|

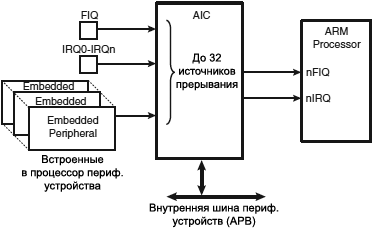

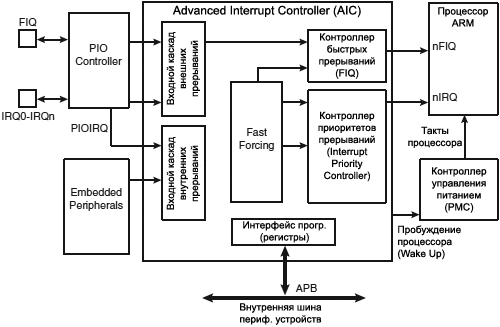

Advanced Interrupt Controller (AIC), ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ ą▓ ą░ą┐ą┐ą░čĆą░čéčāčĆčā AT91SAM7X, čŹč鹊 ą┐čĆąŠą┤ą▓ąĖąĮčāčéčŗą╣ ą▓ąĄą║č鹊čĆąĮčŗą╣ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ čü ą┐ąŠą┤ą┤ąĄčƹȹ║ąŠą╣ 8 čāčĆąŠą▓ąĮąĄą╣ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą▓, čü ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčīčÄ ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮąŠ ą╝ą░čüą║ąĖčĆąŠą▓ą░čéčī ą║ą░ąČą┤ąŠąĄ ąĖąĘ 32 ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄą╝čŗčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. ą×ąĮ čĆą░ąĘčĆą░ą▒ąŠčéą░ąĮ čü čåąĄą╗čīčÄ ą║ą░čĆą┤ąĖąĮą░ą╗čīąĮąŠ čāą╝ąĄąĮčīčłąĖčéčī ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčāčÄ ąĮą░ą│čĆčāąĘą║čā ąĮą░ čÅą┤čĆąŠ ą┐čĆąŠčåąĄčüčüąŠčĆą░, čćč鹊ą▒čŗ čüąĮąĖąĘąĖčéčī ąĘą░čéčĆą░čéčŗ ą┐čĆąŠčåąĄčüčüąŠčĆąĮąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ ąĮą░ ąŠą▒čĆą░ą▒ąŠčéą║čā ą▓ąĮčāčéčĆąĄąĮąĮąĖčģ ąĖ ą▓ąĮąĄčłąĮąĖčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣.

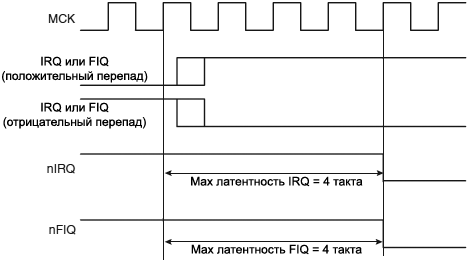

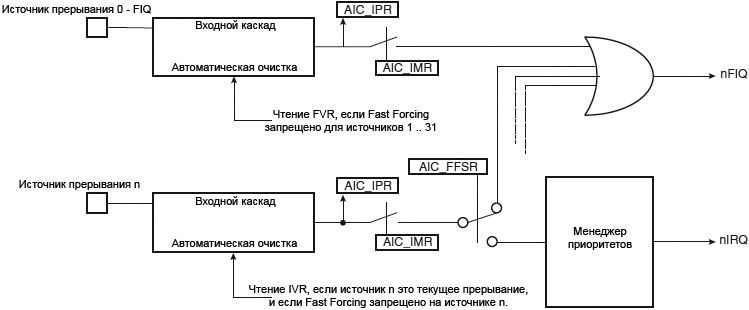

AIC ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčé ą▓čģąŠą┤ FIQ (fast interrupt request, ą▒čŗčüčéčĆčŗą╣ ąĘą░ą┐čĆąŠčü ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ) ąĖ ą▓čģąŠą┤čŗ nIRQ (standard interrupt request, čüčéą░ąĮą┤ą░čĆčéąĮčŗą╣ ąĘą░ą┐čĆąŠčü ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ) ą┐čĆąŠčåąĄčüčüąŠčĆą░ ARM. ąÆčģąŠą┤čŗ AIC čŹč鹊 ą╗ąĖą▒ąŠ čüąĖą│ąĮą░ą╗čŗ ąŠčé ą▓ąĮčāčéčĆąĄąĮąĮąĖčģ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓, ą╗ąĖą▒ąŠ ą▓ąĮąĄčłąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą┐ąŠčüčéčāą┐ą░čÄčēąĖąĄ ą▓ ą▓ąĖą┤ąĄ ą╗ąŠą│ąĖč湥čüą║ąĖčģ čüąĖą│ąĮą░ą╗ąŠą▓ ąĮą░ ą▓čŗą▓ąŠą┤čŗ ą║ąŠčĆą┐čāčüą░ čćąĖą┐ą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░.

8-čāčĆąŠą▓ąĮąĄą▓čŗą╣ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą▓ AIC ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ą┐čĆąĖąŠčĆąĖč鹥čé ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, čĆą░ąĘčĆąĄčłą░čÅ č鹥ą╝ čüą░ą╝čŗą╝ ąŠčüčāčēąĄčüčéą▓ą╗čÅčéčī ąŠą▒čĆą░ą▒ąŠčéą║čā ą▓ ą┐ąĄčĆą▓čāčÄ ąŠč湥čĆąĄą┤čī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čü čüą░ą╝čŗą╝ ą▓čŗčüąŠą║ąĖą╝ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝, ą┤ą░ąČąĄ ąĄčüą╗ąĖ ą▓ ą┤ą░ąĮąĮčŗą╣ ą╝ąŠą╝ąĄąĮčé ą░ą║čéąĖą▓ąĮą░ ąŠą▒čĆą░ą▒ąŠčéą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čü ą╝ąĄąĮąĄąĄ ą▓čŗčüąŠą║ąĖą╝ čāčĆąŠą▓ąĮčÅą╝.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: čéą░ą║ą░čÅ ą┐ąŠą╗ąĄąĘąĮą░čÅ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ąĮą░ąĘąĮą░č湥ąĮąĖčÅ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą▓ ąĖą╝ąĄąĄčéčüčÅ ą┤ą░ą╗ąĄą║ąŠ ąĮąĄ čā ą▓čüąĄčģ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓. ąØą░ą┐čĆąĖą╝ąĄčĆ, AVR RISC ąĖą╝ąĄčÄčé čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮčāčÄ čüąĖčüč鹥ą╝čā ą┐čĆąĖąŠčĆąĖč鹥č鹊ą▓, ą║ č鹊ą╝čā ąČąĄ ą▒ąĄąĘ čüą┐ąĄčåąĖą░ą╗čīąĮąŠą│ąŠ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą▓ąĮčāčéčĆąĖ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ą░ ąĮąĖąĘą║ąŠčāčĆąŠą▓ąĮąĄą▓ąŠą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠąĮąŠ ąĮąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąĄčĆą▓ą░ąĮąŠ ą▒ąŠą╗ąĄąĄ ą┐čĆąĖąŠčĆąĖč鹥čéąĮčŗą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄą╝. ą¤ąŠą┤ąŠą▒ąĮčāčÄ ą┐čĆąŠą▒ą╗ąĄą╝čā čü ą▓čŗč鹥čüąĮąĄąĮąĖąĄą╝ ąĮąĖąĘą║ąŠčāčĆąŠą▓ąĮąĄą▓čŗčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ąĖą╝ąĄčÄčé ą┤ą░ąČąĄ ąŠč湥ąĮčī ą┤ąŠčĆąŠą│ąĖąĄ ą┐čĆąŠčåąĄčüčüąŠčĆčŗ, ąĮą░ą┐čĆąĖą╝ąĄčĆ DSP-ą┐čĆąŠčåąĄčüčüąŠčĆčŗ Blackfin.

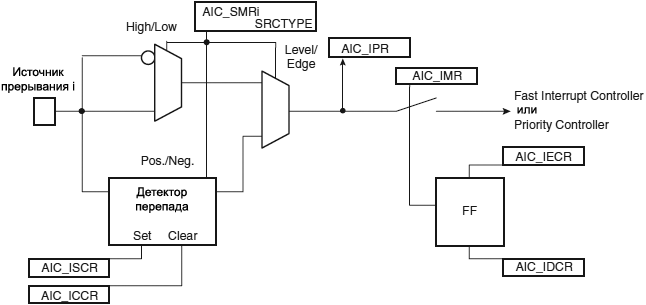

ąÆąĮčāčéčĆąĄąĮąĮąĖąĄ ąĖčüč鹊čćąĮąĖą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą╝ąŠą│čāčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮčŗ ąĮą░ čćčāą▓čüčéą▓ąĖč鹥ą╗čīąĮąŠčüčéčī ą║ čāčĆąŠą▓ąĮčÄ ą╗ąŠą│ąĖč湥čüą║ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ (level sensitive), ą╗ąĖą▒ąŠ ąĮą░ čćčāą▓čüčéą▓ąĖč鹥ą╗čīąĮąŠčüčéčī ą║ ąĄą│ąŠ ą┐ąĄčĆąĄą┐ą░ą┤čā (edge triggered), čé. ąĄ. ą║ ąĖąĘą╝ąĄąĮąĄąĮąĖčÄ čāčĆąŠą▓ąĮčÅ. ąÆąĮąĄčłąĮąĖąĄ ąĖčüč鹊čćąĮąĖą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą╝ąŠąČąĮąŠ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī ąĮą░ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĄ ąŠčé ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą│ąŠ ą┐ąĄčĆąĄą┐ą░ą┤ą░ čāčĆąŠą▓ąĮčÅ (ą╗ąŠą│. 0 -> ą╗ąŠą│. 1), ąŠčé ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠą│ąŠ ą┐ąĄčĆąĄą┐ą░ą┤ą░ čāčĆąŠą▓ąĮčÅ (ą╗ąŠą│. 1 -> ą╗ąŠą│. 0), ą╗ąĖą▒ąŠ ąĮą░ čćčāą▓čüčéą▓ąĖč鹥ą╗čīąĮąŠčüčéčī ą║ čāčĆąŠą▓ąĮčÄ ą╗ąŠą│. 0 ąĖą╗ąĖ ą╗ąŠą│. 1.

ążčāąĮą║čåąĖčÅ ą▒čŗčüčéčĆąŠą│ąŠ ą┐čĆąĖąĮčāą┤ąĖč鹥ą╗čīąĮąŠą│ąŠ ąĘą░ą┐čāčüą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (Fast Forcing) ą┐ąĄčĆąĄąĮą░ą┐čĆą░ą▓ą╗čÅąĄčé ą╗čÄą▒ąŠą╣ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ ąĖą╗ąĖ ą▓ąĮąĄčłąĮąĖą╣ ąĖčüč鹊čćąĮąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮąĖčÅ ą▒čŗčüčéčĆąŠą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą▓ą╝ąĄčüč鹊 ąŠą▒čŗčćąĮąŠą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

ąĀąĖčü. 23-1. ąŻą┐čĆąŠčēąĄąĮąĮą░čÅ ą▒ą╗ąŠą║-čüčģąĄą╝ą░ AIC.

| ą×ą▒čŗčćąĮčŗąĄ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ (ą▒ąĄąĘ ąŠą┐ąĄčĆą░čåąĖąŠąĮąĮčŗą╣ čüąĖčüč鹥ą╝čŗ) |

ą¤čĆąĖą╗ąŠąČąĄąĮąĖčÅ ąĮą░ ąŠčüąĮąŠą▓ąĄ ąŠą┐ąĄčĆą░čåąĖąŠąĮąĮąŠą╣

čüąĖčüč鹥ą╝čŗ (ąŠą▒čŗčćąĮąŠ RTOS) |

| ąöčĆą░ą╣ą▓ąĄčĆčŗ ąŠą┐ąĄčĆą░čåąĖąŠąĮąĮąŠą╣ čüąĖčüč鹥ą╝čŗ |

ąŚą░ą┤ą░čćąĖ ąČąĄčüčéą║ąŠą│ąŠ čĆąĄą░ą╗čīąĮąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ |

| ą×ą▒čĆą░ą▒ąŠčéčćąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ąŠą┐ąĄčĆą░čåąĖąŠąĮąĮąŠą╣ čüąĖčüč鹥ą╝čŗ |

| Advanced Interrupt Controller (AIC) |

| ąÆčüčéčĆąŠąĄąĮąĮčŗąĄ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ |

ąÆąĮąĄčłąĮąĖąĄ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ |

ąĀąĖčü. 23-2. ą×ą┐ąĖčüą░ąĮąĖąĄ ą▓ąĘą░ąĖą╝ąŠą┤ąĄą╣čüčéą▓ąĖčÅ AIC čü ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄą╝.

ąĀąĖčü. 23-3. ą¤ąŠą┤čĆąŠą▒ąĮą░čÅ ą▒ą╗ąŠą║-čüčģąĄą╝ą░ AIC.

ąóą░ą▒ą╗ąĖčåą░ 23-1. ą×ą┐ąĖčüą░ąĮąĖąĄ čüąĖą│ąĮą░ą╗ąŠą▓ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░.

| ą£ąĮąĄą╝ąŠąĮąĖą║ą░ |

ą×ą┐ąĖčüą░ąĮąĖąĄ ą▓čŗą▓ąŠą┤ą░ |

ąóąĖą┐ |

| FIQ |

Fast Interrupt Query (ąĘą░ą┐čĆąŠčü ąĮą░ ą▒čŗčüčéčĆąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ) |

ąÆčģąŠą┤ |

| IRQ0 .. IRQn |

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖčÅ 0 .. n |

ąÆčģąŠą┤ |

[ąŚą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ AIC]

ąĪąĖą│ąĮą░ą╗čŗ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ (I/O). ąĪąĖą│ąĮą░ą╗čŗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ FIQ ąĖ IRQ0 .. IRQn ąŠą▒čŗčćąĮąŠ ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąĖčĆčāčÄčéčüčÅ č湥čĆąĄąĘ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčŗ PIO [2]. ąÆ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą▓ąŠąĘą╝ąŠąČąĮąŠčüč鹥ą╣ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ PIO, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ąŠą│ąŠ ą▓ ą║ąŠąĮą║čĆąĄčéąĮąŠą╝ čéąĖą┐ąĄ ą┐čĆąŠčåąĄčüčüąŠčĆą░, ą▓čŗą▓ąŠą┤čŗ ą║ąŠčĆą┐čāčüą░ čćąĖą┐ą░ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮčŗ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ ąĖčģ ąĮą░ąĘąĮą░č湥ąĮąĮčŗą╝ čäčāąĮą║čåąĖčÅą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ąŁč鹊 ą┐čĆą░ą▓ąĖą╗ąŠ ąĮąĄ ą┤ąĄą╣čüčéą▓čāąĄčé, ą║ąŠą│ą┤ą░ PIO ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╣ ą▓ ą┐čĆąŠčåąĄčüčüąŠčĆąĄ, ą┐čĆąŠąĘčĆą░č湥ąĮ ą┤ą╗čÅ ą┐čĆąŠčģąŠąČą┤ąĄąĮąĖčÅ ą▓čģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░.

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖąĄą╝. AIC ą┐ąŠčüč鹊čÅąĮąĮąŠ ą┐ąŠą╗čāčćą░ąĄčé čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ. Power Management Controller (PMC [3]) ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ ą▓ą╗ąĖčÅąĮąĖčÅ ąĮą░ ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ AIC.

ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▓čŗčģąŠą┤ąŠą▓ AIC, ą╗ąĖą▒ąŠ nIRQ, ą╗ąĖą▒ąŠ or nFIQ, ą┐čĆąĖą▓ąŠą┤ąĖčé ą║ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÄ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ARM, ąĄčüą╗ąĖ ąŠąĮ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ąĖ/čüąĮą░ (čĆąĄąČąĖą╝ ą┐ąŠąĮąĖąČąĄąĮąĮąŠą│ąŠ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ, Idle Mode). ążčāąĮą║čåąĖčÅ General Interrupt Mask ą┐ąŠąĘą▓ąŠą╗čÅąĄčé AIC ą▓čŗą▓ąŠą┤ąĖčéčī ąĖąĘ čüąĮą░ ą┐čĆąŠčåąĄčüčüąŠčĆ ą▒ąĄąĘ ą░ą║čéąĖą▓ą░čåąĖąĖ čüąĖą│ąĮą░ą╗ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐čĆąŠčåąĄčüčüąŠčĆą░, ąŠčüčāčēąĄčüčéą▓ą╗čÅčÅ č鹥ą╝ čüą░ą╝čŗą╝ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖčÄ ą┐čĆąŠčåąĄčüčüąŠčĆąĄ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ.

ąśčüč鹊čćąĮąĖą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. Interrupt Source 0 ą▓čüąĄą│ą┤ą░ ąĮą░ąĘąĮą░č湥ąĮ ąĮą░ FIQ. ąĢčüą╗ąĖ ąĮą░ ą║ąŠčĆą┐čāčüąĄ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ąĮąĄ čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮ ą▓čŗą▓ąŠą┤ FIQ, č鹊 Interrupt Source 0 ąĮąĄ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ.

Interrupt Source 1 ą▓čüąĄą│ą┤ą░ ąĮą░ąĘąĮą░č湥ąĮ ąĮą░ čüąĖčüč鹥ą╝ąĮąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ (System Interrupt). ąŁč鹊 čĆąĄąĘčāą╗čīčéą░čé čüąŠąĄą┤ąĖąĮąĄąĮąĖčÅ čäčāąĮą║čåąĖąĄą╣ ąśąøąś čüąĖą│ąĮą░ą╗ąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čüąĖčüč鹥ą╝ąĮčŗčģ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓, čéą░ą║ąĖčģ ą║ą░ą║ System Timer, Real Time Clock (čćą░čüčŗ čĆąĄą░ą╗čīąĮąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ, RTC), Power Management Controller [3] ąĖ Memory Controller [4]. ąÜąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé čüąĖčüč鹥ą╝ąĮąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ąĄą│ąŠ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ (interrupt service routine, ISR) ą┤ąŠą╗ąČąĄąĮ čüąĮą░čćą░ą╗ą░ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ąĖčüč鹊čćąĮąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ąŁč鹊 ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą┐čāč鹥ą╝ čćč鹥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆąŠą▓ čüąŠčüč鹊čÅąĮąĖčÅ ą▓čŗčłąĄčāą┐ąŠą╝čÅąĮčāčéčŗčģ čüąĖčüč鹥ą╝ąĮčŗčģ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓.

ąśčüč鹊čćąĮąĖą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ 2 .. 31 ą╝ąŠą│čāčé ą▒čŗčéčī ą╗ąĖą▒ąŠ ą┐ąŠą┤ą║ą╗čÄč湥ąĮčŗ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╝ ą║ ą▓čŗčģąŠą┤ą░ą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą▓čüčéčĆąŠąĄąĮąĮčŗčģ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓, ą╗ąĖą▒ąŠ ą║ čüąĖą│ąĮą░ą╗ą░ą╝ ą▓ąĮąĄčłąĮąĖčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. ąÆąĮąĄčłąĮąĖąĄ čüąĖą│ąĮą░ą╗čŗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą╝ąŠą│čāčé ą▒čŗčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮčŗ ą╗ąĖą▒ąŠ ąĮą░ą┐čĆčÅą╝čāčÄ, ą╗ąĖą▒ąŠ č湥čĆąĄąĘ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ PIO.

PIO-ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčŗ ą▓ ą║ąŠąĮč鹥ą║čüč鹥 ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ čĆą░čüčüą╝ą░čéčĆąĖą▓ą░čÄčéčüčÅ ą║ą░ą║ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░. ąĪąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ čüąĖą│ąĮą░ą╗čŗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ PIO Controller ą┐ąŠą┤ą║ą╗čÄčćą░čÄčéčüčÅ ą║ ąĖčüč鹊čćąĮąĖą║ą░ą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ 2 .. 31.

ąśą┤ąĄąĮčéąĖčäąĖą║ą░čåąĖčÅ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ą┐ąŠ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╝čā ąĄą╝čā ąĮąŠą╝ąĄčĆčā ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ąĮą░ čāčĆąŠą▓ąĮąĄ ą┐čĆąŠą┤čāą║čéą░ (čé. ąĄ. čéąĖą┐ą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░), čéą░ą║ ąČąĄ ą║ą░ą║ ąĮąŠą╝ąĄčĆ ą▒ąĖčéą░, čāą┐čĆą░ą▓ą╗čÅčÄčēąĖą╣ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄą╝ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░. ąĪąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ ą┤ą╗čÅ čāą┐čĆąŠčēąĄąĮąĖčÅ ąŠą┐ąĖčüą░ąĮąĖčÅ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮčŗčģ ąŠą┐ąĄčĆą░čåąĖą╣ ąĖ ąĖąĮč鹥čĆč乥ą╣čüą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖčüč鹊čćąĮąĖą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĖą╝ąĄąĮčāčÄčéčüčÅ FIQ, SYS, PID2 .. PID31.

[ążčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ AIC]

ąĀąĄąČąĖą╝ ąĖčüč鹊čćąĮąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. AIC ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčé ą║ą░ąČą┤čŗą╣ ąĖčüč鹊čćąĮąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ą¤ąŠą╗ąĄ SRCTYPE čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ AIC_SMR (Source Mode Register, čĆąĄą│ąĖčüčéčĆ čĆąĄąČąĖą╝ą░ ąĖčüč鹊čćąĮąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ) ą▓čŗą▒ąĖčĆą░ąĄčé čāčüą╗ąŠą▓ąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░.

ąÆąĮčāčéčĆąĄąĮąĮąĖąĄ ąĖčüč鹊čćąĮąĖą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗąĄ ąĮą░ ą▓čŗčģąŠą┤čŗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą▓čüčéčĆąŠąĄąĮąĮčŗčģ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓, ą╝ąŠąČąĮąŠ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī ą╗ąĖą▒ąŠ ą▓ čĆąĄąČąĖą╝ąĄ čćčāą▓čüčéą▓ąĖč鹥ą╗čīąĮąŠčüčéąĖ ą║ čāčĆąŠą▓ąĮčÄ, (level-sensitive mode), ą╗ąĖą▒ąŠ ą▓ čĆąĄąČąĖą╝ąĄ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖčÅ ą┐ąŠ ą┐ąĄčĆąĄą┐ą░ą┤čā čāčĆąŠą▓ąĮčÅ (edge-triggered mode). ąÉą║čéąĖą▓ąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī ą▓ąĮčāčéčĆąĄąĮąĮąĖčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ąĮąĄ ąĖą╝ąĄąĄčé ąĘąĮą░č湥ąĮąĖčÅ ą┤ą╗čÅ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ.

ąÆąĮąĄčłąĮąĖąĄ ąĖčüč鹊čćąĮąĖą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą╝ąŠąČąĮąŠ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī ą╗ąĖą▒ąŠ ą▓ čĆąĄąČąĖą╝ąĄ čćčāą▓čüčéą▓ąĖč鹥ą╗čīąĮąŠčüčéąĖ ą║ čāčĆąŠą▓ąĮčÄ ą╗ąŠą│. 1 (high level-sensitive mode) ąĖą╗ąĖ ą║ čāčĆąŠą▓ąĮčÄ ą╗ąŠą│. 0 (low level-sensitive mode), ąĖą╗ąĖ ą▓ čĆąĄąČąĖą╝ąĄ čćčāą▓čüčéą▓ąĖč鹥ą╗čīąĮąŠčüčéąĖ ą╗ąĖą▒ąŠ ą║ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą╝čā, ą╗ąĖą▒ąŠ ą║ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠą╝čā ą┐ąĄčĆąĄą┐ą░ą┤čā čāčĆąŠą▓ąĮčÅ.

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ąĖčüč鹊čćąĮąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ąÜą░ąČą┤čŗą╣ ąĖčüč鹊čćąĮąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą▓ą║ą╗čÄčćą░čÅ FIQ ą▓ ąĖčüč鹊čćąĮąĖą║ąĄ 0, ą╝ąŠąČąĮąŠ čĆą░ąĘčĆąĄčłąĖčéčī ąĖą╗ąĖ ąĘą░ą┐čĆąĄčéąĖčéčī čü ą┐ąŠą╝ąŠčēčīčÄ čĆąĄą│ąĖčüčéčĆąŠą▓ ą║ąŠą╝ą░ąĮą┤ AIC_IECR (Interrupt Enable Command Register) ąĖ AIC_IDCR (Interrupt Disable Command Register). ąŁč鹊čé ąĮą░ą▒ąŠčĆ čĆąĄą│ąĖčüčéčĆąŠą▓ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé čĆą░ąĘčĆąĄčłą░čéčī ąĖą╗ąĖ ąĘą░ą┐čĆąĄčēą░čéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą▓ ąŠą┤ąĮąŠą╣ ąĖąĮčüčéčĆčāą║čåąĖąĖ. ą£ą░čüą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮą░ ą▓ čĆąĄą│ąĖčüčéčĆąĄ AIC_IMR. ąŚą░ą┐čĆąĄčēąĄąĮąĮąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĮąĄ ą▓ą╗ąĖčÅąĄčé ąĮą░ ąŠą▒čĆą░ą▒ąŠčéą║čā ą┤čĆčāą│ąĖčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣.

ą×čćąĖčüčéą║ą░ ąĖ čāčüčéą░ąĮąŠą▓ą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. ąÆčüąĄ ąĖčüč鹊čćąĮąĖą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮčŗąĄ ąĮą░ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĄ ą┐ąŠ ą┐ąĄčĆąĄą┐ą░ą┤čā (ą▓ą║ą╗čÄčćą░čÅ FIQ ąĮą░ ąĖčüč鹊čćąĮąĖą║ąĄ 0) ą╝ąŠąČąĮąŠ ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮąŠ čāčüčéą░ąĮąŠą▓ąĖčéčī ąĖą╗ąĖ ąŠčćąĖčüčéąĖčéčī ąĘą░ą┐ąĖčüčīčÄ ą▓ čĆąĄą│ąĖčüčéčĆčŗ AIC_ISCR ąĖ AIC_ICCR čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ. ą×čćąĖčüčéą║ą░ ąĖą╗ąĖ čāčüčéą░ąĮąŠą▓ą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣, ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮčŗčģ ąĮą░ čćčāą▓čüčéą▓ąĖč鹥ą╗čīąĮąŠčüčéčī čā čāčĆąŠą▓ąĮčÄ, ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

ą×ą┐ąĄčĆą░čåąĖčÅ ąŠčćąĖčüčéą║ąĖ ąĮąĄą▒čĆąĄąČąĮą░čÅ, ą┐ąŠčüą║ąŠą╗čīą║čā ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┤ąŠą╗ąČąĮą░ ą▓čŗą┐ąŠą╗ąĮąĖčéčī ą┤ąĄą╣čüčéą▓ąĖąĄ ą┤ą╗čÅ ą┐ąĄčĆąĄąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ čüčģąĄą╝čŗ "ąĘą░ą┐ąŠą╝ąĖąĮą░ąĮąĖčÅ", ą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮąĮąŠą╣ ą┐čĆąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖčüč鹊čćąĮąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą▓ čĆąĄąČąĖą╝ąĄ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖčÅ ą┐ąŠ ą┐ąĄčĆąĄą┐ą░ą┤čā (edge-triggered mode). ą×ą┤ąĮą░ą║ąŠ ąŠą┐ąĄčĆą░čåąĖčÅ čāčüčéą░ąĮąŠą▓ą║ąĖ ą┤ąŠčüčéčāą┐ąĮą░ ą┤ą╗čÅ ą░ą▓č鹊č鹥čüčéą░ ąĖą╗ąĖ ą▓ čåąĄą╗čÅčģ ąŠčéą╗ą░ą┤ą║ąĖ. ą×ąĮą░ čéą░ą║ąČąĄ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ąĮą░ ąŠčüąĮąŠą▓ąĄ AIC.

AIC ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąŠčćąĖčēą░ąĄčé č鹥ą║čāčēąĄąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ą║ąŠą│ą┤ą░ čćąĖčéą░ąĄčéčüčÅ čĆąĄą│ąĖčüčéčĆ AIC_IVR (Interrupt Vector Register). ąŁčéą░ ąŠą┐ąĄčĆą░čåąĖčÅ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ č鹊ą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą║ąŠč鹊čĆčŗą╣ AIC ąŠą┐čĆąĄą┤ąĄą╗ąĖą╗ ą║ą░ą║ č鹥ą║čāčēąĄąĄ (čüą╝. ą┤ą░ą╗ąĄąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą▓ Priority Controller). ąÉą▓č鹊ą╝ą░čéąĖč湥čüą║ą░čÅ ąŠčćąĖčüčéą║ą░ čāą╝ąĄąĮčīčłą░ąĄčé ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ąŠą┐ąĄčĆą░čåąĖą╣, čéčĆąĄą▒čāąĄą╝čŗčģ ą┤ą╗čÅ ISR, čéą░ą║ čćč鹊 ą║ąŠą┤čā ISR ąĮąĄ ąĮčāąČąĮąŠ čćąĖčéą░čéčī AIC_IVR. ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ą░čÅ ąŠčćąĖčüčéą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĘą░ą┐čĆąĄčēąĄąĮą░, ąĄčüą╗ąĖ ąĮą░ ąĖčüč鹊čćąĮąĖą║ąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čĆą░ąĘčĆąĄčłąĄąĮą░ čäčāąĮą║čåąĖčÅ Fast Forcing, čéą░ą║ čćč鹊 čüčćąĖčéą░ąĄčéčüčÅ, čćč鹊 čŹč鹊 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čāąĮąĖą║ą░ą╗čīąĮąŠ čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ąĖčüč鹊čćąĮąĖą║ ą▒čŗčüčéčĆąŠą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ FIQ (ą┐ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. ą┤ą░ą╗ąĄąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ "Fast Forcing").

ąÉą▓č鹊ą╝ą░čéąĖč湥čüą║ą░čÅ ąŠčćąĖčüčéą║ą░ ąĖčüč鹊čćąĮąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ 0 ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą┐čĆąĖ čćč鹥ąĮąĖąĖ AIC_FVR.

ąĪčéą░čéčāčü ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ąöą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čĆąĄąĘčāą╗čīčéą░čé čĆą░ą▒ąŠčéčŗ AIC ąŠčéčĆą░ąČą░ąĄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ AIC_IPR (Interrupt Pending Register, čĆąĄą│ąĖčüčéčĆ ąŠąČąĖą┤ą░čÄčēąĖčģ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣), ąĖ čŹč鹊 ą╝ą░čüą║ąĖčĆčāąĄčéčüčÅ čĆąĄą│ąĖčüčéčĆąŠą╝ AIC_IMR (Interrupt Mask Register). AIC_IPR čĆą░ąĘčĆąĄčłą░ąĄčé čĆąĄą░ą╗čīąĮčāčÄ ą░ą║čéąĖą▓ąĮąŠčüčéčī ąĖčüč鹊čćąĮąĖą║ąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣, ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé č鹊ą│ąŠ, ąĘą░ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮčŗ ąŠąĮąĖ ąĖą╗ąĖ ąĮąĄčé.

ą¦č鹥ąĮąĖąĄ AIC_ISR ą┤ą░ąĄčé ąĮąŠą╝ąĄčĆ č鹥ą║čāčēąĄą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (čüą╝. ą┤ą░ą╗ąĄąĄ "Priority Controller"), ąĖ čĆąĄą│ąĖčüčéčĆ AIC_CISR ą┤ą░ąĄčé ąŠą▒čĆą░ąĘ čüąĖą│ąĮą░ą╗ąŠą▓ nIRQ ąĖ nFIQ, ą┐čĆąĖčüčāčéčüčéą▓čāčÄčēąĖčģ ąĮą░ ą┐čĆąŠčåąĄčüčüąŠčĆąĄ.

ąÜą░ąČą┤čŗą╣ ąĖąĘ ą▓čŗčłąĄčāą┐ąŠą╝čÅąĮčāčéčŗčģ čüčéą░čéčāčüąŠą▓ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ąŠą┐čéąĖą╝ąĖąĘą░čåąĖąĖ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą▓ čüąĖčüč鹥ą╝ąĄ.

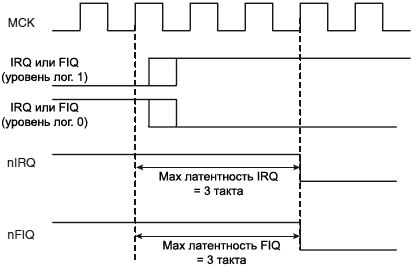

ąĀąĖčü. 23-4. ąÆčģąŠą┤ąĮąŠą╣ ą║ą░čüą║ą░ą┤ ą▓ąĮčāčéčĆąĄąĮąĮąĖčģ ąĖčüč鹊čćąĮąĖą║ąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ (Internal Interrupt Source Input Stage).

ąĀąĖčü. 23-5. ąÆčģąŠą┤ąĮąŠą╣ ą║ą░čüą║ą░ą┤ ą▓ąĮąĄčłąĮąĖčģ ąĖčüč鹊čćąĮąĖą║ąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ (External Interrupt Source Input Stage).

ąøą░č鹥ąĮčéąĮąŠčüčéąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ą¤ąŠą┤ ą╗ą░č鹥ąĮčéąĮąŠčüčéčīčÄ ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░čÄčé ąĘą░ą┤ąĄčƹȹ║čā ąĮą░ čĆąĄą░ą║čåąĖčÄ, ą▓ ą┤ą░ąĮąĮąŠą╝ ą║ąŠąĮč鹥ą║čüč鹥 ąĖą╝ąĄąĄčéčüčÅ ą▓ ą▓ąĖą┤čā ąĘą░ą┤ąĄčƹȹ║ą░ ą╝ąĄąČą┤čā ą┐ąŠčÅą▓ą╗ąĄąĮąĖąĄą╝ čüąŠą▒čŗčéąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĖ ąĘą░ą┐čāčüą║ąŠą╝ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÄ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ą░ (Interrupt Service Routine, ISR). ąōą╗ąŠą▒ą░ą╗čīąĮčŗąĄ ą╗ą░č鹥ąĮčéąĮąŠčüčéąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĘą░ą▓ąĖčüčÅčé ąŠčé ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓, ą▓ą║ą╗čÄčćą░čÅ:

ŌĆó ąÆčĆąĄą╝ąĄąĮąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣.

ŌĆó ą¤čĆąŠąĖąĘąŠčłą╗ąŠ ą╗ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĮą░ čāčĆąŠą▓ąĮąĄ ą┐čĆąŠčåąĄčüčüąŠčĆą░, ąĖą╗ąĖ ąĮą░ čāčĆąŠą▓ąĮąĄ AIC.

ŌĆó ąÆčĆąĄą╝ąĄąĮąĖ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ąĖąĮčüčéčĆčāą║čåąĖąĖ, ą║ąŠč鹊čĆą░čÅ ą▓čŗą┐ąŠą╗ąĮčÅą╗ą░čüčī ą▓ ą╝ąŠą╝ąĄąĮčé ą▓ąŠąĘąĮąĖą║ąĮąŠą▓ąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

ŌĆó ąÆą╗ąĖčÅąĮąĖąĄ ą░ą║čéąĖą▓ąĮąŠčüčéąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ čü ą▒ąŠą╗ąĄąĄ ą▓čŗčüąŠą║ąĖą╝ čāčĆąŠą▓ąĮąĄą╝ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ąĖ čĆąĄčüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖčÅ ą░ą┐ą┐ą░čĆą░čéąĮčŗčģ čüąĖą│ąĮą░ą╗ąŠą▓.

ąÆ čŹč鹊ą╣ čüąĄą║čåąĖąĖ čĆą░čüčüą╝ą░čéčĆąĖą▓ą░čÄčéčüčÅ č鹊ą╗čīą║ąŠ ą░ą┐ą┐ą░čĆą░čéąĮčŗąĄ čĆąĄčüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ. ąŁč鹊 ą┤ą░ąĄčé ą┐ąŠą┤čĆąŠą▒ąĮčāčÄ ąĖąĮč乊čĆą╝ą░čåąĖčÄ ą┐ąŠ ąĖąĮč鹥čĆą▓ą░ą╗ą░ą╝ ą▓čĆąĄą╝ąĄąĮąĖ ą╗ą░č鹥ąĮčéąĮąŠčüčéąĖ ą╝ąĄąČą┤čā čüąŠą▒čŗčéąĖąĄą╝ ąĮą░ ą▓ąĮąĄčłąĮąĄą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĖ ąĖ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (ą▓ čĆąĄąČąĖą╝ąĄ ą┐ąĄčĆąĄą┐ą░ą┤ą░ ąĖą╗ąĖ čāčĆąŠą▓ąĮčÅ), ąĖą╗ąĖ ą░ą║čéąĖą▓ą░čåąĖąĖ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╣ čāčüčéą░ąĮąŠą▓ą║ąĖ čüąĖą│ąĮą░ą╗ą░ nIRQ ąĖą╗ąĖ nFIQ ąĮą░ ą┐čĆąŠčåąĄčüčüąŠčĆąĄ. ąÆčĆąĄą╝čÅ čĆąĄčüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ąĘą░ą▓ąĖčüąĖčé ąŠčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖčüč鹊čćąĮąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĖ ąŠčé ąĄą│ąŠ čéąĖą┐ą░ (ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ ąĖą╗ąĖ ą▓ąĮąĄčłąĮąĖą╣). ąöą╗čÅ čüčéą░ąĮą┤ą░čĆčéąĮąŠą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĖąĮč鹥čĆą▓ą░ą╗čŗ čĆąĄčüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ą┤ą░ąĮčŗ ą▓ ą┐čĆąĄą┤ą┐ąŠą╗ąŠąČąĄąĮąĖąĖ, čćč鹊 ą▓ ą┤ą░ąĮąĮčŗą╣ ą╝ąŠą╝ąĄąĮčé ąĮąĄ ą▓čŗą┐ąŠą╗ąĮčÅčÄčéčüčÅ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ čü ą▒ąŠą╗ąĄąĄ ą▓čŗčüąŠą║ąĖą╝ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝.

ą£čāą╗čīčéąĖą┐ą╗ąĄą║čüąĖčĆąŠą▓ą░ąĮąĖąĄ PIO-ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ [2] ąĮąĄ ą▓ą╗ąĖčÅąĄčé ąĮą░ ą╗ą░č鹥ąĮčéąĮąŠčüčéąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą▓ąĮąĄčłąĮąĖčģ ąĖčüč鹊čćąĮąĖą║ąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

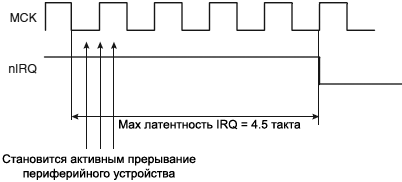

ąĀąĖčü. 23-6. ąÆąĮąĄčłąĮąĄąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą▓ čĆąĄąČąĖą╝ąĄ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖčÅ ą┐ąŠ ą┐ąĄčĆąĄą┐ą░ą┤čā (External Interrupt Edge Triggered Source).

ąĀąĖčü. 23-7. ąÆąĮąĄčłąĮąĄąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą▓ čĆąĄąČąĖą╝ąĄ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖčÅ ą┐ąŠ čāčĆąŠą▓ąĮčÄ (External Interrupt Level Sensitive Source).

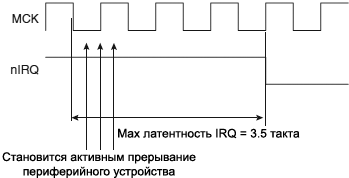

ąĀąĖčü. 23-8. ąÆąĮčāčéčĆąĄąĮąĮąĄąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą▓ čĆąĄąČąĖą╝ąĄ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖčÅ ą┐ąŠ ą┐ąĄčĆąĄą┐ą░ą┤čā (Internal Interrupt Edge Triggered Source).

ąĀąĖčü. 23-9. ąÆąĮčāčéčĆąĄąĮąĮąĄąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą▓ čĆąĄąČąĖą╝ąĄ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖčÅ ą┐ąŠ čāčĆąŠą▓ąĮčÄ (Internal Interrupt Level Sensitive Source).

[ąĪčéą░ąĮą┤ą░čĆčéąĮąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ]

ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą▓ (Priority Controller). 8-čāčĆąŠą▓ąĮąĄą▓čŗą╣ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą▓ čāą┐čĆą░ą▓ą╗čÅąĄčé čüąĖą│ąĮą░ą╗ą░ą╝ąĖ nIRQ ąĮą░ ą┐čĆąŠčåąĄčüčüąŠčĆąĄ, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čüąŠą▒čŗčéąĖą╣ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĮą░ ąĖčüč鹊čćąĮąĖą║ą░čģ 1 .. 31 (ą║čĆąŠą╝ąĄ č鹥čģ, ą║ąŠč鹊čĆčŗąĄ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮčŗ ą▓ Fast Forcing).

ąÜą░ąČą┤čŗą╣ ąĖčüč鹊čćąĮąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĖą╝ąĄąĄčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗą╣ čāčĆąŠą▓ąĄąĮčī ą┐čĆąĖąŠčĆąĖč鹥čéą░ 7 .. 0, čćč鹊 ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ąĘą░ą┐ąĖčüčīčÄ ą┐ąŠą╗čÅ PRIOR ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╝ čĆąĄą│ąĖčüčéčĆąĄ AIC_SMR (Source Mode Register). ąŻčĆąŠą▓ąĄąĮčī 7 čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé čüą░ą╝ąŠą╝čā ą▓čŗčüąŠą║ąŠą╝čā ą┐čĆąĖąŠčĆąĖč鹥čéčā, ąĖ 0 čüą░ą╝ąŠą╝čā ąĮąĖąĘą║ąŠą╝čā. ąÜą░ą║ č鹊ą╗čīą║ąŠ ą┐čĆąŠąĖąĘąŠčłą╗ąŠ čüąŠą▒čŗčéąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą║ą░ą║ čŹč鹊 ą▒čŗą╗ąŠ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąŠ ą┐ąŠą╗ąĄą╝ SRCTYPE ą▓ AIC_SMR (Source Mode Register), čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ čüąĖą│ąĮą░ą╗ nIRQ. ąØąŠą▓ąŠąĄ čüąŠą▒čŗčéąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą╝ąŠąČąĄčé ą┐čĆąŠąĖąĘąŠą╣čéąĖ ąĮą░ ą┤čĆčāą│ąŠą╝ ąĖčüč鹊čćąĮąĖą║ąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ąĖą╗čüčÅ čüąĖą│ąĮą░ą╗, ą▓ čŹč鹊ą╣ čüąĖčéčāą░čåąĖąĖ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą▓ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé č鹥ą║čāčēąĄąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą▓ ą╝ąŠą╝ąĄąĮčé čćč鹥ąĮąĖčÅ AIC_IVR (Interrupt Vector Register). ą¦č鹥ąĮąĖąĄ AIC_IVR čÅą▓ą╗čÅąĄčéčüčÅ č鹊čćą║ąŠą╣ ą▓čģąŠą┤ą░ ą▓ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, čćč鹊 ą┤ą░ąĄčé AIC ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī čüčćąĖčéą░čéčī, čćč鹊 čŹč鹊 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čāčćč鹥ąĮąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣.

ąóąĄą║čāčēąĖą╣ čāčĆąŠą▓ąĄąĮčī ą┐čĆąĖąŠčĆąĖč鹥čéą░ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮ ą║ą░ą║ čāčĆąŠą▓ąĄąĮčī ą┐čĆąĖąŠčĆąĖč鹥čéą░ č鹥ą║čāčēąĄą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

ąĢčüą╗ąĖ ąĮąĄčüą║ąŠą╗čīą║ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ čü ąŠą┤ąĖąĮą░ą║ąŠą▓čŗą╝ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝ ąŠąČąĖą┤ą░čÄčé ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ąĖ čĆą░ąĘčĆąĄčłąĄąĮčŗ ą▓ ą╝ąŠą╝ąĄąĮčé čćč鹥ąĮąĖčÅ AIC_IVR, č鹊 čüąĮą░čćą░ą╗ą░ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čü čüą░ą╝čŗą╝ ąĮąĖąĘą║ąĖą╝ ąĮąŠą╝ąĄčĆąŠą╝ ąĖčüč鹊čćąĮąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

ąĪąĖą│ąĮą░ą╗ nIRQ ą╝ąŠąČąĄčé ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ č鹊ą╗čīą║ąŠ ąĄčüą╗ąĖ čüąŠą▒čŗčéąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐čĆąŠąĖąĘąŠčłą╗ąŠ ąĮą░ ąĖčüč鹊čćąĮąĖą║ąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čü ą▒ąŠą╗ąĄąĄ ą▓čŗčüąŠą║ąĖą╝ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝. ąĢčüą╗ąĖ ą┐čĆąŠąĖąĘąŠčłą╗ąŠ čüąŠą▒čŗčéąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (ąĖą╗ąĖ ąŠąĮąŠ ąŠąČąĖą┤ą░ąĄčé ąŠą▒čĆą░ą▒ąŠčéą║ąĖ) ą▓ąŠ ą▓čĆąĄą╝čÅ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, č鹊 ąĄą│ąŠ ąŠą▒čĆą░ą▒ąŠčéą║ą░ ąŠčéą║ą╗ą░ą┤čŗą▓ą░ąĄčéčüčÅ, ą┐ąŠą║ą░ ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ąĮąĄ ą┐ąŠą║ą░ąČąĄčé AIC ąŠą║ąŠąĮčćą░ąĮąĖąĄ č鹥ą║čāčēąĄą╣ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ AIC_EOICR (End of Interrupt Command Register). ąŚą░ą┐ąĖčüčī AIC_EOICR čÅą▓ą╗čÅąĄčéčüčÅ č鹊čćą║ąŠą╣ ą▓čŗčģąŠą┤ą░ ąĖąĘ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

Interrupt Nesting (ą▓ą╗ąŠąČąĄąĮąĮčŗąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ). ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą▓ čĆąĄą░ą╗ąĖąĘčāąĄčé ą▓ą╗ąŠąČąĄąĮąĮčŗąĄ ą▓čŗąĘąŠą▓čŗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣, čćč鹊ą▒čŗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čü ą▒ąŠą╗ąĄąĄ ą▓čŗčüąŠą║ąĖą╝ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝ ą╝ąŠą│ą╗ąŠ ą▒čŗčéčī ąŠą▒čĆą░ą▒ąŠčéą░ąĮąŠ ąĮą░ č乊ąĮąĄ ą░ą║čéąĖą▓ąĮąŠčüčéąĖ ą╝ąĄąĮąĄąĄ ą┐čĆąĖąŠčĆąĖč鹥čéąĮčŗčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. ąŁč鹊 čéčĆąĄą▒čāąĄčé, čćč鹊ą▒čŗ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ (ISR), čā ą║ąŠč鹊čĆčŗčģ ą┐čĆąĖąŠčĆąĖč鹥čé ą╝ąĄąĮčīčłąĄ, ą┐ąŠą▓č鹊čĆąĮąŠ čĆą░ąĘčĆąĄčłą░ą╗ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĮą░ čāčĆąŠą▓ąĮąĄ ą┐čĆąŠčåąĄčüčüąŠčĆą░.

ąÜąŠą│ą┤ą░ ą┐čĆąŠąĖąĘąŠčłą╗ąŠ ą▒ąŠą╗ąĄąĄ ą┐čĆąĖąŠčĆąĖč鹥čéąĮąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ąĖ čāąČąĄ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ čü ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝ ąĮąĖąČąĄ, čüąĖą│ąĮą░ą╗ nIRQ ą▓čŗčüčéą░ą▓ą╗čÅąĄčéčüčÅ ąĘą░ąĮąŠą▓ąŠ. ąĢčüą╗ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ ąĮą░ čāčĆąŠą▓ąĮąĄ čÅą┤čĆą░, č鹊 č鹥ą║čāčēąĄąĄ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĄčéčüčÅ, ąĖ ąĮąŠą▓čŗą╣ ISR ą┤ąŠą╗ąČąĄąĮ ą┐čĆąŠčćąĖčéą░čéčī AIC_IVR. ąÆ čŹč鹊čé ą╝ąŠą╝ąĄąĮčé č鹥ą║čāčēąĖą╣ ąĮąŠą╝ąĄčĆ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĖ ąĄą│ąŠ čāčĆąŠą▓ąĄąĮčī ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┐čĆąŠčéą░ą╗ą║ąĖą▓ą░ąĄčéčüčÅ ą▓ąŠ ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ ą░ą┐ą┐ą░čĆą░čéąĮčŗą╣ čüč鹥ą║, čéą░ą║ čćč鹊 ąŠąĮąĖ čüąŠčģčĆą░ąĮčÅčÄčéčüčÅ ąĖ ą▓ąŠčüčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄčéčüčÅ, ą║ąŠą│ą┤ą░ ą▒ąŠą╗ąĄąĄ ą┐čĆąĖąŠčĆąĖč鹥čéąĮčŗą╣ ISR ąĘą░ą▓ąĄčĆčłą░ąĄčéčüčÅ, ąĖ ąĘą░ą┐ąĖčüą░ąĮ AIC_EOICR.

AIC ąŠą▒ąŠčĆčāą┤ąŠą▓ą░ąĮ 8-čāčĆąŠą▓ąĮąĄą▓čŗą╝ ą░ą┐ą┐ą░čĆą░čéąĮčŗą╝ čüč鹥ą║ąŠą╝ ą┤ą╗čÅ ą┐ąŠą┤ą┤ąĄčƹȹ║ąĖ 8 ą▓ą╗ąŠąČąĄąĮąĖą╣ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣, čéą░ą║ čćč鹊 ą╝ąŠąČąĮąŠ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čéčī 8 čāčĆąŠą▓ąĮąĄą╣ ą┐čĆąĖąŠčĆąĖč鹥čéą░.

ąÆąĄą║č鹊čĆąĖąĘą░čåąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. ąÉą┤čĆąĄčüą░ ISR, čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ ą║ą░ąČą┤ąŠą╝čā ąĖčüč鹊čćąĮąĖą║čā ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą╝ąŠą│čāčé ą▒čŗčéčī čüąŠčģčĆą░ąĮąĄąĮčŗ ą▓ čĆąĄą│ąĖčüčéčĆą░čģ AIC_SVR1 .. AIC_SVR31 (SVR ąŠąĘąĮą░čćą░ąĄčé Source Vector Register), ąĮąŠą╝ąĄčĆą░ čā čĆąĄą│ąĖčüčéčĆąŠą▓ ą▓ąĄą║č鹊čĆąŠą▓ ąŠčé 1 ą┤ąŠ 31. ąÜąŠą│ą┤ą░ ą┐čĆąŠčåąĄčüčüąŠčĆ čćąĖčéą░ąĄčé AIC_IVR (Interrupt Vector Register), č鹊 ą▓ąŠąĘą▓čĆą░čēą░ąĄčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄ, ąĘą░ą┐ąĖčüą░ąĮąĮąŠąĄ ą▓ AIC_SVR, čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ č鹥ą║čāčēąĄą╝čā ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÄ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▓ąĄą║č鹊čĆąĖąĘą░čåąĖąĄą╣ ąŠą▒čŗčćąĮąŠ ąĮą░ąĘčŗą▓ą░čÄčé ąĮą░ąĘąĮą░č湥ąĮąĖąĄ ą░ą┤čĆąĄčüąŠą▓ ą┤ą╗čÅ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ (Interrupt Service Routine, čüąŠą║čĆą░čēąĄąĮąĮąŠ ISR). ąÆ čŹč鹊ą╝ ąŠą┐ąĖčüą░ąĮąĖąĖ ą┐ąŠą┤ ą▓ąĄą║č鹊čĆąĖąĘą░čåąĖąĄą╣ čéą░ą║ąČąĄ ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░čÄčé ą░ą┐ą┐ą░čĆą░čéąĮčāčÄ ą┐ąŠą┤ą┤ąĄčƹȹ║čā ą┐ąĄčĆąĄą┤ą░čćąĖ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĮą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ISR. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝ ą▓ąĄą║č鹊čĆ čŹč鹊 ą┐čĆąŠčüč鹊 ą░ą┤čĆąĄčü ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ą░ ISR. ąÆąĄą║č鹊čĆ ąĖčüą║ą╗čÄč湥ąĮąĖą╣ ARM čŹč鹊 čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮčŗą╣ ą░ą┤čĆąĄčü 0x00000018, ą║čāą┤ą░ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐čĆąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĖ.

ąĀąĄą│ąĖčüčéčĆčŗ AIC_SVRx ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé čüą┐ąŠčüąŠą▒ ą▓ąĄčéą▓ą╗ąĄąĮąĖčÅ ą▓ ąŠą┤ąĮąŠą╣ ąĖąĮčüčéčĆčāą║čåąĖąĖ ąĮą░ ISR, čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ č鹥ą║čāčēąĄą╝čā ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÄ, čéą░ą║ ą║ą░ą║ AIC_IVR ąŠč鹊ą▒čĆą░ąČąĄąĮ ąĮą░ ą░ą▒čüąŠą╗čÄčéąĮčŗą╣ ą░ą┤čĆąĄčü 0xFFFFF100, ąĖ čéą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝ ą┤ąŠčüčéčāą┐ąĄąĮ ąĖąĘ ą▓ąĄą║č鹊čĆą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ARM ą┐ąŠ ą░ą┤čĆąĄčüčā 0x00000018 čü ą┐ąŠą╝ąŠčēčīčÄ čüą╗ąĄą┤čāčÄčēąĄą╣ ąĖąĮčüčéčĆčāą║čåąĖąĖ:

ąÜąŠą│ą┤ą░ ą┐čĆąŠčåąĄčüčüąŠčĆ ą▓čŗą┐ąŠą╗ąĮčÅąĄčé čŹčéčā ąĖąĮčüčéčĆčāą║čåąĖčÄ, č鹊 ąŠąĮ ąĘą░ą│čĆčāąČą░ąĄčé ąĘąĮą░č湥ąĮąĖąĄ, ą┐čĆąŠčćąĖčéą░ąĮąĮąŠąĄ ąĖąĘ AIC_IVR, ą▓ čüą▓ąŠą╣ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čüč湥čéčćąĖą║, ą┐ąĄčĆąĄčģąŠą┤čÅ čéą░ą║ąĖą╝ čüą┐ąŠčüąŠą▒ąŠą╝ ąĮą░ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą┐čĆą░ą▓ąĖą╗čīąĮąŠą│ąŠ ISR.

ąŁčéą░ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī čćą░čüč鹊 ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ ąŠčüąĮąŠą▓ą░ąĮąŠ ąĮą░ ąŠą┐ąĄčĆą░čåąĖąŠąĮąĮąŠą╣ čüąĖčüč鹥ą╝ąĄ (ą╗ąĖą▒ąŠ RTOS, ą╗ąĖą▒ąŠ ąĮąĄ RTOS). ą×ą┐ąĄčĆą░čåąĖąŠąĮąĮčŗąĄ čüąĖčüč鹥ą╝čŗ čćą░čüč鹊 ąĖą╝ąĄčÄčé ąŠą┤ąĮčā č鹊čćą║čā ą▓čģąŠą┤ą░ ą┤ą╗čÅ ą▓čüąĄčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣, ąĖ ą┐ąĄčĆą▓ą░čÅ ą▓čŗą┐ąŠą╗ąĮčÅąĄą╝ą░čÅ ąĘą░ą┤ą░čćą░ čüąŠčüč鹊ąĖčé ą▓ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖąĖ ąĖčüč鹊čćąĮąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

ą×ą┤ąĮą░ą║ąŠ ą┐čĆąĖ ą┐ąŠčĆčéąĖčĆąŠą▓ą░ąĮąĖąĖ ąŠą┐ąĄčĆą░čåąĖąŠąĮąĮąŠą╣ čüąĖčüč鹥ą╝čŗ ąĮą░ ą┐čĆąŠčåąĄčüčüąŠčĆčŗ AT91 ąĮą░čüč鹊čÅč鹥ą╗čīąĮąŠ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ą┐čĆąĖą╝ąĄąĮčÅčéčī ą▓ąĄą║č鹊čĆąĖąĘą░čåąĖčÄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. ąŁč鹊 ą╝ąŠąČąĮąŠ ą▓čŗą┐ąŠą╗ąĮąĖčéčī ą┐čāč鹥ą╝ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ ą▓čüąĄčģ AIC_SVRx ąĖčüč鹊čćąĮąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, čćč鹊ą▒čŗ ąŠąĮąĖ ą▒čŗą╗ąĖ ąŠą▒čĆą░ą▒ąŠčéą░ąĮčŗ ąŠą┐ąĄčĆą░čåąĖąŠąĮąĮąŠą╣ čüąĖčüč鹥ą╝ąŠą╣ ą┐ąŠ ą░ą┤čĆąĄčüčā ąĄčæ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ąĢčüą╗ąĖ čüą┤ąĄą╗ą░čéčī čéą░ą║, č鹊 ą▓ąĄą║č鹊čĆąĖąĘą░čåąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą┐ąŠąĘą▓ąŠą╗ąĖčé ą║čĆąĖčéąĖč湥čüą║ąŠą╝čā ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÄ ą┐ąĄčĆąĄą┤ą░čéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ąĮą░ čüą┐ąĄčåąĖą░ą╗čīąĮčŗą╣ ąŠč湥ąĮčī ą▒čŗčüčéčĆčŗą╣ ISR, ąĮąĄ ą┐ąĄčĆąĄą┤ą░ą▓ą░čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĮą░ ąŠą▒čŗčćąĮčŗą╣ ISR ąŠą┐ąĄčĆą░čåąĖąŠąĮąĮąŠą╣ čüąĖčüč鹥ą╝čŗ. ąŁč鹊 čāą┐čĆąŠčēą░ąĄčé čĆąĄą░ą╗ąĖąĘą░čåąĖčÄ ąĘą░ą┤ą░čć ąČąĄčüčéą║ąŠą│ąŠ čĆąĄą░ą╗čīąĮąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ (ą▓ą▓ąŠą┤/ą▓čŗą▓ąŠą┤ ą│ąŠą╗ąŠčüąŠą▓čŗčģ ą┤ą░ąĮąĮčŗčģ ąĖą╗ąĖ ąĘą▓čāą║ą░, ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠąĄ ąŠą▒čüą╗čāąČąĖą▓ą░ąĮąĖąĄ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓), čćč鹊ą▒čŗ ąĖčģ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą▒čŗą╗ąŠ ąŠčüčāčēąĄčüčéą▓ą╗ąĄąĮąŠ čŹčäč乥ą║čéąĖą▓ąĮąŠ ąĖ ą┐čĆąŠąĘčĆą░čćąĮąŠ ą┤ą╗čÅ ąĘą░ą┤ą░čć, ą▓čŗą┐ąŠą╗ąĮčÅčÄčēąĖčģčüčÅ ą┐ąŠą┤ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝ ąŠą┐ąĄčĆą░čåąĖąŠąĮąĮąŠą╣ čüąĖčüč鹥ą╝čŗ.

[ISR ąŠą▒čŗčćąĮčŗčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣]

ąŁčéą░ čüąĄą║čåąĖčÅ ą┤ą░ąĄčé ąŠą▒ąĘąŠčĆ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą▒čŗčüčéčĆąŠą╣ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣, ą║ąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ AIC. ąŁč鹊 ąŠą┐ąĖčüą░ąĮąĖąĄ ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčé, čćč鹊 ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčüčé ą┐ąŠąĮąĖą╝ą░ąĄčé ą░čĆčģąĖč鹥ą║čéčāčĆčā ą┐čĆąŠčåąĄčüčüąŠčĆą░ ARM, ąŠčüąŠą▒ąĄąĮąĮąŠ čĆąĄąČąĖą╝čŗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ąĖ čüą▓čÅąĘą░ąĮąĮčŗčģ čü čŹčéąĖą╝ ą▒ąĖčé čüčéą░čéčāčüą░. ąóą░ą║ąČąĄ čŹč鹊 ąŠą┐ąĖčüą░ąĮąĖąĄ ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčé čüą╗ąĄą┤čāčÄčēąĄąĄ:

1. AIC ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ, čĆąĄą│ąĖčüčéčĆčŗ AIC_SVRx ąĘą░ą│čĆčāąČąĄąĮčŗ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╝ąĖ ą░ą┤čĆąĄčüą░ą╝ąĖ ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝ ISR, ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čĆą░ąĘčĆąĄčłąĄąĮčŗ.

2. ą¤ąŠ ą░ą┤čĆąĄčüčā ą▓ąĄą║č鹊čĆą░ ąĖčüą║ą╗čÄč湥ąĮąĖą╣ ARM 0x00000018 ąĮą░čģąŠą┤ąĖčéčüčÅ čéčĆąĄą▒čāąĄą╝ą░čÅ ą┤ą╗čÅ ą▓ąĄą║č鹊čĆąĖąĘą░čåąĖąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ąĖąĮčüčéčĆčāą║čåąĖčÅ

ąÜąŠą│ą┤ą░ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ čüąĖą│ąĮą░ą╗ nIRQ, ąĄčüą╗ąĖ ą▒ąĖčé I čĆąĄą│ąĖčüčéčĆą░ CPSR ą▓ ą╗ąŠą│. 0, č鹊 ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┤ąĄą╣čüčéą▓ąĖą╣ čüą╗ąĄą┤čāčÄčēą░čÅ:

1. CPSR čüąŠčģčĆą░ąĮčÅąĄčéčüčÅ ą▓ SPSR_IRQ, č鹥ą║čāčēąĄąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čüč湥čéčćąĖą║ą░ (PC) ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ą▓ Interrupt link register (R14_irq) ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čüč湥čéčćąĖą║ (R15) ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄą╝ 0x18. ąÆ čüą╗ąĄą┤čāčÄčēąĄą╝ čåąĖą║ą╗ąĄ, ą▓ąŠ ą▓čĆąĄą╝čÅ ą▓čŗą▒ąŠčĆą║ąĖ ąĖąĮčüčéčĆčāą║čåąĖąĖ ą┐ąŠ ą░ą┤čĆąĄčüčā 0x1C, čÅą┤čĆąŠ ARM ą┐ąŠą┤čüčéčĆą░ąĖą▓ą░ąĄčé ąĘąĮą░č湥ąĮąĖąĄ R14_irq, ą┤ąĄą║čĆąĄą╝ąĄąĮčéąĖčĆčāčÅ ąĄą│ąŠ ąĮą░ 4.

2. ą»ą┤čĆąŠ ARM ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ čĆąĄąČąĖą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ąĄčüą╗ąĖ ąŠąĮąŠ ąĄčēąĄ ą▓ ąĮąĄą╝ ąĮąĄ ąĮą░čģąŠą┤ąĖčéčüčÅ.

3. ąÜąŠą│ą┤ą░ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ąĖąĮčüčéčĆčāą║čåąĖčÅ, ąĘą░ą│čĆčāąČąĄąĮąĮą░čÅ ą┐ąŠ ą░ą┤čĆąĄčüčā 0x18, ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čüč湥čéčćąĖą║ ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄą╝, ą┐čĆąŠčćąĖčéą░ąĮąĮčŗą╝ ą▓ AIC_IVR. ą¦č鹥ąĮąĖąĄ AIC_IVR ą┤ą░ąĄčé čüą╗ąĄą┤čāčÄčēąĄąĄ:

ŌĆō ąŻčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ č鹥ą║čāčēąĄąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĮą░ ąŠąČąĖą┤ą░ąĮąĖąĄ, ąĖ čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čü čüą░ą╝čŗą╝ ą▓čŗčüąŠą║ąĖą╝ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝. ąóąĄą║čāčēąĖą╣ čāčĆąŠą▓ąĄąĮčī čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé čāčĆąŠą▓ąĮčÄ ą┐čĆąĖąŠčĆąĖč鹥čéą░ č鹥ą║čāčēąĄą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

ŌĆō ąĪąĮąĖą╝ą░ąĄčéčüčÅ čüąĖą│ąĮą░ą╗ nIRQ ąĮą░ ą┐čĆąŠčåąĄčüčüąŠčĆąĄ. ąöą░ąČąĄ ąĄčüą╗ąĖ ą▓ąĄą║č鹊čĆąĖąĘą░čåąĖčÅ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ, AIC_IVR ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮ, čćč鹊ą▒čŗ čüąĮčÅčéčī čüąĖą│ąĮą░ą╗ nIRQ.

ŌĆō ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąŠčćąĖčēą░ąĄčéčüčÅ, ąĄčüą╗ąĖ ąŠąĮąŠ ą▒čŗą╗ąŠ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąŠ ąĮą░ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĄ ą┐ąŠ ą┐ąĄčĆąĄą┐ą░ą┤čā (edge-triggered).

ŌĆō ąÆ čüč鹥ą║ ą┐čĆąŠčéą░ą╗ą║ąĖą▓ą░ąĄčéčüčÅ č鹥ą║čāčēąĖą╣ čāčĆąŠą▓ąĄąĮčī ąĖ č鹥ą║čāčēąĖą╣ ąĮąŠą╝ąĄčĆ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

ŌĆō ąÆąŠąĘą▓čĆą░čēą░ąĄčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄ, ąĘą░ą┐ąĖčüą░ąĮąĮąŠąĄ ą▓ AIC_SVR, čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ č鹥ą║čāčēąĄą╝čā ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÄ.

4. ą¤čĆąĄą┤čŗą┤čāčēąĖą╣ čłą░ą│ ą┤ą░ąĄčé čŹčäč乥ą║čé ą▓ąĄčéą▓ą╗ąĄąĮąĖčÅ ąĮą░ ISR, čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą┐čĆąŠąĖąĘąŠčłąĄą┤čłąĄą╝čā ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÄ. ąŁč鹊 ą┤ąŠą╗ąČąĮąŠ ąĮą░čćąĖąĮą░čéčīčüčÅ ą┐čāč鹥ą╝ čüąŠčģčĆą░ąĮąĄąĮąĖčÅ link-čĆąĄą│ąĖčüčéčĆą░ (R14_irq) ąĖ SPSR_IRQ. Link-čĆąĄą│ąĖčüčéčĆ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┤ąĄą║čĆąĄą╝ąĄąĮčéąĖčĆąŠą▓ą░ąĮ ąĮą░ 4, ą║ąŠą│ą┤ą░ ąŠąĮ čüąŠčģčĆą░ąĮčÅąĄčéčüčÅ, ąĄčüą╗ąĖ ąŠąĮ ą▓ąŠčüčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ąĮą░ą┐čĆčÅą╝čāčÄ ą▓ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čüč湥čéčćąĖą║ ą┐čĆąĖ ą▓čŗčģąŠą┤ąĄ ąĖąĘ ISR. ąöą╗čÅ čŹč鹊ą│ąŠ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ, ąĮą░ą┐čĆąĖą╝ąĄčĆ, ąĖąĮčüčéčĆčāą║čåąĖčÅ SUB PC, LR, #4.

5. ąæčāą┤čāčēąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą╝ąŠą│čāčé ą▒čŗčéčī ąĘą░č鹥ą╝ ą┤ąĄą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮčŗ ąŠčćąĖčüčéą║ąŠą╣ ą▒ąĖčéą░ I ą▓ CPSR, ą┐ąŠąĘą▓ąŠą╗čÅčÅ č鹥ą╝ čüą░ą╝čŗą╝ čÅą┤čĆčā čāčćąĖčéčŗą▓ą░čéčī ą┐ąŠą▓č鹊čĆąĮčāčÄ čāčüčéą░ąĮąŠą▓ą║čā čüąĖą│ąĮą░ą╗ą░ nIRQ. ąŁč鹊 ą╝ąŠąČąĄčé čüą╗čāčćąĖčéčīčüčÅ, ąĄčüą╗ąĖ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čü ą▒ąŠą╗ąĄąĄ ą▓čŗčüąŠą║ąĖą╝ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝, č湥ą╝ č鹥ą║čāčēąĄąĄ.

6. ą¤ąŠčüą╗ąĄ čŹč鹊ą│ąŠ ISR ą╝ąŠąČąĄčé ą▓čŗą┐ąŠą╗ąĮąĖčéčī čüą▓ąŠąĖ ąĮąĄąŠą▒čģąŠą┤ąĖą╝čŗąĄ ą░ą╗ą│ąŠčĆąĖčéą╝ąĖč湥čüą║ąĖąĄ ą┤ąĄą╣čüčéą▓ąĖčÅ ą┤ą╗čÅ ąŠą▒čüą╗čāąČąĖą▓ą░ąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, čü čüąŠčģčĆą░ąĮąĄąĮąĖąĄą╝ ą▓ čüč鹥ą║ąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗčģ čĆąĄą│ąĖčüčéčĆąŠą▓ ąĖ ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖąĄą╝ ąĖčģ ąĖąĘ čüč鹥ą║ą░ ą┐ąŠčüą╗ąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą▓čüąĄčģ ą┤ąĄą╣čüčéą▓ąĖą╣ ą▓ ą║ąŠąĮčåąĄ ISR. ąÆąŠ ą▓čĆąĄą╝čÅ čŹč鹊ą╣ čäą░ąĘčŗ 6 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čü ą▒ąŠą╗ąĄąĄ ą▓čŗčüąŠą║ąĖą╝ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝ ą╝ąŠąČąĄčé ą┐ąŠą▓č鹊čĆąĖčéčī ą▓čüčÄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī, ąĮą░čćąĖąĮą░čÅ čü čłą░ą│ą░ 1.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĄčüą╗ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąŠ ąĮą░ čćčāą▓čüčéą▓ąĖč鹥ą╗čīąĮąŠčüčéčī ą║ čāčĆąŠą▓ąĮčÄ (level sensitive), č鹊 ą▓ąŠ ą▓čĆąĄą╝čÅ čäą░ąĘčŗ 6 ąĖčüč鹊čćąĮąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąŠčćąĖčēąĄąĮ.

7. ąæąĖčé I ą▓ CPSR ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ą┤ą╗čÅ ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąĄčĆąĄą┤ ą▓čŗčģąŠą┤ąŠą╝, čćč鹊ą▒čŗ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą▒čāą┤ąĄčé ą▓čŗą┐ąŠą╗ąĮąĄąĮąŠ ą▓ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą╝ ą┐ąŠčĆčÅą┤ą║ąĄ.

8. ąĀąĄą│ąĖčüčéčĆ ąŠą║ąŠąĮčćą░ąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (End of Interrupt Command Register, AIC_EOICR) ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮ, čćč鹊ą▒čŗ ą┐ąŠą║ą░ąĘą░čéčī ą┤ą╗čÅ AIC ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĄ č鹥ą║čāčēąĄą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ąŁč鹊 ą┐čĆąĖą▓ąŠą┤ąĖčé ą║ ą▓čŗą▒ąŠčĆą║ąĄ ąĖąĘ čüč鹥ą║ą░ č鹥ą║čāčēąĄą│ąŠ čāčĆąŠą▓ąĮčÅ, ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖčÄ ą┐čĆąĄą┤čŗą┤čāčēąĄą│ąŠ č鹥ą║čāčēąĄą│ąŠ čāčĆąŠą▓ąĮčÅ, ąĄčüą╗ąĖ ąŠąĮ ąĖą╝ąĄąĄčéčüčÅ ą▓ čüč鹥ą║ąĄ. ąĢčüą╗ąĖ ąŠąČąĖą┤ą░ąĄčé ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┤čĆčāą│ąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čü ą╝ąĄąĮčīčłąĖą╝ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝, č湥ą╝ čüčéą░čĆčŗą╣ č鹥ą║čāčēąĖą╣ čāčĆąŠą▓ąĄąĮčī, ąĖą╗ąĖ čü čéą░ą║ąĖą╝ ąČąĄ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝, ąĮąŠ ą┐čĆąĖ ąĮą░ą╗ąĖčćąĖąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čü ą▒ąŠą╗ąĄąĄ ą▓čŗčüąŠą║ąĖą╝ čāčĆąŠą▓ąĮąĄą╝, č湥ą╝ ąĮąŠą▓čŗą╣ č鹥ą║čāčēąĖą╣ čāčĆąŠą▓ąĄąĮčī, č鹊 čüąĖą│ąĮą░ą╗ nIRQ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ čüąĮąŠą▓ą░, ąĮąŠ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĮąĄ ą▒čāą┤ąĄčé ąĘą░ą┐čāčēąĄąĮąŠ ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ, ą┐ąŠč鹊ą╝čā čćč鹊 ą▓ čÅą┤čĆąĄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé I. ąÆąŠčüčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ SPSR_IRQ. ąÆ ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĄ čüąŠčģčĆą░ąĮąĄąĮąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ link-čĆąĄą│ąĖčüčéčĆą░ ą▓ąŠčüčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ąĮą░ą┐čĆčÅą╝čāčÄ ą▓ PC. ąŁč鹊 ą┤ą░ąĄčé čŹčäč乥ą║čé ą▓ąŠąĘą▓čĆą░čéą░ ąĖąĘ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą║ č鹊ą╝čā, čćč鹊 ą▓čŗą┐ąŠą╗ąĮčÅą╗ąŠčüčī ą┐čĆąĄąČą┤ąĄ, ąĖ ąĘą░ą│čĆčāąĘą║ąĖ CPSR čüąŠčģčĆą░ąĮąĄąĮąĮčŗą╝ SPSR, ą╝ą░čüą║ąĖčĆčāčÅ ąĖą╗ąĖ ą┤ąĄą╝ą░čüą║ąĖčĆčāčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čüąŠčüč鹊čÅąĮąĖčÅ, čüąŠčģčĆą░ąĮąĄąĮąĮąŠą│ąŠ ą▓ SPSR_IRQ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▒ąĖčé I ą▓ SPSR ąŠč湥ąĮčī ą▓ą░ąČąĄąĮ. ąĢčüą╗ąĖ ąŠąĮ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, č鹊 čŹč鹊 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 čÅą┤čĆąŠ ARM ą▒čŗą╗ąŠ ąĮą░ ą│čĆą░ąĮąĄ ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą║ąŠą│ą┤ą░ ąĖąĮčüčéčĆčāą║čåąĖčÅ ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖčÅ ą▒čŗą╗ą░ ą┐čĆąĄčĆą▓ą░ąĮą░. ąĪą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ, ą║ąŠą│ą┤ą░ SPSR ą▓ąŠčüčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ, ąĖąĮčüčéčĆčāą║čåąĖčÅ ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖčÅ ąĘą░ą▓ąĄčĆčłą░ąĄčéčüčÅ (ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą╝ą░čüą║ąĖčĆčāąĄčéčüčÅ).

[ąæčŗčüčéčĆąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ (Fast Interrupt)]

ąśčüč鹊čćąĮąĖą║ ą▒čŗčüčéčĆąŠą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. Interrupt source 0 ąĄą┤ąĖąĮčüčéą▓ąĄąĮąĮčŗą╣ ąĖčüč鹊čćąĮąĖą║, ą║ąŠč鹊čĆčŗą╣ ą╝ąŠąČąĄčé ą▓čŗąĘą▓ą░čéčī ąĘą░ą┐čĆąŠčü ą▒čŗčüčéčĆąŠą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ ą┐čĆąŠčåąĄčüčüąŠčĆą░, ąĄčüą╗ąĖ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čäčāąĮą║čåąĖčÅ fast forcing. Interrupt source 0 ąŠą▒čŗčćąĮąŠ ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą║ ą▓čŗą▓ąŠą┤čā FIQ ą║ąŠčĆą┐čāčüą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ąĮą░ą┐čĆčÅą╝čāčÄ, ą╗ąĖą▒ąŠ č湥čĆąĄąĘ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ PIO [2].

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą▒čŗčüčéčĆčŗą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄą╝. ąøąŠą│ąĖą║ą░ Fast Interrupt ą▓ AIC ąĮąĄ ąĖą╝ąĄąĄčé ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. ąĀąĄąČąĖą╝ interrupt source 0, ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮčŗą╣ AIC_SMR0 ąĖ ą┐ąŠą╗ąĄą╝ PRIOR čŹč鹊ą│ąŠ čĆąĄą│ąĖčüčéčĆą░, ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ, ą┤ą░ąČąĄ ąĄčüą╗ąĖ ą▒čāą┤ąĄčé ą┐čĆąŠčćąĖčéą░ąĮąŠ č鹊, čćč鹊 čéčāą┤ą░ ą▒čŗą╗ąŠ ąĘą░ą┐ąĖčüą░ąĮąŠ. ą¤ąŠą╗ąĄ SRCTYPE čĆąĄą│ąĖčüčéčĆą░ AIC_SMR0 čĆą░ąĘčĆąĄčłą░ąĄčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī ąĖčüč鹊čćąĮąĖą║ fast interrupt ąĮą░ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĄ ą┐ąŠ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą╝čā ąĖą╗ąĖ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠą╝čā ą┐ąĄčĆąĄą┐ą░ą┤čā, ąĖą╗ąĖ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī ąĖčüč鹊čćąĮąĖą║ fast interrupt ą┤ą╗čÅ čćčāą▓čüčéą▓ąĖč鹥ą╗čīąĮąŠčüčéąĖ ą║ ą▓čŗčüąŠą║ąŠą╝čā ąĖą╗ąĖ ąĮąĖąĘą║ąŠą╝čā čāčĆąŠą▓ąĮčÄ.

ąŚą░ą┐ąĖčüčī 0x1 ą▓ AIC_IECR (Interrupt Enable Command Register) ąĖ AIC_IDCR (Interrupt Disable Command Register) čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ čĆą░ąĘčĆąĄčłą░ąĄčé ąĖ ąĘą░ą┐čĆąĄčēą░ąĄčé ą▒čŗčüčéčĆąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ. ąæąĖčé 0 čĆąĄą│ąĖčüčéčĆą░ AIC_IMR (Interrupt Mask Register) ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čĆą░ąĘčĆąĄčłąĄąĮąŠ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčēąĄąĮąŠ ą▒čŗčüčéčĆąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ.

ąÆąĄą║č鹊čĆąĖąĘą░čåąĖčÅ Fast Interrupt. ąÉą┤čĆąĄčü ISR ą┤ą╗čÅ ą▒čŗčüčéčĆąŠą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą╝ąŠąČąĄčé ą▒čŗčéčī čüąŠčģčĆą░ąĮąĄąĮ ą▓ čĆąĄą│ąĖčüčéčĆąĄ AIC_SVR0 (Source Vector Register 0). ąŚą░ą┐ąĖčüą░ąĮąĮąŠąĄ ą▓ čŹč鹊čé čĆąĄą│ąĖčüčéčĆ ąĘąĮą░č湥ąĮąĖąĄ ą▓ąŠąĘą▓čĆą░čēą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą┐čĆąŠčåąĄčüčüąŠčĆ čćąĖčéą░ąĄčé AIC_FVR (Fast Vector Register). ąŁč鹊 ą┤ą░ąĄčé ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą▓ąĄčéą▓ą╗ąĄąĮąĖčÅ ąĮą░ ISR ą▓ ąŠą┤ąĮąŠą╣ ąĖąĮčüčéčĆčāą║čåąĖąĖ, čéą░ą║ ą║ą░ą║ AIC_FVR ąŠč鹊ą▒čĆą░ąČąĄąĮ ąĮą░ ą░ą▒čüąŠą╗čÄčéąĮčŗą╣ ą░ą┤čĆąĄčü 0xFFFF F104, čéą░ą║ čćč鹊 ą┤ąŠčüčéčāą┐ąĄąĮ ąĖąĘ ą▓ąĄą║č鹊čĆą░ ą▒čŗčüčéčĆąŠą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ARM ą┐ąŠ ą░ą┤čĆąĄčüčā 0x0000001C čüą╗ąĄą┤čāčÄčēąĄą╣ ąĖąĮčüčéčĆčāą║čåąĖąĄą╣:

ąÜąŠą│ą┤ą░ ą┐čĆąŠčåąĄčüčüąŠčĆ ą▓čŗą┐ąŠą╗ąĮčÅąĄčé čŹčéčā ąĖąĮčüčéčĆčāą║čåąĖčÄ, ąŠąĮ ąĘą░ą│čĆčāąČą░ąĄčé ąĘąĮą░č湥ąĮąĖąĄ, ą┐čĆąŠčćąĖčéą░ąĮąĮąŠąĄ ąĖąĘ AIC_FVR, ą▓ čüą▓ąŠą╣ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čüč湥čéčćąĖą║, ą▓čŗą┐ąŠą╗ąĮčÅčÅ č鹥ą╝ čüą░ą╝čŗą╝ ą┐ąĄčĆąĄčģąŠą┤ ąĮą░ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ISR ą▒čŗčüčéčĆąŠą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ąŁč鹊 čéą░ą║ąČąĄ ą▓čŗą┐ąŠą╗ąĮčÅąĄčé ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║čāčÄ ąŠčćąĖčüčéą║čā ąĖčüč鹊čćąĮąĖą║ą░ ą▒čŗčüčéčĆąŠą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ąĄčüą╗ąĖ ąŠąĮ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ ą▓ čĆąĄąČąĖą╝ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖčÅ ą┐ąŠ ą┐ąĄčĆąĄą┐ą░ą┤čā (edge-triggered mode).

ISR ą▒čŗčüčéčĆąŠą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ąÆ čŹč鹊ą╣ čüąĄą║čåąĖąĖ ą┤ą░ąĄčéčüčÅ ąŠą▒ąĘąŠčĆ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą▒čŗčüčéčĆąŠą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą║ąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ AIC. ąŁč鹊 ąŠą┐ąĖčüą░ąĮąĖąĄ ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčé, čćč鹊 ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčüčé ą┐ąŠąĮąĖą╝ą░ąĄčé ą░čĆčģąĖč鹥ą║čéčāčĆčā ą┐čĆąŠčåąĄčüčüąŠčĆą░ ARM, ąŠčüąŠą▒ąĄąĮąĮąŠ čĆąĄąČąĖą╝čŗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ąĖ čüą▓čÅąĘą░ąĮąĮčŗčģ čü čŹčéąĖą╝ ą▒ąĖčé čüčéą░čéčāčüą░. ąóą░ą║ąČąĄ čŹč鹊 ąŠą┐ąĖčüą░ąĮąĖąĄ ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčé čüą╗ąĄą┤čāčÄčēąĄąĄ:

1. AIC ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ, čĆąĄą│ąĖčüčéčĆ AIC_SVR0 ąĘą░ą│čĆčāąČąĄąĮ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╝ ą░ą┤čĆąĄčüąŠą╝ ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ISR, ąĖ interrupt source 0 čĆą░ąĘčĆąĄčłąĄąĮ.

2. ą¤ąŠ ą░ą┤čĆąĄčüčā ą▒čŗčüčéčĆąŠą│ąŠ ą▓ąĄą║č鹊čĆą░ ąĖčüą║ą╗čÄč湥ąĮąĖą╣ ARM 0x0000001C (FIQ exception vector) ąĮą░čģąŠą┤ąĖčéčüčÅ čéčĆąĄą▒čāąĄą╝ą░čÅ ą┤ą╗čÅ ą▓ąĄą║č鹊čĆąĖąĘą░čåąĖąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ąĖąĮčüčéčĆčāą║čåąĖčÅ

ąÜąŠą│ą┤ą░ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ čüąĖą│ąĮą░ą╗ nFIQ, ąĄčüą╗ąĖ ą▒ąĖčé F čĆąĄą│ąĖčüčéčĆą░ CPSR ą▓ ą╗ąŠą│. 0, č鹊 ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┤ąĄą╣čüčéą▓ąĖą╣ čüą╗ąĄą┤čāčÄčēą░čÅ:

1. CPSR čüąŠčģčĆą░ąĮčÅąĄčéčüčÅ ą▓ SPSR_FIQ, č鹥ą║čāčēąĄąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čüč湥čéčćąĖą║ą░ čüąŠčģčĆą░ąĮčÅąĄčéčüčÅ ą▓ FIQ link-čĆąĄą│ąĖčüčéčĆąĄ (R14_FIQ) ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čüč湥čéčćąĖą║ (R15) ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄą╝ 0x1C. ąØą░ čüą╗ąĄą┤čāčÄčēąĄą╝ čéą░ą║č鹥, ą▓ąŠ ą▓čĆąĄą╝čÅ ą▓čŗą▒ąŠčĆą║ąĖ ą┐ąŠ ą░ą┤čĆąĄčüčā 0x20, čÅą┤čĆąŠ ARM ą┐ąŠą┤čüčéčĆą░ąĖą▓ą░ąĄčé R14_FIQ, ą┤ąĄą║čĆąĄą╝ąĄąĮčéąĖčĆčāčÅ ąĄą│ąŠ ąĮą░ 4.

2. ą»ą┤čĆąŠ ARM ą▓čģąŠą┤ąĖčé ą▓ čĆąĄąČąĖą╝ FIQ.

3. ąÜąŠą│ą┤ą░ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ąĖąĮčüčéčĆčāą║čåąĖčÅ, ąĘą░ą│čĆčāąČąĄąĮąĮą░čÅ ą┐ąŠ ą░ą┤čĆąĄčüčā 0x1C, ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čüč湥čéčćąĖą║ ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄą╝, ą┐čĆąŠčćąĖčéą░ąĮąĮčŗą╝ ąĖąĘ AIC_FVR. ą¦č鹥ąĮąĖąĄ AIC_FVR ą┤ą░ąĄčé čŹčäč乥ą║čé ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą╣ ąŠčćąĖčüčéą║ąĖ ą▒čŗčüčéčĆąŠą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ąĄčüą╗ąĖ ąŠąĮąŠ ą▒čŗą╗ąŠ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąŠ ąĮą░ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĄ ą┐ąŠ ą┐ąĄčĆąĄą┐ą░ą┤čā (edge triggered). ąóąŠą╗čīą║ąŠ ą▓ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ąĮą░ ą┐čĆąŠčåąĄčüčüąŠčĆąĄ ą▒čāą┤ąĄčé čüąĮčÅčé čüąĖą│ąĮą░ą╗ nFIQ.

4. ą¤čĆąĄą┤čŗą┤čāčēąĖą╣ čłą░ą│ čĆą░ąĘčĆąĄčłą░ąĄčé ą▓ąĄčéą▓ą╗ąĄąĮąĖąĄ ąĮą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ISR. ąØąĄčé ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéąĖ čüąŠčģčĆą░ąĮčÅčéčī link-čĆąĄą│ąĖčüčéčĆ R14_FIQ ąĖ čĆąĄą│ąĖčüčéčĆ SPSR_FIQ, ąĄčüą╗ąĖ ąĮąĄ čéčĆąĄą▒čāąĄčéčüčÅ ą▓ą╗ąŠąČąĄąĮąĮąŠčüčéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣.

5. ISR ą╝ąŠąČąĄčé ą▓čŗą┐ąŠą╗ąĮčÅčéčī čüą▓ąŠąĖ ąĮąĄąŠą▒čģąŠą┤ąĖą╝čŗąĄ ą░ą╗ą│ąŠčĆąĖčéą╝ąĖč湥čüą║ąĖąĄ ą┤ąĄą╣čüčéą▓ąĖčÅ. ąØąĄčé ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéąĖ čüąŠčģčĆą░ąĮčÅčéčī čĆąĄą│ąĖčüčéčĆčŗ R8 .. R13, ą┐ąŠč鹊ą╝čā čćč鹊 čĆąĄąČąĖą╝ FIQ ąĖčüą┐ąŠą╗čīąĘčāąĄčé čüą▓ąŠąĖ čüąŠą▒čüčéą▓ąĄąĮąĮčŗąĄ ą▓čŗą┤ąĄą╗ąĄąĮąĮčŗąĄ čĆąĄą│ąĖčüčéčĆčŗ, ąĖ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čīčüą║ąĖąĄ čĆąĄą│ąĖčüčéčĆčŗ R8 .. R13 ąĮą░čģąŠą┤čÅčéčüčÅ ą▓ ąŠčéą┤ąĄą╗čīąĮąŠą╝ ą▒ą░ąĮą║ąĄ. ąöčĆčāą│ąĖąĄ čĆąĄą│ąĖčüčéčĆčŗ R0 .. R7 ą┤ąŠą╗ąČąĮčŗ ą┐ąĄčĆąĄą┤ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ čüąŠčģčĆą░ąĮčÅčéčīčüčÅ ąĖ ą▓ąŠčüčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čéčīčüčÅ ą▓ ą║ąŠąĮčåąĄ ISR (ą┐ąĄčĆąĄą┤ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄą╝ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ čłą░ą│ą░ 6). ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ąĄčüą╗ąĖ ą▒čŗčüčéčĆąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąŠ ąĮą░ čćčāą▓čüčéą▓ąĖč鹥ą╗čīąĮąŠčüčéčī ą║ čāčĆąŠą▓ąĮčÄ (level sensitive), č鹊 ą▓ąŠ ą▓čĆąĄą╝čÅ čŹč鹊ą╣ čäą░ąĘčŗ ąĖčüč鹊čćąĮąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąŠčćąĖčēąĄąĮ, čćč鹊ą▒čŗ čüąĮčÅčéčī čüąĖą│ąĮą░ą╗ interrupt source 0.

6. ąÆ ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĄ Link-čĆąĄą│ąĖčüčéčĆ R14_FOQ ą▓ąŠčüčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▓ PC ą┐ąŠčüą╗ąĄ ą┤ąĄą║čĆąĄą╝ąĄąĮčéą░ ąĮą░ 4 (ąĮą░ą┐čĆąĖą╝ąĄčĆ ąĖąĮčüčéčĆčāą║čåąĖąĄą╣ SUB PC, LR, #4). ąŁč鹊 ą┤ą░ąĄčé čŹčäč乥ą║čé ą▓ąŠąĘą▓čĆą░čéą░ ąĖąĘ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą▓ č鹊čé ą║ąŠą┤, ą║ąŠč鹊čĆčŗą╣ ą▓čŗą┐ąŠą╗ąĮčÅą╗čüčÅ čĆą░ąĮąĄąĄ, ąĘą░ą│čĆčāąĘą║ąĖ CPSR ąĘąĮą░č湥ąĮąĖąĄą╝ SPSR ąĖ ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖą╗ąĖ ą┤ąĄą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖčÅ ą▒čŗčüčéčĆąŠą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ąĘąĮą░č湥ąĮąĖčÅ, čüąŠčģčĆą░ąĮąĄąĮąĮąŠą│ąŠ ą▓ SPSR.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▒ąĖčé F ą▓ SPSR ąĖą╝ąĄąĄčé ą▓ą░ąČąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ. ąĢčüą╗ąĖ ąŠąĮ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, č鹊 čŹč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 čÅą┤čĆąŠ ARM ą║ą░ą║ čĆą░ąĘ čüąŠą▒ąĖčĆą░ą╗ąŠčüčī ą╝ą░čüą║ąĖčĆąŠą▓ą░čéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ FIQ, ą║ąŠą│ą┤ą░ ąĖąĮčüčéčĆčāą║čåąĖčÅ ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖčÅ ą▒čŗą╗ą░ ą┐čĆąĄčĆą▓ą░ąĮą░. ąĪą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ, ą║ąŠą│ą┤ą░ SPSR ą▓ąŠčüčüčéą░ąĮąŠą▓ąĖčéčüčÅ, ą┐čĆąĄčĆą▓ą░ąĮąĮą░čÅ ąĖąĮčüčéčĆčāą║čåąĖčÅ ąĘą░ą▓ąĄčĆčłąĖčéčüčÅ (FIQ ą▒čāą┤ąĄčé ąĘą░ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąŠ).

ąöčĆčāą│ąŠą╣ čüą┐ąŠčüąŠą▒ ąŠą▒čĆą░ą▒ąŠčéą░čéčī ą▒čŗčüčéčĆąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ - ąŠč鹊ą▒čĆą░ąĘąĖčéčī ISR ąĮą░ ą░ą┤čĆąĄčü ARM-ą▓ąĄą║č鹊čĆą░ 0x1C. ąŁč鹊čé ą╝ąĄč鹊ą┤ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą▓ąĄą║č鹊čĆąĖąĘą░čåąĖčÄ, čéą░ą║ čćč鹊 čćč鹥ąĮąĖąĄ AIC_FVR ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮąŠ ą║ą░ą║ ą╝ąŠąČąĮąŠ ą▒ą╗ąĖąČąĄ ą║ ąĮą░čćą░ą╗čā ISR. ą×ą┤ąĮą░ą║ąŠ čŹč鹊čé ą╝ąĄč鹊ą┤ 菹║ąŠąĮąŠą╝ąĖčé ą▓čĆąĄą╝čÅ ą┐čĆąŠčåąĄčüčüąŠčĆą░, ą║ąŠč鹊čĆąŠąĄ ą▒čŗą╗ąŠ ą▒čŗ ą┐ąŠčéčĆą░č湥ąĮąŠ ąĮą░ ąĖąĮčüčéčĆčāą║čåąĖąĖ ą▓ąĄčéą▓ą╗ąĄąĮąĖčÅ ą┐čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ ą▓ąĄą║č鹊čĆąĖąĘą░čåąĖąĖ.

Fast Forcing. ążčāąĮą║čåąĖčÅ Fast Forcing AIC ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐ąĄčĆąĄąĮą░ą┐čĆą░ą▓ą╗čÅčéčī ą╗čÄą▒ąŠą╣ ąŠą▒čŗčćąĮčŗą╣ ąĖčüč鹊čćąĮąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĮą░ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą▒čŗčüčéčĆąŠą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

Fast Forcing čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčēą░ąĄčéčüčÅ ąĘą░ą┐ąĖčüčīčÄ Fast Forcing Enable Register (AIC_FFER) ąĖ Fast Forcing Disable Register (AIC_FFDR) čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ. ąŚą░ą┐ąĖčüčī ą▓ čŹčéąĖ čĆąĄą│ąĖčüčéčĆčŗ ą┐čĆąĖą▓ąŠą┤ąĖčé ą║ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÄ Fast Forcing Status Register (AIC_FFSR), ą║ąŠč鹊čĆčŗą╣ čāą┐čĆą░ą▓ą╗čÅąĄčé čŹč鹊ą╣ čäčāąĮą║čåąĖąĄą╣ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ ąĖą╗ąĖ ą▓ąĮąĄčłąĮąĄą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

ąÜąŠą│ą┤ą░ Fast Forcing čĆą░ąĘčĆąĄčłąĄąĮąŠ, ąĖčüč鹊čćąĮąĖą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░čÄčéčüčÅ čéą░ą║, ą║ą░ą║ čŹč鹊 ą▒čŗą╗ąŠ ąŠą┐ąĖčüą░ąĮąŠ čĆą░ąĮąĄąĄ.

ą¤čĆąĖ čĆą░ąĘčĆąĄčłąĄąĮąĮąŠą╝ Fast Forcing ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ čćčāą▓čüčéą▓ąĖč鹥ą╗čīąĮąŠčüčéąĖ edge/level ąĖ, ą▓ ąĮąĄą║ąŠč鹊čĆčŗčģ čüą╗čāčćą░čÅčģ, ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ą┐ąĄčĆąĄą┐ą░ą┤ą░ ąĖčüč鹊čćąĮąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą▓čüąĄ ąĄčēąĄ ą░ą║čéąĖą▓ąĮąŠ, ąŠą┤ąĮą░ą║ąŠ ąĖčüč鹊čćąĮąĖą║ ąĮąĄ ą╝ąŠąČąĄčé ą▓čŗąĘą▓ą░čéčī ąŠą▒čŗčćąĮąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┤ą╗čÅ ą┐čĆąŠčåąĄčüčüąŠčĆą░, ąĖ ąĄą│ąŠ ąĮąĄ ą▓ąĖą┤ąĖčé čüąĖčüč鹥ą╝ą░ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĖąŠčĆąĖč鹥čéą░.

ąĢčüą╗ąĖ ąĖčüč鹊čćąĮąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ ą▓ čĆąĄąČąĖą╝ level-sensitive, ąĖ ą▒čŗą╗ ąĘą░čģą▓ą░č湥ąĮ ą░ą║čéąĖą▓ąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī, č鹊 Fast Forcing ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ čāčüčéą░ąĮąŠą▓ą║ąĄ ą┤ą╗čÅ čÅą┤čĆą░ čüąĖą│ąĮą░ą╗ą░ nFIQ.

ąĢčüą╗ąĖ ąĖčüč鹊čćąĮąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ ą▓ čĆąĄąČąĖą╝ edge-triggered, ąĖ ą▒čŗą╗ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮ ą░ą║čéąĖą▓ąĮčŗą╣ ą┐ąĄčĆąĄą┐ą░ą┤, č鹊 Fast Forcing ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ čāčüčéą░ąĮąŠą▓ą║ąĄ ą┤ą╗čÅ čÅą┤čĆą░ čüąĖą│ąĮą░ą╗ą░ nFIQ.

ążčāąĮą║čåąĖčÅ Fast Forcing ąĮąĄ ą▓ą╗ąĖčÅąĄčé ąĮą░ ą▒ąĖčé ąŠąČąĖą┤ą░ąĮąĖčÅ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ Interrupt Source 0 pending ą▓ čĆąĄą│ąĖčüčéčĆąĄ ąŠčéą╗ąŠąČąĄąĮąĮčŗčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ (Interrupt Pending Register, AIC_IPR).

ąĀąĄą│ąĖčüčéčĆ ą▓ąĄą║č鹊čĆą░ ą▒čŗčüčéčĆąŠą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (FIQ Vector Register, AIC_FVR) čćąĖčéą░ąĄčé čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ Source Vector Register 0 (AIC_SVR0), ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé č鹊ą│ąŠ, ą║ą░ą║ąŠą╣ ą╝ąŠą│ ą▒čŗčéčī ąĖčüč鹊čćąĮąĖą║ ą▒čŗčüčéčĆąŠą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ą¦č鹥ąĮąĖąĄ FVR ąĮąĄ ąŠčćąĖčēą░ąĄčé Interrupt Source 0, ą║ąŠą│ą┤ą░ čäčāąĮą║čåąĖčÅ Fast Forcing ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ, ąĖ ąĖčüč鹊čćąĮąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąŠčćąĖčēąĄąĮ ąĘą░ą┐ąĖčüčīčÄ ą▓ Interrupt Clear Command Register (AIC_ICCR).

ąÆčüąĄ čĆą░ąĘčĆąĄčłąĄąĮąĮčŗąĄ ąĖ ąŠąČąĖą┤ą░čÄčēąĖąĄ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ąĖčüč鹊čćąĮąĖą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, čā ą║ąŠč鹊čĆčŗčģ čĆą░ąĘčĆąĄčłąĄąĮą░ čäčāąĮą║čåąĖčÅ Fast Forcing, ąĖ ą║ąŠč鹊čĆčŗąĄ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮčŗ ą▓ čĆąĄąČąĖą╝ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖčÅ ą┐ąŠ ą┐ąĄčĆąĄą┐ą░ą┤čā (edge-triggered mode), ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąŠčćąĖčēąĄąĮčŗ ąĘą░ą┐ąĖčüčī ą▓ Interrupt Clear Command Register. ą¤čĆąĖ čŹč鹊ą╝ ąŠąĮąĖ ąŠčćąĖčēą░čÄčéčüčÅ ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ, ą▓ čĆąĄąĘčāą╗čīčéą░č鹥 ą┐čĆąĄą┤ąŠčéą▓čĆą░čēą░ąĄčéčüčÅ ą┐ąŠč鹥čĆąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣.

ą¦č鹥ąĮąĖąĄ AIC_IVR ąĮąĄ ąŠčćąĖčēą░ąĄčé ąĖčüč鹊čćąĮąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, čā ą║ąŠč鹊čĆąŠą│ąŠ čĆą░ąĘčĆąĄčłąĄąĮą░ čäčāąĮą║čåąĖčÅ Fast Forcing.

ąśčüč鹊čćąĮąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ 0, ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąĮčŗą╣ ą┤ą╗čÅ ą▒čŗčüčéčĆąŠą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą┐čĆąŠą┤ąŠą╗ąČą░ąĄčé ąĮąŠčĆą╝ą░ą╗čīąĮčāčÄ čĆą░ą▒ąŠčéčā ąĖ čüčéą░ąĮąŠą▓ąĖčéčüčÅ ąŠą┤ąĮąĖą╝ ąĖąĘ ąĖčüč鹊čćąĮąĖą║ąŠą▓ ą▒čŗčüčéčĆąŠą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

ąĀąĖčü. 23-10. ążčāąĮą║čåąĖčÅ Fast Forcing.

[ąĀąĄąČąĖą╝ ąĘą░čēąĖčéčŗ]

ąĀąĄąČąĖą╝ ąĘą░čēąĖčéčŗ (Protect Mode) ą┐ąŠąĘą▓ąŠą╗čÅąĄčé čćąĖčéą░čéčī čĆąĄą│ąĖčüčéčĆ ą▓ąĄą║č鹊čĆą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (Interrupt Vector Register) ą▒ąĄąĘ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ čüą▓čÅąĘą░ąĮąĮčŗčģ čü čŹčéąĖą╝ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖčģ ąŠą┐ąĄčĆą░čåąĖą╣. ąŁč鹊 ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ, ą║ąŠą│ą┤ą░ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ąŠčéą╗ą░ą┤ą║ą░ čüąĖčüč鹥ą╝čŗ. ąÜąŠą│ą┤ą░ ąŠčéą╗ą░ą┤čćąĖą║, čĆą░ą▒ąŠčéą░čÅ ą╗ąĖą▒ąŠ čü Debug Monitor, ą╗ąĖą▒ąŠ čü ICE ą┐čĆąŠčåąĄčüčüąŠčĆą░ ARM, ąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ąĖ ąŠą▒ąĮąŠą▓ą╗čÅąĄčé ąŠčéą║čĆčŗčéčŗąĄ ąŠą║ąĮą░, ąŠąĮ ą╝ąŠąČąĄčé čćąĖčéą░čéčī čĆąĄą│ąĖčüčéčĆčŗ AIC ąĖ čéą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝ IVR. ąŻ čŹč鹊ą│ąŠ ąĄčüčéčī ąĮąĄąČąĄą╗ą░č鹥ą╗čīąĮčŗąĄ ą┐ąŠčüą╗ąĄą┤čüčéą▓ąĖčÅ:

ŌĆó ąĢčüą╗ąĖ ąŠąČąĖą┤ą░ąĄčé ąŠą▒čĆą░ą▒ąŠčéą║ąĖ čĆą░ąĘčĆąĄčłąĄąĮąĮąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čü ą▒ąŠą╗ąĄąĄ ą▓čŗčüąŠą║ąĖą╝ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝, č湥ą╝ č鹥ą║čāčēąĄąĄ, č鹊 ąŠąĮąŠ ąĮą░čüą╗ą░ąĖą▓ą░ąĄčéčüčÅ (ąĮąĄ ąĘąĮą░čÄ ą║ą░ą║ ą┐ąĄčĆąĄą▓ąĄčüčéąĖ stacked).

ŌĆó ąĢčüą╗ąĖ ąĮąĄčé čĆą░ąĘčĆąĄčłąĄąĮąĮčŗčģ ąŠąČąĖą┤ą░čÄčēąĖčģ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣, ą▒čāą┤ąĄčé ą▓ąŠąĘą▓čĆą░čēąĄąĮ spurious-ą▓ąĄą║č鹊čĆ.

ąÆ ą╗čÄą▒ąŠą╝ čüą╗čāčćą░ąĄ, ąĮąĄąŠą▒čģąŠą┤ąĖą╝ą░ ą║ąŠą╝ą░ąĮą┤ą░ End of Interrupt, čćč鹊ą▒čŗ ą┐ąŠą┤čéą▓ąĄčĆą┤ąĖčéčī ąĖ ą▓ąŠčüčüčéą░ąĮąŠą▓ąĖčéčī ą║ąŠąĮč鹥ą║čüčé AIC. ąŁčéą░ ąŠą┐ąĄčĆą░čåąĖčÅ ąŠą▒čŗčćąĮąŠ ąĮąĄ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ čüąĖčüč鹥ą╝ąŠą╣ ąŠčéą╗ą░ą┤ą║ąĖ, čéą░ą║ ą║ą░ą║ čćč鹊 ąŠčéą╗ą░ąČąĖą▓ą░ąĄą╝ą░čÅ čüąĖčüč鹥ą╝ą░ ąŠą║ą░ąĘčŗą▓ą░ąĄčéčüčÅ ąŠč湥ąĮčī čüąĖą╗čīąĮąŠ ą┐ąŠą┤ą▓ąĄčƹȹĄąĮą░ čĆą░ąĘčĆčāčłąĄąĮąĖčÄ, čćč鹊 ą┐ąĄčĆąĄą▓ąŠą┤ąĖčé ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ ą▓ ąĮąĄąČąĄą╗ą░č鹥ą╗čīąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ.

ąŁč鹊ą│ąŠ ąĖąĘą▒ąĄą│ą░čÄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ Protect Mode. ąŚą░ą┐ąĖčüčī ą┐ąŠą╗čÅ DBGM ą▓ AIC_DCR (Debug Control Register) ą▓ ąĘąĮą░č湥ąĮąĖąĄ 0x1 čĆą░ąĘčĆąĄčłą░ąĄčé Protect Mode.

ąÜąŠą│ą┤ą░ čĆą░ąĘčĆąĄčłąĄąĮ Protect Mode, AIC ą▓čŗą┐ąŠą╗ąĮčÅąĄčé ąĮą░čüą╗ąŠąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ ąĮą░ AIC_IVR ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ąŠą┐ąĄčĆą░čåąĖčÅ ąĘą░ą┐ąĖčüąĖ. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ISR ą┤ąŠą╗ąČąĮčŗ ąĘą░ą┐ąĖčüą░čéčī (ą┐čĆąŠąĖąĘą▓ąŠą╗čīąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ) ą▓ AIC_IVR čüčĆą░ąĘčā ą┐ąŠčüą╗ąĄ ąĄą│ąŠ čćč鹥ąĮąĖčÅ. ąĪ č鹥ą║čāčēąĖą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄą╝ ąŠą▒ąĮąŠą▓ą╗čÅąĄčéčüčÅ ąĮąŠą▓čŗą╣ ą║ąŠąĮč鹥ą║čüčé AIC, ą▓ą║ą╗čÄčćą░čÅ ąĘąĮą░č湥ąĮąĖąĄ Interrupt Status Register (AIC_ISR), č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ AIC_IVR.

ąĪą░ą╝ąŠčüč鹊čÅč鹥ą╗čīąĮąŠąĄ čćč鹥ąĮąĖąĄ AIC_IVR (ąĮą░ą┐čĆąĖą╝ąĄčĆ ąŠčéą╗ą░ą┤čćąĖą║ąŠą╝), ąĮąĄ ąĖąĘą╝ąĄąĮčÅąĄčé ąĮąĖ ą║ąŠąĮč鹥ą║čüčéą░ AIC, ąĮąĖ AIC_ISR. ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗąĄ čćč鹥ąĮąĖčÅ AIC_IVR ą▓čŗą┐ąŠą╗ąĮčÅčÄčéčüčÅ č鹥ą╝ąĖ ąČąĄ ąŠą┐ąĄčĆą░čåąĖčÅą╝ąĖ. ą×ą┤ąĮą░ą║ąŠ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ąĮąĄ ąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čéčī ą┐čĆąŠčåąĄčüčüąŠčĆ ą╝ąĄąČą┤čā čćč鹥ąĮąĖąĄą╝ ąĖ ąĘą░ą┐ąĖčüčīčÄ AIC_IVR ą▓ ISR, čćč鹊 ą│ą░čĆą░ąĮčéąĖčĆčāąĄčé, čćč鹊 ąŠčéą╗ą░ą┤čćąĖą║ ąĮąĄ ą╝ąŠą┤ąĖčäąĖčåąĖčĆčāąĄčé ą║ąŠąĮč鹥ą║čüčé AIC.

ąöą░ą▓ą░ą╣č鹥 ąŠą▒ąŠą▒čēąĖą╝. ąÆ ąĮąŠčĆą╝ą░ą╗čīąĮąŠą╝ čĆą░ą▒ąŠč湥ą╝ čĆąĄąČąĖą╝ąĄ čćč鹥ąĮąĖąĄ AIC_IVR ą▓čŗą┐ąŠą╗ąĮčÅąĄčé ą▓ AIC čüą╗ąĄą┤čāčÄčēąĖąĄ ąŠą┐ąĄčĆą░čåąĖąĖ:

1. ąÆčŗčćąĖčüą╗čÅąĄčé ą░ą║čéąĖą▓ąĮąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ (čü ą▒ąŠą╗ąĄąĄ ą▓čŗčüąŠą║ąĖą╝ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝, č湥ą╝ č鹥ą║čāčēąĄąĄ, ąĖą╗ąĖ spurious-ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ).

2. ą×ą┐čĆąĄą┤ąĄą╗čÅąĄčé ąĖ ą▓ąŠąĘą▓čĆą░čēą░ąĄčé ą▓ąĄą║č鹊čĆ ą░ą║čéąĖą▓ąĮąŠą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

3. ąŚą░ą┐ąŠą╝ąĖąĮą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ.

4. ą¤čĆąŠčéą░ą╗ą║ąĖą▓ą░ąĄčé č鹥ą║čāčēąĖą╣ čāčĆąŠą▓ąĄąĮčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čüč鹥ą║.

5. ą¤ąŠą┤čéą▓ąĄčƹȹ┤ą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ.

ą×ą┤ąĮą░ą║ąŠ ąĄčüą╗ąĖ ą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮ Protect Mode, ą▓čŗą┐ąŠą╗ąĮčÅčÄčéčüčÅ č鹊ą╗čīą║ąŠ ąŠą┐ąĄčĆą░čåąĖąĖ 1 .. 3, ą║ąŠą│ą┤ą░ čćąĖčéą░ąĄčéčüčÅ AIC_IVR. ą×ą┐ąĄčĆą░čåąĖąĖ 4 ąĖ 5 ą▓čŗą┐ąŠą╗ąĮčÅčÄčéčüčÅ AIC, č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ AIC_IVR.

ą¤čĆąŠą│čĆą░ą╝ą╝ą░, ą║ąŠč鹊čĆą░čÅ ąĮą░ą┐ąĖčüą░ąĮą░ ąĖ ąŠčéą╗ą░ąČąĄąĮą░ ą▓ Protect Mode, ą▒čāą┤ąĄčé ą▒ąĄąĘ ą╝ąŠą┤ąĖčäąĖą║ą░čåąĖąĖ ąĮąŠčĆą╝ą░ą╗čīąĮąŠ čĆą░ą▒ąŠčéą░čéčī ąĖ ą▓ Normal Mode. ą×ą┤ąĮą░ą║ąŠ ą▓ Normal Mode ąĘą░ą┐ąĖčüčī AIC_IVR ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé čŹčäč乥ą║čéą░, ąĖ ą╝ąŠąČąĄčé ą▒čŗčéčī čāą┤ą░ą╗ąĄąĮą░ čü čåąĄą╗čīčÄ ąŠą┐čéąĖą╝ąĖąĘą░čåąĖąĖ ą║ąŠą┤ą░.

[ą×čłąĖą▒ąŠčćąĮąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ]

ąÆ AIC ąĄčüčéčī čäčāąĮą║čåąĖčÅ ąĘą░čēąĖčéčŗ ąŠčé spurious (ąŠčłąĖą▒ąŠčćąĮčŗčģ) ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. Spurious-ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąŠ ą║ą░ą║ ą┤ąŠčüčéą░č鹊čćąĮąŠ ą┤ąŠą╗ą│ą░čÅ čāčüčéą░ąĮąŠą▓ą║ą░ ąĖčüč鹊čćąĮąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ AIC, čćč鹊ą▒čŗ čāčüčéą░ąĮąŠą▓ąĖčéčī čüąĖą│ąĮą░ą╗ nIRQ, ąĮąŠ ąĮąĄą┤ąŠčüčéą░č鹊čćąĮąŠ ą┤ąŠą╗ą│ą░čÅ, čćč鹊ą▒čŗ čüčāčēąĄčüčéą▓ąŠą▓ą░čéčī ą▓ ą╝ąŠą╝ąĄąĮčé čćč鹥ąĮąĖčÅ AIC_IVR. ąŁč鹊 čćą░čēąĄ ą▓čüąĄą│ąŠ čüą╗čāčćą░ąĄčéčüčÅ ą▓ čüą╗ąĄą┤čāčÄčēąĖčģ čāčüą╗ąŠą▓ąĖčÅčģ:

ŌĆó ąÆąĮąĄčłąĮąĖą╣ ąĖčüč鹊čćąĮąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ ą▓ čĆąĄąČąĖą╝ čćčāą▓čüčéą▓ąĖč鹥ą╗čīąĮąŠčüčéąĖ ą║ čāčĆąŠą▓ąĮčÄ (level-sensitive mode), ąĖ ą░ą║čéąĖą▓ąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī ą┐čĆąĖčüčāčéčüčéą▓čāąĄčé č鹊ą╗čīą║ąŠ ąĮą░ ą║ąŠčĆąŠčéą║ąŠąĄ ą▓čĆąĄą╝čÅ.

ŌĆó ąÆąĮčāčéčĆąĄąĮąĮąĖą╣ ąĖčüč鹊čćąĮąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ ą▓ čĆąĄąČąĖą╝ čćčāą▓čüčéą▓ąĖč鹥ą╗čīąĮąŠčüčéąĖ ą║ čāčĆąŠą▓ąĮčÄ (level-sensitive mode), ąĖ ą▓čŗčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗, čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▓čüčéčĆąŠąĄąĮąĮąŠą╝čā ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą╝čā čāčüčéčĆąŠą╣čüčéą▓čā, ą░ą║čéąĖą▓ąĖčĆčāąĄčéčüčÅ ąĮą░ ą║ąŠčĆąŠčéą║ąŠąĄ ą▓čĆąĄą╝čÅ (čćč鹊 ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą▓ čüą╗čāčćą░ąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠčé Watchdog [5]).

ŌĆó ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą▓čüąĄą│ąŠ ą╗ąĖčłčī ąĮą░ ąĮąĄčüą║ąŠą╗čīą║ąŠ čéą░ą║č鹊ą▓ čĆą░ąĮčīčłąĄ, č湥ą╝ ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ąĮą░čćąĮąĄčé ąĄą│ąŠ ą╝ą░čüą║ąĖčĆąŠą▓ą░čéčī, čćč鹊 ą▓ čĆąĄąĘčāą╗čīčéą░č鹥 ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ąĖą╝ą┐čāą╗čīčü ąĮą░ ąĖčüč鹊čćąĮąĖą║ąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

AIC ą┤ąĄč鹥ą║čéąĖčĆčāąĄčé spurious-ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą▓ ą╝ąŠą╝ąĄąĮčé, ą║ąŠą│ą┤ą░ čćąĖčéą░ąĄčéčüčÅ AIC_IVR, ą║ąŠą│ą┤ą░ ąĮąĄčé čĆą░ąĘčĆąĄčłąĄąĮąĮčŗčģ, ąŠąČąĖą┤ą░čÄčēąĖčģ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. ąÜąŠą│ą┤ą░ čŹč鹊 ą┐čĆąŠąĖčüčģąŠą┤ąĖčé, AIC ą▓ąĄčĆąĮąĄčé ąĘąĮą░č湥ąĮąĖąĄ, čüąŠčģčĆą░ąĮąĄąĮąĮąŠąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčüč鹊ą╝ ą▓ AIC_SPU (Spurious Vector Register). ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčüčé ą┤ąŠą╗ąČąĄąĮ čüąŠčģčĆą░ąĮąĖčéčī ą░ą┤čĆąĄčü ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ą░ spurious-ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą▓ AIC_SPU ą║ą░ą║ čćą░čüčéčī ą║ąŠą┤ą░ ą▓ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĖ, čćč鹊ą▒čŗ ą║ą░ą║ ą╝ąŠąČąĮąŠ ą▒čŗčüčéčĆąĄąĄ ą▓ąĄčĆąĮčāčéčīčüčÅ ą║ ąĮąŠčĆą╝ą░ą╗čīąĮąŠą╝čā ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÄ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ. ąŁč鹊čé ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčé ą▓ AIC_EOICR ąĖ ą▓čŗą┐ąŠą╗ąĮčÅąĄčé ą▓ąŠąĘą▓čĆą░čé ąĖąĘ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

[ą×ą▒čēąĄąĄ ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣]

ąÆ AIC ąĄčüčéčī ą▒ąĖčé ąŠą▒čēąĄą│ąŠ ąĘą░ą┐čĆąĄčéą░ (ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖčÅ) ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣, General Interrupt Mask (ą▒ąĖčé GMSK ą▓ čĆąĄą│ąĖčüčéčĆąĄ AIC_DCR), ą║ąŠč鹊čĆčŗą╣ ąĮąĄ ą┤ą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅą╝ ą┤ąŠčüčéąĖą│ąĮčāčéčī ą┐čĆąŠčåąĄčüčüąŠčĆą░. ąĪąĖą│ąĮą░ą╗čŗ nIRQ ąĖ nFIQ ą┐ąĄčĆąĄčģąŠą┤čÅčé ą▓ ąĮąĄą░ą║čéąĖą▓ąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ, ąĄčüą╗ąĖ GMSK čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ. ą×ą┤ąĮą░ą║ąŠ čŹčéą░ ą╝ą░čüą║ą░ ąĮąĄ ąĘą░čēąĖčēą░ąĄčé ąŠčé ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ ą┐čĆąŠčåąĄčüčüąŠčĆą░, ąĄčüą╗ąĖ ąŠąĮ ą▓ąŠčłąĄą╗ ą▓ čĆąĄąČąĖą╝ čüąĮą░ (Idle Mode). ąŁčéą░ čäčāąĮą║čåąĖčÅ čāą┐čĆąŠčēą░ąĄčé čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖčÄ ą┐čĆąŠčåąĄčüčüąŠčĆą░ čüąŠ čüą╗ąĄą┤čāčÄčēąĖą╝ čüąŠą▒čŗčéąĖąĄą╝, ąĖ ą║ą░ą║ č鹊ą╗čīą║ąŠ čüąŠą▒čŗčéąĖąĄ ą┐čĆąŠąĖąĘąŠčłą╗ąŠ, ą▒čāą┤čāčé ą▓čŗą┐ąŠą╗ąĮąĄąĮčŗ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ ą┤ąĄą╣čüčéą▓ąĖčÅ ą▒ąĄąĘ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ąØą░čüč鹊čÅč鹥ą╗čīąĮąŠ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ čü ąŠčüč鹊čĆąŠąČąĮąŠčüčéčīčÄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čŹčéčā ą╝ą░čüą║čā.

[ąśąĮč鹥čĆč乥ą╣čü ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ AIC (čĆąĄą│ąĖčüčéčĆčŗ)]

ąæą░ąĘąŠą▓čŗą╣ ą░ą┤čĆąĄčü AIC ąŠč鹊ą▒čĆą░ąČąĄąĮ ąĮą░ ą░ą┤čĆąĄčü 0xFFFFF000, ąĖ ąĘą░ąĮąĖą╝ą░ąĄčé čĆąĄą│ąĖčüčéčĆą░ą╝ąĖ 4-ą║ąĖą╗ąŠą▒ą░ą╣čéąĮąŠąĄ ą░ą┤čĆąĄčüąĮąŠąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ. ąŁč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé čĆąĄą░ą╗ąĖąĘąŠą▓ą░čéčī čäčāąĮą║čåąĖčÄ ą▓ąĄą║č鹊čĆąĖąĘą░čåąĖąĖ, čéą░ą║ ą║ą░ą║ ąĖąĮčüčéčĆčāą║čåąĖąĖ load/store, čĆą░ą▒ąŠčéą░čÄčēąĖąĄ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ PC, ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé č鹊ą╗čīą║ąŠ ┬▒ 4-ą║ąĖą╗ąŠą▒ą░ą╣čéąĮąŠąĄ čüą╝ąĄčēąĄąĮąĖąĄ.

ąóą░ą▒ą╗ąĖčåą░ 23-2. ą×č鹊ą▒čĆą░ąČąĄąĮąĖąĄ ąĮą░ ą┐ą░ą╝čÅčéčī čĆąĄą│ąĖčüčéčĆąŠą▓ AIC.

| ąĪą╝ąĄčēąĄąĮąĖąĄ |

ąĀąĄą│ąĖčüčéčĆ |

ą£ąĮąĄą╝ąŠąĮąĖą║ą░ |

ąöąŠčüčéčāą┐(3) |

ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ |

| 0x0000 |

Source Mode Register 0 |

AIC_SMR0 |

RW |

0x00000000 |

| 0x0004 |

Source Mode Register 1 |

AIC_SMR1 |

RW |

0x00000000 |

| ... |

... |

... |

... |

...

|

| 0x007C |

Source Mode Register 31 |

AIC_SMR31 |

RW |

0x00000000 |

| 0x0080 |

Source Vector Register 0 |

AIC_SVR0 |

RW |

0x00000000 |

| 0x0084 |

Source Vector Register 1 |

AIC_SVR1 |

RW |

0x00000000 |

| ... |

... |

... |

... |

... |

| 0x00FC |

Source Vector Register 31 |

AIC_SVR31 |

RW |

0x00000000 |

| 0x0100 |

Interrupt Vector Register |

AIC_IVR |

RO |

0x00000000 |

| 0x0104 |

FIQ Interrupt Vector Register |

AIC_FVR |

RO |

0x00000000 |

| 0x0108 |

Interrupt Status Register |

AIC_ISR |

RO |

0x00000000 |

| 0x010C |

Interrupt Pending Register(2) |

AIC_IPR |

RO |

0x00000000(1) |

| 0x0110 |

Interrupt Mask Register(2) |

AIC_IMR |

RO |

0x00000000 |

| 0x0114 |

Core Interrupt Status Register |

AIC_CISR |

RO |

0x00000000 |

| 0x0118 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

-- |

-- |

-- |

| 0x011C |

-- |

-- |

-- |

| 0x0120 |

Interrupt Enable Command Register(2) |

AIC_IECR |

WO |

-- |

| 0x0124 |

Interrupt Disable Command Register(2) |

AIC_IDCR |

WO |

-- |

| 0x0128 |

Interrupt Clear Command Register(2) |

AIC_ICCR |

WO |

-- |

| 0x012C |

Interrupt Set Command Register(2) |

AIC_ISCR |

WO |

-- |

| 0x0130 |

End of Interrupt Command Register |

AIC_EOICR |

WO |

-- |

| 0x0134 |

Spurious Interrupt Vector Register |

AIC_SPU |

RW |

0x00000000 |

| 0x0138 |

Debug Control Register |

AIC_DCR |

RW |

0x00000000 |

| 0x013C |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

-- |

-- |

-- |

| 0x0140 |

Fast Forcing Enable Register(2) |

AIC_FFER |

WO |

-- |

| 0x0144 |

Fast Forcing Disable Register(2) |

AIC_FFDR |

WO |

-- |

| 0x0148 |

Fast Forcing Status Register(2) |

AIC_FFSR |

RO |

0x00000000 |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

(1) ąŚąĮą░č湥ąĮąĖąĄ čüą▒čĆąŠčüą░ čŹč鹊ą│ąŠ čĆąĄą│ąĖčüčéčĆą░ ąĘą░ą▓ąĖčüąĖčé ąŠčé čāčĆąŠą▓ąĮčÅ ąĮą░ ą▓ąĮąĄčłąĮąĄą╝ ąĖčüč鹊čćąĮąĖą║ąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. ąÆčüąĄ ą┤čĆčāą│ąĖąĄ ąĖčüč鹊čćąĮąĖą║ąĖ ąŠčćąĖčēą░čÄčéčüčÅ čüą▒čĆąŠčüąŠą╝, čéą░ą║ čćč鹊 ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ ąĮąĄčé ąŠąČąĖą┤ą░ąĮąĖčÅ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ąĖčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣.

(2) ąæąĖč鹊ą▓čŗąĄ ą┐ąŠą╗čÅ PID2..PID31 ąŠčéąĮąŠčüčÅčéčüčÅ ą║ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆą░ą╝ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓, ą║ą░ą║ čŹč鹊 ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąŠ ą▓ čüąĄą║čåąĖąĖ "Peripheral Identifiers" ą┤ą░čéą░čłąĖčéą░ ąĮą░ ą┐čĆąŠčåąĄčüčüąŠčĆ.

(3) WO ąŠąĘąĮą░čćą░ąĄčé č鹊ą╗čīą║ąŠ ąĘą░ą┐ąĖčüčī (Write Only), RW ąŠąĘąĮą░čćą░ąĄčé čćč鹥ąĮąĖąĄ ąĖ ąĘą░ą┐ąĖčüčī (Read Write), RO ąŠąĘąĮą░čćą░ąĄčé č鹊ą╗čīą║ąŠ čćč鹥ąĮąĖąĄ (Read Only).

ąÆ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░čģ AT91SAM7X (AT91SAM7512, AT91SAM7X256, AT91SAM7X128) ą▓čüčéčĆąŠąĄąĮąŠ ą╝ąĮąŠąČąĄčüčéą▓ąŠ čĆą░ąĘąĮąŠą╣ ą░ą┐ą┐ą░čĆą░čéčāčĆčŗ (ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░). ąóą░ą▒ą╗ąĖčåą░ 10-1 ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆčŗ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ (Peripheral Identifiers) ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ čüąĄčĆąĖąĖ AT91SAM7X. ąŻąĮąĖą║ą░ą╗čīąĮčŗąĄ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆčŗ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮčŗ ąĖ ą┤ą╗čÅ AIC (Advanced Interrupt Controller), ąĖ ą┤ą╗čÅ PMC (Power Management Controller) [3].

ąóą░ą▒ą╗ąĖčåą░ 10-1. ąśą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆčŗ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ (Peripheral ID).

| Peripheral ID |

ą£ąĮąĄą╝ąŠąĮąĖą║ą░ |

ą¤ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ |

ąÆąĮąĄčłąĮąĄąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ |

| 0 |

AIC |

Advanced Interrupt Controller |

FIQ |

| 1 |

SYSC(1) |

System Controller |

|

| 2 |

PIOA |

Parallel I/O Controller A(2) |

|

| 3 |

PIOB |

Parallel I/O Controller B(2) |

|

| 4 |

SPI0 |

Serial Peripheral Interface 0(3) |

|

| 5 |

SPI1 |

Serial Peripheral Interface 1(3) |

|

| 6 |

US0 |

USART 0 |

|

| 7 |

US1 |

USART 1 |

|

| 8 |

SSC |

Synchronous Serial Controller |

|

| 9 |

TWI |

Two-wire Interface(4) (I2C) |

|

| 10 |

PWMC |

Pulse Width Modulation Controller |

|

| 11 |

UDP |

USB Device Port(5) |

|

| 12 |

TC0 |

Timer/Counter 0(6) |

|

| 13 |

TC1 |

Timer/Counter 1(6) |

|

| 14 |

TC2 |

Timer/Counter 2(6) |

|

| 15 |

CAN |

CAN Controller(7) |

|

| 16 |

EMAC |

Ethernet MAC |

|

| 17 |

ADC(1) |

Analog-to Digital Converter(8) |

|

| 18-29 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

|

|

| 30 |

AIC |

Advanced Interrupt Controller |

IRQ0 |

| 31 |

AIC |

Advanced Interrupt Controller |

IRQ1 |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

(1) ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖčé SYSC ąĖ ADC ą▓ čĆąĄą│ąĖčüčéčĆą░čģ čāčüčéą░ąĮąŠą▓ą║ąĖ/ąŠčćąĖčüčéą║ąĖ čéą░ą║č鹊ą▓ PMC ąĮąĄ ą┤ą░ąĄčé čŹčäč乥ą║čéą░. System Controller ąĖ ADC čéą░ą║čéąĖčĆčāčÄčéčüčÅ ą┐ąŠčüč鹊čÅąĮąĮąŠ.

(2) ąĪą╝. [2].

(3) ąĪą╝. AT91SAM7 Serial Peripheral Interface (SPI).

(4) ąĪą╝. ARM: ą║ą░ą║ čĆą░ą▒ąŠčéą░čéčī čü ą░ą┐ą┐ą░čĆą░čéąĮčŗą╝ TWI (I2C) ąĮą░ ą┐čĆąĖą╝ąĄčĆąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą╝ąĖą║čĆąŠčüčģąĄą╝ąŠą╣ FM30C256.

(5) ąĪą╝. AT91SAM7X: ąĖąĮč鹥čĆč乥ą╣čü USB (UDP, USB Device Port).

(6) ąĪą╝. ąóą░ą╣ą╝ąĄčĆ/čüč湥čéčćąĖą║ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ AT91SAM7X.

(7) ąĪą╝. AT91SAM7X: ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ CAN.

(8) ąĪą╝. ARM AT91SAM7X256: ą║ą░ą║ čĆą░ą▒ąŠčéą░čéčī čü ADC.

AIC Source Mode Register

ąŁč鹊 čĆąĄą│ąĖčüčéčĆčŗ čĆąĄąČąĖą╝ą░ ąĖčüč鹊čćąĮąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ AIC_SMR0 .. AIC_SMR31.

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| - |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

-

|

- |

- |

- |

- |

- |

- |

- |

- |

SRCTYPE |

- |

- |

PRIOR |

PRIOR: Priority Level

ąŁč鹊 ą┐ąŠą╗ąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčé čāčĆąŠą▓ąĄąĮčī ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┤ą╗čÅ ą▓čüąĄčģ ąĖčüč鹊čćąĮąĖą║ąŠą▓, ą║čĆąŠą╝ąĄ FIQ (source 0). ąŻčĆąŠą▓ąĄąĮčī ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą╝ąŠąČąĄčé ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠčé 0 (čüą░ą╝čŗą╣ ąĮąĖąĘą║ąĖą╣ ą┐čĆąĖąŠčĆąĖč鹥čé) ą┤ąŠ 7 (čüą░ą╝čŗą╣ ą▓čŗčüąŠą║ąĖą╣ ą┐čĆąĖąŠčĆąĖč鹥čé) ą▓ą║ą╗čÄčćąĖč鹥ą╗čīąĮąŠ. ąöą╗čÅ FIQ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čāčĆąŠą▓ąĄąĮčī ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą▓ čüą▓čÅąĘą░ąĮąĮąŠą╝ SMR-čĆąĄą│ąĖčüčéčĆąĄ AIC_SMRx.

SRCTYPE: Interrupt Source Type

ąÉą║čéąĖą▓ąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī ąĖą╗ąĖ ą┐ąĄčĆąĄą┐ą░ą┤, ą┐ąŠ ą║ąŠč鹊čĆąŠą╝čā čüčĆą░ą▒ą░čéčŗą▓ą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ. ąŁč鹊čé ą┐ą░čĆą░ą╝ąĄčéčĆ ąĮąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ ą┤ą╗čÅ ą▓ąĮčāčéčĆąĄąĮąĮąĖčģ ąĖčüč鹊čćąĮąĖą║ąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

| SRCTYPE |

ąÆąĮčāčéčĆąĄąĮąĮąĖąĄ ąĖčüč鹊čćąĮąĖą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ |

ąÆąĮąĄčłąĮąĖąĄ ąĖčüč鹊čćąĮąĖą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ |

| 00 |

ą¦čāą▓čüčéą▓ąĖč鹥ą╗čīąĮąŠčüčéčī ą║ ą╗ąŠą│. 1 |

ą¦čāą▓čüčéą▓ąĖč鹥ą╗čīąĮąŠčüčéčī ą║ ą╗ąŠą│. 0 |

| 01 |

ąĪčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĄ ą┐ąŠ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą╝čā ą┐ąĄčĆąĄą┐ą░ą┤čā čāčĆąŠą▓ąĮčÅ (0 -> 1) |

ąĪčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĄ ą┐ąŠ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠą╝čā ą┐ąĄčĆąĄą┐ą░ą┤čā čāčĆąŠą▓ąĮčÅ (1 -> 0) |

| 10 |

ą¦čāą▓čüčéą▓ąĖč鹥ą╗čīąĮąŠčüčéčī ą║ ą╗ąŠą│. 1 |

ą¦čāą▓čüčéą▓ąĖč鹥ą╗čīąĮąŠčüčéčī ą║ ą╗ąŠą│. 1 |

| 11 |

ąĪčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĄ ą┐ąŠ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą╝čā ą┐ąĄčĆąĄą┐ą░ą┤čā čāčĆąŠą▓ąĮčÅ |

ąĪčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĄ ą┐ąŠ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą╝čā ą┐ąĄčĆąĄą┐ą░ą┤čā čāčĆąŠą▓ąĮčÅ |

AIC Source Vector Register

ąĀąĄą│ąĖčüčéčĆčŗ AIC_SVR0 .. AIC_SVR31 ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ ąĮą░čüčéčĆąŠą╣ą║ąĖ ą░ą┤čĆąĄčüąŠą▓ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| VECTOR |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| VECTOR |

VECTOR: Source Vector

ą¤ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą╝ąŠąČąĄčé čüąŠčģčĆą░ąĮąĖčéčī ą▓ čŹčéąĖčģ čĆąĄą│ąĖčüčéčĆą░čģ ą░ą┤čĆąĄčüą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (ISR) ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

AIC Interrupt Vector Register

ąśą╝čÅ čĆąĄą│ąĖčüčéčĆą░ AIC_IVR, ąŠąĮ čüą╗čāąČąĖčé ą┤ą╗čÅ čćč鹥ąĮąĖčÅ ą░ą┤čĆąĄčüą░ č鹥ą║čāčēąĄą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| IRQV |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| IRQV |

IRQV: Interrupt Vector Register

Interrupt Vector Register čüąŠą┤ąĄčƹȹĖčé ą▓ąĄą║č鹊čĆ, ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮčŗą╣ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╝ ą▓ Source Vector Register, čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ č鹥ą║čāčēąĄą╝čā ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÄ. Source Vector Register ąĖąĮą┤ąĄą║čüąĖčĆčāąĄčéčüčÅ čü ą┐ąŠą╝ąŠčēčīčÄ ąĮąŠą╝ąĄčĆą░ č鹥ą║čāčēąĄą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą║ąŠą│ą┤ą░ ą┐čĆąŠą│čĆą░ą╝ą╝ą░ čćąĖčéą░ąĄčé Interrupt Vector Register.

ąÜąŠą│ą┤ą░ ą▓ ąĮą░čüč鹊čÅčēąĖą╣ ą╝ąŠą╝ąĄąĮčé ąĮąĄčé č鹥ą║čāčēąĄą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ąĖąĘ Interrupt Vector Register ą▒čāą┤ąĄčé ą┐čĆąŠčćąĖčéą░ąĮąŠ ąĘąĮą░č湥ąĮąĖąĄ, čüąŠčģčĆą░ąĮąĄąĮąĮąŠąĄ ą▓ AIC_SPU.

AIC FIQ Vector Register

ąśą╝čÅ čĆąĄą│ąĖčüčéčĆą░ AIC_FVR, ąŠąĮ čüą╗čāąČąĖčé ą┤ą╗čÅ čćč鹥ąĮąĖčÅ ą░ą┤čĆąĄčüą░ č鹥ą║čāčēąĄą│ąŠ ą▒čŗčüčéčĆąŠą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| FIQV |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| FIQV |

FIQV: FIQ Vector Register

FIQ Vector Register čüąŠą┤ąĄčƹȹĖčé ą▓ąĄą║č鹊čĆ, ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮčŗą╣ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╝ ą▓ Source Vector Register 0. ąÜąŠą│ą┤ą░ ą▓ ąĮą░čüč鹊čÅčēąĄąĄ ą▓čĆąĄą╝čÅ ąĮąĄčé ą▒čŗčüčéčĆąŠą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ąĖąĘ FIQ Vector Register ą▒čāą┤ąĄčé ą┐čĆąŠčćąĖčéą░ąĮąŠ ąĘąĮą░č湥ąĮąĖąĄ, čüąŠčģčĆą░ąĮąĄąĮąĮąŠąĄ ą▓ AIC_SPU.

AIC Interrupt Status Register

ąśą╝čÅ čĆąĄą│ąĖčüčéčĆą░ AIC_ISR, ąŠąĮ čüą╗čāąČąĖčé ą┤ą╗čÅ čćč鹥ąĮąĖčÅ ąĮąŠą╝ąĄčĆą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| - |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

-

|

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

IRQID |

IRQID: Current Interrupt Identifier

ą¦č鹥ąĮąĖąĄ Interrupt Status Register ą▓ąĄčĆąĮąĄčé ąĮąŠą╝ąĄčĆ č鹥ą║čāčēąĄą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

AIC Interrupt Pending Register

ąśą╝čÅ čĆąĄą│ąĖčüčéčĆą░ AIC_IPR, ąŠąĮ čüąŠą┤ąĄčƹȹĖčé čäą╗ą░ą│ąĖ ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣, ąŠąČąĖą┤ą░čÄčēąĖčģ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ.

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| PID31 |

PID30 |

PID29 |

PID28 |

PID27 |

PID26 |

PID25 |

PID24 |

PID23 |

PID22 |

PID21 |

PID20 |

PID19 |

PID18 |

PID17 |

PID16 |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| PID15 |

PID14 |

PID13 |

PID12 |

PID11 |

PID10 |

PID9 |

PID8 |

PID7 |

PID6 |

PID5 |

PID4 |

PID3 |

PID2 |

SYS |

FIQ |

FIQ, SYS, PID2, .., PID31: Interrupt Pending

0 čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé čüąŠčüč鹊čÅąĮąĖčÄ, ą║ąŠą│ą┤ą░ ąĮąĄčé ąŠąČąĖą┤ą░čÄčēąĄą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░.

1 čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé čüąŠčüč鹊čÅąĮąĖčÄ, ą║ąŠą│ą┤ą░ ą┤ą╗čÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ ąĖą╝ąĄąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ąŠąČąĖą┤ą░čÄčēąĄąĄ čüą▓ąŠąĄą╣ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ.

AIC Interrupt Mask Register

ąśą╝čÅ čĆąĄą│ąĖčüčéčĆą░ AIC_IMR, ąŠąĮ čüą╗čāąČąĖčé ą┤ą╗čÅ ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖčüč鹊čćąĮąĖą║ąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| PID31 |

PID30 |

PID29 |

PID28 |

PID27 |

PID26 |

PID25 |

PID24 |

PID23 |

PID22 |

PID21 |

PID20 |

PID19 |

PID18 |

PID17 |

PID16 |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| PID15 |

PID14 |

PID13 |

PID12 |

PID11 |

PID10 |

PID9 |

PID8 |

PID7 |

PID6 |

PID5 |

PID4 |

PID3 |

PID2 |

SYS |

FIQ |

FIQ, SYS, PID2, .., PID31: Interrupt Mask

0 ąĘą░ą┐čĆąĄčēą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░.

1 čĆą░ąĘčĆąĄčłą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░.

AIC Core Interrupt Status Register

ąśą╝čÅ čĆąĄą│ąĖčüčéčĆą░ AIC_CISR, ąŠąĮ čüą╗čāąČąĖčé ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ čüąŠčüč鹊čÅąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čÅą┤čĆą░.

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| - |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

-

|

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

-

|

- |

- |

NIRQ |

NIFQ |

NFIQ: NFIQ Status

0 čüąĖą│ąĮą░ą╗ nFIQ ą┤ąĄą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮ.

1 čüąĖą│ąĮą░ą╗ nFIQ ą░ą║čéąĖą▓ąĄąĮ.

NIRQ: NIRQ Status

0 čüąĖą│ąĮą░ą╗ nIRQ ą┤ąĄą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮ.

1 čüąĖą│ąĮą░ą╗ nIRQ ą░ą║čéąĖą▓ąĄąĮ.

AIC Interrupt Enable Command Register

ąśą╝čÅ čĆąĄą│ąĖčüčéčĆą░ AIC_IECR, ąŠąĮ čüą╗čāąČąĖčé ą┤ą╗čÅ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣.

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| PID31 |

PID30 |

PID29 |

PID28 |

PID27 |

PID26 |

PID25 |

PID24 |

PID23 |

PID22 |

PID21 |

PID20 |

PID19 |

PID18 |

PID17 |

PID16 |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| PID15 |

PID14 |

PID13 |

PID12 |

PID11 |

PID10 |

PID9 |

PID8 |

PID7 |

PID6 |

PID5 |

PID4 |

PID3 |

PID2 |

SYS |

FIQ

|

FIQ, SYS, PID2, .., PID31: Interrupt Enable

0 ąĘą░ą┐ąĖčüą░ąĮąĮčŗą╣ ąĮąŠą╗čī ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

1 ąĘą░ą┐ąĖčüą░ąĮąĮą░čÅ ąĄą┤ąĖąĮąĖčåą░ čĆą░ąĘčĆąĄčłą░ąĄčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ.

AIC Interrupt Disable Command Register

ąśą╝čÅ čĆąĄą│ąĖčüčéčĆą░ AIC_IDCR, ąŠąĮ čüą╗čāąČąĖčé ą┤ą╗čÅ ąĘą░ą┐čĆąĄčéą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣.

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| PID31 |

PID30 |

PID29 |

PID28 |

PID27 |

PID26 |

PID25 |

PID24 |

PID23 |

PID22 |

PID21 |

PID20 |

PID19 |

PID18 |

PID17 |

PID16 |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| PID15 |

PID14 |

PID13 |

PID12 |

PID11 |

PID10 |

PID9 |

PID8 |

PID7 |

PID6 |

PID5 |

PID4 |

PID3 |

PID2 |

SYS |

FIQ

|

FIQ, SYS, PID2, .., PID31: Interrupt Disable

0 ąĘą░ą┐ąĖčüą░ąĮąĮčŗą╣ ąĮąŠą╗čī ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

1 ąĘą░ą┐ąĖčüą░ąĮąĮą░čÅ ąĄą┤ąĖąĮąĖčåą░ ąĘą░ą┐čĆąĄčēą░ąĄčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ.

AIC Interrupt Clear Command Register

ąśą╝čÅ čĆąĄą│ąĖčüčéčĆą░ AIC_ICCR, ąŠąĮ čüą╗čāąČąĖčé ą┤ą╗čÅ ąŠčćąĖčüčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣.

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| PID31 |

PID30 |

PID29 |

PID28 |

PID27 |

PID26 |

PID25 |

PID24 |

PID23 |

PID22 |

PID21 |

PID20 |

PID19 |

PID18 |

PID17 |

PID16 |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| PID15 |

PID14 |

PID13 |

PID12 |

PID11 |

PID10 |

PID9 |

PID8 |

PID7 |

PID6 |

PID5 |

PID4 |

PID3 |

PID2 |

SYS |

FIQ

|

FIQ, SYS, PID2, .., PID31: Interrupt Clear

0 ąĘą░ą┐ąĖčüą░ąĮąĮčŗą╣ ąĮąŠą╗čī ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

1 ąĘą░ą┐ąĖčüą░ąĮąĮą░čÅ ąĄą┤ąĖąĮąĖčåą░ ąŠčćąĖčēą░ąĄčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ.

AIC Interrupt Set Command Register

ąśą╝čÅ čĆąĄą│ąĖčüčéčĆą░ AIC_ISCR, ąŠąĮ čüą╗čāąČąĖčé ą┤ą╗čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣.

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| PID31 |

PID30 |

PID29 |

PID28 |

PID27 |

PID26 |

PID25 |

PID24 |

PID23 |

PID22 |

PID21 |

PID20 |

PID19 |

PID18 |

PID17 |

PID16 |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| PID15 |

PID14 |

PID13 |

PID12 |

PID11 |

PID10 |

PID9 |

PID8 |

PID7 |

PID6 |

PID5 |

PID4 |

PID3 |

PID2 |

SYS |

FIQ

|

FIQ, SYS, PID2, .., PID31: Interrupt Set

0 ąĘą░ą┐ąĖčüą░ąĮąĮčŗą╣ ąĮąŠą╗čī ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

1 ąĘą░ą┐ąĖčüą░ąĮąĮą░čÅ ąĄą┤ąĖąĮąĖčåą░ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ.

AIC End of Interrupt Command Register

ąśą╝čÅ čĆąĄą│ąĖčüčéčĆą░ AIC_EOICR, čĆąĄą│ąĖčüčéčĆ ąŠą║ąŠąĮčćą░ąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣.

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| - |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

-

|

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

-

|

- |

- |

NIRQ |

NIFQ

|

End of Interrupt Command Register ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓ ISR, čćč鹊ą▒čŗ ą┐ąŠą║ą░ąĘą░čéčī, čćč鹊 ąŠą▒čĆą░ą▒ąŠčéą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĘą░ą▓ąĄčĆčłąĄąĮą░. ąÆ čŹč鹊čé čĆąĄą│ąĖčüčéčĆ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮąŠ ą╗čÄą▒ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ, ą┐ąŠč鹊ą╝čā čćč鹊 ą┤ą╗čÅ čüąĖą│ąĮą░ą╗ąĖąĘą░čåąĖąĖ ąŠą▒ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĮčāąČąĄąĮ č鹊ą╗čīą║ąŠ čüą░ą╝ čäą░ą║čé ąĘą░ą┐ąĖčüąĖ ą▓ čĆąĄą│ąĖčüčéčĆ.

AIC Spurious Interrupt Vector Register

ąśą╝čÅ čĆąĄą│ąĖčüčéčĆą░ AIC_EOICR, čĆąĄą│ąĖčüčéčĆ ąŠčłąĖą▒ąŠčćąĮąŠą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| SIQV |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| SIQV |

SIQV: Spurious Interrupt Vector Register

ą¤ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą╝ąŠąČąĄčé čüąŠčģčĆą░ąĮąĖčéčī ą▓ čŹč鹊čé čĆąĄą│ąĖčüčéčĆ ą░ą┤čĆąĄčü ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ą░ ąŠčłąĖą▒ąŠčćąĮąŠą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (spurious interrupt). ąŚą░ą┐ąĖčüą░ąĮąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą▒čāą┤ąĄčé ą▓ąŠąĘą▓čĆą░čēąĄąĮąŠ ą▓ AIC_IVR, ąĄčüą╗ąĖ ą┐čĆąŠąĖąĘąŠčłą╗ąŠ spurious-ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĖ ąĘąĮą░č湥ąĮąĖąĄ ą▓ AIC_FVR, ąĄčüą╗ąĖ ą┐čĆąŠąĖąĘąŠčłą╗ąŠ spurious fast interrupt.

AIC Debug Control Register

ąśą╝čÅ čĆąĄą│ąĖčüčéčĆą░ AIC_DEBUG, čüą╗čāąČąĖčé ą┤ą╗čÅ ąĮą░čüčéčĆąŠą╣ą║ąĖ ą┐ąŠą▓ąĄą┤ąĄąĮąĖčÅ AIC ą┐čĆąĖ ąŠčéą╗ą░ą┤ą║ąĄ.

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| - |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

-

|

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

-

|

- |

- |

GMSK |

PROT |

PROT: Protection Mode

0 Protection Mode ąĘą░ą┐čĆąĄčēąĄąĮ.

1 Protection Mode čĆą░ąĘčĆąĄčłąĄąĮ.

GMSK: General Mask

0 čüąĖą│ąĮą░ą╗čŗ nIRQ ąĖ nFIQ ą║ąŠąĮčéčĆąŠą╗ąĖčĆčāčÄčéčüčÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ AIC ąŠą▒čŗčćąĮčŗą╝ ąŠą▒čĆą░ąĘąŠą╝.

1 čüąĖą│ąĮą░ą╗čŗ nIRQ ąĖ nFIQ ą┐ąĄčĆąĄą▓ąĄą┤ąĄąĮčŗ ą▓ čüą▓ąŠąĄ ąĮąĄą░ą║čéąĖą▓ąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ.

AIC Fast Forcing Enable Register

ąśą╝čÅ čĆąĄą│ąĖčüčéčĆą░ AIC_FFER, čüą╗čāąČąĖčé čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ čäčāąĮą║čåąĖąĖ Fast Forcing.

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| PID31 |

PID30 |

PID29 |

PID28 |

PID27 |

PID26 |

PID25 |

PID24 |

PID23 |

PID22 |

PID21 |

PID20 |

PID19 |

PID18 |

PID17 |

PID16 |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |