|

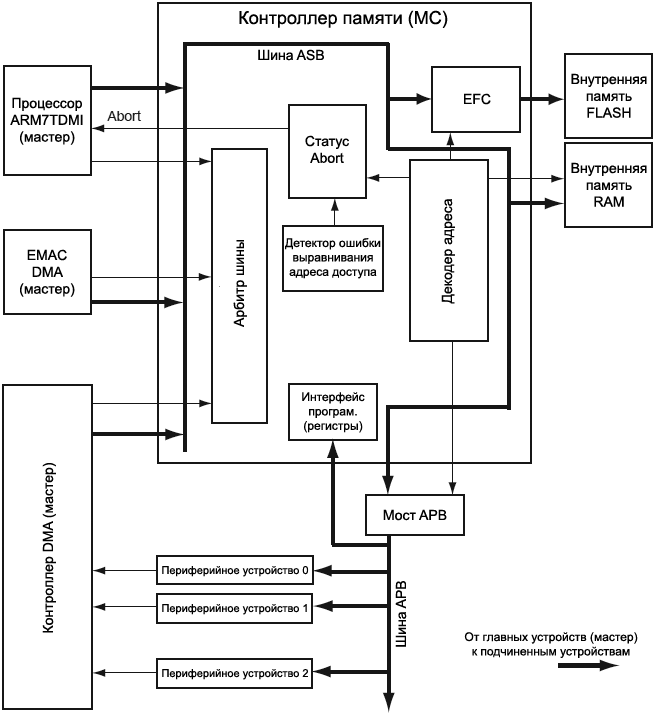

ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą┐ą░ą╝čÅčéąĖ (Memory Controller, MC) ą▓ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░čģ ARM7 ąŠą▒čüą╗čāąČąĖą▓ą░ąĄčé čłąĖąĮčā ASB (čĆą░čüčłąĖčäčĆąŠą▓čŗą▓ą░ąĄčéčüčÅ ą║ą░ą║ ARM System Bus) ąĖ čāą┐čĆą░ą▓ą╗čÅąĄčé ąĘą░ą┐čĆąŠčüą░ą╝ąĖ ą║ ą┐ą░ą╝čÅčéąĖ čüąŠ čüč鹊čĆąŠąĮčŗ ą╝ą░čüč鹥čĆąŠą▓ čłąĖąĮčŗ - ąŠą▒čŗčćąĮąŠ čŹč鹊 čÅą┤čĆąŠ ARM7TDMI ąĖ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ DMA. ąÆ čäčāąĮą║čåąĖąĖ MC ą▓čģąŠą┤ąĖčé ą░čĆą▒ąĖčéčĆ čłąĖąĮčŗ, ą┤ąĄą║ąŠą┤ąĄčĆ ą░ą┤čĆąĄčüą░, čüąĖčüč鹥ą╝ą░ ąŠą▒čüą╗čāąČąĖą▓ą░ąĮąĖčÅ čüąŠčüč鹊čÅąĮąĖčÅ abort, ą┤ąĄč鹥ą║č鹊čĆ ąŠčłąĖą▒ą║ąĖ ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖčÅ ąĖ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą▓čüčéčĆąŠąĄąĮąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ FLASH (Embedded Flash Controller, EFC. ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. [2]).

ąĀąĖčü. 18-1. ąæą╗ąŠą║-čüčģąĄą╝ą░ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ MC.

MC ąŠą▒čüą╗čāąČąĖą▓ą░ąĄčé ą▓ąĮčāčéčĆąĄąĮąĮčÄčÄ čłąĖąĮčā ASB, ąĖ ą▓čŗą┐ąŠą╗ąĮčÅąĄčé ą░čĆą▒ąĖčéčĆą░ąČ ą┤ąŠčüčéčāą┐ą░ ą┤ąŠ čéčĆąĄčģ čāčüčéčĆąŠą╣čüčéą▓ ą╝ą░čüč鹥čĆą░ čłąĖąĮčŗ. MC ą┐ąŠčüčéčĆąŠąĄąĮ ąĖąĘ čüą╗ąĄą┤čāčÄčēąĖčģ ą▒ą╗ąŠą║ąŠą▓:

ŌĆó ąÉčĆą▒ąĖčéčĆ čłąĖąĮčŗ.

ŌĆó ąöąĄą║ąŠą┤ąĄčĆ ą░ą┤čĆąĄčüą░.

ŌĆó ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čüąŠčüč鹊čÅąĮąĖąĄą╝ ąŠą▒čĆčŗą▓ą░ ą┤ąŠčüčéčāą┐ą░ (abort status).

ŌĆó ąöąĄč鹥ą║č鹊čĆ ąŠčłąĖą▒ą║ąĖ ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖčÅ ą░ą┤čĆąĄčüą░ ą┐čĆąĖ ą┤ąŠčüčéčāą┐ąĄ ą║ ą┐ą░ą╝čÅčéąĖ (misalignment detector).

ŌĆó ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą▓čüčéčĆąŠąĄąĮąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ FLASH (Embedded Flash Controller, EFC).

ą¤ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčéčüčÅ, čćč鹊 ą▓čüąĄ ą┤ą░ąĮąĮčŗąĄ čģčĆą░ąĮčÅčéčüčÅ ą▓ ą┐ą░ą╝čÅčéąĖ ą▓ č乊čĆą╝ą░č鹥 little-endian. MC ąĖ ą▓čüąĄ ą╝ą░čüč鹥čĆą░ čłąĖąĮčŗ čĆą░ą▒ąŠčéą░čÄčé č鹊ą╗čīą║ąŠ ą▓ č乊čĆą╝ą░č鹥 ą┤ą░ąĮąĮčŗčģ little-endian [3].

ąÉčĆą▒ąĖčéčĆ čłąĖąĮčŗ. ąÆ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą┐ą░ą╝čÅčéąĖ MC ą▓čüčéčĆąŠąĄąĮ ą┐čĆąŠčüč鹊ą╣ ą░ą┐ą┐ą░čĆą░čéąĮčŗą╣ (ąĮąĄ ąĮą░čüčéčĆą░ąĖą▓ą░ąĄą╝čŗą╣) ą░čĆą▒ąĖčéčĆ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą▓ ą┤ąŠčüčéčāą┐ą░ ą┐ąŠ čłąĖąĮąĄ, ą║ąŠč鹊čĆčŗą╣ ą┤ą░ąĄčé ą┤ąŠčüčéčāą┐ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čłąĖąĮąŠą╣ ąŠą┤ąĮąŠą╝čā ąĖąĘ čéčĆąĄčģ ą│ą╗ą░ą▓ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ (ą╝ą░čüč鹥čĆ). ąŻ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ čüąĄčéąĖ EMAC čüą░ą╝čŗą╣ ą▓čŗčüąŠą║ąĖą╣ ą┐čĆąĖąŠčĆąĖč鹥čé, ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ DMA ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ąĖą╝ąĄąĄčé čüčĆąĄą┤ąĮąĖą╣ ą┐čĆąĖąŠčĆąĖč鹥čé, ąĖ čÅą┤čĆąŠ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ARM (ARM7TDMI) ąĖą╝ąĄąĄčé čüą░ą╝čŗą╣ ąĮąĖąĘą║ąĖą╣ ą┐čĆąĖąŠčĆąĖč鹥čé.

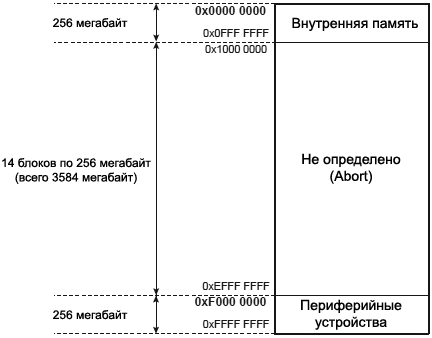

ąöąĄą║ąŠą┤ąĄčĆ ą░ą┤čĆąĄčüą░. ąÆ MC ą▓čüčéčĆąŠąĄąĮ ą┤ąĄą║ąŠą┤ąĄčĆ ą░ą┤čĆąĄčüą░, ą║ąŠč鹊čĆčŗą╣ ą▓ ą┐ąĄčĆą▓čāčÄ ąŠč湥čĆąĄą┤čī ą┤ąĄą║ąŠą┤ąĖčĆčāąĄčé 4 čüčéą░čĆčłąĖčģ ą▒ąĖčéą░ 32-ą▒ąĖčéąĮąŠą╣ čłąĖąĮčŗ ą░ą┤čĆąĄčüą░, ąĖ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé 3 čĆą░ąĘą┤ąĄą╗čīąĮčŗąĄ ąŠą▒ą╗ą░čüčéąĖ ą┐ą░ą╝čÅčéąĖ:

ŌĆó ą×ą┤ąĮąŠ 256-ą╝ąĄą│ą░ą▒ą░ą╣čéąĮąŠąĄ ą░ą┤čĆąĄčüąĮąŠąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ ą┤ą╗čÅ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ.

ŌĆó ą×ą┤ąĮąŠ 256-ą╝ąĄą│ą░ą▒ą░ą╣čéąĮąŠąĄ ą░ą┤čĆąĄčüąĮąŠąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ ą┤ą╗čÅ ą▓čüčéčĆąŠąĄąĮąĮčŗčģ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓.

ŌĆó ąØąĄąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠąĄ ą░ą┤čĆąĄčüąĮąŠąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ čĆą░ąĘą╝ąĄčĆąŠą╝ 3584 ą╝ąĄą│ą░ą▒ą░ą╣čé, čüąŠčüč鹊čÅčēąĄąĄ ąĖčģ 14 ąŠą▒ą╗ą░čüč鹥ą╣ ą┐ą░ą╝čÅčéąĖ ą┐ąŠ 256 ą╝ąĄą│ą░ą▒ą░ą╣čé. ą¤čĆąĖ ą┤ąŠčüčéčāą┐ąĄ ą▓ ąĮąĄąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠąĄ ą░ą┤čĆąĄčüąĮąŠąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ ą▒čāą┤ąĄčé ą▓ąŠąĘą▓čĆą░čēąĄąĮ čüčéą░čéčāčü Abort (ąŠą▒čĆčŗą▓ ąŠą┐ąĄčĆą░čåąĖąĖ ą┤ąŠčüčéčāą┐ą░).

ąĀąĖčü. 18-2. ą×ą▒ą╗ą░čüčéąĖ ą┐ą░ą╝čÅčéąĖ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ARM7.

ąĀą░čüą┐čĆąĄą┤ąĄą╗ąĄąĮąĖąĄ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ ą░ą┤čĆąĄčüąĮąŠą│ąŠ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ą░. ąÆ ą┐čĆąĄą┤ąĄą╗ą░čģ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ ą░ą┤čĆąĄčüąĮąŠą│ąŠ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ą░ ą┤ąĄą║ąŠą┤ąĄčĆ ą░ą┤čĆąĄčüą░ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ MC ą┤ąĄą║ąŠą┤ąĖčĆčāąĄčé ąĄčēąĄ 8 ą▒ąĖčé ą░ą┤čĆąĄčüą░, ą▓čŗą┤ąĄą╗čÅčÅ ąŠą▒ą╗ą░čüčéąĖ čĆą░ąĘą╝ąĄčĆąŠą╝ 1 ą╝ąĄą│ą░ą▒ą░ą╣čé ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĖčģ ą▒ą╗ąŠą║ą░čģ ą┐ą░ą╝čÅčéąĖ ą┐ąŠ 256 ą╝ąĄą│ą░ą▒ą░ą╣čé.

ąÜąŠ ą▓čüąĄą╝ ą▓čŗą┤ąĄą╗ąĄąĮąĮčŗą╝ ąŠą▒ą╗ą░čüčéčÅą╝ ą┐ą░ą╝čÅčéąĖ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą┤ąŠčüčéčāą┐ ą▓ ą┐čĆąĄą┤ąĄą╗ą░čģ 1-ą╝ąĄą│ą░ą▒ą░ą╣čéąĮąŠą│ąŠ ą░ą┤čĆąĄčüąĮąŠą│ąŠ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ą░, ą┐ąŠą▓č鹊čĆčÅčÄčēąĄą│ąŠčüčÅ n čĆą░ąĘ ą▓ čŹč鹊ą╝ ą░ą┤čĆąĄčüąĮąŠą╝ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąĄ, n ą▓čŗčćąĖčüą╗čÅąĄčéčüčÅ ą║ą░ą║ čĆą░ąĘą╝ąĄčĆ ą┐ą░ą╝čÅčéąĖ, ą┐ąŠą┤ąĄą╗ąĄąĮąĮčŗą╣ ąĮą░ 1 ą╝ąĄą│ą░ą▒ą░ą╣čé.

ąÜąŠą│ą┤ą░ ą░ą┤čĆąĄčü ą┤ąŠčüčéčāą┐ą░ ą┐ąŠą┐ą░ą┤ą░ąĄčé ą▓ ąĮąĄąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčāčÄ ąŠą▒ą╗ą░čüčéčī ą┐ą░ą╝čÅčéąĖ, ą┤ąĄą║ąŠą┤ąĄčĆ ą░ą┤čĆąĄčüą░ ą▓ąŠąĘą▓čĆą░čéąĖčé Abort ą╝ą░čüč鹥čĆčā.

ąĀąĖčü. 18-3. ąĀą░čüą┐čĆąĄą┤ąĄą╗ąĄąĮąĖąĄ ą░ą┤čĆąĄčüąŠą▓ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ.

ąÆąĮčāčéčĆąĄąĮąĮčÅčÅ ąŠą▒ą╗ą░čüčéčī ą┐ą░ą╝čÅčéąĖ 0. ą¤ąĄčĆą▓čŗąĄ 32 ą▒ą░ą╣čéą░ čŹč鹊ą╣ ąŠą▒ą╗ą░čüčéąĖ čüąŠą┤ąĄčƹȹ░čé ą░ą┤čĆąĄčüą░ ąĖčüą║ą╗čÄč湥ąĮąĖą╣ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ARM (exception vectors). ąÆ č湥čüčéąĮąŠčüčéąĖ, ąĘą┤ąĄčüčī ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ąĄą║č鹊čĆ čüą▒čĆąŠčüą░ ąĮą░ ą░ą┤čĆąĄčü 0x0 (Reset Vector).

ą¤ąĄčĆąĄą┤ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄą╝ ą║ąŠą╝ą░ąĮą┤čŗ remap ą▓čüčéčĆąŠąĄąĮąĮą░čÅ ą┐ą░ą╝čÅčéčī FLASH ąŠč鹊ą▒čĆą░ąČą░ąĄčéčüčÅ ąĮą░ ą▓ąĮčāčéčĆąĄąĮąĮčÄčÄ ąŠą▒ą╗ą░čüčéčī ą┐ą░ą╝čÅčéąĖ 0, čéą░ą║ čćč鹊 čÅą┤čĆąŠ ARM7TDMI ą▓čŗą▒ąĖčĆą░ąĄčé ąĖąĮčüčéčĆčāą║čåąĖčÄ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ, čüąŠą┤ąĄčƹȹ░čēčāčÄčüčÅ ą▓ ą┐ą░ą╝čÅčéąĖ FLASH. ą¤ąŠčüą╗ąĄ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą║ąŠą╝ą░ąĮą┤čŗ remap ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ ą┐ą░ą╝čÅčéčī SRAM, ąĮą░čģąŠą┤čÅčēą░čÅčüčÅ ą┐ąŠ ą░ą┤čĆąĄčüčā 0x00200000, ąŠč鹊ą▒čĆą░ąČą░ąĄčéčüčÅ ąĮą░ ą▓ąĮčāčéčĆąĄąĮąĮčÄčÄ ąŠą▒ą╗ą░čüčéčī ą┐ą░ą╝čÅčéąĖ 0. ą¤ą░ą╝čÅčéčī, ąŠč鹊ą▒čĆą░ąČąĄąĮąĮą░čÅ ąĮą░ ą▓ąĮčāčéčĆąĄąĮąĮčÄčÄ ąŠą▒ą╗ą░čüčéčī ą┐ą░ą╝čÅčéąĖ 0, ą┤ąŠčüčéčāą┐ąĮą░ ą║ą░ą║ ą┐ąŠ čüą▓ąŠąĄą╝čā ąŠčĆąĖą│ąĖąĮą░ą╗čīąĮąŠą╝čā ą░ą┤čĆąĄčüčā čĆą░ąĘą╝ąĄčēąĄąĮąĖčÅ, čéą░ą║ ąĖ ą┐ąŠ ą░ą┤čĆąĄčüčā 0x0.

ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą▓čŗą┐ąŠą╗ąĮąĄąĮą░ ą║ąŠą╝ą░ąĮą┤ą░ Remap, ą║ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ SRAM ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą┤ąŠčüčéčāą┐ č湥čĆąĄąĘ ą▓ąĮčāčéčĆąĄąĮąĮčÄčÄ ąŠą▒ą╗ą░čüčéčī ą┐ą░ą╝čÅčéąĖ 0.

ąóą░ą║ ą║ą░ą║ ą▓ąĄą║č鹊čĆčŗ ąĖčüą║ą╗čÄč湥ąĮąĖą╣ ARM (Reset, Abort, Data Abort, Prefetch Abort, Undefined Instruction, Interrupt, ąĖ Fast Interrupt) ą┐čĆąĖą▓čÅąĘčŗą▓ą░čÄčéčüčÅ ąŠčé ą░ą┤čĆąĄčüą░ 0x0 ą┤ąŠ ą░ą┤čĆąĄčüą░ 0x20, ą║ąŠą╝ą░ąĮą┤ą░ Remap ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÄ ą┤ąĖąĮą░ą╝ąĖč湥čüą║ąĖ ą┐ąĄčĆąĄąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī čŹčéąĖ ą▓ąĄą║č鹊čĆčŗ ą┐ąŠą┤ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖčÅ.

ąÜąŠą╝ą░ąĮą┤ą░ Remap ą┤ąŠčüčéčāą┐ąĮą░ č湥čĆąĄąĘ ąĖąĮč鹥čĆč乥ą╣čü ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ ą┤ą╗čÅ MC ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ ą▓ ą╗ąŠą│. 1 ą┐ąŠą╗čÅ RCB čĆąĄą│ąĖčüčéčĆą░ MC_RCR (Remap Control Register).

ąöąĄą╣čüčéą▓ąĖąĄ ą║ąŠą╝ą░ąĮą┤čŗ Remap ą╝ąŠąČąĮąŠ ąŠčéą╝ąĄąĮąĖčéčī ą┐ąŠą▓č鹊čĆąĮąŠą╣ ąĘą░ą┐ąĖčüčīčÄ ą▓ 1 ą┐ąŠą╗čÅ RCB čĆąĄą│ąĖčüčéčĆą░ MC_RCR (čé. ąĄ. ą║ąŠą╝ą░ąĮą┤ą░ Remap čĆą░ą▒ąŠčéą░ąĄčé ą┐ąŠ ą┐čĆąĖąĮčåąĖą┐čā čéčĆąĖą│ą│ąĄčĆą░). ąŁč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐čĆąŠčēąĄ ąŠčéą╗ą░ąČąĖą▓ą░čéčī ąŠą┐čĆąĄą┤ąĄą╗čÅąĄą╝čāčÄ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╝ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ąĘą░ą│čĆčāąĘą║ąĖ (boot sequence), čéą░ą║ ą║ą░ą║ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮ ą┐čĆąŠčüč鹊ą╣ čüą┐ąŠčüąŠą▒ ą┐ąĄčĆąĄą▓ąĄčüčéąĖ čćąĖą┐ ą▓ čéčā ąČąĄ čüą░ą╝čāčÄ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÄ, ą║ąŠč鹊čĆą░čÅ ą▒čŗą╗ą░ čüčĆą░ąĘčā ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░.

ąĪčéą░čéčāčü Abort. ąĢčüčéčī 2 ą┐čĆąĖčćąĖąĮčŗ, ą┐ąŠ ą║ąŠč鹊čĆčŗą╝ ą╝ąŠąČąĄčé ą┐čĆąŠąĖąĘąŠą╣čéąĖ ąŠą▒čĆčŗą▓ ąŠą┐ąĄčĆą░čåąĖąĖ ą┤ąŠčüčéčāą┐ą░ ą║ ą┐ą░ą╝čÅčéąĖ (abort):

ŌĆó ą¤ąŠą┐čŗčéą║ą░ ą┤ąŠčüčéčāą┐ą░ ą┐ąŠ ą░ą┤čĆąĄčüčā, čāą║ą░ąĘčŗą▓ą░čÄčēąĄą╝čā ąĮą░ ąĮąĄąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčāčÄ ąŠą▒ą╗ą░čüčéčī ą┐ą░ą╝čÅčéąĖ.

ŌĆó ą¤ąŠą┐čŗčéą║ą░ ą┤ąŠčüčéčāą┐ą░ ą┐ąŠ ąĮąĄą▓čŗčĆąŠą▓ąĮąĄąĮąĮąŠą╝čā ą░ą┤čĆąĄčüčā.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĮąĄą▓čŗčĆąŠą▓ąĮąĄąĮąĮčŗą╣ ą░ą┤čĆąĄčü čŹč鹊 čéą░ą║ąŠą╣ ą▒ą░ą╣č鹊ą▓čŗą╣ ą░ą┤čĆąĄčü ą┐ą░ą╝čÅčéąĖ, ą║ąŠč鹊čĆčŗą╣ ąĮąĄ čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé čéąĖą┐čā ą┤ąŠčüčéčāą┐ą░ ą║ ą┐ą░ą╝čÅčéąĖ (čé. ąĄ. ąĮąĄ ą┤ąĄą╗ąĖčéčüčÅ ąĮą░čåąĄą╗ąŠ ąĮą░ 2 ąĖą╗ąĖ ąĮą░ 4). ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. ąĮąĖąČąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ ą┤ąĄč鹥ą║č鹊čĆą░ ąŠčłąĖą▒ą║ąĖ ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖčÅ.

ąÜąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé abort, ą▓čüąĄą╝ ą╝ą░čüč鹥čĆą░ą╝ čłąĖąĮčŗ ąŠą▒čĆą░čéąĮąŠ ąŠčéą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ čüąĖą│ąĮą░ą╗, ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé č鹊ą│ąŠ, ą║ą░ą║ąŠą╣ ąĖąĘ čŹčéąĖčģ ą╝ą░čüč鹥čĆąŠą▓ ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ą╗ ą┤ąŠčüčéčāą┐. ą×ą┤ąĮą░ą║ąŠ č鹊ą╗čīą║ąŠ čÅą┤čĆąŠ ARM7TDMI ą╝ąŠąČąĄčé čāč湥čüčéčī čüąĖą│ąĮą░ą╗ abort, ąĖ č鹊ą╗čīą║ąŠ ą┐čĆąĖ čāčüą╗ąŠą▓ąĖąĖ, čćč鹊 ąŠąĮąŠ ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ą╗ąŠ ą┤ąŠčüčéčāą┐. ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ DMA ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ąĖ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ EMAC ąĮąĄ ą╝ąŠą│čāčé ąŠą▒čĆą░ą▒ąŠčéą░čéčī ą▓čģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ abort. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ ą╗ąŠą│ąĖč湥čüą║ąĖąĄ čüąŠąĄą┤ąĖąĮąĄąĮąĖčÅ ąŠčéčüčāčéčüčéą▓čāčÄčé ąĮą░ čĆąĖčü. 18-1.

ą¦č鹊ą▒čŗ čāą┐čĆąŠčüčéąĖčéčī ąŠčéą╗ą░ą┤ą║čā ąĖą╗ąĖ ą░ąĮą░ą╗ąĖąĘ ąŠčéą║ą░ąĘą░ ąŠą┐ąĄčĆą░čåąĖąŠąĮąĮąŠą╣ čüąĖčüč鹥ą╝čŗ, ą▓ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ MC ąĖąĮč鹥ą│čĆąĖčĆąŠą▓ą░ąĮ čĆąĄą│ąĖčüčéčĆ čüčéą░čéčāčüą░ Abort (MC_ASR) ąĖ čĆąĄą│ąĖčüčéčĆ ą░ą┤čĆąĄčüą░ Abort (MC_AASR).

ą¤ąŠą╗ąĮčŗą╣ 32-čĆą░ąĘčĆčÅą┤ąĮčŗą╣ ą░ą┤čĆąĄčü, ą║ąŠč鹊čĆčŗą╣ ą▓čŗąĘą▓ą░ą╗ abort, čüąŠčģčĆą░ąĮčÅąĄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ MC_AASR. ą¤ą░čĆą░ą╝ąĄčéčĆčŗ ą┤ąŠčüčéčāą┐ą░ čüąŠčģčĆą░ąĮčÅčÄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ MC_ASR, čćč鹊 ą▓ą║ą╗čÄčćą░ąĄčé:

ŌĆó ąĀą░ąĘą╝ąĄčĆ ąĘą░ą┐čĆąŠčüą░ (ą┐ąŠą╗ąĄ ABTSZ).

ŌĆó ąóąĖą┐ ą┤ąŠčüčéčāą┐ą░ - ą╗ąĖą▒ąŠ čćč鹥ąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ, ą╗ąĖą▒ąŠ ąĘą░ą┐ąĖčüčī, ą╗ąĖą▒ąŠ ą▓čŗą▒ąŠčĆą║ą░ ąĖąĮčüčéčĆčāą║čåąĖąĖ ą║ąŠą┤ą░ (ą┐ąŠą╗ąĄ ABTTYP).

ŌĆó ążą╗ą░ąČą║ąĖ, ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčēąĖąĄ ą┐čĆąĖčćąĖąĮčā abort - ą╗ąĖą▒ąŠ ąĖąĘ-ąĘą░ ą┤ąŠčüčéčāą┐ą░ ą║ ąĮąĄąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą╣ ąŠą▒ą╗ą░čüčéąĖ (ą▒ąĖčé UNDADD), ą╗ąĖą▒ąŠ ąĖąĘ-ąĘą░ ąĮąĄą▓čŗčĆąŠą▓ąĮąĄąĮąĮąŠą│ąŠ ą┤ąŠčüčéčāą┐ą░ (ą▒ąĖčé MISADD).

ŌĆó ąśčüč鹊čćąĮąĖą║, ą║ąŠč鹊čĆčŗą╣ ą▓čŗąĘą▓ą░ą╗ ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ abort (ą▒ąĖčéčŗ MST_EMAC, MST_PDC ąĖ MST_ARM).

ŌĆó ą¤čĆąŠąĖąĘąŠčłąĄą╗ ą╗ąĖ abort ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą╝ą░čüč鹥čĆ, ąĮą░čćąĖąĮą░čÅ čü ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čćč鹥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ (ą▒ąĖčéčŗ SVMST_EMAC, SVMST_PDC ąĖ SVMST_ARM), ąĘą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ ąĖąĮč乊čĆą╝ą░čåąĖąĖ, ąĘą░ą│čĆčāąČąĄąĮąĮąŠą╣ ą▓ ą▒ąĖčéčŗ MST.

ąÆ čüą╗čāčćą░ąĄ, ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖąĘąŠčłąĄą╗ Data Abort (ąŠą▒čĆčŗą▓ ą┤ąŠčüčéčāą┐ą░ ą║ ą┤ą░ąĮąĮčŗą╝) ąŠčé ą┐čĆąŠčåąĄčüčüąŠčĆą░, ą▒čāą┤ąĄčé čüąŠčģčĆą░ąĮąĄąĮ ą░ą┤čĆąĄčü ą┤ąŠčüčéčāą┐ą░. ąŁč鹊 ą┐ąŠą╗ąĄąĘąĮąŠ, ą┐ąŠčüą║ąŠą╗čīą║čā ą┐ąŠąĖčüą║ ąĖąĮčüčéčĆčāą║čåąĖąĖ, ą║ąŠč鹊čĆą░čÅ ą▓čŗąĘą▓ą░ą╗ą░ abort, ą┐ąŠčéčĆąĄą▒čāąĄčé ą┤ąĖąĘą░čüčüąĄą╝ą▒ą╗ąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖąĮčüčéčĆčāą║čåąĖą╣ ąĖ ą┐ąŠą╗ąĮąŠą│ąŠ ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮąĖčÅ ąŠ ą║ąŠąĮč鹥ą║čüč鹥 ą┐čĆąŠčåąĄčüčüąŠčĆą░.

ąÆ čüą╗čāčćą░ąĄ Prefetch Abort (ąŠą▒čĆčŗą▓ ą▓čŗą▒ąŠčĆą║ąĖ ąĖąĮčüčéčĆčāą║čåąĖąĖ) ą░ą┤čĆąĄčü ą╝ąŠąČąĄčé ąĖąĘą╝ąĄąĮąĖčéčīčüčÅ, ą┐ąŠčüą║ąŠą╗čīą║čā ą░ą┤čĆąĄčü ą▓čŗą▒ąŠčĆą║ąĖ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčéčüčÅ ą║ąŠąĮą▓ąĄą╣ąĄčĆąŠą╝ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ARM. ą¤čĆąŠčåąĄčüčüąŠčĆ ARM čāčćąĖčéčŗą▓ą░ąĄčé prefetch abort č鹊ą╗čīą║ąŠ ąĄčüą╗ąĖ ą▓čŗą┐ąŠą╗ąĮčÅą╗ą░čüčī ąĖąĮčüčéčĆčāą║čåąĖčÅ čćč鹥ąĮąĖčÅ, ąĖ ą▓ąŠąĘą╝ąŠąČąĮąŠ, čćč鹊 ą▓ čŹč鹊 ą▓čĆąĄą╝čÅ ą┐čĆąŠąĖąĘąŠčłą╗ąŠ ąĮąĄčüą║ąŠą╗čīą║ąŠ ąŠą▒čĆčŗą▓ąŠą▓ ą┤ąŠčüčéčāą┐ą░. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝ ą┤ą╗čÅ čéą░ą║ąŠą│ąŠ čüą╗čāčćą░čÅ ą┐čĆąĄą┤ą┐ąŠčćčéąĖč鹥ą╗čīąĮąĄąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ čĆąĄą│ąĖčüčéčĆą░ čüą▓čÅąĘąĖ ąŠą▒čĆčŗą▓ą░ ąŠą┐ąĄčĆą░čåąĖąĖ (Abort Link register) ą┐čĆąŠčåąĄčüčüąŠčĆą░ ARM.

ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ EFC. Embedded Flash Controller (EFC) ą▓čüčéčĆąŠąĄąĮ ą▓ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ MC ą┤ą╗čÅ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖčÅ ąĖąĮč鹥čĆč乥ą╣čüą░ ą║ ą▒ą╗ąŠą║ą░ą╝ ą┐ą░ą╝čÅčéąĖ FLASH č湥čĆąĄąĘ ą▓ąĮčāčéčĆąĄąĮąĮčÄčÄ 32-ą▒ąĖčéąĮčāčÄ čłąĖąĮčā. ąŁč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐ąŠą▓čŗčüąĖčéčī ą▒čŗčüčéčĆąŠą┤ąĄą╣čüčéą▓ąĖąĄ ą┐čĆąĖ ą▓čŗą▒ąŠčĆą║ąĄ ą║ąŠą┤ą░ ą▓ čĆąĄąČąĖą╝ąĄ Thumb čü čüąĖčüč鹥ą╝ąŠą╣ 32-ą▒ąĖčéąĮčŗčģ ą▒čāč乥čĆąŠą▓. EFC čéą░ą║ąČąĄ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ąĮą░ą▒ąŠčĆ ą║ąŠą╝ą░ąĮą┤ ą┤ą╗čÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ, čüčéąĖčĆą░ąĮąĖčÅ, ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ ąĮą░ ąĘą░ą┐ąĖčüčī ąĖ čĆą░ąĘą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ čüąŠą┤ąĄčƹȹĖą╝ąŠą│ąŠ ą▓čüčéčĆąŠąĄąĮąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ FLASH.

ąöąĄč鹥ą║č鹊čĆ ąŠčłąĖą▒ą║ąĖ ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖčÅ. ąÆ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąĄ MC ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮ ą┤ąĄč鹥ą║č鹊čĆ ąŠčłąĖą▒ą║ąĖ ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖčÅ ą░ą┤čĆąĄčüą░ ą┤ąŠčüčéčāą┐ą░, ą║ąŠč鹊čĆčŗą╣ ą┐čĆąŠą▓ąĄčĆčÅąĄčé čåąĄą╗ąŠčüčéąĮąŠčüčéčī ą░ą┤čĆąĄčüą░ ą┤ąŠčüčéčāą┐ą░.

ąöą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą┤ąŠčüčéčāą┐ą░, ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé č鹊ą│ąŠ, ą║ą░ą║ąŠą╣ ąĖąĘ ą╝ą░čüč鹥čĆąŠą▓ ąĄą│ąŠ ą┐čĆąŠąĖąĘą▓ąĄą╗, ą┐čĆąŠą▓ąĄčĆčÅąĄčéčüčÅ čĆą░ąĘą╝ąĄčĆ ą┤ąŠčüčéčāą┐ą░ ąĖ ą▒ąĖčéčŗ ą░ą┤čĆąĄčüą░ 0 ąĖ 1. ąĢčüą╗ąĖ ą▒čŗą╗ čéąĖą┐ ą┤ąŠčüčéčāą┐ą░ ą║ čüą╗ąŠą▓čā (32-ą▒ąĖčéąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ) ąĖ ą▒ąĖčéčŗ 0 ąĖ 1 ą░ą┤čĆąĄčüą░ ąĮąĄ čĆą░ą▓ąĮčŗ 0 (čé. ąĄ. ą░ą┤čĆąĄčü ąĮąĄ ą┤ąĄą╗ąĖčéčüčÅ ąĮą░čåąĄą╗ąŠ ąĮą░ 4), č鹊 ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ąŠčłąĖą▒ą║ą░ ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖčÅ ą░ą┤čĆąĄčüą░. ą¤ąŠą┤ąŠą▒ąĮčŗą╝ ąŠą▒čĆą░ąĘąŠą╝, ąĄčüą╗ąĖ čéąĖą┐ ą┤ąŠčüčéčāą┐ą░ ą▒čŗą╗ ą║ ą┐ąŠą╗ąŠą▓ąĖąĮąĄ čüą╗ąŠą▓ą░ (16-ą▒ąĖčéąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ), ąĖ ą┐čĆąĖ čŹč鹊ą╝ ą▒ąĖčé 0 ą░ą┤čĆąĄčüą░ ąĮąĄ čĆą░ą▓ąĄąĮ 0, č鹊 čéą░ą║ąČąĄ ą┤ąĄč鹥ą║čéąĖčĆčāąĄčéčüčÅ ąĮąĄą▓čŗčĆąŠą▓ąĮąĄąĮąĮčŗą╣ ą┤ąŠčüčéčāą┐ ą║ ą┐ą░ą╝čÅčéąĖ. ąÆ ąŠą▒ąŠąĖčģ čéą░ą║ąĖčģ čüą╗čāčćą░čÅčģ ą╝ą░čüč鹥čĆčā ą▒čāą┤ąĄčé ą▓ąŠąĘą▓čĆą░čēąĄąĮ čüčéą░čéčāčü abort, ąĖ ą┤ąŠčüčéčāą┐ ą║ ą┐ą░ą╝čÅčéąĖ ąŠčéą╝ąĄąĮčÅąĄčéčüčÅ. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ą┤ąŠčüčéčāą┐čŗ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ARM, ą║ąŠą│ą┤ą░ ąŠąĮ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖčé ą▓čŗą▒ąŠčĆą║čā ąĖąĮčüčéčĆčāą║čåąĖą╣, ąĮąĄ ą┐čĆąŠą▓ąĄčĆčÅčÄčéčüčÅ.

ą×čłąĖą▒ą║ą░ ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖčÅ ą░ą┤čĆąĄčüą░ ąŠą▒čŗčćąĮąŠ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ąĖąĘ-ąĘą░ ą▒ą░ą│ąŠą▓ ą▓ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą╝ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖąĖ, ą║ąŠą│ą┤ą░ ąĮąĄą┐čĆą░ą▓ąĖą╗čīąĮąŠ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░čÄčéčüčÅ čāą║ą░ąĘą░č鹥ą╗ąĖ. ąóą░ą║ąĖąĄ ąŠčłąĖą▒ą║ąĖ ąĖąĮąŠą│ą┤ą░ čüą╗ąŠąČąĮąŠ ąŠčéą╗ąŠą▓ąĖčéčī ą┐čĆąĖ ąŠčéą╗ą░ą┤ą║ąĄ.

ąŚą░ą┐čĆąŠčłąĄąĮąĮčŗą╣ ą░ą┤čĆąĄčü čüąŠčģčĆą░ąĮčÅąĄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüčéą░čéčāčüą░ Abort Status Register, ąĖ ą░ą┤čĆąĄčü ąĖąĮčüčéčĆčāą║čåąĖąĖ, ą║ąŠč鹊čĆą░čÅ ą▓čŗąĘą▓ą░ą╗ą░ ąŠčłąĖą▒ą║čā ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖčÅ, čüąŠčģčĆą░ąĮčÅąĄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüą▓čÅąĘąĖ ąŠą▒čĆčŗą▓ą░ ąŠą┐ąĄčĆą░čåąĖąĖ ą┐čĆąŠčåąĄčüčüąŠčĆą░ (Abort Link Register), čćč鹊 čāą┐čĆąŠčēą░ąĄčé ą┐ąŠąĖčüą║ ąĖ ąĖčüą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čéą░ą║ąŠą│ąŠ čĆąŠą┤ą░ ąŠčłąĖą▒ąŠą║ ą▓ ą┐čĆąŠą│čĆą░ą╝ą╝ąĄ.

[ąśąĮč鹥čĆč乥ą╣čü ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ MC]

ąÆ čéą░ą▒ą╗ąĖčåąĄ ą┐ąŠą║ą░ąĘą░ąĮ ąŠą▒čēąĖą╣ čüą┐ąĖčüąŠą║ ą▓čüąĄčģ čĆąĄą│ąĖčüčéčĆąŠą▓, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗčģ ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ ą║ MC. ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüąŠą▓ čĆąĄą│ąĖčüčéčĆąŠą▓ ąŠčéčüčćąĖčéčŗą▓ą░ąĄčéčüčÅ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ą░ą┤čĆąĄčüą░ 0xFFFFFF00.

ąóą░ą▒ą╗ąĖčåą░ 18-1. ąĀąĄą│ąĖčüčéčĆčŗ MC.

| ąĪą╝ąĄčēąĄąĮąĖąĄ |

ąĀąĄą│ąĖčüčéčĆ |

ąśą╝čÅ |

ąöąŠčüčéčāą┐ |

ąĪą▒čĆąŠčü |

| 0x0000 |

MC Remap Control Register (čĆąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐čĆąĖą▓čÅąĘą║ąŠą╣ ą┐ą░ą╝čÅčéąĖ) |

MC_RCR |

W |

- |

| 0x0004 |

MC Abort Status Register (čĆąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ ąŠą▒čĆčŗą▓ą░ ąŠą┐ąĄčĆą░čåąĖąĖ) |

MC_ASR |

R |

0x00000000 |

| 0x0008 |

MC Abort Address Status Register (čĆąĄą│ąĖčüčéčĆ ą░ą┤čĆąĄčüą░ čüąŠčüč鹊čÅąĮąĖčÅ ąŠą▒čĆčŗą▓ą░ ąŠą┐ąĄčĆą░čåąĖąĖ) |

MC_AASR |

R |

0x00000000 |

| 0x0010..0x005C |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

|

|

|

| 0x0060 |

ąĀąĄą│ąĖčüčéčĆčŗ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ EFC0 |

ąĪą╝. ąŠą┐ąĖčüą░ąĮąĖąĄ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ EFC [2]. |

| 0x0070 |

ąĀąĄą│ąĖčüčéčĆčŗ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ EFC1* |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ *: EFC1 ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮ č鹊ą╗čīą║ąŠ ą▓ ą┐čĆąŠčåąĄčüčüąŠčĆąĄ AT91SAM7X512.

ąĀąĄą│ąĖčüčéčĆ ą┤ą╗čÅ ą▓čŗą┤ą░čćąĖ ą║ąŠą╝ą░ąĮą┤čŗ Remap (MC Remap Control Register). ąĀą░ą▒ąŠčéą░ąĄčé č鹊ą╗čīą║ąŠ ąĮą░ ąĘą░ą┐ąĖčüčī.

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| - |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| - |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

RCB |

RCB: Remap Command Bit, ą▒ąĖčé ą║ąŠą╝ą░ąĮą┤čŗ Remap.

0: ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ ą▓ą╗ąĖčÅąĮąĖčÅ.

1: ąĘą░ą┐ąĖčüčī ąĄą┤ąĖąĮąĖčåčŗ ą▓ čŹč鹊čé ą║ąŠą╝ą░ąĮą┤ąĮčŗą╣ ą▒ąĖčé čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ čéčĆąĖą│ą│ąĄčĆ, ą┐ąŠą┤ą║ą╗čÄčćą░čÅ ą┐čĆąĖą▓čÅąĘą║čā ą║ ą░ą┤čĆąĄčüčā 0x0 ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ ąŠą┐ąĄčĆą░čéąĖą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ ą┐ąŠ ą░ą┤čĆąĄčüčā 0x00200000 ąĖ ąŠčéą╝ąĄąĮčÅčÅ čŹčéčā ą┐čĆąĖą▓čÅąĘą║čā.

ąĀąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ ąŠą▒čĆčŗą▓ą░ ąŠą┐ąĄčĆą░čåąĖąĖ ą┤ąŠčüčéčāą┐ą░ (MC Abort Status Register). ąĀą░ą▒ąŠčéą░ąĄčé č鹊ą╗čīą║ąŠ ąĮą░ čćč鹥ąĮąĖąĄ.

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| - |

- |

- |

- |

- |

SVMST_ARM |

SVMST_PDC |

SVMST_EMAC |

- |

- |

- |

- |

- |

MST_ARM |

MST_PDC |

MST_EMAC |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| - |

- |

- |

- |

ABTTYP |

ABTSZ |

- |

- |

- |

- |

- |

- |

MISADD |

UNDADD |

UNDADD: Undefined Address Abort Status, čüąŠčüč鹊čÅąĮąĖąĄ ąŠą▒čĆčŗą▓ą░ ąŠą┐ąĄčĆą░čåąĖąĖ ą┐čĆąĖ ą┤ąŠčüčéčāą┐ąĄ ą┐ąŠ ąĮąĄąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą╝čā ą░ą┤čĆąĄčüčā.

0: ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ąŠą▒čĆčŗą▓ ąŠą┐ąĄčĆą░čåąĖąĖ (abort) ąĮąĄ ą▒čŗą╗ ąĖąĘ-ąĘą░ ą┤ąŠčüčéčāą┐ą░ ą║ ąĮąĄąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą╝čā ą░ą┤čĆąĄčüčā ą▓ ą░ą┤čĆąĄčüąĮąŠą╝ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąĄ.

1: ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ąŠą▒čĆčŗą▓ ąŠą┐ąĄčĆą░čåąĖąĖ ą┤ąŠčüčéčāą┐ą░ ą┐čĆąŠąĖąĘąŠčłąĄą╗ ąĖąĘ-ąĘą░ ą┐ąŠą┐čŗčéą║ąĖ ąŠą▒čĆą░čēąĄąĮąĖčÅ ą┐ąŠ ąĮąĄąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą╝čā ą░ą┤čĆąĄčüčā.

MISADD: Misaligned Address Abort Status, čüąŠčüč鹊čÅąĮąĖąĄ ąŠą▒čĆčŗą▓ą░ ąŠą┐ąĄčĆą░čåąĖąĖ ąĖąĘ-ąĘą░ ąĮąĄą▓čŗčĆąŠą▓ąĮąĄąĮąĮąŠą│ąŠ ą┤ąŠčüčéčāą┐ą░.

0: ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ąŠą▒čĆčŗą▓ ąŠą┐ąĄčĆą░čåąĖąĖ (abort) ąĮąĄ ą▒čŗą╗ ąĖąĘ-ąĘą░ ą┐ąŠą┐čŗčéą║ąĖ ą┤ąŠčüčéčāą┐ą░ ą┐ąŠ ąĮąĄą▓čŗą▓čĆąŠą▓ą░ąĮąĄąĮąĮąŠą╝čā ą░ą┤čĆąĄčüčā.

1: ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ąŠą▒čĆčŗą▓ ąŠą┐ąĄčĆą░čåąĖąĖ ą┤ąŠčüčéčāą┐ą░ ą┐čĆąŠąĖąĘąŠčłąĄą╗ ą▒čŗą╗ ąĖąĘ-ąĘą░ ą┐ąŠą┐čŗčéą║ąĖ ą┤ąŠčüčéčāą┐ą░ ą┐ąŠ ąĮąĄą▓čŗą▓čĆąŠą▓ą░ąĮąĄąĮąĮąŠą╝čā ą░ą┤čĆąĄčüčā.

ABTSZ: Abort Size Status, ąĖąĮč乊čĆą╝ą░čåąĖčÅ ąŠčé čĆą░ąĘą╝ąĄčĆąĄ ąŠą┐ąĄčĆą░čåąĖąĖ, ą┐ąŠč鹥čĆą┐ąĄą▓čłąĄą╣ ąŠą▒čĆčŗą▓.

ABTSZ

|

Abort Size |

| 0 |

0 |

ąæą░ą╣čé |

| 0 |

1 |

ą¤ąŠą╗ąŠą▓ąĖąĮą░ čüą╗ąŠą▓ą░ (2 ą▒ą░ą╣čéą░) |

| 1 |

0 |

ąĪą╗ąŠą▓ąŠ (4 ą▒ą░ą╣čéą░) |

| 1 |

1 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ABTTYP: Abort Type Status, ąĖąĮč乊čĆą╝ą░čåąĖčÅ ąŠ čéąĖą┐ąĄ ąŠą┐ąĄčĆą░čåąĖąĖ, ą┐ąŠč鹥čĆą┐ąĄą▓čłąĄą╣ ąŠą▒čĆčŗą▓.

| ABTTYP |

Abort Type |

| 0 |

0 |

ą¦č鹥ąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ |

| 0 |

1 |

ąŚą░ą┐ąĖčüčī ą┤ą░ąĮąĮčŗčģ |

| 1 |

0 |

ąĪą╗ąŠą▓ąŠ (4 ą▒ą░ą╣čéą░) |

| 1 |

1 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

MST_EMAC: EMAC Abort Source, čäą╗ą░ą│ ąĖčüč鹊čćąĮąĖą║ą░ ąŠą┐ąĄčĆą░čåąĖąĖ ąŠą▒čĆčŗą▓ą░ EMAC.

0: ą┐čĆąĖčćąĖąĮąŠą╣ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ ąŠą▒čĆčŗą▓ą░ ąŠą┐ąĄčĆą░čåąĖąĖ ąĮąĄ ą▒čŗą╗ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ EMAC.

1: ą┐ąŠčüą╗ąĄą┤ąĮčÄčÄ ąŠą┐ąĄčĆą░čåąĖčÄ ąŠą▒čĆčŗą▓ą░ ą▓čŗąĘą▓ą░ą╗ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ EMAC.

MST_PDC: PDC Abort Source, čäą╗ą░ą│ ąĖčüč鹊čćąĮąĖą║ą░ ąŠą▒čĆčŗą▓ą░ ąŠą┐ąĄčĆą░čåąĖąĖ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ DMA ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓.

0: ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ąŠą▒ąŠčĆą▓ą░ąĮąĮčŗą╣ ą┤ąŠčüčéčāą┐ ą┐čĆąŠąĖąĘąŠčłąĄą╗ ąĮąĄ ąĖąĘ-ąĘą░ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ DMA.

1: ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ąŠą▒ąŠčĆą▓ą░ąĮąĮčŗą╣ ą┤ąŠčüčéčāą┐ ą┐čĆąŠąĖąĘąŠčłąĄą╗ ąĖąĘ-ąĘą░ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ DMA.

MST_ARM: ARM Abort Source, čäą╗ą░ą│ ąĖčüč鹊čćąĮąĖą║ą░ ąŠą▒čĆčŗą▓ą░ ąŠą┐ąĄčĆą░čåąĖąĖ čÅą┤čĆą░ ARM.

0: ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ąŠą▒ąŠčĆą▓ą░ąĮąĮčŗą╣ ą┤ąŠčüčéčāą┐ ą┐čĆąŠąĖąĘąŠčłąĄą╗ ąĮąĄ ąĖąĘ-ąĘą░ čÅą┤čĆą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░.

1: ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ąŠą▒ąŠčĆą▓ą░ąĮąĮčŗą╣ ą┤ąŠčüčéčāą┐ ą┐čĆąŠąĖąĘąŠčłąĄą╗ ąĖąĘ-ąĘą░ čÅą┤čĆą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░.

SVMST_EMAC: Saved EMAC Abort Source, čüąŠčģčĆą░ąĮąĄąĮąĮčŗą╣ čüčéą░čéčāčü čäą╗ą░ą│ą░ ąĖčüč鹊čćąĮąĖą║ą░ ąŠą▒čĆčŗą▓ą░ EMAC.

0: ąĮąĄ ą▒čŗą╗ąŠ ąŠą▒čĆčŗą▓ą░ EMAC čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čćč鹥ąĮąĖčÅ MC_ASR, ąĖą╗ąĖ čŹč鹊 ą▒čŗą╗ąŠ ąŠą┐ąŠą▓ąĄčēąĄąĮąŠ ą▒ąĖč鹊ą╝ MST_EMAC.

1: ą┐čĆąŠąĖąĘąŠčłąĄą╗ ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ąŠą┤ąĖąĮ ąŠą▒čĆčŗą▓ (abort) EMAC čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čćč鹥ąĮąĖčÅ MC_ASR.

SVMST_PDC: Saved PDC Abort Source, čüąŠčģčĆą░ąĮąĄąĮąĮčŗą╣ čüčéą░čéčāčü čäą╗ą░ą│ą░ ąĖčüč鹊čćąĮąĖą║ą░ ąŠą▒čĆčŗą▓ą░ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ DMA ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓.

0: ąĮąĄ ą▒čŗą╗ąŠ ąŠą▒čĆčŗą▓ą░ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ DMA čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čćč鹥ąĮąĖčÅ MC_ASR, ąĖą╗ąĖ čŹč鹊 ą▒čŗą╗ąŠ ąŠą┐ąŠą▓ąĄčēąĄąĮąŠ ą▒ąĖč鹊ą╝ MST_PDC.

1: ą┐čĆąŠąĖąĘąŠčłąĄą╗ ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ąŠą┤ąĖąĮ ąŠą▒čĆčŗą▓ (abort) DMA čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čćč鹥ąĮąĖčÅ MC_ASR.

SVMST_ARM: Saved ARM Abort Source, čüąŠčģčĆą░ąĮąĄąĮąĮčŗą╣ čüčéą░čéčāčü čäą╗ą░ą│ą░ ąĖčüč鹊čćąĮąĖą║ą░ ąŠą▒čĆčŗą▓ą░ čÅą┤čĆą░ ARM.

0: ąĮąĄ ą▒čŗą╗ąŠ ąŠą▒čĆčŗą▓ą░ ą┤ąŠčüčéčāą┐ą░ čüąŠ čüč鹊čĆąŠąĮčŗ ą┐čĆąŠčåąĄčüčüąŠčĆą░ čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čćč鹥ąĮąĖčÅ MC_ASR, ąĖą╗ąĖ čŹč鹊 ą▒čŗą╗ąŠ ąŠą┐ąŠą▓ąĄčēąĄąĮąŠ ą▒ąĖč鹊ą╝ MST_ARM.

1: ą┐čĆąŠąĖąĘąŠčłąĄą╗ ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ąŠą┤ąĖąĮ ąŠą▒čĆčŗą▓ (abort) ą┤ąŠčüčéčāą┐ą░ čüąŠ čüč鹊čĆąŠąĮčŗ čÅą┤čĆą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ARM čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čćč鹥ąĮąĖčÅ MC_ASR.

ąĀąĄą│ąĖčüčéčĆ ą░ą┤čĆąĄčüą░ ąŠą┐ąĄčĆą░čåąĖąĖ ąŠą▒čĆčŗą▓ą░ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą┐ą░ą╝čÅčéąĖ (MC Abort Address Status Register). ąĀą░ą▒ąŠčéą░ąĄčé č鹊ą╗čīą║ąŠ ąĮą░ čćč鹥ąĮąĖąĄ.

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

ABTADD

|

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| ABTADD |

ABTADD: Abort Address, ą░ą┤čĆąĄčü ąŠą▒čĆčŗą▓ą░ ąŠą┐ąĄčĆą░čåąĖąĖ. ąŚą┤ąĄčüčī čüąŠą┤ąĄčƹȹĖčéčüčÅ ą░ą┤čĆąĄčü ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ ąŠą▒ąŠčĆą▓ą░ąĮąĮąŠą│ąŠ ą┤ąŠčüčéčāą┐ą░.

[ąĪą╗ąŠą▓ą░čĆąĖą║]

APB Advanced Peripheral Bus, ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ čłąĖąĮą░ ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ ą║ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝.

ASB čĆą░čüčłąĖčäčĆąŠą▓čŗą▓ą░ąĄčéčüčÅ ą║ą░ą║ ARM System Bus.

DMA Direct Memory Access, ą┐čĆčÅą╝ąŠą╣ ą┤ąŠčüčéčāą┐ ą║ ą┐ą░ą╝čÅčéąĖ.

EFC Embedded Flash Controller, ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą▓čüčéčĆąŠąĄąĮąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ FLASH.

EMAC Ethernet Media Access Controller, ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ čüąĄčéąĖ Ethernet.

FLASH čéąĖą┐ 菹ĮąĄčĆą│ąŠąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠą╣ ą┐ą░ą╝čÅčéąĖ, ą║ąŠč鹊čĆą░čÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ (ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ) ą▒ą╗ąŠą║ą░ą╝ąĖ čĆą░ąĘą╝ąĄčĆąŠą╝ čüąŠ čüčéčĆą░ąĮąĖčåčā, ąĖ čüąŠčģčĆą░ąĮčÅąĄčé čüą▓ąŠąĖ ą┤ą░ąĮąĮčŗąĄ ą┐ąŠčüą╗ąĄ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ.

RAM Random Access Memory, ąŠą┐ąĄčĆą░čéąĖą▓ąĮą░čÅ ą┐ą░ą╝čÅčéčī, ąŠą▒ąĄčüą┐ąĄčćąĖą▓ą░čÄčēą░čÅ ą┐čĆąŠąĖąĘą▓ąŠą╗čīąĮčŗą╣ ą┤ąŠčüčéčāą┐ ąĮą░ čćč鹥ąĮąĖąĄ ąĖ ąĘą░ą┐ąĖčüčī.

ROM Read-Only Memory, ą┐ąŠčüč鹊čÅąĮąĮą░čÅ, ąĮąĄ ąĖąĘą╝ąĄąĮčÅąĄą╝ą░čÅ ą┐ą░ą╝čÅčéčī, čĆą░ą▒ąŠčéą░čÄčēą░čÅ č鹊ą╗čīą║ąŠ ąĮą░ čćč鹥ąĮąĖąĄ.

SRAM Static RAM, č鹊 ąČąĄ čüą░ą╝ąŠąĄ, čćč鹊 ąĖ RAM. ą¤čĆąŠčüč鹊 ą┐čĆąĄčäąĖą║čü Static ą┐ąŠą┤č湥čĆą║ąĖą▓ą░ąĄčé, čćč鹊 ą┐ą░ą╝čÅčéčī čüčéą░čéąĖč湥čüą║ą░čÅ, ąĮąĄ ą┤ąĖąĮą░ą╝ąĖč湥čüą║ą░čÅ, čé. ąĄ. ąĮąĄ čéčĆąĄą▒čāčÄčéčüčÅ čüą┐ąĄčåąĖą░ą╗čīąĮčŗąĄ ąŠą┐ąĄčĆą░čåąĖąĖ ą┤ą╗čÅ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ čüąŠą┤ąĄčƹȹĖą╝ąŠą│ąŠ ą┐ą░ą╝čÅčéąĖ.

[ąĪčüčŗą╗ą║ąĖ]

1. ARM-based Flash MCU SAM7X512 / SAM7X256 / SAM7X128 DATASHEET site:atmel.com.

2. AT91SAM7 Embedded Flash Controller (EFC).

3. ą¤ąŠčĆčÅą┤ąŠą║ čüą╗ąĄą┤ąŠą▓ą░ąĮąĖčÅ ą▒ą░ą╣čé (endianness). |