|

ąĪč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ (Watchdog Timer, WDT) ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą┐čĆąĄą┤ąŠčéą▓čĆą░čēąĄąĮąĖčÅ ąĘą░ą▓ąĖčüą░ąĮąĖčÅ čüąĖčüč鹥ą╝čŗ, ąĄčüą╗ąĖ ąĄčæ ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┐ąŠą┐ą░ą┤ąĄčé ą▓ ą│ą╗čāčģčāčÄ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║čā (deadlock).

WDT ąŠčüąĮąŠą▓ą░ąĮ ąĮą░ 12-ą▒ąĖčéąĮąŠą╝, čüčćąĖčéą░čÄčēąĖą╝ ą▓ąĮąĖąĘ čüč湥čéčćąĖą║ąĄ, ąĮą░ ą║ąŠč鹊čĆąŠą╝ ą╝ąŠąČąĮąŠ ąĘą░ą┤ą░čéčī čüč鹊čĆąŠąČąĄą▓ąŠą╣ ą┐ąĄčĆąĖąŠą┤ (watchdog period) ą┤ąŠ 16 čüąĄą║čāąĮą┤ (čüč湥čéčćąĖą║ čéą░ą║čéąĖčĆčāąĄčéčüčÅ ą╝ąĄą┤ą╗ąĄąĮąĮčŗą╝ąĖ čéą░ą║čéą░ą╝ąĖ 32.768 ą║ąōčå). WDT ą╝ąŠąČąĄčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ąŠą▒čēąĖą╣ čüą▒čĆąŠčü ąĖą╗ąĖ čüą▒čĆąŠčü č鹊ą╗čīą║ąŠ ą┐čĆąŠčåąĄčüčüąŠčĆą░. ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠ WDT ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ąĄčüą╗ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ ąŠčéą╗ą░ą┤ą║ąĖ (debug mode) ąĖą╗ąĖ ą▓ čĆąĄąČąĖą╝ąĄ ąŠąČąĖą┤ą░ąĮąĖčÅ (idle mode).

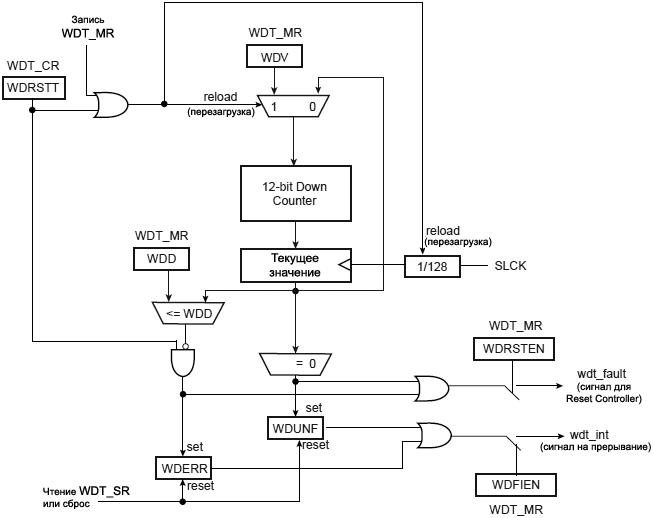

ąĀąĖčü. 16-1. ąæą╗ąŠą║ čüčģąĄą╝ą░ WDT.

[ążčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ WDT]

Watchdog Timer (WDT) ą┐ąŠą╗čāčćą░ąĄčé ą┐ąĖčéą░ąĮąĖąĄ ąŠčé VDDCORE ąĖ ą┐ąĄčĆąĄąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ ą┐čĆąĖ čüą▒čĆąŠčüąĄ ą┐čĆąŠčåąĄčüčüąŠčĆą░. 12-ą▒ąĖčéąĮčŗą╣, čüčćąĖčéą░čÄčēąĖą╣ ą▓ąĮąĖąĘ čüč湥čéčćąĖą║ WDT ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄą╝, ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗą╝ ą▓ ą┐ąŠą╗ąĄ WV čĆąĄą│ąĖčüčéčĆą░ čĆąĄąČąĖą╝ą░ (Mode Register, WDT_MR). WDT ąĖčüą┐ąŠą╗čīąĘčāąĄčé ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą╝ąĄą┤ą╗ąĄąĮąĮčāčÄ čéą░ą║č鹊ą▓čāčÄ čćą░čüč鹊čéčā (Slow Clock), ą┐ąŠą┤ąĄą╗ąĄąĮąĮčāčÄ ąĮą░ 128, čćč鹊ą▒čŗ čāčüčéą░ąĮąŠą▓ąĖčéčī ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮčŗą╣ čüč鹊čĆąŠąČąĄą▓ąŠą╣ ą┐ąĄčĆąĖąŠą┤ 16 čüąĄą║čāąĮą┤ (čéąĖą┐ąŠą▓ą░čÅ čćą░čüč鹊čéą░ Slow Clock čüąŠčüčéą░ą▓ą╗čÅąĄčé 32.768 ą║ąōčå).

ą¤ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ąĘąĮą░č湥ąĮąĖąĄ WV ą▒čāą┤ąĄčé 0xFFF, čćč鹊 čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą╝čā ąĘąĮą░č湥ąĮąĖčÄ čüč湥čéčćąĖą║ą░ čü čĆą░ąĘčĆąĄčłąĄąĮąĮąŠą╣ ą│ąĄąĮąĄčĆą░čåąĖąĄą╣ ą▓ąĮąĄčłąĮąĄą│ąŠ čüą▒čĆąŠčüą░ (ą┐ąŠą╗ąĄ WDRSTEN ą▓ ąĘąĮą░č湥ąĮąĖąĖ 1 ą┐ąŠčüą╗ąĄ Backup Reset). ąŁč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ WDT čĆą░ą▒ąŠčéą░ąĄčé ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░, čé. ąĄ. ą┐ąŠčüą╗ąĄ ą▓ą║ą╗čÄč湥ąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ. ą¤ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą┤ąŠą╗ąČąĄąĮ ą╗ąĖą▒ąŠ ąĘą░ą┐čĆąĄčéąĖčéčī WDT (čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ WDDIS ą▓ WDT_MR), ąĄčüą╗ąĖ ąŠąĮ ąĮąĄ čģąŠč湥čé ąĄą│ąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī, ą╗ąĖą▒ąŠ ą┤ąŠą╗ąČąĄąĮ ą┐ąĄčĆąĄą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī WDT čéą░ą║, čćč鹊ą▒čŗ ąĄą│ąŠ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮčŗą╣ čüč鹊čĆąŠąČąĄą▓ąŠą╣ ą┐ąĄčĆąĖąŠą┤ čüąŠąŠčéą▓ąĄčéčüčéą▓ąŠą▓ą░ą╗ čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÄ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ.

ąĀąĄą│ąĖčüčéčĆ čĆąĄąČąĖą╝ą░ (Watchdog Mode Register, WDT_MR) ą╝ąŠąČąĮąŠ ąĘą░ą┐ąĖčüą░čéčī č鹊ą╗čīą║ąŠ ąŠą┤ąĖąĮ čĆą░ąĘ. ąĪą▒čĆąŠčüąĖčéčī WDT_MR ą╝ąŠąČąĄčé č鹊ą╗čīą║ąŠ čüą▒čĆąŠčü ą┐čĆąŠčåąĄčüčüąŠčĆą░. ąŚą░ą┐ąĖčüčī čĆąĄą│ąĖčüčéčĆą░ WDT_MR ą┐ąĄčĆąĄąĘą░ą│čĆčāąČą░ąĄčé WDT ąĮąŠą▓čŗą╝ąĖ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮčŗą╝ąĖ ą┐ą░čĆą░ą╝ąĄčéčĆą░ą╝ąĖ čĆąĄąČąĖą╝ą░.

ąĢčüą╗ąĖ WDT ą▒čŗą╗ ą┐ąĄčĆąĄąĘą░ą┐čāčēąĄąĮ ąĘą░ą┐ąĖčüčīčÄ ą▓ čĆąĄą│ąĖčüčéčĆ WDT_CR, č鹊 čĆąĄą│ąĖčüčéčĆ WDT_MR ąĮąĄ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ ą▓ č鹥č湥ąĮąĖąĄ 3 ą┐ąĄčĆąĖąŠą┤ąŠą▓ Slow Clock ą┐ąŠčüą╗ąĄ ą╝ąŠą╝ąĄąĮčéą░ ąĘą░ą┐ąĖčüąĖ ą▓ WDT_CR. ąÆ ą╗čÄą▒ąŠą╝ čüą╗čāčćą░ąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ ąĮąŠą▓ąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ ą▓ WDT_MR ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąĖąĮąĖčåąĖąĖčĆčāąĄčé ąĖąĮčüčéčĆčāą║čåąĖčÄ čĆąĄčüčéą░čĆčéą░.

ą¤čĆąĖ ąĮąŠčĆą╝ą░ą╗čīąĮąŠą╝ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĖ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čīčüą║ą░čÅ ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┐ąĄčĆąĄąĘą░ą│čĆčāąČą░ąĄčé WDT čü čĆąĄą│čāą╗čÅčĆąĮčŗą╝ąĖ ąĖąĮč鹥čĆą▓ą░ą╗ą░ą╝ąĖ ą┤ąŠ č鹊ą│ąŠ, ą║ą░ą║ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ąĄą│ąŠ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĄ, ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ čĆąĄą│ąĖčüčéčĆą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ (Control Register, WDT_CR) čü ą▒ąĖč鹊ą╝ WDRSTT ą▓ ąĘąĮą░č湥ąĮąĖąĖ 1. ąóąŠą│ą┤ą░ WDT ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ ą┐ąĄčĆąĄąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄą╝ ąĖąĘ WDT_MR ąĖ ą┐ąĄčĆąĄąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ, ąĖ čéą░ą║ąČąĄ čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ ąĖ ą┐ąĄčĆąĄąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ ą┤ąĄą╗ąĖč鹥ą╗čī ąĮą░ 128 Slow Clock. ąĀąĄą│ąĖčüčéčĆ WDT_CR ąĖą╝ąĄąĄčé ąĘą░čēąĖčéčā ąŠčé ąĘą░ą┐ąĖčüąĖ, ą┐ąŠčŹč鹊ą╝čā ąĄą│ąŠ ąĮąĄą╗čīąĘčÅ čüą╗čāčćą░ą╣ąĮąŠ ąĘą░ą┐ąĖčüą░čéčī ą▒ąĄąĘ čüą┐ąĄčåąĖą░ą╗čīąĮąŠą╣ ąĘą░čēąĖčéąĮąŠą╣ ą┐čĆąŠčåąĄą┤čāčĆčŗ. ąöą╗čÅ ą║ąŠčĆčĆąĄą║čéąĮąŠą╣ ąĘą░ą┐ąĖčüąĖ WDT_CR ą┐čĆąĄą┤čāčüą╝ąŠčéčĆąĄąĮ čüą┐ąĄčåąĖą░ą╗čīąĮčŗą╣, ąČąĄčüčéą║ąŠ ąĘą░ą┤ą░ąĮąĮčŗą╣ ą║ą╗čÄčć ą┤ąŠčüčéčāą┐ą░. ąĢčüą╗ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ąĮąĄ čāčüą┐ąĄą╗ą░ ą┐ąĄčĆąĄąĘą░ą│čĆčāąĘąĖčéčī WDT ą▓ č鹥č湥ąĮąĖąĄ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ ąĘą░čēąĖčéąĮąŠą│ąŠ ą┐ąĄčĆąĖąŠą┤ą░, č鹊 ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ čüąĖą│ąĮą░ą╗ wdt_fault ą▓ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ čüą▒čĆąŠčüą░ (Reset Controller), ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé WDRSTEN ą▓ Mode Register (WDT_MR). ąÜčĆąŠą╝ąĄ č鹊ą│ąŠ, čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé WDUNF ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüąŠčüč鹊čÅąĮąĖčÅ Watchdog Status Register (WDT_SR).

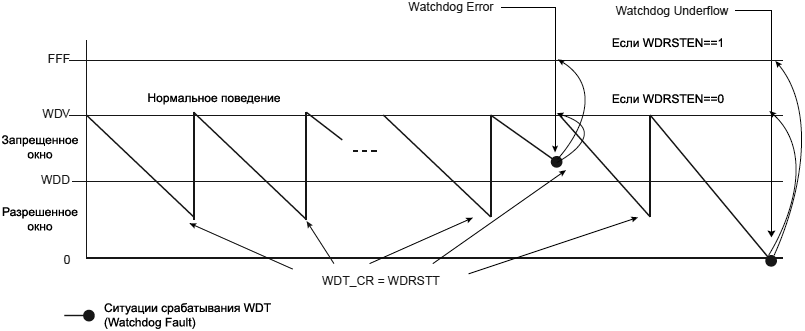

ą¦č鹊ą▒čŗ ą┐čĆąĄą┤ąŠčéą▓čĆą░čéąĖčéčī čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĄ WDT ąĖąĘ-ąĘą░ ąĘą░ą▓ąĖčüą░ąĮąĖčÅ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ, ą┐ąĄčĆąĄąĘą░ą│čĆčāąĘą║ą░ WDT ą┤ąŠą╗ąČąĮą░ ą┐čĆąŠąĖąĘąŠą╣čéąĖ ą▓ ąŠą║ąĮąĄ ą▓čĆąĄą╝ąĄąĮąĖ ą╝ąĄąČą┤čā ąĘąĮą░č湥ąĮąĖčÅą╝ąĖ čüč湥čéčćąĖą║ą░ ąŠčé 0 ą┤ąŠ WDD, ą│ą┤ąĄ WDD ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ čĆąĄą│ąĖčüčéčĆąŠą╝ čĆąĄąČąĖą╝ą░ (WatchDog Mode Register, WDT_MR).

ąøčÄą▒ą░čÅ ą┐ąŠą┐čŗčéą║ą░ ą┐ąĄčĆąĄąĘą░ą┐čāčüčéąĖčéčī WDT, ą║ąŠą│ą┤ą░ ąĄą│ąŠ čüč湥čéčćąĖą║ ąĮą░čģąŠą┤ąĖčéčüčÅ ą╝ąĄąČą┤čā ąĘąĮą░č湥ąĮąĖčÅą╝ąĖ WDV ąĖ WDD, ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ąŠčłąĖą▒ą║ąĄ WDT, ą┤ą░ąČąĄ ąĄčüą╗ąĖ WDT ąĘą░ą┐čĆąĄčēąĄąĮ. ąæąĖčé WDERR ąŠą▒ąĮąŠą▓ąĖčéčüčÅ ą▓ WDT_SR, ąĖ ą▒čāą┤ąĄčé ą▓čŗčüčéą░ą▓ą╗ąĄąĮ čüąĖą│ąĮą░ą╗ wdt_fault ą▓ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ čüą▒čĆąŠčüą░ (Reset Controller).

ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 čŹčéą░ čäčāąĮą║čåąĖčÅ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąĄčēąĄąĮą░ ą┐čāč鹥ą╝ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ąĘąĮą░č湥ąĮąĖčÅ WDD, ą║ąŠč鹊čĆąŠąĄ ą▒čāą┤ąĄčé ą▒ąŠą╗čīčłąĄ ąĖą╗ąĖ čĆą░ą▓ąĮąŠ ąĘąĮą░č湥ąĮąĖčÄ WDV. ąÆ čéą░ą║ąŠą╣ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą┐ąĄčĆąĄąĘą░ą┐čāčüą║ WDT čĆą░ąĘčĆąĄčłąĄąĮ ą▓ąŠ ą▓čüąĄą╝ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąĄą│ąŠ čüč湥čéčćąĖą║ą░ [0; WDV] ą▒ąĄąĘ ą│ąĄąĮąĄčĆą░čåąĖąĖ ąŠčłąĖą▒ą║ąĖ. ąŁč鹊 ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ (ąĘąĮą░č湥ąĮąĖčÅ WDD ąĖ WDV čĆą░ą▓ąĮčŗ).

ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖčé čüąŠčüč鹊čÅąĮąĖčÅ WDUNF (Watchdog Underflow) ąĖ WDERR (Watchdog Error) ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖčÄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé WDFIEN ą▓ čĆąĄą│ąĖčüčéčĆąĄ čĆąĄąČąĖą╝ą░ WDT_MR. ąĪąĖą│ąĮą░ą╗ wdt_fault ą┤ą╗čÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ čüą▒čĆąŠčüą░ ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ čüą▒čĆąŠčüčā WDT, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé WDRSTEN, ą║ą░ą║ čŹč鹊 ą▒čŗą╗ąŠ čāą║ą░ąĘą░ąĮąŠ ą▓ ąŠą┐ąĖčüą░ąĮąĖąĖ ą┐čĆąŠčåąĄą┤čāčĆčŗ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ čüą▒čĆąŠčüą░ (Reset Controller, RSTC [1]). ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ čüą▒čĆą░čüčŗą▓ą░čÄčéčüčÅ ą┐čĆąŠčåąĄčüčüąŠčĆ ąĖ WDT, ąĖ čüą▒čĆąŠčüčÅčéčüčÅ čäą╗ą░ą│ąĖ WDERR ąĖ WDUNF.

ąĢčüą╗ąĖ ą▒čŗą╗ čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮ čüą▒čĆąŠčü, ąĖą╗ąĖ ąĄčüą╗ąĖ ą▒čŗą╗ ą┐čĆąŠčćąĖčéą░ąĮ čĆąĄą│ąĖčüčéčĆ WDT_SR, č鹊 ą▒ąĖčéčŗ čüąŠčüč鹊čÅąĮąĖčÅ čüą▒čĆą░čüčŗą▓ą░čÄčéčüčÅ, ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠčćąĖčēą░ąĄčéčüčÅ, ąĖ čüąĖą│ąĮą░ą╗ wdt_fault ą▓ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ čüą▒čĆąŠčüą░ ąĮąĄ ą▓čŗą┤ą░ąĄčéčüčÅ.

ąŚą░ą┐ąĖčüčī ą▓ WDT_MR ą┐ąĄčĆąĄąĘą░ą│čĆčāąČą░ąĄčé ąĖ ą┐ąĄčĆąĄąĘą░ą┐čāčüą║ą░ąĄčé čüč湥čéčćąĖą║ WDT.

ąÜąŠą│ą┤ą░ ą┐čĆąŠčåąĄčüčüąŠčĆ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ąŠčéą╗ą░ą┤ą║ąĖ (debug state) ąĖą╗ąĖ čĆąĄąČąĖą╝ąĄ ąŠąČąĖą┤ą░ąĮąĖčÅ (idle mode), čüč湥čéčćąĖą║ WDT ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮ. ąŁč鹊 ąĘą░ą▓ąĖčüąĖčé ąŠčé ąĘąĮą░č湥ąĮąĖčÅ, ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ ą▓ ą▒ąĖčéčŗ WDIDLEHLT ąĖ WDDBGHLT čĆąĄą│ąĖčüčéčĆą░ čĆąĄąČąĖą╝ą░ WDT_MR.

ąĀąĖčü. 16-2. ą¤ąŠą▓ąĄą┤ąĄąĮąĖąĄ WDT.

ąöąĖą░ą│čĆą░ą╝ą╝ą░ ąĮą░ čĆąĖčü. 16-2 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą░ą╗ą│ąŠčĆąĖčéą╝ čĆą░ą▒ąŠčéčŗ WDT. ą¦ąĄčĆąĮčŗą╝ąĖ ą║čĆčāąČą║ą░ą╝ąĖ ą┐ąŠą╝ąĄč湥ąĮčŗ ą░ą▓ą░čĆąĖą╣ąĮčŗąĄ čüąĖčéčāą░čåąĖąĖ ą┤ą╗čÅ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ (Watchdog Fault), ą║ąŠč鹊čĆčŗąĄ ą┐čĆąĖą▓ąŠą┤čÅčé ą║ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖčÄ WDT ąĖ čüą▒čĆąŠčüčā čüąĖčüč鹥ą╝čŗ.

[ąĀąĄą│ąĖčüčéčĆčŗ WDT]

ąśąĮč鹥čĆč乥ą╣čü ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ WDT čüąŠčüčéą░ą▓ą╗čÅčÄčé čéčĆąĖ 32-ą▒ąĖčéąĮčŗčģ čĆąĄą│ąĖčüčéčĆą░, ą┐ąŠą║ą░ąĘą░ąĮąĮčŗąĄ ą▓ čéą░ą▒ą╗ąĖčåąĄ 16-1. ąÆ čüč鹊ą╗ą▒čåąĄ "ąĪą╝ąĄčēąĄąĮąĖąĄ" čāą║ą░ąĘą░ąĮąŠ čüą╝ąĄčēąĄąĮąĖąĄ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ą▒ą░ąĘąŠą▓ąŠą│ąŠ ą░ą┤čĆąĄčüą░ AT91C_BASE_WDTC (0xFFFFFD40).

ąóą░ą▒ą╗ąĖčåą░ 16-1. ąÜą░čĆčéą░ ą┐ą░ą╝čÅčéąĖ čĆąĄą│ąĖčüčéčĆąŠą▓ Watchdog Timer (WDT).

| ąĪą╝ąĄčēąĄąĮąĖąĄ |

ąĀąĄą│ąĖčüčéčĆ |

ą£ąĮąĄą╝ąŠąĮąĖą║ą░ |

ąöąŠčüčéčāą┐(1) |

ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ |

| 0x00 |

Control Register (čĆąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ) |

WDT_CR |

WO |

- |

| 0x04 |

Mode Register (čĆąĄą│ąĖčüčéčĆ čĆąĄąČąĖą╝ą░) |

WDT_MR |

RW(2) |

0x3FFF2FFF |

| 0x08 |

Status Register (čĆąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ) |

WDT_SR |

RO |

0x00000000 |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

(1) WO ąŠąĘąĮą░čćą░ąĄčé č鹊ą╗čīą║ąŠ ąĘą░ą┐ąĖčüčī (Write Only), RW ąŠąĘąĮą░čćą░ąĄčé čćč鹥ąĮąĖąĄ ąĖ ąĘą░ą┐ąĖčüčī (Read Write), RO ąŠąĘąĮą░čćą░ąĄčé č鹊ą╗čīą║ąŠ čćč鹥ąĮąĖąĄ (Read Only).

(2) ąŚą░ą┐ąĖčüčī ą▓ č鹥č湥ąĮąĖąĄ čĆą░ą▒ąŠčéčŗ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ ą╝ąŠąČąĮąŠ ąŠčüčāčēąĄčüčéą▓ąĖčéčī ąĮąĄ ą▒ąŠą╗ąĄąĄ ąŠą┤ąĮąŠą│ąŠ čĆą░ąĘą░.

Watchdog Timer Control Register (WDT_CR)

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| KEY |

- |

- |

- |

- |

- |

- |

-

|

- |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

-

|

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

WDRSTT |

WDRSTT: Watchdog Restart

0 ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé čŹčäč乥ą║čéą░.

1 ą┐ąĄčĆąĄąĘą░ą┐čāčüą║ą░ąĄčé čüč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ, ąŠąĮ ąĮą░čćąĖąĮą░ąĄčé ąĘą░ąĮąŠą▓ąŠ čüčćąĖčéą░čéčī ą▓ąĮąĖąĘ ąŠčé ąĘąĮą░č湥ąĮąĖčÅ ą┐ąŠą╗čÅ WDD ą▓ čĆąĄą│ąĖčüčéčĆąĄ WDT_MR.

KEY: Password

ąĪą┐ąĄčåąĖą░ą╗čīąĮąŠąĄ ąĘą░čēąĖčéąĮąŠąĄ ą┐ąŠą╗ąĄ, ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮąĮąŠąĄ ą┤ą╗čÅ ą┐čĆąĄą┤ąŠčéą▓čĆą░čēąĄąĮąĖčÅ čüą╗čāčćą░ą╣ąĮąŠą│ąŠ ą┤ąŠčüčéčāą┐ą░ ąĮą░ ąĘą░ą┐ąĖčüčī ą║ čĆąĄą│ąĖčüčéčĆčā WDT_CR. ąÆ ą┐ąŠą╗ąĄ KEY ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮąŠ ąĘąĮą░č湥ąĮąĖąĄ 0xA5. ąŚą░ą┐ąĖčüčī čüčÄą┤ą░ ą╗čÄą▒ąŠą│ąŠ ą┤čĆčāą│ąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ ąŠčéą╝ąĄąĮąĖčé ąŠą┐ąĄčĆą░čåąĖčÄ ąĘą░ą┐ąĖčüąĖ (čé. ąĄ. čāčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖčéą░ WDRSTT ąĮąĄ ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ą┐ąĄčĆąĄąĘą░ą┐čāčüą║čā WDT).

Watchdog Timer Mode Register (WDT_MR)

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| - |

- |

WDIDLEHLT |

WDDBGHLT |

WDD |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| WDDIS |

WDRPROC |

WDRSTEN |

WDFIEN |

WDV |

WDV: Watchdog Counter Value

ą×ą┐čĆąĄą┤ąĄą╗čÅąĄčé ąĘąĮą░č湥ąĮąĖąĄ, ąĘą░ą│čĆčāąČąĄąĮąĮąŠąĄ ą▓ 12-ą▒ąĖčéąĮčŗą╣ čüč湥čéčćąĖą║ WDT (Watchdog Counter).

WDFIEN: Watchdog Fault Interrupt Enable

0 ąĪąŠą▒čŗčéąĖąĄ čüč鹊čĆąŠąČąĄą▓ąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░ Watchdog Fault (ą┐ąĄčĆąĄą▓ą░ą╗ąĖą▓ą░ąĮąĖąĄ č湥čĆąĄąĘ 0 ąĖą╗ąĖ ąŠčłąĖą▒ą║ą░, underflow ąĖą╗ąĖ error) ąĮąĄ ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÄ.

1 ąĪąŠą▒čŗčéąĖąĄ čüč鹊čĆąŠąČąĄą▓ąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░ (underflow ąĖą╗ąĖ error) ą▓čŗčüčéą░ą▓ąĖčé ąĘą░ą┐čĆąŠčü ąĮą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ.

WDRSTEN: Watchdog Reset Enable

0 ąĪąŠą▒čŗčéąĖąĄ čüč鹊čĆąŠąČąĄą▓ąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░ (underflow ąĖą╗ąĖ error) ąĮąĄ ą┐čĆąĖą▓ąŠą┤ąĖčé ą║ čüą▒čĆąŠčüčā (čé. ąĄ. WDT ąŠčéą║ą╗čÄč湥ąĮ).

1 ąĪąŠą▒čŗčéąĖąĄ čüč鹊čĆąŠąČąĄą▓ąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░ (underflow ąĖą╗ąĖ error) ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ čüą▒čĆąŠčüčā Watchdog reset (čé. ąĄ. WDT čĆą░ą▒ąŠčéą░ąĄčé ąĖ čüą╗ąĄą┤ąĖčé ąĘą░ ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄą╝ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ).

WDRPROC: Watchdog Reset Processor

0 ąĄčüą╗ąĖ WDRSTEN == 1, č鹊 Watchdog fault (underflow ąĖą╗ąĖ error) čüą▒čĆąŠčüąĖčé ą▓čüąĄ (ąĖ ą░ą┐ą┐ą░čĆą░čéčāčĆčā, ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆ).

1 ąĄčüą╗ąĖ WDRSTEN == 1, č鹊 Watchdog fault (underflow ąĖą╗ąĖ error) ą░ą║čéąĖą▓ąĖčĆčāąĄčé čüą▒čĆąŠčü ą┐čĆąŠčåąĄčüčüąŠčĆą░.

WDD: Watchdog Delta Value

ą×ą┐čĆąĄą┤ąĄą╗čÅąĄčé čĆą░ąĘčĆąĄčłąĄąĮąĮąŠąĄ ąŠą║ąĮąŠ ą▓čĆąĄą╝ąĄąĮąĖ (ąĘąĮą░č湥ąĮąĖčÅ čüč湥čéčćąĖą║ą░) ą┤ą╗čÅ ą┐ąĄčĆąĄąĘą░ą│čĆčāąĘą║ąĖ WDT. ąĢčüą╗ąĖ ą▓ ą╝ąŠą╝ąĄąĮčé ąĘą░ą┐ąĖčüąĖ WDT_CR čü WDRSTT = 1 ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░ WDT ą╝ąĄąĮčīčłąĄ ąĖą╗ąĖ čĆą░ą▓ąĮąŠ WDD, č鹊 čŹčéą░ ąĘą░ą┐ąĖčüčī ą┐ąĄčĆąĄąĘą░ą┐čāčüčéąĖčé čéą░ą╣ą╝ąĄčĆ (čŹč鹊 ą┤ąŠą╗ąČąĮą░ ą┐čĆąĖ ąĮąŠčĆą╝ą░ą╗čīąĮąŠą╣ čĆą░ą▒ąŠč鹥 ą┤ąĄą╗ą░čéčī ą┐čĆąŠą│čĆą░ą╝ą╝ą░, čćč鹊ą▒čŗ ą┐čĆąĄą┤ąŠčéą▓čĆą░čéąĖčéčī čüą▒čĆąŠčü čüąĖčüč鹥ą╝čŗ). ąĢčüą╗ąĖ ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░ WDT ą▒ąŠą╗čīčłąĄ WDD, č鹊 ąĘą░ą┐ąĖčüčī WDT_CR čü WDRSTT = 1 ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ąŠčłąĖą▒ą║ąĄ Watchdog error.

WDDBGHLT: Watchdog Debug Halt

0 WDT čĆą░ą▒ąŠčéą░ąĄčé, ą║ąŠą│ą┤ą░ ą┐čĆąŠčåąĄčüčüąŠčĆ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ ąŠčéą╗ą░ą┤ą║ąĖ (debug state).

1 WDT ąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ą║ąŠą│ą┤ą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ ąŠčéą╗ą░ą┤ą║ąĖ.

WDIDLEHLT: Watchdog Idle Halt

0 WDT čĆą░ą▒ąŠčéą░ąĄčé, ą║ąŠą│ą┤ą░ čüąĖčüč鹥ą╝ą░ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ ąŠąČąĖą┤ą░ąĮąĖčÅ (idle mode).

1 WDT ąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ą║ąŠą│ą┤ą░ čüąĖčüč鹥ą╝ą░ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ ąŠąČąĖą┤ą░ąĮąĖčÅ.

WDDIS: Watchdog Disable

0 čĆą░ąĘčĆąĄčłą░ąĄčé čĆą░ą▒ąŠčéčā WDT.

1 ąĘą░ą┐čĆąĄčēą░ąĄčé čĆą░ą▒ąŠčéčā WDT.

Watchdog Timer Status Register (WDT_SR)

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| - |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

-

|

- |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

-

|

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

WDERR |

WDUNF |

WDUNF: Watchdog Underflow

0 čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čćč鹥ąĮąĖčÅ WDT_SR ąĮąĄ ą▒čŗą╗ąŠ čüąŠą▒čŗčéąĖčÅ ą┐ąĄčĆąĄčģąŠą┤ą░ č湥čĆąĄąĘ 0 čüč湥čéčćąĖą║ą░ (Watchdog underflow).

1 ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ąŠą┤ąĖąĮ Watchdog underflow ą┐čĆąŠąĖąĘąŠčłąĄą╗ čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čćč鹥ąĮąĖčÅ WDT_SR.

WDERR: Watchdog Error

0 čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čćč鹥ąĮąĖčÅ WDT_SR ąĮąĄ ą▒čŗą╗ąŠ čüąŠą▒čŗčéąĖčÅ ąŠčłąĖą▒ą║ąĖ WDT (Watchdog error).

1 ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ąŠą┤ąĮą░ ąŠčłąĖą▒ą║ą░ WDT (Watchdog error) ą┐čĆąŠąĖąĘąŠčłą╗ą░ čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čćč鹥ąĮąĖčÅ WDT_SR.

[ąĪčüčŗą╗ą║ąĖ]

1. SAM7X512 / SAM7X256 / SAM7X128 DATASHEET site:microchip.com.

2. ąĪč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ (WatchDog, WDT) ą▓ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░čģ ARM AT91SAM7X. |