|

ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖąĄą╝ (PMC, Power Management Controller) ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąŠą┐čéąĖą╝ąĖąĘąĖčĆąŠą▓ą░čéčī 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ ą║čĆąĖčüčéą░ą╗ą╗ą░ AT91SAM7X ą┐čāč鹥ą╝ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čéą░ą║č鹊ą▓čŗą╝ąĖ čćą░čüč鹊čéą░ą╝ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆą░ (čüąĖčüč鹥ą╝ąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊č鹊ą╣, ąĖ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊č鹊ą╣ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ą║čĆąĖčüčéą░ą╗ą╗ą░). PMC čĆą░ąĘčĆąĄčłą░ąĄčé ąĖą╗ąĖ ąĘą░ą┐čĆąĄčēą░ąĄčé čéą░ą║č鹊ą▓čŗąĄ ą▓čģąŠą┤čŗ ą╝ąĮąŠą│ąĖčģ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ARM.

PMC ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé čüą╗ąĄą┤čāčÄčēąĖąĄ čéą░ą║č鹊ą▓čŗąĄ čćą░čüč鹊čéčŗ:

ŌĆó MCK, Master Clock, ą║ąŠč鹊čĆą░čÅ ą╝ąŠąČąĄčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčīčüčÅ ąŠčé ąĮąĄčüą║ąŠą╗čīą║ąĖčģ čüąŠč鹥ąĮ ą│ąĄčĆčå ą┤ąŠ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ čāčüčéčĆąŠą╣čüčéą▓ą░.

ŌĆó PCK, Processor Clock, čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░, ą║ąŠč鹊čĆą░čÅ ąŠčéą║ą╗čÄčćą░ąĄčéčüčÅ ą┐čĆąĖ ą┐ąĄčĆąĄčģąŠą┤ąĄ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą▓ čĆąĄąČąĖą╝ ąŠąČąĖą┤ą░ąĮąĖčÅ (idle mode).

ŌĆó ąóą░ą║č鹊ą▓čŗąĄ čćą░čüč鹊čéčŗ ą┐ąĄčĆąĖč乥čĆąĖąĖ, Peripheral Clocks, ąŠą▒čŗčćąĮąŠ čŹč鹊 MCK. ąóą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ ą┐ąĄčĆąĖč乥čĆąĖąĖ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčéčüčÅ čĆą░ąĘą╗ąĖčćąĮčŗą╝ ą▓čüčéčĆąŠąĄąĮąĮčŗą╝ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ ą║čĆąĖčüčéą░ą╗ą╗ą░ (USART, SSC, SPI, TWI, TC, MCI ąĖ čé. ą┤.), ąĖ ą┐ąŠą┤ą░čćą░ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ ąĮą░ ą║ą░ąČą┤ąŠąĄ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮąŠ ą║ąŠąĮčéčĆąŠą╗ąĖčĆčāąĄčéčüčÅ (čćč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé čéą░ą║ąČąĄ čāą┐čĆą░ą▓ą╗čÅčéčī 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄą╝ ą║čĆąĖčüčéą░ą╗ą╗ą░). ąöą╗čÅ č鹊ą│ąŠ, čćč鹊ą▒čŗ čāą╝ąĄąĮčīčłąĖčéčī ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ąĖą╝čæąĮ ą┤ą╗čÅ čéą░ą║č鹊ą▓čŗčģ čćą░čüč鹊čé, ą▓ ą┤ą░čéą░čłąĖč鹥 ąĮą░ ą║čĆąĖčüčéą░ą╗ą╗ čéą░ą║č鹊ą▓čŗąĄ čćą░čüč鹊čéčŗ ą┐ąĄčĆąĖč乥čĆąĖąĖ ąĮąŠčüčÅčé ąĖą╝čÅ MCK.

ŌĆó UDP Clock (UDPCK), čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░, čéčĆąĄą▒čāąĄą╝ą░čÅ ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ USB Device Port.

ŌĆó ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗąĄ ą▓čŗčģąŠą┤čŗ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ (Programmable Clock Outputs), ą║ąŠč鹊čĆčŗąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ą▓čŗą▒čĆą░ąĮčŗ ąĖąĘ čéą░ą║č鹊ą▓, ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄą╝čŗčģ čéą░ą║č鹊ą▓čŗą╝ ą│ąĄąĮąĄčĆą░č鹊čĆąŠą╝, ąĖ ą┐ąŠą┤ą░ąĮčŗ ąĮą░ ąĮąŠąČą║ąĖ PCKx.

ą¤čĆąĖą╝. ą┐ąĄčĆąĄą▓ąŠą┤čćąĖą║ą░: "ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮą░čÅ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ ą┤ą╗čÅ čāčüčéčĆąŠą╣čüčéą▓ą░" ąĘą░ą▓ąĖčüąĖčé ąŠčé č鹊ą│ąŠ, ą│ą┤ąĄ čĆą░ą▒ąŠčéą░ąĄčé ą║ąŠą┤ (ą▓ SRAM ąĖą╗ąĖ ą▓ FLASH). ąĢčüą╗ąĖ ą║ąŠą┤ čĆą░ą▒ąŠčéą░ąĄčé ą▓ SRAM, č鹊 čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ čÅą┤čĆą░ ą╝ąŠąČąĄčé ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮą░ ą┤ąŠ 200 ą£ąōčå, ąĄčüą╗ąĖ ąČąĄ ą║ąŠą┤ čĆą░ą▒ąŠčéą░ąĄčé ą▓ąŠ FLASH, č鹊 ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮą░čÅ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ ąĘą░ą▓ąĖčüąĖčé ąŠčé ą║ąŠą╗ąĖč湥čüčéą▓ą░ ąĮą░čüčéčĆąŠąĄąĮąĮčŗčģ čåąĖą║ą╗ąŠą▓ ąŠąČąĖą┤ą░ąĮąĖčÅ ą┐čĆąĖ ą┤ąŠčüčéčāą┐ąĄ ą▓ąŠ FLASH (čüą╝. ą┤ą░ą╗ąĄąĄ čĆą░ąĘą┤ąĄą╗ "ąźą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ ą▓čüčéčĆąŠąĄąĮąĮąŠą╣ FLASH" ąĖ čéą░ą▒ą╗ąĖčåčā "Embedded Flash Wait States"), ąĖ ą╝ąŠąČąĄčé čüąŠčüčéą░ą▓ą╗čÅčéčī ąŠčé 30 ą┤ąŠ 55 ą£ąōčå.

[Master Clock Controller]

ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą│ą╗ą░ą▓ąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ (Master Clock Controller) ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą▓čŗą▒ąŠčĆ ąĖ ą┤ąĄą╗ąĄąĮąĖąĄ ą│ą╗ą░ą▓ąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ Master Clock (MCK). MCK ą▓ ą▓ąĖą┤ąĄ čéą░ą║č鹊ą▓ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčéčüčÅ ą┐ąĄčĆąĖč乥čĆąĖąĖ ąĖ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčā ą┐ą░ą╝čÅčéąĖ.

MCK ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ąĖąĘ čćą░čüč鹊čé, ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄą╝čŗčģ čéą░ą║č鹊ą▓čŗą╝ ą│ąĄąĮąĄčĆą░č鹊čĆąŠą╝ (Clock Generator). ąÆčŗą▒ąŠčĆ ą╝ąĄą┤ą╗ąĄąĮąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ (Slow Clock) ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą╝ąĄą┤ą╗ąĄąĮąĮčŗąĄ čéą░ą║čéčŗ ą┤ą╗čÅ ą▓čüąĄą│ąŠ ą║čĆąĖčüčéą░ą╗ą╗ą░ ą▓ čåąĄą╗ąŠą╝. ąÆčŗą▒ąŠčĆ Main Clock 菹║ąŠąĮąŠą╝ąĖčé ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ ą╝ąŠčēąĮąŠčüčéąĖ čāąĘą╗ąŠą╝ PLL.

Master Clock Controller čüąŠčüč鹊ąĖčé ąĖąĘ čüąĄą╗ąĄą║č鹊čĆą░ čéą░ą║č鹊ą▓ (ą┐ąŠ čüčāčéąĖ čāą┐čĆą░ą▓ą╗čÅąĄą╝čŗą╣ ą║ąŠą╝ą╝čāčéą░č鹊čĆ) ąĖ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ (ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗą╣ ą┤ąĄą╗ąĖč鹥ą╗čī čćą░čüč鹊čéčŗ).

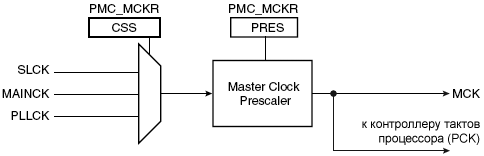

ąÆčŗą▒ąŠčĆ MCK ą┤ąĄą╗ą░ąĄčéčüčÅ ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ ąĘąĮą░č湥ąĮąĖčÅ ą▓ ą┐ąŠą╗ąĄ CSS (Clock Source Selection, ą▓čŗą▒ąŠčĆ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓) čĆąĄą│ąĖčüčéčĆą░ PMC_MCKR (Master Clock Register). ą¤čĆąĄčüą║ą░ą╗ąĄčĆ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéčŗ ą┤ąĄą╗ąĄąĮąĖčÅ čüč鹥ą┐ąĄąĮąĖ 2 ą▓čŗą▒čĆą░ąĮąĮąŠą╣ čćą░čüč鹊čéčŗ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąŠčé 1 ą┤ąŠ 64. ą¤ąŠą╗ąĄ PRES ą▓ čĆąĄą│ąĖčüčéčĆąĄ PMC_MCKR ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčé ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ą┤ąĄą╗ąĄąĮąĖčÅ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░.

ąÜą░ąČą┤čŗą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ PMC_MCKR ą┤ą╗čÅ ąĘą░ą┤ą░ąĮąĖčÅ ąĮąŠą▓ąŠą╣ čćą░čüč鹊čéčŗ MCK, ą▓ čĆąĄą│ąĖčüčéčĆąĄ PMC_SR ąŠčćąĖčēą░ąĄčéčüčÅ ą▒ąĖčé the MCKRDY. ąŁč鹊čé ą▒ąĖčé ą▒čāą┤ąĄčé čćąĖčéą░čéčīčüčÅ ą║ą░ą║ 0, ą┐ąŠą║ą░ ąĮąĄ ąĘą░čüčéą░ą▒ąĖą╗ąĖąĘąĖčĆčāąĄčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄ čćą░čüč鹊čéčŗ MCK. ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖčéą░ MCKRDY ą╝ąŠąČąĄčé ą▓čŗąĘą▓ą░čéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐čĆąŠčåąĄčüčüąŠčĆą░. ąŁčéą░ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą┐ąŠą╗ąĄąĘąĮą░, ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ čü ą▓čŗčüąŠą║ąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ ąĮąĄ ą▒ąŠą╗ąĄąĄ ąĮąĖąĘą║čāčÄ - čćč鹊ą▒čŗ ąĖąĮč乊čĆą╝ąĖčĆąŠą▓ą░čéčī ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠąĄ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖąĄ, čćč鹊 ąĖąĘą╝ąĄąĮąĄąĮąĖąĄ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ ąĘą░ą║ąŠąĮčćąĖą╗ąŠčüčī.

ąĀąĖčü. 25-1. Master Clock Controller.

ą¤ąŠčÅčüąĮąĄąĮąĖčÅ ą║ čĆąĖčüčāąĮą║čā:

CSS ą┐ąŠą╗ąĄ čĆąĄą│ąĖčüčéčĆą░ PMC_MCKR, čāą┐čĆą░ą▓ą╗čÅčÄčēąĄąĄ ą║ąŠą╝ą╝čāčéą░č鹊čĆąŠą╝ ą▓čŗą▒ąŠčĆą░ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ.

PRES ą┐ąŠą╗ąĄ čĆąĄą│ąĖčüčéčĆą░ PMC_MCKR, čāą┐čĆą░ą▓ą╗čÅčÄčēąĄąĄ ą║ąŠčŹčäčäąĖčåąĖąĄąĮč鹊ą╝ ą┤ąĄą╗ąĄąĮąĖčÅ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░.

SLCK Slow Clock, ą╝ąĄą┤ą╗ąĄąĮąĮą░čÅ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ (čćą░čüč鹊čéą░, ą▓čŗčĆą░ą▒ą░čéčŗą▓ą░ąĄą╝ą░čÅ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╝ RC ą│ąĄąĮąĄčĆą░č鹊čĆąŠą╝).

MAINCK ą│ą╗ą░ą▓ąĮą░čÅ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░, ąŠą┐čĆąĄą┤ąĄą╗čÅąĄą╝ą░čÅ čćą░čüč鹊č鹊ą╣ ą║ą▓ą░čĆčåąĄą▓ąŠą│ąŠ čĆąĄąĘąŠąĮą░č鹊čĆą░.

PLLCK čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░, ą┐ąŠą╗čāčćą░ąĄą╝ą░čÅ čü ą▓čŗčģąŠą┤ą░ čāąĘą╗ą░ PLL. PLL čĆą░čüčłąĖčäčĆąŠą▓čŗą▓ą░ąĄčéčüčÅ ą║ą░ą║ Phase Locked Loop, čé. ąĄ. čŹč鹊 ążąÉą¤ą¦, čāąĘąĄą╗ ą│ąĄąĮąĄčĆą░čåąĖąĖ čéą░ą║č鹊ą▓ čü ą┐ąŠą╝ąŠčēčīčÄ ążą░ąĘąŠą▓ąŠą╣ ąÉą▓č鹊ą¤ąŠą┤čüčéčĆąŠą╣ą║ąĖ ą¦ą░čüč鹊čéčŗ.

Master Clock Prescaler ą┐čĆąĄą┤ą┤ąĄą╗ąĖč鹥ą╗čī ą│ą╗ą░ą▓ąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ.

[Processor Clock Controller]

ąĪ ą┐ąŠą╝ąŠčēčīčÄ Processor Clock Controller čĆąĄą░ą╗ąĖąĘčāąĄčéčüčÅ čĆąĄąČąĖą╝ ąŠąČąĖą┤ą░ąĮąĖčÅ ą┐čĆąŠčåąĄčüčüąŠčĆą░ (Processor Idle Mode). ąóą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ PCK ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąĄčēąĄąĮą░ ąĘą░ą┐ąĖčüčīčÄ ą▓ čĆąĄą│ąĖčüčéčĆ PMC_SCDR (System Clock Disable Register). ąóąĄą║čāčēąĄąĄ čüąŠčüč鹊čÅąĮąĖąĄ čŹč鹊ą╣ čćą░čüč鹊čéčŗ (ą╝ąŠąČąĄčé ą┐ąŠąĮą░ą┤ąŠą▒ąĖčéčīčüčÅ ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ą▓ čåąĄą╗čÅčģ ąŠčéą╗ą░ą┤ą║ąĖ) ą╝ąŠąČąĮąŠ ą┐čĆąŠčćąĖčéą░čéčī ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ čüąŠčüč鹊čÅąĮąĖčÅ PMC_SCSR (System Clock Status Register).

ąóą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗ PCK čĆą░ąĘčĆąĄčłąĄąĮ čüčĆą░ąĘčā ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░, ąĖ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąĘą░ąĮąŠą▓ąŠ čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ ą┐čĆąĖ ą▓ąŠąĘąĮąĖą║ąĮąŠą▓ąĄąĮąĖąĖ ą╗čÄą▒ąŠą│ąŠ čĆą░ąĘčĆąĄčłąĄąĮąĮąŠą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ąĀąĄąČąĖą╝ ąŠąČąĖą┤ą░ąĮąĖčÅ Processor Idle Mode ą▓ą║ą╗čÄčćą░ąĄčéčüčÅ ą┐čāč鹥ą╝ ąĘą░ą┐čĆąĄčéą░ PCK, ą║ąŠč鹊čĆčŗą╣ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ ąĘą░ąĮąŠą▓ąŠ ąŠčé čĆą░ąĘčĆąĄčłąĄąĮąĮąŠą│ąŠ ą▒čŗčüčéčĆąŠą│ąŠ (fast interrupt) ąĖą╗ąĖ ąŠą▒čŗčćąĮąŠą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (normal interrupt), ąĖą╗ąĖ ąŠčé čüą▒čĆąŠčüą░ ą║čĆąĖčüčéą░ą╗ą╗ą░.

ąÜąŠą│ą┤ą░ ąĘą░ą┐čĆąĄčēąĄąĮ PCK, č鹥ą║čāčēą░čÅ ąĖąĮčüčéčĆčāą║čåąĖčÅ ąĘą░ą▓ąĄčĆčłą░ąĄčéčüčÅ ą┤ąŠ ąŠčüčéą░ąĮąŠą▓ą║ąĖ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ, ąĮąŠ čŹč鹊 ąĮąĄ ąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ ąŠčé ą┤čĆčāą│ąĖčģ ą╝ą░čüč鹥čĆąŠą▓ ąĮą░ čüąĖčüč鹥ą╝ąĮąŠą╣ čłąĖąĮąĄ.

[USB Clock Controller]

ąóą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊č鹊ą╣ ą┤ą╗čÅ USB čÅą▓ą╗čÅąĄčéčüčÅ ą▓čŗčģąŠą┤ PLL. ąĢčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ USB, č鹊 ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą┤ąŠą╗ąČąĄąĮ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī PLL ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ 48 ą£ąōčå, 92 ą£ąōčå ąĖą╗ąĖ 192 ą£ąōčå čü č鹊čćąĮąŠčüčéčīčÄ +-0.25%, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą▒ąĖčé USBDIV ą▓ čĆąĄą│ąĖčüčéčĆąĄ CKGR_PLLR.

ąÜąŠą│ą┤ą░ ą▓čŗčģąŠą┤ PLL čüčéą░ąĮąŠą▓ąĖčéčüčÅ čüčéą░ą▒ąĖą╗čīąĮčŗą╝, čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▒ąĖčé LOCK: čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ USB ą╝ąŠąČąĄčé ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮą░ ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ UDP ą▓ čĆąĄą│ąĖčüčéčĆąĄ PMC_SCER. ą¦č鹊ą▒čŗ 菹║ąŠąĮąŠą╝ąĖčéčī 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ, ą║ąŠą│ą┤ą░ USB ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ, ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą╝ąŠąČąĄčé čāčüčéą░ąĮąŠą▓ąĖčéčī ą▒ąĖčé UDP ą▓ čĆąĄą│ąĖčüčéčĆąĄ PMC_SCDR. ąæąĖčé UDP ą▓ PMC_SCSR ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą░ą║čéąĖą▓ąĮąŠčüčéčī ą┤ą╗čÅ čŹč鹊ą╣ čćą░čüč鹊čéčŗ. ą¤ąŠčĆčé čāčüčéčĆąŠą╣čüčéą▓ą░ USB čéčĆąĄą▒čāąĄčé ąĖ čüąĖą│ąĮą░ą╗ą░ 48 ą£ąōčå, ąĖ čüąĖą│ąĮą░ą╗ą░ MCK. ąÜą░ą║ čāąČąĄ čāą┐ąŠą╝ąĖąĮą░ą╗ąŠčüčī, MCK ą╝ąŠąČąĄčé čāą┐čĆą░ą▓ą╗čÅčéčīčüčÅ č湥čĆąĄąĘ Master Clock Controller. ąóąĄą║čāčēąĄąĄ čüąŠčüč鹊čÅąĮąĖąĄ ą░ą║čéąĖą▓ąĮąŠčüčéąĖ čéą░ą║č鹊ą▓ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮąŠ č湥čĆąĄąĘ čĆąĄą│ąĖčüčéčĆ PMC_PCSR (Peripheral Clock Status Register).

ąĀąĖčü. 25-2. USB Clock Controller.

[Peripheral Clock Controller]

PMC čāą┐čĆą░ą▓ą╗čÅąĄčé čéą░ą║čéą░ą╝ąĖ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą╣ ą▓čüčéčĆąŠąĄąĮąĮąŠą╣ ą┐ąĄčĆąĖč乥čĆąĖąĖ č湥čĆąĄąĘ Peripheral Clock Controller. ą¤ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą╝ąŠąČąĄčé ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮąŠ čĆą░ąĘčĆąĄčłą░čéčī ąĖą╗ąĖ ąĘą░ą┐čĆąĄčēą░čéčī MCK ą┤ą╗čÅ ą║ą░ąČą┤ąŠą╣ ą┐ąĄčĆąĖč乥čĆąĖąĖ ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ ą▓ čĆąĄą│ąĖčüčéčĆčŗ PMC_PCER (Peripheral Clock Enable) ąĖ PMC_PCDR (Peripheral Clock Disable) čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ.

ąÜąŠą│ą┤ą░ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ ą┤ą╗čÅ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ąĘą░ą┐čĆąĄčēąĄąĮą░, ą┐ąŠą┤ą░čćą░ čéą░ą║č鹊ą▓ ąĮą░ ąĮąĄą│ąŠ ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ ą┐čĆąĄą║čĆą░čēą░ąĄčéčüčÅ. ąóą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ ą┤ą╗čÅ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ čéą░ą║ąČąĄ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąĘą░ą┐čĆąĄčēą░ąĄčéčüčÅ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░.

ąöą╗čÅ ąŠčüčéą░ąĮąŠą▓ą║ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ, čćč鹊ą▒čŗ firmware ąŠąČąĖą┤ą░ą╗ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ č鹥ą║čāčēąĄą╣ ą▓čŗą┐ąŠą╗ąĮčÅąĄą╝ąŠą╣ ąŠą┐ąĄčĆą░čåąĖąĖ ą┐ąĄčĆąĄą┤ ąĘą░ą┐čĆąĄčēąĄąĮąĖąĄą╝ čéą░ą║č鹊ą▓. ąŁč鹊 ą┐ąŠąĘą▓ąŠą╗ąĖčé ąĖąĘą▒ąĄąČą░čéčī ąĖčüą║ą░ąČąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ąĖ ąŠčłąĖą▒ąŠą║ ą▓ ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĖ čüąĖčüč鹥ą╝čŗ.

ąØąŠą╝ąĄčĆ ą▒ąĖčéą░ ą▓ čĆąĄą│ąĖčüčéčĆą░čģ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čéą░ą║čéą░ą╝ąĖ ąĖ čüčéą░čéčāčüą░ ą┐ąĄčĆąĖč乥čĆąĖąĖ (PMC_PCER, PMC_PCDR ąĖ PMC_PCSR) čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčé ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆčā ą┐ąĄčĆąĖč乥čĆąĖąĖ (Peripheral Identifier), ąČąĄčüčéą║ąŠ ąĘą░ą┤ą░ąĮąĮąŠą╝čā ą┐čĆąĖ ą┐čĆąŠąĖąĘą▓ąŠą┤čüčéą▓ąĄ ą║čĆąĖčüčéą░ą╗ą╗ą░. ą×ą▒čŗčćąĮąŠ ąĮąŠą╝ąĄčĆ ą▒ąĖčéą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ąĮąŠą╝ąĄčĆčā ąĖčüč鹊čćąĮąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ąĮą░ąĘąĮą░č湥ąĮąĮąŠą╝čā ą┤ą╗čÅ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░.

[Programmable Clock Output Controller]

PMC čāą┐čĆą░ą▓ą╗čÅąĄčé 4 čüąĖą│ąĮą░ą╗ą░ą╝ąĖ, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠąČąĮąŠ ą▓čŗą▓ąĄčüčéąĖ ąĮą░ ą▓ąĮąĄčłąĮąĖąĄ ąĮąŠąČą║ąĖ ą║čĆąĖčüčéą░ą╗ą╗ą░ PCKx. ąÜą░ąČą┤čŗą╣ ąĖąĘ čŹčéąĖčģ čüąĖą│ąĮą░ą╗ąŠą▓ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ č湥čĆąĄąĘ čĆąĄą│ąĖčüčéčĆčŗ PMC_PCKx.

PCKx ą╝ąŠąČąĄčé ą▒čŗčéčī ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ ą╝ąĄą┤ą╗ąĄąĮąĮčāčÄ čéą░ą║č鹊ą▓čāčÄ čćą░čüč鹊čéčā (Slow clock), ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą║ ą▓čŗčģąŠą┤čā PLL ąĖą╗ąĖ ą║ ą▓čŗčģąŠą┤čā ą│ą╗ą░ą▓ąĮąŠą│ąŠ ą│ąĄąĮąĄčĆą░č鹊čĆą░ čéą░ą║č鹊ą▓ ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ ą┐ąŠą╗čÅ CSS ą▓ čĆąĄą│ąĖčüčéčĆąĄ PMC_PCKx. ąÜą░ąČą┤čŗą╣ ą▓čŗčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ ą╝ąŠąČąĄčé ą▒čŗčéčī čéą░ą║ąČąĄ ą┐ąŠą┤ąĄą╗ąĄąĮ ąĮą░ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé 1 .. 64 (ąĖąĘ čŹč鹊ą│ąŠ čĆčÅą┤ą░ ą▒ąĄčĆčāčéčüčÅ č鹊ą╗čīą║ąŠ č鹥 čćąĖčüą╗ą░, ą║ąŠč鹊čĆčŗąĄ čĆą░ą▓ąĮčŗ čüč鹥ą┐ąĄąĮąĖ 2) ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ ą▓ ą┐ąŠą╗ąĄ PRES (Prescaler) čĆąĄą│ąĖčüčéčĆą░ PMC_PCKx.

ąÜą░ąČą┤čŗą╣ ą▓čŗčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ ą╝ąŠąČąĄčé ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčēąĄąĮ ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ 1 ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé PCKx čĆąĄą│ąĖčüčéčĆąŠą▓ PMC_SCER ąĖ PMC_SCDR. ąóąĄą║čāčēąĄąĄ čüąŠčüč鹊čÅąĮąĖąĄ ą░ą║čéąĖą▓ąĮčŗčģ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗčģ čéą░ą║č鹊ą▓čŗčģ ą▓čŗčģąŠą┤ąŠą▓ ą╝ąŠąČąĮąŠ ą┐ąŠą╗čāčćąĖčéčī čćč鹥ąĮąĖąĄą╝ ą▒ąĖč鹊ą▓ PCKx čĆąĄą│ąĖčüčéčĆą░ PMC_SCSR (System Clock Status Register).

ąÜčĆąŠą╝ąĄ č鹊ą│ąŠ, ą║ą░ą║ ąĖ PCK, ą▒ąĖčé čüčéą░čéčāčüą░ ą▓ čĆąĄą│ąĖčüčéčĆąĄ PMC_SR ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮčŗ ą╗ąĖ ą▓ ą┤ąĄą╣čüčéą▓ąĖč鹥ą╗čīąĮąŠčüčéąĖ ą▒ąĖčéčŗ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ ą▓ čĆąĄą│ąĖčüčéčĆą░čģ Programmable Clock.

ą¤ąŠčüą║ąŠą╗čīą║čā Programmable Clock Controller ąĮąĄ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčé čüą║ą░čćą║ąĖ čäą░ąĘčŗ ą┐čĆąĖ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĖ čéą░ą║č鹊ą▓čŗčģ čćą░čüč鹊čé, č鹊 ą▓ąĄčüčīą╝ą░ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ąĘą░ą┐čĆąĄčéąĖčéčī Programmable Clock ą┐ąĄčĆąĄą┤ ą╗čÄą▒čŗą╝ąĖ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅą╝ąĖ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ, ąĖ ąĘą░č鹥ą╝ ąĘą░ąĮąŠą▓ąŠ čĆą░ąĘčĆąĄčłąĖčéčī ąĖčģ ą┐ąŠčüą╗ąĄ ąŠą║ąŠąĮčćą░ąĮąĖčÅ ą▓čüąĄčģ ą┤ąĄą╣čüčéą▓ąĖą╣ čĆąĄą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ.

[ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ]

1. ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ čĆą░ą▒ąŠčéčŗ Main Oscillator:

ąōą╗ą░ą▓ąĮčŗą╣ ą│ąĄąĮąĄčĆą░č鹊čĆ ą▒čāą┤ąĄčé čĆą░ąĘčĆąĄčłąĄąĮ ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ ą┐ąŠą╗čÅ MOSCEN ą▓ čĆąĄą│ąĖčüčéčĆąĄ CKGR_MOR. ąÆ ąĮąĄą║ąŠč鹊čĆčŗčģ čüą╗čāčćą░čÅčģ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠą╗ąĄąĘąĮąŠ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ą▓čĆąĄą╝čÅ ąĘą░ą┐čāčüą║ą░ (start-up time). ąŁč鹊 ą╝ąŠąČąĮąŠ čüą┤ąĄą╗ą░čéčī ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ ąĘąĮą░č湥ąĮąĖčÅ ą▓ ą┐ąŠą╗ąĄ OSCOUNT čĆąĄą│ąĖčüčéčĆą░ CKGR_MOR.

ąÜą░ą║ č鹊ą╗čīą║ąŠ čĆąĄą│ąĖčüčéčĆ ą▒čŗą╗ ą║ąŠčĆčĆąĄą║čéąĮąŠ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ, ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčüčé ą┤ąŠą╗ąČąĄąĮ ąČą┤ą░čéčī, ą┐ąŠą║ą░ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą┐ąŠą╗ąĄ MOSCS ą▓ čĆąĄą│ąĖčüčéčĆąĄ PMC_SR. ąŁč鹊 ą╝ąŠąČąĮąŠ čüą┤ąĄą╗ą░čéčī ą┐čāč鹥ą╝ ąŠą┐čĆąŠčüą░ čĆąĄą│ąĖčüčéčĆą░ čüčéą░čéčāčüą░ ąĖą╗ąĖ ą┐čāč鹥ą╝ ą┐ąŠą╗čāč湥ąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, čüą▓čÅąĘą░ąĮąĮąŠą│ąŠ čü MOSCS, čćč鹊 ą╝ąŠąČąĮąŠ čĆą░ąĘčĆąĄčłąĖčéčī ą▓ čĆąĄą│ąĖčüčéčĆąĄ PMC_IER. ą¤čĆąĖą╝ąĄčĆ ą║ąŠą┤ą░:

write_register(CKGR_MOR,0x00000701)

ąÆčĆąĄą╝čÅ ąĘą░ą┐čāčüą║ą░ čüąŠčüčéą░ą▓ąĖčé: Start Up Time = 8 * OSCOUNT / SLCK = 56 čåąĖą║ą╗ąŠą▓ ą╝ąĄą┤ą╗ąĄąĮąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ (Slow Clock).

ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą│ą╗ą░ą▓ąĮčŗą╣ ą│ąĄąĮąĄčĆą░č鹊čĆ ą▒čāą┤ąĄčé čĆą░ąĘčĆąĄčłąĄąĮ (ą▒ąĖčé MOSCS čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ) ą┐ąŠčüą╗ąĄ 56 čåąĖą║ą╗ąŠą▓ Slow Clock.

2. ą¤čĆąŠą▓ąĄčĆą║ą░ čćą░čüč鹊čéčŗ Main Oscillator (ąŠą┐čåąĖąŠąĮą░ą╗čīąĮą░čÅ ą┐čĆąŠčåąĄą┤čāčĆą░):

ąÆ ąĮąĄą║ąŠč鹊čĆčŗčģ čüąĖčéčāą░čåąĖčÅčģ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčüčéčā ąĮčāąČąĮąŠ č鹊čćąĮąŠ ąĖąĘą╝ąĄčĆąĖčéčī čćą░čüč鹊čéčā ą│ą╗ą░ą▓ąĮąŠą│ąŠ ą│ąĄąĮąĄčĆą░č鹊čĆą░. ąŁč鹊 ąĖąĘą╝ąĄčĆąĄąĮąĖąĄ ą╝ąŠąČąĮąŠ ąŠčüčāčēąĄčüčéą▓ąĖčéčī č湥čĆąĄąĘ čĆąĄą│ąĖčüčéčĆ CKGR_MCFR.

ąÜą░ą║ č鹊ą╗čīą║ąŠ ą┐ąŠą╗ąĄ MAINRDY ą▓ čĆąĄą│ąĖčüčéčĆąĄ CKGR_MCFR ą▒čāą┤ąĄčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ, ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą╝ąŠąČąĄčé ą┐čĆąŠčćąĖčéą░čéčī ą┐ąŠą╗ąĄ MAINF ą▓ čĆąĄą│ąĖčüčéčĆąĄ CKGR_MCFR. ąŁč鹊 ą┐ąŠą╗ąĄ ą┐čĆąĄą┤ąŠčüčéą░ą▓ąĖčé ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čåąĖą║ą╗ąŠą▓ ąŠčüąĮąŠą▓ąĮąŠą╣ čćą░čüč鹊čéčŗ ąĘą░ 16 čåąĖą║ą╗ąŠą▓ ą╝ąĄą┤ą╗ąĄąĮąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ.

3. ąŻčüčéą░ąĮąŠą▓ą║ą░ PLL ąĖ ą┤ąĄą╗ąĖč鹥ą╗čÅ čćą░čüč鹊čéčŗ:

ąÆčüąĄ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ, ą║ąŠč鹊čĆčŗąĄ ąĮčāąČąĮčŗ ą┤ą╗čÅ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ PLL ąĖ ą┤ąĄą╗ąĖč鹥ą╗čÅ čĆą░ąĘą╝ąĄčēąĄąĮčŗ ą▓ čĆąĄą│ąĖčüčéčĆąĄ CKGR_PLLR.

ą¤ąŠą╗ąĄ DIV ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┤ąĄą╗ąĖč鹥ą╗ąĄą╝, čüčÄą┤ą░ ą╝ąŠąČąĮąŠ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī ąŚąĮą░č湥ąĮąĖąĄ ąŠčé 0 ą┤ąŠ 255. ąÆčŗčģąŠą┤ ą┤ąĄą╗ąĖč鹥ą╗čÅ ą┐ąŠą╗čāčćąĖčé čćą░čüč鹊čéčā ą▓čģąŠą┤ą░ ą┐ąŠą┤ąĄą╗ąĄąĮąĮčāčÄ ąĮą░ ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠą╗čÅ DIV. ą¤ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ DIV čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 0, čćč鹊 čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ą▓čŗą║ą╗čÄč湥ąĮąĮąŠą╝čā ą┤ąĄą╗ąĖč鹥ą╗čÄ.

ą¤ąŠą╗ąĄ OUT ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą░ čćą░čüč鹊čéąĮąŠą│ąŠ ą┤ąĖą░ą┐ą░ąĘąŠąĮą░ PLL B.

ą¤ąŠą╗ąĄ MUL ąĘą░ą┤ą░ąĄčé ą╝ąĮąŠąČąĖč鹥ą╗čī čćą░čüč鹊čéčŗ PLL. ąŁč鹊čé ą┐ą░čĆą░ą╝ąĄčéčĆ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąŠčé 0 ą┤ąŠ 2047. ąĢčüą╗ąĖ MUL čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 0, č鹊 PLL ą▓čŗą║ą╗čÄč湥ąĮą░, ąĖąĮą░č湥 ą▓čŗčģąŠą┤ąĮą░čÅ čćą░čüč鹊čéą░ PLL čĆą░ą▓ąĮą░ ą▓čģąŠą┤ąĮąŠą╣ čćą░čüč鹊č鹥 PLL, čāą╝ąĮąŠąČąĄąĮąĮąŠą╣ ąĮą░ (MUL+1).

ą¤ąŠą╗ąĄ PLLCOUNT čāą║ą░ąĘčŗą▓ą░ąĄčé ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čåąĖą║ą╗ąŠą▓ ą╝ąĄą┤ą╗ąĄąĮąĮčŗčģ čéą░ą║č鹊ą▓ ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé LOCK ą▓ čĆąĄą│ąĖčüčéčĆąĄ PMC_SR, ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ ą║ą░ą║ ą▒čāą┤ąĄčé ąĘą░ą┐ąĖčüą░ąĮ čĆąĄą│ąĖčüčéčĆ CKGR_PLLR.

ąÜą░ą║ č鹊ą╗čīą║ąŠ ąĘą░ą┐ąĖčüą░ąĮ čĆąĄą│ąĖčüčéčĆ PMC_PLL, ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą┤ąŠą╗ąČąĄąĮ ą▓ ą┐čĆąŠą│čĆą░ą╝ą╝ąĄ ąŠąČąĖą┤ą░čéčī čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ LOCK ą▓ čĆąĄą│ąĖčüčéčĆąĄ PMC_SR. ąŁč鹊 ą╝ąŠąČąĮąŠ čüą┤ąĄą╗ą░čéčī ą╗ąĖą▒ąŠ čåąĖą║ą╗ą░ą╝ąĖ ąŠą┐čĆąŠčüą░, ą╗ąĖą▒ąŠ ąŠąČąĖą┤ą░ąĮąĖąĄą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ąĄčüą╗ąĖ čĆą░ąĘčĆąĄčłąĄąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čāčüčéą░ąĮąŠą▓ą║ąĄ ą▒ąĖčéą░ LOCK (čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ čŹč鹊ą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ąĄą╗ą░ąĄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ PMC_IER). ąÆčüąĄ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ ą▓ CKGR_PLLR ą╝ąŠą│čāčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮčŗ ąŠą┤ąĖąĮąŠčćąĮąŠą╣ ąŠą┐ąĄčĆą░čåąĖąĄą╣ ąĘą░ą┐ąĖčüąĖ. ąĢčüą╗ąĖ ąĮą░ ąĮąĄą║ąŠč鹊čĆąŠą╝ čŹčéą░ą┐ąĄ ąĖąĘą╝ąĄąĮąĄąĮčŗ ą┐ąŠą╗čÅ MUL ąĖ/ąĖą╗ąĖ DIV, ą▒ąĖčé LOCK ą┐ąĄčĆąĄą╣ą┤ąĄčé ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ą╗ąŠą│. 0, čćč鹊 ą┐ąŠą║ą░ąČąĄčé ąĮąĄą│ąŠč鹊ą▓ąĮąŠčüčéčī PLL. ąÜąŠą│ą┤ą░ ąĘą░čģą▓ą░čé PLL ą┐čĆąŠąĖąĘąŠčłąĄą╗, ą▒ąĖčé LOCK čüąĮąŠą▓ą░ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ. ą¤ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ąŠą│čĆą░ąĮąĖč湥ąĮ ąŠąČąĖą┤ą░čéčī čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ LOCK, ą┐ąĄčĆąĄą┤ č鹥ą╝ ą║ą░ą║ ąŠąĮ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą▓čŗčģąŠą┤ čéą░ą║č鹊ą▓ PLL.

ą¤ąŠą╗ąĄ USBDIV ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗą╝ ą┤ąĄą╗ąĖč鹥ą╗ąĄą╝ ąĮą░ 1, 2 ąĖą╗ąĖ 4 ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ čéą░ą║č鹊ą▓ USB.

ą¤čĆąĖą╝ąĄčĆ ą║ąŠą┤ą░:

write_register(CKGR_PLLR,0x00040805)

ąĢčüą╗ąĖ PLL ąĖ ą┤ąĄą╗ąĖč鹥ą╗čī čĆą░ąĘčĆąĄčłąĄąĮčŗ, č鹊 ą▓čģąŠą┤ąĮą░čÅ čćą░čüč鹊čéą░ PLL čĆą░ą▓ąĮą░ ą│ą╗ą░ą▓ąĮąŠą╣ čćą░čüč鹊č鹥 (main clock). ąÆčŗčģąŠą┤ąĮą░čÅ čćą░čüč鹊čéą░ PLL čĆą░ą▓ąĮą░ ą▓čģąŠą┤ąĮąŠą╣ čćą░čüč鹊č鹥, čāą╝ąĮąŠąČąĄąĮąĮąŠą╣ ąĮą░ 5. ąÜą░ą║ č鹊ą╗čīą║ąŠ ąĘą░ą┐ąĖčüą░ąĮ čĆąĄą│ąĖčüčéčĆ CKGR_PLLR, ą▒ąĖčé LOCK čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą┐ąŠčüą╗ąĄ 8 čåąĖą║ą╗ąŠą▓ ą╝ąĄą┤ą╗ąĄąĮąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ.

4. ąÆčŗą▒ąŠčĆ čćą░čüč鹊čé Master Clock (MCK) ąĖ Processor Clock (PCK)

ą¦ą░čüč鹊čéčŗ MCK ąĖ PCK ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāčÄčéčüčÅ č湥čĆąĄąĘ čĆąĄą│ąĖčüčéčĆ PMC_MCKR.

ą¤ąŠą╗ąĄ CSS ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą░ ąĖčüč鹊čćąĮąĖą║ą░ ą┤ąĄą╗ąĖč鹥ą╗čÅ ą┤ą╗čÅ MCK. ą¤ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą▓čŗą▒čĆą░ąĮą░ ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖčüč鹊čćąĮąĖą║ą░ ą╝ąĄą┤ą╗ąĄąĮąĮą░čÅ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░.

ą¤ąŠą╗ąĄ PRES ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐čĆąĄčüą║ą░ą╗ąĄčĆąŠą╝ MCK. ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčüčé ą╝ąŠąČąĄčé ą▓čŗą▒čĆą░čéčī ąŠą┤ąĮąŠ ąĖąĘ čĆčÅą┤ą░ ąĘąĮą░č湥ąĮąĖą╣ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéą░ ą┤ąĄą╗ąĄąĮąĖčÅ (1, 2, 4, 8, 16, 32, 64). ąÆčŗčģąŠą┤ąĮą░čÅ čćą░čüč鹊čéą░ MCK čĆą░ą▓ąĮą░ ą▓čģąŠą┤ąĮąŠą╣ čćą░čüč鹊č鹥 ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░, ą┤ąĄą╗ąĄąĮąĮąŠą╣ ąĮą░ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ą▓ ą┐ą░čĆą░ą╝ąĄčéčĆąĄ PRES. ą¤ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ PRES čĆą░ą▓ąĄąĮ 1, čćč鹊 ąŠąĘąĮą░čćą░ąĄčé ąŠčéčüčāčéčüčéą▓ąĖąĄ ą┤ąĄą╗ąĄąĮąĖčÅ, ąĖ ą│ą╗ą░ą▓ąĮą░čÅ čćą░čüč鹊čéą░ ą▒čāą┤ąĄčé čĆą░ą▓ąĮą░ ą╝ąĄą┤ą╗ąĄąĮąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊č鹥.

ąÜą░ą║ č鹊ą╗čīą║ąŠ ąĘą░ą┐ąĖčüą░ąĮ čĆąĄą│ąĖčüčéčĆ PMC_MCKR, ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą┤ąŠą╗ąČąĄąĮ ą▓ ą┐čĆąŠą│čĆą░ą╝ą╝ąĄ ąŠąČąĖą┤ą░čéčī čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ MCKRDY ą▓ čĆąĄą│ąĖčüčéčĆąĄ PMC_SR. ąŁč鹊 ą╝ąŠąČąĮąŠ čüą┤ąĄą╗ą░čéčī ą╗ąĖą▒ąŠ čåąĖą║ą╗ą░ą╝ąĖ ąŠą┐čĆąŠčüą░, ą╗ąĖą▒ąŠ ąŠąČąĖą┤ą░ąĮąĖąĄą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ąĄčüą╗ąĖ čĆą░ąĘčĆąĄčłąĄąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čāčüčéą░ąĮąŠą▓ą║ąĄ ą▒ąĖčéą░ MCKRDY (čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ čŹč鹊ą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ąĄą╗ą░ąĄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ PMC_IER). ąĀąĄą│ąĖčüčéčĆ PMC_MCKR ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ ąŠą┤ąĮąŠą╣ ąŠą┐ąĄčĆą░čåąĖąĄą╣ ąĘą░ą┐ąĖčüąĖ. ąÆąŠčé čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄą╝ą░čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┤ą╗čÅ čĆąĄą│ąĖčüčéčĆą░ PMC_MCKR:

ŌĆó ąĢčüą╗ąĖ ąĮąŠą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┤ą╗čÅ ą┐ąŠą╗čÅ CSS čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé čéą░ą║čéą░ą╝ PLL,

ŌĆō ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī ą┐ąŠą╗ąĄ PRES ą▓ čĆąĄą│ąĖčüčéčĆąĄ PMC_MCKR.

ŌĆō ąČą┤ą░čéčī čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ MCKRDY ą▓ čĆąĄą│ąĖčüčéčĆąĄ PMC_SR.

ŌĆō ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī ą┐ąŠą╗ąĄ CSS ą▓ čĆąĄą│ąĖčüčéčĆąĄ PMC_MCKR.

ŌĆō ąČą┤ą░čéčī čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ MCKRDY ą▓ čĆąĄą│ąĖčüčéčĆąĄ PMC_SR.

ŌĆó ąĢčüą╗ąĖ ąĮąŠą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┤ą╗čÅ ą┐ąŠą╗čÅ CSS čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé čéą░ą║čéą░ą╝ Main Clock ąĖą╗ąĖ Slow Clock,

ŌĆō ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī ą┐ąŠą╗ąĄ CSS ą▓ čĆąĄą│ąĖčüčéčĆąĄ PMC_MCKR.

ŌĆō ąČą┤ą░čéčī čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ MCKRDY ą▓ čĆąĄą│ąĖčüčéčĆąĄ PMC_SR.

ŌĆō ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī ą┐ąŠą╗ąĄ PRES ą▓ čĆąĄą│ąĖčüčéčĆąĄ PMC_MCKR.

ŌĆō ąČą┤ą░čéčī čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ MCKRDY ą▓ čĆąĄą│ąĖčüčéčĆąĄ PMC_SR.

ąĢčüą╗ąĖ ąĮą░ ąĮąĄą║ąŠč鹊čĆąŠą╝ čłą░ą│ąĄ ąŠą┤ąĖąĮ ąĖąĘ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓ CSS ąĖą╗ąĖ PRES ą▒čāą┤ąĄčé ąĖąĘą╝ąĄąĮąĄąĮ, ą▒ąĖčé MCKRDY ą┐ąĄčĆąĄą╣ą┤ąĄčé ą▓ ąĘąĮą░č湥ąĮąĖąĄ ą╗ąŠą│. 0, čćč鹊 ą┐ąŠą║ą░ąČąĄčé č鹥ą║čāčēčāčÄ ąĮąĄą│ąŠč鹊ą▓ąĮąŠčüčéčī MCK ąĖ PCK. ą¤ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą┤ąŠą╗ąČąĄąĮ ąČą┤ą░čéčī, ą┐ąŠą║ą░ ą▒ąĖčé MCKRDY čüąĮąŠą▓ą░ ąĮąĄ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▓ ą╗ąŠą│. 1, ą┐ąĄčĆąĄą┤ č鹥ą╝ ą║ą░ą║ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čéą░ą║čéčŗ MCK ąĖ PCK.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĄčüą╗ąĖ čéą░ą║č鹊ą▓čŗą╣ ą▓čŗčģąŠą┤ PLLx ą▒čŗą╗ ą▓čŗą▒čĆą░ąĮ ą║ą░ą║ MCK, ąĖ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī čĆąĄčłąĖą╗ ą╝ąŠą┤ąĖčäąĖčåąĖčĆąŠą▓ą░čéčī čŹč鹊 ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ ą▓ čĆąĄą│ąĖčüčéčĆ CKGR_PLLR, č鹊 čäą╗ą░ą│ MCKRDY ą┐ąĄčĆąĄą╣ą┤ąĄčé ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ą╗ąŠą│. 0, ąĮą░ ą▓čĆąĄą╝čÅ, ą┐ąŠą║ą░ čåąĄą┐čī PLL čĆą░ąĘąŠčĆą▓ą░ąĮą░. ąÜą░ą║ č鹊ą╗čīą║ąŠ PLL čüąĮąŠą▓ą░ ąĘą░čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆąŠą▓ą░ą╗ą░čüčī, čāčüčéą░ąĮąŠą▓čÅčéčüčÅ ą▒ąĖčéčŗ LOCK ąĖ MCKRDY. ąÜąŠą│ą┤ą░ PLL ąĮąĄ čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆąŠą▓ą░ąĮą░, ą▓čŗą▒ąŠčĆ MCK ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą┐ąĄčĆąĄčģąŠą┤ąĖčé ąĮą░ čćą░čüč鹊čéčā Main Clock. ąöą╗čÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ čüą╝. čüąĄą║čåąĖčÄ 25.8.2. ą┤ą░čéą░čłąĖčéą░ "Clock Switching Waveforms".

ą¤čĆąĖą╝ąĄčĆ ą║ąŠą┤ą░:

write_register(PMC_MCKR,0x00000001)

wait (MCKRDY=1)

write_register(PMC_MCKR,0x00000011)

wait (MCKRDY=1)

ą¤ąŠčüą╗ąĄ čŹčéąĖčģ ąŠą┐ąĄčĆą░čåąĖą╣ čćą░čüč鹊čéą░ MCK čĆą░ą▓ąĮą░ ą│ą╗ą░ą▓ąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊č鹥 (main clock), ą┐ąŠą┤ąĄą╗ąĄąĮąĮąŠą╣ ąĮą░ 16. ą¦ą░čüč鹊čéą░ PCK čĆą░ą▓ąĮą░ čćą░čüč鹊č鹥 MCK.

5. ąÆčŗą▒ąŠčĆ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗčģ čéą░ą║č鹊ą▓ (Programmable clocks)

ąÜą░ą║ čāąČąĄ čāą┐ąŠą╝ąĖąĮą░ą╗ąŠčüčī, ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗąĄ čéą░ą║č鹊ą▓čŗąĄ čćą░čüč鹊čéčŗ čāą┐čĆą░ą▓ą╗čÅčÄčéčüčÅ čĆąĄą│ąĖčüčéčĆą░ą╝ąĖ PMC_SCER, PMC_SCDR ąĖ PMC_SCSR. ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗąĄ čéą░ą║čéčŗ ą╝ąŠą│čāčé ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮčŗ ąĖ/ąĖą╗ąĖ ąĘą░ą┐čĆąĄčēąĄąĮčŗ čĆąĄą│ąĖčüčéčĆą░ą╝ąĖ PMC_SCER ąĖ PMC_SCDR čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ. ąÆ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ąŠą╣ čüąĖčüč鹥ą╝čŗ, ą╝ąŠą│čāčé ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮčŗ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčēąĄąĮčŗ 4 ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗčģ čéą░ą║č鹊ą▓čŗčģ ą▓čŗčģąŠą┤ą░. ąĀąĄą│ąĖčüčéčĆ PMC_SCSR ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé čÅčüąĮčāčÄ ąĖąĮą┤ąĖą║ą░čåąĖčÄ, ą║ą░ą║ą░čÅ ąĖąĘ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗčģ čćą░čüč鹊čé čĆą░ąĘčĆąĄčłąĄąĮą░. ą¤ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ąĘą░ą┐čĆąĄčēąĄąĮčŗ ą▓čüąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗąĄ čéą░ą║čéčŗ. ąĀąĄą│ąĖčüčéčĆčŗ PMC_PCKx ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗčģ čéą░ą║č鹊ą▓.

ą¤ąŠą╗ąĄ CSS ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą░ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ ą┤ą╗čÅ ą┤ąĄą╗ąĖč鹥ą╗čÅ. ąöąŠčüčéčāą┐ąĮąŠ 4 ą▓ą░čĆąĖą░ąĮčéą░ čéą░ą║č鹊ą▓: ą▓čŗą║ą╗čÄč湥ąĮąŠ, main clock, slow clock, PLLCK. ą¤ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ąĘą░ą┤ą░ąĮ ą▓čŗą▒ąŠčĆ ą╝ąĄą┤ą╗ąĄąĮąĮčŗčģ čéą░ą║č鹊ą▓ (slow clock).

ą¤ąŠą╗ąĄ PRES ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐čĆąĄčüą║ą░ą╗ąĄčĆąŠą╝. ą£ąŠąČąĮąŠ ą▓čŗą▒čĆą░čéčī ąŠą┤ąĮąŠ ąĖąĘ ąĘąĮą░č湥ąĮąĖą╣ ą┤ąĄą╗ąĖč鹥ą╗čÅ (1, 2, 4, 8, 16, 32, 64). ąóą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ ą┤ą╗čÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗčģ ą▓čŗčģąŠą┤ąŠą▓ čéą░ą║č鹊ą▓ čĆą░ą▓ąĮą░ ą▓čģąŠą┤ąĮąŠą╣ čćą░čüč鹊č鹥 ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░, ą┐ąŠą┤ąĄą╗ąĄąĮąĮąŠą╣ ąĮą░ ą┐ą░čĆą░ą╝ąĄčéčĆ PRES. ą¤ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą┐ą░čĆą░ą╝ąĄčéčĆ PRES čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1, čćč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ą│ą╗ą░ą▓ąĮą░čÅ čćą░čüč鹊čéą░ čĆą░ą▓ąĮą░ ą╝ąĄą┤ą╗ąĄąĮąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊č鹥.

ąÜą░ą║ č鹊ą╗čīą║ąŠ čĆąĄą│ąĖčüčéčĆ PMC_PCKx ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ, čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēą░čÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝ą░čÅ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮą░, ąĖ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą┤ąŠą╗ąČąĄąĮ ąŠąČąĖą┤ą░čéčī čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ PCKRDYx ą▓ čĆąĄą│ąĖčüčéčĆąĄ PMC_SR. ąÜą░ą║ ąŠą▒čŗčćąĮąŠ, čŹč鹊 ą╝ąŠąČąĮąŠ čüą┤ąĄą╗ą░čéčī čåąĖą║ą╗ą░ą╝ąĖ ąŠą┐čĆąŠčüą░, ą╗ąĖą▒ąŠ ąŠąČąĖą┤ą░ąĮąĖąĄą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, čüą▓čÅąĘą░ąĮąĮąŠą│ąŠ čü ą▒ąĖč鹊ą╝ PCKRDYx (čćč鹊 čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ ą▓ č湥čĆąĄąĘ čĆąĄą│ąĖčüčéčĆ PMC_IER). ąÆčüąĄ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ ą▓ PMC_PCKx ą╝ąŠą│čāčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮčŗ ąĘą░ ąŠą┤ąĮčā ąŠą┐ąĄčĆą░čåąĖčÄ ąĘą░ą┐ąĖčüąĖ.

ąĢčüą╗ąĖ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą╝ąŠą┤ąĖčäąĖčåąĖčĆąŠą▓ą░ąĮčŗ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ CSS ąĖ PRES, č鹊 čüąĮą░čćą░ą╗ą░ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ą┐čĆąĄčēąĄąĮ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗą╣ čéą░ą║č鹊ą▓čŗą╣ ą▓čŗčģąŠą┤. ąŚą░č鹥ą╝ ą╝ąŠąČąĮąŠ ą╝ąĄąĮčÅčéčī ą┐ą░čĆą░ą╝ąĄčéčĆčŗ CSS ąĖ PRES. ąÜą░ą║ č鹊ą╗čīą║ąŠ čŹč鹊 čüą┤ąĄą╗ą░ąĮąŠ, ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą┤ąŠą╗ąČąĄąĮ ąĘą░ąĮąŠą▓ąŠ čĆą░ąĘčĆąĄčłąĖčéčī ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗą╣ ą▓čŗčģąŠą┤ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ, ąĖ ąČą┤ą░čéčī, ą┐ąŠą║ą░ ąĮąĄ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé PCKRDYx.

ą¤čĆąĖą╝ąĄčĆ ą║ąŠą┤ą░:

write_register(PMC_PCK0,0x00000015)

ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗą╣ ą▓čŗčģąŠą┤ 0 ą▓čŗą┤ą░ąĄčé ą│ą╗ą░ą▓ąĮčāčÄ čéą░ą║č鹊ą▓čāčÄ čćą░čüč鹊čéčā (main clock), ą┐ąŠą┤ąĄą╗ąĄąĮąĮčāčÄ ąĮą░ 32.

6. ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓

ąÜą░ą║ č鹊ą╗čīą║ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮčŗ ą▓čüąĄ ą┐čĆąĄą┤čŗą┤čāčēąĖąĄ čłą░ą│ąĖ ą┐ąŠ ąĮą░čüčéčĆąŠą╣ą║ąĄ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ, ą╝ąŠą│čāčé ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮčŗ ąĖ/ąĖą╗ąĖ ąĘą░ą┐čĆąĄčēąĄąĮčŗ čéą░ą║č鹊ą▓čŗąĄ čćą░čüč鹊čéčŗ ą┤ą╗čÅ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ą║čĆąĖčüčéą░ą╗ą╗ą░ č湥čĆąĄąĘ čĆąĄą│ąĖčüčéčĆčŗ PMC_PCER ąĖ PMC_PCDR čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ.

ąÆ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ąŠą╣ čüąĖčüč鹥ą╝čŗ, ą╝ąŠąČąĄčé ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮąŠ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčēąĄąĮąŠ ą┤ąŠ čĆą░ąĘą╗ąĖčćąĮčŗčģ 15 čéą░ą║č鹊ą▓čŗčģ čćą░čüč鹊čé ą┐ąĄčĆąĖč乥čĆąĖąĖ. ąĀąĄą│ąĖčüčéčĆ PMC_PCSR ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé čÅčüąĮčāčÄ ąĖąĮč乊čĆą╝ą░čåąĖčÄ ąŠ č鹊ą╝, ą║ą░ą║ąĖąĄ ąĖąĘ čćą░čüč鹊čé čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐ąĄčĆąĖč乥čĆąĖąĖ čĆą░ąĘčĆąĄčłąĄąĮčŗ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą║ą░ąČą┤ą░čÅ čĆą░ąĘčĆąĄčłąĄąĮąĮą░čÅ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ ą┐ąĄčĆąĖč乥čĆąĖąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé MCK.

ą¤čĆąĖą╝ąĄčĆ ą║ąŠą┤ą░:

//ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ 4 ąĖ 8:

write_register(PMC_PCER,0x00000110)//ąŚą░ą┐čĆąĄčé čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐ąĄčĆąĖč乥čĆąĖąĖ 4:

write_register(PMC_PCDR,0x00000010)

ąÆčĆąĄą╝ąĄąĮąĮčŗąĄ ą┤ąĖą░ą│čĆą░ą╝ą╝čŗ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ čéą░ą║č鹊ą▓čŗčģ čćą░čüč鹊čé ąĖ ąĖčģ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ čüą╝. ą▓ čĆą░ąĘą┤ąĄą╗ąĄ 25.8 "Clock Switching Details" ą┤ą░čéą░čłąĖčéą░ ąĮą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ. ą░ą┤čĆąĄčüą░ čĆąĄą│ąĖčüčéčĆąŠą▓ PMC ąĖ ą┐ąŠą┤čĆąŠą▒ąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ ąĖčģ ą▒ąĖč鹊ą▓ čüą╝. ą▓ čĆą░ąĘą┤ąĄą╗ąĄ 25.9 "Power Management Controller (PMC) User Interface".

[ąĪčüčŗą╗ą║ąĖ]

1. IAR EW ARM: ą│ą┤ąĄ ąĘą░ą┤ą░čÄčéčüčÅ čåąĖą║ą╗čŗ ąŠąČąĖą┤ą░ąĮąĖčÅ (wait state) ą┐čĆąĖ čĆą░ą▒ąŠč鹥 čü flash.

2. ą¤ąĖčéą░ąĮąĖąĄ AT91SAM7X, čĆąĄąČąĖą╝čŗ ą┐ąŠąĮąĖąČąĄąĮąĮąŠą│ąŠ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ. |