|

ąŚą┤ąĄčüčī ą┐ąĄčĆąĄą▓ąĄą┤ąĄąĮ ą┐ąĄčĆąĄą▓ąŠą┤ čĆą░ąĘą┤ąĄą╗ą░ ą┤ą░čéą░čłąĖčéą░ [1], ą┐ąŠčüą▓čÅčēąĄąĮąĮąŠą│ąŠ čéą░ą╣ą╝ąĄčĆčā/čüč湥čéčćąĖą║čā (Timer Counter, čüąŠą║čĆą░čēąĄąĮąĮąŠ TC).

TC ą▓ą║ą╗čÄčćą░ąĄčé čéčĆąĖ ąĖą┤ąĄąĮčéąĖčćąĮčŗčģ 16-ą▒ąĖčéąĮčŗčģ ą║ą░ąĮą░ą╗ą░ čéą░ą╣ą╝ąĄčĆą░/čüč湥čéčćąĖą║ą░. ąÜą░ąČą┤čŗą╣ ą║ą░ąĮą░ą╗ ą╝ąŠąČąĮąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé ą┤čĆčāą│ąĖčģ, čćč鹊ą▒čŗ ąŠąĮąĖ ą▓čŗą┐ąŠą╗ąĮčÅą╗ąĖ čłąĖčĆąŠą║ąĖą╣ čüą┐ąĄą║čéčĆ ą┐čĆąĖą║ą╗ą░ą┤ąĮčŗčģ čäčāąĮą║čåąĖą╣, čéą░ą║ąĖčģ ą║ą░ą║ ąĖąĘą╝ąĄčĆąĄąĮąĖąĄ čćą░čüč鹊čéčŗ, ą┐ąŠą┤čüč湥čé čüąŠą▒čŗčéąĖą╣, ąĖąĘą╝ąĄčĆąĄąĮąĖąĄ ąĖąĮč鹥čĆą▓ą░ą╗ąŠą▓ ą▓čĆąĄą╝ąĄąĮąĖ, ą│ąĄąĮąĄčĆą░čåąĖčÅ ąĖą╝ą┐čāą╗čīčüąŠą▓, č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ ąĘą░ą┤ąĄčƹȹĄą║ ąĖ ą│ąĄąĮąĄčĆą░čåąĖčÅ ą©ąśą£ (pulse width modulation, PWM).

ąŻ ą║ą░ąČą┤ąŠą│ąŠ ą║ą░ąĮą░ą╗ą░ ąĖą╝ąĄąĄčéčüčÅ čéčĆąĖ ą▓ąĮąĄčłąĮąĖčģ čéą░ą║č鹊ą▓čŗčģ ą▓čģąŠą┤ą░, ą┐čÅčéčī ą▓ąĮčāčéčĆąĄąĮąĮąĖčģ čéą░ą║č鹊ą▓čŗčģ ą▓čģąŠą┤ąŠą▓ ąĖ ą┤ą▓ą░ ą╝ąĮąŠą│ąŠčäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮčŗčģ ą▓čģąŠą┤ąĮčŗčģ/ą▓čŗčģąŠą┤ąĮčŗčģ čüąĖą│ąĮą░ą╗ą░, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠąČąĮąŠ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╝. ąÜą░ąČą┤čŗą╣ ą║ą░ąĮą░ą╗ čāą┐čĆą░ą▓ą╗čÅąĄčé ą▓ąĮčāčéčĆąĄąĮąĮąĖą╝ čüąĖą│ąĮą░ą╗ąŠą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą║ąŠč鹊čĆčŗą╣ ą╝ąŠąČąĮąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą┐čĆąŠčåąĄčüčüąŠčĆą░.

ąæą╗ąŠą║ TC ąĖą╝ąĄąĄčé ą┤ą▓ą░ ą│ą╗ąŠą▒ą░ą╗čīąĮčŗčģ čĆąĄą│ąĖčüčéčĆą░, ą║ąŠč鹊čĆčŗą╣ ąŠčéąĮąŠčüąĖčéčüčÅ ą║ąŠ ą▓čüąĄą╝ čéčĆąĄą╝ ą║ą░ąĮą░ą╗ą░ą╝ TC. Block Control Register ą┐ąŠąĘą▓ąŠą╗čÅąĄčé čéčĆąĄą╝ ą║ą░ąĮą░ą╗ą░ą╝ ąĘą░ą┐čāčüčéąĖčéčīčüčÅ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ąŠą┤ąĮąŠą╣ ąĖąĮčüčéčĆčāą║čåąĖąĄą╣. Block Mode Register ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ą▓ąĮąĄčłąĮąĖąĄ ą▓čģąŠą┤čŗ čéą░ą║č鹊ą▓ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą║ą░ąĮą░ą╗ą░, ą┐ąŠąĘą▓ąŠą╗čÅčÅ čüąŠąĄą┤ąĖąĮčÅčéčī ąĖčģ ą▓ čåąĄą┐ąŠčćą║čā.

ąóą░ą▒ą╗ąĖčåą░ 32-1 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą┐čĆąĖčüą▓ąŠąĄąĮąĖąĄ ą▓čģąŠą┤ąŠą▓ čéą░ą║č鹊ą▓ TC ą║ą░ąĮą░ą╗ą░ą╝ 0..2.

ąóą░ą▒ą╗ąĖčåą░ 32-1. ąØą░ąĘąĮą░č湥ąĮąĖąĄ čéą░ą║č鹊ą▓ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ąŠą▓ TC.

| ąśą╝čÅ |

ą×ą┐čĆąĄą┤ąĄą╗ąĄąĮąĖąĄ |

| TIMER_CLOCK1 |

MCK/2 |

| TIMER_CLOCK2 |

MCK/8 |

| TIMER_CLOCK3 |

MCK/32 |

| TIMER_CLOCK4 |

MCK/128 |

| TIMER_CLOCK5 |

MCK/1024 |

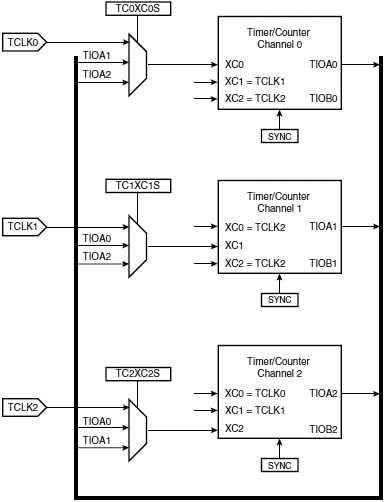

ąØą░ čĆąĖčüčāąĮą║ąĄ ą┐ąŠą║ą░ąĘą░ąĮą░ ą▒ą╗ąŠą║-čüčģąĄą╝ą░ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ TC.

ąĀąĖčü. 32-1. ąæą╗ąŠą║-čüčģąĄą╝ą░ Timer Counter.

ąóą░ą▒ą╗ąĖčåą░ 32-2. ą×ą┐ąĖčüą░ąĮąĖąĄ ąĖą╝ąĄąĮ čüąĖą│ąĮą░ą╗ąŠą▓.

| ąæą╗ąŠą║/ą║ą░ąĮą░ą╗ |

ąśą╝čÅ čüąĖą│ąĮą░ą╗ą░ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| ąĪąĖą│ąĮą░ą╗ ą║ą░ąĮą░ą╗ą░ |

XC0, XC1, XC2 |

ąÆčģąŠą┤čŗ ą▓ąĮąĄčłąĮąĄą│ąŠ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ |

| TIOA |

Capture Mode: ą▓čģąŠą┤ čéą░ą╣ą╝ąĄčĆą░/čüč湥čéčćąĖą║ą░

Waveform Mode: ą▓čŗčģąŠą┤ čéą░ą╣ą╝ąĄčĆą░/čüč湥čéčćąĖą║ą░ |

| TIOB |

Capture Mode: ą▓čģąŠą┤ čéą░ą╣ą╝ąĄčĆą░/čüč湥čéčćąĖą║ą░

Waveform Mode: ą▓čģąŠą┤ ąĖą╗ąĖ ą▓čŗčģąŠą┤ čéą░ą╣ą╝ąĄčĆą░/čüč湥čéčćąĖą║ą░ |

| INT |

ąÆčŗčģąŠą┤ čüąĖą│ąĮą░ą╗ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ |

| SYNC |

ąÆčģąŠą┤ čüąĖą│ąĮą░ą╗ą░ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ |

ąóą░ą▒ą╗ąĖčåą░ 32-3. ąĪą┐ąĖčüąŠą║ ą▓čŗą▓ąŠą┤ąŠą▓ TC.

| ąśą╝čÅ ą▓čŗą▓ąŠą┤ą░ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

ąóąĖą┐ |

| TCLK0-TCLK2 |

ąÆčģąŠą┤ ą▓ąĮąĄčłąĮąĖčģ čéą░ą║č鹊ą▓ |

ąÆčģąŠą┤ |

| TIOA0-TIOA2 |

I/O Line A |

I/O (ą▓čģąŠą┤/ą▓čŗčģąŠą┤) |

| TIOB0-TIOB2 |

I/O Line B |

I/O (ą▓čģąŠą┤/ą▓čŗčģąŠą┤) |

[ąŚą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ TC]

ąĪąĖą│ąĮą░ą╗čŗ I/O. ąŁčéąĖ ąĮąŠąČą║ąĖ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ čüąŠą▓ą╝ąĄčüčéąĖą╝čŗčģ ą▓ąĮąĄčłąĮąĖčģ čāčüčéčĆąŠą╣čüčéą▓, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠą│čāčé ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąĖčĆąŠą▓ą░čéčīčüčÅ čü čüąĖą│ąĮą░ą╗ą░ą╝ąĖ PIO. ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčüčé čüąĮą░čćą░ą╗ą░ ą┤ąŠą╗ąČąĄąĮ ąĮą░čüčéčĆąŠąĖčéčī ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčŗ PIO, čćč鹊ą▒čŗ ą┐čĆąĖčüą▓ąŠąĖčéčī ą▓čŗą▓ąŠą┤čŗ TC ąĖčģ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ čäčāąĮą║čåąĖčÅą╝ [4].

ą£ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčŗ AT91SAM7X ą┐ąŠčüčéą░ą▓ą╗čÅčÄčéčüčÅ ą▓ ą║ąŠčĆą┐čāčüą░čģ LQFP100 ąĖ TFBGA100.

ą£čāą╗čīčéąĖą┐ą╗ąĄą║čüąĖčĆąŠą▓ą░ąĮąĖąĄ ąĮąŠąČąĄą║ TC ąĮą░ PIO-ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąĄ A:

| ąśą╝čÅ ą┐ąŠčĆčéą░ |

ąØąŠą╝ąĄčĆ ą▓čŗą▓ąŠą┤ą░ |

Peripheral A |

Peripheral B |

| LQFP100 |

TFBGA100 |

| PA15 |

23 |

C10 |

SPI0_NPCS3 |

TCLK2 |

ą£čāą╗čīčéąĖą┐ą╗ąĄą║čüąĖčĆąŠą▓ą░ąĮąĖąĄ ąĮąŠąČąĄą║ TC ąĮą░ PIO-ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąĄ B:

| ąśą╝čÅ ą┐ąŠčĆčéą░ |

ąØąŠą╝ąĄčĆ ą▓čŗą▓ąŠą┤ą░ |

Peripheral A |

Peripheral B |

| LQFP100 |

TFBGA100 |

| PB12 |

39 |

B5 |

ETXER |

TCLK0 |

| PB19 |

64 |

D5 |

PWM0 |

TCLK1 |

| PB23 |

69 |

F2 |

TIOA0 |

DCD1 |

| PB24 |

70 |

G2 |

TIOB0 |

DSR1 |

| PB25 |

71 |

F3 |

TIOA1 |

DTR1 |

| PB26 |

72 |

F4 |

TIOB1 |

RI1 |

| PB27 |

9 |

D9 |

TIOA2 |

PWM0 |

| PB28 |

10 |

E8 |

TIOB2 |

PWM1 |

ą¤čĆąĖą╝ąĄčĆ ąĮą░čüčéčĆąŠą╣ą║ąĖ ą░ą┐ą┐ą░čĆą░čéąĮąŠą╣ čäčāąĮą║čåąĖąĖ čüąĖą│ąĮą░ą╗ą░ TIOA10, čćč鹊ą▒čŗ ąŠąĮ č乊čĆą╝ąĖčĆąŠą▓ą░ą╗čüčÅ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ ą║ąŠčĆą┐čāčüą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░:

//ąØąŠąČą║ą░ TIOA0 čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ąĮą░čüčéčĆąŠą╣ą║ąŠą╣ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ PBx:

AT91PS_PIO pPio = AT91C_BASE_PIOB;

//ąØąŠąČą║ą░ TIOA0 ą┐čĆąĖą▓čÅąĘą░ąĮą░ ą║ ą┐ąŠčĆčéčā PB23 ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą╣ čäčāąĮą║čåąĖąĖ A:

u32 periphAenable = AT91C_PB23_TIOA0;

u32 periphBenable = 0;

//ąØą░čüčéčĆąŠą╣ą║ą░ čĆąĄą│ąĖčüčéčĆąŠą▓ PIO:

pPio->PIO_ASR = periphAenable; //ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ čäčāąĮą║čåąĖąĖ Peripheral A

pPio->PIO_BSR = periphBenable; //ąŚą░ą┐čĆąĄčé čäčāąĮą║čåąĖąĖ Peripheral B

pPio->PIO_PDR = (periphAenable | periphBenable);//ąŻčüčéą░ąĮąŠą▓ą║ą░ čĆąĄąČąĖą╝ą░ ą┐ąĄčĆąĖč乥čĆąĖąĖ

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖąĄą╝. TC čéą░ą║čéąĖčĆčāąĄčéčüčÅ č湥čĆąĄąĘ Power Management Controller (PMC) [2], ą┐ąŠčŹč鹊ą╝čā ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčüčé ą┤ąŠą╗ąČąĄąĮ ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮąŠ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī PMC, čćč鹊ą▒čŗ čĆą░ąĘčĆąĄčłąĖčéčī ą┐ąŠą┤ą░čćčā čéą░ą║č鹊ą▓ ąĮą░ Timer Counter.

AT91C_BASE_PMC->PMC_PCER = (1 << AT91C_ID_TC0);

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ. ąŻ TC ąĄčüčéčī čüąĖą│ąĮą░ą╗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗą╣ ą║ Advanced Interrupt Controller (AIC) [3]. ą×ą▒čĆą░ą▒ąŠčéą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ TC čéčĆąĄą▒čāąĄčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ AIC ą┐ąĄčĆąĄą┤ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄą╝ TC.

[ążčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ TC]

ąÆčüąĄ čéčĆąĖ ą║ą░ąĮą░ą╗ą░ TC ąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗ ą┤čĆčāą│ ąŠčé ą┤čĆčāą│ą░ ąĖ čĆą░ą▒ąŠčéą░čÄčé ąĖą┤ąĄąĮčéąĖčćąĮąŠ. ąĀąĄą│ąĖčüčéčĆčŗ ą┤ą╗čÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą║ą░ąĮą░ą╗ą░ ąŠą┐ąĖčüą░ąĮčŗ ąĮąĖąČąĄ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖčģ ą▓čĆąĄąĘą║ą░čģ.

16-bit Counter. ąÜą░ąČą┤čŗą╣ ą║ą░ąĮą░ą╗ ąŠčĆą│ą░ąĮąĖąĘąŠą▓ą░ąĮ ą▓ąŠą║čĆčāą│ 16-čĆą░ąĘčĆčÅą┤ąĮąŠą│ąŠ čüč湥čéčćąĖą║ą░. ąŚąĮą░č湥ąĮąĖąĄ čŹč鹊ą│ąŠ čüč湥čéčćąĖą║ą░ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ ąĮą░ ą║ą░ąČą┤ąŠą╝ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą╝ ą┐ąĄčĆąĄą┐ą░ą┤ąĄ ą▓čŗą▒čĆą░ąĮąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ čéą░ą║č鹊ą▓. ąÜąŠą│ą┤ą░ čüč湥čéčćąĖą║ ą┤ąŠčüčéąĖą│ą░ąĄčé ąĘąĮą░č湥ąĮąĖčÅ 0xFFFF ąĖ ą┐ąĄčĆąĄą▓ą░ą╗ąĖą▓ą░ąĄčé ą║ ąĘąĮą░č湥ąĮąĖčÄ 0x0000, ą┐čĆąŠąĖčüčģąŠą┤ąĖčé čüąŠą▒čŗčéąĖąĄ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ, ąĖ ą┐čĆąĖ čŹč鹊ą╝ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▒ąĖčé COVFS ą▓ čĆąĄą│ąĖčüčéčĆąĄ TC_SR (Status Register).

ąóąĄą║čāčēąĄąĄ ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░ ą┤ąŠčüčéčāą┐ąĮąŠ ą▓ čĆąĄą░ą╗čīąĮąŠą╝ ą▓čĆąĄą╝ąĄąĮąĖ ą┐čāč鹥ą╝ čćč鹥ąĮąĖčÅ Counter Value Register, TC_CV. ąĪč湥čéčćąĖą║ ą╝ąŠąČąĄčé ą▒čŗčéčī čüą▒čĆąŠčłąĄąĮ čéčĆąĖą│ą│ąĄčĆąŠą╝. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░ ą┐ąĄčĆąĄą╣ą┤ąĄčé ą║ 0x0000 ąĮą░ čüą╗ąĄą┤čāčÄčēąĄą╝ ą┤ąŠčüč鹊ą▓ąĄčĆąĮąŠą╝ čéą░ą║č鹥 ą▓čŗą▒čĆą░ąĮąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ.

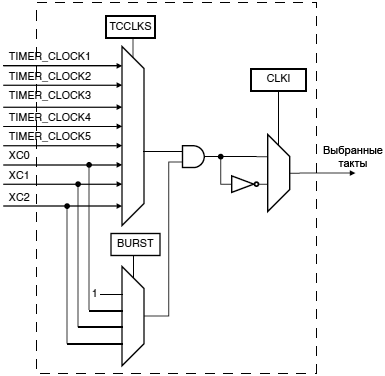

ąÆčŗą▒ąŠčĆ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ. ąØą░ čāčĆąŠą▓ąĮąĄ ą▒ą╗ąŠą║ą░ ą▓čģąŠą┤ąĮčŗąĄ čüąĖą│ąĮą░ą╗čŗ čéą░ą║č鹊ą▓ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą║ą░ąĮą░ą╗ą░ ą╝ąŠąČąĮąŠ ą┐ąŠą┤ą║ą╗čÄčćąĖčéčī ą║ąŠ ą▓ąĮąĄčłąĮąĖą╝ ą▓čģąŠą┤ą░ą╝ TCLK0, TCLK1 ąĖą╗ąĖ TCLK2, ąĖą╗ąĖ ąĖčģ ą╝ąŠąČąĮąŠ ą┐ąŠą┤ą║ą╗čÄčćąĖčéčī ą║ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╝ čüąĖą│ąĮą░ą╗ą░ą╝ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ TIOA0, TIOA1 ąĖą╗ąĖ TIOA2, čćč鹊ą▒čŗ ą║ą░ąĮą░ą╗čŗ čüąŠąĄą┤ąĖąĮčÅą╗ąĖčüčī ą▓ čåąĄą┐ąŠčćą║čā. ąŁč鹊 ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄą╝ TC_BMR (Block Mode), čüą╝. čĆąĖčü. 32-2.

ąĀąĖčü. 32-2. ąÆčŗą▒ąŠčĆ čüąŠąĄą┤ąĖąĮąĄąĮąĖčÅ ą║ą░ąĮą░ą╗ąŠą▓ ą▓ čåąĄą┐ąŠčćą║čā (Clock Chaining Selection).

ąÜą░ąČą┤čŗą╣ ą║ą░ąĮą░ą╗ ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé ą┤čĆčāą│ąĖčģ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĮą░čüčéčĆąŠąĄąĮ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą░ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ ąĖą╗ąĖ ą▓ąĮąĄčłąĮąĄą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ:

ŌĆó ąÆąĮčāčéčĆąĄąĮąĮąĖąĄ čüąĖą│ąĮą░ą╗čŗ čéą░ą║č鹊ą▓: TIMER_CLOCK1, TIMER_CLOCK2, TIMER_CLOCK3, TIMER_CLOCK4, TIMER_CLOCK5.

ŌĆó ąÆąĮąĄčłąĮąĖąĄ čüąĖą│ąĮą░ą╗čŗ čéą░ą║č鹊ą▓: XC0, XC1 ąĖą╗ąĖ XC2.

ąŁč鹊čé ą▓čŗą▒ąŠčĆ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą▒ąĖčéą░ą╝ąĖ TCCLKS ą▓ čĆąĄą│ąĖčüčéčĆąĄ TC_CMR (Channel Mode Register).

ąÆčŗą▒čĆą░ąĮąĮčŗą╣ čéą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąŠąĖąĮą▓ąĄčĆčéąĖčĆąŠą▓ą░ąĮ ą▒ąĖč鹊ą╝ CLKI ą▓ čĆąĄą│ąĖčüčéčĆąĄ TC_CMR. ąŁč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐ąŠą┤čüčćąĖčéčŗą▓ą░čéčī ą┐čĆąŠčéąĖą▓ąŠą┐ąŠą╗ąŠąČąĮčŗąĄ ą┐ąĄčĆąĄą┐ą░ą┤čŗ čéą░ą║č鹊ą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░.

Burst-čäčāąĮą║čåąĖčÅ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé čāą┐čĆą░ą▓ą╗čÅčéčī čéą░ą║č鹊ą▓čŗą╝ čüąĖą│ąĮą░ą╗ąŠą╝ čü ą┐ąŠą╝ąŠčēčīčÄ ą▓ąĮąĄčłąĮąĄą╣ ą╗ąŠą│. 1. ą¤ą░čĆą░ą╝ąĄčéčĆ BURST ą▓ čĆąĄą│ąĖčüčéčĆąĄ TC_CMR ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé čŹč鹊čé čüąĖą│ąĮą░ą╗ (none, XC0, XC1, XC2), čüą╝. čĆąĖčü. 32-3.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▓ ą╗čÄą▒čŗčģ čüą╗čāčćą░čÅčģ, ąĄčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓ąĮąĄčłąĮąĖą╣ čéą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗, ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī ą║ą░ąČą┤ąŠą│ąŠ ąĖąĘ čŹčéąĖčģ čāčĆąŠą▓ąĮąĄą╣ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą▒ąŠą╗čīčłąĄ, č湥ą╝ ą┐ąĄčĆąĖąŠą┤ ą│ą╗ą░ą▓ąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ (master clock, MCK [2]). ąÆąĮąĄčłąĮčÅčÅ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ą▓ 2.5 čĆą░ąĘ ąĮąĖąČąĄ čćą░čüč鹊čéčŗ master clock.

ąĀąĖčü. 32-3. ąÆčŗą▒ąŠčĆ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ.

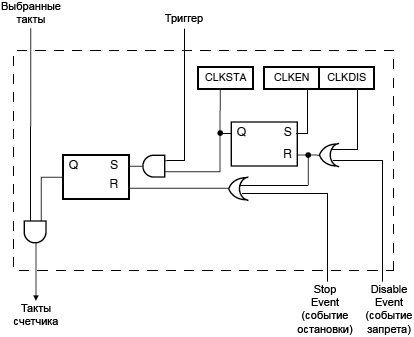

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄą╝. ąóą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ čüč湥čéčćąĖą║ą░ ą╝ąŠąČąĄčé čāą┐čĆą░ą▓ą╗čÅčéčīčüčÅ ą┤ą▓čāą╝čÅ čĆą░ąĘąĮčŗą╝ąĖ čüą┐ąŠčüąŠą▒ą░ą╝ąĖ: ąĄą│ąŠ ą╝ąŠąČąĮąŠ čĆą░ąĘčĆąĄčłąĖčéčī/ąĘą░ą┐čĆąĄčéąĖčéčī ąĖ ąĘą░ą┐čāčüčéąĖčéčī/ąŠčüčéą░ąĮąŠą▓ąĖčéčī, čüą╝. čĆąĖčü. 32-4.

ŌĆó ąóą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ ą╝ąŠąČąĄčé ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮą░ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčēąĄąĮą░ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╝ čü ą┐ąŠą╝ąŠčēčīčÄ ą║ąŠą╝ą░ąĮą┤ CLKEN ąĖ CLKDIS ą▓ čĆąĄą│ąĖčüčéčĆąĄ TC_CCR (TC Channel Control Register). ąÆ čĆąĄąČąĖą╝ąĄ ąĘą░čģą▓ą░čéą░ (Capture Mode) ąŠąĮ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąĄčēąĄąĮ čüąŠą▒čŗčéąĖąĄą╝ ąĘą░ą│čĆčāąĘą║ąĖ RB (RB load event), ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1 ą▒ąĖčé LDBDIS čĆąĄą│ąĖčüčéčĆą░ TC_CMR. ąÆ čĆąĄąČąĖą╝ąĄ ą│ąĄąĮąĄčĆą░čåąĖąĖ čüąĖą│ąĮą░ą╗ą░ (Waveform Mode) čŹč鹊 ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąĄčēąĄąĮąŠ čüąŠą▒čŗčéąĖąĄą╝ čüčĆą░ą▓ąĮąĄąĮąĖčÅ RC (RC Compare event), ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1 ą▒ąĖčé CPCDIS čĆąĄą│ąĖčüčéčĆą░ TC_CMR. ą¤čĆąĖ ąĘą░ą┐čĆąĄč鹥 ą┤ąĄą╣čüčéą▓ąĖčÅ ąĘą░ą┐čāčüą║ą░ ąĖą╗ąĖ ąŠčüčéą░ąĮąŠą▓ą░ (start/stop actions) ąĮąĄ ą┤ą░čÄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░: č鹊ą╗čīą║ąŠ ą║ąŠą╝ą░ąĮą┤ą░ CLKEN ą▓ TC_CCR ą╝ąŠąČąĄčé ą┐ąŠą▓č鹊čĆąĮąŠ čĆą░ąĘčĆąĄčłąĖčéčī čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ. ąÜąŠą│ą┤ą░ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ, čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▒ąĖčé CLKSTA ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüąŠčüč鹊čÅąĮąĖčÅ čéą░ą╣ą╝ąĄčĆą░/čüč湥čéčćąĖą║ą░ TC_SR (TC Status Register).

ŌĆó ąóą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī čéą░ą║ąČąĄ ąĘą░ą┐čāčēąĄąĮąŠ ąĖą╗ąĖ ąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ čüąŠą▒čŗčéąĖąĄą╝, čéčĆąĖą│ą│ąĄčĆ (software, synchro, external ąĖą╗ąĖ compare) ą▓čüąĄą│ą┤ą░ ąĘą░ą┐čāčüą║ą░ąĄčé čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ. ąóą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ RB load event ą▓ Capture Mode (LDBSTOP = 1 ą▓ čĆąĄą│ąĖčüčéčĆąĄ TC_CMR) ąĖą╗ąĖ čüąŠą▒čŗčéąĖąĄą╝ RC Compare ą▓ Waveform Mode (CPCSTOP = 1 ą▓ čĆąĄą│ąĖčüčéčĆąĄ TC_CMR). ąÜąŠą╝ą░ąĮą┤čŗ start ąĖ stop čĆą░ą▒ąŠčéą░čÄčé č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ.

ąĀąĖčü. 32-4. ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄą╝.

ąĀąĄąČąĖą╝čŗ čĆą░ą▒ąŠčéčŗ TC. ąÜą░ąČą┤čŗą╣ ą║ą░ąĮą░ą╗ ą╝ąŠąČąĄčé ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ čĆą░ą▒ąŠčéą░čéčī ą▓ ą┤ą▓čāčģ čĆą░ąĘąĮčŗčģ čĆąĄąČąĖą╝ą░čģ:

ŌĆó ąĀąĄąČąĖą╝ ąĘą░čģą▓ą░čéą░ Capture Mode, ą║ąŠč鹊čĆčŗą╣ ą╝ąŠąČąĄčé ąĖąĘą╝ąĄčĆčÅčéčī ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéąĖ čüąĖą│ąĮą░ą╗ąŠą▓.

ŌĆó ąĀąĄąČąĖą╝ ą│ąĄąĮąĄčĆą░čåąĖąĖ čüąĖą│ąĮą░ą╗ą░ Waveform Mode.

ąĀą░ą▒ąŠčćąĖą╣ čĆąĄąČąĖą╝ TC ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ ą▒ąĖč鹊ą╝ WAVE ą▓ čĆąĄą│ąĖčüčéčĆąĄ TC_CMR (TC Channel Mode Register).

ąÆ Capture Mode čüąĖą│ąĮą░ą╗čŗ TIOA ąĖ TIOB ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāčÄčéčüčÅ ą║ą░ą║ ą▓čģąŠą┤čŗ. ąÆ Waveform Mode čüąĖą│ąĮą░ą╗ TIOA ą▓čüąĄą│ą┤ą░ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ ą║ą░ą║ ą▓čŗčģąŠą┤, ąĖ ąĄčüą╗ąĖ TIOB ąĮąĄ ą▓čŗą▒čĆą░ąĮ ą║ą░ą║ ą▓ąĮąĄčłąĮąĖą╣ čéčĆąĖą│ą│ąĄčĆ, ąŠąĮ č鹊ąČąĄ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ ą║ą░ą║ ą▓čŗčģąŠą┤.

ąóčĆąĖą│ą│ąĄčĆ. ąóčĆąĖą│ą│ąĄčĆ čüą▒čĆą░čüčŗą▓ą░ąĄčé čüč湥čéčćąĖą║ ąĖ ąĘą░ą┐čāčüą║ą░ąĄčé čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čüč湥čéčćąĖą║ą░. ąóčĆąĖ čéąĖą┐ą░ čéčĆąĖą│ą│ąĄčĆąŠą▓ čÅą▓ą╗čÅčÄčéčüčÅ ąŠą▒čēąĖą╝ąĖ ą┤ą╗čÅ ąŠą▒ąŠąĖčģ čĆąĄąČąĖą╝ąŠą▓ Capture/Waveform, ąĖ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ąĖąĘ čŹčéąĖčģ čĆąĄąČąĖą╝ąŠą▓ č湥čéą▓ąĄčĆčéčŗą╣ ą▓ąĮąĄčłąĮąĖą╣ čéčĆąĖą│ą│ąĄčĆ.

ąĪą╗ąĄą┤čāčÄčēąĖąĄ čéčĆąĖą│ą│ąĄčĆčŗ čÅą▓ą╗čÅčÄčéčüčÅ ąŠą▒čēąĖą╝ąĖ ą┤ą╗čÅ ąŠą▒ąŠąĖčģ čĆąĄąČąĖą╝ąŠą▓:

ŌĆó Software Trigger: ąĮą░ ą║ą░ąČą┤ąŠą╝ ą║ą░ąĮą░ą╗ąĄ ąĄčüčéčī ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čéčĆąĖą│ą│ąĄčĆ, ą┤ąŠčüčéčāą┐ąĮčŗą╣ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ SWTRG ą▓ čĆąĄą│ąĖčüčéčĆąĄ TC_CCR.

ŌĆó SYNC: čā ą║ą░ąČą┤ąŠą│ąŠ ą║ą░ąĮą░ą╗ą░ ąĄčüčéčī čüąĖą│ąĮą░ą╗ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ SYNC. ąÜąŠą│ą┤ą░ čŹč鹊čé čüąĖą│ąĮą░ą╗ ą▓čŗčüčéą░ą▓ą╗ąĄąĮ, č鹊 ąŠąĮ ą┤ą░ąĄčé č鹊čé ąČąĄ čŹčäč乥ą║čé, čćč鹊 ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čéčĆąĖą│ą│ąĄčĆ. ąĪąĖą│ąĮą░ą╗čŗ SYNC ą▓čüąĄčģ ą║ą░ąĮą░ą╗ąŠą▓ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄčéčüčÅ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ąĘą░ą┐ąĖčüčīčÄ TC_BCR (Block Control) čü čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╝ ą▒ąĖč鹊ą╝ SYNC.

ŌĆó Compare RC Trigger: ąĮą░ ą║ą░ąČą┤ąŠą╝ ą║ą░ąĮą░ą╗ąĄ čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮąŠ čüčĆą░ą▓ąĮąĄąĮąĖąĄ RC, ąĖ čŹč鹊 ą╝ąŠąČąĄčé ą┐čĆąĄą┤ąŠčüčéą░ą▓ąĖčéčī čéčĆąĖą│ą│ąĄčĆ, ą║ąŠą│ą┤ą░ ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░ čüąŠą▓ą┐ą░ą┤ą░ąĄčé čüąŠ ąĘąĮą░č湥ąĮąĖąĄą╝ čĆąĄą│ąĖčüčéčĆą░ RC, ąĄčüą╗ąĖ ą▓ čĆąĄą│ąĖčüčéčĆąĄ TC_CMR čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé CPCTRG.

ąÜą░ąĮą░ą╗ ą╝ąŠąČąĄčé ą▒čŗčéčī čéą░ą║ąČąĄ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą┤ą╗čÅ ą▓ąĮąĄčłąĮąĄą│ąŠ čéčĆąĖą│ą│ąĄčĆą░. ąÆ Capture Mode ą▓ąĮąĄčłąĮąĖą╣ čéčĆąĖą│ą│ąĄčĆ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą▒čĆą░ąĮ ą╝ąĄąČą┤čā čüąĖą│ąĮą░ą╗ą░ą╝ąĖ TIOA ąĖ TIOB. ąÆ Waveform Mode ą▓ąĮąĄčłąĮąĄąĄ čüąŠą▒čŗčéąĖąĄ ą╝ąŠąČąĄčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčīčüčÅ čüą╗ąĄą┤čāčÄčēąĖą╝ąĖ čüąĖą│ąĮą░ą╗ą░ą╝ąĖ: TIOB, XC0, XC1 ąĖą╗ąĖ XC2. ąŁč鹊 ą▓ąĮąĄčłąĮąĄąĄ čüąŠą▒čŗčéąĖąĄ ąĘą░č鹥ą╝ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąŠ ą┤ą╗čÅ čéčĆąĖą│ą│ąĄčĆą░ ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ ENETRG ą▓ čĆąĄą│ąĖčüčéčĆąĄ TC_CMR.

ąĢčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓ąĮąĄčłąĮąĖą╣ čéčĆąĖą│ą│ąĄčĆ, č鹊 ą┤ą╗čÅ ąĮą░ą┤ąĄąČąĮąŠą│ąŠ ąĄą│ąŠ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī ą▓ąĮąĄčłąĮąĄą│ąŠ ąĖą╝ą┐čāą╗čīčüą░ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą▒ąŠą╗čīčłąĄ, č湥ą╝ ą┐ąĄčĆąĖąŠą┤ master clock.

ąØąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé č鹊ą│ąŠ, ą║ą░ą║ąŠą╣ čéčĆąĖą│ą│ąĄčĆ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ, ąĄą│ąŠ čüą╗ąĄą┤čāąĄčé čāčćąĖčéčŗą▓ą░čéčī ąĮą░ čüą╗ąĄą┤čāčÄčēąĄą╝ ą░ą║čéąĖą▓ąĮąŠą╝ ą┐ąĄčĆąĄą┐ą░ą┤ąĄ ą▓čŗą▒čĆą░ąĮąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ. ąŁč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮąŠ ąŠčéą╗ąĖčćąĮčŗą╝ ąŠčé ąĮčāą╗čÅ čüčĆą░ąĘčā ą┐ąŠčüą╗ąĄ čéčĆąĖą│ą│ąĄčĆą░, ąŠčüąŠą▒ąĄąĮąĮąŠ ą║ąŠą│ą┤ą░ ą▓ ą║ą░č湥čüčéą▓ąĄ čéą░ą║č鹊ą▓ ą▓čŗą▒čĆą░ąĮ čüąĖą│ąĮą░ą╗ čü ąĮąĖąĘą║ąŠą╣ čćą░čüč鹊č鹊ą╣.

Capture Mode (čĆąĄąČąĖą╝ ąĘą░čģą▓ą░čéą░). ąÆ čŹč鹊čé čĆąĄąČąĖą╝ ą▓čģąŠą┤čÅčé ąŠčćąĖčüčéą║ąŠą╣ ą▒ąĖčéą░ WAVE ą▓ čĆąĄą│ąĖčüčéčĆąĄ TC_CMR (Channel Mode Register). Capture Mode ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą║ą░ąĮą░ą╗čā TC ąĖąĘą╝ąĄčĆčÅčéčī ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéąĖ ąĖ čćą░čüč鹊čéčŗ ąĖą╝ą┐čāą╗čīčüąŠą▓ čüąĖą│ąĮą░ą╗ąŠą▓ TIOA ąĖ TIOB, ąĖčģ ą┐ąĄčĆąĖąŠą┤, čüą║ą▓ą░ąČąĮąŠčüčéčī ąĖ čäą░ąĘčā. ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ čüąĖą│ąĮą░ą╗čŗ TIOA ąĖ TIOB ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░čÄčéčüčÅ ą║ą░ą║ ą▓čģąŠą┤čŗ.

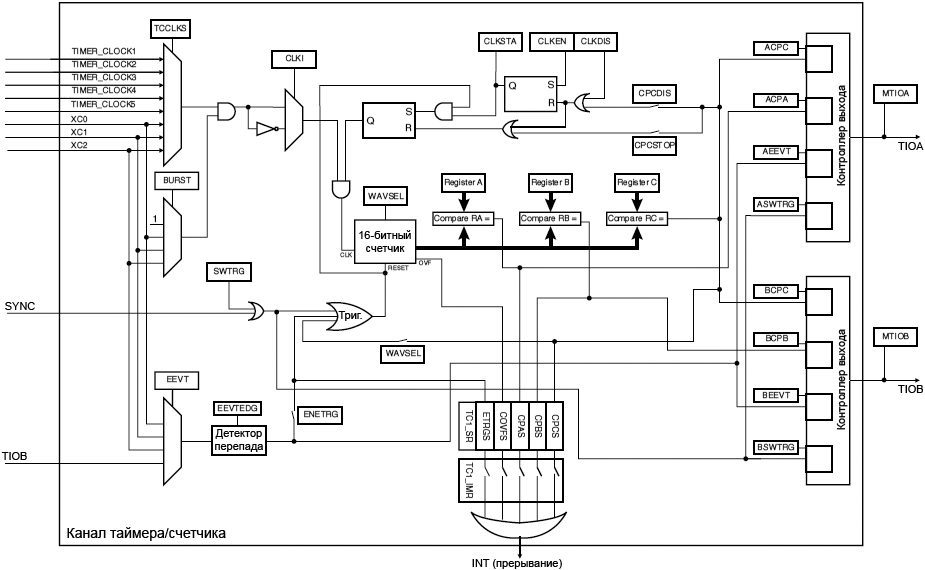

ąĀąĖčü. 32-5 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÄ ą║ą░ąĮą░ą╗ą░ TC, ą║ąŠą│ą┤ą░ ąŠąĮ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ ą▓ Capture Mode.

ąĀąĖčü. 32-5. Capture Mode.

ąĀąĄą│ąĖčüčéčĆčŗ ąĘą░čģą▓ą░čéą░ A ąĖ B. ąĀąĄą│ąĖčüčéčĆčŗ RA ąĖ RB ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą║ą░ą║ čĆąĄą│ąĖčüčéčĆčŗ ąĘą░čģą▓ą░čéą░. ąŁč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ąŠąĮąĖ ą╝ąŠą│čāčé ą▒čŗčéčī ąĘą░ą│čĆčāąČąĄąĮčŗ ąĘąĮą░č湥ąĮąĖąĄą╝ ąĖąĘ čüč湥čéčćąĖą║ą░, ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖąĘąŠčłą╗ąŠ ąĮą░čüčéčĆąŠąĄąĮąĮąŠąĄ čüąŠą▒čŗčéąĖąĄ ąĮą░ čüąĖą│ąĮą░ą╗ąĄ TIOA.

ą¤ą░čĆą░ą╝ąĄčéčĆ LDRA ą▓ čĆąĄą│ąĖčüčéčĆąĄ TC_CMR ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ą┐ąĄčĆąĄą┐ą░ą┤ TIOA ą┤ą╗čÅ ąĘą░ą│čĆčāąĘą║ąĖ čĆąĄą│ąĖčüčéčĆą░ A, ąĖ ą┐ą░čĆą░ą╝ąĄčéčĆ LDRB ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ą┐ąĄčĆąĄą┐ą░ą┤ TIOA ą┤ą╗čÅ ąĘą░ą│čĆčāąĘą║ąĖ čĆąĄą│ąĖčüčéčĆą░ B.

RA ą▒čāą┤ąĄčé ąĘą░ą│čĆčāąČąĄąĮ č鹊ą╗čīą║ąŠ ąĄčüą╗ąĖ ąŠąĮ ąĮąĄ ą▒čŗą╗ ąĘą░ą│čĆčāąČąĄąĮ ą┐ąŠčüą╗ąĄą┤ąĮąĖą╝ąĖ čéčĆąĖą│ą│ąĄčĆąŠą╝, ąĖą╗ąĖ ąĄčüą╗ąĖ RB ą▒čŗą╗ ąĘą░ą│čĆčāąČąĄąĮ ą┐ąŠčüą╗ąĄ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╣ ąĘą░ą│čĆčāąĘą║ąĖ RA.

RB ą▒čāą┤ąĄčé ąĘą░ą│čĆčāąČąĄąĮ č鹊ą╗čīą║ąŠ ąĄčüą╗ąĖ RA ą▒čŗą╗ ąĘą░ą│čĆčāąČąĄąĮ ą┐ąŠčüą╗ąĄą┤ąĮąĖą╝ čéčĆąĖą│ą│ąĄčĆąŠą╝ ąĖą╗ąĖ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╣ ąĘą░ą│čĆčāąĘą║ąŠą╣ RB.

ąŚą░ą│čĆčāąĘą║ą░ RA ąĖą╗ąĖ RB ą┐ąĄčĆąĄą┤ čćč鹥ąĮąĖąĄą╝ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ ąĘą░ą│čĆčāąČąĄąĮąĮąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ čāčüčéą░ąĮąŠą▓ąĖčé čäą╗ą░ą│ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ LOVRS (Overrun Error) ą▓ čĆąĄą│ąĖčüčéčĆąĄ TC_SR (Status Register). ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ čüčéą░čĆąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą▒čāą┤ąĄčé ą┐ąĄčĆąĄąĘą░ą┐ąĖčüą░ąĮąŠ.

ąĪąŠą▒čŗčéąĖčÅ čéčĆąĖą│ą│ąĄčĆą░. ąÆ ą┤ąŠą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ čüąĖą│ąĮą░ą╗čā SYNC, ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą╝čā čéčĆąĖą│ą│ąĄčĆčā ąĖ čéčĆąĖą│ą│ąĄčĆčā čüčĆą░ą▓ąĮąĄąĮąĖčÅ RC Compare čéą░ą║ąČąĄ ą╝ąŠąČąĮąŠ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ą▓ąĮąĄčłąĮąĖą╣ čéčĆąĖą│ą│ąĄčĆ.

ąæąĖčé ABETRG ą▓ čĆąĄą│ąĖčüčéčĆąĄ TC_CMR ą▓čŗą▒ąĖčĆą░ąĄčé ą▓ ą║ą░č湥čüčéą▓ąĄ ą▓ąĮąĄčłąĮąĄą│ąŠ čéčĆąĖą│ą│ąĄčĆą░ ą▓čģąŠą┤ąĮčŗąĄ čüąĖą│ąĮą░ą╗čŗ TIOA ąĖą╗ąĖ TIOB. ą¤ą░čĆą░ą╝ąĄčéčĆ ETRGEDG ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ą┤ąĄč鹥ą║čéąĖčĆčāąĄą╝čŗą╣ ą┐ąĄčĆąĄą┐ą░ą┤ (ąĮą░čĆą░čüčéą░ąĮąĖąĄ čāčĆąŠą▓ąĮčÅ, ąĄą│ąŠ čüą┐ą░ą┤, ąĖą╗ąĖ ąŠą▒ą░ čŹčéąĖčģ ą┐ąĄčĆąĄą┐ą░ą┤ą░) ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą▓ąĮąĄčłąĮąĄą│ąŠ čéčĆąĖą│ą│ąĄčĆą░. ąĢčüą╗ąĖ ETRGEDG = 0 (none), č鹊 ą▓ąĮąĄčłąĮąĖą╣ čéčĆąĖą│ą│ąĄčĆ ąĘą░ą┐čĆąĄčēąĄąĮ.

Waveform Mode. ąÆ čĆąĄąČąĖą╝ ą│ąĄąĮąĄčĆą░čåąĖąĖ čüąĖą│ąĮą░ą╗ą░ ą▓čģąŠą┤čÅčé čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▓ 1 ą▒ąĖčéą░ WAVE čĆąĄą│ąĖčüčéčĆą░ TC_CMR (Channel Mode Register). ąŁč鹊čé čĆąĄąČąĖą╝ ą║ą░ąĮą░ą╗ą░ TC ą│ąĄąĮąĄčĆąĖčĆčāąĄčé 1 ąĖą╗ąĖ 2 čüąĖą│ąĮą░ą╗ą░ PWM čü ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠą╣ čćą░čüč鹊č鹊ą╣ ąĖ ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝ąŠą╣ čüą║ą▓ą░ąČąĮąŠčüčéčīčÄ, ą╗ąĖą▒ąŠ ą│ąĄąĮąĄčĆąĖčĆčāąĄčé čĆą░ąĘąĮčŗąĄ čéąĖą┐čŗ ąŠą┤ąĖąĮąŠčćąĮčŗčģ ąĖą╗ąĖ ą┐ąŠą▓č鹊čĆčÅčÄčēąĖčģčüčÅ ąĖą╝ą┐čāą╗čīčüąŠą▓.

ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ čüąĖą│ąĮą░ą╗ TIOA ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ ą║ą░ą║ ą▓čŗčģąŠą┤, ąĖ ąĄčüą╗ąĖ čüąĖą│ąĮą░ą╗ TIOB ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą║ą░ą║ ą▓ąĮąĄčłąĮąĄąĄ čüąŠą▒čŗčéąĖąĄ (ą┐ą░čĆą░ą╝ąĄčéčĆ EEVT ą▓ TC_CMR), č鹊 ąŠąĮ č鹊ąČąĄ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ ą║ą░ą║ ą▓čŗčģąŠą┤.

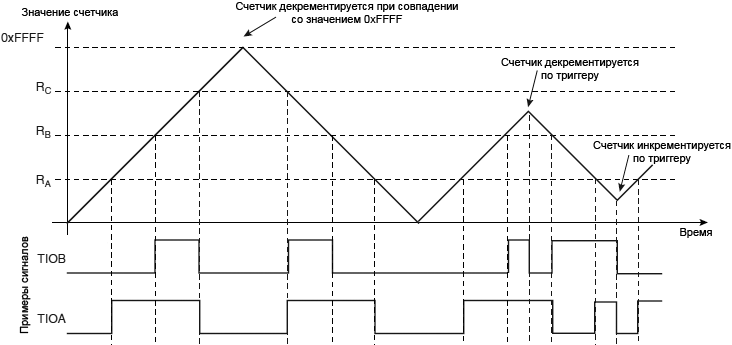

ąØą░ čĆąĖčü. 32-6 ą┐ąŠą║ą░ąĘą░ąĮą░ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą║ą░ąĮą░ą╗ą░ TC, ą║ąŠą│ą┤ą░ ąŠąĮ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ ą▓ čĆąĄąČąĖą╝ąĄ ą│ąĄąĮąĄčĆą░čåąĖąĖ čüąĖą│ąĮą░ą╗ą░ (Waveform Operating Mode).

ąĀąĖčü. 32-6. Waveform Mode.

ąÆčŗą▒ąŠčĆ č乊čĆą╝čŗ ą│ąĄąĮąĄčĆąĖčĆčāąĄą╝ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░. ąÆ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą┐ą░čĆą░ą╝ąĄčéčĆą░ WAVSEL ą▓ čĆąĄą│ąĖčüčéčĆąĄ TC_CMR (Channel Mode Register) ą╝ąĄąĮčÅąĄčéčüčÅ ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ TC_CV.

ąĪ ą╗čÄą▒čŗą╝ ą▓čŗą▒ąŠčĆąŠą╝ ą▓čüąĄ čĆąĄą│ąĖčüčéčĆčŗ RA, RB ąĖ RC ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą║ą░ą║ čĆąĄą│ąĖčüčéčĆčŗ čüčĆą░ą▓ąĮąĄąĮąĖčÅ.

RA Compare ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą▓čŗčģąŠą┤ąŠą╝ TIOA, RB ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą▓čŗčģąŠą┤ąŠą╝ TIOB (ąĄčüą╗ąĖ ąŠąĮ ą║ąŠčĆčĆąĄą║čéąĮąŠ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ), ąĖ RC Compare ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą▓čŗčģąŠą┤ą░ą╝ąĖ TIOA ąĖ/ąĖą╗ąĖ TIOB.

WAVSEL = 00

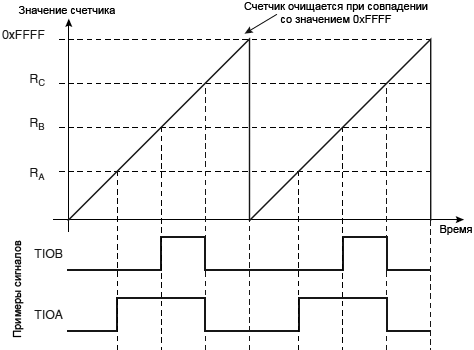

ą¤čĆąĖ WAVSEL = 00 ąĘąĮą░č湥ąĮąĖąĄ TC_CV ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ ąŠčé 0x0000 ą║ 0xFFFF. ąÜą░ą║ č鹊ą╗čīą║ąŠ ą┤ąŠčüčéąĖą│ąĮčāč鹊 ąĘąĮą░č湥ąĮąĖąĄ 0xFFFF, TC_CV čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ. ąśąĮą║čĆąĄą╝ąĄąĮčé TC_CV ąĮą░čćąĖąĮą░ąĄčéčüčÅ ąĘą░ąĮąŠą▓ąŠ, ąĖ čåąĖą║ą╗ ą┐ąŠą▓č鹊čĆčÅąĄčéčüčÅ, čüą╝. čĆąĖčü. 32-7.

ąĀąĖčü. 32-7. WAVSEL= 00 ą▒ąĄąĘ čéčĆąĖą│ą│ąĄčĆą░.

ąĪąŠą▒čŗčéąĖąĄ ą▓ąĮąĄčłąĮąĄą│ąŠ ąĖą╗ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čéčĆąĖą│ą│ąĄčĆą░ ą╝ąŠąČąĄčé čüą▒čĆąŠčüąĖčéčī ąĘąĮą░č湥ąĮąĖąĄ TC_CV. ąÆą░ąČąĮąŠ ąŠčéą╝ąĄčéąĖčéčī, čćč鹊 čéčĆąĖą│ą│ąĄčĆ ą╝ąŠąČąĄčé ą┐čĆąŠąĖąĘąŠą╣čéąĖ ą▓ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé ą▓čĆąĄą╝ąĄąĮąĖ, čüą╝. čĆąĖčü. 32-8.

ąĀąĖčü. 32-8. WAVSEL= 00 čü čéčĆąĖą│ą│ąĄčĆąŠą╝.

ąÆ čŹč鹊ą╣ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ RC Compare ąĮąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąŠ ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ čéčĆąĖą│ą│ąĄčĆą░. ąÆ č鹊 ąČąĄ ą▓čĆąĄą╝čÅ RC Compare ą╝ąŠąČąĄčé ąŠčüčéą░ąĮąŠą▓ąĖčéčī čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čüč湥čéčćąĖą║ą░ (CPCSTOP = 1 ą▓ čĆąĄą│ąĖčüčéčĆąĄ TC_CMR) ąĖ/ąĖą╗ąĖ ąĘą░ą┐čĆąĄčéąĖčéčī čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čüč湥čéčćąĖą║ą░ (CPCDIS = 1 ą▓ čĆąĄą│ąĖčüčéčĆąĄ TC_CMR).

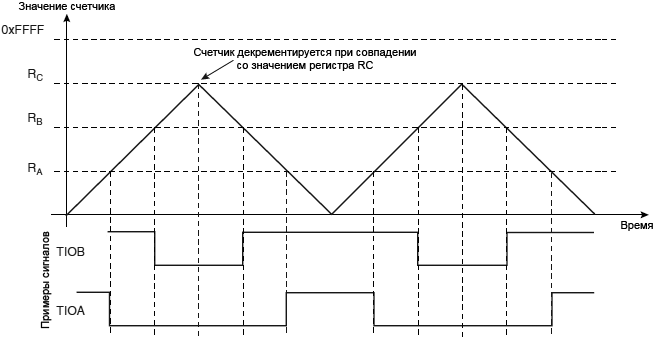

WAVSEL = 10

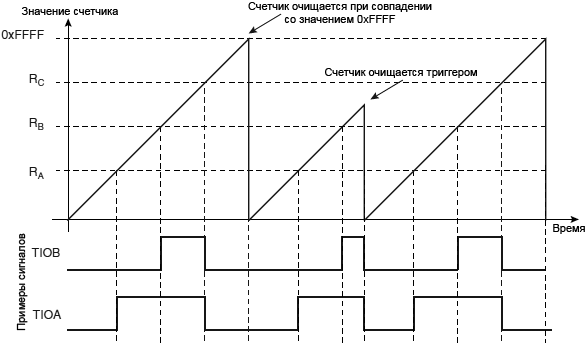

ą¤čĆąĖ WAVSEL = 10 ąĘąĮą░č湥ąĮąĖąĄ TC_CV ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ ąŠ 0 ą┤ąŠ ąĘąĮą░č湥ąĮąĖčÅ RC, ąĘą░č鹥ą╝ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ ą┐čĆąĖ ą┐čĆąĖ RC Compare. ąÜą░ą║ č鹊ą╗čīą║ąŠ TC_CV ą▒čŗą╗ čüą▒čĆąŠčłąĄąĮ, ąŠąĮ ąĮą░čćąĖąĮą░ąĄčé ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆąŠą▓ą░čéčīčüčÅ čüąĮąŠą▓ą░, ąĖ čéą░ą║ ą┤ą░ą╗ąĄąĄ. ąĪą╝. čĆąĖčü. 32-9.

ąĀąĖčü. 32-9. WAVSEL= 10 ą▒ąĄąĘ čéčĆąĖą│ą│ąĄčĆą░.

ąÆą░ąČąĮąŠ ąŠčéą╝ąĄčéąĖčéčī, čćč鹊 TC_CV ą╝ąŠąČąĄčé ą▒čŗčéčī čüą▒čĆąŠčłąĄąĮ ą▓ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé ą▓ąĮąĄčłąĮąĖą╝ čüąŠą▒čŗčéąĖąĄą╝ ąĖą╗ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╝ čéčĆąĖą│ą│ąĄčĆąŠą╝, ąĄčüą╗ąĖ ąŠąĮąĖ ąŠą▒ą░ ą┐čĆą░ą▓ąĖą╗čīąĮąŠ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮčŗ. ąĪą╝. čĆąĖčü. 32-10.

ąĀąĖčü. 32-10. WAVSEL= 10 čü čéčĆąĖą│ą│ąĄčĆąŠą╝.

ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠ RC Compare ą╝ąŠąČąĄčé ąŠčüčéą░ąĮąŠą▓ąĖčéčī čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čüč湥čéčćąĖą║ą░ (CPCSTOP = 1 ą▓ čĆąĄą│ąĖčüčéčĆąĄ TC_CMR) ąĖ/ąĖą╗ąĖ ąĘą░ą┐čĆąĄčéąĖčéčī čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čüč湥čéčćąĖą║ą░ (CPCDIS = 1 ą▓ čĆąĄą│ąĖčüčéčĆąĄ TC_CMR).

WAVSEL = 01

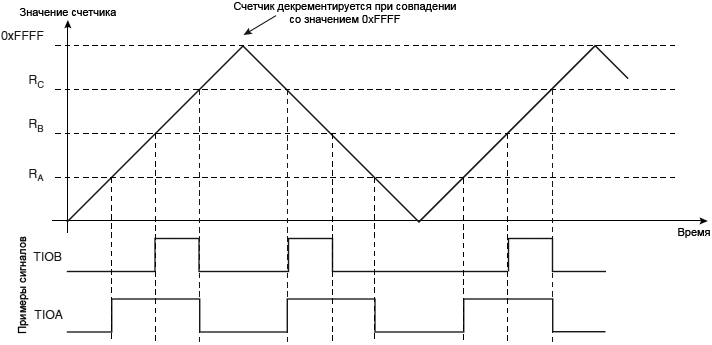

ą¤čĆąĖ WAVSEL = 00 ąĘąĮą░č湥ąĮąĖąĄ TC_CV ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ ąŠčé 0x0000 ą║ 0xFFFF. ąÜą░ą║ č鹊ą╗čīą║ąŠ ą┤ąŠčüčéąĖą│ąĮčāč鹊 ąĘąĮą░č湥ąĮąĖąĄ 0xFFFF, TC_CV ą┤ąĄą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ ą┤ąŠ 0x0000, ąĘą░č鹥ą╝ čüąĮąŠą▓ą░ ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą║ ąĖąĮą║čĆąĄą╝ąĄąĮčéčā, ąĖ čéą░ą║ ą┤ą░ą╗ąĄąĄ. ąĪą╝. čĆąĖčü. 32-11.

ąĀąĖčü. 32-11. WAVSEL = 01 ą▒ąĄąĘ čéčĆąĖą│ą│ąĄčĆą░.

ąóą░ą║ąŠą╣ čéčĆąĖą│ą│ąĄčĆ, ą║ą░ą║ ą▓ąĮąĄčłąĮąĄąĄ čüąŠą▒čŗčéąĖąĄ ąĖą╗ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čéčĆąĖą│ą│ąĄčĆ, ą╝ąŠąČąĄčé ą▓ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé ą▓čĆąĄą╝ąĄąĮąĖ ą╝ąŠą┤ąĖčäąĖčåąĖčĆąŠą▓ą░čéčī TC_CV. ąĢčüą╗ąĖ čéčĆąĖą│ą│ąĄčĆ čüčĆą░ą▒ąŠčéą░ą╗ ą┐čĆąĖ ąĖąĮą║čĆąĄą╝ąĄąĮč鹥 TC_CV, č鹊 TC_CV ąĮą░čćąĮąĄčé ą┤ąĄą║čĆąĄą╝ąĄąĮčéąĖčĆąŠą▓ą░čéčīčüčÅ. ąĢčüą╗ąĖ čéčĆąĖą│ą│ąĄčĆ ą┐čĆąŠąĖąĘąŠčłąĄą╗ ą┐čĆąĖ ą┤ąĄą║čĆąĄą╝ąĄąĮč鹥 TC_CV, č鹊 TC_CV ąĮą░čćąĮąĄčé ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆąŠą▓ą░čéčīčüčÅ. ąĪą╝. čĆąĖčü. 32-12.

ąĀąĖčü. 32-12. WAVSEL = 01 čü čéčĆąĖą│ą│ąĄčĆąŠą╝.

ąÆ čŹč鹊ą╣ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ RC Compare ąĮąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąŠ.

ąÆ č鹊 ąČąĄ ą▓čĆąĄą╝čÅ RC Compare ą╝ąŠąČąĄčé ąŠčüčéą░ąĮąŠą▓ąĖčéčī čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čüč湥čéčćąĖą║ą░ (CPCSTOP = 1 ą▓ čĆąĄą│ąĖčüčéčĆąĄ TC_CMR) ąĖ/ąĖą╗ąĖ ąĘą░ą┐čĆąĄčéąĖčéčī čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čüč湥čéčćąĖą║ą░ (CPCDIS = 1 ą▓ čĆąĄą│ąĖčüčéčĆąĄ TC_CMR).

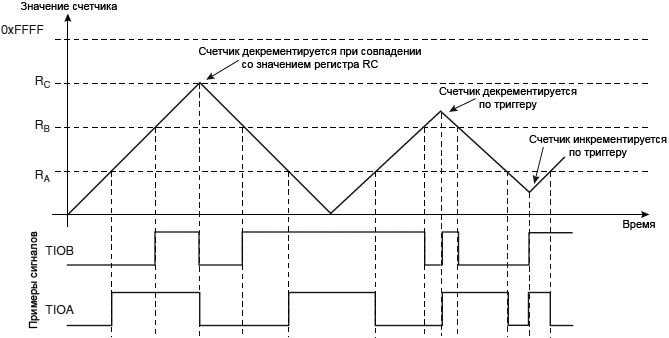

WAVSEL = 11

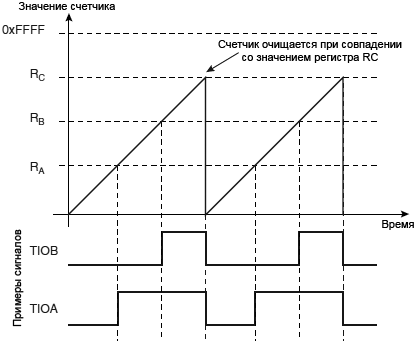

ą¤čĆąĖ WAVSEL = 11 ąĘąĮą░č湥ąĮąĖąĄ TC_CV ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ ąŠčé 0 ą┤ąŠ RC. ąÜą░ą║ č鹊ą╗čīą║ąŠ ą┤ąŠčüčéąĖą│ąĮčāč鹊 ąĘąĮą░č湥ąĮąĖąĄ RC, ąĘąĮą░č湥ąĮąĖąĄ TC_CV ąĮą░čćąĖąĮą░ąĄčé ą┤ąĄą║čĆąĄą╝ąĄąĮčéąĖčĆąŠą▓ą░čéčīčüčÅ ą┤ąŠ 0, ąĘą░č鹥ą╝ čüąĮąŠą▓ą░ ąĮą░čćąĖąĮą░ąĄčé ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆąŠą▓ą░čéčīčüčÅ ą┤ąŠ RC ąĖ čéą░ą║ ą┤ą░ą╗ąĄąĄ. ąĪą╝. čĆąĖčü. 32-13.

ąĀąĖčü. 32-13. WAVSEL = 11 ą▒ąĄąĘ čéčĆąĖą│ą│ąĄčĆą░.

ąóą░ą║ąŠą╣ čéčĆąĖą│ą│ąĄčĆ, ą║ą░ą║ ą▓ąĮąĄčłąĮąĄąĄ čüąŠą▒čŗčéąĖąĄ ąĖą╗ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čéčĆąĖą│ą│ąĄčĆ, ą╝ąŠąČąĄčé ą▓ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé ą▓čĆąĄą╝ąĄąĮąĖ ą╝ąŠą┤ąĖčäąĖčåąĖčĆąŠą▓ą░čéčī TC_CV. ąĢčüą╗ąĖ čéčĆąĖą│ą│ąĄčĆ čüčĆą░ą▒ąŠčéą░ą╗ ą┐čĆąĖ ąĖąĮą║čĆąĄą╝ąĄąĮč鹥 TC_CV, č鹊 TC_CV ąĮą░čćąĮąĄčé ą┤ąĄą║čĆąĄą╝ąĄąĮčéąĖčĆąŠą▓ą░čéčīčüčÅ. ąĢčüą╗ąĖ čéčĆąĖą│ą│ąĄčĆ ą┐čĆąŠąĖąĘąŠčłąĄą╗ ą┐čĆąĖ ą┤ąĄą║čĆąĄą╝ąĄąĮč鹥 TC_CV, č鹊 TC_CV ąĮą░čćąĮąĄčé ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆąŠą▓ą░čéčīčüčÅ. ąĪą╝. čĆąĖčü. 32-14.

ąĀąĖčü. 32-14. WAVSEL = 11 čü čéčĆąĖą│ą│ąĄčĆąŠą╝.

RC Compare ą╝ąŠąČąĄčé ąŠčüčéą░ąĮąŠą▓ąĖčéčī čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čüč湥čéčćąĖą║ą░ (CPCSTOP = 1 ą▓ čĆąĄą│ąĖčüčéčĆąĄ TC_CMR) ąĖ/ąĖą╗ąĖ ąĘą░ą┐čĆąĄčéąĖčéčī čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čüč湥čéčćąĖą║ą░ (CPCDIS = 1 ą▓ čĆąĄą│ąĖčüčéčĆąĄ TC_CMR).

ąÆąĮąĄčłąĮąĖąĄ čüąŠą▒čŗčéąĖčÅ, čāčüą╗ąŠą▓ąĖčÅ čéčĆąĖą│ą│ąĄčĆą░. ąÆąĮąĄčłąĮąĄąĄ čüąŠą▒čŗčéąĖąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąŠ ą┤ą╗čÅ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ąŠą┤ąĮąŠą│ąŠ ąĖąĘ ąĖčüč鹊čćąĮąĖą║ąŠą▓ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ (XC0, XC1, XC2) ąĖą╗ąĖ TIOB. ąóąŠą│ą┤ą░ ą▓čŗą▒čĆą░ąĮąĮąŠąĄ ą▓ąĮąĄčłąĮąĄąĄ čüąŠą▒čŗčéąĖąĄ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą║ą░ą║ čéčĆąĖą│ą│ąĄčĆ.

ą¤ą░čĆą░ą╝ąĄčéčĆ EEVT ą▓ čĆąĄą│ąĖčüčéčĆąĄ TC_CMR ą▓čŗą▒ąĖčĆą░ąĄčé ą▓ąĮąĄčłąĮąĖą╣ čéčĆąĖą│ą│ąĄčĆ. ą¤ą░čĆą░ą╝ąĄčéčĆ EEVTEDG ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ą┐ąĄčĆąĄą┐ą░ą┤ čéčĆąĖą│ą│ąĄčĆą░ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ąĖąĘ ą▓ąŠąĘą╝ąŠąČąĮčŗčģ ą▓ąĮąĄčłąĮąĖčģ čéčĆąĖą│ą│ąĄčĆąŠą▓ (ąĮą░čĆą░čüčéą░ąĮąĖąĄ čāčĆąŠą▓ąĮčÅ, čüą┐ą░ą┤ čāčĆąŠą▓ąĮčÅ, ąĖą╗ąĖ ąŠą▒ą░ čŹčéąĖčģ ą┐ąĄčĆąĄą┐ą░ą┤ą░). ąĢčüą╗ąĖ EEVTEDG ąŠčćąĖčēąĄąĮ (none), č鹊 ą▓ąĮąĄčłąĮąĄąĄ čüąŠą▒čŗčéąĖąĄ ąĮąĄ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąŠ.

ąĢčüą╗ąĖ TIOB ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮ ą║ą░ą║ ą▓ąĮąĄčłąĮąĖą╣ čüąĖą│ąĮą░ą╗ čüąŠą▒čŗčéąĖčÅ (EEVT = 0), č鹊 TIOB ą▒ąŠą╗čīčłąĄ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą║ą░ą║ ą▓čŗčģąŠą┤, ąĖ čĆąĄą│ąĖčüčéčĆ čüčĆą░ą▓ąĮąĄąĮąĖčÅ B ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ čüąĖą│ąĮą░ą╗ąŠą▓ ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ ąĮąĄ ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ąĘą░ą┐čĆąŠčüąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ (IRQ). ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ čŹč鹊čé ą║ą░ąĮą░ą╗ TC ą╝ąŠąČąĄčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī čüąĖą│ąĮą░ą╗ č鹊ą╗čīą║ąŠ ąĮą░ TIOA.

ąÜąŠą│ą┤ą░ ą▓ąĮąĄčłąĮąĄąĄ čüąŠą▒čŗčéąĖąĄ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąŠ, ąŠąĮąŠ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą▓ ą║ą░č湥čüčéą▓ąĄ čéčĆąĖą│ą│ąĄčĆą░ ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ ENETRG ą▓ čĆąĄą│ąĖčüčéčĆąĄ TC_CMR.

ąÆ Capture Mode čüąĖą│ąĮą░ą╗ SYNC ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čéčĆąĖą│ą│ąĄčĆ čéą░ą║ąČąĄ ą┤ąŠčüčéčāą┐ąĮčŗ ą║ą░ą║ čéčĆąĖą│ą│ąĄčĆčŗ. RC Compare čéą░ą║ąČąĄ ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą║ą░ą║ čéčĆąĖą│ą│ąĄčĆ, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą┐ą░čĆą░ą╝ąĄčéčĆą░ WAVSEL.

ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą▓čŗčģąŠą┤ą░. ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą▓čŗčģąŠą┤ą░ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čāčĆąŠą▓ąĮčÅ ąĮą░ TIOA ąĖ TIOB ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü čüąŠą▒čŗčéąĖąĄą╝. ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ TIOB ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ č鹊ą╗čīą║ąŠ ąĄčüą╗ąĖ TIOB ąĮą░čüčéčĆąŠąĄąĮ ą║ą░ą║ ą▓čŗčģąŠą┤ (ąĮąĄ ą║ą░ą║ ąĖčüč鹊čćąĮąĖą║ ą▓ąĮąĄčłąĮąĄą│ąŠ čüąŠą▒čŗčéąĖčÅ).

ąĪą╗ąĄą┤čāčÄčēąĖąĄ čüąŠą▒čŗčéąĖčÅ čāą┐čĆą░ą▓ą╗čÅčÄčé ą▓čŗčģąŠą┤ą░ą╝ąĖ TIOA ąĖ TIOB: ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čéčĆąĖą│ą│ąĄčĆ, ą▓ąĮąĄčłąĮąĄąĄ čüąŠą▒čŗčéąĖąĄ ąĖą╗ąĖ RC Compare. RA Compare čāą┐čĆą░ą▓ą╗čÅąĄčé TIOA, ąĖ RB Compare čāą┐čĆą░ą▓ą╗čÅąĄčé TIOB. ąÜą░ąČą┤ąŠąĄ ąĖąĘ čŹčéąĖčģ čüąŠą▒čŗčéąĖą╣ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąŠ ą┤ą╗čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ, ąŠčćąĖčüčéą║ąĖ ąĖą╗ąĖ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ ą▓čŗčģąŠą┤ą░, ą║ą░ą║ čŹč鹊 ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąŠ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╝ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą╝ ą▓ TC_CMR.

[ąśąĮč鹥čĆč乥ą╣čü ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ TC (čĆąĄą│ąĖčüčéčĆčŗ)]

ąóą░ą▒ą╗ąĖčåą░ 32-4. ą×č鹊ą▒čĆą░ąČąĄąĮąĖąĄ čĆąĄą│ąĖčüčéčĆąŠą▓ čéą░ą╣ą╝ąĄčĆą░/čüč湥čéčćąĖą║ą░ ąĮą░ ą░ą┤čĆąĄčüąĮąŠąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ(1).

| ąĪą╝ąĄčēąĄąĮąĖąĄ |

ąĀąĄą│ąĖčüčéčĆ |

ąśą╝čÅ |

ąöąŠčüčéčāą┐ |

ąĪą▒čĆąŠčü |

| 0x00 + channel ┬Ę 0x40 + 0x00 |

ąĀąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą║ą░ąĮą░ą╗ąŠą╝ |

TC_CCR |

WO |

- |

| 0x00 + channel ┬Ę 0x40 + 0x04 |

ąĀąĄą│ąĖčüčéčĆ čĆąĄąČąĖą╝ą░ ą║ą░ąĮą░ą╗ą░ |

TC_CMR |

RW |

0 |

| 0x00 + channel ┬Ę 0x40 + 0x08 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

|

|

|

| 0x00 + channel ┬Ę 0x40 + 0x0C |

|

|

|

| 0x00 + channel ┬Ę 0x40 + 0x10 |

ąŚąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░ |

TC_CV |

RO |

0 |

| 0x00 + channel ┬Ę 0x40 + 0x14 |

ąĀąĄą│ąĖčüčéčĆ A |

TC_RA |

RW(2) |

0 |

| 0x00 + channel ┬Ę 0x40 + 0x18 |

ąĀąĄą│ąĖčüčéčĆ B |

TC_RB |

RW(2) |

0 |

| 0x00 + channel ┬Ę 0x40 + 0x1C |

ąĀąĄą│ąĖčüčéčĆ C |

TC_RC |

RW |

0 |

| 0x00 + channel ┬Ę 0x40 + 0x20 |

ąĀąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ |

TC_SR |

RO |

0 |

| 0x00 + channel ┬Ę 0x40 + 0x24 |

ąĀąĄą│ąĖčüčéčĆ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ |

TC_IER |

WO |

- |

| 0x00 + channel ┬Ę 0x40 + 0x28 |

ąĀąĄą│ąĖčüčéčĆ ąĘą░ą┐čĆąĄčéą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ |

TC_IDR |

WO |

- |

| 0x00 + channel ┬Ę 0x40 + 0x2C |

ąĀąĄą│ąĖčüčéčĆ ą╝ą░čüą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ |

TC_IMR |

RO |

0 |

| 0xC0 |

ąĀąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą▒ą╗ąŠą║ąŠą╝ |

TC_BCR |

WO |

- |

| 0xC4 |

ąĀąĄą│ąĖčüčéčĆ čĆąĄąČąĖą╝ą░ ą▒ą╗ąŠą║ą░ |

TC_BMR |

RW |

- |

| 0xFC |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

|

|

|

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

1. ąśąĮą┤ąĄą║čü ą║ą░ąĮą░ą╗ą░ (channel) ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąŠčé 0 ą┤ąŠ 2.

2. ąóąŠą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ (read-only, RO), ąĄčüą╗ąĖ WAVE = 0.

3. WO (write-only) ąŠąĘąĮą░čćą░ąĄčé ą┤ąŠčüčéčāą┐ č鹊ą╗čīą║ąŠ ąĮą░ ąĘą░ą┐ąĖčüčī, RW (read-write) ąŠąĘąĮą░čćą░ąĄčé ą┐ąŠą╗ąĮčŗą╣ ą┤ąŠčüčéčāą┐ ąĮą░ čćč鹥ąĮąĖąĄ ąĖ ąĘą░ą┐ąĖčüčī, RO (read-only) ąŠąĘąĮą░čćą░ąĄčé ą┤ąŠčüčéčāą┐ č鹊ą╗čīą║ąŠ ąĮą░ čćč鹥ąĮąĖąĄ.

ąĀąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą▒ą╗ąŠą║ąŠą╝ TC. ąóąĖą┐ ą┤ąŠčüčéčāą┐ą░: č鹊ą╗čīą║ąŠ ąĘą░ą┐ąĖčüčī (WO).

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

-

|

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

-

|

- |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

-

|

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

SYNC

|

SYNC: Synchro Command (ą║ąŠą╝ą░ąĮą┤ą░ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ą║ą░ąĮą░ą╗ąŠą▓)

0 = ąĮąĄ ą┤ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

1 = ą▓čŗčüčéą░ą▓ą╗čÅąĄčé čüąĖą│ąĮą░ą╗ SYNC, ą║ąŠč鹊čĆčŗą╣ ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čéčĆąĖą│ą│ąĄčĆ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ą┤ą╗čÅ ą▓čüąĄčģ ą║ą░ąĮą░ą╗ąŠą▓.

ąĀąĄą│ąĖčüčéčĆ čĆąĄąČąĖą╝ą░ ą▒ą╗ąŠą║ą░ TC. ąóąĖą┐ ą┤ąŠčüčéčāą┐ą░: ą┐ąŠą╗ąĮčŗą╣ (RW).

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

-

|

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

-

|

- |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

-

|

- |

- |

- |

- |

- |

- |

- |

- |

- |

TC2XC2S |

TC1XC1S |

TC0XC0S |

TC0XC0S: External Clock Signal 0 Selection (ą▓čŗą▒ąŠčĆ čüąĖą│ąĮą░ą╗ą░ ą┤ą╗čÅ XC0)

| TC0XC0S |

ąĪąĖą│ąĮą░ą╗, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗą╣ ą║ XC0 |

| 0 |

0 |

TCLK0 |

| 0 |

1 |

none (ąĮąĖč湥ą│ąŠ ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąŠ) |

| 1 |

0 |

TIOA1 |

| 1 |

1 |

TIOA2 |

TC1XC1S: External Clock Signal 1 Selection (ą▓čŗą▒ąŠčĆ čüąĖą│ąĮą░ą╗ą░ ą┤ą╗čÅ XC1)

| TC1XC1S |

ąĪąĖą│ąĮą░ą╗, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗą╣ ą║ XC1 |

| 0 |

0 |

TCLK1 |

| 0 |

1 |

none (ąĮąĖč湥ą│ąŠ ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąŠ) |

| 1 |

0 |

TIOA0 |

| 1 |

1 |

TIOA2 |

TC2XC2S: External Clock Signal 2 Selection (ą▓čŗą▒ąŠčĆ čüąĖą│ąĮą░ą╗ą░ ą┤ą╗čÅ XC2)

| TC2XC2S |

ąĪąĖą│ąĮą░ą╗, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗą╣ ą║ XC2 |

| 0 |

0 |

TCLK2 |

| 0 |

1 |

none (ąĮąĖč湥ą│ąŠ ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąŠ) |

| 1 |

0 |

TIOA0 |

| 1 |

1 |

TIOA1 |

ąĀąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą║ą░ąĮą░ą╗ąŠą╝ TC. ąóąĖą┐ ą┤ąŠčüčéčāą┐ą░: č鹊ą╗čīą║ąŠ ąĘą░ą┐ąĖčüčī (WO).

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

-

|

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

-

|

- |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

-

|

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

SWTRG |

CLKDIS |

CLKEN |

CLKEN: Counter Clock Enable Command (ą║ąŠą╝ą░ąĮą┤ą░ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ čüč湥čéčćąĖą║ą░)

0 = ąĮąĄ ą┤ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

1 = čĆą░ąĘčĆąĄčłą░ąĄčé čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ, ąĄčüą╗ąĖ CLKDIS ąĮąĄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1.

CLKDIS: Counter Clock Disable Command (ą║ąŠą╝ą░ąĮą┤ą░ ąĘą░ą┐čĆąĄčéą░ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ čüč湥čéčćąĖą║ą░)

0 = ąĮąĄ ą┤ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

1 = ąĘą░ą┐čĆąĄčēą░ąĄčé čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ.

SWTRG: Software Trigger Command (ą║ąŠą╝ą░ąĮą┤ą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čéčĆąĖą│ą│ąĄčĆą░)

0 = ąĮąĄ ą┤ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

1 = ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čéčĆąĖą│ą│ąĄčĆ: čüč湥čéčćąĖą║ čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ, ąĖ ąĮą░čćąĖąĮą░ąĄčéčüčÅ ąĄą│ąŠ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ.

ąĀąĄą│ąĖčüčéčĆ čĆąĄąČąĖą╝ą░ ą║ą░ąĮą░ą╗ą░ TC ą▓ čĆąĄąČąĖą╝ąĄ ąĘą░čģą▓ą░čéą░ (WAVE = 0). ąóąĖą┐ ą┤ąŠčüčéčāą┐ą░: ą┐ąŠą╗ąĮčŗą╣ (RW).

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

-

|

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

LDRB |

LDRA |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| WAVE |

CPCTRG |

- |

- |

- |

ABETRG |

ETRGEDG |

LDBDIS |

LDBSTOP |

BURST |

CLKI |

TCCLKS |

TCCLKS: Clock Selection (ą▓čŗą▒ąŠčĆ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ)

| TCCLKS |

ąÆčŗą▒čĆą░ąĮąĮčŗą╣ ąĖčüč鹊čćąĮąĖą║ čéą░ą║č鹊ą▓ |

| 0 |

0 |

0 |

TIMER_CLOCK1 |

| 0 |

0 |

1 |

TIMER_CLOCK2 |

| 0 |

1 |

0 |

TIMER_CLOCK3 |

| 0 |

1 |

1 |

TIMER_CLOCK4 |

| 1 |

0 |

0 |

TIMER_CLOCK5 |

| 1 |

0 |

1 |

XC0 |

| 1 |

1 |

0 |

XC1 |

| 1 |

1 |

1 |

XC2 |

CLKI: Clock Invert (ąĖąĮą▓ąĄčĆčüąĖčÅ čéą░ą║č鹊ą▓)

0 = čüč湥čéčćąĖą║ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ čäčĆąŠąĮč鹊ą╝ ąĮą░čĆą░čüčéą░ąĮąĖčÅ ą╗ąŠą│. čāčĆąŠą▓ąĮčÅ čüąĖą│ąĮą░ą╗ą░ čéą░ą║č鹊ą▓.

1 = čüč湥čéčćąĖą║ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ čüčĆąĄąĘąŠą╝ čüą┐ą░ą┤ą░ ą╗ąŠą│. čāčĆąŠą▓ąĮčÅ čüąĖą│ąĮą░ą╗ą░ čéą░ą║č鹊ą▓.

BURST: Burst Signal Selection (ą▓čŗą▒ąŠčĆ ą▓ąĮąĄčłąĮąĄą│ąŠ čüąĖą│ąĮą░ą╗ą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄą╝)

| BURST |

ąÜą░ą║ čĆą░ą▒ąŠčéą░ąĄčé čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄą╝ |

| 0 |

0 |

ąóą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ ąĮąĄ ą┐ąŠą┤ą░ąĄčéčüčÅ ą┐ąŠčüč鹊čÅąĮąĮąŠ (ąĮąĄčé ą▓ąĮąĄčłąĮąĄą│ąŠ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ) |

| 0 |

1 |

XC0 && ą▓čŗą▒čĆą░ąĮąĮčŗą╣ čüąĖą│ąĮą░ą╗ čéą░ą║č鹊ą▓ |

| 1 |

0 |

XC1 && ą▓čŗą▒čĆą░ąĮąĮčŗą╣ čüąĖą│ąĮą░ą╗ čéą░ą║č鹊ą▓ |

| 1 |

1 |

XC2 && ą▓čŗą▒čĆą░ąĮąĮčŗą╣ čüąĖą│ąĮą░ą╗ čéą░ą║č鹊ą▓ |

LDBSTOP: Counter Clock Stopped with RB Loading (ą▓čŗą▒ąŠčĆ ąŠčüčéą░ąĮąŠą▓ą║ąĖ čüč湥čéą░ ą┐čĆąĖ ąĘą░ą│čĆčāąĘą║ąĄ RB)

0 = čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čüč湥čéčćąĖą║ą░ ąĮąĄ ąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą┐čĆąĖ ąĘą░ą│čĆčāąĘą║ąĄ čĆąĄą│ąĖčüčéčĆą░ RB.

1 = čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čüč湥čéčćąĖą║ą░ ąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą┐čĆąĖ ąĘą░ą│čĆčāąĘą║ąĄ čĆąĄą│ąĖčüčéčĆą░ RB.

LDBDIS: Counter Clock Disable with RB Loading (ą▓čŗą▒ąŠčĆ ąĘą░ą┐čĆąĄčéą░ čüč湥čéą░ ą┐čĆąĖ ąĘą░ą│čĆčāąĘą║ąĄ RB)

0 = čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čüč湥čéčćąĖą║ą░ ąĮąĄ ąĘą░ą┐čĆąĄčēą░ąĄčéčüčÅ ą┐čĆąĖ ąĘą░ą│čĆčāąĘą║ąĄ čĆąĄą│ąĖčüčéčĆą░ RB.

0 = čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čüč湥čéčćąĖą║ą░ ąĘą░ą┐čĆąĄčēą░ąĄčéčüčÅ ą┐čĆąĖ ąĘą░ą│čĆčāąĘą║ąĄ čĆąĄą│ąĖčüčéčĆą░ RB.

ETRGEDG: External Trigger Edge Selection (ą▓čŗą▒ąŠčĆ ą┐ąĄčĆąĄą┐ą░ą┤ą░ ą▓ąĮąĄčłąĮąĄą│ąŠ čéčĆąĖą│ą│ąĄčĆą░)

| ETRGEDG |

ą¤ąĄčĆąĄą┐ą░ą┤ |

| 0 |

0 |

none (ą┐ąĄčĆąĄą┐ą░ą┤ ąĮąĄ ą▓čŗą▒čĆą░ąĮ) |

| 0 |

1 |

ążčĆąŠąĮčé ąĮą░čĆą░čüčéą░ąĮąĖčÅ čāčĆąŠą▓ąĮčÅ (0 -> 1) |

| 1 |

0 |

ąĪą┐ą░ą┤ čāčĆąŠą▓ąĮčÅ (1 -> 0) |

| 1 |

1 |

ąøčÄą▒ąŠą╣ ą┐ąĄčĆąĄą┐ą░ą┤ ą░ą║čéąĖą▓ąĄąĮ |

ABETRG: TIOA or TIOB External Trigger Selection (ą▓čŗą▒ąŠčĆ čüąĖą│ąĮą░ą╗ą░ ą▓ąĮąĄčłąĮąĄą│ąŠ čéčĆąĖą│ą│ąĄčĆą░)

0 = ą▓ ą║ą░č湥čüčéą▓ąĄ ą▓ąĮąĄčłąĮąĄą│ąŠ čéčĆąĖą│ą│ąĄčĆą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ TIOB.

1 = ą▓ ą║ą░č湥čüčéą▓ąĄ ą▓ąĮąĄčłąĮąĄą│ąŠ čéčĆąĖą│ą│ąĄčĆą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ TIOA.

CPCTRG: RC Compare Trigger Enable (čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ čéčĆąĖą│ą│ąĄčĆą░ čüčĆą░ą▓ąĮąĄąĮąĖčÅ RC)

0 = čüąŠą▒čŗčéąĖąĄ RC Compare ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░ ąĮą░ čüč湥čéčćąĖą║ ąĖ ąĄą│ąŠ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ.

1 = čüąŠą▒čŗčéąĖąĄ RC Compare čüą▒čĆą░čüčŗą▓ą░ąĄčé čüč湥čéčćąĖą║ ąĖ ąĘą░ą┐čāčüą║ą░ąĄčé ąĄą│ąŠ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ.

WAVE

0 = čĆą░ąĘčĆąĄčłąĄąĮ čĆąĄąČąĖą╝ čüčĆą░ą▓ąĮąĄąĮąĖčÅ (ą░ą║čéąĖą▓ąĄąĮ Capture Mode).

1 = ąĘą░ą┐čĆąĄčēąĄąĮ čĆąĄąČąĖą╝ čüčĆą░ą▓ąĮąĄąĮąĖčÅ (ą░ą║čéąĖą▓ąĄąĮ Waveform Mode).

LDRA: RA Loading Selection (ą▓čŗą▒ąŠčĆ ą┐ąĄčĆąĄą┐ą░ą┤ąŠą▓ ąĘą░ą│čĆčāąĘą║ąĖ RA)

| LDRA |

ą¤ąĄčĆąĄą┐ą░ą┤ |

| 0 |

0 |

none (ą┐ąĄčĆąĄą┐ą░ą┤ ąĮąĄ ą▓čŗą▒čĆą░ąĮ) |

| 0 |

1 |

ążčĆąŠąĮčé ąĮą░čĆą░čüčéą░ąĮąĖčÅ čāčĆąŠą▓ąĮčÅ TIOA (0 -> 1) |

| 1 |

0 |

ąĪą┐ą░ą┤ čāčĆąŠą▓ąĮčÅ TIOA (1 -> 0) |

| 1 |

1 |

ąøčÄą▒ąŠą╣ ą┐ąĄčĆąĄą┐ą░ą┤ TIOA ą░ą║čéąĖą▓ąĄąĮ |

LDRB: RB Loading Selection (ą▓čŗą▒ąŠčĆ ą┐ąĄčĆąĄą┐ą░ą┤ąŠą▓ ąĘą░ą│čĆčāąĘą║ąĖ RB)

| LDRB |

ą¤ąĄčĆąĄą┐ą░ą┤ |

| 0 |

0 |

none (ą┐ąĄčĆąĄą┐ą░ą┤ ąĮąĄ ą▓čŗą▒čĆą░ąĮ) |

| 0 |

1 |

ążčĆąŠąĮčé ąĮą░čĆą░čüčéą░ąĮąĖčÅ čāčĆąŠą▓ąĮčÅ TIOA (0 -> 1) |

| 1 |

0 |

ąĪą┐ą░ą┤ čāčĆąŠą▓ąĮčÅ TIOA (1 -> 0) |

| 1 |

1 |

ąøčÄą▒ąŠą╣ ą┐ąĄčĆąĄą┐ą░ą┤ TIOA ą░ą║čéąĖą▓ąĄąĮ |

ąĀąĄą│ąĖčüčéčĆ čĆąĄąČąĖą╝ą░ ą║ą░ąĮą░ą╗ą░ TC ą▓ čĆąĄąČąĖą╝ąĄ ą│ąĄąĮąĄčĆą░čåąĖąĖ čüąĖą│ąĮą░ą╗ą░ (WAVE = 1). ąóąĖą┐ ą┤ąŠčüčéčāą┐ą░: ą┐ąŠą╗ąĮčŗą╣ (RW).

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| BSWTRG |

BEEVT |

BCPC |

BCPB |

ASWTRG |

AEEVT |

ACPC |

ACPA |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| WAVE |

WAVSEL |

ENETRG |

EEVT |

EEVTEDG |

CPCDIS |

CPCSTOP |

BURST |

CLKI |

TCCLKS

|

TCCLKS: Clock Selection (ą▓čŗą▒ąŠčĆ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ)

| TCCLKS |

ąÆčŗą▒čĆą░ąĮąĮčŗą╣ ąĖčüč鹊čćąĮąĖą║ čéą░ą║č鹊ą▓ |

| 0 |

0 |

0 |

TIMER_CLOCK1 |

| 0 |

0 |

1 |

TIMER_CLOCK2 |

| 0 |

1 |

0 |

TIMER_CLOCK3 |

| 0 |

1 |

1 |

TIMER_CLOCK4 |

| 1 |

0 |

0 |

TIMER_CLOCK5 |

| 1 |

0 |

1 |

XC0 |

| 1 |

1 |

0 |

XC1 |

| 1 |

1 |

1 |

XC2 |

CLKI: Clock Invert (ąĖąĮą▓ąĄčĆčüąĖčÅ čéą░ą║č鹊ą▓)

0 = čüč湥čéčćąĖą║ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ čäčĆąŠąĮč鹊ą╝ ąĮą░čĆą░čüčéą░ąĮąĖčÅ ą╗ąŠą│. čāčĆąŠą▓ąĮčÅ čüąĖą│ąĮą░ą╗ą░ čéą░ą║č鹊ą▓.

1 = čüč湥čéčćąĖą║ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ čüčĆąĄąĘąŠą╝ čüą┐ą░ą┤ą░ ą╗ąŠą│. čāčĆąŠą▓ąĮčÅ čüąĖą│ąĮą░ą╗ą░ čéą░ą║č鹊ą▓.

BURST: Burst Signal Selection (ą▓čŗą▒ąŠčĆ ą▓ąĮąĄčłąĮąĄą│ąŠ čüąĖą│ąĮą░ą╗ą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄą╝)

| BURST |

ąÜą░ą║ čĆą░ą▒ąŠčéą░ąĄčé čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄą╝ |

| 0 |

0 |

ąóą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ ąĮąĄ ą┐ąŠą┤ą░ąĄčéčüčÅ ą┐ąŠčüč鹊čÅąĮąĮąŠ (ąĮąĄčé ą▓ąĮąĄčłąĮąĄą│ąŠ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ) |

| 0 |

1 |

XC0 && ą▓čŗą▒čĆą░ąĮąĮčŗą╣ čüąĖą│ąĮą░ą╗ čéą░ą║č鹊ą▓ |

| 1 |

0 |

XC1 && ą▓čŗą▒čĆą░ąĮąĮčŗą╣ čüąĖą│ąĮą░ą╗ čéą░ą║č鹊ą▓ |

| 1 |

1 |

XC2 && ą▓čŗą▒čĆą░ąĮąĮčŗą╣ čüąĖą│ąĮą░ą╗ čéą░ą║č鹊ą▓ |

CPCSTOP: Counter Clock Stopped with RC Compare (ąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čéčī čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ą┐čĆąĖ RC Compare)

0 = čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čüč湥čéčćąĖą║ą░ ąĮąĄ ąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ čüč湥čéčćąĖą║ ą┤ąŠčüčéąĖą│ą░ąĄčé ąĘąĮą░č湥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ RC.

1 = čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čüč湥čéčćąĖą║ą░ ąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ čüč湥čéčćąĖą║ ą┤ąŠčüčéąĖą│ą░ąĄčé ąĘąĮą░č湥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ RC.

CPCDIS: Counter Clock Disable with RC Compare (ąĘą░ą┐čĆąĄčēą░čéčī čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ą┐čĆąĖ RC Compare)

0 = čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čüč湥čéčćąĖą║ą░ ąĮąĄ ąĘą░ą┐čĆąĄčēą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ čüč湥čéčćąĖą║ ą┤ąŠčüčéąĖą│ą░ąĄčé ąĘąĮą░č湥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ RC.

1 = čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čüč湥čéčćąĖą║ą░ ąĘą░ą┐čĆąĄčēą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ čüč湥čéčćąĖą║ ą┤ąŠčüčéąĖą│ą░ąĄčé ąĘąĮą░č湥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ RC.

EEVTEDG: External Event Edge Selection (ą▓čŗą▒ąŠčĆ ą┐ąĄčĆąĄą┐ą░ą┤ą░ ą▓ąĮąĄčłąĮąĄą│ąŠ čüąŠą▒čŗčéąĖčÅ)

| EEVTEDG |

ą¤ąĄčĆąĄą┐ą░ą┤ |

| 0 |

0 |

none (ą┐ąĄčĆąĄą┐ą░ą┤ ąĮąĄ ą▓čŗą▒čĆą░ąĮ) |

| 0 |

1 |

ążčĆąŠąĮčé ąĮą░čĆą░čüčéą░ąĮąĖčÅ čāčĆąŠą▓ąĮčÅ (0 -> 1) |

| 1 |

0 |

ąĪą┐ą░ą┤ čāčĆąŠą▓ąĮčÅ (1 -> 0) |

| 1 |

1 |

ąøčÄą▒ąŠą╣ ą┐ąĄčĆąĄą┐ą░ą┤ ą░ą║čéąĖą▓ąĄąĮ |

EEVT: External Event Selection (ą▓čŗą▒ąŠčĆ ą▓ąĮąĄčłąĮąĄą│ąŠ čüąŠą▒čŗčéąĖčÅ)

| EEVTEDG |

ąĪąĖą│ąĮą░ą╗, ą▓čŗą▒čĆą░ąĮąĮčŗą╣ ą║ą░ą║ ą▓ąĮąĄčłąĮąĄąĄ čüąŠą▒čŗčéąĖąĄ |

ąØą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ TIOB |

| 0 |

0 |

TIOB |

ąÆčģąŠą┤(1) |

| 0 |

1 |

XC0 |

ąÆčŗčģąŠą┤ |

| 1 |

0 |

XC1 |

| 1 |

1 |

XC2 |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ (1): ąĄčüą╗ąĖ TIOB ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ą║ą░ą║ čüąĖą│ąĮą░ą╗ ą▓ąĮąĄčłąĮąĄą│ąŠ čüąŠą▒čŗčéąĖčÅ, č鹊 TIOB ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ ą║ą░ą║ ą▓čģąŠą┤, ąĖ ąĮąĄ ą╝ąŠąČąĄčé ą▒ąŠą╗čīčłąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ čüąĖą│ąĮą░ą╗ąŠą▓, ąĖ čüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ąĘą░ą┐čĆąŠčüąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (IRQ).

ENETRG: External Event Trigger Enable (čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ čéčĆąĖą│ą│ąĄčĆą░ ą▓ąĮąĄčłąĮąĄą│ąŠ čüąŠą▒čŗčéąĖčÅ)

0 = ą▓ąĮąĄčłąĮąĄąĄ čüąŠą▒čŗčéąĖąĄ ąĮąĖą║ą░ą║ ąĮąĄ ą▓ą╗ąĖčÅąĄčé ąĮą░ čüč湥čéčćąĖą║ ąĖ ąĄą│ąŠ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ą▓čŗą▒čĆą░ąĮąĮąŠąĄ ą▓ąĮąĄčłąĮąĄąĄ čüąŠą▒čŗčéąĖąĄ č鹊ą╗čīą║ąŠ ą╗ąĖčłčī čāą┐čĆą░ą▓ą╗čÅąĄčé ą▓čŗčģąŠą┤ąŠą╝ TIOA.

1 = ą▓ąĮąĄčłąĮąĄąĄ čüąŠą▒čŗčéąĖąĄ čüą▒čĆą░čüčŗą▓ą░ąĄčé čüč湥čéčćąĖą║ ąĖ ąĘą░ą┐čāčüą║ą░ąĄčé ąĄą│ąŠ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ.

WAVSEL: Waveform Selection (ą▓čŗą▒ąŠčĆ ą▓ą░čĆąĖą░ąĮčéą░ ą│ąĄąĮąĄčĆą░čåąĖąĖ čüąĖą│ąĮą░ą╗ą░)

| WAVSEL |

ąŁčäč乥ą║čé |

| 0 |

0 |

ąĪč湥čé ą▓ą▓ąĄčĆčģ (UP mode) ą▒ąĄąĘ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą│ąŠ čéčĆąĖą│ą│ąĄčĆą░ ą┐čĆąĖ čüąŠą▒čŗčéąĖąĖ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ RC Compare |

| 0 |

1 |

ąĪč湥čé ą▓ą▓ąĄčĆčģ (UP mode) čü ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖą╝ čéčĆąĖą│ą│ąĄčĆąŠą╝ ą┐čĆąĖ čüąŠą▒čŗčéąĖąĖ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ RC Compare |

| 1 |

0 |

ąĪč湥čé ą▓ą▓ąĄčĆčģ ąĖ ą▓ąĮąĖąĘ (UPDOWN mode) ą▒ąĄąĘ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą│ąŠ čéčĆąĖą│ą│ąĄčĆą░ ą┐čĆąĖ čüąŠą▒čŗčéąĖąĖ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ RC Compare |

| 1 |

1 |

ąĪč湥čé ą▓ą▓ąĄčĆčģ ąĖ ą▓ąĮąĖąĘ (UPDOWN mode) čü ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖą╝ čéčĆąĖą│ą│ąĄčĆąŠą╝ ą┐čĆąĖ čüąŠą▒čŗčéąĖąĖ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ RC Compare |

WAVE

0 = ąĘą░ą┐čĆąĄčēąĄąĮ čĆąĄąČąĖą╝ ą│ąĄąĮąĄčĆą░čåąĖąĖ čüąĖą│ąĮą░ą╗ą░ (ą░ą║čéąĖą▓ąĄąĮ Capture Mode).

1 = čĆą░ąĘčĆąĄčłąĄąĮ čĆąĄąČąĖą╝ ą│ąĄąĮąĄčĆą░čåąĖąĖ čüąĖą│ąĮą░ą╗ą░ (ą░ą║čéąĖą▓ąĄąĮ Waveform Mode).

ACPA: RA Compare Effect on TIOA (ą▓ą╗ąĖčÅąĮąĖąĄ čüąŠą▒čŗčéąĖčÅ čüčĆą░ą▓ąĮąĄąĮąĖčÅ RA ąĮą░ čüąĖą│ąĮą░ą╗ TIOA)

| ACPA |

ąŁčäč乥ą║čé |

| 0 |

0 |

none (ąĮąĖč湥ą│ąŠ ąĮąĄ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé) |

| 0 |

1 |

set (čāčüčéą░ąĮąŠą▓ą║ą░ ą▓ ą╗ąŠą│. 1) |

| 1 |

0 |

clear (čüą▒čĆąŠčü ą▓ ą╗ąŠą│. 0) |

| 1 |

1 |

toggle (ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ą▓ ą┐čĆąŠčéąĖą▓ąŠą┐ąŠą╗ąŠąČąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī) |

ACPC: RC Compare Effect on TIOA (ą▓ą╗ąĖčÅąĮąĖąĄ čüąŠą▒čŗčéąĖčÅ čüčĆą░ą▓ąĮąĄąĮąĖčÅ RC ąĮą░ čüąĖą│ąĮą░ą╗ TIOA)

| ACPC |

ąŁčäč乥ą║čé |

| 0 |

0 |

none (ąĮąĖč湥ą│ąŠ ąĮąĄ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé) |

| 0 |

1 |

set (čāčüčéą░ąĮąŠą▓ą║ą░ ą▓ ą╗ąŠą│. 1) |

| 1 |

0 |

clear (čüą▒čĆąŠčü ą▓ ą╗ąŠą│. 0) |

| 1 |

1 |

toggle (ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ą▓ ą┐čĆąŠčéąĖą▓ąŠą┐ąŠą╗ąŠąČąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī) |

AEEVT: External Event Effect on TIOA (ą▓ą╗ąĖčÅąĮąĖąĄ ą▓ąĮąĄčłąĮąĄą│ąŠ čüąŠą▒čŗčéąĖčÅ ąĮą░ čüąĖą│ąĮą░ą╗ TIOA)

| AEEVT |

ąŁčäč乥ą║čé |

| 0 |

0 |

none (ąĮąĖč湥ą│ąŠ ąĮąĄ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé) |

| 0 |

1 |

set (čāčüčéą░ąĮąŠą▓ą║ą░ ą▓ ą╗ąŠą│. 1) |

| 1 |

0 |

clear (čüą▒čĆąŠčü ą▓ ą╗ąŠą│. 0) |

| 1 |

1 |

toggle (ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ą▓ ą┐čĆąŠčéąĖą▓ąŠą┐ąŠą╗ąŠąČąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī) |

ASWTRG: Software Trigger Effect on TIOA (ą▓ą╗ąĖčÅąĮąĖąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čéčĆąĖą│ą│ąĄčĆą░ ąĮą░ čüąĖą│ąĮą░ą╗ TIOA)

| ASWTRG |

ąŁčäč乥ą║čé |

| 0 |

0 |

none (ąĮąĖč湥ą│ąŠ ąĮąĄ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé) |

| 0 |

1 |

set (čāčüčéą░ąĮąŠą▓ą║ą░ ą▓ ą╗ąŠą│. 1) |

| 1 |

0 |

clear (čüą▒čĆąŠčü ą▓ ą╗ąŠą│. 0) |

| 1 |

1 |

toggle (ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ą▓ ą┐čĆąŠčéąĖą▓ąŠą┐ąŠą╗ąŠąČąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī) |

BCPB: RB Compare Effect on TIOB (ą▓ą╗ąĖčÅąĮąĖąĄ čüąŠą▒čŗčéąĖčÅ čüčĆą░ą▓ąĮąĄąĮąĖčÅ RB ąĮą░ čüąĖą│ąĮą░ą╗ TIOB)

| BCPB |

ąŁčäč乥ą║čé |

| 0 |

0 |

none (ąĮąĖč湥ą│ąŠ ąĮąĄ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé) |

| 0 |

1 |

set (čāčüčéą░ąĮąŠą▓ą║ą░ ą▓ ą╗ąŠą│. 1) |

| 1 |

0 |

clear (čüą▒čĆąŠčü ą▓ ą╗ąŠą│. 0) |

| 1 |

1 |

toggle (ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ą▓ ą┐čĆąŠčéąĖą▓ąŠą┐ąŠą╗ąŠąČąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī) |

BCPC: RC Compare Effect on TIOB (ą▓ą╗ąĖčÅąĮąĖąĄ čüąŠą▒čŗčéąĖčÅ čüčĆą░ą▓ąĮąĄąĮąĖčÅ RC ąĮą░ čüąĖą│ąĮą░ą╗ TIOB)

| BCPC |

ąŁčäč乥ą║čé |

| 0 |

0 |

none (ąĮąĖč湥ą│ąŠ ąĮąĄ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé) |

| 0 |

1 |

set (čāčüčéą░ąĮąŠą▓ą║ą░ ą▓ ą╗ąŠą│. 1) |

| 1 |

0 |

clear (čüą▒čĆąŠčü ą▓ ą╗ąŠą│. 0) |

| 1 |

1 |

toggle (ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ą▓ ą┐čĆąŠčéąĖą▓ąŠą┐ąŠą╗ąŠąČąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī) |

BEEVT: External Event Effect on TIOB (ą▓ą╗ąĖčÅąĮąĖąĄ ą▓ąĮąĄčłąĮąĄą│ąŠ čüąŠą▒čŗčéąĖčÅ ąĮą░ čüąĖą│ąĮą░ą╗ TIOB)

| BEEVT |

ąŁčäč乥ą║čé |

| 0 |

0 |

none (ąĮąĖč湥ą│ąŠ ąĮąĄ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé) |

| 0 |

1 |

set (čāčüčéą░ąĮąŠą▓ą║ą░ ą▓ ą╗ąŠą│. 1) |

| 1 |

0 |

clear (čüą▒čĆąŠčü ą▓ ą╗ąŠą│. 0) |

| 1 |

1 |

toggle (ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ą▓ ą┐čĆąŠčéąĖą▓ąŠą┐ąŠą╗ąŠąČąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī) |

BSWTRG: Software Trigger Effect on TIOB (ą▓ą╗ąĖčÅąĮąĖąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čéčĆąĖą│ą│ąĄčĆą░ ąĮą░ čüąĖą│ąĮą░ą╗ TIOB)

| BSWTRG |

ąŁčäč乥ą║čé |

| 0 |

0 |

none (ąĮąĖč湥ą│ąŠ ąĮąĄ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé) |

| 0 |

1 |

set (čāčüčéą░ąĮąŠą▓ą║ą░ ą▓ ą╗ąŠą│. 1) |

| 1 |

0 |

clear (čüą▒čĆąŠčü ą▓ ą╗ąŠą│. 0) |

| 1 |

1 |

toggle (ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ą▓ ą┐čĆąŠčéąĖą▓ąŠą┐ąŠą╗ąŠąČąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī) |

ąĀąĄą│ąĖčüčéčĆ ąĘąĮą░č湥ąĮąĖčÅ čüč湥čéčćąĖą║ą░. ąóąĖą┐ ą┤ąŠčüčéčāą┐ą░: č鹊ą╗čīą║ąŠ čćč鹥ąĮąĖąĄ (RO).

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

-

|

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

-

|

- |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| CV |

CV: Counter Value (ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░)

CV čüąŠą┤ąĄčƹȹĖčé ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░ ą▓ čĆąĄą░ą╗čīąĮąŠą╝ ą▓čĆąĄą╝ąĄąĮąĖ.

ąĀąĄą│ąĖčüčéčĆ A čéą░ą╣ą╝ąĄčĆą░/čüč湥čéčćąĖą║ą░. ąóąĖą┐ ą┤ąŠčüčéčāą┐ą░: č鹊ą╗čīą║ąŠ čćč鹥ąĮąĖąĄ (RO) ąĄčüą╗ąĖ WAVE = 0, ąĖą╗ąĖ ą┐ąŠą╗ąĮčŗą╣ (RW) ąĄčüą╗ąĖ WAVE = 1.

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

-

|

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

-

|

- |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

RA

|

RA: Register A

RA čüąŠą┤ąĄčƹȹĖčé ąĘąĮą░č湥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ A ą▓ čĆąĄą░ą╗čīąĮąŠą╝ ą▓čĆąĄą╝ąĄąĮąĖ.

ąĀąĄą│ąĖčüčéčĆ B čéą░ą╣ą╝ąĄčĆą░/čüč湥čéčćąĖą║ą░. ąóąĖą┐ ą┤ąŠčüčéčāą┐ą░: č鹊ą╗čīą║ąŠ čćč鹥ąĮąĖąĄ (RO) ąĄčüą╗ąĖ WAVE = 0, ąĖą╗ąĖ ą┐ąŠą╗ąĮčŗą╣ (RW) ąĄčüą╗ąĖ WAVE = 1.

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

-

|

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

-

|

- |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

RB

|

RB: Register B

RB čüąŠą┤ąĄčƹȹĖčé ąĘąĮą░č湥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ B ą▓ čĆąĄą░ą╗čīąĮąŠą╝ ą▓čĆąĄą╝ąĄąĮąĖ.

ąĀąĄą│ąĖčüčéčĆ C čéą░ą╣ą╝ąĄčĆą░/čüč湥čéčćąĖą║ą░. ąóąĖą┐ ą┤ąŠčüčéčāą┐ą░: ą┐ąŠą╗ąĮčŗą╣ (RW).

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

-

|

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

-

|

- |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

RC

|

RC: Register C

RC čüąŠą┤ąĄčƹȹĖčé ąĘąĮą░č湥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ C ą▓ čĆąĄą░ą╗čīąĮąŠą╝ ą▓čĆąĄą╝ąĄąĮąĖ.

ąĀąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ čéą░ą╣ą╝ąĄčĆą░/čüč湥čéčćąĖą║ą░. ąóąĖą┐ ą┤ąŠčüčéčāą┐ą░: č鹊ą╗čīą║ąŠ čćč鹥ąĮąĖąĄ (RO).

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

-

|

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

MTIOB |

MTIOA |

CLKSTA |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

-

|

- |

- |

- |

- |

- |

- |

- |

ETRGS |

LDRBS |

LDRAS |

CPCS |

CPBS |

CPAS |

LOVRS |

COVFS |

COVFS: Counter Overflow Status (ą▒čŗą╗ąŠ ą╗ąĖ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĄ čüč湥čéčćąĖą║ą░)

0 = čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čćč鹥ąĮąĖčÅ Status Register ąĮąĄ ą▒čŗą╗ąŠ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ čüč湥čéčćąĖą║ą░.

1 = čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čćč鹥ąĮąĖčÅ Status Register ą▒čŗą╗ąŠ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĄ čüč湥čéčćąĖą║ą░.

LOVRS: Load Overrun Status (ą▒čŗą╗ ą╗ąĖ ą┐čĆąŠą┐čāčüą║ ąĘą░ą│čĆčāąĘą║ąĖ)

0 = ąĮąĄ ą▒čŗą╗ąŠ ą┐čĆąŠą┐čāčüą║ą░ ąĘą░ą│čĆčāąĘą║ąĖ čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čćč鹥ąĮąĖčÅ Status Register, ąĖą╗ąĖ WAVE = 1.

1 = RA ąĖą╗ąĖ RB ą▒čŗą╗ ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ą┤ą▓ą░ąČą┤čŗ ąĘą░ą│čĆčāąČąĄąĮ ą▒ąĄąĘ čćč鹥ąĮąĖčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ čĆąĄą│ąĖčüčéčĆą░ čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čćč鹥ąĮąĖčÅ Status, ąĄčüą╗ąĖ WAVE = 0.

CPAS: RA Compare Status (čüąŠčüč鹊čÅąĮąĖąĄ čüčĆą░ą▓ąĮąĄąĮąĖčÅ RA)

0 = ąĮąĄ ą▒čŗą╗ąŠ RA Compare čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čćč鹥ąĮąĖčÅ Status Register, ąĖą╗ąĖ WAVE = 0.

1 = ą┐čĆąŠąĖąĘąŠčłą╗ąŠ RA Compare čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čćč鹥ąĮąĖčÅ Status Register, ąĄčüą╗ąĖ WAVE = 1.

CPBS: RB Compare Status (čüąŠčüč鹊čÅąĮąĖąĄ čüčĆą░ą▓ąĮąĄąĮąĖčÅ RB)

0 = ąĮąĄ ą▒čŗą╗ąŠ RB Compare čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čćč鹥ąĮąĖčÅ Status Register, ąĖą╗ąĖ WAVE = 0.

1 = ą┐čĆąŠąĖąĘąŠčłą╗ąŠ RB Compare čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čćč鹥ąĮąĖčÅ Status Register, ąĄčüą╗ąĖ WAVE = 1.

CPCS: RC Compare Status (čüąŠčüč鹊čÅąĮąĖąĄ čüčĆą░ą▓ąĮąĄąĮąĖčÅ RC)

0 = ąĮąĄ ą▒čŗą╗ąŠ RC Compare čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čćč鹥ąĮąĖčÅ Status Register, ąĖą╗ąĖ WAVE = 0.

1 = ą┐čĆąŠąĖąĘąŠčłą╗ąŠ RC Compare čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čćč鹥ąĮąĖčÅ Status Register, ąĄčüą╗ąĖ WAVE = 1.

LDRAS: RA Loading Status (čüąŠčüč鹊čÅąĮąĖąĄ ąĘą░ą│čĆčāąĘą║ąĖ RA)

0 = ąĮąĄ ą▒čŗą╗ąŠ ąĘą░ą│čĆčāąĘą║ąĖ RA čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čćč鹥ąĮąĖčÅ Status Register, ąĖą╗ąĖ WAVE = 1.

1 = ą▒čŗą╗ą░ ąĘą░ą│čĆčāąĘą║ą░ RA čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čćč鹥ąĮąĖčÅ Status Register, ąĄčüą╗ąĖ WAVE = 0.

LDRBS: RB Loading Status (čüąŠčüč鹊čÅąĮąĖąĄ ąĘą░ą│čĆčāąĘą║ąĖ RB)

0 = ąĮąĄ ą▒čŗą╗ąŠ ąĘą░ą│čĆčāąĘą║ąĖ RB čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čćč鹥ąĮąĖčÅ Status Register, ąĖą╗ąĖ WAVE = 1.

1 = ą▒čŗą╗ą░ ąĘą░ą│čĆčāąĘą║ą░ RB čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čćč鹥ąĮąĖčÅ Status Register, ąĄčüą╗ąĖ WAVE = 0.

ETRGS: External Trigger Status (čüąŠčüč鹊čÅąĮąĖąĄ ą▓ąĮąĄčłąĮąĄą│ąŠ čéčĆąĖą│ą│ąĄčĆą░)

0 = ąĮąĄ ą▒čŗą╗ąŠ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖčÅ ą▓ąĮąĄčłąĮąĄą│ąŠ čéčĆąĖą│ą│ąĄčĆą░ čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čćč鹥ąĮąĖčÅ Status Register.

1 = ą▒čŗą╗ąŠ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĄ ą▓ąĮąĄčłąĮąĄą│ąŠ čéčĆąĖą│ą│ąĄčĆą░ čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čćč鹥ąĮąĖčÅ Status Register.

CLKSTA: Clock Enabling Status (čüąŠčüč鹊čÅąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ)

0 = čéą░ą║čéčŗ ąĘą░ą┐čĆąĄčēąĄąĮčŗ.

1 = čéą░ą║čéčŗ čĆą░ąĘčĆąĄčłąĄąĮčŗ.

MTIOA: TIOA Mirror (ą╗ąŠą│. čāčĆąŠą▓ąĄąĮčī ąĮą░ TIOA)

0 = TIOA ą▓ ą╗ąŠą│. 0. ąĢčüą╗ąĖ WAVE = 0, č鹊 čŹč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ąĮąŠąČą║ą░ TIOA (ą▓čģąŠą┤) ą▓ ą╗ąŠą│. 0. ąĢčüą╗ąĖ WAVE = 1, č鹊 čŹč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ąĮą░ TIOA (ą▓čŗčģąŠą┤) ą▓čŗą▓ąĄą┤ąĄąĮ čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 0.

1 = TIOA ą▓ ą╗ąŠą│. 1. ąĢčüą╗ąĖ WAVE = 0, č鹊 čŹč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ąĮąŠąČą║ą░ TIOA (ą▓čģąŠą┤) ą▓ ą╗ąŠą│. 1. ąĢčüą╗ąĖ WAVE = 1, č鹊 čŹč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ąĮą░ TIOA (ą▓čŗčģąŠą┤) ą▓čŗą▓ąĄą┤ąĄąĮ čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 1.

MTIOB: TIOB Mirror (ą╗ąŠą│. čāčĆąŠą▓ąĄąĮčī ąĮą░ TIOB)

0 = TIOB ą▓ ą╗ąŠą│. 0. ąĢčüą╗ąĖ WAVE = 0, č鹊 čŹč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ąĮąŠąČą║ą░ TIOB (ą▓čģąŠą┤) ą▓ ą╗ąŠą│. 0. ąĢčüą╗ąĖ WAVE = 1, č鹊 čŹč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ąĮą░ TIOB (ą▓čŗčģąŠą┤) ą▓čŗą▓ąĄą┤ąĄąĮ čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 0.

1 = TIOB ą▓ ą╗ąŠą│. 1. ąĢčüą╗ąĖ WAVE = 0, č鹊 čŹč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ąĮąŠąČą║ą░ TIOB (ą▓čģąŠą┤) ą▓ ą╗ąŠą│. 1. ąĢčüą╗ąĖ WAVE = 1, č鹊 čŹč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ąĮą░ TIOB (ą▓čŗčģąŠą┤) ą▓čŗą▓ąĄą┤ąĄąĮ čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 1.

ąĀąĄą│ąĖčüčéčĆ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ TC. ąóąĖą┐ ą┤ąŠčüčéčāą┐ą░: č鹊ą╗čīą║ąŠ ąĘą░ą┐ąĖčüčī (WO).

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

-

|

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

-

|

- |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

-

|

- |

- |

- |

- |

- |

- |

- |

ETRGS |

LDRBS |

LDRAS |

CPCS |

CPBS |

CPAS |

LOVRS |

COVFS |

COVFS: Counter Overflow (ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĄ čüč湥čéčćąĖą║ą░)

0 = ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

1 = čĆą░ąĘčĆąĄčłą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐čĆąĖ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĖ čüč湥čéčćąĖą║ą░.

LOVRS: Load Overrun

0 = ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

1 = čĆą░ąĘčĆąĄčłą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐čĆąŠą┐čāčüą║ą░ ąĘą░ą│čĆčāąĘą║ąĖ Load Overrun.

CPAS: RA Compare

0 = ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

1 = čĆą░ąĘčĆąĄčłą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ RA Compare.

CPBS: RB Compare

0 = ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

1 = čĆą░ąĘčĆąĄčłą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ RB Compare.

CPCS: RC Compare

0 = ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

1 = čĆą░ąĘčĆąĄčłą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ RC Compare.

LDRAS: RA Loading

0 = ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

1 = čĆą░ąĘčĆąĄčłą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐čĆąĖ ąĘą░ą│čĆčāąĘą║ąĄ RA.

LDRBS: RB Loading

0 = ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

1 = čĆą░ąĘčĆąĄčłą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐čĆąĖ ąĘą░ą│čĆčāąĘą║ąĄ RB.

ETRGS: External Trigger

0 = ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

1 = čĆą░ąĘčĆąĄčłą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą▓ąĮąĄčłąĮąĄą│ąŠ čéčĆąĖą│ą│ąĄčĆą░.

ąĀąĄą│ąĖčüčéčĆ ąĘą░ą┐čĆąĄčéą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ TC. ąóąĖą┐ ą┤ąŠčüčéčāą┐ą░: č鹊ą╗čīą║ąŠ ąĘą░ą┐ąĖčüčī (WO).

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

-

|

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

-

|

- |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

-

|

- |

- |

- |

- |

- |

- |

- |

ETRGS |

LDRBS |

LDRAS |

CPCS |

CPBS |

CPAS |

LOVRS |

COVFS

|

COVFS: Counter Overflow

0 = ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

1 = ąĘą░ą┐čĆąĄčēą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐čĆąĖ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĖ čüč湥čéčćąĖą║ą░.

LOVRS: Load Overrun

0 = ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

1 = ąĘą░ą┐čĆąĄčēą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐čĆąŠą┐čāčüą║ą░ ąĘą░ą│čĆčāąĘą║ąĖ Load Overrun (ąĄčüą╗ąĖ WAVE=0).

CPAS: RA Compare

0 = ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

1 = ąĘą░ą┐čĆąĄčēą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ RA Compare (ąĄčüą╗ąĖ WAVE=1).

CPBS: RB Compare

0 = ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

1 = ąĘą░ą┐čĆąĄčēą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ RB Compare (ąĄčüą╗ąĖ WAVE=1).

CPCS: RC Compare

0 = ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

1 = ąĘą░ą┐čĆąĄčēą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ RC Compare.

LDRAS: RA Loading

0 = ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

1 = ąĘą░ą┐čĆąĄčēą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐čĆąĖ ąĘą░ą│čĆčāąĘą║ąĄ RA (ąĄčüą╗ąĖ WAVE=0).

LDRBS: RB Loading

0 = ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

1 = ąĘą░ą┐čĆąĄčēą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐čĆąĖ ąĘą░ą│čĆčāąĘą║ąĄ RB (ąĄčüą╗ąĖ WAVE=0).

ETRGS: External Trigger

0 = ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

1 = ąĘą░ą┐čĆąĄčēą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą▓ąĮąĄčłąĮąĄą│ąŠ čéčĆąĖą│ą│ąĄčĆą░.

ąĀąĄą│ąĖčüčéčĆ ą╝ą░čüą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čéą░ą╣ą╝ąĄčĆą░/čüč湥čéčćąĖą║ą░. ąóąĖą┐ ą┤ąŠčüčéčāą┐ą░: č鹊ą╗čīą║ąŠ čćč鹥ąĮąĖąĄ (RO).

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

-

|

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

-

|

- |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

-

|

- |

- |

- |

- |

- |

- |

- |

ETRGS |

LDRBS |

LDRAS |

CPCS |

CPBS |

CPAS |

LOVRS |

COVFS

|

COVFS: Counter Overflow

0 = ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ čüč湥čéčćąĖą║ą░ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1 = ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ čüč湥čéčćąĖą║ą░ čĆą░ąĘčĆąĄčłąĄąĮąŠ.

LOVRS: Load Overrun

0 = ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐čĆąŠą┐čāčüą║ą░ ąĘą░ą│čĆčāąĘą║ąĖ Load Overrun ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1 = ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐čĆąŠą┐čāčüą║ą░ ąĘą░ą│čĆčāąĘą║ąĖ Load Overrun čĆą░ąĘčĆąĄčłąĄąĮąŠ.

CPAS: RA Compare

0 = ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ RA Compare ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1 = ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ RA Compare čĆą░ąĘčĆąĄčłąĄąĮąŠ.

CPBS: RB Compare

0 = ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ RB Compare ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1 = ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ RB Compare čĆą░ąĘčĆąĄčłąĄąĮąŠ.

CPCS: RC Compare

0 = ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ RC Compare ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1 = ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ RC Compare čĆą░ąĘčĆąĄčłąĄąĮąŠ.

LDRAS: RA Loading

0 = ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą│čĆčāąĘą║ąĖ RA ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1 = ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą│čĆčāąĘą║ąĖ RA čĆą░ąĘčĆąĄčłąĄąĮąŠ.

LDRBS: RB Loading

0 = ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą│čĆčāąĘą║ąĖ RB ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1 = ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą│čĆčāąĘą║ąĖ RB čĆą░ąĘčĆąĄčłąĄąĮąŠ.

ETRGS: External Trigger

0 = ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą▓ąĮąĄčłąĮąĄą│ąŠ čéčĆąĖą│ą│ąĄčĆą░ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

1 = ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą▓ąĮąĄčłąĮąĄą│ąŠ čéčĆąĖą│ą│ąĄčĆą░ čĆą░ąĘčĆąĄčłąĄąĮąŠ.

[ąĪčüčŗą╗ą║ąĖ]

1. AT91 ARM Thumb-based Microcontrollers AT91SAM7X512 AT91SAM7X256 AT91SAM7X128 site:microchip.com.

2. Power Management Controller ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ AT91SAM7X.

3. Advanced Interrupt Controller ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ AT91SAM7X.

4. AT91SAM7 Parallel Input/Output Controller (PIO). |