|

ąæą╗ąŠą║ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ (Serial Peripheral Interface, SPI) ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé čüąŠą▒ąŠą╣ ą┤čāą┐ą╗ąĄą║čüąĮčŗą╣ ą╗ąĖąĮą║ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ, ąŠą▒ąĄčüą┐ąĄčćąĖą▓ą░čÄčēąĖą╣ ą┤ą▓čāčüč鹊čĆąŠąĮąĮąĖą╣ ąŠą▒ą╝ąĄąĮ čü ą▓ąĮąĄčłąĮąĖą╝ąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ą╝ąĖ ą▓ čĆąĄąČąĖą╝ąĄ ą│ą╗ą░ą▓ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (Master Mode) ąĖą╗ąĖ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (Slave Mode). ąŁč鹊 čéą░ą║ąČąĄ čĆą░ąĘčĆąĄčłą░ąĄčé ąŠą▒ą╝ąĄąĮ ą╝ąĄąČą┤čā ą┐čĆąŠčåąĄčüčüąŠčĆą░ą╝ąĖ, ąĄčüą╗ąĖ ą║ čĆą░ąĘčĆą░ą▒ą░čéčŗą▓ą░ąĄą╝ąŠą╣ čüąĖčüč鹥ą╝ąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą▓ąĮąĄčłąĮąĖą╣ ą┐čĆąŠčåąĄčüčüąŠčĆ.

ą¤ąŠ čüčāčéąĖ SPI čŹč鹊 ą┐čĆąŠčüč鹊 čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░, ą║ąŠč鹊čĆčŗą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ ą┐ąĄčĆąĄą┤ą░ąĄčé ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ ą┤čĆčāą│ąĖčģ čāčüčéčĆąŠą╣čüčéą▓ SPI [2]. ąÆąŠ ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ąŠą┤ąĮą░ ąĖąĘ čüąĖčüč鹥ą╝ SPI ą┤ąĄą╣čüčéą▓čāąĄčé ą║ą░ą║ "master", čāą┐čĆą░ą▓ą╗čÅčÅ ą┐ąŠč鹊ą║ąŠą╝ ą┤ą░ąĮąĮčŗčģ, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ ą┤čĆčāą│ąĖąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ ąĮą░ čłąĖąĮąĄ SPI ą┤ąĄą╣čüčéą▓čāčÄčé ą║ą░ą║ "slave" ą▓ą┤ą▓ąĖą│ą░čÅ ą▓ čüąĄą▒čÅ ą┤ą░ąĮąĮčŗąĄ ąĖ ą▓čŗą┤ą▓ąĖą│ą░čÅ ąĖčģ ąĮą░ čłąĖąĮčā ą┐ąŠ čéą░ą║č鹊ą▓ąŠą╝čā čüąĖą│ąĮą░ą╗čā, ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄą╝ąŠą╝čā čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ master. ąĀą░ąĘąĮčŗąĄ CPU ą╝ąŠą│čāčé ą┐čĆąĄą┤ą┐čĆąĖąĮčÅčéčī ą┐ąŠą┐čŗčéą║ąĖ čüčéą░čéčī ą╝ą░čüč鹥čĆą░ą╝ąĖ, č鹊ą│ą┤ą░ ą▒čāą┤ąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┐čĆąŠč鹊ą║ąŠą╗ čü ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ ą╝ą░čüč鹥čĆą░ą╝ąĖ ąĮą░ čłąĖąĮąĄ (Multiple Master Protocol) ą▓ ąŠčéą╗ąĖčćąĖąĄ ąŠčé čüą╗čāčćą░čÅ, ą║ąŠą│ą┤ą░ ąĮą░ čłąĖąĮąĄ SPI č鹊ą╗čīą║ąŠ ąŠą┤ąĮąŠ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą╝ą░čüč鹥čĆ, ą░ ą▓čüąĄ ąŠčüčéą░ą╗čīąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗąĄ (Single Master Protocol, čŹč鹊čé ą▓ą░čĆąĖą░ąĮčé ą┐čĆąŠč鹊ą║ąŠą╗ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čćą░čēąĄ ą▓čüąĄą│ąŠ). ąÆ ą┐čĆąŠč鹊ą║ąŠą╗ąĄ čü ąŠą┤ąĮąĖą╝ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ ą╝ą░čüč鹥čĆ ą┤ą░ąĮąĮčŗąĄ ą╝ąŠą│čāčé ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčīčüčÅ čüčĆą░ąĘčā ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗą╝ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝. ąöą╗čÅ ą┐čĆąŠč鹊ą║ąŠą╗ą░ čü ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ master ą▓čüąĄ čĆą░ą▓ąĮąŠ ą▓ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé ą▓čĆąĄą╝ąĄąĮąĖ ąĮą░ ąŠą┤ąĮąŠą╣ čłąĖąĮąĄ ą┤ąŠą╗ąČąĮąŠ ąĮą░čģąŠą┤ąĖčéčīčüčÅ č鹊ą╗čīą║ąŠ ąŠą┤ąĮąŠ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą╝ą░čüč鹥čĆ, čé. ąĄ. ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī ą┤ą░ąĮąĮčŗąĄ ą┐ąŠ čłąĖąĮąĄ ą╝ąŠąČąĄčé č鹊ą╗čīą║ąŠ ąŠą┤ąĮąŠ čāčüčéčĆąŠą╣čüčéą▓ąŠ. ą¤ąŠą┤ąŠą▒ąĮčŗą╝ ąŠą▒čĆą░ąĘąŠą╝, ą║ąŠą│ą┤ą░ ą╝ą░čüč鹥čĆ ą┐ąĄčĆąĄą┤ą░ąĄčé ą┐ąŠ čłąĖąĮąĄ SPI ą┤ą░ąĮąĮčŗąĄ ą▓čüąĄą╝ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ slave, ą▓ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé ą▓čĆąĄą╝ąĄąĮąĖ č鹊ą╗čīą║ąŠ ąŠą┤ąĮąŠ čāčüčéčĆąŠą╣čüčéą▓ąŠ slave ą╝ąŠąČąĄčé ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī ą┤ą░ąĮąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓čā master.

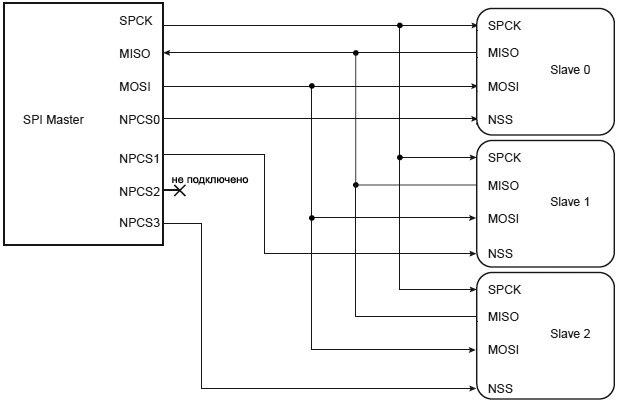

Slave-čāčüčéčĆąŠą╣čüčéą▓ąŠ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ą▓ąĮąĄčłąĮąĖą╝ čüąĖą│ąĮą░ą╗ąŠą╝ NSS, ą║ąŠč鹊čĆčŗą╣ ą┐čĆąĖčģąŠą┤ąĖčé ą┤ą╗čÅ ąĮąĄą│ąŠ ąŠčé čāčüčéčĆąŠą╣čüčéą▓ą░ Master. ąĢčüą╗ąĖ ąĮą░ čłąĖąĮąĄ SPI ą┐čĆąĖčüčāčéčüčéą▓čāąĄčé ąĮąĄčüą║ąŠą╗čīą║ąŠ čāčüčéčĆąŠą╣čüčéą▓ slave, master ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ąŠčéą┤ąĄą╗čīąĮčŗąĄ čüąĖą│ąĮą░ą╗čŗ ą▓čŗą▒ąŠčĆą║ąĖ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ slave (NPCS).

ąĪąĖčüč鹥ą╝ą░ SPI čüąŠčüč鹊ąĖčé ąĖąĘ 2 čüąĖą│ąĮą░ą╗ąŠą▓ ą┤ą░ąĮąĮčŗčģ ąĖ ą┤ą▓čāčģ čüąĖą│ąĮą░ą╗ąŠą▓ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ:

ŌĆó Master Out Slave In (MOSI): čŹč鹊 čüąĖą│ąĮą░ą╗ ą┤ą░ąĮąĮčŗčģ, ą║ąŠč鹊čĆčŗąĄ master ą▓čŗą┤ą▓ąĖą│ą░ąĄčé ąĮą░ ą▓čģąŠą┤čŗ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ (slave).

ŌĆó Master In Slave Out (MISO): čŹč鹊 čüąĖą│ąĮą░ą╗ ą┤ą░ąĮąĮčŗčģ, ą║ąŠč鹊čĆčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ slave ą▓čŗą┤ą▓ąĖą│ą░ąĄčé ąĮą░ ą▓čģąŠą┤ ą│ą╗ą░ą▓ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (master). ąŚą┤ąĄčüčī ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮąŠ ą▒ąŠą╗čīčłąĄ ąŠą┤ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ slave, ą┐ąĄčĆąĄą┤ą░čÄčēąĖčģ ą┤ą░ąĮąĮčŗąĄ ą▓ čĆą░ąĘąĮčŗąĄ ą╝ąŠą╝ąĄąĮčéčŗ ą▓čĆąĄą╝ąĄąĮąĖ.

ŌĆó Serial Clock (SPCK): čŹč鹊 čāą┐čĆą░ą▓ą╗čÅčÄčēąĖą╣ čüąĖą│ąĮą░ą╗, ą║ąŠč鹊čĆčŗą╣ ą│ąĄąĮąĄčĆąĖčĆčāąĄčé master, čĆąĄą│čāą╗ąĖčĆčāčÅ č鹥ą╝ čüą░ą╝čŗą╝ ą┐ąŠč鹊ą║ ą┤ą░ąĮąĮčŗčģ č湥čĆąĄąĘ MOSI ąĖ MISO. Master ą╝ąŠąČąĄčé ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī ą┤ą░ąĮąĮčŗąĄ čü čĆą░ąĘą╗ąĖčćąĮčŗą╝ąĖ čüą║ąŠčĆąŠčüčéčÅą╝ąĖ; čüąĖą│ąĮą░ą╗ SPCK ą┐ąĄčĆąĄą║ą╗čÄčćą░ąĄčéčüčÅ ąŠą┤ąĖąĮ čĆą░ąĘ ąĮą░ ą║ą░ąČą┤čŗą╣ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗą╣ ą▒ąĖčé.

ŌĆó Slave Select (NSS): čŹč鹊čé čāą┐čĆą░ą▓ą╗čÅčÄčēąĖą╣ čüąĖą│ąĮą░ą╗ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé slave-čāčüčéčĆąŠą╣čüčéą▓čā ą▓čŗą║ą╗čÄčćąĖčéčüčÅ ąĖ ą▓ą║ą╗čÄčćąĖčéčīčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ.

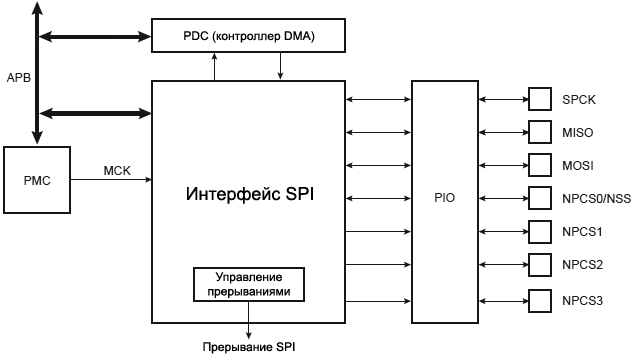

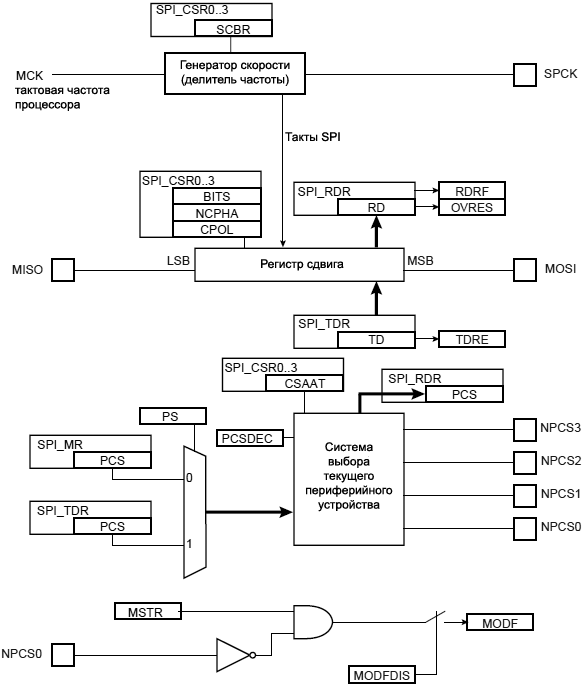

ąĀąĖčü. 28-1. ą×ą▒čēą░čÅ ą▒ą╗ąŠą║-čüčģąĄą╝ą░ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ SPI ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ARM7 (čüąĄą╝ąĄą╣čüčéą▓ąŠ AT91SAM7 ą║ąŠą╝ą┐ą░ąĮąĖąĖ Atmel).

ą¤ąŠčÅčüąĮąĄąĮąĖčÅ ą║ čĆąĖčü. 28-1: APB ąŠąĘąĮą░čćą░ąĄčé Advanced Peripheral Bus (ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ čłąĖąĮą░ ąŠą▒ą╝ąĄąĮą░ čü ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ), PMC ąŠąĘąĮą░čćą░ąĄčé Power Management Controller (ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖąĄą╝), MCK ąŠąĘąĮą░čćą░ąĄčé ą│ą╗ą░ą▓ąĮčāčÄ čéą░ą║č鹊ą▓čāčÄ čćą░čüč鹊čéčā čÅą┤čĆą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░, PIO ąŠąĘąĮą░čćą░ąĄčé ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠą│ąŠ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ (čüą╝. [4]).

ąĀąĖčü. 28-2. ą¤čĆąĖą╝ąĄčĆ ą▒ą╗ąŠą║-čüčģąĄą╝čŗ ą┐čĆąĖą╝ąĄąĮąĄąĮąĖčÅ SPI ą▓ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĖ.

ąóą░ą▒ą╗ąĖčåą░ 28-1. ą×ą┐ąĖčüą░ąĮąĖąĄ čüąĖą│ąĮą░ą╗ąŠą▓ SPI.

ąśą╝čÅ ą▓čŗą▓ąŠą┤ą░

|

ą×ą┐ąĖčüą░ąĮąĖąĄ čüąĖą│ąĮą░ą╗ą░

|

ąóąĖą┐ čüąĖą│ąĮą░ą╗ą░

|

| Master |

Slave |

| MISO |

Master In Slave Out (ą▓čģąŠą┤ ą│ą╗ą░ą▓ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ąĖ ą▓čŗčģąŠą┤ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ) |

ą▓čģąŠą┤ |

ą▓čŗčģąŠą┤ |

| MOSI |

Master Out Slave In (ą▓čŗčģąŠą┤ ą│ą╗ą░ą▓ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ąĖ ą▓čģąŠ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ) |

ą▓čŗčģąŠą┤ |

ą▓čģąŠą┤ |

| SPCK |

Serial Clock (čüąĖą│ąĮą░ą╗ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ) |

ą▓čŗčģąŠą┤ |

ą▓čģąŠą┤ |

| NPCS1..NPCS3 |

Peripheral Chip Select (čüąĖą│ąĮą░ą╗čŗ ą▓čŗą▒ąŠčĆą║ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ąĮą░ čłąĖąĮąĄ SPI) |

ą▓čŗčģąŠą┤ |

ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ |

| NPCS0/NSS |

Peripheral Chip Select/Slave Select (ą▓čŗą▒ąŠčĆą║ą░ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░/ą▓čŗą▒ąŠčĆą║ą░ ą▓ čĆąĄąČąĖą╝ąĄ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░) |

ą▓čŗčģąŠą┤ |

ą▓čģąŠą┤ |

ąÆčüąĄ ą▓čŗą▓ąŠą┤čŗ, ą┐ąĄčĆąĄčćąĖčüą╗ąĄąĮąĮčŗąĄ ą▓ čéą░ą▒ą╗ąĖčåąĄ, ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝ ąĮą░čüčéčĆąŠąĄąĮčŗ ą║ą░ą║ ą▓čģąŠą┤čŗ ąĖ ą▓čŗčģąŠą┤čŗ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄą╝ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ PIO.

[ąŚą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ SPI ąŠčé ą┤čĆčāą│ąĖčģ čĆąĄčüčāčĆčüąŠą▓]

ą¤ąŠčĆčéčŗ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░. ąØąŠąČą║ąĖ, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą┤ą╗čÅ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ą║ ą▓ąĮąĄčłąĮąĖą╝ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ SPI, ą╝ąŠą│čāčé ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąĖčĆąŠą▓ą░čéčīčüčÅ čü ą┤čĆčāą│ąĖą╝ąĖ ą░ą┐ą┐ą░čĆą░čéąĮčŗą╝ąĖ čäčāąĮą║čåąĖčÅą╝ąĖ ąĖ ą┐ąŠčĆčéą░ą╝ąĖ GPIO. ą£čāą╗čīčéąĖą┐ą╗ąĄą║čüąĖčĆąŠą▓ą░ąĮąĖąĄ čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ PIO [4] čü ą┐ąŠą╝ąŠčēčīčÄ ą▓čŗą▒ąŠčĆą░ čäčāąĮą║čåąĖą╣ ą┐ąĄčĆąĖč乥čĆąĖąĖ A ąĖ B. ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčüčé ą┤ąŠą╗ąČąĄąĮ čüąĮą░čćą░ą╗ą░ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčŗ PIO, čćč鹊ą▒čŗ ąĮą░ąĘąĮą░čćąĖčéčī ą▓čŗą▓ąŠą┤čŗ SPI ą┤ą╗čÅ čüą▓ąŠąĖčģ čäčāąĮą║čåąĖą╣ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░.

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖąĄą╝. SPI ą╝ąŠąČąĄčé čéą░ą║čéąĖčĆąŠą▓ą░čéčīčüčÅ č湥čĆąĄąĘ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖąĄą╝ (Power Management Controller, PMC) [5], čéą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ čüąĮą░čćą░ą╗ą░ ąĮą░čüčéčĆąŠąĖčéčī čĆąĄą│ąĖčüčéčĆčŗ PMC, čćč鹊ą▒čŗ čĆą░ąĘčĆąĄčłąĖčéčī čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ SPI.

ąŁč鹊čé ą┐čĆąĖą╝ąĄčĆ ąĖąĘ ą▒ąĖą▒ą╗ąĖąŠč鹥ą║ąĖ FatFs-07c.

#include "at91sam7x512/AT91SAM7X512.h"

#include < pio/pio.h >

#define PPIO_BASE_SPI AT91C_BASE_PIOA

#define PIN_SPI1_MISO {1 << 24, AT91C_BASE_PIOA, AT91C_ID_PIOA, PIO_PERIPH_B, PIO_PULLUP}

#define PIN_SPI1_MOSI {1 << 23, AT91C_BASE_PIOA, AT91C_ID_PIOA, PIO_PERIPH_B, PIO_DEFAULT}

#define PIN_SPI1_SPCK {1 << 22, AT91C_BASE_PIOA, AT91C_ID_PIOA, PIO_PERIPH_B, PIO_DEFAULT}

#define PIN_MMC_CS {1 << 21, AT91C_BASE_PIOA, AT91C_ID_PIOA, PIO_PERIPH_B, PIO_DEFAULT}

#define CARD_SELECT_PIN AT91C_PIO_PA21

#define AT91C_BASE_SPI AT91C_BASE_SPI1

#define PSPI_BASE AT91C_BASE_SPI1

#define AT91C_ID_SPI AT91C_ID_SPI1

#define PINS_MMC PIN_SPI1_MISO, PIN_SPI1_MOSI, PIN_SPI1_SPCK, PIN_MMC_CS

const Pin pinsMMC[] = {PINS_MMC};

static void AT91_spiSetSpeed(BYTE speed)

{

DWORD reg;

if ( speed < SPI_SCBR_MIN ) speed = SPI_SCBR_MIN;

if ( speed > 1 ) speed &= 0xFE;

reg = PSPI_BASE->SPI_CSR[SPI_CSR_NUM];

reg = ( reg & ~(DWORD)(AT91C_SPI_SCBR) ) | ( (DWORD)speed << 8 );

PSPI_BASE->SPI_CSR[SPI_CSR_NUM] = reg;

}

/*-----------------------------------------------------------------------*/

/* ąśąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ ąĖąĮč鹥čĆč乥ą╣čüą░ SPI */

/*-----------------------------------------------------------------------*/

static void init_spi( void )

{

PIO_Configure(pinsMMC, PIO_LISTSIZE(pinsMMC)); //ąĮąŠąČą║ąĖ ą║ą░čĆčéčŗ SD (SPI)

// ąĀą░ąĘčĆąĄčłąĖčéčī čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ SPI.

AT91C_BASE_PMC->PMC_PCER = ( 1 << AT91C_ID_SPI );

// ąŚą░ą┐čĆąĄčé SPI:

PSPI_BASE->SPI_CR = AT91C_SPI_SPIDIS;

// ąĪą▒čĆąŠčü ąĖ čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ SPI. ąÆčüąĄ ą▓čŗą│ą╗čÅą┤ąĖčé čéą░ą║, čćč鹊 ą┤ą╗čÅ ąĮą░ą┤ąĄąČąĮąŠą│ąŠ čüą▒čĆąŠčüą░

// SPI čéčĆąĄą▒čāąĄčéčüčÅ 2 ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗčģ čüą▒čĆąŠčüą░:

PSPI_BASE->SPI_CR = AT91C_SPI_SWRST;

PSPI_BASE->SPI_CR = AT91C_SPI_SWRST;

PSPI_BASE->SPI_CR = AT91C_SPI_SPIEN;

// ąĀąĄąČąĖą╝ SPI: master, FDIV=0, čäčāąĮą║čåąĖčÅ fault detection ąĘą░ą┐čĆąĄčēąĄąĮą░:

PSPI_BASE->SPI_MR = AT91C_SPI_MSTR | AT91C_SPI_MODFDIS;

// ąØą░čüčéčĆąŠą╣ą║ą░ čĆąĄą│ąĖčüčéčĆą░ chip-select:

// 8 ąĮą░ čäčĆąĄą╣ą╝, CPOL=1, ClockPhase=0, DLYBCT = 0

PSPI_BASE->SPI_CSR[SPI_CSR_NUM] = AT91C_SPI_CPOL | AT91C_SPI_BITS_8;

// ąØą░ ą▓čĆąĄą╝čÅ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ ą║ą░čĆčéčŗ SD čāčüčéą░ąĮąŠą▓ąĖčéčī ą╝ą░ą╗čāčÄ čüą║ąŠčĆąŠčüčéčī:

AT91_spiSetSpeed(0xFE);

}

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ąŻ ąĖąĮč鹥čĆč乥ą╣čüą░ SPI ąĖą╝ąĄąĄčéčüčÅ čüąĖą│ąĮą░ą╗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗą╣ ą║ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčā ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ (Advanced Interrupt Controller, AIC). ąĀą░ą▒ąŠčéą░ čü SPI ą┐ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅą╝ čéčĆąĄą▒čāąĄčé ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮąŠą│ąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ AIC ą┐ąĄčĆąĄą┤ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄą╝ SPI.

[ążčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ SPI]

ąĀąĄąČąĖą╝čŗ čĆą░ą▒ąŠčéčŗ. SPI čĆą░ą▒ąŠčéą░ąĄčé ą▓ čĆąĄąČąĖą╝ąĄ Master (ą│ą╗ą░ą▓ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮą░ čłąĖąĮąĄ) ąĖą╗ąĖ ą▓ čĆąĄąČąĖą╝ąĄ Slave (ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮą░ čłąĖąĮąĄ). ąĀą░ą▒ąŠčéą░ ą▓ čĆąĄąČąĖą╝ąĄ Master ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ ąĘą░ą┐ąĖčüčīčÄ 1 ą▓ ą▒ąĖčé MSTR čĆąĄą│ąĖčüčéčĆą░ čĆąĄąČąĖą╝ą░ SPI_MR. ąÆčŗą▓ąŠą┤čŗ NPCS0 .. NPCS3 ą▓čüąĄ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāčÄčéčüčÅ ą║ą░ą║ ą▓čŗčģąŠą┤čŗ, ą▓čŗą▓ąŠą┤ SPCK čéą░ą║ąČąĄ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ ą║ą░ą║ ą▓čŗčģąŠą┤ ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ čéą░ą║č鹊ą▓, čüąĖą│ąĮą░ą╗ MISO ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčéčüčÅ ą║ąŠ ą▓čģąŠą┤čā ą┐čĆąĖąĄą╝ąĮąĖą║ą░ ąĖ MOSI ą▒čāą┤ąĄčé čāą┐čĆą░ą▓ą╗čÅčéčīčüčÅ ą▓čŗčģąŠą┤ąŠą╝ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░.

ąĢčüą╗ąĖ ą▒ąĖčé MSTR ąĘą░ą┐ąĖčüą░ąĮ ą║ą░ą║ 0, č鹊 SPI čĆą░ą▒ąŠčéą░ąĄčé ą▓ čĆąĄąČąĖą╝ąĄ Slave. MISO čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ą▓čŗčģąŠą┤ąŠą╝ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░, MOSI ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčéčüčÅ ą║ąŠ ą▓čģąŠą┤čā ą┐čĆąĖąĄą╝ąĮąĖą║ą░, ąĮąŠąČą║ą░ SPCK čüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▓čģąŠą┤ąŠą╝ ąĖ ą┐ąŠą╗čāčćą░ąĄčé čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ąŠčé ą▓ąĮąĄčłąĮąĄą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ master ą┤ą╗čÅ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ čĆą░ą▒ąŠčéčŗ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ ąĖ ą┐čĆąĖąĄą╝ąĮąĖą║ą░. ąÆčŗą▓ąŠą┤ NPCS0 čüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▓čģąŠą┤ąŠą╝, ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą║ą░ą║ čüąĖą│ąĮą░ą╗ ą▓čŗą▒ąŠčĆą║ąĖ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (Slave Select signal, NSS). ąÆčŗą▓ąŠą┤čŗ NPCS1 .. NPCS3 ąĮąĖą║ą░ą║ ąĮąĄ čāą┐čĆą░ą▓ą╗čÅčÄčéčüčÅ, ąĖ ą╝ąŠą│čāčé ą▒čŗčéčī ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮčŗ ą┤ą╗čÅ ą┤čĆčāą│ąĖčģ čåąĄą╗ąĄą╣ (ąĮą░ą┐čĆąĖą╝ąĄčĆ, ą║ą░ą║ ą┐ąŠčĆčéčŗ GPIO).

ą¤čĆąŠčåąĄčüčü ąŠą▒ą╝ąĄąĮą░ ą┤ą░ąĮąĮčŗą╝ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ ąĖą┤ąĄąĮčéąĖčćąĮąŠ ą┤ą╗čÅ ąŠą▒ąŠąĖčģ čĆąĄąČąĖą╝ąŠą▓ čĆą░ą▒ąŠčéčŗ. ąōąĄąĮąĄčĆą░č鹊čĆ čüą║ąŠčĆąŠčüčéąĖ ą░ą║čéąĖą▓ąĖąĘąĖčĆčāąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą▓ čĆąĄąČąĖą╝ąĄ Master - ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ čéą░ą║č鹊ą▓ SPCK.

ą¤ąĄčĆąĄą┤ą░čćą░ ąĖ ą┐čĆąĖąĄą╝ ą┤ą░ąĮąĮčŗčģ. ąÆąŠąĘą╝ąŠąČąĮčŗ 4 ą║ąŠą╝ą▒ąĖąĮą░čåąĖąĖ ą┐ąŠą╗čÅčĆąĮąŠčüčéąĖ ąĖ čäą░ąĘčŗ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čć ą┤ą░ąĮąĮčŗčģ ą▓ ąŠą▒ąŠąĖčģ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅčģ (4 čĆą░ąĘąĮčŗčģ, ąĮąĄčüąŠą▓ą╝ąĄčüčéąĖą╝čŗčģ ą┤čĆčāą│ čü ą┤čĆčāą│ąŠą╝ č乊čĆą╝ą░čéą░). ą¤ąŠą╗čÅčĆąĮąŠčüčéčī čéą░ą║č鹊ą▓ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ ą▒ąĖč鹊ą╝ CPOL čĆąĄą│ąĖčüčéčĆą░ ą▓čŗą▒ąŠčĆą║ąĖ čćąĖą┐ą░ (Chip Select Register, SPI_CSR0 .. SPI_CSR3). ążą░ąĘą░ čéą░ą║č鹊ą▓ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ ą▒ąĖč鹊ą╝ NCPHA č鹊ą│ąŠ ąČąĄ čĆąĄą│ąĖčüčéčĆą░. ąŁčéąĖ 2 ą┐ą░čĆą░ą╝ąĄčéčĆą░ ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčé ą░ą║čéąĖą▓ąĮčŗąĄ ą┐ąĄčĆąĄą┐ą░ą┤čŗ čéą░ą║č鹊ą▓ ą┤ą╗čÅ ą╝ąŠą╝ąĄąĮčéą░ ą▓čĆąĄą╝ąĄąĮąĖ, ą║ąŠą│ą┤ą░ ą┤ą░ąĮąĮčŗąĄ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮčŗ ąĖ ą┐čĆąŠčćąĖčéą░ąĮčŗ. ąÜą░ąČą┤čŗą╣ ąĖąĘ čŹčéąĖčģ 2 ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓ ąĖą╝ąĄąĄčé 2 ą▓ąŠąĘą╝ąŠąČąĮčŗčģ čüąŠčüč鹊čÅąĮąĖčÅ, čćč鹊 ąĖ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé 4 č乊čĆą╝ą░čéą░. ą¦č鹊ą▒čŗ ąŠą▒ą╝ąĄąĮ ą┤ą░ąĮąĮčŗą╝ąĖ ą▒čŗą╗ ą▓ąŠąĘą╝ąŠąČąĄąĮ, ąŠą▒ąĄ čüč鹊čĆąŠąĮčŗ ąŠą▒ą╝ąĄąĮą░ ą┐ąŠ čłąĖąĮąĄ SPI ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮčŗ čüąŠą▓ą╝ąĄčüčéąĖą╝čŗą╝ ą┤čĆčāą│ čü ą┤čĆčāą│ąŠą╝ ąŠą▒čĆą░ąĘąŠą╝. ąĢčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ąĮąĄčüą║ąŠą╗čīą║ąŠ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ čü čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮąŠą╣, čĆą░ąĘą╗ąĖčćąĮąŠą╣ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĄą╣ č乊čĆą╝ą░čéą░, čāčüčéčĆąŠą╣čüčéą▓ąŠ master ą┤ąŠą╗ąČąĮąŠ ą┐ąĄčĆąĄą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī čüą░ą╝ąŠ čüąĄą▒čÅ ą┤ą╗čÅ ąŠą▒ą╝ąĄąĮą░ ą┤ą░ąĮąĮčŗą╝ąĖ čü ą║ą░ąČą┤čŗą╝ ąŠčéą┤ąĄą╗čīąĮčŗą╝ slave-čāčüčéčĆąŠą╣čüčéą▓ąŠą╝.

ąóą░ą▒ą╗ąĖčåą░ 28-2. ą¤ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą║ąŠą╝ą▒ąĖąĮą░čåąĖąĖ ąĮą░čüčéčĆąŠąĄą║ ą▒ąĖčé CPOL ąĖ NCPHA, ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčēąĖčģ 4 čĆąĄąČąĖą╝ą░ (č乊čĆą╝ą░čéą░) č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ.

| SPI Mode |

CPOL |

NCPHA |

| 0 |

0 |

1 |

| 1 |

0 |

0 |

| 2 |

1 |

1 |

| 3 |

1 |

0 |

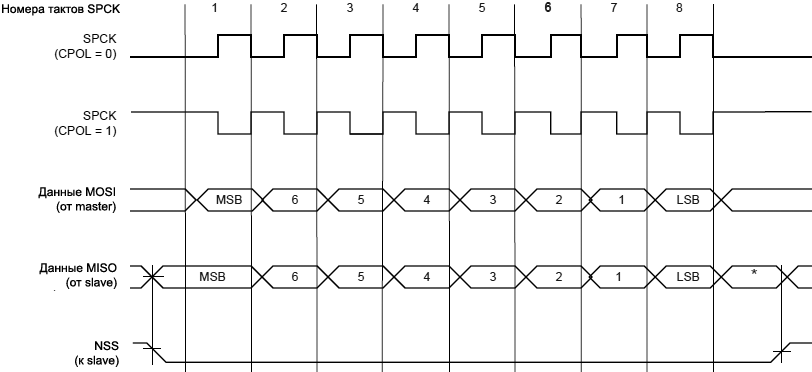

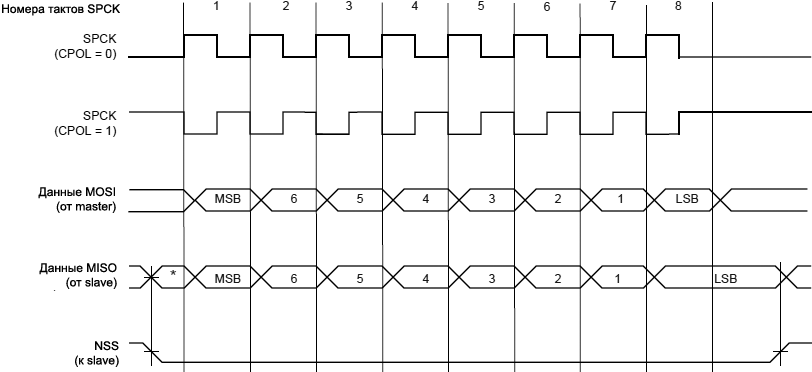

ąØą░ čĆąĖčüčāąĮą║ą░čģ 28-3 ąĖ 28-4 ą┐ąŠą║ą░ąĘą░ąĮčŗ ą┐čĆąĖą╝ąĄčĆčŗ ą┐ąĄčĆąĄą┤ą░čć ą┤ą░ąĮąĮčŗčģ ą┤ą╗čÅ čäčĆąĄą╣ą╝ą░ 8 ą▒ąĖčé.

ąĀąĖčü. 28-3. ążąŠčĆą╝ą░čé ą┤ą░ąĮąĮčŗčģ SPI ą┤ą╗čÅ ą▓ą░čĆąĖą░ąĮčéą░ ąĮą░čüčéčĆąŠą╣ą║ąĖ NCPHA=1.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ *: ą▓ čŹč鹊ą╝ ą╝ąĄčüč鹥 ąĘąĮą░č湥ąĮąĖąĄ čāčĆąŠą▓ąĮčÅ ąĮąĄ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąŠ, ąĮąŠ ąŠą▒čŗčćąĮąŠ ąĘą┤ąĄčüčī ą▒čāą┤ąĄčé ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčéą░ MSB ąŠčé ą┐čĆąĄą┤čŗą┤čāčēąĄą│ąŠ ą┐čĆąĖąĮčÅč鹊ą│ąŠ čäčĆąĄą╣ą╝ą░.

ąĀąĖčü. 28-4. ążąŠčĆą╝ą░čé ą┤ą░ąĮąĮčŗčģ SPI ą┤ą╗čÅ ą▓ą░čĆąĖą░ąĮčéą░ ąĮą░čüčéčĆąŠą╣ą║ąĖ NCPHA=0.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ *: ą▓ čŹč鹊ą╝ ą╝ąĄčüč鹥 ąĘąĮą░č湥ąĮąĖąĄ čāčĆąŠą▓ąĮčÅ ąĮąĄ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąŠ, ąĮąŠ ąŠą▒čŗčćąĮąŠ ąĘą┤ąĄčüčī ą▒čāą┤ąĄčé ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčéą░ LSB ąŠčé ą┐čĆąĄą┤čŗą┤čāčēąĄą│ąŠ ą┐ąĄčĆąĄą┤ą░ąĮąĮąŠą│ąŠ čäčĆąĄą╣ą╝ą░.

[ąĀąĄąČąĖą╝čŗ čĆą░ą▒ąŠčéčŗ Master]

ąÜąŠą│ą┤ą░ SPI čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ Master, čéą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗ ąĖąĮč鹥čĆč乥ą╣čüą░ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╝ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗą╝ ą│ąĄąĮąĄčĆą░č鹊čĆąŠą╝ čüą║ąŠčĆąŠčüčéąĖ. ąŁč鹊 ą┐ąŠą╗ąĮąŠčüčéčīčÄ čāą┐čĆą░ą▓ą╗čÅąĄčé ąŠą▒ą╝ąĄąĮąŠą╝ ą┤ą░ąĮąĮčŗą╝ąĖ ą▓ ąŠą▒ąŠąĖčģ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅčģ ą┐čĆąĖ ąŠą▒ą╝ąĄąĮąĄ čüąŠ slave-čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗą╝ąĖ ą║ čłąĖąĮąĄ SPI. ąśąĮč鹥čĆč乥ą╣čü SPI čāą┐čĆą░ą▓ą╗čÅąĄčé čüąĖą│ąĮą░ą╗ąŠą╝ ą▓čŗą▒ąŠčĆą║ąĖ slave-čāčüčéčĆąŠą╣čüčéą▓ą░ ąĖ čüąĖą│ąĮą░ą╗ąŠą╝ čéą░ą║č鹊ą▓ SPCK.

ąÆ ąĖąĮč鹥čĆč乥ą╣čüąĄ SPI ąĖą╝ąĄąĄčéčüčÅ 2 čĆąĄą│ąĖčüčéčĆą░ ą┤ą╗čÅ čāą┤ąĄčƹȹĖą▓ą░ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ, čĆąĄą│ąĖčüčéčĆ ą┐ąĄčĆąĄą┤ą░čćąĖ (Transmit Data Register, SPI_TDR) ąĖ čĆąĄą│ąĖčüčéčĆ ą┐čĆąĖąĄą╝ą░ (Receive Data Register, SPI_RDR), ąĖ ąŠą┤ąĖąĮ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░. ąĀąĄą│ąĖčüčéčĆčŗ SPI_TDR ąĖ SPI_RDR ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé ą┐ąĄčĆąĄąĮąŠčü ą┤ą░ąĮąĮčŗčģ čü ą┐ąŠčüč鹊čÅąĮąĮąŠą╣ čüą║ąŠčĆąŠčüčéčīčÄ.

ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ SPI čĆą░ąĘčĆąĄčłąĄąĮ, ąŠą▒ą╝ąĄąĮ ą┤ą░ąĮąĮčŗą╝ąĖ ąĮą░čćąĖąĮą░ąĄčéčüčÅ čü ą╝ąŠą╝ąĄąĮčéą░, ą║ąŠą│ą┤ą░ ą┐čĆąŠčåąĄčüčüąŠčĆ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčé čĆąĄą│ąĖčüčéčĆ SPI_TDR. ąŁčéąĖ ąĘą░ą┐ąĖčüą░ąĮąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ ą┐ąĄčĆąĄą╝ąĄčēą░čÄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░, ąĖ ąĮą░ čłąĖąĮąĄ SPI ąĮą░čćąĖąĮą░ąĄčéčüčÅ ą┐čĆąŠčåąĄčüčü ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ą▓ ąŠą▒ąŠąĖčģ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅčģ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ. ąÆ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ ą┤ą░ąĮąĮčŗąĄ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ čüą┤ą▓ąĖą│ą░ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ ą▓čŗą┤ą▓ąĖą│ą░čÄčéčüčÅ ąĮą░ čüąĖą│ąĮą░ą╗ MOSI ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ čüą┤ą▓ąĖą│ą░, ą┤ą░ąĮąĮčŗąĄ čü čüąĖą│ąĮą░ą╗ą░ MISO ą▓ą┤ą▓ąĖą│ą░čÄčéčüčÅ ą▒ąĖčé ąĘą░ ą▒ąĖč鹊ą╝ ą▓ č鹊čé ąČąĄ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░. ą¤čĆąĖąĄą╝ ą┤ą░ąĮąĮčŗčģ ąĮąĄ ą╝ąŠąČąĄčé ąŠčüčāčēąĄčüčéą▓ą╗čÅčéčīčüčÅ ą▒ąĄąĘ ą┐ąĄčĆąĄą┤ą░čćąĖ, čŹčéąĖ 2 ą┐čĆąŠčåąĄčüčüą░ ąŠčüčāčēąĄčüčéą▓ą╗čÅčÄčéčüčÅ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ.

ąĢčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮą░čÅ ą▓čŗą▒ąŠčĆą║ą░ čüąĖą│ąĮą░ą╗ą░ą╝ąĖ NPCS[3:0], č鹊 ą┐ąĄčĆąĄą┤ ąĘą░ą┐ąĖčüčīčÄ ą▓ čĆąĄą│ąĖčüčéčĆ SPI_TDR ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą┐čĆą░ą▓ąĖą╗čīąĮąŠ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ ą┐ąŠą╗ąĄ PCS ą▓ ą┤ą░ąĮąĮčŗčģ, ąĘą░ą┐ąĖčüčŗą▓ą░ąĄą╝čŗčģ ą▓ čŹč鹊čé čĆąĄą│ąĖčüčéčĆ, čćč鹊ą▒čŗ ą▒čŗą╗ąŠ ą▓čŗą▒čĆą░ąĮąŠ ąĮčāąČąĮąŠąĄ slave-čāčüčéčĆąŠą╣čüčéą▓ąŠ. ą£ąŠąČąĄčé čéą░ą║ąČąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮą░čÅ ą▓čŗą▒ąŠčĆą║ą░ slave-čāčüčéčĆąŠą╣čüčéą▓ ą┐čāč鹥ą╝ ą┐čĆąŠčüč鹊ą│ąŠ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čāčĆąŠą▓ąĮčÅą╝ąĖ ą┐ąŠčĆč鹊ą▓ GPIO.

ąĢčüą╗ąĖ ąĮąŠą▓čŗąĄ ą┤ą░ąĮąĮčŗąĄ ą▒čŗą╗ąĖ ąĘą░ą┐ąĖčüą░ąĮčŗ ą▓ SPI_TDR ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐čĆąŠčåąĄčüčüą░ ą┐ąĄčĆąĄą┤ą░čćąĖ, č鹊 ą┐ąĄčĆąĄą┤ą░čćą░ čĆą░ąĮąĄąĄ ąĘą░ą┐ąĖčüą░ąĮąĮčŗčģ ą▓ čĆąĄą│ąĖčüčéčĆ SPI_TDR ą┤ą░ąĮąĮčŗčģ ą▒čāą┤ąĄčé ą┐čĆąŠą┤ąŠą╗ąČą░čéčīčüčÅ ą┤ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ č鹥ą║čāčēąĄą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ. ą¤ąŠčüą╗ąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ č鹥ą║čāčēąĄą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐čĆąĖąĮčÅčéčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą▒čāą┤čāčé ą┐ąĄčĆąĄą┤ą░ąĮčŗ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ čüą┤ą▓ąĖą│ą░ ą▓ čĆąĄą│ąĖčüčéčĆ SPI_RDR, ąĖ č鹊ą╗čīą║ąŠ čćč鹊 ąĘą░ą┐ąĖčüą░ąĮąĮčŗąĄ ąĮąŠą▓čŗąĄ ą┤ą░ąĮąĮčŗąĄ ąĖąĘ SPI_TDR ą▒čāą┤čāčé ąĘą░ą│čĆčāąČąĄąĮčŗ ą▓ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░, ąĖ ąĮą░čćąĮąĄčéčüčÅ ąĮąŠą▓ą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░.

ą£ąŠą╝ąĄąĮčé ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐ąĄčĆąĄąĮąŠčüą░ ą▓ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ ąĘą░ą┐ąĖčüą░ąĮąĮčŗčģ ą▓ SPI_TDR ą┤ą░ąĮąĮčŗčģ ąĖąĮą┤ąĖčåąĖčĆčāąĄčéčüčÅ ą▒ąĖč鹊ą╝ TDRE (Transmit Data Register Empty, čé. ąĄ. ą▒ąĖčé čäą╗ą░ą│ą░ ąŠą┐čāčüč鹊賹ĄąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ ą┐ąĄčĆąĄą┤ą░čćąĖ) čĆąĄą│ąĖčüčéčĆą░ čüąŠčüč鹊čÅąĮąĖčÅ (Status Register, SPI_SR). ąÜąŠą│ą┤ą░ ąĮąŠą▓čŗąĄ ą┤ą░ąĮąĮčŗąĄ ąĘą░ą┐ąĖčüą░ąĮčŗ ą▓ SPI_TDR, čŹč鹊čé ą▒ąĖčé ąŠčćąĖčēą░ąĄčéčüčÅ. ąæąĖčé TDRE ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ąĘą░ą┐čāčüą║ą░ ą║ą░ąĮą░ą╗ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ DMA (Transmit PDC channel).

ąŚą░ą▓ąĄčĆčłąĄąĮąĖąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčéčüčÅ čäą╗ą░ą│ąŠą╝ TXEMPTY ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_SR. ąĢčüą╗ąĖ ąĘą░ą┤ąĄčƹȹ║ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ (ą┐ąŠą╗ąĄ DLYBCT ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_CSR0 .. SPI_CSR3) ą▒ąŠą╗čīčłąĄ 0 ą┤ą╗čÅ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ, č鹊 čäą╗ą░ą│ TXEMPTY čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą┐ąŠčüą╗ąĄ ąĖčüč鹥č湥ąĮąĖčÅ čŹč鹊ą╣ ąĘą░ą┤ąĄčƹȹ║ąĖ. ąÆ čŹč鹊čé ą╝ąŠą╝ąĄąĮčé ą▓čĆąĄą╝ąĄąĮąĖ ą│ą╗ą░ą▓ąĮą░čÅ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░ (MCK) ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą║ą╗čÄč湥ąĮą░.

ą£ąŠą╝ąĄąĮčé ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖčÅ ą┐čĆąĖąĮčÅčéčŗčģ ą┤ą░ąĮąĮčŗčģ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ čüą┤ą▓ąĖą│ą░ ą▓ čĆąĄą│ąĖčüčéčĆ SPI_RDR ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčéčüčÅ ą▒ąĖč鹊ą╝ RDRF (Receive Data Register Full, čĆąĄą│ąĖčüčéčĆ ą┤ą░ąĮąĮčŗčģ ą┐čĆąĖąĄą╝ą░ ąĘą░ą┐ąŠą╗ąĮąĄąĮ) ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüąŠčüč鹊čÅąĮąĖčÅ SPI_SR. ąÜąŠą│ą┤ą░ ą┐čĆąĖąĮčÅčéčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┐čĆąŠčćąĖčéą░ąĮčŗ, ą▒ąĖčé RDRF ąŠčćąĖčēą░ąĄčéčüčÅ.

ąĢčüą╗ąĖ čĆąĄą│ąĖčüčéčĆ ą┐čĆąĖąĄą╝ą░ SPI_RDR ąĮąĄ ą▒čŗą╗ ą┐čĆąŠčćąĖčéą░ąĮ ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ą┐ąŠčüčéčāą┐ąĖą╗ąĖ ąĮąŠą▓čŗąĄ ą┤ą░ąĮąĮčŗąĄ (čé. ąĄ. ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ąĮąĄ čāčüą┐ąĄą╗ą░ ąĖčģ ą┐čĆąŠčćąĖčéą░čéčī), č鹊 čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ ąŠčłąĖą▒ą║ąĖ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ ą┐čĆąĖąĄą╝ą░ (Overrun Error, OVRES) ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüąŠčüč鹊čÅąĮąĖčÅ SPI_SR. ą¤ąŠą║ą░ čŹč鹊čé čäą╗ą░ą│ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ą┤ą░ąĮąĮčŗąĄ ąĘą░ą│čĆčāąČąĄąĮčŗ ą▓ SPI_RDR. ą¤ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą┤ąŠą╗ąČąĄąĮ ą┐čĆąŠčćąĖčéą░čéčī čĆąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ SPI_SR, čćč鹊ą▒čŗ ąŠčćąĖčüčéąĖčéčī ą▒ąĖčé OVRES.

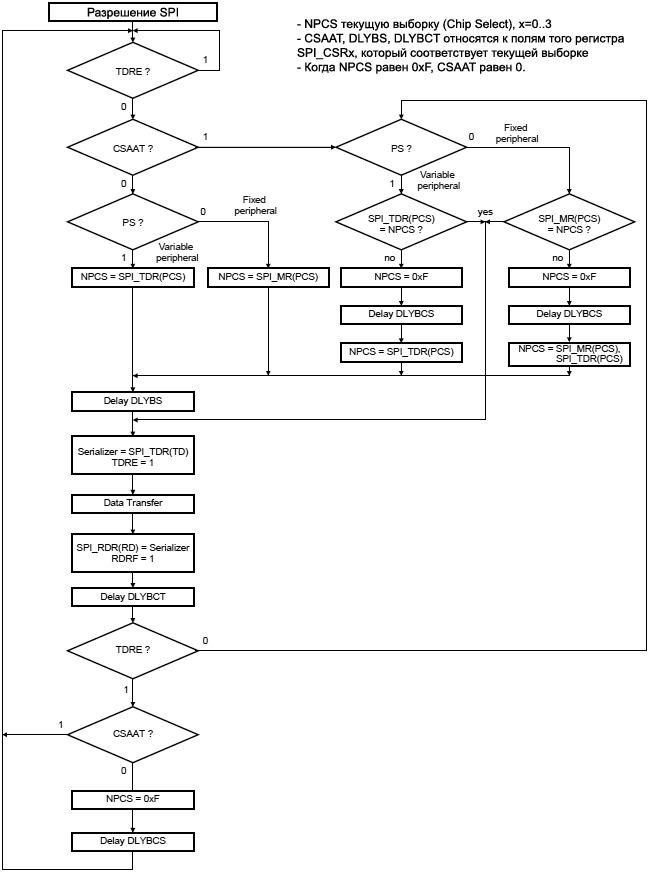

ąĀąĖčü. 28-5 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé SPI, ą║ąŠą│ą┤ą░ ąŠąĮ čĆą░ą▒ąŠčéą░ąĄčé ą▓ čĆąĄąČąĖą╝ąĄ Master. ąĀąĖčü. 28-6 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą┐čĆąŠčåąĄčüčü ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ąŠą▒ą╝ąĄąĮą░ ą┤ą░ąĮąĮčŗčģ.

ąĀąĖčü. 28-5. ąæą╗ąŠą║-čüčģąĄą╝ą░ SPI ą▓ čĆąĄąČąĖą╝ąĄ Master.

ąĀąĖčü. 28-6. ąÉą╗ą│ąŠčĆąĖčéą╝ ą┐ąŠą┤ą┤ąĄčƹȹ║ąĖ čĆąĄąČąĖą╝ą░ čĆą░ą▒ąŠčéčŗ Master.

ąōąĄąĮąĄčĆą░čåąĖčÅ čéą░ą║č鹊ą▓. ąóą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗ SPI, ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčēąĖą╣ čüą║ąŠčĆąŠčüčéčī ą┐ąĄčĆąĄą┤ą░čćąĖ (SPCK), ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ąĮą░ ą▒ą░ąĘąĄ čćą░čüč鹊čéčŗ ą┐čĆąŠčåąĄčüčüąŠčĆą░ (MCK), ą┐ąŠą┤ąĄą╗ąĄąĮąĮąŠą╣ ąĮą░ ąĘąĮą░č湥ąĮąĖąĄ ą╝ąĄąČą┤čā 1 ąĖ 255.

ąŁč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąŠčüčāčēąĄčüčéą▓ą╗čÅčéčī ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮčāčÄ čĆą░ą▒ąŠčćčāčÄ čüą║ąŠčĆąŠčüčéčī ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ąŠ čćą░čüč鹊čéčŗ ą┐čĆąŠčåąĄčüčüąŠčĆą░, ąĖ ą╝ąĖąĮąĖą╝ą░ą╗čīąĮčāčÄ čüą║ąŠčĆąŠčüčéčī ą┐ąĄčĆąĄą┤ą░čćąĖ ąĮą░ čćą░čüč鹊č鹥 ą▒ąĖčé MCK/255. ąŚąĮą░č湥ąĮąĖąĄ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéą░ ą┤ąĄą╗ąĄąĮąĖčÅ ąĘą░ą┤ą░ąĄčéčüčÅ ą┐ąŠą╗ąĄą╝ SCBR čĆąĄą│ąĖčüčéčĆą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą▓čŗą▒ąŠčĆą║ąŠą╣ (Chip Select Register, SPI_CSR0 .. SPI_CSR3).

ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ ą┐ąŠą╗čÅ SCBR ąĘąĮą░č湥ąĮąĖąĄą╝ 0 ąĘą░ą┐čĆąĄčēąĄąĮąŠ. ąĪčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ, ą║ąŠą│ą┤ą░ ą┐ąŠą╗ąĄ SCBR čĆą░ą▓ąĮąŠ 0, ą╝ąŠąČąĄčé ą┐čĆąĖą▓ąĄčüčéąĖ ą║ ąĮąĄą┐čĆąĄą┤čüą║ą░ąĘčāąĄą╝čŗą╝ čĆąĄąĘčāą╗čīčéą░čéą░ą╝.

ą¤ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ ą┐ąŠą╗ąĄ SCBR čĆą░ą▓ąĮąŠ 0, ąĖ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą┤ąŠą╗ąČąĄąĮ ąĘą░ą┐ąĖčüą░čéčī čéčāą┤ą░ ą┤ąŠą┐čāčüčéąĖą╝ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ (1..255) ą┐ąĄčĆąĄą┤ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄą╝ ą┐ąĄčĆą▓ąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ.

ąöąĄą╗ąĖč鹥ą╗čī SCBR ą▓ą╝ąĄčüč鹥 čü ą┤čĆčāą│ąĖą╝ąĖ ą┐ą░čĆą░ą╝ąĄčéčĆą░ą╝ąĖ, ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčēąĖą╝ąĖ č乊čĆą╝ą░čé, ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮąŠ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ą░ą┐ą┐ą░čĆą░čéąĮąŠą╣ ą▓čŗą▒ąŠčĆą║ąĖ čćąĖą┐ą░ čü ą┐ąŠą╝ąŠčēčīčÄ čĆąĄą│ąĖčüčéčĆąŠą▓ ą▓čŗą▒ąŠčĆą║ąĖ (Chip Select Registers, SPI_CSR0 .. SPI_CSR3). ąŁč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą░ą┤ą░ą┐čéąĖčĆąŠą▓ą░čéčī SPI ą║ čüą║ąŠčĆąŠčüčéąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ą║ą░ąČą┤ąŠą│ąŠ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮąŠą│ąŠ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ą▒ąĄąĘ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéąĖ ą┐ąĄčĆąĄą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ SPI.

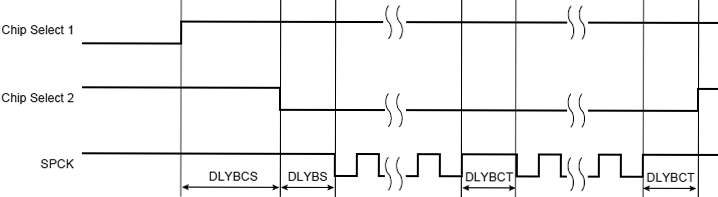

ąŚą░ą┤ąĄčƹȹ║ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ. ąĀąĖčü. 28-7 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ą▓čŗą▒ąŠčĆą║ąĖ ą▓ąĮąĄčłąĮąĖčģ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ (chip select) ąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĮą░ ąŠą┤ąĮąŠą╝ ąĖ č鹊ą╝ ąČąĄ čüąĖą│ąĮą░ą╗ąĄ ą▓čŗą▒ąŠčĆą║ąĖ. ą£ąŠą│čāčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮčŗ 3 ąĘą░ą┤ąĄčƹȹ║ąĖ, čćč鹊ą▒čŗ ąĖąĘą╝ąĄąĮąĖčéčī č乊čĆą╝čā čüąĖą│ąĮą░ą╗ąŠą▓ ąĖąĮč鹥čĆč乥ą╣čüą░ SPI:

ŌĆó ąŚą░ą┤ąĄčƹȹ║ą░ ą▓ ąĖąĘą╝ąĄąĮąĄąĮąĖąĖ čüąĖą│ąĮą░ą╗ąŠą▓ ą▓čŗą▒ąŠčĆą║ąĖ, ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝ą░čÅ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ą┤ą╗čÅ ą▓čüąĄčģ ą▓čŗą▒ąŠčĆąŠą║ ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ ą┐ąŠą╗čÅ DLYBCS ą▓ čĆąĄą│ąĖčüčéčĆąĄ čĆąĄąČąĖą╝ą░ SPI_MR. ąŁč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą▓čüčéą░ą▓ą╗čÅčéčī ąĘą░ą┤ąĄčƹȹ║čā ą┐ąĄčĆąĄą┤ ąŠčüą▓ąŠą▒ąŠąČą┤ąĄąĮąĖąĄą╝ čüąĖą│ąĮą░ą╗ą░ ą▓čŗą▒ąŠčĆą║ąĖ ąĖ ą┐ąĄčĆąĄą┤ ą▓čŗčüčéą░ą▓ą╗ąĄąĮąĖąĄą╝ ąĮąŠą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ą▓čŗą▒ąŠčĆą║ąĖ.

ŌĆó ąŚą░ą┤ąĄčƹȹ║ą░ ą┐ąĄčĆąĄą┤ SPCK, ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝ą░čÅ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą╣ ą▓čŗą▒ąŠčĆą║ąĖ ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ ą┐ąŠą╗čÅ DLYBS ą▓ čĆąĄą│ąĖčüčéčĆą░čģ SPI_CSR0 .. SPI_CSR3. ąŁč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąĮą░čćąĖąĮą░čéčī ą▓čŗą┤ą░ą▓ą░čéčī čüąĖą│ąĮą░ą╗ SPCK čü ąĮąĄą║ąŠč鹊čĆąŠą╣ ąĘą░ą┤ąĄčƹȹ║ąŠą╣ ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą▒čŗą╗ ą░ą║čéąĖą▓ąĖąĘąĖčĆąŠą▓ą░ąĮ čüąĖą│ąĮą░ą╗ ą▓čŗą▒ąŠčĆą║ąĖ.

ŌĆó ąŚą░ą┤ąĄčƹȹ║ą░ ą╝ąĄąČą┤čā ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╝ąĖ ą┐ąĄčĆąĄą┤ą░čćą░ą╝ąĖ, čéą░ą║ąČąĄ ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝ą░čÅ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą╣ ą▓čŗą▒ąŠčĆą║ąĖ ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ ą┐ąŠą╗čÅ DLYBCT ą▓ čĆąĄą│ąĖčüčéčĆą░čģ SPI_CSR0 .. SPI_CSR3. ąŁč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą▓čüčéą░ą▓ą╗čÅčéčī ąĘą░ą┤ąĄčƹȹ║čā ą╝ąĄąČą┤čā ą┤ą▓čāą╝čÅ ą┐ąĄčĆąĄą┤ą░čćą░ą╝ąĖ ąĮą░ ąŠą┤ąĮąŠą╝ ąĖ č鹊ą╝ ąČąĄ ą░ą║čéąĖą▓ąĮąŠą╝ čüąĖą│ąĮą░ą╗ąĄ ą▓čŗą▒ąŠčĆą║ąĖ.

ąĀąĖčü. 28-7. ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗąĄ ąĘą░ą┤ąĄčƹȹ║ąĖ.

ąÆčüąĄ ą▓čŗčłąĄą┐ąĄčĆąĄčćąĖčüą╗ąĄąĮąĮčŗąĄ ąĘą░ą┤ąĄčƹȹ║ąĖ ą┐ąŠąĘą▓ąŠą╗čÅčÄčé ą░ą┤ą░ą┐čéąĖčĆąŠą▓ą░čéčī ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ SPI ą┤ą╗čÅ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗčģ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗčģ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ SPI, čćč鹊ą▒čŗ čüą║ąŠčĆąŠčüčéčī ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ ą▓čĆąĄą╝ąĄąĮąĖ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ čüąĖą│ąĮą░ą╗ą░ ą▓čŗą▒ąŠčĆą║ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓ąŠą▓ą░ą╗ąĖ ą┤ąŠą┐čāčüčéąĖą╝čŗą╝ ąĘąĮą░č湥ąĮąĖčÅą╝ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą║ąŠąĮą║čĆąĄčéąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░.

ąĪąĖą│ąĮą░ą╗čŗ ą▓čŗą▒ąŠčĆą║ąĖ. ąÆąĮąĄčłąĮąĖąĄ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗąĄ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ SPI ą░ą║čéąĖą▓ąĖąĘąĖčĆčāčÄčéčüčÅ čüąĖą│ąĮą░ą╗ą░ą╝ąĖ ą▓čŗą▒ąŠčĆą║ąĖ NPCS0 .. NPCS3. ą¤ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą▓čüąĄ čüąĖą│ąĮą░ą╗čŗ NPCS ąĮąĄ ą░ą║čéąĖą▓ąĮčŗ ą┐ąĄčĆąĄą┤ ąĮą░čćą░ą╗ąŠą╝ ąĖ ą┐ąŠčüą╗ąĄ ąŠą║ąŠąĮčćą░ąĮąĖčÅ ą║ą░ąČą┤ąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ.

ąÆčŗą▒ąŠčĆą║ą░ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮą░ ą┤ą▓čāą╝čÅ čĆą░ąĘąĮčŗą╝ąĖ čüą┐ąŠčüąŠą▒ą░ą╝ąĖ:

ŌĆó ążąĖą║čüąĖčĆąŠą▓ą░ąĮąĮą░čÅ ą▓čŗą▒ąŠčĆą║ą░ (Fixed Peripheral Select): SPI ąŠą▒ą╝ąĄąĮąĖą▓ą░ąĄčéčüčÅ ą┤ą░ąĮąĮčŗą╝ąĖ č鹊ą╗čīą║ąŠ čü ąŠą┤ąĮąĖą╝ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗą╝ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝.

ŌĆó ąśąĘą╝ąĄąĮčÅąĄą╝ą░čÅ ą▓čŗą▒ąŠčĆą║ą░ (Variable Peripheral Select): ą╝ąŠąČąĮąŠ ąŠą▒ą╝ąĄąĮąĖą▓ą░čéčīčüčÅ ą┤ą░ąĮąĮčŗą╝ąĖ ą▒ąŠą╗ąĄąĄ č湥ą╝ čü ąŠą┤ąĮąĖą╝ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗą╝ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝.

ąĀą░ą▒ąŠčéą░ Fixed Peripheral Select ą░ą║čéąĖą▓ąĖąĘąĖčĆčāąĄčéčüčÅ ąĘą░ą┐ąĖčüčīčÄ 0 ą▓ ą▒ąĖčé PS čĆąĄą│ąĖčüčéčĆą░ čĆąĄąČąĖą╝ą░ SPI_MR. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ č鹥ą║čāčēąĄąĄ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ, ą║ąŠč鹊čĆąŠąĄ ą▒čāą┤ąĄčé ą▓čŗą▒čĆą░ąĮąŠ, ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą┐ąŠą╗ąĄą╝ PCS čĆąĄą│ąĖčüčéčĆą░ SPI_MR, ąĖ ą┐ąŠą╗ąĄ PCS ą▓ čĆąĄą│ąĖčüčéčĆąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ SPI_TDR ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

ąĀą░ą▒ąŠčéą░ Variable Peripheral Select ą░ą║čéąĖą▓ąĖąĘąĖčĆčāąĄčéčüčÅ ąĘą░ą┐ąĖčüčīčÄ ą▒ąĖčéą░ PS ą▓ 1. ąóąŠą│ą┤ą░ ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą▓čŗą▒ąŠčĆą║ąŠą╣ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┐ąŠą╗ąĄ PCS ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_TDR. ąŁč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ąĮąŠą▓ą░čÅ ą▓čŗą▒ąŠčĆą║ą░ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮą░ ą▓ą╝ąĄčüč鹥 čü ą║ą░ąČą┤čŗą╝ąĖ ąĮąŠą▓čŗą╝ąĖ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗą╝ąĖ ą┤ą░ąĮąĮčŗą╝ąĖ.

Fixed Peripheral Selection ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąŠčĆą│ą░ąĮąĖąĘąŠą▓ą░čéčī ą┐ąĄčĆąĄą┤ą░čćąĖ ą▒čāč乥čĆą░ čü ąŠą┤ąĮąĖą╝ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝. ą¤čĆąĖ čŹč鹊ą╝ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ PDC (DMA) ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ąŠą┐čéąĖą╝ą░ą╗čīąĮčŗą╝ ą▓ čüą╝čŗčüą╗ąĄ 菹║ąŠąĮąŠą╝ąĖąĖ ą┐ą░ą╝čÅčéąĖ čüą┐ąŠčüąŠą▒ąŠą╝, čéą░ą║ ą║ą░ą║ čĆą░ąĘą╝ąĄčĆ ą║ą░ąČą┤ąŠą╣ čÅč湥ą╣ą║ąĖ ą▒čāč乥čĆą░ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗčģ ą┤ą░ąĮąĮčŗčģ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą▒čĆą░ąĮ ą╗ąĖą▒ąŠ 8 (1 ą▒ą░ą╣čé), ą╗ąĖą▒ąŠ 16 ą▒ąĖčé (2 ą▒ą░ą╣čéą░). ą×ą┤ąĮą░ą║ąŠ ąĖąĘą╝ąĄąĮąĄąĮąĖąĄ ą▓čŗą▒ąŠčĆą║ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ čéčĆąĄą▒čāąĄčé ą┐ąĄčĆąĄą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ čĆąĄąČąĖą╝ą░ SPI_MR (čćč鹊ą▒čŗ čāą┐čĆą░ą▓ą╗čÅčéčī ąĄą│ąŠ ą┐ąŠą╗ąĄą╝ PCS).

Variable Peripheral Selection ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąŠčüčāčēąĄčüčéą▓ą╗čÅčéčī ą┐ąĄčĆąĄą┤ą░čćąĖ ą▒čāč乥čĆą░ čü ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ ą▒ąĄąĘ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéąĖ ą┐ąĄčĆąĄą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ čĆąĄąČąĖą╝ą░ SPI_MR. ąöą░ąĮąĮčŗąĄ, ąĘą░ą┐ąĖčüčŗą▓ą░ąĄą╝čŗąĄ ą▓ čĆąĄą│ąĖčüčéčĆ SPI_TDR, ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čłąĖčĆąĖąĮąŠą╣ ą▓ 32 ą▒ąĖčéą░, ąĖ ą▓ ąĮąĖčģ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮčŗ ą║ą░ą║ čĆąĄą░ą╗čīąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗąĄ ą┤ą░ąĮąĮčŗąĄ, čéą░ą║ąĖ ąĖ ąĮą░čüčéčĆąŠą╣ą║ą░ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą║ąĖ ąĮčāąČąĮąŠą│ąŠ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░. ąśčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ PDC (DMA) ą▓ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ čéčĆąĄą▒čāąĄčé ą▒čāč乥čĆąŠą▓, ą│ą┤ąĄ ą║ą░ąČą┤ą░čÅ čÅč湥ą╣ą║ą░ 32-ą▒ąĖčéąĮą░čÅ, ą│ą┤ąĄ ą┤ą░ąĮąĮčŗąĄ ąĮą░čģąŠą┤čÅčéčüčÅ ą▓ ą╝ą╗ą░ą┤čłąĖčģ ą▒ąĖčéą░čģ čÅč湥ą╣ą║ąĖ, ą┐ąŠą╗čÅ PCS ąĖ LASTXFER ąĮą░čģąŠą┤čÅčéčüčÅ ą▓ čüčéą░čĆčłąĖčģ ą▒ąĖčéą░čģ, ąŠą┤ąĮą░ą║ąŠ SPI ą▓čüąĄ ąĄčēąĄ čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü ą▓čŗą▒čĆą░ąĮąĮčŗą╝ ą║ąŠą╗ąĖč湥čüčéą▓ąŠą╝ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗčģ čüąĖą│ąĮą░ą╗ą░ą╝ąĖ MOSI ąĖ MISO ą▒ąĖčé (ąŠčé 8 ą┤ąŠ 16), ą║ą░ą║ čŹč鹊 ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąŠ ą▓ čĆąĄą│ąĖčüčéčĆą░čģ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓čŗą▒ąŠčĆą║ąĖ. ąŁč鹊 ąĮąĄ ąŠč湥ąĮčī ąŠą┐čéąĖą╝ą░ą╗čīąĮąŠ čü č鹊čćą║ąĖ ąĘčĆąĄąĮąĖčÅ čĆą░ąĘą╝ąĄčĆą░ ą┐ą░ą╝čÅčéąĖ, ą▓čŗą┤ąĄą╗čÅąĄą╝ąŠą╣ ą┐ąŠą┤ ą▒čāč乥čĆčŗ, ąŠą┤ąĮą░ą║ąŠ ąŠč湥ąĮčī čŹčäč乥ą║čéąĖą▓ąĮąŠ ą▓ ą┐ą╗ą░ąĮąĄ ąŠą▒ą╝ąĄąĮą░ ą┤ą░ąĮąĮčŗą╝ąĖ čü ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ ą▒ąĄąĘ ą║ą░ą║ąŠą│ąŠ-ą╗ąĖą▒ąŠ ą▓ą╝ąĄčłą░č鹥ą╗čīčüčéą▓ą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░ (čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąĄčĆąĄą┤ą░č湥ą╣ ą┤ą░ąĮąĮčŗčģ ą▒ąĄčĆąĄčé ąĮą░ čüąĄą▒čÅ čüąĖčüč鹥ą╝ą░ DMA).

ąöąĄą║ąŠą┤ąĖčĆąŠą▓ą░ąĮąĖąĄ čüąĖą│ąĮą░ą╗ąŠą▓ ą▓čŗą▒ąŠčĆą║ąĖ. ą¤ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą╝ąŠąČąĄčé ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī čĆą░ą▒ąŠčéčā SPI čü ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ ą▓ ą║ąŠą╗ąĖč湥čüčéą▓ąĄ ą┤ąŠ 15, ąĄčüą╗ąĖ ąŠčüčāčēąĄčüčéą▓ą╗čÅčéčī ą░ą┐ą┐ą░čĆą░čéąĮąŠąĄ ą┤ąĄą║ąŠą┤ąĖčĆąŠą▓ą░ąĮąĖąĄ čüąĖą│ąĮą░ą╗ąŠą▓ ą▓čŗą▒ąŠčĆą║ąĖ NPCS0..NPCS3 čü ą┐ąŠą╝ąŠčēčīčÄ ą▓ąĮąĄčłąĮąĄą│ąŠ ą┤ąĄčłąĖčäčĆą░č鹊čĆą░. ąŁč鹊 ą╝ąŠąČąĮąŠ čĆą░ąĘčĆąĄčłąĖčéčī ąĘą░ą┐ąĖčüčīčÄ ą▒ąĖčéą░ PCSDEC čĆąĄą│ąĖčüčéčĆą░ čĆąĄąČąĖą╝ą░ SPI_MR ą▓ ąĘąĮą░č湥ąĮąĖąĄ 1.

ąÜąŠą│ą┤ą░ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą▓čŗą▒ąŠčĆą║ą░ą╝ąĖ ą▒ąĄąĘ ą┤ąĄą║ąŠą┤ąĖčĆąŠą▓ą░ąĮąĖčÅ (PCSDEC=0), č鹊 SPI ą│ą░čĆą░ąĮčéąĖčĆčāąĄčé, čćč鹊 ą▓ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé ą▓čĆąĄą╝ąĄąĮąĖ ą▒čāą┤ąĄčé ą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮąŠ (čé. ąĄ. ą┐ąĄčĆąĄą▓ąĄą┤ąĄąĮąŠ ą▓ čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 0) ąĮąĄ ą▒ąŠą╗čīčłąĄ ąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ą▓čŗą▒ąŠčĆą║ąĖ, ą▓čüąĄ ąŠčüčéą░ą╗čīąĮčŗąĄ čüąĖą│ąĮą░ą╗čŗ ą▓čŗą▒ąŠčĆą║ąĖ ąŠčüčéą░ąĮčāčéčüčÅ ą▓ ąĮąĄą░ą║čéąĖą▓ąĮąŠą╝ čüąŠčüč鹊čÅąĮąĖąĖ (ą╗ąŠą│. 1). ą¤čĆąĖč湥ą╝ ąĄčüą╗ąĖ ąŠčłąĖą▒ąŠčćąĮąŠ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮčŗ ą▓ ą╗ąŠą│. 0 ą┤ą░ąČąĄ 2 ą▒ąĖčéą░ ą▓ ą┐ąŠą╗ąĄ PCS, č鹊 ą▒čāą┤ąĄčé ą▓čŗą▒čĆą░ąĮ č鹊ą╗čīą║ąŠ čćąĖą┐ čü ą╝ąĄąĮčīčłąĖą╝ ą┐ąŠčĆčÅą┤ą║ąŠą▓čŗą╝ ąĮąŠą╝ąĄčĆąŠą╝.

ąÜąŠą│ą┤ą░ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą▓čŗą▒ąŠčĆą║ą░ą╝ąĖ čü ą┐čĆąĖą╝ąĄąĮąĄąĮąĖąĄą╝ ą▓ąĮąĄčłąĮąĄą│ąŠ ą┤ąĄą║ąŠą┤ąĖčĆąŠą▓ą░ąĮąĖčÅ (PCSDEC=1), č鹊 SPI ąĮą░ą┐čĆčÅą╝čāčÄ ą▓čŗą▓ąŠą┤ąĖčé ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠą╗čÅ PCS ą╗ąĖą▒ąŠ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ čĆąĄąČąĖą╝ą░ SPI_MR, ą╗ąĖą▒ąŠ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ ą┐ąĄčĆąĄą┤ą░čćąĖ SPI_TDR (ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ąĘąĮą░č湥ąĮąĖčÅ ą▒ąĖčéą░ PS).

ąóą░ą║ ą║ą░ą║ SPI čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ąĖčüčģąŠą┤ąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 0xF ą┤ą╗čÅ ąĮąĄą░ą║čéąĖą▓ąĮąŠą│ąŠ čüąŠčüč鹊čÅąĮąĖčÅ ą╗ąĖąĮąĖą╣ ą▓čŗą▒ąŠčĆą║ąĖ (čé. ąĄ. ą▓čüąĄ ą╗ąĖąĮąĖąĖ ą▓čŗą▒ąŠčĆą║ąĖ ąĮą░čģąŠą┤čÅčéčüčÅ ąĮą░ čāčĆąŠą▓ąĮąĄ ą╗ąŠą│. 1), ą║ąŠą│ą┤ą░ ąĮąĄčé ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą║ą░ą║ąĖčģ-ą╗ąĖą▒ąŠ ą┐ąĄčĆąĄą┤ą░čć, č鹊 ą╝ąŠąČąĄčé ą▒čŗčéčī ą┤ąĄą║ąŠą┤ąĖčĆąŠą▓ą░ąĮąŠ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą║ąĖ ąĮąĄ ą▒ąŠą╗ąĄąĄ 15 ą▓ąĮąĄčłąĮąĖčģ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ SPI.

ąŻ SPI ąĖą╝ąĄąĄčéčüčÅ č鹊ą╗čīą║ąŠ 4 čĆąĄą│ąĖčüčéčĆą░ ą▓čŗą▒ąŠčĆą║ąĖ čćąĖą┐ą░, ą░ ąĮąĄ 15. ąÆ čĆąĄąĘčāą╗čīčéą░č鹥, ą║ąŠą│ą┤ą░ ą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮ čĆąĄąČąĖą╝ ą┤ąĄą║ąŠą┤ąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓čŗą▒ąŠčĆą║ąĖ (PCSDEC=1), ą║ą░ąČą┤čŗą╣ čĆąĄą│ąĖčüčéčĆ ą▓čŗą▒ąŠčĆą║ąĖ ą╝ąŠąČąĄčé ąĘą░ą┤ą░čéčī ą▓čŗą▒ąŠčĆą║čā č鹊ą╗čīą║ąŠ ą┤ąŠ 4 ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓. ąØą░ą┐čĆąĖą╝ąĄčĆ, SPI_CRS0 ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ ą┤ąĄą║ąŠą┤ąĖčĆčāąĄą╝čŗčģ ą▓ąĮąĄčłąĮąĄ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ąŠčé 0 ą┤ąŠ 3, čćč鹊 čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ąĘąĮą░č湥ąĮąĖčÅą╝ ą┐ąŠą╗čÅ PCS ąŠčé 0x0 ą┤ąŠ 0x3. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą┤ąŠą╗ąČąĄąĮ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī, čćč鹊 čüąŠą▓ą╝ąĄčüčéąĖą╝čŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┐ąŠą┤ą║ą╗čÄč湥ąĮčŗ ą║ ą┤ąĄą║ąŠą┤ąĖčĆąŠą▓ą░ąĮąĮčŗą╝ ą▓čŗą▒ąŠčĆą║ą░ą╝ 0 .. 3, 4 .. 7, 8 .. 11 ąĖ 12 .. 14.

ąĪąĮčÅčéąĖąĄ čüąĖą│ąĮą░ą╗ą░ ą▓čŗą▒ąŠčĆą║ąĖ. ąÆ ąĮąŠčĆą╝ą░ą╗čīąĮąŠą╝ čĆąĄąČąĖą╝ąĄ čĆą░ą▒ąŠčéčŗ ą║ą░ą║ č鹊ą╗čīą║ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮą░ ą┐ąĄčĆąĄą┤ą░čćą░ ą┐ąŠčüą╗ąĄą┤ąĮąĖčģ ąĘą░ą┐ąĖčüą░ąĮąĮčŗčģ ą▓ čĆąĄą│ąĖčüčéčĆ SPI_TDR ą┤ą░ąĮąĮčŗčģ, ą▓čüąĄ čüąĖą│ąĮą░ą╗čŗ NPCS ą┐ąĄčĆąĄčģąŠą┤čÅčé ą▓ ą╗ąŠą│. 1. ąŁč鹊 ą╝ąŠąČąĄčé ą┐čĆąĖą▓ąĄčüčéąĖ ą║ ąŠčłąĖą▒ą║ąĄ, ąĄčüą╗ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆ čüą╗ąĖčłą║ąŠą╝ ą┤ąŠą╗ą│ąŠ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ąĖ ą║ą░ą║ čüą╗ąĄą┤čüčéą▓ąĖąĄ ą╝ąŠąČąĄčé čāčüą╗ąŠąČąĮąĖčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖąĄ ąĮąĄą║ąŠč鹊čĆčŗčģ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓, ą║ąŠč鹊čĆčŗąĄ čéčĆąĄą▒čāčÄčé, čćč鹊ą▒čŗ čüąĖą│ąĮą░ą╗ ą▓čŗą▒ąŠčĆą║ąĖ ąŠčüčéą░ą▓ą░ą╗čüčÅ ą░ą║čéąĖą▓ąĮčŗą╝ ą▓ąŠ ą▓čĆąĄą╝čÅ ą▓čüąĄą│ąŠ ąĮą░ą▒ąŠčĆą░ ą┐ąĄčĆąĄą┤ą░čć.

ą¦č鹊ą▒čŗ čāą┐čĆąŠčüčéąĖčéčī čĆą░ą▒ąŠčéčā čü čéą░ą║ąĖą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ, ą▓ čĆąĄą│ąĖčüčéčĆąĄ ą▓čŗą▒ąŠčĆą║ąĖ (SPI_CSR0 .. SPI_CSR3) ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ ą▒ąĖčé CSAAT (Chip Select Active After Transfer) ą▓ čüąŠčüč鹊čÅąĮąĖąĄ 1. ąŁč鹊 ą┐ąŠąĘą▓ąŠą╗ąĖčé ąŠčüčéą░ą▓ą░čéčīčüčÅ čüąĖą│ąĮą░ą╗čā ą▓čŗą▒ąŠčĆą║ąĖ ą▓ čüą▓ąŠąĄą╝ č鹥ą║čāčēąĄą╝ ą░ą║čéąĖą▓ąĮąŠą╝ čüąŠčüč鹊čÅąĮąĖąĖ (ą▓ ą╗ąŠą│. 0), ą┐ąŠą║ą░ ąĮąĄ ą┐ąŠčéčĆąĄą▒čāąĄčéčüčÅ ąŠą▒ą╝ąĄąĮ čü ą┤čĆčāą│ąĖą╝ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝.

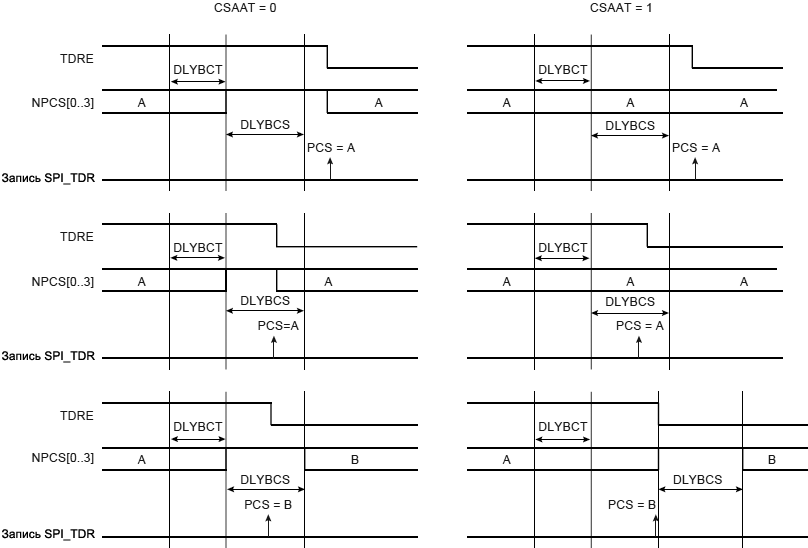

ąØą░ čĆąĖčü. 28-8 ą┐ąŠą║ą░ąĘą░ąĮčŗ čüą╗čāčćą░ąĖ čĆą░ąĘą╗ąĖčćąĮąŠą╣ ąŠčéą╝ąĄąĮčŗ ą▓čŗą▒ąŠčĆą║ąĖ, čćč鹊 čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ą▒ąĖč鹊ą╝ CSAAT.

ąĀąĖčü. 28-8. ąĀąĄąČąĖą╝čŗ ąŠčéą╝ąĄąĮčŗ ą▓čŗą▒ąŠčĆą║ąĖ.

ąöąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čüąŠčüč鹊čÅąĮąĖčÅ ąŠčéą║ą░ąĘą░ (Mode Fault Detection). ąĀąĄąČąĖą╝ ąŠčéą║ą░ąĘą░ ą┤ąĄč鹥ą║čéąĖčĆčāąĄčéčüčÅ, ą║ąŠą│ą┤ą░ SPI ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ ą▓ čĆąĄąČąĖą╝ąĄ Master, ąĮą░ čłąĖąĮąĄ SPI ąĮą░čģąŠą┤ąĖčéčüčÅ ąĮąĄčüą║ąŠą╗čīą║ąŠ čāčüčéčĆąŠą╣čüčéą▓ master, ąĖ ą┐čĆąĖ čŹč鹊ą╝ ą▓ąĮąĄčłąĮąĖą╣ master (ąŠčłąĖą▒ąŠčćąĮąŠ) čāčüčéą░ąĮąŠą▓ąĖą╗ ą░ą║čéąĖą▓ąĮčŗą╣ ąĮąĖąĘą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī ąĮą░ čüąĖą│ąĮą░ą╗ąĄ NPCS0/NSS. NPCS0, MOSI, MISO ąĖ SPCK ą┤ą╗čÅ čĆąĄąČąĖą╝ą░ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ą╝ą░čüč鹥čĆąŠą▓ ąĮą░ čłąĖąĮąĄ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ ą┤ą╗čÅ ą▒čāč乥čĆą░ čü ąŠčéą║čĆčŗčéčŗą╝ čüč鹊ą║ąŠą╝ čü ą┐ąŠą╝ąŠčēčīčÄ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ PIO (čüą╝. [4]), čéą░ą║ čćč鹊 čéčĆąĄą▒čāąĄčéčüčÅ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖąĄ ą▓ąĮąĄčłąĮąĖčģ ą▓ąĄčĆčģąĮąĖčģ ąĮą░ą│čĆčāąĘąŠčćąĮčŗčģ čĆąĄąĘąĖčüč鹊čĆąŠą▓ (pull-up), čćč鹊ą▒čŗ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī ą┐ąŠčÅą▓ą╗ąĄąĮąĖąĄ ą▓čŗčüąŠą║ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ ąĮą░ čüąĖą│ąĮą░ą╗ą░čģ čłąĖąĮčŗ (ą▓ąĮčāčéčĆąĄąĮąĮąĖąĄ pull-up ą╝ąŠą│čāčé ą┐ąŠą┤ąŠą╣čéąĖ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ą╝ą░ą╗čŗčģ čüą║ąŠčĆąŠčüč鹥ą╣ ą┐ąĄčĆąĄą┤ą░čć).

ąÜąŠą│ą┤ą░ ą▒čŗą╗ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮ ąŠčéą║ą░ąĘ (mode fault), ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüąŠčüč鹊čÅąĮąĖčÅ SPI_SR čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé MODF, ą┐ąŠą║ą░ čĆąĄą│ąĖčüčéčĆ SPI_SR ąĮąĄ ą▒čāą┤ąĄčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ ą┐čĆąŠčćąĖčéą░ąĮ, ąĖ SPI ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąĘą░ą┐čĆąĄčēą░ąĄčéčüčÅ ąĘą░ą┐ąĖčüčīčÄ ą▓ ą╗ąŠą│. 1 ą▒ąĖčéą░ SPIEN čāą┐čĆą░ą▓ą╗čÅčÄčēąĄą│ąŠ čĆąĄą│ąĖčüčéčĆą░ SPI_CR.

ą¤ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ čüčģąĄą╝čŗ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ Mode Fault čĆą░ąĘčĆąĄčłąĄąĮčŗ. ą¤ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą╝ąŠąČąĄčé ąĘą░ą┐čĆąĄčéąĖčéčī ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ Mode Fault ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ MODFDIS ą▓ čĆąĄą│ąĖčüčéčĆąĄ čĆąĄąČąĖą╝ą░ SPI_MR.

[ąĀąĄąČąĖą╝ čĆą░ą▒ąŠčéčŗ Slave]

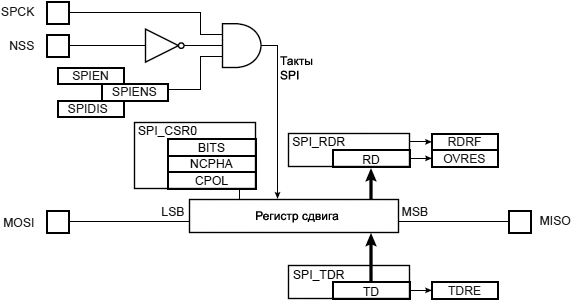

ą¤čĆąĖ čĆą░ą▒ąŠč鹥 ą▓ čĆąĄąČąĖą╝ąĄ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ čłąĖąĮčŗ SPI (Slave Mode), SPI ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčé ą▒ąĖčéčŗ ą┤ą░ąĮąĮčŗčģ ą┐ąŠ čéą░ą║čéą░ą╝, ą┐ąŠčüčéčāą┐ą░čÄčēąĖą╝ čüąĮą░čĆčāąČąĖ ąŠčé ą▓čŗą▓ąŠą┤ą░ SPCK (čüąĖą│ąĮą░ą╗čŗ čéą░ą║č鹊ą▓ ą│ąĄąĮąĄčĆąĖčĆčāčÄčéčüčÅ ą▓ąĮąĄčłąĮąĖą╝ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ master).

SPI ąČą┤ąĄčé ą░ą║čéąĖą▓ą░čåąĖąĖ (ą┐ąĄčĆąĄčģąŠą┤ą░ ą▓ ą╗ąŠą│. 0) čüąĖą│ąĮą░ą╗ą░ NSS ą┐ąĄčĆąĄą┤ ąĮą░čćą░ą╗ąŠą╝ ą┐čĆąĖąĄą╝ą░ čüąĖą│ąĮą░ą╗ąŠą▓ čéą░ą║č鹊ą▓ ąŠčé ą▓ąĮąĄčłąĮąĄą│ąŠ ą│ą╗ą░ą▓ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░. ąÜąŠą│ą┤ą░ NSS ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ ą╗ąŠą│. 0, čéą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗ ą┐čĆąŠčģąŠą┤ąĖčé ą┐čĆąŠą▓ąĄčĆą║čā č湥čĆąĄąĘ ą▒ą╗ąŠą║ čüąĄčĆąĖą░ą╗ąĖąĘą░č鹊čĆą░, ą║ąŠč鹊čĆčŗą╣ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčé č鹊 ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ąĖčé, ą║ąŠč鹊čĆąŠąĄ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąŠ ą▓ ą┐ąŠą╗ąĄ BITS čĆąĄą│ąĖčüčéčĆą░ ą▓čŗą▒ąŠčĆą║ąĖ 0 (Chip Select Register 0, SPI_CSR0). ąæąĖčéčŗ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░čÄčéčüčÅ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü čäą░ąĘąŠą╣ ąĖ ą┐ąŠą╗čÅčĆąĮąŠčüčéčīčÄ, ą║ąŠč鹊čĆčŗąĄ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮčŗ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ ą▒ąĖčéą░ą╝ąĖ NCPHA ąĖ CPOL čĆąĄą│ąĖčüčéčĆą░ SPI_CSR0. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ą▒ąĖčéčŗ BITS, CPOL ąĖ NCPHA ą┤čĆčāą│ąĖčģ čĆąĄą│ąĖčüčéčĆąŠą▓ ą▓čŗą▒ąŠčĆą║ąĖ (SPI_CSR1 .. SPI_CSR3) ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░čÄčé ąĮąĖą║ą░ą║ąŠą│ąŠ ą▓ą╗ąĖčÅąĮąĖčÅ ąĮą░ ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ SPI, ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ ą▓ Slave Mode.

ąæąĖčéčŗ ą┐ąŠ čéą░ą║čéą░ą╝ SPCK ą▓čŗą┤ą▓ąĖą│ą░čÄčéčüčÅ č湥čĆąĄąĘ čüąĖą│ąĮą░ą╗ MISO ąĖ ąŠčåąĖčäčĆąŠą▓čŗą▓ą░čÄčéčüčÅ ąĮą░ čüąĖą│ąĮą░ą╗ąĄ MOSI.

ąÜąŠą│ą┤ą░ ą▓čüąĄ ą▒ąĖčéčŗ čäčĆąĄą╣ą╝ą░ ąŠą▒čĆą░ą▒ąŠčéą░ąĮčŗ, ą┐čĆąĖąĮčÅčéčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┐ąĄčĆąĄą╝ąĄčēą░čÄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ ą┐čĆąĖąĄą╝ą░ SPI_RDR, ąĖ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▒ąĖčé RDRF ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüąŠčüč鹊čÅąĮąĖčÅ SPI_SR. ąĢčüą╗ąĖ čĆąĄą│ąĖčüčéčĆ SPI_RDR ąĮąĄ ą▒čŗą╗ ą┐čĆąŠčćąĖčéą░ąĮ ą┐ąĄčĆąĄą┤ ą┐ąŠčüčéčāą┐ą╗ąĄąĮąĖąĄą╝ ąĮąŠą▓čŗčģ ą┤ą░ąĮąĮčŗčģ (ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ąĮąĄ čāčüą┐ąĄą╗ą░ čŹč鹊 čüą┤ąĄą╗ą░čéčī), č鹊 čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé ąŠčłąĖą▒ą║ąĖ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ (Overrun Error, OVRES) ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_SR. ą¤ąŠą║ą░ čŹč鹊čé čäą╗ą░ą│ OVRES čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ą┤ą░ąĮąĮčŗąĄ ąŠčüčéą░čÄčéčüčÅ ąĘą░ą│čĆčāąČąĄąĮąĮčŗą╝ąĖ ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_RDR. ą¦č鹊ą▒čŗ ąŠčćąĖčüčéąĖčéčī ą▒ąĖčé OVRES, ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┤ąŠą╗ąČąĮą░ ą┐čĆąŠčćąĖčéą░čéčī čĆąĄą│ąĖčüčéčĆ SPI_SR.

ąÜąŠą│ą┤ą░ ąĮą░čćąĖąĮą░ąĄčéčüčÅ ą┐ąĄčĆąĄą┤ą░čćą░, ą┤ą░ąĮąĮčŗąĄ ą▓čŗą┤ą▓ąĖą│ą░čÄčéčüčÅ ąĮą░čĆčāąČčā ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ čüą┤ą▓ąĖą│ą░. ąĢčüą╗ąĖ ąĮąĄ ą▒čŗą╗ąĖ ąĘą░ą┐ąĖčüą░ąĮčŗ ą┤ą░ąĮąĮčŗąĄ ą▓ čĆąĄą│ąĖčüčéčĆ ą┐ąĄčĆąĄą┤ą░čćąĖ SPI_TDR, č鹊 ą▒čāą┤čāčé ą┐ąĄčĆąĄą┤ą░ąĮčŗ ą┐ąŠčüą╗ąĄą┤ąĮąĖąĄ ą┐čĆąĖąĮčÅčéčŗąĄ ą┤ą░ąĮąĮčŗąĄ. ąĢčüą╗ąĖ čü ą╝ąŠą╝ąĄąĮčéą░ čüą▒čĆąŠčüą░ ąĮąĄ ą▒čŗą╗ąŠ ą┐čĆąĖąĮčÅč鹊 ąĮąĖą║ą░ą║ąĖčģ ą┤ą░ąĮąĮčŗčģ, č鹊 ą▓čüąĄ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗąĄ ą▒ąĖčéčŗ ą▒čāą┤čāčé ą┐ąĄčĆąĄą┤ą░ąĮčŗ ą║ą░ą║ ąĮčāą╗ąĖ, čéą░ą║ ą║ą░ą║ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ čüą▒čĆą░čüčŗą▓ą░ąĄčé čüą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą▓ 0.

ąÜąŠą│ą┤ą░ ą┐ąĄčĆą▓čŗąĄ ą┤ą░ąĮąĮčŗąĄ ą▒čŗą╗ąĖ ąĘą░ą┐ąĖčüą░ąĮčŗ ą▓ čĆąĄą│ąĖčüčéčĆ ą┐ąĄčĆąĄą┤ą░čćąĖ SPI_TDR, ąŠąĮąĖ ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ ą┐ąĄčĆąĄą╝ąĄčēą░čÄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░, ąĖ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▒ąĖčé TDRE ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüąŠčüč鹊čÅąĮąĖčÅ SPI_SR. ąĢčüą╗ąĖ ą┐ąŠčüą╗ąĄ čŹč鹊ą│ąŠ čüčĆą░ąĘčā ąĘą░ą┐ąĖčüą░ąĮčŗ ąĮąŠą▓čŗąĄ ą┤ą░ąĮąĮčŗąĄ, č鹊 ąŠąĮąĖ ąŠčüčéą░ąĮčāčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI_TDR (ąĮąĄ ą▒čāą┤čāčé ą┐ąŠą║ą░ ą┐ąĄčĆąĄą┤ą░ąĮčŗ ą▓ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░) ą┤ąŠ č鹥čģ ą┐ąŠčĆ, ą┐ąŠą║ą░ ąĮąĄ ąĘą░ą▓ąĄčĆčłąĖčéčüčÅ ą┐ąĄčĆąĄą┤ą░čćą░, čé. ąĄ. NSS ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ ą╗ąŠą│. 0, ąĖ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ SPCK ą┐čĆąŠčłą╗ąŠ čéčĆąĄą▒čāąĄą╝ąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą┤ąŠą┐čāčüčéąĖą╝čŗčģ čéą░ą║č鹊ą▓. ąÜąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą┐ąĄčĆąĄą┤ą░čćą░, ą┐ąŠčüą╗ąĄą┤ąĮąĖąĄ ąĘą░ą┐ąĖčüą░ąĮąĮčŗąĄ ą▓ čĆąĄą│ąĖčüčéčĆ SPI_TDR ą┤ą░ąĮąĮčŗąĄ ą┐ąĄčĆąĄą╝ąĄčēą░čÄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░, ąĖ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▒ąĖčé TDRE ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüąŠčüč鹊čÅąĮąĖčÅ SPI_SR. ąŁč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé čćą░čüčéčŗąĄ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ ą║čĆąĖčéąĖč湥čüą║ąĖčģ ą┐ąĄčĆąĄą╝ąĄąĮąĮčŗčģ čü ąŠą┤ąĖąĮąŠčćąĮčŗą╝ąĖ ą┐ąĄčĆąĄą┤ą░čćą░ą╝ąĖ.

ąŚą░č鹥ą╝ ąĮąŠą▓čŗąĄ ą┤ą░ąĮąĮčŗąĄ ąĘą░ą│čĆčāąČą░čÄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ ą┐ąĄčĆąĄą┤ą░čćąĖ SPI_TDR. ąÆ č鹊ą╝ čüą╗čāčćą░ąĄ, ą║ąŠą│ą┤ą░ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĮąĄ ą│ąŠč鹊ą▓čŗ ąĮąŠą▓čŗąĄ ą┤ą░ąĮąĮčŗąĄ, čé. ąĄ. ąŠąĮąĖ ąĮąĄ ą▒čŗą╗ąĖ ąĘą░ą┐ąĖčüą░ąĮčŗ ą▓ čĆąĄą│ąĖčüčéčĆ SPI_TDR čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╣ ąĘą░ą│čĆčāąĘą║ąĖ SPI_TDR ą▓ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░, č鹊 čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ ąŠčüčéą░ąĮąĄčéčüčÅ ąĮąĄ ąĖąĘą╝ąĄąĮąĄąĮąĮčŗą╝, ąĖ ą▒čāą┤čāčé ą┐ąĄčĆąĄą┤ą░ąĮčŗ ą┐ąŠčüą╗ąĄą┤ąĮąĖąĄ ą┐čĆąĖąĮčÅčéčŗąĄ ą┤ą░ąĮąĮčŗąĄ.

ąØą░ čĆąĖčü. 28-9 ą┐ąŠą║ą░ąĘą░ąĮą░ ą▒ą╗ąŠą║-čüčģąĄą╝ą░ SPI ą▓ Slave Mode.

ąĀąĖčü. 28-9. ążčāąĮą║čåąĖąŠąĮą░ą╗čīąĮą░čÅ čüčģąĄą╝ą░ čĆąĄąČąĖą╝ą░ čĆą░ą▒ąŠčéčŗ Slave.

[ąśąĮč鹥čĆč乥ą╣čü ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ SPI]

ąÆ čéą░ą▒ą╗ąĖčåąĄ ąĮąĖąČąĄ ą┐ąŠą║ą░ąĘą░ąĮčŗ čĆąĄą│ąĖčüčéčĆčŗ SPI. ąÆ ą║čĆą░ą╣ąĮąĄą╝ ą╗ąĄą▓ąŠą╝ čüč鹊ą╗ą▒čåąĄ ą┐ąŠą║ą░ąĘą░ąĮąŠ čüą╝ąĄčēąĄąĮąĖąĄ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ąĮą░čćą░ą╗čīąĮąŠą│ąŠ ą▒ą░ąĘąŠą▓ąŠą│ąŠ ą░ą┤čĆąĄčüą░ ąĖąĮč鹥čĆč乥ą╣čüą░. ąØą░ą┐čĆąĖą╝ąĄčĆ, čā ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ AT91SAM7X128, AT91SAM7X256, AT91SAM7X512 ąĄčüčéčī ą┤ą▓ą░ ąĖąĮč鹥čĆč乥ą╣čüą░ SPI: SPI0 ąĖ SPI1. ąŻ ąĖąĮč鹥čĆč乥ą╣čüą░ SPI0 ą▒ą░ąĘąŠą▓čŗą╣ ą░ą┤čĆąĄčü čĆą░ą▓ąĄąĮ 0xFFFE0000 (čĆą░ą▓ąĄąĮ ą░ą┤čĆąĄčüčā čĆąĄą│ąĖčüčéčĆą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ AT91C_SPI0_CR), ą░ čā SPI1 ą▒ą░ąĘąŠą▓čŗą╣ ą░ą┤čĆąĄčü 0xFFFE4000 (čĆą░ą▓ąĄąĮ ą░ą┤čĆąĄčüčā čĆąĄą│ąĖčüčéčĆą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ AT91C_SPI1_CR).

ąóą░ą▒ą╗ąĖčåą░ 28-3. ąĀąĄą│ąĖčüčéčĆčŗ SPI.

| ąĪą╝ąĄčēąĄąĮąĖąĄ |

ąĀąĄą│ąĖčüčéčĆ |

ąśą╝čÅ |

ąöąŠčüčéčāą┐ |

ąĪą▒čĆąŠčü |

| 0x0000 |

Control Register (čĆąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ) |

SPI_CR |

W |

- |

| 0x0004 |

Mode Register (čĆąĄą│ąĖčüčéčĆ čĆąĄąČąĖą╝ą░) |

SPI_MR |

R/W |

0x00000000 |

| 0x0008 |

Receive Data Register (čĆąĄą│ąĖčüčéčĆ ą┤ą░ąĮąĮčŗčģ ą┐čĆąĖąĄą╝ą░) |

SPI_RDR |

R |

0x00000000 |

| 0x000C |

Transmit Data Register (čĆąĄą│ąĖčüčéčĆ ą┤ą░ąĮąĮčŗčģ ą┐ąĄčĆąĄą┤ą░čćąĖ) |

SPI_TDR |

W |

- |

| 0x0010 |

Status Register (čĆąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ) |

SPI_SR |

R |

0x000000F0 |

| 0x0014 |

Interrupt Enable Register (čĆąĄą│ąĖčüčéčĆ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣) |

SPI_IER |

W |

- |

| 0x0018 |

Interrupt Disable Register (čĆąĄą│ąĖčüčéčĆ ąĘą░ą┐čĆąĄčéą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣) |

SPI_IDR |

W |

- |

| 0x001C |

Interrupt Mask Register (čĆąĄą│ąĖčüčéčĆ ą╝ą░čüą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣) |

SPI_IMR |

R |

0x00000000 |

| 0x0020..0x002C |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

- |

- |

- |

| 0x0030 |

Chip Select Register 0 (čĆąĄą│ąĖčüčéčĆ ą▓čŗą▒ąŠčĆą║ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ 0) |

SPI_CSR0 |

R/W |

0x00000000 |

| 0x0034 |

Chip Select Register 1 (čĆąĄą│ąĖčüčéčĆ ą▓čŗą▒ąŠčĆą║ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ 1) |

SPI_CSR1 |

R/W |

0x00000000 |

| 0x0038 |

Chip Select Register 2 (čĆąĄą│ąĖčüčéčĆ ą▓čŗą▒ąŠčĆą║ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ 2) |

SPI_CSR2 |

R/W |

0x00000000 |

| 0x003C |

Chip Select Register 3 (čĆąĄą│ąĖčüčéčĆ ą▓čŗą▒ąŠčĆą║ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ 3) |

SPI_CSR3 |

R/W |

0x00000000 |

| 0x004C..0x00FC |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

- |

- |

- |

| 0x100..0x124 |

ąśčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ PDC (DMA), čüą╝. [6] |

|

|

|

ąĀąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ SPI (SPI Control Register). ąĀą░ą▒ąŠčéą░ąĄčé č鹊ą╗čīą║ąŠ ąĮą░ ąĘą░ą┐ąĖčüčī.

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

-

|

- |

- |

- |

- |

- |

- |

LASTXFER |

- |

- |

- |

- |

- |

- |

-

|

- |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

-

|

- |

- |

- |

- |

- |

- |

- |

SWRST |

- |

- |

- |

- |

- |

SPIDIS |

SPIEN |

SPIEN: SPI Enable, čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ čĆą░ą▒ąŠčéčŗ SPI.

0 = ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé čŹčäč乥ą║čéą░.

1 = čĆą░ąĘčĆąĄčłą░ąĄčé ą┤ą╗čÅ SPI ą┐ąĄčĆąĄą┤ą░čćčā ąĖ ą┐čĆąĖąĄą╝ ą┤ą░ąĮąĮčŗčģ.

SPIDIS: SPI Disable, ąĘą░ą┐čĆąĄčé čĆą░ą▒ąŠčéčŗ SPI.

0 = ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé čŹčäč乥ą║čéą░.

1 = ąĘą░ą┐čĆąĄčēą░ąĄčé SPI.

ąÜą░ą║ č鹊ą╗čīą║ąŠ SPIDIS čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, SPI ąĘą░ą▓ąĄčĆčłą░ąĄčé čüą▓ąŠąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ.

ąÆčüąĄ ą▓čŗą▓ąŠą┤čŗ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ ą▓čģąŠą┤ą░, ąĖ ąĮąĖą║ą░ą║ąĖąĄ ą┤ą░ąĮąĮčŗąĄ ąĮąĄ ą┐čĆąĖąĮąĖą╝ą░čÄčéčüčÅ ąĖ ąĮąĄ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ.

ąĢčüą╗ąĖ ą▓ ą╝ąŠą╝ąĄąĮčé čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ SPIDIS ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą┐ąĄčĆąĄą┤ą░čćą░, č鹊 ą┐ąĄčĆąĄą┤ ąĘą░ą┐čĆąĄč鹊ą╝ SPI ąŠąĮą░ ąĘą░ą▓ąĄčĆčłą░ąĄčéčüčÅ.

ąĢčüą╗ąĖ ą┐čĆąĖ ąĘą░ą┐ąĖčüąĖ čĆąĄą│ąĖčüčéčĆą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąŠą▒ą░ ą▒ąĖčéą░, ąĖ SPIEN ąĖ SPIDIS čĆą░ą▓ąĮčŗ 1, č鹊 SPI ąĘą░ą┐čĆąĄčēą░ąĄčéčüčÅ.

SWRST: SPI Software Reset, ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čüą▒čĆąŠčü SPI.

0 = ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé čŹčäč乥ą║čéą░.

1 = čüą▒čĆą░čüčŗą▓ą░ąĄčé SPI. ąæčāą┤ąĄčé ą▓čŗą┐ąŠą╗ąĮąĄąĮ ą▓čŗąĘą▓ą░ąĮąĮčŗą╣ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╝ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖąĄą╝ ą░ą┐ą┐ą░čĆą░čéąĮčŗą╣ čüą▒čĆąŠčü ąĖąĮč鹥čĆč乥ą╣čüą░ SPI.

ą¤ąŠčüą╗ąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čüą▒čĆąŠčüą░ SPI ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ Slave Mode. ą¤čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čüą▒čĆąŠčü ąĮąĄ ą▓ą╗ąĖčÅąĄčé ąĮą░ ą║ą░ąĮą░ą╗čŗ PDC.

LASTXFER: Last Transfer, ą┐ąŠčüą╗ąĄą┤ąĮčÅčÅ ą┐ąĄčĆąĄą┤ą░čćą░.

0 = ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé čŹčäč乥ą║čéą░.

1 = čü č鹥ą║čāčēąĄą│ąŠ NPCS ą▒čāą┤ąĄčé čüąĮčÅčéą░ ą▓čŗą▒ąŠčĆą║ą░ ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ąĘą░ą┐ąĖčüą░ąĮąĮčŗąĄ ą▓ čĆąĄą│ąĖčüčéčĆ ą┐ąĄčĆąĄą┤ą░čćąĖ (SPI_TDR) ą┤ą░ąĮąĮčŗąĄ ą▒čŗą╗ąĖ ą┐ąĄčĆąĄą┤ą░ąĮčŗ. ąÜąŠą│ą┤ą░ ą▒ąĖčé CSAAT čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąĘą░ą║čĆčŗčéčī ąŠą▒ą╝ąĄąĮ čü č鹥ą║čāčēąĖą╝ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ ą┐čāč鹥ą╝ ą┐ąĄčĆąĄą▓ąŠą┤ą░ ą▓ ą╗ąŠą│. 1 čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ čüąĖą│ąĮą░ą╗ą░ ą▓čŗą▒ąŠčĆą║ąĖ NPCS, ą║ą░ą║ č鹊ą╗čīą║ąŠ ą┐ąĄčĆąĄą┤ą░čćą░ čüąŠą┤ąĄčƹȹĖą╝ąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░ ą┤ą░ąĮąĮčŗčģ ąĘą░ą▓ąĄčĆčłąĖčéčüčÅ.

ąŁč鹊 ą┐ąŠą╗ąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ č鹊ą╗čīą║ąŠ č鹊ą│ą┤ą░, ą║ąŠą│ą┤ą░ ą░ą║čéąĖą▓ąĄąĮ čĆąĄąČąĖą╝ ąĖąĘą╝ąĄąĮčÅąĄą╝ąŠą╣ ą▓čŗą▒ąŠčĆą║ąĖ ą▓ąĮąĄčłąĮąĖčģ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ (Variable Peripheral Select, PS = 1).

ąĀąĄą│ąĖčüčéčĆ čĆąĄąČąĖą╝ą░ SPI (SPI Mode Register). ąĀą░ą▒ąŠčéą░ąĄčé ąĮą░ čćč鹥ąĮąĖąĄ ąĖ ąĮą░ ąĘą░ą┐ąĖčüčī.

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| DLYBCS |

- |

- |

- |

- |

PCS |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

-

|

- |

- |

- |

- |

- |

- |

- |

LLB |

- |

- |

MODFDIS |

- |

PCSDEC |

PS |

MSTR |

MSTR: Master/Slave Mode, čĆąĄąČąĖą╝ čĆą░ą▒ąŠčéčŗ SPI - ą║ą░ą║ ą│ą╗ą░ą▓ąĮąŠąĄ ąĖą╗ąĖ ą║ą░ą║ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ.

0 = SPI ą▓ čĆąĄąČąĖą╝ąĄ Slave (ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ).

1 = SPI ą▓ čĆąĄąČąĖą╝ąĄ Master (ą│ą╗ą░ą▓ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ).

PS: Peripheral Select, ą┐čĆąĖąĮčåąĖą┐ ą▓čŗą▒ąŠčĆą║ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓.

0 = Fixed Peripheral Select, čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮčŗą╣ ą▓čŗą▒ąŠčĆ ą┐ąĄčĆąĖč乥čĆąĖąĖ.

1 = Variable Peripheral Select, ąĖąĘą╝ąĄąĮčÅąĄą╝čŗą╣ ą▓čŗą▒ąŠčĆ ą┐ąĄčĆąĖč乥čĆąĖąĖ.

PCSDEC: Chip Select Decode, čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ą▓ąĮąĄčłąĮąĄą│ąŠ ą┤ąĄą║ąŠą┤ąĄčĆą░ ą▓čŗą▒ąŠčĆą║ąĖ.

0 = ą▓čŗą▒ąŠčĆą║ą░ ą▓ąĮąĄčłąĮąĖčģ čāčüčéčĆąŠą╣čüčéą▓ ąĮą░ą┐čĆčÅą╝čāčÄ ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčéčüčÅ ą║ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗą╝ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝, ą▒ąĄąĘ ą▓ąĮąĄčłąĮąĄą│ąŠ ą┤ąĄčłąĖčäčĆą░č鹊čĆą░.

1 = č湥čéčŗčĆąĄ čüąĖą│ąĮą░ą╗ą░ ą▓čŗą▒ąŠčĆą║ąĖ ą┐ąŠą┤ą║ą╗čÄčćą░čÄčéčüčÅ ą║ ą┤ąĄą║ąŠą┤ąĄčĆčā 4-ą▓-16.

ąÜąŠą│ą┤ą░ PCSDEC čĆą░ą▓ąĄąĮ 1, ą╝ąŠą│čāčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčīčüčÅ ą┤ąŠ 15 ą▓čŗą▒ąŠčĆąŠą║ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ SPI čü ą┐ąŠą╝ąŠčēčīčÄ ą▓ąĮąĄčłąĮąĄą╣ ą┤ąĄą║ąŠą┤ąĖčĆčāčÄčēąĄą╣ čüčģąĄą╝čŗ. ąĀąĄą│ąĖčüčéčĆčŗ ą▓čŗą▒ąŠčĆą║ąĖ (SPI_CSRx) ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčé čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ čŹčéąĖčģ 15 ą▓čŗą▒ąŠčĆąŠą║, ą┐ąŠą┤čćąĖąĮčÅčÅčüčī čüą╗ąĄą┤čāčÄčēąĖą╝ ą┐čĆą░ą▓ąĖą╗ą░ą╝:

SPI_CSR0 ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé čüąĖą│ąĮą░ą╗čŗ ą▓čŗą▒ąŠčĆą║ąĖ 0 .. 3.

SPI_CSR1 ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé čüąĖą│ąĮą░ą╗čŗ ą▓čŗą▒ąŠčĆą║ąĖ 4 .. 7.

SPI_CSR2 ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé čüąĖą│ąĮą░ą╗čŗ ą▓čŗą▒ąŠčĆą║ąĖ 8 .. 11.

SPI_CSR3 ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé čüąĖą│ąĮą░ą╗čŗ ą▓čŗą▒ąŠčĆą║ąĖ 12 .. 14.

MODFDIS: Mode Fault Detection, ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ąŠčéą║ą░ąĘą░ čĆąĄąČąĖą╝ą░ čĆą░ą▒ąŠčéčŗ čü ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ ą╝ą░čüč鹥čĆą░ą╝ąĖ ąĮą░ čłąĖąĮąĄ.

0 = čĆąĄąČąĖą╝ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ąŠčéą║ą░ąĘą░ čĆą░ąĘčĆąĄčłąĄąĮ.

1 = čĆąĄąČąĖą╝ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ąŠčéą║ą░ąĘą░ ąĘą░ą┐čĆąĄčēąĄąĮ.

LLB: Local Loopback Enable, čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ ąĘą░ą╝čŗą║ą░ąĮąĖčÅ ą▓čģąŠą┤ą░ ą┤ą░ąĮąĮčŗčģ ąĮą░ ą▓čŗčģąŠą┤.

0 = ą┐ąĄčéą╗čÅ ąĘą░ą║ąŠą╗čīčåąŠą▓čŗą▓ą░ąĮąĖčÅ ąĘą░ą┐čĆąĄčēąĄąĮą░ (ąĮąŠčĆą╝ą░ą╗čīąĮčŗą╣ čĆąĄąČąĖą╝ čĆą░ą▒ąŠčéčŗ).

1 = ą▓čģąŠą┤ ą┤ą░ąĮąĮčŗčģ čüąŠąĄą┤ąĖąĮąĄąĮ čü ą▓čŗčģąŠą┤ąŠą╝ (ą┐čĆąĖą╝ąĄąĮčÅąĄčéčüčÅ ą┤ą╗čÅ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ).

LLB čāą┐čĆą░ą▓ą╗čÅąĄčé ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖąĄą╝ ą┐ąĄčéą╗ąĖ ąŠą▒čĆą░čéąĮąŠą╣ čüą▓čÅąĘąĖ ą┤ą╗čÅ ąĘą░ą║ąŠą╗čīčåąŠą▓čŗą▓ą░ąĮąĖčÅ čüąĄčĆąĖą░ą╗ąĖąĘą░č鹊čĆą░ ą┤ą░ąĮąĮčŗčģ, čćč鹊 ą┐čĆąĖą╝ąĄąĮčÅąĄčéčüčÅ ą┤ą╗čÅ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ č鹊ą╗čīą║ąŠ ą▓ čĆąĄąČąĖą╝ąĄ Master (MISO ą▓ąĮčāčéčĆąĖ ą║čĆąĖčüčéą░ą╗ą╗ą░ ą╗ąŠą│ąĖč湥čüą║ąĖ čüąŠąĄą┤ąĖąĮčÅąĄčéčüčÅ čü MOSI).

PCS: Peripheral Chip Select, ą▓čŗą▒ąŠčĆą║ą░ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░.

ąŁč鹊 ą┐ąŠą╗ąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą▓ č鹊ą╝ čüą╗čāčćą░ąĄ, ą║ąŠą│ą┤ą░ čĆą░ą▒ąŠčéą░ąĄčé čĆąĄąČąĖą╝ čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮąŠą╣ ą▓čŗą▒ąŠčĆą║ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ (Fixed Peripheral Select, PS = 0).

PCS = xxx0 NPCS[3:0] = 1110

PCS = xx01 NPCS[3:0] = 1101

PCS = x011 NPCS[3:0] = 1011

PCS = 0111 NPCS[3:0] = 0111

PCS = 1111 ąĘą░ą┐čĆąĄčēąĄąĮąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ (ą▓čŗą▒ąŠčĆą║ą░ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ąĮąĄ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ)

ąŚą┤ąĄčüčī x ąŠąĘąĮą░čćą░ąĄčé ą╗čÄą▒ąŠąĄ ą▓ąŠąĘą╝ąŠąČąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ čāčĆąŠą▓ąĮčÅ. ąĢčüą╗ąĖ PCSDEC = 1, č鹊 ąĘąĮą░č湥ąĮąĖąĄ PCS ąĮą░ą┐čĆčÅą╝čāčÄ ą┐ąŠą┐ą░ą┤ą░ąĄčé ąĮą░ ą▓ąĮąĄčłąĮąĖąĄ čüąĖą│ąĮą░ą╗čŗ ą▓čŗčģąŠą┤ą░ NPCS[3:0] (ą┤ą╗čÅ č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓čŗą▒ąŠčĆąŠą║ ą┤ąŠą╗ąČąĮą░ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ čüčģąĄą╝ą░ ą▓ąĮąĄčłąĮąĄą╣ ą┤ąĄčłąĖčäčĆą░čåąĖąĖ).

DLYBCS: Delay Between Chip Selects, ąĘą░ą┤ąĄčƹȹ║ą░ ą╝ąĄąČą┤čā čüąĖą│ąĮą░ą╗ą░ą╝ąĖ ą▓čŗą▒ąŠčĆą║ąĖ.

ąŁč鹊 ą┐ąŠą╗ąĄ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ąĘą░ą┤ąĄčƹȹ║čā ąŠčé ąĮąĄą░ą║čéąĖą▓ąĮąŠą│ąŠ čüąŠčüč鹊čÅąĮąĖčÅ čüąĖą│ąĮą░ą╗ą░ NPCS ą┤ąŠ ą░ą║čéąĖą▓ą░čåąĖąĖ ą┤čĆčāą│ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ NPCS. ąÆčĆąĄą╝čÅ DLYBCS ą│ą░čĆą░ąĮčéąĖčĆčāąĄčé ąŠčéčüčāčéčüčéą▓ąĖąĄ ą┐ąĄčĆąĄą║čĆčŗčéąĖčÅ ą▓ąŠ ą▓čĆąĄą╝ąĄąĮąĖ ą▓čŗą▒ąŠčĆąŠą║ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗčģ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓, ąĖ čĆąĄčłą░ąĄčé ą║ąŠąĮą║čāčĆąĄąĮčåąĖčÄ ą┐ąŠ čłąĖąĮąĄ, ą║ąŠą│ą┤ą░ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ ąĖą╝ąĄčÄčé ą▒ąŠą╗čīčłąĖąĄ, ą┐ą╗ą░ą▓ą░čÄčēąĖąĄ ą▓čĆąĄą╝ąĄąĮą░ čĆąĄą░ą║čåąĖąĖ.

ąĢčüą╗ąĖ DLYBCS ą╝ąĄąĮčīčłąĄ ąĖą╗ąĖ čĆą░ą▓ąĮąŠ 6, č鹊 ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą▒čāą┤ąĄčé ą▓čüčéą░ą▓ą╗ąĄąĮą░ ąĘą░ą┤ąĄčƹȹ║ą░ ą▓ 6 ą┐ąĄčĆąĖąŠą┤ąŠą▓ čéą░ą║č鹊ą▓ MCK. ąśąĮą░č湥 ą┤ą╗čÅ ą▓čŗčćąĖčüą╗ąĄąĮąĖčÅ ą▓čĆąĄą╝ąĄąĮąĖ ąĘą░ą┤ąĄčƹȹ║ąĖ ą▒čāą┤ąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ čüą╗ąĄą┤čāčÄčēą░čÅ č乊čĆą╝čāą╗ą░:

DLYBCS

ąŚą░ą┤ąĄčƹȹ║ą░ ą╝ąĄąČą┤čā ą▓čŗą▒ąŠčĆą║ą░ą╝ąĖ = --------

MCK

ąĀąĄą│ąĖčüčéčĆ ą┤ą░ąĮąĮčŗčģ ą┐čĆąĖąĄą╝ą░ SPI (SPI Receive Data Register). ąĀą░ą▒ąŠčéą░ąĄčé č鹊ą╗čīą║ąŠ ąĮą░ čćč鹥ąĮąĖąĄ.

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

-

|

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

PCS |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| RD |

RD: Receive Data, ą┐čĆąĖąĮčÅčéčŗąĄ ą┤ą░ąĮąĮčŗąĄ. ąöą░ąĮąĮčŗąĄ, ą║ąŠč鹊čĆčŗąĄ ą┐čĆąĖąĮčÅą╗ ąĖąĮč鹥čĆč乥ą╣čü SPI, čüąŠčģčĆą░ąĮčÅčÄčéčüčÅ ą▓ čŹč鹊ą╝ ą┐ąŠą╗ąĄ čü ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖąĄą╝ ą▓ą┐čĆą░ą▓ąŠ. ąØąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą▒ąĖčéčŗ čĆą░ą▓ąĮčŗ 0.

PCS: Peripheral Chip Select, ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą║ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓.

ąóąŠą╗čīą║ąŠ ą▓ čĆąĄąČąĖą╝ąĄ Master čŹčéąĖ ą▒ąĖčéčŗ ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčé čāčĆąŠą▓ąĮąĖ ąĮą░ čüąĖą│ąĮą░ą╗ą░čģ ą▓čŗą▒ąŠčĆą║ąĖ NPCS ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ. ąśąĮą░č湥 čŹčéąĖ ą▒ąĖčéčŗ ą▒čāą┤čāčé čćąĖčéą░čéčīčüčÅ ą║ą░ą║ 0.

ąĀąĄą│ąĖčüčéčĆ ą┤ą░ąĮąĮčŗčģ ą┐ąĄčĆąĄą┤ą░čćąĖ SPI (SPI Transmit Data Register). ąĀą░ą▒ąŠčéą░ąĄčé č鹊ą╗čīą║ąŠ ąĮą░ ąĘą░ą┐ąĖčüčī.

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

-

|

- |

- |

- |

- |

- |

- |

LASTXFER |

- |

- |

- |

- |

PCS |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| TD |

TD: Transmit Data, ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗąĄ ą┤ą░ąĮąĮčŗąĄ. ąÆ čŹč鹊ą╝ čĆąĄą│ąĖčüčéčĆąĄ čüąŠčģčĆą░ąĮčÅčÄčéčüčÅ ą┤ą░ąĮąĮčŗąĄ, ą║ąŠč鹊čĆčŗąĄ ą┤ąŠą╗ąČąĄąĮ ą┐ąĄčĆąĄą┤ą░čéčī ąĖąĮč鹥čĆč乥ą╣čü SPI. ąöą░ąĮąĮčŗąĄ čüąŠčģčĆą░ąĮčÅčÄčéčüčÅ ą▓ čŹč鹊ą╝ ą┐ąŠą╗ąĄ čü ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖąĄą╝ ą▓ą┐čĆą░ą▓ąŠ.

PCS: Peripheral Chip Select, ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą║ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓.

ąŁč鹊 ą┐ąŠą╗ąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ ą░ą║čéąĖą▓ąĄąĮ čĆąĄąČąĖą╝ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą╣ ą▓čŗą▒ąŠčĆą║ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ (Variable Peripheral Select, PS = 1). ąĢčüą╗ąĖ PCSDEC = 0:

PCS = xxx0 NPCS[3:0] = 1110

PCS = xx01 NPCS[3:0] = 1101

PCS = x011 NPCS[3:0] = 1011

PCS = 0111 NPCS[3:0] = 0111

PCS = 1111 ąĘą░ą┐čĆąĄčēąĄąĮąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ (ą▓čŗą▒ąŠčĆą║ą░ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ąĮąĄ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ)

ąŚą┤ąĄčüčī x ąŠąĘąĮą░čćą░ąĄčé ą╗čÄą▒ąŠąĄ ą▓ąŠąĘą╝ąŠąČąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ čāčĆąŠą▓ąĮčÅ. ąĢčüą╗ąĖ PCSDEC = 1, č鹊 ąĘąĮą░č湥ąĮąĖąĄ PCS ąĮą░ą┐čĆčÅą╝čāčÄ ą┐ąŠą┐ą░ą┤ą░ąĄčé ąĮą░ ą▓ąĮąĄčłąĮąĖąĄ čüąĖą│ąĮą░ą╗čŗ ą▓čŗčģąŠą┤ą░ NPCS[3:0] (ą┤ą╗čÅ č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓čŗą▒ąŠčĆąŠą║ ą┤ąŠą╗ąČąĮą░ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ čüčģąĄą╝ą░ ą▓ąĮąĄčłąĮąĄą╣ ą┤ąĄčłąĖčäčĆą░čåąĖąĖ).

LASTXFER: Last Transfer, ą┐ąŠčüą╗ąĄą┤ąĮčÅčÅ ą┐ąĄčĆąĄą┤ą░čćą░.

0 = ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé čŹčäč乥ą║čéą░.

1 = č鹥ą║čāčēąĖąĄ ą▓čŗą▒ąŠčĆą║ąĖ NPCS ą▒čāą┤čāčé ą┐ąĄčĆąĄą▓ąĄą┤ąĄąĮčŗ ą▓ ąĮąĄą░ą║čéąĖą▓ąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą▒čāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ąĘą░ą┐ąĖčüą░ąĮąĮčŗą╣ ą▓ čĆąĄą│ąĖčüčéčĆ ą┐ąĄčĆąĄą┤ą░čćąĖ SPI_TDR čäčĆąĄą╣ą╝ ą┤ą░ąĮąĮčŗčģ. ąÜąŠą│ą┤ą░ ą▒ąĖčé CSAAT čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąĘą░ą║čĆčŗčéčī ąŠą▒ą╝ąĄąĮ čü č鹥ą║čāčēąĖą╝ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ ą┐čāč鹥ą╝ ą┐ąĄčĆąĄą▓ąŠą┤ą░ ą▓ ą▓čŗčüąŠą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī čüąĖą│ąĮą░ą╗ą░ NPCS, čéą░ą║ č鹊ą╗čīą║ąŠ ą┐ąĄčĆąĄą┤ą░čćą░ ąĘą░ą▓ąĄčĆčłąĖčéčüčÅ.

ąŁč鹊 ą┐ąŠą╗ąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ č鹊ą╗čīą║ąŠ ąĄčüą╗ąĖ ą░ą║čéąĖą▓ąĄąĮ čĆąĄąČąĖą╝ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą╣ ą▓čŗą▒ąŠčĆą║ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ (Variable Peripheral Select, PS = 1).

ąĀąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ SPI (SPI Status Register). ąĀą░ą▒ąŠčéą░ąĄčé č鹊ą╗čīą║ąŠ ąĮą░ čćč鹥ąĮąĖąĄ.

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

-

|

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

SPIENS |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| - |

- |

- |

- |

- |

- |

TXEMPTY |

NSSR |

TXBUFE |

RXBUFF |

ENDTX |

ENDRX |

OVRES |

MODF |

TDRE |

RDRF |

RDRF: Receive Data Register Full, čĆąĄą│ąĖčüčéčĆ ą┤ą░ąĮąĮčŗčģ ą┐čĆąĖąĄą╝ą░ ąĘą░ą┐ąŠą╗ąĮąĄąĮ ąĮąŠą▓čŗą╝ąĖ ą┤ą░ąĮąĮčŗą╝ąĖ.

0 = ąĮąĄ ą▒čŗą╗ąŠ ą┐čĆąĖąĮčÅč鹊 ąĮąŠą▓čŗčģ ą┤ą░ąĮąĮčŗčģ čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čćč鹥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ SPI_RDR.

1 = ą▒čŗą╗ ą┐čĆąĖąĮčÅčé ąĮąŠą▓čŗą╣ čäčĆąĄą╣ą╝ ą┤ą░ąĮąĮčŗčģ čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čćč鹥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ SPI_RDR.

TDRE: Transmit Data Register Empty, čĆąĄą│ąĖčüčéčĆ ą┤ą░ąĮąĮčŗčģ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐čāčüčé.

0 = ą┤ą░ąĮąĮčŗąĄ, ą║ąŠč鹊čĆčŗąĄ ą▒čŗą╗ąĖ ąĘą░ą┐ąĖčüą░ąĮčŗ ą▓ čĆąĄą│ąĖčüčéčĆ SPI_TDR, ąĄčēąĄ ąĮąĄ ą┐ąŠą┐ą░ą╗ąĖ ą▓ čüąĄčĆąĖą░ą╗ąĖąĘą░č鹊čĆ.

1 = ą┤ą░ąĮąĮčŗąĄ, ą║ąŠč鹊čĆčŗąĄ ą▒čŗą╗ąĖ ąĘą░ą┐ąĖčüą░ąĮčŗ ą▓ čĆąĄą│ąĖčüčéčĆ SPI_TDR, ą┐ąŠą┐ą░ą╗ąĖ ą▓ čüąĄčĆąĖą░ą╗ąĖąĘą░č鹊čĆ, ąĖ čĆąĄą│ąĖčüčéčĆ SPI_TDR ą│ąŠč鹊ą▓ ą║ ą┐ąŠą╗čāč湥ąĮąĖčÄ ąĮąŠą▓čŗčģ ą┤ą░ąĮąĮčŗčģ.

TDRE čĆą░ą▓ąĄąĮ 0, ą║ąŠą│ą┤ą░ SPI ąĘą░ą┐čĆąĄčēąĄąĮ, ąĖą╗ąĖ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░. ąÜąŠą╝ą░ąĮą┤ą░, čĆą░ąĘčĆąĄčłą░čÄčēą░čÅ SPI, čāčüčéą░ąĮąŠą▓ąĖčé čŹč鹊čé ą▒ąĖčé ą▓ 1.

MODF: Mode Fault Error, ąŠčłąĖą▒ą║ą░ čĆąĄąČąĖą╝ą░.

0 = čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čćč鹥ąĮąĖčÅ SPI_SR ąĮąĄ ą▒čŗą╗ąŠ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąŠ čüąŠčüč鹊čÅąĮąĖąĄ Mode Fault.

1 = čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čćč鹥ąĮąĖčÅ SPI_SR ą▒čŗą╗ąŠ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąŠ čüąŠčüč鹊čÅąĮąĖąĄ Mode Fault.

OVRES: Overrun Error Status, čäą╗ą░ą│ ąŠčłąĖą▒ą║ąĖ, čüą▓čÅąĘą░ąĮąĮąŠą╣ čü ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĄą╝ ąĮą░ ą┐čĆąĖąĄą╝ąĄ.

0 = čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čćč鹥ąĮąĖčÅ SPI_SR ąĮąĄ ą▒čŗą╗ąŠ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąŠ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ ą┐čĆąĖąĄą╝ą░.

1 = čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čćč鹥ąĮąĖčÅ SPI_SR ą▒čŗą╗ąŠ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąŠ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĄ ą┐čĆąĖąĄą╝ą░.

ą¤ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĄ (overrun) ą┐čĆąŠąĖčüčģąŠą┤ąĖčé, ą║ąŠą│ą┤ą░ čĆąĄą│ąĖčüčéčĆ SPI_RDR ą▒čŗą╗ ąĘą░ą│čĆčāąČąĄąĮ ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ą┤ą▓ą░ąČą┤čŗ čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čćč鹥ąĮąĖčÅ SPI_RDR.

ENDRX: End of RX buffer, ąŠą║ąŠąĮčćą░ąĮąĖąĄ ą▒čāč乥čĆą░ ą┐čĆąĖąĄą╝ą░.

0 = čĆąĄą│ąĖčüčéčĆ čüč湥čéčćąĖą║ą░ ą┐čĆąĖąĄą╝ą░ (Receive Counter Register) ąĮąĄ ą┤ąŠčüčéąĖą│ ąĮčāą╗čÅ čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╣ ąĘą░ą┐ąĖčüąĖ ą▓ čĆąĄą│ąĖčüčéčĆčŗ SPI_RCR(1) ąĖą╗ąĖ SPI_RNCR(1).

1 = čĆąĄą│ąĖčüčéčĆ čüč湥čéčćąĖą║ą░ ą┐čĆąĖąĄą╝ą░ ą┤ąŠčüčéąĖą│ ąĮčāą╗čÅ čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╣ ąĘą░ą┐ąĖčüąĖ ą▓ čĆąĄą│ąĖčüčéčĆčŗ SPI_RCR(1) ąĖą╗ąĖ SPI_RNCR(1).

ENDTX: End of TX buffer, ąŠą║ąŠąĮčćą░ąĮąĖąĄ ą▒čāč乥čĆą░ ą┐ąĄčĆąĄą┤ą░čćąĖ.

0 = čĆąĄą│ąĖčüčéčĆ čüč湥čéčćąĖą║ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ (Transmit Counter Register) ąĮąĄ ą┤ąŠčüčéąĖą│ ąĮčāą╗čÅ čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╣ ąĘą░ą┐ąĖčüąĖ ą▓ čĆąĄą│ąĖčüčéčĆčŗ SPI_TCR(1) ąĖą╗ąĖ SPI_TNCR(1).

1 = čĆąĄą│ąĖčüčéčĆ čüč湥čéčćąĖą║ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ąŠčüčéąĖą│ ąĮčāą╗čÅ čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╣ ąĘą░ą┐ąĖčüąĖ ą▓ čĆąĄą│ąĖčüčéčĆčŗ SPI_TCR(1) ąĖą╗ąĖ SPI_TNCR(1).

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ (1): čĆąĄą│ąĖčüčéčĆčŗ SPI_RCR, SPI_RNCR, SPI_TCR, SPI_TNCR čäąĖąĘąĖč湥čüą║ąĖ ąĮą░čģąŠą┤čÅčéčüčÅ ą▓ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąĄ ą┐čĆčÅą╝ąŠą│ąŠ ą┤ąŠčüčéčāą┐ą░ ą║ ą┐ą░ą╝čÅčéąĖ (PDC, čüą╝. [6]).

RXBUFF: RX Buffer Full, ą▒čāč乥čĆ ą┐čĆąĖąĄą╝ą░ ąĘą░ą┐ąŠą╗ąĮąĄąĮ.

0 = ą▓ čĆąĄą│ąĖčüčéčĆą░čģ SPI_RCR(1) ąĖą╗ąĖ SPI_RNCR(1) ąĮą░čģąŠą┤ąĖčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄ, ąŠčéą╗ąĖčćąĮąŠąĄ ąŠčé 0.

1 = ą▓ ąŠą▒ąŠąĖčģ čĆąĄą│ąĖčüčéčĆą░čģ SPI_RCR(1) ąĖ SPI_RNCR(1) ąĮą░čģąŠą┤ąĖčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄ 0.

TXBUFE: TX Buffer Empty, ą▒čāč乥čĆ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐čāčüčé.

0 = ą▓ čĆąĄą│ąĖčüčéčĆą░čģ SPI_TCR(1) ąĖą╗ąĖ SPI_TNCR(1) ąĮą░čģąŠą┤ąĖčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄ, ąŠčéą╗ąĖčćąĮąŠąĄ ąŠčé 0.

1 = ą▓ ąŠą▒ąŠąĖčģ čĆąĄą│ąĖčüčéčĆą░čģ SPI_TCR(1) ąĖ SPI_TNCR(1) ąĮą░čģąŠą┤ąĖčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄ 0.

NSSR: NSS Rising, ąĮą░čĆą░čüčéą░ąĮąĖąĄ čüąĖą│ąĮą░ą╗ą░ ą▓čŗą▒ąŠčĆą║ąĖ.

0 = ąĮąĄ ą▒čŗą╗ąŠ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąŠ ąĮą░čĆą░čüčéą░ąĮąĖąĄ čāčĆąŠą▓ąĮčÅ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ NSS čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čćč鹥ąĮąĖčÅ.

1 = ą▒čŗą╗ąŠ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąŠ ąĮą░čĆą░čüčéą░ąĮąĖąĄ čāčĆąŠą▓ąĮčÅ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ NSS čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ čćč鹥ąĮąĖčÅ.

TXEMPTY: Transmission Registers Empty, čĆąĄą│ąĖčüčéčĆčŗ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐čāčüčéčŗ.

0 = ą▓ ą╝ąŠą╝ąĄąĮčé, ą║ąŠą│ą┤ą░ ą┤ą░ąĮąĮčŗąĄ č鹊ą╗čīą║ąŠ čćč鹊 ą▒čŗą╗ąĖ ąĘą░ą┐ąĖčüą░ąĮčŗ ą▓ čĆąĄą│ąĖčüčéčĆ SPI_TDR.

1 = čĆąĄą│ąĖčüčéčĆ SPI_TDR ąĖ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ ąŠą▒ą░ ą┐čāčüčéčŗ. ąĢčüą╗ąĖ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮą░ ąĘą░ą┤ąĄčƹȹ║ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ, TXEMPTY čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą┐ąŠčüą╗ąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ čŹč鹊ą╣ ąĘą░ą┤ąĄčƹȹ║ąĖ.

SPIENS: SPI Enable Status, čüąŠčüč鹊čÅąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ SPI.

0 = SPI ąĘą░ą┐čĆąĄčēąĄąĮ.

1 = SPI čĆą░ąĘčĆąĄčłąĄąĮ.

ąĀąĄą│ąĖčüčéčĆ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ SPI (SPI Interrupt Enable Register). ąĀą░ą▒ąŠčéą░ąĄčé č鹊ą╗čīą║ąŠ ąĮą░ ąĘą░ą┐ąĖčüčī.

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

-

|

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| - |

- |

- |

- |

- |

- |

TXEMPTY |

NSSR |

TXBUFE |

RXBUFF |

ENDTX |

ENDRX |

OVRES |

MODF |

TDRE |

RDRF |

RDRF: Receive Data Register Full Interrupt Enable, čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĮąŠčüčéąĖ čĆąĄą│ąĖčüčéčĆą░ ą┤ą░ąĮąĮčŗčģ ą┐čĆąĖąĄą╝ą░.

TDRE: SPI Transmit Data Register Empty Interrupt Enable, čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ ąŠą┐čāčüč鹊賹ĄąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ ą┤ą░ąĮąĮčŗčģ ą┐ąĄčĆąĄą┤ą░čćąĖ.

MODF: Mode Fault Error Interrupt Enable, čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ ąŠčłąĖą▒ą║ąĖ čĆąĄąČąĖą╝ą░.

OVRES: Overrun Error Interrupt Enable, čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ ąŠčłąĖą▒ą║ąĖ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ ą┐čĆąĖąĄą╝ą░.

ENDRX: End of Receive Buffer Interrupt Enable, čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ ąŠą║ąŠąĮčćą░ąĮąĖčÅ ą▒čāč乥čĆą░ ą┐čĆąĖąĄą╝ą░.

ENDTX: End of Transmit Buffer Interrupt Enable, čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ ąŠą║ąŠąĮčćą░ąĮąĖčÅ ą▒čāč乥čĆą░ ą┐ąĄčĆąĄą┤ą░čćąĖ.

RXBUFF: Receive Buffer Full Interrupt Enable, čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĖčÅ ą▒čāč乥čĆą░ ą┐čĆąĖąĄą╝ą░.

TXBUFE: Transmit Buffer Empty Interrupt Enable, čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ ąŠą┐čāčüč鹊賹ĄąĮąĖčÅ ą▒čāč乥čĆą░ ą┐ąĄčĆąĄą┤ą░čćąĖ.

NSSR: NSS Rising Interrupt Enable, čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ ąĮą░čĆą░čüčéą░ąĮąĖčÅ čüąĖą│ąĮą░ą╗ą░ NSS.

TXEMPTY: Transmission Registers Empty Enable, čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ ąŠą┐čāčüč鹊賹ĄąĮąĖčÅ čĆąĄą│ąĖčüčéčĆąŠą▓ ą┐ąĄčĆąĄą┤ą░čćąĖ.

0 = ąĮąĄ ą┤ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

1 = čĆą░ąĘčĆąĄčłą░ąĄčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ.

ąĀąĄą│ąĖčüčéčĆ ąĘą░ą┐čĆąĄčéą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ SPI (SPI Interrupt Disable Register). ąĀą░ą▒ąŠčéą░ąĄčé č鹊ą╗čīą║ąŠ ąĮą░ ąĘą░ą┐ąĖčüčī. ąÆčüąĄ ą▒ąĖčéčŗ č鹥 ąČąĄ čüą░ą╝čŗąĄ, čćč鹊 ąĖ čā čĆąĄą│ąĖčüčéčĆą░ SPI_IER, č鹊ą╗čīą║ąŠ ąĘą░ą┐ąĖčüčī ą▓ ąĮąĖčģ 1 ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąŠą▒čĆą░čéąĮąŠąĄ ą┤ąĄą╣čüčéą▓ąĖąĄ - ąĮąĄ čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ, ą░ ąĘą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

0 = ąĮąĄ ą┤ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

1 = ąĘą░ą┐čĆąĄčēą░ąĄčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ.

ąĀąĄą│ąĖčüčéčĆ ą╝ą░čüą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ SPI (SPI Interrupt Mask Register). ąĀą░ą▒ąŠčéą░ąĄčé č鹊ą╗čīą║ąŠ ąĮą░ čćč鹥ąĮąĖąĄ. ąÆčüąĄ ą▒ąĖčéčŗ č鹥 ąČąĄ čüą░ą╝čŗąĄ, čćč鹊 ąĖ čā čĆąĄą│ąĖčüčéčĆąŠą▓ SPI_IER ąĖ SPI_IER, č鹊ą╗čīą║ąŠ ąĘą┤ąĄčüčī ąŠąĮąĖ ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčé čüąŠčüč鹊čÅąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąĮąŠčüčéąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

0 = čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĮąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ.

1 = čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ.

ąĀąĄą│ąĖčüčéčĆčŗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą▓čŗą▒ąŠčĆą║ąŠą╣ SPI (SPI Chip Select Register). ąĀą░ą▒ąŠčéą░ąĄčé ąĮą░ čćč鹥ąĮąĖąĄ ąĖ ąĮą░ ąĘą░ą┐ąĖčüčī.

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| DLYBCT |

DLYBS |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| SCBR |

BITS |

CSAAT |

- |

NCPHA |

CPOL |

CPOL: Clock Polarity, ą┐ąŠą╗čÅčĆąĮąŠčüčéčī čéą░ą║č鹊ą▓ ą▒ąĖčé.

0 = ąĮąĄą░ą║čéąĖą▓ąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ ąĘąĮą░č湥ąĮąĖčÅ, ą║ąŠą│ą┤ą░ SPCK ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ą╗ąŠą│. 0.

1 = ąĮąĄą░ą║čéąĖą▓ąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ ąĘąĮą░č湥ąĮąĖčÅ, ą║ąŠą│ą┤ą░ SPCK ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ą╗ąŠą│. 1.

CPOL ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ ąĮąĄą░ą║čéąĖą▓ąĮąŠą│ąŠ čüąŠčüč鹊čÅąĮąĖčÅ čéą░ą║č鹊ą▓ ą▒ąĖčé (SPCK). ąæąĖčé CPOL čüąŠą▓ą╝ąĄčüčéąĮąŠ čü ą▒ąĖč鹊ą╝ NCPHA ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą░ ą▓ąĘą░ąĖą╝ąŠą┤ąĄą╣čüčéą▓ąĖčÅ ą╝ąĄąČą┤čā čéą░ą║čéą░ą╝ąĖ/ą┤ą░ąĮąĮčŗą╝ąĖ ą│ą╗ą░ą▓ąĮčŗčģ ąĖ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ąĮą░ čłąĖąĮąĄ SPI.

NCPHA: Clock Phase, čäą░ąĘą░ čéą░ą║č鹊ą▓ ą▒ąĖčé.

0 = ą┤ą░ąĮąĮčŗąĄ ą╝ąĄąĮčÅčÄčé čüą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠ čäčĆąŠąĮčéčā ąĮą░čĆą░čüčéą░ąĮąĖčÅ čāčĆąŠą▓ąĮčÅ čéą░ą║č鹊ą▓ SPCK, ąĖ ąĘąĮą░č湥ąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ ąĘą░čģą▓ą░čéčŗą▓ą░ąĄčéčüčÅ ą┐ąŠ ą┐ąŠčüą╗ąĄą┤čāčÄčēąĄą╝čā čüą┐ą░ą┤čā čāčĆąŠą▓ąĮčÅ čéą░ą║č鹊ą▓ SPCK.

1 = ą┤ą░ąĮąĮčŗąĄ ąĘą░čģą▓ą░čéčŗą▓ą░čÄčéčüčÅ ą┐ąŠ čäčĆąŠąĮčéčā ąĮą░čĆą░čüčéą░ąĮąĖčÅ čāčĆąŠą▓ąĮčÅ čéą░ą║č鹊ą▓ SPCK, ąĖ ą┤ą░ąĮąĮčŗąĄ ą╝ąĄąĮčÅčÄčé čüą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠ ą┐ąŠčüą╗ąĄą┤čāčÄčēąĄą╝čā čüą┐ą░ą┤čā čāčĆąŠą▓ąĮčÅ čéą░ą║č鹊ą▓ SPCK.

NCPHA ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé, ą║ą░ą║ąŠą╣ ą┐ąĄčĆąĄą┐ą░ą┤ SPCK ą┐čĆąĖą▓ąŠą┤ąĖčé ą║ ąĖąĘą╝ąĄąĮąĄąĮąĖčÄ čüąĖą│ąĮą░ą╗ą░ ą┤ą░ąĮąĮčŗčģ, ąĖ ą║ą░ą║ąŠą╣ ą┐ąĄčĆąĄą┐ą░ą┤ ą┐čĆąĖą▓ąŠą┤ąĖčé ą║ čüčćąĖčéčŗą▓ą░ąĮąĖčÄ ąĘąĮą░č湥ąĮąĖčÅ ą▒ąĖčéą░ ą┤ą░ąĮąĮčŗčģ. ąæąĖčé NCPHA čüąŠą▓ą╝ąĄčüčéąĮąŠ čü ą▒ąĖč鹊ą╝ CPOL ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą░ ą▓ąĘą░ąĖą╝ąŠą┤ąĄą╣čüčéą▓ąĖčÅ ą╝ąĄąČą┤čā čéą░ą║čéą░ą╝ąĖ/ą┤ą░ąĮąĮčŗą╝ąĖ ą│ą╗ą░ą▓ąĮčŗčģ ąĖ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ąĮą░ čłąĖąĮąĄ SPI.

CSAAT: Chip Select Active After Transfer, ą░ą║čéąĖą▓ąĄąĮ ą╗ąĖ čüąĖą│ąĮą░ą╗ ą▓čŗą▒ąŠčĆą║ąĖ ą┐ąŠčüą╗ąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ.

0 = čüąĖą│ąĮą░ą╗ ą▓čŗą▒ąŠčĆą║ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┐ąĄčĆąĄą╣ą┤ąĄčé ą▓ 1, ą║ą░ą║ č鹊ą╗čīą║ąŠ ą▒čāą┤ąĄčé ą▓čŗą┐ąŠą╗ąĮąĄąĮą░ ą┐ąŠčüą╗ąĄą┤ąĮčÅčÅ ą┐ąĄčĆąĄą┤ą░čćą░.

1 = čüąĖą│ąĮą░ą╗ ą▓čŗą▒ąŠčĆą║ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ąĮąĄ ą┐ąĄčĆąĄą╣ą┤ąĄčé ą▓ 1, ą║ą░ą║ č鹊ą╗čīą║ąŠ ą▒čāą┤ąĄčé ą▓čŗą┐ąŠą╗ąĮąĄąĮą░ ą┐ąŠčüą╗ąĄą┤ąĮčÅčÅ ą┐ąĄčĆąĄą┤ą░čćą░. ąĪąĖą│ąĮą░ą╗ ą▓čŗą▒ąŠčĆą║ąĖ ąŠčüčéą░ąĮąĄčéčüčÅ ą░ą║čéąĖą▓ąĮčŗą╝ (ą╗ąŠą│. 0), ą┐ąŠą║ą░ ąĮąĄ ą▒čāą┤ąĄčé ąĘą░ą┐čĆąŠčłąĄąĮą░ ą┐ąĄčĆąĄą┤ą░čćą░ ąĮą░ ą┤čĆčāą│ąŠą╝ ą▓čŗą▒čĆą░ąĮąĮąŠą╝ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą╝ čāčüčéčĆąŠą╣čüčéą▓ąĄ.

BITS: Bits Per Transfer, ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ąĖčé ą▓ąŠ čäčĆąĄą╣ą╝ąĄ ą┤ą░ąĮąĮčŗčģ.

ąŁč鹊 ą┐ąŠą╗ąĄ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé, čüą║ąŠą╗čīą║ąŠ ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ ą▒čāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ąĮąŠ ąĖ ą┐čĆąĖąĮčÅč鹊. ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ ąĮąĄ ą┤ąŠą╗ąČąĮčŗ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ.

| BITS |

ąÜąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ |

| 0000 |

8 |

| 0001 |

9 |

| 0010 |

10 |

| 0011 |

11 |

| 0100 |

12 |

| 0101 |

13 |

| 0110 |

14 |

| 0111 |

15 |

| 1000 |

16 |

| 1001 .. 1111 |

ąÆčüąĄ čŹčéąĖ ąĘąĮą░č湥ąĮąĖčÅ ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ. |

SCBR: Serial Clock Baud Rate, ąĮą░čüčéčĆąŠą╣ą║ą░ čüą║ąŠčĆąŠčüčéąĖ.

ąÆ čĆąĄąČąĖą╝ąĄ Master ąĖąĮč鹥čĆč乥ą╣čü SPI ąĖčüą┐ąŠą╗čīąĘčāąĄčé čüč湥čéčćąĖą║ ą┐ąŠ ą╝ąŠą┤čāą╗čÄ, čćč鹊ą▒čŗ ąĘą░ą┤ą░ą▓ą░čéčī čéčĆąĄą▒čāąĄą╝čāčÄ čüą║ąŠčĆąŠčüčéčī č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą▒ąĖčé SPCK. ą¦ą░čüč鹊čéą░ ą▒ąĖčé SPCK ą┐ąŠą╗čāčćą░ąĄčéčüčÅ ą┐čāč鹥ą╝ ą┤ąĄą╗ąĄąĮąĖčÅ ą│ą╗ą░ą▓ąĮąŠą╣ čćą░čüč鹊čéčŗ čéą░ą║č鹊ą▓ ą┐čĆąŠčåąĄčüčüąŠčĆą░ MCK. ąĪą║ąŠčĆąŠčüčéčī ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ąĘą░ą┐ąĖčüčīčÄ ąĘąĮą░č湥ąĮąĖčÅ ą▓ ą┐ąŠą╗ąĄ SCBR ąŠčé 1 ą┤ąŠ 255. ąĪą╗ąĄą┤čāčÄčēąĄąĄ ą▓čŗčĆą░ąČąĄąĮąĖąĄ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé čćą░čüč鹊čéčā ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ čéą░ą║č鹊ą▓ SPCK:

MCK

SPCK Baudrate = ------

SCBR

ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ ą┐ąŠą╗čÅ SCBR ąĘąĮą░č湥ąĮąĖąĄą╝ 0 ąĘą░ą┐čĆąĄčēąĄąĮąŠ. ąŚą░ą┐čāčüą║ ą┐ąĄčĆąĄą┤ą░čćąĖ, ą║ąŠą│ą┤ą░ SCBR čĆą░ą▓ąĮąŠ 0, ą╝ąŠąČąĄčé ą┐čĆąĖą▓ąĄčüčéąĖ ą║ ąĮąĄą┐čĆąĄą┤čüą║ą░ąĘčāąĄą╝čŗą╝ čĆąĄąĘčāą╗čīčéą░čéą░ą╝. ą¤ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ SCBR čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ ą▓ 0, ąĖ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą┤ąŠą╗ąČąĄąĮ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī ą▓ ą┐ąŠą╗ąĄ SCBR ąĮąĄąĮčāą╗ąĄą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┐ąĄčĆąĄą┤ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄą╝ ą┐ąĄčĆą▓ąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ.

DLYBS: Delay Before SPCK, ąĘą░ą┤ąĄčƹȹ║ą░ ą┐ąĄčĆąĄą┤ čéą░ą║čéą░ą╝ąĖ.

ąŁč鹊 ą┐ąŠą╗ąĄ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ąĘą░ą┤ąĄčƹȹ║čā ąŠčé ą╝ąŠą╝ąĄąĮčéą░ ą░ą║čéąĖą▓ąĖąĘą░čåąĖąĖ ą▓čŗą▒ąŠčĆą║ąĖ NPCS ą┤ąŠ ą┐ąĄčĆą▓ąŠą│ąŠ ą┐ąĄčĆąĄą┐ą░ą┤ą░ čéą░ą║č鹊ą▓ SPCK.

ąÜąŠą│ą┤ą░ DLYBS čĆą░ą▓ąĮąŠ 0, ąĘą░ą┤ąĄčƹȹ║ą░ ą╝ąĄąČą┤čā ą┐ąŠčÅą▓ą╗ąĄąĮąĖąĄą╝ ą┤ąŠą┐čāčüčéąĖą╝ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ NPCS ąĖ ą┐ąĄčĆąĄą┐ą░ą┤ąŠą╝ SPCK čüąŠčüčéą░ą▓ą╗čÅąĄčé 1/2 ąŠčé ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéąĖ ą┐ąĄčĆąĖąŠą┤ą░ SPCK.

ąśąĮą░č湥 ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖąĄ ąĘą░ą┤ąĄčƹȹ║ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čüą╗ąĄą┤čāčÄčēąĄąĄ ą▓čŗčĆą░ąČąĄąĮąĖąĄ:

DLYBS

Delay Before SPCK = -------

MCK

DLYBCT: Delay Between Consecutive Transfers, ąĘą░ą┤ąĄčƹȹ║ą░ ą╝ąĄąČą┤čā čüą╗ąĄą┤čāčÄčēąĖą╝ąĖ ą┤čĆčāą│ ąĘą░ ą┤čĆčāą│ąŠą╝ ą┐ąĄčĆąĄą┤ą░čćą░ą╝ąĖ.

ąŁč鹊 ą┐ąŠą╗ąĄ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ąĘą░ą┤ąĄčƹȹ║čā ą╝ąĄąČą┤čā ą┤ą▓čāą╝čÅ čüąŠčüąĄą┤ąĮąĖą╝ąĖ ą┐ąĄčĆąĄą┤ą░čćą░ą╝ąĖ čü ąŠą┤ąĮąĖą╝ ąĖ č鹥ą╝ ąČąĄ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ ą▒ąĄąĘ čüąĮčÅčéąĖčÅ čüąĖą│ąĮą░ą╗ą░ ą▓čŗą▒ąŠčĆą║ąĖ. ąŁčéą░ ąĘą░ą┤ąĄčƹȹ║ą░ ą▓čüąĄą│ą┤ą░ ą▓čüčéą░ą▓ą╗čÅąĄčéčüčÅ ą┐ąŠčüą╗ąĄ ą║ą░ąČą┤ąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖ ą┐ąĄčĆąĄą┤ čüąĮčÅčéąĖąĄą╝ čüąĖą│ąĮą░ą╗ą░ ą▓čŗą▒ąŠčĆą║ąĖ, ąĄčüą╗ąĖ čŹč鹊 ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ.

ąÜąŠą│ą┤ą░ DLYBCT čĆą░ą▓ąĮąŠ 0, č鹊 ąĘą░ą┤ąĄčƹȹ║ą░ ą╝ąĄąČą┤čā čüąŠčüąĄą┤ąĮąĖą╝ąĖ ą┐ąĄčĆąĄą┤ą░čćą░ą╝ąĖ ąĮąĄ ą▓čüčéą░ą▓ą╗čÅąĄčéčüčÅ, ąĖ čéą░ą║čéčŗ ą▒ąĖčé čüąŠčģčĆą░ąĮčÅčÄčé čüą▓ąŠą╣ čĆą░ą▒ąŠčćąĖą╣ čåąĖą║ą╗ ą┐ąŠ ą▓čüąĄą╝ ą┐ąĄčĆąĄą┤ą░čćą░ą╝ čäčĆąĄą╣ą╝ąŠą▓ ą┤ą░ąĮąĮčŗčģ.

ąśąĮą░č湥 ą▒čāą┤ąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ čüą╗ąĄą┤čāčÄčēąĄąĄ ą▓čŗčĆą░ąČąĄąĮąĖąĄ ą┤ą╗čÅ ą▓čŗčćąĖčüą╗ąĄąĮąĖčÅ ąĘą░ą┤ąĄčƹȹ║ąĖ:

32 * DLYBCT

ąŚą░ą┤ąĄčƹȹ║ą░ ą╝ąĄąČą┤čā čüąŠčüąĄą┤ąĮąĖą╝ąĖ ą┐ąĄčĆąĄą┤ą░čćą░ą╝ąĖ = -------------

MCK

[ąĪčüčŗą╗ą║ąĖ]

1. SAM7X512 / SAM7X256 / SAM7X128 DATASHEET site:atmel.com.

2. ąśąĮč鹥čĆč乥ą╣čü SPI.

3. AT91SAM7X: čĆą░ą▒ąŠčéą░ čü ą┐ąŠčĆč鹊ą╝ SPI ą▓ čĆąĄąČąĖą╝ąĄ master.

4. AT91SAM7 Parallel Input/Output Controller (PIO).

5. Power Management Controller ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ AT91SAM7X.

6. AT91SAM7X: ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ PDC. |