|

ąÆ ą┐čĆąŠčåąĄčüčüąŠčĆą░čģ Blackfin ADSP-BF538 ąĖ ADSP-BF538F ąĖą╝ąĄąĄčéčüčÅ 3 čāąĮąĖą▓ąĄčĆčüą░ą╗čīąĮčŗčģ ą░čüąĖąĮčģčĆąŠąĮąĮčŗčģ ą┐čĆąĖąĄą╝ąŠą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ (universal asynchronous receiver/transmitters, UART), čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮąĮčŗčģ ą║ą░ą║ ą▓ąĮčāčéčĆąĄąĮąĮąĄąĄ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐čĆąŠčåąĄčüčüąŠčĆą░ BF538 [2]. UART ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ą┐ąŠą╗ąĮčŗą╣ ą┤čāą┐ą╗ąĄą║čü, ąĖ čÅą▓ą╗čÅąĄčéčüčÅ čüąŠą▓ą╝ąĄčüčéąĖą╝čŗą╝ čü ą┐ąŠą┐čāą╗čÅčĆąĮčŗą╝ ąĖąĮą┤čāčüčéčĆąĖą░ą╗čīąĮčŗą╝ čüčéą░ąĮą┤ą░čĆč鹊ą╝ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ą┐ąŠčĆčéą░ ą║ąŠą╝ą┐čīčÄč鹥čĆąŠą▓ PC (RS-232, COM-ą┐ąŠčĆčé). ąŚą┤ąĄčüčī ą┐čĆąĖą▓ąĄą┤ąĄąĮ ą┐ąĄčĆąĄą▓ąŠą┤ čĆą░ąĘą┤ąĄą╗ą░ UART PORT CONTROLLERS ą┤ą░čéą░čłąĖčéą░ [1].

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▓ č鹥ą║čüč鹥 čüčéą░čéčīąĖ ąŠą▒ąĄ ą╝ąŠą┤ąĄą╗ąĖ Blackfin ADSP-BF538 ąĖ ADSP-BF538F ą▒čāą┤čāčé ą┤ą╗čÅ ą┐čĆąŠčüč鹊čéčŗ ąŠą▒ąŠąĘąĮą░čćą░čéčīčüčÅ ą┐čĆąŠčüč鹊 ą║ą░ą║ BF538. ąØąĄą┐ąŠąĮčÅčéąĮčŗąĄ ą░ą▒ą▒čĆąĄą▓ąĖą░čéčāčĆčŗ ąĖ č鹥čĆą╝ąĖąĮčŗ čüą╝. ą▓ čĆą░ąĘą┤ąĄą╗ąĄ "ąĪą╗ąŠą▓ą░čĆąĖą║" čüčéą░čéčīąĖ [2].

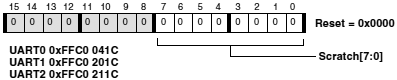

ąÆ čéą░ą▒ą╗ąĖčåąĄ ąĮąĖąČąĄ ą┐čĆąĖą▓ąĄą┤ąĄąĮą░ čåąŠą║ąŠą╗ąĄą▓ą║ą░ ąĮąŠąČąĄą║ ą┐ąŠčĆč鹊ą▓ UART0, UART1, UART2 ą┤ą╗čÅ ą┐čĆąŠčåąĄčüčüąŠčĆą░ BF538. ąĪč鹊ąĖčé ąĘą░ą╝ąĄčéąĖčéčī, čćč鹊 ą┐ąŠčĆčé UART0 ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą▓čŗą┤ąĄą╗ąĄąĮąĮčŗąĄ ą▓čŗą▓ąŠą┤čŗ ą┤ą╗čÅ čüąĖą│ąĮą░ą╗ąŠą▓ RXD ąĖ TXD, ą░ čā ą┐ąŠčĆč鹊ą▓ UART1 ąĖ UART2 čäčāąĮą║čåąĖąĖ UART čüąŠą▓ą╝ąĄčēąĄąĮčŗ čü čäčāąĮą║čåąĖčÅą╝ąĖ ą┐ąŠčĆč鹊ą▓ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ (GPIO). ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčāčÄ ąĖąĮč乊čĆą╝ą░čåąĖčÄ ą┐ąŠ ą┐ąŠčĆčéą░ą╝ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ (GPIO) čüą╝. ą▓ čüčéą░čéčīąĄ [4].

| ąĪąĖą│ąĮą░ą╗ |

UART0 |

UART1 |

UART2 |

| RXD |

ą▓čŗą▓. T1

RX0 |

ą▓čŗą▓. C5

PD10 |

ą▓čŗą▓. W14

PD12 |

| TXD |

ą▓čŗą▓. R1

TX0 |

ą▓čŗą▓. C6

PD11 |

ą▓čŗą▓. W15

PD13 |

ąÜą░ąČą┤čŗą╣ UART ą┐čĆąĄąŠą▒čĆą░ąĘčāąĄčé ą┤ą░ąĮąĮčŗąĄ ą╝ąĄąČą┤čā ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╝ ąĖ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮčŗą╝ č乊čĆą╝ą░čéą░ą╝ąĖ. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ąŠą▒ą╝ąĄąĮ ą┤ą░ąĮąĮčŗą╝ąĖ čüą╗ąĄą┤čāąĄčé ą░čüąĖąĮčģčĆąŠąĮąĮąŠą╝čā ą┐čĆąŠč鹊ą║ąŠą╗čā, ą║ąŠč鹊čĆčŗą╣ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé čĆą░ąĘą╗ąĖčćąĮčŗąĄ ą┤ą╗ąĖąĮčŗ čüą╗ąŠą▓ą░, čüč鹊ą┐-ą▒ąĖčéčŗ ąĖ ąŠą┐čåąĖąĖ ą│ąĄąĮąĄčĆą░čåąĖąĖ ąĖ ą┐čĆąŠą▓ąĄčĆą║ąĖ č湥čéąĮąŠčüčéąĖ ą▒ąĖčé. ąÜą░ąČą┤čŗą╣ UART ąĖą╝ąĄąĄčé ą░ą┐ą┐ą░čĆą░čéąĮčāčÄ ą┐ąŠą┤ą┤ąĄčƹȹ║čā ą│ąĄąĮąĄčĆą░čåąĖąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ - ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą╝ąŠą│čāčé ą▒čŗčéčī čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮčŗ ąŠčé 12 čĆą░ąĘąĮčŗčģ čüąŠą▒čŗčéąĖą╣, čüą▓čÅąĘą░ąĮąĮčŗčģ čü ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ UART. ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠ ą║ą░ąČą┤čŗą╣ UART ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ą┐ąŠą╗čāą┤čāą┐ą╗ąĄą║čüąĮčŗą╣ ą┐čĆąŠč鹊ą║ąŠą╗ IrDA┬« (Infrared Data Association) SIR (čüą║ąŠčĆąŠčüčéčī 9.6/115.2 Kbps), čŹčéą░ čäčāąĮą║čåąĖčÅ čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ ą▓čŗą▒ąŠčĆąŠą╝ čĆąĄąČąĖą╝ą░.

ąĪąĖą│ąĮą░ą╗čŗ čüąŠčüč鹊čÅąĮąĖčÅ ąĖ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą╝ąŠą┤ąĄą╝ą░ (modem status and control) ąĮąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčéčüčÅ ą╝ąŠą┤čāą╗čÅą╝ąĖ UART, ąŠą┤ąĮą░ą║ąŠ čŹč鹊čé čäčāąĮą║čåąĖąŠąĮą░ą╗ ą╝ąŠąČąĄčé ą▒čŗčéčī čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ ą▓čŗą▓ąŠą┤ąŠą▓ ą┐ąŠčĆč鹊ą▓ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ ąŠą▒čēąĄą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ (GPIO).

ąÜą░ąČą┤čŗą╣ UART ąĖą╝ąĄąĄčé ą┐ąŠą┤ą┤ąĄčƹȹ║čā čüąŠ čüč鹊čĆąŠąĮčŗ čüąĖčüč鹥ą╝čŗ DMA [3] ą┤ą╗čÅ čĆą░ąĘą┤ąĄą╗čīąĮčŗčģ ą╝ą░čüč鹥čĆ-ą║ą░ąĮą░ą╗ąŠą▓ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖ ą┐čĆąĖąĄą╝ą░ (TX DMA ąĖ RX DMA). ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, UART ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ą╗ąĖą▒ąŠ ą▓ čĆąĄąČąĖą╝ąĄ DMA, ą╗ąĖą▒ąŠ ą▓ čĆąĄąČąĖą╝ąĄ ąŠą▒čŗčćąĮąŠą│ąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ ą┤ąŠčüčéčāą┐ą░, ą▒ąĄąĘ DMA. ąĀąĄąČąĖą╝ ą▒ąĄąĘ DMA čéčĆąĄą▒čāąĄčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąŠč鹊ą║ąŠą╝ ą┤ą░ąĮąĮčŗčģ ą╗ąĖą▒ąŠ čü ą┐ąŠą╝ąŠčēčīčÄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣, ą╗ąĖą▒ąŠ ą▒ąĄąĘ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣, ą┐ąŠ ąŠą┐čĆąŠčüčā čäą╗ą░ą│ąŠą▓ ą▓ čĆąĄą│ąĖčüčéčĆą░čģ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ (polling). ą£ąĄč鹊ą┤ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ DMA ą▒ąŠą╗ąĄąĄ čŹčäč乥ą║čéąĖą▓ąĄąĮ, ą┐ąŠč鹊ą╝čā čćč鹊 čéčĆąĄą▒čāąĄčé ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠą│ąŠ ą▓ą╝ąĄčłą░č鹥ą╗čīčüčéą▓ą░ čüąŠ čüč鹊čĆąŠąĮčŗ ą┐čĆąŠčåąĄčüčüąŠčĆą░ - čüąĖčüč鹥ą╝ą░ DMA ą▒ąĄčĆąĄčé ąĮą░ čüąĄą▒čÅ ąŠą┐ąĄčĆą░čåąĖčÄ ą┐ąŠ ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖčÄ ą┤ą░ąĮąĮčŗčģ ą╝ąĄąČą┤čā ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ UART ąĖ ą┐ą░ą╝čÅčéčīčÄ. ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčāčÄ ąĖąĮč乊čĆą╝ą░čåąĖčÄ ąŠ čüąĖčüč鹥ą╝ąĄ DMA čüą╝. ą▓ čüčéą░čéčīąĄ [3].

ąÆą╝ąĄčüč鹥 čü UART0 ą┤ą╗čÅ čäčāąĮą║čåąĖąĖ ą░ą▓č鹊čéą┤ąĄč鹥ą║čéą░ čüą║ąŠčĆąŠčüčéąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ (autobaud) ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą╗čÄą▒ąŠąĄ ąĖąĘ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ čéą░ą╣ą╝ąĄčĆą░. ąöą╗čÅ UART1 ąĖ UART2 čäčāąĮą║čåąĖčÅ ą░ą▓č鹊ą┤ąĄč鹥ą║čéą░ čüą║ąŠčĆąŠčüčéąĖ ąĮąĄ ą┤ąŠčüčéčāą┐ąĮą░. ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ ą┐čĆąŠ čéą░ą╣ą╝ąĄčĆčŗ ą╝ąŠąČąĮąŠ ą┐čĆąŠčćąĖčéą░čéčī ą▓ čĆą░ąĘą┤ąĄą╗ąĄ "Timers" [1].

[ążąŠčĆą╝ą░čé čäčĆąĄą╣ą╝ą░ UART]

ąÜą░ąČą┤čŗą╣ UART čüą╗ąĄą┤čāąĄčé čüčéą░ąĮą┤ą░čĆčéąĮąŠą╝čā ą░čüąĖąĮčģčĆąŠąĮąĮąŠą╝čā ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą╝čā ą┐čĆąŠč鹊ą║ąŠą╗čā ąŠą▒ą╝ąĄąĮą░ ą┤ą░ąĮąĮčŗą╝ąĖ čüąŠ čüą╗ąĄą┤čāčÄčēąĖą╝ąĖ ąĮą░čüčéčĆą░ąĖą▓ą░ąĄą╝čŗą╝ąĖ ąŠą┐čåąĖčÅą╝ąĖ:

ŌĆó 5..8 ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ.

ŌĆó 1, 1.5 ąĖą╗ąĖ 2 čüč鹊ą┐-ą▒ąĖčéą░.

ŌĆó ąōąĄąĮąĄčĆą░čåąĖčÅ/ą┐čĆąŠą▓ąĄčĆą║ą░ č湥čéąĮąŠčüčéąĖ: None (ąŠčéą║ą╗čÄč湥ąĮąŠ), even (ą┐čĆąŠą▓ąĄčĆą║ą░ ąĮą░ č湥čéąĮąŠčüčéčī) ąĖą╗ąĖ odd (ą┐čĆąŠą▓ąĄčĆą║ą░ ąĮą░ ąĮąĄč湥čéąĮąŠčüčéčī).

ŌĆó Baud rate (čüą║ąŠčĆąŠčüčéčī čüą╗ąĄą┤ąŠą▓ą░ąĮąĖčÅ ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ) = SCLK / (16 x Divisor), ą│ą┤ąĄ SCLK čŹč鹊 čćą░čüč鹊čéą░ čüąĖčüč鹥ą╝ąĮąŠą╣ čłąĖąĮčŗ ą┐čĆąŠčåąĄčüčüąŠčĆą░, ąĖ Divisor čŹč鹊 ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ą┤ąĄą╗ąĄąĮąĖčÅ, ą║ąŠč鹊čĆčŗą╣ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ ą▓ ą╗čÄą▒ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ąŠčé 1 ą┤ąŠ 65536.

ą¤ąŠ čüčéą░ąĮą┤ą░čĆčéčā ą║ą░ąČą┤ąŠąĄ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ąŠąĄ čüą╗ąŠą▓ąŠ ą┤ą░ąĮąĮčŗčģ (ą░čüąĖąĮčģčĆąŠąĮąĮčŗą╣ čäčĆąĄą╣ą╝) čéčĆąĄą▒čāčÄčé ąĮą░ą╗ąĖčćąĖčÅ čüčéą░čĆč鹊ą▓ąŠą│ąŠ ą▒ąĖčéą░ ąĖ ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ąŠą┤ąĮąŠą│ąŠ čüč鹊ą┐ąŠą▓ąŠą│ąŠ ą▒ąĖčéą░. ąóą░ą║ąČąĄ ąŠą┐čåąĖąŠąĮą░ą╗čīąĮąŠ ą╝ąŠąČąĄčé ą┐čĆąĖčüčāčéčüčéą▓ąŠą▓ą░čéčī ą▒ąĖčé č湥čéąĮąŠčüčéąĖ, ą║ąŠč鹊čĆčŗą╣ čüąŠąĘą┤ą░ąĄčéčüčÅ ąŠčé ą┤ąĖą░ą┐ą░ąĘąŠąĮą░ ą▒ąĖčé ąŠčé 7 ą┤ąŠ 12. ążąŠčĆą╝ą░čé ą┐čĆąĖąĮąĖą╝ą░ąĄą╝ąŠą│ąŠ ąĖ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ąŠą│ąŠ čäčĆąĄą╣ą╝ą░ čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ čĆąĄą│ąĖčüčéčĆąŠą╝ Line control register (UARTx_LCR). ąöą░ąĮąĮčŗąĄ ą▓čüąĄą│ą┤ą░ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ čéą░ą║, čćč鹊 čüą░ą╝čŗą╣ ą╝ą╗ą░ą┤čłąĖą╣ ą▒ąĖčé čüą╗ąŠą▓ą░ (least significant bit, LSB) ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą┐ąĄčĆą▓čŗą╝, ąĖ ąĘą░ ąĮąĖą╝ ąĖą┤čāčé ą▒ąĖčéčŗ ą┐ąŠ ąĮą░čĆą░čüčéą░ąĮąĖčÄ čüčéą░čĆčłąĖąĮčüčéą▓ą░, čüą░ą╝čŗą╣ čüčéą░čĆčłąĖą╣ ą▒ąĖčé čüą╗ąŠą▓ą░ (most significant bit, MSB) ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą┐ąŠčüą╗ąĄą┤ąĮąĖą╝. ąØą░ čĆąĖčü. 12-1 ą┐ąŠą║ą░ąĘą░ąĮą░ čäąĖąĘąĖč湥čüą║ą░čÅ ą┤ąĖą░ą│čĆą░ą╝ą╝ą░ čéąĖą┐ąĖčćąĮąŠą│ąŠ ą┐ąŠč鹊ą║ą░ ą▒ąĖčé, ą║ąŠč鹊čĆčŗą╣ ą╝ąŠąČąĮąŠ čāą▓ąĖą┤ąĄčéčī ąĮą░ ą▓čŗą▓ąŠą┤ąĄ TX.

ąĀąĖčü. 12-1. ąÜą░ą║ ą▓čŗą│ą╗čÅą┤ąĖčé ą┐ąŠč鹊ą║ ą▒ąĖčé ąĮą░ ą▓čŗą▓ąŠą┤ąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ TX.

[ąĀąĄą│ąĖčüčéčĆčŗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĖ čüąŠčüč鹊čÅąĮąĖčÅ UART]

ą¤čĆąŠčåąĄčüčüąŠčĆ BF538 ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ąĮą░ą▒ąŠčĆ čĆąĄą│ąĖčüčéčĆąŠą▓ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĖ čüąŠčüč鹊čÅąĮąĖčÅ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ UART, ą║ąŠč鹊čĆčŗąĄ ą▓čŗą┐ąŠą╗ąĮąĄąĮčŗ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü ąŠą▒čēąĄą┐čĆąĖąĮčÅčéčŗą╝ąĖ ąĖąĮą┤čāčüčéčĆąĖą░ą╗čīąĮčŗą╝ąĖ čüčéą░ąĮą┤ą░čĆčéą░ą╝ąĖ. ąŁč鹊 čĆąĄą│ąĖčüčéčĆčŗ, ąŠč鹊ą▒čĆą░ąČąĄąĮąĮčŗąĄ ąĮą░ ą░ą┤čĆąĄčüą░ą╝ ą┐ą░ą╝čÅčéąĖ, čéą░ą║ ąĮą░ąĘčŗą▓ą░ąĄą╝čŗąĄ memory-mapped registers (MMR), ą║ąŠč鹊čĆčŗąĄ ąĖą╝ąĄčÄčé čłąĖčĆąĖąĮčā ą▓ 1 ą▒ą░ą╣čé, ąĖ ą╝ąŠą│čāčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮčŗ/ąĘą░ą┐ąĖčüą░ąĮčŗ ą▓ ąŠą▒čēąĄą╝ ą░ą┤čĆąĄčüąĮąŠą╝ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąĄ ą┐ą░ą╝čÅčéąĖ ą║ą░ą║ ą┐ąŠą╗čā-čüą╗ąŠą▓ą░ (2 ą▒ą░ą╣čéą░), ą│ą┤ąĄ čüčéą░čĆčłąĖą╣ ą▒ą░ą╣čé ąĘą░ą┐ąŠą╗ąĮąĄąĮ ąĮčāą╗ąĄą╝.

ąĪ čåąĄą╗čīčÄ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖčÅ čüąŠ čüčéą░ąĮą┤ą░čĆčéąĮčŗą╝ąĖ ąĖąĮą┤čāčüčéčĆąĖą░ą╗čīąĮčŗą╝ąĖ ąĖąĮč鹥čĆč乥ą╣čüą░ą╝ąĖ, ąĮąĄčüą║ąŠą╗čīą║ąŠ čĆąĄą│ąĖčüčéčĆąŠą▓ ą┐čĆąĖą▓čÅąĘą░ąĮčŗ ą║ ąŠą┤ąĮąŠą╝čā ą░ą┤čĆąĄčüčā. ąĀąĄą│ąĖčüčéčĆčŗ ąĘą░čēąĄą╗ą║ąĖ ą┤ąĄą╗ąĖč鹥ą╗čÅ (divisor latch registers, UARTx_DLH ąĖ UARTx_DLL) ąĖčüą┐ąŠą╗čīąĘčāčÄčé ąŠą▒čēąĖą╣ ą░ą┤čĆąĄčü čü čĆąĄą│ąĖčüčéčĆąŠą╝ ą▒čāč乥čĆą░ ą┐ąĄčĆąĄą┤ą░čćąĖ (transmit holding register, UARTx_THR), čĆąĄą│ąĖčüčéčĆąŠą╝ ą▒čāč乥čĆą░ ą┐čĆąĖąĄą╝ą░ (receive buffer register, UARTx_RBR) ąĖ čĆąĄą│ąĖčüčéčĆąŠą╝ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ (interrupt enable register, UARTx_IER). ąæąĖčé ąĘą░čēąĄą╗ą║ąĖ ą┤ąĄą╗ąĖč鹥ą╗čÅ (divisor latch access bit, DLAB) ą▓ čĆąĄą│ąĖčüčéčĆąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą╗ąĖąĮąĖąĄą╣ (line control register, UARTx_LCR) čāą┐čĆą░ą▓ą╗čÅąĄčé ąĮą░ą▒ąŠčĆąŠą╝ čĆąĄą│ąĖčüčéčĆąŠą▓, ą║ąŠč鹊čĆčŗą╣ ą┤ąŠčüčéčāą┐ąĄąĮ ą▓ ąĮą░čüč鹊čÅčēąĖą╣ ą╝ąŠą╝ąĄąĮčé. ąöą╗čÅ ą┤ąŠčüčéčāą┐ą░ ą║ čŹčéąĖą╝ čĆąĄą│ąĖčüčéčĆą░ą╝ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠąĄ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖąĄ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī 16-čĆą░ąĘčĆčÅą┤ąĮčŗąĄ ąĖąĮčüčéčĆčāą║čåąĖąĖ ąĘą░ą│čĆčāąĘą║ąĖ/čüąŠčģčĆą░ąĮąĄąĮąĖčÅ (16-bit word load/store instructions).

ąĀą░ąĘą┤ąĄą╗čīąĮčāčÄ ą▒čāč乥čĆąĖąĘą░čåąĖčÄ ąĖą╝ąĄčÄčé ąĖ ą║ą░ąĮą░ą╗ ą┐ąĄčĆąĄą┤ą░čćąĖ, ąĖ ą║ą░ąĮą░ą╗ ą┐čĆąĖąĄą╝ą░. ąĀąĄą│ąĖčüčéčĆ UARTx_THR ą▒čāč乥čĆąĖąĘąĖčĆčāąĄčé čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ (transmit shift register, TSR) ąĖ čĆąĄą│ąĖčüčéčĆ UARTx_RBR ą▒čāč乥čĆąĖąĘąĖčĆčāąĄčé čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ ą┐čĆąĖąĄą╝ą░ (receive shift register, LSR). ąĀąĄą│ąĖčüčéčĆčŗ čüą┤ą▓ąĖą│ą░ ąĮąĄą┤ąŠčüčéčāą┐ąĮčŗ ą┤ą╗čÅ ą┐čĆčÅą╝ąŠą│ąŠ ą┤ąŠčüčéčāą┐ą░ čüąŠ čüč鹊čĆąŠąĮčŗ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖčÅ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĮą░ ą▓čüąĄčģ čĆąĖčüčāąĮą║ą░čģ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą▒ąĖčéčŗ čĆąĄą│ąĖčüčéčĆąŠą▓ ąĘą░ą║čĆą░čłąĄąĮčŗ čüąĄčĆčŗą╝ čåą▓ąĄč鹊ą╝.

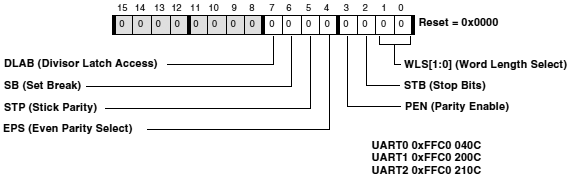

ąĀąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą╗ąĖąĮąĖąĄą╣ (UART line control register, UARTx_LCR) čāą┐čĆą░ą▓ą╗čÅąĄčé č乊čĆą╝ą░č鹊ą╝ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ąŠą│ąŠ ąĖ ą┐čĆąĖąĮąĖą╝ą░ąĄą╝ąŠą│ąŠ čäčĆąĄą╣ą╝ąŠą▓ (čā ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ąŠą│ąŠ ąĖ ą┐čĆąĖąĮąĖą╝ą░ąĄą╝ąŠą│ąŠ čäčĆąĄą╣ą╝ąŠą▓ ą▓čüąĄą│ą┤ą░ č乊čĆą╝ą░čé ąŠą┤ąĖąĮą░ą║ąŠą▓čŗą╣, čüą╝. čĆąĖčü. 12-2). ąæąĖčé SB čĆą░ą▒ąŠčéą░ąĄčé ą┤ą░ąČąĄ č鹊ą│ą┤ą░, ą║ąŠą│ą┤ą░ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ ą┤ą╗čÅ UART ąĘą░ą┐čĆąĄčēąĄąĮą░. ą¤ąŠčüą║ąŠą╗čīą║čā ą▓čŗą▓ąŠą┤ TX ąŠą▒čŗčćąĮąŠ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ąŠąČąĖą┤ą░ąĮąĖčÅ ąĖą╝ąĄąĄčé čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 1, č鹊 ąŠąĮ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą║ą░ą║ ą▓čŗą▓ąŠą┤ čäą╗ą░ą│ą░, ąĄčüą╗ąĖ UART ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ.

ąĀąĖčü. 12-2. UART Line Control Register (UARTx_LCR).

DLAB (Divisor Latch Access). ąæąĖčé ąĘą░čēąĄą╗ą║ąĖ ą┤ąĄą╗ąĖč鹥ą╗čÅ. 1: čĆą░ąĘčĆąĄčłą░ąĄčé ą┤ąŠčüčéčāą┐ ą║ UARTx_DLL ąĖ UARTx_DLH, 0: čĆą░ąĘčĆąĄčłą░ąĄčé ą┤ąŠčüčéčāą┐ ą║ UARTx_THR, UARTx_RBR ąĖ UARTx_IER. ąæąĖčé ąĮčāąČąĄąĮ ą┐ąŠč鹊ą╝čā, čćč鹊 čŹčéąĖ čĆąĄą│ąĖčüčéčĆčŗ ąĖčüą┐ąŠą╗čīąĘčāčÄčé ąŠą┤ąĖąĮ ąĖ č鹊čé ąČąĄ ą░ą┤čĆąĄčü MMR.

SB (Set Break). ąæąĖčé čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čüąŠčüč鹊čÅąĮąĖąĄą╝ ą╗ąĖąĮąĖąĄą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ. 0: ąŠą▒čŗčćąĮčŗą╣ čĆąĄąČąĖą╝, 1: - ą┐čĆąĖąĮčāą┤ąĖč鹥ą╗čīąĮčŗą╣ ą▓čŗą▓ąŠą┤ ą╗ąŠą│. 0 ąĮą░ ą▓čŗą▓ąŠą┤ TX.

STP (Stick Parity). ąĢčüą╗ąĖ ą▒ąĖčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ąĖ PEN = 1, č鹊 ą┐čĆąĖąĮčāą┤ąĖč鹥ą╗čīąĮąŠ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé č湥čéąĮąŠčüčéčī ą▓ ąĘą░ą┤ą░ąĮąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ. EPS = 1 č湥čéąĮąŠčüčéčī ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ąĖ ą┐čĆąŠą▓ąĄčĆčÅąĄčéčüčÅ ą║ą░ą║ 0, EPS = 0 č湥čéąĮąŠčüčéčī ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ąĖ ą┐čĆąŠą▓ąĄčĆčÅąĄčéčüčÅ ą║ą░ą║ 1.

EPS (Even Parity Select). ąæąĖčé ąĮą░čüčéčĆąŠą╣ą║ąĖ č湥čéąĮąŠčüčéąĖ. 1: Even parity (ą┐čĆąŠą▓ąĄčĆą║ą░ ąĮą░ č湥čéąĮąŠčüčéčī), 0: Odd parity (ą┐čĆąŠą▓ąĄčĆą║ą░ ąĮą░ ąĮąĄč湥čéąĮąŠčüčéčī). ąæąĖčé čĆą░ą▒ąŠčéą░ąĄčé, ą║ąŠą│ą┤ą░ PEN = 1 ąĖ STP = 0.

PEN (Parity Enable). ąæąĖčé čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ąĖ ą┐čĆąŠą▓ąĄčĆą║ąĖ č湥čéąĮąŠčüčéąĖ. 1: ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī ąĖ ą┐čĆąŠą▓ąĄčĆčÅčéčī č湥čéąĮąŠčüčéčī, 0: ąĖąĮč乊čĆą╝ą░čåąĖčÅ č湥čéąĮąŠčüčéąĖ ąĮąĄ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ąĖ ąĮąĄ ą┐čĆąŠą▓ąĄčĆčÅąĄčéčüčÅ (čŹč鹊čé ą▓ą░čĆąĖą░ąĮčé ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čćą░čēąĄ ą▓čüąĄą│ąŠ).

STB (Stop Bits). ąØą░čüčéčĆą░ąĖą▓ą░ąĄčé čüč鹊ą┐-ą▒ąĖčé čäčĆąĄą╣ą╝ą░. 1: 2 čüč鹊ą┐-ą▒ąĖčéą░ ą┤ą╗čÅ ą┤ą╗ąĖąĮ čüą╗ąŠą▓ą░ ąĮąĄ 5 ą▒ąĖčé, ąĖą╗ąĖ 1.5 čüč鹊ą┐-ą▒ąĖčéą░ ą┤ą╗čÅ ą┤ą╗ąĖąĮ čüą╗ąŠą▓ą░ ą▓ 5 ą▒ąĖčé. 0: 1 čüč鹊ą┐-ą▒ąĖčé ą┤ą╗čÅ ą▓čüąĄčģ ą┤ą╗ąĖąĮ čüą╗ąŠą▓ą░, čŹč鹊čé ą▓ą░čĆąĖą░ąĮčé ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čćą░čēąĄ ą▓čüąĄą│ąŠ.

WLS[1:0] (Word Length Select). ąÆčŗą▒ąŠčĆ ą┤ą╗ąĖąĮčŗ čüą╗ąŠą▓ą░. 00: 5 ą▒ąĖčé, 01: 6 ą▒ąĖčé, 10: 7 ą▒ąĖčé, 11: 8 ą▒ąĖčé. ą¤ąŠčüą╗ąĄą┤ąĮąĖą╣ ą▓ą░čĆąĖą░ąĮčé ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čćą░čēąĄ ą▓čüąĄą│ąŠ.

ąĀąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą╝ąŠą┤ąĄą╝ąŠą╝ (modem control register, UARTx_MCR) čāą┐čĆą░ą▓ą╗čÅąĄčé ą┐ąŠčĆč鹊ą╝ UART, ą║ą░ą║ čŹč鹊 ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 12-3. ąźąŠčéčÅ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠčüčéčī ą╝ąŠą┤ąĄą╝ą░ ąĮąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ ą▓ąĮąĄčłąĮąĖą╝ąĖ ą▓čŗą▓ąŠą┤ą░ą╝ąĖ, čĆąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą╝ąŠą┤ąĄą╝ąŠą╝ ą▓čüąĄ ąČąĄ ą▒čŗą╗ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮ ą┤ą╗čÅ ą┐ąŠą┤ą┤ąĄčƹȹ║ąĖ čĆąĄąČąĖą╝ą░ ąĘą░ą║ąŠą╗čīčåąŠą▓čŗą▓ą░ąĮąĖčÅ (loop back mode). ąŁč鹊čé čĆąĄąČąĖą╝ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čüą░ą╝ąŠč鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ, ą▓ ąĮąĄą╝ ą┐čĆąĖąĮčāą┤ąĖč鹥ą╗čīąĮąŠ ą▓ąĮąĄčłąĮąĖą╣ ą▓čŗą▓ąŠą┤ TX ą┐ąĄčĆąĄą▓ąŠą┤ąĖčéčüčÅ ą▓ ą╗ąŠą│ 1, ąĖ ą▓ąĮąĄčłąĮąĖą╣ ą▓čģąŠą┤ąĮąŠą╣ ą▓čŗą▓ąŠą┤ ąŠčéą║ą╗čÄčćą░ąĄčéčüčÅ ąŠčé RX, ąĖ ą┐čĆąĖąĄą╝/ą┐ąĄčĆąĄą┤ą░čćą░ čüąŠąĄą┤ąĖąĮčÅčÄčéčüčÅ ą┤čĆčāą│ ąĮą░ ą┤čĆčāą│ą░ ą▓ąĮčāčéčĆąĖ ą║čĆąĖčüčéą░ą╗ą╗ą░.

ąĀąĖčü. 12-3. UART Modem Control Register (UARTx_MCR).

ąĀąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ ą╗ąĖąĮąĖąĖ (UART line status register, UARTx_LSR), čüąŠą┤ąĄčƹȹĖčé ąĖąĮč乊čĆą╝ą░čåąĖčÄ ąŠ čüąŠčüč鹊čÅąĮąĖąĖ UART, čüą╝. čĆąĖčü. 12-4. ąŁč鹊čé čĆąĄą│ąĖčüčéčĆ ą┤ąŠčüčéčāą┐ąĄąĮ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ, čćč鹊 ą▓ą┐ąŠą╗ąĮąĄ ą╗ąŠą│ąĖčćąĮąŠ.

ąĀąĖčü. 12-4. UART Line Status Register (UARTx_LSR).

TEMT (TSR and UARTx_THR Empty). ąæąĖčé čüąŠčüč鹊čÅąĮąĖčÅ ąŠą┐čāčüč鹊賹ĄąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ čüą┤ą▓ąĖą│ą░ ąĖ ą▒čāč乥čĆą░ ą┐ąĄčĆąĄą┤ą░čćąĖ. 0: čĆąĄą│ąĖčüčéčĆčŗ ąĘą░ą┐ąŠą╗ąĮąĄąĮčŗ, 1: ąŠą▒ą░ ą┐čāčüčéčŗ.

THRE (THR Empty). ąæąĖčé čüąŠčüč鹊čÅąĮąĖčÅ ąŠą┐čāčüč鹊賹ĄąĮąĖčÅ ą▒čāč乥čĆą░ ą┐ąĄčĆąĄą┤ą░čćąĖ. 0: THR ąĮąĄ ą┐čāčüčé, 1: THR ą┐čāčüčé.

BI (Break interrupt). 0: ąĮąĄčé čüąĖą│ąĮą░ą╗ąĖąĘą░čåąĖąĖ ąŠą▒čĆčŗą▓ą░ ą┐ąŠč鹊ą║ą░ (No break interrupt), 1: čüąŠčüč鹊čÅąĮąĖąĄ ąŠą▒čĆčŗą▓ą░ ą┐ąŠč鹊ą║ą░ ąĮą░ ą╗ąĖąĮąĖąĖ (Break interrupt; čŹč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 čüąĖą│ąĮą░ą╗ RX čāą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą╗ąŠą│. 0 ą┤ąŠą╗čīčłąĄ, č湥ą╝ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮą░čÅ ą┤ą╗ąĖąĮą░ čüą╗ąŠą▓ą░).

FE (Framing Error). ąæąĖčé ąŠčłąĖą▒ą║ąĖ čäčĆąĄą╣ą╝ą░. 0: ąŠčłąĖą▒ą║ąĖ ąĮąĄčé, 1: ąŠčłąĖą▒ą║ą░ ąĮąĄą┤ąŠą┐čāčüčéąĖą╝ąŠą│ąŠ čüč鹊ą┐-ą▒ąĖčéą░ (ąŠąĮ ąĮąĄ čĆą░ą▓ąĄąĮ ą╗ąŠą│. 0).

PE (Parity Error). ąæąĖčé ąŠčłąĖą▒ą║ąĖ ą┐čĆąŠą▓ąĄčĆą║ąĖ č湥čéąĮąŠčüčéąĖ. 0: ąĮąĄčé ąŠčłąĖą▒ą║ąĖ, 1: ąŠčłąĖą▒ą║ą░ č湥čéąĮąŠčüčéąĖ.

OE (Overrun Error). ąæąĖčé ą┐ąŠč鹥čĆąĖ ą┤ą░ąĮąĮčŗčģ ąĮą░ ą┐čĆąĖąĄą╝ąĄ (ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĄ ą┐čĆąĖąĄą╝ą░). 0: ąĮąĄčé ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ, 1: čĆąĄą│ąĖčüčéčĆ UARTx_RBR ąĮąĄ ą▒čŗą╗ ą┐čĆąŠčćąĖčéą░ąĮ ą▓ ą╝ąŠą╝ąĄąĮčé ą┐čĆąĖąĄą╝ą░ ąĮąŠą▓ąŠą│ąŠ čäčĆąĄą╣ą╝ą░, ą┐ąŠčŹč鹊ą╝čā UARTx_RBR ą▒čŗą╗ ą┐ąĄčĆąĄąĘą░ą┐ąĖčüą░ąĮ ąĮąŠą▓čŗą╝ąĖ ą┤ą░ąĮąĮčŗą╝ąĖ, ąĖ ą┐čĆąĖąĮčÅčéčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┐čĆąĄą┤čŗą┤čāčēąĄą│ąŠ čäčĆąĄą╣ą╝ą░ ą▒čŗą╗ąĖ ą┐ąŠč鹥čĆčÅąĮčŗ.

DR (Data Ready). ąōąŠč鹊ą▓ąĮąŠčüčéčī ą┤ą░ąĮąĮčŗčģ ąĮą░ ą┐čĆąĖąĄą╝ąĄ. 0: ąĮąŠą▓čŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┐ąŠą║ą░ ąĮąĄ ą┐ąŠčüčéčāą┐ąĖą╗ąĖ, 1: čĆąĄą│ąĖčüčéčĆ UARTx_RBR čüąŠą┤ąĄčƹȹĖčé ąĮąŠą▓čŗąĄ ą┐čĆąĖąĮčÅčéčŗąĄ ą┤ą░ąĮąĮčŗąĄ.

ąæąĖčéčŗ break interrupt (BI), overrun error (OE), parity error (PE) ąĖ framing error (FE) ąŠčćąĖčēą░čÄčéčüčÅ, ą║ąŠą│ą┤ą░ čćąĖčéą░ąĄčéčüčÅ čĆąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ ą╗ąĖąĮąĖąĖ UARTx_LSR. ąæąĖčé data ready (DR) ąŠčćąĖčēą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ čćąĖčéą░ąĄčéčüčÅ čĆąĄą│ąĖčüčéčĆ ą▒čāč乥čĆą░ ą┐čĆąĖąĄą╝ą░ UARTx_RBR.

ąśąĘ-ąĘą░ ą┤ąĄčüčéčĆčāą║čéąĖą▓ąĮąŠą╣ ą┐čĆąĖčĆąŠą┤čŗ čŹčéąĖčģ ąŠą┐ąĄčĆą░čåąĖą╣ čćč鹥ąĮąĖčÅ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą┐čĆąĄą┤ą┐čĆąĖąĮčÅčéčŗ čüą┐ąĄčåąĖą░ą╗čīąĮčŗąĄ ą╝ąĄčĆčŗ. ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčāčÄ ąĖąĮč乊čĆą╝ą░čåąĖčÄ čüą╝. ą▓ čĆą░ąĘą┤ąĄą╗ą░čģ "ąĪą┐ąĄą║čāą╗čÅčéąĖą▓ąĮąŠąĄ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ čćč鹥ąĮąĖčÅ ą┐ą░ą╝čÅčéąĖ" ąĖ "ą¤ąŠą▓ąĄą┤ąĄąĮąĖąĄ čćč鹥ąĮąĖčÅ ą┐ą░ą╝čÅčéąĖ ą┐ąŠ čāčüą╗ąŠą▓ąĖčÄ" čüčéą░čéčīąĖ [5].

ąæąĖčé THRE ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą║ą░ąĮą░ą╗ ą┐ąĄčĆąĄą┤ą░čćąĖ UART ą│ąŠč鹊ą▓ ą║ ą┐ąŠą╗čāč湥ąĮąĖčÄ ąĮąŠą▓čŗčģ ą┤ą░ąĮąĮčŗčģ, ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠąĄ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖąĄ ą╝ąŠąČąĄčé ąĘą░ą┐ąĖčüą░čéčī čĆąĄą│ąĖčüčéčĆ UARTx_THR. ąŚą░ą┐ąĖčüčī ą▓ UARTx_THR ąŠčćąĖčüčéąĖčé ą▒ąĖčé THRE. ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čüąĮąŠą▓ą░, ą║ąŠą│ą┤ą░ ą┤ą░ąĮąĮčŗąĄ ą▒čāą┤čāčé ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ čüą║ąŠą┐ąĖčĆąŠą▓ą░ąĮčŗ ąĖąĘ UARTx_THR ą▓ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ (TSR). ą£ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąŠą▓ąĄčĆąĄąĮ ą▒ąĖčé TEMT, čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ą╝ąŠą╝ąĄąĮčé, ą║ąŠą│ą┤ą░ ą▒čŗą╗ą░ ąĘą░ą▓ąĄčĆčłąĄąĮą░ ąĮąĄą┤ą░ą▓ąĮąŠ ąĮą░čćą░čéą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░.

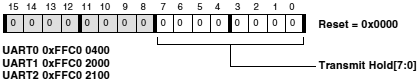

ąŚą░ą┐ąĖčüčī ą▓ čĆąĄą│ąĖčüčéčĆ ą▒čāč乥čĆą░ ą┐ąĄčĆąĄą┤ą░čćąĖ (UART transmit holding register, UARTx_THR) ąĖąĮąĖčåąĖąĖčĆčāąĄčé ą┐ąĄčĆąĄą┤ą░čćčā čäčĆąĄą╣ą╝ą░. ąŚą░ą┐ąĖčüą░ąĮąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą▒čāą┤čāčé ą┐ąĄčĆąĄą╝ąĄčēąĄąĮčŗ ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ (transmit shift register, TSR), ąŠčéą║čāą┤ą░ ą┤ą░ąĮąĮčŗąĄ ą▒čāą┤čāčé ą▓čŗą┤ą▓ąĖą│ą░čéčīčüčÅ ąĮą░ ą▓ąĮąĄčłąĮąĖą╣ ą▓čŗą▓ąŠą┤ TX čüąŠ čüą║ąŠčĆąŠčüčéčīčÄ, čĆą░ą▓ąĮąŠą╣ SCLK / (16 x Divisor), ą▓ą╝ąĄčüč鹥 čü ą▒ąĖčéą░ą╝ąĖ čüčéą░čĆčéą░, čüč鹊ą┐ą░, č湥čéąĮąŠčüčéąĖ - čéą░ą║ č乊čĆą╝ąĖčĆčāąĄčéčüčÅ čüčéą░ąĮą┤ą░čĆčéąĮčŗą╣ ą░čüąĖąĮčģčĆąŠąĮąĮčŗą╣ čäčĆąĄą╣ą╝. ąÆčüąĄ čäčĆąĄą╣ą╝čŗ ąĮą░čćąĖąĮą░čÄčéčüčÅ čü ą┐ąĄčĆąĄčģąŠą┤ą░ 1 -> 0 ąĮą░ ą╗ąĖąĮąĖąĖ TX (čŹč鹊 čüąĖą│ąĮą░ą╗ąĖąĘąĖčĆčāąĄčé ąŠ ąĮą░čćą░ą╗ąĄ čüčéą░čĆč鹊ą▓ąŠą│ąŠ ą▒ąĖčéą░, ą┐ąŠ čŹč鹊ą╝čā ą╝ąŠą╝ąĄąĮčéčā ą▒čāą┤ąĄčé čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆąŠą▓ą░čéčīčüčÅ ą┐čĆąĖąĄą╝ ąĮą░ čüč鹊čĆąŠąĮąĄ ą┐ąŠą╗čāčćą░č鹥ą╗čÅ ą┤ą░ąĮąĮčŗčģ). ą¤ąĄčĆąĄąĮąŠčü ą┤ą░ąĮąĮčŗčģ ąĖąĘ UARTx_THR ą▓ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ čāčüčéą░ąĮąŠą▓ąĖčé ą▒ąĖčé THRE čĆąĄą│ąĖčüčéčĆą░ čüčéą░čéčāčüą░ ą╗ąĖąĮąĖąĖ UARTx_LSR.

ąĀąĄą│ąĖčüčéčĆ UARTx_THR ą┤ąŠčüčéčāą┐ąĄąĮ č鹊ą╗čīą║ąŠ ąĮą░ ąĘą░ą┐ąĖčüčī, ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčé ąŠą┤ąĖąĮ ąĖ č鹊čé ąČąĄ ą░ą┤čĆąĄčü MMR, čćč鹊 ąĖ čĆąĄą│ąĖčüčéčĆčŗ UARTx_RBR ąĖ UARTx_DLL. ą¦č鹊ą▒čŗ ą┐ąŠą╗čāčćąĖčéčī ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ ą┤ąŠčüčéčāą┐ ą║ UARTx_THR, ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąŠčćąĖčēąĄąĮ ą▒ąĖčé DLAB ą▓ čĆąĄą│ąĖčüčéčĆąĄ UARTx_LCR. ąÜąŠą│ą┤ą░ ą▒ąĖčé DLAB ąŠčćąĖčēąĄąĮ, ąĘą░ą┐ąĖčüčī ą┐ąŠ ą░ą┤čĆąĄčüčā čĆąĄą│ąĖčüčéčĆą░ UARTx_THR ą▒čāą┤ąĄčé ąŠčüčāčēąĄčüčéą▓ą╗čÅčéčī ąĘą░ą┐ąĖčüčī ą▓ čĆąĄą│ąĖčüčéčĆ ą▒čāč乥čĆą░ ą┐ąĄčĆąĄą┤ą░čćąĖ, ą░ čćč鹥ąĮąĖąĄ ą┐ąŠ č鹊ą╝čā ąČąĄ ą░ą┤čĆąĄčüčā ą▒čāą┤ąĄčé ąŠčüčāčēąĄčüčéą▓ą╗čÅčéčī čćč鹥ąĮąĖąĄ ą▒čāč乥čĆą░ ą┐čĆąĖąĄą╝ą░ UARTx_RBR. ąóą░ą║ąŠąĄ čüąŠą▓ą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░ ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┐ąŠč鹊ą╝čā, čćč鹊 UARTx_THR ą┤ąŠčüčéčāą┐ąĄąĮ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ąĘą░ą┐ąĖčüąĖ, ą░ UARTx_RBR ą┤ąŠčüčéčāą┐ąĄąĮ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą▒čāč乥čĆčŗ ą┐čĆąĖąĄą╝ą░ ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖą╝ąĄčÄčé ąŠą┤ąĖąĮ ąĖ č鹊čé ąČąĄ ą░ą┤čĆąĄčü MMR.

ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ą┤ą░ąĮąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ, ąĮą░čćąĖąĮą░čÅ čü čüą░ą╝ąŠą│ąŠ ą╝ą╗ą░ą┤čłąĄą│ąŠ ą▒ąĖčéą░ (LSB), ą┤ą░ą╗ąĄąĄ ą▒ąĖčéčŗ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ą┐ąŠąŠč湥čĆąĄą┤ąĮąŠ ą┐ąŠ čüčéą░čĆčłąĖąĮčüčéą▓čā. ą×ą║ą░ąĮčćąĖą▓ą░ąĄčéčüčÅ ą┐ąĄčĆąĄą┤ą░čćą░ ą┤ą░ąĮąĮčŗčģ čüą░ą╝čŗą╝ čüčéą░čĆčłąĖą╝ ą▒ąĖč鹊ą╝ (MSB), ąĘą░ čüčéą░čĆčłąĖą╝ ą▒ąĖč鹊ą╝ ą┤ą░ąĮąĮčŗčģ čüą╗ąĄą┤čāąĄčé ąŠą┐čåąĖąŠąĮą░ą╗čīąĮąŠ ą▒ąĖčé č湥čéąĮąŠčüčéąĖ ąĖ ą┤ą░ą╗ąĄąĄ čüč鹊ą┐-ą▒ąĖčéčŗ (ąŠą┤ąĖąĮ, ą┐ąŠą╗č鹊čĆą░ ąĖą╗ąĖ ą┤ą▓ą░ čüč鹊ą┐-ą▒ąĖčéą░).

ąĀąĖčü. 12-5. UART Transmit Holding Register (UARTx_THR).

ąŁč鹊 čĆąĄą│ąĖčüčéčĆ ą▒čāč乥čĆą░ ą┐čĆąĖąĄą╝ą░ (UART Receive Buffer, UARTx_RBR). ą×ą┐ąĄčĆą░čåąĖčÅ ą┐čĆąĖąĄą╝ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčé č鹊čé ąČąĄ č乊čĆą╝ą░čé čäčĆąĄą╣ą╝ą░, čćč鹊 ąĖ ą┐ąĄčĆąĄą┤ą░čćą░, ąĘą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ ą║ąŠą╗ąĖč湥čüčéą▓ą░ čüč鹊ą┐-ą▒ąĖč鹊ą▓, ą┤ą╗čÅ ą║ąŠč鹊čĆčŗčģ ą▓čüąĄą│ą┤ą░ ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčéčüčÅ 1 čüč鹊ą┐-ą▒ąĖčé. ą¤ąŠčüą╗ąĄ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ čüčéą░čĆč鹊ą▓ąŠą│ąŠ ą▒ąĖčéą░ ą┐čĆąĖąĮąĖą╝ą░ąĄą╝ąŠąĄ čüą╗ąŠą▓ąŠ ą▓ą┤ą▓ąĖą│ą░ąĄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ ą┐čĆąĖąĄą╝ą░ (receive shift register, RSR) čüąŠ čüą║ąŠčĆąŠčüčéčīčÄ (čćą░čüč鹊č鹊ą╣ čüą╗ąĄą┤ąŠą▓ą░ąĮąĖčÅ ą▒ąĖčé), ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą╣ ą║ą░ą║ SCLK / (16 x divisor). ą¤ąŠčüą╗ąĄ ą┐čĆąĖąĄą╝ą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ą▒ąĖčé (ą▓ą║ą╗čÄčćą░čÅ čüč鹊ą┐-ą▒ąĖčé) ąŠą▒ąĮąŠą▓ą╗čÅčÄčéčüčÅ ą┤ą░ąĮąĮčŗąĄ ąĖ ą╗čÄą▒ą░čÅ čüčéą░čéčāčüąĮą░čÅ ąĖąĮč乊čĆą╝ą░čåąĖčÅ, ąĖ ą┤ą░ąĮąĮčŗąĄ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą┐ąĄčĆąĄą╝ąĄčēą░čÄčéčüčÅ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ čüą┤ą▓ąĖą│ą░ ą▓ ą▒čāč乥čĆ ą┐čĆąĖąĄą╝ą░ UARTx_RBR. ą¤ąŠčüą╗ąĄ ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖčÅ čüą╗ąŠą▓ą░ ą┤ą░ąĮąĮčŗčģ ą▓ UARTx_RBR ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╣ ąĘą░ą┤ąĄčƹȹ║ąĖ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ąŠą▒ąĮąŠą▓ą╗čÅąĄčéčüčÅ čäą╗ą░ą│ ą│ąŠč鹊ą▓ąĮąŠčüčéąĖ ą┤ą░ąĮąĮčŗčģ DR ą▓ čĆąĄą│ąĖčüčéčĆąĄ UARTx_LSR.

ą¦ą░čüč鹊čéą░ ąŠčåąĖčäčĆąŠą▓ą║ąĖ ą▓čģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ą┤ą░ąĮąĮčŗčģ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé čü 16-ą║čĆą░čéąĮąŠą╣ čćą░čüč鹊č鹊ą╣ čüą╗ąĄą┤ąŠą▓ą░ąĮąĖčÅ ą▒ąĖčé (baud rate * 16), ą║ą░ą║ ą╝ąŠąČąĮąŠ ą▒ą╗ąĖąČąĄ ą║ ąŠąČąĖą┤ą░ąĄą╝ąŠą╣ čüąĄčĆąĄą┤ąĖąĮąĄ ą▒ąĖčéą░. ąśąĘ-ąĘą░ č鹊ą│ąŠ, čćč鹊 ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ čćą░čüč鹊čéą░ ą▓čŗą▒ąŠčĆą║ąĖ ąĮąĄ č鹊čćąĮąŠ čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé čüą║ąŠčĆąŠčüčéąĖ ą┐čĆąĖąĮąĖą╝ą░ąĄą╝ąŠą│ąŠ ą┐ąŠč鹊ą║ą░ ą┤ą░ąĮąĮčŗčģ, č鹊čćą║ą░ ą▓čŗą▒ąŠčĆą║ąĖ čüą╝ąĄčēą░ąĄčéčüčÅ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ čüąĄčĆąĄą┤ąĖąĮčŗ ą║ą░ąČą┤ąŠą│ąŠ ą▒ąĖčéą░. ąóąŠčćą║ą░ ą▓čŗą▒ąŠčĆą║ąĖ čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆčāąĄčéčüčÅ ą║ą░ąČą┤čŗą╣ čĆą░ąĘ ąĘą░ąĮąŠą▓ąŠ ą┐ąŠ ąĮą░čćą░ą╗čā čüčéą░čĆč鹊ą▓ąŠą│ąŠ ą▒ąĖčéą░, čéą░ą║ čćč鹊 ąŠčłąĖą▒ą║ą░ ąĮąĄčüąŠąŠčéą▓ąĄčéčüčéą▓ąĖčÅ čüą║ąŠčĆąŠčüč鹥ą╣ ąĮą░ą║ą░ą┐ą╗ąĖą▓ą░ąĄčéčüčÅ ą┐ąŠ ą▓čüąĄą╣ ą┤ą╗ąĖąĮąĄ ą┐čĆąĖąĮąĖą╝ą░ąĄą╝ąŠą│ąŠ čüą╗ąŠą▓ą░ (ąĮą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╝ ą▒ąĖč鹥 čüą╝ąĄčēąĄąĮąĖąĄ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ąŠąČąĖą┤ą░ąĄą╝ąŠą│ąŠ čåąĄąĮčéčĆą░ čüčéą░ąĮąŠą▓ąĖčéčüčÅ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮčŗą╝). ążąĖą╗čīčéčĆ ą┐čĆąĖąĄą╝ą░ čāą┤ą░ą╗čÅąĄčé čüą╗čāčćą░ą╣ąĮčŗąĄ ąĖą╝ą┐čāą╗čīčüčŗ, ą║ąŠč鹊čĆčŗąĄ ą┐ąŠ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéąĖ ą╝ąĄąĮčīčłąĄ ą┤ą▓čāčģ ą┐ąĄčĆąĖąŠą┤ąŠą▓ čéą░ą║č鹊ą▓ ą▓čŗą▒ąŠčĆą║ąĖ.

ąĀąĄą│ąĖčüčéčĆ UARTx_RBR ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ, ąĖ ąŠąĮ ąĖčüą┐ąŠą╗čīąĘčāąĄčé č鹊čé ąČąĄ čüą░ą╝čŗą╣ ą░ą┤čĆąĄčü, čćč鹊 ąĖ čĆąĄą│ąĖčüčéčĆ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ąĘą░ą┐ąĖčüąĖ UARTx_THR ąĖ čĆąĄą│ąĖčüčéčĆ UARTx_DLL. ą¦č鹊ą▒čŗ ą┐ąŠą╗čāčćąĖčéčī ą┤ąŠčüčéčāą┐ ą║ UARTx_RBR, ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąŠčćąĖčēąĄąĮ ą▒ąĖčé DLAB ą▓ čĆąĄą│ąĖčüčéčĆąĄ UARTx_LCR. ąÜąŠą│ą┤ą░ ą▒ąĖčé DLAB ąŠčćąĖčēąĄąĮ, ąĘą░ą┐ąĖčüčī ą┐ąŠ MMR-ą░ą┤čĆąĄčüčā ą┤ą╗čÅ čĆąĄą│ąĖčüčéčĆą░ UARTx_RBR ą┐ąŠą╝ąĄčüčéąĖčé ą┤ą░ąĮąĮčŗąĄ ą▓ čĆąĄą│ąĖčüčéčĆ UARTx_THR, ą░ čćč鹥ąĮąĖąĄ ą▓ąĄčĆąĮąĄčé ą┤ą░ąĮąĮčŗąĄ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ UARTx_RBR.

ąĀąĖčü. 12-6. UART Receive Buffer Register (UARTx_RBR).

ąĀąĄą│ąĖčüčéčĆ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ (UART interrupt enable register, UARTx_IER) ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ąĘą░ą┐čĆąŠčüąŠą▓ ą║ čüąĖčüč鹥ą╝ąĄ ą┤ą╗čÅ ąŠą┐čāčüč鹊賹ĄąĮąĖčÅ ąĖą╗ąĖ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĖčÅ čĆąĄą│ąĖčüčéčĆąŠą▓ ą┤ą░ąĮąĮčŗčģ UART (čüą╝. čĆąĖčü. 12-7). ąŚą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ čĆą░ą▒ąŠčéčŗ ą┐ąŠ ą┐čĆąĖąĮčåąĖą┐čā ąŠą┐čĆąŠčüą░ (ą▒ąĄąĘ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣), ą▓ čŹč鹊ą╝ čĆąĄą│ąĖčüčéčĆąĄ ąŠą▒čŗčćąĮąŠ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą▒ąĖčéčŗ ERBFI ąĖ/ąĖą╗ąĖ ETBEI.

ąĀąĖčü. 12-7. UART Interrupt Enable Register (UARTx_IER).

ELSI (Enable RX status interrupt). ąæąĖčé čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čüąŠčüč鹊čÅąĮąĖčÅ ą┐čĆąĖąĄą╝ąĮąŠą╣ ą╗ąĖąĮąĖąĖ. 0: ąĮąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣, 1: ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čüąŠčüč鹊čÅąĮąĖčÅ ą╗ąĖąĮąĖąĖ ą┐čĆąĖąĄą╝ą░, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą╗čÄą▒ąŠą╣ ąĖąĘ ą▒ąĖčé UARTx_LSR[4:1] (ą▒ąĖčéčŗ čüčéą░čéčāčüą░ BI, FE, PE, OE).

ERBFI (Enable Receive Buffer Full interrupt). ąæąĖčé čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĖčÄ ą▒čāč乥čĆą░ ą┐čĆąĖąĄą╝ą░. 0: ąĮąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣, 1: ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ RX, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé DR ą▓ čĆąĄą│ąĖčüčéčĆąĄ UARTx_LSR.

ETBEI (Enable Transmit Buffer Empty interrupt). ąæąĖčé čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ ąŠą┐čāčüč鹊賹ĄąĮąĖčÄ ą▒čāč乥čĆą░ ą┐ąĄčĆąĄą┤ą░čćąĖ. 0: ąĮąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣, 1: ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ TX, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé THRE ą▓ čĆąĄą│ąĖčüčéčĆąĄ UARTx_LSR.

ąŻčüčéą░ąĮąŠą▓ą║ą░ čŹč鹊ą│ąŠ čĆąĄą│ąĖčüčéčĆą░ ą▒ąĄąĘ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ čüąĖčüč鹥ą╝čŗ DMA ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ č鹊ą╝čā, čćč鹊 ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ UART č湥čĆąĄąĘ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą▒čāą┤ąĄčé ąŠą┐ąŠą▓ąĄčēą░čéčī ą┐čĆąŠčåąĄčüčüąŠčĆ ąŠ čüąŠą▒čŗčéąĖčÅčģ, čüą▓čÅąĘą░ąĮąĮčŗčģ čü ą┤ą░ąĮąĮčŗą╝ąĖ. ąöą╗čÅ ą┐čĆą░ą▓ąĖą╗čīąĮąŠą╣ čĆą░ą▒ąŠčéčŗ ą▓ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮčŗ čüąĖčüč鹥ą╝ąĮčŗąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ąĖ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮčŗ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ (ISR). ąöą╗čÅ ąŠą▒čĆą░čéąĮąŠą╣ čüąŠą▓ą╝ąĄčüčéąĖą╝ąŠčüčéąĖ UARTx_IIR ą▓čüąĄ ąĄčēąĄ ą║ąŠčĆčĆąĄą║čéąĮąŠ ąŠčéčĆą░ąČą░ąĄčé čüąŠčüč鹊čÅąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

ążčāąĮą║čåąĖąĖ UART čĆą░čüą┐čĆąĄą┤ąĄą╗ąĄąĮčŗ ą┐ąŠ 3 ąŠčéą┤ąĄą╗čīąĮčŗą╝ ą║ą░ąĮą░ą╗ą░ą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠą╣ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ, ą┐čĆąĖąĄą╝ą░ ą┤ą░ąĮąĮčŗčģ, čüąŠą▒čŗčéąĖą╣ čüąŠčüč鹊čÅąĮąĖčÅ ą╗ąĖąĮąĖąĖ, ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé č鹊ą│ąŠ, čĆą░ąĘčĆąĄčłąĄąĮ DMA ąĖą╗ąĖ ąĮąĄčé.

ąÜąŠą│ą┤ą░ čĆą░ąĘčĆąĄčłąĄąĮ DMA, UART ąĖčüą┐ąŠą╗čīąĘčāąĄčé DMA ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ą╝ąĄąČą┤čā ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ UART ąĖ ą┐ą░ą╝čÅčéčīčÄ ą┐čĆąŠčåąĄčüčüąŠčĆą░. ąöąŠčüčéčāą┐ąĮčŗ ąŠčéą┤ąĄą╗čīąĮčŗąĄ ą║ą░ąĮą░ą╗čŗ DMA ą┤ą╗čÅ ąŠą┐ąĄčĆą░čåąĖą╣ ą┐čĆąĖąĄą╝ą░ ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ. ą×ą▒čĆą░ą▒ąŠčéą║ą░ čüąŠą▒čŗčéąĖą╣ ąŠčłąĖą▒ą║ąĖ ą╗ąĖąĮąĖąĖ ą╝ąŠąČąĄčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮą░ ą┐ąŠą╗ąĮąŠčüčéčīčÄ ąŠčéą┤ąĄą╗čīąĮąŠ ąŠčé ą┐čĆąĖąĄą╝ą░/ą┐ąĄčĆąĄą┤ą░čćąĖ.

ąĀąĄą│ąĖčüčéčĆ UARTx_IER ąŠč鹊ą▒čĆą░ąČąĄąĮ ąĮą░ č鹊čé ąČąĄ čüą░ą╝čŗą╣ ą░ą┤čĆąĄčü MMR, čćč鹊 ąĖ čĆąĄą│ąĖčüčéčĆ UARTx_DLH. ą¦č鹊ą▒čŗ ą┐ąŠą╗čāčćąĖčéčī ą┤ąŠčüčéčāą┐ ą║ UARTx_IER, ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąŠčćąĖčēąĄąĮ ą▒ąĖčé DLAB ą▓ čĆąĄą│ąĖčüčéčĆąĄ UARTx_LCR.

ą¦č鹊ą▒čŗ čĆą░ąĘčĆąĄčłąĖčéčī UART DMA, čüąĮą░čćą░ą╗ą░ ąĮą░čüčéčĆą░ąĖą▓ą░čÄčéčüčÅ čüąĖčüč鹥ą╝ąĮčŗąĄ čāą┐čĆą░ą▓ą╗čÅčÄčēąĖąĄ čĆąĄą│ąĖčüčéčĆčŗ DMA [3], ąĖ ąĘą░č鹥ą╝ čĆą░ąĘčĆąĄčłą░čÄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ UART čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčé ERBFI ąĖ/ąĖą╗ąĖ ETBEI ą▓ čĆąĄą│ąĖčüčéčĆąĄ UARTx_IER. ą¤čĆąĖčćąĖąĮą░ ą▓ č鹊ą╝, čćč鹊 ą╗ąĖąĮąĖąĖ ąĘą░ą┐čĆąŠčüą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤čāą▒ą╗ąĖčĆčāčÄčéčüčÅ ą║ą░ą║ ą╗ąĖąĮąĖąĖ ąĘą░ą┐čĆąŠčüą░ DMA. ąÆ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé č鹊ą│ąŠ, čĆą░ąĘčĆąĄčłąĄąĮ DMA ąĖą╗ąĖ ąĮąĄčé ą┐čĆąĖ ą┐čĆąĖąĄą╝ąĄ čŹčéąĖčģ ąĘą░ą┐čĆąŠčüąŠą▓, ą▒ą╗ąŠą║ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ DMA ą╗ąĖą▒ąŠ ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ą┐čĆčÅą╝ąŠą╣ ą┤ąŠčüčéčāą┐ ą║ ą┐ą░ą╝čÅčéąĖ, ą╗ąĖą▒ąŠ ą┐ąĄčĆąĄą┤ą░ąĄčé ąĘą░ą┐čĆąŠčü ą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ UART č湥čĆąĄąĘ ą▒ą╗ąŠą║ čüąĖčüč鹥ą╝ąĮąŠą╣ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. ą×ą┤ąĮą░ą║ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠčłąĖą▒ą║ąĖ UART ą▓čüąĄą│ą┤ą░ ą┐čĆąĖčģąŠą┤ąĖčé ąĮą░ą┐čĆčÅą╝čāčÄ ą▓ ą▒ą╗ąŠą║ čüąĖčüč鹥ą╝ąĮąŠą╣ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣, ą┐ąŠą╗ąĮąŠčüčéčīčÄ ą╝ąĖąĮčāčÅ ą▒ą╗ąŠą║ DMA.

ąæąĖčé ELSI čĆą░ąĘčĆąĄčłą░ąĄčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĮą░ ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠą╝ ą║ą░ąĮą░ą╗ąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą║ąŠą│ą┤ą░ ą▓ąŠąĘąĮąĖą║ą░ąĄčé ą╗čÄą▒ąŠąĄ ąĖąĘ čüą╗ąĄą┤čāčÄčēąĖčģ čāčüą╗ąŠą▓ąĖą╣ ą┐ąŠ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╝ ą▒ąĖčéą░ą╝ ą▓ čĆąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ ą╗ąĖąĮąĖąĖ UARTx_LSR:

ŌĆó Receive overrun error (OE), ąŠčłąĖą▒ą║ą░ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ ą┐čĆąĖąĄą╝ą░

ŌĆó Receive parity error (PE), ąŠčłąĖą▒ą║ą░ č湥čéąĮąŠčüčéąĖ ą┐čĆąĖąĄą╝ą░

ŌĆó Receive framing error (FE), ąŠčłąĖą▒ą║ą░ čäčĆąĄą╣ą╝ą░ ą┐čĆąĖąĄą╝ą░

ŌĆó Break interrupt (BI), čüąĖą│ąĮą░ą╗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠč鹊ą║ą░ ą┤ą░ąĮąĮčŗčģ ąĮą░ ą┐čĆąĖąĄą╝ąĄ

ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé ETBEI ą▓ čĆąĄą│ąĖčüčéčĆąĄ UARTx_IER, ą╝ąŠą┤čāą╗čī UART ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ ą▓čŗą┤ą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĖą╗ąĖ ąĘą░ą┐čĆąŠčü DMA. ąÜąŠą│ą┤ą░ ąĖąĮąĖčåąĖąĖčĆčāąĄčéčüčÅ ą┐ąĄčĆąĄą┤ą░čćą░ čüčéčĆąŠą║ąĖ (ąĖą╗ąĖ ą▒ą╗ąŠą║ą░ ą┤ą░ąĮąĮčŗčģ), č鹊 ąĮąĄ čéčĆąĄą▒čāąĄčéčüčÅ ąĮąĖą║ą░ą║ą░čÅ čüą┐ąĄčåąĖą░ą╗čīąĮą░čÅ ąŠą▒čĆą░ą▒ąŠčéą║ą░ ą┤ą╗čÅ ą┐ąĄčĆą▓ąŠą│ąŠ čüąĖą╝ą▓ąŠą╗ą░. ąŻčüčéą░ąĮąŠą▓ąĖč鹥 ą▒ąĖčé ETBEI, ąĖ ą┐ąŠąĘą▓ąŠą╗čīč鹥 ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝ąĄ ISR ąĘą░ą│čĆčāąĘąĖčéčī ą┐ąĄčĆą▓čŗą╣ čüąĖą╝ą▓ąŠą╗ ąĖąĘ ą┐ą░ą╝čÅčéąĖ ąĖ ąĘą░ą┐ąĖčüą░čéčī ąĄą│ąŠ ą▓ čĆąĄą│ąĖčüčéčĆ UARTx_THR, ą║ą░ą║ ąŠą▒čŗčćąĮąŠ. ąĪąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ, ą▒ąĖčé ETBEI ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąŠčćąĖčēąĄąĮ, ąĄčüą╗ąĖ ąĘą░ą▓ąĄčĆčłąĄąĮą░ ą┐ąĄčĆąĄą┤ą░čćą░ čüčéčĆąŠą║ąĖ.

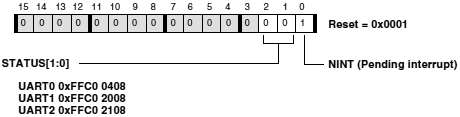

ą¤ąŠ čüąŠąŠą▒čĆą░ąČąĄąĮąĖčÅą╝ čüąŠą▓ą╝ąĄčüčéąĖą╝ąŠčüčéąĖ ą▓čüąĄ ąĄčēąĄ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčéčüčÅ čĆąĄą│ąĖčüčéčĆ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░čåąĖąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ (UART interrupt identification register, UARTx_IIR), ą║ąŠč鹊čĆčŗą╣ ąŠčéčĆą░ąČą░ąĄčé čüąŠčüč鹊čÅąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ UART. ąĪčéą░ąĮą┤ą░čĆčéąĮčŗą╣ ą╝ąĄč鹊ą┤ čĆą░ą▒ąŠčéčŗ čü UART (ąĮą░ą┐čĆąĖą╝ąĄčĆ, ą║ą░ą║ąŠą╣-č鹊 ą│ąŠč鹊ą▓čŗą╣ ąĖčüčģąŠą┤ąĮčŗą╣ ą║ąŠą┤, ą║ąŠč鹊čĆčŗą╣ čā ąÆą░čü ąĄčüčéčī ąĖ ąĄą│ąŠ ąĮčāąČąĮąŠ ą┐ąŠ ą║ą░ą║ąĖą╝-č鹊 ą┐čĆąĖčćąĖąĮą░ą╝ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī) ą╝ąŠąČąĄčé ą┐ąŠčéčĆąĄą▒ąŠą▓ą░čéčī ąŠą▒čŖąĄą┤ąĖąĮąĄąĮąĖąĄ ą▓čüąĄčģ ąĖčüč鹊čćąĮąĖą║ąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ąĮą░ 1 ą║ą░ąĮą░ą╗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣, ąĖ ąŠą▒čüą╗čāąČąĖą▓ą░čéčī ąĖčģ ą▓ ąŠą┤ąĮąŠą╝ ISR. ąŁč鹊 ą╝ąŠąČąĮąŠ ą┤ąŠčüčéąĖčćčī ą┐čāč鹥ą╝ ą│ą╗ąŠą▒ą░ą╗čīąĮąŠą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ ą▓čüąĄčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ UART ąĮą░ ąŠą┤ąĖąĮ ąĖ č鹊čé ąČąĄ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ ISR, čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ čüąĖčüč鹥ą╝ąĮčŗčģ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ (system interrupt controllers, SICx).

ąæčāą┤čāčćąĖ ąŠčćąĖčēąĄąĮąĮčŗą╝, ą▒ąĖčé ąŠąČąĖą┤ą░čÄčēąĄą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (pending interrupt bit, NINT) čüąĖą│ąĮą░ą╗ąĖąĘąĖčĆčāąĄčé ąŠ č鹊ą╝, čćč鹊 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠąČąĖą┤ą░ąĄčé ąŠą▒čĆą░ą▒ąŠčéą║ąĖ. ą¤ąŠą╗ąĄ STATUS ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąŠąČąĖą┤ą░čÄčēąĄąĄ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, čā ą║ąŠč鹊čĆąŠą│ąŠ čüą░ą╝čŗą╣ ą▓čŗčüąŠą║ąĖą╣ ą┐čĆąĖąŠčĆąĖč鹥čé; ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠą┐čāčüč鹊賹ĄąĮąĖčÅ UARTx_THR ąĖą╝ąĄąĄčé čüą░ą╝čŗą╣ ąĮąĖąĘą║ąĖą╣ ą┐čĆąĖąŠčĆąĖč鹥čé. ąÆ č鹊ą╝ čüą╗čāčćą░ąĄ, ą║ąŠą│ą┤ą░ čüąĖą│ąĮą░ą╗ąĖąĘąĖčĆčāčÄčé čüčĆą░ąĘčā ąŠą▒ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, UARTx_IIR čćąĖčéą░ąĄčéčüčÅ ą║ą░ą║ 0x06.

ąÜąŠą│ą┤ą░ ąŠąČąĖą┤ą░ąĄčé ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ UART, ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (ISR) ąĮčāąČą┤ą░ąĄčéčüčÅ ą▓ čÅą▓ąĮąŠą╣ ąŠčćąĖčüčéą║ąĄ ąĘą░čēąĄą╗ą║ąĮčāč鹊ą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĖ. ąØąĖąČąĄ ąĮą░ čĆąĖčü. 12-8 ą┐ąŠą║ą░ąĘą░ąĮčŗ ąĘą░čēąĄą╗ą║ąĖą▓ą░ąĄą╝čŗąĄ ą▒ąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ UARTx_IIR, ąĖ ąĮąĖąČąĄ ą▓ ąŠą┐ąĖčüą░ąĮąĖąĖ ą▒ąĖčé ą┐ąŠą║ą░ąĘą░ąĮąŠ, ą║ą░ą║ ąĖąĘ ąĮčāąČąĮąŠ ąŠčćąĖčēą░čéčī.

ąĀąĖčü. 12-8. UART Interrupt Identification Register (UARTx_IIR).

STATUS[1:0]. ą×čüąĮąŠą▓ąĮčŗąĄ ąĘą░čēąĄą╗ą║ąĖ čüąŠčüč鹊čÅąĮąĖčÅ.

00: ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ

01: čĆąĄą│ąĖčüčéčĆ UARTx_THR ą┐čāčüčé. ąŚą░ą┐ąĖčüčī UARTx_THR ąĖą╗ąĖ čćč鹥ąĮąĖąĄ UARTx_IIR ąŠčćąĖčüčéąĖčé ąĘą░ą┐čĆąŠčü ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

10: ą┐čĆąĖąĮčÅčéčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą│ąŠč鹊ą▓čŗ ą║ čćč鹥ąĮąĖčÄ. ą¦č鹥ąĮąĖąĄ UARTx_RBR ąŠčćąĖčüčéąĖčé ąĘą░ą┐čĆąŠčü ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

11: ąĖąĘą╝ąĄąĮąĄąĮąĖąĄ čüąŠčüč鹊čÅąĮąĖčÅ ą╗ąĖąĮąĖąĖ ą┐čĆąĖąĄą╝ą░. ą¦č鹥ąĮąĖąĄ UARTx_LSR ąŠčćąĖčüčéąĖčé ąĘą░ą┐čĆąŠčü ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

ąŚą░ą┐čĆąŠčü ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ TX ąŠčćąĖčēą░ąĄčéčüčÅ ąĘą░ą┐ąĖčüčīčÄ ąĮąŠą▓čŗčģ ą┤ą░ąĮąĮčŗčģ ą▓ čĆąĄą│ąĖčüčéčĆ UARTx_THR ąĖą╗ąĖ čćč鹥ąĮąĖąĄą╝ čĆąĄą│ąĖčüčéčĆą░ UARTx_IIR. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ ąĮą░ čüą┐ąĄčåąĖą░ą╗čīąĮčāčÄ čĆąŠą╗čī čćč鹥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ UARTx_IIR ą▓ č鹊ą╝ čüą╗čāčćą░ąĄ, ą║ąŠą│ą┤ą░ ISR ąĮąĄ ąČąĄą╗ą░ąĄčé ą▒ąŠą╗čīčłąĄ ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī ą┤ą░ąĮąĮčŗąĄ. ąĢčüą╗ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠąĄ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖąĄ ąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ą┐ąĄčĆąĄą┤ą░čćčā, ąŠąĮąŠ ą┤ąŠą╗ąČąĮąŠ ą┐čĆąŠčćąĖčéą░čéčī UARTx_IIR ą┤ą╗čÅ čüą▒čĆąŠčüą░ ąĘą░ą┐čĆąŠčüą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ą¤ąŠą║ą░ čĆąĄą│ąĖčüčéčĆ UARTx_IIR čćąĖčéą░ąĄčéčüčÅ ą║ą░ą║ 0x04 ąĖą╗ąĖ 0x06 (čŹč鹊 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ąŠąČąĖą┤ą░ąĄčé ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┤čĆčāą│ąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą▒ąŠą╗ąĄąĄ ą▓čŗčüąŠą║ąĖą╝ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝), ąĘą░čēąĄą╗ą║ą░ ąŠą┐čāčüč鹊賹ĄąĮąĖčÅ UARTx_THR ąĮąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠčćąĖčēąĄąĮą░ čćč鹥ąĮąĖąĄą╝ UARTx_IIR.

ą£ąŠąČąĄčé ą▓ąŠąĘąĮąĖą║ąĮčāčéčī deadlock (ą▒ąĄąĘą▓čŗčģąŠą┤ąĮą░čÅ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ą░ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ), ąĄčüą╗ąĖ ą╗ąĖą▒ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čüąŠčüč鹊čÅąĮąĖčÅ ą╗ąĖąĮąĖąĖ, ą╗ąĖą▒ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐čĆąĖąĄą╝ą░ ą┤ą░ąĮąĮčŗčģ ą▒čŗą╗ąŠ ąĮą░ąĘąĮą░č湥ąĮąŠ čü ą╝ąĄąĮčīčłąĖą╝ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝ ą╝ąĄąĮčīčłąĄ (ąĮą░ąĘąĮą░č湥ąĮąĖąĄ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą▓ ą┤ąĄą╗ą░ąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄą╝ SICx), č湥ą╝ čā ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠą┐čāčüč鹊賹ĄąĮąĖčÅ ą▒čāč乥čĆą░ ą┐ąĄčĆąĄą┤ą░čćąĖ. ą¦č鹊ą▒čŗ ąĖąĘą▒ąĄąČą░čéčī čéą░ą║ąŠą╣ čüąĖčéčāą░čåąĖąĖ, ą▓čüąĄą│ą┤ą░ ąĮą░ąĘąĮą░čćą░ą╣č鹥 čüą░ą╝ąŠąĄ ąĮąĖąĘą║ąŠąĄ ą┐ąŠ ą┐čĆąĖąŠčĆąĖč鹥čéčā ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čüčĆąĄą┤ąĖ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą▓ UART čüąŠą▒čŗčéąĖčÄ ąŠą┐čāčüč鹊賹ĄąĮąĖčÅ ą▒čāč乥čĆą░ UARTx_THR.

ąśąĘ-ąĘą░ ą┤ąĄčüčéčĆčāą║čéąĖą▓ąĮąŠą╣ ą┐čĆąĖčĆąŠą┤čŗ čŹčéąĖčģ ąŠą┐ąĄčĆą░čåąĖą╣ čćč鹥ąĮąĖčÅ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą┐čĆąĄą┤ą┐čĆąĖąĮčÅčéčŗ čüą┐ąĄčåąĖą░ą╗čīąĮčŗąĄ ą╝ąĄčĆčŗ. ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčāčÄ ąĖąĮč乊čĆą╝ą░čåąĖčÄ čüą╝. ą▓ čĆą░ąĘą┤ąĄą╗ą░čģ "ąĪą┐ąĄą║čāą╗čÅčéąĖą▓ąĮąŠąĄ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ čćč鹥ąĮąĖčÅ ą┐ą░ą╝čÅčéąĖ" ąĖ "ą¤ąŠą▓ąĄą┤ąĄąĮąĖąĄ čćč鹥ąĮąĖčÅ ą┐ą░ą╝čÅčéąĖ ą┐ąŠ čāčüą╗ąŠą▓ąĖčÄ" čüčéą░čéčīąĖ [5].

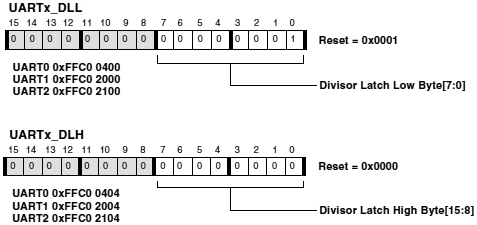

ą¦ą░čüč鹊čéą░ čüą╗ąĄą┤ąŠą▓ą░ąĮąĖčÅ ą▒ąĖčé ąĘą░ą▓ąĖčüąĖčé ąŠčé čüąĖčüč鹥ą╝ąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ (system clock, SCLK) ąĖ ąĘąĮą░č湥ąĮąĖčÅ 16-čĆą░ąĘčĆčÅą┤ąĮąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░ ą┤ą╗čÅ ąĮą░čüčéčĆąŠą╣ą║ąĖ ą┤ąĄą╗ąĖč鹥ą╗čÅ (divisor). ąŚąĮą░č湥ąĮąĖąĄ divisor ą┐ąŠą┤ąĄą╗ąĄąĮąŠ ąĮą░ ą┤ą▓ą░ ą▒ą░ą╣čéą░ - čĆąĄą│ąĖčüčéčĆ ą╝ą╗ą░ą┤čłąĄą│ąŠ ą▒ą░ą╣čéą░ ąĘą░čēąĄą╗ą║ąĖ ą┤ąĄą╗ąĖč鹥ą╗čÅ (UART divisor latch low byte register, UART_DLL) ąĖ čĆąĄą│ąĖčüčéčĆ čüčéą░čĆčłąĄą│ąŠ ą▒ą░ą╣čéą░ ąĘą░čēąĄą╗ą║ąĖ ą┤ąĄą╗ąĖč鹥ą╗čÅ (UART divisor latch high byte register, UARTx_DLH). ąŁčéąĖ čĆąĄą│ąĖčüčéčĆčŗ ą▓ą╝ąĄčüč鹥 č乊čĆą╝ąĖčĆčāąĄčé 16-čĆą░ąĘčĆčÅą┤ąĮčŗą╣ divisor (čüą╝. čĆąĖčü. 12-9). ą¦ą░čüč鹊čéą░ čüą╗ąĄą┤ąŠą▓ą░ąĮąĖčÅ ą▒ąĖčé, ąĖą╗ąĖ čüą║ąŠčĆąŠčüčéčī (baud rate) ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗčćąĖčüą╗ąĄąĮą░ ą┐ąŠ čüą╗ąĄą┤čāčÄčēąĄą╝čā ą▓čŗčĆą░ąČąĄąĮąĖčÄ:

BAUD RATE = SCLK/(16 x divisor)

ąĢčüą╗ąĖ ąŠą▒ą░ čĆąĄą│ąĖčüčéčĆą░, ąĖ UARTx_DLL, ąĖ UARTx_DLH čĆą░ą▓ąĮčŗ 0, č鹊 divisor == 65536.

ąĀąĖčü. 12-9. UART Divisor Latch Low Byte Register (UARTx_DLL) ąĖ UART Divisor Latch High Byte Register (UARTx_DLH).

ąĀąĄą│ąĖčüčéčĆ UART_DLL ąŠč鹊ą▒čĆą░ąČąĄąĮ ąĮą░ č鹊čé ąČąĄ MMR-ą░ą┤čĆąĄčü, čćč鹊 ąĖ čĆąĄą│ąĖčüčéčĆčŗ UARTx_THR ąĖ UARTx_RBR. ąĀąĄą│ąĖčüčéčĆ UARTx_DLH ąŠč鹊ą▒čĆą░ąČąĄąĮ ąĮą░ č鹊čé ąČąĄ čüą░ą╝čŗą╣ MMR-ą░ą┤čĆąĄčü, čćč鹊 ąĖ čĆąĄą│ąĖčüčéčĆ UARTx_IER. ąöąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé DLAB ą▓ čĆąĄą│ąĖčüčéčĆąĄ UARTx_LCR, čćč鹊ą▒čŗ ą╝ąŠąČąĮąŠ ą▒čŗą╗ąŠ ą┐ąŠą╗čāčćąĖčéčī ą┤ąŠčüčéčāą┐ ą║ čĆąĄą│ąĖčüčéčĆą░ą╝ ąĘą░čēąĄą╗ą║ąĖ UART divisor. ą¤ąŠčüą║ąŠą╗čīą║čā čāčüčéą░ąĮąŠą▓ą║ą░ divisor ąŠą▒čŗčćąĮąŠ ą┤ąĄą╗ą░ąĄčéčüčÅ ąŠą┤ąĖąĮ čĆą░ąĘ ą▓ ą╝ąŠą╝ąĄąĮčé ąĮą░čüčéčĆąŠą╣ą║ąĖ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓ UART ą┐ąĄčĆąĄą┤ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝, č鹊 čéą░ą║ą░čÅ ą░ą┤čĆąĄčüą░čåąĖčÅ ąĮąĄ čüąŠąĘą┤ą░ąĄčé ą┐čĆąŠą▒ą╗ąĄą╝ ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ ą║ ą▒čāč乥čĆą░ą╝ ą┤ą░ąĮąĮčŗčģ UART ąĖ ą║ čĆąĄą│ąĖčüčéčĆčā čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣.

ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 16-ą▒ąĖčéąĮčŗą╣ divisor ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ąĮą░čüčéčĆąŠąĄąĮ ąĘąĮą░č湥ąĮąĖčÅą╝ąĖ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ čĆąĄą│ąĖčüčéčĆąŠą▓ UARTx_DLH ąĖ UARTx_DLL, ą▓ čĆąĄąĘčāą╗čīčéą░č鹥 č湥ą│ąŠ ą┐ąŠą╗čāčćą░ąĄčéčüčÅ 0x0001, ąĖ UART ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ čĆą░ą▒ąŠčéą░ąĄčé ąĮą░ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠ ą▓ąŠąĘą╝ąŠąČąĮąŠą╣ čüą║ąŠčĆąŠčüčéąĖ. ąĢčüą╗ąĖ UART ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ, ąĘą░ą┐čĆąĄčé čéą░ą║č鹊ą▓ UART 菹║ąŠąĮąŠą╝ąĖčé 菹ĮąĄčĆą│ąĖčÄ, ą┐ąŠčéčĆąĄą▒ą╗čÅąĄą╝čāčÄ ąŠčé ąĖčüč鹊čćąĮąĖą║ą░ ą┐ąĖčéą░ąĮąĖčÅ. ąĀąĄą│ąĖčüčéčĆčŗ UARTx_DLH ąĖ UARTx_DLL ą╝ąŠą│čāčé ą▒čŗčéčī ąĮą░čüčéčĆąŠąĄąĮčŗ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╝ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖąĄą╝ ą┤ąŠ ąĖą╗ąĖ ą┐ąŠčüą╗ąĄ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ UCEN.

ąÆ čéą░ą▒ą╗ąĖčåąĄ 12-1 ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮčŗ ą┐čĆąĖą╝ąĄčĆčŗ ą║ąŠčŹčäčäąĖčåąĖąĄąĮč鹊ą▓ ą┤ąĄą╗ąĄąĮąĖčÅ divide, čéčĆąĄą▒čāąĄą╝čŗąĄ ą┤ą╗čÅ ą┐ąŠą┤ą┤ąĄčƹȹ║ąĖ ąĮą░ąĖą▒ąŠą╗ąĄąĄ čĆą░čüą┐čĆąŠčüčéčĆą░ąĮąĄąĮąĮčŗčģ čüčéą░ąĮą┤ą░čĆčéąĮčŗčģ čüą║ąŠčĆąŠčüč鹥ą╣.

ąóą░ą▒ą╗ąĖčåą░ 12-1. ą¤čĆąĖą╝ąĄčĆčŗ UART Baud Rate (čüą║ąŠčĆąŠčüčéąĖ ą┐ąŠč鹊ą║ą░ ą▒ąĖčé) ą┤ą╗čÅ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ čüąĖčüč鹥ą╝ąĮąŠą╣ čłąĖąĮčŗ (SCLK) 100 ą£ąōčå.

| ąĪą║ąŠčĆąŠčüčéčī |

DL |

ąĀąĄą░ą╗čīąĮą░čÅ čüą║ąŠčĆąŠčüčéčī |

% ąŠčłąĖą▒ą║ąĖ |

| 2400 |

2604 |

2400.15 |

0.006 |

| 4800 |

1302 |

4800.31 |

0.007 |

| 9600 |

651 |

9600.61 |

0.006 |

| 19200 |

326 |

19171.78 |

0.147 |

| 38400 |

163 |

38343.56 |

0.147 |

| 57600 |

109 |

57339.45 |

0.452 |

| 115200 |

54 |

115740.74 |

0.469 |

| 921600 |

7 |

892857.14 |

3.119 |

| 6250000 |

1 |

6250000 |

- |

ąóčēą░č鹥ą╗čīąĮąŠ ą▓čŗą▒ąĖčĆą░ą╣č鹥 čćą░čüč鹊čéčā ą┤ą╗čÅ SCLK, ą┐ąŠč鹊ą╝čā čćč鹊 čŹč鹊 ą┐ąŠąĘą▓ąŠą╗ąĖčé č鹊čćąĮąĄąĄ ą▓čŗą┤ąĄčƹȹ░čéčī čĆčÅą┤ čüčéą░ąĮą┤ą░čĆčéąĮčŗčģ čüą║ąŠčĆąŠčüč鹥ą╣ RS-232.

ąĪąŠą┤ąĄčƹȹĖą╝ąŠąĄ 8-ą▒ąĖčéąĮąŠą│ąŠ UART scratch register (UARTx_SCR), ą║ąŠč鹊čĆčŗąĄ ą┐ąŠą║ą░ąĘą░ąĮ ąĮą░ čĆąĖčü. 12-10, ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ čĆą░ą▓ąĮąŠ 0x00. ą×ąĮ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą║ą░ą║ čģčĆą░ąĮąĖą╗ąĖčēąĄ ą┤ą░ąĮąĮčŗčģ ąŠą▒čēąĄą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ, ąĖ ąŠąĮ ąĮąĖą║ą░ą║ ąĮąĄ čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéčāčĆąŠą╣ UART.

ąĀąĖčü. 12-10. UART Scratch Register (UARTx_SCR).

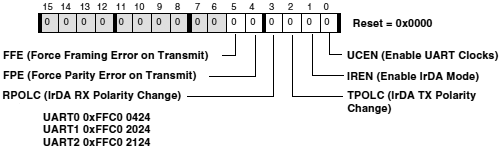

ąĀąĄą│ąĖčüčéčĆ ąŠą▒čēąĄą│ąŠ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ UART (UART global control register, UARTx_GCTL) čüąŠą┤ąĄčƹȹĖčé ą▒ąĖčé čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┤ą╗čÅ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ UART ąĖ ą┤ą╗čÅ ą▓ą║ą╗čÄč湥ąĮąĖčÅ čĆąĄąČąĖą╝ą░ IrDA.

ąĀąĖčü. 12-11. UART Global Control Register (UARTx_GCTL).

FFE (Force Framing Error on Transmit). 1: ą┐čĆąĖąĮčāą┤ąĖč鹥ą╗čīąĮąŠ ą▓čŗčüčéą░ą▓ąĖčéčī ąŠčłąĖą▒ą║čā, 0: ąĮąŠčĆą╝ą░ą╗čīąĮąŠąĄ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĄ.

FPE (Force Parity Error on Transmit). 1: ą┐čĆąĖąĮčāą┤ąĖč鹥ą╗čīąĮąŠ ą▓čŗčüčéą░ą▓ąĖčéčī ąŠčłąĖą▒ą║čā, 0: ąĮąŠčĆą╝ą░ą╗čīąĮąŠąĄ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĄ.

RPOLC (IrDA RX Polarity Change). 1: čüąŠčüč鹊čÅąĮąĖčÄ ąŠąČąĖą┤ą░ąĮąĖčÅ ą╗ąĖąĮąĖąĖ ą┐čĆąĖąĄą╝ą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ą╗ąŠą│. 1, 0: čüąŠčüč鹊čÅąĮąĖčÄ ąŠąČąĖą┤ą░ąĮąĖčÅ ą╗ąĖąĮąĖąĖ ą┐čĆąĖąĄą╝ą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ą╗ąŠą│. 0.

TPOLC (IrDA TX Polarity Change). 1: čüąŠčüč鹊čÅąĮąĖčÄ ąŠąČąĖą┤ą░ąĮąĖčÅ ą╗ąĖąĮąĖąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ą╗ąŠą│. 1, 0: čüąŠčüč鹊čÅąĮąĖčÄ ąŠąČąĖą┤ą░ąĮąĖčÅ ą╗ąĖąĮąĖąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ą╗ąŠą│. 0.

IREN (Enable IrDA Mode). 1: čĆą░ąĘčĆąĄčłąĖčéčī čĆąĄąČąĖą╝ IrDA, 0: ąĘą░ą┐čĆąĄčéąĖčéčī čĆąĄąČąĖą╝ IrDA.

UCEN (Enable UART Clocks). 1: čĆą░ąĘčĆąĄčłąĖčéčī čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ UART. 0: ąĘą░ą┐čĆąĄčéąĖčéčī čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ UART.

ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ą▒ąĖčé UCEN ąĮąĄ ą┐čĆąĖčüčāčéčüčéą▓ąŠą▓ą░ą╗ ą▓ ą┐čĆąĄą┤čŗą┤čāčēąĖčģ čĆąĄą░ą╗ąĖąĘą░čåąĖčÅčģ UART. ą×ąĮ ą▒čŗą╗ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮ ą┤ą╗čÅ čŹą║ąŠąĮąŠą╝ąĖąĖ 菹ĮąĄčĆą│ąĖąĖ ą┤ą╗čÅ čüą╗čāčćą░ąĄą▓, ą║ąŠą│ą┤ą░ UART ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ. ą¤čĆąĖ ą┐ąŠčĆčéąĖčĆąŠą▓ą░ąĮąĖąĖ ą║ąŠą┤ą░ čāą▒ąĄą┤ąĖč鹥čüčī, čćč鹊 čĆą░ąĘčĆąĄčłąĖą╗ąĖ čŹč鹊čé ą▒ąĖčé, ąĖąĮą░č湥 UART čĆą░ą▒ąŠčéą░čéčī ąĮąĄ ą▒čāą┤ąĄčé.

ąæąĖčéčŗ ąĮą░čüčéčĆąŠą╣ą║ąĖ ą┐ąŠą╗čÅčĆąĮąŠčüčéąĖ ą┐čĆąĖąĄą╝ą░ ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ RPOLC ąĖ TPOLC čĆą░ą▒ąŠčéą░čÄčé č鹊ą╗čīą║ąŠ ą▓ čüą╗čāčćą░ąĄ čĆą░ąĘčĆąĄčłąĄąĮąĮąŠą│ąŠ čĆąĄąČąĖą╝ą░ IrDA. ąöą▓ą░ ą▒ąĖčéą░ ą┐čĆąĖąĮčāą┤ąĖč鹥ą╗čīąĮąŠą│ąŠ ą▓čŗčüčéą░ą▓ą╗ąĄąĮąĖčÅ ąŠčłąĖą▒ą║ąĖ FPE ąĖ FFE ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮčŗ ą┤ą╗čÅ čåąĄą╗ąĄą╣ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ. ą×ąĮąĖ ą┐ąŠą╗ąĄąĘąĮčŗ ą┤ą╗čÅ ąŠčéą╗ą░ą┤ą║ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖčÅ, ąŠčüąŠą▒ąĄąĮąĮąŠ ą▓ čĆąĄąČąĖą╝ąĄ ąĘą░ą║ąŠą╗čīčåąŠą▓čŗą▓ą░ąĮąĖčÅ ą▓čģąŠą┤ą░ ąĮą░ ą▓čŗčģąŠą┤ (loop back mode).

[ąĀą░ą▒ąŠčéą░ čü UART ą▒ąĄąĘ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ DMA]

ąÆ čĆąĄąČąĖą╝ąĄ ą▒ąĄąĘ DMA ą┤ą░ąĮąĮčŗąĄ ą┐ąĄčĆąĄą╝ąĄčēą░čÄčéčüčÅ ą╝ąĄąČą┤čā čĆąĄą│ąĖčüčéčĆą░ą╝ąĖ UART ąĖ ą┐ą░ą╝čÅčéčīčÄ čÅą┤čĆąŠą╝ ą┐čĆąŠčåąĄčüčüąŠčĆą░. ą¦č鹊ą▒čŗ ą┐čĆąĄą┤ąŠčéą▓čĆą░čéąĖčéčī ą║ą░ą║čāčÄ-ą╗ąĖą▒ąŠ ą┐ąŠč鹥čĆčÄ ą┤ą░ąĮąĮčŗčģ ą▓ ąŠą▒čēąĄą╝ ą┐ąŠč鹊ą║ąĄ čĆąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ ą╗ąĖąĮąĖąĖ UARTx_LSR ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą┤ą▓ą░ čüą┐ąĄčåąĖą░ą╗čīąĮčŗčģ čäą╗ą░ą│ą░ THRE (čäą╗ą░ą│ ąŠą┐čāčüč鹊賹ĄąĮąĖčÅ ą▒čāč乥čĆą░) ąĖ DR (čäą╗ą░ą│ ą│ąŠč鹊ą▓ąĮąŠčüčéąĖ ą┤ą░ąĮąĮčŗčģ). ą¦č鹊ą▒čŗ ą┐ąĄčĆąĄą┤ą░čéčī čüąĖą╝ą▓ąŠą╗, ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ąĘą░ą│čĆčāąČą░ąĄčé ąĄą│ąŠ ą▓ čĆąĄą│ąĖčüčéčĆ UARTx_THR. ąöą╗čÅ č鹊ą│ąŠ, čćč鹊ą▒čŗ ą┐ąĄčĆąĄą┤ą░čéčī čüą╗ąĄą┤čāčÄčēąĖą╣ čüąĖą╝ą▓ąŠą╗, ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ ąŠčéčüą╗ąĄą┤ąĖčéčī čäą╗ą░ą│ ąŠą┐čāčüč鹊賹ĄąĮąĖčÅ ą▒čāč乥čĆą░, ąĖ čüąĮąŠą▓ą░ ąĘą░ą│čĆčāąĘąĖčéčī ą▓ čĆąĄą│ąĖčüčéčĆ UARTx_THR ą║ąŠą┤ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ąŠą│ąŠ čüąĖą╝ą▓ąŠą╗ą░. ą¤čĆąĖąĮčÅčéčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮčŗ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ UARTx_RBR, čäą░ą║čé ąĮą░ą╗ąĖčćąĖčÅ ąĮąŠą▓čŗčģ ą┤ą░ąĮąĮčŗčģ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮ čćč鹥ąĮąĖąĄą╝ ą▒ąĖčéą░ ą│ąŠč鹊ą▓ąĮąŠčüčéąĖ ą┤ą░ąĮąĮčŗčģ. ą¤čĆąŠčåąĄčüčüąŠčĆ ą┤ąŠą╗ąČąĄąĮ ą║ą░ąČą┤čŗą╣ čĆą░ąĘ čćąĖčéą░čéčī ąĖą╗ąĖ ąĘą░ą┐ąĖčüčŗą▓ą░čéčī č鹊ą╗čīą║ąŠ ąŠą┤ąĖąĮ čüąĖą╝ą▓ąŠą╗.

ążą╗ą░ą│ THRE čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą▒čāč乥čĆ ą┐ąĄčĆąĄą┤ą░čćąĖ UARTx_THR ą│ąŠč鹊ą▓ ą║ ąĘą░ą┐ąĖčüąĖ ąĮąŠą▓čŗčģ ą┤ą░ąĮąĮčŗčģ, ąĖ ąŠčćąĖčēą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą┐čĆąŠčåąĄčüčüąŠčĆ ąĘą░ą│čĆčāąĘąĖą╗ ą▓ UARTx_THR ąĮąŠą▓čŗąĄ ą┤ą░ąĮąĮčŗąĄ. ąŚą░ą┐ąĖčüčī UARTx_THR, ą║ąŠą│ą┤ą░ ąŠąĮ ąĄčēąĄ ąĮąĄ ąŠą┐čāčüč鹊賹Ėą╗čüčÅ, ą┐ąĄčĆąĄąĘą░ą┐ąĖčłąĄčé čĆąĄą│ąĖčüčéčĆ ąĮąŠą▓čŗą╝ ąĘąĮą░č湥ąĮąĖąĄą╝, ąĖ ą┐čĆąĄą┤čŗą┤čāčēąĖą╣ čüąĖą╝ą▓ąŠą╗ ąĮąĄ ą▒čāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ąĮ.

ążą╗ą░ą│ DR čüąĖą│ąĮą░ą╗ąĖąĘąĖčĆčāąĄčé, čćč鹊 ą▓ UARTx_RBR ą┐ąŠčÅą▓ąĖą╗ąĖčüčī ąĮąŠą▓čŗąĄ ą┤ą░ąĮąĮčŗąĄ. ąŁč鹊čé čäą╗ą░ą│ ąŠčćąĖčēą░ąĄčéčüčÅ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ, ą║ąŠą│ą┤ą░ ą┐čĆąŠčåąĄčüčüąŠčĆ čćąĖčéą░ąĄčé ąĖąĘ UARTx_RBR. ą¦č鹥ąĮąĖąĄ UARTx_RBR, ą┐čĆąŠąĖąĘąŠčłąĄą┤čłąĄąĄ ą┤ąŠ čāčüčéą░ąĮąŠą▓ą║ąĖ čäą╗ą░ą│ą░ DR ą▓ąŠąĘą▓čĆą░čéąĖčé ą┐čĆąĄą┤čŗą┤čāčēąĄąĄ ą┐čĆąĖąĮčÅč鹊ąĄ ąĘąĮą░č湥ąĮąĖąĄ. ąÜąŠą│ą┤ą░ UARTx_RBR ąĮąĄ ą▒čŗą╗ ą┐čĆąŠčćąĖčéą░ąĮ ą▓ąŠ ą▓čĆąĄą╝čÅ, ąĮąŠą▓čŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┐ąĄčĆąĄčéčĆčāčé č鹥, čćč鹊 čāąČąĄ ąĖą╝ąĄčÄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ UARTx_RBR, ąĖ ą▒čāą┤ąĄčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čäą╗ą░ą│ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ ą┐čĆąĖąĄą╝ą░ (overrun, OE).

ąĪ ąĘą░ą┐čĆąĄčēąĄąĮąĮčŗą╝ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅą╝ąĖ čŹčéąĖ čäą╗ą░ą│ąĖ čüąŠčüč鹊čÅąĮąĖčÅ ą┤ąŠą╗ąČąĮčŗ ą┐ąŠčüč鹊čÅąĮąĮąŠ, čåąĖą║ą╗ąĖč湥čüą║ąĖ ąŠą┐čĆą░čłąĖą▓ą░čéčīčüčÅ, čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ą╝ąŠą╝ąĄąĮčé ą▓čĆąĄą╝ąĄąĮąĖ, ą║ąŠą│ą┤ą░ ą┤ą░ąĮąĮčŗąĄ ą┤ąŠčüčéčāą┐ąĮčŗ ą┤ą╗čÅ ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖčÅ. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 čéą░ą║ąŠą╣ ąŠą┐čĆąŠčü ąĖąĮč鹥ąĮčüąĖą▓ąĮąŠ ąĘą░čéčĆą░ą│ąĖą▓ą░ąĄčé ą▓čŗčćąĖčüą╗ąĖč鹥ą╗čīąĮčŗą╣ čĆąĄčüčāčĆčü ą┐čĆąŠčåąĄčüčüąŠčĆą░, ą┐ąŠčŹč鹊ą╝čā čéą░ą║ąŠą╣ ą┐čĆąĖąĮčåąĖą┐ čĆą░ą▒ąŠčéčŗ ą▒ąĄąĘ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ąŠą▒čŗčćąĮąŠ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓ čüąĖčüč鹥ą╝ą░čģ čĆąĄą░ą╗čīąĮąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ čü čåąĖčäčĆąŠą▓ąŠą╣ ąŠą▒čĆą░ą▒ąŠčéą║ąŠą╣ čüąĖą│ąĮą░ą╗ąŠą▓. ą¤čĆąŠą│čĆą░ą╝ą╝ąĮąŠąĄ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖąĄ ą╝ąŠąČąĄčé ąĘą░ą┐ąĖčüą░čéčī ą┤ąŠ 2 čüą╗ąŠą▓ ą▓ čĆąĄą│ąĖčüčéčĆ UARTx_THR ą┐ąĄčĆąĄą┤ čĆą░ąĘčĆąĄčłąĄąĮąĖąĄą╝ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ UART. ąÜą░ą║ č鹊ą╗čīą║ąŠ ą▒čāą┤ąĄčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé UCEN, čŹčéąĖ 2 čüą╗ąŠą▓ą░ ą▒čāą┤čāčé ąŠčéą┐čĆą░ą▓ą╗ąĄąĮčŗ.

ąÉą╗čīč鹥čĆąĮą░čéąĖą▓ąĮąŠ ąĘą░ą┐ąĖčüąĖ ąĖ čćč鹥ąĮąĖčÅ UART ą╝ąŠą│čāčé ą▒čŗčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮčŗ ą▓ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ą░čģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (ISR). ą×čéą┤ąĄą╗čīąĮčŗąĄ ą╗ąĖąĮąĖąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮčŗ ą┤ą╗čÅ čüąŠą▒čŗčéąĖą╣ UART TX, UART RX ąĖ UART Error. ąĪąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ čŹčéąĖą╝ čüąŠą▒čŗčéąĖčÅą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą╝ąŠą│čāčé ą▒čŗčéčī ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮąŠ čĆą░ąĘčĆąĄčłąĄąĮčŗ ąĮą░čüčéčĆąŠą╣ą║ąŠą╣ čĆąĄą│ąĖčüčéčĆą░ UARTx_IER.

ą×ą▒čĆą░ą▒ąŠčéčćąĖą║ąĖ ISR ą╝ąŠą│čāčé ąŠčåąĄąĮąĖčéčī ą┐ąŠą╗ąĄ ą▒ąĖčé čüąŠčüč鹊čÅąĮąĖčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░čåąĖąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ UART (UARTx_IIR), čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ąĖčüč鹊čćąĮąĖą║, čüąĖą│ąĮą░ą╗ąĖąĘąĖčĆčāčÄčēąĖą╣ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄą╝. ąĢčüą╗ąĖ čüąĖą│ąĮą░ą╗ ą┐ąŠčüčéčāą┐ąĖą╗ ą▒ąŠą╗čīčłąĄ č湥ą╝ ąŠčé ąŠą┤ąĮąŠą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░, ą┐ąŠą╗ąĄ čüąŠčüč鹊čÅąĮąĖčÅ ą┐ąŠą║ą░ąČąĄčé ąŠą┤ąĖąĮ ąĖąĘ ąĮąĖčģ, čā ą║ąŠč鹊čĆąŠą│ąŠ ą▓čŗčłąĄ ą┐čĆąĖąŠčĆąĖč鹥čé. ą¤čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čéą░ą║ąČąĄ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĮą░ąĘąĮą░č湥ąĮčŗ ąĖ ą┤ąĄą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮčŗ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄą╝ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐čĆąŠčåąĄčüčüąŠčĆą░. ą×ą▒čĆą░ą▒ąŠčéčćąĖą║ąĖ ISR ą┤ąŠą╗ąČąĮčŗ čÅą▓ąĮąŠ ąŠčćąĖčüčéąĖčéčī ąĘą░čēąĄą╗ą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ UARTx_IIR, čüą╝. čĆąĖčü. 12-8.

[ąĀą░ą▒ąŠčéą░ čü UART č湥čĆąĄąĘ DMA]

ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ą▓čŗą┤ąĄą╗čÅčÄčéčüčÅ ąŠčéą┤ąĄą╗čīąĮčŗąĄ ą║ą░ąĮą░ą╗čŗ DMA ą┤ą╗čÅ ą┐čĆąĖąĄą╝ą░ (RX) ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ (TX), čćč鹊ą▒čŗ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ, ą▒ąĄąĘ ą┐čĆčÅą╝ąŠą│ąŠ čāčćą░čüčéąĖčÅ ą┐čĆąŠčåąĄčüčüąŠčĆą░, ą┐ąĄčĆąĄą╝ąĄčēą░čéčī ą┤ą░ąĮąĮčŗąĄ ą╝ąĄąČą┤čā ą░ą┐ą┐ą░čĆą░čéčāčĆąŠą╣ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ UART ąĖ ą┐ą░ą╝čÅčéčīčÄ ą┐čĆąŠčåąĄčüčüąŠčĆą░. ą¤čĆąŠą│čĆą░ą╝ą╝ąĮąŠąĄ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖąĄ ąĮąĄ ą┐ąĄčĆąĄą╝ąĄčēą░ąĄčé ą┤ą░ąĮąĮčŗąĄ, ą║ą░ą║ ą┐čĆąĖ čĆą░ą▒ąŠč鹥 ą▒ąĄąĘ DMA (ą┐ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅą╝ ąĖą╗ąĖ ą▒ąĄąĘ), ąŠąĮąŠ ą┐čĆąŠčüč鹊 ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮąŠ ąĮą░čüčéčĆą░ąĖą▓ą░ąĄčé ą┐ąŠą┤čģąŠą┤čÅčēąĄąĄ ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ ą╗ąĖą▒ąŠ č湥čĆąĄąĘ ą╝ąĄčģą░ąĮąĖąĘą╝ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą▓, ą╗ąĖą▒ąŠ ą▓ čĆąĄąČąĖą╝ąĄ ą░ą▓č鹊ą▒čāč乥čĆą░.

ąÆ ą║ą░ąĮą░ą╗ąĄ UART DMA ąĮąĄ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčéčüčÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ą▒čāč乥čĆąĖąĘą░čåąĖąĖ, čéą░ą║ čćč鹊 čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅ ą║ ąĘą░ą┤ąĄčƹȹ║ą░ą╝ ąŠčüčéą░čÄčéčüčÅ čéą░ą║ąĖą╝ąĖ ąČąĄ, ą║ą░ą║ ąĖ ą┤ą╗čÅ čĆąĄąČąĖą╝ą░ ą▒ąĄąĘ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ DMA. ą×ą┤ąĮą░ą║ąŠ č鹥ą┐ąĄčĆčī ąĘą░ą┤ąĄčƹȹ║ą░ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą░ą║čéąĖą▓ąĮąŠčüčéčīčÄ čłąĖąĮčŗ ąĖ ą╝ąĄčģą░ąĮąĖąĘą╝ąŠą╝ ą░čĆą▒ąĖčéčĆą░ąČą░, ąĖ ąĮą░ ąĘą░ą┤ąĄčƹȹ║čā ąĮąĄ ą▓ą╗ąĖčÅąĄčé ąĘą░ą│čĆčāąĘą║ą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą▓čŗčćąĖčüą╗ąĄąĮąĖčÅą╝ąĖ ąĖ ą┐čĆąĖąŠčĆąĖč鹥čéčŗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčāčÄ ąĖąĮč乊čĆą╝ą░čåąĖčÄ ą┐ąŠ DMA čüą╝. ą▓ čüčéą░čéčīąĄ [3].

ą×ą▒čĆą░ą▒ąŠčéčćąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ DMA ą┤ąŠą╗ąČąĄąĮ čÅą▓ąĮąŠ ąĘą░ą┐ąĖčüą░čéčī ąĄą┤ąĖąĮąĖčåčŗ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ čĆąĄą│ąĖčüčéčĆčŗ čüčéą░čéčāčüą░ DMA IRQ, čćč鹊ą▒čŗ ąŠčćąĖčüčéąĖčéčī ąĘą░čēąĄą╗ą║ąĮčāčéčŗą╣ ąĘą░ą┐čĆąŠčü ąĮą░ ąŠą▒čĆą░ą▒ąŠčéą║čā ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

ąöą╗čÅ č鹊ą│ąŠ, čćč鹊ą▒čŗ čĆą░ąĘčĆąĄčłąĖčéčī UART DMA, čüąĮą░čćą░ą╗ą░ ąĮą░čüčéčĆą░ąĖą▓ą░čÄčéčüčÅ čüąĖčüč鹥ą╝ąĮčŗąĄ čĆąĄą│ąĖčüčéčĆčŗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ DMA, ąĖ ąĘą░č鹥ą╝ čĆą░ąĘčĆąĄčłą░čÄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ UART ERBFI ąĖ/ąĖą╗ąĖ ETBEI ą▓ čĆąĄą│ąĖčüčéčĆąĄ UARTx_IER. ąóą░ą║ ąĮą░čüčéčĆą░ąĖą▓ą░ąĄčéčüčÅ DMA ą┐ąŠč鹊ą╝čā, čćč鹊 ą╗ąĖąĮąĖąĖ ąĘą░ą┐čĆąŠčüą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤čāą▒ą╗ąĖčĆčāčÄčéčüčÅ ą║ą░ą║ ą╗ąĖąĮąĖąĖ ąĘą░ą┐čĆąŠčüą░ DMA. ąÆ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé č鹊ą│ąŠ, čĆą░ąĘčĆąĄčłąĄąĮ DMA ąĖą╗ąĖ ąĮąĄčé, ą┐čĆąĖ ą┐ąŠčüčéčāą┐ą╗ąĄąĮąĖąĖ čŹčéąĖčģ ąĘą░ą┐čĆąŠčüąŠą▓ ą▒ą╗ąŠą║ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ DMA ą╗ąĖą▒ąŠ ą▒čāą┤ąĄčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ą┐čĆčÅą╝ąŠą╣ ą┤ąŠčüčéčāą┐ ą║ ą┐ą░ą╝čÅčéąĖ, ą╗ąĖą▒ąŠ ą┐ąĄčĆąĄą┤ą░čüčé ąĘą░ą┐čĆąŠčü ą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ UART ąĮą░ ą▒ą╗ąŠą║ąĄ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ čüąĖčüč鹥ą╝ąĮčŗčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. ą×ą┤ąĮą░ą║ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠčłąĖą▒ą║ąĖ UART ąĮą░ą┐čĆčÅą╝čāčÄ ą┐ąŠčüčéčāą┐ą░ąĄčé ą▓ ą▒ą╗ąŠą║ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ čüąĖčüč鹥ą╝ąĮčŗčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣, ą┐ąŠą╗ąĮąŠčüčéčīčÄ ą┐čĆąŠą┐čāčüą║ą░čÅ ą▒ą╗ąŠą║ DMA.

UART DMA ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé 8-čĆą░ąĘčĆčÅą┤ąĮąŠąĄ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĄ.

[ąĀą░ą▒ąŠčéą░ čü UART ą▓ čüą╝ąĄčłą░ąĮąĮčŗčģ čĆąĄąČąĖą╝ą░čģ]

ąĀąĄąČąĖą╝čŗ ą▒ąĄąĘ DMA ąĖ čü DMA ąĖčüą┐ąŠą╗čīąĘčāčÄčé čĆą░ąĘąĮčŗąĄ ą╝ąĄčģą░ąĮąĖąĘą╝čŗ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ. ąĪą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ, ą╗čÄą▒ąŠą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ąŠą▒ą╝ąĄąĮ ą┤ą░ąĮąĮčŗą╝ąĖ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ą▓ąĄčĆčłąĄąĮ ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ą▒čāą┤ąĄčé ą┐čĆąŠąĖąĘą▓ąĄą┤ąĄąĮąŠ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ąĖąĘ čĆąĄąČąĖą╝ą░ ą▒ąĄąĘ DMA ą▓ čĆąĄąČąĖą╝ čü DMA, ąĖą╗ąĖ ąĮą░ąŠą▒ąŠčĆąŠčé. ąöčĆčāą│ąĖą╝ąĖ čüą╗ąŠą▓ą░ą╝ąĖ, ą┐ąĄčĆąĄą┤ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄą╝ ąŠčé ą┐ąĄčĆąĄą┤ą░čćąĖ ą▒ąĄąĘ DMA ą║ ą┐ąĄčĆąĄą┤ą░čćąĖ č湥čĆąĄąĘ DMA ąĮčāąČąĮąŠ čāą▒ąĄą┤ąĖčéčīčüčÅ, čćč鹊 ąŠą▒ą░ čĆąĄą│ąĖčüčéčĆą░, ąĖ UARTx_THR, ąĖ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ (TSR) ą┐čāčüčéčŗ, ą┐čāč鹥ą╝ ą┐čĆąŠą▓ąĄčĆą║ąĖ ą▒ąĖč鹊ą▓ čüąŠčüč鹊čÅąĮąĖčÅ THRE ąĖ TEMT ą▓ čĆąĄą│ąĖčüčéčĆąĄ UARTx_LSR. ąśąĮą░č湥 ą┐čĆąŠčåąĄčüčüąŠčĆ ą▒čāą┤ąĄčé ąČą┤ą░čéčī, ą┐ąŠą║ą░ ąĮąĄ ąŠčćąĖčüčéąĖčéčüčÅ 2-ą▒ąĖčéąĮąŠąĄ ą┐ąŠą╗ąĄ čüąŠčüč鹊čÅąĮąĖčÅ ą▒čāč乥čĆą░ DMA ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╝ čĆąĄą│ąĖčüčéčĆąĄ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ UART DMA (UARTx_CONFIG_TX).

ą¤čĆąĖ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĖ ąĖąĘ DMA ą▓ čĆą░ą▒ąŠčéčā ą▒ąĄąĘ DMA čāą▒ąĄą┤ąĖč鹥čüčī, čćč鹊 ąŠą▒ą░ ą║ą░ąĮą░ą╗ą░ DMA - ą║ą░ąĮą░ą╗ DMA ą┐čĆąĖąĄą╝ą░ (RX) ąĖ ą║ą░ąĮą░ą╗ DMA ą┐ąĄčĆąĄą┤ą░čćąĖ (TX) - ą┐ąŠą╗ąĮąŠčüčéčīčÄ ą┐ąĄčĆąĄą┤ą░ą╗ąĖ čüą▓ąŠąĖ ą┤ą░ąĮąĮčŗąĄ, ą▓ą║ą╗čÄčćą░čÅ ą┤ą░ąĮąĮčŗąĄ, ą║ąŠč鹊čĆčŗąĄ čüąŠą┤ąĄčƹȹ░čéčüčÅ ą▓ čüč鹥ą║ą░čģ DMA FIFO. ąÆ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ DMA RX ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą┐ąŠčüą╗ąĄą┤ąĮąĄąĄ čüą╗ąŠą▓ąŠ ą┤ą░ąĮąĮčŗčģ ą▒čŗą╗ąŠ ąĘą░ą┐ąĖčüą░ąĮąŠ ą▓ ą┐ą░ą╝čÅčéčī (ąĖ ą┐ąŠą║ąĖąĮčāą╗ąŠ DMA FIFO), ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ DMA TX ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą┐ąŠčüą╗ąĄą┤ąĮąĄąĄ čüą╗ąŠą▓ąŠ ą┤ą░ąĮąĮčŗčģ ą┐ąŠą║ąĖąĮčāą╗ąŠ ą┐ą░ą╝čÅčéčī (ąĖ ą▓ąŠčłą╗ąŠ ą▓ DMA FIFO). ą¤čĆąŠčåąĄčüčüąŠčĆ ą┤ąŠą╗ąČąĄąĮ ą┐ąŠą┤ąŠąČą┤ą░čéčī, ą┐ąŠą║ą░ ąĮąĄ ąŠą┐čāčüč鹊賹ĖčéčüčÅ TX FIFO ą┐čāč鹥ą╝ ą┐čĆąŠą▓ąĄčĆą║ąĖ ą▒ąĖčéą░ čüąŠčüč鹊čÅąĮąĖčÅ DMA_RUN ą▓ ą║ą░ąĮą░ą╗ąĄ TX čĆąĄą│ąĖčüčéčĆą░ IRQ_STATUS - ą▒ąĖčé ą┤ąŠą╗ąČąĄąĮ ąŠčćąĖčüčéąĖčéčīčüčÅ, ąĖ č鹊ą╗čīą║ąŠ ą┐ąŠčüą╗ąĄ čŹč鹊ą│ąŠ ą╝ąŠąČąĮąŠ ą▒ąĄąĘąŠą┐ą░čüąĮąŠ ąĘą░ą┐čĆąĄčéąĖčéčī ą║ą░ąĮą░ą╗ DMA.

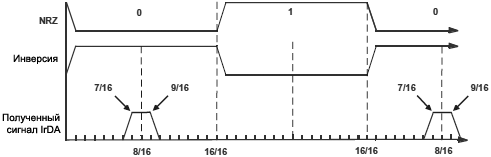

ą×čéą┤ąĄą╗čīąĮąŠ ąŠčé čüčéą░ąĮą┤ą░čĆčéąĮąŠą╣ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠčüčéąĖ RS-232/RS485, ą╝ąŠą┤čāą╗čī UART čéą░ą║ąČąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ą┐ąŠą╗čāą┤čāą┐ą╗ąĄą║čüąĮčŗą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ąŠą▒ą╝ąĄąĮ ą┤ą░ąĮąĮčŗą╝ąĖ č湥čĆąĄąĘ čüąĖą│ąĮą░ą╗čŗ ąĖąĮčäčĆą░ą║čĆą░čüąĮąŠą│ąŠ ą┤ąĖą░ą┐ą░ąĘąŠąĮą░ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü čĆąĄą║ąŠą╝ąĄąĮą┤ą░čåąĖčÅą╝ąĖ ąŠčé Infrared Data Association (IrDA). ążąĖąĘąĖč湥čüą║ąĖą╣ čüą╗ąŠą╣ ą┐čĆąŠč鹊ą║ąŠą╗ą░ ąĖąĘą▓ąĄčüč鹥ąĮ ą║ą░ą║ IrDA SIR (čüą║ąŠčĆąŠčüčéčī 9.6/115.2 Kbps), ąŠąĮ ąŠčüąĮąŠą▓ą░ąĮ ąĮą░ ą╝ąŠą┤čāą╗čÅčåąĖąĖ ą┐ąŠ ą┐čĆąĖąĮčåąĖą┐čā "ą▓ąŠąĘą▓čĆą░čéą░ ą║ ąĮčāą╗čÄ čü ąĖąĮą▓ąĄčĆčüąĖąĄą╣" (return-to-zero-inverted, RZI). ą£ąŠą┤čāą╗čÅčåąĖčÅ čü ą┐ąŠąĘąĖčåąĖąĄą╣ ąĖą╝ą┐čāą╗čīčüą░ (pulse position modulation) ąĮąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ.

ąĪ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ 16x čéą░ą║č鹊ą▓ čüą║ąŠčĆąŠčüčéąĖ ą┤ą░ąĮąĮčŗčģ, č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ ą╝ąŠą┤čāą╗čÅčåąĖąĖ RZI ą┤ąŠčüčéąĖą│ą░ąĄčéčüčÅ ą┐čāč鹥ą╝ ąĖąĮą▓ąĄčĆčéąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖ ą╝ąŠą┤čāą╗ąĖčĆąŠą▓ą░ąĮąĖčÅ ą║ąŠą┤ą░ "ą▒ąĄąĘ ą▓ąŠąĘą▓čĆą░čéą░ ą║ ąĮčāą╗čÄ" (non-return-to-zero, NRZ), ą║ąŠč鹊čĆčŗą╣ ąĮąŠčĆą╝ą░ą╗čīąĮąŠ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą╝ąŠą┤čāą╗ąĄą╝ UART. ąØą░ čüč鹊čĆąŠąĮąĄ ą┐čĆąĖąĄą╝ą░ 16x čéą░ą║čéčŗ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ ąŠą║ąĮą░ ą▓čŗą▒ąŠčĆą║ąĖ ąĖą╝ą┐čāą╗čīčüą░ IrDA, ąĖąĘ ą║ąŠč鹊čĆąŠą│ąŠ ą▓ąŠčüčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą║ąŠą┤ NRZ, ą╝ąŠą┤čāą╗ąĖčĆąŠą▓ą░ąĮąĮčŗą╣ RZI.

ą¤ąŠą┤ą┤ąĄčƹȹ║ą░ IrDA čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ IREN ą▓ čĆąĄą│ąĖčüčéčĆąĄ ąŠą▒čēąĄą│ąŠ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ UART (UART global control register, UARTx_GCTL). ą¤čĆąĖą╗ąŠąČąĄąĮąĖąĄ IrDA čéčĆąĄą▒čāąĄčé ą┐čĆąĖą╝ąĄąĮąĄąĮąĖčÅ ą▓ąĮąĄčłąĮąĖčģ čéčĆą░ąĮčüąĖą▓ąĄčĆąŠą▓.

ą×ą┐ąĖčüą░ąĮąĖąĄ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ IrDA. ą¦č鹊ą▒čŗ ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ąĖą╝ą┐čāą╗čīčü IrDA, ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗą╣ ą╝ąŠą┤čāą╗ąĄą╝ UART, čüąĮą░čćą░ą╗ą░ ąŠą▒čŗčćąĮčŗą╣ ą▓čŗą▓ąŠą┤ NRZ ąĖąĮą▓ąĄčĆčéąĖčĆčāąĄčéčüčÅ čéą░ą║, čćč鹊 0 ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą║ą░ą║ ąĖą╝ą┐čāą╗čīčü ą╗ąŠą│. 1 ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčīčÄ 16 ą┐ąĄčĆąĖąŠą┤ąŠą▓ čéą░ą║č鹊ą▓ UART, ąĖ 1 ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą║ą░ą║ ąĖą╝ą┐čāą╗čīčü ą╗ąŠą│. 0 ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčīčÄ 16 ą┐ąĄčĆąĖąŠą┤ąŠą▓ čéą░ą║č鹊ą▓ UART. ąŚą░č鹥ą╝ ąĮą░čćą░ą╗čīąĮčŗą╣ čüčĆąĄąĘ ąĖą╝ą┐čāą╗čīčüą░ ąĘą░ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ąĮą░ 6 ą┐ąĄčĆąĖąŠą┤ąŠą▓ čéą░ą║č鹊ą▓ UART. ą¤ąŠą┤ąŠą▒ąĮčŗą╝ ąŠą▒čĆą░ąĘąŠą╝ ąĘą░ą▓ąĄčĆčłą░čÄčēąĖą╣ čüčĆąĄąĘ ąĖą╝ą┐čāą╗čīčüą░ ąŠą▒čĆąĄąĘą░ąĄčéčüčÅ ąĮą░ 8 ą┐ąĄčĆąĖąŠą┤ąŠą▓ čéą░ą║č鹊ą▓ UART. ąÆ čĆąĄąĘčāą╗čīčéą░č鹥 ą┐ąŠą╗čāčćą░ąĄčéčüčÅ čüąĖą│ąĮą░ą╗ ąĖąĘąĮą░čćą░ą╗čīąĮąŠą│ąŠ 0 ą║ą░ą║ ąĖą╝ą┐čāą╗čīčü ą╗ąŠą│. 1 č鹊ą╗čīą║ąŠ ąĮą░ 3/16 ą┐ąĄčĆąĖąŠą┤ąŠą▓ čéą░ą║č鹊ą▓ ą▓ 16-čéą░ą║č鹊ą▓ąŠą╝ ą┐ąĄčĆąĖąŠą┤ąĄ UART. ąśą╝ą┐čāą╗čīčü čåąĄąĮčéčĆąĖčĆčāąĄčéčüčÅ ą▓ąŠąĘą╗ąĄ čüąĄčĆąĄą┤ąĖąĮčŗ ą▓čĆąĄą╝ąĄąĮąĖ ą▒ąĖčéą░, ą║ą░ą║ čŹč鹊 ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 12-12. ą¤ąŠą╗čāč湥ąĮąĮčŗą╣ ąĖą╝ą┐čāą╗čīčü IrDA ą┐ąŠčüčéčāą┐ą░ąĄčé ąĮą░ ą▓ąĮąĄčłąĮąĖą╣ ą┤čĆą░ą╣ą▓ąĄčĆ ąĖąĮčäčĆą░ą║čĆą░čüąĮąŠą│ąŠ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░.

ąĀąĖčü. 12-12. ąśą╝ą┐čāą╗čīčü ą┐ąĄčĆąĄą┤ą░čćąĖ IrDA.

ąŁč鹊čé ą╝ąĄč鹊ą┤ ą╝ąŠą┤čāą╗čÅčåąĖąĖ ą│ą░čĆą░ąĮčéąĖčĆčāąĄčé, čćč鹊 ą▓čŗčģąŠą┤ąĮą░čÅ čłąĖčĆąĖąĮą░ ąĖą╝ą┐čāą╗čīčüą░ ąŠčé UART ą┐ąŠą╗čāčćąĖčéčüčÅ ą┤ą╗čÅ ą╗ąŠą│. 1 ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčīčÄ ą▓ 3 čéą░ą║čéą░ ąĮą░ ą║ą░ąČą┤čŗąĄ 16 čéą░ą║č鹊ą▓čŗčģ ąĖą╝ą┐čāą╗čīčüąŠą▓ UART. ąÜą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▓ čéą░ą▒ą╗ąĖčåąĄ 12-1, ąŠčłąĖą▒ą║ą░ čāčüčéą░ąĮąŠą▓ą║ąĖ čüą║ąŠčĆąŠčüčéąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐ąŠą╗čāčćą░ąĄčéčüčÅ ąŠč湥ąĮčī ą╝ą░ą╗ąŠą╣, ąĖ ą▓čģąŠą┤ąĖčé ą▓ ą┤ąŠą┐čāčüą║ąĖ čüčéą░ąĮą┤ą░čĆčéą░ ą▒ąŠą╗čīčłąĖąĮčüčéą▓ą░ ąĖąĮčäčĆą░ą║čĆą░čüąĮčŗčģ čéčĆą░ąĮčüąĖą▓ąĄčĆąŠą▓.

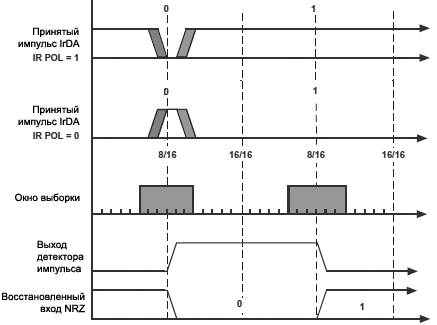

ą×ą┐ąĖčüą░ąĮąĖąĄ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ IrDA. ążčāąĮą║čåąĖčÅ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ IrDA ą▒ąŠą╗ąĄąĄ čüą╗ąŠąČąĮą░, č湥ą╝ čäčāąĮą║čåąĖčÅ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░. ą¤čĆąĖąĄą╝ąĮąĖą║ ą┤ąŠą╗ąČąĄąĮ ą▓čŗą┤ąĄą╗ąĖčéčī ąĖą╝ą┐čāą╗čīčü IrDA, ąĖ ą▓čŗčĆąĄąĘą░čéčī čłčāą╝. ą¦č鹊ą▒čŗ ą┤ąŠčüčéąĖčćčī čŹč鹊ą│ąŠ, ą┐čĆąĖąĄą╝ąĮąĖą║ ąĖčēąĄčé ąĖą╝ą┐čāą╗čīčü IrDA ą▓ čāąĘą║ąŠą╝ ąŠą║ąĮąĄ, čåąĄąĮčéčĆąĖčĆąŠą▓ą░ąĮąĮąŠą╝ ą┐ąŠčüąĄčĆąĄą┤ąĖąĮąĄ ąŠąČąĖą┤ą░ąĄą╝ąŠą│ąŠ ąĖą╝ą┐čāą╗čīčüą░.

ążąĖą╗čīčéčĆą░čåąĖčÅ ą┐ąŠą╝ąĄčģ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ąŠčéčüč湥č鹊ą╝ 16 čüąĖčüč鹥ą╝ąĮčŗčģ čéą░ą║č鹊ą▓ ąŠčé ą▓čĆąĄą╝ąĄąĮąĖ, ą║ąŠą│ą┤ą░ ą┐ąŠčÅą▓ąĖą╗čüčÅ ąĮą░čćą░ą╗čīąĮčŗą╣ ąĖą╝ą┐čāą╗čīčü. ąĢčüą╗ąĖ ąĖą╝ą┐čāą╗čīčü ą┐čĆąŠą┐ą░ą╗, ą║ąŠą│ą┤ą░ čüč湥čéčćąĖą║ ąĘą░ą▓ąĄčĆčłąĖą╗ čüč湥čé, č鹊 čŹč鹊čé ąĖą╝ą┐čāą╗čīčü čüčćąĖčéą░ąĄčéčüčÅ ą┐ąŠą╝ąĄčģąŠą╣. ąśąĮą░č湥 čüčćąĖčéą░ąĄčéčüčÅ, čćč鹊 ą┐čĆąĖąĮčÅčé 0. ąŁč鹊 ą┤ąŠą┐čāčüčéąĖą╝ąŠ, ą┐ąŠč鹊ą╝čā čćč鹊 ą┐ąŠą╝ąĄčģąĖ, ą┐ąŠčüčéčāą┐ą░čÄčēąĖąĄ č湥čĆąĄąĘ ą┐ą░čĆą░ąĘąĖčéąĮčŗąĄ ąĄą╝ą║ąŠčüčéąĮčŗąĄ čüą▓čÅąĘąĖ ą▓ čćąĖą┐ąĄ ąŠą▒čŗčćąĮąŠ ą▒čŗą▓ą░čÄčé ąĮąĄ ą┤ą╗ąĖąĮąĮąĄąĄ, č湥ą╝ čćą░čüčéčī ą┐ąĄčĆąĖąŠą┤ą░ čüąĖčüč鹥ą╝ąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ. ąśčüč鹊čćąĮąĖą║ąĖ ą┐ąŠą╝ąĄčģ, ąĮą░čģąŠą┤čÅčēąĖąĄčüčÅ ą▓ąĮąĄ čćąĖą┐ą░, ąĖ ąĮąĄ čÅą▓ą╗čÅčÄčēąĖąĄčüčÅ čćą░čüčéčīčÄ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░, ą╝ąŠą│čāčé ą▒čŗčéčī čāčüčéčĆą░ąĮąĄąĮčŗ ą┐ąŠą┤čģąŠą┤čÅčēąĖą╝ 菹║čĆą░ąĮąĖčĆąŠą▓ą░ąĮąĖąĄą╝. ąÆ ą║ą░č湥čüčéą▓ąĄ ą┤čĆčāą│ąŠą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ ą┐ąŠą╝ąĄčģ ąŠčüčéą░ąĄčéčüčÅ č鹊ą╗čīą║ąŠ čüąŠą▒čüčéą▓ąĄąĮąĮčŗą╣ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║. ą¤čĆąŠčåąĄčüčüąŠčĆ čĆą░čüčüčćąĖčéą░ąĮ ąĮą░ č鹊, čćč鹊 ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé čüą┐ąĄčåąĖčäąĖą║ą░čåąĖąĖ. ąĢčüą╗ąĖ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ ąĮą░čĆčāčłą░ąĄčé čüčéą░ąĮą┤ą░čĆčé, č鹊 ą╝ąŠą│čāčé ą▒čŗčéčī ą┐ąŠą╗čāč湥ąĮčŗ ąĮąĄą┐čĆąĄą┤čüą║ą░ąĘčāąĄą╝čŗąĄ čĆąĄąĘčāą╗čīčéą░čéčŗ. 4-čĆą░ąĘčĆčÅą┤ąĮčŗą╣ čüč湥čéčćąĖą║ ą┤ąŠą▒ą░ą▓ą╗čÅąĄčé ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗą╣ ąĮąĄą┤ąŠčĆąŠą│ąŠą╣ čāčĆąŠą▓ąĄąĮčī ąĘą░čēąĖčéčŗ. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ą┐ąŠčüą║ąŠą╗čīą║čā čüąĖčüč鹥ą╝ąĮą░čÅ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ ą╝ąŠąČąĄčé ą╝ąĄąĮčÅčéčīčüčÅ ą▓ čĆą░ąĘąĮčŗčģ čüąĖčüč鹥ą╝ą░čģ, čüą░ą╝ą░čÅ ą┤ą╗ąĖč鹥ą╗čīąĮą░čÅ ą┤ąŠą┐čāčüą║ą░ąĄą╝ą░čÅ ą┐ąŠą╝ąĄčģą░ ąŠą▒čĆą░čéąĮąŠ ą┐čĆąŠą┐ąŠčĆčåąĖąŠąĮą░ą╗čīąĮą░ čüąĖčüč鹥ą╝ąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊č鹥.

ą×ą║ąĮąŠ ą▓čŗą▒ąŠčĆą║ąĖ ą┐čĆąĖąĄą╝ą░ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą┐ąŠ čüč湥čéčćąĖą║čā, ą║ąŠč鹊čĆčŗą╣ čéą░ą║čéąĖčĆčāąĄčéčüčÅ ąĮą░ 16x čćą░čüč鹊č鹥 ąŠčé čćą░čüč鹊čéčŗ čüą╗ąĄą┤ąŠą▓ą░ąĮąĖčÅ ą▒ąĖčé. ą×ą║ąĮąŠ ą▓čŗą▒ąŠčĆą║ąĖ ą┐ąĄčĆąĄčüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆčāąĄčéčüčÅ čü ą║ą░ąČą┤čŗą╝ čüčéą░čĆč鹊ą▓čŗą╝ ą▒ąĖč鹊ą╝, ą┐čāč鹥ą╝ čåąĄąĮčéčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ąŠą║ąĮą░ ą▓čŗą▒ąŠčĆą║ąĖ ą▓ąŠą║čĆčāą│ čüčéą░čĆč鹊ą▓ąŠą│ąŠ ą▒ąĖčéą░.

ą¤ąŠą╗čÅčĆąĮąŠčüčéčī ą┐čĆąĖąĮąĖą╝ą░ąĄą╝čŗčģ ą┤ą░ąĮąĮčŗčģ ą╝ąŠąČąĮąŠ ą▓čŗą▒čĆą░čéčī, ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāčÅ ą▒ąĖčé IRPOL. ąĀąĖčü. 12-13 ą┤ą░ąĄčé ą┐čĆąĖą╝ąĄčĆčŗ ą║ą░ąČą┤ąŠą│ąŠ čéąĖą┐ą░ ą┐ąŠą╗čÅčĆąĮąŠčüčéąĖ.

ŌĆó IRPOL = 0 ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčé, čćč鹊 ąĮą░ ą▓čģąŠą┤ąĄ ą▓ čĆąĄąČąĖą╝ąĄ ąŠąČąĖą┤ą░ąĮąĖčÅ 0, ąĖ ą║ą░ąČą┤čŗą╣ ą░ą║čéąĖą▓ąĮčŗą╣ ą┐ąĄčĆąĄčģąŠą┤ ą╗ąŠą│. 1 čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ąĘąĮą░č湥ąĮąĖčÄ ą╗ąŠą│. 0 UART NRZ.

ŌĆó IRPOL = 1 ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčé, čćč鹊 ąĮą░ ą▓čģąŠą┤ąĄ ą▓ čĆąĄąČąĖą╝ąĄ ąŠąČąĖą┤ą░ąĮąĖčÅ 1, ąĖ ą║ą░ąČą┤čŗą╣ ą░ą║čéąĖą▓ąĮčŗą╣ ą┐ąĄčĆąĄčģąŠą┤ ą╗ąŠą│. 0 čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ąĘąĮą░č湥ąĮąĖčÄ ą╗ąŠą│. 0 UART NRZ.

ąĀąĖčü. 12-13. ąöąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ąĖą╝ą┐čāą╗čīčüą░ IrDA ą▓ ą┐čĆąĖąĄą╝ąĮąĖą║ąĄ.

ąŚą░ą│ąŠą╗ąŠą▓ąŠčćąĮčŗą╣ čäą░ą╣ą╗ ą┤ą╗čÅ ą╝ąŠą┤čāą╗čÅ ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝ UARTapp.cpp:

#ifndef __UARTAPP__

#define __UARTAPP__

#define UART0 0

#define UART2 2

#define UART0_MMR_OFFSET 0x0000

#define UART2_MMR_OFFSET 0x1D00

//ą┤ą╗čÅ SIC_ISR0, SIC_IWR0, SIC_IMASK0

#define UART0_RX_IRQ 0x00004000

//ąöą╗čÅ SIC_ISR1, SIC_IWR1, SIC_IMASK1:

#define UART1_RX_IRQ DMA16_IRQ

#define UART2_RX_IRQ DMA18_IRQ

#define UART0_TXBUFSIZE 256

#define UART0_TXBUFMASK (UART0_TXBUFSIZE-1)

#define UART0_RXBUFSIZE 256

#define UART0_RXBUFMASK (UART0_RXBUFSIZE-1)

#define UART2_TXBUFSIZE 256

#define UART2_TXBUFMASK (UART0_TXBUFSIZE-1)

#define UART2_RXBUFSIZE 256

#define UART2_RXBUFMASK (UART0_RXBUFSIZE-1)

extern section ("sdram0") u8 bufTXuart0[UART0_TXBUFSIZE];

extern u16 inTXuart0, outTXuart0;

extern section ("sdram0") u8 bufRXuart0[UART0_RXBUFSIZE];

extern u16 inRXuart0, outRXuart0;

extern section ("sdram0") u8 bufTXuart2[UART2_TXBUFSIZE];

extern u16 inTXuart2, outTXuart2;

extern section ("sdram0") u8 bufRXuart2[UART2_RXBUFSIZE];

extern u16 inRXuart2, outRXuart2;

void InitUART (u8 uartnum);

void UARTpoll (void);

void UartPuts (u8 uartnum, char *msg);

#endif //__UARTAPP__

ą£ąŠą┤čāą╗čī ąŠčüąĮąŠą▓ąĮčŗčģ ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝, čĆą░ą▒ąŠčéą░čÄčēąĖčģ čü UART0 ąĖ UART2:

//UARTapp.cpp: ą╝ąŠą┤čāą╗čī ą┤ą╗čÅ ą║ąŠąĮčüąŠą╗ąĖ, čĆą░ą▒ąŠčéą░čÄčēąĄą╣ č湥čĆąĄąĘ UART0 (DD2 FT231XQ).

#include < cdefBF538.h >

#include < stdint.h >

#include < string.h >

#include < services_types.h >

#include "uart-debug/ADSP-BF538-UART.h"

#include "UARTapp.h"

//ąÜąŠą╗čīčåąĄą▓čŗąĄ ą▒čāč乥čĆčŗ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖ ą┐čĆąĖąĄą╝ą░ ą┤ą╗čÅ UART0:

section ("sdram0") u8 bufTXuart0[UART0_TXBUFSIZE];

u16 inTXuart0, outTXuart0;

section ("sdram0") u8 bufRXuart0[UART0_RXBUFSIZE];

u16 inRXuart0, outRXuart0;

//ąÜąŠą╗čīčåąĄą▓čŗąĄ ą▒čāč乥čĆčŗ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖ ą┐čĆąĖąĄą╝ą░ ą┤ą╗čÅ UART2:

section ("sdram0") u8 bufTXuart2[UART2_TXBUFSIZE];

u16 inTXuart2, outTXuart2;

section ("sdram0") u8 bufRXuart2[UART2_RXBUFSIZE];

u16 inRXuart2, outRXuart2;

EX_REENTRANT_HANDLER(UartInterruptsHandlerData);

//***************************************

//* Function Name : short UartGpioInit(unsigned char UartNum)

//* Description : ąØą░čüčéčĆą░ąĖą▓ą░ąĄčé ąĮąŠąČą║ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆą░, ąĘą░ą┤ąĄą╣čüčéą▓ąŠą▓ą░ąĮąĮčŗąĄ ą┐ąŠą┤ UART.

//*

//* Parameters : ąĮąĄčé

//* Returns : NULL, ąĄčüą╗ąĖ ą▓čüąĄ OK, ąĖąĮą░č湥 ąĄčüą╗ąĖ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ.

//* Globals : ąĮąĄčé

short UartGpioInit(u8 UartNum)

{

switch (UartNum) {

case 0: break;

#if defined __ADSPBF538__

case 1: *pPORTDIO_FER &= ~(PD10|PD11);

break;

case 2: *pPORTDIO_FER &= ~(PD12|PD13);

break;

#endif

#if defined __ADSPBF539__

case 1: *pGPIO_D_CNFG &= ~(PD10|PD11);

break;

case 2: *pGPIO_D_CNFG &= ~(PD12|PD13);

break;

#endif

default:

return -1;

}

return 0;

}

void UARTpoll (void)

{

//ą×ą▒čĆą░ą▒ąŠčéą║ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ UART0

if(inTXuart0 != outTXuart0)

{

//ąÆ ą▒čāč乥čĆąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ čćč鹊-č鹊 ąĄčüčéčī

if (*pUART0_LSR & TEMT)

{

//ą£ąŠąČąĮąŠ ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī

*pUART0_THR = bufTXuart0[outTXuart0];

outTXuart0++;

outTXuart0 &= UART0_TXBUFMASK;

}

}

//ą×ą▒čĆą░ą▒ąŠčéą║ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ UART2

if(inTXuart2 != outTXuart2)

{

//ąÆ ą▒čāč乥čĆąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ čćč鹊-č鹊 ąĄčüčéčī

if (*pUART2_LSR & TEMT)

{

//ą£ąŠąČąĮąŠ ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī

*pUART2_THR = bufTXuart2[outTXuart2];

outTXuart2++;

outTXuart2 &= UART2_TXBUFMASK;

}

}

}

/***************************************

* Function Name : UartInterruptsHandlerData

* Description : čüčéą░ąĮą┤ą░čĆčéąĮčŗą╣ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą┐čĆąĖąĄą╝ą░ ą┤ą░ąĮąĮčŗčģ UART.

* ąŠąĮ ąŠą┤ąĖąĮ ą┤ą╗čÅ ą▓čüąĄčģ ą┐ąŠčĆč鹊ą▓ UART.

*

* Parameters : ąĮąĄčé

* Returns : ąĮąĄčé

* Globals : ąĮąĄčé

//EX_INTERRUPT_HANDLER(UartInterruptsHandlerData)

EX_REENTRANT_HANDLER(UartInterruptsHandlerData)

{

u16 UartMmrOffset = 0;

u8 UartNum = 0;

u32 SicIsr0 = 0;

u32 SicIsr1 = 0;

SicIsr0 = *pSIC_ISR0;

SicIsr1 = *pSIC_ISR1;

// ąŁč鹊čé ą║ąŠą┤ ą┐čĆąĖą▓čÅąĘą░ąĮ ą║ ąĮą░čüčéčĆąŠą╣ą║ą░ą╝, ą║ąŠč鹊čĆčŗąĄ čüą┤ąĄą╗ą░ąĮčŗ ą▓ čäčāąĮą║čåąĖąĖ UartInterruptsInit.

//ą×ą┐čĆąĄą┤ąĄą╗ąĄąĮąĖąĄ, ąĮą░ ą║ą░ą║ąŠą╣ ą┐ąŠčĆčé UARTx ą┐čĆąĖčłąĄą╗ čüąĖą╝ą▓ąŠą╗:

if (SicIsr0 & UART0_RX_IRQ)

{

UartMmrOffset = UART0_MMR_OFFSET;

UartNum = 0;

}

else if (SicIsr1 & UART1_RX_IRQ)

{

UartMmrOffset = UART1_MMR_OFFSET;

UartNum = 1;

}

else if (SicIsr1 & UART2_RX_IRQ)

{

UartMmrOffset = UART2_MMR_OFFSET;

UartNum = 2;

}

else

{

asm("EMUEXCPT; jump 0;");

}

//ą¦č鹥ąĮąĖąĄ ą┐čĆąĖąĮčÅč鹊ą│ąŠ čüąĖą╝ą▓ąŠą╗ą░:

volatile u16 *pUartRbr = (volatile u16*) (UART0_RBR + UartMmrOffset);

if (0==UartNum)

{

bufRXconsole[inRXconsole] = *pUartRbr;

inRXconsole++;

inRXconsole &= UARTCONS_RXBUFMASK;

}

else if (2==UartNum)

{

bufRXdebug[inRXdebug] = *pUartRbr;

inRXdebug++;

inRXdebug &= UARTDEBUG_RXBUFMASK;

}

else

{

bufRXdebug[inRXdebug] = '?';

inRXdebug++;

inRXdebug &= UARTDEBUG_RXBUFMASK;

}

ssync();

}

//***************************************

//* Function Name : short UartInterruptsInit(unsigned char UartNum)

//* Description : ąĮą░čüčéčĆąŠą╣ą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ąĖ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐čĆąĖąĄą╝ą░ ą┤ą░ąĮąĮčŗčģ.

//*

//* Parameters : ąĮąŠą╝ąĄčĆ ą┐ąŠčĆčéą░ UART

//* Returns : NULL, ąĄčüą╗ąĖ ą▓čüąĄ OK, ąĖąĮą░č湥 ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠąĄ čćąĖčüą╗ąŠ.

//* Globals : ąĮąĄčé

short UartInterruptsInit(u8 UartNum)

{

u16 UartMmrOffset = 0;

switch (UartNum)

{

case 0:

UartMmrOffset = UART0_MMR_OFFSET;

*pSIC_IAR1 |= PX_IVG(UART0_PERIPHERAL_RX_INT_ID, IVG_UART_DATA);

*pSIC_IMASK0 |= UART0_RX_IRQ;

break;

case 1:

UartMmrOffset = UART1_MMR_OFFSET;

*pSIC_IAR3 |= PX_IVG(UART1_PERIPHERAL_RX_INT_ID, IVG_UART_DATA);

*pSIC_IMASK1 |= UART1_RX_IRQ;

break;

case 2:

UartMmrOffset = UART2_MMR_OFFSET;

*pSIC_IAR5 |= PX_IVG(UART2_PERIPHERAL_RX_INT_ID, IVG_UART_DATA);

*pSIC_IMASK1 |= UART2_RX_IRQ;

break;

default:

return -1;

}

register_handler_ex(IVG_UART_DATA, UartInterruptsHandlerData, EX_INT_ENABLE);

volatile u16 *pUartIer = (volatile u16*) (UART0_IER + UartMmrOffset);

//*pUartIer = (ELSI|ERBFI);

*pUartIer = ERBFI;

return 0;

}

//***************************************

//* Function Name : short UartInitTerminal(unsigned char UartNum, unsigned long UartBitrate)

//* Description : ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčé UART ą┤ą╗čÅ ąŠą▒ą╝ąĄąĮą░ čü PC-č鹥čĆą╝ąĖąĮą░ą╗ąŠą╝: 8 ą▒ąĖčé, no parity, 1 stop bit.

//*

//* Parameters : ąĮąŠą╝ąĄčĆ ą┐ąŠčĆčéą░ UART, ąĘąĮą░č湥ąĮąĖąĄ čüą║ąŠčĆąŠčüčéąĖ UART (ą▒ąŠą┤)

//* Returns : NULL, ąĄčüą╗ąĖ ą▓čüąĄ OK, ąĖąĮą░č湥 ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ. is returned.

//* Globals : ąĮąĄčé

short UartInitTerminal(u8 UartNum, u32 UartBitrate)

{

u16 UartMmrOffset = 0;

u16 UartDivisor = 0;

switch (UartNum) {

case 0: UartMmrOffset = UART0_MMR_OFFSET; break;

case 1: UartMmrOffset = UART1_MMR_OFFSET; break;

case 2: UartMmrOffset = UART2_MMR_OFFSET; break;

default: printf("%s(): UART%d is not available.\n",__func__,UartNum); return -1;

}

volatile u16 *pUartGctl = (volatile u16*) (UART0_GCTL + UartMmrOffset);

volatile u16 *pUartLcr = (volatile u16*) (UART0_LCR + UartMmrOffset);

volatile u16 *pUartMcr = (volatile u16*) (UART0_MCR + UartMmrOffset);

if (*pUartGctl & UCEN) { return 0; } // UART čāąČąĄ čĆą░ąĘčĆąĄčłąĄąĮ

UartGpioInit(UartNum);

UartSetBitrate(UartNum, UartBitrate);

// ąĀą░ąĘčĆąĄčłąĖčéčī čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ UART:

*pUartGctl = UCEN;

// ąĪą▒čĆąŠčü ą▒ąĖčéą░ LOOP_ENA ą│ą░čĆą░ąĮčéąĖčĆčāąĄčé, čćč鹊 čĆąĄąČąĖą╝ Loopback ąĘą░ą┐čĆąĄčēąĄąĮ:

*pUartMcr = 0;

// ą¤čĆąĖą╝ąĄąĮąĖčéčī ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÄ UART:

*pUartLcr = WLS(8);

UartInterruptsInit(UartNum);

return 0;

}

//***************************************

//* Function Name : short UartPutc(unsigned char UartNum, char c)

//* Description : čäčāąĮą║čåąĖčÅ ą┐ąŠą╝ąĄčēą░ąĄčé ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗą╣ čüąĖą╝ą▓ąŠą╗ ą▓ ą║ąŠą╗čīčåąĄą▓ąŠą╣ ą▒čāč乥čĆ ą┐ąĄčĆąĄą┤ą░čćąĖ.

//*

//* Parameters : ąĮąŠą╝ąĄčĆ ą┐ąŠčĆčéą░ UART, čüąĖą╝ą▓ąŠą╗ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ

//* Returns : NULL, ąĄčüą╗ąĖ ą▓čüąĄ OK, ąĖąĮą░č湥 ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ.

//* Globals : ąĮąĄčé

short UartPutc(u8 UartNum, char c)

{

u16 UartMmrOffset = 0;

u8* bufptr;

u16 *in, bufmask;

if (UART0==UartNum)

{

bufptr = bufTXuart0;

in = &inTXuart0;

bufmask = UART0_TXBUFMASK;

}

else

{

bufptr = bufTXdebug;

in = &inTXdebug;

bufmask = UARTDEBUG_TXBUFMASK;

}

bufptr[*in] = c;

(*in)++;

(*in) &= bufmask;

return 0;

}

//***************************************

//* Function Name : short UartPuts(unsigned char UartNum, char *c)

//* Description : čäčāąĮą║čåąĖčÅ ą┐ąĄčĆąĄą┤ą░ąĄčé čüčéčĆąŠą║čā, ą║ąŠč鹊čĆą░čÅ ą┤ąŠą╗ąČąĮą░ ąĘą░ą▓ąĄčĆčłą░čéčīčüčÅ ąĮčāą╗ąĄą╝

//* (NULL-terminated string, ASCIIZ, čüčéčĆąŠą║ą░ čüčéąĖą╗čÅ čÅąĘčŗą║ą░ C).

//*

//* Parameters : ąĮąŠą╝ąĄčĆ ą┐ąŠčĆčéą░ UART, čāą║ą░ąĘą░č鹥ą╗čī ąĮą░ čüčéčĆąŠą║čā ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ.

//* Returns : NULL, ąĄčüą╗ąĖ ą▓čüąĄ OK, ąĖąĮą░č湥 ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ.

//* Globals : ąĮąĄčé

short UartPuts(u8 UartNum, char *c)

{

while (*c) {

UartPutc(UartNum, *c);

#if(0) // ąŠą▒ čŹč鹊ą╝ ą╝ąŠąČąĄčé ą┐ąŠąĘą░ą▒ąŠčéąĖčéčīčüčÅ uprintf

if (*c == '\n') { // 0x0A, ąĮąŠą▓ą░čÅ čüčéčĆąŠą║ą░?

UartPutc(UartNum, '\r'); // 0x0D, ą▓čüčéą░ą▓ą║ą░ carriage return

return 0;

}

else if (*c == '\r') { // 0x0D, carriage return?

UartPutc(UartNum, '\n'); // 0x0A, ą▓čüčéą░ą▓ą║ą░ čüąĖą╝ą▓ąŠą╗ą░ ąĮąŠą▓ąŠą╣ čüčéčĆąŠą║ąĖ

return 0;

}

else { c++; }

#else

c++;

#endif

}

return 0;

}

//ąśąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆčāąĄčé ą┐ąŠčĆčé UART

void InitUART (u8 uartnum)

{

//ą×čćąĖčüčéą║ą░ ą║ąŠą╗čīčåąĄą▓ąŠą│ąŠ ą▒čāč乥čĆą░:

if (0==uartnum)

{

inTXuart0 = 0; outTXuart0 = 0;

}

else if (2==uartnum)

{

inTXuart2 = 0; outTXuart2 = 0;

}

//ąØą░čüčéčĆąŠą╣ą║ą░ ą┐ąŠčĆčéą░ UART:

UartInitTerminal(uartnum,

115200);

}

ą£ąŠą┤čāą╗čī ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ (main.cpp):

//*****************************************************************************

// ą¤čĆąĖą╝ąĄčĆ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ą┤ą╗čÅ Blackfin ADSP-BF538, ąĖčüą┐ąŠą╗čīąĘčāčÄčēąĖą╣ ą┐ąŠčĆčéčŗ UART0 ąĖ UART2.

// ą¤čĆąĖąĄą╝ čüąĖą╝ą▓ąŠą╗ąŠą▓ ąĮą░čüčéčĆąŠąĄąĮ ą┐ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅą╝, čüąĖą╝ą▓ąŠą╗čŗ ą┐ąŠą┐ą░ą┤ą░čÄčé ą▓ ą║ąŠą╗čīčåąĄą▓čŗąĄ ą▒čāč乥čĆčŗ

// bufRXuart0 ąĖ bufRXuart2 (ąŠą▒čĆą░ą▒ąŠčéą║ą░ ą┤ą░ąĮąĮčŗčģ ą▓ ą║ąŠą╗čīčåąĄą▓čŗčģ ą▒čāč乥čĆą░čģ ą┤ą╗čÅ čāą┐čĆąŠčēąĄąĮąĖčÅ

// ąĮąĄ čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮą░).

//

// ą¤ąĄčĆąĄą┤ą░čćą░ čéą░ą║ąČąĄ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ č湥čĆąĄąĘ ą║ąŠą╗čīčåąĄą▓čŗąĄ ą▒čāč乥čĆčŗ (bufTXuart0

// ąĖ bufTXuart2), ą┤ą░ąĮąĮčŗąĄ ą▓ ą║ąŠą╗čīčåąĄą▓ąŠą╣ ą▒čāč乥čĆ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐ąŠą╝ąĄčēą░ąĄčéčüčÅ ą▓čŗąĘąŠą▓ąŠą╝

// UartPuts, ą┐ąĄčĆąĄą┤ą░čćą░ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą┐ąŠčüąĖą╝ą▓ąŠą╗čīąĮąŠ ą▓čŗąĘąŠą▓ą░ą╝ąĖ UARTpoll.

//*****************************************************************************

#include "Units\Timer.h"

#include "pins.h"

#include "WEX025664.h"

#include "delay.h"

#include "uart-debug/BfDebugger.h"

#include "strval.h"

#include "UARTapp.h"

int main()

{

InitCore();

ConfigureInputs();

ConfigureOutputs();

PowerON();

InitUART(0);

InitUART(2);

Beep(100);

while(1)

{

if(buttonApressed())

{

Beep(100);

UartPuts(UART0, "test UART0\r\n");

}

if(buttonBpressed())

{

Beep(200);

UartPuts(UART2, "test UART2\r\n");

}

UARTpoll();

// ąóčāčé ą╝ąŠąČąĮąŠ ą▓čüčéą░ą▓ąĖčéčī ą▓čŗąĘąŠą▓čŗ ą┐čĆąŠčåąĄą┤čāčĆ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą▒čāč乥čĆąŠą▓ ą┐čĆąĖąĄą╝ą░

// bufRXuart0 ąĖ bufRXuart2, ą░ čéą░ą║ąČąĄ ą┤čĆčāą│ąŠą╣ ą┐ąĄčĆąĖąŠą┤ąĖč湥čüą║ąĖ ą▓čŗąĘčŗą▓ą░ąĄą╝čŗą╣

// ą║ąŠą┤.

}

}

[ąĪčüčŗą╗ą║ąĖ]

1. ADSP-BF538/ADSP-BF538F Blackfin® Processor Hardware Reference site:analog.com.

2. Blackfin ADSP-BF538.

3. ADSP-BF538: DMA.

4. ADSP-BF538: čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąŠčĆčéą░ą╝ąĖ GPIO C, D, E.

5. ą¤ą░ą╝čÅčéčī Blackfin.

6. Blackfin: č乊čĆą╝ą░čéąĖčĆąŠą▓ą░ąĮąĮčŗą╣ ą▓čŗą▓ąŠą┤ ą▓ ąŠą║ąĮąŠ č鹥čĆą╝ąĖąĮą░ą╗ą░ č湥čĆąĄąĘ UART.

7. Blackfin ą┐ąĖčłąĄą╝ ą┤čĆą░ą╣ą▓ąĄčĆ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ą┐ąŠčĆčéą░ site:kit-e.ru. |