|

ąŻ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ ADSP-BF538/ADSP-BF538F Blackfin (ą┤ą░ą╗ąĄąĄ ą▓ č鹥ą║čüč鹥 ą┐čĆąŠčüč鹊 BF538) ąĄčüčéčī ą▒ąŠą│ą░čéčŗą╣ ąĮą░ą▒ąŠčĆ čĆą░ąĘą╗ąĖčćąĮčŗčģ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą▓ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅčģ. ążčāąĮą║čåąĖčÅ GPIO (general-purpose input/output, ą┐ąŠčĆčéčŗ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ ąŠą▒čēąĄą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ) ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąĖčĆčāčÄčéčüčÅ ąĮą░ ą▓čŗą▓ąŠą┤ą░čģ ą║ąŠčĆą┐čāčüą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░ čü čäčāąĮą║čåąĖčÅą╝ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓. ążčāąĮą║čåąĖąŠąĮą░ą╗ GPIO ą╝ąŠąČąĄčé ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą▓čŗą▓ąŠą┤ą░ ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮąŠ - ą▓ą╝ąĄčüč鹊 čäčāąĮą║čåąĖąŠąĮą░ą╗ą░ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓.

ąÆčŗą▓ąŠą┤čŗ GPIO čüą│čĆčāą┐ą┐ąĖčĆąŠą▓ą░ąĮčŗ ą▓ ą┐ąŠčĆčéčŗ C, D, E (ąĄčüčéčī čéą░ą║ąČąĄ ąĖ ą┐ąŠčĆčé F, ąĮąŠ ąĄą│ąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ ąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ ąĖą╝ąĄąĄčé ąŠčéą╗ąĖčćąĖčÅ, ą┐ąŠčŹč鹊ą╝čā ą┐ąŠčĆčé F čĆą░čüčüą╝ąŠčéčĆąĄąĮ ą▓ ąŠčéą┤ąĄą╗čīąĮąŠą╣ čüčéą░čéčīąĄ [2]). ąÜą░ąČą┤čŗą╣ ą▓čŗą▓ąŠą┤ ą▓ ą│čĆčāą┐ą┐ąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮąŠ. ąĢčüą╗ąĖ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ, ą┐čĆąĖą╝ąĄąĮčÅčÄčēąĄąĄ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ, ąĮąĄ čéčĆąĄą▒čāąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą▓čüąĄčģ ą▓čŗą▓ąŠą┤ąŠą▓ čŹč鹊ą│ąŠ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░, č鹊 ą▓čüąĄ ąĮąĄąĮčāąČąĮčŗąĄ ą▓čŗą▓ąŠą┤čŗ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ą╝ąŠą│čāčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ ą║ą░ą║ ą┐ąŠčĆčéčŗ GPIO. ąÆ čéą░ą▒ą╗ąĖčåąĄ 15-1 ą┐ąŠą║ą░ąĘą░ąĮąŠ, ą║ą░ą║ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┐čĆąĖą▓čÅąĘą░ąĮčŗ ą║ ą┐ąŠčĆčéą░ą╝ GPIO.

ąóą░ą▒ą╗ąĖčåą░ 15-1. ą£čāą╗čīčéąĖą┐ą╗ąĄą║čüąĖčĆąŠą▓ą░ąĮąĖąĄ čäčāąĮą║čåąĖą╣ GPIO ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ąĮą░ ą▓čŗą▓ąŠą┤ą░čģ ą┐čĆąŠčåąĄčüčüąŠčĆą░.

| ą¤ąŠčĆčé |

ą×čüąĮąŠą▓ąĮą░čÅ čäčāąĮą║čåąĖčÅ (ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ) |

ąÉą╗čīč鹥čĆąĮą░čéąĖą▓ąĮą░čÅ čäčāąĮą║čåąĖčÅ |

| Port C |

CAN

GPIO |

PC1:0

PC9:4 |

| Port D |

SPI1

SPI2

UART1

UART2 |

PD4:0

PD9:5

PD11:10

PD13:12 |

| Port E |

SPORT2

SPORT3 |

PE7:0

PE15:8 |

ążčāąĮą║čåąĖąĖ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ, ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčŗąĄ čäčāąĮą║čåąĖąĖ. ążčāąĮą║čåąĖąĖ, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠąČąĮąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ ąĮą░čüčéčĆąŠąĖčéčī ąĮą░ ą▓čŗą▓ąŠą┤ą░čģ ą┐čĆąŠčåąĄčüčüąŠčĆą░ (čé. ąĄ. ąĖąĘą╝ąĄąĮąĖčéčī ąĖčģ ą┐ąĄčĆą▓ąŠąĮą░čćą░ą╗čīąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ąĮą░ ą┤čĆčāą│ąŠąĄ), ąĮą░ąĘčŗą▓ą░čÄčéčüčÅ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčŗą╝ąĖ. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą║ą░ąČą┤čŗą╣ ą▓čŗą▓ąŠą┤ ą┐ąŠčĆčéą░ ą╝ąŠąČąĄčé ąĮąĄčüčéąĖ 2 ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ ą▓čŗą▒ąĖčĆą░ąĄą╝čŗąĄ čäčāąĮą║čåąĖąĖ - čäčāąĮą║čåąĖčÅ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ, ąĖą╗ąĖ ą┐ąĄčĆą▓ąĖčćąĮą░čÅ, ąŠčüąĮąŠą▓ąĮą░čÅ čäčāąĮą║čåąĖčÅ (ą║ąŠč鹊čĆą░čÅ čĆą░ą▒ąŠčéą░ąĄčé ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ / ą▓ą║ą╗čÄč湥ąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ) ąĖ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮą░čÅ čäčāąĮą║čåąĖčÅ.

ążčāąĮą║čåąĖąŠąĮą░ą╗ GPIO ą┐ąŠčĆč鹊ą▓ C, D ąĖ E ąŠčéą╗ąĖčćą░ąĄčéčüčÅ ąŠčé ą┐ąŠčĆčéą░ F ą┤ą▓čāą╝čÅ ą╝ąŠą╝ąĄąĮčéą░ą╝ąĖ:

1. ąØą░ ą┐ąŠčĆčéą░čģ C, D ąĖ E ąĮąĄčé ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ čüąŠčüč鹊čÅąĮąĖčÄ ą╗ąŠą│. čāčĆąŠą▓ąĮčÅ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ ąĖ ą┐ąŠ ą┐ąĄčĆąĄą┐ą░ą┤ą░ą╝ čŹč鹊ą│ąŠ čāčĆąŠą▓ąĮčÅ.

2. ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ GPIO ąĖ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ąĮą░ ą┐ąŠčĆčéą░čģ C, D ąĖ E ąĮąĖą║ą░ą║ ąĮąĄ čüą▓čÅąĘą░ąĮąŠ čü čćč鹥ąĮąĖąĄą╝ ąĖ ąĘą░ą┐ąĖčüčīčÄ ą╗čÄą▒čŗčģ čĆąĄą│ąĖčüčéčĆąŠą▓ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░.

ąĪčĆą░ąĘčā ą┐ąŠčüą╗ąĄ čüąĖčüč鹥ą╝ąĮąŠą│ąŠ čüą▒čĆąŠčüą░ ą▓ąĄčüčī čäčāąĮą║čåąĖąŠąĮą░ą╗ GPIO ąĘą░ą┐čĆąĄčēąĄąĮ, ąĖ ą▓čŗą▓ąŠą┤čŗ ą┐ąĄčĆąĄą║ą╗čÄčćą░čÄčéčüčÅ ąĮą░ ąŠą▒čüą╗čāąČąĖą▓ą░ąĮąĖąĄ čäčāąĮą║čåąĖą╣ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ ą▓čŗą▓ąŠą┤ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (ą│ą┤ąĄ ą╝ąŠą│ą╗ą░ ą▒čŗ ą▒čŗčéčī čäčāąĮą║čåąĖčÅ GPIO) čĆą░ą▒ąŠčéą░ąĄčé ą┐ąŠ čüą▓ąŠąĄą╝čā ąĮą░ąĘąĮą░č湥ąĮąĖčÄ, ą║ą░ą║ ąĄčüą╗ąĖ ą▒čŗ čŹč鹊ą╝čā ą▓čŗą▓ąŠą┤čā ą▒čŗą╗ąŠ ąĮą░ąĘąĮą░č湥ąĮąŠ čĆą░ą▒ąŠčéą░čéčī ą┤ą╗čÅ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░, ą▒ąĄąĘ ąĮą░ą╗ąĖčćąĖčÅ ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ čäčāąĮą║čåąĖąŠąĮą░ą╗ą░ GPIO. ąØąŠ ą▓čŗą▓ąŠą┤ ą╝ąŠąČąĄčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ąĮą░ čĆą░ą▒ąŠčéčā ą║ą░ą║ GPIO ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ ą▒ąĖčéą░ ą▓ čĆąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ GPIO (PORTxIO_FER). ąÜą░ą║ č鹊ą╗čīą║ąŠ ą▓čŗą▓ąŠą┤ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą▓ čĆą░ą▒ąŠč鹥 ą║ą░ą║ GPIO, ąĄą│ąŠ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čĆą░ą▒ąŠčéčŗ (ą▓čģąŠą┤ čŹč鹊 ąĖą╗ąĖ ą▓čŗčģąŠą┤) ą╝ąŠąČąĮąŠ čāčüčéą░ąĮąŠą▓ąĖčéčī, ąĖčüą┐ąŠą╗čīąĘčāčÅ čĆąĄą│ąĖčüčéčĆčŗ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ GPIO (PORTxIO_DIR). ą£ąŠąČąĮąŠ ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮąŠ ąĘą░ą┤ą░čéčī ą▓čŗčģąŠą┤ąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┤ą╗čÅ GPIO ą┐ąĄčĆąĄą┤ ąĄą│ąŠ ąĮą░čüčéčĆąŠą╣ą║ąŠą╣ ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ ą▓ čĆąĄąČąĖą╝ąĄ ą▓čŗčģąŠą┤ą░.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĖą╝ąĄąĮą░ čĆąĄą│ąĖčüčéčĆąŠą▓ ą┤ą╗čÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ GPIO ąĖčüą┐ąŠą╗čīąĘčāčÄčé ą┐čĆąĄčäąĖą║čü PORTxIO, ą│ą┤ąĄ ą▒čāą║ą▓ą░ x ą╝ąŠąČąĄčé ą▒čŗčéčī C, D ąĖą╗ąĖ E.

ąĢčüčéčī ąĮąĄčüą║ąŠą╗čīą║ąŠ ą╝ąĄč鹊ą┤ąŠą▓ ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą▓čŗčģąŠą┤ąĮčŗą╝ čāčĆąŠą▓ąĮąĄą╝ GPIO čü ą┐ąŠą╝ąŠčēčīčÄ ąĘą░ą┐ąĖčüąĖ ąĘąĮą░č湥ąĮąĖą╣ ą▓ čĆąĄą│ąĖčüčéčĆčŗ. ąŁčéąĖ čĆąĄą│ąĖčüčéčĆčŗ čüą╗ąĄą┤čāčÄčēąĖąĄ: čĆąĄą│ąĖčüčéčĆ ą┤ą░ąĮąĮčŗčģ (GPIO data, PORTxIO), čĆąĄą│ąĖčüčéčĆ čāčüčéą░ąĮąŠą▓ą║ąĖ (PORTxIO_SET), čĆąĄą│ąĖčüčéčĆ ąŠčćąĖčüčéą║ąĖ (PORTxIO_CLEAR), ąĖ čĆąĄą│ąĖčüčéčĆ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ čāčĆąŠą▓ąĮčÅ ą▓ ą┐čĆąŠčéąĖą▓ąŠą┐ąŠą╗ąŠąČąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ (PORTxIO_TOGGLE). ąöą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čüąŠčüč鹊čÅąĮąĖąĄą╝ ą▓čŗčģąŠą┤ąŠą▓ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą╝ąĄč鹊ą┤ ąĘą░ą┐ąĖčüą░čéčī-1-ą┤ą╗čÅ_ą┤ąĄą╣čüčéą▓ąĖčÅ, čćč鹊 čāčüčéčĆą░ąĮčÅąĄčé ą┐čĆąŠą▒ą╗ąĄą╝čŗ ą║ąŠą│ąĄčĆąĄąĮčéąĮąŠčüčéąĖ, ąŠą▒čŗčćąĮąŠ ą▓ąŠąĘąĮąĖą║ą░čÄčēąĖąĄ čü ą╝ąĄč鹊ą┤ą░ą╝ąĖ ą┤ąŠčüčéčāą┐ą░ čéąĖą┐ą░ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ read-modify-write.

ą×ą▒ą░ čŹčéąĖ č鹥čĆą╝ąĖąĮą░ čüą▓čÅąĘą░ąĮčŗ čü ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéčīčÄ čāą┐čĆą░ą▓ą╗čÅčéčī čüąŠčüč鹊čÅąĮąĖąĄą╝ č鹊ą╗čīą║ąŠ ąŠą┤ąĮąŠą│ąŠ ą▒ąĖčéą░ ąĘą░ ąŠą┤ąĮčā ąŠą┐ąĄčĆą░čåąĖčÄ. ą¤ąŠčüą║ąŠą╗čīą║čā ą▒ąĖčéčŗ, čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ ą▓čŗą▓ąŠą┤ą░ą╝ ą┐ąŠčĆč鹊ą▓, ąŠą▒čŖąĄą┤ąĖąĮąĄąĮčŗ ą▓ čüą╗ąŠą▓ąŠ čĆą░ąĘčĆčÅą┤ąĮąŠčüčéčīčÄ 16 ą▒ąĖčé, č鹊 čéčĆą░ą┤ąĖčåąĖąŠąĮąĮčŗą╝ čüą┐ąŠčüąŠą▒ąŠą╝ ą┐ąŠą╝ąĄąĮčÅčéčī čüąŠčüč鹊čÅąĮąĖąĄ č鹊ą╗čīą║ąŠ ąŠą┤ąĮąŠą│ąŠ ą▒ąĖčéą░ ą╝ąŠąČąĮąŠ č鹊ą╗čīą║ąŠ čü ą┐ąŠą╝ąŠčēčīčÄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ąŠą┐ąĄčĆą░čåąĖą╣ ą┐čĆąŠčćąĖčéą░čéčī, ą┐ąŠą╝ąĄąĮčÅčéčī ą┐čĆąŠčćąĖčéą░ąĮąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ąĖ ąĘą░ą┐ąĖčüą░čéčī. ąŁč鹊 ą║ą░ą║ čĆą░ąĘ ąĖ ąĮą░ąĘčŗą▓ą░ąĄčéčüčÅ ąŠą┐ąĄčĆą░čåąĖąĄą╣ read-modify-write.

ą¤čĆąŠą▒ą╗ąĄą╝ą░ čü ąŠą┐ąĄčĆą░čåąĖąĄą╣ read-modify-write čüąŠčüč鹊ąĖčé ą▓ č鹊ą╝, čćč鹊 čü čéčĆą░ą┤ąĖčåąĖąŠąĮąĮčŗą╝ ą┤ąŠčüčéčāą┐ąŠą╝ ą║ čĆąĄą│ąĖčüčéčĆą░ą╝ čéą░ą║ąŠąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą▒ąĖčéą░ą╝ąĖ čéčĆčāą┤ąĮąŠ čüą┤ąĄą╗ą░čéčī ą░č鹊ą╝ą░čĆąĮčŗą╝. ąÆąŠčé čéčāčé ą║ą░ą║ čĆą░ąĘ ąĖ ą┐čĆąĖčģąŠą┤ąĖčé ąĮą░ ą┐ąŠą╝ąŠčēčī ą┐čĆąĖąĮčåąĖą┐ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą▒ąĖčéą░ą╝ąĖ write-1-to-ą┤ąĄą╣čüčéą▓ąĖąĄ (ąĘą░ą┐ąĖčüą░čéčī ą╗ąŠą│. 1, čćč鹊ą▒čŗ ą▓čŗą┐ąŠą╗ąĮąĖčéčī ą┤ąĄą╣čüčéą▓ąĖąĄ) - ą▒ą╗ą░ą│ąŠą┤ą░čĆčÅ ąĮą░ą╗ąĖčćąĖčÄ ąŠčéą┤ąĄą╗čīąĮąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą┤ąĄą╣čüčéą▓ąĖčÅ (čüą▒čĆąŠčü, čāčüčéą░ąĮąŠą▓ą║ą░, ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ) ą┐ąŠčÅą▓ą╗čÅąĄčéčüčÅ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą░č鹊ą╝ą░čĆąĮąŠ čāą┐čĆą░ą▓ą╗čÅčéčī ąĘąĮą░č湥ąĮąĖąĄą╝ ą╗čÄą▒ąŠą│ąŠ ąŠčéą┤ąĄą╗čīąĮąŠą│ąŠ ą▒ąĖčéą░ (ąĖą╗ąĖ ąĮą░ą▒ąŠčĆą░ ą▒ąĖč鹊ą▓) ąĘą░ ąŠą┤ąĮąŠ ą▒čŗčüčéčĆąŠąĄ ą┤ąĄą╣čüčéą▓ąĖąĄ.

ąÆ čéą░ą▒ą╗ąĖčåą░čģ 15-2, 15-3 ąĖ 15-4 ą┐ąĄčĆąĄčćąĖčüą╗ąĄąĮčŗ ą▓čüąĄ ą▓čŗą▓ąŠą┤čŗ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓, čā ą║ąŠč鹊čĆčŗčģ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĮą░ąĘąĮą░č湥ąĮą░ čäčāąĮą║čåąĖčÅ GPIO. ąÜą░ąČą┤čŗą╣ ą┐ąŠčĆčé GPIO ąĖą╝ąĄąĄčé ą┐ąŠą╗ąĮčŗą╣ ąĮą░ą▒ąŠčĆ čĆąĄą│ąĖčüčéčĆąŠą▓, čüą▓čÅąĘą░ąĮąĮčŗčģ čü čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝ GPIO čŹč鹊ą│ąŠ ą┐ąŠčĆčéą░. ąØąŠą╝ąĄčĆą░ ą▒ąĖčé ą▓ čŹčéąĖčģ čéą░ą▒ą╗ąĖčåą░čģ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮčŗ ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ ą║ ą╗čÄą▒ąŠą╝čā ąĖąĘ čŹčéąĖčģ čĆąĄą│ąĖčüčéčĆąŠą▓ GPIO, ą┐ąŠč鹊ą╝čā čćč鹊 ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮą░čÅ ą┐ąŠąĘąĖčåąĖčÅ ą▒ąĖčéą░ čŹč鹊ą│ąŠ ą┐ąŠčĆčéą░ čüąŠčģčĆą░ąĮčÅąĄčéčüčÅ ą┤ą╗čÅ ą▓čüąĄčģ čĆąĄą│ąĖčüčéčĆąŠą▓ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ GPIO. ąØą░ą┐čĆąĖą╝ąĄčĆ, ąĄčüą╗ąĖ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ CAN, č鹊 2 ą▓čŗą▓ąŠą┤ą░ CAN (CANTX ąĖ CANRX) ą╝ąŠą│čāčé ą▒čŗčéčī ąŠčüą▓ąŠą▒ąŠąČą┤ąĄąĮčŗ ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ ą▓ ą║ą░č湥čüčéą▓ąĄ GPIO ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖč鹊ą▓ 0 ąĖ 1 (čé. ąĄ. ąĘą░ą┐ąĖčüąĖ ą╗ąŠą│. 1 ą▓ ą▒ąĖčéčŗ 0 ąĖ 1) čĆąĄą│ąĖčüčéčĆą░ PORTCIO_FER. ąØą░čćąĖąĮą░čÅ čü čŹč鹊ą│ąŠ ą╝ąŠą╝ąĄąĮčéą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠąĄ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖąĄ ą╝ąŠąČąĄčé čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī čŹčéąĖ ą▓čŗą▓ąŠą┤čŗ ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ą┤čĆčāą│ ąŠčé ą┤čĆčāą│ą░ (ąĮą░ą┐čĆąĖą╝ąĄčĆ, ą║ą░ą║ ą▓čģąŠą┤ ąĖą╗ąĖ ą▓čŗčģąŠą┤), ąĖ čéą░ą║ąČąĄ ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ą┤čĆčāą│ ąŠčé ą┤čĆčāą│ą░ čāą┐čĆą░ą▓ą╗čÅčéčī čŹčéąĖą╝ąĖ ą▓čŗą▓ąŠą┤ą░ą╝ąĖ ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ ą╗ąŠą│. 0 ąĖ ą╗ąŠą│. 1 ą▓ ą▒ąĖčéčŗ 0 ąĖ 1 čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖčģ čĆąĄą│ąĖčüčéčĆąŠą▓ GPIO ą┐ąŠčĆčéą░ C.

ąóą░ą▒ą╗ąĖčåą░ 15-2. GPIO Port C ąĖ ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąĖčĆąŠą▓ą░ąĮąĖąĄ čäčāąĮą║čåąĖą╣.

| ąÆčŗą▓ąŠą┤ GPIO ą┐ąŠčĆčéą░ C |

ąÆčŗą▓ąŠą┤ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░, ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąĖčĆąŠą▓ą░ąĮąĮčŗą╣ čü čäčāąĮą║čåąĖąĄą╣ GPIO |

ąĪąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ čĆą░ąĘčĆčÅą┤čŗ čĆąĄą│ąĖčüčéčĆąŠą▓ GPIO |

| PC0 |

CAN ą┐ąĄčĆąĄą┤ą░čćą░ (CANTX) |

0 |

| PC1 |

CAN ą┐čĆąĖąĄą╝ (CANRX) |

1 |

| PC4-9 |

GPIO (ąĮąĄčé ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąĖčĆąŠą▓ą░ąĮąĖčÅ čü ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ) |

4-9 |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▓čŗą▓ąŠą┤čŗ PC1 ąĖ PC4 (čĆą░ąĘčĆčÅą┤čŗ 1 ąĖ 4) ą╝ąŠą│čāčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ ą║ą░ą║ GPIO, ąŠą┤ąĮą░ą║ąŠ ąĮą░ą┤ąŠ ąĖą╝ąĄčéčī ą▓ ą▓ąĖą┤čā, čćč鹊 ą▓ čĆąĄąČąĖą╝ąĄ ą▓čģąŠą┤ą░ čŹč鹊 5V-tolerant ą▓čģąŠą┤, ą░ ą▓ čĆąĄąČąĖą╝ąĄ ą▓čŗčģąŠą┤ą░ čŹč鹊 ą▓čŗčģąŠą┤ čü ąŠčéą║čĆčŗčéčŗą╝ čüč鹊ą║ąŠą╝. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą▓ čĆąĄąČąĖą╝ąĄ ą▓čŗčģąŠą┤ą░ čŹčéąĖ ą▓čŗą▓ąŠą┤čŗ ą╝ąŠą│čāčé ą▒čŗčéčī ą┐ąĄčĆąĄą▓ąĄą┤ąĄąĮčŗ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ą╗ąŠą│. 0, ąĄčüą╗ąĖ ąĘą░ą┐ąĖčüą░čéčī ą▓ čĆąĄą│ąĖčüčéčĆ ą┤ą░ąĮąĮčŗčģ ąĘąĮą░č湥ąĮąĖąĄ 0, ąĮąŠ ąĄčüą╗ąĖ ąĘą░ą┐ąĖčüą░čéčī ą╗ąŠą│. 1, č鹊 ą▓čŗą▓ąŠą┤ ą┐ąĄčĆąĄą╣ą┤ąĄčé ą▓ čéčĆąĄčéčīąĄ čüąŠčüč鹊čÅąĮąĖąĄ (čüąŠčüč鹊čÅąĮąĖąĄ ąŠčéą║ą╗čÄč湥ąĮąŠ). ąóą░ą║ čćč鹊 ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ąĮą░ ą▓čŗčģąŠą┤ąĄ ą┐ąŠą╗ąĮąŠčåąĄąĮąĮąŠą╣ ą╗ąŠą│. 1 ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ą┐ąŠą┤ą║ą╗čÄčćąĖčéčī ą║ ą▓čŗą▓ąŠą┤ą░ą╝ PC1 ąĖ PC4 ą▓ąĮąĄčłąĮąĖą╣ pull-up čĆąĄąĘąĖčüč鹊čĆ.

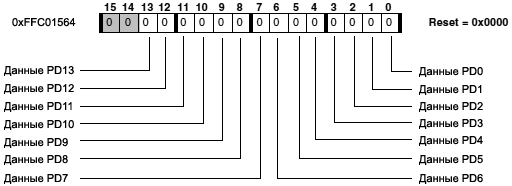

ąóą░ą▒ą╗ąĖčåą░ 15-3. GPIO Port D ąĖ ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąĖčĆąŠą▓ą░ąĮąĖąĄ čäčāąĮą║čåąĖą╣.

| ąÆčŗą▓ąŠą┤ GPIO ą┐ąŠčĆčéą░ D |

ąÆčŗą▓ąŠą┤ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░, ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąĖčĆąŠą▓ą░ąĮąĮčŗą╣ čü čäčāąĮą║čåąĖąĄą╣ GPIO |

ąĪąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ čĆą░ąĘčĆčÅą┤čŗ čĆąĄą│ąĖčüčéčĆąŠą▓ GPIO |

| PD0 |

SPI1 Master Out Slave In (MOSI1) |

0 |

| PD1 |

SPI1 Master In Slave Out (MISO1) |

1 |

| PD2 |

SPI1 Clock (SCK1) |

2 |

| PD3 |

SPI1 Slave Select Input (~SPI1SS) |

3 |

| PD4 |

SPI1 Slave Select Enable (~SPI1SEL1) |

4 |

| PD5 |

SPI2 Master Out Slave In (MOSI2) |

5 |

| PD6 |

SPI2 Master In Slave Out (MISO2) |

6 |

| PD7 |

SPI2 Clock (SCK2) |

7 |

| PD8 |

SPI2 Slave Select Input (~SPI2SS) |

8 |

| PD9 |

SPI2 Slave Select Enable (~SPI2SEL1) |

9 |

| PD10 |

UART1 Receive (RX1) |

10 |

| PD11 |

UART1 Transmit (TX1) |

11 |

| PD12 |

UART2 Receive (RX2) |

12 |

| PD13 |

UART2 Transmit (TX2) |

13 |

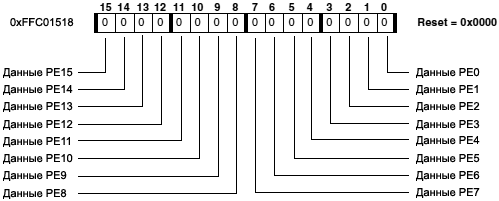

ąóą░ą▒ą╗ąĖčåą░ 15-4. GPIO Port E ąĖ ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąĖčĆąŠą▓ą░ąĮąĖąĄ čäčāąĮą║čåąĖą╣.

| ąÆčŗą▓ąŠą┤ GPIO ą┐ąŠčĆčéą░ E |

ąÆčŗą▓ąŠą┤ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░, ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąĖčĆąŠą▓ą░ąĮąĮčŗą╣ čü čäčāąĮą║čåąĖąĄą╣ GPIO |

ąĪąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ čĆą░ąĘčĆčÅą┤čŗ čĆąĄą│ąĖčüčéčĆąŠą▓ GPIO |

| PE0 |

SPORT2 Receive Serial Clock (RSCLK2) |

0 |

| PE1 |

SPORT2 Receive Frame Sync (RFS2) |

1 |

| PE2 |

SPORT2 Receive Data Primary (DR2PRI) |

2 |

| PE3 |

SPORT2 Receive Data Secondary (DR2SEC) |

3 |

| PE4 |

SPORT2 Transmit Serial Clock (TSCLK2) |

4 |

| PE5 |

SPORT2 Transmit Frame Sync (TFS2) |

5 |

| PE6 |

SPORT2 Transmit Data Primary (DT2PRI) |

6 |

| PE7 |

SPORT2 Transmit Data Secondary (DT2SEC) |

7 |

| PE8 |

SPORT3 Receive Serial Clock (RSCLK3) |

8 |

| PE9 |

SPORT3 Receive Frame Sync (RFS3) |

9 |

| PE10 |

SPORT3 Receive Data Primary (DR3PRI) |

10 |

| PE11 |

SPORT3 Receive Data Secondary (DR3SEC) |

11 |

| PE12 |

SPORT3 Transmit Serial Clock (TSCLK3) |

12 |

| PE13 |

SPORT3 Transmit Frame Sync (TFS3) |

13 |

| PE14 |

SPORT3 Transmit Data Primary (DT3PRI) |

14 |

| PE15 |

SPORT3 Transmit Data Secondary (DT3SEC) |

15 |

[ą×č鹊ą▒čĆą░ąČą░ąĄą╝čŗąĄ ąĮą░ ą┐ą░ą╝čÅčéčī čĆąĄą│ąĖčüčéčĆčŗ GPIO]

ąĀąĄą│ąĖčüčéčĆčŗ, ą║ąŠč鹊čĆčŗą╝ąĖ čāą┐čĆą░ą▓ą╗čÅčÄčéčüčÅ GPIO, čÅą▓ą╗čÅčÄčéčüčÅ čćą░čüčéčīčÄ ąŠą▒ą╗ą░čüčéąĖ ą┐ą░ą╝čÅčéąĖ čüąĖčüč鹥ą╝ąĮčŗčģ čĆąĄą│ąĖčüčéčĆąŠą▓, ąŠč鹊ą▒čĆą░ąČąĄąĮąĮčŗčģ ąĮą░ ąŠą▒čēąĄąĄ ą░ą┤čĆąĄčüąĮąŠąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ ą┐čĆąŠčåąĄčüčüąŠčĆą░ (memory-mapped registers, čüąŠą║čĆą░čēąĄąĮąĮąŠ MMR). ąÉą┤čĆąĄčüą░ čĆąĄą│ąĖčüčéčĆąŠą▓ GPIO MMR ą┤ą░ąĮčŗ ą▓ ą¤čĆąĖą╗ąŠąČąĄąĮąĖąĖ B. ąöąŠčüčéčāą┐ ą║ čĆąĄą│ąĖčüčéčĆą░ą╝ GPIO čüąŠ čüč鹊čĆąŠąĮčŗ čÅą┤čĆą░ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ č湥čĆąĄąĘ čüąĖčüč鹥ą╝ąĮčāčÄ čłąĖąĮčā.

ąĀąĄą│ąĖčüčéčĆ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ čäčāąĮą║čåąĖąĖ GPIO (GPIO function enable register, PORTxIO_FER) čÅą▓ą╗čÅąĄčéčüčÅ čĆąĄą│ąĖčüčéčĆąŠą╝ čü ą┤ąŠčüčéčāą┐ąŠą╝ ąĮą░ čćč鹥ąĮąĖąĄ ąĖ ąĘą░ą┐ąĖčüčī. ąÜą░ąČą┤ą░čÅ ą┐ąŠąĘąĖčåąĖčÅ ą▒ąĖčéą░ ą▓ čŹč鹊ą╝ čĆąĄą│ąĖčüčéčĆąĄ čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ąŠčéą┤ąĄą╗čīąĮąŠą╝čā ą▓čŗą▓ąŠą┤čā GPIO (ąĘą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ čĆą░ąĘčĆčÅą┤ąŠą▓, ą┐ąŠą╝ąĄč湥ąĮąĮčŗčģ ąĮą░ čĆąĖčüčāąĮą║ą░čģ čüąĄčĆčŗą╝ čåą▓ąĄč鹊ą╝). ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ čĆą░ą▓ąĮąŠ 0x0000. ąÆ čŹč鹊ą╝ čüąŠčüč鹊čÅąĮąĖąĖ ą▓čüąĄ čäčāąĮą║čåąĖąĖ GPIO ą▓čŗą▓ąŠą┤ą░ ąĘą░ą┐čĆąĄčēąĄąĮčŗ, ąĖ čĆą░ą▒ąŠčéą░ ą▓čŗą▓ąŠą┤ą░ ąĘą░ą▓ąĖčüąĖčé ąŠčé čäčāąĮą║čåąĖąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░, čüą▓čÅąĘą░ąĮąĮąŠą│ąŠ čü čŹčéąĖą╝ ą▓čŗą▓ąŠą┤ąŠą╝. ąøąŠą│. 1, ąĘą░ą┐ąĖčüą░ąĮąĮą░čÅ ą▓ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčāčÄ ą┐ąŠąĘąĖčåąĖčÄ ą▒ąĖčéą░ PORTxIO_FER, ąĘą░ą┐čĆąĄčēą░ąĄčé čäčāąĮą║čåąĖčÄ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ąĮą░ čŹč鹊ą╝ ą▓čŗą▓ąŠą┤ąĄ ąĖ čĆą░ąĘčĆąĄčłą░ąĄčé čĆą░ą▒ąŠčéčā ą▓čŗą▓ąŠą┤ą░ ą║ą░ą║ GPIO. ąŚą░ą┐ąĖčüčī ą╗ąŠą│. 0 ą▓ąŠąĘą▓čĆą░čēą░ąĄčé čäčāąĮą║čåąĖčÄ ą▓čŗą▓ąŠą┤ą░ ą┐ąŠą┤ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝. ą¦č鹥ąĮąĖąĄ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗčģ ą▒ąĖč鹊ą▓ PORTxIO_FER ą▓čüąĄą│ą┤ą░ ą▓ąĄčĆąĮąĄčé ąĘąĮą░č湥ąĮąĖąĄ 0, ą┐čĆąĖ čŹč鹊ą╝ ąĘą░ą┐ąĖčüčī ą▓ čŹčéąĖ ą▒ąĖčéčŗ ąĮąĄ ą┤ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

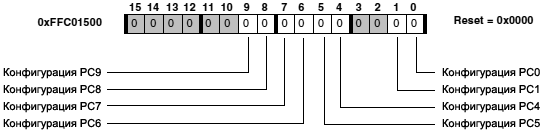

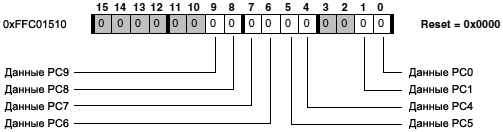

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ ą║ čĆąĖčü. 15-1:

ŌĆó ąæąĖčéčŗ PC1 ąĖ PC4 (čĆą░ąĘčĆčÅą┤čŗ 1 ąĖ 4) ą╝ąŠą│čāčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ ą║ą░ą║ GPIO, ąĮąŠ ąŠąĮąĖ čĆą░ą▒ąŠčéą░čÄčé ą║ą░ą║ 5V-tolerant ą▓čģąŠą┤ ąĖą╗ąĖ ą║ą░ą║ ą▓čŗčģąŠą┤ čü ąŠčéą║čĆčŗčéčŗą╝ čüč鹊ą║ąŠą╝ (ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čĆą░ą▒ąŠčéčŗ ą┐ąŠčĆčéą░).

ŌĆó ąæąĖčéčŗ ąŠčé PC4 ą┤ąŠ PC9 (čĆą░ąĘčĆčÅą┤čŗ 4 .. 9) ą▓čüąĄą│ą┤ą░ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ ą║ą░ą║ GPIO ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé č鹊ą│ąŠ, čćč鹊 ąĘą░ą┐ąĖčüą░ąĮąŠ ą▓ čŹčéąĖ ą▒ąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ PORTCIO_FER (čé. ąĄ. ąĮą░ čŹčéąĖčģ ą▓čŗą▓ąŠą┤ą░čģ ąĮąĄčé čäčāąĮą║čåąĖąŠąĮą░ą╗ą░ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓).

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ ą║ čĆąĖčü. 15-1 ąĖ 15-2: ą┐ąŠą╝ąĄč湥ąĮąĮčŗąĄ čüąĄčĆčŗą╝ čåą▓ąĄč鹊ą╝ ą▒ąĖčéčŗ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ąĖ ą▓čüąĄą│ą┤ą░ čćąĖčéą░čÄčéčüčÅ ą║ą░ą║ 0. ąŚą░ą┐ąĖčüčī ą▓ čŹčéąĖ ą▒ąĖčéčŗ ąĮąĄ ą┤ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

ąĀąĖčü. 15-1. GPIO Port C Function Enable Register (PORTCIO_FER).

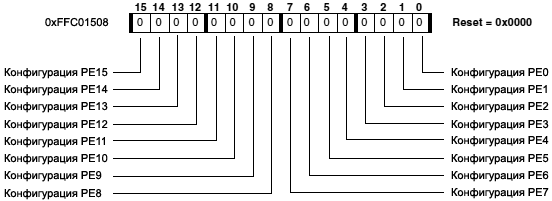

ąĀąĖčü. 15-2. GPIO Port D Function Enable Register (PORTDIO_FER).

ąĀąĖčü. 15-3. GPIO Port E Function Enable Register (PORTEIO_FER).

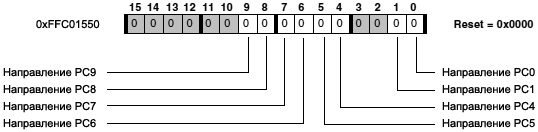

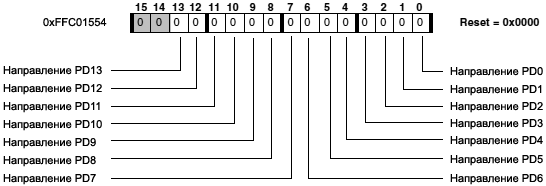

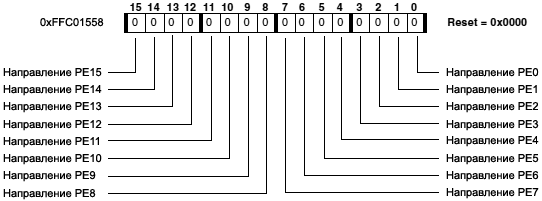

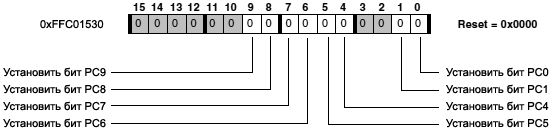

ąĀąĄą│ąĖčüčéčĆ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ GPIO (GPIO direction register, PORTxIO_DIR) čÅą▓ą╗čÅąĄčéčüčÅ čĆąĄą│ąĖčüčéčĆąŠą╝ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ ąĖ ąĘą░ą┐ąĖčüąĖ. ąÜą░ąČą┤ą░čÅ ą┐ąŠąĘąĖčåąĖčÅ ą▒ąĖčéą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą╝čā ą▓čŗą▓ąŠą┤čā GPIO (ąĘą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ čĆą░ąĘčĆčÅą┤ąŠą▓, ą┐ąŠą╝ąĄč湥ąĮąĮčŗčģ ąĮą░ čĆąĖčüčāąĮą║ą░čģ čüąĄčĆčŗą╝ čåą▓ąĄč鹊ą╝). ąĢčüą╗ąĖ ą▓čŗą▓ąŠą┤ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą║ą░ą║ GPIO (čü ą┐ąŠą╝ąŠčēčīčÄ čĆąĄą│ąĖčüčéčĆą░ PORTxIO_FER), č鹊 ąĘą░ą┐ąĖčüą░ąĮąĮą░čÅ ą▓ ą▒ąĖčé PORTxIO_DIR ą╗ąŠą│. 1 čĆą░ąĘčĆąĄčłą░ąĄčé čĆą░ą▒ąŠčéčā ą▓čŗą▓ąŠą┤ą░ GPIO ą║ą░ą║ ą▓čŗčģąŠą┤ą░, ą┐ąĄčĆąĄą▓ąŠą┤čÅ ąĄą│ąŠ ą▓čŗčģąŠą┤ąĮąŠą╣ čāčĆąŠą▓ąĄąĮčī ą▓ čüąŠčüč鹊čÅąĮąĖąĄ, ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠąĄ čĆąĄą│ąĖčüčéčĆąŠą╝ PORTxIO. ąĢčüą╗ąĖ ąĘą░ą┐ąĖčüą░čéčī ą╗ąŠą│. 0 ą▓ čĆą░ąĘčĆčÅą┤ PORTxIO_DIR, č鹊 čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▓čŗą▓ąŠą┤ GPIO ą▒čāą┤ąĄčé čĆą░ą▒ąŠčéą░čéčī ą║ą░ą║ ą▓čģąŠą┤. ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ ą┤ą╗čÅ čĆąĄą│ąĖčüčéčĆą░ PORTxIO_DIR čĆą░ą▓ąĮąŠ 0x0000, čćč鹊 ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ąĮą░čüčéčĆą░ąĖą▓ą░ąĄčé ą▓čüąĄ ą▓čŗą▓ąŠą┤čŗ ą┐ąŠčĆčéą░ ą║ą░ą║ ą▓čģąŠą┤čŗ (ąĄčüą╗ąĖ ą║ąŠąĮąĄčćąĮąŠ ą▓čŗą▓ąŠą┤čŗ ą┐ąŠčĆčéą░ ą┐ąĄčĆąĄą▓ąĄą┤ąĄąĮčŗ ą▓ čĆąĄąČąĖą╝ čĆą░ą▒ąŠčéčŗ GPIO). ą¦č鹥ąĮąĖąĄ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗčģ ą▒ąĖč鹊ą▓ (ą┐ąŠą╝ąĄč湥ąĮčŗ ąĮą░ čĆąĖčüčāąĮą║ą░čģ čüąĄčĆčŗą╝ čåą▓ąĄč鹊ą╝) ą▓čüąĄą│ą┤ą░ ą▓ąŠąĘą▓čĆą░čēą░ąĄčé 0, ąĘą░ą┐ąĖčüčī ą▓ ąĮąĖčģ ąĮąĄ ą┤ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ ą║ čĆąĖčü. 15-4: ą▓čŗą▓ąŠą┤čŗ PC1 ąĖ PC4 (čĆą░ąĘčĆčÅą┤čŗ 1 ąĖ 4) ą╝ąŠą│čāčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ ą║ą░ą║ GPIO, ąŠą┤ąĮą░ą║ąŠ ąĮą░ą┤ąŠ ąĖą╝ąĄčéčī ą▓ ą▓ąĖą┤čā, čćč鹊 ą▓ čĆąĄąČąĖą╝ąĄ ą▓čģąŠą┤ą░ čŹč鹊 5V-tolerant ą▓čģąŠą┤, ą░ ą▓ čĆąĄąČąĖą╝ąĄ ą▓čŗčģąŠą┤ą░ čŹč鹊 ą▓čŗčģąŠą┤ čü ąŠčéą║čĆčŗčéčŗą╝ čüč鹊ą║ąŠą╝. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą▓ čĆąĄąČąĖą╝ąĄ ą▓čŗčģąŠą┤ą░ čŹčéąĖ ą▓čŗą▓ąŠą┤čŗ ą╝ąŠą│čāčé ą▒čŗčéčī ą┐ąĄčĆąĄą▓ąĄą┤ąĄąĮčŗ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ą╗ąŠą│. 0, ąĄčüą╗ąĖ ąĘą░ą┐ąĖčüą░čéčī ą▓ čĆąĄą│ąĖčüčéčĆ ą┤ą░ąĮąĮčŗčģ ąĘąĮą░č湥ąĮąĖąĄ 0, ąĮąŠ ąĄčüą╗ąĖ ąĘą░ą┐ąĖčüą░čéčī ą╗ąŠą│. 1, č鹊 ą▓čŗą▓ąŠą┤ ą┐ąĄčĆąĄą╣ą┤ąĄčé ą▓ čéčĆąĄčéčīąĄ čüąŠčüč鹊čÅąĮąĖąĄ (čüąŠčüč鹊čÅąĮąĖąĄ ąŠčéą║ą╗čÄč湥ąĮąŠ). ąóą░ą║ čćč鹊 ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ąĮą░ ą▓čŗčģąŠą┤ąĄ ą┐ąŠą╗ąĮąŠčåąĄąĮąĮąŠą╣ ą╗ąŠą│. 1 ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ą┐ąŠą┤ą║ą╗čÄčćąĖčéčī ą║ ą▓čŗą▓ąŠą┤ą░ą╝ PC1 ąĖ PC4 ą▓ąĮąĄčłąĮąĖą╣ pull-up čĆąĄąĘąĖčüč鹊čĆ.

ąĀąĖčü. 15-4. GPIO Port C Direction Register (PORTCIO_DIR).

ąĀąĖčü. 15-5. GPIO Port D Direction Register (PORTDIO_DIR).

ąĀąĖčü. 15-6. GPIO Port E Direction Register (PORTEIO_DIR).

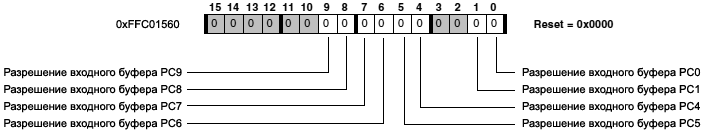

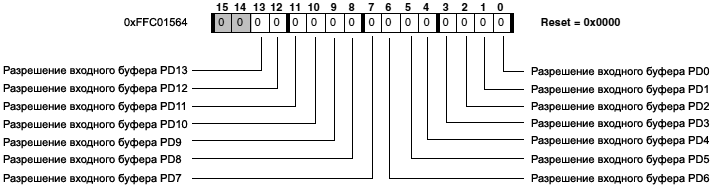

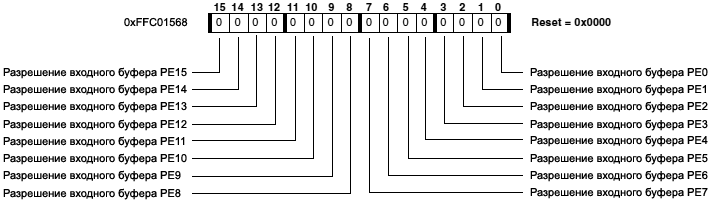

ąĀąĄą│ąĖčüčéčĆ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą▓čģąŠą┤ą░ GPIO (GPIO input enable register, PORTxIO_INEN) ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ čĆą░ą▒ąŠčéčŗ ą▓čģąŠą┤ąĮčŗčģ ą▒čāč乥čĆąŠą▓ ą┤ą╗čÅ ą╗čÄą▒ąŠą│ąŠ ą▓čŗą▓ąŠą┤ą░ GPIO, ą║ąŠč鹊čĆčŗą╣ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą║ą░ą║ ą▓čģąŠą┤. ąĢčüą╗ąĖ ąŠčüčéą░ą▓ąĖčéčī ą▓čģąŠą┤ąĮąŠą╣ ą▒čāč乥čĆ ąĘą░ą┐čĆąĄčēąĄąĮąĮčŗą╝, č鹊 čŹč鹊 čāčüčéčĆą░ąĮčÅąĄčé ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéčī ą┐ąŠą┤ą║ą╗čÄčćą░čéčī ą▓ąĮąĄčłąĮąĖąĄ ą┐ąŠą┤čéčÅą│ąĖą▓ą░čÄčēąĖąĄ čĆąĄąĘąĖčüč鹊čĆčŗ (pull-up ąĖą╗ąĖ pull-down) ą▓ čåąĄą╗čīčÄ ą┐ąŠą╗čāč湥ąĮąĖčÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą│ąŠ ą╗ąŠą│. čāčĆąŠą▓ąĮčÅ ąĮą░ ą▓čģąŠą┤ąĄ, ą║ąŠą│ą┤ą░ ąŠčéą┤ąĄą╗čīąĮčŗąĄ ą▓čŗą▓ąŠą┤čŗ GPIO ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ čüąĖčüč鹥ą╝ąŠą╣. ą¤ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą▓čģąŠą┤ąĮčŗąĄ ą▒čāč乥čĆčŗ ąĘą░ą┐čĆąĄčēąĄąĮčŗ. ą¦č鹥ąĮąĖąĄ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗčģ ą▒ąĖčé PORTxIO_INEN (ąĮą░ čĆąĖčüčāąĮą║ą░čģ ąŠąĮąĖ ą┐ąŠą╝ąĄč湥ąĮčŗ čüąĄčĆčŗą╝ čåą▓ąĄč鹊ą╝) ą▓čüąĄą│ą┤ą░ ą▓ąĄčĆąĮąĄčé ąĘąĮą░č湥ąĮąĖąĄ 0, ąĘą░ą┐ąĖčüčī ą▓ čŹčéąĖ ą▒ąĖčéčŗ ąĮąĄ ą┤ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

ąĢčüą╗ąĖ ą▓čŗą▓ąŠą┤ GPIO čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą║ą░ą║ ą▓čģąŠą┤, č鹊 ąŠą▒čÅąĘą░č鹥ą╗čīąĮąŠ čéą░ą║ąČąĄ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé ą▓ čĆąĄą│ąĖčüčéčĆąĄ PORTxIO_INEN.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ ą║ čĆąĖčü. 15-7: ą▒ąĖčéčŗ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą▒čāč乥čĆą░ ą┤ą╗čÅ PC1 ąĖ PC4 (čĆą░ąĘčĆčÅą┤čŗ 1 ąĖ 4) ą╝ąŠą│čāčé ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ, ą║ąŠą│ą┤ą░ čŹčéąĖ ą▓čŗą▓ąŠą┤čŗ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ ą║ą░ą║ GPIO. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ą▓ čĆąĄąČąĖą╝ąĄ ą▓čģąŠą┤ą░ ą▓čŗą▓ąŠą┤čŗ PC1 ąĖ PC4 ą╝ąŠą│čāčé ą▒čŗčéčī 5V-tolerant (čé. ąĄ. ą┤ąŠą┐čāčüą║ą░čéčī čĆą░ą▒ąŠčéčā čü ą╗ąŠą│. čāčĆąŠą▓ąĮčÅą╝ąĖ 5V, ą┤ą░ąČąĄ ąĄčüą╗ąĖ čŹč鹊 ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą▓čŗčłąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ VDDEXT, ą║ąŠč鹊čĆąŠąĄ ąŠą▒čŗčćąĮąŠ čüąŠčüčéą░ą▓ą╗čÅąĄčé 3.3V).

ąĀąĖčü. 15-7. GPIO Port C Input Enable Register (PORTCIO_INEN).

ąĀąĖčü. 15-8. GPIO Port D Input Enable Register (PORTDIO_INEN).

ąĀąĖčü. 15-9. GPIO Port E Input Enable Register (PORTEIO_INEN).

[ąĀąĄą│ąĖčüčéčĆčŗ ą╗ąŠą│ąĖč湥čüą║ąĖčģ ąĘąĮą░č湥ąĮąĖą╣ GPIO]

ąŻ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ąĄčüčéčī 4 čĆąĄą│ąĖčüčéčĆą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą╗ąŠą│ąĖč湥čüą║ąĖą╝ąĖ čāčĆąŠą▓ąĮčÅą╝ąĖ GPIO (GPIO value registers):

ŌĆó GPIO data register (PORTxIO), čĆąĄą│ąĖčüčéčĆ ą┤ą░ąĮąĮčŗčģ GPIO.

ŌĆó GPIO set register (PORTxIO_SET), čĆąĄą│ąĖčüčéčĆ ą┤ą╗čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ čĆą░ąĘčĆčÅą┤ąŠą▓ GPIO.

ŌĆó GPIO clear register (PORTxIO_CLEAR), čĆąĄą│ąĖčüčéčĆ ą┤ą╗čÅ čüą▒čĆąŠčüą░ čĆą░ąĘčĆčÅą┤ąŠą▓ GPIO.

ŌĆó GPIO toggle register (PORTxIO_TOGGLE), čĆąĄą│ąĖčüčéčĆ ą┤ą╗čÅ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ą▓ ą┐čĆąŠčéąĖą▓ąŠą┐ąŠą╗ąŠąČąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ čĆą░ąĘčĆčÅą┤ąŠą▓ GPIO.

ąŁčéąĖ čĆąĄą│ąĖčüčéčĆčŗ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ čüą╗ąĄą┤čāčÄčēąĖčģ čåąĄą╗ąĄą╣:

ŌĆó ą¦č鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ą╗ąŠą│. čāčĆąŠą▓ąĄąĮčī ąĮą░ ą╗čÄą▒čŗčģ ą▓čŗą▓ąŠą┤ą░čģ GPIO, ąĮą░čüčéčĆąŠąĄąĮąĮčŗčģ ą║ą░ą║ ą▓čģąŠą┤čŗ.

ŌĆó ąŚą░ą┤ą░čéčī ąĮčāąČąĮčŗą╣ ą╗ąŠą│. čāčĆąŠą▓ąĄąĮčī ąĮą░ ą╗čÄą▒čŗčģ ą▓čŗą▓ąŠą┤ą░čģ GPIO, ąĮą░čüčéčĆąŠąĄąĮąĮčŗčģ ą║ą░ą║ ą▓čŗčģąŠą┤čŗ.

ąÜą░ąČą┤čŗą╣ ą▓čŗą▓ąŠą┤ GPIO ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╝ ą▒ąĖč鹊ą╝ ą▓ ą║ą░ąČą┤ąŠą╝ ąĖąĘ čŹčéąĖčģ 4 čĆąĄą│ąĖčüčéčĆąŠą▓. ą¦č鹥ąĮąĖąĄ ą╗čÄą▒ąŠą│ąŠ ąĖąĘ čŹčéąĖčģ čĆąĄą│ąĖčüčéčĆąŠą▓ ą┤ą░čüčé ą╗ąŠą│ąĖč湥čüą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī ąĮą░ čŹčéąĖčģ ą▓čŗą▓ąŠą┤ą░čģ GPIO - čé. ąĄ. ą▓ąŠąĘą▓čĆą░čēąĄąĮąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą▒čāą┤ąĄčé čüąŠąŠčéą▓ąĄčéčüčéą▓ąŠą▓ą░čéčī čüąŠčüč鹊čÅąĮąĖčÄ ą▓čŗčģąŠą┤ąŠą▓ (ąĄčüą╗ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ ą▓čŗą▓ąŠą┤čŗ GPIO ąĮą░čüčéčĆąŠąĄąĮčŗ ą║ą░ą║ ą▓čŗčģąŠą┤) ąĖą╗ąĖ ąĘąĮą░č湥ąĮąĖčÄ ą╗ąŠą│ąĖč湥čüą║ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░, ą┐ąŠą┤ą░ąĮąĮąŠą│ąŠ ąĮą░ ą▓čģąŠą┤ (ąĄčüą╗ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ ą▓čŗą▓ąŠą┤čŗ GPIO ąĮą░čüčéčĆąŠąĄąĮčŗ ą║ą░ą║ ą▓čģąŠą┤).

ą¦č鹥ąĮąĖąĄ ą▓čüąĄčģ čŹčéąĖčģ 4 čĆąĄą│ąĖčüčéčĆąŠą▓ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ ą┤ą░čüčé 0x0000, ą┐ąŠč鹊ą╝čā čćč鹊 čŹčéąĖ ą▓čŗą▓ąŠą┤čŗ ąĮąĄ čĆą░ąĘčĆąĄčłąĄąĮčŗ, ą┤ą░ąČąĄ ąĄčüą╗ąĖ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ ąŠąĮąĖ ąĮą░čģąŠą┤čÅčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ čĆą░ą▒ąŠčéčŗ ą▓čģąŠą┤ą░.

ąŁč鹊 čĆąĄą│ąĖčüčéčĆ ą┤ą░ąĮąĮčŗčģ GPIO (GPIO data register, PORTxIO). ąĢčüą╗ąĖ ą▓čŗą▓ąŠą┤ ąĖą╗ąĖ ą▓čŗą▓ąŠą┤čŗ ąĮą░čüčéčĆąŠąĄąĮčŗ ą║ą░ą║ ą▓čŗčģąŠą┤čŗ GPIO, č鹊 ąĘą░ą┐ąĖčüčŗą▓ą░ąĄą╝ąŠąĄ ą▓ čĆąĄą│ąĖčüčéčĆ ą┤ą░ąĮąĮčŗčģ ąĘąĮą░č湥ąĮąĖąĄ ąĮą░ą┐čĆčÅą╝čāčÄ ą▒čāą┤ąĄčé ąĘą░ą┤ą░ą▓ą░čéčī čüąŠčüč鹊čÅąĮąĖąĄ ą▓čŗčģąŠą┤ąŠą▓ GPIO. ą¤čĆąĖ čćč鹥ąĮąĖąĖ čŹč鹊ą│ąŠ čĆąĄą│ąĖčüčéčĆą░ ą▒čāą┤ąĄčé ą▓ąŠąĘą▓čĆą░čēąĄąĮąŠ ąĘąĮą░č湥ąĮąĖąĄ ą╗ąŠą│ąĖč湥čüą║ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ ąĮą░ ą▓čŗą▓ąŠą┤ą░čģ GPIO. ą¦č鹥ąĮąĖąĄ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗčģ ą▒ąĖč鹊ą▓ ą┤ą░ąĮąĮčŗčģ GPIO ą▓čüąĄą│ą┤ą░ ą▓ąĄčĆąĮąĄčé 0, ąĘą░ą┐ąĖčüčī ą▓ čŹčéąĖ ą▒ąĖčéčŗ ąĮąĄ ą┤ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░ (ąĮą░ čĆąĖčüčāąĮą║ą░čģ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą▒ąĖčéčŗ ą┐ąŠą╝ąĄč湥ąĮčŗ čüąĄčĆčŗą╝ čåą▓ąĄč鹊ą╝).

ąĀąĖčü. 15-10. GPIO Port C Data Register (PORTCIO).

ąĀąĖčü. 15-11. GPIO Port D Data Register (PORTDIO).

ąĀąĖčü. 15-12. GPIO Port E Data Register (PORTEIO).

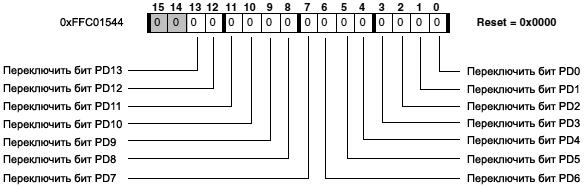

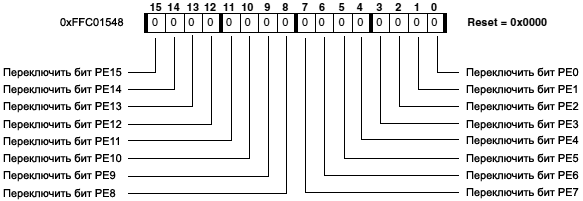

ąĀąĄą│ąĖčüčéčĆčŗ čāčüčéą░ąĮąŠą▓ą║ąĖ (GPIO set, PORTxIO_SET), čüą▒čĆąŠčüą░ (GPIO clear, PORTxIO_CLEAR) ąĖ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ (GPIO toggle, PORTxIO_TOGGLE) čĆą░ąĘčĆčÅą┤ąŠą▓ GPIO ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ ą┐ąŠą▒ąĖčéąĮąŠą│ąŠ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą▓čŗčģąŠą┤ą░ą╝ąĖ GPIO. ąŁč鹊čé ą╝ąĄčģą░ąĮąĖąĘą╝ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓ąŠ ąĖąĘą▒ąĄąČą░ąĮąĖąĄ ą┐ąŠč鹥ąĮčåąĖą░ą╗čīąĮčŗčģ ą┐čĆąŠą▒ą╗ąĄą╝ ąĮąĄ čéčĆą░ą┤ąĖčåąĖąŠąĮąĮčŗčģ ąĮąĄ ą░č鹊ą╝ą░čĆąĮčŗčģ ąŠą┐ąĄčĆą░čåąĖą╣ čéąĖą┐ą░ read-modify-write (ą┐čĆąŠčćąĖčéą░čéčī-ąĖąĘą╝ąĄąĮąĖčéčī-ąĘą░ą┐ąĖčüą░čéčī). ą¦č鹥ąĮąĖąĄ čŹčéąĖčģ čĆąĄą│ąĖčüčéčĆąŠą▓ ą▓ąĄčĆąĮąĄčé čüąŠčüč鹊čÅąĮąĖąĄ ą▓čŗą▓ąŠą┤ąŠą▓ GPIO. ą¦č鹥ąĮąĖąĄ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗčģ ą▒ąĖč鹊ą▓ čŹčéąĖčģ čĆąĄą│ąĖčüčéčĆąŠą▓ ą▓čüąĄą│ą┤ą░ ą▓ąĄčĆąĮąĄčé 0, ąĘą░ą┐ąĖčüčī ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░ (ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą▒ąĖčéčŗ ąĮą░ čĆąĖčüčāąĮą║ą░čģ ą┐ąŠą╝ąĄč湥ąĮčŗ čüąĄčĆčŗą╝ čåą▓ąĄč鹊ą╝).

ąĀąĖčü. 15-13. GPIO Port C Set Register (PORTCIO_SET).

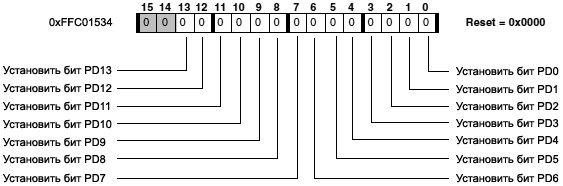

ąĀąĖčü. 15-14. GPIO Port D Set Register (PORTDIO_SET).

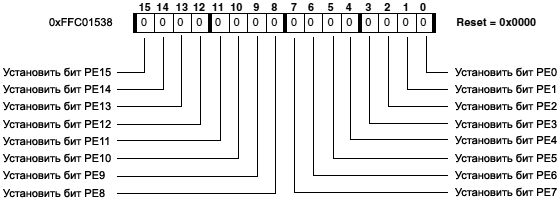

ąĀąĖčü. 15-15. GPIO Port E Set Register (PORTEIO_SET).

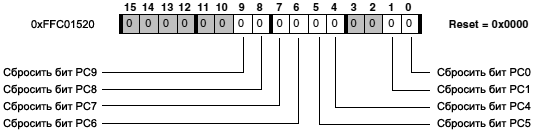

ąĀąĖčü. 15-16. GPIO Port C Clear Register (PORTCIO_CLEAR).

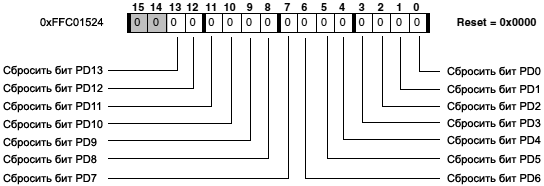

ąĀąĖčü. 15-17. GPIO Port D Clear Register (PORTDIO_CLEAR).

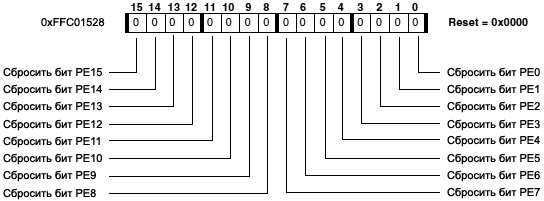

ąĀąĖčü. 15-18. GPIO Port E Clear Register (PORTEIO_CLEAR).

ąĀąĖčü. 15-19. GPIO Port C Toggle Register (PORTCIO_TOGGLE).

ąĀąĖčü. 15-20. GPIO Port D Toggle Register (PORTDIO_TOGGLE).

ąĀąĖčü. 15-21. GPIO Port E Toggle Register (PORTEIO_TOGGLE).

ąÆ ą║ą░č湥čüčéą▓ąĄ ą┐čĆąĖą╝ąĄčĆą░ č鹊ą│ąŠ, ą║ą░ą║ čĆą░ą▒ąŠčéą░čÄčé čŹčéąĖ čĆąĄą│ąĖčüčéčĆčŗ, ą┐čĆąĄą┤ą┐ąŠą╗ąŠąČąĖą╝, čćč鹊 PD0 čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą║ą░ą║ ą▓čŗčģąŠą┤ (PORTDIO_FER = 0x0001 ąĖ PORTDIO_DIR = 0x0001). ąŚą░ą┐ąĖčüčī 0x0001 ą▓ čĆąĄą│ąĖčüčéčĆ PORTDIO_SET ą┐ąĄčĆąĄą▓ąĄą┤ąĄčé ąĮąŠąČą║čā ą▓čŗčģąŠą┤ą░ PD0 ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ą╗ąŠą│. 1 ą▒ąĄąĘ ą▓ą╗ąĖčÅąĮąĖčÅ ąĮą░ čüąŠčüč鹊čÅąĮąĖąĄ ą┤čĆčāą│ąĖčģ ą▓čŗą▓ąŠą┤ąŠą▓ GPIO. ąŚą░ą┐ąĖčüčī 0x0001 ą▓ čĆąĄą│ąĖčüčéčĆ PORTDIO_CLEAR ą┐ąĄčĆąĄą▓ąĄą┤ąĄčé ą▓čŗčģąŠą┤ąĮąŠą╣ čāčĆąŠą▓ąĄąĮčī ą▓čŗą▓ąŠą┤ą░ PD0 ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ą╗ąŠą│. 0 ą▒ąĄąĘ ą▓ą╗ąĖčÅąĮąĖčÅ ąĮą░ čüąŠčüč鹊čÅąĮąĖąĄ ą┤čĆčāą│ąĖčģ ą▓čŗą▓ąŠą┤ąŠą▓ GPIO. ąŚą░ą┐ąĖčüčī 0x0001 ą▓ čĆąĄą│ąĖčüčéčĆ PORTDIO_TOGGLE ą┐ąŠą╝ąĄąĮčÅąĄčé čüąŠčüč鹊čÅąĮąĖąĄ ąĮą░ ą▓čŗčģąŠą┤ąĄ PD0 ąĮą░ ą┐čĆąŠčéąĖą▓ąŠą┐ąŠą╗ąŠąČąĮąŠąĄ ąŠčé č鹥ą║čāčēąĄą│ąŠ čüąŠčüč鹊čÅąĮąĖčÅ, ą▒ąĄąĘ ą▓ą╗ąĖčÅąĮąĖčÅ ąĮą░ ą┤čĆčāą│ąĖąĄ ą▓čŗą▓ąŠą┤čŗ GPIO.

ąŚą░ą┐ąĖčüčī 0 ą▓ ą╗čÄą▒ąŠą╣ ąĖąĘ čŹčéąĖčģ čĆąĄą│ąĖčüčéčĆąŠą▓ ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

ą¦č鹥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆąŠą▓ PORTxIO_SET ąĖą╗ąĖ PORTxIO_CLEAR ą▓ąŠąĘą▓čĆą░čéąĖčé čüą╗ąĄą┤čāčÄčēąĄąĄ:

ŌĆó 0 ą┤ą╗čÅ ą▓čŗą▓ąŠą┤ąŠą▓ GPIO, ą║ąŠč鹊čĆčŗąĄ ąĮą░čüčéčĆąŠąĄąĮčŗ ą║ą░ą║ ą▓čŗčģąŠą┤čŗ, ąĖ ą┐ąĄčĆąĄą▓ąĄą┤ąĄąĮčŗ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ą╗ąŠą│. 0.

ŌĆó 1 ą┤ą╗čÅ ą▓čŗą▓ąŠą┤ąŠą▓ GPIO, ą║ąŠč鹊čĆčŗąĄ ąĮą░čüčéčĆąŠąĄąĮčŗ ą║ą░ą║ ą▓čŗčģąŠą┤čŗ, ąĖ ą┐ąĄčĆąĄą▓ąĄą┤ąĄąĮčŗ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ą╗ąŠą│. 1.

ŌĆó ąŻčĆąŠą▓ąĄąĮčī ą▓čģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ą┤ą╗čÅ ą▓čŗą▓ąŠą┤ąŠą▓ GPIO, ąĮą░čüčéčĆąŠąĄąĮąĮčŗčģ ą║ą░ą║ ą▓čģąŠą┤čŗ (ąĖ čā ą║ąŠč鹊čĆčŗčģ čĆą░ąĘčĆąĄčłąĄąĮčŗ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ ą▓čģąŠą┤ąĮčŗąĄ ą▒čāč乥čĆčŗ).

[ąæčŗčüčéčĆąŠą┤ąĄą╣čüčéą▓ąĖąĄ / ą┐čĆąŠą┐čāčüą║ąĮą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī]

ąÆčŗą▓ąŠą┤čŗ GPIO čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆąŠą▓ą░ąĮčŗ čü čüąĖčüč鹥ą╝ąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊č鹊ą╣ (SCLK). ąÜąŠą│ą┤ą░ ą▓čŗą▓ąŠą┤čŗ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ ą║ą░ą║ ą▓čŗčģąŠą┤čŗ, ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗąĄ GPIO ą╝ąŠą│čāčé ą╝ąĄąĮčÅčéčī čüą▓ąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ ąĮą░ ą║ą░ąČą┤ąŠą╝ ą┐ąĄčĆąĄą┐ą░ą┤ąĄ čüąĖčüč鹥ą╝ąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ (ąĮąĄ ą┐čāčéą░ą╣č鹥 čü čćą░čüč鹊č鹊ą╣ čÅą┤čĆą░ CCLK!).

ąĀąĄą│ąĖčüčéčĆčŗ ą┐čĆąŠčåąĄčüčüąŠčĆą░ Blackfin, ąŠč鹊ą▒čĆą░ąČąĄąĮąĮčŗąĄ ąĮą░ ą░ą┤čĆąĄčüąĮąŠąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ ą┐ą░ą╝čÅčéąĖ (memory-mapped registers, MMR) ąĮą░čģąŠą┤čÅčéčüčÅ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ą░ą┤čĆąĄčüąŠą▓ 0xFFE00000 .. 0xFFFFFFFF.

ąÜąŠ ą▓čüąĄą╝ MMR čÅą┤čĆą░ ą┤ąŠčüčéčāą┐ ą┤ąŠą╗ąČąĄąĮ ąŠčüčāčēąĄčüčéą▓ą╗čÅčéčīčüčÅ ą║ą░ą║ 32-ą▒ąĖčéąĮąŠąĄ čćč鹥ąĮąĖąĄ ąĖą╗ąĖ ąĘą░ą┐ąĖčüčī.

ąÆ čŹč鹊ą╝ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĖ ą┐ąĄčĆąĄčćąĖčüą╗ąĄąĮčŗ ą░ą┤čĆąĄčüą░ MMR čÅą┤čĆą░ ąĖčģ ąĖą╝ąĄąĮą░. ą¦č鹊ą▒čŗ ą┐ąŠą╗čāčćąĖčéčī ą▒ąŠą╗čīčłąĄ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ą┐čĆąŠ MMR, čüą╝. čüč鹊ą╗ą▒ąĄčå "ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ ą▓ čĆą░ąĘą┤ąĄą╗ąĄ".

ąĀąĄą│ąĖčüčéčĆčŗ GPIO port C, D, E (0xFFC0 1500 ŌĆō 0xFFC0 15FF)

ąóą░ą▒ą╗ąĖčåą░ B-13. ąĀąĄą│ąĖčüčéčĆčŗ GPIO Port C.

| ąÉą┤čĆąĄčü MMR |

ąśą╝čÅ čĆąĄą│ąĖčüčéčĆą░ |

ąĪą╝. čüąĄą║čåąĖčÄ |

| 0xFFC0 1500 |

PORTCIO_FER |

ąĀąĄą│ąĖčüčéčĆ PORTxIO_FER |

| 0xFFC0 1550 |

PORTCIO_DIR |

ąĀąĄą│ąĖčüčéčĆ PORTxIO_DIR |

| 0xFFC0 1560 |

PORTCIO_INEN |

ąĀąĄą│ąĖčüčéčĆ PORTxIO_INEN |

| 0xFFC0 1510 |

PORTCIO |

ąĀąĄą│ąĖčüčéčĆ PORTxIO |

| 0xFFC0 1520 |

PORTCIO_CLEAR |

ąĀąĄą│ąĖčüčéčĆčŗ PORTxIO_SET, PORTxIO_CLEAR ąĖ PORTxIO_TOGGLE |

| 0xFFC0 1530 |

PORTCIO_SET |

| 0xFFC0 1540 |

PORTCIO_TOGGLE |

ąóą░ą▒ą╗ąĖčåą░ B-14. ąĀąĄą│ąĖčüčéčĆčŗ GPIO Port D.

| ąÉą┤čĆąĄčü MMR |

ąśą╝čÅ čĆąĄą│ąĖčüčéčĆą░ |

ąĪą╝. čüąĄą║čåąĖčÄ |

| 0xFFC0 1504 |

PORTDIO_FER |

ąĀąĄą│ąĖčüčéčĆ PORTxIO_FER |

| 0xFFC0 1554 |

PORTDIO_DIR |

ąĀąĄą│ąĖčüčéčĆ PORTxIO_DIR |

| 0xFFC0 1564 |

PORTDIO_INEN |

ąĀąĄą│ąĖčüčéčĆ PORTxIO_INEN |

| 0xFFC0 1514 |

PORTDIO |

ąĀąĄą│ąĖčüčéčĆ PORTxIO |

| 0xFFC0 1524 |

PORTDIO_CLEAR |

ąĀąĄą│ąĖčüčéčĆčŗ PORTxIO_SET, PORTxIO_CLEAR ąĖ PORTxIO_TOGGLE |

| 0xFFC0 1534 |

PORTDIO_SET |

| 0xFFC0 1544 |

PORTDIO_TOGGLE |

ąóą░ą▒ą╗ąĖčåą░ B-15. ąĀąĄą│ąĖčüčéčĆčŗ GPIO Port E.

| ąÉą┤čĆąĄčü MMR |

ąśą╝čÅ čĆąĄą│ąĖčüčéčĆą░ |

ąĪą╝. čüąĄą║čåąĖčÄ |

| 0xFFC0 1508 |

PORTEIO_FER |

ąĀąĄą│ąĖčüčéčĆ PORTxIO_FER |

| 0xFFC0 1558 |

PORTEIO_DIR |

ąĀąĄą│ąĖčüčéčĆ PORTxIO_DIR |

| 0xFFC0 1568 |

PORTEIO_INEN |

ąĀąĄą│ąĖčüčéčĆ PORTxIO_INEN |

| 0xFFC0 1518 |

PORTEIO |

ąĀąĄą│ąĖčüčéčĆ PORTxIO |

| 0xFFC0 1528 |

PORTEIO_CLEAR |

ąĀąĄą│ąĖčüčéčĆčŗ PORTxIO_SET, PORTxIO_CLEAR ąĖ PORTxIO_TOGGLE |

| 0xFFC0 1538 |

PORTEIO_SET |

| 0xFFC0 1548 |

PORTEIO_TOGGLE |

ąĀąĄą│ąĖčüčéčĆčŗ GPIO port F (0xFFC0 0700 ŌĆō 0xFFC0 07FF)

Table B-16. ąĀąĄą│ąĖčüčéčĆčŗ GPIO Port F.

| ąÉą┤čĆąĄčü MMR |

ąśą╝čÅ čĆąĄą│ąĖčüčéčĆą░ |

ąĪą╝. čüąĄą║čåąĖčÄ |

| 0xFFC0 0700 |

PORTFIO_FLAG_D |

ąĀąĄą│ąĖčüčéčĆ PORTFIO |

| 0xFFC0 0704 |

PORTEIO_FLAG_CLEAR |

ąĀąĄą│ąĖčüčéčĆčŗ PORTFIO_SET, PORTFIO_CLEAR ąĖ PORTFIO_TOGGLE |

| 0xFFC0 0708 |

PORTFIO_FLAG_SET |

| 0xFFC0 070C |

PORTFIO_FLAG_TOGGLE |

| 0xFFC0 0710 |

PORTFIO_MASKA |

ą×ą▒ąĘąŠčĆ čĆąĄą│ąĖčüčéčĆąŠą▓ ą╝ą░čüą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ GPIO F |

| 0xFFC0 0714 |

PORTFIO_MASKA_CLEAR |

| 0xFFC0 0718 |

PORTFIO_MASKA_SET |

| 0xFFC0 071C |

PORTFIO_MASKA_TOGGLE |

| 0xFFC0 0720 |

PORTFIO_MASKB |

| 0xFFC0 0724 |

PORTFIO_MASKB_CLEAR |

| 0xFFC0 0728 |

PORTFIO_MASKB_SET |

| 0xFFC0 072C |

PORTFIO_MASKB_TOGGLE |

| 0xFFC0 0730 |

PORTFIO_DIR |

ąĀąĄą│ąĖčüčéčĆ PORTFIO_DIR |

| 0xFFC0 0734 |

PORTFIO_POLAR |

ąĀąĄą│ąĖčüčéčĆ PORTFIO_POLAR |

| 0xFFC0 0738 |

PORTFIO_EDGE |

ąĀąĄą│ąĖčüčéčĆ PORTFIO_EDGE |

| 0xFFC0 073C |

PORTFIO_BOTH |

ąĀąĄą│ąĖčüčéčĆ PORTFIO_BOTH |

| 0xFFC0 0740 |

PORTFIO_INEN |

ąĀąĄą│ąĖčüčéčĆ PORTFIO_INEN |

[ąĪčüčŗą╗ą║ąĖ]

1. ADSP-BF538/ADSP-BF538F Blackfin® Processor Hardware Reference site:analog.com.

2. ADSP-BF538: čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąŠčĆčéą░ą╝ąĖ GPIO F. |