|

ą¤čĆąŠčåąĄčüčüąŠčĆ ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą┐čĆčÅą╝ąŠą╣ ą┤ąŠčüčéčāą┐ ą║ ą┐ą░ą╝čÅčéąĖ (direct memory access, DMA) ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ą╝ąĄąČą┤čā ąŠą▒ą╗ą░čüčéčÅą╝ąĖ ą┐ą░ą╝čÅčéąĖ ąĖą╗ąĖ ą╝ąĄąČą┤čā ąŠą▒ą╗ą░čüčéčīčÄ ą┐ą░ą╝čÅčéąĖ ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝. ą¤čĆąŠčåąĄčüčüąŠčĆ ą╝ąŠąČąĄčé ąĘą░ą┤ą░čéčī ąŠą┐ąĄčĆą░čåąĖąĖ ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ąĖ ą▓ąĄčĆąĮčāčéčīčüčÅ ą║ ąĮąŠčĆą╝ą░ą╗čīąĮąŠą╝čā ą┐ąŠč鹊ą║čā ą▓čŗčćąĖčüą╗ąĄąĮąĖą╣. ą¤čĆąĖ čŹč鹊ą╝ ą┐ąĄčĆąĄąĮąŠčü ą┤ą░ąĮąĮčŗčģ ą┐ąŠą╗ąĮąŠčüčéčīčÄ ą▒ąĄčĆąĄčé ąĮą░ čüąĄą▒čÅ ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ DMA, čĆą░ą▒ąŠčéą░čÅ ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé čÅą┤čĆą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĘą┤ąĄčüčī ą┐čĆąĖą▓ąĄą┤ąĄąĮ ą┐ąĄčĆąĄą▓ąŠą┤ čĆą░ąĘą┤ąĄą╗ą░ ą┤ą░čéą░čłąĖčéą░ Analog Devices [1], ą┐ąŠčüą▓čÅčēąĄąĮąĮąŠą│ąŠ DMA Blackfin ADSP-BF538. ąÆčüąĄ ąĮąĄą┐ąŠąĮčÅčéąĮčŗąĄ čüąŠą║čĆą░čēąĄąĮąĖčÅ ąĖ č鹥čĆą╝ąĖąĮčŗ, ą▓čüčéčĆąĄčćą░čÄčēąĖąĄčüčÅ ą▓ č鹥ą║čüč鹥, čüą╝. ą▓ čĆą░ąĘą┤ąĄą╗ąĄ "ąĪą╗ąŠą▓ą░čĆąĖą║" čüčéą░čéčīąĖ [3].

ąÆ ą┐čĆąŠčåąĄčüčüąŠčĆąĄ ąĄčüčéčī ą┤ą▓ąĄ ą┐ąŠą┤čüąĖčüč鹥ą╝čŗ DMA: DMA ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ 0 ąĖ DMA ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ 1. ąŁčéąĖ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčŗ DMA ąŠą┤ąĖąĮą░ą║ąŠą▓čŗąĄ ą▓ čüą╝čŗčüą╗ąĄ ąŠą┐ąĖčüą░ąĮąĖčÅ, ą║ąŠč鹊čĆąŠąĄ ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮąŠ ą▓ čŹč鹊ą╣ čüčéą░čéčīąĄ.

ąÜ ą┤ą▓čāą╝ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ą╝ DMA ą┐čĆąĖą▓čÅąĘą░ąĮčŗ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗąĄ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░, čé. ąĄ. ą║ą░ąČą┤čŗą╣ ąĖąĘ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ ąĖą╝ąĄąĄčé čüą▓ąŠą╣ ąĮą░ą▒ąŠčĆ ąŠą▒čüą╗čāąČąĖą▓ą░ąĄą╝čŗčģ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓, ą║ąŠč鹊čĆčŗąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčéčüčÅ čäčāąĮą║čåąĖąĄą╣ DMA. ą¤čĆąĖą▓čÅąĘą║ą░ čŹčéą░ ąČąĄčüčéą║ą░čÅ, ąĖ ąĄčæ ąĮąĄą╗čīąĘčÅ ą┐ąĄčĆąĄą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī, ąŠąĮą░ ąĘą░ą▓ąĖčüąĖčé č鹊ą╗čīą║ąŠ ąŠčé čéąĖą┐ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ąŠą│ąŠ ą┐čĆąŠčåąĄčüčüąŠčĆą░.

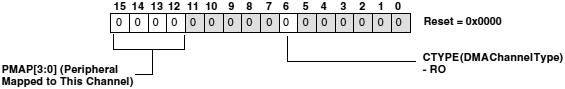

ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ ą┐čĆąŠ ą┐čĆąĖą▓čÅąĘą║ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ čüą╝. ą▓čĆąĄąĘą║čā "ąĀąĄą│ąĖčüčéčĆčŗ DMAx_PERIPHERAL_MAP, MDMAx_yy_PERIPHERAL_MAP", čéą░ą▒ą╗ąĖčåčŗ 9-7 ąĖ 9-8.

ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆčŗ DMA ą╝ąŠą│čāčé ą▓čŗą┐ąŠą╗ąĮčÅčéčī ąĮąĄčüą║ąŠą╗čīą║ąŠ čéąĖą┐ąŠą▓ ą┐ąĄčĆąĄą┤ą░čć ą┤ą░ąĮąĮčŗčģ:

ŌĆó ą£ąĄąČą┤čā ą┐ą░ą╝čÅčéčīčÄ ąĖ ą┐ą░ą╝čÅčéčīčÄ DMA (MDMA), ą┐ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. čĆą░ąĘą┤ąĄą╗ "DMA ą┤ą╗čÅ ą┐ąĄčĆąĄčüčŗą╗ąŠą║ ą┐ąŠ ą┐ą░ą╝čÅčéąĖ".

ŌĆó ą£ąĄąČą┤čā ą┐ą░ą╝čÅčéčīčÄ ąĖ SPI, ą┐ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. [2].

ŌĆó ą£ąĄąČą┤čā ą┐ą░ą╝čÅčéčīčÄ ąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╝ ą┐ąŠčĆč鹊ą╝ (SPORT), ą┐ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. [4].

ŌĆó ą£ąĄąČą┤čā ą┐ą░ą╝čÅčéčīčÄ ąĖ ą┐ąŠčĆč鹊ą╝ UART, ą┐ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. [5].

ŌĆó ą£ąĄąČą┤čā ą┐ą░ą╝čÅčéčīčÄ ąĖ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮčŗą╝ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ ąĖąĮč鹥čĆč乥ą╣čüąŠą╝ (PPI), ą┐ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. "Parallel Peripheral Interface" [1].

ąÆ čüąĖčüč鹥ą╝ąĄ ąĄčüčéčī 14 DMA-čüąŠą▓ą╝ąĄčüčéąĖą╝čŗčģ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓, ą▓ą║ą╗čÄčćą░čÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčŗ ą┐ą░ą╝čÅčéąĖ DMA (MDMA0ŌĆō1).

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ ą┐ąĄčĆąĄą▓ąŠą┤čćąĖą║ą░: čÅ ąĮąĄ čüą╝ąŠą│ ąĮą░čüčćąĖčéą░čéčī 14 ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓, čā ą╝ąĄąĮčÅ ą┐ąŠą╗čāčćą░ąĄčéčüčÅ č鹊ą╗čīą║ąŠ 13: PPI, SPORT0, SPORT1, SPORT2, SPORT3, SPI0, SPI1, SPI2, UART0, UART1, UART2, MDMA0, MDMA1. ą¤ąŠčģąŠąČąĄ, ą▓ ą┤ą░čéą░čłąĖč鹥 [1] ą▓ čŹč鹊ą╝ ą╝ąĄčüč鹥 ąŠą┐ąĄčćą░čéą║ą░.

ąĢčüčéčī ą▓čüąĄą│ąŠ 28 ą║ą░ąĮą░ą╗ąŠą▓ DMA, čüą╝. čéą░ą▒ą╗ąĖčåčā 9-1.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ ą┐ąĄčĆąĄą▓ąŠą┤čćąĖą║ą░: ą┐ąŠčģąŠąČąĄ, čćč鹊 čéčāčé čüąĮąŠą▓ą░ ąŠą┐ąĄčćą░čéą║ą░: ą▓ čéą░ą▒ą╗ąĖčåąĄ 9-1 ąĮąĄ 28 ą║ą░ąĮą░ą╗ąŠą▓, ą░ 26.

ąóą░ą▒ą╗ąĖčåą░ 9-1. ąÜą░ąĮą░ą╗čŗ DMA.

| PDMA: ą┐čĆąĖąĄą╝/ą┐ąĄčĆąĄą┤ą░čćą░ PPI |

PDMA: UART0 ą┐ąĄčĆąĄą┤ą░čćą░ |

| PDMA: SPORT0 ą┐čĆąĖąĄą╝ |

PDMA: UART1 ą┐čĆąĖąĄą╝ |

| PDMA: SPORT0 ą┐ąĄčĆąĄą┤ą░čćą░ |

PDMA: UART1 ą┐ąĄčĆąĄą┤ą░čćą░ |

| PDMA: SPORT1 ą┐čĆąĖąĄą╝ |

PDMA: UART2 ą┐čĆąĖąĄą╝ |

| PDMA: SPORT1 ą┐ąĄčĆąĄą┤ą░čćą░ |

PDMA: UART2 ą┐ąĄčĆąĄą┤ą░čćą░ |

| PDMA: SPORT2 ą┐čĆąĖąĄą╝ |

MDMA0: stream0 ą┐ąĄčĆąĄą┤ą░čćą░ (ą╝ąĄčüč鹊 ąĮą░ąĘąĮą░č湥ąĮąĖčÅ) |

| PDMA: SPORT2 ą┐ąĄčĆąĄą┤ą░čćą░ |

MDMA0: stream0 ą┐čĆąĖąĄą╝ (ąĖčüč鹊čćąĮąĖą║) |

| PDMA: SPORT3 ą┐čĆąĖąĄą╝ |

MDMA0: stream1 ą┐ąĄčĆąĄą┤ą░čćą░ (ą╝ąĄčüč鹊 ąĮą░ąĘąĮą░č湥ąĮąĖčÅ) |

| PDMA: SPORT3 ą┐ąĄčĆąĄą┤ą░čćą░ |

MDMA0: stream1 ą┐čĆąĖąĄą╝ (ąĖčüč鹊čćąĮąĖą║) |

| PDMA: ą┐čĆąĖąĄą╝/ą┐ąĄčĆąĄą┤ą░čćą░ SPI0 |

MDMA1: stream0 ą┐ąĄčĆąĄą┤ą░čćą░ (ą╝ąĄčüč鹊 ąĮą░ąĘąĮą░č湥ąĮąĖčÅ) |

| PDMA: ą┐čĆąĖąĄą╝/ą┐ąĄčĆąĄą┤ą░čćą░ SPI1 |

MDMA1: stream0 ą┐čĆąĖąĄą╝ (ąĖčüč鹊čćąĮąĖą║) |

| PDMA: ą┐čĆąĖąĄą╝/ą┐ąĄčĆąĄą┤ą░čćą░ SPI2 |

MDMA1: stream1 ą┐ąĄčĆąĄą┤ą░čćą░ (ą╝ąĄčüč鹊 ąĮą░ąĘąĮą░č湥ąĮąĖčÅ) |

| PDMA: UART0 ą┐čĆąĖąĄą╝ |

MDMA1: stream1 ą┐čĆąĖąĄą╝ (ąĖčüč鹊čćąĮąĖą║) |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: PDMA ąŠąĘąĮą░čćą░ąĄčé DMA ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓, MDMA ąŠąĘąĮą░čćą░ąĄčé DMA ąĮą░ ą┐ą░ą╝čÅčéąĖ.

ąÆ čŹč鹊ą╣ čüčéą░čéčīąĄ ąŠą┐ąĖčüą░ąĮčŗ čäčāąĮą║čåąĖąĖ, ąŠą▒čēąĖąĄ ą┤ą╗čÅ ą▓čüąĄčģ ą║ą░ąĮą░ą╗ąŠą▓ DMA, ąĖ čéą░ą║ąČąĄ ąŠą┐ąĖčüą░ąĮąŠ, ą║ą░ą║ ąĮą░čüčéčĆąŠąĖčéčī ąŠą┐ąĄčĆą░čåąĖąĖ DMA. ą¤ąŠą┤čĆąŠą▒ąĮąŠčüčéąĖ, ąŠčéąĮąŠčüčÅčēąĖąĄčüčÅ ą║ ą║ą░ąČą┤ąŠą╝čā ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą╝čā čāčüčéčĆąŠą╣čüčéą▓čā, čüą╝. ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╝ čĆą░ąĘą┤ąĄą╗ąĄ ą┤ą░čéą░čłąĖčéą░, ą┐ąŠčüą▓čÅčēąĄąĮąĮąŠą╝ čŹč鹊ą╝čā ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą╝čā čāčüčéčĆąŠą╣čüčéą▓čā (ąĮą░ą┐čĆąĖą╝ąĄčĆ ą┤ą╗čÅ SPI čüą╝. [2]). ąśąĮč乊čĆą╝ą░čåąĖčÄ ą┐ąŠ ą▒čŗčüčéčĆąŠą┤ąĄą╣čüčéą▓ąĖčÄ ąĖ ą░čĆą▒ąĖčéčĆą░ąČčā čłąĖąĮčŗ ą┤ą╗čÅ ąŠą┐ąĄčĆą░čåąĖą╣ DMA ą╝ąŠąČąĮąŠ ąĮą░ą╣čéąĖ ą▓ čĆą░ąĘą┤ąĄą╗ąĄ "DAB, DCB, and DEB Performance" [1].

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: DAB ąŠąĘąĮą░čćą░ąĄčé DMA acces bus, DCB ąŠąĘąĮą░čćą░ąĄčé DMA core bus, DEB ąŠąĘąĮą░čćą░ąĄčé DMA external bus.

DMA-ą┐ąĄčĆąĄą┤ą░čćąĖ ą▓ ą┐čĆąŠčåąĄčüčüąŠčĆąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ąĮą░ ą▒ą░ąĘąĄ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ ąĖą╗ąĖ ąĮą░ ą▒ą░ąĘąĄ čĆąĄą│ąĖčüčéčĆą░. ą¤ąĄčĆąĄą┤ą░čćąĖ DMA, ąŠčüąĮąŠą▓ą░ąĮąĮčŗąĄ ąĮą░ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąĄ, čéčĆąĄą▒čāčÄčé ąĮą░čüčéčĆąŠą╣ą║ąĖ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓, čüąŠčģčĆą░ąĮąĄąĮąĮčŗčģ ą▓ ą┐ą░ą╝čÅčéąĖ, čćč鹊ą▒čŗ ąĖąĮąĖčåąĖąĖčĆąŠą▓ą░čéčī ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī DMA. ąŁč鹊čé ą▓ąĖą┤ ą┐ąĄčĆąĄą┤ą░čć ą┐ąŠąĘą▓ąŠą╗čÅąĄčé čüąŠąĄą┤ąĖąĮąĖčéčī ą▓ čåąĄą┐ąŠčćą║čā ąĮąĄčüą║ąŠą╗čīą║ąŠ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüč鹥ą╣ DMA. ą¤čĆąĖ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĖ DMA ąĮą░ ąŠčüąĮąŠą▓ąĄ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ ą║ą░ąĮą░ą╗ DMA ą╝ąŠąČąĄčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą╣ ąĮą░čüčéčĆąŠą╣ą║ąĖ ąĖ ąĘą░ą┐čāčüą║ą░ ą┤čĆčāą│ąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ DMA, ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ ą║ą░ą║ č鹥ą║čāčēą░čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ąĘą░ą▓ąĄčĆčłąĖą╗ą░čüčī.

ą¤ąĄčĆąĄą┤ą░čćąĖ DMA ąĮą░ ąŠčüąĮąŠą▓ąĄ čĆąĄą│ąĖčüčéčĆą░ ą┐ąŠąĘą▓ąŠą╗čÅčÄčé ą┐čĆąŠčåąĄčüčüąŠčĆčā ąĮą░ą┐čĆčÅą╝čāčÄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī čĆąĄą│ąĖčüčéčĆčŗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ DMA ą┤ą╗čÅ ąĖąĮąĖčåąĖą░čåąĖąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ DMA. ą¤ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÄ čāą┐čĆą░ą▓ą╗čÅčÄčēąĖąĄ čĆąĄą│ąĖčüčéčĆčŗ ą╝ąŠą│čāčé ą▒čŗčéčī ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąŠą▒ąĮąŠą▓ą╗ąĄąĮčŗ čüą▓ąŠąĖą╝ąĖ ąŠčĆąĖą│ąĖąĮą░ą╗čīąĮčŗą╝ąĖ ąĘąĮą░č湥ąĮąĖčÅą╝ąĖ ąĮą░čüčéčĆąŠą╣ą║ąĖ ą┤ą╗čÅ ą┐čĆąŠą┤ąŠą╗ąČąĄąĮąĖąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ, ąĄčüą╗ąĖ čŹč鹊 ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ.

[DMA ąĖ čĆąĄą│ąĖčüčéčĆčŗ MMR DMA]

ąöą╗čÅ čāą┤ąŠą▒čüčéą▓ą░ ąŠą▒čüčāąČą┤ąĄąĮąĖąĄ ą▓ čŹč鹊ą╣ čüčéą░čéčīąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčé čüčéą░ąĮą┤ą░čĆčéąĮčŗąĄ (ąĮąĄ ą┐čĆąĖą▓čÅąĘą░ąĮąĮčŗąĄ ą║ ą║ą░ą║ąŠą╣-č鹊 ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą╣ ą░ą┐ą┐ą░čĆą░čéčāčĆąĄ) ąĖą╝ąĄąĮą░ ą┤ą╗čÅ čĆąĄą│ąĖčüčéčĆąŠą▓ DMA ąĖ ą┐ą░ą╝čÅčéąĖ DMA.

ąĪčéą░ąĮą┤ą░čĆčéąĮčŗąĄ ąĖą╝ąĄąĮą░ čĆąĄą│ąĖčüčéčĆąŠą▓ ą┐ąĄčĆąĄčćąĖčüą╗ąĄąĮčŗ ą▓ čéą░ą▒ą╗ąĖčåąĄ 9-2. ąĪčéą░ąĮą┤ą░čĆčéąĮčŗąĄ ąĖą╝ąĄąĮą░ čĆąĄą│ąĖčüčéčĆąŠą▓ ą┐ą░ą╝čÅčéąĖ DMA ą┐ąĄčĆąĄčćąĖčüą╗ąĄąĮčŗ ą▓ čéą░ą▒ą╗ąĖčåąĄ 9-4. ą¤čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ ą▓ ą┐čĆąŠą│čĆą░ą╝ą╝ąĄ čüčéą░ąĮą┤ą░čĆčéąĮčŗąĄ ąĖą╝ąĄąĮą░ ą┤ąŠą┐ąŠą╗ąĮčÅčÄčéčüčÅ ą┐čĆąĄčäąĖą║čüą░ą╝ąĖ, ąŠą▒ąŠąĘąĮą░čćą░čÄčēąĖą╝ąĖ ą║ą░ąĮą░ą╗ DMA (ąĮą░ą┐čĆąĖą╝ąĄčĆ, START_ADDR ą▒čāą┤ąĄčé ąĖą╝ąĄąĮąŠą▓ą░čéčīčüčÅ ą║ą░ą║ DMA3_START_ADDR ąĖą╗ąĖ DMA4_START_ADDR, ąĖ čé. ą┐.).

ąĀąĄą│ąĖčüčéčĆčŗ DMA ą┐ąŠą┐ą░ą┤ą░čÄčé ą▓ 3 ą║ą░č鹥ą│ąŠčĆąĖąĖ:

ŌĆó ąóąĄą║čāčēąĖąĄ čĆąĄą│ąĖčüčéčĆčŗ, čéą░ą║ąĖąĄ ą║ą░ą║ DMAx_CURR_ADDR ąĖ DMAx_CURR_X_COUNT.

ŌĆó ąĀąĄą│ąĖčüčéčĆčŗ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓, čéą░ą║ąĖąĄ ą║ą░ą║ DMAx_CONFIG ąĖ DMAx_X_COUNT.

ŌĆó ąĀąĄą│ąĖčüčéčĆčŗ čüąŠčüč鹊čÅąĮąĖčÅ ąĖ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ, čéą░ą║ąĖąĄ ą║ą░ą║ DMAx_IRQ_STATUS ąĖ DMAx_PERIPHERAL_MAP.

ąæčāą║ą▓ą░ x ą▓ ąĖą╝ąĄąĮą░čģ DMAx ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé ąŠčéą┤ąĄą╗čīąĮąŠąĄ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ, ą║ąŠč鹊čĆąŠąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé DMA. ąØą░ą┐čĆąĖą╝ąĄčĆ, ą┤ą╗čÅ DMA čü ą┐čĆąĖą▓čÅąĘą║ąŠą╣ ą║ą░ąĮą░ą╗ą░ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ DMA6_CONFIG ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé čĆąĄą│ąĖčüčéčĆ DMA_CONFIG ą┤ą╗čÅ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┐čĆąĖąĄą╝ą░ UART0. ąöą╗čÅ ą┐čĆąĖą▓čÅąĘąŠą║ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą║ą░ąĮą░ą╗ąŠą▓ DMA čüą╝. čéą░ą▒ą╗ąĖčåčŗ 9-5 ąĖ 9-7 ą▓ąŠ ą▓čĆąĄąĘą║ąĄ "ąĀąĄą│ąĖčüčéčĆčŗ DMAx_PERIPHERAL_MAP, MDMAx_yy_PERIPHERAL_MAP" (ą┐čĆąĖą▓čÅąĘą║ą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąĄčĆąĄą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮą░ č湥čĆąĄąĘ čĆąĄą│ąĖčüčéčĆčŗ DMAx_PERIPHERAL_MAP, MDMAx_yy_PERIPHERAL_MAP).

ąóąŠą╗čīą║ąŠ čĆąĄą│ąĖčüčéčĆčŗ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓ ą╝ąŠą│čāčé ą▒čŗčéčī ąĮą░ą┐čĆčÅą╝čāčÄ ąĘą░ą│čĆčāąČąĄąĮčŗ ąĖąĘ 菹╗ąĄą╝ąĄąĮč鹊ą▓ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░; 菹╗ąĄą╝ąĄąĮčéčŗ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ ą┐ąĄčĆąĄčćąĖčüą╗ąĄąĮčŗ ą▓ čéą░ą▒ą╗ąĖčåąĄ 9-3.

ąÆ čéą░ą▒ą╗ąĖčåąĄ 9-2 ą┐ąĄčĆąĄčćąĖčüą╗ąĄąĮčŗ čüčéą░ąĮą┤ą░čĆčéąĮčŗąĄ (ą▒ąĄąĘ ą┐čĆąĄčäąĖą║čüąŠą▓ DMAx) ąĖą╝ąĄąĮą░ čĆąĄą│ąĖčüčéčĆąŠą▓ DMA. ąöą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░ čéą░ą▒ą╗ąĖčåą░ čéą░ą║ąČąĄ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüą╝ąĄčēąĄąĮąĖąĄ MMR, ą║čĆą░čéą║ąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░, ą║ą░č鹥ą│ąŠčĆąĖčÄ čĆąĄą│ąĖčüčéčĆą░ ąĖ ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░.

ąóą░ą▒ą╗ąĖčåą░ 9-2. ąĪčéą░ąĮą┤ą░čĆčéąĮčŗąĄ ąĖą╝ąĄąĮą░ čĆąĄą│ąĖčüčéčĆąŠą▓ MMR ą┤ą╗čÅ DMA.

| ąĪą╝ąĄčēąĄąĮąĖąĄ MMR |

ąśą╝čÅ |

ą×ą┐ąĖčüą░ąĮąĖąĄ MMR |

ąÜą░č鹥ą│ąŠčĆąĖčÅ čĆąĄą│ąĖčüčéčĆą░ |

ąŚąĮą░čć. ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ |

| 0x00 |

NEXT_DESC_PTR |

ąŻą║ą░ąĘą░č鹥ą╗čī čüą▓čÅąĘąĖ ąĮą░ čüą╗ąĄą┤čāčÄčēąĖą╣ ą┤ąĄčüą║čĆąĖą┐č鹊čĆ. |

ą¤ą░čĆą░ą╝ąĄčéčĆ |

0x0000 0000 |

| 0x04 |

START_ADDR |

ąØą░čćą░ą╗čīąĮčŗą╣ ą░ą┤čĆąĄčü č鹥ą║čāčēąĄą│ąŠ ą▒čāč乥čĆą░. |

ą¤ą░čĆą░ą╝ąĄčéčĆ |

0x0000 0000 |

| 0x08 |

DMA_CONFIG |

ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ DMA, ą▓ą║ą╗čÄčćą░čÅ ą▒ąĖčé čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ DMA. |

ą¤ą░čĆą░ą╝ąĄčéčĆ |

0x0000 |

| 0x0C |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

|

|

|

| 0x10 |

X_COUNT |

ąĪč湥čéčćąĖą║ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čåąĖą║ą╗ą░. |

ą¤ą░čĆą░ą╝ąĄčéčĆ |

0x0001 |

| 0x14 |

X_MODIFY |

ąśąĮą║čĆąĄą╝ąĄąĮčé ą░ą┤čĆąĄčüą░ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čåąĖą║ą╗ą░ ą▓ ą▒ą░ą╣čéą░čģ. |

ą¤ą░čĆą░ą╝ąĄčéčĆ |

0x0002 |

| 0x18 |

Y_COUNT |

ąĪč湥čéčćąĖą║ ą▓ąĮąĄčłąĮąĄą│ąŠ čåąĖą║ą╗ą░ (č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čĆąĄąČąĖą╝ą░ 2D). |

ą¤ą░čĆą░ą╝ąĄčéčĆ |

0x0001 |

| 0x1C |

Y_MODIFY |

ąśąĮą║čĆąĄą╝ąĄąĮčé ą░ą┤čĆąĄčüą░ ą▓ąĮąĄčłąĮąĄą│ąŠ čåąĖą║ą╗ą░ ą▓ ą▒ą░ą╣čéą░čģ. |

ą¤ą░čĆą░ą╝ąĄčéčĆ |

0x0002 |

| 0x20 |

CURR_DESC_PTR |

ąŻą║ą░ąĘą░č鹥ą╗čī č鹥ą║čāčēąĄą│ąŠ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░. |

ąóąĄą║čāčēąĄąĄ ąĘąĮą░č湥ąĮąĖąĄ |

|

| 0x24 |

CURR_ADDR |

ąóąĄą║čāčēąĖą╣ ą░ą┤čĆąĄčü DMA |

ąóąĄą║čāčēąĄąĄ ąĘąĮą░č湥ąĮąĖąĄ |

|

| 0x28 |

IRQ_STATUS |

ąĀąĄą│ąĖčüčéčĆ čüčéą░čéčāčüą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ąĪąŠą┤ąĄčƹȹĖčé čüąŠčüč鹊čÅąĮąĖąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ, čüąŠčüč鹊čÅąĮąĖąĄ ąŠčłąĖą▒ą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĖ čüąŠčüč鹊čÅąĮąĖąĄ ą║ą░ąĮą░ą╗ą░ (ą┐ąĄčĆąĄą┤ą░ąĄčé ą┤ą░ąĮąĮčŗąĄ/ą▓čŗą▒ąŠčĆą║ą░ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░/ą┐ą░čāąĘą░). |

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ |

|

| 0x2C |

PERIPHERAL_MAP |

ą×č鹊ą▒čĆą░ąČąĄąĮąĖąĄ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ąĮą░ ą║ą░ąĮą░ą╗ DMA. ąĪąŠą┤ąĄčƹȹĖčé 4-ą▒ąĖčéąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ, čāą║ą░ąĘčŗą▓ą░čÄčēąĄąĄ, ą║ ą║ą░ą║ąŠą╝čā ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą╝čā čāčüčéčĆąŠą╣čüčéą▓čā ą┐čĆąĖą▓čÅąĘą░ąĮ ą║ą░ąĮą░ą╗ DMA (ą┤ą╗čÅ ą║ą░ąĮą░ą╗ąŠą▓ MDMA čŹč鹊 ą┐ąŠą╗ąĄ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ, čé. ąĄ. ą┐čĆąĖą▓čÅąĘą║čā ą╝ąĄąĮčÅčéčī ąĮąĄą╗čīąĘčÅ). |

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ |

|

| 0x30 |

CURR_X_COUNT |

ąóąĄą║čāčēąĖą╣ čüč湥čéčćąĖą║ (1D) ąĖą╗ąĖ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ X-čüč湥čéčćąĖą║ čüčéčĆąŠą║ąĖ (2D), čüčćąĖčéą░ąĄčé ą▓ąĮąĖąĘ ąŠčé X_COUNT. |

ąóąĄą║čāčēąĄąĄ ąĘąĮą░č湥ąĮąĖąĄ |

|

| 0x34 |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

|

|

|

| 0x38 |

CURR_Y_COUNT |

ąóąĄą║čāčēąĖą╣ čüč湥čéčćąĖą║ čüčéčĆąŠą║ (č鹊ą╗čīą║ąŠ ą┤ą╗čÅ 2D), čüčćąĖčéą░ąĄčé ą▓ąĮąĖąĘ ąŠčé Y_COUNT. |

ąóąĄą║čāčēąĄąĄ ąĘąĮą░č湥ąĮąĖąĄ |

|

| 0x3C |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

|

|

|

ąÆčüąĄ čĆąĄą│ąĖčüčéčĆčŗ DMA ą┤ąŠčüčéčāą┐ąĮčŗ ą║ą░ą║ 16-ą▒ąĖčéąĮčŗąĄ čÅč湥ą╣ą║ąĖ ą┐ą░ą╝čÅčéąĖ. ą×ą┤ąĮą░ą║ąŠ čüą╗ąĄą┤čāčÄčēąĖąĄ čĆąĄą│ąĖčüčéčĆčŗ ą╝ąŠą│čāčé ą▒čŗčéčī ą┤ąŠčüčéčāą┐ąĮčŗ ą║ą░ą║ 32-čĆą░ąĘčĆčÅą┤ąĮčŗąĄ čĆąĄą│ąĖčüčéčĆčŗ: NEXT_DESC_PTR, START_ADDR, CURR_DESC_PTR, CURR_ADDR. ąÜąŠą│ą┤ą░ ą║ čŹčéąĖą╝ č湥čéčŗčĆąĄą╝ čĆąĄą│ąĖčüčéčĆą░ą╝ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą┤ąŠčüčéčāą┐ ą║ą░ą║ ą║ 16-ą▒ąĖčéąĮčŗą╝ čÅč湥ą╣ą║ą░ą╝, č鹊 ą┤ąŠčüčéčāą┐ąĮčŗ ąĖčģ ą╝ą╗ą░ą┤čłąĖąĄ 16 ą▒ąĖčé.

[ą¤ąŠ ą║ą░ą║ąŠą╝čā ą┐čĆąĖąĮčåąĖą┐čā ąĖą╝ąĄąĮčāčÄčéčüčÅ čĆąĄą│ąĖčüčéčĆčŗ DMA MMR]

ą¦č鹊ą▒čŗ ąĮąĄ ą┐ąĄčĆąĄą┐čāčéą░čéčī ąĖą╝ąĄąĮą░ 菹╗ąĄą╝ąĄąĮč鹊ą▓ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ ąĖ čüčéą░ąĮą┤ą░čĆčéąĮčŗąĄ ąĖą╝ąĄąĮą░ čĆąĄą│ąĖčüčéčĆąŠą▓ DMA, ą▓ čŹč鹊ą╣ čüčéą░čéčīąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čüą╗ąĄą┤čāčÄčēąĖą╣ ą┐čĆąĖąĮčåąĖą┐ ąĖą╝ąĄąĮąŠą▓ą░ąĮąĖčÅ ą▓ čéą░ą▒ą╗ąĖčåąĄ 9-3, ą│ą┤ąĄ:

ŌĆó ąĪčéą░ąĮą┤ą░čĆčéąĮčŗąĄ ąĖą╝ąĄąĮą░ ą▓ ą╗ąĄą▓ąŠą╝ čüč鹊ą╗ą▒čåąĄ ąĮąĄ ą┐čĆąĖą▓čÅąĘą░ąĮčŗ ą▓ ą┤ąĄą╣čüčéą▓ąĖč鹥ą╗čīąĮąŠčüčéąĖ ą║ čĆąĄčüčāčĆčüą░ą╝ ą┐čĆąŠčåąĄčüčüąŠčĆą░.

ŌĆó ąĪčĆąĄą┤ąĮąĖą╣ čüč鹊ą╗ą▒ąĄčå ą┐ąĄčĆąĄčćąĖčüą╗čÅąĄčé čüą┐ąĄčåąĖčäąĖč湥čüą║ąŠąĄ ąĖą╝čÅ MMR. ąóąŠą╗čīą║ąŠ čüą┐ąĄčåąĖčäąĖč湥čüą║ąĖąĄ ąĖą╝ąĄąĮą░ MMR ąŠč鹊ą▒čĆą░ąČąĄąĮčŗ ąĮą░ čĆąĄčüčāčĆčüčŗ ą┐čĆąŠčåąĄčüčüąŠčĆą░.

ŌĆó ąÆ DMAx ą▒čāą║ą▓ą░ x ąŠą▒ąŠąĘąĮą░čćą░ąĄčé ąĮąŠą╝ąĄčĆ ą║ą░ąĮą░ą╗ą░ DMA. ąØą░ą┐čĆąĖą╝ąĄčĆ, DMA3_IRQ_STATUS čÅą▓ą╗čÅąĄčéčüčÅ IRQ_STATUS MMR ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ DMA ąĮąŠą╝ąĄčĆ 3.

ŌĆó ąØąŠą╝ąĄčĆ ą║ą░ąĮą░ą╗ą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĮą░ąĘąĮą░č湥ąĮ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ, ą╗ąĖą▒ąŠ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ (č湥čĆąĄąĘ čĆąĄą│ąĖčüčéčĆčŗ DMAx_PERIPHERAL_MAP, MDMAx_yy_PERIPHERAL_MAP). ąØąŠą╝ąĄčĆą░ ą║ą░ąĮą░ą╗ąŠą▓ DMA ąĖ ą┐čĆąĖą▓čÅąĘą║čā ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ čüą╝. ą▓ čéą░ą▒ą╗ąĖčåą░čģ 9-5 ąĖ 9-7 (ą▓čĆąĄąĘą║ą░ "ąĀąĄą│ąĖčüčéčĆčŗ DMAx_PERIPHERAL_MAP, MDMAx_yy_PERIPHERAL_MAP").

ŌĆó ą¤ąŠčüą╗ąĄą┤ąĮąĖą╣ čüč鹊ą╗ą▒ąĄčå ą┐ąĄčĆąĄčćąĖčüą╗čÅąĄčé ą╝ą░ą║čĆąŠčüčŗ, ąĮą░ąĘąĮą░č湥ąĮąĮčŗąĄ ą║ą░ąČą┤ąŠą╝čā 菹╗ąĄą╝ąĄąĮčéčā ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ ą▓ ą┐ą░ą╝čÅčéąĖ.

ŌĆó ąśą╝čÅ ą╝ą░ą║čĆąŠčüą░ ą▓ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╝ čüč鹊ą╗ą▒čåąĄ ąĮčāąČąĮąŠ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čÅčüąĮąŠčüčéąĖ, čćč鹊ą▒čŗ ą┐ąŠąĮčÅčéąĮąĄąĄ ąŠą▒čüčāą┤ąĖčéčī ą┐čĆąĖąĮčåąĖą┐ čĆą░ą▒ąŠčéčŗ ą┐ąŠą┤čüąĖčüč鹥ą╝čŗ DMA.

ŌĆó ąÆ ą╗ąĄą▓ąŠą╝ čüč鹊ą╗ą▒čåąĄ ą┐ąĄčĆąĄčćąĖčüą╗ąĄąĮčŗ čüčéą░ąĮą┤ą░čĆčéąĮčŗąĄ ąĖą╝ąĄąĮą░ MMR, ą║ąŠč鹊čĆčŗąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą▓ ąŠą▒čüčāąČą┤ąĄąĮąĖąĖ ąŠčüąĮąŠą▓ąĮąŠą│ąŠ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐ąŠą┤čüąĖčüč鹥ą╝čŗ DMA.

ąóą░ą▒ą╗ąĖčåą░ 9-3. ą¤čĆąĖąĮčåąĖą┐čŗ ąĖą╝ąĄąĮąŠą▓ą░ąĮąĖčÅ DMA MMR ąĖ 菹╗ąĄą╝ąĄąĮč鹊ą▓ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░.

| ą×ą▒čēąĄąĄ ąĖą╝čÅ |

ą¤ąŠą╗ąĮąŠąĄ ąĖą╝čÅ PDMA MMR (x = ąĮąŠą╝ąĄčĆčā ą║ą░ąĮą░ą╗ą░) |

ąśą╝čÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ 菹╗ąĄą╝ąĄąĮčéą░ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ ą▓ ą┐ą░ą╝čÅčéąĖ |

| DMA_CONFIG |

DMAx_CONFIG |

DMACFG |

| NEXT_DESC_PTR |

DMAx_NEXT_DESC_PTR |

NDPH (čüčéą░čĆčłąĖąĄ 16 ą▒ąĖčé), NDPL (ą╝ą╗ą░ą┤čłąĖąĄ 16 ą▒ąĖčé) |

| START_ADDR |

DMAx_START_ADDR |

SAH (čüčéą░čĆčłąĖąĄ 16 ą▒ąĖčé), SAL (ą╝ą╗ą░ą┤čłąĖąĄ 16 ą▒ąĖčé) |

| X_COUNT |

DMAx_X_COUNT |

XCNT |

| Y_COUNT |

DMAx_Y_COUNT |

YCNT |

| X_MODIFY |

DMAx_X_MODIFY |

XMOD |

| Y_MODIFY |

DMAx_Y_MODIFY |

YMOD |

| CURR_DESC_PTR |

DMAx_CURR_DESC_PTR |

- |

| CURR_ADDR |

DMAx_CURR_ADDR |

- |

| CURR_X_COUNT |

DMAx_CURR_X_COUNT |

- |

| CURR_Y_COUNT |

DMAx_CURR_Y_COUNT |

- |

| IRQ_STATUS |

DMAx_IRQ_STATUS |

- |

| PERIPHERAL_MAP |

DMAx_PERIPHERAL_MAP |

- |

[ą¤ąŠ ą║ą░ą║ąŠą╝čā ą┐čĆąĖąĮčåąĖą┐čā ąĖą╝ąĄąĮčāčÄčéčüčÅ čĆąĄą│ąĖčüčéčĆčŗ ą┐ą░ą╝čÅčéąĖ DMA]

ąśą╝ąĄąĮą░ čĆąĄą│ąĖčüčéčĆąŠą▓ ą┐ą░ą╝čÅčéąĖ DMA (čé. ąĄ. MDMA) ąĮąĄčüą║ąŠą╗čīą║ąŠ ąŠčéą╗ąĖčćą░čÄčéčüčÅ ąŠčé ąĖą╝ąĄąĮ ą┤čĆčāą│ąĖčģ čĆąĄą│ąĖčüčéčĆąŠą▓ DMA (čé. ąĄ. PDMA). ą¤ąŠč鹊ą║ąĖ ą┐ą░ą╝čÅčéąĖ DMA ąĮąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ą┐ąĄčĆąĄąĮą░ąĘąĮą░č湥ąĮčŗ ąĮą░ čĆą░ąĘąĮčŗąĄ ą║ą░ąĮą░ą╗čŗ, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░, čüą▓čÅąĘą░ąĮąĮčŗąĄ čü DMA, ą╝ąŠą│čāčé ą▒čŗčéčī ą┐čĆąĖą▓čÅąĘą░ąĮčŗ ą║ ą╗čÄą▒ąŠą╝čā ą║ą░ąĮą░ą╗čā DMA ąŠčé 0 ą┤ąŠ 21.

ąŻ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ąĄčüčéčī 2 ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ DMA. ąÜą░ąČą┤čŗą╣ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ čüąŠą┤ąĄčƹȹĖčé 2 ą┐ąŠč鹊ą║ą░ ą┐ą░ą╝čÅčéąĖ DMA. ąæčāą║ą▓ą░ x ąŠą▒ąŠąĘąĮą░čćą░ąĄčé, ą║ ą║ą░ą║ąŠą╝čā ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčā DMA ą┐čĆąĖąĮą░ą┤ą╗ąĄąČąĖčé ą║ą░ąĮą░ą╗, ą░ čā ą▒čāą║ą▓ yy ą╝ąŠąČąĄčé ą▒čŗčéčī 4 ą▓ąŠąĘą╝ąŠąČąĮčŗčģ ąĘąĮą░č湥ąĮąĖčÅ:

ŌĆó S0, ąĖčüč鹊čćąĮąĖą║ ą┐ą░ą╝čÅčéąĖ DMA ą┐ąŠč鹊ą║ą░ 0

ŌĆó D0, ą╝ąĄčüč鹊 ąĮą░ąĘąĮą░č湥ąĮąĖčÅ ą┐ą░ą╝čÅčéąĖ DMA ą┐ąŠč鹊ą║ą░ 0

ŌĆó S1, ąĖčüč鹊čćąĮąĖą║ ą┐ą░ą╝čÅčéąĖ DMA ą┐ąŠč鹊ą║ą░ 1

ŌĆó D1, ą╝ąĄčüč鹊 ąĮą░ąĘąĮą░č湥ąĮąĖčÅ ą┐ą░ą╝čÅčéąĖ DMA ą┐ąŠč鹊ą║ą░ 1

ąÆ čéą░ą▒ą╗ąĖčåąĄ 9-4 ą┐ąŠą║ą░ąĘą░ąĮąŠ čüąŠą│ą╗ą░čłąĄąĮąĖąĄ ą┐ąŠ ąĖą╝ąĄąĮąŠą▓ą░ąĮąĖčÄ ą┤ą╗čÅ čĆąĄą│ąĖčüčéčĆąŠą▓ ą┐ą░ą╝čÅčéąĖ DMA.

ąóą░ą▒ą╗ąĖčåą░ 9-4. ą¤čĆąĖąĮčåąĖą┐ ąĖą╝ąĄąĮąŠą▓ą░ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆąŠą▓ ą┐ą░ą╝čÅčéąĖ DMA.

| ą×ą▒čēąĄąĄ ąĖą╝čÅ |

ą¤ąŠą╗ąĮąŠąĄ ąĖą╝čÅ MDMA MMR (x = 0 ąĖą╗ąĖ 1, ąŠą▒ąŠąĘąĮą░čćą░ąĄčé ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ DMA; yy = S0, S1, D0 ąĖą╗ąĖ D1) |

ąśą╝čÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ 菹╗ąĄą╝ąĄąĮčéą░ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ ą▓ ą┐ą░ą╝čÅčéąĖ |

| DMA_CONFIG |

MDMAx_yy_CONFIG |

DMACFG |

| NEXT_DESC_PTR |

MDMAx_yy_NEXT_DESC_PTR |

NDPH (čüčéą░čĆčłąĖąĄ 16 ą▒ąĖčé), NDPL (ą╝ą╗ą░ą┤čłąĖąĄ 16 ą▒ąĖčé) |

| START_ADDR |

MDMAx_yy_START_ADDR |

SAH (čüčéą░čĆčłąĖąĄ 16 ą▒ąĖčé), SAL (ą╝ą╗ą░ą┤čłąĖąĄ 16 ą▒ąĖčé) |

| X_COUNT |

MDMAx_yy_X_COUNT |

XCNT |

| Y_COUNT |

MDMAx_yy_Y_COUNT |

YCNT |

| X_MODIFY |

MDMAx_yy_X_MODIFY |

XMOD |

| Y_MODIFY |

MDMAx_yy_Y_MODIFY |

YMOD |

| CURR_DESC_PTR |

MDMAx_yy_CURR_DESC_PTR |

- |

| CURR_ADDR |

MDMAx_yy_CURR_ADDR |

- |

| CURR_X_COUNT |

MDMAx_yy_CURR_X_COUNT |

- |

| CURR_Y_COUNT |

MDMAx_yy_CURR_Y_COUNT |

- |

| IRQ_STATUS |

MDMAx_yy_IRQ_STATUS |

- |

| PERIPHERAL_MAP |

MDMAx_yy_PERIPHERAL_MAP |

- |

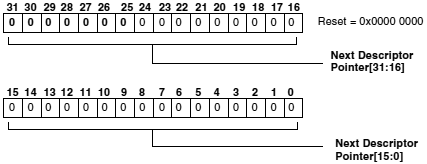

ąĀąĄą│ąĖčüčéčĆ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ čāą║ą░ąĘą░č鹥ą╗čÅ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ NEXT_DESC_PTR ąĘą░ą┤ą░ąĄčé, ą│ą┤ąĄ ąĮą░ą╣čéąĖ ąĮą░čćą░ą╗ąŠ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ ą▒ą╗ąŠą║ą░ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░, ą│ą┤ąĄ ąŠą┐ąĖčüą░ąĮą░ ą░ą║čéąĖą▓ąĮąŠčüčéčī DMA, ą║ąŠą│ą┤ą░ ąĘą░ą▓ąĄčĆčłąĖčéčüčÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ č鹥ą║čāčēąĄą│ąŠ ą▒ą╗ąŠą║ą░ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░. ąŁč鹊čé čĆąĄą│ąĖčüčéčĆ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą▓ čĆąĄąČąĖą╝ą░čģ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ ą╝ąŠą┤ąĄą╗ąĄą╣ ą╝ą░ą╗ąŠą│ąŠ ąĖ ą▒ąŠą╗čīčłąŠą│ąŠ čüą┐ąĖčüą║ą░. ąÆ ąĮą░čćą░ą╗ąĄ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ ą▓čŗą▒ąĖčĆą░čÄčéčüčÅ ą╗čÄą▒ąŠą╣ ąĖąĘ čŹčéąĖčģ čĆąĄąČąĖą╝ąŠą▓, 32-ą▒ąĖčéą░ NEXT_DESC_PTR ą║ąŠą┐ąĖčĆčāčÄčéčüčÅ ą▓ CURR_DESC_PTR. ąŚą░č鹥ą╝, ą▓ąŠ ą▓čĆąĄą╝čÅ ą▓čŗą▒ąŠčĆą║ąĖ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░, čĆąĄą│ąĖčüčéčĆ CURR_DESC_PTR ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ ą┐ąŠčüą╗ąĄ ą║ą░ąČą┤ąŠą│ąŠ ą┐čĆąŠčćąĖčéą░ąĮąĮąŠą│ąŠ 菹╗ąĄą╝ąĄąĮčéą░ ą▓ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąĄ.

ąÆ čĆąĄąČąĖą╝ą░čģ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ ą╝ąŠą┤ąĄą╗ąĄą╣ ą╝ą░ą╗ąŠą│ąŠ ąĖ ą▒ąŠą╗čīčłąŠą│ąŠ čüą┐ąĖčüą║ą░ čĆąĄą│ąĖčüčéčĆ NEXT_DESC_PTR, ąĮąŠ ąĮąĄ CURR_DESC_PTR, ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĮą░ą┐čĆčÅą╝čāčÄ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ č湥čĆąĄąĘ MMR-ą┤ąŠčüčéčāą┐ ą┐ąĄčĆąĄą┤ ąĮą░čćą░ą╗ąŠą╝ čĆą░ą▒ąŠčéčŗ DMA.

ąÆ čĆąĄąČąĖą╝ąĄ ą╝ą░čüčüąĖą▓ą░ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą▓ čĆąĄą│ąĖčüčéčĆ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ čāą║ą░ąĘą░č鹥ą╗čÅ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ ąĖą│ąĮąŠčĆąĖčĆčāąĄčéčüčÅ, ąĖ ą▓čŗą▒ąŠčĆą║ą░ čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ č鹊ą╗čīą║ąŠ č湥čĆąĄąĘ čĆąĄą│ąĖčüčéčĆ CURR_DESC_PTR.

ąĀąĖčü. 9-1. Next Descriptor Pointer Register (DMAx_NEXT_DESC_PTR / MDMAx_yy_NEXT_DESC_PTR).

ąöą╗čÅ čŹč鹊ą│ąŠ čĆąĄą│ąĖčüčéčĆą░ ą┤ąŠčüčéčāą┐ąĄąĮ ą┤ąŠčüčéčāą┐ ąĮą░ čćč鹥ąĮąĖąĄ ąĖ ąĘą░ą┐ąĖčüčī ą┤ąŠ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą║ą░ąĮą░ą╗ą░, ąĖ ą┐ąŠčüą╗ąĄ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą║ą░ąĮą░ą╗ą░ ą┤ąŠčüčéčāą┐ąĄąĮ ą┤ąŠčüčéčāą┐ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ.

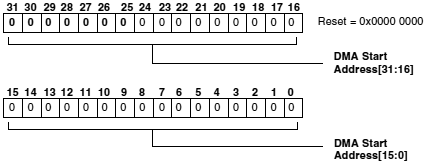

ąĀąĄą│ąĖčüčéčĆ ą░ą┤čĆąĄčüą░ ąĮą░čćą░ą╗ą░ START_ADDR, ą┐ąŠą║ą░ąĘą░ąĮąĮčŗą╣ ąĮą░ čĆąĖčü. 9-2, čüąŠą┤ąĄčƹȹĖčé ąĮą░čćą░ą╗čīąĮčŗą╣ ą░ą┤čĆąĄčü ą▒čāč乥čĆą░ ą┤ą░ąĮąĮčŗčģ, ąĮą░ ą║ąŠč鹊čĆčŗą╣ ą▓ ąĮą░čüč鹊čÅčēąĖą╣ ą╝ąŠą╝ąĄąĮčé ąĮą░čåąĄą╗ąĄąĮ DMA.

ąĀąĖčü. 9-2. Start Address Register (DMAx_START_ADDR, MDMAx_yy_START_ADDR).

ąöą╗čÅ čŹč鹊ą│ąŠ čĆąĄą│ąĖčüčéčĆą░ ą┤ąŠčüčéčāą┐ąĄąĮ ą┤ąŠčüčéčāą┐ ąĮą░ čćč鹥ąĮąĖąĄ ąĖ ąĘą░ą┐ąĖčüčī ą┤ąŠ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą║ą░ąĮą░ą╗ą░, ąĖ ą┐ąŠčüą╗ąĄ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą║ą░ąĮą░ą╗ą░ ą┤ąŠčüčéčāą┐ąĄąĮ ą┤ąŠčüčéčāą┐ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ.

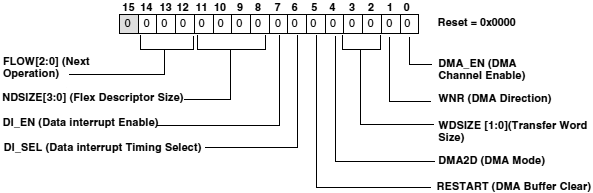

ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ DMA_CONFIG, ą┐ąŠą║ą░ąĘą░ąĮąĮčŗą╣ ąĮą░ čĆąĖčü. 9-3, ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ąĮą░čüčéčĆąŠą╣ą║ąĖ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓ ąĖ čĆąĄąČąĖą╝ąŠą▓ čĆą░ą▒ąŠčéčŗ DMA. ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 ąĘą░ą┐ąĖčüčī ą▓ čĆąĄą│ąĖčüčéčĆ DMA_CONFIG ą▓ąŠ ą▓čĆąĄą╝čÅ čĆą░ą▒ąŠčéčŗ DMA ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ąŠčłąĖą▒ą║ąĄ DMA ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé č鹊ą│ąŠ, čćč鹊 ą▓ ą▒ąĖčé DMA_EN ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ 0.

ąĀąĖčü. 9-3. Configuration Register (DMAx_CONFIG / MDMAx_yy_CONFIG).

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: čüąĄčĆčŗą╝ čåą▓ąĄč鹊ą╝ ą┐ąŠą╝ąĄč湥ąĮčŗ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą▒ąĖčéčŗ.

ąöą╗čÅ čŹč鹊ą│ąŠ čĆąĄą│ąĖčüčéčĆą░ ą┤ąŠčüčéčāą┐ąĄąĮ ą┤ąŠčüčéčāą┐ ąĮą░ čćč鹥ąĮąĖąĄ ąĖ ąĘą░ą┐ąĖčüčī ą┤ąŠ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą║ą░ąĮą░ą╗ą░, ąĖ ą┐ąŠčüą╗ąĄ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą║ą░ąĮą░ą╗ą░ ą┤ąŠčüčéčāą┐ąĄąĮ ą┤ąŠčüčéčāą┐ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ.

FLOW[2:0] (Next Operation). ą×ą┐čĆąĄą┤ąĄą╗čÅąĄčé čüą╗ąĄą┤čāčÄčēčāčÄ ąŠą┐ąĄčĆą░čåąĖčÄ DMA, ą║ąŠč鹊čĆą░čÅ ąĮą░čćąĮąĄčéčüčÅ ąĘą░ č鹥ą║čāčēąĄą╣:

0x0 - Stop, ąŠčüčéą░ąĮąŠą▓ą║ą░ ą░ą║čéąĖą▓ąĮąŠčüčéąĖ DMA ąĮą░ čŹč鹊ą╝ ą║ą░ąĮą░ą╗ąĄ. ąÜąŠą│ą┤ą░ č鹥ą║čāčēąĖą╣ čĆą░ą▒ąŠčćąĖą╣ ą▒ą╗ąŠą║ ąĘą░ą▓ąĄčĆčłąĖčéčüčÅ, ą║ą░ąĮą░ą╗ DMA ąŠčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ, ą┐ąŠčüą╗ąĄ čüąĖą│ąĮą░ą╗ąĖąĘą░čåąĖąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄą╝ (ąĄčüą╗ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ). ąæąĖčé čüąŠčüč鹊čÅąĮąĖčÅ DMA_RUN ą▓ čĆąĄą│ąĖčüčéčĆąĄ DMAx_IRQ_STATUS ą┐ąŠą╝ąĄąĮčÅąĄčéčüčÅ ąŠčé 1 ą║ 0, ą▒ąĖčé DMA_EN ą▓ čĆąĄą│ąĖčüčéčĆąĄ DMAx_CONFIG ąŠčüčéą░ąĮąĄčéčüčÅ ąĮąĄąĖąĘą╝ąĄąĮąĮčŗą╝. ąÆ čŹč鹊ą╝ čüąŠčüč鹊čÅąĮąĖąĖ ą║ą░ąĮą░ą╗ ąĮą░čģąŠą┤ąĖčéčüčÅ ąĮą░ ą┐ą░čāąĘąĄ. ą¤čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ą▓čüąĄ ąĄčēąĄ ąŠčéčäąĖą╗čīčéčĆąŠą▓čŗą▓ą░čÄčéčüčÅ ą▒ą╗ąŠą║ąŠą╝ DMA. ąÜą░ąĮą░ą╗ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąĄčĆąĄąĘą░ą┐čāčēąĄąĮ ą┐čĆąŠčüč鹊 ą┤čĆčāą│ąŠą╣ ąĘą░ą┐ąĖčüčīčÄ ą▓ DMAx_CONFIG čü čāą║ą░ąĘą░ąĮąĖąĄą╝ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ čĆą░ą▒ąŠč湥ą│ąŠ ą▒ą╗ąŠą║ą░, ą▓ ą║ąŠč鹊čĆąŠą╝ DMA_EN čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1.

0x1 - čĆąĄąČąĖą╝ ą░ą▓č鹊ą▒čāč乥čĆą░. ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ąĄčüą║čĆąĖą┐č鹊čĆčŗ ą▓ ą┐ą░ą╝čÅčéąĖ. ąÆą╝ąĄčüč鹊 čŹč鹊ą│ąŠ DMA ą▓čŗą┐ąŠą╗ąĮčÅąĄčé ą┐ąŠčüč鹊čÅąĮąĮčŗąĄ ą║čĆčāą│ąŠą▓čŗąĄ ą┐čĆąŠčģąŠą┤čŗ ą┐ąŠ ą▒čāč乥čĆčā, ąŠčüąĮąŠą▓ą░ąĮąĮčŗąĄ ąĮą░ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮčŗąĄ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╝ ąĮą░čüčéčĆąŠą╣ą║ąĖ DMAx MMR. ą¤čĆąĖ ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĖ čĆą░ą▒ąŠč湥ą│ąŠ ą▒ą╗ąŠą║ą░ čĆąĄą│ąĖčüčéčĆčŗ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓ ą┐ąĄčĆąĄąĘą░ą│čĆčāąČą░čÄčéčüčÅ ą▓ č鹥ą║čāčēąĖąĄ čĆąĄą│ąĖčüčéčĆčŗ, ąĖ DMA ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ ą▓ąŠąĘąŠą▒ąĮąŠą▓ąĖčéčüčÅ ą▒ąĄąĘ čāčćą░čüčéąĖčÅ ą┐čĆąŠčåąĄčüčüąŠčĆą░. ąĀąĄąČąĖą╝ ą░ą▓č鹊ą▒čāč乥čĆą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮ ąĘą░ą┐ąĖčüčīčÄ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╝ 0 ą▓ ą▒ąĖčé DMA_EN čĆąĄą│ąĖčüčéčĆą░ DMAx_CONFIG.

0x4 - ą╝ą░čüčüąĖą▓ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą▓. ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ą┤ąĄčüą║čĆąĖą┐č鹊čĆ ąĖąĘ ą┐ą░ą╝čÅčéąĖ, ą▓ ą║ąŠč鹊čĆąŠą╝ ąĮąĄčé 菹╗ąĄą╝ąĄąĮč鹊ą▓ NDPH ąĖą╗ąĖ NDPL. ą¤ąŠčüą║ąŠą╗čīą║čā ą┤ąĄčüą║čĆąĖą┐č鹊čĆ ąĮąĄ čüąŠą┤ąĄčƹȹĖčé ąĘą░ą┐ąĖčüčī čüą╗ąĄą┤čāčÄčēąĄą│ąŠ čāą║ą░ąĘą░č鹥ą╗čÅ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░, ą┐ąŠą┤čüąĖčüč鹥ą╝ą░ DMA ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ CURR_DESC_PTR ą┤ą╗čÅ ą┐ąĄčĆąĄčłą░ą│ąĖą▓ą░ąĮąĖčÅ ą┐ąŠ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ą╝, čćč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą│čĆčāą┐ą┐ąĄ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą▓ čüą╗ąĄą┤ąŠą▓ą░čéčī ą▓ ą┐ą░ą╝čÅčéąĖ ąŠą┤ąĮąŠą╝čā ąĘą░ ą┤čĆčāą│ąĖą╝, ąĮą░ą┐ąŠą┤ąŠą▒ąĖąĄ ą╝ą░čüčüąĖą▓ą░.

0x6 - čüą┐ąĖčüąŠą║ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą▓ (ą╝ą░ą╗ą░čÅ ą╝ąŠą┤ąĄą╗čī). ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ą┤ąĄčüą║čĆąĖą┐č鹊čĆ ąĖąĘ ą┐ą░ą╝čÅčéąĖ, ą▓ ą║ąŠč鹊čĆąŠą╝ čüąŠą┤ąĄčƹȹĖčéčüčÅ ą┐ąŠą╗ąĄ NDPL, ąĮąŠ ąĮąĄ NDPH. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, čüčéą░čĆčłąĖąĄ 16 čüą╗ąĄą┤čāčÄčēąĄą│ąŠ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ ą▒ąĄčĆčāčéčüčÅ ąŠčé čüčéą░čĆčłąĖčģ ą▒ąĖčé ą▓ čĆąĄą│ąĖčüčéčĆąĄ NEXT_DESC_PTR, čćč鹊 ąŠą│čĆą░ąĮąĖčćąĖą▓ą░ąĄčé ą▓čüąĄ ą┤ąĄčüą║čĆąĖą┐č鹊čĆčŗ ąŠą▒ą╗ą░čüčéčīčÄ čüčéčĆą░ąĮąĖčåčŗ ą┐ą░ą╝čÅčéąĖ 64 ą║ąĖą╗ąŠą▒ą░ą╣čéą░.

0x7 - čüą┐ąĖčüąŠą║ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą▓ (ą▒ąŠą╗čīčłą░čÅ ą╝ąŠą┤ąĄą╗čī). ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ą┤ąĄčüą║čĆąĖą┐č鹊čĆ ąĖąĘ ą┐ą░ą╝čÅčéąĖ, ą║ąŠč鹊čĆčŗą╣ ą▓ą║ą╗čÄčćą░ąĄčé NDPH ąĖ NDPL, čćč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┤ąŠčüčéąĖčćčī ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą╣ ą│ąĖą▒ą║ąŠčüčéąĖ ą┤ą╗čÅ čĆą░ąĘą╝ąĄčēąĄąĮąĖčÅ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą▓ ą▓ ą┐ą░ą╝čÅčéąĖ.

NDSIZE[3:0] (Flex Descriptor Size). ą×ą┐čĆąĄą┤ąĄą╗čÅąĄčé čĆą░ąĘą╝ąĄčĆ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░. ąŁč鹊 ą┐ąŠą╗ąĄ ąĘą░ą┤ą░ąĄčé ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čĆąĄą│ąĖčüčéčĆąŠą▓ DMA MMR ą┤ą╗čÅ ąĘą░ą│čĆčāąĘą║ąĖ ąĖąĘ 菹╗ąĄą╝ąĄąĮč鹊ą▓ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ ą▓ ą┐ą░ą╝čÅčéąĖ. ąŁč鹊 ą┐ąŠą╗ąĄ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī čĆą░ą▓ąĮąŠ 0, ąĄčüą╗ąĖ ąĮčāąČąĮą░ ąŠčüčéą░ąĮąŠą▓ą║ą░ ąĖą╗ąĖ čĆąĄąČąĖą╝ ą░ą▓č鹊ą▒čāč乥čĆą░. ąĢčüą╗ąĖ NDSIZE ąĖ FLOW čāą║ą░ąĘčŗą▓ą░čÄčé ą┤ąĄčüą║čĆąĖą┐č鹊čĆ, ą║ąŠč鹊čĆčŗą╣ čĆą░čüčłąĖčĆčÅąĄčéčüčÅ ąĘą░ ą┐čĆąĄą┤ąĄą╗čŗ YMOD, ą▓ąŠąĘąĮąĖą║ąĮąĄčé ąŠčłąĖą▒ą║ą░ DMA.

0000 - čéčĆąĄą▒čāąĄčéčüčÅ ąĄčüą╗ąĖ Stop ąĖą╗ąĖ čĆąĄąČąĖą╝ ą░ą▓č鹊ą▒čāč乥čĆą░

0001 - 1001 - čĆą░ąĘą╝ąĄčĆ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░

1010 - 1111 - ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ

DI_EN (Data interrupt Enable). 0: ąĮąĄ čĆą░ąĘčĆąĄčłą░čéčī ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠčüą╗ąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ čĆą░ą▒ąŠč湥ą│ąŠ ą▒ą╗ąŠą║ą░, 1: čĆą░ąĘčĆąĄčłąĖčéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠčüą╗ąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ čĆą░ą▒ąŠč湥ą│ąŠ ą▒ą╗ąŠą║ą░.

DI_SEL (Data interrupt Timing Select). ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ ą┤ą╗čÅ ID-ąŠą┐ąĄčĆą░čåąĖąĖ. 0: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠčüą╗ąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ čéčĆą░ąĮčüč乥čĆą░ ą▓čüąĄą│ąŠ ą▒čāč乥čĆą░ (ą▓ąĮąĄčłąĮąĖą╣ čåąĖą║ą╗), 1: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠčüą╗ąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą║ą░ąČą┤ąŠą╣ čüčéčĆąŠą║ąĖ (ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čåąĖą║ą╗) č鹊ą╗čīą║ąŠ ą┤ą╗čÅ 2D. ąŁč鹊čé ą▒ąĖčé čāą║ą░ąĘčŗą▓ą░ąĄčé ą▓čĆąĄą╝čÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ: ą┐ąŠčüą╗ąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą▓čüąĄą│ąŠ ą▒čāč乥čĆą░ ąĖą╗ąĖ ą┐ąŠčüą╗ąĄ ą║ą░ąČą┤ąŠą╣ čüčéčĆąŠą║ąĖ ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╝ čåąĖą║ą╗ąĄ. ąŁč鹊čé ą▒ąĖčé ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖčÅ 2D DMA.

RESTART (DMA Buffer Clear). ą¤ąĄčĆąĄąĘą░ą┐čāčüą║, ąŠčćąĖčüčéą║ą░ ą▒čāč乥čĆą░ DMA. 0: čüąŠčģčĆą░ąĮčÅčéčī ą┤ą░ąĮąĮčŗąĄ DMA FIFO ą╝ąĄąČą┤čā čĆą░ą▒ąŠčćąĖą╝ąĖ ą▒ą╗ąŠą║ą░ą╝ąĖ, 1: ąŠčéą▒čĆąŠčüąĖčéčī DMA FIFO ą┐ąĄčĆąĄą┤ ąĮą░čćą░ą╗ąŠą╝ čĆą░ą▒ąŠč湥ą│ąŠ ą▒ą╗ąŠą║ą░. ąŁč鹊čé ą▒ąĖčé čāą║ą░ąĘčŗą▓ą░ąĄčé, ą┤ąŠą╗ąČąĮčŗ ą╗ąĖ ą┐čĆąĖąĮčÅčéčŗąĄ ą┤ą░ąĮąĮčŗąĄ čāą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ ą▓ FIFO ą┤ą░ąĮąĮčŗčģ ą║ą░ąĮą░ą╗ą░ (RESTART=0), ąĖą╗ąĖ ąČąĄ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąŠčéą▒čĆąŠčłąĄąĮčŗ (RESTART=1) ą┐ąĄčĆąĄą┤ ąĮą░čćą░ą╗ąŠą╝ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ čĆą░ą▒ąŠč湥ą│ąŠ ą▒ą╗ąŠą║ą░. ą¤čĆąĖąĮčÅčéčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą▒čāą┤čāčé ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąŠčéą▒čĆąŠčłąĄąĮčŗ, ą║ąŠą│ą┤ą░ DMA_EN ąĖąĘą╝ąĄąĮčÅąĄčéčüčÅ ąŠčé 0 ą║ 1, ąŠą▒čŗčćąĮąŠ ą║ąŠą│ą┤ą░ ą║ą░ąĮą░ą╗ čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ ą▓ ą┐ąĄčĆą▓čŗą╣ čĆą░ąĘ. ą¤čĆąĖąĮčÅčéčŗąĄ ą┤ą░ąĮąĮčŗąĄ FIFO ąŠą▒čŗčćąĮąŠ ą┤ąŠą╗ąČąĮčŗ čüąŠčģčĆą░ąĮčÅčéčīčüčÅ ą╝ąĄąČą┤čā čĆą░ą▒ąŠčćąĖą╝ąĖ ą▒ą╗ąŠą║ą░ą╝ąĖ, ąĄčüą╗ąĖ čĆą░ą▒ąŠčćąĖąĄ ą▒ą╗ąŠą║ąĖ čüąŠčüčéą░ą▓ą╗čÅčÄčé ą┐čĆąŠą┤ąŠą╗ąČą░čÄčēąĖą╣čüčÅ ą┐ąŠč鹊ą║ ą┤ą░ąĮąĮčŗčģ. ą×ą┤ąĮą░ą║ąŠ ąĄčüą╗ąĖ ąĮąŠą▓čŗą╣ čĆą░ą▒ąŠčćąĖą╣ ą▒ą╗ąŠą║ ąĘą░ą┐čāčüą║ą░ąĄčé ąĮąŠą▓čŗą╣ ą┐ąŠč鹊ą║ ą┤ą░ąĮąĮčŗčģ, ą▒ąĖčé RESTART ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1, čćč鹊ą▒čŗ ąŠčćąĖčüčéąĖčéčī čĆą░ąĮąĄąĄ ą┐čĆąĖąĮčÅčéčŗąĄ ą┤ą░ąĮąĮčŗąĄ.

DMA2D (DMA Mode). 0: ą╗ąĖąĮąĄą╣ąĮčŗą╣ čĆąĄąČąĖą╝, 1: ą┤ą▓čāčģą╝ąĄčĆąĮčŗą╣ (2D). ąŁč鹊čé ą▒ąĖčé čāą║ą░ąĘčŗą▓ą░ąĄčé, ą║ą░ą║ ą┤ąŠą╗ąČąĄąĮ čĆą░ą▒ąŠčéą░čéčī čĆąĄąČąĖą╝ DMA - ą▓ąŠą▓ą╗ąĄą║ą░čéčī č鹊ą╗čīą║ąŠ X_COUNT ąĖ X_MODIFY (ąŠą┤ąĮąŠą╝ąĄčĆąĮčŗą╣ DMA) ąĖą╗ąĖ čéą░ą║ąČąĄ ą▓ąŠą▓ą╗ąĄą║ą░čéčī Y_COUNT ąĖ Y_MODIFY (ą┤ą▓čāčģą╝ąĄčĆąĮčŗą╣ DMA).

WDSIZE[1:0] (Transfer Word Size). ąĀą░ąĘą╝ąĄčĆ čüą╗ąŠą▓ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ:

00 - 8-ą▒ąĖčéąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ

01 - 16-ą▒ąĖčéąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ

10 - 32-ą▒ąĖčéąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ

11 - ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ

ą¤ąŠą┤čüąĖčüč鹥ą╝ą░ DMA ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ą┐ąĄčĆąĄą┤ą░čćąĖ 8-, 16- ąĖą╗ąĖ 32-čĆą░ąĘčĆčÅą┤ąĮčŗčģ 菹╗ąĄą╝ąĄąĮč鹊ą▓. ąÜą░ąČą┤čŗą╣ ąĘą░ą┐čĆąŠčü/ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮąĖąĄ čĆąĄąĘčāą╗čīčéą░čéą░ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ąĘą░ ąŠą┤ąĖąĮ ą┤ąŠčüčéčāą┐ ą║ ą┐ą░ą╝čÅčéąĖ (ąĮąĄčüą╝ąŠčéčĆčÅ ąĮą░ č鹊, čćč鹊 čéčĆąĄą▒čāąĄčéčüčÅ 2 čåąĖą║ą╗ą░ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ 32-ą▒ąĖčéąĮčŗčģ ą┤ą░ąĮąĮčŗčģ č湥čĆąĄąĘ 16-ą▒ąĖčéąĮčŗą╣ ą┐ąŠčĆčé ą┐ą░ą╝čÅčéąĖ), ąĖą╗ąĖ č湥čĆąĄąĘ 16-ą▒ąĖčéąĮčāčÄ čłąĖąĮčā DAB. ąĀą░ąĘą╝ąĄčĆčŗ ąĖąĮą║čĆąĄą╝ąĄąĮčéą░ čāą║ą░ąĘą░č鹥ą╗čÅ ą░ą┤čĆąĄčüą░ DMA (čłą░ą│ąĖ) ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą║čĆą░čéąĮčŗ čĆą░ąĘą╝ąĄčĆčā ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ąŠą│ąŠ 菹╗ąĄą╝ąĄąĮčéą░: 1 ą┤ą╗čÅ 8 ą▒ąĖčé, 2 ą┤ą╗čÅ 16 ą▒ąĖčé, 4 ą┤ą╗čÅ 32 ą▒ąĖčé.

ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčāčÄ ąĖąĮč乊čĆą╝ą░čåąĖčÄ ą┐čĆąŠ č鹊, ą║ą░ą║ ąĮą░čüčéčĆą░ąĖą▓ą░ąĄčéčüčÅ ą║ą░ąČą┤čŗą╣ ą║ą░ąĮą░ą╗ DMA ą┤ą╗čÅ ą┐ąŠą┤ą┤ąĄčƹȹ║ąĖ čĆą░ąĘąĮčŗčģ ą┤ą╗ąĖąĮ ą┐ąĄčĆąĄą┤ą░čćąĖ, čüą╝. ą▓čĆąĄąĘą║čā "ąĀąĄą│ąĖčüčéčĆčŗ DMAx_PERIPHERAL_MAP, MDMAx_yy_PERIPHERAL_MAP".

WNR (DMA Direction). ąØą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ DMA. 0: čćč鹥ąĮąĖąĄ ą┐ą░ą╝čÅčéąĖ čüąŠ čüč鹊čĆąŠąĮčŗ DMA (ą┐ąĄčĆąĄą┤ą░čćą░), 1: ąĘą░ą┐ąĖčüčī ą┐ą░ą╝čÅčéąĖ čüąŠ čüč鹊čĆąŠąĮčŗ DMA (ą┐čĆąĖąĄą╝).

DMA_EN (DMA Channel Enable). 0: ąĘą░ą┐čĆąĄčé ą║ą░ąĮą░ą╗ą░ DMA, 1: čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ą║ą░ąĮą░ą╗ą░ DMA. ąÜąŠą│ą┤ą░ ą║ą░ąĮą░ą╗ DMA ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ čĆą░ąĘčĆąĄčłąĄąĮ, ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠčé ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ąŠąĘąĮą░čćą░čÄčé ąĘą░ą┐čĆąŠčüčŗ DMA. ąÜąŠą│ą┤ą░ ą║ą░ąĮą░ą╗ ąĘą░ą┐čĆąĄčēąĄąĮ, ą▒ą╗ąŠą║ DMA ąĖą│ąĮąŠčĆąĖčĆčāąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ąĖ ą┐ąĄčĆąĄą┤ą░ąĄčé ąĄą│ąŠ ąĮą░ą┐čĆčÅą╝čāčÄ ą▓ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. ą¦č鹊ą▒čŗ ąĖąĘą▒ąĄąČą░čéčī ąĮąĄą┐čĆąĄą┤čüą║ą░ąĘčāąĄą╝ąŠą│ąŠ ą┐ąŠą▓ąĄą┤ąĄąĮąĖčÅ, ą┐ąŠąĘą░ą▒ąŠčéčīč鹥čüčī ąŠ čĆą░ąĘčĆąĄčłąĄąĮąĖąĖ ą║ą░ąĮą░ą╗ą░ DMA ą┐ąĄčĆąĄą┤ čĆą░ąĘčĆąĄčłąĄąĮąĖąĄą╝ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░, ąĖ ąŠ ąĘą░ą┐čĆąĄč鹥 ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┐ąĄčĆąĄą┤ ąĘą░ą┐čĆąĄč鹊ą╝ ą║ą░ąĮą░ą╗ą░ DMA.

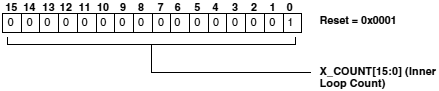

ąöą╗čÅ ą┤ą▓čāčģą╝ąĄčĆąĮčŗčģ ą┐ąĄčĆąĄą┤ą░čć DMA (2D DMA) ąĖą╝ąĄčÄčéčüčÅ čĆąĄą│ąĖčüčéčĆčŗ čüč湥čéčćąĖą║ą░ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čåąĖą║ą╗ą░ (Inner Loop Count, X_COUNT), ą┐ąŠą║ą░ąĘą░ąĮąĮčŗąĄ ąĮą░ čĆąĖčü. 9-4. ąöą╗čÅ ąŠą┤ąĮąŠą╝ąĄčĆąĮčŗčģ ą┐ąĄčĆąĄą┤ą░čć DMA (1D DMA), ąŠąĮąĖ čāą║ą░ąĘčŗą▓ą░čÄčé ą║ąŠą╗ąĖč湥čüčéą▓ąŠ 菹╗ąĄą╝ąĄąĮč鹊ą▓ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ. ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. čĆą░ąĘą┤ąĄą╗ "ąöą▓čāčģą╝ąĄčĆąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ DMA". ąŚąĮą░č湥ąĮąĖąĄ 0 ą┤ą╗čÅ X_COUNT čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé 65536 菹╗ąĄą╝ąĄąĮčéą░ą╝.

ąĀąĖčü. 9-4. Inner Loop Count Register (DMAx_X_COUNT / MDMAx_yy_X_COUNT).

ąöą╗čÅ čŹč鹊ą│ąŠ čĆąĄą│ąĖčüčéčĆą░ ą┤ąŠčüčéčāą┐ąĄąĮ ą┤ąŠčüčéčāą┐ ąĮą░ čćč鹥ąĮąĖąĄ ąĖ ąĘą░ą┐ąĖčüčī ą┤ąŠ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą║ą░ąĮą░ą╗ą░, ąĖ ą┐ąŠčüą╗ąĄ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą║ą░ąĮą░ą╗ą░ ą┤ąŠčüčéčāą┐ąĄąĮ ą┤ąŠčüčéčāą┐ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ.

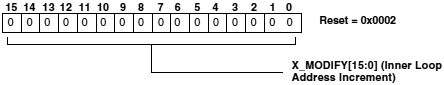

ąĀąĄą│ąĖčüčéčĆčŗ ąĖąĮą║čĆąĄą╝ąĄąĮčéą░ ą░ą┤čĆąĄčüą░ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čåąĖą║ą╗ą░ (inner loop address increment, X_MODIFY) čüąŠą┤ąĄčƹȹ░čé čćąĖčüą╗ąŠ čüąŠ ąĘąĮą░ą║ąŠą╝ ą▓ č乊čĆą╝ą░č鹥 ą┤ą▓ąŠąĖčćąĮąŠą│ąŠ ą┤ąŠą┐ąŠą╗ąĮąĄąĮąĖčÅ ą┤ąŠ 2 ą┤ą╗čÅ ąĖąĮą║čĆąĄą╝ąĄąĮčéą░ ą▒ą░ą╣č鹊ą▓ąŠą│ąŠ ą░ą┤čĆąĄčüą░. ąöą╗čÅ 1D DMA čŹč鹊čé ąĖąĮą║čĆąĄą╝ąĄąĮčé čÅą▓ą╗čÅąĄčéčüčÅ čłą░ą│ąŠą╝, ą║ąŠč鹊čĆčŗą╣ ą┐čĆąĖą║ą╗ą░ą┤čŗą▓ą░ąĄčéčüčÅ ą┐ąŠčüą╗ąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ ą║ą░ąČą┤ąŠą│ąŠ 菹╗ąĄą╝ąĄąĮčéą░.

ąöą╗čÅ 2D DMA čŹč鹊čé ąĖąĮą║čĆąĄą╝ąĄąĮčé ąĮą░ą║ą╗ą░ą┤čŗą▓ą░ąĄčéčüčÅ ą┐ąŠčüą╗ąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ ą║ą░ąČą┤ąŠą│ąŠ 菹╗ąĄą╝ąĄąĮčéą░ ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╝ čåąĖą║ą╗ąĄ, ą┤ąŠ ąĮąĄą│ąŠ, ąĮąŠ ąĮąĄ ą▓ą║ą╗čÄčćą░čÅ ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ 菹╗ąĄą╝ąĄąĮčé ą▓ ą║ą░ąČą┤ąŠą╝ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╝ čåąĖą║ą╗ąĄ (ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čĆą░ąĘą▓ąĄčĆčéą║ąĖ ą║ą░ą┤čĆą░). ą¤ąŠčüą╗ąĄ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ 菹╗ąĄą╝ąĄąĮčéą░ ą▓ ą║ą░ąČą┤ąŠą╝ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╝ čåąĖą║ą╗ąĄ ą▓ą╝ąĄčüč鹊 čŹč鹊ą│ąŠ ą┐čĆąĖą║ą╗ą░ą┤čŗą▓ą░ąĄčéčüčÅ Y_MODIFY, ąĘą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ čüą░ą╝ąŠą│ąŠ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▓ ą║ą░ąČą┤ąŠą╝ čĆą░ą▒ąŠč湥ą╝ ą▒ą╗ąŠą║ąĄ. X_MODIFY ą▓čüąĄą│ą┤ą░ ą┐čĆąĖą║ą╗ą░ą┤čŗą▓ą░ąĄčéčüčÅ ąĮą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╣ ą┐ąĄčĆąĄą┤ą░č湥 čĆą░ą▒ąŠč湥ą│ąŠ ą▒ą╗ąŠą║ą░.

ą¤ąŠą╗ąĄ X_MODIFY ą╝ąŠąČąĄčé ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ ą▓ 0. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ DMA ą┐ąŠčüč鹊čÅąĮąĮąŠ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ąŠčé ąŠą┤ąĮąŠą│ąŠ ąĖ č鹊ą│ąŠ ąČąĄ ą░ą┤čĆąĄčüą░. ąŁč鹊 ą┐ąŠą╗ąĄąĘąĮąŠ, ąĮą░ą┐čĆąĖą╝ąĄčĆ, ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ą╝ąĄąČą┤čā čĆąĄą│ąĖčüčéčĆąŠą╝ ą┤ą░ąĮąĮčŗčģ ąĖ ą▓ąĮąĄčłąĮąĖą╝ ąŠč鹊ą▒čĆą░ąČąĄąĮąĮčŗą╝ ąĮą░ ą┐ą░ą╝čÅčéčī ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝.

ąĀąĖčü. 9-5. Inner Loop Address Increment Register (DMAx_X_MODIFY / MDMAx_yy_X_MODIFY).

ąöą╗čÅ čŹč鹊ą│ąŠ čĆąĄą│ąĖčüčéčĆą░ ą┤ąŠčüčéčāą┐ąĄąĮ ą┤ąŠčüčéčāą┐ ąĮą░ čćč鹥ąĮąĖąĄ ąĖ ąĘą░ą┐ąĖčüčī ą┤ąŠ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą║ą░ąĮą░ą╗ą░, ąĖ ą┐ąŠčüą╗ąĄ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą║ą░ąĮą░ą╗ą░ ą┤ąŠčüčéčāą┐ąĄąĮ ą┤ąŠčüčéčāą┐ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ.

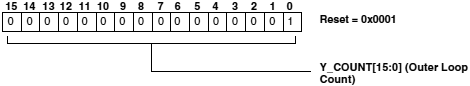

ąöą╗čÅ čĆąĄąČąĖą╝ą░ 2D DMA čĆąĄą│ąĖčüčéčĆčŗ ą▓ąĮąĄčłąĮąĄą│ąŠ čåąĖą║ą╗ą░ (outer loop count, Y_COUNT) čüąŠą┤ąĄčƹȹ░čé čüč湥čéčćąĖą║ ą▓ąĮąĄčłąĮąĄą│ąŠ čåąĖą║ą╗ą░. ąŁč鹊 ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ 1D DMA. ąÆ čŹč鹊ą╝ čĆąĄą│ąĖčüčéčĆąĄ čüąŠą┤ąĄčƹȹĖčéčüčÅ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čüčéčĆąŠą║ ą▓ąŠ ą▓ąĮąĄčłąĮąĄą╝ čåąĖą║ą╗ąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ 2D DMA. ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. čĆą░ąĘą┤ąĄą╗ "ąöą▓čāčģą╝ąĄčĆąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ DMA".

ąĀąĖčü. 9-6. Outer Loop Count Register (DMAx_Y_COUNT / MDMAx_yy_Y_COUNT).

ąöą╗čÅ čŹč鹊ą│ąŠ čĆąĄą│ąĖčüčéčĆą░ ą┤ąŠčüčéčāą┐ąĄąĮ ą┤ąŠčüčéčāą┐ ąĮą░ čćč鹥ąĮąĖąĄ ąĖ ąĘą░ą┐ąĖčüčī ą┤ąŠ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą║ą░ąĮą░ą╗ą░, ąĖ ą┐ąŠčüą╗ąĄ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą║ą░ąĮą░ą╗ą░ ą┤ąŠčüčéčāą┐ąĄąĮ ą┤ąŠčüčéčāą┐ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ.

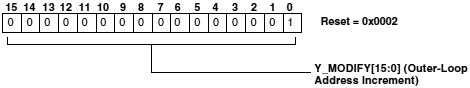

ąĀąĄą│ąĖčüčéčĆčŗ ąĖąĮą║čĆąĄą╝ąĄąĮčéą░ ą░ą┤čĆąĄčüą░ ą▓ąĮąĄčłąĮąĄą│ąŠ čåąĖą║ą╗ą░ ( outer loop address increment, Y_MODIFY) čüąŠą┤ąĄčƹȹ░čé čćąĖčüą╗ąŠ čüąŠ ąĘąĮą░ą║ąŠą╝ ą▓ č乊čĆą╝ą░č鹥 ą┤ą▓ąŠąĖčćąĮąŠą│ąŠ ą┤ąŠą┐ąŠą╗ąĮąĄąĮąĖčÅ ą┤ąŠ 2 ą┤ą╗čÅ ąĖąĮą║čĆąĄą╝ąĄąĮčéą░ ą▒ą░ą╣č鹊ą▓ąŠą│ąŠ ą░ą┤čĆąĄčüą░. ąŁč鹊 ąĖąĮą║čĆąĄą╝ąĄąĮčé ą▒ą░ą╣č鹊ą▓ąŠą│ąŠ ą░ą┤čĆąĄčüą░, ą║ąŠč鹊čĆčŗą╣ ą┐čĆąĖą║ą╗ą░ą┤čŗą▓ą░ąĄčéčüčÅ ą┐ąŠčüą╗ąĄ ą║ą░ąČą┤ąŠą│ąŠ ą┤ąĄą║čĆąĄą╝ąĄąĮčéą░ CURR_Y_COUNT, ąĘą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ 菹╗ąĄą╝ąĄąĮčéą░ ą▓ 2D-ą╝ą░čüčüąĖą▓ąĄ, ą║ąŠą│ą┤ą░ čéą░ą║ąČąĄ ąĖčüč鹥ą║ą░ąĄčé CURR_Y_COUNT. ąŚąĮą░č湥ąĮąĖąĄ čÅą▓ą╗čÅąĄčéčüčÅ čüą╝ąĄčēąĄąĮąĖąĄą╝ ą╝ąĄąČą┤čā ą┐ąŠčüą╗ąĄą┤ąĮąĖą╝ čüą╗ąŠą▓ąŠą╝ ą▓ ąŠą┤ąĮąŠą╣ "čüčéčĆąŠą║ąĄ" ąĖ ą┐ąĄčĆą▓čŗą╝ čüą╗ąŠą▓ąŠą╝ ą▓ čüą╗ąĄą┤čāčÄčēąĄą╣ "čüčéčĆąŠą║ąĄ". ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. čĆą░ąĘą┤ąĄą╗ "ąöą▓čāčģą╝ąĄčĆąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ DMA".

ąĀąĖčü. 9-7. Outer Loop Address Increment Register (DMAx_Y_MODIFY / MDMAx_yy_Y_MODIFY).

ąöą╗čÅ čŹč鹊ą│ąŠ čĆąĄą│ąĖčüčéčĆą░ ą┤ąŠčüčéčāą┐ąĄąĮ ą┤ąŠčüčéčāą┐ ąĮą░ čćč鹥ąĮąĖąĄ ąĖ ąĘą░ą┐ąĖčüčī ą┤ąŠ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą║ą░ąĮą░ą╗ą░, ąĖ ą┐ąŠčüą╗ąĄ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą║ą░ąĮą░ą╗ą░ ą┤ąŠčüčéčāą┐ąĄąĮ ą┤ąŠčüčéčāą┐ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ.

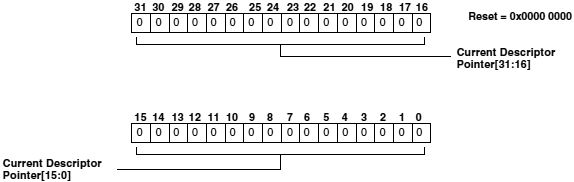

ąĀąĄą│ąĖčüčéčĆčŗ čāą║ą░ąĘą░č鹥ą╗čÅ č鹥ą║čāčēąĄą│ąŠ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ (current descriptor pointer, CURR_DESC_PTR) čüąŠą┤ąĄčƹȹ░čé ą░ą┤čĆąĄčü ą┐ą░ą╝čÅčéąĖ ą┤ą╗čÅ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ 菹╗ąĄą╝ąĄąĮčéą░ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ ą┤ą╗čÅ ąĘą░ą│čĆčāąĘą║ąĖ. ąöą╗čÅ ąĮą░čüčéčĆąŠąĄą║ čĆąĄąČąĖą╝ą░ FLOW, ą║ąŠč鹊čĆčŗą╣ ą▓ąŠą▓ą╗ąĄą║ą░ąĄčé ą┤ąĄčüą║čĆąĖą┐č鹊čĆčŗ (FLOW=4, 6 ąĖą╗ąĖ 7), čŹč鹊čé čĆąĄą│ąĖčüčéčĆ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ čŹą╗ąĄą╝ąĄąĮč鹊ą▓ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ ą▓ ą┐ąŠą┤čģąŠą┤čÅčēąĖąĄ MMR ą┤ąŠ ąĮą░čćą░ą╗ą░ čĆą░ą▒ąŠč湥ą│ąŠ ą▒ą╗ąŠą║ą░ DMA. ąöą╗čÅ čĆąĄąČąĖą╝ąŠą▓ čüą┐ąĖčüą║ą░ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą▓ (FLOW=6 ąĖą╗ąĖ 7), čŹč鹊čé čĆąĄą│ąĖčüčéčĆ ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆčāąĄčéčüčÅ ąĖąĘ NEXT_DESC_PTR ą┐ąĄčĆąĄą┤ ąĘą░ą│čĆčāąĘą║ąŠą╣ ą║ą░ąČą┤ąŠą│ąŠ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░. ąŚą░č鹥ą╝ ą░ą┤čĆąĄčü ą▓ CURR_DESC_PTR ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ čü ą║ą░ąČą┤čŗą╝ ą┐čĆąŠčćąĖčéą░ąĮąĮčŗą╝ 菹╗ąĄą╝ąĄąĮč鹊ą╝ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░. ąÜąŠą│ą┤ą░ ą▓ąĄčüčī ą┤ąĄčüą║čĆąĖą┐č鹊čĆ ą┐čĆąŠčćąĖčéą░ąĮ, CURR_DESC_PTR čüąŠą┤ąĄčƹȹĖčé ąĘąĮą░č湥ąĮąĖąĄ Descriptor Start Address + Descriptor Size (ą║ąŠą╗ąĖč湥čüčéą▓ąŠ 菹╗ąĄą╝ąĄąĮč鹊ą▓).

ąöą╗čÅ čĆąĄąČąĖą╝ą░ ą╝ą░čüčüąĖą▓ą░ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą▓ (FLOW=4) čŹč鹊čé čĆąĄą│ąĖčüčéčĆ, ąĮąŠ ąĮąĄ čĆąĄą│ąĖčüčéčĆ NEXT_DESC_PTR, ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ ą┤ąŠčüčéčāą┐ąŠą╝ č湥čĆąĄąĘ MMR ą┐ąĄčĆąĄą┤ ąĮą░čćą░ą╗ąŠą╝ ąŠą┐ąĄčĆą░čåąĖąĖ DMA.

ąĀąĖčü. 9-8. Current Descriptor Pointer Register (DMAx_CURR_DESC_PTR / MDMAx_yy_CURR_DESC_PTR).

ąöą╗čÅ čŹč鹊ą│ąŠ čĆąĄą│ąĖčüčéčĆą░ ą┤ąŠčüčéčāą┐ąĄąĮ ą┤ąŠčüčéčāą┐ ąĮą░ čćč鹥ąĮąĖąĄ ąĖ ąĘą░ą┐ąĖčüčī ą┤ąŠ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą║ą░ąĮą░ą╗ą░, ąĖ ą┐ąŠčüą╗ąĄ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą║ą░ąĮą░ą╗ą░ ą┤ąŠčüčéčāą┐ąĄąĮ ą┤ąŠčüčéčāą┐ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ.

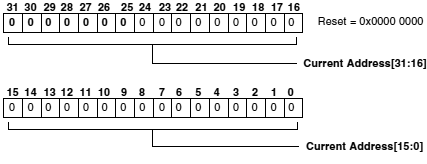

ąĀąĄą│ąĖčüčéčĆčŗ č鹥ą║čāčēąĄą│ąŠ ą░ą┤čĆąĄčüą░ (current address, CURR_ADDR), ą┐ąŠą║ą░ąĘą░ąĮąĮčŗąĄ ąĮą░ čĆąĖčü. 9-9, čüąŠą┤ąĄčƹȹ░čé ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮąĮčŗą╣ ą░ą┤čĆąĄčü ą┐ąĄčĆąĄą┤ą░čćąĖ DMA ą┤ą╗čÅ ąĖą╝ąĄčÄčēąĄą╣čüčÅ čüąĄčüčüąĖąĖ DMA. ąÆ ąĮą░čćą░ą╗ąĄ čüąĄčüčüąĖąĖ DMA čŹč鹊čé čĆąĄą│ąĖčüčéčĆ ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ START_ADDR, ąĖ ą┤ą░ą╗ąĄąĄ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ čü ą║ą░ąČą┤ąŠą╣ ą┐ąĄčĆąĄą┤ą░č湥ą╣. ąĀąĄą│ąĖčüčéčĆ č鹥ą║čāčēąĄą│ąŠ ą░ą┤čĆąĄčüą░ čüąŠą┤ąĄčƹȹĖčé 32 ą▒ąĖčéą░.

ąĀąĖčü. 9-9. Current Address Register (DMAx_CURR_ADDR / MDMAx_yy_CURR_ADDR).

ąöą╗čÅ čŹč鹊ą│ąŠ čĆąĄą│ąĖčüčéčĆą░ ą┤ąŠčüčéčāą┐ąĄąĮ ą┤ąŠčüčéčāą┐ ąĮą░ čćč鹥ąĮąĖąĄ ąĖ ąĘą░ą┐ąĖčüčī ą┤ąŠ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą║ą░ąĮą░ą╗ą░, ąĖ ą┐ąŠčüą╗ąĄ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą║ą░ąĮą░ą╗ą░ ą┤ąŠčüčéčāą┐ąĄąĮ ą┤ąŠčüčéčāą┐ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ.

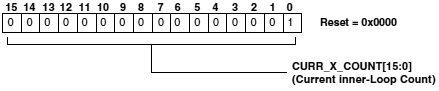

ąĀąĄą│ąĖčüčéčĆ č鹥ą║čāčēąĄą│ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čüč湥čéčćąĖą║ą░ čåąĖą║ą╗ą░ (current inner loop count, CURR_X_COUNT) ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄą╝ X_COUNT ą▓ ą╝ąŠą╝ąĄąĮčé ąĮą░čćą░ą╗ą░ ą║ą░ąČą┤ąŠą╣ čüąĄčüčüąĖąĖ DMA session (ą┤ą╗čÅ 1D DMA) ąĖ čéą░ą║ąČąĄ ą┐ąŠčüą╗ąĄ ąŠą║ąŠąĮčćą░ąĮąĖčÅ ą║ą░ąČą┤ąŠą╣ čüčéčĆąŠą║ąĖ DMA (ą┤ą╗čÅ 2D DMA). ąśąĮą░č湥 ąŠąĮ ą▒čāą┤ąĄčé ą┤ąĄą║čĆąĄą╝ąĄąĮčéąĖčĆąŠą▓ą░čéčīčüčÅ ą║ą░ąČą┤čŗą╣ čĆą░ąĘ ą┐čĆąĖ ą┐ąĄčĆąĄą┤ą░č湥 菹╗ąĄą╝ąĄąĮčéą░. ąÜąŠą│ą┤ą░ čĆąĄą│ąĖčüčéčĆ čüč湥čéčćąĖą║ą░ ąŠą▒ąĮčāą╗čÅąĄčéčüčÅ, čŹč鹊 ąŠąĘąĮą░čćą░ąĄčé ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĄ DMA. ąöą╗čÅ 2D DMA, CURR_X_COUNT čĆą░ą▓ąĄąĮ 0 č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ ą┐ąĄčĆąĄą┤ą░čćą░ ąĘą░ą▓ąĄčĆčłąĖčéčüčÅ ą┐ąŠą╗ąĮąŠčüčéčīčÄ. ą£ąĄąČą┤čā čüčéčĆąŠą║ą░ą╝ąĖ ąŠąĮ čĆą░ą▓ąĄąĮ X_COUNT.

ąĀąĖčü. 9-10. Current Inner Loop Count Register (DMAx_CURR_X_COUNT / MDMAx_yy_CURR_X_COUNT).

ąöą╗čÅ čŹč鹊ą│ąŠ čĆąĄą│ąĖčüčéčĆą░ ą┤ąŠčüčéčāą┐ąĄąĮ ą┤ąŠčüčéčāą┐ ąĮą░ čćč鹥ąĮąĖąĄ ąĖ ąĘą░ą┐ąĖčüčī ą┤ąŠ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą║ą░ąĮą░ą╗ą░, ąĖ ą┐ąŠčüą╗ąĄ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą║ą░ąĮą░ą╗ą░ ą┤ąŠčüčéčāą┐ąĄąĮ ą┤ąŠčüčéčāą┐ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ.

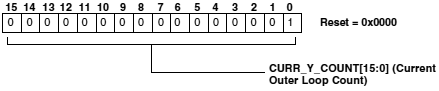

ąĀąĄą│ąĖčüčéčĆ č鹥ą║čāčēąĄą│ąŠ ą▓ąĮąĄčłąĮąĄą│ąŠ čüč湥čéčćąĖą║ą░ (current outer loop count, CURR_Y_COUNT) ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄą╝ Y_COUNT ą▓ ą╝ąŠą╝ąĄąĮčé ąĮą░čćą░ą╗ą░ ą║ą░ąČą┤ąŠą╣ čüąĄčüčüąĖąĖ 2D DMA. ą×ąĮ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ 1D DMA. ąŁč鹊čé čĆąĄą│ąĖčüčéčĆ ą┤ąĄą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ ą║ą░ąČą┤čŗą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ čĆąĄą│ąĖčüčéčĆ CURR_X_COUNT ąĖčüč鹥ą║ą░ąĄčé ą┐čĆąĖ ąŠą┐ąĄčĆą░čåąĖąĖ 2D DMA (ą┐čĆąĖ ąĄą│ąŠ ą┐ąĄčĆąĄčģąŠą┤ąĄ ąŠčé 1 ą║ X_COUNT ąĖą╗ąĖ ąŠčé 1 ą║ 0), čćč鹊 ąŠąĘąĮą░čćą░ąĄčé ą┐ąŠą╗ąĮčāčÄ ą┐ąĄčĆąĄą┤ą░čćčā čüčéčĆąŠą║ąĖ. ą¤ąŠčüą╗ąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ čüąĄčüčüąĖąĖ 2D DMA ąĘąĮą░č湥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆąŠą▓ CURR_Y_COUNT=1 ąĖ CURR_X_COUNT=0.

ąĀąĖčü. 9-11. Current Outer Loop Count Register (DMAx_CURR_Y_COUNT / MDMAx_yy_CURR_Y_COUNT).

ąöą╗čÅ čŹč鹊ą│ąŠ čĆąĄą│ąĖčüčéčĆą░ ą┤ąŠčüčéčāą┐ąĄąĮ ą┤ąŠčüčéčāą┐ ąĮą░ čćč鹥ąĮąĖąĄ ąĖ ąĘą░ą┐ąĖčüčī ą┤ąŠ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą║ą░ąĮą░ą╗ą░, ąĖ ą┐ąŠčüą╗ąĄ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą║ą░ąĮą░ą╗ą░ ą┤ąŠčüčéčāą┐ąĄąĮ ą┤ąŠčüčéčāą┐ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ.

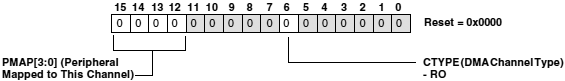

ąÜą░ąČą┤čŗą╣ čĆąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓čÅąĘą║ąĖ ą┐ąĄčĆąĖč乥čĆąĖąĖ ą║ą░ąĮą░ą╗ą░ DMA PERIPHERAL_MAP čüąŠą┤ąĄčƹȹĖčé ą▒ąĖčéčŗ ą┤ą╗čÅ:

ŌĆó ą¤čĆąĖą▓čÅąĘą║ąĖ ą║ą░ąĮą░ą╗ą░ ą║ čüą┐ąĄčåąĖčäąĖč湥čüą║ąŠą╝čā ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą╝čā čāčüčéčĆąŠą╣čüčéą▓čā.

ŌĆó ąśą┤ąĄąĮčéąĖčäąĖą║ą░čåąĖąĖ, čÅą▓ą╗čÅąĄčéčüčÅ ą╗ąĖ ą║ą░ąĮą░ą╗ ą║ą░ąĮą░ą╗ąŠą╝ DMA ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ąĖą╗ąĖ ą║ą░ąĮą░ą╗ąŠą╝ DMA ą┐ą░ą╝čÅčéąĖ.

ąĢčüčéčī 2 ąĮą░ą▒ąŠčĆą░ čĆąĄą│ąĖčüčéčĆąŠą▓ PERIPHERAL_MAP. ą×ą┤ąĖąĮ ąĮą░ą▒ąŠčĆ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ąŠą▓, čüą▓čÅąĘą░ąĮąĮčŗčģ čü DMA ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ 0, ąĖ ą┤čĆčāą│ąŠą╣ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ąŠą▓, čüą▓čÅąĘą░ąĮąĮčŗčģ čü DMA ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ 1. ą¤ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ ąĮą░ąĘąĮą░čćą░čÄčéčüčÅ ąĮą░ ą║ąŠąĮą║čĆąĄčéąĮčŗą╣ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ (0 ąĖą╗ąĖ 1). ąŁč鹊 ąĮą░ąĘąĮą░č湥ąĮąĖąĄ čäąĖą║čüąĖčĆąŠą▓ą░ąĮąŠ, ąĖ ąĮąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą▒čĆą░ąĮąŠ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╝ (ąĮą░ąĘąĮą░č湥ąĮąĖąĄ ą┤ą╗čÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ 0 ą┐čĆąĖą▓ąĄą┤ąĄąĮąŠ ą▓ čéą░ą▒ą╗ąĖčåąĄ 9-5, ą┤ą╗čÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ 1 ą▓ čéą░ą▒ą╗ąĖčåąĄ 9-7).

ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī 1:1 čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĄ ą▓ ą┐čĆąĖą▓čÅąĘą║ąĄ ą║ą░ąĮą░ą╗ąŠą▓ DMA ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓. ą¤ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ąŠčéą▓ąĄčćą░ąĄčé ąĘą░ č鹊, čćč鹊ą▒čŗ ąĮąĄ ą▒čŗą╗ąŠ ą┐čĆąĖą▓čÅąĘą░ąĮąŠ ąĮąĄčüą║ąŠą╗čīą║ąŠ ą║ą░ąĮą░ą╗ąŠą▓ DMA ą║ ąŠą┤ąĮąŠą╝čā ąĖ č鹊ą╝čā ąČąĄ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą╝čā čāčüčéčĆąŠą╣čüčéą▓čā, ąĖ čćč鹊 ąĮąĄčüą║ąŠą╗čīą║ąŠ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ąĮąĄ ą┐čĆąĖą▓čÅąĘą░ąĮąŠ ą║ ąŠą┤ąĮąŠą╝čā ąĖ č鹊ą╝čā ąČąĄ ą┐ąŠčĆčéčā DMA. ąĢčüą╗ąĖ ą▓čüąĄ-čéą░ą║ąĖ ąĮąĄčüą║ąŠą╗čīą║ąŠ ą║ą░ąĮą░ą╗ąŠą▓ ą┐čĆąĖą▓čÅąĘą░ąĮąŠ ąĮą░ ąŠą┤ąĮąŠ ąĖ č鹊 ąČąĄ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ, č鹊 ą▒čāą┤ąĄčé ą┐ąŠą┤ą║ą╗čÄč湥ąĮ č鹊ą╗čīą║ąŠ ąŠą┤ąĖąĮ ą║ą░ąĮą░ą╗ (ą║ą░ąĮą░ą╗ čü čüą░ą╝čŗą╝ ąĮąĖąĘą║ąĖą╝ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝). ąĢčüą╗ąĖ ą║ ą║ą░ąĮą░ą╗čā ą┐čĆąĖą▓čÅąĘą░ąĮąŠ ąĮąĄ čüčāčēąĄčüčéą▓čāčÄčēąĄąĄ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ (ąĮą░ą┐čĆąĖą╝ąĄčĆ, ą▓ ą┐ąŠą╗ąĄ PMAP ąĘą░ą┐ąĖčüą░ąĮąŠ ąĘąĮą░č湥ąĮąĖąĄ 0xF), č鹊 ą║ą░ąĮą░ą╗ ą▒čāą┤ąĄčé ąĘą░ą┐čĆąĄčēąĄąĮ - ąĘą░ą┐čĆąŠčüčŗ DMA ąĖą│ąĮąŠčĆąĖčĆčāčÄčéčüčÅ, ąĖ ąĮąĄ ą▒čāą┤čāčé ą▓čŗą┤ą░ą▓ą░čéčīčüčÅ čćč鹥ąĮąĖčÅ/ąĘą░ą┐ąĖčüąĖ DMA. ąŚą░ą┐čĆąŠčüčŗ DMA čéą░ą║ąČąĄ ąĮąĄ ą┐ąĄčĆąĄąĮą░ą┐čĆą░ą▓ą╗čÅčÄčéčüčÅ ąŠčé ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ą║ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčā ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣.

ąØąĖąČąĄ ą┐čĆąĖą▓ąĄą┤ąĄąĮ ą┐čĆąĖą╝ąĄčĆ čłą░ą│ąŠą▓ ą┤ą╗čÅ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą▓ ą║ą░ąĮą░ą╗ą░ DMA ą┤ą▓čāčģ ą║ą░ąĮą░ą╗ąŠą▓. ąŻą▒ąĄą┤ąĖč鹥čüčī, čćč鹊 ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą║ą░ąĮą░ą╗čŗ 6 ąĖ 7.

1. ąŻą▒ąĄą┤ąĖč鹥čüčī, čćč鹊 DMA ąĘą░ą┐čĆąĄčēąĄąĮ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ąŠą▓ 6 ąĖ 7.

2. ąŚą░ą┐ąĖčłąĖč鹥 ą▓ DMA6_PERIPHERAL_MAP ąĘąĮą░č湥ąĮąĖąĄ 0x7000, ąĖ ą▓ DMA7_PERIPHERAL_MAP ąĘąĮą░č湥ąĮąĖąĄ 0x6000.

3. ąĀą░ąĘčĆąĄčłąĖč鹥 ą║ą░ąĮą░ą╗ DMA 6 ąĖ/ąĖą╗ąĖ 7.

[DMA ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ 0]

ąĀąĖčü. 9-12. DMA Controller 0 Peripheral Map Register (DMAx_PERIPHERAL_MAP / MDMAx_yy_PERIPHERAL_MAP).

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: čüąĄčĆčŗą╝ čåą▓ąĄč鹊ą╝ ą┐ąŠą╝ąĄč湥ąĮčŗ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą▒ąĖčéčŗ.

ąöą╗čÅ čŹč鹊ą│ąŠ čĆąĄą│ąĖčüčéčĆą░ ą┤ąŠčüčéčāą┐ąĄąĮ ą┤ąŠčüčéčāą┐ ąĮą░ čćč鹥ąĮąĖąĄ ąĖ ąĘą░ą┐ąĖčüčī ą┤ąŠ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą║ą░ąĮą░ą╗ą░, ąĖ ą┐ąŠčüą╗ąĄ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą║ą░ąĮą░ą╗ą░ ą┤ąŠčüčéčāą┐ąĄąĮ ą┤ąŠčüčéčāą┐ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ.

PMAP[3:0] (Peripheral Mapped to This Channel). ą¤čĆąĖą▓čÅąĘą║ą░ ą║ą░ąĮą░ą╗ą░ ą║ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą╝čā čāčüčéčĆąŠą╣čüčéą▓čā:

0x0 - PPI

0x1 - SPORT0 RX

0x2 - SPORT0 TX

0x3 - SPORT1 RX

0x4 - SPORT1 TX

0x5 - SPI0

0x6 - UART0 RX

0x7 - UART0 TX

CTYPE (DMA Channel Type). ąóąĖą┐ ą║ą░ąĮą░ą╗ą░, ą▒ąĖčé č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ. 0: ą║ą░ąĮą░ą╗ DMA ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░, 1: ą║ą░ąĮą░ą╗ DMA ą┐ą░ą╝čÅčéąĖ.

[DMA ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ 1]

ąĀąĖčü. 9-13. DMA Controller 1 Peripheral Map Register (DMAx_PERIPHERAL_MAP / MDMAx_yy_PERIPHERAL_MAP).

ąöą╗čÅ čŹč鹊ą│ąŠ čĆąĄą│ąĖčüčéčĆą░ ą┤ąŠčüčéčāą┐ąĄąĮ ą┤ąŠčüčéčāą┐ ąĮą░ čćč鹥ąĮąĖąĄ ąĖ ąĘą░ą┐ąĖčüčī ą┤ąŠ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą║ą░ąĮą░ą╗ą░, ąĖ ą┐ąŠčüą╗ąĄ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą║ą░ąĮą░ą╗ą░ ą┤ąŠčüčéčāą┐ąĄąĮ ą┤ąŠčüčéčāą┐ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ.

PMAP[3:0] (Peripheral Mapped to This Channel). ą¤čĆąĖą▓čÅąĘą║ą░ ą║ą░ąĮą░ą╗ą░ ą║ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą╝čā čāčüčéčĆąŠą╣čüčéą▓čā:

0x0 - SPORT2 RX

0x1 - SPORT2 TX

0x2 - SPORT3 RX

0x3 - SPORT3 TX

0x4 - ąĮąĄ ąĮą░ąĘąĮą░č湥ąĮąŠ

0x5 - ąĮąĄ ąĮą░ąĘąĮą░č湥ąĮąŠ

0x6 - SPI1

0x7 - SPI2

0x8 - UART1 RX

0x9 - UART1 TX

0xa - UART2 RX

0xb - UART2 TX

CTYPE (DMA Channel Type). ąóąĖą┐ ą║ą░ąĮą░ą╗ą░, ą▒ąĖčé č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ. 0: ą║ą░ąĮą░ą╗ DMA ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░, 1: ą║ą░ąĮą░ą╗ DMA ą┐ą░ą╝čÅčéąĖ.

[ą¤čĆąĖą▓čÅąĘą║ą░ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ą║ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ą╝ DMA 0 ąĖ 1]

ąÆ čéą░ą▒ą╗ąĖčåą░čģ 9-5 ąĖ 9-7 ą┐ąĄčĆąĄčćąĖčüą╗ąĄąĮčŗ ą┤ą▓ąŠąĖčćąĮčŗąĄ ąĮą░čüčéčĆąŠą╣ą║ąĖ ą║ą░čĆčéčŗ ą┐čĆąĖą▓čÅąĘą║ąĖ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░, ą║ąŠč鹊čĆąŠąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé DMA.

ąóą░ą▒ą╗ąĖčåą░ 9-5. ąØą░ąĘąĮą░č湥ąĮąĮčŗąĄ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┤ą╗čÅ DMA Controller 0.

| ąÜą░ąĮą░ą╗ DMA |

ą¤čĆąĖą▓čÅąĘą║ą░ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ |

ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą┤ą╗čÅ PERIPHERAL_MAP (ą┤ą▓ąŠąĖčćąĮąŠąĄ) |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ |

| DMA0 (čüą░ą╝čŗą╣ ą▓čŗčüąŠą║ąĖą╣ ą┐čĆąĖąŠčĆąĖč鹥čé) |

PPI |

0000 0000 0000 0000 |

|

| DMA1 |

SPORT0 RX |

0001 0000 0000 0000 |

|

| DMA2 |

SPORT0 TX |

0010 0000 0000 0000 |

|

| DMA3 |

SPORT1 RX |

0011 0000 0000 0000 |

|

| DMA4 |

SPORT1 TX |

0100 0000 0000 0000 |

|

| DMA5 |

SPI0 |

0101 0000 0000 0000 |

|

| DMA6 |

UART0 RX |

0110 0000 0000 0000 |

|

| DMA7 |

UART0 TX |

0111 0000 0000 0000 |

|

| MDMA0_D0 |

ą¤ąŠč鹊ą║ 0 DMA ą┐ąŠ ą┐ą░ą╝čÅčéąĖ, TX (ą╝ąĄčüč鹊 ąĮą░ąĘąĮą░č湥ąĮąĖčÅ) |

0000 0000 0100 0000 |

ąĮąĄ ą┐ąĄčĆąĄąĮą░ąĘąĮą░čćą░ąĄčéčüčÅ |

| MDMA0_S0 |

ą¤ąŠč鹊ą║ 0 DMA ą┐ąŠ ą┐ą░ą╝čÅčéąĖ, RX (ąĖčüč鹊čćąĮąĖą║) |

0000 0000 0100 0000 |

ąĮąĄ ą┐ąĄčĆąĄąĮą░ąĘąĮą░čćą░ąĄčéčüčÅ |

| MDMA0_D1 |

ą¤ąŠč鹊ą║ 1 DMA ą┐ąŠ ą┐ą░ą╝čÅčéąĖ, TX (ą╝ąĄčüč鹊 ąĮą░ąĘąĮą░č湥ąĮąĖčÅ) |

0000 0000 0100 0000 |

ąĮąĄ ą┐ąĄčĆąĄąĮą░ąĘąĮą░čćą░ąĄčéčüčÅ |

| MDMA0_S1 (čüą░ą╝čŗą╣ ąĮąĖąĘą║ąĖą╣ ą┐čĆąĖąŠčĆąĖč鹥čé) |

ą¤ąŠč鹊ą║ 1 DMA ą┐ąŠ ą┐ą░ą╝čÅčéąĖ, RX (ąĖčüč鹊čćąĮąĖą║) |

0000 0000 0100 0000 |

ąĮąĄ ą┐ąĄčĆąĄąĮą░ąĘąĮą░čćą░ąĄčéčüčÅ |

ąóą░ą▒ą╗ąĖčåą░ 9-6. ąśą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆčŗ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┤ą╗čÅ 4-ą▒ąĖčéąĮąŠą│ąŠ ą┐ąŠą╗čÅ PMAP ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ DMA 0.

| ą¤ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ |

Ōä¢ PMAP ID (ą┤ą▓ąŠąĖčćąĮčŗą╣ č乊čĆą╝ą░čé) |

| PPI |

0000 |

| SPORT0 RX |

0001 |

| SPORT0 TX |

0010 |

| SPORT1 RX |

0011 |

| SPORT1 TX |

0100 |

| SPI |

0101 |

| UART0 RX |

0110 |

| UART0 TX |

0111 |

ąóą░ą▒ą╗ąĖčåą░ 9-7. ąØą░ąĘąĮą░č湥ąĮąĮčŗąĄ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┤ą╗čÅ DMA Controller 1.

| ąÜą░ąĮą░ą╗ DMA |

ą¤čĆąĖą▓čÅąĘą║ą░ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ |

ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą┤ą╗čÅ PERIPHERAL_MAP (ą┤ą▓ąŠąĖčćąĮąŠąĄ) |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ |

| DMA8 (čüą░ą╝čŗą╣ ą▓čŗčüąŠą║ąĖą╣ ą┐čĆąĖąŠčĆąĖč鹥čé) |

SPORT2 RX |

0000 0000 0000 0000 |

|

| DMA9 |

SPORT2 TX |

0001 0000 0000 0000 |

|

| DMA10 |

SPORT3 RX |

0010 0000 0000 0000 |

|

| DMA11 |

SPORT3 TX |

0011 0000 0000 0000 |

|

| DMA12 |

ąĮąĄ ąĮą░ąĘąĮą░č湥ąĮąŠ |

0100 0000 0000 0000 |

|

| DMA13 |

ąĮąĄ ąĮą░ąĘąĮą░č湥ąĮąŠ |

0101 0000 0000 0000 |

|

| DMA14 |

SPI1 |

0110 0000 0000 0000 |

|

| DMA15 |

SPI2 |

0111 0000 0000 0000 |

|

| DMA16 |

UART1 RX |

1000 0000 0000 0000 |

|

| DMA17 |

UART1 TX |

1001 0000 0000 0000 |

|

| DMA18 |

UART2 RX |

1010 0000 0000 0000 |

|

| DMA19 |

UART2 TX |

1011 0000 0000 0000 |

|

| MDMA1_D0 |

ą¤ąŠč鹊ą║ 2 DMA ą┐ąŠ ą┐ą░ą╝čÅčéąĖ, TX (ą╝ąĄčüč鹊 ąĮą░ąĘąĮą░č湥ąĮąĖčÅ) |

0000 0000 0100 0000 |

ąĮąĄ ą┐ąĄčĆąĄąĮą░ąĘąĮą░čćą░ąĄčéčüčÅ |

| MDMA1_S0 |

ą¤ąŠč鹊ą║ 2 DMA ą┐ąŠ ą┐ą░ą╝čÅčéąĖ, RX (ąĖčüč鹊čćąĮąĖą║) |

0000 0000 0100 0000 |

ąĮąĄ ą┐ąĄčĆąĄąĮą░ąĘąĮą░čćą░ąĄčéčüčÅ |

| MDMA1_D1 |

ą¤ąŠč鹊ą║ 1 DMA ą┐ąŠ ą┐ą░ą╝čÅčéąĖ, TX (ą╝ąĄčüč鹊 ąĮą░ąĘąĮą░č湥ąĮąĖčÅ) |

0000 0000 0100 0000 |

ąĮąĄ ą┐ąĄčĆąĄąĮą░ąĘąĮą░čćą░ąĄčéčüčÅ |

| MDMA1_S1 (čüą░ą╝čŗą╣ ąĮąĖąĘą║ąĖą╣ ą┐čĆąĖąŠčĆąĖč鹥čé) |

ą¤ąŠč鹊ą║ 1 DMA ą┐ąŠ ą┐ą░ą╝čÅčéąĖ, RX (ąĖčüč鹊čćąĮąĖą║) |

0000 0000 0100 0000 |

ąĮąĄ ą┐ąĄčĆąĄąĮą░ąĘąĮą░čćą░ąĄčéčüčÅ |

ąóą░ą▒ą╗ąĖčåą░ 9-8. ąśą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆčŗ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┤ą╗čÅ 4-ą▒ąĖčéąĮąŠą│ąŠ ą┐ąŠą╗čÅ PMAP ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ DMA 1.

| ą¤ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ |

Ōä¢ PMAP ID (ą┤ą▓ąŠąĖčćąĮčŗą╣ č乊čĆą╝ą░čé) |

| SPORT2 RX |

0000 |

| SPORT2 TX |

0001 |

| SPORT3 RX |

0010 |

| SPORT3 TX |

0011 |

| ąĮąĄ ąĮą░ąĘąĮą░č湥ąĮąŠ |

0100 |

| ąĮąĄ ąĮą░ąĘąĮą░č湥ąĮąŠ |

0101 |

| SPI1 |

0110 |

| SPI2 |

0111 |

| UART1 RX |

1000 |

| UART1 TX |

1001 |

| UART2 RX |

1010 |

| UART2 TX |

1011 |

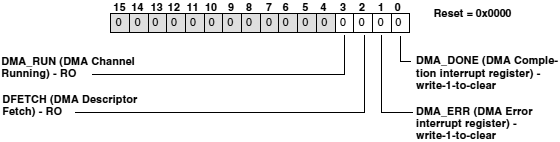

ąĀąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (IRQ_STATUS), ą┐ąŠą║ą░ąĘą░ąĮąĮčŗą╣ ąĮą░ čĆąĖčü. 9-14, čüąŠą┤ąĄčƹȹĖčé ą▒ąĖčéčŗ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ą║ą░ąĮą░ą╗ą░ DMA:

ŌĆó ąĀą░ąĘčĆąĄčłąĄąĮ ą╗ąĖ ąĖ čĆą░ą▒ąŠčéą░ąĄčé ą╗ąĖ ą║ą░ąĮą░ą╗, čĆą░ąĘčĆąĄčłąĄąĮ ąĮąŠ ąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ąĖą╗ąĖ ąĘą░ą┐čĆąĄčēąĄąĮ.

ŌĆó ąÆčŗą▒čĆą░ąĮčŗ ą╗ąĖ ą┤ą░ąĮąĮčŗąĄ ąĖą╗ąĖ ą┤ąĄčüą║čĆąĖą┐č鹊čĆ DMA.

ŌĆó ąæčŗą╗ąŠ ą╗ąĖ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąŠ ą│ą╗ąŠą▒ą░ą╗čīąĮąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ DMA, ąĖą╗ąĖ ą▒čŗą╗ąŠ ą▓čŗčüčéą░ą▓ą╗ąĄąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą║ą░ąĮą░ą╗ą░.

ŌĆó ąæčŗą╗ą░ ą╗ąĖ ąĘą░čäąĖą║čüąĖčĆąŠą▓ą░ąĮą░ ąŠčłąĖą▒ą║ą░ DMA.

ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ DMA_DONE ą▓čŗčüčéą░ą▓ą╗čÅąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą▒čŗą╗ ąĘą░ą▓ąĄčĆčłąĄąĮ ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ą┤ąŠčüčéčāą┐ ą║ ą┐ą░ą╝čÅčéąĖ (čćč鹥ąĮąĖąĄ ąĖą╗ąĖ ąĘą░ą┐ąĖčüčī). ąöą╗čÅ ą┐ąĄčĆąĄą┤ą░čć (čćč鹥ąĮąĖąĄ ą┐ą░ą╝čÅčéąĖ) ą┤ą░ąĮąĮčŗąĄ ą┐ąĄčĆąĄą╝ąĄčēą░čÄčéčüčÅ ą▓ čüč鹊čĆąŠąĮčā ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░, ąĘą┤ąĄčüčī ą╝ąŠąČąĄčé ą▒čŗčéčī ą┤ąŠ 4 čüą╗ąŠą▓ ą┤ą░ąĮąĮčŗčģ ą▓ ą║ą░ąĮą░ą╗ąĄ DMA, ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖąĘąŠčłą╗ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ. ąÆ čŹč鹊čé ą╝ąŠą╝ąĄąĮčé ą▒čāą┤ąĄčé ąĮąŠčĆą╝ą░ą╗čīąĮčŗą╝ ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ ąĘą░ą┐čāčüčéąĖčéčī čüą╗ąĄą┤čāčÄčēąĖą╣ čĆą░ą▒ąŠčćąĖą╣ ą▒ą╗ąŠą║. ą×ą┤ąĮą░ą║ąŠ ąĄčüą╗ąĖ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÄ ąĮčāąČąĮąŠ ąĘąĮą░čéčī, ą║ąŠą│ą┤ą░ ą▓ ą┤ąĄą╣čüčéą▓ąĖč鹥ą╗čīąĮąŠčüčéąĖ ą┐ąŠčüą╗ąĄą┤ąĮąĖąĄ ą┤ą░ąĮąĮčŗąĄ ą▒čŗą╗ąĖ ą┐ąĄčĆąĄą┤ą░ąĮčŗ ą▓ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ, ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÄ ąĮčāąČąĮąŠ ąŠą┐čĆą░čłąĖą▓ą░čéčī ą▒ąĖčé DMA_RUN - čŹč鹊čé čäą╗ą░ą│ čĆą░ą▓ąĄąĮ 1, ą┐ąŠą║ą░ ąĄčüčéčī ąĮąĄ ą┤ąŠčüčéą░ą▓ą╗ąĄąĮąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą▓ FIFO.

ą¤čĆąŠčåąĄčüčüąŠčĆ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ą│ąĖą▒ą║čāčÄ čüčéčĆčāą║čéčāčĆčā ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ čü čéčĆąĄą╝čÅ ąĖčüč鹊čćąĮąĖą║ą░ą╝ąĖ. ą×čéą┤ąĄą╗čīąĮčŗąĄ čāčĆąŠą▓ąĮąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ IRQ ą▓čŗą┤ąĄą╗ąĄąĮčŗ ą┤ą╗čÅ ą┤ą░ąĮąĮčŗčģ, ąŠčłąĖą▒ąŠą║ ą┐ąĄčĆąĖč乥čĆąĖąĖ ąĖ ąŠčłąĖą▒ąŠą║ DMA:

ŌĆó ą¤čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ąŠčéąĮąŠčüčÅčēąĖąĄčüčÅ ą║ ą┤ą░ąĮąĮčŗą╝ (čüą╝. čéą░ą▒ą╗ąĖčåčā 9-7).

ŌĆó ą¤čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠčłąĖą▒ą║ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░.

ŌĆó ą¤čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠčłąĖą▒ą║ąĖ DMA (ąĮą░ą┐čĆąĖą╝ąĄčĆ, ąŠčłąĖą▒ą║ą░ ą▓ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąĄ ąĖą╗ąĖ ąŠčłąĖą▒ą║ą░ čłąĖąĮčŗ).

ąÆčüąĄ ą║ą░ąĮą░ą╗čŗ DMA ąŠą▒čŖąĄą┤ąĖąĮčÅčÄčéčüčÅ ą┐ąŠ ąśąøąś ąĮą░ ąŠą┤ąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠčłąĖą▒ą║ąĖ DMA čüąĖčüč鹥ą╝ąĮąŠą│ąŠ čāčĆąŠą▓ąĮčÅ. ą×čéą┤ąĄą╗čīąĮčŗąĄ čüą╗ąŠą▓ą░ IRQ_STATUS ą║ą░ąČą┤ąŠą│ąŠ ą║ą░ąĮą░ą╗ą░ ą╝ąŠą│čāčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮčŗ ą┤ą╗čÅ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░čåąĖąĖ ą║ą░ąĮą░ą╗ą░, ąĮą░ ą║ąŠč鹊čĆąŠą╝ ą┐čĆąŠąĖąĘąŠčłą╗ą░ ąŠčłąĖą▒ą║ą░ DMA.

ąĀąĖčü. 9-14. Interrupt Status Register (DMAx_IRQ_STATUS / MDMAx_yy_IRQ_STATUS).

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: čüąĄčĆčŗą╝ čåą▓ąĄč鹊ą╝ ą┐ąŠą╝ąĄč湥ąĮčŗ ąĮąĄąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą▒ąĖčéčŗ.

DMA_RUN (DMA Channel Running). ąĪąŠčüč鹊čÅąĮąĖąĄ ą║ą░ąĮą░ą╗ą░ DMA, ą▒ąĖčé č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ. ąŁč鹊čé ą▒ąĖčé ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▓ 1, ą║ąŠą│ą┤ą░ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ čĆąĄą│ąĖčüčéčĆ DMA_CONFIG. 0: čŹč鹊čé ą║ą░ąĮą░ą╗ DMA ąĘą░ą┐čĆąĄčēąĄąĮ, ąĖą╗ąĖ ąŠąĮ čĆą░ąĘčĆąĄčłąĄąĮ, ąĮąŠ ąĮą░čģąŠą┤ąĖčéčüčÅ ąĮą░ ą┐ą░čāąĘąĄ (FLOW mode 0), 1: čŹč鹊čé ą║ą░ąĮą░ą╗ DMA čĆą░ąĘčĆąĄčłąĄąĮ ąĖ čĆą░ą▒ąŠčéą░ąĄčé, čé. ąĄ. ą╗ąĖą▒ąŠ ą┐ąĄčĆąĄą┤ą░ąĄčé ą┤ą░ąĮąĮčŗąĄ, ą╗ąĖą▒ąŠ ą┤ąĄą╗ą░ąĄčé ą▓čŗą▒ąŠčĆą║čā ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ DMA.

DFETCH (DMA Descriptor Fetch). ąæąĖčé č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ, ąŠąĮ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▓ 1, ą║ąŠą│ą┤ą░ čĆąĄą│ąĖčüčéčĆ DMA_CONFIG ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ čü čĆąĄąČąĖą╝ą░ą╝ąĖ FLOW 4ŌĆō7. 0: čŹč鹊čé ą║ą░ąĮą░ą╗ DMA ąĘą░ą┐čĆąĄčēąĄąĮ, ąĖą╗ąĖ ąŠąĮ čĆą░ąĘčĆąĄčłąĄąĮ, ąĮąŠ ąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮ (FLOW mode 0), 1: čŹč鹊čé ą║ą░ąĮą░ą╗ čĆą░ąĘčĆąĄčłąĄąĮ ąĖ ą▓ ąĮą░čüč鹊čÅčēąĖą╣ ą╝ąŠą╝ąĄąĮčé ą┤ąĄą╗ą░ąĄčé ą▓čŗą▒ąŠčĆą║čā ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░.

DMA_ERR (DMA Error interrupt register). ąæąĖčé, ą║ąŠč鹊čĆčŗą╣ ąŠčćąĖčēą░ąĄčéčüčÅ ąŠą┐ąĄčĆą░čåąĖąĄą╣ W1C (write-1-to-clear, ąĘą░ą┐ąĖčüą░čéčī 1 ą┤ą╗čÅ ąŠčćąĖčüčéą║ąĖ). 0: ąĮąĄčé ąŠčłąĖą▒ą║ąĖ DMA, 1: ą┐čĆąŠąĖąĘąŠčłą╗ą░ ąŠčłąĖą▒ą║ą░ DMA, ąĖ ą▓čŗčüčéą░ą▓ą╗ąĄąĮąŠ ą│ą╗ąŠą▒ą░ą╗čīąĮąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ DMA. ą¤ąŠčüą╗ąĄ ą▓ąŠąĘąĮąĖą║ąĮąŠą▓ąĄąĮąĖčÅ čŹč鹊ą╣ ąŠčłąĖą▒ą║ąĖ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ č鹥ą║čāčēąĖčģ čĆąĄą│ąĖčüčéčĆąŠą▓ DMA ąĮąĄ ąĘą░ą┤ą░ąĮąŠ. ąĀąĄą│ąĖčüčéčĆčŗ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓ ąĖ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąŠčüčéą░čÄčéčüčÅ ąĮąĄ ąĖąĘą╝ąĄąĮąĄąĮąĮčŗą╝ąĖ.

DMA_DONE (DMA Completion interrupt register). 0: ą┤ą╗čÅ čŹč鹊ą│ąŠ ą║ą░ąĮą░ą╗ą░ ąĮąĄ ą▒čŗą╗ąŠ ą▓čŗčüčéą░ą▓ą╗ąĄąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, 1: čĆą░ą▒ąŠčéą░ DMA ąĘą░ą▓ąĄčĆčłąĄąĮą░, ąĖ ą┤ą╗čÅ čŹč鹊ą│ąŠ ą║ą░ąĮą░ą╗ą░ DMA ą▓čŗčüčéą░ą▓ą╗ąĄąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ.

ąóą░ą▒ą╗ąĖčåą░ 9-9. ą¤čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ąŠčéąĮąŠčüčÅčēąĖąĄčüčÅ ą║ ą┤ą░ąĮąĮčŗą╝.

| ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| - |

ąöą╗čÅ čŹč鹊ą│ąŠ čĆą░ą▒ąŠč湥ą│ąŠ ą▒ą╗ąŠą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą╝ąŠą│čāčé ą▒čŗčéčī ąĘą░ą┐čĆąĄčēąĄąĮčŗ. |

| ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ |

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠčé ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░, ąĮąĄ ąŠčéąĮąŠčüčÅčēąĄąĄčüčÅ ą║ DMA. |

| ąŚą░ą▓ąĄčĆčłąĄąĮąĖąĄ čüčéčĆąŠą║ąĖ |

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ DMA ą╝ąŠąČąĄčé ą┐čĆąŠąĖąĘąŠą╣čéąĖ ą┐ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĖ čüčéčĆąŠą║ąĖ (ą║ąŠą│ą┤ą░ ąĖčüč鹥ą║ CURR_X_COUNT). |

| ąŚą░ą▓ąĄčĆčłąĄąĮąĖąĄ ą▒čāč乥čĆą░ |

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ DMA ą╝ąŠąČąĄčé ą┐čĆąŠąĖąĘąŠą╣čéąĖ ą┐ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▓čüąĄą│ąŠ ą▒čāč乥čĆą░ (ą║ąŠą│ą┤ą░ ąĖčüč鹥ą║ą╗ąĖ CURR_X_COUNT ąĖ CURR_Y_COUNT). |

ążą╗ą░ą│ DMA_DONE čÅą▓ą╗čÅąĄčéčüčÅ čäą╗ą░ą│ąŠą╝ čéąĖą┐ą░ W1C (write-1-clear), čé. ąĄ. ą┤ą╗čÅ ąĄą│ąŠ čüą▒čĆąŠčüą░ ąĮčāąČąĮąŠ ą▓ ą┐ąŠąĘąĖčåąĖčÄ čäą╗ą░ą│ą░ ą┐ąŠ ą╝ą░čüą║ąĄ ąĘą░ą┐ąĖčüą░čéčī ąĄą┤ąĖąĮąĖčåčā. ą¤čĆąĖą╝ąĄčĆ ISR, ą│ą┤ąĄ ą┤ąĄą╗ą░ąĄčéčüčÅ ąŠčćąĖčüčéą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐čĆąĖąĄą╝ą░ ą▒ą╗ąŠą║ą░ ą┤ą░ąĮąĮčŗčģ č湥čĆąĄąĘ SPORT3:

EX_REENTRANT_HANDLER(ADC_data_ISR)

{

*pDMA10_IRQ_STATUS |= 0x0001;

TOGGLEVD10();

}

ąÜąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ąŠčé čĆąĄąČąĖą╝ą░ DMA ą║ čĆąĄąČąĖą╝čā ą▒ąĄąĘ DMA, ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠčé ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĘą░ą┐čĆąĄčēąĄąĮčŗ ą┐čĆąĖ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĖ čĆąĄąČąĖą╝ą░ (č湥čĆąĄąĘ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ čĆąĄą│ąĖčüčéčĆčŗ ąĖą╗ąĖ ą╝ą░čüą║ąĖ SIC_IMASKx), čćč鹊ą▒čŗ ąĮąĄąČąĄą╗ą░č鹥ą╗čīąĮąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĮąĄ ą▒čŗą╗ąŠ čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąŠ ąĮą░ ąŠą▒čēąĄą╣ ą╗ąĖąĮąĖąĖ ąĘą░ą┐čĆąŠčüą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (ą┐ąŠčüą║ąŠą╗čīą║čā ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ DMA čüąŠą▓ą╝ąĄčēąĄąĮąŠ čü ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄą╝ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░).

[ąōąĖą▒ą║ą░čÅ čüčéčĆčāą║čéčāčĆą░ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░]

ąōąĖą▒ą║ąĖąĄ ą┤ąĄčüą║čĆąĖą┐č鹊čĆčŗ DMA čÅą▓ą╗čÅčÄčéčüčÅ čüčéčĆčāą║čéčāčĆą░ą╝ąĖ čü ą┐ąĄčĆąĄą╝ąĄąĮąĮčŗą╝ čĆą░ąĘą╝ąĄčĆąŠą╝ ą┤ą░ąĮąĮčŗčģ, ąŠčéą║čāą┤ą░ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆčŗ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓ DMA. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī čĆąĄą│ąĖčüčéčĆąŠą▓ ą▓ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąĄ ąĖąĘąĮą░čćą░ą╗čīąĮąŠ čäąĖą║čüąĖčĆąŠą▓ą░ąĮą░ (ą▓ ą┐čĆąĄą┤ąĄą╗ą░čģ 3 čĆą░ąĘąĮčŗčģ, ąĮąŠ ą┐ąŠčģąŠąČąĖčģ ą▓ą░čĆąĖą░ąĮč鹊ą▓), ąŠą┤ąĮą░ą║ąŠ ą┤ą╗ąĖąĮą░ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ ą┐ąŠą╗ąĮąŠčüčéčīčÄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ. ąĀąĄą│ąĖčüčéčĆčŗ ą║ą░ąĮą░ą╗ą░ DMA čāą┐ąŠčĆčÅą┤ąŠč湥ąĮčŗ čéą░ą║, čćč鹊 čćą░čēąĄ ą▓čüąĄą│ąŠ ąĘą░ą│čĆčāąČą░ąĄą╝čŗąĄ čĆąĄą│ąĖčüčéčĆčŗ ą┐čĆąĖ ąŠą▒čĆą░ą▒ąŠčéą║ąĄ čĆą░ą▒ąŠč湥ą│ąŠ ą▒ą╗ąŠą║ą░ ąĖą╝ąĄčÄčé čüą░ą╝čŗąĄ ą╝ą╗ą░ą┤čłąĖąĄ ą░ą┤čĆąĄčüą░ MMR. ą¤čĆąĖ ąĘą░ą┐čāčüą║ąĄ ą┐ąŠą┤čüąĖčüč鹥ą╝čŗ DMA ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą╝ąŠąČąĄčé ą▓čŗą▒čĆą░čéčī - ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ąĖą╗ąĖ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┤ąĄčüą║čĆąĖą┐č鹊čĆčŗ. ąĢčüą╗ąĖ ą┤ąĄčüą║čĆąĖą┐č鹊čĆčŗ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ, č鹊 ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą╝ąŠąČąĄčé ąĘą░ą┐ąĖčüą░čéčī čĆąĄą│ąĖčüčéčĆčŗ DMA MMR ąĮą░ą┐čĆčÅą╝čāčÄ, ą┐ąŠčüą╗ąĄ č湥ą│ąŠ ąĘą░ą┐čāčüčéąĖčéčī DMA, ąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą╗ąĖą▒ąŠ čĆąĄąČąĖą╝ ą░ą▓č鹊ą▒čāč乥čĆą░ (Autobuffer), ąĄčüą╗ąĖ ąĮą░ą┤ąŠ ą┐ąŠ čåąĖą║ą╗čā ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī ąŠą┤ąĖąĮ ąĖ č鹊čé ąČąĄ ą▒čāč乥čĆ, ą╗ąĖą▒ąŠ čĆąĄąČąĖą╝ ąŠčüčéą░ąĮąŠą▓ą║ąĖ (Stop) ą┤ą╗čÅ ąŠą┤ąĖąĮąŠčćąĮčŗčģ ą┐ąĄčĆąĄą┤ą░čć ą▒čāč乥čĆą░.

ąöą╗čÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą▓ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčé ą┐ąŠą╗ąĄ NDSIZE ą▓ čĆąĄą│ąĖčüčéčĆąĄ DMAx_CONFIG ą║ąŠą╗ąĖč湥čüčéą▓ąŠą╝ čĆąĄą│ąĖčüčéčĆąŠą▓ DMA, ą║ąŠč鹊čĆčŗąĄ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĘą░ą│čĆčāąČąĄąĮčŗ ąĖąĘ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░, ąĮą░čćąĖąĮą░čÅ čü čüą░ą╝ąŠą│ąŠ ą╝ą╗ą░ą┤čłąĄą│ąŠ ą░ą┤čĆąĄčüą░ MMR. ą¤ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą╝ąŠąČąĄčé ą▓čŗą▒čĆą░čéčī čĆą░ąĘą╝ąĄčĆ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ ąŠčé ąŠą┤ąĮąŠą╣ ąĘą░ą┐ąĖčüąĖ (ą╝ą╗ą░ą┤čłąĖąĄ 16 ą▒ąĖčé START_ADDR) ą┤ąŠ 9 ąĘą░ą┐ąĖčüąĄą╣ (ą┐ąŠą╗ąĮąŠčüčéčīčÄ ą▓čüąĄ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ DMA).

ąśą╝ąĄąĄčéčüčÅ 3 ą▓ą░čĆąĖą░ąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ąĘąĮą░č湥ąĮąĖą╣ ą▓ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąĄ - ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé č鹊ą│ąŠ, ą▓ą║ą╗čÄč湥ąĮ ąĖą╗ąĖ ąĮąĄ čāą║ą░ąĘą░č鹥ą╗čī ąĮą░ čüą╗ąĄą┤čāčÄčēąĖą╣ ą┤ąĄčüą║čĆąĖą┐č鹊čĆ, ąĖ ąĄčüą╗ąĖ ą▓ą║ą╗čÄč湥ąĮ, č鹊 ą║ą░ą║ąŠą╣ čā ąĮąĄą│ąŠ ą▓ąĖą┤.

1. ąŻą║ą░ąĘą░č鹥ą╗čī ąĮą░ čüą╗ąĄą┤čāčÄčēąĖą╣ ą┤ąĄčüą║čĆąĖą┐č鹊čĆ ąĮąĄ ą▓ą║ą╗čÄč湥ąĮ (čĆąĄąČąĖą╝ ą╝ą░čüčüąĖą▓ą░ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą▓).

2. ąÆą║ą╗čÄč湥ąĮčŗ ą╝ą╗ą░ą┤čłąĖąĄ 16 ą▒ąĖčé čüą╗ąĄą┤čāčÄčēąĄą│ąŠ čāą║ą░ąĘą░č鹥ą╗čÅ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ (čüą┐ąĖčüąŠą║ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░, ą╝ą░ą╗ą░čÅ ą╝ąŠą┤ąĄą╗čī).

3. ąÆą║ą╗čÄč湥ąĮčŗ ą┐ąŠą╗ąĮąŠčüčéčīčÄ ą▓čüąĄ 32 ą▒ąĖčéą░ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ čāą║ą░ąĘą░č鹥ą╗čÅ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ (čüą┐ąĖčüąŠą║ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░, ą▒ąŠą╗čīčłą░čÅ ą╝ąŠą┤ąĄą╗čī).

ąÆčüąĄ ą┤čĆčāą│ąĖąĄ čĆąĄą│ąĖčüčéčĆčŗ, ą║ąŠč鹊čĆčŗąĄ ąĮąĄ ąĘą░ą│čĆčāąČą░čÄčéčüčÅ ąĖąĘ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░, čüąŠčģčĆą░ąĮčÅčÄčé čüą▓ąŠąĖ ą┐čĆąĄą┤čŗą┤čāčēąĖąĄ ąĘąĮą░č湥ąĮąĖčÅ (čģąŠčéčÅ čĆąĄą│ąĖčüčéčĆčŗ CURR_ADDR, CURR_X_COUNT, CURR_Y_COUNT ą┐ąĄčĆąĄąĘą░ą│čĆčāąČą░čÄčéčüčÅ ą╝ąĄąČą┤čā ąĘą░čģą▓ą░č鹊ą╝ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ ąĖ ąĘą░ą┐čāčüą║ąŠą╝ ąŠą┐ąĄčĆą░čåąĖąĖ DMA).

ą×čüąĮąŠą▓ąĮčŗąĄ ąĮą░čüčéčĆąŠą╣ą║ąĖ DMA, ą║ąŠč鹊čĆčŗąĄ ąĮąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ ąĖąĘą╝ąĄąĮąĖčéčī ąĖąĘ ąŠą┤ąĮąŠą│ąŠ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ ą║ čüą╗ąĄą┤čāčÄčēąĄą╝čā ą▓ čåąĄą┐ąŠčćą║ąĄ (ą╝ą░ą╗ą░čÅ ąĖą╗ąĖ ą▒ąŠą╗čīčłą░čÅ ą╝ąŠą┤ąĄą╗ąĖ čüą┐ąĖčüą║ąŠą▓ ąĖą╗ąĖ čĆąĄąČąĖą╝ ą╝ą░čüčüąĖą▓ą░ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą▓): ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ DMA, čĆą░ąĘą╝ąĄčĆ čüą╗ąŠą▓ą░, ąŠą▒ą╗ą░čüčéčī ą┐ą░ą╝čÅčéąĖ (ąĖą╝ąĄąĄčéčüčÅ ą▓ ą▓ąĖą┤čā ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ą╝ąĄąČą┤čā ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ ąĖ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéčīčÄ).

ą×ą┤ąĮą░ čåąĄą┐ąŠčćą║ą░ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą▓ ąĮąĄ ą╝ąŠąČąĄčé čāą┐čĆą░ą▓ą╗čÅčéčī ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčīčÄ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▒čāč乥čĆąŠą▓ ą┤ą░ąĮąĮčŗčģ, ą║ąŠč鹊čĆčŗąĄ čĆą░ąĘą╝ąĄčēąĄąĮčŗ ą▓ čĆą░ąĘąĮčŗčģ ą▓ąĖą┤ą░čģ ą┐ą░ą╝čÅčéąĖ. ąÆą╝ąĄčüč鹊 čŹč鹊ą│ąŠ čüąŠąĘą┤ą░ą╣č鹥 ąŠčéą┤ąĄą╗čīąĮčŗąĄ ą│čĆčāą┐ą┐čŗ (čåąĄą┐ąŠčćą║ąĖ) ą▒čāč乥čĆąŠą▓ ą┤ą░ąĮąĮčŗčģ ą┤ą╗čÅ čĆą░ąĘąĮčŗčģ ą▓ąĖą┤ąŠą▓ ą┐ą░ą╝čÅčéąĖ, ąĮąŠ ąĮąĄ čüąŠąĄą┤ąĖąĮčÅą╣č鹥 čåąĄą┐ąŠčćą║ąĖ čĆą░ąĘąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ ą▓ą╝ąĄčüč鹥. ąĪąĮą░čćą░ą╗ą░ ą┐ąĄčĆąĄą┤ą░ą╣č鹥 ą┐ąĄčĆą▓čāčÄ čåąĄą┐ąŠčćą║čā, ą┤ąŠąČą┤ąĖč鹥čüčī ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą▓ čŹč鹊ą╣ ą┐ąĄčĆą▓ąŠą╣ čåąĄą┐ąŠčćą║ąĄ ąĖ ąĘą░č鹥ą╝ ąĮą░čćąĮąĖč鹥 ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī čüą╗ąĄą┤čāčÄčēčāčÄ čåąĄą┐ąŠčćą║čā MMR-ąĘą░ą┐ąĖčüčīčÄ ą▓ DMA_CONFIG.

ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 čģąŠčéčÅ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą┤ąŠą╗ąČąĄąĮ čĆą░ąĘą╝ąĄčüčéąĖčéčī ą║ą░ąČą┤čŗą╣ ąĖąĘ ą▒čāč乥čĆąŠą▓ ą▓ čåąĄą┐ąŠčćą║ąĄ ą▓ ąŠą┤ąĮąŠą╝ ąĖ č鹊ą╝ ąČąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąĄ ą┐ą░ą╝čÅčéąĖ, čüčéčĆčāą║čéčāčĆčŗ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą▓ čüą░ą╝ąĖ ą┐ąŠ čüąĄą▒ąĄ ą╝ąŠą│čāčé ą▒čŗčéčī čĆą░ąĘą╝ąĄčēąĄąĮčŗ ą▓ ą╗čÄą▒ąŠą╣ ąŠą▒ą╗ą░čüčéąĖ ą┐ą░ą╝čÅčéąĖ, ąĖ ą╝ąŠą│čāčé čüąŠąĘą┤ą░ą▓ą░čéčī čüčüčŗą╗ą║čā ąĖąĘ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ ą▓ ąŠą┤ąĮąŠą╣ ąŠą▒ą╗ą░čüčéąĖ ą┐ą░ą╝čÅčéąĖ ąĮą░ ą┤ąĄčüą║čĆąĖą┐č鹊čĆ ą▓ ą┤čĆčāą│ąŠą╣ ąŠą▒ą╗ą░čüčéąĖ ą┐ą░ą╝čÅčéąĖ, ą▒ąĄąĘ ąŠą│čĆą░ąĮąĖč湥ąĮąĖą╣.

ąÆ čéą░ą▒ą╗ąĖčåąĄ 9-10 ą┐ąŠą║ą░ąĘą░ąĮčŗ čüą╝ąĄčēąĄąĮąĖčÅ ą┤ą╗čÅ čŹą╗ąĄą╝ąĄąĮč鹊ą▓ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ ą▓ čéčĆąĄčģ ą▓čŗčłąĄ ąŠą┐ąĖčüą░ąĮąĮčŗčģ čĆąĄąČąĖą╝ą░čģ. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ąĖą╝ąĄąĮą░ ą▓ čéą░ą▒ą╗ąĖčåąĄ ą┐ąĄčĆąĄčćąĖčüą╗čÅčÄčé 菹╗ąĄą╝ąĄąĮčéčŗ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ ą▓ ą┐ą░ą╝čÅčéąĖ, ąĮąŠ čŹč鹊 ąĮąĄ ą░ą║čéčāą░ą╗čīąĮčŗąĄ MMR, ą▓ ą║ąŠč鹊čĆčŗąĄ ąŠąĮąĖ ą▓čĆąĄą╝čÅ ąŠčé ą▓čĆąĄą╝ąĄąĮąĖ ąĘą░ą│čĆčāąČą░čÄčéčüčÅ.

ąóą░ą▒ą╗ąĖčåą░ 9-10. ąĀąĄą│ąĖčüčéčĆčŗ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓ ąĖ čüą╝ąĄčēąĄąĮąĖčÅ ą▓ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąĄ.

| ąĪą╝ąĄčēąĄąĮąĖąĄ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ |

ąĀąĄąČąĖą╝ ą╝ą░čüčüąĖą▓ą░ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą▓ |

ąĀąĄąČąĖą╝ ą╝ą░ą╗ąŠą╣ ą╝ąŠą┤ąĄą╗ąĖ čüą┐ąĖčüą║ą░ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą▓ |

ąĀąĄąČąĖą╝ ą▒ąŠą╗čīčłąŠą╣ ą╝ąŠą┤ąĄą╗ąĖ čüą┐ąĖčüą║ą░ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą▓ |

| 0x00 |

SAL |

NDPL |

NDPL |

| 0x02 |

SAH |

SAL |

NDPH |

| 0x04 |

DMACFG |

SAH |

SAL |

| 0x06 |

XCNT |

DMACFG |

SAH |

| 0x08 |

XMOD |

XCNT |

DMACFG |

| 0x0A |

YCNT |

XMOD |

XCNT |

| 0x0C |

YMOD |

YCNT |

XMOD |

| 0x0E |

|

YMOD |

YCNT |

| 0x10 |

|

|

YMOD |

[ąöą▓čāčģą╝ąĄčĆąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ DMA]

ąöą▓čāčģą╝ąĄčĆąĮčŗąĄ DMA ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé ą┐čĆąŠąĖąĘą▓ąŠą╗čīąĮčŗąĄ čĆą░ąĘą╝ąĄčĆčŗ čüčéčĆąŠą║ ąĖ čüč鹊ą╗ą▒čåąŠą▓ ą┤ąŠ 64K x 64K 菹╗ąĄą╝ąĄąĮč鹊ą▓, ą║ą░ą║ ąĖ ą┐čĆąŠąĖąĘą▓ąŠą╗čīąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ X_MODIFY ąĖ Y_MODIFY ą┤ąŠ ┬▒32K ą▒ą░ą╣čé. ąæąŠą╗ąĄąĄ č鹊ą│ąŠ, Y_MODIFY ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠčéčĆąĖčåą░č鹥ą╗čīąĮčŗą╝, čćč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé čĆąĄą░ą╗ąĖąĘąŠą▓ą░čéčī ą┐ąŠč鹊ą║ąĖ ą┤ą░ąĮąĮčŗčģ čü č湥čĆąĄą┤ąŠą▓ą░ąĮąĖąĄą╝ (interleaved data stream). X_COUNT ąĖ Y_COUNT ąĘą░ą┤ą░čÄčé čĆą░ąĘą╝ąĄčĆčŗ čüčéčĆąŠą║ ąĖ čüč鹊ą╗ą▒čåąŠą▓, ą│ą┤ąĄ X_COUNT ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī 2 ąĖą╗ąĖ ą▒ąŠą╗čīčłąĄ.

ąØą░čćą░ą╗čīąĮčŗą╣ ą░ą┤čĆąĄčü ąĖ ąĘąĮą░č湥ąĮąĖčÅ ą┤ą╗čÅ ą╝ąŠą┤ąĖčäąĖą║ą░čåąĖąĖ čāą║ą░ąĘčŗą▓ą░čÄčéčüčÅ ą▓ ą▒ą░ą╣čéą░čģ, ąĖ ąŠąĮąĖ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą▓čŗčĆąŠą▓ąĮąĄąĮčŗ ąĮą░ čĆą░ąĘą╝ąĄčĆ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ąŠą│ąŠ čüą╗ąŠą▓ą░ DMA (WDSIZE[1:0] ą▓ čĆąĄą│ąĖčüčéčĆąĄ DMA_CONFIG). ą×čłąĖą▒ą║ą░ ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖčÅ ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ąŠčłąĖą▒ą║ąĄ DMA.

ąŚąĮą░č湥ąĮąĖąĄ X_MODIFY čÅą▓ą╗čÅąĄčéčüčÅ ą▒ą░ą╣č鹊ą▓čŗą╝ ąĖąĮą║čĆąĄą╝ąĄąĮč鹊ą╝ ą░ą┤čĆąĄčüą░, ą║ąŠč鹊čĆčŗą╣ ą┐čĆąĖą╝ąĄąĮčÅąĄčéčüčÅ ą┐ąŠčüą╗ąĄ ą║ą░ąČą┤ąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ, ą║ąŠą│ą┤ą░ ą┤ąĄą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ CURR_X_COUNT. ąŚąĮą░č湥ąĮąĖąĄ X_MODIFY ąĮąĄ ą┐čĆąĖą╝ąĄąĮčÅąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čüč湥čéčćąĖą║ čåąĖą║ą╗ą░ ąŠą║ą░ąĮčćąĖą▓ą░ąĄčé čüą▓ąŠąĄ ą┤ąĄą║čĆąĄą╝ąĄąĮčéąĖčĆąŠą▓ą░ąĮąĖąĄ CURR_X_COUNT čü ą┐ąĄčĆąĄčģąŠą┤ąŠą╝ ąŠčé 1 ą║ 0, ąĘą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ čüą╗čāčćą░ąĄą▓, ą║ąŠą│ą┤ą░ čŹč鹊 ą┐čĆąĖą║ą╗ą░ą┤čŗą▓ą░ąĄčéčüčÅ ąĮą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╣ ą┐ąĄčĆąĄą┤ą░č湥, ą║ąŠą│ą┤ą░ CURR_Y_COUNT čĆą░ą▓ąĄąĮ 1 ąĖ CURR_X_COUNT ą┤ąĄą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ ąŠčé 1 ą║ 0.

ąŚąĮą░č湥ąĮąĖąĄ Y_MODIFY čÅą▓ą╗čÅąĄčéčüčÅ ą▒ą░ą╣č鹊ą▓čŗą╝ ąĖąĮą║čĆąĄą╝ąĄąĮč鹊ą╝ ą░ą┤čĆąĄčüą░, ą║ąŠč鹊čĆčŗą╣ ą┐čĆąĖą╝ąĄąĮčÅąĄčéčüčÅ ą┐ąŠčüą╗ąĄ ą║ą░ąČą┤ąŠą│ąŠ ą┤ąĄą║čĆąĄą╝ąĄąĮčéą░ CURR_Y_COUNT. ą×ą┤ąĮą░ą║ąŠ ąĘąĮą░č湥ąĮąĖąĄ Y_MODIFY ąĮąĄ ą┐čĆąĖą║ą╗ą░ą┤čŗą▓ą░ąĄčéčüčÅ ą║ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╝čā 菹╗ąĄą╝ąĄąĮčéčā ą▓ ą╝ą░čüčüąĖą▓ąĄ, ą┐ąŠ ą║ąŠč鹊čĆąŠą╝čā čüčćąĖčéą░ąĄčé čüč湥čéčćąĖą║ ą▓ąĮąĄčłąĮąĄą│ąŠ čåąĖą║ą╗ą░ (CURR_Y_COUNT), ą║ąŠą│ą┤ą░ ąŠąĮ ąĘą░ą▓ąĄčĆčłą░ąĄčé ą┤ąĄą║čĆąĄą╝ąĄąĮčéąĖčĆąŠą▓ą░ąĮąĖąĄ ą┐čĆąĖ ą┐ąĄčĆąĄčģąŠą┤ąĄ ąŠčé 1 ą║ 0.

ą¤ąŠčüą╗ąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ CURR_Y_COUNT=1, CURR_X_COUNT=0, ąĖ CURR_ADDR čĆą░ą▓ąĄąĮ ą░ą┤čĆąĄčüčā ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ 菹╗ąĄą╝ąĄąĮčéą░ ą┐ą╗čÄčü X_MODIFY. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ąĄčüą╗ąĖ ą║ą░ąĮą░ą╗ DMA ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ ą┤ą╗čÅ ą░ą▓č鹊ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ (čĆąĄąČąĖą╝ ą░ą▓č鹊ą▒čāč乥čĆą░), č鹊 čŹčéąĖ čĆąĄą│ąĖčüčéčĆčŗ ąĘą░ą│čĆčāąČą░čÄčéčüčÅ ąĖąĘ X_COUNT, Y_COUNT, ąĖ START_ADDR, ą║ą░ą║ čŹč鹊 ą▒čŗą╗ąŠ ą┐čĆąĖ ą┐ąĄčĆą▓ąŠą╣ ą┐ąĄčĆąĄą┤ą░č湥.

X_MODIFY = 1

X_COUNT = 16

Y_MODIFY = N-15 (čüą╝ąĄčēąĄąĮąĖąĄ ąŠčé ą║ąŠąĮčåą░ ąŠą┤ąĮąŠą╣ čüčéčĆąŠą║ąĖ ą┤ąŠ ąĮą░čćą░ą╗ą░ čüą╗ąĄą┤čāčÄčēąĄą╣)

Y_COUNT = 8

ąŁč鹊 ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ čüą╗ąĄą┤čāčÄčēąĖą╝ čüą╝ąĄčēąĄąĮąĖčÅą╝ ą░ą┤čĆąĄčüą░ ąŠčé ąĮą░čćą░ą╗čīąĮąŠą│ąŠ ą░ą┤čĆąĄčüą░:

0,1,2,...15,

N,N+1, ... N+15,

2N, 2N+1,... 2N+15, ...

7N, 7N+1,... 7N+15,

0, ...

X_MODIFY = (N*M)

X_COUNT = 3

Y_MODIFY = 1 - 2(N*M) (ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠąĄ)

Y_COUNT = (N*M)

ąŁč鹊 ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ čüą╗ąĄą┤čāčÄčēąĖą╝ čüą╝ąĄčēąĄąĮąĖčÅą╝ ą░ą┤čĆąĄčüą░ ąŠčé ąĮą░čćą░ą╗čīąĮąŠą│ąŠ ą░ą┤čĆąĄčüą░:

0, (N*M), 2(N*M),

1, (N*M)+1, 2(N*M)+1,

2, (N*M)+2, 2(N*M)+2,

...

(N*M)-1, 2(N*M)-1, 3(N*M)-1,

0, ...

[ąÉą╗ą│ąŠčĆąĖčéą╝ čĆą░ą▒ąŠčéčŗ DMA]

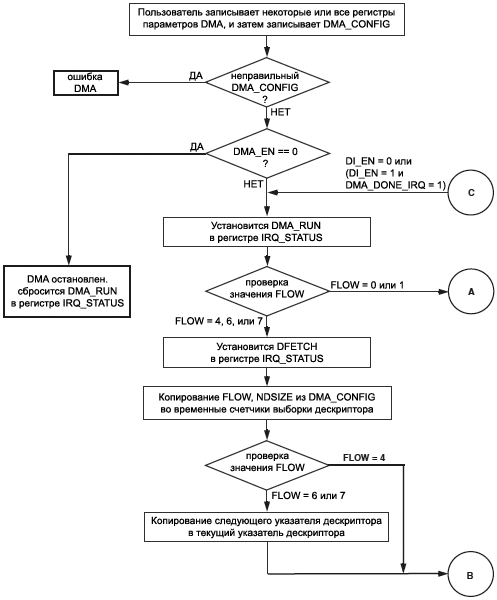

ąØą░ čĆąĖčüčāąĮą║ą░čģ 9-15 ąĖ 9-16 ą┐ąŠą║ą░ąĘą░ąĮ ą┐čĆąŠčåąĄčüčü DMA, čüąŠčüč鹊čÅčēąĖą╣ ąĖąĘ 2 čćą░čüč鹥ą╣.

ąĀąĖčü. 9-15. ąĀą░ą▒ąŠčéą░ DMA čü č鹊čćą║ąĖ ąĘčĆąĄąĮąĖčÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ DMA (čćą░čüčéčī 1 ąĖąĘ 2).

ąĀąĖčü. 9-16. ąĀą░ą▒ąŠčéą░ DMA čü č鹊čćą║ąĖ ąĘčĆąĄąĮąĖčÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ DMA (čćą░čüčéčī 2 ąĖąĘ 2).

[ą¤čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮą░čÅ ąĮą░čüčéčĆąŠą╣ą║ą░ DMA]

ąÆ čŹč鹊ą╝ čĆą░ąĘą┤ąĄą╗ąĄ čĆą░čüčüą╝ą░čéčĆąĖą▓ą░ąĄčéčüčÅ ąĘą░ą┐čāčüą║ DMA "čü ąĮčāą╗čÅ". ąĪąĖčéčāą░čåąĖčÅ ą▒čāą┤ąĄčé ą┐ąŠčģąŠąČą░ ąĮą░ ąĘą░ą┐čāčüą║ DMA, ą║ąŠą│ą┤ą░ ąŠąĮ ą▓čüčéą░ą╗ ąĮą░ ą┐ą░čāąĘčā ą▓ čĆąĄąČąĖą╝ąĄ FLOW = 0.

ą¤ąĄčĆąĄą┤ ąĖąĮąĖčåąĖą░čåąĖąĄą╣ DMA ą▓ ą┐ąĄčĆą▓čŗą╣ čĆą░ąĘ ąĮą░ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮąĮąŠą╝ ą║ą░ąĮą░ą╗ąĄ čāą▒ąĄą┤ąĖč鹥čüčī ą▓ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ ą▓čüąĄčģ čĆąĄą│ąĖčüčéčĆąŠą▓ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓. ą×čüąŠą▒ąĄąĮąĮąŠ ą▓ąĮąĖą╝ą░č鹥ą╗čīąĮąŠ ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆčāą╣č鹥 čüčéą░čĆčłąĖąĄ 16 ą▒ąĖčé čĆąĄą│ąĖčüčéčĆąŠą▓ NEXT_DESC_PTR ąĖ START_ADDR, ą┐ąŠč鹊ą╝čā čćč鹊 ąĖąĮą░č湥 ą║ ąĮąĖą╝ ą╝ąŠąČąĄčé ąĮąĄ ą▒čŗčéčī ą┤ąŠčüčéčāą┐ą░, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą▓čŗą▒čĆą░ąĮąĮąŠą│ąŠ čĆąĄąČąĖą╝ą░ FLOW.

ąöą╗čÅ ąĘą░ą┐čāčüą║ą░ ąŠą┐ąĄčĆą░čåąĖąĖ DMA ąĮą░ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮąĮąŠą╝ ą║ą░ąĮą░ą╗ąĄ čüąĮą░čćą░ą╗ą░ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĮą░ą┐čĆčÅą╝čāčÄ ąĘą░ą┐ąĖčüą░ąĮčŗ ą▓čüąĄ ąĖą╗ąĖ ąĮąĄą║ąŠč鹊čĆčŗąĄ čĆąĄą│ąĖčüčéčĆčŗ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓ DMA. ąØą░ čŹč鹊ą╝ čłą░ą│ąĄ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮčŗ ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ čĆąĄą│ąĖčüčéčĆ NEXT_DESC_PTR (ąĖą╗ąĖ CURR_DESC_PTR ą▓ čĆąĄąČąĖą╝ąĄ FLOW = 4), ąŠą┤ąĮą░ą║ąŠ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą╝ąŠąČąĄčé ąĘą░čģąŠč鹥čéčī ąĘą░ą┐ąĖčüą░čéčī ą┤čĆčāą│ąĖąĄ čĆąĄą│ąĖčüčéčĆčŗ DMA, ą║ąŠč鹊čĆčŗąĄ ą║ąŠąĮąĄčćąĮąŠ ą╝ąŠą│čāčé ą▒čŗčéčī čüčéą░čéąĖč湥čüą║ąĖą╝ąĖ ą┐čĆąĖ ą░ą║čéąĖą▓ąĮąŠčüčéąĖ DMA (ąĮą░ą┐čĆąĖą╝ąĄčĆ, čŹč鹊 X_MODIFY, Y_MODIFY). ąĪąŠą┤ąĄčƹȹĖą╝ąŠąĄ NDSIZE ąĖ FLOW ą▓ DMA_CONFIG čāą║ą░ąČąĄčé, ą║ą░ą║ąĖąĄ čĆąĄą│ąĖčüčéčĆčŗ, ąĄčüą╗ąĖ čéą░ą║ąŠą▓čŗąĄ ąĖą╝ąĄčÄčéčüčÅ, ąĘą░čģą▓ą░čéčŗą▓ą░čÄčéčüčÅ ąĖąĘ 菹╗ąĄą╝ąĄąĮč鹊ą▓ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ ą▓ ą┐ą░ą╝čÅčéąĖ. ą¤ąŠčüą╗ąĄ ą▓čŗą▒ąŠčĆą║ąĖ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░, ąĄčüą╗ąĖ ąŠąĮ ąĄčüčéčī, ąĮą░čüčéčĆąŠą╣ą║ą░ ąĘą░ą▓ąĄčĆčłąĄąĮą░, ąĮą░čćąĮąĄčéčüčÅ ąŠą┐ąĄčĆą░čåąĖčÅ DMA ą┐ąŠčüą╗ąĄ ąĘą░ą┐ąĖčüąĖ DMA_CONFIG čü ą▒ąĖč鹊ą╝ DMA_EN = 1.

ąÜąŠą│ą┤ą░ DMA_CONFIG ąĘą░ą┐ąĖčüą░ąĮ ąĮą░ą┐čĆčÅą╝čāčÄ, ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ DMA čĆą░čüą┐ąŠąĘąĮą░ąĄčé čŹč鹊čé čäą░ą║čé ą║ą░ą║ čüą┐ąĄčåąĖą░ą╗čīąĮąŠąĄ čāčüą╗ąŠą▓ąĖąĄ ąĘą░ą┐čāčüą║ą░, ą║ąŠč鹊čĆąŠąĄ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé, ą║ąŠą│ą┤ą░ ąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ DMA ą▓ ą┐ąĄčĆą▓čŗą╣ čĆą░ąĘ ąĮą░ čŹč鹊ą╝ ą║ą░ąĮą░ą╗ąĄ ąĖą╗ąĖ ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą┐ąŠą┤čüąĖčüč鹥ą╝ą░ DMA ą▒čŗą╗ą░ ąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮą░ (ą┐čĆąĖ FLOW = 0). ąÜąŠą│ą┤ą░ ą▓čŗą▒ąŠčĆą║ą░ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ ąĘą░ą▓ąĄčĆčłąĖą╗ą░čüčī ąĖ DMA_EN=1, č鹊 ą▒čŗą╗ ą┐čĆąŠčćąĖčéą░ąĮ 菹╗ąĄą╝ąĄąĮčé ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ DMACFG ą▓ čĆąĄą│ąĖčüčéčĆ DMA_CONFIG, čćč鹊 ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčéčüčÅ ą║ą░ą║ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ (ą┐ąĄčĆąĄą┤ čŹčéąĖą╝ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┤ąŠčüčéąĖą│ą░ąĄčéčüčÅ ą┐čĆčÅą╝ąŠą╣ ąĘą░ą┐ąĖčüčīčÄ ą▓ DMA_CONFIG).

ąÜą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 9-15 ąĖ 9-16, ą┐čĆąĖ ąĘą░ą┐čāčüą║ąĄ ą▒ąĖčéčŗ FLOW ąĖ NDSIZE čĆąĄą│ąĖčüčéčĆą░ DMA_CONFIG ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčé ą┐čĆąŠčåąĄčüčü ąĮą░čüčéčĆąŠą╣ą║ąĖ DMA. ąŚąĮą░č湥ąĮąĖąĄ FLOW ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé, ąĘą░ą│čĆčāąĘąĖčéčī ą╗ąĖ č鹥ą║čāčēąĖąĄ čĆąĄą│ąĖčüčéčĆčŗ ąĖčģ 菹╗ąĄą╝ąĄąĮč鹊ą▓ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ ą▓ ą┐ą░ą╝čÅčéąĖ, č鹊ą│ą┤ą░ ą║ą░ą║ ą▒ąĖčéčŗ NDSIZE ą┤ąĄčéą░ą╗ąĖąĘąĖčĆčāčÄčé, ą║ą░ą║ ą╝ąĮąŠą│ąŠ 菹╗ąĄą╝ąĄąĮč鹊ą▓ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ ą▒čāą┤ąĄčé ą▓čŗą▒čĆą░ąĮąŠ ą┐ąĄčĆąĄą┤ ąĘą░ą┐čāčüą║ąŠą╝ DMA. ąĀąĄą│ąĖčüčéčĆčŗ DMA, ąĮąĄ ą▓ą║ą╗čÄč湥ąĮąĮčŗąĄ ą▓ ą┤ąĄčüą║čĆąĖą┐č鹊čĆ, ąĮąĄ ą╝ąŠą┤ąĖčäąĖčåąĖčĆčāąĄčéčüčÅ, ąĖ ą▓ ąĮąĖčģ ąŠčüčéą░čÄčéčüčÅ ą┐čĆąĄą┤čŗą┤čāčēąĖąĄ ąĘąĮą░č湥ąĮąĖčÅ. ąæąŠą╗ąĄąĄ č鹊ą│ąŠ, ąĘąĮą░č湥ąĮąĖčÅ čüą▒čĆąŠčüą░ DMA MMR ąĮąĖą║ąŠą│ą┤ą░ ąĮąĄ ą▓ąŠčüčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄčéčüčÅ, ąĘą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ čüąĖčéčāą░čåąĖąĖ čüąĖčüč鹥ą╝ąĮąŠą│ąŠ čüą▒čĆąŠčüą░.

ąĢčüą╗ąĖ ąĘąĮą░č湥ąĮąĖąĄ FLOW ąĘą░ą┤ą░ąĄčé čĆąĄąČąĖą╝čŗ ą╝ąŠą┤ąĄą╗ąĄą╣ ą╝ą░ą╗ąŠą│ąŠ ąĖą╗ąĖ ą▒ąŠą╗čīčłąŠą│ąŠ čüą┐ąĖčüą║ą░ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą▓, č鹊 NEXT_DESC_PTR ą║ąŠą┐ąĖčĆčāąĄčéčüčÅ ą▓ CURR_DESC_PTR. ąŚą░č鹥ą╝ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą▓čŗą▒ąŠčĆą║ą░ ąĮąŠą▓čŗčģ 菹╗ąĄą╝ąĄąĮč鹊ą▓ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ ąĖąĘ ą┐ą░ą╝čÅčéąĖ, ąĖąĮą┤ąĄą║čüąĖčĆąŠą▓ą░ąĮąĮčŗčģ č湥čĆąĄąĘ CURR_DESC_PTR, ą║ąŠč鹊čĆčŗą╣ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ ą┐ąŠčüą╗ąĄ ą║ą░ąČą┤ąŠą╣ ą▓čŗą▒ąŠčĆą║ąĖ. ąĢčüą╗ąĖ NDPL ąĖ/ąĖą╗ąĖ NDPH čÅą▓ą╗čÅčÄčéčüčÅ čćą░čüčéčīčÄ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░, č鹊 čŹčéąĖ ąĘąĮą░č湥ąĮąĖčÅ ąĘą░ą│čĆčāąČą░čÄčéčüčÅ ą▓ NEXT_DESC_PTR, ąŠą┤ąĮą░ą║ąŠ ą▓čŗą▒ąŠčĆą║ą░ č鹥ą║čāčēąĄą│ąŠ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ ą┐čĆąŠą┤ąŠą╗ąČą░ąĄčéčüčÅ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ CURR_DESC_PTR. ą¤ąŠčüą╗ąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą▓čŗą▒ąŠčĆą║ąĖ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ CURR_DESC_PTR čāą║ą░ąĘčŗą▓ą░ąĄčé ąĮą░ čüą╗ąĄą┤čāčÄčēąĄąĄ 16-ą▒ąĖčéąĮąŠąĄ čüą╗ąŠą▓ąŠ ą▓ ą┐ą░ą╝čÅčéąĖ ą┐ąŠčüą╗ąĄ ą║ąŠąĮčåą░ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░.

ąĢčüą╗ąĖ ąĮąĖ NDPH, ąĮąĖ NDPL ąĮąĄ čÅą▓ą╗čÅčÄčéčüčÅ čćą░čüčéčīčÄ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ (čé. ąĄ. čĆąĄąČąĖą╝ ą╝ą░čüčüąĖą▓ą░ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą▓, FLOW = 4), č鹊 ąĮąĄ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖąĄ ąĖąĘ NDPH/NDPL ą▓ CURR_DESC_PTR. ąÆą╝ąĄčüč鹊 čŹč鹊ą│ąŠ ąĖąĮą┤ąĄą║čüąĖčĆąŠą▓ą░ąĮąĮą░čÅ ą▓čŗą▒ąŠčĆą║ą░ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ ąĮą░čćąĖąĮą░ąĄčéčüčÅ čüąŠ ąĘąĮą░č湥ąĮąĖčÅ ą▓ CURR_DESC_PTR.

ąĢčüą╗ąĖ DMACFG ąĮąĄ čÅą▓ą╗čÅąĄčéčüčÅ čćą░čüčéčīčÄ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░, č鹊 čāą┐čĆą░ą▓ą╗čÅčÄčé čĆą░ą▒ąŠč鹊ą╣ ą┐čĆąĄą┤čŗą┤čāčēąĖąĄ ąĮą░čüčéčĆąŠą╣ą║ąĖ DMA_CONFIG (ą║ąŠč鹊čĆčŗąĄ ą▒čŗą╗ąĖ ąĘą░ą┐ąĖčüą░ąĮčŗ ą┤ąŠčüčéčāą┐ąŠą╝ ą║ MMR ą┐čĆąĖ ąĮą░čüčéčĆąŠą╣ą║ąĄ). ąĢčüą╗ąĖ DMACFG ą▓čģąŠą┤ąĖčé ą▓ ą┤ąĄčüą║čĆąĖą┐č鹊čĆ, č鹊 ąĘąĮą░č湥ąĮąĖąĄ DMA_CONFIG, ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮąŠąĄ ą┤ąŠčüčéčāą┐ąŠą╝ ą║ MMR, čāą┐čĆą░ą▓ą╗čÅąĄčé č鹊ą╗čīą║ąŠ ąĘą░ą│čĆčāąĘą║ąŠą╣ ą┐ąĄčĆą▓ąŠą│ąŠ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ ąĖąĘ ą┐ą░ą╝čÅčéąĖ. ą¤ąŠčüą╗ąĄą┤čāčÄčēąĄąĄ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĄ DMA čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ą╝ą╗ą░ą┤čłąĖą╝ ą▒ą░ą╣č鹊ą╝ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ DMACFG ąĖ čĆąĄą│ąĖčüčéčĆą░ą╝ąĖ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓, ąĘą░ą│čĆčāąČąĄąĮąĮčŗčģ ąĖąĘ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░. ąæąĖčéčŗ DI_EN, DI_SEL, DMA2D, WDSIZE ąĖ WNR, ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮčŗąĄ čĆą░ąĮąĄąĄ ą┤ąŠčüčéčāą┐ąŠą╝ č湥čĆąĄąĘ MMR, ą▒čāą┤čāčé ąĖą│ąĮąŠčĆąĖčĆąŠą▓ą░ąĮčŗ.

ąæąĖčéčŗ čüąŠčüč鹊čÅąĮąĖčÅ DMA_RUN ąĖ DFETCH ą▓ čĆąĄą│ąĖčüčéčĆąĄ IRQ_STATUS ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčé čüčéą░čéčāčü ą║ą░ąĮą░ą╗ą░ DMA. ą¤ąŠčüą╗ąĄ ąĘą░ą┐ąĖčüąĖ DMA_CONFIG ą▒ąĖčéčŗ DMA_RUN ąĖ DFETCH ą╝ąŠą│čāčé ą▒čŗčéčī ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą▓ 1. ą¤čĆąĖ ą┐ąĄčĆą▓ąŠą╣ ąĘą░ą│čĆčāąĘą║ąĄ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ ąĖąĘ ą┐ą░ą╝čÅčéąĖ ąĮąĄ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą┤ą░ąĮąĮčŗčģ.

ą¤ąŠčüą╗ąĄ ą▓čŗčłąĄąŠą┐ąĖčüą░ąĮąĮčŗčģ čłą░ą│ąŠą▓ č鹥ą║čāčēąĖąĄ čĆąĄą│ąĖčüčéčĆčŗ ąĘą░ą│čĆčāąČą░čÄčéčüčÅ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąĖąĘ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖčģ 菹╗ąĄą╝ąĄąĮč鹊ą▓ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░, ą┐ąĄčĆąĄąĘą░ą┐ąĖčüčŗą▓ą░čÅ čüą▓ąŠąĄ ą┐čĆąĄą┤čŗą┤čāčēąĄąĄ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ:

ŌĆó START_ADDR ą║ąŠą┐ąĖčĆčāąĄčéčüčÅ ą▓ CURR_ADDR

ŌĆó X_COUNT ą║ąŠą┐ąĖčĆčāąĄčéčüčÅ ą▓ CURR_X_COUNT

ŌĆó Y_COUNT ą║ąŠą┐ąĖčĆčāąĄčéčüčÅ ą▓ CURR_Y_COUNT

ąŚą░č鹥ą╝ ąĮą░čćąĖąĮą░ąĄčéčüčÅ ąŠą┐ąĄčĆą░čåąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ DMA, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 9-16.

[ą×ą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ DMA]

ą¤ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĖ čĆą░ą▒ąŠč湥ą│ąŠ ą▒ą╗ąŠą║ą░ ą║ąŠąĮčéčĆąŠą╗ąĄčĆ DMA ąĘą░ą▓ąĄčĆčłą░ąĄčé ą┐ąĄčĆąĄą┤ą░čćčā ą▓čüąĄčģ ą┤ą░ąĮąĮčŗčģ ą╝ąĄąČą┤čā ą┐ą░ą╝čÅčéčīčÄ ąĖ ą▒ą╗ąŠą║ąŠą╝ DMA. ąĢčüą╗ąĖ čŹč鹊 čĆą░ąĘčĆąĄčłąĄąĮąŠ ą▒ąĖč鹊ą╝ DI_EN, č鹊 ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ čüąĖą│ąĮą░ą╗ąĖąĘąĖčĆčāąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄą╝ čÅą┤čĆčā ąĮą░čüčéčāą┐ą╗ąĄąĮąĖąĄ čŹč鹊ą│ąŠ čüąŠą▒čŗčéąĖčÅ, ąĖ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ą▒ąĖčé DMA_DONE ą▓ čĆąĄą│ąĖčüčéčĆąĄ IRQ_STATUS ą║ą░ąĮą░ą╗ą░.

ąÜąŠą│ą┤ą░ ą▒ąĖčéčŗ FLOW ąŠčćąĖčēąĄąĮčŗ, (= 0), ąŠą┐ąĄčĆą░čåąĖčÅ ąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ąŠčćąĖčüčéą║ąŠą╣ ą▒ąĖčéą░ DMA_RUN ą▓ čĆąĄą│ąĖčüčéčĆąĄ IRQ_STATUS ą┐ąŠčüą╗ąĄ ą╗čÄą▒ąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ą▓ ą║ą░ąĮą░ą╗čīąĮąŠą╝ DMA FIFO, ą║ąŠą│ą┤ą░ ą┤ą░ąĮąĮčŗąĄ ą▒čŗą╗ąĖ ą┐ąĄčĆąĄą┤ą░ąĮčŗ ą▓ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ.

ąÆąŠ ą▓čĆąĄą╝čÅ ą▓čŗą▒ąŠčĆą║ąĖ ą▓ čĆąĄąČąĖą╝ą░čģ FLOW 4, 6 ąĖ 7, ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ DMA čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ą▓ 1 ą▒ąĖčé DFETCH čĆąĄą│ąĖčüčéčĆą░ IRQ_STATUS. ąÆ čŹč鹊ą╝ ą╝ąĄčüč鹥 čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĄ DMA ąĘą░ą▓ąĖčüąĖčé ąŠčé č鹊ą│ąŠ, ą║ą░ą║ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ FLOW, čé. ąĄ. 4, 6 ąĖą╗ąĖ 7:

FLOW = 4 (ą╝ą░čüčüąĖą▓ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą▓): ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ąĮąŠą▓čŗą╣ ą┤ąĄčüą║čĆąĖą┐č鹊čĆ ąĖąĘ ą┐ą░ą╝čÅčéąĖ ą▓ čĆąĄą│ąĖčüčéčĆčŗ DMA č湥čĆąĄąĘ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ CURR_DESC_PTR, ą║ąŠą│ą┤ą░ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ CURR_DESC_PTR. ąĀą░ąĘą╝ąĄčĆ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ ą▒ąĄčĆąĄčéčüčÅ ąĖąĘ ą┐ąŠą╗čÅ NDSIZE čĆąĄą│ąĖčüčéčĆą░ DMA_CONFIG ą┤ąŠ ąĮą░čćą░ą╗ą░ ą▓čŗą▒ąŠčĆą║ąĖ.

FLOW = 6 (ą╝ąŠą┤ąĄą╗čī ą╝ą░ą╗ąŠą│ąŠ čüą┐ąĖčüą║ą░ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą▓): ą║ąŠą┐ąĖčĆčāąĄčéčüčÅ 32-ą▒ąĖčéąĮčŗą╣ NEXT_DESC_PTR ą▓ CURR_DESC_PTR. ąöą░ą╗ąĄąĄ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ą┤ąĄčüą║čĆąĖą┐č鹊čĆ ąĖąĘ ą┐ą░ą╝čÅčéąĖ ą▓ čĆąĄą│ąĖčüčéčĆčŗ DMA č湥čĆąĄąĘ ąĮąŠą▓ąŠąĄ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ CURR_DESC_PTR, ą║ąŠą│ą┤ą░ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ CURR_DESC_PTR. ą¤ąĄčĆą▓čŗą╣ 菹╗ąĄą╝ąĄąĮčé ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ą▓ ąĮąŠą▓ąŠąĄ 16-ą▒ąĖčéąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┤ą╗čÅ ą╝ą╗ą░ą┤čłąĖčģ 16 ą▒ąĖčé čĆąĄą│ąĖčüčéčĆą░ NEXT_DESC_PTR, ąĘą░ čŹčéąĖą╝ 菹╗ąĄą╝ąĄąĮč鹊ą╝ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ ąĖą┤čāčé ąŠčüčéą░ą╗čīąĮčŗąĄ 菹╗ąĄą╝ąĄąĮčéčŗ. ąĪčéą░čĆčłąĖąĄ 16 ą▒ąĖčé NEXT_DESC_PTR čüąŠčģčĆą░ąĮčÅčÄčé čüą▓ąŠąĄ ą┐čĆąĄąČąĮąĄąĄ ąĘąĮą░č湥ąĮąĖąĄ. ąŁč鹊 ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą▒ąŠą╗ąĄąĄ ą║ąŠčĆąŠčéą║ąĖą╣ ąĖ čŹčäč乥ą║čéąĖą▓ąĮčŗą╣ ą┤ąĄčüą║čĆąĖą┐č鹊čĆ ą┐ąŠ čüčĆą░ą▓ąĮąĄąĮąĖčÄ čü ą╝ąŠą┤ąĄą╗čīčÄ ą▒ąŠą╗čīčłąŠą│ąŠ čüą┐ąĖčüą║ą░, čćč鹊 ą┐ąŠą┤čģąŠą┤ąĖčé ą┤ą╗čÅ ą┐čĆąĖą╗ąŠąČąĄąĮąĖą╣, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠą│čāčé čĆą░ąĘą╝ąĄčüčéąĖčéčī ą┤ąĄčüą║čĆąĖą┐č鹊čĆčŗ ą║ą░ąĮą░ą╗ą░ ą▓ ą┐čĆąĄą┤ąĄą╗ą░čģ ą▒ą╗ąŠą║ą░ ą┐ą░ą╝čÅčéąĖ čĆą░ąĘą╝ąĄčĆąŠą╝ 64 ą║ąĖą╗ąŠą▒ą░ą╣čéą░.

FLOW = 7 (ą╝ąŠą┤ąĄą╗čī ą▒ąŠą╗čīčłąŠą│ąŠ čüą┐ąĖčüą║ą░ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓): ą║ąŠą┐ąĖčĆčāąĄčéčüčÅ 32-ą▒ąĖčéąĮčŗą╣ NEXT_DESC_PTR ą▓ CURR_DESC_PTR. ąöą░ą╗ąĄąĄ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ą┤ąĄčüą║čĆąĖą┐č鹊čĆ ąĖąĘ ą┐ą░ą╝čÅčéąĖ ą▓ čĆąĄą│ąĖčüčéčĆčŗ DMA č湥čĆąĄąĘ ąĮąŠą▓ąŠąĄ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ CURR_DESC_PTR, ą║ąŠą│ą┤ą░ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ CURR_DESC_PTR. ą¤ąĄčĆą▓čŗąĄ 菹╗ąĄą╝ąĄąĮčéčŗ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ ąĘą░ą│čĆčāąČą░čÄčé ąĮąŠą▓ąŠąĄ 32-ą▒ąĖčéąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┤ą╗čÅ ą┐ąŠą╗ąĮąŠą│ąŠ NEXT_DESC_PTR, ą┤ą░ą╗ąĄąĄ ąĖą┤čāčé ąŠčüčéą░ą╗čīąĮčŗąĄ 菹╗ąĄą╝ąĄąĮčéčŗ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░. ąĪčéą░čĆčłąĖąĄ 16 ą▒ąĖčé NEXT_DESC_PTR ą╝ąŠą│čāčé ąŠčéą╗ąĖčćą░čéčīčüčÅ ąŠčé čüą▓ąŠąĄą│ąŠ ą┐čĆąĄą┤čŗą┤čāčēąĄą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ. ąŁč鹊 ą┤ą░ąĄčé ą▒ąŠą╗ąĄąĄ ą│ąĖą▒ą║čāčÄ ą┐ąŠą┤ą┤ąĄčƹȹ║čā čüą┐ąĖčüą║ą░ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą▓, ą║ąŠč鹊čĆčŗąĄ č鹥ą┐ąĄčĆčī ą╝ąŠą│čāčé ąĮą░čģąŠą┤ąĖčéčīčüčÅ ą▓ ą╗čÄą▒ąŠą╣ ąŠą▒ą╗ą░čüčéąĖ ą┐ą░ą╝čÅčéąĖ - ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣, ą▓ąĮąĄčłąĮąĄą╣, ąĖą╗ąĖ ą┤ą░ąČąĄ ą▓ ROM.

ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ąĄčüą╗ąĖ ąĮčāąČąĮąŠ čüą▓čÅąĘą░čéčī čåąĄą┐ąŠčćą║čā ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą▓, ą│ą┤ąĄ ąŠą┤ąĮą░ čćą░čüčéčī čåąĄą┐ąŠčćą║ąĖ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ąŠą▒ą╗ą░čüčéąĖ 64 ą║ąĖą╗ąŠą▒ą░ą╣čéą░, ą░ ą▓č鹊čĆą░čÅ čćą░čüčéčī ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ąĮąĄ čŹč鹊ą╣ ąŠą▒ą╗ą░čüčéąĖ, č鹊 č鹊ą╗čīą║ąŠ ą▓ ąŠą┤ąĮąŠą╝ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąĄ ąĮčāąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī FLOW=7 ŌĆō ą┐čĆąŠčüč鹊 ą┐ąŠč鹊ą╝čā, čćč鹊 ą▓ ąĮąĄą╝ ą▒čāą┤ąĄčé čüąŠą┤ąĄčƹȹ░čéčīčüčÅ čüčüčŗą╗ą║ą░ ą┤ą╗čÅ ą▓čŗčģąŠą┤ą░ ąĘą░ ą┐čĆąĄą┤ąĄą╗čŗ 64 ą║ąĖą╗ąŠą▒ą░ą╣čéąĮąŠą╣ ąŠą▒ą╗ą░čüčéąĖ ą┐ą░ą╝čÅčéąĖ. ąÆčüąĄ ąŠčüčéą░ą╗čīąĮčŗąĄ ą┤ąĄčüą║čĆąĖą┐č鹊čĆčŗ, čüąŠąĄą┤ąĖąĮąĄąĮąĮčŗąĄ ą▓ą╝ąĄčüč鹥, ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą▓čüąĄ č鹥 ąČąĄ ąŠą▒ą╗ą░čüčéąĖ ą┐ą░ą╝čÅčéąĖ 64 ą║ąĖą╗ąŠą▒ą░ą╣čéą░ čü ąĮą░čüčéčĆąŠą╣ą║ąŠą╣ FLOW = 6.

FLOW = 1, 4, 6 ąĖą╗ąĖ 7 (ą░ą▓č鹊ą▒čāč乥čĆ, ą╝ą░čüčüąĖą▓ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą▓, ą╝ą░ą╗ą░čÅ ą╝ąŠą┤ąĄą╗čī čüą┐ąĖčüą║ą░ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą▓ ąĖą╗ąĖ ą▒ąŠą╗čīčłą░čÅ ą╝ąŠą┤ąĄą╗čī čüą┐ąĖčüą║ą░ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ) ąĘą░ą│čĆčāąČą░čÄčé (ąĖą╗ąĖ ą┐ąĄčĆąĄąĘą░ą│čĆčāąČą░čÄčé) č鹥ą║čāčēąĖąĄ čĆąĄą│ąĖčüčéčĆčŗ:

CURR_ADDR ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ąĖąĘ START_ADDR,

CURR_X_COUNT ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ąĖąĘ X_COUNT,

CURR_Y_COUNT ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ąĖąĘ Y_COUNT

ąŚą░č鹥ą╝ ąŠčćąĖčēą░ąĄčéčüčÅ ą▒ąĖčé DFETCH ą▓ čĆąĄą│ąĖčüčéčĆąĄ IRQ_STATUS, ą┐ąŠčüą╗ąĄ č湥ą│ąŠ čüąĮąŠą▓ą░ ąĮą░čćąĖąĮą░ąĄčéčüčÅ ą┐ąĄčĆąĄą┤ą░čćą░ DMA, ą║ą░ą║ čŹč鹊 ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 9-16.

[ąÜą░ą║ ąŠčüčéą░ąĮąŠą▓ąĖčéčī ą┐ąĄčĆąĄą┤ą░čćąĖ DMA]

ąÆ čĆąĄąČąĖą╝ąĄ FLOW = 0 DMA ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąŠčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą┐ąŠčüą╗ąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ čĆą░ą▒ąŠč湥ą│ąŠ ą▒ą╗ąŠą║ą░.

ąĢčüą╗ąĖ ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ DMA ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą╝ą░čüčüąĖą▓ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą▓, ąĖ ąĄčüą╗ąĖ ą║ą░ąČą┤čŗą╣ ą┤ąĄčüą║čĆąĖą┐č鹊čĆ čüąŠą┤ąĄčƹȹĖčé 菹╗ąĄą╝ąĄąĮčé DMACFG, č鹊 ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ 菹╗ąĄą╝ąĄąĮčé DMACFG ą┤ąŠą╗ąČąĄąĮ čüąŠą┤ąĄčƹȹ░čéčī ąĮą░čüčéčĆąŠą╣ą║čā FLOW = 0, čćč鹊ą▒čŗ ą║ąŠčĆčĆąĄą║čéąĮąŠ ąŠčüčéą░ąĮąŠą▓ąĖčéčī čĆą░ą▒ąŠčéčā ą║ą░ąĮą░ą╗ą░ DMA.