|

ąÆ čŹč鹊ą╝ ą░ą┐ąĮąŠčāč鹥 ąŠą▒čüčāąČą┤ą░ąĄčéčüčÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ą░ą╝čÅčéčīčÄ ą║čŹčłą░ ą┤ą╗čÅ čüąĄą╝ąĄą╣čüčéą▓ą░ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ Blackfin┬« ą║ąŠą╝ą┐ą░ąĮąĖąĖ Analog Devices (ą┐ąĄčĆąĄą▓ąŠą┤ ą┤ą░čéą░čłąĖčéą░ EE-271 [1]). ą¤čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮčŗ ą┐ąŠą┐čāą╗čÅčĆąĮčŗąĄ čüčģąĄą╝čŗ ą║čŹčłąĖčĆąŠą▓ą░ąĮąĖčÅ, ąĖ ą┐ąŠą┤čĆąŠą▒ąĮąŠ čĆą░čüčüą╝ą░čéčĆąĖą▓ą░ąĄčéčüčÅ ą║čŹčłąĖčĆąŠą▓ą░ąĮąĖąĄ ąĖąĮčüčéčĆčāą║čåąĖą╣ ąĖ ą║čŹčłąĖčĆąŠą▓ą░ąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ. ą×ą┐ąĖčüą░ąĮąĮčŗąĄ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ ą┤ąŠčüčéčāą┐ąĮčŗ ąĮą░ ą▓čüąĄčģ ą╝ąŠą┤ąĄą╗čÅčģ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ Blackfin. ąÆą╝ąĄčüč鹥 čü čŹčéąĖą╝ ą░ą┐ąĮąŠčāč鹊ą╝ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮčŗ ą┐čĆąĖą╝ąĄčĆčŗ ą║ąŠą┤ą░ [7], ą┤ąĄą╝ąŠąĮčüčéčĆąĖčĆčāčÄčēąĖąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą║čŹčłąĖčĆąŠą▓ą░ąĮąĖąĄą╝ ą┐ą░ą╝čÅčéąĖ. ą¤čĆąĖą╝ąĄčĆčŗ ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┤ą╗čÅ ą▓čüąĄčģ ą╝ąŠą┤ąĄą╗ąĄą╣ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ čüąĄą╝ąĄą╣čüčéą▓ą░ Blackfin.

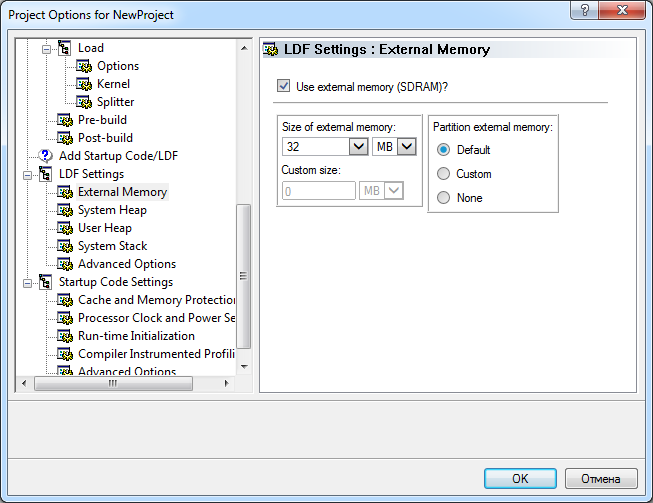

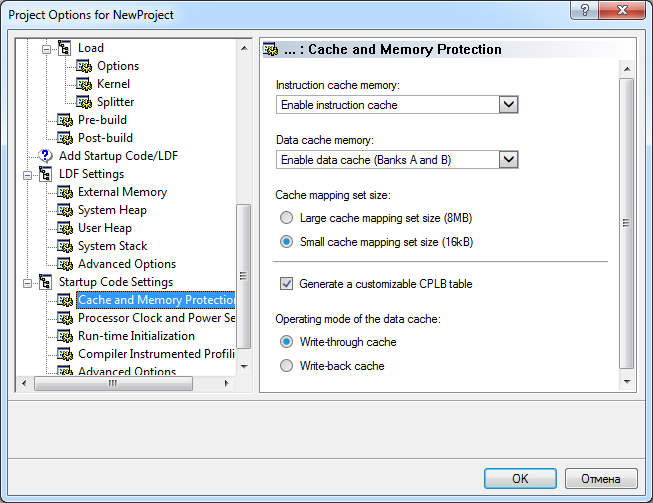

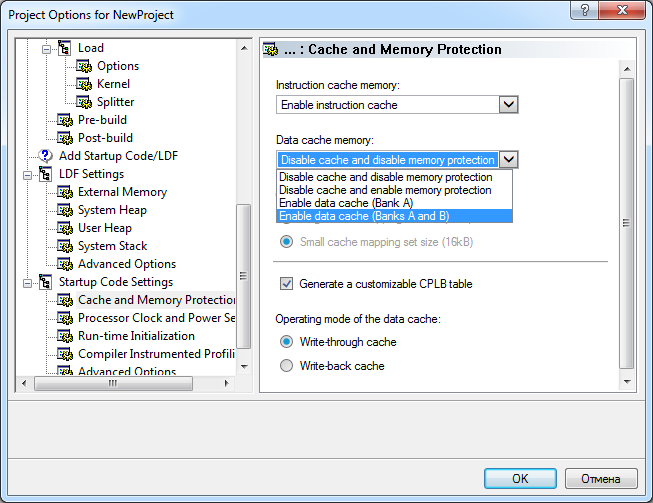

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĮą░ąĘą▓ą░ąĮąĖčÅ ąĮąĄą║ąŠč鹊čĆčŗčģ č鹥čĆą╝ąĖąĮąŠą▓ ą┤ą╗čÅ ą▒ąŠą╗ąĄąĄ čÅčüąĮąŠą│ąŠ ą┐ąŠąĮąĖą╝ą░ąĮąĖčÅ čüą╝čŗčüą╗ą░ ąŠčüčéą░ą▓ą╗ąĄąĮčŗ ą▓ č鹥ą║čüč鹥 ą▒ąĄąĘ ą┐ąĄčĆąĄą▓ąŠą┤ą░. ą×ą▒čŖčÅčüąĮąĄąĮąĖąĄ č鹥čĆą╝ąĖąĮąŠą▓ č鹥čģąĮąŠą╗ąŠą│ąĖąĖ ą║čŹčłąĖčĆąŠą▓ą░ąĮąĖčÅ ąĄčüčéčī ą▓ čĆą░ąĘą┤ąĄą╗ąĄ "ą×ą▒čēą░čÅ ą║ąŠąĮčåąĄą┐čåąĖčÅ ą║čŹčłąĖčĆąŠą▓ą░ąĮąĖčÅ -> ąóąĄčĆą╝ąĖąĮąŠą╗ąŠą│ąĖčÅ ą║čŹčłą░". ąóą░ą║ąČąĄ ąĮąĄąĘąĮą░ą║ąŠą╝čŗąĄ č鹥čĆą╝ąĖąĮčŗ ąĖ čüąŠą║čĆą░čēąĄąĮąĖčÅ čüą╝. ą▓ čĆą░ąĘą┤ąĄą╗ąĄ ąĪą╗ąŠą▓ą░čĆąĖą║ čŹč鹊ą╣ čüčéą░čéčīąĖ ąĖ čüčéą░čéčīąĖ [2].

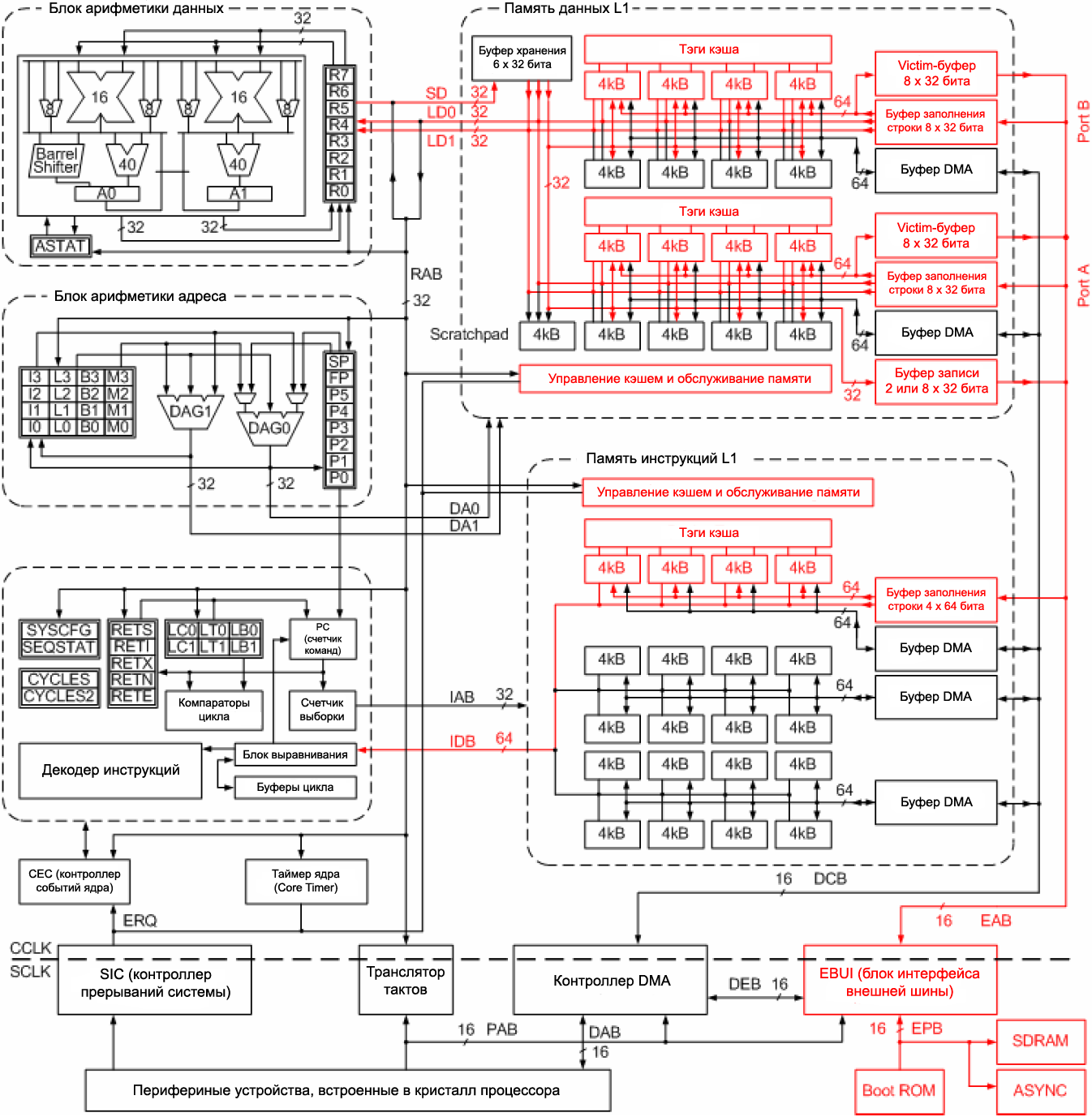

ąĀąĖčü. 1. ąæą╗ąŠą║-ą┤ąĖą░ą│čĆą░ą╝ą╝ą░ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ADSP-BF533.

Barrel Shifter, ASTAT, A1, A0, ... ą░ą┐ą┐ą░čĆą░čéąĮčŗąĄ čāąĘą╗čŗ čÅą┤čĆą░, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą▓ čüąĖčüč鹥ą╝ąĄ ą║ąŠą╝ą░ąĮą┤ (čāąĘąĄą╗ čüą┤ą▓ąĖą│ą░ ąĮą░ čāą║ą░ąĘą░ąĮąĮąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ąĖčé ąĘą░ 1 čéą░ą║čé, čĆąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ, ą░ą║ą║čāą╝čāą╗čÅč鹊čĆčŗ, ...).

CEC Core Event Controller.

DAG1, DAG0 Data Address Generator.

SIC System Interrupt Controller.

SD, LD0, LD1, RAB, DA0, DA1, IAB, IDB, PAB, DAB, DEB, EAB, EPB, DCB ą▓ąĮčāčéčĆąĄąĮąĮąĖąĄ čłąĖąĮčŗ ą░ą┤čĆąĄčüą░ ąĖ ą┤ą░ąĮąĮčŗčģ.

Scratchpad čüą┐ąĄčåąĖą░ą╗čīąĮą░čÅ ą┐ą░ą╝čÅčéčī ą┤ą╗čÅ ą▓čĆąĄą╝ąĄąĮąĮčŗčģ ą┤ą░ąĮąĮčŗčģ.

SDRAM, ASYNC čłąĖąĮčŗ ą┤ą╗čÅ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ - ą┤ąĖąĮą░ą╝ąĖč湥čüą║ąŠą╣ ąĖ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą╣.

ąÆ čŹč鹊ą╝ čĆą░ąĘą┤ąĄą╗ąĄ ąŠą┐ąĖčüčŗą▓ą░čÄčéčüčÅ ąŠą▒čēąĖąĄ ą┐čĆąĖąĮčåąĖą┐čŗ ąĖ č鹥čĆą╝ąĖąĮąŠą╗ąŠą│ąĖčÅ, ą┐čĆąĖą╝ąĄąĮčÅąĄą╝čŗąĄ ą▓ ą║čŹčłąĖčĆąŠą▓ą░ąĮąĖąĖ ą║ąŠą┤ą░ ąĖ ą┤ą░ąĮąĮčŗčģ.

ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą┐ą░ą╝čÅčéąĖ. ąĪąĖčüč鹥ą╝čŗ, ą║ąŠč鹊čĆčŗąĄ čéčĆąĄą▒čāčÄčé ą▒ąŠą╗čīčłąŠą╣ ąŠą▒čŖąĄą╝ ą┐ą░ą╝čÅčéąĖ, ąŠą▒čŗčćąĮąŠ čĆą░čüą┐čĆąĄą┤ąĄą╗čÅčÄčé ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čāčÄ ą┐ą░ą╝čÅčéčī ą┐ąŠ ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ čāčĆąŠą▓ąĮčÅą╝. ą¤ą░ą╝čÅčéčī čüą░ą╝ąŠą│ąŠ ą▓ąĄčĆčģąĮąĄą│ąŠ čāčĆąŠą▓ąĮčÅ (ą░ą┐ą┐ą░čĆą░čéąĮąŠ ąĮą░čģąŠą┤čÅčēą░čÅčüčÅ ą▒ą╗ąĖąČąĄ ą▓čüąĄą│ąŠ ą║ čÅą┤čĆčā ą┐čĆąŠčåąĄčüčüąŠčĆą░, čéą░ą║ ąĮą░ąĘčŗą▓ą░ąĄą╝ą░čÅ ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ ą┐ą░ą╝čÅčéčī L1) ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé čüą░ą╝čŗą╣ ą▓čŗčüąŠą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī ą▒čŗčüčéčĆąŠą┤ąĄą╣čüčéą▓ąĖčÅ, ąĖ čŹčéą░ ą┐ą░ą╝čÅčéčī čüą░ą╝ą░čÅ ą┤ąŠčĆąŠą│ą░čÅ. ą¤ą░ą╝čÅčéčī ą▒ąŠą╗ąĄąĄ ąĮąĖąĘą║ąĖčģ čāčĆąŠą▓ąĮąĄą╣ čéčĆąĄą▒čāčÄčé ąĮąĄčüą║ąŠą╗čīą║ąŠ čåąĖą║ą╗ąŠą▓ ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ ą║ čÅč湥ą╣ą║ą░ą╝, ąĮąŠ čüč鹊ąĖčé ą┤ąĄčłąĄą▓ą╗ąĄ (ąĮą░ą┐čĆąĖą╝ąĄčĆ, ą║ čéą░ą║ąŠą╣ ą┐ą░ą╝čÅčéąĖ ąŠčéąĮąŠčüąĖčéčüčÅ ą▓ąĮąĄčłąĮčÅčÅ ą┤ąĖąĮą░ą╝ąĖč湥čüą║ą░čÅ ą┐ą░ą╝čÅčéčī SDRAM).

ą¤ą░ą╝čÅčéčī ą║čŹčłą░ - čŹč鹊 čüą┐ąĄčåąĖą░ą╗čīąĮąŠ ą▓čŗą┤ąĄą╗ąĄąĮąĮą░čÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ ą║čŹčłą░ ą┐ą░ą╝čÅčéčī ą▓čŗčüąŠą║ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ (L1). ą×ąĮą░ ąĘą░čēąĖčēąĄąĮą░ ąŠčé ą┐čĆčÅą╝ąŠą│ąŠ ą┤ąŠčüčéčāą┐ą░ ą║ą░ą║ čüąŠ čüč鹊čĆąŠąĮčŗ čÅą┤čĆą░, čéą░ą║ ąĖ čüąŠ čüč鹊čĆąŠąĮčŗ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓. ą¤čĆąĖą╝ąĄąĮąĄąĮąĖąĄ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą║čŹčłą░ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąĮą░čģąŠą┤ąĖčéčīčüčÅ čüąĄą║čåąĖčÅą╝ ąĖąĮčüčéčĆčāą║čåąĖą╣ ąĖ ą┤ą░ąĮąĮčŗčģ ąĮą░čģąŠą┤ąĖčéčīčüčÅ ą▓ ą┐ą░ą╝čÅčéąĖ ąĮąĖąĘą║ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ (ąŠą▒čŗčćąĮąŠ SDRAM), čéą░ą║ čćč鹊 ąĮą░ąĖą▒ąŠą╗ąĄąĄ čćą░čüč鹊 ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą┤ą░ąĮąĮčŗąĄ ąĖ/ąĖą╗ąĖ ą║ąŠą┤ (ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé č鹊ą│ąŠ, ą║ą░ą║ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą║čŹčł) ą║ąŠą┐ąĖčĆčāąĄčéčüčÅ ą▓ ą┐ą░ą╝čÅčéčī ą║čŹčłą░ čü ą┐ąŠą╝ąŠčēčīčÄ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą║čŹčłą░. ąöąŠčüč鹊ą▓ąĄčĆąĮą░čÅ ą║ąŠą┐ąĖčÅ ą▓ ą║čŹčłąĄ čĆą░ą▒ąŠčéą░ąĄčé ąĮą░ą╝ąĮąŠą│ąŠ ą▒čŗčüčéčĆąĄąĄ, č湥ą╝ ąŠčĆąĖą│ąĖąĮą░ą╗čīąĮą░čÅ ą╝ąĄą┤ą╗ąĄąĮąĮą░čÅ ą┐ą░ą╝čÅčéčī (ąĖąĮčüčéčĆčāą║čåąĖąĖ ąĖ ą┤ą░ąĮąĮčŗąĄ ą┤ąŠčüčéčāą┐ąĮčŗ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą║ąĖ ąĘą░ 1 čåąĖą║ą╗ čÅą┤čĆą░), ą┐ąŠčüą║ąŠą╗čīą║čā čŹč鹊 čüą░ą╝ą░čÅ ą▒čŗčüčéčĆą░čÅ ą┐ą░ą╝čÅčéčī L1. ąÉčĆčģąĖč鹥ą║čéčāčĆą░ ą║čŹčłą░ ąŠčüąĮąŠą▓ą░ąĮą░ ąĮą░ ą┐čĆąĖąĮčåąĖą┐ąĄ, čćč鹊 ą░ą┤čĆąĄčüąĮąŠąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ ą┐ą░ą╝čÅčéąĖ ą┤ąĄą╗ąĖčéčüčÅ ąĮą░ ą▒ą╗ąŠą║ąĖ čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ čĆą░ąĘą╝ąĄčĆą░ (ą║ąŠč鹊čĆčŗąĄ ą▓ č鹥čĆą╝ąĖąĮąŠą╗ąŠą│ąĖąĖ ą║čŹčłąĖčĆąŠą▓ą░ąĮąĖčÅ ąĮą░ąĘčŗą▓ą░čÄčéčüčÅ čüčéčĆąŠą║ą░ą╝ąĖ ą║čŹčłą░). ąĪčéčĆąŠą║ąĖ ą║čŹčłą░ čüčćąĖčéą░čÄčéčüčÅ čüą░ą╝čŗą╝ąĖ ą╝ą░ą╗ąĄąĮčīą║ąĖą╝ąĖ ą║čāčüąŠčćą║ą░ą╝ąĖ ą┐ą░ą╝čÅčéąĖ, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠąČąĮąŠ ą┐ąĄčĆąĄą┤ą░čéčī ą║ą░ą║ ą║ąŠą┐ąĖčÄ ąĖąĘ ą▓ąĮąĄčłąĮąĄą╣ (ą╝ąĄą┤ą╗ąĄąĮąĮąŠą╣) ą┐ą░ą╝čÅčéąĖ ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮčÄčÄ ą┐ą░ą╝čÅčéčī ą║čŹčłą░ L1, ąĄčüą╗ąĖ ą▒čŗą╗ ąĘą░čäąĖą║čüąĖčĆąŠą▓ą░ąĮ ą┐čĆąŠą╝ą░čģ ą║čŹčłą░.

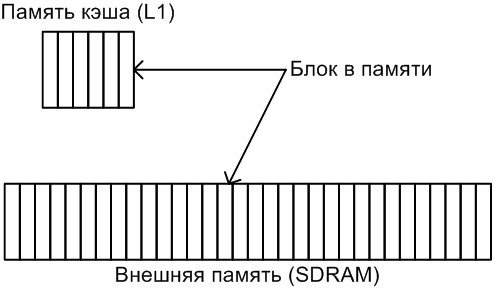

ą×ą▒čĆą░čēąĄąĮąĖąĄ ą║ ą┐ą░ą╝čÅčéąĖ ąĖą┤ąĄąĮčéąĖčäąĖčåąĖčĆčāąĄčéčüčÅ ą║ą░ą║ čüčüčŗą╗ą║ą░ ąĮą░ ąĮąĄą║ąĖą╣ ąŠčéą┤ąĄą╗čīąĮčŗą╣ ą▒ą╗ąŠą║ ą┐ą░ą╝čÅčéąĖ. ąØą░ čĆąĖčü. 2 ą┐ąŠą║ą░ąĘą░ąĮą░ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ, ą▓ ą║ąŠč鹊čĆąŠą╣ ąŠą▒ą╗ą░čüčéčī ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ ą┐ąŠą┤ąĄą╗ąĄąĮą░ ąĮą░ 24 ą▒ą╗ąŠą║ą░ ą┐ą░ą╝čÅčéąĖ, ąĖ ą┐ą░ą╝čÅčéčī ą║čŹčłą░ ą┐ąŠą┤ąĄą╗ąĄąĮą░ ąĮą░ 6 ą▒ą╗ąŠą║ąŠą▓ (čŹč鹊 ą┐čĆąĖą╝ąĄčĆ ąŠčüąĮąŠą▓ąĮąŠą╣ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą┐ą░ą╝čÅčéąĖ. ąÜąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ą╗ąŠą║ąŠą▓ ą┐ą░ą╝čÅčéąĖ ą╝ąŠąČąĄčé ą▓ ą┤ąĄą╣čüčéą▓ąĖč鹥ą╗čīąĮąŠčüčéąĖ ąŠčéą╗ąĖčćą░čéčīčüčÅ ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą╝ąŠą┤ąĄą╗ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆą░ Blackfin). ąĀą░ąĘą╝ąĄčĆ ą▒ą╗ąŠą║ą░ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ ąĖ ą▒ą╗ąŠą║ą░ ą┐ą░ą╝čÅčéąĖ ą║čŹčłą░ ąŠą┤ąĖąĮą░ą║ąŠą▓čŗą╣. ą¤ąŠčüą║ąŠą╗čīą║čā ą▓čüąĄą│ą┤ą░ ą┐ą░ą╝čÅčéčī ą║čŹčłą░ ą┐ąŠ čĆą░ąĘą╝ąĄčĆčā čüąŠčüč鹊ąĖčé ąĖąĘ 6 ą▒ą╗ąŠą║ąŠą▓ (ą║ą░ą║ ą▓ čŹč鹊ą╝ čćą░čüčéąĮąŠą╝ ą┐čĆąĖą╝ąĄčĆąĄ), č鹊 ą╝ąŠąČąĄčé ą▒čŗčéčī č鹊ą╗čīą║ąŠ 6 ą▒ą╗ąŠą║ąŠą▓ ą┤ą░ąĮąĮčŗčģ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ, ą║ąŠč鹊čĆčŗąĄ ą▒čāą┤čāčé ą┤ąŠčüčéčāą┐ąĮčŗ ą║ą░ą║ ą║čŹčłąĖčĆčāąĄą╝ą░čÅ ą║ąŠą┐ąĖčÅ.

ąĀąĖčü. 2. ą¤čĆąĖ ą║čŹčłąĖčĆąŠą▓ą░ąĮąĖąĖ ąŠą▒ą╗ą░čüčéčī ą┐ą░ą╝čÅčéąĖ ą┐ąŠą┤ąĄą╗ąĄąĮą░ ąĮą░ ą▒ą╗ąŠą║ąĖ čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ čĆą░ąĘą╝ąĄčĆą░.

ąóąĄčĆą╝ąĖąĮąŠą╗ąŠą│ąĖčÅ ą║čŹčłą░

ŌĆó Way, ą┐čāčéčī: ą╝ą░čüčüąĖą▓ čüčéčĆąŠą║ čģčĆą░ąĮąĖą╗ąĖčēą░ ą▓ m-way ą║čŹčłąĄ.

ŌĆó Locked way, ąĘą░ą▒ą╗ąŠą║ąĖčĆąŠą▓ą░ąĮąĮčŗą╣ ą┐čāčéčī: ąĄčüą╗ąĖ way ą▓ čüąŠčüč鹊čÅąĮąĖąĖ locked (ąĘą░ą▒ą╗ąŠą║ąĖčĆąŠą▓ą░ąĮ), č鹊 ąŠąĮ ąĮąĄ čāčćą░čüčéą▓čāąĄčé ą▓ ą┐ąŠą╗ąĖčéąĖą║ąĄ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ ą║čŹčłą░ "čüą░ą╝čŗą╣ ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╣" (least-recently used, LRU).

ŌĆó Set, ąĮą░ą▒ąŠčĆ: ą│čĆčāą┐ą┐ą░ ąŠą▒ą╗ą░čüč鹥ą╣ čģčĆą░ąĮąĄąĮąĖčÅ m-way ą▓ ą┐čāčéąĖ (way) ą║čŹčłą░ m-way. ą×čéą┤ąĄą╗čīąĮčŗą╣ ą▒ą╗ąŠą║ ą┐ą░ą╝čÅčéąĖ ą┐čĆąĖą▓čÅąĘą░ąĮ ą║ čüą┐ąĄčåąĖčäąĖčćąĮąŠą╝čā ąĮą░ą▒ąŠčĆčā. ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą║čŹčłą░ ą▓čŗą▒ąĖčĆą░ąĄčé way ą▓ąĮčāčéčĆąĖ ąĮą░ą▒ąŠčĆą░ set.

ŌĆó ąĪčéčĆąŠą║ą░ ą║čŹčłą░, cache-line: 32-ą▒ą░ą╣čéąĮčŗą╣ ąĮąĄą┐čĆąĄčĆčŗą▓ąĮčŗą╣ ą▒ą╗ąŠą║ ą┐ą░ą╝čÅčéąĖ ą║ąŠč鹊čĆčŗą╣ ą▒čŗą╗ ą┐ąĄčĆąĄą┤ą░ąĮ ą║ą░ą║ ą║ąŠą┐ąĖčÅ ąĖąĘ/ą▓ ą┐ą░ą╝čÅčéčī ą▓čŗčüąŠą║ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ ą▓/ąĖąĘ ą║čŹčłą░.

ŌĆó Dirty/clean, ą│čĆčÅąĘąĮą░čÅ/čćąĖčüčéą░čÅ): čüąŠčüč鹊čÅąĮąĖąĄ čüčéčĆąŠą║ąĖ ą║čŹčłą░, ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčēą░čÅ ąĮą░ą╗ąĖčćąĖąĄ ąĖą╗ąĖ ąŠčéčüčāčéčüčéą▓ąĖąĄ čĆą░čüčģąŠąČą┤ąĄąĮąĖą╣ ąŠčĆąĖą│ąĖąĮą░ą╗čīąĮąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ ą▓ąŠ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╣ ąĄą╝čā ą║ąŠą┐ąĖąĖ ą▓ čüčéčĆąŠą║ąĄ ą║čŹčłą░. ąĢčüą╗ąĖ čĆą░ąĘą╗ąĖčćąĖčÅ ąĄčüčéčī, čé. ąĄ. ąĮąĄčé čüąĖąĮčģčĆąŠąĮąĮąŠčüčéąĖ ą╝ąĄąČą┤čā ą║čŹčłąĄą╝ ąĖ ą║čŹčłąĖčĆčāąĄą╝ąŠą╣ ą┐ą░ą╝čÅčéčīčÄ, č鹊 čüčéčĆąŠą║ą░ ą│čĆčÅąĘąĮą░čÅ, ąĄčüą╗ąĖ ą┤ą░ąĮąĮčŗąĄ ą▓ ąŠčĆąĖą│ąĖąĮą░ą╗ąĄ ąĖą╗ąĖ ą║čŹčłąĄ ąĮąĄ ą▒čŗą╗ąĖ ą┐ąŠą╝ąĄąĮčÅąĮčŗ, č鹊 čüčéčĆąŠą║ą░ čćąĖčüčéą░čÅ.

ŌĆó Cache hit, ą┐ąŠą┐ą░ą┤ą░ąĮąĖąĄ ą▓ ą║čŹčł: ą┐čĆąŠčåąĄčüčüąŠčĆ ąŠą▒čĆą░ą╗čüčÅ ą║ ą▒ą╗ąŠą║čā ą┐ą░ą╝čÅčéąĖ (ąĮą░čģąŠą┤čÅčēąĄą╝čāčüčÅ ą▓ ąŠčüąĮąŠą▓ąĮąŠą╣, ą╝ąĄą┤ą╗ąĄąĮąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ), ą║ąŠč鹊čĆą░čÅ čāąČąĄ ąĖą╝ąĄąĄčé ą┤ąŠčüč鹊ą▓ąĄčĆąĮčāčÄ ą║ąŠą┐ąĖčÄ ą▓ ą║čŹčłąĄ. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ą┐čĆąŠčåąĄčüčüąŠčĆ čüčĆą░ąĘčā ą┐ąŠą╗čāčćąĖčé ą┤ą░ąĮąĮčŗąĄ ąĖąĘ ą║čŹčłą░, čü ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠą╣ ąĘą░ą┤ąĄčƹȹ║ąŠą╣.

ŌĆó Cache miss, ą┐čĆąŠą╝ą░čģ ą║čŹčłą░: ą┐čĆąŠčåąĄčüčüąŠčĆ ąŠą▒čĆą░čéąĖą╗čüčÅ ą║ ą▒ą╗ąŠą║čā ą┐ą░ą╝čÅčéąĖ, ą║ąŠč鹊čĆčŗą╣ ą┐ąŠą║ą░ ąĮąĄ ą┤ąŠčüčéčāą┐ąĄąĮ ą▓ ą║čŹčłąĄ. ąÜąŠą│ą┤ą░ ą┐čĆąŠąĖąĘąŠčłąĄą╗ ą┐čĆąŠą╝ą░čģ ą║čŹčłą░, ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą║čŹčłą░ ą┤ąĄą╗ą░ąĄčé ą║ąŠą┐ąĖčĆąŠą▓ą░ąĮąĖąĄ ą▒ą╗ąŠą║ą░ ą▓ ą┐ą░ą╝čÅčéčī ą║čŹčłą░ ąĖąĘ ąĮąĖąĘą║ąŠčāčĆąŠą▓ąĮąĄą▓ąŠą╣ ą┐ą░ą╝čÅčéąĖ.

ŌĆó Victim, "ąČąĄčĆčéą▓ą░": ą│čĆčÅąĘąĮą░čÅ čüčéčĆąŠą║ą░ ą║čŹčłą░ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮą░ ą▓ ąĮąĖąĘą║ąŠčāčĆąŠą▓ąĮąĄą▓čāčÄ ą┐ą░ą╝čÅčéčī ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ą╝ąŠąČąĮąŠ ą▒čāą┤ąĄčé ąĄčæ ąŠčüą▓ąŠą▒ąŠą┤ąĖčéčī ą┤ą╗čÅ ąĘą░ą┐ąĖčüąĖ ą▓ ą║čŹčł ąĮąŠą▓čŗčģ ą┤ą░ąĮąĮčŗčģ (čüą╝. victim buffer ąĮą░ čĆąĖčü. 1).

ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗąĄ ą┐ąŠą┤čĆąŠą▒ąĮąŠčüčéąĖ ą┐ąŠ č鹥čĆą╝ąĖąĮąŠą╗ąŠą│ąĖąĖ ą║čŹčłąĖčĆąŠą▓ą░ąĮąĖčÅ ą╝ąŠąČąĮąŠ ą┐ąŠą╗čāčćąĖčéčī ąĖąĘ čĆą░ąĘą┤ąĄą╗ą░ "Memory" ą┤ą░čéą░čłąĖčéą░ "Blackfin Processor Programming Reference".

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▓ ą┐ąŠčüą╗ąĄą┤čāčÄčēąĄą╝ ąĖąĘą╗ąŠąČąĄąĮąĖąĖ ą▒čāą┤čāčé ą▓ąĘą░ąĖą╝ąŠąĘą░ą╝ąĄąĮčÅąĄą╝ąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ čüą╗ąŠą▓ą░ line (čüčéčĆąŠą║ą░), cache-line (čüčéčĆąŠą║ą░ ą║čŹčłą░) ąĖ cache-block (ą▒ą╗ąŠą║ ą║čŹčłą░). ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą▒ą╗ąŠą║ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé ąŠą▒ą╗ą░čüčéčī čéą░ą║ąŠą│ąŠ ąČąĄ čĆą░ąĘą╝ąĄčĆą░, ą║ą░ą║ čüčéčĆąŠą║ą░ ą║čŹčłą░.

[ąĀą░ąĘą╝ąĄčēąĄąĮąĖąĄ ą▒ą╗ąŠą║ą░]

ąśčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ 3 ąŠčüąĮąŠą▓ąĮčŗąĄ čüčģąĄą╝čŗ ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐čĆąĖąĮčÅčéąĖčÅ čĆąĄčłąĄąĮąĖčÅ, ą│ą┤ąĄ čĆą░ąĘą╝ąĄčüčéąĖčéčī ą┐čĆąĖčģąŠą┤čÅčēąĖą╣ ą▒ą╗ąŠą║ ą▓ ą┐ą░ą╝čÅčéąĖ ą║čŹčłą░.

ą║čŹčł čü ą┐čĆčÅą╝ąŠą╣ ą┐čĆąĖą▓čÅąĘą║ąŠą╣ (Direct Mapped Cache). ąÆ čŹč鹊ą╣ čüčģąĄą╝ąĄ ą║ą░ąČą┤čŗą╣ ą▒ą╗ąŠą║ ą┐ą░ą╝čÅčéąĖ ąĮąĖąĘą║ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ ąĖą╝ąĄąĄčé č鹊ą╗čīą║ąŠ ąŠą┤ąĖąĮ čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮčŗą╣ ą▒ą╗ąŠą║ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ ą▓ ą║čŹčłąĄ. ąŚą┤ąĄčüčī ą┐čĆąĖčüčāčéčüčéą▓čāąĄčé ą┐čĆąĖą▓čÅąĘą║ą░ ąŠą┤ąĖąĮ-ą║-ąŠą┤ąĮąŠą╝čā ąŠčé ąĮąĖąĘą║ąŠčāčĆąŠą▓ąĮąĄą▓ąŠą╣ ą┐ą░ą╝čÅčéąĖ ą║ ą┐ą░ą╝čÅčéąĖ ą║čŹčłą░. ą¤čĆąĖą▓čÅąĘą║ą░ ąŠčüąĮąŠą▓čŗą▓ą░ąĄčéčüčÅ ąĮą░ ą░ą┤čĆąĄčüąĄ ą▒ą╗ąŠą║ą░ ą▓ ą┐ą░ą╝čÅčéąĖ ąĮąĖąĘą║ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ. ąŁčéą░ čüčģąĄą╝ą░ ąĮą░ąĖą▒ąŠą╗ąĄąĄ ą┐čĆąŠčüčéą░, ąĖ ąĖą╝ąĄąĄčé čüą░ą╝čāčÄ ąĮąĖąĘą║čāčÄ ą│ąĖą▒ą║ąŠčüčéčī ą▓ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ.

ą¤ąŠą╗ąĮąŠ-ą░čüčüąŠčåąĖą░čéąĖą▓ąĮčŗą╣ ą║čŹčł (Fully Associative Cache). ą¤ąŠ čŹč鹊ą╣ čüčģąĄą╝ąĄ ą▒ą╗ąŠą║ ą▓ ąŠčüąĮąŠą▓ąĮąŠą╣ (ą╝ąĄą┤ą╗ąĄąĮąĮąŠą╣) ą┐ą░ą╝čÅčéąĖ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą╝ąĄąĮąĄąĮ ąĮą░ ą▒ą╗ąŠą║ ą▓ ą┐ą░ą╝čÅčéąĖ ą║čŹčłą░. ą¤čĆąĖą▓čÅąĘą║ą░ ą▒ą╗ąŠą║ąŠą▓ ą┐ąŠą╗ąĮąŠčüčéčīčÄ čüą╗čāčćą░ą╣ąĮą░. ąŁčéą░ čüčéčĆą░č鹥ą│ąĖčÅ ąĖą╝ąĄąĄčé čüą░ą╝čāčÄ čüą╗ąŠąČąĮąŠčüčéčī ą▓ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĖ, ąĮąŠ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé čüą░ą╝čāčÄ ą▓čŗčüąŠą║čāčÄ ą│ąĖą▒ą║ąŠčüčéčī ą▓ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ.

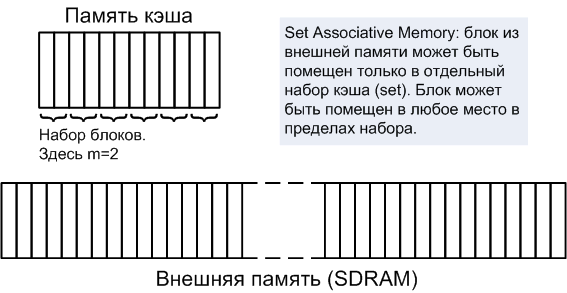

ąØą░ą▒ąŠčĆ ą░čüčüąŠčåąĖą░čéąĖą▓ąĮąŠą│ąŠ ą║čŹčłą░ (Set Associative Cache). ą¤ą░ą╝čÅčéčī ą║čŹčłą░ čĆą░ąĘą▒ąĖčéą░ ąĮą░ ąĮą░ą▒ąŠčĆčŗ. ąØą░ą▒ąŠčĆ (set) čüąŠčüč鹊ąĖčé ąĖąĘ ąĮąĄą║ąŠč鹊čĆąŠą│ąŠ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ą▒ą╗ąŠą║ąŠą▓. ąøčÄą▒ąŠą╣ ą▒ą╗ąŠą║ ą▓ ą┐ą░ą╝čÅčéąĖ ąĮąĖąĘą║ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ ąĖą╝ąĄąĄčé čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮčŗą╣ ąĮą░ą▒ąŠčĆ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ ą▓ ą║čŹčłąĄ (ą║čāą┤ą░ ąŠąĮ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠą╝ąĄčēąĄąĮ). ą¤ąŠčüčéčāą┐ą░čÄčēąĖą╣ ą▒ą╗ąŠą║ ą╝ąŠąČąĄčé ąĘą░ą╝ąĄąĮąĖčéčī ą╗čÄą▒čŗąĄ ą▒ą╗ąŠą║ąĖ ą▓ąĮčāčéčĆąĖ ą┐čĆąĖą▓čÅąĘą░ąĮąĮąŠą│ąŠ ąĮą░ą▒ąŠčĆą░. ąĢčüą╗ąĖ ą▓ ąĮą░ą▒ąŠčĆąĄ ąĄčüčéčī m ą▒ą╗ąŠą║ąŠą▓, č鹊 ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą║čŹčłą░ ąĮą░ąĘčŗą▓ą░ąĄčéčüčÅ m-way set associative. ąŁč鹊čé ą╝ąĄč鹊ą┤ čĆą░ąĘą╝ąĄčēąĄąĮąĖčÅ ą▒ą╗ąŠą║ą░ čÅą▓ą╗čÅąĄčéčüčÅ ą║ąŠą╝ą┐čĆąŠą╝ąĖčüčüąĮčŗą╝ ą┐ąŠ čüą╗ąŠąČąĮąŠčüčéąĖ ąĖ ą│ąĖą▒ą║ąŠčüčéąĖ. ąĀąĖčü. 3 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą┐ą░ą╝čÅčéčī 2-way set associate.

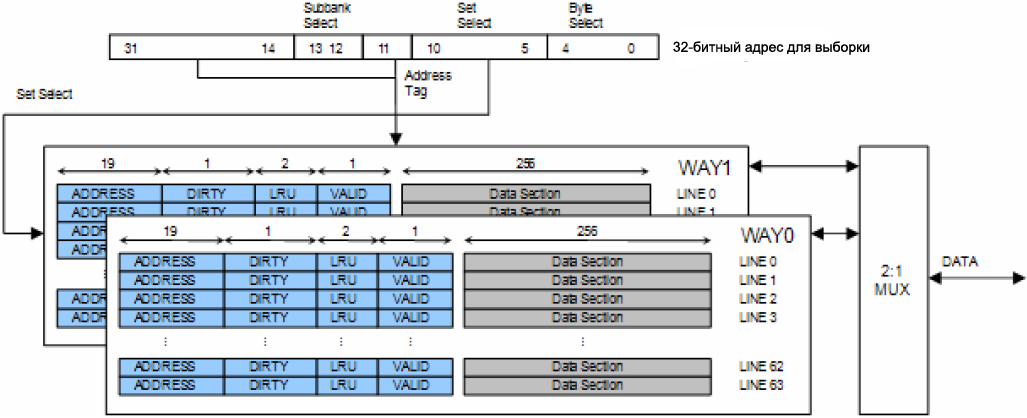

ąĀąĖčü. 3. ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą┐ą░ą╝čÅčéąĖ ą┤ą╗čÅ 2-way set associative cache.

ą¤ąĄčĆą▓čŗąĄ 2 čüčģąĄą╝čŗ čÅą▓ą╗čÅčÄčéčüčÅ čüą┐ąĄčåąĖą░ą╗čīąĮčŗą╝ąĖ čüą╗čāčćą░čÅą╝ąĖ set associative cache (direct mapped ą┤ą╗čÅ m = 1, ąĖ fully associative ą┤ą╗čÅ m = ą║ąŠą╗ąĖč湥čüčéą▓čā čüčéčĆąŠą║ ą║čŹčłą░).

[ąŚą░ą╝ąĄąĮą░ ą▒ą╗ąŠą║ą░]

ąØą░ čĆąĖčü. 4 ą┐ąŠą║ą░ąĘą░ąĮąŠ čüčĆą░ą▓ąĮąĄąĮąĖąĄ ąĘą░ą╝ąĄąĮčŗ ą▒ą╗ąŠą║ą░ ą┤ą╗čÅ 1-way ąĖ 4-way set associative cache. ąĀą░čüčüą╝ąŠčéčĆąĖą╝ ą╗ąĖąĮąĄą╣ąĮčŗą╣ ą┐ąŠč鹊ą║ č湥čĆąĄąĘ ą▒ąŠą╗čīčłąŠą╣ čåąĖą║ą╗ ą▓ ą┐čĆąŠą│čĆą░ą╝ą╝ąĄ, čĆą░čüą┐ąŠą╗ąŠąČąĄąĮąĮčŗą╣ ą▓ąŠ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ. ąÜąŠą│ą┤ą░ čÅč湥ą╣ą║ąĖ ą║čŹčłą░ ą▒čŗą╗ąĖ ą┐ąĄčĆąĄąĘą░ą┐ąĖčüą░ąĮčŗ ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ąŠąĮąĖ ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ, ą║čŹčł čüčćąĖčéą░ąĄčéčüčÅ "ą┐ąŠą▓čĆąĄąČą┤ąĄąĮąĮčŗą╝". ąæąŠą╗ąĄąĄ ą▓ąĄčĆąŠčÅčéąĮąŠ ąĮą░ą╗ąĖčćąĖąĄ čéčĆąĄą▒čāąĄą╝ąŠą╣ ąĖąĮčüčéčĆčāą║čåąĖąĖ ą┤ą╗čÅ ą┐ąŠą▓č鹊čĆąĮąŠą│ąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą▓ 4-way ą║čŹčłąĄ, č湥ą╝ ą▓ 1-way ą║čŹčłąĄ. ąÜąŠą┤ ą┤ąŠą╗ąČąĄąĮ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┐ąŠą▓č鹊čĆąĮąŠ, čćč鹊ą▒čŗ ą┐ąŠą╗čāčćąĖčéčī ą┐čĆąĄąĖą╝čāčēąĄčüčéą▓ąŠ ą▓ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ ą║čŹčłą░.

ąĀąĖčü. 4. ą¤čĆąĖą╝ąĄčĆčŗ čĆą░ąĘą╝ąĄčēąĄąĮąĖčÅ ą▒ą╗ąŠą║ą░.

ąÆ ą║čŹčłąĄ čü ą┐čĆčÅą╝ąŠą╣ ą┐čĆąĖą▓čÅąĘą║ąŠą╣ (direct mapped cache), ą▓čüąĄą│ą┤ą░ ą╝ąĄčüč鹊 ą▓ąĮčāčéčĆąĖ ą║čŹčłą░ čäąĖą║čüąĖčĆąŠą▓ą░ąĮąŠ, ą▓ ą║ąŠč鹊čĆąŠą╝ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠą╝ąĄčēąĄąĮą░ ą║čŹčłąĖčĆčāąĄą╝ą░čÅ (ą▓ąĮąĄčłąĮčÅčÅ) ą┐ą░ą╝čÅčéčī. ą×ą┤ąĮą░ą║ąŠ, ą▓ čĆą░ąĘą╝ąĄčēąĄąĮąĖąĖ ą▒ą╗ąŠą║ą░ čü ą┐ąŠą╗ąĮąŠ-čüą▓čÅąĘą░ąĮąĮčŗą╝ ą║čŹčłąĄą╝ (fully associative) ąĖą╗ąĖ čü ąĮą░ą▒ąŠčĆąŠą╝ čüą▓čÅąĘą░ąĮąĮąŠą│ąŠ ą║čŹčłą░ (set-associative), ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą▒čĆą░ąĮąŠ ąĮąĄčüą║ąŠą╗čīą║ąŠ ą╝ąĄčüčé ą┐čĆąĖ čüąŠą▒čŗčéąĖąĖ ą┐čĆąŠą╝ą░čģą░ ą║čŹčłą░. ąæą╗ąŠą║ąĖ, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ąĘą░ą╝ąĄąĮąĄąĮčŗ, ąĮą░ąĘčŗą▓ą░čÄčéčüčÅ "čāčćą░čüčéą▓čāčÄčēąĖą╝ąĖ" ą▒ą╗ąŠą║ą░ą╝ąĖ. ąÆąŠčé ąĮąĄą║ąŠč鹊čĆčŗąĄ čüčéčĆą░č鹥ą│ąĖąĖ, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ čćą░čēąĄ ą▓čüąĄą│ąŠ ą▓ ą▓čŗą▒ąŠčĆąĄ ą▒ą╗ąŠą║ą░ ą║čŹčłą░ ą┤ą╗čÅ ąĘą░ą╝ąĄąĮčŗ:

ŌĆó ąĪą╗čāčćą░ą╣ąĮą░čÅ ąĘą░ą╝ąĄąĮą░: ą▒ą╗ąŠą║ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ čüą╗čāčćą░ą╣ąĮąŠ ąĖąĘ čāčćą░čüčéą▓čāčÄčēąĖčģ ą▒ą╗ąŠą║ąŠą▓. ą£ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą│ąĄąĮąĄčĆą░č鹊čĆ ą┐čüąĄą▓ą┤ąŠčüą╗čāčćą░ą╣ąĮčŗčģ čćąĖčüąĄą╗, čćč鹊ą▒čŗ ą▓čŗą▒čĆą░čéčī ą▒ą╗ąŠą║ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ. ąŁč鹊 čüą░ą╝čŗą╣ ą┐čĆąŠčüčéą░čÅ, ąĮąŠ ąĮą░ąĖą╝ąĄąĮąĄąĄ čŹčäč乥ą║čéąĖą▓ąĮą░čÅ čĆąĄą░ą╗ąĖąĘą░čåąĖčÅ.

ŌĆó ąŚą░ą╝ąĄąĮą░ ą┐ąŠ ą┐čĆąĖąĮčåąĖą┐čā FIFO (First in first out, FIFO; ą┐čĆąĖąĮčåąĖą┐ ą┐ąĄčĆą▓čŗą╝ ąĘą░čłąĄą╗, ą┐ąĄčĆą▓čŗą╝ ą▓čŗčłąĄą╗): ą▓čģąŠą┤čÅčēąĖą╣ ą▒ą╗ąŠą║ ąĘą░ą╝ąĄąĮčÅąĄčé čüą░ą╝čŗą╣ čüčéą░čĆčŗą╣ ąĖąĘ čāčćą░čüčéą▓čāčÄčēąĖčģ ą▒ą╗ąŠą║ąŠą▓.

ŌĆó ąŚą░ą╝ąĄąĮą░ LRU (Least-recently used, LRU; ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╣, čé. ąĄ. ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╣ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠ ą┤ą░ą▓ąĮąŠ): ą┐ąŠ čŹč鹊ą╣ čüčģąĄą╝ąĄ ą▓čüąĄ ą┤ąŠčüčéčāą┐čŗ ą║ ą▒ą╗ąŠą║ą░ą╝ ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ. ąæčāą┤ąĄčé ą▓čŗą▒čĆą░ąĮ č鹊čé ą▒ą╗ąŠą║ ą┤ą╗čÅ ąĘą░ą╝ąĄąĮčŗ, ą║ ą║ąŠč鹊čĆąŠą╝čā ąĮąĄ ą▒čŗą╗ąŠ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ ąŠą▒čĆą░čēąĄąĮąĖčÅ čüą░ą╝ąŠąĄ ą┤ą╗ąĖč鹥ą╗čīąĮąŠąĄ ą▓čĆąĄą╝čÅ. LRU ą┐ąŠą╗ą░ą│ą░ąĄčéčüčÅ ąĮą░ ą╝ąĄčüčéąĮčŗąĄ čāčüą╗ąŠą▓ąĖčÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ: ąĄčüą╗ąĖ č鹊ą╗čīą║ąŠ čćč鹊 ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĮčŗąĄ ą▒ą╗ąŠą║ąĖ čüą║ąŠčĆąĄąĄ ą▓čüąĄą│ąŠ ąŠą┐čÅčéčī ą▓ ą▒ą╗ąĖąČą░ą╣čłąĄąĄ ą▓čĆąĄą╝čÅ ą┐ąŠąĮą░ą┤ąŠą▒čÅčéčüčÅ, č鹊 čģąŠčĆąŠčłąĖą╝ ą║ą░ąĮą┤ąĖą┤ą░č鹊ą╝ ą┤ą╗čÅ ąĘą░ą╝ąĄąĮčŗ ą▒čāą┤ąĄčé ą▒ą╗ąŠą║, ą║ąŠč鹊čĆčŗą╣ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ą╗čüčÅ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠ ą┤ą░ą▓ąĮąŠ.

ŌĆó ą£ąŠą┤ąĖčäąĖčåąĖčĆąŠą▓ą░ąĮąĮčŗą╣ ą┐čĆąĖąĮčåąĖą┐ ąĘą░ą╝ąĄąĮčŗ LRU: "ą╝ąŠą┤ąĖčäąĖčåąĖčĆąŠą▓ą░ąĮąĮčŗą╣" ą▓ čüą╗čāčćą░ąĄ ą┐čĆąŠčåąĄčüčüąŠčĆą░ Blackfin ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ą▒ąĖčé 8 (CPLB_LRUPRIO) ą▓ čĆąĄą│ąĖčüčéčĆą░čģ ą┤ą░ąĮąĮčŗčģ CPLB čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ąĖą╗ąĖ ąŠčćąĖčēąĄąĮ (čüą╝. čĆąĖčü. 17 ąĖ 18). ąŻ čŹč鹊ą│ąŠ ą▒ąĖčéą░ ą┐čĆąĖąŠčĆąĖč鹥čé ą▓čŗčłąĄ, č湥ą╝ čā ą┐ąŠą╗ąĖčéąĖą║ąĖ ąĘą░ą╝ąĄąĮčŗ LRU. ąĪąŠą│ą╗ą░čüąĮąŠ čüčģąĄą╝ąĄ ą╝ąŠą┤ąĖčäąĖčåąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ LRU, ą▒ą╗ąŠą║čā ą┐čĆąĖčüą▓ą░ąĖą▓ą░ąĄčéčüčÅ ąĮąĖąĘą║ąĖą╣ ą┐čĆąĖąŠčĆąĖč鹥čé ąĖą╗ąĖ ą▓čŗčüąŠą║ąĖą╣ ą┐čĆąĖąŠčĆąĖč鹥čé.

ąĢčüą╗ąĖ ą┐ąŠčüčéčāą┐ą░čÄčēąĖą╣ ą▒ą╗ąŠą║ ąĖą╝ąĄąĄčé ąĮąĖąĘą║ąĖą╣ ą┐čĆąĖąŠčĆąĖč鹥čé, č鹊 č鹊ą╗čīą║ąŠ ą▒ą╗ąŠą║ąĖ čü ąĮąĖąĘą║ąĖą╝ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝ ą╝ąŠą│čāčé čāčćą░čüčéą▓ąŠą▓ą░čéčī ą▓ ąĘą░ą╝ąĄąĮąĄ ą║čŹčłą░.

ąĢčüą╗ąĖ ą┐ąŠčüčéčāą┐ą░čÄčēąĖą╣ ą▒ą╗ąŠą║ ąĖą╝ąĄąĄčé ą▓čŗčüąŠą║ąĖą╣ ą┐čĆąĖąŠčĆąĖč鹥čé, č鹊 ą▓čüąĄ ąĮąĖąĘą║ąŠ-ą┐čĆąĖąŠčĆąĖč鹥čéąĮčŗąĄ ą▒ą╗ąŠą║ąĖ ą▒čāą┤čāčé čāčćą░čüčéą▓ąŠą▓ą░čéčī ą▓ ąĘą░ą╝ąĄąĮąĄ ą║čŹčłą░. ąĢčüą╗ąĖ ąĮąĄčé ąĮąĖąĘą║ąŠą┐čĆąĖąŠčĆąĖč鹥čéąĮčŗčģ ą▒ą╗ąŠą║ąŠą▓, č鹊 ą▓čŗčüąŠą║ąŠą┐čĆąĖąŠčĆąĖč鹥čéąĮčŗąĄ ą▒ą╗ąŠą║ąĖ ą╝ąŠą│čāčé čāčćą░čüčéą▓ąŠą▓ą░čéčī ą▓ ą┐ąŠą╗ąĖčéąĖą║ąĄ ąĘą░ą╝ąĄąĮčŗ. ą¤ąŠą╗ąĖčéąĖą║ą░ LRU ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą░ ą▒ą╗ąŠą║ą░-ąČąĄčĆčéą▓čŗ ą┤ą╗čÅ ąĘą░ą╝ąĄąĮčŗ čüčĆąĄą┤ąĖ čāčćą░čüčéą▓čāčÄčēąĖčģ ą▒ą╗ąŠą║ąŠą▓.

ąØąĄ ą▓čüąĄ ą▒ą╗ąŠą║ąĖ ą╝ąŠą│čāčé čüąŠą┤ąĄčƹȹ░čéčī ą▓ čüąĄą▒ąĄ ą┤ąŠčüč鹊ą▓ąĄčĆąĮčāčÄ ąĖąĮč乊čĆą╝ą░čåąĖčÄ. ąØą░ą┐čĆąĖą╝ąĄčĆ, ą▓ ą╝ąŠą╝ąĄąĮčé čüčéą░čĆčéą░ čüąĖčüč鹥ą╝čŗ ą▓ ą║čŹčłąĄ ąĮąĄ čüąŠą┤ąĄčƹȹĖčéčüčÅ ą▓ąŠąŠą▒čēąĄ ąĮąĖą║ą░ą║ąĖčģ ą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗčģ ą┤ą░ąĮąĮčŗčģ. ąæą╗ąŠą║ąĖ ą║čŹčłą░ ą▒čāą┤čāčé ąĘą░ą┐ąŠą╗ąĮčÅčéčīčüčÅ ą▓čüčÅą║ąĖą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ ą▒čāą┤čāčé ą┐čĆąŠąĖčüčģąŠą┤ąĖčéčī ąŠą▒čĆą░čēąĄąĮąĖčÅ ą║ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ čü ą┐čĆąŠą╝ą░čģą░ą╝ąĖ ą╝ąĖą╝ąŠ ą║čŹčłą░. ą£ąĄčģą░ąĮąĖąĘą╝ ą┤ąŠą╗ąČąĄąĮ ąĖą┤ąĄąĮčéąĖčäąĖčåąĖčĆąŠą▓ą░čéčī, čüąŠą┤ąĄčƹȹĖčéčüčÅ ą╗ąĖ ą▓ ą▒ą╗ąŠą║ąĄ ą║čŹčłą░ ą┤ąŠčüč鹊ą▓ąĄčĆąĮą░čÅ ąĖąĮč乊čĆą╝ą░čåąĖčÅ. ą¦č鹊ą▒čŗ ą┐čĆąŠą▓ąĄčĆąĖčéčī čŹč鹊, čü ą║ą░ąČą┤čŗą╝ ą▒ą╗ąŠą║ąŠą╝ ą║čŹčłą░ čüą▓čÅąĘčŗą▓ą░ąĄčéčüčÅ čéą░ą║ ąĮą░ąĘčŗą▓ą░ąĄą╝čŗą╣ ą▒ąĖčé ą┤ąŠčüč鹊ą▓ąĄčĆąĮąŠčüčéąĖ, "valid" ą▒ąĖčé. ąÜąŠą│ą┤ą░ ą▓ ą║čŹčłąĄ ąĮą░čģąŠą┤čÅčéčüčÅ ą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ, čüąŠą▓ą┐ą░ą┤ą░čÄčēąĖąĄ čü čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╝ ą▒ą╗ąŠą║ąŠą╝ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ, č鹊 valid-ą▒ąĖčé ą┤ą╗čÅ čŹč鹊ą│ąŠ ą▒ą╗ąŠą║ą░ ą║čŹčłą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ.

ąÆ ą┤ąŠą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ valid-ą▒ąĖčéčā, ą║ą░ąČą┤čŗą╣ ą▒ą╗ąŠą║ ą▓ ą║čŹčłąĄ čéą░ą║ąČąĄ ąĖą╝ąĄąĄčé ą┐čĆąĖą▓čÅąĘą░ąĮąĮčŗą╣ ą║ ąĮąĄą╝čā čé菹│ ą░ą┤čĆąĄčüą░. ąŁč鹊čé ą░ą┤čĆąĄčü ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé čäąĖąĘąĖč湥čüą║ąĖą╣ ą░ą┤čĆąĄčü ą║čŹčłąĖčĆčāąĄą╝ąŠą│ąŠ ą▒ą╗ąŠą║ą░ ą▓ąŠ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ. ąÜąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ąŠą▒čĆą░čēąĄąĮąĖąĄ ą║ ą▒ą╗ąŠą║čā ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ, ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą║čŹčłą░ čüčĆą░ą▓ąĮąĖą▓ą░ąĄčé ą▓ąĮąĄčłąĮąĖą╣ ą░ą┤čĆąĄčü čü čé菹│ą░ą╝ąĖ ą░ą┤čĆąĄčüą░ ą║čŹčłą░ (čā ą▒ą╗ąŠą║ąŠą▓, ą║ąŠč鹊čĆčŗąĄ ąĖą╝ąĄčÄčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╝ valid-ą▒ąĖčé), čćč鹊ą▒čŗ ąĮą░ą╣čéąĖ ąĮą░ą▒ąŠčĆ ą┤ą░ąĮąĮčŗčģ, ą║ąŠč鹊čĆčŗą╣ ą╝ąŠąČąĄčé čüąŠą┤ąĄčƹȹ░čéčī čŹč鹊čé ą▒ą╗ąŠą║. ąĢčüą╗ąĖ ą░ą┤čĆąĄčü ą▒ą╗ąŠą║ą░ čüąŠą▓ą┐ą░ą┤ą░ąĄčé čü ąŠą┤ąĮąĖą╝ ąĖąĘ č鹥ą│ąŠą▓ ą░ą┤čĆąĄčüą░ ą║čŹčłą░, č鹊 ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą┐ąŠą┐ą░ą┤ą░ąĮąĖąĄ ą▓ ą║čŹčł (čé. ąĄ. ą▓ ą║čŹčłąĄ ąĮą░ą╣ą┤ąĄąĮą░ ąĖąĮč乊čĆą╝ą░čåąĖčÅ, čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēą░čÅ ąĘą░ą┐čĆą░čłąĖą▓ą░ąĄą╝ąŠą╝čā ą▒ą╗ąŠą║čā ąĖąĘ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ).

ąÆ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ set-associative cache ą║ą░ąČą┤čŗą╣ ą░ą┤čĆąĄčü ą┐ą░ą╝čÅčéąĖ ą╝ąŠąČąĄčé čĆą░čüčüą╝ą░čéčĆąĖą▓ą░čéčīčüčÅ ą║ą░ą║ ą║ąŠą╝ą▒ąĖąĮą░čåąĖčÅ čéčĆąĄčģ ą┐ąŠą╗ąĄą╣ (čüą╝. čéą░ą▒ą╗ąĖčåčā 1). ą¤ąĄčĆą▓ąŠąĄ ą┤ąĄą╗ąĄąĮąĖąĄ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą╝ąĄąČą┤čā ą░ą┤čĆąĄčüąŠą╝ ą▒ą╗ąŠą║ą░ ąĖ čüą╝ąĄčēąĄąĮąĖąĄą╝ ą▒ą╗ąŠą║ą░. ą¤ąŠčüą╗ąĄ čŹč鹊ą│ąŠ ą░ą┤čĆąĄčü ą▒ą╗ąŠą║ą░ (čäčĆąĄą╣ą╝) ą╝ąŠąČąĄčé ą▒čŗčéčī čéą░ą║ąČąĄ ą┐ąŠą┤ąĄą╗ąĄąĮ ąĮą░ ą┐ąŠą╗ąĄ čé菹│ą░ ąĖ ą┐ąŠą╗ąĄ ąĖąĮą┤ąĄą║čüą░.

ąóą░ą▒ą╗ąĖčåą░ 1. ąĀą░ąĘą▒ąĖąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░.

ąÉą┤čĆąĄčü ą▒ą╗ąŠą║ą░

|

ąĪą╝ąĄčēąĄąĮąĖąĄ ą▒ą╗ąŠą║ą░

|

| ą¤ąŠą╗ąĄ čé菹│ą░ |

ą¤ąŠą╗ąĄ ąĖąĮą┤ąĄą║čüą░ |

| ąśčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ ą║čŹčłą░, čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ą┐ąŠą┐ą░ą┤ą░ąĮąĖąĄ ąĖą╗ąĖ ą┐čĆąŠą╝ą░čģ ą║čŹčłą░ |

ąśčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą┐čĆąĖą▓čÅąĘą║ąĖ čāą║ą░ąĘą░ąĮąĮąŠą│ąŠ ą▒ą╗ąŠą║ą░ ą║ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą╝čā ąĮą░ą▒ąŠčĆčā (set) |

ąśčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą░ čüą╗ąŠą▓ą░ ą▓ ą┐čĆąĄą┤ąĄą╗ą░čģ čāą║ą░ąĘą░ąĮąĮąŠą│ąŠ ą▒ą╗ąŠą║ą░ |

ą¤ąŠą╗ąĄ čüą╝ąĄčēąĄąĮąĖčÅ ą▒ą╗ąŠą║ą░ ą▓čŗą▒ąĖčĆą░ąĄčé ąĮčāąČąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ąĖąĘ ą▒ą╗ąŠą║ą░. ą¤ąŠą╗ąĄ ąĖąĮą┤ąĄą║čüą░ ą▓čŗą▒ąĖčĆą░ąĄčé ąĮą░ą▒ąŠčĆ, ąĖ ą┐ąŠą╗ąĄ čé菹│ą░ čüčĆą░ą▓ąĮąĖą▓ą░ąĄčéčüčÅ čü čŹčéąĖą╝, čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ą┐ąŠą┐ą░ą┤ą░ąĮąĖąĄ ą▓ ą║čŹčł.

[ąĪčéčĆą░č鹥ą│ąĖčÅ ąĘą░ą┐ąĖčüąĖ]

ąŚą┤ąĄčüčī čĆą░čüčüą╝ą░čéčĆąĖą▓ą░čÄčéčüčÅ ą┤ą▓ąĄ čĆą░ąĘąĮčŗąĄ ą┐čĆąŠą▒ą╗ąĄą╝čŗ, ą▓ąŠąĘąĮąĖą║ą░čÄčēąĖąĄ ą┐čĆąĖ ąŠą┐ąĄčĆą░čåąĖąĖ ąĘą░ą┐ąĖčüąĖ ą▓ ą┐ą░ą╝čÅčéčī, čüą▓čÅąĘą░ąĮąĮąŠą╣ čü ą┤ą░ąĮąĮčŗą╝ąĖ ą║čŹčłą░.

ą×ą┐ąĄčĆą░čåąĖčÅ ąĘą░ą┐ąĖčüąĖ ą▓ čüą╗čāčćą░ąĄ ą┐ąŠą┐ą░ą┤ą░ąĮąĖčÅ ą▓ ą║čŹčł. ąŚą┤ąĄčüčī ąĖą╝ąĄąĄčéčüčÅ 2 ąŠčüąĮąŠą▓ąĮčŗąĄ ąŠą┐čåąĖąĖ ą┐čĆąĖ ąĘą░ą┐ąĖčüąĖ ą┤ą░ąĮąĮčŗčģ ąŠą▒čĆą░čéąĮąŠ ą▓ąŠ ą▓ąĮąĄčłąĮčÄčÄ ą┐ą░ą╝čÅčéčī:

ŌĆó Write-through (WT), čüą║ą▓ąŠąĘąĮą░čÅ ąĘą░ą┐ąĖčüčī: ąĖąĮč乊čĆą╝ą░čåąĖčÅ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ ą║ą░ą║ ą▓ ą▒ą╗ąŠą║ ą║čŹčłą░, čéą░ą║ ąĖ ą▓ ą▒ą╗ąŠą║ ąŠčĆąĖą│ąĖąĮą░ą╗čīąĮąŠą╣ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ, čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╣ ą▒ą╗ąŠą║čā ą║čŹčłą░. ą¤ąŠą▓ąĄą┤ąĄąĮąĖąĄ/čüą║ąŠčĆąŠčüčéčī čĆą░ą▒ąŠčéčŗ čŹč鹊ą╣ čüčģąĄą╝čŗ ą┐ąŠą┤ąŠą▒ąĮčŗ ą┐čĆąŠčüč鹊ą╣ ąĘą░ą┐ąĖčüąĖ ą▓ąŠ ą▓ąĮąĄčłąĮčÄčÄ ą┐ą░ą╝čÅčéčī, ą║ąŠą│ą┤ą░ ą║čŹčł ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ.

ŌĆó Write-back (WB), ąŠą▒čĆą░čéąĮą░čÅ ąĘą░ą┐ąĖčüčī: ąĖąĮč乊čĆą╝ą░čåąĖčÅ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą▓ ą▒ą╗ąŠą║ ą║čŹčłą░. ą¤čĆąĖ ą╝ąŠą┤ąĖčäąĖą║ą░čåąĖąĖ ąĖąĘą╝ąĄąĮąĄąĮąĮą░čÅ čüčéčĆąŠą║ą░ ą║čŹčłą░ (victim cache-line) ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ ą▓ąŠ ą▓ąĮąĄčłąĮčÄčÄ ą┐ą░ą╝čÅčéčī č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ čŹč鹊čé ą▒ą╗ąŠą║ ą║čŹčłą░ ąĘą░ą╝ąĄąĮčÅąĄčéčüčÅ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąŠą┐ąĄčĆą░čåąĖčÅ čüąŠčģčĆą░ąĮąĄąĮąĖčÅ (store), ąŠčüąŠą▒ąĄąĮąĮąŠ ą▓ čĆąĄąČąĖą╝ąĄ čĆą░ą▒ąŠčéčŗ WT, ą▒čāą┤ąĄčé ąŠą▒ąĮąŠą▓ą╗čÅčéčī č鹊ą╗čīą║ąŠ ą╝ąŠą┤ąĖčäąĖčåąĖčĆąŠą▓ą░ąĮąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ. ąØąĄ ą▒čāą┤ąĄčé ąŠčüčāčēąĄčüčéą▓ą╗čÅčéčīčüčÅ čåąĄą╗ąŠą╣ čüčéčĆąŠą║ąĖ ą║čŹčłą░ ą▓ąŠ ą▓ąĮąĄčłąĮčÄčÄ ą┐ą░ą╝čÅčéčī, ąĄčüą╗ąĖ čŹč鹊 ąĮąĄ čéčĆąĄą▒čāąĄčéčüčÅ.

ą¦č鹊ą▒čŗ čāą╝ąĄąĮčīčłąĖčéčī čćą░čüč鹊čéčā ąŠą▒čĆą░čéąĮąŠą╣ ąĘą░ą┐ąĖčüąĖ ą▒ą╗ąŠą║ąŠą▓ ą┐čĆąĖ ąĘą░ą╝ąĄąĮąĄ, ąŠą▒čŗčćąĮąŠ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čäąĖčćą░, ąĮą░ąĘčŗą▓ą░ąĄą╝ą░čÅ "ą│čĆčÅąĘąĮčŗą╣ ą▒ąĖčé", dirty-ą▒ąĖčé. ąŁč鹊 ą▒ąĖčé čüąŠčüč鹊čÅąĮąĖčÅ, ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčēąĖą╣ ą│čĆčÅąĘąĮčŗą╣ ą▒ą╗ąŠą║ ą▓ ą║čŹčłąĄ ąĖą╗ąĖ ąĮąĄčé (ą┐ąŠą┤ "ą│čĆčÅąĘąĮčŗą╝" ą▒ą╗ąŠą║ąŠą╝ ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčéčüčÅ ą╝ąŠą┤ąĖčäąĖčåąĖčĆąŠą▓ą░ąĮąĮčŗą╣ ą▒ą╗ąŠą║; ąĄčüą╗ąĖ ą▒ą╗ąŠą║ ą║čŹčłą░ ąĮąĄ ą▒čŗą╗ ą╝ąŠą┤ąĖčäąĖčåąĖčĆąŠą▓ą░ąĮ, č鹊 ąŠąĮ čüčćąĖčéą░ąĄčéčüčÅ "čćąĖčüčéčŗą╝"). ą¦ąĖčüčéčŗą╣ ą▒ą╗ąŠą║ ąĮąĄ ą▒čāą┤ąĄčé ąĘą░ą┐ąĖčüą░ąĮ ąŠą▒čĆą░čéąĮąŠ ą┐čĆąĖ ąĘą░ą╝ąĄąĮąĄ čŹč鹊ą│ąŠ ą▒ą╗ąŠą║ą░. ąźąŠčéčÅ ą╝ąĮąŠą│ąŠąĄ ąĘą░ą▓ąĖčüąĖčé ąŠčé ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ, ąĮąŠ čĆąĄąČąĖą╝ WB čĆą░ą▒ąŠčéą░ąĄčé čŹčäč乥ą║čéąĖą▓ąĮąĄąĄ ą┐čĆąĖą╝ąĄčĆąĮąŠ ąĮą░ 10..15%, č湥ą╝ čĆąĄąČąĖą╝ WT. ąĀąĄąČąĖą╝ WT ą╗čāčćčłąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī, ą║ąŠą│ą┤ą░ ą┤ąŠą╗ąČąĮą░ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ ą║ąŠą│ąĄčĆąĄąĮčéąĮąŠčüčéčī ą╝ąĄąČą┤čā ą┤ą▓čāą╝čÅ ąĖą╗ąĖ ą▒ąŠą╗čīčłąĖą╝ ą║ąŠą╗ąĖč湥čüčéą▓ąŠą╝ čĆąĄčüčāčĆčüąŠą▓ (ąĮą░ą┐čĆąĖą╝ąĄčĆ, DMA ąĖ čÅą┤čĆąŠ).

ą×ą┐ąĄčĆą░čåąĖąĖ ąĘą░ą┐ąĖčüąĖ čü ą┐čĆąŠą╝ą░čģą░ą╝ąĖ ą║čŹčłą░. ą¤ąŠčüą║ąŠą╗čīą║čā ą┤ą░ąĮąĮčŗąĄ ąĮąĄ ą▒čŗą╗ąĖ ąĮąĄąŠą▒čģąŠą┤ąĖą╝čŗ ą┐čĆąĖ ąĘą░ą┐ąĖčüąĖ, ąĘą┤ąĄčüčī ąĄčüčéčī ą┤ą▓ąĄ ąŠą┐čåąĖąĖ ą┐čĆąĖ ą┐čĆąŠą╝ą░čģąĄ ą║čŹčłą░ ąĮą░ ąĘą░ą┐ąĖčüąĖ:

ŌĆó Write allocate, ą▓čŗą┤ąĄą╗ąĄąĮąĖąĄ ą▒ą╗ąŠą║ą░ ą┐čĆąĖ ąĘą░ą┐ąĖčüąĖ: ą┐čĆąĖ ą┐čĆąŠą╝ą░čģąĄ ą║čŹčłą░ ą▓čŗą┤ąĄą╗čÅąĄčéčüčÅ ą▒ą╗ąŠą║, ąĘą░ ą║ąŠč鹊čĆčŗą╝ ą┐čĆąŠąĖčüčģąŠą┤čÅčé ą┤ąĄą╣čüčéą▓ąĖčÅ, ą║ą░ą║ ą┐čĆąĖ ą┐ąŠą┐ą░ą┤ą░ąĮąĖąĖ ą▓ ą║čŹčł, ąŠą┐ąĖčüą░ąĮąĮčŗąĄ ą▓čŗčłąĄ. ą¤ąŠ čéą░ą║ąŠą╣ čüčģąĄą╝ąĄ ą┐čĆąŠą╝ą░čģ ą╝ąĖą╝ąŠ ą║čŹčłą░ ą┐čĆąĖ ąĘą░ą┐ąĖčüąĖ čĆą░ą▒ąŠčéą░ąĄčé čéą░ą║ ąČąĄ, ą║ą░ą║ ą┐čĆąŠą╝ą░čģ ą╝ąĖą╝ąŠ ą║čŹčłą░ ą┐čĆąĖ čćč鹥ąĮąĖąĖ. ąĪąĮą░čćą░ą╗ą░ čüčéčĆąŠą║ą░ ą║čŹčłą░ ąĘą░čģą▓ą░čéčŗą▓ą░ąĄčéčüčÅ ąĖąĘ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ, ą┐ąĄčĆąĄą┤ č鹥ą╝ ą║ą░ą║ ąŠą▒ąĮąŠą▓ąĖčéčī ą║ą░ą║ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ ą║čŹčł, čéą░ą║ ąĖ ą▓ąĮąĄčłąĮčÄčÄ ą┐ą░ą╝čÅčéčī.

ŌĆó No-write allocate, ą▒ąĄąĘ ą▓čŗą┤ąĄą╗ąĄąĮąĖčÅ ą▒ą╗ąŠą║ą░ ą┐čĆąĖ ąĘą░ą┐ąĖčüąĖ: ą┐čĆąĖ čŹč鹊ą╣ čüčģąĄą╝ąĄ ą┐čĆąŠą╝ą░čģąĖ ą║čŹčłą░ ą┐čĆąĖ ąĘą░ą┐ąĖčüąĖ ąĮąĖą║ą░ą║ ąĮąĄ ą▓ą╗ąĖčÅčÄčé ąĮą░ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ ą║čŹčłą░. ąæą╗ąŠą║ ą▒čāą┤ąĄčé ą╝ąŠą┤ąĖčäąĖčåąĖčĆąŠą▓ą░ąĮ č鹊ą╗čīą║ąŠ ą▓ąŠ ą▓ąĮąĄčłąĮąĄą╣ ąĮąĖąĘą║ąŠčāčĆąŠą▓ąĮąĄą▓ąŠą╣ (ą╝ąĄą┤ą╗ąĄąĮąĮąŠą╣) ą┐ą░ą╝čÅčéąĖ, ąĖ ąĮąĄ ą▒čāą┤ąĄčé ą║čŹčłąĖčĆąŠą▓ą░čéčīčüčÅ.

[ą£ąŠą┤ąĄą╗čī ą║čŹčłą░, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ą░čÅ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą╝ Blackfin]

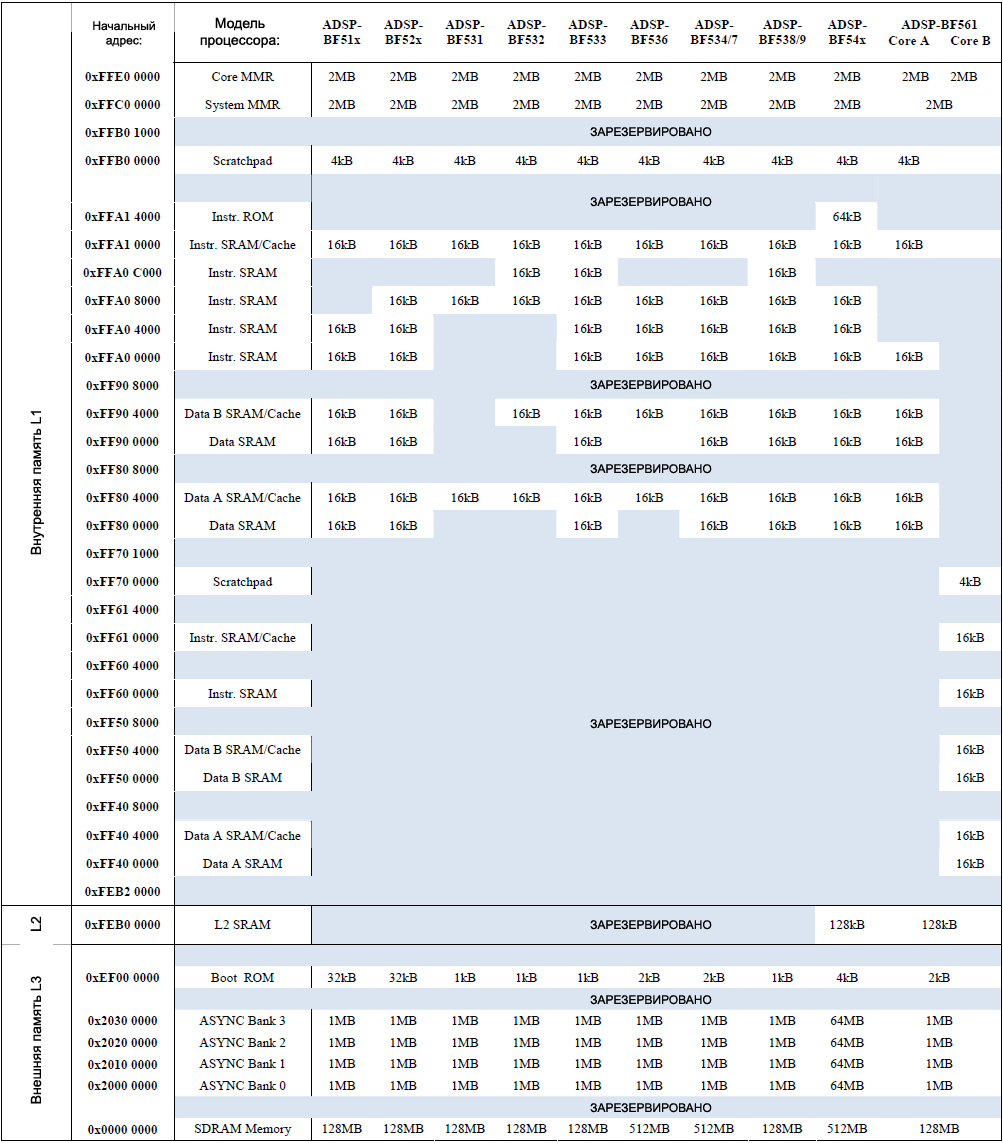

ąŻ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ Blackfin ąĄčüčéčī ą┤ąŠ 3 čāčĆąŠą▓ąĮąĄą╣ ąĖąĄčĆą░čĆčģąĖąĖ ą┐ą░ą╝čÅčéąĖ - L1, L2, L3 - čćč鹊ą▒čŗ ą┐čĆąĄą┤ąŠčüčéą░ą▓ąĖčéčī ąĮąĄą║ąĖą╣ ą║ąŠą╝ą┐čĆąŠą╝ąĖčüčü ą╝ąĄąČą┤čā ąŠą▒čŖąĄą╝ąŠą╝ ą┐ą░ą╝čÅčéąĖ ąĖ ą▒čŗčüčéčĆąŠą┤ąĄą╣čüčéą▓ąĖąĄą╝ (ą┐ą░ą╝čÅčéčī L2 ąĄčüčéčī č鹊ą╗čīą║ąŠ čā ą┤ą▓čāčģčÅą┤ąĄčĆąĮąŠą│ąŠ ADSP-BF561). ą¤ą░ą╝čÅčéčī L1 ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé čüą░ą╝ąŠąĄ ą▓čŗčüąŠą║ąŠąĄ ą▒čŗčüčéčĆąŠą┤ąĄą╣čüčéą▓ąĖąĄ ą┐čĆąĖ čüą░ą╝ąŠą╣ ą╝ą░ą╗ąŠą╣ ąĄą╝ą║ąŠčüčéąĖ. ąóąĖą┐čŗ ą┐ą░ą╝čÅčéąĖ L2 ąĖ L3 ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÄčé ąŠą▒čŖąĄą╝čŗ ą▒ąŠą╗čīčłąĄ, č湥ą╝ L1, ąŠą┤ąĮą░ą║ąŠ ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ ą║ ąĮąĖą╝ ąŠą▒čŗčćąĮąŠ čéčĆąĄą▒čāąĄčéčüčÅ ąĮąĄčüą║ąŠą╗čīą║ąŠ čéą░ą║č鹊ą▓.

ąŻ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ Blackfin ąĄčüčéčī ą▒ą░ąĮą║ąĖ ą┐ą░ą╝čÅčéąĖ L1 ą┤ą░ąĮąĮčŗčģ ąĖ ąĖąĮčüčéčĆčāą║čåąĖą╣, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠąČąĮąŠ ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī ą║ą░ą║ SRAM ąĖą╗ąĖ ą║ą░ą║ ą║čŹčł. ąÜąŠą│ą┤ą░ ą┐ą░ą╝čÅčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮą░ ą║ą░ą║ ą║čŹčł, č鹊 ą║ ąĮąĄą╣ ąĮąĄ ąĖą╝ąĄčÄčé ą┐čĆčÅą╝ąŠą│ąŠ ą┤ąŠčüčéčāą┐ą░ ąĮąĖ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ DMA, ąĮąĖ ąĖąĮčüčéčĆčāą║čåąĖąĖ ąĘą░ą│čĆčāąĘą║ąĖ/čüąŠčģčĆą░ąĮąĄąĮąĖčÅ čÅą┤čĆą░. ąŻ ą▓čüąĄčģ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ Blackfin ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą║čŹčłą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą┐ąŠčćčéąĖ ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠ (čüą╝. čéą░ą▒ą╗ąĖčåčā 2), ąĮąŠ ą┐ąŠčüą╗ąĄą┤čāčÄčēąĄąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ ą▒čāą┤ąĄčé ąŠčüąĮąŠą▓ą░ąĮą░ ąĮą░ ą┐čĆąĖą╝ąĄčĆąĄ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ ADSP-BF533.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ ą┐ą░ą╝čÅčéčī L1 ą┐čĆąŠčåąĄčüčüąŠčĆą░ Blackfin ą┐ąŠą┤ą║ą╗čÄč湥ąĮą░ č湥čĆąĄąĘ čłąĖąĮčā External Access Bus (EAB) ą║ ą▒ą╗ąŠą║čā ą▓ąĮąĄčłąĮąĄą╣ čłąĖąĮčŗ External Bus Interface Unit (EBIU), ą║ąŠč鹊čĆčŗą╣ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčé ą┤ąŠčüčéčāą┐čŗ ą║ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ (ąĮą░ą┐čĆąĖą╝ąĄčĆ ą║ ą┐ą░ą╝čÅčéąĖ SDRAM). ąøčÄą▒ą░čÅ č鹥ą║čāčēą░čÅ ą░ą║čéąĖą▓ąĮąŠčüčéčī EAB ąĮąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąĄčĆą▓ą░ąĮą░, ąĮą░čćą░č鹊ąĄ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĖąĄ čüčéčĆąŠą║ąĖ ą║čŹčłą░ ąŠą▒čÅąĘą░č鹥ą╗čīąĮąŠ ąĘą░ą║ąŠąĮčćąĖčéčüčÅ.

ąóą░ą▒ą╗ąĖčåą░ 2. ąÜą░čĆčéą░ ą┐ą░ą╝čÅčéąĖ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ Blackfin.

[ąÜąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ ą║čŹčłą░ ąĖąĮčüčéčĆčāą║čåąĖą╣ Blackfin]

ą×čĆą│ą░ąĮąĖąĘą░čåąĖčÅ ą║čŹčłą░. ąŻ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ADSP-BF533 ąĖą╝ąĄąĄčéčüčÅ 80 ą║ąĖą╗ąŠą▒ą░ą╣čé ą▓čüčéčĆąŠąĄąĮąĮąŠą╣ ą▓ ą║čĆąĖčüčéą░ą╗ą╗ ą┐ą░ą╝čÅčéąĖ ąĖąĮčüčéčĆčāą║čåąĖą╣. 64 ą║ąĖą╗ąŠą▒ą░ą╣čéą░ ą┐ą░ą╝čÅčéąĖ ąĖąĮčüčéčĆčāą║čåąĖą╣ ą┤ąŠčüčéčāą┐ąĮčŗ ą║ą░ą║ SRAM ąĖąĮčüčéčĆčāą║čåąĖą╣. ą×čüčéą░ą╗čīąĮčŗąĄ 16 ą║ąĖą╗ąŠą▒ą░ą╣čé ą┐ą░ą╝čÅčéąĖ ą╝ąŠąČąĮąŠ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī ą║ą░ą║ ą║čŹčł ąĖąĮčüčéčĆčāą║čåąĖą╣, ą╗ąĖą▒ąŠ ą╝ąŠąČąĮąŠ ąĖčģ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą║ą░ą║ SRAM ąĖąĮčüčéčĆčāą║čåąĖą╣. ąÆ čéą░ą▒ą╗ąĖčåąĄ 2 ą┐ąŠą║ą░ąĘą░ąĮą░ ą║ąŠą╝ą▒ąĖąĮąĖčĆąŠą▓ą░ąĮąĮą░čÅ ą║ą░čĆčéą░ ą┐ą░ą╝čÅčéąĖ ą┤ą╗čÅ ą▓čüąĄčģ ą┤ąŠčüčéčāą┐ąĮčŗčģ ą▓ ąĮą░čüč鹊čÅčēąĄąĄ ą▓čĆąĄą╝čÅ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ čüąĄą╝ąĄą╣čüčéą▓ą░ Blackfin.

ąŻ ą▓čüąĄčģ ą╝ąŠą┤ąĄą╗ąĄą╣ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ Blackfin ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčéčüčÅ ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą┐ą░ą╝čÅčéąĖ ąĖąĮčüčéčĆčāą║čåąĖą╣, ą║ąŠč鹊čĆąŠąĄ ą╝ąŠąČąĮąŠ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī ą╗ąĖą▒ąŠ ą║ą░ą║ ą║čŹčł ąĖąĮčüčéčĆčāą║čåąĖą╣, ą╗ąĖą▒ąŠ ą║ą░ą║ SRAM. ąØą░čćą░ą╗čīąĮčŗą╣ ą░ą┤čĆąĄčü ą▓ ą║ą░čĆč鹥 ą┐ą░ą╝čÅčéąĖ ą▓čüąĄą│ą┤ą░ ąŠą┤ąĖąĮą░ą║ąŠą▓čŗą╣.

ąÜąŠą│ą┤ą░ čŹčéą░ ą┐ą░ą╝čÅčéčī čĆą░ąĘčĆąĄčłąĄąĮą░ ą┤ą╗čÅ ą║čŹčłą░, ą┐ą░ą╝čÅčéčī ąĖąĮčüčéčĆčāą║čåąĖą╣ čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ 4-way set associative memory. ąÜą░ąČą┤čŗą╣ ąĖąĘ 4 ą┐čāč鹥ą╣ ą╝ąŠąČąĮąŠ ąĘą░ą▒ą╗ąŠą║ąĖčĆąŠą▓ą░čéčī ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ. ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą║čŹčłą░ ąĖąĮčüčéčĆčāą║čåąĖą╣ ą╝ąŠąČąĮąŠ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī ą┤ą╗čÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą╝ąŠą┤ąĖčäąĖčåąĖčĆąŠą▓ą░ąĮąĮąŠą╣ ą┐ąŠą╗ąĖčéąĖą║ąĖ LRU (čüą╝. ą▓čĆąĄąĘą║čā "ą×ą▒čēą░čÅ ą║ąŠąĮčåąĄą┐čåąĖčÅ ą║čŹčłąĖčĆąŠą▓ą░ąĮąĖčÅ"), ąĖą╗ąĖ ą┐čĆąŠčüčéčāčÄ ą┐ąŠą╗ąĖčéąĖą║čā LRU ą┤ą╗čÅ ą┐čĆąĖąĮčÅčéąĖčÅ čĆąĄčłąĄąĮąĖčÅ ą┐ąŠ ąĘą░ą╝ąĄąĮąĄ čüčéčĆąŠą║ąĖ ą║čŹčłą░.

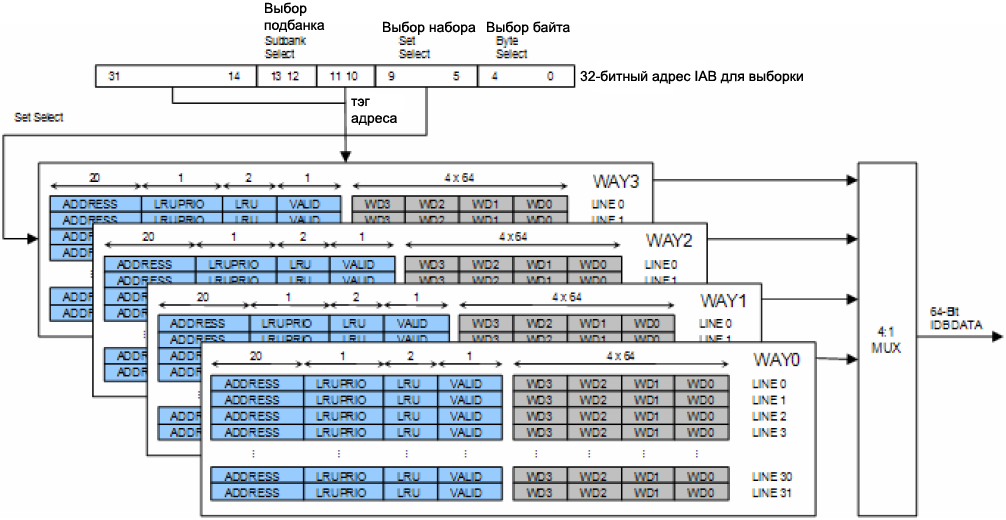

ŌĆó 16 ą║ąĖą╗ąŠą▒ą░ą╣čéąĮčŗą╣ ą║čŹčł ąŠčĆą│ą░ąĮąĖąĘąŠą▓ą░ąĮ ą║ą░ą║ 4 ą┐ąŠą┤ą▒ą░ąĮą║ą░ ą┐ąŠ 4 ą║ąĖą╗ąŠą▒ą░ą╣čéą░ ą║ą░ąČą┤čŗą╣. ą¤ąŠą┤ą▒ą░ąĮą║ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ą▒ąĖčéą░ą╝ąĖ ą░ą┤čĆąĄčüą░ ą┐ą░ą╝čÅčéąĖ [13:12].

ŌĆó ąÜą░ąČą┤čŗą╣ 4 ą║ąĖą╗ąŠą▒ą░ą╣čéąĮčŗą╣ ą┐ąŠą┤ą▒ą░ąĮą║ čüąŠčüč鹊ąĖčé ąĖąĘ 32 ąĮą░ą▒ąŠčĆąŠą▓. ąØą░ą▒ąŠčĆ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ą▒ąĖčéą░ą╝ąĖ ą░ą┤čĆąĄčüą░ ą┐ą░ą╝čÅčéąĖ [9:5].

ŌĆó ąÜą░ąČą┤čŗą╣ ąĮą░ą▒ąŠčĆ čüąŠčüč鹊ąĖčé ąĖąĘ 4 ą┐čāč鹥ą╣ (way). ą¤čāčéčī ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ ą║čŹčłą░ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü ą┐ąŠą╗ąĖčéąĖą║ąŠą╣ čĆą░ąĘą╝ąĄčēąĄąĮąĖčÅ čüčéčĆąŠą║ąĖ ą║čŹčłą░. ą¤čāčéąĖ ą╝ąŠąČąĮąŠ ąĖą┤ąĄąĮčéąĖčäąĖčåąĖčĆąŠą▓ą░čéčī ą▒ąĖčéą░ą╝ąĖ ą░ą┤čĆąĄčüą░ [11:10] ą▓ SRAM.

ŌĆó ąöčĆčāą│ąĖą╝ąĖ čüą╗ąŠą▓ą░ą╝ąĖ, ąĮą░ą▒ąŠčĆ 0 (set-0) ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé č湥čéčŗčĆąĄ ą┐čāčéąĖ ą┤ą╗čÅ čüčéčĆąŠą║ąĖ 0 (line-0).

ŌĆó ąĀą░ąĘą╝ąĄčĆ čüčéčĆąŠą║ąĖ ą║čŹčłą░ (ą┤ą╗čÅ čćč鹥ąĮąĖčÅ ą▓ čüą╗čāčćą░ąĄ ą┐čĆąŠą╝ą░čģą░ ą║čŹčłą░) čĆą░ą▓ąĄąĮ 32 ą▒ą░ą╣čéą░.

ąÆąĮąĄčłąĮąĖą╣ ą┐ąŠčĆčé čćč鹥ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ (ą┤ą╗čÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą║čŹčłą░) ąĖą╝ąĄąĄčé čłąĖčĆąĖąĮčā 64 ą▒ąĖčéą░ (8 ą▒ą░ą╣čé). ąĪą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ, ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą║čŹčłą░ čćąĖčéą░ąĄčé ą▓čüčÄ čüčéčĆąŠą║čā ą║čŹčłą░ ą║ą░ą║ ą┐ą░čćą║čā ąĖąĘ č湥čéčŗčĆąĄčģ 8-ą▒ą░ą╣čéąĮčŗčģ ą║čāčüą║ąŠą▓ ą┤ą░ąĮąĮčŗčģ.

ąŻ ą║ą░ąČą┤ąŠą╣ čüčéčĆąŠą║ąĖ ąĄčüčéčī čé菹│, čüą▓čÅąĘą░ąĮąĮčŗą╣ čü ąĮąĄą╣. ąó菹│ čüąŠčüč鹊ąĖčé ąĖąĘ čüą╗ąĄą┤čāčÄčēąĖčģ 4 čćą░čüč鹥ą╣:

ŌĆó 20-ą▒ąĖčéąĮčŗą╣ č鹥ą│ ą░ą┤čĆąĄčüą░: čüčĆą░ą▓ąĮąĖą▓ą░ąĄčéčüčÅ čü ą░ą┤čĆąĄčüąŠą╝ ą┐ą░ą╝čÅčéąĖ, čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ą┐ąŠą┐ą░ą┤ą░ąĮąĖąĄ ą▓ ą║čŹčł ąĖą╗ąĖ ą┐čĆąŠą╝ą░čģ ą║čŹčłą░.

ŌĆó LRU Priority: ą┐čĆąĖąŠčĆąĖč鹥čé ą┤ą╗čÅ ą╝ąŠą┤ąĖčäąĖčåąĖčĆąŠą▓ą░ąĮąĮąŠą╣ ą┐ąŠą╗ąĖčéąĖą║ąĖ LRU.

ŌĆó LRU State: čüąŠčüč鹊čÅąĮąĖąĄ LRU, ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ ą║čŹčłą░ ą┤ą╗čÅ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐ąŠą╗ąĖčéąĖą║ąĖ LRU.

ŌĆó Valid-ą▒ąĖčé: ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą┤ąŠčüč鹊ą▓ąĄčĆąĮąŠčüčéčī ą┤ą░ąĮąĮčŗčģ čüčéčĆąŠą║ąĖ.

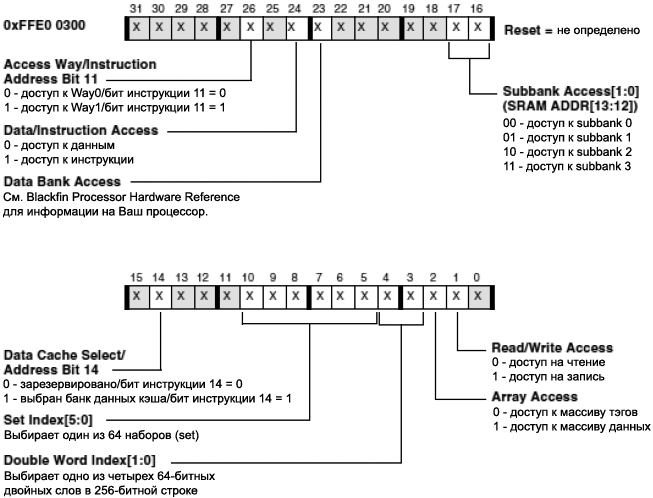

32-ą▒ąĖčéąĮą░čÅ ąŠą▒ą╗ą░čüčéčī ą░ą┤čĆąĄčüą░ ą┐čĆąĖą▓čÅąĘą░ąĮą░ ą║ ąŠą▒ą╗ą░čüčéąĖ ą┐ą░ą╝čÅčéąĖ ą║čŹčłą░ čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝:

ŌĆó ąÆčŗą▒ąŠčĆ ą┐ąŠą┤ą▒ą░ąĮą║ą░ (Subbank Select): ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ąŠčéą┤ąĄą╗čīąĮčŗą╣ 4 ą║ąĖą╗ąŠą▒ą░ą╣čéąĮčŗą╣ ą┐ąŠą┤ą▒ą░ąĮą║.

ŌĆó ąÆčŗą▒ąŠčĆ ąĮą░ą▒ąŠčĆą░ (Set Select): ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ąĮą░ą▒ąŠčĆ ąĖąĘ 32 ąĮą░ą▒ąŠčĆąŠą▓ ą║čŹčłą░.

ŌĆó ąÆčŗą▒ąŠčĆ ą▒ą░ą╣čéą░ (Byte Select): ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ą▒ą░ą╣čé ąĖąĘ ą┤ą░ąĮąĮąŠą╣ čüčéčĆąŠą║ąĖ.

ąØą░ čĆąĖčü. 5 ą┐ąŠą║ą░ąĘą░ąĮąŠ, ą║ą░ą║ ąŠčĆą│ą░ąĮąĖąĘąŠą▓ą░ąĮ 4 ą║ąĖą╗ąŠą▒ą░ą╣čéąĮčŗą╣ ą┐ąŠą┤ą▒ą░ąĮą║ ą║čŹčłą░ ąĖąĮčüčéčĆčāą║čåąĖą╣. ąÜą░ąČą┤čŗą╣ 4 ą║ąĖą╗ąŠą▒ą░ą╣čéąĮčŗą╣ ą┐ąŠą┤ą▒ą░ąĮą║ąĖ ąĖą╝ąĄąĄčé ąŠą┤ąĖąĮą░ą║ąŠą▓čāčÄ čüčéčĆčāą║čéčāčĆčā.

ąĀąĖčü. 5. ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą║čŹčłą░ ąĖąĮčüčéčĆčāą║čåąĖą╣ ą┤ą╗čÅ ąŠą┤ąĮąŠą│ąŠ ą┐ąŠą┤ą▒ą░ąĮą║ą░, ą┐čĆąĖą╝ąĄąĮąĄąĮą░ ąŠčĆą│ą░ąĮąĖąĘą░čåąĖčÅ ą║čŹčłą░ 4-way set associative.

ąóą░ą▒ą╗ąĖčåą░ 3. ą¤ąŠą╗ąĖčéąĖą║ą░ ąĘą░ą╝ąĄąĮčŗ ą┤ą╗čÅ ą║čŹčłą░ ąĖąĮčüčéčĆčāą║čåąĖą╣ Blackfin.

ąĪąĖčéčāą░čåąĖčÅ

|

ąĪčéčĆą░č鹥ą│ąĖčÅ |

| ąóąŠą╗čīą║ąŠ ąŠą┤ąĖąĮ ąĮąĄą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗą╣ way ą▓ ąĮą░ą▒ąŠčĆąĄ (set) |

ą¤čĆąĖčģąŠą┤čÅčēąĖą╣ ą▒ą╗ąŠą║ ąĘą░ą╝ąĄąĮąĖčé čŹč鹊čé ą▒ą╗ąŠą║ |

| ąæąŠą╗čīčłąĄ ąŠą┤ąĮąŠą│ąŠ ąĮąĄą┤ąŠčüč鹊ą▓ąĄčĆąĮąŠą│ąŠ way ą▓ ą║čŹčłąĄ |

ąØąĄą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗą╣ way ą▒čāą┤ąĄčé ąĘą░ą╝ąĄąĮąĄąĮ ą▓ čéą░ą║ąŠą╝ ą┐ąŠčĆčÅą┤ą║ąĄ: ą┐ąĄčĆą▓čŗą╝ way0, ąĘą░č鹥ą╝ way1, way2, ąĖ ą▓ ą║ąŠąĮčåąĄ way3. |

| ąÆ ą║čŹčłąĄ ąĮąĄčé ąĮąĄą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗčģ way |

ąæčāą┤ąĄčé ąĘą░ą╝ąĄąĮąĄąĮ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╣ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠ ą┤ą░ą▓ąĮąŠ way (Last-recently used, LRU). ąöą╗čÅ ą╝ąŠą┤ąĖčäąĖčåąĖčĆąŠą▓ą░ąĮąĮąŠą╣ ą┐ąŠą╗ąĖčéąĖą║ąĖ LRU: way čü ą▓čŗčüąŠą║ąĖą╝ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝ ąĮąĄ ą▒čāą┤ąĄčé ąĘą░ą╝ąĄąĮąĄąĮ, ąĄčüą╗ąĖ ąĖą╝ąĄąĄčéčüčÅ ą▓ čŹč鹊ą╝ ąĮą░ą▒ąŠčĆąĄ way čü ąĮąĖąĘą║ąĖą╝ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝. ąØąĖąĘą║ąŠą┐čĆąĖąŠčĆąĖč鹥čéąĮčŗą╣ ą▒ą╗ąŠą║ ąĮąĄ ą╝ąŠąČąĄčé ąĘą░ą╝ąĄąĮąĖčéčī ą▓čŗčüąŠą║ąŠą┐čĆąĖąŠčĆąĖč鹥čéąĮčŗą╣. ąĢčüą╗ąĖ čā ą▓čüąĄčģ way ą▓čŗčüąŠą║ąĖą╣ ą┐čĆąĖąŠčĆąĖč鹥čé, č鹊 way čü ąĮąĖąĘą║ąĖą╝ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝ ąĮąĄ ą╝ąŠąČąĄčé ą║čŹčłąĖčĆąŠą▓ą░čéčīčüčÅ. |

ą¤ąŠą┐ą░ą┤ą░ąĮąĖčÅ/ą┐čĆąŠą╝ą░čģąĖ ą║čŹčłą░ ąĖ ąĘą░ą╝ąĄąĮą░ čüčéčĆąŠą║ąĖ ą║čŹčłą░. ą¤ąŠą┐ą░ą┤ą░ąĮąĖąĄ ą▓ ą║čŹčł ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą┐čāč鹥ą╝ čüčĆą░ą▓ąĮąĄąĮąĖčÅ čüčéą░čĆčłąĖčģ 18 ą▒ąĖčé ąĖ ą▒ąĖč鹊ą▓ 11 ąĖ 10 ą░ą┤čĆąĄčüą░ ą▓čŗą▒ąŠčĆą║ąĖ ąĖąĮčüčéčĆčāą║čåąĖąĖ čü č鹥ą│ąŠą╝ ą░ą┤čĆąĄčüą░ ą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗčģ čüčéčĆąŠą║, ąĮą░čģąŠą┤čÅčēąĖčģčüčÅ ą▓ ą┤ą░ąĮąĮčŗą╣ ą╝ąŠą╝ąĄąĮčé ą▓ ąĮą░ą▒ąŠčĆąĄ ą║čŹčłą░. ąĢčüą╗ąĖ čüčĆą░ą▓ąĮąĄąĮąĖąĄ čü č鹥ą│ąŠą╝ ą░ą┤čĆąĄčüą░ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüąŠą▓ą┐ą░ą┤ąĄąĮąĖąĄ, č鹊 ą┐ąŠą╗čāčćą░ąĄčéčüčÅ ą┐ąŠą┐ą░ą┤ą░ąĮąĖąĄ ą▓ ą║čŹčł. ąĢčüą╗ąĖ čüčĆą░ą▓ąĮąĄąĮąĖąĄ ąĮąĄ ą┤ą░ą╗ąŠ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą│ąŠ čĆąĄąĘčāą╗čīčéą░čéą░, č鹊 ą┐ąŠą╗čāčćą░ąĄčéčüčÅ ą┐čĆąŠą╝ą░čģ ą╝ąĖą╝ąŠ ą║čŹčłą░.

ą¤čĆąĄą┤ą┐ąŠą╗ąŠąČąĖą╝, čćč鹊 ą┐čĆąŠąĖąĘąŠčłąĄą╗ ą┤ąŠčüčéčāą┐ ą┐ąŠ ą░ą┤čĆąĄčüčā 0x10374956. ąŁč鹊čé ą░ą┤čĆąĄčü ą┐čĆąĖą▓čÅąĘą░ąĮ ą║ set-10 ą┐ąŠą┤ą▒ą░ąĮą║ą░ 0. ąĪčéą░čĆčłąĖąĄ 18 ą▒ąĖčé ąĖ ą▒ąĖčéčŗ 11-10 čŹč鹊ą│ąŠ ą░ą┤čĆąĄčüą░ (č乊čĆą╝ąĖčĆčāčÄčé čüą╗ąŠą▓ąŠ čé菹│ą░) ą▒čāą┤čāčé čüčĆą░ą▓ąĮąĖą▓ą░čéčīčüčÅ čüąŠ ą▓čüąĄą╝ąĖ ą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗą╝ąĖ čé菹│ą░ą╝ąĖ (čā ą║ąŠč鹊čĆčŗčģ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ valid-ą▒ąĖčé) ą▓ ąĮą░ą▒ąŠčĆąĄ set-10.

ą¤čĆąĖ ą┐čĆąŠą╝ą░čģąĄ ą║čŹčłą░ ą▒ą╗ąŠą║ ą┐ą░ą╝čÅčéąĖ ąĖąĮčüčéčĆčāą║čåąĖą╣ ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ą┤ąŠčüčéčāą┐ ąĮą░ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĖąĄ čüčéčĆąŠą║ąĖ ą║čŹčłą░, čćč鹊ą▒čŗ ą┐ąŠą╗čāčćąĖčéčī ąĮąĄą┤ąŠčüčéą░čÄčēčāčÄ čüčéčĆąŠą║čā ą║čŹčłą░ ąĖąĘ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ. ą»ą┤čĆąŠ ą┐čĆąĖąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé čĆą░ą▒ąŠčéčā, ą┐ąŠą║ą░ ąĮąĄ ą▒čāą┤ąĄčé ą▓ąŠąĘą▓čĆą░čēąĄąĮąŠ čåąĄą╗ąĄą▓ąŠąĄ čüą╗ąŠą▓ąŠ ąĖąĮčüčéčĆčāą║čåąĖąĖ ąĖąĘ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ.

ąÉą┤čĆąĄčü ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ ą║ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ čÅą▓ą╗čÅąĄčéčüčÅ ą░ą┤čĆąĄčüąŠą╝ čåąĄą╗ąĄą▓ąŠą│ąŠ čüą╗ąŠą▓ą░ ąĖąĮčüčéčĆčāą║čåąĖąĖ. ąæą╗ąŠą║ ąĘą░ą╝ąĄąĮčŗ čüčéčĆąŠą║ąĖ ą║čŹčłą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą▒ąĖčéčŗ Valid ąĖ LRU (ąĮą░ čĆą░ąĘą▒ą╗ąŠą║ąĖčĆąŠą▓ą░ąĮąĮčŗčģ ą┐čāčéčÅčģ, unlocked ways), čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī, ą║ą░ą║ąŠą╣ ą▒ą╗ąŠą║ (ąĖąĘ ąĖą╝ąĄčÄčēąĖčģčüčÅ ą▒ą╗ąŠą║ąŠą▓ ą▓ ąĮą░ą▒ąŠčĆąĄ) ą▒čāą┤ąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ąĮąŠą▓ąŠą╣ čüčéčĆąŠą║ąĖ ą║čŹčłą░. ąÆ čéą░ą▒ą╗ąĖčåąĄ 3 ą┐ąŠą║ą░ąĘą░ąĮąŠ, ą║ą░ą║ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ą┐ąŠą╗ąĖčéąĖą║ą░ ąĘą░ą╝ąĄąĮčŗ čüčéčĆąŠą║ąĖ ą║čŹčłą░.

ąŚą░ą┐ąŠą╗ąĮąĄąĮąĖąĄ čüčéčĆąŠą║ąĖ ą║čŹčłą░ čüąŠčüč鹊ąĖčé ąĖąĘ ąĘą░čģą▓ą░čéą░ 32 ą▒ą░ą╣čé (ąŠą┤ąĖąĮ ą▒ą╗ąŠą║) ą┤ą░ąĮąĮčŗčģ ąĖąĘ ą┐ą░ą╝čÅčéąĖ. ąÉą┤čĆąĄčü ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ čćč鹥ąĮąĖčÅ čÅą▓ą╗čÅąĄčéčüčÅ ą░ą┤čĆąĄčüąŠą╝ čåąĄą╗ąĄą▓ąŠą│ąŠ čüą╗ąŠą▓ą░ ąĖąĮčüčéčĆčāą║čåąĖąĖ. ą¤čĆąĖ ąŠčéą▓ąĄč鹥 ąĮą░ ąĘą░ą┐čĆąŠčü čćč鹥ąĮąĖčÅ čüčéčĆąŠą║ąĖ ąŠčé ą▒ą╗ąŠą║ą░ ąĖąĮčüčéčĆčāą║čåąĖą╣ ą┐ą░ą╝čÅčéąĖ ą▓ąĮąĄčłąĮčÅčÅ ą┐ą░ą╝čÅčéčī ą▓ąĄčĆąĮąĄčé čüąĮą░čćą░ą╗ą░ 64-ą▒ąĖčéąĮąŠąĄ čüą╗ąŠą▓ąŠ čåąĄą╗ąĄą▓ąŠą╣ ąĖąĮčüčéčĆčāą║čåąĖąĖ. ąĪą╗ąĄą┤čāčÄčēąĖąĄ 3 čüą╗ąŠą▓ą░ ą▒čāą┤čāčé ąĘą░čģą▓ą░čéčŗą▓ą░čéčīčüčÅ ą┤čĆčāą│ ąĘą░ ą┤čĆčāą│ąŠą╝ ą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ą░ą┤čĆąĄčüą░čģ, ą║ą░ą║ čŹč鹊 ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▓ čéą░ą▒ą╗ąĖčåąĄ 4.

ąóą░ą▒ą╗ąĖčåą░ 4. ą¤ąŠčĆčÅą┤ąŠą║ ą▓čŗą▒ąŠčĆą║ąĖ čüą╗ąŠą▓ą░ čüčéčĆąŠą║ąĖ ą║čŹčłą░ ąĖąĮčüčéčĆčāą║čåąĖą╣.

ą”ąĄą╗ąĄą▓ąŠąĄ čüą╗ąŠą▓ąŠ

|

ą¤ąŠčĆčÅą┤ąŠą║ ą▓čŗą▒ąŠčĆą║ąĖ ą┤ą╗čÅ čüą╗ąĄą┤čāčÄčēąĖčģ čéčĆąĄčģ čüą╗ąŠą▓ |

| WD0 |

WD0, WD1, WD2, WD3 |

| WD1 |

WD1, WD2, WD3, WD0 |

| WD2 |

WD2, WD3, WD0, WD1 |

| WD3 |

WD3, WD0, WD1, WD2 |

ąÜąŠą│ą┤ą░ ą▒ą╗ąŠą║ ą║čŹčłą░ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ąĖąĘ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ, ą║ą░ąČą┤ąŠąĄ 64-ą▒ąĖčéąĮąŠąĄ čüą╗ąŠą▓ąŠ ą▒čāč乥čĆąĖąĘąĖčĆčāąĄčéčüčÅ ą▓ 4-čÅč湥ąĄčćąĮąŠą╝ ą▒čāč乥čĆąĄ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĖčÅ čüčéčĆąŠą║ąĖ, ą┐ąĄčĆąĄą┤ č鹥ą╝ ą║ą░ą║ ąŠąĮąŠ ą▒čāą┤ąĄčé ąĘą░ą┐ąĖčüą░ąĮąŠ ą▓ 4 ą║ąĖą╗ąŠą▒ą░ą╣čéąĮčŗą╣ ą▒ą░ąĮą║ ą┐ą░ą╝čÅčéąĖ. ąæčāč乥čĆ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĖčÅ čüčéčĆąŠą║ąĖ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé čÅą┤čĆčā ą┐ąŠą╗čāčćąĖčéčī ą┤ą░ąĮąĮčŗąĄ ąĖąĘ ąĮąŠą▓ąŠą╣ čüčéčĆąŠą║ąĖ ą║čŹčłą░ ą▓ąŠ ą▓čĆąĄą╝čÅ, ą║ąŠą│ą┤ą░ čüčéčĆąŠą║ą░ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ąĖąĘ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ, ą▒ąĄąĘ ąŠąČąĖą┤ą░ąĮąĖčÅ, ą┐ąŠą║ą░ ą▓čüčÅ čüčéčĆąŠą║ą░ ą▒čāą┤ąĄčé ąĘą░ą┐ąĖčüą░ąĮą░ ą▓ ą║čŹčł.

ŌĆó ą║čŹčł ą▓čŗą║ą╗čÄč湥ąĮ: ą┤ąĄą╗ą░ąĄčéčüčÅ ą▓čŗą▒ąŠčĆą║ą░ 64 ą▒ąĖčé / 8 ą▒ą░ą╣čé

ŌĆó ą║čŹčł ą▓ą║ą╗čÄč湥ąĮ: ą▓čüąĄą│ą┤ą░ ą┤ąĄą╗ą░ąĄčéčüčÅ ą▓čŗą▒ąŠčĆą║ą░ 256 ą▒ąĖčé / 32 ą▒ą░ą╣čé (čāčüą║ąŠčĆąĄąĮąĮąŠąĄ ą┐ą░ą║ąĄčéąĮąŠąĄ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĖąĄ)

ŌĆó ą¤ąŠčüą║ąŠą╗čīą║čā ąĖąĮč鹥čĆč乥ą╣čü ą║ SDRAM (ą▓ąĮąĄčłąĮčÅčÅ ą┐ą░ą╝čÅčéčī) ąĮą░ ą▒ąŠą╗čīčłąĖąĮčüčéą▓ąĄ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ Blackfin ąĖą╝ąĄąĄčé čłąĖčĆąĖąĮčā 16 ą▒ąĖčé, č鹊 ą║ą░ąČą┤ą░čÅ ą▓čŗą▒ąŠčĆą║ą░ ąĖąĮčüčéčĆčāą║čåąĖąĖ čüąŠčüč鹊ąĖčé ąĖąĘ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ 16-ą▒ąĖčéąĮčŗčģ ą┤ąŠčüčéčāą┐ąŠą▓ ą║ ą┐ą░ą╝čÅčéąĖ.

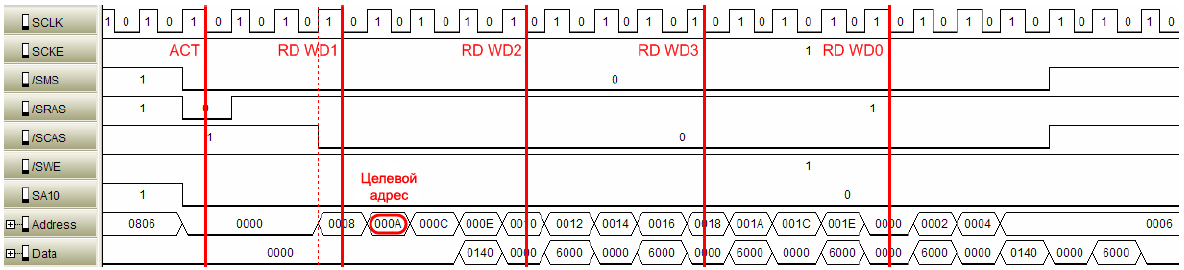

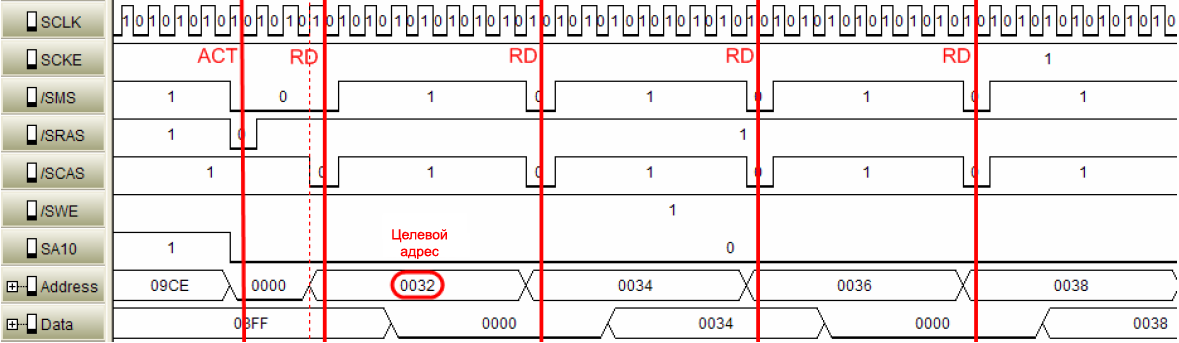

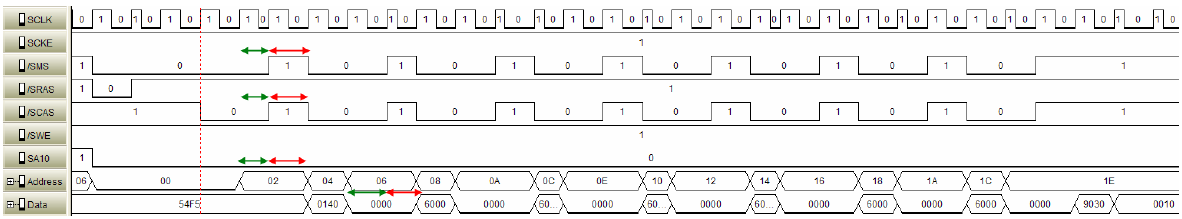

ąØą░ čĆąĖčü. 6 ą┐ąŠą║ą░ąĘą░ąĮą░ ą▓čŗą▒ąŠčĆą║ą░ ąĖąĮčüčéčĆčāą║čåąĖąĖ ąĖąĘ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ SDRAM (čåąĄą╗ąĄą▓ąŠą╣ ą░ą┤čĆąĄčü 0x000Ah), ą║ąŠą│ą┤ą░ ą║čŹčł ąĖąĮčüčéčĆčāą║čåąĖą╣ ą▓čŗą║ą╗čÄč湥ąĮ. ą¤čĆąĖ čŹč鹊ą╝ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ 64-ą▒ąĖčéąĮčŗą╣ ą▒ą╗ąŠą║ (ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮ ą║ą░ą║ WDx). ąØą░čćą░ą╗čīąĮčŗą╣ ą░ą┤čĆąĄčü ą▒ą╗ąŠą║ą░ 0x0008h, ą┐ąŠčüą║ąŠą╗čīą║čā ą┤ąŠčüčéčāą┐ (ą▓čŗą▒ąŠčĆą║ą░ ąĖąĮčüčéčĆčāą║čåąĖąĖ) ą▓čŗčĆąŠą▓ąĮąĄąĮ ąĮą░ ą│čĆą░ąĮąĖčåčā ą▓ 64 ą▒ąĖčéą░.

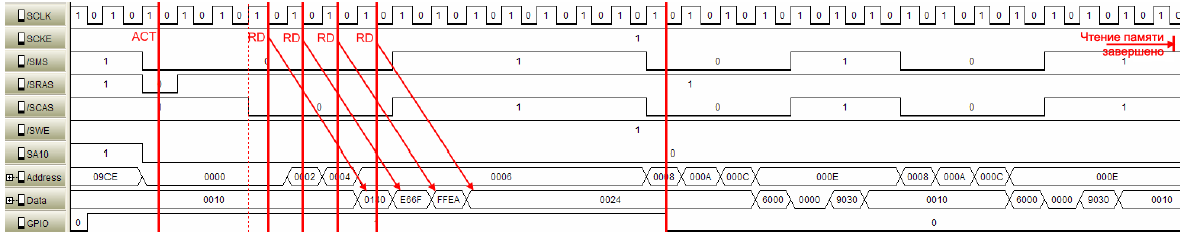

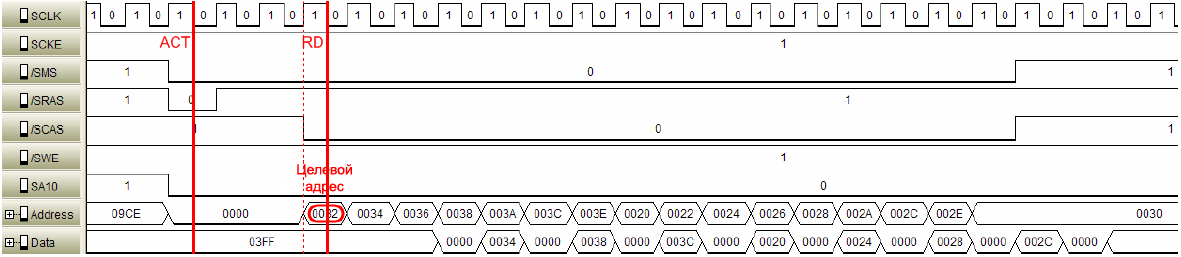

ąĀąĖčü. 7 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé č鹊čé ąČąĄ čüą░ą╝čŗą╣ ą┤ąŠčüčéčāą┐, ą║ąŠą│ą┤ą░ ą║čŹčł ąĖąĮčüčéčĆčāą║čåąĖą╣ ą▓ą║ą╗čÄč湥ąĮ. ąØą░čćą░ą╗čīąĮčŗą╣ ą░ą┤čĆąĄčü ąŠčüčéą░ą╗čüčÅ čĆą░ą▓ąĮčŗą╝ 0x0008h. ąŁč鹊 ąĮą░čćą░ą╗ąŠ WD1. WD2 ąĮą░čćąĖąĮą░ąĄčéčüčÅ čü ą░ą┤čĆąĄčüą░ 0x0010h, ąĖ WD3 ąĮą░čćąĖąĮą░ąĄčéčüčÅ čü ą░ą┤čĆąĄčüą░ 0x0018h. WD0 čü ą░ą┤čĆąĄčüąŠą╝ 0x0000h čÅą▓ą╗čÅąĄčéčüčÅ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╣ čćą░čüčéčīčÄ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ąŠą│ąŠ ą▒ą╗ąŠą║ą░ ą║čŹčłą░.

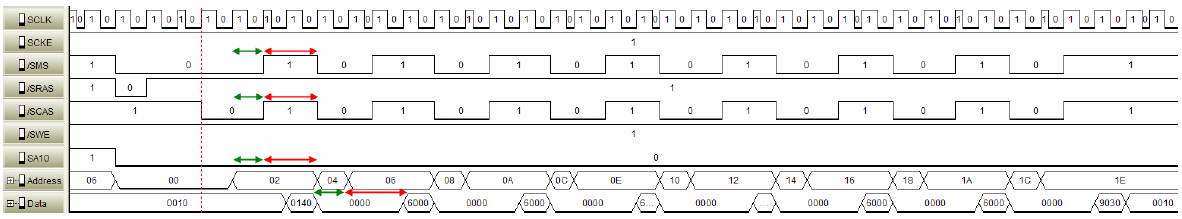

ąĀąĖčü. 8 ąĖ 9 ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčé ąĘą░ą┤ąĄčƹȹ║ąĖ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą┤ą╗čÅ ąĖąĮčüčéčĆčāą║čåąĖą╣, čüąŠčģčĆą░ąĮąĄąĮąĮčŗčģ ą▓ąŠ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ (ąĮą░čćą░ą╗čīąĮčŗą╣ ą░ą┤čĆąĄčü 0x00000). ąĪąĖą│ąĮą░ą╗ "GPIO" ą┐ąĄčĆąĄą║ą╗čÄčćąĖčéčüčÅ ąĖąĘ 1 ą▓ 0 čäčāąĮą║čåąĖąĄą╣, čĆą░čüą┐ąŠą╗ąŠąČąĄąĮąĮąŠą╣ ą▓ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ. ąŁčéą░ čäčāąĮą║čåąĖčÅ ą▒čāą┤ąĄčé ą▓čŗą│ą╗čÅą┤ąĄčéčī ą┐čĆąĖą╝ąĄčĆąĮąŠ čéą░ą║, ą║ą░ą║ ąĮą░ čŹč鹊ą╝ ą╗ąĖčüčéąĖąĮą│ąĄ:

[--SP] = (R7:7,P5:5);

P5.H = hi(FIO_FLAG_C);

P5.L = hi(FIO_FLAG_C);

R7 = 0x20 (z);

w[P5] = R7;

ssync;

(R7:7,P5:5) = [SP++];

rts;

ąöą╗čÅ ą┤ąŠčüčéčāą┐ą░ ą║ ą┐ą░ą╝čÅčéąĖ SDRAM ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ąĮąĄčüą║ąŠą╗čīą║ąŠ ąŠą┐ąĄčĆą░čåąĖą╣ ą┐čĆąĖ čäą░ą║čéąĖč湥čüą║ąŠą╝ čćč鹥ąĮąĖąĖ ą┐ą░ą╝čÅčéąĖ (RD: ąŠąĘąĮą░čćą░ąĄčé ą║ąŠą╝ą░ąĮą┤čā čćč鹥ąĮąĖčÅ). ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ ą┐čĆąŠ ą▒čŗčüčéčĆąŠą┤ąĄą╣čüčéą▓ąĖąĄ SDRAM čüą╝. čĆą░ąĘą┤ąĄą╗ "ąĪąŠąŠą▒čĆą░ąČąĄąĮąĖčÅ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéąĖ".

ąĀąĖčü. 8 ąĖ 9 ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčé ą┤ąŠčüčéčāą┐ ą║ čüą┐ąĄčåąĖčäąĖčćąĮąŠą╝čā ą▒ą░ąĮą║čā ą▓ ą┐ą░ą╝čÅčéąĖ SDRAM. ąĪąĮą░čćą░ą╗ą░ čåąĄą╗ąĄą▓ą░čÅ čüčéčĆąŠą║ą░ (row, ąĖą╝ąĄąĄčéčüčÅ ą▓ ą▓ąĖą┤čā ąĮąĄ čüčéčĆąŠą║ą░ ą║čŹčłą░, ą░ čüčéčĆąŠą║ą░ SDRAM) ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ąŠčéą║čĆčŗčéą░ ą▓ ąŠčéą┤ąĄą╗čīąĮąŠą╝ ą▒ą░ąĮą║ąĄ (ACT: ą║ąŠą╝ą░ąĮą┤ą░ Active).

ą¤ąŠčüą╗ąĄ ąĘą░ą┤ąĄčƹȹ║ąĖ ACTIVE-to-READ-or-WRITE (tRCD, ąĘą┤ąĄčüčī čŹč鹊 3 čéą░ą║čéą░ SCLK), ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠčéą┐čĆą░ą▓ą╗ąĄąĮą░ ą║ąŠą╝ą░ąĮą┤ą░ čćč鹥ąĮąĖčÅ. ą¤ąŠčüą╗ąĄ ąĘą░ą┤ąĄčƹȹ║ąĖ ą▓čŗčüčéą░ą▓ą╗ąĄąĮąĖčÅ čüąĖą│ąĮą░ą╗ą░ čüč鹊ą╗ą▒čåą░ CAS (CL, ąĘą┤ąĄčüčī čŹč鹊 3 čéą░ą║čéą░ SCLK), čüčéą░ąĮąŠą▓ąĖčéčüčÅ ą┤ąŠčüčéčāą┐ąĮąŠą╣ ą┐ąĄčĆą▓ą░čÅ ą┐ąŠčĆčåąĖčÅ ą┤ą░ąĮąĮčŗčģ.

ąöąŠ ąĮą░čüč鹊čÅčēąĄą│ąŠ ą╝ąŠą╝ąĄąĮčéą░ ąĘą░ą┤ąĄčƹȹ║ą░ ą┤ąŠčüčéčāą┐ą░ čü ą▓ą║ą╗čÄč湥ąĮąĮčŗą╝ ą║čŹčłąĄą╝ ąĖ čü ą▓čŗą║ą╗čÄč湥ąĮąĮčŗą╝ ą║čŹčłąĄą╝ ą┐ąŠą║ą░ ąŠą┤ąĖąĮą░ą║ąŠą▓ą░čÅ. ąöą╗čÅ ą┐ąĄčĆą▓ąŠą│ąŠ 64-ą▒ąĖčéąĮąŠą│ąŠ ą▒ą╗ąŠą║ą░ ąĖąĮčüčéčĆčāą║čåąĖą╣ ąĮąĄčé ąĮąĖą║ą░ą║ąĖčģ ąŠčéą╗ąĖčćąĖą╣, ą▓čĆąĄą╝čÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠąĄ. ą¤ąŠčüą╗ąĄ ą┐čĆąĖą╝ąĄčĆąĮąŠ 10 čéą░ą║č鹊ą▓ SCLK ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą┐ąĄčĆą▓ą░čÅ ąĖąĮčüčéčĆčāą║čåąĖčÅ.

ąöąŠčüč鹊ąĖąĮčüčéą▓ąŠ ą║čŹčłą░ ąĖąĮčüčéčĆčāą║čåąĖą╣ ą┐čĆąŠčÅą▓ą╗čÅąĄčéčüčÅ ą┤ą╗čÅ čüą╗ąĄą┤čāčÄčēąĄą╣ ą┐ąŠčĆčåąĖąĖ ą║ąŠą┤ą░ ŌĆō ąĖ ąŠą▒čŗčćąĮąŠ ą┐čĆąŠčåąĄčüčü ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ą╗ąĖąĮąĄąĄąĮ ŌĆō ą║ąŠč鹊čĆčŗą╣ ą▓čŗčćąĖčéčŗą▓ą░ąĄčéčüčÅ ą┐ąŠčüą╗ąĄ ą┐ąĄčĆą▓ąŠą│ąŠ 64-ą▒ąĖčéąĮąŠą│ąŠ ą▒ą╗ąŠą║ą░. ąÆ čüčĆą░ą▓ąĮąĄąĮąĖąĖ čüąŠ čüčéčĆąŠą║ąŠą╣ ą║čŹčłą░ ą▓ 256 ą▒ąĖčé, čŹč鹊 ąĘą░ą╣ą╝ąĄčé ąŠą║ąŠą╗ąŠ 4x11 (ą┐ą╗čÄčü ACT) čéą░ą║č鹊ą▓ SCLK, ą┐ąŠą║ą░ ą┐ąŠčüą╗ąĄą┤ąĮčÅčÅ ą┐ąŠčĆčåąĖčÅ ą┤ą░ąĮąĮčŗčģ ąĮąĄ ą▒čāą┤ąĄčé ą┤ąŠčüčéčāą┐ąĮą░ ąĮą░ EAB, ą║ąŠą│ą┤ą░ ą║čŹčł ąĖąĮčüčéčĆčāą║čåąĖą╣ ąĮąĄ čĆą░ąĘčĆąĄčłąĄąĮ.

ąÜąŠą│ą┤ą░ ą║čŹčł ąĖąĮčüčéčĆčāą║čåąĖą╣ čĆą░ąĘčĆąĄčłąĄąĮ, čéą░ ąČąĄ čüą░ą╝ą░čÅ ąŠą┐ąĄčĆą░čåąĖčÅ ą▓čŗą┐ąŠą╗ąĮąĖčéčüčÅ ąĘą░ 21 čéą░ą║čé SCLK (ą▓ą║ą╗čÄčćą░čÅ ACT).

ąĀąĖčü. 6. ąÆčŗą▒ąŠčĆą║ą░ ąĖąĮčüčéčĆčāą║čåąĖąĖ, ą║ąŠą│ą┤ą░ ą║čŹčł ąŠčéą║ą╗čÄč湥ąĮ.

ąĀąĖčü. 7. ąÆčŗą▒ąŠčĆą║ą░ ąĖąĮčüčéčĆčāą║čåąĖąĖ, ą║ąŠą│ą┤ą░ ą║čŹčł ą▓ą║ą╗čÄč湥ąĮ.

ąĀąĖčü. 8. ąŚą░ą┤ąĄčƹȹ║ą░ čü ąĖąĮčüčéčĆčāą║čåąĖąĄą╣, ą║ąŠą│ą┤ą░ ą║čŹčł ąŠčéą║ą╗čÄč湥ąĮ.

ąĀąĖčü. 9. ąŚą░ą┤ąĄčƹȹ║ą░ čü ąĖąĮčüčéčĆčāą║čåąĖąĄą╣, ą║ąŠą│ą┤ą░ ą║čŹčł ą▓ą║ą╗čÄč湥ąĮ.

[ąÜąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ ą║čŹčłą░ ą┤ą░ąĮąĮčŗčģ Blackfin]

ą×čĆą│ą░ąĮąĖąĘą░čåąĖčÅ ą║čŹčłą░. ąŻ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ADSP-BF533 ąĖą╝ąĄąĄčéčüčÅ 64 ą║ąĖą╗ąŠą▒ą░ą╣čéą░ ą▓čüčéčĆąŠąĄąĮąĮąŠą╣ ą▓ ą║čĆąĖčüčéą░ą╗ą╗ ą┐ą░ą╝čÅčéąĖ ą┤ą░ąĮąĮčŗčģ. 32 ą║ąĖą╗ąŠą▒ą░ą╣čéą░ ą┐ą░ą╝čÅčéąĖ ą┤ą░ąĮąĮčŗčģ ą┤ąŠčüčéčāą┐ąĮčŗ ą║ą░ą║ SRAM ą┤ą░ąĮąĮčŗčģ. ą×čüčéą░ą╗čīąĮą░čÅ čćą░čüčéčī - ąĄčēąĄ 32 ą║ąĖą╗ąŠą▒ą░ą╣čéą░ ą┐ą░ą╝čÅčéąĖ - ą┤ąŠčüčéčāą┐ąĮą░ ą║ą░ą║ 2 ąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗčģ ą▒ą░ąĮą║ą░ ą┐ą░ą╝čÅčéąĖ ą┐ąŠ 16 ą║ąĖą╗ąŠą▒ą░ą╣čé, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠąČąĮąŠ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī ą╗ąĖą▒ąŠ ą║ą░ą║ ą║čŹčł ą┤ą░ąĮąĮčŗčģ, ą╗ąĖą▒ąŠ ą║ą░ą║ SRAM ą┤ą░ąĮąĮčŗčģ.

ąØąĄą║ąŠč鹊čĆčŗąĄ ą╝ąŠą┤ąĄą╗ąĖ čüąĄą╝ąĄą╣čüčéą▓ą░ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ Blackfin ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÄčé č鹊ą╗čīą║ąŠ ąŠą┤ąĖąĮ ą▒ą░ąĮą║ ą┐ą░ą╝čÅčéąĖ ą┤ą░ąĮąĮčŗčģ, ą║ąŠč鹊čĆčŗą╣ ą╝ąŠąČąĮąŠ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī ą╗ąĖą▒ąŠ ą║ą░ą║ ą║čŹčł ą┤ą░ąĮąĮčŗčģ, ą╗ąĖą▒ąŠ ą║ą░ą║ SRAM. ą¤ąŠą┤čĆąŠą▒ąĮąŠčüčéąĖ čüą╝. ą▓ čéą░ą▒ą╗ąĖčåąĄ 2.

ąÜąŠą│ą┤ą░ ą║čŹčł ą┤ą░ąĮąĮčŗčģ čĆą░ąĘčĆąĄčłąĄąĮ, č鹊 ąŠąĮ čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą┐ą░ą╝čÅčéčī 2-way set associative. ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą║čŹčłą░ ą┤ą░ąĮąĮčŗčģ ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą┐ąŠą╗ąĖčéąĖą║čā LRU ą┤ą╗čÅ ąĘą░ą╝ąĄąĮčŗ čüčéčĆąŠą║ąĖ ą║čŹčłą░ (ąŠąĮ ąĮąĄ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą╝ąŠą┤ąĖčäąĖčåąĖčĆąŠą▓ą░ąĮąĮčāčÄ ą┐ąŠą╗ąĖčéąĖą║čā LRU, ą║ą░ą║ čŹč鹊 ąĖą╝ąĄąĄčé ą╝ąĄčüč鹊 čü ą║čŹčłąĄą╝ ąĖąĮčüčéčĆčāą║čåąĖą╣).

ŌĆó ąÆ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą║ąŠą╗ąĖč湥čüčéą▓ą░ ą▒ą░ąĮą║ąŠą▓, čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĮčŗčģ ą║ą░ą║ ą║čŹčł, ą║čŹčł ą┤ą░ąĮąĮčŗčģ ą╝ąŠąČąĄčé ąĘą░ąĮąĖą╝ą░čéčī ą╗ąĖą▒ąŠ 16 ą║ąĖą╗ąŠą▒ą░ą╣čé (ąŠą┤ąĖąĮ ą▒ą░ąĮą║), ą╗ąĖą▒ąŠ 32 ą║ąĖą╗ąŠą▒ą░ą╣čéą░ (ą┤ą▓ą░ ą▒ą░ąĮą║ą░).

ŌĆó ąÜą░ąČą┤čŗą╣ 16 ą║ąĖą╗ąŠą▒ą░ą╣čéąĮčŗą╣ ą▒ą░ąĮą║ ą║čŹčłą░ ą┤ą░ąĮąĮčŗčģ ąŠčĆą│ą░ąĮąĖąĘąŠą▓ą░ąĮ ą║ą░ą║ č湥čéčŗčĆąĄ 4-ą║ąĖą╗ąŠą▒ą░ą╣čéąĮčŗčģ ą┐ąŠą▒ą░ąĮą║ą░. ą¤ąŠą┤ą▒ą░ąĮą║ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ą┐ąŠ ą▒ąĖčéą░ą╝ ą░ą┤čĆąĄčüą░ ą┐ą░ą╝čÅčéąĖ [13:12].

ŌĆó ąÜą░ąČą┤čŗą╣ 4-ą║ąĖą╗ąŠą▒ą░ą╣čéąĮčŗą╣ ą┐ąŠą┤ą▒ą░ąĮą║ čüąŠčüč鹊ąĖčé ąĖąĘ 64 ąĮą░ą▒ąŠčĆąŠą▓ (set). ąØą░ą▒ąŠčĆ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ą▒ąĖčéą░ą╝ąĖ ą░ą┤čĆąĄčüą░ ą┐ą░ą╝čÅčéąĖ [10:5].

ŌĆó ąÜą░ąČą┤čŗą╣ ąĮą░ą▒ąŠčĆ čüąŠčüč鹊ąĖčé ąĖąĘ 2 ą┐čāč鹥ą╣ (way). ą¤čāčéčī ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ ą║čŹčłą░ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü ą┐ąŠą╗ąĖčéąĖą║ąŠą╣ čĆą░ąĘą╝ąĄčēąĄąĮąĖčÅ čüčéčĆąŠą║ąĖ ą║čŹčłą░. ą¤čāčéąĖ ą╝ąŠąČąĮąŠ ąĖą┤ąĄąĮčéąĖčäąĖčåąĖčĆąŠą▓ą░čéčī ą┐ąŠ ą▒ąĖčéčā ą░ą┤čĆąĄčüą░ [11] ą▓ SRAM.

ŌĆó ąöčĆčāą│ąĖą╝ąĖ čüą╗ąŠą▓ą░ą╝ąĖ, ąĮą░ą▒ąŠčĆ set-0 ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮ ą┤ą▓čāą╝čÅ ą┐čāčéčÅą╝ąĖ čüčéčĆąŠą║ąĖ line-0.

ŌĆó ąĀą░ąĘą╝ąĄčĆ čüčéčĆąŠą║ąĖ ą║čŹčłą░ (ą║ąŠč鹊čĆą░čÅ ą┐ąŠą┤ą╗ąĄąČąĖčé čćč鹥ąĮąĖčÄ ą┐čĆąĖ ą┐čĆąŠą╝ą░čģąĄ ą╝ąĖą╝ąŠ ą║čŹčłą░) čüąŠčüčéą░ą▓ą╗čÅąĄčé 32 ą▒ą░ą╣čéą░.

ą¤ąŠą┤ąŠą▒ąĮąŠ ą║čŹčłčā ąĖąĮčüčéčĆčāą║čåąĖąĖ, ą║ą░ąČą┤ą░čÅ čüčéčĆąŠą║ą░ ą║čŹčłą░ ąĖą╝ąĄąĄčé čüą▓čÅąĘą░ąĮąĮčāčÄ čü ąĮąĄą╣ ą┐ąŠčĆčåąĖčÄ č鹥ą│ą░ (čüą╝. čĆąĖčü. 10):

ŌĆó 19-ą▒ąĖčéąĮčŗą╣ č鹥ą│ ą░ą┤čĆąĄčüą░: čüčĆą░ą▓ąĮąĖą▓ą░ąĄčéčüčÅ čü ą░ą┤čĆąĄčüąŠą╝ ą┐ą░ą╝čÅčéąĖ, čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ą┐ąŠą┐ą░ą┤ą░ąĮąĖąĄ ą▓ ą║čŹčł ąĖą╗ąĖ ą┐čĆąŠą╝ą░čģ ą╝ąĖą╝ąŠ ą║čŹčłą░.

ŌĆó Dirty-ą▒ąĖčé: čŹč鹊čé ą▒ąĖčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 čüčéčĆąŠą║ą░ ą║čŹčłą░ ą▒čŗą╗ą░ ą╝ąŠą┤ąĖčäąĖčåąĖčĆąŠą▓ą░ąĮą░.

ŌĆó LRU state: ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ ą║čŹčłą░ ą┤ą╗čÅ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ ą┐ąŠą╗ąĖčéąĖą║ąĖ LRU.

ŌĆó Valid-ą▒ąĖčé: ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą┤ąŠčüč鹊ą▓ąĄčĆąĮąŠčüčéčī ą┤ą░ąĮąĮčŗčģ čüčéčĆąŠą║ąĖ ą║čŹčłą░.

32-ą▒ąĖčéąĮąŠąĄ ą░ą┤čĆąĄčüąĮąŠąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ ą┐čĆąĖą▓čÅąĘą░ąĮąŠ ą║ ą┐ą░ą╝čÅčéąĖ ą║čŹčłą░ čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝ (čüą╝. čĆąĖčü. 10):

ŌĆó Subbank select (ą▓čŗą▒ąŠčĆ ą┐ąŠą┤ą▒ą░ąĮą║ą░): ą▓čŗą▒ąĖčĆą░ąĄčé ąŠčéą┤ąĄą╗čīąĮčŗą╣ 4-ą║ąĖą╗ąŠą▒ą░ą╣čéąĮčŗą╣ ą┐ąŠą┤ą▒ą░ąĮą║.

ŌĆó Set select (ą▓čŗą▒ąŠčĆ ąĮą░ą▒ąŠčĆą░): ą▓čŗą▒ąĖčĆą░ąĄčé ąĮą░ą▒ąŠčĆ (set) ąĖąĘ 64 ąĮą░ą▒ąŠčĆąŠą▓ ą║čŹčłą░.

ŌĆó Byte select (ą▓čŗą▒ąŠčĆ ą▒ą░ą╣čéą░): ą▓čŗą▒ąĖčĆą░ąĄčé ą▒ą░ą╣čé ąĖąĘ ąĖą╝ąĄčÄčēąĄą╣čüčÅ čüčéčĆąŠą║ąĖ.

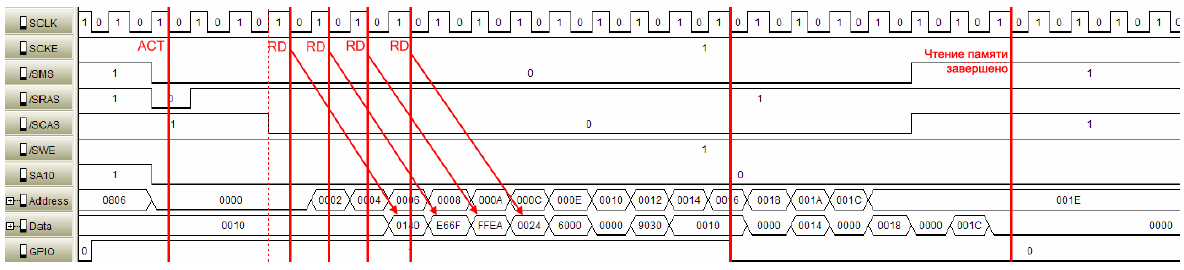

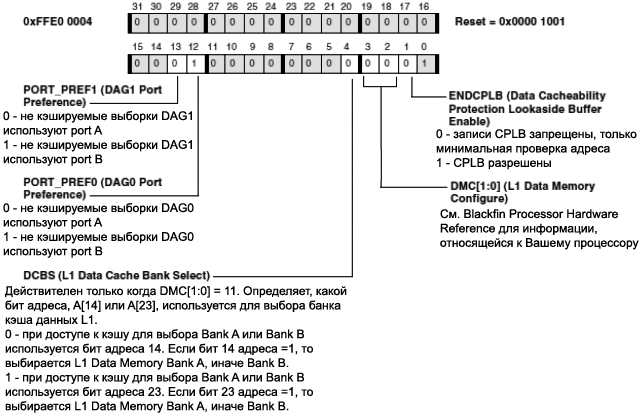

ąØą░ čĆąĖčü. 10 ą┐ąŠą║ą░ąĘą░ąĮąŠ, ą║ą░ą║ ąŠčĆą│ą░ąĮąĖąĘąŠą▓ą░ąĮ 4-ą║ąĖą╗ąŠą▒ą░ą╣ąĮčéąĮčŗą╣ ą┐ąŠą┤ą▒ą░ąĮą║ ą║čŹčłą░ ą┤ą░ąĮąĮčŗčģ. ąÜąŠą│ą┤ą░ ąŠą▒ą░ ą▒ą░ąĮą║ą░ ą┤ą░ąĮąĮčŗčģ čĆą░ąĘčĆąĄčłąĄąĮčŗ ą┤ą╗čÅ ą║čŹčłą░, č鹊 ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čüąŠčüč鹊čÅąĮąĖčÅ ą▒ąĖčéą░ DCBS ą╗ąĖą▒ąŠ ą▒ąĖčé 14 (ą║ą░ąČą┤čŗąĄ 16 ą║ąĖą╗ąŠą▒ą░ą╣čé) ąĖą╗ąĖ ą▒ąĖčé 23 (ą║ą░ąČą┤čŗąĄ 8 ą╝ąĄą│ą░ą▒ą░ą╣čé) ą░ą┤čĆąĄčüąĮąŠą│ąŠ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą░ ąŠą┤ąĮąŠą│ąŠ ąĖąĘ 16-ą║ąĖą╗ąŠą▒ą░ą╣čéąĮčŗčģ ą▒ą░ąĮą║ąŠą▓ ą┤ą░ąĮąĮčŗčģ (čüą╝. čĆąĖčü. 11).

ąöąŠčüčéčāą┐ ąĮą░ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĖąĄ čüčéčĆąŠą║ąĖ ą║čŹčłą░ čüąŠčüč鹊ąĖčé ąĖąĘ ąĘą░čģą▓ą░čéą░ 32 ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ ąĖąĘ ą┐ą░ą╝čÅčéąĖ. ąÉą┤čĆąĄčü ą┤ą╗čÅ čéčĆą░ąĮčüč乥čĆą░ čćč鹥ąĮąĖčÅ čŹč鹊 ą░ą┤čĆąĄčü čåąĄą╗ąĄą▓ąŠą│ąŠ čüą╗ąŠą▓ą░ ą┤ą░ąĮąĮčŗčģ. ą¤čĆąĄą┤ą┐ąŠą╗ąŠąČąĖą╝, čćč鹊 ąĖą╝ąĄą╗ ą╝ąĄčüč鹊 ą┤ąŠčüčéčāą┐ I/O ąĮą░ čćč鹥ąĮąĖąĄ 16-ą▒ąĖčéąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ, ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ąŠčéą▓ąĄčé ąĮą░ ąĘą░ą┐čĆąŠčü čćč鹥ąĮąĖčÅ čüčéčĆąŠą║ąĖ ąŠčé ą▒ą╗ąŠą║ą░ čćč鹥ąĮąĖčÅ ą┐ą░ą╝čÅčéąĖ, ą▓ąĮąĄčłąĮčÅčÅ ą┐ą░ą╝čÅčéčī ą▓ąŠąĘą▓čĆą░čéąĖčé čüąĮą░čćą░ą╗ą░ 16-ą▒ąĖčéąĮąŠąĄ čåąĄą╗ąĄą▓ąŠąĄ čüą╗ąŠą▓ąŠ ą┤ą░ąĮąĮčŗčģ. ąĪą╗ąĄą┤čāčÄčēąĖąĄ 15 čüą╗ąŠą▓ ą▒čāą┤čāčé ąĘą░čģą▓ą░č湥ąĮčŗ ą┤čĆčāą│ ąĘą░ ą┤čĆčāą│ąŠą╝ ą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ą░ą┤čĆąĄčüą░čģ, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▓ čéą░ą▒ą╗ąĖčåąĄ 5.

ąóą░ą▒ą╗ąĖčåą░ 5. ą¤ąŠčĆčÅą┤ąŠą║ ą▓čŗą▒ąŠčĆą║ąĖ čüą╗ąŠą▓ą░ čüčéčĆąŠą║ąĖ ą║čŹčłą░ ą┤ą░ąĮąĮčŗčģ.

ą”ąĄą╗ąĄą▓ąŠąĄ čüą╗ąŠą▓ąŠ

|

ą¤ąŠčĆčÅą┤ąŠą║ ą▓čŗą▒ąŠčĆą║ąĖ ą┤ą╗čÅ čüą╗ąĄą┤čāčÄčēąĖčģ 15 čüą╗ąŠą▓ |

| WD0 |

WD0, ..., WD15 |

| WD1 |

WD1, ..., WD15, WD0 |

| WD2 |

WD2, ..., WD15, WD0, WD1 |

| WD15 |

WD15, WD0, ..., WD14 |

ąÜąŠą│ą┤ą░ čüčéčĆąŠą║ą░ ą║čŹčłą░ ąĘą░ą▒ąĖčĆą░ąĄčéčüčÅ ąĖąĘ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ, ą║ą░ąČą┤ąŠąĄ 32-ą▒ąĖčéąĮąŠąĄ čüą╗ąŠą▓ąŠ ą▒čāč乥čĆąĖąĘčāąĄčéčüčÅ ą▓ 8-čÅč湥ąĄčćąĮąŠą╝ ą▒čāč乥čĆąĄ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĖčÅ čüčéčĆąŠą║ąĖ (line fill buffer), ą┐ąĄčĆąĄą┤ ąĘą░ą┐ąĖčüčīčÄ ą▓ 4-ą║ąĖą╗ąŠą▒ą░ą╣čéąĮčŗą╣ ą▒ą░ąĮą║ ą┐ą░ą╝čÅčéąĖ. ąæčāč乥čĆ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĖčÅ čüčéčĆąŠą║ąĖ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé čÅą┤čĆčā ą┐ąŠą╗čāčćąĖčéčī ą┤ąŠčüčéčāą┐ ą║ ą┤ą░ąĮąĮčŗą╝ ąĖąĘ ąĮąŠą▓ąŠą╣ čüčéčĆąŠą║ąĖ ą║čŹčłą░ ą║ą░ą║ ą║ čüčéčĆąŠą║ąĄ, ą┐ąŠą╗čāčćą░ąĄą╝ąŠą╣ ąĖąĘ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ, ą▒ąĄąĘ ąŠąČąĖą┤ą░ąĮąĖčÅ, ą┐ąŠą║ą░ čüčéčĆąŠą║ą░ ą▒čāą┤ąĄčé ąĘą░ą┐ąĖčüą░ąĮą░ ą▓ ą║čŹčł.

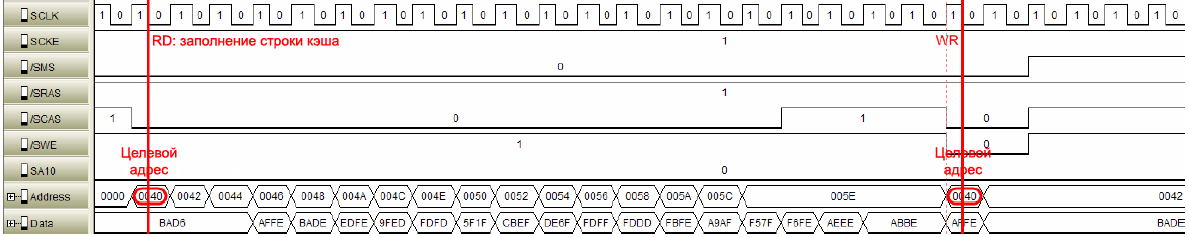

ąÆ ąŠčéą╗ąĖčćąĖąĄ ąŠčé ąĖąĮčüčéčĆčāą║čåąĖą╣, ą┤ą░ąĮąĮčŗąĄ ąŠą▒čŗčćąĮąŠ ą╝ąŠą┤ąĖčäąĖčåąĖčĆčāčÄčéčüčÅ ąĖ ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ ąŠą▒čĆą░čéąĮąŠ ą▓ąŠ (ą▓ąĮąĄčłąĮčÄčÄ) ą┐ą░ą╝čÅčéčī. ąøčÄą▒ą░čÅ ą║čŹčłąĖčĆčāąĄą╝ą░čÅ ąŠą┤ąĖąĮąŠčćąĮą░čÅ (ąĮąĄ ą┐ą░ą║ąĄčéąĮą░čÅ) ąĘą░ą┐ąĖčüčī čÅą┤čĆą░ ą▓ąŠ ą▓ąĮąĄčłąĮčÄčÄ ą┐ą░ą╝čÅčéčī ą┐čĆąŠąĖčüčģąŠą┤ąĖčé č湥čĆąĄąĘ ą▒čāč乥čĆ ąĘą░ą┐ąĖčüąĖ. ąōą╗čāą▒ąĖąĮą░ čŹč鹊ą│ąŠ ą▒čāč乥čĆą░ ą╝ąŠąČąĄčé ąĖąĘą╝ąĄąĮčÅčéčīčüčÅ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü ąĮą░čüčéčĆąŠą╣ą║ą░ą╝ąĖ ą▓ čĆąĄą│ąĖčüčéčĆąĄ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ (interrupt priority register, IPRIO).

ąóčĆąĄčéąĖą╣ ą▒čāč乥čĆ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ ą│čĆčÅąĘąĮąŠą╣ čüčéčĆąŠą║ąĖ ą║čŹčłą░, ą║ąŠč鹊čĆą░čÅ čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ (flush) ąĖą╗ąĖ ąĘą░ą╝ąĄąĮčÅąĄčéčüčÅ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĖąĄą╝ čüčéčĆąŠą║ąĖ ą║čŹčłą░ ąĖ ąĘą░č鹥ą╝ ą┤ą╗čÅ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ ą┐ą░ą║ąĄčéąĮąŠą╣ ąŠą┐ąĄčĆą░čåąĖąĖ ąĘą░ą┐ąĖčüąĖ ąĮą░ čłąĖąĮąĄ, čćč鹊ą▒čŗ ą▓čŗą┐ąŠą╗ąĮąĖčéčī ąŠą▒čĆą░čéąĮąŠąĄ ą║ąŠą┐ąĖčĆąŠą▓ą░ąĮąĖąĄ čüčéčĆąŠą║ąĖ ą▓ąŠ ą▓ąĮąĄčłąĮčÄčÄ ą┐ą░ą╝čÅčéčī. ąŁč鹊čé ą▒čāč乥čĆ ąĮą░ąĘčŗą▓ą░ąĄčéčüčÅ "ą▒čāč乥čĆąŠą╝ ąČąĄčĆčéą▓čŗ", victim-ą▒čāč乥čĆ. ą×ąĮ čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮ ąĮą░ą┐ąŠą┤ąŠą▒ąĖąĄ ą▒čāč乥čĆą░ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĖčÅ čüčéčĆąŠą║ąĖ, ą║ą░ą║ FIFO ą│ą╗čāą▒ąĖąĮąŠą╣ 8 čÅč湥ąĄą║, čā ą║ą░ąČą┤ąŠą╣ čłąĖčĆąĖąĮą░ 32 ą▒ąĖčéą░ (čüą╝. čĆąĖčü. 1).

ąĀąĖčü. 10. ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą║čŹčłą░ ą┤ą░ąĮąĮčŗčģ ą┤ą╗čÅ ąŠą┤ąĮąŠą│ąŠ ą┐ąŠą┤ą▒ą░ąĮą║ą░ ŌĆō 2-way set associative.

ąĀąĖčü. 11. ą¤čĆąĖą▓čÅąĘą║ą░ ą║čŹčłą░ ą┤ą░ąĮąĮčŗčģ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü ą▒ąĖč鹊ą╝ DCBS.

ąĀąĖčü. 12. ąÆčŗą▒ąŠčĆą║ą░ ą┤ą░ąĮąĮčŗčģ, ą║ąŠą│ą┤ą░ ą║čŹčł ą▓čŗą║ą╗čÄč湥ąĮą░.

ąĀąĖčü. 13. ąÆčŗą▒ąŠčĆą║ą░ ą┤ą░ąĮąĮčŗčģ, ą║ąŠą│ą┤ą░ ą║čŹčł ą▓ą║ą╗čÄč湥ąĮą░.

ąÆčŗą▒ąŠčĆą║ą░ ą┤ą░ąĮąĮčŗčģ ąĖąĘ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ

ŌĆó ą║čŹčł ą▓čŗą║ą╗čÄč湥ąĮą░: ą┤ąŠčüčéčāą┐ čłąĖčĆąĖąĮąŠą╣ 1 ą▒ą░ą╣čé, 2 ą▒ą░ą╣čéą░ ąĖą╗ąĖ 4 ą▒ą░ą╣čéą░

ŌĆó ą║čŹčł ą▓ą║ą╗čÄč湥ąĮą░: ą▓čüąĄą│ą┤ą░ ą┤ąĄą╗ą░ąĄčéčüčÅ ą▓čŗą▒ąŠčĆą║ą░ 256 ą▒ąĖčé / 32 ą▒ą░ą╣čéą░ (ą┐ą░ą║ąĄčéąĮąŠąĄ čāčüą║ąŠčĆąĄąĮąĮąŠąĄ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĖąĄ)

ŌĆó ą¤ąŠčüą║ąŠą╗čīą║čā ąĖąĮč鹥čĆč乥ą╣čü SDRAM ąĮą░ ą▒ąŠą╗čīčłąĖąĮčüčéą▓ąĄ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ Blackfin 16-ą▒ąĖčéąĮčŗą╣, č鹊 ą║ą░ąČą┤čŗą╣ ą┤ąŠčüčéčāą┐ ą▒čāą┤ąĄčé čłąĖčĆąĖąĮąŠą╣ 16 ą▒ąĖčé. ą¤čĆąĖ ą┤ąŠčüčéčāą┐ąĄ ą║ ą▒ą░ą╣čéčā ą╝ą╗ą░ą┤čłąĖą╣ ąĖą╗ąĖ čüčéą░čĆčłąĖą╣ ą▒ą░ą╣čé ą╝ą░čüą║ąĖčĆčāąĄčéčüčÅ čüąĖą│ąĮą░ą╗ąŠą╝ SDQM.

ąĀąĖčü. 12 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą┤ąŠčüčéčāą┐ ą║ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ ąĮą░ čćč鹥ąĮąĖąĄ 16-ą▒ąĖčéąĮčŗčģ ą┤ą░ąĮąĮčŗčģ (čåąĄą╗ąĄą▓ąŠą╣ ą░ą┤čĆąĄčü 0x0032h). ą║čŹčł ą┤ą░ąĮąĮčŗčģ ą▓čŗą║ą╗čÄč湥ąĮ. ąöą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą┤ąŠčüčéčāą┐ą░ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ąŠą┤ąĮąŠ 16-ą▒ąĖčéąĮąŠąĄ čüą╗ąŠą▓ąŠ.

ąĀąĖčü. 13 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé č鹊čé ąČąĄ čüą░ą╝čŗą╣ ą┤ąŠčüčéčāą┐, ąĮąŠ čü ą▓ą║ą╗čÄč湥ąĮąĮčŗą╝ ą║čŹčłąĄą╝ ą┤ą░ąĮąĮčŗčģ. ąŚą┤ąĄčüčī ąĮą░čćą░ą╗čīąĮčŗą╣ ą░ą┤čĆąĄčü 0x0032h. ąöčĆčāą│ąĖąĄ ą┤ą░ąĮąĮčŗąĄ, ą┐čĆąĖąĮą░ą┤ą╗ąĄąČą░čēąĖąĄ čŹč鹊ą╣ ą║čŹčłąĖčĆčāąĄą╝ąŠą╣ čüčéčĆąŠą║ąĄ ą▒čāą┤čāčé ą▓čŗą▒čĆą░ąĮčŗ čéą░ą║, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▓ čéą░ą▒ą╗ąĖčåąĄ 5.

ą£ąĄč鹊ą┤čŗ ąĘą░ą┐ąĖčüąĖ ą║čŹčłą░. ąÆąĮąĄčłąĮčÅčÅ ą┐ą░ą╝čÅčéčī ą┐ąŠą┤ąĄą╗ąĄąĮą░ ąĮą░ čĆą░ąĘąĮčŗąĄ čüčéčĆą░ąĮąĖčåčŗ (ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗąĄ č湥čĆąĄąĘ čĆąĄą│ąĖčüčéčĆčŗ ąĘą░čēąĖčéčŗ ą▒čāč乥čĆąŠą▓ ą┤ą░ąĮąĮčŗčģ ą║čŹčłą░ - data cache protection lookaside buffers, čĆąĄą│ąĖčüčéčĆčŗ DCPLB). ąÉčéčĆąĖą▒čāčéčŗ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą╣ čüčéčĆą░ąĮąĖčåčŗ ą╝ąŠąČąĮąŠ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ. ąÜą░ą║ ą▒čāą┤ąĄčé ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▓ čüą╗ąĄą┤čāčÄčēąĄą╣ čüąĄą║čåąĖąĖ, čüčéčĆą░ąĮąĖčåčŗ ą┐ą░ą╝čÅčéąĖ ą╝ąŠą│čāčé ą▒čŗčéčī:

ŌĆó ąĪą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ ą╗ąĖą▒ąŠ ą▓ čĆąĄąČąĖą╝ąĄ ąĘą░ą┐ąĖčüąĖ write-back WB, ą╗ąĖą▒ąŠ ą▓ čĆąĄąČąĖą╝ąĄ ąĘą░ą┐ąĖčüąĖ write-through WT (ą▒ąĖčé CPLB_WT).

ŌĆó ąĪą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ ą┤ą╗čÅ ą▓čŗą┤ąĄą╗ąĄąĮąĖčÅ čüčéčĆąŠą║ ą║čŹčłą░ ą╗ąĖą▒ąŠ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ, ą╗ąĖą▒ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ ąĖ ąĘą░ą┐ąĖčüąĖ (ą▒ąĖčé CPLB_L1_AOW).

ąóą░ą▒ą╗ąĖčåą░ 6. ą¤ąŠą▓ąĄą┤ąĄąĮąĖąĄ ą▓ čüą┐ąĄčåąĖčäąĖč湥čüą║ąŠą╣ čüąĖčéčāą░čåąĖąĖ ąĘą░ą┐ąĖčüąĖ.

|

ąĪčéčĆąŠą║ą░ ą║čŹčłą░ ą┤ąŠčüč鹊ą▓ąĄčĆąĮą░čÅ (valid) |

ąĪčéčĆąŠą║ą░ ą║čŹčłą░ ąĮąĄą┤ąŠčüč鹊ą▓ąĄčĆąĮą░čÅ (invalid) |

WT

AOW=0 |

ą×ą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ čüčéčĆąŠą║ąĖ ą║čŹčłą░ ąĖ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ |

ą×ą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ č鹊ą╗čīą║ąŠ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ |

WT

AOW=1 |

ą×ą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ čüčéčĆąŠą║ąĖ ą║čŹčłą░ ąĖ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ |

ąÆčŗą▒ąŠčĆą║ą░ čüčéčĆąŠą║ąĖ ą║čŹčłą░

ą×ą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ čüčéčĆąŠą║ąĖ ą║čŹčłą░

ą×ą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ |

| WB |

ą×ą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ č鹊ą╗čīą║ąŠ čüčéčĆąŠą║ąĖ ą║čŹčłą░ |

ąÆčŗą▒ąŠčĆą║ą░ čüčéčĆąŠą║ąĖ ą║čŹčłą░

ą×ą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ čüčéčĆąŠą║ąĖ ą║čŹčłą░ |

ąóą░ą▒ą╗ąĖčåą░ 6 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ ą▓ čĆą░ąĘą╗ąĖčćąĮčŗčģ ą╝ąĄč鹊ą┤ą░čģ ąĘą░ą┐ąĖčüąĖ ą║čŹčłą░. ąĀąĖčü. 14 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüąĖčéčāą░čåąĖčÄ, ą║ąŠą│ą┤ą░ ą║čŹčł ą┤ą░ąĮąĮčŗčģ čĆą░ąĘčĆąĄčłąĄąĮ ą▓ čĆąĄąČąĖą╝ąĄ write-through (WT), ąĖ čü čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╝ ą▒ąĖč鹊ą╝ CPLB_L1_AOW. ąśąĮąĖčåąĖąĖčĆčāąĄčéčüčÅ ą┤ąŠčüčéčāą┐ ąĮą░ ąĘą░ą┐ąĖčüčī ą┐ąŠ ą░ą┤čĆąĄčüčā 0x0040h. ąĪąĮą░čćą░ą╗ą░ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĖąĄ čüčéčĆąŠą║ąĖ ą║čŹčłą░, ąĘą░č鹥ą╝ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ąĘą░ą┐ąĖčüčī ą▓ąŠ ą▓ąĮąĄčłąĮčÄčÄ ą┐ą░ą╝čÅčéčī.

ąĀąĖčü. 14. ąÆčŗą▒ąŠčĆą║ą░ ą┤ą░ąĮąĮčŗčģ čü ą▓ą║ą╗čÄč湥ąĮąĮčŗą╝ ą║čŹčłąĄą╝, ą║ąŠą│ą┤ą░ ą▓ą║ą╗čÄč湥ąĮ čĆąĄąČąĖą╝ ąĘą░ą┐ąĖčüąĖ write-through ąĖ čĆą░ąĘčĆąĄčłąĄąĮ AOW.

ąæą╗ąŠą║ ąĘą░čēąĖčéčŗ ą┐ą░ą╝čÅčéąĖ ąĖ ą║čŹčłą░ (Memory Protection and Cache Unit). ą¤čĆąŠčåąĄčüčüąŠčĆ Blackfin čüąŠą┤ąĄčƹȹĖčé ąŠčüąĮąŠą▓ą░ąĮąĮčŗą╣ ąĮą░ čüčéčĆą░ąĮąĖčåą░čģ ą▒ą╗ąŠą║ ąĘą░čēąĖčéčŗ ą┐ą░ą╝čÅčéąĖ Memory Protection and Cache Unit (MPCU), ą║ąŠč鹊čĆčŗą╣ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą║ąŠąĮčéčĆąŠą╗čī ąĮą░ą┤ ą║čŹčłąĖčĆąŠą▓ą░ąĮąĖąĄą╝ ą┤ąĖą░ą┐ą░ąĘąŠąĮąŠą▓ ą┐ą░ą╝čÅčéąĖ ąĖ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą░čéčĆąĖą▒čāčéą░ą╝ąĖ ąĘą░čēąĖčéčŗ ąĮą░ čāčĆąŠą▓ąĮąĄ čüčéčĆą░ąĮąĖčåčŗ. MPCU čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮ ą║ą░ą║ ą▒ą╗ąŠą║ąĖ 16-čÅč湥ąĄčćąĮąŠą╣, ą░ą┤čĆąĄčüčāąĄą╝ąŠą╣ ą┐ąŠ čüąŠą┤ąĄčƹȹĖą╝ąŠą╝čā ą┐ą░ą╝čÅčéąĖ (content addressable memory, CAM). ąÜą░ąČą┤ą░čÅ čÅč湥ą╣ą║ą░ ąĮą░ąĘčŗą▓ą░ąĄčéčüčÅ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą╝ cacheability protection lookaside buffer (CPLB). ążčāąĮą║čåąĖąŠąĮą░ą╗ MPCU ą▓ą║ą╗čÄčćą░ąĄčé:

ŌĆó ąæčāč乥čĆčŗ ą║čŹčłąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖ ąĘą░čēąĖčéčŗ (Caching and protection lookaside buffers, CPLB)

ŌĆó ąĪą▓ąŠą╣čüčéą▓ą░ ą║čŹčłą░/ąĘą░čēąĖčéčŗ, ąŠą┐čĆąĄą┤ąĄą╗čÅąĄą╝čŗąĄ ąĮą░ ą▒ą░ąĘąĄ čüčéčĆą░ąĮąĖčåčŗ ą┐ą░ą╝čÅčéąĖ (čĆą░ąĘą╝ąĄčĆą░ą╝ąĖ 1 ą║ąĖą╗ąŠą▒ą░ą╣čé, 4 ą║ąĖą╗ąŠą▒ą░ą╣čéą░, 1 ą╝ąĄą│ą░ą▒ą░ą╣čé ąĖ 4 ą╝ąĄą│ą░ą▒ą░ą╣čéą░)

ŌĆó ąŚą░čēąĖčéą░ ą┤ąŠčüčéčāą┐ą░ čĆąĄąČąĖą╝ąŠą▓ User/supervisor, ąĖ ąĘą░čēąĖčéą░ ąĘą░ą┤ą░čćą░/ąĘą░ą┤ą░čćą░

ąŚą░čēąĖčéą░ ą▒čāč乥čĆąŠą▓ ą║čŹčłą░ (Cacheability Protection Lookaside Buffers, CPLB). ąÜą░ąČą┤ą░čÅ ąĘą░ą┐ąĖčüčī ą▓ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░čģ CPLB ąĘą░ą┤ą░ąĄčé ą░čéčĆąĖą▒čāčéčŗ ą║čŹčłąĖčĆčāąĄą╝ąŠčüčéąĖ ąĖ ąĘą░čēąĖčéčŗ ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą╣ čüčéčĆą░ąĮąĖčåčŗ ą┐ą░ą╝čÅčéąĖ. ąŚą░ą┐ąĖčüąĖ CPLB ą┐ąŠą┤ąĄą╗ąĄąĮčŗ ą╝ąĄąČą┤čā CPLB ąĖąĮčüčéčĆčāą║čåąĖą╣ ąĖ ą┤ą░ąĮąĮčŗčģ. 16 ąĘą░ą┐ąĖčüąĄą╣ CPLB (ąĮą░ąĘčŗą▓ą░ąĄą╝čŗčģ ICPLB) ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ ąĘą░ą┐čĆąŠčüąŠą▓ ą▓čŗą▒ąŠčĆą║ąĖ ąĖąĮčüčéčĆčāą║čåąĖąĖ. ąöčĆčāą│ąĖąĄ 16 ąĘą░ą┐ąĖčüąĄą╣ CPLB (ąĮą░ąĘčŗą▓ą░ąĄą╝čŗčģ DCPLB) ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ čéčĆą░ąĮąĘą░ą║čåąĖą╣ ą┤ą░ąĮąĮčŗčģ. ąŻčüčéą░ąĮąŠą▓ą║ą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖčģ ą▒ąĖčé ą▓ čĆąĄą│ąĖčüčéčĆą░čģ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ą░ą╝čÅčéčīčÄ ąĖąĮčüčéčĆčāą║čåąĖą╣ (IMEM_CONTROL) ąĖ čĆąĄą│ąĖčüčéčĆą░čģ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ą░ą╝čÅčéčīčÄ ą┤ą░ąĮąĮčŗčģ (DMEM_CONTROL) čĆą░ąĘčĆąĄčłą░čÄčé čĆą░ą▒ąŠčéčā ICPLB ąĖ DCPLB. ąÜą░ąČą┤ą░čÅ ąĘą░ą┐ąĖčüčī CPLB čüąŠčüč鹊ąĖčé ąĖąĘ ą┐ą░čĆčŗ 32-ą▒ąĖčéąĮčŗčģ ąĘąĮą░č湥ąĮąĖą╣. ą¤ąĄčĆąĄą┤ ąĘą░ą│čĆčāąĘą║ąŠą╣ ą┤ą░ąĮąĮčŗčģ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ ą▓ ą╗čÄą▒ąŠą╣ CPLB čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēą░čÅ ą│čĆčāą┐ą┐ą░ ąĖąĘ 16 CPLB ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ąĘą░ą┐čĆąĄčēąĄąĮą░ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ ą▒ąĖč鹊ą▓ ENICPLB ąĖą╗ąĖ ENDCPLB ą▓ čĆąĄą│ąĖčüčéčĆąĄ IMEM_CONTROL ąĖą╗ąĖ DMEM_CONTROL čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ.

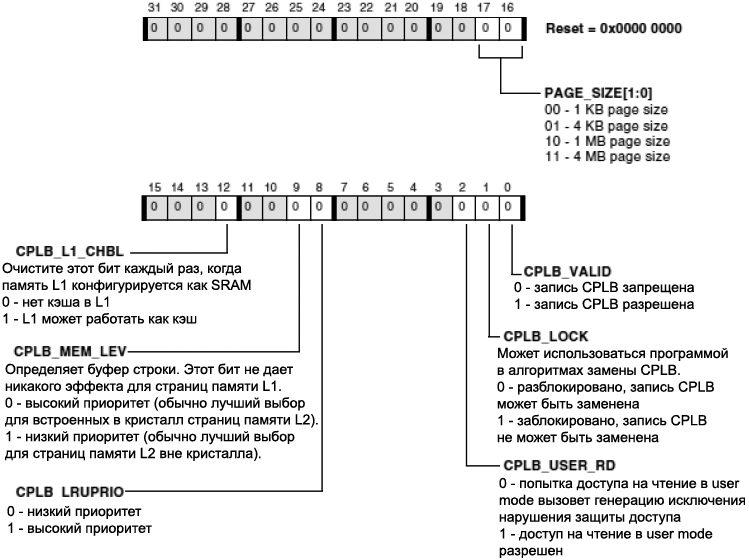

ąöą╗čÅ ą▓čŗą▒ąŠčĆąŠą║ ąĖąĮčüčéčĆčāą║čåąĖą╣: ICPLB_ADDR[n] ąĘą░ą┤ą░ąĄčé ąĮą░čćą░ą╗čīąĮčŗą╣ ą░ą┤čĆąĄčü čüčéčĆą░ąĮąĖčåčŗ, ąŠą┐ąĖčüą░ąĮąĮąŠą╣ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą╝ CPLB. ICPLB_DATA[n] ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé čüą▓ąŠą╣čüčéą▓ą░ čüčéčĆą░ąĮąĖčåčŗ, ąŠą┐ąĖčüą░ąĮąĮąŠą╣ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą╝ CPLB. ąØą░ čĆąĖčü. 15 ą┐ąŠą║ą░ąĘą░ąĮčŗ čĆą░ąĘą╗ąĖčćąĮčŗąĄ ą▒ąĖč鹊ą▓čŗąĄ ą┐ąŠą╗čÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ ICPLB_DATA ąĖ ąĖčģ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠčüčéčī.

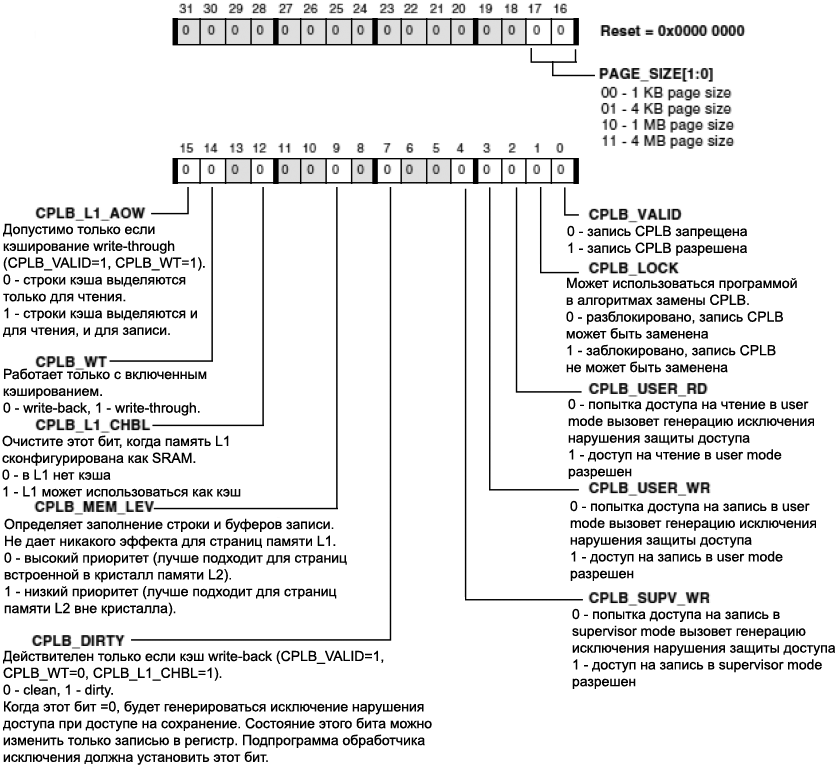

ąöą╗čÅ ąŠą┐ąĄčĆą░čåąĖą╣ čü ą┤ą░ąĮąĮčŗą╝ąĖ: DCPLB_ADDR[m] ąĘą░ą┤ą░ąĄčé ąĮą░čćą░ą╗čīąĮčŗą╣ ą░ą┤čĆąĄčü čüčéčĆą░ąĮąĖčåčŗ, ąŠą┐ąĖčüą░ąĮąĮąŠą╣ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą╝ CPLB. DCPLB_DATA[m] ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé čüą▓ąŠą╣čüčéą▓ą░ čüčéčĆą░ąĮąĖčåčŗ, ąŠą┐ąĖčüą░ąĮąĮąŠą╣ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą╝ CPLB. ąĀąĖčü. 16 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čĆą░ąĘą╗ąĖčćąĮčŗąĄ ą▒ąĖč鹊ą▓čŗąĄ ą┐ąŠą╗čÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ DCPLB_DATA ąĖ ąĖčģ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠčüčéčī.

ąśčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ CPLB

ŌĆó ąĢčüą╗ąĖ ą║čŹčł čĆą░ąĘčĆąĄčłąĄąĮą░: CPLB ą┤ąŠą╗ąČąĮčŗ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ čüą▓ąŠą╣čüčéą▓ ą║čŹčłą░.

ŌĆó ąĢčüą╗ąĖ ą║čŹčł ąĘą░ą┐čĆąĄčēąĄąĮą░: CPLB ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ąĘą░čēąĖčéčŗ čüčéčĆą░ąĮąĖčå ą┐ą░ą╝čÅčéąĖ.

ŌĆó ąĢčüą╗ąĖ CPLB ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ, č鹊 ą┤ąŠą╗ąČąĮą░ čüčāčēąĄčüčéą▓ąŠą▓ą░čéčī ą┐čĆą░ą▓ąĖą╗čīąĮąŠ ąĮą░čüčéčĆąŠąĄąĮąĮą░čÅ ąĘą░ą┐ąĖčüčī CPLB ą┤ąŠ č鹊ą│ąŠ, ą║ą░ą║ ą▒čāą┤ąĄčé čüą┤ąĄą╗ą░ąĮą░ ą┐ąŠą┐čŗčéą║ą░ ą┤ąŠčüčéčāą┐ą░ ą║ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą╣ ąŠą▒ą╗ą░čüčéąĖ ą┐ą░ą╝čÅčéąĖ. ąśąĮą░č湥 ą▒čāą┤ąĄčé čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąŠ ąĖčüą║ą╗čÄč湥ąĮąĖąĄ.

ŌĆó ąĢčüčéčī ą┤ą▓ą░ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ CPLB ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ - ą┤ą╗čÅ ą┐ą░ą╝čÅčéąĖ ą┤ą░ąĮąĮčŗčģ scratchpad ąĖ ą┤ą╗čÅ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ą░ ą░ą┤čĆąĄčüąŠą▓ MMR čüąĖčüč鹥ą╝čŗ ąĖ čÅą┤čĆą░. ąŁčéąĖ ą┤ąĄčüą║čĆąĖą┐č鹊čĆčŗ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčé ą▓čŗčłąĄčāą║ą░ąĘą░ąĮąĮčŗąĄ ąŠą▒ą╗ą░čüčéąĖ ą║ą░ą║ ąĮąĄ ą║čŹčłąĖčĆčāąĄą╝čŗąĄ, čéą░ą║ čćč鹊 ąĮąĄ ąĮčāąČąĮčŗ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗąĄ CPLB ą┤ą╗čÅ ąĮą░čüčéčĆąŠą╣ą║ąĖ čŹčéąĖčģ čĆąĄą│ąĖąŠąĮąŠą▓ ą┐ą░ą╝čÅčéąĖ.

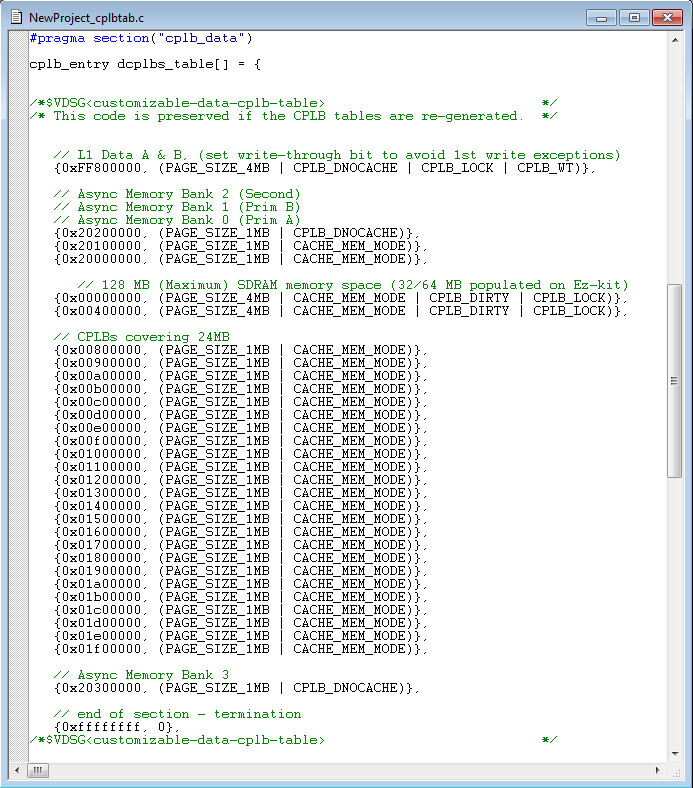

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĄčüą╗ąĖ ą┤ą╗čÅ čŹč鹊ą╣ ąŠą▒ą╗ą░čüčéąĖ ąĮą░čüčéčĆąŠąĄąĮčŗ ą┐čĆą░ą▓ąĖą╗čīąĮčŗąĄ CPLB, č鹊 CPLB ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą▒čāą┤čāčé ąĖą│ąĮąŠčĆąĖčĆąŠą▓ą░ąĮčŗ. ąØą░ ąĮąŠą▓čŗčģ čćą╗ąĄąĮą░čģ čüąĄą╝ąĄą╣čüčéą▓ą░ Blackfin, čéą░ą║ąĖčģ ą║ą░ą║ ADSP-BF51x, ADSP-BF52x ąĖ ADSP-BF54x, ą▓čüčéčĆąŠąĄąĮąĮą░čÅ ą▓ ą║čĆąĖčüčéą░ą╗ą╗ ą┐ą░ą╝čÅčéčī ą┐čĆąŠą│čĆą░ą╝ą╝ boot ROM (ą┐ą░ą╝čÅčéčī č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ) ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé čäčāąĮą║čåąĖąĖ (SysControl()) ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ ą║ čĆąĄą│ąĖčüčéčĆą░ą╝ PLL ąĖ čĆąĄą│ąĖčüčéčĆą░ą╝ čĆąĄą│čāą╗čÅč鹊čĆą░ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ. ąóą░ą║ąČąĄ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠ ą┤ąŠčüčéčāą┐ąĮčŗ ą▓ąĮčāčéčĆąĄąĮąĮąĖąĄ L1 ROM ąĖąĮčüčéčĆčāą║čåąĖą╣ ąĖ/ąĖą╗ąĖ L2 SRAM. ąöą╗čÅ ą▓čüąĄčģ čŹčéąĖčģ čüą╗čāčćą░ąĄą▓ čéčĆąĄą▒čāąĄčéčüčÅ ą┐čĆą░ą▓ąĖą╗čīąĮąŠ ąĮą░čüčéčĆąŠąĄąĮąĮčŗą╣ ą┤ąĄčüą║čĆąĖą┐č鹊čĆ CPLB (ąĖąĮčüčéčĆčāą║čåąĖą╣ ąĖ ą┤ą░ąĮąĮčŗčģ). ąĪą╝. ą┤ą░čéą░čłąĖčé ąĮą░ ą┐čĆąŠčåąĄčüčüąŠčĆ ąĖą╗ąĖ čéą░ą▒ą╗ąĖčåčā 2 ą┤ą╗čÅ ą┐ąŠą┤čĆąŠą▒ąĮąŠčüč鹥ą╣ ąŠ č鹊ą╝, ą║ą░ą║ąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą┐ą░ą╝čÅčéąĖ ąĖą╝ąĄąĄčéčüčÅ ą▓ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą│ąŠ ą┐čĆąŠčåąĄčüčüąŠčĆą░ čüąĄą╝ąĄą╣čüčéą▓ą░ Blackfin.

ąĀąĖčü. 15. ąæąĖč鹊ą▓čŗąĄ ą┐ąŠą╗čÅ ąĖ ąĖčģ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠąĄ ąĮą░ąĘąĮą░č湥ąĮąĖąĄ ą┤ą╗čÅ čĆąĄą│ąĖčüčéčĆąŠą▓ ICPLB_DATA.

ąĀąĖčü. 16. ąæąĖč鹊ą▓čŗąĄ ą┐ąŠą╗čÅ ąĖ ąĖčģ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠąĄ ąĮą░ąĘąĮą░č湥ąĮąĖąĄ ą┤ą╗čÅ čĆąĄą│ąĖčüčéčĆąŠą▓ DCPLB_DATA.

[ąĪčéčĆą░ąĮąĖčåčŗ ą┐ą░ą╝čÅčéąĖ ąĖ ą░čéčĆąĖą▒čāčéčŗ čüčéčĆą░ąĮąĖčåčŗ]

ąÜą░ąČą┤ą░čÅ ąĘą░ą┐ąĖčüčī CPLB čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ą┤ąŠą┐čāčüčéąĖą╝ąŠą╣ čüčéčĆą░ąĮąĖčåąĄ ą┐ą░ą╝čÅčéąĖ. ąÜą░ąČą┤čŗą╣ ą░ą┤čĆąĄčü ą▓ ą┐čĆąĄą┤ąĄą╗ą░čģ čüčéčĆą░ąĮąĖčåčŗ ąĖčüą┐ąŠą╗čīąĘčāąĄčé ąŠą┤ąĮąĖ ąĖ č鹥 ąČąĄ ąŠą▒čēąĖąĄ ą░čéčĆąĖą▒čāčéčŗ, ąĘą░ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ čŹč鹊ą╣ čüčéčĆą░ąĮąĖčåčŗ. ąöąĄčüą║čĆąĖą┐č鹊čĆ ą░ą┤čĆąĄčüą░ xCPLB_ADDR[n] ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą▒ą░ąĘąŠą▓čŗą╣ ą░ą┤čĆąĄčü ą┐ąŠą╗ąŠąČąĄąĮąĖčÅ čüčéčĆą░ąĮąĖčåčŗ ą▓ ą┐ą░ą╝čÅčéąĖ. ąĪą╗ąŠą▓ąŠ čüą▓ąŠą╣čüčéą▓ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ xCPLB_DATA[n] ąĘą░ą┤ą░ąĄčé čĆą░ąĘą╝ąĄčĆ ąĖ ą░čéčĆąĖą▒čāčéčŗ ą┤ą╗čÅ čŹč鹊ą╣ čüčéčĆą░ąĮąĖčåčŗ. ąĀąĖčü. 15 ąĖ čĆąĖčü. 16 ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčé čĆą░ąĘą╗ąĖčćąĮčŗąĄ ą▒ąĖč鹊ą▓čŗąĄ ą┐ąŠą╗čÅ ąĖ ąĖčģ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠčüčéčī ą▓ čĆąĄą│ąĖčüčéčĆą░čģ ICPLB_DATAx ąĖ DCPLB_DATAx čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ. ąØąĖąČąĄ ą┤ą░ąĮąŠ ą║ąŠčĆąŠčéą║ąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ ą┐ąŠą╗ąĄą╣ ą▒ąĖčé.

Page Size (čĆą░ąĘą╝ąĄčĆ čüčéčĆą░ąĮąĖčåčŗ). ąÉčĆčģąĖč鹥ą║čéčāčĆą░ ą┐ą░ą╝čÅčéąĖ Blackfin ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé 4 čĆą░ąĘą╗ąĖčćąĮčŗąĄ čĆą░ąĘą╝ąĄčĆą░ čüčéčĆą░ąĮąĖčåčŗ: 1 ą║ąĖą╗ąŠą▒ą░ą╣čé, 4 ą║ąĖą╗ąŠą▒ą░ą╣čé, 1 ą╝ąĄą│ą░ą▒ą░ą╣čé ąĖą╗ąĖ 4 ą╝ąĄą│ą░ą▒ą░ą╣čéą░. ąĪčéčĆą░ąĮąĖčåčŗ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą▓čŗčĆąŠą▓ąĮąĄąĮčŗ ą┐ąŠ ą│čĆą░ąĮąĖčåą░ą╝ čüčéčĆą░ąĮąĖčå, ą░ą┤čĆąĄčü ą║ąŠč鹊čĆčŗčģ ą┤ąŠą╗ąČąĄąĮ ąĮą░čåąĄą╗ąŠ ą┤ąĄą╗ąĖčéčīčüčÅ ąĮą░ čĆą░ąĘą╝ąĄčĆ čüčéčĆą░ąĮąĖčåčŗ.

Cache-Line Allocation (ą▓čŗą┤ąĄą╗ąĄąĮąĖąĄ čüčéčĆąŠą║ąĖ ą║čŹčłą░). ąĀą░ąĘčĆąĄčłąĄąĮą░ ą║čŹčł čéąĖą┐ą░ write-through, čćč鹊 ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮąŠ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ą┐ą░ą╝čÅčéąĖ ą┤ą░ąĮąĮčŗčģ. ąæąĖčé CPLB_L1_AOW ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé, ąĖąĮąĖčåąĖąĖčĆąŠą▓ą░ąĮąŠ ą╗ąĖ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĖąĄ čüčéčĆąŠą║ąĖ ą║čŹčłą░ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ ąĖą╗ąĖ čéą░ą║ąČąĄ ąĖ ą┤ą╗čÅ ąĘą░ą┐ąĖčüąĖ. ąöą╗čÅ ąĘą░ą┐ąĖčüąĄą╣, čü ą║ąŠč鹊čĆčŗą╝ąĖ ą▒ąĖčé CPLB_L1_AOW ąĮąĄ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ, ą║čŹčł ą▓ąĄą┤ąĄčé čüąĄą▒čÅ čéą░ą║, ą║ą░ą║ ą▒čāą┤č鹊 ąĄčæ ąĮąĄčé. ąĢčüą╗ąĖ čŹč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, č鹊 ąĘą░ą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║čŹčłą░ čüčĆą░ą▒ą░čéčŗą▓ą░ąĄčé ą┐ąŠčüą╗ąĄ č湥ą│ąŠ ąĖą┤ąĄčé ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ ąĖą╗ąĖ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ.

Write-Through/Write-Back Flag (čäą╗ą░ą│ čéąĖą┐ą░ ą║čŹčłą░). ąŁč鹊čé čäą╗ą░ą│ ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ą┐ą░ą╝čÅčéąĖ ą┤ą░ąĮąĮčŗčģ. ą×ąĮ čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ą░čéčĆąĖą▒čāčéčā (ą▒ąĖčé CPLB_WT), čĆą░ąĘčĆąĄčłą░čÄčēąĄą╝čā čĆąĄąČąĖą╝ write-through ą┤ą╗čÅ ą┤ą░ąĮąĮčŗčģ, ą║ąŠą│ą┤ą░ ą▒ąĖčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ. ą¤ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ (CPLB_WT = 0) ą░ą║čéąĖą▓ąĄąĮ čĆąĄąČąĖą╝ write-back.

Cacheable/Non-cacheable Flag (čäą╗ą░ą│ ą║čŹčłąĖčĆąŠą▓ą░čéčī/ąĮąĄ ą║čŹčłąĖčĆąŠą▓ą░čéčī). ąĢčüą╗ąĖ čüčéčĆą░ąĮąĖčåą░ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮą░ ą║ą░ą║ ąĮąĄ ą║čŹčłąĖčĆčāąĄą╝ą░čÅ (CPLB_L1_CHBL = 0), č鹊 ą┐čĆąĖ ą┤ąŠčüčéčāą┐ąĄ ą║ čŹč鹊ą╣ čüčéčĆą░ąĮąĖčåąĄ ą║čŹčł ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ. ąĪčéčĆą░ąĮąĖčåčŗ ą┐ą░ą╝čÅčéąĖ ą╝ąŠą│čāčé ą▒čŗčéčī ąĮą░ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮčŗ ą║ą░ą║ ą║čŹčłąĖčĆčāąĄą╝čŗąĄ, ą║ąŠą│ą┤ą░:

ŌĆó ąŻčüčéčĆąŠą╣čüčéą▓ąŠ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ (I/O) ąŠč鹊ą▒čĆą░ąČąĄąĮąŠ ąĮą░ ą░ą┤čĆąĄčü ą┐ą░ą╝čÅčéąĖ.

ŌĆó ąÜąŠą┤, ąĮą░čģąŠą┤čÅčēąĖą╣čüčÅ ą▓ čŹč鹊ą╣ čüčéčĆą░ąĮąĖčåąĄ, ą▓čŗąĘčŗą▓ą░ąĄčéčüčÅ ąĮąĄčćą░čüč鹊 (ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą╝ąŠąČąĄčé ąĮąĄ ąČąĄą╗ą░čéčī ąĄą│ąŠ ą║čŹčłąĖčĆąŠą▓ą░čéčī).

ŌĆó ąÜąŠą┤ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ 菹║čüčéčĆąĄą╝ą░ą╗čīąĮąŠ ąĮąĄą╗ąĖąĮąĄą╣ąĮčŗą╣.

LRU Priority (ą┐čĆąĖąŠčĆąĖč鹥čé LRU). ąŁč鹊čé ą░čéčĆąĖą▒čāčé (CPLB_LRUPRIO) ą┤ąŠčüčéčāą┐ąĄąĮ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ CPLB ą┐ą░ą╝čÅčéąĖ ąĖąĮčüčéčĆčāą║čåąĖą╣. ą×ąĮ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ą┐čĆąĖąŠčĆąĖč鹥čé LRU (low/high, ąĮąĖąĘą║ąĖą╣/ą▓čŗčüąŠą║ąĖą╣) ą┤ą╗čÅ čāą║ą░ąĘą░ąĮąĮąŠą╣ čüčéčĆą░ąĮąĖčåčŗ. ąŁč鹊 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą╝ąŠą┤ąĖčäąĖčåąĖčĆąŠą▓ą░ąĮąĮąŠą╣ ą┐ąŠą╗ąĖčéąĖą║ąĖ LRU (čüą╝. čĆą░ąĘą┤ąĄą╗čŗ "ąĀą░ąĘą╝ąĄčēąĄąĮąĖąĄ ą▒ą╗ąŠą║ą░", "ąŚą░ą╝ąĄąĮą░ ą▒ą╗ąŠą║ą░").

Dirty/Modified Flag (čäą╗ą░ą│ ą░ą║čéčāą░ą╗čīąĮąŠą│ąŠ čüąŠčüč鹊čÅąĮąĖčÅ ą╝ąŠą┤ąĖčäąĖčåąĖčĆąŠą▓ą░ąĮąĮąŠčüčéąĖ ą║čŹčłą░). ąæąĖčé CPLB_DIRTY ą┤ą░ąĄčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčüčéčā ą▓čŗą▒ąŠčĆ ą┤ą╗čÅ čüąĖą│ąĮą░ą╗ąĖąĘą░čåąĖąĖ ąŠ č鹊ą╝, čćč鹊 ą┐čĆąŠąĖąĘąŠčłąĄą╗ (ą┐ąĄčĆą▓čŗą╣) ą┤ąŠčüčéčāą┐ ąĮą░ ąĘą░ą┐ąĖčüčī ą▓ąŠ ą▓ąĮąĄčłąĮčÄčÄ ą┐ą░ą╝čÅčéčī. ą¤čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮąĮčŗą╣ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ą┐ą░ą╝čÅčéąĖ ą┤ą░ąĮąĮčŗčģ, čŹč鹊čé ą░čéčĆąĖą▒čāčé ą┤ąŠčüč鹊ą▓ąĄčĆąĄąĮ č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ čüčéčĆą░ąĮąĖčåą░ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮą░ ą║ą░ą║ ą║čŹčłąĖčĆčāąĄą╝ą░čÅ ą▓ čĆąĄąČąĖą╝ąĄ write-back. ąŁč鹊čé ą▒ąĖčé ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ ą┤ą╗čÅ čüąŠčģčĆą░ąĮąĄąĮąĖčÅ ą┤ąŠčüčéčāą┐ąŠą▓ ą║ čŹč鹊ą╣ čüčéčĆą░ąĮąĖčåąĄ. ąÜąŠą│ą┤ą░ čŹč鹊čé ą▒ąĖčé ąŠčćąĖčēąĄąĮ, čéąĖąŠ ą┤ąŠčüčéčāą┐ ą║ čŹč鹊ą╣ čüčéčĆą░ąĮąĖčåąĄ ą▓čŗąĘčŗą▓ą░ąĄčé ąĖčüą║ą╗čÄč湥ąĮąĖąĄ (EXCAUSE 0x23). ą×ą▒čĆą░ą▒ąŠčéčćąĖą║ ąĖčüą║ą╗čÄč湥ąĮąĖčÅ ą┤ąŠą╗ąČąĄąĮ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čéčī čŹč鹊čé ą▒ąĖčé, čćč鹊ą▒čŗ ą┐ąŠą╝ąĄčéąĖčéčī čüčéčĆą░ąĮąĖčåčā ą║ą░ą║ ą│čĆčÅąĘąĮčāčÄ.

Write Access Permission Flags (čäą╗ą░ą│ąĖ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ąĮą░ ą╝ąŠą┤ąĖčäąĖą║ą░čåąĖčÄ ą┐ą░ą╝čÅčéąĖ). CPLB ą┤ą╗čÅ ą┐ą░ą╝čÅčéąĖ ą┤ą░ąĮąĮčŗčģ ąĖą╝ąĄčÄčé 2 čäą╗ą░ą│ą░, ą║ąŠč鹊čĆčŗąĄ čĆą░ąĘčĆąĄčłą░čÄčé/ąĘą░ą┐čĆąĄčēą░čÄčé ą┤ąŠčüčéčāą┐ ąĮą░ ąĘą░ą┐ąĖčüčī ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēčāčÄ čüčéčĆą░ąĮąĖčåčā ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮąŠ ą┤ą╗čÅ čĆąĄąČąĖą╝ą░ čüčāą┐ąĄčĆą▓ąĖąĘąŠčĆą░ (CPLB_SUPV_WR) ąĖ ą┤ą╗čÅ čĆąĄąČąĖą╝ą░ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ (CPLB_USER_WR).

User Read Access Permission Flag (čäą╗ą░ą│ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┤ąŠčüčéčāą┐ą░ ąĮą░ čćč鹥ąĮąĖąĄ ą┤ą╗čÅ čĆąĄąČąĖą╝ą░ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ). ąŁč鹊čé ą░čéčĆąĖą▒čāčé (CPLB_USER_RD) čĆą░ąĘčĆąĄčłą░ąĄčé/ąĘą░ą┐čĆąĄčēą░ąĄčé čćč鹥ąĮąĖčÅ čŹč鹊ą╣ čüčéčĆą░ąĮąĖčåčŗ ą║ąŠą┤ąŠą╝, čĆą░ą▒ąŠčéą░čÄčēąĄą╝ ą▓ user mode.

Lock Flag (čäą╗ą░ą│ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ). ąÜąŠą│ą┤ą░ ą▒ąĖčé CPLB_LOCK, čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēą░čÅ ąĘą░ą┐ąĖčüčī CPLB ąĘą░ą▒ą╗ąŠą║ąĖčĆąŠą▓ą░ąĮą░. ąŁč鹊čé ą░čéčĆąĖą▒čāčé ą┐ąŠą╗ąĄąĘąĄąĮ ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┤ąĖąĮą░ą╝ąĖč湥čüą║ąŠą╣ ą┐ą░ą╝čÅčéčīčÄ. ąÜąŠą│ą┤ą░ ąĘą░ą┐ąĖčüčī CPLB ąĘą░ą▒ą╗ąŠą║ąĖčĆąŠą▓ą░ąĮą░, ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ ąĖčüą║ą╗čÄč湥ąĮąĖčÅ ą┐čĆąŠą╝ą░čģą░ CPLB ąĮąĄ čĆą░čüčüą╝ą░čéčĆąĖą▓ą░ąĄčé čŹč鹊čé ą▒ą╗ąŠą║ ą┤ą╗čÅ ąĘą░ą╝ąĄąĮčŗ.

ąÉčéčĆąĖą▒čāčéčŗ čüčéčĆą░ąĮąĖčåčŗ, čüą▓čÅąĘą░ąĮąĮčŗąĄ čü čĆą░ąĘčĆąĄčłąĄąĮąĖąĄą╝ čćč鹥ąĮąĖčÅ/ąĘą░ą┐ąĖčüąĖ ą┐ąŠąĘą▓ąŠą╗čÅčÄčé čĆąĄą░ą╗ąĖąĘąŠą▓ą░čéčī ąĘą░čēąĖčéčā ą┐ą░ą╝čÅčéąĖ. ąŁč鹊 ą╝ąŠąČąĄčé ą┐ąŠčéčĆąĄą▒ąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą┐čĆąĖą╗ąŠąČąĄąĮąĖą╣ čĆąĄą░ą╗čīąĮąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ, ą▓ ą║ąŠč鹊čĆčŗčģ ą▓čüąĄ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ čĆą░ąĘą┤ąĄą╗ąĄąĮąŠ ąĮą░ ą║ąŠą┤ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ ąĖ ą║ąŠą┤ ąŠą┐ąĄčĆą░čåąĖąŠąĮąĮąŠą╣ čüąĖčüč鹥ą╝čŗ. ąÜąŠą┤ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ ą╝ąŠąČąĄčé ąĖą╝ąĄčéčī ąĮąĄčüą║ąŠą╗čīą║ąŠ čĆą░ąĘąĮčŗčģ ą┐ąŠč鹊ą║ąŠą▓, ą┐čĆąĖč湥ą╝ ą║ą░ąČą┤čŗą╣ ą┐ąŠč鹊ą║ ąĖą╝ąĄąĄčé čüąŠą▒čüčéą▓ąĄąĮąĮčŗąĄ čĆąĄčüčāčĆčüčŗ ą┐ą░ą╝čÅčéąĖ, ą║ąŠč鹊čĆčŗąĄ ąĮąĄą┤ąŠčüčéčāą┐ąĮčŗ ą┤ą╗čÅ ą┤čĆčāą│ąĖčģ ą┐ąŠč鹊ą║ąŠą▓. ą×ą┤ąĮą░ą║ąŠ čÅą┤čĆąŠ ąŠą┐ąĄčĆą░čåąĖąŠąĮąĮąŠą╣ čüąĖčüč鹥ą╝čŗ ą╝ąŠąČąĄčé ą┐ąŠą╗čāčćąĖčéčī ą┤ąŠčüčéčāą┐ ą║ąŠ ą▓čüąĄą╝ čĆąĄčüčāčĆčüą░ą╝ ą┐ą░ą╝čÅčéąĖ. ąŁčéą░ ąĘą░ą┤ą░čćą░ ą╝ąŠąČąĄčé ą▒čŗčéčī čĆąĄčłąĄąĮą░ ąĮą░čüčéčĆąŠą╣ą║ąŠą╣ čĆą░ąĘąĮčŗčģ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖą╣ CPLB ą▓ čĆą░ąĘąĮčŗčģ ą┐ąŠč鹊ą║ą░čģ.

ąÜąŠą│ą┤ą░ CPLB čĆą░ąĘčĆąĄčłąĄąĮčŗ, ą┤ąŠą╗ąČąĮą░ čüčāčēąĄčüčéą▓ąŠą▓ą░čéčī ą┤ąŠą┐čāčüčéąĖą╝ą░čÅ ąĘą░ą┐ąĖčüčī CPLB ą░ čéą░ą▒ą╗ąĖčåąĄ CPLB ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą░ą┤čĆąĄčüą░, ą▓ ą║ąŠč鹊čĆčŗą╣ ą┤ąĄą╗ą░ąĄčéčüčÅ ą┤ąŠčüčéčāą┐. ąĢčüą╗ąĖ ąĮąĄčé ą┤ąŠą┐čāčüčéąĖą╝čŗčģ ąĘą░ą┐ąĖčüąĄą╣ ą┤ą╗čÅ čüčéčĆą░ąĮąĖčå, ą║ ą║ąŠč鹊čĆčŗą╝ ą┐čĆąŠąĖąĘąŠčłą╗ąŠ ąŠą▒čĆą░čēąĄąĮąĖąĄ, č鹊 ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ąĖčüą║ą╗čÄč湥ąĮąĖąĄ CPLB.

[ąĀąĄą│ąĖčüčéčĆčŗ čüąŠčüč鹊čÅąĮąĖčÅ CPLB (CPLB Status Registers)]

MPCU ąĖą╝ąĄąĄčé 2 ąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗčģ čĆąĄą│ąĖčüčéčĆą░ čüąŠčüč鹊čÅąĮąĖčÅ: ąŠą┤ąĖąĮ ą┤ą╗čÅ čüčéą░čéčāčüą░ ICPLB (čĆąĖčü. 17), ąĖ ąŠą┤ąĖąĮ ą┤ą╗čÅ čüčéą░čéčāčüą░ DCPLB (čĆąĖčü. 18).

FAULT_ILLADDR. ą¤čĆąŠąĖąĘąŠčłą╗ą░ ą┐ąŠą┐čŗčéą║ą░ ąĘą░ą┐ąĖčüąĖ ą▓ ą┐ą░ą╝čÅčéčī, ą║ąŠč鹊čĆą░čÅ ąĮąĄ čüčāčēąĄčüčéą▓čāąĄčé.

FAULT_DAG. ąŁč鹊čé ą▒ąĖčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 DAG0 ąĖą╗ąĖ DAG1 ą┐čĆąĖą▓ąĄą╗ ą║ ąĮąĄą┐čĆą░ą▓ąĖą╗čīąĮąŠą╝čā ą┤ąŠčüčéčāą┐čā ą║ ą┤ą░ąĮąĮčŗą╝ (č鹊ą╗čīą║ąŠ DCPLB).

FAULT_USERSUPV. ąöąŠčüčéčāą┐ ą▒čŗą╗ čüą┤ąĄą╗ą░ąĮ ą╗ąĖą▒ąŠ ą▓ čĆąĄąČąĖą╝ąĄ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ (user mode), ą╗ąĖą▒ąŠ ą▓ čĆąĄąČąĖą╝ąĄ čüčāą┐ąĄčĆą▓ąĖąĘąŠčĆą░ (supervisor mode).

FAULT_RW. ąöąŠčüčéčāą┐ ą║ ą┤ą░ąĮąĮčŗą╝ ą▒čŗą╗ ą╗ąĖą▒ąŠ ąĮą░ čćč鹥ąĮąĖąĄ, ą╗ąĖą▒ąŠ ąĮą░ ąĘą░ą┐ąĖčüčī (č鹊ą╗čīą║ąŠ DCPLB).

FAULT. ąĪąŠčüč鹊čÅąĮąĖąĄ ą┐ąŠą┐ą░ą┤ą░ąĮąĖčÅ/ą┐čĆąŠą╝ą░čģą░ (hit/miss) čüą▓čÅąĘą░ąĮąĮąŠą╣ ąĘą░ą┐ąĖčüąĖ CPLB.

ąĀąĖčü. 17. ąæąĖč鹊ą▓čŗąĄ ą┐ąŠą╗čÅ ąĖ ąĖčģ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠčüčéčī ą┤ą╗čÅ čĆąĄą│ąĖčüčéčĆą░ čüąŠčüč鹊čÅąĮąĖčÅ ICPLB.

ąĀąĖčü. 18. ąæąĖč鹊ą▓čŗąĄ ą┐ąŠą╗čÅ ąĖ ąĖčģ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠčüčéčī ą┤ą╗čÅ čĆąĄą│ąĖčüčéčĆą░ čüąŠčüč鹊čÅąĮąĖčÅ DCPLB.

Table 7. ąĪąŠą▒čŗčéąĖčÅ CPLB, ą║ąŠč鹊čĆčŗąĄ ą▓čŗąĘčŗą▓ą░čÄčé ąĖčüą║ą╗čÄč湥ąĮąĖčÅ [6].

| ąśčüą║ą╗čÄč湥ąĮąĖąĄ (Exception) |

EXCAUSE [5:0] |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ/ą┐čĆąĖą╝ąĄčĆčŗ |

| ąØą░čĆčāčłąĄąĮąĖąĄ ąĘą░čēąĖčéčŗ ą┤ąŠčüčéčāą┐ą░ CPLB ą║ ą┤ą░ąĮąĮčŗą╝ |

0x23 |

ąĪą┤ąĄą╗ą░ąĮą░ ą┐ąŠą┐čŗčéą║ą░ ą┤ąŠčüčéčāą┐ą░ ą║ čĆąĄčüčāčĆčüčā čüčāą┐ąĄčĆą▓ąĖąĘąŠčĆą░ (čüą╝. [6]), ą╗ąĖą▒ąŠ ąĮąĄą┤ąŠą┐čāčüčéąĖą╝čŗą╣ ą┤ąŠčüčéčāą┐ ą║ ą┐ą░ą╝čÅčéąĖ. ąŁčéą░ ąĘą░ą┐ąĖčüčī ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čüąĖą│ąĮą░ą╗ąĖąĘą░čåąĖąĖ ąŠ ąĮą░čĆčāčłąĄąĮąĖąĖ ąĘą░čēąĖčéčŗ, ą║ ą║ąŠč鹊čĆąŠą╝čā ą┐čĆąĖą▓ąĄą╗ ąĮąĄ čĆą░ąĘčĆąĄčłąĄąĮąĮčŗą╣ ą┤ąŠčüčéčāą┐ ą║ ą┐ą░ą╝čÅčéąĖ, ąĖ čŹč鹊 ąĘą░ą┤ą░ąĮąŠ ą▒ą╗ąŠą║ąŠą╝ MPCU ąĖ CPLB. |

| ąØą░čĆčāčłąĄąĮąĖąĄ ą┤ąŠčüčéčāą┐ą░ ą║ ą┤ą░ąĮąĮčŗą╝, čüą▓čÅąĘą░ąĮąĮąŠąĄ čü ąĮąĄą▓čŗčĆąŠą▓ąĮąĄąĮąĮčŗą╝ ą░ą┤čĆąĄčüąŠą╝ |

0x24 |

ąæčŗą╗ą░ ą┐ąŠą┐čŗčéą║ą░ ąĮąĄą▓čŗčĆąŠą▓ąĮąĄąĮąĮąŠą│ąŠ ą┤ąŠčüčéčāą┐ą░ ą║ ą┤ą░ąĮąĮčŗą╝ ą┐ą░ą╝čÅčéąĖ ąĖą╗ąĖ ą┤ą░ąĮąĮčŗą╝ ą║čŹčłą░. |

| ą¤čĆąŠą╝ą░čģ CPLB ą┐čĆąĖ ą┤ąŠčüčéčāą┐ąĄ ą║ ą┤ą░ąĮąĮčŗą╝ |

0x26 |

ąśčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ MPCU ą┤ą╗čÅ čüąĖą│ąĮą░ą╗ąĖąĘą░čåąĖąĖ ąŠ ą┐čĆąŠą╝ą░čģąĄ CPLB ą┐čĆąĖ ą┤ąŠčüčéčāą┐ąĄ ą║ ą┤ą░ąĮąĮčŗą╝. |

| ą£ąĮąŠąČąĄčüčéą▓ąĄąĮąĮąŠąĄ ą┐ąŠą┐ą░ą┤ą░ąĮąĖąĄ CPLB ą┐čĆąĖ ą┤ąŠčüčéčāą┐ąĄ ą║ ą┤ą░ąĮąĮčŗą╝ |

0x27 |

ąÉą┤čĆąĄčüčā ą▓čŗą▒ąŠčĆą║ąĖ ą┤ą░ąĮąĮčŗčģ čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ą▒ąŠą╗čīčłąĄ ąŠą┤ąĮąŠą╣ ąĘą░ą┐ąĖčüąĖ CPLB. |

| ąØą░čĆčāčłąĄąĮąĖąĄ ąĘą░čēąĖčéčŗ CPLB ą┐čĆąĖ ą▓čŗą▒ąŠčĆą║ąĄ ąĖąĮčüčéčĆčāą║čåąĖąĖ |

0x2B |

ąØąĄą┤ąŠą┐čāčüčéąĖą╝čŗą╣ ą┤ąŠčüčéčāą┐ ą▓čŗą▒ąŠčĆą║ąĖ ąĖąĮčüčéčĆčāą║čåąĖąĖ (ąĮą░čĆčāčłąĄąĮąĖąĄ ąĘą░čēąĖčéčŗ ą┐ą░ą╝čÅčéąĖ). |

| ą¤čĆąŠą╝ą░čģ CPLB ą┐čĆąĖ ą▓čŗą▒ąŠčĆą║ąĄ ąĖąĮčüčéčĆčāą║čåąĖąĖ |

0x2C |

ą¤čĆąŠą╝ą░čģ CPLB ą┐čĆąĖ ą▓čŗą▒ąŠčĆą║ąĄ ąĖąĮčüčéčĆčāą║čåąĖąĖ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ. |

| ą£ąĮąŠąČąĄčüčéą▓ąĄąĮąĮąŠąĄ ą┐ąŠą┐ą░ą┤ą░ąĮąĖąĄ CPLB ą┐čĆąĖ ą▓čŗą▒ąŠčĆą║ąĄ ąĖąĮčüčéčĆčāą║čåąĖąĖ |

0x2D |

ąÉą┤čĆąĄčüčā ą▓čŗą▒ąŠčĆą║ąĖ ąĖąĮčüčéčĆčāą║čåąĖąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ą▒ąŠą╗čīčłąĄ ąŠą┤ąĮąŠą╣ ąĘą░ą┐ąĖčüąĖ CPLB. |

[ąśčüą║ą╗čÄč湥ąĮąĖčÅ čüąĄą║ą▓ąĄąĮčüąŠčĆą░, čüą▓čÅąĘą░ąĮąĮčŗąĄ čü CPLB]

ąÆ čĆąĄą│ąĖčüčéčĆą░čģ ICPLB_DATAx ąĖ DCPLB_DATAx ąĮąĄą║ąŠč鹊čĆčŗąĄ ą┐ąŠą╗ąĖčéąĖą║ąĖ ą┤ąŠčüčéčāą┐ą░ (čćč鹥ąĮąĖąĄ/ąĘą░ą┐ąĖčüčī ą▓ user mode ąĖ supervisor mode) ą╝ąŠą│čāčé ą▒čŗčéčī ąĘą░ą┤ą░ąĮčŗ ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗčģ ąŠą▒ą╗ą░čüč鹥ą╣ ą┐ą░ą╝čÅčéąĖ. ąØą░čĆčāčłąĄąĮąĖąĄ ą┐čĆą░ą▓ąĖą╗ ą┤ąŠčüčéčāą┐ą░ ą┐čĆąĖą▓ąŠą┤ąĖčé ą║ ąĖčüą║ą╗čÄč湥ąĮąĖčÅą╝ čüąĄą║ą▓ąĄąĮčüąŠčĆą░.

ą¤čĆąĖčćąĖąĮąŠą╣ ąĖčüą║ą╗čÄč湥ąĮąĖčÅ ą╝ąŠąČąĄčé ą▒čŗčéčī čćč鹥ąĮąĖąĄ ąĖąĘ ą┐ąŠą╗čÅ ą▒ąĖčé EXCAUSE čĆąĄą│ąĖčüčéčĆą░ čüąŠčüč鹊čÅąĮąĖčÅ čüąĄą║ą▓ąĄąĮčüąŠčĆą░ (sequencer status register, SEQSTAT). ąÆ čéą░ą▒ą╗ąĖčåąĄ 7 ą┐ąŠą║ą░ąĘą░ąĮ čüą┐ąĖčüąŠą║ ą▓čüąĄčģ ąĖčüą║ą╗čÄč湥ąĮąĖą╣, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠą│čāčé ą┐ąŠčüčéčāą┐ą░čéčī ąŠčé CPLB.

[ąóą░ą▒ą╗ąĖčåą░ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą▓ čüčéčĆą░ąĮąĖčåčŗ (Page Descriptor Table)]

ą×ą▒čŗčćąĮąŠ ąŠčüąĮąŠą▓ą░ąĮąĮą░čÅ ąĮą░ ą┐ą░ą╝čÅčéąĖ čüčéčĆčāą║čéčāčĆą░ ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ CPLB ąĮą░ąĘčŗą▓ą░ąĄčéčüčÅ page descriptor table (čéą░ą▒ą╗ąĖčåą░ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą▓ čüčéčĆą░ąĮąĖčå, PDT). ąÆčüąĄ ą┐ąŠč鹥ąĮčåąĖą░ą╗čīąĮąŠ ąĮąĄąŠą▒čģąŠą┤ąĖą╝čŗąĄ ąĘą░ą┐ąĖčüąĖ CPLB ą╝ąŠą│čāčé ą▒čŗčéčī čüąŠčģčĆą░ąĮąĄąĮčŗ ą▓ PDT (ą║ąŠč鹊čĆą░čÅ ąŠą▒čŗčćąĮąŠ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ SRAM). ąÜąŠą│ą┤ą░ ąĮčāąČąĮąŠ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī CPLB, ą║ąŠą┤ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ą╝ąŠąČąĄčé ą▓ąĘčÅčéčī ąĘą░ą┐ąĖčüąĖ CPLB ąĖąĘ PDT ąĖ ąĘą░ą┐ąŠą╗ąĮąĖčéčī ąĖčģ ą▓ čĆąĄą│ąĖčüčéčĆčŗ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ CPLB.

ąöą╗čÅ ą╝ą░ą╗ąŠą╣/ą┐čĆąŠčüč鹊ą╣ ą╝ąŠą┤ąĄą╗ąĖ ą┐ą░ą╝čÅčéąĖ ąĖąĮąŠą│ą┤ą░ ą╝ąŠąČąĮąŠ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ąĮą░ą▒ąŠčĆ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą▓ CPLB, ą║ąŠč鹊čĆčŗą╣ ą┐ąŠą╝ąĄčüčéąĖčéčüčÅ ą▓ 32 ąĘą░ą┐ąĖčüąĖ CPLB (16 ICPLB ąĖ 16 DCPLB). ąŁč鹊čé čéąĖą┐ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ ąĮą░ąĘčŗą▓ą░ąĄčéčüčÅ ą║ą░ą║ čüčéą░čéąĖč湥čüą║ą░čÅ ą╝ąŠą┤ąĄą╗čī čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ą░ą╝čÅčéąĖ. ą¤čĆąĖą╝ąĄčĆ Example1 (1) ąĖčüą┐ąŠą╗čīąĘčāąĄčé čüčéą░čéąĖč湥čüą║čāčÄ ą╝ąŠą┤ąĄą╗čī čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ą░ą╝čÅčéąĖ.

ąöą╗čÅ čüą╗ąŠąČąĮčŗčģ ą╝ąŠą┤ąĄą╗ąĄą╣ ą┐ą░ą╝čÅčéąĖ ą▓ PDT ą╝ąŠą│čāčé ą▒čŗčéčī ąĘą░ą┐ąĖčüąĖ CPLB, ą║ąŠč鹊čĆčŗąĄ ąĮąĄ čāą║ą╗ą░ą┤čŗą▓ą░čÄčéčüčÅ ą▓ ą┤ąŠčüčéčāą┐ąĮčŗąĄ 16 čĆąĄą│ąĖčüčéčĆąŠą▓ CPLB. ąöą╗čÅ čŹčéąĖčģ čāčüą╗ąŠą▓ąĖą╣ CPLB ą╝ąŠąČąĄčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ čüąĮą░čćą░ą╗ą░ čü čŹčéąĖą╝ąĖ ą╗čÄą▒čŗą╝ąĖ 16 ąĘą░ą┐ąĖčüčÅą╝ąĖ. ąÜąŠą│ą┤ą░ ą┐čĆąŠčåąĄčüčüąŠčĆ ąŠą▒čĆą░čēą░ąĄčéčüčÅ ą║ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą╝čā ą╝ąĄčüčéčā ą▓ ą┐ą░ą╝čÅčéąĖ, ą║ąŠč鹊čĆą░čÅ ąĮąĄ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮą░ č湥čĆąĄąĘ ąĘą░ą┐ąĖčüąĖ CPLB, ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ąĖčüą║ą╗čÄč湥ąĮąĖąĄ, ąĖ ą░ą┤čĆąĄčü ą▓čŗąĘą▓ą░ą▓čłąĄą╣ ąŠčłąĖą▒ą║čā ą┐ą░ą╝čÅčéąĖ čüąŠčģčĆą░ąĮčÅąĄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ ąŠčłąĖą▒ą║ąĖ ą░ą┤čĆąĄčüą░ (Fault Address register, xCPLB_FAULT_ADDR). ą×ą▒čĆą░ą▒ąŠčéčćąĖą║ ąĖčüą║ą╗čÄč湥ąĮąĖčÅ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čŹč鹊čé ą░ą┤čĆąĄčü ą┤ą╗čÅ ą┐ąŠąĖčüą║ą░ ąĮčāąČąĮąŠą╣ ąĘą░ą┐ąĖčüąĖ CPLB ą▓ PDT. ą×ą┤ąĮą░ ąĖąĘ čüčāčēąĄčüčéą▓čāčÄčēąĖčģ ąĘą░ą┐ąĖčüąĄą╣ CPLB ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą╝ąĄąĮąĄąĮą░ čŹč鹊ą╣ ąĮąŠą▓ąŠą╣ ąĮą░ą╣ą┤ąĄąĮąĮąŠą╣ ąĘą░ą┐ąĖčüčīčÄ CPLB, ą▓ąĘčÅč鹊ą╣ ąĖąĘ PDT.

ą¤ąŠą╗ąĖčéąĖą║ą░ ąĘą░ą╝ąĄąĮą░ CPLB ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąŠčüč鹊ą╣ ąĖą╗ąĖ čüą╗ąŠąČąĮąŠą╣, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čéčĆąĄą▒ąŠą▓ą░ąĮąĖą╣ čüąĖčüč鹥ą╝čŗ. ą£ąŠąČąĄčé ą┐čĆąŠąĖąĘąŠą╣čéąĖ čéą░ą║, čćč鹊 ą▒ąŠą╗čīčłąĄ č湥ą╝ ąŠą┤ąĮąŠ ąŠą▒čĆą░čēąĄąĮąĖąĄ ą║ ą┐ą░ą╝čÅčéąĖ, ą┤ą╗čÅ ą║ąŠč鹊čĆąŠą╣ ąĮąĄčé ąĘą░ą┐ąĖčüąĖ ą▓ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░čģ. ąÆ čéą░ą║ąĖčģ čāčüą╗ąŠą▓ąĖčÅčģ ąĖčüą║ą╗čÄč湥ąĮąĖčÅ ą┐čĆąĖąŠčĆąĖč鹥ąĘąĖčĆčāčÄčéčüčÅ ąĖ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░čÄčéčüčÅ ą▓ čüą╗ąĄą┤čāčÄčēąĄą╝ ą┐ąŠčĆčÅą┤ą║ąĄ:

1. ą¤čĆąŠą╝ą░čģąĖ čüčéčĆą░ąĮąĖčåčŗ ą┤ą╗čÅ ąĖąĮčüčéčĆčāą║čåąĖą╣.

2. ą¤čĆąŠą╝ą░čģąĖ čüčéčĆą░ąĮąĖčåčŗ ąĮą░ DAG0.

3. ą¤čĆąŠą╝ą░čģąĖ čüčéčĆą░ąĮąĖčåčŗ ąĮą░ DAG1.

ą¤čĆąĖą╝ąĄčĆ ą║ąŠą┤ą░ ą▓ Example2 (2) ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ ąĖčüą║ą╗čÄč湥ąĮąĖą╣ ą┤ą╗čÅ ą┐čĆąŠą╝ą░čģąŠą▓ DCPLB (čüą╝. čéą░ą▒ą╗ąĖčåčā 7: EXCAUSE 0x26). ą×ąĮ ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą║ą░čĆčāčüąĄą╗čīąĮčŗą╣ ą╝ąĄč鹊ą┤ čłąĄą┤čāą╗ąĖąĮą│ą░ (round-robin) ą┤ą╗čÅ ąĘą░ą╝ąĄąĮčŗ DCPLB.

[ąĪąŠąŠą▒čĆą░ąČąĄąĮąĖčÅ, ą║ą░čüą░čÄčēąĖąĄčüčÅ ą║ąŠą│ąĄčĆąĄąĮčéąĮąŠčüčéąĖ ą║čŹčłą░]

ąĢčüą╗ąĖ ą▓ąĮąĄčłąĮąĖą╣ ąĖčüč鹊čćąĮąĖą║ (ąĮą░ą┐čĆąĖą╝ąĄčĆ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ DMA) ąŠą▒čĆą░čēą░ąĄčéčüčÅ ą║ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ, ą║ąŠč鹊čĆą░čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮą░ ą║ą░ą║ ą║čŹčłąĖčĆčāąĄą╝ą░čÅ, ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčüčé ą┤ąŠą╗ąČąĄąĮ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī ą║ąŠą│ąĄčĆąĄąĮčéąĮąŠčüčéčī ą┐ą░ą╝čÅčéąĖ. ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą║čŹčłą░ ąĮąĄ ąĘąĮą░ąĄčé ąĮąĖ ąŠ ą║ą░ą║ąĖčģ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅčģ, ą║ąŠč鹊čĆčŗąĄ ą▒čŗą╗ąĖ čüą┤ąĄą╗ą░ąĮčŗ ąĮąĄ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą╝. ą¤čĆąŠčüč鹊ą╣ ąŠą┐čĆąŠčü ą┐ą░ą╝čÅčéąĖ čĆą░ą▒ąŠčéą░čéčī ąĮąĄ ą▒čāą┤ąĄčé.

ą¤čĆąĖą╝ąĄčĆ ą┤ą╗čÅ čéą░ą║ąŠą╣ čüąĖčéčāą░čåąĖąĖ - ą║ąŠą╗čīčåąĄą▓ąŠą╣ ą▒čāč乥čĆ, ą║ąŠč鹊čĆčŗą╣ čģčĆą░ąĮąĖčéčüčÅ ą▓ąŠ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ. ąöą░ąĮąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ą╝ąĄąČą┤čā čŹčéąĖą╝ ą▒čāč乥čĆąŠą╝ ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ ąĖąĮč鹥čĆč乥ą╣čüąŠą╝ (ąĮą░ą┐čĆąĖą╝ąĄčĆ, ą║ą░ą║ąŠą╣-č鹊 ą┐ąŠč鹊ą║ ą░čāą┤ąĖąŠą┤ą░ąĮąĮčŗčģ). ą»ą┤čĆąŠ ą┤ąŠą╗ąČąĮąŠ čüą┤ąĄą╗ą░čéčī ąĮąĄą║ąŠč鹊čĆčŗąĄ ą▓čŗčćąĖčüą╗ąĄąĮąĖčÅ ąĖ ąĘą░ą┐ąĖčüą░čéčī ą┤ą░ąĮąĮčŗąĄ ąŠą▒čĆą░čéąĮąŠ ą▓ ą▒čāč乥čĆ, ąŠčéą║čāą┤ą░ ą┤ą░ąĮąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ąŠą▒čĆą░čéąĮąŠ ą▓ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ąČąĄą╗ą░č鹥ą╗čīąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čüčéčĆą░č鹥ą│ąĖčÄ write-through (čüą║ą▓ąŠąĘąĮą░čÅ ąĘą░ą┐ąĖčüčī). ąÆ čéą░ą▒ą╗ąĖčåąĄ 8 ą┐ąŠą║ą░ąĘą░ąĮčŗ čüčéą░ą┤ąĖąĖ ą║ąŠąĮą▓ąĄą╣ąĄčĆą░ ąĖąĮčüčéčĆčāą║čåąĖą╣ ą┐čĆąŠčåąĄčüčüąŠčĆą░ Blackfin.

ąóą░ą▒ą╗ąĖčåą░ 8. ąĪčéą░ą┤ąĖąĖ ą║ąŠąĮą▓ąĄą╣ąĄčĆą░ ąĖąĮčüčéčĆčāą║čåąĖą╣.

| Instr Fetch 1 (ą▓čŗą▒ąŠčĆą║ą░ ąĖąĮčüčéčĆčāą║čåąĖąĖ 1) |

| Instr Fetch 2 (ą▓čŗą▒ąŠčĆą║ą░ ąĖąĮčüčéčĆčāą║čåąĖąĖ 2) |

| Instr Fetch 3 (ą▓čŗą▒ąŠčĆą║ą░ ąĖąĮčüčéčĆčāą║čåąĖąĖ 3) |

| Instr Dec (ą┤ąĄą║ąŠą┤ąĖčĆąŠą▓ą░ąĮąĖąĄ ąĖąĮčüčéčĆčāą║čåąĖąĖ) |

| Addr Calc (ą▓čŗčćąĖčüą╗ąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░) |

| Data Fetch 1 (ą▓čŗą▒ąŠčĆą║ą░ ą┤ą░ąĮąĮčŗčģ 1) |

| Data Fetch 2 (ą▓čŗą▒ąŠčĆą║ą░ ą┤ą░ąĮąĮčŗčģ 2) |

| Ex 1 |

| Ex 2 |

| Write-Back |

ąØą░ čüčéą░ą┤ąĖąĖ 1 (IF1) ą░ą┤čĆąĄčü ąĖąĮčüčéčĆčāą║čåąĖąĖ ą▓čŗą┤ą░ąĄčéčüčÅ ąĮą░ čłąĖąĮčā ą┤ąŠčüčéčāą┐ą░ ą║ ąĖąĮčüčéčĆčāą║čåąĖąĖ (Instruction Access Bus, IAB). ąÆ čŹč鹊ą╣ čäą░ąĘąĄ ąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ čüčĆą░ą▓ąĮąĄąĮąĖąĄ čé菹│ąŠą▓ ą║čŹčłą░ ąĖąĮčüčéčĆčāą║čåąĖąĖ.

ąØą░ čüčéą░ą┤ąĖąĖ 6 (DF1) ą░ą┤čĆąĄčü ą┤ą░ąĮąĮčŗčģ ą▓čŗą┤ą░ąĄčéčüčÅ ąĮą░ čłąĖąĮčā ą┤ąŠčüčéčāą┐ą░ ą║ ą┤ą░ąĮąĮčŗą╝ (Data Access Buses, DA0 ąĖ DA1). ąÆ čŹč鹊ą╣ čäą░ąĘąĄ ąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ čüčĆą░ą▓ąĮąĄąĮąĖąĄ čé菹│ąŠą▓ ą║čŹčłą░ ą┤ą░ąĮąĮčŗčģ.

ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ ą┐čĆąŠ ą║ąŠąĮą▓ąĄą╣ąĄčĆ ąĖąĮčüčéčĆčāą║čåąĖą╣ čüą╝. čĆą░ąĘą┤ąĄą╗ "Program Sequencer" ą▓ čĆčāą║ąŠą▓ąŠą┤čüčéą▓ąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąŠčåąĄčüčüąŠčĆą░ Blackfin [3].

[ą×ą▒čĆą░ą▒ąŠčéą║ą░ ą║čŹčłą░ ąĖąĮčüčéčĆčāą║čåąĖąĖ ąĖ ą┤ą░ąĮąĮčŗčģ]

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą║čŹčłą░. ą║čŹčłąĖ ąĖąĮčüčéčĆčāą║čåąĖąĖ ąĖ ą┤ą░ąĮąĮčŗčģ ą╝ąŠą│čāčé ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮčŗ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčēąĄąĮčŗ ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ą┤čĆčāą│ ąŠčé ą┤čĆčāą│ą░ ą┐čāč鹥ą╝ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆąŠą▓ IMEM_CONTROL ąĖ DMEM_CONTROL čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ. ą¤čĆąĖą╝ąĄčĆ ą┤ąĄą╝ąŠąĮčüčéčĆąĖčĆčāąĄčé, ą║ą░ą║ ą╝ąŠąČąĮąŠ čĆą░ąĘčĆąĄčłąĖčéčī ą║čŹčłąĖ ą┤ą░ąĮąĮčŗčģ/ąĖąĮčüčéčĆčāą║čåąĖąĖ:

ŌĆó ą¤ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ čĆą░ąĘčĆąĄčłąĖčéčī ą║čŹčł, ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĮą░čüčéčĆąŠąĄąĮčŗ ąĖ čĆą░ąĘčĆąĄčłąĄąĮčŗ ą║ąŠčĆčĆąĄą║čéąĮčŗąĄ ą┤ąĄčüą║čĆąĖą┐č鹊čĆčŗ CPLB.

ŌĆó ąÜąŠą│ą┤ą░ ą┐ą░ą╝čÅčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮą░ ą║ą░ą║ ą║čŹčł, ą║ ąĮąĄą╣ ąĮąĄą╗čīąĘčÅ ą┐ąŠą╗čāčćąĖčéčī ą┤ąŠčüčéčāą┐ ąĮą░ą┐čĆčÅą╝čāčÄ (ąĮąĖ čüąŠ čüč鹊čĆąŠąĮčŗ čÅą┤čĆą░, ąĮąĖ č湥čĆąĄąĘ DMA).

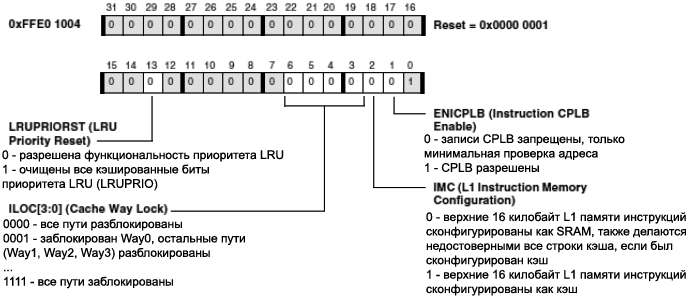

Instruction Memory Control Register (IMEM_CONTROL). ąĀąĖčü. 19 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čĆą░ąĘą╗ąĖčćąĮčŗąĄ ą▒ąĖč鹊ą▓čŗąĄ ą┐ąŠą╗čÅ ąĖ ąĖčģ čäčāąĮą║čåąĖąŠąĮą░ą╗ čĆąĄą│ąĖčüčéčĆą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ą░ą╝čÅčéčīčÄ ąĖąĮčüčéčĆčāą║čåąĖą╣ IMEM_CONTROL.

LRU Priority Reset (čüą▒čĆąŠčü ą┐čĆąĖąŠčĆąĖč鹥čéą░ LRU). ąæąĖčé LRUPRIORST ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ čüą▒čĆąŠčüą░ ą▓čüąĄčģ ą▒ąĖč鹊ą▓ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą║čŹčłąĖčĆąŠą▓ą░ąĮąĖčÅ LRU.

Instruction Cache Locking by Way (čüą┐ąŠčüąŠą▒ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ ą║čŹčłąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖąĮčüčéčĆčāą║čåąĖą╣). ą║čŹčł ąĖąĮčüčéčĆčāą║čåąĖą╣ ąĖą╝ąĄąĄčé 4 ąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗčģ ą▒ąĖčéą░ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ (čŹčéąĖ ą▒ąĖčéčŗ ą┤ąŠčüčéčāą┐ąĮčŗ ą▓ čĆąĄą│ąĖčüčéčĆąĄ IMEM_CONTROL), ą║ąŠč鹊čĆčŗąĄ ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┤ą╗čÅ ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠą╣ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ č湥čéčŗčĆąĄčģ ą┐čāč鹥ą╣.

ąÜąŠą│ą┤ą░ ąŠčéą┤ąĄą╗čīąĮčŗą╣ ą┐čāčéčī ąĘą░ą▒ą╗ąŠą║ąĖčĆąŠą▓ą░ąĮ (čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé ILOC ą▓ čĆąĄą│ąĖčüčéčĆąĄ IMEM_CONTROL), ąŠąĮ ąĮąĄ čāčćą░čüčéą▓čāąĄčé ą▓ ą┐ąŠą╗ąĖčéąĖą║ąĄ ąĘą░ą╝ąĄąĮčŗ čüčéčĆąŠą║ąĖ ą║čŹčłą░. ąśąĮčüčéčĆčāą║čåąĖąĖ, ą║čŹčłąĖčĆąŠą▓ą░ąĮąĮčŗąĄ ąĖąĘ ąĘą░ą▒ą╗ąŠą║ąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ ą┐čāčéąĖ, ą╝ąŠąČąĮąŠ čāą┤ą░ą╗ąĖčéčī č鹊ą╗čīą║ąŠ čü ą┐ąŠą╝ąŠčēčīčÄ ąĖąĮčüčéčĆčāą║čåąĖąĖ IFLUSH.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ą░ ą║čŹčłą░ ą┐čĆąĄą┤ąŠčéą▓čĆą░čēą░ąĄčé ąŠčé ą▓čŗą▒ąŠčĆą░ ą┤ą╗čÅ ąĘą░ą╝ąĄąĮčŗ č鹊ą╗čīą║ąŠ ą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗąĄ čüčéčĆąŠą║ąĖ ą║čŹčłą░. ąØąĄą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗąĄ čüčéčĆąŠą║ąĖ ą║čŹčłą░, čüąŠčģčĆą░ąĮąĄąĮąĮčŗąĄ ą▓ ąĘą░ą▒ą╗ąŠą║ąĖčĆąŠą▓ą░ąĮąĮąŠą╝ ą┐čāčéąĖ, ą▓čüąĄ ąĄčēąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ą▓čŗą▒čĆą░ąĮčŗ ą┤ą╗čÅ ąĘą░ą╝ąĄąĮčŗ. ąŁč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ą┐čĆąŠą╝ą░čģąĖ ą║čŹčłą░ ą▓ ąĮąĄą┤ąŠčüč鹊ą▓ąĄčĆąĮčāčÄ ąĘą░ą┐ąĖčüčī ą┐čĆąĖą▓ąĄą┤čāčé ą║ č鹊ą╝čā, čćč鹊 čŹčéą░ ąĘą░ą┐ąĖčüčī ą▒čāą┤ąĄčé ą▓čŗą▒čĆą░ąĮą░ ą┤ą╗čÅ ąĘą░ą╝ąĄąĮčŗ ąĮąŠą▓ąŠą╣ čüčéčĆąŠą║ąŠą╣ ą║čŹčłą░.