|

[ą×ą▒čĆą░ą▒ąŠčéą║ą░ čüąŠą▒čŗčéąĖą╣]

ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ čüąŠą▒čŗčéąĖą╣ ą┐čĆąŠčåąĄčüčüąŠčĆą░ Blackfin ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčé ą▓čüąĄ ą░čüąĖąĮčģčĆąŠąĮąĮčŗąĄ ąĖ čüąĖąĮčģčĆąŠąĮąĮčŗąĄ čüąŠą▒čŗčéąĖčÅ ą┤ą╗čÅ ą┐čĆąŠčåąĄčüčüąŠčĆą░. ą×ą▒čĆą░ą▒ąŠčéą║ą░ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą╝ čüąŠą▒čŗčéąĖą╣ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ą║ą░ą║ ąĮą░čüčéčĆąŠą╣ą║čā ą┐čĆąĖąŠčĆąĖč鹥č鹊ą▓, čéą░ą║ ąĖ ąĖčģ ą▓ą╗ąŠąČąĄąĮąĮąŠčüčéčī. ąÆą╗ąŠąČąĄąĮąĮąŠčüčéčī ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą▒čŗčéčī ą░ą║čéąĖą▓ąĮčŗą╝ąĖ čüčĆą░ąĘčā ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ą░ą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ (čüąŠą▒čŗčéąĖą╣). ą¤čĆąĖąŠčĆąĖč鹥ąĘą░čåąĖčÅ ą│ą░čĆą░ąĮčéąĖčĆčāąĄčé, čćč鹊 ąŠą▒čüą╗čāąČąĖą▓ą░ąĮąĖąĄ čüąŠą▒čŗčéąĖčÅ čü čüą░ą╝čŗą╝ ą▒ąŠą╗čīčłąĖą╝ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝ ąĖą╝ąĄąĄčé ą┐čĆąĄąĖą╝čāčēąĄčüčéą▓ąŠ ą┐ąĄčĆąĄą┤ ąŠą▒čüą╗čāąČąĖą▓ą░ąĮąĖąĄą╝ čüąŠą▒čŗčéąĖčÅ čü ą╝ąĄąĮčīčłąĖą╝ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝. ą¤čĆąĖ čŹč鹊ą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čü ą╝ąĄąĮčīčłąĖą╝ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗč鹥čüąĮąĄąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄą╝ ą▒ąŠą╗ąĄąĄ ą▓čŗčüąŠą║ąĖą╝ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝ (ą▒ąŠą╗ąĄąĄ ą┐čĆąĖąŠčĆąĖč鹥čéąĮąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠą║ą░ąČąĄčéčüčÅ ą▓ą╗ąŠąČąĄąĮąĮčŗą╝ ą▓ ą╝ąĄąĮąĄąĄ ą┐čĆąĖąŠčĆąĖč鹥čéąĮąŠąĄ).

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĘą┤ąĄčüčī ą┐čĆąĖą▓ąĄą┤ąĄąĮ ą┐ąĄčĆąĄą▓ąŠą┤ čćą░čüčéąĖ ą┤ąŠą║čāą╝ąĄąĮčéą░čåąĖąĖ [1], ą┐ąŠčüą▓čÅčēąĄąĮąĮąŠą╣ ąŠą▒čüą╗čāąČąĖą▓ą░ąĮąĖčÄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. ąØąĄąĘąĮą░ą║ąŠą╝čŗąĄ č鹥čĆą╝ąĖąĮčŗ ąĖ čüąŠą║čĆą░čēąĄąĮąĖčÅ čüą╝. ą▓ čĆą░ąĘą┤ąĄą╗ąĄ "ąĪą╗ąŠą▓ą░čĆąĖą║" čüčéą░čéčīąĖ [2], ą░ čéą░ą║ąČąĄ ą▓ąŠ ą▓čĆąĄąĘą║ą░čģ čüčéą░čéčīąĖ [2] ąĖ čŹč鹊ą╣ čüčéą░čéčīąĖ.

ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ą┐ąŠą┤ čüą╗ąŠą▓ąŠą╝ "čüąŠą▒čŗčéąĖąĄ" (event) ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░čÄčéčüčÅ ą▓čüąĄ čéąĖą┐čŗ ą░ą║čéąĖą▓ąĮąŠčüčéąĖ ą┐čĆąŠčåąĄčüčüąŠčĆą░. ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ čüąŠą▒čŗčéąĖą╣ ą▓čüąĄą│ąŠ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé 5 čĆą░ąĘą╗ąĖčćąĮčŗčģ čüąŠą▒čŗčéąĖą╣: Emulation, Reset, NMI, Exception, ąĖ 7 čłčé. Interrupt. ąÆčüąĄą│ąŠ ąĖą╝ąĄąĄčéčüčÅ 16 čüąŠą▒čŗčéąĖą╣, čü ąĮąŠą╝ąĄčĆą░ą╝ąĖ ąŠčé 0 ą┤ąŠ 15, ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ ąĖą╝ čĆąĄą│ąĖčüčéčĆčŗ ą▓ąĄą║č鹊čĆąŠą▓ čüąŠą▒čŗčéąĖą╣ EVT0 .. EVT15.

| Event Ōä¢ |

ąÜą╗ą░čüčü čüąŠą▒čŗčéąĖčÅ |

ą£ąĮąĄą╝ąŠąĮąĖą║ą░ |

| ąĪąŠą▒čŗčéąĖčÅ čÅą┤čĆą░ |

| EVT0 |

Emulation (ąŠčéą╗ą░ą┤čćąĖą║ JTAG) |

EMU |

| EVT1 |

Reset (čüą▒čĆąŠčü) |

RST |

| EVT2 |

NMI (ąĮąĄ ą╝ą░čüą║ąĖčĆčāąĄą╝ąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ) |

NMI |

| EVT3 |

Exception (ąĖčüą║ą╗čÄč湥ąĮąĖąĄ) |

EVX |

| EVT4 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

GBLDIS |

| EVT5 |

Hardware Error (ą░ą┐ą┐ą░čĆą░čéąĮą░čÅ ąŠčłąĖą▒ą║ą░) |

IVHW |

| ąĪąŠą▒čŗčéąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ |

| EVT6 |

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą│čĆčāą┐ą┐čŗ ą┐čĆąĖąŠčĆąĖč鹥čéą░ 6 |

IVG6 |

| EVT7 |

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą│čĆčāą┐ą┐čŗ ą┐čĆąĖąŠčĆąĖč鹥čéą░ 7 |

IVG7 |

| EVT8 |

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą│čĆčāą┐ą┐čŗ ą┐čĆąĖąŠčĆąĖč鹥čéą░ 8 |

IVG8 |

| EVT9 |

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą│čĆčāą┐ą┐čŗ ą┐čĆąĖąŠčĆąĖč鹥čéą░ 9 |

IVG9 |

| EVT10 |

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą│čĆčāą┐ą┐čŗ ą┐čĆąĖąŠčĆąĖč鹥čéą░ 10 |

IVG10 |

| EVT11 |

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą│čĆčāą┐ą┐čŗ ą┐čĆąĖąŠčĆąĖč鹥čéą░ 11 |

IVG11 |

| EVT12 |

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą│čĆčāą┐ą┐čŗ ą┐čĆąĖąŠčĆąĖč鹥čéą░ 12 |

IVG12 |

| EVT13 |

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą│čĆčāą┐ą┐čŗ ą┐čĆąĖąŠčĆąĖč鹥čéą░ 13 |

IVG13 |

| EVT14 |

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą│čĆčāą┐ą┐čŗ ą┐čĆąĖąŠčĆąĖč鹥čéą░ 14 |

IVG14 |

| EVT15 |

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą│čĆčāą┐ą┐čŗ ą┐čĆąĖąŠčĆąĖč鹥čéą░ 15 |

IVG15 |

"ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ" (interrupt) čŹč鹊 čüąŠą▒čŗčéąĖąĄ, ą║ąŠč鹊čĆąŠąĄ ą╝ąĄąĮčÅąĄčé ąĮąŠčĆą╝ą░ą╗čīąĮčŗą╣ čģąŠą┤ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ (ąĮąĄ čüą▒čĆą░čüčŗą▓ą░čÅ ąĄą│ąŠ), ą░čüąĖąĮčģčĆąŠąĮąĮąŠ čü ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčīčÄ ąĄčæ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ. ąŁč鹊 ąŠčéą╗ąĖčćą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠčé ąĖčüą║ą╗čÄč湥ąĮąĖčÅ (exception), ą║ąŠč鹊čĆąŠąĄ ą┐čĆąĖą▓čÅąĘą░ąĮąŠ ą║ čģąŠą┤čā ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ (ą▓ąŠąĘąĮąĖą║ą░ąĄčé čüąĖąĮčģčĆąŠąĮąĮąŠ čü ą┐ąŠč鹊ą║ąŠą╝ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą║ąŠą╝ą░ąĮą┤).

ąŁč鹊 ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝ą░, ąŠčéą╗ąĖčćą░čÄčēą░čÅčüčÅ ąŠčé ąŠą▒čŗčćąĮąŠą╣ č鹊ą╗čīą║ąŠ č鹥ą╝, čćč鹊 ą┤ą╗čÅ ąĄčæ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ąŠčéą┤ąĄą╗čīąĮčŗą╣ čüč鹥ą║ (čüč鹥ą║ čüčāą┐ąĄčĆą▓ąĖąĘąŠčĆą░), ąĖ ą┤ą╗čÅ ą▓ąŠąĘą▓čĆą░čéą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤čĆčāą│ąŠą╣ čĆąĄą│ąĖčüčéčĆ (RETI ą▓ą╝ąĄčüč鹊 čĆąĄą│ąĖčüčéčĆą░ RETS).

ąöą╗čÅ čāą┤ąŠą▒čüčéą▓ą░ ąĮą░ą┐ąĖčüą░ąĮąĖčÅ ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą▓ čüčĆąĄą┤ąĄ VisualDSP ąĖą╝ąĄčÄčéčüčÅ čüą┐ąĄčåąĖą░ą╗čīąĮčŗąĄ ą╝ą░ą║čĆąŠčüčŗ EX_INTERRUPT_HANDLER ąĖ EX_REENTRANT_HANDLER, ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗąĄ ą▓ ąĘą░ą│ąŠą╗ąŠą▓ąŠčćąĮąŠą╝ čäą░ą╣ą╗ąĄ Blackfin\include\sys\exception.h (ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ą║ą░čéą░ą╗ąŠą│ąĄ čāčüčéą░ąĮąŠą▓ą║ąĖ VisualDSP). ą×čéą╗ąĖčćąĖąĄ čŹčéąĖčģ ą╝ą░ą║čĆąŠčüąŠą▓ ą▓ č鹊ą╝, čćč鹊 ą▓ ą┐ąĄčĆą▓čŗą╣ ą╝ą░ą║čĆąŠčü EX_INTERRUPT_HANDLER ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čü ąŠčéą║ą╗čÄč湥ąĮąĮąŠą╣ ą▓ą╗ąŠąČąĄąĮąĮąŠčüčéčīčÄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ (čé. ąĄ. čŹč鹊čé ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ ąĮąĄą╗čīąĘčÅ ąĮąĖč湥ą╝ ą┐čĆąĄčĆą▓ą░čéčī, ą┤ą░ąČąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄą╝ čü ą▒ąŠą╗ąĄąĄ ą▓čŗčüąŠą║ąĖą╝ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝), ą░ ą▓č鹊čĆąŠą╣ ą╝ą░ą║čĆąŠčü EX_REENTRANT_HANDLER ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ąŠą▒čĆą░ą▒ąŠčéčćąĖą║, ą║ąŠč鹊čĆčŗą╣ ą╝ąŠąČąĮąŠ ą┐čĆąĄčĆčŗą▓ą░čéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄą╝ čü ą▒ąŠą╗ąĄąĄ ą▓čŗčüąŠą║ąĖą╝ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝.

ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą┐ąŠą┤ą┤ąĄčƹȹ║čā 5 ąŠčéą┤ąĄą╗čīąĮčŗčģ čéąĖą┐ąŠą▓ čüąŠą▒čŗčéąĖą╣:

Emulation ŌĆō ą┐ąĄčĆąĄą▓ąŠą┤ąĖčé ą┐čĆąŠčåąĄčüčüąŠčĆ ą▓ čĆąĄąČąĖą╝ 菹╝čāą╗čÅčåąĖąĖ (ąŠčéą╗ą░ą┤ą║ą░), čćč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐ąŠčüčŗą╗ą░čéčī ą┐čĆąŠčåąĄčüčüąŠčĆčā čüą┐ąĄčåąĖą░ą╗čīąĮčŗąĄ ą║ąŠą╝ą░ąĮą┤čŗ ąĖ čāą┐čĆą░ą▓ą╗čÅčéčī ąĖą╝ č湥čĆąĄąĘ ąĖąĮč鹥čĆč乥ą╣čü JTAG, ąĖ ą┐ąŠą╗čāčćą░čéčī ąĖąĘ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ąŠčéą╗ą░ą┤ąŠčćąĮčāčÄ ąĖąĮč乊čĆą╝ą░čåąĖčÄ.

Reset ŌĆō čüą▒čĆą░čüčŗą▓ą░ąĄčé ą┐čĆąŠčåąĄčüčüąŠčĆ.

Nonmaskable Interrupt (NMI) ŌĆō ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čüč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ ąĖą╗ąĖ ą▓čģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ NMI ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ą┤ą╗čÅ ą┐čĆąŠčåąĄčüčüąŠčĆą░ čŹč鹊 čüąŠą▒čŗčéąĖąĄ. ąĪąŠą▒čŗčéąĖąĄ NMI čćą░čüč鹊 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą║ą░ą║ čüąĖą│ąĮą░ą╗ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ čüąĖčüč鹥ą╝čŗ, čćč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐čĆą░ą▓ąĖą╗čīąĮąŠ ąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ ą▓čŗą┐ąŠą╗ąĮąĖčéčī ą┐čĆąŠčåąĄą┤čāčĆčā ąŠčéą║ą╗čÄč湥ąĮąĖčÅ.

Exceptions (ąĖčüą║ą╗čÄč湥ąĮąĖčÅ) ŌĆō čüąŠą▒čŗčéąĖčÅ, čüąĖąĮčģčĆąŠąĮąĮčŗąĄ čü ą┐ąŠč鹊ą║ąŠą╝ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ. ą¤čĆąĖ čŹč鹊ą╝ ąĖčüą║ą╗čÄč湥ąĮąĖąĄ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ą▒čāą┤ąĄčé čĆą░ąĘčĆąĄčłąĄąĮąŠ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ąĖąĮčüčéčĆčāą║čåąĖąĖ, ą║ąŠč鹊čĆą░čÅ ą▓čŗąĘą▓ą░ą╗ą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄ. ąśčüą║ą╗čÄč湥ąĮąĖčÅ ą╝ąŠą│čāčé ą▓čŗąĘą▓ą░čéčī čéą░ą║ąĖąĄ čüąŠą▒čŗčéąĖčÅ, ą║ą░ą║ ąĮą░čĆčāčłąĄąĮąĖąĄ ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ąĖą╗ąĖ ąĮąĄąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮą░čÅ ąĖąĮčüčéčĆčāą║čåąĖčÅ.

Interrupts (ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ) ŌĆō čüąŠą▒čŗčéąĖčÅ, ą░čüąĖąĮčģčĆąŠąĮąĮčŗąĄ ą┐ąŠ ąŠčéąĮąŠčłąĄąĮąĖčÄ ą║ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÄ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ. ą×ąĮąĖ ą▓čŗąĘčŗą▓ą░čÄčéčüčÅ čüąĖą│ąĮą░ą╗ą░ą╝ąĖ ąĖčģ ą▓čģąŠą┤ąĮčŗčģ ą┐ąŠčĆč鹊ą▓, čéą░ą╣ą╝ąĄčĆąŠą▓ ąĖ ą┤čĆčāą│ąĖčģ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓.

ąÜą░ąČą┤ąŠąĄ čüąŠą▒čŗčéąĖąĄ ąĖą╝ąĄąĄčé čüą▓čÅąĘą░ąĮąĮčŗą╣ čü ąĮąĖą╝ čĆąĄą│ąĖčüčéčĆ ą┤ą╗čÅ čģčĆą░ąĮąĄąĮąĖčÅ ą░ą┤čĆąĄčüą░ ą▓ąŠąĘą▓čĆą░čéą░ ąĖ čüą▓čÅąĘą░ąĮąĮąŠą╣ ąĖąĮčüčéčĆčāą║čåąĖąĖ ą▓ąŠąĘą▓čĆą░čéą░ ąĖąĘ čüąŠą▒čŗčéąĖčÅ. ąÜąŠą│ą┤ą░ čüčĆą░ą▒ąŠčéą░ą╗ąŠ čüąŠą▒čŗčéąĖąĄ, čüąŠčüč鹊čÅąĮąĖąĄ ą┐čĆąŠčåąĄčüčüąŠčĆą░ čüąŠčģčĆą░ąĮčÅąĄčéčüčÅ ą▓ čüč鹥ą║ čüčāą┐ąĄčĆą▓ąĖąĘąŠčĆą░.

ąĀąĄąČąĖą╝ čüčāą┐ąĄčĆą▓ąĖąĘąŠčĆą░ - čŹč鹊 ą║ąŠą│ą┤ą░ čÅą┤čĆąŠ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą▓čŗą┐ąŠą╗ąĮčÅąĄčé ą║ąŠą┤ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ąĪč鹥ą║ čüčāą┐ąĄčĆą▓ąĖąĘąŠčĆą░ - čüč鹥ą║ ą║ąŠą┤ą░ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ (ą┤ą╗čÅ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ąŠčéą┤ąĄą╗čīąĮčŗą╣ čüč鹥ą║).

ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ čüąŠą▒čŗčéąĖą╣ ą┐čĆąŠčåąĄčüčüąŠčĆą░ čüąŠčüč鹊ąĖčé ąĖąĘ 2 čüčéą░ą┤ąĖą╣: System Interrupt Controller (SIC) ąĖ Core Event Controller (CEC). SIC čĆą░ą▒ąŠčéą░ąĄčé čüąŠą▓ą╝ąĄčüčéąĮąŠ čü CEC ą┤ą╗čÅ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖčÅ ą┐čĆąĖąŠčĆąĖč鹥ąĘą░čåąĖąĖ ąĖ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą▓čüąĄą╝ąĖ čüąŠą▒čŗčéąĖčÅą╝ąĖ čüąĖčüč鹥ą╝čŗ. ąÜąŠąĮčåąĄą┐čéčāą░ą╗čīąĮąŠ ą░čĆčģąĖč鹥ą║čéčāčĆą░ čāčüčéčĆąŠąĄąĮą░ čéą░ą║, čćč鹊 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠčé ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┐ąŠą┐ą░ą┤ą░čÄčé ą▓ SIC, ąĖ ą┤ą░ą╗ąĄąĄ ąĮą░ą┐čĆčÅą╝čāčÄ ą┐ąĄčĆąĄąĮą░ą┐čĆą░ą▓ą╗čÅčÄčéčüčÅ ą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠą▒čēąĄą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ CEC.

System Interrupt Controller (SIC). ąĪąĖčüč鹥ą╝ąĮčŗą╣ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ (System Interrupt Controller) ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą┐čĆąĖą▓čÅąĘą║čā ąĖ ą╝ą░čĆčłčĆčāčéąĖąĘą░čåąĖčÄ čüąŠą▒čŗčéąĖą╣ ąŠčé ą╝ąĮąŠąČąĄčüčéą▓ą░ ąĖčüč鹊čćąĮąĖą║ąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ąŠčé ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ąĮą░ ą┐čĆąĖąŠčĆąĖč鹥ąĘąĖčĆąŠą▓ą░ąĮąĮčŗąĄ ą▓čģąŠą┤čŗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ąŠą▒čēąĄą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ CEC ("ąŠą▒čēąĄą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ" ąŠčéčĆą░ąČą░ąĄčé č鹊čé čäą░ą║čé, čćč鹊 ąŠąĮąĖ ą╝ąŠą│čāčé ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░čéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠčé ą╗čÄą▒ąŠą│ąŠ ą░ą┐ą┐ą░čĆą░čéąĮąŠą│ąŠ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ - ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé č鹊ą│ąŠ, ą║ą░ą║ čŹč鹊 ąĮą░čüčéčĆąŠąĖčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčüčé). ąźąŠčéčÅ ą┐čĆąŠčåąĄčüčüąŠčĆ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą┐čĆąĖą▓čÅąĘą║čā ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ (ą║ąŠč鹊čĆą░čÅ čüą░ą╝ą░ ąĮą░čüčéčĆą░ąĖą▓ą░ąĄčéčüčÅ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░), ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą╝ąŠąČąĄčé ą┐ąŠą╝ąĄąĮčÅčéčī ą┐čĆąĖą▓čÅąĘą║čā (ąĖ č鹥ą╝ čüą░ą╝čŗą╝ ą┐čĆąĖąŠčĆąĖč鹥čé ąŠą▒čĆą░ą▒ąŠčéą║ąĖ) čüąĖą│ąĮą░ą╗ąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ąŠčé ą┐ąĄčĆąĖč乥čĆąĖąĖ ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ ą┐ąŠą┤čģąŠą┤čÅčēąĖčģ ąĘąĮą░č湥ąĮąĖą╣ ą▓ čĆąĄą│ąĖčüčéčĆčŗ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ (Interrupt Assignment Registers, IAR).

Core Event Controller (CEC). ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ čüąŠą▒čŗčéąĖą╣ čÅą┤čĆą░ (Core Event Controller) ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé 9 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ąŠą▒čēąĄą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ (general-purpose interrupts, IVG15ŌĆō7) ą▓ ą┤ąŠą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ ą▓čŗą┤ąĄą╗ąĄąĮąĮąŠą╝čā (ąĮąĄ ąĮą░čüčéčĆą░ąĖą▓ą░ąĄą╝ąŠą╝čā) ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÄ ąĖ čüąŠą▒čŗčéąĖčÅą╝ ąĖčüą║ą╗čÄč湥ąĮąĖčÅ. ąśąĘ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ąŠą▒čēąĄą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ ąĄčüčéčī 2 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čü čüą░ą╝čŗą╝ ąĮąĖąĘą║ąĖą╝ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝ (IVG15, IVG14), ą║ąŠč鹊čĆčŗąĄ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░čéčī ą┤ą╗čÅ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ąŠą▓ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣, ąŠčüčéą░ą▓ą╗čÅčÅ ą▓čģąŠą┤čŗ 7 ą▒ąŠą╗ąĄąĄ ą┐čĆąĖąŠčĆąĖč鹥čéąĮčŗčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ (IVG13-IVG7) ą┤ą╗čÅ ą┐ąŠą┤ą┤ąĄčƹȹ║ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓.

| ąśčüč鹊čćąĮąĖą║ čüąŠą▒čŗčéąĖčÅ |

ąÆąĄą║č鹊čĆ EVT |

| ąŁą╝čāą╗čÅčåąĖčÅ (čüą░ą╝čŗą╣ ą▓čŗčüąŠą║ąĖą╣ ą┐čĆąĖąŠčĆąĖč鹥čé) |

EMU |

| ąĪą▒čĆąŠčü |

RST |

| NMI (ąĮąĄą╝ą░čüą║ąĖčĆčāąĄą╝ąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ) |

NMI |

| Exception (ąĖčüą║ą╗čÄč湥ąĮąĖąĄ) |

EVX |

| ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

- |

| Hardware Error (ą░ą┐ą┐ą░čĆą░čéąĮą░čÅ ąŠčłąĖą▒ą║ą░) |

IVHW |

| Core Timer (čéą░ą╣ą╝ąĄčĆ čÅą┤čĆą░) |

IVTMR |

ąÆ čĆąĄą│ąĖčüčéčĆą░čģ SIC_IARx ą┐ąŠčüą╗ąĄ čüčéą░čĆčéą░ čüąĖčüč鹥ą╝čŗ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą┐čĆąŠą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ ą┐čĆąĖą▓čÅąĘą║ą░ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ą║ čüąĖčüč鹥ą╝ąĮčŗą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅą╝ (čüąŠą▒čŗčéąĖčÅą╝), ąĖ čüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ ąĮą░ąĘąĮą░čćą░čÄčéčüčÅ ąĖčģ ą┐čĆąĖąŠčĆąĖč鹥čéčŗ.

ąóą░ą▒ą╗ąĖčåą░ 4-6. ą¤čĆąĖą▓čÅąĘą║ą░ čüąĖčüč鹥ą╝ąĮčŗčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ąŠčé ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ą║ čüąŠą▒čŗčéąĖčÅą╝ čÅą┤čĆą░ (System and Core Event Mapping).

| ąśčüč鹊čćąĮąĖą║ čüąŠą▒čŗčéąĖčÅ |

ąÆąĄą║č鹊čĆ EVT |

| PLL Wake-Up Interrupt |

IVG7 |

| DMA Controller 0 Error |

| DMA Controller 1 Error |

| PPI Error Interrupt |

| SPORT0 Error Interrupt |

| SPORT1 Error Interrupt |

| SPORT2 Error Interrupt |

| SPORT3 Error Interrupt |

| SPI0 Error Interrupt |

| SPI1 Error Interrupt |

| SPI2 Error Interrupt |

| UART0 Error Interrupt |

| UART1 Error Interrupt |

| UART2 Error Interrupt |

| CAN Error Interrupt |

| ą¤čĆąĄčĆčŗą▓ą░ąĮąĖčÅ Real-Time Clock |

IVG8 |

| DMA0 Interrupt (PPI) |

| DMA1 Interrupt (SPORT0 Rx) |

IVG9 |

| DMA2 Interrupt (SPORT0 Tx) |

| DMA3 Interrupt (SPORT1 Rx) |

| DMA4 Interrupt (SPORT1 Tx) |

| DMA8 Interrupt (SPORT2 Rx) |

| DMA9 Interrupt (SPORT2 Tx) |

| DMA10 Interrupt (SPORT3 Rx) |

| DMA11 Interrupt (SPORT3 Tx) |

| DMA5 Interrupt (SPI0) |

IVG10 |

| DMA14 Interrupt (SPI1) |

| DMA15 Interrupt (SPI2) |

| DMA6 Interrupt (UART0 Rx) |

| DMA7 Interrupt (UART0 Tx) |

| DMA16 Interrupt (UART1 Rx) |

| DMA17 Interrupt (UART1 Tx) |

| DMA18 Interrupt (UART2 Rx) |

| DMA19 Interrupt (UART2 Tx) |

| ą¤čĆąĄčĆčŗą▓ą░ąĮąĖčÅ Timer0, Timer1, Timer2 |

IVG11 |

| ą¤čĆąĄčĆčŗą▓ą░ąĮąĖčÅ TWI0, TWI1 |

| CAN Receive Interrupt |

| CAN Transmit Interrupt |

| ą¤čĆąĄčĆčŗą▓ą░ąĮąĖčÅ A ąĖ B ą┐ąŠčĆčéą░ F GPIO |

IVG12 |

| MDMA0 Stream 0 Interrupt |

IVG13 |

| MDMA0 Stream 1 Interrupt |

| MDMA1 Stream 0 Interrupt |

| MDMA1 Stream 1 Interrupt |

| Software Watchdog Timer |

ą×čćąĖčēą░čéčī č鹥čéčĆą░ą┤čŗ čĆąĄą│ąĖčüčéčĆąŠą▓ SIC_IARx čāą┤ąŠą▒ąĮąŠ čü ą┐ąŠą╝ąŠčēčīčÄ ą╝ą░ą║čĆąŠčüą░ PX_IVG_CLR (Peripheral Interrupt ID). ąŚą┤ąĄčüčī Peripheral Interrupt ID čŹč鹊 ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (ą╝ąŠąČąĮąŠ ą┐ąŠčüą╝ąŠčéčĆąĄčéčī ą▓ čéą░ą▒ą╗ąĖčåąĄ 4-7). ą£ą░ą║čĆąŠčü PX_IVG_CLR ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮ ą▓ ąĘą░ą│ąŠą╗ąŠą▓ą║ąĄ VisualDSP 5.0\Blackfin\include\defBF532.h. ą¤čĆąĖą╝ąĄčĆ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ:

// ą×čćąĖčēą░ąĄčé čāčĆąŠą▓ąĄąĮčī IVG ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ 11 (čŹč鹊 SPORT1 RX):

*pSIC_IAR1 &= PX_IVG_CLR(11);

ą¤čĆąĖą╝ąĄčĆ ą║ąŠą┤ą░ ąŠčćąĖčüčéą║ąĖ ą▓čüąĄčģ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ąĖ ą┐čĆąĖą▓čÅąĘą║ąĖ ą║ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝:

void ClearPeripherialPriorityAndMap (void)

{

for(int i =0;i<8;++i)

{

// ą×čćąĖčüčéą║ą░ čāčĆąŠą▓ąĮąĄą╣ IVG ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓:

*pSIC_IAR0 &= PX_IVG_CLR(i);

*pSIC_IAR1 &= PX_IVG_CLR(i+8);

*pSIC_IAR2 &= PX_IVG_CLR(i+16);

*pSIC_IAR3 &= PX_IVG_CLR(i+24);

*pSIC_IAR4 &= PX_IVG_CLR(i+32);

*pSIC_IAR5 &= PX_IVG_CLR(i+40);

*pSIC_IAR6 &= PX_IVG_CLR(i+48);

}

}

ąÜčĆąŠą╝ąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĖą▓čÅąĘą║ąĖ, ąŠčéą┤ąĄą╗čīąĮčŗąĄ ąĖčüč鹊čćąĮąĖą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą╝ąŠą│čāčé ą▒čŗčéčī ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮčŗ (ąĘą░ą┐čĆąĄčēąĄąĮčŗ) ą▓ SIC.

[ą×ą▒čĆą░ą▒ąŠčéą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ čüąĖčüč鹥ą╝ąŠą╣]

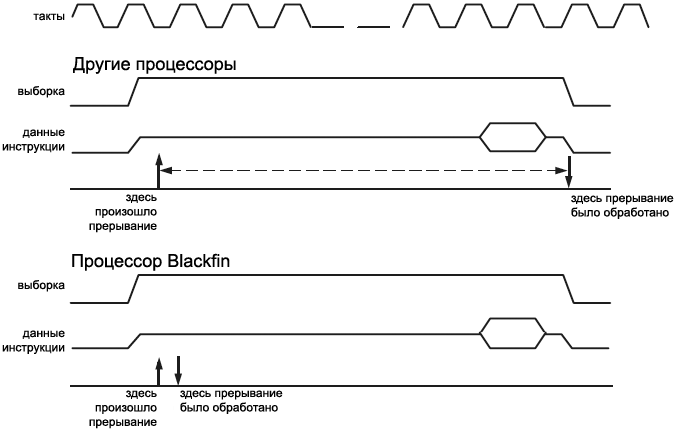

ąØą░ čĆąĖčü. 4-4 ą┐ąŠą║ą░ąĘą░ąĮąŠ, ą║ą░ą║ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ (Interrupt A) ą┤ą╗čÅ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčéčüčÅ, čćč鹊 ą┤ą╗čÅ ąĮąĄą│ąŠ čĆą░ąĘčĆąĄčłąĄąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ).

ąĀąĖčü. 4-4. ąæą╗ąŠą║-ą┤ąĖą░ą│čĆą░ą╝ą╝ą░ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▓ čüą║ąŠą▒ą║ą░čģ ą┐ąŠą║ą░ąĘą░ąĮčŗ ąĖą╝ąĄąĮą░ MMR (čĆąĄą│ąĖčüčéčĆąŠą▓, ąŠč鹊ą▒čĆą░ąČąĄąĮąĮčŗčģ ąĮą░ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ ą┐ą░ą╝čÅčéąĖ ą┐čĆąŠčåąĄčüčüąŠčĆą░).

ąÆąŠčé ąŠą┐ąĖčüą░ąĮąĖąĄ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (Interrupt A) ą┐ąŠ čłą░ą│ą░ą╝:

1. ąÆ čĆąĄą│ąĖčüčéčĆą░čģ SIC_ISR ąĘą░ą┐ąŠą╝ąĖąĮą░ąĄčéčüčÅ ąĘą░ą┐čĆąŠčü, ąĖ ą┤ąĄą╗ą░ąĄčéčüčÅ ą┐čĆąŠą▓ąĄčĆą║ą░ - ą▓čŗčüčéą░ą▓ą╗ąĄąĮąŠ ą╗ąĖ ąĄčēąĄ ąĮąĄ ąŠą▒čüą╗čāąČąĄąĮąĮąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ (čé. ąĄ. ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠą║ą░ ąĄčēąĄ ąĮąĄ ąŠčćąĖčüčéąĖą╗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ).

2. ą¤čĆąŠą▓ąĄčĆčÅčÄčéčüčÅ čĆąĄą│ąĖčüčéčĆčŗ SIC_IWR čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī, čćč鹊 čÅą┤čĆąŠ ąĮčāąČąĮąŠ ą▓čŗą▓ąĄčüčéąĖ ąĖąĘ čüąŠčüč鹊čÅąĮąĖčÅ ąŠąČąĖą┤ą░ąĮąĖčÅ (idle state) ąĖ/ąĖą╗ąĖ čĆą░ąĘą▒čāą┤ąĖčéčī ąĄą│ąŠ, ą▓čŗą▓ąĄą┤čÅ ąĖąĘ čĆąĄąČąĖą╝ą░ čüąĮą░, ą▒ą░ąĘąĖčĆčāčÅčüčī ąĮą░ čŹč鹊ą╝ ąĘą░ą┐čĆąŠčüąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

3. ąĀąĄą│ąĖčüčéčĆčŗ SIC_IMASK čĆą░ąĘčĆąĄčłą░čÄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠčé ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ąĮą░ čāčĆąŠą▓ąĮąĄ čüąĖčüč鹥ą╝čŗ. ąĢčüą╗ąĖ Interrupt A čĆą░ąĘčĆąĄčłąĄąĮąŠ, č鹊 ąŠą▒čĆą░ą▒ąŠčéą║ą░ ąĘą░ą┐čĆąŠčüą░ ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą║ čłą░ą│čā 4.

4. ąĀąĄą│ąĖčüčéčĆčŗ SIC_IARx ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčé ą┐čĆąĖą▓čÅąĘą║čā ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą┐ąĄčĆąĖč乥čĆąĖąĖ ą║ ąĮą░ą▒ąŠčĆčā ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ąŠą▒čēąĄą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ čÅą┤čĆą░ (general-purpose core interrupts) IVG7 ŌĆō IVG15. ą¤čĆąĖą▓čÅąĘą║ą░ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ą┐čĆąĖąŠčĆąĖč鹥čé ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┤ą╗čÅ Interrupt A (ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé č鹊ą│ąŠ ą║ ą║ą░ą║ąŠą╝čā ąĖąĘ IVG7 ŌĆō IVG15 ąŠąĮąŠ ą┐čĆąĖą▓čÅąĘą░ąĮąŠ).

5. ąĀąĄą│ąĖčüčéčĆ ILAT ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ CEC ą┤ąŠą▒ą░ą▓ą╗čÅąĄčé Interrupt A ą║ ą╗ąŠą│čā ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣, ąĘą░čģą▓ą░č湥ąĮąĮčŗčģ čÅą┤čĆąŠą╝, ąĮąŠ ą┐ąŠą║ą░ ąĄčēąĄ ąĮąĄ ąŠą▒čĆą░ą▒ąŠčéą░ąĮąĮčŗčģ.

6. ąĀąĄą│ąĖčüčéčĆ IMASK ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ CEC čĆą░ąĘčĆąĄčłą░ąĄčé čüąŠą▒čŗčéąĖčÅ čĆą░ąĘąĮčŗčģ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą▓ čÅą┤čĆą░. ąĢčüą╗ąĖ čüąŠą▒čŗčéąĖąĄ IVGx, čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ Interrupt A, čĆą░ąĘčĆąĄčłąĄąĮąŠ, č鹊 ą┐čĆąŠčåąĄčüčü ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą║ čłą░ą│čā 7.

7. ąśąĘ čéą░ą▒ą╗ąĖčåčŗ ą▓ąĄą║č鹊čĆąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ (Event Vector Table, čĆąĄą│ąĖčüčéčĆčŗ EVTx) ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ą┐ąŠą┤čģąŠą┤čÅčēąĖą╣ ą▓ąĄą║č鹊čĆ ą┤ą╗čÅ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (interrupt service routine, ISR), ą▓ ąĮą░čłąĄą╝ ą┐čĆąĖą╝ąĄčĆąĄ čŹč鹊 ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ ą┤ą╗čÅ Interrupt A.

8. ąÜąŠą│ą┤ą░ ą▓ąĄą║č鹊čĆ čüąŠą▒čŗčéąĖčÅ Interrupt A ą▓ą▓ąĄą┤ąĄąĮ ą▓ ą║ąŠąĮą▓ąĄą╣ąĄčĆ čÅą┤čĆą░, čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą┐ąŠą┤čģąŠą┤čÅčēąĖą╣ ą▒ąĖčé IPEND, ą║ąŠč鹊čĆčŗą╣ ąŠčćąĖčēą░ąĄčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé ILAT. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, IPEND ąŠčéčüą╗ąĄąČąĖą▓ą░ąĄčé ą▓čüąĄ ąŠąČąĖą┤ą░čÄčēąĖąĄ (ąŠčéą╗ąŠąČąĄąĮąĮčŗąĄ) ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą░ čéą░ą║ąČąĄ č鹥, ą║ąŠč鹊čĆčŗąĄ ą▓ ąĮą░čüč鹊čÅčēąĖą╣ ą╝ąŠą╝ąĄąĮčé ąŠą▒čüą╗čāąČąĖą▓ą░čÄčéčüčÅ.

9. ąÜąŠą│ą┤ą░ ą▓čŗą┐ąŠą╗ąĮąĖčéčüčÅ ISR ą┤ą╗čÅ Interrupt A, ąĖąĮčüčéčĆčāą║čåąĖčÅ RTI ąŠčćąĖčüčéąĖčé ą┐ąŠą┤čģąŠą┤čÅčēąĖą╣ ą▒ąĖčé IPEND. ą×ą┤ąĮą░ą║ąŠ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé SIC_ISR ąĮąĄ ąŠčćąĖčēą░ąĄčéčüčÅ, ą┐ąŠą║ą░ ISR ąĮąĄ ąŠčćąĖčüčéąĖčé ą╝ąĄčģą░ąĮąĖąĘą╝, ą║ąŠč鹊čĆčŗą╣ čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ą╗ Interrupt A, ąĖą╗ąĖ ą┐ąŠą║ą░ ISR ąĮąĄ ąŠčćąĖčüčéąĖčé čŹč鹊čé ą▒ąĖčé.

ąØčāąČąĮąŠ ąĘą░ą╝ąĄčéąĖčéčī, čćč鹊 čüąŠą▒čŗčéąĖčÅ emulation, reset, NMI ąĖ exception, ą║ą░ą║ ąĖ ą░ą┐ą┐ą░čĆą░čéąĮą░čÅ ąŠčłąĖą▒ą║ą░ (hardware error, IVHW) ąĖ ąĘą░ą┐čĆąŠčüčŗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čéą░ą╣ą╝ąĄčĆą░ čÅą┤čĆą░ (core timer, IVTMR), ą▓ą▓ąŠą┤čÅčé čåąĄą┐ąŠčćą║čā ąŠą▒čĆą░ą▒ąŠčéą║čā ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ąĮą░ čāčĆąŠą▓ąĮąĄ ILAT, čéą░ą║ čćč鹊 ąĮą░ ąĮąĖčģ ąĮąĄ ą▓ą╗ąĖčÅčÄčé čĆąĄą│ąĖčüčéčĆčŗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čāčĆąŠą▓ąĮčÅ čüąĖčüč鹥ą╝čŗ (SIC_IWR, SIC_ISR, SIC_IMASK, SIC_IARx).

ąĢčüą╗ąĖ ąĮąĄčüą║ąŠą╗čīą║ąŠ ąĖčüč鹊čćąĮąĖą║ąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĖčüą┐ąŠą╗čīąĘčāčÄčé ąŠą┤ąĮąŠ ąŠą▒čēąĄąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čÅą┤čĆą░, č鹊 ISR ą┤ąŠą╗ąČąĄąĮ čüą░ą╝ ąĖą┤ąĄąĮčéąĖčäąĖčåąĖčĆąŠą▓ą░čéčī ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ, ą║ąŠč鹊čĆąŠąĄ čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ą╗ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ. ąóą░ą║ čćč鹊 ą┤ą╗čÅ ISR ą╝ąŠąČąĄčé ą┐ąŠąĮą░ą┤ąŠą▒ąĖčéčīčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ ąŠą┐čĆąŠčüąĖčéčī ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ, čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī, ą║ą░ą║ąŠąĄ ą┤ąĄą╣čüčéą▓ąĖąĄ ąĮčāąČąĮąŠ ą┐čĆąĄą┤ą┐čĆąĖąĮčÅčéčī ą┤ą╗čÅ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

[ąĪąĖčüč鹥ą╝ąĮčŗąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠčé ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓]

ąĪąĖčüč鹥ą╝ą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ąĖą╝ąĄąĄčé ąĮąĄčüą║ąŠą╗čīą║ąŠ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓, ą┐ąŠčŹč鹊ą╝čā ą┤ą╗čÅ ąĖčģ ąŠą▒čüą╗čāąČąĖą▓ą░ąĮąĖčÅ ą╝ąŠąČąĄčé ą┐ąŠčéčĆąĄą▒ąŠą▓ą░čéčīčüčÅ ą┐ąŠą┤ą┤ąĄčƹȹ║ą░ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. ąÆ čéą░ą▒ą╗ąĖčåąĄ 4-7 ą┐ąĄčĆąĄčćąĖčüą╗ąĄąĮčŗ:

ŌĆó ąśčüč鹊čćąĮąĖą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠčé ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ (čüč鹊ą╗ą▒ąĄčå Peripheral Interrupt Source).

ŌĆó ąśą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąĄčĆąĖč乥čĆąĖąĖ (čüč鹊ą╗ą▒ąĄčå Peripheral Interrupt ID) - čćąĖčüą╗ąŠą▓čŗąĄ ą║ąŠą┤čŗ, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą┤ą╗čÅ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĖčÅ čüąĖčüč鹥ą╝ąĮčŗčģ čĆąĄą│ąĖčüčéčĆąŠą▓ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ (system interrupt assignment registers, SIC_IARx). ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. ąŠą┐ąĖčüą░ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆąŠą▓ SIC_IARx ą▓ąŠ ą▓čĆąĄąĘą║ąĄ "ąĀąĄą│ąĖčüčéčĆčŗ SIC_IARx".

ŌĆó ą¤čĆąĖą▓čÅąĘą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ąŠą▒čēąĄą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ (General-purpose interrupt) čÅą┤čĆą░, ą┐čĆąĖčüą▓ąŠąĄąĮąĮąŠąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ (čüč鹊ą╗ą▒ąĄčå Reset Defaults). ąŚą┤ąĄčüčī ą┐ąĄčĆąĄčćąĖčüą╗ąĄąĮčŗ ąĖą╝ąĄąĮą░ ą▓ąĄą║č鹊čĆąŠą▓ EVT.

ŌĆó ąśą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čÅą┤čĆą░ (core interrupt ID, čüč鹊ą╗ą▒ąĄčå Core Interrupt ID), ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╣ ą▓ čĆąĄą│ąĖčüčéčĆą░čģ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ čüąĖčüč鹥ą╝ąĮčŗčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ (system interrupt assignment registers, SIC_IARx).

ąóą░ą▒ą╗ąĖčåą░ 4-7. ąĪąŠčüč鹊čÅąĮąĖąĄ ąĖčüč鹊čćąĮąĖą║ąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░.

| Peripheral Interrupt Source |

Peripheral Interrupt ID |

Reset Defaults |

Core Interrupt ID |

| PLL Wake-Up Interrupt |

0 |

IVG7 |

0 |

| DMA Controller 0 Error (generic) |

1 |

| PPI Error Interrupt |

2 |

| SPORT0 Error Interrupt |

3 |

| SPORT1 Error Interrupt |

4 |

| SPI0 Error Interrupt |

5 |

| UART0 Error Interrupt |

6 |

| ą¤čĆąĄčĆčŗą▓ą░ąĮąĖčÅ Real-Time Clock (ą▒čāą┤ąĖą╗čīąĮąĖą║, čüąĄą║čāąĮą┤čŗ, ą╝ąĖąĮčāčéčŗ, čćą░čüčŗ, ąŠą▒čĆą░čéąĮčŗą╣ ąŠčéčüč湥čé čüąĄą║čāąĮą┤) |

7 |

IVG8 |

1 |

| DMA0 Interrupt (PPI) |

8 |

| DMA1 Interrupt (SPORT0 Rx) |

9 |

IVG9 |

2 |

| DMA2 Interrupt (SPORT0 Tx) |

10 |

| DMA3 Interrupt (SPORT1 Rx) |

11 |

| DMA4 Interrupt (SPORT1 Tx) |

12 |

| DMA5 Interrupt (SPI0) |

13 |

IVG10 |

3 |

| DMA6 Interrupt (UART0 Rx) |

14 |

| DMA7 Interrupt (UART0 Tx) |

15 |

| ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ Timer0 |

16 |

IVG11 |

4 |

| ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ Timer1 |

17 |

| ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ Timer2 |

18 |

| ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ A GPIO (ą┐ąŠčĆčé F) |

19 |

IVG12 |

5 |

| ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ B GPIO (ą┐ąŠčĆčé F) |

20 |

| DMA 8/9 interrupt (MDMA Stream 0) |

21 |

IVG13 |

6 |

| DMA 10/11 interrupt (MDMA Stream 1) |

22 |

| Software Watchdog Timer interrupt |

23 |

| DMA controller 1 error (generic) |

24 |

IVG7 |

0 |

| SPORT2 error interrupt |

25 |

| SPORT3 error interrupt |

26 |

| SPI1 error interrupt |

28 |

| SPI2 error interrupt |

29 |

| UART1 error interrupt |

30 |

| UART2 error interrupt |

31 |

| CAN error interrupt |

32 |

| DMA 8 interrupt (SPORT2 receive) |

33 |

IVG9 |

2 |

| DMA 9 interrupt (SPORT2 transmit) |

34 |

| DMA 10 interrupt (SPORT3 receive) |

35 |

| DMA 11 interrupt (SPORT3 transmit) |

36 |

| DMA 12 interrupt |

37 |

| DMA 13 interrupt |

38 |

| DMA 14 interrupt (SPI1) |

39 |

IVG10 |

3 |

| DMA 15 interrupt (SPI2) |

40 |

| DMA 16 interrupt (UART1 RX) |

41 |

| DMA 17 interrupt (UART1 TX) |

42 |

| DMA 18 interrupt (UART2 RX) |

43 |

| DMA 19 interrupt (UART2 TX) |

44 |

| TWI0 interrupt |

45 |

IVG11 |

4 |

| TWI1 interrupt |

46 |

| CAN receive interrupt |

47 |

| CAN transmit interrupt |

48 |

| MDMA1 stream 0 (memory DMA) |

49 |

IVG13 |

6 |

| MDMA1 stream 1 (memory DMA) |

50 |

| ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

51..63 |

- |

- |

ąĪčéčĆčāą║čéčāčĆą░ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ą│ąĖą▒ą║ąŠ ąĮą░čüčéčĆą░ąĖą▓ą░ąĄčéčüčÅ. ą¤ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ ąĮąĄčüą║ąŠą╗čīą║ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ čüąŠą▓ą╝ąĄčüčéąĮąŠ ąĖčüą┐ąŠą╗čīąĘčāčÄčé ąŠą┤ąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čÅą┤čĆą░ ąŠą▒čēąĄą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ, ą║ą░ą║ čŹč鹊 ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▓ čĆą░ąĘą┤ąĄą╗ąĄ "System Interrupt" čĆčāą║ąŠą▓ąŠą┤čüčéą▓ą░ ([3] ą┤ą╗čÅ BF538).

ą×ą▒čĆą░ą▒ąŠčéčćąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą║ąŠč鹊čĆčŗą╣ ą┤ąŠą╗ąČąĄąĮ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čéčī ąŠą▒čĆą░ą▒ąŠčéą║čā ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ąĖčüč鹊čćąĮąĖą║ąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ąŠčé ą░ą┐ą┐ą░čĆą░čéčāčĆčŗ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓, ą┤ąŠą╗ąČąĄąĮ ąŠą┐čĆąŠčüąĖčéčī čĆąĄą│ąĖčüčéčĆčŗ čŹč鹊ą╣ ą░ą┐ą┐ą░čĆą░čéčāčĆčŗ (ą┐čĆąĖą▓čÅąĘą░ąĮąĮčŗąĄ ą║ ą┐ą░ą╝čÅčéąĖ čĆąĄą│ąĖčüčéčĆčŗ, memory mapped registers, MMR), čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī, ą║ą░ą║ąŠąĄ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ą╗ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ.

ąĢčüą╗ąĖ ą┐čĆąĖą▓čÅąĘą║ą░ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ (čüą╝. ą▓čĆąĄąĘą║čā "ą¤čĆąĖą▓čÅąĘą║ąĖ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą▓ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ" ąĖą╗ąĖ čĆą░ąĘą┤ąĄą╗ "System Interrupt" čĆčāą║ąŠą▓ąŠą┤čüčéą▓ą░ [3] ą┤ą╗čÅ BF538), č鹊 ą▓ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą▓čģąŠą┤čÅčé č鹊ą╗čīą║ąŠ čüą╗ąĄą┤čāčÄčēąĖąĄ čłą░ą│ąĖ:

ŌĆó ąÆ čéą░ą▒ą╗ąĖčåčā ą▓ąĄą║č鹊čĆąŠą▓ čÅą┤čĆą░ Event Vector Table (EVT) ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ ą░ą┤čĆąĄčü ą▓ąĄą║č鹊čĆą░ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

ŌĆó ąśąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆčāąĄčéčüčÅ čĆąĄą│ąĖčüčéčĆ IMASK.

ŌĆó ąöąĄą╝ą░čüą║ąĖčĆčāąĄčéčüčÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ą▓ čĆąĄą│ąĖčüčéčĆąĄ SIC_IMASK.

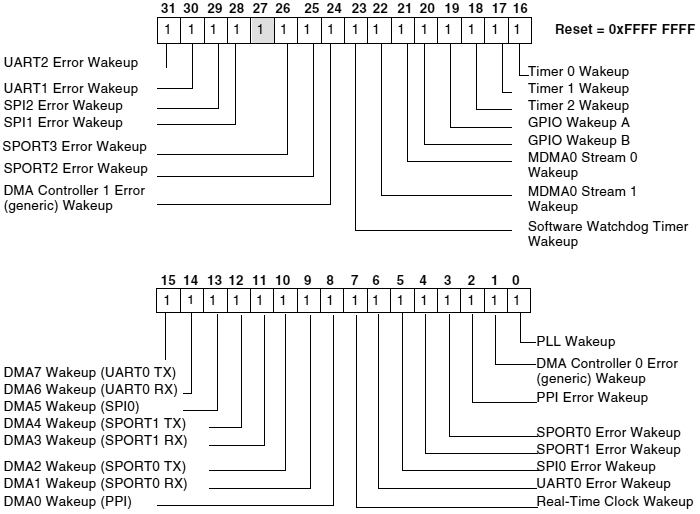

ąÆ ą┐čĆąŠčåąĄčüčüąŠčĆą░čģ čüąĄą╝ąĄą╣čüčéą▓ą░ Blackfin ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠą┤ąĖąĮ ąĖą╗ąĖ ąĮąĄčüą║ąŠą╗čīą║ąŠ čĆąĄą│ąĖčüčéčĆąŠą▓ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ čüąĖčüč鹥ą╝čŗ ą┐ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÄ (System Interrupt Wakeup-Enable registers, SIC_IWR). ąÆ ą┐čĆąŠčåąĄčüčüąŠčĆąĄ ADSP-BF538 čéą░ą║ąĖčģ čĆąĄą│ąĖčüčéčĆąŠą▓ ą┤ą▓ą░: SIC_IWR1 ąĖ SIC_IWR0.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▓ąĄąĘą┤ąĄ, ą│ą┤ąĄ ą▓ č鹥ą║čüč鹥 ą▓čüčéčĆąĄčćą░ąĄčéčüčÅ ADSP-BF538 ąĖą╗ąĖ BF538, ąĖą╝ąĄąĄčéčüčÅ ą▓ ą▓ąĖą┤čā 2 ą╝ąŠą┤ąĄą╗ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆą░: ADSP-BF538 ąĖ ADSP-BF538F.

ąĀąĄą│ąĖčüčéčĆčŗ SIC_IWR1 ąĖ SIC_IWR0 ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÄčé ą┐čĆąĖą▓čÅąĘą║čā ąĖčüč鹊čćąĮąĖą║ąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠčé ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ą║ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčā ą┤ąĖąĮą░ą╝ąĖč湥čüą║ąŠą│ąŠ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖąĄą╝ (Dynamic Power Management Controller, DPMC). ąøčÄą▒ąŠąĄ ąĖąĘ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ą╝ąŠąČąĄčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąŠ ą┤ą╗čÅ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ čÅą┤čĆą░ - ą▓čŗą▓ąŠą┤ą░ ąĄą│ąŠ ąĖąĘ čüąŠčüč鹊čÅąĮąĖčÅ ąŠąČąĖą┤ą░ąĮąĖčÅ (idle state) ąĖą╗ąĖ čĆąĄąČąĖą╝ą░ čüąĮą░ (Sleep mode) ą┤ą╗čÅ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, čćč鹊 ą┤ąĄą╗ą░ąĄčéčüčÅ ą┐čĆąŠčüčéčŗą╝ čĆą░ąĘčĆąĄčłąĄąĮąĖąĄą╝ ą┐ąŠą┤čģąŠą┤čÅčēąĄą│ąŠ ą▒ąĖčéą░ ą▓ čĆąĄą│ąĖčüčéčĆą░čģ SIC_IWRx. ą×ą▒čĆą░čéąĖč鹥čüčī ą║ čĆą░ąĘą┤ąĄą╗čā "System Interrupt" čĆčāą║ąŠą▓ąŠą┤čüčéą▓ą░ ą┐ąŠ ą░ą┐ą┐ą░čĆą░čéčāčĆąĄ ą┐čĆąŠčåąĄčüčüąŠčĆą░ (čé. ąĄ. [3] ą┤ą╗čÅ BF538). ąĢčüą╗ąĖ ąĖčüč鹊čćąĮąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠčé ą░ą┐ą┐ą░čĆą░čéčāčĆčŗ čĆą░ąĘčĆąĄčłąĄąĮ ą▓ SIC_IWRx, ąĖ čÅą┤čĆąŠ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ ąĖą╗ąĖ ą┐ąŠą╝ąĄčēąĄąĮąŠ ą▓ čĆąĄąČąĖą╝ čüąĮą░, č鹊 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čāą║ą░ąČąĄčé DPMC ąĖąĮąĖčåąĖąĖčĆąŠą▓ą░čéčī ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ, čćč鹊ą▒čŗ ą╝ąŠąČąĮąŠ ą▒čŗą╗ąŠ ąŠą▒čĆą░ą▒ąŠčéą░čéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ. ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 čŹč鹊čé čĆąĄąČąĖą╝ čĆą░ą▒ąŠčéčŗ ą╝ąŠąČąĄčé ą┤ąŠą▒ą░ą▓ąĖčéčī ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčāčÄ ąĘą░ą┤ąĄčƹȹ║čā ą▓ ąŠą▒čĆą░ą▒ąŠčéą║čā ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čāą┐čĆą░ą▓ą╗čÅąĄą╝ąŠą│ąŠ čüąŠčüč鹊čÅąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ. ąöą╗čÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ą┐ąŠ čĆąĄąČąĖą╝ą░ą╝ ą┐ąĖčéą░ąĮąĖčÅ ąĖ čüąŠčüč鹊čÅąĮąĖčÄ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ąĖ čÅą┤čĆą░ čüą╝. čĆą░ąĘą┤ąĄą╗ "Dynamic Power Management" ą▓ čĆčāą║ąŠą▓ąŠą┤čüčéą▓ąĄ ą┐ąŠ ą░ą┐ą┐ą░čĆą░čéčāčĆąĄ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ([3] ą┤ą╗čÅ BF538).

ą¤ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ, ą║ą░ą║ čŹč鹊 ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▓ čĆą░ąĘą┤ąĄą╗ąĄ "System Interrupt" ([3] ą┤ą╗čÅ BF538), ą▓čüąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą▒čāą┤čāčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ąĘą░ą┐čĆąŠčü ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ ą┤ą╗čÅ čÅą┤čĆą░. ą×ą┤ąĮą░ą║ąŠ ą┤ą╗čÅ ąĮąĄą║ąŠč鹊čĆčŗčģ ą┐čĆąĖą╗ąŠąČąĄąĮąĖą╣ ą╝ąŠąČąĄčé ą┐ąŠąĮą░ą┤ąŠą▒ąĖčéčīčüčÅ ąĘą░ą┐čĆąĄčéąĖčéčī čŹčéčā čäčāąĮą║čåąĖčÄ ą┤ą╗čÅ ąĮąĄą║ąŠč鹊čĆčŗčģ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓.

ąĀąĄą│ąĖčüčéčĆ SIC_IWR ąĮąĖą║ą░ą║ ąĮąĄ ą▓ą╗ąĖčÅąĄčé ąĮą░ ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ ą┐čĆąŠčåąĄčüčüąŠčĆą░, ąĄčüą╗ąĖ čÅą┤čĆąŠ ąĮąĄ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ ąĖą╗ąĖ ąĮąĄ ą┐ąŠą╝ąĄčēąĄąĮąŠ ą▓ čĆąĄąČąĖą╝ čüąĮą░. ąæąĖčéčŗ ą▓ čŹč鹊ą╝ čĆąĄą│ąĖčüčéčĆąĄ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčé ą░ąĮą░ą╗ąŠą│ąĖčćąĮčŗą╝ ą▒ąĖčéą░ą╝ ą▓ čĆąĄą│ąĖčüčéčĆą░čģ System Interrupt Mask (SIC_IMASK) ąĖ Interrupt Status (SIC_ISR).

ą¤ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ ą▓čüąĄ ą┤ąĄą╣čüčéą▓ąĖč鹥ą╗čīąĮčŗąĄ ą▒ąĖčéčŗ ą▓ čĆąĄą│ąĖčüčéčĆą░čģ SIC_IWRx ą▒čāą┤čāčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą▓ ą╗ąŠą│. 1, čćč鹊 čĆą░ąĘčĆąĄčłąĖčé čäčāąĮą║čåąĖčÄ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ ą┤ą╗čÅ ą▓čüąĄčģ čĆą░ąĘčĆąĄčłąĄąĮąĮčŗčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. ą¤ąĄčĆąĄą┤ čĆą░ąĘčĆąĄčłąĄąĮąĖąĄą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆčāą╣č鹥 čŹč鹊čé čĆąĄą│ąĖčüčéčĆ ą▓ ą▓ ą┐čĆąŠčåąĄą┤čāčĆąĄ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ, ą║ąŠč鹊čĆą░čÅ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą▓ ą║ąŠą┤ąĄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ (ą┤ąŠ ą▓čģąŠą┤ą░ ą▓ ą▒ąĄčüą║ąŠąĮąĄčćąĮčŗą╣ čåąĖą║ą╗ čäčāąĮą║čåąĖąĖ main). ąĀąĄą│ąĖčüčéčĆ SIC_IWRx ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮ ąĖą╗ąĖ ąĘą░ą┐ąĖčüą░ąĮ ą▓ ą╗čÄą▒ąŠąĄ ą▓čĆąĄą╝čÅ. ą¦č鹊ą▒čŗ ąĘą░čēąĖčéąĖčéčīčüčÅ čüą╗čāčćą░ą╣ąĮčŗčģ ąŠčłąĖą▒ąŠą║ ąĖą╗ąĖ ą┐ąŠč鹥čĆąĖ ą░ą║čéąĖą▓ąĮąŠčüčéąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, čŹč鹊čé čĆąĄą│ąĖčüčéčĆ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮ č鹊ą╗čīą║ąŠ č鹊ą│ą┤ą░, ą║ąŠą│ą┤ą░ ąĘą░ą┐čĆąĄčēąĄąĮčŗ ą▓čüąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠčé ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓.

ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 čäčāąĮą║čåąĖčÅ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ ąĮąĄ ąĘą░ą▓ąĖčüąĖčé ąŠčé čäčāąĮą║čåąĖąĖ ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ąó. ąĄ. ąĄčüą╗ąĖ ąĖčüč鹊čćąĮąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čĆą░ąĘčĆąĄčłąĄąĮ ą▓ SIC_IWR, ąĮąŠ ąĘą░ą┐čĆąĄčēąĄąĮ ą▓ SIC_IMASK (ąĘą░ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮ), č鹊 čÅą┤čĆąŠ ą▓čüąĄ čĆą░ą▓ąĮąŠ ą┐čĆąŠčüąĮąĄčéčüčÅ ąŠčé čŹč鹊ą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĖ ą▓čŗą╣ą┤ąĄčé ąĖąĘ ąŠąČąĖą┤ą░ąĮąĖčÅ ąĖą╗ąĖ čüąĮą░, ąŠą┤ąĮą░ą║ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĮąĄ ą▒čāą┤ąĄčé čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąŠ (ą║ąŠą┤ ISR ąĮąĄ ąĘą░ą┐čāčüčéąĖčéčüčÅ).

ąØą░čüčéčĆąŠą╣ą║ą░ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą┤ą╗čÅ čĆąĄą│ąĖčüčéčĆą░ SIC_IWR0 ą┐čĆąŠčåąĄčüčüąŠčĆą░ ADSP-BF538:

ąØą░čüčéčĆąŠą╣ą║ą░ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą┤ą╗čÅ čĆąĄą│ąĖčüčéčĆą░ SIC_IWR1 ą┐čĆąŠčåąĄčüčüąŠčĆą░ ADSP-BF538:

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą┤ą╗čÅ ą▓čüąĄčģ ą▒ąĖčé 0 ąŠąĘąĮą░čćą░ąĄčé ąĘą░ą┐čĆąĄčé čäčāąĮą║čåąĖąĖ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ, 1 čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ čŹč鹊ą╣ čäčāąĮą║čåąĖąĖ.

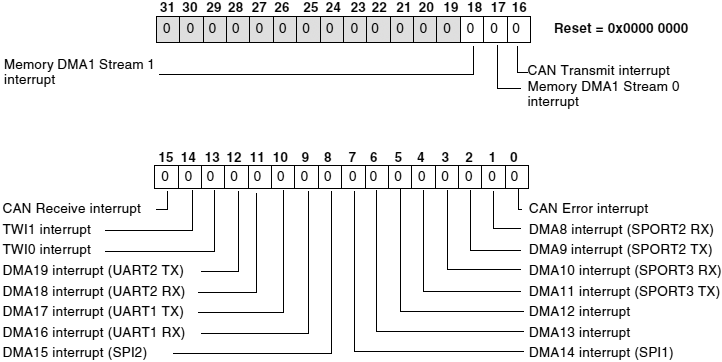

ąĪąĖčüč鹥ą╝ąĮčŗą╣ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (System Interrupt Controller, SIC) BF538 ąĖą╝ąĄąĄčé 2 čĆąĄą│ąĖčüčéčĆą░ čüąŠčüč鹊čÅąĮąĖčÅ, ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮąĮčŗčģ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ: System Interrupt Status registers (SIC_ISR1 ąĖ SIC_ISR0). ąÜą░ąČą┤čŗą╣ ą▒ąĖčé ą▓ čŹč鹊ą╝ čĆąĄą│ąĖčüčéčĆąĄ čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ąŠą┤ąĮąŠą╝čā ąĖąĘ ąĖčüč鹊čćąĮąĖą║ąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠčé ą░ą┐ą┐ą░čĆą░čéčāčĆčŗ. ąæąĖčé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ SIC ą┤ąĄč鹥ą║čéąĖčĆčāąĄčé ą▓čŗčüčéą░ą▓ą╗ąĄąĮąĮąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ąĖ čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ SIC ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ą╗, čćč鹊 ą▒čŗą╗ąŠ čüąĮčÅč鹊 ąĮą░ ą▓čģąŠą┤ąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠčé ą┐ąĄčĆąĖč乥čĆąĖąĖ. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ą┤ą╗čÅ ąĮąĄą║ąŠč鹊čĆčŗčģ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓, čéą░ą║ąĖčģ ą║ą░ą║ ą┐ąŠčĆčéčŗ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ ąŠą▒čēąĄą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ (general-purpose I/O, GPIO), ą░čüąĖąĮčģčĆąŠąĮąĮčŗąĄ ą▓čģąŠą┤čŗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą╝ąŠą│čāčé ą┐čĆąŠą╣čéąĖ ą╝ąĮąŠą│ąŠ čåąĖą║ą╗ąŠą▓ ąĘą░ą┤ąĄčƹȹ║ąĖ ąŠčé ą╝ąŠą╝ąĄąĮčéą░, ą║ąŠą│ą┤ą░ ISR ąĖąĮąĖčåąĖąĖčĆąŠą▓ą░ą╗ ąŠčćąĖčüčéą║čā ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (ąŠą▒čŗčćąĮąŠ ąĘą░ą┐ąĖčüčīčÄ ą▓ čüąĖčüč鹥ą╝ąĮčŗą╣ MMR) ą┤ąŠ ą▓čĆąĄą╝ąĄąĮąĖ, ą║ąŠą│ą┤ą░ SIC ąŠą┐čĆąĄą┤ąĄą╗ąĖčé, čćč鹊 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą▒čŗą╗ąŠ čüąĮčÅč鹊.

ąÆ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé č鹊ą│ąŠ, ą║ą░ą║ ąĖčüč鹊čćąĮąĖą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐čĆąĖą▓čÅąĘą░ąĮčŗ ą║ąŠ ą▓čģąŠą┤ą░ą╝ ą│čĆčāą┐ą┐ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ IVGx, ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (ISR) ą╝ąŠąČąĄčé ą▓ąĘą░ąĖą╝ąŠą┤ąĄą╣čüčéą▓ąŠą▓ą░čéčī čü ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ ą▒ąĖčéą░ą╝ąĖ čüąŠčüč鹊čÅąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ąĖčüč鹊čćąĮąĖą║ - ąŠčéą║čāą┤ą░ ą┐čĆąĖčłą╗ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ. ą×ą┤ąĮąŠą╣ ąĖąĘ ą┐ąĄčĆą▓čŗčģ ąĖąĮčüčéčĆčāą║čåąĖą╣ ą▓ ą║ąŠą┤ąĄ ISR ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī čćč鹥ąĮąĖąĄ SIC_ISRx, čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ąŠą┤ąĖąĮ ąĖąĘ ąŠą▒čēąĖčģ ąĖčüč鹊čćąĮąĖą║ąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą┤ą╗čÅ čŹč鹊ą╣ ą│čĆčāą┐ą┐čŗ. ISR ą┤ąŠą╗ąČąĄąĮ ą┐ąŠą╗ąĮąŠčüčéčīčÄ ąŠą▒čĆą░ą▒ąŠčéą░čéčī ą▓čüąĄ ąŠąČąĖą┤ą░čÄčēąĖąĄ ąŠą▒čēąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ąŠ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ąĖąĮčüčéčĆčāą║čåąĖąĖ RTI (ą▓čŗčģąŠą┤ ąĖąĘ ISR), ą║ąŠč鹊čĆą░čÅ čĆą░ąĘčĆąĄčłąĖčé ą┐ąŠčüą╗ąĄą┤čāčÄčēąĖąĄ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ąĮą░ čŹč鹊ą╝ ą▓čģąŠą┤ąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ IVGx.

ąÆą░ąČąĮąŠ: ą║ąŠą│ą┤ą░ ISR ąĘą░ą▓ąĄčĆčłą░ąĄčéčüčÅ, ąĖąĮčüčéčĆčāą║čåąĖčÅ RTI ąŠčćąĖčüčéąĖčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé ą▓ čĆąĄą│ąĖčüčéčĆąĄ IPEND. ą×ą┤ąĮą░ą║ąŠ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé ą▓ čĆąĄą│ąĖčüčéčĆąĄ SIC_ISR ąĮąĄ ą▒čāą┤ąĄčé ąŠčćąĖčēąĄąĮ, ą┐ąŠą║ą░ ISR ąĮąĄ ąŠčćąĖčüčéąĖčé ą╝ąĄčģą░ąĮąĖąĘą╝, ą║ąŠč鹊čĆčŗą╣ čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ą╗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ.

ąÆąŠ ą╝ąĮąŠą│ąĖčģ čüąĖčüč鹥ą╝ą░čģ ąĖą╝ąĄąĄčéčüčÅ ąĮąĄ čéą░ą║ ą╝ąĮąŠą│ąŠ ą░ą┐ą┐ą░čĆą░čéąĮčŗčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ąŠčé čāčüčéčĆąŠą╣čüčéą▓, ą║ąŠč鹊čĆčŗąĄ ąĮą░ą┤ąŠ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░čéčī, čéą░ą║ čćč鹊 ąĄčüčéčī ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ąĮą░ąĘąĮą░čćąĖčéčī ąĮą░ ą║ą░ąČą┤ąŠąĄ ąĖąĘ čéą░ą║ąĖčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ čāąĮąĖą║ą░ą╗čīąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī ą┐čĆąĖąŠčĆąĖč鹥čéą░ (čé. ąĄ. ąĮą░ čāąĮąĖą║ą░ą╗čīąĮčŗą╣ ą▓čģąŠą┤/ą│čĆčāą┐ą┐čā ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ IVGx). ą¤ąŠ ą║čĆą░ą╣ąĮąĄą╣ ą╝ąĄčĆąĄ, ąĮčāąČąĮąŠ čüčéą░čĆą░čéčīčüčÅ ą┐čĆąŠąĄą║čéąĖčĆąŠą▓ą░čéčī čüąĖčüč鹥ą╝čŗ ąĖą╝ąĄąĮąĮąŠ čéą░ą║. ąÆ čéą░ą║ąĖčģ čĆą░ąĘčĆą░ą▒ąŠčéą║ą░čģ ąŠč湥ąĮčī čĆąĄą┤ą║ąŠ ąĮą░ą┤ąŠ ą▒čāą┤ąĄčé čćąĖčéą░čéčī SIC_ISR (ąĄčüą╗ąĖ čŹč鹊 ą▓ąŠąŠą▒čēąĄ ą║ąŠą│ą┤ą░-ąĮąĖą▒čāą┤čī ą┐ąŠąĮą░ą┤ąŠą▒ąĖčéčüčÅ), ą┐ąŠč鹊ą╝čā čćč鹊 ą║ą░ąČą┤čŗą╣ ISR ą▒čāą┤ąĄčé čüąŠąŠčéą▓ąĄčéčüčéą▓ąŠą▓ą░čéčī čüčéčĆąŠą│ąŠ ąŠą┤ąĮąŠą╝čā ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÄ ąŠčé ąŠą┤ąĮąŠą│ąŠ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░.

ąØą░ čĆąĄą│ąĖčüčéčĆ SIC_ISR ąĮąĄ ą▓ą╗ąĖčÅąĄčé čüąŠčüč鹊čÅąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ System Interrupt Mask (SIC_IMASK), ąĖ SIC_ISR ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮ ą▓ ą╗čÄą▒ąŠąĄ ą▓čĆąĄą╝čÅ. ąŚą░ą┐ąĖčüčī SIC_ISR ąĮąĖą║ą░ą║ ąĮąĄ ą▓ą╗ąĖčÅąĄčé ąĮą░ ąĄą│ąŠ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ.

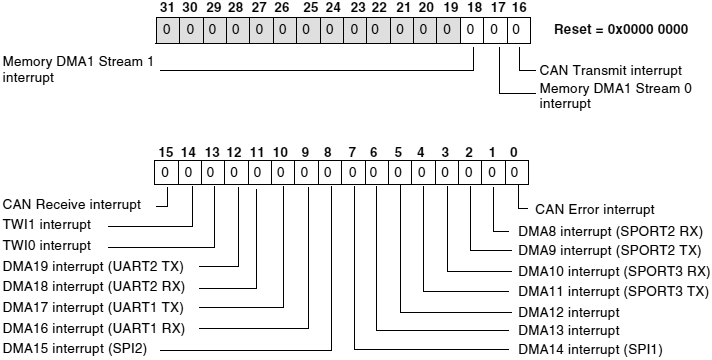

ąĀąĖčü. 4-8. System Interrupt Status Register 0 (SIC_ISR0).

ąĀąĖčü. 4-9. System Interrupt Status Register 1 (SIC_ISR1).

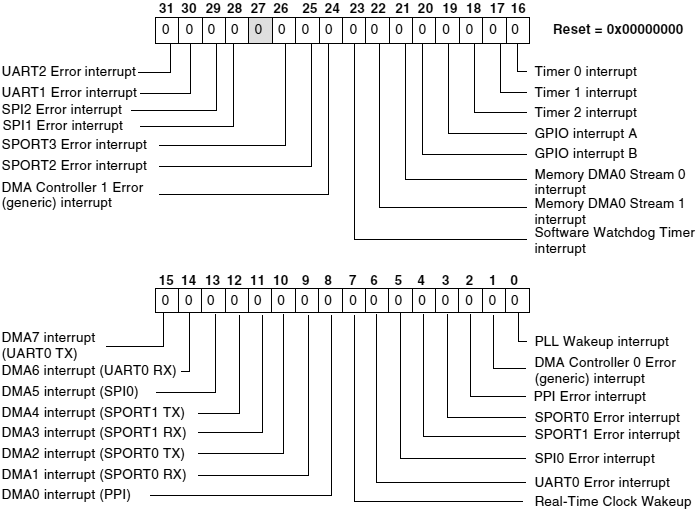

ąÆ ą┐čĆąŠčåąĄčüčüąŠčĆą░čģ čüąĄą╝ąĄą╣čüčéą▓ą░ Blackfin ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠą┤ąĖąĮ ąĖą╗ąĖ ąĮąĄčüą║ąŠą╗čīą║ąŠ čĆąĄą│ąĖčüčéčĆąŠą▓ ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (System Interrupt Mask register, SIC_IMASK). ąÆ ą┐čĆąŠčåąĄčüčüąŠčĆąĄ ADSP-BF538 čéą░ą║ąĖčģ čĆąĄą│ąĖčüčéčĆąŠą▓ ą┤ą▓ą░: SIC_IMASK1 ąĖ SIC_IMASK0. ąŁčéąĖ čĆąĄą│ąĖčüčéčĆčŗ ą┐ąŠąĘą▓ąŠą╗čÅčÄčé čĆą░ąĘčĆąĄčłą░čéčī/ąĘą░ą┐čĆąĄčēą░čéčī ą║ą░ąČą┤čŗą╣ ąĖąĘ ąĖčüč鹊čćąĮąĖą║ąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĮą░ čüąĖčüč鹥ą╝ąĮąŠą╝ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ (System Interrupt Controller, SIC), ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé č鹊ą│ąŠ, ą▒čŗą╗ąŠ ąĖą╗ąĖ ąĮąĄčé čĆą░ąĘčĆąĄčłąĄąĮąŠ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ.

ąĪą▒čĆąŠčü ą┐čĆąĖąĮčāą┤ąĖč鹥ą╗čīąĮąŠ čüą▒čĆą░čüčŗą▓ą░ąĄčé ą▓čüąĄ ą▒ąĖčéčŗ SIC_IMASKx ą▓ ąĮčāą╗ąĖ, č湥ą╝ ąĘą░ą┐čĆąĄčēą░čÄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠčé ą▓čüąĄčģ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓. ąŚą░ą┐ąĖčüčī 1 ą▓ ąĮčāąČąĮčŗą╣ ą▒ąĖčé čĆą░ąĘčĆąĄčłą░ąĄčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ.

ąźąŠčéčÅ čŹčéąĖ čĆąĄą│ąĖčüčéčĆčŗ ą╝ąŠą│čāčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮčŗ ąĖą╗ąĖ ąĘą░ą┐ąĖčüą░ąĮčŗ ą▓ ą╗čÄą▒ąŠąĄ ą▓čĆąĄą╝čÅ (ą▓ čĆąĄąČąĖą╝ąĄ Supervisor), ąŠąĮąĖ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆąŠą▓ą░ąĮčŗ ą▓ ą┐čĆąŠčåąĄą┤čāčĆąĄ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ąĮą░čüčéčĆąŠąĄą║ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░, ą┤ąŠ č鹊ą│ąŠ, ą║ą░ą║ ą▒čāą┤čāčé ą│ą╗ąŠą▒ą░ą╗čīąĮąŠ čĆą░ąĘčĆąĄčłąĄąĮčŗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

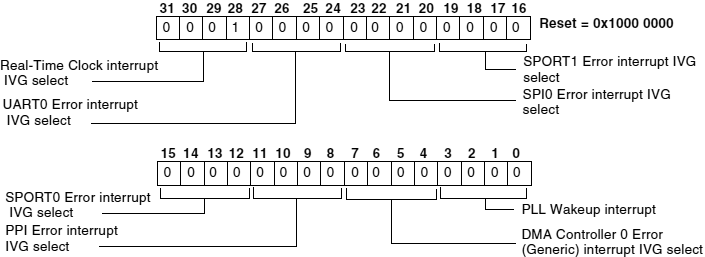

ąĀąĖčü. 4-10. System Interrupt Mask Register 0 (SIC_IMASK0).

ąĀąĖčü. 4-11. System Interrupt Mask Register 1 (SIC_IMASK1).

ą×čéąĮąŠčüąĖč鹥ą╗čīąĮčŗąĄ ą┐čĆąĖąŠčĆąĖč鹥čéčŗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ąŠčé ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ą╝ąŠą│čāčé ą▒čŗčéčī ąĮą░čüčéčĆąŠąĄąĮčŗ ą┐čāč鹥ą╝ ą┐čĆąĖą▓čÅąĘą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠčé ą┐ąĄčĆąĖč乥čĆąĖąĖ ą║ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╝čā čāčĆąŠą▓ąĮčÄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ čÅą┤čĆą░ (čé. ąĄ. ą║ ąĮčāąČąĮąŠą╣ ą│čĆčāą┐ą┐ąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ IVGx). ą¤čĆąĖą▓čÅąĘą║ą░ čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ čĆąĄą│ąĖčüčéčĆą░ą╝ąĖ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ čüąĖčüč鹥ą╝ąĮčŗčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ (System Interrupt Assignment Registers, SIC_IARx) - ą▓ ąĮąĖčģ ą┤ąĄą╗ą░ąĄčéčüčÅ ąĮą░ąĘąĮą░č湥ąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ąŠą┤ąĮąŠą╣ ąĖąĘ ą│čĆčāą┐ą┐ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ąŠą▒čēąĄą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ IVGx (ąĮą░ą┐ąŠą╝ąĮčÄ, čćč鹊 ą║ą░ąČą┤ą░čÅ ą│čĆčāą┐ą┐ą░ IVGx ąĖą╝ąĄąĄčé ąČąĄčüčéą║ąŠ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī ą┐čĆąĖąŠčĆąĖč鹥čéą░). ąĢčüą╗ąĖ ąŠą┤ąĮąŠą╣ ą│čĆčāą┐ą┐ąĄ ąĮą░ąĘąĮą░č湥ąĮąŠ ą▒ąŠą╗čīčłąĄ ąŠą┤ąĮąŠą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąĄčĆąĖč乥čĆąĖąĖ, č鹊 ąŠąĮąĖ, ą▒čāą┤čāčćąĖ čĆą░ąĘčĆąĄčłąĄąĮčŗ, čĆą░ą▒ąŠčéą░čÄčé ą▓ ąŠą▒čŖąĄą┤ąĖąĮąĄąĮąĖąĄą╝ ą┐ąŠ ąśąøąś ą▓ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ąĄ ISR, ą▒ąĄąĘ ą║ą░ą║ąŠą│ąŠ-č鹊 ą░ą┐ą┐ą░čĆą░čéąĮąŠą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ ą┐čĆąĖąŠčĆąĖč鹥čéą░ (čé. ąĄ. ą▓ ą┐čĆąĄą┤ąĄą╗ą░čģ ąŠą┤ąĮąŠą╣ ą│čĆčāą┐ą┐čŗ IVGx ą▓čüąĄ ąĖčüč鹊čćąĮąĖą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ čĆą░ą▓ąĮąŠą┐čĆą░ą▓ąĮčŗ). ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠąĄ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖąĄ ą╝ąŠąČąĄčé ą┐čĆąĖąŠčĆąĖč鹥ąĘąĖčĆąŠą▓ą░čéčī ąŠą▒čĆą░ą▒ąŠčéą║čā ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą│čĆčāą┐ą┐čŗ IVGx čéą░ą║, ą║ą░ą║ čŹč鹊 čéčĆąĄą▒čāąĄčéčüčÅ ą▓ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĖ.

ąöą╗čÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ąŠą▒čēąĄą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ IVGx, ą║ąŠą│ą┤ą░ ąĮą░ ąŠą┤ąĮčā ą│čĆčāą┐ą┐čā ą┐čĆąĖą▓čÅąĘą░ąĮąŠ ąĮąĄčüą║ąŠą╗čīą║ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą░ą┐ą┐ą░čĆą░čéčāčĆčŗ, ąĮčāąČąĮąŠ čüą┐ąĄčåąĖą░ą╗čīąĮąŠ ą┐ąŠąĘą░ą▒ąŠčéąĖčéčīčüčÅ ąŠ ą║ąŠčĆčĆąĄą║čéąĮąŠą╣ ąŠą▒čĆą░ą▒ąŠčéą║ąĄ čüąŠ čüč鹊čĆąŠąĮčŗ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ą▓čüąĄčģ ąŠąČąĖą┤ą░čÄčēąĖčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣, ą┐čĆąĖą▓čÅąĘą░ąĮąĮčŗčģ ą║ ąŠą┤ąĮąŠą╝čā ą▓čģąŠą┤čā IVGx. ą¤čĆąŠą│čĆą░ą╝ą╝ąĮąŠąĄ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖąĄ ą┤ąŠą╗ąČąĮąŠ čüą░ą╝ąŠ ą▓ čüą▓ąŠąĄą╝ ą║ąŠą┤ąĄ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░čéčī ą┐čĆąĖąŠčĆąĖč鹥čé ąŠą▒čēąĖčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą▓ ą┐čĆąĄą┤ąĄą╗ą░čģ ąŠą┤ąĮąŠą╣ ą│čĆčāą┐ą┐čŗ IVGx.

ąĀąĄą│ąĖčüčéčĆčŗ SIC_IARx ą╝ąŠą│čāčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮčŗ ąĖą╗ąĖ ąĘą░ą┐ąĖčüą░ąĮčŗ ą▓ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé ą▓ čĆąĄąČąĖą╝ąĄ Supervisor. ą×ą┤ąĮą░ą║ąŠ ąČąĄą╗ą░č鹥ą╗čīąĮąŠ ąĖčģ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī ą▓ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čüą▒čĆąŠčüą░ (Reset interrupt service routine) ą┤ąŠ ą│ą╗ąŠą▒ą░ą╗čīąĮąŠą│ąŠ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. ą¦č鹊ą▒čŗ ąĘą░čēąĖčéąĖčéčīčüčÅ ąŠčé ąŠčłąĖą▒ąŠą║ ąĖą╗ąĖ čüą╗čāčćą░ą╣ąĮąŠą╣ ą┐ąŠč鹥čĆąĖ ą░ą║čéąĖą▓ąĮąŠčüčéąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, čŹčéąĖ čĆąĄą│ąĖčüčéčĆčŗ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮčŗ č鹊ą╗čīą║ąŠ č鹊ą│ą┤ą░, ą║ąŠą│ą┤ą░ ą▓čüąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠčé ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ąĘą░ą┐čĆąĄčēąĄąĮčŗ.

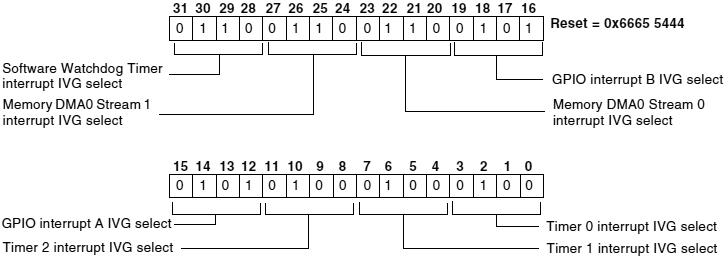

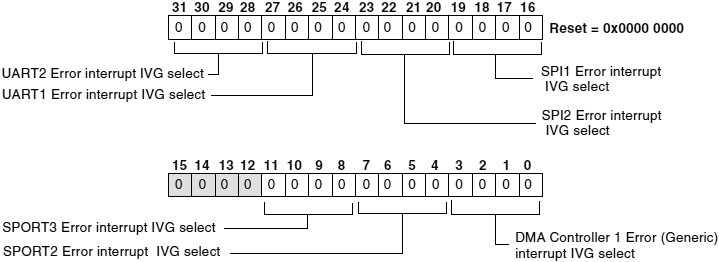

ąĀąĖčü. 4-12. System Interrupt Assignment Register 0 (SIC_IAR0).

ąĀąĖčü. 4-13. System Interrupt Assignment Register 0 (SIC_IAR1).

ąĀąĖčü. 4-14. System Interrupt Assignment Register 0 (SIC_IAR2).

ąĀąĖčü. 4-15. System Interrupt Assignment Register 0 (SIC_IAR3).

ąĀąĖčü. 4-16. System Interrupt Assignment Register 0 (SIC_IAR4).

ąĀąĖčü. 4-17. System Interrupt Assignment Register 0 (SIC_IAR5).

ąĀąĖčü. 4-18. System Interrupt Assignment Register 0 (SIC_IAR6).

| ąÆčŗą▒ąŠčĆ IVG ą┤ą╗čÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ |

ąæąĖčéčŗ SIC_IARx

(ą▓ą╝ąĄčüč鹊 N ą┐ąŠą┤čüčéą░ą▓ą╗čÅąĄčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄ ąĖąĘ čéą░ą▒ą╗ąĖčåčŗ 4-8) |

| SIC_IAR0, ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ 0x1000 0000 |

| Real-Time Clock interrupt |

SIC_IAR0, 0xN... .... |

| UART0 Error interrupt |

SIC_IAR0, 0x.N.. .... |

| SPI0 Error interrupt |

SIC_IAR0, 0x..N. .... |

| SPORT1 Error interrupt |

SIC_IAR0, 0x...N .... |

| SPORT0 Error interrupt |

SIC_IAR0, 0x.... N... |

| PPI Error interrupt |

SIC_IAR0, 0x.... .N.. |

| DMA Controller 0 Error (Generic) interrupt |

SIC_IAR0, 0x.... ..N. |

| PLL Wakeup interrupt |

SIC_IAR0, 0x.... ...N |

| SIC_IAR1, ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ 0x3332 2221 |

| DMA7 (UART TX) interrupt |

SIC_IAR1, 0xN... .... |

| DMA6 (UART RX) interrupt |

SIC_IAR1, 0x.N.. .... |

| DMA5 (SPI) interrupt |

SIC_IAR1, 0x..N. .... |

| DMA4 (SPORT1 TX) interrupt |

SIC_IAR1, 0x...N .... |

| DMA3 (SPORT1 RX) interrupt |

SIC_IAR1, 0x.... N... |

| DMA2 (SPORT0 TX) interrupt |

SIC_IAR1, 0x.... .N.. |

| DMA1 (SPORT0 RX) interrupt |

SIC_IAR1, 0x.... ..N. |

| DMA0 (PPI) interrupt |

SIC_IAR1, 0x.... ...N |

| SIC_IAR2, ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ 0x6665 5444 |

| Software Watchdog Timer interrupt |

SIC_IAR2, 0xN... .... |

| Memory DMA0 Stream 1 interrupt |

SIC_IAR2, 0x.N.. .... |

| Memory DMA0 Stream 0 interrupt |

SIC_IAR2, 0x..N. .... |

| GPIO interrupt B (ą┐ąŠčĆčé F) |

SIC_IAR2, 0x...N .... |

| GPIO interrupt A (ą┐ąŠčĆčé F) |

SIC_IAR2, 0x.... N... |

| Timer 2 interrupt |

SIC_IAR2, 0x.... .N.. |

| Timer 1 interrupt |

SIC_IAR2, 0x.... ..N. |

| Timer 0 interrupt |

SIC_IAR2, 0x.... ...N |

| SIC_IAR3, ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ 0x0000 0000 |

| UART2 Error interrupt |

SIC_IAR3, 0xN... .... |

| UART1 Error interrupt |

SIC_IAR3, 0x.N.. .... |

| SPI2 Error interrupt |

SIC_IAR3, 0x..N. .... |

| SPI1 Error interrupt |

SIC_IAR3, 0x...N .... |

| --- (ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ) --- |

SIC_IAR3, 0x.... 0... |

| SPORT3 Error interrupt |

SIC_IAR3, 0x.... .N.. |

| SPORT2 Error interrupt |

SIC_IAR3, 0x.... ..N. |

| DMA Controller 1 Error (Generic) interrupt |

SIC_IAR3, 0x.... ...N |

| SIC_IAR4, ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ 0x3222 2220 |

| DMA14 (SPI1) interrupt |

SIC_IAR4, 0xN... .... |

| DMA13 interrupt |

SIC_IAR4, 0x.N.. .... |

| DMA12 interrupt |

SIC_IAR4, 0x..N. .... |

| DMA11 (SPORT3 TX) interrupt |

SIC_IAR4, 0x...N .... |

| DMA10 (SPORT3 RX) interrupt |

SIC_IAR4, 0x.... N... |

| DMA9 (SPORT2 TX) interrupt |

SIC_IAR4, 0x.... .N.. |

| DMA8 (SPORT2 RX) interrupt |

SIC_IAR4, 0x.... ..N. |

| CAN Error interrupt |

SIC_IAR4, 0x.... ...N |

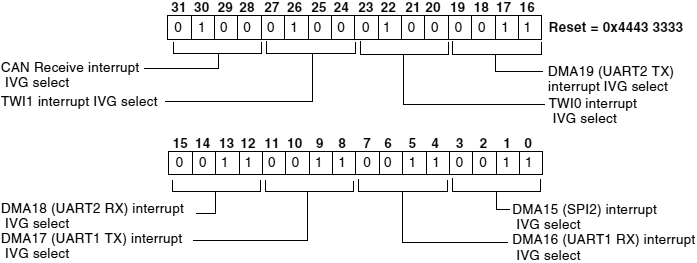

| SIC_IAR5, ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ 0x4443 3333 |

| CAN Receive interrupt |

SIC_IAR5, 0xN... .... |

| TWI1 interrupt |

SIC_IAR5, 0x.N.. .... |

| TWI0 interrupt |

SIC_IAR5, 0x..N. .... |

| DMA19 (UART2 TX) interrupt |

SIC_IAR5, 0x...N .... |

| DMA18 (UART2 RX) interrupt |

SIC_IAR5, 0x.... N... |

| DMA17 (UART1 TX) interrupt |

SIC_IAR5, 0x.... .N.. |

| DMA16 (UART1 RX) interrupt |

SIC_IAR5, 0x.... ..N. |

| DMA15 (SPI2) interrupt |

SIC_IAR5, 0x.... ...N |

| SIC_IAR6, ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ 0x0044 4664 |

| --- (ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ) --- |

SIC_IAR6, 0x0... .... |

| --- (ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ) --- |

SIC_IAR6, 0x.0.. .... |

| --- (ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ) --- |

SIC_IAR6, 0x..4. .... |

| --- (ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ) --- |

SIC_IAR6, 0x...4 .... |

| --- (ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ) --- |

SIC_IAR6, 0x.... 4... |

| Memory DMA1 Stream 1 interrupt |

SIC_IAR6, 0x.... .N.. |

| Memory DMA1 Stream 0 interrupt |

SIC_IAR6, 0x.... ..N. |

| CAN Transmit interrupt |

SIC_IAR6, 0x.... ...N |

ąÆ čéą░ą▒ą╗ąĖčåąĄ 4-8 ą┐ąĄčĆąĄčćąĖčüą╗ąĄąĮčŗ ąĘąĮą░č湥ąĮąĖčÅ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą░ ą│čĆčāą┐ą┐čŗ ą▓ąĄą║č鹊čĆą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (Interrupt Vector Group, IVGx), ą║ąŠč鹊čĆčŗąĄ ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ ą▓ č鹥čéčĆą░ą┤čŗ čĆąĄą│ąĖčüčéčĆąŠą▓ SIC_IARx.

ąóą░ą▒ą╗ąĖčåą░ 4-8. ąØąŠą╝ąĄčĆą░ IVGx ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą░.

| ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠą▒čēąĄą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ |

ąŚąĮą░č湥ąĮąĖčÅ ą┤ą╗čÅ ąĘą░ą┐ąĖčüąĖ ą▓ SIC_IARx |

| IVG7 |

0 |

| IVG8 |

1 |

| IVG9 |

2 |

| IVG10 |

3 |

| IVG11 |

4 |

| IVG12 |

5 |

| IVG13 |

6 |

| IVG14 |

7 |

| IVG15 |

8 |

ąŻčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čéčī ąĘąĮą░č湥ąĮąĖąĄ č鹥čéčĆą░ą┤ čĆąĄą│ąĖčüčéčĆąŠą▓ SIC_IARx čāą┤ąŠą▒ąĮąŠ čü ą┐ąŠą╝ąŠčēčīčÄ ą╝ą░ą║čĆąŠčüą░ PX_IVG (Peripheral Interrupt ID, IVGx). ąŚą┤ąĄčüčī Peripheral Interrupt ID čŹč鹊 ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (ą╝ąŠąČąĮąŠ ą┐ąŠčüą╝ąŠčéčĆąĄčéčī ą▓ čéą░ą▒ą╗ąĖčåąĄ 4-7), ą░ IVGx čŹč鹊 ąĘąĮą░č湥ąĮąĖąĄ ąĖąĘ čéą░ą▒ą╗ąĖčåčŗ 4-8. ą£ą░ą║čĆąŠčü PX_IVG ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮ ą▓ ąĘą░ą│ąŠą╗ąŠą▓ą║ąĄ VisualDSP 5.0\Blackfin\include\defBF532.h. ą¤čĆąĖą╝ąĄčĆ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ:

*pSIC_IAR1 |= PX_IVG(11, 8);// ąŻčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ #11 (SPORT1 RX) ąĮą░ IVG8

[ąĀąĄą│ąĖčüčéčĆčŗ Core Event Controller (CEC)]

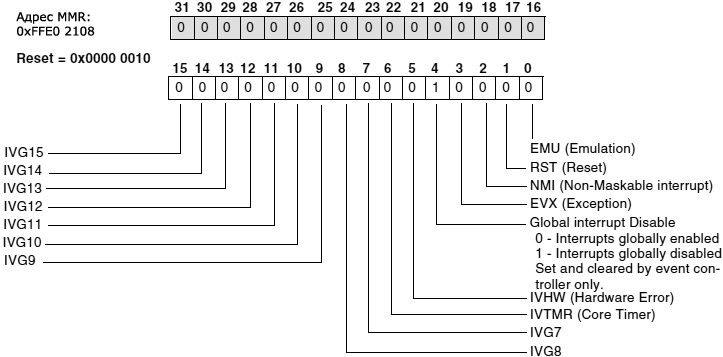

ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ čüąŠą▒čŗčéąĖą╣ ąĖčüą┐ąŠą╗čīąĘčāąĄčé 3 čĆąĄą│ąĖčüčéčĆą░ MMR čÅą┤čĆą░ ą┤ą╗čÅ ą║ąŠąŠčĆą┤ąĖąĮąĖčĆąŠą▓ą░ąĮąĖčÅ ąŠčéą╗ąŠąČąĄąĮąĮčŗčģ ąĘą░ą┐čĆąŠčüąŠą▓ čüąŠą▒čŗčéąĖą╣ (ą┐ąŠą┤ą┤ąĄčƹȹ║ą░ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą▓ ąĖ ą▓ą╗ąŠąČąĄąĮąĮąŠčüčéąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣). ąÆ ą║ą░ąČą┤ąŠą╝ ąĖąĘ čŹčéąĖčģ MMR ą╝ą╗ą░ą┤čłąĖąĄ 16 ą▒ąĖčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčé 16 čāčĆąŠą▓ąĮčÅą╝ čüąŠą▒čŗčéąĖą╣ (čé. ąĄ. ą┐čĆąĖąŠčĆąĖč鹥čéą░ą╝). ąØą░ą┐čĆąĖą╝ąĄčĆ, ą▒ąĖčé 0 čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé čüą░ą╝ąŠą╝čā ą┐čĆąĖąŠčĆąĖč鹥čéąĮąŠą╝čā čāčĆąŠą▓ąĮčÄ čüąŠą▒čŗčéąĖą╣, čĆąĄąČąĖą╝čā 菹╝čāą╗čÅčåąĖąĖ (Emulator mode). ąÆąŠčé čŹčéąĖ čĆąĄą│ąĖčüčéčĆčŗ:

ŌĆó IMASK - interrupt mask, ą╝ą░čüą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

ŌĆó ILAT - interrupt latch, ąĘą░čģą▓ą░čé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

ŌĆó IPEND - interrupts pending, ąŠčéą╗ąŠąČąĄąĮąĮčŗąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

ąÜ čŹčéąĖą╝ 3 čĆąĄą│ąĖčüčéčĆą░ą╝ ą╝ąŠąČąĮąŠ ą┐ąŠą╗čāčćąĖčéčī ą┤ąŠčüčéčāą┐ č鹊ą╗čīą║ąŠ ą▓ čĆąĄąČąĖą╝ąĄ čüčāą┐ąĄčĆą▓ąĖąĘąŠčĆą░ (Supervisor mode).

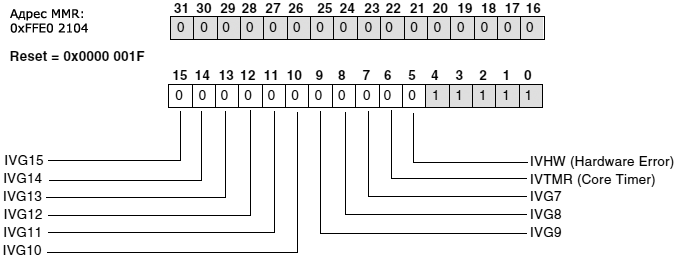

ąĀąĄą│ąĖčüčéčĆ ą╝ą░čüą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ čÅą┤čĆą░ (Core Interrupt Mask register, IMASK, ąĮąĄ ą┐čāčéą░čéčī čü čĆąĄą│ąĖčüčéčĆą░ą╝ąĖ SIC_IMASKx) ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, ą║ą░ą║ąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ ą▒čĆą░čéčī čāčĆąŠą▓ąĮąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. ąĀąĄą│ąĖčüčéčĆ IMASK ą╝ąŠąČąĮąŠ čćąĖčéą░čéčī ąĖ ąĘą░ą┐ąĖčüčŗą▓ą░čéčī (ąĮąŠ č鹊ą╗čīą║ąŠ ą▓ čĆąĄąČąĖą╝ąĄ čüčāą┐ąĄčĆą▓ąĖąĘąŠčĆą░). ąśą╝ąĄčÄčé ąĘąĮą░č湥ąĮąĖčÅ ą▒ąĖčéčŗ [15:5]; ąŠčüčéą░ą╗čīąĮčŗąĄ ą▒ąĖčéčŗ [4:0] ąČąĄčüčéą║ąŠ ąĘą░ą║ąŠą┤ąĖčĆąŠą▓ą░ąĮčŗ ą▓ 1, ąĖ čüąŠą▒čŗčéąĖčÅ ąŠčé čŹčéąĖčģ čāčĆąŠą▓ąĮąĄą╣ ą▓čüąĄą│ą┤ą░ čĆą░ąĘčĆąĄčłąĄąĮčŗ. ąĢčüą╗ąĖ IMASK[N] == 1 ąĖ ILAT[N] == 1, č鹊 ą▒čāą┤ąĄčé ą▓ąĘčÅč鹊 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ N, ąĄčüą╗ąĖ ą┐ąŠą║ą░ ąĮąĄ ą▒čŗą╗ąŠ čĆą░čüą┐ąŠąĘąĮą░ąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čü ą▒ąŠą╗ąĄąĄ ą▓čŗčüąŠą║ąĖą╝ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝. ąĢčüą╗ąĖ IMASK[N] == 0 ąĖ ILAT[N] čüčéą░ą╗ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄą╝ N, č鹊 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĮąĄ ą▒čāą┤ąĄčé ą▓ąĘčÅč鹊, ąĖ ILAT[N] ąŠčüčéą░ąĮąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╝.

ąĀąĖčü. 4-5. Core Interrupt Mask Register.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą┤ą╗čÅ ą▓čüąĄčģ ą▒ąĖčé 0 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ (ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąŠ), 1 čĆą░ąĘčĆąĄčłąĄąĮąŠ. ą¤ąŠą╝ąĄč湥ąĮąĮčŗąĄ čüąĄčĆčŗą╝ čåą▓ąĄč鹊ą╝ ą▒ąĖčéčŗ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ.

ąÜą░ąČą┤čŗą╣ ą▒ąĖčé čĆąĄą│ąĖčüčéčĆą░ ąĘą░čģą▓ą░čéą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čÅą┤čĆą░ (Core Interrupt Latch register, ILAT) ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą▒čŗą╗ąŠ ąĘą░čģą▓ą░č湥ąĮąŠ, ąŠą┤ąĮą░ą║ąŠ ą┐ąŠą║ą░ ąĄčēąĄ ąĮąĄ ą┐čĆąĖąĮčÅč鹊 ą┐čĆąŠčåąĄčüčüąŠčĆąŠą╝ ą▓ ąŠą▒čĆą░ą▒ąŠčéą║čā (čüą╝. čĆąĖčü. 4-6). ąæąĖčé ą▒čāą┤ąĄčé čüą▒čĆąŠčłąĄąĮ ą┤ąŠ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą┐ąĄčĆą▓ąŠą╣ ąĖąĮčüčéčĆčāą║čåąĖąĖ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╝ ISR. ąÆ č鹊čćą║ąĄ, ą║ąŠą│ą┤ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐čĆąĖąĮčÅč鹊 ą┐čĆąŠčåąĄčüčüąŠčĆąŠą╝, ą▒ąĖčé ILAT[N] ą▒čāą┤ąĄčé ąŠčćąĖčēąĄąĮ, ąĖ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ą▒čāą┤ąĄčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé IPEND[N]. ąĀąĄą│ąĖčüčéčĆ ILAT ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮ ą▓ čĆąĄąČąĖą╝ąĄ čüčāą┐ąĄčĆą▓ąĖąĘąŠčĆą░. ąŚą░ą┐ąĖčüčī ą▓ ILAT ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ąŠčćąĖčüčéą║ąĖ ą▒ąĖčé (ą▓ čĆąĄąČąĖą╝ąĄ čüčāą┐ąĄčĆą▓ąĖąĘąŠčĆą░). ą¦č鹊ą▒čŗ ąŠčćąĖčüčéąĖčéčī ą▒ąĖčé N ą▓ ILAT, čüąĮą░čćą░ą╗ą░ čāą▒ąĄą┤ąĖč鹥čüčī, čćč鹊 IMASK[N] == 0, ąĖ ąĘą░č鹥ą╝ ąĘą░ą┐ąĖčłąĖč鹥 ILAT[N] = 1. ąŁč鹊 ąĘą░ą┐ąĖčüčī čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ č鹊ą│ą┤ą░, ą║ąŠą│ą┤ą░ ąĮčāąČąĮąŠ ąŠčćąĖčüčéąĖčéčī (ąŠčéą╝ąĄąĮąĖčéčī) ąĘą░čģą▓ą░č湥ąĮąĮčŗąĄ ąĘą░ą┐čĆąŠčüčŗ ąĮą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą▓ą╝ąĄčüč鹊 č鹊ą│ąŠ, čćč鹊ą▒čŗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą▒čŗą╗ąŠ ąŠą▒čĆą░ą▒ąŠčéą░ąĮąŠ.

ąśąĮčüčéčĆčāą║čåąĖčÅ RAISE ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ ą╗čÄą▒ąŠą│ąŠ ą▒ąĖčéą░ ąŠčé ILAT[15] ą┤ąŠ ILAT[5], ąĖ čéą░ą║ąČąĄ ą▒ąĖčéčŗ ILAT[2] ąĖą╗ąĖ ILAT[1].

ąóąŠą╗čīą║ąŠ ą░ą┐ą┐ą░čĆą░čéąĮčŗą╣ čüąĖą│ąĮą░ą╗ JTAG TRST ą╝ąŠąČąĄčé ąŠčćąĖčüčéąĖčéčī ILAT[0].

ąöą╗čÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣, ą║ąŠč鹊čĆčŗąĄ čāąČąĄ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░čÄčéčüčÅ, ą▒ąĖčé ILAT čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╣ ą│čĆčāą┐ą┐čŗ IVG ąĮąĄ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ, ąĄčüą╗ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ąĮąŠą▓ąŠ čüčĆą░ą▒ąŠčéą░ąĄčé ą▓ čüąĖčüč鹥ą╝ąĄ ąĮą░ čāčĆąŠą▓ąĮąĄ ąĖčüč鹊čćąĮąĖą║ą░. ą×ą┤ąĮą░ą║ąŠ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé ą▓ čĆąĄą│ąĖčüčéčĆąĄ SIC_ISR ąŠčüčéą░ąĮąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╝. ą¤ąŠčŹč鹊ą╝čā ą┤ą░ąČąĄ ąĄčüą╗ąĖ ą▒ąĖčé ILAT ą┤ą╗čÅ ąŠčéą┤ąĄą╗čīąĮąŠą│ąŠ IVG ąĮąĄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ą▓ čŹč鹊ą╝ ą┐čĆąŠčåąĄčüčüąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĮąĄ ą▒čāą┤čāčé ą┐ąŠč鹥čĆčÅąĮčŗ; ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ SIC ą┐ąŠą┤čéą▓ąĄčĆą┤ąĖą╗ ą▒čŗ čŹčéčā ąĖąĮč乊čĆą╝ą░čåąĖčÄ ą▓ąĮčāčéčĆąĄąĮąĮąĄ ą┤ą╗čÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ CEC.

ąĀąĖčü. 4-6. Core Interrupt Latch Register.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ ą┤ą╗čÅ ą▒ąĖčéą░ 0 ąĘą░ą▓ąĖčüąĖčé ąŠčé 菹╝čāą╗čÅč鹊čĆą░. ąöą╗čÅ ą▓čüąĄčģ ą▒ąĖčé 0 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĮąĄ ąĘą░čģą▓ą░č湥ąĮąŠ, 1 ąĘą░čģą▓ą░č湥ąĮąŠ. ą¤ąŠą╝ąĄč湥ąĮąĮčŗąĄ čüąĄčĆčŗą╝ čåą▓ąĄč鹊ą╝ ą▒ąĖčéčŗ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ.

ąĀąĄą│ąĖčüčéčĆ ąŠąČąĖą┤ą░čÄčēąĖčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ čÅą┤čĆą░ (Core Interrupt Pending register, IPEND) ąŠčéčüą╗ąĄąČąĖą▓ą░ąĄčé ą▓čüąĄ ą▓ą╗ąŠąČąĄąĮąĮčŗąĄ ą▓ ąĮą░čüč鹊čÅčēąĖą╣ ą╝ąŠą╝ąĄąĮčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (čüą╝. čĆąĖčü. 4-7). ąÜą░ąČą┤čŗą╣ ą▒ąĖčé ą▓ IPEND ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čüąĄą╣čćą░čü ą░ą║čéąĖą▓ąĮąŠ ąĖą╗ąĖ ą▓ą╗ąŠąČąĄąĮąŠ ąĮą░ ąĮąĄą║ąŠč鹊čĆąŠą╝ čāčĆąŠą▓ąĮąĄ. ąĀąĄą│ąĖčüčéčĆ IPEND ą╝ąŠąČąĮąŠ ą┐čĆąŠčćąĖčéą░čéčī ą▓ čĆąĄąČąĖą╝ąĄ čüčāą┐ąĄčĆą▓ąĖąĘąŠčĆą░, ąĮąŠ ąĮąĄą╗čīąĘčÅ ąĘą░ą┐ąĖčüą░čéčī. ąæąĖčé IPEND[4] ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ čüąŠą▒čŗčéąĖą╣ ą┤ą╗čÅ ą▓čĆąĄą╝ąĄąĮąĮąŠą│ąŠ ąĘą░ą┐čĆąĄčéą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ąĮą░ ą▓čģąŠą┤ąĄ ąĖ ą▓čŗčģąŠą┤ąĄ ISR.

ąÜąŠą│ą┤ą░ čüąŠą▒čŗčéąĖąĄ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčéčüčÅ, čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé ą▓ čĆąĄą│ąĖčüčéčĆąĄ IPEND. ąĪą░ą╝čŗą╣ ą╝ą╗ą░ą┤čłąĖą╣ ą▒ąĖčé ą▓ IPEND, ą║ąŠč鹊čĆčŗą╣ čüąĄą╣čćą░čü čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé č鹊 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ą║ąŠč鹊čĆąŠąĄ ą▓ ąĮą░čüč鹊čÅčēąĖą╣ ą╝ąŠą╝ąĄąĮčé ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčéčüčÅ. ąŁč鹊 ą▒čāą┤ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čü čüą░ą╝čŗą╝ ą▓čŗčüąŠą║ąĖą╝ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝ čüčĆąĄą┤ąĖ ą▓čüąĄčģ ą▓čŗą┐ąŠą╗ąĮčÅąĄą╝čŗčģ ą▓ ąĮą░čüč鹊čÅčēąĖą╣ ą╝ąŠą╝ąĄąĮčé, ąĖ ą▓čüąĄ ąŠčüčéą░ą╗čīąĮčŗąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ąĄčüą╗ąĖ ąŠąĮąĖ č鹊ąČąĄ ą░ą║čéąĖą▓ąĮčŗ, ą▓ ąĮą░čüč鹊čÅčēąĖą╣ ą╝ąŠą╝ąĄąĮčé ą▒čāą┤čāčé ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ (ą▓čŗč鹥čüąĮąĄąĮčŗ). ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą▓ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé ą▓čĆąĄą╝ąĄąĮąĖ IPEND čüąŠą┤ąĄčƹȹĖčé ą▓ čüąĄą▒ąĄ čüąŠčüč鹊čÅąĮąĖąĄ ą▓čüąĄčģ ą▓ą╗ąŠąČąĄąĮąĮčŗčģ ą┤čĆčāą│ ą▓ ą┤čĆčāą│ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣.

ąĀąĖčü. 4-7. Core Interrupt Pending Register.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą┤ą╗čÅ ą▓čüąĄčģ ą▒ąĖčé, ąĘą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ ą▒ąĖčéą░ 4, ą╗ąŠą│. 0 ąŠąĘąĮą░čćą░ąĄčé ąŠčéčüčāčéčüčéą▓ąĖąĄ ą┐ąŠčüčéą░ą▓ą╗ąĄąĮąĮąŠą│ąŠ ą▓ ąŠč湥čĆąĄą┤čī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, 1 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠčüčéą░ą▓ą╗ąĄąĮąŠ ą▓ ąŠč湥čĆąĄą┤čī ąĖą╗ąĖ ą░ą║čéąĖą▓ąĮąŠ (ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčéčüčÅ ISR).

[Event Vector Table]

ąóą░ą▒ą╗ąĖčåą░ ą▓ąĄą║č鹊čĆąŠą▓ čüąŠą▒čŗčéąĖą╣ (Event Vector Table, EVT) čŹč鹊 ą░ą┐ą┐ą░čĆą░čéąĮą░čÅ čéą░ą▒ą╗ąĖčåą░ ąĖąĘ 16 ąĘą░ą┐ąĖčüąĄą╣, ą║ą░ąČą┤ą░čÅ 32 ą▒ąĖčéą░ ą┤ą╗ąĖąĮąŠą╣. ąÜą░ąČą┤ą░čÅ ąĘą░ą┐ąĖčüčī EVT čüąŠą┤ąĄčƹȹĖčé ą▓čģąŠą┤ ą▓ ą┐čĆąŠčåąĄą┤čāčĆčā ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą║ą░ąČą┤ąŠą│ąŠ ą▓ąŠąĘą╝ąŠąČąĮąŠą│ąŠ čüąŠą▒čŗčéąĖčÅ čÅą┤čĆą░. ąŚą░ą┐ąĖčüąĖ EVT ą┤ąŠčüčéčāą┐ąĮčŗ ą║ą░ą║ MMR, ąĖ ą║ą░ąČą┤ą░čÅ ąĘą░ą┐ąĖčüčī ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮą░ ą┐čĆąĖ čüą▒čĆąŠčüąĄ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╝ ą░ą┤čĆąĄčüąŠą╝ ą▓ąĄą║č鹊čĆą░ ą┤ą╗čÅ ISR. ąÜąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé čüąŠą▒čŗčéąĖąĄ, č鹊 ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą┐ąĄčĆąĄą┤ą░čćą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ (ą▓čŗąĘąŠą▓ąŠą╝ ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ) ą┐ąŠ ąĮą░čćą░ą╗čīąĮąŠą╝čā ą░ą┤čĆąĄčüčā, čüąŠčģčĆą░ąĮąĄąĮąĮąŠą╝čā ą▓ EVT ą┤ą╗čÅ čŹč鹊ą│ąŠ čüąŠą▒čŗčéąĖčÅ.

ąÉčĆčģąĖč鹥ą║čéčāčĆą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī čāąĮąĖą║ą░ą╗čīąĮčŗąĄ ą░ą┤čĆąĄčüą░ ą▓ ą║ą░ąČą┤čŗą╣ ąĖąĘ ą▓ąĄą║č鹊čĆąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ; čéą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ąĮąĄčé ąČąĄčüčéą║ąŠą╣ čäąĖą║čüą░čåąĖąĖ ą┐ąŠą╗ąŠąČąĄąĮąĖčÅ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ąŠą▓ ą▓ąĄą║č鹊čĆąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą▓ ą┐ą░ą╝čÅčéąĖ ąĮą░ ą▒ą░ąĘąĄ ą║ą░ą║ąŠą│ąŠ-č鹊 ą░ą┤čĆąĄčüą░. ąŁč鹊čé ą┐ąŠą┤čģąŠą┤ ą╝ąĖąĮąĖą╝ąĖąĘąĖčĆčāąĄčé ąĘą░ą┤ąĄčƹȹ║čā, ą┐ąŠč鹊ą╝čā čćč鹊 ąĮąĄ ąĮčāąČąĮą░ ą║ąŠą╝ą░ąĮą┤ą░ ą┤ą░ą╗čīąĮąĄą│ąŠ ą┐ąĄčĆąĄčģąŠą┤ą░ (long jump) ąĖąĘ čéą░ą▒ą╗ąĖčåčŗ ą▓ąĄą║č鹊čĆąŠą▓ ą▓ čĆąĄą░ą╗čīąĮčŗą╣ ą║ąŠą┤ ISR (čé. ąĄ. ą▓ EVT čāąČąĄ ą║ą░ą║ ą▒čŗ ąĘą░ą║čŹčłąĖčĆąŠą▓ą░ąĮčŗ).

ąÆ čéą░ą▒ą╗ąĖčåąĄ 4-8 ą┐ąĄčĆąĄčćąĖčüą╗ąĄąĮčŗ čüąŠą▒čŗčéąĖčÅ ą┐ąŠ ą┐čĆąĖąŠčĆąĖč鹥čéčā. ąÜą░ąČą┤ąŠąĄ čüąŠą▒čŗčéąĖąĄ ąĖą╝ąĄąĄčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé ą▓ čĆąĄą│ąĖčüčéčĆą░čģ čüąŠčüč鹊čÅąĮąĖčÅ ILAT, IMASK ąĖ IPEND.

ąóą░ą▒ą╗ąĖčåą░ 4-8. ąóą░ą▒ą╗ąĖčåą░ ą▓ąĄą║č鹊čĆąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (EVT) čÅą┤čĆą░.

| ąÆąĄą║č鹊čĆ EVT |

ąÜą╗ą░čüčü čüąŠą▒čŗčéąĖą╣ |

ąĀąĄą│ąĖčüčéčĆ ą▓ąĄą║č鹊čĆą░ |

ąÉą┤čĆąĄčü MMR |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ |

| EMU |

ąŁą╝čāą╗čÅčåąĖčÅ |

EVT0 |

0xFFE02000 |

ąĪą░ą╝čŗą╣ ą▓čŗčüąŠą║ąĖą╣ ą┐čĆąĖąŠčĆąĖč鹥čé. ąÉą┤čĆąĄčü ą▓ąĄą║č鹊čĆą░ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčéčüčÅ č湥čĆąĄąĘ ąĖąĮč鹥čĆč乥ą╣čü JTAG. |

| RST |

ąĪą▒čĆąŠčü |

EVT1 |

0xFFE02004 |

|

| NMI |

ąØąĄą╝ą░čüą║ąĖčĆčāąĄą╝ąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ |

EVT2 |

0xFFE02008 |

|

| EVX |

Exception |

EVT3 |

0xFFE0200C |

|

| ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

EVT4 |

0xFFE02010 |

ąĀąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąĮčŗą╣ ą▓ąĄą║č鹊čĆ |

| IVHW |

Hardware Error |

EVT5 |

0xFFE02014 |

|

| IVTMR |

ąóą░ą╣ą╝ąĄčĆ čÅą┤čĆą░ |

EVT6 |

0xFFE02018 |

|

| IVG7 |

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ 7 |

EVT7 |

0xFFE0201C |

ąĪąĖčüč鹥ą╝ąĮąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ |

| IVG8 |

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ 8 |

EVT8 |

0xFFE02020 |

ąĪąĖčüč鹥ą╝ąĮąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ |

| IVG9 |

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ 9 |

EVT9 |

0xFFE02024 |

ąĪąĖčüč鹥ą╝ąĮąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ |

| IVG10 |

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ 10 |

EVT10 |

0xFFE02028 |

ąĪąĖčüč鹥ą╝ąĮąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ |

| IVG11 |

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ 11 |

EVT11 |

0xFFE0202C |

ąĪąĖčüč鹥ą╝ąĮąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ |

| IVG12 |

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ 12 |

EVT12 |

0xFFE02030 |

ąĪąĖčüč鹥ą╝ąĮąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ |

| IVG13 |

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ 13 |

EVT13 |

0xFFE02034 |

ąĪąĖčüč鹥ą╝ąĮąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ |

| IVG14 |

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ 14 |

EVT14 |

0xFFE02038 |

ąĪąĖčüč鹥ą╝ąĮąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ |

| IVG15 |

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ 15 |

EVT15 |

0xFFE0203C |

ą¤čĆąŠą│čĆą░ą╝ą╝ąĮąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ |

ąĀąĄą│ąĖčüčéčĆ ą┐ąĄčĆąĄąĮą░ąĘąĮą░č湥ąĮąĖčÅ čéą░ą▒ą╗ąĖčåčŗ ą▓ąĄą║č鹊čĆąŠą▓ čüąŠą▒čŗčéąĖą╣ (event vector table override, EVT_OVERRIDE) ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ąĖčüč鹊čćąĮąĖą║ ą░ą┤čĆąĄčüąŠą▓ ą┤ą╗čÅ ą▓ąĄą║č鹊čĆąŠą▓ ą│čĆčāą┐ą┐ (ą▓čģąŠą┤ąŠą▓) ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ IVG7-IVG15. ąØą░ą┐čĆąĖą╝ąĄčĆ, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé ą▓ EVT_OVERRIDE, ą║ąŠč鹊čĆčŗą╣ čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé IVG7, č鹊 ą▓ąĄą║č鹊čĆą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ IVG7 ąĖą╝ąĄčÄčé č鹊čé ąČąĄ ą░ą┤čĆąĄčü, čćč鹊 ąĖ ą┐čĆąĖ čüą▒čĆąŠčüąĄ čÅą┤čĆą░ (ą░ą┤čĆąĄčü ą▓ ą╝ąĄčüč鹥 EVT7 ąĖą│ąĮąŠčĆąĖčĆčāąĄčéčüčÅ, ą║ąŠą│ą┤ą░ čŹč鹊 ą┐ąĄčĆąĄąĮą░ąĘąĮą░č湥ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ). ąŚą░ą┐ąĖčüčī EVT ą┤ą╗čÅ čüąŠą▒čŗčéąĖčÅ Reset (IVG1) čŹč鹊 ą░ą┤čĆąĄčü, čü ą║ąŠč鹊čĆąŠą│ąŠ čÅą┤čĆąĄ čüčéą░čĆčéčāąĄčé ą║ą░ą║ č鹊ą╗čīą║ąŠ čüą▒čĆąŠčü čüąĮąĖą╝ą░ąĄčéčüčÅ.

ąóą░ą▒ą╗ąĖčåą░ 4-9. ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ EVT_OVERRIDE.

| Ōä¢ ą▒ąĖčéą░ |

ąśą╝čÅ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| 15 |

IVG1 |

0: ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī EVT1 ą┤ą╗čÅ ą▓ąĄą║č鹊čĆą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ RAISE 1.

1: ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą░ą┤čĆąĄčü ą▓ąĄą║č鹊čĆą░ Reset ą┤ą╗čÅ ą▓ąĄą║č鹊čĆą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ RAISE 1 (ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ). |

| 14:8 |

- |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

| 7 |

IVG15 |

0: ąĮąĄčé ąĮąĖą║ą░ą║ąĖčģ ą┤ąĄą╣čüčéą▓ąĖą╣.

1: čĆą░ąĘčĆąĄčłąĖčéčī ą┐ąĄčĆąĄąĮą░ąĘąĮą░č湥ąĮąĖąĄ. |

| 6 |

IVG14 |

0: ąĮąĄčé ąĮąĖą║ą░ą║ąĖčģ ą┤ąĄą╣čüčéą▓ąĖą╣.

1: čĆą░ąĘčĆąĄčłąĖčéčī ą┐ąĄčĆąĄąĮą░ąĘąĮą░č湥ąĮąĖąĄ. |

| 5 |

IVG13 |

0: ąĮąĄčé ąĮąĖą║ą░ą║ąĖčģ ą┤ąĄą╣čüčéą▓ąĖą╣.

1: čĆą░ąĘčĆąĄčłąĖčéčī ą┐ąĄčĆąĄąĮą░ąĘąĮą░č湥ąĮąĖąĄ. |

| 4 |

IVG12 |

0: ąĮąĄčé ąĮąĖą║ą░ą║ąĖčģ ą┤ąĄą╣čüčéą▓ąĖą╣.

1: čĆą░ąĘčĆąĄčłąĖčéčī ą┐ąĄčĆąĄąĮą░ąĘąĮą░č湥ąĮąĖąĄ. |

| 3 |

IVG11 |

0: ąĮąĄčé ąĮąĖą║ą░ą║ąĖčģ ą┤ąĄą╣čüčéą▓ąĖą╣.

1: čĆą░ąĘčĆąĄčłąĖčéčī ą┐ąĄčĆąĄąĮą░ąĘąĮą░č湥ąĮąĖąĄ. |

| 2 |

IVG10 |

0: ąĮąĄčé ąĮąĖą║ą░ą║ąĖčģ ą┤ąĄą╣čüčéą▓ąĖą╣.

1: čĆą░ąĘčĆąĄčłąĖčéčī ą┐ąĄčĆąĄąĮą░ąĘąĮą░č湥ąĮąĖąĄ. |

| 1 |

IVG9 |

0: ąĮąĄčé ąĮąĖą║ą░ą║ąĖčģ ą┤ąĄą╣čüčéą▓ąĖą╣.

1: čĆą░ąĘčĆąĄčłąĖčéčī ą┐ąĄčĆąĄąĮą░ąĘąĮą░č湥ąĮąĖąĄ. |

| 0 |

IVG8 |

0: ąĮąĄčé ąĮąĖą║ą░ą║ąĖčģ ą┤ąĄą╣čüčéą▓ąĖą╣.

1: čĆą░ąĘčĆąĄčłąĖčéčī ą┐ąĄčĆąĄąĮą░ąĘąĮą░č湥ąĮąĖąĄ. |

[ąĀąĄą│ąĖčüčéčĆčŗ ąĖ ąĖąĮčüčéčĆčāą║čåąĖąĖ ą▓ąŠąĘą▓čĆą░čéą░]

ąśčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ ą┐ąĄčĆąĄąĮą░ąĘąĮą░č湥ąĮąĖčÅ EVT ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┤čĆčāą│ąĖą╝ čüąŠą▒čŗčéąĖčÅą╝ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą░ą┤čĆąĄčü ą▓ąĄą║č鹊čĆ čüą▒čĆąŠčüą░ Reset ą║ą░ą║ čüą▓ąŠą╣ čüąŠą▒čüčéą▓ąĄąĮąĮčŗą╣ ą░ą┤čĆąĄčü ą▓ąĄą║č鹊čĆą░, ą▓ą╝ąĄčüč鹊 čüą▓ąŠąĄą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĮąŠą│ąŠ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą░ą┤čĆąĄčüą░. ąŁč鹊čé ą┐ąŠą┤čģąŠą┤ čāčüčéčĆą░ąĮčÅąĄčé ą┐ąŠčéčĆąĄą▒ąĮąŠčüčéčī ą┤ą▓ąŠą╣ąĮąŠą╣ ą║ąŠčüą▓ąĄąĮąĮąŠą╣ ą░ą┤čĆąĄčüą░čåąĖąĖ, čćč鹊ą▒čŗ ą▓čŗą┐ąŠą╗ąĮąĖčéčī ą┐ąĄčĆąĄčģąŠą┤ ąĮą░ ą▓ąĮąĄčłąĮąĄ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮąĮčŗą╣ ą░ą┤čĆąĄčü ą┐čĆąĖ čüą▒čĆąŠčüąĄ.

ą¤čĆąĖą╝ąĄčĆąĮąŠ čéą░ą║, ą║ą░ą║ čĆąĄą│ąĖčüčéčĆ RETS čāą┐čĆą░ą▓ą╗čÅąĄčé ąĖąĮčüčéčĆčāą║čåąĖčÅą╝ąĖ ą▓čŗąĘąŠą▓ą░ CALL ąĖ ą▓ąŠąĘą▓čĆą░čéą░ RTS, čéą░ą║ ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĖ ąĖčüą║ą╗čÄč湥ąĮąĖčÅ ąĖčüą┐ąŠą╗čīąĘčāčÄčé ą░ą┐ą┐ą░čĆą░čéąĮčŗą╣ čüč鹥ą║ čĆąĄą│ąĖčüčéčĆąŠą▓ čü ąŠą┤ąĮąŠą╣ ąĘą░ą┐ąĖčüčīčÄ. ąĢčüą╗ąĖ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, čüąĄą║ą▓ąĄąĮčüąĄčĆ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ čüąŠčģčĆą░ąĮčÅąĄčé ą░ą┤čĆąĄčü ą▓ąŠąĘą▓čĆą░čéą░ ą▓ čĆąĄą│ąĖčüčéčĆ RETI ą┤ąŠ ą┐ąĄčĆąĄčüą║ąŠą║ą░ ąĮą░ ą▓ąĄą║č鹊čĆ čüąŠą▒čŗčéąĖčÅ. ąóąĖą┐ąĖčćąĮą░čÅ ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ISR ąĘą░ą▓ąĄčĆčłą░ąĄčéčüčÅ ąĖąĮčüčéčĆčāą║čåąĖąĄą╣ RTI, ą║ąŠč鹊čĆą░čÅ ą║ąŠą╝ą░ąĮą┤čāąĄčé čüąĄą║ą▓ąĄąĮčüąĄčĆčā ą┐ąĄčĆąĄąĘą░ą│čĆčāąĘąĖčéčī ąĘąĮą░č湥ąĮąĖąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čüč湥čéčćąĖą║ą░ (Program Counter, PC) ąĘąĮą░č湥ąĮąĖąĄą╝ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ RETI. ąĪą╗ąĄą┤čāčÄčēąĖą╣ ą┐čĆąĖą╝ąĄčĆ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą┐čĆąŠčüčéčāčÄ ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝čā ISR.

isr:

[--SP] = (R7:0, P5:0); /* ą┐čĆąŠč鹊ą╗ą║ąĮčāčéčī (push) ą▓ čüč鹥ą║ čĆąĄą│ąĖčüčéčĆčŗ čÅą┤čĆą░ */

[--SP] = ASTAT; /* ą┐čĆąŠč鹊ą╗ą║ąĮčāčéčī (push) ą▓ čüč鹥ą║ čüčéą░čéčāčü ą░čĆąĖčäą╝ąĄčéąĖą║ąĖ */

/* ąŚą┤ąĄčüčī ąĮčāąČąĮąŠ čĆą░ąĘą╝ąĄčüčéąĖčéčī ą║ąŠą┤ ą░ą╗ą│ąŠčĆąĖčéą╝ą░ ISR */

...

ASTAT = [SP++]; /* ą▓čŗą▒čĆą░čéčī (pop) ąĖąĘ čüč鹥ą║ą░ čüčéą░čéčāčü ą░čĆąĖčäą╝ąĄčéąĖą║ąĖ */

(R7:0, P5:0) = [SP++]; /* ą▓čŗą▒čĆą░čéčī (pop) ąĖąĘ čüč鹥ą║ą░ čĆąĄą│ąĖčüčéčĆčŗ čÅą┤čĆą░ */

RTI; /* ą▓ąŠąĘą▓čĆą░čé ąĖąĘ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ */

isr.end:

ąØąĄčé ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéąĖ ąĘą░ą▒ąŠčéąĖčéčīčüčÅ ąŠ čüąŠą┤ąĄčƹȹĖą╝ąŠą╝ čĆąĄą│ąĖčüčéčĆą░ RETI, ą║ąŠą│ą┤ą░ ąĘą░ą┐čĆąĄčēąĄąĮą░ ą▓ą╗ąŠąČąĄąĮąĮąŠčüčéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. ą×ą┤ąĮą░ą║ąŠ ąĄčüą╗ąĖ ą▓ą╗ąŠąČąĄąĮąĮąŠčüčéčī ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮą░, ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐čĆąĄčĆą▓ą░ąĮ (ą▓čŗč鹥čüąĮąĄąĮ) ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄą╝ čü ą▒ąŠą╗ąĄąĄ ą▓čŗčüąŠą║ąĖą╝ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝, č鹊 čĆąĄą│ąĖčüčéčĆ RETI ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čüąŠčģčĆą░ąĮąĄąĮ, čüą║ąŠčĆąĄąĄ ą▓čüąĄą│ąŠ ą▓ čüč鹥ą║ (čģąŠčéčÅ ąĮąĄ ąŠą▒čÅąĘą░č鹥ą╗čīąĮąŠ ąĖą╝ąĄąĮąĮąŠ ą▓ čüč鹥ą║, ą╝ąŠąČąĮąŠ ąĖ ą▓ ą┤čĆčāą│ąŠąĄ ą╝ąĄčüč鹊 ą┐ą░ą╝čÅčéąĖ).

ąźąĖčéčĆąŠčüčéčī ą▓ č鹊ą╝, čćč鹊 ą┤ąŠčüčéčāą┐ ą║ čĆąĄą│ąĖčüčéčĆčā RETI ąĖą╝ąĄąĄčé ąĮąĄčÅą▓ąĮčŗą╣ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗą╣ čŹčäč乥ą║čé - čćč鹥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ RETI čĆą░ąĘčĆąĄčłą░ąĄčé ą▓ą╗ąŠąČąĄąĮąĮąŠčüčéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. ąŚą░ą┐ąĖčüčī ą▓ RETI čüąĮąŠą▓ą░ ąĘą░ą┐čĆąĄčēą░ąĄčé ą▓ą╗ąŠąČąĄąĮąĮąŠčüčéčī. ąŁčéą░ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąŠą▒čĆą░ą▒ąŠčéčćąĖą║čā ISR čĆą░ąĘą▒ąĖčéčī čüą░ą╝ąŠą│ąŠ čüąĄą▒čÅ ąĮą░ ą┐čĆąĄčĆčŗą▓ą░ąĄą╝čŗąĄ ąĖ ąĮąĄ ą┐čĆąĄčĆčŗą▓ą░ąĄą╝čŗąĄ čüąĄą║čåąĖąĖ ą║ąŠą┤ą░. ąØą░ą┐čĆąĖą╝ąĄčĆ:

isr:

[--SP] = (R7:0, P5:0); /* ą┐čĆąŠč鹊ą╗ą║ąĮčāčéčī ą▓ čüč鹥ą║ čĆąĄą│ąĖčüčéčĆčŗ čÅą┤čĆą░ */

[--SP] = ASTAT; /* ą┐čĆąŠč鹊ą╗ą║ąĮčāčéčī ą▓ čüč鹥ą║ čüčéą░čéčāčü ą░čĆąĖčäą╝ąĄčéąĖą║ąĖ */

/* ąÆ čŹč鹊ą╝ ą╝ąĄčüč鹥 ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čĆą░ąĘą╝ąĄčēąĄąĮ ą║čĆąĖčéąĖč湥čüą║ąĖą╣, ą░č鹊ą╝ą░čĆąĮąŠ ą▓čŗą┐ąŠą╗ąĮčÅąĄą╝čŗą╣ ą║ąŠą┤: */

...

[--SP] = RETI; /* čĆą░ąĘčĆąĄčłąĖčéčī ą▓ą╗ąŠąČąĄąĮąĮąŠčüčéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ */

/* ąÆ čŹč鹊ą╝ ą╝ąĄčüč鹥 ąĮčāąČąĮąŠ čĆą░ąĘą╝ąĄčüčéąĖčéčī ąŠčüąĮąŠą▓ąĮąŠą╣ ą║ąŠą┤ ą░ą╗ą│ąŠčĆąĖčéą╝ą░ ISR,

ą║ąŠč鹊čĆčŗą╣ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąĄčĆą▓ą░ąĮ ą▒ąŠą╗ąĄąĄ ą┐čĆąĖąŠčĆąĖč鹥čéąĮčŗą╝ąĖ ISR: */

...

RETI = [SP++]; /* čüąĮąŠą▓ą░ ąĘą░ą┐čĆąĄčé ą▓ą╗ąŠąČąĄąĮąĮąŠčüčéąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ */

/* ąŚą┤ąĄčüčī ą╝ąŠąČąĮąŠ čĆą░ąĘą╝ąĄčüčéąĖčéčī ąĄčēąĄ ąŠą┤ąĮčā čüąĄą║čåąĖčÄ ą║čĆąĖčéąĖč湥čüą║ąŠą│ąŠ,

ą░č鹊ą╝ą░čĆąĮąŠ ą▓čŗą┐ąŠą╗ąĮčÅąĄą╝ąŠą│ąŠ ą║ąŠą┤ą░: */

ASTAT = [SP++]; /* ą▓čŗą▒čĆą░čéčī ąĖąĘ čüč鹥ą║ą░ čüčéą░čéčāčü ą░čĆąĖčäą╝ąĄčéąĖą║ąĖ */

(R7:0, P5:0) = [SP++]; /* ą▓čŗą▒čĆą░čéčī ąĖąĘ čüč鹥ą║ą░ čĆąĄą│ąĖčüčéčĆčŗ čÅą┤čĆą░ */

RTI; /* ą▓ąŠąĘą▓čĆą░čé ąĖąĘ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ */

isr.end:

ą¤ąŠąĮčÅčéąĖąĄ "ą░č鹊ą╝ą░čĆąĮąŠčüčéčī" ąŠąĘąĮą░čćą░ąĄčé "ąĮąĄą┤ąĄą╗ąĖą╝čŗą╣" - ą┐ąŠčłą╗ąŠ ąŠčé č鹊ą│ąŠ, čćč鹊 ą░č鹊ą╝čŗ ą║ą░ą║ ą▒čŗ ąĮąĄ ą┤ąĄą╗čÅčéčüčÅ (ą┐ąŠ ą║čĆą░ą╣ąĮąĄą╣ ą╝ąĄčĆąĄ čĆą░ąĘą┤ąĄą╗ąĖčéčī ąŠč湥ąĮčī čéčĆčāą┤ąĮąŠ). ąÆ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĖ ą╝ąĮąŠą│ąŠąĘą░ą┤ą░čćąĮčŗčģ čüąĖčüč鹥ą╝ (ąĖą╗ąĖ čüąĖčüč鹥ą╝ čü ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅą╝ąĖ, čćč鹊 ą▓ ą┤ą░ąĮąĮąŠą╝ ą║ąŠąĮč鹥ą║čüč鹥 ąŠą┤ąĮąŠ ąĖ č鹊 ąČąĄ) ąĄčüčéčī čéą░ą║ąŠąĄ ą┐ąŠąĮčÅčéąĖąĄ, ą║ą░ą║ ą░č鹊ą╝ą░čĆąĮą░čÅ ąŠą┐ąĄčĆą░čåąĖčÅ. ąŁč鹊 čéą░ą║ą░čÅ ąŠą┐ąĄčĆą░čåąĖčÅ ą▓ ą┐čĆąŠą│čĆą░ą╝ą╝ąĄ, ą║ąŠč鹊čĆą░čÅ, ą▒čāą┤čāčćąĖ ąĘą░ą┐čāčēąĄąĮąĮąŠą╣, ąĮąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąĄčĆą▓ą░ąĮą░ ąĮąĖą║ą░ą║ąĖą╝ ą┤čĆčāą│ąĖą╝ ą▓čŗą┐ąŠą╗ąĮčÅčÄčēąĖą╝čüčÅ ą║ąŠą┤ąŠą╝ (ąĮą░ą┐čĆąĖą╝ąĄčĆ, ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ąŠą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ), ą┤ą░ąČąĄ ąĮą░ ąĮąĄą║ąŠč鹊čĆąŠąĄ ą▓čĆąĄą╝čÅ.

ąóą░ą║ąČąĄ ąĄčüčéčī čéą░ą║ąŠąĄ ą┐ąŠąĮčÅčéąĖąĄ, ą║ą░ą║ ą░č鹊ą╝ą░čĆąĮčŗą╣ ą┤ąŠčüčéčāą┐ ą║ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą╣. ąØą░ą┐čĆąĖą╝ąĄčĆ, ąŠą▒čŗčćąĮąŠ 32-čĆą░ąĘčĆčÅą┤ąĮą░čÅ ą┐čĆąŠčåąĄčüčüąŠčĆąĮą░čÅ čüąĖčüč鹥ą╝ą░ ąĮąĄ ą╝ąŠąČąĄčé ą▒ąĄąĘ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖčÅ ą░č鹊ą╝ą░čĆąĮąŠčüčéąĖ ą┤ąŠčüčéčāą┐ą░ ą║ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą╣ čĆą░ąĘą╝ąĄčĆąŠą╝ ą▒ąŠą╗čīčłąĄ 32 ą▒ąĖčéą░ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī čāčüą┐ąĄčłąĮąŠąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĄ ąŠą┐ąĄčĆą░čåąĖąĖ. ąÜ ą┐čĆąĖą╝ąĄčĆčā, ąĮčāąČąĮąŠ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆąŠą▓ą░čéčī 64 ą▒ąĖčéąĮąŠąĄ čćąĖčüą╗ąŠ ąĘą░ ąĮąĄčüą║ąŠą╗čīą║ąŠ ąŠčéą┤ąĄą╗čīąĮčŗčģ ąŠą┐ąĄčĆą░čåąĖą╣ (čüąĮą░čćą░ą╗ą░ čāą▓ąĄą╗ąĖčćąĖčéčī ąĮą░ 1 ą╝ą╗ą░ą┤čłčāčÄ ą┐ąŠą╗ąŠą▓ąĖąĮčā ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą╣, čāč湥čüčéčī ą┐ąĄčĆąĄąĮąŠčü, ąĖ ą┐čĆąĖ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéąĖ čāą▓ąĄą╗ąĖčćąĖčéčī ąĮą░ 1 ą▓č鹊čĆčāčÄ ą┐ąŠą╗ąŠą▓ąĖąĮčā ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą╣). ąĢčüą╗ąĖ ąĮąĄ ąŠą▒ąĄčüą┐ąĄčćąĖčéčī ą░č鹊ą╝ą░čĆąĮąŠčüčéčī čŹč鹊ą╣ ąŠą┐ąĄčĆą░čåąĖąĖ, č鹊 ą┐ąŠą┐čŗčéą║ą░ čćč鹥ąĮąĖčÅ čŹč鹊ą╣ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą╣ ąĖąĘ ą▒ąŠą╗ąĄąĄ ą┐čĆąĖąŠčĆąĖč鹥čéąĮąŠą│ąŠ ą┐ąŠč鹊ą║ą░ (ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ) ą╝ąŠąČąĄčé ą┤ą░čéčī ąĮąĄą▓ąĄčĆąĮčŗą╣ čĆąĄąĘčāą╗čīčéą░čé. ą×ą▒ąĄčüą┐ąĄč湥ąĮąĖąĄ ą░č鹊ą╝ą░čĆąĮąŠčüčéąĖ ąŠą┐ąĄčĆą░čåąĖąĖ ą┤ąŠčüčéčāą┐ą░ ą║ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą╣ čāčüčéčĆą░ąĮčÅąĄčé čŹčéčā ą┐čĆąŠą▒ą╗ąĄą╝čā.

ąöą╗čÅ ąĮąĄą║ąŠč鹊čĆčŗčģ ą┐ąĄčĆąĄą╝ąĄąĮąĮčŗčģ ąĮąĄ ąĮčāąČąĮąŠ ąŠą▒ąĄčüą┐ąĄčćąĖą▓ą░čéčī ą░č鹊ą╝ą░čĆąĮąŠčüčéčī ą┤ąŠčüčéčāą┐ą░ - čŹč鹊 č鹥 ą┐ąĄčĆąĄą╝ąĄąĮąĮčŗąĄ, ą┤ąŠčüčéčāą┐ ą║ ą║ąŠč鹊čĆčŗą╝ ą┐čĆąŠčåąĄčüčüąŠčĆ ą╝ąŠąČąĄčé ąŠčüčāčēąĄčüčéą▓ąĖčéčī ąĘą░ ąŠą┤ąĮčā ąĖąĮčüčéčĆčāą║čåąĖčÄ ą░čüčüąĄą╝ą▒ą╗ąĄčĆą░. ąØą░ą┐čĆąĖą╝ąĄčĆ, ąĖąĮą║čĆąĄą╝ąĄąĮčé ą▒ą░ą╣čéą░ ąĮą░ 8-ą▒ąĖčéąĮąŠą╝ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąĄ ąĖąĘąĮą░čćą░ą╗čīąĮąŠ ą░č鹊ą╝ą░čĆąĮą░čÅ ąŠą┐ąĄčĆą░čåąĖčÅ.

ąĢčüą╗ąĖ ąĮąĄ čéčĆąĄą▒čāąĄčéčüčÅ ąĖą╝ąĄčéčī ą▓ ISR ąĮąĄ ą┐čĆąĄčĆčŗą▓ą░ąĄą╝čŗą╣ ą║ąŠą┤, č鹊 čģąŠčĆąŠčłąĄą╣ ą┐čĆą░ą║čéąĖą║ąŠą╣ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą▒čāą┤ąĄčé čĆą░ąĘčĆąĄčłąĖčéčī ą▓ą╗ąŠąČąĄąĮąĮąŠčüčéčī ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ. ąŁč鹊 ą┐čĆąĄą┤ąŠčéą▓čĆą░čéąĖčé ąĮąĄąČąĄą╗ą░č鹥ą╗čīąĮčāčÄ ąĘą░ą┤ąĄčƹȹ║čā ą┤ą╗čÅ ąĘą░ą┐čāčüą║ą░ ą▓čŗčüąŠą║ąŠą┐čĆąĖąŠčĆąĖč鹥čéąĮčŗčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. ą¤čĆąĖą╝ąĄčĆ:

isr:

[--SP] = RETI; /* čĆą░ąĘčĆąĄčłąĖčéčī ą▓ą╗ąŠąČąĄąĮąĮąŠčüčéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ */

[--SP] = (R7:0, P5:0); /* ą▓ą┤ą▓ąĖąĮčāčéčī ą▓ čüč鹥ą║ (push) čĆąĄą│ąĖčüčéčĆčŗ čÅą┤čĆą░ */

[--SP] = ASTAT; /* ą▓ą┤ą▓ąĖąĮčāčéčī ą▓ čüč鹥ą║ (push) čäą╗ą░ą│ąĖ ą░čĆąĖčäą╝ąĄčéąĖč湥čüą║ąĖčģ ąŠą┐ąĄčĆą░čåąĖą╣ */

/* ąÆ čŹč鹊ą╝ ą╝ąĄčüč鹥 ąĮčāąČąĮąŠ čĆą░ąĘą╝ąĄčüčéąĖčéčī ą║ąŠą┤ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ: */

...

ASTAT = [SP++]; /* ą▓ąŠčüčüčéą░ąĮąŠą▓ąĖčéčī ąĖąĘ čüč鹥ą║ą░ (pop) čäą╗ą░ą│ąĖ ą░čĆąĖčäą╝ąĄčéąĖč湥čüą║ąĖčģ ąŠą┐ąĄčĆą░čåąĖą╣ */

(R7:0, P5:0) = [SP++]; /* ą▓ąŠčüčüčéą░ąĮąŠą▓ąĖčéčī ąĖąĘ čüč鹥ą║ą░ (pop) čĆąĄą│ąĖčüčéčĆčŗ čÅą┤čĆą░ */

RETI = [SP++]; /* ąĘą░ą┐čĆąĄčé ą▓ą╗ąŠąČąĄąĮąĮąŠčüčéąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ */

RTI; /* ą▓ąŠąĘą▓čĆą░čé ąĖąĘ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ */

isr.end:

ą¤ąŠą┤čĆąŠą▒ąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ č鹥čģąĮąĖą║ąĖ čüą╝. ą▓ čĆą░ąĘą┤ąĄą╗ąĄ "ąÆą╗ąŠąČąĄąĮąĮąŠčüčéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣". ąĪąŠą▒čŗčéąĖčÅ čŹą╝čāą╗čÅčåąĖąĖ, NMI ąĖ ąĖčüą║ą╗čÄč湥ąĮąĖčÅ ąĖčüą┐ąŠą╗čīąĘčāčÄčé č鹥čģąĮąĖą║čā ąĮą░ą┐ąŠą┤ąŠą▒ąĖąĄ "ąĮąŠčĆą╝ą░ą╗čīąĮčŗčģ" ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ (čé. ąĄ. ą▒ąĄąĘ ą▓ą╗ąŠąČąĄąĮąĮąŠčüčéąĖ). ą×ą┤ąĮą░ą║ąŠ ąŠąĮąĖ ąĖą╝ąĄčÄčé čüą▓ąŠą╣ čüąŠą▒čüčéą▓ąĄąĮąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ ą▓ąŠąĘą▓čĆą░čéą░ ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēčāčÄ ąĄą╝čā ąĖąĮčüčéčĆčāą║čåąĖčÄ ą▓ąŠąĘą▓čĆą░čéą░. ąóą░ą▒ą╗ąĖčåą░ 4-10 ą┤ą░ąĄčé ąŠą▒ąĘąŠčĆ čŹčéąĖčģ ąĖąĮčüčéčĆčāą║čåąĖą╣ ąĖ čĆąĄą│ąĖčüčéčĆąŠą▓.

ąóą░ą▒ą╗ąĖčåą░ 4-10. ąĀąĄą│ąĖčüčéčĆčŗ ąĖ ąĖąĮčüčéčĆčāą║čåąĖąĖ ą▓ąŠąĘą▓čĆą░čéą░.

| ąśą╝čÅ |

ąÜą╗ą░čüčü čüąŠą▒čŗčéąĖą╣ |

ąĀąĄą│ąĖčüčéčĆ ą░ą┤čĆąĄčüą░

ą▓ąŠąĘą▓čĆą░čéą░ |

ąśąĮčüčéčĆčāą║čåąĖčÅ

ą▓ąŠąĘą▓čĆą░čéą░ |

| EMU |

ąŁą╝čāą╗čÅčåąĖčÅ |

RETE |

RTE |

| RST |

ąĪą▒čĆąŠčü |

RETI |

RTI |

| NMI |

ąØąĄą╝ą░čüą║ąĖčĆčāąĄą╝ąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ |

RETN |

RTN |

| EVX |

Exception |

RETX |

RTX |

| ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

- |

- |

| IVHW |

Hardware Error |

RETI |

RTI |

| IVTMR |

ąóą░ą╣ą╝ąĄčĆ čÅą┤čĆą░ |

| IVG7 |

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ 7 |

| IVG8 |

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ 8 |

| IVG9 |

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ 9 |

| IVG10 |

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ 10 |

| IVG11 |

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ 11 |

| IVG12 |

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ 12 |

| IVG13 |

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ 13 |

| IVG14 |

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ 14 |

| IVG15 |

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ 15 |

ąÆčŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ąĖąĮčüčéčĆčāą║čåąĖą╣ RTX, RTN ąĖą╗ąĖ RTE ą▓ čüąŠą▒čŗčéąĖąĖ čü ą╝ąĄąĮčīčłąĖą╝ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝. ąśąĮčüčéčĆčāą║čåąĖąĖ RTX, RTN ąĖ RTE čĆą░ąĘčĆą░ą▒ąŠčéą░ąĮčŗ ą┤ą╗čÅ ą▓ąŠąĘą▓čĆą░čéą░ ąĖąĘ ąĖčüą║ą╗čÄč湥ąĮąĖčÅ (eXception), NMI ąĖ čüąŠą▒čŗčéąĖčÅ čŹą╝čāą╗čÅčåąĖąĖ (Emulator) čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ. ąØąĄ ąĖčüą┐ąŠą╗čīąĘčāą╣č鹥 ąĖčģ ą┤ą╗čÅ ą▓ąŠąĘą▓čĆą░čéą░ ąĖąĘ čüąŠą▒čŗčéąĖčÅ čü ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝ ąĮąĖąČąĄ. ąöą╗čÅ ą▓ąŠąĘą▓čĆą░čéą░ ąĖąĘ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĖčüą┐ąŠą╗čīąĘčāą╣č鹥 ąĖąĮčüčéčĆčāą║čåąĖčÄ RTI. ą×čłąĖą▒ąŠčćąĮąŠąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ ąĖąĮčüčéčĆčāą║čåąĖą╣ ą▓ąŠąĘą▓čĆą░čéą░ ą╝ąŠąČąĄčé ą┐čĆąĖą▓ąĄčüčéąĖ ą║ ąĮąĄą┐čĆąĄą┤čüą║ą░ąĘčāąĄą╝čŗą╝ čĆąĄąĘčāą╗čīčéą░čéą░ą╝.

ąÆ čüą╗čāčćą░ąĄ RTX ą▒čāą┤ąĄčé ą░ą┐ą┐ą░čĆą░čéąĮąŠ ąŠčćąĖčēąĄąĮ ą▒ąĖčé IPEND[3]. ąÆ čüą╗čāčćą░ąĄ RTI ą▓ čĆąĄą│ąĖčüčéčĆąĄ IPEND ą▒čāą┤ąĄčé ą░ą┐ą┐ą░čĆą░čéąĮąŠ ąŠčćąĖčēąĄąĮ ąĄą┤ąĖąĮąĖčćąĮčŗą╣ ą▒ąĖčé, čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÄ čü čüą░ą╝čŗą╝ ą▓čŗčüąŠą║ąĖą╝ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝.

[Emulation Interrupt (ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠčéą╗ą░ą┤ą║ąĖ)]

ąĪąŠą▒čŗčéąĖąĄ 菹╝čāą╗čÅčåąĖąĖ ą┐ąĄčĆąĄą▓ąŠą┤ąĖčé ą┐čĆąŠčåąĄčüčüąŠčĆ ą▓ čĆąĄąČąĖą╝ 菹╝čāą╗čÅčåąĖąĖ (Emulation mode), ą│ą┤ąĄ ąĖąĮčüčéčĆčāą║čåąĖąĖ čćąĖčéą░čÄčéčüčÅ ąĖąĘ ąĖąĮč鹥čĆč乥ą╣čüą░ JTAG. ąŁč鹊 čüą░ą╝ąŠąĄ ą▓čŗčüąŠą║ąŠąĄ ą┐ąŠ ą┐čĆąĖąŠčĆąĖč鹥čéčā ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┤ą╗čÅ čÅą┤čĆą░. ąöąĄčéą░ą╗čīąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ ą┐čĆąŠčåąĄčüčüą░ 菹╝čāą╗čÅčåąĖąĖ čüą╝. ą▓ čĆą░ąĘą┤ąĄą╗ąĄ Blackfin Processor Debug čĆčāą║ąŠą▓ąŠą┤čüčéą▓ą░ ą┐ąŠ ą░ą┐ą┐ą░čĆą░čéčāčĆąĄ ąÆą░čłąĄą│ąŠ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ([3] ą┤ą╗čÅ BF538).

[Reset Interrupt (ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čüą▒čĆąŠčüą░)]

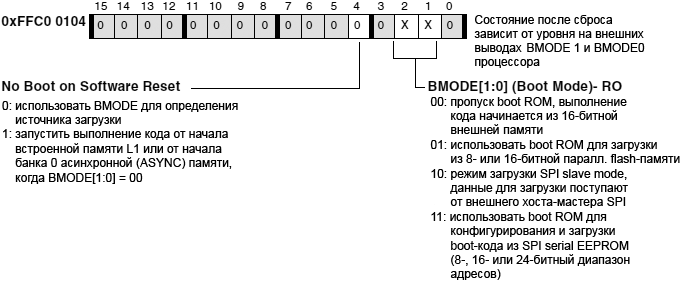

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čüą▒čĆąŠčüą░ (RST) ą╝ąŠąČąĄčé ą▒čŗčéčī ąĖąĮąĖčåąĖąĖčĆąŠą▓ą░ąĮąŠ č湥čĆąĄąĘ ą▓čŗą▓ąŠą┤ ~RESET ąĖą╗ąĖ ą┐čĆąĖ čüąŠą▒čŗčéąĖąĖ ąĖčüč鹥č湥ąĮąĖčÅ čéą░ą╣ą╝ą░čāčéą░ čüč鹊čĆąŠąČąĄą▓ąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░ (watchdog timer). ąŁč鹊 ą╝ąĄčüč鹊 ąŠčéą╗ąĖčćą░ąĄčéčüčÅ ąŠčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ č鹥ą╝, čćč鹊 ąĄą│ąŠ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ. ąŚą░ą┐ąĖčüčī ą┐ąŠ čŹč鹊ą╝čā ą░ą┤čĆąĄčüčā ą╝ąĄąĮčÅąĄčé čĆąĄą│ąĖčüčéčĆ, ąĮąŠ ąĮąĄ ą╝ąĄąĮčÅąĄčé ą▓ąĄą║č鹊čĆą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą┐čĆąĖ čüą▒čĆąŠčüąĄ. ą¤čĆąŠčåąĄčüčüąŠčĆ ą▓čüąĄą│ą┤ą░ ą┐čĆąĖ čüą▒čĆąŠčüąĄ ą┐ąĄčĆąĄčģąŠą┤ąĖčé ąĮą░ ą▓ąĄą║č鹊čĆ čüą▒čĆąŠčüą░.

ąĪąŠčüč鹊čÅąĮąĖąĄ čüą▒čĆąŠčüą░ (Reset state) ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆčāąĄčé ą╗ąŠą│ąĖą║čā ą┐čĆąŠčåąĄčüčüąŠčĆą░, ą┐ąĄčĆąĄą▓ąŠą┤čÅ ąĄčæ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ (ąĖčüčģąŠą┤ąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ). ąÆąŠ ą▓čĆąĄą╝čÅ Reset state ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ąĖ ąŠą┐ąĄčĆą░čåąĖąŠąĮąĮą░čÅ čüąĖčüč鹥ą╝ą░ ąĮąĄ ą▓čŗą┐ąŠą╗ąĮčÅčÄčéčüčÅ. ąóą░ą║čéčŗ ą▓ąŠ ą▓čĆąĄą╝čÅ Reset state ąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄčéčüčÅ.

ą¤čĆąŠčåąĄčüčüąŠčĆ ąŠčüčéą░ąĄčéčüčÅ ą▓ Reset state, ą┐ąŠą║ą░ ą▓ąĮąĄčłąĮčÅčÅ ą╗ąŠą│ąĖą║ą░ čāą┤ąĄčƹȹĖą▓ą░ąĄčé ą▓ ą░ą║čéąĖą▓ąĮąŠą╝ čāčĆąŠą▓ąĮąĄ ą▓ąĮąĄčłąĮąĖą╣ čüąĖą│ąĮą░ą╗ ~RESET. ąÜą░ą║ č鹊ą╗čīą║ąŠ čŹč鹊čé čüąĖą│ąĮą░ą╗ ą┐ąĄčĆąĄčüčéą░ąĮąĄčé ą▒čŗčéčī ą░ą║čéąĖą▓ąĮčŗą╝, ą┐čĆąŠčåąĄčüčüąŠčĆ ąĘą░ą▓ąĄčĆčłą░ąĄčé ą┐čĆąŠčåąĄą┤čāčĆčā čüą▒čĆąŠčüą░ ąĖ ą┐ąĄčĆąĄą║ą╗čÄčćą░ąĄčéčüčÅ ą▓ čĆąĄąČąĖą╝ čüčāą┐ąĄčĆą▓ąĖąĘąŠčĆą░ Supervisor, ą│ą┤ąĄ ą▓čŗą┐ąŠą╗ąĮčÅąĄčé ą║ąŠą┤ ą┐ąŠ ą▓ąĄą║č鹊čĆčā čüąŠą▒čŗčéąĖčÅ čüą▒čĆąŠčüą░.

ą¤čĆąŠą│čĆą░ą╝ą╝ą░ ą▓ čĆąĄąČąĖą╝ąĄ čüčāą┐ąĄčĆą▓ąĖąĘąŠčĆą░ (Supervisor mode) ąĖą╗ąĖ čĆąĄąČąĖą╝ąĄ 菹╝čāą╗čÅčåąĖąĖ (Emulation mode) ą╝ąŠąČąĄčé ą▓čŗąĘą▓ą░čéčī Reset state ą▒ąĄąĘ ą▓ąŠą▓ą╗ąĄč湥ąĮąĖčÅ ą▓ąĮąĄčłąĮąĄą│ąŠ čüąĖą│ąĮą░ą╗ą░ ~RESET. ąŁč鹊 ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą▓čŗą┤ą░č湥ą╣ Reset-ą▓ąĄčĆčüąĖąĖ ąĖąĮčüčéčĆčāą║čåąĖąĖ RAISE.

ą¤čĆąŠą│čĆą░ą╝ą╝čŗ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ą▓ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čīčüą║ąŠą╝ čĆąĄąČąĖą╝ąĄ (User mode) ąĮąĄ ą╝ąŠą│čāčé ą▓čŗąĘą▓ą░čéčī Reset state, ąĘą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ čüąĖčüč鹥ą╝ąĮąŠą│ąŠ ą▓čŗąĘąŠą▓ą░, ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮąĮąŠą│ąŠ čÅą┤čĆąŠą╝ ąŠą┐ąĄčĆą░čåąĖąŠąĮąĮąŠą╣ čüąĖčüč鹥ą╝čŗ. ąÆ čéą░ą▒ą╗ąĖčåąĄ 3-5 ą┐ąŠą║ą░ąĘą░ąĮąŠ čüąŠčüč鹊čÅąĮąĖąĄ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą┐čĆąĖ čüą▒čĆąŠčüąĄ.

ąóą░ą▒ą╗ąĖčåą░ 3-5. ąĪąŠčüč鹊čÅąĮąĖąĄ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą┐čĆąĖ čüą▒čĆąŠčüąĄ.

| ąŁą╗ąĄą╝ąĄąĮčé |

ą×ą┐ąĖčüą░ąĮąĖąĄ čüąŠčüč鹊čÅąĮąĖčÅ čüą▒čĆąŠčüą░ |

| ą»ą┤čĆąŠ |

| ąĀą░ą▒ąŠčćąĖą╣ čĆąĄąČąĖą╝ |

ąĀąĄąČąĖą╝ čüčāą┐ąĄčĆą▓ąĖąĘąŠčĆą░ ą▓ čüąŠą▒čŗčéąĖąĖ čüą▒čĆąŠčüą░, čéą░ą║čéčŗ ąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ. |

| ąĀąĄąČąĖą╝ ąŠą║čĆčāą│ą╗ąĄąĮąĖčÅ (Rounding Mode) |

ąØąĄčüą╝ąĄčēąĄąĮąĮąŠąĄ ąŠą║čĆčāą│ą╗ąĄąĮąĖąĄ (Unbiased rounding). |

| ąĪč湥čéčćąĖą║ąĖ čåąĖą║ą╗ą░ |

ąŚą░ą┐čĆąĄčēąĄąĮčŗ, ąŠą▒ąĮčāą╗ąĄąĮčŗ. |

| DAG-čĆąĄą│ąĖčüčéčĆčŗ (I, L, B, M) |

ąĪą╗čāčćą░ą╣ąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ (ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąŠčćąĖčēąĄąĮčŗ ą┐čĆąĖ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ). |

| ąĀąĄą│ąĖčüčéčĆčŗ ą┤ą░ąĮąĮčŗčģ ąĖ ą░ą┤čĆąĄčüą░ |

ąĪą╗čāčćą░ą╣ąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ (ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąŠčćąĖčēąĄąĮčŗ ą┐čĆąĖ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ). |

| IPEND, IMASK, ILAT |

ą×čćąĖčēąĄąĮčŗ, ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą│ą╗ąŠą▒ą░ą╗čīąĮąŠ ąĘą░ą┐čĆąĄčēąĄąĮčŗ ą▒ąĖč鹊ą╝ 4 čĆąĄą│ąĖčüčéčĆą░ IPEND. |

| ąæčāč乥čĆčŗ CPLB |

ąŚą░ą┐čĆąĄčēąĄąĮčŗ. |

| ą¤ą░ą╝čÅčéčī ąĖąĮčüčéčĆčāą║čåąĖą╣ L1 |

SRAM (ą║čŹčłąĖčĆąŠą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ). |

| ą¤ą░ą╝čÅčéčī ą┤ą░ąĮąĮčŗčģ L1 |

SRAM (ą║čŹčłąĖčĆąŠą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ). |

| ąæąĖčéčŗ ą┤ąŠčüč鹊ą▓ąĄčĆąĮąŠčüčéąĖ ą║čŹčłą░ |

ąØąĄ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčé ą┤ąĄą╣čüčéą▓ąĖč鹥ą╗čīąĮąŠčüčéąĖ. |

| ąĪąĖčüč鹥ą╝ą░ |

| ąĀąĄąČąĖą╝čŗ ąĘą░ą│čĆčāąĘą║ąĖ |

ą×ą┐čĆąĄą┤ąĄą╗čÅčÄčéčüčÅ ą╗ąŠą│. čāčĆąŠą▓ąĮčÅą╝ąĖ ą▓čŗą▓ąŠą┤ąŠą▓ BMODE ą▓ ą╝ąŠą╝ąĄąĮčé čüą▒čĆąŠčüą░. |

| ąóą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ MSEL |

ąöą╗čÅ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗčģ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ąĘąĮą░č湥ąĮąĖą╣ čüą╝. ąŠą┐ąĖčüą░ąĮąĖąĄ ą┐ąŠą╗čÅ MSEL čĆąĄą│ąĖčüčéčĆą░ PLL_CTL ą▓ ą░ą┐ą┐ą░čĆą░čéąĮąŠą╝ čĆčāą║ąŠą▓ąŠą┤čüčéą▓ąĄ ą┐ąŠ ą┐čĆąŠčåąĄčüčüąŠčĆčā ([3] ą┤ą╗čÅ BF538). |

| ąĀąĄąČąĖą╝ ą┐čĆąŠą┐čāčüą║ą░ PLL (PLL Bypass Mode) |

ąŚą░ą┐čĆąĄčēąĄąĮ. |

| VCO/Core Clock Ratio |

ąĪą╝. ąŠą┐ąĖčüą░ąĮąĖąĄ ą┐ąŠą╗čÅ CSEL čĆąĄą│ąĖčüčéčĆą░ PLL_DIV ą▓ ą░ą┐ą┐ą░čĆą░čéąĮąŠą╝ čĆčāą║ąŠą▓ąŠą┤čüčéą▓ąĄ ą┐ąŠ ąÆą░čłąĄą╝čā ą┐čĆąŠčåąĄčüčüąŠčĆčā ([3] ą┤ą╗čÅ BF538). |

| VCO/System Clock Ratio |

ąĪą╝. ąŠą┐ąĖčüą░ąĮąĖąĄ ą┐ąŠą╗čÅ SSEL čĆąĄą│ąĖčüčéčĆą░ PLL_DIV ą▓ ą░ą┐ą┐ą░čĆą░čéąĮąŠą╝ čĆčāą║ąŠą▓ąŠą┤čüčéą▓ąĄ ą┐ąŠ ąÆą░čłąĄą╝čā ą┐čĆąŠčåąĄčüčüąŠčĆčā ([3] ą┤ą╗čÅ BF538). |

| ąóą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ |

ąŚą░ą┐čĆąĄčēąĄąĮąŠ. |

[ąĪą▒čĆąŠčü čüąĖčüč鹥ą╝čŗ ąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ]

ąÆ čéą░ą▒ą╗ąĖčåąĄ 3-6 ąŠą┐ąĖčüą░ąĮčŗ 5 čéąĖą┐ąŠą▓ čüą▒čĆąŠčüą░. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ą▓čüąĄ čüą▒čĆąŠčüčŗ ąĘą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čüą▒čĆąŠčüą░ (System Software), čüą▒čĆą░čüčŗą▓ą░čÄčé čÅą┤čĆąŠ ą┐čĆąŠčåąĄčüčüąŠčĆą░.

ąóą░ą▒ą╗ąĖčåą░ 3-6. ąÆąĖą┤čŗ čüą▒čĆąŠčüą░.

| Reset |

ąśčüč鹊čćąĮąĖą║ |

ąĀąĄąĘčāą╗čīčéą░čé |

| Hardware Reset |

ą¤ąŠą┤ą░čćą░ čüąĖą│ąĮą░ą╗ą░ ąĮą░ ą▓čŗą▓ąŠą┤ ~RESET. |

ąĪą▒čĆą░čüčŗą▓ą░ąĄčé ą║ą░ą║ čÅą┤čĆąŠ, čéą░ą║ ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░, ą▓ą║ą╗čÄčćą░čÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą┤ąĖąĮą░ą╝ąĖč湥čüą║ąŠą│ąŠ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖąĄą╝ (Dynamic Power Management Controller, DPMC). ąóą░ą║ąČąĄ čüą▒čĆą░čüčŗą▓ą░ąĄčé ą▒ąĖčé No Boot ą▓ čĆąĄą│ąĖčüčéčĆąĄ SYSCR. |

| System Software Reset |

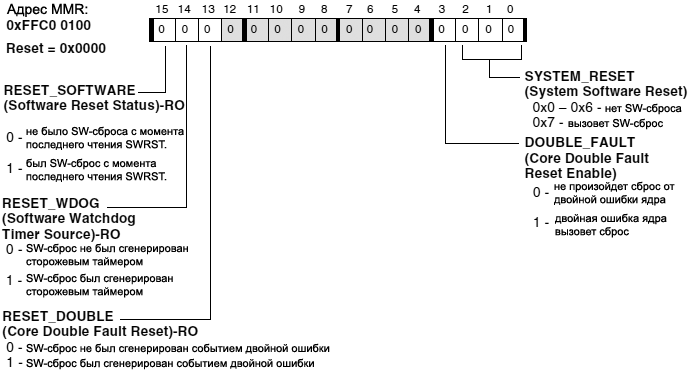

ąŚą░ą┐ąĖčüčī b#111 ą▓ ą▒ąĖčéčŗ [2:0] čüąĖčüč鹥ą╝ąĮąŠą│ąŠ MMR SWRST ą┐ąŠ ą░ą┤čĆąĄčüčā 0xFFC00100 ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą╝čā čüą▒čĆąŠčüčā čüąĖčüč鹥ą╝čŗ. |

ąĪą▒čĆą░čüčŗą▓ą░čÄčéčüčÅ č鹊ą╗čīą║ąŠ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░, ąĖčüą║ą╗čÄčćą░čÅ ą▒ą╗ąŠą║ąĖ RTC ąĖ DPMC. DPMC čüą▒čĆą░čüčŗą▓ą░ąĄčé č鹊ą╗čīą║ąŠ No Boot ą▓ ą▒ąĖč鹥 Software Reset čĆąĄą│ąĖčüčéčĆą░ SYSCR. ą»ą┤čĆąŠ ąĮąĄ čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ąĘą░ą│čĆčāąĘą║ąĖ ąĮąĄ ąĖąĮąĖčåąĖąĖčĆčāąĄčéčüčÅ. |

| Watchdog Timer Reset |

ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ čüč鹊čĆąŠąČąĄą▓ąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░ ą╝ąŠąČąĄčé ą▓čŗąĘą▓ą░čéčī čŹč鹊čé čéąĖą┐ čüą▒čĆąŠčüą░, ąĄčüą╗ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ąĮąĄ čāčüą┐ąĄą╗ą░ ą┐ąĄčĆąĄąĘą░ą│čĆčāąĘąĖčéčī čéą░ą╣ą╝ąĄčĆ (ąĮą░ą┐čĆąĖą╝ąĄčĆ ą┐ąŠą▓ąĖčüą╗ą░). |

ąĪą▒čĆą░čüčŗą▓ą░ąĄčé ą║ą░ą║ čÅą┤čĆąŠ, čéą░ą║ ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░, ąĘą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ ą▒ą╗ąŠą║ą░ RTC ąĖ ą▒ąŠą╗čīčłąĖąĮčüčéą▓ą░ čāąĘą╗ąŠą▓ DPMC (Watchdog Timer reset ąĮąĄ čĆą░ą▒ąŠčéą░ąĄčé, ąĄčüą╗ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ čüąĮą░). ąĀąĄą│ąĖčüčéčĆ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čüą▒čĆąŠčüą░ (Software Reset register, SWRST) ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮ, čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī, čćč鹊 ąĖčüč鹊čćąĮąĖą║ąŠą╝ čüą▒čĆąŠčüą░ ą▒čŗą╗ čüč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ. |

| Core Double-Fault Reset |

ąÜąŠą│ą┤ą░ čŹč鹊 čĆą░ąĘčĆąĄčłąĄąĮąŠ ą▒ąĖč鹊ą╝ DOUBLE_FAULT ą▓ čĆąĄą│ąĖčüčéčĆąĄ SWRST, čŹč鹊čé čüą▒čĆąŠčü ą▒čāą┤ąĄčé ą▓čŗąĘą▓ą░ąĮ ą▓čģąŠą┤ąŠą╝ čÅą┤čĆą░ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ą┤ą▓ąŠą╣ąĮąŠą╣ ąŠčłąĖą▒ą║ąĖ. |

ąĪą▒čĆą░čüčŗą▓ą░ąĄčé ą║ą░ą║ čÅą┤čĆąŠ, čéą░ą║ ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░, ąĖčüą║ą╗čÄčćą░čÅ ą▒ą╗ąŠą║ RTC ąĖ ą▒ąŠą╗čīčłąĖąĮčüčéą▓ąŠ čāąĘą╗ąŠą▓ DPMC. ąĀąĄą│ąĖčüčéčĆ SWRST ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮ, čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī, čćč鹊 ąĖčüč鹊čćąĮąĖą║ąŠą╝ čüą▒čĆąŠčüą░ ą▒čŗą╗ Core Double Fault. |

| Core-Only Software Reset |

ąŁč鹊čé čüą▒čĆąŠčü ą▓čŗąĘčŗą▓ą░ąĄčéčüčÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄą╝ ąĖąĮčüčéčĆčāą║čåąĖąĖ RAISE 1, ąĖą╗ąĖ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čüą▒čĆąŠčüą░ (Software Reset, SYSRST) ą▓ čĆąĄą│ąĖčüčéčĆąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąŠčéą╗ą░ą┤ą║ąŠą╣ (Debug Control register, DBGCTL) č湥čĆąĄąĘ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠąĄ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖąĄ ą┐ąŠą┤ą┤ąĄčƹȹ║ąĖ 菹╝čāą╗čÅč鹊čĆą░ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ ą┐ąŠčĆčéą░ JTAG. ąĀąĄą│ąĖčüčéčĆ DBGCTL ąĮąĄ ą▓ąĖą┤ąĄąĮ ąĮą░ ą║ą░čĆč鹥 ą┐ą░ą╝čÅčéąĖ ą┐čĆąŠčåąĄčüčüąŠčĆą░. |

ąĪą▒čĆą░čüčŗą▓ą░ąĄčé č鹊ą╗čīą║ąŠ čÅą┤čĆąŠ. ą¤ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ ąĮąĄ čĆą░čüą┐ąŠąĘąĮą░čÄčé čŹč鹊čé čüą▒čĆąŠčü. |

Hardware Reset (ą░ą┐ą┐ą░čĆą░čéąĮčŗą╣ čüą▒čĆąŠčü). ąĪą▒čĆąŠčü ą║čĆąĖčüčéą░ą╗ą╗ą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░ čÅą▓ą╗čÅąĄčéčüčÅ ą░čüąĖąĮčģčĆąŠąĮąĮčŗą╝ čüąŠą▒čŗčéąĖąĄą╝ čüą▒čĆąŠčüą░. ąöą╗čÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠą│ąŠ čüą▒čĆąŠčüą░ ą▓čģąŠą┤ąĮąŠą╣ ą▓čŗą▓ąŠą┤ ~RESET ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąĄčĆąĄą▓ąĄą┤ąĄąĮ ąĖąĘ ą░ą║čéąĖą▓ąĮąŠą│ąŠ čüąŠčüč鹊čÅąĮąĖčÅ (ą╗ąŠą│. 0) ą▓ ąĮąĄą░ą║čéąĖą▓ąĮąŠąĄ (ą╗ąŠą│. 1), ą┐ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. ą┤ą░čéą░čłąĖčé ąĮą░ ą┐čĆąŠčåąĄčüčüąŠčĆ.