|

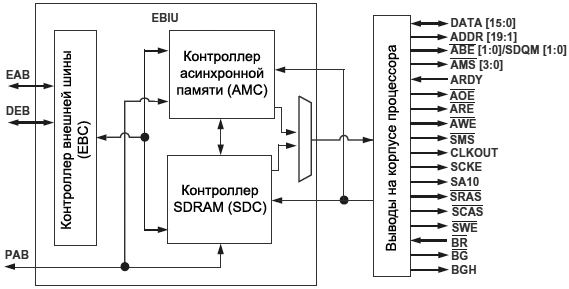

ąÆ čŹč鹊ą╣ čüčéą░čéčīąĄ ą┐čĆąĖą▓ąĄą┤ąĄąĮ ą┐ąĄčĆąĄą▓ąŠą┤ čĆą░ąĘą┤ąĄą╗ą░ "18. EXTERNAL BUS INTERFACE UNIT" ą┤ą░čéą░čłąĖčéą░ [1]. ą×ą┐ąĖčüą░ąĮ ą▒ą╗ąŠą║ ąĖąĮč鹥čĆč乥ą╣čüą░ čü ą▓ąĮąĄčłąĮąĄą╣ čłąĖąĮąŠą╣ (external bus interface unit, EBIU) ą┐čĆąŠčåąĄčüčüąŠčĆą░ ADSP-BF538. ąæą╗ąŠą║ EBIU ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą┐čĆąŠąĘčĆą░čćąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü ą┤ą╗čÅ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ą▓ąĮąĄčłąĮąĖčģ ą╝ąĖą║čĆąŠčüčģąĄą╝ ą┐ą░ą╝čÅčéąĖ. ąĪ ąĄą│ąŠ ą┐ąŠą╝ąŠčēčīčÄ ą┐čĆąŠčåąĄčüčüąŠčĆ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ą▓ąĮąĄčłąĮąĄąĄ čüąĖąĮčģčĆąŠąĮąĮąŠąĄ ą┤ąĖąĮą░ą╝ąĖč湥čüą║ąŠąĄ ą×ąŚąŻ (SDRAM), ąĖ čüąŠą▓ą╝ąĄčüčéąĖą╝ čüąŠ čüčéą░ąĮą┤ą░čĆčéą░ą╝ąĖ PC100 ąĖ PC133 SDRAM. EBIU čéą░ą║ąČąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ą░čüąĖąĮčģčĆąŠąĮąĮčŗąĄ ąĖąĮč鹥čĆč乥ą╣čüčŗ ą┤ą╗čÅ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ą┐ą░ą╝čÅčéąĖ SRAM, ROM, FIFO, FLASH, ąĖ čćąĖą┐ąŠą▓ ASIC/FPGA.

ąĪąĖčüč鹥ą╝ą░ EBIU ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčé ąĘą░ą┐čĆąŠčüčŗ ą║ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ čüąŠ čüč鹊čĆąŠąĮčŗ čÅą┤čĆą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ąĖą╗ąĖ ą║ą░ąĮą░ą╗ą░ DMA. ą¤čĆąĖąŠčĆąĖč鹥čé ąĘą░ą┐čĆąŠčüąŠą▓ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą▓ąĮąĄčłąĮąĄą╣ čłąĖąĮčŗ. ąÉą┤čĆąĄčü ąĘą░ą┐čĆąŠčüą░ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé, č湥ą╝ ą▒čāą┤ąĄčé ąŠą▒čĆą░ą▒ąŠčéą░ąĮ ąĘą░ą┐čĆąŠčü - ą╗ąĖą▒ąŠ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ EBIU SDRAM, ą╗ąĖą▒ąŠ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ EBIU.

EBIU čéą░ą║čéąĖčĆčāąĄčéčüčÅ ąŠčé čüąĖčüč鹥ą╝ąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ (SCLK). ąÆčüąĄ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ čüąĖąĮčģčĆąŠąĮąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗąĄ ą║ ą┐čĆąŠčåąĄčüčüąŠčĆčā, čĆą░ą▒ąŠčéą░čÄčé ąĮą░ čćą░čüč鹊č鹥 SCLK. ąĪąŠąŠčéąĮąŠčłąĄąĮąĖąĄ ą╝ąĄąČą┤čā čćą░čüč鹊č鹊ą╣ čÅą┤čĆą░ (CCLK) ąĖ čćą░čüč鹊č鹊ą╣ SCLK ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ č湥čĆąĄąĘ MMR-čĆąĄą│ąĖčüčéčĆ čüąĖčüč鹥ą╝čŗ čäą░ąĘąŠą▓ąŠą╣ ą░ą▓č鹊ą┐ąŠą┤čüčéčĆąŠą╣ą║ąĖ čćą░čüč鹊čéčŗ (phase-locked loop, PLL). ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ ą┐čĆąŠ čŹč鹊 čüą╝. čĆą░ąĘą┤ąĄą╗čŗ "Core Clock/System Clock Ratio Control" ą┤ą░čéą░čłąĖčéą░ [1] (ąĖą╗ąĖ "ąóą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ" ąĖ "ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čüąŠąŠčéąĮąŠčłąĄąĮąĖąĄą╝ čćą░čüč鹊čé CCLK/SCLK" [5]).

ąĀąĖčü. 18-1. ąÜą░čĆčéą░ čĆą░čüą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ ą░ą┤čĆąĄčüąĮąŠą│ąŠ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ą░ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ (External Memory Map).

ąÉą┤čĆąĄčüąĮąŠąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 18-1. ą×ą┤ąĮą░ ąŠą▒ą╗ą░čüčéčī ą┐ą░ą╝čÅčéąĖ ą▓čŗą┤ąĄą╗ąĄąĮą░ ą┤ą╗čÅ ą┐ąŠą┤ą┤ąĄčƹȹ║ąĖ SDRAM. ą¤ą░čĆą░ą╝ąĄčéčĆčŗ ąĖąĮč鹥čĆą▓ą░ą╗ąŠą▓ ą▓čĆąĄą╝ąĄąĮąĖ ąĖąĮč鹥čĆč乥ą╣čüą░ SDRAM ąĖ čĆą░ąĘą╝ąĄčĆ ąŠą▒ą╗ą░čüčéąĖ SDRAM ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāčÄčéčüčÅ. ąĀą░ąĘą╝ąĄčĆ ąŠą▒ą╗ą░čüčéąĖ ą┐ą░ą╝čÅčéąĖ SDRAM ą╝ąŠąČąĄčé ąĮą░čģąŠą┤ąĖčéčīčüčÅ ą▓ ą┐čĆąĄą┤ąĄą╗ą░čģ ąŠčé 16 ą┤ąŠ 512 ą╝ąĄą│ą░ą▒ą░ą╣čé.

ąÜą░ą║ ą┐ąŠą┤ą║ą╗čÄčćąĖčéčī ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ SDRAM, ą║ąŠč鹊čĆčŗąĄ ą╝ąĄąĮčīčłąĄ 16 ą╝ąĄą│ą░ą▒ą░ą╣čé ą┐ąŠ ąŠą▒čŖąĄą╝čā ą┐ą░ą╝čÅčéąĖ, čüą╝. čĆą░ąĘą┤ąĄą╗ "Using SDRAMs Smaller Than 16M Byte" ą┤ą░čéą░čłąĖčéą░ [1].

ąØą░čćą░ą╗čīąĮčŗą╣ ą░ą┤čĆąĄčü ąŠą▒ą╗ą░čüčéąĖ ą┐ą░ą╝čÅčéąĖ SDRAM 0x00000000. ą×ą▒ą╗ą░čüčéčī ąŠčé ą║ąŠąĮčåą░ ąŠą▒ą╗ą░čüčéąĖ ą┐ą░ą╝čÅčéąĖ SDRAM ą┤ąŠ ą░ą┤čĆąĄčüą░ 0x20000000 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮą░.

ąĪą╗ąĄą┤čāčÄčēąĖąĄ 4 ąŠą▒ą╗ą░čüčéąĖ ą┐ą░ą╝čÅčéąĖ ą▓čŗą┤ąĄą╗ąĄąĮčŗ ą┤ą╗čÅ ą┐ąŠą┤ą┤ąĄčƹȹ║ąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ. ąÜą░ąČą┤ą░čÅ ąŠą▒ą╗ą░čüčéčī ą░čüąĖąĮčģčĆąŠąĮąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮą░ ą┤ą╗čÅ ą┐ąŠą┤ą┤ąĄčƹȹ║ąĖ ąŠčéą╗ąĖčćą░čÄčēąĖčģčüčÅ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą┐ą░ą╝čÅčéąĖ. ąÜą░ąČą┤ą░čÅ ąŠą▒ą╗ą░čüčéčī ąĖą╝ąĄąĄčé čüą▓ąŠą╣ ąŠčéą┤ąĄą╗čīąĮčŗą╣ ą▓čŗčģąŠą┤ ą▓čŗą▒ąŠčĆą║ąĖ, čüąĖą│ąĮą░ą╗ ąĮą░ ą║ąŠč鹊čĆąŠą╝ ą│ąĄąĮąĄčĆąĖčĆčāąĄčé EBIU.

ąöą░ą╗ąĄąĄ ąĖą┤ąĄčé ąŠą▒ą╗ą░čüčéčī ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ. ą×ą▒čĆą░čēąĄąĮąĖčÅ ą║ čŹč鹊ą╣ ąŠą▒ą╗ą░čüčéąĖ ąĮąĄ ą▒čāą┤ąĄčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī čéčĆą░ąĮąĘą░ą║čåąĖąĖ ą┐ąŠ ą▓ąĮąĄčłąĮąĄą╣ čłąĖąĮąĄ. ąŚą░ą┐ąĖčüąĖ ą▓ čŹčéčā ąŠą▒ą╗ą░čüčéčī ąĮąĄ ą┤ą░ą┤čāčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░, ąĖ čćč鹥ąĮąĖčÅ ą▓ąĄčĆąĮčāčé ąĮąĄąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ. EBIU ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ąŠčłąĖą▒ą║čā ąŠą▒čĆą░čēąĄąĮąĖčÅ ą┐ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ čłąĖąĮąĄ, čćč鹊 ą▓čŗąĘąŠą▓ąĄčé ą│ąĄąĮąĄčĆą░čåąĖčÄ ą░ą┐ą┐ą░čĆą░čéąĮąŠą│ąŠ ąĖčüą║ą╗čÄč湥ąĮąĖčÅ (hardware exception) ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ čüąŠ čüč鹊čĆąŠąĮčŗ čÅą┤čĆą░ ąĖ ąŠą┐čåąĖąŠąĮą░ą╗čīąĮąŠ ą╝ąŠąČąĄčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠčé ą║ą░ąĮą░ą╗ą░ DMA.

ąØą░ čĆąĖčü. 18-2 ą┐ąŠą║ą░ąĘą░ąĮą░ ą║ąŠąĮčåąĄą┐čéčāą░ą╗čīąĮą░čÅ ą▒ą╗ąŠą║-ą┤ąĖą░ą│čĆą░ą╝ą╝ą░ EBIU ąĖ ąĄą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüąŠą▓. ąØą░ą┤č湥čĆą║ąĖą▓ą░ąĮąĖąĄ ąĮą░ą┤ ąĖą╝ąĄąĮąĄą╝ čüąĖą│ąĮą░ą╗ą░ ąĮą░ čĆąĖčüčāąĮą║ąĄ (ąĖą╗ąĖ ą┐čĆąĄčäąĖą║čü ~ ą▓ č鹥ą║čüč鹥) ąŠąĘąĮą░čćą░ąĄčé ą░ą║čéąĖą▓ąĮčŗą╣ ąĮąĖąĘą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī čŹč鹊ą│ąŠ čüąĖą│ąĮą░ą╗ą░.

ąĀąĖčü. 18-2. External Bus Interface Unit (EBIU).

ą¤ąŠčüą║ąŠą╗čīą║čā ą▓ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé ą▓čĆąĄą╝ąĄąĮąĖ ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠčüčāčēąĄčüčéą▓ą╗ąĄąĮąŠ ąŠą▒čĆą░čēąĄąĮąĖąĄ č鹊ą╗čīą║ąŠ ą║ ąŠą┤ąĮąŠą╝čā čāčüčéčĆąŠą╣čüčéą▓čā ą┐ą░ą╝čÅčéąĖ, č鹊 čüąĖą│ąĮą░ą╗čŗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ, ą░ą┤čĆąĄčüą░ ąĖ ą┤ą░ąĮąĮčŗčģ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ čéąĖą┐ą░ ą┐ą░ą╝čÅčéąĖ ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąĖčĆąŠą▓ą░ąĮčŗ ą┤čĆčāą│ čü ą┤čĆčāą│ąŠą╝ ąĮą░ ą▓čŗą▓ąŠą┤ą░čģ ą┐čĆąŠčåąĄčüčüąŠčĆą░. ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ (asynchronous memory controller, AMC) ąĖ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą┤ąĖąĮą░ą╝ąĖč湥čüą║ąŠą╣ čüąĖąĮčģčĆąŠąĮąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ (SDRAM controller, SDC) čŹčäč乥ą║čéąĖą▓ąĮąŠ čāą┐čĆą░ą▓ą╗čÅčÄčé ąŠą▒čēąĖą╝ąĖ ą▓čŗą▓ąŠą┤ą░ą╝ąĖ ą║ąŠčĆą┐čāčüą░ ą║čĆąĖčüčéą░ą╗ą╗ą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░.

[ąÆąĮčāčéčĆąĄąĮąĮąĖąĄ ąĖąĮč鹥čĆč乥ą╣čüčŗ ą┐ą░ą╝čÅčéąĖ]

EBIU čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮąŠąĄ ą║ ą┐čĆąŠčåąĄčüčüąŠčĆčā ą┐ąŠ čéčĆąĄą╝ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╝ čłąĖąĮą░ą╝:

ŌĆó External access bus (EAB). ąŁčéą░ čłąĖąĮą░ ąŠą▒čüą╗čāąČąĖą▓ą░ąĄčé ą▒ą╗ąŠą║ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ą░ą╝čÅčéčīčÄ čÅą┤čĆą░ ąŠčé ąĖą╝ąĄąĮąĖ ąĘą░ą┐čĆąŠčüąŠą▓ čÅą┤čĆą░ ą║ ą▓ąĮąĄčłąĮąĄą╣ čłąĖąĮąĄ.

ŌĆó DMA external bus (DEB). ąŁčéą░ čłąĖąĮą░ ąŠą▒čüą╗čāąČąĖą▓ą░ąĄčé ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ DMA ąŠčé ąĖą╝ąĄąĮąĖ ąĘą░ą┐čĆąŠčüąŠą▓ ą║ą░ąĮą░ą╗ą░ DMA ą║ ą▓ąĮąĄčłąĮąĄą╣ čłąĖąĮąĄ.

ŌĆó Peripheral access bus (PAB). ąŁčéą░ čłąĖąĮą░ ąŠą▒čüą╗čāąČąĖą▓ą░ąĄčé ąĘą░ą┐čĆąŠčüčŗ čÅą┤čĆą░ ą║ čüąĖčüč鹥ą╝ąĮčŗą╝ MMR.

ąŁčéąĖ čüąĖąĮčģčĆąŠąĮąĮčŗąĄ ąĖąĮč鹥čĆč乥ą╣čüčŗ, čéą░ą║čéąĖčĆčāąĄą╝čŗąĄ čü čćą░čüč鹊č鹊ą╣ SCLK, ą┤ąŠčüčéčāą┐ąĮčŗ ą║ą░ą║ čĆąĄą│ąĖčüčéčĆčŗ EBIU. EAB ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą┤ąŠčüčéčāą┐ ąĖ ą║ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą╣ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ, ąĖ ą║ čüąĖąĮčģčĆąŠąĮąĮąŠą╣ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ DRAM. ąÆąĮąĄčłąĮąĖą╣ ą┤ąŠčüčéčāą┐ čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ą╗ąĖą▒ąŠ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ (AMC), ą╗ąĖą▒ąŠ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ SDRAM (SDC), ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ ą░ą┤čĆąĄčüą░, ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ą▓čłąĄą│ąŠčüčÅ ą▓ ąĘą░ą┐čĆąŠčüąĄ ą║ EBIU. ą¤ąŠčüą║ąŠą╗čīą║čā AMC ąĖ SDC ąĖčüą┐ąŠą╗čīąĘčāčÄčé ąŠą┤ąĖąĮ ąĖ č鹊čé ąČąĄ ąĖąĮč鹥čĆč乥ą╣čü ą║ ą▓ąĮąĄčłąĮąĖą╝ ą▓čŗą▓ąŠą┤ą░ą╝ ą┐čĆąŠčåąĄčüčüąŠčĆą░, ą┤ąŠčüčéčāą┐ ą║ ą▓ąĮąĄčłąĮąĖą╝ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ą╝ ą┐ą░ą╝čÅčéąĖ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ, ąĖ ą┤ąŠą╗ąČąĄąĮ čāą┐čĆą░ą▓ą╗čÅčéčīčüčÅ ąĮą░ ą▒ą░ąĘąĄ ąĘą░ą┐čĆąŠčüąŠą▓ ąŠčé EAB.

ą©ąĖąĮą░ PAB ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ ą║ čĆąĄą│ąĖčüčéčĆą░ą╝ čüąŠčüč鹊čÅąĮąĖčÅ ąĖ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ EBIU, ą┐čĆąĖą▓čÅąĘą░ąĮąĮčŗą╝ ą║ čÅč湥ą╣ą║ą░ą╝ ą┐ą░ą╝čÅčéąĖ (MMR). PAB čĆą░ąĘą┤ąĄą╗čīąĮąŠ ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčéčüčÅ ą║ AMC ąĖ SDC, čéą░ą║ čćč鹊 ąĮąĄ ąĮčāąČąĄąĮ ą░čĆą▒ąĖčéčĆą░ąČ ą┤ą╗čÅ čĆą░čüą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ čåąĖą║ą╗ąŠą▓ ą┤ąŠčüčéčāą┐ą░ ąŠčé čłąĖąĮčŗ EAB.

ąøąŠą│ąĖą║ą░ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą▓ąĮąĄčłąĮąĄą╣ čłąĖąĮčŗ (external bus controller, EBC) ą┤ąŠą╗ąČąĮą░ ą▓čŗą┐ąŠą╗ąĮčÅčéčī ą░čĆą▒ąĖčéčĆą░ąČ ąĘą░ą┐čĆąŠčüąŠą▓ ą┤ąŠčüčéčāą┐ą░ ą║ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ, ą┐čĆąĖčģąŠą┤čÅčēąĖčģ ąŠčé čłąĖąĮ EAB ąĖ DEB. ąøąŠą│ąĖą║ą░ EBC ą┐ąĄčĆąĄąĮą░ą┐čĆą░ą▓ą╗čÅąĄčé ąĘą░ą┐čĆąŠčüčŗ čćč鹥ąĮąĖčÅ ąĖ ąĘą░ą┐ąĖčüąĖ ąĮą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą┐ą░ą╝čÅčéąĖ, ą▒ą░ąĘąĖčĆčāčÅčüčī ąĮą░ ą▓čŗą▒ąŠčĆąĄ čłąĖąĮčŗ. ąÆčŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą┤ąŠčüčéčāą┐ą░ ą┤ą╗čÅ AMC ąĖ SDC ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ č湥čĆąĄąĘ ąŠą▒čēąĖąĄ ą╗ąŠą│ąĖč湥čüą║ąĖąĄ čüčģąĄą╝čŗ ą▓ąĮąĄčłąĮąĖčģ ą▓čŗą▓ąŠą┤ąŠą▓. ąŁč鹊 čĆą░ą▒ąŠčéą░ąĄčé ą┐ąŠ ą┐čĆąĖąĮčåąĖą┐čā ą║ąŠąĮą▓ąĄą╣ąĄčĆą░, ą▓ č鹊ą╝ ą┐ąŠčĆčÅą┤ą║ąĄ, ą║ąŠč鹊čĆčŗą╣ ąĘą░ą┤ą░ąĄčé ą░čĆą▒ąĖčéčĆ EBC. ąÆ ą▒ąŠą╗čīčłąĖąĮčüčéą▓ąĄ čüą╗čāčćą░ąĄą▓ čéčĆą░ąĮąĘą░ą║čåąĖąĖ ąŠčé čÅą┤čĆą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ąĖą╝ąĄčÄčé ą┐čĆąĖąŠčĆąĖč鹥čé ą┐ąĄčĆąĄą┤ ą┤ąŠčüčéčāą┐ąŠą╝ ąŠčé DMA. ą×ą┤ąĮą░ą║ąŠ, ąĄčüą╗ąĖ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ DMA ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ą╗ čćčĆąĄąĘą╝ąĄčĆąĮąŠąĄ čĆąĄąĘąĄčĆą▓ąĮąŠąĄ ą║ąŠą┐ąĖčĆąŠą▓ą░ąĮąĖąĄ čéčĆą░ąĮąĘą░ą║čåąĖą╣, č鹊 ąŠąĮ ą╝ąŠąČąĄčé ąĘą░ą┐čĆąŠčüąĖčéčī ą▓čĆąĄą╝ąĄąĮąĮąŠąĄ ą┐ąŠą▓čŗčłąĄąĮąĖąĄ ą┐čĆąĖąŠčĆąĖč鹥čéą░ čüą▓ąŠąĖčģ ąĘą░ą┐čĆąŠčüąŠą▓ ą┐ąĄčĆąĄą┤ ąĘą░ą┐čĆąŠčüą░ą╝ąĖ čüąŠ čüč鹊čĆąŠąĮčŗ čÅą┤čĆą░.

[ąÆąĮąĄčłąĮąĖąĄ ąĖąĮč鹥čĆč乥ą╣čüčŗ ą┐ą░ą╝čÅčéąĖ]

ąÜą░ą║ čāąČąĄ čāą┐ąŠą╝ąĖąĮą░ą╗ąŠčüčī, ąĖ AMC, ąĖ SDC ąĖčüą┐ąŠą╗čīąĘčāčÄčé ąŠą┤ąĖąĮ ąĖ č鹊čé ąČąĄ ą▓ąĮąĄčłąĮąĖą╣ čäąĖąĘąĖč湥čüą║ąĖą╣ ąĖąĮč鹥čĆč乥ą╣čü ą▓čŗą▓ąŠą┤ąŠą▓ ą║čĆąĖčüčéą░ą╗ą╗ą░ ą┤ą╗čÅ čüąĖą│ąĮą░ą╗ąŠą▓ ą░ą┤čĆąĄčüą░ ąĖ ą┤ą░ąĮąĮčŗčģ, ąĖ ą┤ą░ąČąĄ ąŠą▒čēąĖąĄ ą▓čŗą▓ąŠą┤čŗ ą┤ą╗čÅ ąĮąĄą║ąŠč鹊čĆčŗčģ čüąĖą│ąĮą░ą╗ąŠą▓ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ. ąÆąŠčé ą▓čŗą▓ąŠą┤čŗ, ą║ąŠč鹊čĆčŗąĄ čÅą▓ą╗čÅčÄčéčüčÅ ąŠą▒čēąĖą╝ąĖ:

ŌĆó ADDR[19:1], čłąĖąĮą░ ą░ą┤čĆąĄčüą░

ŌĆó DATA[15:0], čłąĖąĮą░ ą┤ą░ąĮąĮčŗčģ

ŌĆó ABE[1:0]/SDQM[1:0], čüąĖą│ąĮą░ą╗čŗ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą▒ą░ą╣čéą░ AMC (AMC byte enable)/ą╝ą░čüą║ąĖ ą┤ą░ąĮąĮčŗčģ SDC (SDC data masks)

ŌĆó BR, BG, BGH, čüąĖą│ąĮą░ą╗čŗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┤ąŠčüčéčāą┐ą░ ą▓ąĮąĄčłąĮąĄą╣ čłąĖąĮčŗ

ąöčĆčāą│ąĖąĄ čüąĖą│ąĮą░ą╗čŗ ąĮąĄ ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąĖčĆčāčÄčéčüčÅ ą╝ąĄąČą┤čā ą┤ą▓čāą╝čÅ ą║ąŠąĮčéčĆąŠą╗ąĄčĆą░ą╝ąĖ. ąÆ čéą░ą▒ą╗ąĖčåą░čģ 18-1 ąĖ 18-2 ąŠą┐ąĖčüą░ąĮčŗ čüąĖą│ąĮą░ą╗čŗ, čüą▓čÅąĘą░ąĮąĮčŗąĄ čü ą║ą░ąČą┤čŗą╝ ąĖąĘ ąĖąĮč鹥čĆč乥ą╣čüąŠą▓. ąÆ čüč鹊ą╗ą▒čåąĄ ąóąĖą┐ ą▒čāą║ą▓ą░ą╝ąĖ ą┐ąŠą╝ąĄč湥ąĮ čéąĖą┐ čüąĖą│ąĮą░ą╗ą░: I ąŠąĘąĮą░čćą░ąĄčé ą▓čģąŠą┤, O ą▓čŗčģąŠą┤.

ąóą░ą▒ą╗ąĖčåą░ 18-1. ąĪąĖą│ąĮą░ą╗čŗ ąĖąĮč鹥čĆč乥ą╣čüą░ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ.

| ąĪąĖą│ąĮą░ą╗ |

ąóąĖą┐ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| DATA[15:0] |

I/O |

ąÆąĮąĄčłąĮčÅčÅ čłąĖąĮą░ ą┤ą░ąĮąĮčŗčģ. |

| ADDR[19:1] |

O |

ąÆąĮąĄčłąĮčÅčÅ čłąĖąĮą░ ą░ą┤čĆąĄčüą░. |

| ~AMS[3:0] |

O |

ąÆčŗą▒ąŠčĆą║ąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝ ą▒ą░ąĮą║ąŠą▓ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ. |

| ~AWE |

O |

ąĪąĖą│ąĮą░ą╗ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┤ą╗čÅ ąĘą░ą┐ąĖčüąĖ (write enable). |

| ~ARE |

O |

ąĪąĖą│ąĮą░ą╗ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ (read enable). |

| ~AOE |

O |

ąĪąĖą│ąĮą░ą╗ ą┤ą╗čÅ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą▓čŗčģąŠą┤ąĮčŗčģ ą▒čāč乥čĆąŠą▓ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ. ąÆ ą▒ąŠą╗čīčłąĖąĮčüčéą▓ąĄ čüą╗čāčćą░ąĄą▓ čüąĖą│ąĮą░ą╗ ~AOE ą┤ąŠą╗ąČąĄąĮ ą┐ąŠą┤ą║ą╗čÄčćą░čéčīčüčÅ ą║ ą▓čŗą▓ąŠą┤čā ą▓čŗą▒ąŠčĆą║ąĖ ~OE ą▓ąĮąĄčłąĮąĄą╣ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą┐ą░ą╝čÅčéąĖ, ą▓ą║ą╗čÄč湥ąĮąĮąŠą╣ ą▓ ą░ą┤čĆąĄčüąĮąŠąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ ą▓ąĮąĄčłąĮąĄą╣ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ(1). |

| ARDY |

I |

ą×čéą▓ąĄčé ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą┐ą░ą╝čÅčéąĖ, čüąŠąŠą▒čēą░čÄčēąĖą╣ ąŠ čüą▓ąŠąĄą╣ ą│ąŠč鹊ą▓ąĮąŠčüčéąĖ. ąÆąĮąĖą╝ą░ąĮąĖąĄ: čŹč鹊 čüąĖąĮčģčĆąŠąĮąĮčŗą╣ ą▓čģąŠą┤. |

| ~ABE[1:0]/SDQM[1:0] |

O |

ąĪąĖą│ąĮą░ą╗čŗ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą▒ą░ą╣čé. |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ 1: ąŠą▒čĆą░čéąĖč鹥čüčī ą║ ą┤ą░čéą░čłąĖčéčā ąĮą░ ą┐čĆąŠčåąĄčüčüąŠčĆčŗ ADSP-BF538/ADSP-BF538F [1] ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ą┐ąŠ ąĖąĮč鹥čĆą▓ą░ą╗ą░ą╝ ą▓čĆąĄą╝ąĄąĮąĖ ą╝ąĄąČą┤čā čüąĖą│ąĮą░ą╗ą░ą╝ąĖ ~AOE ąĖ ~ARE, čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī, ą║ą░ą║ąŠą╣ čüąĖą│ąĮą░ą╗ ąĖąĮč鹥čĆč乥ą╣čüą░ ąĮčāąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą▓ čüąĖčüč鹥ą╝ąĄ.

ąóą░ą▒ą╗ąĖčåą░ 18-2. ąĪąĖą│ąĮą░ą╗čŗ ąĖąĮč鹥čĆč乥ą╣čüą░ SDRAM.

| ąĪąĖą│ąĮą░ą╗ |

ąóąĖą┐ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| DATA[15:0] |

I/O |

ąÆąĮąĄčłąĮčÅčÅ čłąĖąĮą░ ą┤ą░ąĮąĮčŗčģ. |

| ADDR[19:18], ADDR[16:1] |

O |

ąÆąĮąĄčłąĮčÅčÅ čłąĖąĮą░ ą░ą┤čĆąĄčüą░. ą¤ąŠą┤ą║ą╗čÄčćą░ąĄčéčüčÅ ą║ ą▓čģąŠą┤ą░ą╝ ą░ą┤čĆąĄčüą░ ą╝ąĖą║čĆąŠčüčģąĄą╝ SDRAM. ąÆčŗčģąŠą┤čŗ ą┤ą╗čÅ ą░ą┤čĆąĄčüą░ ą▒ą░ąĮą║ą░ ADDR[19:18] ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮčŗ ą║ ą▓čŗą▓ąŠą┤ą░ą╝ BA[1:0] ą╝ąĖą║čĆąŠčüčģąĄą╝ SDRAM. |

| ~SRAS |

O |

ąĪčéčĆąŠą▒ čüčéčĆąŠą║, ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčéčüčÅ ą║ ą▓čŗą▓ąŠą┤čā ~RAS ą╝ąĖą║čĆąŠčüčģąĄą╝ SDRAM. |

| ~SCAS |

O |

ąĪčéčĆąŠą▒ čüč鹊ą╗ą▒čåąŠą▓, ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčéčüčÅ ą║ ą▓čŗą▓ąŠą┤čā ~CAS ą╝ąĖą║čĆąŠčüčģąĄą╝ SDRAM. |

| ~SWE |

O |

ąĪąĖą│ąĮą░ą╗ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ąĘą░ą┐ąĖčüąĖ, ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčéčüčÅ ą║ ą▓čŗą▓ąŠą┤čā ~WE ą╝ąĖą║čĆąŠčüčģąĄą╝ SDRAM. |

| ~ABE[1:0]/SDQM[1:0] |

O |

ąĪąĖą│ąĮą░ą╗čŗ ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ, ą┐ąŠą┤ą║ą╗čÄčćą░čÄčéčüčÅ ą║ ą▓čŗą▓ąŠą┤ą░ą╝ DQM ą╝ąĖą║čĆąŠčüčģąĄą╝ SDRAM. |

| ~SMS |

O |

ąĪąĖą│ąĮą░ą╗ ą▓čŗą▒ąŠčĆą║ąĖ ą┐ą░ą╝čÅčéąĖ ą┤ą╗čÅ ą▒ą░ąĮą║ą░ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ, čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ ą┐ąŠą┤ SDRAM. ą¤ąŠą┤ą║ą╗čÄčćą░ąĄčéčüčÅ ą║ ą▓čŗą▓ąŠą┤ą░ą╝ ą▓čŗą▒ąŠčĆą║ąĖ ~CS ą╝ąĖą║čĆąŠčüčģąĄą╝ SDRAM. |

| SA10 |

O |

ąÆčŗą▓ąŠą┤ A10 ą┤ą╗čÅ ą╝ąĖą║čĆąŠčüčģąĄą╝ SDRAM. ąśąĮč鹥čĆč乥ą╣čü SDRAM ąĖčüą┐ąŠą╗čīąĘčāąĄčé čŹč鹊čé ą▓čŗą▓ąŠą┤, čćč鹊ą▒čŗ ą╝ąŠąČąĮąŠ ą▒čŗą╗ąŠ ą▓čŗą┐ąŠą╗ąĮąĖčéčī ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ SDRAM, ą┐ąŠą║ą░ AMC ąĖčüą┐ąŠą╗čīąĘčāąĄčé čłąĖąĮčā. ą¤ąŠą┤ą║ą╗čÄčćą░ąĄčéčüčÅ ą║ ą▓čŗą▓ąŠą┤čā A[10] ą╝ąĖą║čĆąŠčüčģąĄą╝ SDRAM. |

| SCKE |

O |

ąÆčŗą▓ąŠą┤ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ čéą░ą║č鹊ą▓, ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčéčüčÅ ą║ ą▓čŗą▓ąŠą┤čā CKE ą╝ąĖą║čĆąŠčüčģąĄą╝ SDRAM. |

| CLKOUT |

O |

ąÆčŗčģąŠą┤ ą┤ą╗čÅ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ SDRAM. ą¤ąĄčĆąĄą║ą╗čÄčćą░ąĄčéčüčÅ čü čćą░čüč鹊č鹊ą╣ čüąĖčüč鹥ą╝ąĮąŠą╣ čłąĖąĮčŗ ą┐čĆąŠčåąĄčüčüąŠčĆą░ SCLK. ą¤ąŠą┤ą║ą╗čÄčćą░ąĄčéčüčÅ ą║ ą▓čŗą▓ąŠą┤čā CLK ą╝ąĖą║čĆąŠčüčģąĄą╝ SDRAM. |

[ą£ąŠą┤ąĄą╗čī ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ EBIU]

ąöą╗čÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ EBIU ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čüąĖčüč鹥ą╝ą░ čĆąĄą│ąĖčüčéčĆąŠą▓, ą┐čĆąĖą▓čÅąĘą░ąĮąĮčŗčģ ą║ ą░ą┤čĆąĄčüą░ą╝ ą┐ą░ą╝čÅčéąĖ (memory-mapped registers, MMR). ąŁč鹊 6 čĆąĄą│ąĖčüčéčĆąŠą▓ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĖ 1 čĆąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ EBIU:

ŌĆó Asynchronous memory global control register (EBIU_AMGCTL), ą│ą╗ąŠą▒ą░ą╗čīąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą╣ ą┐ą░ą╝čÅčéčīčÄ.

ŌĆó Asynchronous memory bank control 0 register (EBIU_AMBCTL0), čĆąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą▒ą░ąĮą║ąŠą╝ 0 ą░čüąĖąĮčģčĆąŠąĮąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ.

ŌĆó Asynchronous memory bank control 1 register (EBIU_AMBCTL1), čĆąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą▒ą░ąĮą║ąŠą╝ 1 ą░čüąĖąĮčģčĆąŠąĮąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ.

ŌĆó SDRAM memory global control register (EBIU_SDGCTL), ą│ą╗ąŠą▒ą░ą╗čīąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ą░ą╝čÅčéčīčÄ SDRAM.

ŌĆó SDRAM memory bank control register (EBIU_SDBCTL), čĆąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą▒ą░ąĮą║ą░ą╝ąĖ ą┐ą░ą╝čÅčéąĖ SDRAM.

ŌĆó SDRAM refresh rate control register (EBIU_SDRRC), čĆąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čüą║ąŠčĆąŠčüčéčīčÄ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ SDRAM.

ŌĆó SDRAM control status register (EBIU_SDSTAT), čĆąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ SDRAM.

ąÜą░ąČą┤čŗą╣ ąĖąĘ čŹčéąĖčģ čĆąĄą│ąĖčüčéčĆąŠą▓ ą▒čāą┤ąĄčé ą┐ąŠą┤čĆąŠą▒ąĮąŠ ąŠą┐ąĖčüą░ąĮ ą▓ čüąĄą║čåąĖčÅčģ, ą┐ąŠčüą▓čÅčēąĄąĮąĮčŗčģ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ą╝ AMC ąĖ SDC.

[ąöąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ąŠčłąĖą▒ąŠą║]

EBIU ąŠčéą▓ąĄčćą░ąĄčé ąĮą░ ą╗čÄą▒čāčÄ ąŠą┐ąĄčĆą░čåąĖčÄ čü čłąĖąĮąŠą╣ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ą░ą┤čĆąĄčüąŠą▓ 0x00000000 ŌĆō 0xEEFFFFFF, ą┤ą░ąČąĄ ąĄčüą╗ąĖ čŹčéą░ ąŠą┐ąĄčĆą░čåąĖčÅ ą┐ąŠ čłąĖąĮąĄ ą┐ąŠą┐ą░ą┤ą░ąĄčé ąĮą░ ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąĮčŗą╣ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčēąĄąĮąĮčŗą╣ ą░ą┤čĆąĄčü ą┐ą░ą╝čÅčéąĖ ąĖą╗ąĖ čäčāąĮą║čåąĖąĖ. EBIU ąŠčéą▓ąĄčćą░ąĄčé ą┐ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÄ ąŠą┐ąĄčĆą░čåąĖąĖ ąĮą░ čłąĖąĮąĄ, ą▓čŗčüčéą░ą▓ą╗čÅčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ąĮąŠą╝ąĄčĆ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ, ą║ą░ą║ čŹč鹊 ą▒čŗą╗ąŠ čāą║ą░ąĘą░ąĮąŠ ą╝ą░čüč鹥čĆąŠą╝ čłąĖąĮčŗ, ąĖ ą▓čŗčüčéą░ą▓ą╗čÅčÅ čüąĖą│ąĮą░ą╗čŗ ąŠčłąĖą▒ą║ąĖ čłąĖąĮčŗ ą┤ą╗čÅ čüą╗ąĄą┤čāčÄčēąĖčģ čüąŠą▒čŗčéąĖą╣ ąŠčłąĖą▒ą║ąĖ:

ŌĆó ąøčÄą▒ąŠą╣ ą┤ąŠčüčéčāą┐ ą║ ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąĮąŠą╣ ąŠą▒ą╗ą░čüčéąĖ ą┐ą░ą╝čÅčéąĖ, ąĮąĄ ąĮą░čģąŠą┤čÅčēąĄą╣čüčÅ ąĮą░ ą║čĆąĖčüčéą░ą╗ą╗ąĄ čćąĖą┐ą░.

ŌĆó ąøčÄą▒ąŠą╣ ą┤ąŠčüčéčāą┐ ą║ ąĘą░ą┐čĆąĄčēąĄąĮąĮąŠą╝čā ą▓ąĮąĄčłąĮąĄą╝čā ą▒ą░ąĮą║čā ą┐ą░ą╝čÅčéąĖ.

ŌĆó ąøčÄą▒ąŠą╣ ą┤ąŠčüčéčāą┐ ą║ ąŠčéčüčāčéčüčéą▓čāčÄčēąĄą╣ ąŠą▒ą╗ą░čüčéąĖ ą┐ą░ą╝čÅčéąĖ ą▒ą░ąĮą║ą░ SDRAM.

ąĢčüą╗ąĖ ąĘą░ą┐čĆąŠčü čÅą┤čĆą░ ą┐čĆąĖą▓ąĄą╗ ą║ ąŠčłąĖą▒ą║ąĄ ą┤ąŠčüčéčāą┐ą░ ą┐ąŠ čłąĖąĮąĄ, č鹊 ą│ąĄąĮąĄčĆąĖčĆčāąĄą╝čŗą╣ ąŠčéą▓ąĄčé ąŠčłąĖą▒ą║ąĖ ąŠčé EBIU ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ HWE čÅą┤čĆą░ (čŹč鹊 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąŠ). ąĢčüą╗ąĖ ąĘą░ą┐čĆąŠčü ą╝ą░čüč鹥čĆą░ DMA ą┐čĆąĖą▓ąĄą╗ ą║ ąŠčłąĖą▒ą║ąĄ ą┤ąŠčüčéčāą┐ą░ ą┐ąŠ čłąĖąĮąĄ, č鹊 ąŠčłąĖą▒ą║ą░ čłąĖąĮčŗ ąĘą░čģą▓ą░čéčŗą▓ą░ąĄčéčüčÅ ą▓ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąĄ ąĖ ąŠą┐čåąĖąŠąĮą░ą╗čīąĮąŠ ą╝ąŠąČąĄčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┤ą╗čÅ čÅą┤čĆą░.

[ąśąĮč鹥čĆč乥ą╣čü ą░čüąĖąĮčģčĆąŠąĮąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ (Asynchronous Memory Interface)]

ąśąĮč鹥čĆč乥ą╣čü ą░čüąĖąĮčģčĆąŠąĮąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐čĆąŠąĘčĆą░čćąĮąŠ ą┐ąŠą┤ą║ą╗čÄčćąĖčéčī ą║ ą┐čĆąŠčåąĄčüčüąŠčĆą░ čĆą░ąĘą╗ąĖčćąĮčŗąĄ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą┐ą░ą╝čÅčéąĖ ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░. ąŁč鹊 ą▓ą║ą╗čÄčćą░ąĄčé ą┐ą░ą╝čÅčéčī SRAM, ROM, EPROM, flash, ąĖ čćąĖą┐čŗ ą╗ąŠą│ąĖą║ąĖ FPGA/ASIC. ą¤ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ 4 ąŠą▒ą╗ą░čüčéąĖ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ. ąÜą░ąČą┤ą░čÅ ąĖąĘ ąĮąĖčģ ąĖą╝ąĄąĄčé ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮčŗą╣ čüąĖą│ąĮą░ą╗ ą▓čŗą▒ąŠčĆą║ąĖ ą┐ą░ą╝čÅčéąĖ, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▓ čéą░ą▒ą╗ąĖčåąĄ 18-3.

ąóą░ą▒ą╗ąĖčåą░ 18-3. ąöąĖą░ą┐ą░ąĘąŠąĮčŗ ą░ą┤čĆąĄčüąŠą▓ ą▒ą░ąĮą║ą░ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ.

| ąĪąĖą│ąĮą░ą╗ ą▓čŗą▒ąŠčĆą║ąĖ ą▒ą░ąĮą║ą░ |

ąØą░čćą░ą╗čīąĮčŗą╣ ą░ą┤čĆąĄčü |

ąÜąŠąĮąĄčćąĮčŗą╣ ą░ą┤čĆąĄčü |

| ~AMS[3] |

0x20300000 |

0x203FFFFF |

| ~AMS[2] |

0x20200000 |

0x202FFFFF |

| ~AMS[1] |

0x20100000 |

0x201FFFFF |

| ~AMS[0] |

0x20000000 |

0x200FFFFF |

ąöąĄą║ąŠą┤ąĖčĆąŠą▓ą░ąĮąĖąĄ ą░ą┤čĆąĄčüą░ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ. ąöąĖą░ą┐ą░ąĘąŠąĮ ą░ą┤čĆąĄčüą░, čüą▓čÅąĘą░ąĮąĮčŗą╣ čü ą║ą░ąČą┤čŗą╝ ą▒ą░ąĮą║ąŠą╝ ą┐ą░ą╝čÅčéąĖ čäąĖą║čüąĖčĆąŠą▓ą░ąĮ, ąĖ ąĖą╝ąĄąĄčé čĆą░ąĘą╝ąĄčĆ ą▓ 1 ą╝ąĄą│ą░ą▒ą░ą╣čé; ąŠą┤ąĮą░ą║ąŠ ąĮąĄ ąŠą▒čÅąĘą░č鹥ą╗čīąĮąŠ ą┤ąŠą╗ąČąĮčŗ ąĖą╝ąĄčéčīčüčÅ ą▓ ąĮą░ą╗ąĖčćąĖąĖ ą▓čüąĄ čĆą░ąĘčĆąĄčłąĄąĮąĮčŗąĄ ą▒ą░ąĮą║ąĖ ą┐ą░ą╝čÅčéąĖ. ąÆ ąŠčéą╗ąĖčćąĖąĄ ąŠčé ą┐ą░ą╝čÅčéąĖ SDRAM, ą║ąŠč鹊čĆą░čÅ ą╝ąŠąČąĄčé ąĮčāąČą┤ą░čéčīčüčÅ ą▓ ą┐ąŠą┤ą┤ąĄčƹȹ║ąĄ ąŠč湥ąĮčī ą▒ąŠą╗čīčłąĖčģ čüčéčĆčāą║čéčāčĆ, ą┐ąĄčĆąĄą║čĆčŗą▓ą░čÄčēąĖčģ ąĮąĄčüą║ąŠą╗čīą║ąŠ ą▒ą░ąĮą║ąŠą▓ ą┐ą░ą╝čÅčéąĖ, ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ą┐čĆąŠčüč鹊 ąŠą▒ąĄčüą┐ąĄčćąĖčéčī ąŠą│čĆą░ąĮąĖč湥ąĮąĖąĄ ą┤ą╗čÅ ą║ąŠą┤ą░ ąĖ čüčéčĆčāą║čéčāčĆ ą┤ą░ąĮąĮčŗčģ, čćč鹊ą▒čŗ ąŠąĮąĖ ąĮą░čģąŠą┤ąĖą╗ąĖčüčī ą▓ ą┐čĆąĄą┤ąĄą╗ą░čģ ąŠą┤ąĮąŠą│ąŠ ąĖąĘ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄą╝čŗčģ ą▒ą░ąĮą║ąŠą▓ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ (ąĖąĘ-ąĘą░ ą┐čĆąĖčĆąŠą┤čŗ čéąĖą┐ąŠą▓ ą║ąŠą┤ą░ ąĖą╗ąĖ ą┤ą░ąĮąĮčŗčģ, ą║ąŠč鹊čĆčŗąĄ čģčĆą░ąĮčÅčéčüčÅ ą▓ čŹč鹊ą╣ ą┐ą░ą╝čÅčéąĖ).

ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ąĮąĄ ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮąĮčŗąĄ ą▒ą░ąĮą║ąĖ ą┐ą░ą╝čÅčéąĖ, ąĖą╗ąĖ čćą░čüčéąĖčćąĮąŠ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĮčŗąĄ ą▒ą░ąĮą║ąĖ AMC ąĮąĄ ą┐čĆąĖą▓ąĄą┤čāčé ą║ ąŠčłąĖą▒ą║ąĄ čłąĖąĮčŗ, ąĖ ą▒čāą┤čāčé ąŠą▒čĆą░čēą░čéčīčüčÅ ą║ ą┤ąŠą┐čāčüčéąĖą╝čŗą╝ ą░ą┤čĆąĄčüą░ą╝ AMC.

ąĪąĖą│ąĮą░ą╗čŗ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ ą▒čŗą╗ąĖ ą┐ąĄčĆąĄčćąĖčüą╗ąĄąĮčŗ ą▓ čéą░ą▒ą╗ąĖčåąĄ 18-1. ąśąĮč鹥čĆą▓ą░ą╗čŗ ą▓čĆąĄą╝ąĄąĮąĖ ąĮą░ čŹčéąĖčģ ą▓čŗą▓ąŠą┤ą░čģ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāčÄčéčüčÅ, čćč鹊ą▒čŗ ą╝ąŠąČąĮąŠ ą▒čŗą╗ąŠ ą│ąĖą▒ą║ąŠ ąĮą░čüčéčĆą░ąĖą▓ą░čéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ą║ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ čü čĆą░ąĘąĮčŗą╝ąĖ čüą║ąŠčĆąŠčüčéčÅą╝ąĖ ą┤ąŠčüčéčāą┐ą░. ą¤čĆąĖą╝ąĄčĆčŗ ąĖąĮč鹥čĆč乥ą╣čüąŠą▓ čüą╝. ą▓ čĆą░ąĘą┤ąĄą╗ąĄ "21. System Design" ą┤ą░čéą░čłąĖčéą░ [1].

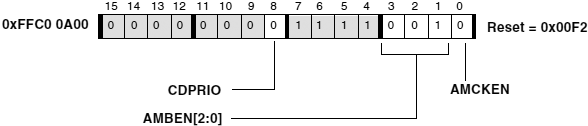

ąōą╗ąŠą▒ą░ą╗čīąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą╣ ą┐ą░ą╝čÅčéčīčÄ (asynchronous memory global control register, EBIU_AMGCTL), ą┐ąŠą║ą░ąĘą░ąĮąĮčŗą╣ ąĮą░ čĆąĖčü. 18-3, ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčé ąŠą▒čēąĖąĄ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░. ąĀąĄą│ąĖčüčéčĆ EBIU_AMGCTL čüąŠą┤ąĄčƹȹĖčé ą▒ąĖčéčŗ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą▒ą░ąĮą║ąŠą▓ ąĖ ą┤čĆčāą│čāčÄ ąĖąĮč乊čĆą╝ą░čåąĖčÄ. ąĀąĄą│ąĖčüčéčĆ EBIU_AMGCTL ąĮąĄ ą┤ąŠą╗ąČąĄąĮ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčīčüčÅ, ą║ąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ AMC. ąĀąĄą│ąĖčüčéčĆ EBIU_AMGCTL ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąŠčüą╗ąĄą┤ąĮąĖą╝ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄą╝čŗą╝ čāą┐čĆą░ą▓ą╗čÅčÄčēąĖą╝ čĆąĄą│ąĖčüčéčĆąŠą╝, ą║ąŠą│ą┤ą░ ą┐čĆąŠčåąĄčüčüąŠčĆ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ ą║ ą▓ąĮąĄčłąĮąĖą╝ ą░čüąĖąĮčģčĆąŠąĮąĮčŗą╝ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝.

ąöą╗čÅ č鹥čģ ą▓ąĮąĄčłąĮąĖčģ čāčüčéčĆąŠą╣čüčéą▓, ą┤ą╗čÅ ą║ąŠč鹊čĆčŗčģ ąĮčāąČąĄąĮ čéą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗, ą╝ąŠąČąĄčé ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮ ą▓čŗčģąŠą┤ CLKOUT, ąĄčüą╗ąĖ ą▓ čĆąĄą│ąĖčüčéčĆąĄ EBIU_AMGCTL čāčüčéą░ąĮąŠą▓ąĖčéčī ą▒ąĖčé AMCKEN. ąÆ čüąĖčüč鹥ą╝ą░čģ, ą║ąŠč鹊čĆčŗąĄ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčé CLKOUT, čāčüčéą░ąĮąŠą▓ąĖč鹥 ą▓ 0 ą▒ąĖčé AMCKEN.

ąĀąĖčü. 18-3. Asynchronous Memory Global Control Register (EBIU_AMGCTL).

CDPRIO. 0: čā čÅą┤čĆą░ ą┐čĆąĖąŠčĆąĖč鹥čé ą┐ąĄčĆąĄą┤ DMA ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ ą║ ą▓ąĮąĄčłąĮąĖą╝ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝, 1: ą┐čĆąĖąŠčĆąĖč鹥čé čā DMA ą┐ąĄčĆąĄą┤ čÅą┤čĆąŠą╝.

AMBEN[2:0]. ąæąĖčéčŗ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą░čüąĖąĮčģčĆąŠąĮąĮčŗčģ ą▒ą░ąĮą║ąŠą▓ ą┐ą░ą╝čÅčéąĖ:

000 - ą▓čüąĄ ą▒ą░ąĮą║ąĖ ąĘą░ą┐čĆąĄčēąĄąĮčŗ

001 - čĆą░ąĘčĆąĄčłąĄąĮ Bank0

010 - čĆą░ąĘčĆąĄčłąĄąĮčŗ Bank0 ąĖ Bank1

011 - čĆą░ąĘčĆąĄčłąĄąĮčŗ Bank0, Bank1 ąĖ Bank2

1xx - čĆą░ąĘčĆąĄčłąĄąĮčŗ ą▓čüąĄ ą▒ą░ąĮą║ąĖ (Bank0, Bank1, Bank2, Bank3)

AMCKEN. 0: ąĘą░ą┐čĆąĄčé ą▓čŗą┤ą░čćąĖ CLKOUT ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ ą║ čĆąĄą│ąĖąŠąĮą░ą╝ ą▓ąĮąĄčłąĮąĄą╣ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ, 1: čĆą░ąĘčĆąĄčłąĖčéčī ą▓čŗą┤ą░čćčā CLKOUT.

[ą×ąĮą╗ą░ą╣ąĮ-ą║ą░ą╗čīą║čāą╗čÅč鹊čĆ ą┤ą╗čÅ čĆąĄą│ąĖčüčéčĆą░ EBIU_AMGCTL]

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▓ ą┐ąŠą╗čÅ čĆąĄą│ąĖčüčéčĆą░ EBIU_AMGCTL ą┐čĆąŠčüčéą░ą▓ą╗ąĄąĮčŗ ąĘąĮą░č湥ąĮąĖčÅ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ, ą║ąŠč鹊čĆčŗąĄ ąŠąĮąĖ ą┐ąŠą╗čāčćą░čÄčé ą┐čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ (čüą▒čĆąŠčüąĄ ą┐čĆąŠčåąĄčüčüąŠčĆą░).

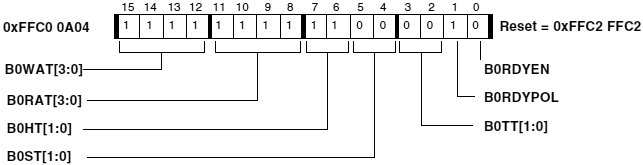

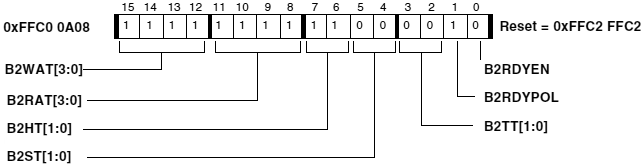

ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ EBIU ąĖą╝ąĄąĄčé 2 čĆąĄą│ąĖčüčéčĆą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą▒ą░ąĮą║ą░ą╝ąĖ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ (asynchronous memory bank control registers, EBIU_AMBCTL0 ąĖ EBIU_AMBCTL1, čüą╝. čĆąĖčü. 18-4 .. 18-7). ą×ąĮąĖ čüąŠą┤ąĄčƹȹ░čé ą▒ąĖčéčŗ čüč湥čéčćąĖą║ąŠą▓ ą┤ą╗čÅ ąĮą░čüčéčĆąŠą╣ą║ąĖ, čüčéčĆąŠą▒ąĖčĆąŠą▓ą░ąĮąĖčÅ, ą▓čĆąĄą╝ąĄąĮąĖ čāą┤ąĄčƹȹ░ąĮąĖčÅ, ą▒ąĖčéčŗ ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ čéąĖą┐ą░ ą┐ą░ą╝čÅčéąĖ ąĖ čĆą░ąĘą╝ąĄčĆą░, ąĖ ą▒ąĖčéčŗ ą┤ą╗čÅ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ARDY. ąŁčéąĖ čĆąĄą│ąĖčüčéčĆčŗ ąĮąĄ ą┤ąŠą╗ąČąĮčŗ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčīčüčÅ, ą║ąŠą│ą┤ą░ AMC ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ.

ą£ąŠą│čāčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮčŗ čüą╗ąĄą┤čāčÄčēąĖąĄ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ ą▓čĆąĄą╝ąĄąĮąĖ AMC:

ŌĆó Setup (ą▓čĆąĄą╝čÅ ąĮą░ čāčüčéą░ąĮąŠą▓ą║čā): ą▓čĆąĄą╝čÅ ą╝ąĄąČą┤čā ąĮą░čćą░ą╗ąŠą╝ čåąĖą║ą╗ą░ ą┐ą░ą╝čÅčéąĖ (~AMS[x]==0) ąĖ ą▓čŗčüčéą░ą▓ą╗ąĄąĮąĖąĄą╝ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ čćč鹥ąĮąĖčÅ (~ARE==0) ąĖą╗ąĖ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ąĘą░ą┐ąĖčüąĖ (~AWE==0).

ŌĆó Read access (ą┤ąŠčüčéčāą┐ ąĮą░ čćč鹥ąĮąĖąĄ): ą▓čĆąĄą╝čÅ ą╝ąĄąČą┤čā ą▓čŗčüčéą░ą▓ą╗ąĄąĮąĖąĄą╝ čĆą░ąĘčĆąĄčłąĄąĮąĖąĄą╝ čćč鹥ąĮąĖčÅ (~ARE==0) ąĖ čüąĮčÅčéąĖąĄą╝ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ čćč鹥ąĮąĖčÅ (~ARE==1).

ŌĆó Write access (ą┤ąŠčüčéčāą┐ ąĮą░ ąĘą░ą┐ąĖčüčī): ą▓čĆąĄą╝čÅ ą╝ąĄąČą┤čā ą▓čŗčüčéą░ą▓ą╗ąĄąĮąĖąĄą╝ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ąĘą░ą┐ąĖčüąĖ (~AWE==0) ąĖ čüąĮčÅčéąĖąĄą╝ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ąĘą░ą┐ąĖčüąĖ (~AWE==1).

ŌĆó Hold (čāą┤ąĄčƹȹ░ąĮąĖąĄ): ą▓čĆąĄą╝čÅ ą╝ąĄąČą┤čā čüąĮčÅčéąĖąĄą╝ čüąĖą│ąĮą░ą╗ą░ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ čćč鹥ąĮąĖčÅ (~ARE==1) ąĖą╗ąĖ čüąĖą│ąĮą░ą╗ą░ ąĘą░ą┐ąĖčüąĖ (~AWE==1) ąĖ ą║ąŠąĮčåąŠą╝ čåąĖą║ą╗ą░ ą┐ą░ą╝čÅčéąĖ (~AMS[x]==1).

ąÜą░ąČą┤čŗą╣ ąĖąĘ čŹčéąĖčģ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ ą▓ ąĄą┤ąĖąĮąĖčåą░čģ čéą░ą║č鹊ą▓ EBIU. ąÆąŠčé ą╝ąĖąĮąĖą╝ą░ą╗čīąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ ą┤ą╗čÅ čŹčéąĖčģ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓:

ŌĆó Setup Ōēź 1 čåąĖą║ą╗ą░

ŌĆó Read access Ōēź 1 čåąĖą║ą╗ą░

ŌĆó Write access Ōēź 1 čåąĖą║ą╗ą░

ŌĆó Hold Ōēź 0 čåąĖą║ą╗ąŠą▓

ąĀąĖčü. 18-4. Asynchronous Memory Bank Control 0 Register (ą▒ąĖčéčŗ 31..16).

ąĀąĖčü. 18-5. Asynchronous Memory Bank Control 0 Register (ą▒ąĖčéčŗ 15..0).

ąĀąĖčü. 18-6. Asynchronous Memory Bank Control 1 Register (ą▒ąĖčéčŗ 31..16).

ąĀąĖčü. 18-7. Asynchronous Memory Bank Control 1 Register (ą▒ąĖčéčŗ 15..0).

BnWAT[3:0]. ąÆčĆąĄą╝čÅ ą┤ąŠčüčéčāą┐ą░ ąĮą░ ąĘą░ą┐ąĖčüčī ą┤ą╗čÅ ą▒ą░ąĮą║ą░ n (ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čåąĖą║ą╗ąŠą▓, ą▓ č鹥č湥ąĮąĖąĄ ą║ąŠč鹊čĆčŗčģ ~AWE ąŠčüčéą░ąĄčéčüčÅ ą▓ ą░ą║čéąĖą▓ąĮąŠą╝ čüąŠčüč鹊čÅąĮąĖąĖ):

0000 čŹč鹊 ąĘąĮą░č湥ąĮąĖąĄ ąĮąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ

0001..1111 ąŠčé 1 ą┤ąŠ 15 čåąĖą║ą╗ąŠą▓

BnRAT[3:0]. ąÆčĆąĄą╝čÅ ą┤ąŠčüčéčāą┐ą░ ąĮą░ čćč鹥ąĮąĖąĄ ą┤ą╗čÅ ą▒ą░ąĮą║ą░ n (ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čåąĖą║ą╗ąŠą▓, ą▓ č鹥č湥ąĮąĖąĄ ą║ąŠč鹊čĆčŗčģ ~ARE ąŠčüčéą░ąĄčéčüčÅ ą▓ ą░ą║čéąĖą▓ąĮąŠą╝ čüąŠčüč鹊čÅąĮąĖąĖ):

0000 čŹč鹊 ąĘąĮą░č湥ąĮąĖąĄ ąĮąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ

0001..1111 ąŠčé 1 ą┤ąŠ 15 čåąĖą║ą╗ąŠą▓

BnHT[1:0]. ąÆčĆąĄą╝čÅ čāą┤ąĄčƹȹ░ąĮąĖčÅ (hold) ą┤ą╗čÅ ą▒ą░ąĮą║ą░ n (ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čåąĖą║ą╗ąŠą▓ ą╝ąĄąČą┤čā ą┐ąĄčĆąĄčģąŠą┤ąŠą╝ ~AWE ąĖą╗ąĖ ~ARE ą▓ ąĮąĄą░ą║čéąĖą▓ąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ ąĖ ą┐ąĄčĆąĄčģąŠą┤ąŠą╝ ~AOE ą▓ ąĮąĄą░ą║čéąĖą▓ąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ):

00 ąĘą░ą┤ąĄčƹȹ║ą░ 0 čåąĖą║ą╗ąŠą▓

01 ąĘą░ą┤ąĄčƹȹ║ą░ 1 čåąĖą║ą╗

10 ąĘą░ą┤ąĄčƹȹ║ą░ 2 čåąĖą║ą╗ą░

11 ąĘą░ą┤ąĄčƹȹ║ą░ 3 čåąĖą║ą╗ą░

BnST[1:0]. ąÆčĆąĄą╝čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ (setup) ą┤ą╗čÅ ą▒ą░ąĮą║ą░ n (ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čåąĖą║ą╗ąŠą▓ ą┐ąŠčüą╗ąĄ ą┐ąĄčĆąĄčģąŠą┤ą░ ~AOE ą▓ ą░ą║čéąĖą▓ąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ ąĖ ą┐ąĄčĆąĄą┤ ą┐ąĄčĆąĄčģąŠą┤ąŠą╝ ~AWE ąĖą╗ąĖ ~ARE ą▓ ą░ą║čéąĖą▓ąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ):

00 ąĘą░ą┤ąĄčƹȹ║ą░ 4 čåąĖą║ą╗ą░

01 ąĘą░ą┤ąĄčƹȹ║ą░ 1 čåąĖą║ą╗

10 ąĘą░ą┤ąĄčƹȹ║ą░ 2 čåąĖą║ą╗ą░

11 ąĘą░ą┤ąĄčƹȹ║ą░ 3 čåąĖą║ą╗ą░

BnTT[1:0]. ąÆčĆąĄą╝čÅ ą┐ąĄčĆąĄčģąŠą┤ą░ (transition time) ą┤ą╗čÅ ą▒ą░ąĮą║ą░ n (ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čåąĖą║ą╗ąŠą▓, ą▓čüčéą░ą▓ą╗ąĄąĮąĮčŗčģ ą┐ąŠčüą╗ąĄ ą┤ąŠčüčéčāą┐ą░ ąĮą░ čćč鹥ąĮąĖąĄ ą┤ą╗čÅ čŹč鹊ą│ąŠ ą▒ą░ąĮą║ą░ ąĖ ą┐ąĄčĆąĄą┤ ą┤ąŠčüčéčāą┐ąŠą╝ ąĮą░ ąĘą░ą┐ąĖčüčī ą▓ čŹč鹊čé ąČąĄ ą▒ą░ąĮą║, ąĖą╗ąĖ ą┤ąŠčüčéčāą┐ąŠą╝ ąĮą░ čćč鹥ąĮąĖąĄ ą▓ ą┤čĆčāą│ąŠą╣ ą▒ą░ąĮą║):

00 ąĘą░ą┤ąĄčƹȹ║ą░ 4 čåąĖą║ą╗ą░

01 ąĘą░ą┤ąĄčƹȹ║ą░ 1 čåąĖą║ą╗

10 ąĘą░ą┤ąĄčƹȹ║ą░ 2 čåąĖą║ą╗ą░

11 ąĘą░ą┤ąĄčƹȹ║ą░ 3 čåąĖą║ą╗ą░

BnRDYPOL. ą¤ąŠą╗čÅčĆąĮąŠčüčéčī čüąĖą│ąĮą░ą╗ą░ ADRY ą┤ą╗čÅ ą▒ą░ąĮą║ą░ n. 0: čéčĆą░ąĮąĘą░ą║čåąĖčÅ ąĘą░ą▓ąĄčĆčłą░ąĄčéčüčÅ, ąĄčüą╗ąĖ ARDY ą┐čĆąŠčćąĖčéą░ąĮ ą║ą░ą║ ą╗ąŠą│. 0, 1: čéčĆą░ąĮąĘą░ą║čåąĖčÅ ąĘą░ą▓ąĄčĆčłą░ąĄčéčüčÅ, ąĄčüą╗ąĖ ARDY ą┐čĆąŠčćąĖčéą░ąĮ ą║ą░ą║ ą╗ąŠą│. 1.

BnRDYEN. ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ čĆą░ą▒ąŠčéčŗ čüąĖą│ąĮą░ą╗ą░ ADRY ą┤ą╗čÅ ą▒ą░ąĮą║ą░ n. 0: ąĖą│ąĮąŠčĆąĖčĆąŠą▓ą░čéčī ARDY ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ ą║ čŹč鹊ą╝čā ą▒ą░ąĮą║čā, 1: ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ąĖčüč鹥č湥čé ąĘą░ą┤ąĄčƹȹ║ą░ ą┤ąŠčüčéčāą┐ą░, ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čüąŠčüč鹊čÅąĮąĖąĄ ą▓čģąŠą┤ą░ ARDY ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ čéčĆą░ąĮąĘą░ą║čåąĖąĖ (ą│ąŠč鹊ą▓ą░ ąĖą╗ąĖ ąĮąĄ ą│ąŠč鹊ą▓ą░ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ ą┐ą░ą╝čÅčéąĖ).

[ą×ąĮą╗ą░ą╣ąĮ-ą║ą░ą╗čīą║čāą╗čÅč鹊čĆ ą┤ą╗čÅ čĆąĄą│ąĖčüčéčĆąŠą▓ EBIU_AMBCTL0 ąĖ EBIU_AMBCTL1]

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▓ ą┐ąŠą╗čÅ čĆąĄą│ąĖčüčéčĆąŠą▓ EBIU_AMBCTL0 ąĖ EBIU_AMBCTL1 ą┐čĆąŠčüčéą░ą▓ą╗ąĄąĮčŗ ąĘąĮą░č湥ąĮąĖčÅ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ, ą║ąŠč鹊čĆčŗąĄ ąŠąĮąĖ ą┐ąŠą╗čāčćą░čÄčé ą┐čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ (čüą▒čĆąŠčüąĄ ą┐čĆąŠčåąĄčüčüąŠčĆą░).

[ą¤čĆąĄą┤ąŠčéą▓čĆą░čēąĄąĮąĖąĄ ą║ąŠąĮčäą╗ąĖą║čéąĮąŠą╣ čüąĖčéčāą░čåąĖąĖ ą┐čĆąĖ ąŠą▒čĆą░čēąĄąĮąĖąĖ ą║ čłąĖąĮąĄ]

ąśąĘ-ąĘą░ č鹊ą│ąŠ, čćč鹊 čłąĖąĮą░ čü 3 čüąŠčüč鹊čÅąĮąĖčÅą╝ąĖ čüąŠą▓ą╝ąĄčüčéąĮąŠ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ ą▓ čüąĖčüč鹥ą╝ąĄ, ą▓ą░ąČąĮąŠ ąĖąĘą▒ąĄą│ą░čéčī ą║ąŠąĮčäą╗ąĖą║č鹊ą▓ ąĮą░ čłąĖąĮąĄ. ąÜąŠąĮčäą╗ąĖą║čéčŗ ą┐čĆąĖą▓ąĄą┤čāčé ą║ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ą┐ąŠč鹥čĆąĖ ą┐ąŠčéčĆąĄą▒ą╗čÅąĄą╝ąŠą╣ ą╝ąŠčēąĮąŠčüčéąĖ, ąĖ ą╝ąŠąČąĄčé ą┐čĆąĖą▓ąĄčüčéąĖ ą║ ąŠčéą║ą░ąĘčā čāčüčéčĆąŠą╣čüčéą▓ą░. ąÜąŠąĮčäą╗ąĖą║čé ą╝ąŠąČąĄčé ą┐čĆąŠąĖąĘąŠą╣čéąĖ, ą║ąŠą│ą┤ą░ ąŠą┤ąĮąŠ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąŠčüą▓ąŠą▒ąŠąČą┤ą░ąĄčé čłąĖąĮčā, ą░ ą┤čĆčāą│ąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĘą░ąĮąĖą╝ą░ąĄčé. ąĢčüą╗ąĖ ą┐ąĄčĆą▓ąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ čüą╗ąĖčłą║ąŠą╝ ą╝ąĄą┤ą╗ąĄąĮąĮąŠ ą┐ąĄčĆąĄą▓ąŠą┤ąĖčé čüą▓ąŠąĖ ą▓čŗčģąŠą┤čŗ ą▓ čéčĆąĄčéčīąĄ čüąŠčüč鹊čÅąĮąĖąĄ, ąĖ ą▓č鹊čĆąŠąĄ čüą╗ąĖčłą║ąŠą╝ ą▒čŗčüčéčĆąŠ ą▓ą║ą╗čÄčćą░ąĄčéčüčÅ, č鹊 ąĮą░ ą▓čŗčģąŠą┤ą░čģ čāčüčéčĆąŠą╣čüčéą▓ ą▓ąŠąĘąĮąĖą║ąĮčāčé čüą║ą▓ąŠąĘąĮčŗąĄ č鹊ą║ąĖ.

ą£ąŠą│čāčé ą┐čĆąŠąĖąĘąŠą╣čéąĖ ą┤ą▓ą░ čüą╗čāčćą░čÅ čü ą║ąŠąĮčäą╗ąĖą║čéą░ą╝ąĖ. ą¤ąĄčĆą▓čŗą╣ čŹč鹊 čćč鹥ąĮąĖąĄ, ąĘą░ ą║ąŠč鹊čĆčŗą╝ čüą╗ąĄą┤čāąĄčé ąĘą░ą┐ąĖčüčī ą▓ ąŠą┤ąĮąŠ ąĖ č鹊 ąČąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ ą┐ą░ą╝čÅčéąĖ. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ą┤čĆą░ą╣ą▓ąĄčĆ čłąĖąĮčŗ ą┤ą░ąĮąĮčŗčģ ą┐ąŠč鹥ąĮčåąĖą░ą╗čīąĮąŠ ą╝ąŠąČąĄčé ą▓čüčéčāą┐ąĖčéčī ą▓ ą║ąŠąĮčäą╗ąĖą║čé čü ą░ą┤čĆąĄčüčāąĄą╝čŗą╝ ąĮą░ čćč鹥ąĮąĖąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ ą┐ą░ą╝čÅčéąĖ. ąÆč鹊čĆąŠą╣ čüą╗čāčćą░ą╣ - čćč鹥ąĮąĖąĄ ąĖąĘ čĆą░ąĘąĮčŗčģ ąŠą▒ą╗ą░čüč鹥ą╣ ą┐ą░ą╝čÅčéąĖ. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ 2 ą▓ąĮąĄčłąĮąĖčģ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┐ą░ą╝čÅčéąĖ ą╝ąŠą│čāčé ą┐ąŠč鹥ąĮčåąĖą░ą╗čīąĮąŠ ą▓ąŠą╣čéąĖ ą▓ ą║ąŠąĮčäą╗ąĖą║čé ą┤čĆčāą│ čü ą┤čĆčāą│ąŠą╝ ą▓ ą╝ąŠą╝ąĄąĮčé ą┐ąĄčĆąĄčģąŠą┤ą░ ą╝ąĄąČą┤čā ą┤ą▓čāą╝čÅ ąŠą┐ąĄčĆą░čåąĖčÅą╝ąĖ čćč鹥ąĮąĖčÅ.

ą¦č鹊ą▒čŗ ąĖąĘą▒ąĄąČą░čéčī ą║ąŠąĮčäą╗ąĖą║čéą░, ą┐čĆą░ą▓ąĖą╗čīąĮąŠ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāą╣č鹥 ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĄčģąŠą┤ą░ ą╝ąĄąČą┤čā ą▒ą░ąĮą║ą░ą╝ąĖ (bank transition time) ą▓ čĆąĄą│ąĖčüčéčĆą░čģ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą▒ą░ąĮą║ą░ą╝ąĖ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ. ąŁč鹊 ą┐ąŠąĘą▓ąŠą╗ąĖčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĄ ąĮą░čüčéčĆąŠąĖčéčī ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čåąĖą║ą╗ąŠą▓ ą╝ąĄąČą┤čā čŹčéąĖą╝ąĖ čéąĖą┐ą░ą╝ąĖ ą┤ąŠčüčéčāą┐ą░ ąĮą░ ą▒ą░ąĘąĄ ą┐ąŠ ą▒ą░ąĘąĄ ą▒ą░ąĮą║-ą▒ą░ąĮą║. ą£ąĖąĮąĖą╝ą░ą╗čīąĮąŠ EBIU ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé 1 čåąĖą║ą╗ ąĮą░ ą┐ąĄčĆąĄčģąŠą┤.

[ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą▓čģąŠą┤ąŠą╝ ARDY]

ąÜą░ąČą┤čŗą╣ ą▒ą░ąĮą║ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ ą┤ą╗čÅ ąŠą┐čĆąŠčüą░ ą▓čģąŠą┤ą░ ARDY ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ čéą░ą╣ą╝ąĄčĆ ą┤ąŠčüčéčāą┐ą░ čćč鹥ąĮąĖčÅ ąĖą╗ąĖ ąĘą░ą┐ąĖčüąĖ ą┤ąŠčüčćąĖčéą░ąĄčé ą┤ąŠ ą║ąŠąĮčåą░ ą▓ąĮąĖąĘ, ąĖą╗ąĖ ą┤ą╗čÅ ąĖą│ąĮąŠčĆąĖčĆąŠą▓ą░ąĮąĖčÅ čŹč鹊ą│ąŠ ą▓čģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░. ąÆ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé č鹊ą│ąŠ, čĆą░ąĘčĆąĄčłąĄąĮ ąĖą╗ąĖ ąĮąĄčé ARDY ą▓ ąŠą║ąĮąĄ ą▓čŗą▒ąŠčĆą║ąĖ, ARDY ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ čĆą░čüčłąĖčĆąĄąĮąĖčÅ ą▓čĆąĄą╝ąĄąĮąĖ ą┤ąŠčüčéčāą┐ą░, ą║ą░ą║ čŹč鹊 čéčĆąĄą▒čāąĄčéčüčÅ. ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 ARDY ąŠą┐čĆą░čłąĖą▓ą░ąĄčéčüčÅ čüąĖąĮčģčĆąŠąĮąĮąŠ, ą┐ąŠčŹč鹊ą╝čā:

ŌĆó ąÆčŗčüčéą░ą▓ą╗ąĄąĮąĖąĄ ąĖ čüąĮčÅčéąĖąĄ ARDY ą┤ą╗čÅ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą┤ąŠą╗ąČąĮąŠ čāą┤ąŠą▓ą╗ąĄčéą▓ąŠčĆčÅčéčī ą┤ą░čéą░čłąĖčéčā ą▓ ą║ąŠąĮč鹥ą║čüč鹥 ą▓čĆąĄą╝ąĄąĮ setup ąĖ hold. ąĢčüą╗ąĖ ąĮąĄ čāą┤ąŠą▓ą╗ąĄčéą▓ąŠčĆčÅčÄčéčüčÅ čŹčéąĖ čüąĖąĮčģčĆąŠąĮąĮčŗąĄ ąŠą│čĆą░ąĮąĖč湥ąĮąĖčÅ, č鹊 čŹč鹊 ą╝ąŠąČąĄčé ą┐čĆąĖą▓ąĄčüčéąĖ ą║ čüą╗čāčćą░ą╣ąĮąŠ-ąĮąĄčüčéą░ą▒ąĖą╗čīąĮąŠą╝čā ą▓ąĮčāčéčĆąĄąĮąĮąĄą╝čā ą┐ąŠą▓ąĄą┤ąĄąĮąĖčÄ. ąĪąĖą│ąĮą░ą╗ CLKOUT ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą┤ąŠą╗ąČąĄąĮ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░ąĮąĖčÅ čüąĖąĮčģčĆąŠąĮąĮčŗčģ ą┐ąĄčĆąĄčģąŠą┤ąŠą▓ ARDY.

ŌĆó ąÆčŗą▓ąŠą┤ ARDY ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čüčéą░ą▒ąĖą╗čīąĮčŗą╝ (ąĮą░ ą▓čĆąĄą╝čÅ ą▓čŗčüčéą░ą▓ą╗ąĄąĮąĖčÅ ąĖą╗ąĖ čüąĮčÅčéąĖčÅ čāčĆąŠą▓ąĮčÅ) ąĮą░ ą▓ąĮąĄčłąĮąĄą╝ ąĖąĮč鹥čĆč乥ą╣čüą░ ąĮą░ ą▓čĆąĄą╝čÅ čåąĖą║ą╗ą░ ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čüč湥čéčćąĖą║ ą▒ą░ąĮą║ą░ ą┤ąŠčüčéąĖą│ąĮąĄčé 0; čé. ąĄ. ą▒ąŠą╗čīčłąĄ ąŠą┤ąĮąŠą│ąŠ čåąĖą║ą╗ą░ CLKOUT ą┐ąĄčĆąĄą┤ ąĘą░ą┐ą╗ą░ąĮąĖčĆąŠą▓ą░ąĮąĮčŗą╝ ąĮą░čĆą░čüčéą░ąĮąĖąĄą╝ čāčĆąŠą▓ąĮčÅ ~AWE ąĖą╗ąĖ ~ARE. ąŁč鹊 ąŠą┐čĆąĄą┤ąĄą╗ąĖčé, ą▒čāą┤ąĄčé ą╗ąĖ ą▓čĆąĄą╝čÅ ą┤ąŠčüčéčāą┐ą░ čĆą░čüčłąĖčĆąĄąĮąŠ, ąĖą╗ąĖ ąĮąĄčé.

ŌĆó ąÜą░ą║ č鹊ą╗čīą║ąŠ ą▓čĆąĄą╝čÅ čéčĆą░ąĮąĘą░ą║čåąĖąĖ ą▒čŗą╗ąŠ čĆą░čüčłąĖčĆąĄąĮąŠ ąĖąĘ-ąĘą░ č鹊ą│ąŠ, čćč鹊 ARDY ą▒čŗą╗ ąŠą┐čĆąŠčłąĄąĮ ą▓ "ąĘą░ąĮčÅč鹊ą╝" čüąŠčüč鹊čÅąĮąĖąĖ, čéčĆą░ąĮąĘą░ą║čåąĖčÅ ą▒čāą┤ąĄčé ąĘą░ą▓ąĄčĆčłąĄąĮą░ ąĮą░ ąŠą┤ąĖąĮ čåąĖą║ą╗ ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ARDY ą▒čāą┤ąĄčé ąĘą░č鹥ą╝ ąŠą┐čĆąŠčłąĄąĮ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ "ą│ąŠč鹊ą▓".

ą¤ąŠą╗čÅčĆąĮąŠčüčéčī čüąĖą│ąĮą░ą╗ą░ ARDY ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą▒ą░ąĮą║ą░ ąŠčéą┤ąĄą╗čīąĮąŠ. ą¤ąŠčüą║ąŠą╗čīą║čā ARDY ąĮąĄ ąŠą┐čĆą░čłąĖą▓ą░ąĄčéčüčÅ, ą┐ąŠą║ą░ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą┤ąŠčüčéčāą┐ ą║ ą▒ą░ąĮą║čā, ą┤ą╗čÅ ą║ąŠč鹊čĆąŠą│ąŠ čĆą░ąĘčĆąĄčłąĄąĮąŠ ą▓čŗčüčéą░ą▓ą╗ąĄąĮąĖąĄ ARDY, č鹊 ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ARDY ąĮąĄ ąĮčāąČą┤ą░ąĄčéčüčÅ ą▓ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĖ. ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčāčÄ ąĖąĮč乊čĆą╝ą░čåąĖčÄ čüą╝. ą▓ čĆą░ąĘą┤ąĄą╗ąĄ "ąöąŠą▒ą░ą▓ą╗ąĄąĮąĖąĄ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗčģ čåąĖą║ą╗ąŠą▓ ąŠąČąĖą┤ą░ąĮąĖčÅ".

[ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗąĄ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ ą▓čĆąĄą╝ąĄąĮąĖ EBIU]

ąĪąŠąŠčéąĮąŠčłąĄąĮąĖčÅ ąĖąĮč鹥čĆą▓ą░ą╗ąŠą▓ ą▓čĆąĄą╝ąĄąĮąĖ ąĘą░ą▓ąĖčüąĖčé ąŠčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ AMC, čÅą▓ą╗čÅąĄčéčüčÅ ą╗ąĖ ąĖąĮąĖčåąĖąĖčĆąŠą▓ą░ąĮąĖąĄ čéčĆą░ąĮąĘą░ą║čåąĖąĖ ąŠčé čÅą┤čĆą░ ąĖą╗ąĖ ąŠčé DMA ą┐ąŠ ą┐ą░ą╝čÅčéąĖ (memory DMA, MDMA), ąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ čéčĆą░ąĮąĘą░ą║čåąĖą╣ (ąĘą░ čćč鹥ąĮąĖąĄą╝ čüą╗ąĄą┤čāąĄčé čćč鹥ąĮąĖąĄ, ąĘą░ čćč鹥ąĮąĖąĄą╝ čüą╗ąĄą┤čāąĄčé ąĘą░ą┐ąĖčüčī, ąĖ čéą░ą║ ą┤ą░ą╗ąĄąĄ).

ąÉčüąĖąĮčģčĆąŠąĮąĮčŗąĄ ą┤ąŠčüčéčāą┐čŗ čüąŠ čüč鹊čĆąŠąĮčŗ čÅą┤čĆą░. ąØąĄą║ąŠč鹊čĆčŗąĄ ą┤ąŠčüčéčāą┐čŗ ą║ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ ą▓čŗąĘčŗą▓ą░čÄčéčüčÅ ąĖąĮčüčéčĆčāą║čåąĖčÅą╝ąĖ čÅą┤čĆą░ ąĮą░ą┐ąŠą┤ąŠą▒ąĖąĄ:

R0.L = W[P0++] ; čćč鹥ąĮąĖąĄ ąĖąĘ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ (P0 čāą║ą░ąĘčŗą▓ą░ąĄčé ąĮą░ čÅč湥ą╣ą║čā ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ)

ąĖą╗ąĖ:

W[P0++] = R0.L ; ąĘą░ą┐ąĖčüčī ą▓ąŠ ą▓ąĮąĄčłąĮčÄčÄ ą┐ą░ą╝čÅčéčī.

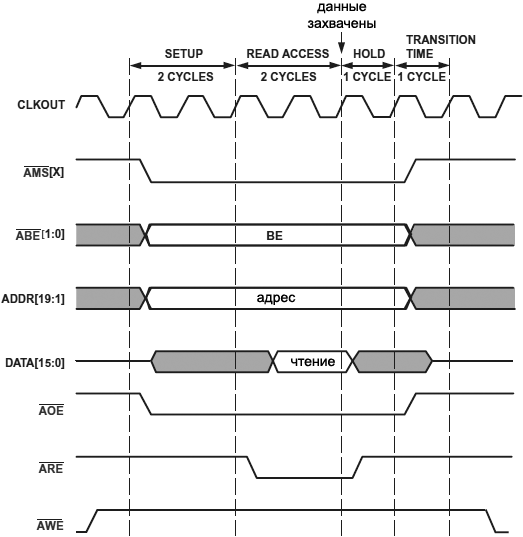

ąÉčüąĖąĮčģčĆąŠąĮąĮčŗąĄ čćč鹥ąĮąĖčÅ. ąØą░ čĆąĖčü. 18-8 ą┐ąŠą║ą░ąĘą░ąĮ čåąĖą║ą╗ čłąĖąĮčŗ ą┐čĆąĖ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą╝ čćč鹥ąĮąĖąĖ čü ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮčŗą╝ąĖ ą┐ą░čĆą░ą╝ąĄčéčĆą░ą╝ąĖ setup = 2 čåąĖą║ą╗ą░, ą┤ąŠčüčéčāą┐ ąĮą░ čćč鹥ąĮąĖąĄ = 2 čåąĖą║ą╗ą░, hold = 1 čåąĖą║ą╗, transition time = 1 čåąĖą║ą╗. ą”ąĖą║ą╗čŗ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą│ąŠ čćč鹥ąĮąĖčÅ ą┐ąŠ čłąĖąĮąĄ ą┐čĆąŠąĖčüčģąŠą┤čÅčé čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝:

1. ąÆ ąĮą░čćą░ą╗ąĄ ą┐ąĄčĆąĖąŠą┤ą░ setup čüąĖą│ąĮą░ą╗čŗ ~AMS[x], čłąĖąĮčŗ ą░ą┤čĆąĄčüą░ ąĖ ~ABE[1:0] čüčéą░ąĮąŠą▓čÅčéčüčÅ ą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗą╝ąĖ, ąĖ ą▓čŗčüčéą░ą▓ą╗čÅąĄčéčüčÅ ~AOE.

2. ąÆ ą╝ąŠą╝ąĄąĮčé ąĮą░čćą░ą╗ą░ ą┐ąĄčĆąĖąŠą┤ą░ ą┤ąŠčüčéčāą┐ą░ ąĮą░ čćč鹥ąĮąĖąĄ ąĖ ą┐ąŠčüą╗ąĄ 2 čéą░ą║č鹊ą▓ setup ą▓čŗčüčéą░ą▓ą╗čÅąĄčéčüčÅ ~ARE.

3. ąÆ ą╝ąŠą╝ąĄąĮčé ąĮą░čćą░ą╗ą░ ą┐ąĄčĆąĖąŠą┤ą░ hold, čćąĖčéą░ąĄą╝čŗąĄ ą┤ą░ąĮąĮčŗąĄ ąŠą┐čĆą░čłąĖą▓ą░čÄčéčüčÅ ą┐ąŠ čäčĆąŠąĮčéčā čéą░ą║čéą░ EBIU. ąĪąĖą│ąĮą░ą╗ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ ~ARE čüąĮąĖą╝ą░ąĄčéčüčÅ ą┐ąŠčüą╗ąĄ čŹč鹊ą│ąŠ čäčĆąŠąĮčéą░ čéą░ą║čéą░.

4. ą¤ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ą┐ąĄčĆąĖąŠą┤ą░ hold čüąĖą│ąĮą░ą╗ ~AOE čüąĮąĖą╝ą░ąĄčéčüčÅ ą┤ąŠ ą╝ąŠą╝ąĄąĮčéą░, ą┐ąŠą║ą░ ąĘą░ čŹčéąĖą╝ čåąĖą║ą╗ąŠą╝ čłąĖąĮčŗ ąĮąĄ ą┐ąŠčüą╗ąĄą┤čāąĄčé ą┤čĆčāą│ąŠąĄ ą░čüąĖąĮčģčĆąŠąĮąĮąŠąĄ čćč鹥ąĮąĖąĄ ą▓ čéčā ąČąĄ čüą░ą╝čāčÄ ąŠą▒ą╗ą░čüčéčī ą┐ą░ą╝čÅčéąĖ. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ~AMS[x] čüąĮąĖą╝ą░ąĄčéčüčÅ ą┤ąŠ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ čåąĖą║ą╗ą░ ąŠą▒čĆą░čēąĄąĮąĖčÅ ą▓ č鹊čé ąČąĄ ą▒ą░ąĮą║ ą┐ą░ą╝čÅčéąĖ.

5. ąĢčüą╗ąĖ ą▓ąĮčāčéčĆąĄąĮąĮąĄ ąĮąĄ ą┐ąŠčüčéą░ą▓ą╗ąĄąĮąŠ ą▓ ąŠč湥čĆąĄą┤čī ą┤čĆčāą│ąŠąĄ čćč鹥ąĮąĖąĄ ą▓ č鹊čé ąČąĄ ą▒ą░ąĮą║, AMC ą┤ąŠą▒ą░ą▓ą╗čÅąĄčé ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čåąĖą║ą╗ąŠą▓ ą┤ą╗čÅ ą┐ąĄčĆąĄčģąŠą┤ą░ ą╝ąĄąČą┤čā ąŠą▒ą╗ą░čüčéčÅą╝ąĖ ą┐ą░ą╝čÅčéąĖ.

ąĀąĖčü. 18-8. ą”ąĖą║ą╗čŗ čĆą░ą▒ąŠčéčŗ čłąĖąĮčŗ ą┐čĆąĖ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą╝ čćč鹥ąĮąĖąĖ.

ąöąŠčüčéčāą┐ ąĮą░ čćč鹥ąĮąĖąĄ ąĘą░ą▓ąĄčĆčłą░ąĄčéčüčÅ čüąĮčÅčéąĖąĄą╝ čüąĖą│ąĮą░ą╗ąŠą▓ ~AMSx ąĖ ~AOE. ąŚą┤ąĄčüčī ą┐čĆąĖčüčāčéčüčéą▓čāčÄčé ąĮąĄčüą║ąŠą╗čīą║ąŠ čåąĖą║ą╗ąŠą▓ ąŠąČąĖą┤ą░ąĮąĖčÅ ą┤ąŠ ąĮą░čćą░ą╗ą░ čüą╗ąĄą┤čāčÄčēąĄą╣ ąŠą┐ąĄčĆą░čåąĖąĖ čćč鹥ąĮąĖčÅ. ąÜąŠą╗ąĖč湥čüčéą▓ąŠ čåąĖą║ą╗ąŠą▓ ąŠąČąĖą┤ą░ąĮąĖčÅ čÅą▓ą╗čÅąĄčéčüčÅ čäčāąĮą║čåąĖąĄą╣ ąŠčé čüąŠąŠčéąĮąŠčłąĄąĮąĖčÅ CCLK/SCLK. ąÜąŠą╗ąĖč湥čüčéą▓ąŠ čåąĖą║ą╗ąŠą▓ ąŠąČąĖą┤ą░ąĮąĖčÅ ą┤ą╗čÅ CCLK/SCLK=3 ą▒čāą┤ąĄčé 6, 4 ą┤ą╗čÅ CCLK/SCLK=5, ąĖ 3 ą┤ą╗čÅ CCLK/SCLK=10.

ąÉčüąĖąĮčģčĆąŠąĮąĮčŗąĄ ąĘą░ą┐ąĖčüąĖ. ąØą░ čĆąĖčü. 18-9 ą┐ąŠą║ą░ąĘą░ąĮ čåąĖą║ą╗ čłąĖąĮčŗ ą┐čĆąĖ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą╣ ąĘą░ą┐ąĖčüąĖ, ąĘą░ ą║ąŠč鹊čĆąŠą╣ čüą╗ąĄą┤čāąĄčé čåąĖą║ą╗ čćč鹥ąĮąĖčÅ ą▓ č鹊ą╝ ąČąĄ ą▒ą░ąĮą║ąĄ, čü ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮčŗą╝ąĖ ą┐ą░čĆą░ą╝ąĄčéčĆą░ą╝ąĖ setup = 2 čåąĖą║ą╗ą░, ą┤ąŠčüčéčāą┐ ąĮą░ ąĘą░ą┐ąĖčüčī = 2 čåąĖą║ą╗ą░, ą┤ąŠčüčéčāą┐ ąĮą░ čćč鹥ąĮąĖąĄ = 3 čåąĖą║ą╗ą░, hold = 1 čåąĖą║ą╗, transition time = 1 čåąĖą║ą╗. ą”ąĖą║ą╗čŗ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą╣ ąĘą░ą┐ąĖčüąĖ ą┐ąŠ čłąĖąĮąĄ ą┐čĆąŠąĖčüčģąŠą┤čÅčé čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝:

1. ąÆ ąĮą░čćą░ą╗ąĄ ą┐ąĄčĆąĖąŠą┤ą░ setup čüąĖą│ąĮą░ą╗čŗ ~AMS[x], čłąĖąĮčŗ ą░ą┤čĆąĄčüą░, ą┤ą░ąĮąĮčŗčģ, ąĖ ~ABE[1:0] čüčéą░ąĮąŠą▓čÅčéčüčÅ ą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗą╝ąĖ.

2. ąÆ ą╝ąŠą╝ąĄąĮčé ąĮą░čćą░ą╗ą░ ą┐ąĄčĆąĖąŠą┤ą░ ą┤ąŠčüčéčāą┐ą░ ąĮą░ ąĘą░ą┐ąĖčüčī ą▓čŗčüčéą░ą▓ą╗čÅąĄčéčüčÅ ~AWE.

3. ąÆ ą╝ąŠą╝ąĄąĮčé ąĮą░čćą░ą╗ą░ ą┐ąĄčĆąĖąŠą┤ą░ hold čüąĖą│ąĮą░ą╗ ~AWE čüąĮąĖą╝ą░ąĄčéčüčÅ.

ą”ąĖą║ą╗čŗ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą│ąŠ čćč鹥ąĮąĖčÅ ą┐ąŠ čłąĖąĮąĄ ą┐čĆąŠąĖčüčģąŠą┤čÅčé čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝:

1. ąÆ ąĮą░čćą░ą╗ąĄ ą┐ąĄčĆąĖąŠą┤ą░ setup čüąĖą│ąĮą░ą╗čŗ ~AMS[x], čłąĖąĮčŗ ą░ą┤čĆąĄčüą░ ąĖ ~ABE[1:0] čüčéą░ąĮąŠą▓čÅčéčüčÅ ą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗą╝ąĖ, ąĖ ą▓čŗčüčéą░ą▓ą╗čÅąĄčéčüčÅ ~AOE.

2. ąÆ ą╝ąŠą╝ąĄąĮčé ąĮą░čćą░ą╗ą░ ą┐ąĄčĆąĖąŠą┤ą░ ą┤ąŠčüčéčāą┐ą░ ąĮą░ čćč鹥ąĮąĖąĄ ą▓čŗčüčéą░ą▓ą╗čÅąĄčéčüčÅ ~ARE.

3. ąÆ ą╝ąŠą╝ąĄąĮčé ąĮą░čćą░ą╗ą░ ą┐ąĄčĆąĖąŠą┤ą░ hold čćąĖčéą░ąĄą╝čŗąĄ ą┤ą░ąĮąĮčŗąĄ ąŠą┐čĆą░čłąĖą▓ą░čÄčéčüčÅ ą┐ąŠ ąĮą░čĆą░čüčéą░ąĮąĖčÄ čäčĆąŠąĮčéą░ čüąĖą│ąĮą░ą╗ą░ čéą░ą║č鹊ą▓ EBIU. ąĪąĖą│ąĮą░ą╗ ~ARE čüąĮąĖą╝ą░ąĄčéčüčÅ ą┐ąŠčüą╗ąĄ čŹč鹊ą│ąŠ čäčĆąŠąĮčéą░ čéą░ą║č鹊ą▓.

4. ą¤ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ą┐ąĄčĆąĖąŠą┤ą░ hold čüąĖą│ąĮą░ą╗ą░ ~AOE čüąĮąĖą╝ą░ąĄčéčüčÅ ą┤ąŠ ą╝ąŠą╝ąĄąĮčéą░, ą┐ąŠą║ą░ ąĘą░ čŹčéąĖą╝ čåąĖą║ą╗ąŠą╝ čłąĖąĮčŗ ąĮąĄ ą┐ąŠčüą╗ąĄą┤čāąĄčé ą┤čĆčāą│ąŠąĄ ą░čüąĖąĮčģčĆąŠąĮąĮąŠąĄ čćč鹥ąĮąĖąĄ ą▓ čéčā ąČąĄ čüą░ą╝čāčÄ ąŠą▒ą╗ą░čüčéčī ą┐ą░ą╝čÅčéąĖ. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ~AMS[x] čüąĮąĖą╝ą░ąĄčéčüčÅ ą┤ąŠ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ čåąĖą║ą╗ą░ ąŠą▒čĆą░čēąĄąĮąĖčÅ ą▓ č鹊čé ąČąĄ ą▒ą░ąĮą║ ą┐ą░ą╝čÅčéąĖ.

5. ąĢčüą╗ąĖ ą▓ąĮčāčéčĆąĄąĮąĮąĄ ąĮąĄ ą┐ąŠčüčéą░ą▓ą╗ąĄąĮąŠ ą▓ ąŠč湥čĆąĄą┤čī ą┤čĆčāą│ąŠąĄ čćč鹥ąĮąĖąĄ ą▓ č鹊čé ąČąĄ ą▒ą░ąĮą║, AMC ą┤ąŠą▒ą░ą▓ą╗čÅąĄčé ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čåąĖą║ą╗ąŠą▓ ą┤ą╗čÅ ą┐ąĄčĆąĄčģąŠą┤ą░ ą╝ąĄąČą┤čā ąŠą▒ą╗ą░čüčéčÅą╝ąĖ ą┐ą░ą╝čÅčéąĖ.

ąĀąĖčü. 18-9. ą”ąĖą║ą╗čŗ čĆą░ą▒ąŠčéčŗ čłąĖąĮčŗ ą┐čĆąĖ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą╣ ąĘą░ą┐ąĖčüąĖ ąĖ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą╝ čćč鹥ąĮąĖąĖ.

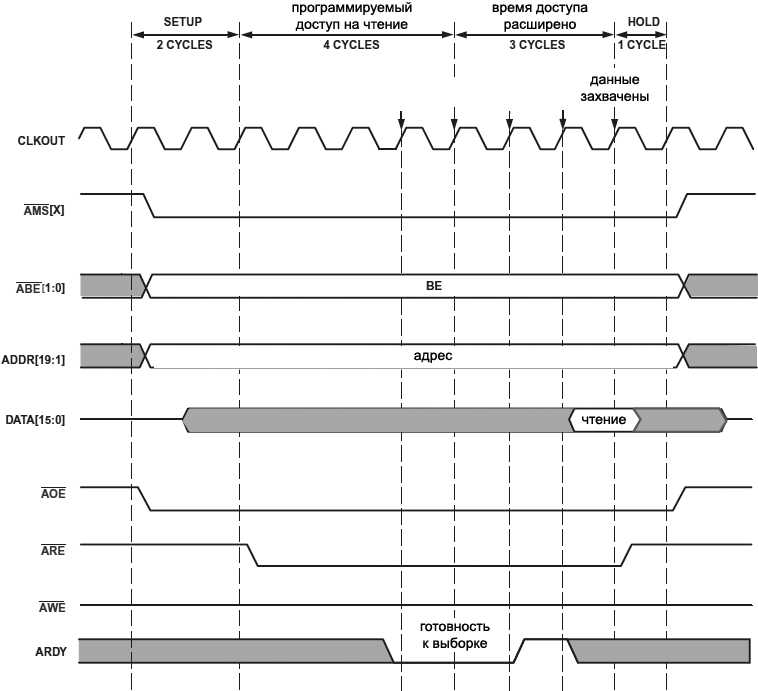

ąöąŠą▒ą░ą▓ą╗ąĄąĮąĖąĄ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗčģ čåąĖą║ą╗ąŠą▓ ąŠąČąĖą┤ą░ąĮąĖčÅ. ąÆčŗą▓ąŠą┤ ARDY ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą▓čüčéą░ą▓ą║ąĖ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗčģ čéą░ą║č鹊ą▓ ąŠąČąĖą┤ą░ąĮąĖčÅ (wait states). ąŁč鹊čé ą▓čģąŠą┤ ąŠą┐čĆą░čłąĖą▓ą░ąĄčéčüčÅ čüąĖąĮčģčĆąŠąĮąĮąŠ čü ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊č鹊ą╣ EBIU. EBIU ąĮą░čćąĖąĮą░ąĄčé ąŠą┐čĆą░čłąĖą▓ą░čéčī ARDY ąĮą░ 1 čéą░ą║č鹊ą▓čŗą╣ čåąĖą║ą╗ ą┐ąĄčĆąĄą┤ ąŠą║ąŠąĮčćą░ąĮąĖąĄą╝ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ ą┐ąĄčĆąĖąŠą┤ą░ čüčéčĆąŠą▒ąĖčĆąŠą▓ą░ąĮąĖčÅ. ąĢčüą╗ąĖ ARDY ąŠą┐čĆąŠčłąĄąĮ ą║ą░ą║ ąĮąĄ ą▓čŗčüčéą░ą▓ą╗ąĄąĮąĮčŗą╣, č鹊 ą┐ąĄčĆąĖąŠą┤ ą┤ąŠčüčéčāą┐ą░ čĆą░čüčłąĖčĆčÅąĄčéčüčÅ. ąŚą░č鹥ą╝ ą▓čŗą▓ąŠą┤ ARDY ą┐čĆąŠą┤ąŠą╗ąČą░ąĄčé ąŠą┐čĆą░čłąĖą▓ą░čéčīčüčÅ ąĮą░ ą║ą░ąČą┤ąŠą╝ ą┐ąŠčüą╗ąĄą┤čāčÄčēąĄą╝ čéą░ą║č鹊ą▓ąŠą╝ ą┐ąĄčĆąĄą┐ą░ą┤ąĄ. ą¦ąĖčéą░ąĄą╝čŗąĄ ą┤ą░ąĮąĮčŗąĄ ąĘą░čēąĄą╗ą║ąĖą▓ą░čÄčéčüčÅ ąĮą░ čéą░ą║č鹊ą▓ąŠą╝ ą┐ąĄčĆąĄą┐ą░ą┤ąĄ ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ARDY ą▒čŗą╗ ąŠą┐čĆąŠčłąĄąĮ ą║ą░ą║ ą▓čŗčüčéą░ą▓ą╗ąĄąĮąĮčŗą╣. ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ čćč鹥ąĮąĖčÅ ąĖą╗ąĖ ąĘą░ą┐ąĖčüąĖ ąŠčüčéą░ąĄčéčüčÅ ą▓čŗčüčéą░ą▓ą╗ąĄąĮąĮčŗą╝ ąĮą░ ąŠą┤ąĖąĮ čéą░ą║čé ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ARDY ą▒čŗą╗ ą┐čĆąŠčćąĖčéą░ąĮ ą║ą░ą║ ą▓čŗčüčéą░ą▓ą╗ąĄąĮąĮčŗą╣. ą¤čĆąĖą╝ąĄčĆ čŹč鹊ą│ąŠ ą┐ąŠą▓ąĄą┤ąĄąĮąĖčÅ ą┐ąŠą║ą░ąĘą░ąĮ ąĮą░ čĆąĖčü. 18-10, ą│ą┤ąĄ setup = 2 čåąĖą║ą╗ą░, ą▓čĆąĄą╝čÅ ą┤ąŠčüčéčāą┐ą░ ąĮą░ čćč鹥ąĮąĖąĄ = 4 čåąĖą║ą╗ą░, ąĖ hold = 1 čåąĖą║ą╗. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ą┐ąĄčĆąĖąŠą┤ ą┤ąŠčüčéčāą┐ą░ ąĮą░ čćč鹥ąĮąĖąĄ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ąĮą░ 2 čåąĖą║ą╗ą░, čćč鹊ą▒čŗ ą▓čģąŠą┤ ARDY ą┤ąĄą╣čüčéą▓ąĖč鹥ą╗čīąĮąŠ ą╝ąŠą│ čĆą░ą▒ąŠčéą░čéčī.

ąĀąĖčü. 18-10. ąöąŠą▒ą░ą▓ą╗ąĄąĮąĖąĄ čéą░ą║č鹊ą▓ ąŠąČąĖą┤ą░ąĮąĖčÅ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ ARDY.

ąĪąĖą│ąĮą░ą╗čŗ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą▒ą░ą╣čéą░. ąÆčŗą▓ąŠą┤čŗ ~ABE[1:0] ąŠą▒ą░ ąĮą░čģąŠą┤čÅčéčüčÅ ą▓ ą╗ąŠą│. 0 ą┐čĆąĖ ą▓čüąĄčģ ą░čüąĖąĮčģčĆąŠąĮąĮčŗčģ čćč鹥ąĮąĖčÅčģ ąĖ 16-ą▒ąĖčéąĮčŗčģ ą░čüąĖąĮčģčĆąŠąĮąĮčŗčģ ąĘą░ą┐ąĖčüčÅčģ. ąÜąŠą│ą┤ą░ ą┤ąĄą╗ą░ąĄčéčüčÅ ą░čüąĖąĮčģčĆąŠąĮąĮą░čÅ ąĘą░ą┐ąĖčüčī ą▓ čüčéą░čĆčłąĖą╣ ą▒ą░ą╣čé 16-ą▒ąĖčéąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ, č鹊 ~ABE1 = 0 ąĖ ~ABE0 = 1. ąÜąŠą│ą┤ą░ ą░čüąĖąĮčģčĆąŠąĮąĮą░čÅ ąĘą░ą┐ąĖčüčī ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą▓ ą╝ą╗ą░ą┤čłąĖą╣ ą▒ą░ą╣čé 16-ą▒ąĖčéąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ, ~ABE1 = 1 ąĖ ~ABE0 = 0.

[ąÆčüčéčĆąŠąĄąĮąĮą░čÅ ą▓ ą║čĆąĖčüčéą░ą╗ą╗ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą┐ą░ą╝čÅčéčī FLASH]

ąÆ ą║čĆąĖčüčéą░ą╗ą╗ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ ą╝ą░čĆąŠą║ ADSP-BF538F4 ąĖ ADSP-BF538F8 ą▓čüčéčĆąŠąĄąĮą░ ą┐ą░ą╝čÅčéčī FLASH. ąŁčéą░ ą┐ą░ą╝čÅčéčī FLASH ąĖą╝ąĄąĄčé ąŠčéą┤ąĄą╗čīąĮčŗą╣ čüąĖą│ąĮą░ą╗ ą▓čŗą▒ąŠčĆą║ąĖ ą▓ąĮčāčéčĆąĖ ą║ąŠčĆą┐čāčüą░, ąĖ ąŠąĮ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąĖą▓čÅąĘą░ąĮ ą║ ą╗čÄą▒ąŠą╝čā ąĖąĘ 4 ą░čüąĖąĮčģčĆąŠąĮąĮčŗčģ ą▒ą░ąĮą║ąŠą▓ ą┐ą░ą╝čÅčéąĖ ą┐čāč鹥ą╝ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ą▓čŗą▓ąŠą┤ą░ ~FCE ą║ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╝čā ą▓čŗą▓ąŠą┤čā ~AMSx. ąĢčüą╗ąĖ ą▓čŗą▓ąŠą┤ ~FCE ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą║ ą▓čŗą▓ąŠą┤čā ~AMS0, č鹊 ą┐čĆąŠčåąĄčüčüąŠčĆ ąĘą░ą│čĆčāąĘąĖčéčüčÅ ąĖąĘ čŹč鹊ą╣ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ FLASH.

[ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ SDRAM (SDC)]

ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ SDRAM ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐čĆąŠčåąĄčüčüąŠčĆčā ąŠą▒ą╝ąĄąĮąĖą▓ą░čéčīčüčÅ ą┤ą░ąĮąĮčŗą╝ąĖ čü čüąĖąĮčģčĆąŠąĮąĮąŠą╣ ą┤ąĖąĮą░ą╝ąĖč湥čüą║ąŠą╣ ą┐ą░ą╝čÅčéčīčÄ DRAM (SDRAM) ąĮą░ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą╣ čćą░čüč鹊č鹥, ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą╣ ą▓ ą┤ą░čéą░čłąĖč鹥 ąĮą░ ą┐čĆąŠčåąĄčüčüąŠčĆ ADSP-BF538/ADSP-BF538F. ąæą╗ą░ą│ąŠą┤ą░čĆčÅ SDC ą┐čĆąŠčåąĄčüčüąŠčĆ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ą┐čĆąŠąĘčĆą░čćąĮčŗą╣ ą┤ą╗čÅ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ąĖąĮč鹥čĆč乥ą╣čü čü ąŠą┤ąĮąĖą╝ ą▓ąĮąĄčłąĮąĖą╝ ą▒ą░ąĮą║ąŠą╝ čüčéą░ąĮą┤ą░čĆčéąĮčŗčģ ą╝ąĖą║čĆąŠčüčģąĄą╝ SDRAM ąŠą▒čŖąĄą╝ąŠą╝ ąŠčé 64 ą┤ąŠ 512 ą╝ąĄą│ą░ą▒ąĖčéą░, ą▓ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅčģ x4, x8 ąĖ x16. ą¤čĆąĖ čŹč鹊ą╝ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮą░čÅ ąŠą▒čēą░čÅ ąĄą╝ą║ąŠčüčéčī ą┐ą░ą╝čÅčéąĖ SDRAM ą╝ąŠąČąĄčé ą▒čŗčéčī ą┤ąŠ 512 ą╝ąĄą│ą░ą▒ą░ą╣čé. ąæą░ąĮą║ SDRAM čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ą▓čŗčģąŠą┤ąŠą╝ ą▓čŗą▒ąŠčĆą║ąĖ ą┐ą░ą╝čÅčéąĖ ~SMS. ąśąĮč鹥čĆč乥ą╣čü ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąĮą░čüčéčĆą░ąĖą▓ą░čéčī ąŠą┐čåąĖąĖ ąĖąĮč鹥čĆą▓ą░ą╗ąŠą▓ ą▓čĆąĄą╝ąĄąĮąĖ, čćč鹊ą▒čŗ ą╝ąŠąČąĮąŠ ą▒čŗą╗ąŠ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čéčī ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗąĄ ą▒čāč乥čĆčŗ ą╝ąĄąČą┤čā ą┐čĆąŠčåąĄčüčüąŠčĆąŠą╝ ąĖ SDRAM, ąĖ čŹčéąĖą╝ ą║ąŠą╝ą┐ąĄąĮčüąĖčĆąŠą▓ą░čéčī ąĄą╝ą║ąŠčüčéąĮčāčÄ ąĮą░ą│čĆčāąĘą║čā ą▒ąŠą╗čīčłąĖčģ ąŠą▒čŖąĄą╝ąŠą▓ ą┐ą░ą╝čÅčéąĖ.

ąĪąŠčüč鹊čÅąĮąĖąĄ ą▓čüąĄčģ ą▓čģąŠą┤ąŠą▓ ąĖąĮč鹥čĆč乥ą╣čüą░ čüčćąĖčéčŗą▓ą░ąĄčéčüčÅ ą┐ąŠ čäčĆąŠąĮčéčā čüąĖą│ąĮą░ą╗ą░ čéą░ą║č鹊ą▓ SDRAM ąĮą░ ą▓čŗą▓ąŠą┤ąĄ CLKOUT. ąÆčüąĄ ą▓čŗčģąŠą┤čŗ ąĖąĮč鹥čĆč乥ą╣čüą░ ą▒čāą┤čāčé ą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗą╝ąĖ ą┐čĆąĖ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą╝ ą┐ąĄčĆąĄą┐ą░ą┤ąĄ čüąĖą│ąĮą░ą╗ą░ čéą░ą║č鹊ą▓ SDRAM ąĮą░ ą▓čŗą▓ąŠą┤ąĄ CLKOUT.

ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, EBIU SDC ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą┐čĆąŠąĘčĆą░čćąĮčŗą╣ ą░ą┐ą┐ą░čĆą░čéąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü ą║ čüčéą░ąĮą┤ą░čĆčéąĮčŗą╝ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ą╝ ą┐ą░ą╝čÅčéąĖ SDRAM. ąÆąŠčé ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ ąĖąĮč鹥čĆč乥ą╣čüą░ SDC:

ŌĆó ą¤ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčéčüčÅ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ SDRAM ąĮą░ 64 ą╝ąĄą│ą░ą▒ąĖčéą░, 128 ą╝ąĄą│ą░ą▒ąĖčé, 256 ą╝ąĄą│ą░ą▒ąĖčé, 512 ą╝ąĄą│ą░ą▒ąĖčé čü ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅą╝ąĖ čłąĖąĮčŗ ą┤ą░ąĮąĮčŗčģ x4, x8 ąĖ x16.

ŌĆó ą¤ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ąŠą▒čēąĖą╣ ąŠą▒čŖąĄą╝ ą┤ąŠ 512 ą╝ąĄą│ą░ą▒ą░ą╣čé ą┤ą╗čÅ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ SDRAM.

ŌĆó ą¤ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčéčüčÅ čüčéčĆą░ąĮąĖčåčŗ SDRAM čĆą░ąĘą╝ąĄčĆą░ą╝ąĖ 512 ą▒ą░ą╣čé, 1 ą║ąĖą╗ąŠą▒ą░ą╣čé, 2 ą║ąĖą╗ąŠą▒ą░ą╣čéą░ ąĖ 4 ą║ąĖą╗ąŠą▒ą░ą╣čéą░.

ŌĆó ąÆ ą┐čĆąĄą┤ąĄą╗ą░čģ SDRAM ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ 4 ą▓ąĮčāčéčĆąĄąĮąĮąĖčģ ą▒ą░ąĮą║ą░.

ŌĆó ąśčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗą╣ čüč湥čéčćąĖą║ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ ą┤ą╗čÅ čüąŠą│ą╗ą░čüąŠą▓ą░ąĮąĖčÅ čĆą░ąĘą╗ąĖčćąĮčŗčģ čéą░ą║č鹊ą▓čŗčģ čćą░čüč鹊čé ąĖ čéčĆąĄą▒čāąĄą╝ąŠą╣ čćą░čüč鹊čéčŗ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ SDRAM.

ŌĆó ą¤čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ąĮąĄčüą║ąŠą╗čīą║ąŠ ąŠą┐čåąĖą╣ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĖąĮč鹥čĆą▓ą░ą╗ą░ą╝ąĖ ą▓čĆąĄą╝ąĄąĮąĖ ą┤ą╗čÅ ą┐ąŠą┤ą┤ąĄčƹȹ║ąĖ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗčģ ą▒čāč乥čĆąŠą▓ ą╝ąĄąČą┤čā ą┐čĆąŠčåąĄčüčüąŠčĆąŠą╝ ąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ą╝ąĖ SDRAM.

ŌĆó ąśčüą┐ąŠą╗čīąĘčāąĄčé ąŠčéą┤ąĄą╗čīąĮčŗą╣ ą▓čŗą▓ąŠą┤ (SA10), ą║ąŠč鹊čĆčŗą╣ čĆą░ąĘčĆąĄčłą░ąĄčé SDC ą┤ąĄą╗ą░čéčī ą┐čĆąĄą┤ąĘą░čĆčÅą┤ SDRAM ą┐ąĄčĆąĄą┤ ą▓čŗą┤ą░č湥ą╣ ą║ąŠą╝ą░ąĮą┤čŗ ą░ą▓č鹊ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ (auto-refresh) ąĖą╗ąĖ čüą░ą╝ąŠąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ (self-refresh), ą┐ąŠą║ą░ AMC čāą┐čĆą░ą▓ą╗čÅąĄčé ą┐ąŠčĆč鹊ą╝ EBIU.

ŌĆó ą¤ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé čüą░ą╝ąŠąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ ą┤ą╗čÅ čüčéą░ąĮą┤ą░čĆčéąĮčŗčģ ą╝ąĖą║čĆąŠčüčģąĄą╝ čüą░ą╝ąŠąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ ąŠčéą┤ąĄą╗čīąĮąŠą│ąŠ ą╝ą░čüčüąĖą▓ą░ ą┤ą╗čÅ ą╝ąŠą▒ąĖą╗čīąĮčŗčģ SDRAM.

ŌĆó ą¤čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé 2 ąŠą┐čåąĖąĖ ą┤ą╗čÅ ąĘą░ą┐čāčüą║ą░ (power-up) SDRAM.

ŌĆó ą¤čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą┤ąŠčüčéčāą┐ ą║ ą▒ą░ąĮą║ą░ą╝ SDRAM čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ č湥čĆąĄą┤ąŠą▓ą░ąĮąĖčÅ.

ąöą╗čÅ ą▒ąŠą╗čīčłąĄą╣ čÅčüąĮąŠčüčéąĖ čüą╗ąĄą┤čāąĄčé ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ąĮąĄą║ąŠč鹊čĆčŗąĄ č鹥čĆą╝ąĖąĮčŗ, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą▓ ąŠą┐ąĖčüą░ąĮąĖąĖ čüąĖčüč鹥ą╝čŗ SDRAM.

ąÜąŠą╝ą░ąĮą┤ą░ Bank Activate. ąÜąŠą╝ą░ąĮą┤ą░ ą░ą║čéąĖą▓ą░čåąĖąĖ ą▒ą░ąĮą║ą░ ą┐čĆąĖą▓ąŠą┤ąĖčé SDRAM ą║ ąŠčéą║čĆčŗčéąĖčÄ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ ą▒ą░ąĮą║ą░ (čāą║ą░ąĘą░ąĮąĮąŠą│ąŠ ą┐ąŠ ą░ą┤čĆąĄčüčā ą▒ą░ąĮą║ą░) ą▓ čüčéčĆąŠą║ąĄ (čāą║ą░ąĘą░ąĮąĮąŠą╝ ą░ą┤čĆąĄčüąŠą╝ čüčéčĆąŠą║ąĖ). ąÜąŠą│ą┤ą░ bank activate command ą▓čŗą┤ą░ąĄčéčüčÅ ą┤ą╗čÅ SDRAM, SDRAM ąŠčéą║čĆčŗą▓ą░ąĄčé ąĮąŠą▓čŗą╣ ą░ą┤čĆąĄčü čüčéčĆąŠą║ąĖ ą▓ čüą┐ąĄčåąĖą░ą╗čīąĮąŠą╝ ą▒ą░ąĮą║ąĄ. ą¤ą░ą╝čÅčéčī ą▓ ąŠčéą║čĆčŗč鹊ą╝ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╝ ą▒ą░ąĮą║ąĄ ąĖ čüčéčĆąŠą║ą░ ąĮą░ąĘčŗą▓ą░ąĄčéčüčÅ ąŠčéą║čĆčŗč鹊ą╣ čüčéčĆą░ąĮąĖčåąĄą╣. ąÜąŠą╝ą░ąĮą┤ą░ ą░ą║čéąĖą▓ą░čåąĖąĖ ą▒ą░ąĮą║ą░ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą▓čŗą┤ą░ąĮą░ ą┐ąĄčĆąĄą┤ ą║ąŠą╝ą░ąĮą┤ąŠą╣ čćč鹥ąĮąĖčÅ ąĖą╗ąĖ ąĘą░ą┐ąĖčüąĖ.

Burst Length. ą¤ą░čĆą░ą╝ąĄčéčĆ burst length (ą┤ą╗ąĖąĮą░ ą▒ą╗ąŠą║ą░) ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čüą╗ąŠą▓, ą║ąŠč鹊čĆąŠąĄ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ SDRAM čüąŠčģčĆą░ąĮčÅąĄčé ąĖą╗ąĖ ą┐ąĄčĆąĄą┤ą░ąĄčé ą┐ąŠčüą╗ąĄ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ąŠą┤ąĮąŠą╣ ą║ąŠą╝ą░ąĮą┤čŗ ąĘą░ą┐ąĖčüąĖ ąĖą╗ąĖ čćč鹥ąĮąĖčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ. ą¤ą░čĆą░ą╝ąĄčéčĆ burst length ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗčģ ą▒ąĖčé ą▓ čĆąĄą│ąĖčüčéčĆ čĆąĄąČąĖą╝ą░ SDRAM (SDRAM mode register) ą▓ąŠ ą▓čĆąĄą╝čÅ ąŠą┐ąĄčĆą░čåąĖąĖ ąĘą░ą┐čāčüą║ą░ SDRAM (power-up sequence).

ąźąŠčéčÅ SDC ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé č鹊ą╗čīą║ąŠ čĆąĄąČąĖą╝ burst length = 1, ą▓ąŠ ą▓čĆąĄą╝čÅ ąŠą▒ą╝ąĄąĮą░ ą▒ą╗ąŠą║ąŠą╝ čü SDRAM, ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ SDC ą▓čŗą┤ą░ąĄčé ą║ąŠą╝ą░ąĮą┤čā čćč鹥ąĮąĖčÅ ąĖą╗ąĖ ąĘą░ą┐ąĖčüąĖ ą║ą░ąČą┤čŗą╣ čåąĖą║ą╗, ąĖ čüąŠčģčĆą░ąĮčÅąĄčé ą┤ąŠčüčéčāą┐ ą║ ą┤ą░ąĮąĮčŗą╝. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, čŹčäč乥ą║čéąĖą▓ąĮą░čÅ burst length ąĮą░ą╝ąĮąŠą│ąŠ ą▒ąŠą╗čīčłąĄ 1. ąöčĆčāą│ąĖą╝ąĖ čüą╗ąŠą▓ą░ą╝ąĖ, čāčüčéą░ąĮąŠą▓ą║ą░ burst length = 1 ąĮąĄ čāą╝ąĄąĮčīčłą░ąĄčé ą┐ąŠą╗ąŠčüčā ą┐čĆąŠą┐čāčüą║ą░ąĮąĖčÅ ą┐čĆąĖ ąŠą▒ą╝ąĄąĮąĄ čü SDRAM.

ąÜąŠą╝ą░ąĮą┤ą░ Burst Stop. ąÜąŠą╝ą░ąĮą┤ą░ ąŠčüčéą░ąĮąŠą▓ą║ąĖ ą▒ą╗ąŠą║ą░ čŹč鹊 ąŠą┤ąĖąĮ ąĖąĘ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ čüą┐ąŠčüąŠą▒ąŠą▓ ąĘą░ą▓ąĄčĆčłąĖčéčī ąĖą╗ąĖ ą┐čĆąĄčĆą▓ą░čéčī ąŠą┐ąĄčĆą░čåąĖčÄ ą▒ą╗ąŠčćąĮąŠą│ąŠ čćč鹥ąĮąĖčÅ ąĖą╗ąĖ ąĘą░ą┐ąĖčüąĖ.

ą¤ąŠčüą║ąŠą╗čīą║čā SDRAM burst length ą▓čüąĄą│ą┤ą░ ąČąĄčüčéą║ąŠ ąĘą░ą┤ą░ąĮą░ ą▓ 1, č鹊 SDC ąĮąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ą║ąŠą╝ą░ąĮą┤čā burst stop.

Burst Type. ą¤ą░čĆą░ą╝ąĄčéčĆ čéąĖą┐ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▒ą╗ąŠą║ą░ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ą┐ąŠčĆčÅą┤ąŠą║ ą░ą┤čĆąĄčüąŠą▓, ą▓ ą║ąŠč鹊čĆąŠą╝ SDRAM ą┐ąĄčĆąĄą┤ą░ąĄčé ą▒ą╗ąŠčćąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┐ąŠčüą╗ąĄ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą║ąŠą╝ą░ąĮą┤čŗ čćč鹥ąĮąĖčÅ ąĖą╗ąĖ čüąŠčģčĆą░ąĮčÅąĄčé ą▒ą╗ąŠčćąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┐ąŠčüą╗ąĄ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą║ąŠą╝ą░ąĮą┤čŗ ąĘą░ą┐ąĖčüąĖ. ą¤ą░čĆą░ą╝ąĄčéčĆ burst type ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ąĘą░ą┐čāčüą║ą░ SDRAM (power-up sequence).

ą¤ąŠčüą║ąŠą╗čīą║čā SDRAM burst length ą▓čüąĄą│ą┤ą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ ą║ą░ą║ 1, č鹊 burst type ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą▓ą╗ąĖčÅąĮąĖčÅ. ą×ą┤ąĮą░ą║ąŠ SDC ą▓čüąĄą│ą┤ą░ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé burst type ąĮą░ čéąĖą┐ č鹊ą╗čīą║ąŠ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ą┤ąŠčüčéčāą┐ą░ (sequential-accesses-only) ą▓ ą╝ąŠą╝ąĄąĮčé ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ąĘą░ą┐čāčüą║ą░ SDRAM.

CAS Latency (CL). ąøą░č鹥ąĮčéąĮąŠčüčéčī čüčéčĆąŠą▒ą░ ą░ą┤čĆąĄčüą░ čüč鹊ą╗ą▒čåą░ (CAS) čŹč鹊 ąĘą░ą┤ąĄčƹȹ║ą░ ą▓ čéą░ą║č鹊ą▓čŗčģ čåąĖą║ą╗ą░čģ ą╝ąĄąČą┤čā ą╝ąŠą╝ąĄąĮč鹊ą╝, ą║ąŠą│ą┤ą░ SDRAM ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ą╗ą░ ą║ąŠą╝ą░ąĮą┤čā čćč鹥ąĮąĖčÅ, ąĖ ą╝ąŠą╝ąĄąĮč鹊ą╝, ą║ąŠą│ą┤ą░ ąŠąĮą░ ą┐čĆąĄą┤ąŠčüčéą░ą▓ąĖą╗ą░ ą┤ą░ąĮąĮčŗąĄ ąĮą░ čüą▓ąŠąĖčģ ą▓čŗčģąŠą┤ąĮčŗčģ ą▓čŗą▓ąŠą┤ą░čģ. CAS latency ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ čĆąĄąČąĖą╝ą░ SDRAM (SDRAM mode register) ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ąĘą░ą┐čāčüą║ą░ (power-up sequence) SDRAM.

ąÜą╗ą░čüčü čüą║ąŠčĆąŠčüčéąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝ SDRAM ąĖ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ą░čÅ ą▓ čüąĖčüč鹥ą╝ąĄ, ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ąĘąĮą░č湥ąĮąĖąĄ ą┤ą╗čÅ ą┐ą░čĆą░ą╝ąĄčéčĆą░ CAS latency. SDC ą╝ąŠąČąĄčé ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čéčī CAS latency čĆą░ąĘą╝ąĄčĆąŠą╝ 2 ąĖą╗ąĖ 3 čéą░ą║č鹊ą▓čŗčģ čåąĖą║ą╗ą░. ąÆčŗą▒čĆą░ąĮąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ CAS latency ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąŠ ą▓ ąŠą▒čēąĖą╣ čĆąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ SDRAM (SDRAM memory global control register, EBIU_SDGCTL) ą┐ąĄčĆąĄą┤ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčīčÄ ąĘą░ą┐čāčüą║ą░ SDRAM. ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. ą▓ąŠ ą▓čĆąĄąĘą║ąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ EBIU_SDGCTL.

CBR (CAS Before RAS) Refresh ąĖą╗ąĖ Auto-Refresh. ąÜąŠą│ą┤ą░ SDC ąĖčüč鹥č湥čé čüč湥čéčćąĖą║ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ, SDC ą┤ąĄą╗ą░ąĄčé ą┐čĆąĄą┤ąĘą░čĆčÅą┤ ą▓čüąĄčģ 4 ą▒ą░ąĮą║ąŠą▓ SDRAM ąĖ ąĘą░č鹥ą╝ ą▓čŗą┤ą░ąĄčé ą┤ą╗čÅ ąĮąĖčģ ą║ąŠą╝ą░ąĮą┤čā ą░ą▓č鹊ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ (auto-refresh command). ąŁč鹊 ą┐čĆąĖą▓ąŠą┤ąĖčé ą║ SDRAM ą║ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą▓ąĮčāčéčĆąĖ čüąĄą▒čÅ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čåąĖą║ą╗ą░ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ CBR. ąÜąŠą│ą┤ą░ ą▓ąĮčāčéčĆąĄąĮąĮąĄąĄ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ ąĘą░ą▓ąĄčĆčłąĖčéčüčÅ, ą▓čüąĄ 4 ą▓ąĮčāčéčĆąĄąĮąĮąĖąĄ ą▒ą░ąĮą║ą░ SDRAM ą┐ąŠą╗čāčćą░čé ą┐čĆąĄą┤ąĘą░čĆčÅą┤.

ążčāąĮą║čåąĖčÅ ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓čŗą▓ąŠą┤ą░ą╝ąĖ DQM. ąÆčŗą▓ąŠą┤čŗ SDQM[1:0] ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÄčé ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖčÅ ą▒ą░ą╣čé ą┐čĆąĖ 8-ą▒ąĖčéąĮčŗčģ ąĘą░ą┐ąĖčüčÅčģ ą▓ SDRAM. ąÆčŗą▓ąŠą┤čŗ DQM ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ ą▓čģąŠą┤ąĮąŠą│ąŠ ą▒čāč乥čĆą░ SDRAM ą┐čĆąĖ ąŠą┐ąĄčĆą░čåąĖčÅčģ čćą░čüčéąĖčćąĮąŠą╣ ąĘą░ą┐ąĖčüąĖ. ąÆčŗą▓ąŠą┤čŗ SDQM[1:0] ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ąĮą░ čåąĖą║ą╗ą░čģ čćą░čüčéąĖčćąĮąŠą│ąŠ čćč鹥ąĮąĖčÅ. ąöą╗čÅ čåąĖą║ą╗ąŠą▓ ąĘą░ą┐ąĖčüąĖ čā ą╝ą░čüąŠą║ ą┤ą░ąĮąĮčŗčģ ąĘą░ą┤ąĄčƹȹ║ą░ čüąŠčüčéą░ą▓ą╗čÅąĄčé 0 čåąĖą║ą╗ąŠą▓, čćč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąĘą░ą┐ąĖčüčŗą▓ą░čéčī ą┤ą░ąĮąĮčŗąĄ, ą│ą┤ąĄ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▓čŗą▓ąŠą┤ SDQM[x] ąŠą┐čĆą░čłąĖą▓ą░ąĄčéčüčÅ ą║ą░ą║ čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 0, ąĖ ą▒ą╗ąŠą║ąĖčĆčāąĄčé ąĘą░ą┐ąĖčüčī, ą║ąŠą│ą┤ą░ SDQM[x] ąŠą┐čĆą░čłąĖą▓ą░ąĄčéčüčÅ ą║ą░ą║ ą╗ąŠą│. 1 - ąĮą░ ą▒ą░ą╣č鹊ą▓ąŠą╣ ą▒ą░ąĘąĄ (ą▒ą░ą╣čé-ąĘą░-ą▒ą░ą╣č鹊ą╝).

Internal Bank. ąŁč鹊 ąĮąĄčüą║ąŠą╗čīą║ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĖčģ ą▒ą░ąĮą║ąŠą▓, čĆą░čüą┐ąŠą╗ąŠąČąĄąĮąĮčŗčģ ą▓ ąĖą╝ąĄčÄčēąĄą╣čüčÅ SDRAM. SDC ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ąŠą▒čĆą░čēąĄąĮąĖčÅ ą║ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╝ ą▒ą░ąĮą║ą░ą╝ čü č湥čĆąĄą┤ąŠą▓ą░ąĮąĖąĄą╝. ąÉą┤čĆąĄčü ą▒ą░ąĮą║ą░ ą╝ąŠąČąĄčé čüčćąĖčéą░čéčīčüčÅ čćą░čüčéčīčÄ ą░ą┤čĆąĄčüą░ čüčéčĆąŠą║ąĖ. SDC ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčé, čćč鹊 ą▓čüąĄ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ SDRAM, ą║ąŠč鹊čĆčŗąĄ ą║ ąĮąĄą╝čā ą┐ąŠą┤ą║ą╗čÄč湥ąĮčŗ, ąĖą╝ąĄčÄčé 4 ą▓ąĮčāčéčĆąĄąĮąĮąĖčģ ą▒ą░ąĮą║ą░, ąĖ ą┐ąŠąĘą▓ąŠą╗čÅčÄčé ąĖą╝ąĄčéčī ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ ą▒ą░ąĮą║ą░ ąĖą╝ąĄčéčī čāąĮąĖą║ą░ą╗čīąĮčŗą╣ ą░ą┤čĆąĄčü čüčéčĆąŠą║ąĖ.

Mode Register. ąĀąĄą│ąĖčüčéčĆ čĆąĄąČąĖą╝ą░ - ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ SDRAM čüąŠą┤ąĄčƹȹ░čé ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čĆąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ, ą║ąŠč鹊čĆčŗą╣ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąĘą░ą┤ą░čéčī čüčéą░ąĮą┤ą░čĆčé, ą┐ąŠ ą║ąŠč鹊čĆąŠą╝čā ą▒čāą┤ąĄčé čĆą░ą▒ąŠčéą░čéčī čāčüčéčĆąŠą╣čüčéą▓ąŠ SDRAM. ą¤ąŠčüą╗ąĄ ą▓ą║ą╗čÄč湥ąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ ąĖ ą┐ąĄčĆąĄą┤ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄą╝ čćč鹥ąĮąĖčÅ ąĖą╗ąĖ ąĘą░ą┐ąĖčüąĖ ąŠą▒ą╗ą░čüčéąĖ ą┐ą░ą╝čÅčéąĖ SDRAM, ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ ą┤ąŠą╗ąČąĮąŠ ą┐ąĄčĆąĄą║ą╗čÄčćąĖčéčī SDC ąĮą░ ąĘą░ą┐ąĖčüčī ą▓ čĆąĄą│ąĖčüčéčĆ čĆąĄąČąĖą╝ą░ SDRAM. ąŚą░ą┐ąĖčüčī ą▓ SDRAM mode register ą┐ąĄčĆąĄą║ą╗čÄčćą░ąĄčéčüčÅ ąĘą░ą┐ąĖčüčīčÄ 1 ą▓ ą▒ąĖčé PSSE ąŠą▒čēąĄą│ąŠ čĆąĄą│ąĖčüčéčĆą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ SDRAM (SDRAM memory global control register, EBIU_SDGCTL), ąĖ ąĘą░č鹥ą╝ ą▓čŗą┤ą░ąĄčé ą┐ąĄčĆąĄą┤ą░čćčā čćč鹥ąĮąĖčÅ ąĖą╗ąĖ ąĘą░ą┐ąĖčüąĖ ą┤ą╗čÅ ąŠą▒ą╝ąĄąĮą░ čü ą░ą┤čĆąĄčüąĮčŗą╝ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠą╝ SDRAM. ą¤ąĄčĆą▓ąŠąĮą░čćą░ą╗čīąĮą░čÅ ąŠą┐ąĄčĆą░čåąĖčÅ čćč鹥ąĮąĖčÅ ąĖą╗ąĖ ąĘą░ą┐ąĖčüąĖ ą▓čŗąĘčŗą▓ą░ąĄčé čüčéą░čĆčé ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ąĘą░ą┐čāčüą║ą░ SDRAM (SDRAM power-up sequence), ą║ąŠč鹊čĆą░čÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčé čĆąĄą│ąĖčüčéčĆ čĆąĄąČąĖą╝ą░ SDRAM ą┐ą░čĆą░ą╝ąĄčéčĆąŠą╝ CAS latency ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ EBIU_SDGCTL. ą¤ąĄčĆą▓ąŠąĮą░čćą░ą╗čīąĮąŠąĄ čćč鹥ąĮąĖąĄ ąĖą╗ąĖ ąĘą░ą┐ąĖčüčī SDRAM ąĘą░ąĮąĖą╝ą░čÄčé ą╝ąĮąŠą│ąŠ čåąĖą║ą╗ąŠą▓ ą┤ąŠ čüą▓ąŠąĄą│ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ.

ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ą┤ą╗čÅ ą▒ąŠą╗čīčłąĖąĮčüčéą▓ą░ ą┐čĆąĖą╗ąŠąČąĄąĮąĖą╣ SDRAM power-up sequence ąĖ ąĘą░ą┐ąĖčüčī ą▓ čĆąĄą│ąĖčüčéčĆ čĆąĄąČąĖą╝ą░ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮčŗ č鹊ą╗čīą║ąŠ 1 čĆą░ąĘ. ąÜą░ą║ č鹊ą╗čīą║ąŠ power-up sequence ąĘą░ą▓ąĄčĆčłąĖą╗ą░čüčī, ą▒ąĖčé PSSE ąĮąĄ ą┤ąŠą╗ąČąĄąĮ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čéčīčüčÅ čüąĮąŠą▓ą░, ąĘą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ čüą╗čāčćą░ąĄą▓, ą║ąŠą│ą┤ą░ ąĮą░ą┤ąŠ ą┐ąŠą╝ąĄąĮčÅčéčī čĆąĄą│ąĖčüčéčĆ čĆąĄąČąĖą╝ą░. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ąŠą▒čĆą░čéąĖč鹥čüčī ą║ čĆą░ąĘą┤ąĄą╗čā "Managing SDRAM Refresh During PLL Transitions" ą▓ ą┤ą░čéą░čłąĖč鹥 [1].

ą£ąĖą║čĆąŠčüčģąĄą╝čŗ SDRAM čü ąĮąĖąĘą║ąĖą╝ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄą╝ ą╝ąŠą│čāčé čéą░ą║ąČąĄ čüąŠą┤ąĄčƹȹ░čéčī čĆąĄą│ąĖčüčéčĆ čĆą░čüčłąĖčĆąĄąĮąĮąŠą│ąŠ čĆąĄąČąĖą╝ą░ (extended mode register). EBIU čĆą░ąĘčĆąĄčłą░ąĄčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ extended mode register ą▓ąŠ ą▓čĆąĄą╝čÅ ą▓ą║ą╗čÄč湥ąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ č湥čĆąĄąĘ ą▒ąĖčé EMREN čĆąĄą│ąĖčüčéčĆą░ EBIU_SDGCTL.

Page Size. ąĀą░ąĘą╝ąĄčĆ čüčéčĆą░ąĮąĖčåčŗ čŹč鹊 ąŠą▒čŖąĄą╝ ą┐ą░ą╝čÅčéąĖ, čā ą║ąŠč鹊čĆąŠą╣ ąŠą┤ąĖąĮą░ą║ąŠą▓čŗą╣ ą░ą┤čĆąĄčü čüčéčĆąŠą║ąĖ, ąĖ ą║ ą║ąŠč鹊čĆąŠą╝čā ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠą╗čāč湥ąĮ ą┤ąŠčüčéčāą┐ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╝ąĖ ą║ąŠą╝ą░ąĮą┤ą░ą╝ąĖ čćč鹥ąĮąĖčÅ ąĖą╗ąĖ ąĘą░ą┐ąĖčüąĖ ą▒ąĄąĘ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéąĖ ą░ą║čéąĖą▓ąĖčĆąŠą▓ą░čéčī ą┤čĆčāą│čāčÄ čüčéčĆąŠą║čā ą┐ą░ą╝čÅčéąĖ. ąĀą░ąĘą╝ąĄčĆ čüčéčĆą░ąĮąĖčåčŗ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗčćąĖčüą╗ąĄąĮ ą┤ą╗čÅ 16-čĆą░ąĘčĆčÅą┤ąĮčŗčģ ą▒ą░ąĮą║ąŠą▓ SDRAM ą┐ąŠ čüą╗ąĄą┤čāčÄčēąĄą╣ č乊čĆą╝čāą╗ąĄ:

page size = 2(CAW + 1)

ąŚą┤ąĄčüčī CAW čŹč鹊 čłąĖčĆąĖąĮą░ ą░ą┤čĆąĄčüą░ čüč鹊ą╗ą▒čåą░ SDRAM. ąĢą┤ąĖąĮąĖčćą║ą░ ą┤ąŠą▒ą░ą▓ą╗čÅąĄčéčüčÅ ą┐ąŠč鹊ą╝čā, čćč鹊 ą▒ą░ąĮą║ SDRAM ąĖą╝ąĄąĄčé čłąĖčĆąĖąĮčā 16 (čé. ąĄ. 1 ą░ą┤čĆąĄčü čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé 2 ą▒ą░ą╣čéą░ą╝).

ąÜąŠą╝ą░ąĮą┤ą░ Pre-Charge. ąÜąŠą╝ą░ąĮą┤ą░ ą┐čĆąĄą┤ąĘą░čĆčÅą┤ą░ ąĘą░ą║čĆčŗą▓ą░ąĄčé ąŠčéą┤ąĄą╗čīąĮčŗą╣ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ ą▒ą░ąĮą║ ą▓ ą░ą║čéąĖą▓ąĮąŠą╣ čüčéčĆą░ąĮąĖčåąĄ ąĖą╗ąĖ ą▓čüąĄ ą▓ąĮčāčéčĆąĄąĮąĮąĖąĄ ą▒ą░ąĮą║ąĖ ąĮą░ čüčéčĆą░ąĮąĖčåąĄ.

SDRAM Bank. ąæą░ąĮą║ SDRAM čŹč鹊 ąŠą▒ą╗ą░čüčéčī ą┐ą░ą╝čÅčéąĖ, ą║ąŠč鹊čĆą░čÅ ą╝ąŠąČąĄčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮą░ ąĮą░ čĆą░ąĘą╝ąĄčĆ 16 ą╝ąĄą│ą░ą▒ą░ą╣čé, 32 ą╝ąĄą│ą░ą▒ą░ą╣čéą░, 64 ą╝ąĄą│ą░ą▒ą░ą╣čéą░, 128 ą╝ąĄą│ą░ą▒ą░ą╣čé, 256 ą╝ąĄą│ą░ą▒ą░ą╣čé ąĖą╗ąĖ 512 ą╝ąĄą│ą░ą▒ą░ą╣čé, ąĖ ąŠąĮą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą▒čĆą░ąĮą░ č湥čĆąĄąĘ ą╗ąŠą│. 0 ąĮą░ ą▓čŗą▓ąŠą┤ąĄ ~SMS.

ąØąĄ ą┐čāčéą░ą╣č鹥 č鹥čĆą╝ąĖąĮ "SDRAM internal bank" (ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ ą▒ą░ąĮą║ SDRAM), ą║ąŠč鹊čĆčŗą╣ ąŠčéąĮąŠčüąĖčéčüčÅ ą║ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╝čā čüąŠą┤ąĄčƹȹĖą╝ąŠą╝čā SDRAM, ąĖ ą║ąŠč鹊čĆčŗą╣ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ą┐ąŠ ą░ą┤čĆąĄčüčā ą▒ą░ąĮą║ą░, čü č鹥čĆą╝ąĖąĮąŠą╝ "ą▒ą░ąĮą║ SDRAM" ąĖą╗ąĖ "external bank" (ą▓ąĮąĄčłąĮąĖą╣ ą▒ą░ąĮą║), ą║ąŠč鹊čĆčŗą╣ ąŠčéąĮąŠčüąĖčéčüčÅ ą║ąŠ ą▓čüąĄą╝čā ą╝ą░čüčüąĖą▓čā ą┐ą░ą╝čÅčéąĖ SDRAM, ą║ąŠč鹊čĆčŗą╣ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ą▓čŗą▓ąŠą┤ąŠą╝ ~SMS.

Self-Refresh, čüą░ą╝ąŠąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ. ąÜąŠą│ą┤ą░ SDRAM čĆą░ą▒ąŠčéą░ąĄčé ą▓ čĆąĄąČąĖą╝ąĄ čüą░ą╝ąŠąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ, ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čéą░ą╣ą╝ąĄčĆ ą╝ąĖą║čĆąŠčüčģąĄą╝ SDRAM ąĖąĮąĖčåąĖąĖčĆčāąĄčé ą┐ąĄčĆąĖąŠą┤ąĖč湥čüą║ąĖąĄ čåąĖą║ą╗ąĖ ą░ą▓č鹊ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ, ą▒ąĄąĘ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéąĖ ą▓ąĮąĄčłąĮąĄą│ąŠ ą▓čģąŠą┤ą░ ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ. SDC ą┤ąŠą╗ąČąĄąĮ ą▓čŗą┤ą░čéčī čüąĄčĆąĖčÄ ą║ąŠą╝ą░ąĮą┤, ą▓ą║ą╗čÄčćą░čÅ ą║ąŠą╝ą░ąĮą┤čā self-refresh, čćč鹊ą▒čŗ ą┐ąĄčĆąĄą▓ąĄčüčéąĖ SDRAM ą▓ čŹč鹊čé čĆąĄąČąĖą╝ ą┐ąŠąĮąĖąČąĄąĮąĮąŠą│ąŠ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ, ąĖ ą┤ąŠą╗ąČąĄąĮ ą▓čŗą┤ą░čéčī ą┤čĆčāą│čāčÄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą║ąŠą╝ą░ąĮą┤ ą┤ą╗čÅ ą▓čŗčģąŠą┤ą░ ąĖąĘ čĆąĄąČąĖą╝ą░ self-refresh. ąÆčģąŠą┤ ą▓ čĆąĄąČąĖą╝ self-refresh ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ č湥čĆąĄąĘ ąŠą▒čēąĖą╣ čĆąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ SDRAM (SDRAM memory global control register, EBIU_SDGCTL), ąĖ ą╗čÄą▒ąŠą╣ ą┤ąŠčüčéčāą┐ ą║ ą░ą┤čĆąĄčüąĮąŠą╝čā ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓čā SDRAM ą┐čĆąĖą▓ąŠą┤ąĖčé SDC ą║ ą▓čŗą▓ąŠą┤čā SDRAM ąĖąĘ čĆąĄąČąĖą╝ą░ self-refresh. ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. čĆą░ąĘą┤ąĄą╗ "ąÆčģąŠą┤ ą▓ čĆąĄąČąĖą╝ Self-Refresh (SRFS) ąĖ ą▓čŗčģąŠą┤ ąĖąĘ ąĮąĄą│ąŠ".

tRAS. ąŁč鹊 ąĮąĄąŠą▒čģąŠą┤ąĖą╝ą░čÅ ąĘą░ą┤ąĄčƹȹ║ą░ ą╝ąĄąČą┤čā ą▓čŗą┤ą░č湥ą╣ ą║ąŠą╝ą░ąĮą┤čŗ ą░ą║čéąĖą▓ą░čåąĖąĖ ą▒ą░ąĮą║ą░ ąĖ ą▓čŗą┤ą░č湥ą╣ ą║ąŠą╝ą░ąĮą┤čŗ pre-charge, ąĖ ą╝ąĄąČą┤čā ą║ąŠą╝ą░ąĮą┤ąŠą╣ self-refresh ąĖ ą▓čŗčģąŠą┤ąŠą╝ ąĖąĘ čĆąĄąČąĖą╝ą░ self-refresh. ąæąĖč鹊ą▓ąŠąĄ ą┐ąŠą╗ąĄ TRAS ą▓ ąŠą▒čēąĄą╝ čĆąĄą│ąĖčüčéčĆąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ SDRAM (EBIU_SDGCTL) čüąŠą┤ąĄčƹȹĖčé 4 ą▒ąĖčéą░, ąĖ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąŠ ą▓ ąĘąĮą░č湥ąĮąĖąĄ ąŠčé 1 ą┤ąŠ 15 (ąĘą░ą┤ąĄčƹȹ║ą░ ą▓ čéą░ą║č鹊ą▓čŗčģ čåąĖą║ą╗ą░čģ). ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. čĆą░ąĘą┤ąĄą╗ "ąÆčŗą▒ąŠčĆ ąĘą░ą┤ąĄčƹȹ║ąĖ Selecting the Bank Activate Command Delay (TRAS)".

tRC. ąŁč鹊 ąĮąĄąŠą▒čģąŠą┤ąĖą╝ą░čÅ ąĘą░ą┤ąĄčƹȹ║ą░ ą╝ąĄąČą┤čā ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╝ąĖ ą▓čŗą┤ą░čćą░ą╝ąĖ ą║ąŠą╝ą░ąĮą┤ ą░ą║čéąĖą▓ą░čåąĖąĖ ą▒ą░ąĮą║ą░ ą▓ č鹊čé ąČąĄ čüą░ą╝čŗą╣ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ ą▒ą░ąĮą║ SDRAM. ąŁčéą░ ąĘą░ą┤ąĄčƹȹ║ą░ ąĮąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮą░ ąĮą░ą┐čĆčÅą╝čāčÄ. ąŚą░ą┤ąĄčƹȹ║ą░ tRC ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą▓čŗą┤ąĄčƹȹ░ąĮą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╝ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄą╝ ą┐ąŠą╗ąĄą╣ TRAS ąĖ TRP, čćč鹊ą▒čŗ ąŠą▒ąĄčüą┐ąĄčćąĖčéčī čāčüą╗ąŠą▓ąĖąĄ tRAS + tRP Ōēź tRC.

tRCD. ąŁč鹊 ąĮąĄąŠą▒čģąŠą┤ąĖą╝ą░čÅ ąĘą░ą┤ąĄčƹȹ║ą░ ą╝ąĄąČą┤čā ą║ąŠą╝ą░ąĮą┤ąŠą╣ ą░ą║čéąĖą▓ą░čåąĖąĖ ą▒ą░ąĮą║ą░ ąĖ ąĮą░čćą░ą╗ąŠą╝ ą┐ąĄčĆą▓ąŠą╣ ą║ąŠą╝ą░ąĮą┤čŗ čćč鹥ąĮąĖčÅ ąĖą╗ąĖ ąĘą░ą┐ąĖčüąĖ. ąæąĖč鹊ą▓ąŠąĄ ą┐ąŠą╗ąĄ TRCD ą▓ ąŠą▒čēąĄą╝ čĆąĄą│ąĖčüčéčĆąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ SDRAM (EBIU_SDGCTL) čüąŠą┤ąĄčƹȹĖčé 3 ą▒ąĖčéą░, ąĖ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąŠ ą▓ ąĘąĮą░č湥ąĮąĖčÅ ąŠčé 1 ą┤ąŠ 7 (ąĘą░ą┤ąĄčƹȹ║ą░ ą▓ čéą░ą║č鹊ą▓čŗčģ čåąĖą║ą╗ą░čģ).

tRFC. ąŁč鹊 čéčĆąĄą▒čāąĄą╝ą░čÅ ąĘą░ą┤ąĄčƹȹ║ą░ ą╝ąĄąČą┤čā ą▓čŗą┤ą░č湥ą╣ ą║ąŠą╝ą░ąĮą┤čŗ auto-refresh ąĖ ą║ąŠą╝ą░ąĮą┤čŗ ą░ą║čéąĖą▓ą░čåąĖąĖ ą▒ą░ąĮą║ą░, ąĖ ą╝ąĄąČą┤čā ą▓čŗą┤ą░čćą░ą╝ąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ą║ąŠą╝ą░ąĮą┤ auto-refresh. ąŁčéą░ ąĘą░ą┤ąĄčƹȹ║ą░ ąĮąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮą░ ąĮą░ą┐čĆčÅą╝čāčÄ, ąĖ ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčéčüčÅ, čćč鹊 ąŠąĮą░ čĆą░ą▓ąĮą░ tRC. ąŚą░ą┤ąĄčƹȹ║ą░ tRC ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą▓čŗą┤ąĄčƹȹ░ąĮą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╝ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄą╝ ą┐ąŠą╗ąĄą╣ TRAS ąĖ TRP, čćč鹊ą▒čŗ ąŠą▒ąĄčüą┐ąĄčćąĖčéčī čāčüą╗ąŠą▓ąĖąĄ tRAS + tRP Ōēź tRC.

tRP. ąŁč鹊 čéčĆąĄą▒čāąĄą╝ą░čÅ ąĘą░ą┤ąĄčƹȹ║ą░ ą╝ąĄąČą┤čā ą▓čŗą┤ą░č湥ą╣ ą║ąŠą╝ą░ąĮą┤čŗ pre-charge ąĖ ą▓čŗą┤ą░č湥ą╣ ą║ąŠą╝ą░ąĮą┤:

ŌĆó ą║ąŠą╝ą░ąĮą┤ą░ ą░ą║čéąĖą▓ą░čåąĖąĖ ą▒ą░ąĮą║ą░

ŌĆó ą║ąŠą╝ą░ąĮą┤ą░ auto-refresh

ŌĆó ą║ąŠą╝ą░ąĮą┤ą░ self-refresh

ąæąĖč鹊ą▓ąŠąĄ ą┐ąŠą╗ąĄ TRP ą▓ ąŠą▒čēąĄą╝ čĆąĄą│ąĖčüčéčĆąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ SDRAM (EBIU_SDGCTL) čüąŠą┤ąĄčƹȹĖčé 3 ą▒ąĖčéą░, ąĖ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮą░ ą▓ ąĘąĮą░č湥ąĮąĖąĄ ąŠčé 1 ą┤ąŠ 7 (ąĘą░ą┤ąĄčƹȹ║ą░ ą▓ čéą░ą║č鹊ą▓čŗčģ čåąĖą║ą╗ą░čģ). ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. čĆą░ąĘą┤ąĄą╗ "ąÆčŗą▒ąŠčĆ ąĘą░ą┤ąĄčƹȹ║ąĖ Pre-Charge (TRP)".

tRRD. ąŁč鹊 čéčĆąĄą▒čāąĄą╝ą░čÅ ąĘą░ą┤ąĄčƹȹ║ą░ ą╝ąĄąČą┤čā ą▓čŗą┤ą░č湥ą╣ ą║ąŠą╝ą░ąĮą┤čŗ ą░ą║čéąĖą▓ą░čåąĖąĖ ą▒ą░ąĮą║ą░ A ą▓čŗą┤ą░č湥ą╣ ą║ąŠą╝ą░ąĮą┤čŗ ą░ą║čéąĖą▓ą░čåąĖąĖ ą▒ą░ąĮą║ą░ B. ąŁčéą░ ąĘą░ą┤ąĄčƹȹ║ą░ ąĮąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮą░ ąĮą░ą┐čĆčÅą╝čāčÄ ąĖ ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčéčüčÅ, čćč鹊 ąŠąĮą░ čĆą░ą▓ąĮą░ tRCD + 1.

tWR. ąŁč鹊 čéčĆąĄą▒čāąĄą╝ą░čÅ ąĘą░ą┤ąĄčƹȹ║ą░ ą╝ąĄąČą┤čā ą║ąŠą╝ą░ąĮą┤ąŠą╣ ąĘą░ą┐ąĖčüąĖ (ą║ąŠč鹊čĆą░čÅ ą▓čŗąĘčŗą▓ą░ąĄčé ąĘą░ą┐ąĖčüčī ą┤ą░ąĮąĮčŗčģ) ąĖ ą║ąŠą╝ą░ąĮą┤ąŠą╣ pre-charge. ąæąĖč鹊ą▓ąŠąĄ ą┐ąŠą╗ąĄ TWR ą▓ ąŠą▒čēąĄą╝ čĆąĄą│ąĖčüčéčĆąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ SDRAM (EBIU_SDGCTL) čüąŠą┤ąĄčƹȹĖčé 2 ą▒ąĖčéą░, ąĖ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąŠ ą▓ ąĘąĮą░č湥ąĮąĖčÅ ąŠčé 1 ą┤ąŠ 3 čéą░ą║č鹊ą▓čŗčģ čåąĖą║ą╗ą░ ąĘą░ą┤ąĄčƹȹ║ąĖ.

tXSR. ąŁč鹊 čéčĆąĄą▒čāąĄą╝ą░čÅ ąĘą░ą┤ąĄčƹȹ║ą░ ą╝ąĄąČą┤čā ą▓čŗčģąŠą┤ąŠą╝ ąĖąĘ čĆąĄąČąĖą╝ą░ self-refresh ąĖ ą▓čŗą┤ą░č湥ą╣ ą║ąŠą╝ą░ąĮą┤čŗ auto-refresh. čéą░ ąĘą░ą┤ąĄčƹȹ║ą░ ąĮąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮą░ ąĮą░ą┐čĆčÅą╝čāčÄ ąĖ ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčéčüčÅ, čćč鹊 ąŠąĮą░ čĆą░ą▓ąĮą░ tRC. ąŚą░ą┤ąĄčƹȹ║ą░ tRC ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą▓čŗą┤ąĄčƹȹ░ąĮą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╝ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄą╝ ą┐ąŠą╗ąĄą╣ TRAS ąĖ TRP, čćč鹊ą▒čŗ ąŠą▒ąĄčüą┐ąĄčćąĖčéčī čāčüą╗ąŠą▓ąĖąĄ tRAS + tRP Ōēź tRC.

[ą¤ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄą╝čŗąĄ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ SDRAM]

ąÆ čéą░ą▒ą╗ąĖčåąĄ 18-4 ą┐ąŠą║ą░ąĘą░ąĮčŗ ą▓čüąĄ ą▓ąŠąĘą╝ąŠąČąĮčŗąĄ čĆą░ąĘą╝ąĄčĆčŗ ą▒ą░ąĮą║ą░, ąĘąĮą░č湥ąĮąĖčÅ čłąĖčĆąĖąĮčŗ ą▒ą░ąĮą║ą░ ąĖ ą┤ąĖčüą║čĆąĄčéąĮčŗąĄ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ SDRAM, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠąČąĮąŠ ąĮą░ą┐čĆčÅą╝čāčÄ ą┐ąŠą┤ą║ą╗čÄčćąĖčéčī ą║ SDC.

ąóą░ą▒ą╗ąĖčåą░ 18-4. ą¤ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄą╝čŗąĄ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą┤ąĖčüą║čĆąĄčéąĮčŗčģ ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓ SDRAM.

| ąĀą░ąĘą╝ąĄčĆ ą┐ą░ą╝čÅčéąĖ čüąĖčüč鹥ą╝čŗ, ą╝ąĄą│ą░ą▒ą░ą╣čé |

ąĀą░ąĘą╝ąĄčĆ čüąĖčüč鹥ą╝ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ |

ą£ąĖą║čĆąŠčüčģąĄą╝čŗ SDRAM |

ąÜąŠą╗ąĖč湥čüčéą▓ąŠ ą╝ąĖą║čĆąŠčüčģąĄą╝ |

| 8 |

4M x 16 |

4M x 4 |

4 |

| 8 |

4M x 16 |

4M x 16 |

1 |

| 16 |

8M x 16 |

8M x 8 |

2 |

| 16 |

8M x 16 |

8M x 16 |

1 |

| 32 |

16M x 16 |

16M x 4 |

4 |

| 32 |

16M x 16 |

16M x 8 |

2 |

| 32 |

16M x 16 |

16M x 16 |

1 |

| 64 |

64M x 16 |

32M x 4 |

4 |

| 64 |

64M x 16 |

32M x 8 |

2 |

| 64 |

64M x 16 |

32M x 16 |

1 |

| 128 |

128M x 16 |

64M x 4 |

4 |

| 128 |

128M x 16 |

64M x 8 |

2 |

| 128 |

128M x 16 |

64M x 16 |

1 |

[ą¤čĆąĖą╝ąĄčĆčŗ ą▒ą╗ąŠą║-ą┤ąĖą░ą│čĆą░ą╝ą╝ čüąĖčüč鹥ą╝ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ SDRAM]

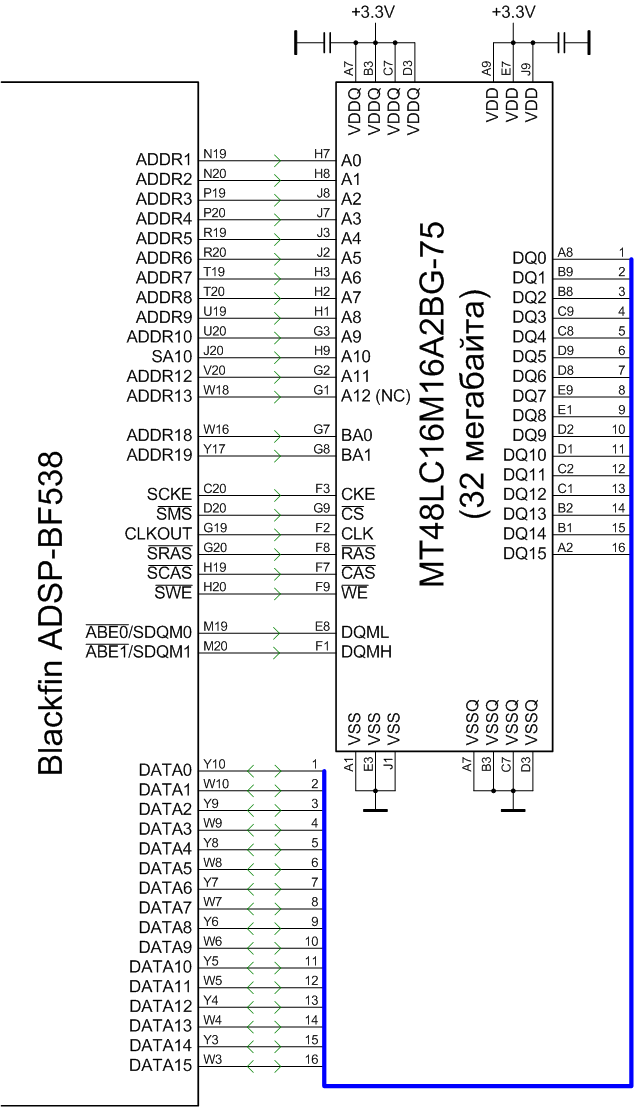

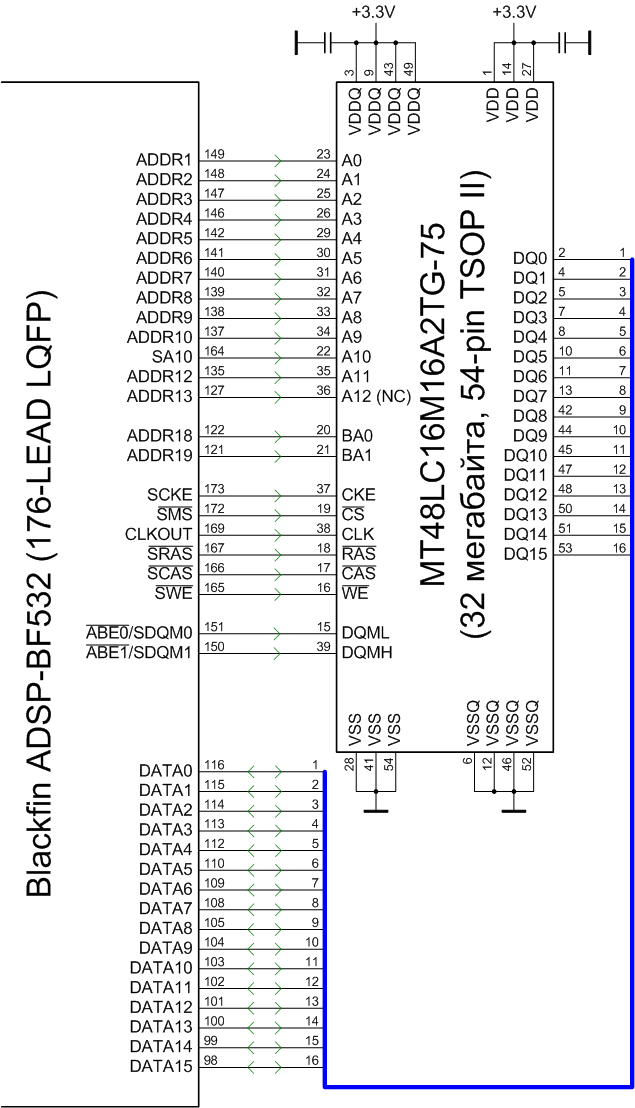

ąØą░ čĆąĖčü. 18-11a ąĖ 18-11b ą┐ąŠą║ą░ąĘą░ąĮą░ ą▒ą╗ąŠą║-ą┤ąĖą░ą│čĆą░ą╝ą╝ą░ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ą┐čĆąŠčåąĄčüčüąŠčĆą░ Blackfin ą║ SDRAM. ąÆ čŹč鹊ą╝ ą┐čĆąĖą╝ąĄčĆąĄ ąĖąĮč鹥čĆč乥ą╣čü SDRAM ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą║ ą┤ą▓čāą╝ 64 ą╝ąĄą│ą░ą▒ąĖčéąĮčŗą╝ (x8 čłąĖąĮą░ ą┤ą░ąĮąĮčŗčģ) ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ą╝ SDRAM, čćč鹊ą▒čŗ čüč乊čĆą╝ąĖčĆąŠą▓ą░čéčī ą▓ąĮąĄčłąĮąĖą╣ ą▒ą░ąĮą║ ą┐ą░ą╝čÅčéąĖ čĆą░ąĘą╝ąĄčĆąŠą╝ 16 ą╝ąĄą│ą░ą▒ą░ą╣čé. ąØą░ ąŠą▒ąĄ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ SDRAM ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠ ą┐ąŠą┤ą║ą╗čÄč湥ąĮčŗ čłąĖąĮčŗ ą░ą┤čĆąĄčüą░ ąĖ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ.

ąÆ SDC ąĖą╝ąĄąĄčéčüčÅ ąŠčéą┤ąĄą╗čīąĮčŗą╣ ą▓čŗą▓ąŠą┤ ą░ą┤čĆąĄčüą░ (SA10) ą┤ą╗čÅ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą║ąŠą╝ą░ąĮą┤čŗ auto-refresh ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠ čü ą╗čÄą▒čŗą╝ ą░čüąĖąĮčģčĆąŠąĮąĮčŗą╝ ą┤ąŠčüčéčāą┐ąŠą╝ ą║ ą┐ą░ą╝čÅčéąĖ. ąŁč鹊čé ąŠčéą┤ąĄą╗čīąĮčŗą╣ ą▓čŗą▓ąŠą┤ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé SDC ą▓čŗą┤ą░čéčī ą║ąŠą╝ą░ąĮą┤čā pre-charge ą┤ą╗čÅ SDRAM ą┐ąĄčĆąĄą┤ ą▓čŗą┤ą░č湥ą╣ ą║ąŠą╝ą░ąĮą┤čŗ auto-refresh.

ąĀąĖčü. 18-11a. ą¤čĆąĖą╝ąĄčĆ čüąĖčüč鹥ą╝čŗ čü 16 ą╝ąĄą│ą░ą▒ą░ą╣čéą░ą╝ąĖ SDRAM ąĮą░ 2 ą╝ąĖą║čĆąŠčüčģąĄą╝ą░čģ.

ąĀąĖčü. 18-11b. ą¤čĆąĖą╝ąĄčĆ čüąĖčüč鹥ą╝čŗ čü 32 ą╝ąĄą│ą░ą▒ą░ą╣čéą░ą╝ąĖ SDRAM ąĮą░ 1 ą╝ąĖą║čĆąŠčüčģąĄą╝ąĄ (MT48LC16M16A2BG-75 ą▓ ą║ąŠčĆą┐čāčüąĄ 54-ball FBGA, ą┐čĆąŠčåąĄčüčüąŠčĆ ADSP-BF538 ą▓ ą║ąŠčĆą┐čāčüąĄ 316-ball Pb-free CSP_BGA).

ąĀąĖčü. 18-11c. ą¤čĆąĖą╝ąĄčĆ čüąĖčüč鹥ą╝čŗ čü 32 ą╝ąĄą│ą░ą▒ą░ą╣čéą░ą╝ąĖ SDRAM ąĮą░ 1 ą╝ąĖą║čĆąŠčüčģąĄą╝ąĄ (MT48LC16M16A2TG-75 ą▓ ą║ąŠčĆą┐čāčüąĄ 54 ą▓čŗą▓ąŠą┤ąŠą▓ TSOP, ADSP-BF532 ą▓ ą║ąŠčĆą┐čāčüąĄ 176 ą▓čŗą▓ąŠą┤ąŠą▓ LQFP).

//ąÜąŠą┤ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ ADSP-BF532 (ą┐ąŠą┤čģąŠą┤ąĖčé ąĖ ą┤ą╗čÅ ADSP-BF538) SDRAM

// (ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ MT48LC16M16A2BG-75, čłąĖąĮą░ 16 ą▒ąĖčé, čĆą░ąĘą╝ąĄčĆ 32 ą╝ąĄą│ą░ą▒ą░ą╣čéą░)

// čćą░čüč鹊čéą░ čłąĖąĮčŗ SCLK=32.768 ą£ąōčå.

#include < cdefBF532.h >

void InitSDRAM (void)

{

/////////////////////////////////////////////

// SDRAM Refresh Rate Control Register:

*pEBIU_SDRRC = 252;

ssync();

/////////////////////////////////////////////

// SDRAM Memory Bank Control Register:

*pEBIU_SDBCTL = EBCAW_9 | // EBCAW = 01 (9 ą▒ąĖčé čłąĖčĆąĖąĮą░ ą░ą┤čĆąĄčüą░ čüč鹊ą╗ą▒čåą░)

EBSZ_32 | // EBSZ = 01 (32 ą╝ąĄą│ą░ą▒ą░ą╣čéą░ čĆą░ąĘą╝ąĄčĆ ą▓ąĮąĄčłąĮąĄą│ąŠ ą▒ą░ąĮą║ą░)

EBE; // EBE = 1 (čĆą░ąĘčĆąĄčłąĄąĮ ą▓ąĮąĄčłąĮąĖą╣ ą▒ą░ąĮą║ SDRAM)

ssync();

/////////////////////////////////////////////

// SDRAM Memory Global Control Register:

*pEBIU_SDGCTL = //FBBRW | ą▓ąĖąĘčāą░ą╗čīąĮąŠ ąĮąĄ ą▓ąĖą┤ąĮąŠ ą▓ą╗ąĖčÅąĮąĖąĄ čŹč鹊ą│ąŠ ą▒ąĖčéą░ ąĮą░ čüą║ąŠčĆąŠčüčéčī

//ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ąĘą░ą┐čāčüą║ą░ SDRAM power-up sequence ą┐ąŠčüą╗ąĄ ą┐ąĄčĆą▓ąŠą│ąŠ ą┤ąŠčüčéčāą┐ą░ ą║ SDRAM:

PSS |

//SDRAM tWR:

TWR_1 |

//SDRAM tRCD:

TRCD_1 |

//SDRAM tRP:

TRP_1 |

//SDRAM tRAS:

TRAS_1 |

//ą×ą▒ąĮąŠą▓ą╗čÅčÄčéčüčÅ ą▓čüąĄ ą▒ą░ąĮą║ąĖ:

PASR_ALL|

//SDRAM CAS latency:

CL_2 |

//ąĀą░ąĘčĆąĄčłąĖčéčī ą▓čŗą┤ą░čćčā CLKOUT, SRAS, SCAS, SWE, SDQM[1:0]:

SCTLE;

ssync();

}

ą¤čĆąŠąĄą║čé [2] VisualDSP++ 5.0 ą┤ą╗čÅ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ SDRAM (ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ MT48LC16M16A2BG-75, čłąĖąĮą░ 16 ą▒ąĖčé, čĆą░ąĘą╝ąĄčĆ 32 ą╝ąĄą│ą░ą▒ą░ą╣čéą░) ą┐ąŠą┤čģąŠą┤ąĖčé ą┤ą╗čÅ ADSP-BF532 ąĖ ADSP-BF538 (ą║ąŠą╝ą┐ąĖą╗ąĖčĆąŠą▓ą░čéčī ąĮą░ą┤ąŠ ą┤ą╗čÅ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ADSP-BF532).

ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠ ą▓čŗą▓ąŠą┤ SA10 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé SDC ą▓ąŠą╣čéąĖ ą▓ čĆąĄąČąĖą╝ self-refresh ąĖ ą▓čŗą╣čéąĖ ąĖąĘ ąĮąĄą│ąŠ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠ čü ą╗čÄą▒čŗą╝ ą░čüąĖąĮčģčĆąŠąĮąĮčŗą╝ ą┤ąŠčüčéčāą┐ąŠą╝ ą║ ą┐ą░ą╝čÅčéąĖ. ąÆčŗą▓ąŠą┤ SA10 (ą▓ą╝ąĄčüč鹊 ą▓čŗą▓ąŠą┤ą░ ADDR[11]) ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĮą░ą┐čĆčÅą╝čāčÄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą║ ą▓čŗą▓ąŠą┤čā A10 ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ SDRAM. ąÆąŠ ą▓čĆąĄą╝čÅ ą║ąŠą╝ą░ąĮą┤čŗ pre-charge ą▓čŗą▓ąŠą┤ SA10 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ, čćč鹊ą▒čŗ ą┐ąŠą║ą░ąĘą░čéčī, čćč鹊 pre-charge ą▓čüąĄ ąĄčēąĄ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮąŠ. ąÆąŠ ą▓čĆąĄą╝čÅ ą║ąŠą╝ą░ąĮą┤čŗ ą░ą║čéąĖą▓ą░čåąĖąĖ ą▒ą░ąĮą║ą░ ą▓čŗą▓ąŠą┤ąĖčé ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ ą▒ąĖčé ą░ą┤čĆąĄčüą░ čüčéčĆąŠą║ąĖ, ą║ąŠč鹊čĆčŗą╣ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąĖčĆąŠą▓ą░ąĮ ąĮą░ ą▓čģąŠą┤ A10 SDRAM. ąÆąŠ ą▓čĆąĄą╝čÅ ą║ąŠą╝ą░ąĮą┤ čćč鹥ąĮąĖčÅ ąĖ ąĘą░ą┐ąĖčüąĖ SA10 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ąĘą░ą┐čĆąĄčéą░ čäčāąĮą║čåąĖąĖ auto-pre-charge ą╝ąĖą║čĆąŠčüčģąĄą╝ SDRAM.

ąĪąĖčüč鹥ą╝čŗ SDRAM ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčé ą▓čŗą▓ąŠą┤ ADDR[11].

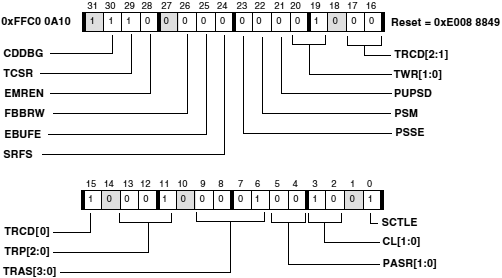

ą×ą▒čēąĖą╣ čĆąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ SDRAM (SDRAM memory global control register, EBIU_SDGCTL) čüąŠą┤ąĄčƹȹĖčé ą▓ čüąĄą▒ąĄ ą▓čüąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗąĄ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ, čüą▓čÅąĘą░ąĮąĮčŗąĄ čü ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĄą╣ ąĖ čäąĖąĘąĖč湥čüą║ąĖą╝ąĖ ą┐ą░čĆą░ą╝ąĄčéčĆą░ą╝ąĖ ą▓čĆąĄą╝ąĄąĮąĖ ą┤ąŠčüčéčāą┐ą░ ą║ SDRAM. ąØą░ čĆąĖčü. 18-12 ą┐ąŠą║ą░ąĘą░ąĮčŗ ą▒ąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ EBIU_SDGCTL (čüąĄčĆčŗą╝ čåą▓ąĄč鹊ą╝ ą┐ąŠą╝ąĄč湥ąĮčŗ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą▒ąĖčéčŗ).

ąĀąĖčü. 18-12. SDRAM Memory Global Control Register (EBIU_SDGCTL).

ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ą▓čüąĄ ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąĮčŗąĄ ą▒ąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ EBIU_SDGCTL (ą┐ąŠą║ą░ąĘą░ąĮčŗ ąĮą░ čĆąĖčüčāąĮą║ąĄ čüąĄčĆčŗą╝ čåą▓ąĄč鹊ą╝) ą┤ąŠą╗ąČąĮčŗ ą▓čüąĄą│ą┤ą░ ąĘą░ą┐ąĖčüčŗą▓ą░čéčīčüčÅ ąĮčāą╗čÅą╝ąĖ.

CDDBG. ąŚą░ą┐čĆąĄčé čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐čĆąĖ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮąĖąĖ čłąĖąĮčŗ ą▓ąĮąĄčłąĮąĄą╝čā ą╝ą░čüč鹥čĆčā. ąæąĖčé CDDBG ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčēąĄąĮąĖčÅ čāą┐čĆą░ą▓ą╗čÅčÄčēąĖčģ čüąĖą│ąĮą░ą╗ąŠą▓ SDRAM, ą║ąŠą│ą┤ą░ ą▓ąĮąĄčłąĮąĖą╣ ąĖąĮč鹥čĆč乥ą╣čü ą┐ą░ą╝čÅčéąĖ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮ ą▓ąĮąĄčłąĮąĄą╝čā ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčā. ąĢčüą╗ąĖ čŹč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1, č鹊 čāą┐čĆą░ą▓ą╗čÅčÄčēąĖąĄ čüąĖą│ąĮą░ą╗čŗ ą┐ąĄčĆąĄčģąŠą┤čÅčé ą▓ čéčĆąĄčéčīąĄ čüąŠčüč鹊čÅąĮąĖąĄ, ą║ąŠą│ą┤ą░ ą░ą║čéąĖą▓ąĮąŠ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮąĖąĄ ą┤ąŠčüčéčāą┐ą░ ą║ ą▓ąĮąĄčłąĮąĄą╣ čłąĖąĮąĄ ą┤čĆčāą│ąŠą╝čā ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčā. ąśąĮą░č湥 čŹčéąĖ čüąĖą│ąĮą░ą╗čŗ ą┐čĆąŠą┤ąŠą╗ąČą░čé čāą┐čĆą░ą▓ą╗čÅčéčīčüčÅ ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮąĖčÅ ą┤ąŠčüčéčāą┐ą░. ąĢčüą╗ąĖ ą▒ąĖčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ąĖ ą║ ą▓ąĮąĄčłąĮąĄą╣ čłąĖąĮąĄ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮ ą┤ąŠčüčéčāą┐, č鹊 čüčćąĖčéą░ąĄčéčüčÅ, čćč鹊 ą▓čüąĄ ą▓ąĮčāčéčĆąĄąĮąĮąĖąĄ ą▒ą░ąĮą║ąĖ SDRAM ąĖąĘą╝ąĄąĮčÅčÄčéčüčÅ ą▓ąĮąĄčłąĮąĖą╝ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝. ąŁč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ąĮą░ ą║ą░ąČą┤ąŠą╝ ą▒ą░ąĮą║ąĄ čéčĆąĄą▒čāąĄčéčüčÅ pre-charge ą┐ąĄčĆąĄą┤ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝, ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ąĘą░ąĮąŠą▓ąŠ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą║ąŠąĮčéčĆąŠą╗čī ąĮą░ą┤ ą▓ąĮąĄčłąĮąĄą╣ čłąĖąĮąŠą╣. ąŁč鹊 ą▓ą╗ąĖčÅąĄčé ąĮą░ čüąĖą│ąĮą░ą╗čŗ ~SRAS, ~SCAS, ~SWE, ~SMS, SA10, SCKE ąĖ CLKOUT.

TCSR. ą×ą┐čĆąĄą┤ąĄą╗čÅąĄčé č鹥čĆą╝ąŠą║ąŠą╝ą┐ąĄąĮčüąĖčĆąŠą▓ą░ąĮąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┤ą╗čÅ čüą░ą╝ąŠąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ čĆą░čüčłąĖčĆąĄąĮąĮąŠą│ąŠ čĆąĄąČąĖą╝ą░ (extended mode register) SDRAM. 0: 45┬░C, 1:85┬░C.

EMREN. 0: ąĘą░ą┐čĆąĄčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ čĆą░čüčłąĖčĆąĄąĮąĮąŠą│ąŠ čĆąĄąČąĖą╝ą░, 1: čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ. ąæąĖčé EMREN čĆą░ąĘčĆąĄčłą░ąĄčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ čĆą░čüčłąĖčĆąĄąĮąĮąŠą│ąŠ čĆąĄąČąĖą╝ą░ ą┐čĆąĖ ąĘą░ą┐čāčüą║ąĄ SDRAM. ąĀąĄą│ąĖčüčéčĆ čĆą░čüčłąĖčĆąĄąĮąĮąŠą│ąŠ čĆąĄąČąĖą╝ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čŹąĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄą╝ SDRAM ą┤ą╗čÅ ą╝ąŠą▒ąĖą╗čīąĮčŗčģ ą┐čĆąĖą╗ąŠąČąĄąĮąĖą╣ (ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą┐ą░ą╝čÅčéąĖ čü ą┐ąŠąĮąĖąČąĄąĮąĮčŗą╝ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄą╝). ąĢčüą╗ąĖ čĆą░ąĘčĆąĄčłąĄąĮ ą▒ąĖčé EMREN, č鹊 ą▒ąĖčéčŗ TCSR ąĖ PASR[1:0] čāą┐čĆą░ą▓ą╗čÅčÄčé ąĘąĮą░č湥ąĮąĖąĄą╝, ąĘą░ą┐ąĖčüą░ąĮąĮčŗą╝ ą▓ čĆąĄą│ąĖčüčéčĆ čĆą░čüčłąĖčĆąĄąĮąĮąŠą│ąŠ čĆąĄąČąĖą╝ą░. ąæąĖčéčŗ PASR ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčé, čüą║ąŠą╗čīą║ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĖčģ ą▒ą░ąĮą║ąŠą▓ SDRAM ą▒čāą┤čāčé ąŠą▒ąĮąŠą▓ą╗ąĄąĮčŗ ą▓ąŠ ą▓čĆąĄą╝čÅ self-refresh. ąæąĖčé TCSR čüąĖą│ąĮą░ą╗ąĖąĘąĖčĆčāąĄčé ą┤ą╗čÅ SDRAM ąĮą░ąĖčģčāą┤čłąĖą╣ ą┤ąĖą░ą┐ą░ąĘąŠąĮ č鹥ą╝ą┐ąĄčĆą░čéčāčĆ ą┤ą╗čÅ čüąĖčüč鹥ą╝čŗ, ąĖ ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čŹč鹊ą│ąŠ ą║ą░ą║ čćą░čüč鹊 ąĮčāąČąĮąŠ ąŠą▒ąĮąŠą▓ą╗čÅčéčī ą▓ąĮčāčéčĆąĄąĮąĮąĖąĄ ą▒ą░ąĮą║ąĖ SDRAM ą▓ąŠ ą▓čĆąĄą╝čÅ self-refresh.

FBBRW. ąæčŗčüčéčĆčŗą╣ ą┐ąĄčĆąĄčģąŠą┤ ą╝ąĄąČą┤čā čĆąĄąČąĖą╝ą░ą╝ąĖ čćč鹥ąĮąĖčÅ ąĖ ąĘą░ą┐ąĖčüąĖ, 0: ąĘą░ą┐čĆąĄčēąĄąĮąŠ, 1: čĆą░ąĘčĆąĄčłąĄąĮąŠ. ąæąĖčé FBBRW čĆą░ąĘčĆąĄčłą░ąĄčé čćč鹥ąĮąĖąĄ SDRAM, ąĘą░ ą║ąŠč鹊čĆčŗą╝ čüą╗ąĄą┤čāąĄčé ąĘą░ą┐ąĖčüčī, ą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ čåąĖą║ą╗ą░čģ. ąÆąŠ ą╝ąĮąŠą│ąĖčģ čüąĖčüč鹥ą╝ą░čģ čŹč鹊 ąĮąĄą▓ąŠąĘą╝ąŠąČąĮąŠ, ą┐ąŠč鹊ą╝čā čćč鹊 ą▓čĆąĄą╝čÅ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ ą▓čŗą▓ąŠą┤ąŠą▓ ą┤ą░ąĮąĮčŗčģ SDRAM čüą╗ąĖčłą║ąŠą╝ ą▓ąĄą╗ąĖą║ąŠ, čćč鹊 ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ą║ąŠąĮčäą╗ąĖą║čéčā ąĮą░ čłąĖąĮąĄ čü ąŠą┐ąĄčĆą░čåąĖąĄą╣ ąĘą░ą┐ąĖčüąĖ ą┐čĆąŠčåąĄčüčüąŠčĆą░. ąÜąŠą│ą┤ą░ čŹč鹊čé ą▒ąĖčé čĆą░ą▓ąĄąĮ 0, ą▓čüčéą░ą▓ą╗čÅąĄčéčüčÅ čéą░ą║č鹊ą▓čŗą╣ čåąĖą║ą╗ ą╝ąĄąČą┤čā ą┤ąŠčüčéčāą┐ąŠą╝ ąĮą░ čćč鹥ąĮąĖąĄ, ąĘą░ ą║ąŠč鹊čĆčŗą╝ ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ čüą╗ąĄą┤čāąĄčé ą┤ąŠčüčéčāą┐ ąĮą░ ąĘą░ą┐ąĖčüčī.

EBUFE. 0: ąĘą░ą┐čĆąĄčēą░ąĄčé ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčāčÄ ąĘą░ą┤ąĄčƹȹ║čā čüąĖą│ąĮą░ą╗ąŠą▓ ą░ą┤čĆąĄčüą░ ąĖ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ ą▓ąĮąĄčłąĮąĄą│ąŠ ą▒čāč乥čĆą░, 1: čĆą░ąĘčĆąĄčłą░ąĄčé. ąæąĖčé EBUFE ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčéą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĖąĮč鹥čĆą▓ą░ą╗ą░ą╝ąĖ ą▓čĆąĄą╝ąĄąĮąĖ ą▓ąĮąĄčłąĮąĄą│ąŠ ą▒čāč乥čĆą░. ąÆ čüąĖčéčāą░čåąĖčÅčģ, ą│ą┤ąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą▒čāč乥čĆąĖąĘąŠą▓ą░ąĮąĮčŗąĄ ą╝ąŠą┤čāą╗ąĖ SDRAM ąĖą╗ąĖ ą┤ąĖčüą║čĆąĄčéąĮčŗąĄ čĆąĄą│ąĖčüčéčĆčŗ-ą▒čāč乥čĆčŗ ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čāą┐čĆą░ą▓ą╗čÅčÄčēąĖą╝ąĖ ą▓čģąŠą┤ą░ą╝ąĖ SDRAM, EBUFE ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1. ąśčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ čŹč鹊ą╣ čāčüčéą░ąĮąŠą▓ą║ąĖ ą┤ąŠą▒ą░ą▓ą╗čÅąĄčé čåąĖą║ą╗ ą▒čāč乥čĆąĖąĘą░čåąĖąĖ ą┤ą░ąĮąĮčŗčģ ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ąŠą▓ ąĮą░ čćč鹥ąĮąĖąĄ ąĖ ąĘą░ą┐ąĖčüčī. ąĪą╝. "ąŻčüčéą░ąĮąŠą▓ą║ą░ ąŠą┐čåąĖąĖ čéą░ą╣ą╝ąĖąĮą│ą░ ą▒čāč乥čĆąĖąĘą░čåąĖąĖ SDRAM (EBUFE)" ą┤ą╗čÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ą┐ąŠ ą┐ąŠą▓ąŠą┤čā ą▒ąĖčéą░ EBUFE.

SRFS. 0: ąĘą░ą┐čĆąĄčé čüą░ą╝ąŠąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ SDRAM, 1: čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ. ąÜąŠą│ą┤ą░ ą▒ąĖčé SRFS čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1, čüčĆą░ą▒ą░čéčŗą▓ą░ąĄčé čĆąĄąČąĖą╝ self-refresh. ąÜą░ą║ č鹊ą╗čīą║ąŠ SDC ąĘą░ą▓ąĄčĆčłąĖčé ą░ą║čéąĖą▓ąĮčāčÄ ą┐ąĄčĆąĄą┤ą░čćčā, SDC ą▓čŗą┐ąŠą╗ąĮąĖčé ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą║ąŠą╝ą░ąĮą┤ ą┤ą╗čÅ ą┐ąĄčĆąĄą▓ąŠą┤ą░ SDRAM ą▓ čĆąĄąČąĖą╝ self-refresh. ąĪą╗ąĄą┤čāčÄčēąĖą╣ ą┤ąŠčüčéčāą┐ ą║ čĆą░ąĘčĆąĄčłąĄąĮąĮąŠą╝čā ą▒ą░ąĮą║čā SDRAM ąĘą░čüčéą░ą▓ąĖčé SDC ą▓čŗą┐ąŠą╗ąĮąĖčéčī ą║ąŠą╝ą░ąĮą┤čŗ ą┤ą╗čÅ ą▓čŗčģąŠą┤ą░ SDRAM ąĖąĘ čĆąĄąČąĖą╝ą░ self-refresh ąĖ ąŠčüčāčēąĄčüčéą▓ąĖčéčī ą┤ąŠčüčéčāą┐. ąĪą╝. čĆą░ąĘą┤ąĄą╗ "ąÆčģąŠą┤ ą▓ čĆąĄąČąĖą╝ Self-Refresh (SRFS) ąĖ ą▓čŗčģąŠą┤ ąĖąĘ ąĮąĄą│ąŠ" ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ą┐ąŠ ą▒ąĖčéčā SRFS.

PSSE. ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ąĘą░ą┐čāčüą║ą░ SDRAM power-up sequence. 0: ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░, 1: čĆą░ąĘčĆąĄčłą░ąĄčé power-up sequence ą┐čĆąĖ čüą╗ąĄą┤čāčÄčēąĄą╝ ąŠą▒čĆą░čēąĄąĮąĖąĖ ą║ SDRAM.

PSM. ą×ą┐čĆąĄą┤ąĄą╗čÅąĄčé, ą║ą░ą║ ą▒čāą┤ąĄčé čĆą░ą▒ąŠčéą░čéčī SDRAM power-up sequence. 0: ąŠą┐ąĄčĆą░čåąĖąĖ Pre-charge, 8 čåąĖą║ą╗ąŠą▓ CBR refresh, čāčüčéą░ąĮąŠą▓ą║ą░ čĆąĄą│ąĖčüčéčĆą░ čĆąĄąČąĖą╝ą░ (mode register SDRAM). 1: ąŠą┐ąĄčĆą░čåąĖąĖ Pre-charge, čāčüčéą░ąĮąŠą▓ą║ą░ čĆąĄą│ąĖčüčéčĆą░ čĆąĄąČąĖą╝ą░ (mode register SDRAM), 8 čåąĖą║ą╗ąŠą▓ CBR.

ąæąĖčéčŗ PSM ąĖ PSSE čĆą░ą▒ąŠčéą░čÄčé čüąŠą▓ą╝ąĄčüčéąĮąŠ, čćč鹊ą▒čŗ čāą║ą░ąĘą░čéčī ąĖ ą▓čŗąĘą▓ą░čéčī čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą▓ą║ą╗čÄč湥ąĮąĖčÅ SDRAM (power-up sequence, ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ). ąĢčüą╗ąĖ PSM čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1, č鹊 SDC ą▓čŗą┐ąŠą╗ąĮčÅąĄčé ą║ąŠą╝ą░ąĮą┤čā pre-charge, ąĘą░ ą║ąŠč鹊čĆąŠą╣ ą▓čŗą┤ą░ąĄčé ą║ąŠą╝ą░ąĮą┤čā ąĘą░ą│čĆčāąĘą║ąĖ čĆąĄą│ąĖčüčéčĆą░ čĆąĄąČąĖą╝ą░, ąĖ ąĘą░č鹥ą╝ ą▓čŗą┐ąŠą╗ąĮčÅąĄčé 8 čåąĖą║ą╗ąŠą▓ auto-refresh. ąĢčüą╗ąĖ ą▒ąĖčé PSM ąŠčćąĖčēąĄąĮ, č鹊 SDC ą▓čŗą┐ąŠą╗ąĮčÅąĄčé ą║ąŠą╝ą░ąĮą┤čā, ąĘą░ ą║ąŠč鹊čĆąŠą╣ čüą╗ąĄą┤čāąĄčé 8 čåąĖą║ą╗ąŠą▓ auto-refresh, ąĖ ąĘą░č鹥ą╝ ąĖą┤ąĄčé ą║ąŠą╝ą░ąĮą┤ą░ ąĘą░ą│čĆčāąĘą║ąĖ čĆąĄą│ąĖčüčéčĆą░ čĆąĄąČąĖą╝ą░. ąöąŠą╗ąČąĮčŗ ą┐čĆąŠąĖąĘąŠą╣čéąĖ 2 čüąŠą▒čŗčéąĖčÅ ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ SDC ą▓čŗą┐ąŠą╗ąĮąĖčé SDRAM power-up sequence:

ŌĆó ąæąĖčé PSSE ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1 čćč鹊ą▒čŗ čĆą░ąĘčĆąĄčłąĖčéčī SDRAM power-up sequence.

ŌĆó ąöąŠčüčéčāą┐ ąĮą░ čćč鹥ąĮąĖąĄ ąĖą╗ąĖ ąĘą░ą┐ąĖčüčī ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮ ą┤ą╗čÅ čĆą░ąĘčĆąĄčłąĄąĮąĮąŠą│ąŠ ą░ą┤čĆąĄčüąĮąŠą│ąŠ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ą░, čćč鹊ą▒čŗ ą┐čĆąĄą┤ąŠčüčéą░ą▓ąĖčéčī ą▓ąĮąĄčłąĮčÄčÄ čłąĖąĮčā ą┤ą╗čÅ SDC, čéą░ą║ čćč鹊ą▒čŗ ą╝ąŠą│ą╗ą░ ą┐čĆąŠą╣čéąĖ SDRAM power-up sequence.

ą¤čĆąŠąĖąĘąŠą╣ą┤ąĄčé SDRAM power-up sequence, ąĘą░ ą║ąŠč鹊čĆąŠą╣ ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ čüą╗ąĄą┤čāąĄčé ą┐ąĄčĆąĄą┤ą░čćą░ čćč鹥ąĮąĖčÅ ąĖą╗ąĖ ąĘą░ą┐ąĖčüąĖ, ą║ąŠč鹊čĆą░čÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ą╗ą░čüčī ą┤ą╗čÅ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖčÅ SDRAM power-up sequence. ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 ąĘą░ą┤ąĄčƹȹ║ą░ ą┤ą╗čÅ ą┐ąĄčĆą▓ąŠą╣ ąŠą┐ąĄčĆą░čåąĖąĖ ą┤ąŠčüčéčāą┐ą░ ą║ SDRAM ą┤ąŠą▓ąŠą╗čīąĮąŠ ą▒ąŠą╗čīčłą░čÅ ąĖąĘ-ąĘą░ č鹊ą│ąŠ, čćč鹊 SDRAM power-up sequence ąĘą░ąĮąĖą╝ą░ąĄčé ą╝ąĮąŠąČąĄčüčéą▓ąŠ čéą░ą║č鹊ą▓ ą┤ą╗čÅ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ.

ą¤ąĄčĆąĄą┤ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄą╝ SDC power-up sequence čāą▒ąĄą┤ąĖč鹥čüčī, čćč鹊 SDRAM ą┐ąŠą╗čāčćą░ąĄčé čüčéą░ą▒ąĖą╗čīąĮąŠąĄ ą┐ąĖčéą░ąĮąĖąĄ ą┐čĆą░ą▓ąĖą╗čīąĮąŠ čéą░ą║čéąĖčĆčāąĄčéčüčÅ ąĮąĄą║ąŠč鹊čĆčŗą╣ ą┐čĆąŠą╝ąĄąČčāč鹊ą║ ą▓čĆąĄą╝ąĄąĮąĖ, ą║ą░ą║ čŹč鹊 čāą║ą░ąĘą░ąĮąŠ ą▓ ą┤ą░čéą░čłąĖč鹥 ąĮą░ SDRAM.

PUPSD. ą×ą┐čĆąĄą┤ąĄą╗čÅąĄčé ąĘą░ą┤ąĄčƹȹ║čā ąĘą░ą┐čāčüą║ą░ power-up. 0: ąĮąĄčé ąĘą░ą┤ąĄčƹȹ║ąĖ ą┐ąĄčĆąĄą┤ ą┐ąĄčĆą▓ąŠą╣ ą║ąŠą╝ą░ąĮą┤ąŠą╣ Pre-charge, 1: ą┤ąŠą▒ą░ą▓ąĖčéčüčÅ 15 čéą░ą║č鹊ą▓ ąĘą░ą┤ąĄčƹȹ║ąĖ ą┐ąĄčĆąĄą┤ ą┐ąĄčĆą▓ąŠą╣ ą║ąŠą╝ą░ąĮą┤ąŠą╣ Pre-charge. ąæąĖčé ąĘą░ą┤ąĄčƹȹ║ąĖ ąĘą░ą┐čāčüą║ą░ power-up (PUPSD) ąŠą┐čåąĖąŠąĮą░ą╗čīąĮąŠ ąĘą░ą┤ąĄčƹȹĖą▓ą░ąĄčé power-up start sequence ąĮą░ 15 čéą░ą║č鹊ą▓ SCLK. ąŁč鹊 ą┐ąŠą╗ąĄąĘąĮąŠ ą┤ą╗čÅ ą╝ąĮąŠą│ąŠą┐čĆąŠčåąĄčüčüąŠčĆąĮčŗčģ čüąĖčüč鹥ą╝, ą║ąŠč鹊čĆčŗąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčé ąŠą▒čēčāčÄ ą▓ąĮąĄčłąĮčÄčÄ ą┐ą░ą╝čÅčéčī SDRAM. ąĢčüą╗ąĖ čłąĖąĮą░ ą▒čŗą╗ą░ čĆą░ąĮąĄąĄ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮą░ ą┤čĆčāą│ąŠą╝čā ą┐čĆąŠčåąĄčüčüąŠčĆčā ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ą▒čŗą╗ąĖ ą▓čŗą┐ąŠą╗ąĮąĄąĮčŗ power-up ąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮ čĆąĄąČąĖą╝ self-refresh, ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ą▓ą╗ą░ą┤ąĄąĮąĖčÅ čłąĖąĮąŠą╣, č鹊 ą▒ąĖčé PUPSD ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░ąĮąĖčÅ ą┤ąŠčüčéą░č鹊čćąĮąŠą│ąŠ ą┐ąĄčĆąĖąŠą┤ą░ ąĮąĄą░ą║čéąĖą▓ąĮąŠčüčéąĖ ąŠčé self-refresh ą┤ąŠ ą┐ąĄčĆą▓ąŠą╣ ą║ąŠą╝ą░ąĮą┤čŗ pre-charge ą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ power-up, čćč鹊ą▒čŗ čāą┤ąŠą▓ą╗ąĄčéą▓ąŠčĆąĖčéčī ą▓čĆąĄą╝ąĄąĮąĖ ą▓čŗčģąŠą┤ą░ ąĖąĘ self-refresh (tXSR) ą╝ąĖą║čĆąŠčüčģąĄą╝ SDRAM.

TWR[1:0]. ąŚą░ą┤ą░ąĄčé ą▓čĆąĄą╝čÅ SDRAM tWR ą▓ čéą░ą║č鹊ą▓čŗčģ čåąĖą║ą╗ą░čģ, ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ą▓čŗą▒ąŠčĆ ąĘą░ą┤ąĄčƹȹ║ąĖ ą┐čĆąĄą┤ąĘą░čĆčÅą┤ą░ ą┤ą╗čÅ ąĘą░ą┐ąĖčüąĖ (Write to Pre-Charge Delay, TWR). ąŚąĮą░č湥ąĮąĖąĄ tWR ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé čéčĆąĄą▒čāąĄą╝čāčÄ ąĘą░ą┤ąĄčƹȹ║čā (ą▓ čéą░ą║čéą░čģ) ą╝ąĄąČą┤čā ą╝ąŠą╝ąĄąĮč鹊ą╝ ą▓čĆąĄą╝ąĄąĮąĖ, ą║ąŠą│ą┤ą░ SDC ą▓čŗą┤ą░ąĄčé ą║ąŠą╝ą░ąĮą┤čā ąĘą░ą┐ąĖčüąĖ (ą║ąŠč鹊čĆą░čÅ ąĘą░ą┐čāčüą║ą░ąĄčé ąĘą░ą┐ąĖčüčī ą┤ą░ąĮąĮčŗčģ) ąĖ ą║ąŠą╝ą░ąĮą┤ąŠą╣ pre-charge. ąŁč鹊čé ą┐ą░čĆą░ą╝ąĄčéčĆ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÄ čāą┤ąŠą▓ą╗ąĄčéą▓ąŠčĆčÅčéčī čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅ ą┐ąŠ ąĮąĄąŠą▒čģąŠą┤ąĖą╝čŗą╝ ąĖąĮč鹥čĆą▓ą░ą╗ą░ą╝ ą▓čĆąĄą╝ąĄąĮąĖ čüąŠ čüč鹊čĆąŠąĮčŗ ą╝ąĖą║čĆąŠčüčģąĄą╝ SDRAM.

ąæąĖčéčŗ TWR ą▓ čĆąĄą│ąĖčüčéčĆąĄ EBIU_SDGCTL ą▓čŗą▒ąĖčĆą░čÄčé ąĘąĮą░č湥ąĮąĖąĄ tWR, ą╝ąŠąČąĮąŠ ą▓čŗą▒čĆą░čéčī ąŠčé 1 ą┤ąŠ 3 čéą░ą║č鹊ą▓čŗčģ čåąĖą║ą╗ąŠą▓. ąØą░ą┐čĆąĖą╝ąĄčĆ: TWR = 00 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ, TWR = 01 ąĘą░ą┤ąĄčƹȹ║ą░ 1 čéą░ą║č鹊ą▓čŗą╣ čåąĖą║ą╗, TWR = 10 ąĘą░ą┤ąĄčƹȹ║ą░ 2 čéą░ą║č鹊ą▓čŗčģ čåąĖą║ą╗ą░, TWR = 11 ąĘą░ą┤ąĄčƹȹ║ą░ 3 čéą░ą║č鹊ą▓čŗčģ čåąĖą║ą╗ą░.

TRCD[2:1]. ąĪčéą░čĆčłąĖąĄ ą▒ąĖčéčŗ ą┐ąŠą╗čÅ, ą║ąŠč鹊čĆąŠąĄ ąĘą░ą┤ą░ąĄčé ą▓čĆąĄą╝čÅ SDRAM tRCD ą▓ čéą░ą║č鹊ą▓čŗčģ čåąĖą║ą╗ą░čģ.

TRCD. ą£ą╗ą░ą┤čłąĖą╣ ą▒ąĖčé ą┐ąŠą╗čÅ, ą║ąŠč鹊čĆąŠąĄ ąĘą░ą┤ą░ąĄčé ą▓čĆąĄą╝čÅ SDRAM tRCD ą▓ čéą░ą║č鹊ą▓čŗčģ čåąĖą║ą╗ą░čģ.

ąæąĖčéčŗ TRCD[2:0] ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčé ą▓čŗą▒ąŠčĆ ąĘą░ą┤ąĄčƹȹ║ąĖ ą╝ąĄąČą┤čā čüčéčĆąŠą▒ą░ą╝ąĖ čüčéčĆąŠą║ąĖ ąĖ čüč鹊ą╗ą▒čåą░ (RAS to CAS Delay, TRCD). ąŚąĮą░č湥ąĮąĖąĄ tRCD (ąĘą░ą┤ąĄčƹȹ║ą░ ą╝ąĄąČą┤čā RAS ąĖ CAS) ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ąĘą░ą┤ąĄčƹȹ║čā ą┤ą╗čÅ ą┐ąĄčĆą▓ąŠą╣ ą║ąŠą╝ą░ąĮą┤čŗ čćč鹥ąĮąĖčÅ ąĖą╗ąĖ ąĘą░ą┐ąĖčüąĖ ą┐ąŠčüą╗ąĄ ą║ąŠą╝ą░ąĮą┤čŗ ą░ą║čéąĖą▓ą░čåąĖąĖ čüčéčĆąŠą║ąĖ, čāą║ą░ąĘą░ąĮąĮąŠą╣ ą▓ čéą░ą║č鹊ą▓čŗčģ čåąĖą║ą╗ą░čģ. ą¤ą░čĆą░ą╝ąĄčéčĆ tRCD ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐čĆąŠčåąĄčüčüąŠčĆčā ą░ą┤ą░ą┐čéąĖčĆąŠą▓ą░čéčīčüčÅ ą┐ąŠą┤ čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅ ąĖąĮč鹥čĆą▓ą░ą╗ąŠą▓ ą▓čĆąĄą╝ąĄąĮąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝ SDRAM čüąĖčüč鹥ą╝čŗ.

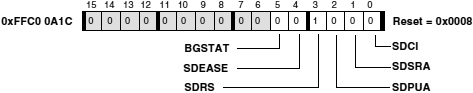

ąæąĖčéčŗ tRCD ą▓ čĆąĄą│ąĖčüčéčĆąĄ EBIU_SDGCTL ą┐ąŠąĘą▓ąŠą╗čÅčÄčé ą▓čŗą▒čĆą░čéčī ąĘąĮą░č湥ąĮąĖąĄ tRCD, ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą▒čĆą░ąĮąŠ ą╗čÄą▒ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ąŠčé 1 ą┤ąŠ 7. ąØą░ą┐čĆąĖą╝ąĄčĆ: TRCD = 000 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ (ąĮąĄ ą┤ą░ąĄčé čŹčäč乥ą║čéą░), TRCD = 001 ąĘą░ą┤ąĄčƹȹ║ą░ 1 čéą░ą║č鹊ą▓čŗą╣ čåąĖą║ą╗, TRCD = 010 ąĘą░ą┤ąĄčƹȹ║ą░ 2 čéą░ą║č鹊ą▓čŗčģ čåąĖą║ą╗ą░, TRCD = 111 ąĘą░ą┤ąĄčƹȹ║ą░ 7 čéą░ą║č鹊ą▓čŗčģ čåąĖą║ą╗ąŠą▓.