|

ąŻ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ADSP-BF538 Blackfin ąĄčüčéčī 3 čłčéčāą║ąĖ SPI-čüąŠą▓ą╝ąĄčüčéąĖą╝čŗčģ ąĖąĮč鹥čĆč乥ą╣čüą░ (čćč鹊 čéą░ą║ąŠąĄ SPI čüą╝. [2]). ą×ą▒čŗčćąĮąŠ čā SPI ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ 4 čüąĖą│ąĮą░ą╗čīąĮčŗčģ ą▓čŗą▓ąŠą┤ą░: 2 ą┤ą╗čÅ ą┐čĆąĖąĄą╝ą░ ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ, 1 ą┤ą╗čÅ čéą░ą║č鹊ą▓, ąĖ ąĄčēąĄ ąŠą┤ąĖąĮ ą┤ą╗čÅ ą┐ąŠą┤ą░čćąĖ čüąĖą│ąĮą░ą╗ą░ ą▓čŗą▒ąŠčĆą║ąĖ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą╝čā čāčüčéčĆąŠą╣čüčéą▓čā (ąĖąĮąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ 3 čüąĖą│ąĮą░ą╗ą░, ą║ąŠą│ą┤ą░ ąĮąĄ ąĮčāąČąĮąŠ ą┤ą░ą▓ą░čéčī čüąĖą│ąĮą░ą╗ ą▓čŗą▒ąŠčĆą║ąĖ, ąĖą╗ąĖ ą┤ą░ąČąĄ 2 čüąĖą│ąĮą░ą╗ą░, ąĄčüą╗ąĖ čéčĆąĄą▒čāąĄčéčüčÅ ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī ą┤ą░ąĮąĮčŗąĄ č鹊ą╗čīą║ąŠ ą▓ ąŠą┤ąĮąŠą╝ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĖ). ąÆ čéą░ą║ąŠą╣ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą╝ąŠąČąĮąŠ ąŠčĆą│ą░ąĮąĖąĘąŠą▓ą░čéčī ą┤ąŠčüčéą░č鹊čćąĮąŠ ą▒čŗčüčéčĆčŗą╣ ą┤čāą┐ą╗ąĄą║čüąĮčŗą╣ ą║ą░ąĮą░ą╗ čüą▓čÅąĘąĖ. SPI ą┐čĆąŠčåąĄčüčüąŠčĆą░ BF538 ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé čĆą░ą▒ąŠčéčā ą▓ čĆąĄąČąĖą╝ąĄ master, slave, ą░ čéą░ą║ąČąĄ čĆąĄąČąĖą╝ čü ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ master. ą£ąŠąČąĮąŠ ą╝ąĄąĮčÅčéčī čüą║ąŠčĆąŠčüčéčī ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖ ą┐ąŠą╗čÅčĆąĮąŠčüčéčī/čäą░ąĘčā čüąĖą│ąĮą░ą╗ą░ čéą░ą║č鹊ą▓. ąśčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ ą┤čĆą░ą╣ą▓ąĄčĆą░ čü ąŠčéą║čĆčŗčéčŗą╝ čüč鹊ą║ąŠą╝ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čéčī čüčåąĄąĮą░čĆąĖą╣ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ čü ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ master ą▒ąĄąĘ ąŠą┐ą░čüąĮąŠčüčéąĖ čüą║ą▓ąŠąĘąĮčŗčģ č鹊ą║ąŠą▓ ą╝ąĄąČą┤čā ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ ą▓čŗčģąŠą┤ą░ą╝ąĖ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: čéą░ą╝, ą│ą┤ąĄ ą▓ č鹥ą║čüč鹥 ą▒čāą┤ąĄčé čāą║ą░ąĘą░ąĮąŠ ADSP-BF538 ąĖą╗ąĖ ą┐čĆąŠčüč鹊 BF538, ąĖą╝ąĄąĄčéčüčÅ ą▓ ą▓ąĖą┤čā ą┤ą▓ąĄ ą╝ąŠą┤ąĄą╗ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ADSP-BF538 ąĖ ADSP-BF538F. ąØąĄą┐ąŠąĮčÅčéąĮčŗąĄ č鹥čĆą╝ąĖąĮčŗ ąĖ čüąŠą║čĆą░čēąĄąĮąĖčÅ čüą╝. ą▓ čĆą░ąĘą┤ąĄą╗ąĄ "ąĪą╗ąŠą▓ą░čĆąĖą║" čüčéą░čéčīąĖ [5].

ąÆąŠčé čéąĖą┐ąĖčćąĮčŗąĄ ą┐čĆąĖą╝ąĄčĆčŗ ą┐čĆąĖą╝ąĄąĮąĄąĮąĖčÅ ąĖąĮč鹥čĆč乥ą╣čüą░ SPI ą▓ 菹╗ąĄą║čéčĆąŠąĮąĖą║ąĄ:

ŌĆó ą×ą▒ą╝ąĄąĮ ą┤ą░ąĮąĮčŗą╝ąĖ čü ą┤čĆčāą│ąĖą╝ąĖ CPU ąĖą╗ąĖ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ą╝ąĖ.

ŌĆó ą¤ąŠą┤ą║ą╗čÄč湥ąĮąĖąĄ ą░ą┐ą┐ą░čĆą░čéąĮčŗčģ ą║ąŠą┤ąĄą║ąŠą▓.

ŌĆó ą£ąĖą║čĆąŠčüčģąĄą╝čŗ ą░ąĮą░ą╗ąŠą│ąŠ-čåąĖčäčĆąŠą▓čŗčģ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░č鹥ą╗ąĄą╣ (ADC).

ŌĆó ą£ąĖą║čĆąŠčüčģąĄą╝čŗ čåąĖčäčĆąŠ-ą░ąĮą░ą╗ąŠą│ąŠą▓čŗčģ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░č鹥ą╗ąĄą╣ (DAC).

ŌĆó ą¤čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░č鹥ą╗ąĖ čćą░čüč鹊čé ą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ.

ŌĆó ą”ąĖčäčĆąŠą▓čŗąĄ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ąĖ ąĖ ą┐čĆąĖąĄą╝ąĮąĖą║ąĖ ą░čāą┤ąĖąŠ-čüčéą░ąĮą┤ą░čĆč鹊ą▓ SP/DIF ąĖą╗ąĖ AES/EBU.

ŌĆó ąöąĖčüą┐ą╗ąĄąĖ LCD, OLED.

ŌĆó ąĀąĄą│ąĖčüčéčĆčŗ čüą┤ą▓ąĖą│ą░, čĆą░čüčłąĖčĆąĖč鹥ą╗ąĖ ą┐ąŠčĆč鹊ą▓ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░.

ŌĆó ąÜčĆąĖčüčéą░ą╗ą╗čŗ FPGA čü 菹╝čāą╗čÅčåąĖąĄą╣ ąĖąĮč鹥čĆč乥ą╣čüą░ SPI.

ŌĆó ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ ą╝ąĖą║čĆąŠčüčģąĄą╝ ą┐ą░ą╝čÅčéąĖ ąĖ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓.

ŌĆó ą¤ąŠą┤ą║ą╗čÄč湥ąĮąĖąĄ ą╝ąĖą║čĆąŠčüčģąĄą╝ ą┐ą░ą╝čÅčéąĖ, ą▓ č鹊ą╝ čćąĖčüą╗ąĄ ąĖ FLASH-ą║ą░čĆčé SD/miniSD/microSD.

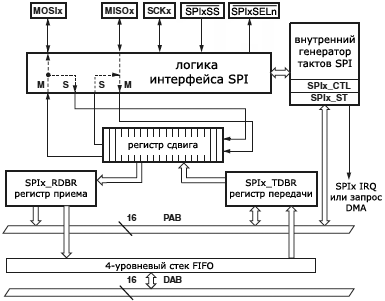

ąØą░ čĆąĖčü. 10-1 ą┐ąŠą║ą░ąĘą░ąĮą░ ą▒ą╗ąŠą║-čüčģąĄą╝ą░ SPI ą┐čĆąŠčåąĄčüčüąŠčĆą░ Blackfin. ąŚą┤ąĄčüčī MOSIx čŹč鹊 čüąĖą│ąĮą░ą╗ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ą▓čŗčģąŠą┤ master ą▓čģąŠą┤ slave, MISOx čüąĖą│ąĮą░ą╗ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ą▓čģąŠą┤ master ą▓čŗčģąŠą┤ slave, SCKx čŹč鹊 čüąĖą│ąĮą░ą╗ čéą░ą║č鹊ą▓, ~SPIxSS čŹč鹊 čüąĖą│ąĮą░ą╗ ą▓čŗą▒ąŠčĆą║ąĖ ą┤ą╗čÅ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (ą▓ą╝ąĄčüč鹊 x ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠą┤čüčéą░ą▓ą╗ąĄąĮą░ čåąĖčäčĆą░ 0, 1 ąĖą╗ąĖ 2). ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ąĮą░ ą┤ąĖą░ą│čĆą░ą╝ą╝ąĄ čüąĖą│ąĮą░ą╗čŗ MOSIx, MISOx, SCKx ą┐ąŠą║ą░ąĘą░ąĮčŗ ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╝ąĖ ą┐ąŠč鹊ą╝čā, čćč鹊 ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĘą░ą▓ąĖčüąĖčé ąŠčé čĆąĄąČąĖą╝ą░ čĆą░ą▒ąŠčéčŗ SPI - čŹč鹊 ą╝ąŠąČąĄčé ą▒čŗčéčī čĆąĄąČąĖą╝ master (ą│ą╗ą░ą▓ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮą░ čłąĖąĮąĄ) ąĖą╗ąĖ čĆąĄąČąĖą╝ slave (ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ). ąØąŠ ąĮą░ čüą░ą╝ąŠą╝ ą┤ąĄą╗ąĄ ą▓ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé ą▓čĆąĄą╝ąĄąĮąĖ ą┐ąŠčĆčé SPI ą╝ąŠąČąĄčé ą▒čŗčéčī ąĮą░čüčéčĆąŠąĄąĮ ą╗ąĖą▒ąŠ ą║ą░ą║ master, ą╗ąĖą▒ąŠ ą║ą░ą║ slave, ą┐ąŠčŹč鹊ą╝čā ą▓čüąĄ čüąĖą│ąĮą░ą╗čŗ ą▒čāą┤čāčé ąĖčüą║ą╗čÄčćąĖč鹥ą╗čīąĮąŠ ąŠą┤ąĮąŠąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╝ąĖ.

ąĀąĖčü. 10-1. ąæą╗ąŠą║-ą┤ąĖą░ą│čĆą░ą╝ą╝ą░ SPI.

| ąÆčŗą▓ąŠą┤ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| MOSIx |

Master Output Slave Input: ą▓čŗčģąŠą┤ ą┤ą░ąĮąĮčŗčģ ą│ą╗ą░ą▓ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ąĖ ą▓čģąŠą┤ ą┤ą░ąĮąĮčŗčģ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ. |

| MISOx |

Master Input Slave Output: ą▓čģąŠą┤ ą┤ą░ąĮąĮčŗčģ ą│ą╗ą░ą▓ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ąĖ ą▓čŗčģąŠą┤ ą┤ą░ąĮąĮčŗčģ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ. |

| SCKx |

ąóą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗, ą║ąŠč鹊čĆčŗą╣ ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ą│ą╗ą░ą▓ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ. ąöą╗čÅ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ čŹč鹊čé čüąĖą│ąĮą░ą╗ čÅą▓ą╗čÅąĄčéčüčÅ ą▓čģąŠą┤ąŠą╝. |

| ~SPIxSS |

ąĪąĖą│ąĮą░ą╗ ą░ą║čéąĖą▓ą░čåąĖąĖ ą┤ą╗čÅ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░, ą▓čŗčüčéą░ą▓ą╗čÅąĄą╝čŗą╣ ą│ą╗ą░ą▓ąĮčŗą╝ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝. ąÉą║čéąĖą▓ąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 0. ąöą╗čÅ ą┐čĆąŠčåąĄčüčüąŠčĆą░ Blackfin čŹč鹊čé čüąĖą│ąĮą░ą╗ ą▓čüąĄą│ą┤ą░ čÅą▓ą╗čÅąĄčéčüčÅ ą▓čģąŠą┤ąŠą╝, ąĮąŠ ąĄą│ąŠ čäčāąĮą║čåąĖčÅ čĆą░ąĘą╗ąĖčćą░ąĄčéčüčÅ ą┤ą╗čÅ čĆąĄąČąĖą╝ąŠą▓ master ąĖ slave. ąÜąŠą│ą┤ą░ Blackfin čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ SPI (slave), č鹊 čŹč鹊 čüąĖą│ąĮą░ą╗ ą▓čŗą▒ąŠčĆą║ąĖ ą┤ą╗čÅ ąĮąĄą│ąŠ. ąÜąŠą│ą┤ą░ Blackfin čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą│ą╗ą░ą▓ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ SPI (master), č鹊 čŹč鹊čé ą▓čģąŠą┤ čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ čüąĖą│ąĮą░ą╗ ąŠčłąĖą▒ą║ąĖ. |

| ~SPIxSELn |

ąĪąĖą│ąĮą░ą╗ ą░ą║čéąĖą▓ą░čåąĖąĖ ą┤ą╗čÅ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░, ą▓čŗčüčéą░ą▓ą╗čÅąĄą╝čŗą╣ ą│ą╗ą░ą▓ąĮčŗą╝ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝. ąÉą║čéąĖą▓ąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 0. ąöą╗čÅ ą┐čĆąŠčåąĄčüčüąŠčĆą░ Blackfin čŹč鹊čé čüąĖą│ąĮą░ą╗ čÅą▓ą╗čÅąĄčéčüčÅ ą▓čŗčģąŠą┤ąŠą╝. |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▓ą╝ąĄčüč鹊 ą▒čāą║ą▓čŗ x ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠą┤čüčéą░ą▓ą╗ąĄąĮą░ čåąĖčäčĆą░ 0, 1 ąĖą╗ąĖ 2, ąŠą▒ąŠąĘąĮą░čćą░čÄčēą░čÅ ąĮąŠą╝ąĄčĆ ąĖąĮč鹥čĆč乥ą╣čüą░ SPI. ąÆą╝ąĄčüč鹊 ą▒čāą║ą▓čŗ n ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠą┤čüčéą░ą▓ą╗ąĄąĮą░ čåąĖčäčĆą░ 1 ą┤ą╗čÅ ąĖąĮč鹥čĆč乥ą╣čüąŠą▓ SPI1 ąĖ SPI2, ąĖą╗ąĖ čåąĖčäčĆą░ 1..7 ą┤ą╗čÅ ąĖąĮč鹥čĆč乥ą╣čüą░ SPI0.

ąśąĮč鹥čĆč乥ą╣čü SPI ą▓ čüčāčēąĮąŠčüčéąĖ ą┐ąŠčüčéčĆąŠąĄąĮ ąĮą░ ąŠčüąĮąŠą▓ąĄ čĆąĄą│ąĖčüčéčĆą░ čüą┤ą▓ąĖą│ą░, ą║ąŠč鹊čĆčŗą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ ą┐ąĄčĆąĄą┤ą░ąĄčé ąĖ ą┐čĆąĖąĮąĖą╝ą░ąĄčé ą▒ąĖčéčŗ ą┤ą░ąĮąĮčŗčģ, ą┐ąŠ ąŠą┤ąĮąŠą╝čā ą▒ąĖčéčā ąĘą░ čéą░ą║čé čüąĖą│ąĮą░ą╗ą░ SCKx - čéą░ą║ąĖą╝ čüą┐ąŠčüąŠą▒ąŠą╝ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ąŠą▒ą╝ąĄąĮ čü ą┤čĆčāą│ąĖą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ SPI. ąöą░ąĮąĮčŗąĄ SPI ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ąĖ ą┐čĆąĖąĮąĖą╝ą░čÄčéčüčÅ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ - ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą┐ąĄčĆąĄą┤ą░čćą░, ą┤ą░ąĮąĮčŗąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ ą▓čŗą┤ą▓ąĖą│ą░čÄčéčüčÅ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ čüą┤ą▓ąĖą│ą░ č湥čĆąĄąĘ ą▓čŗčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ ą┤ą░ąĮąĮčŗčģ ąĖ ą▓ čŹč鹊 ąČąĄ ą▓čĆąĄą╝čÅ č湥čĆąĄąĘ ą▓čģąŠą┤ ą┤ą░ąĮąĮčŗčģ ą▓ą┤ą▓ąĖą│ą░čÄčéčüčÅ ą▓ č鹊čé ąČąĄ čüą░ą╝čŗą╣ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░, ąĮąŠ čü ą┤čĆčāą│ąŠą│ąŠ ąĄą│ąŠ ą║ąŠąĮčåą░. ąĪąĖąĮčģčĆąŠčüąĖą│ąĮą░ą╗ SCKx čāą┐čĆą░ą▓ą╗čÅąĄčé čüą┤ą▓ąĖą│ąŠą╝ ąĖ ą▓čŗą▒ąŠčĆą║ąŠą╣ ą┤ą░ąĮąĮčŗčģ.

ąÆąŠ ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĄą┤ą░čć ą┤ą░ąĮąĮčŗčģ SPI ąŠą┤ąĮąŠ ąĖąĘ čāčüčéčĆąŠą╣čüčéą▓ ąĮą░ čłąĖąĮąĄ čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą│ą╗ą░ą▓ąĮąŠąĄ (master), ą│ą┤ąĄ ąŠąĮąŠ čāą┐čĆą░ą▓ą╗čÅąĄčé ą┐ąŠč鹊ą║ąŠą╝ ą┤ą░ąĮąĮčŗčģ ą│ąĄąĮąĄčĆą░čåąĖąĄą╣ čüąĖą│ąĮą░ą╗ą░ čéą░ą║č鹊ą▓ ąĖ čüąĖą│ąĮą░ą╗ą░ ą▓čŗą▒ąŠčĆą║ąĖ ą┤ą╗čÅ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (~SPIxSS). ąöčĆčāą│ąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮą░ čłąĖąĮąĄ čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠąĄ (slave), ąĖ ą┐čĆąĖąĮąĖą╝ą░ąĄčé ąĮąŠą▓čŗąĄ ą┤ą░ąĮąĮčŗąĄ ąŠčé master ą▓ čüą▓ąŠą╣ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ č湥čĆąĄąĘ čüąĖą│ąĮą░ą╗ ą┐čĆąĖąĄą╝ą░ (MOSI), ąĖ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ą┐ąĄčĆąĄą┤ą░ąĄčé ą┤ą░ąĮąĮčŗąĄ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ čüą┤ą▓ąĖą│ą░ č湥čĆąĄąĘ čüą▓ąŠą╣ čüąĖą│ąĮą░ą╗ ą┐ąĄčĆąĄą┤ą░čćąĖ (MISO).

ąśąĮąŠą│ą┤ą░ čüąĖčüč鹥ą╝ą░ ąŠą▒ą╝ąĄąĮą░ ą┐ąŠčüčéčĆąŠąĄąĮą░ čéą░ą║, čćč鹊 ą║ čłąĖąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąŠ ąĮąĄčüą║ąŠą╗čīą║ąŠ čāčüčéčĆąŠą╣čüčéą▓ SPI. ąóąŠą│ą┤ą░ ą│ą╗ą░ą▓ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ (ąŠą▒čŗčćąĮąŠ čŹč鹊 ą┐čĆąŠčåąĄčüčüąŠčĆ ąĖą╗ąĖ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ) ą╝ąŠąČąĄčé ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī ą┤ą░ąĮąĮčŗąĄ ą▓čüąĄą╝ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ ąĮą░ čłąĖąĮąĄ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ (čŹč鹊čé čĆąĄąČąĖą╝ ąĄčēąĄ ąĮą░ąĘčŗą▓ą░ąĄčéčüčÅ čłąĖčĆąŠą║ąŠą▓ąĄčēą░ąĮąĖąĄą╝, broadcast mode). ą×ą┤ąĮą░ą║ąŠ ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī ą┤ą░ąĮąĮčŗąĄ ąĮą░ čłąĖąĮčā ą╝ąŠąČąĄčé č鹊ą╗čīą║ąŠ ąŠą┤ąĮąŠ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ. ąŁč鹊ą│ąŠ ą╝ąŠąČąĮąŠ ą┤ąŠą▒ąĖčéčīčüčÅ ą▓ broadcast mode ą┤ą╗čÅ SPI0, ą│ą┤ąĄ ąĮąĄčüą║ąŠą╗čīą║ąŠ čāčüčéčĆąŠą╣čüčéą▓ ą╝ąŠą│čāčé ą▒čŗčéčī ą▓čŗą▒čĆą░ąĮčŗ ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ąŠčé master, ąĮąŠ č鹊ą╗čīą║ąŠ ąŠą┤ąĮąŠ slave-čāčüčéčĆąŠą╣čüčéą▓ąŠ ą╝ąŠąČąĄčé ąŠčéą┐čĆą░ą▓ą╗čÅčéčī ą┤ą░ąĮąĮčŗąĄ ąŠą▒čĆą░čéąĮąŠ ą║ master. ąÆ čāčüą╗ąŠą▓ąĖčÅčģ čĆą░ą▒ąŠčéčŗ čü ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ master ąĮą░ čłąĖąĮąĄ (multimaster) ąĖą╗ąĖ čü ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ ąĮą░ čłąĖąĮąĄ (multislave), ą║ąŠą│ą┤ą░ ąĮąĄčüą║ąŠą╗čīą║ąŠ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ čüąŠąĄą┤ąĖąĮąĄąĮčŗ ą┤čĆčāą│ čü ą┤čĆčāą│ąŠą╝ č湥čĆąĄąĘ čüą▓ąŠąĖ ą┐ąŠčĆčéčŗ SPI, ą▓čüąĄ ą▓čŗą▓ąŠą┤čŗ MOSIx čüąŠąĄą┤ąĖąĮčÅčÄčéčüčÅ ą┤čĆčāą│ čü ą┤čĆčāą│ąŠą╝, ą║ą░ą║ ąĖ ą▓čŗą▓ąŠą┤čŗ MISOx ąĖ SCKx.

ąöą╗čÅ čüąĖčéčāą░čåąĖąĖ multislave ą┐čĆąŠčåąĄčüčüąŠčĆ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī 7 ą▓čŗą▓ąŠą┤ąŠą▓ GPIO ą┐ąŠčĆčéą░ F, PF1ŌĆōPF7, ą║ąŠč鹊čĆčŗąĄ ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮčŗ ą┤ą╗čÅ ą┐ąŠą┤ą░čćąĖ čüąĖą│ąĮą░ą╗ąŠą▓ ą▓čŗą▒ąŠčĆą║ąĖ ą┤ą╗čÅ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ą┐ąŠčĆčéą░ SPI0. ąöą╗čÅ SPI1 ąĖ SPI2 ą┐čĆąŠčåąĄčüčüąŠčĆ ąĖčüą┐ąŠą╗čīąĘčāąĄčé ąŠą┤ąĖąĮ ą▓čŗą▓ąŠą┤ GPIO ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ą▓čŗą▒ąŠčĆą║ąĖ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░: SPI1 ąĖčüą┐ąŠą╗čīąĘčāąĄčé PD4, ąĖ SPI2 ąĖčüą┐ąŠą╗čīąĘčāąĄčé PD9.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą┐ąŠą┤čĆąŠą▒ąĮąĄąĄ ą┐čĆąŠ GPIO ą┐ąŠčĆčéą░ F čüą╝. [3].

ą¤ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ ą▓čüąĄ ą▒ą╗ąŠą║ąĖ SPI ą┐čĆąŠčåąĄčüčüąŠčĆą░ ąĘą░ą┐čĆąĄčēąĄąĮčŗ, ąĖ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ ą▓ čĆąĄąČąĖą╝ slave.

ąÆ čéą░ą▒ą╗ąĖčåą░čģ ą┐čĆąĖą▓ąĄą┤ąĄąĮą░ čåąŠą║ąŠą╗ąĄą▓ą║ą░ ąĮąŠąČąĄą║ 316-ą▓čŗą▓ąŠą┤ąĮąŠą│ąŠ ą║ąŠčĆą┐čāčüą░ CSP BGA ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ Blackfin ADSP-BF538, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗčģ ą║ SPI0, SPI1, SPI2.

[SPI0]

| ąÆčŗą▓ąŠą┤ |

ąØąŠąČą║ą░ CSP BGA |

| MOSI0 |

G2 |

| MISO0 |

F2 |

| SCK0 |

G1 |

| ~SPI0SS/PF0 |

F1 |

| ~SPI0SEL1/PF1 |

E1 |

| ~SPI0SEL2/PF2 |

E2 |

| ~SPI0SEL3/PF3 |

B4 |

| ~SPI0SEL4/PF4 |

D1 |

| ~SPI0SEL5/PF5 |

D2 |

| ~SPI0SEL6/PF6 |

C1 |

| ~SPI0SEL7/PF7 |

C2 |

[SPI1]

| ąÆčŗą▓ąŠą┤ |

ąØąŠąČą║ą░ CSP BGA |

| MOSI1/PD0 |

C16 |

| MISO1/PD1 |

C14 |

| SCK1/PD2 |

C17 |

| ~SPI1SS/PD3 |

C15 |

| ~SPI1SEL1/PD4 |

C13 |

[SPI2]

| ąÆčŗą▓ąŠą┤ |

ąØąŠąČą║ą░ CSP BGA |

| MOSI2/PD5 |

C9 |

| MISO2/PD6 |

C10 |

| SCK2/PD7 |

C11 |

| ~SPI2SS/PD8 |

C8 |

| ~SPI2SEL1/PD9 |

C7 |

[ąĪąĖą│ąĮą░ą╗ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ SCKx]

SCKx čŹč鹊 čüąĖą│ąĮą░ą╗ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ SPI. ą×ąĮ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ master-čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ ąĮą░ čłąĖąĮąĄ, ąĖ čāą┐čĆą░ą▓ą╗čÅąĄčé čüą║ąŠčĆąŠčüčéčīčÄ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ą▓ ąŠą▒ąŠąĖčģ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅčģ. ąŻčüčéčĆąŠą╣čüčéą▓ąŠ master ą╝ąŠąČąĄčé ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī ą┤ą░ąĮąĮčŗąĄ čü čĆą░ąĘąĮčŗą╝ąĖ čüą║ąŠčĆąŠčüčéčÅą╝ąĖ. ąŚą░ ąŠą┤ąĖąĮ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗą╣ ą▒ąĖčé čüąĖą│ąĮą░ą╗ SCKx ą┐čĆąŠčģąŠą┤ąĖčé 1 ą┐ąĄčĆąĖąŠą┤ čüą▓ąŠąĄą│ąŠ čüąĖą│ąĮą░ą╗ą░. ąÜąŠą│ą┤ą░ čāčüčéčĆąŠą╣čüčéą▓ąŠ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąŠ ą║ą░ą║ master, čŹč鹊čé čüąĖą│ąĮą░ą╗ čā ąĮąĄą│ąŠ čüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▓čŗčģąŠą┤ąŠą╝, ą░ ą║ąŠą│ą┤ą░ ą║ą░ą║ slave, č鹊 ą▓čģąŠą┤ąŠą╝.

ąóą░ą║čéčŗ SCKx ą▓čŗčĆą░ą▒ą░čéčŗą▓ą░čÄčéčüčÅ ąĮąĄ ą┐ąŠčüč鹊čÅąĮąĮąŠ, ą░ č鹊ą╗čīą║ąŠ ą▓ąŠ ą▓čĆąĄą╝čÅ ą░ą║čéąĖą▓ąĮąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ, ąĖ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ąĖą╝ą┐čāą╗čīčüąŠą▓ čéą░ą║č鹊ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ą▒ąĖč鹊ą▓ąŠą╣ ą┤ą╗ąĖąĮąĄ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ąŠą│ąŠ čüą╗ąŠą▓ą░ (čäčĆąĄą╣ą╝ą░). ąÜąŠą╗ąĖč湥čüčéą▓ąŠ ą░ą║čéąĖą▓ąĮčŗčģ čéą░ą║č鹊ą▓čŗčģ ą┐ąĄčĆąĄą┐ą░ą┤ąŠą▓ čĆą░ą▓ąĮąŠ ą║ąŠą╗ąĖč湥čüčéą▓čā ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ, ą┐ąŠčÅą▓ą╗čÅčÄčēąĖčģčüčÅ ą┤čĆčāą│ ąĘą░ ą┤čĆčāą│ąŠą╝ ąĮą░ čüąĖą│ąĮą░ą╗ą░čģ MISOx ąĖ MOSIx. ą¤ąŠą┤čćąĖąĮąĄąĮąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ ąĖą│ąĮąŠčĆąĖčĆčāčÄčé čéą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗, ąĄčüą╗ąĖ ą▓čģąŠą┤ ą▓čŗą▒ąŠčĆą║ąĖ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (čüąĖą│ąĮą░ą╗ ~SPIxSS, ą║ąŠč鹊čĆčŗą╣ ą│ąĄąĮąĄčĆąĖčĆčāąĄčé master) ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ąĮąĄą░ą║čéąĖą▓ąĮąŠą╝ čüąŠčüč鹊čÅąĮąĖąĖ (ą╗ąŠą│. 1).

SCKx ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą▓čŗą┤ą▓ąĖą│ą░ąĮąĖčÅ ąĮą░čĆčāąČčā ąĖ ą▓ą┤ą▓ąĖą│ą░ąĮąĖčÅ ą▓ąĮčāčéčĆčī ą┤ą░ąĮąĮčŗčģ č湥čĆąĄąĘ ą▓čŗą▓ąŠą┤čŗ MOSIx ąĖ MISOx čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ. ą¤ąŠą╗čÅčĆąĮąŠčüčéčī ąĖ čäą░ąĘą░ čéą░ą║č鹊ą▓ ą┐ąŠ ąŠčéąĮąŠčłąĄąĮąĖčÄ ą║ čüąĖą│ąĮą░ą╗čā ą┤ą░ąĮąĮčŗčģ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ čü ą┐ąŠą╝ąŠčēčīčÄ čĆąĄą│ąĖčüčéčĆą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ SPI (SPI control register, SPIx_CTL), ąĖ ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčé č乊čĆą╝ą░čé ą┐ąĄčĆąĄą┤ą░čćąĖ (čüą╝. čĆą░ąĘą┤ąĄą╗ "ążąŠčĆą╝ą░čéčŗ ą┐ąĄčĆąĄą┤ą░čćąĖ SPI").

ąĪąĖą│ąĮą░ą╗ SCK0 ą▓čŗą┤ąĄą╗ąĄąĮ ą┤ą╗čÅ ąĖčüą║ą╗čÄčćąĖč鹥ą╗čīąĮąŠą│ąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą┐ąŠą┤ čéą░ą║čéčŗ SPI. ąĪąĖą│ąĮą░ą╗čŗ SCK1 ąĖ SCK2 čÅą▓ą╗čÅčÄčéčüčÅ ą▓čŗą▓ąŠą┤ą░ą╝ąĖ GPIO, čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ PD2 ąĖ PD7. ąŻą▒ąĄą┤ąĖč鹥čüčī, čćč鹊 čĆąĄą│ąĖčüčéčĆ PORTDIO_FER ąĮą░čüčéčĆąŠąĄąĮ ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ čŹčéąĖčģ ą▓čŗą▓ąŠą┤ąŠą▓ ą║ą░ą║ čüąĖą│ąĮą░ą╗ąŠą▓ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (ą┐ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. [4]).

[ąÆčģąŠą┤: čüąĖą│ąĮą░ą╗ ą▓čŗą▒ąŠčĆą║ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ~SPIxSS]

ąŁč鹊 čüąĖą│ąĮą░ą╗ ą▓čŗą▒ąŠčĆą║ąĖ ą┤ą╗čÅ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ čłąĖąĮčŗ SPI, ą║ąŠč鹊čĆčŗą╣ ą▓čŗčĆą░ą▒ą░čéčŗą▓ą░ąĄčé ą│ą╗ą░ą▓ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ. ąĪąĖą│ąĮą░ą╗ ą░ą║čéąĖą▓ąĄąĮ ą┐čĆąĖ ą╗ąŠą│. 0, ąĖ čŹčéąĖą╝ čāčĆąŠą▓ąĮąĄą╝ čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ čĆą░ą▒ąŠčéą░ ą▒ą╗ąŠą║ą░ SPI ą┐čĆąŠčåąĄčüčüąŠčĆą░, ą║ąŠą│ą┤ą░ SPI čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą║ą░ą║ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ. ąĪąĖą│ąĮą░ą╗ ~SPIxSS čĆą░ą▒ąŠčéą░ąĄčé č鹊ą╗čīą║ąŠ ą║ą░ą║ ą▓čģąŠą┤, ąĖ ą▓ąĄą┤ąĄčé čüąĄą▒čÅ ą║ą░ą║ čüąĖą│ąĮą░ą╗ chip-select. ąÜąŠą│ą┤ą░ SPI ą┐čĆąŠčåąĄčüčüąŠčĆą░ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą║ą░ą║ čāčüčéčĆąŠą╣čüčéą▓ąŠ master, čüąĖą│ąĮą░ą╗ ~SPIxSS ą╝ąŠąČąĄčé ą┤ąĄą╣čüčéą▓ąŠą▓ą░čéčī ą║ą░ą║ ą▓čģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ ąŠčłąĖą▒ą║ąĖ, ą║ąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ąŠą▒ą╝ąĄąĮ ą┤ą░ąĮąĮčŗą╝ąĖ ąĮą░ čłąĖąĮąĄ čü ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ master (čĆąĄąČąĖą╝ multimaster). ąÆ čĆąĄąČąĖą╝ąĄ multimaster, ąĄčüą╗ąĖ ą▓čŗčüčéą░ą▓ą╗ąĄąĮ čüąĖą│ąĮą░ą╗ ~SPIxSS ą┤ą╗čÅ master (ą┐ąĄčĆąĄą▓ąĄą┤ąĄąĮ ą▓ ą╗ąŠą│. 0), ąĖ čĆą░ąĘčĆąĄčłąĄąĮ ą▒ąĖčé PSSE ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPIx_CTL, č鹊 ą┐čĆąŠąĖąĘąŠčłą╗ą░ ąŠčłąĖą▒ą║ą░. ąŁč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ą┤čĆčāą│ąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐čŗčéą░ąĄčéčüčÅ čüčéą░čéčī master-ąŠą╝ čłąĖąĮčŗ SPI.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▒ąĖčé PSSE ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPIx_CTL čĆą░ąĘčĆąĄčłą░ąĄčé čäčāąĮą║čåąĖčÄ čĆąĄą░ą│ąĖčĆąŠą▓ą░ąĮąĖčÅ ąĮą░ ą▓ąĮąĄčłąĮąĖą╣ čüąĖą│ąĮą░ą╗ ąŠčłąĖą▒ą║ąĖ. ąÜąŠą│ą┤ą░ PSSE = 1, ą▓čģąŠą┤ ~SPIxSS čüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▓čģąŠą┤ąŠą╝ ąŠčłąĖą▒ą║ąĖ ą▓ čĆąĄąČąĖą╝ąĄ master. ąśąĮą░č湥 ~SPIxSS ąĖą│ąĮąŠčĆąĖčĆčāąĄčéčüčÅ.

ąĪąĖą│ąĮą░ą╗ ~SPI0SS ąĖčüą┐ąŠą╗čīąĘčāąĄčé č鹊čé ąČąĄ čüą░ą╝čŗą╣ ą▓čŗą▓ąŠą┤, čćč鹊 ąĖ PF0. ąŻą▒ąĄą┤ąĖč鹥čüčī, čćč鹊 ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄč鹥 PF0 ą║ą░ą║ ą▓čŗčģąŠą┤, ą║ąŠą│ą┤ą░ čģąŠčéąĖč鹥 ąĄą│ąŠ ąĘą░ą┤ąĄą╣čüčéą▓ąŠą▓ą░čéčī ą▓ ą║ą░č湥čüčéą▓ąĄ čüąĖą│ąĮą░ą╗ą░ ~SPI0SS. ąĪąĖą│ąĮą░ą╗čŗ ~SPI1SS ąĖ ~SPI2SS čŹč鹊 ą▓čŗą▓ąŠą┤čŗ GPIO (PD3 ąĖ PD8, čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ). ąŻą▒ąĄą┤ąĖč鹥čüčī, čćč鹊 čĆąĄą│ąĖčüčéčĆ PORTDIO_FER ą┐čĆą░ą▓ąĖą╗čīąĮąŠ ąĮą░čüčéčĆąŠąĖą╗ čŹčéąĖ ą▓čŗą▓ąŠą┤čŗ ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ čüąŠą▓ą╝ąĄčüčéąĮąŠ čü ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ (ą┐ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. [4]).

[Master Out Slave In (MOSIx)]

ąÆčŗą▓ąŠą┤ MOSI0 ą▓čŗą┤ąĄą╗ąĄąĮ ą┤ą╗čÅ ąĖčüą║ą╗čÄčćąĖč鹥ą╗čīąĮąŠą│ąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą┐ąŠą┤ ą┤ą░ąĮąĮčŗąĄ SPI0, ą░ ą▓čŗą▓ąŠą┤čŗ MOSI1 ąĖ MOSI2 ąĮąĄčüčāčé čéą░ą║ąČąĄ ąŠą▒čēčāčÄ čäčāąĮą║čåąĖčÄ GPIO (PD0 ąĖ PD5 čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ). ąŻą▒ąĄą┤ąĖč鹥čüčī, čćč鹊 ą▓ čĆąĄą│ąĖčüčéčĆąĄ PORTDIO_FER ą▒ąĖčéčŗ 0 ąĖ 5 ąĮą░čüčéčĆąŠąĄąĮčŗ ą┐ąŠą┤ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ (ą┐ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. [4]).

ąÆčŗą▓ąŠą┤ MOSIx čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą▓čŗčģąŠą┤ ą│ą╗ą░ą▓ąĮąŠą│ąŠ ąĖ ą▓čģąŠą┤ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (master-out-slave-in, čüąŠą║čĆą░čēąĄąĮąĮąŠ MOSI). ąĢčüą╗ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą║ą░ą║ master, ą▓čŗą▓ąŠą┤ MOSIx čüčéą░ąĮąŠą▓ąĖčéčüčÅ čüąĖą│ąĮą░ą╗ąŠą╝ ą┐ąĄčĆąĄą┤ą░čćąĖ (ą▓čŗčģąŠą┤ąŠą╝), č湥čĆąĄąĘ ą║ąŠč鹊čĆčŗą╣ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ą┤ą░ąĮąĮčŗąĄ ą║ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą╝čā čāčüčéčĆąŠą╣čüčéą▓čā. ąĢčüą╗ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą║ą░ą║ slave (ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ), č鹊 ą▓čŗą▓ąŠą┤ MOSIx čüčéą░ąĮąŠą▓ąĖčéčüčÅ čüąĖą│ąĮą░ą╗ąŠą╝ ą┐čĆąĖąĄą╝ą░ (ą▓čģąŠą┤), č湥čĆąĄąĘ ą║ąŠč鹊čĆčŗą╣ ą┐ąŠčüčéčāą┐ą░čÄčé ą▓čģąŠą┤ąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ąŠčé ą│ą╗ą░ą▓ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░. ą¤čĆąĖ ą▓ąĘą░ąĖą╝ąŠą┤ąĄą╣čüčéą▓ąĖąĖ ą┐ąŠ čłąĖąĮąĄ SPI ą┤ą░ąĮąĮčŗąĄ ą▓čŗą┤ą▓ąĖą│ą░čÄčéčüčÅ ąĮą░čĆčāąČčā ąĖąĘ ą▓čŗą▓ąŠą┤ą░ MOSIx ą│ą╗ą░ą▓ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ąĖ ą▓ą┤ą▓ąĖą│ą░čÄčéčüčÅ ą▓ąĮčāčéčĆčī č湥čĆąĄąĘ MOSIx ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░.

[Master In Slave Out (MISOx)]

ąÆčŗą▓ąŠą┤ MISOx čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą▓čģąŠą┤ ą│ą╗ą░ą▓ąĮąŠą│ąŠ ąĖ ą▓čŗčģąŠą┤ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (master-in-slave-out, čüąŠą║čĆą░čēąĄąĮąĮąŠ MISO). ąĢčüą╗ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą║ą░ą║ master, ą▓čŗą▓ąŠą┤ MISOx čüčéą░ąĮąŠą▓ąĖčéčüčÅ čüąĖą│ąĮą░ą╗ąŠą╝ ą┐čĆąĖąĄą╝ą░ (ą▓čģąŠą┤), ąĮą░ ą║ąŠč鹊čĆčŗą╣ ą┐ąŠčüčéčāą┐ą░čÄčé ą┤ą░ąĮąĮčŗąĄ ąŠčé ą│ą╗ą░ą▓ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░. ąĢčüą╗ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą║ą░ą║ slave, ą▓čŗą▓ąŠą┤ MISOx čüčéą░ąĮąŠą▓ąĖčéčüčÅ čüąĖą│ąĮą░ą╗ąŠą╝ ą┐ąĄčĆąĄą┤ą░čćąĖ (ą▓čŗčģąŠą┤), ą║ąŠč鹊čĆčŗą╣ ą┐ąĄčĆąĄą┤ą░ąĄčé ą┤ą░ąĮąĮčŗąĄ ą║ ą│ą╗ą░ą▓ąĮąŠą╝čā čāčüčéčĆąŠą╣čüčéą▓čā. ą¤čĆąĖ ą▓ąĘą░ąĖą╝ąŠą┤ąĄą╣čüčéą▓ąĖąĖ ą┐ąŠ čłąĖąĮąĄ SPI ą┤ą░ąĮąĮčŗąĄ ą▓čŗą┤ą▓ąĖą│ą░čÄčéčüčÅ ąĮą░čĆčāąČčā ąĖąĘ ą▓čŗą▓ąŠą┤ą░ MISOx ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ąĖ ą▓ą┤ą▓ąĖą│ą░čÄčéčüčÅ ą▓ąĮčāčéčĆčī č湥čĆąĄąĘ MISOx ą│ą╗ą░ą▓ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░. ąŚą┤ąĄčüčī čüą╗ąĄą┤čāąĄčé čüą┤ąĄą╗ą░čéčī ąĮąĄčüą║ąŠą╗čīą║ąŠ ą▓ą░ąČąĮčŗčģ ąĘą░ą╝ąĄčćą░ąĮąĖą╣.

ŌĆó ąÆčŗą▓ąŠą┤ MISO0 ą▓čŗą┤ąĄą╗ąĄąĮ ą┤ą╗čÅ ąĖčüą║ą╗čÄčćąĖč鹥ą╗čīąĮąŠą│ąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą▓ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą╝ čāčüčéčĆąŠą╣čüčéą▓ąĄ SPI0, ą░ ą▓čŗą▓ąŠą┤čŗ MISO1 ąĖ MISO2 ąĮąĄčüčāčé čéą░ą║ąČąĄ ąŠą▒čēčāčÄ čäčāąĮą║čåąĖčÄ GPIO (PD1 ąĖ PD6 čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ). ąŻą▒ąĄą┤ąĖč鹥čüčī, čćč鹊 ą▓ čĆąĄą│ąĖčüčéčĆąĄ PORTDIO_FER ą▒ąĖčéčŗ 1 ąĖ 6 ąĮą░čüčéčĆąŠąĄąĮčŗ ą┐ąŠą┤ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ (ą┐ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. [4]).

ŌĆó ą¤čĆąĖ čĆą░ą▒ąŠč鹥 ą▓ čüąĖčüč鹥ą╝ąĄ multislave č鹊ą╗čīą║ąŠ ąŠą┤ąĮąŠą╝čā čāčüčéčĆąŠą╣čüčéą▓čā slave čĆą░ąĘčĆąĄčłąĄąĮąŠ ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī ą┤ą░ąĮąĮčŗąĄ.

ŌĆó ą¤čĆąŠčåąĄčüčüąŠčĆ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą│čĆčāąČąĄąĮ č湥čĆąĄąĘ čüą▓ąŠą╣ ąĖąĮč鹥čĆč乥ą╣čü SPI0, čćč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąĘą░ą│čĆčāąĘąĖčéčī ąĖ ąĘą░ą┐čāčüčéąĖčéčī ąĖčüą┐ąŠą╗ąĮčÅąĄą╝čŗą╣ ą║ąŠą┤ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ.

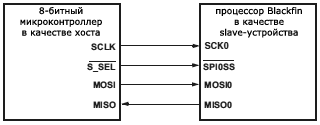

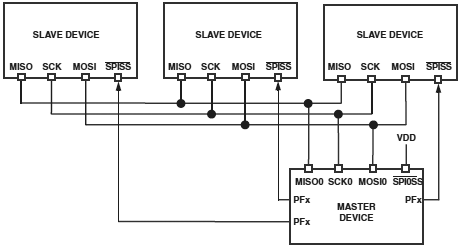

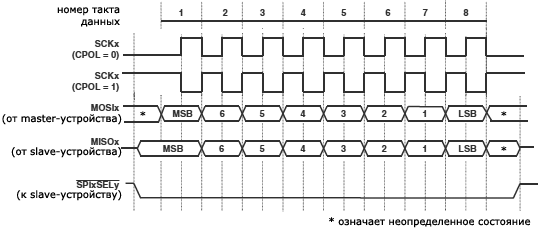

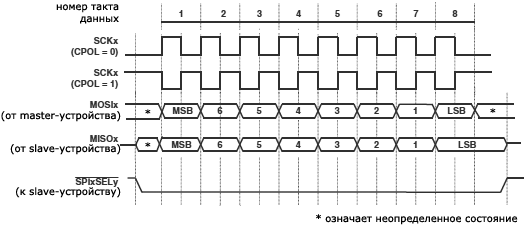

ą¤čĆąĖą╝ąĄčĆ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ SPI ą┐ąŠą║ą░ąĘą░ąĮ ąĮą░ čĆąĖčü. 10-2, ąĘą┤ąĄčüčī ą┐čĆąŠčåąĄčüčüąŠčĆ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą║ą░ą║ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ SPI (slave). 8-čĆą░ąĘčĆčÅą┤ąĮčŗą╣ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą│ą╗ą░ą▓ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ (SPI master).

ąĀąĖčü. 10-2. ą¤čĆąŠčåąĄčüčüąŠčĆ BF538 ą▓ ą║ą░č湥čüčéą▓ąĄ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ SPI.

[ąÆčŗčģąŠą┤čŗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ]

ąÜą░ąČą┤čŗą╣ ą╝ąŠą┤čāą╗čī SPI ąĖą╝ąĄąĄčé 2 ą▓čŗčģąŠą┤ąĮčŗčģ čüąĖą│ąĮą░ą╗ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠčłąĖą▒ą║ąĖ.

ą¤ąŠą▓ąĄą┤ąĄąĮąĖąĄ čüąĖą│ąĮą░ą╗ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ (SPI data interrupt) ąĘą░ą▓ąĖčüąĖčé ąŠčé ą▒ąĖč鹊ą▓ąŠą│ąŠ ą┐ąŠą╗čÅ ąĖąĮąĖčåąĖą░čåąĖąĖ TIMOD ą▓ čĆąĄą│ąĖčüčéčĆąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ SPI (SPIx_CTL). ąÆ čĆąĄąČąĖą╝ąĄ DMA (TIMOD = 1X), ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ ą┤ąĄą╣čüčéą▓čāąĄčé ą║ą░ą║ ąĘą░ą┐čĆąŠčü DMA, ąĖ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ, ą║ąŠą│ą┤ą░ DMA FIFO ą│ąŠč鹊ą▓ąŠ ą║ ąĘą░ą┐ąĖčüąĖ (TIMOD = 11) ąĖą╗ąĖ ą║ čćč鹥ąĮąĖčÄ (TIMOD = 10). ąÆ čĆąĄąČąĖą╝ąĄ ą▒ąĄąĘ DMA (TIMOD = 0X), ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ, ą║ąŠą│ą┤ą░ čĆąĄą│ąĖčüčéčĆ SPIx_TDBR ą│ąŠč鹊ą▓ ą║ ąĘą░ą┐ąĖčüąĖ (TIMOD = 01), ąĖą╗ąĖ ą║ąŠą│ą┤ą░ čĆąĄą│ąĖčüčéčĆ SPIx_RDBR ą│ąŠč鹊ą▓ ą║ čćč鹥ąĮąĖčÄ (TIMOD = 00).

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠčłąĖą▒ą║ąĖ SPI ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ master, ą║ąŠą│ą┤ą░ ą▓ąŠąĘąĮąĖą║ą░ąĄčé ąŠčłąĖą▒ą║ą░ čĆąĄąČąĖą╝ą░ (mode fault error), ą║ą░ą║ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ DMA, čéą░ą║ ąĖ ą▒ąĄąĘ DMA. ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠčłąĖą▒ą║ąĖ ą╝ąŠąČąĄčé ą▒čŗčéčī čéą░ą║ąČąĄ čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąŠ ą▓ čĆąĄąČąĖą╝ąĄ DMA, ą║ąŠą│ą┤ą░ ą▒čŗą╗ą░ ąĮąĄą┤ąŠą│čĆčāąĘą║ą░ ą┤ą░ąĮąĮčŗčģ, underflow (TXE ą┐čĆąĖ TIMOD = 11) ąĖą╗ąĖ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ, overflow (RBSY ą┐čĆąĖ TIMOD = 10). ąæąĄąĘ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ DMA ą▒ąĖčéčŗ čüąŠą▒čŗčéąĖčÅ underflow ąĖ overflow čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄčé ą▒ąĖčéčŗ TXE ąĖ RBSY ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPIx_STAT, ąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐čĆąĖ čŹč鹊ą╝ ąĮąĄ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ.

ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ ą┐čĆąŠ čŹčéąĖ ą▓čŗčģąŠą┤čŗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čüą╝. ą▓čĆąĄąĘą║čā "ąĀąĄą│ąĖčüčéčĆ SPIx_CTL".

[ąĀąĄą│ąĖčüčéčĆčŗ SPI]

ąŻ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ SPI ąĄčüčéčī ąĮąĄčüą║ąŠą╗čīą║ąŠ čĆąĄą│ąĖčüčéčĆąŠą▓, ą┤ąŠčüčéčāą┐ąĮčŗčģ ąĖąĘ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ. ąØąĄą║ąŠč鹊čĆčŗąĄ ąĖąĘ čŹčéąĖčģ čĆąĄą│ąĖčüčéčĆąŠą▓ čéą░ą║ąČąĄ ą┤ąŠčüčéčāą┐ąĮčŗ č湥čĆąĄąĘ čłąĖąĮčā DMA. 4 čĆąĄą│ąĖčüčéčĆą░ čüąŠą┤ąĄčƹȹ░čé ąĖąĮč乊čĆą╝ą░čåąĖčÄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĖ čüąŠčüč鹊čÅąĮąĖčÅ: SPIx_BAUD, SPIx_CTL, SPIx_FLG ąĖ SPIx_STAT. 2 čĆąĄą│ąĖčüčéčĆą░ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ ą▒čāč乥čĆąĖąĘą░čåąĖąĖ ą┤ą░ąĮąĮčŗčģ ą┐čĆąĖąĄą╝ą░ ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ: SPIx_RDBR ąĖ SPIx_TDBR. ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ ą┐čĆąŠ čĆąĄą│ąĖčüčéčĆčŗ DMA čüą╝. [6]. ąĀąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ SFDR čÅą▓ą╗čÅąĄčéčüčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╝ ą┤ą╗čÅ ą╝ąŠą┤čāą╗čÅ SPI, ąĖ ą║ ąĮąĄą╝čā ąĮąĄčé ą┐čĆčÅą╝ąŠą│ąŠ ą┤ąŠčüčéčāą┐ą░.

ąĀąĄą│ąĖčüčéčĆčŗ čüąŠčüč鹊čÅąĮąĖčÅ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ čĆą░ąĘąĮčŗčģ čüąŠą▒čŗčéąĖą╣, ą▓ č鹊ą╝ čćąĖčüą╗ąĄ ąĖ ąŠčłąĖą▒ąŠą║, ą┐ąŠą┤čĆąŠą▒ąĮąĄąĄ ą┐čĆąŠ čŹč鹊 čüą╝. čĆą░ąĘą┤ąĄą╗ "ąĪąĖą│ąĮą░ą╗čŗ ąŠčłąĖą▒ąŠą║ ąĖ čäą╗ą░ą│ąĖ". ą×ą▒ąĘąŠčĆ čäčāąĮą║čåąĖą╣ čĆąĄą│ąĖčüčéčĆąŠą▓ čüą╝. ą▓ čéą░ą▒ą╗ąĖčåąĄ 10-3.

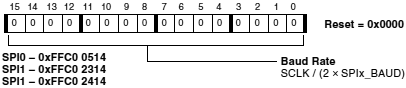

ąĀąĄą│ąĖčüčéčĆ čüą║ąŠčĆąŠčüčéąĖ (SPI baud rate register, SPIx_BAUD) ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ čüą║ąŠčĆąŠčüčéąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▓ čāčüčéčĆąŠą╣čüčéą▓ąĄ master. ąÜąŠą│ą┤ą░ čāčüčéčĆąŠą╣čüčéą▓ąŠ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąŠ ą║ą░ą║ slave, ąĘą░ą┐ąĖčüą░ąĮąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą▓ čŹč鹊ą╝ čĆąĄą│ąĖčüčéčĆąĄ ąĖą│ąĮąŠčĆąĖčĆčāąĄčéčüčÅ. ąóą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░, ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčēą░čÅ čüą║ąŠčĆąŠčüčéčī, ą▓čŗčćąĖčüą╗čÅąĄčéčüčÅ ą┐ąŠ č乊čĆą╝čāą╗ąĄ:

ą¦ą░čüč鹊čéą░ SCKx = SCLK/(2 x SPIx_BAUD)

ąŚą┤ąĄčüčī SCLK čŹč鹊 čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ čüąĖčüč鹥ą╝ąĮąŠą╣ čłąĖąĮčŗ ą┐čĆąŠčåąĄčüčüąŠčĆą░, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ą░čÅ ą┤ą╗čÅ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓. ąŚą░ą┐ąĖčüčī ąĘąĮą░č湥ąĮąĖą╣ 0 ąĖą╗ąĖ 1 ą▓ čŹč鹊čé čĆąĄą│ąĖčüčéčĆ ąĘą░ą┐čĆąĄčēą░ąĄčé ą│ąĄąĮąĄčĆą░čåąĖčÄ čéą░ą║č鹊ą▓ SPI. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠ ą▓ąŠąĘą╝ąŠąČąĮą░čÅ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ ą┤ą░ąĮąĮčŗčģ ą╝ąŠąČąĄčé ą▒čŗčéčī 1/4 ąŠčé čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ čüąĖčüč鹥ą╝ąĮąŠą╣ čłąĖąĮčŗ.

ąĀąĖčü. 10-3. SPI Baud Rate Register (SPIx_BAUD).

ąÆ čéą░ą▒ą╗ąĖčåąĄ 10-1 ą┐ąĄčĆąĄčćąĖčüą╗ąĄąĮąŠ ąĮąĄčüą║ąŠą╗čīą║ąŠ ą┐čĆąĖą╝ąĄčĆąŠą▓ čéą░ą║č鹊ą▓čŗčģ čćą░čüč鹊čé ą│ą╗ą░ą▓ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ SPI.

ąóą░ą▒ą╗ąĖčåą░ 10-1. ą¤čĆąĖą╝ąĄčĆčŗ SPI Master Baud Rate.

ąŚąĮą░č湥ąĮąĖąĄ SPIx_BAUD

ą┤ąĄčüčÅčéąĖčćąĮąŠąĄ |

ąÜąŠčŹčäčäąĖčåąĖąĄąĮčé ą┤ąĄą╗ąĄąĮąĖčÅ

|

ąĪą║ąŠčĆąŠčüčéčī ą┐čĆąĖ SCLK==100 ą£ąōčå |

| 0 |

ąĮąĄ ą┤ąŠčüčéčāą┐ąĮąŠ |

ąĮąĄ ą┤ąŠčüčéčāą┐ąĮąŠ |

| 1 |

ąĮąĄ ą┤ąŠčüčéčāą┐ąĮąŠ |

ąĮąĄ ą┤ąŠčüčéčāą┐ąĮąŠ |

| 2 |

4 |

25 ą£ąōčå |

| 3 |

6 |

16.7 ą£ąōčå |

| 4 |

8 |

12.5 ą£ąōčå |

| 65535 (0xFFFF) |

131070 |

763 ąōčå |

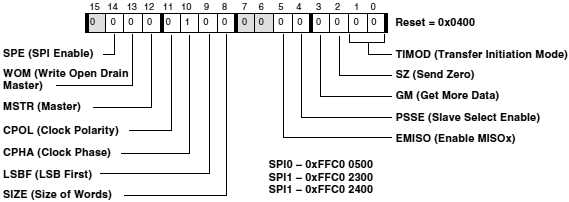

ąĀąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ (SPI control register, SPIx_CTL) ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ čĆą░ą▒ąŠčéčŗ ą╝ąŠą┤čāą╗čÅ SPI. ąŁč鹊čé čĆąĄą│ąĖčüčéčĆ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ąĖąĮč鹥čĆč乥ą╣čüą░ SPI, ą▓čŗą▒ąŠčĆą░ čĆąĄąČąĖą╝ą░ master ąĖą╗ąĖ slave ąĖ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ č乊čĆą╝ą░čéą░ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ąĖ čĆą░ąĘą╝ąĄčĆą░ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ąŠą│ąŠ čüą╗ąŠą▓ą░ ą▓ ą▒ąĖčéą░čģ (čĆą░ąĘą╝ąĄčĆ čäčĆąĄą╣ą╝ą░).

ą¤ąŠą┤ č鹥čĆą╝ąĖąĮąŠą╝ "čüą╗ąŠą▓ąŠ" ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčéčüčÅ ą╝ąĖąĮąĖą╝ą░ą╗čīąĮčŗą╣ ą▒ą╗ąŠą║ ą▒ąĖčé, ą║ąŠč鹊čĆčŗą╣ ą╝ąŠąČąĄčé ą▒čŗčéčī ą╗ąĖą▒ąŠ 8, ą╗ąĖą▒ąŠ 16 ą▒ąĖčé, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą▒ąĖčéą░ ą┤ą╗ąĖąĮčŗ čüą╗ąŠą▓ą░ (SIZE) ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPIx_CTL. ąŚą┤ąĄčüčī ąĄčüčéčī čéą░ą║ąČąĄ 2 čüą┐ąĄčåąĖą░ą╗čīąĮčŗčģ ą▒ąĖčéą░, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ą╝ąŠą┤ąĖčäąĖčåąĖčĆąŠą▓ą░ąĮčŗ ą░ą┐ą┐ą░čĆą░čéąĮąŠ: SPE ąĖ MSTR.

ąĀąĖčü. 10-4. SPI Control Register (SPIx_CTL).

SPE (SPI Enable). ąŁč鹊čé ą▒ąĖčé čĆą░ąĘčĆąĄčłą░ąĄčé čĆą░ą▒ąŠčéčā ą░ą┐ą┐ą░čĆą░čéčāčĆčŗ SPI. 0: SPI ąĘą░ą┐čĆąĄčēąĄąĮ, 1: čĆą░ąĘčĆąĄčłąĄąĮ.

WOM (Write Open Drain Master). ą×ą┐čĆąĄą┤ąĄą╗čÅąĄčé čéąĖą┐ ą▒čāč乥čĆąŠą▓ ą▓čŗčģąŠą┤ąŠą▓ ą▓ čĆąĄąČąĖą╝ąĄ master. 0: ąŠą▒čŗčćąĮčŗąĄ (ą┤ą▓čāčģčéą░ą║čéąĮčŗąĄ) ą▓čŗčģąŠą┤ąĮčŗąĄ ą▒čāč乥čĆčŗ, 1: ą▒čāč乥čĆ čü ąŠčéą║čĆčŗčéčŗą╝ ą║ąŠą╗ą╗ąĄą║č鹊čĆąŠą╝, čéčĆąĄą▒čāčÄčēąĖą╝ ąĮą░ čüąĖą│ąĮą░ą╗čīąĮąŠą╣ čłąĖąĮąĄ ąĮą░ą╗ąĖčćąĖčÅ ą┐ąŠą┤čéčÅą│ąĖą▓ą░čÄčēąĄą│ąŠ ą▓ąĄčĆčģąĮąĄą│ąŠ čĆąĄąĘąĖčüč鹊čĆą░ (pull-up).

MSTR (Master). 0: ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠąĄ (slave) čāčüčéčĆąŠą╣čüčéą▓ąŠ, 1: ą│ą╗ą░ą▓ąĮąŠąĄ (master) čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮą░ čłąĖąĮąĄ SPI.

CPOL (Clock Polarity). ą¤ąŠą╗čÅčĆąĮąŠčüčéčī čéą░ą║č鹊ą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ SCKx. 0: ą┤ą╗čÅ čüąĖą│ąĮą░ą╗ą░ čéą░ą║č鹊ą▓ SCKx ą░ą║čéąĖą▓ąĮą░čÅ ą╗ąŠą│. 1, 1: ą░ą║čéąĖą▓ąĮčŗą╣ ą╗ąŠą│. 0.

CPHA (Clock Phase). ążą░ąĘą░ čéą░ą║č鹊ą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ SCKx, čéą░ą║ąČąĄ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé čĆąĄąČąĖą╝ čĆą░ą▒ąŠčéčŗ. 0: SCKx ąĮą░čćąĖąĮą░ąĄčé ą┐ąĄčĆąĄą║ą╗čÄčćą░čéčīčüčÅ ą┐ąŠčüąĄčĆąĄą┤ąĖąĮąĄ ą▒ąĖčéą░ ą┤ą░ąĮąĮčŗčģ, ą▓čŗą▓ąŠą┤čŗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ čāą┐čĆą░ą▓ą╗čÅčÄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ. 1: SCKx ąĮą░čćąĖąĮą░ąĄčé ą┐ąĄčĆąĄą║ą╗čÄčćą░čéčīčüčÅ ą▓ ą╝ąŠą╝ąĄąĮčé ą┐ąŠčÅą▓ą╗ąĄąĮąĖčÅ ą┐ąĄčĆą▓ąŠą│ąŠ ą▒ąĖčéą░, ą▓čŗą▓ąŠą┤čŗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ ą┤ąŠą╗ąČąĮčŗ ą┐ąĄčĆąĄą║ą╗čÄčćą░čéčīčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ.

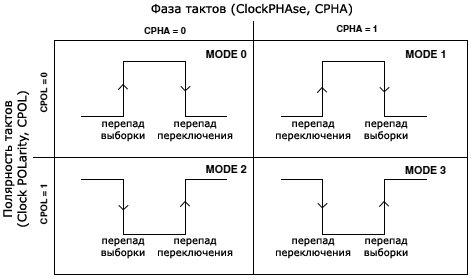

ąæąĖčéčŗ CPOL ąĖ CPHA ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčé č乊čĆą╝ą░čé čäčĆąĄą╣ą╝ą░ SPI.

LSBF (LSB First). 0: čüčéą░čĆčłąĖą╣ ą▒ąĖčé (Most Significant Bit, MSB) ą┤ą░ąĮąĮčŗčģ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą┐ąĄčĆą▓čŗą╝, 1: ą╝ą╗ą░ą┤čłąĖą╣ ą▒ąĖčé (Least Significant Bit, LSB) ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą┐ąĄčĆą▓čŗą╝.

SIZE (Size of Words). ą×ą┐čĆąĄą┤ąĄą╗čÅąĄčé ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ąĖčé ą▓ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ąŠą╝ čüą╗ąŠą▓ąĄ. 0: 8 ą▒ąĖčé, 1: 16 ą▒ąĖčé.

EMISO (Enable MISOx). ąæąĖčé EMISO čĆą░ąĘčĆąĄčłą░ąĄčé ą▓čŗą▓ąŠą┤ MISOx ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ ą▓ ą║ą░č湥čüčéą▓ąĄ ą▓čŗčģąŠą┤ą░. ąŁč鹊 ąĮčāąČąĮąŠ ą▓ čüąĖčüč鹥ą╝ą░čģ multislave, ą║ąŠą│ą┤ą░ master čģąŠč湥čé ą┐ąĄčĆąĄą┤ą░čéčī ą┤ą░ąĮąĮčŗąĄ ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ čüčĆą░ąĘčā (broadcast). ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ č鹊ą╗čīą║ąŠ ąŠą┤ąĮąŠą╝čā čāčüčéčĆąŠą╣čüčéą▓čā slave ą╝ąŠąČąĮąŠ ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī ą┤ą░ąĮąĮčŗąĄ ąŠą▒čĆą░čéąĮąŠ ą║ master. ąŚą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ č鹊ą│ąŠ slave, ąŠčé ą║ąŠč鹊čĆąŠą│ąŠ master čģąŠč湥čé ą┐čĆąĖąĮčÅčéčī ą┤ą░ąĮąĮčŗąĄ, ą▓čüąĄ ą┤čĆčāą│ąĖąĄ slave-čāčüčéčĆąŠą╣čüčéą▓ą░ ą┤ąŠą╗ąČąĮčŗ ąŠčćąĖčüčéąĖčéčī čŹč鹊čé ą▒ąĖčé.

PSSE (Slave Select Enable). ąæąĖčé PSSE ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ čĆą░ą▒ąŠčéčŗ ą▓čģąŠą┤ą░ ~SPIxSS ą▓ čĆąĄąČąĖą╝ąĄ master. ąÜąŠą│ą┤ą░ ą▓čģąŠą┤ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ, ~SPIxSS ą╝ąŠąČąĮąŠ ąĘą░ą┐čĆąĄčéąĖčéčī, ąŠčüčéą░ą▓ąĖą▓ čŹč鹊čé ą▓čŗą▓ąŠą┤ čüą▓ąŠą▒ąŠą┤ąĮčŗą╝ ą┤ą╗čÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą▓ ą║ą░č湥čüčéą▓ąĄ ą▓čŗą▓ąŠą┤ą░ ą┐ąŠčĆčéą░ GPIO. 0: ą▓čģąŠą┤ ąĘą░ą┐čĆąĄčēąĄąĮ (ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą║ą░ą║ GPIO), 1: ą▓čģąŠą┤ čĆą░ąĘčĆąĄčłąĄąĮ.

GM (Get More Data). ą×ą┐čĆąĄą┤ąĄą╗čÅąĄčé ą┐ąŠą╗čāč湥ąĮąĖąĄ ąĖą╗ąĖ ąŠčéą▒čĆą░čüčŗą▓ą░ąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ, ą║ąŠą│ą┤ą░ SPIx_RDBR ąĘą░ą┐ąŠą╗ąĮąĄąĮ. 0: ą┐čĆąĖčģąŠą┤čÅčēąĖąĄ ą┤ą░ąĮąĮčŗąĄ ąŠčéą▒čĆą░čüčŗą▓ą░čÄčéčüčÅ, 1: ą┐čĆąŠą┤ąŠą╗ąČąĄąĮąĖąĄ ą┐čĆąĖąĄą╝ą░ ą┤ą░ąĮąĮčŗčģ, ą║ąŠč鹊čĆčŗą╣ ąĘą░čéčĆąĄčé ą┐čĆąĄą┤čŗą┤čāčēąĖąĄ ą┤ą░ąĮąĮčŗąĄ.

SZ (Send Zero). ą¦č鹊 ą┐ąŠčüčŗą╗ą░čéčī, ą║ąŠą│ą┤ą░ SPIx_TDBR ą┐čāčüčé. 0: ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī ą┐ąŠčüą╗ąĄą┤ąĮąĄąĄ čüą╗ąŠą▓ąŠ, 1: ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī ąĮčāą╗ąĖ.

TIMOD. ą¤ąŠą╗ąĄ TIMOD ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čāą║ą░ąĘą░ąĮąĖčÅ ą┤ąĄą╣čüčéą▓ąĖčÅ, ą║ąŠč鹊čĆąŠąĄ ąĮą░čćąĖąĮą░ąĄčé ą┐ąĄčĆąĄą┤ą░čćąĖ ą▓/ąĖąĘ ą▒čāč乥čĆąŠą▓ ą┐čĆąĖąĄą╝ą░/ą┐ąĄčĆąĄą┤ą░čćąĖ.

| ąæąĖčéčŗ TIMOD |

ą×ą┐ąĖčüą░ąĮąĖąĄ

|

| 00 |

ąĢčüą╗ąĖ ą┐ąŠą╗ąĄ TIMOD čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ ą▓ 00, č鹊 čéčĆą░ąĮąĘą░ą║čåąĖčÅ ą┐ąŠčĆčéą░ SPI ąĮą░čćąĮąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą┐čĆąŠčćąĖčéą░ąĮ ą▒čāč乥čĆ ą┐čĆąĖąĄą╝ą░ SPIx_RDBR. ąöą░ąĮąĮčŗąĄ ąŠčé ą┐ąĄčĆą▓ąŠą│ąŠ čćč鹥ąĮąĖčÅ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąŠčéą▒čĆąŠčłąĄąĮčŗ, ą┐ąŠč鹊ą╝čā čćč鹊 čćč鹥ąĮąĖąĄ ą┤ąŠą╗ąČąĮąŠ ąĖąĮąĖčåąĖąĖčĆąŠą▓ą░čéčī ą┐ąĄčĆą▓čāčÄ čéčĆą░ąĮąĘą░ą║čåąĖčÄ ą┐ąŠčĆčéą░ SPI. ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ, ą║ąŠą│ą┤ą░ čĆąĄą│ąĖčüčéčĆ SPIx_RDBR ą▒čāą┤ąĄčé ąĘą░ą┐ąŠą╗ąĮąĄąĮ. |

| 01 |

ąÜąŠą│ą┤ą░ ą┐ąŠą╗ąĄ TIMOD čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ ą▓ 01, čéčĆą░ąĮąĘą░ą║čåąĖčÅ ąĖąĮąĖčåąĖąĖčĆčāąĄčéčüčÅ ą┐čĆąĖ ąĘą░ą┐ąĖčüąĖ ą▒čāč乥čĆą░ ą┐ąĄčĆąĄą┤ą░čćąĖ SPIx_TDBR. ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ, ą║ąŠą│ą┤ą░ SPIx_TDBR ą┐čāčüčé. |

| 10 |

ąŚąĮą░č湥ąĮąĖąĄ 10 ą┤ą╗čÅ ą┐ąŠą╗čÅ TIMOD ą▓čŗą▒ąĖčĆą░ąĄčé čĆąĄąČąĖą╝ ą┐čĆąĖąĄą╝ą░ DMA, ąĖ ą┐ąĄčĆą▓ą░čÅ čéčĆą░ąĮąĘą░ą║čåąĖčÅ ąĮą░čćąĖąĮą░ąĄčéčüčÅ ą┐čāč鹥ą╝ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĖąĄą╝ą░ SPI čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ DMA. ą¤ąŠčüą╗ąĄą┤čāčÄčēąĖąĄ ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮčŗąĄ čéčĆą░ąĮąĘą░ą║čåąĖąĖ (ą┐ąĄčĆąĄą┤ą░čćąĖ ą▒ą╗ąŠą║ąŠą▓ čüą╗ąŠą▓) ąĖąĮąĖčåąĖąĖčĆčāčÄčéčüčÅ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖą╝ąĖ DMA-čćč鹥ąĮąĖčÅą╝ąĖ čĆąĄą│ąĖčüčéčĆą░ SPIx_RDBR, ą║ą░ą║ č鹊ą╗čīą║ąŠ ą▒čāč乥čĆ SPI DMA FIFO ąŠą║ą░ąČąĄčéčüčÅ ąĮąĄ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĮčŗą╝. |

| 11 |

ąŚąĮą░č湥ąĮąĖąĄ 11 ą┤ą╗čÅ ą┐ąŠą╗čÅ TIMOD ą▓čŗą▒ąĖčĆą░ąĄčé čĆąĄąČąĖą╝ ą┐ąĄčĆąĄą┤ą░čćąĖ DMA, ąĖ ą▓ čŹč鹊ą╝ čüą╗čāčćą░ąĄ čéčĆą░ąĮąĘą░ą║čåąĖčÅ ąĮą░čćąĖąĮą░ąĄčéčüčÅ ą┐čāč鹥ą╝ DMA-ąĘą░ą┐ąĖčüąĖ čĆąĄą│ąĖčüčéčĆą░ SPIx_TDBR. ą¤ąĄčĆą▓ą░čÅ DMA-ąĘą░ą┐ąĖčüčī ąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ čĆą░ąĘčĆąĄčłąĄąĮąĖąĄą╝ SPI ą▓ čĆąĄąČąĖą╝ąĄ DMA, ą┐ąŠčüą╗ąĄ č湥ą│ąŠ ąĮą░čćąĖąĮą░ąĄčéčüčÅ ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčīčüčÅ ą┐ąĄčĆą▓čŗą╣ ą▒ą╗ąŠą║ ą┤ą░ąĮąĮčŗčģ ą▒ąĄąĘ čāčćą░čüčéąĖčÅ ą┐čĆąŠčåąĄčüčüąŠčĆą░, ą┐ąŠą┤ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝ DMA. ą¤ąŠčüą╗ąĄą┤čāčÄčēąĖąĄ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖąĄ DMA-ąĘą░ą┐ąĖčüąĖ ąĮą░čćąĖąĮą░čÄčéčüčÅ, ą║ą░ą║ č鹊ą╗čīą║ąŠ SPI DMA FIFO ąŠą║ą░ąČąĄčéčüčÅ ąĮąĄ ą┐čāčüčé. |

ąæąĖčéčŗ SPE ąĖ MSTR ą╝ąŠą│čāčé ą▒čŗčéčī ą╝ąŠą┤ąĖčäąĖčåąĖčĆąŠą▓ą░ąĮčŗ ą░ą┐ą┐ą░čĆą░čéčāčĆąŠą╣, ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé MODF ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüąŠčüč鹊čÅąĮąĖčÅ. ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. ą▓čĆąĄąĘą║čā "Mode Fault Error (MODF)".

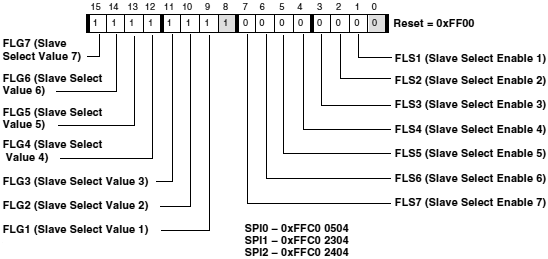

ąĢčüą╗ąĖ SPI čĆą░ąĘčĆąĄčłąĄąĮ ą║ą░ą║ master, č鹊 SPI ąĖčüą┐ąŠą╗čīąĘčāąĄčé čĆąĄą│ąĖčüčéčĆ čäą╗ą░ą│ąŠą▓ (SPI flag register, SPIx_FLG) ą┤ą╗čÅ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┤ąŠ 7 ą▓čŗą▓ąŠą┤ąŠą▓ GPIO ą┐ąŠčĆčéą░ F ą┤ą╗čÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮčŗčģ čüąĖą│ąĮą░ą╗ąŠą▓ ą▓čŗą▒ąŠčĆą║ąĖ slave-čāčüčéčĆąŠą╣čüčéą▓. ąÆ čĆąĄąČąĖą╝ąĄ slave ą▒ąĖčéčŗ SPIx_FLG ąĮąĄ ąĖą╝ąĄčÄčé ąĮąĖą║ą░ą║ąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ, ąĖ ą║ą░ąČą┤čŗą╣ SPI ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą▓čģąŠą┤ SPIxSS ą▓ ą║ą░č湥čüčéą▓ąĄ čüąĖą│ąĮą░ą╗ą░ ą▓čŗą▒ąŠčĆą║ąĖ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░.

ąØąĖąČąĄ ąĮą░ čĆąĖčüčāąĮą║ąĄ ą┐ąŠą║ą░ąĘą░ąĮąŠ čĆą░čüą┐čĆąĄą┤ąĄą╗ąĄąĮąĖąĄ ą▒ąĖčé ą┤ą╗čÅ ą┐ąŠčĆčéą░ SPI0. ąöą╗čÅ ą┐ąŠčĆč鹊ą▓ SPI1 ąĖ SPI2 ąĖą╝ąĄčÄčé ąĘąĮą░č湥ąĮąĖąĄ č鹊ą╗čīą║ąŠ ą▒ąĖčéčŗ FLG1 ąĖ FLS1, ąŠčüčéą░ą╗čīąĮčŗąĄ ą▒ąĖčéčŗ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ. ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ ą┐čĆąŠ ąŠčéą╗ąĖčćąĖčÅ ą▓ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĖ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ ą┤ą╗čÅ čĆą░ąĘąĮčŗčģ ą╝ąŠą┤čāą╗ąĄą╣ SPI čüą╝. čĆą░ąĘą┤ąĄą╗ "ą×čüąŠą▒ąĄąĮąĮąŠčüčéąĖ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ SPI1 ąĖ SPI2".

ąĀąĖčü. 10-5. SPIx Flag Register (SPIx_FLG).

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: čüąĄčĆčŗą╝ čåą▓ąĄč鹊ą╝ ą┐ąŠą╝ąĄč湥ąĮčŗ ą▒ąĖčéčŗ, ą║ąŠč鹊čĆčŗąĄ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ.

ąĀąĄą│ąĖčüčéčĆ SPI0_FLG čüąŠą┤ąĄčƹȹĖčé 2 ąĮą░ą▒ąŠčĆą░ ą▒ąĖčé, ą║ąŠč鹊čĆčŗąĄ čĆą░ą▒ąŠčéą░čÄčé čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝.

ŌĆó Slave select enable (FLSx).

ąÜą░ąČą┤čŗą╣ ąĖąĘ ą▒ąĖčé FLSx čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ą▓čŗą▓ąŠą┤ą░ą╝ GPIO ą┐ąŠčĆčéą░ F (PFx). ąÜąŠą│ą┤ą░ ą▒ąĖčé FLSx čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▓čŗą▓ąŠą┤ PFx čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ą║ą░ą║ čüąĖą│ąĮą░ą╗ ą▓čŗą▒ąŠčĆą║ąĖ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (slave select). ąØą░ą┐čĆąĖą╝ąĄčĆ, ąĄčüą╗ąĖ FLS1 čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ SPI0_FLG, č鹊 PF1 čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ą║ą░ą║ slave select (SPI0SEL1). ąÆ čéą░ą▒ą╗ąĖčåąĄ 10-2 ą┐ąŠą║ą░ąĘą░ąĮą░ čüą▓čÅąĘčī ą▒ąĖč鹊ą▓ FLSx ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖčģ ą▓čŗą▓ąŠą┤ąŠą▓ PFx.

ąĢčüą╗ąĖ ą▒ąĖčé FLSx ąĮąĄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, č鹊 čĆąĄą│ąĖčüčéčĆčŗ GPIO ą┐ąŠčĆčéą░ F (PORTFIO_DIR ąĖ ą┤čĆčāą│ąĖąĄ) ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāčÄčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▓čŗą▓ąŠą┤ PFx ąĖ čāą┐čĆą░ą▓ą╗čÅčÄčé ąĄą│ąŠ ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄą╝ ą┤ą╗čÅ SPI0.

ŌĆó Slave select value (FLGx).

ąÜąŠą│ą┤ą░ ą▓čŗą▓ąŠą┤ PFx čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą║ą░ą║ ą▓čŗčģąŠą┤ čüąĖą│ąĮą░ą╗ą░ slave select ą┤ą╗čÅ SPI0, ą▒ąĖčéčŗ FLGx ą╝ąŠą│čāčé ąŠą┐čĆąĄą┤ąĄą╗čÅčéčī ąĘąĮą░č湥ąĮąĖąĄ, ą║ąŠč鹊čĆąŠąĄ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ąĮą░ ą▓čŗčģąŠą┤.

ąĢčüą╗ąĖ CPHA = 1 ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI0_CTL, č鹊 ą▓čŗčģąŠą┤ąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╝ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝ ą▒ąĖčéą░ą╝ąĖ FLGx. ą¤čĆąŠč鹊ą║ąŠą╗ SPI ą┐ąŠąĘą▓ąŠą╗čÅąĄčé čüąĖą│ąĮą░ą╗čā slave select ąŠčüčéą░ą▓ą░čéčīčüčÅ ą░ą║čéąĖą▓ąĮčŗą╝ (ą▓ ą╗ąŠą│. 0), ą╗ąĖą▒ąŠ ąĮąĄą░ą║čéąĖą▓ąĮčŗą╝ ą╝ąĄąČą┤čā ą┐ąĄčĆąĄą┤ą░čćą░ą╝ąĖ čüą╗ąŠą▓. ą¤ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą┤ąŠą╗ąČąĄąĮ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ čāčüčéą░ąĮąŠą▓ąĖčéčī ąĖą╗ąĖ čüą▒čĆąŠčüąĖčéčī čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ ą▒ąĖčéčŗ FLGx. ąØą░ą┐čĆąĖą╝ąĄčĆ, čćč鹊ą▒čŗ čāą┐čĆą░ą▓ą╗čÅčéčī PF3 ą▓ ą║ą░č湥čüčéą▓ąĄ čüąĖą│ąĮą░ą╗ą░ slave select, ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé FLS3 ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI0_FLG. ą×čćąĖčüčéą║ą░ FLG3 ą┐ąĄčĆąĄą▓ąĄą┤ąĄčé ą▓čŗčģąŠą┤ PF3 ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ą╗ąŠą│. 0, čāčüčéą░ąĮąŠą▓ą║ą░ FLG3 ą┐ąĄčĆąĄą▓ąĄą┤ąĄčé PF3 ą▓ ą╗ąŠą│. 1. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, PF3 ą╝ąŠąČąĄčé ą┐ąĄčĆąĄą║ą╗čÄčćą░čéčīčüčÅ ą▓ ą╗ąŠą│. 1 ąĖ ą╗ąŠą│. 0 ą╝ąĄąČą┤čā ą┐ąĄčĆąĄą┤ą░čćą░ą╝ąĖ ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ ąĖ čüą▒čĆąŠčüą░ ą▒ąĖčéą░ FLG3. ąśąĮą░č湥 PF3 ą┤ąŠą╗ąČąĄąĮ ąŠčüčéą░ą▓ą░čéčīčüčÅ ą░ą║čéąĖą▓ąĮčŗą╝ (ą╗ąŠą│. 0) ą╝ąĄąČą┤čā ą┐ąĄčĆąĄą┤ą░čćą░ą╝ąĖ, čćč鹊ą▒čŗ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ, ą┤ą╗čÅ ą║ąŠč鹊čĆąŠą│ąŠ ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮ čüąĖą│ąĮą░ą╗ ą▓čŗą▒ąŠčĆą║ąĖ, ą╝ąŠą│ą╗ąŠ ą┐ąŠą╗čāčćąĖčéčī (ąĖ ąŠčéą┐čĆą░ą▓ąĖčéčī, ąĄčüą╗ąĖ čŹč鹊 ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ) ą┤ą░ąĮąĮčŗąĄ.

ąĢčüą╗ąĖ CPHA = 0 ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI0_CTL, č鹊 ą░ą┐ą┐ą░čĆą░čéčāčĆą░ SPI čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ą▓čŗčģąŠą┤ąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ čüąĖą│ąĮą░ą╗ą░ ą▓čŗą▒ąŠčĆą║ąĖ, ąĖ ą▒ąĖčéčŗ FLGx ąĖą│ąĮąŠčĆąĖčĆčāčÄčéčüčÅ. ą¤čĆąŠč鹊ą║ąŠą╗ SPI čéčĆąĄą▒čāąĄčé, čćč鹊ą▒čŗ čüąĖą│ąĮą░ą╗ slave select ą▒čŗą╗ąŠ ąĮąĄą░ą║čéąĖą▓ąĮčŗą╝ ą╝ąĄąČą┤čā ą┐ąĄčĆąĄą┤ą░čćą░ą╝ąĖ čüą╗ąŠą▓. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ą░ą┐ą┐ą░čĆą░čéčāčĆą░ SPI čāą┐čĆą░ą▓ą╗čÅąĄčé ą▓čŗą▓ąŠą┤ą░ą╝ąĖ. ąØą░ą┐čĆąĖą╝ąĄčĆ, ą┤ą╗čÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ PF3 ą▓ ą║ą░č湥čüčéą▓ąĄ čüąĖą│ąĮą░ą╗ą░ slave select, ąĮčāąČąĮąŠ č鹊ą╗čīą║ąŠ čāčüčéą░ąĮąŠą▓ąĖčéčī ą▒ąĖčé FLS3 ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPIx_FLG. ąØąĄčé ąĮąĖą║ą░ą║ąŠą╣ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéąĖ čéą░ą║ąČąĄ čāą┐čĆą░ą▓ą╗čÅčéčī ąĘąĮą░č湥ąĮąĖąĄą╝ ą▒ąĖčéą░ FLG3, ą┐ąŠč鹊ą╝čā čćč鹊 ą░ą┐ą┐ą░čĆą░čéčāčĆą░ SPI ą▒čāą┤ąĄčé ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ čüą░ą╝ą░ čāą┐čĆą░ą▓ą╗čÅčéčī ą▓čŗą▓ąŠą┤ąŠą╝ PF3 ą║ą░ą║ čüąĖą│ąĮą░ą╗ąŠą╝ ą▓čŗą▒ąŠčĆą║ąĖ ą┤ą╗čÅ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░.

ąóą░ą▒ą╗ąĖčåą░ 10-2. ą¤čĆąĖą▓čÅąĘą║ą░ ą▒ąĖč鹊ą▓ čĆąĄą│ąĖčüčéčĆą░ SPI0_FLG ą║ ą▓čŗą▓ąŠą┤ą░ą╝ PFx.

| ąæąĖčé |

ąśą╝čÅ

|

ążčāąĮą║čåąĖčÅ |

ąÆčŗą▓ąŠą┤ PFx |

ą¤ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ |

| 0 |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

0 |

| 1 |

FLS1 |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ SPI0SEL1 |

PF1 |

0 |

| 2 |

FLS2 |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ SPI0SEL2 |

PF2 |

0 |

| 3 |

FLS3 |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ SPI0SEL3 |

PF3 |

0 |

| 4 |

FLS4 |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ SPI0SEL4 |

PF4 |

0 |

| 5 |

FLS5 |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ SPI0SEL5 |

PF5 |

0 |

| 6 |

FLS6 |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ SPI0SEL6 |

PF6 |

0 |

| 7 |

FLS7 |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ SPI0SEL7 |

PF7 |

0 |

| 8 |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

1 |

| 9 |

FLG1 |

ąŚąĮą░č湥ąĮąĖąĄ SPI0SEL1 |

PF1 |

1 |

| 10 |

FLG2 |

ąŚąĮą░č湥ąĮąĖąĄ SPI0SEL2 |

PF2 |

1 |

| 11 |

FLG3 |

ąŚąĮą░č湥ąĮąĖąĄ SPI0SEL3 |

PF3 |

1 |

| 12 |

FLG4 |

ąŚąĮą░č湥ąĮąĖąĄ SPI0SEL4 |

PF4 |

1 |

| 13 |

FLG5 |

ąŚąĮą░č湥ąĮąĖąĄ SPI0SEL5 |

PF5 |

1 |

| 14 |

FLG6 |

ąŚąĮą░č湥ąĮąĖąĄ SPI0SEL6 |

PF6 |

1 |

| 15 |

FLG7 |

ąŚąĮą░č湥ąĮąĖąĄ SPI0SEL7 |

PF7 |

1 |

[ąÆčŗčģąŠą┤čŗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ ~SPI0SEL7..SPI0SEL1. ąśčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ ą▒ąĖč鹊ą▓ FLS čĆąĄą│ąĖčüčéčĆą░ SPI0_FLG ą┤ą╗čÅ SPI multislave]

ąæąĖčéčŗ FLSx ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI0_FLG ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą▓ čĆą░ą▒ąŠč湥ą╝ ąŠą║čĆčāąČąĄąĮąĖąĖ čü ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ ąĮą░ čłąĖąĮąĄ SPI (multislave). ąØą░ą┐čĆąĖą╝ąĄčĆ, ąĄčüą╗ąĖ ąĮą░ čłąĖąĮąĄ ąĄčüčéčī 8 čāčüčéčĆąŠą╣čüčéą▓ SPI, ą▓ą║ą╗čÄčćą░čÅ čāčüčéčĆąŠą╣čüčéą▓ąŠ master, č鹊 ą┐čĆąŠčåąĄčüčüąŠčĆ master ą╝ąŠąČąĄčé ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čéčī čéčĆą░ąĮąĘą░ą║čåąĖąĖ SPI čü ą┤čĆčāą│ąĖą╝ąĖ 7 slave-čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ. ąŁčéą░ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ čéčĆąĄą▒čāąĄčé ąĮą░ą╗ąĖčćąĖčÅ č鹊ą╗čīą║ąŠ ąŠą┤ąĮąŠą│ąŠ master-čāčüčéčĆąŠą╣čüčéą▓ą░. ąØą░ą┐čĆąĖą╝ąĄčĆ, ą┐čĆąĄą┤ą┐ąŠą╗ąŠąČąĖą╝, čćč鹊 SPI0 čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ master. 7 ą▓čŗą▓ąŠą┤ąŠą▓ ą┐ąŠčĆčéą░ GPIO F (PF1ŌĆōPF7) ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą║ą░ąČą┤čŗą╣ ą║ ą▓čŗą▓ąŠą┤ą░ą╝ ~SPIxSS ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ SPI. ąÆ čéą░ą║ąŠą╣ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą▒ąĖčéčŗ FLSx ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI0_FLG ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ čéčĆąĄą╝čÅ čĆą░ąĘąĮčŗą╝ąĖ čüą┐ąŠčüąŠą▒ą░ą╝ąĖ.

ąöą╗čÅ ą▓ą░čĆąĖą░ąĮč鹊ą▓ 1 ąĖ 2 ą┐čĆąŠčåąĄčüčüąŠčĆ čÅą▓ą╗čÅąĄčéčüčÅ master, ąĖ 7 ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ / ą▓ąĮąĄčłąĮąĖčģ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ čĆą░ą▒ąŠčéą░čÄčé č湥čĆąĄąĘ SPI ą║ą░ą║ slave-čāčüčéčĆąŠą╣čüčéą▓ą░. ą¤čĆąŠčåąĄčüčüąŠčĆ ą╝ąŠąČąĄčé:

1. ą¤ąĄčĆąĄą┤ą░čéčī ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ ą▓čüąĄčģ čüąĄą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ SPI ą▓ čĆąĄąČąĖą╝ąĄ broadcast. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ą▓čüąĄ ą▒ąĖčéčŗ FLSx čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ.

2. ą¤ąĄčĆąĄą┤ą░čéčī ąĖ ą┐čĆąĖąĮčÅčéčī ą┤ą░ąĮąĮčŗąĄ ąŠčé ą║ą░ąČą┤ąŠą│ąŠ slave-čāčüčéčĆąŠą╣čüčéą▓ą░ SPI ą┐ąŠ ąŠčéą┤ąĄą╗čīąĮąŠčüčéąĖ. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ čéčĆąĄą▒čāąĄčéčüčÅ ąĖąĘą▒ąĖčĆą░č鹥ą╗čīąĮąŠąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą▒ąĖčéą░ą╝ąĖ FLSx.

ąöą╗čÅ ą▓ą░čĆąĖą░ąĮčéą░ 3 ą▓čüąĄ 8 čāčüčéčĆąŠą╣čüčéą▓ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗąĄ č湥čĆąĄąĘ ą┐ąŠčĆčéčŗ SPI ą╝ąŠą│čāčé ą▒čŗčéčī čéą░ą║ąČąĄ ą┤čĆčāą│ąĖą╝ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆą░ą╝ąĖ.

3. ąĢčüą╗ąĖ ą▓čüąĄ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ čéą░ą║ąČąĄ čÅą▓ą╗čÅčÄčéčüčÅ ą┐čĆąŠčåąĄčüčüąŠčĆą░ą╝ąĖ, č鹊 ąĘą░ą┐čĆą░čłąĖą▓ą░čÄčēąĖą╣ ą╝ąŠąČąĄčé ą┐čĆąĖąĮčÅčéčī ą┤ą░ąĮąĮčŗąĄ č鹊ą╗čīą║ąŠ ąŠčé ąŠą┤ąĮąŠą│ąŠ ą┐čĆąŠčåąĄčüčüąŠčĆą░ (čćč鹊 ą╝ąŠąČąĮąŠ ąŠčĆą│ą░ąĮąĖąĘąŠą▓ą░čéčī, ąŠčćąĖčüčéąĖą▓ ą▒ąĖčé EMISO ą▓ ąŠčüčéą░ą╗čīąĮčŗčģ čłąĄčüčéąĖ slave-ą┐čĆąŠčåąĄčüčüąŠčĆą░čģ) ąĘą░ ąŠą┤ąĖąĮ čĆą░ąĘ, ąĖ ą╝ąŠąČąĄčé ą┐ąĄčĆąĄą┤ą░čéčī ą┤ą░ąĮąĮčŗąĄ čüčĆą░ąĘčā ą▓čüąĄą╝ slave-ą┐čĆąŠčåąĄčüčüąŠčĆą░ą╝ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ (broadcast). ąŁčéą░ čäčāąĮą║čåąĖčÅ EMISO ą╝ąŠąČąĄčé ą▒čŗčéčī čéą░ą║ąČąĄ ą┤ąŠčüčéčāą┐ąĮą░ ąĖ ą▓ ą┤čĆčāą│ąĖčģ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░čģ. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čäčāąĮą║čåąĖčÄ EMISO ą▓ ą╗čÄą▒čŗą╝ ą┤čĆčāą│ąĖą╝ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ SPI, ą║ąŠč鹊čĆąŠąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé čéą░ą║čāčÄ čäčāąĮą║čåąĖčÄ.

ąØą░ čĆąĖčü. 10-6 ą┐ąŠą║ą░ąĘą░ąĮ ąŠą┤ąĖąĮ ą┐čĆąŠčåąĄčüčüąŠčĆ ą▓ ą║ą░č湥čüčéą▓ąĄ master čü čéčĆąĄą╝čÅ ą┤čĆčāą│ąĖą╝ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆą░ą╝ąĖ (ąĖą╗ąĖ čŹč鹊 ą╝ąŠą│čāčé ą▒čŗčéčī ą┤čĆčāą│ąĖąĄ SPI-čüąŠą▓ą╝ąĄčüčéąĖą╝čŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░) ą▓ čĆąĄąČąĖą╝ąĄ slave.

ąĀąĖčü. 10-6. ąĪčåąĄąĮą░čĆąĖą╣, ą│ą┤ąĄ ąŠą┤ąĖąĮ Master ąĖ ąĮąĄčüą║ąŠą╗čīą║ąŠ čāčüčéčĆąŠą╣čüčéą▓ Slave.

[ą×čüąŠą▒ąĄąĮąĮąŠčüčéąĖ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ SPI1 ąĖ SPI2]

ąÆąĄčüčī čäčāąĮą║čåąĖąŠąĮą░ą╗, ąŠą┐ąĖčüą░ąĮąĮčŗą╣ ą▓čŗčłąĄ ą┤ą╗čÅ SPI0 ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą▓čŗčģąŠą┤ą░ą╝ąĖ ą▓čŗą▒ąŠčĆą║ąĖ slave-select, čéą░ą║ąČąĄ čüą┐čĆą░ą▓ąĄą┤ą╗ąĖą▓ ąĖ ą┤ą╗čÅ SPI1 ąĖ SPI2. ą×ą┤ąĮą░ą║ąŠ, ą┐ąŠčüą║ąŠą╗čīą║čā SPI1 ąĖ SPI2 ą╝ąŠą│čāčé čāą┐čĆą░ą▓ą╗čÅčéčī ą║ą░ąČą┤čŗą╣ č鹊ą╗čīą║ąŠ ąŠą┤ąĮąĖą╝ ą▓čŗčģąŠą┤ąĮčŗą╝ čüąĖą│ąĮą░ą╗ąŠą╝ slave-select, č鹊 čĆąĄą░ą╗čīąĮčŗą╝ čäčāąĮą║čåąĖąŠąĮą░ą╗ąŠą╝ ą▓ čĆąĄą│ąĖčüčéčĆą░čģ SPIx_FLG ąŠą▒ą╗ą░ą┤ą░čÄčé č鹊ą╗čīą║ąŠ ą▒ąĖčéčŗ FLS1/FLG1. ą×čüčéą░ą╗čīąĮčŗąĄ ą▒ąĖčéčŗ ą▓ čĆąĄą│ąĖčüčéčĆą░čģ SPIx_FLG ą┤ą╗čÅ SPI1 ąĖ SPI2 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ. ąöą╗čÅ SPI1 ąĖąĘą╝ąĄąĮąĄąĮąĖąĄ čüąŠčüč鹊čÅąĮąĖčÅ čŹčéąĖčģ ą▒ąĖč鹊ą▓ ą▓ą╗ąĖčÅąĄčé ąĮą░ ą▓čŗą▓ąŠą┤ PD4 pin. ąöą╗čÅ SPI2 ąĖąĘą╝ąĄąĮąĄąĮąĖąĄ čüąŠčüč鹊čÅąĮąĖčÅ čŹčéąĖčģ ą▒ąĖč鹊ą▓ ą▓ą╗ąĖčÅąĄčé ąĮą░ ą▓čŗą▓ąŠą┤ PD9. ąŻą┤ąŠčüč鹊ą▓ąĄčĆčīč鹥čüčī, čćč鹊 čĆąĄą│ąĖčüčéčĆ PORTDIO_FER ą┐čĆą░ą▓ąĖą╗čīąĮąŠ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą┤ą╗čÅ ąĮą░čüčéčĆąŠą╣ą║ąĖ čŹčéąĖčģ ą▓čŗą▓ąŠą┤ąŠą▓ ą┐ąŠą┤ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝. ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. čĆąĖčü. 15-8 ąĖ 15-10 ą▓ čüčéą░čéčīąĄ [4].

ąĀąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ (SPI status register, SPIx_STAT) ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą╝ąŠą╝ąĄąĮčéą░, ą║ąŠą│ą┤ą░ ą┐ąĄčĆąĄą┤ą░čćą░ SPI ąĘą░ą▓ąĄčĆčłąĖą╗ą░čüčī, ąĖą╗ąĖ ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖąĘąŠčłą╗ą░ ąŠčłąĖą▒ą║ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ/ą┐čĆąĖąĄą╝ą░. ąĀąĄą│ąĖčüčéčĆ SPIx_STAT ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮ ą▓ ą╗čÄą▒ąŠąĄ ą▓čĆąĄą╝čÅ. ąØąĄą║ąŠč鹊čĆčŗąĄ ą▒ąĖčéčŗ ą▓ SPIx_STAT ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮčŗ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ (RO, Read Only) - čŹč鹊 ą▒ąĖčéčŗ, ą║ąŠč鹊čĆčŗąĄ ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮčŗ ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ąĖąĮč乊čĆą╝ą░čåąĖąĖ (ą▒ąĖčéčŗ RXS, TXS, SPIF). ąŁčéąĖ ą▒ąĖčéčŗ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄčéčüčÅ ąĖ ąŠčćąĖčēą░čÄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ.

ąØąĄą║ąŠč鹊čĆčŗąĄ ą▒ąĖčéčŗ ą╝ąŠąČąĮąŠ čüą▒čĆąŠčüąĖčéčī (č鹊ą╗čīą║ąŠ čüą▒čĆąŠčüąĖčéčī, čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄčéčüčÅ ąŠąĮąĖ ą░ą┐ą┐ą░čĆą░čéąĮąŠ), ąĄčüą╗ąĖ ąĘą░ą┐ąĖčüą░čéčī ą▓ ąĮąĖčģ ą╗ąŠą│. 1 (čéą░ą║ ąĮą░ąĘčŗą▓ą░ąĄą╝ą░čÅ č鹥čģąĮąŠą╗ąŠą│ąĖčÅ W1C, čé. ąĄ. Write-1-Clear, ąĘą░ą┐ąĖčüą░čéčī ą╗ąŠą│. 1 ą┤ą╗čÅ ąŠčćąĖčüčéą║ąĖ). ąŁč鹊 ą▒ąĖčéčŗ TXCOL, RBSY, TXE, MODF - ąŠąĮąĖ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ąĄčüą╗ąĖ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ąŠčłąĖą▒ą║ą░. ąæčāą┤čāčćąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╝ąĖ, ąŠąĮąĖ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čüą▒čĆąŠčłąĄąĮčŗ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ. ąØą░ą┐čĆąĖą╝ąĄčĆ, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé TXE, č鹊 ą▓ čĆąĄą│ąĖčüčéčĆ SPIx_STAT ąĮčāąČąĮąŠ ąĘą░ą┐ąĖčüą░čéčī čćąĖčüą╗ąŠ 0x0004 (ą╗ąŠą│. 1 ą▓ ą┐ąŠąĘąĖčåąĖąĖ ą▒ąĖčéą░ TXE), č鹊ą│ą┤ą░ TXE čüą▒čĆąŠčüąĖčéčüčÅ.

ąæąĖčéčŗ TXCOL, RBSY, TXE, MODF čüą▒čĆą░čüčŗą▓ą░čÄčéčüčÅ ą┐čĆąĖ čüą▒čĆąŠčüąĄ ą┐čĆąŠčåąĄčüčüąŠčĆą░, ąĮąŠ ąĮąĄ čüą▒čĆą░čüčŗą▓ą░čÄčéčüčÅ, ąĄčüą╗ąĖ ąĘą░ą┐čĆąĄčéąĖčéčī SPI.

ąĀąĖčü. 10-7. SPI Status Register (SPIx_STAT).

TXCOL (Transmit Collision Error). ąæąĖčé čéąĖą┐ą░ W1C, čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čüą▒čĆąŠčłąĄąĮ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ ąĘą░ą┐ąĖčüčīčÄ ą╗ąŠą│. 1. ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ą╝ąŠą│ą╗ąĖ ą▒čŗčéčī ą┐ąĄčĆąĄą┤ą░ąĮčŗ ąĖčüą┐ąŠčĆč湥ąĮąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ.

RXS (RX Data Buffer register). ąæąĖčé čéąĖą┐ą░ RO, č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ. 0 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ą▒čāč乥čĆ ą┐čĆąĖąĄą╝ą░ ą┐čāčüčé, 1 čćč鹊 ą▒čāč乥čĆ ą┐čĆąĖąĄą╝ą░ ąĘą░ą┐ąŠą╗ąĮąĄąĮ ą┐čĆąĖąĮčÅčéčŗą╝ąĖ ą┤ą░ąĮąĮčŗą╝ąĖ.

RBSY (Receive Error). ąæąĖčé čéąĖą┐ą░ W1C, čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čüą▒čĆąŠčłąĄąĮ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ ąĘą░ą┐ąĖčüčīčÄ ą╗ąŠą│. 1. ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ą▒čŗą╗ąĖ ą┐čĆąĖąĮčÅčéčŗ ą┤ą░ąĮąĮčŗąĄ, ą║ąŠą│ą┤ą░ ą▒čāč乥čĆ ą┐čĆąĖąĄą╝ą░ ą▒čŗą╗ ąĘą░ą┐ąŠą╗ąĮąĄąĮ (ąĮąĄ ą┐čĆąŠčćąĖčéą░ąĮ ą▓ąŠą▓čĆąĄą╝čÅ, čé. ąĄ. ą┐čĆąŠąĖąĘąŠčłą╗ąŠ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĄ ąĮą░ ą┐čĆąĖąĄą╝ąĄ, RX overflow).

TXS (SPIx_TDBR Data Buffer register). ąæąĖčé čéąĖą┐ą░ RO, č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ. 0 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ą▒čāč乥čĆ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐čāčüčé, 1 čćč鹊 ą▒čāč乥čĆ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĘą░ą┐ąŠą╗ąĮąĄąĮ ą┤ą░ąĮąĮčŗą╝ąĖ, ą║ąŠč鹊čĆčŗąĄ ąĄčēąĄ ąĮąĄ ąŠčéą┐čĆą░ą▓ą╗ąĄąĮčŗ.

TXE (Transmission Error). ąæąĖčé čéąĖą┐ą░ W1C, čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čüą▒čĆąŠčłąĄąĮ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ ąĘą░ą┐ąĖčüčīčÄ ą╗ąŠą│. 1. ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ą┐čĆąŠąĖąĘąŠčłą╗ą░ ą┐ąĄčĆąĄą┤ą░čćą░, ą║ąŠą│ą┤ą░ ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPIx_TDBR ąĮąĄ ą▒čŗą╗ąŠ ąĮąŠą▓čŗčģ ą┤ą░ąĮąĮčŗčģ (čĆąĄą│ąĖčüčéčĆ ąĮąĄ ą▒čŗą╗ ąĘą░ą┐ąŠą╗ąĮąĄąĮ ą▓ąŠą▓čĆąĄą╝čÅ, čé. ąĄ. ą┐čĆąŠąĖąĘąŠčłą╗ą░ ąĮąĄą┤ąŠą│čĆčāąĘą║ą░ ąĮą░ ą┐ąĄčĆąĄą┤ą░č湥, TX underflow).

MODF (Mode Fault Error). ąæąĖčé čéąĖą┐ą░ W1C, čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čüą▒čĆąŠčłąĄąĮ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ ąĘą░ą┐ąĖčüčīčÄ ą╗ąŠą│. 1. ąŻčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▓ čāčüčéčĆąŠą╣čüčéą▓ąĄ master, ą║ąŠą│ą┤ą░ ą┤čĆčāą│ąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐čŗčéą░ąĄčéčüčÅ čüčéą░čéčī master.

SPIF (SPI Finished). ąæąĖčé čéąĖą┐ą░ RO, č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ. ąŻčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ąĘą░ą▓ąĄčĆčłąĄąĮą░ ą┐ąĄčĆąĄą┤ą░čćą░ ąŠą┤ąĮąŠą│ąŠ čüą╗ąŠą▓ą░ (čäčĆąĄą╣ą╝ą░).

ąæčāč乥čĆ ą┐ąĄčĆąĄą┤ą░čćąĖ čüčéą░ąĮąŠą▓ąĖčéčüčÅ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĮčŗą╝, ą║ąŠą│ą┤ą░ ą▓ ąĮąĄą│ąŠ (čé. ąĄ. ą▓ čĆąĄą│ąĖčüčéčĆ SPIx_TDBR) ąĘą░ą┐ąĖčüą░ąĮčŗ ą┤ą░ąĮąĮčŗąĄ, ąĖ čüčéą░ąĮąŠą▓ąĖčéčüčÅ ą┐čāčüčéčŗą╝, ą║ąŠą│ą┤ą░ ąĮą░čćąĖąĮą░ąĄčéčüčÅ ą┐ąĄčĆąĄą┤ą░čćą░, ąĖ ąĘąĮą░č湥ąĮąĖąĄ ą▒čāč乥čĆą░ ąĘą░ą│čĆčāąČąĄąĮąŠ ą▓ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░. ąæčāč乥čĆ ą┐čĆąĖąĄą╝ą░ čüčéą░ąĮąŠą▓ąĖčéčüčÅ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĮčŗą╝ ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ, ą║ąŠą│ą┤ą░ ąĘąĮą░č湥ąĮąĖąĄ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ čüą┤ą▓ąĖą│ą░ ąĘą░ą│čĆčāąČąĄąĮąŠ ą▓ ą▒čāč乥čĆ ą┐čĆąĖąĄą╝ą░ (čé. ąĄ. ą▓ čĆąĄą│ąĖčüčéčĆ SPIx_RDBR). ąæčāč乥čĆ ą┐čĆąĖąĄą╝ą░ ąŠą┐čāčüč鹊賹░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ SPIx_RDBR ą┐čĆąŠčćąĖčéą░ąĮ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╝ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖąĄą╝.

ąæąĖčé SPIF ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ (čé. ąĄ. ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░) čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ. ą×ąĮ čéą░ą║ąČąĄ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ąĘą░ą┐čĆąĄčēą░ąĄčéčüčÅ ą┐ąŠčĆčé SPI.

ą¤čĆąĖ ą▓čģąŠą┤ąĄ ą▓ čĆąĄąČąĖą╝ DMA ą▒čāč乥čĆ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖ ą▒čāč乥čĆ ą┐čĆąĖąĄą╝ą░ čüčéą░ąĮąŠą▓čÅčéčüčÅ ą┐čāčüčéčŗą╝ąĖ. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą▒ąĖčéčŗ TXS ąĖ RXS ąĖąĘąĮą░čćą░ą╗čīąĮąŠ ąŠčćąĖčēąĄąĮčŗ ą┐ąŠčüą╗ąĄ ą▓čģąŠą┤ą░ ą▓ čĆąĄąČąĖą╝ DMA. ąÜąŠą│ą┤ą░ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ DMA, č鹊 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ DMA_DONE čüąĖą│ąĮą░ą╗ąĖąĘąĖčĆčāąĄčé ąŠčé č鹊ą╝, čćč鹊 DMA FIFO ą┐čāčüčé. ą×ą┤ąĮą░ą║ąŠ ą▓ čŹč鹊čé ą╝ąŠą╝ąĄąĮčé ą▓čüąĄ ąĄčēąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ą┤ą░ąĮąĮčŗąĄ ą▓ SPI DMA FIFO, ąŠąČąĖą┤ą░čÄčēąĖąĄ čüą▓ąŠąĄą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą╝čā ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖčÄ čéčĆąĄą▒čāąĄčéčüčÅ ąŠą┐čĆą░čłąĖą▓ą░čéčī ą▒ąĖčé TXS ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPIx_STAT, ą┐ąŠą║ą░ ąŠąĮ ąĮąĄ čüčéą░ąĮąĄčé ą╗ąŠą│. 0 ą┤ą╗čÅ ą┤ą▓čāčģ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ čćč鹥ąĮąĖą╣, ąĖ č鹊ą╗čīą║ąŠ č鹊ą│ą┤ą░ ą╝ąŠąČąĮąŠ čüčćąĖčéą░čéčī ą▒čāč乥čĆ SPI DMA FIFO ąŠą┐čāčüč鹊賹ĄąĮąĮčŗą╝ (čé. ąĄ. č鹊ą╗čīą║ąŠ č鹊ą│ą┤ą░ ąĄą│ąŠ ą╝ąŠąČąĮąŠ ąĘą░ą┐ąŠą╗ąĮčÅčéčī ąĮąŠą▓čŗą╝ąĖ ą┤ą░ąĮąĮčŗą╝ąĖ). ąÜąŠą│ą┤ą░ ąĘą░č鹥ą╝ ą▒ąĖčé SPIF ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ ą╗ąŠą│. 1, čŹč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ą▒čŗą╗ąŠ ą┐ąĄčĆąĄą┤ą░ąĮąŠ ą┐ąŠčüą╗ąĄą┤ąĮąĄąĄ čüą╗ąŠą▓ąŠ.

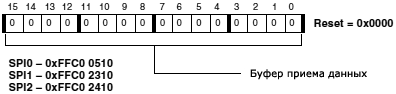

ąĀąĄą│ąĖčüčéčĆ ą▒čāč乥čĆą░ ą┐ąĄčĆąĄą┤ą░čćąĖ (SPI transmit data buffer register, SPIx_TDBR) čÅą▓ą╗čÅąĄčéčüčÅ 16-ą▒ąĖčéąĮčŗą╝ čĆąĄą│ąĖčüčéčĆąŠą╝, ą┤ąŠčüčéčāą┐ąĮčŗą╝ ąĮą░ čćč鹥ąĮąĖąĄ ąĖ ąĘą░ą┐ąĖčüčī. ą¤ąĄčĆąĄą┤ ą┐ąĄčĆąĄą┤ą░č湥ą╣ ą┤ą░ąĮąĮčŗąĄ ąĘą░ą│čĆčāąČą░čÄčéčüčÅ ą▓ čŹč鹊čé čĆąĄą│ąĖčüčéčĆ. ąĪčĆą░ąĘčā ą┐ąĄčĆąĄą┤ ąĮą░čćą░ą╗ąŠą╝ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ą┤ą░ąĮąĮčŗąĄ ą▓ SPIx_TDBR ąĘą░ą│čĆčāąČą░čÄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ ą┤ą░ąĮąĮčŗčģ (shift data register, SFDR). ą¦č鹥ąĮąĖąĄ SPIx_TDBR ą╝ąŠąČąĄčé ą┐čĆąŠąĖąĘąŠą╣čéąĖ ą▓ ą╗čÄą▒ąŠąĄ ą▓čĆąĄą╝čÅ, čćč鹊 ąĮąĖą║ą░ą║ ąĮąĄ ą▓ą╗ąĖčÅąĄčé ąĮą░ ąĖąĮąĖčåąĖąĖčĆąŠą▓ą░ąĮąĖąĄ ą┐ąĄčĆąĄą┤ą░čć SPI ąĖą╗ąĖ ąĮą░ čüą░ą╝čā ą┐ąĄčĆąĄą┤ą░čćčā.

ąÜąŠą│ą┤ą░ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ čĆą░ąĘčĆąĄčłąĄąĮ DMA, ą┐ąŠą┤čüąĖčüč鹥ą╝ą░ DMA ąĘą░ą│čĆčāąČą░ąĄčé ą┤ą░ąĮąĮčŗąĄ ą▓ čŹč鹊čé čĆąĄą│ąĖčüčéčĆ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ čüčĆą░ąĘčā ą┐ąĄčĆąĄą┤ ąĮą░čćą░ą╗ąŠą╝ ą┐ąĄčĆąĄą┤ą░čćąĖ. ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ąĮąĄ čüą╗ąĄą┤čāąĄčé ąĘą░ą┐ąĖčüčŗą▓ą░čéčī ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ ą┤ą░ąĮąĮčŗąĄ ą▓ SPIx_TDBR, ą┐ąŠč鹊ą╝čā čćč鹊 čŹč鹊 ą┐ąĄčĆąĄąĘą░ą┐ąĖčłąĄčé č鹥 ą┤ą░ąĮąĮčŗąĄ, ą║ąŠč鹊čĆčŗąĄ ą▒čŗą╗ąĖ ąĘą░ą┐ąĖčüą░ąĮčŗ DMA.

ąÜąŠą│ą┤ą░ DMA čĆą░ąĘčĆąĄčłąĄąĮ ą┤ą╗čÅ ą┐čĆąĖąĄą╝ą░, čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ SPIx_TDBR ą┐ąŠčüč鹊čÅąĮąĮąŠ ą┐ąŠą▓č鹊čĆąĮąŠ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ (ą┐ąĄčĆąĄą┤ą░čćą░ č湥čĆąĄąĘ SPI ą▓čüąĄą│ą┤ą░ ą┤čāą┐ą╗ąĄą║čüąĮą░čÅ). ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ąĘą░ą┐ąĖčüčī ą▓ SPIx_TDBR čĆą░ąĘčĆąĄčłąĄąĮą░, ąĖ ąĘą░ą┐ąĖčüą░ąĮąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą▒čāą┤čāčé ą┐ąĄčĆąĄą┤ą░ąĮčŗ.

ąĢčüą╗ąĖ ą▒ąĖčé čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░č湥ą╣ ąĮčāą╗ąĄą╣ (send zeros control bit, SZ ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPIx_CTL) čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, č鹊 ą┐čĆąĖ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗčģ ąŠą▒čüč鹊čÅč鹥ą╗čīčüčéą▓ą░čģ čĆąĄą│ąĖčüčéčĆ SPIx_TDBR ą╝ąŠąČąĄčé ą▒čŗčéčī čüą▒čĆąŠčłąĄąĮ ą▓ 0.

ąĢčüą╗ąĖ ą▓ SPIx_TDBR ą▒čāą┤ąĄčé ą▓čŗą┐ąŠą╗ąĮąĄąĮąŠ ąĮąĄčüą║ąŠą╗čīą║ąŠ ąĘą░ą┐ąĖčüąĄą╣ ą▓ąŠ ą▓čĆąĄą╝čÅ ą▓čŗą┐ąŠą╗ąĮčÅčÄčēąĄą╣čüčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ, č鹊 ą▒čāą┤čāčé ą┐ąĄčĆąĄą┤ą░ąĮčŗ č鹊ą╗čīą║ąŠ č鹥 ą┤ą░ąĮąĮčŗąĄ, čćč鹊 ą▒čŗą╗ąĖ ąĘą░ą┐ąĖčüą░ąĮčŗ ą▓ ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ čĆą░ąĘ. ą¤čĆąĄą┤čŗą┤čāčēąĖąĄ ąĘąĮą░č湥ąĮąĖčÅ, ą║ąŠč鹊čĆčŗąĄ ą▒čŗą╗ąĖ ąĘą░ą┐ąĖčüą░ąĮčŗ ą▓ SPIx_TDBR ą┤ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ, ąĮąĄ ą▒čāą┤čāčé ą┐ąĄčĆąĄą┤ą░ąĮčŗ. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą╝ąĮąŠąČąĄčüčéą▓ąĄąĮąĮą░čÅ ąĘą░ą┐ąĖčüčī ą▓ SPIx_TDBR ą▓ąŠąĘą╝ąŠąČąĮą░, ąĮąŠ čŹč鹊 ąĮąĄ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ.

ąĀąĖčü. 10-8. SPI Transmit Data Buffer Register (SPIx_TDBR).

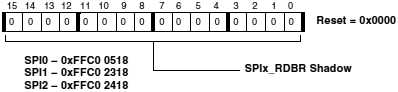

ąĀąĄą│ąĖčüčéčĆ ą▒čāč乥čĆą░ ą┐čĆąĖąĄą╝ą░ (SPI receive data buffer register, SPIx_RDBR) čÅą▓ą╗čÅąĄčéčüčÅ 16-ą▒ąĖčéąĮčŗą╝ čĆąĄą│ąĖčüčéčĆąŠą╝, ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮąĮčŗą╝ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ. ą¤ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗąĄ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ čüą┤ą▓ąĖą│ą░ ąĘą░ą│čĆčāąČą░čÄčéčüčÅ ą▓ SPIx_RDBR. ą¤čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ DMA ąĮą░ ą┐čĆąĖąĄą╝ąĄ ą┤ą░ąĮąĮčŗąĄ ą▓ SPIx_RDBR ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą▓čŗčćąĖčéčŗą▓ą░čÄčéčüčÅ ą┐ąŠą┤čüąĖčüč鹥ą╝ąŠą╣ DMA. ąÜąŠą│ą┤ą░ SPIx_RDBR čćąĖčéą░ąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ, ą▒ąĖčé RXS ąŠčćąĖčēą░ąĄčéčüčÅ, ąĖ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĖąĮąĖčåąĖąĖčĆąŠą▓ą░ąĮą░ ąĮąŠą▓ą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░ SPI (ąĄčüą╗ąĖ TIMOD = 00).

ąĀąĖčü. 10-9. SPI Receive Data Buffer Register (SPIx_RDBR).

ąóąĄąĮąĄą▓ąŠą╣ čĆąĄą│ąĖčüčéčĆ ą▒čāč乥čĆą░ ą┐čĆąĖąĄą╝ą░ (SPI RDBR shadow register, SPIx_SHADOW) ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮ ą┤ą╗čÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą▓ ąŠčéą╗ą░ą┤ą║ąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖčÅ. ąŁč鹊čé čĆąĄą│ąĖčüčéčĆ ąĖą╝ąĄąĄčé ą░ą┤čĆąĄčü, ąŠčéą╗ąĖčćą░čÄčēąĖą╣čüčÅ ąŠčé ą░ą┤čĆąĄčüą░ ą▒čāč乥čĆą░ ą┐čĆąĖąĄą╝ą░ SPIx_RDBR, ąĮąŠ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ SPIx_SHADOW ąĖą┤ąĄąĮčéąĖčćąĮąŠ čüąŠą┤ąĄčƹȹĖą╝ąŠą╝čā SPIx_RDBR. ąÜąŠą│ą┤ą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠąĄ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖąĄ čćąĖčéą░ąĄčé SPIx_RDBR, ą▒ąĖčé RXS ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPIx_STAT ąŠčćąĖčēą░ąĄčéčüčÅ, ąĖ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĖąĮąĖčåąĖąĖčĆąŠą▓ą░ąĮą░ ą┐ąĄčĆąĄą┤ą░čćą░ SPI (ąĄčüą╗ąĖ TIMOD = 00 ą▓ SPIx_CTL). ą¤čĆąĖ čćč鹥ąĮąĖąĖ čĆąĄą│ąĖčüčéčĆą░ SPIx_SHADOW ąĮąĄ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ąĮąĖą║ą░ą║ąĖčģ ą░ą┐ą┐ą░čĆą░čéąĮčŗčģ ą┤ąĄą╣čüčéą▓ąĖą╣. ąĀąĄą│ąĖčüčéčĆ SPIx_SHADOW ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ.

ąĀąĖčü. 10-10. SPI RDBR Shadow Register (SPIx_SHADOW).

ąÆ čéą░ą▒ą╗ąĖčåąĄ 10-3 ąŠą▒ąŠą▒čēąĄąĮčŗ čäčāąĮą║čåąĖąĖ čĆąĄą│ąĖčüčéčĆąŠą▓ SPI.

ąóą░ą▒ą╗ąĖčåą░ 10-3. ąØą░ąĘąĮą░č湥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆąŠą▓ SPI.

| ąśą╝čÅ čĆąĄą│ąĖčüčéčĆą░ |

ążčāąĮą║čåąĖčÅ |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ |

| SPIx_CTL |

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąŠčĆč鹊ą╝ SPI |

ąæąĖčéčŗ SPE ąĖ MSTR ą▓ čŹč鹊ą╝ čĆąĄą│ąĖčüčéčĆąĄ čéą░ą║ąČąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ąĖąĘą╝ąĄąĮąĄąĮčŗ ą░ą┐ą┐ą░čĆą░čéčāčĆąŠą╣ (ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ MODF). |

| SPIx_FLG |

ążą╗ą░ą│ąĖ ą┐ąŠčĆčéą░ SPI |

ąæąĖčéčŗ 0 ąĖ 8 ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI0_FLG ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ. ąÆ čĆąĄą│ąĖčüčéčĆą░čģ SPI1_FLG ąĖ SPI2_FLG ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ ą▓čüąĄ ą▒ąĖčéčŗ, ąĘą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ FLS1 ąĖ FLG1. |

| SPIx_STAT |

ąĪąŠčüč鹊čÅąĮąĖąĄ ą┐ąŠčĆčéą░ SPI |

ąæąĖčé SPIF ą╝ąŠąČąĄčé ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ąŠčćąĖčüčéą║ąŠą╣ ą▒ąĖčéą░ SPE ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPIx_CTL. |

| SPIx_TDBR |

ąæčāč乥čĆ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐ąŠčĆčéą░ SPI |

ąĪąŠą┤ąĄčƹȹĖą╝ąŠąĄ čŹč鹊ą│ąŠ čĆąĄą│ąĖčüčéčĆą░ čéą░ą║ąČąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĖąĘą╝ąĄąĮąĄąĮąŠ ą░ą┐ą┐ą░čĆą░čéąĮąŠ (ą▒ą╗ąŠą║ąŠą╝ DMA, ąĖ/ąĖą╗ąĖ ą║ąŠą│ą┤ą░ ą▒ąĖčé SZ=1 ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPIx_CTL). |

| SPIx_RDBR |

ąæčāč乥čĆ ą┐čĆąĖąĄą╝ą░ ą┐ąŠčĆčéą░ SPI |

ąÜąŠą│ą┤ą░ čŹč鹊čé čĆąĄą│ąĖčüčéčĆ čćąĖčéą░ąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╝ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖąĄą╝, čüčĆą░ą▒ą░čéčŗą▓ą░ąĄčé ą░ą┐ą┐ą░čĆą░čéąĮąŠąĄ čüąŠą▒čŗčéąĖąĄ. |

| SPIx_BAUD |

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čüą║ąŠčĆąŠčüčéčīčÄ ą┐ąŠčĆčéą░ SPI |

ąŚąĮą░č湥ąĮąĖčÅ 0 ąĖ 1 ą▓ čŹč鹊ą╝ čĆąĄą│ąĖčüčéčĆąĄ ąĘą░ą┐čĆąĄčēą░čÄčé ą│ąĄąĮąĄčĆą░čåąĖčÄ čéą░ą║č鹊ą▓ SCKx. |

| SPIx_SHADOW |

ąöą░ąĮąĮčŗąĄ ą┐ąŠčĆčéą░ SPI |

ąÆ čĆąĄą│ąĖčüčéčĆąĄ ą┐ąŠčÅą▓ą╗čÅąĄčéčüčÅ č鹊 ąČąĄ čüą░ą╝ąŠąĄ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ, čćč鹊 ąĖ ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPIx_RDBR, ąŠą┤ąĮą░ą║ąŠ ą┐čĆąĖ čćč鹥ąĮąĖąĖ čĆąĄą│ąĖčüčéčĆą░ SPIx_SHADOW ąĮąĄ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ąĮąĖą║ą░ą║ąĖčģ ą┤ąĄą╣čüčéą▓ąĖą╣. |

[ążąŠčĆą╝ą░čéčŗ ą┐ąĄčĆąĄą┤ą░čćąĖ SPI]

SPI ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé 4 čĆą░ąĘąĮčŗčģ ą║ąŠą╝ą▒ąĖąĮą░čåąĖąĖ čäą░ąĘčŗ ąĖ ą┐ąŠą╗čÅčĆąĮąŠčüčéąĖ čéą░ą║č鹊ą▓ ą▒ąĖčé (SPI čĆąĄąČąĖą╝čŗ 0-3). ąŁčéąĖ ą║ąŠą╝ą▒ąĖąĮą░čåąĖąĖ ą▓čŗą▒ąĖčĆą░čÄčéčüčÅ ą▒ąĖčéą░ą╝ąĖ CPOL ąĖ CPHA ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPIx_CTL, ą║ą░ą║ čŹč鹊 ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 10-11.

ąĀąĖčü. 10-11. ąĀąĄąČąĖą╝čŗ čĆą░ą▒ąŠčéčŗ SPI.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą┐ąĄčĆąĄą┐ą░ą┤ ą▓čŗą▒ąŠčĆą║ąĖ - čŹč鹊 ąĖąĘą╝ąĄąĮąĄąĮąĖąĄ ą╗ąŠą│ąĖč湥čüą║ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ čéą░ą║č鹊ą▓ ą▓ ą╝ąŠą╝ąĄąĮčé čüčćąĖčéčŗą▓ą░ąĮąĖčÅ ąĘąĮą░č湥ąĮąĖčÅ ą▒ąĖčéą░ ą┤ą░ąĮąĮčŗčģ. ą¤ąĄčĆąĄą┐ą░ą┤ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ - ą╝ąŠą╝ąĄąĮčé ą▓čŗą▓ąŠą┤ą░ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ ą▒ąĖčéą░ ą┤ą░ąĮąĮčŗčģ.

ąĀąĖčüčāąĮą║ąĖ 10-12 ąĖ 10-13 ą┤ąĄą╝ąŠąĮčüčéčĆąĖčĆčāčÄčé ą┤ą▓ą░ ą▒ą░ąĘąŠą▓čŗčģ č乊čĆą╝ą░čéą░ ą┐ąĄčĆąĄą┤ą░čćąĖ, ąĘą░ą┤ą░ąĮąĮčŗąĄ ą▒ąĖč鹊ą╝ CPHA. ą¤ąŠą║ą░ąĘą░ąĮčŗ ąĮą░ ą║ą░ąČą┤ąŠą╝ čĆąĖčüčāąĮą║ąĄ ą┐ąŠą║ą░ąĘą░ąĮąŠ 2 č乊čĆą╝čŗ čüąĖą│ąĮą░ą╗ą░ ą┤ą╗čÅ SCKx - ąŠą┤ąĖąĮ ą┤ą╗čÅ CPOL = 0, ą┤čĆčāą│ąŠą╣ ą┤ą╗čÅ CPOL = 1. ąöąĖą░ą│čĆą░ą╝ą╝čŗ ą╝ąŠą│čāčé ą▒čŗčéčī ąĖąĮč鹥čĆą┐čĆąĄčéąĖčĆąŠą▓ą░ąĮčŗ ą║ą░ą║ ą┤ąĖą░ą│čĆą░ą╝ą╝čŗ čāčüčéčĆąŠą╣čüčéą▓ą░ master ąĖą╗ąĖ slave, ą┐ąŠčüą║ąŠą╗čīą║čā čüąĖą│ąĮą░ą╗čŗ SCKx, MISOx ąĖ MOSIx ąĮą░ą┐čĆčÅą╝čāčÄ čüąŠąĄą┤ąĖąĮąĄąĮčŗ ą╝ąĄąČą┤čā čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ master ąĖ slave. ąĪąĖą│ąĮą░ą╗ MISOx čÅą▓ą╗čÅąĄčéčüčÅ ą▓čŗčģąŠą┤ąŠą╝ slave-čāčüčéčĆąŠą╣čüčéą▓ą░ (ą┐ąĄčĆąĄą┤ą░čćą░ ąŠčé ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░), ąĖ čüąĖą│ąĮą░ą╗ MOSIx čÅą▓ą╗čÅąĄčéčüčÅ ą▓čŗčģąŠą┤ąŠą╝ master (ą┐ąĄčĆąĄą┤ą░čćą░ ąŠčé ą│ą╗ą░ą▓ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░). ąĪąĖą│ąĮą░ą╗ SCKx ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ master, ąĖ čüąĖą│ąĮą░ą╗ ~SPIxSS čÅą▓ą╗čÅąĄčéčüčÅ ą▓čģąŠą┤ąŠą╝ ą▓čŗą▒ąŠčĆą║ąĖ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (slave device select input), ąĮą░ ą║ąŠč鹊čĆčŗą╣ ą┐čĆąĖčģąŠą┤ąĖčé ą▓čŗą▒ąŠčĆą║ą░ ąŠčé čāčüčéčĆąŠą╣čüčéą▓ą░ master. ąØą░ ą┤ąĖą░ą│čĆą░ą╝ą╝ą░čģ ą┐ąŠą║ą░ąĘą░ąĮą░ 8-ą▒ąĖčéąĮą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░ (SIZE = 0), ą┐čĆąĖ ą┐ąĄčĆąĄą┤ą░č湥 ą┐ąĄčĆą▓čŗą╝ čüą░ą╝ąŠą│ąŠ ąĘąĮą░čćąĖą╝ąŠą│ąŠ ą▒ąĖčéą░, most significant bit, MSB (LSBF = 0). ąĀą░ąĘčĆąĄčłąĄąĮą░ ą╗čÄą▒ą░čÅ ą║ąŠą╝ą▒ąĖąĮą░čåąĖčÅ ą▒ąĖčé SIZE ąĖ LSBF ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPIx_CTL. ąØą░ą┐čĆąĖą╝ąĄčĆ, ą┤čĆčāą│ąŠą╣ ą▓ąŠąĘą╝ąŠąČąĮąŠą╣ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĄą╣ ą╝ąŠąČąĄčé ą▒čŗčéčī 16-ą▒ąĖčéąĮą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░, ą║ąŠą│ą┤ą░ čüą░ą╝čŗą╣ ą╝ąĄąĮąĄąĄ ąĘąĮą░čćąĖą╝čŗą╣ ą▒ąĖčé (least significant bit, LSB) ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą┐ąĄčĆą▓čŗą╝.

ą¤ąŠą╗čÅčĆąĮąŠčüčéčī ąĖ čäą░ąĘą░ čéą░ą║č鹊ą▓ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ąĮą░čüčéčĆąŠąĄąĮą░ ąĖą┤ąĄąĮčéąĖčćąĮąŠ ą┤ą╗čÅ čāčüčéčĆąŠą╣čüčéą▓ master ąĖ slave, ą║ąŠč鹊čĆčŗąĄ ą▓ąŠą▓ą╗ąĄč湥ąĮčŗ ą▓ ąŠą▒ą╝ąĄąĮ ą┤čĆčāą│ čü ą┤čĆčāą│ąŠą╝. ążąŠčĆą╝ą░čé ą┐ąĄčĆąĄą┤ą░čćąĖ ąŠčé master ą╝ąŠąČąĄčé ą▒čŗčéčī ąĖąĘą╝ąĄąĮąĄąĮ ą╝ąĄąČą┤čā ą┐ąĄčĆąĄą┤ą░čćą░ą╝ąĖ, čćč鹊ą▒čŗ čāą┤ąŠą▓ą╗ąĄčéą▓ąŠčĆąĖčéčī čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅą╝ slave-čāčüčéčĆąŠą╣čüčéą▓ą░.

ąÜąŠą│ą┤ą░ CPHA = 0, ą╗ąĖąĮąĖčÅ ą▓čŗą▒ąŠčĆą║ąĖ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ąĮąĄ ą░ą║čéąĖą▓ąĮą░ (ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą╗ąŠą│. 1) ą╝ąĄąČą┤čā ą║ą░ąČą┤ąŠą╣ ą┐ąĄčĆąĄą┤ą░č湥ą╣ čäčĆąĄą╣ą╝ą░. ąŁč鹊 čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą░ą┐ą┐ą░čĆą░čéąĮąŠą╣ ą╗ąŠą│ąĖą║ąŠą╣ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ SPI. ąÜąŠą│ą┤ą░ CPHA = 1, ą╗ąĖąĮąĖčÅ ą▓čŗą▒ąŠčĆą║ąĖ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ~SPIxSS ą╝ąŠąČąĄčé ą╗ąĖą▒ąŠ ąŠčüčéą░ą▓ą░čéčīčüčÅ ą░ą║čéąĖą▓ąĮąŠą╣ (ą▓čüąĄ ą▓čĆąĄą╝čÅ ąŠčüčéą░ą▓ą░čéčīčüčÅ ą▓ ą╗ąŠą│. 0) ą╝ąĄąČą┤čā čüą╗ąĄą┤čāčÄčēąĖą╝ąĖ ą┤čĆčāą│ ąĘą░ ą┤čĆčāą│ąŠą╝ ą┐ąĄčĆąĄą┤ą░čćą░ą╝ąĖ čäčĆąĄą╣ą╝ą░, ą╗ąĖą▒ąŠ čüčéą░ąĮąŠą▓ąĖčéčīčüčÅ ąĮąĄą░ą║čéąĖą▓ąĮąŠą╣ ą╝ąĄąČą┤čā ą┐ąĄčĆąĄą┤ą░čćą░ą╝ąĖ (ą┐ąĄčĆąĄčģąŠą┤ąĖčéčī ą▓ ą╗ąŠą│. 1). ąŁč鹊 ą┤ąŠą╗ąČąĮąŠ čāą┐čĆą░ą▓ą╗čÅčéčīčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ, ą┐čāč鹥ą╝ ą╝ą░ąĮąĖą┐čāą╗čÅčåąĖąĖ čüąŠą┤ąĄčƹȹĖą╝čŗą╝ čĆąĄą│ąĖčüčéčĆą░ SPIx_FLG.

ąØą░ čĆąĖčü. 10-12 ą┐ąŠą║ą░ąĘą░ąĮ ą┐čĆąŠč鹊ą║ąŠą╗ ą┐ąĄčĆąĄą┤ą░čćąĖ SPI ą┤ą╗čÅ CPHA = 0. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 SCKx ąĮą░čćąĖąĮą░ąĄčé ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ą┐ąŠčüąĄčĆąĄą┤ąĖąĮąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ, SIZE = 0 ąĖ LSBF = 0.

ąĀąĖčü. 10-12. ą¤čĆąŠč鹊ą║ąŠą╗ ą┐ąĄčĆąĄą┤ą░čćąĖ SPI (č乊čĆą╝ą░čé čäčĆąĄą╣ą╝ą░) ą┤ą╗čÅ CPHA = 0.

ąØą░ čĆąĖčü. 10-13 ą┐ąŠą║ą░ąĘą░ąĮ ą┐čĆąŠč鹊ą║ąŠą╗ ą┐ąĄčĆąĄą┤ą░čćąĖ SPI ą┤ą╗čÅ CPHA = 1. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 SCKx ąĮą░čćąĖąĮą░ąĄčé ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ą▓ ą╝ąŠą╝ąĄąĮčé ąĮą░čćą░ą╗ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ, SIZE = 0 ąĖ LSBF = 0.

ąĀąĖčü. 10-13. ą¤čĆąŠč鹊ą║ąŠą╗ ą┐ąĄčĆąĄą┤ą░čćąĖ SPI (č乊čĆą╝ą░čé čäčĆąĄą╣ą╝ą░) ą┤ą╗čÅ CPHA = 1.

[ą×čüąĮąŠą▓ąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ čĆą░ą▒ąŠčéčŗ SPI]

ąśąĮč鹥čĆč乥ą╣čü SPI ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą▓ ąŠą▒ą╝ąĄąĮąĄ čü ąŠą┤ąĮąĖą╝ čāčüčéčĆąŠą╣čüčéą▓ąŠ master ąĮą░ čłąĖąĮąĄ, ąĖ ą▓ čüąĖčéčāą░čåąĖčÅčģ, ą║ąŠą│ą┤ą░ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ master ą╝ąŠą│čāčé čüčéą░ąĮąŠą▓ąĖčéčīčüčÅ ąĮąĄčüą║ąŠą╗čīą║ąŠ čāčüčéčĆąŠą╣čüčéą▓ (čĆą░ą▒ąŠč湥ąĄ ąŠą║čĆčāąČąĄąĮąĖąĄ multimaster). ąÆ ą╗čÄą▒ąŠą╝ čüą╗čāčćą░ąĄ ąŠą┤ąĮąŠąĖą╝ąĄąĮąĮčŗąĄ čüąĖą│ąĮą░ą╗čŗ MOSIx, MISOx ąĖ SCKx čüąŠąĄą┤ąĖąĮčÅčÄčéčüčÅ ą┤čĆčāą│ čü ą┤čĆčāą│ąŠą╝ ąĮą░ą┐čĆčÅą╝čāčÄ. ą¤ąĄčĆąĄą┤ą░čćą░ ąĖ ą┐čĆąĖąĄą╝ ą╝ąĄąČą┤čā ą┤ą▓čāą╝čÅ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ SPI ą▓čüąĄą│ą┤ą░ ąĮą░čćąĖąĮą░čÄčéčüčÅ ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ (čé. ąĄ. ą┐ąĄčĆąĄą┤ą░čćą░ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ą┤čāą┐ą╗ąĄą║čüąĮą░čÅ), ąĘą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ ą▓čŗą▒ąŠčĆą░ čĆąĄąČąĖą╝ą░ čłąĖčĆąŠą║ąŠą▓ąĄčēą░ąĮąĖčÅ (broadcast), ą║ąŠą│ą┤ą░ ąĮą░ čłąĖąĮąĄ ą┐čĆąĖčüčāčéčüčéą▓čāčÄčé ąĮąĄčüą║ąŠą╗čīą║ąŠ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓. ąÆ čĆąĄąČąĖą╝ąĄ broadcast ąĮąĄčüą║ąŠą╗čīą║ąŠ slave-čāčüčéčĆąŠą╣čüčéą▓ ą╝ąŠą│čāčé ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮčŗ ąĮą░ ą┐čĆąĖąĄą╝, ąĮąŠ č鹊ą╗čīą║ąŠ ąŠą┤ąĮąŠą╝čā ąĖąĘ ąĮąĖčģ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮą░ ą┐ąĄčĆąĄą┤ą░čćą░, ąĖąĮą░č湥 ąĮąĄčüą║ąŠą╗čīą║ąŠ ą▓čŗčģąŠą┤ąŠą▓ ą╝ąŠą│čāčé ą┐ąŠčĆąŠą┤ąĖčéčī ąĮą░ čüąĖą│ąĮą░ą╗ąĄ MISO čüą║ą▓ąŠąĘąĮčŗąĄ č鹊ą║ąĖ. ąĢčüą╗ąĖ ą┐ąĄčĆąĄą┤ą░čćą░ ąĖą╗ąĖ ą┐čĆąĖąĄą╝ ąĮąĄ čéčĆąĄą▒čāąĄčéčüčÅ, č鹊 čŹč鹊 ą╝ąŠąČąĮąŠ ą┐čĆąŠčüč鹊 ąĖą│ąĮąŠčĆąĖčĆąŠą▓ą░čéčī. ąÆ čŹč鹊ą╝ čĆą░ąĘą┤ąĄą╗ąĄ ąŠą┐ąĖčüčŗą▓ą░čÄčéčüčÅ čüąĖą│ąĮą░ą╗čŗ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ, čĆą░ą▒ąŠčéą░ SPI ą▓ ą║ą░č湥čüčéą▓ąĄ master ąĖ ą▓ ą║ą░č湥čüčéą▓ąĄ slave, ąĖ ą│ąĄąĮąĄčĆą░čåąĖčÅ ąŠčłąĖą▒ąŠą║.

ąöąŠą╗ąČąĮčŗ ą▒čŗčéčī ą┐čĆąĄą┤ą┐čĆąĖąĮčÅčéčŗ ą╝ąĄčĆčŗ ą┐čĆąĄą┤ąŠčüč鹊čĆąŠąČąĮąŠčüčéąĖ, čćč鹊ą▒čŗ ąĮąĄ ą┤ąŠą┐čāčüčéąĖčéčī ą┐ąŠčĆčćąĖ ą┤ą░ąĮąĮčŗčģ, ą║ąŠą│ą┤ą░ ą╝ąĄąĮčÅąĄčéčüčÅ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą╝ąŠą┤čāą╗čÅ SPI. ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ąĮąĄ ą┤ąŠą╗ąČąĮą░ ą╝ąĄąĮčÅčéčīčüčÅ ą┐čĆąĖ ą┐ąĄčĆąĄą┤ą░č湥 ą┤ą░ąĮąĮčŗčģ. ą¤ąŠą╗čÅčĆąĮąŠčüčéčī čéą░ą║č鹊ą▓ ą┤ąŠą╗ąČąĮą░ ą╝ąĄąĮčÅčéčīčüčÅ č鹊ą╗čīą║ąŠ č鹊ą│ą┤ą░, ą║ąŠą│ą┤ą░ ąĮąĄčé ą▓čŗą▒čĆą░ąĮąĮčŗčģ slave-čāčüčéčĆąŠą╣čüčéą▓. ąśčüą║ą╗čÄč湥ąĮąĖąĄą╝ ąĖąĘ čŹč鹊ą│ąŠ ą╝ąŠąČąĄčé ą▒čŗčéčī čüąĖčéčāą░čåąĖčÅ, ą║ąŠą│ą┤ą░ ąĮą░ čłąĖąĮąĄ SPI ąĄčüčéčī č鹊ą╗čīą║ąŠ ąŠą┤ąĖąĮ master ąĖ č鹊ą╗čīą║ąŠ ąŠą┤ąĮąŠ čāčüčéčĆąŠą╣čüčéą▓ąŠ slave, CPHA = 1, ąĖ ą▓čģąŠą┤ slave-čāčüčéčĆąŠą╣čüčéą▓ą░ čāąČąĄ ą┐ąĄčĆąĄą▓ąĄą┤ąĄąĮ ą▓ ą░ą║čéąĖą▓ąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ (ą╗ąŠą│. 0). ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ slave ą▓čüąĄą│ą┤ą░ ą▓čŗą▒čĆą░ąĮ, ąĖ čüąĖčéčāą░čåąĖąĖ ą┐ąŠčĆčćąĖ ą┤ą░ąĮąĮčŗčģ ą╝ąŠąČąĮąŠ ąĖąĘą▒ąĄąČą░čéčī ą┐čāč鹥ą╝ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ slave-čāčüčéčĆąŠą╣čüčéą▓ą░ č鹊ą╗čīą║ąŠ ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ ąŠą▒ą░ čāčüčéčĆąŠą╣čüčéą▓ą░, ąĖ master, ąĖ slave.

ąÆ čüąĖčüč鹥ą╝ą░čģ multimaster (ą║ąŠą│ą┤ą░ ąĮą░ čłąĖąĮąĄ SPI ą▓ čĆą░ąĘąĮčŗąĄ ą╝ąŠą╝ąĄąĮčéčŗ ą▓čĆąĄą╝ąĄąĮąĖ ą╝ąŠą│čāčé čüčéą░ąĮąŠą▓ąĖčéčīčüčÅ ą│ą╗ą░ą▓ąĮčŗą╝ąĖ čĆą░ąĘąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░) ąĖą╗ąĖ ą▓ čüąĖčüč鹥ą╝ą░čģ multislave (ą║ąŠą│ą┤ą░ ąĮą░ čłąĖąĮąĄ SPI ąĄčüčéčī ąĮąĄčüą║ąŠą╗čīą║ąŠ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓), ą▓čŗą▓ąŠą┤čŗ ą▓čŗčģąŠą┤ą░ ą┤ą░ąĮąĮčŗčģ (MOSIx ąĖ MISOx) ą╝ąŠą│čāčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ ą║ą░ą║ ą▓čŗčģąŠą┤čŗ čü ąŠčéą║čĆčŗčéčŗą╝ąĖ čüč鹊ą║ą░ą╝ąĖ, čćč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐čĆąĄą┤ąŠčéą▓čĆą░čéąĖčéčī ą┐ąŠčÅą▓ą╗ąĄąĮąĖąĄ čüą║ą▓ąŠąĘąĮčŗčģ č鹊ą║ąŠą▓, ą║ąŠą│ą┤ą░ ąĮą░ ą▓čŗčģąŠą┤ą░čģ ą┐ąŠčÅą▓ą╗čÅčÄčéčüčÅ ą┐čĆąŠčéąĖą▓ąŠą┐ąŠą╗ąŠąČąĮčŗąĄ čāčĆąŠą▓ąĮąĖ (čüą║ą▓ąŠąĘąĮčŗąĄ č鹊ą║ąĖ ą╝ąŠą│čāčé ą┐čĆąĖą▓ąĄčüčéąĖ ą║ ą┐ąŠą▓čŗčłąĄąĮąĮąŠą╝čā ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÄ č鹊ą║ą░ ąĖ ą┤ą░ąČąĄ ą║ ą▓čŗčģąŠą┤čā ąĖąĘ čüčéčĆąŠčÅ ą▓čŗčģąŠą┤ąĮčŗčģ ą▒čāč乥čĆąŠą▓ ą┐ąŠčĆčéą░). ąÆ čéą░ą║ąŠą╣ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ čéčĆąĄą▒čāąĄčéčüčÅ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖąĄ ą▓ąĮąĄčłąĮąĄą│ąŠ ą▓ąĄčĆčģąĮąĄą│ąŠ ąĮą░ą│čĆčāąĘąŠčćąĮąŠą│ąŠ čĆąĄąĘąĖčüč鹊čĆą░ (pull-up) ą╝ąĄąČą┤čā čłąĖąĮąŠą╣ ą┐ąĖčéą░ąĮąĖčÅ VDDEXT ąĖ čüąĖą│ąĮą░ą╗ąŠą╝ ą┤ą░ąĮąĮčŗčģ, čĆą░ą▒ąŠčéą░čÄčēąĄą╝ ąĮą░ ąŠčéą║čĆčŗčéčŗčģ čüč鹊ą║ą░čģ (MOSIx ąĖ/ąĖą╗ąĖ MISOx).

ą×ą┐čåąĖąĄą╣ ąŠčéą║čĆčŗč鹊ą│ąŠ čüč鹊ą║ą░ čāą┐čĆą░ą▓ą╗čÅąĄčé ą▒ąĖčé WOM. ąÜąŠą│ą┤ą░ ą▒ąĖčé WOM čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ąĖ SPI čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą║ą░ą║ master, ą▓čŗą▓ąŠą┤ MOSIx čüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▓čŗčģąŠą┤ąŠą╝ čü čéčĆąĄą╝čÅ čüąŠčüč鹊čÅąĮąĖčÅą╝ąĖ, ą║ąŠą│ą┤ą░ ąĮą░ ąĮąĄą╝ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą╗ąŠą│. 1 (čé. ąĄ. ąŠčéą║čĆčŗčéčŗą╣ čüč鹊ą║ ą┐ąĄčĆąĄčüčéą░ąĄčé ąĘą░ą╝čŗą║ą░čéčī ą╗ąĖąĮąĖčÄ MOSIx ąĮą░ GND). ąØąŠ ą║ąŠą│ą┤ą░ ąĮą░ ą▓čŗčģąŠą┤ MOSIx ą▓čŗą▓ąŠą┤ąĖčéčüčÅ ą╗ąŠą│. 0, č鹊 ą▓čŗčģąŠą┤ ą┐ąĄčĆąĄčüčéą░ąĄčé ą▒čŗčéčī ą▓ čéčĆąĄčéčīąĄą╝ čüąŠčüč鹊čÅąĮąĖąĖ (ą┐ąŠč鹊ą╝čā čćč鹊 ąŠčéą║čĆčŗčéčŗą╣ čüč鹊ą║ ą┐čĆąĖčéčÅą│ąĖą▓ą░ąĄčé čüąĖą│ąĮą░ą╗ MOSIx ą║ GND). ąÉąĮą░ą╗ąŠą│ąĖčćąĮąŠ, ą║ąŠą│ą┤ą░ WOM čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ąĖ SPI čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą▓ čĆąĄąČąĖą╝ąĄ slave, ą▓čŗą▓ąŠą┤ MISOx čüčéą░ąĮąŠą▓ąĖčéčüčÅ čü ąŠčéą║čĆčŗčéčŗą╝ čüč鹊ą║ąŠą╝, ąĖ ą╝ąŠąČąĄčé ą┐ąĄčĆąĄčģąŠą┤ąĖčéčī ą▓ čéčĆąĄčéčīąĄ čüąŠčüč鹊čÅąĮąĖąĄ, ą║ąŠą│ą┤ą░ ąĮą░ ąĮąĄą│ąŠ ą▓čŗą▓ąŠą┤ąĖčéčüčÅ ą╗ąŠą│. 1.

[ąóą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ SPI]

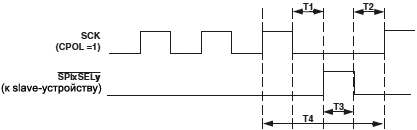

ąóą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗ SCKx ą▓čŗą┤ą░ąĄčéčüčÅ ąĮą░ čłąĖąĮčā ąĮąĄ ą┐ąŠčüč鹊čÅąĮąĮąŠ, ą░ č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ ą░ą║čéąĖą▓ąĮą░ ą┐ąĄčĆąĄą┤ą░čćą░ čäčĆąĄą╣ą╝ą░, čé. ąĄ. ą║ąŠą│ą┤ą░ ą▒ąĖčéčŗ čüą╗ąŠą▓ą░ ą┤ą░ąĮąĮčŗčģ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ą┐ąŠ čłąĖąĮąĄ SPI. ąÜąŠą╗ąĖč湥čüčéą▓ąŠ ą░ą║čéąĖą▓ąĮčŗčģ ą┐ąĄčĆąĄą┐ą░ą┤ąŠą▓ čéą░ą║č鹊ą▓ č鹊čćąĮąŠ čĆą░ą▓ąĮąŠ ą║ąŠą╗ąĖč湥čüčéą▓čā ą▒ąĖčé, ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗčģ ą┐ąŠ čüąĖą│ąĮą░ą╗ą░ą╝ ą┤ą░ąĮąĮčŗčģ MISO ąĖ MOSI. ą£ą░ą║čüąĖą╝ą░ą╗čīąĮą░čÅ čćą░čüč鹊čéą░ čéą░ą║č鹊ą▓ ą╝ąŠąČąĄčé ą▒čŗčéčī 1/4 ąŠčé čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ SCLK. ąöą╗čÅ čāčüčéčĆąŠą╣čüčéą▓ master čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ 16-ą▒ąĖčéąĮčŗą╝ ąĘąĮą░č湥ąĮąĖąĄą╝ ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPIx_BAUD. ąöą╗čÅ slave-čāčüčéčĆąŠą╣čüčéą▓ ąĘąĮą░č湥ąĮąĖąĄ SPIx_BAUD ąĖą│ąĮąŠčĆąĖčĆčāąĄčéčüčÅ. ąÜąŠą│ą┤ą░ čāčüčéčĆąŠą╣čüčéą▓ąŠ SPI čÅą▓ą╗čÅąĄčéčüčÅ master, čüąĖą│ąĮą░ą╗ SCKx čüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▓čŗčģąŠą┤ąŠą╝. ąÜąŠą│ą┤ą░ čāčüčéčĆąŠą╣čüčéą▓ąŠ SPI čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ slave, čüąĖą│ąĮą░ą╗ SCKx čüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▓čģąŠą┤ąŠą╝. Slave-čāčüčéčĆąŠą╣čüčéą▓ą░ ąĖą│ąĮąŠčĆąĖčĆčāčÄčé čüąĖą│ąĮą░ą╗ SCKx, ąĄčüą╗ąĖ ąĖčģ čüąĖą│ąĮą░ą╗ ą▓čŗą▒ąŠčĆą║ąĖ čüčéą░ąĮąŠą▓ąĖčéčüčÅ ąĮąĄą░ą║čéąĖą▓ąĮčŗą╝ (high).

ąĪąĖą│ąĮą░ą╗ SCKx ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą▓ą┤ą▓ąĖą│ą░ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ą▓ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ ąĖ ą▓čŗčéą░ą╗ą║ąĖą▓ą░ąĮąĖčÅ ąĖčģ ąĮą░čĆčāąČčā ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ čüą┤ą▓ąĖą│ą░ č湥čĆąĄąĘ čüąĖą│ąĮą░ą╗čŗ ą┤ą░ąĮąĮčŗčģ MISOx ąĖ MOSIx čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ. ąöą░ąĮąĮčŗąĄ ą▓čüąĄą│ą┤ą░ ą▓čŗą┤ą▓ąĖą│ą░čÄčéčüčÅ ą┐ąŠ ąŠą┤ąĮąŠą╝čā ą▒ąĖčéčā ąĮą░ ąŠą┤ąĖąĮ ą┐ąĄčĆąĄą┐ą░ą┤ čéą░ą║č鹊ą▓ (0 -> 1 ąĖą╗ąĖ 1 -> 0, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ), ąĖ ą▓čŗą▒ąŠčĆą║ą░ ą┤ą░ąĮąĮčŗčģ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ąĮą░ ą┐čĆąŠčéąĖą▓ąŠą┐ąŠą╗ąŠąČąĮąŠą╝ ą┐ąĄčĆąĄą┐ą░ą┤ąĄ (1 -> 0 ąĖą╗ąĖ 0 -> 1). ą¤ąŠą╗čÅčĆąĮąŠčüčéčī ąĖ čäą░ąĘą░ čéą░ą║č鹊ą▓ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPIx_CTL ąĖ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé č乊čĆą╝ą░čé čäčĆąĄą╣ą╝ą░ (čĆąĖčü. 10-11).

[ąĀą░ą▒ąŠčéą░ ą▓ čĆąĄąČąĖą╝ąĄ ą│ą╗ą░ą▓ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (Master)]

ą£ąĄąČą┤čā ą┐ąŠčĆčéą░ą╝ąĖ SPI0 ąĖ SPI1/SPI2 ąĄčüčéčī ąŠčéą╗ąĖčćąĖčÅ, čüą▓čÅąĘą░ąĮąĮčŗąĄ čü ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĄą╣ ąĮąŠąČąĄą║ ąĖ čü čüąĖą│ąĮą░ą╗ą░ą╝ąĖ ą▓čŗą▒ąŠčĆą║ąĖ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓.

SPI0. ąÜąŠą│ą┤ą░ SPI0 čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą║ą░ą║ master (ąĖ ąĮąĄ ą▓čŗą▒čĆą░ąĮ čĆąĄąČąĖą╝ DMA), ąĖąĮč鹥čĆč乥ą╣čü čĆą░ą▒ąŠčéą░ąĄčé ą┐ąŠ čüą╗ąĄą┤čāčÄčēąĄą╝čā ą░ą╗ą│ąŠčĆąĖčéą╝čā.

1. ą»ą┤čĆąŠ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčé čĆąĄą│ąĖčüčéčĆ SPI0_FLG, č湥ą╝ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ąŠą┤ąĖąĮ ąĖą╗ąĖ ą▒ąŠą╗čīčłąĄąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čäą╗ą░ą│ąŠą▓ ą▓čŗą▒ąŠčĆą║ąĖ (SPI flag select bits, FLSx). ąŁč鹊 ą│ą░čĆą░ąĮčéąĖčĆčāąĄčé, čćč鹊 ąĮąĄ ą▒čāą┤čāčé ą▓čŗą▒čĆą░ąĮčŗ ąĮąĖą║ą░ą║ąĖąĄ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ ąĮą░ čłąĖąĮąĄ, ą┐ąŠą║ą░ master ąĮąĄ ą▒čāą┤ąĄčé čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ.

2. ą»ą┤čĆąŠ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčé čĆąĄą│ąĖčüčéčĆčŗ SPI0_BAUD ąĖ SPI0_CTL, č湥ą╝ čĆą░ąĘčĆąĄčłą░ąĄčé čĆą░ą▒ąŠčéčā čāčüčéčĆąŠą╣čüčéą▓ą░ ą▓ čĆąĄąČąĖą╝ąĄ master, ąĖ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčé čüąĖčüč鹥ą╝čā SPI, ąĘą░ą┤ą░ą▓ą░čÅ ą┤ą╗ąĖąĮčā čüą╗ąŠą▓ą░, č乊čĆą╝ą░čé ą┐ąĄčĆąĄą┤ą░čćąĖ, čüą║ąŠčĆąŠčüčéčī ąĖ ą┤čĆčāą│ąĖąĄ ąĮąĄąŠą▒čģąŠą┤ąĖą╝čŗąĄ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ.

3. ąĢčüą╗ąĖ CPHA = 1, čÅą┤čĆąŠ ą░ą║čéąĖą▓ąĖčĆčāąĄčé ąĮčāąČąĮąŠąĄ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ (ąĖą╗ąĖ ąĮąĄčüą║ąŠą╗čīą║ąŠ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓) ą┐čāč鹥ą╝ ąŠčćąĖčüčéą║ąĖ ąŠą┤ąĮąŠą│ąŠ (ąĖą╗ąĖ ą▒ąŠą╗čīčłąĄą│ąŠ ą║ąŠą╗ąĖč湥čüčéą▓ą░) ą▒ąĖč鹊ą▓ FLGx ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI0_FLG.

4. ąæąĖčéčŗ TIMOD ą▓ SPI0_CTL ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčé čĆąĄąČąĖą╝ ąĖąĮąĖčåąĖą░čåąĖąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ SPI. ą¤ąĄčĆąĄą┤ą░čćą░ ąĮą░ čłąĖąĮąĄ SPI ąĮą░čćąĖąĮą░ąĄčéčüčÅ ą╗ąĖą▒ąŠ ą┐čĆąĖ ąĘą░ą┐ąĖčüąĖ ą┤ą░ąĮąĮčŗčģ čÅą┤čĆąŠą╝ ą▓ ą▒čāč乥čĆ ą┐ąĄčĆąĄą┤ą░čćąĖ (SPI0_TDBR), ą╗ąĖą▒ąŠ ą┐čĆąĖ čćč鹥ąĮąĖąĖ ą┤ą░ąĮąĮčŗčģ ąĖąĘ ą▒čāč乥čĆą░ ą┐čĆąĖąĄą╝ą░ (SPI0_RDBR).

5. ąŚą░č鹥ą╝ SPI ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ąĖą╝ą┐čāą╗čīčüčŗ čéą░ą║č鹊ą▓ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ SCK0, ąĖ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ą▓čŗą┤ą▓ąĖą│ą░ąĄčé ą┤ą░ąĮąĮčŗąĄ ąĮą░čĆčāąČčā č湥čĆąĄąĘ čüą▓ąŠą╣ ą▓čŗčģąŠą┤ MOSI0, ąĖ ą▓ą┤ą▓ąĖą│ą░ąĄčé ą┤ą░ąĮąĮčŗąĄ ą▓ąĮčāčéčĆčī č湥čĆąĄąĘ čüą▓ąŠą╣ ą▓čģąŠą┤ MISO0. ą¤ąĄčĆąĄą┤ čüą┤ą▓ąĖą│ąŠą╝ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ čüąŠą┤ąĄčƹȹĖą╝čŗą╝ čĆąĄą│ąĖčüčéčĆą░ SPI0_TDBR. ą¤ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ čĆąĄą│ąĖčüčéčĆą░ čüą┤ą▓ąĖą│ą░ ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ą▓ SPI0_RDBR (ą▒čāč乥čĆ ą┐čĆąĖąĄą╝ą░).

6. ąĪ ą║ą░ąČą┤čŗą╝ ąĮąŠą▓čŗą╝ ąĖąĮąĖčåąĖąĖčĆąŠą▓ą░ąĮąĖąĄą╝ ą┐ąĄčĆąĄą┤ą░čćąĖ SPI ą┐čĆąŠą┤ąŠą╗ąČąĖčé ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī ąĖ ą┐čĆąĖąĮąĖą╝ą░čéčī čüą╗ąŠą▓ą░ ą┤ą░ąĮąĮčŗčģ, ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü ąĮą░čüčéčĆąŠąĄąĮąĮčŗą╝ čĆąĄąČąĖą╝ąŠą╝ ąĖąĮąĖčåąĖą░čåąĖąĖ (čüą╝. ą▒ąĖčéčŗ TIMOD čĆąĄą│ąĖčüčéčĆąĄ SPIx_CTL).

SPI1 ąĖ SPI2. ąöą╗čÅ SPI1 ąĖ SPI2 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čéą░ ąČąĄ čüą░ą╝ą░čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī, ąŠčéą╗ąĖčćąĖąĄ č鹊ą╗čīą║ąŠ ą▓ č鹊ą╝, čćč鹊 čÅą┤čĆąŠ ą┤ąŠą╗ąČąĮąŠ čüąĮą░čćą░ą╗ą░ ą┐čĆąŠą▓ąĄčĆąĖčéčī, čćč鹊 ą▓čŗą▓ąŠą┤čŗ GPIO, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą┤ą╗čÅ ą┐ąŠčĆč鹊ą▓ SPIx, ąĮąĄ čĆą░ą▒ąŠčéą░čÄčé ą║ą░ą║ ą┐ąŠčĆčéčŗ GPIO. ą¤ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą▓čŗą▓ąŠą┤čŗ ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮčŗ ą┤ą╗čÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ SPI1 ąĖ SPI2 (ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčāčÄ ąĖąĮč乊čĆą╝ą░čåąĖčÄ ą┐čĆąŠ ąĮą░čüčéčĆąŠą╣ą║čā ą┐ąŠčĆč鹊ą▓ GPIO čüą╝. ą▓ čüčéą░čéčīąĄ [4]). ąĢčüą╗ąĖ ą▒čāč乥čĆ ą┐ąĄčĆąĄą┤ą░čćąĖ ąŠčüčéą░ąĄčéčüčÅ ą┐čāčüčéčŗą╝ ąĖą╗ąĖ ą▒čāč乥čĆ ą┐čĆąĖąĄą╝ą░ ąŠčüčéą░ąĄčéčüčÅ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĮčŗą╝, č鹊 čāčüčéčĆąŠą╣čüčéą▓ąŠ čĆą░ą▒ąŠčéą░ąĄčé ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü čüąŠčüč鹊čÅąĮąĖčÅą╝ąĖ ą▒ąĖč鹊ą▓ SZ ąĖ GM ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPIx_CTL. ąĢčüą╗ąĖ SZ = 1, ąĖ ą▒čāč乥čĆ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐čāčüčé, č鹊 čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐ąŠčüč鹊čÅąĮąĮąŠ ą┐ąĄčĆąĄą┤ą░ąĄčé ąĮčāą╗ąĖ č湥čĆąĄąĘ ą▓čŗą▓ąŠą┤ MOSIx. ą×ą┤ąĮąŠ čüą╗ąŠą▓ąŠ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą╣ ąĮąŠą▓ąŠą╣ ą║ąŠą╝ą░ąĮą┤čŗ ąĖąĮąĖčåąĖą░čåąĖąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ. ąĢčüą╗ąĖ SZ = 0, ąĖ ą▒čāč乥čĆ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐čāčüčé, čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐ąŠčüč鹊čÅąĮąĮąŠ ą┐ąĄčĆąĄą┤ą░ąĄčé ą┐ąŠčüą╗ąĄą┤ąĮąĄąĄ čüą╗ąŠą▓ąŠ, ą║ąŠč鹊čĆąŠąĄ ą▒čŗą╗ąŠ ą┐ąĄčĆąĄą┤ą░ąĮąŠ ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ čĆą░ąĘ čĆą░ąĮąĄąĄ, ą┤ąŠ č鹊ą│ąŠ ą║ą░ą║ ą▒čāč乥čĆ ą┐ąĄčĆąĄą┤ą░čćąĖ ąŠą┐čāčüč鹊賹Ėą╗čüčÅ. ąĢčüą╗ąĖ GM = 1, ąĖ ą▒čāč乥čĆ ą┐čĆąĖąĄą╝ą░ ą┐ąŠą╗ąŠąĮ, čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐čĆąŠą┤ąŠą╗ąČąĖčé ą┐čĆąĖąĮąĖą╝ą░čéčī ąĮąŠą▓čŗąĄ ą┤ą░ąĮąĮčŗąĄ ąĖąĘ ą▓čŗą▓ąŠą┤ą░ MISOx, ą┐ąĄčĆąĄąĘą░ą┐ąĖčüčŗą▓ą░čÅ čüčéą░čĆčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą▓ ą▒čāč乥čĆąĄ ą┐čĆąĖąĄą╝ą░ SPIx_RDBR. ąĢčüą╗ąĖ GM = 0, ąĖ ą▒čāč乥čĆ ą┐čĆąĖąĄą╝ą░ ą┐ąŠą╗ąŠąĮ, č鹊 ą┐čĆąĖčģąŠą┤čÅčēąĖąĄ ą┤ą░ąĮąĮčŗąĄ ą▒čāą┤čāčé ąŠčéą▒čĆąŠčłąĄąĮčŗ, ąĖ ą▒čāč乥čĆ ą┐čĆąĖąĄą╝ą░ SPIx_RDBR ąĮąĄ ą▒čāą┤ąĄčé ąŠą▒ąĮąŠą▓ą╗čÅčéčīčüčÅ.

[ąĀąĄąČąĖą╝čŗ ą┐ąĄčĆąĄą┤ą░čćąĖ. ąśąĮąĖčåąĖą░čåąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ąŠčé ą│ą╗ą░ą▓ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░]

ąÜąŠą│ą┤ą░ čāčüčéčĆąŠą╣čüčéą▓ąŠ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąŠ ą║ą░ą║ master, ąĖąĮąĖčåąĖą░čåąĖčÅ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą┐ąŠą╗ąĄą╝ TIMOD - ą┤ą▓čāą╝čÅ ą▒ąĖčéą░ą╝ąĖ ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPIx_CTL. ąØą░ ąŠčüąĮąŠą▓ąĄ čŹčéąĖčģ ą┤ą▓čāčģ ą▒ąĖčé ąĖ čüąŠčüč鹊čÅąĮąĖčÅ ąĖąĮč鹥čĆč乥ą╣čüą░ ąĮąŠą▓ą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░ ąĮą░čćąĮąĄčéčüčÅ ą╗ąĖą▒ąŠ ą┐čĆąĖ čćč鹥ąĮąĖąĖ SPIx_RDBR, ą╗ąĖą▒ąŠ ą┐čĆąĖ ąĘą░ą┐ąĖčüąĖ SPIx_TDBR. ąŁčéą░ ąĖąĮč乊čĆą╝ą░čåąĖčÅ čüą▓ąĄą┤ąĄąĮą░ ą▓ čéą░ą▒ą╗ąĖčåąĄ 10-4.

ąĢčüą╗ąĖ ą┐ąŠčĆčé SPI čĆą░ąĘčĆąĄčłąĄąĮ čü TIMOD = 01 ąĖą╗ąĖ TIMOD = 11, ą░ą┐ą┐ą░čĆą░čéčāčĆą░ ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ ą▓čŗą┤ą░ąĄčé ą┐ąĄčĆą▓ąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĖą╗ąĖ ąĘą░ą┐čĆąŠčü DMA.

ąóą░ą▒ą╗ąĖčåą░ 10-4. ąśąĮąĖčåąĖą░čåąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐ąŠ čłąĖąĮąĄ SPI.

| TIMOD |

ążčāąĮą║čåąĖčÅ

|

ąÜąŠą│ą┤ą░ ąĖąĮąĖčåąĖąĖčĆčāąĄčéčüčÅ ą┐ąĄčĆąĄą┤ą░čćą░ |

ąöąĄą╣čüčéą▓ąĖąĄ, ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ |

| 00 |

ą¤ąĄčĆąĄą┤ą░čćą░ ąĖ ą┐čĆąĖąĄą╝. |

ąśąĮąĖčåąĖąĖčĆčāąĄčéčüčÅ ąĮąŠą▓ą░čÅ ąŠą┤ąĖąĮąŠčćąĮą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░ čüą╗ąŠą▓ą░ ą┐čĆąĖ čćč鹥ąĮąĖąĖ SPIx_RDBR ąĖ ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĖ ą┐čĆąĄą┤čŗą┤čāčēąĄą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ. |

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą░ą║čéąĖą▓ąĮąŠ, ą║ąŠą│ą┤ą░ ą▒čāč乥čĆ ą┐čĆąĖąĄą╝ą░ ąĘą░ą┐ąŠą╗ąĮąĄąĮ.

ą¦č鹥ąĮąĖąĄ SPIx_RDBR ąŠčćąĖčēą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ. |

| 01 |

ą¤ąĄčĆąĄą┤ą░čćą░ ąĖ ą┐čĆąĖąĄą╝. |

ąśąĮąĖčåąĖąĖčĆčāąĄčéčüčÅ ąĮąŠą▓ą░čÅ ąŠą┤ąĖąĮąŠčćąĮą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░ čüą╗ąŠą▓ą░ ą┐čĆąĖ ąĘą░ą┐ąĖčüąĖ SPIx_TDBR ąĖ ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĖ ą┐čĆąĄą┤čŗą┤čāčēąĄą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ. |

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą░ą║čéąĖą▓ąĮąŠ, ą║ąŠą│ą┤ą░ ą▒čāč乥čĆ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐čāčüčé.

ąŚą░ą┐ąĖčüčī ą▓ SPIx_TDBR ąŠčćąĖčēą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ. |

| 10 |

ą¤čĆąĖąĄą╝ ą┐ąŠą┤ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝ DMA |

ąśąĮąĖčåąĖąĖčĆčāąĄčéčüčÅ ą┐ąĄčĆąĄą┤ą░čćą░ ąĮąŠą▓ąŠą│ąŠ ą▒ą╗ąŠą║ą░ čüą╗ąŠą▓ ą┐čĆąĖ čĆą░ąĘčĆąĄčłąĄąĮąĖąĖ SPI ą┤ą╗čÅ čĆąĄąČąĖą╝ą░ DMA. ą¤ąĄčĆąĄą┤ą░čćą░ ąŠčéą┤ąĄą╗čīąĮąŠą│ąŠ čüą╗ąŠą▓ą░ ąĮą░čćąĖąĮą░ąĄčéčüčÅ čü čćč鹥ąĮąĖčÅ ą▒ą╗ąŠą║ąŠą╝ DMA čĆąĄą│ąĖčüčéčĆą░ SPIx_RDBR ąĖ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ. |

ąŚą░ą┐čĆą░čłąĖą▓ą░ąĄčé čćč鹥ąĮąĖčÅ DMA, ą║ą░ą║ č鹊ą╗čīą║ąŠ SPI DMA FIFO ąĮąĄ ą┐čāčüčé. |

| 11 |

ą¤ąĄčĆąĄą┤ą░čćą░ ą┐ąŠą┤ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝ DMA |

ąśąĮąĖčåąĖąĖčĆčāąĄčéčüčÅ ą┐ąĄčĆąĄą┤ą░čćą░ ąĮąŠą▓ąŠą│ąŠ ą▒ą╗ąŠą║ą░ čüą╗ąŠą▓ ą┐čĆąĖ čĆą░ąĘčĆąĄčłąĄąĮąĖąĖ SPI ą┤ą╗čÅ čĆąĄąČąĖą╝ą░ DMA. ą¤ąĄčĆąĄą┤ą░čćą░ ąŠčéą┤ąĄą╗čīąĮąŠą│ąŠ čüą╗ąŠą▓ą░ ąĮą░čćąĖąĮą░ąĄčéčüčÅ čü ąĘą░ą┐ąĖčüąĖ ą▒ą╗ąŠą║ąŠą╝ DMA čĆąĄą│ąĖčüčéčĆą░ SPIx_TDBR ąĖ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ. |

ąŚą░ą┐čĆą░čłąĖą▓ą░ąĄčé ąĘą░ą┐ąĖčüąĖ DMA, ą║ą░ą║ č鹊ą╗čīą║ąŠ SPI DMA FIFO ąĮąĄ ąĘą░ą┐ąŠą╗ąĮąĄąĮ. |

[ąĀą░ą▒ąŠčéą░ ą▓ čĆąĄąČąĖą╝ąĄ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░]

ąÜąŠą│ą┤ą░ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮą░čüčéčĆąŠąĄąĮąŠ ą║ą░ą║ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠąĄ (ąĖ ąĮąĄ ą▓čŗą▒čĆą░ąĮ čĆąĄąČąĖą╝ DMA), ąĮą░čćą░ą╗ąŠ ą┐ąĄčĆąĄą┤ą░čćąĖ čüčĆą░ą▒ą░čéčŗą▓ą░ąĄčé ą┐čĆąĖ ą┐ąĄčĆąĄčģąŠą┤ąĄ čüąĖą│ąĮą░ą╗ą░ ~SPIxSS ą▓ ą░ą║čéąĖą▓ąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ (ą╗ąŠą│. 0), ąĖą╗ąĖ ą┐ąŠ ą┐ąĄčĆą▓ąŠą╝čā ą░ą║čéąĖą▓ąĮąŠą╝čā ą┐ąĄčĆąĄą┐ą░ą┤čā čéą░ą║č鹊ą▓ (SCKx) - ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čüąŠčüč鹊čÅąĮąĖčÅ ą▒ąĖčéą░ CPHA ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPIx_CTL.

ąÆąŠčé čłą░ą│ąĖ, ąĖą╗ą╗čÄčüčéčĆąĖčĆčāčÄčēąĖąĄ čĆą░ą▒ąŠčéčā SPI ą▓ čĆąĄąČąĖą╝ąĄ slave:

1. ą»ą┤čĆąŠ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčé čĆąĄą│ąĖčüčéčĆ SPIx_CTL, čćč鹊ą▒čŗ ąĮą░čüčéčĆąŠąĖčéčī čĆąĄąČąĖą╝ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ čüąŠąĄą┤ąĖąĮąĄąĮąĖčÅ čéą░ą║, čćč鹊ą▒čŗ ą▒čŗčéčī čüąŠą▓ą╝ąĄčüčéąĖą╝čŗą╝ čü č乊čĆą╝ą░č鹊ą╝ ą┐ąĄčĆąĄą┤ą░čćąĖ, ąĮą░čüčéčĆąŠąĄąĮąĮčŗą╝ ąĮą░ čüč鹊čĆąŠąĮąĄ SPI master.

2. ą¦č鹊ą▒čŗ ą┐ąŠą┤ą│ąŠč鹊ą▓ąĖčéčī ą┐ąĄčĆąĄą┤ą░čćčā ą┤ą░ąĮąĮčŗčģ, čÅą┤čĆąŠ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčé čŹčéąĖ ą┤ą░ąĮąĮčŗąĄ ą▓ ą▒čāč乥čĆ ą┐ąĄčĆąĄą┤ą░čćąĖ SPIx_TDBR.

3. ąÜą░ą║ č鹊ą╗čīą║ąŠ ąĮą░ ą▓čģąŠą┤ąĄ ~SPIxSS ą┐ąŠčÅą▓ąĖą╗čüčÅ čüą┐ą░ą┤ čāčĆąŠą▓ąĮčÅ (ą┐ąĄčĆąĄčģąŠą┤ ąŠčé ą╗ąŠą│. 1 ą║ ą╗ąŠą│. 0), čāčüčéčĆąŠą╣čüčéą▓ąŠ slave ąĮą░čćąĖąĮą░ąĄčé ą▓čŗą┤ą▓ąĖą│ą░čéčī ą┤ą░ąĮąĮčŗąĄ ąĮą░čĆčāąČčā č湥čĆąĄąĘ čüą▓ąŠą╣ ą▓čŗčģąŠą┤ MISO, ąĖ ą▓ą┤ą▓ąĖą│ą░čéčī ą┤ą░ąĮąĮčŗąĄ ą▓ąĮčāčéčĆčī č湥čĆąĄąĘ čüą▓ąŠą╣ ą▓čģąŠą┤ MOSI ą┐ąŠ ą┐ąĄčĆąĄą┐ą░ą┤ą░ą╝ čüąĖą│ąĮą░ą╗ą░ SCKx, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ąĮą░čüčéčĆąŠąĄą║ ą▒ąĖčé CPHA ąĖ CPOL čĆąĄą│ąĖčüčéčĆą░ SPIx_CTL.

4. ą¤čĆąĖąĄą╝/ą┐ąĄčĆąĄą┤ą░čćą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą┤ąŠ č鹊ą│ąŠ ą╝ąŠą╝ąĄąĮčéą░, ą║ą░ą║ čüčéą░ąĮąĄčé ąĮąĄą░ą║čéąĖą▓ąĮčŗą╝ čüąĖą│ąĮą░ą╗ ~SPIxSS, ąĖą╗ąĖ ą┐ąŠą║ą░ slave ąĮąĄ ą┐ąŠą╗čāčćąĖčé ąĮčāąČąĮąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čéą░ą║č鹊ą▓čŗčģ ąĖą╝ą┐čāą╗čīčüąŠą▓ SCKx.

5. Slave-čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐čĆąŠą┤ąŠą╗ąČąĖčé ą┐čĆąĖąĮąĖą╝ą░čéčī/ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī čü ą║ą░ąČą┤čŗą╝ čüą┐ą░ą┤ąŠą╝ ~SPIxSS ąĖ/ąĖą╗ąĖ čéą░ą║č鹊ą▓čŗą╝ ą┐ąĄčĆąĄą┐ą░ą┤ąŠą╝ SCKx.

ąöą╗čÅ SPI1 ąĖ SPI2 ą▓čŗą▓ąŠą┤čŗ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ SPI ąĮąĄ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ ą║ą░ą║ ą▓čŗą▓ąŠą┤čŗ ą┐ąŠčĆč鹊ą▓ GPIO, ą┐ąŠą┤čĆąŠą▒ąĮąĄąĄ ą┐čĆąŠ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ ą┐ąŠčĆč鹊ą▓ GPIO čüą╝. [4].

ąĢčüą╗ąĖ ą▒čāč乥čĆ ą┐ąĄčĆąĄą┤ą░čćąĖ ąŠčüčéą░ąĄčéčüčÅ ą┐čāčüčéčŗą╝, ąĖą╗ąĖ ą▒čāč乥čĆ ą┐čĆąĖąĄą╝ą░ ąŠčüčéą░ąĄčéčüčÅ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĮčŗą╝, č鹊 čāčüčéčĆąŠą╣čüčéą▓ąŠ čĆą░ą▒ąŠčéą░ąĄčé ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü ąĮą░čüčéčĆąŠą╣ą║ąŠą╣ ą▒ąĖčé SZ ąĖ GM čĆąĄą│ąĖčüčéčĆą░ SPIx_CTL. ąĢčüą╗ąĖ SZ = 1 ąĖ ą▒čāč乥čĆ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐čāčüčé, čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐ąŠčüč鹊čÅąĮąĮąŠ ą┐ąĄčĆąĄą┤ą░ąĄčé ąĮčāą╗ąĖ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ MISOx. ąĢčüą╗ąĖ SZ = 0, ąĖ ą▒čāč乥čĆ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐čāčüčé, č鹊 čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐ąŠčüč鹊čÅąĮąĮąŠ ą┐ąĄčĆąĄą┤ą░ąĄčé ą┐ąŠčüą╗ąĄą┤ąĮąĄąĄ čüą╗ąŠą▓ąŠ ą┤ą░ąĮąĮčŗčģ, ą║ąŠč鹊čĆąŠąĄ ą▒čŗą╗ąŠ ą┐ąĄčĆąĄą┤ą░ąĮąŠ ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ čĆą░ąĘ ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ą▒čāč乥čĆ ą┐ąĄčĆąĄą┤ą░čćąĖ ąŠą┐čāčüč鹊賹Ėą╗čüčÅ. ąĢčüą╗ąĖ GM = 1, ąĖ ą▒čāč乥čĆ ą┐čĆąĖąĄą╝ą░ ą┐ąŠą╗ąŠąĮ, čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐čĆąŠą┤ąŠą╗ąČąĖčé ą┐čĆąĖąĮąĖą╝ą░čéčī ąĮąŠą▓čŗąĄ ą┤ą░ąĮąĮčŗąĄ čü ą▓čŗą▓ąŠą┤ą░ MOSIx, ą┐ąĄčĆąĄąĘą░ą┐ąĖčüčŗą▓ą░čÅ čüčéą░čĆčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPIx_RDBR. ąĢčüą╗ąĖ GM = 0, ąĖ ą▒čāč乥čĆ ą┐čĆąĖąĄą╝ą░ ą┐ąŠą╗ąŠąĮ, č鹊 ą┐čĆąĖčģąŠą┤čÅčēąĖąĄ ą┤ą░ąĮąĮčŗąĄ ąŠčéą▒čĆą░čüčŗą▓ą░čÄčéčüčÅ, ąĖ čĆąĄą│ąĖčüčéčĆ SPIx_RDBR ąĮąĄ ąŠą▒ąĮąŠą▓ą╗čÅąĄčéčüčÅ.

ąōąŠč鹊ą▓ąĮąŠčüčéčī ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ą║ ą┐ąĄčĆąĄą┤ą░č湥. ąÜąŠą│ą┤ą░ čāčüčéčĆąŠą╣čüčéą▓ąŠ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąŠ ą║ą░ą║ slave, ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ą▓čŗą┐ąŠą╗ąĮąĖčéčī ą┤ąĄą╣čüčéą▓ąĖčÅ, ą┐ąŠą║ą░ąĘą░ąĮąĮčŗąĄ ą▓ čéą░ą▒ą╗ąĖčåąĄ 10-5, čćč鹊ą▒čŗ ą┐ąŠą┤ą│ąŠč鹊ą▓ąĖčéčī čāčüčéčĆąŠą╣čüčéą▓ąŠ ą║ ąĮąŠą▓ąŠą╣ ą┐ąĄčĆąĄą┤ą░č湥.

ąóą░ą▒ą╗ąĖčåą░ 10-5. ą¤ąŠą┤ą│ąŠč鹊ą▓ą║ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ.

| TIMOD |

ążčāąĮą║čåąĖčÅ

|

ąöąĄą╣čüčéą▓ąĖąĄ, ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ |

| 00 |

ą¤ąĄčĆąĄą┤ą░čćą░ ąĖ ą┐čĆąĖąĄą╝. |

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą░ą║čéąĖą▓ąĮąŠ, ą║ąŠą│ą┤ą░ ą▒čāč乥čĆ ą┐čĆąĖąĄą╝ą░ ąĘą░ą┐ąŠą╗ąĮąĄąĮ.

ą¦č鹥ąĮąĖąĄ SPIx_RDBR ąŠčćąĖčēą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ. |

| 01 |

ą¤ąĄčĆąĄą┤ą░čćą░ ąĖ ą┐čĆąĖąĄą╝. |

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą░ą║čéąĖą▓ąĮąŠ, ą║ąŠą│ą┤ą░ ą▒čāč乥čĆ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐čāčüčé.

ąŚą░ą┐ąĖčüčī ą▓ SPIx_TDBR ąŠčćąĖčēą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ. |

| 10 |

ą¤čĆąĖąĄą╝ ą┐ąŠą┤ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝ DMA |

ąŚą░ą┐čĆą░čłąĖą▓ą░ąĄčé čćč鹥ąĮąĖčÅ DMA, ą║ą░ą║ č鹊ą╗čīą║ąŠ SPI DMA FIFO ąĮąĄ ą┐čāčüčé. |

| 11 |

ą¤ąĄčĆąĄą┤ą░čćą░ ą┐ąŠą┤ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝ DMA |

ąŚą░ą┐čĆą░čłąĖą▓ą░ąĄčé ąĘą░ą┐ąĖčüąĖ DMA, ą║ą░ą║ č鹊ą╗čīą║ąŠ SPI DMA FIFO ąĮąĄ ąĘą░ą┐ąŠą╗ąĮąĄąĮ. |

[ąĪąĖą│ąĮą░ą╗čŗ ąŠčłąĖą▒ąŠą║ ąĖ čäą╗ą░ą│ąĖ]

ąæąĖčé MODF ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPIx_STAT čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ, ą║ąŠą│ą┤ą░ ą▓čģąŠą┤ ~SPIxSS čāčüčéčĆąŠą╣čüčéą▓ą░, čĆą░ą▒ąŠčéą░čÄčēąĄą│ąŠ ą║ą░ą║ master, ą┐ąĄčĆąĄą▓ąŠą┤ąĖčéčüčÅ ą▓ ą╗ąŠą│. 0 ą║ą░ą║ąĖą╝-č鹊 ą┤čĆčāą│ąĖą╝ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ ą▓ čüąĖčüč鹥ą╝ąĄ. ąŁč鹊 ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą▓ čüąĖčüč鹥ą╝ą░čģ multimaster, ą│ą┤ąĄ ą┤čĆčāą│ąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ čéą░ą║ąČąĄ ą┐čŗčéą░ąĄčéčüčÅ ą┐ąĄčĆąĄą╣čéąĖ ą▓ čĆąĄąČąĖą╝ master. ą¦č鹊ą▒čŗ čĆą░ąĘčĆąĄčłąĖčéčī čŹčéčā čäčāąĮą║čåąĖčÄ, ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé PSSE ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPIx_CTL. ąÜąŠąĮą║čāčĆąĄąĮčåąĖčÅ ą┤čĆčāą│ čü ą┤čĆčāą│ąŠą╝ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ą▓čŗčģąŠą┤ąŠą▓ ą╝ąŠąČąĄčé ą┐čĆąĖą▓ąĄčüčéąĖ ą║ ą┐ąŠą▓čĆąĄąČą┤ąĄąĮąĖčÄ ą▓čŗčģąŠą┤ąĮčŗčģ ą▒čāč乥čĆąŠą▓. ąÜą░ą║ č鹊ą╗čīą║ąŠ ąŠą▒ąĮą░čĆčāąČąĄąĮą░ čŹčéą░ ąŠčłąĖą▒ą║ą░, ą┐čĆąŠąĖčüčģąŠą┤čÅčé čüą╗ąĄą┤čāčÄčēąĖąĄ ą┤ąĄą╣čüčéą▓ąĖčÅ:

ŌĆó ą×čćąĖčēą░ąĄčéčüčÅ čāą┐čĆą░ą▓ą╗čÅčÄčēąĖą╣ ą▒ąĖčé MSTR ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPIx_CTL, čćč鹊 ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčé ąĖąĮč鹥čĆč乥ą╣čü SPI ą║ą░ą║ slave.

ŌĆó ą×čćąĖčēą░ąĄčéčüčÅ čāą┐čĆą░ą▓ą╗čÅčÄčēąĖą╣ ą▒ąĖčé SPE ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPIx_CTL, č湥ą╝ ąĘą░ą┐čĆąĄčēą░ąĄčéčüčÅ čĆą░ą▒ąŠčéą░ čüąĖčüč鹥ą╝čŗ SPI.

ŌĆó ąŻčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▒ąĖčé čüąŠčüč鹊čÅąĮąĖčÅ MODF ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPIx_STAT.

ŌĆó ąōąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠčłąĖą▒ą║ąĖ SPI.

ąŁčéąĖ 4 čāčüą╗ąŠą▓ąĖčÅ čüąŠčģčĆą░ąĮčÅčÄčéčüčÅ, ą┐ąŠą║ą░ ą▒ąĖčé MODF ąĮąĄ ą▒čāą┤ąĄčé ąŠčćąĖčēąĄąĮ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ. ą¤ąŠą║ą░ ą▒ąĖčé MODF ąĮąĄ ą▒čāą┤ąĄčé ąŠčćąĖčēąĄąĮ, SPI ąĮąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ąĮąŠą▓ąŠ čĆą░ąĘčĆąĄčłąĄąĮ, ą┤ą░ąČąĄ ą▓ ą║ą░č湥čüčéą▓ąĄ slave-čāčüčéčĆąŠą╣čüčéą▓ą░. ąÉą┐ą┐ą░čĆą░čéčāčĆą░ ąĮąĄ ą┤ą░ąĄčé ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÄ čāčüčéą░ąĮąŠą▓ąĖčéčī ąĮąĖ ą▒ąĖčé SPE, ąĮąĖ ą▒ąĖčé MSTR, ą┐ąŠą║ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé MODF.