|

ąÆ čŹč鹊ą╣ čüčéą░čéčīąĄ ą┐čĆąĖą▓ąĄą┤ąĄąĮ ą┐ąĄčĆąĄą▓ąŠą┤ ą┤ą░čéą░čłąĖčéą░ Atmel AVR151 [1], čĆą░čüčüą║ą░ąĘčŗą▓ą░čÄčēąĄą│ąŠ ą┐čĆąŠ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ą┐ąŠčĆčé SPI. ąŚą┤ąĄčüčī ąŠą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ, ą║ą░ą║ ąĮą░čüčéčĆąŠąĖčéčī ąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ ą▓ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ AVR čāąĘąĄą╗ Serial Peripheral Interface (SPI) [2]. ąæąŠą╗čīčłąĖąĮčüčéą▓ąŠ AVR čāąČąĄ ąĖą╝ąĄčÄčé ą▓ čüą▓ąŠąĄą╝ čüąŠčüčéą░ą▓ąĄ ą╝ąŠą┤čāą╗čī SPI, ąĖ ą╝ąŠą│čāčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ čéą░ą║, ą║ą░ą║ ąŠą┐ąĖčüą░ąĮąŠ ą▓ čŹč鹊ą╝ ą┤ą░čéą░čłąĖč鹥. ą¤ąŠčüą╗ąĄ ąĮąĄą▒ąŠą╗čīčłąŠą│ąŠ 菹║čüą║čāčĆčüą░ ą▓ č鹥ąŠčĆąĖčÄ SPI ą▒čāą┤ąĄčé ą┐ąŠą║ą░ąĘą░ąĮąŠ, ą║ą░ą║ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī SPI AVR ą▓ čĆąĄąČąĖą╝ąĄ ą│ą╗ą░ą▓ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (Master Mode) ąĖ ą▓ čĆąĄąČąĖą╝ąĄ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (Slave Mode).

ąĀą░čüčüą╝ą░čéčĆąĖą▓ą░ąĄą╝čŗąĄ ą▓ąŠą┐čĆąŠčüčŗ:

ŌĆó ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▓čŗą▓ąŠą┤ąŠą▓ ą┐ąŠčĆčéą░ SPI.

ŌĆó ąĪąĖčüč鹥ą╝čŗ čü ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ.

ŌĆó ąöąĖą░ą│čĆą░ą╝ą╝čŗ ą▓čĆąĄą╝ąĄąĮąĖ SPI.

ŌĆó ąÜąŠąĮčäą╗ąĖą║čéčŗ ą┐ąĄčĆąĄą┤ą░čć SPI.

ŌĆó ąŁą╝čāą╗čÅčåąĖčÅ SPI.

ŌĆó ą¤čĆąĖą╝ąĄčĆčŗ ą║ąŠą┤ą░, čĆą░ą▒ąŠčéą░čÄčēąĖąĄ ą┐ąŠ ą┐čĆąĖąĮčåąĖą┐čā ąŠą┐čĆąŠčüą░.

ŌĆó ą¤čĆąĖą╝ąĄčĆčŗ ą║ąŠą┤ą░, čĆą░ą▒ąŠčéą░čÄčēąĖąĄ ą┐ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅą╝.

[ą×ą▒čēąĄąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ SPI]

SPI ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąŠčüčāčēąĄčüčéą▓ąĖčéčī ą▒čŗčüčéčĆčŗą╣ čüąĖąĮčģčĆąŠąĮąĮčŗą╣ ąŠą▒ą╝ąĄąĮ ą┤ą░ąĮąĮčŗą╝ąĖ ą╝ąĄąČą┤čā AVR ąĖ čĆą░ąĘą╗ąĖčćąĮčŗą╝ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ą╝ąĖ, ąĖą╗ąĖ ą╝ąĄąČą┤čā ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ AVR. ąÆ ą▒ąŠą╗čīčłąĖąĮčüčéą▓ąĄ čéąĖą┐ąŠą▓ AVR ąĖąĮč鹥čĆč乥ą╣čü SPI ąĮąĄčüąĄčé ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠąĄ ąĮą░ąĘąĮą░č湥ąĮąĖąĄ - ąŠąĮ ą┐čĆąĖą╝ąĄąĮčÅąĄčéčüčÅ ą┤ą╗čÅ ą▓ąĮčāčéčĆąĖčüčģąĄą╝ąĮąŠą│ąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐ą░ą╝čÅčéąĖ ąĖ čäčīčĹʹŠą▓ (In System Programming, čüąŠą║čĆą░čēąĄąĮąĮąŠ ISP. ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠ čüą╝. ą░ą┐ąĮąŠčāčé AVR910). ąÆąĘą░ąĖą╝ąŠą┤ąĄą╣čüčéą▓ąĖąĄ ą╝ąĄąČą┤čā ą┤ą▓čāą╝čÅ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ SPI ą▓čüąĄą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą║ą░ą║ ąŠą▒ą╝ąĄąĮ ą╝ąĄąČą┤čā ą│ą╗ą░ą▓ąĮčŗą╝ ąĖ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗą╝ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ (master device ąĖ slave device). ąÆ čüčĆą░ą▓ąĮąĄąĮąĖąĖ čü čĆą░ąĘą╗ąĖčćąĮčŗą╝ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ (ą┤ą░čéčćąĖą║ąĖ č鹥ą╝ą┐ąĄčĆą░čéčāčĆčŗ, ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą┐ą░ą╝čÅčéąĖ, čĆą░čüčłąĖčĆąĖč鹥ą╗ąĖ ą┐ąŠčĆč鹊ą▓ ąĖ čé. ą┤.), ą║ąŠč鹊čĆčŗąĄ ą╝ąŠą│čāčé čĆą░ą▒ąŠčéą░čéčī č鹊ą╗čīą║ąŠ ą▓ čĆąĄąČąĖą╝ąĄ slave, ąĖąĮč鹥čĆč乥ą╣čü SPI ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ AVR ą╝ąŠąČąĄčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą┐ąŠ ą▓čŗą▒ąŠčĆčā ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčüčéą░ ą║ą░ą║ ą▓ čĆąĄąČąĖą╝ master, čéą░ą║ ąĖ ą▓ čĆąĄąČąĖą╝ slave. ąĀąĄąČąĖą╝ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ ą╝ą░čüč鹥čĆą░ (master bit, MSTR) ą▓ čĆąĄą│ąĖčüčéčĆąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ SPI (SPI control register, SPCR). ąöą╗čÅ ą▓čŗą▓ąŠą┤ą░ ~SS ąĮčāąČąĮąŠ čāč湥čüčéčī ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗąĄ čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅ ą┐ąŠ ąĮą░čüčéčĆąŠą╣ą║ąĄ, čćč鹊 ą▒čāą┤ąĄčé ąŠą┐ąĖčüą░ąĮąŠ ą▓ čüąĄą║čåąĖąĖ "ąĪąĖčüč鹥ą╝čŗ čü ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ. ąĀą░ą▒ąŠčéą░ ą▓čŗą▓ąŠą┤ą░ ~SS". ą£ą░čüč鹥čĆ čÅą▓ą╗čÅąĄčéčüčÅ čāą┐čĆą░ą▓ą╗čÅčÄčēąĄą╣ čćą░čüčéčīčÄ čüąĖčüč鹥ą╝čŗ, ąĖ ąŠąĮ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé čéą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗, ąĮą░ ą║ąŠč鹊čĆąŠą╝ ąŠčüąĮąŠą▓čŗą▓ą░ąĄčéčüčÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ąŠą▒ą╝ąĄąĮ ą┤ą░ąĮąĮčŗą╝ąĖ ą┐ąŠ čłąĖąĮąĄ SPI. ą¤ąŠą┤čćąĖąĮąĄąĮąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ (slave device) ąĮąĄ ą│ąĄąĮąĄčĆąĖčĆčāąĄčé čüąĖą│ąĮą░ą╗ čéą░ą║č鹊ą▓, čéą░ą║ čćč鹊 ąŠąĮąŠ ąĮąĄ ą╝ąŠąČąĄčé čüčéą░ąĮąŠą▓ąĖčéčīčüčÅ ą░ą║čéąĖą▓ąĮčŗą╝ čüą░ą╝ąŠčüč鹊čÅč鹥ą╗čīąĮąŠ. ąŻčüčéčĆąŠą╣čüčéą▓ąŠ slave ą┐čĆąŠčüč鹊 ąŠčéą┐čĆą░ą▓ą╗čÅąĄčé ąĖ ą┐čĆąĖąĮąĖą╝ą░ąĄčé ą┤ą░ąĮąĮčŗąĄ, č鹊ą╗čīą║ąŠ ąĄčüą╗ąĖ master ą│ąĄąĮąĄčĆąĖčĆčāąĄčé čéčĆąĄą▒čāąĄą╝čŗą╣ čéą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗.

ą×ą┤ąĮą░ą║ąŠ master ą│ąĄąĮąĄčĆąĖčĆčāąĄčé čéą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗ č鹊ą╗čīą║ąŠ ą▓ ą╝ąŠą╝ąĄąĮčé ąŠčéą┐čĆą░ą▓ą║ąĖ ą┤ą░ąĮąĮčŗčģ. ąŁč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ąĄčüą╗ąĖ ąĮčāąČąĮąŠ ą┐čĆąŠčćąĖčéą░čéčī ą┤ą░ąĮąĮčŗąĄ ąĖąĘ slave, č鹊 master ą┤ąŠą╗ąČąĄąĮ ą┐ąŠčüą╗ą░čéčī ą║ą░ą║ąĖąĄ-č鹊 ą┤ą░ąĮąĮčŗąĄ ą▓ slave, čé. ąĄ. čćč鹥ąĮąĖąĄ ąĖ ąĘą░ą┐ąĖčüčī ą┐ąŠ čłąĖąĮąĄ SPI ą┐čĆąŠąĖčüčģąŠą┤čÅčé ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: čŹč鹊 ą╝ąŠąČąĄčé ą▓ąĮąĄčüčéąĖ ą┐čāčéą░ąĮąĖčåčā, ąĄčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ "ą┐ą░čüčüąĖą▓ąĮčŗąĄ" ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ ąĮą░ą┐ąŠą┤ąŠą▒ąĖąĄ ą┤ą░čéčćąĖą║ąŠą▓. ąØąĄ ą▓čüąĄą│ą┤ą░ čÅą▓ą╗čÅąĄčéčüčÅ č湥čéą║ąŠą╣ ą║ąŠąĮčåąĄą┐čåąĖčÅ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéąĖ ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī čüą╗čāčćą░ą╣ąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ č鹊ą│ąŠ, čćč鹊ą▒čŗ ą┤ą░ąĮąĮčŗąĄ ą┐čĆąŠčćąĖčéą░čéčī.

[2.1. ą¤ąĄčĆąĄą┤ą░čćą░ ą┤ą░ąĮąĮčŗčģ ą╝ąĄąČą┤čā Master ąĖ Slave]

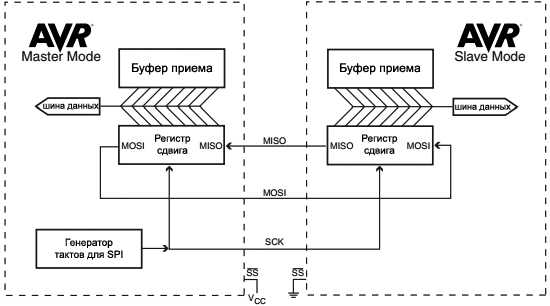

ąÆąĘą░ąĖą╝ąŠą┤ąĄą╣čüčéą▓ąĖąĄ ą╝ąĄąČą┤čā ą│ą╗ą░ą▓ąĮčŗą╝ ąĖ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗą╝ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ AVR ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 1. ąŚą┤ąĄčüčī čĆą░ą▒ąŠčéą░čÄčé ą┤čĆčāą│ čü ą┤čĆčāą│ąŠą╝ ą┤ą▓ą░ ąĖą┤ąĄąĮčéąĖčćąĮčŗąĄ ą┐ąŠ čéąĖą┐čā čāčüčéčĆąŠą╣čüčéą▓ą░. ąøąĄą▓ąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąŠ ą║ą░ą║ master, ą░ ą┐čĆą░ą▓ąŠąĄ ą║ą░ą║ slave. ąĪąĖą│ąĮą░ą╗čŗ MISO, MOSI ąĖ SCK ą┐ąŠą┤ą║ą╗čÄč湥ąĮčŗ ą║ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╝ čüąĖą│ąĮą░ą╗ą░ą╝ ą┐čĆąŠčéąĖą▓ąŠą┐ąŠą╗ąŠąČąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (MISO-MISO, MOSI-MOSI, SCK-SCK). ąĀąĄąČąĖą╝ (master ąĖą╗ąĖ slave) ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé, ą║ą░ą║ ą▒čāą┤čāčé čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░čéčī čŹčéąĖ čüąĖą│ąĮą░ą╗čŗ - ą║ą░ą║ ą▓čģąŠą┤ ąĖą╗ąĖ ą║ą░ą║ ą▓čŗčģąŠą┤. ą¤ąŠčüą║ąŠą╗čīą║čā ą▒ąĖčéčŗ čüą┤ą▓ąĖą│ą░čÄčéčüčÅ ą▓ slave (ąŠą▒ą╝ąĄąĮ ą▓ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĖ ąŠčé ą│ą╗ą░ą▓ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ą║ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą╝čā) ąĖ ą▓čŗą┤ą▓ąĖą│ą░čÄčéčüčÅ ąĖąĘ slave (ąŠą▒ą╝ąĄąĮ ą▓ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĖ ąŠčé ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ą║ ą│ą╗ą░ą▓ąĮąŠą╝čā) ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ą▓ ąŠą┤ąĮąŠą╝ čéą░ą║č鹊ą▓ąŠą╝ čåąĖą║ą╗ąĄ, č鹊 ąŠą▒ą░ 8-ą▒ąĖčéąĮčŗčģ čüą┤ą▓ąĖą│ąŠą▓čŗčģ čĆąĄą│ąĖčüčéčĆą░ ą┐čĆąĖąĄą╝ą░ ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▒čāą┤čāčé ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░čéčīčüčÅ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ. ąŁč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ą┐ąŠčüą╗ąĄ ą┐čĆąŠčģąŠąČą┤ąĄąĮąĖčÅ 8 ąĖą╝ą┐čāą╗čīčüąŠą▓ čéą░ą║č鹊ą▓ SCK ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą┐ąŠą╗ąĮčŗą╣ čåąĖą║ą╗ ąŠą▒ą╝ąĄąĮą░ ą┤ą░ąĮąĮčŗą╝ąĖ ą▓ ąŠą▒ąĄ čüč鹊čĆąŠąĮčŗ.

ąĀąĖčü. 1. ąóąĖą┐ąĖčćąĮą░čÅ ąŠčĆą│ą░ąĮąĖąĘą░čåąĖčÅ ąŠą▒ą╝ąĄąĮą░ ą┤ą░ąĮąĮčŗą╝ąĖ č湥čĆąĄąĘ SPI.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĖąĘ-ąĘą░ č鹊ą│ąŠ, čćč鹊 ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčŗ AVR ąĮą░čłą┐ąĖą│ąŠą▓ą░ąĮčŗ čĆą░ąĘą╗ąĖčćąĮąŠą╣ ą┐ąĄčĆąĖč乥čĆąĖąĄą╣, ąĖ čüčāčēąĄčüčéą▓čāąĄčé ą╝ąĮąŠąČąĄčüčéą▓ąŠ čĆą░ąĘąĮąŠą▓ąĖą┤ąĮąŠčüč鹥ą╣ čéąĖą┐ąŠą▓ AVR čü čĆą░ąĘą╗ąĖčćąĮčŗą╝ ąĮą░ą▒ąŠčĆąŠą╝ ą▓čüčéčĆąŠąĄąĮąĮčŗčģ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓, ą▓čüčéčĆąĄčćą░ąĄčéčüčÅ ąĖąĮąŠą│ą┤ą░ ąĮąĄą║ąŠč鹊čĆą░čÅ ą┐čāčéą░ąĮąĖčåą░ ą▓ ą╝ąĮąĄą╝ąŠąĮąĖč湥čüą║ąĖčģ ąŠą▒ąŠąĘąĮą░č湥ąĮąĖčÅčģ čĆąĄą│ąĖčüčéčĆąŠą▓ ąĖ čüąĖą│ąĮą░ą╗ąŠą▓. ąŁč鹊 ąĮąĄ ą┤ąŠą╗ąČąĮąŠ ąÆą░čü čüą╝čāčēą░čéčī, ą┐čĆąŠčüč鹊 ą▓ąĮąĖą╝ą░č鹥ą╗čīąĮąŠ ą┐čĆąŠčćąĖčéą░ą╣č鹥 ą┤ą░čéą░čłąĖčé ąĮą░ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╣ ąÆą░ą╝ąĖ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ AVR.

ąÜ ą┐čĆąĖą╝ąĄčĆčā, ą▓ čŹč鹊ą╝ ą┤ą░čéą░čłąĖč鹥 čéą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗ SPI ąŠą▒ąŠąĘąĮą░čćą░ąĄčéčüčÅ ą║ą░ą║ SCK. ąØąŠ ą▓ č鹊 ąČąĄ ą▓čĆąĄą╝čÅ čā ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ AT90USB162 ą┐ąŠą┤ ąĖą╝ąĄąĮąĄą╝ SCK čäąĖą│čāčĆąĖčĆčāąĄčé čéą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗ ą┤ą╗čÅ ąĖąĮč鹥čĆč乥ą╣čüą░ PS/2, ą░ ą┤ą╗čÅ SPI čéą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗ ąĮąŠčüąĖčé ą┤čĆčāą│ąŠąĄ ąĖą╝čÅ: SCLK.

ąĪąĖčüč鹥ą╝ą░ SPI AVR ąĖą╝ąĄąĄčé ąŠą┤ąĖąĮąŠčćąĮčāčÄ ą▒čāč乥čĆąĖąĘą░čåąĖčÄ ą▓ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖ ą┤ą▓ąŠą╣ąĮčāčÄ ą▒čāč乥čĆąĖąĘą░čåąĖčÄ ą▓ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĖ ą┐čĆąĖąĄą╝ą░. ąŁč鹊 ą▓ą╗ąĖčÅąĄčé ąĮą░ č鹊, ą║ą░ą║ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ąŠą▒čĆą░ą▒ąŠčéą║ą░ ą┤ą░ąĮąĮčŗčģ:

1. ąØąŠą▓čŗąĄ ą▒ą░ą╣čéčŗ ą┤ą╗čÅ ąŠčéą┐čĆą░ą▓ą║ąĖ ąĮąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮčŗ ą▓ čĆąĄą│ąĖčüčéčĆ ą┤ą░ąĮąĮčŗčģ (SPDR) / čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░, ą┐ąŠą║ą░ ąĮąĄ ąĘą░ą▓ąĄčĆčłąĖčéčüčÅ ą┐ąŠą╗ąĮčŗą╣ čåąĖą║ą╗ čüą┤ą▓ąĖą│ą░.

2. ą¤čĆąĖąĮčÅčéčŗąĄ ą▒ą░ą╣čéčŗ ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ ą▓ ą▒čāč乥čĆ ą┐čĆąĖąĄą╝ą░ ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ ą┐ąŠčüą╗ąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ.

3. ąæčāč乥čĆ ą┐čĆąĖąĄą╝ą░ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮ ą┐ąĄčĆąĄą┤ ąĮą░čćą░ą╗ąŠą╝ čüą╗ąĄą┤čāčÄčēąĄą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ, ąĖąĮą░č湥 ą┤ą░ąĮąĮčŗąĄ ą▒čāą┤čāčé ą┐ąŠč鹥čĆčÅąĮčŗ.

4. ą¦č鹥ąĮąĖąĄ SPDR ą▓ąĄčĆąĮąĄčé ą┤ą░ąĮąĮčŗąĄ ąĖąĘ ą▒čāč乥čĆą░ ą┐čĆąĖąĄą╝ą░.

ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą┐ąĄčĆąĄą┤ą░čćą░ ąĘą░ą▓ąĄčĆčłąĖčéčüčÅ, ą▒čāą┤ąĄčé ą▓čŗčüčéą░ą▓ą╗ąĄąĮ SPI Interrupt Flag (SPIF) ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI Status Register (SPSR). ąŁč鹊 ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖčÄ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ąĄčüą╗ąĖ ąŠąĮąŠ čĆą░ąĘčĆąĄčłąĄąĮąŠ, ąĖ ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé ą│ą╗ąŠą▒ą░ą╗čīąĮąŠą│ąŠ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖčéą░ SPI Interrupt Enable (SPIE) ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPCR čĆą░ąĘčĆąĄčłąĖčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠčé ą╝ąŠą┤čāą╗čÅ SPI, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ čāčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖčéą░ I ą▓ čĆąĄą│ąĖčüčéčĆąĄ SREG ą│ą╗ąŠą▒ą░ą╗čīąĮąŠ čĆą░ąĘčĆąĄčłą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

[2.2. ąÆčŗą▓ąŠą┤čŗ SPI]

SPI čüčéą░ąĮą┤ą░čĆčéąĮąŠ čüąŠčüč鹊ąĖčé ąĖąĘ 4 čüąĖą│ąĮą░ą╗čīąĮčŗčģ ą╗ąĖąĮąĖą╣ [2]. ąŁč鹊 čéą░ą║čéčŗ čüą┤ą▓ąĖą│ą░ (shift clock, SCK), ą▓čŗčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ ą│ą╗ą░ą▓ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (Master Out Slave In MOSI), ą▓čģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ ą│ą╗ą░ą▓ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (Master In Slave Out, MISO) ąĖ čüąĖą│ąĮą░ą╗ą░ ą▓čŗą▒ąŠčĆą║ąĖ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ čü ą░ą║čéąĖą▓ąĮčŗą╝ čāčĆąŠą▓ąĮąĄą╝ ą╗ąŠą│. 0 (Slave Select, ~SS). ąÜąŠą│ą┤ą░ ąĖąĮč鹥čĆč乥ą╣čü SPI čĆą░ąĘčĆąĄčłąĄąĮ, č鹊 ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ ą▓čŗą▓ąŠą┤ąŠą▓ MOSI, MISO, SCK ąĖ ~SS ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąĮą░ąĘąĮą░čćą░čÄčéčüčÅ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü čéą░ą▒ą╗ąĖčåąĄą╣ ąĮąĖąČąĄ.

ąóą░ą▒ą╗ąĖčåą░ 2-1. ą¤ąĄčĆąĄąĮą░ąĘąĮą░č湥ąĮąĖąĄ čĆąĄąČąĖą╝ą░ čĆą░ą▒ąŠčéčŗ (ą▓čģąŠą┤ ąĖą╗ąĖ ą▓čŗčģąŠą┤) ą▓čŗą▓ąŠą┤ąŠą▓ AVR ą▓ čĆąĄąČąĖą╝ąĄ SPI.

| ąĪąĖą│ąĮą░ą╗ |

ąØą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą▓ čĆąĄąČąĖą╝ąĄ Master |

ąØą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą▓ čĆąĄąČąĖą╝ąĄ Slave |

| MOSI |

ą×ą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčüč鹊ą╝ |

ąÆčģąŠą┤ |

| MISO |

ąÆčģąŠą┤ |

ą×ą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčüč鹊ą╝ |

| SCK |

ą×ą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčüč鹊ą╝ |

ąÆčģąŠą┤ |

| ~SS |

ą×ą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčüč鹊ą╝ |

ąÆčģąŠą┤ |

ąÆ čéą░ą▒ą╗ąĖčåąĄ ą┐ąŠą║ą░ąĘą░ąĮąŠ, čćč鹊 ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāčÄčéčüčÅ č鹊ą╗čīą║ąŠ ą▓čģąŠą┤ąĮčŗąĄ čüąĖą│ąĮą░ą╗čŗ (čé. ąĄ. č鹊ą╗čīą║ąŠ ą▓čģąŠą┤čŗ ąĮąĄ čéčĆąĄą▒čāąĄčéčüčÅ čüą┐ąĄčåąĖą░ą╗čīąĮąŠ ąĮą░čüčéčĆą░ąĖą▓ą░čéčī č湥čĆąĄąĘ čĆąĄą│ąĖčüčéčĆ DDRx). ąØąŠ ą▓čŗčģąŠą┤ąĮčŗąĄ čüąĖą│ąĮą░ą╗čŗ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čüą┐ąĄčåąĖą░ą╗čīąĮąŠ ąĮą░čüčéčĆąŠąĄąĮčŗ ą▓čĆčāčćąĮčāčÄ, ą┐ąŠą┤ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝ firmware ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░. ąŁč鹊 ąĮčāąČąĮąŠ ą┤ą╗čÅ čāčüčéčĆą░ąĮąĄąĮąĖčÅ ą║ąŠąĮčäą╗ąĖą║č鹊ą▓ ąĖ čüą╗čāčćą░ą╣ąĮąŠą│ąŠ ą┐ąŠą▓čĆąĄąČą┤ąĄąĮąĖčÅ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ ą┤čĆą░ą╣ą▓ąĄčĆą░ ą┐ąŠčĆčéą░.

[2.3. ąĪąĖčüč鹥ą╝čŗ čü ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ. ąĀą░ą▒ąŠčéą░ ą▓čŗą▓ąŠą┤ą░ ~SS]

ąĪąĖą│ąĮą░ą╗ Slave Select (~SS) ąĖą│čĆą░ąĄčé čåąĄąĮčéčĆą░ą╗čīąĮčāčÄ čĆąŠą╗čī ą▓ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĖ SPI. ąÆ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čĆąĄąČąĖą╝ą░ čĆą░ą▒ąŠčéčŗ ą┐ąŠčĆčéą░ SPI AVR, ą▓čŗą▓ąŠą┤ ~SS ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖą╗ąĖ ą░ą║čéąĖą▓ąĖąĘą░čåąĖąĖ čāčüčéčĆąŠą╣čüčéą▓. ąÆčŗą▓ąŠą┤ ~SS ą╝ąŠąČąĮąŠ čüčĆą░ą▓ąĮąĖčéčī čü čüąĖą│ąĮą░ą╗ąŠą╝ chip select (CS), čā ą║ąŠč鹊čĆąŠą│ąŠ ąĄčüčéčī ąĮąĄčüą║ąŠą╗čīą║ąŠ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗčģ ą▓ąŠąĘą╝ąŠąČąĮąŠčüč鹥ą╣.

ąĢčüą╗ąĖ ą▓čŗą▓ąŠą┤ ~SS čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą║ą░ą║ ą▓čģąŠą┤ ą▓ čĆąĄąČąĖą╝ąĄ master, č鹊 ą▓čŗą▓ąŠą┤ ~SS ą┤ąŠą╗ąČąĄąĮ čāą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą╗ąŠą│. 1, čćč鹊ą▒čŗ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī, čćč鹊 čāčüčéčĆąŠą╣čüčéą▓ąŠ ą▒čāą┤ąĄčé čĆą░ą▒ąŠčéą░čéčī ą║ą░ą║ master SPI. ąøąŠą│. 0 ąĮą░ ą▓čģąŠą┤ąĄ ~SS ą┐ąĄčĆąĄą║ą╗čÄčćąĖčé SPI ą▓ čĆąĄąČąĖą╝ slave, ąĖ ą░ą┐ą┐ą░čĆą░čéčāčĆą░ SPI ą▒čāą┤ąĄčé ą▓čŗą┐ąŠą╗ąĮčÅčéčī čüą╗ąĄą┤čāčÄčēąĖąĄ ą┤ąĄą╣čüčéą▓ąĖčÅ:

1. ąæąĖčé ą│ą╗ą░ą▓ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (master bit, MSTR) ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPI Control Register (SPCR) ąŠčćąĖčēą░ąĄčéčüčÅ, ąĖ čüąĖčüč鹥ą╝ą░ SPI čüčéą░ąĮąŠą▓ąĖčéčüčÅ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą╣. ąØą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čĆą░ą▒ąŠčéčŗ ą▓čŗą▓ąŠą┤ąŠą▓ (ą▓čģąŠą┤ ąĖą╗ąĖ ą▓čŗčģąŠą┤) ą┐ąĄčĆąĄą║ą╗čÄčćą░ąĄčéčüčÅ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü čéą░ą▒ą╗ąĖčåąĄą╣ 2-1.

2. ąŻčüčéą░ąĮąŠą▓ąĖčéčüčÅ SPI Interrupt Flag (SPIF) ą▓ SPI Status Register (SPSR). ąĢčüą╗ąĖ čĆą░ąĘčĆąĄčłąĄąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ SPI, ąĖ ą│ą╗ąŠą▒ą░ą╗čīąĮąŠ čĆą░ąĘčĆąĄčłąĄąĮčŗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, č鹊 ą▓čŗą┐ąŠą╗ąĮąĖčéčüčÅ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ SPI.

ąóą░ą║ąŠąĄ čüčéčĆą░ąĮąĮąŠąĄ ąĮą░ ą┐ąĄčĆą▓čŗą╣ ą▓ąĘą│ą╗čÅą┤ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠą╗ąĄąĘąĮčŗą╝, ą║ąŠą│ą┤ą░ ą▓ čüąĖčüč鹥ą╝ąĄ ąĄčüčéčī ąĮąĄčüą║ąŠą╗čīą║ąŠ ą│ą╗ą░ą▓ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ - čćč鹊ą▒čŗ ąĖąĘą▒ąĄąČą░čéčī ą┐ąŠą┐čŗčéą║čā ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠą│ąŠ ąĘą░čģą▓ą░čéą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čłąĖąĮąŠą╣ SPI čüčĆą░ąĘčā ą┤ą▓čāą╝čÅ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ master. ąĢčüą╗ąĖ ąČąĄ ą▓čŗą▓ąŠą┤ ~SS čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą║ą░ą║ ą▓čŗčģąŠą┤, č鹊 ąŠąĮ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą║ą░ą║ ąŠą▒čŗčćąĮčŗą╣ ą┐ąŠčĆčé ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ ąŠą▒čēąĄą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ (GPIO), ą║ąŠč鹊čĆčŗą╣ ąĮąĖą║ą░ą║ ąĮąĄ čüą▓čÅąĘą░ąĮ čü čüąĖčüč鹥ą╝ąŠą╣ SPI.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▓ čüą╗čāčćą░čÅčģ, ą║ąŠą│ą┤ą░ AVR čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą▓ čĆąĄąČąĖą╝ąĄ master, ąĖ ąŠąĮ ąĮąĄ ą╝ąŠąČąĄčé ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī čüąŠčüč鹊čÅąĮąĖąĄ ą╗ąŠą│. 1 ą▓čŗą▓ąŠą┤ą░ ~SS ą╝ąĄąČą┤čā ą┤ą▓čāą╝čÅ ą┐ąĄčĆąĄą┤ą░čćą░ą╝ąĖ, ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąŠą▓ąĄčĆąĄąĮ ą▒ąĖčé čüąŠčüč鹊čÅąĮąĖčÅ MSTR ą┐ąĄčĆąĄą┤ ąĘą░ą┐ąĖčüčīčÄ ąĮąŠą▓ąŠą│ąŠ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ąŠą│ąŠ ą▒ą░ą╣čéą░. ąÜą░ą║ č鹊ą╗čīą║ąŠ ą▒ąĖčé MSTR ą▒čŗą╗ ąŠčćąĖčēąĄąĮ ąĮąĖąĘą║ąĖą╝ čāčĆąŠą▓ąĮąĄą╝ čüąĖą│ąĮą░ą╗ą░ ~SS, ą▒ąĖčé MSTR čüąĮąŠą▓ą░ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą║ąŠą┤ąŠą╝ firmware, čćč鹊ą▒čŗ ąŠą┐čÅčéčī čĆą░ąĘčĆąĄčłąĖčéčī čĆą░ą▒ąŠčéčā SPI ą▓ čĆąĄąČąĖą╝ąĄ master.

ąÆ čĆąĄąČąĖą╝ąĄ slave ą▓čŗą▓ąŠą┤ ~SS ą▓čüąĄą│ą┤ą░ čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą▓čģąŠą┤. ąÜąŠą│ą┤ą░ ~SS čāą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ą▓ ą╗ąŠą│. 0, č鹊 SPI ą░ą║čéąĖą▓ąĖąĘąĖčĆčāąĄčéčüčÅ, ąĖ MISO čüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▓čŗčģąŠą┤ąŠą╝, ąĄčüą╗ąĖ čŹč鹊 ą▒čŗą╗ąŠ čĆą░ąĮąĄąĄ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąŠ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╝. ąÆčüąĄ ą┤čĆčāą│ąĖąĄ ą▓čŗą▓ąŠą┤čŗ SPI ąŠčüčéą░čÄčéčüčÅ čĆą░ą▒ąŠčéą░čéčī ą║ą░ą║ ą▓čģąŠą┤čŗ. ąÜąŠą│ą┤ą░ ~SS ą▓ ą╗ąŠą│. 1, č鹊 ą▓čüąĄ ą▓čŗą▓ąŠą┤čŗ SPI čüčéą░ąĮąŠą▓čÅčéčüčÅ ą▓čģąŠą┤ą░ą╝ąĖ, ąĖ SPI ą┤ąĄą░ą║čéąĖą▓ąĖčĆčāąĄčéčüčÅ, čŹč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ąŠąĮ ąĮąĄ ą▒čāą┤ąĄčé ą┐čĆąĖąĮąĖą╝ą░čéčī ą┐ąŠčüčéčāą┐ą░čÄčēąĖąĄ ą┤ą░ąĮąĮčŗąĄ. ąÆ čéą░ą▒ą╗ąĖčåąĄ 2-2 ą┐ąŠą║ą░ąĘą░ąĮ ąŠą▒ąĘąŠčĆ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓čŗą▓ąŠą┤ą░ ~SS.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▓ čĆąĄąČąĖą╝ąĄ slave ą╗ąŠą│ąĖą║ą░ SPI ą▒čāą┤ąĄčé čüą▒čĆąŠčłąĄąĮą░, ą║ą░ą║ č鹊ą╗čīą║ąŠ čāčĆąŠą▓ąĄąĮčī ą▓čŗą▓ąŠą┤ą░ ~SS ą▒čŗą╗ ą┐ąĄčĆąĄą▓ąĄą┤ąĄąĮ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ą╗ąŠą│. 1. ąóą░ą║ čćč鹊 ąĄčüą╗ąĖ ą▓čŗą▓ąŠą┤ ~SS ą┐ąŠą╗čāčćąĖą╗ čüąĮą░čĆčāąČąĖ ą╗ąŠą│. 1 ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ, č鹊 ą┐ąĄčĆąĄą┤ą░čćą░ ąĖ ą┐čĆąĖąĄą╝ SPI ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ ąŠčüčéą░ąĮąŠą▓čÅčéčüčÅ, ąĖ ą┤ą░ąĮąĮčŗąĄ ą╝ąŠą│čāčé čüčćąĖčéą░čéčīčüčÅ ą┐ąŠč鹥čĆčÅąĮąĮčŗą╝ąĖ.

ąóą░ą▒ą╗ąĖčåą░ 2-2. ą×ą▒ąĘąŠčĆ čäčāąĮą║čåąĖą╣ ą▓čŗą▓ąŠą┤ą░ ~SS.

| ąĀąĄąČąĖą╝ |

ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ~SS |

ąøąŠą│. čāčĆąŠą▓ąĄąĮčī ąĮą░ ~SS |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| Slave |

ąÆčüąĄą│ą┤ą░ ą▓čģąŠą┤ |

1 |

Slave ą┤ąĄą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮ (ąĮąĄ ą▓čŗą▒čĆą░ąĮ) |

| 0 |

Slave ą░ą║čéąĖą▓ąĄąĮ (ą▓čŗą▒čĆą░ąĮ) |

Master

|

ąÆčģąŠą┤ |

1 |

Master ą░ą║čéąĖą▓ąĄąĮ (ą▓čŗą▒čĆą░ąĮ) |

| 0 |

Master ą┤ąĄą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮ, ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮ ą▓ čĆąĄąČąĖą╝ slave |

| ąÆčŗčģąŠą┤ |

1 |

Master ą░ą║čéąĖą▓ąĄąĮ (ą▓čŗą▒čĆą░ąĮ) |

| 0 |

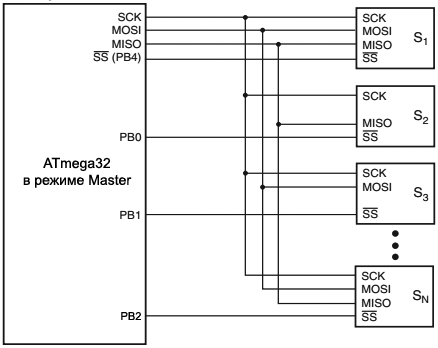

ąÜą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▓ čéą░ą▒ą╗ąĖčåąĄ 2-2, ą▓čŗą▓ąŠą┤ ~SS ą▓ čĆąĄąČąĖą╝ąĄ slave ą▓čüąĄą│ą┤ą░ čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą▓čģąŠą┤. ąØąĖąĘą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī ą░ą║čéąĖą▓ąĖčĆčāąĄčé čĆą░ą▒ąŠčéčā SPI, ą░ ą▓čŗčüąŠą║ąĖą╣ ą┤ąĄą░ą║čéąĖą▓ąĖčĆčāąĄčé. ąÆ čüąĖčüč鹥ą╝ąĄ čü ąŠą┤ąĮąĖą╝ ą│ą╗ą░ą▓ąĮčŗą╝ ąĖ ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ (Single Master Multiple Slave), ą│ą┤ąĄ AVR čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą║ą░ą║ master, ą▓čŗą▓ąŠą┤ ~SS ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ ą║ą░ą║ ą▓čŗčģąŠą┤, ąĖ ą▓ąŠąĘą╝ąŠąČąĮą░čÅ čüčģąĄą╝ą░ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ą┐ąŠą║ą░ąĘą░ąĮą░ ąĮą░ čĆąĖčü. 2-1. ąÜąŠą╗ąĖč湥čüčéą▓ąŠ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓, ą║ąŠč鹊čĆąŠąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮąŠ ą║ čŹč鹊ą╝čā ą│ą╗ą░ą▓ąĮąŠą╝čā AVR, ąŠą│čĆą░ąĮąĖč湥ąĮąŠ č鹊ą╗čīą║ąŠ ą║ąŠą╗ąĖč湥čüčéą▓ąŠą╝ čüą▓ąŠą▒ąŠą┤ąĮčŗčģ ą▓čŗą▓ąŠą┤ąŠą▓ GPIO, ąĮą░ ą║ąŠč鹊čĆčŗčģ ą╝ąŠąČąĮąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čéčī čüąĖą│ąĮą░ą╗ ą▓čŗą▒ąŠčĆą║ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░.

ąĀąĖčü. 2-1. ą¤čĆąĖą╝ąĄčĆ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ą║ ąŠą┤ąĮąŠą╝čā ą│ą╗ą░ą▓ąĮąŠą╝čā čāčüčéčĆąŠą╣čüčéą▓čā AVR.

ąÆąŠąĘą╝ąŠąČąĮąŠčüčéčī ą┐ąŠą┤ą║ą╗čÄčćąĖčéčī ąĮąĄčüą║ąŠą╗čīą║ąŠ čāčüčéčĆąŠą╣čüčéą▓ ą▓ ąŠą┤ąĮąŠą╣ ąĖ č鹊ą╣ ąČąĄ čłąĖąĮąĄ SPI ąŠčüąĮąŠą▓čŗą▓ą░ąĄčéčüčÅ ąĮą░ čäą░ą║č鹥, čćč鹊 ą▓ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé ą▓čĆąĄą╝ąĄąĮąĖ ą╝ąŠą│čāčé ą▒čŗčéčī ą░ą║čéąĖą▓ąĮčŗ ąĖ ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī ą┤ą░ąĮąĮčŗąĄ č鹊ą╗čīą║ąŠ 2 čāčüčéčĆąŠą╣čüčéą▓ą░ SPI - č鹊ą╗čīą║ąŠ ąŠą┤ąĮąŠ master ąĖ č鹊ą╗čīą║ąŠ ąŠą┤ąĮąŠ slave. ąĪąĖą│ąĮą░ą╗čīąĮčŗąĄ ą╗ąĖąĮąĖąĖ MISO, MOSI ąĖ SCK ą▓čüąĄčģ ąŠčüčéą░ą╗čīąĮčŗčģ slave-čāčüčéčĆąŠą╣čüčéą▓ ąŠčüčéą░čÄčéčüčÅ ą▓ čéčĆąĄčéčīąĄą╝ čüąŠčüč鹊čÅąĮąĖąĖ (čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĮčŗą╝ąĖ ą║ą░ą║ ą▓čģąŠą┤čŗ čü ą▓čŗčüąŠą║ąĖą╝ ą▓čģąŠą┤ąĮčŗą╝ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄą╝ ąĖ ąŠčéą║ą╗čÄč湥ąĮąĮčŗą╝ąĖ pullup-čĆąĄąĘąĖčüč鹊čĆą░ą╝ąĖ). ą×čłąĖą▒ąŠčćąĮą░čÅ čĆąĄą░ą╗ąĖąĘą░čåąĖčÅ (ąĮą░ą┐čĆąĖą╝ąĄčĆ, ąĄčüą╗ąĖ 2 ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ą░ ą▒čāą┤čāčé ą░ą║čéąĖą▓ąĖąĘąĖčĆąŠą▓ą░ąĮčŗ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ) ą╝ąŠąČąĄčé ą┐čĆąĖą▓ąĄčüčéąĖ ą║ ąĘą░ą╝čŗą║ą░ąĮąĖčÄ ą┤čĆčāą│ ąĮą░ ą┤čĆčāą│ą░ ą▓čŗčģąŠą┤ąŠą▓ CMOS ąĖ čüą║ą▓ąŠąĘąĮčŗą╝ č鹊ą║ą░ą╝, č湥ą│ąŠ čüą╗ąĄą┤čāąĄčé ąĖąĘą▒ąĄą│ą░čéčī. ąĀąĄąĘąĖčüč鹊čĆčŗ ąŠčé 1 ą┤ąŠ 10 ą║ą×ą╝ ą╝ąŠą│čāčé ą▒čŗčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮčŗ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ čü ą▓čŗą▓ąŠą┤ą░ą╝ąĖ SPI, čćč鹊ą▒čŗ ą┐čĆąĄą┤ąŠčéą▓čĆą░čéąĖčéčī ą┐ąĄčĆąĄą│čĆčāąĘą║čā ą▓čŗčģąŠą┤ąĮčŗčģ ą▒čāč乥čĆąŠą▓ CMOS ą┐čĆąĖ ąŠčłąĖą▒ąŠčćąĮąŠą╝ ąĘą░ą╝čŗą║ą░ąĮąĖąĖ ą▓čŗčģąŠą┤ąŠą▓ ą┤čĆčāą│ ąĮą░ ą┤čĆčāą│ą░, ą║ąŠą│ą┤ą░ ąĮą░ čŹčéąĖčģ ą▓čŗčģąŠą┤ą░čģ ą┐čĆąĖčüčāčéčüčéą▓čāčÄčé čĆą░ąĘąĮčŗąĄ ą╗ąŠą│ąĖč湥čüą║ąĖąĄ čāčĆąŠą▓ąĮąĖ. ą×ą┤ąĮą░ą║ąŠ ąĖą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 čŹč鹊 ą╝ąŠąČąĄčé ą┐ąŠą▓ą╗ąĖčÅčéčī ąĮą░ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠ ą▓ąŠąĘą╝ąŠąČąĮčāčÄ čüą║ąŠčĆąŠčüčéčī ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ąĖąĘ-ąĘą░ ą┐ą░čĆą░ąĘąĖčéąĮąŠą╣ ąĄą╝ą║ąŠčüčéąĖ čüąĖą│ąĮą░ą╗ąŠą▓ čłąĖąĮčŗ SPI.

ą×ą┤ąĮąŠąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ SPI čéčĆąĄą▒čāčÄčé č鹊ą╗čīą║ąŠ čüąĖą│ąĮą░ą╗ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖ ąŠą┤ąĖąĮ ąĖąĘ čüąĖą│ąĮą░ą╗ąŠą▓ ą┤ą░ąĮąĮčŗčģ. ąÜą░ą║ąŠą╣ ąĖą╝ąĄąĮąĮąŠ čüąĖą│ąĮą░ą╗ ą┤ą░ąĮąĮčŗčģ - MISO ąĖą╗ąĖ MOSI - ą▒čāą┤ąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ, ąĘą░ą▓ąĖčüąĖčé ąŠčé ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮąĖčÅ čāčüčéčĆąŠą╣čüčéą▓ą░. ą¤čĆąŠčüčéčŗąĄ čüąĄąĮčüąŠčĆčŗ, ą║ ą┐čĆąĖą╝ąĄčĆčā, ą┐čĆąŠčüč鹊 ąŠčéą┐čĆą░ą▓ą╗čÅčÄčé ą┤ą░ąĮąĮčŗąĄ (ą║ą░ą║ S2 ąĮą░ čĆąĖčü. 2-1), ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ ą▓ąĮąĄčłąĮąĖą╣ DAC ą┐čĆąŠčüč鹊 ą┐čĆąĖąĮąĖą╝ą░ąĄčé ą┤ą░ąĮąĮčŗąĄ (ą║ą░ą║ S3 ąĮą░ čĆąĖčü. 2-1).

[2.4. ąöąĖą░ą│čĆą░ą╝ą╝čŗ ą▓čĆąĄą╝ąĄąĮąĖ SPI]

ąŻ SPI ąĄčüčéčī 4 čĆąĄąČąĖą╝ą░ čĆą░ą▒ąŠčéčŗ SPI, ąŠčé 0 ą┤ąŠ 3 (Mode 0 .. Mode 3). ąŁčéąĖ čĆąĄąČąĖą╝čŗ ą┐ąŠ čüčāčēąĄčüčéą▓čā čāą┐čĆą░ą▓ą╗čÅčÄčé ą╝ąĄč鹊ą┤ąŠą╝, ą║ą░ą║ ą┤ą░ąĮąĮčŗąĄ ą▓ą┤ą▓ąĖą│ą░čÄčéčüčÅ ąĖą╗ąĖ ą▓čŗą┤ą▓ąĖą│ą░čÄčéčüčÅ č湥čĆąĄąĘ SPI. ąÜąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą┤ą▓čāą╝čÅ ą▒ąĖčéą░ą╝ąĖ ą▓ SPI control register (SPCR). ą¤ąŠą╗čÅčĆąĮąŠčüčéčī čéą░ą║č鹊ą▓ čāą║ą░ąĘčŗą▓ą░ąĄčéčüčÅ čāą┐čĆą░ą▓ą╗čÅčÄčēąĖą╝ ą▒ąĖč鹊ą╝ CPOL, ą║ąŠč鹊čĆčŗą╝ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ą░ą║čéąĖą▓ąĮčŗą╣ ą╗ąŠą│. 1 ąĖą╗ąĖ ą╗ąŠą│. 0 čāčĆąŠą▓ąĄąĮčī ą┤ą╗čÅ čéą░ą║č鹊ą▓. ąŻą┐čĆą░ą▓ą╗čÅčÄčēąĖą╣ ą▒ąĖčé čäą░ąĘčŗ čéą░ą║č鹊ą▓ CPHA ą▓čŗą▒ąĖčĆą░ąĄčé ąŠą┤ąĖąĮ ąĖąĘ ą┤ą▓čāčģ čäčāąĮą┤ą░ą╝ąĄąĮčéą░ą╗čīąĮąŠ čĆą░ąĘąĮčŗčģ č乊čĆą╝ą░čéą░ ą┐ąĄčĆąĄą┤ą░čćąĖ. ą¦č鹊ą▒čŗ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī ą┐čĆą░ą▓ąĖą╗čīąĮčŗą╣ ąŠą▒ą╝ąĄąĮ ą┤ą░ąĮąĮčŗą╝ąĖ ą╝ąĄąČą┤čā master ąĖ slave, ąŠą▒ą░ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┤ąŠą╗ąČąĮčŗ čĆą░ą▒ąŠčéą░čéčī ą▓ ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠą╝ čĆąĄąČąĖą╝ąĄ. ąŁč鹊 ą╝ąŠąČąĄčé ą┐ąŠčéčĆąĄą▒ąŠą▓ą░čéčī ą┐ąĄčĆąĄą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ master, čćč鹊ą▒čŗ čüąŠąŠčéą▓ąĄčéčüčéą▓ąŠą▓ą░čéčī čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅą╝ čĆą░ąĘąĮčŗčģ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ slave (ą║ąŠą│ą┤ą░ ąŠą┤ąĖąĮ master čĆą░ą▒ąŠčéą░ąĄčé č湥čĆąĄąĘ ąŠą┤ąĮčā čłąĖąĮčā SPI čü ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ slave).

ąÆąŠąĘą╝ąŠąČąĮčŗąĄ ą║ąŠą╝ą▒ąĖąĮą░čåąĖąĖ ą▒ąĖč鹊ą▓ CPOL ąĖ CPHA ąĘą░ą┤ą░čÄčé čĆą░ąĘą╗ąĖčćąĮčŗąĄ čĆąĄąČąĖą╝čŗ SPI ą║ą░ą║ čŹč鹊 ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▓ čéą░ą▒ą╗ąĖčåąĄ 2-3. ą¤ąŠčüą║ąŠą╗čīą║čā čéčāčé ąĮąĄčé č湥čéą║ąŠą│ąŠ čüčéą░ąĮą┤ą░čĆčéą░, ąĖ čŹčéąĖ čĆąĄąČąĖą╝čŗ ąĮą░ąĘčŗą▓ą░čÄčéčüčÅ ą┐ąŠ-čĆą░ąĘąĮąŠą╝čā ą▓ čĆą░ąĘąĮąŠą╣ ą╗ąĖč鹥čĆą░čéčāčĆąĄ, č鹊 ą║ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÄ SPI čüą╗ąĄą┤čāąĄčé ą┐ąŠą┤ąŠą╣čéąĖ čü ąŠčüąŠą▒čŗą╝ ą▓ąĮąĖą╝ą░ąĮąĖąĄą╝.

ąóą░ą▒ą╗ąĖčåą░ 2-3. ąÜąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ čĆąĄąČąĖą╝ą░ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ SPI.

| Mode |

CPOL |

CPHA |

ą¤ąĄčĆąĄą┐ą░ą┤ SCK ą┤ą╗čÅ čüą┤ą▓ąĖą│ą░ |

ą¤ąĄčĆąĄą┐ą░ą┤ SCK ą┤ą╗čÅ ąĘą░čģą▓ą░čéą░ |

| 0 |

0 |

0 |

1 -> 0 |

0 -> 1 |

| 1 |

0 |

1 |

0 -> 1 |

1 -> 0 |

| 2 |

1 |

0 |

0 -> 1 |

1 -> 0 |

| 3 |

1 |

1 |

1 -> 0 |

0 -> 1 |

ą¤ąŠą╗čÅčĆąĮąŠčüčéčī čéą░ą║č鹊ą▓ (čüąŠčüč鹊čÅąĮąĖąĄ CPOL) ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĘąĮą░čćąĖč鹥ą╗čīąĮąŠą│ąŠ čŹčäč乥ą║čéą░ ąĮą░ č乊čĆą╝ą░čé ą┐ąĄčĆąĄą┤ą░čćąĖ. ąĪą╝ąĄąĮą░ čüąŠčüč鹊čÅąĮąĖčÅ čŹč鹊ą│ąŠ ą▒ąĖčéą░ č鹊ą╗čīą║ąŠ ą╗ąĖčłčī ą┐čĆąĖą▓ąŠą┤ąĖčé ą║ ąĖąĮą▓ąĄčĆčéąĖčĆąŠą▓ą░ąĮąĖčÄ čüąĖą│ąĮą░ą╗ą░ čéą░ą║č鹊ą▓ (ą░ą║čéąĖą▓ąĮčŗą╣ ą▓čŗčüąŠą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī čüčéą░ąĮąŠą▓ąĖčéčüčÅ ą░ą║čéąĖą▓ąĮčŗą╝ ąĮąĖąĘą║ąĖą╝, ąĖ ąĮąĖąĘą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī čüąŠčüč鹊čÅąĮąĖąĄ ąŠąČąĖą┤ą░ąĮąĖčÅ ą╝ąĄąĮčÅąĄčéčüčÅ ąĮą░ ą▓čŗčüąŠą║ąĖą╣, ąĖ ąĮą░ąŠą▒ąŠčĆąŠčé). ąŻčüčéą░ąĮąŠą▓ą║ą░ čäą░ąĘčŗ (čüąŠčüč鹊čÅąĮąĖąĄ CPHA) ąĮą░ą┐čĆąŠčéąĖą▓, ą▓čŗą▒ąĖčĆą░ąĄčé ąŠą┤ąĖąĮ ąĖąĘ ą┤ą▓čāčģ čĆą░ąĘąĮčŗčģ čĆąĄąČąĖą╝ąŠą▓ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ, ą║ąŠč鹊čĆčŗąĄ ą┐ąŠą┤čĆąŠą▒ąĮąĄąĄ ą▒čāą┤čāčé čĆą░čüčüą╝ąŠčéčĆąĄąĮčŗ ą▓ čüą╗ąĄą┤čāčÄčēąĖčģ ą┤ą▓čāčģ čĆą░ąĘą┤ąĄą╗ą░čģ. ą¤ąŠčüą║ąŠą╗čīą║čā čüąĖą│ąĮą░ą╗čŗ MOSI, MISO čāčüčéčĆąŠą╣čüčéą▓ master ąĖ slave ąĮą░ą┐čĆčÅą╝čāčÄ čüąŠąĄą┤ąĖąĮąĄąĮčŗ ą┤čĆčāą│ čü ą┤čĆčāą│ąŠą╝, č鹊 ą┤ąĖą░ą│čĆą░ą╝ą╝čŗ ą▓čĆąĄą╝ąĄąĮąĖ ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčé č乊čĆą╝čā čüąĖą│ąĮą░ą╗ąŠą▓ čüčĆą░ąĘčā ąŠ ąŠą▒ąŠąĖčģ čāčüčéčĆąŠą╣čüčéą▓ master ąĖ slave. ąĪąĖą│ąĮą░ą╗ ~SS čÅą▓ą╗čÅąĄčéčüčÅ ą▓čģąŠą┤ąŠą╝ ą▓čŗą▒ąŠčĆą║ąĖ čā ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░. ąÆčŗą▓ąŠą┤ ~SS čāčüčéčĆąŠą╣čüčéą▓ą░ master ąĮąĄ ą┐ąŠą║ą░ąĘą░ąĮ ąĮą░ ą┤ąĖą░ą│čĆą░ą╝ą╝ą░čģ. ą×ąĮ ąĮąĄ ą░ą║čéąĖą▓ąĄąĮ ą┐čĆąĖ ą╗ąŠą│. 1 ąĮą░ ~SS (ąĄčüą╗ąĖ ~SS ą▒čŗą╗ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą║ą░ą║ ą▓čģąŠą┤), ąĖą╗ąĖ ą▓čŗčģąŠą┤ ~SS ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ ą║ą░ą║ ą▓čŗčģąŠą┤ąĮąŠą╣ ą┐ąŠčĆčé, č鹊ą│ą┤ą░ ąŠąĮ ą╝ąŠąČąĄčé čāą┐čĆą░ą▓ą╗čÅčéčīčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ ąĖ čĆą░ą▒ąŠčéą░čéčī ą║ą░ą║ ąŠą▒čŗčćąĮčŗą╣ ą┐ąŠčĆčé GPIO.

[2.5. CPHA=0 CPOL=0 (Mode 0) ąĖ CPHA=0 CPOL=1 (Mode 1)]

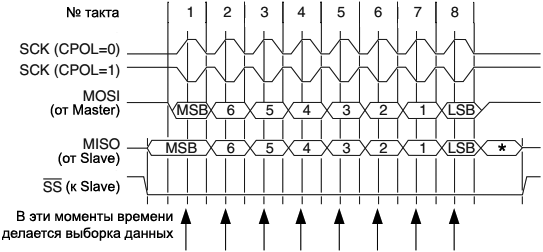

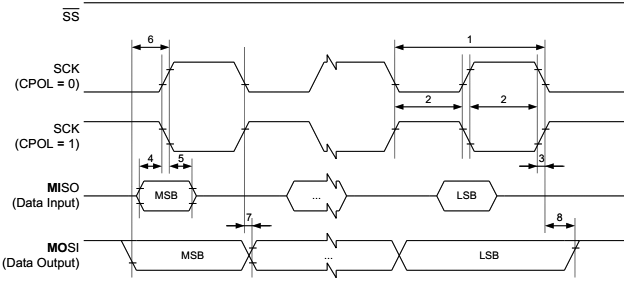

ążąŠčĆą╝ą░ čüąĖą│ąĮą░ą╗ąŠą▓ SPI, ą║ąŠą│ą┤ą░ CPHA=0, ą┐ąŠą║ą░ąĘą░ąĮą░ ąĮą░ čĆąĖčü. 2-2. ąöą╗čÅ čüąĖą│ąĮą░ą╗ą░ SCK ą┐ąŠą║ą░ąĘą░ąĮąŠ 2 ą▓ą░čĆąĖą░ąĮčéą░ č乊čĆą╝čŗ: ą║ąŠą│ą┤ą░ CPOL=0 ąĖ ą║ąŠą│ą┤ą░ CPOL=1.

ąĀąĖčü. 2-2. ążąŠčĆą╝ą░čé ą┐ąĄčĆąĄą┤ą░čćąĖ SPI, ą║ąŠą│ą┤ą░ CPHA=0.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: čüąŠčüč鹊čÅąĮąĖąĄ * ąĮąĄ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąŠ, ąĮąŠ ąŠą▒čŗčćąĮąŠ čüą░ą╝čŗą╣ čüčéą░čĆčłąĖą╣ ą▒ąĖčé (MSB) ą┐čĆąĖąĮčÅč鹊ą│ąŠ čüąĖą╝ą▓ąŠą╗ą░. MSB ąŠąĘąĮą░čćą░ąĄčé Most Significant Bit (čüą░ą╝čŗą╣ čüčéą░čĆčłąĖą╣ ą▒ąĖčé), LSB ąŠąĘąĮą░čćą░ąĄčé Least Significant Bit (čüą░ą╝čŗą╣ ą╝ą╗ą░ą┤čłąĖą╣ ą▒ąĖčé).

ąÜąŠą│ą┤ą░ SPI čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą▓ čĆąĄąČąĖą╝ąĄ slave, ą┐ąĄčĆąĄą┤ą░čćą░ ąĮą░čćąĖąĮą░ąĄčéčüčÅ ą┐ąŠ čüą┐ą░ą┤čā čüąĖą│ąĮą░ą╗ą░ ~SS. ąŁč鹊 ą░ą║čéąĖą▓ąĖčĆčāąĄčé ą░ą┐ą┐ą░čĆą░čéčāčĆčā SPI slave-čāčüčéčĆąŠą╣čüčéą▓ą░, ąĖ ąĘąĮą░č湥ąĮąĖąĄ MSB ą▓ ą▓čŗą▓ąŠą┤ąĖą╝ąŠą╝ ą▒ą░ą╣č鹥, čüąŠčģčĆą░ąĮąĄąĮąĮąŠą╝ ą▓ čĆąĄą│ąĖčüčéčĆąĄ ą┤ą░ąĮąĮčŗčģ (SPDR), ą▓čŗą▓ąŠą┤ąĖčéčüčÅ ąĮą░ čüąĖą│ąĮą░ą╗ MISO. ąöąĄą╣čüčéą▓ąĖč鹥ą╗čīąĮą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░ ąĮą░čćąĮąĄčéčüčÅ, ą║ąŠą│ą┤ą░ čāčüčéčĆąŠą╣čüčéą▓ąŠ master ąĘą░ą┐ąĖčłąĄčé ą▓ čüą▓ąŠąĄą╝ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą╝ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖąĖ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ čĆąĄą│ąĖčüčéčĆą░ SPDR. ąŁč鹊 ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ą│ąĄąĮąĄčĆą░čåąĖąĖ čéą░ą║č鹊ą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░. ąÆ čüą╗čāčćą░čÅčģ, ą║ąŠą│ą┤ą░ CPHA=0, čüąĖą│ąĮą░ą╗ SCK ąŠčüčéą░ąĄčéčüčÅ ą▓ 0 ą┤ą╗čÅ ą┐ąĄčĆą▓ąŠą╣ ą┐ąŠą╗ąŠą▓ąĖąĮčŗ ą┐ąĄčĆą▓ąŠą│ąŠ čåąĖą║ą╗ą░ SCK. ąŁč鹊 ą│ą░čĆą░ąĮčéąĖčĆčāąĄčé čüčéą░ą▒ąĖą╗čīąĮąŠčüčéčī čüąĖą│ąĮą░ą╗ą░ ąĮą░ ą▓čģąŠą┤ą░čģ ą║ą░ą║ master, čéą░ą║ ąĖ slave. ąöą░ąĮąĮčŗąĄ ąĮą░ ą▓čģąŠą┤ąĮčŗčģ čüąĖą│ąĮą░ą╗čīąĮčŗčģ ą╗ąĖąĮąĖčÅčģ ą▒čāą┤čāčé ą┐čĆąŠčćąĖčéą░ąĮčŗ ą┐ąŠ ą┐ąĄčĆąĄčģąŠą┤čā čüąĖą│ąĮą░ą╗ą░ SCK ąĖąĘ ąĮąĄą░ą║čéąĖą▓ąĮąŠą│ąŠ čüąŠčüč鹊čÅąĮąĖčÅ ą▓ ą░ą║čéąĖą▓ąĮąŠąĄ (ąĮą░čĆą░čüčéą░ąĮąĖąĄ čüąĖą│ąĮą░ą╗ą░, ąĄčüą╗ąĖ CPOL=0, ąĖ čüą┐ą░ą┤ čüąĖą│ąĮą░ą╗ą░, ąĄčüą╗ąĖ CPOL=1). ą¤ąĄčĆąĄčģąŠą┤ čüąĖą│ąĮą░ą╗ą░ SCK ąĖąĘ ą░ą║čéąĖą▓ąĮąŠą│ąŠ čüąŠčüč鹊čÅąĮąĖčÅ ą▓ ąĮąĄą░ą║čéąĖą▓ąĮąŠąĄ (čüą┐ą░ą┤ čüąĖą│ąĮą░ą╗ą░, ąĄčüą╗ąĖ CPOL=0, ąĖ ąĮą░čĆą░čüčéą░ąĮąĖąĄ, ąĄčüą╗ąĖ CPOL=1) ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ čüą┤ą▓ąĖą│čā ą┤ą░ąĮąĮčŗčģ ąĮą░ 1 ą▒ąĖčé, čéą░ą║ čćč鹊 čüą╗ąĄą┤čāčÄčēąĖą╣ ą▒ąĖčéčŗ ą▒čāą┤ąĄčé ą▓čŗą▓ąĄą┤ąĄąĮ ąĮą░ čüąĖą│ąĮą░ą╗čŗ MOSI ąĖ MISO.

ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą▒čāą┤čāčé ąĘą░ą▓ąĄčĆčłąĄąĮčŗ 8 ąĖą╝ą┐čāą╗čīčüąŠą▓ čéą░ą║č鹊ą▓, čåąĖą║ą╗ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▒ą░ą╣čéą░ ą▒čāą┤ąĄčé ąĘą░ą▓ąĄčĆčłąĄąĮ. ąÆ ąŠą▒ąŠąĖčģ čāčüčéčĆąŠą╣čüčéą▓ą░čģ (master ąĖ slave) čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ SPI interrupt flag (SPIF), ąĖ ą┐čĆąĖąĮčÅčéčŗą╣ ą▒ą░ą╣čé ą┐ąŠą┐ą░ą┤ąĄčé ą▓ ą▒čāč乥čĆ ą┐čĆąĖąĄą╝ą░.

[2.6. CPHA=1 CPOL=0 (Mode 2) ąĖ CPHA=1 CPOL=1 (Mode 3)]

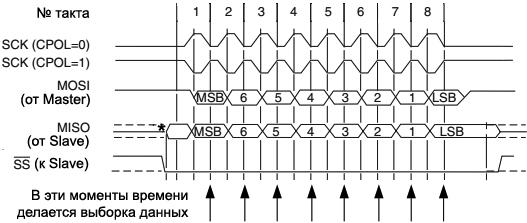

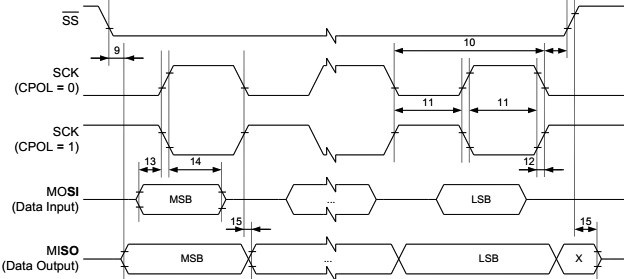

ążąŠčĆą╝ą░ čüąĖą│ąĮą░ą╗ąŠą▓ SPI, ą║ąŠą│ą┤ą░ CPHA=1, ą┐ąŠą║ą░ąĘą░ąĮą░ ąĮą░ čĆąĖčü. 2-3. ąöą╗čÅ čüąĖą│ąĮą░ą╗ą░ SCK ą┐ąŠą║ą░ąĘą░ąĮąŠ 2 ą▓ą░čĆąĖą░ąĮčéą░ č乊čĆą╝čŗ: ą║ąŠą│ą┤ą░ CPOL=0 ąĖ ą║ąŠą│ą┤ą░ CPOL=1.

ąĀąĖčü. 2-3. ążąŠčĆą╝ą░čé ą┐ąĄčĆąĄą┤ą░čćąĖ SPI, ą║ąŠą│ą┤ą░ CPHA=1.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: čüąŠčüč鹊čÅąĮąĖąĄ * ąĮąĄ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąŠ, ąĮąŠ ąŠą▒čŗčćąĮąŠ čüą░ą╝čŗą╣ ą╝ą╗ą░ą┤čłąĖą╣ ą▒ąĖčé (LSB) čĆą░ąĮąĄąĄ ą┐ąĄčĆąĄą┤ą░ąĮąĮąŠą│ąŠ čüąĖą╝ą▓ąŠą╗ą░. MSB ąŠąĘąĮą░čćą░ąĄčé Most Significant Bit (čüą░ą╝čŗą╣ čüčéą░čĆčłąĖą╣ ą▒ąĖčé), LSB ąŠąĘąĮą░čćą░ąĄčé Least Significant Bit (čüą░ą╝čŗą╣ ą╝ą╗ą░ą┤čłąĖą╣ ą▒ąĖčé).

ąÜą░ą║ ąĖ ą▓ ą┐čĆąĄą┤čŗą┤čāčēąĖčģ ą┤ą▓čāčģ čüą╗čāčćą░čÅčģ (ąŠą┐ąĖčüą░ąĮąĮčŗą╝ąĖ ą▓ 2.5), čüą┐ą░ą┤ čāčĆąŠą▓ąĮčÅ ąĮą░ ~SS ą▓čŗą▒ąĖčĆą░ąĄčé ąĖ ą░ą║čéąĖčĆčāąĄčé čāčüčéčĆąŠą╣čüčéą▓ąŠ slave. ąÆ čüčĆą░ą▓ąĮąĄąĮąĖąĖ čü ą┤ą▓čāą╝čÅ ą┐čĆąĄą┤čŗą┤čāčēąĖą╝ąĖ čüą╗čāčćą░čÅą╝ąĖ (ąŠą┐ąĖčüą░ąĮąĮčŗą╝ąĖ ą▓ 2.5), ą│ą┤ąĄ CPHA=0, ąĘą┤ąĄčüčī ą┐ąĄčĆąĄą┤ą░čćą░ ąĮąĄ ąĮą░čćąĖąĮą░ąĄčéčüčÅ, ąĖ ą▓ čŹč鹊čé ą╝ąŠą╝ąĄąĮčé MSB ąĮąĄ ą▓čŗą▓ąŠą┤ąĖčéčüčÅ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ slave.

ąöąĄą╣čüčéą▓ąĖč鹥ą╗čīąĮą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░ ąĮą░čćąĖąĮą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠąĄ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ master ąĘą░ą┐ąĖčłąĄčé ą▒ą░ą╣čé ą▓ SPDR, ąĖ ąĮą░čćąĮąĄčéčüčÅ ą│ąĄąĮąĄčĆą░čåąĖčÅ čüąĖą│ąĮą░ą╗ą░ čéą░ą║č鹊ą▓ SCK. ą¤ąĄčĆą▓čŗą╣ ą┐ąĄčĆąĄčģąŠą┤ čüąĖą│ąĮą░ą╗ą░ ąĖąĘ ąĮąĄą░ą║čéąĖą▓ąĮąŠą│ąŠ čüąŠčüč鹊čÅąĮąĖčÅ ą▓ ą░ą║čéąĖą▓ąĮąŠąĄ (ąĮą░čĆą░čüčéą░ąĮąĖąĄ čüąĖą│ąĮą░ą╗ą░, ąĄčüą╗ąĖ CPOL=0, ąĖ čüą┐ą░ą┤ čüąĖą│ąĮą░ą╗ą░, ąĄčüą╗ąĖ CPOL=1) ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ą▓čŗą▓ąŠą┤čā MSB ą▒ą░ą╣čéą░ (ą║ąŠč鹊čĆčŗą╣ ą▒čŗą╗ ąĘą░ą┐ąĖčüą░ąĮ ą▓ SPDR) ą║ą░ą║ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ master, čéą░ą║ ąĖ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ slave. ąÜą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 2-3, ąĘą┤ąĄčüčī ąĮąĄčé ąĘą░ą┤ąĄčƹȹ║ąĖ ą▓ ą┐ąŠą╗ąŠą▓ąĖąĮčā čéą░ą║čéą░ SCK, ą║ą░ą║ čŹč鹊 ą▒čŗą╗ąŠ ą▓ čĆąĄąČąĖą╝ą░čģ Mode 0 ąĖ Mode 1. ąĪąĖą│ąĮą░ą╗ SCK ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ ą╝ąĄąĮčÅąĄčé čüą▓ąŠą╣ čāčĆąŠą▓ąĄąĮčī čü ąĮą░čćą░ą╗ąŠą╝ ą┐ąĄčĆą▓ąŠą│ąŠ čéą░ą║čéą░ SCK. ąöą░ąĮąĮčŗąĄ ąĮą░ ą▓čģąŠą┤ąĮčŗčģ čüąĖą│ąĮą░ą╗ą░čģ ą▒čāą┤čāčé ą┐čĆąŠčćąĖčéą░ąĮčŗ ą┐ąŠ ą┐ąĄčĆąĄčģąŠą┤čā čüąĖą│ąĮą░ą╗ą░ SCK ąĖąĘ ą░ą║čéąĖą▓ąĮąŠą│ąŠ čüąŠčüč鹊čÅąĮąĖčÅ ą▓ ąĮąĄą░ą║čéąĖą▓ąĮąŠąĄ (čüą┐ą░ą┤ čüąĖą│ąĮą░ą╗ą░, ąĄčüą╗ąĖ CPOL=0, ąĖ ąĮą░čĆą░čüčéą░ąĮąĖąĄ, ąĄčüą╗ąĖ CPOL=1).

ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą▒čāą┤čāčé ąĘą░ą▓ąĄčĆčłąĄąĮčŗ 8 ąĖą╝ą┐čāą╗čīčüąŠą▓ čéą░ą║č鹊ą▓, čåąĖą║ą╗ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▒ą░ą╣čéą░ ą▒čāą┤ąĄčé ąĘą░ą▓ąĄčĆčłąĄąĮ. ąÆ ąŠą▒ąŠąĖčģ čāčüčéčĆąŠą╣čüčéą▓ą░čģ (master ąĖ slave) čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ SPI interrupt flag (SPIF), ąĖ ą┐čĆąĖąĮčÅčéčŗą╣ ą▒ą░ą╣čé ą┐ąŠą┐ą░ą┤ąĄčé ą▓ ą▒čāč乥čĆ ą┐čĆąĖąĄą╝ą░.

2.6.1. ą¦č鹊 ąĮčāąČąĮąŠ čāč湥čüčéčī ąĮą░ ą▓čŗčüąŠą║ąĖčģ čüą║ąŠčĆąŠčüčéčÅčģ ąŠą▒ą╝ąĄąĮą░

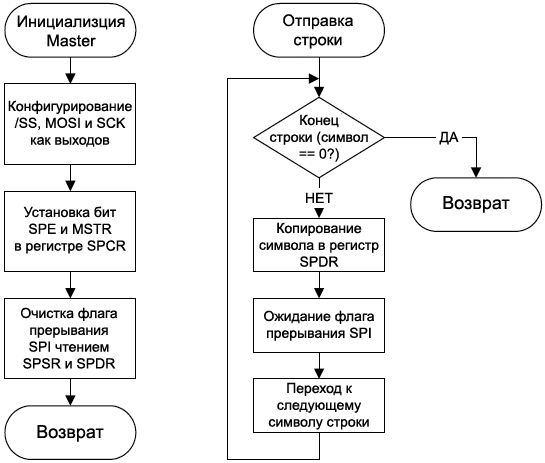

ąŻčüčéčĆąŠą╣čüčéą▓ą░, ą║ąŠč鹊čĆčŗąĄ čĆą░ą▒ąŠčéą░čÄčé ąĮą░ ą▓čŗčüąŠą║ąĖčģ čéą░ą║č鹊ą▓čŗčģ čćą░čüč鹊čéą░čģ, ąĖ ą╝ąŠą┤čāą╗ąĖ SPI, ą║ąŠč鹊čĆčŗąĄ čüą┐ąŠčüąŠą▒ąĮčŗ ą║ čĆą░ą▒ąŠč鹥 ąĮą░ čüą║ąŠčĆąŠčüčéčÅčģ, ą┤ąŠčģąŠą┤čÅčēąĖčģ ą┤ąŠ ą┐ąŠą╗ąŠą▓ąĖąĮčŗ ą┐ąĄčĆąĖąŠą┤ą░ čüąĖčüč鹥ą╝ąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ, ą┤ąŠą╗ąČąĮčŗ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ čéą░ą║, čćč鹊ą▒čŗ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ ąĖ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ ą▒čŗą╗ąŠ ą▒ąŠą╗ąĄąĄ č鹊čćąĮąŠąĄ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĄ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ. ąØą░ čüą╗ąĄą┤čāčÄčēąĖčģ ą┤ą▓čāčģ ą┤ąĖą░ą│čĆą░ą╝ą╝ą░čģ ą┐ąŠą║ą░ąĘą░ąĮą░ č乊čĆą╝ą░ čüąĖą│ąĮą░ą╗ąŠą▓ ą┤ą╗čÅ AVR ą▓ čĆąĄąČąĖą╝ąĄ master ąĖ čĆąĄąČąĖą╝ąĄ slave ą┤ą╗čÅ SPI Mode 0 ąĖ Mode 1. ąóąŠčćąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ ąŠč鹊ą▒čĆą░ąČą░ąĄą╝čŗčģ ąĖąĮč鹥čĆą▓ą░ą╗ąŠą▓ ą▓čĆąĄą╝ąĄąĮąĖ ąĘą░ą▓ąĖčüčÅčé ąŠčé čĆą░ąĘą╗ąĖčćąĮčŗčģ čéąĖą┐ąŠą▓ čāčüčéčĆąŠą╣čüčéą▓, ąĖ ąĮąĄ ąŠą▒čüčāąČą┤ą░čÄčéčüčÅ ą▓ čŹč鹊ą╝ ą░ą┐ąĮąŠčāč鹥. ą×ą┤ąĮą░ą║ąŠ ą┐čĆąĖąĮčåąĖą┐ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓čüąĄčģ čāčüčéčĆąŠą╣čüčéą▓ ąŠą┤ąĖąĮ ąĖ č鹊čé ąČąĄ, čéą░ą║ čćč鹊 ą┤ą╗čÅ ąĮąĖčģ ą▓čüąĄčģ ąĮčāąČąĮąŠ ą┐čĆąĖąĮąĖą╝ą░čéčī ą▓ąŠ ą▓ąĮąĖą╝ą░ąĮąĖąĄ čüą╗ąĄą┤čāčÄčēąĖąĄ čüąŠąŠą▒čĆą░ąČąĄąĮąĖčÅ.

ąĀąĖčü. 2-4. ąöąĖą░ą│čĆą░ą╝ą╝čŗ ą▓čĆąĄą╝ąĄąĮąĖ Master.

ą£ąĖąĮąĖą╝ą░ą╗čīąĮčŗąĄ čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅ ą║ ąĖąĮč鹥čĆą▓ą░ą╗ą░ą╝ čéą░ą║č鹊ą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ą┐ąŠą║ą░ąĘą░ąĮčŗ ąĮą░ čĆąĖčüčāąĮą║ą░čģ ą╝ąĄčéą║ą░ą╝ąĖ "1" ąĖ "2". ąŚąĮą░č湥ąĮąĖąĄ "1" čāą║ą░ąĘčŗą▓ą░ąĄčé ą┐ąĄčĆąĖąŠą┤ SCK, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ "2" čāą║ą░ąĘčŗą▓ą░ąĄčé ą▓čĆąĄą╝ąĄąĮą░ ą▓čŗčüąŠą║ąŠą│ąŠ / ąĮąĖąĘą║ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ čéą░ą║č鹊ą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░. ą£ą░ą║čüąĖą╝ą░ą╗čīąĮąŠąĄ ą▓čĆąĄą╝čÅ ąĮą░čĆą░čüčéą░ąĮąĖčÅ ąĖ čüą┐ą░ą┤ą░ čüąĖą│ąĮą░ą╗ą░ SCK čāą║ą░ąĘą░ąĮąŠ ą╝ąĄčéą║ąŠą╣ "3". ąŁč鹊 ą┐ąĄčĆą▓čŗąĄ 3 ąĖąĮč鹥čĆą▓ą░ą╗ą░ ą▓čĆąĄą╝ąĄąĮąĖ AVR master, ą║ąŠč鹊čĆčŗąĄ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą┐čĆąŠą▓ąĄčĆąĄąĮčŗ ąĮą░ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĄ čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅą╝ slave-čāčüčéčĆąŠą╣čüčéą▓ą░.

ąÆčĆąĄą╝čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ (Setup time) "4" ąĖ ą▓čĆąĄą╝čÅ čāą┤ąĄčƹȹ░ąĮąĖčÅ (Hold time) "5" čÅą▓ą╗čÅčÄčéčüčÅ ą▓ą░ąČąĮčŗą╝ąĖ ąĖąĮč鹥čĆą▓ą░ą╗ą░ą╝ąĖ, ą┐ąŠč鹊ą╝čā čćč鹊 ąŠąĮąĖ čāą║ą░ąĘčŗą▓ą░čÄčé čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅ ą║ AVR, ąŠą┐čĆąĄą┤ąĄą╗čÅąĄą╝čŗąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖąĄą╝ ą║ slave-čāčüčéčĆąŠą╣čüčéą▓čā. ąŁčéąĖ ąĖąĮč鹥čĆą▓ą░ą╗čŗ ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčé, čüą║ąŠą╗čīą║ąŠ ą▓čĆąĄą╝ąĄąĮąĖ ą┤ąŠą╗ąČąĮąŠ ą┐čĆąŠą╣čéąĖ ą┤ąŠ čéą░ą║č鹊ą▓ąŠą│ąŠ ą┐ąĄčĆąĄą┐ą░ą┤ą░ slave, ą┐ąŠčüą╗ąĄ č湥ą│ąŠ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą│ąŠč鹊ą▓čŗ ą┤ąŠą┐čāčüčéąĖą╝čŗąĄ ą▓čŗčģąŠą┤ąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ, ąĖ čüą║ąŠą╗čīą║ąŠ ą▓čĆąĄą╝ąĄąĮąĖ ą┐ąŠčüą╗ąĄ čéą░ą║č鹊ą▓ąŠą│ąŠ ą┐ąĄčĆąĄą┐ą░ą┤ą░ čŹčéąĖ ą┤ą░ąĮąĮčŗąĄ ą┤ąŠą╗ąČąĮčŗ čāą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ ą▓ ą┤ąŠą┐čāčüčéąĖą╝ąŠą╝ čüąŠčüč鹊čÅąĮąĖąĖ.

ą¦č鹊 ąĄčüą╗ąĖ ą▓čĆąĄą╝čÅ Setup ąĖ Hold ą┤ąŠčüčéą░č鹊čćąĮąŠ ą▓ąĄą╗ąĖą║ąĖ, čćč鹊ą▒čŗ slave ą┐ąŠčģąŠą┤ąĖą╗ąŠ ą║ čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅą╝ AVR, ą┐ąŠą┤ąŠą╣ą┤ąĄčé ą╗ąĖ AVR ą║ čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅą╝ slave?

ąÆčĆąĄą╝čÅ "6" (Out ą║ SCK) čāą║ą░ąĘčŗą▓ą░ąĄčé ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠąĄ ą▓čĆąĄą╝čÅ, ą║ąŠą│ą┤ą░ AVR ąĖą╝ąĄąĄčé ą│ąŠč鹊ą▓čŗąĄ ą┤ąĄą╣čüčéą▓ąĖč鹥ą╗čīąĮčŗąĄ ą▓čŗčģąŠą┤ąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┤ąŠ ą┐ąŠčÅą▓ą╗ąĄąĮąĖčÅ čéą░ą║č鹊ą▓ąŠą│ąŠ ą┐ąĄčĆąĄą┐ą░ą┤ą░. ąŁč鹊 ą▓čĆąĄą╝čÅ ą╝ąŠąČąĮąŠ čüčĆą░ą▓ąĮąĖčéčī čü ą▓čĆąĄą╝ąĄąĮąĄą╝ Setup "4" slave-čāčüčéčĆąŠą╣čüčéą▓ą░.

The time "7" (SCK ą║ Out) ąĘą░ą┤ą░ąĄčé ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠąĄ ą▓čĆąĄą╝čÅ, ą┐ąŠčüą╗ąĄ ą║ąŠč鹊čĆąŠą│ąŠ AVR ą▓čŗą▓ąŠą┤ąĖčé čüą╗ąĄą┤čāčÄčēąĖą╣ ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ, ą░ ą▓čĆąĄą╝čÅ "8" (SCK ą║ Out high) čāą║ą░ąĘčŗą▓ą░ąĄčé ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠąĄ ą▓čĆąĄą╝čÅ, ą║ąŠą│ą┤ą░ ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ čüąĖą│ąĮą░ą╗ą░ MOSI ą▓ ą▓ąĄčĆąĮąŠą╝ ąĘąĮą░č湥ąĮąĖąĖ ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ ą║ą░ą║ SCK ą▒čŗą╗ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ąŠą▒čĆą░čéąĮąŠ ą║ čüąŠčüč鹊čÅąĮąĖčÄ ąŠąČąĖą┤ą░ąĮąĖčÅ (idle state).

ąĀąĖčü. 2-5. ąöąĖą░ą│čĆą░ą╝ą╝čŗ ą▓čĆąĄą╝ąĄąĮąĖ Slave.

ą¤čĆąĖąĮčåąĖą┐ č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą┤ąĖą░ą│čĆą░ą╝ą╝ ą▓ čĆąĄąČąĖą╝ąĄ slave č鹊čé ąČąĄ čüą░ą╝čŗą╣, ą║ą░ą║ ąŠąĮ ą▒čŗą╗ čĆą░ąĮąĄąĄ ąŠą┐ąĖčüą░ąĮ ą┤ą╗čÅ čĆąĄąČąĖą╝ą░ master. ąŁč鹊 ą┐ąŠč鹊ą╝čā, čćč鹊 ą┐čĆąĖ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĖ čĆąŠą╗ąĄą╣ ą╝ąĄąČą┤čā master ąĖ slave čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅ ą║ ąĖąĮč鹥čĆą▓ą░ą╗ą░ą╝ čéą░ą║ąČąĄ ąĖąĮą▓ąĄčĆčéąĖčĆčāčÄčéčüčÅ. ą£ąĖąĮąĖą╝ą░ą╗čīąĮčŗąĄ ąĖąĮč鹥čĆą▓ą░ą╗čŗ čĆąĄąČąĖą╝ą░ master č鹥ą┐ąĄčĆčī čüčéą░ąĮąŠą▓čÅčéčüčÅ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮčŗą╝ąĖ ąĖąĮč鹥čĆą▓ą░ą╗ą░ą╝ąĖ, ąĖ ąĮą░ąŠą▒ąŠčĆąŠčé.

[2.7. ąÜąŠąĮčäą╗ąĖą║čéčŗ ą▓ ą┐ąĄčĆąĄą┤ą░č湥 SPI]

ąÜąŠą╗ą╗ąĖąĘąĖčÅ ąĘą░ą┐ąĖčüąĖ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé, ąĄčüą╗ąĖ ąĘą░ą┐ąĖčüą░ąĮ SPDR, ą║ąŠą│ą┤ą░ ą┐ąĄčĆąĄą┤ą░čćą░ ąĄčēąĄ ąĮąĄ ąĘą░ą▓ąĄčĆčłąĖą╗ą░čüčī. ą¤ąŠčüą║ąŠą╗čīą║čā čŹč鹊čé čĆąĄą│ąĖčüčéčĆ ąĖą╝ąĄąĄčé č鹊ą╗čīą║ąŠ ąŠą┤ąĖąĮąŠčćąĮčāčÄ ą▒čāč乥čĆąĖąĘą░čåąĖčÄ ą┤ą╗čÅ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ, č鹊 ąĘą░ą┐ąĖčüčī ą▓ SPDR ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ąĘą░ą┐ąĖčüąĖ ą┤ą░ąĮąĮčŗčģ ąĮąĄą┐ąŠčüčĆąĄą┤čüčéą▓ąĄąĮąĮąŠ ą▓ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ SPI. ą¤ąŠčüą║ąŠą╗čīą║čā čŹčéą░ ąŠą┐ąĄčĆą░čåąĖčÅ ąĘą░ą┐ąĖčüąĖ ą┐ąŠą▓čĆąĄą┤ąĖą╗ą░ ą▒čŗ ą┤ą░ąĮąĮčŗąĄ č鹥ą║čāčēąĄą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ, ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ąŠčłąĖą▒ą║ą░ ą║ąŠą╗ą╗ąĖąĘąĖąĖ ąĘą░ą┐ąĖčüąĖ (write-collision error) ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ WCOL ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPSR. ąŚą░ą┐ąĖčüčī ą┐čĆąĖ čŹč鹊ą╝ ąĮąĄ ą▒čāą┤ąĄčé ą▓čŗą┐ąŠą╗ąĮąĄąĮą░, ąĖ č鹥ą║čāčēą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░ ą┐čĆąŠą┤ąŠą╗ąČąĖčéčüčÅ ą▒ąĄąĘ ą┐ąŠą╝ąĄčģ.

ą×čłąĖą▒ą║ą░ ą║ąŠą╗ą╗ąĖąĘąĖąĖ ąĘą░ą┐ąĖčüąĖ ąŠą▒čŗčćąĮąŠ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą▓ čāčüčéčĆąŠą╣čüčéą▓ąĄ slave, ą┐ąŠč鹊ą╝čā čćč鹊 slave ąĮąĖą║ą░ą║ ąĮąĄ čāą┐čĆą░ą▓ą╗čÅąĄčé ą╝ąŠą╝ąĄąĮč鹊ą╝, ą║ąŠą│ą┤ą░ master ąĮą░čćąĮąĄčé ą┐ąĄčĆąĄą┤ą░čćčā. ą×ą┤ąĮą░ą║ąŠ master ąĘąĮą░ąĄčé, ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą┐ąĄčĆąĄą┤ą░čćą░. ąóą░ą║ čćč鹊 master ąĮąĄ ą┤ąŠą╗ąČąĄąĮ ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ąŠčłąĖą▒ą║ąĖ ą║ąŠą╗ą╗ąĖąĘąĖąĖ ąĘą░ą┐ąĖčüąĖ, čģąŠčéčÅ ą╗ąŠą│ąĖą║ą░ SPI ą╝ąŠąČąĄčé ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░čéčī čŹčéąĖ ąŠčłąĖą▒ą║ąĖ ą║ą░ą║ ą▓ čĆąĄąČąĖą╝ąĄ master, čéą░ą║ ąĖ ą▓ čĆąĄąČąĖą╝ąĄ slave.

[2.8. ąŁą╝čāą╗čÅčåąĖčÅ SPI]

ąÜąŠą│ą┤ą░ SPI 菹╝čāą╗ąĖčĆčāąĄčéčüčÅ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ 菹╝čāą╗čÅč鹊čĆą░ ą░ą┐ą┐ą░čĆą░čéčāčĆčŗ ICE200, ąĖą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 ą▓ ą┤ąĄą╣čüčéą▓ąĖč鹥ą╗čīąĮąŠčüčéąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ ą▓ čŹč鹊ą╝ 菹╝čāą╗čÅč鹊čĆąĄ ąĮąĄ ąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄčéčüčÅ ąĮą░ č鹊čćą║ąĄ ąŠčüčéą░ąĮąŠą▓ą░ (break point), ą░ ą┐čĆąŠą┤ąŠą╗ąČą░čÄčé čĆą░ą▒ąŠčéą░čéčī čü č鹊ą╣ čüą║ąŠčĆąŠčüčéčīčÄ, ą║ąŠč鹊čĆą░čÅ ą▒čŗą╗ą░ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮą░.

ąÜąŠą│ą┤ą░ SPI 菹╝čāą╗ąĖčĆčāąĄčéčüčÅ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ ICEPRO, č鹊 ąĖąĮč鹥čĆą▓ą░ą╗čŗ ą▓čĆąĄą╝ąĄąĮąĖ ą▒čāą┤čāčé ą╝ąĄąĮąĄąĄ č鹊čćąĮčŗ, č湥ą╝ ąĄčüą╗ąĖ ą▒čŗ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ą╗čüčÅ čĆąĄą░ą╗čīąĮčŗą╣ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ čüą░ą╝ ą┐ąŠ čüąĄą▒ąĄ. ą¤čĆąĖčćąĖąĮą░ ą▓ č鹊ą╝, čćč鹊 čā ICEPRO ą▒ąŠą╗čīčłąĄ ą┤ą╗ąĖąĮą░ čåąĄą┐ąĄą╣ čüąĖą│ąĮą░ą╗ąŠą▓ - čŹč鹊 čéą░ čåąĄąĮą░, ą║ąŠč鹊čĆčāčÄ ą╝čŗ ą▓čŗąĮčāąČą┤ąĄąĮčŗ ąĘą░ą┐ą╗ą░čéąĖčéčī ąĘą░ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą░ą┐ą│čĆąĄą╣ą┤ą░ ąĖ ą┐ąŠą╗čāč湥ąĮąĖąĄ ą│ąĖą▒ą║ąŠčüčéąĖ ą▓ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ.

[2.9. ąØą░čüčéčĆąŠą╣ą║ą░ SPI]

ąÜąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ SPI ą▓ čĆąĄąČąĖą╝ąĄ master ą▒čāą┤ąĄčé ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▓ ą┤ą▓čāą╝čÅ čĆą░ąĘąĮčŗą╝ąĖ čüą┐ąŠčüąŠą▒ą░ą╝ąĖ. ą¤ąĄčĆą▓čŗą╣ ą┐čĆąĖą╝ąĄčĆ ą┐ąŠą║ą░ąČąĄčé čĆąĄą░ą╗ąĖąĘą░čåąĖčÄ ąŠą▒ą╝ąĄąĮą░ č湥čĆąĄąĘ SPI, ą║ąŠą│ą┤ą░ č鹥ą║čāčēąĄąĄ čüąŠčüč鹊čÅąĮąĖąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐ąŠą╗čāčćą░čÄčé ąŠą┐čĆąŠčüąŠą╝ čäą╗ą░ą│ąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (polling). ąÆč鹊čĆąŠą╣ ą┐čĆąĖą╝ąĄčĆ ą┐ąŠą║ą░ąČąĄčé, ą║ą░ą║ čĆąĄą░ą╗ąĖąĘąŠą▓ą░čéčī ąŠą▒ą╝ąĄąĮ ą┤ą░ąĮąĮčŗą╝ąĖ čü čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝ ą┐ąŠč鹊ą║ąŠą╝ ą┐ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅą╝.

ą×ą▒ą╝ąĄąĮ ą┤ą░ąĮąĮčŗą╝ąĖ ą╝ąĄąČą┤čā ą┤ą▓čāą╝čÅ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ AVR ą▒čāą┤ąĄčé ą┐ąŠą║ą░ąĘą░ąĮ ą▓ ą▓ąĖą┤ąĄ ąŠčéą┐čĆą░ą▓ą║ąĖ č鹥ą║čüčéą░ "Text String" ąŠčé čāčüčéčĆąŠą╣čüčéą▓ą░ master ą║ čāčüčéčĆąŠą╣čüčéą▓čā slave. ą¤čĆąĖąĮčÅčéčŗąĄ čüąĖą╝ą▓ąŠą╗čŗ ą▒čāą┤čāčé čüčĆą░ą▓ąĮąĄąĮčŗ čü ąŠąČąĖą┤ą░ąĄą╝čŗą╝ąĖ, ąĖ čĆąĄąĘčāą╗čīčéą░čé ą┐čĆąŠą▓ąĄčĆą║ąĖ ą▒čāą┤ąĄčé ą▓čŗą▓ąĄą┤ąĄąĮ ą▓ ą┐ąŠčĆčé D. ąŁčéąĖ čĆąĄąĘčāą╗čīčéą░čéčŗ čģąŠčĆąŠčłąŠ ą┐ąŠą┤čģąŠą┤čÅčé ą║ ą┤ą╗čÅ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ ąĮą░ 2 ą┐ą╗ą░čéą░čģ čĆą░ąĘčĆą░ą▒ąŠčéčćąĖą║ą░ ąĮą░ą┐ąŠą┤ąŠą▒ąĖąĄ STK500.

ąÆąŠ ą▓čüąĄčģ ą┐čĆąĖą╝ąĄčĆą░čģ, ą┐ąŠą║ą░ąĘą░ąĮąĮčŗčģ ąĘą┤ąĄčüčī, SPI ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ ą▓ Mode 0, ąĖ MSB ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą┐ąĄčĆą▓čŗą╝. ąŁč鹊 ą┤ąŠčüčéąĖą│ą░ąĄčéčüčÅ čüą▒čĆąŠčüąŠą╝ ą▓ 0 ą▒ąĖč鹊ą▓ CPOL, CPHA ąĖ DORD ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPCR. ąÆ č鹊ą╝ ąČąĄ čĆąĄą│ąĖčüčéčĆąĄ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▒ąĖčé SPE, čĆą░ąĘčĆąĄčłą░čÄčēąĖą╣ čĆą░ą▒ąŠčéčā SPI. ąóą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ SCK ąĘą░ą┤ą░ąĄčéčüčÅ CK/4 ą▓ ą┐ąĄčĆą▓ąŠą╝ ą┐čĆąĖą╝ąĄčĆąĄ (čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąŠč鹊ą║ąŠą╝ ą┐ąŠ ąŠą┐čĆąŠčüčā) ąĖ CK/16 ą▓ ą║ąŠą┤ąĄ ą▓č鹊čĆąŠą│ąŠ ą┐čĆąĖą╝ąĄčĆą░ (čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąŠč鹊ą║ąŠą╝ ą┐ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅą╝).

ąóą░ą▒ą╗ąĖčåą░ 2-4. ąØą░čüčéčĆąŠą╣ą║ą░ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ SPI ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ AT90USB162 ą▒ąĖčéą░ą╝ąĖ SPI2X (čĆąĄą│ąĖčüčéčĆ SPSR), ąĖ ą▒ąĖčéą░ą╝ąĖ SPR1, SPR0 (čĆąĄą│ąĖčüčéčĆ SPCR). ą¦ą░čüč鹊čéą░ CK ąĖ fosc čŹč鹊 čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ čÅą┤čĆą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░.

| SPI2X |

SPR1 |

SPR0 |

ąóą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ SCK |

| 0 |

0 |

0 |

fosc/4 |

| 0 |

0 |

1 |

fosc/16 |

| 0 |

1 |

0 |

fosc/64 |

| 0 |

1 |

1 |

fosc/128 |

| 1 |

0 |

0 |

fosc/2 |

| 1 |

0 |

1 |

fosc/8 |

| 1 |

1 |

0 |

fosc/32 |

| 1 |

1 |

1 |

fosc/64 |

ąöą╗čÅ čüčĆą░ą▓ąĮąĄąĮąĖčÅ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖą╣ SPI ą▓ čĆą░ąĘąĮčŗčģ ą┐čĆąĖą╝ąĄčĆą░čģ ąĮčāąČąĮąŠ ąŠą▒čĆą░čéąĖčéčī ą▓ąĮąĖą╝ą░ąĮąĖąĄ ąĮą░ čāčüčéą░ąĮąŠą▓ą║čā ą▒ąĖčéą░ ą▓čŗą▒ąŠčĆą░ Master / Slave (MSTR) ąĖ ą▒ąĖčéą░ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ SPI Interrupt Enable (SPIE).

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

1. ą¤ąŠčüą║ąŠą╗čīą║čā ąŠą▒ą░ ą┐čĆąĖą╝ąĄčĆą░ ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčé ą┐ąĄčĆąĄą┤ą░čćčā ą╝ąĄąČą┤čā ąŠą┤ąĮąĖą╝ master ąĖ ąŠą┤ąĮąĖą╝ slave, č鹊 ąĮąĄ čéčĆąĄą▒čāąĄčéčüčÅ ą┐čĆąŠą▓ąĄčĆčÅčéčī, čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą╗ąĖ ą▒ąĖčé MSTR ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ master ąĮą░čćąĮąĄčé ąĮąŠą▓čāčÄ ą┐ąĄčĆąĄą┤ą░čćčā. ąŁč鹊čé ą║ąŠą┤ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┤ąŠą▒ą░ą▓ą╗ąĄąĮ ą▓ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ, ą│ą┤ąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ąĮąĄčüą║ąŠą╗čīą║ąŠ čāčüčéčĆąŠą╣čüčéą▓ master.

2. ąźąŠčéčÅ čāčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖč鹊ą▓ ą▓čŗą▒ąŠčĆą░ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ (Clock Rate Select bits) ąĮąĄ ą┤ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░ ą▓ čĆąĄąČąĖą╝ąĄ slave, ąĮčāąČąĮąŠ čāą┤ąŠčüč鹊ą▓ąĄčĆąĖčéčüčÅ, čćč鹊 čüąĖčüč鹥ą╝ąĮą░čÅ čćą░čüč鹊čéą░ (CK) slave-čāčüčéčĆąŠą╣čüčéą▓ą░ ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ą▓ 4 čĆą░ąĘą░ ą▓čŗčłąĄ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ SPI (SCK).

3. ą×čćąĖčüčéą║ą░ ąŠąČąĖą┤ą░čÄčēąĖčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ SPI ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą┐čāčüčéčŗą╝ ą┤ąŠčüčéčāą┐ąŠą╝ ą║ SPSR ąĖ SPDR.

ąÆą╝ąĄčüč鹥 čü čŹčéąĖą╝ ą░ą┐ąĮąŠčāč鹊ą╝ ą┐ąŠčüčéą░ą▓ą╗čÅčÄčéčüčÅ 2 čäą░ą╣ą╗ą░ ąĖčüčģąŠą┤ąĮąŠą│ąŠ ą║ąŠą┤ą░ ąĮą░ čÅąĘčŗą║ąĄ C.

ą¦č鹊ą▒čŗ ąĘą░ą┐čāčüčéąĖčéčī ą║ąŠą┤, ąĮą░čüčéčĆąŠą╣č鹥 2 ą┐ą╗ą░čéčŗ STK500, ą║ą░ą║ čŹč鹊 ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 2-6. ąÜąŠą┤ ąĮą░ą┐ąĖčüą░ąĮ ą┤ą╗čÅ ATmega162, ąĮąŠ ą╝ąŠąČąĄčé ą▒čŗčéčī čüą║ąŠą╝ą┐ąĖą╗ąĖčĆąŠą▓ą░ąĮ ą┤ą╗čÅ ą╗čÄą▒čŗčģ AVR, čā ą║ąŠč鹊čĆčŗčģ ąĄčüčéčī ą░ą┐ą┐ą░čĆą░čéąĮčŗą╣ SPI ąĖ ą┐ąŠčĆčéčŗ PORTA, PORTB ąĖ PORTD.

ąĀąĖčü. 2-6. ąØą░čüčéčĆąŠą╣ą║ą░ ą░ą┐ą┐ą░čĆą░čéčāčĆčŗ.

2.9.1. ą¤čĆąĖą╝ąĄčĆ 1 - ąŠą▒ą╝ąĄąĮ ą┤ą░ąĮąĮčŗą╝ąĖ č湥čĆąĄąĘ SPI ą┐ąŠ ą┐čĆąĖąĮčåąĖą┐čā ąŠą┐čĆąŠčüą░

2.9.1.1. ąØą░ čüč鹊čĆąŠąĮąĄ Master:

ąĢčüą╗ąĖ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, č鹊 ąĮčāąČąĮąŠ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī č鹊ą╗čīą║ąŠ ą╗ąĖčłčī ą░ą┐ą┐ą░čĆą░čéčāčĆčā SPI ąĖ ą▓čŗą▓ąŠą┤čŗ čüąĖą│ąĮą░ą╗ąŠą▓ ąŠą▒ą╝ąĄąĮą░. ąÆ čŹč鹊ą╝ ą┐čĆąĖą╝ąĄčĆąĄ ą▓ą░ąČąĮąŠ ąĮą░čüčéčĆąŠąĖčéčī ą▓čŗą▓ąŠą┤ ~SS ą║ą░ą║ ą▓čŗčģąŠą┤ąĮąŠą╣ ą┐ąŠčĆčé. ąŁč鹊 ą┤ąĄą╗ą░ąĄčéčüčÅ ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ą▒čāą┤ąĄčé čĆą░ąĘčĆąĄčłąĄąĮą░ čĆą░ą▒ąŠčéą░ SPI ą▓ čĆąĄąČąĖą╝ąĄ master. ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ SPI, ą║ąŠą│ą┤ą░ ~SS čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą║ą░ą║ ą▓čģąŠą┤, ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ č鹊ą╝čā, čćč鹊 SPI ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ ą┐ąĄčĆąĄą║ą╗čÄčćąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ slave, ąĄčüą╗ąĖ ą║ ą▓čŗą▓ąŠą┤čā ~SS ą▒čāą┤ąĄčé ą┐čĆąĖą╗ąŠąČąĄąĮ ąĮąĖąĘą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī. ąÆ čĆąĄąČąĖą╝ąĄ slave ą▓čŗą▓ąŠą┤ ~SS ą▓čüąĄą│ą┤ą░ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ ą║ą░ą║ ą▓čģąŠą┤ (čüą╝. čĆąĖčü. 2-7). ąśčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ ąŠą┐čĆąŠčüą░ ą┤ą░ąĄčé čüą░ą╝čŗą╣ ą▒čŗčüčéčĆčŗą╣ ąŠą▒ą╝ąĄąĮ ą┤ą░ąĮąĮčŗą╝ąĖ, ą┐ąŠčŹč鹊ą╝čā ą▓ čĆąĄąČąĖą╝ąĄ master čéą░ą║ąŠą╣ ą┐čĆąĖąĮčåąĖą┐ čĆą░ą▒ąŠčéčŗ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čćą░čēąĄ ą▓čüąĄą│ąŠ.

ąĀąĖčü. 2-7. Master, čĆą░ą▒ąŠčéą░čÄčēąĖą╣ ą┐ąŠ ąŠą┐čĆąŠčüčā - ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ ąĖ ą┐ąĄčĆąĄą┤ą░čćą░.

2.9.1.2. ąØą░ čüč鹊čĆąŠąĮąĄ Slave:

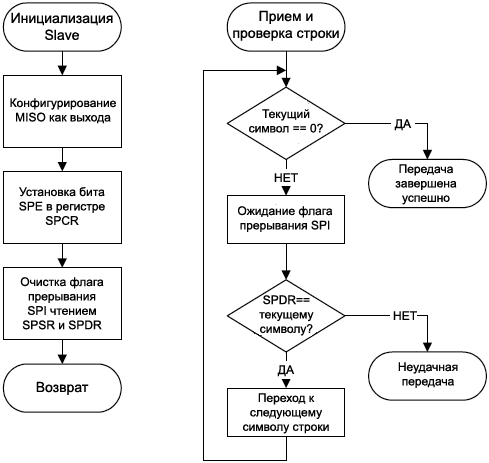

ąöą╗čÅ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ AVR ą▓ čĆąĄąČąĖą╝ąĄ SPI slave ąĮąĄčé ąĮčāąČą┤čŗ ą┐čĆąĖą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ ą║ą░ą║ąŠą│ąŠ-ą╗ąĖą▒ąŠ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą│ąŠ ą┐ąŠčĆčÅą┤ą║ą░ ą┐čĆąĖ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ čĆąĄą│ąĖčüčéčĆąŠą▓. ąÆčŗą▓ąŠą┤ MISO ąĮą░čüčéčĆą░ąĖą▓ą░ąĄčéčüčÅ ą║ą░ą║ ą▓čŗčģąŠą┤, ąĖ ą▓čüąĄ ąŠčüčéą░ą╗čīąĮčŗąĄ ą▓čŗą▓ąŠą┤čŗ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąĮą░čüčéčĆą░ąĖą▓ą░čÄčéčüčÅ ą║ą░ą║ ą▓čģąŠą┤čŗ, ą║ąŠą│ą┤ą░ čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ čĆą░ą▒ąŠčéą░ SPI (čüą╝. čéą░ą▒ą╗ąĖčåčā 2-8). ąöą╗čÅ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ SPI AVR ą▓ čĆąĄąČąĖą╝ąĄ slave ąĮčāąČąĮąŠ čüą▒čĆąŠčüąĖčéčī ą▓ 0 ą▒ąĖčé MSTR. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ą▒ąĖčéčŗ ą▓čŗą▒ąŠčĆą░ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ SPR0 ąĖ SPR1 ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░čÄčé ąĮąĖą║ą░ą║ąŠą│ąŠ ą▓ą╗ąĖčÅąĮąĖčÅ, ą┐ąŠč鹊ą╝čā čćč鹊 ą┐čĆąŠąĖčüčģąŠą┤ąĖčé čüąĖąĮčģčĆąŠąĮąĮčŗą╣ ąŠą▒ą╝ąĄąĮ ą┤ą░ąĮąĮčŗą╝ąĖ ą┐ąŠ čéą░ą║čéą░ą╝ master-čāčüčéčĆąŠą╣čüčéą▓ą░.

ąÆčüąĄ ą┤čĆčāą│ąĖąĄ ąĮą░čüčéčĆąŠą╣ą║ąĖ čĆąĄą│ąĖčüčéčĆą░ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ SPI (SPCR) ą▒čāą┤čāčé čéą░ą║ąĖą╝ąĖ ąČąĄ, ą║ą░ą║ ąĖ ą▓ čĆąĄąČąĖą╝ąĄ master. ąŁč鹊 ą▓ą░ąČąĮąŠ ą┤ą╗čÅ ą│ą░čĆą░ąĮčéąĖąĖ čāčüą┐ąĄčłąĮąŠą│ąŠ ąŠą▒ą╝ąĄąĮą░ ą┤ą░ąĮąĮčŗą╝ąĖ ą╝ąĄąČą┤čā ą┤ą▓čāą╝čÅ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ.

ąĀąĖčü. 2-8. Slave, čĆą░ą▒ąŠčéą░čÄčēąĖą╣ ą┐ąŠ ąŠą┐čĆąŠčüčā - ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ ąĖ ą┐čĆąĖąĄą╝.

2.9.2. ą¤čĆąĖą╝ąĄčĆ 2 - ąŠą▒ą╝ąĄąĮ č湥čĆąĄąĘ SPI ą┐ąŠą┤ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣

ą×ą▒ą╝ąĄąĮ ą┤ą░ąĮąĮčŗą╝ąĖ ą┐ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅą╝ ą▓ čĆąĄąČąĖą╝ąĄ master ąĖą╝ąĄąĄčé čüą╝čŗčüą╗ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī, č鹊ą╗čīą║ąŠ ąĄčüą╗ąĖ ą│ąĄąĮąĄčĆąĖčĆčāąĄą╝ą░čÅ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ SCK ą┐ąŠą╗čāčćą░ąĄčéčüčÅ ą▒ąŠą╗čīčłąĖą╝ ą┤ąĄą╗ąĖč鹥ą╗ąĄą╝ čüąĖčüč鹥ą╝ąĮąŠą╣ čćą░čüč鹊čéčŗ (ąĮą░ą┐ąŠą┤ąŠą▒ąĖąĄ 64 ąĖą╗ąĖ 128). ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ą┐čĆąŠčåąĄčüčüąŠčĆ ą╝ąŠąČąĄčé ą┤ąĄą╗ą░čéčī čćč鹊-č鹊 ąĄčēąĄ, ą▓ą╝ąĄčüč鹊 č鹊ą│ąŠ čćč鹊ą▒čŗ čéčāą┐ąŠ ąČą┤ą░čéčī ą╝ąŠą╝ąĄąĮčéą░, ą║ąŠą│ą┤ą░ ą╝ąŠąČąĮąŠ ą┐ąĄčĆąĄą┤ą░čéčī/ą┐čĆąĖąĮčÅčéčī ąŠč湥čĆąĄą┤ąĮąŠą╣ ą▒ą░ą╣čé (čüąŠą▒čüčéą▓ąĄąĮąĮąŠ ą▓ čŹč鹊ą╝ ąĖ ąĘą░ą║ą╗čÄčćą░ąĄčéčüčÅ ą┤ąŠčüč鹊ąĖąĮčüčéą▓ąŠ ą╝ąĄč鹊ą┤ą░ čĆą░ą▒ąŠčéčŗ ą┐ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅą╝). ąÆ čĆąĄąČąĖą╝ąĄ slave, ą║ąŠą│ą┤ą░ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮąĄ ąĘąĮą░ąĄčé, ą║ąŠą│ą┤ą░ ąĖą╝ąĄąĮąĮąŠ ąĮą░čćąĮąĄčéčüčÅ ą┐ąĄčĆąĄą┤ą░čćą░, ą▓ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ ą┐ąŠą┤ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą┐ąŠąĮąĖąČąĄąĮąĖąĄ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ SPI čéčĆąĄą▒čāąĄčéčüčÅ ą┤ą╗čÅ č鹊ą│ąŠ, čćč鹊ą▒čŗ čāčüą┐ąĄčéčī čüčĆąĄą░ą│ąĖčĆąŠą▓ą░čéčī ąĮą░ ąĮą░čćą░ą╗ąŠ ą┐ąĄčĆąĄą┤ą░čćąĖ, ąĖ ąĖąĘą▒ąĄąČą░čéčī ąŠčłąĖą▒ąŠą║ ą║ąŠą╗ą╗ąĖąĘąĖą╣ ąĘą░ą┐ąĖčüąĖ.

2.9.2.1. ąØą░ čüč鹊čĆąŠąĮąĄ Master:

ąśąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ SPI ą┐čĆąŠąĖčüčģąŠą┤ąĖčé č鹊čćąĮąŠ čéą░ą║ ąČąĄ, ą║ą░ą║ ąĖ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ master ą▓ ą┐ąĄčĆą▓ąŠą╝ ą┐čĆąĖą╝ąĄčĆąĄ. ąÜą░ą║ ąĖ čĆą░ąĮčīčłąĄ, ą▓ čĆąĄąČąĖą╝ąĄ master čüąĮą░čćą░ą╗ą░ ąĮą░čüčéčĆą░ąĖą▓ą░ąĄčéčüčÅ ą▓čŗą▓ąŠą┤ ~SS ą║ą░ą║ ą▓čŗčģąŠą┤, ąĖ č鹊ą╗čīą║ąŠ ą┐ąŠč鹊ą╝ ą╝ąŠąČąĮąŠ čĆą░ąĘčĆąĄčłąĖčéčī čĆą░ą▒ąŠčéčā SPI. ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ SPI čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ SPIE ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPCR.

ąĀąĖčü. 2-9. Master, čĆą░ą▒ąŠčéą░čÄčēąĖą╣ ą┐ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅą╝ - ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ ąĖ ą┐ąĄčĆąĄą┤ą░čćą░.

2.9.2.2. ąØą░ čüč鹊čĆąŠąĮąĄ Slave:

ąŻčüčéčĆąŠą╣čüčéą▓ąŠ slave ąĮąĄ ąĘąĮą░ąĄčé, ą║ąŠą│ą┤ą░ master ąĘą░ą┐čāčüčéąĖčé ąĮąŠą▓čŗą╣ ąŠą▒ą╝ąĄąĮ ą┤ą░ąĮąĮčŗą╝ąĖ. ą¤čĆąĄčĆčŗą▓ą░ąĮąĖčÅ - ąŠčéą╗ąĖčćąĮą░čÅ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī čĆąĄą░ą│ąĖčĆąŠą▓ą░čéčī ąĮą░ čüąŠą▒čŗčéąĖčÅ, ą║ąŠą│ą┤ą░ ąĘą░čĆą░ąĮąĄąĄ ąĮąĄ ąĖąĘą▓ąĄčüčéąĮąŠ, ą║ąŠą│ą┤ą░ ąŠąĮąĖ ą┐čĆąŠąĖąĘąŠą╣ą┤čāčé, ąĖ ąĖą╝ąĄąĮąĮąŠ čéą░ą║ąĖą╝ čüą┐ąŠčüąŠą▒ąŠą╝ čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮą░ čĆą░ą▒ąŠčéą░ SPI ą▓ čĆąĄąČąĖą╝ąĄ slave.

ąÆ čŹč鹊ą╝ ą┐čĆąĖą╝ąĄčĆąĄ ąŠčüąĮąŠą▓ąĮą░čÅ ą┐čĆąŠą│čĆą░ą╝ą╝ą░ (č鹥ą╗ąŠ čäčāąĮą║čåąĖąĖ main) ąĘą░ąĮąĖą╝ą░ąĄčéčüčÅ ąŠą┐ąŠą▓ąĄčēąĄąĮąĖčÅą╝ąĖ ąŠą▒ ąŠčłąĖą▒ą║ą░čģ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖ čüąŠą▒čŗčéąĖčÅčģ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ.

ąĀąĖčü. 2-10. Slave, čĆą░ą▒ąŠčéą░čÄčēąĖą╣ ą┐ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅą╝ - ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ ąĖ ą┐čĆąĖąĄą╝.

[ąśčüčģąŠą┤ąĮčŗą╣ ą║ąŠą┤ ą┐čĆąĖą╝ąĄčĆąŠą▓]

Atmel ą┐čĆąĄą┤ąŠčüčéą░ą▓ąĖą╗ą░ ą┤ą╗čÅ ą░ą┐ąĮąŠčāčéą░ AVR151 ą┐čĆąĖą╝ąĄčĆčŗ ąĖčüčģąŠą┤ąĮąŠą│ąŠ ą║ąŠą┤ą░ ą┤ą╗čÅ IAR. ąśčüčģąŠą┤ąĮčŗą╣ ą║ąŠą┤ ą┐čĆąĖą╝ąĄčĆąŠą▓ ą╝ąŠąČąĮąŠ čüą║ą░čćą░čéčī čü čüą░ą╣čéą░ Atmel, ą╗ąĖą▒ąŠ ą┐ąŠ čüčüčŗą╗ą║ąĄ [3] (čü ą║ąŠą╝ą╝ąĄąĮčéą░čĆąĖčÅą╝ąĖ ą▓ ą║ąŠą┤ąĄ, ą┐ąĄčĆąĄą▓ąĄą┤ąĄąĮąĮčŗą╝ąĖ ąĮą░ čĆčāčüčüą║ąĖą╣ čÅąĘčŗą║).

//***************************************************************************

// A P P L I C A T I O N N O T E F O R T H E A V R F A M I L Y

//

// Number : AVR151

// File Name : "avr151_Master.c"

// Title : ąØą░čüčéčĆąŠą╣ą║ą░ ąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ SPI

// Date : 00.09.20

// Version : 1.0

// Target MCU : ąøčÄą▒ąŠą╣ AVR, ąĖą╝ąĄčÄčēąĖą╣ ąĮą░ ą▒ąŠčĆčéčā SPI

//

// ą×ą¤ąśąĪąÉąØąśąĢ

// ąŁč鹊čé ą░ą┐ąĮąŠčāčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, ą║ą░ą║ čĆą░ąĘčĆąĄčłąĖčéčī ąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ ą▓ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ

// ą░ą┐ą┐ą░čĆą░čéąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü SPI ą▓ čĆąĄąČąĖą╝ąĄ Master.

//

// ąŁč鹊čé čäą░ą╣ą╗ čüąŠą┤ąĄčƹȹĖčé ą║ąŠą┤ ą▓čüąĄčģ ą┐čĆąĖą╝ąĄčĆąŠą▓. ąöą╗čÅ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ ą╝ąĄąČą┤čā ą┐čĆąĖą╝ąĄčĆą░ą╝ąĖ ąÆą░ą╝

// ąĮčāąČąĮąŠ ą▒čāą┤ąĄčé ą▓čŗąĘčŗą▓ą░čéčī čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝čŗ (čüą╝. ąĮąĖąČąĄ ą║ąŠą╝ą╝ąĄąĮčéą░čĆąĖąĖ ą▓ ąŠčüąĮąŠą▓ąĮąŠą╣

// ą┐čĆąŠą│čĆą░ą╝ą╝ąĄ, čé. ąĄ. ą▓ čäčāąĮą║čåąĖąĖ main).

//

// Modified 2004-10-25 RAA

//**************************************************************************

#include "inavr.h"

#include "ioavr.h"

char* TextString = "AVR communicating via the SPI"+0x00;

char* PtrToStrChar; // ąŻą║ą░ąĘą░č鹥ą╗čī ąĮą░ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗą╣ čüąĖą╝ą▓ąŠą╗ ą▓ čüčéčĆąŠą║ąĄ

char ClearToSend = 1; // ążą╗ą░ą│ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ąŠčéą┐čĆą░ą▓ą║ąĖ čüčéčĆąŠą║ąĖ.

// ą×ą▒čĆą░ą▒ąŠčéčćąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čĆąĄąČąĖą╝ą░ Master (ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąŠč鹊ą║ąŠą╝ ą┐ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅą╝)

#pragma vector=SPI_STC_vect

__interrupt void ISR_SPI (void)

{

PtrToStrChar++; // ąŻą║ą░ąĘą░čéčī ąĮą░ čüą╗ąĄą┤čāčÄčēąĖą╣ čüąĖą╝ą▓ąŠą╗ ą▓ čüčéčĆąŠą║ąĄ,

if (*PtrToStrChar != 0) // ąĄčüą╗ąĖ čŹč鹊 ąĄčēąĄ ąĮąĄ ą║ąŠąĮąĄčå čüčéčĆąŠą║ąĖ.

{

SPDR = *PtrToStrChar; // ą×čéą┐čĆą░ą▓ąĖčéčī čüąĖą╝ą▓ąŠą╗ č湥čĆąĄąĘ SPI.

}

else

{

ClearToSend = 1; // ąĢčüą╗ąĖ ą┤ąŠčłą╗ąĖ ą┤ąŠ ą║ąŠąĮčåą░ čüčéčĆąŠą║ąĖ, čĆą░ąĘčĆąĄčłąĖčéčī

// ąŠčéą┐čĆą░ą▓ą║čā čüą╗ąĄą┤čāčÄčēąĄą╣ čüčéčĆąŠą║ąĖ.

}

// ą¤ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ čĆąĄąČąĖą╝ą░ Master čü čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝ ą┐ąŠč鹊ą║ąŠą╝ ą┐ąŠ ąŠą┐čĆąŠčüčā.

void Init_Master (void)

{

volatile char IOReg;

// ąØą░čüčéčĆąŠąĖčéčī PB4(/SS), PB5(MOSI), PB7(SCK) ą║ą░ą║ ą▓čŗčģąŠą┤čŗ:

DDRB = (1 << PB4)|(1 << PB5)|(1 << PB7);

// ąĀą░ąĘčĆąĄčłąĖčéčī SPI ą▓ čĆąĄąČąĖą╝ąĄ Master Mode čü čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊č鹊ą╣ SCK = CK/4:

SPCR = (1 << SPE)|(1 << MSTR);

IOReg = SPSR; // ąŠčćąĖčüčéąĖčéčī ą▒ąĖčé SPIF ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPSR

IOReg = SPDR;

}

// ą¤ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ čĆąĄąČąĖą╝ą░ Master čü čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝ ą┐ąŠč鹊ą║ąŠą╝ ą┐ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅą╝.

void Init_Master_IntContr (void)

{

volatile char IOReg;

// ąØą░čüčéčĆąŠąĖčéčī PB4(/SS), PB5(MOSI), PB7(SCK) ą║ą░ą║ ą▓čŗčģąŠą┤čŗ:

DDRB = (1 << PB4)|(1 << PB5)|(1 << PB7);

// ąĀą░ąĘčĆąĄčłąĖčéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ SPI ąĖ čĆąĄąČąĖą╝ SPI Master čü čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊č鹊ą╣ SCK = CK/16:

SPCR = (1 << SPIE)|(1 << SPE)|(1 << MSTR)|(1 << SPR0);

IOReg = SPSR; // ą×čćąĖčüčéąĖčéčī ą▒ąĖčé SPIF ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPSR.

IOReg = SPDR;

__enable_interrupt(); // ąōą╗ąŠą▒ą░ą╗čīąĮąŠ čĆą░ąĘčĆąĄčłąĖčéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

}

// ą¤ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ąŠčéą┐čĆą░ą▓ą║ąĖ čĆąĄąČąĖą╝ą░ Master (ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ ą┐ąŠ ąŠą┐čĆąŠčüčā)

void Master_Send (void)

{

PtrToStrChar = TextString; // ąŻčüčéą░ąĮąŠą▓ąĖčéčī čāą║ą░ąĘą░č鹥ą╗čī ąĮą░ ąĮą░čćą░ą╗ąŠ čüčéčĆąŠą║ąĖ.

while (*PtrToStrChar != 0) // ą”ąĖą║ą╗ "ąĄčüą╗ąĖ ąĮąĄ ą║ąŠąĮąĄčå čüčéčĆąŠą║ąĖ", č鹊 ..

{

SPDR = *PtrToStrChar; // .. ąŠčéą┐čĆą░ą▓ąĖčéčī čüąĖą╝ą▓ąŠą╗ č湥čĆąĄąĘ SPI,

while (!(SPSR & (1 << SPIF))); // ąČą┤ą░čéčī ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ąŠčéą┐čĆą░ą▓ą║ąĖ čüąĖą╝ą▓ąŠą╗ą░,

PtrToStrChar++; // ą┐ąĄčĆąĄą╣čéąĖ ą║ čüą╗ąĄą┤čāčÄčēąĄą╝čā čüąĖą╝ą▓ąŠą╗čā ą▓ čüčéčĆąŠą║ąĄ.

}

}

// ą¤ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ąŠčéą┐čĆą░ą▓ą║ąĖ čĆąĄąČąĖą╝ą░ Master (ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ ą┐ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅą╝)

void Master_Send_IntContr (void)

{

if (ClearToSend == 1) // ąĢčüą╗ąĖ ą┐ąĄčĆąĄą┤ą░čćą░ ąĮąĄ ąĖą┤ąĄčé, č鹊 ..

{

PtrToStrChar = TextString; // .. čāčüčéą░ąĮąŠą▓ąĖčéčī čāą║ą░ąĘą░č鹥ą╗čī ąĮą░ ąĮą░čćą░ą╗ąŠ čüčéčĆąŠą║ąĖ,

// ąĘą░ą┐čāčüčéąĖčéčī ąĮąŠą▓čāčÄ ą┐ąĄčĆąĄą┤ą░čćčā ą┐čāč鹥ą╝ ąŠčéą┐čĆą░ą▓ą║ąĖ

SPDR = *PtrToStrChar; // ą┐ąĄčĆą▓ąŠą│ąŠ čüąĖą╝ą▓ąŠą╗ą░ ąĮąŠą▓ąŠą╣ čüčéčĆąŠą║ąĖ,

ClearToSend = 0; // ąĘą░ą▒ą╗ąŠą║ąĖčĆąŠą▓ą░čéčī ąĖąĮąĖčåąĖą░čåąĖčÄ ąĮąŠą▓čŗčģ ą┐ąĄčĆąĄą┤ą░čć.

}

}

void main (void)

{

char KeyPressed = false;

DDRD = 0xFF;

PORTD = 0x00;

// ąöą╗čÅ ą¤čĆąĖą╝ąĄčĆą░ 1 čĆą░čüą║ąŠą╝ą╝ąĄąĮčéąĖčĆčāą╣č鹥 čüą╗ąĄą┤čāčÄčēčāčÄ čüčéčĆąŠą║čā:

Init_Master (); // ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ ą┐ąŠ ąŠą┐čĆąŠčüčā

// ąöą╗čÅ ą¤čĆąĖą╝ąĄčĆą░ 2 čĆą░čüą║ąŠą╝ą╝ąĄąĮčéąĖčĆčāą╣č鹥 čüą╗ąĄą┤čāčÄčēčāčÄ čüčéčĆąŠą║čā:

// Init_Master_IntContr(); // ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ ą┐ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅą╝

while (1)

{

if (PINA != 0xFF)

{

if (KeyPressed == false)

{

KeyPressed = true;

PORTD = ~PORTD; // ą¤ąĄčĆąĄą║ą╗čÄčćąĖčéčī ą▓ ą┐čĆąŠčéąĖą▓ąŠą┐ąŠą╗ąŠąČąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ ą▓čŗčģąŠą┤čŗ

// ą┐ąŠčĆčéą░ D (čéčāą┤ą░ ą┐ąŠą┤ą║ą╗čÄč湥ąĮčŗ čüą▓ąĄč鹊ą┤ąĖąŠą┤čŗ).

// ąöą╗čÅ ą¤čĆąĖą╝ąĄčĆą░ 1 čĆą░čüą║ąŠą╝ą╝ąĄąĮčéąĖčĆčāą╣č鹥 čüą╗ąĄą┤čāčÄčēčāčÄ čüčéčĆąŠą║čā:

Master_Send ();

// ąöą╗čÅ ą¤čĆąĖą╝ąĄčĆą░ 2 čĆą░čüą║ąŠą╝ą╝ąĄąĮčéąĖčĆčāą╣č鹥 čüą╗ąĄą┤čāčÄčēčāčÄ čüčéčĆąŠą║čā:

// Master_Send_IntContr();

}

}

else

KeyPressed = false;

}

}

//***************************************************************************

// A P P L I C A T I O N N O T E F O R T H E A V R F A M I L Y

//

// Number : AVR151

// File Name : "avr151_Master.c"

// Title : ąØą░čüčéčĆąŠą╣ą║ą░ ąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ SPI

// Date : 00.09.20

// Version : 1.0

// Target MCU : ąøčÄą▒ąŠą╣ AVR, ąĖą╝ąĄčÄčēąĖą╣ ąĮą░ ą▒ąŠčĆčéčā SPI

//

// ą×ą¤ąśąĪąÉąØąśąĢ

// ąŁč鹊čé ą░ą┐ąĮąŠčāčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, ą║ą░ą║ čĆą░ąĘčĆąĄčłąĖčéčī ąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ ą▓ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ

// ą░ą┐ą┐ą░čĆą░čéąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü SPI ą▓ čĆąĄąČąĖą╝ąĄ Slave.

//

// ąŁč鹊čé čäą░ą╣ą╗ čüąŠą┤ąĄčƹȹĖčé ą║ąŠą┤ ą▓čüąĄčģ ą┐čĆąĖą╝ąĄčĆąŠą▓. ąöą╗čÅ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ ą╝ąĄąČą┤čā ą┐čĆąĖą╝ąĄčĆą░ą╝ąĖ ąÆą░ą╝

// ąĮčāąČąĮąŠ ą▒čāą┤ąĄčé ą▓čŗąĘčŗą▓ą░čéčī čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝čŗ (čüą╝. ąĮąĖąČąĄ ą║ąŠą╝ą╝ąĄąĮčéą░čĆąĖąĖ ą▓ ąŠčüąĮąŠą▓ąĮąŠą╣

// ą┐čĆąŠą│čĆą░ą╝ą╝ąĄ, čé. ąĄ. ą▓ čäčāąĮą║čåąĖąĖ main).

//

// Modified 2004-10-25 RAA

//**************************************************************************

#include "inavr.h"

#include "ioavr.h"

#define Error 0x01

#define Success 0x02

char TransmitState = 0x00;

char* TextString = "AVR communicating via the SPI"+0x00;

// ą×ą▒čĆą░ą▒ąŠčéčćąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čĆąĄąČąĖą╝ą░ Slave (ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąŠč鹊ą║ąŠą╝ ą┐ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅą╝)

#pragma vector=SPI_STC_vect

__interrupt void ISR_SPI (void)

{

if (SPDR != *TextString) // ą¤čĆąŠą▓ąĄčĆą║ą░ ąĮą░ ąŠčłąĖą▒ą║ąĖ ą┐čĆąĖ ą┐ąĄčĆąĄą┤ą░č湥

{

TransmitState = Error; // ą×čłąĖą▒ą║ą░!

SPCR &= ~(1 << SPIE); // ąŚą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ SPI.

}

else

{

TextString++; // ą¤ąĄčĆąĄą╣čéąĖ ą║ čüą╗ąĄą┤čāčÄčēąĄą╝čā čüąĖą╝ą▓ąŠą╗čā,

if (*TextString == 0) // ą┐čĆąŠą▓ąĄčĆąĖčéčī ąĮą░ ą║ąŠąĮąĄčå čüčéčĆąŠą║ąĖ

{

TransmitState = Success; // ą¤čĆąĖąĄą╝ čüčéčĆąŠą║ąĖ čāčüą┐ąĄčłąĮąŠ ąĘą░ą▓ąĄčĆčłąĄąĮ.

SPCR &= ~(1 << SPIE); // ąŚą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ SPI.

}

}

}

// ą¤ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ čĆąĄąČąĖą╝ą░ Slave čü čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝ ą┐ąŠč鹊ą║ąŠą╝ ą┐ąŠ ąŠą┐čĆąŠčüčā.

void Init_Slave (void)

{

volatile char IOReg;

// ąØą░čüčéčĆąŠą╣ą║ą░ PB6(MISO) ą║ą░ą║ ą▓čŗčģąŠą┤ą░:

DDRB = (1 << PB6);

// ąĀą░ąĘčĆąĄčłąĖčéčī SPI ą▓ čĆąĄąČąĖą╝ąĄ Slave čü čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊č鹊ą╣ SCK = CK/4:

SPCR = (1 << SPE);

IOReg = SPSR; // ą×čćąĖčüčéąĖčéčī ą▒ąĖčé SPIF ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPSR.

IOReg = SPDR;

DDRD = 0xFF; // ąØą░čüčéčĆąŠąĖčéčī čĆą░ąĘčĆčÅą┤čŗ ą┐ąŠčĆčéą░ D ą║ą░ą║ ą▓čŗčģąŠą┤čŗ.

}

// ą¤ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ čĆąĄąČąĖą╝ą░ Slave čü čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝ ą┐ąŠč鹊ą║ąŠą╝ ą┐ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅą╝.

void Init_Slave_IntContr (void)

{

volatile char IOReg;

// ąØą░čüčéčĆąŠą╣ą║ą░ PB6(MISO) ą║ą░ą║ ą▓čŗčģąŠą┤ą░:

DDRB = (1 << PB6);

// ąĀą░ąĘčĆąĄčłąĖčéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ SPI ąĖ čĆą░ąĘčĆąĄčłąĖčéčī SPI ą▓ čĆąĄąČąĖą╝ąĄ Slave čü čéą░ą║č鹊ą▓ąŠą╣

// čćą░čüč鹊č鹊ą╣ SCK = CK/4:

SPCR = (1 << SPIE)|(1 << SPE);

IOReg = SPSR; // ą×čćąĖčüčéąĖčéčī ą▒ąĖčé SPIF ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPSR.

IOReg = SPDR;

DDRD = 0xFF; // ąØą░čüčéčĆąŠąĖčéčī čĆą░ąĘčĆčÅą┤čŗ ą┐ąŠčĆčéą░ D ą║ą░ą║ ą▓čŗčģąŠą┤čŗ.

__enable_interrupt(); // ąōą╗ąŠą▒ą░ą╗čīąĮąŠ čĆą░ąĘčĆąĄčłąĖčéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

}

// ą¤ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┐čĆąĖąĄą╝ą░ ą▓ čĆąĄąČąĖą╝ąĄ Slave (čü čĆą░ą▒ąŠč鹊ą╣ ą┐ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅą╝)

void Slave_Receive_IntContr (void)

{

while (1)

{

switch (TransmitState)

{// ąśąĮą┤ąĖą║ą░čåąĖčÅ ąŠčłąĖą▒ą║ąĖ ąĖą╗ąĖ čāčüą┐ąĄčłąĮąŠą│ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐čĆąĖąĄą╝ą░ čüą▓ąĄč鹊ą┤ąĖąŠą┤ą░ą╝ąĖ,

// ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗą╝ąĖ ą║ ą┐ąŠčĆčéčā D:

case 0x00:

PORTD = 0x00;

break;

case Error:

PORTD = 0xF0;

break;

case Success:

PORTD = 0xAA;

break;

}

}

}

// ą¤ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┐čĆąĖąĄą╝ą░ ą▓ čĆąĄąČąĖą╝ąĄ Slave (čü čĆą░ą▒ąŠč鹊ą╣ ą┐ąŠ ąŠą┐čĆąŠčüčā)

void Slave_Receive (void)

{

// ą”ąĖą║ą╗, ą┐ąŠą║ą░ ąĮąĄ ą┤ąŠą╣ą┤ąĄą╝ ą┤ąŠ ą║ąŠąĮčåą░ čüčéčĆąŠą║ąĖ, ąĖą╗ąĖ ąĮąĄ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ąŠčłąĖą▒ą║ą░:

while ((*TextString != 0) && (TransmitState != Error))

{

while (!(SPSR & (1 << SPIF))); // ą×ąČąĖą┤ą░ąĮąĖąĄ ą╝ąŠą╝ąĄąĮčéą░ ą┐čĆąĖąĄą╝ą░ čüąĖą╝ą▓ąŠą╗ą░.

// ą¤čĆąŠą▓ąĄčĆą║ą░: ą┐čĆą░ą▓ąĖą╗čīąĮąŠ ą╗ąĖ ą┐čĆąĖąĮčÅčé čüąĖą╝ą▓ąŠą╗:

if (SPDR != *TextString)

TransmitState = Error;

else

TextString++; // ą¤ąĄčĆąĄą╣čéąĖ ą║ čüą╗ąĄą┤čāčÄčēąĄą╝čā čüąĖą╝ą▓ąŠą╗čā

// output result transmission status on Port D

if (TransmitState == Error)

PORTD = 0xF0;

else

PORTD = 0xAA;

while (1);

}

void main (void)

{

// ąöą╗čÅ ą¤čĆąĖą╝ąĄčĆą░ 1 čĆą░čüą║ąŠą╝ą╝ąĄąĮčéąĖčĆčāą╣č鹥 čüą╗ąĄą┤čāčÄčēąĖąĄ ą┤ą▓ąĄ čüčéčĆąŠą║ąĖ:

Init_Slave();

Slave_Receive();

// ąöą╗čÅ ą¤čĆąĖą╝ąĄčĆą░ 2 čĆą░čüą║ąŠą╝ą╝ąĄąĮčéąĖčĆčāą╣č鹥 čüą╗ąĄą┤čāčÄčēąĖąĄ ą┤ą▓ąĄ čüčéčĆąŠą║ąĖ:

// Init_Slave_IntContr();

// Slave_Receive_IntContr();

}

[ąĪčüčŗą╗ą║ąĖ]

1. AVR151: Setup And Use of The SPI site:atmel.com.

2. ąśąĮč鹥čĆč乥ą╣čü SPI.

3. 150219AVR-apnouts.zip - ą░čĆčģąĖą▓ čü ą░ą┐ąĮąŠčāčéą░ą╝ąĖ ąĖ ąĖčüčģąŠą┤ąĮčŗą╝ ą║ąŠą┤ąŠą╝.

4. ATmega328: SPI. |

ąÜąŠą╝ą╝ąĄąĮčéą░čĆąĖąĖ

ą¦ą░čüč鹊čéą░ ą║ą▓ą░čĆčåą░ 14.7456 ą£ąōčå, ą╝ąĖą║čĆčāčģą░ ą┐ą░ą╝čÅčéąĖ ą┐ąŠ ą┤ą░čéą░čłąĖčéčā ą┤ąĄčƹȹĖčé ą┤ąŠ 20 ą£ąōčå. ąóąŠ ąĄčüčéčī čćč鹊 ą▒čŗ čĆą░ą▒ąŠčéą░čéčī ąĮą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĮčāąČąĮąŠ ą┐čĆąĖąĮčāą┤ąĖč鹥ą╗čīąĮąŠ ąĖ ąŠčüąĮąŠą▓ą░č鹥ą╗čīąĮąŠ ąĘą░ąĮąĖąČą░čéčī čćą░čüč鹊čéčā čłąĖąĮčŗ?

microsin: ąĘą░ąĮąĖąČą░čéčī čéą░ą║č鹊ą▓čāčÄ čćą░čüč鹊čéčā master SCK ą▓ čüą╗čāčćą░ąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą┤ą╗čÅ ąŠą▒ą╝ąĄąĮą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą╝ąŠąČąĄčé ą┐ąŠąĮą░ą┤ąŠą▒ąĖčéčīčüčÅ č鹊ą╗čīą║ąŠ ą▓ č鹊ą╝ čüą╗čāčćą░ąĄ, ąĄčüą╗ąĖ ąĮčāąČąĮčŗ ąĖąĮč鹥ąĮčüąĖą▓ąĮčŗąĄ ą▓čŗčćąĖčüą╗ąĄąĮąĖčÅ ąĮą░ č乊ąĮąĄ ą┤ą╗ąĖč鹥ą╗čīąĮąŠą│ąŠ ąĖąĮč鹥ąĮčüąĖą▓ąĮąŠą│ąŠ ąŠą▒ą╝ąĄąĮą░ č湥čĆąĄąĘ SPI. ą¤ąŠąĮčÅčéąĮąŠ ą┐ąŠč湥ą╝čā - ą┐čĆąĖ ą▓čŗčüąŠą║ąŠą╣ čćą░čüč鹊č鹥 ąŠą▒ą╝ąĄąĮą░ ą┐čĆąŠčåąĄčüčüąŠčĆ ą▒čāą┤ąĄčé ą▓čŗąĮčāąČą┤ąĄąĮ ą┐ąŠčćčéąĖ ą▓čüąĄ ą▓čĆąĄą╝čÅ ąĮą░čģąŠą┤ąĖčéčīčüčÅ ą▓ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ SPI, ąĖ ąĮą░ ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐ąŠč鹊ą║ ą▓čŗčćąĖčüą╗ąĄąĮąĖą╣ ą▓čĆąĄą╝ąĄąĮąĖ ąĮąĄ ąŠčüčéą░ąĮąĄčéčüčÅ.

ą» ą┐čĆą░ą▓ąĖą╗čīąĮąŠ ą┐ąŠąĮčÅą╗, ą┤ą╗čÅ ą║ąŠčĆčĆąĄą║čéąĮąŠą╣ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ čĆą░ą▒ąŠčéčŗ čü ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ slave čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ ąČąĄą╗ą░č鹥ą╗čīąĮąŠ ą┐čĆąĖą╝ąĄąĮčÅčéčī č鹊čé ąĖą╗ąĖ ąĖąĮąŠą╣ ą┤ąĄą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąŠčĆ ąĖąĘ 74 ą╗ąŠą│ąĖą║ąĖ, ą│ą┤ąĄ čāą┐čĆą░ą▓ą╗čÅąĄą╝čŗą╣ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ SPI čüąĖą│ąĮą░ą╗ ~SS ą┐ąŠą┤ą░ąĄčéčüčÅ ąĮą░ ą▓čģąŠą┤, ą░ ą▓čŗą▒ąŠčĆ "ą║ą╗ąĖąĄąĮčéą░" ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ąĮąŠą│ą░ą╝ąĖ?

microsin: ą▓čŗ ą▓čüąĄ ą┐ąŠąĮčÅą╗ąĖ ą┐čĆą░ą▓ąĖą╗čīąĮąŠ, ąĮąŠ ą╝ąĮąĄ ąŠč湥ąĮčī čüą╗ąŠąČąĮąŠ ą┐čĆąĖą┤čāą╝ą░čéčī čüąĖčéčāą░čåąĖčÄ, ą║ąŠą│ą┤ą░ čéą░ą║ąŠą╣ ą┤ąĄą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąŠčĆ (ą┤ąĄčłąĖčäčĆą░č鹊čĆ) ą╝ąŠąČąĄčé ą┐ąŠąĮą░ą┤ąŠą▒ąĖčéčīčüčÅ. ą×ą▒čŗčćąĮąŠ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ąĮą░ čłąĖąĮąĄ SPI ąĮąĄą╝ąĮąŠą│ąŠ, ąĖ ąĮąĖą║ą░ą║ąŠą╣ ą┤ąĄą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąŠčĆ ąĮąĄ ąĮčāąČąĄąĮ - ą▓čŗą▒ąŠčĆą║ą░ą╝ąĖ ąĮąĄą┐ąŠčüčĆąĄą┤čüčéą▓ąĄąĮąĮąŠ ą╝ąŠąČąĄčé čāą┐čĆą░ą▓ą╗čÅčéčī ą│ą╗ą░ą▓ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ čłąĖąĮčŗ, čāą┐čĆą░ą▓ą╗čÅčÄčēąĖą╣ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ .

microsin: čĆąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ SPCR, ą▒ąĖčé Bit 5 ŌĆō DORD: Data Order.

microsin: ą┤ą╗čÅ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐ąŠą┤ąŠą▒ąĮčŗčģ ą║ąŠąĮčäą╗ąĖą║č鹊ą▓ ą║ą░ą║ čĆą░ąĘ ąĖ ą┐čĆąĖą┤čāą╝ą░ąĮčŗ čüąĖą│ąĮą░ą╗čŗ ą▓čŗą▒ąŠčĆą║ąĖ ~SS. ąĢčüą╗ąĖ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ ~SS ąĮąĄ ą░ą║čéąĖą▓ąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī (ą╗ąŠą│. 1), č鹊 ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐ąĄčĆąĄą▓ąŠą┤ąĖčé čüą▓ąŠą╣ ą▓čŗčģąŠą┤ MISO ą▓ čéčĆąĄčéčīąĄ (ąŠčéą║ą╗čÄč湥ąĮąĮąŠąĄ) čüąŠčüč鹊čÅąĮąĖąĄ.

RSS ą╗ąĄąĮčéą░ ą║ąŠą╝ą╝ąĄąĮčéą░čĆąĖąĄą▓ čŹč鹊ą╣ ąĘą░ą┐ąĖčüąĖ