|

ąŚą┤ąĄčüčī ą┐čĆąĖą▓ąĄą┤ąĄąĮ ą┐ąĄčĆąĄą▓ąŠą┤ ą┤ą░čéą░čłąĖčéą░ ą┐ąŠ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčā ATmega328 (ATmega48, ATmega88, ATmega168), ą║ą░čüą░čÄčēąĖąĄčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠą│ąŠ ą▒ą╗ąŠą║ą░ ąĖąĮč鹥čĆč乥ą╣čüą░ SPI.

ą×čüąĮąŠą▓ąĮčŗąĄ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ ąĖąĮč鹥čĆč乥ą╣čüą░:

ŌĆó ą¤ąŠą╗ąĮąŠą┤čāą┐ą╗ąĄą║čüąĮą░čÅ, čéčĆąĄčģą┐čĆąŠą▓ąŠą┤ąĮą░čÅ, čüąĖąĮčģčĆąŠąĮąĮą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░ ą┤ą░ąĮąĮčŗčģ

ŌĆó ąÆąŠąĘą╝ąŠąČąĮąŠčüčéčī čĆą░ą▒ąŠčéčŗ ą▓ čĆąĄąČąĖą╝ąĄ Master ąĖą╗ąĖ Slave

ŌĆó ą¤ąĄčĆąĄą┤ą░čćą░ ą┤ą░ąĮąĮčŗčģ čü čĆą░ąĘąĮčŗą╝ ą┐ąŠčĆčÅą┤ą║ąŠą╝ čüą╗ąĄą┤ąŠą▓ą░ąĮąĖčÅ ą▒ąĖčé - čüąĮą░čćą░ą╗ą░ LSB ąĖą╗ąĖ čüąĮą░čćą░ą╗ą░ MSB

ŌĆó 7 ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗčģ čüą║ąŠčĆąŠčüč鹥ą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ

ŌĆó ążą╗ą░ą│ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, čüąĖą│ąĮą░ą╗ąĖąĘąĖčĆčāčÄčēąĖą╝ ąŠą▒ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ

ŌĆó ążą╗ą░ą│ ąĘą░čēąĖčéčŗ ąŠčé ą║ąŠą╗ą╗ąĖąĘąĖąĖ ąĘą░ą┐ąĖčüąĖ

ŌĆó ąÆąŠąĘą╝ąŠąČąĮąŠčüčéčī ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ ąĖąĘ čĆąĄąČąĖą╝ą░ čüąĮą░ (Idle Mode)

ŌĆó ąĀąĄąČąĖą╝ Master SPI čāą┤ą▓ąŠąĄąĮąĮąŠą╣ čüą║ąŠčĆąŠčüčéąĖ (CK/2)

[ą×ą┐ąĖčüą░ąĮąĖąĄ ąŠčüąĮąŠą▓ąĮčŗčģ ą▓ąŠąĘą╝ąŠąČąĮąŠčüč鹥ą╣ SPI]

ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü (Serial Peripheral Interface, SPI) ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąŠčüčāčēąĄčüčéą▓ą╗čÅčéčī ą▓čŗčüąŠą║ąŠčüą║ąŠčĆąŠčüčéąĮąŠą╣ ąŠą▒ą╝ąĄąĮ ą┤ą░ąĮąĮčŗą╝ąĖ ą╝ąĄąČą┤čā ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ą╝ąĖ ATmega48A/PA/88A/PA/168A/PA/328/P ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ, ą╗ąĖą▒ąŠ čü ą┤čĆčāą│ąĖą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ ąĮą░ ąŠčüąĮąŠą▓ąĄ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░čģ (AVR, ARM, STM32 ąĖ čé. ą┐.). ąśąĮč鹥čĆč乥ą╣čü USART ą╝ąŠąČąĄčé č鹊ąČąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ Master SPI, čüą╝. čĆą░ąĘą┤ąĄą╗ "USART ą▓ čĆąĄąČąĖą╝ąĄ SPI". ąæąĖčé PRSPI ą▓ čĆąĄą│ąĖčüčéčĆąĄ PRR (Power Reduction Register) ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮ ą▓ 0, čćč鹊ą▒čŗ ą╝ąŠą│ čĆą░ą▒ąŠčéą░čéčī ą▒ą╗ąŠą║ SPI.

ąÜą░ą║ čüą╗ąĄą┤čāąĄčé ąĖąĘ čüą▓ąŠąĄą│ąŠ ąĮą░ąĘą▓ą░ąĮąĖčÅ, čĆąĄą│ąĖčüčéčĆ PRR ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮ ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čüąĮąĖąČąĄąĮąĖąĄą╝ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ąĘą░ čüč湥čé ąŠčéą║ą╗čÄč湥ąĮąĖčÅ ąĮąĄą║ąŠč鹊čĆčŗčģ ą░ą┐ą┐ą░čĆą░čéąĮčŗčģ ą▒ą╗ąŠą║ąŠą▓ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ - TWI (I2C), Timer/Counter2, Timer/Counter0, Timer/Counter1, SPI, USART0, ADC. ą¤ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ (ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ ąĖą╗ąĖ ą▓ą║ą╗čÄč湥ąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ) ą▓čüąĄ ą▒ąĖčéčŗ ą▓ čĆąĄą│ąĖčüčéčĆąĄ PRR ąŠą▒ąĮčāą╗ąĄąĮčŗ, čćč鹊 čĆą░ąĘčĆąĄčłą░ąĄčé čĆą░ą▒ąŠčéčā ą▓čŗčłąĄą┐ąĄčĆąĄčćąĖčüą╗ąĄąĮąĮąŠą│ąŠ ąŠą▒ąŠčĆčāą┤ąŠą▓ą░ąĮąĖčÅ, ą▓ č鹊ą╝ čćąĖčüą╗ąĄ ąĖ SPI.

PRSPI: Power Reduction Serial Peripheral Interface. ąæąĖčé PRSPI ą▓ čĆąĄą│ąĖčüčéčĆąĄ PRR ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąŠčéą║ą╗čÄčćąĖčéčī ąĖąĮč鹥čĆč乥ą╣čü SPI (ąĄčüą╗ąĖ ąĘą░ą┐ąĖčüą░čéčī ą▓ čŹč鹊čé ą▒ąĖčé ą╗ąŠą│. 1) ąĖ č鹥ą╝ čüą░ą╝čŗą╝ čüąĮąĖąĘąĖčéčī ąŠą▒čēąĄąĄ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ. ąĢčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ ą░ą┐ą┐ą░čĆą░čéąĮčŗą╣ čĆąĄąČąĖą╝ ąŠčéą╗ą░ą┤ą║ąĖ (debugWIRE On-chip Debug System), čŹč鹊čé ą▒ąĖčé ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮ ą▓ ą╗ąŠą│. 1. ąŚą░ą┐ąĖčüčī ą▓ ą╗ąŠą│. 1 čŹč鹊ą│ąŠ ą▒ąĖčéą░ ą▓čŗą║ą╗čÄčćą░ąĄčé SPI ą┐čāč鹥ą╝ ąŠčüčéą░ąĮąŠą▓ą║ąĖ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ čŹč鹊ą│ąŠ ą╝ąŠą┤čāą╗čÅ. ąÜąŠą│ą┤ą░ SPI čüąĮąŠą▓ą░ ą▓čŗą╣ą┤ąĄčé ąĖąĘ čüąĮą░, ąŠąĮ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ąĮąŠą▓ąŠ ą┐ąĄčĆąĄąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆąŠą▓ą░ąĮ, čćč鹊ą▒čŗ ąŠą▒ąĄčüą┐ąĄčćąĖčéčī čüą▓ąŠąĄ ą║ąŠčĆčĆąĄą║čéąĮąŠąĄ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĄ.

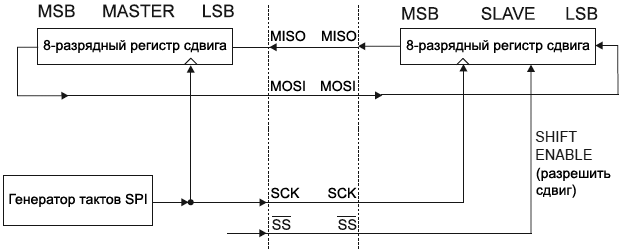

ąØąĖąČąĄ ą┐ąŠą║ą░ąĘą░ąĮą░ ą┤ąĖą░ą│čĆą░ą╝ą╝ą░ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ą▒ą╗ąŠą║ą░ SPI.

ąĀąĖčü. 19-1. ąæą╗ąŠą║-ą┤ąĖą░ą│čĆą░ą╝ą╝ą░ SPI.

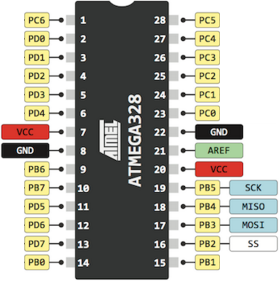

ąĀąĖčü. 19-1a. ąĀą░čüą┐ąŠą╗ąŠąČąĄąĮąĖąĄ (čåąŠą║ąŠą╗ąĄą▓ą║ą░) ą▓čŗą▓ąŠą┤ąŠą▓ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ATmega328P, ąĘą░ą┤ąĄą╣čüčéą▓ąŠą▓ą░ąĮąĮčŗčģ ą┐ąŠą┤ čäčāąĮą║čåąĖčÄ SPI (SCK, MISO, MOSI, ~SS) ą┤ą╗čÅ ą║ąŠčĆą┐čāčüą░ DIP28.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: čåąŠą║ąŠą╗ąĄą▓ą║čā ą▓čŗą▓ąŠą┤ąŠą▓ SPI ą┤ą╗čÅ ą┤čĆčāą│ąĖčģ ą║ąŠčĆą┐čāčüąŠą▓ ąĖ ą┤čĆčāą│ąĖčģ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ AVR čüą╝. ą┤ą░čéą░čłąĖčé ąĮą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ. ąöą╗čÅ ATmega328 čüą╝. [4].

ąÜą░ą║ čüąŠąĄą┤ąĖąĮčÅčÄčéčüčÅ ą┤čĆčāą│ čü ą┤čĆčāą│ąŠą╝ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┐čĆąŠčåąĄčüčüąŠčĆčŗ ą▓ čĆąĄąČąĖą╝ą░čģ Master ąĖ Slave, ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 19-2. ąĪąĖčüč鹥ą╝ą░ čüąŠčüč鹊ąĖčé ąĖčģ 2 čĆąĄą│ąĖčüčéčĆąŠą▓ čüą┤ą▓ąĖą│ą░, ąĖ ą│ąĄąĮąĄčĆą░č鹊čĆą░ čéą░ą║č鹊ą▓ ąĖąĮč鹥čĆč乥ą╣čüą░, čĆą░ą▒ąŠčéą░čÄčēąĄą│ąŠ ąĮą░ čüč鹊čĆąŠąĮąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ Master. SPI Master ąĖąĮąĖčåąĖąĖčĆčāąĄčé čåąĖą║ą╗ ąŠą▒ą╝ąĄąĮą░, ą║ąŠą│ą┤ą░ ą┐ąĄčĆąĄą▓ąŠą┤ąĖčé ą▓čŗą▓ąŠą┤ ą▓čŗą▒ąŠčĆą║ąĖ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (Slave Select, ~SS) ą▓ ą╗ąŠą│. 0. ąŻčüčéčĆąŠą╣čüčéą▓ą░ Master ąĖ Slave ą┐ąŠą┤ą│ąŠčéą░ą▓ą╗ąĖą▓ą░čÄčé ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ ąŠčéą┐čĆą░ą▓ą║ąĖ ą▓ ąĖčģ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖčģ čĆąĄą│ąĖčüčéčĆą░čģ čüą┤ą▓ąĖą│ą░, ąĖ Master ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ąĮą░ ą▓čŗą▓ąŠą┤ąĄ SCK čéą░ą║č鹊ą▓čŗąĄ ąĖą╝ą┐čāą╗čīčüčŗ, ąĮąĄąŠą▒čģąŠą┤ąĖą╝čŗąĄ ą┤ą╗čÅ ąŠą▒ą╝ąĄąĮą░ ą┤ą░ąĮąĮčŗą╝ąĖ. ąöą░ąĮąĮčŗąĄ ą▓čüąĄą│ą┤ą░ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ą▓ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĖ ąŠčé Master ą║ Slave č湥čĆąĄąĘ ą▓čŗą▓ąŠą┤ MOSI (Master Out ŌĆō Slave In), ąĖ ą▓ ąŠą▒čĆą░čéąĮąŠą╝ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĖ ą▓čüąĄą│ą┤ą░ č湥čĆąĄąĘ ą▓čŗą▓ąŠą┤ MISO (Master In ŌĆō Slave Out). ą¤ąŠčüą╗ąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ ą║ą░ąČą┤ąŠą│ąŠ ą┐ą░ą║ąĄčéą░ ą┤ą░ąĮąĮčŗčģ Master ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčé čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖčÄ čāčüčéčĆąŠą╣čüčéą▓ą░ Slave ą┐čāč鹥ą╝ ą┐ąĄčĆąĄą▓ąŠą┤ą░ ą▓ ą╗ąŠą│. 1 ą▓čŗą▓ąŠą┤ą░ ~SS.

ąĀąĖčü. 19-2. ąÆąĘą░ąĖą╝ąŠą┤ąĄą╣čüčéą▓ąĖąĄ SPI Master - SPI Slave.

Master. ąÜąŠą│ą┤ą░ ąĖąĮč鹥čĆč乥ą╣čü SPI čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą▓ čĆąĄąČąĖą╝ąĄ Master, č鹊 ąĮąĄčé ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą│ąŠ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čüąŠčüč鹊čÅąĮąĖąĄą╝ čüąĖą│ąĮą░ą╗ą░ ~SS. ąŁč鹊 ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ąŠą▒čĆą░ą▒ąŠčéą░ąĮąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ ą║ąŠą┤ąŠą╝ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ą╝ąŠąČąĄčé ąĮą░čćą░čéčīčüčÅ ąŠą▒ą╝ąĄąĮ ą┤ą░ąĮąĮčŗą╝ąĖ. ąÜąŠą│ą┤ą░ ą╗ąĖąĮąĖčÅ ~SS čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮą░ (čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ Slave ą▓čŗą▒čĆą░ąĮąŠ), ąĘą░ą┐ąĖčüčī ą▒ą░ą╣čéą░ ą▓ čĆąĄą│ąĖčüčéčĆ ą┤ą░ąĮąĮčŗčģ SPI ąĘą░ą┐čāčüčéąĖčé ą│ąĄąĮąĄčĆą░čåąĖčÄ čéą░ą║č鹊ą▓ SPI, ąĖ ą░ą┐ą┐ą░čĆą░čéčāčĆą░ ąĖąĮč鹥čĆč乥ą╣čüą░ ą▓čŗą┤ą▓ąĖą│ą░ąĄčé 8 ą▒ąĖčé ąĖ ą┐ąĄčĆąĄą┤ą░ąĄčé ąĖčģ čāčüčéčĆąŠą╣čüčéą▓čā Slave. ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą▒ą░ą╣čé ą▓čŗą┤ą▓ąĖąĮčāčé, ą│ąĄąĮąĄčĆą░č鹊čĆ čéą░ą║č鹊ą▓ SPI ąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ, ąĖ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ ąŠą║ąŠąĮčćą░ąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ (SPIF). ąĢčüą╗ąĖ čĆą░ąĘčĆąĄčłąĄąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ SPI (čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ SPI Interrupt Enable, SPIE ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPCR, č鹊 ą▒čāą┤ąĄčé ą▓čŗčüčéą░ą▓ą╗ąĄąĮ ąĘą░ą┐čĆąŠčü ąĮą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ. Master ą╝ąŠąČąĄčé ą┐čĆąŠą┤ąŠą╗ąČąĖčéčī ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī ą┤čĆčāą│ąĖąĄ ą▒ą░ą╣čéčŗ ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ ą▓ čĆąĄą│ąĖčüčéčĆ SPDR, ąĖą╗ąĖ čüąĖą│ąĮą░ą╗ąĖąĘąĖčĆąŠą▓ą░čéčī ąŠą▒ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ą┐ą░ą║ąĄčéą░ ą┐ąĄčĆąĄą▓ąŠą┤ąŠą╝ ą▓ ą╗ąŠą│. 1 ą▓čŗą▓ąŠą┤ą░ ~SS. ą¤ąŠčüą╗ąĄą┤ąĮąĖą╣ ą┐čĆąĖčłąĄą┤čłąĖą╣ ą▒ą░ą╣čé ą▒čāą┤ąĄčé čüąŠčģčĆą░ąĮąĄąĮ ą▓ ą▒čāč乥čĆąĮąŠą╝ čĆąĄą│ąĖčüčéčĆąĄ ą┤ą╗čÅ ą┐ąŠčüą╗ąĄą┤čāčÄčēąĄą│ąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ.

Slave. ąÜąŠą│ą┤ą░ čāčüčéčĆąŠą╣čüčéą▓ąŠ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąŠ ą║ą░ą║ Slave, ąĖąĮč鹥čĆč乥ą╣čü SPI ą▒čāą┤ąĄčé ąŠčüčéą░ą▓ą░čéčīčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ čüąĮą░, ą║ąŠą│ą┤ą░ ą▓čŗą▓ąŠą┤ MISO ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čéčĆąĄčéčīąĄą╝ (ąŠčéą║ą╗čÄč湥ąĮąĮąŠą╝) čüąŠčüč鹊čÅąĮąĖąĖ, ą┐ąŠą║ą░ ą▓čŗą▓ąŠą┤ ~SS čāą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ą▓ ą╗ąŠą│. 1. ąÆ čŹč鹊ą╝ čüąŠčüč鹊čÅąĮąĖąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą╝ąŠąČąĄčé ąŠą▒ąĮąŠą▓ąĖčéčī čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ čĆąĄą│ąĖčüčéčĆą░ ą┤ą░ąĮąĮčŗčģ (SPI Data Register, SPDR), ąĮąŠ ą┤ą░ąĮąĮčŗąĄ ąĮąĄ ą▒čāą┤čāčé ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčīčüčÅ ąĮą░čĆčāąČčā ą┐ąŠ čéą░ą║čéą░ą╝ SCK, ą┐ąŠą║ą░ ą▓čŗą▓ąŠą┤ ~SS ąĮąĄ ą▒čāą┤ąĄčé ą┐ąĄčĆąĄą▓ąĄą┤ąĄąĮ ą▓ ą╗ąŠą│. 0. ąÜą░ą║ č鹊ą╗čīą║ąŠ ąŠą┤ąĖąĮ ą▒ą░ą╣čé ą┐ąŠą╗ąĮąŠčüčéčīčÄ čüą┤ą▓ąĖąĮčāčé, ą▒čāą┤ąĄčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čäą╗ą░ą│ ąŠą║ąŠąĮčćą░ąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ SPIF. ąĢčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (SPI Interrupt Enable bit, SPIE) ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPCR, č鹊 ą▒čāą┤ąĄčé ą▓čŗčüčéą░ą▓ą╗ąĄąĮ ąĘą░ą┐čĆąŠčü ąĮą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ. Slave ą╝ąŠąČąĄčé ą┐čĆąŠą┤ąŠą╗ąČąĖčéčī čĆą░ąĘą╝ąĄčēą░čéčī ąĮąŠą▓čŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ ąŠčéą┐čĆą░ą▓ą║ąĖ ą▓ čĆąĄą│ąĖčüčéčĆ SPDR ą┐ąĄčĆąĄą┤ čćč鹥ąĮąĖąĄą╝ ą┐čĆąĖčģąŠą┤čÅčēąĖčģ ą┤ą░ąĮąĮčŗčģ. ą¤ąŠčüą╗ąĄą┤ąĮąĖą╣ ą┐čĆąĖčłąĄą┤čłąĖą╣ ą▒ą░ą╣čé ą▒čāą┤ąĄčé čüąŠčģčĆą░ąĮąĄąĮ ą▓ ą▒čāč乥čĆąĮąŠą╝ čĆąĄą│ąĖčüčéčĆąĄ ą┤ą╗čÅ ą┐ąŠčüą╗ąĄą┤čāčÄčēąĄą│ąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ.

ąÆ čüąĖčüč鹥ą╝ąĄ ąĄčüčéčī ąŠą┤ąĖąĮąŠčćąĮą░čÅ ą▒čāč乥čĆąĖąĘą░čåąĖčÅ ą▓ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖ ą┤ą▓ąŠą╣ąĮą░čÅ ą▒čāč乥čĆąĖąĘą░čåąĖčÅ ą▓ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĖ ą┐čĆąĖąĄą╝ą░. ąŁč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗąĄ ą▒ą░ą╣čéčŗ ąĮąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮčŗ ą▓ čĆąĄą│ąĖčüčéčĆ ą┤ą░ąĮąĮčŗčģ SPI (SPI Data Register, SPDR), ą┐ąŠą║ą░ ąĮąĄ ą▒čāą┤ąĄčé ąŠčüčāčēąĄčüčéą▓ą╗ąĄąĮ ą┐ąŠą╗ąĮčŗą╣ čåąĖą║ą╗ čüą┤ą▓ąĖą│ą░ č鹥ą║čāčēąĄą│ąŠ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ąŠą│ąŠ ą▒ą░ą╣čéą░. ą×ą┤ąĮą░ą║ąŠ ą║ąŠą│ą┤ą░ ą┐čĆąĖąĮąĖą╝ą░čÄčéčüčÅ ą┤ą░ąĮąĮčŗąĄ, ą┐čĆąĖąĮčÅčéčŗą╣ čüąĖą╝ą▓ąŠą╗ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ ą┤ą░ąĮąĮčŗčģ SPI (SPDR) ą┤ąŠ č鹊ą│ąŠ, ą║ą░ą║ čüą╗ąĄą┤čāčÄčēąĖą╣ ą▒ą░ą╣čé ą▒čāą┤ąĄčé ą▓ą┤ą▓ąĖąĮčāčé ą▓ ąĖąĮč鹥čĆč乥ą╣čü, ąĖąĮą░č湥 ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ čāąČąĄ ą┐čĆąĖąĮčÅčéčŗą╣ ą▒ą░ą╣čé ą▒čāą┤ąĄčé ą┐ąŠč鹥čĆčÅąĮ. ąÆ čĆąĄąČąĖą╝ąĄ SPI Slave čāą┐čĆą░ą▓ą╗čÅčÄčēą░čÅ ą╗ąŠą│ąĖą║ą░ ą▒čāą┤ąĄčé ąŠčéčüą╗ąĄąČąĖą▓ą░čéčī ą┐čĆąĖčģąŠą┤čÅčēąĖą╣ čüąĖą│ąĮą░ą╗ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ SCK. ą¦č鹊ą▒čŗ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī ą┐čĆą░ą▓ąĖą╗čīąĮčāčÄ čĆą░ą▒ąŠčéčā čŹč鹊ą│ąŠ čüąĖą│ąĮą░ą╗ą░, čéčĆąĄą▒čāąĄčéčüčÅ ą▓čŗą┐ąŠą╗ąĮąĖčéčī čāčüą╗ąŠą▓ąĖčÅ ą┤ą╗čÅ ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠ ą┤ąŠą┐čāčüčéąĖą╝čŗčģ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüč鹥ą╣ čéą░ą║č鹊ą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░:

ąöą╗ąĖč鹥ą╗čīąĮąŠčüčéčī ą╗ąŠą│. 0 ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą▒ąŠą╗čīčłąĄ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéąĖ 2 čéą░ą║č鹊ą▓ čÅą┤čĆą░ CPU.

ąöą╗ąĖč鹥ą╗čīąĮąŠčüčéčī ą╗ąŠą│. 1 ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą▒ąŠą╗čīčłąĄ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéąĖ 2 čéą░ą║č鹊ą▓ čÅą┤čĆą░ CPU.

ąÜąŠą│ą┤ą░ SPI čĆą░ąĘčĆąĄčłąĄąĮ, ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čĆą░ą▒ąŠčéčŗ čüąĖą│ąĮą░ą╗ąŠą▓ ą▓čŗą▓ąŠą┤ąŠą▓ is MOSI, MISO, SCK ąĖ ~SS ą┐ąĄčĆąĄąĮą░ąĘąĮą░čćą░ąĄčéčüčÅ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü čéą░ą▒ą╗ąĖčåąĄą╣ 19-1. ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ ą┐čĆąŠ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠąĄ ą┐ąĄčĆąĄąĮą░ąĘąĮą░č湥ąĮąĖąĄ čäčāąĮą║čåąĖą╣ ą▓čŗą▓ąŠą┤ąŠą▓ čüą╝. "ąÉą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčŗąĄ čäčāąĮą║čåąĖąĖ ą▓čŗą▓ąŠą┤ąŠą▓ ą┐ąŠčĆčéą░" ą▓ čüčéą░čéčīąĄ [4].

ąóą░ą▒ą╗ąĖčåą░ 19-1. ąÜą░ą║ ą╝ąĄąĮčÅčÄčé čüą▓ąŠčÄ čäčāąĮą║čåąĖčÄ ą▓čŗą▓ąŠą┤čŗ SPI ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čĆąĄąČąĖą╝ą░ čĆą░ą▒ąŠčéčŗ Master/Slave(1).

ąÆčŗą▓ąŠą┤

|

ąØą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ, Master SPI |

ąØą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ, Slave SPI |

| MOSI |

ą×ą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╝ (DDRxn) |

ąÆčģąŠą┤ |

| MISO |

ąÆčģąŠą┤ |

ą×ą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╝ (DDRxn) |

| SCK |

ą×ą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╝ (DDRxn) |

ąÆčģąŠą┤ |

| ~SS |

ą×ą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╝ (DDRxn) |

ąÆčģąŠą┤ |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ (1): ą┤ą╗čÅ ą┐čāąĮą║č鹊ą▓ čéą░ą▒ą╗ąĖčåčŗ "ą×ą┐čĆąĄą┤ąĄą╗ąĄąĮąŠ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╝" ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čĆą░ą▒ąŠčéčŗ ą▓čŗą▓ąŠą┤ąŠą▓ SPI ąĘą░ą▓ąĖčüąĖčé ąŠčé ąĮą░čüčéčĆąŠą╣ą║ąĖ ą▓čŗą▓ąŠą┤ąŠą▓ ą┐ąŠčĆčéą░ B ąĖ ąĖčģ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčŗčģ čäčāąĮą║čåąĖą╣ (čüą╝. "ąÉą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčŗąĄ čäčāąĮą║čåąĖąĖ ą▓čŗą▓ąŠą┤ąŠą▓ ą┐ąŠčĆčéą░" ą▓ čüčéą░čéčīąĄ [4]).

ąÆ čüą╗ąĄą┤čāčÄčēąĄą╝ ą║ąŠą┤ąĄ ą┐ąŠą║ą░ąĘą░ąĮąŠ, ą║ą░ą║ ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆąŠą▓ą░čéčī SPI ą▓ čĆąĄąČąĖą╝ąĄ Master, ąĖ ą║ą░ą║ ą▓čŗą┐ąŠą╗ąĮąĖčéčī ą┐čĆąŠčüčéčāčÄ ą┐ąĄčĆąĄą┤ą░čćčā. DDR_SPI ą▓ ą┐čĆąĖą╝ąĄčĆą░čģ ąĘą░ą╝ąĄąĮčÅąĄčéčüčÅ ą┤ąĄą╣čüčéą▓ąĖč鹥ą╗čīąĮčŗą╝ čĆąĄą│ąĖčüčéčĆąŠą╝, ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčēąĖą╝ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ ąĮąŠąČą║ąĖ ą▓čŗą▓ąŠą┤ą░ (čŹč鹊 ąĘą░ą▓ąĖčüąĖčé ąŠčé ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░, ąĖ ą╝ąŠąČąĄčé ą▒čŗčéčī, ą║ ą┐čĆąĖą╝ąĄčĆčā DDRB, ąĄčüą╗ąĖ ą┐čĆąĖą╝ąĄąĮčÅąĄčéčüčÅ ATmega328). DD_MOSI, DD_MISO ąĖ DD_SCK ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĘą░ą╝ąĄąĮąĄąĮčŗ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╝ąĖ ąĮąŠą╝ąĄčĆą░ą╝ąĖ ą▒ąĖčé, ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčēąĖą╝ąĖ ąĮąŠąČą║ąĖ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░. ąØą░ą┐čĆąĖą╝ąĄčĆ, ąĄčüą╗ąĖ MOSI ąĮą░čģąŠą┤ąĖčéčüčÅ ąĮą░ ąĮąŠąČą║ąĄ ą┐ąŠčĆčéą░ PB3 (ą║ą░ą║ čŹč鹊 čā ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ATmega328 [4]), č鹊 ąĘą░ą╝ąĄąĮąĖč鹥 DD_MOSI ąĮą░ ąĖą╝čÅ ąĮąŠą╝ąĄčĆą░ ąĮąŠąČą║ąĖ ą┐ąŠčĆčéą░ DDB3 ąĖ ąĘą░ą╝ąĄąĮąĖč鹥 DDR_SPI ąĮą░ ąĖą╝čÅ čĆąĄą│ąĖčüčéčĆą░ DDRB.

ą¤čĆąĖą╝ąĄčĆ ą║ąŠą┤ą░ ąĮą░ ą░čüčüąĄą╝ą▒ą╗ąĄčĆąĄ:

SPI_MasterInit:

; ąØą░čüčéčĆąŠą╣ą║ą░ MOSI ąĖ SCK ą║ą░ą║ ą▓čŗčģąŠą┤, ą▓čüąĄ ąŠčüčéą░ą╗čīąĮčŗąĄ čüąĖą│ąĮą░ą╗čŗ ą║ą░ą║ ą▓čģąŠą┤:

ldi r17,(1 << DD_MOSI)|(1 << DD_SCK)

out DDR_SPI,r17

; ąĀą░ąĘčĆąĄčłąĖčéčī čĆą░ą▒ąŠčéčā SPI, čĆąĄąČąĖą╝ Master, čāčüčéą░ąĮąŠą▓ąĖčéčī čüą║ąŠčĆąŠčüčéčī čéą░ą║č鹊ą▓ fck/16:

ldi r17,(1 << SPE)|(1 << MSTR)|(1 << SPR0)

out SPCR,r17

ret

SPI_MasterTransmit:

; ąŚą░ą┐čāčüą║ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ (r16):

out SPDR,r16

Wait_Transmit:

; ą×ąČąĖą┤ą░ąĮąĖąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ

in r16, SPSR

sbrs r16, SPIF

rjmp Wait_Transmit

ret

ą¤čĆąĖą╝ąĄčĆ ą║ąŠą┤ą░ ąĮą░ čÅąĘčŗą║ąĄ C:

void SPI_MasterInit(void)

{

/* ąØą░čüčéčĆąŠą╣ą║ą░ MOSI ąĖ SCK ą║ą░ą║ ą▓čŗčģąŠą┤,

ą▓čüąĄ ąŠčüčéą░ą╗čīąĮčŗąĄ čüąĖą│ąĮą░ą╗čŗ ą║ą░ą║ ą▓čģąŠą┤: */

DDR_SPI = (1 << DD_MOSI)|(1 << DD_SCK);

/* ąĀą░ąĘčĆąĄčłąĖčéčī čĆą░ą▒ąŠčéčā SPI, čĆąĄąČąĖą╝ Master,

čāčüčéą░ąĮąŠą▓ąĖčéčī čüą║ąŠčĆąŠčüčéčī čéą░ą║č鹊ą▓ fck/16: */

SPCR = (1 << SPE)|(1 << MSTR)|(1 << SPR0);

}

void SPI_MasterTransmit(char cData)

{

/* ąŚą░ą┐čāčüą║ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ: */

SPDR = cData;

/* ą×ąČąĖą┤ą░ąĮąĖąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ: */

while(!(SPSR & (1 << SPIF)));

}

ąÆ čŹč鹊ą╣ ą┤ąŠą║čāą╝ąĄąĮčéą░čåąĖąĖ čüąŠą┤ąĄčƹȹ░čéčüčÅ ą┐čĆąŠčüčéčŗąĄ ą┐čĆąĖą╝ąĄčĆčŗ ą║ąŠą┤ą░, ą║ąŠč鹊čĆčŗąĄ ą║čĆą░čéą║ąŠ ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčé, ą║ą░ą║ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čĆą░ąĘą╗ąĖčćąĮčŗąĄ čćą░čüčéąĖ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░. ąŁčéąĖ ą┐čĆąĖą╝ąĄčĆčŗ ą║ąŠą┤ą░ ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░čÄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ čüą┐ąĄčåąĖą░ą╗čīąĮčŗčģ ą┐ąŠą┤ą║ą╗čÄčćą░ąĄą╝čŗčģ ąĘą░ą│ąŠą╗ąŠą▓ąŠčćąĮčŗčģ čäą░ą╣ą╗ąŠą▓. ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 ąĮąĄ ą▓čüąĄ ą┐ąŠčüčéą░ą▓čēąĖą║ąĖ ą║ąŠą╝ą┐ąĖą╗čÅč鹊čĆąŠą▓ čÅąĘčŗą║ą░ C ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÄčé ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖąĄ ąĖą╝ąĄąĮ ą┤ą╗čÅ ą▒ąĖčé čĆąĄą│ąĖčüčéčĆąŠą▓ ą▓ čäą░ą╣ą╗ą░čģ ąĘą░ą│ąŠą╗ąŠą▓ą║ąŠą▓, ąĖ ąŠč乊čĆą╝ą╗ąĄąĮąĖąĄ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čéą░ą║ąČąĄ ąĘą░ą▓ąĖčüąĖčé ąŠčé ą┐ąŠą┤ą┤ąĄčƹȹ║ąĖ čĆą░čüčłąĖčĆąĄąĮąĖčÅą╝ąĖ čüąĖąĮčéą░ą║čüąĖčüą░ ą║ąŠą╝ą┐ąĖą╗čÅč鹊čĆą░ čÅąĘčŗą║ą░ C. ąöą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ą┐ąŠą┤čĆąŠą▒ąĮąŠčüč鹥ą╣ ą┐ąŠąČą░ą╗čāą╣čüčéą░ ą┐čĆąŠą║ąŠąĮčüčāą╗čīčéąĖčĆčāą╣č鹥čüčī čü ą┤ąŠą║čāą╝ąĄąĮčéą░čåąĖąĄą╣ ąĮą░ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╣ ąÆą░ą╝ąĖ ą║ąŠą╝ą┐ąĖą╗čÅč鹊čĆ C.

ąöą╗čÅ čĆąĄą│ąĖčüčéčĆąŠą▓ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░, ąĮą░čģąŠą┤čÅčēąĖčģčüčÅ ą▓ čĆą░čüčłąĖčĆąĄąĮąĮąŠą╣ ąŠą▒ą╗ą░čüčéąĖ ą░ą┤čĆąĄčüąĮąŠą│ąŠ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ą░ AVR (extended I/O map), ąĖąĮčüčéčĆčāą║čåąĖąĖ IN, OUT, SBIS, SBIC, CBI ąĖ SBI ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĘą░ą╝ąĄąĮąĄąĮčŗ ąĮą░ ąĖąĮčüčéčĆčāą║čåąĖąĖ, ą║ąŠč鹊čĆčŗąĄ ą┐ąŠąĘą▓ąŠą╗čÅčÄčé ą┐ąŠą╗čāčćąĖčéčī ą┤ąŠčüčéčāą┐ ą▓ čŹčéčā ąŠą▒ą╗ą░čüčéčī. ą×ą▒čŗčćąĮąŠ ąĖąĮčüčéčĆčāą║čåąĖąĖ LDS ąĖ STS ą║ąŠą╝ą▒ąĖąĮąĖčĆčāčÄčéčüčÅ čü SBRS, SBRC, SBR ąĖ CBR.

ąĪą╗ąĄą┤čāčÄčēąĖąĄ ą┐čĆąĖą╝ąĄčĆčŗ ą║ąŠą┤ą░ ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčé ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÄ SPI ą▓ čĆąĄąČąĖą╝ąĄ Slave, ąĖ ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčé ą║ą░ą║ ą▓čŗą┐ąŠą╗ąĮąĖčéčī ą┐čĆąŠčüč鹥ą╣čłąĖą╣ ą┐čĆąĖąĄą╝ ą┤ą░ąĮąĮčŗčģ.

ą¤čĆąĖą╝ąĄčĆ ą║ąŠą┤ą░ ąĮą░ ą░čüčüąĄą╝ą▒ą╗ąĄčĆąĄ:

SPI_SlaveInit:

; ąØą░čüčéčĆąŠą╣ą║ą░ ąĮąŠąČą║ąĖ ą┐ąŠčĆčéą░ MISO ą║ą░ą║ ą▓čŗčģąŠą┤,

; ą▓čüąĄ ąŠčüčéą░ą╗čīąĮčŗąĄ čüąĖą│ąĮą░ą╗čŗ ą║ą░ą║ ą▓čģąŠą┤:

ldi r17,(1 << DD_MISO)

out DDR_SPI,r17

; ąĀą░ąĘčĆąĄčłąĖčéčī čĆą░ą▒ąŠčéčā SPI:

ldi r17,(1 << SPE)

out SPCR,r17

ret

SPI_SlaveReceive:

; ą×ąČąĖą┤ą░ąĮąĖąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐čĆąĖąĄą╝ą░:

in r16, SPSR

sbrs r16, SPIF

rjmp SPI_SlaveReceive

; ą¦č鹥ąĮąĖąĄ ą┐čĆąĖąĮčÅčéčŗčģ ą┤ą░ąĮąĮčŗčģ ąĖ ą▓ąŠąĘą▓čĆą░čé:

in r16,SPDR

ret

ą¤čĆąĖą╝ąĄčĆ ą║ąŠą┤ą░ ąĮą░ čÅąĘčŗą║ąĄ C:

void SPI_SlaveInit(void)

{

/* ąØą░čüčéčĆąŠą╣ą║ą░ ąĮąŠąČą║ąĖ ą┐ąŠčĆčéą░ MISO ą║ą░ą║ ą▓čŗčģąŠą┤,

ą▓čüąĄ ąŠčüčéą░ą╗čīąĮčŗąĄ čüąĖą│ąĮą░ą╗čŗ ą║ą░ą║ ą▓čģąŠą┤: */

DDR_SPI = (1 << DD_MISO);

/* ąĀą░ąĘčĆąĄčłąĖčéčī čĆą░ą▒ąŠčéčā SPI: */

SPCR = (1 << SPE);

}

char SPI_SlaveReceive(void)

{

/* ą×ąČąĖą┤ą░ąĮąĖąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐čĆąĖąĄą╝ą░: */

while(!(SPSR & (1 << SPIF)));

/* ą¦č鹥ąĮąĖąĄ ą┐čĆąĖąĮčÅčéčŗčģ ą┤ą░ąĮąĮčŗčģ ąĖ ą▓ąŠąĘą▓čĆą░čé: */

return SPDR;

}

[ążčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠčüčéčī ą▓čŗą▓ąŠą┤ą░ ~SS]

Slave Mode (ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ SPI). ąÜąŠą│ą┤ą░ SPI čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą▓ čĆąĄąČąĖą╝ąĄ Slave, ą▓čŗą▓ąŠą┤ ą┐ąŠčĆčéą░ ą┤ą╗čÅ čüąĖą│ąĮą░ą╗ą░ Slave Select (~SS) ą▓čüąĄą│ą┤ą░ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąĮą░čüčéčĆą░ąĖą▓ą░ąĄčéčüčÅ ą║ą░ą║ ą▓čģąŠą┤. ąÜąŠą│ą┤ą░ ~SS ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ą╗ąŠą│. 0, ą░ą║čéąĖą▓ąĖčĆčāąĄčéčüčÅ ą▒ą╗ąŠą║ SPI, ąĖ ą▓čŗą▓ąŠą┤ MISO čüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▓čŗčģąŠą┤ąŠą╝ (ą▓čŗčģąŠą┤ąĖčé ąĖąĘ čéčĆąĄčéčīąĄą│ąŠ čüąŠčüč鹊čÅąĮąĖčÅ, ąĖą╗ąĖ ąĖąĘ čüąŠčüč鹊čÅąĮąĖčÅ ą▓čģąŠą┤ą░), ąĄčüą╗ąĖ čŹč鹊 ą▒čŗą╗ąŠ čĆą░ąĮąĄąĄ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąŠ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╝ ąĮą░čüčéčĆąŠą╣ą║ąŠą╣ ą▒ąĖč鹊ą▓ čĆąĄą│ąĖčüčéčĆą░ DDRx. ąÆčüąĄ ą┤čĆčāą│ąĖąĄ čüąĖą│ąĮą░ą╗čŗ SPI ąŠčüčéą░čÄčéčüčÅ ą▓čģąŠą┤ą░ą╝ąĖ. ąÜąŠą│ą┤ą░ ~SS ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ą╗ąŠą│. 1, č鹊 ą▓čüąĄ ą▓čŗą▓ąŠą┤čŗ čüčéą░ąĮąŠą▓čÅčéčüčÅ ą▓čģąŠą┤ą░ą╝ąĖ, ąĖ ą▒ą╗ąŠą║ SPI ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ ą┐ą░čüčüąĖą▓ąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ, čé. ąĄ. ąŠąĮ ąĮąĄ ą▒čāą┤ąĄčé ą┐čĆąĖąĮąĖą╝ą░čéčī ą┤ą░ąĮąĮčŗąĄ. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ą╗ąŠą│ąĖą║ą░ SPI ą▒čāą┤ąĄčé čüą▒čĆąŠčłąĄąĮą░, ą║ąŠą│ą┤ą░ čüąĖą│ąĮą░ą╗ ~SS ą┐ąĄčĆąĄą▓ąŠą┤ąĖčéčüčÅ ą▓ ą╗ąŠą│. 1.

ąÆčŗą▓ąŠą┤ ~SS ą┐ąŠą╗ąĄąĘąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┤ą╗čÅ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ą┐ą░ą║ąĄčéą░ / ą▒ą░ą╣čéą░, čćč鹊ą▒čŗ čüąŠčģčĆą░ąĮąĖčéčī čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĄ ą╝ąĄąČą┤čā čüč湥čéčćąĖą║ąŠą╝ ą▒ąĖčé ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ SPI ąĖ ą│ąĄąĮąĄčĆą░č鹊čĆąŠą╝ čéą░ą║č鹊ą▓ čäčĆąĄą╣ą╝ą░ ą│ą╗ą░ą▓ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ SPI. ąÜąŠą│ą┤ą░ ~SS ą┐ąĄčĆąĄą▓ąŠą┤ąĖčéčüčÅ ą▓ ą╗ąŠą│. 1, ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ SPI ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ čüą▒čĆąŠčüąĖčé ą╗ąŠą│ąĖą║čā ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖ ą┐čĆąĖąĄą╝ą░, ąĖ ą▓čüąĄ čćą░čüčéąĖčćąĮąŠ ą┐čĆąĖąĮčÅčéčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüą┤ą▓ąĖą│ą░ ą▒čāą┤čāčé ąŠčéą▒čĆąŠčłąĄąĮčŗ.

Master Mode (ą│ą╗ą░ą▓ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ SPI). ąÜąŠą│ą┤ą░ SPI čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą▓ čĆąĄąČąĖą╝ąĄ Master (čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé MSTR ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPCR), ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą╝ąŠąČąĄčé ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čĆą░ą▒ąŠčéčŗ ą▓čŗą▓ąŠą┤ą░ ~SS (ą▓čģąŠą┤ čŹč鹊 ą▒čāą┤ąĄčé ąĖą╗ąĖ ą▓čŗčģąŠą┤).

ąĢčüą╗ąĖ ~SS čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą║ą░ą║ ą▓čŗčģąŠą┤, č鹊 ą▓čŗą▓ąŠą┤ čüčéą░ąĮąŠą▓ąĖčéčüčÅ ąŠą▒čŗčćąĮčŗą╝ ą▓čŗčģąŠą┤ąŠą╝ GPIO, čĆą░ą▒ąŠčéą░ ą║ąŠč鹊čĆąŠą│ąŠ ąĮąĖą║ą░ą║ ą░ą┐ą┐ą░čĆą░čéąĮąŠ ąĮąĄ čüą▓čÅąĘą░ąĮąŠ čü ą▒ą╗ąŠą║ąŠą╝ SPI. ą×ą▒čŗčćąĮąŠ čŹčéąĖą╝ ą▓čŗą▓ąŠą┤ąŠą╝ ą╝ąŠąČąĮąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ čāą┐čĆą░ą▓ą╗čÅčéčī čüąŠčüč鹊čÅąĮąĖąĄą╝ ą▓čģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ~SS ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ SPI.

ąĢčüą╗ąĖ ~SS čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą║ą░ą║ ą▓čģąŠą┤, ąŠąĮ ą┤ąŠą╗ąČąĄąĮ čāą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą╗ąŠą│. 1, čćč鹊ą▒čŗ ą╝ąŠą│ čĆą░ą▒ąŠčéą░čéčī Master SPI. ąĢčüą╗ąĖ ą▓čŗą▓ąŠą┤ ~SS ą▒čāą┤ąĄčé ą┐ąĄčĆąĄą▓ąĄą┤ąĄąĮ ą▓ ą╗ąŠą│. 0 ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ąĖ čüčģąĄą╝ą░ą╝ąĖ, ą║ąŠą│ą┤ą░ SPI čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą▓ čĆąĄąČąĖą╝ąĄ Master čü ~SS čĆą░ą▒ąŠčéą░čÄčēąĖą╝ ą║ą░ą║ ą▓čģąŠą┤, č鹊 ą▒ą╗ąŠą║ SPI ąĖąĮč鹥čĆą┐čĆąĄčéąĖčĆčāąĄčé čŹč鹊 čüąŠčüč鹊čÅąĮąĖąĄ čéą░ą║, čćč鹊 ą┤čĆčāą│ąŠąĄ ą│ą╗ą░ą▓ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĘą░ąĮčÅą╗ąŠ čłąĖąĮčā SPI ąĖ ąĮą░čćąĖąĮą░ąĄčé ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī ą┤ą░ąĮąĮčŗąĄ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą╝čā čāčüčéčĆąŠą╣čüčéą▓čā. ąŁčéą░ čüąĖčéčāą░čåąĖčÅ ąŠčéąĮąŠčüąĖčéčüčÅ ą║ čüčåąĄąĮą░čĆąĖčÄ, ą║ąŠą│ą┤ą░ ąĮą░ čłąĖąĮąĄ SPI ąĖą╝ąĄąĄčéčüčÅ ąĮąĄčüą║ąŠą╗čīą║ąŠ ą│ą╗ą░ą▓ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ (Master), ąĖ ąŠąĮąĖ ą║ąŠąĮą║čāčĆąĖčĆčāčÄčé ą┤čĆčāą│ čü ą┤čĆčāą│ąŠą╝ ąĮą░ ą┤ąŠčüčéčāą┐ ą║ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą╝čā čāčüčéčĆąŠą╣čüčéą▓čā SPI (Slave). ą¦č鹊ą▒čŗ ąĖąĘą▒ąĄąČą░čéčī ą║ąŠą╗ą╗ąĖąĘąĖąĖ ąĮą░ čłąĖąĮąĄ, ą▒ą╗ąŠą║ SPI ą┐čĆąĄą┤ą┐čĆąĖąĮąĖą╝ą░ąĄčé čüą╗ąĄą┤čāčÄčēąĖąĄ ą┤ąĄą╣čüčéą▓ąĖčÅ:

1. ąæąĖčé MSTR ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPCR ąŠčćąĖčēą░ąĄčéčüčÅ, ąĖ čüąĖčüč鹥ą╝ą░ SPI ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ čĆąĄąČąĖą╝ Slave. ąÆ čĆąĄąĘčāą╗čīčéą░č鹥 čāčüčéčĆąŠą╣čüčéą▓ąŠ SPI ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ čĆąĄąČąĖą╝ Slave, ąĖ ą▓čŗą▓ąŠą┤čŗ MOSI ąĖ SCK čüčéą░ąĮąŠą▓čÅčéčüčÅ ą▓čģąŠą┤ą░ą╝ąĖ.

2. ąŻčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ čäą╗ą░ą│ SPIF ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPSR, ąĖ ąĄčüą╗ąĖ čĆą░ąĘčĆąĄčłąĄąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ SPI, ąĖ I-ą▒ąĖčé ą▓ čĆąĄą│ąĖčüčéčĆąĄ SREG čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ (ą│ą╗ąŠą▒ą░ą╗čīąĮąŠ čĆą░ąĘčĆąĄčłąĄąĮčŗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ), č鹊 ąĘą░ą┐čāčüčéąĖčéčüčÅ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ SPI.

ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ąĄčüą╗ąĖ ą┐ąĄčĆąĄą┤ą░čćą░ SPI ą▓ čĆąĄąČąĖą╝ąĄ Master čĆą░ą▒ąŠčéą░ąĄčé ą┐ąŠą┤ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣, ąĖ ąĄčüčéčī ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ą▓čģąŠą┤ąĮąŠą│ąŠ ą╗ąŠą│. čāčĆąŠą▓ąĮčÅ čüąĖą│ąĮą░ą╗ą░ ~SS, č鹊 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┤ąŠą╗ąČąĮąŠ ą▓čüąĄą│ą┤ą░ ą┐čĆąŠą▓ąĄčĆčÅčéčī, čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą╗ąĖ ą▓čüąĄ ąĄčēąĄ ą▒ąĖčé MSTR. ąĢčüą╗ąĖ ą▒ąĖčé MSTR ą▒čŗą╗ ąŠčćąĖčēąĄąĮ ą▓čŗą▒ąŠčĆą║ąŠą╣ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░, č鹊 ąŠąĮ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ, čćč鹊ą▒čŗ čüąĮąŠą▓ą░ čĆą░ąĘčĆąĄčłąĖčéčī čĆą░ą▒ąŠčéčā čĆąĄąČąĖą╝ą░ SPI Master.

[ąĀąĄąČąĖą╝čŗ č乊čĆą╝ą░čéą░ ą┤ą░ąĮąĮčŗčģ]

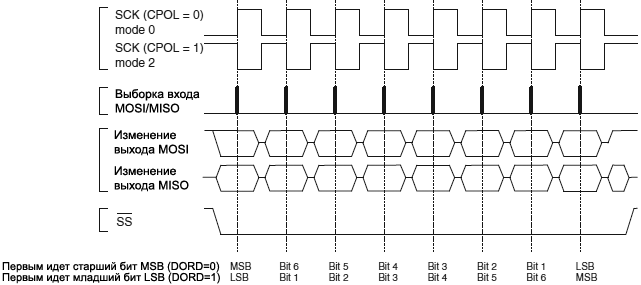

ąśą╝ąĄąĄčéčüčÅ 4 ą▓ąŠąĘą╝ąŠąČąĮčŗąĄ ą║ąŠą╝ą▒ąĖąĮą░čåąĖąĖ čäą░ąĘčŗ ąĖ ą┐ąŠą╗čÅčĆąĮąŠčüčéąĖ SCK ą┐ąŠ ąŠčéąĮąŠčłąĄąĮąĖčÄ ą║ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╝ ą┤ą░ąĮąĮčŗą╝, čćč鹊 čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ą▒ąĖčéą░ą╝ąĖ CPHA ąĖ CPOL čĆąĄą│ąĖčüčéčĆą░ SPCR. ążąŠčĆą╝ą░čéčŗ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ SPI ą┐ąŠą║ą░ąĘą░ąĮčŗ ąĮą░ čĆąĖčü. 19-3 ąĖ 19-4. ąæąĖčéčŗ ą┤ą░ąĮąĮčŗčģ ą▓čŗą┤ą▓ąĖą│ą░čÄčéčüčÅ ąĮą░čĆčāąČčā ąĖ ąĘą░čģą▓ą░čéčŗą▓ą░čÄčéčüčÅ ą┐čĆąĖ ą┐čĆąĖąĄą╝ąĄ ąĮą░ ą┐čĆąŠčéąĖą▓ąŠą┐ąŠą╗ąŠąČąĮčŗčģ ą┐ąĄčĆąĄą┐ą░ą┤ą░čģ čüąĖą│ąĮą░ą╗ą░ SCK, čćč鹊 ą│ą░čĆą░ąĮčéąĖčĆčāąĄčé ą┤ąŠčüčéą░č鹊čćąĮąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▓čĆąĄą╝ąĄąĮąĖ ą┤ą╗čÅ čüčéą░ą▒ąĖą╗čīąĮąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ čüąĖą│ąĮą░ą╗ąŠą▓ ą┤ą░ąĮąĮčŗčģ. ążąŠčĆą╝ą░čéčŗ čäčĆąĄą╣ą╝ą░ ą┤ą░ąĮąĮčŗčģ ą┐ąŠą║ą░ąĘą░ąĮčŗ ąĮą░ čĆąĖčü. 19-3 ąĖ 19-4, ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü čéą░ą▒ą╗ąĖčåąĄą╣ 19-2.

ąóą░ą▒ą╗ąĖčåą░ 19-2. ążąŠčĆą╝ą░čéčŗ ą┤ą░ąĮąĮčŗčģ SPI.

| SPI mode |

ąØą░čüčéčĆąŠą╣ą║ą░ |

ąØą░čćą░ą╗čīąĮčŗą╣ ą┐ąĄčĆąĄą┐ą░ą┤ |

ąÜąŠąĮąĄčćąĮčŗą╣ ą┐ąĄčĆąĄą┐ą░ą┤ |

| 0 |

CPOL=0, CPHA=0 |

ąÆčŗą▒ąŠčĆą║ą░ čüąĖą│ąĮą░ą╗ą░ (ąĮą░čĆą░čüčéą░ąĮąĖąĄ čāčĆąŠą▓ąĮčÅ) |

ąŻčüčéą░ąĮąŠą▓ą║ą░ čüąĖą│ąĮą░ą╗ą░ (čüą┐ą░ą┤ čāčĆąŠą▓ąĮčÅ) |

| 1 |

CPOL=0, CPHA=1 |

ąŻčüčéą░ąĮąŠą▓ą║ą░ čüąĖą│ąĮą░ą╗ą░ (ąĮą░čĆą░čüčéą░ąĮąĖąĄ čāčĆąŠą▓ąĮčÅ) |

ąÆčŗą▒ąŠčĆą║ą░ čüąĖą│ąĮą░ą╗ą░ (čüą┐ą░ą┤ čāčĆąŠą▓ąĮčÅ) |

| 2 |

CPOL=1, CPHA=0 |

ąÆčŗą▒ąŠčĆą║ą░ čüąĖą│ąĮą░ą╗ą░ (čüą┐ą░ą┤ čāčĆąŠą▓ąĮčÅ) |

ąŻčüčéą░ąĮąŠą▓ą║ą░ čüąĖą│ąĮą░ą╗ą░ (ąĮą░čĆą░čüčéą░ąĮąĖąĄ čāčĆąŠą▓ąĮčÅ) |

| 3 |

CPOL=1, CPHA=1 |

ąŻčüčéą░ąĮąŠą▓ą║ą░ čüąĖą│ąĮą░ą╗ą░ (čüą┐ą░ą┤ čāčĆąŠą▓ąĮčÅ) |

ąÆčŗą▒ąŠčĆą║ą░ čüąĖą│ąĮą░ą╗ą░ (ąĮą░čĆą░čüčéą░ąĮąĖąĄ čāčĆąŠą▓ąĮčÅ) |

ąĀąĖčü. 19-3. ążąŠčĆą╝ą░čé ą┐ąĄčĆąĄą┤ą░čćąĖ SPI, ą║ąŠą│ą┤ą░ CPHA = 0.

ąĀąĖčü. 19-4. ążąŠčĆą╝ą░čé ą┐ąĄčĆąĄą┤ą░čćąĖ SPI, ą║ąŠą│ą┤ą░ CPHA = 1.

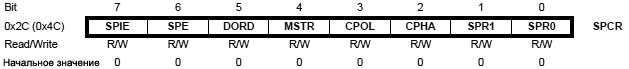

[ą×ą┐ąĖčüą░ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆąŠą▓]

ąĀąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ SPI.

Bit 7 ŌĆō SPIE: SPI Interrupt Enable

ąŁč鹊čé ą▒ąĖčé, ąĄčüą╗ąĖ ąŠąĮ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1, čĆą░ąĘčĆąĄčłą░ąĄčé ą▓čŗą┐ąŠą╗ąĮąĖčéčīčüčÅ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║čā ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ SPI (ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ąĖą╗čüčÅ ą▒ąĖčé SPIF ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPSR, ąĖ ąĄčüą╗ąĖ čĆą░ąĘčĆąĄčłąĄąĮčŗ ą│ą╗ąŠą▒ą░ą╗čīąĮčŗąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ I-ą▒ąĖčéą░ ą▓ čĆąĄą│ąĖčüčéčĆąĄ SREG).

Bit 6 ŌĆō SPE: SPI Enable

ąÜąŠą│ą┤ą░ ą▒ąĖčé SPE čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ ą╗ąŠą│. 1, č鹊 čĆą░ą▒ąŠčéą░ SPI čĆą░ąĘčĆąĄčłąĄąĮą░.

Bit 5 ŌĆō DORD: Data Order

ąÜąŠą│ą┤ą░ ą▓ ą▒ąĖčé DORD ąĘą░ą┐ąĖčüą░ąĮą░ ą╗ąŠą│. 1, č鹊 ą┐ąĄčĆą▓čŗą╝ ą▒čāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ąĮ ą╝ą╗ą░ą┤čłąĖą╣ ą▒ąĖčé (Least Significant Bit, LSB) 8-ą▒ąĖčéąĮąŠą│ąŠ čüą╗ąŠą▓ą░ ą┤ą░ąĮąĮčŗčģ. ąÜąŠą│ą┤ą░ DORD čüą▒čĆąŠčłąĄąĮ ą▓ ą╗ąŠą│. 0 (čüąŠčüč鹊čÅąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ), čüąĮą░čćą░ą╗ą░ ą▒čāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčīčüčÅ čüčéą░čĆčłąĖą╣ ą▒ąĖčé (Most Significant Bit, MSB).

Bit 4 ŌĆō MSTR: Master/Slave Select

ąŁč鹊čé ą▒ąĖčé ą▓čŗą▒ąĄčĆąĄčé čĆąĄąČąĖą╝ Master SPI, ą║ąŠą│ą┤ą░ ą▓ ąĮąĄą│ąŠ ąĘą░ą┐ąĖčüą░ąĮą░ ą╗ąŠą│. 1, ąĖ čĆąĄąČąĖą╝ Slave SPI, ą║ąŠą│ą┤ą░ ą▓ ąĮąĄą│ąŠ ąĘą░ą┐ąĖčüą░ąĮ ą╗ąŠą│. 0. ąĢčüą╗ąĖ ~SS čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą║ą░ą║ ą▓čģąŠą┤ ąĖ ą┐ąŠą┤čéčÅąĮčāčé ą║ ą╗ąŠą│. 0, ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ ą╗ąŠą│. 1 ą▒ąĖčé MSTR, č鹊 ą▒ąĖčé MSTR čüą▒čĆąŠčüąĖčéčüčÅ ą▓ ą╗ąŠą│. 0, ąĖ čāčüčéą░ąĮąŠą▓čÅčéčüčÅ ą▒ąĖčé SPIF ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPSR. ąöą╗čÅ č鹊ą│ąŠ, čćč鹊ą▒čŗ čüąĮąŠą▓ą░ ąĘą░čĆą░ą▒ąŠčéą░ą╗ čĆąĄąČąĖą╝ Master, ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą┤ąŠą╗ąČąĄąĮ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ čāčüčéą░ąĮąŠą▓ąĖčéčī ą▒ąĖčé MSTR.

Bit 3 ŌĆō CPOL: Clock Polarity

ąÜąŠą│ą┤ą░ čŹč鹊čé ą▒ąĖčé ąĘą░ą┐ąĖčüą░ąĮ ą▓ ą╗ąŠą│. 1, SCK ąĮą░čģąŠą┤ąĖčéčüčÅ ąĮą░ čāčĆąŠą▓ąĮąĄ ą╗ąŠą│. 1 ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ąŠąČąĖą┤ą░ąĮąĖčÅ. ąÜąŠą│ą┤ą░ ą▓ CPOL ąĘą░ą┐ąĖčüą░ąĮ ą╗ąŠą│. 0, č鹊 SCK ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ąŠąČąĖą┤ą░ąĮąĖčÅ ą▒čāą┤ąĄčé ąĮą░ čāčĆąŠą▓ąĮąĄ ą╗ąŠą│. 0. ąĪą╝. čĆąĖčü. 19-3 ąĖ 19-4 ą┤ą╗čÅ ą┐čĆąĖą╝ąĄčĆą░. ążčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠčüčéčī CPOL ą┐ąŠą║ą░ąĘą░ąĮą░ ą▓ čéą░ą▒ą╗ąĖčåąĄ ąĮąĖąČąĄ:

ąóą░ą▒ą╗ąĖčåą░ 19-3. ąÜą░ą║ čĆą░ą▒ąŠčéą░ąĄčé CPOL.

| CPOL |

ąØą░čćą░ą╗čīąĮčŗą╣ ą┐ąĄčĆąĄą┐ą░ą┤ |

ąÜąŠąĮąĄčćąĮčŗą╣ ą┐ąĄčĆąĄą┐ą░ą┤ |

| 0 |

ąØą░čĆą░čüčéą░ąĮąĖąĄ čāčĆąŠą▓ąĮčÅ |

ąĪą┐ą░ą┤ čāčĆąŠą▓ąĮčÅ |

| 1 |

ąĪą┐ą░ą┤ čāčĆąŠą▓ąĮčÅ |

ąØą░čĆą░čüčéą░ąĮąĖąĄ čāčĆąŠą▓ąĮčÅ |

Bit 2 ŌĆō CPHA: Clock Phase

ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖčéą░ čäą░ąĘčŗ (CPHA) ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé, ą║ą░ą║ ą▒čāą┤ąĄčé čüčćąĖčéčŗą▓ą░čéčīčüčÅ ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ - ą┐ąŠ ąĮą░čćą░ą╗čīąĮąŠą╝čā (ą┐ąĄčĆą▓ąŠą╝čā) ąĖą╗ąĖ ą┐ąŠ ąĘą░ą▓ąĄčĆčłą░čÄčēąĄą╝čā (ą┐ąŠčüą╗ąĄą┤ąĮąĄą╝čā) ą┐ąĄčĆąĄą┐ą░ą┤čā čāčĆąŠą▓ąĮčÅ SCK. ąĪą╝. čĆąĖčü. 19-3 ąĖ 19-4 ą┤ą╗čÅ ą┐čĆąĖą╝ąĄčĆą░. ążčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠčüčéčī CPHA ą┐ąŠą║ą░ąĘą░ąĮą░ ą▓ čéą░ą▒ą╗ąĖčåąĄ ąĮąĖąČąĄ:

ąóą░ą▒ą╗ąĖčåą░ 19-3. ąÜą░ą║ čĆą░ą▒ąŠčéą░ąĄčé CPOL.

| CPHA |

ąØą░čćą░ą╗čīąĮčŗą╣ ą┐ąĄčĆąĄą┐ą░ą┤ |

ąÜąŠąĮąĄčćąĮčŗą╣ ą┐ąĄčĆąĄą┐ą░ą┤ |

| 0 |

ąĪčćąĖčéčŗą▓ą░ąĮąĖąĄ čāčĆąŠą▓ąĮčÅ ą┤ą░ąĮąĮčŗčģ |

ąŻčüčéą░ąĮąŠą▓ą║ą░ čāčĆąŠą▓ąĮčÅ ą┤ą░ąĮąĮčŗčģ |

| 1 |

ąŻčüčéą░ąĮąŠą▓ą║ą░ čāčĆąŠą▓ąĮčÅ ą┤ą░ąĮąĮčŗčģ |

ąĪčćąĖčéčŗą▓ą░ąĮąĖąĄ čāčĆąŠą▓ąĮčÅ ą┤ą░ąĮąĮčŗčģ |

Bits 1, 0 ŌĆō SPR1, SPR0: ą▓čŗą▒ąŠčĆ čüą║ąŠčĆąŠčüčéąĖ čüą╗ąĄą┤ąŠą▓ą░ąĮąĖčÅ čéą░ą║č鹊ą▓ SPI

ąŁčéąĖ ą┤ą▓ą░ ą▒ąĖčéą░ čāą┐čĆą░ą▓ą╗čÅčÄčé čćą░čüč鹊č鹊ą╣ čüą╗ąĄą┤ąŠą▓ą░ąĮąĖčÅ ąĖą╝ą┐čāą╗čīčüąŠą▓ SCK, ą║ąŠą│ą┤ą░ čāčüčéčĆąŠą╣čüčéą▓ąŠ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąŠ ą║ą░ą║ Master. SPR1 ąĖ SPR0 ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░čÄčé ąĮąĖą║ą░ą║ąŠą│ąŠ ą▓ą╗ąĖčÅąĮąĖčÅ, ą║ąŠą│ą┤ą░ čāčüčéčĆąŠą╣čüčéą▓ąŠ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąŠ ą║ą░ą║ Slave. ąŚą░ą▓ąĖčüąĖą╝ąŠčüčéčī čćą░čüč鹊čéčŗ čéą░ą║č鹊ą▓ SCK ąĖ čćą░čüč鹊čéčŗ ą│ąĄąĮąĄčĆą░č鹊čĆą░ čéą░ą║č鹊ą▓ čüąĖčüč鹥ą╝čŗ (Oscillator Clock frequency, fOSC) ą┐ąŠą║ą░ąĘą░ąĮą░ ą▓ čéą░ą▒ą╗ąĖčåąĄ:

| SPI2X |

SPR1 |

SPR0 |

ą¦ą░čüč鹊čéą░ SCK |

| 0 |

0 |

0 |

fOSC/4 |

| 0 |

0 |

1 |

fOSC/16 |

| 0 |

1 |

0 |

fOSC/64 |

| 0 |

1 |

1 |

fOSC/128 |

| 1 |

0 |

0 |

fOSC/2 |

| 1 |

0 |

1 |

fOSC/8 |

| 1 |

1 |

0 |

fOSC/32 |

| 1 |

1 |

1 |

fOSC/64 |

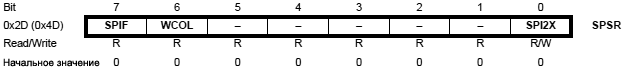

ąĀąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ SPI.

Bit 7 ŌĆō SPIF: SPI Interrupt Flag

ąÜąŠą│ą┤ą░ ąĘą░ą▓ąĄčĆčłąĄąĮą░ ą┐ąĄčĆąĄą┤ą░čćą░ čäčĆąĄą╣ą╝ą░ ą┤ą░ąĮąĮčŗčģ, čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ čäą╗ą░ą│ SPIF. ąĢčüą╗ąĖ ą▒ąĖčé SPIE ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPCR čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ąĖ čĆą░ąĘčĆąĄčłąĄąĮčŗ ą│ą╗ąŠą▒ą░ą╗čīąĮčŗąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, č鹊 ąĘą░ą┐čāčüčéąĖčéčüčÅ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ąĢčüą╗ąĖ ~SS ąĮą░čüčéčĆąŠąĄąĮ ą║ą░ą║ ą▓čģąŠą┤ ą▓ čĆąĄąČąĖą╝ąĄ SPI Master, ąĖ ą▓čģąŠą┤ ~SS ą┐ąĄčĆąĄą▓ąĄą┤ąĄąĮ ą▓ ą╗ąŠą│. 0, č鹊 čŹč鹊 čüąŠą▒čŗčéąĖąĄ čéą░ą║ąČąĄ čāčüčéą░ąĮąŠą▓ąĖčé čäą╗ą░ą│ SPIF. SPIF ąŠčćąĖčēą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą║ąŠą│ą┤ą░ ą▓čŗą┐ąŠą╗ąĮąĖčéčüčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ąÉą╗čīč鹥čĆąĮą░čéąĖą▓ąĮąŠ ą▒ąĖčé SPIF ąŠčćąĖčēą░ąĄčéčüčÅ ą┐ąĄčĆą▓čŗą╝ čćč鹥ąĮąĖąĄą╝ čĆąĄą│ąĖčüčéčĆą░ čüąŠčüč鹊čÅąĮąĖčÅ SPSR, ą║ąŠą│ą┤ą░ ą▒ąĖčé SPIF čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ąĖ ą┐ąŠčüą╗ąĄą┤čāčÄčēąĖą╝ ą┤ąŠčüčéčāą┐ąŠą╝ ą║ čĆąĄą│ąĖčüčéčĆčā ą┤ą░ąĮąĮčŗčģ SPI (SPDR).

Bit 6 ŌĆō WCOL: Write COLlision Flag

ąæąĖčé WCOL čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ, ąĄčüą╗ąĖ ą▓ čĆąĄą│ąĖčüčéčĆ ą┤ą░ąĮąĮčŗčģ SPI (SPDR) ąĘą░ą┐ąĖčüą░ąĮčŗ ą┤ą░ąĮąĮčŗąĄ ą▓ č鹊čé ą╝ąŠą╝ąĄąĮčé, ą║ąŠą│ą┤ą░ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą┐ąĄčĆąĄą┤ą░čćą░. ąæąĖčé WCOL (ąĖ ą▓ą╝ąĄčüč鹥 čü ąĮąĖą╝ ą▒ąĖčé SPIF) ąŠčćąĖčüčéčÅčéčüčÅ ą┐ąĄčĆą▓čŗą╝ čćč鹥ąĮąĖąĄą╝ čĆąĄą│ąĖčüčéčĆą░ čüąŠčüč鹊čÅąĮąĖčÅ SPI čü čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╝ ą▒ąĖč鹊ą╝ WCOL, ąĖ ą┐ąŠčüą╗ąĄą┤čāčÄčēąĖą╝ ą┤ąŠčüčéčāą┐ąŠą╝ ą║ čĆąĄą│ąĖčüčéčĆčā ą┤ą░ąĮąĮčŗčģ SPI (SPDR).

Bit [5:1] ŌĆō Reserved

ąŁčéąĖ ą▒ąĖčéčŗ ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ ą▓ ATmega48A/PA/88A/PA/168A/PA/328/P ąĖ ą▓čüąĄą│ą┤ą░ čćąĖčéą░čÄčéčüčÅ ą║ą░ą║ 0.

Bit 0 ŌĆō SPI2X: Double SPI Speed Bit

ąÜąŠą│ą┤ą░ ą▓ čŹč鹊čé ą▒ąĖčé ąĘą░ą┐ąĖčüą░ąĮą░ ą╗ąŠą│. 1, č鹊 čüą║ąŠčĆąŠčüčéčī SPI (čé. ąĄ. čćą░čüč鹊čéą░ čéą░ą║č鹊ą▓ SCK) čāą┤ą▓ą░ąĖą▓ą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ SPI čĆą░ą▒ąŠčéą░ąĄčé ą▓ čĆąĄąČąĖą╝ąĄ Master (čüą╝. čéą░ą▒ą╗ąĖčåčā 19-5). ąŁč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ą╝ąĖąĮąĖą╝ą░ą╗čīąĮčŗą╣ ą┐ąĄčĆąĖąŠą┤ SCK čüąŠčüčéą░ą▓ąĖčé 2 čéą░ą║čéą░ čÅą┤čĆą░ CPU. ąÜąŠą│ą┤ą░ SPI čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą║ą░ą║ Slave, čĆą░ą▒ąŠčéą░ SPI ą│ą░čĆą░ąĮčéąĖčĆčāąĄčéčüčÅ ąĮą░ čćą░čüč鹊čéą░čģ fOSC/4 ąĖą╗ąĖ ąĮąĖąČąĄ.

ąóą░ą║ąČąĄ ąĖąĮč鹥čĆč乥ą╣čü SPI ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ ATmega48A/PA/88A/PA/168A/PA/328/P ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ą▓ąĮčāčéčĆąĖčüčģąĄą╝ąĮąŠą│ąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ (ISP), čéą░ą║ čćč鹊 čü ą┐ąŠą╝ąŠčēčīčÄ ą▓ąĮąĄčłąĮąĄą│ąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ą░č鹊čĆą░ ISP ą╝ąŠąČąĮąŠ ąĘą░ą┐ąĖčüą░čéčī ąĖ ą┐čĆąŠčćąĖčéą░čéčī ą┐ą░ą╝čÅčéčī ą┐čĆąŠą│čĆą░ą╝ą╝ (FLASH), 菹ĮąĄčĆą│ąŠąĮąĄąĘą░ą▓ąĖčüąĖą╝čāčÄ ą┐ą░ą╝čÅčéčī (EEPROM) ąĖ čäčīčÄąĘčŗ (ą┐ąŠą┤čĆąŠą▒ąĮąŠčüčéąĖ čüą╝. ą▓ ą┤ą░čéą░čłąĖč鹥 ąĮą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ).

ąĀąĄą│ąĖčüčéčĆ ą┤ą░ąĮąĮčŗčģ SPI.

ąĀąĄą│ąĖčüčéčĆ ą┤ą░ąĮąĮčŗčģ SPI ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ / ąĘą░ą┐ąĖčüąĖ ą┐čĆąĖąĮąĖą╝ą░ąĄą╝čŗčģ ąĖ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗčģ ą┤ą░ąĮąĮčŗčģ. ąĀąĄą│ąĖčüčéčĆ SPDR čĆą░čüą┐ąŠą╗ąŠąČąĄąĮ ą▓ ąŠą▒ą╗ą░čüčéąĖ čäą░ą╣ą╗ą░ čĆąĄą│ąĖčüčéčĆąŠą▓ AVR, ąĖ čüą╗čāąČąĖčé ą┤ą╗čÅ ąŠą▒ą╝ąĄąĮą░ ą┤ą░ąĮąĮčŗą╝ąĖ čü čĆąĄą│ąĖčüčéčĆą░ą╝ąĖ čüą┤ą▓ąĖą│ą░ SPI. ąŚą░ą┐ąĖčüčī ą▓ SPDR ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆčāąĄčé ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ. ą¦č鹥ąĮąĖąĄ SPDR ą▓čŗą┐ąŠą╗ąĮčÅąĄčé čćč鹥ąĮąĖąĄ ą▒čāč乥čĆą░ čĆąĄą│ąĖčüčéčĆą░ čüą┤ą▓ąĖą│ą░ SPI.

[ąĪčüčŗą╗ą║ąĖ]

1. AVR151: ąĮą░čüčéčĆąŠą╣ą║ą░ ąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ SPI.

2. ąśąĮč鹥čĆč乥ą╣čü SPI.

3. ATmega328: USART ą▓ čĆąĄąČąĖą╝ąĄ SPI.

4. GPIO ąĖ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčŗąĄ čäčāąĮą║čåąĖąĖ ą┐ąŠčĆčéą░. |