|

ą×čüąĮąŠą▓ąĮčŗąĄ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ:

ŌĆó ą¤ąŠą╗ąĮčŗą╣ ą┤čāą┐ą╗ąĄą║čü, čéčĆąĄčģą┐čĆąŠą▓ąŠą┤ąĮčŗą╣, čüąĖąĮčģčĆąŠąĮąĮčŗą╣ ąŠą▒ą╝ąĄąĮ ą┤ą░ąĮąĮčŗą╝ąĖ

ŌĆó ąĀą░ą▒ąŠčéą░ č鹊ą╗čīą║ąŠ ą▓ čĆąĄąČąĖą╝ąĄ ą│ą╗ą░ą▓ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (Master)

ŌĆó ą¤ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčéčüčÅ ą▓čüąĄ 4 čĆąĄąČąĖą╝ą░ čĆą░ą▒ąŠčéčŗ SPI (Mode 0, 1, 2 ąĖ 3)

ŌĆó ą£ąŠąČąĮąŠ ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī ą┐ąĄčĆą▓čŗą╝ ąĖą╗ąĖ ą╝ą╗ą░ą┤čłąĖą╣ (LSB), ąĖą╗ąĖ čüčéą░čĆčłąĖą╣ (MSB) ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ

ŌĆó ąĀą░ą▒ąŠčéą░ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ ąŠč湥čĆąĄą┤ąĖ (ą┤ą▓ąŠą╣ąĮą░čÅ ą▒čāč乥čĆąĖąĘą░čåąĖčÅ)

ŌĆó ąōąĄąĮąĄčĆą░č鹊čĆ čüą║ąŠčĆąŠčüčéąĖ čü ą▓čŗčüąŠą║ąŠą╣ čĆą░ąĘčĆąĄčłą░čÄčēąĄą╣ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčīčÄ

ŌĆó ąĀą░ą▒ąŠčéą░ ąĮą░ ą▓čŗčüąŠą║ąŠą╣ čüą║ąŠčĆąŠčüčéąĖ (fXCKmax = fCK/2)

ŌĆó ąōąĖą▒ą║ą░čÅ čüąĖčüč鹥ą╝ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣

ąæą╗ąŠą║ čāąĮąĖą▓ąĄčĆčüą░ą╗čīąĮąŠą│ąŠ čüąĖąĮčģčĆąŠąĮąĮąŠą│ąŠ ąĖ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą│ąŠ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ ąĖ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ USART (Universal Synchronous and Asynchronous serial Receiver and Transmitter) ą╝ąŠąČąĄčé čĆą░ą▒ąŠčéą░čéčī ą▓ čĆąĄąČąĖą╝ąĄ, čüąŠą▓ą╝ąĄčüčéąĖą╝ąŠą╝ čü master SPI.

ąŻčüčéą░ąĮąŠą▓ą║ą░ ąŠą▒ąŠąĖčģ ą▒ąĖčé UMSELn1:0 ą▓ ą╗ąŠą│. 1 čĆą░ąĘčĆąĄčłą░ąĄčé čĆą░ą▒ąŠčéčā USART ą▓ ą╗ąŠą│ąĖą║ąĄ MSPIM (ą░ą▒ą▒čĆąĄą▓ąĖą░čéčāčĆą░ čĆą░čüčłąĖčäčĆąŠą▓čŗą▓ą░ąĄčéčüčÅ ą║ą░ą║ Master SPI mode). ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ čĆą░ą▒ąŠčéčŗ čāą┐čĆą░ą▓ą╗čÅčÄčēą░čÅ ą╗ąŠą│ąĖą║ą░ SPI master ą┐ąŠą╗čāčćą░ąĄčé ą┐čĆčÅą╝ąŠąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ąĮą░ą┤ ą░ą┐ą┐ą░čĆą░čéčāčĆąŠą╣ USART. ąŁčéąĖ ą░ą┐ą┐ą░čĆą░čéąĮčŗąĄ čĆąĄčüčāčĆčüčŗ ą▓ą║ą╗čÄčćą░čÄčé čĆąĄą│ąĖčüčéčĆčŗ čüą┤ą▓ąĖą│ą░ ąĖ ą▒čāč乥čĆčŗ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ ąĖ ą┐čĆąĖąĄą╝ąĮąĖą║ą░, ą░ čéą░ą║ąČąĄ ą│ąĄąĮąĄčĆą░č鹊čĆ čüą║ąŠčĆąŠčüčéąĖ (baud rate generator). ąĀą░ą▒ąŠčéą░ ą│ąĄąĮąĄčĆą░č鹊čĆą░ ą▒ąĖčéą░ č湥čéąĮąŠčüčéąĖ ąĖ ą▒ą╗ąŠą║ą░ ąĄą│ąŠ ą┐čĆąŠą▓ąĄčĆą║ąĖ, ą░ ą╗ąŠą│ąĖą║ą░ ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ąĖ čéą░ą║č鹊ą▓, ą╗ąŠą│ąĖą║ą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ RX ąĖ TX ą▓ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ąŠčéą║ą╗čÄčćą░čÄčéčüčÅ. ąøąŠą│ąĖą║ą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ USART RX ąĖ TX ąĘą░ą╝ąĄąĮčÅąĄčéčüčÅ ąŠą▒čēąĄą╣ ą╗ąŠą│ąĖą║ąŠą╣ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąŠą▒ą╝ąĄąĮąŠą╝ SPI. ą×ą┤ąĮą░ą║ąŠ ą╗ąŠą│ąĖą║ą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą▓čŗą▓ąŠą┤ą░ą╝ąĖ ąĖ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ąĖą┤ąĄąĮčéąĖčćąĮą░ ą┤ą╗čÅ ąŠą▒ąŠąĖčģ čĆąĄąČąĖą╝ąŠą▓ čĆą░ą▒ąŠčéčŗ (USART ąĖ SPI).

ąÉą┤čĆąĄčüą░ čĆąĄą│ąĖčüčéčĆąŠą▓ I/O ąŠčüčéą░čÄčéčüčÅ ą┤ą╗čÅ ąŠą▒ąŠąĖčģ čĆąĄąČąĖą╝ąŠą▓ ąŠą┤ąĖąĮą░ą║ąŠą▓čŗą╝ąĖ. ą×ą┤ąĮą░ą║ąŠ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠčüčéčī ąĮąĄą║ąŠč鹊čĆčŗčģ čāą┐čĆą░ą▓ą╗čÅčÄčēąĖčģ čĆąĄą│ąĖčüčéčĆąŠą▓ ą┐čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ MSPIM ą╝ąĄąĮčÅąĄčéčüčÅ.

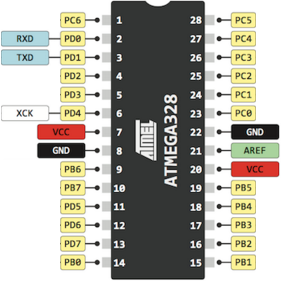

ąØą░ čĆąĖčüčāąĮą║ąĄ ą▓ ą║ą░č湥čüčéą▓ąĄ ą┐čĆąĖą╝ąĄčĆą░ ą┐ąŠą║ą░ąĘą░ąĮčŗ ąĮąŠąČą║ąĖ USART (RXD, TXD, XCK) ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ATmega328P ą▓ ą║ąŠčĆą┐čāčüąĄ DIP28, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą║ą░ą║ SPI.

[ąōąĄąĮąĄčĆą░čåąĖčÅ čéą░ą║č鹊ą▓]

ąøąŠą│ąĖą║ą░ ą│ąĄąĮąĄčĆą░čåąĖąĖ čéą░ą║č鹊ą▓ čüąŠąĘą┤ą░ąĄčé ą▒ą░ąĘąŠą▓čāčÄ čéą░ą║č鹊ą▓čāčÄ čćą░čüč鹊čéčā ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ ąĖ ą┐čĆąĖąĄą╝ąĮąĖą║ą░. ąöą╗čÅ čĆąĄąČąĖą╝ą░ USART MSPIM ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ č鹊ą╗čīą║ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ ąĖ ą▓čŗą┤ą░čćą░ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čéą░ą║č鹊ą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ąĮą░čĆčāąČčā (čé. ąĄ. čĆą░ą▒ąŠčéą░ č鹊ą╗čīą║ąŠ ą▓ čĆąĄąČąĖą╝ąĄ ą│ą╗ą░ą▓ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░, SPI master). ąÆ čĆąĄą│ąĖčüčéčĆąĄ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ DDRx ą▒ąĖčé ą┤ą╗čÅ ą▓čŗą▓ąŠą┤ą░ XCKn (čāčüą╗ąŠą▓ąĮąŠ ąŠą▒ąŠąĘąĮą░čćąĖą╝ ąĮąŠą╝ąĄčĆ čŹč鹊ą│ąŠ ą▒ąĖčéą░ DDR_XCKn) ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ ą╗ąŠą│. 1 (čćč鹊ą▒čŗ ąŠąĮ čĆą░ą▒ąŠčéą░ą╗ ą║ą░ą║ ą▓čŗčģąŠą┤), čćč鹊ą▒čŗ ą║ąŠčĆčĆąĄą║čéąĮąŠ čĆą░ą▒ąŠčéą░ą╗ čĆąĄąČąĖą╝ USART MSPIM. ą¢ąĄą╗ą░č鹥ą╗čīąĮąŠ čāčüčéą░ąĮąŠą▓ąĖčéčī ą▒ąĖčé DDR_XCKn ą┤ąŠ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ čĆą░ą▒ąŠčéčŗ USART ą▓ čĆąĄąČąĖą╝ąĄ MSPIM (čé. ąĄ. ą┤ąŠ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▓ ą╗ąŠą│. 1 ą▒ąĖč鹊ą▓ TXENn ąĖ RXENn).

ąōąĄąĮąĄčĆą░čåąĖčÅ čéą░ą║č鹊ą▓ ą▓ čĆąĄąČąĖą╝ąĄ MSPIM ąĖą┤ąĄąĮčéąĖčćąĮą░ čĆąĄąČąĖą╝čā ą│ąĄąĮąĄčĆą░čåąĖąĖ čéą░ą║č鹊ą▓ ą▓ USART synchronous master mode. ąóą░ą║ čćč鹊 čüą║ąŠčĆąŠčüčéčī (baud rat) ąĖą╗ąĖ ąĮą░čüčéčĆąŠą╣ą║ą░ UBRRn ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗčćąĖčüą╗ąĄąĮą░ ą┐ąŠ č鹊ą╣ ąČąĄ č乊čĆą╝čāą╗ąĄ, čüą╝. čéą░ą▒ą╗ąĖčåčā 21-1:

ąóą░ą▒ą╗ąĖčåą░ 21-1. ąÆčŗčĆą░ąČąĄąĮąĖčÅ ą┤ą╗čÅ ą▓čŗčćąĖčüą╗ąĄąĮąĖčÅ ąĮą░čüčéčĆąŠą╣ą║ąĖ čĆąĄą│ąĖčüčéčĆą░ čüą║ąŠčĆąŠčüčéąĖ (Baud Rate Register).

ąĀąĄąČąĖą╝

|

ąÆčŗčĆą░ąČąĄąĮąĖąĄ ą┤ą╗čÅ

ą▓čŗčćąĖčüą╗ąĄąĮąĖčÅ čüą║ąŠčĆąŠčüčéąĖ |

ąÆčŗčĆą░ąČąĄąĮąĖąĄ ą┤ą╗čÅ ą▓čŗčćąĖčüą╗ąĄąĮąĖčÅ

ąĘąĮą░č湥ąĮąĖčÅ UBRRn |

| ąĪąĖąĮčģčĆąŠąĮąĮčŗą╣, Master |

fOSC

BAUD = -----------

2*(UBRRn+1) |

fOSC

UBRRn = -------- - 1

2*BAUD |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: baud rate (čüą║ąŠčĆąŠčüčéčī ą▒ąĖčé) ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮą░ ą▓ ą▒ąĖčéą░čģ ąĮą░ čüąĄą║čāąĮą┤čā (bps).

BAUD Baud rate (ą▓ ą▒ąĖčéą░čģ/čüąĄą║, bps)

fOSC čćą░čüč鹊čéą░ čüąĖčüč鹥ą╝ąĮąŠą│ąŠ čéą░ą║č鹊ą▓ąŠą│ąŠ ą│ąĄąĮąĄčĆą░č鹊čĆą░ (System Oscillator clock frequency)

UBRRn čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ čĆąĄą│ąĖčüčéčĆąŠą▓ UBRRnH ąĖ UBRRnL (0-4095)

[ąĀąĄąČąĖą╝čŗ čäčĆąĄą╣ą╝ą░ ą┤ą░ąĮąĮčŗčģ SPI Data ąĖ ą┤ąĖą░ą│čĆą░ą╝ą╝čŗ]

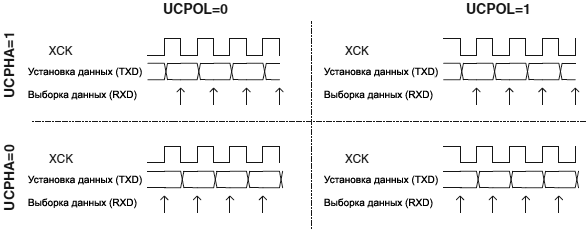

ąśą╝ąĄčÄčéčüčÅ 4 ą║ąŠą╝ą▒ąĖąĮą░čåąĖąĖ čäą░ąĘčŗ ąĖ ą┐ąŠą╗čÅčĆąĮąŠčüčéąĖ XCKn (ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓ ą║ą░č湥čüčéą▓ąĄ čüąĖą│ąĮą░ą╗ą░ SCK ąĖąĮč鹥čĆč乥ą╣čüą░ SPI) ą┐ąŠ ąŠčéąĮąŠčłąĄąĮąĖčÄ ą║ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╝ ą┤ą░ąĮąĮčŗą╝. ąŁčéąĖ ą║ąŠą╝ą▒ąĖąĮą░čåąĖąĖ ąĘą░ą┤ą░čÄčé č乊čĆą╝ą░čé čäčĆąĄą╣ą╝ą░ (čĆąĄąČąĖą╝ 0, 1, 2 ąĖ 3), čćč鹊 ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ čāą┐čĆą░ą▓ą╗čÅčÄčēąĖą╝ąĖ ą▒ąĖčéą░ą╝ąĖ UCPHAn ąĖ UCPOLn. ąöąĖą░ą│čĆą░ą╝ą╝čŗ ą▓čĆąĄą╝ąĄąĮąĖ ąŠą▒ą╝ąĄąĮą░ ą┤ą░ąĮąĮčŗą╝ąĖ ą┐ąŠą║ą░ąĘą░ąĮčŗ ąĮą░ čĆąĖčü. 21-1. ą¤ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗąĄ ą▒ąĖčéčŗ ą┤ą░ąĮąĮčŗčģ ą▓čŗą┤ą▓ąĖą│ą░čÄčéčüčÅ ąĮą░čĆčāąČčā, ąĖ ą▓čģąŠą┤ąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ąĘą░čēąĄą╗ą║ąĖą▓ą░čÄčéčüčÅ ąĮą░ ą┐čĆąĖąĄą╝ąĄ ą▓ ą┐čĆąŠčéąĖą▓ąŠą┐ąŠą╗ąŠąČąĮčŗčģ ą┐ąĄčĆąĄą┐ą░ą┤ą░čģ čéą░ą║č鹊ą▓ XCKn, ą│ą░čĆą░ąĮčéąĖčĆčāčÅ ą┤ąŠčüčéą░č鹊čćąĮąŠąĄ ą▓čĆąĄą╝čÅ ą┤ą╗čÅ čüčéą░ą▒ąĖą╗ąĖąĘą░čåąĖąĖ ą┤ą░ąĮąĮčŗčģ. ążčāąĮą║čåąĖąŠąĮą░ą╗ ą▒ąĖč鹊ą▓ UCPOLn ąĖ UCPHAn čüčāą╝ą╝ą░čĆąĮąŠ ą┐ąŠą║ą░ąĘą░ąĮ ą▓ čéą░ą▒ą╗ąĖčåąĄ 21-2. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ąĄčüą╗ąĖ ą┐ąŠą╝ąĄąĮčÅčéčī čŹčéąĖ ą▒ąĖčéčŗ ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐čĆąŠąĖčüčģąŠą┤čÅčēąĄą│ąŠ ąŠą▒ą╝ąĄąĮą░ ą┐ąŠą▓čĆąĄą┤ąĖčé č乊čĆą╝ąĖčĆčāąĄą╝čŗąĄ ąĖ ą┐čĆąĖąĮąĖą╝ą░ąĄą╝čŗąĄ čäčĆąĄą╣ą╝čŗ ą┤ą░ąĮąĮčŗčģ.

ąóą░ą▒ą╗ąĖčåą░ 21-2. ąÜą░ą║ čĆą░ą▒ąŠčéą░čÄčé ą▒ąĖčéčŗ UCPOLn ąĖ UCPHAn.

| UCPOLn |

UCPHAn |

SPI Mode |

ąØą░čćą░ą╗čīąĮčŗą╣ ą┐ąĄčĆąĄą┐ą░ą┤ |

ąŚą░ą▓ąĄčĆčłą░čÄčēąĖą╣ ą┐ąĄčĆąĄą┐ą░ą┤ |

| 0 |

0 |

0 |

ąÆčŗą▒ąŠčĆą║ą░ čüąĖą│ąĮą░ą╗ą░ (ą┐ąŠ ąĮą░čĆą░čüčéą░ąĮąĖčÄ čāčĆąŠą▓ąĮčÅ) |

ąŻčüčéą░ąĮąŠą▓ą║ą░ čüąĖą│ąĮą░ą╗ą░ (ą┐ąŠ čüą┐ą░ą┤čā čāčĆąŠą▓ąĮčÅ) |

| 0 |

1 |

1 |

ąŻčüčéą░ąĮąŠą▓ą║ą░ čüąĖą│ąĮą░ą╗ą░ (ą┐ąŠ ąĮą░čĆą░čüčéą░ąĮąĖčÄ čāčĆąŠą▓ąĮčÅ) |

ąÆčŗą▒ąŠčĆą║ą░ čüąĖą│ąĮą░ą╗ą░ (ą┐ąŠ čüą┐ą░ą┤čā čāčĆąŠą▓ąĮčÅ) |

| 1 |

0 |

2 |

ąÆčŗą▒ąŠčĆą║ą░ čüąĖą│ąĮą░ą╗ą░ (ą┐ąŠ čüą┐ą░ą┤čā čāčĆąŠą▓ąĮčÅ) |

ąŻčüčéą░ąĮąŠą▓ą║ą░ čüąĖą│ąĮą░ą╗ą░ (ą┐ąŠ ąĮą░čĆą░čüčéą░ąĮąĖčÄ čāčĆąŠą▓ąĮčÅ) |

| 1 |

1 |

3 |

ąŻčüčéą░ąĮąŠą▓ą║ą░ čüąĖą│ąĮą░ą╗ą░ (ą┐ąŠ čüą┐ą░ą┤čā čāčĆąŠą▓ąĮčÅ) |

ąÆčŗą▒ąŠčĆą║ą░ čüąĖą│ąĮą░ą╗ą░ (ą┐ąŠ ąĮą░čĆą░čüčéą░ąĮąĖčÄ čāčĆąŠą▓ąĮčÅ) |

ąĀąĖčü. 21-1. ąöąĖą░ą│čĆą░ą╝ą╝čŗ ą▓čĆąĄą╝ąĄąĮąĖ ąŠą▒ą╝ąĄąĮą░ ą┤ą░ąĮąĮčŗą╝ąĖ ą┤ą╗čÅ čĆą░ąĘąĮčŗčģ ąĮą░čüčéčĆąŠąĄą║ UCPHAn ąĖ UCPOLn.

[ążąŠčĆą╝ą░čéčŗ čäčĆąĄą╣ą╝ą░ ą┤ą░ąĮąĮčŗčģ]

ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ čäčĆąĄą╣ą╝ ą┤ą╗čÅ čĆąĄąČąĖą╝ą░ MSPIM ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ą┐ąĄčĆąĄą┤ą░čćčā ąŠą┤ąĮąŠą│ąŠ čüąĖą╝ą▓ąŠą╗ą░, čüąŠčüč鹊čÅčēąĄą│ąŠ ąĖąĘ 8 ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ. ąĀąĄąČąĖą╝ USART MSPIM ąĖą╝ąĄąĄčé 2 ą┤ąŠą┐čāčüčéąĖą╝čŗčģ č乊čĆą╝ą░čéą░ čäčĆąĄą╣ą╝ą░:

ŌĆó 8-ą▒ąĖčéąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ čü ą┐ąĄčĆą▓čŗą╝ čüčéą░čĆčłąĖą╝ ą▒ąĖč鹊ą╝ (MSB ąĖą┤ąĄčé ą┐ąĄčĆą▓čŗą╝)

ŌĆó 8-ą▒ąĖčéąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ čü ą┐ąĄčĆą▓čŗą╝ ą╝ą╗ą░ą┤čłąĖą╝ ą▒ąĖč鹊ą╝ (LSB ąĖą┤ąĄčé ą┐ąĄčĆą▓čŗą╝)

ążčĆąĄą╣ą╝ ąĮą░čćąĖąĮą░ąĄčéčüčÅ čü ą┐ąĄčĆąĄą┤ą░čćąĖ ą╝ą╗ą░ą┤čłąĄą│ąŠ (LSB) ąĖą╗ąĖ čüčéą░čĆčłąĄą│ąŠ (MSB) ą▒ąĖčéą░ ą┤ą░ąĮąĮčŗčģ. ąŚą░č鹥ą╝ ąĖą┤čāčé čüą╗ąĄą┤čāčÄčēąĖąĄ ą┐ąŠ čüčéą░čĆčłąĖąĮčüčéą▓čā ą▒ąĖčéčŗ, ą▓čüąĄą│ąŠ ą▓ąŠčüąĄą╝čī, ąĘą░ą║ą░ąĮčćąĖą▓ą░čÅčüčī čüčéą░čĆčłąĖą╝ ąĖą╗ąĖ ą╝ą╗ą░ą┤čłąĖą╝ ą▒ąĖč鹊ą╝ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ. ąÜąŠą│ą┤ą░ čäčĆąĄą╣ą╝ ą┐ąĄčĆąĄą┤ą░ąĮ ą┐ąŠą╗ąĮąŠčüčéčīčÄ, ąĘą░ ąĮąĖą╝ čüčĆą░ąĘčā čüą╗ąĄą┤čāąĄčé čüą╗ąĄą┤čāčÄčēąĖą╣ čäčĆąĄą╣ą╝, ąĖą╗ąĖ ą╗ąĖąĮąĖčÅ ąŠą▒ą╝ąĄąĮą░ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ąŠąČąĖą┤ą░ąĮąĖčÅ (ą╗ąŠą│. 1).

ąæąĖčéčŗ UDORDn ą▓ čĆąĄą│ąĖčüčéčĆąĄ UCSRnC čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄčé č乊čĆą╝ą░čé čäčĆąĄą╣ą╝ą░, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╣ USART ą▓ čĆąĄąČąĖą╝ąĄ MSPIM. ą¤čĆąĖąĄą╝ąĮąĖą║ ąĖ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ ąĖčüą┐ąŠą╗čīąĘčāčÄčé ąŠą┤ąĮčā ąĖ čéčā ąČąĄ ąĮą░čüčéčĆąŠą╣ą║čā. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 čüą╝ąĄąĮą░ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▓ ą╗čÄą▒ąŠą╝ ąĖąĘ čŹčéąĖčģ ą▒ąĖč鹊ą▓ ą┐ąŠą▓čĆąĄą┤čÅčé ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗą╣ ąĖ ą┐čĆąĖąĮąĖą╝ą░ąĄą╝čŗą╣ ą▓ ąĮą░čüč鹊čÅčēąĖą╣ ą╝ąŠą╝ąĄąĮčé čäčĆąĄą╣ą╝čŗ.

16-ą▒ąĖčéąĮą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░ ą┤ą░ąĮąĮčŗčģ ą▓ąŠąĘą╝ąŠąČąĮąŠ ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ ą┤ą▓čāčģ ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ ą▓ čĆąĄą│ąĖčüčéčĆ UDRn. ą¤ąĄčĆąĄą┤ą░čćą░ UART ąĘą░ą▓ąĄčĆčłąĖčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄą╝, ą║ąŠč鹊čĆąŠąĄ ą▒čāą┤ąĄčé čüąĖą│ąĮą░ą╗ąĖąĘąĖčĆąŠą▓ą░čéčī ąŠ č鹊ą╝, čćč鹊 16-ą▒ąĖčéąĮą░čÅ ą▓ąĄą╗ąĖčćąĖąĮą░ ą┐ąŠą╗ąĮąŠčüčéčīčÄ ą▓čŗą┤ą▓ąĖąĮčāčéą░.

ąśąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ USART MSPIM. USART ą▓ čĆąĄąČąĖą╝ąĄ MSPIM ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆčāąĄčéčüčÅ ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ą╝ąŠąČąĄčé ą┐čĆąŠąĖąĘąŠą╣čéąĖ ą╗čÄą▒ąŠą╣ ąŠą▒ą╝ąĄąĮ ą┤ą░ąĮąĮčŗą╝ąĖ. ą¤čĆąŠčåąĄčüčü ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ ąŠą▒čŗčćąĮąŠ čüąŠčüč鹊ąĖčé ąĖąĘ čāčüčéą░ąĮąŠą▓ą║ąĖ čüą║ąŠčĆąŠčüčéąĖ (baud rate), čāčüčéą░ąĮąŠą▓ą║ąĖ čĆąĄąČąĖą╝ą░ ą│ą╗ą░ą▓ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▓ ą╗ąŠą│. 1 ą▒ąĖčéą░ DDR_XCKn), čāčüčéą░ąĮąŠą▓ą║ąĖ č乊čĆą╝ą░čéą░ čäčĆąĄą╣ą╝ą░ ąĖ čĆą░ąĘčĆąĄčłąĄąĮąĖąĖ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ ąĖ ą┐čĆąĖąĄą╝ąĮąĖą║ą░. ąØąĄąĘą░ą▓ąĖą╝ąŠą╝ąŠ ą╝ąŠąČąĄčé čĆą░ą▒ąŠčéą░čéčī č鹊ą╗čīą║ąŠ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║. ąöą╗čÅ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖčÅ USART čü čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝ ą┐ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅą╝ ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐čĆąŠčåąĄą┤čāčĆčŗ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čüą▒čĆąŠčłąĄąĮ čäą╗ą░ą│ ą│ą╗ąŠą▒ą░ą╗čīąĮąŠą│ąŠ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ (ą▒ąĖčé I ą▓ čĆąĄą│ąĖčüčéčĆąĄ SREG), čćč鹊ą▒čŗ ą▓čĆąĄą╝ąĄąĮąĮąŠ ąĘą░ą┐čĆąĄčéąĖčéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: čćč鹊ą▒čŗ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮčāčÄ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÄ ą▓čŗčģąŠą┤ą░ XCKn, čĆąĄą│ąĖčüčéčĆ čüą║ąŠčĆąŠčüčéąĖ (baud-rate register, UBRRn) ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąŠą▒ąĮčāą╗ąĄąĮ ą▓ ą╝ąŠą╝ąĄąĮčé čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░. ąÆ ą║ąŠąĮčéčĆą░čüč鹥 čü ąĮąŠčĆą╝ą░ą╗čīąĮčŗą╝ čĆąĄąČąĖą╝ąŠą╝ čĆą░ą▒ąŠčéčŗ USART, čĆąĄą│ąĖčüčéčĆ UBRRn ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮąŠ ąĮčāąČąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ čĆą░ąĘčĆąĄčłąĄąĮ, ąĮąŠ ą┐ąĄčĆąĄą┤ ąĮą░čćą░ą╗ąŠą╝ ą┐ąĄčĆą▓ąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ. ąŻčüčéą░ąĮąŠą▓ą║ą░ UBRRn ą▓ ąĮąŠą╗čī ą┐ąĄčĆąĄą┤ čĆą░ąĘčĆąĄčłąĄąĮąĖąĄą╝ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ ąĮąĄ ąŠą▒čÅąĘą░č鹥ą╗čīąĮą░, ąĄčüą╗ąĖ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ čüčĆą░ąĘčā ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░, ą┐ąŠč鹊ą╝čā čćč鹊 čüą▒čĆąŠčü ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąŠą▒ąĮčāą╗čÅąĄčé UBRRn.

ą¤ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ čüą┤ąĄą╗ą░čéčī ą┐ąŠą▓č鹊čĆąĮčāčÄ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÄ ą┐čĆąĖ ąĖąĘą╝ąĄąĮąĄąĮąĖąĖ čüą║ąŠčĆąŠčüčéąĖ, čĆąĄąČąĖą╝ą░ ą┤ą░ąĮąĮčŗčģ ąĖą╗ąĖ č乊čĆą╝ą░čéą░ čäčĆąĄą╣ą╝ą░, čāą▒ąĄą┤ąĖč鹥čüčī, čćč鹊 ąĮąĄ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ąŠą▒ą╝ąĄąĮ ą┤ą░ąĮąĮčŗą╝ąĖ ą┐čĆąĖ ąĖąĘą╝ąĄąĮąĄąĮąĖąĖ ąĮą░čüčéčĆąŠąĄą║ čĆąĄą│ąĖčüčéčĆąŠą▓. ążą╗ą░ą│ TXCn ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą┐čĆąŠą▓ąĄčĆą║ąĖ, ąĘą░ą▓ąĄčĆčłąĖą╗ ą╗ąĖ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ ą▓čüąĄ čüą▓ąŠąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ, ąĖ čäą╗ą░ą│ RXCn ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą┐čĆąŠą▓ąĄčĆą║ąĖ, čćč鹊 ąĮąĄ ąŠčüčéą░ą╗ąŠčüčī ąĮąĄ ą┐čĆąŠčćąĖčéą░ąĮąĮčŗčģ ą┤ą░ąĮąĮčŗčģ ą▓ ą▒čāč乥čĆąĄ ą┐čĆąĖąĄą╝ą░. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 čäą╗ą░ą│ TXCn ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąŠčćąĖčēąĄąĮ ą┐ąĄčĆąĄą┤ ą║ą░ąČą┤ąŠą╣ ą┐ąĄčĆąĄą┤ą░č湥ą╣ (ą┤ąŠ č鹊ą│ąŠ, ą║ą░ą║ ą▒čāą┤ąĄčé ąĘą░ą┐ąĖčüą░ąĮ UDRn), ąĄčüą╗ąĖ ąŠąĮ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čŹč鹊ą╣ čåąĄą╗ąĖ.

ąØąĖąČąĄ ą┤ą░ąĮčŗ ą┐čĆąŠčüčéčŗąĄ ą┐čĆąĖą╝ąĄčĆčŗ ą║ąŠą┤ą░ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ USART (ąĮą░ ą░čüčüąĄą╝ą▒ą╗ąĄčĆąĄ ąĖ ąĮą░ C, čü 菹║ą▓ąĖą▓ą░ą╗ąĄąĮčéąĮčŗą╝ čäčāąĮą║čåąĖąŠąĮą░ą╗ąŠą╝). ą¤čĆąĖą╝ąĄčĆčŗ ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░čÄčé čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąŠč鹊ą║ąŠą╝ ą┤ą░ąĮąĮčŗčģ ą┐ąŠ ąŠą┐čĆąŠčüčā (ą▒ąĄąĘ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣). ąĪą║ąŠčĆąŠčüčéčī ąĘą░ą┤ą░ąĄčéčüčÅ ą║ą░ą║ ą┐ą░čĆą░ą╝ąĄčéčĆ čäčāąĮą║čåąĖąĖ ąĮą░čüčéčĆąŠą╣ą║ąĖ. ąöą╗čÅ ą║ąŠą┤ą░ ąĮą░ ą░čüčüąĄą╝ą▒ą╗ąĄčĆąĄ ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčéčüčÅ, čćč鹊 ą┐ą░čĆą░ą╝ąĄčéčĆ baud rate čüąŠčģčĆą░ąĮąĄąĮ ą▓ čĆąĄą│ąĖčüčéčĆąŠą▓ąŠą╣ ą┐ą░čĆąĄ r17:r16.

ą¤čĆąĖą╝ąĄčĆ ą║ąŠą┤ą░ ąĮą░ ą░čüčüąĄą╝ą▒ą╗ąĄčĆąĄ:

USART_Init:

clr r18

out UBRRnH,r18

out UBRRnL,r18

; ąØą░čüčéčĆąŠą╣ą║ą░ ąĮąŠąČą║ąĖ ą┐ąŠčĆčéą░ XCKn ą║ą░ą║ ą▓čŗčģąŠą┤ą░, čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ čĆąĄąČąĖą╝ą░ Master:

sbi XCKn_DDR, XCKn

; ąŻčüčéą░ąĮąŠą▓ą║ą░ čĆąĄąČąĖą╝ą░ MSPIM ąĖ čĆąĄąČąĖą╝ą░ 0 ą┤ą╗čÅ ą┤ą░ąĮąĮčŗčģ SPI:

ldi r18, (1 << UMSELn1)|(1 << UMSELn0)|(0 << UCPHAn)|(0 << UCPOLn)

out UCSRnC,r18

; ąĀą░ąĘčĆąĄčłąĖčéčī ą┐čĆąĖąĄą╝ąĮąĖą║ ąĖ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║:

ldi r18, (1 << RXENn)|(1 << TXENn)

out UCSRnB,r18

; ąØą░čüčéčĆąŠą╣ą║ą░ baud rate.

; ąÆąØąśą£ąÉąØąśąĢ: čüą║ąŠčĆąŠčüčéčī (Baud Rate) ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮą░

; ą┐ąŠčüą╗ąĄ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░!

out UBRRnH, r17

out UBRRnL, r18

ret

ą¤čĆąĖą╝ąĄčĆ ą║ąŠą┤ą░ ąĮą░ čÅąĘčŗą║ąĄ C:

void USART_Init( unsigned int baud )

{

UBRRn = 0;

/* ąØą░čüčéčĆąŠą╣ą║ą░ ąĮąŠąČą║ąĖ ą┐ąŠčĆčéą░ XCKn ą║ą░ą║ ą▓čŗčģąŠą┤ą░, čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ čĆąĄąČąĖą╝ą░ Master: */

XCKn_DDR |= (1<<XCKn);

/* ąŻčüčéą░ąĮąŠą▓ą║ą░ čĆąĄąČąĖą╝ą░ MSPIM ąĖ čĆąĄąČąĖą╝ą░ 0 ą┤ą╗čÅ ą┤ą░ąĮąĮčŗčģ SPI: */

UCSRnC = (1 << UMSELn1)|(1 << UMSELn0)|(0 << UCPHAn)|(0 << UCPOLn);

/* ąĀą░ąĘčĆąĄčłąĖčéčī ą┐čĆąĖąĄą╝ąĮąĖą║ ąĖ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║: */

UCSRnB = (1 << RXENn)|(1 << TXENn);

/* ąØą░čüčéčĆąŠą╣ą║ą░ baud rate.

ąÆąØąśą£ąÉąØąśąĢ: čüą║ąŠčĆąŠčüčéčī (Baud Rate) ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮą░

ą┐ąŠčüą╗ąĄ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░! */

UBRRn = baud;

}

ąÆ čŹč鹊ą╣ ą┤ąŠą║čāą╝ąĄąĮčéą░čåąĖąĖ čüąŠą┤ąĄčƹȹ░čéčüčÅ ą┐čĆąŠčüčéčŗąĄ ą┐čĆąĖą╝ąĄčĆčŗ ą║ąŠą┤ą░, ą║ąŠč鹊čĆčŗąĄ ą║čĆą░čéą║ąŠ ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčé, ą║ą░ą║ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čĆą░ąĘą╗ąĖčćąĮčŗąĄ čćą░čüčéąĖ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░. ąŁčéąĖ ą┐čĆąĖą╝ąĄčĆčŗ ą║ąŠą┤ą░ ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░čÄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ čüą┐ąĄčåąĖą░ą╗čīąĮčŗčģ ą┐ąŠą┤ą║ą╗čÄčćą░ąĄą╝čŗčģ ąĘą░ą│ąŠą╗ąŠą▓ąŠčćąĮčŗčģ čäą░ą╣ą╗ąŠą▓. ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 ąĮąĄ ą▓čüąĄ ą┐ąŠčüčéą░ą▓čēąĖą║ąĖ ą║ąŠą╝ą┐ąĖą╗čÅč鹊čĆąŠą▓ čÅąĘčŗą║ą░ C ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÄčé ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖąĄ ąĖą╝ąĄąĮ ą┤ą╗čÅ ą▒ąĖčé čĆąĄą│ąĖčüčéčĆąŠą▓ ą▓ čäą░ą╣ą╗ą░čģ ąĘą░ą│ąŠą╗ąŠą▓ą║ąŠą▓, ąĖ ąŠč乊čĆą╝ą╗ąĄąĮąĖąĄ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čéą░ą║ąČąĄ ąĘą░ą▓ąĖčüąĖčé ąŠčé ą┐ąŠą┤ą┤ąĄčƹȹ║ąĖ čĆą░čüčłąĖčĆąĄąĮąĖčÅą╝ąĖ čüąĖąĮčéą░ą║čüąĖčüą░ ą║ąŠą╝ą┐ąĖą╗čÅč鹊čĆą░ čÅąĘčŗą║ą░ C. ąöą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ą┐ąŠą┤čĆąŠą▒ąĮąŠčüč鹥ą╣ ą┐ąŠąČą░ą╗čāą╣čüčéą░ ą┐čĆąŠą║ąŠąĮčüčāą╗čīčéąĖčĆčāą╣č鹥čüčī čü ą┤ąŠą║čāą╝ąĄąĮčéą░čåąĖąĄą╣ ąĮą░ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╣ ąÆą░ą╝ąĖ ą║ąŠą╝ą┐ąĖą╗čÅč鹊čĆ C.

ąöą╗čÅ čĆąĄą│ąĖčüčéčĆąŠą▓ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░, ąĮą░čģąŠą┤čÅčēąĖčģčüčÅ ą▓ čĆą░čüčłąĖčĆąĄąĮąĮąŠą╣ ąŠą▒ą╗ą░čüčéąĖ ą░ą┤čĆąĄčüąĮąŠą│ąŠ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ą░ AVR (extended I/O map), ąĖąĮčüčéčĆčāą║čåąĖąĖ IN, OUT, SBIS, SBIC, CBI ąĖ SBI ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĘą░ą╝ąĄąĮąĄąĮčŗ ąĮą░ ąĖąĮčüčéčĆčāą║čåąĖąĖ, ą║ąŠč鹊čĆčŗąĄ ą┐ąŠąĘą▓ąŠą╗čÅčÄčé ą┐ąŠą╗čāčćąĖčéčī ą┤ąŠčüčéčāą┐ ą▓ čŹčéčā ąŠą▒ą╗ą░čüčéčī. ą×ą▒čŗčćąĮąŠ ąĖąĮčüčéčĆčāą║čåąĖąĖ LDS ąĖ STS ą║ąŠą╝ą▒ąĖąĮąĖčĆčāčÄčéčüčÅ čü SBRS, SBRC, SBR ąĖ CBR.

[ą×ą▒ą╝ąĄąĮ ą┤ą░ąĮąĮčŗą╝ąĖ]

ąśčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ USART ą▓ čĆąĄąČąĖą╝ąĄ MSPIM čéčĆąĄą▒čāąĄčé čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░, čé. ąĄ. ą▒ąĖčé TXENn ą▓ čĆąĄą│ąĖčüčéčĆąĄ UCSRnB čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ ą╗ąŠą│. 1. ąÜąŠą│ą┤ą░ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ čĆą░ąĘčĆąĄčłąĄąĮ, ąŠą▒čŗčćąĮą░čÅ čĆą░ą▒ąŠčéą░ ą┐ąŠčĆčéą░ GPIO ąĮą░ ą▓čŗą▓ąŠą┤ąĄ TxDn ą┐ąĄčĆąĄąĮą░ąĘąĮą░čćą░ąĄčéčüčÅ, ąĖ čŹčéą░ ąĮąŠąČą║ą░ čüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▓čŗčģąŠą┤ąŠą╝ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ą┤ą░ąĮąĮčŗčģ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░. ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ čÅą▓ą╗čÅąĄčéčüčÅ ąĮąĄ ąŠą▒čÅąĘą░č鹥ą╗čīąĮčŗą╝, ąĖ čŹč鹊 ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▓ ą╗ąŠą│. 1 ą▒ąĖčéą░ RXENn ą▓ čĆąĄą│ąĖčüčéčĆąĄ UCSRnB. ąÜąŠą│ą┤ą░ ą┐čĆąĖąĄą╝ąĮąĖą║ čĆą░ąĘčĆąĄčłąĄąĮ, ąŠą▒čŗčćąĮąŠąĄ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĄ ą▓čŗą▓ąŠą┤ą░ ą┐ąŠčĆčéą░ GPIO ąĮą░ ą▓čŗą▓ąŠą┤ąĄ RxDn ą┐ąĄčĆąĄąĮą░ąĘąĮą░čćą░ąĄčéčüčÅ, ąĖ čŹč鹊čé ą▓čŗą▓ąŠą┤ čüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▓čģąŠą┤ąŠą╝ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ą┤ą░ąĮąĮčŗčģ ą┐čĆąĖąĄą╝ąĮąĖą║ą░. ąÆ ąŠą▒ąŠąĖčģ čüą╗čāčćą░čÅčģ čüąĖą│ąĮą░ą╗ XCKn ą▒čāą┤ąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮ ą║ą░ą║ čéą░ą║čéčŗ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ąŠą▒ą╝ąĄąĮą░ ą┤ą░ąĮąĮčŗą╝ąĖ ąĖ ą┤ą╗čÅ ą┐čĆąĖąĄą╝ąĮąĖą║ą░, ąĖ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░.

ą¤ąŠčüą╗ąĄ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ USART ą│ąŠč鹊ą▓ ą║ ąŠą▒ą╝ąĄąĮčā ą┤ą░ąĮąĮčŗą╝ąĖ. ą×ą▒ą╝ąĄąĮ ą┤ą░ąĮąĮčŗą╝ąĖ ąĖąĮąĖčåąĖąĖčĆčāąĄčéčüčÅ ąĘą░ą┐ąĖčüčīčÄ ą▓ čĆąĄą│ąĖčüčéčĆ UDRn ą┐ąŠ ą░ą┤čĆąĄčüčā, ąĮą░čģąŠą┤čÅčēąĄą╝čüčÅ ą▓ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąĄ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ čüąĖčüč鹥ą╝čŗ ą║ąŠą╝ą░ąĮą┤. ąŁč鹊 ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą║ą░ą║ ą┤ą╗čÅ ą┐čĆąĖąĄą╝ą░, čéą░ą║ ąĖ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ, ą┐ąŠčüą║ąŠą╗čīą║čā ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ čāą┐čĆą░ą▓ą╗čÅąĄčé č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖąĄą╝ čéą░ą║č鹊ą▓ ą▒ąĖčé. ąöą░ąĮąĮčŗąĄ, ąĘą░ą┐ąĖčüą░ąĮąĮčŗąĄ ą▓ UDRn, ą┐ąĄčĆąĄą╝ąĄčēą░čÄčéčüčÅ ąĖąĘ ą▒čāč乥čĆą░ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▓ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░, ą║ąŠą│ą┤ą░ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ ą│ąŠč鹊ą▓ ą║ ą┐ąĄčĆąĄą┤ą░č湥 ąĮąŠą▓ąŠą│ąŠ čäčĆąĄą╣ą╝ą░.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: čćč鹊ą▒čŗ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čéčī ą▓čģąŠą┤ąĮąŠą╣ ą▒čāč乥čĆ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüąĖąĮčģčĆąŠąĮąĮąŠčüčéąĖ čü ą║ąŠą╗ąĖč湥čüčéą▓ąŠą╝ ą┐ąĄčĆąĄą┤ą░ąĮąĮčŗčģ ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ, čĆąĄą│ąĖčüčéčĆ UDRn ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮ ą┐čĆąĖ ą║ą░ąČą┤ąŠą╣ ąŠčéą┐čĆą░ą▓ą║ąĄ ą▒ą░ą╣čéą░. ąĀą░ą▒ąŠčéą░ ą▓čģąŠą┤ąĮąŠą│ąŠ ą▒čāč乥čĆą░ ąĖą┤ąĄąĮčéąĖčćąĮą░ ąŠą▒čŗčćąĮąŠą╝čā čĆąĄąČąĖą╝čā čĆą░ą▒ąŠčéčŗ USART, čé. ąĄ. ąĄčüą╗ąĖ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĄ, č鹊 ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ą┐čĆąĖąĮčÅčéčŗą╣ čüąĖą╝ą▓ąŠą╗ ą▒čāą┤ąĄčé ą┐ąŠč鹥čĆčÅąĮ, ą▓ ą▒čāč乥čĆąĄ ąĮąĄ ą▒čāą┤čāčé ąĮą░čģąŠą┤ąĖčéčīčüčÅ ą┤ą░ąĮąĮčŗąĄ, ą║ąŠč鹊čĆčŗąĄ ą┐čĆąĖčłą╗ąĖ ą┐ąĄčĆą▓čŗą╝ąĖ. ąŁč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ąĄčüą╗ąĖ ąĮą░ą┤ąŠ ą┐ąĄčĆąĄą┤ą░čéčī 4 ą▒ą░ą╣čéą░, čüąĮą░čćą░ą╗ą░ ą▒ą░ą╣čé 1, ą┐ąŠč鹊ą╝ ą▒ą░ą╣čéčŗ 2, 3 ąĖ 4, ąĖ čĆąĄą│ąĖčüčéčĆ UDRn ąĮąĄ ą▒čŗą╗ ą┐čĆąŠčćąĖčéą░ąĮ ą┐ąŠčüą╗ąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą▓čüąĄčģ ą┐ąĄčĆąĄą┤ą░čć, č鹊 ą┐čĆąĖąĮčÅčéčŗą╣ ą▒ą░ą╣čé 3 ą▒čāą┤ąĄčé ą┐ąŠč鹥čĆčÅąĮ, ąĖ ąĮąĄ ą▒čāą┤ąĄčé ą┐čĆąĖąĮčÅčé ą▒ą░ą╣čé 1.

ąĪą╗ąĄą┤čāčÄčēąĖąĄ ą┐čĆąĖą╝ąĄčĆčŗ ą║ąŠą┤ą░ ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčé ą┐čĆąŠčüč鹊ą╣ ąŠą▒ą╝ąĄąĮ ą┤ą░ąĮąĮčŗą╝ąĖ č湥čĆąĄąĘ USART ą▓ čĆąĄąČąĖą╝ąĄ MSPIM, ą▒ą░ąĘąĖčĆčāčÅčüčī ąĮą░ ąŠą┐čĆąŠčüąĄ čäą╗ą░ą│ą░ ąŠą┐čāčüč鹊賹ĄąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ ą┤ą░ąĮąĮčŗčģ (Data Register Empty, UDREn) ąĖ čäą╗ą░ą│ą░ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐čĆąĖąĄą╝ą░ (Receive Complete, RXCn). USART ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆąŠą▓ą░ąĮ ą┐ąĄčĆąĄą┤ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ čäčāąĮą║čåąĖąĖ ąŠą▒ą╝ąĄąĮą░. ąöą╗čÅ ą║ąŠą┤ą░ ąĮą░ ą░čüčüąĄą╝ą▒ą╗ąĄčĆąĄ ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčéčüčÅ, čćč鹊 ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ čüąŠčģčĆą░ąĮčÅčÄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ R16, ąĖ ą┐čĆąĖąĮčÅčéčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┤ąŠčüčéčāą┐ąĮčŗ ą▓ č鹊ą╝ ąČąĄ čüą░ą╝ąŠą╝ čĆąĄą│ąĖčüčéčĆąĄ (R16) ą┐ąŠčüą╗ąĄ ą▓ąŠąĘą▓čĆą░čéą░ ąĖąĘ čäčāąĮą║čåąĖąĖ.

ążčāąĮą║čåąĖčÅ ą┐čĆąŠčüč鹊 ąČą┤ąĄčé, ą┐ąŠą║ą░ ą▒čāč乥čĆ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĮąĄ ąŠą┐čāčüč鹊賹ĖčéčüčÅ, ą┐čāč鹥ą╝ ą┐čĆąŠą▓ąĄčĆą║ąĖ čäą╗ą░ą│ą░ UDREn, ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ą╝ąŠąČąĮąŠ ąĘą░ą│čĆčāąĘąĖčéčī ąĮąŠą▓čŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ. ąŚą░č鹥ą╝ čäčāąĮą║čåąĖčÅ ąČą┤ąĄčé ą┐ąŠčÅą▓ą╗ąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ą▓ ą▒čāč乥čĆąĄ ą┐čĆąĖąĄą╝ą░, ą┐čāč鹥ą╝ ą┐čĆąŠą▓ąĄčĆą║ąĖ čäą╗ą░ą│ą░ RXCn, ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮąŠ ąĖąĘ ą▒čāč乥čĆą░ ą┐čĆąĖąĮčÅč鹊ąĄ ąĘąĮą░č湥ąĮąĖąĄ.

ą¤čĆąĖą╝ąĄčĆ ą║ąŠą┤ą░ ąĮą░ ą░čüčüąĄą╝ą▒ą╗ąĄčĆąĄ:

USART_MSPIM_Transfer:

; ą×ąČąĖą┤ą░ąĮąĖąĄ ąŠą┐čāčüč鹊賹ĄąĮąĖčÅ ą▒čāč乥čĆą░ ą┐ąĄčĆąĄą┤ą░čćąĖ.

in r16, UCSRnA

sbrs r16, UDREn

rjmp USART_MSPIM_Transfer

; ą¤ąŠą╝ąĄčüčéąĖčéčī ą┤ą░ąĮąĮčŗąĄ (r16) ą▓ ą▒čāč乥čĆ ą┤ą╗čÅ ąŠčéą┐čĆą░ą▓ą║ąĖ ą┤ą░ąĮąĮčŗčģ:

out UDRn,r16

; ą×ąČąĖą┤ą░ąĮąĖąĄ ą┐čĆąĖąĮčÅčéčŗčģ ą┤ą░ąĮąĮčŗčģ.

USART_MSPIM_Wait_RXCn:

in r16, UCSRnA

sbrs r16, RXCn

rjmp USART_MSPIM_Wait_RXCn

; ą¤ąŠą╗čāčćąĖčéčī ąĖ ą▓ąĄčĆąĮčāčéčī č湥čĆąĄąĘ R16 ą┐čĆąĖąĮčÅčéčŗąĄ ą┤ą░ąĮąĮčŗąĄ:

in r16, UDRn

ret

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą┐čĆąĖą▓ąĄą┤ąĄąĮąĮčŗą╣ ą▓čŗčłąĄ ą║ąŠą┤ ą░čüčüąĄą╝ą▒ą╗ąĄčĆą░ čüą╗ąĄą┤čāąĄčé čĆą░čüčüą╝ą░čéčĆąĖą▓ą░čéčī čüą║ąŠčĆąĄąĄ ą║ą░ą║ ą┐čüąĄą▓ą┤ąŠą║ąŠą┤, č鹊ą╗čīą║ąŠ ą╗ąĖčłčī ą┤ąĄą╝ąŠąĮčüčéčĆąĖčĆčāčÄčēąĖą╣ ąŠą▒čēąĖą╣ ą░ą╗ą│ąŠčĆąĖčéą╝, čćč鹊 ąĘą░ą╝ąĄčéąĖą╗ ąŠą┤ąĖąĮ ąĖąĘ ą┐ąŠčüąĄčéąĖč鹥ą╗ąĄą╣ čüą░ą╣čéą░ ąØąĖą║ąŠą╗ą░ą╣, ą▓čŗčĆą░ąČą░čÄ ąĄą╝čā ą▒ąŠą╗čīčłčāčÄ ą▒ą╗ą░ą│ąŠą┤ą░čĆąĮąŠčüčéčī. ąöąĄą╗ąŠ ą▓ č鹊ą╝, čćč鹊 čĆąĄą│ąĖčüčéčĆ R16 čĆą░ąĮąĄąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ą╗čüčÅ ą║ą░ą║ ą▓čĆąĄą╝ąĄąĮąĮą░čÅ čÅč湥ą╣ą║ą░ ą┐ą░ą╝čÅčéąĖ ą┤ą╗čÅ ą░ąĮą░ą╗ąĖąĘą░ ąŠą┐čāčüč鹊賹ĄąĮąĖčÅ ą▒čāč乥čĆą░ ą┐ąĄčĆąĄą┤ą░čćąĖ, ąĖ ą┤ą╗čÅ ąŠčéą┐čĆą░ą▓ą║ąĖ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┤čĆčāą│ąŠą╣ čĆąĄą│ąĖčüčéčĆ (čüą╝. ą║ąŠą╝ą╝ąĄąĮčéą░čĆąĖą╣ ą▓ ą║ąŠąĮčåąĄ čüčéą░čéčīąĖ). ąøąĖą▒ąŠ ą┐ąĄčĆąĄą┤ ąŠčéą┐čĆą░ą▓ą║ąŠą╣ ąĮčāąČąĮąŠ ą┐ąŠą╝ąĄčēą░čéčī ą▓ R16 ąŠčéą┐čĆą░ą▓ą╗čÅąĄą╝čŗąĄ ą┤ą░ąĮąĮčŗąĄ.

ą¤čĆąĖą╝ąĄčĆ ą║ąŠą┤ą░ ąĮą░ čÅąĘčŗą║ąĄ C:

unsigned char USART_Receive( void )

{

/* ą×ąČąĖą┤ą░ąĮąĖąĄ ąŠą┐čāčüč鹊賹ĄąĮąĖčÅ ą▒čāč乥čĆą░ ą┐ąĄčĆąĄą┤ą░čćąĖ. */

while ( !( UCSRnA & (1 << UDREn)) );

/* ą¤ąŠą╝ąĄčüčéąĖčéčī ą┤ą░ąĮąĮčŗąĄ (r16) ą▓ ą▒čāč乥čĆ ą┤ą╗čÅ ąŠčéą┐čĆą░ą▓ą║ąĖ ą┤ą░ąĮąĮčŗčģ: */

UDRn = data;

/* ą×ąČąĖą┤ą░ąĮąĖąĄ ą┐čĆąĖąĮčÅčéčŗčģ ą┤ą░ąĮąĮčŗčģ. */

while ( !(UCSRnA & (1 << RXCn)) );

/* ą¤ąŠą╗čāčćąĖčéčī ąĖ ą▓ąĄčĆąĮčāčéčī č湥čĆąĄąĘ R16 ą┐čĆąĖąĮčÅčéčŗąĄ ą┤ą░ąĮąĮčŗąĄ: */

return UDRn;

}

ążą╗ą░ą│ąĖ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ ąĖ ą┐čĆąĖąĄą╝ąĮąĖą║ą░, ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ążą╗ą░ą│ąĖ RXCn, TXCn ąĖ UDREn, ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą▓ čĆąĄąČąĖą╝ąĄ USART MSPIM ąĖą┤ąĄąĮčéąĖčćąĮčŗ ąĖąĘ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖčÄ ą▓ ąŠą▒čŗčćąĮąŠą╝ čĆąĄąČąĖą╝ąĄ USART. ą×ą┤ąĮą░ą║ąŠ čäą╗ą░ą│ąĖ čüąŠčüč鹊čÅąĮąĖčÅ ąŠčłąĖą▒ą║ąĖ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ (receiver error status flags FE, DOR ąĖ PE) ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ąĖ ą▓čüąĄą│ą┤ą░ čćąĖčéą░čÄčéčüčÅ ą║ą░ą║ 0.

ąŚą░ą┐čĆąĄčé ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ ąĖą╗ąĖ ą┐čĆąĖąĄą╝ąĮąĖą║ą░. ąŚą░ą┐čĆąĄčé ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ ąĖą╗ąĖ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ ą▓ čĆąĄąČąĖą╝ąĄ USART MSPIM ąĖą┤ąĄąĮčéąĖč湥ąĮ ąĘą░ą┐čĆąĄčéčā ą▓ ąŠą▒čŗčćąĮąŠą╝ čĆąĄąČąĖą╝ąĄ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖčÅ USART.

[ąĪčĆą░ą▓ąĮąĄąĮąĖąĄ AVR USART MSPIM ąĖ AVR SPI]

USART ą▓ čĆąĄąČąĖą╝ąĄ MSPIM ą┐ąŠą╗ąĮąŠčüčéčīčÄ čüąŠą▓ą╝ąĄčüčéąĖą╝ čü AVR SPI ą▓ čüą╗ąĄą┤čāčÄčēąĖčģ ą░čüą┐ąĄą║čéą░čģ:

ŌĆó ąöąĖą░ą│čĆą░ą╝ą╝čŗ čüąĖą│ąĮą░ą╗ąŠą▓ čĆąĄąČąĖą╝ą░ Master.

ŌĆó ążčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠčüčéčī ą▒ąĖčéą░ UCPOLn ąĖą┤ąĄąĮčéąĖčćąĮą░ čäčāąĮą║čåąĖąŠąĮą░ą╗čā ą▒ąĖčéą░ CPOL SPI.

ŌĆó ążčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠčüčéčī ą▒ąĖčéą░ UCPHAn ąĖą┤ąĄąĮčéąĖčćąĮą░ čäčāąĮą║čåąĖąŠąĮą░ą╗čā ą▒ąĖčéą░ CPHA SPI.

ŌĆó ążčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠčüčéčī ą▒ąĖčéą░ UDORDn ąĖą┤ąĄąĮčéąĖčćąĮą░ čäčāąĮą║čåąĖąŠąĮą░ą╗čā ą▒ąĖčéą░ DORD SPI.

ą×ą┤ąĮą░ą║ąŠ, ą┐ąŠčüą║ąŠą╗čīą║čā čĆąĄąČąĖą╝ USART MSPIM ąĘą░ą┤ąĄą╣čüčéą▓čāąĄčé čĆąĄčüčāčĆčüčŗ USART, č鹊 ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ USART ą▓ čĆąĄąČąĖą╝ąĄ MSPIM ąĮąĄčüą║ąŠą╗čīą║ąŠ ąŠčéą╗ąĖčćą░ąĄčéčüčÅ ą▓ čüčĆą░ą▓ąĮąĄąĮąĖąĖ čü čĆąĄąČąĖą╝ąŠą╝ SPI. ąÆ ą┤ąŠą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ čĆą░ąĘą╗ąĖčćąĖčÅą╝ ą▓ ą▒ąĖčéą░čģ čāą┐čĆą░ą▓ą╗čÅčÄčēąĖčģ čĆąĄą│ąĖčüčéčĆąŠą▓, ąĖ ą▓ č鹊ą╝, čćč鹊 ą▓ USART MSPIM ą▓ąŠąĘą╝ąŠąČąĮą░ čĆą░ą▒ąŠčéą░ č鹊ą╗čīą║ąŠ ą║ą░ą║ Master, čéą░ą║ąČąĄ ąĄčüčéčī čüą╗ąĄą┤čāčÄčēąĖąĄ ąŠčéą╗ąĖčćąĖčÅ ą╝ąĄąČą┤čā čĆąĄąČąĖą╝ą░ą╝ąĖ USART MSPIM ąĖ ąŠą▒čŗčćąĮčŗą╝ SPI:

ŌĆó USART MSPIM ą▓ą║ą╗čÄčćą░ąĄčé ą▒čāč乥čĆąĖąĘą░čåąĖčÄ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ (ą┤ą▓ąŠą╣ąĮčāčÄ). ąŻ SPI ąĮąĄčé ą▒čāč乥čĆą░.

ŌĆó ą¤čĆąĖąĄą╝ąĮąĖą║ čĆąĄąČąĖą╝ą░ USART MSPIM ą▓ą║ą╗čÄčćą░ąĄčé ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī ą▒čāč乥čĆą░.

ŌĆó ążą╗ą░ą│ SPI WCOL (Write Collision, ą║ąŠą╗ą╗ąĖąĘąĖčÅ ąĘą░ą┐ąĖčüąĖ) ąŠčéčüčāčéčüčéą▓čāąĄčé ą▓ čĆąĄąČąĖą╝ąĄ USART MSPIM.

ŌĆó ąØąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ą┤ą▓ąŠą╣ąĮą░čÅ čüą║ąŠčĆąŠčüčéčī SPI (SPI2X). ą×ą┤ąĮą░ą║ąŠ č鹊ą│ąŠ ąČąĄ čüą░ą╝ąŠą│ąŠ čŹčäč乥ą║čéą░ ą╝ąŠąČąĮąŠ ą┤ąŠčüčéąĖčćčī ąĮą░čüčéčĆąŠą╣ą║ąŠą╣ UBRRn.

ŌĆó ąÆčĆąĄą╝čÅ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠčéą╗ąĖčćą░ąĄčéčüčÅ.

ŌĆó ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą▓čŗą▓ąŠą┤ą░ą╝ąĖ ąŠčéą╗ąĖčćą░ąĄčéčüčÅ, ą┐ąŠčüą║ąŠą╗čīą║čā ą▓ čĆąĄąČąĖą╝ąĄ USART MSPIM ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ č鹊ą╗čīą║ąŠ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĄ Master.

ąĪčĆą░ą▓ąĮąĄąĮąĖąĄ ą▓čŗą▓ąŠą┤ąŠą▓ USART ą▓ čĆąĄąČąĖą╝ąĄ MSPIM ąĖ ą▓čŗą▓ąŠą┤ąŠą▓ SPI ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▓ čéą░ą▒ą╗ąĖčåąĄ 21-3.

ąóą░ą▒ą╗ąĖčåą░ 21-3. ąĪčĆą░ą▓ąĮąĄąĮąĖąĄ ą▓čŗą▓ąŠą┤ąŠą▓ USART MSPIM ąĖ SPI.

USART

MSPIM |

SPI |

ąÜąŠą╝ą╝ąĄąĮčéą░čĆąĖą╣ |

| TxDn |

MOSI |

ąóąŠą╗čīą║ąŠ ą║ą░ą║ ą▓čŗčģąŠą┤ čĆąĄąČąĖą╝ą░ Master |

| RxDn |

MISO |

ąóąŠą╗čīą║ąŠ ą║ą░ą║ ą▓čģąŠą┤ čĆąĄąČąĖą╝ą░ Master |

| XCKn |

SCK |

ążčāąĮą║čåąĖąŠąĮą░ą╗ ąŠą┤ąĖąĮą░ą║ąŠą▓čŗą╣ |

| - |

~SS |

ąØąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ USART MSPIM |

[ą×ą┐ąĖčüą░ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆąŠą▓]

ąÆ čŹč鹊ą╣ čüąĄą║čåąĖąĖ ąŠą┐ąĖčüą░ąĮčŗ čĆąĄą│ąĖčüčéčĆčŗ USART, ą║ąŠč鹊čĆčŗąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ USART ą▓ čĆąĄąČąĖą╝ąĄ SPI (MSPIM).

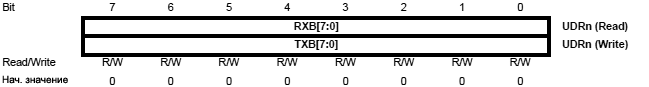

ąĀąĄą│ąĖčüčéčĆ ą┤ą░ąĮąĮčŗčģ USART.

ążčāąĮą║čåąĖčÅ ąĖ ąŠą┐ąĖčüą░ąĮąĖąĄ ą▒ąĖčé čĆąĄą│ąĖčüčéčĆą░ ą┤ą░ąĮąĮčŗčģ USART (UDRn) ą▓ čĆąĄąČąĖą╝ąĄ MSPIM ąĖą┤ąĄąĮčéąĖčćąĮčŗ čĆą░ą▒ąŠč鹥 USART ą▓ ąŠą▒čŗčćąĮąŠą╝ čĆąĄąČąĖą╝ąĄ.

ąĀąĄą│ąĖčüčéčĆ ą▒čāč乥čĆą░ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ (USART Transmit Data Buffer Register) ąĖ čĆąĄą│ąĖčüčéčĆ ą▒čāč乥čĆą░ ą┐čĆąĖąĄą╝ą░ ą┤ą░ąĮąĮčŗčģ (USART Receive Data Buffer Register) ąĖčüą┐ąŠą╗čīąĘčāčÄčé č鹊čé ąČąĄ čüą░ą╝čŗą╣ ą░ą┤čĆąĄčü I/O, ą║ąŠč鹊čĆčŗą╣ ąĮą░ąĘčŗą▓ą░ąĄčéčüčÅ čĆąĄą│ąĖčüčéčĆąŠą╝ ą┤ą░ąĮąĮčŗčģ USART (USART Data Register, ąĖą╗ąĖ UDRn). ąĀąĄą│ąĖčüčéčĆ ą▒čāč乥čĆą░ ą┐ąĄčĆąĄą┤ą░čćąĖ (Transmit Data Buffer Register, TXB) ą▒čāą┤ąĄčé ą╝ąĄčüč鹊ą╝ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ, ą║ąŠč鹊čĆčŗąĄ ąĘą░ą┐ąĖčüą░ąĮčŗ ą┐ąŠ ą░ą┤čĆąĄčüčā čĆąĄą│ąĖčüčéčĆą░ UDRn. ą¦č鹥ąĮąĖąĄ ą┐ąŠ ą░ą┤čĆąĄčüčā čĆąĄą│ąĖčüčéčĆą░ UDRn ą▓ąĄčĆąĮąĄčé čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ čĆąĄą│ąĖčüčéčĆą░ ą▒čāč乥čĆą░ ą┐čĆąĖąĄą╝ą░ ą┤ą░ąĮąĮčŗčģ (Receive Data Buffer Register, RXB).

ąæčāč乥čĆ ą┐ąĄčĆąĄą┤ą░čćąĖ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮ č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čäą╗ą░ą│ UDREn ą▓ čĆąĄą│ąĖčüčéčĆąĄ UCSRnA. ąöą░ąĮąĮčŗąĄ, ąĘą░ą┐ąĖčüą░ąĮąĮčŗąĄ ą▓ UDRn, ą║ąŠą│ą┤ą░ ąĮąĄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čäą╗ą░ą│ UDREn, ą▒čāą┤čāčé ąĖą│ąĮąŠčĆąĖčĆąŠą▓ą░čéčīčüčÅ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ąŠą╝ USART. ąÜąŠą│ą┤ą░ ą┤ą░ąĮąĮčŗąĄ ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ ą▓ ą▒čāč乥čĆ ą┐ąĄčĆąĄą┤ą░čćąĖ, ąĖ čĆą░ąĘčĆąĄčłąĄąĮ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║, ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ ąĘą░ą│čĆčāąĘąĖčé ą┤ą░ąĮąĮčŗąĄ ą▓ ą┤ą░ąĮąĮčŗąĄ ą▓ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ, ą║ąŠą│ą┤ą░ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ ą┐čāčüčé. ąóąŠą│ą┤ą░ ą┤ą░ąĮąĮčŗąĄ ą▒čāą┤čāčé ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčīčüčÅ č湥čĆąĄąĘ ą▓čŗą▓ąŠą┤ TxDn.

ąæčāč乥čĆ ą┐čĆąĖąĄą╝ą░ čüąŠčüč鹊ąĖčé ąĖąĘ ą┤ą▓čāčģčāčĆąŠą▓ąĮąĄą▓ąŠą│ąŠ FIFO. FIFO ą▒čāą┤ąĄčé ą╝ąĄąĮčÅčéčī čüą▓ąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé č鹊ą│ąŠ, ą║ą░ą║ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ąŠą▒čĆą░čēąĄąĮąĖąĄ ą║ ą▒čāč乥čĆčā ą┐čĆąĖąĄą╝ą░. ąśąĘ-ąĘą░ čéą░ą║ąŠą│ąŠ ą┐ąŠą▓ąĄą┤ąĄąĮąĖčÅ ą▒čāč乥čĆą░ ą┐čĆąĖąĄą╝ą░ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāą╣č鹥 ąĖąĮčüčéčĆčāą║čåąĖąĖ Read-Modify-Write (SBI ąĖ CBI) ą┐ąŠ ą░ą┤čĆąĄčüčā čĆąĄą│ąĖčüčéčĆą░ UDRn. ąæčāą┤čīč鹥 ąŠčüč鹊čĆąŠąČąĮčŗ, ą║ąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄč鹥 ąĖąĮčüčéčĆčāą║čåąĖąĖ ą┐čĆąŠą▓ąĄčĆą║ąĖ ą▒ąĖčé (SBIC ąĖ SBIS), ą┐ąŠčüą║ąŠą╗čīą║čā ąŠąĮąĖ čéą░ą║ąČąĄ ą▒čāą┤čāčé ą╝ąĄąĮčÅčéčī čüąŠčüč鹊čÅąĮąĖąĄ FIFO.

ąĀąĄą│ąĖčüčéčĆ A čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĖ čüčéą░čéčāčüą░ USART.

Bit 7 ŌĆō RXCn: USART Receive Complete

ąŁč鹊čé ą▒ąĖčé čäą╗ą░ą│ą░ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ąĖą╝ąĄčÄčéčüčÅ ąĮąĄ ą┐čĆąŠčćąĖčéą░ąĮąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą▓ ą▒čāč乥čĆąĄ ą┐čĆąĖąĄą╝ą░, ąĖ ąŠčćąĖčēą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą▒čāč乥čĆ ą┐čĆąĖąĄą╝ą░ ą┐čāčüčé (čé. ąĄ. ą║ąŠą│ą┤ą░ ą▓ ąĮąĄą╝ ąĮąĄ čüąŠą┤ąĄčƹȹĖčéčüčÅ ąĮąĄ ą┐čĆąŠčćąĖčéą░ąĮąĮčŗčģ ą┤ą░ąĮąĮčŗčģ). ąĢčüą╗ąĖ ą┐čĆąĖąĄą╝ąĮąĖą║ ąĘą░ą┐čĆąĄčēąĄąĮ, č鹊 ą▒čāč乥čĆ ą┐čĆąĖąĄą╝ą░ čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ ąĖ ą▒ąĖčé RXCn ą▒čāą┤ąĄčé ą┐ąŠčüč鹊čÅąĮąĮąŠ čćąĖčéą░čéčīčüčÅ ą║ą░ą║ 0. ążą╗ą░ą│ RXCn ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐čĆąĖąĄą╝ą░ (Receive Complete interrupt, čüą╝. ąŠą┐ąĖčüą░ąĮąĖąĄ ą▒ąĖčéą░ RXCIEn).

Bit 6 ŌĆō TXCn: USART Transmit Complete

ąŁč鹊čé čäą╗ą░ą│ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą┐ąŠą╗ąĮčŗą╣ čäčĆąĄą╣ą╝ ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüą┤ą▓ąĖą│ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ (Transmit Shift Register) ą▓čŗą┤ą▓ąĖąĮčāą╗čüčÅ ąĮą░čĆčāąČčā ąĖ ą▓ ąĮą░čüč鹊čÅčēąĖą╣ ą╝ąŠą╝ąĄąĮčé ą▓ ą▒čāč乥čĆąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ (UDRn) ąĮąĄčé ąĮąŠą▓čŗčģ ą┤ą░ąĮąĮčŗčģ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ. ążą╗ą░ą│ TXCn ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąŠčćąĖčēą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ (transmit complete interrupt), ąĖą╗ąĖ čŹč鹊čé ą▒ąĖčé ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠčćąĖčēąĄąĮ ąĘą░ą┐ąĖčüčīčÄ ą▓ ąĮąĄą│ąŠ ą╗ąŠą│. 1. ążą╗ą░ą│ TXCn ą╝ąŠąČąĄčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ (Transmit Complete interrupt, čüą╝. ąŠą┐ąĖčüą░ąĮąĖąĄ ą▒ąĖčéą░ TXCIEn).

Bit 5 ŌĆō UDREn: USART Data Register Empty

ążą╗ą░ą│ UDREn ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, ą│ąŠč鹊ą▓ ą╗ąĖ ą▒čāč乥čĆ ą┐ąĄčĆąĄą┤ą░čćąĖ (UDRn) ą║ ą┐ąŠą╗čāč湥ąĮąĖčÄ ąĮąŠą▓čŗčģ ą┤ą░ąĮąĮčŗčģ. ąĢčüą╗ąĖ UDREn čćąĖčéą░ąĄčéčüčÅ ą║ą░ą║ ą╗ąŠą│. 1, č鹊 ą▒čāč乥čĆ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐čāčüčé, ąĖ čéą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝ ą│ąŠč鹊ą▓ ą║ ąĘą░ą┐ąĖčüąĖ ąĮąŠą▓čŗčģ ą┤ą░ąĮąĮčŗčģ. ążą╗ą░ą│ UDREn ą╝ąŠąČąĄčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠą┐čāčüč鹊賹ĄąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ ą┤ą░ąĮąĮčŗčģ (Data Register Empty interrupt, čüą╝. ąŠą┐ąĖčüą░ąĮąĖąĄ ą▒ąĖčéą░ UDRIE). UDREn čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░, čćč鹊ą▒čŗ ą┐ąŠą║ą░ąĘą░čéčī ą│ąŠč鹊ą▓ąĮąŠčüčéčī ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░.

Bit 4:0 ŌĆō ą▒ąĖčéčŗ, ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąĮčŗąĄ ą▓ čĆąĄąČąĖą╝ąĄ MSPIM

ąÜąŠą│ą┤ą░ USART ą▓ čĆąĄąČąĖą╝ąĄ MSPIM, čŹčéąĖ ą▒ąĖčéčŗ ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ ą┤ą╗čÅ ą▒čāą┤čāčēąĄą│ąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ. ąöą╗čÅ čüąŠą▓ą╝ąĄčüčéąĖą╝ąŠčüčéąĖ čü ą▒čāą┤čāčēąĖą╝ąĖ ą╝ąŠą┤ąĄą╗čÅą╝ąĖ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ ą▓ čŹčéąĖ ą▒ąĖčéčŗ ąĮčāąČąĮąŠ ąĘą░ą┐ąĖčüą░čéčī ąĮčāą╗ąĖ, ą║ąŠą│ą┤ą░ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ čĆąĄą│ąĖčüčéčĆ UCSRnA.

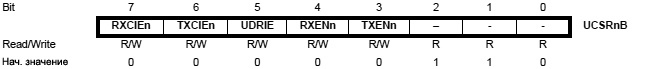

ąĀąĄą│ąĖčüčéčĆ B čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĖ čüčéą░čéčāčüą░ USART.

Bit 7 ŌĆō RXCIEn: RX Complete Interrupt Enable

ąŚą░ą┐ąĖčüčī čŹč鹊ą│ąŠ ą▒ąĖčéą░ ą▓ ą╗ąŠą│. 1 čĆą░ąĘčĆąĄčłą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čäą╗ą░ą│čā RXCn. ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐čĆąĖąĄą╝ą░ (USART Receive Complete interrupt) ą▒čāą┤ąĄčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčīčüčÅ č鹊ą╗čīą║ąŠ ąĄčüą╗ąĖ ą▒ąĖčé RXCIEn čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ ą╗ąŠą│. 1, čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ ą╗ąŠą│. 1 čäą╗ą░ą│ ą│ą╗ąŠą▒ą░ą╗čīąĮąŠą│ąŠ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ (Global Interrupt Flag, I-ą▒ąĖčé ą▓ čĆąĄą│ąĖčüčéčĆąĄ SREG), ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé RXCn ą▓ čĆąĄą│ąĖčüčéčĆąĄ UCSRnA.

Bit 6 ŌĆō TXCIEn: TX Complete Interrupt Enable

ąŚą░ą┐ąĖčüčī čŹč鹊ą│ąŠ ą▒ąĖčéą░ ą▓ ą╗ąŠą│. 1 čĆą░ąĘčĆąĄčłą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čäą╗ą░ą│čā TXCn. ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ (USART Transmit Complete interrupt) ą▒čāą┤ąĄčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčīčüčÅ č鹊ą╗čīą║ąŠ ąĄčüą╗ąĖ ą▒ąĖčé TXCIEn ąĘą░ą┐ąĖčüą░ąĮ ą▓ ą╗ąŠą│. 1, čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ ą╗ąŠą│. 1 čäą╗ą░ą│ ą│ą╗ąŠą▒ą░ą╗čīąĮąŠą│ąŠ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ (Global Interrupt Flag, I-ą▒ąĖčé ą▓ čĆąĄą│ąĖčüčéčĆąĄ SREG), ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé TXCn ą▓ čĆąĄą│ąĖčüčéčĆąĄ UCSRnA.

Bit 5 ŌĆō UDRIE: USART Data Register Empty Interrupt Enable

ąŚą░ą┐ąĖčüčī čŹč鹊ą│ąŠ ą▒ąĖčéą░ ą▓ ą╗ąŠą│. 1 čĆą░ąĘčĆąĄčłą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ čäą╗ą░ą│čā UDREn. ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠą┐čāčüč鹊賹ĄąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ ą┤ą░ąĮąĮčŗčģ (Data Register Empty interrupt) ą▒čāą┤ąĄčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčīčüčÅ č鹊ą╗čīą║ąŠ ąĄčüą╗ąĖ ąĘą░ą┐ąĖčüą░ąĮ ą▓ ą╗ąŠą│. 1 ą▒ąĖčé UDRIE, čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ ą╗ąŠą│. 1 čäą╗ą░ą│ ą│ą╗ąŠą▒ą░ą╗čīąĮąŠą│ąŠ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ (Global Interrupt Flag, I-ą▒ąĖčé ą▓ čĆąĄą│ąĖčüčéčĆąĄ SREG), ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé UDREn ą▓ čĆąĄą│ąĖčüčéčĆąĄ UCSRnA.

Bit 4 ŌĆō RXENn: Receiver Enable

ąŚą░ą┐ąĖčüčī čŹč鹊ą│ąŠ ą▒ąĖčéą░ ą▓ ą╗ąŠą│. 1 čĆą░ąĘčĆąĄčłą░ąĄčé čĆą░ą▒ąŠčéčā ą┐čĆąĖąĄą╝ąĮąĖą║ą░ USART ą▓ čĆąĄąČąĖą╝ąĄ MSPIM. ą¤čĆąĖąĄą╝ąĮąĖą║, ą▒čāą┤čāčćąĖ čĆą░ąĘčĆąĄčłąĄąĮąĮčŗą╝, ą┐ąĄčĆąĄąĮą░ąĘąĮą░čćąĖčé ąŠą▒čŗčćąĮąŠąĄ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĄ ąĮąŠąČą║ąĖ ą┐ąŠčĆčéą░ ą┤ą╗čÅ čüąĖą│ąĮą░ą╗ą░ RxDn. ąŚą░ą┐čĆąĄčé ą┐čĆąĖąĄą╝ąĮąĖą║ą░ čüą▒čĆąŠčüąĖčé čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ ą▒čāč乥čĆą░ ą┐čĆąĖąĄą╝ą░. ąĢčüą╗ąĖ ą▓ čĆąĄąČąĖą╝ąĄ MSPIM čĆą░ąĘčĆąĄčłąĖčéčī č鹊ą╗čīą║ąŠ ą┐čĆąĖąĄą╝ąĮąĖą║ (ąĮą░ą┐čĆąĖą╝ąĄčĆ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ RXENn=1 ąĖ TXENn=0), č鹊 čŹč鹊 ąĮąĄ ą▒čāą┤ąĄčé ąĖą╝ąĄčéčī ąĮąĖą║ą░ą║ąŠą│ąŠ čüą╝čŗčüą╗ą░, ą┐ąŠč鹊ą╝čā čćč鹊 č鹊ą╗čīą║ąŠ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ čāą┐čĆą░ą▓ą╗čÅąĄčé č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖąĄą╝ čéą░ą║č鹊ą▓ ą▒ąĖčé, ąĖ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ č鹊ą╗čīą║ąŠ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĄ Master.

Bit 3 ŌĆō TXENn: Transmitter Enable

ąŚą░ą┐ąĖčüčī čŹč鹊ą│ąŠ ą▒ąĖčéą░ ą▓ ą╗ąŠą│. 1 čĆą░ąĘčĆąĄčłą░ąĄčé čĆą░ą▒ąŠčéčā ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ USART. ą¤ąĄčĆąĄą┤ą░čéčćąĖą║, ą▒čāą┤čāčćąĖ čĆą░ąĘčĆąĄčłąĄąĮąĮčŗą╝, ą┐ąĄčĆąĄąĮą░ąĘąĮą░čćąĖčé ąŠą▒čŗčćąĮąŠąĄ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĄ ąĮąŠąČą║ąĖ ą┐ąŠčĆčéą░ ą┤ą╗čÅ čüąĖą│ąĮą░ą╗ą░ TxDn. ąŚą░ą┐čĆąĄčé ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ (ąĘą░ą┐ąĖčüčī ą▓ TXENn ą╗ąŠą│. 0) ąĮąĄ ą▒čāą┤ąĄčé čŹčäč乥ą║čéąĖą▓ąĮčŗą╝, ą┐ąŠą║ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé č鹥ą║čāčēą░čÅ ąĖ ąŠčéą╗ąŠąČąĄąĮąĮą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░, čé. ąĄ. ą┐ąŠą║ą░ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ (Transmit Shift Register) ąĖ čĆąĄą│ąĖčüčéčĆ ą▒čāč乥čĆą░ ą┐ąĄčĆąĄą┤ą░čćąĖ (Transmit Buffer Register) čüąŠą┤ąĄčƹȹ░čé ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ. ąÜąŠą│ą┤ą░ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ ąĘą░ą┐čĆąĄčēąĄąĮ, ąŠąĮ ą▒ąŠą╗čīčłąĄ ąĮąĄ ą▒čāą┤ąĄčé ą┐ąĄčĆąĄąĮą░ąĘąĮą░čćą░čéčī ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ ąĮąŠąČą║ąĖ ą┐ąŠčĆčéą░ TxDn.

Bit 2:0 ŌĆō ą▒ąĖčéčŗ, ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąĮčŗąĄ ą▓ čĆąĄąČąĖą╝ąĄ MSPIM

ąÜąŠą│ą┤ą░ USART ą▓ čĆąĄąČąĖą╝ąĄ MSPIM, čŹčéąĖ ą▒ąĖčéčŗ ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ ą┤ą╗čÅ ą▒čāą┤čāčēąĄą│ąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ. ąöą╗čÅ čüąŠą▓ą╝ąĄčüčéąĖą╝ąŠčüčéąĖ čü ą▒čāą┤čāčēąĖą╝ąĖ ą╝ąŠą┤ąĄą╗čÅą╝ąĖ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ ą▓ čŹčéąĖ ą▒ąĖčéčŗ ąĮčāąČąĮąŠ ąĘą░ą┐ąĖčüą░čéčī ąĮčāą╗ąĖ, ą║ąŠą│ą┤ą░ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ čĆąĄą│ąĖčüčéčĆ UCSRnB.

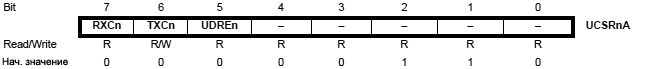

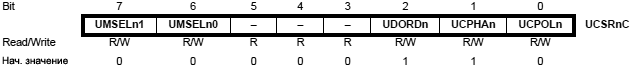

ąĀąĄą│ąĖčüčéčĆ C čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĖ čüčéą░čéčāčüą░ USART.

Bit 7:6 ŌĆō UMSELn1:0: USART Mode Select

ąŁčéąĖ ą▒ąĖčéčŗ ą▓čŗą▒ąĖčĆą░čÄčé čĆąĄąČąĖą╝ čĆą░ą▒ąŠčéčŗ USART, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▓ čéą░ą▒ą╗ąĖčåąĄ 21-4 (ąŠą┐ąĖčüą░ąĮąĖąĄ čĆą░ą▒ąŠčéčŗ USART ą▓ ąŠą▒čŗčćąĮąŠą╝ čĆąĄąČąĖą╝ąĄ čüą╝. ą▓ ą┤ą░čéą░čłąĖč鹥). ąĀąĄąČąĖą╝ MSPIM čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ąŠą▒ą░ ą▒ąĖčéą░ UMSELn čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą▓ ą╗ąŠą│. 1. ąæąĖčéčŗ UDORDn, UCPHAn ąĖ UCPOLn ą╝ąŠą│čāčé ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ č鹥ą╝ąĖ ąČąĄ čüą░ą╝čŗą╝ąĖ ąŠą┐ąĄčĆą░čåąĖčÅą╝ąĖ ąĘą░ą┐ąĖčüąĖ, ą║ąŠą│ą┤ą░ čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ čĆąĄąČąĖą╝ MSPIM.

ąóą░ą▒ą╗ąĖčåą░ 21-4. ąØą░čüčéčĆąŠą╣ą║ąĖ ą▒ąĖč鹊ą▓ UMSELn.

| UMSELn1 |

UMSELn0 |

ąĀąĄąČąĖą╝ čĆą░ą▒ąŠčéčŗ |

| 0 |

0 |

ąÉčüąĖąĮčģčĆąŠąĮąĮčŗą╣ USART |

| 0 |

1 |

ąĪąĖąĮčģčĆąŠąĮąĮčŗą╣ USART |

| 1 |

0 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

| 1 |

1 |

Master SPI (MSPIM) |

Bit 5:3 ŌĆō ą▒ąĖčéčŗ, ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąĮčŗąĄ ą▓ čĆąĄąČąĖą╝ąĄ MSPIM

ąÜąŠą│ą┤ą░ USART ą▓ čĆąĄąČąĖą╝ąĄ MSPIM, čŹčéąĖ ą▒ąĖčéčŗ ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ ą┤ą╗čÅ ą▒čāą┤čāčēąĄą│ąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ. ąöą╗čÅ čüąŠą▓ą╝ąĄčüčéąĖą╝ąŠčüčéąĖ čü ą▒čāą┤čāčēąĖą╝ąĖ ą╝ąŠą┤ąĄą╗čÅą╝ąĖ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ ą▓ čŹčéąĖ ą▒ąĖčéčŗ ąĮčāąČąĮąŠ ąĘą░ą┐ąĖčüą░čéčī ąĮčāą╗ąĖ, ą║ąŠą│ą┤ą░ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ čĆąĄą│ąĖčüčéčĆ UCSRnC.

Bit 2 ŌĆō UDORDn: Data Order

ąÜąŠą│ą┤ą░ čŹč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ ą╗ąŠą│. 1, ą╝ą╗ą░ą┤čłąĖą╣ ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ (LSB) ą▒čāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ąĮ ą┐ąĄčĆą▓čŗą╝. ąÜąŠą│ą┤ą░ čŹč鹊čé ą▒ąĖčé čüą▒čĆąŠčłąĄąĮ ą▓ ą╗ąŠą│. 0, ą▒čāą┤ąĄčé čüąĮą░čćą░ą╗ą░ ą┐ąĄčĆąĄą┤ą░ąĮ čüčéą░čĆčłąĖą╣ ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ (MSB). ąöą╗čÅ ą┐ąŠą┤čĆąŠą▒ąĮąŠčüč鹥ą╣ čüą╝. čĆą░ąĘą┤ąĄą╗, ą│ą┤ąĄ ąŠą┐ąĖčüą░ąĮčŗ č乊čĆą╝ą░čéčŗ čäčĆąĄą╣ą╝ą░.

Bit 1 ŌĆō UCPHAn: Clock Phase

ąØą░čüčéčĆąŠą╣ą║ą░ ą▒ąĖčéą░ UCPHAn ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé, ą▓ ą║ą░ą║ąŠą╣ ą╝ąŠą╝ąĄąĮčé ą▒čāą┤čāčé čüčćąĖčéčŗą▓ą░čéčīčüčÅ ą┤ą░ąĮąĮčŗąĄ - ą┐ąŠ ą╗ąĖą┤ąĖčĆčāčÄčēąĄą╝čā ą┐ąĄčĆąĄą┐ą░ą┤čā čéą░ą║č鹊ą▓ XCKn (ąĮą░čćą░ą╗čīąĮčŗą╣ ą┐ąĄčĆąĄą┐ą░ą┤), ąĖą╗ąĖ ą┐ąŠ ąĘą░ą▓ąĄčĆčłą░čÄčēąĄą╝čā (ą┐ąŠčüą╗ąĄą┤ąĮąĄą╝čā) ą┐ąĄčĆąĄą┐ą░ą┤čā XCKn. ąŚą░ ą┐ąŠą┤čĆąŠą▒ąĮąŠčüčéčÅą╝ąĖ ąŠą▒čĆą░čéąĖč鹥čüčī ą║ ąŠą┐ąĖčüą░ąĮąĖčÄ čĆąĄąČąĖą╝ąŠą▓ ą┤ą░ąĮąĮčŗčģ ą▓ čĆą░ąĘą┤ąĄą╗ąĄ "ąĀąĄąČąĖą╝čŗ čäčĆąĄą╣ą╝ą░ ą┤ą░ąĮąĮčŗčģ SPI Data ąĖ ą┤ąĖą░ą│čĆą░ą╝ą╝čŗ".

Bit 0 ŌĆō UCPOLn: Clock Polarity

ąØą░čüčéčĆąŠą╣ą║ą░ ą▒ąĖčéą░ UCPOLn ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ą┐ąŠą╗čÅčĆąĮąŠčüčéčī čéą░ą║č鹊ą▓ XCKn. ąÜąŠą╝ą▒ąĖąĮą░čåąĖąĖ ąĮą░čüčéčĆąŠąĄą║ ą▒ąĖčé UCPOLn ąĖ UCPHAn ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčé, ą║ą░ą║ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ąĖ ą┐čĆąĖąĮąĖą╝ą░čÄčéčüčÅ ą┤ą░ąĮąĮčŗąĄ ą┐ąŠ ąŠčéąĮąŠčłąĄąĮąĖčÄ ą║ čéą░ą║č鹊ą▓ąŠą╝čā čüąĖą│ąĮą░ą╗čā, čé. ąĄ. ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╣ č乊čĆą╝ą░čé čäčĆąĄą╣ą╝ą░. ąŚą░ ą┐ąŠą┤čĆąŠą▒ąĮąŠčüčéčÅą╝ąĖ ąŠą▒čĆą░čéąĖč鹥čüčī ą║ ąŠą┐ąĖčüą░ąĮąĖčÄ čĆąĄąČąĖą╝ąŠą▓ ą┤ą░ąĮąĮčŗčģ ą▓ čĆą░ąĘą┤ąĄą╗ąĄ "ąĀąĄąČąĖą╝čŗ čäčĆąĄą╣ą╝ą░ ą┤ą░ąĮąĮčŗčģ SPI Data ąĖ ą┤ąĖą░ą│čĆą░ą╝ą╝čŗ".

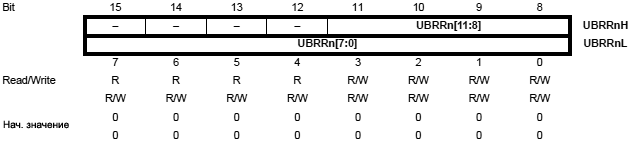

ą¤ą░čĆą░ čĆąĄą│ąĖčüčéčĆąŠą▓, ąŠčéą▓ąĄčćą░čÄčēąĖčģ ąĘą░ ąĮą░čüčéčĆąŠą╣ą║čā čüą║ąŠčĆąŠčüčéąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖ ą┐čĆąĖąĄą╝ą░.

ążčāąĮą║čåąĖčÅ ąĖ ąŠą┐ąĖčüą░ąĮąĖąĄ čŹčéąĖčģ ą▒ąĖčé ą▓ čĆąĄąČąĖą╝ąĄ MSPIM čüąŠą▓ą┐ą░ą┤ą░ąĄčé čü ąŠą┐ąĖčüą░ąĮąĖąĄą╝, ą║ąŠą│ą┤ą░ USART čĆą░ą▒ąŠčéą░ąĄčé ą▓ čüą▓ąŠąĖčģ ąŠą▒čŗčćąĮčŗčģ čĆąĄąČąĖą╝ą░čģ.

Bit 15:12 ŌĆō ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ

ąŁčéąĖ ą▒ąĖčéčŗ ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ ą┤ą╗čÅ ą▒čāą┤čāčēąĄą│ąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ. ąöą╗čÅ čüąŠą▓ą╝ąĄčüčéąĖą╝ąŠčüčéąĖ čü ą▒čāą┤čāčēąĖą╝ąĖ ą╝ąŠą┤ąĄą╗čÅą╝ąĖ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ ą▓ čŹčéąĖ ą▒ąĖčéčŗ ąĮčāąČąĮąŠ ąĘą░ą┐ąĖčüą░čéčī ąĮčāą╗ąĖ, ą║ąŠą│ą┤ą░ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ čĆąĄą│ąĖčüčéčĆ UBRRnH.

Bit 11:0 ŌĆō UBRR[11:0]: USART Baud Rate Register

ąŁčéąĖ ą▒ąĖčéčŗ ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčé čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ 12-ą▒ąĖčéąĮąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░, ą║ąŠč鹊čĆčŗą╣ ąĘą░ą┤ą░ąĄčé čüą║ąŠčĆąŠčüčéčī ą┐ąĄčĆąĄą┤ą░čćąĖ (USART baud rate). ąĀąĄą│ąĖčüčéčĆ UBRRnH čüąŠą┤ąĄčƹȹĖčé 4 čüčéą░čĆčłąĖčģ ą▒ąĖčéą░, ąĖ čĆąĄą│ąĖčüčéčĆ UBRRnL čüąŠą┤ąĄčƹȹĖčé 8 ą╝ą╗ą░ą┤čłąĖčģ ą▒ąĖčé čüą║ąŠčĆąŠčüčéąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ USART. ąĢčüą╗ąĖ ąĖąĘą╝ąĄąĮąĖčéčī ąĘąĮą░č湥ąĮąĖąĄ čŹčéąĖčģ ą▒ąĖčé "ąĮą░ ą╗ąĄčéčā", ą║ąŠą│ą┤ą░ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ č鹥ą║čāčēą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░ ąĖ ą┐čĆąĖąĄą╝ čäčĆąĄą╣ą╝ą░, č鹊 čŹčéąĖ čäčĆąĄą╣ą╝čŗ ą▒čāą┤čāčé ąĖčüą┐ąŠčĆč湥ąĮčŗ. ąŚą░ą┐ąĖčüčī ą▓ UBRRnL ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠą╝čā ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÄ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░, ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčēąĄą│ąŠ čüą║ąŠčĆąŠčüčéčī USART.

[ąĪčüčŗą╗ą║ąĖ]

1. AVR151: ąĮą░čüčéčĆąŠą╣ą║ą░ ąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ SPI.

2. ATmega328: SPI.

3. ąśąĮč鹥čĆč乥ą╣čü SPI. |

ąÜąŠą╝ą╝ąĄąĮčéą░čĆąĖąĖ

ąÜąŠą│ą┤ą░ čŹč鹊čé čäą╗ą░ą│ ą▓čŗčüčéą░ą▓ą╗ąĄąĮ, ą┤ą░ąĮąĮčŗąĄ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ R16 ą┐ąŠą╝ąĄčēą░čÄčéčüčÅ ą┤ą╗čÅ ąŠčéą┐čĆą░ą▓ą║ąĖ ą┐ąŠ USART: out UDRn,r16. ąÉ ą┤ąŠ čŹč鹊ą│ąŠ ą▓ R16 ą┐ąĖčģą░ą╗ąĖčüčī čäą╗ą░ą│ąĖ ąĖąĘ čüą╗čāąČąĄą▒ąĮąŠą│ąŠ UCSRnA. ąó.ąĄ. ąĄčüą╗ąĖ ą║č鹊-č鹊 čĆą░ąĮąĄąĄ ąĘą░ą┐ąĖčģąĮąĄčé ą▓ R16 čüą▓ąŠąĖ ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ ąŠčéą┐čĆą░ą▓ą║ąĖ, ąĖ ą┤ą░ą╗ąĄąĄ ąĮą░čćąĮąĄčé ą┐čĆąŠą▓ąĄčĆčÅčéčī čäą╗ą░ą│ąĖ ą▓čŗčłąĄčāą║ą░ąĘą░ąĮąĮčŗą╝ ą║čāčüą║ąŠą╝ ą║ąŠą┤ą░, č鹊 ąŠąĮ čŹčéąĖ ą┤ą░ąĮąĮčŗąĄ ąĘą░čéčĆąĄčé.

ąÜąŠčĆčĆąĄą║čéąĮąŠ ą▒čāą┤ąĄčé čĆą░ą▒ąŠčéą░čéčī čüą╗ąĄą┤čāčÄčēąĖą╣ ą║čāčüąŠą║ ą║ąŠą┤ą░:

ldi r17,0xNN ; ą│ą┤ąĄ 0xNN ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ ąŠčéą┐čĆą░ą▓ą║ąĖ

USART_MSPIM_Tra nsfer:

; ą×ąČąĖą┤ą░ąĮąĖąĄ ąŠą┐čāčüč鹊賹ĄąĮąĖčÅ ą▒čāč乥čĆą░ ą┐ąĄčĆąĄą┤ą░čćąĖ.

in r16, UCSRnA

sbrs r16, UDREn

rjmp USART_MSPIM_Tra nsfer

; ą¤ąŠą╝ąĄčüčéąĖčéčī ą┤ą░ąĮąĮčŗąĄ (r17) ą▓ ą▒čāč乥čĆ ą┤ą╗čÅ ąŠčéą┐čĆą░ą▓ą║ąĖ ą┤ą░ąĮąĮčŗčģ:

out UDRn,r17

ą¤ąĄčĆąĄą┤ą░čćčā ą┤ą░ąĮąĮčŗčģ ąĮą░ ąŠą┤ąĮąŠą╝ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąĄ, ą▒ą╗ą░ą│ąŠą┤ą░čĆčÅ čüčéą░čéčīąĄ, čāčüą┐ąĄčłąĮąŠ ąŠčĆą│ą░ąĮąĖąĘąŠą▓ą░ą╗, ąĮąŠ čü ą┐čĆąĖąĄą╝ąŠą╝ ąĮąĖč湥ą│ąŠ ąĮąĄ ą┐ąŠą╗čāčćą░ąĄčéčüčÅ.

ąÜą░ą║ ą┐čĆą░ą▓ąĖą╗čīąĮąŠ ą┐čĆąĖąĮąĖą╝ą░čéčī ąŠčéą┐čĆą░ą▓ą╗ąĄąĮąĮčŗąĄ čéą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝ ą┤ą░ąĮąĮčŗąĄ? ąĢčüą╗ąĖ ą▓ąŠąĘą╝ąŠąČąĮąŠ ą┐ąŠą║ą░ąČąĖč鹥 ą┐čĆąĖą╝ąĄčĆ čĆą░ą▒ąŠčćąĖą╣.

microsin: čā ATmega328 ąĮąĄčé čäčāąĮą║čåąĖąĖ DMA, ą┐ąŠčŹč鹊ą╝čā ą┐čĆąĖą┤ąĄčéčüčÅ ąŠčĆą│ą░ąĮąĖąĘąŠą▓ą░čéčī ą┐čĆąĖąĄą╝ ą┐ąŠ ąŠą┤ąĮąŠą╝čā ą▒ą░ą╣čéčā, čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. ąöą╗čÅ ą▓čŗčüąŠą║ąŠčüą║ąŠčĆąŠčüčéąĮąŠ ą│ąŠ ą┐čĆąĖąĄą╝ą░ ą▓ąŠąĘą╝ąŠąČąĮąŠ ą┐čĆąĖą┤ąĄčéčüčÅ ąĮą░ą┐ąĖčüą░čéčī ąĮą░ ą░čüčüąĄą╝ą▒ą╗ąĄčĆąĄ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (ISR), ąĖ ąŠą▒ąĄčüą┐ąĄčćąĖčéčī, čćč鹊ą▒čŗ ą▓ ą╝ąŠą╝ąĄąĮčé ą┐čĆąĖąĄą╝ą░ SPI ąĮąĄ čüčĆą░ą▒ą░čéčŗą▓ą░ą╗ąĖ ą▒ąŠą╗ąĄąĄ ą▓čŗčüąŠą║ąŠą┐čĆąĖąŠčĆąĖč鹥čé ąĮčŗąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ąöą╗čÅ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖčÅ ą│ą░čĆą░ąĮčéąĖąĖ čåąĄą╗ąŠčüčéąĮąŠčüčéąĖ ą┤ą░ąĮąĮčŗčģ ą┐čĆąĖ ą┐čĆąĖąĄą╝ąĄ ąĖąĮąŠą│ą┤ą░ ą┐čĆąĖčģąŠą┤ąĖčéčüčÅ ąŠčĆą│ą░ąĮąĖąĘąŠą▓ą░čéčī ą┐čĆąŠą▓ąĄčĆą║čā ą┤ą░ąĮąĮčŗčģ ą┐ąŠ ą║ąŠąĮčéčĆąŠą╗čīąĮąŠą╣ čüčāą╝ą╝ąĄ, ąĖ ą┐čĆąŠč鹊ą║ąŠą╗ ą┤ąŠą╗ąČąĄąĮ ą┐čĆąĄą┤čāčüą╝ą░čéčĆąĖą▓ą░čéčī ą┐čĆąŠčåąĄą┤čāčĆčā ą┐ąŠą▓č鹊čĆąĮąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▓ čüą╗čāčćą░ąĄ ąŠčłąĖą▒ąŠą║.

RSS ą╗ąĄąĮčéą░ ą║ąŠą╝ą╝ąĄąĮčéą░čĆąĖąĄą▓ čŹč鹊ą╣ ąĘą░ą┐ąĖčüąĖ