|

ąÆ čŹč鹊ą╣ čüčéą░čéčīąĄ čĆą░čüčüą╝ąŠčéčĆąĄąĮčŗ ą┐čĆą░ą║čéąĖč湥čüą║ąĖąĄ ą┐čĆąĖą╝ąĄčĆčŗ čĆą░ą▒ąŠčéčŗ čü ą┐ąŠčĆč鹊ą╝ SPI (ą▓ čĆąĄąČąĖą╝ąĄ Master) ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ ARM7 ą║ąŠą╝ą┐ą░ąĮąĖąĖ Atmel (AT91SAM7X128, AT91SAM7X256, AT91SAM7X512) ąĮą░ čÅąĘčŗą║ąĄ C (ą▓ čüčĆąĄą┤ąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ IAR Embedded Workbench). ąśąĮč鹥čĆč乥ą╣čü SPI čłąĖčĆąŠą║ąŠ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą▓čŗčüąŠą║ąŠčüą║ąŠčĆąŠčüčéąĮąŠą╣ čüą▓čÅąĘąĖ ą╝ąĄąČą┤čā ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ą╝ąĖ, čĆą░ą▒ąŠčéčŗ čü ą║ą░čĆčéą░ą╝ąĖ ą┐ą░ą╝čÅčéąĖ SD (ąĖą╗ąĖ SDHC, ąĖą╗ąĖ MMC), čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą▓ąĮąĄčłąĮąĄą╣ ą┐ąĄčĆąĖč乥čĆąĖąĄą╣ ąĖ ą┤čĆčāą│ąĖčģ čåąĄą╗ąĄą╣. ąØą░ą┐čĆąĖą╝ąĄčĆ, LCD ą▓ ąĮąĄą║ąŠč鹊čĆčŗčģ č鹥ą╗ąĄč乊ąĮą░čģ ą┐ąŠą┤ą║ą╗čÄč湥ąĮčŗ č湥čĆąĄąĘ SPI, ąĖąĮč鹥čĆč乥ą╣čü ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ISP ą┤ą╗čÅ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ AVR ąĖ ą┤ą╗čÅ ą╝ąĮąŠą│ąĖčģ ą┤čĆčāą│ąĖčģ - ą▓čüąĄ č鹊čé ąČąĄ SPI.

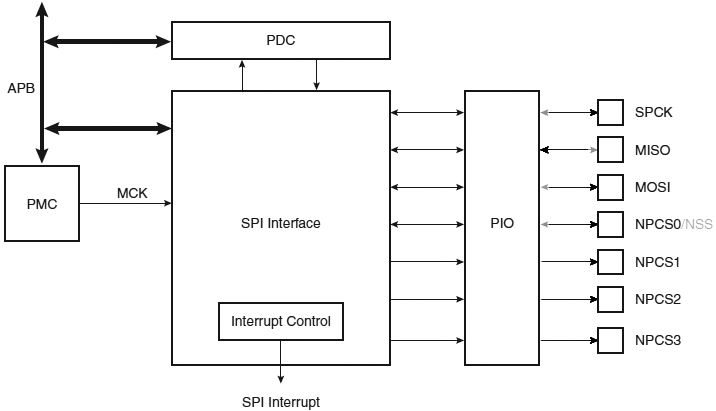

[ą¤ąŠčĆčé SPI ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ ARM7]

ąÆ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ARM7 ą▓čüčéčĆąŠąĄąĮčŗ 2 ą┐ąŠčĆčéą░ SPI: SPI0 ąĖ SPI1, ą║ąŠč鹊čĆčŗąĄ ąĖą╝ąĄčÄčé ąŠą┤ąĖąĮą░ą║ąŠą▓čŗąĄ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāčÄčéčüčÅ ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠ. ą¤ąŠčĆčé SPI ą╝ąŠąČąĄčé ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī ą┤ą░ąĮąĮčŗąĄ (čüą╗ąŠą▓ąŠ ąŠčé 8 ą┤ąŠ 16 ą▒ąĖčé ą┤ą╗ąĖąĮąŠą╣) ą║ą░ą║ ą┐ąŠą┤ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╝ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝, čéą░ą║ ąĖ ą▓ čĆąĄąČąĖą╝ąĄ DMA. ąÆčüąĄ čüąĖą│ąĮą░ą╗čŗ ąĖąĮč鹥čĆč乥ą╣čüą░ SPI (ą▓čŗą▒ąŠčĆą║ą░ ą▓ąĮąĄčłąĮąĄą│ąŠ čćąĖą┐ą░ CS, čéą░ą║čéčŗ SPCK, ą▓čŗčģąŠą┤ąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ MOSI, ą▓čģąŠą┤ąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ MISO) ą│ąĄąĮąĄčĆąĖčĆčāčÄčéčüčÅ ąĖ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░čÄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ. ąöą░ąĮąĮčŗąĄ ą▓čŗą┤ą▓ąĖą│ą░čÄčéčüčÅ ą┐ąŠą▒ąĖčéąĮąŠ, ą┐čĆąĖ čŹč鹊ą╝ ą▓ąŠąĘą╝ąŠąČąĮčŗ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ą║ą░ą║ ą┐čĆąĖąĄą╝, čéą░ą║ ąĖ ą┐ąĄčĆąĄą┤ą░čćą░ ą┤ą░ąĮąĮčŗčģ (ą┐ąŠą╗ąĮčŗą╣ ą┤čāą┐ą╗ąĄą║čü). ąØą░ čĆąĖčüčāąĮą║ąĄ ą┐čĆąĖą▓ąĄą┤ąĄąĮą░ čāą┐čĆąŠčēąĄąĮąĮą░čÅ ą▒ą╗ąŠą║-čüčģąĄą╝ą░ SPI.

ą¤ąŠčÅčüąĮąĄąĮąĖčÅ ą║ čāą┐čĆąŠčēąĄąĮąĮąŠą╣ ą▒ą╗ąŠą║-čüčģąĄą╝ąĄ: čüąĄčĆčŗą╝ čåą▓ąĄč鹊ą╝ ą┐ąŠą╝ąĄč湥ąĮčŗ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĖ čüąĖą│ąĮą░ą╗čŗ, ąŠčéąĮąŠčüčÅčēąĖąĄčüčÅ ą║ čĆąĄąČąĖą╝čā slave SPI (ą▓ ą┤ą░ąĮąĮąŠą╣ čüčéą░čéčīąĄ ąĮąĄ čĆą░čüčüą╝ą░čéčĆąĖą▓ą░ąĄčéčüčÅ).

APB - čłąĖąĮą░ Advanced Peripheral Bus, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮą░čÅ ą║ MCU (ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ ą╝ąĖąĮą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░).

PMC - Power Management Controller, čüą╝. ąĪą╗ąŠą▓ą░čĆąĖą║.

PDC - Peripheral DMA Controller, čüą╝. ąĪą╗ąŠą▓ą░čĆąĖą║.

MCK - čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░, ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮąĮą░čÅ ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ ą┐ąĄčĆąĖč乥čĆąĖąĖ SPI.

SPI Interface - ą┐ąĄčĆąĖč乥čĆąĖčÅ (ą░ą┐ą┐ą░čĆą░čéčāčĆą░) SPI, ą▓čüčéčĆąŠąĄąĮąĮą░čÅ ą▓ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ARM7.

Interrupt Control - čüąĖčüč鹥ą╝ą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅą╝ąĖ SPI.

SPI Interrupt - čüąĖą│ąĮą░ą╗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠčé ą┐ąĄčĆąĖč乥čĆąĖąĖ SPI.

PIO - ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ (I/O) PIO Controller A ąĖą╗ąĖ PIO Controller B, ą║ąŠč鹊čĆčŗą╣ ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮ ą┤ą╗čÅ ą║ąŠą╝ą╝čāčéą░čåąĖąĖ čäčāąĮą║čåąĖą╣ ąĮąŠąČąĄą║ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ (čüą╝. čéą░ą▒ą╗ąĖčåčŗ 10-2 ąĖ 10-3).

SPCK - ą▓ąĮąĄčłąĮčÅčÅ ąĮąŠąČą║ą░, čéą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗ SPI, čüą╝. ąĪą╗ąŠą▓ą░čĆąĖą║.

MISO - ą▓ąĮąĄčłąĮčÅčÅ ąĮąŠąČą║ą░, ą▓čģąŠą┤ ą┤ą░ąĮąĮčŗčģ ą▓ čĆąĄąČąĖą╝ąĄ master, čüą╝. ąĪą╗ąŠą▓ą░čĆąĖą║.

MOSI - ą▓ąĮąĄčłąĮčÅčÅ ąĮąŠąČą║ą░, ą▓čŗčģąŠą┤ ą┤ą░ąĮąĮčŗčģ ą▓ čĆąĄąČąĖą╝ąĄ master, čüą╝. ąĪą╗ąŠą▓ą░čĆąĖą║.

NSS - ą▓ąĮąĄčłąĮčÅčÅ ąĮąŠąČą║ą░, ą▓čģąŠą┤ ą┤ą╗čÅ čüąĖą│ąĮą░ą╗ą░ ą▓čŗą▒ąŠčĆą║ąĖ ą▓ čĆąĄąČąĖą╝ąĄ slave, ą▓ čŹč鹊ą╣ čüčéą░čéčīąĄ ąĮąĄ čĆą░čüčüą╝ą░čéčĆąĖą▓ą░ąĄčéčüčÅ.

NPCS0, NPCS1, NPCS2, NPCS3 - ą▓ąĮąĄčłąĮąĖąĄ ąĮąŠąČą║ąĖ, ą▓čŗčģąŠą┤ąĮčŗąĄ čüąĖą│ąĮą░ą╗čŗ ą┤ą╗čÅ ąŠčĆą│ą░ąĮąĖąĘą░čåąĖąĖ ą▓čŗą▒ąŠčĆą░ ą▓ąĮąĄčłąĮąĖčģ slave-čāčüčéčĆąŠą╣čüčéą▓, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗčģ ą║ čłąĖąĮąĄ SPI.

ąóą░ą▒ą╗ąĖčåą░ 10-2. ą£čāą╗čīčéąĖą┐ą╗ąĄą║čüąĖčĆąŠą▓ą░ąĮąĖąĄ ąĮąŠąČąĄą║ ą║čĆąĖčüčéą░ą╗ą╗ą░ ARM7 ą┤ą╗čÅ PIO Controller A, ąŠčéąĮąŠčüčÅčēąĄąĄčüčÅ ą║ SPI.

| Pin Ōä¢ |

I/O Line |

Peripheral A |

Peripheral B |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ |

| 86 |

PA2 |

SCK0 |

SPI1_NPCS1 |

High-Drive |

| 85 |

PA3 |

RTS0 |

SPI1_NPCS2 |

High-Drive |

| 88 |

PA4 |

CTS0 |

SPI1_NPCS3 |

|

| 91 |

PA7 |

SCK1 |

SPI0_NPCS1 |

|

| 13 |

PA8 |

RTS1 |

SPI0_NPCS2 |

|

| 14 |

PA9 |

CTS1 |

SPI0_NPCS3 |

|

| 20 |

PA12 |

SPI0_NPCS0 |

|

|

| 21 |

PA13 |

SPI0_NPCS1 |

PCK1 |

|

| 22 |

PA14 |

SPI0_NPCS2 |

IRQ1 |

|

| 23 |

PA15 |

SPI0_NPCS3 |

TCLK2 |

|

| 24 |

PA16 |

SPI0_MISO |

|

|

| 25 |

PA17 |

SPI0_MOSI |

|

|

| 26 |

PA18 |

SPI0_SPCK |

|

|

| 49 |

PA21 |

TF |

SPI1_NPCS0 |

|

| 50 |

PA22 |

|

SPI1_SPCK |

|

| 55 |

PA23 |

|

SPI1_MOSI |

|

| 56 |

PA24 |

|

SPI1_MISO |

|

| 59 |

PA25 |

|

SPI1_NPCS1 |

|

| 60 |

PA26 |

|

SPI1_NPCS2 |

|

| 75 |

PA29 |

|

SPI1_NPCS3 |

|

ąóą░ą▒ą╗ąĖčåą░ 10-3. ą£čāą╗čīčéąĖą┐ą╗ąĄą║čüąĖčĆąŠą▓ą░ąĮąĖąĄ ąĮąŠąČąĄą║ ą║čĆąĖčüčéą░ą╗ą╗ą░ ARM7 ą┤ą╗čÅ PIO Controller B, ąŠčéąĮąŠčüčÅčēąĄąĄčüčÅ ą║ SPI.

| Pin Ōä¢ |

I/O Line |

Peripheral A |

Peripheral B |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ |

| 44 |

PB10 |

EXT2 |

SPI1_NPCS1 |

|

| 45 |

PB11 |

EXT3 |

SPI1_NPCS2 |

|

| 30 |

PB13 |

ERX2 |

SPI0_NPCS1 |

|

| 29 |

PB14 |

ERX3 |

SPI0_NPCS2 |

|

| 53 |

PB16 |

ECOL |

SPI1_NPCS3 |

|

| 36 |

PB17 |

ERXCK |

SPI0_NPCS3 |

|

ą¤ąŠčÅčüąĮąĄąĮąĖčÅ ą║ čéą░ą▒ą╗ąĖčåą░ą╝:

Pin Ōä¢ - ąĮąŠą╝ąĄčĆą░ ąĮąŠąČąĄą║ ą║ąŠčĆą┐čāčüą░ LQFP100 ą┤ą╗čÅ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ AT91SAM7X128, AT91SAM7X256, AT91SAM7X512.

I/O Line - ą╝ąĮąĄą╝ąŠąĮąĖč湥čüą║ąŠąĄ ąĖą╝čÅ ąĮąŠąČą║ąĖ čćąĖą┐ą░, čüąŠą┤ąĄčƹȹ░čēąĄąĄ ą▓ čüąĄą▒ąĄ ąĮąŠą╝ąĄčĆ ą▒ąĖčéą░ (ąŠčé 0 ą┤ąŠ 31) ąĖ ąĖą╝čÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ PIO (A ąĖą╗ąĖ B).

Peripheral A, Peripheral B - ą▓ą░čĆąĖą░ąĮčéčŗ ąĮą░čüčéčĆąŠąĄą║ ąĮąŠąČąĄą║ ą║ą░ą║ ą┐ąĄčĆąĖč乥čĆąĖčÅ A ąĖą╗ąĖ ą┐ąĄčĆąĖč乥čĆąĖčÅ B. ąĪąĄčĆčŗą╝ čłčĆąĖčäč鹊ą╝ ą┐ąŠą╝ąĄč湥ąĮčŗ ąĮąĄ ąŠčéąĮąŠčüčÅčēąĖąĄčüčÅ ą║ SPI ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą┐ąĄčĆąĖč乥čĆąĖąĖ ą┤ą╗čÅ ąĮąŠąČąĄą║, ą░ ąČąĖčĆąĮčŗą╝ čłčĆąĖčäč鹊ą╝ - ą▓ą░čĆąĖą░ąĮčé ąĮą░čüčéčĆąŠą╣ą║ąĖ ą┤ą╗čÅ ą¤čĆąĖą╝ąĄčĆą░ 1 (čüą╝. ą┤ą░ą╗ąĄąĄ).

High-Drive - ąĮąŠąČą║ąĖ ą▓čŗą▒ąŠčĆąŠą║ ą┤ą╗čÅ ą▓ąĮąĄčłąĮąĖčģ slave-čāčüčéčĆąŠą╣čüčéą▓ čłąĖąĮčŗ SPI, ąŠą▒ą╗ą░ą┤ą░čÄčēąĖąĄ ą┐ąŠą▓čŗčłąĄąĮąĮąŠą╣ ąĮą░ą│čĆčāąĘąŠčćąĮąŠą╣ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčīčÄ.

ą×čĆą│ą░ąĮąĖąĘą░čåąĖčÅ ą▓čŗą▒ąŠčĆą║ąĖ ą▓ąĮąĄčłąĮąĖčģ čćąĖą┐ąŠą▓, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗčģ ą┐ąŠ SPI (slave čāčüčéčĆąŠą╣čüčéą▓ čłąĖąĮčŗ SPI) ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┤ąĄą╗ą░čéčī ą░ą┐ą┐ą░čĆą░čéąĮčāčÄ ą▓čŗą▒ąŠčĆą║čā ą┤ąŠ 4 čćąĖą┐ąŠą▓ ą▒ąĄąĘ ą┐čĆąĖą╝ąĄąĮąĄąĮąĖčÅ ą┤ąĄčłąĖčäčĆą░č鹊čĆą░, ąĖ ą┤ąŠ 15 čćąĖą┐ąŠą▓ čü ą┐čĆąĖą╝ąĄąĮąĄąĮąĖąĄą╝ ą▓ąĮąĄčłąĮąĄą│ąŠ ą┤ąĄčłąĖčäčĆą░č鹊čĆą░ 4x16. ąĪąĖą│ąĮą░ą╗ ą▓čŗą▒ąŠčĆą║ąĖ CS ą╝ąŠąČąĄčé čéą░ą║ąČąĄ ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčīčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ. ąśąĮč鹥čĆč乥ą╣čü SPI čģąŠčĆąŠčłąŠ ąŠą┐ąĖčüą░ąĮ ą▓ ą┤ą░čéą░čłąĖč鹥, ąĖ ąĖą╝ąĄąĄčé ą┤ąŠą▓ąŠą╗čīąĮąŠ ą┐čĆąŠčüč鹊ą╣ ąĖąĮč鹥čĆč乥ą╣čü ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ (ąĮą░ą▒ąŠčĆ čĆąĄą│ąĖčüčéčĆąŠą▓ SPI). ą£ąŠąČąĮąŠ ąĘą░ą┤ą░čéčī ąĮą░ą▒ąŠčĆ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą┐ąŠ čüąŠą▒čŗčéąĖčÅą╝ SPI (ąŠą┐čāčüč鹊賹ĄąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ ą┐ąĄčĆąĄą┤ą░čćąĖ, ąŠą║ąŠąĮčćą░ąĮąĖąĄ ą┐čĆąĖąĄą╝ą░ čüą╗ąŠą▓ą░, ąŠčłąĖą▒ą║ą░ čĆąĄąČąĖą╝ą░ ąĖ ą┤čĆčāą│ąĖąĄ čüąŠą▒čŗčéąĖčÅ). ąöą╗čÅ ąĮą░čćą░ą╗ą░ čĆą░ą▒ąŠčéčŗ čü SPI ąĮčāąČąĮąŠ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī ąĮąŠąČą║ąĖ čćąĖą┐ą░ ąĮą░ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ ą┐ąĄčĆąĖč乥čĆąĖąĖ SPI, ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī PMC ąĮą░ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ą┐ąĄčĆąĖč乥čĆąĖąĖ SPI, ąĘą░ą┤ą░čéčī čüą║ąŠčĆąŠčüčéčī, ąĮą░čüčéčĆąŠąĖčéčī čüąĖčüč鹥ą╝čā ą▓čŗą▒ąŠčĆą║ąĖ ą▓ąĮąĄčłąĮąĖčģ čćąĖą┐ąŠą▓ ąĖ ą┤čĆčāą│ąĖąĄ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ.

[ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą▓čŗą▒ąŠčĆą║ąŠą╣ ą▓ąĮąĄčłąĮąĖčģ čćąĖą┐ąŠą▓ (slave-čāčüčéčĆąŠą╣čüčéą▓ą░ SPI)]

ą¦ąĖą┐ ARM7 ąĖą╝ąĄąĄčé 4 ą▓čŗą▓ąŠą┤ą░, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮčŗ ą║ą░ą║ ą░ą┐ą┐ą░čĆą░čéąĮčŗąĄ ą▓čŗčģąŠą┤čŗ ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ąĖ slave-čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ ąĮą░ čłąĖąĮąĄ SPI (NPCS0/NSS, NPCS1, NPCS2, NPCS3). ąÆčŗą▒ąŠčĆą║ą░ slave-čāčüčéčĆąŠą╣čüčéą▓ SPI (ą░ą┐ą┐ą░čĆą░čéąĮąŠąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čüąĖą│ąĮą░ą╗ą░ą╝ąĖ CS) ąĮą░čüčéčĆą░ąĖą▓ą░ąĄčéčüčÅ č湥čĆąĄąĘ čĆąĄą│ąĖčüčéčĆčŗ SPI_MR (ą▒ąĖč鹊ą▓čŗąĄ ą┐ąŠą╗čÅ PS, PCSDEC, PCS, DLYBCS) ąĖ SPI_CSRx (ą┐ąŠą╗čÅ CSAAT, DLYBS, DLYBCT). ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠąĄ ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ čüąĖą│ąĮą░ą╗ą░ ą▓čŗą▒ąŠčĆą║ąĖ ąĮą░čüčéčĆą░ąĖą▓ą░ąĄčéčüčÅ čéą░ą║ąČąĄ č湥čĆąĄąĘ čĆąĄą│ąĖčüčéčĆčŗ SPI_CR (ą▒ąĖčé LASTXFER) ąĖ SPI_TDR (ą▒ąĖčé LASTXFER, ą┐ąŠą╗ąĄ PCS). ąÆ ąŠčĆą│ą░ąĮąĖąĘą░čåąĖąĖ ą▓čŗą▒ąŠčĆą║ąĖ ą▓ąŠąĘą╝ąŠąČąĮčŗ čüą╗ąĄą┤čāčÄčēąĖąĄ ą▓ą░čĆąĖą░ąĮčéčŗ:

1. ąÆčŗą▒ąŠčĆ čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮąŠą╣ ą┐ąĄčĆąĖč乥čĆąĖąĖ, ą║ąŠą│ą┤ą░ SPI_MR.PS=0, SPI_MR.PCSDEC=0. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ąĮą░ ąĮąŠąČą║ą░čģ NPCS0, NPCS1, NPCS2, NPCS3 čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą╗ąŠą│ąĖč湥čüą║ąĖą╣ čüąĖą│ąĮą░ą╗ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü ą┐ąŠą╗ąĄą╝ PCS čĆąĄą│ąĖčüčéčĆą░ SPI_MR. ąöą╗čÅ ą┐ąŠą╗čÅ SPI_MR.PCS ą┤ąŠą┐čāčüčéąĖą╝čŗ ąĘąĮą░č湥ąĮąĖčÅ 14 (0xE, 1110b, ą░ą║čéąĖą▓ąĮą░ ą▓čŗą▒ąŠčĆą║ą░ NPCS0), 13 (0xD, 1101b, ą░ą║čéąĖą▓ąĮą░ ą▓čŗą▒ąŠčĆą║ą░ NPCS1), 11 (0xB, 1011b, ą░ą║čéąĖą▓ąĮą░ ą▓čŗą▒ąŠčĆą║ą░ NPCS2), 7 (0x7, 0111b, ą░ą║čéąĖą▓ąĮą░ ą▓čŗą▒ąŠčĆą║ą░ NPCS3). ą¤ąŠą╗ąĄ PCS čĆąĄą│ąĖčüčéčĆą░ ą┐ąĄčĆąĄą┤ą░čćąĖ SPI_TDR ą┐čĆąĖ čŹč鹊ą╝ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ. ąÆą░čĆąĖą░ąĮčé čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮąŠą╣ ą┐ąĄčĆąĖč乥čĆąĖąĖ ą┐čĆąĖą╝ąĄąĮčÅąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ąĮčāąČąĮąŠ ą▓ąĄčüčéąĖ ą┐ąĄčĆąĄą┤ą░čćčā ą▓ čĆąĄąČąĖą╝ąĄ DMA č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ąŠą┤ąĮąŠą│ąŠ čćąĖą┐ą░ (SPI_TDR.PCS ą┐čĆąĖ čŹč鹊ą╝ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ąĮąĄą╗čīąĘčÅ). ąöą╗čÅ č鹊ą│ąŠ, čćč鹊ą▒čŗ ąĘą░ą┐čāčüčéąĖčéčī ą┐ąĄčĆąĄą┤ą░čćčā DMA ą┤ą╗čÅ ą┤čĆčāą│ąŠą│ąŠ čćąĖą┐ą░, ąĮčāąČąĮąŠ ą┐ąĄčĆąĄčāčüčéą░ąĮąŠą▓ąĖčéčī ą┐ąŠą╗ąĄ SPI_MR.PCS.

2. ąÆčŗą▒ąŠčĆ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą╣ ą┐ąĄčĆąĖč乥čĆąĖąĖ, ą║ąŠą│ą┤ą░ SPI_MR.PS=1, SPI_MR.PCSDEC=0. ąŁč鹊čé čĆąĄąČąĖą╝ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé čĆą░ą▒ąŠčéą░čéčī ą▒ąĄąĘ DMA ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ čü ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ slave-čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ ąĮą░ čłąĖąĮąĄ SPI. ą¤ąŠą╗ąĄ SPI_MR.PCS č鹥ą┐ąĄčĆčī ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą░ą║čéąĖą▓ąĖąĘą░čåąĖąĖ čüąĖą│ąĮą░ą╗ąŠą▓ ą▓čŗą▒ąŠčĆąŠą║, ą░ ą┐čĆąĖą╝ąĄąĮčÅąĄčéčüčÅ ą┐ąŠą╗ąĄ PCS čĆąĄą│ąĖčüčéčĆą░ ą┐ąĄčĆąĄą┤ą░čćąĖ, SPI_TDR.PCS. ąöą╗čÅ ą┐ąŠą╗čÅ SPI_TDR.PCS ą┤ąŠą┐čāčüčéąĖą╝čŗ ąĘąĮą░č湥ąĮąĖčÅ 14 (0xE, 1110b, ą░ą║čéąĖą▓ąĮą░ ą▓čŗą▒ąŠčĆą║ą░ NPCS0), 13 (0xD, 1101b, ą░ą║čéąĖą▓ąĮą░ ą▓čŗą▒ąŠčĆą║ą░ NPCS1), 11 (0xB, 1011b, ą░ą║čéąĖą▓ąĮą░ ą▓čŗą▒ąŠčĆą║ą░ NPCS2), 7 (0x7, 0111b, ą░ą║čéąĖą▓ąĮą░ ą▓čŗą▒ąŠčĆą║ą░ NPCS3).

3. ąÆčŗą▒ąŠčĆ čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮąŠą╣ ą┐ąĄčĆąĖč乥čĆąĖąĖ čü ą▓ąĮąĄčłąĮąĖą╝ ą┤ąĄčłąĖčäčĆą░č鹊čĆąŠą╝, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗą╝ ą║ ąĮąŠąČą║ą░ą╝ NPCS0 .. NPCS3, ą║ąŠą│ą┤ą░ SPI_MR.PS=0, SPI_MR.PCSDEC=1. ąŁč鹊čé čĆąĄąČąĖą╝ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą▓čŗą▒čĆą░čéčī ą╗čÄą▒ąŠąĄ ąĖąĘ 15 slave-čāčüčéčĆąŠą╣čüčéą▓, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗčģ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠ ą║ čłąĖąĮąĄ SPI. ąöą╗čÅ ą▓čŗą▒ąŠčĆą║ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄ ąĖąĘ ą┐ąŠą╗čÅ SPI_MR.PCS, ą┤ąŠą┐čāčüčéąĖą╝čŗ ąĘąĮą░č湥ąĮąĖčÅ ąŠčé 0 ą┤ąŠ 14. ą¤ąŠą╗ąĄ PCS čĆąĄą│ąĖčüčéčĆą░ ą┐ąĄčĆąĄą┤ą░čćąĖ SPI_TDR ą┐čĆąĖ čŹč鹊ą╝ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ. ąŁč鹊čé ą▓ą░čĆąĖą░ąĮčé čéą░ą║ąČąĄ, ą║ą░ą║ ąĖ ą▓ą░čĆąĖą░ąĮčé 1, ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐ąŠ čłąĖąĮąĄ SPI č湥čĆąĄąĘ DMA.

4. ąÆčŗą▒ąŠčĆ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą╣ ą┐ąĄčĆąĖč乥čĆąĖąĖ čü ą▓ąĮąĄčłąĮąĖą╝ ą┤ąĄčłąĖčäčĆą░č鹊čĆąŠą╝, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗą╝ ą║ ąĮąŠąČą║ą░ą╝ NPCS0 .. NPCS3, ą║ąŠą│ą┤ą░ SPI_MR.PS=1, SPI_MR.PCSDEC=1. ąŁč鹊čé čĆąĄąČąĖą╝ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą▓čŗą▒čĆą░čéčī ą╗čÄą▒ąŠąĄ ąĖąĘ 15 slave-čāčüčéčĆąŠą╣čüčéą▓, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗčģ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠ ą║ čłąĖąĮąĄ SPI. ąöą╗čÅ ą▓čŗą▒ąŠčĆą║ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄ ąĖąĘ ą┐ąŠą╗čÅ SPI_TDR.PCS, ą┤ąŠą┐čāčüčéąĖą╝čŗ ąĘąĮą░č湥ąĮąĖčÅ ąŠčé 0 ą┤ąŠ 14. ą¤ąŠą╗ąĄ PCS čĆąĄą│ąĖčüčéčĆą░ ą┐ąĄčĆąĄą┤ą░čćąĖ SPI_MR ą┐čĆąĖ čŹč鹊ą╝ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ. ąŁč鹊čé ą▓ą░čĆąĖą░ąĮčé čéą░ą║ąČąĄ, ą║ą░ą║ ąĖ ą▓ą░čĆąĖą░ąĮčé 2, ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐ąŠ čłąĖąĮąĄ SPI ą▒ąĄąĘ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ DMA.

ąØą░ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī čüąĖą│ąĮą░ą╗ą░ ą▓čŗą▒ąŠčĆą║ąĖ ą▓ą╗ąĖčÅčÄčé čüą╗ąĄą┤čāčÄčēąĖąĄ čĆąĄą│ąĖčüčéčĆčŗ ąĖ ąĖčģ ą┐ąŠą╗čÅ:

SPI_MR.DLYBCS čŹč鹊 ą┐ąŠą╗ąĄ ą▓ą╗ąĖčÅąĄčé ąĮą░ ąĘą░ą┤ąĄčƹȹ║čā ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą╗čÅ ą▓čüąĄčģ čĆąĄąČąĖą╝ąŠą▓ č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓čŗą▒ąŠčĆąŠą║ (čĆąĄąČąĖą╝čŗ 1..4). ąśą╝ąĄąĄčé čüą╝čŗčüą╗ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┐čĆąĖ ąĮą░ą╗ąĖčćąĖąĖ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ slave-čāčüčéčĆąŠą╣čüčéą▓ ąĮą░ čłąĖąĮąĄ SPI. ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ čŹč鹊ą│ąŠ ą┐ąŠą╗čÅ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąĘą░ą┤ą░čéčī ą▓čĆąĄą╝čÅ ąĘą░ą┤ąĄčƹȹ║ąĖ ą╝ąĄąČą┤čā ąŠčéą║ą░ąĘąŠą╝ ąŠčé ą▓čŗą▒ąŠčĆą░ ąŠą┤ąĮąŠą│ąŠ slave-čāčüčéčĆąŠą╣čüčéą▓ą░ ą▓ ą┐ąŠą╗čīąĘčā ą▓čŗą▒ąŠčĆą░ ą┤čĆčāą│ąŠą│ąŠ, čćč鹊 ą│ą░čĆą░ąĮčéąĖčĆčāąĄčé ąŠčéčüčāčéčüčéą▓ąĖąĄ ą║ąŠąĮčäą╗ąĖą║č鹊ą▓ ąĮą░ čłąĖąĮąĄ SPI. ąó. ąĄ. ąĘą░ą┤ąĄčƹȹ║ą░ ą▓čüčéą░ą▓ą╗čÅąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą┐čĆąĖ ą┐ąĄčĆąĄčģąŠą┤ąĄ čü ąŠą┤ąĮąŠą│ąŠ slave-čāčüčéčĆąŠą╣čüčéą▓ą░ ąĮą░ ą┤čĆčāą│ąŠąĄ. ąĢčüą╗ąĖ ą┐ąŠą╗ąĄ DLYBCS ą╝ąĄąĮčīčłąĄ ąĖą╗ąĖ čĆą░ą▓ąĮąŠ 6, č鹊 ą▓čĆąĄą╝čÅ ąĘą░ą┤ąĄčƹȹ║ąĖ ą▒čāą┤ąĄčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ ą▓ ąĘąĮą░č湥ąĮąĖąĄ 6 ą┐ąĄčĆąĖąŠą┤ąŠą▓ MCK (ąĖą╗ąĖ 6*N ą┐ąĄčĆąĖąŠą┤ąŠą▓ MCK, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ ą┐ąŠą╗ąĄ SPI_MR.FDIV). ąÆ ą┐čĆąŠčéąĖą▓ąĮąŠą╝ čüą╗čāčćą░ąĄ ąĘą░ą┤ąĄčƹȹ║ą░ ą▓čŗčćąĖčüą╗čÅąĄčéčüčÅ ą┐ąŠ č乊čĆą╝čāą╗ąĄ DLYBCS/MCK (ąĄčüą╗ąĖ FDIV=0) ąĖą╗ąĖ (DLYBCS*N)/MCK (ąĄčüą╗ąĖ FDIV=1).

SPI_CSRx.DLYBS čŹč鹊 ą┐ąŠą╗ąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ ąŠčéą┤ąĄą╗čīąĮąŠ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą╣ ąĮąŠąČą║ąĖ NPCSx (NPCS0 .. NPCS3), ąĖ ą▓ą╗ąĖčÅąĄčé ąĮą░ ąĘą░ą┤ąĄčƹȹ║čā ą╝ąĄąČą┤čā čüą┐ą░ą┤ąŠą╝ ąĮą░ ąĮąŠąČą║ąĄ NPCSx (ą░ą║čéąĖą▓ąĖąĘą░čåąĖčÅ ą▓čŗą▒ąŠčĆą║ąĖ) ąĖ ą┐ąŠčÅą▓ą╗ąĄąĮąĖąĄą╝ čéą░ą║č鹊ą▓ SPCK. ąĢčüą╗ąĖ ą┐ąŠą╗ąĄ DLYBS=0, č鹊 ą▓čĆąĄą╝čÅ ąĘą░ą┤ąĄčƹȹ║ąĖ čüąŠčüčéą░ą▓ą╗čÅąĄčé ą┐ąŠą╗ą┐ąĄčĆąĖąŠą┤ą░ čćą░čüč鹊čéčŗ SPCK. ąÆ ą┐čĆąŠčéąĖą▓ąĮąŠą╝ čüą╗čāčćą░ąĄ ą▓čĆąĄą╝čÅ ąĘą░ą┤ąĄčƹȹ║ąĖ ą▓čŗčćąĖčüą╗čÅąĄčéčüčÅ ą┐ąŠ č乊čĆą╝čāą╗ąĄ DLYBS/MCK (ąĄčüą╗ąĖ FDIV=0) ąĖą╗ąĖ (32 * DLYBCS)/MCK (ąĄčüą╗ąĖ FDIV=1).

SPI_CSRx.DLYBCT čŹč鹊 ą┐ąŠą╗ąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ ąŠčéą┤ąĄą╗čīąĮąŠ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą╣ ąĮąŠąČą║ąĖ NPCSx (NPCS0 .. NPCS3), ąĖ ą▓ą╗ąĖčÅąĄčé ąĮą░ ąĘą░ą┤ąĄčƹȹ║čā ą╝ąĄąČą┤čā ą╝ąĄąČą┤čā ą┤ą▓čāą╝čÅ ąŠčéą┤ąĄą╗čīąĮčŗą╝ąĖ ą┐ąĄčĆąĄą┤ą░čćą░ą╝ąĖ, ą┐čĆąĖčģąŠą┤čÅčēąĖą╝ąĖčüčÅ ąĮą░ ąŠą┤ąĮąŠ ąĖ č鹊 ąČąĄ slave-čāčüčéčĆąŠą╣čüčéą▓ąŠ. ąÜąŠą│ą┤ą░ ą┐ąŠą╗ąĄ DLYBCT=0, č鹊 ąĮąĖą║ą░ą║ąŠą╣ ąĘą░ą┤ąĄčƹȹ║ąĖ ąĮąĄčé, ąĖ čüąĖąĮčģčĆąŠčüąĖą│ąĮą░ą╗ SPCK čüąŠčģčĆą░ąĮčÅąĄčé čüą▓ąŠą╣ čĆą░ą▒ąŠčćąĖą╣ čåąĖą║ą╗, ą║ąŠč鹊čĆčŗą╣ ą▒čŗą╗ ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ. ąśąĮą░č湥 ą▓čĆąĄą╝čÅ ąĘą░ą┤ąĄčƹȹ║ąĖ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ čāčĆą░ą▓ąĮąĄąĮąĖąĄą╝ (32 * DLYBCT)/MCK + SCBR/(2 * MCK) (ąĄčüą╗ąĖ FDIV=0), ąĖą╗ąĖ čāčĆą░ą▓ąĮąĄąĮąĖąĄą╝ (32 * 32 * DLYBCT)/MCK + (32 * SCBR)/(2 * MCK) (ąĄčüą╗ąĖ FDIV=1).

ąÆąĮąĖą╝ą░ąĮąĖąĄ: ą┐čĆąĖ ą┐ąĄčĆąĄąĮą░čüčéčĆąŠą╣ą║ąĄ ą▓čŗą▒ąŠčĆą║ąĖ ąĮąĄ ąĘą░ą▒čŗą▓ą░ą╣č鹥 ąŠ čĆąĄą│ąĖčüčéčĆą░čģ SPI_CSRx - čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▓čŗą▒ąŠčĆą║ąĄ čĆąĄą│ąĖčüčéčĆ čéą░ą║ąČąĄ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą║ąŠčĆčĆąĄą║čéąĮąŠ ąĮą░čüčéčĆąŠąĄąĮ, ąĖąĮą░č湥 ą┐ąĄčĆąĄą┤ą░čćą░ ąĖ ą┐čĆąĖąĄą╝ ą▒čāą┤čāčé ąĮąĄą▓ąŠąĘą╝ąŠąČąĮčŗ (ąĮąĄ ą▒čāą┤čāčé ą║ąŠčĆčĆąĄą║čéąĮąŠ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čéčīčüčÅ čäą╗ą░ą│ąĖ SPIO_SR.TDRE, SPIO_SR.TXBUFE, SPIO_SR.RDRF).

[ąØą░čüčéčĆąŠą╣ą║ą░ čüą║ąŠčĆąŠčüčéąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ SPI]

ąĪą║ąŠčĆąŠčüčéčī ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐ąŠ čłąĖąĮąĄ SPI ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊č鹊ą╣, ą▓čŗą▓ąŠą┤ąĖą╝ąŠą╣ ąĮą░ ąĮąŠąČą║čā čüąĖąĮčģčĆąŠčüąĖą│ąĮą░ą╗ą░ SPCK. ąŁč鹊čé čüąĖą│ąĮą░ą╗ ą│ąĄąĮąĄčĆąĖčĆčāąĄčé master čłąĖąĮčŗ SPI, ą▓ ąĮą░čłąĄą╝ čüą╗čāčćą░ąĄ čŹč鹊 ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ARM7. ą¦ą░čüč鹊čéą░ SPCK ą▓ą╗ąĖčÅąĄčé ąĮą░ čüą║ąŠčĆąŠčüčéčī ą┐ąĄčĆąĄą┤ą░čćąĖ, ąĖ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą┐ąŠą╗ąĄą╝ SPI_MR.FDIV ąĖ ą┐ąŠą╗ąĄą╝ SPI_CSRx.SCBR. ąÆ ą┐ąŠą╗ąĄ SCBR ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮąŠ ąĘąĮą░č湥ąĮąĖąĄ ąŠčé 1 ą┤ąŠ 255, ąĘąĮą░č湥ąĮąĖąĄ 0 ąĘą░ą┐čĆąĄčēąĄąĮąŠ (ąĄčüą╗ąĖ ąĘą░ą┐ąĖčüą░čéčī 0, č鹊 ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ čüčéą░ąĮąĄčé ąĮąĄą┐čĆąĄą┤čüą║ą░ąĘčāąĄą╝čŗą╝). ąĪą║ąŠčĆąŠčüčéčī ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ čāčĆą░ą▓ąĮąĄąĮąĖąĄą╝ MCK/SCBR (ąĄčüą╗ąĖ FDIV=0), MCK/(32 * SCBR) (ąĄčüą╗ąĖ FDIV=1).

[ążąŠčĆą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ čüąĖą│ąĮą░ą╗ą░ čéą░ą║č鹊ą▓ SPCK]

ążąŠčĆą╝ą░čé ą┐ąĄčĆąĄą┤ą░čćąĖ ąĘą░ą▓ąĖčüąĖčé ąŠčé čäą░ąĘčŗ čüąĖąĮčģčĆąŠčüąĖą│ąĮą░ą╗ą░ SPCK ą┐ąŠ ąŠčéąĮąŠčłąĄąĮąĖčÄ ą║ čüąĖą│ąĮą░ą╗čā ą┤ą░ąĮąĮčŗčģ (MOSI, MISO). ąŁč鹊 ąĮą░čüčéčĆą░ąĖą▓ą░ąĄčéčüčÅ ą┐ąŠą╗čÅą╝ąĖ NCPHA ąĖ CPOL čĆąĄą│ąĖčüčéčĆąŠą▓ SPI_CSRx. ą¤ąŠą╗ąĄ SPI_CSRx.CPOL ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ą┐ąŠą╗čÅčĆąĮąŠčüčéčī čüąĖąĮčģčĆąŠčüąĖą│ąĮą░ą╗ą░: ąĄčüą╗ąĖ SPI_CSRx.CPOL=0, č鹊 ąĮąĄą░ą║čéąĖą▓ąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ SPCK ą╗ąŠą│. 0, ą░ ąĄčüą╗ąĖ SPI_CSRx.CPOL=1, č鹊 ąĮąĄą░ą║čéąĖą▓ąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ SPCK ą╗ąŠą│. 1. ą¤ąŠą╗ąĄ SPI_CSRx.NCPHA ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé čäą░ąĘčā čüąĖąĮčģčĆąŠčüąĖą│ąĮą░ą╗ą░. ąÆą╝ąĄčüč鹥 ą┐ąŠą╗čÅ ą┐ąŠą╗čÅ CPOL ąĖ NCPHA ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčé 4 ą▓ą░čĆąĖą░ąĮčéą░ č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ čüąĖą│ąĮą░ą╗ą░ SPCK.

1. NCPHA=0, CPOL=0. ąöą░ąĮąĮčŗąĄ čäąĖą║čüąĖčĆčāčÄčéčüčÅ ą┐ąŠ čüą┐ą░ą┤čā SPCK, ą╝ąĄąĮčÅčÄčéčüčÅ ą┐ąŠ čäčĆąŠąĮčéčā SPCK, ąĮą░čćą░ą╗čīąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ SPCK ą╗ąŠą│. 0.

2. NCPHA=0, CPOL=1. ąöą░ąĮąĮčŗąĄ čäąĖą║čüąĖčĆčāčÄčéčüčÅ ą┐ąŠ čäčĆąŠąĮčéčā SPCK, ą╝ąĄąĮčÅčÄčéčüčÅ ą┐ąŠ čüą┐ą░ą┤čā SPCK, ąĮą░čćą░ą╗čīąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ SPCK ą╗ąŠą│. 1.

3. NCPHA=1, CPOL=0. ąöą░ąĮąĮčŗąĄ čäąĖą║čüąĖčĆčāčÄčéčüčÅ ą┐ąŠ čäčĆąŠąĮčéčā SPCK, ą╝ąĄąĮčÅčÄčéčüčÅ ą┐ąŠ čüą┐ą░ą┤čā SPCK, ąĮą░čćą░ą╗čīąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ SPCK ą╗ąŠą│. 0.

4. NCPHA=1, CPOL=1. ąöą░ąĮąĮčŗąĄ čäąĖą║čüąĖčĆčāčÄčéčüčÅ ą┐ąŠ čüą┐ą░ą┤čā SPCK, ą╝ąĄąĮčÅčÄčéčüčÅ ą┐ąŠ čäčĆąŠąĮčéčā SPCK, ąĮą░čćą░ą╗čīąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ SPCK ą╗ąŠą│. 1.

[ą¤ąĄčĆąĄą┤ą░čćą░ SPI čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ DMA / ą▒ąĄąĘ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ DMA]

ąÜąŠą│ą┤ą░ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ DMA, č鹊 ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą▒čĆą░ąĮ ą╗čÄą▒ąŠą╣ ą▓ą░čĆąĖą░ąĮčé ąĮą░čüčéčĆąŠą╣ą║ąĖ ą┐ąĄčĆąĖč乥čĆąĖąĖ (ą╗čÄą▒čŗąĄ ąĘąĮą░č湥ąĮąĖčÅ SPI_MR.PS, SPI_MR.PCSDEC), ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą┐čĆąĖą╝ąĄąĮčÅąĄą╝ąŠą╣ čüčģąĄą╝čŗ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ slave-čāčüčéčĆąŠą╣čüčéą▓, ąĖčģ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ąĖ ą┐čĆąĄą┤ą┐ąŠčćč鹥ąĮąĖą╣ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčüčéą░.

ąÜąŠą│ą┤ą░ DMA ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ, č鹊 ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ ą┐ąŠ ąĮą░čüčéčĆąŠą╣ą║ąĄ ą▓čŗą▒ąŠčĆą║ąĖ slave-čāčüčéčĆąŠą╣čüčéą▓ ąĮąĄčüą║ąŠą╗čīą║ąŠ čüčāąČą░čÄčéčüčÅ, ąĄčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ąĮąĄčüą║ąŠą╗čīą║ąŠ slave-čāčüčéčĆąŠą╣čüčéą▓ ąĮą░ čłąĖąĮąĄ SPI. ą¤čĆąĖčćąĖąĮą░ ą▓ č鹊ą╝, čćč鹊 ą┐čĆąĖ ą┐ąĄčĆąĄą┤ą░č湥 ąŠą┤ąĮąŠą│ąŠ ą▒ą╗ąŠą║ą░ ą┤ą░ąĮąĮčŗčģ č湥čĆąĄąĘ DMA ąĮąĄą╗čīąĘčÅ ą┐ąĄčĆąĄąĮą░čüčéčĆąŠąĖčéčī čĆąĄą│ąĖčüčéčĆ SPI_MR. ąóą░ą║ čćč鹊 ą╝ąŠąČąĮąŠ ąĘą░ą┤ą░čéčī čĆąĄąČąĖą╝ čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮąŠą╣ ą┐ąĄčĆąĖč乥čĆąĖąĖ (SPI_MR.PS=0), čü ą┤ąĄą║ąŠą┤ąĄčĆąŠą╝ ąĖą╗ąĖ ą▒ąĄąĘ (SPI_MR.PCSDEC=0 ąĖą╗ąĖ SPI_MR.PCSDEC=1), č鹊ą│ą┤ą░ ą▒čāč乥čĆ PDC ą╝ąŠąČąĮąŠ ą▓čŗą▒čĆą░čéčī 8-ą▒ąĖčéąĮčŗą╣ ąĖą╗ąĖ 16-ą▒ąĖčéąĮčŗą╣ (ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą▓čŗą▒čĆą░ąĮąĮąŠą│ąŠ č乊čĆą╝ą░čéą░ ą┐ąĄčĆąĄą┤ą░čćąĖ). ąÆ ą┐čĆąĄą┤ąĄą╗ą░čģ ą┐ąĄčĆąĄą┤ą░čćąĖ ąŠą┤ąĮąŠą│ąŠ ą▒ą╗ąŠą║ą░ č湥čĆąĄąĘ DMA ą╝ąŠąČąĮąŠ ą▓ąĄčüčéąĖ ąŠą▒ą╝ąĄąĮ č鹊ą╗čīą║ąŠ čü ąŠą┤ąĮąĖą╝ slave-čāčüčéčĆąŠą╣čüčéą▓ąŠą╝, ąĮąŠ čĆą░čüčģąŠą┤ ą┐ą░ą╝čÅčéąĖ ąĮą░ ą▒čāč乥čĆčŗ DMA ą┐ąŠą╗čāčćą░ąĄčéčüčÅ čŹą║ąŠąĮąŠą╝ąĖčćąĮčŗą╝. ąĢčüą╗ąĖ ąČąĄ ą▓čŗą▒čĆą░čéčī ą┤ą╗čÅ DMA čĆąĄąČąĖą╝ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą╣ ą┐ąĄčĆąĖč乥čĆąĖąĖ (SPI_MR.PS=1), čü ą┤ąĄą║ąŠą┤ąĄčĆąŠą╝ ąĖą╗ąĖ ą▒ąĄąĘ (SPI_MR.PCSDEC=0 ąĖą╗ąĖ SPI_MR.PCSDEC=1), č鹊 č鹊ą│ą┤ą░ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ 32-ą▒ąĖčéąĮčŗą╣ ą▒čāč乥čĆ DMA, ą▓ ą┤ą░ąĮąĮčŗčģ ą║ąŠč鹊čĆąŠą│ąŠ ąĘą░ą┐ąŠą╗ąĮąĄąĮčŗ ą┐ąŠą╗čÅ ą▓čŗą▒ąŠčĆą░ slave-čāčüčéčĆąŠą╣čüčéą▓ą░ ąĖ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą▓čŗą▒ąŠčĆą║ąĖ. ąŁč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą▓ ą┐čĆąĄą┤ąĄą╗ą░čģ ąŠą┤ąĮąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ DMA ą▓ąĄčüčéąĖ ąŠą▒ą╝ąĄąĮ čü ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ slave-čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ, ąŠą┤ąĮą░ą║ąŠ čāą▓ąĄą╗ąĖčćąĖą▓ą░ąĄčé ąĮą░ą║ą╗ą░ą┤ąĮčŗąĄ čĆą░čüčģąŠą┤čŗ ą┐ąŠ ą┐ą░ą╝čÅčéąĖ ą┐ąŠą┤ ą▒čāč乥čĆčŗ DMA. ąöą╗čÅ ąĘą░ą┐čāčüą║ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▓ čĆąĄąČąĖą╝ąĄ DMA čéą░ą║ąČąĄ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ą░ ąĮą░čüčéčĆąŠą╣ą║ą░ čĆąĄą│ąĖčüčéčĆąŠą▓ PDC.

[ąśąĮč鹥čĆč乥ą╣čü ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ SPI]

ą¤ąŠą┤ ąĖąĮč鹥čĆč乥ą╣čüąŠą╝ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ ą┐ąŠąĮąĖą╝ą░ąĄčéčüčÅ ą║ą░čĆčéą░ ą┐ą░ą╝čÅčéąĖ čĆąĄą│ąĖčüčéčĆąŠą▓ SPI. ą¦ąĄčĆąĄąĘ čŹčéąĖ čĆąĄą│ąĖčüčéčĆčŗ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą║ą░ą║ ąŠą▒ą╝ąĄąĮ ą┤ą░ąĮąĮčŗą╝ąĖ, čéą░ą║ ąĖ ąĮą░čüčéčĆąŠą╣ą║ą░, čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ SPI, ą┐ąŠą╗čāč湥ąĮąĖąĄ ąĄą│ąŠ čüąŠčüč鹊čÅąĮąĖčÅ ąĖ čĆą░ą▒ąŠčéą░ čü SPI č湥čĆąĄąĘ DMA. ąŻ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ AT91SAM7X ą┤ą▓ą░ ąĖąĮč鹥čĆč乥ą╣čüą░ SPI, ąĖ ą║ą░ąČą┤ąŠą╝čā čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé 2 ą▒ą╗ąŠą║ą░ ą░ą┤čĆąĄčüąĮąŠą│ąŠ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ą░. ąöą╗čÅ SPI0 čŹč鹊 ą░ą┤čĆąĄčüąĮąŠąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ 0xFFFE0000..0xFFFE0124, ą┤ą╗čÅ SPI1 0xFFFE4000..0xFFFE4124. ąÆ čéą░ą▒ą╗ąĖčåąĄ ąĮąĖąČąĄ ą┐ąĄčĆąĄčćąĖčüą╗ąĄąĮčŗ ą▓čüąĄ čĆąĄą│ąĖčüčéčĆčŗ, ą║čĆą░čéą║ąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ ąĖčģ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ, ą░ čéą░ą║ąČąĄ čüą╝ąĄčēąĄąĮąĖąĄ ą▓ ą░ą┤čĆąĄčüąĮąŠą╝ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąĄ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ą▒ą░ąĘąŠą▓ąŠą│ąŠ ą░ą┤čĆąĄčüą░ (ą▒ą░ąĘąŠą▓čŗą╣ ą░ą┤čĆąĄčü ą┤ą╗čÅ SPI0 čĆą░ą▓ąĄąĮ 0xFFFE0000, ą░ ą┤ą╗čÅ SPI1 0xFFFE4000).

| ąĪą╝ąĄčēąĄąĮąĖąĄ |

ąĀąĄą│ąĖčüčéčĆ |

ąśą╝čÅ |

ąöąŠčüčéčāą┐ |

ąĪą▒čĆąŠčü |

| 0x000 |

Control Register (čĆąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ) |

SPI_CR |

W |

- |

| 0x004 |

Mode Register (čĆąĄą│ąĖčüčéčĆ čĆąĄąČąĖą╝ą░) |

SPI_MR |

R/W |

0 |

| 0x008 |

Receive Data Register (ą┤ą░ąĮąĮčŗąĄ ą┐čĆąĖąĄą╝ą░) |

SPI_RDR |

R |

0 |

| 0x00C |

Transmit Data Register (ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗąĄ ą┤ą░ąĮąĮčŗąĄ) |

SPI_TDR |

W |

- |

| 0x010 |

Status Register (čĆąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ) |

SPI_SR |

R |

0x000000F0 |

| 0x014 |

Interrupt Enable Register (čĆąĄą│ąĖčüčéčĆ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣) |

SPI_IER |

W |

- |

| 0x018 |

Interrupt Disable Register (čĆąĄą│ąĖčüčéčĆ ąĘą░ą┐čĆąĄčēąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣) |

SPI_IDR |

W |

- |

| 0x01C |

Interrupt Mask Register (čĆąĄą│ąĖčüčéčĆ ą╝ą░čüą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣) |

SPI_IMR |

R |

0 |

| 0x020..0x02C |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ (ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ) |

|

|

|

| 0x030 |

Chip Select Register 0 (čĆąĄą│ąĖčüčéčĆ ą▓čŗą▒ąŠčĆą║ąĖ 0) |

SPI_CSR0 |

R/W |

0 |

| 0x034 |

Chip Select Register 1 (čĆąĄą│ąĖčüčéčĆ ą▓čŗą▒ąŠčĆą║ąĖ 1) |

SPI_CSR1 |

R/W |

0 |

| 0x038 |

Chip Select Register 2 (čĆąĄą│ąĖčüčéčĆ ą▓čŗą▒ąŠčĆą║ąĖ 2) |

SPI_CSR2 |

R/W |

0 |

| 0x03C |

Chip Select Register 3 (čĆąĄą│ąĖčüčéčĆ ą▓čŗą▒ąŠčĆą║ąĖ 3) |

SPI_CSR3 |

R/W |

0 |

| 0x040..0x0FC |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ (ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ) |

|

|

|

| 0x100..0x124 |

ąĀąĄą│ąĖčüčéčĆčŗ PDC (čüą╝. [5]). |

|

|

|

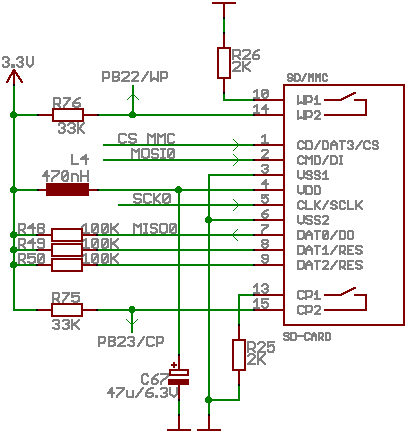

ąŚą░ ąŠčüąĮąŠą▓čā ą┐čĆąĖą╝ąĄčĆą░ ą▓ąĘčÅčé čĆą░ą▒ąŠčćąĖą╣ ą║ąŠą┤ ąĖąĘ ą▒ąĖą▒ą╗ąĖąŠč鹥ą║ąĖ EFSL (čĆą░ą▒ąŠčéą░ čü ą║ą░čĆčéą░ą╝ąĖ SD/SDHC/MMC ą┐ąŠ SPI ą▓ ąŠą┤ąĮąŠą▒ąĖčéąĮąŠą╝ čĆąĄąČąĖą╝ąĄ). ąśčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┐ąŠčĆčé SPI1, ą┤ą░ąĮąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ą┐ąŠ 8 ą▒ąĖčé, ą▓čŗą▒ąŠčĆą║ą░ č乊čĆą╝ąĖčĆčāąĄčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮąŠą╣ ą┐ąĄčĆąĖč乥čĆąĖąĖ, č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ąŠą┤ąĮąŠą│ąŠ slave-čāčüčéčĆąŠą╣čüčéą▓ą░ (čüčéą░ąĮą┤ą░čĆčéąĮą░čÅ ą║ą░čĆčéą░ ą┐ą░ą╝čÅčéąĖ SD/SDHC/MMC [1]), DMA ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ. ąĪąĖą│ąĮą░ą╗ ą▓čŗą▒ąŠčĆą║ąĖ č乊čĆą╝ąĖčĆčāąĄčéčüčÅ ąĮą░ ą║ą░ąČą┤čŗą╣ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗą╣ / ą┐čĆąĖąĮąĖą╝ą░ąĄą╝čŗą╣ ą▒ą░ą╣čé. ąĀą░čüčüą╝ą░čéčĆąĖą▓ą░ąĄčéčüčÅ č鹊ą╗čīą║ąŠ ąĮąĖąĘą║ąŠčāčĆąŠą▓ąĮąĄą▓čŗą╣ ą║ąŠą┤, ą║ąŠč鹊čĆčŗą╣ ąŠčéąĮąŠčüąĖčéčüčÅ ą║ ąĮą░čüčéčĆąŠą╣ą║ąĄ SPI ąĖ ą┐čĆąĖąĄą╝čā/ą┐ąĄčĆąĄą┤ą░č湥 ą▒ą░ą╣čéą░ (ąĮąĄčé ą║ąŠą┤ą░ ąĮą░čüčéčĆąŠą╣ą║ąĖ čĆąĄąČąĖą╝ą░ ą║ą░čĆčéčŗ ąĖ ą┐ąŠą┤ą┤ąĄčƹȹ║ąĖ ą┐čĆąŠč鹊ą║ąŠą╗ą░). ą¤čĆąĖą╝ąĄčĆ čäąĖąĘąĖč湥čüą║ąŠą│ąŠ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ą║ą░čĆčéčŗ ą┐ą░ą╝čÅčéąĖ čüą╝. ą▓ [1].

ą¤ąŠą┤ą║ą╗čÄč湥ąĮąĖąĄ ą║ą░čĆčéčŗ ą┐ą░ą╝čÅčéąĖ SD/SDHC/MMC ą╝ą░ą║ąĄčéąĮąŠą╣ ą┐ą╗ą░čéčŗ Olimex SAM7-EX256-REV-B.

ąØą░čüčéčĆąŠą╣ą║ą░

ą¤ąĄčĆąĄą┤ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ SPI ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ąĮą░čüčéčĆąŠąĖčéčī, ąĖ ąĮą░čüčéčĆąŠą╣ą║ą░ ąĘą░ą║ą╗čÄčćą░ąĄčéčüčÅ ą▓ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĖ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ PMC, ąĮą░čüčéčĆąŠą╣ą║ąĄ č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓čŗą▒ąŠčĆą║ąĖ ąĖ ąĮą░čüčéčĆąŠą╣ą║ąĄ čüą║ąŠčĆąŠčüčéąĖ SPI. ą¤čĆąĖą╝ąĄčĆ ąĮą░čüčéčĆąŠą╣ą║ąĖ ą┐čĆąĖą▓ąĄą┤ąĄąĮ ą▓ ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝ąĄ if_spiInit, ą║ąŠč鹊čĆą░čÅ ą┐čĆąĖąĮąĖą╝ą░ąĄčé ą▓ ą║ą░č湥čüčéą▓ąĄ ą┐ą░čĆą░ą╝ąĄčéčĆą░ ą▒ą░ąĘąŠą▓čŗą╣ ą░ą┤čĆąĄčü ąĖąĮč鹥čĆč乥ą╣čüą░ SPI. ąØą░ą┐čĆąĖą╝ąĄčĆ, ą┤ą╗čÅ SPI0 ą▒ą░ąĘąŠą▓čŗą╣ ą░ą┤čĆąĄčü čĆą░ą▓ąĄąĮ AT91C_BASE_SPI0 (0xFFFE0000), ą░ ą┤ą╗čÅ SPI1 ą▒ą░ąĘąŠą▓čŗą╣ ą░ą┤čĆąĄčü čĆą░ą▓ąĄąĮ AT91C_BASE_SPI1 (0xFFFE4000).

#define SPI_CSR_NUM 0 //ąĮąŠą╝ąĄčĆ ą▓čŗą▒ąŠčĆą║ąĖ ą┤ą╗čÅ ą║ą░čĆčéčŗ SD/SDHC/MMC, čüąĖą│ąĮą░ą╗ CS

#define SPI_MR_PCS ((0<<0)|(1<<1)|(1<<2)|(1<<3))

#define PIN_SPI1_MISO {1 << 24, AT91C_BASE_PIOA, AT91C_ID_PIOA, PIO_PERIPH_B, PIO_PULLUP}

#define PIN_SPI1_MOSI {1 << 23, AT91C_BASE_PIOA, AT91C_ID_PIOA, PIO_PERIPH_B, PIO_DEFAULT}

#define PIN_SPI1_SPCK {1 << 22, AT91C_BASE_PIOA, AT91C_ID_PIOA, PIO_PERIPH_B, PIO_DEFAULT}

#define PIN_SPI1_CS {1 << 21, AT91C_BASE_PIOA, AT91C_ID_PIOA, PIO_PERIPH_B, PIO_DEFAULT}

#define PINS_MMC PIN_SPI1_MISO, PIN_SPI1_MOSI, PIN_SPI1_SPCK, PIN_SPI1_CS

#define SDCARD_BASE_SPI AT91C_BASE_SPI1#define SDCARD_ID_SPI AT91C_ID_SPI1

#define SDCARD_SPI_SCBR_MIN 2

const Pin pinsMMC[] = {PINS_MMC};

void if_spiInit(hwInterface *iface)

{

////////////////////////////////////////////////////////////////////////

// ąØą░čćą░ą╗ąŠ ąĮą░čüčéčĆąŠą╣ą║ąĖ SPI

AT91PS_SPI pSPI = SDCARD_BASE_SPI;

AT91PS_PMC pPMC = AT91C_BASE_PMC;

PIO_Configure(pinsMMC, PIO_LISTSIZE(pinsMMC)); //ąĮą░čüčéčĆąŠą╣ą║ą░ ąĮąŠąČąĄą║ SPI

// ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ PMC: čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą┤ą╗čÅ SPI

pPMC->PMC_PCER = ( (euint32) 1 << SDCARD_ID_SPI ); //ID čŹč鹊 ą┐čĆąŠčüč鹊 ąĮąŠą╝ąĄčĆ ą▒ąĖčéą░

// SPI enable and reset

pSPI->SPI_CR = AT91C_SPI_SPIEN | AT91C_SPI_SWRST;

// ąĀąĄąČąĖą╝ SPI: master, čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮą░čÅ ą┐ąĄčĆąĖč乥čĆąĖčÅ, FDIV=0,

// ąĘą░ą┐čĆąĄčé ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ ąŠčłąĖą▒ąŠčćąĮąŠą╣ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ

pSPI->SPI_MR = AT91C_SPI_MSTR | AT91C_SPI_PS_FIXED | AT91C_SPI_MODFDIS;

// čāčüčéą░ąĮąŠą▓ą║ą░ ą┐ąŠą╗čÅ PCS ą┤ą╗čÅ čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ čĆąĄąČąĖą╝ą░ ą▓čŗą▒ąŠčĆą░ ą┐ąĄčĆąĖč乥čĆąĖąĖ

pSPI->SPI_MR |= ( (SPI_MR_PCS << 16) & AT91C_SPI_PCS );

// ąØą░čüčéčĆąŠą╣ą║ą░ čĆąĄą│ąĖčüčéčĆą░ SPI_CSR0:

// 8 ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ ąĮą░ 1 ą┐ąĄčĆąĄą┤ą░čćčā, CPOL=1, ClockPhase=0, DLYBCT=0

pSPI->SPI_CSR[SPI_CSR_NUM] = AT91C_SPI_CPOL | AT91C_SPI_BITS_8;

// ąØą░čüčéčĆąŠą╣ą║ą░ čüą║ąŠčĆąŠčüčéąĖ SPI (FE ą┐ąŠą┐ą░ą┤ąĄčé ą▓ ą┐ąŠą╗ąĄ SCBR, čćč鹊 ąŠą▒ąĄčüą┐ąĄčćąĖčé

// ą╝ą░ą╗čāčÄ čüą║ąŠčĆąŠčüčéčī, ąĮąĄąŠą▒čģąŠą┤ąĖą╝čāčÄ ą┤ą╗čÅ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ ą║ą░čĆčéčŗ ą┐ą░ą╝čÅčéąĖ).

if_spiSetSpeed(0xFE);

// ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ čĆą░ą▒ąŠčéčŗ SPI

pSPI->SPI_CR = AT91C_SPI_SPIEN;

// ąÜąŠąĮąĄčå ąĮą░čüčéčĆąŠą╣ą║ąĖ SPI

////////////////////////////////////////////////////////////////////////

// ą×čéą┐čĆą░ą▓ą║ą░ 20 ą║ąŠą╝ą░ąĮą┤ SPI, ą║ąŠą│ą┤ą░ ą║ą░čĆčéą░ ąĮąĄ ą▓čŗą▒čĆą░ąĮą░.

for(u8 i=0;i<21;i++)

{

if_spiSend(iface,0xFF);

}

}

ą¤ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ąĮą░čüčéčĆąŠą╣ą║ąĖ čüą║ąŠčĆąŠčüčéąĖ if_spiSetSpeed ąĘą░ą┐ąŠą╗ąĮčÅąĄčé ą┐ąŠą╗ąĄ SCBR čĆąĄą│ąĖčüčéčĆą░ SPI_CSR0 čü ą┐čĆąŠą▓ąĄčĆą║ąŠą╣ ąĮą░ ą║ąŠčĆčĆąĄą║čéąĮąŠčüčéčī ą▓čģąŠą┤ąĮąŠą│ąŠ ą┐ą░čĆą░ą╝ąĄčéčĆą░ SCBRval.

void if_spiSetSpeed (u8 SCBRval)

{

u32 reg;

AT91PS_SPI pSPI = SDCARD_BASE_SPI;

if ( SCBRval < SDCARD_SPI_SCBR_MIN )

SCBRval = SDCARD_SPI_SCBR_MIN;

if ( SCBRval > 1 )

SCBRval &= 0xFE;

reg = pSPI->SPI_CSR[SPI_CSR_NUM];

reg = ( reg & ~(u32)(AT91C_SPI_SCBR) ) | ( (u32)SCBRval << 8 );

pSPI->SPI_CSR[SPI_CSR_NUM] = reg;

}

ą¤ąĄčĆąĄą┤ą░čćą░ ąĖ ą┐čĆąĖąĄą╝

ą¤ąĄčĆąĄą┤ą░čćą░ ąĖ ą┐čĆąĖąĄą╝ ą┐čĆąŠąĖčüčģąŠą┤čÅčé ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ, ą┐ąŠčüą║ąŠą╗čīą║čā SPI ą┤čāą┐ą╗ąĄą║čüąĮčŗą╣ (čā ąĮąĄą│ąŠ ąŠčéą┤ąĄą╗čīąĮčŗąĄ ą╗ąĖąĮąĖąĖ ą┤ą╗čÅ ą┐čĆąĖąĄą╝ą░ ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ, MISO ąĖ MOSI). ą¤ąĄčĆąĄą┤ą░čćą░ ąĖ ą┐čĆąĖąĄą╝ ąŠčüčāčēąĄčüčéą▓ą╗čÅčÄčéčüčÅ ą▓čŗąĘąŠą▓ąŠą╝ čäčāąĮą║čåąĖąĖ if_spiSend. ąØą░ ą▓čģąŠą┤ąĄ čā ąĮąĄčæ ą▒ą░ąĘąŠą▓čŗą╣ ą░ą┤čĆąĄčü ąĖąĮč鹥čĆč乥ą╣čüą░ SPI (iface), ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗą╣ ą▒ą░ą╣čé outgoing, ą░ ąĮą░ ą▓čŗčģąŠą┤ąĄ čäčāąĮą║čåąĖčÅ ą▓ąŠąĘą▓čĆą░čēą░ąĄčé ą┐čĆąĖąĮčÅčéčŗą╣ ą▒ą░ą╣čé.

u8 if_spiSend(hwInterface *iface, u8 outgoing)

{

u8 incoming;

AT91PS_SPI pSPI = SDCARD_BASE_SPI;

//ąŠąČąĖą┤ą░ąĮąĖąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ

while( !( pSPI->SPI_SR & AT91C_SPI_TDRE ) );

//ąĘą░ą┐čāčüą║ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▒ą░ą╣čéą░

pSPI->SPI_TDR = (u16)( outgoing );

//ąŠąČąĖą┤ą░ąĮąĖąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐čĆąĖąĄą╝ą░

while( !( pSPI->SPI_SR & AT91C_SPI_RDRF ) );

//čüčćąĖčéčŗą▓ą░ąĮąĖąĄ ąĖ ą▓ąŠąĘą▓čĆą░čé ą┐ąŠą╗čāč湥ąĮąĮąŠą│ąŠ ą▒ą░ą╣čéą░

incoming = (u8)( pSPI->SPI_RDR );

return incoming;

}

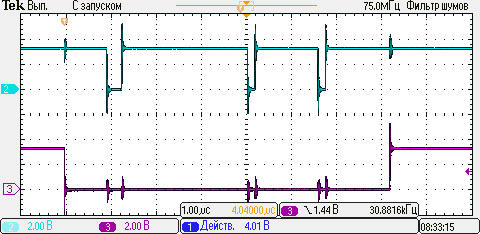

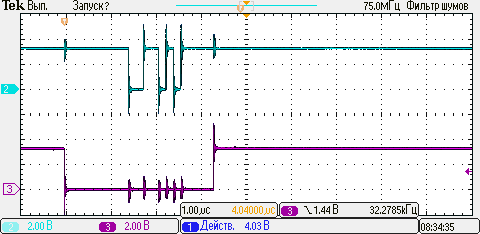

ąÆ ą¤čĆąĖą╝ąĄčĆąĄ 1 ą▓čŗą▒ąŠčĆą║ą░ slave-čāčüčéčĆąŠą╣čüčéą▓ą░ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ ąĮą░ ą║ą░ąČą┤čŗą╣ ą┐ąŠčüčŗą╗ą░ąĄą╝čŗą╣ ą▒ą░ą╣čé (ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą▒ą╗ąŠą║ ą┤ą░ąĮąĮčŗčģ ąĖąĘ 4 ą▒ą░ą╣čé 00 FF 0F 0F):

ąśąĮąŠą│ą┤ą░ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ, čćč鹊ą▒čŗ ą▓čŗą▒ąŠčĆą║ą░ slave-čāčüčéčĆąŠą╣čüčéą▓ą░ (NPCSx) ą┐čĆąŠąĖčüčģąŠą┤ąĖą╗ą░ ąĮąĄ ąĮą░ ą║ą░ąČą┤čŗą╣ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗą╣ ą▒ą░ą╣čé, ą░ čüčéą░ąĮąŠą▓ąĖą╗ą░čüčī ą░ą║čéąĖą▓ąĮąŠą╣ ą▓ č鹥č湥ąĮąĖąĄ ą▓čüąĄą│ąŠ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ąŠą│ąŠ ą▒ą╗ąŠą║ą░ ą┤ą░ąĮąĮčŗčģ (ą╝ą░čüčüąĖą▓ą░ ą▒ą░ą╣čé). ąöą╗čÅ čŹč鹊ą│ąŠ ąĄčüčéčī ąĮąĄčüą║ąŠą╗čīą║ąŠ ą▓ąŠąĘą╝ąŠąČąĮąŠčüč鹥ą╣. ąÆ čŹč鹊ą╝ ą┐čĆąĖą╝ąĄčĆąĄ ą┐ąŠą║ą░ąĘą░ąĮąŠ, ą║ą░ą║ čāą┐čĆą░ą▓ą╗čÅčéčī ą▓čŗą▒ąŠčĆą║ąŠą╣ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ. ąöą╗čÅ čŹč鹊ą│ąŠ ąĮčāąČąĮąŠ ą┐ąĄčĆąĄąĘą░ą┤ą░čéčī ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖąĄ ąĮąŠąČą║ąĖ PIN_SPI1_CS ąĖąĘ ą┐čĆąĄą┤čŗą┤čāčēąĄą│ąŠ ą┐čĆąĖą╝ąĄčĆą░ ąĮą░ ąŠą▒čŗčćąĮčŗą╣ ą┐ąŠčĆčé ą▓ą▓ąŠą┤ą░ ą▓čŗą▓ąŠą┤ą░, ą░ ąĮąĄ ąĮą░ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖąĄ ą║ ą┐ąĄčĆąĖč乥čĆąĖąĖ (PIO_PERIPH_A ąĮą░ą┤ąŠ ąĘą░ą╝ąĄąĮąĖčéčī ąĮą░ PIO_OUTPUT_1):

//#define PIN_SPI0_CS {1 << 12, AT91C_BASE_PIOA, AT91C_ID_PIOA, PIO_PERIPH_A, PIO_DEFAULT}

#define PIN_SPI0_CS {1 << 12, AT91C_BASE_PIOA, AT91C_ID_PIOA, PIO_OUTPUT_1, PIO_DEFAULT}

ą¤čĆąĖ ą┐ąĄčĆąĄą┤ą░č湥 ą▒ą╗ąŠą║ą░ ą┤ą░ąĮąĮčŗčģ ąĮčāąČąĮąŠ č鹥ą┐ąĄčĆčī ąĖąĘ ą║ąŠą┤ą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī ą╗ąŠą│ąĖč湥čüą║ąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ ąĮąŠąČą║ąĖ ą▓čŗą▒ąŠčĆą║ąĖ. ąÆ ą┐čĆąĖą╝ąĄčĆąĄ ą║ąŠą┤ą░ ąĮąĖąČąĄ ą┐ąŠą║ą░ąĘą░ąĮąŠ, ą║ą░ą║ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ čāą┐čĆą░ą▓ą╗čÅčéčī ą▓čŗą▒ąŠčĆą║ąŠą╣ (SPI1_NPCS0). ąÆ Gameduino ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą▒ą╗ąŠą║ ą┤ą░ąĮąĮčŗčģ ąĖąĘ ą▒čāč乥čĆą░ buffer (ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ ą┐ąŠčĆč鹊ą▓, ą║ąŠą┤ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ SPI ąŠčüčéą░čÄčéčüčÅ ą▒ąĄąĘ ąĖąĘą╝ąĄąĮąĄąĮąĖą╣).

//ą▓čŗą▒ąŠčĆą║čā ąŠą┐čāčüą║ą░ąĄą╝ ą▓ 0 ą┐ąĄčĆąĄą┤ ąŠčéą┐čĆą░ą▓ą║ąŠą╣ ą▒ą╗ąŠą║ą░ ą▒ą░ą╣čé

PIO_Clear(&pinsGAMEDUINO[3]);

for (int idx=0; idx<sizeof(buffer); idx++)

{

//ąŠąČąĖą┤ą░ąĮąĖąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ

while( !( pSPI->SPI_SR & AT91C_SPI_TDRE ) );

//ąĘą░ą┐čāčüą║ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▒ą░ą╣čéą░

pSPI->SPI_TDR = buffer[idx];

//ąŠąČąĖą┤ą░ąĮąĖąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐čĆąĖąĄą╝ą░

while( !( pSPI->SPI_SR & AT91C_SPI_RDRF ) );

//čüčćąĖčéčŗą▓ą░ąĮąĖąĄ ą┐ąŠą╗čāč湥ąĮąĮąŠą│ąŠ ą▒ą░ą╣čéą░

incoming = (u8)( pSPI->SPI_RDR );

}

//ą▓ąŠąĘą▓čĆą░čēą░ąĄą╝ ą▓čŗą▒ąŠčĆą║čā ą▓ 1 ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▒ą╗ąŠą║ą░ ą▒ą░ą╣čé

PIO_Set(&pinsGAMEDUINO[3]);

ąÆ čĆąĄąĘčāą╗čīčéą░č鹥 ą┐ąŠą╗čāčćąĖčéčüčÅ čéą░ą║ą░čÅ ąŠčüčåąĖą╗ą╗ąŠą│čĆą░ą╝ą╝ą░ (ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą▒ą╗ąŠą║ ą┤ą░ąĮąĮčŗčģ ąĖąĘ 4 ą▒ą░ą╣čé 00 FF 0F 0F, čüčĆą░ą▓ąĮąĖč鹥 čü ąŠčüčåąĖą╗ą╗ąŠą│čĆą░ą╝ą╝ąŠą╣ ąĖąĘ ą¤čĆąĖą╝ąĄčĆą░ 1):

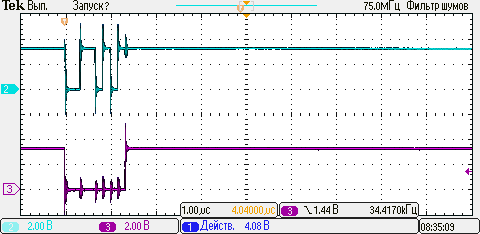

ąÆ čŹč鹊ą╝ ą┐čĆąĖą╝ąĄčĆąĄ 8-ą▒ąĖčéąĮčŗąĄ ą┐ąŠčüčŗą╗ą║ąĖ ą┤ą░ąĮąĮčŗčģ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ąĄą┤ąĖąĮčŗą╝ ą▒ą╗ąŠą║ąŠą╝ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ DMA. ą¤čĆąĄąĖą╝čāčēąĄčüčéą▓ąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ DMA ą▓ čüą╗ąĄą┤čāčÄčēąĄą╝: ą╝ąŠąČąĮąŠ ąĮą░ą┐ąĖčüą░čéčī ą┐čĆąŠą│čĆą░ą╝ą╝čā čéą░ą║, čćč鹊 ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ čüą╝ąŠąČąĄčé ąĘą░ąĮąĖą╝ą░čéčīčüčÅ ą┤čĆčāą│ąŠą╣ čĆą░ą▒ąŠč鹊ą╣, čćč鹊 ąĘąĮą░čćąĖč鹥ą╗čīąĮąŠ čāčüą║ąŠčĆčÅąĄčé ąŠą▒čĆą░ą▒ąŠčéą║čā ą┤ą░ąĮąĮčŗčģ. ąÆ čŹč鹊ą╝ ą┐čĆąĖą╝ąĄčĆąĄ ą┤ą╗čÅ čāą┐čĆąŠčēąĄąĮąĖčÅ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┐čĆąŠčüč鹊 ąŠąČąĖą┤ą░ąĮąĖąĄ ąŠą║ąŠąĮčćą░ąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐čāč鹥ą╝ ąŠą┐čĆąŠčüą░ ą▒ąĖčéą░ čüčéą░čéčāčüą░ SPI_SR.TXBUFE, čģąŠčéčÅ ą▓ čĆąĄą░ą╗čīąĮąŠą╣ ąĘą░ą┤ą░č湥 ą╗čāčćčłąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┤ą╗čÅ čüąĖą│ąĮą░ą╗ąĖąĘą░čåąĖąĖ ąŠą▒ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▒ą╗ąŠą║ą░ ą┤ą░ąĮąĮčŗčģ. ąÆčŗą▒ąŠčĆą║ą░ slave-čāčüčéčĆąŠą╣čüčéą▓ą░ ą╝ąŠąČąĄčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčīčüčÅ ą║ą░ą║ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ, čéą░ą║ ąĖ ą░ą┐ą┐ą░čĆą░čéąĮąŠ (ą┐ąŠ čäą╗ą░ąČą║čā useCSHW).

//ąĮą░ą▒ąŠčĆ ąĮąŠąČąĄą║ SPI ą┤ą╗čÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠą│ąŠ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą▓čŗą▒ąŠčĆą║ąŠą╣

#define PINS_GAMEDUINO_CSHW PIN_SPI0_MISO, PIN_SPI0_MOSI, PIN_SPI0_SPCK, PIN_SPI0_CSHW

const Pin pinsGAMEDUINO_CSHW[] = {PINS_GAMEDUINO_CSHW};

//ąĮą░ą▒ąŠčĆ ąĮąŠąČąĄą║ SPI ą┤ą╗čÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą▓čŗą▒ąŠčĆą║ąŠą╣

#define PINS_GAMEDUINO_CSSW PIN_SPI0_MISO, PIN_SPI0_MOSI, PIN_SPI0_SPCK, PIN_SPI0_CSSW

const Pin pinsGAMEDUINO_CSSW[] = {PINS_GAMEDUINO_CSSW};

//ą▒čāč乥čĆ DMA ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ

u32 TXSPIDMAbuf[(4+ZXSPECTRUM_SCREEN_SIZE)];

void init_spi_Gameduino (void)

{

if (useCSHW)

PIO_Configure(pinsGAMEDUINO_CSHW, PIO_LISTSIZE(pinsGAMEDUINO_CSHW));

else

PIO_Configure(pinsGAMEDUINO_CSSW, PIO_LISTSIZE(pinsGAMEDUINO_CSSW));

AT91C_BASE_PMC->PMC_PCER = ( 1 << GAMEDUINO_ID_SPI );

// ąŚą░ą┐čĆąĄčé SPI

GAMEDUINO_BASE_SPI->SPI_CR = AT91C_SPI_SPIDIS;

// ąśąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ PDC (DMA) ą┤ą╗čÅ SPI:

// ąĘą░ą┐čĆąĄčé PDC TX ąĖ RX

GAMEDUINO_BASE_SPI->SPI_PTCR = AT91C_PDC_TXTDIS | AT91C_PDC_RXTDIS;

// ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ čüč湥čéčćąĖą║ąŠą▓ ąĖ čāą║ą░ąĘą░č鹥ą╗ąĄą╣ ąĮą░ ą▒čāč乥čĆ ą▓ 0

// "čüą╗ąĄą┤čāčÄčēąĖą╣" ą▒čāč乥čĆ TX

GAMEDUINO_BASE_SPI->SPI_TNPR = 0;

GAMEDUINO_BASE_SPI->SPI_TNCR = 0;

// "čüą╗ąĄą┤čāčÄčēąĖą╣" ą▒čāč乥čĆ RX

GAMEDUINO_BASE_SPI->SPI_RNPR = 0;

GAMEDUINO_BASE_SPI->SPI_RNCR = 0;

// ą▒čāč乥čĆ TX

GAMEDUINO_BASE_SPI->SPI_TPR = 0;

GAMEDUINO_BASE_SPI->SPI_TCR = 0;

// ą▒čāč乥čĆ RX

GAMEDUINO_BASE_SPI->SPI_RPR = 0;

GAMEDUINO_BASE_SPI->SPI_RCR = 0;

// ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ SPI ąĖ ąĄą│ąŠ čüą▒čĆąŠčü

// "ąÜą░ąČąĄčéčüčÅ, čćč鹊 čā ą╝ą░čłąĖąĮčŗ čüąŠčüč鹊čÅąĮąĖą╣ ą┤ą╗čÅ revB ą▓ąĄčĆčüąĖąĖ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī

// 2 ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗčģ čüą▒čĆąŠčüą░ SPI, čüą▒čĆąŠčü ą┐čĆąŠčłąĄą╗ čāčüą┐ąĄčłąĮąŠ."

GAMEDUINO_BASE_SPI->SPI_CR = AT91C_SPI_SWRST;

GAMEDUINO_BASE_SPI->SPI_CR = AT91C_SPI_SWRST;

GAMEDUINO_BASE_SPI->SPI_CR = AT91C_SPI_SPIEN;

// ąĀąĄąČąĖą╝ SPI: master, FDIV=0, ąĘą░ą┐čĆąĄčé ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ąŠčłąĖą▒ą║ąĖ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ.

GAMEDUINO_BASE_SPI->SPI_MR = AT91C_SPI_MSTR | AT91C_SPI_MODFDIS;

// ąŻčüčéą░ąĮąŠą▓ą║ą░ čĆąĄą│ąĖčüčéčĆą░ ą▓čŗą▒ąŠčĆą║ąĖ čćąĖą┐ą░:

// 8 ą▒ąĖčé ąĮą░ ą┐ąĄčĆąĄą┤ą░čćčā, CPOL=1, ClockPhase=0, DLYBCT = 0

GAMEDUINO_BASE_SPI->SPI_CSR[SPI_CSR_NUM] = AT91C_SPI_CPOL | AT91C_SPI_BITS_8;

// ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ čĆą░ą▒ąŠčéčŗ SPI

GAMEDUINO_BASE_SPI->SPI_CR = AT91C_SPI_SPIEN;

}

void send_block_to_Gameduino (void *buf, int bytes)

{

int idx;

init_spi_Gameduino();

LED(1);

if (!useCSHW)

PIO_Clear(&pinsGAMEDUINO_CSSW[3]);

//ą┐ąĄčĆąĄą┤ą░čćą░

if (GAMEDUINO_BASE_SPI->SPI_MR & AT91C_SPI_PS)

{

//ą¤ąŠą┤ą│ąŠč鹊ą▓ą║ą░ ą▒čāč乥čĆą░ DMA, ąĄčüą╗ąĖ SPI_MR.PS=1 (čĆąĄąČąĖą╝ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą╣ ą┐ąĄčĆąĖč乥čĆąĖąĖ)

for (idx=0; idx<(bytes-1); idx++)

{

TXSPIDMAbuf[idx] = ((u8*)buf)[idx];

}

TXSPIDMAbuf[idx] = ((u8*)buf)[idx] | AT91C_SPI_LASTXFER;

while (0 == SPI_WriteBuffer(GAMEDUINO_BASE_SPI, TXSPIDMAbuf, bytes));

}

else

while (0 == SPI_WriteBuffer(GAMEDUINO_BASE_SPI, buf, bytes));

//ąŠąČąĖą┤ą░ąĮąĖąĄ ąŠą║ąŠąĮčćą░ąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ

while (0 == (GAMEDUINO_BASE_SPI->SPI_SR & AT91C_SPI_TXBUFE));

if (!useCSHW)

PIO_Set(&pinsGAMEDUINO_CSSW[3]);

LED(0);

close_spi_Gameduino();

}

//------------------------------------------------------------------------------

/// ą¤ąŠčüčŗą╗ą░ąĄčé čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ ą▒čāč乥čĆą░ buffer č湥čĆąĄąĘ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ SPI,

/// ąĖčüą┐ąŠą╗čīąĘčāčÅ PDC ą┤ą╗čÅ ąŠą▒čüą╗čāąČąĖą▓ą░ąĮąĖčÅ čéčĆą░ąĮąĘą░ą║čåąĖąĖ.

/// \param spi čāą║ą░ąĘą░č鹥ą╗čī ąĮą░ 菹║ąĘąĄą╝ą╗čÅčĆ AT91S_SPI.

/// \param buffer čāą║ą░ąĘą░č鹥ą╗čī ąĮą░ ąŠčéą┐čĆą░ą▓ą╗čÅąĄą╝čŗą╣ ą▒čāč乥čĆ.

/// \param length ą┤ą╗ąĖąĮą░ ą┤ą░ąĮąĮčŗčģ ą▓ ą▒čāč乥čĆąĄ.

//------------------------------------------------------------------------------

unsigned char SPI_WriteBuffer(AT91S_SPI *spi,

void *buffer,

unsigned int length)

{

// ą¤čĆąŠą▓ąĄčĆą║ą░, ą┐čāčüčé ą╗ąĖ ą┐ąĄčĆą▓čŗą╣ ą▒ą░ąĮą║:

if (spi->SPI_TCR == 0)

{

spi->SPI_TPR = (unsigned int) buffer;

spi->SPI_TCR = length;

spi->SPI_PTCR = AT91C_PDC_TXTEN;

return 1;

}

// ą¤čĆąŠą▓ąĄčĆą║ą░, ą┐čāčüčé ą╗ąĖ ą▓č鹊čĆąŠą╣ ą▒ą░ąĮą║:

else if (spi->SPI_TNCR == 0)

{

spi->SPI_TNPR = (unsigned int) buffer;

spi->SPI_TNCR = length;

return 1;

}

// ąØąĄčé čüą▓ąŠą▒ąŠą┤ąĮčŗčģ ą▒ą░ąĮą║ąŠą▓:

return 0;

}

ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ą▓ čüą╗čāčćą░ąĄ ą▓čŗą▒ąŠčĆą░ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą╣ ą┐ąĄčĆąĖč乥čĆąĖąĖ SPI_MR.PS=1 ą┤ą╗čÅ DMA ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čüą┐ąĄčåąĖą░ą╗čīąĮąŠ ą┐ąŠą┤ą│ąŠč鹊ą▓ą╗ąĄąĮąĮčŗą╣ 32-ą▒ąĖčéąĮčŗą╣ ą▒čāč乥čĆ. ąÆ ą┐ąŠčüą╗ąĄą┤ąĮčÄčÄ čÅč湥ą╣ą║čā ą▒čāč乥čĆą░ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ ą┐čĆąĖąĘąĮą░ą║ SPI_TDR.LASTXFER, ą║ąŠč鹊čĆčŗą╣ ąĮčāąČąĄąĮ ą┤ą╗čÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠą│ąŠ ą▓ąŠąĘą▓čĆą░čéą░ čüąĖą│ąĮą░ą╗ą░ ą▓čŗą▒ąŠčĆą║ąĖ ą▓ ąĮąĄą░ą║čéąĖą▓ąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ. ąØą░ ą┐ąĄčĆą▓ąŠą╣ ąŠčüčåąĖą╗ą╗ąŠą│čĆą░ą╝ą╝ąĄ DMA čĆą░ą▒ąŠčéą░ąĄčé čü ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ č乊čĆą╝ąĖčĆčāąĄą╝ąŠą╣ ą▓čŗą▒ąŠčĆą║ąŠą╣, ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ 8-ą▒ąĖčéąĮčŗą╣ ą▒čāč乥čĆ DMA (ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą▒ą╗ąŠą║ ą┤ą░ąĮąĮčŗčģ ąĖąĘ 4 ą▒ą░ą╣čé 00 FF 0F 0F):

ąØą░ ą▓č鹊čĆąŠą╣ ąŠčüčåąĖą╗ą╗ąŠą│čĆą░ą╝ą╝ąĄ DMA čĆą░ą▒ąŠčéą░ąĄčé ą▓ą╝ąĄčüč鹥 čü ą░ą┐ą┐ą░čĆą░čéąĮąŠ č乊čĆą╝ąĖčĆčāąĄą╝ąŠą╣ ą▓čŗą▒ąŠčĆą║ąŠą╣, ą┤ą╗čÅ čŹč鹊ą│ąŠ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ 32-ą▒ąĖčéąĮčŗą╣ ą▒čāč乥čĆ DMA (ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą▒ą╗ąŠą║ ą┤ą░ąĮąĮčŗčģ ąĖąĘ 4 ą▒ą░ą╣čé 00 FF 0F 0F):

[ąĪą╗ąŠą▓ą░čĆąĖą║]

CS čüąĖą│ąĮą░ą╗ ą▓čŗą▒ąŠčĆą║ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ ąĮą░ čłąĖąĮąĄ SPI. ąĢčüą╗ąĖ čŹč鹊 ą▓čģąŠą┤, č鹊 ą┤ą╗čÅ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ARM7 ąŠąĮ ąĮą░ąĘčŗą▓ą░ąĄčéčüčÅ čéą░ą║ąČąĄ NSS (ą▓ čŹč鹊ą╣ čüčéą░čéčīąĄ ąĮąĄ čĆą░čüčüą╝ą░čéčĆąĖą▓ą░ąĄčéčüčÅ), ą░ ąĄčüą╗ąĖ ą▓čŗčģąŠą┤, č鹊 NPCSx (NPCS0, NPCS1, NPCS2, NPCS3).

DMA ą░ą▒ą▒čĆąĄą▓ąĖą░čéčāčĆą░ ąŠčé Direct Memory Access, čćč鹊 ąŠąĘąĮą░čćą░ąĄčé "ą┐čĆčÅą╝ąŠą╣ ą┤ąŠčüčéčāą┐ ą║ ą┐ą░ą╝čÅčéąĖ". ąśą╝ąĄąĄčéčüčÅ ą▓ ą▓ąĖą┤čā, čćč鹊 ą┐ąĄčĆąĖč乥čĆąĖčÅ (ą▓ ąĮą░čłąĄą╝ čüą╗čāčćą░ąĄ čŹč鹊 ąĖąĮč鹥čĆč乥ą╣čü SPI) ą┐ąŠą╗čāčćą░ąĄčé ą┤ąŠčüčéčāą┐ ą║ ą┐ą░ą╝čÅčéąĖ ą▒ąĄąĘ čāčćą░čüčéąĖčÅ ą▓čŗčćąĖčüą╗ąĖč鹥ą╗čīąĮąŠą│ąŠ čÅą┤čĆą░ ARM, čćč鹊 čĆą░ąĘą│čĆčāąČą░ąĄčé čÅą┤čĆąŠ ą┤ą╗čÅ ą┤čĆčāą│ąĖčģ ąĘą░ą┤ą░čć ąĖ čāčüą║ąŠčĆčÅąĄčé čĆą░ą▒ąŠčéčā firmware. ąĪą╝. čéą░ą║ąČąĄ PDC.

MMC MultiMedia Card - čéąĖą┐ąŠčĆą░ąĘą╝ąĄčĆ čüčéą░ąĮą┤ą░čĆčéąĮčŗčģ ą║ą░čĆčé ą┐ą░ą╝čÅčéąĖ (ąŠą▒čŗčćąĮąŠ ąĄą╝ą║ąŠčüčéčīčÄ ą┤ąŠ 512 ą╝ąĄą│ą░ą▒ą░ą╣čé). ąŁč鹊 čāąČąĄ čāčüčéą░čĆąĄą▓čłąĖą╣ čéąĖą┐ ą║ą░čĆčé, ą║ąŠč鹊čĆčŗą╣ ąĮąĄ ą▓čŗą┐čāčüą║ą░ąĄčéčüčÅ. ą×ąĮ čäąĖąĘąĖč湥čüą║ąĖ čüąŠą▓ą╝ąĄčüčéąĖą╝ čü č乊čĆą╝ą░č鹊ą╝ SD čüąĮąĖąĘčā ą▓ą▓ąĄčĆčģ, čé. ąĄ. ą║ą░čĆčéčā MMC ą╝ąŠąČąĮąŠ ą▓čüčéą░ą▓ąĖčéčī ą▓ čüą╗ąŠčé ą┤ą╗čÅ ą║ą░čĆčé SD, ąĮąŠ ąĮąĄ ąĮą░ąŠą▒ąŠčĆąŠčé (ą║ą░čĆčéą░ MMC č鹊ąĮčīčłąĄ, ąĖą╝ąĄąĄčé č鹊ą╗čēąĖąĮčā 1.45 ą╝ą╝, ą░ ą║ą░čĆčéą░ SD ąĖą╝ąĄąĄčé č鹊ą╗čēąĖąĮčā 2.1 ą╝ą╝). ąĪą╝. čéą░ą║ąČąĄ SD, SDHC.

MISO Master Input Slave Output ą┐čĆąŠą▓ąŠą┤ čłąĖąĮčŗ SPI, ą▓čģąŠą┤ ą│ą╗ą░ą▓ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (master), ą▓čŗčģąŠą┤ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ (slave).

MOSI Master Output Slave Input ą┐čĆąŠą▓ąŠą┤ čłąĖąĮčŗ SPI, ą▓čŗčģąŠą┤ ą│ą╗ą░ą▓ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (master), ą▓čģąŠą┤ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ (slave).

PMC Power Management Controller - ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖąĄą╝, ą║ąŠč鹊čĆčŗą╣ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ąĮčāčéčĆąĖ čćąĖą┐ą░ ARM7. ąØą░ąĘą▓ą░ąĮąĖąĄ ąĮąĄą╝ąĮąŠą│ąŠ ąĮąĄąŠč湥ą▓ąĖą┤ąĮąŠąĄ, ą┐ąŠčüą║ąŠą╗čīą║čā ąĮą░ čüą░ą╝ąŠą╝ ą┤ąĄą╗ąĄ PMC ąŠčéą▓ąĄčćą░ąĄčé ąĘą░ ą▓ą║ą╗čÄč湥ąĮąĖąĄ/ą▓čŗą║ą╗čÄč湥ąĮąĖąĄ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐ąĄčĆąĖč乥čĆąĖąĖ (ą▓ ąĮą░čłąĄą╝ čüą╗čāčćą░ąĄ PMC ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ąĮą░čüčéčĆąŠąĖčéčī, čćč鹊ą▒čŗ ąĘą░čĆą░ą▒ąŠčéą░ą╗ąŠ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ą┐ąĄčĆąĖč乥čĆąĖąĖ SPI).

PDC Peripheral DMA Controller, ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą┐čĆčÅą╝ąŠą│ąŠ ą┤ąŠčüčéčāą┐ą░ ą║ ą┐ą░ą╝čÅčéąĖ. ąĪą╝. čéą░ą║ąČąĄ DMA.

SD ą║ą░čĆčéčŗ Security Digital (ąĖąĮąŠą│ą┤ą░ ąĖčģ ąĮą░ąĘčŗą▓ą░čÄčé SDC, Security Digital Card) - čéąĖą┐ąŠčĆą░ąĘą╝ąĄčĆ čüčéą░ąĮą┤ą░čĆčéąĮčŗčģ ą║ą░čĆčé ą┐ą░ą╝čÅčéąĖ čĆą░ąĘą╝ąĄčĆąŠą╝ ą┤ąŠ 2 ą│ąĖą│ą░ą▒ą░ą╣čé ą▓ą║ą╗čÄčćąĖč鹥ą╗čīąĮąŠ. ąÜą░čĆčéčŗ SD ąĖ SDHC ąĖą╝ąĄčÄčé ąŠą┤ąĖąĮą░ą║ąŠą▓čŗą╣ čéąĖą┐ąŠčĆą░ąĘą╝ąĄčĆ. ąĪą╝. čéą░ą║ąČąĄ MMC, SDHC.

SDHC ą║ą░čĆčéčŗ Secure Digital High Capacity - čéąĖą┐ąŠčĆą░ąĘą╝ąĄčĆ čüčéą░ąĮą┤ą░čĆčéąĮčŗčģ ą║ą░čĆčé ą┐ą░ą╝čÅčéąĖ ą┐ąŠą▓čŗčłąĄąĮąĮąŠą╣ ąĄą╝ą║ąŠčüčéąĖ (ą┤ąŠ 32 ą│ąĖą│ą░ą▒ą░ą╣čé ą▓ą║ą╗čÄčćąĖč鹥ą╗čīąĮąŠ). ąÜą░čĆčéčŗ SD ąĖ SDHC ąĖą╝ąĄčÄčé ąŠą┤ąĖąĮą░ą║ąŠą▓čŗą╣ čéąĖą┐ąŠčĆą░ąĘą╝ąĄčĆ. ąĪą╝. čéą░ą║ąČąĄ MMC, SD.

SPI Serial Peripheral Interface, ą┐ąŠą┐čāą╗čÅčĆąĮą░čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮą░čÅ čłąĖąĮą░ ą┤ą╗čÅ ąŠą▒ą╝ąĄąĮą░ ą┤ą░ąĮąĮčŗą╝ąĖ. ą©ąĖąĮą░ ąĖą╝ąĄąĄčé ą░čĆčģąĖč鹥ą║čéčāčĆčā č鹊čćą║ą░-č鹊čćą║ą░, čé. ąĄ. ąĮą░ čłąĖąĮąĄ ą▓ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé ą▓čĆąĄą╝ąĄąĮąĖ ą╝ąŠąČąĄčé ą┐čĆąĖčüčāčéčüčéą▓ąŠą▓ą░čéčī č鹊ą╗čīą║ąŠ 2 ą░ą║čéąĖą▓ąĮčŗčģ čāčćą░čüčéąĮąĖą║ą░ ąŠą▒ą╝ąĄąĮą░ ą┤ą░ąĮąĮčŗą╝ąĖ - ą│ą╗ą░ą▓ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ (SPI master) ąĖ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ (SPI slave). ą£ąĄąČą┤čā master ąĖ slave ą▓ąŠąĘą╝ąŠąČąĄąĮ ą┤čāą┐ą╗ąĄą║čüąĮčŗą╣ ąŠą▒ą╝ąĄąĮ ą┤ą░ąĮąĮčŗą╝ąĖ.

SPI_CR SPI Control Register - čĆąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ SPI.

SPI_MR SPI Mode Register - čĆąĄą│ąĖčüčéčĆ čĆąĄąČąĖą╝ą░ SPI.

SPI_CSRx SPI Chip Select Register - čĆąĄą│ąĖčüčéčĆ ą▓čŗą▒ąŠčĆą░ čćąĖą┐ą░ SPI. ąśą╝ąĄąĄčéčüčÅ 4 čĆąĄą│ąĖčüčéčĆą░ SPI_CSRx: SPI_CSR0, SPI_CSR1, SPI_CSR2, SPI_CSR3.

SPCK čéą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗ čłąĖąĮčŗ SPI, ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ master (ą▓ ąĮą░čłąĄą╝ čüą╗čāčćą░ąĄ čŹč鹊 ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ARM7).

[ąĪčüčŗą╗ą║ąĖ]

1. ąÜą░ą║ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą║ą░čĆčéčŗ ą┐ą░ą╝čÅčéąĖ MMC/SDC.

2. ą£ą░ą║ąĄčéąĮą░čÅ ą┐ą╗ą░čéą░ AT91SAM7X.

3. ąśčüčģąŠą┤ąĮčŗą╣ ą║ąŠą┤, ąĖą╗ą╗čÄčüčéčĆąĖčĆčāčÄčēąĖą╣ čĆą░ą▒ąŠčéčā čü SPI - ą┐čĆąŠąĄą║čé 121003ZX-screen-test. ą¤ąĄčĆąĄą┤ą░ąĄčéčüčÅ čŹą║čĆą░ąĮ ZX Spectrum ą▓ ą░ą┤ą░ą┐č鹥čĆ Gameduino, 菹║čĆą░ąĮčŗ ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ ą▓ ą║ą░čéą░ą╗ąŠą│ SCR ą║ą░čĆčéčŗ SD. ą£ąŠąČąĮąŠ čéą░ą║ąČąĄ ąĘą░ą┐čāčüčéąĖčéčī ąĮą░ ą┐ąĄčĆąĄą┤ą░čćčā ą┐ąŠ SPI č鹊ą╗čīą║ąŠ ąŠą┤ąĖąĮ čäą░ą╣ą╗ test.bin ą┐čĆąŠąĖąĘą▓ąŠą╗čīąĮąŠą│ąŠ čĆą░ąĘą╝ąĄčĆą░ (ąŠčé 1 ą┤ąŠ 6912 ą▒ą░ą╣čé).

4. Gameduino: 菹║čĆą░ąĮ ą┤ą╗čÅ ZX Spectrum.

5. AT91SAM7X: ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ PDC. |

ąÜąŠą╝ą╝ąĄąĮčéą░čĆąĖąĖ

microsin: čĆąĄą░ą╗ąĖąĘą░čåąĖčÄ čäčāąĮą║čåąĖąĖ SPI_WriteBuffer čüą╝. ą▓ ą╝ąŠą┤čāą╗ąĄ spi.c ą▒ąĖą▒ą╗ąĖąŠč鹥ą║ IAR. ąöąŠą▒ą░ą▓ąĖą╗ ą▓ čüčéą░čéčīčÄ ą║ąŠą┤ čŹč鹊ą╣ čäčāąĮą║čåąĖąĖ, čüą╝. ą▓čĆąĄąĘą║čā čü ą¤čĆąĖą╝ąĄčĆąŠą╝ 3.

RSS ą╗ąĄąĮčéą░ ą║ąŠą╝ą╝ąĄąĮčéą░čĆąĖąĄą▓ čŹč鹊ą╣ ąĘą░ą┐ąĖčüąĖ