|

ąóąĄčģąĮąŠą╗ąŠą│ąĖčÅ ą┐čĆčÅą╝ąŠą│ąŠ ą┤ąŠčüčéčāą┐ą░ ą║ ą┐ą░ą╝čÅčéąĖ DMA (Direct Memory Access) ą▓ ą╝ąĖą║čĆąŠą┐čĆąŠčåąĄčüčüąŠčĆą░čģ ąĖ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░čģ ą┐čĆąĖą╝ąĄąĮčÅąĄčéčüčÅ ą┤ą╗čÅ čĆą░ąĘą│čĆčāąĘą║ąĖ CPU ąŠčé čĆčāčéąĖąĮąĮčŗčģ ąŠą┐ąĄčĆą░čåąĖą╣ ą┐ąŠ ą┐ąĄčĆąĄčüčŗą╗ą║ąĄ ą┤ą░ąĮąĮčŗčģ ą╝ąĄąČą┤čā ąŠą┐ąĄčĆą░čéąĖą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéčīčÄ (RAM, SRAM) ąĖ čĆą░ąĘą╗ąĖčćąĮčŗą╝ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ (UART, SPI, ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčŗ ą┤ąĖčüą┐ą╗ąĄčÅ ąĖ čé. ą┤.). ą¤ąŠčüą║ąŠą╗čīą║čā ą┐čĆąĖ čŹč鹊ą╝ ą┐ąĄčĆąĄčüčŗą╗ą║ą░ą╝ąĖ ą┤ą░ąĮąĮčŗčģ ąĘą░ąĮąĖą╝ą░ąĄčéčüčÅ ąŠčéą┤ąĄą╗čīąĮąŠąĄ ą░ą┐ą┐ą░čĆą░čéąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ (ąĮąĄ CPU), č鹊 ą▒čŗčüčéčĆąŠą┤ąĄą╣čüčéą▓ąĖąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ ąĖ čŹčäč乥ą║čéąĖą▓ąĮąŠčüčéčī čĆą░ą▒ąŠčéčŗ ąĘąĮą░čćąĖč鹥ą╗čīąĮąŠ ą┐ąŠą▓čŗčłą░ąĄčéčüčÅ. ą¤ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ DMA ą▓ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░čģ Atmel čüąĄčĆąĖą╣ AT91SAM ąĮą░ąĘčŗą▓ą░ąĄčéčüčÅ PDC (čĆą░čüčłąĖčäčĆąŠą▓čŗą▓ą░ąĄčéčüčÅ ą║ą░ą║ Peripheral DMA Controller). ąŚą┤ąĄčüčī ą┐ąĄčĆąĄą▓ąĄą┤ąĄąĮ ą║čāčüąŠą║ ą┤ą░čéą░čłąĖčéą░ ąĮą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ AT91SAM7X512 (ą░ čéą░ą║ąČąĄ AT91SAM7X128, AT91SAM7X256), ą┐ąŠčüą▓čÅčēąĄąĮąĮčŗą╣ PDC.

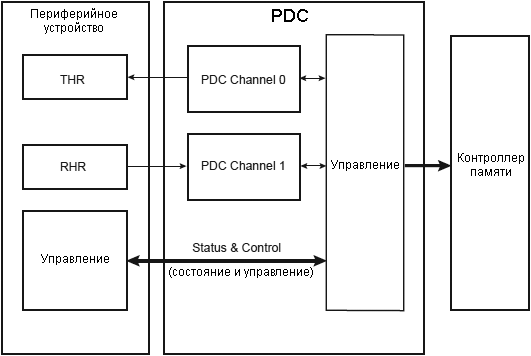

[ą×ą▒čēąĖą╣ ąŠą▒ąĘąŠčĆ PDC AT91SAM7X]

Peripheral DMA Controller (PDC) ą┐ąĄčĆąĄą┤ą░ąĄčé ą┤ą░ąĮąĮčŗąĄ ą╝ąĄąČą┤čā ąŠą┐ąĄčĆą░čéąĖą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéčīčÄ ąĖ ą▓čüčéčĆąŠąĄąĮąĮčŗą╝ąĖ ą▓ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ, čéą░ą║ąĖą╝ąĖ ą║ą░ą║ UART, USART, SSC, SPI, MCI. ąöą╗čÅ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ AT91SAM7X128, AT91SAM7X256 ąĖ AT91SAM7X512 ąŠą┐ąĄčĆą░čéąĖą▓ąĮą░čÅ ą┐ą░ą╝čÅčéčī ą╝ąŠąČąĄčé ą▒čŗčéčī č鹊ą╗čīą║ąŠ ą▓čüčéčĆąŠąĄąĮąĮą░čÅ (SRAM), č鹊ą│ą┤ą░ ą║ą░ą║ ą┤čĆčāą│ąĖąĄ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčŗ, ąŠčüąĮą░čēąĄąĮąĮčŗąĄ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ, ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čéą░ą║ąČąĄ ą┐ą░ą╝čÅčéčī, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčāčÄ čüąĮą░čĆčāąČąĖ (čüčéą░čéąĖč湥čüą║čāčÄ ąĖą╗ąĖ ą┤ąĖąĮą░ą╝ąĖč湥čüą║čāčÄ). ąśčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ PDC ą┐ąŠąĘą▓ąŠą╗čÅąĄčé čāčüčéčĆą░ąĮąĖčéčī ą▓ą╝ąĄčłą░č鹥ą╗čīčüčéą▓ąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą╣ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ CPU ą┤ą╗čÅ ą┐ąŠą┤ą┤ąĄčƹȹ║ąĖ ą┐čĆąŠčåąĄą┤čāčĆ ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ, ąĖ čüąĮąĖą╝ą░ąĄčé čü CPU ąĮą░ą│čĆčāąĘą║čā ąĮą░ ą┐ąĄčĆąĄčüčŗą╗ą║čā ą┤ą░ąĮąĮčŗčģ ąĖ ąŠą▒čĆą░ą▒ąŠčéą║čā ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. ąŁč鹊 ąĘąĮą░čćąĖč鹥ą╗čīąĮąŠ čüąĮąĖąČą░ąĄčé ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čåąĖą║ą╗ąŠą▓, čéčĆąĄą▒čāąĄą╝čŗčģ ą┤ą╗čÅ ą┐ąĄčĆąĄąĮąŠčüą░ ą┤ą░ąĮąĮčŗčģ, ąĖ ą▓ čĆąĄąĘčāą╗čīčéą░č鹥 čüąĮąĖąČą░ąĄčé 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ ąĖ ą┐ąŠą▓čŗčłą░ąĄčé čüą║ąŠčĆąŠčüčéčī čĆą░ą▒ąŠčéčŗ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ.

ąÜą░ąĮą░ą╗čŗ PDC čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮčŗ ą▓ ą▓ąĖą┤ąĄ ą┐ą░čĆ, ą║ą░ąČą┤ą░čÅ ą┐ą░čĆą░ ą▓čŗą┤ąĄą╗ąĄąĮą░ ą┤ą╗čÅ ąŠčéą┤ąĄą╗čīąĮąŠą│ąŠ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░. ą×ą┤ąĖąĮ ą║ą░ąĮą░ą╗ ą▓ ą┐ą░čĆąĄ ą▓čŗą┤ąĄą╗ąĄąĮ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ ą┐čĆąĖąĄą╝ą░, ą┤čĆčāą│ąŠą╣ ą║ą░ąĮą░ą╗ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ UART, USART, SSC ąĖ SPI.

ą¤čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ (čĆąĄą│ąĖčüčéčĆčŗ) ą║ą░ąĮą░ą╗ąŠą▓ PDC ąĖąĮč鹥ą│čĆąĖčĆąŠą▓ą░ąĮčŗ ą▓ ą░ą┤čĆąĄčüąĮąŠąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ ą║ą░ąČą┤ąŠą│ąŠ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░. ą×ąĮ čüąŠą┤ąĄčƹȹĖčé:

ŌĆó 32-ą▒ąĖčéąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ čāą║ą░ąĘą░č鹥ą╗čÅ ąĮą░ ą┐ą░ą╝čÅčéčī

ŌĆó 16-ą▒ąĖčéąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ čüč湥čéčćąĖą║ą░ ą┐ąĄčĆąĄąĮąŠčüąĖą╝čŗčģ ą▒ą░ą╣čé

ŌĆó 32-ą▒ąĖčéąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ čāą║ą░ąĘą░č鹥ą╗čÅ ąĮą░ ą┐ą░ą╝čÅčéčī

ŌĆó 16-ą▒ąĖčéąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ čüč湥čéčćąĖą║ą░ ą┐ąĄčĆąĄąĮąŠčüąĖą╝čŗčģ ą▒ą░ą╣čé

ąĪąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ (UART, USART, SSC, SPI) ą┐ąĄčĆąĄą║ą╗čÄčćą░ąĄčé ą┐ąĄčĆąĄą┤ą░čćąĖ PDC čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ čüąĖą│ąĮą░ą╗ąŠą▓ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖ ą┐čĆąĖąĄą╝ą░. ąÜąŠą│ą┤ą░ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┐ąĄčĆąĄąĮąĄčüąĄąĮčŗ, čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╝ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠą║ąŠąĮčćą░ąĮąĖčÅ ą┐čĆąŠčåąĄą┤čāčĆčŗ ą┐ąĄčĆąĄąĮąŠčüą░ ą┤ą░ąĮąĮčŗčģ (čŹč鹊 ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąĖąĄą╝ ąĖą╗ąĖ ą┐ąĄčĆąĄą┤ą░čćą░).

ąĀąĖčü. 22-1. ąæą╗ąŠą║-čüčģąĄą╝ą░ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą┐čĆčÅą╝ąŠą│ąŠ ą┤ąŠčüčéčāą┐ą░ ą║ ą┐ą░ą╝čÅčéąĖ PDC (Peripheral DMA Controller).

ąÆ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░čģ AT91SAM7X512 (ą░ čéą░ą║ąČąĄ AT91SAM7X128, AT91SAM7X256) čäčāąĮą║čåąĖčÅą╝ąĖ PDC (DMA) ąŠčüąĮą░čēąĄąĮčŗ čüą╗ąĄą┤čāčÄčēąĖąĄ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░: SPI0, SPI1, USART0, USART1, SSC. ąÜ čüąŠąČą░ą╗ąĄąĮąĖčÄ, ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ USB, CAN, Ethernet čäčāąĮą║čåąĖčÅą╝ąĖ DMA ąĮąĄ ąŠčüąĮą░čēąĄąĮčŗ.

[ążčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ PDC]

ąśąĮč鹥čĆč乥ą╣čü ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ ą║ą░ąĮą░ą╗ąŠą▓ PDC (ą║ą░ąĮą░ą╗ ą┐čĆąĖąĄą╝ą░, ą║ą░ąĮą░ą╗ ą┐ąĄčĆąĄą┤ą░čćąĖ) ą┐ąŠąĘą▓ąŠą╗čÅčÄčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčüčéčā čāą┐čĆą░ą▓ą╗čÅčéčī ą┐ąŠč鹊ą║ą░ą╝ąĖ ą┤ą░ąĮąĮčŗčģ ąĖ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī ąĖčģ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą║ą░ąĮą░ą╗ą░. ąśąĮč鹥čĆč乥ą╣čü ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ ą║ą░ąĮą░ą╗ą░ PDC ąĖąĮč鹥ą│čĆąĖčĆąŠą▓ą░ąĮ ą▓ ąĖąĮč鹥čĆč乥ą╣čü ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░, ą║ ą║ąŠč鹊čĆąŠą╝čā PDC ąŠčéąĮąŠčüąĖčéčüčÅ, čüąŠ čüą╝ąĄčēąĄąĮąĖąĄą╝ ą░ą┤čĆąĄčüą░ 0x100 (ą║ą░čĆčéčā čĆąĄą│ąĖčüčéčĆąŠą▓ PDC čüą╝. ą▓ čĆą░ąĘą┤ąĄą╗ąĄ "ąśąĮč鹥čĆč乥ą╣čü ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ PDC"). ąØą░ ą║ą░ąČą┤ąŠąĄ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐čĆąĖčģąŠą┤ąĖčéčüčÅ ą┐ąŠ 4 32-ą▒ąĖčéąĮčŗčģ čĆąĄą│ąĖčüčéčĆą░ (RPR, RNPR, TPR ąĖ TNPR, ąŠ ąĮąĖčģ ą┐ąŠą┤čĆąŠą▒ąĮąĄąĄ ą▓ čĆą░ąĘą┤ąĄą╗ąĄ "ąŻą║ą░ąĘą░č鹥ą╗ąĖ ąĮą░ ą┐ą░ą╝čÅčéčī") ąĖ 4 16-ą▒ąĖčéąĮčŗčģ čĆąĄą│ąĖčüčéčĆą░ (RCR, RNCR, TCR ąĖ TNCR, ąŠ ąĮąĖčģ ą┐ąŠą┤čĆąŠą▒ąĮąĄąĄ ą▓ čĆą░ąĘą┤ąĄą╗ąĄ "ąĪč湥čéčćąĖą║ąĖ ą┐ąĄčĆąĄąĮąŠčüą░ ą┤ą░ąĮąĮčŗčģ").

ąĀą░ąĘą╝ąĄčĆ ą▒čāč乥čĆą░ ą▓ ąĄą┤ąĖąĮąĖčåą░čģ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗčģ ą┐ąŠčĆčåąĖą╣ ą┤ą░ąĮąĮčŗčģ (ąĄą┤ąĖąĮąĖčåą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▒ą░ą╣čé, 2 ą▒ą░ą╣čéą░ ąĖą╗ąĖ 4 ą▒ą░ą╣čéą░) ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ ą▓ 16-ą▒ąĖčéąĮąŠą╝ čüč湥čéčćąĖą║ąĄ ą┐ąĄčĆąĄčüčŗą╗ą║ąĖ (TCR, TNCR ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖą╗ąĖ RCR, RNCR ą┤ą╗čÅ ą┐čĆąĖąĄą╝ą░). ąĪč湥čéčćąĖą║ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮ ą▓ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé, čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī, čüą║ąŠą╗čīą║ąŠ ąĄą┤ąĖąĮąĖčå ą┤ą░ąĮąĮčŗčģ ąŠčüčéą░ą╗ąŠčüčī ą┐ąĄčĆąĄą┤ą░čéčī ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą║ą░ąĮą░ą╗ą░.

ąæą░ąĘąŠą▓čŗą╣ ą░ą┤čĆąĄčü ą┐ąĄčĆąĄčüčŗą╗ą║ąĖ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ ą▓ 32-ą▒ąĖčéąĮąŠą╝ čāą║ą░ąĘą░č鹥ą╗ąĄ ąĮą░ ą┐ą░ą╝čÅčéčī. ąŁčéąĖą╝ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą╝ąĄčüč鹊 ą┐ąĄčĆą▓ąŠą│ąŠ ą░ą┤čĆąĄčüą░ ą▓ ą▒ą╗ąŠą║ąĄ ą┐ą░ą╝čÅčéąĖ, ą║čāą┤ą░ ą▒čāą┤ąĄčé ąŠčüčāčēąĄčüčéą▓ą╗čÅčéčīčüčÅ ą┤ąŠčüčéčāą┐. ąÆ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé ą▓čĆąĄą╝ąĄąĮąĖ ą╝ąŠąČąĮąŠ ą┐čĆąŠčćąĖčéą░čéčī ąĘąĮą░č湥ąĮąĖąĄ čŹč鹊ą│ąŠ čāą║ą░ąĘą░č鹥ą╗čÅ, ąĖ ą┐ąŠ ąĮąĄą╝čā ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ą╝ąĄčüč鹊 ąĮą░ąĘąĮą░č湥ąĮąĖčÅ čüą╗ąĄą┤čāčÄčēąĄą╣ ą┐ąŠčĆčåąĖąĖ ą┤ą░ąĮąĮčŗčģ. PDC ąĖą╝ąĄąĄčé ą▓čŗą┤ąĄą╗ąĄąĮąĮčŗąĄ čĆąĄą│ąĖčüčéčĆčŗ čüąŠčüč鹊čÅąĮąĖčÅ, ą║ąŠč鹊čĆčŗąĄ ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčé - čĆą░ąĘčĆąĄčłąĄąĮ ąĖą╗ąĖ ąĮąĄčé ą┐ąĄčĆąĄąĮąŠčü ą┤ą░ąĮąĮčŗčģ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą║ą░ąĮą░ą╗ą░. ąĪčéą░čéčāčü ą║ą░ąČą┤ąŠą│ąŠ ą║ą░ąĮą░ą╗ą░ čĆą░ąĘą╝ąĄčēąĄąĮ ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüąŠčüč鹊čÅąĮąĖčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░. ą¤ąĄčĆąĄą┤ą░čćąĖ ą╝ąŠą│čāčé ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮčŗ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčēąĄąĮčŗ č湥čĆąĄąĘ čāčüčéą░ąĮąŠą▓ą║čā ą▒ąĖčé TXTEN/TXTDIS (ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ) ąĖ RXTEN/RXTDIS (ą┤ą╗čÅ ą┐čĆąĖąĄą╝ą░) ą▓ čĆąĄą│ąĖčüčéčĆąĄ PDC Transfer Control Register. ąŁčéąĖ ą▒ąĖčéčŗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┤ąĄą╗ą░čÄčé ą▓ąŠąĘą╝ąŠąČąĮčŗą╝ ą▒ąĄąĘąŠą┐ą░čüąĮąŠ čćąĖčéą░čéčī čĆąĄą│ąĖčüčéčĆčŗ čāą║ą░ąĘą░č鹥ą╗ąĄą╣ ąĖ čüč湥čéčćąĖą║ąŠą▓ - ą▒ąĄąĘ čĆąĖčüą║ą░, čćč鹊 ąŠąĮąĖ ąĖąĘą╝ąĄąĮčÅčéčüčÅ ą╝ąĄąČą┤čā čćč鹥ąĮąĖčÅą╝ąĖ.

PDC ą▓čŗčüčéą░ą▓ą╗čÅąĄčé čäą╗ą░ą│ąĖ čüčéą░čéčāčüą░ ą▓ čĆąĄą│ąĖčüčéčĆčŗ čüąŠčüč鹊čÅąĮąĖčÅ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (ENDRX, ENDTX, RXBUFF ąĖ TXBUFE).

ENDRX čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ čĆąĄą│ąĖčüčéčĆ PERIPH_RCR (čüč湥čéčćąĖą║ ą┐čĆąĖąĄą╝ą░) ą┤ąŠčüčéąĖą│ą░ąĄčé ąĮčāą╗čÅ.

RXBUFF čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ąŠą▒ą░ čüč湥čéčćąĖą║ą░ ą┐čĆąĖąĄą╝ą░, ąĖ PERIPH_RCR, ąĖ PERIPH_RNCR ą┤ąŠčüčéąĖą│ą╗ąĖ ąĮčāą╗čÅ.

ENDTX čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ čĆąĄą│ąĖčüčéčĆ PERIPH_TCR (čüč湥čéčćąĖą║ ą┐ąĄčĆąĄą┤ą░čćąĖ) ą┤ąŠčüčéąĖą│ ąĮčāą╗čÅ.

TXBUFE čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ąŠą▒ą░ čüč湥čéčćąĖą║ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ, ąĖ PERIPH_TCR ąĖ PERIPH_TNCR ą┤ąŠčüčéąĖą│ą╗ąĖ ąĮčāą╗čÅ.

ąŁčéąĖ čäą╗ą░ą│ąĖ čüčéą░čéčāčüą░ ąŠą┐ąĖčüą░ąĮčŗ ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüčéą░čéčāčüą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (peripheral status register). ąÜ ą┐čĆąĖą╝ąĄčĆčā, ąĄčüą╗ąĖ čŹč鹊 ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ SPI, č鹊 čŹč鹊 ą▒čāą┤ąĄčé čĆąĄą│ąĖčüčéčĆ čüčéą░čéčāčüą░ SPI_SR.

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ |

SPIENS |

| - |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

r |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ |

TXEMPTY |

NSSR |

TXBUFE |

RXBUFF |

ENDTX |

ENDRX |

OVRES |

MODF |

TDRE |

RDRF |

| - |

- |

- |

- |

- |

- |

r |

r |

r |

r |

r |

r |

r |

r |

r |

r |

ąØąĄ ą▒čāą┤čā ą┐čĆąĖą▓ąŠą┤ąĖčéčī ąŠą┐ąĖčüą░ąĮąĖąĄ ą▓čüąĄčģ čäą╗ą░ą│ąŠą▓ (ąĘą░ ą┐ąŠą┤čĆąŠą▒ąĮąŠčüčéčÅą╝ąĖ ąŠą▒čĆą░čēą░ą╣č鹥čüčī ą║ ą┤ą░čéą░čłąĖčéčā). ąØą░čü čüąĄą╣čćą░čü ąĖąĮč鹥čĆąĄčüčāčÄčé č鹊ą╗čīą║ąŠ čäą╗ą░ą│ąĖ, ą║ąŠč鹊čĆčŗąĄ ąŠčéąĮąŠčüčÅčéčüčÅ ą║ PDC:

ŌĆó ENDRX: End of RX buffer (ą┐čĆąĖąĘąĮą░ą║ ąŠą║ąŠąĮčćą░ąĮąĖčÅ ą▒čāč乥čĆą░ ą┐čĆąĖąĄą╝ą░)

0 = Receive Counter Register (čüč湥čéčćąĖą║ ą┐čĆąĖąĄą╝ą░) ąĮąĄ ą┤ąŠčüčéąĖą│ 0 čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╣ ąĘą░ą┐ąĖčüąĖ ą▓ SPI_RCR(1) ąĖą╗ąĖ ą▓ SPI_RNCR(1).

1 = Receive Counter Register (čüč湥čéčćąĖą║ ą┐čĆąĖąĄą╝ą░) ą┤ąŠčüčéąĖą│ 0 čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╣ ąĘą░ą┐ąĖčüąĖ ą▓ SPI_RCR(1) ąĖą╗ąĖ ą▓ SPI_RNCR(1).

ŌĆó ENDTX: End of TX buffer (ą┐čĆąĖąĘąĮą░ą║ ąŠą║ąŠąĮčćą░ąĮąĖčÅ ą▒čāč乥čĆą░ ą┐ąĄčĆąĄą┤ą░čćąĖ)

0 = Transmit Counter Register (čüč湥čéčćąĖą║ ą┐ąĄčĆąĄą┤ą░čćąĖ) ąĮąĄ ą┤ąŠčüčéąĖą│ 0 čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╣ ąĘą░ą┐ąĖčüąĖ ą▓ SPI_TCR(1) ąĖą╗ąĖ ą▓ SPI_TNCR(1).

1 = Transmit Counter Register (čüč湥čéčćąĖą║ ą┐ąĄčĆąĄą┤ą░čćąĖ) ą┤ąŠčüčéąĖą│ 0 čü ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╣ ąĘą░ą┐ąĖčüąĖ ą▓ SPI_TCR(1) ąĖą╗ąĖ ą▓ SPI_TNCR(1).

ŌĆó RXBUFF: RX Buffer Full (ą▒čāč乥čĆ ą┐čĆąĖąĄą╝ą░ ąĘą░ą┐ąŠą╗ąĮąĄąĮ)

0 = SPI_RCR(1) ąĖą╗ąĖ SPI_RNCR(1) ąĖą╝ąĄčÄčé ąĘąĮą░č湥ąĮąĖąĄ, ąĮąĄ čĆą░ą▓ąĮąŠąĄ 0.

1 = ą×ą▒ą░ čĆąĄą│ąĖčüčéčĆą░, ąĖ SPI_RCR(1), ąĖ SPI_RNCR(1) čĆą░ą▓ąĮčŗ 0.

ŌĆó TXBUFE: TX Buffer Empty (ą▒čāč乥čĆ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐čāčüčé)

0 = SPI_TCR(1) ąĖą╗ąĖ SPI_TNCR(1) ąĖą╝ąĄčÄčé ąĘąĮą░č湥ąĮąĖąĄ, ąĮąĄ čĆą░ą▓ąĮąŠąĄ 0.

1 = ą×ą▒ą░ čĆąĄą│ąĖčüčéčĆą░, ąĖ SPI_TCR(1), ąĖ SPI_TNCR(1) čĆą░ą▓ąĮčŗ 0.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ (1). ąĀąĄą│ąĖčüčéčĆčŗ SPI_RCR, SPI_RNCR, SPI_TCR, SPI_TNCR čäąĖąĘąĖč湥čüą║ąĖ čĆą░ąĘą╝ąĄčēąĄąĮčŗ ą▓ PDC, čģąŠčéčÅ ąĮą░čģąŠą┤čÅčéčüčÅ ą▓ ą░ą┤čĆąĄčüąĮąŠą╝ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąĄ ąĖąĮč鹥čĆč乥ą╣čüą░ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ SPI.

[ąŻą║ą░ąĘą░č鹥ą╗ąĖ ąĮą░ ą┐ą░ą╝čÅčéčī (Memory Pointers)]

ąÜą░ąČą┤ąŠąĄ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ (UART, SPI ąĖ čé. ą┐.) čüąŠąĄą┤ąĖąĮąĄąĮąŠ čü PDC ą┤ą▓čāą╝čÅ ą║ą░ąĮą░ą╗ą░ą╝ąĖ - ą║ą░ąĮą░ą╗ąŠą╝ ą┐čĆąĖąĄą╝ą░ ąĖ ą║ą░ąĮą░ą╗ąŠą╝ ą┐ąĄčĆąĄą┤ą░čćąĖ. ąÜą░ąČą┤čŗą╣ ą║ą░ąĮą░ą╗ čüąĮą░ą▒ąČąĄąĮ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╝ 32-ą▒ąĖčéąĮčŗą╝ čāą║ą░ąĘą░č鹥ą╗ąĄą╝ ąĮą░ ą┐ą░ą╝čÅčéčī. ąÜą░ąČą┤čŗą╣ čāą║ą░ąĘą░č鹥ą╗čī ąĮą░ ą┐ą░ą╝čÅčéčī čāą║ą░ąĘčŗą▓ą░ąĄčé ąĮą░ ą║ą░ą║ąŠąĄ-č鹊 ą╝ąĄčüč鹊 ą▓ ą░ą┤čĆąĄčüąĮąŠą╝ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąĄ ą┐ą░ą╝čÅčéąĖ (čŹčéą░ ą▓čüčéčĆąŠąĄąĮąĮą░čÅ ą▓ čćąĖą┐ ąŠą┐ąĄčĆą░čéąĖą▓ąĮą░čÅ ą┐ą░ą╝čÅčéčī ą║ą░ą║ čā ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ AT91SAM7X, ąĖą╗ąĖ čŹč鹊 ą╝ąŠąČąĄčé ą▒čŗčéčī ą┤ą░ąČąĄ ą▓ąĮąĄčłąĮčÅčÅ ą┐ą░ą╝čÅčéčī, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮą░čÅ č湥čĆąĄąĘ ą▓ąĮąĄčłąĮčÄčÄ čłąĖąĮčā ąĖ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą┐ą░ą╝čÅčéąĖ).

ąÆ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čéąĖą┐ą░ ą┐ąĄčĆąĄąĮąŠčüą░ ą┤ą░ąĮąĮčŗčģ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (ą┐ąŠą▒ą░ą╣čéąĮąŠ, ą┐ąŠą╗čāčüą╗ąŠą▓ą░ą╝ąĖ ą▓ 2 ą▒ą░ą╣čéą░ ąĖą╗ąĖ čüą╗ąŠą▓ą░ą╝ąĖ ą┐ąŠ 4 ą▒ą░ą╣čéą░), čāą║ą░ąĘą░č鹥ą╗čī ąĮą░ ą┐ą░ą╝čÅčéčī čü ą║ą░ąČą┤ąŠą╣ ą┐ąĄčĆąĄą┤ą░č湥ą╣ ą┐ąŠčĆčåąĖąĖ ą┤ą░ąĮąĮčŗčģ ą▒čāą┤ąĄčé ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆąŠą▓ą░ąĮ ąĮą░ 1, 2 ąĖą╗ąĖ 4.

ąĢčüą╗ąĖ čāą║ą░ąĘą░č鹥ą╗čī ąĮą░ ą┐ą░ą╝čÅčéčī ą▒čŗą╗ ą┐ąĄčĆąĄą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ ą▓ąŠ ą▓čĆąĄą╝čÅ ą░ą║čéąĖą▓ąĮąŠą╣ ąŠą┐ąĄčĆą░čåąĖąĖ PDC, č鹊 ą░ą┤čĆąĄčü ą┐ąĄčĆąĄąĮąŠčüą░ ą┤ą░ąĮąĮčŗčģ ą┐ąŠą╝ąĄąĮčÅąĄčéčüčÅ, ąĖ PDC ą▒čāą┤ąĄčé ą▓čŗą┐ąŠą╗ąĮčÅčéčī ą┐ąĄčĆąĄąĮąŠčü ą┤ą░ąĮąĮčŗčģ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ ąĮąŠą▓čŗčģ ą░ą┤čĆąĄčüąŠą▓ (ąŠą▒čŗčćąĮąŠ čéą░ą║ ąĮąĖą║ąŠą│ą┤ą░ ąĮąĄ ą┤ąĄą╗ą░čÄčé, čāą║ą░ąĘą░č鹥ą╗ąĖ ą┐ąĄčĆąĄąĮą░čüčéčĆą░ąĖą▓ą░čÄčé ą┐ąĄčĆąĄą┤ ąĮą░čćą░ą╗ąŠą╝ ąŠą┐ąĄčĆą░čåąĖąĖ ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ, ąĖą╗ąĖ ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ąŠą┐ąĄčĆą░čåąĖąĖ ą┐ąŠ ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖčÄ ą┤ą░ąĮąĮčŗčģ).

[ąĪč湥čéčćąĖą║ąĖ ą┐ąĄčĆąĄąĮąŠčüą░ ą┤ą░ąĮąĮčŗčģ (Transfer Counters)]

ąśą╝ąĄąĄčéčüčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ 16-ą▒ąĖčéąĮčŗą╣ čüč湥čéčćąĖą║ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą║ą░ąĮą░ą╗ą░, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╣ ą┤ą╗čÅ ą┐ąŠą┤čüč湥čéą░ čāąČąĄ ą┐ąĄčĆąĄą┤ą░ąĮąĮčŗčģ ą┤ą░ąĮąĮčŗčģ ąĖąĘ ą▓čüąĄą│ąŠ ą▒ą╗ąŠą║ą░. ąĪč湥čéčćąĖą║ąĖ ą┤ąĄą║čĆąĄą╝ąĄąĮčéąĖčĆčāčÄčéčüčÅ ą┐ąŠčüą╗ąĄ ą┐ąĄčĆąĄąĮąŠčüą░ ą║ą░ąČą┤ąŠą╣ ąŠčéą┤ąĄą╗čīąĮąŠą╣ ą┐ąŠčĆčåąĖąĖ ą┤ą░ąĮąĮčŗčģ. ąÜąŠą│ą┤ą░ čüč湥čéčćąĖą║ ą┤ąŠčüčéąĖą│ą░ąĄčé 0, č鹊 ą┐ąĄčĆąĄąĮąŠčü ą┤ą░ąĮąĮčŗčģ ąĘą░ą▓ąĄčĆčłąĄąĮ, ąĖ PDC ąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ą┐čĆąŠčåąĄą┤čāčĆčā ą┐ąĄčĆąĄąĮąŠčüą░ ą┤ą░ąĮąĮčŗčģ.

ąĢčüą╗ąĖ Next Counter Register (čüč湥čéčćąĖą║ ą┤ą╗čÅ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ ą┐ąĄčĆąĄąĮąŠčüą░) čĆą░ą▓ąĄąĮ 0, č鹊 PDC ąĘą░ą┐čĆąĄčēą░ąĄčé ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ąĮą░ čüą╗ąĄą┤čāčÄčēčāčÄ ąŠą┐ąĄčĆą░čåąĖčÄ ą┐ąĄčĆąĄąĮąŠčüą░ ąĖ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ čäą╗ą░ą│ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ (TNCR ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖ RNCR ą┤ą╗čÅ ą┐čĆąĖąĄą╝ą░).

ąĢčüą╗ąĖ čüč湥čéčćąĖą║ ą▒čŗą╗ ą┐ąĄčĆąĄą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ ą▓ąŠ ą▓čĆąĄą╝čÅ ą░ą║čéąĖą▓ąĮąŠą╣ ąŠą┐ąĄčĆą░čåąĖąĖ PDC, č鹊 ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą┐ąĄčĆąĄą┤ą░čć (ąĖą╗ąĖ ą┐čĆąĖąĄą╝ąŠą▓) ą┐ąŠčĆčåąĖą╣ ą┤ą░ąĮąĮčŗčģ ąŠą▒ąĮąŠą▓ą╗čÅąĄčéčüčÅ, ąĖ PDC čüčćąĖčéą░ąĄčé ą┐ąĄčĆąĄą┤ą░čćąĖ (ąĖą╗ąĖ ą┐čĆąĖąĄą╝čŗ) ąŠčé ąĮąŠą▓ąŠą╣ ą▓ąĄą╗ąĖčćąĖąĮčŗ čüč湥čéčćąĖą║ą░ (ąŠą▒čŗčćąĮąŠ čéą░ą║ ąĮąĖą║ąŠą│ą┤ą░ ąĮąĄ ą┤ąĄą╗ą░čÄčé, čüč湥čéčćąĖą║ąĖ ąĮą░čüčéčĆą░ąĖą▓ą░čÄčé ą┐ąĄčĆąĄą┤ ąĮą░čćą░ą╗ąŠą╝ ą┐ąĄčĆąĄąĮąŠčüą░ ą┤ą░ąĮąĮčŗčģ, ą║ąŠą│ą┤ą░ ą┐čĆąŠčåąĄčüčü ą┐ąĄčĆąĄąĮąŠčüą░ ąĄčēąĄ ąĮąĄ ą░ą║čéąĖą▓ąĄąĮ, ąĖą╗ąĖ čāąČąĄ ąĘą░ą▓ąĄčĆčłąĄąĮ).

ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆąŠą▓ Next Counter/Pointer ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąŠčĆą│ą░ąĮąĖąĘąŠą▓ą░čéčī ą┐ąĄčĆąĄą┤ą░čćčā ą▒čāč乥čĆąŠą▓ ą┐ąŠ čåąĄą┐ąŠčćą║ąĄ. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ čüč湥čéčćąĖą║ąĖ ą┐ąĄčĆąĄąĮąŠčüą░ ą┤ąĄą║čĆąĄą╝ąĄąĮčéąĖčĆčāčÄčéčüčÅ ą▓ ą┐čĆąŠčåąĄčüčüąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ ą║ą░ą║ ąŠą▒čŗčćąĮąŠ, ąĮąŠ ą║ąŠą│ą┤ą░ čüč湥čéčćąĖą║ ą┐ąĄčĆąĄąĮąŠčüą░ ą┤ąŠčüčéąĖą│ ąĮčāą╗čÅ, č鹊 ąĘąĮą░č湥ąĮąĖčÅ ąĖąĘ čĆąĄą│ąĖčüčéčĆąŠą▓ Next Counter/Pointer ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąĘą░ą│čĆčāąČą░čÄčéčüčÅ ą▓ č鹥ą║čāčēąĖąĄ čĆąĄą│ąĖčüčéčĆčŗ Counter/Pointer, ąĖ ą┐čĆąŠčåąĄčüčü ą┐ąĄčĆąĄąĮąŠčüą░ ą┤ą░ąĮąĮčŗčģ ą▓ąŠąĘąŠą▒ąĮąŠą▓ą╗čÅąĄčéčüčÅ. ąÆ čŹč鹊čé ą╝ąŠą╝ąĄąĮčé ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ąĖ ą╝ąŠąČąĮąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ ąĘą░ą│čĆčāąĘąĖčéčī ą▓ čĆąĄą│ąĖčüčéčĆčŗ Next Counter/Pointer ąĘąĮą░č湥ąĮąĖąĄ ą┤ą╗čÅ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ ą▒čāč乥čĆą░. ąóą░ą║ąĖą╝ čüą┐ąŠčüąŠą▒ąŠą╝ ąŠčĆą│ą░ąĮąĖąĘčāčÄčé ąĮąĄą┐čĆąĄčĆčŗą▓ąĮčāčÄ ą▓ąŠ ą▓čĆąĄą╝ąĄąĮąĖ ą┐ąĄčĆąĄą┤ą░čćčā, ą┐čĆąĖ čŹč鹊ą╝ CPU ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ąŠč湥ąĮčī ąĮąĄąĘąĮą░čćąĖč鹥ą╗čīąĮąŠ.

ąöą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą║ą░ąĮą░ą╗ą░ 2 ą▒ąĖčéą░ čüčéą░čéčāčüą░ ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčé ąŠą║ąŠąĮčćą░ąĮąĖąĄ č鹥ą║čāčēąĄą│ąŠ ą▒čāč乥čĆą░ (ENDRX, ENTX) ąĖ ąŠą║ąŠąĮčćą░ąĮąĖąĄ čüčĆą░ąĘčā ą┤ą▓čāčģ ą▒čāč乥čĆąŠą▓, ąĖ č鹥ą║čāčēąĄą│ąŠ ąĖ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ (RXBUFF, TXBUFE). ąŁčéąĖ ą▒ąĖčéčŗ ąĮą░čģąŠą┤čÅčéčüčÅ ą┐čĆčÅą╝ąŠ ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüąŠčüč鹊čÅąĮąĖčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░, ąĖ ą╝ąŠą│čāčé ą▓čŗąĘčŗą▓ą░čéčī čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąŠčüą░ ąĮą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┤ą╗čÅ AIC (Advanced Interrupt Controller). ążą╗ą░ą│ąĖ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąŠčćąĖčēą░čÄčéčüčÅ, ą║ąŠą│ą┤ą░ ą▒čŗą╗ ąĘą░ą┐ąĖčüą░ąĮ ąŠą┤ąĖąĮ ąĖąĘ čĆąĄą│ąĖčüčéčĆąŠą▓-čüč湥čéčćąĖą║ą▓ (Counter ąĖą╗ąĖ Next Counter Register).

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą║ąŠą│ą┤ą░ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ Next Counter Register ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ą▓ Counter Register, ąĘąĮą░č湥ąĮąĖąĄ Next Counter Register čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ ą▓ 0.

[ą¤čĆąŠčåąĄčüčüčŗ ą┐ąĄčĆąĄąĮąŠčüą░ ą┤ą░ąĮąĮčŗčģ (Data Transfers)]

ą¤ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐ąĄčĆąĄą║ą╗čÄčćą░ąĄčé ą┐ąĄčĆąĄąĮąŠčüčŗ ą┤ą░ąĮąĮčŗčģ PDC čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ čüąĖą│ąĮą░ą╗ąŠą▓ ą│ąŠč鹊ą▓ąĮąŠčüčéąĖ ą║ ą┐ąĄčĆąĄą┤ą░č湥 (TXRDY) ąĖ ą┐čĆąĖąĄą╝čā (RXRDY).

ąÜąŠą│ą┤ą░ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐čĆąĖąĮčÅą╗ąŠ ą┐ąŠčüčéčāą┐ąĖą▓čłąĖąĄ ą┤ą░ąĮąĮčŗąĄ (ąĮą░ą┐čĆąĖą╝ąĄčĆ, čüąĖą╝ą▓ąŠą╗, ą┐ąŠčüčéčāą┐ąĖą▓čłąĖą╣ ąĮą░ UART), ąŠąĮąŠ ą┐ąŠčüčŗą╗ą░ąĄčé čüąĖą│ąĮą░ą╗ Receive Ready ą║ PDC, ą║ąŠč鹊čĆčŗą╣ ąĘą░č鹥ą╝ ąĘą░ą┐čĆą░čłąĖą▓ą░ąĄčé ą┤ąŠčüčéčāą┐ ą║ čüąĖčüč鹥ą╝ąĮąŠą╣ čłąĖąĮąĄ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░. ąÜąŠą│ą┤ą░ ą┤ąŠčüčéčāą┐ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮ, PDC ąĘą░ą┐čāčüą║ą░ąĄčé čćč鹥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ Receive Holding Register (RHR) ąĖ ąĘą░č鹥ą╝ ą┐ąĄčĆąĄą║ą╗čÄčćą░ąĄčéčüčÅ ąĮą░ ąĘą░ą┐ąĖčüčī ą┐čĆąĖąĮčÅčéčŗčģ ą┤ą░ąĮąĮčŗčģ ą▓ ą┐ą░ą╝čÅčéčī. ą¤ąŠčüą╗ąĄ ą┐čĆąĖąĄą╝ą░ ą║ą░ąČą┤ąŠą╣ ą┐ąŠčĆčåąĖąĖ ą┤ą░ąĮąĮčŗčģ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ čāą║ą░ąĘą░č鹥ą╗čī ąĮą░ ą┐ą░ą╝čÅčéčī PDC ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ, ąĖ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ąŠčüčéą░ą▓čłąĖčģčüčÅ ą┐čĆąĖąĄą╝ąŠą▓ (čüč湥čéčćąĖą║) ą┤ąĄą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ. ąÜąŠą│ą┤ą░ ą┐čĆąĖąĮčÅčé ą▓ąĄčüčī ą▒ą╗ąŠą║ ą┤ą░ąĮąĮčŗčģ, č鹊 ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą╝čā čāčüčéčĆąŠą╣čüčéą▓čā ą┐ąŠčüčŗą╗ą░ąĄčéčüčÅ čüąĖą│ąĮą░ą╗, ąĖ ą┐čĆąĖąĄą╝ ą┤ą░ąĮąĮčŗčģ ąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ. ąóą░ ąČąĄ čüą░ą╝ą░čÅ ą┐čĆąŠčåąĄą┤čāčĆą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ąĖ ą┐čĆąĖ ą┐ąĄčĆąĄą┤ą░č湥, č鹊ą╗čīą║ąŠ ą▓ ąŠą▒čĆą░čéąĮąŠą╝ ą┐ąŠčĆčÅą┤ą║ąĄ (čé. ąĄ. čüąĮą░čćą░ą╗ą░ čüčćąĖčéčŗą▓ą░ąĄčéčüčÅ ą┐ąŠčĆčåąĖčÅ ą┤ą░ąĮąĮčŗčģ ąĖąĘ ą┐ą░ą╝čÅčéąĖ, ąĖ ąĘą░č鹥ą╝ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą▓ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ).

[ą¤čĆąĖąŠčĆąĖč鹥čé ąĘą░ą┐čĆąŠčüąŠą▓ PDC (PDC Transfer Requests)]

ąÜą░ąČą┤čŗą╣ Peripheral DMA Controller ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčé ąĘą░ą┐čĆąŠčüčŗ ąĮą░ ą┐ąĄčĆąĄąĮąŠčü ą┤ą░ąĮąĮčŗčģ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü ą┐čĆąĖąŠčĆąĖč鹥čéą░ą╝ąĖ, čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮčŗą╝ąĖ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą╣ ą╝ąŠą┤ąĄą╗ąĖ čćąĖą┐ą░. ąŁčéąĖ ą┐čĆąĖąŠčĆąĖč鹥čéčŗ ąĘą░ą┤ą░ąĮčŗ ą▓ ą┤ą░čéą░čłąĖč鹥 ąĮą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ. ą¤čĆąĖąŠčĆąĖč鹥čé ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮčŗčģ ąĘą░ą┐čĆąŠčüąŠą▓ ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠą│ąŠ čéąĖą┐ą░ (ą┐čĆąĖąĄą╝ąĮąĖą║ ąĖą╗ąĖ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║), ą┐čĆąŠąĖąĘąŠčłąĄą┤čłąĖąĄ ąĮą░ ąŠą┤ąĖąĮą░ą║ąŠą▓čŗčģ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ą░čģ, ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą┐ąŠ ąĮčāą╝ąĄčĆą░čåąĖąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓.

ąĢčüą╗ąĖ ąĘą░ą┐čĆąŠčüčŗ ąĮą░ ą┐ąĄčĆąĄąĮąŠčü ą┐ąŠčüčéčāą┐ąĖą╗ąĖ ąĮąĄ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ, č鹊 ąŠąĮąĖ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░čÄčéčüčÅ ą▓ ą┐ąŠčĆčÅą┤ą║ąĄ ąĖčģ ą┐ąŠčüčéčāą┐ą╗ąĄąĮąĖčÅ. ąŚą░ą┐čĆąŠčüčŗ ąŠčé ą┐čĆąĖąĄą╝ąĮąĖą║ąŠą▓ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░čÄčéčüčÅ ą▓ ą┐ąĄčĆą▓čāčÄ ąŠč湥čĆąĄą┤čī, ąĖ ąĘą░č鹥ą╝ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░čÄčéčüčÅ ąĘą░ą┐čĆąŠčüčŗ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ąŠą▓.

[ąśąĮč鹥čĆč乥ą╣čü ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ PDC]

ąÆčüąĄ čĆąĄą│ąĖčüčéčĆčŗ ą▓ čéą░ą▒ą╗ąĖčåąĄ ą┤ąŠčüčéčāą┐ąĮčŗ ąĖ ąĮą░ čćč鹥ąĮąĖąĄ ąĖ ąĘą░ą┐ąĖčüčī (ą┤ąŠčüčéčāą┐ Read-write), ą║čĆąŠą╝ąĄ čĆąĄą│ąĖčüčéčĆą░ PERIPH_PTCR (ą┤ąŠčüčéčāą┐ Write-only) ąĖ čĆąĄą│ąĖčüčéčĆą░ PERIPH_PTSR (ą┤ąŠčüčéčāą┐ Read-only). ąóą░ą║ąČąĄ čā ą▓čüąĄčģ čĆąĄą│ąĖčüčéčĆąŠą▓, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠąČąĮąŠ čćąĖčéą░čéčī, ąĮą░čćą░ą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ čĆą░ą▓ąĮąŠ 0.

ąóą░ą▒ą╗ąĖčåą░ 22-1. ąÜą░čĆčéą░ čĆąĄą│ąĖčüčéčĆąŠą▓ PDC, ą┐čĆąĖą▓čÅąĘą░ąĮąĮą░čÅ ą║ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą╝čā čāčüčéčĆąŠą╣čüčéą▓čā.

| ąĪą╝ąĄčēąĄąĮąĖąĄ |

ąĀąĄą│ąĖčüčéčĆ |

ąśą╝čÅ |

ąöąŠčüčéčāą┐ |

ąĪą▒čĆąŠčü |

| 0x100 |

Receive Pointer Register |

PERIPH_RPR |

R/W |

0 |

| 0x104 |

Receive Counter Register |

PERIPH_RCR |

R/W |

0 |

| 0x108 |

Transmit Pointer Register |

PERIPH_TPR |

R/W |

0 |

| 0x10C |

Transmit Counter Register |

PERIPH_TCR |

R/W |

0 |

| 0x110 |

Receive Next Pointer Register |

PERIPH_RNPR |

R/W |

0 |

| 0x114 |

Receive Next Counter Register |

PERIPH_RNCR |

R/W |

0 |

| 0x118 |

Transmit Next Pointer Register |

PERIPH_TNPR |

R/W |

0 |

| 0x11C |

Transmit Next Counter Register |

PERIPH_TNCR |

R/W |

0 |

| 0x120 |

PDC Transfer Control Register |

PERIPH_PTCR |

W |

- |

| 0x124 |

PDC Transfer Status Register |

PERIPH_PTSR |

R |

0 |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą┐čĆąĖčüčéą░ą▓ą║ą░ PERIPH ąĘą░ą╝ąĄąĮčÅąĄčéčüčÅ ąĮą░ ąĖą╝čÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░. ąÆčüąĄ 10 čĆąĄą│ąĖčüčéčĆąŠą▓ PDC ą┐čĆąĖą▓čÅąĘą░ąĮčŗ ą║ ąŠą▒ą╗ą░čüčéąĖ ą┐ą░ą╝čÅčéąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ čü ąŠą┤ąĮąĖą╝ ąĖ č鹥ą╝ ąČąĄ čüą╝ąĄčēąĄąĮąĖąĄą╝, ą║ąŠč鹊čĆąŠąĄ ąŠčéąĮąŠčüąĖčéčüčÅ ą║ čŹč鹊ą╝čā ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą╝čā čāčüčéčĆąŠą╣čüčéą▓čā. ąŁč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ą░ą┤čĆąĄčüą░ ą┤ą╗čÅ čĆąĄą│ąĖčüčéčĆąŠą▓ PDC čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ čüą╝ąĄčēąĄąĮąĖą╣ ąĮčāąČąĮąŠą│ąŠ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (DBGU, USART, SSC, SPI, MCI ąĖ čé. ą┤.).

PDC Receive Pointer Register (PERIPH_RPR). 32-ą▒ąĖčéąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ, ą║ąŠč鹊čĆčŗą╣ čāą║ą░ąĘčŗą▓ą░ąĄčé ąĮą░ ą░ą┤čĆąĄčü, ą║čāą┤ą░ ą▒čāą┤ąĄčé ąĘą░ą┐ąĖčüą░ąĮą░ čüą╗ąĄą┤čāčÄčēą░čÅ ą┐čĆąĖąĮąĖą╝ą░ąĄą╝ą░čÅ ą┐ąŠčĆčåąĖčÅ ą┤ą░ąĮąĮčŗčģ (RXPTR: Receive Pointer Address). ąöąŠčüčéčāą┐ąĄąĮ ąĖ ąĮą░ čćč鹥ąĮąĖąĄ, ąĖ ąĮą░ ąĘą░ą┐ąĖčüčī.

PDC Receive Counter Register (PERIPH_RCR). 16-ą▒ąĖčéąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ, ą▓ ą║ąŠč鹊čĆąŠą╝ čüąŠą┤ąĄčƹȹĖčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░ ąŠčüčéą░ą▓čłąĖčģčüčÅ ą┤ą╗čÅ ą┐čĆąĖąĄą╝ą░ ą┐ąŠčĆčåąĖą╣ ą┤ą░ąĮąĮčŗčģ (RXCTR: Receive Counter Value). ąöąŠčüčéčāą┐ąĄąĮ ąĖ ąĮą░ čćč鹥ąĮąĖąĄ, ąĖ ąĮą░ ąĘą░ą┐ąĖčüčī.

PDC Transmit Pointer Register (PERIPH_TPR). 32-ą▒ąĖčéąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ, ą║ąŠč鹊čĆčŗą╣ čāą║ą░ąĘčŗą▓ą░ąĄčé ąĮą░ ą░ą┤čĆąĄčü, ąŠčéą║čāą┤ą░ ą▒čāą┤ąĄčé ą┐čĆąŠčćąĖčéą░ąĮą░ čüą╗ąĄą┤čāčÄčēą░čÅ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ą░čÅ ą┐ąŠčĆčåąĖčÅ ą┤ą░ąĮąĮčŗčģ (TXPTR: Transmit Pointer Address). ąöąŠčüčéčāą┐ąĄąĮ ąĖ ąĮą░ čćč鹥ąĮąĖąĄ, ąĖ ąĮą░ ąĘą░ą┐ąĖčüčī.

PDC Transmit Counter Register (PERIPH_TCR). 16-ą▒ąĖčéąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ, ą▓ ą║ąŠč鹊čĆąŠą╝ čüąŠą┤ąĄčƹȹĖčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░ ąŠčüčéą░ą▓čłąĖčģčüčÅ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐ąŠčĆčåąĖą╣ ą┤ą░ąĮąĮčŗčģ (TXCTR: Transmit Counter Value). ąöąŠčüčéčāą┐ąĄąĮ ąĖ ąĮą░ čćč鹥ąĮąĖąĄ, ąĖ ąĮą░ ąĘą░ą┐ąĖčüčī. ąÜąŠą│ą┤ą░ ą┤ąŠčüčéąĖą│ą░ąĄčé ąĮčāą╗čÅ, č鹊 ą┐čĆąŠčåąĄčüčü ą┐ąĄčĆąĄą┤ą░čćąĖ č湥čĆąĄąĘ DMA ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ.

PDC Receive Next Pointer Register (PERIPH_RNPR). ąöąŠčüčéčāą┐ąĄąĮ ąĖ ąĮą░ čćč鹥ąĮąĖąĄ, ąĖ ąĮą░ ąĘą░ą┐ąĖčüčī. ąĀąĄą│ąĖčüčéčĆ čüąŠą┤ąĄčƹȹĖčé 32-ą▒ąĖčéąĮąŠąĄ ą┐ąŠą╗ąĄ RXNPTR: Receive Next Pointer Address. ąŁč鹊 ą░ą┤čĆąĄčü (čāą║ą░ąĘą░č鹥ą╗čī) ąĮą░ čüą╗ąĄą┤čāčÄčēąĖą╣ ą▒čāč乥čĆ, ą║ąŠč鹊čĆčŗą╣ ą▒čāą┤ąĄčé ą┤ą░ą╗ąĄąĄ ąĮą░ą┐ąŠą╗ąĮčÅčéčīčüčÅ ą┐čĆąĖąĮąĖą╝ą░ąĄą╝čŗą╝ąĖ ą┤ą░ąĮąĮčŗą╝ąĖ, ą║ąŠą│ą┤ą░ ąĘą░ą┐ąŠą╗ąĮąĖčéčüčÅ č鹥ą║čāčēąĖą╣ ą▒čāč乥čĆ.

PDC Receive Next Counter Register (PERIPH_RNCR). ąöąŠčüčéčāą┐ąĄąĮ ąĖ ąĮą░ čćč鹥ąĮąĖąĄ, ąĖ ąĮą░ ąĘą░ą┐ąĖčüčī. ąĀąĄą│ąĖčüčéčĆ čüąŠą┤ąĄčƹȹĖčé 16-ą▒ąĖčéąĮąŠąĄ ą┐ąŠą╗ąĄ RXNCR: Receive Next Counter Value. ąŁč鹊 ą░ą┤čĆąĄčü (čāą║ą░ąĘą░č鹥ą╗čī) ąĮą░ čüą╗ąĄą┤čāčÄčēąĖą╣ ą▒čāč乥čĆ, ą║ąŠč鹊čĆčŗą╣ ą▒čāą┤ąĄčé ą┤ą░ą╗ąĄąĄ ąĘą░ą┐ąŠą╗ąĮčÅčéčīčüčÅ, ą║ąŠą│ą┤ą░ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĖčéčüčÅ č鹥ą║čāčēąĖą╣ ą▒čāč乥čĆ.

PDC Transmit Next Pointer Register (PERIPH_TNPR). ąöąŠčüčéčāą┐ąĄąĮ ąĖ ąĮą░ čćč鹥ąĮąĖąĄ, ąĖ ąĮą░ ąĘą░ą┐ąĖčüčī. ąĀąĄą│ąĖčüčéčĆ čüąŠą┤ąĄčƹȹĖčé 32-ą▒ąĖčéąĮąŠąĄ ą┐ąŠą╗ąĄ TXNPTR: Transmit Next Pointer Address. ąŁč鹊 ą░ą┤čĆąĄčü (čāą║ą░ąĘą░č鹥ą╗čī) ąĮą░ čüą╗ąĄą┤čāčÄčēąĖą╣ ą▒čāč乥čĆ, ą║ąŠč鹊čĆčŗą╣ ą▒čāą┤ąĄčé ą┤ą░ą╗ąĄąĄ ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčīčüčÅ, ą║ąŠą│ą┤ą░ ąŠą┐čāčüč鹊賹ĖčéčüčÅ č鹥ą║čāčēąĖą╣ ą▒čāč乥čĆ.

PDC Transmit Next Counter Register (PERIPH_TNCR). ąöąŠčüčéčāą┐ąĄąĮ ąĖ ąĮą░ čćč鹥ąĮąĖąĄ, ąĖ ąĮą░ ąĘą░ą┐ąĖčüčī. ąĪąŠą┤ąĄčƹȹĖčé 16-ą▒ąĖčéąĮąŠąĄ ą┐ąŠą╗ąĄ čüč湥čéčćąĖą║ą░ TXNCR: Transmit Next Counter Value ą┤ą╗čÅ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ ą▒čāč乥čĆą░ ą┐ąĄčĆąĄą┤ą░čćąĖ.

PDC Transfer Control Register (PERIPH_PTCR). ąöąŠčüčéčāą┐ąĄąĮ č鹊ą╗čīą║ąŠ ąĮą░ ąĘą░ą┐ąĖčüčī. ąŁč鹊 čĆąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░č湥ą╣, čüąŠą┤ąĄčƹȹĖčé čüą╗ąĄą┤čāčÄčēąĖąĄ ą┐ąŠą╗čÅ:

ŌĆó RXTEN: Receiver Transfer Enable

0 = ąØąĄ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖčé čŹčäč乥ą║čéą░.

1 = ąĀą░ąĘčĆąĄčłą░ąĄčé ą▓čŗą┤ą░čćčā ąĘą░ą┐čĆąŠčüąŠą▓ PDC ą┐čĆąĖąĄą╝ąĮąĖą║ą░, ąĄčüą╗ąĖ ąĮąĄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé RXTDIS.

ŌĆó RXTDIS: Receiver Transfer Disable

0 = ąØąĄ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖčé čŹčäč乥ą║čéą░.

1 = ąŚą░ą┐čĆąĄčēą░ąĄčé ąĘą░ą┐čĆąŠčüčŗ PDC ąŠčé ą┐čĆąĖąĄą╝ąĮąĖą║ą░.

ŌĆó TXTEN: Transmitter Transfer Enable

0 = ąØąĄ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖčé čŹčäč乥ą║čéą░.

1 = ąĀą░ąĘčĆąĄčłą░ąĄčé ą▓čŗą┤ą░čćčā ąĘą░ą┐čĆąŠčüąŠą▓ PDC ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░.

ŌĆó TXTDIS: Transmitter Transfer Disable

0 = ąØąĄ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖčé čŹčäč乥ą║čéą░.

1 = ąŚą░ą┐čĆąĄčēą░ąĄčé ąĘą░ą┐čĆąŠčüčŗ PDC ąŠčé ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░.

PDC Transfer Status Register (PERIPH_PTSR). ąöąŠčüčéčāą┐ąĄąĮ č鹊ą╗čīą║ąŠ ąĮą░ čćč鹥ąĮąĖąĄ. ąĪąŠą┤ąĄčƹȹĖčé č鹊ą╗čīą║ąŠ 2 ą▒ąĖčéą░, ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčēąĖąĄ čĆą░ą▒ąŠč湥ąĄ čüąŠčüč鹊čÅąĮąĖąĄ PDC ą┤ą╗čÅ ą┤ą░ąĮąĮąŠą│ąŠ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░.

ŌĆó RXTEN: Receiver Transfer Enable

0 = ąŚą░ą┐čĆąŠčüčŗ PDC ąŠčé ą┐čĆąĖąĄą╝ąĮąĖą║ą░ ąĘą░ą┐čĆąĄčēąĄąĮčŗ.

1 = ąŚą░ą┐čĆąŠčüčŗ PDC ąŠčé ą┐čĆąĖąĄą╝ąĮąĖą║ą░ čĆą░ąĘčĆąĄčłąĄąĮčŗ.

ŌĆó TXTEN: Transmitter Transfer Enable

0 = ąŚą░ą┐čĆąŠčüčŗ PDC ąŠčé ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ ąĘą░ą┐čĆąĄčēąĄąĮčŗ.

1 = ąŚą░ą┐čĆąŠčüčŗ PDC ąŠčé ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ čĆą░ąĘčĆąĄčłąĄąĮčŗ.

[ą¤čĆąĖą╝ąĄčĆčŗ čĆą░ą▒ąŠčéčŗ c ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ AT91SAM7X č湥čĆąĄąĘ DMA]

ąÆ čŹč鹊ą╝ ą┐čĆąĖą╝ąĄčĆąĄ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ AT91SAM7X ą▓ąĄą┤ąĄčé ąŠą▒ą╝ąĄąĮ čü DSP Blackfin č湥čĆąĄąĘ ą┐ąŠčĆčé SSC čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ DMA. ą¦č鹊ą▒čŗ ąĮąĄ ąĘą░ą│čĆąŠą╝ąŠąČą┤ą░čéčī ą┐čĆąĖą╝ąĄčĆ, ąĮąĄą║ąŠč鹊čĆčŗąĄ ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ąŠą┐čāčēąĄąĮčŗ (ąĮą░ą┐čĆąĖą╝ąĄčĆ, ą▓čŗčćąĖčüą╗ąĄąĮąĖąĄ CRC16). ą¤čĆąĖąĄą╝ ąĖ ą┐ąĄčĆąĄą┤ą░čćą░ ąĘą░ą┐čāčüą║ą░čÄčéčüčÅ ą┐ąŠąŠč湥čĆąĄą┤ąĮąŠ. AT91SAM7X ąŠąČąĖą┤ą░ąĄčé ą┐ą░ą║ąĄčé DSP (ą┐ąŠčüč鹊čÅąĮąĮąŠ čĆą░ą▒ąŠčéą░ąĄčé ąĮą░ ą┐čĆąĖąĄą╝), ąĖ čüčĆą░ąĘčā ą┐ąŠčüą╗ąĄ ą┐ąŠą╗čāč湥ąĮąĖčÅ ą┐ą░ą║ąĄčéą░ ą┐ąĄčĆąĄą║ą╗čÄčćą░ąĄčéčüčÅ ąĮą░ ą┐ąĄčĆąĄą┤ą░čćčā ąĖ ą▓čŗą┤ą░ąĄčé ąŠčéą▓ąĄčé. ąóą░ą║ą░čÅ ą╝ąŠą┤ąĄą╗čī ąŠą▒ą╝ąĄąĮą░ ą┤ą░ąĮąĮčŗą╝ąĖ ą▓čŗą▒čĆą░ąĮą░ ą┤ą╗čÅ čāą┐čĆąŠčēąĄąĮąĖčÅ ąŠčéą╗ą░ą┤ą║ąĖ ą┐čĆąŠč鹊ą║ąŠą╗ą░. ą¤ą░ą║ąĄčéčŗ ąĖ ąĮą░ ą┐čĆąĖąĄą╝ąĄ, ąĖ ąĮą░ ą┐ąĄčĆąĄą┤ą░č湥 ąĖą╝ąĄčÄčé ąŠą┤ąĖąĮą░ą║ąŠą▓čāčÄ čüčéčĆčāą║čéčāčĆčā ąĖ čĆą░ąĘą╝ąĄčĆ 560 ą▒ą░ą╣čé. ąÜą░ąČą┤čŗą╣ ą┐ą░ą║ąĄčé ą▓ ąĮą░čćą░ą╗ąĄ ąĖą╝ąĄąĄčé čüąĖąĮčģčĆąŠąĘą░ą│ąŠą╗ąŠą▓ąŠą║ ąĖąĘ 6 ą▒ą░ą╣čé 0xA5, ą▓ ą║ąŠąĮčåąĄ ą║ąŠąĮčéčĆąŠą╗čīąĮčāčÄ čüčāą╝ą╝čā CRC16 ąĖ ą╝ą░čĆą║ąĄčĆ ą║ąŠąĮčåą░ ą┐ą░ą║ąĄčéą░ ąĖąĘ 6 ą▒ą░ą╣čé 0xE6. ą× ąĮą░čćą░ą╗ąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ DSP ąŠą┐ąŠą▓ąĄčēą░ąĄčé čüą┐ąĄčåąĖą░ą╗čīąĮčŗą╝ ą╗ąŠą│ąĖč湥čüą║ąĖą╝ čüąĖą│ąĮą░ą╗ąŠą╝, ą┐ąŠ ą║ąŠč鹊čĆąŠą╝čā čüčĆą░ą▒ą░čéčŗą▓ą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ISR_INTdsp, ąĘą░ą┐čāčüą║ą░čÅ ą┐čĆąĖąĄą╝ąĮąĖą║ SSC. AT91SAM7X ąŠą┐ąŠą▓ąĄčēą░ąĄčé ąŠ ąĮą░čćą░ą╗ąĄ čüą▓ąŠąĄą╣ ą┐ąĄčĆąĄą┤ą░č湥 ą░ąĮą░ą╗ąŠą│ąĖčćąĮčŗą╝ čüąĖą│ąĮą░ą╗ąŠą╝ outINTarm. ąŚą┤ąĄčüčī ąŠą┐ąĖčüą░ąĮ č鹊ą╗čīą║ąŠ ąŠą┤ąĖąĮ ąĖąĘ ą▓ąŠąĘą╝ąŠąČąĮčŗčģ ą╝ąĮąŠą│ąŠčćąĖčüą╗ąĄąĮąĮčŗčģ ą▓ą░čĆąĖą░ąĮč鹊ą▓ ąŠčĆą│ą░ąĮąĖąĘą░čåąĖąĖ ąŠą▒ą╝ąĄąĮą░ ą┤ą░ąĮąĮčŗą╝ąĖ č湥čĆąĄąĘ SSC, ą┐ąŠčŹč鹊ą╝čā ąĮąĄ ąĮčāąČąĮąŠ ąĄą│ąŠ ą┐čĆąĖąĮąĖą╝ą░čéčī ą║ą░ą║ ą┤ąŠą│ą╝čā.

ą×ą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ ą▓čüą┐ąŠą╝ąŠą│ą░č鹥ą╗čīąĮčŗčģ čéąĖą┐ąŠą▓:

#define SSC_A5_LEN 6 /*čüąĖąĮčģčĆąŠą▒ą░ą╣čéčŗ ąĮą░čćą░ą╗ą░ 0xA5*/

#define SSC_CMD_LEN 2 /*ą║ąŠą┤ ą║ąŠą╝ą░ąĮą┤čŗ*/

#define SSC_SERVICE_LEN 32 /*čüąĄčĆą▓ąĖčüąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ*/

#define SSC_DATA_LEN 512

#define SSC_CRC_LEN 2

#define SSC_E6_LEN 6 /*čüąĖąĮčģčĆąŠą▒ą░ą╣čéčŗ ą║ąŠąĮčåą░ 0xE6*/

#define SSC_HEADER_LEN (SSC_A5_LEN+SSC_CMD_LEN+SSC_SERVICE_LEN)

#define SSC_TAIL_LEN (2/*CRC*/+SSC_E6_LEN)

#define SSC_BLOCK_LEN (SSC_HEADER_LEN + SSC_DATA_LEN + SSC_TAIL_LEN)

#define SSC_BIT_PER_FRAME 32

#define FillSscHeader(buf) memset(buf, 0xA5, SSC_A5_LEN)

#define FillSscFooter(buf) memset(&(buf[SSC_BLOCK_LEN-SSC_E6_LEN]), 0xE6, SSC_E6_LEN)

//ą▒ąĖčéčŗ tSSC.flags

#define SSCRX_HANDLER_UPDATED (1 << 0) //ąŠą▒ąĮąŠą▓ą╗ąĄąĮ čģąĄąĮą┤ą╗ąĄčĆ ą┐čĆąĖąĄą╝ą░

#define SSCTX_HANDLER_UPDATED (1 << 1) //ąŠą▒ąĮąŠą▓ą╗ąĄąĮ čģąĄąĮą┤ą╗ąĄčĆ ą┐ąĄčĆąĄą┤ą░čćąĖ

#define SSCTX_PACKET_UPDATED (1 << 2) //ąŠą▒ąĮąŠą▓ąĖą╗čüčÅ ą▒čāč乥čĆ ą┐ąĄčĆąĄą┤ą░čćąĖ. ąŁč鹊 ąĘąĮą░čćąĖčé, čćč鹊 ą┐ąĄčĆąĄą┤ ąĘą░ą┐čāčüą║ąŠą╝ ą┐ąĄčĆąĄą┤ą░čćąĖ

// ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ ISR ą┤ąŠą╗ąČąĄąĮ ąŠą▒ąĮąŠą▓ąĖčéčī ą┤ą░ąĮąĮčŗąĄ ą▓ ą▒čāč乥čĆąĄ PDC (DMA).

#define SSCRX_CANDATA (1 << 3) //ąĄčüčéčī ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ CAN

#define SSCRX_NEWCANDATA (1 << 4) //ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ CAN ą┐čĆąĖčłą╗ąĖ č鹊ą╗čīą║ąŠ čćč鹊

#define SSCTX_UPDATE_DSP_RQ (1 << 5) //čüąĖą│ąĮą░ą╗ ą▓čŗąĘą▓ą░čéčī TXhandler, čćč鹊ą▒čŗ ą┐ąŠą┤ą│ąŠč鹊ą▓ąĖčéčī ąĮąŠą▓čŗąĄ ą┤ą░ąĮąĮčŗąĄ

// ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą╗čÅ DSP. ążą╗ą░ą│ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▓ ą╗čÄą▒ąŠą╝ ą╝ąĄčüč鹥

// ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ, ą░ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčéčüčÅ ąĖ čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ

// ą▓ DSPhandler (čåąĖą║ą╗ main).

#define SSCTX_DSP_PAUSE (1 << 6) //ą┐ą░čāąĘą░ ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ DSP

#define SSCTX_COMPLETED (1 << 7) //ą┐ąĄčĆąĄą┤ą░čćą░ ą┐ąŠą╗ąĮąŠčüčéčīčÄ ąĘą░ą▓ąĄčĆčłąĄąĮą░

typedef __packed struct _SSC

{

u8 pdcbufRX[SSC_BLOCK_LEN]; // ą▒čāč乥čĆ PDC (DMA) ą┐čĆąĖąĄą╝ą░

u8 pdcbufTX[SSC_BLOCK_LEN]; // ą▒čāč乥čĆ PDC (DMA) ą┐ąĄčĆąĄą┤ą░čćąĖ

u8 bufRX [SSC_BLOCK_LEN-(SSC_A5_LEN+SSC_E6_LEN)]; // ą▓čŗčģąŠą┤ąĮąŠą╣ ą▒čāč乥čĆ ą┐čĆąĖąĄą╝ą░

u8 bufTX [SSC_BLOCK_LEN-(SSC_A5_LEN+SSC_E6_LEN)]; // ą▓čŗčģąŠą┤ąĮąŠą╣ ą▒čāč乥čĆ ą┐ąĄčĆąĄą┤ą░čćąĖ

void (*RXhandler)(u8 idxSSCrx);

void (*TXhandler)(void);

u8 tail_detected; // čüąĖąĮčģčĆąŠą▒ą░ą╣čéčŗ ą║ąŠąĮčåą░ 0xE6 0xE6 0xE6 0xE6 0xE6 0xE6 ą┐čĆąŠčłą╗ąĖ

u8 txflags; // čäą╗ą░ą│ąĖ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ

u8 rxflags; // čäą╗ą░ą│ąĖ ą┤ą╗čÅ ą┐čĆąĖąĄą╝ą░

u32 rectimeout;

int reciv_shift;

tERRSSCcounters errcnt;

tSSCcounters cnt;

} tSSC;

typedef __packed struct _ERRSSCcounters

{

u32 missheader; // čüč湥čéčćąĖą║ ąĮąĄ ąĮą░ą╣ą┤ąĄąĮąĮčŗčģ ąĘą░ą│ąŠą╗ąŠą▓ą║ąŠą▓

u32 crc; // čüč湥čéčćąĖą║ ąŠčłąĖą▒ąŠą║ CRC

u32 timeout; // ąŠčłąĖą▒ą║ą░ čéą░ą╣ą╝ą░čāčéą░

}tERRSSCcounters;

typedef __packed struct _SSCcounters

{

u32 tx; // čüą║ąŠą╗čīą║ąŠ ą▒čŗą╗ąŠ ą┐ąĄčĆąĄą┤ą░čć

u32 rx; // čüą║ąŠą╗čīą║ąŠ ą▒čŗą╗ąŠ čāčüą┐ąĄčłąĮčŗčģ ą┐čĆąĖąĄą╝ąŠą▓

u32 intdsp;

u32 rxOK; // čüą║ąŠą╗čīą║ąŠ ą▒čŗą╗ąŠ čāčüą┐ąĄčłąĮčŗčģ ą┐čĆąĖąĄą╝ąŠą▓

}tSSCcounters;

typedef __packed struct _SSC

{

u8 pdcbufRX[SSC_BLOCK_LEN]; // ą▒čāč乥čĆ PDC (DMA) ą┐čĆąĖąĄą╝ą░

u8 pdcbufTX[SSC_BLOCK_LEN]; // ą▒čāč乥čĆ PDC (DMA) ą┐ąĄčĆąĄą┤ą░čćąĖ

u8 bufRX [SSC_BLOCK_LEN-(SSC_A5_LEN+SSC_E6_LEN)]; // ą▓čŗčģąŠą┤ąĮąŠą╣ ą▒čāč乥čĆ ą┐čĆąĖąĄą╝ą░

u8 bufTX [SSC_BLOCK_LEN-(SSC_A5_LEN+SSC_E6_LEN)]; // ą▓čŗčģąŠą┤ąĮąŠą╣ ą▒čāč乥čĆ ą┐ąĄčĆąĄą┤ą░čćąĖ

void (*RXhandler)(u8 idxSSCrx);

void (*TXhandler)(void);

u8 tail_detected; // čüąĖąĮčģčĆąŠą▒ą░ą╣čéčŗ ą║ąŠąĮčåą░ 0xE6 0xE6 0xE6 0xE6 0xE6 0xE6 ą┐čĆąŠčłą╗ąĖ

u8 txflags; // čäą╗ą░ą│ąĖ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ

u8 rxflags; // čäą╗ą░ą│ąĖ ą┤ą╗čÅ ą┐čĆąĖąĄą╝ą░

u32 rectimeout;

int reciv_shift;

tERRSSCcounters errcnt;

tSSCcounters cnt;

} tSSC;

//ąŠą▒čēą░čÅ čüčģąĄą╝ą░ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ąŠą│ąŠ ą▒ą╗ąŠą║ą░, ą▓čüąĄą│ąŠ 6+546+6 = 558 ą▒ą░ą╣čé

typedef __packed struct _TRawBlock

{

//u8 A5[6]; //0xA5 0xA5 0xA5 0xA5 0xA5 0xA5

u16 cmd; //ą║ąŠą┤ ą║ąŠą╝ą░ąĮą┤čŗ

u8 serv[32]; //čüąĄčĆą▓ąĖčüąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ, ą║ąŠč鹊čĆčŗąĄ ąĘą░ą▓ąĖčüčÅčé ąŠčé ą║ąŠą╝ą░ąĮą┤čŗ

u8 data[512]; //512 ą▒ą░ą╣čé ą┐ąŠą╗ąĄąĘąĮčŗčģ ą┤ą░ąĮąĮčŗčģ

u16 CRC16; //2 ą▒ą░ą╣čéą░ CRC

//u8 E6[6]; //0xE6 0xE6 0xE6 0xE6 0xE6 0xE6 čüąĖąĮčģčĆąŠą▒ą░ą╣čéčŗ ą║ąŠąĮčåą░

}TRawBlock;

extern tSSC vSSC; //čüą╗čāąČąĄą▒ąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┐ąŠčĆčéą░ SSC

ą×ą▒čēąĖąĄ ą┐ąĄčĆąĄą╝ąĄąĮąĮčŗąĄ (ą▒čāč乥čĆčŗ ą┐čĆąĖąĄą╝ą░ ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ, čüčéą░čéąĖčüčéąĖą║ą░ ąĖ čé. ą┐.), ą▓čüą┐ąŠą╝ąŠą│ą░č鹥ą╗čīąĮčŗąĄ ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝čŗ:

tSSC vSSC; //čüą╗čāąČąĄą▒ąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┐ąŠčĆčéą░ SSC

void FillSscHeader (u8 *buf)

{

memset(buf, 0xA5, SSC_A5_LEN);

}

void FillSscFooter (u8 *buf)

{

//čüčćąĖčéą░ąĄą╝ CRC

((TRawBlock*)buf)->CRC16 = CRC_START_VAL;

AddCRC16(&(buf[6]), 2+32+512, (u16*)&((TRawBlock*)buf)->CRC16);

//ąĘą░ą┐ąŠą╗ąĮčÅąĄą╝ čģą▓ąŠčüčé - čłąĄčüčéčī ą▒ą░ą╣čé 0xE6

memset(&(buf[SSC_BLOCK_LEN-SSC_E6_LEN]), 0xE6, SSC_E6_LEN);

}

//ą┐čĆąŠčåąĄą┤čāčĆą░ ąĘą░ą┐čāčüą║ą░ąĄčé ąŠčéą┐čĆą░ą▓ą║čā ą▒čāč乥čĆą░ vSSC.pdcbufTX

void SSCtransmit (void)

{

u16 donetimeout = 0;

FillSscHeader(vSSC.pdcbufTX);

FillSscFooter(vSSC.pdcbufTX);

//ąŚą░ą┐čāčüčéąĖą╝ ą┐ąĄčĆąĄą┤ą░čćčā.

while (!vSSC.txdone)

{

donetimeout++;

if (donetimeout > 20000)

vSSC.txdone = true;

}

//ą┤ą░ąĄą╝ čüąĖą│ąĮą░ą╗ ą┤ą╗čÅ DSP (čüą▒čĆą░čüčŗą▓ą░ąĄą╝ ą▓ 0)

PIO_Configure(&outINTarm, 1);

vSSC.txdone = false;

#if (SSC_BIT_PER_FRAME < = 8)

SSC_WriteBuffer(AT91C_BASE_SSC, (void *) vSSC.pdcbufTX, SSC_BLOCK_LEN);

#elif (SSC_BIT_PER_FRAME < = 16)

SSC_WriteBuffer(AT91C_BASE_SSC, (void *) vSSC.pdcbufTX, SSC_BLOCK_LEN/2);

#elif (SSC_BIT_PER_FRAME < = 32)

SSC_WriteBuffer(AT91C_BASE_SSC, (void *) vSSC.pdcbufTX, SSC_BLOCK_LEN/4);

#else

#error "SSC_BIT_PER_FRAME invalid"

#endif

//čĆą░ąĘčĆąĄčłąĖą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖčÄ ą┐ąĄčĆąĄą┤ą░čćąĖ

SSC_EnableInterrupts(AT91C_BASE_SSC, AT91C_SSC_TXBUFE);

//čĆą░ąĘčĆąĄčłą░ąĄą╝ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║

SSC_EnableTransmitter(AT91C_BASE_SSC);

vSSC.cnt.tx++;

}

void setSSChandlers (void rx(void), void tx(void))

{

vSSC.RXhandler = rx;

vSSC.TXhandler = tx;

}

ąÜąŠą┤ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ SSC:

void ConfigureSSC (u32 baudrate)

{

//ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠčé čüąĖą│ąĮą░ą╗ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ ąŠčé DSP

PIO_EnableIt(&inINTdsp);

//čüą▒čĆą░čüčŗą▓ą░ąĄą╝ ą┐ąĄčĆąĄą╝ąĄąĮąĮčŗąĄ SSC

vSSC.cnt.tx = 0;

vSSC.cnt.rx = 0;

vSSC.cnt.rxOK = 0;

vSSC.tail_detected = false;

vSSC.txflags = SSCTX_COMPLETED;

vSSC.rxflags = 0;

vSSC.errcnt.missheader = 0;

vSSC.errcnt.crc = 0;

vSSC.errcnt.timeout = 0;

vSSC.rectimeout = 0;

vSSC.reciv_shift = 0;

memset(vSSC.pdcbufRX, 0, SSC_BLOCK_LEN);

memset(vSSC.bufRX, 0, SSC_BLOCK_LEN);

FillSscHeader(vSSC.pdcbufTX);

FillSscFooter(vSSC.pdcbufTX);

//ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝ ąĮąŠąČą║ąĖ čā SSC

PIO_Configure(SSC_pins, PIO_LISTSIZE(SSC_pins));

SSC_Configure(AT91C_BASE_SSC,

AT91C_ID_SSC,

baudrate,

BOARD_MCK);

//ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ ąĖ ą┐čĆąĖąĄą╝ąĮąĖą║:

SSC_ConfigureTransmitter(AT91C_BASE_SSC,

(AT91C_SSC_CKS_DIV | AT91C_SSC_CKO_CONTINOUS | AT91C_SSC_START_FALL_RF |

SSC_STTDLY(0) | SSC_PERIOD(33) | AT91C_SSC_CKI),

(SSC_DATLEN(SSC_BIT_PER_FRAME) | SSC_DATNB(1) | SSC_FSLEN(1) | AT91C_SSC_FSOS_POSITIVE));

SSC_ConfigureReceiver(AT91C_BASE_SSC,

(AT91C_SSC_CKS_RK | AT91C_SSC_START_FALL_RF | SSC_STTDLY(0) | AT91C_SSC_CKI),

(SSC_DATLEN(SSC_BIT_PER_FRAME) | SSC_DATNB(1) | SSC_FSLEN(1)));

//ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝ ąĖ čĆą░ąĘčĆąĄčłą░ąĄą╝ SSC interrupt

AIC_ConfigureIT(AT91C_ID_SSC, AT91C_AIC_PRIOR_LOWEST+2, ISR_Ssc);

AIC_EnableIT(AT91C_ID_SSC);

}

ą×ą▒čĆą░ą▒ąŠčéčćąĖą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣:

//------------------------------------------------------------------------------

/// Interrupt handler ą┤ą╗čÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠčé DSP (ą┐ąĄčĆąĄčģąŠą┤ ą▓ ąĮąŠą╗ąĖą║ čüąĖą│ąĮą░ą╗ąĖąĘąĖčĆčāąĄčé

/// ąŠ ąĮą░čćą░ą╗ąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ).

//------------------------------------------------------------------------------

void ISR_INTdsp (void)

{

if (!PIO_Get(&inINTdsp))

{

vSSC.cnt.intdsp++;

//ąØą░čüčéčĆąŠąĖą╝ ą┐čĆąĖąĄą╝

AT91C_BASE_SSC->SSC_RCR = 0;

#if (SSC_BIT_PER_FRAME < = 8)

SSC_ReadBuffer(AT91C_BASE_SSC, vSSC.pdcbufRX, SSC_BLOCK_LEN);

#elif (SSC_BIT_PER_FRAME < = 16)

SSC_ReadBuffer(AT91C_BASE_SSC, vSSC.pdcbufRX, SSC_BLOCK_LEN/2);

#elif (SSC_BIT_PER_FRAME < = 32)

SSC_ReadBuffer(AT91C_BASE_SSC, vSSC.pdcbufRX, SSC_BLOCK_LEN/4);

#else

#error "SSC_BIT_PER_FRAME invalid"

#endif

SSC_EnableReceiver(AT91C_BASE_SSC);

SSC_EnableInterrupts(AT91C_BASE_SSC, AT91C_SSC_RXBUFF);

}

}

//------------------------------------------------------------------------------

/// Interrupt handler for the SSC. ąĪčĆą░ą▒ą░čéčŗą▓ą░ąĄčé ąĮą░ čüąŠą▒čŗčéąĖčÅ ąŠą║ąŠąĮčćą░ąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ,

/// ąŠą║ąŠąĮčćą░ąĮąĖčÅ ą┐čĆąĖąĄą╝ą░. ąĪąĖą│ąĮą░ą╗ąĖąĘąĖčĆčāąĄčé ąŠą▒ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ.

//------------------------------------------------------------------------------

void ISR_Ssc(void)

{

unsigned int status = AT91C_BASE_SSC->SSC_SR;

u16 RX_RECV_CRC, RX_CALC_CRC;

TDspAnsw *dspAnsw;

u16 *pCnt;

u32 rxidx;

if ((status & AT91C_SSC_TXBUFE)/* ą▒čāč乥čĆ DMA ą┐čāčüčé */ &&

(status & AT91C_SSC_TXENA)/* ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ ą▓ą║ą╗čÄč湥ąĮ */)

{

// ą¤ąĄčĆąĄą┤ą░čćą░ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ PDC ąĘą░ą║ąŠąĮč湥ąĮą░

SSC_DisableInterrupts(AT91C_BASE_SSC, AT91C_SSC_ENDTX | AT91C_SSC_TXBUFE);

AT91C_BASE_SSC->SSC_PTCR = AT91C_PDC_TXTDIS;

//ąČą┤ąĄą╝, ą║ąŠą│ą┤ą░ ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ čäčĆąĄą╣ą╝ ą▓čŗčüą║ąŠčćąĖčé ąĖąĘ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░

while (!(AT91C_BASE_SSC->SSC_SR & AT91C_SSC_TXEMPTY));

//čĆą░ąĮčīčłąĄ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ą╗ąĖ ą▓ 1, ą░ č鹥ą┐ąĄčĆčī ą┤ąĄą╗ą░ąĄą╝ ą▓čŗą▓ąŠą┤ PIN_PB23_INTARM_INPUT ą▓čģąŠą┤ąŠą╝

// čü ąĮą░ą│čĆčāąĘąŠčćąĮčŗą╝ čĆąĄąĘąĖčüč鹊čĆąŠą╝, čćč鹊 ą┤ąĄą╗ą░ąĄčé č鹊 ąČąĄ čüą░ą╝ąŠąĄ.

PIO_Configure(&inINTarm, 1);

SSC_DisableTransmitter(AT91C_BASE_SSC);

vSSC.txflags |= SSCTX_COMPLETED;

}

if ((status & AT91C_SSC_RXBUFF/* ą▒čāč乥čĆ DMA ą┐ąŠą╗ąŠąĮ */) &&

(status & AT91C_SSC_RXENA/* ą┐čĆąĖąĄą╝ąĮąĖą║ ą▓ą║ą╗čÄč湥ąĮ */))

{

// ą¤čĆąĖąĄą╝ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ PDC ąĘą░ą║ąŠąĮč湥ąĮ

SSC_DisableInterrupts(AT91C_BASE_SSC, AT91C_SSC_RXBUFF);

AT91C_BASE_SSC->SSC_PTCR = AT91C_PDC_RXTDIS;

SSC_DisableReceiver(AT91C_BASE_SSC);

vSSC.cnt.rx++;

///////////////////////////////////////////////////

// ą×ą▒čĆą░ą▒ąŠčéą║ą░ ą┐čĆąĖčłąĄą┤čłąĄą│ąŠ ą┐ą░ą║ąĄčéą░. ą¤čĆąŠą▓ąĄčĆąĖą╝, čćč鹊 ą┐čĆąĖąĮčÅą╗ąĖ,

// ąĖčēąĄą╝ ą▓ ą▒čāč乥čĆąĄ ąĮą░čćą░ą╗ąŠ ą┤ą░ąĮąĮčŗčģ ą┐ąŠ čüąĖąĮčģčĆąŠą▒ą░ą╣čéą░ą╝.

rxidx = 0;

while (rxidx<20)

{

if (vSSC.pdcbufRX[rxidx++] == 0xA5)

break;

}

while (rxidx<20)

{

if (vSSC.pdcbufRX[rxidx++] != 0xA5)

break;

}

if (rxidx>=20)

{

//ąĮąĄ ąĮą░ą╣ą┤ąĄąĮ ą║ąŠąĮąĄčå čüąĖąĮčģčĆąŠąĘą░ą│ąŠą╗ąŠą▓ą║ą░ (0xA5) ą▓ ą┐čĆąĄą┤ąĄą╗ą░čģ ą┐ąĄčĆą▓čŗčģ 10 ą▒ą░ą╣čé

vSSC.errcnt.missheader++;

return;

}

//ąĘą░ą│ąŠą╗ąŠą▓ąŠą║ čüčéą░čĆčéą░ ąĮą░ą╣ą┤ąĄąĮ

rxidx--;

//rxidx čāą║ą░ąĘčŗą▓ą░ąĄčé ąĮą░ ą║ąŠą╝ą░ąĮą┤čā cmd

vSSC.reciv_shift = rxidx - SSC_A5_LEN;

//ą┐čĆąŠą▓ąĄčĆąĖą╝ CRC, ą┤ą╗čÅ č湥ą│ąŠ ą║ąŠą┐ąĖčĆčāąĄą╝ ą▓ RX_RECV_CRC ą┐čĆąĖąĮčÅčéčāčÄ CRC

memcpy(&RX_RECV_CRC, &(vSSC.pdcbufRX[rxidx + (SSC_CMD_LEN+SSC_SERVICE_LEN+SSC_DATA_LEN)]), 2);

RX_CALC_CRC = CRC_START_VAL;

AddCRC16(&(vSSC.pdcbufRX[rxidx]), (SSC_CMD_LEN+SSC_SERVICE_LEN+SSC_DATA_LEN), &RX_CALC_CRC);

if (RX_RECV_CRC != RX_CALC_CRC)

{

vSSC.errcnt.crc++;

return;

}

else

{

///////////////////////////////////////////////////

// ąÜąŠąĮąĄčå ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĖčłąĄą┤čłąĄą│ąŠ ą┐ą░ą║ąĄčéą░.

// ąĢčüą╗ąĖ ą╝čŗ ąĘą┤ąĄčüčī, ąĘąĮą░čćąĖčé čāčüą┐ąĄčłąĮąŠ ąĘą░ą▓ąĄčĆčłąĄąĮ ą┐čĆąĖąĄą╝.

memcpy(vSSC.bufRX, vSSC.pdcbufRX+rxidx, (SSC_BLOCK_LEN-(SSC_A5_LEN+SSC_E6_LEN)));

dspAnsw = (TDspAnsw*)vSSC.bufRX;

dspstate.rxcmd = dspAnsw->cmd;

vSSC.cnt.rxOK++;

((TRawBlock*)vSSC.bufRX)->CRC16 = CRC_START_VAL;

AddCRC16(&(vSSC.bufRX[6]), 2+32+512, (u16*)&((TRawBlock*)vSSC.bufRX)->CRC16);

}

///////////////////////////////////////////////////

// ą×čéą▓ąĄčéąĮą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░ ą▓ čüč鹊čĆąŠąĮčā DSP

if (vSSC.txflags & SSCTX_PACKET_UPDATED)

{

FillSscHeader(vSSC.pdcbufTX);

memcpy(vSSC.pdcbufTX+SSC_A5_LEN, vSSC.bufTX, SSC_BLOCK_LEN-(SSC_A5_LEN+SSC_E6_LEN));

FillSscFooter(vSSC.pdcbufTX);

vSSC.txflags &= ~SSCTX_PACKET_UPDATED;

}

if ((0==(vSSC.txflags & SSCTX_HANDLER_UPDATED)) && (0!=pdcTXpacket->cmd))

{

SSCtransmit();

}

}/* if: ą▒čāč乥čĆ DMA ą┐ąŠą╗ąŠąĮ ąĖ ą┐čĆąĖąĄą╝ąĮąĖą║ ą▓ą║ą╗čÄč湥ąĮ */

}

ąÆ čŹč鹊ą╝ ą┐čĆąĖą╝ąĄčĆąĄ 8-ą▒ąĖčéąĮčŗąĄ ą┐ąŠčüčŗą╗ą║ąĖ ą┤ą░ąĮąĮčŗčģ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ąĄą┤ąĖąĮčŗą╝ ą▒ą╗ąŠą║ąŠą╝ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ DMA. ą¤čĆąĄąĖą╝čāčēąĄčüčéą▓ąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ DMA ą▓ čüą╗ąĄą┤čāčÄčēąĄą╝: ą╝ąŠąČąĮąŠ ąĮą░ą┐ąĖčüą░čéčī ą┐čĆąŠą│čĆą░ą╝ą╝čā čéą░ą║, čćč鹊 ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ čüą╝ąŠąČąĄčé ąĘą░ąĮąĖą╝ą░čéčīčüčÅ ą┤čĆčāą│ąŠą╣ čĆą░ą▒ąŠč鹊ą╣, čćč鹊 ąĘąĮą░čćąĖč鹥ą╗čīąĮąŠ čāčüą║ąŠčĆčÅąĄčé ąŠą▒čĆą░ą▒ąŠčéą║čā ą┤ą░ąĮąĮčŗčģ. ąÆ čŹč鹊ą╝ ą┐čĆąĖą╝ąĄčĆąĄ ą┤ą╗čÅ čāą┐čĆąŠčēąĄąĮąĖčÅ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┐čĆąŠčüč鹊 ąŠąČąĖą┤ą░ąĮąĖąĄ ąŠą║ąŠąĮčćą░ąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐čāč鹥ą╝ ąŠą┐čĆąŠčüą░ ą▒ąĖčéą░ čüčéą░čéčāčüą░ SPI_SR.TXBUFE, čģąŠčéčÅ ą▓ čĆąĄą░ą╗čīąĮąŠą╣ ąĘą░ą┤ą░č湥 ą╗čāčćčłąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┤ą╗čÅ čüąĖą│ąĮą░ą╗ąĖąĘą░čåąĖąĖ ąŠą▒ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▒ą╗ąŠą║ą░ ą┤ą░ąĮąĮčŗčģ. ąÆčŗą▒ąŠčĆą║ą░ slave-čāčüčéčĆąŠą╣čüčéą▓ą░ ą╝ąŠąČąĄčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčīčüčÅ ą║ą░ą║ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ, čéą░ą║ ąĖ ą░ą┐ą┐ą░čĆą░čéąĮąŠ (ą┐ąŠ čäą╗ą░ąČą║čā useCSHW).

//ąĮą░ą▒ąŠčĆ ąĮąŠąČąĄą║ SPI ą┤ą╗čÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠą│ąŠ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą▓čŗą▒ąŠčĆą║ąŠą╣

#define PINS_GAMEDUINO_CSHW PIN_SPI0_MISO, PIN_SPI0_MOSI, PIN_SPI0_SPCK, PIN_SPI0_CSHW

const Pin pinsGAMEDUINO_CSHW[] = {PINS_GAMEDUINO_CSHW};

//ąĮą░ą▒ąŠčĆ ąĮąŠąČąĄą║ SPI ą┤ą╗čÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą▓čŗą▒ąŠčĆą║ąŠą╣

#define PINS_GAMEDUINO_CSSW PIN_SPI0_MISO, PIN_SPI0_MOSI, PIN_SPI0_SPCK, PIN_SPI0_CSSW

const Pin pinsGAMEDUINO_CSSW[] = {PINS_GAMEDUINO_CSSW};

//ą▒čāč乥čĆ DMA ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ

u32 TXSPIDMAbuf[(4+ZXSPECTRUM_SCREEN_SIZE)];

void init_spi_Gameduino (void)

{

if (useCSHW)

PIO_Configure(pinsGAMEDUINO_CSHW, PIO_LISTSIZE(pinsGAMEDUINO_CSHW));

else

PIO_Configure(pinsGAMEDUINO_CSSW, PIO_LISTSIZE(pinsGAMEDUINO_CSSW));

AT91C_BASE_PMC->PMC_PCER = ( 1 << GAMEDUINO_ID_SPI );

// ąŚą░ą┐čĆąĄčé SPI

GAMEDUINO_BASE_SPI->SPI_CR = AT91C_SPI_SPIDIS;

// ąśąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ PDC (DMA) ą┤ą╗čÅ SPI:

// ąĘą░ą┐čĆąĄčé PDC TX ąĖ RX

GAMEDUINO_BASE_SPI->SPI_PTCR = AT91C_PDC_TXTDIS | AT91C_PDC_RXTDIS;

// ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ čüč湥čéčćąĖą║ąŠą▓ ąĖ čāą║ą░ąĘą░č鹥ą╗ąĄą╣ ąĮą░ ą▒čāč乥čĆ ą▓ 0

// "čüą╗ąĄą┤čāčÄčēąĖą╣" ą▒čāč乥čĆ TX

GAMEDUINO_BASE_SPI->SPI_TNPR = 0;

GAMEDUINO_BASE_SPI->SPI_TNCR = 0;

// "čüą╗ąĄą┤čāčÄčēąĖą╣" ą▒čāč乥čĆ RX

GAMEDUINO_BASE_SPI->SPI_RNPR = 0;

GAMEDUINO_BASE_SPI->SPI_RNCR = 0;

// ą▒čāč乥čĆ TX

GAMEDUINO_BASE_SPI->SPI_TPR = 0;

GAMEDUINO_BASE_SPI->SPI_TCR = 0;

// ą▒čāč乥čĆ RX

GAMEDUINO_BASE_SPI->SPI_RPR = 0;

GAMEDUINO_BASE_SPI->SPI_RCR = 0;

// ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ SPI ąĖ ąĄą│ąŠ čüą▒čĆąŠčü

// "ąÜą░ąČąĄčéčüčÅ, čćč鹊 čā ą╝ą░čłąĖąĮčŗ čüąŠčüč鹊čÅąĮąĖą╣ ą┤ą╗čÅ revB ą▓ąĄčĆčüąĖąĖ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī

// 2 ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗčģ čüą▒čĆąŠčüą░ SPI, čüą▒čĆąŠčü ą┐čĆąŠčłąĄą╗ čāčüą┐ąĄčłąĮąŠ."

GAMEDUINO_BASE_SPI->SPI_CR = AT91C_SPI_SWRST;

GAMEDUINO_BASE_SPI->SPI_CR = AT91C_SPI_SWRST;

GAMEDUINO_BASE_SPI->SPI_CR = AT91C_SPI_SPIEN;

// ąĀąĄąČąĖą╝ SPI: master, FDIV=0, ąĘą░ą┐čĆąĄčé ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ąŠčłąĖą▒ą║ąĖ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ.

GAMEDUINO_BASE_SPI->SPI_MR = AT91C_SPI_MSTR | AT91C_SPI_MODFDIS;

// ąŻčüčéą░ąĮąŠą▓ą║ą░ čĆąĄą│ąĖčüčéčĆą░ ą▓čŗą▒ąŠčĆą║ąĖ čćąĖą┐ą░:

// 8 ą▒ąĖčé ąĮą░ ą┐ąĄčĆąĄą┤ą░čćčā, CPOL=1, ClockPhase=0, DLYBCT = 0

GAMEDUINO_BASE_SPI->SPI_CSR[SPI_CSR_NUM] = AT91C_SPI_CPOL | AT91C_SPI_BITS_8;

// ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ čĆą░ą▒ąŠčéčŗ SPI

GAMEDUINO_BASE_SPI->SPI_CR = AT91C_SPI_SPIEN;

}

void send_block_to_Gameduino (void *buf, int bytes)

{

int idx;

init_spi_Gameduino();

LED(1);

if (!useCSHW)

PIO_Clear(&pinsGAMEDUINO_CSSW[3]);

//ą┐ąĄčĆąĄą┤ą░čćą░

if (GAMEDUINO_BASE_SPI->SPI_MR & AT91C_SPI_PS)

{

//ą¤ąŠą┤ą│ąŠč鹊ą▓ą║ą░ ą▒čāč乥čĆą░ DMA, ąĄčüą╗ąĖ SPI_MR.PS=1 (čĆąĄąČąĖą╝ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą╣ ą┐ąĄčĆąĖč乥čĆąĖąĖ)

for (idx=0; idx<(bytes-1); idx++)

{

TXSPIDMAbuf[idx] = ((u8*)buf)[idx];

}

TXSPIDMAbuf[idx] = ((u8*)buf)[idx] | AT91C_SPI_LASTXFER;

while (0 == SPI_WriteBuffer(GAMEDUINO_BASE_SPI, TXSPIDMAbuf, bytes));

}

else

while (0 == SPI_WriteBuffer(GAMEDUINO_BASE_SPI, buf, bytes));

//ąŠąČąĖą┤ą░ąĮąĖąĄ ąŠą║ąŠąĮčćą░ąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ

while (0 == (GAMEDUINO_BASE_SPI->SPI_SR & AT91C_SPI_TXBUFE));

if (!useCSHW)

PIO_Set(&pinsGAMEDUINO_CSSW[3]);

LED(0);

close_spi_Gameduino();

}

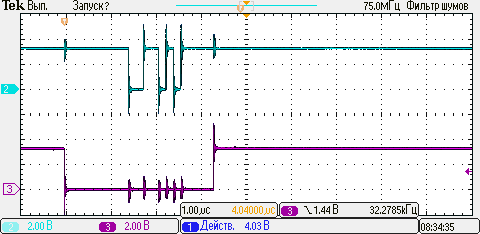

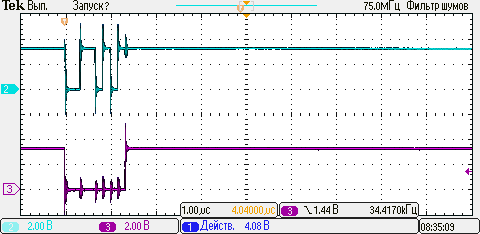

ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ą▓ čüą╗čāčćą░ąĄ ą▓čŗą▒ąŠčĆą░ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą╣ ą┐ąĄčĆąĖč乥čĆąĖąĖ SPI_MR.PS=1 ą┤ą╗čÅ DMA ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čüą┐ąĄčåąĖą░ą╗čīąĮąŠ ą┐ąŠą┤ą│ąŠč鹊ą▓ą╗ąĄąĮąĮčŗą╣ 32-ą▒ąĖčéąĮčŗą╣ ą▒čāč乥čĆ. ąÆ ą┐ąŠčüą╗ąĄą┤ąĮčÄčÄ čÅč湥ą╣ą║čā ą▒čāč乥čĆą░ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ ą┐čĆąĖąĘąĮą░ą║ SPI_TDR.LASTXFER, ą║ąŠč鹊čĆčŗą╣ ąĮčāąČąĄąĮ ą┤ą╗čÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠą│ąŠ ą▓ąŠąĘą▓čĆą░čéą░ čüąĖą│ąĮą░ą╗ą░ ą▓čŗą▒ąŠčĆą║ąĖ ą▓ ąĮąĄą░ą║čéąĖą▓ąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ. ąØą░ ą┐ąĄčĆą▓ąŠą╣ ąŠčüčåąĖą╗ą╗ąŠą│čĆą░ą╝ą╝ąĄ DMA čĆą░ą▒ąŠčéą░ąĄčé čü ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ č乊čĆą╝ąĖčĆčāąĄą╝ąŠą╣ ą▓čŗą▒ąŠčĆą║ąŠą╣, ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ 8-ą▒ąĖčéąĮčŗą╣ ą▒čāč乥čĆ DMA (ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą▒ą╗ąŠą║ ą┤ą░ąĮąĮčŗčģ ąĖąĘ 4 ą▒ą░ą╣čé 00 FF 0F 0F):

ąØą░ ą▓č鹊čĆąŠą╣ ąŠčüčåąĖą╗ą╗ąŠą│čĆą░ą╝ą╝ąĄ DMA čĆą░ą▒ąŠčéą░ąĄčé ą▓ą╝ąĄčüč鹥 čü ą░ą┐ą┐ą░čĆą░čéąĮąŠ č乊čĆą╝ąĖčĆčāąĄą╝ąŠą╣ ą▓čŗą▒ąŠčĆą║ąŠą╣, ą┤ą╗čÅ čŹč鹊ą│ąŠ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ 32-ą▒ąĖčéąĮčŗą╣ ą▒čāč乥čĆ DMA (ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą▒ą╗ąŠą║ ą┤ą░ąĮąĮčŗčģ ąĖąĘ 4 ą▒ą░ą╣čé 00 FF 0F 0F):

ą¤ąŠčüą║ąŠą╗čīą║čā ąĖ ą┐čĆąĖąĄą╝, ąĖ ą┐ąĄčĆąĄą┤ą░čćą░ SPI čĆą░ą▒ąŠčéą░čÄčé ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ, č鹊 ą▓čüąĄ, čćč鹊 ąĮčāąČąĮąŠ čüą┤ąĄą╗ą░čéčī ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ/ą┐čĆąĖąĄą╝ą░ č湥čĆąĄąĘ DMA, čŹč鹊 ą┐ąŠą┤ą│ąŠč鹊ą▓ąĖčéčī 2 ą▒čāč乥čĆą░ (ąŠą┤ąĖąĮ ą┤ą╗čÅ ą┐čĆąĖąĄą╝ą░, ą┤čĆčāą│ąŠą╣ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ), ąĘą░ą│čĆčāąĘąĖčéčī čĆąĄą│ąĖčüčéčĆčŗ DMA ąĖ ą▓ąĘą▓ąĄčüčéąĖ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ą▒ąĖčéčŗ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĖąĄą╝ą░ ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ. ąÆčüąĄ ą▓ąĄčüčī ąŠčüčéą░ą╗čīąĮąŠą╣ ą║ąŠą┤ ąŠčüčéą░ąĄčéčüčÅ ą▒ąĄąĘ ąĖąĘą╝ąĄąĮąĄąĮąĖą╣.

//////////////////////////////////////////////////////////////////////////

// ą¤ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ąĘą░ą┐čāčüą║ą░ąĄčé ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čćčā ąĖ ą┐čĆąĖąĄą╝ č湥čĆąĄąĘ DMA.

// ąĢčüą╗ąĖ ą┐ąĄčĆąĄą┤ą░čćą░ čāčüą┐ąĄčłąĮąŠ ąĘą░ą┐čāčēąĄąĮą░, č鹊 ą▒čāą┤ąĄčé ą▓ąŠąĘą▓čĆą░čēąĄąĮąŠ 1, ąĖąĮą░č湥 (ąĄčüą╗ąĖ

// ą▓čüąĄ ą▒ą░ąĮą║ąĖ ąĘą░ąĮčÅčéčŗ) ą▒čāą┤ąĄčé ą▓ąŠąĘą▓čĆą░čēąĄąĮ 0.

unsigned char SPI_RWbuf(AT91S_SPI *spi,

void *rxbuf, void *txbuf,

unsigned int length)

{

#if !defined(CHIP_SPI_DMA)

// ą¤čĆąŠą▓ąĄčĆą║ą░ ą┤ąŠčüčéčāą┐ąĮąŠčüčéąĖ ą┐ąĄčĆą▓ąŠą│ąŠ ą▒ą░ąĮą║ą░

if (spi->SPI_TCR == 0)

{

spi->SPI_RPR = (unsigned int) rxbuf;

spi->SPI_TPR = (unsigned int) txbuf;

spi->SPI_RCR = length;

spi->SPI_TCR = length;

spi->SPI_PTCR = (AT91C_PDC_RXTEN | AT91C_PDC_TXTEN);

return 1;

}

// ą¤čĆąŠą▓ąĄčĆą║ą░ ą┤ąŠčüčéčāą┐ąĮąŠčüčéąĖ ą▓č鹊čĆąŠą│ąŠ ą▒ą░ąĮą║ą░

else if (spi->SPI_TNCR == 0)

{

spi->SPI_RNPR = (unsigned int) rxbuf;

spi->SPI_TNPR = (unsigned int) txbuf;

spi->SPI_RNCR = length;

spi->SPI_TNCR = length;

return 1;

}

#endif

// ąØąĄčé čüą▓ąŠą▒ąŠą┤ąĮčŗčģ ą▒ą░ąĮą║ąŠą▓

return 0;

}

[ąĪčüčŗą╗ą║ąĖ]

1. AT91SAM7X: čĆą░ą▒ąŠčéą░ čü ą┐ąŠčĆč鹊ą╝ SPI ą▓ čĆąĄąČąĖą╝ąĄ master. |