|

лњ ЛЇЛѓлЙл╣ ЛЂЛѓл░ЛѓЛїлх лЙл┐лИЛЂл░лйл░ Лђл░лиЛђл░л▒лЙЛѓл║л░ лйл░ л░л┐л┐л░Лђл░ЛѓЛЃЛђлх FPGA Gameduino [1] ЛЇл║Лђл░лйл░ л┐лЙл┐ЛЃл╗ЛЈЛђлйлЙл│лЙ лйлхл║лЙл│л┤л░ 8-л▒лИЛѓлйлЙл│лЙ л║лЙл╝л┐ЛїЛјЛѓлхЛђл░ ZX Spectrum.

[лдлИЛёЛђлЙл▓л░ЛЈ ЛЂЛЁлхл╝лЙЛѓлхЛЁлйлИл║л░ лИ ZX Spectrum]

лњлЙ л▓Лђлхл╝лхлйл░ ЛЂл▓лЙлхл│лЙ ЛЂлЙл▓лхЛѓЛЂл║лЙл│лЙ л┤лхЛѓЛЂЛѓл▓л░ л╝лйлх лЙЛЄлхлйЛї ЛЂлИл╗ЛїлйлЙ л┐лЙл▓лхлил╗лЙ л┐лЙлилйл░л║лЙл╝лИЛѓЛїЛЂЛЈ ЛЂ ЛєлИЛёЛђлЙл▓лЙл╣ ЛЂЛЁлхл╝лЙЛѓлхЛЁлйлИл║лЙл╣ л┐лЙ л╗л░л▒лЙЛђл░ЛѓлЙЛђлйлЙл╝ЛЃ л┐Лђл░л║ЛѓлИл║ЛЃл╝ЛЃ (лЙлй л┐ЛЃл▒л╗лИл║лЙл▓л░л╗ЛЂЛЈ л▓ лХЛЃЛђлйл░л╗лх "лал░л┤лИлЙ") лйл░ лЙЛЂлйлЙл▓лх 155 ЛЂлхЛђлИлИ ЛєлИЛёЛђлЙл▓ЛІЛЁ лИлйЛѓлхл│Лђл░л╗ЛїлйЛІЛЁ л╝лИл║ЛђлЙЛЂЛЁлхл╝. лћл╗ЛЈ л┐лЙл┤ЛђлЙЛЂЛѓл║л░ ЛЇЛѓлЙ л▒ЛІл╗ лил░ЛЁл▓л░ЛѓЛІл▓л░ЛјЛЅлИл╣ л╝лИЛђ л▒лхЛЂл║лЙлйлхЛЄлйЛІЛЁ л▓лЙлил╝лЙлХлйлЙЛЂЛѓлхл╣ л┐лЙ ЛЂлИлйЛѓлхлиЛЃ л░л▓ЛѓлЙл╝л░ЛѓлЙл▓. люлЙлХлйлЙ л▒ЛІл╗лЙ л┤л░лХлх ЛЂлЙл▒Лђл░ЛѓЛї ЛЂл▓лЙл╣ ЛЂлЙл▒ЛЂЛѓл▓лхлйлйЛІл╣ л▓ЛІЛЄлИЛЂл╗лИЛѓлхл╗Лї, лйлЙ... лйл░ л┐Лђл░л║ЛѓлИл║лх л╝лИл║ЛђлЙЛЂЛЁлхл╝ ЛЁл▓л░Лѓл░л╗лЙ Лђл░лил▓лх ЛЄЛѓлЙ л┐лЙл╝лЙЛђл│л░ЛѓЛї ЛЂл▓лхЛѓлЙл┤лИлЙл┤лЙл╝ лИ л┐лЙл│лЙлйЛЈЛѓЛї лйл░ 7-ЛЂлхл│л╝лхлйЛѓлйлЙл╝ лИлйл┤лИл║л░ЛѓлЙЛђлх лЙл▒Лђл░ЛѓлйЛІл╣ лЙЛѓЛЂЛЄлхЛѓ. люлИл║ЛђлЙЛЂЛЁлхл╝ЛІ, л░ лЙЛЂлЙл▒лхлйлйлЙ ЛєлИЛёЛђлЙл▓ЛІлх л▒ЛІл╗лИ ЛѓлЙл│л┤л░ лйл░ л▓лхЛЂ лилЙл╗лЙЛѓл░ лИ л┤лЙл▒ЛІл▓л░л╗лИЛЂЛї ЛЂлЙ ЛЂл▓л░л╗лЙл║, Лђл░лил▓л░л╗лЙл▓ Лєл▓лхЛѓлйлЙл│лЙ л╝лхЛѓл░л╗л╗л░ лИ лИли ЛЂЛѓл░ЛђлЙл╣ л░л┐л┐л░Лђл░ЛѓЛЃЛђЛІ. лъл┤лйл░л║лЙ лЙЛЅЛЃЛЅлхлйлИлх ЛѓлЙл│лЙ, ЛЄЛѓлЙ лйл░ ЛЃЛђлЙл▓лйлх л╗лЙл│лИЛЄлхЛЂл║лИЛЁ ЛЂЛЁлхл╝ л╝лЙлХлйлЙ ЛЂл┤лхл╗л░ЛѓЛї л▓ЛЂлх, ЛЄЛѓлЙ "л┤ЛЃЛѕл░ л┐лЙлХлхл╗л░лхЛѓ" ЛЂЛёлЙЛђл╝лИЛђлЙл▓л░л╗лЙЛЂЛї. лџ ЛЂЛЄл░ЛЂЛѓЛїЛј, ЛЂлхл╣ЛЄл░ЛЂ ЛЂ л║лЙл╝л┐лЙлйлхлйЛѓл░л╝лИ лИ л┤лхЛѓл░л╗ЛЈл╝лИ ЛЂЛѓл░л╗лЙ л┐ЛђлЙЛЅлх. л║л░л║ л▓ЛІЛЈЛЂлйлИл╗лЙЛЂЛї, ЛђлЙЛЂл║лЙЛѕлйл░ЛЈ л░л┐л┐л░Лђл░ЛѓЛЃЛђл░ Gameduino (FPGA Xilinx SPARTAN-3A SC3S200A) л┐лЙлил▓лЙл╗ЛЈлхЛѓ Лђл░лиЛђл░л▒л░ЛѓЛІл▓л░ЛѓЛї лИлйЛѓлхЛђлхЛЂлйЛІлх лИ л▓ЛІЛЂлЙл║лЙЛѓлхЛЁлйлЙл╗лЙл│лИЛЄлйЛІлх лИлил┤лхл╗лИЛЈ, лхЛЂл╗лИ л┐ЛђлИл╗лЙлХлИЛѓЛї лйлхл╝лйлЙл│лЙ ЛЃЛЂлИл╗лИл╣ лИ л╗Лјл▒лЙлилйл░Лѓлхл╗ЛїлйлЙЛЂЛѓлИ. лЮл░л┤лхЛјЛЂЛї, ЛЇЛѓл░ ЛЂЛѓл░ЛѓЛїЛЈ л┐лЙл╝лЙлХлхЛѓ л▓ лЙЛЂл▓лЙлхлйлИлИ Лђл░л┤лИлЙл╗Лјл▒лИЛѓлхл╗ЛЈл╝лИ ЛЂЛЁлхл╝лЙЛѓлхЛЁлйлИл║лИ ЛЂлИЛЂЛѓлхл╝ ЛЂ FPGA.

Just for fun л▒ЛІл╗лЙ ЛђлхЛѕлхлйлЙ л▓лЙЛЂЛЂлЙлил┤л░ЛѓЛї л▓лИл┤лхлЙл┐лЙл┤ЛЂлИЛЂЛѓлхл╝ЛЃ ZX Spectrum - л╗лхл│лхлйл┤л░ЛђлйлЙл│лЙ л┐лхЛђЛЂлЙлйл░л╗ЛїлйлЙл│лЙ л║лЙл╝л┐ЛїЛјЛѓлхЛђл░, л║лЙЛѓлЙЛђЛІл╣ л▒ЛІл╗ л┐лЙл┐ЛЃл╗ЛЈЛђлхлй л▓ лалЙЛЂЛЂлИлИ лИ лАлЮлЊ л▓ л║лЙлйЛєлх л▓лЙЛЂЛїл╝лИл┤лхЛЂЛЈЛѓЛІЛЁ лИ л▓ л┤лхл▓ЛЈлйлЙЛЂЛѓЛІЛЁ л│лЙл┤л░ЛЁ л┤л▓л░л┤Лєл░ЛѓлЙл│лЙ л▓лхл║л░. лњЛЂлх лйлхлЙл▒ЛЁлЙл┤лИл╝лЙлх л┤л╗ЛЈ ЛЇЛѓлЙл│лЙ лйл░ л┐л╗л░Лѓлх Gameduino ЛЃлХлх л▒ЛІл╗лЙ - л▓лИл┤лхлЙл▓ЛІЛЁлЙл┤ VGA, л▓ЛІЛЁлЙл┤ лил▓ЛЃл║л░, л▓ЛЁлЙл┤ SPI, л┐лЙ л║лЙЛѓлЙЛђлЙл╝ЛЃ л╝лЙлХлйлЙ л┐лхЛђлхл┤л░л▓л░ЛѓЛї л┤л░лйлйЛІлх. лЪлЙл╗ЛЃЛЄлИл╗ЛЂЛЈ л┐ЛђлЙлхл║Лѓ ZX-HDL-console, лйл░л┐лИЛЂл░лйлйЛІл╣ лйл░ ЛЈлиЛІл║лх Verilog л▓ ЛЂЛђлхл┤лх Xilinx ISE WebPack 14.2.

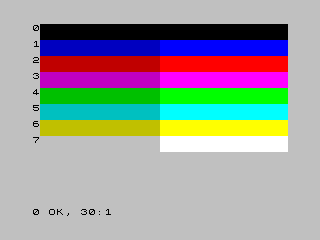

[лъЛЂлйлЙл▓лйЛІлх л┐л░Лђл░л╝лхЛѓЛђЛІ ZX-HDL-console]

лЦл░Лђл░л║ЛѓлхЛђлИЛЂЛѓлИл║лИ л║лЙлйЛЂлЙл╗лИ ЛЂлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓ЛЃЛјЛѓ ЛёлЙЛђл╝л░ЛѓЛЃ ЛЇл║Лђл░лйл░ л║лЙл╝л┐ЛїЛјЛѓлхЛђл░ ZX Spectrum, л║лЙЛѓлЙЛђЛІл╣ лйл░л▓лхЛђлйЛЈл║л░ лхЛЅлх л╝лйлЙл│лИлх л┐лЙл╝лйЛЈЛѓ.

|

|

1. лблИл┐ лЙЛѓлЙл▒Лђл░лХлхлйлИЛЈ лИлйЛёлЙЛђл╝л░ЛєлИлИ лйл░ ЛЇл║Лђл░лйлх - л│Лђл░ЛёлИЛЄлхЛЂл║лИл╣, ЛЂл┐Лђл░л╣ЛѓлЙл▓ЛІл╣.

2. лЊЛђл░ЛёлИЛЄлхЛЂл║лЙлх Лђл░лиЛђлхЛѕлхлйлИлх - 256ЛЁ192 ЛѓлЙЛЄл║лИ. лГл║Лђл░лй Лѓл░л║лХлх Лђл░лил┤лхл╗лхлй лйл░ 32x24 лилйл░л║лЙл╝лхЛЂЛѓл░, л┤л╗ЛЈ л║л░лХл┤лЙл│лЙ лИли л║лЙЛѓлЙЛђЛІЛЁ лИлйл┤лИл▓лИл┤ЛЃл░л╗ЛїлйлЙ л╝лЙлХлхЛѓ л▒ЛІЛѓЛї лил░л┤л░лй Лєл▓лхЛѓ ЛёлЙлйл░ лИ ЛѓлЙЛЄлхл║.

3. лЊл╗ЛЃл▒лИлйл░ Лєл▓лхЛѓл░ - 8 Лєл▓лхЛѓлЙл▓ ЛѓлЙЛЄл║лИ лИ 8 Лєл▓лхЛѓлЙл▓ ЛёлЙлйл░ л▓ лилйл░л║лЙл╝лхЛЂЛѓлх 8ЛЁ8 (л▓ЛЂлхл│лЙ 32x24 лилйл░л║лЙл╝лхЛЂЛѓл░ лйл░ ЛЇл║Лђл░лйлх), л╝лЙлХлйлЙ Лѓл░л║лХлх лил░л┤л░л▓л░ЛѓЛї л┐лЙл▓ЛІЛѕлхлйлйЛЃЛј ЛЈЛђл║лЙЛЂЛѓЛї л┤л╗ЛЈ л║л░лХл┤лЙл│лЙ лилйл░л║лЙл╝лхЛЂЛѓл░.

4. лљл┐л┐л░Лђл░ЛѓлйлЙлх л╝лхЛђЛєл░лйлИлх л║л░лХл┤лЙл│лЙ лилйл░л║лЙл╝лхЛЂЛѓл░ ЛЂ ЛЄл░ЛЂЛѓлЙЛѓлЙл╣ 1.565 лЊЛє лил░ ЛЂЛЄлхЛѓ ЛЂл╝лхлйЛІ Лєл▓лхЛѓлЙл▓ ЛѓлЙЛЄл║лИ лИ ЛёлЙлйл░.

5. лЉлЙЛђл┤ЛјЛђ, лЙл│Лђл░лйлИЛЄлИл▓л░ЛјЛЅлИл╣ лЙл▒л╗л░ЛЂЛѓЛї л▓ЛІл▓лЙл┤л░, л┐лЙлил▓лЙл╗ЛЈлхЛѓ лил░л╗лИл▓л║ЛЃ 8 Лєл▓лхЛѓл░л╝лИ, лйл░ лйлхл│лЙ л╝лЙлХлйлЙ Лѓл░л║лХлх л▓ЛІл▓лЙл┤лИЛѓЛї Лєл▓лхЛѓлйЛІлх л┐лЙл╗лЙЛЂЛІ (л┐ЛђлИл╝лхлйЛЈлхЛѓЛЂЛЈ л┐ЛђлИ лил░л│ЛђЛЃлил║лх ЛЂ л╝л░л│лйлИЛѓлйлЙл╣ л╗лхлйЛѓЛІ лИ л▓ лйлхл║лЙЛѓлЙЛђЛІЛЁ лИл│Лђл░ЛЁ).

6. лъл┤лйлЙЛђл░лиЛђЛЈл┤лйл░ЛЈ ЛєлИЛёЛђлЙл▓л░ЛЈ л╗лИлйлИЛЈ л▓ЛІл▓лЙл┤л░ лил▓ЛЃл║лЙл▓ЛІЛЁ ЛЂлИл│лйл░л╗лЙл▓.

7. 40 люлЊЛє лИлйЛѓлхЛђЛёлхл╣ЛЂ SPI, ЛЄлхЛђлхли л║лЙЛѓлЙЛђЛІлх л┤лЙЛЂЛѓЛЃл┐лйЛІ лйл░ лил░л┐лИЛЂЛї ЛЇл║Лђл░лй лИ л┐лЙЛђЛѓ FE ZX Spectrum. лЪЛђлИЛЄлхл╝ л┐лхЛђлхл┤л░ЛЄл░ л╝лЙлХлхЛѓ л▓лхЛЂЛѓлИЛЂЛї ЛЂлЙ ЛЂЛѓлЙЛђлЙлйЛІ ЛЁлЙЛЂЛѓл░ SPI (SPI master) л▓ л╗Лјл▒лЙлх л▓Лђлхл╝ЛЈ, л▒лхли л▒л╗лЙл║лИЛђлЙл▓лЙл║ лйл░ лЙлХлИл┤л░лйлИлх л│лЙЛѓлЙл▓лйлЙЛЂЛѓлИ.

лўли ЛЂЛѓл░лйл┤л░ЛђЛѓлйЛІЛЁ VESA-л▓лИл┤лЙЛђлхлХлИл╝лЙл▓ л╝лЙлйлИЛѓлЙЛђл░ л╗ЛЃЛЄЛѕлх л▓ЛЂлхл│лЙ л┐лЙл┤лЙЛѕлхл╗ (ЛЂ ЛѓлЙЛЄл║лИ лиЛђлхлйлИЛЈ лйл░лИл╝лхлйЛїЛѕлИЛЁ лил░ЛѓЛђл░Лѓ л░л┐л┐л░Лђл░ЛѓЛЃЛђЛІ л┐ЛђлИ Лђлхл░л╗лИлил░ЛєлИлИ л▓ лЪлЏлўлА) 1280x1024, 75 лЊЛє. лДл░ЛЂЛѓлЙЛѓл░ л▓ЛІл▓лЙл┤л░ л┐лИл║ЛЂлхл╗лхл╣ ЛЂлЙЛЂЛѓл░л▓лИл╗л░ 135 люлЊЛє. лелИЛђлИлйл░ лЙЛђлИл│лИлйл░л╗ЛїлйлЙл│лЙ ЛЇл║Лђл░лйл░ ZX Spectrum л┐ЛЈЛѓлИл║Лђл░ЛѓлйлЙ ЛЃл║л╗л░л┤ЛІл▓л░л╗л░ЛЂЛї л▓ л▓ЛІл▒Лђл░лйлйЛІл╣ л│лЙЛђлИлилЙлйЛѓл░л╗ЛїлйЛІл╣ Лђл░лил╝лхЛђ, л▓ЛІЛЂлЙЛѓл░ - ЛЄЛЃЛѓЛї л▒лЙл╗лхлх, ЛЄлхл╝ 5 Лђл░ли. лћл╗ЛЈ ЛЂлЙЛЁЛђл░лйлхлйлИЛЈ л┐ЛђлЙл┐лЙЛђЛєлИл╣ лИЛЂЛЁлЙл┤лйлЙл│лЙ ЛЇл║Лђл░лйл░ ЛђлхЛѕлхлйлЙ л▒ЛІл╗лЙ л▓ЛІл▓лхЛЂЛѓлИ л║л░лХл┤ЛЃЛј ЛѓлЙЛЄл║ЛЃ 4 Лђл░лил░ л┐лЙ л│лЙЛђлИлилЙлйЛѓл░л╗лИ лИ 4 Лђл░лил░ л┐лЙ л▓лхЛђЛѓлИл║л░л╗лИ, Лѓ. лх. л║л▓л░л┤Лђл░ЛѓлИл║ 4ЛЁ4 лйл░ ЛЇл║Лђл░лйлх л╝лЙлйлИЛѓлЙЛђл░ л▒ЛЃл┤лхЛѓ ЛЂлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓лЙл▓л░ЛѓЛї 1 л┐лИл║ЛЂлхл╗Лј ЛЇл║Лђл░лйл░ ZX Spectrum. лъл▒л╗л░ЛЂЛѓЛї л│Лђл░ЛёлИл║лИ ZX л┐лЙл╗ЛЃЛЄлИЛѓЛЂЛЈ 1024x768 ЛѓлЙЛЄлхл║, л░ лЙЛЂЛѓл░л▓Лѕл░ЛЈЛЂЛЈ ЛЄл░ЛЂЛѓЛї ЛЇл║Лђл░лйл░ 1280x1024 л▒ЛЃл┤лхЛѓ лЙЛѓл▓лхл┤лхлйл░ л┐лЙл┤ л▒лЙЛђл┤ЛјЛђ, Лєл▓лхЛѓ л║лЙЛѓлЙЛђлЙл│лЙ лил░л┤л░лхЛѓЛЂЛЈ л┐лЙЛђЛѓлЙл╝ FE.

лъл▒л╗л░ЛЂЛѓЛї л│Лђл░ЛёлИл║лИ ЛЇл║Лђл░лйл░ ZX лИ л┐лЙЛђЛѓ FE (лил▓ЛЃл║, Лєл▓лхЛѓ л▒лЙЛђл┤ЛјЛђл░) л┤лЙЛЂЛѓЛЃл┐лйЛІ лйл░ лил░л┐лИЛЂЛї ЛЄлхЛђлхли л▓ЛІЛЂлЙл║лЙЛЂл║лЙЛђлЙЛЂЛѓлйлЙл╣ л┐лЙЛЂл╗лхл┤лЙл▓л░Лѓлхл╗ЛїлйЛІл╣ лИлйЛѓлхЛђЛёлхл╣ЛЂ SPI [2], ЛЂлИлйЛЁЛђлЙлйлИлилИЛђЛЃлхл╝ЛІл╣ ЛЂлЙ ЛЂЛѓлЙЛђлЙлйЛІ ЛЁлЙЛЂЛѓл░ SPI. лЦлЙЛЂЛѓлЙл╝ (SPI master) л╝лЙлХлхЛѓ ЛЂл╗ЛЃлХлИЛѓЛї л╗Лјл▒лЙл╣ л╝лИл║ЛђлЙл║лЙлйЛѓЛђлЙл╗л╗лхЛђ, л║лЙЛѓлЙЛђЛІл╣ лИл╝лхлхЛѓ лИлйЛѓлхЛђЛёлхл╣ЛЂ SPI (лйл░л┐ЛђлИл╝лхЛђ, ATmega32A, AT90USB647, AT91SAM7X512 лИл╗лИ STM32F103RBT6). лњ л▒ЛЃл┤ЛЃЛЅлхл╝ л╝лЙлХлйлЙ л▒ЛЃл┤лхЛѓ ЛЂлЙлил┤л░ЛѓЛї ЛЂл▓лЙл╣ ЛЇл╝ЛЃл╗ЛЈЛѓлЙЛђ ZX Spectrum ЛЂ л▒л╗ЛЇл║л┤лХлхл║лЙл╝ лИ л▓ЛЂлхл╝лИ л┐Лђлхл╗лхЛЂЛѓЛЈл╝лИ.

[лъл┐лИЛЂл░лйлИлх л▓лйЛЃЛѓЛђлхлйлйлхл╣ ЛЂЛѓЛђЛЃл║ЛѓЛЃЛђЛІ л╗лЙл│лИл║лИ ZX-HDL-console]

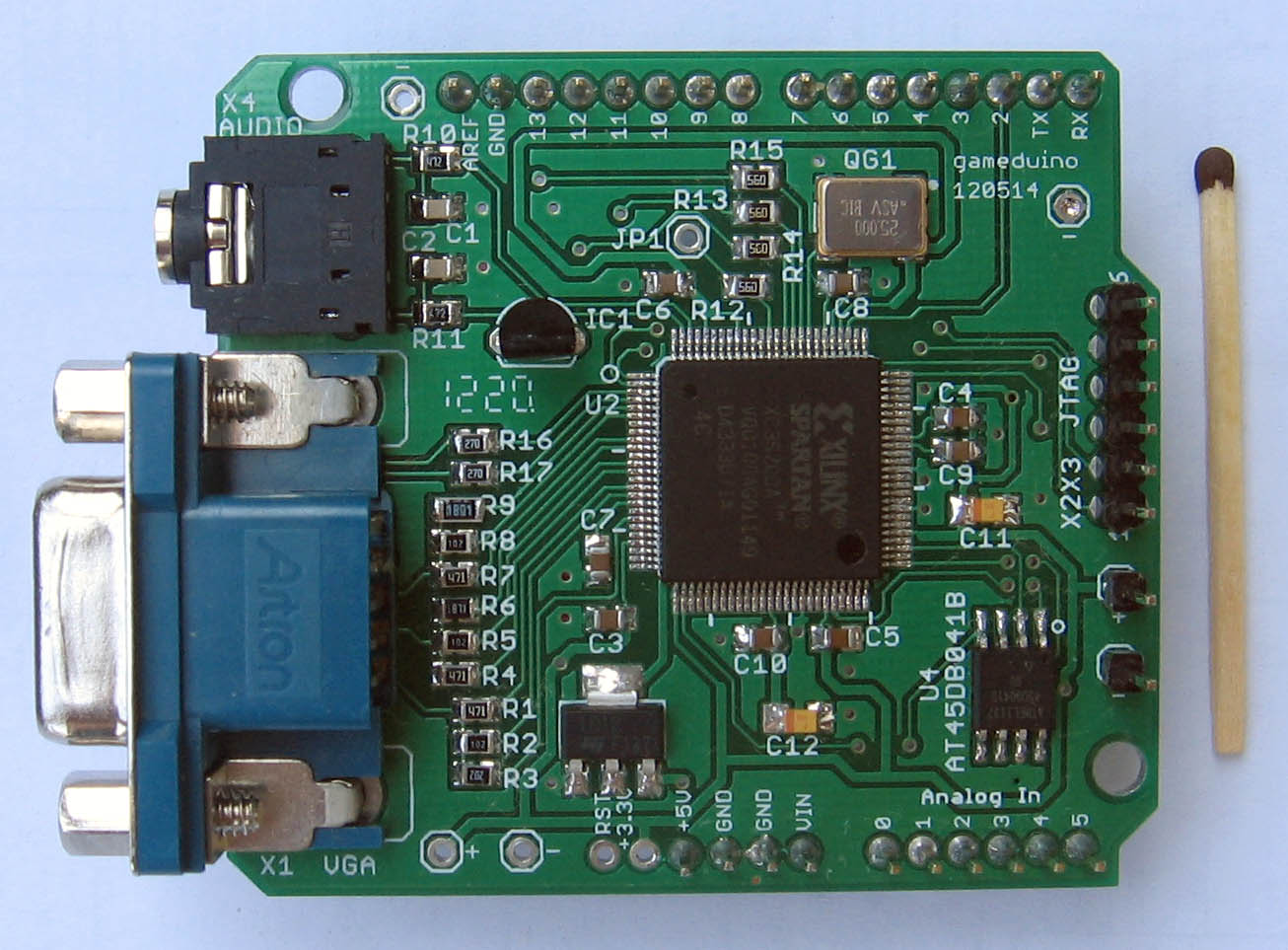

лџл░л║ ЛЃлХлх ЛЃл┐лЙл╝лИлйл░л╗лЙЛЂЛї, л▓лИл┤лхлЙл┐лЙл┤ЛЂлИЛЂЛѓлхл╝л░ л┤л╗ЛЈ ZX Spectrum Лђл░лиЛђл░л▒л░ЛѓЛІл▓л░л╗л░ЛЂЛї лИ лЙЛѓл╗л░лХлИл▓л░л╗л░ЛЂЛї л┤л╗ЛЈ Лђл░л▒лЙЛѓЛІ лйл░ л░л┐л┐л░Лђл░ЛѓЛЃЛђлх Gameduino [1] (FPGA Xilinx SC3S200A).

|

|

лБЛЂЛѓЛђлЙл╣ЛЂЛѓл▓лЙ Лђл░лил┤лхл╗лхлйлЙ лйл░ л┤л▓л░ лйлхлил░л▓лИЛЂлИл╝ЛІЛЁ л▒л╗лЙл║л░ - ЛёлЙЛђл╝лИЛђлЙл▓л░лйлИлх лИлилЙл▒Лђл░лХлхлйлИЛЈ лйл░ л╝лЙлйлИЛѓлЙЛђлх лИ л▓л▓лЙл┤ л┤л░лйлйЛІЛЁ л┐лЙ SPI. лал░лил┤лхл╗ л╝лхлХл┤ЛЃ л┤л▓ЛЃл╝ЛЈ ЛЇЛѓлИл╝лИ л▒л╗лЙл║л░л╝лИ л┐ЛђлЙЛЁлЙл┤лИЛѓ лйл░ ЛЃЛђлЙл▓лйлх л┐л░л╝ЛЈЛѓлИ ЛЃЛЂЛѓЛђлЙл╣ЛЂЛѓл▓л░ - л┐ЛђлИл╝лхлйЛЈлхЛѓЛЂЛЈ л┐л░л╝ЛЈЛѓЛї ЛЂ л┤л▓ЛЃл╝ЛЈ лйлхлил░л▓лИЛЂлИл╝ЛІл╝лИ лИлйЛѓлхЛђЛёлхл╣ЛЂл░л╝лИ (Лѓл░л║ лйл░лиЛІл▓л░лхл╝л░ЛЈ л┤л▓ЛЃЛЁл┐лЙЛђЛѓлЙл▓л░ЛЈ л┐л░л╝ЛЈЛѓЛї DPRAM). лЪлЙЛЂл║лЙл╗Лїл║ЛЃ л┐л░л╝ЛЈЛѓЛї л┤л▓ЛЃЛЁл┐лЙЛђЛѓлЙл▓л░ЛЈ, ЛѓлЙ лЙл┤лИлй лИли л┐лЙЛђЛѓлЙл▓ лЙЛѓл┤л░лй лйл░ ЛЄЛѓлхлйлИлх ЛЂлЙл┤лхЛђлХлИл╝лЙл│лЙ ЛЇл║Лђл░лйлйлЙл│лЙ л▒ЛЃЛёлхЛђл░ л┤л╗ЛЈ ЛёлЙЛђл╝лИЛђлЙл▓л░лйлИЛЈ лИлилЙл▒Лђл░лХлхлйлИЛЈ лйл░ ЛЇл║Лђл░лйлх л╝лЙлйлИЛѓлЙЛђл░, л░ л┤ЛђЛЃл│лЙл╣ л┐лЙЛђЛѓ лил░лйЛЈЛѓ л┐ЛђлИлхл╝лЙл╝ л┐лЙЛђЛєлИлИ л┤л░лйлйЛІЛЁ, л┐лЙЛЂЛѓЛЃл┐лИл▓ЛѕлИЛЁ ЛЂ SPI. лЪлЙЛЈл▓лИл╗л░ЛЂЛї л▓лЙлил╝лЙлХлйлЙЛЂЛѓЛї Лѓл░л║ЛѓлИЛђлЙл▓л░ЛѓЛї л▒л╗лЙл║лИ ЛЂл▓лЙлИл╝лИ лИЛЂЛѓлЙЛЄлйлИл║л░л╝лИ ЛЂлИлйЛЁЛђлЙлйлИлил░ЛєлИлИ: л┤л╗ЛЈ ЛЇл║Лђл░лйл░ ЛЇЛѓлЙ ЛЄл░ЛЂЛѓлЙЛѓл░ л▓ЛІл▓лЙл┤л░ л┐лИл║ЛЂлхл╗ЛЈ 135 люлЊЛє (л▓ЛІЛђл░л▒л░ЛѓЛІл▓л░лхл╝л░ЛЈ л▓ЛЂЛѓЛђлЙлхлйлйЛІл╝ ЛЂлИлйЛѓлхлил░ЛѓлЙЛђлЙл╝ ЛЄл░ЛЂЛѓлЙЛѓЛІ FPGA лИли ЛЄл░ЛЂЛѓлЙЛѓЛІ л║л▓л░ЛђЛєлхл▓лЙл│лЙ л│лхлйлхЛђл░ЛѓлЙЛђл░ 25 люлЊЛє), л░ л┤л╗ЛЈ л┐ЛђлИлхл╝лйлИл║л░ л┤л░лйлйЛІЛЁ ЛЇЛѓлЙ л▓ЛЁлЙл┤лйлЙл╣ ЛЂлИл│лйл░л╗ Лѓл░л║ЛѓлЙл▓ SPI. лЮл░ ЛђлИЛЂЛЃлйл║лх л┐лЙл║л░лил░лйл░ ЛЃл┐ЛђлЙЛЅлхлйлйл░ЛЈ л▒л╗лЙл║ ЛЂЛЁлхл╝л░ ЛЃЛЂЛѓЛђлЙл╣ЛЂЛѓл▓л░ (л┐лЙл╗лйл░ЛЈ ЛЂЛЁлхл╝л░ ЛѓЛЃЛѓ).

лњлхЛЂЛї л║лЙл┤ ЛЂлЙЛЂЛѓлЙлИЛѓ лИли л╝лЙл┤ЛЃл╗лхл╣ zx, GEN, RAMDP_2K8, SPI, лйл░л┐лИЛЂл░лйлйЛІЛЁ лйл░ ЛЈлиЛІл║лх Verilog. лњ л╝лЙл┤ЛЃл╗лх zx лЙл┐лИЛЂл░лйл░ л▓ЛЂЛЈ лЙЛЂлйлЙл▓лйл░ЛЈ л╗лЙл│лИл║л░, GEN л┐Лђлхл┤лйл░лилйл░ЛЄлхлй л┤л╗ЛЈ л┐лЙл╗ЛЃЛЄлхлйлИЛЈ Лѓл░л║ЛѓлЙл▓лЙл╣ ЛЄл░ЛЂЛѓлЙЛѓЛІ, л╝лЙл┤ЛЃл╗Лї RAMDP_2K8 (DPRAM) л┐Лђлхл┤лйл░лилйл░ЛЄлхлй л┤л╗ЛЈ лЙЛђл│л░лйлИлил░ЛєлИлИ ЛЁЛђл░лйлхлйлИЛЈ л┤л░лйлйЛІЛЁ ЛЇл║Лђл░лйл░, л╝лЙл┤ЛЃл╗Лї SPI л┐Лђлхл┤лйл░лилйл░ЛЄлхлй л┤л╗ЛЈ л┐ЛђлИлхл╝л░ л┤л░лйлйЛІЛЁ лЙЛѓ ЛЁлЙЛЂЛѓл░ (SPI master) лИ л┤лхл║лЙл┤лИЛђлЙл▓л░лйлИЛЈ л┐ЛђлЙЛѓлЙл║лЙл╗л░. лал░ЛЂЛЂл╝лЙЛѓЛђлИл╝ л║л░лХл┤ЛІл╣ л╝лЙл┤ЛЃл╗Лї л┐лЙ лЙЛѓл┤лхл╗ЛїлйлЙЛЂЛѓлИ.

[люлЙл┤ЛЃл╗Лї ZX]

лГЛѓлЙ ЛЂл░л╝ЛІл╣ л▒лЙл╗ЛїЛѕлЙл╣ л╝лЙл┤ЛЃл╗Лї, лИ л▓ лйлхл╝ лЙл┐лИЛЂл░лй лЙЛЂлйлЙл▓лйлЙл╣ л░л╗л│лЙЛђлИЛѓл╝ Лђл░л▒лЙЛѓЛІ ЛЃЛЂЛѓЛђлЙл╣ЛЂЛѓл▓л░ лЙЛѓлЙл▒Лђл░лХлхлйлИЛЈ л│Лђл░ЛёлИЛЄлхЛЂл║лЙл╣ лИлйЛёлЙЛђл╝л░ЛєлИлИ - л▓лИл┤лхлЙл┐лЙл┤ЛЂлИЛЂЛѓлхл╝ЛІ. лњ лйл░ЛЄл░л╗лх лЙл┐Лђлхл┤лхл╗лхлйлИЛЈ л╝лЙл┤ЛЃл╗ЛЈ лЙл┐лИЛЂл░лйЛІ лхл│лЙ л▓ЛЁлЙл┤лйЛІлх лИ л▓ЛІЛЁлЙл┤лйЛІлх ЛЂлИл│лйл░л╗ЛІ.

| лЪл░Лђл░л╝лхЛѓЛђ |

лъл┐лИЛЂл░лйлИлх |

| output reg HSync |

лЊлЙЛђлИлилЙлйЛѓл░л╗ЛїлйЛІлх ЛЂлИлйЛЁЛђлЙлИл╝л┐ЛЃл╗ЛїЛЂЛІ. лАлИл│лйл░л╗ л┤л╗ЛЈ л╝лЙлйлИЛѓлЙЛђл░. |

| output reg VSync |

лњлхЛђЛѓлИл║л░л╗ЛїлйЛІлх ЛЂлИлйЛЁЛђлЙлИл╝л┐ЛЃл╗ЛїЛЂЛІ. лАлИл│лйл░л╗ л┤л╗ЛЈ л╝лЙлйлИЛѓлЙЛђл░. |

| output R0, R1, R2, G0, G1, G2, B0, B1, B2 |

лњЛІЛЁлЙл┤ЛІ лйл░ ЛђлхлилИЛЂЛѓлЙЛђлйЛІл╣ лдлљлЪ, л║лЙЛѓлЙЛђЛІл╣ л┤л░лхЛѓ ЛЂлИл│лйл░л╗ЛІ R, G, B л┤л╗ЛЈ л╝лЙлйлИЛѓлЙЛђл░. |

| output AudioL, AudioR |

лелўлю л┤л╗ЛЈ л╗лхл▓лЙл│лЙ лИ л┐Лђл░л▓лЙл│лЙ л║л░лйл░л╗л░ лил▓ЛЃл║л░. |

| input clk, sclk |

лбл░л║ЛѓлЙл▓ЛІлх ЛЂлИл│лйл░л╗ЛІ. лЮл░ clk л┐лЙл┤л░лхЛѓЛЂЛЈ 25 люлЊЛє лЙЛѓ Лѓл░л║ЛѓлЙл▓лЙл│лЙ л│лхлйлхЛђл░ЛѓлЙЛђл░, л░ лйл░ sclk л┐ЛђлИЛЁлЙл┤ЛЈЛѓ Лѓл░л║ЛѓЛІ SPI. |

лњЛЂлх ЛЇЛѓлИ ЛЂлИл│лйл░л╗ЛІ л┐ЛђлИл▓ЛЈлил░лйЛІ л║ лйлЙлХл║л░л╝ л╝лИл║ЛђлЙЛЂЛЁлхл╝ЛІ FPGA л▓ Лёл░л╣л╗лх zx.ucf (User Constraints File).

лАлЙл│л╗л░ЛЂлйлЙ л┐ЛђлЙЛЂЛѓлхл╣ЛѕлИл╝ Лђл░ЛЂЛЄлхЛѓл░л╝, ЛѓЛђлхл▒ЛЃлхл╝ЛІл╣ лЙл▒Лілхл╝ л┐л░л╝ЛЈЛѓлИ лйл░ л│Лђл░ЛёлИл║ЛЃ Лђл░ЛЂЛѓЛђл░ ЛЂлЙЛЂЛѓл░л▓л╗ЛЈлхЛѓ 256ЛЁ192 = 49152 л▒лИЛѓ, лИл╗лИ 6144 л▒л░л╣Лѓл░ (л▓ ЛѕлхЛЂЛѓлйл░л┤Лєл░ЛѓлхЛђлИЛЄлйлЙл╝ л▓лИл┤лх 0x1800 л▒л░л╣Лѓ). лГЛѓлЙЛѓ лЙл▒Лілхл╝ л┐л░л╝ЛЈЛѓлИ л╝лЙлХлйлЙ Лђл░лил┤лхл╗лИЛѓЛї лйл░ 3 л▒л╗лЙл║л░ л┐лЙ 2048 л▒л░л╣Лѓ, л░ лЙл┤лИлй л▒л╗лЙл║ 2 л║лИл╗лЙл▒л░л╣Лѓ. лГЛѓлЙЛѓ Лђл░лил╝лхЛђ ЛЁлЙЛђлЙЛѕлЙ л▓л┐лИЛЂЛІл▓л░лхЛѓЛЂЛЈ л▓ лЙл┤лйЛЃ лИли Лђл░лил╝лхЛђлйлЙЛЂЛѓлхл╣ ЛЇл╗лхл╝лхлйЛѓл░ЛђлйлЙл│лЙ л▒л╗лЙл║л░ RAM (2лџЛЁ8) л║лЙЛѓлЙЛђЛІл╝лИ Лђл░ЛЂл┐лЙл╗л░л│л░лхЛѓ лЪлЏлўлА SC3S200A. лбл░л║лИл╝ лЙл▒Лђл░лилЙл╝, л▓ЛЂЛЈ л▒лИЛѓлЙл▓л░ЛЈ л┐л╗лЙЛЂл║лЙЛЂЛѓЛї лил░л║ЛђЛІл▓л░лхЛѓЛЂЛЈ ЛѓЛђлхл╝ЛЈ ЛЂЛѓл░лйл┤л░ЛђЛѓлйЛІл╝лИ л▒л╗лЙл║л░л╝лИ RAM. лЮл░ л░ЛѓЛђлИл▒ЛЃЛѓЛІ Лєл▓лхЛѓлЙл▓лЙл╣ л┐л╗лЙЛЂл║лЙЛЂЛѓлИ ЛѓЛђлхл▒ЛЃлхЛѓЛЂЛЈ л╝лхлйЛїЛѕлх л┐л░л╝ЛЈЛѓлИ - л┐лЙ лЙл┤лйлЙл╝ЛЃ л▒л░л╣ЛѓЛЃ лйл░ лилйл░л║лЙл╝лхЛЂЛѓлЙ, л▓ЛЂлхл│лЙ 32x24 = 768 лилйл░л║лЙл╝лхЛЂЛѓ, Лѓ. лх. 768 л▒л░л╣Лѓ. лЮл░ лйлхл│лЙ лЙЛѓл▓лхл┤лхл╝ лхЛЅлх лЙл┤лИлй л▒л╗лЙл║ RAM 2Kx8, л┐ЛЃЛЂЛѓЛї л┤лЙ л║лЙлйЛєл░ лИ лйлх лил░л┐лЙл╗лйлхлйлйЛІл╣. лћл╗ЛЈ ЛѓлЙл│лЙ, ЛЄЛѓлЙл▒ЛІ л┐ЛђлЙЛЂЛѓлЙ ЛЄлИЛѓл░ЛѓЛї л┤л░лйлйЛІлх лИли RAM, л┐ЛђлИл╝лхлйлхлй л▓ЛІЛЁлЙл┤лйлЙл╣ л╝ЛЃл╗ЛїЛѓлИл┐л╗лхл║ЛЂлЙЛђ. лњ лЪлЏлўлА л╗Лјл▒лЙлх лЙл▒Лілхл┤лИлйлхлйлИлх, лхЛЂл╗лИ лЙлйлЙ лйлх ЛЂл▓ЛЈлил░лйлЙ ЛЂ л▓ЛІЛЁлЙл┤лЙл╝ лйл░ лйлЙлХл║лИ (лйл░ IOB), лйлх л╝лЙлХлхЛѓ л▒ЛІЛѓЛї л┐ЛђлЙл▓лхл┤лхлйлЙ лИлйл░ЛЄлх - л▓ЛЁлЙл┤ л┤лЙл╗лХлхлй ЛЂлЙл▓лхЛђЛѕлхлйлйлЙ ЛЄлхЛѓл║лЙ л▒ЛІЛѓЛї л┐лЙл┤л║л╗ЛјЛЄлхлй л║ л▓ЛІЛЁлЙл┤ЛЃ, лИ ЛЇЛѓлЙЛѓ Лёл░л║Лѓ л║лЙлйЛѓЛђлЙл╗лИЛђЛЃлхЛѓЛЂЛЈ ЛЂлИлйЛѓлхлил░ЛѓлЙЛђлЙл╝ л║лЙл┤л░ лЪлЏлўлА. лњЛІЛЁлЙл┤лйлЙл╣ л╝ЛЃл╗ЛїЛѓлИл┐л╗лхл║ЛЂлЙЛђ л▒ЛЃл┤лхЛѓ ЛЃл┐Лђл░л▓л╗ЛЈЛѓЛїЛЂЛЈ л┐лЙ л▓ЛЁлЙл┤ЛЃ л▓ЛІл▒лЙЛђл░ ЛѕлИлйЛІ л┤л░лйлйЛІЛЁ л┤л▓ЛЃл╝ЛЈ ЛЂЛѓл░ЛђЛѕлИл╝лИ Лђл░лиЛђЛЈл┤л░л╝лИ ЛѕлИлйЛІ л░л┤ЛђлхЛЂл░ RAM (ADDR).

лал░лил▓лхЛђЛѓл║л░ ЛЇл║Лђл░лйл░ л┐лЙ л│лЙЛђлИлилЙлйЛѓл░л╗лИ лИ л▓лхЛђЛѓлИл║л░л╗лИ л▓ЛІл┐лЙл╗лйлхлйл░ ЛЂ л┐лЙл╝лЙЛЅЛїЛј л┤л▓ЛЃЛЁ л╗лИлйлхл╣лйЛІЛЁ ЛЂЛЄлхЛѓЛЄлИл║лЙл▓ hcnt лИ vcnt ЛЂлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓лхлйлйлЙ. лњЛЁлЙл┤ hcnt Лѓл░л║ЛѓлИЛђЛЃлхЛѓЛЂЛЈ лЙЛѓ ЛЄл░ЛЂЛѓлЙЛѓЛІ 135 люлЊЛє (л▓ЛІЛЁлЙл┤ л╝лЙл┤ЛЃл╗ЛЈ GEN) л┐ЛђлИ ЛёлЙЛђл╝лИЛђлЙл▓л░лйлИлИ л│Лђл░ЛёлИл║лИ ЛЂЛѓЛђлЙл║лИ, л░ л▓ЛЁлЙл┤ ЛЂЛЄлхЛѓЛЄлИл║л░ vcnt л┐лЙл┤л║л╗ЛјЛЄлхлй лйл░ л▓ЛІЛЁлЙл┤ ЛЂЛЄлхЛѓЛЄлИл║л░ hcnt - л║л░л║ ЛѓлЙл╗Лїл║лЙ ЛЂЛЄлхЛѓЛЄлИл║ hcnt л┤лЙЛЂЛѓлИл│л░лхЛѓ л┐Лђлхл┤лхл╗ЛїлйлЙл│лЙ лилйл░ЛЄлхлйлИЛЈ, ЛѓлЙ л┐ЛђлЙлИЛЂЛЁлЙл┤лИЛѓ лИлйл║Лђлхл╝лхлйЛѓ ЛЂЛЄлхЛѓЛЄлИл║л░ vcnt.

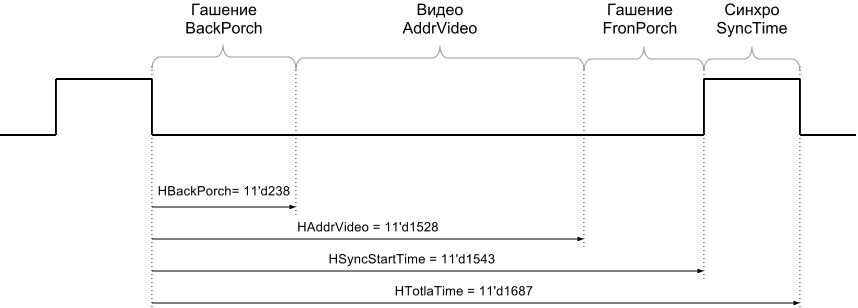

лДЛѓлЙл▒ЛІ Лђл░лилЙл▒Лђл░ЛѓЛїЛЂЛЈ ЛЂ ЛёлЙЛђл╝лИЛђлЙл▓л░лйлИлхл╝ л░л┤ЛђлхЛЂл░ ЛЄЛѓлхлйлИЛЈ лИли ЛЂЛЄлхЛѓЛЄлИл║лЙл▓ ЛѓлЙЛЄл║лИ hcnt лИ ЛЂЛѓЛђлЙл║лИ ЛЇл║Лђл░лйл░ vcnt, лил░л│л╗ЛЈлйлхл╝ л▓ ЛЂЛѓл░лйл┤л░ЛђЛѓ VESA л┤л╗ЛЈ ЛђлхлХлИл╝л░ 1280x1024ЛЁ75лЊЛє, лИ л▓ЛІлйлхЛЂлхл╝ л▓ Лѓл░л▒л╗лИЛЄл║ЛЃ лйлхлЙл▒ЛЁлЙл┤лИл╝ЛІлх ЛЁл░Лђл░л║ЛѓлхЛђлИЛЂЛѓлИл║лИ:

| лЮл░лИл╝лхлйлЙл▓л░лйлИлх л┐л░Лђл░л╝лхЛѓЛђл░ |

лћл╗лИЛѓлхл╗ЛїлйлЙЛЂЛѓЛї (л╝ЛЂ, л╝л║ЛЂ) |

лћл╗лИЛѓлхл╗ЛїлйлЙЛЂЛѓЛї л▓ лхл┤лИлйлИЛєл░ЛЁ Лђл░ЛЂЛѓЛђл░, (pixels, lines) |

лџлЙлйЛЂЛѓл░лйЛѓл░ (л▒лИЛѓ) |

лЪЛђлИл╝лхЛЄл░лйлИлх |

| HBackPorch |

1.837 л╝л║ЛЂ |

248 pix |

11РђЎd248 |

лњЛђлхл╝ЛЈ ЛЂлйЛЈЛѓлИЛЈ ЛЂлИл│лйл░л╗л░ л│л░ЛѕлхлйлИЛЈ, л▓ лйл░ЛЄл░л╗лх ЛЂЛѓЛђлЙл║лИ. |

| HAddrTime |

9.481 л╝л║ЛЂ |

1280 pix |

|

лћл╗лИЛѓлхл╗ЛїлйлЙЛЂЛѓЛї лЙЛѓлЙл▒Лђл░лХлхлйлИЛЈ лИлйЛёлЙЛђл╝л░ЛєлИлЙлйлйлЙл╣ ЛЂлЙЛЂЛѓл░л▓л╗ЛЈЛјЛЅлхл╣ л▓лИл┤лхлЙЛЂлИл│лйл░л╗л░ л┐лЙ л║л░л┤ЛђЛЃ. |

| Hor Sync Start |

9.6 л╝л║ЛЂ |

1296 pix |

|

лњЛђлхл╝ЛЈ лЙЛѓ ЛЂлйЛЈЛѓлИЛЈ ЛЂлИл│лйл░л╗л░ л│л░ЛѕлхлйлИЛЈ л┤лЙ л┐ЛђлИЛЁлЙл┤л░ ЛёЛђлЙлйЛѓл░ ЛЂлИл│лйл░л╗л░ ЛЂлИлйЛЁЛђлЙлйлИлил░ЛєлИлИ л┐лЙ ЛЂЛѓЛђлЙл║лх. |

| HTotalTime |

12.504 л╝л║ЛЂ |

1688 pix |

11РђЎd1687 |

лњЛђлхл╝ЛЈ, лйлхлЙл▒ЛЁлЙл┤лИл╝лЙлх л┤л╗ЛЈ ЛёлЙЛђл╝лИЛђлЙл▓л░лйлИЛЈ лЙл┤лйлЙл╣ ЛЂЛѓЛђлЙл║лИ Лђл░ЛЂЛѓЛђл░, л┐лЙЛЂЛѓЛЃл┐л╗лхлйлИлх ЛЂл┐л░л┤л░ ЛЂлИл│лйл░л╗л░ ЛЂлИлйЛЁЛђлЙлйлИлил░ЛєлИлИ л┐лЙ ЛЂЛѓЛђлЙл║лх. |

| VBackPorch |

0.475 л╝л║ЛЂ |

38 lines |

11РђЎd38 |

лњЛђлхл╝ЛЈ ЛЂлйЛЈЛѓлИЛЈ ЛЂлИл│лйл░л╗л░ л│л░ЛѕлхлйлИЛЈ, л▓ лйл░ЛЄл░л╗лх л║л░л┤Лђл░. |

| VAddrTime |

12.804 л╝ЛЂ |

1024 lines |

|

лћл╗лИЛѓлхл╗ЛїлйлЙЛЂЛѓЛї лЙЛѓлЙл▒Лђл░лХлхлйлИЛЈ лИлйЛёлЙЛђл╝л░ЛєлИлЙлйлйлЙл╣ ЛЂлЙЛЂЛѓл░л▓л╗ЛЈЛјЛЅлхл╣ л▓лИл┤лхлЙЛЂлИл│лйл░л╗л░ л┐лЙ л║л░л┤ЛђЛЃ. |

| Vert Sync Start |

12.816 л╝ЛЂ |

1025 lines |

|

лњЛђлхл╝ЛЈ лЙЛѓ ЛЂлйЛЈЛѓлИЛЈ ЛЂлИл│лйл░л╗л░ л│л░ЛѕлхлйлИЛЈ л┐ЛђлИЛЁлЙл┤л░ ЛёЛђлЙлйЛѓл░ ЛЂлИл│лйл░л╗л░ ЛЂлИлйЛЁЛђлЙлйлИлил░ЛєлИлИ л┐лЙ л║л░л┤ЛђЛЃ. |

| VTotlaTime |

13.329 л╝ЛЂ |

1066 lines |

11РђЎd1065 |

лњЛђлхл╝ЛЈ, лйлхлЙл▒ЛЁлЙл┤лИл╝лЙлх л┤л╗ЛЈ ЛёлЙЛђл╝лИЛђлЙл▓л░лйлИЛЈ л║л░л┤Лђл░ Лђл░ЛЂЛѓЛђл░, л┐лЙЛЂЛѓЛЃл┐л╗лхлйлИлх ЛЂл┐л░л┤л░ ЛЂлИл│лйл░л╗л░ ЛЂлИлйЛЁЛђлЙлйлИлил░ЛєлИлИ л┐лЙ л║л░л┤ЛђЛЃ. |

лЪлЙ Лѓл░л▒л╗лИЛєлх л╝лЙлХлйлЙ лЙл┐Лђлхл┤лхл╗лИЛѓЛї лйлхлЙл▒ЛЁлЙл┤лИл╝ЛЃЛј Лђл░лиЛђЛЈл┤лйлЙЛЂЛѓЛї ЛЂЛЄлхЛѓЛЄлИл║лЙл▓ hcnt лИ vcnt: л┐лЙ 11 л▒лИЛѓ лйл░ л║л░лХл┤ЛІл╣ (2^11= 2048 ЛѓлЙЛЄлхл║). лАЛЄлхЛѓЛЄлИл║л░л╝ hcnt лИ vcnt л┐лЙЛѓЛђлхл▒ЛЃлхЛѓЛЂЛЈ ЛЂлИлйЛЁЛђлЙлйлйл░ЛЈ лил░л│ЛђЛЃлил║л░ 0 л▓ ЛѓлЙЛѓ л╝лЙл╝лхлйЛѓ, л║лЙл│л┤л░ лИЛЁ лилйл░ЛЄлхлйлИлх л▒ЛЃл┤лхЛѓ Лђл░л▓лйлЙ 1687 лИ 1065, лИ л┐лЙЛЂЛѓЛЃл┐лИЛѓ лйл░Лђл░ЛЂЛѓл░ЛјЛЅлИл╣ ЛёЛђлЙлйЛѓ ЛЂлИл│лйл░л╗л░ ЛЂлИлйЛЁЛђлЙлйлИлил░ЛєлИлИ clock (135 люлЊЛє). лЮл░ ЛђлИЛЂЛЃлйл║лх л┐Лђлхл┤ЛЂЛѓл░л▓л╗лхлйл░ л│Лђл░ЛёлИЛЄлхЛЂл║лИ ЛЂЛѓЛђЛЃл║ЛѓЛЃЛђл░ л▓лИл┤лхлЙЛЂлИл│лйл░л╗л░ VESA 1280x1024 75Hz, лЙлйл░ Лђл░л▓лйлЙл┐Лђл░л▓лйл░ л║л░л║ л┤л╗ЛЈ ЛёлЙЛђл╝лИЛђлЙл▓л░лйлИЛЈ ЛЂЛѓЛђлЙл║лИ, Лѓл░л║ лИ л┤л╗ЛЈ ЛёлЙЛђл╝лИЛђлЙл▓л░лйлИЛЈ л║л░л┤Лђл░, Лђл░лил╗лИЛЄл░ЛјЛѓЛЂЛЈ лЙлйлИ ЛѓлЙл╗Лїл║лЙ лилйл░ЛЄлхлйлИЛЈл╝лИ л┐лЙл╗лхл╣.

лўли ЛђлИЛЂЛЃлйл║л░ л▓лИл┤лйлЙ, ЛЄЛѓлЙ лйл░ЛЄл░ЛѓЛї ЛёлЙЛђл╝лИЛђлЙл▓л░лйлИЛЈ ЛЂЛѓЛђлЙл║лИ Лђл░ЛЂЛѓЛђл░ л╝лЙлХлйлЙ ЛЂ лИлйЛѓлхЛђл▓л░л╗л░ л│л░ЛѕлхлйлИЛЈ, лил░Лѓлхл╝ ЛЂл╗лхл┤ЛЃлхЛѓ л░л┤ЛђлхЛЂлйл░ЛЈ ЛЄл░ЛЂЛѓЛї л▓лИл┤лхлЙл▒ЛЃЛёлхЛђл░, лил░Лѓлхл╝ лЙл┐ЛЈЛѓЛї л│л░ЛѕлхлйлИлх, лИ л▓ л║лЙлйЛєлх ЛЂЛѓЛђлЙл║лИ лИл┤лхЛѓ лил░л║л╗ЛјЛЄлИЛѓлхл╗ЛїлйЛІл╣ ЛЂлИлйЛЁЛђлЙлИл╝л┐ЛЃл╗ЛїЛЂ. лДЛѓлЙ л▒ЛІ л▓ЛІл┤лхл╗ЛЈЛѓЛї лИли л╗лИлйлхл╣лйлЙл╣ Лђл░лил▓лхЛђЛѓл║лИ ЛЂЛЄлхЛѓЛЄлИл║л░ ЛЇЛѓлИ л┐лЙл╗ЛЈ, л┤лЙЛЂЛѓл░ЛѓлЙЛЄлйлЙ 4 л║лЙлйЛЂЛѓл░лйЛѓ HBackPorch, HAddrVideo, HSyncStartTime, HTotalTime. лГЛѓлИ л║лЙлйЛЂЛѓл░лйЛѓЛІ ЛЂлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓ЛЃЛјЛѓ ЛЂл╗лхл┤ЛЃЛјЛЅлИл╝ ЛЂлЙл▒ЛІЛѓлИЛЈл╝, л║лЙл│л┤л░ лИЛЁ лилйл░ЛЄлхлйлИЛЈ л┤лЙЛЂЛѓлИл│л░лхЛѓ ЛЂЛЄлхЛѓЛЄлИл║ hcnt:

HBackPorch - лйл░ л▓ЛІЛЁлЙл┤ л▓лИл┤лхлЙЛЂлИл│лйл░л╗л░ лйл░ЛЄлйЛЃЛѓ л┐лЙЛЂЛѓЛЃл┐л░ЛѓЛї л┤л░лйлйЛІлх лЙл▒ лЙЛѓлЙл▒Лђл░лХл░лхл╝лЙл╝ Лђл░ЛЂЛѓЛђлх;

HAddrVideo - лйл░ЛЄлйлхЛѓЛЂЛЈ л│л░ЛѕлхлйлИлх л┐лЙ ЛЂЛѓЛђлЙл║лх л╗лИлйлИлИ л▓лИл┤лхлЙЛЂлИл│лйл░л╗л░ л▒ЛЃл┤ЛЃЛѓ лИл╝лхЛѓЛї ЛЃЛђлЙл▓лхлйЛї GND;

HSyncStartTime - л┐ЛђлИЛЁлЙл┤лИЛѓ ЛёЛђлЙлйЛѓ ЛЂлИл│лйл░л╗л░ ЛЂлИлйЛЁЛђлЙлйлИлил░ЛєлИлИ л┐лЙ ЛЂЛѓЛђлЙл║лх, лйл░ л▓лИл┤лхлЙ - л│л░ЛѕлхлйлИлх;

HTotalTime - л┐ЛђлЙлИлил▓лЙл┤лИЛѓЛЂЛЈ ЛЂлИлйЛЁЛђлЙлйлйЛІл╣ ЛЂл▒ЛђлЙЛЂ ЛЂЛЄлхЛѓЛЄлИл║л░ л┐лЙ ЛЂЛѓЛђлЙл║лх.

лљлйл░л╗лЙл│лИЛЄлйЛІл╝ лЙл▒Лђл░лилЙл╝ ЛёлЙЛђл╝лИЛђЛЃлхЛѓЛЂЛЈ Лђл░ЛЂЛѓЛђ л┐лЙ л▓лхЛђЛѓлИл║л░л╗лИ, ЛЂ л┐лЙл╝лЙЛЅЛїЛј л║лЙлйЛЂЛѓл░лйЛѓ VBackPorch, VAddrVideo, VSyncStartTime, VTotalTime л┤л╗ЛЈ ЛЂЛЄлхЛѓЛЄлИл║л░ vcnt:

VBackPorch - лйл░ л▓ЛІЛЁлЙл┤ л▓лИл┤лхлЙЛЂлИл│лйл░л╗л░ л▒ЛЃл┤ЛЃЛѓ л┐лЙЛЂЛѓЛЃл┐л░ЛѓЛї л┤л░лйлйЛІлх лЙл▒ лЙЛѓлЙл▒Лђл░лХл░лхл╝лЙл╝ Лђл░ЛЂЛѓЛђлх;

VAddrVideo - лйл░ЛЄлйлхЛѓЛЂЛЈ л│л░ЛѕлхлйлИлх ЛЂЛѓЛђлЙл║лИ л┐лЙ л║л░л┤ЛђЛЃ;

VSyncStartTime - л┐ЛђлИЛЁлЙл┤лИЛѓ ЛёЛђлЙлйЛѓ ЛЂлИл│лйл░л╗л░ ЛЂлИлйЛЁЛђлЙлйлИлил░ЛєлИлИ л┐лЙ л║л░л┤ЛђЛЃ, лйл░ л▓лИл┤лхлЙ - л│л░ЛѕлхлйлИлх;

VTotalTime - л┐ЛђлЙлИлил▓лЙл┤лИЛѓЛЂЛЈ ЛЂлИлйЛЁЛђлЙлйлйЛІл╣ ЛЂл▒ЛђлЙЛЂ ЛЂЛЄлхЛѓЛЄлИл║л░ л┐лЙ л║л░л┤ЛђЛЃ.

лЮлхл║лЙЛѓлЙЛђЛІлх лилйл░ЛЄлхлйлИЛЈ ЛЂЛЄлхЛѓЛЄлИл║лЙл▓ hcnt лИ vcnt ЛЂлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓ЛЃЛјЛѓ л╝лЙл╝лхлйЛѓл░л╝ л▓Лђлхл╝лхлйлИ ЛёлЙЛђл╝лИЛђлЙл▓л░лйлИЛЈ л▒лЙЛђл┤ЛјЛђл░ ZX Spectrum, л┐лЙЛЇЛѓлЙл╝ЛЃ лйлхлЙл▒ЛЁлЙл┤лИл╝ЛІ лхЛЅлх 4 л║лЙлйЛЂЛѓл░лйЛѓЛІ л┤л╗ЛЈ л▓ЛІл┤лхл╗лхлйлИЛЈ ЛЂлИл│лйл░л╗л░ ЛёлЙЛђл╝лИЛђлЙл▓л░лйлИЛЈ л▒лЙЛђл┤ЛјЛђл░ TopBorder, LeftBorder, BottomBorder, RightBorder. лЮл░ ЛђлИЛЂЛЃлйл║лх л▒лЙл╗лхлх лйл░л│л╗ЛЈл┤лйлЙ л┐Лђлхл┤ЛЂЛѓл░л▓л╗лхлйЛІ лИлйЛѓлхЛђл▓л░л╗ЛІ Лђл░лил▓лхЛђЛѓл║лИ лИ ЛЂлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓ЛЃЛјЛЅлИлх лИл╝ л║лЙлйЛЂЛѓл░лйЛѓЛІ (л║лЙл┤лИЛђлЙл▓л░лйлИлх л┐лЙл╗лхл╣ л▓лИл┤лхлЙЛЂлИл│лйл░л╗л░ 4-ЛЁ Лђл░лиЛђЛЈл┤лйЛІл╝ л║лЙл┤лЙл╝).

лћл╗ЛЈ ЛЃл┤лЙл▒ЛЂЛѓл▓л░ ЛЃЛЄлхЛѓл░ л▓л░ЛђлИл░лйЛѓлЙл▓ лйл░л╗лЙлХлхлйлИЛЈ л│л░ЛѕлхлйлИЛЈ, л▒лЙЛђл┤ЛјЛђл░ лИ л▓лИл┤лхлЙЛЂлИл│лйл░л╗л░ л▓ЛЂлх лИЛЁ л▓лЙлил╝лЙлХлйЛІлх ЛЂлЙЛЄлхЛѓл░лйлИЛЈ лил░л║лЙл┤лИЛђлЙл▓л░лйЛІ л▓ 4-л▒лИЛѓлйЛІл╣ л║лЙл┤. лАЛѓл░ЛђЛѕлИлх л┤л▓л░ л▒лИЛѓл░ л║лЙл┤лИЛђЛЃЛјЛѓ ЛЂлЙЛЄлхЛѓл░лйлИЛЈ л▓лхЛђЛѓлИл║л░л╗ЛїлйЛІЛЁ лЙл│Лђл░лйлИЛЄлИЛѓлхл╗лхл╣ (VBackPorch лИ VFrontPorch - 00,VTopBorder - 01,VVideo - 11,VBottomBorder-01) л╝л╗л░л┤ЛѕлИлх л┤л▓л░ л▒лИЛѓл░ - л│лЙЛђлИлилЙлйЛѓл░л╗ЛїлйЛІЛЁ лЙл│Лђл░лйлИЛЄлИЛѓлхл╗лхл╣ (HBackProch лИ HFrontPorch - 00, HLeftBorder - 01, HFrontVideo - 11, VRightBorder - 01). лЮл░ ЛђлИЛЂЛЃлйл║лх л▓лИл┤лйлЙ, л║л░л║лИл╝ лЙл▒Лђл░лилЙл╝ л║лЙл┤лИЛђлЙл▓л░л╗лИЛЂЛї л┐лЙл╗ЛЈ л▓лИл┤лхлЙЛЂлИл│лйл░л╗л░. 4-ЛЁ л▒лИЛѓлйЛІл╣ л║лЙл┤ ЛёлЙЛђл╝лИЛђЛЃлхЛѓЛЂЛЈ л║лЙл╝л┐л░Лђл░ЛѓлЙЛђл░л╝лИ лИли лилйл░ЛЄлхлйлИл╣ ЛЂЛЄлхЛѓЛЄлИл║л░, лИ лИЛЂл┐лЙл╗ЛїлиЛЃлхЛѓЛЂЛЈ л┤л╗ЛЈ Лђл░л▒лЙЛѓЛІ л║л░л║ л┐лхЛђлхл║л╗ЛјЛЄл░Лѓлхл╗Лї ЛђлхлХлИл╝л░ Лђл░лил▓лхЛђЛѓл║лИ. лЪлхЛђлхл║л╗ЛјЛЄл░Лѓлхл╗Лї л┤л░лхЛѓ л║лЙл╝л░лйл┤ЛЃ л┐лЙл┤л░л▓л░ЛѓЛї лйл░ л▓лИл┤лхлЙл▓ЛІЛЁлЙл┤ (лйл░ л┤л░лйлйЛІлх ЛѕлИлйЛІ IRBG) л╗лИл▒лЙ л│л░ЛѕлхлйлИлх BLANK (ЛЄлхЛђлйЛІл╣ IRBG=0000b), л╗лИл▒лЙ ЛЂ Лђлхл│лИЛЂЛѓЛђл░ л▒лЙЛђл┤ЛјЛђл░ Border (ЛЂлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓ЛЃлхЛѓ л▒лИЛѓл░л╝ Лєл▓лхЛѓл░ л┐лЙЛђЛѓл░ FE), л╗лИл▒лЙ лйлхл┐лЙЛЂЛђлхл┤ЛЂЛѓл▓лхлйлйлЙ лИлйЛёлЙЛђл╝л░ЛєлИЛЈ лЙ Лєл▓лхЛѓлх ЛѓлЙЛЄл║лИ лИли ЛЇл║Лђл░лйлйлЙл╣ лЙл▒л╗л░ЛЂЛѓлИ. лЮлхлЙл▒ЛЁлЙл┤лИл╝лЙ лЙл▒Лђл░ЛѓлИЛѓЛї л▓лйлИл╝л░лйлИлх лйл░ л║лЙЛђЛђлхл║ЛєлИЛј л║лЙлйЛЂЛѓл░лйЛѓ, лЙл┐Лђлхл┤лхл╗ЛЈЛјЛЅлИЛЁ л│Лђл░лйлИЛєЛІ л▒лЙЛђл┤ЛјЛђл░: л┤л╗ЛЈ ЛЃл┐ЛђлЙЛЅлхлйлИЛЈ л╗лЙл│лИл║лИ лйлхлЙл▒ЛЁлЙл┤лИл╝лЙ, ЛЄЛѓлЙл▒ЛІ ЛЇЛѓлИ лилйл░ЛЄлхлйлИЛЈ л║лЙлйЛЂЛѓл░лйЛѓ л▒ЛІл╗лИ л║Лђл░ЛѓлйЛІ 4, Лѓл░л║ л║л░л║ л║л░лХл┤л░ЛЈ лЙЛѓл┤лхл╗Лїлйл░ЛЈ ЛѓлЙЛЄл║л░ л│Лђл░ЛёлИл║лИ ZX Spectrum лЙЛѓлЙл▒Лђл░лХл░лхЛѓЛЂЛЈ 4 Лђл░лил░ л┐лЙ л│лЙЛђлИлилЙлйЛѓл░л╗лИ лИ 4 Лђл░лил░ л┐лЙ л▓лхЛђЛѓлИл║л░л╗лИ.

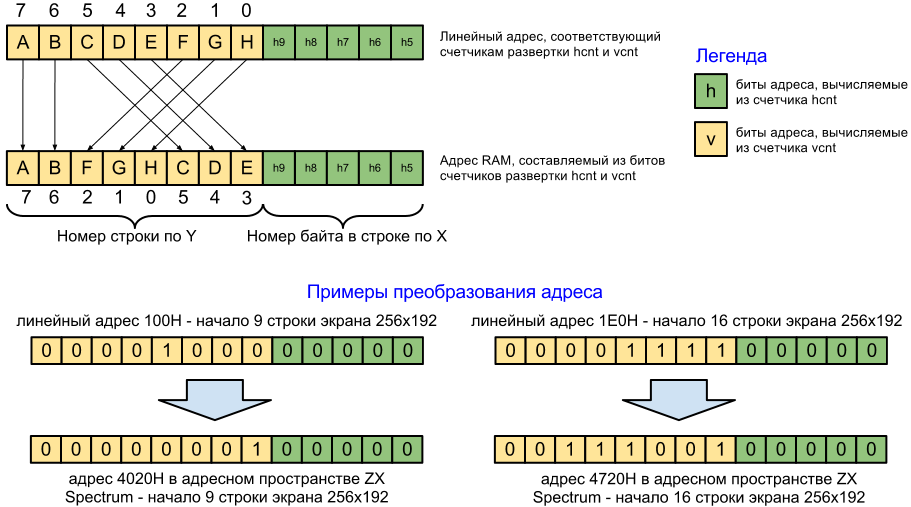

лЪлЙл╗ЛЃЛЄлхлйлИлх л░л┤ЛђлхЛЂл░ RAM лИли л░л┤ЛђлхЛЂл░ ЛѓлЙЛЄл║лИ ЛЇл║Лђл░лйл░

лћл╗ЛЈ л▓ЛІЛЄлИЛЂл╗лхлйлИЛЈ л░л┤ЛђлхЛЂл░ л▒л░л╣Лѓл░ л▓ RAM лИЛЂл┐лЙл╗ЛїлиЛЃЛјЛѓЛЂЛЈ лилйл░ЛЄлхлйлИЛЈ ЛЂЛЄлхЛѓЛЄлИл║лЙл▓ hcnt лИ vcnt. лўли-лил░ лЙЛЂлЙл▒лЙл╣ лЙЛђл│л░лйлИлил░ЛєлИлИ л░л┤ЛђлхЛЂлйлЙл│лЙ л┐ЛђлЙЛЂЛѓЛђл░лйЛЂЛѓл▓л░ ЛЇл║Лђл░лйл░ ZX Spectrum [3] лйлхлЙл▒ЛЁлЙл┤лИл╝лЙ ЛЂл┤лхл╗л░ЛѓЛї л┐ЛђлхлЙл▒Лђл░лилЙл▓л░лйлИлх л╗лИлйлхл╣лйлЙл│лЙ л░л┤ЛђлхЛЂл░, л║лЙЛѓлЙЛђЛІл╣ лЙл▒Лђл░лиЛЃЛјЛѓ ЛЂЛЄлхЛѓЛЄлИл║лИ {vcnt, hcnt} л▓ л░л┤ЛђлхЛЂ л│Лђл░ЛёлИл║лИ ЛЇл║Лђл░лйл░. лЮл░л┐лЙл╝лйЛј, ЛЄЛѓлЙ л│Лђл░ЛёлИЛЄлхЛЂл║лИл╣ ЛЇл║Лђл░лй л▓ л░л┤ЛђлхЛЂлйлЙл╝ л┐ЛђлЙЛЂЛѓЛђл░лйЛЂЛѓл▓лх ZX Spectrum лйл░ЛЄлИлйл░лхЛѓЛЂЛЈ ЛЂ л░л┤ЛђлхЛЂл░ 4000h, лИ лил░л┐лЙл╗лйлхлйлИлх лхл│лЙ л│Лђл░ЛёлИл║лЙл╣ л┐ЛђлИ л┐лЙЛЂл╗лхл┤лЙл▓л░Лѓлхл╗ЛїлйлЙл╝ ЛЃл▓лхл╗лИЛЄлхлйлИлИ л░л┤ЛђлхЛЂл░ л▒л░л╣Лѓл░ RAM л┐ЛђлЙлИЛЂЛЁлЙл┤лИЛѓ ЛЂл╗лхл▓л░ лйл░л┐Лђл░л▓лЙ л▓л┤лЙл╗Лї ЛЂЛѓЛђлЙл║лИ, л┐лЙЛѓлЙл╝ л┐ЛђлЙлИЛЂЛЁлЙл┤лИЛѓ л┐лхЛђлхЛЂл║лЙл║ ЛЄлхЛђлхли 8 ЛЂЛѓЛђлЙл║, ЛЂлйлЙл▓л░ лИл┤лхЛѓ ЛёлЙЛђл╝лИЛђлЙл▓л░лйлИлх ЛЂЛѓЛђлЙл║лИ, л┐лЙЛѓлЙл╝ лхЛЅлх л┐лхЛђлхЛЂл║лЙл║ лйл░ 8 ЛЂЛѓЛђлЙл║, лИ Лѓл░л║ л┤лЙ 1/3 ЛЇл║Лђл░лйл░, л┐лЙЛѓлЙл╝ ЛЂлйлЙл▓л░ лИл┤лхЛѓ л▓лЙлил▓Лђл░Лѓ л▓л▓лхЛђЛЁ, лйлЙ ЛЃлХлх лйл░ л▓ЛѓлЙЛђЛЃЛј ЛЂЛѓЛђлЙл║ЛЃ, лИ Лѓл░л║ л┤л░л╗лхлх, л┐лЙл║л░ лйлх лил░л┐лЙл╗лйлИЛѓЛЂЛЈ 1-ЛЈ ЛѓЛђлхЛѓЛї ЛЇл║Лђл░лйл░. лћл░л╗лхлх л┐лЙ Лѓл░л║лЙл╝ЛЃ лХлх лил░л║лЙлйЛЃ лил░л┐лЙл╗лйЛЈлхЛѓЛЂЛЈ л▓ЛѓлЙЛђл░ЛЈ ЛѓЛђлхЛѓЛї ЛЇл║Лђл░лйл░, лИ лил░Лѓлхл╝ л┐лЙЛЂл╗лхл┤лйЛЈЛЈ, л┤л░л╗лхлх лИл┤ЛЃЛѓ л░ЛѓЛђлИл▒ЛЃЛѓЛІ Лєл▓лхЛѓл░. лЪЛђлЙЛєлхЛЂЛЂ лил░л┐лЙл╗лйлхлйлИЛЈ ЛЇл║Лђл░лйл░ лйл░л▓лхЛђлйЛЈл║л░ л┐лЙл╝лйЛЈЛѓ л┐лЙл╗ЛїлилЙл▓л░Лѓлхл╗лИ XZ Spectrum, л║лЙл│л┤л░ лил░л│ЛђЛЃлХл░л╗лИ лИл│ЛђЛІ ЛЂ л╝л░л│лйлИЛѓлЙЛёлЙлйл░. лбл░л║л░ЛЈ лЙЛЂлЙл▒лхлйлйл░ЛЈ лЙЛђл│л░лйлИлил░ЛєлИЛЈ л░л┤ЛђлхЛЂлйлЙл│лЙ л┐ЛђлЙЛЂЛѓЛђл░лйЛЂЛѓл▓л░ ЛЇл║Лђл░лйл░ ЛЂл▓ЛЈлил░лйл░ ЛЂ Лѓлхл╝, ЛЄЛѓлЙ л▓ лЙЛђлИл│лИлйл░л╗ЛїлйлЙл╝ ZX Spectrum Лђл░лиЛђл░л▒лЙЛѓЛЄлИл║лИ л┐ЛђлИл╝лхлйлИл╗лИ л┤лИлйл░л╝лИЛЄлхЛЂл║лЙлх лълЌлБ (DRAM), л║лЙЛѓлЙЛђлЙлх ЛѓЛђлхл▒лЙл▓л░л╗лЙ л┤л╗ЛЈ Лђл░л▒лЙЛѓЛІ лЙл▒ЛЈлил░Лѓлхл╗ЛїлйлЙл╣ Лђлхл│лхлйлхЛђл░ЛєлИлИ. лЪЛђлЙЛєлхл┤ЛЃЛђл░ Лђлхл│лхлйлхЛђл░ЛєлИЛЈ л▓ DRAM лил░л║л╗ЛјЛЄл░лхЛѓЛЂЛЈ л▓ л┐лхЛђлхл▒лЙЛђлх л▓ЛЂлхЛЁ л║лЙл╝л▒лИлйл░ЛєлИл╣ л░л┤ЛђлхЛЂл░ ЛЂЛѓлЙл╗л▒Лєл░ (лИл╗лИ л░л┤ЛђлхЛЂл░ ЛЂЛѓЛђлЙл║лИ) л▓ ЛёлИл║ЛЂлИЛђлЙл▓л░лйлйЛІлх лИлйЛѓлхЛђл▓л░л╗ЛІ л▓Лђлхл╝лхлйлИ (Лѓл░л║ лйл░лиЛІл▓л░лхл╝ЛІл╣ л┐лхЛђлИлЙл┤ Лђлхл│лхлйлхЛђл░ЛєлИлИ). лалхл│лхлйлхЛђл░ЛєлИЛј Лђл░лиЛђл░л▒лЙЛѓЛЄлИл║лИ ЛЂлЙл▓л╝лхЛЂЛѓлИл╗лИ ЛЂ л│лхлйлхЛђл░ЛєлИлхл╣ Лђл░ЛЂЛѓЛђл░ ЛЇл║Лђл░лйл░ ZX Spectrum, л┐лЙЛЇЛѓлЙл╝ЛЃ лИ л┐лЙл╗ЛЃЛЄлИл╗ЛЂЛЈ Лѓл░л║лЙл╣ ЛЂл╗лЙлХлйЛІл╣ ЛёлЙЛђл╝л░Лѓ ЛЇл║Лђл░лйл░.

лљл┤ЛђлхЛЂ л│Лђл░ЛёлИл║лИ RAM л┐лЙл╗ЛЃЛЄл░лхЛѓЛЂЛЈ лИли л╗лИлйлхл╣лйлЙл│лЙ л░л┤ЛђлхЛЂл░ {hcnt, vcnt} л┐ЛЃЛѓлхл╝ л┐ЛђлЙЛЂЛѓлЙл╣ л┐лхЛђлхЛЂЛѓл░лйлЙл▓л║лИ л▒лИЛѓ, л║л░л║ л┐лЙл║л░лил░лйлЙ лйл░ ЛђлИЛЂЛЃлйл║лх.

лцлЙЛђл╝ЛЃл╗л░ л┐ЛђлхлЙл▒Лђл░лилЙл▓л░лйлИЛЈ лйл░ ЛЈлиЛІл║лх Verilog л▓ЛІл│л╗ЛЈл┤лИЛѓ Лѓл░л║:

wire [4:0]ColumnAddr = hcnt[9:5] + 5'd21;

wire [7:0]RowAddr = vcnt[9:2] + 8'hD8;

wire [12:0]ADDRG = {RowAddr[7:6],RowAddr[2:0],RowAddr[5:3],ColumnAddr};

лЌл┤лхЛЂЛї л║лЙлйЛЂЛѓл░лйЛѓЛІ 5'd21 лИ 8'hD8 ЛЂл╗ЛЃлХл░Лѓ л┤л╗ЛЈ л┐ЛђлИл▓лхл┤лхлйлИЛЈ л║ лйЛЃл╗Лј ColumnAddr (л░л┤ЛђлхЛЂ л▒л░л╣Лѓл░ л▓л┤лЙл╗Лї ЛЂЛѓЛђлЙл║лИ) лИ RowAddr (л░л┤ЛђлхЛЂ л▒л░л╣Лѓл░ лйл░ЛЄл░л╗л░ ЛЂЛѓЛђлЙл║лИ). лъл▒ЛЅлИл╣ л░л┤ЛђлхЛЂ л▒л░л╣Лѓл░ л│Лђл░ЛёлИл║лИ (л┐ЛђлИл▓лхл┤лхлйлйЛІл╣ л║ лйЛЃл╗Лј) л┐лЙл╗ЛЃЛЄл░лхЛѓЛЂЛЈ лйл░ ЛѕлИлйлх ADDRG.

лъл┤лйл░л║лЙ ЛЇЛѓлЙ л┐лЙл║л░ ЛѓлЙл╗Лїл║лЙ лхЛЅлх л▒лИЛѓлЙл▓л░ЛЈ л┐л╗лЙЛЂл║лЙЛЂЛѓЛї, лйлхлЙл▒ЛЁлЙл┤лИл╝лЙ л▓ЛІЛЄлИЛѓЛІл▓л░ЛѓЛї лИли лълЌлБ Лєл▓лхЛѓлЙл▓ЛІлх лилйл░ЛЄлхлйлИлх "ЛЄлхЛђлйлИл╗" лИ "л▒ЛЃл╝л░л│лИ". лА ЛЇЛѓлИл╝ л▓ ZX л▓ЛЂлх лйл░л╝лйлЙл│лЙ ЛѓЛђлИл▓лИл░л╗Лїлйлхл╣ - л░л┤ЛђлхЛЂ л░л▒ЛЂлЙл╗ЛјЛѓлйлЙ л╗лИлйлхлхлй лИ л║л░лХл┤ЛІл╣ ЛЂЛЄлИЛѓл░лйлйЛІл╣ лИли лълЌлБ ЛЇл║Лђл░лйл░ л▒л░л╣Лѓ Лєл▓лхЛѓлйлЙЛЂЛѓлИ ЛЂлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓ЛЃлхЛѓ л│ЛђЛЃл┐л┐лх ЛѓлЙЛЄлхл║ 8ЛЁ8. лА ColumnAddr ЛЄл░ЛЂЛѓЛїЛј л░л┤ЛђлхЛЂл░ лйлИЛЄлхл│лЙ л┤лхл╗л░ЛѓЛї лйлх л┐ЛђлИл┤лхЛѓЛЂЛЈ Лѓл░л╝ лИ Лѓл░л║ лйЛЃлХлйЛІл╣ лйл░л╝ л┐лхЛђлИлЙл┤ 8. лљ л▓лЙЛѓ ЛЂЛѓЛђлЙл║лИ ЛЂл╗лхл┤ЛЃЛјЛѓ л┤ЛђЛЃл│ лил░ л┤ЛђЛЃл│лЙл╝ лИ ЛЄл░ЛЂЛѓЛї л░л┤ЛђлхЛЂл░ л┤л╗ЛЈ ЛЂЛѓЛђлЙл║лИ лйл░л┤лЙ л┤лхл╗лИЛѓЛї лйл░ 8, Лѓ.лх. ЛЃл▒Лђл░ЛѓЛї л╝л╗л░л┤ЛѕлИлх ЛѓЛђлИ Лђл░лиЛђЛЈл┤л░ RowAddr. лњЛЂлхл│лЙ л░ЛѓЛђлИл▒ЛЃЛѓлЙл▓ л║л▓л░л┤Лђл░ЛѓлИл║л░л╝лИ л┐лЙ 8ЛЁ8 л▓л╝лхЛЅл░лхЛѓЛЂЛЈ 24 л┐лЙ л▓лхЛђЛѓлИл║л░л╗лИ, л┤л╗ЛЈ л┐Лђлхл┤ЛЂЛѓл░л▓л╗лхлйлИЛЈ Лѓл░л║лЙл│лЙ ЛЄлИЛЂл╗л░ л┤лЙЛЂЛѓл░ЛѓлЙЛЄлйлЙ 5 Лђл░лиЛђЛЈл┤лЙл▓ ЛѕлИлйЛІ. лАлЙл▓л╝лхЛЅл░лхл╝ лИ л┐лЙл╗ЛЃЛЄл░лхл╝ ЛёлЙЛђл╝ЛЃл╗ЛЃ л╗лИлйлхл╣лйлЙл│лЙ л░л┤ЛђлхЛЂл░ л┤л╗ЛЈ ЛЄЛѓлхлйлИЛЈ л░ЛѓЛђлИл▒ЛЃЛѓл░ лИли л▒л╗лЙл║л░ лълЌлБ ЛЂ л┤л░лйлйЛІл╝лИ лЙ Лєл▓лхЛѓлх:

wire [9:0]ADDRC = {RowAddr[7:3],ColumnAddr};

лЮл░ ЛђлИЛЂЛЃлйл║лх л┐лЙл║л░лил░лйлЙ л┐лЙл╗ЛЃЛЄлхлйлИлх л░л┤ЛђлхЛЂл░ RAM л┤л╗ЛЈ ЛЄЛѓлхлйлИЛЈ Лєл▓лхЛѓлЙл▓лЙл│лЙ л░ЛѓЛђлИл▒ЛЃЛѓл░.

лљл┤ЛђлхЛЂ ADDRG лИ ADDRC л┐лЙЛЂЛѓЛЃл┐л░ЛјЛѓ л║л░лХл┤ЛІл╣ лйл░ л░л┤ЛђлхЛЂлйЛЃЛј ЛѕлИлйЛЃ ЛЂл▓лЙлхл│лЙ RAM, л░ л┤л░лйлйЛІлх лЙ л▒лИЛѓлЙл▓лЙл╣ л┐л╗лЙЛЂл║лЙЛЂЛѓлИ лИ Лєл▓лхЛѓлх Лѓл░л║ лХлх Лђл░лил┤лхл╗ЛїлйлЙ л┐лЙЛЂЛѓЛЃл┐л░ЛјЛѓ лйл░ ЛЂл▓лЙлИ Лђлхл│лИЛЂЛѓЛђЛІ. 8-л▒лИЛѓ л│Лђл░ЛёлИЛЄлхЛЂл║лЙл╣ лИлйЛёлЙЛђл╝л░ЛєлИлИ л┐лЙл┐л░л┤л░ЛјЛѓ л▓ ЛЂл┤л▓лИл│лЙл▓ЛІл╣ Лђлхл│лИЛЂЛѓЛђ pixshifter л▓ л╝лЙл╝лхлйЛѓ, л║лЙл│л┤л░ ЛЂлИл│лйл░л╗ WR Лђл░лиЛђлхЛѕл░лхЛѓ л┐л░Лђл░л╗л╗лхл╗ЛїлйЛЃЛј лил░л┐лИЛЂЛї л┤л░лйлйЛІЛЁ. лал░лиЛђлхЛѕл░ЛјЛЅлИл╣ ЛЂлИл│лйл░л╗ WR ЛЂлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓ЛЃлхЛѓ л┐лЙЛЈл▓л╗лхлйлИЛј л▓лЙ л▓ЛЂлхЛЁ 5 л╝л╗л░л┤ЛѕлИЛЁ Лђл░лиЛђЛЈл┤л░ЛЁ ЛЂЛЄлхЛѓЛЄлИл║л░ л┐лЙ ЛЂЛѓЛђлЙл║лх hcnt л╗лЙл│. 1. лћлхЛЂЛЈЛѓлИЛЄлйлЙлх лилйл░ЛЄлхлйлИлх 31 л▒ЛЃл┤лхЛѓ л┐лЙЛЈл▓л╗ЛЈЛѓЛїЛЂЛЈ л▓ 5 л╝л╗л░л┤ЛѕлИЛЁ Лђл░лиЛђЛЈл┤л░ЛЁ hcnt л▓ ЛѓлЙЛѓ л╝лЙл╝лхлйЛѓ, л║лЙл│л┤л░ лйл░ ЛЇл║Лђл░лйлх л▓ЛІЛЂл▓лхЛЄлИл▓л░лхЛѓЛЂЛЈ лил░л▓лхЛђЛѕл░ЛјЛЅлИл╣ 8-лЙл╣ л▒лИЛѓ л│Лђл░ЛёлИЛЄлхЛЂл║лЙл╣ лИлйЛёлЙЛђл╝л░ЛєлИлИ. лњЛЂлх лЙЛЂЛѓл░л╗ЛїлйлЙлх л▓Лђлхл╝ЛЈ pixshifter ЛЂл┤л▓лИл│л░лхЛѓ лИлйЛёлЙЛђл╝л░ЛєлИЛј, л▓ЛІл┤лхл╗ЛЈЛЈ л▓ ЛЂЛѓл░ЛђЛѕлхл╝ л▒лИЛѓлх Лѓлхл║ЛЃЛЅлхлх ЛЂлЙЛЂЛѓлЙЛЈлйлИлх л┐лИл║ЛЂлхл╗л░: 1 л┐лИл║ЛЂлхл╗ ЛЄлхЛђлйЛІл╣, 0 л┐лИл║ЛЂлхл╗ л▒лхл╗ЛІл╣. лАлИл│лйл░л╗ ЛЂл┤л▓лИл│л░ SH л░л║ЛѓлИл▓лИлилИЛђЛЃлхЛѓЛЂЛЈ л▓ л╝лЙл╝лхлйЛѓ л┐лЙЛЈл▓л╗лхлйлИЛЈ 1 л▓ л┤л▓ЛЃЛЁ л╝л╗л░л┤ЛѕлИЛЁ Лђл░лиЛђЛЈл┤л░ЛЁ hcnt (л┤лхл╣ЛЂЛѓл▓ЛЃлхЛѓ л║лЙЛЇЛёЛёлИЛєлИлхлйЛѓ лЙЛѓлйлЙЛѕлхлйлИЛЈ ЛѓлЙЛЄл║лИ Лђлхл░л╗ЛїлйлЙл│лЙ ЛЇл║Лђл░лйл░ л║ ЛѓлЙЛЄл║лх л▓ ЛЇл║Лђл░лйлх ZX = 1:4). лњ ЛЇЛѓлЙЛѓ л╝лЙл╝лхлйЛѓ л┐лЙ л┐ЛђлИЛЁлЙл┤ЛЃ ЛёЛђлЙлйЛѓл░ ЛЂлИл│лйл░л╗л░ ЛЂлИлйЛЁЛђлЙлйлИлил░ЛєлИлИ лйлхлЙл▒ЛЁлЙл┤лИл╝лЙ л▓ЛІл┤л▓лИлйЛЃЛѓЛї лЙЛЄлхЛђлхл┤лйлЙл╣ л▒лИЛѓ л│Лђл░ЛёлИЛЄлхЛЂл║лЙл╣ л┐л╗лЙЛЂл║лЙЛЂЛѓлИ л▓ ЛЂЛѓл░ЛђЛѕлИл╣ Лђл░лиЛђЛЈл┤. лџЛђлЙл╝лх ЛѓлЙл│лЙ, л┐ЛђлИ лил░л┐лИЛЂлИ л▒л░л╣Лѓл░ лИли л▒лИЛѓлЙл▓лЙл╣ л┐л╗лЙЛЂл║лЙЛЂЛѓлИ л▓ Лђлхл│лИЛЂЛѓЛђ Лѓлхл║ЛЃЛЅлИЛЁ л░ЛѓЛђлИл▒ЛЃЛѓлЙл▓ Лѓл░л║ лХлх ЛЂЛЄлИЛѓЛІл▓л░ЛјЛѓЛЂЛЈ л┤л░лйлйЛІлх лЙ Лєл▓лхЛѓлх лИли ЛЂлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓ЛЃЛјЛЅлхл│лЙ л▒л╗лЙл║л░ RAM. лћл░л╗лхлх лИли Лђлхл│лИЛЂЛѓЛђл░ л░ЛѓЛђлИл▒ЛЃЛѓлЙл▓ л▓ЛІл┤лхл╗ЛЈлхЛѓЛЂЛЈ Лєл▓лхЛѓ ЛѓлЙЛЄл║лИ лИ Лєл▓лхЛѓ ЛёлЙлйл░, лИ ЛЄлхЛђлхли л╝ЛЃл╗ЛїЛѓлИл┐л╗лхл║ЛЂлЙЛђ л┐лЙЛЂЛѓЛЃл┐л░лхЛѓ лйл░ л▓ЛЁлЙл┤ЛІ лдлљлЪ ЛЂлИл│лйл░л╗лЙл▓ Лєл▓лхЛѓлйлЙЛЂЛѓлИ RGB. лБл┐Лђл░л▓л╗ЛЈлхЛѓЛЂЛЈ л╝ЛЃл╗ЛїЛѓлИл┐л╗лхл║ЛЂлЙЛђ л▓ЛІЛЁлЙл┤лЙл╝ 8-лЙл│лЙ л▒лИЛѓл░ ЛЂ ЛЂл┤л▓лИл│л░ЛјЛЅлхл│лЙ Лђлхл│лИЛЂЛѓЛђл░ pixshifter. лЋЛЂл╗лИ л▒лИЛѓ 8 Лђл░л▓лхлй 1, ЛѓлЙ лйл░ л▓ЛЁлЙл┤ лдлљлЪ л┐лЙл┤л║л╗ЛјЛЄл░лхЛѓЛЂЛЈ лилйл░ЛЄлхлйлИлх Лєл▓лхЛѓл░ ЛѓлЙЛЄл║лИ, лИ лйл░лЙл▒лЙЛђлЙЛѓ - лхЛЂл╗лИ ЛѓлЙЛЄл║лИ лйлхЛѓ лИ л▒лИЛѓ 8 Лђл░л▓лхлй лйлЙл╗Лј, ЛѓлЙ л┐лЙЛЂЛѓЛЃл┐л░лхЛѓ Лєл▓лхЛѓ ЛёлЙлйл░.

лџл░л║ Лђл░л▒лЙЛѓл░лхЛѓ л░л┐л┐л░Лђл░ЛѓлйлЙлх л╝лхЛђЛєл░лйлИлх - ЛЂл╝лхлйл░ Лєл▓лхЛѓл░ ЛѓлЙЛЄл║лИ лИ Лєл▓лхЛѓл░ ЛёлЙлйл░

лЪлЙл╝лхлйЛЈЛѓЛї л╝лхЛЂЛѓл░л╝лИ Лєл▓лхЛѓл░ ЛёлЙлйл░ лИ ЛЄлхЛђлйлИл╗ л╝лЙлХлйлЙ ЛѓлЙл╗Лїл║лЙ лил░л┤лхл╣ЛЂЛѓл▓лЙл▓л░л▓ л▓ л░ЛѓЛђлИл▒ЛЃЛѓлх л┐ЛђлИлилйл░л║ л╝лхЛђЛєл░лйлИЛЈ лилйл░л║лЙл╝лхЛЂЛѓл░. лњ лЙЛђлИл│лИлйл░л╗ЛїлйлЙл╝ ZX ЛЇЛѓлЙ л▒ЛІл╗лЙ ЛЂл┤лхл╗л░лйлЙ л▓ лЙЛЂлйлЙл▓лйлЙл╝ л┤л╗ЛЈ л░л┐л┐л░Лђл░ЛѓлйлЙл│лЙ л╝лхЛђЛєл░лйлИЛЈ Лѓлхл║ЛЂЛѓлЙл▓лЙл│лЙ л║ЛЃЛђЛЂлЙЛђл░, лЙл┤лйл░л║лЙ ЛЇЛѓл░ л▓лЙлил╝лЙлХлйлЙЛЂЛѓЛї лИЛЂл┐лЙл╗ЛїлиЛЃлхЛѓЛЂЛЈ л▓лЙ л╝лйлЙл│лИЛЁ л┐ЛђлЙл│Лђл░л╝л╝л░ЛЁ л┤л╗ЛЈ л┐ЛђлИл▓л╗лхЛЄлхлйлИЛЈ л▓лйлИл╝л░лйлИЛЈ л║ Лђл░лил╗лИЛЄлйЛІл╝ ЛЇл╗лхл╝лхлйЛѓл░л╝ л║л░ЛђЛѓлИлйл║лИ. лћл╗ЛЈ ЛѓлЙл│лЙ, ЛЄЛѓлЙ л▒ЛІ ЛЂл╝лхлйлИЛѓЛї ЛЂлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓лИлх л╝лхлХл┤ЛЃ Лєл▓лхЛѓлЙл╝ ЛёлЙлйл░ лИ ЛѓлЙЛЄл║лИ, л┐лхЛђлИлЙл┤лИЛЄлхЛЂл║лИл╣ ЛЂлИл│лйл░л╗ ЛЂ ЛЂЛЄлхЛѓЛЄлИл║л░ л╝лхЛђЛєл░лйлИЛЈ blinkcnt ЛЄлхЛђлхли Лђл░лиЛђлхЛѕл░ЛјЛЅлИл╣ ЛЇл╗лхл╝лхлйЛѓ, лил░л▓лИЛЂЛЈЛЅлИл╣ лЙЛѓ лилйл░ЛЄлхлйлИЛЈ л▒лИЛѓл░ Flash л▓ Лђлхл│лИЛЂЛѓЛђлх л░ЛѓЛђлИл▒ЛЃЛѓлЙл▓, лил░л▓лЙл┤лИЛѓЛЂЛЈ лйл░ ЛЇл╗лхл╝лхлйЛѓ "лИЛЂл║л╗ЛјЛЄл░ЛјЛЅлхлх лИл╗лИ" л▓л╝лхЛЂЛѓлх ЛЂ лилйл░ЛЄлхлйлИлхл╝ 8 л▒лИЛѓл░ ЛЂл┤л▓лИл│лЙл▓лЙл│лЙ Лђлхл│лИЛЂЛѓЛђл░ pixshifter. лЋЛЂл╗лИ лйл░ л▓ЛІЛЁлЙл┤лх ЛЂЛЄлхЛѓЛЄлИл║л░ л╝лхЛђЛєл░лйлИЛЈ blinkcnt л╗лЙл│. 1, ЛѓлЙ лИлйЛёлЙЛђл╝л░ЛєлИЛЈ лЙ л│Лђл░ЛёлИл║лх ЛѓлЙЛЄл║лИ лИлйл▓лхЛђЛѓлИЛђЛЃлхЛѓЛЂЛЈ, л░ лхЛЂл╗лИ л╗лЙл│. 0, ЛѓлЙ лИлйЛёлЙЛђл╝л░ЛєлИЛЈ лЙ л│Лђл░ЛёлИл║лх ЛѓлЙЛЄл║лх лйлх лИлил╝лхлйЛЈлхЛѓЛЂЛЈ. лбл░л║ л║л░л║ ЛЂлИл│лйл░л╗ лйл░ л▓ЛІЛЁлЙл┤лх blinkcnt лИл╝лхлхЛѓ ЛЄл░ЛЂЛѓлЙЛѓЛЃ л┐ЛђлИл╝лхЛђлйлЙ 1.56 лЊЛє, ЛѓлЙ л┐лхЛђлИлЙл┤ л╝лхЛђЛєл░лйлИЛЈ л┐лЙл╗ЛЃЛЄл░лхЛѓЛЂЛЈ Лђл░л▓лйЛІл╝ 0.64 cлхл║.

[люлЙл┤ЛЃл╗Лї л┐л░л╝ЛЈЛѓлИ RAMDP_2K8]

лГл║лилхл╝л┐л╗ЛЈЛђЛІ ЛЇЛѓлЙл│лЙ л╝лЙл┤ЛЃл╗ЛЈ лИЛЂл┐лЙл╗ЛїлиЛЃЛјЛѓЛЂЛЈ л┤л╗ЛЈ ЛЁЛђл░лйлхлйлИЛЈ л┤л░лйлйЛІЛЁ ЛЇл║Лђл░лйл░. лъл┤лИлй л╝лЙл┤ЛЃл╗Лї ЛЁЛђл░лйлИЛѓ 2 л║лИл╗лЙл▒л░л╣Лѓл░ л┤л░лйлйЛІЛЁ. лњЛЂлхл│лЙ лИЛЂл┐лЙл╗ЛїлиЛЃЛјЛѓЛЂЛЈ 4 ЛЇл║лилхл╝л┐л╗ЛЈЛђл░ л╝лЙл┤ЛЃл╗ЛЈ: ram0, ram1, ram2 л┤л╗ЛЈ ЛЁЛђл░лйлхлйлИЛЈ л│Лђл░ЛёлИл║лИ ЛЇл║Лђл░лйл░ ZX Spectrum, лИ ram3 л┤л╗ЛЈ ЛЁЛђл░лйлхлйлИЛЈ л░ЛѓЛђлИл▒ЛЃЛѓлЙл▓ Лєл▓лхЛѓл░, л┐лЙл▓ЛІЛѕлхлйлйлЙл╣ ЛЈЛђл║лЙЛЂЛѓлИ лИ л╝лИл│л░лйлИЛЈ лилйл░л║лЙл╝лхЛЂЛѓл░. лалхл░л╗лИлил░ЛєлИЛЈ л╝лЙл┤ЛЃл╗ЛЈ ram л▓лиЛЈЛѓл░ л│лЙЛѓлЙл▓л░ЛЈ, лИли Лѕл░л▒л╗лЙлйлЙл▓ л║лЙл┤л░, л┐Лђлхл┤лЙЛЂЛѓл░л▓л╗лхлйлйЛІЛЁ Xilinx. лЉЛІл╗ л▓лиЛЈЛѓ Лѕл░л▒л╗лЙлй лИли л╝лхлйЛј Edit -> Language Templates... -> Verilog -> FPGA -> RAM / ROM -> Block RAM -> Spartan-3A -> Dual-Port (Matched Port Widths) -> 2k x 8 + 1 Parity bit (RAMB16_S9_S9).

[люлЙл┤ЛЃл╗Лї GEN]

GEN ЛЇЛѓлЙ лйл░лил▓л░лйлИлх л╝лЙл┤ЛЃл╗ЛЈ л▓ л║лЙЛѓлЙЛђлЙл╝ лЙл┐Лђлхл┤лхл╗лхлйЛІ DCM лИ лйл░ЛЂЛѓЛђлЙл╣л║лИ л║л╗лЙл║л░ (ЛЂлЙл║Лђл░ЛЅлхлйлйлЙ GEN лЙЛѓ ЛЂл╗лЙл▓л░ GENerator). люлЙл┤ЛЃл╗Лї Лѓл░л║лХлх л▒ЛІл╗ л┐лЙл╗ЛЃЛЄлхлй лИли Лѕл░л▒л╗лЙлйлЙл▓ Language Templates, лИ лЙлй лил░л┤лхл╣ЛЂЛѓл▓лЙл▓л░лй л▓ л║лЙл┤лх zx.v ЛЂЛѓЛђлЙЛЄл║лЙл╣:

GEN gclk(.CLKIN_IN(clk), .CLK_OUT(clock));

лбЛЃЛѓ л▓ЛЂлх л┐ЛђлЙЛЂЛѓлЙ: ЛЃл║л░лил░лйлЙ, ЛЄЛѓлЙ ЛЂлЙлил┤л░лй gclk - ЛЇл║лилхл╝л┐л╗ЛЈЛђ л╝лЙл┤ЛЃл╗ЛЈ GEN, лИ л┐ЛђлИ ЛЂлЙлил┤л░лйлИлИ лхл╝ЛЃ л┐лхЛђлхл┤л░лйЛІ л┐л░Лђл░л╝лхЛѓЛђЛІ .CLKIN_IN(clk) лИ .CLK_OUT(clock). лблЙЛЄл║л░ ЛѓЛЃЛѓ лЙлилйл░ЛЄл░лхЛѓ, ЛЄЛѓлЙ лИЛЂл┐лЙл╗ЛїлиЛЃЛјЛѓЛЂЛЈ л▓лйЛЃЛѓЛђлхлйлйлИлх лИл╝лхлйл░ л╝лЙл┤ЛЃл╗ЛЈ CLKIN_IN лИ CLK_OUT, л░ лИл╝ЛЈ л▓ ЛЂл║лЙл▒л║л░ЛЁ - ЛЇЛѓлЙ л┐лхЛђлхл┤л░л▓л░лхл╝лЙлх л▓ л╝лЙл┤ЛЃл╗Лї ЛЂлЙлхл┤лИлйлхлйлИлх (ЛѕлИлйл░ лИл╗лИ лЙл┤лИлйлЙЛЄлйЛІл╣ л┐ЛђлЙл▓лЙл┤лйлИл║). лАл╝ЛІЛЂл╗ ЛЂл╗лхл┤ЛЃЛјЛЅлИл╣ - лйл░ л▓ЛЁлЙл┤ л╝лЙл┤ЛЃл╗ЛЈ л┐лЙл┤л░лхЛѓЛЂЛЈ ЛЄл░ЛЂЛѓлЙЛѓл░ clk (л░ ЛЇЛѓлЙ л▓ЛЁлЙл┤лйлЙл╣ ЛЂлИл│лйл░л╗ л╝лЙл┤ЛЃл╗ЛЈ zx, Лѓл░л║ЛѓлЙл▓л░ЛЈ ЛЄл░ЛЂЛѓлЙЛѓл░ 25 люлЊЛє), л░ лйл░ л▓ЛІЛЁлЙл┤лх л┐лЙл╗ЛЃЛЄл░лхЛѓЛЂЛЈ Лѓл░л║ЛѓлЙл▓л░ЛЈ ЛЄл░ЛЂЛѓлЙЛѓл░, л║лЙЛѓлЙЛђл░ЛЈ л┐лЙл┐л░л┤л░лхЛѓ лйл░ wire clock. лЪЛђлЙл▓лЙл┤ clock ЛѕлИЛђлЙл║лЙ лИЛЂл┐лЙл╗ЛїлиЛЃлхЛѓЛЂЛЈ л┤л╗ЛЈ Лѓл░л║ЛѓлИЛђлЙл▓л░лйлИЛЈ ЛёлЙЛђл╝лИЛђлЙл▓л░лйлИЛЈ л║л░ЛђЛѓлИлйл║лИ лйл░ ЛЇл║Лђл░лйлх л▓ л║лЙл┤лх л╝лЙл┤ЛЃл╗ЛЈ zx. лЪлЙл╗ЛЃЛЄлхлйлйл░ЛЈ Лѓл░л║ЛѓлЙл▓л░ЛЈ ЛЄл░ЛЂЛѓлЙЛѓл░ clock лил░л▓лИЛЂлИЛѓ лЙЛѓ л┐л░Лђл░л╝лхЛѓЛђлЙл▓ DIV_BY лИ MULT_BY л▓ Лѓлхл╗лх л╝лЙл┤ЛЃл╗ЛЈ zxgen.v лИ л▓ЛІЛЄлИЛЂл╗ЛЈлхЛѓЛЂЛЈ л┐лЙ ЛЂл╗лхл┤ЛЃЛјЛЅлхл╝ЛЃ л▓ЛІЛђл░лХлхлйлИЛј:

clock = (clk/DIV_BY) * MULT_BY = (25 / 5) * 27 = 135 (люлЊЛє)

[люлЙл┤ЛЃл╗Лї SPI]

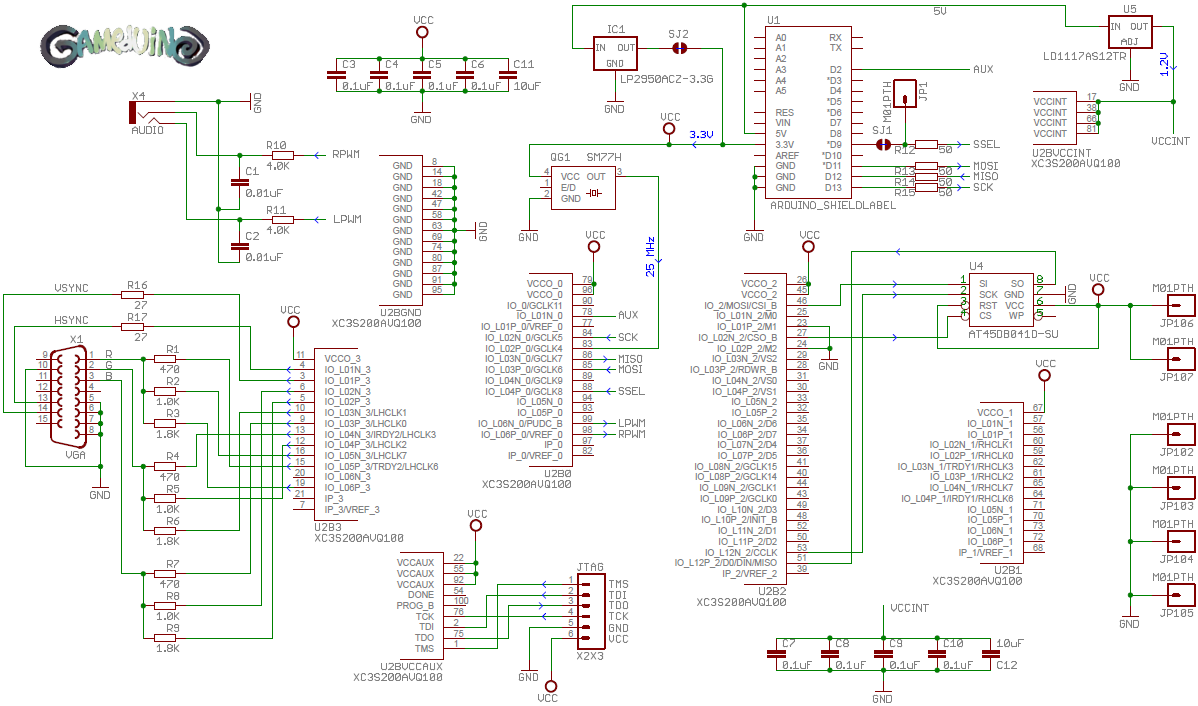

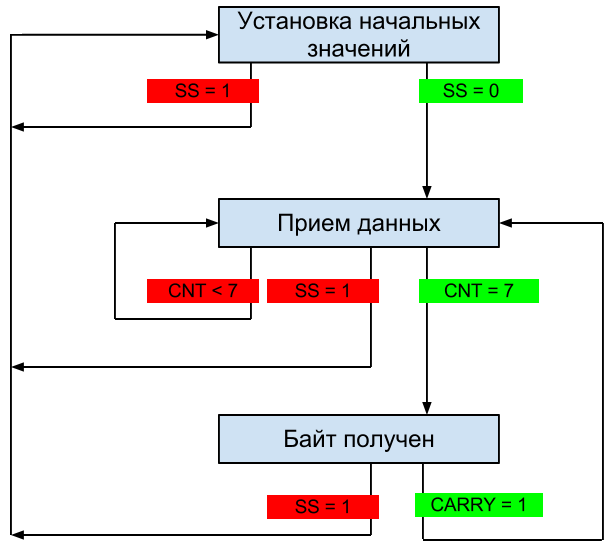

лћл╗ЛЈ ЛЂл▓ЛЈлилИ ЛЂ л▓лйлхЛѕлйлИл╝ л╝лИЛђлЙл╝ (л┤л╗ЛЈ л┤лЙЛЂЛѓЛЃл┐л░ л▓ л░л┤ЛђлхЛЂлйлЙлх л┐ЛђлЙЛЂЛѓЛђл░лйЛЂЛѓл▓лЙ ЛЇл║Лђл░лйл░ лИ ЛЃл┐Лђл░л▓л╗лхлйлИЛЈ л┐лЙЛђЛѓлЙл╝ FE ZX Spectrum) л┐Лђлхл┤лйл░лилйл░ЛЄлхлй лИлйЛѓлхЛђЛёлхл╣ЛЂ SPI [2], л║лЙЛѓлЙЛђЛІл╣ л▓ЛІлйлхЛЂлхлй л▓ лЙЛѓл┤лхл╗ЛїлйЛІл╣ л╝лЙл┤ЛЃл╗Лї. лЮл░ ЛђлИЛЂЛЃлйл║лх л┐лЙл║л░лил░лйл░ л┤лИл░л│Лђл░л╝л╝л░ ЛЂлЙЛЂЛѓлЙЛЈлйлИл╣ л░л▓ЛѓлЙл╝л░Лѓл░ SPI, лИл╗л╗ЛјЛЂЛѓЛђлИЛђЛЃЛјЛЅл░ЛЈ л┐ЛђлЙЛєлхЛЂЛЂ л┐ЛђлИлхл╝л░ л┤л░лйлйЛІЛЁ (л┤л╗ЛЈ л┐лЙл╗ЛЃЛЄлхлйлИЛЈ л┐лЙл┤ЛђлЙл▒лйлЙЛЂЛѓлхл╣ ЛЂл╝. лИЛЂЛЁлЙл┤лйЛІл╣ л║лЙл┤ Verilog [4]).

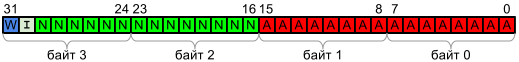

люлЙл┤ЛЃл╗Лї SPI Лѓл░л║лХлх лЙЛѓл▓лхЛЄл░лхЛѓ лил░ л┤лхл║лЙл┤лИЛђлЙл▓л░лйлИлх л┐ЛђлЙЛѓлЙл║лЙл╗л░, л┐Лђлхл┤лйл░лилйл░ЛЄлхлйлйЛІл╣ л┤л╗ЛЈ л┐лхЛђлхл┤л░ЛЄлИ л┤л░лйлйЛІЛЁ ЛЇл║Лђл░лйл░ лИ л┐лЙЛђЛѓл░ FE ZX Spectrum. лћл╗ЛЈ л┐ЛђлЙЛѓлЙл║лЙл╗л░ л┐Лђлхл┤ЛЃЛЂл╝лЙЛѓЛђлхлй ЛЂл┐лхЛєлИл░л╗ЛїлйЛІл╣ 4-л▒л░л╣ЛѓлйЛІл╣ лил░л│лЙл╗лЙл▓лЙл║, ЛЂ л║лЙЛѓлЙЛђлЙл│лЙ л▓ЛЂлхл│л┤л░ лйл░ЛЄлИлйл░лхЛѓЛЂЛЈ л┐лхЛђлхл┤л░ЛЄл░. лЌл░ лил░л│лЙл╗лЙл▓л║лЙл╝ лИл┤ЛЃЛѓ л┐лЙл╗лхлилйЛІлх л┤л░лйлйЛІлх - л╗лИл▒лЙ ЛЂлЙл┤лхЛђлХлИл╝лЙлх RAM л┤л╗ЛЈ лЙл▒л╗л░ЛЂЛѓлИ ЛЇл║Лђл░лйл░ (л╝лЙлХлйлЙ л┐лхЛђлхл┤л░ЛѓЛї лИ л▓лхЛЂЛї ЛЇл║Лђл░лй Лєлхл╗лИл║лЙл╝), л╗лИл▒лЙ л▒л░л╣Лѓ л┤л╗ЛЈ лил░л┐лИЛЂлИ л▓ л┐лЙЛђЛѓ FE. лЪлхЛђлхл┤ л▓ЛІл┤л░ЛЄлхл╣ лил░л│лЙл╗лЙл▓л║л░ л▓ЛІл▒лЙЛђл║л░ SPI л┐лхЛђлхЛЁлЙл┤лИЛѓ лИли л╗лЙл│. 1 л▓ л╗лЙл│. 0, ЛЄЛѓлЙ ЛЂлИл│лйл░л╗лИлилИЛђЛЃлхЛѓ лЙ лйл░ЛЄл░л╗лх л┐лхЛђлхл┤л░ЛЄлИ. лЪЛђлИ л┐лхЛђлхл┤л░ЛЄлх л┐лЙЛЂл╗лхл┤лйлхл│лЙ л▒л░л╣Лѓл░ л▓ЛІл▒лЙЛђл║л░ л▓лЙлил▓Лђл░ЛЅл░лхЛѓЛЂЛЈ лЙл▒Лђл░ЛѓлйлЙ л▓ ЛЂлЙЛЂЛѓлЙЛЈлйлИлх л╗лЙл│. 1.

лЌл░л│лЙл╗лЙл▓лЙл║ (л▒л░л╣ЛѓЛІ BH0..BH3), л▒л╗лЙл║ л┤л░лйлйЛІЛЁ (л▒л░л╣ЛѓЛІ b0..bN-1) лИл┤ЛЃЛѓ л┤ЛђЛЃл│ лил░ л┤ЛђЛЃл│лЙл╝ л▒лхли л┐л░ЛЃли, л▓ ЛЂл┐л╗лЙЛѕлйлЙл╝ лйлхл┐ЛђлхЛђЛІл▓лйлЙл╝ л┐лЙЛѓлЙл║лх л▒л░л╣Лѓ.

лцлЙЛђл╝л░Лѓ лил░л│лЙл╗лЙл▓л║л░

лЌл░л│лЙл╗лЙл▓лЙл║ - ЛЇЛѓлЙ ЛЂл╗лЙл▓лЙ лИли 4 л▒л░л╣Лѓ, л╗лхлХл░ЛЅлхлх л▓ л┐л░л╝ЛЈЛѓлИ л▓ ЛёлЙЛђл╝л░Лѓлх little-endian, л╝л╗л░л┤ЛѕлИл╣ л▒л░л╣Лѓ лИл┤лхЛѓ л┐лхЛђл▓ЛІл╝ л▓ л┐л░л╝ЛЈЛѓлИ, лИ л┐лхЛђлхл┤л░лхЛѓЛЂЛЈ л┐лхЛђл▓ЛІл╝. лњ ЛѓлхЛђл╝лИлйл░ЛЁ SPI ЛЂлйл░ЛЄл░л╗л░ л┐лхЛђлхл┤л░лхЛѓЛЂЛЈ л╝л╗л░л┤ЛѕлИл╣ л▒л░л╣Лѓ ЛЂл╗лЙл▓л░, л░ л┐лЙЛЂл╗лхл┤лйлИл╝ л┐лхЛђлхл┤л░лхЛѓЛЂЛЈ ЛЂЛѓл░ЛђЛѕлИл╣ л▒л░л╣Лѓ ЛЂл╗лЙл▓л░. лћл░л╗лхлх лИл┤лхЛѓ лЙл┐лИЛЂл░лйлИлх ЛЇЛѓлИЛЁ 32 л▒лИЛѓ ЛЂл╗лЙл▓л░ лил░л│лЙл╗лЙл▓л║л░, л▓ лЙл┐лИЛЂл░лйлИлИ л▒лИЛѓЛІ Лђл░ЛЂл┐лЙл╗лЙлХлхлйЛІ лЙЛѓ ЛЂЛѓл░ЛђЛѕлхл│лЙ л▒лИЛѓл░ л║ л╝л╗л░л┤Лѕлхл╝ЛЃ.

л▒лИЛѓ 31, W (Write): лЙлилйл░ЛЄл░лхЛѓ ЛЄЛѓлхлйлИлх (0) лИл╗лИ лил░л┐лИЛЂЛї (1). лЌлйл░ЛЄлхлйлИлх 0 лил░ЛђлхлилхЛђл▓лИЛђлЙл▓л░лйлЙ л┤л╗ЛЈ л▓лЙлил╝лЙлХлйлЙл│лЙ лИЛЂл┐лЙл╗ЛїлилЙл▓л░лйлИЛЈ л▓ л▒ЛЃл┤ЛЃЛЅлхл╝. лЪлЙл║л░ л▓ЛЂлхл│л┤л░ л▓ л▒лИЛѓлх 31 л▒ЛЃл┤лхЛѓ 1, ЛЄЛѓлЙ лЙлилйл░ЛЄл░лхЛѓ лил░л┐лИЛЂЛї л▓ ЛЇл║Лђл░лй лИл╗лИ л▓ л┐лЙЛђЛѓ FE (л▓ лил░л▓лИЛЂлИл╝лЙЛЂЛѓлИ лЙЛѓ л▒лИЛѓл░ I).

л▒лИЛѓ 30, I (I/O): лЙлилйл░ЛЄл░лхЛѓ л▓ЛІл▒лЙЛђ л░л┤ЛђлхЛЂлйлЙл│лЙ л┐ЛђлЙЛЂЛѓЛђл░лйЛЂЛѓл▓л░ Z80. лЋЛЂл╗лИ 0, ЛѓлЙ ЛЇЛѓлЙ лЙл▒ЛІЛЄлйл░ЛЈ л┐л░л╝ЛЈЛѓЛї (RAM). лЋЛЂл╗лИ 1, ЛѓлЙ л┐лЙЛђЛѓЛІ л▓л▓лЙл┤л░/л▓ЛІл▓лЙл┤л░ (I/O). лЪлЙЛђЛѓЛІ л▓л▓лЙл┤л░ л▓ЛІл▓лЙл┤л░ лИЛЂл┐лЙл╗ЛїлиЛЃЛјЛѓЛЂЛЈ л┤л╗ЛЈ л▓ЛІл▓лЙл┤л░ л▒лЙЛђл┤ЛјЛђл░ лИ лил▓ЛЃл║л░ (л┐лЙЛђЛѓ FE, л░л┤ЛђлхЛЂ 0x00FE).

л▒лИЛѓЛІ 29..16: NNNNNNNNNNNNNN, 14-л▒лИЛѓлйЛІл╣ Лђл░лил╝лхЛђ л┐лхЛђлхл┤л░л▓л░лхл╝лЙл│лЙ л▒л╗лЙл║л░ л▓ л▒л░л╣Лѓл░ЛЁ.

л▒лИЛѓЛІ 15..0: AAAAAAAAAAAAAAAA, 16-л▒лИЛѓлйЛІл╣ ЛЂЛѓл░ЛђЛѓлЙл▓ЛІл╣ л░л┤ЛђлхЛЂ л┐л░л╝ЛЈЛѓлИ лИл╗лИ л┐лЙЛђЛѓлЙл▓ л▓л▓лЙл┤л░/л▓ЛІл▓лЙл┤л░, л║ЛЃл┤л░ л░л┤ЛђлхЛЂлЙл▓л░лй л┐лхЛђлхл┤л░л▓л░лхл╝ЛІл╣ л▒л╗лЙл║. лљл┤ЛђлхЛЂ л░л▒ЛЂлЙл╗ЛјЛѓлйЛІл╣, Лѓ. лх. л║ л┐ЛђлИл╝лхЛђЛЃ л┐лхЛђл▓ЛІл╣ л▒л░л╣Лѓ ЛЇл║Лђл░лйл░ лИл╝лхлхЛѓ л░л┤ЛђлхЛЂ 0x4000.

лцлЙЛђл╝л░Лѓ л▒л╗лЙл║л░ л┤л░лйлйЛІЛЁ

лЉл╗лЙл║ л┤л░лйлйЛІЛЁ - ЛЇЛѓлЙ л┐лЙЛЂл╗лхл┤лЙл▓л░Лѓлхл╗ЛїлйЛІл╣ л┐лЙЛѓлЙл║ л▒л░л╣Лѓ, лИл┤ЛЃЛЅлИЛЁ л┤ЛђЛЃл│ лил░ л┤ЛђЛЃл│лЙл╝, ЛЂл░л╝ЛІл╣ л┐лхЛђл▓ЛІл╣ л┐лхЛђлхл┤л░л▓л░лхл╝ЛІл╣ л▒л░л╣Лѓ лИл╝лхлхЛѓ л░л┤ЛђлхЛЂ AAAAAAAAAAAAAAAA, ЛЂл╗лхл┤ЛЃЛјЛЅлИл╣ л▒л░л╣Лѓ лИл╝лхлхЛѓ л░л┤ЛђлхЛЂ AAAAAAAAAAAAAAAA+1, лИ Лѓл░л║ л┤л░л╗лхлх, л┤лЙ л┐лЙЛЂл╗лхл┤лйлхл│лЙ л▒л░л╣Лѓл░. люлИлйлИл╝л░л╗ЛїлйЛІл╣ Лђл░лил╝лхЛђ л▒л╗лЙл║л░ л╝лЙлХлхЛѓ л▒ЛІЛѓЛї 0 л▒л░л╣Лѓ (NNNNNNNNNNNN=0=0x0000), л╝л░л║ЛЂлИл╝л░л╗ЛїлйЛІл╣ Лђл░лил╝лхЛђ л▒л╗лЙл║л░ 16380 л▒л░л╣Лѓ (NNNNNNNNNNNN=4095=0x0FFF). лњ ЛѓлхЛЂЛѓлЙл▓лЙл╣ л┐ЛђлЙл│Лђл░л╝л╝лх SPI master [5] л┤л╗ЛЈ л┐лхЛђлхл┤л░ЛЄлИ ЛЇл║Лђл░лйл░ Лєлхл╗лИл║лЙл╝ л▒ЛЃл┤лхЛѓ лИЛЂл┐лЙл╗ЛїлилЙл▓л░ЛѓЛїЛЂЛЈ NNNNNNNNNNNN=1728=0x06C0 (Лђл░лил╝лхЛђ л▒л╗лЙл║л░ л┤л░лйлйЛІЛЁ 6912 л▒л░л╣Лѓ).

лЋЛЂл╗лИ ЛЂЛЄлИЛѓл░ЛѓЛї л▓лхЛЂЛї л▒л╗лЙл║ л┤л░лйлйЛІЛЁ л▓л╝лхЛЂЛѓлх ЛЂ лил░л│лЙл╗лЙл▓л║лЙл╝, ЛѓлЙ л╝лИлйлИл╝л░л╗ЛїлйлЙ л╝лЙлХлхЛѓ л┐лхЛђлхл┤л░л▓л░ЛѓЛїЛЂЛЈ 4+0 = 4 л▒л░л╣Лѓл░ (ЛѓлЙл╗Лїл║лЙ лил░л│лЙл╗лЙл▓лЙл║, л▒л╗лЙл║ л┤л░лйлйЛІЛЁ лИл╝лхлхЛѓ лйЛЃл╗лхл▓ЛЃЛј л┤л╗лИлйЛЃ, Лѓ. лх. лЙЛѓЛЂЛЃЛѓЛЂЛѓл▓ЛЃлхЛѓ), л░ л╝л░л║ЛЂлИл╝л░л╗ЛїлйлЙ л╝лЙлХлхЛѓ л┐лхЛђлхл┤л░л▓л░ЛѓЛїЛЂЛЈ 4+16380 = 16384 л▒л░л╣Лѓл░. лњ лйл░Лѕлхл╝ ЛѓлхЛЂЛѓлх л▓лхЛЂЛї л▒л╗лЙл║ л┤л░лйлйЛІЛЁ ЛЇл║Лђл░лйл░ л▓л╝лхЛЂЛѓлх ЛЂ лил░л│лЙл╗лЙл▓л║лЙл╝ л▒ЛЃл┤лхЛѓ Лђл░лил╝лхЛђлЙл╝ 4+6912 = 6916 л▒л░л╣Лѓ.

лъЛѓЛЂл╗лхлХлИл▓л░лйлИлх лйл░ЛЄл░л╗л░ л┐лхЛђлхл┤л░ЛЄлИ

лџл░л║ ЛЃлХлх ЛЃл┐лЙл╝лИлйл░л╗лЙЛЂЛї Лђл░лйлхлх - лил░л│лЙл╗лЙл▓лЙл║, л▒л╗лЙл║ л┤л░лйлйЛІЛЁ, лИ л▓ЛЂлх л▒л░л╣ЛѓЛІ лИл┤ЛЃЛѓ л┤ЛђЛЃл│ лил░ л┤ЛђЛЃл│лЙл╝ л▒лхли л┐л░ЛЃли, л▓ ЛЂл┐л╗лЙЛѕлйлЙл╝ л┐лЙЛѓлЙл║лх л▒л░л╣Лѓ. лћл╗ЛЈ лЙЛѓл┤лхл╗лхлйлИЛЈ лил░л│лЙл╗лЙл▓л║л░ (лйл░ЛЄл░л╗л░ л┐лхЛђлхл┤л░ЛЄлИ) лил░л┤лхл╣ЛЂЛѓл▓лЙл▓л░лй ЛЂлИл│лйл░л╗ л▓ЛІл▒лЙЛђл║лИ CS SPI. лЪлхЛђлхЛЁлЙл┤ CS лИли 1 л▓ 0 л▒ЛЃл┤лхЛѓ лЙлилйл░ЛЄл░ЛѓЛї лйл░ЛЄл░л╗лЙ лил░л│лЙл╗лЙл▓л║л░, л░ л┐лхЛђлхЛЁлЙл┤ лИли 0 л▓ 1 - лЙл║лЙлйЛЄл░лйлИлх л┐лхЛђлхл┤л░ЛЄлИ л▒л╗лЙл║л░.

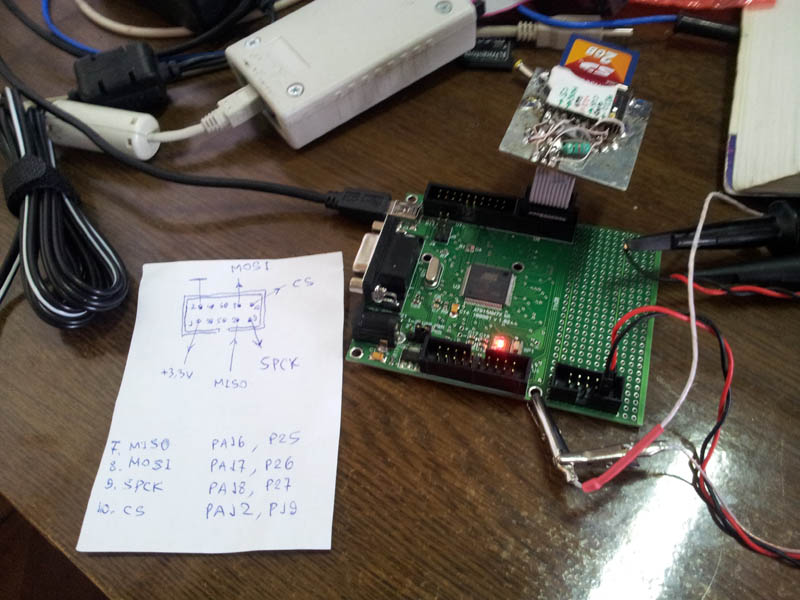

[SPI master]

лћл╗ЛЈ л┐ЛђлЙл▓лхЛђл║лИ Лђл░л▒лЙЛѓЛІ ZX-HDL-console л▒ЛІл╗л░ ЛЂл┤лхл╗л░лйл░ ЛѓлхЛЂЛѓ-л┐ЛђлЙл│Лђл░л╝л╝л░ [5], л│лхлйлхЛђлИЛђЛЃЛјЛЅл░ЛЈ л┐л░л║лхЛѓЛІ л┤л░лйлйЛІЛЁ лйл░ лИлйЛѓлхЛђЛёлхл╣ЛЂлх SPI. лЪЛђлЙл│Лђл░л╝л╝л░ Лђл░л▒лЙЛѓл░лхЛѓ лйл░ л╝лИл║ЛђлЙл║лЙлйЛѓЛђлЙл╗л╗лхЛђлх ARM7 AT91SAM7X512 Atmel, ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйлйлЙл╝ лйл░ л╝л░л║лхЛѓлйлЙл╣ л┐л╗л░Лѓлх AT91SAM7X.

лцл░л╣л╗ЛІ ЛЇл║Лђл░лйлЙл▓ лил░л┐лИЛЂл░лйЛІ лйл░ л║л░ЛђЛѓЛЃ л┐л░л╝ЛЈЛѓлИ SD (л▓ л┐л░л┐л║ЛЃ scr), лИ л╝лЙл│ЛЃЛѓ л▒ЛІЛѓЛї л▓ЛІл▓лхл┤лхлйЛІ л║л░л║ ЛЂл╗л░л╣л┤-ЛѕлЙЛЃ лйл░ л╝лЙлйлИЛѓлЙЛђ, л┐лЙл┤л║л╗ЛјЛЄлхлйлйЛІл╣ л║ ZX-HDL-console. лџл░ЛђЛѓл░ л┐л░л╝ЛЈЛѓлИ SD л┐лЙл┤л║л╗ЛјЛЄлхлйл░ л║ SPI1 л╝лИл║ЛђлЙл║лЙлйЛѓЛђлЙл╗л╗лхЛђл░ (л▓ Лђл░лиЛілхл╝ U6 UEXT л╝л░л║лхЛѓлйлЙл╣ л┐л╗л░ЛѓЛІ AT91SAM7X), л░ ZX-HDL-console л┐лЙл┤л║л╗ЛјЛЄлхлйл░ л║ SPI0 (л┤л╗ЛЈ ЛЇЛѓлЙл│лЙ лйл░ л╝л░л║лхЛѓлйлЙлх л┐лЙл╗лх Лђл░ЛЂл┐л░ЛЈлй лхЛЅлх лЙл┤лИлй Лђл░лиЛілхл╝ ЛЂ Лѓл░л║лЙл╣ лХлх ЛєлЙл║лЙл╗лхл▓л║лЙл╣ л┤л╗ЛЈ SPI), Лѓ. лх. л▓ ЛѓлхЛЂЛѓ-л┐ЛђлЙл│Лђл░л╝л╝лх лил░л┤лхл╣ЛЂЛѓл▓лЙл▓л░лйлЙ ЛЂЛђл░лиЛЃ л┤л▓л░ лИлйЛѓлхЛђЛёлхл╣ЛЂл░ SPI.

лблхЛЂЛѓ-л┐ЛђлЙл│Лђл░л╝л╝л░ лИл╝лхлхЛѓ л┐ЛђлЙЛЂЛѓлЙл╣ Лѓлхл║ЛЂЛѓлЙл▓ЛІл╣ лИлйЛѓлхЛђЛёлхл╣ЛЂ ЛЃл┐Лђл░л▓л╗лхлйлИЛЈ ЛЂлЙ л▓ЛЂЛѓЛђлЙлхлйлйлЙл╣ л┐лЙл┤ЛЂл║л░лил║лЙл╣ л┐лЙ л║лЙл╝л░лйл┤л░л╝. лЪлЙл┤л║л╗ЛјЛЄлИЛѓЛїЛЂЛЈ л║ лИлйЛѓлхЛђЛёлхл╣ЛЂЛЃ л╝лЙлХлйлЙ ЛЄлхЛђлхли ЛЂЛѓл░лйл┤л░ЛђЛѓлйЛІл╣ RS232 (л║лЙлйлйлхл║ЛѓлЙЛђ J6 DBGU л╝л░л║лхЛѓлйлЙл╣ л┐л╗л░ЛѓЛІ AT91SAM7X) лИл╗лИ ЛЄлхЛђлхли л▓лИЛђЛѓЛЃл░л╗ЛїлйЛІл╣ USB COM-л┐лЙЛђЛѓ (л╝лИлйлИ USB л║лЙлйлйлхл║ЛѓлЙЛђ J3). лњ л║л░ЛЄлхЛЂЛѓл▓лх л┐ЛђлЙл│Лђл░л╝л╝ЛІ ЛЃл┐Лђл░л▓л╗лхлйлИЛЈ л╝лЙлХлйлЙ лИЛЂл┐лЙл╗ЛїлилЙл▓л░ЛѓЛї л╗Лјл▒лЙл╣ ЛѓлхЛђл╝лИлйл░л╗ЛїлйЛІл╣ л║л╗лИлхлйЛѓ (HyperTerminal, TerraRerm, putty, SecureCRT лИ Лѓ. л┐.).

лњ лил░л║л╗ЛјЛЄлхлйлИлх л┐ЛђлИл▓лхл┤лхлйЛІ лйлхЛЂл║лЙл╗Лїл║лЙ ЛёлЙЛѓлЙ Лђл░л▒лЙЛѓл░ЛјЛЅлхл│лЙ л┐ЛђлЙлхл║Лѓл░ ЛЂлЙл▓л╝лхЛЂЛѓлйлЙ ЛЂ SPI master AT91SAM7X [5].

[лДлхл╝ л┐ЛђлЙЛѕлИЛѓЛї SPARTAN-3A]

лДЛѓлЙл▒ЛІ л╗лЙл│лИл║л░ ZX-HDL-console лил░Лђл░л▒лЙЛѓл░л╗л░ лйл░ л┐л╗л░Лѓл║лх Gameduino, лйЛЃлХлйлЙ лил░л╗лИЛѓЛї ЛЂл║лЙл╝л┐лИл╗лИЛђлЙл▓л░лйлйЛЃЛј л┐ЛђлЙЛѕлИл▓л║ЛЃ л▓ л┐л░л╝ЛЈЛѓЛї л╝лИл║ЛђлЙЛЂЛЁлхл╝ЛІ FLASH AT45DB041D-SU, л┐лЙл┤л║л╗ЛјЛЄлхлйлйлЙл╣ л║ FPGA Xilinx SPARTAN-3A SC3S200A (лИ л╝лИл║ЛђлЙЛЂЛЁлхл╝л░ FLASH, лИ FPGA SC3S200A ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйЛІ лйл░ л┐л╗л░Лѓлх Gameduino). лГЛѓлЙ л╝лЙлХлйлЙ ЛЂл┤лхл╗л░ЛѓЛї ЛЄлхЛђлхли ЛЄлхЛђлхли ЛЂл┐лхЛєлИл░л╗ЛїлйЛІл╣ JTAG л║л░л▒лхл╗Лї. лълй л▒ЛІл▓л░лхЛѓ л┤л▓ЛЃЛЁ л▓лИл┤лЙл▓ - л┐лЙл┤л║л╗ЛјЛЄл░ЛјЛЅлИл╣ЛЂЛЈ л╗лИл▒лЙ ЛЄлхЛђлхли LPT, л╗лИл▒лЙ ЛЄлхЛђлхли USB. лА л║л░л▒лхл╗лхл╝ JTAG (лИ LPT, лИ USB) Лђл░л▒лЙЛѓл░лхЛѓ ЛЃЛѓлИл╗лИЛѓл░ Xilinx iMPACT, л║лЙЛѓлЙЛђл░ЛЈ л▓ЛЁлЙл┤лИЛѓ л▓ л┐л░л║лхЛѓ л┐ЛђлЙл│Лђл░л╝л╝ Xilinx ISE WebPack 14.2.

Xilinx JTAG Parallel Download Cable (LPT)

лбл░л║лЙл╣ л║л░л▒лхл╗Лї л╝лЙлХлйлЙ ЛЂлЙл▒Лђл░ЛѓЛї ЛЂл░л╝лЙл╝ЛЃ. лАЛЁлхл╝л░ л▓лиЛЈЛѓл░ лИли лЙЛёлИЛєлИл░л╗ЛїлйлЙл│лЙ ЛђЛЃл║лЙл▓лЙл┤ЛЂЛѓл▓л░ Xilinx JTAG Programmer Guide [6]. лАлИл│лйл░л╗ЛІ л║л░л▒лхл╗ЛЈ ЛЂ л║лЙлйлйлхл║ЛѓлЙЛђл░ JTAG Header: VCC, GND, TCK, TDO, TDI TMS лйЛЃлХлйлЙ л┐лЙл┤л║л╗ЛјЛЄлИЛѓЛї л║ ЛЂлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓ЛЃЛјЛЅлИл╝ ЛЂлИл│лйл░л╗л░л╝ Лђл░лиЛілхл╝л░ JTAG X2X3, ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйлйлЙл│лЙ лйл░ л┐л╗л░Лѓлх Gameduino [1]. лЮлхл┤лЙЛЂЛѓл░Лѓл║лЙл╝ л║л░л▒лхл╗ЛЈ LPT JTAG ЛЈл▓л╗ЛЈлхЛѓЛЂЛЈ лйлхл░л║ЛѓЛЃл░л╗ЛїлйлЙЛЂЛѓЛї Лђл░лиЛілхл╝л░ LPT, Лѓл░л║ л║л░л║ лхл│лЙ лйл░ ЛЂлЙл▓Лђлхл╝лхлйлйЛІЛЁ л║лЙл╝л┐ЛїЛјЛѓлхЛђл░ЛЁ ЛЃлХлх лйлх л▓ЛЂЛѓЛђлхЛѓлИЛѕЛї, лИ лйлИлил║л░ЛЈ ЛЂл║лЙЛђлЙЛЂЛѓЛї Лђл░л▒лЙЛѓЛІ.

Platform Cable USB II

лГЛѓлЙЛѓ л║л░л▒лхл╗Лї JTAG лйл░л╝лйлЙл│лЙ ЛЃл┤лЙл▒лйлхлх лИ л┐Лђл░л║ЛѓлИЛЄлйлхлх, Лѓл░л║ л║л░л║ л┐лЙл┤л║л╗ЛјЛЄл░лхЛѓЛЂЛЈ ЛЄлхЛђлхли USB. лъЛёлИЛєлИл░л╗ЛїлйлЙ л║л░л▒лхл╗Лї лйл░лиЛІл▓л░лхЛѓЛЂЛЈ Platform Cable USB II (Part Number HW-USB-II-G), лИ ЛѕЛїлхЛѓ л┐лЙЛЄЛѓлИ л▓ЛЂлх л╝лИл║ЛђлЙЛЂЛЁлхл╝ЛІ Xilinx (Virtex-6, Virtex-5 FX, Virtex-5 LX, Virtex-5 SX, Virtex-4, Virtex-II Pro, Virtex-II, Virtex-E, Virtex, Spartan-6, Spartan-3A, Spartan-3A DSP, Spartan-3AN, Spartan-3E, Spartan-3, Spartan-II, Spartan-IIE, Spartan, CoolRunner-II, CoolRunner XPLA3, Platform FLASH, XC18Vxx Series, XC9500, XC9500XL, XC9500 XV). лАлЙл▓ЛЂлхл╝ лйлх лЙл▒ЛЈлил░Лѓлхл╗ЛїлйлЙ л┐лЙл║ЛЃл┐л░ЛѓЛї лЙЛђлИл│лИлйл░л╗ЛїлйЛІл╣ л║л░л▒лхл╗Лї лЙЛѓ Xilinx, лйл░ ebay.com л╝лЙлХлйлЙ лйл░л╣ЛѓлИ лйл░л╝лйлЙл│лЙ л┤лхЛѕлхл▓л╗лх л║лИЛѓл░л╣ЛЂл║лИл╣ л░лйл░л╗лЙл│, л║лЙЛѓлЙЛђЛІл╣ Лђл░л▒лЙЛѓл░лхЛѓ ЛѓлЙЛЄлйлЙ Лѓл░л║ лХлх (л║л╗ЛјЛЄлхл▓ЛІлх ЛЂл╗лЙл▓л░ л┤л╗ЛЈ л┐лЙлИЛЂл║л░ Xilinx Platform Cable USB Compatible FPGA CPLD JTAG).

[лАл╗лЙл▓л░ЛђлИл║]

CPLD Complex Programmable Logic Device, л┤лЙЛЂл╗лЙл▓лйлЙ л┐лхЛђлхл▓лЙл┤лИЛѓЛЂЛЈ л║л░л║ ЛЂл╗лЙлХлйлЙлх л┐ЛђлЙл│Лђл░л╝л╝лИЛђЛЃлхл╝лЙлх л╗лЙл│лИЛЄлхЛЂл║лЙлх ЛЃЛЂЛѓЛђлЙл╣ЛЂЛѓл▓лЙ, л┐лЙ ЛЂл╝ЛІЛЂл╗ЛЃ ЛЇЛѓлЙ ЛѓлЙ лХлх ЛЂл░л╝лЙлх, ЛЄЛѓлЙ лИ лЪлЏлўлА. лъл▒ЛІЛЄлйлЙ л┐лЙл┤ CPLD л┐лЙлйлИл╝л░ЛјЛѓЛЂЛЈ л╝лИл║ЛђлЙЛЂЛЁлхл╝ЛІ ЛЂл╗лЙлХлйлхлх, ЛЄлхл╝ PAL (Programmable Array Logic), лйлЙ л┐ЛђлЙЛЅлх, ЛЄлхл╝ FPGA. лњ CPLD лИ PAL, л▓ лЙЛѓл╗лИЛЄлИлх лЙЛѓ FPGA, лЙл▒ЛІЛЄлйлЙ л┐ЛђлИл╝лхлйЛЈлхЛѓЛЂЛЈ л▓ЛЂЛѓЛђлЙлхлйлйл░ЛЈ ЛЇлйлхЛђл│лЙлйлхлил░л▓лИЛЂлИл╝л░ЛЈ л┐л░л╝ЛЈЛѓЛї л┤л╗ЛЈ ЛЁЛђл░лйлхлйлИЛЈ л╗лЙл│лИл║лИ.

DCM Digital Clock Manager, л╝лЙл┤ЛЃл╗Лї ЛЃл┐Лђл░л▓л╗лхлйлИЛЈ Лѓл░л║ЛѓлЙл▓лЙл╣ ЛЄл░ЛЂЛѓлЙЛѓлЙл╣. лАл┐лхЛєлИл░л╗Лїлйл░ЛЈ ЛЂЛЁлхл╝л░ л▓лйЛЃЛѓЛђлИ FPGA, л║лЙЛѓлЙЛђл░ЛЈ лЙЛѓл▓лхЛЄл░лхЛѓ лил░ ЛёлЙЛђл╝лИЛђлЙл▓л░лйлИлх Лѓл░л║ЛѓлЙл▓лЙл╣ ЛЄл░ЛЂЛѓлЙЛѓЛІ л┤л╗ЛЈ Лђл░л▒лЙЛѓЛІ л╗лЙл│лИл║лИ.

DPRAM Dual Port RAM, л┤л▓ЛЃЛЁл┐лЙЛђЛѓлЙл▓лЙлх лълЌлБ. лАл┐лхЛєлИл░л╗Лїлйл░ЛЈ л┐л░л╝ЛЈЛѓЛї ЛЂ л┤л▓ЛЃл╝ЛЈ ЛёлИлилИЛЄлхЛЂл║лИл╝лИ лИлйЛѓлхЛђЛёлхл╣ЛЂл░л╝лИ л┤лЙЛЂЛѓЛЃл┐л░ л║ ЛЂлЙл┤лхЛђлХлИл╝лЙл╝ЛЃ.

FPGA, лЪлЏлўлА Field Programmable Gate Array, лЪЛђлЙл│Лђл░л╝л╝лИЛђЛЃлхл╝л░ЛЈ лЏлЙл│лИЛЄлхЛЂл║л░ЛЈ лўлйЛѓлхл│Лђл░л╗Лїлйл░ЛЈ лАЛЁлхл╝л░ - ЛЂл┐лхЛєлИл░л╗Лїлйл░ЛЈ л╝лИл║ЛђлЙЛЂЛЁлхл╝л░, л┐Лђлхл┤лйл░лилйл░ЛЄлхлйлйл░ЛЈ л┤л╗ЛЈ ЛЂлЙлил┤л░лйлИЛЈ л┐ЛђлЙлИлил▓лЙл╗ЛїлйлЙл╣ ЛєлИЛёЛђлЙл▓лЙл╣ ЛЂЛЁлхл╝ЛІ, л╗лЙл│лИл║л░ л║лЙЛѓлЙЛђлЙл╣ л┐ЛђлЙл│Лђл░л╝л╝лИЛђЛЃлхЛѓЛЂЛЈ л┐лЙл╗ЛїлилЙл▓л░Лѓлхл╗лхл╝. лАлЙл▓л╝лхЛЂЛѓлйлЙ ЛЂ FPGA лЙл▒ЛІЛЄлйлЙ л┐ЛђлИл╝лхлйЛЈлхЛѓЛЂЛЈ л▓лйлхЛѕлйЛЈЛЈ ЛЇлйлхЛђл│лЙлйлхлил░л▓лИЛЂлИл╝л░ЛЈ л┐л░л╝ЛЈЛѓЛї л┤л╗ЛЈ ЛЁЛђл░лйлхлйлИЛЈ л╗лЙл│лИл║лИ. лЏлЙл│лИл║л░ Лѓл░л║лХлх л╝лЙлХлхЛѓ лил░л│ЛђЛЃлХл░ЛѓЛїЛЂЛЈ лИли л▓лйлхЛѕлйлхл│лЙ лИлйЛѓлхл╗л╗лхл║ЛѓЛЃл░л╗ЛїлйлЙл│лЙ ЛЃЛЂЛѓЛђлЙл╣ЛЂЛѓл▓л░ (л╝лИл║ЛђлЙл║лЙлйЛѓЛђлЙл╗л╗лхЛђ).

IOB Input-Output Block, л▒л╗лЙл║ л▓л▓лЙл┤л░-л▓ЛІл▓лЙл┤л░, ЛЂл┐лхЛєлИл░л╗Лїлйл░ЛЈ ЛЂЛЁлхл╝л░ л▓ FPGA, л║лЙЛѓлЙЛђл░ЛЈ лЙЛѓл▓лхЛЄл░лхЛѓ лил░ л║лЙлйЛёлИл│ЛЃЛђл░ЛєлИЛј л▓ЛІл▓лЙл┤лЙл▓ л╝лИл║ЛђлЙЛЂЛЁлхл╝ЛІ.

HDL Hardware Description Language, ЛЈлиЛІл║ лЙл┐лИЛЂл░лйлИЛЈ л░л┐л┐л░Лђл░ЛѓЛЃЛђЛІ. лъл▒ЛЅлхлх лйл░лил▓л░лйлИлх л▓ЛЂлхЛЁ ЛЈлиЛІл║лЙл▓ЛІЛЁ ЛЂЛђлхл┤ЛЂЛѓл▓, л║лЙЛѓлЙЛђЛІлх л┐ЛђлИл╝лхлйЛЈЛјЛѓЛЂЛЈ л┤л╗ЛЈ Лђл░лиЛђл░л▒лЙЛѓл║лИ FPGA лИ CPLD. лџ HDL-ЛЈлиЛІл║л░л╝ лЙЛѓлйлЙЛЂЛЈЛѓЛЂЛЈ ЛЂл░л╝ЛІлх л┐лЙл┐ЛЃл╗ЛЈЛђлйЛІлх ЛЈлиЛІл║лИ Verilog лИ VHDL.

RAM, лълЌлБ Random Access Memory, лИл╗лИ лъл┐лхЛђл░ЛѓлИл▓лйлЙлх лЌл░л┐лЙл╝лИлйл░ЛјЛЅлхлх лБЛЂЛѓЛђлЙл╣ЛЂЛѓл▓лЙ.

SPI Serial Peripheral Interface, л┐лЙЛЂл╗лхл┤лЙл▓л░Лѓлхл╗ЛїлйЛІл╣ л┐лхЛђлИЛёлхЛђлИл╣лйЛІл╣ лИлйЛѓлхЛђЛёлхл╣ЛЂ. лЪлЙл┤ЛђлЙл▒лйлхлх ЛЂл╝. [2].

Verilog лАлИ-л┐лЙл┤лЙл▒лйЛІл╣ ЛЈлиЛІл║ лЙл┐лИЛЂл░лйлИЛЈ л╗лЙл│лИл║лИ, л┐ЛђлИл╝лхлйЛЈлхл╝ЛІл╣ л┤л╗ЛЈ Лђл░лиЛђл░л▒лЙЛѓл║лИ ЛЂлЙл┤лхЛђлХлИл╝лЙл│лЙ FPGA.

VESA Video Electronics Standards Association - лЙЛђл│л░лйлИлил░ЛєлИЛЈ, лил░лйлИл╝л░ЛјЛЅл░ЛЈЛЂЛЈ Лђл░лиЛђл░л▒лЙЛѓл║лЙл╣ ЛЂЛѓл░лйл┤л░ЛђЛѓлЙл▓ л▓ЛІл▓лЙл┤л░ л▓лИл┤лхлЙлИлйЛёлЙЛђл╝л░ЛєлИлИ. лњ ЛЇЛѓлЙл╣ ЛЂЛѓл░ЛѓЛїлх л┐лЙл┤ л░л▒л▒Лђлхл▓лИл░ЛѓЛЃЛђлЙл╣ VESA л┐лЙл┤Лђл░лиЛЃл╝лхл▓л░ЛјЛѓЛЂЛЈ ЛЂЛѓл░лйл┤л░ЛђЛѓлйЛІлх л▓лИл┤лхлЙЛђлхлХлИл╝ЛІ л┤л╗ЛЈ л║лЙл╝л┐ЛїЛјЛѓлхЛђлйЛІЛЁ л╝лЙлйлИЛѓлЙЛђлЙл▓.

[лАЛЂЛІл╗л║лИ]

1. Gameduino: лИл│ЛђлЙл▓лЙл╣ л░л┤л░л┐ЛѓлхЛђ л┤л╗ЛЈ л╝лИл║ЛђлЙл║лЙлйЛѓЛђлЙл╗л╗лхЛђлЙл▓.

2. лўлйЛѓлхЛђЛёлхл╣ЛЂ SPI.

3. лъЛђл│л░лйлИлил░ЛєлИЛЈ ЛЇл║Лђл░лйл░ ZX Spectrum site:zxdesign.info.

4. 121108ZX-HDL-console-pub.zip - лИЛЂЛЁлЙл┤лйЛІл╣ л║лЙл┤ Verilog-л┐ЛђлЙлхл║Лѓл░ ZX-HDL-console (Xilinx ISE WebPack 14.2), ЛёлЙЛѓлЙл│Лђл░ЛёлИлИ, л┤лЙл║ЛЃл╝лхлйЛѓл░ЛєлИЛЈ.

5. AT91SAM7X: Лђл░л▒лЙЛѓл░ ЛЂ л┐лЙЛђЛѓлЙл╝ SPI л▓ ЛђлхлХлИл╝лх master.

6. Xilinx JTAG Programmer Guide pdf site:xilinx.com - ЛђЛЃл║лЙл▓лЙл┤ЛЂЛѓл▓лЙ л┐лЙ л┐ЛђлЙл│Лђл░л╝л╝лИЛђлЙл▓л░лйлИЛј ЛЄлИл┐лЙл▓ FPGA Xilinx ЛЄлхЛђлхли лИлйЛѓлхЛђЛёлхл╣ЛЂ JTAG. |