|

ąÆ ą┐čĆąŠčåąĄčüčüąĄ 菹▓ąŠą╗čÄčåąĖąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝ ą┤ąĖąĮą░ą╝ąĖč湥čüą║ąŠą╣ ą┐ą░ą╝čÅčéąĖ ą┐čĆąŠąĖąĘąŠčłąĄą╗ ą┐ąĄčĆąĄčģąŠą┤ ąŠčé čüąĖąĮčģčĆąŠąĮąĮčŗčģ ą╝ąĖą║čĆąŠčüčģąĄą╝ čü ąŠą┤ąĖąĮąŠčćąĮąŠą╣ čüą║ąŠčĆąŠčüčéčīčÄ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ (single data rate synchronous DRAM, čüąŠą║čĆą░čēąĄąĮąĮąŠ SDR, ąĖą╗ąĖ SDRAM) ą║ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ą╝ ą┤ąĖąĮą░ą╝ąĖč湥čüą║ąŠą╣ ą┐ą░ą╝čÅčéąĖ čü ą┤ą▓ąŠą╣ąĮąŠą╣ čüą║ąŠčĆąŠčüčéčīčÄ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ (double data rate synchronous DRAM, čüąŠą║čĆą░čēąĄąĮąĮąŠ DDR). ąźąŠčéčÅ ą▓ ąŠą▒ąŠąĖčģ čŹčéąĖčģ č鹥čģąĮąŠą╗ąŠą│ąĖčÅčģ ą╝ąĮąŠą│ąŠ ąŠą▒čēąĄą│ąŠ, DDR ą▓čüąĄ ąČąĄ ą┐čĆąĄą┤ą╗ą░ą│ą░ąĄčé ąĘąĮą░čćąĖč鹥ą╗čīąĮčŗąĄ čāą╗čāčćčłąĄąĮąĖčÅ.

ąĢčüą╗ąĖ ą║ąŠčĆąŠčéą║ąŠ, č鹊 ą┐ą░ą╝čÅčéčī DDR ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé čüąĖąĮčģčĆąŠąĮąĮčŗą╣ ąĘą░čģą▓ą░čé ą┤ą░ąĮąĮčŗčģ ąĮą░ čāą┤ą▓ąŠąĄąĮąĮąŠą╣ čćą░čüč鹊č鹥 čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, čāčüčéčĆąŠą╣čüčéą▓ąŠ DDR266 ąĮą░ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊č鹥 133 ą£ąōčå ą┤ą░čüčé ą┐ąĖą║ąŠą▓čāčÄ ą┐ąŠą╗ąŠčüčā ą┐čĆąŠą┐čāčüą║ą░ąĮąĖčÅ ą┤ą╗čÅ ą┤ą░ąĮąĮčŗčģ 266 ą╝ąĄą│ą░ą▒ąĖčé/čüąĄą║, ąĖą╗ąĖ 2.1 ą│ąĖą│ą░ą▒ą░ą╣čé/čüąĄą║ ą┤ą╗čÅ ą╝ąŠą┤čāą╗ąĄą╣ x64 DIMM. ąŁč鹊 čüčéą░ą╗ąŠ čĆąĄą░ą╗čīąĮčŗą╝ čü ą┐ąŠčÅą▓ą╗ąĄąĮąĖąĄą╝ ą░čĆčģąĖč鹥ą║čéčāčĆčŗ ą┤ą▓ąŠą╣ąĮąŠą╣ čāą┐čĆąĄąČą┤ą░čÄčēąĄą╣ ą▓čŗą▒ąŠčĆą║ąĖ (2n-prefetch architecture), ą│ą┤ąĄ ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ čłąĖąĮą░ ą┤ą░ąĮąĮčŗčģ ą▓ 2 čĆą░ąĘą░ čłąĖčĆąĄ ą▓ąĮąĄčłąĮąĄą╣ čłąĖąĮčŗ ą┤ą░ąĮąĮčŗčģ, ąĖ ą┤ą░ąĮąĮčŗąĄ ąĘą░čģą▓ą░čéčŗą▓ą░čÄčéčüčÅ ą┤ą▓ą░ąČą┤čŗ ąĘą░ 1 čéą░ą║čé. ą¦č鹊ą▒čŗ ąŠą▒ąĄčüą┐ąĄčćąĖčéčī čåąĄą╗ąŠčüčéąĮąŠčüčéčī čüąĖą│ąĮą░ą╗ąŠą▓ ąĮą░ ą▓čŗčüąŠą║ąŠą╣ čüą║ąŠčĆąŠčüčéąĖ, ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ DDR SDRAM ą┐čĆąĖą╝ąĄąĮčÅčÄčé ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╣ čüčéčĆąŠą▒ ą┤ą░ąĮąĮčŗčģ ąĖ ąĖąĮč鹥čĆč乥ą╣čü SSTL_2 čü ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╝ąĖ ą▓čģąŠą┤ą░ą╝ąĖ ąĖ čüąĖą│ąĮą░ą╗ą░ą╝ąĖ čéą░ą║č鹊ą▓.

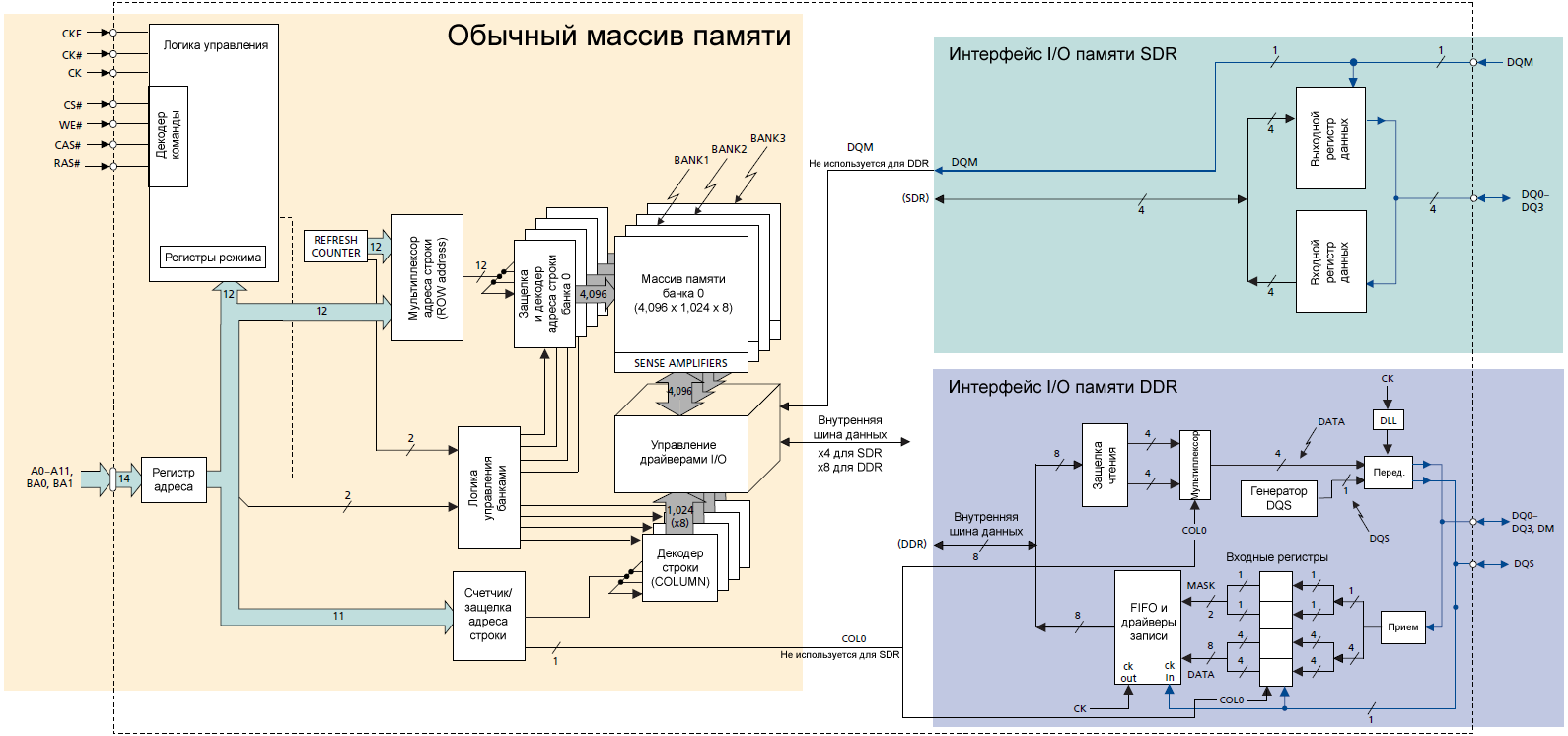

ą”ąĄą╗čī čŹč鹊ą│ąŠ ą░ą┐ąĮąŠčāčéą░ (ą┐ąĄčĆąĄą▓ąŠą┤ [1]) - ą┐čĆąĄą┤ąŠčüčéą░ą▓ąĖčéčī ąŠą▒ąĘąŠčĆ ą░čĆčģąĖč鹥ą║čéčāčĆčŗ 2n-prefetch, čłąĖąĮčŗ ą┤ą░ąĮąĮčŗčģ ąĮą░ ąŠčüąĮąŠą▓ąĄ čüčéčĆąŠą▒ąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖ ąĖąĮč鹥čĆč乥ą╣čüą░ SSTL_2, čé. ąĄ. č鹥čģąĮąŠą╗ąŠą│ąĖą╣, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗčģ ą▓ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░čģ DDR SDRAM. ąŁč鹊 čéą░ą║ąČąĄ ą┐čĆąŠą╗čīąĄčé čüą▓ąĄčé ąĮą░ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮčŗąĄ ąŠčéą╗ąĖčćąĖčÅ ą╝ąĄąČą┤čā SDR (ąŠą▒čŗčćąĮą░čÅ čüąĖąĮčģčĆąŠąĮąĮą░čÅ ą┐ą░ą╝čÅčéčī) ąĖ čāą╗čāčćčłąĄąĮąĮąŠą╣ č鹥čģąĮąŠą╗ąŠą│ąĖąĄą╣ ą┐ą░ą╝čÅčéąĖ DDR. ą¤ąŠą┤čĆąŠą▒ąĮąŠ ą┐čĆąŠ ą┤ąĖąĘą░ą╣ąĮ ąĖ ą║čĆąĖč鹥čĆąĖąĖ ąĖąĮč鹥čĆą▓ą░ą╗ąŠą▓ ą▓čĆąĄą╝ąĄąĮąĖ ą┤ą╗čÅ čüąĖčüč鹥ą╝, ąŠčüąĮąŠą▓ą░ąĮąĮčŗčģ ąĮą░ DDR SDRAM, čüą╝. ą┤ą░čéą░čłąĖčéčŗ ą║ąŠą╝ą┐ą░ąĮąĖąĖ Micron [3].

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąŠą▒čŖčÅčüąĮąĄąĮąĖąĄ ąĮąĄą┐ąŠąĮčÅčéąĮčŗčģ č鹥čĆą╝ąĖąĮąŠą▓ ąĖ čüąŠą║čĆą░čēąĄąĮąĖą╣ čüą╝. ą▓ čüčéą░čéčīąĄ [4].

ąóą░ą▒ą╗ąĖčåą░ 1. ąÜčĆą░čéą║ąĖą╣ ąŠą▒ąĘąŠčĆ č鹥čģąĮąŠą╗ąŠą│ąĖą╣ SDR ąĖ DDR.

| ą¤ą░čĆą░ą╝ąĄčéčĆ |

SDR |

DDR |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ |

| DQM |

ąöąÉ |

ąĮąĄčé |

ąśčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą╝ą░čüą║ąĖ ąĘą░ą┐ąĖčüąĖ ą┤ą░ąĮąĮčŗčģ ąĖ čćč鹥ąĮąĖčÅ OE. |

| DM (Data Mask) |

ąĮąĄčé |

ąöąÉ |

ąŚą░ą╝ąĄąĮčÅąĄčé DQM, ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖčÅ ąĘą░ą┐ąĖčüąĖ ą┤ą░ąĮąĮčŗčģ. |

| DQS (Data Strobe) |

ąĮąĄčé |

ąöąÉ |

ąØąŠą▓čŗą╣ čüąĖą│ąĮą░ą╗, ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ąĘą░čģą▓ą░čéą░ ą┤ą░ąĮąĮčŗčģ. |

| CK# (System Clock) |

ąĮąĄčé |

ąöąÉ |

ąØąŠą▓čŗą╣ čüąĖą│ąĮą░ą╗, ą┐ąŠčüą║ąŠą╗čīą║čā DDR ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗąĄ čüąĖą│ąĮą░ą╗čŗ čéą░ą║č鹊ą▓. |

| VREF |

ąĮąĄčé |

ąöąÉ |

ą×ą┐ąŠčĆąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┤ą╗čÅ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗčģ ą▓čģąŠą┤ąŠą▓ (čāčĆąŠą▓ąĄąĮčī ąĮą░ ąĮąĄą╝ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ąĮą░ ą┐ąŠą╗ąŠą▓ąĖąĮąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ, VDD/2). |

| VDD ąĖ VDDQ |

3.3V |

2.5V |

ąŻ DDR čāą╝ąĄąĮčīčłąĄąĮąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ ąĖ ą┐ąŠąĮąĖąČąĄąĮąĮą░čÅ ą┐ąŠčéčĆąĄą▒ą╗čÅąĄą╝ą░čÅ ą╝ąŠčēąĮąŠčüčéčī. |

| ąĪąĖą│ąĮą░ą╗čīąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü |

LVTTL |

SSTL_2 |

DDR ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣ ą▓ą▓ąŠą┤/ą▓čŗą▓ąŠą┤ (I/O). |

| ąØą░ą│čĆčāąĘąŠčćąĮą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī ą▓čŗčģąŠą┤ąŠą▓ |

ążąĖą║čüąĖčĆąŠą▓ą░ąĮąĮą░čÅ |

ąśąĘą╝ąĄąĮčÅąĄą╝ą░čÅ |

ąŻčüčéčĆąŠą╣čüčéą▓ą░ x16 DDR ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÄčé ąŠą┐čåąĖčÄ čüąĮąĖąČąĄąĮąĖčÅ ą╝ąŠčēąĮąŠčüčéąĖ ą▓čŗčģąŠą┤ąĮčŗčģ ą┤čĆą░ą╣ą▓ąĄčĆąŠą▓. |

| ąĪą║ąŠčĆąŠčüčéčī ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ |

1x |

2x |

DDR ą┐ąĄčĆąĄą╝ąĄčēą░ąĄčé ą┤ą░ąĮąĮčŗąĄ ąĮą░ ą┤ą▓ąŠą╣ąĮąŠą╣ čćą░čüč鹊č鹥 čéą░ą║č鹊ą▓. |

| ąÉčĆčģąĖč鹥ą║čéčāčĆą░ |

ąĪąĖąĮčģčĆąŠąĮąĮą░čÅ |

ąĪąĖąĮčģčĆąŠąĮąĮą░čÅ ą┐ąŠ ąŠčéąĮąŠčłąĄąĮąĖčÄ ą║ ąĖčüč鹊čćąĮąĖą║čā ą┤ą░ąĮąĮčŗčģ |

DDR ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╣ čüčéčĆąŠą▒ ą┤ą░ąĮąĮčŗčģ. |

ąĀąĖčü. 1. ążčāąĮą║čåąĖąŠąĮą░ą╗čīąĮą░čÅ ą▒ą╗ąŠą║-čüčģąĄą╝ą░ ą╝ą░čüčüąĖą▓ą░ ą┐ą░ą╝čÅčéąĖ 2M čÅč湥ąĄą║, ą║ą░ąČą┤ą░čÅ ą┐ąŠ 4 čĆą░ąĘčĆčÅą┤ą░, čü ąĖąĮč鹥čĆč乥ą╣čüąŠą╝ SDR ąĖ ąĖąĮč鹥čĆč乥ą╣čüąŠą╝ DDR.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ ą║ čĆąĖčü. 1:

REFRESH COUNTER - čüč湥čéčćąĖą║ (čüčéčĆąŠą║) ą┤ą╗čÅ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ čÅč湥ąĄą║ ą┐ą░ą╝čÅčéąĖ.

SENSE AMPLIFIERS - čāčüąĖą╗ąĖč鹥ą╗ąĖ čüčćąĖčéčŗą▓ą░ąĮąĖčÅ ąĘą░čĆčÅą┤ą░ ąĮą░ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆą░čģ čÅč湥ąĄą║ ą┐ą░ą╝čÅčéąĖ.

[ą×čéą╗ąĖčćąĖčÅ čäčāąĮą║čåąĖąŠąĮą░ą╗ą░ DDR ąĖ SDR]

ąóąĄčģąĮąŠą╗ąŠą│ąĖčÅ SDR SDRAM čģąŠčĆąŠčłąŠ ąĖąĘą▓ąĄčüčéąĮą░ ąĖ ąĄčæ ą┐čĆąĖąĮčåąĖą┐čŗ ąŠą▒čŗčćąĮąŠ čģąŠčĆąŠčłąŠ ą┐ąŠąĮąĖą╝ą░čÄčé čĆą░ąĘčĆą░ą▒ąŠčéčćąĖą║ąĖ. ąóą░ą║ čćč鹊 čüąŠčüčĆąĄą┤ąŠč鹊čćąĖą╝čüčÅ ąĮą░ ą▓ąŠą┐čĆąŠčüą░čģ ąŠčéą╗ąĖčćąĖą╣ DDR ąŠčé SDR.

ąĢčüą╗ąĖ ą┐ąŠčüą╝ąŠčéčĆąĄčéčī ąĮą░ ą▒ą╗ąŠą║-ą┤ąĖą░ą│čĆą░ą╝ą╝čŗ 32M x 4 SDR ąĖ DDR, č鹊 ą▓ąĖą┤ąĮąŠ, čćč鹊 čÅą┤čĆąŠ čÅč湥ąĄą║ ą┐ą░ą╝čÅčéąĖ čā ąĮąĖčģ ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠąĄ (čüą╝. čĆąĖčü. 1). ą×ą▒ąĄ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ąĖą╝ąĄčÄčé ąŠą┤ąĖąĮą░ą║ąŠą▓čāčÄ ą░ą┤čĆąĄčüą░čåąĖčÄ ąĖ čāą┐čĆą░ą▓ą╗čÅčÄčēąĖą╣ ąĖąĮč鹥čĆč乥ą╣čü ą║ąŠą╝ą░ąĮą┤; čā ąŠą▒ąŠąĖčģ čüąĖčüč鹥ą╝ą░ ą┐ą░ą╝čÅčéąĖ ą┐ąŠčüčéčĆąŠąĄąĮą░ ąĮą░ ąŠčüąĮąŠą▓ąĄ 4 ą▒ą░ąĮą║ąŠą▓ ą╝ą░čüčüąĖą▓ąŠą▓ ą┐ą░ą╝čÅčéąĖ; ąĖ ąŠą▒ąĄ ąĮą░ą╗ą░ą│ą░čÄčé ąŠą┤ąĖąĮą░ą║ąŠą▓čŗąĄ čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅ ą║ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÄ ą╝ą░čüčüąĖą▓ąŠą▓ ą┐ą░ą╝čÅčéąĖ. ążčāąĮą┤ą░ą╝ąĄąĮčéą░ą╗čīąĮčŗąĄ ąŠčéą╗ąĖčćąĖčÅ ą║čĆąŠčÄčéčüčÅ ąĖą╝ąĄąĮąĮąŠ ą▓ ąĖąĮč鹥čĆč乥ą╣čüąĄ ą┤ą░ąĮąĮčŗčģ.

ąśąĮč鹥čĆč乥ą╣čü ą┐ą░ą╝čÅčéąĖ SDR ąĖą╝ąĄąĄčé ą┐ąŠą╗ąĮąŠčüčéčīčÄ čüąĖąĮčģčĆąŠąĮąĮčŗą╣ ą┤ąĖąĘą░ą╣ąĮ, ą│ą┤ąĄ ą┤ą░ąĮąĮčŗąĄ ąĘą░čģą▓ą░čéčŗą▓ą░čÄčéčüčÅ č鹊ą╗čīą║ąŠ ą┐ąŠ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą╝čā ą┐ąĄčĆąĄą┐ą░ą┤čā čüąĖą│ąĮą░ą╗ą░ čéą░ą║č鹊ą▓. ąŻ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ čłąĖąĮčŗ ą┤ą░ąĮąĮčŗčģ čéą░ą║ą░čÅ ąČąĄ čłąĖčĆąĖąĮą░, ą║ą░ą║ ąĖ čā ą▓ąĮąĄčłąĮąĄą╣, ąĖ ą┤ą░ąĮąĮčŗąĄ ąĘą░čēąĄą╗ą║ąĖą▓ą░čÄčéčüčÅ ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ ą╝ą░čüčüąĖą▓ ą┐ą░ą╝čÅčéąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ, ą┐ąŠ ą╝ąĄčĆąĄ ąĖčģ ą┐ąĄčĆąĄą┤ą░čćąĖ č湥čĆąĄąĘ ą▒čāč乥čĆčŗ I/O. ą¤ą░ą╝čÅčéčī SDR čéą░ą║ąČąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé čüąĖą│ąĮą░ą╗ DQM, ą║ąŠč鹊čĆčŗą╣ ą┤ąĄą╣čüčéą▓čāąĄčé ą║ą░ą║ ą╝ą░čüą║ą░ ą┤ą░ąĮąĮčŗčģ ą▓ąŠ ą▓čĆąĄą╝čÅ ąŠą┐ąĄčĆą░čåąĖąĖ ąĘą░ą┐ąĖčüąĖ (WRITE), ąĖą╗ąĖ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą▓čŗčģąŠą┤ąŠą▓ ą┤ą╗čÅ ąŠą┐ąĄčĆą░čåąĖąĖ čćč鹥ąĮąĖčÅ (READ).

ąöą░ąĮąĮčŗąĄ ą┐ą░ą╝čÅčéąĖ DDR ąĖą╝ąĄčÄčé č湥čüčéąĮčŗą╣ čüąĖąĮčģčĆąŠąĮąĮčŗą╣ ą┤ąĖąĘą░ą╣ąĮ ą┐ąŠ ąŠčéąĮąŠčłąĄąĮąĖčÄ ą║ ąĖčüč鹊čćąĮąĖą║čā (source-synchronous), ą│ą┤ąĄ ą┤ą░ąĮąĮčŗąĄ ąĘą░čģą▓ą░čéčŗą▓ą░čÄčéčüčÅ ą┤ą▓ą░ąČą┤čŗ čü ą┐ąŠą╝ąŠčēčīčÄ ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮąŠą│ąŠ čüčéčĆąŠą▒ą░ ą┤ą░ąĮąĮčŗčģ. ąŚą┤ąĄčüčī čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮą░ ą░čĆčģąĖč鹥ą║čéčāčĆą░ ą┤ą▓ąŠą╣ąĮąŠą╣ čāą┐čĆąĄąČą┤ą░čÄčēąĄą╣ ą▓čŗą▒ąŠčĆą║ąĖ 2n-prefetch, ą│ą┤ąĄ ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ čłąĖąĮą░ ą┤ą░ąĮąĮčŗčģ ą▓ 2 čĆą░ąĘą░ čłąĖčĆąĄ ą▓ąĮąĄčłąĮąĄą╣ čłąĖąĮčŗ. ąŁč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé čÅč湥ą╣ą║ą░ą╝ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ ą┐ą░čĆą░ą╝ąĖ ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī ą┤ą░ąĮąĮčŗąĄ ą▒čāč乥čĆą░ą╝ I/O. ąŻ DDR ąĮąĄčé čüąĖą│ąĮą░ą╗ą░ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą▓čŗčģąŠą┤ą░ ą┤ą╗čÅ ąŠą┐ąĄčĆą░čåąĖą╣ čćč鹥ąĮąĖčÅ (READ), ąĮąŠ DDR ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ą║ąŠą╝ą░ąĮą┤čā BURST TERMINATE, čćč鹊ą▒čŗ ą▒čŗčüčéčĆąŠ ąĘą░ą▓ąĄčĆčłąĖčéčī ą┐čĆąŠčåąĄčüčü čćč鹥ąĮąĖčÅ. ąÆąŠ ą▓čĆąĄą╝čÅ ąŠą┐ąĄčĆą░čåąĖąĖ ąĘą░ą┐ąĖčüąĖ (WRITE) ą┤ąŠčüčéčāą┐ąĮčŗ čüąĖą│ąĮą░ą╗čŗ DM, čćč鹊ą▒čŗ ą┐ąŠąĘą▓ąŠą╗ąĖčéčī ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖąĄ ąĮąĄą┤ąŠą┐čāčüčéąĖą╝čŗčģ ą┤ą░ąĮąĮčŗčģ ąĘą░ą┐ąĖčüąĖ.

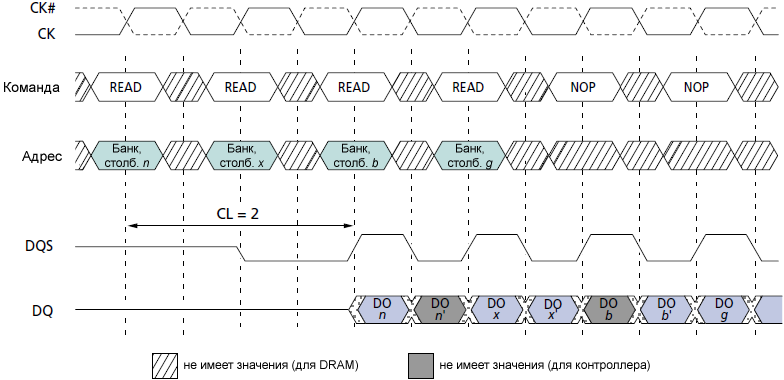

ą©ąĖąĮą░ ą║ąŠą╝ą░ąĮą┤ DDR čüąŠčüč鹊ąĖčé ąĖąĘ čüąĖą│ąĮą░ą╗ąŠą▓ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ čéą░ą║č鹊ą▓ (clock enable, CKE), ą▓čŗą▒ąŠčĆą║ąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ (chip select, CS#), ą░ą┤čĆąĄčüą░ čüčéčĆąŠą║ąĖ (row) ąĖ ą░ą┤čĆąĄčüą░ čüč鹊ą╗ą▒čåą░ (column), ą░ą┤čĆąĄčüą░ ą▒ą░ąĮą║ą░, ąĖ čüąĖą│ąĮą░ą╗ą░ ąĘą░ą┐ąĖčüąĖ (write enable, WE#), ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 4. ąÜąŠą╝ą░ąĮą┤čŗ ą▓ą▓ąŠą┤čÅčéčüčÅ ą┐ąŠ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮčŗą╝ ą┐ąĄčĆąĄą┐ą░ą┤ą░ą╝ čéą░ą║č鹊ą▓, ąĖ ą┤ą░ąĮąĮčŗąĄ ą┐ąŠčÅą▓ą╗čÅčÄčéčüčÅ ą║ą░ą║ ą┐ąŠ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮčŗą╝, čéą░ą║ ąĖ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮčŗą╝ ą┐ąĄčĆąĄą┐ą░ą┤ą░ą╝ čüąĖą│ąĮą░ą╗ą░ čéą░ą║č鹊ą▓.

ą¤ą░ą╝čÅčéčī DDR ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčāčÄ ą┐ą░čĆčā ą┤ą╗čÅ čüąĖčüč鹥ą╝ąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ, ą┐ąŠčŹč鹊ą╝čā čüąĖą│ąĮą░ą╗ čéą░ą║ąŠą▓ ąĖą╝ąĄąĄčé 2 ą╗ąĖąĮąĖąĖ: čéą░ą║čé CK ąĖ ą║ąŠą╝ą┐ą╗ąĄą╝ąĄąĮčéą░čĆąĮčŗą╣ ąĄą╝čā CK#. ą¤ąŠą╗ąŠąČąĖč鹥ą╗čīąĮčŗą╝ ą┐ąĄčĆąĄą┐ą░ą┤ąŠą╝ ą┤ą╗čÅ DDR ąĮą░ąĘčŗą▓ą░čÄčé ą╝ąŠą╝ąĄąĮčé ą▓čĆąĄą╝ąĄąĮąĖ, ą║ąŠą│ą┤ą░ čāčĆąŠą▓ąĄąĮčī čüąĖą│ąĮą░ą╗ą░ čéą░ą║č鹊ą▓ ą┐ąĄčĆąĄčüąĄą║ą░ąĄčé čüą┐ą░ą┤ą░čÄčēąĖą╣ čāčĆąŠą▓ąĄąĮčī ą║ąŠą╝ą┐ą╗ąĄą╝ąĄąĮčéą░čĆąĮąŠą│ąŠ ąĄą╝čā čüąĖą│ąĮą░ą╗ą░, ąĖ č鹥čĆą╝ąĖąĮ ąĮąĄą│ą░čéąĖą▓ąĮąŠą│ąŠ ą┐ąĄčĆąĄą┐ą░ą┤ą░ čéą░ą║č鹊ą▓ ąŠą▒ąŠąĘąĮą░čćą░ąĄčé ą╝ąŠą╝ąĄąĮčé, ą║ąŠą│ą┤ą░ čüą┐ą░ą┤ čāčĆąŠą▓ąĮčÅ čüąĖą│ąĮą░ą╗ą░ čéą░ą║č鹊ą▓ ą┐ąĄčĆąĄčüąĄą║ą░ąĄčéčüčÅ čü ąĮą░čĆą░čüčéą░čÄčēąĖą╝ čāčĆąŠą▓ąĮąĄą╝ ą║ąŠą╝ą┐ą╗ąĄą╝ąĄąĮčéą░čĆąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░.

ąÉčĆčģąĖč鹥ą║čéčāčĆą░ 2n-Prefetch. ąóąĄčĆą╝ąĖąĮ DDR (ąĖą╗ąĖ DDRI) ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čüą┐ąĄčåąĖą░ą╗čīąĮąŠ čüą▓čÅąĘą░ąĮ čü čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ 2n-prefetch, ą┐ąŠčüą║ąŠą╗čīą║čā ą▒čāą┤čāčēąĖąĄ čĆą░ąĘčĆą░ą▒ąŠčéą║ąĖ ą▓ ąŠą▒ą╗ą░čüčéąĖ ą┤ąĖąĮą░ą╝ąĖč湥čüą║ąŠą╣ ą┐ą░ą╝čÅčéąĖ (DDRII) ą▒čāą┤čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą░čĆčģąĖč鹥ą║čéčāčĆčā 4n-prefetch.

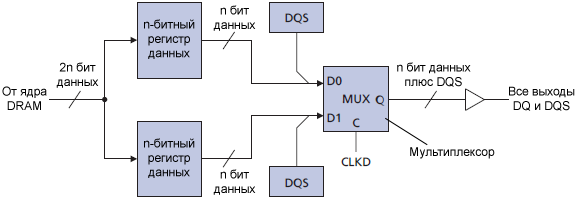

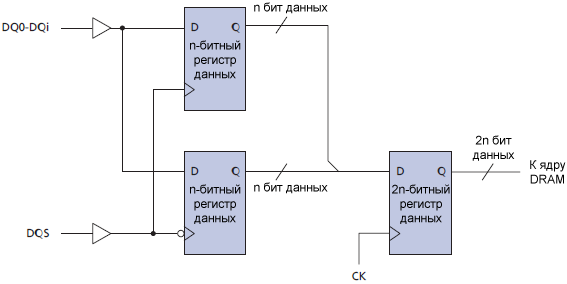

ąöą╗čÅ ą▓ąĄąĮą┤ąŠčĆą░ DRAM č鹥čĆą╝ąĖąĮ 2n-prefetch ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ čłąĖąĮą░ ą┤ą░ąĮąĮčŗčģ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┤ą▓ąŠą╣ąĮąŠą╣ čłąĖčĆąĖąĮčŗ ą┐ąŠ čüčĆą░ą▓ąĮąĄąĮąĖčÄ čü ą▓ąĮąĄčłąĮąĄą╣ čłąĖąĮąŠą╣ ą┤ą░ąĮąĮčŗčģ, ąĖ čéą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝ čćą░čüč鹊čéą░ ą┤ąŠčüčéčāą┐ą░ ą║ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╝čā čüč鹊ą╗ą▒čåčā ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓ 2 čĆą░ąĘą░ ą╝ąĄąĮčīčłąĄ čüą║ąŠčĆąŠčüčéąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▓ąĮąĄčłąĮąĖčģ ą┤ą░ąĮąĮčŗčģ. ą¤ąŠčŹč鹊ą╝čā ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ąŠą┤ąĖąĮąŠčćąĮąŠą│ąŠ ą┤ąŠčüčéčāą┐ą░ ąĮą░ čćč鹥ąĮąĖčÅ ą▓ąĮčāčéčĆąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčéčüčÅ 2 ą▓ąĮąĄčłąĮąĖčģ čüą╗ąŠą▓ą░ ą┤ą░ąĮąĮčŗčģ (ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 2). ą¤ąŠą┤ąŠą▒ąĮčŗą╝ ąŠą▒čĆą░ąĘąŠą╝ ą▓ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ 2 ą▓ąĮąĄčłąĮąĖčģ čüą╗ąŠą▓ą░ ą┤ą░ąĮąĮčŗčģ, ą║ąŠą│ą┤ą░ čŹčéąĖ 2 ąĘą░ą┐ąĖčüąĖ ą▓ąĮčāčéčĆąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ ą║ąŠą╝ą▒ąĖąĮąĖčĆčāčÄčéčüčÅ ą▓ ąŠą┤ąĖąĮ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ ą┤ąŠčüčéčāą┐ ąĮą░ ąĘą░ą┐ąĖčüčī (ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 3).

ąĀąĖčü. 2. ąŻą┐čĆąŠčēąĄąĮąĮą░čÅ ą▒ą╗ąŠą║-čüčģąĄą╝ą░ 2n-Prefetch READ.

ąĀąĖčü. 3. ąŻą┐čĆąŠčēąĄąĮąĮą░čÅ ą▒ą╗ąŠą║-čüčģąĄą╝ą░ 2n-Prefetch WRITE.

ąØą░ ą▓ąĄčĆčģąĮąĄą╝ čāčĆąŠą▓ąĮąĄ, čü č鹊čćą║ąĖ ąĘčĆąĄąĮąĖčÅ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ, 2n-prefetch ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ą┤ąŠčüčéčāą┐ ą║ ą┤ą░ąĮąĮčŗą╝ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą┐ą░čĆą░ą╝ąĖ; ąĮą░ą┐čĆąĖą╝ąĄčĆ, ąŠą┤ąĖąĮąŠčćąĮčŗą╣ ą┤ąŠčüčéčāą┐ ąĮą░ čćč鹥ąĮąĖąĄ ą┤ąĄą╗ą░ąĄčé ą▓čŗą▒ąŠčĆą║čā ą┤ą▓čāčģ čüą╗ąŠą▓ ą┤ą░ąĮąĮčŗčģ; ąĖ ą┐čĆąĖ ąŠą┤ąĖąĮąŠčćąĮąŠą╝ ą┤ąŠčüčéčāą┐ąĄ ąĮą░ ąĘą░ą┐ąĖčüčī ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮčŗ ą┤ą▓ą░ čüą╗ąŠą▓ą░ ą┤ą░ąĮąĮčŗčģ (ąĖ/ąĖą╗ąĖ ą╝ą░čüąŠą║ ą▒ąĖč鹊ą▓ ą┤ą░ąĮąĮčŗčģ). ąŁč鹊 ą▓ą╗ąĖčÅąĄčé ąĖ ąĮą░ ą╝ąĖąĮąĖą╝ą░ą╗čīąĮčŗą╣ čĆą░ąĘą╝ąĄčĆ ą┐ą░ą║ąĄčéą░ (burst size), ąĖ ąĮą░ ąĮąĄ ą╝ąĖąĮąĖą╝ą░ą╗čīąĮčŗąĄ ąŠą▒čĆčŗą▓čŗ ą┐ą░ą║ąĄč鹊ą▓. ą£ąĖąĮąĖą╝ą░ą╗čīąĮčŗą╣ čĆą░ąĘą╝ąĄčĆ ą┐ą░ą║ąĄčéą░ ą░čĆčģąĖč鹥ą║čéčāčĆčŗ 2n-prefetch čüąŠčüčéą░ą▓ą╗čÅąĄčé 2 ą┐ąĄčĆąĄąĮąŠčüą░ ą▓ąĮąĄčłąĮąĖčģ ą┤ą░ąĮąĮčŗčģ.

ąĀąĖčü. 4. ą¤čĆąĖą╝ąĄčĆ čüąĖą│ąĮą░ą╗ąŠą▓ ąĮą░ čłąĖąĮąĄ ą┤ą╗čÅ ąŠą┐ąĄčĆą░čåąĖąĖ WRITE čāčüčéčĆąŠą╣čüčéą▓ą░ DDR.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ ą║ čĆąĖčü. 4:

CA = Column Address, ą░ą┤čĆąĄčü čüč鹊ą╗ą▒čåą░.

RA = Row Address, ą░ą┤čĆąĄčü čüčéčĆąŠą║ąĖ.

Ai = čüą░ą╝čŗą╣ ąĘąĮą░čćąĖą╝čŗą╣ ą┐ąŠ ą▓ąĄčüčā čĆą░ąĘčĆčÅą┤ ą░ą┤čĆąĄčüą░.

BA = Bank Address, ą░ą┤čĆąĄčü ą▒ą░ąĮą║ą░.

EN AP = Enable Auto Precharge, čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ čäčāąĮą║čåąĖąĖ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą│ąŠ ą┐čĆąĄą┤ąĘą░čĆčÅą┤ą░.

DIS AP = Disable Auto Precharge, ąĘą░ą┐čĆąĄčé čäčāąĮą║čåąĖąĖ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą│ąŠ ą┐čĆąĄą┤ąĘą░čĆčÅą┤ą░.

ą£ąĖąĮąĖą╝ą░ą╗čīąĮčŗąĄ ąĖąĮč鹥čĆą▓ą░ą╗čŗ ą▓čĆąĄą╝ąĄąĮąĖ (Time Slots). ąöą╗čÅ ąŠą┐ąĄčĆą░čåąĖą╣ READ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą╝ąŠąČąĄčé ą▓čŗą▒čĆą░čéčī ąĖą│ąĮąŠčĆ ą╗čÄą▒ąŠą│ąŠ ąĖąĘ čŹčéąĖčģ ą┤ą▓čāčģ čüą╗ąŠą▓, ąĮąŠ ąĖąĮč鹥čĆą▓ą░ą╗čŗ ą▓čĆąĄą╝ąĄąĮąĖ ą┤ą╗čÅ ąŠą▒ąŠąĖčģ ą▓čüąĄ čĆą░ą▓ąĮąŠ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čüąŠą▒ą╗čÄą┤ąĄąĮčŗ (čüą╝. čĆąĖčü. 5). ą¤ąŠą┤ąŠą▒ąĮčŗą╝ ąŠą▒čĆą░ąĘąŠą╝ ą┤ą╗čÅ ąŠą┐ąĄčĆą░čåąĖą╣ WRITE ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą╝ąŠąČąĄčé ą╝ą░čüą║ąĖčĆąŠą▓ą░čéčī ą╗čÄą▒ąŠąĄ ąĖąĘ čŹčéąĖčģ ą┤ą▓čāčģ čüą╗ąŠą▓, ąĮąŠ ąŠą┐čÅčéčī-čéą░ą║ąĖ ąŠąĮąĖ ąĘą░ą╣ą╝čāčé čüą▓ąŠąĖ čüą╗ąŠčéčŗ ą▓čĆąĄą╝ąĄąĮąĖ (čüą╝. čĆąĖčü. 6). ąöą╗čÅ ą║ą░ąČą┤ąŠą╣ ą▓čŗą┤ą░ąĮąĮąŠą╣ ą║ąŠą╝ą░ąĮą┤čŗ READ ąĖą╗ąĖ WRITE (ąĖ ą░ą┤čĆąĄčüą░ čüč鹊ą╗ą▒čåą░) ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÄčéčüčÅ 2 čüą╗ąŠą▓ą░ ą┤ą░ąĮąĮčŗčģ. ą¤ąŠčüą║ąŠą╗čīą║čā čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐čĆąĖą╝ąĄąĮčÅąĄčé ą┤ą▓ąŠą╣ąĮčāčÄ čüą║ąŠčĆąŠčüčéčī ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ, ą║ą░ą║ ąĖ 2n-prefetch, č鹊 ąŠą┐čéąĖą╝ą░ą╗čīąĮąŠ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą╝ąĖąĮąĖą╝čāą╝ 2 čüą╗ąŠą▓ą░ ą┤ą░ąĮąĮčŗčģ (čéą░ą║ ą║ą░ą║ ą║ąŠą╝ą░ąĮą┤čŗ ąĮąĄ ą╝ąŠą│čāčé ą▓čŗą┤ą░ą▓ą░čéčīčüčÅ ą▒ąŠą╗ąĄąĄ čćą░čüč鹊).

ąĀąĖčü. 5. ą£ąĖąĮąĖą╝ą░ą╗čīąĮčŗą╣ ąĖąĮč鹥čĆą▓ą░ą╗ ą▓čĆąĄą╝ąĄąĮąĖ ą┤ą╗čÅ 2n-Prefetch READ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ ą║ čĆąĖčü. 5:

1. ą¤ąŠą║ą░ąĘą░ąĮą░ ąŠą┐ąĄčĆą░čåąĖčÅ ą▓čŗą▓ąŠą┤ą░ ą┤ą░ąĮąĮčŗčģ DO n, ąĮą░čćąĖąĮą░čÅ ąŠčé čüč鹊ą╗ą▒čåą░ n, ąĖ čéą░ą║ ą┤ą░ą╗ąĄąĄ.

2. n', ąĖ čé. ą┤. čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé čüą╗ąĄą┤čāčÄčēąĄą╝čā ąĘą░ DO n čüą╗ąŠą▓čā ą┤ą░ąĮąĮčŗčģ, ąĖ čé. ą┤., ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮčŗą╝ ą┐ąŠčĆčÅą┤ą║ąŠą╝ ą▓čŗą┤ą░čćąĖ ą┐ą░ą║ąĄčéą░.

3. ąÆ ą┐ąŠą║ą░ąĘą░ąĮąĮčŗčģ čüą╗čāčćą░čÅčģ ą┤ą╗ąĖąĮą░ ą┐ą░ą║ąĄčéą░ (Burst Length, BL) = 2, 4 ąĖą╗ąĖ 8.

4. ą×ą┐ąĄčĆą░čåąĖąĖ READ ą┤ą╗čÅ ą░ą║čéąĖą▓ąĮčŗčģ čüčéčĆąŠą║ ą▓ ą╗čÄą▒čŗčģ ą▒ą░ąĮą║ą░čģ.

5. ą¤ąŠą║ą░ąĘą░ąĮąŠ čü ąĮąŠą╝ąĖąĮą░ą╗čīąĮčŗą╝ąĖ ąĖąĮč鹥čĆą▓ą░ą╗ą░ą╝ąĖ tAC ąĖ tDQSQ.

6. ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ čģąŠč湥čé ą┐ąŠą╗čāčćąĖčéčī ą┐ąĄčĆą▓čŗąĄ 2 čüą╗ąŠą▓ą░ ą┤ą╗čÅ ą┐ąĄčĆą▓ąŠą╣ ą║ąŠą╝ą░ąĮą┤čŗ READ, ąŠą▒ą░ čüą╗ąŠą▓ą░ ą┤ą╗čÅ ą▓č鹊čĆąŠą╣ ą║ąŠą╝ą░ąĮą┤čŗ, ąĖ ą▓č鹊čĆąŠąĄ ąĖąĘ 2 čüą╗ąŠą▓ ą┤ą╗čÅ čéčĆąĄčéčīąĄą╣ ą║ąŠą╝ą░ąĮą┤čŗ.

ąĀąĖčü. 6. ą£ąĖąĮąĖą╝ą░ą╗čīąĮčŗą╣ ąĖąĮč鹥čĆą▓ą░ą╗ ą▓čĆąĄą╝ąĄąĮąĖ ą┤ą╗čÅ 2n-Prefetch WRITE.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ ą║ čĆąĖčü. 6:

1. ą¤ąŠą║ą░ąĘą░ąĮą░ ąŠą┐ąĄčĆą░čåąĖčÅ ą▓ą▓ąŠą┤ą░ ą┤ą░ąĮąĮčŗčģ DI b, ą│ą┤ąĄ čüą╗ąŠą▓ąŠ ą┤ą░ąĮąĮčŗčģ čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé čüč鹊ą╗ą▒čåčā b, ąĖ čé. ą┤.

2. b', ąĖ čé. ą┤. čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ą▓čģąŠą┤ąĮąŠą╝čā čüą╗ąŠą▓čā ą┤ą░ąĮąĮčŗčģ, ą║ąŠč鹊čĆąŠąĄ ąĖą┤ąĄčé ąĘą░ DI b, ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮčŗą╝ ą┐ąŠčĆčÅą┤ą║ąŠą╝ ą┐ą░ą║ąĄčéą░.

3. ąÆ ą┐ąŠą║ą░ąĘą░ąĮąĮčŗčģ čüą╗čāčćą░čÅčģ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮą░čÅ ą┤ą╗ąĖąĮą░ ą┐ą░ą║ąĄčéą░ (Burst Length, BL) = 2, 4 ąĖą╗ąĖ 8.

4. ąÜą░ąČą┤ą░čÅ ą║ąŠą╝ą░ąĮą┤ą░ WRITE ą╝ąŠąČąĄčé ąŠčéąĮąŠčüąĖčéčīčüčÅ ą║ ą╗čÄą▒ąŠą╝čā ą▒ą░ąĮą║čā.

5. ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ čģąŠč湥čé ąĘą░ą┐ąĖčüą░čéčī ą┐ąĄčĆą▓čŗąĄ 2 čüą╗ąŠą▓ą░ ą┤ą╗čÅ ą┐ąĄčĆą▓ąŠą╣ ą║ąŠą╝ą░ąĮą┤čŗ WRITE, ąŠą▒ą░ čüą╗ąŠą▓ą░ ą┤ą╗čÅ ą▓č鹊čĆąŠą╣, ąĖ ą▓č鹊čĆąŠąĄ čüą╗ąŠą▓ąŠ ąĖąĘ ą┤ą▓čāčģ čüą╗ąŠą▓ čéčĆąĄčéčīąĄą╣.

ąöą╗čÅ ąĮąĄ ą╝ąĖąĮąĖą╝ą░ą╗čīąĮčŗčģ ą┐ąŠ ą┤ą╗ąĖąĮąĄ ą┐ą░ą║ąĄč鹊ą▓ READ (4 ąĖą╗ąĖ 8 čüą╗ąŠą▓) čŹč鹊 ą┐ąŠą╝ąŠą│ą░ąĄčé čüą▓čÅąĘą░čéčī ą║ą░ąČą┤čŗą╣ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮčŗą╣ ą┐ąĄčĆąĄą┐ą░ą┤ čü ą┐ą░čĆąŠą╣ čüą╗ąŠą▓ ą┤ą░ąĮąĮčŗčģ. ąóą░ą║ąĖą╝ čüą┐ąŠčüąŠą▒ąŠą╝ ąŠą▒čĆčŗą▓čŗ ą║ąŠą╝ą░ąĮą┤ READ ą┐čĆąŠčēąĄ ą┐ąŠąĮčÅčéčī. ąØą░ą┐čĆąĖą╝ąĄčĆ, čü ą┤ą╗ąĖąĮąŠą╣ ą┐ą░ą║ąĄčéą░ (burst length, BL) = 8, ą║ąŠą╝ą░ąĮą┤ą░ čćč鹥ąĮąĖčÅ READ, ąĘą░ ą║ąŠč鹊čĆąŠą╣ ąĖą┤čāčé 3 ą┐čĆąĄčĆčŗą▓ą░čÄčēąĖąĄ ą║ąŠą╝ą░ąĮą┤čŗ, ąĮčāąČą┤ą░ąĄčéčüčÅ ą▓ ą┤ąŠčüčéčāą┐ąĄ ą║ąŠ ą▓čüąĄą╝čā ą┐ą░ą║ąĄčéčā. ąĢčüą╗ąĖ ą║ąŠą╝ą░ąĮą┤ą░, ąŠą▒čĆčŗą▓ą░čÄčēą░čÅ ą┐ą░ą║ąĄčé, ą┐čĆąĖą║ą╗ą░ą┤čŗą▓ą░ąĄčéčüčÅ ąĮą░ ą┐ąĄčĆą▓ąŠą╝ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą╝ ą┐ąĄčĆąĄą┐ą░ą┤ąĄ, čüą╗ąĄą┤čāčÄčēąĄą╝ ąĘą░ ą║ąŠą╝ą░ąĮą┤ąŠą╣ READ, č鹊 ą▒čāą┤ąĄčé ąŠčüčāčēąĄčüčéą▓ą╗ąĄąĮ ą┤ąŠčüčéčāą┐ č鹊ą╗čīą║ąŠ ą║ ą┤ą▓čāą╝ čüą╗ąŠą▓ą░ą╝; ąĄčüą╗ąĖ ą║ąŠą╝ą░ąĮą┤ą░, ą┐čĆąĄčĆčŗą▓ą░čÄčēą░čÅ ą┐ą░ą║ąĄčé, ą▒čāą┤ąĄčé ą┐čĆąĖą╗ąŠąČąĄąĮą░ ąĮą░ ą▓č鹊čĆąŠą╝ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą╝ ą┐ąĄčĆąĄą┐ą░ą┤ąĄ čéą░ą║č鹊ą▓ ąĘą░ ą║ąŠą╝ą░ąĮą┤ąŠą╣ READ, č鹊 ą┤ąŠčüčéčāą┐ ą▒čāą┤ąĄčé ąŠčüčāčēąĄčüčéą▓ą╗ąĄąĮ č鹊ą╗čīą║ąŠ ą║ 4 čüą╗ąŠą▓ą░ą╝, ąĖ čé. ą┐. (čüą╝. čĆąĖčü. 7).

ąĀąĖčü. 7. ąĪą▓čÅąĘčī čüą╗ąŠč鹊ą▓ ą║ąŠą╝ą░ąĮą┤ ąĖ čćąĖčéą░ąĄą╝čŗčģ ą┤ą░ąĮąĮčŗčģ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ ą║ čĆąĖčü. 7:

1. DO n čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ą▓čŗą▓ąŠą┤čā ą┤ą░ąĮąĮčŗčģ ąĖąĘ čüč鹊ą╗ą▒čåą░ n.

2. ąÜąŠą╝ą░ąĮą┤čŗ NOP ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅčÄčé ą╗čÄą▒čāčÄ ą┤ąŠą┐čāčüčéąĖą╝čāčÄ ąĮąĄ ą┐čĆąĄčĆčŗą▓ą░čÄčēčāčÄ ą┐ą░ą║ąĄčé ą║ąŠą╝ą░ąĮą┤čā.

3. ąÜąŠą╝ą░ąĮą┤čŗ BST ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅčÄčé ą╗čÄą▒čāčÄ ą┤ąŠą┐čāčüčéąĖą╝čāčÄ ą┐čĆąĄčĆčŗą▓ą░čÄčēčāčÄ ą┐ą░ą║ąĄčé ą║ąŠą╝ą░ąĮą┤čā.

4. ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čüą╗ąŠčéą░ą╝ąĖ ą║ąŠą╝ą░ąĮą┤ ą┐ąŠą╝ąĄč湥ąĮčŗ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą╣ ą┐ą░čĆčŗ; ąĄčüą╗ąĖ ą┐čĆąĄčĆčŗą▓ą░čÄčēą░čÅ ą║ąŠą╝ą░ąĮą┤ą░ ą┐čĆąĖą║ą╗ą░ą┤čŗą▓ą░ąĄčéčüčÅ ą▓ ą║ąŠąĮčéčĆąŠą╗ąĖčĆčāąĄą╝ąŠą╝ čüą╗ąŠč鹥 ą║ąŠą╝ą░ąĮą┤čŗ ą┤ą╗čÅ ąĖą╝ąĄčÄčēąĄą╣čüčÅ ą┐ą░čĆčŗ čüą╗ąŠą▓ ą┤ą░ąĮąĮčŗčģ, č鹊 čŹčéą░ ą┐ą░čĆą░ ąĮąĄ ą▒čāą┤ąĄčé ą┐čĆąŠčćąĖčéą░ąĮą░.

5. ą¤ą░čĆą░ 1 ą▓čüąĄą│ą┤ą░ ą▒čāą┤ąĄčé ą▓čŗą▓ąĄą┤ąĄąĮą░ (ąĮą░ą┐čĆąĖą╝ąĄčĆ, čŹč鹊 ą┐ą░ą║ąĄčé ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠą╣ ą┤ą╗ąĖąĮčŗ), ą║ąŠą│ą┤ą░ ą┐čĆąĖą╝ąĄąĮčÅąĄčéčüčÅ ą║ąŠą╝ą░ąĮą┤ą░ READ.

ąÜąŠąĮčåąĄą┐čåąĖčÅ čüą▓čÅąĘąĖ ą┐ą░čĆ ą┤ą░ąĮąĮčŗčģ čü ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮčŗą╝ąĖ ą┐ąĄčĆąĄą┐ą░ą┤ą░ą╝ąĖ čéą░ą║č鹊ą▓ čéą░ą║ąČąĄ ąŠčéąĮąŠčüąĖčéčüčÅ ąĖ ą║ ąŠą┐ąĄčĆą░čåąĖčÅą╝ WRITE. ą×ą┤ąĮą░ą║ąŠ, čćč鹊ą▒čŗ ą┐ąŠą╗ąĮąŠčüčéčīčÄ ą┐ąŠąĮčÅčéčī ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖąĄ ąĖ ąŠčüčéą░ąĮąŠą▓ą║čā ąĘą░ą┐ąĖčüčŗą▓ą░ąĄą╝čŗčģ ą┤ą░ąĮąĮčŗčģ, ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī čāčćč鹥ąĮą░ ą╗ą░č鹥ąĮčéąĮąŠčüčéčī ąŠą┐ąĄčĆą░čåąĖąĖ WRITE ąĖ ą┤ąĖą░ą│čĆą░ą╝ą╝čŗ ą▓čĆąĄą╝ąĄąĮąĖ čłąĖąĮčŗ ą┤ą░ąĮąĮčŗčģ, ąŠčüąĮąŠą▓ą░ąĮąĮąŠą╣ ąĮą░ čüčéčĆąŠą▒ąĖčĆąŠą▓ą░ąĮąĖąĖ. ąóąĄą┐ąĄčĆčī ąĮčāąČąĮąŠ čāą┐ąŠą╝čÅąĮčāčéčī ąŠ č鹊ą╝, čćč鹊 ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮčŗąĄ ą┐ąĄčĆąĄą┐ą░ą┤čŗ ą┤ą╗čÅ ąŠą┐ąĄčĆą░čåąĖą╣ WRITE ąĖąĮč鹥čĆąĄčüčāčÄčé ąĮą░čü ą┐ąŠ-ą┤čĆčāą│ąŠą╝čā, č湥ą╝ ą║ą░ą║ ą┤ą╗čÅ ąŠą┐ąĄčĆą░čåąĖą╣ READ. ą¤čĆąĖčćąĖąĮą░ ąŠčéą╗ąĖčćąĖą╣ ąĘą░ą║ą╗čÄčćą░ąĄčéčüčÅ ą▓ ąĘą░ą┤ąĄčƹȹ║ą░čģ (latencies), ąĖ ą┐ąŠčŹč鹊ą╝čā ą┤ąŠčüčéčāą┐ ą║ ą╝ą░čüčüąĖą▓čā ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą▓ ąĮą░čćą░ą╗ąĄ ąŠą┐ąĄčĆą░čåąĖąĖ READ, ąĮąŠ ą▓ ą╝ąŠą╝ąĄąĮčé ąŠą║ąŠąĮčćą░ąĮąĖčÅ ąŠą┐ąĄčĆą░čåąĖąĖ WRITE. ążą░ą║čéąĖč湥čüą║ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ ą┐ąĄčĆąĄą┐ą░ą┤čŗ ąĘą░ą▓ąĖčüčÅčé ąŠčé č鹊ą│ąŠ, ą║ą░ą║ą░čÅ ą┐čĆąĖą╝ąĄąĮčÅąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░čÄčēą░čÅ ą║ąŠą╝ą░ąĮą┤ą░, čćč鹊 ą▒čāą┤ąĄčé ą┐ąŠą║ą░ąĘą░ąĮąŠ ą┐ąŠąĘąČąĄ.

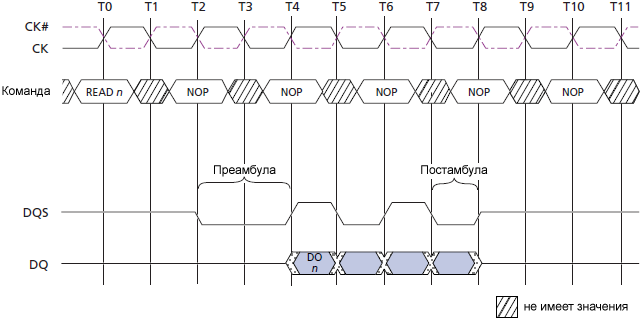

ą©ąĖąĮą░ ą┤ą░ąĮąĮčŗčģ, ąŠčüąĮąŠą▓ą░ąĮąĮą░čÅ ąĮą░ čüčéčĆąŠą▒ąĖčĆąŠą▓ą░ąĮąĖąĖ. ąÆ ą┐ąŠą╗ąĮąŠčüčéčīčÄ čüąĖąĮčģčĆąŠąĮąĮąŠą╣ čüąĖčüč鹥ą╝ąĄ ą▓čŗą▓ąŠą┤ ąĖ ąĘą░čģą▓ą░čé ą┤ą░ąĮąĮčŗčģ ą┐čĆąŠąĖčüčģąŠą┤čÅčé ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ąŠą▒čēąĄą╣, ą┐ąŠčüč鹊čÅąĮąĮąŠ čĆą░ą▒ąŠčéą░čÄčēąĄą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊č鹥 čüąĖčüč鹥ą╝čŗ (system clock). ą×ą┤ąĮą░ą║ąŠ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮą░čÅ čüą║ąŠčĆąŠčüčéčī ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą╗čÅ čéą░ą║ąŠą╣ čüąĖčüč鹥ą╝čŗ ą┤ąŠčüčéąĖą│ą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ čüčāą╝ą╝ą░ ą▓čĆąĄą╝ąĄąĮąĖ ą┤ąŠčüčéčāą┐ą░ ąĮą░ ą▓čŗą▓ąŠą┤ ąĖ ą▓čĆąĄą╝ąĄąĮ ąĘą░ą┤ąĄčƹȹĄą║ čāą║ą╗ą░ą┤čŗą▓ą░ąĄčéčüčÅ ą▓ ą▒ąĖč鹊ą▓čŗą╣ ąĖąĮč鹥čĆą▓ą░ą╗ (ą▓ąĄą╗ąĖčćąĖąĮčā, ąŠą▒čĆą░čéąĮčāčÄ čüą║ąŠčĆąŠčüčéąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ). ąźąŠčéčÅ ą│ąĄąĮąĄčĆą░čåąĖčÅ ąŠčéą╗ąŠąČąĄąĮąĮčŗčģ čéą░ą║č鹊ą▓ ą┤ą╗čÅ čĆą░ąĮąĮąĄą│ąŠ ą┐ąŠčüčéčāą┐ą╗ąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ąĖ/ąĖą╗ąĖ ą┐ąŠąĘą┤ąĮąĄą│ąŠ ąĘą░čģą▓ą░čéą░ ą┤ą░ąĮąĮčŗčģ ą┐ąŠąĘą▓ąŠą╗čÅčé ą┐ąŠą▓čŗčüąĖčéčī čüą║ąŠčĆąŠčüčéčī ą┐ąĄčĆąĄą┤ą░čćąĖ, čŹčéąĖ č鹥čģąĮąĖą║ąĖ ąĮąĄ čāčćąĖčéčŗą▓ą░čÄčé č鹊čé čäą░ą║čé, čćč鹊 ąŠą║ąĮąŠ ą┤ąŠą┐čāčüčéąĖą╝čŗčģ ą┤ą░ąĮąĮčŗčģ (čéą░ą║ ąĮą░ąĘčŗą▓ą░ąĄą╝čŗą╣ "ą│ą╗ą░ąĘ ą┤ą░ąĮąĮčŗčģ", data eye) ą┐ąĄčĆąĄą╝ąĄčēą░ąĄčéčüčÅ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ą╗čÄą▒ąŠą│ąŠ čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ čéą░ą║č鹊ą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ - ąĖąĘ-ąĘą░ ąĖąĘą╝ąĄąĮąĄąĮąĖą╣ č鹥ą╝ą┐ąĄčĆą░čéčāčĆčŗ, ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ ąĖą╗ąĖ ąĮą░ą│čĆčāąĘą║ąĖ. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, čćč鹊ą▒čŗ ą▓čüąĄ čĆą░ą▓ąĮąŠ ą┤ąŠčüčéąĖčćčī ą▓čŗčüąŠą║ąĖčģ čüą║ąŠčĆąŠčüč鹥ą╣ ą┤ą░ąĮąĮčŗčģ, ą┤ą╗čÅ čāčüčéčĆąŠą╣čüčéą▓ DDR ą┤ąŠą▒ą░ą▓ą╗ąĄąĮčŗ čüčéčĆąŠą▒čŗ čüąĖą│ąĮą░ą╗ąŠą▓ ą┤ą░ąĮąĮčŗčģ. ąĪčéčĆąŠą▒čŗ čüąĖą│ąĮą░ą╗ąŠą▓ ą┤ą░ąĮąĮčŗčģ ąĮąĄ čÅą▓ą╗čÅčÄčéčüčÅ ą┐ąŠčüč鹊čÅąĮąĮąŠ ą│ąĄąĮąĄčĆąĖčĆčāąĄą╝čŗą╝ąĖ, ą║ą░ą║ čüąĖą│ąĮą░ą╗čŗ čéą░ą║č鹊ą▓, ąĖ ąŠąĮąĖ ą│ąĄąĮąĄčĆąĖčĆčāčÄčéčüčÅ ą▓čŗą▓ąŠą┤čÅčēąĖą╝ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ (ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ ą┐ą░ą╝čÅčéąĖ ą┤ą╗čÅ ąŠą┐ąĄčĆą░čåąĖą╣ WRITE, ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ą╝ąĖ DRAM ą┤ą╗čÅ ąŠą┐ąĄčĆą░čåąĖą╣ READ). ąØą░ čāčĆąŠą▓ąĮąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ DRAM ą┤ą╗čÅ ąŠą┐ąĄčĆą░čåąĖą╣ READ čüąĖą│ąĮą░ą╗čŗ čüčéčĆąŠą▒ą░ ą┤ą░ąĮąĮčŗčģ (DQS) čŹčäč乥ą║čéąĖą▓ąĮąŠ ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮčŗ ą║ą░ą║ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗąĄ ą▓čŗčģąŠą┤čŗ ą┤ą░ąĮąĮčŗčģ (DQ) čü ąĘą░čĆą░ąĮąĄąĄ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗą╝ čłą░ą▒ą╗ąŠąĮąŠą╝; ą┤ą╗čÅ ąŠą┐ąĄčĆą░čåąĖą╣ WRITE čüąĖą│ąĮą░ą╗čŗ čüčéčĆąŠą▒ą░ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą║ą░ą║ čéą░ą║čéčŗ ą┤ą╗čÅ ąĘą░čģą▓ą░čéą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖčģ ą▓čģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ. ąØą░ čāčĆąŠą▓ąĮąĄ ą┐ąĄčćą░čéąĮąŠą╣ ą┐ą╗ą░čéčŗ čüąĖą│ąĮą░ą╗čŗ čüčéčĆąŠą▒ą░ ąĖą╝ąĄčÄčé ąĮą░ą│čĆčāąĘą║čā, ąĖą┤ąĄąĮčéąĖčćąĮčāčÄ čüąĖą│ąĮą░ą╗ą░ą╝ ą┤ą░ąĮąĮčŗčģ, ąĖ čĆą░ąĘą▓ąŠą┤čÅčéčüčÅ ą┐čĆąŠą▓ąŠą┤ąĮąĖą║ą░ą╝ąĖ č鹊čćąĮąŠ čéą░ą║ ąČąĄ.

ąóčāčé čüč鹊ąĖčé čüą┤ąĄą╗ą░čéčī ą╝ą░ą╗ąĄąĮčīą║ąŠąĄ ąŠčéčüčéčāą┐ą╗ąĄąĮąĖąĄ, čćč鹊ą▒čŗ ą┐ąŠą║ą░ąĘą░čéčī čüąŠąŠčéąĮąŠčłąĄąĮąĖąĄ čüąĖą│ąĮą░ą╗ąŠą▓ čüčéčĆąŠą▒ą░ ą║ ą┤ą░ąĮąĮčŗą╝ (strobe-to-data). ąŁč鹊 č鹥čģąĮąĖč湥čüą║ąŠąĄ ąĘą░ą╝ąĄčćą░ąĮąĖąĄ č乊ą║čāčüąĖčĆčāąĄčéčüčÅ ąĮą░ čéąĖą┐ąĖčćąĮčŗčģ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅčģ ą┐ą░ą╝čÅčéąĖ ą┤ąĄčüą║č鹊ą┐ąŠą▓ PC, ą║ąŠč鹊čĆčŗąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčé x64 ą╝ąŠą┤čāą╗ąĖ DIMM, ą┐ąŠčüčéčĆąŠąĄąĮąĮčŗąĄ ąĖąĘ x8 ąĖą╗ąĖ x16 ą╝ąĖą║čĆąŠčüčģąĄą╝ DRAM. ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆčŗ ą┤ą╗čÅ čŹčéąĖčģ ą┐čĆąĖą╗ąŠąČąĄąĮąĖą╣ ą▒čāą┤čāčé čĆą░ąĘčĆą░ą▒ąŠčéą░ąĮčŗ čü ąŠą┤ąĮąĖą╝ čüčéčĆąŠą▒ąŠą╝ ąĮą░ ą▒ą░ą╣čé; ąĮą░ą┐čĆąĖą╝ąĄčĆ, ąĘą┤ąĄčüčī ą▒čāą┤ąĄčé ąŠą┤ąĖąĮ čüčéčĆąŠą▒ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ x8 DRAM, ąĖą╗ąĖ 2 čüčéčĆąŠą▒ą░ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ x16.

ąöčĆčāą│ąĖąĄ čéąĖą┐čŗ ą┐čĆąĖą╗ąŠąČąĄąĮąĖą╣ ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┤čĆčāą│ąĖąĄ čüąŠąŠčéąĮąŠčłąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗąĄ/čüčéčĆąŠą▒. ąØą░ą┐čĆąĖą╝ąĄčĆ, čüąĄčĆą▓ąĄčĆčŗ ąĖčüą┐ąŠą╗čīąĘčāčÄčé x72 ą╝ąŠą┤čāą╗ąĖ DIMM, ąŠčüąĮąŠą▓ą░ąĮąĮčŗąĄ ąĮą░ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░čģ x4, čćč鹊 čéčĆąĄą▒čāąĄčé ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓, ą│ąĄąĮąĄčĆąĖčĆčāčÄčēąĖčģ ąŠčéą┤ąĄą╗čīąĮčŗą╣ čüčéčĆąŠą▒ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą╣ č湥čéą▓ąĄčĆą║ąĖ ą▒ąĖčé, ąĖ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčŗ ą┤ą╗čÅ ą│čĆą░čäąĖą║ąĖ ąĖą╗ąĖ ą┐čĆąĖą╗ąŠąČąĄąĮąĖą╣ ą║ąŠą╝ą╝čāąĮąĖą║ą░čåąĖą╣ ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ąŠčé ąŠą┤ąĮąŠą│ąŠ ą┤ąŠ 4 čüčéčĆąŠą▒ąŠą▓ ąĮą░ 32 ą▒ąĖčéą░. ą¤čĆąŠą┤ą▓ąĖąĮčāčéčŗąĄ č鹥čģąĮąĖą║ąĖ ą╝ąŠą│čāčé ą▒čŗčéčī ąĘą░ą┤ąĄą╣čüčéą▓ąŠą▓ą░ąĮčŗ ą┤ą╗čÅ čüą╝ąĄčłąĖą▓ą░ąĮąĖčÅ ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖčÅ čĆą░ąĘą╗ąĖčćąĮčŗčģ ąŠčéąĮąŠčłąĄąĮąĖą╣ ą┤ą░ąĮąĮčŗąĄ/čüčéčĆąŠą▒ ą▓ čüąĖčüč鹥ą╝ąĄ, ąĮąŠ čéą░ą║ąĖąĄ čüą╗čāčćą░ąĖ ąĘą┤ąĄčüčī ąĮąĄ čĆą░čüčüą╝ą░čéčĆąĖą▓ą░čÄčéčüčÅ. ąÆ čŹč鹊ą╝ ą░ą┐ąĮąŠčāč鹥 čüą┤ąĄą╗ą░ąĮ č乊ą║čāčü ą┤ą╗čÅ čüąŠąŠčéąĮąŠčłąĄąĮąĖčÅ ąŠą┤ąĮąŠą│ąŠ čüčéčĆąŠą▒ą░ ąĮą░ 1 ą▒ą░ą╣čé. ąĪąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖčÅ ąĖ ąŠą┐ąĖčüą░ąĮąĮčŗąĄ ą▓čŗčćąĖčüą╗ąĄąĮąĖčÅ ą┐čĆąĖą╝ąĄąĮčÅčÄčéčüčÅ ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ą║ ą║ą░ąČą┤ąŠą╣ ą│čĆčāą┐ą┐ąĄ čüąĖą│ąĮą░ą╗ąŠą▓.

ąöą╗čÅ ąŠą┐ąĄčĆą░čåąĖą╣ čćč鹥ąĮąĖčÅ (READ) čüąĖą│ąĮą░ą╗čŗ čüčéčĆąŠą▒ą░ ą┤ą░ąĮąĮčŗčģ ą▓čŗčĆąŠą▓ąĮąĄąĮčŗ ą┐ąŠ čüčĆąĄąĘčā čü čüąĖą│ąĮą░ą╗ą░ą╝ąĖ ą┤ą░ąĮąĮčŗčģ, čŹč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ą▓čüąĄ ą┤ą░ąĮąĮčŗąĄ ąĖ čüčéčĆąŠą▒čŗ ą┤ą░ąĮąĮčŗčģ čéą░ą║čéąĖčĆčāčÄčéčüčÅ ą▓ čāčüčéčĆąŠą╣čüčéą▓ąĄ ąŠą┤ąĖąĮą░ą║ąŠą▓čŗą╝ čüąĖą│ąĮą░ą╗ąŠą╝, ąĖ ą▓čüąĄ ą┐ąĄčĆąĄčģąŠą┤čŗ čāčĆąŠą▓ąĮąĄą╣ ą▓čŗčģąŠą┤ąŠą▓ ą▒čāą┤čāčé ąĮąŠą╝ąĖąĮą░ą╗čīąĮąŠ ą┐čĆąŠąĖčüčģąŠą┤ąĖčéčī ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ. ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą▒čāą┤ąĄčé ą▓ąĮčāčéčĆąĖ čüąĄą▒čÅ ąĘą░ą┤ąĄčƹȹĖą▓ą░čéčī ą┐čĆąĖąĮąĖą╝ą░ąĄą╝čŗą╣ čüčéčĆąŠą▒ ą║ čåąĄąĮčéčĆčā ą┐čĆąĖąĮčÅč鹊ą│ąŠ "ą│ą╗ą░ąĘą░ ą┤ą░ąĮąĮčŗčģ".

ąöą╗čÅ ąŠą┐ąĄčĆą░čåąĖą╣ ąĘą░ą┐ąĖčüąĖ (WRITE) ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą┤ąŠą╗ąČąĄąĮ ą┐čĆąĄą┤ąŠčüčéą░ą▓ąĖčéčī čüčéčĆąŠą▒čŗ ą┤ą░ąĮąĮčŗčģ, ą▓čŗčĆąŠą▓ąĮąĄąĮąĮčŗąĄ ą┐ąŠ čåąĄąĮčéčĆčā ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ čüą▓ąŠąĖčģ ą┤ą░ąĮąĮčŗčģ. ąóą░ą║ čćč鹊 ą┐ąĄčĆąĄą┐ą░ą┤čŗ čāčĆąŠą▓ąĮčÅ čüčéčĆąŠą▒ąŠą▓ ą┐čĆąŠąĖčüčģąŠą┤čÅčé ąĮąŠą╝ąĖąĮą░ą╗čīąĮąŠ čü čäą░ąĘąŠą╣ 90 ą│čĆą░ą┤čāčüąŠą▓ (ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ) ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ą┐ąĄčĆąĄą┐ą░ą┤ąŠą▓ čāčĆąŠą▓ąĮčÅ ą┤ą░ąĮąĮčŗčģ. ąŻčüčéčĆąŠą╣čüčéą▓ąŠ DRAM ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą▓ąĮčāčéčĆąĄąĮąĮčÄčÄ ą┐ąŠą┤čģąŠą┤čÅčēčāčÄ ą╝ą░čĆčłčĆčāčéąĖąĘą░čåąĖčÄ čüčéčĆąŠą▒ąŠą▓ ąĖ ą┤ą░ąĮąĮčŗčģ čéą░ą║, čćč鹊ą▒čŗ čüčéčĆąŠą▒čŗ ą╝ąŠą│ą╗ąĖ ą▒čŗčéčī ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮčŗ ąĮą░ą┐čĆčÅą╝čāčÄ ą┤ą╗čÅ ąĘą░čģą▓ą░čéą░ ą▓čģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ą┐čĆąĖčćąĖąĮą░ čĆą░ąĘą╗ąĖčćąĖą╣ ąŠą┐ąĄčĆą░čåąĖą╣ READ ąĖ WRITE čüąŠčüč鹊ąĖčé ą▓ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ čĆą░ąĘąĮčŗčģ čüčģąĄą╝ ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖčÅ, čćč鹊ą▒čŗ čüčģąĄą╝ą░ ąĘą░ą┤ąĄčƹȹ║ąĖ ą▒čŗą╗ą░ čüąŠčüčĆąĄą┤ąŠč鹊č湥ąĮą░ ą▓ ąŠą┤ąĮąŠą╝ ą╝ąĄčüč鹥 (ą▓ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąĄ), ąĖ ąĮąĄ ą┤ąŠą╗ąČąĮą░ čéąĖčĆą░ąČąĖčĆąŠą▓ą░čéčīčüčÅ čü ą║ą░ąČą┤čŗą╝ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ DRAM, ąĮą░čģąŠą┤čÅčēąĖą╝čüčÅ ą▓ čüąĖčüč鹥ą╝ąĄ. ąŁč鹊čé ą┐ąŠą┤čģąŠą┤, ą║ą░ą║ ąŠąČąĖą┤ą░ąĄčéčüčÅ, ą▒čāą┤ąĄčé ą┐ąĄčĆąĄąĮąĄčüąĄąĮ ą▓ ą▒čāą┤čāčēąĄą╝ ąĮą░ čüą╗ąĄą┤čāčÄčēąĖąĄ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą┤ąĖąĘą░ą╣ąĮą░ DDR, čćč鹊ą▒čŗ čāčüąŠą▓ąĄčĆčłąĄąĮčüčéą▓ąŠą▓ą░čéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčāčÄ ąĖąĮčäčĆą░čüčéčĆčāą║čéčāčĆčā.

ą¤čĆąĄą░ą╝ą▒čāą╗ą░ ąĖ ą┐ąŠčüčéą░ą╝ą▒čāą╗ą░. ą©ą░ą▒ą╗ąŠąĮ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓ ą▓čĆąĄą╝ąĄąĮąĖ čüčéčĆąŠą▒ą░ ą┤ą░ąĮąĮčŗčģ čüąŠčüč鹊ąĖčé ąĖąĘ ą┐ąŠčĆčåąĖą╣ ą┐čĆąĄą░ą╝ą▒čāą╗čŗ, ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ ąĖ ą┐ąŠčüčéą░ą╝ą▒čāą╗čŗ. ąĀąĖčü. 8 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čłą░ą▒ą╗ąŠąĮ čüčéčĆąŠą▒ą░ ąĖ ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ ą┤ą╗čÅ ąŠą┐ąĄčĆą░čåąĖą╣ READs, ąĖ čĆąĖčü. 9 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé č鹊 ąČąĄ čüą░ą╝ąŠąĄ ą┤ą╗čÅ ąŠą┐ąĄčĆą░čåąĖą╣ WRITE. ą¤ąŠčĆčåąĖčÅ ą┐čĆąĄą░ą╝ą▒čāą╗čŗ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ąŠą║ąĮąŠ ą▓čĆąĄą╝ąĄąĮąĖ ą┤ą╗čÅ ą┐čĆąĖąĮąĖą╝ą░čÄčēąĄą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░, čćč鹊ą▒čŗ čĆą░ąĘčĆąĄčłąĖčéčī ąĄą│ąŠ čüčģąĄą╝čā ąĘą░čģą▓ą░čéą░ ą┤ą░ąĮąĮčŗčģ, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ ąĖąĘą▓ąĄčüčéąĮčŗą╣/ą┤ąŠą┐čāčüčéąĖą╝čŗą╣ čāčĆąŠą▓ąĄąĮčī ą┐čĆąĖčüčāčéčüčéą▓čāąĄčé ą▓ čüąĖą│ąĮą░ą╗ąĄ čüčéčĆąŠą▒ą░, čćč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąĖąĘą▒ąĄąČą░čéčī ą╗ąŠąČąĮčŗčģ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖą╣ čüčģąĄą╝čŗ ąĘą░čģą▓ą░čéą░. ąŚą░ ą┐čĆąĄą░ą╝ą▒čāą╗ąŠą╣ čüčéčĆąŠą▒čŗ ą▒čāą┤čāčé ą┐ąĄčĆąĄą║ą╗čÄčćą░čéčīčüčÅ čü č鹊ą╣ ąČąĄ čćą░čüč鹊č鹊ą╣, čćč鹊 ąĖ čéą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗, ą▓ č鹥č湥ąĮąĖąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐ą░ą║ąĄčéą░ ą┤ą░ąĮąĮčŗčģ (data burst). ąÜą░ąČą┤čŗą╣ ą┐ąĄčĆąĄčģąŠą┤ ą▓ ą╗ąŠą│. 1 ąĖ ą▓ ą╗ąŠą│. 0 čüą▓čÅąĘą░ąĮ čü ą┐ąĄčĆąĄą┤ą░č湥ą╣ ąŠą┤ąĮąŠą╣ ą┐ąŠčĆčåąĖąĖ ą┤ą░ąĮąĮčŗčģ. ą£ą░ą╗čŗą╣ ąĖąĮč鹥čĆą▓ą░ą╗ ą▓čĆąĄą╝ąĄąĮąĖ ąĘą░ ą┐ąŠčüą╗ąĄą┤ąĮąĖą╝ ą┐ąĄčĆąĄčģąŠą┤ąŠą╝ ąĮą░ąĘčŗą▓ą░ąĄčéčüčÅ ą┐ąŠčüčéą░ą╝ą▒čāą╗ąŠą╣. ąæąŠą╗čīčłąĖąĮčüčéą▓ąŠ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ ąĖą╝ąĄčÄčé ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ ąĖčüč鹊čćąĮąĖą║ čéą░ą║č鹊ą▓ čü čćą░čüč鹊č鹊ą╣ ą▓ 2 čĆą░ąĘą░ ą▓čŗčłąĄ čćą░čüč鹊čéčŗ čéą░ą║č鹊ą▓ ą┐ą░ą╝čÅčéąĖ, čéą░ą║ čćč鹊 ą│ąĄąĮąĄčĆą░čåąĖčÅ čüčéčĆąŠą▒ą░, čüą┤ą▓ąĖąĮčāč鹊ą│ąŠ ą┐ąŠ čäą░ąĘąĄ ąĮą░ 90 ą│čĆą░ą┤čāčüąŠą▓ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ą┤ą░ąĮąĮčŗčģ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą┤ąŠą▓ąŠą╗čīąĮąŠ ą┐čĆąŠčüč鹊. ą×ą▒čŗčćąĮąŠ ą┤ą░ąĮąĮčŗąĄ ąĖ čüčéčĆąŠą▒ čéą░ą║čéąĖčĆčāčÄčéčüčÅ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ ą┤ą▓čāą║čĆą░čéąĮąŠą╣ čćą░čüč鹊čéčŗ čéą░ą║č鹊ą▓, čü ą┤ą░ąĮąĮčŗą╝ąĖ, ą┐ąŠčüčéčāą┐ą░čÄčēąĖą╝ąĖ ąĮą░ ą▓čŗčģąŠą┤ ą┐ąŠ ą┐ąĄčĆąĄą┐ą░ą┤ą░ą╝ čü ąŠą┤ąĮąŠą╣ ą┐ąŠą╗čÅčĆąĮąŠčüčéčīčÄ, ąĖ čüčéčĆąŠą▒čŗ ą┐ąĄčĆąĄą║ą╗čÄčćą░čÄčéčüčÅ ą┐ąŠ ą┐ąĄčĆąĄą┐ą░ą┤ą░ą╝ čéą░ą║č鹊ą▓ ą┐čĆąŠčéąĖą▓ąŠą┐ąŠą╗ąŠąČąĮąŠą╣ ą┐ąŠą╗čÅčĆąĮąŠčüčéąĖ. ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠ ą┐čĆąĖą▓ą╗ąĄą║ą░ąĄčéčüčÅ ąĘą░ą┤ąĄčƹȹ║ą░ ą┐čĆąĖčģąŠą┤čÅčēąĄą│ąŠ čüčéčĆąŠą▒ą░ ą┤ą╗čÅ ąŠą┐ąĄčĆą░čåąĖą╣ READ, čćč鹊 ą┐ąŠą┤čĆąŠą▒ąĮąŠ čĆą░čüčüą╝ą░čéčĆąĖą▓ą░ąĄčéčüčÅ ą▓ ąŠčéą┤ąĄą╗čīąĮąŠą╝ ą░ą┐ąĮąŠčāč鹥.

ąĀąĖčü. 8. ą©ą░ą▒ą╗ąŠąĮ DQS ą┤ą╗čÅ ąŠą┐ąĄčĆą░čåąĖąĖ READ, ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčēąĖą╣ ą┐čĆąĄą░ą╝ą▒čāą╗čā ąĖ ą┐ąŠčüčéą░ą╝ą▒čāą╗čā.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ ą║ čĆąĖčü. 8:

1. DO n čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ą▓čŗą▓ąŠą┤čā ą┤ą░ąĮąĮčŗčģ ą┤ą╗čÅ čüč鹊ą╗ą▒čåą░ n.

2. ąöą╗ąĖąĮą░ ą┐ą░ą║ąĄčéą░ (Burst Length, BL) = 4, CAS latency = 2.

3. ąóčĆąĖ čüą╗ąĄą┤čāčÄčēąĖąĄ ą┤čĆčāą│ ąĘą░ ą┤čĆčāą│ąŠą╝ 菹╗ąĄą╝ąĄąĮčéą░ ą┤ą░ąĮąĮčŗčģ ą┐ąŠčÅą▓ą╗čÅčÄčéčüčÅ ą▓ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮąŠą╝ ą┐ąŠčĆčÅą┤ą║ąĄ ą┐ąŠčüą╗ąĄ DO n.

4. ąöą╗čÅ ąĖą╗ą╗čÄčüčéčĆą░čåąĖąĖ čüąĖą│ąĮą░ą╗čŗ ą┐ąŠą║ą░ąĘą░ąĮčŗ čü tAC ąĖ tDQSQ = 0.

ąĀąĖčü. 9. ą©ą░ą▒ą╗ąŠąĮ DQS ą┤ą╗čÅ ąŠą┐ąĄčĆą░čåąĖąĖ WRITE, ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčēąĖą╣ ą┐čĆąĄą░ą╝ą▒čāą╗čā ąĖ ą┐ąŠčüčéą░ą╝ą▒čāą╗čā.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ ą║ čĆąĖčü. 9:

1. DI b čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ą▓čģąŠą┤ąĮčŗą╝ ą┤ą░ąĮąĮčŗą╝ ą┤ą╗čÅ čüč鹊ą╗ą▒čåą░ b.

2. ą¤ąŠčüčéčāą┐ą░čÄčé čéčĆąĖ čüą╗ąĄą┤čāčÄčēąĖąĄ ą┤čĆčāą│ ąĘą░ ą┤čĆčāą│ąŠą╝ ą▓čģąŠą┤ąĮčŗčģ 菹╗ąĄą╝ąĄąĮčéą░ ą┤ą░ąĮąĮčŗčģ ą▓ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮąŠą╝ ą┐ąŠčĆčÅą┤ą║ąĄ ą┐ąŠčüą╗ąĄ DI b.

3. ą¤ąŠą║ą░ąĘą░ąĮ ą┐ą░ą║ąĄčé ąĖąĘ 4 菹╗ąĄą╝ąĄąĮč鹊ą▓ ą┤ą░ąĮąĮčŗčģ.

4. ąöą╗čÅ ąĖą╗ą╗čÄčüčéčĆą░čåąĖąĖ ą┐ąŠą║ą░ąĘą░ąĮ ąĮąŠą╝ąĖąĮą░ą╗čīąĮčŗą╣ ąĖąĮč鹥čĆą▓ą░ą╗ tDQSS ąĖ ą▒ąĄąĘ ą▒ąĖč鹊ą▓ DM.

ąöą╗čÅ ą┐ąĄčĆąĄčģąŠą┤ą░čģ ąŠčé čćč鹥ąĮąĖčÅ ą║ čćč鹥ąĮąĖčÄ (read-to-read) čłąĖąĮčŗ ą┤ą░ąĮąĮčŗčģ, ą│ą┤ąĄ ąŠą┐ąĄčĆą░čåąĖąĖ READ ą┐čĆąŠąĖčüčģąŠą┤čÅčé ąĖąĘ čĆą░ąĘąĮčŗčģ čäąĖąĘąĖč湥čüą║ąĖčģ ą▒ą░ąĮą║ąŠą▓ DRAM, ąĖą╗ąĖ ą┤ą╗čÅ ą┐ąĄčĆąĄčģąŠą┤ąŠą▓ ąŠčé čćč鹥ąĮąĖčÅ ą║ ąĘą░ą┐ąĖčüąĖ (read-to-write) čłąĖąĮčŗ ą┤ą░ąĮąĮčŗčģ (ąĮą░ą┐čĆąĖą╝ąĄčĆ, ą┐ąĄčĆąĄčģąŠą┤čŗ ąĖąĘ čüąŠčüč鹊čÅąĮąĖčÅ, ą║ąŠą│ą┤ą░ ąŠąĮąŠ čāčüčéčĆąŠą╣čüčéą▓ąŠ čāą┐čĆą░ą▓ą╗čÅąĄčé čłąĖąĮąŠą╣ ą┤ą░ąĮąĮčŗčģ, ą║ čüąŠčüč鹊čÅąĮąĖčÄ, ą║ąŠą│ą┤ą░ ą┤čĆčāą│ąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ čāą┐čĆą░ą▓ą╗čÅąĄčé čłąĖąĮąŠą╣ ą┤ą░ąĮąĮčŗčģ), ąĖą╝ąĄčÄčéčüčÅ čüąĖą│ąĮą░ą╗čŗ čüčéčĆąŠą▒ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ, ąĖ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ ąĮčāąČąĄąĮ ą┐ąŠą╗ąĮčŗą╣ čłą░ą▒ą╗ąŠąĮ čüčéčĆąŠą▒ą░ (ą▓ą║ą╗čÄčćą░čÅ ą┐čĆąĄą░ą╝ą▒čāą╗čŗ ąĖ ą┐ąŠčüčéą░ą╝ą▒čāą╗čŗ). ąÜąŠąĮčüąĄčĆą▓ą░čéąĖą▓ąĮčŗą╣ ą┐ąŠą┤čģąŠą┤ čĆąĄčłąĄąĮąĖčÅ ą┐čĆąŠą▒ą╗ąĄą╝čŗ - čüąŠčüč鹊ąĖčé ą▓ čĆą░čüą┐ąŠą╗ąŠąČąĄąĮąĖąĖ ąĖąĮč鹥čĆą▓ą░ą╗ąŠą▓ ą╝ąĄąČą┤čā ąĘą░ą┐čĆąŠčüą░ą╝ąĖ, čéą░ą║ čćč鹊ą▒čŗ ą┐ąŠčüčéą░ą╝ą▒čāą╗ą░ ąŠčé ą┐ąĄčĆą▓ąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ąĘą░ą▓ąĄčĆčłąĖą╗ą░čüčī ą┤ąŠ ąĮą░čćą░ą╗ą░ ą┐čĆąĄą░ą╝ą▒čāą╗čŗ ąŠčé ą┤čĆčāą│ąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗąĄ ą┐ą░ą║ąĄčéčŗ READ ąĖąĘ ąŠą┤ąĮąŠą│ąŠ ąĖ č鹊ą│ąŠ ąČąĄ ą▒ą░ąĮą║ą░ DRAM ą▓čŗą┐ąŠą╗ąĮčÅčÄčéčüčÅ čĆą░čüčłąĖčĆąĄąĮąĖąĄą╝ ą┐ąŠčĆčåąĖąĖ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ čłą░ą▒ą╗ąŠąĮą░ čüčéčĆąŠą▒ą░ ą┤ą░ąĮąĮčŗčģ (ą┐ąŠčüčéą░ą╝ą▒čāą╗ą░ ąĖ ą┐čĆąĄą░ą╝ą▒čāą╗ą░ ąĮąĄ ąĮčāąČąĮą░ ą╝ąĄąČą┤čā čüą╗ąĄą┤čāčÄčēąĖą╝ąĖ ą┤čĆčāą│ ąĘą░ ą┤čĆčāą│ąŠą╝ ą┐ą░ą║ąĄčéą░ą╝ąĖ READ ąĖąĘ ąŠą┤ąĮąŠą│ąŠ ąĖ č鹊ą│ąŠ ąČąĄ čāčüčéčĆąŠą╣čüčéą▓ą░). ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗąĄ ą┐ą░ą║ąĄčéčŗ WRITE čéą░ą║ąČąĄ ą▓ąŠąĘą╝ąŠąČąĮčŗ, ą┤ą░ąČąĄ ąĄčüą╗ąĖ ąŠąĮąĖ ąŠčüčāčēąĄčüčéą▓ą╗čÅčÄčéčüčÅ ą▓ čĆą░ąĘąĮčŗąĄ čäąĖąĘąĖč湥čüą║ąĖąĄ ą▒ą░ąĮą║ąĖ DRAM. ąŁč鹊 ąĮąĄčüą║ąŠą╗čīą║ąŠ ą╝ąĄąĮąĄąĄ ąĖąĮčéčāąĖčéąĖą▓ąĮąŠ ą┐ąŠč鹊ą╝čā čćč鹊, ą▓ ąŠčéą╗ąĖčćąĖąĄ ąŠčé čüą╗čāčćą░čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ čćč鹥ąĮąĖą╣ (READ) ąĖąĘ ąŠą┤ąĮąŠą│ąŠ ąĖ č鹊ą│ąŠ ąČąĄ ąĖčüč鹊čćąĮąĖą║ą░, ą╝ąĄčüč鹊 ąĮą░ąĘąĮą░č湥ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ą▓ DRAM ą┤ą╗čÅ ą▓č鹊čĆąŠą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ą┐ą░ą║ąĄčéą░ WRITE ąĮąĄčé čüą┐ąŠčüąŠą▒ą░ čāąĘąĮą░čéčī, čćč鹊 ą┐ąĄčĆą▓čŗą╣ ą┐ą░ą║ąĄčé WRITE ąŠčüčāčēąĄčüčéą▓ą╗čÅą╗čüčÅ ą▓ ą┤čĆčāą│ąŠą╣ ą▒ą░ąĮą║ DRAM. ąŁč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 DRAM ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čüą┐ąŠčüąŠą▒ąĮčŗ ą┐čĆąĖąĮąĖą╝ą░čéčī čĆą░ąĘąĮčŗąĄ ą▓čĆąĄą╝ąĄąĮą░ ą┐čĆąĄą░ą╝ą▒čāą╗čŗ, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé č鹊ą│ąŠ, ą║ą░ą║ą░čÅ ą▒čŗą╗ą░ ą┐ąĄčĆąĄą┤ čŹčéąĖą╝ ą░ą║čéąĖą▓ąĮąŠčüčéčī ąĘą░ą┐ąĖčüąĖ ąĮą░ čłąĖąĮąĄ.

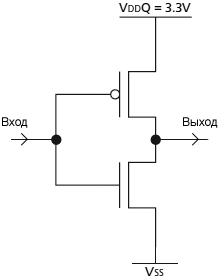

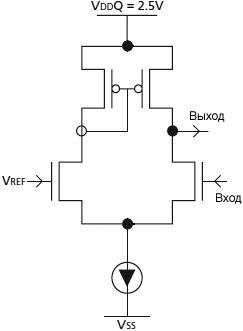

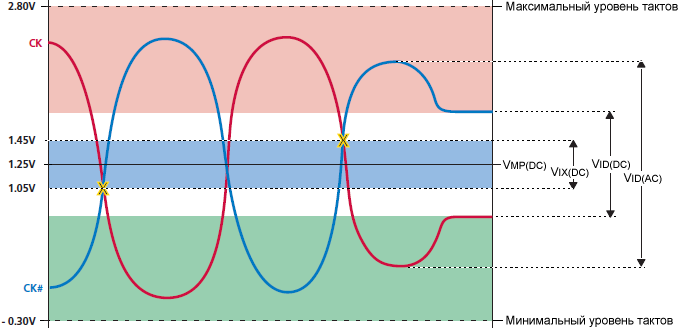

ąśąĮč鹥čĆč乥ą╣čü SSTL_2. ą¤čĆąĄą┤čŗą┤čāčēąĖąĄ č鹥čģąĮąŠą╗ąŠą│ąĖąĖ ą┐ą░ą╝čÅčéąĖ SDR ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ą╗ąĖ LVTTL ąĖ čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮčŗąĄ čāčĆąŠą▓ąĮąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┤ą╗čÅ ąĖąĮč鹥čĆč乥ą╣čüą░ ą┐ąĄčĆąĄą┤ą░čćąĖ čüąĖą│ąĮą░ą╗ąŠą▓. ą£ąĖą║čĆąŠčüčģąĄą╝čŗ DDR SDRAM ąĘą░ą┤ąĄą╣čüčéą▓čāčÄčé ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗąĄ ą▓čģąŠą┤čŗ ąĖ ąŠą┐ąŠčĆąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┤ą╗čÅ ą▓čüąĄčģ čüąĖą│ąĮą░ą╗ąŠą▓ ąĖąĮč鹥čĆč乥ą╣čüą░. ąŁč鹊čé ąĖąĮč鹥čĆč乥ą╣čü ąĮą░ąĘčŗą▓ą░ąĄčéčüčÅ SSTL_2, ąĖ ąŠąĮ čĆą░ą▒ąŠčéą░ąĄčé ąĮą░ čüą┐ąĄčåąĖą░ą╗čīąĮąŠą╣ ą╗ąŠą│ąĖą║ąĄ čü čāčĆąŠą▓ąĮčÅą╝ąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ 2.5V. SSTL_2 čÅą▓ą╗čÅąĄčéčüčÅ ąĖąĮą┤čāčüčéčĆąĖą░ą╗čīąĮčŗą╝ čüčéą░ąĮą┤ą░čĆč鹊ą╝, ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗą╝ ą┤ąŠą║čāą╝ąĄąĮč鹊ą╝ JEDEC #EIA/JESD8-9. ąźąŠčéčÅ ąĮąĄą║ąŠč鹊čĆčŗąĄ DRAM ą▒čāą┤čāčé ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čéčī čüąĮąĖąČąĄąĮąĮčŗą╣ ą┐ąŠ ą╝ąŠčēąĮąŠčüčéąĖ ą▓čŗčģąŠą┤, ą▒ąŠą╗čīčłąĖąĮčüčéą▓ąŠ ą▒čāą┤ąĄčé čüąŠą▓ą╝ąĄčüčéąĖą╝ąŠ čü čāčĆąŠą▓ąĮčÅą╝ąĖ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ SSTL_2 Class II.

ąÆčŗą│ąŠą┤čŗ ąĖąĮč鹥čĆč乥ą╣čüą░ SSTL_2 ą▓ą║ą╗čÄčćą░čÄčé čüąĖą╝ą╝ąĄčéčĆąĖčÄ ą┤ą╗čÅ ąĮąĖąĘą║ąŠą│ąŠ ąĖ ą▓čŗčüąŠą║ąŠą│ąŠ ą╗ąŠą│ąĖč湥čüą║ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ, čāą╗čāčćčłąĄąĮąĮčāčÄ čåąĄą╗ąŠčüčéąĮąŠčüčéčī ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░, ą┐ąŠą▓čŗčłąĄąĮąĮčāčÄ ąĘą░čēąĖčéčā ąŠčé čłčāą╝ą░, čéą░ą║ ą║ą░ą║ ąĮą░ ą▓čģąŠą┤ąĮčŗąĄ čāčĆąŠą▓ąĮąĖ ą╝ąĄąĮčīčłąĄ ą▓ą╗ąĖčÅčÄčé ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ.

ąöčĆą░ą╣ą▓ąĄčĆčŗ ą▓čŗčģąŠą┤ą░ ąĖ ą┐čĆąĖąĄą╝ąĮąĖą║ąĖ. ąÆčŗčģąŠą┤ąĮčŗąĄ ą▒čāč乥čĆčŗ ąĖ ą▓čģąŠą┤ąĮčŗąĄ ą┐čĆąĖąĄą╝ąĮąĖą║ąĖ ą┐ąŠą╝ąĄąĮčÅą╗ąĖčüčī ąŠčé LVTTL ą║ SSTL_2. ąÆčŗčģąŠą┤ąĮą░čÅ ą╗ąŠą│ąĖą║ą░ ą▒čāč乥čĆą░ ąĮąĄ ą┐ąŠą╝ąĄąĮčÅą╗ą░čüčī, ąĮąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ VDDQ ą┤ą╗čÅ DDR ą┐ąĄčĆąĄčłą╗ąŠ ąŠčé 3.3V ą║ 2.5V.

ąÆčģąŠą┤ąĮčŗąĄ ą┐čĆąĖąĄą╝ąĮąĖą║ąĖ ą╝ąĖą│čĆąĖčĆąŠą▓ą░ą╗ąĖ ąŠčé ąŠą▒čŗčćąĮąŠą│ąŠ ą║ą░čüą║ą░ą┤ą░ ąĮą░ n-ą║ą░ąĮą░ą╗čīąĮąŠą╝ ąĖ p-ą║ą░ąĮą░ą╗čīąĮąŠą╝ čéčĆą░ąĮąĘąĖčüč鹊čĆą░čģ ą║ čāčüąĖą╗ąĖč鹥ą╗čÄ čü ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╝ ą▓čģąŠą┤ąŠą╝. ąæąŠą╗ąĄąĄ čüą╗ąŠąČąĮčŗą╣ ą┐čĆąĖąĄą╝ąĮąĖą║, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╣ ą▓ DDR, ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą▒ąŠą╗čīčłčāčÄ ą┐ąŠą╗ąŠčüčā ą┐čĆąŠą┐čāčüą║ą░ąĮąĖčÅ ąĖ ą╝ąĄąĮčīčłčāčÄ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéčī ąŠčé č鹥ą╝ą┐ąĄčĆą░čéčāčĆčŗ, čćč鹊ą▒čŗ ą┐ąŠą▓čŗčüąĖčéčī ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ ą┐čĆąĖąĄą╝ą░ ą▓ ą▒ąŠą╗ąĄąĄ ąČąĄčüčéą║ąĖčģ čāčüą╗ąŠą▓ąĖčÅčģ ą┐ąĄčĆąĄą┤ą░čćąĖ čüąĖą│ąĮą░ą╗ą░. ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ VREF ą▒čŗą╗ąŠ ą┤ąŠą▒ą░ą▓ą╗ąĄąĮąŠ, čćč鹊ą▒čŗ čāą╗čāčćčłąĖčéčī čĆą░ą▒ąŠčéčā ą┐čĆąĖ ąĖąĘą╝ąĄąĮąĄąĮąĖąĖ č鹥ą╝ą┐ąĄčĆą░čéčāčĆčŗ ąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ VDD.

|

|

| ąĀąĖčü. 10. ąóąĖą┐ąĖčćąĮčŗą╣ ą┐čĆąĖąĄą╝ąĮąĖą║ LVCMOS. |

ąĀąĖčü. 11. ąóąĖą┐ąĖčćąĮčŗą╣ ą┐čĆąĖąĄą╝ąĮąĖą║ SSTL_2. |

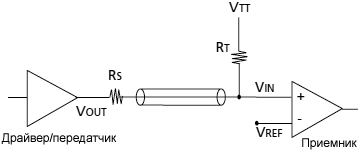

ąĪąĖą│ąĮą░ą╗čŗ I/O. ąóąĖą┐ąĖčćąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü SSTL_2 ą▓ą║ą╗čÄčćą░ąĄčé ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠąĄ č鹥čĆą╝ąĖąĮąĖčĆčāčÄčēąĄąĄ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ ąĖ ą▓ąĄčĆčģąĮąĖą╣ ąĮą░ą│čĆčāąĘąŠčćąĮčŗą╣ čĆąĄąĘąĖčüč鹊čĆ (pull-up), ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗąĄ ą║ č鹥čĆą╝ąĖąĮąĖčĆčāčÄčēąĄą╝čā ąĮą░ą┐čĆčÅąČąĄąĮąĖčÄ, čüą╝. čĆąĖčü. 12a. ąśąĮč鹥čĆč乥ą╣čü SSTL_2 ąĖčüą┐ąŠą╗čīąĘčāąĄčé ąŠą┐ąŠčĆąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĖ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗąĄ ą▓čģąŠą┤čŗ ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ ą╗ąŠą│ąĖč湥čüą║ąĖčģ čāčĆąŠą▓ąĮąĄą╣. ą×ą┐ąŠčĆąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą║ą░ą║ ą┐ąŠą╗ąŠą▓ąĖąĮą░ ąŠčé ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ, ąĖ č鹥čĆą╝ąĖąĮąĖčĆčāčÄčēąĄąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ čĆą░ą▓ąĮąŠ ąŠą┐ąŠčĆąĮąŠą╝čā ąĮą░ą┐čĆčÅąČąĄąĮąĖčÄ (VDD = 2.5V, VREF = VTT = 1.25V).

ąĀąĖčü. 12a. ąóąĖą┐ąĖčćąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü SSTL_2.

ąĀąĖčü. 12b. ąóąĖą┐ąĖčćąĮčŗąĄ čāčĆąŠą▓ąĮąĖ ąĖąĮč鹥čĆč乥ą╣čüą░ SSTL_2.

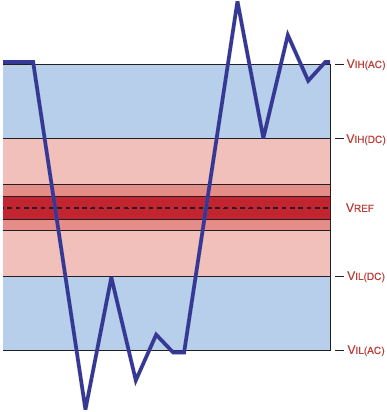

ąöą╗čÅ ąĖąĮč鹥čĆč乥ą╣čüą░ SSTL_2 ąĖą╝ąĄčÄčéčüčÅ ą▓čģąŠą┤ąĮčŗąĄ čāčĆąŠą▓ąĮąĖ DC (ą┐ąŠčüč鹊čÅąĮąĮčŗą╣ č鹊ą║) ąĖ AC (ą┐ąĄčĆąĄą╝ąĄąĮąĮčŗą╣ č鹊ą║). ą×ą▒čŗčćąĮąŠ DRAM ąĮą░čćąĮčāčé ą┐ąĄčĆąĄą║ą╗čÄčćą░čéčīčüčÅ ą║ ąĮąŠą▓ąŠą╝čā ą╗ąŠą│ąĖč湥čüą║ąŠą╝čā čāčĆąŠą▓ąĮčÄ, ą║ąŠą│ą┤ą░ ą▓čģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ ą┐ąĄčĆąĄčģąŠą┤ąĖčé č湥čĆąĄąĘ čåąĄą╗ąĄą▓ąŠą╣ čāčĆąŠą▓ąĄąĮčī DC, ąĖ ą▒čāą┤ąĄčé ąĘą░čģą▓ą░č湥ąĮ, ą║ąŠą│ą┤ą░ ą▓čģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ ą┐ąĄčĆąĄčüąĄč湥čé ą▓čģąŠą┤ąĮąŠą╣ čāčĆąŠą▓ąĄąĮčī AC. ąÜą░ą║ č鹊ą╗čīą║ąŠ ą╗ąŠą│ąĖč湥čüą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī ą▒čŗą╗ ąĘą░čģą▓ą░č湥ąĮ, ąŠąĮ ąŠčüčéą░ąĮąĄčéčüčÅ ąĘą░čģą▓ą░č湥ąĮąĮčŗą╝, ą┐ąŠą║ą░ ą▓čģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ ąĮąĄ ą┐ąĄčĆąĄą╣ą┤ąĄčé ąŠą▒čĆą░čéąĮąŠ č湥čĆąĄąĘ čāčĆąŠą▓ąĄąĮčī DC. ąĪą╝. čĆąĖčü. 12b, ą│ą┤ąĄ ą┐ąŠą║ą░ąĘą░ąĮ čéąĖą┐ąĖčćąĮčŗą╣ ą▓čģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ SSTL_2.

[ąźą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ ą┐ąŠ ą┐ąŠčüč鹊čÅąĮąĮąŠą╝čā č鹊ą║čā (DC) ąĖ čĆą░ą▒ąŠčćąĖąĄ čāčüą╗ąŠą▓ąĖčÅ]

ą¤ą░čĆą░ą╝ąĄčéčĆčŗ ą▓ čéą░ą▒ą╗ąĖčåąĄ ąĘą░ą┤ą░ąĮčŗ ą┤ą╗čÅ čāčüą╗ąŠą▓ąĖą╣ 0┬░C Ōēż TA Ōēż +70┬░C; VDD = +2.5V ┬▒0.2V, VDDQ = +2.5V ┬▒0.2V.

| ą¤ą░čĆą░ą╝ąĄčéčĆ/čāčüą╗ąŠą▓ąĖąĄ |

ąĪąĖą╝ą▓ąŠą╗ |

MIN |

MAX |

ąĢą┤. |

| ą×ą┐ąŠčĆąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ I/O |

VREF |

0.49 x VDDQ |

0.51 x VDDQ |

V |

| ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ I/O ą▓ čāčüą╗ąŠą▓ąĖčÅčģ ąĮą░ą│čĆčāąĘą║ąĖ (ą▓ čüąĖčüč鹥ą╝ąĄ) |

VTT |

VREF - 0.04 |

VREF + 0.04 |

V |

| ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ ą▓čŗčüąŠą║ąŠą│ąŠ ą▓čģąŠą┤ąĮąŠą│ąŠ čāčĆąŠą▓ąĮčÅ (ą╗ąŠą│. 1) |

VIH(DC) |

VREF + 0.15 |

VDD + 0.3 |

V |

| ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮąĖąĘą║ąŠą│ąŠ ą▓čģąŠą┤ąĮąŠą│ąŠ čāčĆąŠą▓ąĮčÅ (ą╗ąŠą│. 0) |

VIL(DC) |

-0.3 |

VREF - 0.15 |

V |

| ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ ą▓čŗčüąŠą║ąŠą│ąŠ ą▓čģąŠą┤ąĮąŠą│ąŠ čāčĆąŠą▓ąĮčÅ (ą╗ąŠą│. 1) AC |

VIH(AC) |

VREF + 0.310 |

- |

V |

| ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮąĖąĘą║ąŠą│ąŠ ą▓čģąŠą┤ąĮąŠą│ąŠ čāčĆąŠą▓ąĮčÅ (ą╗ąŠą│. 0) AC |

VIL(AC) |

- |

VREF - 0.310 |

V |

ąóą░ą║č鹊ą▓čŗąĄ ą▓čģąŠą┤čŗ. ą¦č鹊ą▒čŗ ą┐ąŠą▓čŗčüąĖčéčī č鹊čćąĮąŠčüčéčī ąĖ čāą╝ąĄąĮčīčłąĖčéčī čŹčäč乥ą║čé ą┤ąČąĖčéč鹥čĆą░ čéą░ą║č鹊ą▓, ą▓ DDR ą▒čŗą╗ąĖ ą┤ąŠą▒ą░ą▓ą╗ąĄąĮčŗ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗąĄ čéą░ą║čéčŗ. ąŻčüčéčĆąŠą╣čüčéą▓ą░ SDR ąĖčüą┐ąŠą╗čīąĘčāčÄčé čüčĆąĄą┤ąĮčÄčÄ č鹊čćą║čā ą┐čĆąĖ ąĮą░čĆą░čüčéą░ąĮąĖąĖ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą│ąŠ ą┐ąĄčĆąĄą┐ą░ą┤ą░ čéą░ą║č鹊ą▓, čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ą╝ąŠą╝ąĄąĮčé ąĘą░čģą▓ą░čéą░ ą┤ą░ąĮąĮčŗčģ, čéą░ą║ čćč鹊 ą┤ą╗čÅ čŹč鹊ą│ąŠ ą╝ąŠą╝ąĄąĮčéą░ ą▓ąŠąĘą╝ąŠąČąĮąŠ ą┤čĆąŠąČą░ąĮąĖąĄ čäą░ąĘčŗ ą▓čŗą▒ąŠčĆą║ąĖ (ą┐ąŠą▓čŗčłąĄąĮąĮčŗą╣ ą┤ąČąĖčéč鹥čĆ čéą░ą║č鹊ą▓). ąŻčüčéčĆąŠą╣čüčéą▓ą░ DDR ąĖčüą┐ąŠą╗čīąĘčāčÄčé č鹊čćą║čā ą┐ąĄčĆąĄčüąĄč湥ąĮąĖčÅ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗčģ čüąĖą│ąĮą░ą╗ąŠą▓ CK ąĖ CK#. ąśčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ č鹊čćą║ąĖ ą┐ąĄčĆąĄčüąĄč湥ąĮąĖčÅ ą▓ą╝ąĄčüč鹊 čüčĆąĄą┤ąĮąĄą╣ č鹊čćą║ąĖ ą┐ąŠą╝ąŠą│ą░čÄčé čüąĮąĖąĘąĖčéčī čŹčäč乥ą║čé ą┤ąČąĖčéč鹥čĆą░ ąĖ ą┐ąŠą▓čŗčüąĖčéčī ą║ą░č湥čüčéą▓ąŠ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ. ąóą░ą║ąČąĄ čéą░ą║čéčŗ, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ DDR, čĆą░ą▒ąŠčéą░čÄčé čü čāč湥č鹊ą╝ ąĮą░ą▒ąŠčĆą░ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓, ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗčģ JEDEC (čüą╝. čĆąĖčü. 13).

ąĀąĖčü. 13. ąóąĖą┐ąĖčćąĮą░čÅ ąŠčüčåąĖą╗ą╗ąŠą│čĆą░ą╝ą╝ą░ čéą░ą║č鹊ą▓ SSTL_2.

[ą×ą▒čēąĖąĄ ąĘą░ą╝ąĄčćą░ąĮąĖčÅ]

ąĪčģąŠąČąĄčüčéčī čģčĆą░ąĮąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ą▓ SDR ąĖ DDR SDRAM ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÄčé ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čÅą╝ ą╝ąĖą║čĆąŠčüčģąĄą╝ DRAM ą▓čŗąĖą│čĆčŗčł ą▓ 菹║ąŠąĮąŠą╝ąĖąĖ ąĮą░ ą┐čĆąŠčåąĄčüčüąĄ ą┐čĆąŠąĖąĘą▓ąŠą┤čüčéą▓ą░, ąĖ ą┐čĆąĖ čŹč鹊ą╝ ą┐ąŠą╗čāčćą░čéčī ą▒ąŠą╗čīčłčāčÄ ą▓čŗą│ąŠą┤čā, čüą▓čÅąĘą░ąĮąĮčāčÄ čü ąĮąŠą▓čŗą╝ąĖ ą║ą░č湥čüčéą▓ą░ą╝ąĖ ą┐ąŠą╗čāčćą░ąĄą╝ąŠą│ąŠ ą┐čĆąŠą┤čāą║čéą░. ąŁčéą░ čüčģąŠąČąĄčüčéčī čéą░ą║ąČąĄ ą┐ąŠą╝ąŠą│ą░ąĄčé čĆą░ąĘčĆą░ą▒ąŠčéčćąĖą║čā ą╗čāčćčłąĄ ą┐ąŠąĮčÅčéčī čüčāčéčī DDR, ąĖ ą┐ąŠąĘą▓ąŠą╗ąĖčéčī ąĄą╝čā ą┐čĆąĖą╝ąĄąĮąĖčéčī ąŠą┐čéąĖą╝ą░ą╗čīąĮčŗąĄ č鹥čģąĮąĖą║ąĖ ą┐čĆąĄą┤čŗą┤čāčēąĖčģ čĆą░ąĘčĆą░ą▒ąŠč鹊ą║ ą▓ ąĮąŠą▓čŗčģ ą┐ą╗ą░čéč乊čĆą╝ą░čģ DDR. ąźąŠčéčÅ čüčģąĄą╝čŗ ą░ą┤čĆąĄčüą░čåąĖąĖ, čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅ ą║ čĆą░ąĘą▓ąŠą┤ą║ąĄ ąĖ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┤ą╗čÅ DDR ą┐ąŠčćčéąĖ čéą░ą║ąĖąĄ ąČąĄ, ą║ą░ą║ čā SDR, ą┐ąŠą╗čāčćą░ąĄčéčüčÅ ą┤ą▓ąŠą╣ąĮąŠąĄ čāą▓ąĄą╗ąĖč湥ąĮąĖąĄ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéąĖ ą▓ą╝ąĄčüč鹥 čü ą▓čŗąĖą│čĆčŗčłąĄą╝ ą▓ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĖ. ąØą░ą┐čĆąĖą╝ąĄčĆ, ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ ą╝ąŠčēąĮąŠčüčéąĖ ą┤ą╗čÅ DDR ąĮą░ą╝ąĮąŠą│ąŠ ą╝ąĄąĮčīčłąĄ, č湥ą╝ ą┤ą╗čÅ čüčĆą░ą▓ąĮąĖą╝ąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ SDR, ąĖ ą┐ąĖą║ąŠą▓čŗąĄ čüą║ąŠčĆąŠčüčéąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ą╝ąŠą│čāčé ą┐čĆąĄą▓čŗčüąĖčéčī 2.1 ą│ąĖą│ą░ą▒ą░ą╣čéą░/čüąĄą║ ą┤ą╗čÅ čüčéą░ąĮą┤ą░čĆčéąĮčŗčģ ą╝ąŠą┤čāą╗ąĄą╣ x64 DDR DIMM.

[ąĪčüčŗą╗ą║ąĖ]

1. TN-46-05 GENERAL DDR SDRAM FUNCTIONALITY site:micron.com.

2. SDRAM Tutorial site:embeddedmicro.com.

3. Micron DDR SDRAM.

4. SDR SDRAM MT48LC16M16A2. |

ąÜąŠą╝ą╝ąĄąĮčéą░čĆąĖąĖ

ąöą╗ąĖąĮą░ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ ą│ąŠ čćč鹥ąĮąĖčÅ 2, 4, 8 ąĘą░ą┤ą░ąĄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ mode, ą▓ ą╝ąĖą║čĆąŠčüčģąĄą╝ąĄ DDR, ąĮą░ą┐čĆąĖą╝ąĄčĆ ą▓ ąŠą┤ąĮąŠą╣ ąĖąĘ ą┐čĆąŠčüą╝ąŠčéčĆąĄąĮąĮčŗčģ ą╝ąĮąŠą╣ DDR2 č鹊ą╗čīą║ąŠ 4 ąĖą╗ąĖ 8, 2čģ ąĮąĄčé.

RSS ą╗ąĄąĮčéą░ ą║ąŠą╝ą╝ąĄąĮčéą░čĆąĖąĄą▓ čŹč鹊ą╣ ąĘą░ą┐ąĖčüąĖ