|

[ą×čüąĮąŠą▓ąĮčŗąĄ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ MT48LC16M16A2]

ŌĆó ą£ąĖą║čĆąŠčüčģąĄą╝ą░ čüąŠą▓ą╝ąĄčüčéąĖą╝ą░ čü ą╝ąŠą┤čāą╗čÅą╝ąĖ ą┐ą░ą╝čÅčéąĖ PC100 ąĖ PC133.

ŌĆó ą¤ąŠą╗ąĮąŠčüčéčīčÄ čüąĖąĮčģčĆąŠąĮąĮą░ (čŹč鹊 SDR-ą┐ą░ą╝čÅčéčī); ą▓čüąĄ čüąĖą│ąĮą░ą╗čŗ čĆąĄą│ąĖčüčéčĆąĖčĆčāčÄčéčüčÅ ą┐ąŠ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą╝čā čäčĆąŠąĮčéčā čüąĖčüč鹥ą╝ąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ (system clock).

ŌĆó ąĀą░ą▒ąŠčéą░ąĄčé ąĮą░ ąŠčüąĮąŠą▓ąĄ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ ą║ąŠąĮą▓ąĄą╣ąĄčĆą░; ą░ą┤čĆąĄčü čüč鹊ą╗ą▒čåą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĖąĘą╝ąĄąĮąĄąĮ ąĮą░ ą╗čÄą▒ąŠą╝ čéą░ą║č鹥.

ŌĆó ąÆąĮčāčéčĆąĄąĮąĮąĖąĄ ą▒ą░ąĮą║ąĖ ą┤ą╗čÅ čüą║čĆčŗčéąĖčÅ ą┤ąŠčüčéčāą┐ą░ ą║ čüčéčĆąŠą║ąĄ / ą┐čĆąĄą┤ąĘą░čĆčÅą┤ą░ (precharge).

ŌĆó ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗąĄ ą┤ą╗ąĖąĮčŗ ą┐ą░ą║ąĄčéąĮčŗčģ ą┐ąĄčĆąĄą┤ą░čć: 1, 2, 4, 8 ąĖ ą┐ąŠą╗ąĮą░čÅ čüčéčĆą░ąĮąĖčåą░.

ŌĆó ąÉą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖą╣ ą┐čĆąĄą┤ąĘą░čĆčÅą┤ (auto precharge), ą▓ą║ą╗čÄčćą░čÅ čĆąĄąČąĖą╝čŗ ą║ąŠąĮą║čāčĆąĄąĮčéąĮąŠą│ąŠ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą│ąŠ ą┐čĆąĄą┤ąĘą░čĆčÅą┤ą░ ąĖ ą░ą▓č鹊ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ą┤ąĖąĮą░ą╝ąĖč湥čüą║ąŠą╣ ą┐ą░ą╝čÅčéąĖ (auto refresh).

ŌĆó ąĀąĄąČąĖą╝ čüą░ą╝ąŠąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ (self refresh). ąŁč鹊čé čĆąĄąČąĖą╝ ąĮąĄą┤ąŠčüčéčāą┐ąĄąĮ ąĮą░ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░čģ AT.

ŌĆó Auto refresh:

ŌĆō 64 ą╝čü, 8192 čéą░ą║čéą░ (ąĖčüą┐ąŠą╗ąĮąĄąĮąĖąĄ commercial ąĖ industrial).

ŌĆō 16 ą╝čü, 8192 čéą░ą║čéą░ (ąĖčüą┐ąŠą╗ąĮąĄąĮąĖąĄ automotive)

ŌĆó ąÆčģąŠą┤čŗ ąĖ ą▓čŗčģąŠą┤čŗ, čüąŠą▓ą╝ąĄčüčéąĖą╝čŗąĄ čü ą╗ąŠą│ąĖą║ąŠą╣ LVTTL (Low Voltage TTL, čé. ąĄ. ąĮąĖąĘą║ąŠą▓ąŠą╗čīčéąĮą░čÅ čéčĆą░ąĮąĘąĖčüč鹊čĆąĮą░čÅ ą╗ąŠą│ąĖą║ą░).

ŌĆó ą×ą┤ąĖąĮ ąĖčüč鹊čćąĮąĖą║ ą┐ąĖčéą░ąĮąĖčÅ 3.3V ┬▒0.3V.

ą£ąĖą║čĆąŠčüčģąĄą╝ą░ MT48LC16M16A2 čüąŠą┤ąĄčƹȹĖčé 256 ą╝ąĄą│ą░ą▒ąĖčé čÅč湥ąĄą║ ą┐ą░ą╝čÅčéąĖ (32 ą╝ąĄą│ą░ą▒ą░ą╣čéą░), ąŠčĆą│ą░ąĮąĖąĘąŠą▓ą░ąĮąĮčŗčģ ą║ą░ą║ 4 ą▒ą░ąĮą║ą░ 16-čĆą░ąĘčĆčÅą┤ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ, ą┐ąŠ 4M čÅč湥ąĄą║ ą▓ ą║ą░ąČą┤ąŠą╝ ą▒ą░ąĮą║ąĄ.

ąśą╝ąĄąĄčéčüčÅ 3 ą▓ą░čĆąĖą░ąĮčéą░ čäąĖąĘąĖč湥čüą║ąŠą╣ ąŠčĆą│ą░ąĮąĖąĘą░čåąĖąĖ ą╝ą░čüčüąĖą▓ą░ ą┐ą░ą╝čÅčéąĖ ąĖąĘ 256M ą▒ąĖčé (32 ą╝ąĄą│ą░ą▒ą░ą╣čéą░), čüą╝. čéą░ą▒ą╗ąĖčåčā.

| ą×ą┐čåąĖąĖ |

ą£ą░čĆą║ąĖčĆąŠą▓ą║ą░ |

| MT48LC64M4A2 64M x 4 (16M čÅč湥ąĄą║ x 4 x 4 ą▒ą░ąĮą║ą░) |

64M4 |

| MT48LC32M8A2 32M x 8 (8M čÅč湥ąĄą║ x 8 x 4 ą▒ą░ąĮą║ą░) |

32M8 |

| MT48LC16M16A2 16M x 16 (4M čÅč湥ąĄą║ x 16 x 4 ą▒ą░ąĮą║ą░) |

16M16 |

| ą×ą┐čåąĖąĖ |

ą£ą░čĆą║ąĖčĆąŠą▓ą║ą░ |

| ą¤ą╗ą░čüčéąĖą║ąŠą▓čŗąĄ ą║ąŠčĆą┐čāčüą░ OCPL (off-center parting line) |

| 54-pin TSOP II OCPL (400 mil), čüčéą░ąĮą┤ą░čĆčéąĮąŠąĄ ą╗čāąČąĄąĮąĖąĄ |

TG |

| 54-pin TSOP II OCPL (400 mil), Pb-free |

P |

| TFBGA |

| 60-ball TFBGA (x4, x8) (8mm x 16mm) |

FB |

| 60-ball TFBGA (x4, x8) (8mm x 16mm) Pb-free |

BB |

| VFBGA |

| 54-ball VFBGA (x16) (8mm x 14 mm) |

FG1 |

| 54-ball VFBGA (x16) (8mm x 14 mm) Pb-free |

BG1 |

| 54-ball VFBGA (x16) (8mm x 8 mm) |

F42 |

| 54-ball VFBGA (x16) (8mm x 8 mm) Pb-free |

B42 |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

1. ąöąŠčüčéčāą┐ąĮąŠ č鹊ą╗čīą║ąŠ ą▓ čĆąĄą▓ąĖąĘąĖąĖ D.

2. ąöąŠčüčéčāą┐ąĮąŠ č鹊ą╗čīą║ąŠ ą▓ čĆąĄą▓ąĖąĘąĖąĖ G.

ą¤ą░čĆą░ą╝ąĄčéčĆčŗ, ą▓ą╗ąĖčÅčÄčēąĖąĄ ąĮą░ čüą║ąŠčĆąŠčüčéčī čĆą░ą▒ąŠčéčŗ:

ŌĆó ąÆčĆąĄą╝čÅ ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖčÅ 2 čéą░ą║čéą░ (Write recovery, tWR = 2 CLK), ą╝ą░čĆą║ąĖčĆąŠą▓ą║ą░ A2.

ŌĆó ąÆčĆąĄą╝čÅ čéą░ą║čéą░, čüą╝. čéą░ą▒ą╗ąĖčåčā:

| ą×ą┐čåąĖąĖ |

ą£ą░čĆą║ąĖčĆąŠą▓ą║ą░ |

| 6 ąĮčü ąĖ CL = 3 (č鹊ą╗čīą║ąŠ ą▓ ąŠčĆą│ą░ąĮąĖąĘą░čåąĖąĖ x8, x16) |

-6A |

| 7.5 ąĮčü ąĖ CL = 3 (PC133) |

-75 (ą┤ąŠčüčéčāą┐ąĮąŠ č鹊ą╗čīą║ąŠ ą▓ čĆąĄą▓ąĖąĘąĖąĖ D) |

| 7.5 ąĮčü ąĖ CL = 2 (PC133) |

-7E |

ąóą░ą▒ą╗ąĖčåą░ 1. ąÜą╗čÄč湥ą▓čŗąĄ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ ą▓čĆąĄą╝ąĄąĮąĖ.

| Speed Grade |

ąóą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░, ą£ąōčå |

tRCD-tRP-CL |

tRCD (ąĮčü) |

tRP (ąĮčü) |

CL (ąĮčü) |

| -6A |

167 |

3-3-3 |

18 |

18 |

18 |

| -75 |

133 |

3-3-3 |

20 |

20 |

20 |

| -7E |

133 |

2-2-2 |

15 |

15 |

15 |

ąóą░ą▒ą╗ąĖčåą░ 2. ąÉą┤čĆąĄčüą░čåąĖčÅ.

| ą¤ą░čĆą░ą╝ąĄčéčĆ |

64M x 4 |

32M x 8 |

16M x 16 |

| ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ |

16M čÅč湥ąĄą║ x 4, 4 ą▒ą░ąĮą║ą░ |

8M čÅč湥ąĄą║ x 8, 4 ą▒ą░ąĮą║ą░ |

4M čÅč湥ąĄą║ x 16, 4 ą▒ą░ąĮą║ą░ |

| ąĪč湥čéčćąĖą║ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ (čüčéčĆąŠą║) |

8K |

| ąÉą┤čĆąĄčü čüčéčĆąŠą║ąĖ |

8K A[12:0] |

| ąÉą┤čĆąĄčü ą▒ą░ąĮą║ą░ |

4 BA[1:0] |

| ąÉą┤čĆąĄčü čüč鹊ą╗ą▒čåą░ |

2K A[9:0], A11 |

1K A[9:0] |

512 A[8:0] |

ąóą░ą▒ą╗ąĖčåą░ 3. ą£ą░čĆą║ąĖčĆąŠą▓ą║ą░ ą║ąŠčĆą┐čāčüąŠą▓ ą╝ąĖą║čĆąŠčüčģąĄą╝.

| ą£ą░čĆą║ąĖčĆąŠą▓ą║ą░ |

ąÉčĆčģąĖč鹥ą║čéčāčĆą░ |

ąóąĖą┐ ą║ąŠčĆą┐čāčüą░ |

| MT48LC64M4A2TG |

64M x 4 |

54-pin TSOP II |

| MT48LC64M4A2P |

| MT48LC64M4A2FB1 |

60-ball FBGA |

| MT48LC64M4A2BB1 |

| MT48LC32M8A2TG |

32M x 8 |

54-pin TSOP II |

| MT48LC32M8A2P |

| MT48LC32M8A2FB1 |

60-ball FBGA |

| MT48LC32M8A2BB1 |

| MT48LC16M16A2TG |

16M x 16 |

54-pin TSOP II |

| MT48LC16M16A2P |

| MT48LC16M16A2FG |

54-ball FBGA |

| MT48LC16M16A2BG |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ 1: FBGA Device Decoder: www.micron.com/decoder.

ą£ąĖą║čĆąŠčüčģąĄą╝čŗ 256 ą╝ąĄą│ą░ą▒ąĖčé SDRAM (ą▓ ąŠą┐čåąĖčÅčģ 16M x 4 x 4 ą▒ą░ąĮą║ą░, 8M x 8 x 4 ą▒ą░ąĮą║ą░, ąĖ 4M x 16 x 4 ą▒ą░ąĮą║ą░) čŹč鹊 DRAM ąĮą░ ąŠčüąĮąŠą▓ąĄ 4 ą▒ą░ąĮą║ąŠą▓ ą┐ą░ą╝čÅčéąĖ, čĆą░ą▒ąŠčéą░čÄčēąĄąĄ ąĮą░ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĖ 3.3V č湥čĆąĄąĘ čüąĖąĮčģčĆąŠąĮąĮčŗą╣ ą▓ąĮąĄčłąĮąĖą╣ ąĖąĮč鹥čĆč乥ą╣čü. ą£ąĖą║čĆąŠčüčģąĄą╝ą░ ąĖąĘą│ąŠč鹊ą▓ą╗ąĄąĮą░ ą┐ąŠ č鹥čģąĮąŠą╗ąŠą│ąĖąĖ ą▓čŗčüąŠą║ąŠčüą║ąŠčĆąŠčüčéąĮąŠą╣ CMOS, ąĖ čÅą▓ą╗čÅąĄčéčüčÅ ą╝ąĖą║čĆąŠčüčģąĄą╝ąŠą╣ ą┤ąĖąĮą░ą╝ąĖč湥čüą║ąŠą╣ ą┐ą░ą╝čÅčéąĖ čü ą┐čĆąŠąĖąĘą▓ąŠą╗čīąĮčŗą╝ ą┤ąŠčüčéčāą┐ąŠą╝, čüąŠčüč鹊čÅčēąĄą╣ ąĖąĘ 268435456 ą▒ąĖčé ą┐ą░ą╝čÅčéąĖ. ąÆąĮčāčéčĆąĖ ąŠąĮą░ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮą░ ą║ą░ą║ 4 ą▒ą░ąĮą║ą░ ą┤ąĖąĮą░ą╝ąĖč湥čüą║ąŠą│ąŠ ą×ąŚąŻ (DRAM) čü čüąĖąĮčģčĆąŠąĮąĮčŗą╝ ąĖąĮč鹥čĆč乥ą╣čüąŠą╝ (ą▓čüąĄ čüąĖą│ąĮą░ą╗čŗ ą▓čŗą▓ąŠą┤ąŠą▓ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ čĆąĄą│ąĖčüčéčĆąĖčĆčāčÄčéčüčÅ ą┐ąŠ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą╝čā ą┐ąĄčĆąĄą┐ą░ą┤čā čüąĖą│ąĮą░ą╗ą░ čéą░ą║č鹊ą▓ CLK). ą¤čĆąĖ 4-čĆą░ąĘčĆčÅą┤ąĮąŠą╣ ąŠą┐čåąĖąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ (MT48LC64M4A2) ą║ą░ąČą┤čŗą╣ ąĖąĘ č湥čéčŗčĆąĄčģ ą▒ą░ąĮą║ąŠą▓ ąĮą░ 67108864 ą▒ąĖčé ąŠčĆą│ą░ąĮąĖąĘąŠą▓ą░ąĮ ą║ą░ą║ 8192 čüčéčĆąŠą║ ąĮą░ 2048 čüč鹊ą╗ą▒čåąŠą▓ čÅč湥ąĄą║ ą┐ąŠ 4 ą▒ąĖčéą░ ą║ą░ąČą┤ą░čÅ. ą¤čĆąĖ 8-čĆą░ąĘčĆčÅą┤ąĮąŠą╣ ąŠą┐čåąĖąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ (MT48LC32M8A2) ą║ą░ąČą┤čŗą╣ ąĖąĘ 4 ą▒ą░ąĮą║ąŠą▓ ąĮą░ 67108864 ą▒ąĖčé ąŠčĆą│ą░ąĮąĖąĘąŠą▓ą░ąĮ ą║ą░ą║ 8192 čüčéčĆąŠą║ ąĮą░ 1024 čüč鹊ą╗ą▒čåąŠą▓ čÅč湥ąĄą║ ą┐ąŠ 8 ą▒ąĖčé ą║ą░ąČą┤ą░čÅ. ą¤čĆąĖ 16-čĆą░ąĘčĆčÅą┤ąĮąŠą╣ ąŠą┐čåąĖąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ (MT48LC16M16A2) ą║ą░ąČą┤čŗą╣ ąĖąĘ 4 ą▒ą░ąĮą║ąŠą▓ ąĮą░ 67108864 ą▒ąĖčé ąŠčĆą│ą░ąĮąĖąĘąŠą▓ą░ąĮ ą║ą░ą║ 8192 čüčéčĆąŠą║ ąĮą░ 512 čüč鹊ą╗ą▒čåąŠą▓ čÅč湥ąĄą║ ą┐ąŠ 16 ą▒ąĖčé ą║ą░ąČą┤ą░čÅ.

ąöąŠčüčéčāą┐ ąĮą░ čćč鹥ąĮąĖąĄ ąĖ ąĘą░ą┐ąĖčüčī SDRAM ąŠčĆąĖąĄąĮčéąĖčĆąŠą▓ą░ąĮ ąĮą░ ą┐ą░ą║ąĄčéąĮčāčÄ ą┐ąĄčĆąĄą┤ą░čćčā; ą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą┤ąŠčüčéčāą┐ čüčéą░čĆčéčāąĄčé ąĮą░ ą▓čŗą▒čĆą░ąĮąĮąŠą╣ čÅč湥ą╣ą║ąĄ, ąĖ ą┐čĆąŠą┤ąŠą╗ąČą░ąĄčéčüčÅ ą┤ą╗čÅ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ ą║ąŠą╗ąĖč湥čüčéą▓ą░ čÅč湥ąĄą║. ąöąŠčüčéčāą┐ ąĮą░čćąĖąĮą░ąĄčéčüčÅ čü čĆąĄą│ąĖčüčéčĆą░čåąĖąĄą╣ ą║ąŠą╝ą░ąĮą┤čŗ ACTIVE (ą░ą║čéąĖą▓ą░čåąĖčÅ), ąĘą░ ą║ąŠč鹊čĆąŠą╣ čüą╗ąĄą┤čāąĄčé ą║ąŠą╝ą░ąĮą┤ą░ READ (čćč鹥ąĮąĖąĄ) ąĖą╗ąĖ WRITE (ąĘą░ą┐ąĖčüčī). ąæąĖčéčŗ ą░ą┤čĆąĄčüą░, čüąŠą▓ą┐ą░ą┤ą░čÄčēąĖąĄ čü ą║ąŠą╝ą░ąĮą┤ąŠą╣ ACTIVE, ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą░ ą▒ą░ąĮą║ą░ ąĖ čüčéčĆąŠą║ąĖ, ą║ ą║ąŠč鹊čĆčŗą╝ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą┤ąŠčüčéčāą┐ (čüąĖą│ąĮą░ą╗čŗ BA[1:0] ą▓čŗą▒ąĖčĆą░čÄčé ą▒ą░ąĮą║; A[12:0] ą▓čŗą▒ąĖčĆą░čÄčé čüčéčĆąŠą║čā). ąæąĖčéčŗ ą░ą┤čĆąĄčüą░ (x4: A[9:0], A11; x8: A[9:0]; x16: A[8:0]), čüąŠą▓ą┐ą░ą┤ą░čÄčēąĖąĄ čü ą║ąŠą╝ą░ąĮą┤ąŠą╣ READ ąĖą╗ąĖ WRITE, ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ ąĮą░čćą░ą╗čīąĮąŠą│ąŠ ą┐ąŠą╗ąŠąČąĄąĮąĖčÅ čüč鹊ą╗ą▒čåą░ ą┐čĆąĖ ą┐ą░ą║ąĄčéąĮąŠą╝ ą┤ąŠčüčéčāą┐ąĄ.

SDRAM ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗąĄ ą┤ą╗ąĖąĮčŗ ą┐ą░ą║ąĄč鹊ą▓ čćč鹥ąĮąĖčÅ ąĖą╗ąĖ ąĘą░ą┐ąĖčüąĖ (read / write burst lengths, BL) ąĖąĘ 1, 2, 4 ąĖą╗ąĖ 8 čÅč湥ąĄą║, ąĖą╗ąĖ ąĮą░ ą┐ąŠą╗ąĮčāčÄ čüčéčĆą░ąĮąĖčåčā, čü ąŠą┐čåąĖąĄą╣ ąŠą▒čĆčŗą▓ą░ ą┐ą░ą║ąĄčéąĮąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ (burst terminate). ą£ąŠąČąĄčé ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮą░ čäčāąĮą║čåąĖčÅ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą│ąŠ ą┐čĆąĄą┤ąĘą░čĆčÅą┤ą░ (auto precharge), čćč鹊ą▒čŗ ąŠčüčāčēąĄčüčéą▓ą╗čÅą╗čüčÅ čüą░ą╝ąŠčüč鹊čÅč鹥ą╗čīąĮčŗą╣, ąĘą░ą┐čāčüą║ą░ąĄą╝čŗą╣ ą▓ ą┐ąŠ ąĖąĮč鹥čĆą▓ą░ą╗ą░ą╝ ą▓čĆąĄą╝ąĄąĮąĖ ą┐čĆąĄą┤ąĘą░čĆčÅą┤ čüčéčĆąŠą║ąĖ (self-timed row precharge), ą║ąŠč鹊čĆčŗą╣ ąĖąĮąĖčåąĖąĖčĆčāąĄčéčüčÅ ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖčÄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐ą░ą║ąĄčéą░ (end burst sequence).

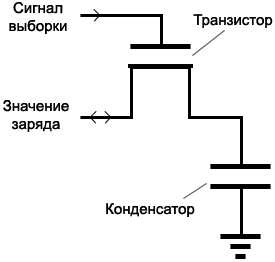

ąæą░ąĘąŠą▓čŗą╝ 菹╗ąĄą╝ąĄąĮč鹊ą╝ čģčĆą░ąĮąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ą▓ąĮčāčéčĆąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝ DRAM čÅą▓ą╗čÅąĄčéčüčÅ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ. ąÜąŠąĮą┤ąĄąĮčüą░č鹊čĆ čŹč鹊 čéą░ą║ąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ, ą║ąŠč鹊čĆąŠąĄ ą╝ąŠąČąĄčé čģčĆą░ąĮąĖčéčī ą▓ čüąĄą▒ąĄ ąĘą░čĆčÅą┤ 菹╗ąĄą║čéčĆąĖč湥čüčéą▓ą░. ąÆčŗ ą╝ąŠąČąĄč鹥 ą┐čĆąĄą┤čüčéą░ą▓ąĖčéčī ąĄą│ąŠ čüąĄą▒ąĄ ą║ą░ą║ ąĮąĄą║čāčÄ ąĄą╝ą║ąŠčüčéčī, ą▓ąŠąĘą┤čāčłąĮčŗą╣ čłą░čĆąĖą║. ąóą░ą║ ąČąĄ, ą║ą░ą║ ą╝čŗ ąĘą░ą┐ąŠą╗ąĮčÅąĄą╝ čłą░čĆąĖą║ ą▓ąŠąĘą┤čāčģąŠą╝ ąĖą╗ąĖ ą│ą░ąĘąŠą╝, ą╝čŗ ą╝ąŠąČąĄą╝ ąĘą░ą┐ąŠą╗ąĮąĖčéčī ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ ąĮąĄą║ąŠč鹊čĆčŗą╝ ąĘą░čĆčÅą┤ąŠą╝ (ą┐ąĄčĆąĄą▓ąŠą┤ ąĖąĘ [3]).

ąæą░ąĘąŠą▓ą░čÅ čÅč湥ą╣ą║ą░ ą┐ą░ą╝čÅčéąĖ DRAM ą▓čŗą│ą╗čÅą┤ąĖčé, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ čāą┐čĆąŠčēąĄąĮąĮąŠ ąĮą░ ą║ą░čĆčéąĖąĮą║ąĄ ąĮąĖąČąĄ.

ąŚą┤ąĄčüčī ą╝čŗ ą▓ąĖą┤ąĖą╝ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ, ą║ąŠč鹊čĆčŗą╣ ą╝ąŠąČąĄčé čģčĆą░ąĮąĖčéčī ą▓ čüąĄą▒ąĄ ąĘą░čĆčÅą┤, ąĖ čéčĆą░ąĮąĘąĖčüč鹊čĆ, ą║ąŠč鹊čĆčŗą╣ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą╗ąĖą▒ąŠ ą┐ąŠą╝ąĄčüčéąĖčéčī ąĘą░čĆčÅą┤ ą▓ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ (ąĘą░ą┐ąĖčüčī), ą╗ąĖą▒ąŠ ą▓čŗą▓ąĄčüčéąĖ ąĘą░čĆčÅą┤ ąĮą░čĆčāąČčā (čćč鹥ąĮąĖąĄ). ąóą░ą║ąĖąĄ čÅč湥ą╣ą║ąĖ čüąŠą▒čĆą░ąĮčŗ ą▓ ą▒ąŠą╗čīčłąĖąĄ 2D-ą╝ą░čüčüąĖą▓čŗ, ąĖ čā čŹčéąĖčģ ą╝ą░čüčüąĖą▓ąŠą▓ ąĄčüčéčī čüčéčĆąŠą║ąĖ (rows) ąĖ čüč鹊ą╗ą▒čåčŗ (columns).

ąÜąŠą│ą┤ą░ ąÆčŗ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄč鹥 ą┤ą░ąĮąĮčŗąĄ ą▓ DRAM, ąĘą░čĆčÅąČąĄąĮąĮčŗą╣ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ą╗ąŠą│. 1 ąĖąĮč乊čĆą╝ą░čåąĖąĖ, ą░ ąŠčéčüčāčéčüčéą▓ąĖąĄ ąĘą░čĆčÅą┤ą░ ąĮą░ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆąĄ čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ą╗ąŠą│. 0.

ąÜąŠą│ą┤ą░ ąÆčŗ čüčćąĖčéčŗą▓ą░ąĄč鹥 ą┤ą░ąĮąĮčŗąĄ ąĖąĘ DRAM, ąĘą░čĆčÅą┤ ąĮą░ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆąĄ ąĖąĘą╝ąĄčĆčÅąĄčéčüčÅ čü ą┐ąŠą╝ąŠčēčīčÄ čüą┐ąĄčåąĖą░ą╗čīąĮąŠą╣ čüčģąĄą╝čŗ, čéą░ą║ ąĮą░ąĘčŗą▓ą░ąĄą╝ąŠą│ąŠ čāčüąĖą╗ąĖč鹥ą╗čÅ čüąŠą┤ąĄčƹȹĖą╝ąŠą│ąŠ čÅč湥ą╣ą║ąĖ (sense amplifier). ąĢčüą╗ąĖ čāčüąĖą╗ąĖč鹥ą╗čī ąŠą┐čĆąĄą┤ąĄą╗ąĖą╗ ąĮą░ą╗ąĖčćąĖąĄ ąĘą░čĆčÅą┤ą░ ąĮą░ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆąĄ, č鹊 ąŠąĮ ą▓čŗą▓ąĄą┤ąĄčé ą╗ąŠą│. 1, ąĖąĮą░č湥 ą▒čāą┤ąĄčé ą▓čŗą▓ąĄą┤ąĄąĮ ą╗ąŠą│. 0.

ąŚą┤ąĄčüčī ąĄčüčéčī 2 ąŠčüąĮąŠą▓ąĮčŗąĄ ą┐čĆąŠą▒ą╗ąĄą╝čŗ, ą║ąŠč鹊čĆčŗąĄ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą┐čĆąĄąŠą┤ąŠą╗ąĄąĮčŗ ą▓ ą┤ąĖąĘą░ą╣ąĮąĄ DRAM. ąÆąŠ-ą┐ąĄčĆą▓čŗčģ, čćč鹥ąĮąĖąĄ ąĘą░čĆčÅą┤ą░ ąĖąĘ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆą░ ą┐čĆąĖą▓ąŠą┤ąĖčé ą║ čāč鹥čćą║ąĄ ąĘą░čĆčÅą┤ą░. ąŁč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ą▓čüąĄ čćč鹥ąĮąĖčÅ ąĖąĘ čÅč湥ąĄą║ ą┤ąĄčüčéčĆčāą║čéąĖą▓ąĮčŗ ą┤ą╗čÅ ąĮą░čģąŠą┤čÅčēąĄą╣čüčÅ ą▓ čÅč湥ą╣ą║ą░čģ ąĖąĮč乊čĆą╝ą░čåąĖąĖ. ąÜą░ą║ č鹊ą╗čīą║ąŠ ąÆčŗ ą┐čĆąŠčćąĖčéą░ą╗ąĖ ą┐ąŠčĆčåąĖčÄ ą┤ą░ąĮąĮčŗčģ ąĖąĘ DRAM, č鹊 čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēą░čÅ ąĖąĮč乊čĆą╝ą░čåąĖčÅ ą▓ ą┐čĆąŠčćąĖčéą░ąĮąĮčŗčģ čÅč湥ą╣ą║ą░čģ ąĮąĄ ą╝ąŠąČąĄčé čüčćąĖčéą░čéčīčüčÅ ą┤ą░ą╗ąĄąĄ ą┤ąŠčüč鹊ą▓ąĄčĆąĮąŠą╣. ą¦č鹊ą▒čŗ ąĖčüą┐čĆą░ą▓ąĖčéčī čŹčéčā čüąĖčéčāą░čåąĖčÄ, ą┤ą░ąĮąĮčŗąĄ čüčĆą░ąĘčā ąČąĄ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮčŗ ąŠą▒čĆą░čéąĮąŠ ą▓ čŹčéąĖ čÅč湥ą╣ą║ąĖ, ąĖ čŹč鹊čé ą┐čĆąŠčåąĄčüčü ąĮą░ąĘčŗą▓ą░ąĄčéčüčÅ ą┐čĆąĄą┤ąĘą░čĆčÅą┤ąŠą╝ (precharging). ą¤čĆąĖą╝. ą┐ąĄčĆąĄą▓ąŠą┤čćąĖą║ą░: ą▒ąŠą╗ąĄąĄ ą╗ąŠą│ąĖčćąĮąŠ čŹč鹊 ąĮą░ąĘą▓ą░čéčī ą┐ąŠčüčéąĘą░čĆčÅą┤ąŠą╝, ąĮąŠ ą▓čüąĄ-čéą░ą║ąĖ čĆąĄčłąĖą╗ ą┐ąĄčĆąĄą▓ąŠą┤ąĖčéčī ą▒čāą║ą▓ą░ą╗čīąĮąŠ.

ą¦č鹊ą▒čŗ čüą┤ąĄą╗ą░čéčī ąĖąĮč鹥čĆč乥ą╣čü ą┤ą░ąĮąĮčŗčģ ą║ DRAM ą▒ąŠą╗ąĄąĄ čŹčäč乥ą║čéąĖą▓ąĮčŗą╝, ą▓čüčÅ čüčéčĆąŠą║ą░ ą╝ą░čüčüąĖą▓ą░ ą┤ą░ąĮąĮčŗčģ ą┐čĆąĖ ąŠą▒čĆą░čēąĄąĮąĖąĖ ą║ ąĮąĄą╝čā ą▓čŗčćąĖčéčŗą▓ą░ąĄčéčüčÅ čåąĄą╗ąĖą║ąŠą╝ ą▓ ą▒čāč乥čĆ čüčéčĆąŠą║ąĖ. ą¤čĆąŠčåąĄčüčü čćč鹥ąĮąĖčÅ čüčéčĆąŠą║ąĖ ą▓ čŹč鹊čé ą▒čāč乥čĆ ąĮą░ąĘčŗą▓ą░ąĄčéčüčÅ ą░ą║čéąĖą▓ą░čåąĖąĄą╣ čüčéčĆąŠą║ąĖ, ąĖą╗ąĖ ąŠčéą║čĆčŗčéąĖąĄą╝ čüč鹊ą║ąĖ. ąÜą░ą║ č鹊ą╗čīą║ąŠ čüčéčĆąŠą║ą░ ąŠčéą║čĆčŗčéą░, ą┤ą░ąĮąĮčŗąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮčŗ ąĖą╗ąĖ ąĘą░ą┐ąĖčüą░ąĮčŗ ą▓ ą╗čÄą▒ąŠą╣ čüč鹊ą╗ą▒ąĄčå čüčéčĆąŠą║ąĖ ą▒ąĄąĘ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéąĖ ąŠčéą║čĆčŗą▓ą░čéčī čüčéčĆąŠą║čā ą┐ąŠą▓č鹊čĆąĮąŠ.

ą×ą┤ąĮą░ą║ąŠ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ą▓ ąŠą┤ąĮąŠą╝ ą▒ą░ąĮą║ąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠčéą║čĆčŗčéą░ č鹊ą╗čīą║ąŠ ąŠą┤ąĮą░ čüčéčĆąŠą║ą░. ą¦č鹊ą▒čŗ ą┐čĆąŠčćąĖčéą░čéčī ą┤čĆčāą│čāčÄ čüčéčĆąŠą║čā ą▓ č鹊ą╝ ąČąĄ ą▒ą░ąĮą║ąĄ, čéčĆąĄą▒čāąĄčéčüčÅ ą▓čŗą┐ąŠą╗ąĮąĖčéčī precharge č鹥ą║čāčēąĄą╣ ąŠčéą║čĆčŗč鹊ą╣ čüčéčĆąŠą║ąĖ, ąĖ ą┐ąŠčüą╗ąĄ čŹč鹊ą│ąŠ ą╝ąŠąČąĮąŠ ąŠčéą║čĆčŗčéčī ąĮąŠą▓čāčÄ čüčéčĆąŠą║čā.

ąÆč鹊čĆą░čÅ čäčāąĮą┤ą░ą╝ąĄąĮčéą░ą╗čīąĮą░čÅ ą┐čĆąŠą▒ą╗ąĄą╝ą░ DRAM, ąĖąĘ-ąĘą░ ą║ąŠč鹊čĆąŠą╣ čŹčéčā ą┐ą░ą╝čÅčéčī ąĮą░ąĘčŗą▓ą░čÄčé ą┤ąĖąĮą░ą╝ąĖč湥čüą║ąĖą╝ ą×ąŚąŻ (dynamic RAM, čüąŠą║čĆą░čēąĄąĮąĮąŠ DRAM) čüąŠčüč鹊ąĖčé ą▓ čāč鹥čćą║ąĄ ąĘą░čĆčÅą┤ą░, ą┤ą░ąČąĄ ą║ąŠą│ą┤ą░ čéčĆą░ąĮąĘąĖčüč鹊čĆ čÅč湥ą╣ą║ąĖ ąĘą░ą║čĆčŗčé. ąŁč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ą║ą░ą║ č鹊ą╗čīą║ąŠ ą▓ čÅč湥ą╣ą║ąĄ ą┐ąŠčÅą▓ąĖą╗čüčÅ ąĘą░čĆčÅą┤, ąĖąĘ-ąĘą░ ą┤ąĄč乥ą║č鹊ą▓ ą▓ ą┤ąĖ菹╗ąĄą║čéčĆąĖą║ą░ ą▓ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆąĄ, ąĖ ąĖąĘ-ąĘą░ ąĮąĄ ą▒ąĄčüą║ąŠąĮąĄčćąĮąŠą│ąŠ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖčÅ ąĘą░ą║čĆčŗč鹊ą│ąŠ ą║ą░ąĮą░ą╗ą░ čéčĆą░ąĮąĘąĖčüč鹊čĆą░ ąĮą░čćąĖąĮą░ąĄčéčüčÅ ą┐ąŠčüč鹥ą┐ąĄąĮąĮčŗą╣ čüą░ą╝ąŠą┐čĆąŠąĖąĘą▓ąŠą╗čīąĮčŗą╣ čĆą░ąĘčĆčÅą┤ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆą░. ąŁč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ąĄčüą╗ąĖ ąĮąĄ ą┐čĆąĄą┤ą┐čĆąĖąĮčÅčéčī ąĮąĖą║ą░ą║ąĖčģ čüą┐ąĄčåąĖą░ą╗čīąĮčŗčģ ą╝ąĄčĆ, č鹊 č湥čĆąĄąĘ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠąĄ ą▓čĆąĄą╝čÅ ąĘą░čĆčÅą┤ ąĖčüč湥ąĘąĮąĄčé ąĖ ąĖąĮč乊čĆą╝ą░čåąĖčÅ ą▓ ą┐ą░ą╝čÅčéąĖ ą▒čāą┤ąĄčé ą┐ąŠč鹥čĆčÅąĮą░.

ą¦č鹊ą▒čŗ čĆąĄčłąĖčéčī čŹčéčā ą┐čĆąŠą▒ą╗ąĄą╝čā, ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą┐ąĄčĆąĖąŠą┤ąĖč湥čüą║ąŠąĄ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ ą║ą░ąČą┤ąŠą╣ čüčéčĆąŠą║ąĖ ą╝ą░čüčüąĖą▓ą░ ą┐ą░ą╝čÅčéąĖ (refresh). ą×ą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ čüąŠčüč鹊ąĖčé ąĖąĘ ąŠą▒čŗčćąĮąŠą│ąŠ čćč鹥ąĮąĖčÅ čüčéčĆąŠą║ąĖ, ąĖ ą┐ąŠčüą╗ąĄą┤čāčÄčēąĄą╣ ąĘą░ą┐ąĖčüąĖ čüčćąĖčéą░ąĮąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ąŠą▒čĆą░čéąĮąŠ. ąŁč鹊čé ą┐čĆąŠčåąĄčüčü ą│ą░čĆą░ąĮčéąĖčĆčāąĄčé, čćč鹊 ą▓ąŠ ą▓čüąĄčģ čÅč湥ą╣ą║ą░čģ ą▒čāą┤ąĄčé ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ąĘą░čĆčÅą┤.

ąÆčĆąĄą╝čÅ, ą▓ č鹥č湥ąĮąĖąĄ ą║ąŠč鹊čĆąŠą│ąŠ ąŠą▒čÅąĘą░č鹥ą╗čīąĮąŠ ą┤ąŠą╗ąČąĮą░ ą┐čĆąŠąĖąĘąŠą╣čéąĖ ąŠą┐ąĄčĆą░čåąĖčÅ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ, ąĘą░ą▓ąĖčüąĖčé ąŠčé č鹥čģąĮąŠą╗ąŠą│ąĖąĖ ąĖąĘą│ąŠč鹊ą▓ą╗ąĄąĮąĖčÅ DRAM. ą×ą▒čŗčćąĮąŠ čŹč鹊 ą▓čĆąĄą╝čÅ čüąŠčüčéą░ą▓ą╗čÅąĄčé ą┐čĆąĖą▒ą╗ąĖąĘąĖč鹥ą╗čīąĮąŠ 64 ą╝čü, čé. ąĄ. ą│ą░čĆą░ąĮčéąĖčĆčāąĄčéčüčÅ, čćč鹊 ą▓ č鹥č湥ąĮąĖąĖ 64 ą╝čü čÅč湥ą╣ą║ą░ ą┐ą░ą╝čÅčéąĖ ą▒čāą┤ąĄčé ą┤ąŠčüč鹊ą▓ąĄčĆąĮąŠ čģčĆą░ąĮąĖčéčī čüą▓ąŠčÄ ąĖąĮč乊čĆą╝ą░čåąĖčÄ ą▒ąĄąĘ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ. ąÜą░ą║ č鹊ą╗čīą║ąŠ čŹč鹊 ą▓čĆąĄą╝čÅ ą┐čĆąŠčłą╗ąŠ, čéčĆąĄą▒čāąĄčéčüčÅ ą▓čŗą┐ąŠą╗ąĮąĖčéčī ą╗ąĖą▒ąŠ čćč鹥ąĮąĖąĄ + ą┐čĆąĄą┤ąĘą░čĆčÅą┤ čüčéčĆąŠą║ąĖ, ą╗ąĖą▒ąŠ ą▓čŗą┐ąŠą╗ąĮąĖčéčī ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ čüčéčĆąŠą║ąĖ.

ą×ą▒čŗčćąĮąŠ SDRAM čüą░ą╝ą░ čāą╝ąĄąĄčé ą▓čŗą┐ąŠą╗ąĮčÅčéčī ąŠą┐ąĄčĆą░čåąĖčÄ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ, ąĖ ąĖą╝ąĄąĄčé ą▓ąĮčāčéčĆąĖ čüąĄą▒čÅ čüč湥čéčćąĖą║ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ čüčéčĆąŠą║ (refresh counter). ąØąŠ ąÆčŗ ą▓čüąĄ ąĄčēąĄ ą┤ąŠą╗ąČąĮčŗ čāą║ą░ąĘą░čéčī ą╝ąĖą║čĆąŠčüčģąĄą╝ąĄ SDRAM, čćč鹊 ą┐ąŠčĆą░ ą▓čŗą┐ąŠą╗ąĮąĖčéčī ąŠą┐ąĄčĆą░čåąĖčÄ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ. ą¤čĆąŠčåąĄą┤čāčĆą░ą╝ąĖ ąĘą░ą┐čāčüą║ą░ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ, ąŠčéą║čĆčŗčéąĖčÅ ąĖ ąĘą░ą║čĆčŗčéąĖčÅ čüčéčĆąŠą║, ąĮą░čüčéčĆąŠą╣ą║ąŠą╣ ą┐čĆąĄą┤ąĘą░čĆčÅą┤ąŠą╝ ą┐čĆąĖ čćč鹥ąĮąĖąĖ ąŠą▒čŗčćąĮąŠ ąĘą░ąĮąĖą╝ą░ąĄčéčüčÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ SDRAM, ą┐ąŠąĘą▓ąŠą╗čÅčÅ ą┐čĆąŠčåąĄčüčüąŠčĆčā ą┐čĆąŠąĘčĆą░čćąĮąŠ ąŠą▒čĆą░čēą░čéčīčüčÅ ą║ SDRAM ą║ą░ą║ ą║ ąŠą▒čŗčćąĮąŠą╝čā čüčéą░čéąĖč湥čüą║ąŠą╝čā ą×ąŚąŻ.

[ą¦ąĄą╝ ąŠčéą╗ąĖčćą░čÄčéčüčÅ DRAM ąĖ SDRAM]

ą×čéą╗ąĖčćąĖčÅ čŹčéąĖčģ ą┤ą▓čāčģ ą▓ąĖą┤ąŠą▓ ą┤ąĖąĮą░ą╝ąĖč湥čüą║ąŠą│ąŠ ą×ąŚąŻ čüąŠčüč鹊ąĖčé ą▓ č鹊ą╝, čćč鹊 SDRAM čĆą░ą▒ąŠčéą░ąĄčé čüąĖąĮčģčĆąŠąĮąĮąŠ, ą░ DRAM ąĮąĄčé. ąÆčüąĄ, čćč鹊 čŹč鹊 ąĘąĮą░čćąĖčé - SDRAM ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą▓ąĮąĄčłąĮąĖą╣ čéą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗, ą░ DRAM ąĄą│ąŠ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčé. ąöąŠčüč鹊ąĖąĮčüčéą▓ąŠ SDRAM ą▓ č鹊ą╝, čćč鹊 ąĄą│ąŠ ą▓čģąŠą┤čŗ ąĖ ą▓čŗčģąŠą┤čŗ čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆąŠą▓ą░ąĮčŗ ą┐čĆąĖ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖąĖ ą║ č湥ą╝čā ą▒čŗ č鹊 ąĮąĖ ą▒čŗą╗ąŠ, ąĖ ą║ąŠą│ą┤ą░ čéą░ą║ą░čÅ ą┐ą░ą╝čÅčéčī ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčéčüčÅ ą║ čéą░ą║ąĖą╝ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗą╝ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ ą║ą░ą║ FPGA, ą╝ąŠąČąĮąŠ ą┐ąŠą╗čāčćąĖčéčī ąĮąĄą║ąŠč鹊čĆčŗą╣ ą▓čŗąĖą│čĆčŗčł ą▓ čüą║ąŠčĆąŠčüčéąĖ čĆą░ą▒ąŠčéčŗ čü ą┐čĆąĖą╝ąĄąĮąĄąĮąĖąĄą╝ č鹥čģąĮąŠą╗ąŠą│ąĖąĖ ą║ąŠąĮą▓ąĄą╣ąĄčĆą░.

ą£ąĖą║čĆąŠčüčģąĄą╝čŗ SDRAM ąĮą░ą╝ąĮąŠą│ąŠ ą▒ąŠą╗ąĄąĄ čĆą░čüą┐čĆąŠčüčéčĆą░ąĮąĄąĮčŗ, č湥ą╝ ąŠą▒čŗčćąĮčŗąĄ, ąĮąĄ čüąĖąĮčģčĆąŠąĮąĮčŗąĄ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ DRAM.

ąóą░ą║ąČąĄ čüč鹊ąĖčé ąŠčéą╝ąĄčéąĖčéčī, čćč鹊 ą┐ą░ą╝čÅčéčī DDR (čĆą░čüčłąĖčäčĆąŠą▓čŗą▓ą░ąĄčéčüčÅ ą║ą░ą║ Double Data Rate) RAM, ąŠ ą║ąŠč鹊čĆąŠą╣ ą╝čŗ ąŠą▒čŗčćąĮąŠ čüą╗čŗčłąĖą╝ ą▓ ą║ąŠąĮč鹥ą║čüč鹥 ą║ąŠą╝ą┐čīčÄč鹥čĆąŠą▓, čÅą▓ą╗čÅąĄčéčüčÅ čĆą░ąĘąĮąŠą▓ąĖą┤ąĮąŠčüčéčīčÄ ą┐ą░ą╝čÅčéąĖ SDRAM.

ą¦č鹊ą▒čŗ ą┤ąŠčüčéąĖčćčī ą▓čŗčüąŠą║ąŠą╣ čüą║ąŠčĆąŠčüčéąĖ čĆą░ą▒ąŠčéčŗ, ą▓ąĮčāčéčĆąĖ 256 ą╝ąĄą│ą░ą▒ąĖčé SDRAM ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą║ąŠąĮą▓ąĄą╣ąĄčĆąĮą░čÅ ą░čĆčģąĖč鹥ą║čéčāčĆą░. ą×ąĮą░ čüąŠą▓ą╝ąĄčüčéąĖą╝ą░ čü ą░čĆčģąĖč鹥ą║čéčāčĆą░ą╝ąĖ ą┤ą▓čāą║čĆą░čéąĮąŠą╣ čāą┐čĆąĄąČą┤ą░čÄčēąĄą╣ ą▓čŗą▒ąŠčĆą║ąĖ (2n rule of prefetch), ąĮąŠ ąŠąĮą░ čéą░ą║ąČąĄ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą╝ąĄąĮčÅčéčī ą░ą┤čĆąĄčü čüč鹊ą╗ą▒čåą░ ąĮą░ ą║ą░ąČą┤ąŠą╝ čéą░ą║č鹥, čćč鹊ą▒čŗ ą┤ąŠčüčéąĖčćčī ą▓čŗčüąŠą║ąŠą╣ čüą║ąŠčĆąŠčüčéąĖ čĆą░ą▒ąŠčéčŗ ąĖ ą┐ąŠą╗ąĮąŠčüčéčīčÄ čĆąĄą░ą╗ąĖąĘąŠą▓ą░čéčī ą┐čĆąŠąĖąĘą▓ąŠą╗čīąĮčŗą╣ ą┤ąŠčüčéčāą┐ ą║ čÅč湥ą╣ą║ą░ą╝ ą┐ą░ą╝čÅčéąĖ. ą¤čĆąĄą┤ąĘą░čĆčÅą┤ ąŠą┤ąĮąŠą│ąŠ ą▒ą░ąĮą║ą░, ą┐ąŠą║ą░ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą┤ąŠčüčéčāą┐ ą║ ąŠą┤ąĮąŠą╝čā ąĖąĘ čéčĆąĄčģ ą┤čĆčāą│ąĖčģ ą▒ą░ąĮą║ąŠą▓, ą▒čāą┤ąĄčé čüą║čĆčŗą▓ą░čéčī čéą░ą║čéčŗ ą┐čĆąĄą┤ąĘą░čĆčÅą┤ą░ (PRECHARGE) ąĖ ąŠą▒ąĄčüą┐ąĄčćąĖčé čüą║ą▓ąŠąĘąĮąŠą╣, ą┐čĆąŠąĖąĘą▓ąŠą╗čīąĮčŗą╣ ą┤ąŠčüčéčāą┐ ą║ ą┤ą░ąĮąĮčŗą╝ ąĮą░ ą▓čŗčüąŠą║ąŠą╣ čüą║ąŠčĆąŠčüčéąĖ.

ąŁą▓ąŠą╗čÄčåąĖčÅ ą╝ąĖą║čĆąŠčüčģąĄą╝ ą┤ąĖąĮą░ą╝ąĖč湥čüą║ąŠą╣ ą┐ą░ą╝čÅčéąĖ ą┐čĆąŠčłą╗ą░ ąŠčé čüąĖąĮčģčĆąŠąĮąĮčŗčģ DRAM čü ąŠą┤ąĖąĮąŠčćąĮąŠą╣ ą┐čĆąŠą┐čāčüą║ąĮąŠą╣ (SDR) ą║ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ą╝ čü ą┤ą▓ąŠą╣ąĮąŠą╣ ą┐čĆąŠą┐čāčüą║ąĮąŠą╣ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčīčÄ (double data rate synchronous DRAM, DDR). ąźąŠčéčÅ ą┐čĆąĖąĮčåąĖą┐ čĆą░ą▒ąŠčéčŗ čŹčéąĖčģ č鹥čģąĮąŠą╗ąŠą│ąĖą╣ ą▓ąŠ ą╝ąĮąŠą│ąŠą╝ čüąŠą▓ą┐ą░ą┤ą░ąĄčé, DDR čéą░ą║ąČąĄ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ąĘąĮą░čćąĖč鹥ą╗čīąĮčŗąĄ čāą╗čāčćčłąĄąĮąĖčÅ ą┐ąŠčéčĆąĄą▒ąĖč鹥ą╗čīčüą║ąĖčģ čüą▓ąŠą╣čüčéą▓ ą╝ąĖą║čĆąŠčüčģąĄą╝ ą┐ą░ą╝čÅčéąĖ.

ąÆ ąŠą▒čēąĄą╝ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą┐ą░ą╝čÅčéąĖ DDR ą┐ąŠąĘą▓ąŠą╗čÅčÄčé ą┐ąŠą▓čŗčüąĖčéčī čüą║ąŠčĆąŠčüčéčī ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ą▓ 2 čĆą░ąĘą░, čé. ąĄ. čüąĖąĮčģčĆąŠąĮąĮąŠ čü ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮčŗą╝ ąĖ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮčŗą╝ ą┐ąĄčĆąĄą┐ą░ą┤ą░ą╝ąĖ čéą░ą║č鹊ą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░. ąó. ąĄ. čćą░čüč鹊čéą░ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ą┐ąŠą╗čāčćą░ąĄčéčüčÅ čāą┤ą▓ąŠąĄąĮąĮąŠą╣. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, čāčüčéčĆąŠą╣čüčéą▓ąŠ DDR266, čĆą░ą▒ąŠčéą░čÄčēąĄąĄ ąĮą░ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊č鹥 133 ą£ąōčå, ąĖą╝ąĄąĄčé ą┐ąĖą║ąŠą▓čāčÄ čüą║ąŠčĆąŠčüčéčī ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ 266 Mb/s, ąĖą╗ąĖ 2.1 GB/s ą┤ą╗čÅ ą╝ąŠą┤čāą╗ąĄą╣ x64 DIMM. ąŁč鹊 čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮąŠ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ ą┤ą▓ąŠą╣ąĮąŠą╣ ą▓čŗą▒ąŠčĆą║ąĖ čüą╗ąŠą▓ą░ (2n-prefetch architecture) ą│ą┤ąĄ ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ čłąĖąĮą░ ą┤ą░ąĮąĮčŗčģ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą▓ą░ąČą┤čŗ ąĮą░ čüą▓ąŠčÄ ą┐ąŠą╗ąĮčāčÄ čłąĖčĆąĖąĮčā, ąĖ ą▓čŗčģąŠą┤ąĮą░čÅ čłąĖąĮą░ ą┤ą░ąĮąĮčŗčģ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą▓ą░ąČą┤čŗ ąĮą░ ą║ą░ąČą┤čŗą╣ ą┐ąĄčĆąĖąŠą┤ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ. ą¦č鹊ą▒čŗ ąŠą▒ąĄčüą┐ąĄčćąĖčéčī čéą░ą║čāčÄ ą▓čŗčüąŠą║čāčÄ čüą║ąŠčĆąŠčüčéčī ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖ ą║ą░č湥čüčéą▓ąŠ ą▓čŗčüąŠą║ąŠčüą║ąŠčĆąŠčüčéąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░, ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ DDR SDRAM ąĖčüą┐ąŠą╗čīąĘčāčÄčé ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╣ čüčéčĆąŠą▒ ą┤ą░ąĮąĮčŗčģ, ąĖąĮč鹥čĆč乥ą╣čü SSTL_2 čü ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╝ąĖ ą▓čģąŠą┤ą░ą╝ąĖ ąĖ čéą░ą║čéą░ą╝ąĖ.

ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ čŹč鹊ą╣ č鹥čģąĮąŠą╗ąŠą│ąĖąĖ čüą╝. ą▓ ą┤ą░čéą░čłąĖč鹥 TN4605.pdf [2]. ąóą░ą╝ čéą░ą║ąČąĄ čĆą░čüčüą╝ą░čéčĆąĖą▓ą░čÄčéčüčÅ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮčŗąĄ čĆą░ąĘą╗ąĖčćąĖčÅ ą╝ąĄąČą┤čā SDR ąĖ čāą╗čāčćčłąĄąĮąĮąŠą╣ č鹥čģąĮąŠą╗ąŠą│ąĖąĄą╣ ą┐ą░ą╝čÅčéąĖ DDR. ąÜčĆąĖč鹥čĆąĖąĖ ą┤ąĖąĘą░ą╣ąĮą░ ąĖ ąĖąĮč鹥čĆą▓ą░ą╗ąŠą▓ ą▓čĆąĄą╝ąĄąĮąĖ ą┤ą╗čÅ čüąĖčüč鹥ą╝, ąŠčüąĮąŠą▓ą░ąĮąĮčŗčģ ąĮą░ DDR SDRAM, čüą╝. ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖčģ ą┤ą░čéą░čłąĖčéą░čģ ąĮą░ čüą░ą╣č鹥 ą║ąŠą╝ą┐ą░ąĮąĖąĖ Micron (http://www.micron.com/ddrsdram).

256 ą╝ąĄą│ą░ą▒ąĖčéąĮą░čÅ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ SDRAM ą▒čŗą╗ą░ čĆą░ąĘčĆą░ą▒ąŠčéą░ąĮą░ ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ ą▓ čüąĖčüč鹥ą╝ą░čģ, ą│ą┤ąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ 3.3V. ą¤čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčéčüčÅ čĆąĄąČąĖą╝ ą░ą▓č鹊ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ (auto refresh mode) ą▓ą╝ąĄčüč鹥 čü čĆąĄąČąĖą╝ąŠą╝ 菹ĮąĄčĆą│ąŠčüą▒ąĄčĆąĄąČąĄąĮąĖčÅ (power-saving, power-down mode). ąÆčüąĄ ą▓čģąŠą┤čŗ ąĖ ą▓čŗčģąŠą┤čŗ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ čüąŠą▓ą╝ąĄčüčéąĖą╝čŗ čü ą╗ąŠą│ąĖą║ąŠą╣ LVTTL.

ą£ąĖą║čĆąŠčüčģąĄą╝ą░ SDRAM ą┤ą░ąĄčé čüčāčēąĄčüčéą▓ąĄąĮąĮčŗą╣ ą▓čŗąĖą│čĆčŗčł ą▓ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéąĖ ą┤ąĖąĮą░ą╝ąĖč湥čüą║ąŠą╣ ą┐ą░ą╝čÅčéąĖ, ą▓ą║ą╗čÄčćą░čÅ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī čüąĖąĮčģčĆąŠąĮąĮąŠą╣ ą┐ą░ą║ąĄčéąĮąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĮą░ ą▓čŗčüąŠą║ąŠą╣ čüą║ąŠčĆąŠčüčéąĖ čü ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą╣ ą│ąĄąĮąĄčĆą░čåąĖąĄą╣ ą░ą┤čĆąĄčüą░ čüč鹊ą╗ą▒čåą░, ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī č湥čĆąĄą┤ąŠą▓ą░ąĮąĖčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĖčģ ą▒ą░ąĮą║ąŠą▓ ą┤ą╗čÅ čüą║čĆčŗčéąĖčÅ ą▓čĆąĄą╝ąĄąĮąĖ ą┐čĆąĄą┤ąĘą░čĆčÅą┤ą░, ąĖ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī čüą╗čāčćą░ą╣ąĮąŠ ą╝ąĄąĮčÅčéčī ą░ą┤čĆąĄčüą░ čüč鹊ą╗ą▒čåąŠą▓ ąĮą░ ą║ą░ąČą┤ąŠą╝ čéą░ą║č鹥 ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐ą░ą║ąĄčéąĮąŠą│ąŠ ą┤ąŠčüčéčāą┐ą░.

ą×ą┐čåąĖčÅ ą╝ąĖą║čĆąŠčüčģąĄą╝, ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮąĮčŗčģ ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ ą▓ čĆą░čüčłąĖčĆąĄąĮąĮąŠą╝ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ č鹥ą╝ą┐ąĄčĆą░čéčāčĆ ą░ą▓č鹊ą╝ąŠą▒ąĖą╗čīąĮąŠą╣ ą┐čĆąŠą╝čŗčłą╗ąĄąĮąĮąŠčüčéąĖ (automotive temperature, AT), ąĖą╝ąĄąĄčé čüą╗ąĄą┤čāčÄčēąĖąĄ ąŠčüąŠą▒ąĄąĮąĮąŠčüčéąĖ:

ŌĆó ą¤ąĄčĆąĖąŠą┤ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ 16 ą╝čü.

ŌĆó ąĪą░ą╝ąŠąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ (self refresh) ąĮąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ.

ŌĆó ąóąĄą╝ą┐ąĄčĆą░čéčāčĆą░ ąŠą║čĆčāąČą░čÄčēąĄą│ąŠ ą▓ąŠąĘą┤čāčģą░ ąĖ ą║ąŠčĆą┐čāčüą░ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ąĮąĄ ą╝ąŠąČąĄčé ą▓čŗčģąŠą┤ąĖčéčī ąĘą░ ą┐čĆąĄą┤ąĄą╗čŗ ą┤ąĖą░ą┐ą░ąĘąŠąĮą░ ŌĆō40 .. +105 ┬░C.

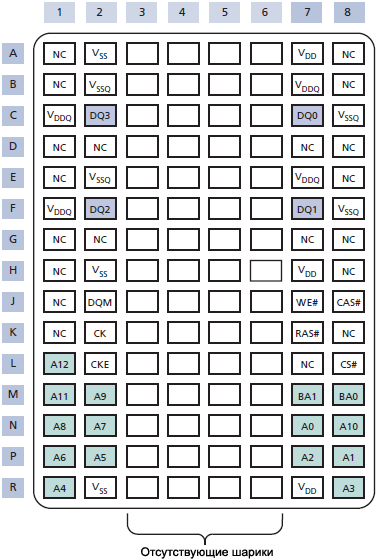

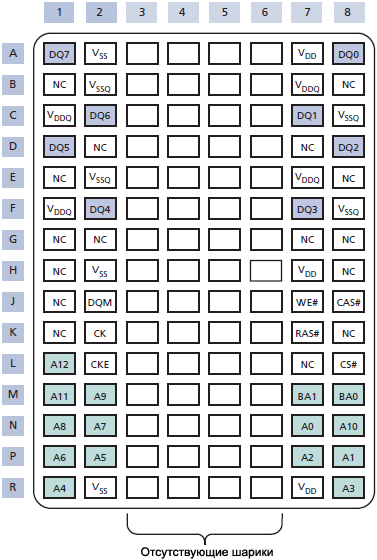

ąĀąĖčü. 3. ążčāąĮą║čåąĖąŠąĮą░ą╗čīąĮą░čÅ ą▒ą╗ąŠą║-čüčģąĄą╝ą░ MT48LC16M16A2 (ąŠčĆą│ą░ąĮąĖąĘą░čåąĖčÅ 16M čÅč湥ąĄą║ x 16 ą▒ąĖčé).

ąĀąĖčü. 4. 54-Pin TSOP (ą▓ąĖą┤ čüą▓ąĄčĆčģčā).

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

1. ąĪąĖą╝ą▓ąŠą╗ # ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 čŹč鹊čé čüąĖą│ąĮą░ą╗ ąĖą╝ąĄąĄčé ą░ą║čéąĖą▓ąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 0. ąĪąĖą╝ą▓ąŠą╗ č湥čĆčéčŗ (-) ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 čäčāąĮą║čåąĖčÅ ą▓čŗą▓ąŠą┤ąŠą▓ ąŠą┐čåąĖą╣ x8 ąĖ x4 čéą░ą║ą░čÅ ąČąĄ, ą║ą░ą║ ąĖ čäčāąĮą║čåąĖčÅ ąŠą┐čåąĖąĖ x16.

2. ąÜąŠčĆą┐čāčü ą╝ąŠąČąĄčé ą▒čŗčéčī ą║ą░ą║ čü ą╝ąĄčéą║ąŠą╣ čĆą░čüą┐ąŠą╗ąŠąČąĄąĮąĖčÅ ą▓čŗą▓ąŠą┤ąŠą▓, čéą░ą║ ąĖ ą▒ąĄąĘ ąĮąĄčæ.

| 64M x 4, ą║ąŠčĆą┐čāčü FB 8x16 ą╝ą╝ |

32M x 8, ą║ąŠčĆą┐čāčü FB 8x16 ą╝ą╝ |

|

|

ąĀąĖčü. 5. 60-Ball FBGA (ą▓ąĖą┤ čüą▓ąĄčĆčģčā).

ąĀąĖčü. 6. 54-Ball VFBGA (ą▓ąĖą┤ čüą▓ąĄčĆčģčā).

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ 1: ą▓čŗą▓ąŠą┤čŗ ą▓ ą┐ąŠąĘąĖčåąĖčÅčģ A4, A5 ąĖ A6 ąŠčéčüčāčéčüčéą▓čāčÄčé ą▓ čäąĖąĘąĖč湥čüą║ąŠą╝ ą║ąŠčĆą┐čāčüąĄ. ąŁčéąĖ ą┐ąŠąĘąĖčåąĖąĖ ą┐čāčüčéčŗąĄ - čüčéčĆąŠą║ąĖ 4, 5 ąĖ 6 čüčāčēąĄčüčéą▓čāčÄčé, ąĮąŠ ąĮą░ ąĮąĖčģ ąĮąĄčé čłą░čĆąĖą║ąŠą▓ ą┐čĆąĖą┐ąŠčÅ.

ąóą░ą▒ą╗ąĖčåą░ 4. ą×ą┐ąĖčüą░ąĮąĖąĄ ą▓čŗą▓ąŠą┤ąŠą▓. ąÆ čüč鹊ą╗ą▒čåąĄ "ąóąĖą┐" ą▒čāą║ą▓ą░ I ąŠąĘąĮą░čćą░ąĄčé ą▓čģąŠą┤, I/O ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╣ čüąĖą│ąĮą░ą╗ (ą║ąŠč鹊čĆčŗą╣ ą╝ąŠąČąĄčé čĆą░ą▒ąŠčéą░čéčī ą║ą░ą║ ą▓čģąŠą┤ ąĖ ą║ą░ą║ ą▓čŗčģąŠą┤), P ąŠąĘąĮą░čćą░ąĄčé ą┐ąĖčéą░ąĮąĖąĄ.

| ą£ąĮąĄą╝ąŠąĮąĖą║ą░ |

ąóąĖą┐ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| CLK |

I |

ąÆąĮąĄčłąĮąĖą╣ čéą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗, ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄą╝čŗą╣ čüąĖčüč鹥ą╝ąŠą╣, ą│ą┤ąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ SDRAM. ąÆčüąĄ ą▓čģąŠą┤ąĮčŗąĄ čüąĖą│ąĮą░ą╗čŗ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčéčüčÅ ą┐ąŠ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą╝čā ą┐ąĄčĆąĄą┐ą░ą┤čā čŹč鹊ą│ąŠ čéą░ą║č鹊ą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░. ąĪąĖą│ąĮą░ą╗ CLK čéą░ą║ąČąĄ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčé ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čüč湥čéčćąĖą║ ą┐ą░ą║ąĄčéą░ (burst counter) ąĖ čāą┐čĆą░ą▓ą╗čÅąĄčé ą▓čŗčģąŠą┤ąĮčŗą╝ąĖ čĆąĄą│ąĖčüčéčĆą░ą╝ąĖ. |

| CKE |

I |

ClocK Enable: čüąĖą│ąĮą░ą╗ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ. ąøąŠą│. 1 ą░ą║čéąĖą▓ąĖčĆčāąĄčé ą┤ąĄą╣čüčéą▓ąĖąĄ čéą░ą║č鹊ą▓ CLK, ą╗ąŠą│. 0 ą┤ąĄą░ą║čéąĖą▓ąĖčĆčāąĄčé. ąöąĄą░ą║čéąĖą▓ą░čåąĖčÅ čéą░ą║č鹊ą▓ ą┐čĆąĖą▓ąŠą┤ąĖčé ą║ ą▓čŗą║ą╗čÄč湥ąĮąĖčÄ ą┐čĆąĄą┤ąĘą░čĆčÅą┤ą░ (PRECHARGE) ąĖ čäčāąĮą║čåąĖąĖ čüą░ą╝ąŠąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ (SELF REFRESH), ą▓čüąĄ ą▒ą░ąĮą║ąĖ ą┐ąĄčĆąĄčģąŠą┤čÅčé ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ąŠąČąĖą┤ą░ąĮąĖčÅ (idle). ą×čéą║ą╗čÄčćą░ąĄčéčüčÅ čĆąĄąČąĖą╝ active (ą░ą║čéąĖą▓ąĮąŠčüčéčī čüčéčĆąŠą║ąĖ ą▓ ą╗čÄą▒ąŠą╝ ą▒ą░ąĮą║ąĄ), ąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą┐ą░ą║ąĄčéąĮčŗą╣ ą┤ąŠčüčéčāą┐, ąĖ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ čĆąĄąČąĖą╝ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ąĖ čéą░ą║č鹊ą▓ CLOCK SUSPEND. CKE čĆą░ą▒ąŠčéą░ąĄčé čüąĖąĮčģčĆąŠąĮąĮąŠ čü ąŠčüčéą░ą╗čīąĮčŗą╝ąĖ čüąĖą│ąĮą░ą╗ą░ą╝ąĖ, ąĘą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ čüą╗čāčćą░čÅ, ą║ąŠą│ą┤ą░ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ ą▓ąŠčłą╗ą░ ą▓ čĆąĄąČąĖą╝ power-down ąĖ čüą╗čāčćą░čÅ, ą║ąŠą│ą┤ą░ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ ą▓ąŠčłą╗ą░ ą▓ čĆąĄąČąĖą╝ self refresh. ąÆ čŹčéąĖčģ ą┤ą▓čāčģ čüą╗čāčćą░čÅčģ CKE čüčéą░ąĮąŠą▓ąĖčéčüčÅ ą░čüąĖąĮčģčĆąŠąĮąĮčŗą╝ ą┤ąŠ ą╝ąŠą╝ąĄąĮčéą░ ą▓čŗčģąŠą┤ą░ ąĖąĘ ąĖčģ čĆąĄąČąĖą╝ąŠą▓. ąæčāč乥čĆčŗ ą▓čģąŠą┤ą░, ą▓ą║ą╗čÄčćą░čÅ CLK, ąĘą░ą┐čĆąĄčēąĄąĮčŗ ą▓ąŠ ą▓čĆąĄą╝čÅ čĆąĄąČąĖą╝ąŠą▓ power-down ąĖ self refresh, č鹥ą╝ čüą░ą╝čŗą╝ ąŠą▒ąĄčüą┐ąĄčćąĖą▓ą░čÅ ąĮąĖąĘą║ąŠąĄ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ 菹ĮąĄčĆą│ąĖąĖ. CKE ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠčüč鹊čÅąĮąĮąŠ ą┐ąŠą┤čéčÅąĮčāčé ą║ ą╗ąŠą│. 1 ąĖą╗ąĖ ąĘą░ą╝ą║ąĮčāčé ąĮą░ ą┐ą╗čÄčü ą┐ąĖčéą░ąĮąĖčÅ. |

| CS# |

I |

Chip Select: čüąĖą│ąĮą░ą╗ ą▓čŗą▒ąŠčĆą║ąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ. CS#=0 čĆą░ąĘčĆąĄčłą░ąĄčé, ąĖ CS#=1 ąĘą░ą┐čĆąĄčēą░ąĄčé ą┤ąĄą║ąŠą┤ąĄčĆ ą║ąŠą╝ą░ąĮą┤čŗ. ąÆčüąĄ ą║ąŠą╝ą░ąĮą┤čŗ ą╝ą░čüą║ąĖčĆčāčÄčéčüčÅ, ą║ąŠą│ą┤ą░ CS#=1, ąĮąŠ ąĘą░ą┐čāčēąĄąĮąĮčŗąĄ ą┐ą░ą║ąĄčéčŗ READ/WRITE ą┐čĆąŠą┤ąŠą╗ąČą░čé čüą▓ąŠčÄ čĆą░ą▒ąŠčéčā, ąĖ ą▓čģąŠą┤čŗ DQM čüąŠčģčĆą░ąĮčÅčé ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓čŗčģąŠą┤ąŠą▓ ą┤ą░ąĮąĮčŗčģ DQ. ąĪąĖą│ąĮą░ą╗ CS# ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą▓čŗą▒ąŠčĆą░ ą▓ąĮąĄčłąĮąĄą│ąŠ ą▒ą░ąĮą║ą░ ą┐ą░ą╝čÅčéąĖ ą▓ čüąĖčüč鹥ą╝ą░čģ, ą│ą┤ąĄ ąĄčüčéčī ąĮąĄčüą║ąŠą╗čīą║ąŠ ą▒ą░ąĮą║ąŠą▓. ąĪąĖą│ąĮą░ą╗ CS# čüčćąĖčéą░ąĄčéčüčÅ čćą░čüčéčīčÄ ą║ąŠą┤ą░ ą║ąŠą╝ą░ąĮą┤čŗ. |

| CAS#, RAS#, WE# |

I |

ąĪąĖą│ąĮą░ą╗čŗ ą▓čŗą▒ąŠčĆą║ąĖ čüč鹊ą╗ą▒čåą░, ą▓čŗą▒ąŠčĆą║ąĖ čüčéčĆąŠą║ąĖ ąĖ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ąĘą░ą┐ąĖčüąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ. ąŁčéąĖ čüąĖą│ąĮą░ą╗čŗ čüąŠą▓ą╝ąĄčüčéąĮąŠ čü čüąĖą│ąĮą░ą╗ąŠą╝ CS# ąĘą░ą┤ą░čÄčé ą║ąŠą┤ ą║ąŠą╝ą░ąĮą┤čŗ, ą▓ ą║ąŠč鹊čĆčāčÄ ą▓čģąŠą┤ąĖčé ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ SDRAM. |

| DQM (ąŠą┐čåąĖąĖ x4 ąĖ x8) |

I |

ą£ą░čüą║ą░ ą▓čģąŠą┤ą░/ą▓čŗčģąŠą┤ą░. ąĢčüą╗ąĖ DQM ą░ąĮą░ą╗ąĖąĘąĖčĆčāąĄčéčüčÅ ą║ą░ą║ ą╗ąŠą│. 1, č鹊 čŹč鹊 ą▓čģąŠą┤ąĮą░čÅ ą╝ą░čüą║ą░ ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ ąĮą░ ąĘą░ą┐ąĖčüčī, ąĖ čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ą▓čŗčģąŠą┤ą░ ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ ąĮą░ čćč鹥ąĮąĖąĄ. ąÆčģąŠą┤ąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą╝ą░čüą║ąĖčĆčāčÄčéčüčÅ ą▓ąŠ ą▓čĆąĄą╝čÅ čåąĖą║ą╗ą░ WRITE. ąÆčŗčģąŠą┤ąĮčŗąĄ ą▒čāč乥čĆčŗ ąĮą░čģąŠą┤čÅčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ High-Z (čü ą╗ą░č鹥ąĮčéąĮąŠčüčéčīčÄ ą▓ 2 čéą░ą║čéą░) ą▓ąŠ ą▓čĆąĄą╝čÅ čåąĖą║ą╗ą░ READ. LDQM čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé D[7:0], ąĖ UDQM čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé DQ[15:8]. ąŻ čüąĖą│ąĮą░ą╗ąŠą▓ LDQM ąĖ UDQM čéą░ą║ąĖąĄ ąČąĄ čüąŠčüč鹊čÅąĮąĖčÅ, ą║ąŠą│ą┤ą░ ą▓ č鹥ą║čüč鹥 čāą┐ąŠą╝ąĖąĮą░ąĄčéčüčÅ čüąĖą│ąĮą░ą╗ DQM. |

| DQML, DQMH (ąŠą┐čåąĖčÅ x16) |

| LDQM, UDQM (54-ball ą║ąŠčĆą┐čāčü) |

| BA[1:0] |

I |

ąÉą┤čĆąĄčü ą▒ą░ąĮą║ą░. ąŁč鹊čé ą░ą┤čĆąĄčü ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé, ą║ ą║ą░ą║ąŠą╝čā ąĖąĘ 4 ą▒ą░ąĮą║ąŠą▓ ąŠčéąĮąŠčüčÅčéčüčÅ ą▓čŗą┐ąŠą╗ąĮčÅąĄą╝čŗąĄ ą║ąŠą╝ą░ąĮą┤čŗ ACTIVE, READ, WRITE ąĖą╗ąĖ PRECHARGE. |

| A[12:0] |

I |

ąÉą┤čĆąĄčüąĮčŗąĄ ą▓čģąŠą┤čŗ. A[12:0] ą░ąĮą░ą╗ąĖąĘąĖčĆčāčÄčéčüčÅ ą▓ąŠ ą▓čĆąĄą╝čÅ ą║ąŠą╝ą░ąĮą┤čŗ ACTIVE (ą║ąŠą│ą┤ą░ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą░ą┤čĆąĄčü čüčéčĆąŠą║ąĖ A[12:0]) ąĖ ą▓ąŠ ą▓čĆąĄą╝čÅ ą║ąŠą╝ą░ąĮą┤čŗ READ ąĖą╗ąĖ WRITE (ą║ąŠą│ą┤ą░ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą░ą┤čĆąĄčü čüč鹊ą╗ą▒čåą░ A[9:0] ąĖ A11 ą┤ą╗čÅ ąŠą┐čåąĖąĖ x4; A[9:0] ą┤ą╗čÅ ąŠą┐čåąĖąĖ x8; A[8:0] ą┤ą╗čÅ ąŠą┐čåąĖąĖ x16; A10 ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé čäčāąĮą║čåąĖčÄ auto precharge), čćč鹊ą▒čŗ ą▓čŗą▒čĆą░čéčī ąŠą┤ąĮčā ąĖąĘ čÅč湥ąĄą║ ą╝ą░čüčüąĖą▓ą░ ą┐ą░ą╝čÅčéąĖ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╝ ą▒ą░ąĮą║ąĄ. A10 ą░ąĮą░ą╗ąĖąĘąĖčĆčāąĄčéčüčÅ ą▓ąŠ ą▓čĆąĄą╝čÅ ą║ąŠą╝ą░ąĮą┤čŗ PRECHARGE, čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī, ą┤ąŠą╗ąČąĮčŗ ą╗ąĖ ą▒čŗčéčī ą┐čĆąĄą┤ąĘą░čĆčÅąČąĄąĮčŗ ą▓čüąĄ ą▒ą░ąĮą║ąĖ (ą║ąŠą│ą┤ą░ A10=1) ąĖą╗ąĖ č鹊ą╗čīą║ąŠ ąŠą┤ąĖąĮ ą▒ą░ąĮą║, ą▓čŗą▒čĆą░ąĮąĮčŗą╣ čüąĖą│ąĮą░ą╗ą░ą╝ąĖ BA[1:0] (ą║ąŠą│ą┤ą░ A10=0). ąÆčģąŠą┤čŗ ą░ą┤čĆąĄčüą░ čéą░ą║ąČąĄ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÄčé ą║ąŠą┤ ąŠą┐ąĄčĆą░čåąĖąĖ ą▓ąŠ ą▓čĆąĄą╝čÅ ą║ąŠą╝ą░ąĮą┤čŗ LOAD MODE REGISTER. |

| DQ[15:0] (ąŠą┐čåąĖčÅ x16) |

I/O |

ą©ąĖąĮą░ ą┤ą░ąĮąĮčŗčģ. |

| DQ[7:0] (ąŠą┐čåąĖčÅ x8) |

| DQ[3:0] (ąŠą┐čåąĖčÅ x4) |

| VDDQ |

P |

ą¤ą╗čÄčü ą┐ąĖčéą░ąĮąĖčÅ ą┤ą╗čÅ ą▒čāč乥čĆąŠą▓ DQ. |

| VSSQ |

P |

ąŚąĄą╝ą╗čÅ ą┐ąĖčéą░ąĮąĖčÅ ą┤ą╗čÅ ą▒čāč乥čĆąŠą▓ DQ. |

| VDD |

P |

ą¤ą╗čÄčü ą┐ąĖčéą░ąĮąĖčÅ 3.3V┬▒0.3V. |

| VSS |

P |

ą×ą▒čēąĖą╣ ą┐čĆąŠą▓ąŠą┤ ą┤ą╗čÅ ą▓čüąĄčģ čüąĖą│ąĮą░ą╗ąŠą▓ ąĖ ą╝ąĖąĮčāčü ą┐ąĖčéą░ąĮąĖčÅ. |

| NC |

- |

ąŁčéąĖ ą▓čŗą▓ąŠą┤čŗ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąŠčüčéą░ą▓ą╗ąĄąĮčŗ ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗą╝ąĖ. ąöą╗čÅ ą▓ąĄčĆčüąĖą╣ ą╝ąĖą║čĆąŠčüčģąĄą╝ x4 ąĖ x8 ą▓čŗą▓ąŠą┤ G1 ąĮąĖą║čāą┤ą░ ąĮąĄ ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčéčüčÅ, ąŠą┤ąĮą░ą║ąŠ ą▓ ą▒čāą┤čāčēąĖčģ čĆą░ąĘčĆą░ą▒ąŠčéą║ą░čģ ąŠąĮ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ. |

ąĪą╝. čéą░ą▒ą╗ąĖčåčŗ 5, 6 čĆą░ąĘą┤ąĄą╗ą░ "Temperature and Thermal Impedance" ą┤ą░čéą░čłąĖčéą░ [1]. ąÆčüąĄ ą┤ą░čéą░čłąĖčéčŗ ą╝ąŠąČąĮąŠ čüą║ą░čćą░čéčī ą┐ąŠ čüčüčŗą╗ą║ąĄ [4].

ąĪčéčĆąĄčüčüąŠą▓čŗąĄ čāčüą╗ąŠą▓ąĖčÅ, ą▓ ą║ąŠč鹊čĆčŗčģ ą┐čĆąĄą▓čŗčłą░čÄčéčüčÅ ąĘąĮą░č湥ąĮąĖčÅ ą▓ čéą░ą▒ą╗ąĖčåąĄ 7, ą╝ąŠą│čāčé ą┐čĆąĖą▓ąĄčüčéąĖ ą║ ąĮąĄąŠą▒čĆą░čéąĖą╝ąŠą╝čā ą┐ąŠą▓čĆąĄąČą┤ąĄąĮąĖčÄ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ. ąŁčéąĖ čüčéčĆąĄčüčüąŠą▓čŗąĄ ą┐čĆąĄą┤ąĄą╗čīąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ čāą║ą░ąĘą░ąĮčŗ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čĆąĄą╣čéąĖąĮą│ą░, ąĖ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ ą▓ čŹčéąĖčģ čāčüą╗ąŠą▓ąĖčÅčģ ąĖą╗ąĖ čü ąĖčģ ą┐čĆąĄą▓čŗčłąĄąĮąĖąĄą╝ ą▒čāą┤ąĄčé ąŠąĘąĮą░čćą░čéčī, čćč鹊 čĆą░ą▒ąŠčćąĖąĄ ą┤ą░ąĮąĮčŗąĄ čüą┐ąĄčåąĖčäąĖą║ą░čåąĖąĖ ąĮąĄą▓ąŠąĘą╝ąŠąČąĮąŠ ą▒čāą┤ąĄčé ą┐čĆąĖą╝ąĄąĮąĖčéčī. ąöąĄą╣čüčéą▓ąĖąĄ čŹčéąĖčģ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮčŗčģ čāčüą╗ąŠą▓ąĖą╣ ą┤ą╗ąĖč鹥ą╗čīąĮąŠąĄ ą▓čĆąĄą╝čÅ ą╝ąŠąČąĄčé ą┐ąŠą▓ą╗ąĖčÅčéčī ąĮą░ ąĮą░ą┤ąĄąČąĮąŠčüčéčī čĆą░ą▒ąŠčéčŗ ą╝ąĖą║čĆąŠčüčģąĄą╝.

ąóą░ą▒ą╗ąĖčåą░ 7. ą¤čĆąĄą┤ąĄą╗čīąĮčŗąĄ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ (Absolute Maximum Ratings).

| ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ/č鹥ą╝ą┐ąĄčĆą░čéčāčĆą░ |

ąĪąĖą╝ą▓ąŠą╗ |

MIN |

MAX |

ąĢą┤. |

| ą¤ąĖčéą░ąĮąĖąĄ VDD/VDDQ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ VSS |

VDD/VDDQ |

-1 |

4.6 |

V |

| ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮą░ ą▓čģąŠą┤ą░čģ, ą▓čŗą▓ąŠą┤ą░čģ NC ąĖą╗ąĖ čłą░čĆąĖą║ą░čģ I/O ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ VSS |

VIN |

-1 |

4.6 |

| ąóąĄą╝ą┐ąĄčĆą░čéčāčĆą░ čģčĆą░ąĮąĄąĮąĖčÅ (ą┐ą╗ą░čüčéąĖą║) |

TSTG |

-55 |

150 |

┬░C |

| ąĀą░čüčüąĄąĖą▓ą░ąĄą╝ą░čÅ ą╝ąŠčēąĮąŠčüčéčī |

- |

- |

1 |

ąÆčé |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ ą║ čéą░ą▒ą╗ąĖčåąĄ 7: čĆą░ąĘąĮąĖčåą░ ą╝ąĄąČą┤čā VDD ąĖ VDDQ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą▓čüąĄą│ą┤ą░ ąĮąĄ ą▒ąŠą╗čīčłąĄ 0.3V. VDDQ ąĮąĄ ą┤ąŠą╗ąČąĮąŠ ą┐čĆąĄą▓čŗčłą░čéčī VDD.

ąóą░ą▒ą╗ąĖčåą░ 8. ąŁą╗ąĄą║čéčĆąĖč湥čüą║ąĖąĄ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ ąĖ čĆą░ą▒ąŠčćąĖąĄ čāčüą╗ąŠą▓ąĖčÅ ą┤ą╗čÅ ą┐ąŠčüč鹊čÅąĮąĮąŠą│ąŠ č鹊ą║ą░, DC. ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ 1..3 ą║ čéą░ą▒ą╗ąĖčåąĄ 8 ąŠčéąĮąŠčüčÅčéčüčÅ ą║ąŠ ą▓čüąĄą╝ čāčüą╗ąŠą▓ąĖčÅą╝; VDD/VDDQ = 3.3V┬▒0.3V.

| ą¤ą░čĆą░ą╝ąĄčéčĆ/čāčüą╗ąŠą▓ąĖąĄ |

ąĪąĖą╝ą▓ąŠą╗ |

MIN |

MAX |

ąĢą┤. |

ą¤čĆąĖą╝. |

| ąØą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ |

VDD/VDDQ |

3 |

3.6 |

V |

|

| ąøąŠą│. 1 ą┤ą╗čÅ ą▓čüąĄčģ ą▓čģąŠą┤ąŠą▓ |

VIH |

2 |

VDD+0.3 |

V |

4 |

| ąøąŠą│. 0 ą┤ą╗čÅ ą▓čüąĄčģ ą▓čģąŠą┤ąŠą▓ |

VIL |

-0.3 |

0.8 |

V |

4 |

| ąÆčŗčģąŠą┤ąĮąŠą╣ čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 1 ą┐čĆąĖ č鹊ą║ąĄ ąĮą░ą│čĆčāąĘą║ąĖ IOUT = ŌĆō4 ą╝ąÉ |

VOH |

2.4 |

- |

V |

|

| ąÆčŗčģąŠą┤ąĮąŠą╣ čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 0 ą┐čĆąĖ č鹊ą║ąĄ ąĮą░ą│čĆčāąĘą║ąĖ IOUT = 4 ą╝ąÉ |

VOL |

- |

0.4 |

V |

|

| ąÆčģąŠą┤ąĮąŠą╣ č鹊ą║ čāč鹥čćą║ąĖ: ąĮą░ ą╗čÄą▒ąŠą╝ ą▓čģąŠą┤ąĄ 0V Ōēż VIN Ōēż VDD (ą▓čüąĄ ą┤čĆčāą│ąĖąĄ ąĮąĄ č鹥čüčéąĖčĆčāąĄą╝čŗąĄ čłą░čĆąĖą║ąĖ ą┐ąŠą┤ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄą╝ 0V) |

IL |

-5 |

5 |

╬╝A |

|

| ąÆčŗčģąŠą┤ąĮąŠą╣ č鹊ą║ čāč鹥čćą║ąĖ: ą▒čāč乥čĆčŗ ą▓čŗčģąŠą┤ąŠą▓ DQ ąĘą░ą┐čĆąĄčēąĄąĮčŗ; 0V Ōēż VOUT Ōēż VDDQ |

IOZ |

-5 |

5 |

╬╝A |

|

| ąĀą░ą▒ąŠčćą░čÅ č鹥ą╝ą┐ąĄčĆą░čéčāčĆą░ ąĖčüą┐ąŠą╗ąĮąĄąĮąĖčÅ Commercial |

TA |

0 |

70 |

┬░C |

|

| ąĀą░ą▒ąŠčćą░čÅ č鹥ą╝ą┐ąĄčĆą░čéčāčĆą░ ąĖčüą┐ąŠą╗ąĮąĄąĮąĖčÅ Industrial |

-40 |

85 |

|

| ąĀą░ą▒ąŠčćą░čÅ č鹥ą╝ą┐ąĄčĆą░čéčāčĆą░ ąĖčüą┐ąŠą╗ąĮąĄąĮąĖčÅ Automotive |

-40 |

105 |

|

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ ą║ čéą░ą▒ą╗ąĖčåąĄ 8:

1. ąÆčüąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ čāą║ą░ąĘą░ąĮčŗ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ VSS.

2. ą£ąĖąĮąĖą╝ą░ą╗čīąĮčŗąĄ čüą┐ąĄčåąĖčäąĖą║ą░čåąĖąĖ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ č鹊ą│ąŠ, čćč鹊ą▒čŗ ą┐ąŠą║ą░ąĘą░čéčī ą▓čĆąĄą╝čÅ čåąĖą║ą╗ą░, ąĮą░ ą║ąŠč鹊čĆąŠą╝ ą┐čĆą░ą▓ąĖą╗čīąĮąŠąĄ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĄ ą▓ąŠ ą▓čüąĄą╝ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ č鹥ą╝ą┐ąĄčĆą░čéčāčĆ; 0┬░C Ōēż TA Ōēż +70┬░C (ąĖčüą┐ąŠą╗ąĮąĄąĮąĖąĄ commercial), ŌĆō40┬░C Ōēż TA Ōēż +85┬░C (ąĖčüą┐ąŠą╗ąĮąĄąĮąĖąĄ industrial), ąĖ ŌĆō40┬░C Ōēż TA Ōēż +105┬░C (ąĖčüą┐ąŠą╗ąĮąĄąĮąĖąĄ automotive).

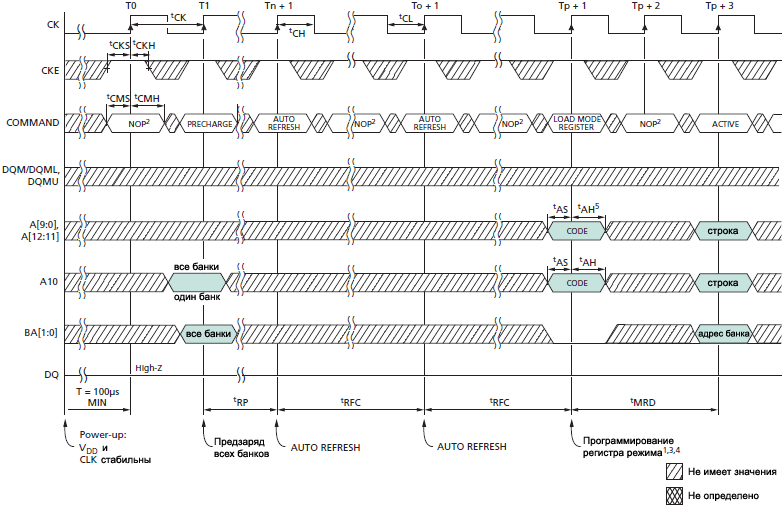

3. ąóčĆąĄą▒čāąĄčéčüčÅ ąĮą░čćą░ą╗čīąĮą░čÅ ą┐ą░čāąĘą░ 100 ą╝ą║čü ą┐ąŠčüą╗ąĄ ą▓ą║ą╗čÄč湥ąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ, ąĘą░ ą║ąŠč鹊čĆąŠą╣ čüą╗ąĄą┤čāčÄčé 2 ą║ąŠą╝ą░ąĮą┤čŗ AUTO REFRESH, ą┐ąĄčĆąĄą┤ č鹥ą╝ ą║ą░ą║ ą│ą░čĆą░ąĮčéąĖčĆčāąĄčéčüčÅ ą║ąŠčĆčĆąĄą║čéąĮąŠąĄ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĄ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ (VDD ąĖ VDDQ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĘą░ą┐ąĖčéą░ąĮčŗ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ. VSS ąĖ VSSQ ą┤ąŠą╗ąČąĮčŗ ąĖą╝ąĄčéčī ąŠą┤ąĖąĮą░ą║ąŠą▓čŗą╣ ą┐ąŠč鹥ąĮčåąĖą░ą╗). ąöą▓ąĄ ą║ąŠą╝ą░ąĮą┤čŗ AUTO REFRESH ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą┐ąŠą▓č鹊čĆąĄąĮčŗ ą║ą░ąČą┤čŗą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ ą┐čĆąĄą▓čŗčłąĄąĮ čéčĆąĄą▒čāąĄą╝čŗą╣ ąĖąĮč鹥čĆą▓ą░ą╗ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ tREF.

4. ą¤ąĄčĆąĄą│čĆčāąĘą║ą░ ą┐ąŠ ą▓čģąŠą┤čā VIH: (overshoot): VIH,max = VDDQ + 2V ą┤ą╗čÅ ąĖą╝ą┐čāą╗čīčüą░ čłąĖčĆąĖąĮąŠą╣ Ōēż 3 ąĮčü, ąĖ čłąĖčĆąĖąĮą░ ąĖą╝ą┐čāą╗čīčüą░ ąĮąĄ ą┤ąŠą╗ąČąĮą░ ą┐čĆąĄą▓čŗčłą░čéčī 1/3 ąŠčé ą┐ąĄčĆąĖąŠą┤ą░ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ. ą¤ąĄčĆąĄą│čĆčāąĘą║ą░ ą┐ąŠ ą▓čģąŠą┤čā VIL (undershoot): VIL,min = ŌĆō2V ą┤ą╗čÅ ąĖą╝ą┐čāą╗čīčüą░ čłąĖčĆąĖąĮąŠą╣ Ōēż3 ąĮčü.

ąóą░ą▒ą╗ąĖčåą░ 9. ą¤ą░čĆą░ąĘąĖčéąĮą░čÅ ąĄą╝ą║ąŠčüčéčī. ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ 1 ąŠčéąĮąŠčüąĖčéčüčÅ ą║ąŠ ą▓čüąĄą╝ ą┐ą░čĆą░ą╝ąĄčéčĆą░ą╝ ąĖ čāčüą╗ąŠą▓ąĖčÅą╝.

| ąÜąŠčĆą┐čāčü |

ą¤ą░čĆą░ą╝ąĄčéčĆ |

ąĪąĖą╝ą▓ąŠą╗ |

MIN |

MAX |

ąĢą┤. |

ą¤čĆąĖą╝. |

| TSOP |

ąÆčģąŠą┤ąĮą░čÅ ąĄą╝ą║ąŠčüčéčī CLK |

CL1 |

2.5 |

3.5 |

ą┐ąż |

2 |

| ąÆčģąŠą┤ąĮą░čÅ ąĄą╝ą║ąŠčüčéčī ą▓čüąĄčģ ą┤čĆčāą│ąĖčģ ą▓čģąŠą┤ąĮčŗčģ čłą░čĆąĖą║ąŠą▓čŗčģ ą▓čŗą▓ąŠą┤ąŠą▓ |

CL2 |

2.5 |

3.8 |

3 |

| ąĢą╝ą║ąŠčüčéčī ą▓čŗą▓ąŠą┤ąŠą▓ DQ (ą▓čģąŠą┤/ą▓čŗčģąŠą┤) |

CL0 |

4 |

6 |

4 |

| FBGA |

ąÆčģąŠą┤ąĮą░čÅ ąĄą╝ą║ąŠčüčéčī CLK |

CL1 |

1.5 |

3.5 |

5 |

| ąÆčģąŠą┤ąĮą░čÅ ąĄą╝ą║ąŠčüčéčī ą▓čüąĄčģ ą┤čĆčāą│ąĖčģ ą▓čģąŠą┤ąĮčŗčģ čłą░čĆąĖą║ąŠą▓čŗčģ ą▓čŗą▓ąŠą┤ąŠą▓ |

CL2 |

1.5 |

3.8 |

6 |

| ąĢą╝ą║ąŠčüčéčī ą▓čŗą▓ąŠą┤ąŠą▓ DQ (ą▓čģąŠą┤/ą▓čŗčģąŠą┤) |

CL0 |

3 |

6 |

7 |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ ą║ čéą░ą▒ą╗ąĖčåąĄ 9:

1. ą¤ą░čĆą░ą╝ąĄčéčĆčŗ čüąĮčÅčéčŗ ą┐čĆąĖ čāčüą╗ąŠą▓ąĖčÅčģ VDD, VDDQ = 3.3V; f=1 ą£ąōčå, TA = 25┬░C; č鹥čüčéąĖčĆčāąĄą╝čŗą╣ ą▓čŗą▓ąŠą┤ čüą╝ąĄčēąĄąĮ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄą╝ 1.4V.

2. PC100 ąĘą░ą┤ą░ąĄčé ą╝ą░ą║čüąĖą╝čāą╝ 4 ą┐ąż.

3. PC100 ąĘą░ą┤ą░ąĄčé ą╝ą░ą║čüąĖą╝čāą╝ 5 ą┐ąż.

4. PC100 ąĘą░ą┤ą░ąĄčé ą╝ą░ą║čüąĖą╝čāą╝ 6.5 ą┐ąż.

5. PC133 ąĘą░ą┤ą░ąĄčé ą╝ąĖąĮąĖą╝čāą╝ 2.5 ą┐ąż.

6. PC133 ąĘą░ą┤ą░ąĄčé ą╝ąĖąĮąĖą╝čāą╝ 2.5 ą┐ąż.

7. PC133 ąĘą░ą┤ą░ąĄčé ą╝ąĖąĮąĖą╝čāą╝ 3.0 ą┐ąż.

ąóą░ą▒ą╗ąĖčåą░ 10. ąĪą┐ąĄčåąĖčäąĖą║ą░čåąĖčÅ ąĖ čāčüą╗ąŠą▓ąĖčÅ č鹊ą║ą░ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ IDD ą┤ą╗čÅ ąŠą┐čåąĖą╣ x4, x8, x16 čĆąĄą▓ąĖąĘąĖąĖ D. ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ 1..5 ąŠčéąĮąŠčüąĖčéčüčÅ ą║ąŠ ą▓čüąĄą╝ ą┐ą░čĆą░ą╝ąĄčéčĆą░ą╝ ąĖ čāčüą╗ąŠą▓ąĖčÅą╝; VDD/VDDQ = +3.3V ┬▒0.3V.

ą¤ą░čĆą░ą╝ąĄčéčĆ/čāčüą╗ąŠą▓ąĖąĄ

|

ąĪąĖą╝ą▓ąŠą╗

|

MAX

|

ąĢą┤.

|

ą¤čĆąĖą╝.

|

| -6A |

-7E |

-75 |

| ą¤ąŠčéčĆąĄą▒ą╗čÅąĄą╝čŗą╣ čĆą░ą▒ąŠčćąĖą╣ č鹊ą║: ą░ą║čéąĖą▓ąĮčŗą╣ čĆąĄąČąĖą╝ Burst = 2; READ ąĖą╗ąĖ WRITE; tRC = tRC (MIN). |

IDD1 |

135 |

135 |

125 |

mA |

6, 7, 8, 9 |

| ą¤ąŠčéčĆąĄą▒ą╗čÅąĄą╝čŗą╣ č鹊ą║ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ąŠąČąĖą┤ą░ąĮąĖčÅ: čĆąĄąČąĖą╝ Power-down; ą▓čüąĄ ą▒ą░ąĮą║ąĖ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ąŠąČąĖą┤ą░ąĮąĖčÅ; CKE=0. |

IDD2 |

2 |

2 |

2 |

9 |

| ą¤ąŠčéčĆąĄą▒ą╗čÅąĄą╝čŗą╣ č鹊ą║ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ąŠąČąĖą┤ą░ąĮąĖčÅ: ą░ą║čéąĖą▓ąĮčŗą╣ čĆąĄąČąĖą╝; CKE=1; CS#=1; ą▓čüąĄ ą▒ą░ąĮą║ąĖ ą░ą║čéąĖą▓ąĮčŗ ą┐ąŠčüą╗ąĄ ąĖąĮč鹥čĆą▓ą░ą╗ą░ tRCD; ąĮąĖą║ą░ą║ąĖąĄ ąŠą┐ąĄčĆą░čåąĖąĖ ą┤ąŠčüčéčāą┐ą░ ąĮąĄ ąŠčüčāčēąĄčüčéą▓ą╗čÅčÄčéčüčÅ. |

IDD3 |

40 |

40 |

40 |

6, 8, 9, 10 |

| ą¤ąŠčéčĆąĄą▒ą╗čÅąĄą╝čŗą╣ čĆą░ą▒ąŠčćąĖą╣ č鹊ą║: čĆąĄąČąĖą╝ ą┐ą░ą║ąĄčéą░ (burst); READ ąĖą╗ąĖ WRITE; ą▓čüąĄ ą▒ą░ąĮą║ąĖ ą░ą║čéąĖą▓ąĮčŗ. |

IDD4 |

135 |

135 |

135 |

6, 7, 8, 9 |

| ąóąŠą║ čüąŠčüč鹊čÅąĮąĖčÅ auto refresh: CKE=1; CS#=1. |

tRFC = tRFC (MIN) |

IDD5 |

285 |

285 |

270 |

6, 7, 8, 9, 10, 11 |

| tRFC = 7.813 ą╝ą║čü |

IDD6 |

3.5 |

3.5 |

3.5 |

| tRFC = 1.953 ą╝ą║čü (AT) |

IDD6 |

8 |

8 |

8 |

| ąóąŠą║ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ ą▓ čĆąĄąČąĖą╝ąĄ self refresh: CKE Ōēż 0.2V |

ąĪčéą░ąĮą┤ą░čĆčéąĮąŠąĄ ąĖčüą┐ąŠą╗ąĮąĄąĮąĖąĄ |

IDD7 |

2.5 |

2.5 |

2.5 |

|

| Low power (L) |

IDD7 |

- |

1.5 |

1.5 |

12 |

ąóą░ą▒ą╗ąĖčåą░ 11. ąĪą┐ąĄčåąĖčäąĖą║ą░čåąĖčÅ ąĖ čāčüą╗ąŠą▓ąĖčÅ č鹊ą║ą░ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ IDD ą┤ą╗čÅ ąŠą┐čåąĖą╣ x4, x8, x16 čĆąĄą▓ąĖąĘąĖąĖ G. ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ 1..5 ąŠčéąĮąŠčüąĖčéčüčÅ ą║ąŠ ą▓čüąĄą╝ ą┐ą░čĆą░ą╝ąĄčéčĆą░ą╝ ąĖ čāčüą╗ąŠą▓ąĖčÅą╝; VDD/VDDQ = +3.3V ┬▒0.3V.

ą¤ą░čĆą░ą╝ąĄčéčĆ/čāčüą╗ąŠą▓ąĖąĄ

|

ąĪąĖą╝ą▓ąŠą╗

|

MAX

|

ąĢą┤.

|

ą¤čĆąĖą╝.

|

| -6A |

-7E |

| ą¤ąŠčéčĆąĄą▒ą╗čÅąĄą╝čŗą╣ čĆą░ą▒ąŠčćąĖą╣ č鹊ą║: ą░ą║čéąĖą▓ąĮčŗą╣ čĆąĄąČąĖą╝ Burst = 2; READ ąĖą╗ąĖ WRITE; tRC = tRC (MIN). |

IDD1 |

100 |

100 |

mA |

6, 7, 8, 9 |

| ą¤ąŠčéčĆąĄą▒ą╗čÅąĄą╝čŗą╣ č鹊ą║ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ąŠąČąĖą┤ą░ąĮąĖčÅ: čĆąĄąČąĖą╝ Power-down; ą▓čüąĄ ą▒ą░ąĮą║ąĖ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ąŠąČąĖą┤ą░ąĮąĖčÅ; CKE=0. |

IDD2 |

2.5 |

2.5 |

9 |

| ą¤ąŠčéčĆąĄą▒ą╗čÅąĄą╝čŗą╣ č鹊ą║ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ąŠąČąĖą┤ą░ąĮąĖčÅ: ą░ą║čéąĖą▓ąĮčŗą╣ čĆąĄąČąĖą╝; CKE=1; CS#=1; ą▓čüąĄ ą▒ą░ąĮą║ąĖ ą░ą║čéąĖą▓ąĮčŗ ą┐ąŠčüą╗ąĄ ąĖąĮč鹥čĆą▓ą░ą╗ą░ tRCD; ąĮąĖą║ą░ą║ąĖąĄ ąŠą┐ąĄčĆą░čåąĖąĖ ą┤ąŠčüčéčāą┐ą░ ąĮąĄ ąŠčüčāčēąĄčüčéą▓ą╗čÅčÄčéčüčÅ. |

IDD3 |

35 |

35 |

6, 8, 9, 10 |

| ą¤ąŠčéčĆąĄą▒ą╗čÅąĄą╝čŗą╣ čĆą░ą▒ąŠčćąĖą╣ č鹊ą║: čĆąĄąČąĖą╝ ą┐ą░ą║ąĄčéą░ (burst); READ ąĖą╗ąĖ WRITE; ą▓čüąĄ ą▒ą░ąĮą║ąĖ ą░ą║čéąĖą▓ąĮčŗ. |

IDD4 |

100 |

100 |

6, 7, 8, 9 |

| ąóąŠą║ čüąŠčüč鹊čÅąĮąĖčÅ auto refresh: CKE=1; CS#=1. |

tRFC = tRFC (MIN) |

IDD5 |

150 |

150 |

6, 7, 8, 9, 10, 11 |

| tRFC = 7.813 ą╝ą║čü |

IDD6 |

4 |

4 |

| tRFC = 1.953 ą╝ą║čü (AT) |

IDD6 |

8 |

8 |

| ąóąŠą║ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ ą▓ čĆąĄąČąĖą╝ąĄ self refresh: CKE Ōēż 0.2V |

ąĪčéą░ąĮą┤ą░čĆčéąĮąŠąĄ ąĖčüą┐ąŠą╗ąĮąĄąĮąĖąĄ |

IDD7 |

3 |

3 |

|

| Low power (L) |

IDD7 |

1.5 |

1.5 |

12 |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ ą║ čéą░ą▒ą╗ąĖčåą░ą╝ 10 ąĖ 11:

1. ąÆčüąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ čāą║ą░ąĘą░ąĮčŗ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ VSS.

2. ą£ąĖąĮąĖą╝ą░ą╗čīąĮčŗąĄ čüą┐ąĄčåąĖčäąĖą║ą░čåąĖąĖ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ č鹊ą│ąŠ, čćč鹊ą▒čŗ ą┐ąŠą║ą░ąĘą░čéčī ą▓čĆąĄą╝čÅ čåąĖą║ą╗ą░, ąĮą░ ą║ąŠč鹊čĆąŠą╝ ą┐čĆą░ą▓ąĖą╗čīąĮąŠąĄ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĄ ą▓ąŠ ą▓čüąĄą╝ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ č鹥ą╝ą┐ąĄčĆą░čéčāčĆ; 0┬░C Ōēż TA Ōēż +70┬░C (ąĖčüą┐ąŠą╗ąĮąĄąĮąĖąĄ commercial), ŌĆō40┬░C Ōēż TA Ōēż +85┬░C (ąĖčüą┐ąŠą╗ąĮąĄąĮąĖąĄ industrial), ąĖ ŌĆō40┬░C Ōēż TA Ōēż +105┬░C (ąĖčüą┐ąŠą╗ąĮąĄąĮąĖąĄ automotive).

3. ąóčĆąĄą▒čāąĄčéčüčÅ ąĮą░čćą░ą╗čīąĮą░čÅ ą┐ą░čāąĘą░ 100 ą╝ą║čü ą┐ąŠčüą╗ąĄ ą▓ą║ą╗čÄč湥ąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ, ąĘą░ ą║ąŠč鹊čĆąŠą╣ čüą╗ąĄą┤čāčÄčé 2 ą║ąŠą╝ą░ąĮą┤čŗ AUTO REFRESH, ą┐ąĄčĆąĄą┤ č鹥ą╝ ą║ą░ą║ ą│ą░čĆą░ąĮčéąĖčĆčāąĄčéčüčÅ ą║ąŠčĆčĆąĄą║čéąĮąŠąĄ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĄ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ (VDD ąĖ VDDQ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĘą░ą┐ąĖčéą░ąĮčŗ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ. VSS ąĖ VSSQ ą┤ąŠą╗ąČąĮčŗ ąĖą╝ąĄčéčī ąŠą┤ąĖąĮą░ą║ąŠą▓čŗą╣ ą┐ąŠč鹥ąĮčåąĖą░ą╗). ąöą▓ąĄ ą║ąŠą╝ą░ąĮą┤čŗ AUTO REFRESH ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą┐ąŠą▓č鹊čĆąĄąĮčŗ ą║ą░ąČą┤čŗą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ ą┐čĆąĄą▓čŗčłąĄąĮ čéčĆąĄą▒čāąĄą╝čŗą╣ ąĖąĮč鹥čĆą▓ą░ą╗ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ tREF.

4. ąĀą░ą▒ąŠčéą░ ą┐ąŠ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą╝čā č鹊ą║čā (AC) ąĖ č鹥čüč鹊ą▓čŗąĄ čāčüą╗ąŠą▓ąĖčÅ ą┤ą╗čÅ IDD ą┤ą░ąĮčŗ ą┐čĆąĖ VIL = 0V ąĖ VIH = 3.0V, ąĖąĘą╝ąĄčĆąĖč鹥ą╗čīąĮčŗą╣ ąŠą┐ąŠčĆąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī 1.5V. ąĢčüą╗ąĖ ą▓čģąŠą┤ąĮąŠąĄ ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĄčģąŠą┤ą░ ą▒ąŠą╗čīčłąĄ 1 ąĮčü, č鹊 ą▓čĆąĄą╝čÅ ąĖąĘą╝ąĄčĆčÅąĄčéčüčÅ ąŠčé VIL, max ąĖ VIH,min ąĖ ąĮąĄ ą┤ąŠą╗čīčłąĄ ąŠčé čüčĆąĄą┤ąĮąĄą╣ č鹊čćą║ąĖ 1.5V. CLK ą▓čüąĄą│ą┤ą░ ąĖą╝ąĄąĄčé č鹊čćą║čā ą┐ąĄčĆąĄčģąŠą┤ą░ 1.5V. ąĪą╝. č鹥čģąĮąĖč湥čüą║ąŠąĄ čāą║ą░ąĘą░ąĮąĖąĄ TN-48-09 ą║ąŠą╝ą┐ą░ąĮąĖąĖ Micron.

5. ąĪą┐ąĄčåąĖčäąĖą║ą░čåąĖąĖ IDD č鹥čüčéąĖčĆąŠą▓ą░ą╗ąĖčüčī ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą▒čŗą╗ąŠ ą║ąŠčĆčĆąĄą║čéąĮąŠ ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆąŠą▓ą░ąĮąŠ.

6. IDD ąĘą░ą▓ąĖčüąĖčé ąŠčé ąĘą░ą│čĆčāąĘą║ąĖ ą▓čŗčģąŠą┤ą░ ąĖ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ. ąŻą║ą░ąĘą░ąĮąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ ą▒čŗą╗ąĖ ą┐ąŠą╗čāč湥ąĮčŗ čü ą╝ąĖąĮąĖą╝ą░ą╗čīąĮčŗą╝ ą▓čĆąĄą╝ąĄąĮąĄą╝ čéą░ą║čéą░ ąĖ ąŠčéą║čĆčŗčéčŗą╝ąĖ ą▓čŗčģąŠą┤ą░ą╝ąĖ.

7. ąóąŠą║ IDD ą▒čāą┤ąĄčé čāą▓ąĄą╗ąĖčćąĖą▓ą░čéčīčüčÅ ąĖą╗ąĖ čāą╝ąĄąĮčīčłą░čéčīčüčÅ ą┐čĆąŠą┐ąŠčĆčåąĖąŠąĮą░ą╗čīąĮąŠ ąĖąĘą╝ąĄąĮąĄąĮąĖčÄ čćą░čüč鹊čéčŗ ą┐čĆąĖ čāčüą╗ąŠą▓ąĖčÅčģ ąĖčüą┐čŗčéą░ąĮąĖčÅ.

8. ą¤ąĄčĆąĄčģąŠą┤čŗ ą╝ąĄąČą┤čā ą░ą┤čĆąĄčüą░ą╝ąĖ ą┐čĆąŠąĖčüčģąŠą┤čÅčé ą▓ čüčĆąĄą┤ąĮąĄą╝ ą║ą░ąČą┤čŗąĄ 2 čéą░ą║čéą░.

9. ąöą╗čÅ -75 ą┐ą░čĆą░ą╝ąĄčéčĆ CL = 3 ąĖ tCK = 7.5 ąĮčü; ą┤ą╗čÅ -7E ą┐ą░čĆą░ą╝ąĄčéčĆ CL = 2 ąĖ tCK = 7.5 ąĮčü.

10. ąöčĆčāą│ąĖąĄ ą▓čģąŠą┤ąĮčŗąĄ čüąĖą│ąĮą░ą╗čŗ ą╝ąŠą│čāčé ą╝ąĄąĮčÅčéčīčüčÅ ąĮąĄ čćą░čēąĄ č湥ą╝ ą║ą░ąČą┤čŗąĄ 2 čéą░ą║čéą░, ąĖ ą┐čĆąĖ ą┤ąŠą┐čāčüčéąĖą╝čŗčģ čāčĆąŠą▓ąĮčÅčģ VIH ąĖą╗ąĖ VIL.

11. CKE=1 ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĖąŠą┤ą░ ą║ąŠą╝ą░ąĮą┤čŗ REFRESH tRFC (MIN), ąĖąĮą░č湥 CKE-0. ąøąĖą╝ąĖčé IDD6 ąĖą╝ąĄąĄčé ą┤ąĄą╣čüčéą▓ąĖč鹥ą╗čīąĮąŠąĄ ąĮąŠą╝ąĖąĮą░ą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ, ąĖ ąĮąĄ čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ąŠčłąĖą▒ą║ąĄ.

12. ąĀą░ąĘčĆąĄčłą░ąĄčé ą▓čüčéčĆąŠąĄąĮąĮąŠąĄ ą▓ čćąĖą┐ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ ąĖ čüč湥čéčćąĖą║ąĖ ą░ą┤čĆąĄčüą░.

13. PC100 ąĘą░ą┤ą░ąĄčé ą╝ą░ą║čüąĖą╝čāą╝ 4 ą┐ąż.

14. PC100 ąĘą░ą┤ą░ąĄčé ą╝ą░ą║čüąĖą╝čāą╝ 5 ą┐ąż.

ąóą░ą▒ą╗ąĖčåą░ 12. ąŁą╗ąĄą║čéčĆąĖč湥čüą║ąĖąĄ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ ąĖ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄą╝čŗąĄ čĆą░ą▒ąŠčćąĖąĄ čāčüą╗ąŠą▓ąĖčÅ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą│ąŠ č鹊ą║ą░ (AC). ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ 1..5 ąŠčéąĮąŠčüčÅčéčüčÅ ą║ąŠ ą▓čüąĄą╝ ą┐ą░čĆą░ą╝ąĄčéčĆą░ą╝ ąĖ čāčüą╗ąŠą▓ąĖčÅą╝.

ą¤ą░čĆą░ą╝ąĄčéčĆ

|

ąĪąĖą╝ą▓ąŠą╗

|

-6A |

-7E |

-75 |

ąĢą┤. |

ą¤čĆąĖą╝.

|

| min |

max |

min |

max |

min |

max |

| ąÆčĆąĄą╝čÅ ą┤ąŠčüčéčāą┐ą░ ąŠčé CLK (ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮčŗą╣ ą┐ąĄčĆąĄą┐ą░ą┤) |

CL=3 |

tAC(3) |

- |

5.4 |

- |

5.4 |

- |

5.4 |

ąĮčü |

7 |

| CL=2 |

tAC(2) |

- |

7.56 |

- |

5.4 |

- |

6 |

7 |

| CL=1 |

tAC(1) |

- |

176 |

- |

- |

- |

- |

7 |

| ąÆčĆąĄą╝čÅ čāą┤ąĄčƹȹ░ąĮąĖčÅ |

tAH |

0.8 |

- |

0.8 |

- |

0.8 |

- |

|

| ąÆčĆąĄą╝čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ ą░ą┤čĆąĄčüą░ |

tAS |

1.5 |

- |

1.5 |

- |

1.5 |

- |

|

| ą©ąĖčĆąĖąĮą░ ąĖąĮč鹥čĆą▓ą░ą╗ą░ ą╗ąŠą│. 1 čéą░ą║č鹊ą▓ CLK |

|

tCH |

2.5 |

- |

2.5 |

- |

2.5 |

- |

|

| ą©ąĖčĆąĖąĮą░ ąĖąĮč鹥čĆą▓ą░ą╗ą░ ą╗ąŠą│. 0 čéą░ą║č鹊ą▓ CLK |

|

tCL |

2.5 |

- |

2.5 |

- |

2.5 |

- |

|

| ąÆčĆąĄą╝čÅ ą┐ąĄčĆąĖąŠą┤ą░ čéą░ą║č鹊ą▓ |

CL=3 |

tCK(3) |

6 |

- |

7 |

- |

7.5 |

- |

8 |

| CL=2 |

tCK(2) |

106 |

- |

7.5 |

- |

10 |

- |

8 |

| CL=1 |

tCK(1) |

206 |

- |

- |

- |

- |

- |

8 |

| ąÆčĆąĄą╝čÅ čāą┤ąĄčƹȹ░ąĮąĖčÅ CKE |

tCKH |

0.8 |

- |

0.8 |

- |

0.8 |

- |

|

| ąÆčĆąĄą╝čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ CKE |

tCKS |

1.5 |

- |

1.5 |

- |

1.5 |

- |

|

| ąÆčĆąĄą╝čÅ čāą┤ąĄčƹȹ░ąĮąĖčÅ CS#, RAS#, CAS#, WE#, DQM |

tCMH |

0.8 |

- |

0.8 |

- |

0.8 |

- |

|

| ąÆčĆąĄą╝čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ CS#, RAS#, CAS#, WE#, DQM |

tCMS |

1.5 |

- |

1.5 |

- |

1.5 |

- |

|

| ąÆčĆąĄą╝čÅ čāą┤ąĄčƹȹ░ąĮąĖčÅ ą▓čģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ |

tDH |

0.8 |

- |

0.8 |

- |

0.8 |

- |

|

| ąÆčĆąĄą╝čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▓čģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ |

tCMS |

1.5 |

- |

1.5 |

- |

1.5 |

- |

|

| ąÆčĆąĄą╝čÅ High-Z ą▓čŗčģąŠą┤ą░ ą┤ą░ąĮąĮčŗčģ |

CL=3 |

tHZ(3) |

- |

5.4 |

- |

5.4 |

- |

5.4 |

9 |

| CL=2 |

tHZ(2) |

- |

7.56 |

- |

5.4 |

- |

6 |

9 |

| CL=1 |

tHZ(1) |

- |

176 |

- |

- |

- |

- |

9 |

| ąÆčĆąĄą╝čÅ Low-Z ą▓čŗčģąŠą┤ą░ ą┤ą░ąĮąĮčŗčģ |

tLZ |

1 |

- |

1 |

- |

1 |

- |

|

| ąÆčĆąĄą╝čÅ čāą┤ąĄčƹȹ░ąĮąĖčÅ ą▓čŗčģąŠą┤ą░ ą┤ą░ąĮąĮčŗčģ (ą┐ąŠą┤ ąĮą░ą│čĆčāąĘą║ąŠą╣) |

tOH |

3 |

- |

3 |

- |

3 |

- |

|

| ąÆčĆąĄą╝čÅ čāą┤ąĄčƹȹ░ąĮąĖčÅ ą▓čŗčģąŠą┤ą░ ą┤ą░ąĮąĮčŗčģ (ą▒ąĄąĘ ąĮą░ą│čĆčāąĘą║ąĖ) |

tOHn |

1.8 |

- |

1.8 |

- |

1.8 |

- |

10 |

| ą¤ąĄčĆąĄčģąŠą┤ ąŠčé ą║ąŠą╝ą░ąĮą┤čŗ ACTIVE ą║ ą║ąŠą╝ą░ąĮą┤ąĄ PRECHARGE |

tRAS |

42 |

120,000 |

37 |

120,000 |

44 |

120,000 |

|

| ą¤ąĄčĆąĄčģąŠą┤ ąŠčé ą║ąŠą╝ą░ąĮą┤čŗ ACTIVE ą║ ą║ąŠą╝ą░ąĮą┤ąĄ ACTIVE |

tRC |

60 |

- |

60 |

- |

66 |

- |

11 |

| ąŚą░ą┤ąĄčƹȹ║ą░ ą┐ąĄčĆąĄčģąŠą┤ą░ ąŠčé ą║ąŠą╝ą░ąĮą┤čŗ ACTIVE ą║ ą║ąŠą╝ą░ąĮą┤ąĄ READ ąĖą╗ąĖ WRITE |

tRCD |

18 |

- |

15 |

- |

20 |

- |

|

| ą¤ąĄčĆąĖąŠą┤ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ (8192 čüčéčĆąŠą║ąĖ) |

tREF |

- |

64 |

- |

64 |

- |

64 |

ą╝čü |

|

| ą¤ąĄčĆąĖąŠą┤ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ ą┤ą╗čÅ ąĖčüą┐ąŠą╗ąĮąĄąĮąĖčÅ AT (8192 čüčéčĆąŠą║ąĖ) |

tREFAT |

- |

16 |

- |

16 |

- |

16 |

|

| ą¤ąĄčĆąĖąŠą┤ AUTO REFRESH |

tRFC |

60 |

- |

66 |

- |

66 |

- |

ąĮčü |

|

| ą¤ąĄčĆąĖąŠą┤ ą║ąŠą╝ą░ąĮą┤čŗ PRECHARGE |

tRP |

18 |

- |

15 |

- |

20 |

- |

|

| ąśąĮč鹥čĆą▓ą░ą╗ ąŠčé ą║ąŠą╝ą░ąĮą┤čŗ ACTIVE ą┤ą╗čÅ ą▒ą░ąĮą║ą░ a ą┤ąŠ ą║ąŠą╝ą░ąĮą┤čŗ ACTIVE ą┤ą╗čÅ ą▒ą░ąĮą║ą░ b |

tRRD |

12 |

- |

14 |

- |

15 |

- |

|

| ąÆčĆąĄą╝čÅ ą┐ąĄčĆąĄčģąŠą┤ą░ |

tT |

0.3 |

1.2 |

0.3 |

1.2 |

0.3 |

1.2 |

12 |

| ąÆčĆąĄą╝čÅ ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖčÅ ąĘą░ą┐ąĖčüąĖ (WRITE recovery) |

tWR |

1CLK + 6 ąĮčü |

- |

1CLK + 7 ąĮčü |

- |

1CLK + 7.5 ąĮčü |

- |

13 |

| 12 |

- |

14 |

- |

15 |

- |

14 |

| ąśąĮč鹥čĆą▓ą░ą╗ ą╝ąĄąČą┤čā ą▓čŗčģąŠą┤ąŠą╝ ąĖąĘ SELF REFRESH ą┤ąŠ ą║ąŠą╝ą░ąĮą┤čŗ ACTIVE |

tXSR |

67 |

- |

67 |

- |

75 |

- |

15 |

ąóą░ą▒ą╗ąĖčåą░ 13. ążčāąĮą║čåąĖąŠąĮą░ą╗čīąĮčŗąĄ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ AC. ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ 2..5 ąŠčéąĮąŠčüčÅčéčüčÅ ą║ąŠ ą▓čüąĄą╝ ą┐ą░čĆą░ą╝ąĄčéčĆą░ą╝ ąĖ čāčüą╗ąŠą▓ąĖčÅą╝.

ą¤ą░čĆą░ą╝ąĄčéčĆ

|

ąĪąĖą╝ą▓ąŠą╗

|

-6A |

-7E |

-75 |

ąĢą┤. |

ą¤čĆąĖą╝.

|

| ąśąĮč鹥čĆą▓ą░ą╗ ą╝ąĄąČą┤čā ą┐ąŠčüą╗ąĄą┤ąĮąĖą╝ąĖ ą▓čģąŠą┤ąĮčŗą╝ąĖ ą┤ą░ąĮąĮčŗą╝ąĖ ą┤ąŠ ą║ąŠą╝ą░ąĮą┤čŗ ąŠčüčéą░ąĮąŠą▓ą║ąĖ ą┐ą░ą║ąĄčéą░ (STOP) |

tBDL |

1 |

1 |

1 |

tCK |

16 |

| ąśąĮč鹥čĆą▓ą░ą╗ ąŠčé ą║ąŠą╝ą░ąĮą┤čŗ READ/WRITE ą┤ąŠ ą║ąŠą╝ą░ąĮą┤čŗ READ/WRITE |

tCCD |

1 |

1 |

1 |

16 |

| ąśąĮč鹥čĆą▓ą░ą╗ ąŠčé ą┐ąŠčüą╗ąĄą┤ąĮąĖčģ ą┤ą░ąĮąĮčŗčģ ą┤ąŠ ąĮąŠą▓ąŠą╣ ą║ąŠą╝ą░ąĮą┤čŗ READ/WRITE |

tCDL |

1 |

1 |

1 |

16 |

| ąśąĮč鹥čĆą▓ą░ą╗ ąŠčé CKE ą┤ąŠ ąĘą░ą┐čĆąĄčéą░ čéą░ą║č鹊ą▓ ąĖą╗ąĖ ą▓čģąŠą┤ą░ ą▓ čĆąĄąČąĖą╝ power-down |

tCKED |

1 |

1 |

1 |

17 |

| ąśąĮč鹥čĆą▓ą░ą╗ ąŠčé ą▓čģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ ą┤ąŠ ą║ąŠą╝ą░ąĮą┤čŗ ACTIVE |

tDAL |

5 |

4 |

5 |

18, 19 |

| ąśąĮč鹥čĆą▓ą░ą╗ ąŠčé ą▓čģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ ą┤ąŠ ą║ąŠą╝ą░ąĮą┤čŗ PRECHARGE |

tDPL |

2 |

2 |

2 |

19, 20 |

| ąŚą░ą┤ąĄčƹȹ║ą░ ąŠčé DQM ą┤ąŠ ą▓čģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ |

tDQD |

0 |

0 |

0 |

16 |

| ąŚą░ą┤ąĄčƹȹ║ą░ ąŠčé DQM ą┤ąŠ ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ą▓ąŠ ą▓čĆąĄą╝čÅ ąŠą┐ąĄčĆą░čåąĖąĖ WRITE |

tDQM |

0 |

0 |

0 |

16 |

| ąŚą░ą┤ąĄčƹȹ║ą░ ąŠčé DQM ą┤ąŠ High-Z ą▓ąŠ ą▓čĆąĄą╝čÅ ąŠą┐ąĄčĆą░čåąĖąĖ READ |

tDQZ |

2 |

2 |

2 |

16 |

| ąŚą░ą┤ąĄčƹȹ║ą░ ąŠčé ą║ąŠą╝ą░ąĮą┤čŗ WRITE ą┤ąŠ ą▓čģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ |

tDWD |

0 |

0 |

0 |

16 |

| ąśąĮč鹥čĆą▓ą░ą╗ ąŠčé ą║ąŠą╝ą░ąĮą┤čŗ LOAD MODE REGISTER ą┤ąŠ ą║ąŠą╝ą░ąĮą┤čŗ ACTIVE ąĖą╗ąĖ REFRESH |

tMRD |

2 |

2 |

2 |

21 |

| ąśąĮč鹥čĆą▓ą░ą╗ ąŠčé CKE ą┤ąŠ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ čéą░ą║č鹊ą▓ ąĖą╗ąĖ ą▓čŗčģąŠą┤ą░ ąĖąĘ čĆąĄąČąĖą╝ą░ power-down |

tPED |

1 |

1 |

1 |

17 |

| ąśąĮč鹥čĆą▓ą░ą╗ ąŠčé ą┐ąŠčüą╗ąĄą┤ąĮąĖčģ ą▓čģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ ą┤ąŠ ą║ąŠą╝ą░ąĮą┤čŗ PRECHARGE |

tRDL |

2 |

2 |

2 |

19, 20 |

| ą¤ąĄčĆąĄčģąŠą┤ ą║ High-Z ą▓čŗčģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ ąŠčé ą║ąŠą╝ą░ąĮą┤čŗ PRECHARGE |

CL=3 |

tROH(3) |

3 |

3 |

3 |

16 |

| CL=2 |

tROH(2) |

2 |

2 |

2 |

16 |

| CL=1 |

tROH(1) |

1 |

- |

- |

16 |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

1. ą£ąĖąĮąĖą╝ą░ą╗čīąĮčŗąĄ čüą┐ąĄčåąĖčäąĖą║ą░čåąĖąĖ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ č鹊ą│ąŠ, čćč鹊ą▒čŗ ą┐ąŠą║ą░ąĘą░čéčī ą▓čĆąĄą╝čÅ čåąĖą║ą╗ą░, ąĮą░ ą║ąŠč鹊čĆąŠą╝ ą┐čĆą░ą▓ąĖą╗čīąĮąŠąĄ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĄ ą▓ąŠ ą▓čüąĄą╝ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ č鹥ą╝ą┐ąĄčĆą░čéčāčĆ; 0┬░C Ōēż TA Ōēż +70┬░C (ąĖčüą┐ąŠą╗ąĮąĄąĮąĖąĄ commercial), ŌĆō40┬░C Ōēż TA Ōēż +85┬░C (ąĖčüą┐ąŠą╗ąĮąĄąĮąĖąĄ industrial), ąĖ ŌĆō40┬░C Ōēż TA Ōēż +105┬░C (ąĖčüą┐ąŠą╗ąĮąĄąĮąĖąĄ automotive).

2. ąóčĆąĄą▒čāąĄčéčüčÅ ąĮą░čćą░ą╗čīąĮą░čÅ ą┐ą░čāąĘą░ 100 ą╝ą║čü ą┐ąŠčüą╗ąĄ ą▓ą║ą╗čÄč湥ąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ, ąĘą░ ą║ąŠč鹊čĆąŠą╣ čüą╗ąĄą┤čāčÄčé 2 ą║ąŠą╝ą░ąĮą┤čŗ AUTO REFRESH, ą┐ąĄčĆąĄą┤ č鹥ą╝ ą║ą░ą║ ą│ą░čĆą░ąĮčéąĖčĆčāąĄčéčüčÅ ą║ąŠčĆčĆąĄą║čéąĮąŠąĄ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĄ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ (VDD ąĖ VDDQ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĘą░ą┐ąĖčéą░ąĮčŗ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ. VSS ąĖ VSSQ ą┤ąŠą╗ąČąĮčŗ ąĖą╝ąĄčéčī ąŠą┤ąĖąĮą░ą║ąŠą▓čŗą╣ ą┐ąŠč鹥ąĮčåąĖą░ą╗). ąöą▓ąĄ ą║ąŠą╝ą░ąĮą┤čŗ AUTO REFRESH ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą┐ąŠą▓č鹊čĆąĄąĮčŗ ą║ą░ąČą┤čŗą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ ą┐čĆąĄą▓čŗčłąĄąĮ čéčĆąĄą▒čāąĄą╝čŗą╣ ąĖąĮč鹥čĆą▓ą░ą╗ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ tREF.

3. ąÆ ą┤ąŠą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ čāą┤ąŠą▓ą╗ąĄčéą▓ąŠčĆąĄąĮąĖčÄ čüą┐ąĄčåąĖčäąĖą║ą░čåąĖąĖ ąĮą░ čüą║ąŠčĆąŠčüčéčī ą┐ąĄčĆąĄčģąŠą┤ąŠą▓, čéą░ą║čéčŗ ąĖ CKE ą┤ąŠą╗ąČąĮčŗ ą╝ąŠąĮąŠč鹊ąĮąĮąŠ ąŠčüčāčēąĄčüčéą▓ą╗čÅčéčī ą┐ąĄčĆąĄčģąŠą┤čŗ ą╝ąĄąČą┤čā čāčĆąŠą▓ąĮčÅą╝ąĖ VIH ąĖ VIL (ąĖą╗ąĖ ą╝ąĄąČą┤čā čāčĆąŠą▓ąĮčÅą╝ąĖ VIL ąĖ VIH).

4. ąÆčŗčģąŠą┤čŗ ąŠą▒ą╝ąĄčĆčÅą╗ąĖčüčī ąĮą░ čāčĆąŠą▓ąĮąĄ 1.5V čüąŠ čüą╗ąĄą┤čāčÄčēąĄą╣ 菹║ą▓ąĖą▓ą░ą╗ąĄąĮčéąĮąŠą╣ ąĮą░ą│čĆčāąĘą║ąŠą╣:

5. ą¤čĆąĖą▓ąĄą┤ąĄąĮčŗ ą┤ą░ąĮąĮčŗąĄ čāčüą╗ąŠą▓ąĖą╣ čĆą░ą▒ąŠčéčŗ AC ąĖ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ IDD ą┐čĆąĖ VIL=0V ąĖ VIH=3.0V čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ čāčĆąŠą▓ąĮčÅ ąĖąĘą╝ąĄčĆąĄąĮąĖčÅ 1.5V. ąĢčüą╗ąĖ ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĄčģąŠą┤ą░ ą▓čģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ą▒ąŠą╗čīčłąĄ 1 ąĮčü, č鹊 ą▓čĆąĄą╝čÅ ąĖąĘą╝ąĄčĆčÅąĄčéčüčÅ ą╝ąĄąČą┤čā VIL,max ąĖ VIH,min ąĖ ąĮąĄ ą┤ą░ą╗čīčłąĄ ąŠčé čüčĆąĄą┤ąĮąĄą╣ č鹊čćą║ąĖ 1.5V. ąĪąĖą│ąĮą░ą╗ CLK ą▓čüąĄą│ą┤ą░ ą┤ąŠą╗ąČąĄąĮ ą░ąĮą░ą╗ąĖąĘąĖčĆąŠą▓ą░čéčīčüčÅ ą▓ ą╝ąŠą╝ąĄąĮčé ą┐ąĄčĆąĄčģąŠą┤ą░ č湥čĆąĄąĘ čāčĆąŠą▓ąĄąĮčī 1.5V. ąĪą╝. č鹥čģąĮąĖč湥čüą║ąŠąĄ čāą║ą░ąĘą░ąĮąĖąĄ TN-48-09 ą║ąŠą╝ą┐ą░ąĮąĖąĖ Micron.

6. ąØąĄ ą┐čĆąĖą╝ąĄąĮąĖą╝ąŠ ą┤ą╗čÅ čĆąĄą▓ąĖąĘąĖąĖ D.

7. tAC ą┤ą╗čÅ -75/-7E ąĮą░ CL=3 ą▒ąĄąĘ ąĮą░ą│čĆčāąĘą║ąĖ čüąŠčüčéą░ą▓ą╗čÅąĄčé 4.6 ąĮčü, ąĖ čŹč鹊 ą│ą░čĆą░ąĮčéąĖčĆčāąĄčéčüčÅ ą┐čĆąŠčåąĄčüčüąŠą╝ čĆą░ąĘčĆą░ą▒ąŠčéą║ąĖ.

8. ą¦ą░čüč鹊čéą░ čéą░ą║č鹊ą▓ ą┤ąŠą╗ąČąĮą░ ąŠčüčéą░ą▓ą░čéčīčüčÅ ą┐ąŠčüč鹊čÅąĮąĮąŠą╣ (čüčéą░ą▒ąĖą╗čīąĮčŗąĄ čéą░ą║čéčŗ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮčŗ ą║ą░ą║ čüąĖą│ąĮą░ą╗, čāą┤ąŠą▓ą╗ąĄčéą▓ąŠčĆčÅčÄčēąĖą╣ ąĖąĮč鹥čĆą▓ą░ą╗ą░ą╝ ą▓čĆąĄą╝ąĄąĮąĖ, čāą║ą░ąĘą░ąĮąĮčŗą╝ąĖ ą▓ čüą┐ąĄčåąĖčäąĖą║ą░čåąĖąĖ ą┤ą╗čÅ ą▓čŗą▓ąŠą┤ą░ čéą░ą║č鹊ą▓) ą▓ąŠ ą▓čĆąĄą╝čÅ čüąŠčüč鹊čÅąĮąĖą╣ ą┤ąŠčüčéčāą┐ą░ ąĖą╗ąĖ ą┐čĆąĄą┤ąĘą░čĆčÅą┤ą░ (ą║ąŠą╝ą░ąĮą┤čŗ READ, WRITE, ą▓ą║ą╗čÄčćą░čÅ tWR, ąĖ ą║ąŠą╝ą░ąĮą┤čŗ PRECHARGE). CKE ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ čüąĮąĖąČąĄąĮąĖčÅ čüą║ąŠčĆąŠčüčéąĖ ąŠą▒ą╝ąĄąĮą░ ą┤ą░ąĮąĮčŗą╝ąĖ.

9. tHZ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ą▓čĆąĄą╝čÅ, ąĮą░ ą║ąŠč鹊čĆąŠą╝ ą▓čŗčģąŠą┤ ą┤ąŠčüčéąĖą│ą░ąĄčé ąŠčéą║ą╗čÄč湥ąĮąĮąŠą│ąŠ čüąŠčüč鹊čÅąĮąĖčÅ; čŹč鹊 ąĮąĄ ąŠčéąĮąŠčüąĖčéčüčÅ ą║ čāčĆąŠą▓ąĮčÅą╝ VOH ąĖą╗ąĖ VOL. ą¤ąŠčüą╗ąĄą┤ąĮąĖą╣ ą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗą╣ 菹╗ąĄą╝ąĄąĮčé ą┤ą░ąĮąĮčŗčģ ą▒čāą┤ąĄčé čāą┤ąŠą▓ą╗ąĄčéą▓ąŠčĆčÅčéčī tOH ą┤ąŠ ą┐ąĄčĆąĄčģąŠą┤ą░ ą║ čüąŠčüč鹊čÅąĮąĖčÄ High-Z.

10. ą¤ą░čĆą░ą╝ąĄčéčĆ ą│ą░čĆą░ąĮčéąĖčĆčāąĄčéčüčÅ ą┐čĆąŠčåąĄčüčüąŠą╝ čĆą░ąĘčĆą░ą▒ąŠčéą║ąĖ.

11. ą£ąĖą║čĆąŠčüčģąĄą╝čŗ DRAM ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą▓čĆąĄą╝čÅ ąŠčé ą▓čĆąĄą╝ąĄąĮąĖ ą░ą┤čĆąĄčüąŠą▓ą░ąĮčŗ, ą║ąŠą│ą┤ą░ ą║ ąĮąĖą╝ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą┤ąŠčüčéčāą┐. ąØąĄą┐čĆąŠą┐ąŠčĆčåąĖąŠąĮą░ą╗čīąĮčŗą╣ ą┤ąŠčüčéčāą┐ ą║ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗą╝ ą░ą┤čĆąĄčüą░ą╝ čüčéčĆąŠą║ąĖ ą╝ąŠąČąĄčé ą┐čĆąĖą▓ąĄčüčéąĖ ą║ čüąĮąĖąČąĄąĮąĖčÄ ą▓čĆąĄą╝ąĄąĮąĖ ąČąĖąĘąĮąĖ ąĖąĘą┤ąĄą╗ąĖčÅ.

12. ąźą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ AC ą┐čĆąĄą┤ą┐ąŠą╗ą░ą│ą░čÄčé tT = 1 ąĮčü.

13. ąóąŠą╗čīą║ąŠ ą┤ą╗čÅ čĆąĄąČąĖą╝ą░ auto precharge. ąæčÄą┤ąČąĄčé ą▓čĆąĄą╝ąĄąĮąĖ precharge (tRP) ąĮą░čćąĖąĮą░ąĄčéčüčÅ ąŠčé 6 ąĮčü ą┤ą╗čÅ -6A, 7 ąĮčü ą┤ą╗čÅ -7E ąĖ 7.5 ąĮčü ą┤ą╗čÅ -75 ą┐ąŠčüą╗ąĄ ą┐ąĄčĆą▓ąŠą╣ ąĘą░ą┤ąĄčƹȹ║ąĖ čéą░ą║č鹊ą▓, ą┐ąŠčüą╗ąĄ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╣ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĮąŠą╣ ąŠą┐ąĄčĆą░čåąĖąĖ WRITE.

14. ąóąŠą╗čīą║ąŠ ą┤ą╗čÅ čĆąĄąČąĖą╝ą░ ą┐čĆąĄą┤ąĘą░čĆčÅą┤ą░ (precharge).

15. ąÆąŠ ą▓čĆąĄą╝čÅ čŹč鹊ą│ąŠ ą┐ąĄčĆąĖąŠą┤ą░ CLK ą┤ąŠą╗ąČąĄąĮ ą┐ąĄčĆąĄą║ą╗čÄčćąĖčéčīčüčÅ ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ 2 čĆą░ąĘą░.

16. ąóčĆąĄą▒čāąĄą╝čŗąĄ čéą░ą║čéčŗ čāą║ą░ąĘą░ąĮčŗ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠčüčéčīčÄ JEDEC ąĖ ąĮąĄ ąĘą░ą▓ąĖčüčÅčé ąŠčé ą╗čÄą▒ąŠą│ąŠ ą┐ą░čĆą░ą╝ąĄčéčĆą░ ą▓čĆąĄą╝ąĄąĮąĖ.

17. ąśąĮč鹥čĆą▓ą░ą╗čŗ ą▓čĆąĄą╝ąĄąĮąĖ čāą║ą░ąĘą░ąĮčŗ ą▓ ą┐ąĄčĆąĖąŠą┤ą░čģ čéą░ą║č鹊ą▓ tCKS. ąóą░ą║čé (čéą░ą║čéčŗ) čāą║ą░ąĘą░ąĮčŗ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ąŠčĆąĖąĄąĮčéąĖčĆąŠą▓ą║ąĖ ąĮą░ ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠą╣ čüą║ąŠčĆąŠčüčéąĖ čåąĖą║ą╗ąŠą▓.

18. ąśąĮč鹥čĆą▓ą░ą╗ ą▓čĆąĄą╝ąĄąĮąĖ čāą║ą░ąĘą░ąĮ ą┐ąŠ tWR ą┐ą╗čÄčü tRP. ąóą░ą║čé (čéą░ą║čéčŗ) čāą║ą░ąĘą░ąĮčŗ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ąŠčĆąĖąĄąĮčéąĖčĆąŠą▓ą║ąĖ ąĮą░ ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠą╣ čüą║ąŠčĆąŠčüčéąĖ čåąĖą║ą╗ąŠą▓.

19. ą×čüąĮąŠą▓ą░ąĮąŠ ąĮą░ tCK = 7.5 ąĮčü ą┤ą╗čÅ -75 ąĖ -7E, 6 ąĮčü ą┤ą╗čÅ -6A.

20. ąśąĮč鹥čĆą▓ą░ą╗ ą▓čĆąĄą╝ąĄąĮąĖ čāą║ą░ąĘą░ąĮ ą┐ąŠ tWR.

21. JEDEC ąĖ PC100 ąĘą░ą┤ą░čÄčé 3 čéą░ą║čéą░.

ą¤ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ SDRAM čüą╝ąŠąČąĄčé ąĮąŠčĆą╝ą░ą╗čīąĮąŠ čĆą░ą▒ąŠčéą░čéčī, ąŠąĮą░ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆąŠą▓ą░ąĮą░. ąÆ ą┐ąŠčüą╗ąĄą┤čāčÄčēąĖčģ čüąĄą║čåąĖčÅ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮąŠ ą┐ąŠą┤čĆąŠą▒ąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ, ąĄčæ čĆąĄą│ąĖčüčéčĆąŠą▓, ąĖ ą║ą░ą║ ąŠąĮą░ čĆą░ą▒ąŠčéą░ąĄčé.

[ąÜąŠą╝ą░ąĮą┤čŗ]

ąÆ čéą░ą▒ą╗ąĖčåąĄ 14 ą┐čĆąĖą▓ąĄą┤ąĄąĮą░ ą║čĆą░čéą║ą░čÅ čüą┐čĆą░ą▓ą║ą░ ą┐ąŠ ą┤ąŠčüčéčāą┐ąĮčŗą╝ ą║ąŠą╝ą░ąĮą┤ą░ą╝, ąĖ ą┤ą░ą╗ąĄąĄ ą┤ą░ąĮąŠ ą┐ąŠą┤čĆąŠą▒ąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ ą║ą░ąČą┤ąŠą╣ ą║ąŠą╝ą░ąĮą┤čŗ. ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗąĄ čéą░ą▒ą╗ąĖčåčŗ ąĖčüčéąĖąĮąĮąŠčüčéąĖ (čéą░ą▒ą╗ąĖčåčŗ 15..17) ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÄčé ąĖąĮč乊čĆą╝ą░čåąĖčÄ ąŠ ą┐ąĄčĆąĄčģąŠą┤ą░čģ ą╝ąĄąČą┤čā č鹥ą║čāčēąĖą╝ ąĖ čüą╗ąĄą┤čāčÄčēąĖą╝ čüąŠčüč鹊čÅąĮąĖąĄą╝ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ SDRAM.

ąóą░ą▒ą╗ąĖčåą░ 14. ąóą░ą▒ą╗ąĖčåą░ ąĖčüčéąĖąĮąĮąŠčüčéąĖ - ą║ąŠą╝ą░ąĮą┤čŗ ąĖ čĆą░ą▒ąŠčéą░ DQM. 0 ąŠąĘąĮą░čćą░ąĄčé ą╗ąŠą│. 0, 1 ą╗ąŠą│. 1, x ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 čāčĆąŠą▓ąĄąĮčī čüąĖą│ąĮą░ą╗ą░ ąĮąĄ ąĖą╝ąĄąĄčé ąĘąĮą░č湥ąĮąĖčÅ.

| ąśą╝čÅ ą║ąŠą╝ą░ąĮą┤čŗ (čäčāąĮą║čåąĖčÅ) |

CS# |

RAS# |

CAS# |

WE# |

DQM |

ADDR |

DQ |

ą¤čĆąĖą╝. |

| COMMAND INHIBIT (NOP) |

1 |

x |

x |

x |

x |

x |

x |

|

| NO OPERATION (NOP) |

0 |

1 |

1 |

1 |

x |

x |

x |

|

| ACTIVE (ą▓čŗą▒ąŠčĆ ą▒ą░ąĮą║ą░ ąĖ ą░ą║čéąĖą▓ą░čåąĖčÅ čüčéčĆąŠą║ąĖ) |

0 |

0 |

1 |

1 |

x |

ą▒ą░ąĮą║/čüčéčĆąŠą║ą░ |

x |

2 |

| READ (ą▓čŗą▒ąŠčĆ ą▒ą░ąĮą║ą░ ąĖ čüč鹊ą╗ą▒čåą░, ąĖ ąĘą░ą┐čāčüą║ ą┐ą░ą║ąĄčéą░ READ) |

0 |

1 |

0 |

1 |

0/1 |

ą▒ą░ąĮą║/čüč鹊ą╗ą▒ąĄčå |

x |

3 |

| WRITE (ą▓čŗą▒ąŠčĆ ą▒ą░ąĮą║ą░ ąĖ čüč鹊ą╗ą▒čåą░, ąĖ ąĘą░ą┐čāčüą║ ą┐ą░ą║ąĄčéą░ WRITE) |

0 |

1 |

0 |

0 |

ą┤ą░ąĮąĮčŗąĄ |

3 |

| BURST TERMINATE |

0 |

1 |

1 |

0 |

x |

x |

Active |

4 |

| PRECHARGE (ą┤ąĄą░ą║čéąĖą▓ą░čåąĖčÅ čüčéčĆąŠą║ąĖ ą▓ ą▒ą░ąĮą║ąĄ ąĖą╗ąĖ ą▒ą░ąĮą║ą░čģ) |

0 |

0 |

1 |

0 |

x |

code |

x |

5 |

| AUTO REFRESH ąĖą╗ąĖ SELF REFRESH (ą▓čģąŠą┤ ą▓ čĆąĄąČąĖą╝ čüą░ą╝ąŠąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ) |

0 |

0 |

0 |

1 |

x |

x |

x |

6, 7 |

| LOAD MODE REGISTER |

0 |

0 |

0 |

0 |

x |

op-code |

x |

8 |

| ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ąĘą░ą┐ąĖčüąĖ/čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ą▓čŗčģąŠą┤ąŠą▓ |

x |

x |

x |

x |

0 |

x |

Active |

9 |

| ąŚą░ą┐čĆąĄčé ąĘą░ą┐ąĖčüąĖ/ąŠčéą║ą╗čÄč湥ąĮąĖąĄ ą▓čŗčģąŠą┤ąŠą▓ |

x |

x |

x |

x |

1 |

x |

High-Z |

9 |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ ą║ čéą░ą▒ą╗ąĖčåąĄ 14 (ą┐čĆąĖą╝ąĄčćą░ąĮąĖąĄ 1 ą┐čĆąĖą╝ąĄąĮąĖą╝ąŠ ą┤ą╗čÅ ą▓čüąĄčģ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓ ąĖ čāčüą╗ąŠą▓ąĖą╣):

1. CKE = ą╗ąŠą│. 1 ą┤ą╗čÅ ą▓čüąĄčģ ą║ąŠą╝ą░ąĮą┤, ą║čĆąŠą╝ąĄ SELF REFRESH.

2. ąĪąĖą│ąĮą░ą╗čŗ A[0:n] ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÄčé ą░ą┤čĆąĄčü čüčéčĆąŠą║ąĖ (ą│ą┤ąĄ An čüą░ą╝čŗą╣ ąĘąĮą░čćą░čēąĖą╣ ą▒ąĖčé ą░ą┤čĆąĄčüą░), BA0 ąĖ BA1 ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčé, ą║ą░ą║ąŠą╣ ą▒ą░ąĮą║ ą┤ąĄą╗ą░ąĄčéčüčÅ ą░ą║čéąĖą▓ąĮčŗą╝.

3. ąĪąĖą│ąĮą░ą╗čŗ A[0:i] ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÄčé ą░ą┤čĆąĄčü čüč鹊ą╗ą▒čåą░ (ą│ą┤ąĄ i čüą░ą╝čŗą╣ čüčéą░čĆčłąĖą╣ ą▒ąĖčé ą░ą┤čĆąĄčüą░ čüč鹊ą╗ą▒čåą░ ą┤ą╗čÅ ąĖą╝ąĄčÄčēąĄą╣čüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠą╣ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ čāčüčéčĆąŠą╣čüčéą▓ą░). A10 = ą╗ąŠą│. 1 čĆą░ąĘčĆąĄčłą░ąĄčé čäčāąĮą║čåąĖčÄ auto precharge (ąĮąĄ ą┐ąŠčüč鹊čÅąĮąĮąŠ), A10 = ą╗ąŠą│. 0 ąĘą░ą┐čĆąĄčēą░ąĄčé čäčāąĮą║čåąĖčÄ auto precharge. BA0 ąĖ BA1 ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčé, ą║ą░ą║ąŠą╣ ą▒ą░ąĮą║ čćąĖčéą░ąĄčéčüčÅ ąĖą╗ąĖ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ.

4. ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą║ąŠą╝ą░ąĮą┤čŗ BURST TERMINATE ąŠčüčéą░ąĮąŠą▓ąĖčéčī ą┐ą░ą║ąĄčé ą┤ą░ąĮąĮčŗčģ (data burst), čéą░ą║ čćč鹊 čŹčéą░ ą║ąŠą╝ą░ąĮą┤ą░ ą╝ąŠą│ą╗ą░ ą▒čŗ čüąŠą▓ą┐ą░čüčéčī čü ą┤ą░ąĮąĮčŗą╝ąĖ ąĮą░ čłąĖąĮąĄ. ą×ą┤ąĮą░ą║ąŠ čüč鹊ą╗ą▒ąĄčå DQ ąĖą╝ąĄąĄčé čüąŠčüč鹊čÅąĮąĖąĄ "DonŌĆÖt Care" (ąĮąĄ ąĖą╝ąĄąĄčé ąĘąĮą░č湥ąĮąĖčÅ), čćč鹊ą▒čŗ ą┐ąŠą║ą░ąĘą░čéčī, čćč鹊 ą║ąŠą╝ą░ąĮą┤ą░ BURST TERMINATE ą╝ąŠąČąĄčé ą┐ąŠčÅą▓ąĖčéčīčüčÅ, ą║ąŠą│ą┤ą░ ąĮąĄčé ą┤ą░ąĮąĮčŗčģ.

5. A10 = ą╗ąŠą│. 0: BA0, BA1 ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčé ą▒ą░ąĮą║, ą┤ą╗čÅ ą║ąŠč鹊čĆąŠą│ąŠ ą┤ąĄą╗ą░ąĄčéčüčÅ precharge. A10 = ą╗ąŠą│. 1: ą┤ą╗čÅ ą▓čüąĄčģ ą▒ą░ąĮą║ąŠą▓ ą┤ąĄą╗ą░ąĄčéčüčÅ precharge, ąĖ čüąŠčüč鹊čÅąĮąĖąĄ BA0, BA1 ąĮąĄ ąĖą╝ąĄąĄčé ąĘąĮą░č湥ąĮąĖčÅ (DonŌĆÖt Care).

6. ąŁčéą░ ą║ąŠą╝ą░ąĮą┤ą░ AUTO REFRESH, ąĄčüą╗ąĖ CKE = ą╗ąŠą│. 1, ąĖ SELF REFRESH, ąĄčüą╗ąĖ CKE = ą╗ąŠą│. 0.

7. ąÆąĮčāčéčĆąĄąĮąĮąĖą╣ čüč湥čéčćąĖą║ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ (refresh counter) čāą┐čĆą░ą▓ą╗čÅąĄčé ą░ą┤čĆąĄčüą░čåąĖąĄą╣ čüčéčĆąŠą║; čüąŠčüč鹊čÅąĮąĖąĄ ą▓čüąĄčģ ą▓čģąŠą┤ąŠą▓ ąĖ ąĮąŠąČąĄą║ I/O ąĮąĄ ąĖą╝ąĄąĄčé ąĘąĮą░č湥ąĮąĖčÅ, ą║čĆąŠą╝ąĄ CKE.

8. A[11:0] ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ą║ąŠą┤ ąŠą┐ąĄčĆą░čåąĖąĖ (opcode), ąĘą░ą┐ąĖčüčŗą▓ą░ąĄą╝čŗą╣ ą▓ čĆąĄą│ąĖčüčéčĆ čĆąĄąČąĖą╝ą░.

9. ąÉą║čéąĖą▓ąĖčĆčāąĄčé ąĖą╗ąĖ ą┤ąĄą░ą║čéąĖą▓ąĖčĆčāąĄčé DQ ą▓ąŠ ą▓čĆąĄą╝čÅ ąŠą┐ąĄčĆą░čåąĖą╣ WRITE (ą▒ąĄąĘ ąĘą░ą┤ąĄčƹȹ║ąĖ čéą░ą║č鹊ą▓, zero-clock delay) ąĖ ąŠą┐ąĄčĆą░čåąĖą╣ čćč鹥ąĮąĖčÅ READ (ąĘą░ą┤ąĄčƹȹ║ą░ 2 čéą░ą║čéą░).

COMMAND INHIBIT. ążčāąĮą║čåąĖčÅ ąĘą░ą┐čĆąĄčéą░ ą║ąŠą╝ą░ąĮą┤čŗ (COMMAND INHIBIT) ą┐čĆąĄą┤ąŠčéą▓čĆą░čēą░ąĄčé ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ąĮąŠą▓čŗčģ ą║ąŠą╝ą░ąĮą┤ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝, ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé č鹊ą│ąŠ, čĆą░ąĘčĆąĄčłąĄąĮ čüąĖą│ąĮą░ą╗ CLK ąĖą╗ąĖ ąĮąĄčé. ąŁčäč乥ą║čé čéą░ą║ąŠą╣, čćč鹊 čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮąĄ ą▓čŗą▒čĆą░ąĮąŠ. ąØą░ ąŠą┐ąĄčĆą░čåąĖąĖ, ą║ąŠč鹊čĆčŗąĄ čāąČąĄ ą┐čĆąŠąĖčüčģąŠą┤čÅčé, čŹčéą░ ą║ąŠą╝ą░ąĮą┤ą░ ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą▓ą╗ąĖčÅąĮąĖčÅ.

NO OPERATION (NOP). ąÜąŠą╝ą░ąĮą┤ą░ NOP (ąĮąĄčé ąŠą┐ąĄčĆą░čåąĖąĖ) ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą┐čāčüč鹊ą╣ ąŠą┐ąĄčĆą░čåąĖąĖ ąĮą░ ą▓čŗą▒čĆą░ąĮąĮąŠą╝ čāčüčéčĆąŠą╣čüčéą▓ąĄ (CS# = ą╗ąŠą│. 0). ąŁč鹊 ą┐čĆąĄą┤ąŠčéą▓čĆą░čēą░ąĄčé čĆąĄą│ąĖčüčéčĆą░čåąĖčÄ ąĮąĄąČąĄą╗ą░č鹥ą╗čīąĮčŗčģ ą║ąŠą╝ą░ąĮą┤ ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ąĖ (idle) ąĖą╗ąĖ čüąŠčüč鹊čÅąĮąĖą╣ ąŠąČąĖą┤ą░ąĮąĖčÅ (wait states). ąØą░ ąŠą┐ąĄčĆą░čåąĖąĖ, ą║ąŠč鹊čĆčŗąĄ čāąČąĄ ą┐čĆąŠąĖčüčģąŠą┤čÅčé, čŹčéą░ ą║ąŠą╝ą░ąĮą┤ą░ ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą▓ą╗ąĖčÅąĮąĖčÅ.

LOAD MODE REGISTER (LMR). ąĀąĄą│ąĖčüčéčĆčŗ čĆąĄąČąĖą╝ą░ ąĘą░ą│čĆčāąČą░čÄčéčüčÅ č湥čĆąĄąĘ ą▓čģąŠą┤čŗ A[n:0] (ąĘą┤ąĄčüčī An čüą░ą╝čŗą╣ čüčéą░čĆčłąĖą╣ čĆą░ąĘčĆčÅą┤ ą░ą┤čĆąĄčüą░), BA0 ąĖ BA1 (čüą╝. ąŠą┐ąĖčüą░ąĮąĖąĄ Mode Register). ąÜąŠą╝ą░ąĮą┤ą░ LOAD MODE REGISTER ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą┤ą░ąĮą░ č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ ą▓čüąĄ ą▒ą░ąĮą║ąĖ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ idle, ąĖ ą┐ąŠčüą╗ąĄą┤čāčÄčēą░čÅ ą▓čŗą┐ąŠą╗ąĮčÅąĄą╝ą░čÅ ą║ąŠą╝ą░ąĮą┤ą░ ąĮąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą┤ą░ąĮą░ ą┤ąŠ ą╝ąŠą╝ąĄąĮčéą░ tMRD.

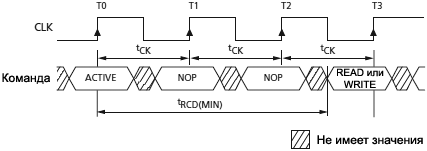

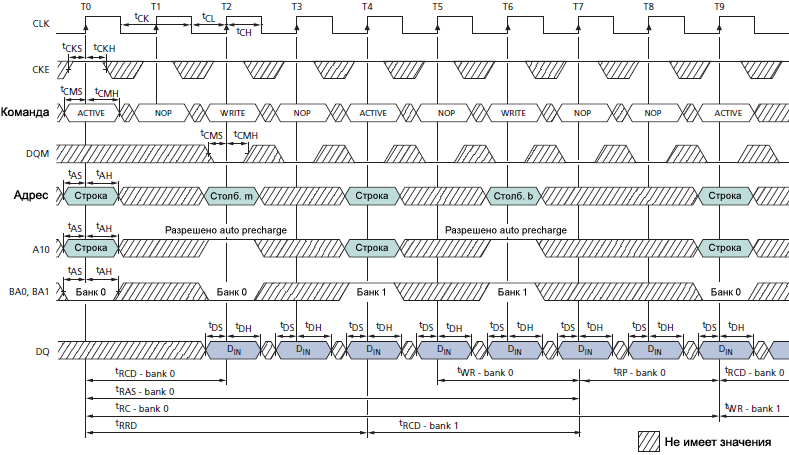

ACTIVE. ąÜąŠą╝ą░ąĮą┤ą░ ACTIVE ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą░ą║čéąĖą▓ą░čåąĖąĖ čüčéčĆąŠą║ąĖ ą▓ ąŠčéą┤ąĄą╗čīąĮąŠą╝ ą▒ą░ąĮą║ąĄ ą┤ą╗čÅ ą┐ąŠčüą╗ąĄą┤čāčÄčēąĄą│ąŠ ą┤ąŠčüčéčāą┐ą░. ąŚąĮą░č湥ąĮąĖčÅ ąĮą░ ą▓čģąŠą┤ą░čģ BA0, BA1 ą▓čŗą▒ąĖčĆą░čÄčé ą▒ą░ąĮą║, ąĖ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮąĮčŗą╣ ą░ą┤čĆąĄčü ą▓čŗą▒ąĖčĆą░ąĄčé čüčéčĆąŠą║čā. ąŁčéą░ čüčéčĆąŠą║ą░ ąŠčüčéą░ąĄčéčüčÅ ą░ą║čéąĖą▓ąĮąŠą╣, ą┐ąŠą║ą░ ą┤ą╗čÅ čŹč鹊ą│ąŠ ą▒ą░ąĮą║ą░ ąĮąĄ ą▒čāą┤ąĄčé ą▓čŗą┤ą░ąĮą░ ą║ąŠą╝ą░ąĮą┤ą░ PRECHARGE. ąÜąŠą╝ą░ąĮą┤ą░ PRECHARGE ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą▓čŗą┤ą░ąĮą░ ą┐ąĄčĆąĄą┤ ąŠčéą║čĆčŗčéąĖąĄą╝ ą┤čĆčāą│ąŠą╣ čüčéčĆąŠą║ąĖ ą▓ č鹊ą╝ ąČąĄ čüą░ą╝ąŠą╝ ą▒ą░ąĮą║ąĄ.

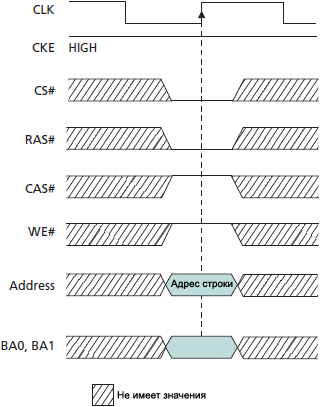

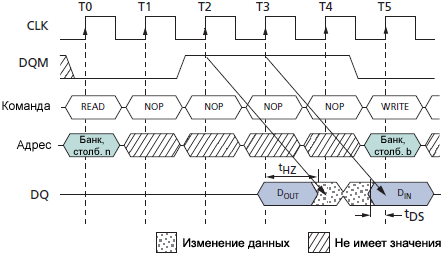

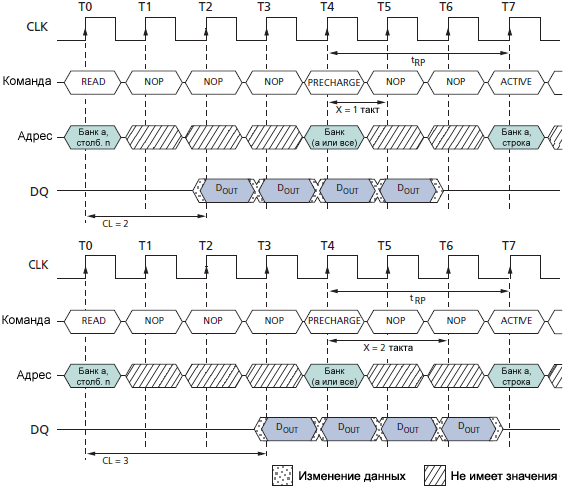

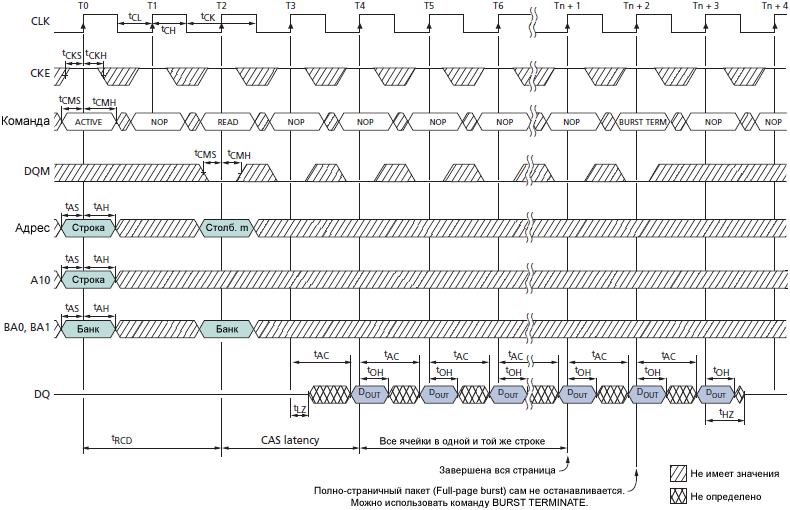

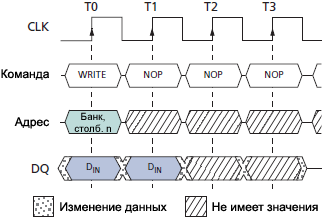

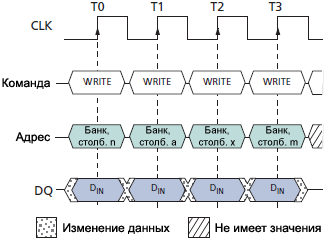

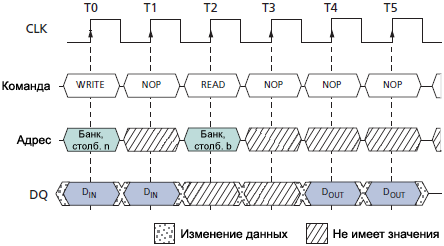

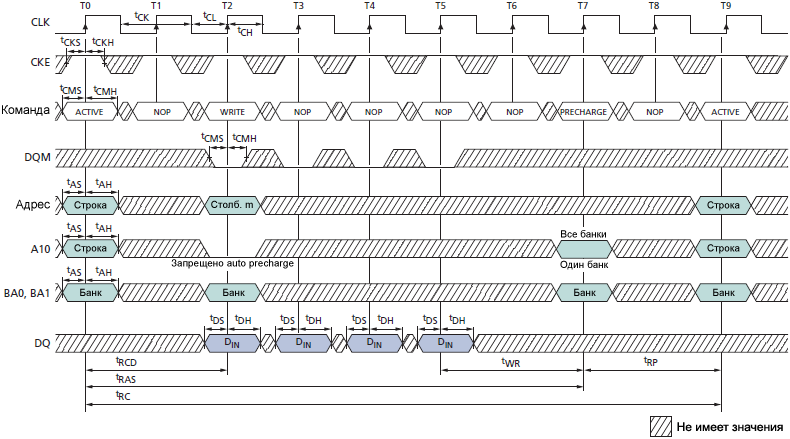

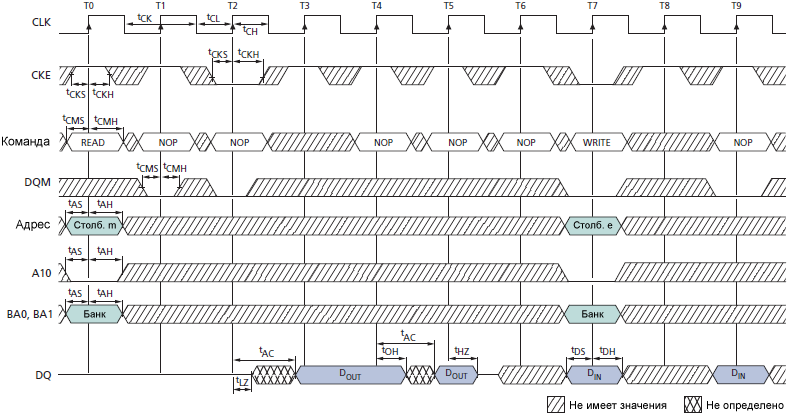

ąĀąĖčü. 14. ąÜąŠą╝ą░ąĮą┤ą░ ACTIVE.

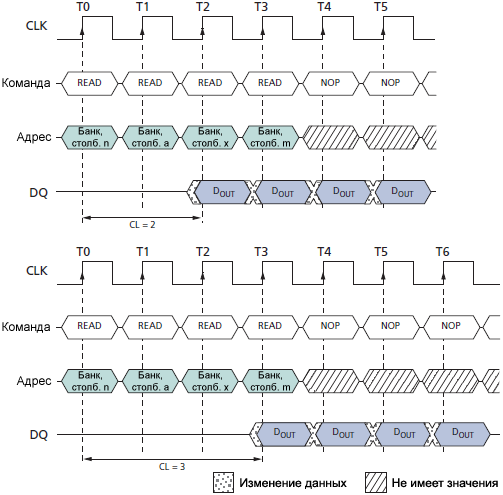

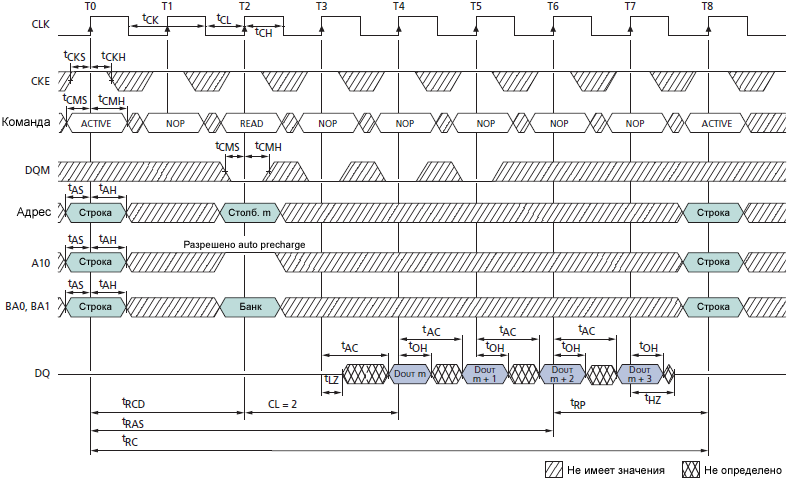

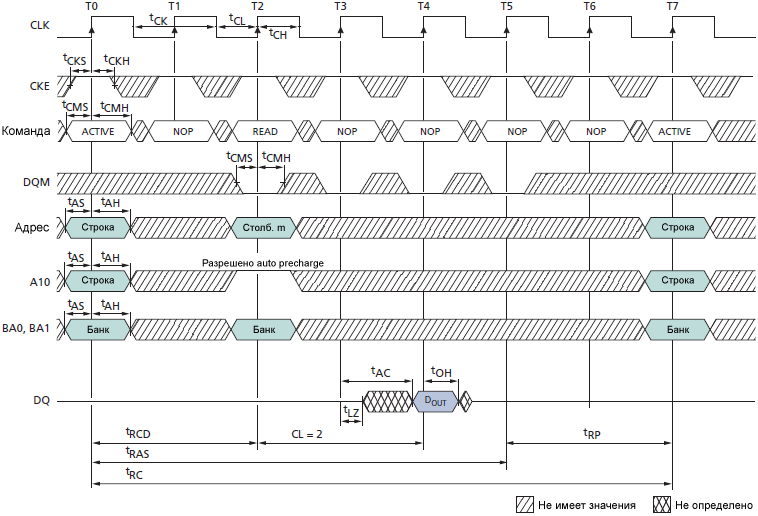

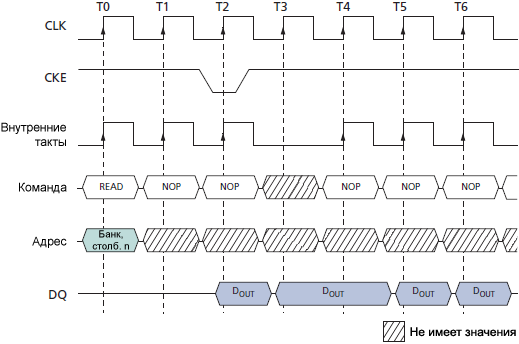

READ. ąÜąŠą╝ą░ąĮą┤ą░ čćč鹥ąĮąĖčÅ (READ) ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ąĖąĮąĖčåąĖą░čåąĖąĖ ą┤ąŠčüčéčāą┐ą░ ą┐ą░ą║ąĄčéąĮčŗą╝ čćč鹥ąĮąĖąĄą╝ ą┤ą╗čÅ ą░ą║čéąĖą▓ąĮąŠą╣ čüčéčĆąŠą║ąĖ. ąŚąĮą░č湥ąĮąĖčÅ ąĮą░ ą▓čģąŠą┤ą░čģ BA0, BA1 ą▓čŗą▒ąĖčĆą░čÄčé ą▒ą░ąĮą║; ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮąĮčŗą╣ ą░ą┤čĆąĄčü ą▓čŗą▒ąĖčĆą░ąĄčé čüčéą░čĆč鹊ą▓ąŠąĄ ą┐ąŠą╗ąŠąČąĄąĮąĖąĄ čüč鹊ą╗ą▒čåą░. ąŚąĮą░č湥ąĮąĖąĄ ąĮą░ ą▓čģąŠą┤ąĄ A10 ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé, ą┤ąŠą╗ąČąĮąŠ ą╗ąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ auto precharge. ąĢčüą╗ąĖ ą▓čŗą▒čĆą░ąĮąŠ auto precharge, č鹊 ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖčÄ ą┐ą░ą║ąĄčéą░ čćč鹥ąĮąĖčÅ (READ burst) ą┤ą╗čÅ čüčéčĆąŠą║ąĖ, ą║ ą║ąŠč鹊čĆąŠą╣ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą┤ąŠčüčéčāą┐, ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ precharge; ąĄčüą╗ąĖ auto precharge ąĮąĄ ą▓čŗą▒čĆą░ąĮąŠ, čüčéčĆąŠą║ą░ ąŠčüčéą░ąĄčéčüčÅ ąŠčéą║čĆčŗč鹊ą╣ ą┤ą╗čÅ ą┐ąŠčüą╗ąĄą┤čāčÄčēąĖčģ ą┤ąŠčüčéčāą┐ąŠą▓. ąĪčćąĖčéčŗą▓ą░ąĄą╝čŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┐ąŠčÅą▓ą╗čÅčÄčéčüčÅ ąĮą░ DQ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü čāčĆąŠą▓ąĮčÅčģ ąĮą░ ą▓čģąŠą┤ą░čģ DQM ąĮą░ 2 čéą░ą║čéą░ čĆą░ąĮčīčłąĄ. ąĢčüą╗ąĖ čüąĖą│ąĮą░ą╗ DQM ą▒čŗą╗ ąĘą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ ą║ą░ą║ ą╗ąŠą│. 1, č鹊 čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ ą▓čŗčģąŠą┤čŗ DQ ą▒čāą┤čāčé ą▓ čüąŠčüč鹊čÅąĮąĖąĖ High-Z ąĮą░ 2 čéą░ą║čéą░ ą┐ąŠąĘąČąĄ; ąĄčüą╗ąĖ DQM čüąĖą│ąĮą░ą╗ ąĘą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ ą▓ ą╗ąŠą│. 0, č鹊 ąĮą░ DQ ą▒čāą┤čāčé ą▓čŗą▓ąĄą┤ąĄąĮčŗ ą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ.

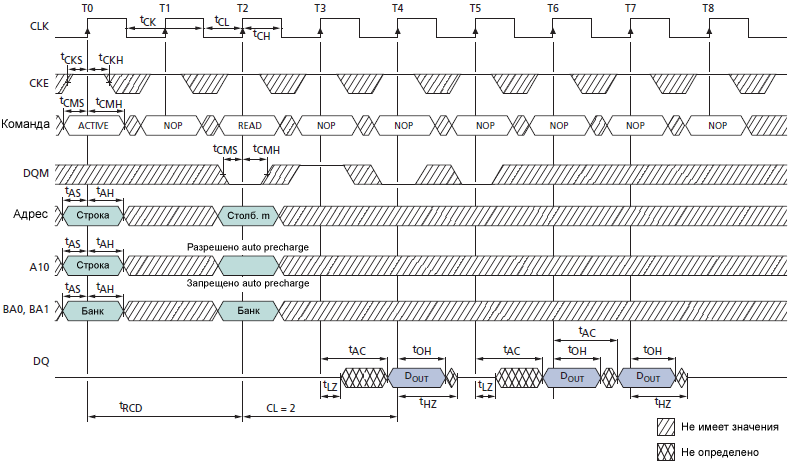

ąĀąĖčü. 15. ąÜąŠą╝ą░ąĮą┤ą░ READ (EN AP = čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ auto precharge, DIS AP = ąĘą░ą┐čĆąĄčé auto precharge).

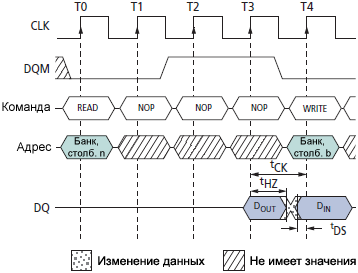

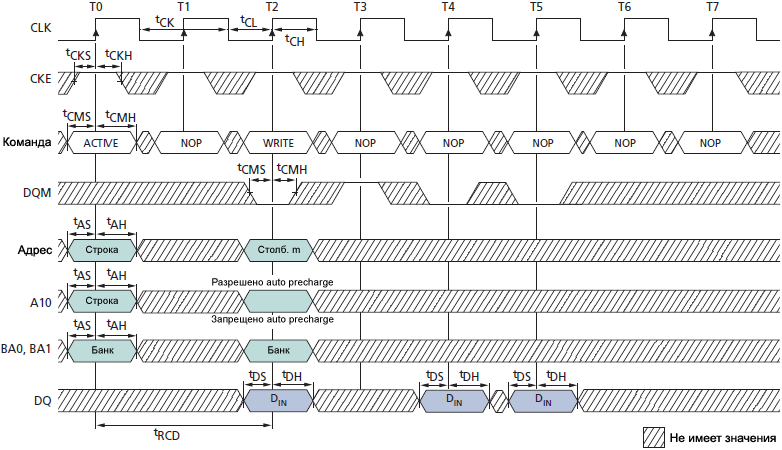

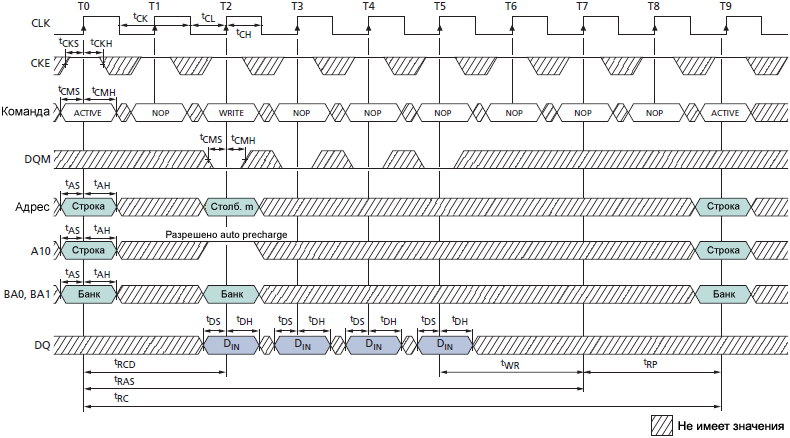

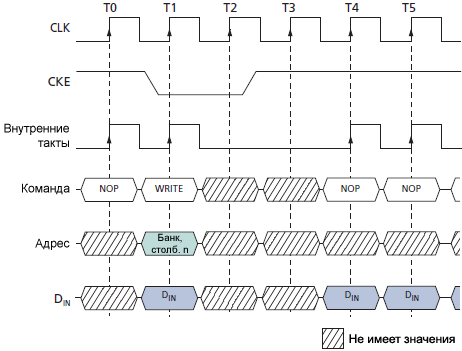

WRITE. ąÜąŠą╝ą░ąĮą┤ą░ ąĘą░ą┐ąĖčüąĖ (WRITE) ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ąĖąĮąĖčåąĖą░čåąĖąĖ ą┤ąŠčüčéčāą┐ą░ ą┐ą░ą║ąĄčéąĮąŠą╣ ąĘą░ą┐ąĖčüąĖ (burst write) ąĮą░ ą░ą║čéąĖą▓ąĮąŠą╣ čüčéčĆąŠą║ąĄ. ąŚąĮą░č湥ąĮąĖčÅ ąĮą░ ą▓čģąŠą┤ą░čģ BA0, BA1 ą▓čŗą▒ąĖčĆą░čÄčé ą▒ą░ąĮą║; ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮąĮčŗą╣ ą░ą┤čĆąĄčü ą▓čŗą▒ąĖčĆą░ąĄčé čüčéą░čĆč鹊ą▓ąŠąĄ ą┐ąŠą╗ąŠąČąĄąĮąĖąĄ čüč鹊ą╗ą▒čåą░. ąŚąĮą░č湥ąĮąĖąĄ ąĮą░ ą▓čģąŠą┤ąĄ A10 ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé, ą┤ąŠą╗ąČąĮąŠ ą╗ąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ auto precharge. ąĢčüą╗ąĖ ą▓čŗą▒čĆą░ąĮąŠ auto precharge, č鹊 ą┤ą╗čÅ čüčéčĆąŠą║ąĖ, ą║ ą║ąŠč鹊čĆąŠą╣ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą┤ąŠčüčéčāą┐, ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ precharge ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖčÄ ą┐ą░ą║ąĄčéą░ ąĘą░ą┐ąĖčüąĖ (write burst); ąĄčüą╗ąĖ auto precharge ąĮąĄ ą▓čŗą▒čĆą░ąĮąŠ, č鹊 čüčéčĆąŠą║ą░ ąŠčüčéą░ąĄčéčüčÅ ąŠčéą║čĆčŗč鹊ą╣ ą┤ą╗čÅ ą┐ąŠčüą╗ąĄą┤čāčÄčēąĖčģ ą┤ąŠčüčéčāą┐ąŠą▓. ąÆčģąŠą┤ąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ, ą┐ąŠčÅą▓ą╗čÅčÄčēąĖąĄčüčÅ ąĮą░ DQ, ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ ą▓ ą╝ą░čüčüąĖą▓ ą┐ą░ą╝čÅčéąĖ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü čāčĆąŠą▓ąĮčÅą╝ąĖ ą▓čģąŠą┤ąĮąŠą╣ ą╗ąŠą│ąĖą║ąĖ čüąĖą│ąĮą░ą╗ąŠą▓ DQM, ą┐ąŠčÅą▓ą╗čÅčÄčēąĖą╝ąĖčüčÅ ą▓ą╝ąĄčüč鹥 čü ą┤ą░ąĮąĮčŗą╝ąĖ. ąĢčüą╗ąĖ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮąĮčŗą╣ čüąĖą│ąĮą░ą╗ DQM ąĘą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ ą║ą░ą║ ą╗ąŠą│. 0, č鹊 čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ ą┤ą░ąĮąĮčŗąĄ ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ ą▓ ą┐ą░ą╝čÅčéčī; ąĄčüą╗ąĖ čüąĖą│ąĮą░ą╗ DQM čĆąĄą│ąĖčüčéčĆąĖčĆčāąĄčéčüčÅ ą║ą░ą║ ą╗ąŠą│. 1, č鹊 čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ ą▓čģąŠą┤čŗ ą┤ą░ąĮąĮčŗčģ ąĖą│ąĮąŠčĆąĖčĆčāčÄčéčüčÅ ąĖ ą║ąŠą╝ą░ąĮą┤ą░ WRITE ąĮąĄ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą┤ą╗čÅ čŹč鹊ą╣ čÅč湥ą╣ą║ąĖ ą▒ą░ą╣čéą░/čüč鹊ą╗ą▒čåą░.

ąĀąĖčü. 16. ąÜąŠą╝ą░ąĮą┤ą░ WRITE (EN AP = čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ auto precharge, DIS AP = ąĘą░ą┐čĆąĄčé auto precharge).

PRECHARGE. ąÜąŠą╝ą░ąĮą┤ą░ PRECHARGE ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą┤ąĄą░ą║čéąĖą▓ą░čåąĖąĖ ąŠčéą║čĆčŗč鹊ą╣ čüčéčĆąŠą║ąĖ ą▓ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą╝ ą▒ą░ąĮą║ąĄ ąĖą╗ąĖ ąŠčéą║čĆčŗč鹊ą╣ čüčéčĆąŠą║ąĖ ą▓ąŠ ą▓čüąĄčģ ą▒ą░ąĮą║ą░čģ. ąæą░ąĮą║ (ą▒ą░ąĮą║ąĖ) ą▒čāą┤ąĄčé ą┤ąŠčüčéčāą┐ąĄąĮ ą┤ą╗čÅ ą┐ąŠčüą╗ąĄą┤čāčÄčēąĄą│ąŠ ą┤ąŠčüčéčāą┐ą░ ą║ čüčéčĆąŠąĄą║ ąĮą░ čāą║ą░ąĘą░ąĮąĮąŠąĄ ą▓čĆąĄą╝čÅ (tRP) ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą▓čŗą┤ą░ąĮą░ ą║ąŠą╝ą░ąĮą┤ą░ PRECHARGE. ąÆčģąŠą┤ A10 ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé, ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą╗ąĖ ą┐čĆąĄą┤ąĘą░čĆčÅą┤ ąĮą░ ąŠą┤ąĮąŠą╝ ąĖą╗ąĖ ą▓čüąĄčģ ą▒ą░ąĮą║ą░čģ, ąĖ ą▓ čüą╗čāčćą░ąĄ, ą║ąŠą│ą┤ą░ precharge ą┤ąĄą╗ą░ąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ąŠą┤ąĮąŠą│ąŠ ą▒ą░ąĮą║ą░, ą▓čģąŠą┤čŗ BA0 ąĖ BA1 ą▓čŗą▒ąĖčĆą░čÄčé čŹč鹊čé ą▒ą░ąĮą║. ąśąĮą░č湥 čāčĆąŠą▓ąĮąĖ ąĮą░ BA0 ąĖ BA1 ąĮąĄ ąĖą╝ąĄčÄčé ąĘąĮą░č湥ąĮąĖčÅ. ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą▒ą░ąĮą║ ą┐čĆąĄą┤ąĘą░čĆčÅąČąĄąĮ, ąŠąĮ ąŠčüčéą░ąĄčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ąŠąČąĖą┤ą░ąĮąĖčÅ (idle state), ąĖ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮ ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ą┤ą╗čÅ čŹč鹊ą│ąŠ ą▒ą░ąĮą║ą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮą░ ą║ąŠą╝ą░ąĮą┤ą░ READ ąĖą╗ąĖ WRITE.

ąĀąĖčü. 17. ąÜąŠą╝ą░ąĮą┤ą░ PRECHARGE.

BURST TERMINATE. ąÜąŠą╝ą░ąĮą┤ą░ ąŠčüčéą░ąĮąŠą▓ą║ąĖ ą┐ą░ą║ąĄčéą░ (BURST TERMINATE) ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ąŠą▒čĆčŗą▓ą░ ą┐ąĄčĆąĄą┤ą░čć ą┐ą░ą║ąĄčéą░ čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮąŠą╣ ą┤ą╗ąĖąĮčŗ (fixed-length burst), ą╗ąĖą▒ąŠ ąĮąĄą┐čĆąĄčĆčŗą▓ąĮčŗčģ ą┐ąĄčĆąĄą┤ą░čć čüčéčĆą░ąĮąĖčå (continuous page burst). ąĪą░ą╝ą░čÅ ą┐ąŠčüą╗ąĄą┤ąĮčÅčÅ ąĘą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮąĮą░čÅ ą║ąŠą╝ą░ąĮą┤ą░ READ ąĖą╗ąĖ WRITE, ą▓čŗą┤ą░ąĮąĮą░čÅ ą┐ąĄčĆąĄą┤ BURST TERMINATE, ą▒čāą┤ąĄčé ąŠą▒ąŠčĆą▓ą░ąĮą░.

[ąĀąĄąČąĖą╝čŗ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ]

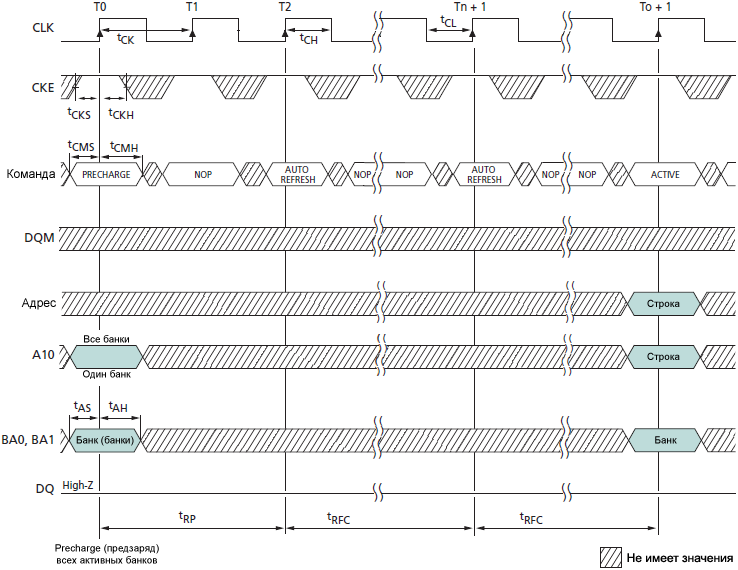

AUTO REFRESH. AUTO REFRESH ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ąĮąŠčĆą╝ą░ą╗čīąĮąŠą│ąŠ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖčÅ SDRAM ąĖ čŹč鹊 ą░ąĮą░ą╗ąŠą│ąĖčćąĮąŠ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÄ CAS#-BEFORE-RAS# (CBR) ą▓ ąŠą▒čŗčćąĮčŗčģ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░čģ DRAM. ąŁčéą░ ą║ąŠą╝ą░ąĮą┤ą░ ąĮąĄ ą┤ąĄą╣čüčéą▓čāąĄčé ą┐ąŠčüč鹊čÅąĮąĮąŠ, ąĖ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą▓čŗą┤ą░ąĮą░ ą║ą░ąČą┤čŗą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ čéčĆąĄą▒čāąĄčéčüčÅ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ ą┤ąĖąĮą░ą╝ąĖč湥čüą║ąŠą╣ ą┐ą░ą╝čÅčéąĖ. ąÆčüąĄ ą░ą║čéąĖą▓ąĮčŗąĄ ą▒ą░ąĮą║ąĖ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą┐čĆąĄą┤ąĘą░čĆčÅąČąĄąĮčŗ (precharge) ą┐ąĄčĆąĄą┤ ą▓čŗą┤ą░č湥ą╣ ą║ąŠą╝ą░ąĮą┤čŗ AUTO REFRESH. ąÜąŠą╝ą░ąĮą┤ą░ AUTO REFRESH ąĮąĄ ą┤ąŠą╗ąČąĮą░ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ, ą┐ąŠą║ą░ ąĮąĄ ąĖčüč鹥č湥čé ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠąĄ ą▓čĆąĄą╝čÅ ąĖąĮč鹥čĆą▓ą░ą╗ą░ tRP ą┐ąŠčüą╗ąĄ ą║ąŠą╝ą░ąĮą┤čŗ PRECHARGE, ą║ą░ą║ čŹč鹊 ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▓ čüąĄą║čåąĖąĖ Bank/Row Activation.

ąÉą┤čĆąĄčüą░čåąĖčÅ ą┐čĆąĖ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĖ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╝ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ. ąŁč鹊 ą┤ąĄą╗ą░ąĄčé čüąŠčüč鹊čÅąĮąĖąĄ ą▒ąĖč鹊ą▓ ą░ą┤čĆąĄčüą░ ąĮąĄ ąĘąĮą░čćąĖą╝čŗą╝ąĖ (ą╗ąŠą│ąĖč湥čüą║ąĖąĄ čāčĆąŠą▓ąĮąĖ ąĮą░ ąĮąĖčģ ąĮąĄ ąĖą╝ąĄčÄčé ąĘąĮą░č湥ąĮąĖčÅ) ą▓ąŠ ą▓čĆąĄą╝čÅ ą║ąŠą╝ą░ąĮą┤čŗ AUTO REFRESH. ąØąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé čłąĖčĆąĖąĮčŗ čāčüčéčĆąŠą╣čüčéą▓ą░, 256M SDRAM čéčĆąĄą▒čāąĄčé 8192 čåąĖą║ą╗ąŠą▓ AUTO REFRESH ą║ą░ąČą┤čŗąĄ 64 ą╝čü (ą┤ą╗čÅ ąĖčüą┐ąŠą╗ąĮąĄąĮąĖą╣ commercial ąĖ industrial) ąĖą╗ąĖ 16 ą╝čü (ą┤ą╗čÅ ąĖčüą┐ąŠą╗ąĮąĄąĮąĖčÅ automotive). ą¤čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮąĖąĄ čĆą░čüą┐čĆąŠčüčéčĆą░ąĮčÅąĄą╝ąŠą╣ ą║ąŠą╝ą░ąĮą┤čŗ AUTO REFRESH ą║ą░ąČą┤čŗąĄ 7.813 ą╝ą║čü (ą┤ą╗čÅ ąĖčüą┐ąŠą╗ąĮąĄąĮąĖą╣ commercial ąĖ industrial) ąĖą╗ąĖ 1.953 ą╝ą║čü (ą┤ą╗čÅ ąĖčüą┐ąŠą╗ąĮąĄąĮąĖčÅ automotive) ą▒čāą┤ąĄčé čāą┤ąŠą▓ą╗ąĄčéą▓ąŠčĆčÅčéčī čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÄ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ ąĖ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī, čćč鹊 ą▒čāą┤ąĄčé ąŠą▒ąĮąŠą▓ą╗ąĄąĮą░ ą║ą░ąČą┤ą░čÅ čüčéčĆąŠą║ą░. ąÉą╗čīč鹥čĆąĮą░čéąĖą▓ąĮąŠ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą┤ą░ąĮąŠ 8192 ą║ąŠą╝ą░ąĮą┤ AUTO REFRESH ą┐ą░ą║ąĄč鹊ą╝ čü ąĖąĮč鹥čĆą▓ą░ą╗ąŠą╝ ąĮąĄ ą╝ąĄąĮčīčłąĄ tRFC, čé. ąĄ. ą║ą░ąČą┤čŗąĄ 64 ą╝čü (ą┤ą╗čÅ ąĖčüą┐ąŠą╗ąĮąĄąĮąĖą╣ commercial ąĖ industrial) ąĖą╗ąĖ 16 ą╝čü (ą┤ą╗čÅ ąĖčüą┐ąŠą╗ąĮąĄąĮąĖčÅ automotive).

SELF REFRESH. ąÜąŠą╝ą░ąĮą┤ą░ SELF REFRESH ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ čüąŠčģčĆą░ąĮąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ą▓ SDRAM, ą┤ą░ąČąĄ ąĄčüą╗ąĖ ąŠčüčéą░ą╗čīąĮą░čÅ čüąĖčüč鹥ą╝ą░ ą▓čŗą║ą╗čÄč湥ąĮą░. ąÆ čĆąĄąČąĖą╝ąĄ self refresh ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ SDRAM čüąŠčģčĆą░ąĮčÅąĄčé čüą▓ąŠąĖ ą┤ą░ąĮąĮčŗąĄ ą┐čĆąĖ ąŠčéčüčāčéčüčéą▓ąĖąĖ ą▓ąĮąĄčłąĮąĄą│ąŠ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ (ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ čüą░ą╝ąŠąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ ą▒ąĄąĘ čāčćą░čüčéąĖčÅ ą▓ąĮąĄčłąĮąĄą│ąŠ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░).

ąÜąŠą╝ą░ąĮą┤ą░ SELF REFRESH ąĖąĮąĖčåąĖąĖčĆčāąĄčéčüčÅ ąĮą░ą┐ąŠą┤ąŠą▒ąĖąĄ ą║ąŠą╝ą░ąĮą┤čŗ AUTO REFRESH, ąĘą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ č鹊ą│ąŠ, čćč鹊 CKE ąĘą░ą┐čĆąĄčēąĄąĮ (ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą╗ąŠą│. 0). ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ąĘą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮą░ ą║ąŠą╝ą░ąĮą┤ą░ SELF REFRESH, ą▓čüąĄ ą▓čģąŠą┤čŗ SDRAM ą┐ąĄčĆąĄčģąŠą┤čÅčé ą▓ čüąŠčüč鹊čÅąĮąĖąĄ "ąĮąĄ ąĖą╝ąĄąĄčé ąĘąĮą░č湥ąĮąĖčÅ", ą║čĆąŠą╝ąĄ čüąĖą│ąĮą░ą╗ą░ CKE, ą║ąŠč鹊čĆčŗą╣ ą┤ąŠą╗ąČąĄąĮ ąŠčüčéą░ą▓ą░čéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą╗ąŠą│. 0.

ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ čĆąĄąČąĖą╝ čüą░ą╝ąŠąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ (self refresh) ą▒čŗą╗ ąĘą░ą┐čāčēąĄąĮ, SDRAM ąĖčüą┐ąŠą╗čīąĘčāąĄčé čüą▓ąŠąĄ ą▓ąĮčāčéčĆąĄąĮąĮąĄąĄ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ, čüą░ą╝ąŠčüč鹊čÅč鹥ą╗čīąĮąŠ ą▓čŗą┐ąŠą╗ąĮčÅčÅ čåąĖą║ą╗čŗ AUTO REFRESH. ą£ąĖą║čĆąŠčüčģąĄą╝ą░ SDRAM ą┤ąŠą╗ąČąĮą░ ąŠčüčéą░ą▓ą░čéčīčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ čüą░ą╝ąŠąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ ąĮą░ ą╝ąĖąĮąĖą╝ą░ą╗čīąĮčŗą╣ ą┐ąĄčĆąĖąŠą┤, čĆą░ą▓ąĮčŗą╣ tRAS, ąĖ ą╝ąŠąČąĄčé ąŠčüčéą░ą▓ą░čéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą░ą╝ąŠąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ ą▒ąĄčüą║ąŠąĮąĄčćąĮąŠ ą┤ąŠą╗ą│ąŠ, ą┐ąŠą║ą░ ąĮą░ ą╝ąĖą║čĆąŠčüčģąĄą╝čā ą┐ąŠą┤ą░ąĄčéčüčÅ ą┐ąĖčéą░ąĮąĖąĄ, ąĖ ą┐ąŠą║ą░ čŹč鹊čé čĆąĄąČąĖą╝ ąĮąĄąŠą▒čģąŠą┤ąĖą╝.

ą¤čĆąŠčåąĄą┤čāčĆą░ ą▓čŗčģąŠą┤ą░ ąĖąĘ čüą░ą╝ąŠąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ čéčĆąĄą▒čāąĄčé ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą║ąŠą╝ą░ąĮą┤. ąĪąĮą░čćą░ą╗ą░ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ąĘą░čüčéą░ą▒ąĖą╗ąĖąĘąĖčĆąŠą▓ą░ąĮą░ čćą░čüč鹊čéą░ čéą░ą║č鹊ą▓ CLK (čüčéą░ą▒ąĖą╗čīąĮąŠčüčéčī čéą░ą║č鹊ą▓ ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 čüąĖą│ąĮą░ą╗ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ čāą┤ąŠą▓ą╗ąĄčéą▓ąŠčĆčÅąĄčé čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅą╝, ąĘą░ą┤ą░ąĮąĮčŗą╝ ą▓ čüą┐ąĄčåąĖčäąĖą║ą░čåąĖąĖ ą┤ą╗čÅ čéą░ą║č鹊ą▓, čüą╝. ą▓čĆąĄąĘą║čā "ąŁą╗ąĄą║čéčĆąĖč湥čüą║ąĖąĄ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ AC") ą┤ąŠ č鹊ą│ąŠ, ą║ą░ą║ čüąĖą│ąĮą░ą╗ CKE ą┐ąĄčĆąĄą╣ą┤ąĄčé ą▓ ą╗ąŠą│. 1. ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ CKE ą┐ąĄčĆąĄą╣ą┤ąĄčé ą▓ ą╗ąŠą│. 1, ąĮą░ SDRAM ąĮčāąČąĮąŠ ą▓čŗą┤ą░čéčī ą║ąŠą╝ą░ąĮą┤čŗ NOP (ą▓ č鹥č湥ąĮąĖąĄ ą╝ąĖąĮąĖą╝čāą╝ 2 čéą░ą║č鹊ą▓) ą┤ą╗čÅ tXSR, ą┐ąŠč鹊ą╝čā čćč鹊 čéčĆąĄą▒čāąĄčéčüčÅ ą▓čĆąĄą╝čÅ ą┤ą╗čÅ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą╗čÄą▒ąŠą│ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ ą┐čĆąŠčåąĄčüčüą░ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ.

ą¤čĆąĖ ą▓čŗčģąŠą┤ąĄ ąĖąĘ čĆąĄąČąĖą╝ą░ čüą░ą╝ąŠąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ ą║ąŠą╝ą░ąĮą┤čŗ AUTO REFRESH ą┤ąŠą╗ąČąĮčŗ ą▓čŗą┤ą░ą▓ą░čéčīčüčÅ čü čāą║ą░ąĘą░ąĮąĮčŗą╝ąĖ ąĖąĮč鹥čĆą▓ą░ą╗ą░ą╝ąĖ, čéą░ą║ ą║ą░ą║ ąĖ SELF REFRESH ąĖ AUTO REFRESH ąĖčüą┐ąŠą╗čīąĘčāčÄčé ąŠą┤ąĖąĮ ąĖ č鹊čé ąČąĄ čüč湥čéčćąĖą║ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ čüčéčĆąŠą║.

ąĀąĄąČąĖą╝ čüą░ą╝ąŠąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ (self refresh) ąĮąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ą╝ąĖ ą▓ č鹥ą╝ą┐ąĄčĆą░čéčāčĆąĮąŠą╝ ąĖčüą┐ąŠą╗ąĮąĄąĮąĖąĖ ą┤ą╗čÅ ą░ą▓č鹊ą╝ąŠą▒ąĖą╗čīąĮąŠą╣ ą┐čĆąŠą╝čŗčłą╗ąĄąĮąĮąŠčüčéąĖ (automotive temperature devices, AT).

ąóą░ą▒ą╗ąĖčåą░ 15. ąóą░ą▒ą╗ąĖčåą░ ąĖčüčéąĖąĮąĮąŠčüčéąĖ ŌĆō č鹥ą║čāčēąĄąĄ čüąŠčüč鹊čÅąĮąĖąĄ ą▒ą░ąĮą║ n, ą║ąŠą╝ą░ąĮą┤ą░ ą┤ą╗čÅ ą▒ą░ąĮą║ą░ n. 0 ąŠąĘąĮą░čćą░ąĄčé ą╗ąŠą│. 0, 1 ą╗ąŠą│. 1, x ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 čāčĆąŠą▓ąĄąĮčī čüąĖą│ąĮą░ą╗ą░ ąĮąĄ ąĖą╝ąĄąĄčé ąĘąĮą░č湥ąĮąĖčÅ.

| ąóąĄą║čāčēąĄąĄ čüąŠčüč鹊čÅąĮąĖąĄ |

CS# |

RAS# |

CAS# |

WE# |

ąÜąŠą╝ą░ąĮą┤ą░/ą┤ąĄą╣čüčéą▓ąĖąĄ |

ą¤čĆąĖą╝. |

| ąøčÄą▒ąŠąĄ |

1 |

x |

x |

x |

COMMAND INHIBIT (ąĘą░ą┐čĆąĄčé ą║ąŠą╝ą░ąĮą┤čŗ, NOP/ą┐čĆąŠą┤ąŠą╗ąČąĖčéčī ą┐čĆąĄą┤čŗą┤čāčēčāčÄ ąŠą┐ąĄčĆą░čåąĖčÄ) |

|

| 0 |

1 |

1 |

1 |

NO OPERATION (ąĮąĖą║ą░ą║ąŠą│ąŠ ą┤ąĄą╣čüčéą▓ąĖčÅ, NOP/ą┐čĆąŠą┤ąŠą╗ąČąĖčéčī ą┐čĆąĄą┤čŗą┤čāčēčāčÄ ąŠą┐ąĄčĆą░čåąĖčÄ) |

|

| Idle (ąŠąČąĖą┤ą░ąĮąĖąĄ) |

0 |

0 |

1 |

1 |

ACTIVE (ą▓čŗą▒ąŠčĆ ąĖ ą░ą║čéąĖą▓ą░čåąĖčÅ čüčéčĆąŠą║ąĖ) |

|

| 0 |

0 |

0 |

1 |

AUTO REFRESH (ą░ą▓č鹊ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ) |

7 |

| 0 |

0 |

0 |

0 |

LOAD MODE REGISTER (ąĘą░ą│čĆčāąĘą║ą░ čĆąĄą│ąĖčüčéčĆą░ čĆąĄąČąĖą╝ą░) |

7 |

| 0 |

0 |

1 |

0 |

PRECHARGE |

8 |

| Row active (čüčéčĆąŠą║ą░ ą░ą║čéąĖą▓ąĮą░) |

0 |

1 |

0 |

1 |

READ (ą▓čŗą▒ąŠčĆ čüč鹊ą╗ą▒čåą░ ąĖ ąĘą░ą┐čāčüą║ ą┐ą░ą║ąĄčéą░ čćč鹥ąĮąĖčÅ, READ burst) |

9 |

| 0 |

1 |

0 |

0 |

WRITE (ą▓čŗą▒ąŠčĆ čüč鹊ą╗ą▒čåą░ ąĖ ąĘą░ą┐čāčüą║ ą┐ą░ą║ąĄčéą░ ąĘą░ą┐ąĖčüąĖ, WRITE burst) |

9 |

| 0 |

0 |

1 |

0 |

PRECHARGE (ą┤ąĄą░ą║čéąĖą▓ą░čåąĖčÅ čüčéčĆąŠą║ąĖ ą▓ ą▒ą░ąĮą║ąĄ ąĖą╗ąĖ ą▒ą░ąĮą║ą░čģ) |

10 |

| Read, čćč鹥ąĮąĖąĄ (čäčāąĮą║čåąĖčÅ auto precharge ąĘą░ą┐čĆąĄčēąĄąĮą░) |

0 |

1 |

0 |

1 |

READ (ą▓čŗą▒ąŠčĆ čüč鹊ą╗ą▒čåą░ ąĖ ąĘą░ą┐čāčüą║ ąĮąŠą▓ąŠą│ąŠ ą┐ą░ą║ąĄčéą░ čćč鹥ąĮąĖčÅ, READ burst) |

9 |

| 0 |

1 |

0 |

0 |

WRITE (ą▓čŗą▒ąŠčĆ čüč鹊ą╗ą▒čåą░ ąĖ ąĘą░ą┐čāčüą║ ą┐ą░ą║ąĄčéą░ ąĘą░ą┐ąĖčüąĖ, WRITE burst) |

9 |

| 0 |

0 |

1 |

0 |

PRECHARGE (ąŠą▒čĆčŗą▓ ą┐ą░ą║ąĄčéą░ READ, ąĘą░ą┐čāčüą║ ą┐čĆąĄą┤ąĘą░čĆčÅą┤ą░) |

10 |

| 0 |

1 |

1 |

0 |

BURST TERMINATE (ąŠą▒čĆčŗą▓ ą┐ą░ą║ąĄčéą░) |

11 |

| Write, ąĘą░ą┐ąĖčüčī (čäčāąĮą║čåąĖčÅ auto precharge ąĘą░ą┐čĆąĄčēąĄąĮą░) |

0 |

1 |

0 |

1 |

READ (ą▓čŗą▒ąŠčĆ čüč鹊ą╗ą▒čåą░ ąĖ ąĘą░ą┐čāčüą║ ą┐ą░ą║ąĄčéą░ čćč鹥ąĮąĖčÅ, READ burst) |

9 |

| 0 |

1 |

0 |

0 |

WRITE (ą▓čŗą▒ąŠčĆ čüč鹊ą╗ą▒čåą░ ąĖ ąĘą░ą┐čāčüą║ ąĮąŠą▓ąŠą│ąŠ ą┐ą░ą║ąĄčéą░ ąĘą░ą┐ąĖčüąĖ, WRITE burst) |

9 |

| 0 |

0 |

1 |

0 |

PRECHARGE (ąŠą▒čĆčŗą▓ ą┐ą░ą║ąĄčéą░ WRITE, ąĘą░ą┐čāčüą║ ą┐čĆąĄą┤ąĘą░čĆčÅą┤ą░) |

10 |

| 0 |

1 |

1 |

0 |

BURST TERMINATE (ąŠą▒čĆčŗą▓ ą┐ą░ą║ąĄčéą░) |

11 |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ ą║ čéą░ą▒ą╗ąĖčåąĄ 15 (ąĖąĘ ąĮąĖčģ 1..6 ąŠčéąĮąŠčüčÅčéčüčÅ ą║ąŠ ą▓čüąĄą╝ ą┐ą░čĆą░ą╝ąĄčéčĆą░ą╝ ąĖ čāčüą╗ąŠą▓ąĖčÅą╝):

1. ąŁčéą░ čéą░ą▒ą╗ąĖčåą░ ąŠčéąĮąŠčüąĖčéčüčÅ ą║ čüąĖčéčāą░čåąĖčÅą╝, ą║ąŠą│ą┤ą░ CKEn-1 ą▒čŗą╗ ą╗ąŠą│. 1, ąĖ CKEn ą╗ąŠą│. 1 (čüą╝. čéą░ą▒ą╗ąĖčåčā 17) ąĖ čŹč鹊 ą┐čĆąŠąĖąĘąŠčłą╗ąŠ ą┐ąŠčüą╗ąĄ tXSR (ąĄčüą╗ąĖ ą┐čĆąĄą┤čŗą┤čāčēąĄąĄ čüąŠčüč鹊čÅąĮąĖąĄ ą▒čŗą╗ąŠ self refresh).

2. ąŁčéą░ čéą░ą▒ą╗ąĖčåą░ čüą┐ąĄčåąĖčäąĖčćąĮą░ ą┤ą╗čÅ ą▒ą░ąĮą║ą░, ąĘą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ čüą┐ąĄčåąĖą░ą╗čīąĮąŠ ąŠą│ąŠą▓ąŠčĆąĄąĮąĮčŗčģ čüąĖčéčāą░čåąĖą╣ (ąĮą░ą┐čĆąĖą╝ąĄčĆ, č鹥ą║čāčēąĄąĄ čüąŠčüč鹊čÅąĮąĖąĄ ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą│ąŠ ą▒ą░ąĮą║ą░, ąĖ ą┐ąŠą║ą░ąĘą░ąĮąĮčŗąĄ ą║ąŠą╝ą░ąĮą┤čŗ ą╝ąŠą│čāčé ą▒čŗčéčī ą▓čŗą┤ą░ąĮčŗ ą║ čŹč鹊ą╝čā ą▒ą░ąĮą║čā, ą║ąŠą│ą┤ą░ ąŠąĮ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čéą░ą║ąŠą╝ čüąŠčüč鹊čÅąĮąĖąĖ). ąśčüą║ą╗čÄč湥ąĮąĖčÅ čĆą░čüčüą╝ą░čéčĆąĖą▓ą░čÄčéčüčÅ ąĮąĖąČąĄ.

3. ą×ą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ č鹥ą║čāčēąĄą│ąŠ čüąŠčüč鹊čÅąĮąĖčÅ:

Idle: ą▒ą░ąĮą║ ą▒čŗą╗ ą┐čĆąĄą┤ąĘą░čĆčÅąČąĄąĮ, ąĖ ą┐čĆąŠčłąĄą╗ ąĖąĮč鹥čĆą▓ą░ą╗ tRP.

Row active: ą▒ą░ąĮą║ ą▒čŗą╗ ą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮ, ąĖ ą┐čĆąŠčłą╗ąŠ ą▓čĆąĄą╝čÅ tRCD. ąØąĄ ą┐čĆąŠąĖčüčģąŠą┤čÅčé ąŠą┐ąĄčĆą░čåąĖąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐ą░ą║ąĄč鹊ą▓ ą┤ą░ąĮąĮčŗčģ (data bursts), ąĮąĄ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą┤ąŠčüčéčāą┐ ą║ ą┐ą░ą╝čÅčéąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ, ąĖ ąĮąĄ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą┤ąŠčüčéčāą┐ ą║ ąĄčæ čĆąĄą│ąĖčüčéčĆą░ą╝.

Read: ąĖąĮąĖčåąĖąĖčĆąŠą▓ą░ąĮą░ ąŠą┐ąĄčĆą░čåąĖčÅ ą┐ą░ą║ąĄčéąĮąŠą│ąŠ čćč鹥ąĮąĖčÅ (READ burst) čü ąĘą░ą┐čĆąĄč鹊ą╝ auto precharge, ąĖ ąŠąĮą░ ą┐ąŠą║ą░ ąĮąĄ ąĘą░ą▓ąĄčĆčłąĄąĮą░ ąĖą╗ąĖ ą┐ąŠą║ą░ ąĮąĄ ąŠą▒ąŠčĆą▓ą░ąĮą░.

Write: ąĖąĮąĖčåąĖąĖčĆąŠą▓ą░ąĮą░ ąŠą┐ąĄčĆą░čåąĖčÅ ą┐ą░ą║ąĄčéąĮąŠą╣ ąĘą░ą┐ąĖčüąĖ (WRITE burst) čü ąĘą░ą┐čĆąĄč鹊ą╝ auto precharge, ąĖ ąŠąĮą░ ą┐ąŠą║ą░ ąĮąĄ ąĘą░ą▓ąĄčĆčłąĄąĮą░ ąĖą╗ąĖ ą┐ąŠą║ą░ ąĮąĄ ąŠą▒ąŠčĆą▓ą░ąĮą░.