|

CoolRunnerвДҐ-II —Н—В–Њ —Б–µ–Љ–µ–є—Б—В–≤–Њ CPLD (Complex Programmable Logic Device) –Њ—В –Ї–Њ–Љ–њ–∞–љ–Є–Є Xilinx. CoolRunner-II –њ–Њ–Ї–∞–Ј—Л–≤–∞–µ—В –≤—Л–і–∞—О—Й–Є–µ—Б—П –њ–∞—А–∞–Љ–µ—В—А—Л –њ–Њ —Б–Њ–Њ—В–љ–Њ—И–µ–љ–Є—О –њ—А–Њ–Є–Ј–≤–Њ–і–Є—В–µ–ї—М–љ–Њ—Б—В—М/—Н–љ–µ—А–≥–Њ–њ–Њ—В—А–µ–±–ї–µ–љ–Є–µ –Ј–∞ –≤–њ–Њ–ї–љ–µ –і–Њ—Б—В—Г–њ–љ—Л–µ —Ж–µ–љ—Л, —Б —И–Є—А–Њ–Ї–Є–Љ –∞—Б—Б–Њ—А—В–Є–Љ–µ–љ—В–Њ–Љ –Ї–Њ—А–њ—Г—Б–Њ–≤ –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ. –≠—В–Њ—В –∞–њ–љ–Њ—Г—В (–њ–µ—А–µ–≤–Њ–і XAPP376 [1]) —Б–Њ—Б—А–µ–і–Њ—В–Њ—З–µ–љ –љ–∞ –Њ–њ–Є—Б–∞–љ–Є–Є, –Ї–∞–Ї CoolRunner-II CPLD —Б–Њ–Ј–і–∞–µ—В –ї–Њ–≥–Є—З–µ—Б–Ї—Г—О —Б—Е–µ–Љ—Г –љ–∞ –Њ—Б–љ–Њ–≤–µ —Б–≤–Њ–µ–є —Д–∞–±—А–Є–Ї–Є CMOS. –°–Ї–Њ—А–µ–µ –≤—Б–µ–≥–Њ –Т–∞–Љ –љ–Є–Ї–Њ–≥–і–∞ –љ–µ –њ–Њ–љ–∞–і–Њ–±–Є—В—Б—П –≤–љ–Є–Ї–∞—В—М –≤–Њ –≤—Б–µ —В–Њ–љ–Ї–Њ—Б—В–Є –≤–љ—Г—В—А–µ–љ–љ–µ–≥–Њ —Г—Б—В—А–Њ–є—Б—В–≤–∞, –Ї–Њ—В–Њ—А–Њ–µ –Ј–і–µ—Б—М –Њ–њ–Є—Б—Л–≤–∞–µ—В—Б—П, –њ–Њ—В–Њ–Љ—Г —З—В–Њ –Я–Ю —А–∞–Ј—А–∞–±–Њ—В–Ї–Є –∞–≤—В–Њ–Љ–∞—В–Є—З–µ—Б–Ї–Є –Њ–±—А–∞–±–Њ—В–∞–µ—В –Т–∞—И –њ—А–Њ–µ–Ї—В —В–∞–Ї–Є–Љ –Њ–±—А–∞–Ј–Њ–Љ, —З—В–Њ–±—Л –і–∞—В—М –љ–∞–Є–ї—Г—З—И–Є–µ –њ–Њ–Ї–∞–Ј–∞—В–µ–ї–Є —Б–Ї–Њ—А–Њ—Б—В–Є –Є –њ–Њ—В—А–µ–±–ї–µ–љ–Є—П —Н–љ–µ—А–≥–Є–Є, –њ—А–Є –Љ–Є–љ–Є–Љ–∞–ї—М–љ–Њ–Љ –≤–Љ–µ—И–∞—В–µ–ї—М—Б—В–≤–µ –њ–Њ–ї—М–Ј–Њ–≤–∞—В–µ–ї—П –≤ –≤–Є–і–µ –љ–∞—Б—В—А–Њ–є–Ї–Є –њ—А–Њ–µ–Ї—В–∞. –Т —В–µ—Е —Б–ї—Г—З–∞—П—Е, –Ї–Њ–≥–і–∞ –Т—Л —Е–Њ—В–Є—В–µ —Г–Ј–љ–∞—В—М, –Ї–∞–Ї–Є–Љ –Њ–±—А–∞–Ј–Њ–Љ CoolRunner-II –і–µ–ї–∞–µ—В —Б–≤–Њ—О –Љ–∞–≥–Є—О, —Н—В–Њ—В –∞–њ–љ–Њ—Г—В –і–Њ–ї–ґ–µ–љ –њ–Њ–Љ–Њ—З—М —Г–і–Њ–≤–ї–µ—В–≤–Њ—А–Є—В—М –≤—Б–µ –њ–Њ—В—А–µ–±–љ–Њ—Б—В–Є. –Ф–ї—П –Њ–±—Й–µ–є –Є–љ—Д–Њ—А–Љ–∞—Ж–Є–Є –њ–Њ —Б–µ–Љ–µ–є—Б—В–≤—Г CoolRunner-II —Б–Љ. CoolRunner-II Family Data Sheet (ds90 [2]) –Є –і–∞—В–∞—И–Є—В—Л, –њ–Њ—Б–≤—П—Й–µ–љ–љ—Л–µ –Њ—В–і–µ–ї—М–љ—Л–Љ —Г—Б—В—А–Њ–є—Б—В–≤–∞–Љ. –Т—Б–µ –љ–µ–њ–Њ–љ—П—В–љ—Л–µ —В–µ—А–Љ–Є–љ—Л –Є —Б–Њ–Ї—А–∞—Й–µ–љ–Є—П —Б–Љ. –≤ –°–ї–Њ–≤–∞—А–Є–Ї–µ [3].

[–Р—А—Е–Є—В–µ–Ї—В—Г—А–∞ –љ–∞ –≤–µ—А—Е–љ–µ–Љ —Г—А–Њ–≤–љ–µ]

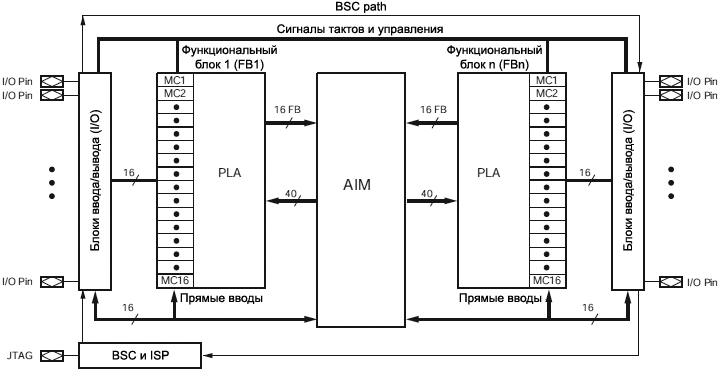

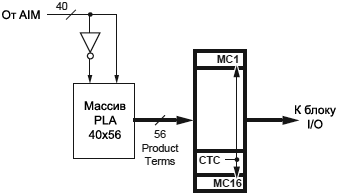

–†–Є—Б. 1 –њ–Њ–Ї–∞–Ј—Л–≤–∞–µ—В –Њ–±—Й—Г—О —Б—Е–µ–Љ—Г –∞—А—Е–Є—В–µ–Ї—В—Г—А—Л CoolRunner-II. –Ч–і–µ—Б—М –Њ–љ–∞ –љ–∞–њ–Њ–Љ–Є–љ–∞–µ—В –±–Њ–ї—М—И–Є–љ—Б—В–≤–Њ –і—А—Г–≥–Є—Е CPLD. –Э–Њ–ґ–Ї–Є –≤–≤–Њ–і–∞/–≤—Л–≤–Њ–і–∞ (I/O pin) –Њ–Ї—А—Г–ґ–∞—О—В —З–Є–њ, –≤ –Ї–Њ—В–Њ—А–Њ–Љ –Є–Љ–µ–µ—В—Б—П –љ–µ—Б–Ї–Њ–ї—М–Ї–Њ –њ—А–Њ–≥—А–∞–Љ–Љ–Є—А—Г–µ–Љ—Л—Е —Д—Г–љ–Ї—Ж–Є–Њ–љ–∞–ї—М–љ—Л—Е –±–ї–Њ–Ї–Њ–≤ (Function Block, FB), –Ї–Њ—В–Њ—А—Л–µ –Љ–Њ–ґ–љ–Њ —Б–Њ–µ–і–Є–љ—П—В—М –і—А—Г–≥ —Б –і—А—Г–≥–Њ–Љ –Є –≤–љ–µ—И–љ–Є–Љ –Љ–Є—А–Њ–Љ —З–µ—А–µ–Ј –њ—А–Њ–і–≤–Є–љ—Г—В—Г—О –Љ–∞—В—А–Є—Ж—Г –≤–љ—Г—В—А–µ–љ–љ–Є—Е —Б–Њ–µ–і–Є–љ–µ–љ–Є–є Advanced Interconnect Matrix (AIM). –Э–Њ–ґ–Ї–Є –Ї–Њ—А–њ—Г—Б–∞ –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ—Л –Є –µ—С –Љ–∞—В—А–Є—Ж–∞ AIM –њ–Њ—Б—В–∞–≤–ї—П–µ—В –≤—Е–Њ–і–љ—Л–µ –њ–µ—А–µ–Љ–µ–љ–љ—Л–µ –≤ FB, –Ї–Њ—В–Њ—А—Л–є —А–µ–∞–ї–Є–Ј—Г–µ—В –љ—Г–ґ–љ—Г—О –ї–Њ–≥–Є–Ї—Г, –Є –Њ—В–њ—А–∞–≤–ї—П–µ—В –µ—С —А–µ–Ј—Г–ї—М—В–∞—В—Л –Њ–±—А–∞—В–љ–Њ –≤–Њ –≤–љ–µ—И–љ–Є–є –Љ–Є—А.

–†–Є—Б. 1. –Р—А—Е–Є—В–µ–Ї—В—Г—А–∞ CoolRunner-II CPLD.

[–Р—А—Е–Є—В–µ–Ї—В—Г—А–∞ FB]

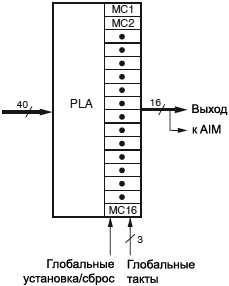

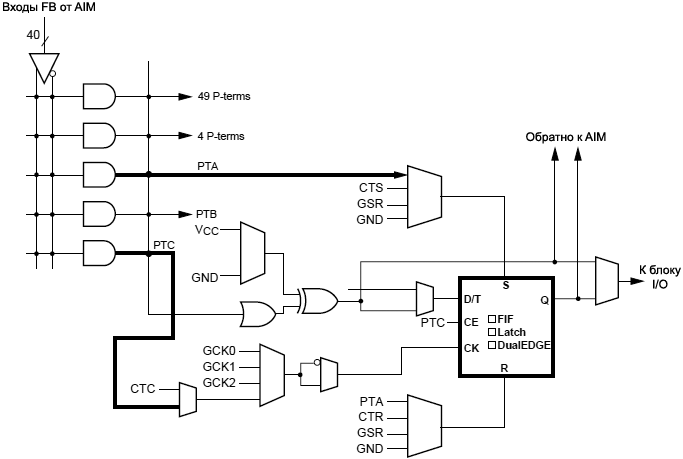

CoolRunner-II Function Block (—А–Є—Б. 2) –њ—А–Є–љ–Є–Љ–∞–µ—В 40 –≤—Е–Њ–і–љ—Л—Е —Б–Є–≥–љ–∞–ї–Њ–≤ –Њ—В AIM, –Є –љ–∞–њ—А—П–Љ—Г—О –њ–Њ–і–Ї–ї—О—З–∞–µ—В –Є—Е –Ї –Љ–∞—Б—Б–Є–≤—Г –њ—А–Њ–≥—А–∞–Љ–Љ–Є—А—Г–µ–Љ–Њ–є –ї–Њ–≥–Є–Ї–Є (Programmable Logic Array, PLA), –Ї–Њ—В–Њ—А—Л–є —А–∞–±–Њ—В–∞–µ—В –њ–Њ –≤—Б–µ–Љ—Г –±–ї–Њ–Ї—Г FB. 16 –Љ–∞–Ї—А–Њ—П—З–µ–µ–Ї —А–µ–∞–ї–Є–Ј—Г—О—В –Ї–Њ–Љ–±–Є–љ–∞—Ж–Є–Є –ї–Њ–≥–Є–Ї–Є PLA, –Є –љ–∞–Ј–љ–∞—З–∞—О—В —Б–Є–≥–љ–∞–ї—Л –љ–∞ —А–∞–Ј–ї–Є—З–љ—Л–µ –Ї–Њ–Љ–њ–Њ–љ–µ–љ—В—Л –Љ–∞–Ї—А–Њ—П—З–µ–є–Ї–Є - —В—А–Є–≥–≥–µ—А—Л (flip-flops), –њ—А–Њ–њ—Г—Б–Ї–∞—О—Й–Є–µ –Љ—Г–ї—М—В–Є–њ–ї–µ–Ї—Б–Њ—А—Л (bypass multiplexors), —В–∞–Ї—В–Њ–≤—Л–µ —Б–Є–≥–љ–∞–ї—Л (clock), —Б–Є–≥–љ–∞–ї—Л —Б–±—А–Њ—Б–∞ (reset), –Є —В. –і. –†–µ–Ј—Г–ї—М—В–Є—А—Г—О—Й–Є–µ —Б–Є–≥–љ–∞–ї—Л –Љ–∞—А—И—А—Г—В–Є–Ј–Є—А—Г—О—В—Б—П –Њ–±—А–∞—В–љ–Њ –Ї AIM –і–ї—П –і–Њ–њ–Њ–ї–љ–Є—В–µ–ї—М–љ–Њ–≥–Њ —Б–Њ–µ–і–Є–љ–µ–љ–Є—П —Б –і—А—Г–≥–Є–Љ–Є FB, –Є–ї–Є –і–ї—П –≤—Л–≤–Њ–і–∞ –Є–Ј —З–Є–њ–∞ —З–µ—А–µ–Ј –љ–Њ–ґ–Ї–Є –≤—Л—Е–Њ–і–Њ–≤. –Ю–±—А–∞—В–Є—В–µ –≤–љ–Є–Љ–∞–љ–Є–µ, —З—В–Њ –≥–ї–Њ–±–∞–ї—М–љ—Л–µ —А–µ—Б—Г—А—Б—Л (—В–∞–Ї—В–Њ–≤—Л–є —Б–Є–≥–љ–∞–ї, —Б–Є–≥–љ–∞–ї—Л —Г—Б—В–∞–љ–Њ–≤–Ї–Є/—Б–±—А–Њ—Б–∞) –і–Њ—Б—В—Г–њ–љ—Л –Є–љ–і–Є–≤–Є–і—Г–∞–ї—М–љ–Њ –і–ї—П –Ї–∞–ґ–і–Њ–є —П—З–µ–є–Ї–Є, –µ—Б–ї–Є —Н—В–Њ –љ–µ–Њ–±—Е–Њ–і–Є–Љ–Њ. –Я–Ю —А–∞–Ј—А–∞–±–Њ—В–Ї–Є –љ–∞–Ј–љ–∞—З–∞–µ—В —Б–Є–≥–љ–∞–ї—Л –њ–µ—А–µ–Љ–µ–љ–љ—Л—Е –љ–∞ —А–∞–Ј–ї–Є—З–љ—Л–µ FB, –Є —Г–њ—А–∞–≤–ї—П–µ—В –≤–љ—Г—В—А–µ–љ–љ–Є–Љ–Є —Б–Њ–µ–і–Є–љ–µ–љ–Є—П–Љ–Є FB –Ї–∞–Ї —Б –ї–Њ–≥–Є—З–µ—Б–Ї–Є–Љ–Є —А–µ—Б—Г—А—Б–∞–Љ–Є, —В–∞–Ї –Є —Б –≥–ї–Њ–±–∞–ї—М–љ—Л–Љ–Є —А–µ—Б—Г—А—Б–∞–Љ–Є.

–†–Є—Б. 2. CoolRunner-II CPLD Function Block.

[–Ь–∞–Ї—А–Њ—П—З–µ–є–Ї–∞]

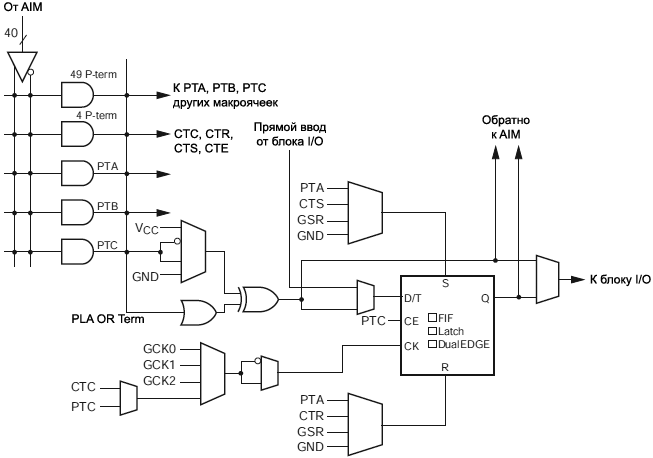

–Х—Б–ї–Є –Ј–∞–≥–ї—П–љ—Г—В—М –≤–љ—Г—В—А—М FB, —В–Њ –Љ—Л —Г–≤–Є–і–Є–Љ —В–∞–Љ 16 –Љ–∞–Ї—А–Њ—П—З–µ–µ–Ї. –Т –Њ—В–ї–Є—З–Є–µ –Њ—В –і—А—Г–≥–Є—Е –∞—А—Е–Є—В–µ–Ї—В—Г—А CPLD, –ї–Њ–≥–Є—З–µ—Б–Ї–Є–µ –≥—А–∞–љ–Є—Ж—Л –≤ FB –љ–µ—Б–Ї–Њ–ї—М–Ї–Њ –љ–µ—З–µ—В–Ї–Є–µ. –°–ї–Њ–ґ–љ–Њ –Є–Ј–Њ–ї–Є—А–Њ–≤–∞—В—М —Б–њ–µ—Ж–Є—Д–Є—З–µ—Б–Ї–Є–µ –ї–Њ–≥–Є—З–µ—Б–Ї–Є–µ —А–µ—Б—Г—А—Б—Л, –Ї–Њ—В–Њ—А—Л–µ –≤—Л–і–µ–ї–µ–љ—Л –љ–∞ –Њ—В–і–µ–ї—М–љ—Л–µ –Љ–∞–Ї—А–Њ—П—З–µ–є–Ї–Є - –Є–Ј-–Ј–∞ –≤–Њ–Ј–Љ–Њ–ґ–љ–Њ—Б—В–Є –≤–љ—Г—В—А–µ–љ–љ–Є—Е —Б–Њ–µ–і–Є–љ–µ–љ–Є–є —Б –њ–Њ–Љ–Њ—Й—М—О PLA. –†–Є—Б. 3 –њ–Њ–і—А–Њ–±–љ–Њ –њ–Њ–Ї–∞–Ј—Л–≤–∞–µ—В –Љ–∞–Ї—А–Њ—П—З–µ–є–Ї—Г CoolRunner-II –Ї –Ї–Њ—В–Њ—А–Њ–є –Љ—Л –±—Г–і–µ–Љ —З–∞—Б—В–Њ –Њ–±—А–∞—Й–∞—В—М—Б—П –≤ —Н—В–Њ–Љ –Њ–њ–Є—Б–∞–љ–Є–Є. –≠—В–∞ PLA —А–∞–Ј–Љ–µ—Й–µ–љ–∞ –≤ –ї–µ–≤–Њ–є —З–∞—Б—В–Є —А–Є—Б—Г–љ–Ї–∞. –Я—А–Є –њ–µ—А–µ–Љ–µ—Й–µ–љ–Є–Є –њ–Њ —А–Є—Б—Г–љ–Ї—Г –≤–њ—А–∞–≤–Њ –Љ—Л —Г–≤–Є–і–Є–Љ —В—А–Є–≥–≥–µ—А, —Г –Ї–Њ—В–Њ—А–Њ–≥–Њ –µ—Б—В—М —Б–Є–≥–љ–∞–ї —А–∞–Ј—А–µ—И–µ–љ–Є—П —В–∞–Ї—В–Є—А–Њ–≤–∞–љ–Є—П (clock enable, CE), –Є —Г–≤–Є–і–Є–Љ –љ–µ—Б–Ї–Њ–ї—М–Ї–Њ —В—А–∞–њ–µ—Ж–µ–Є–і–∞–ї—М–љ—Л—Е –Љ—Г–ї—М—В–Є–њ–ї–µ–Ї—Б–Њ—А–Њ–≤. –£ —Н—В–Є—Е –Љ—Г–ї—М—В–Є–њ–ї–µ–Ї—Б–Њ—А–Њ–≤ —П–≤–љ–Њ –љ–µ –њ–Њ–Ї–∞–Ј–∞–љ—Л –Є—Е —Б–Є–≥–љ–∞–ї—Л –≤—Л–±–Њ—А–Ї–Є –Є –±–Є—В—Л, –Ї–Њ—В–Њ—А—Л–µ –і–µ–ї–∞—О—В –≤—Л–±–Њ—А–Ї—Г. –≠—В–Є –±–Є—В—Л –љ–∞—Е–Њ–і—П—В—Б—П –≤ –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Њ–љ–љ–Њ–є –њ–∞–Љ—П—В–Є, –Є –Њ–љ–Є –Љ–µ–љ—П—О—В—Б—П –њ—А–Є –њ—А–Њ–≥—А–∞–Љ–Љ–Є—А–Њ–≤–∞–љ–Є–Є —П—З–µ–µ–Ї –≤–љ—Г—В—А–µ–љ–љ–µ–є —Н–љ–µ—А–≥–Њ–љ–µ–Ј–∞–≤–Є—Б–Є–Љ–Њ–є –њ–∞–Љ—П—В–Є CPLD (—Н—В–Є–Љ –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ–∞ CPLD –Є –Њ—В–ї–Є—З–∞–µ—В—Б—П –Њ—В –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ—Л FPGA - –њ–µ—А–≤–∞—П –Є–Љ–µ–µ—В –љ–∞ –±–Њ—А—В—Г —Н–љ–µ—А–≥–Њ–љ–µ–Ј–∞–≤–Є—Б–Є–Љ—Г—О –њ–∞–Љ—П—В—М, –∞ –≤—В–Њ—А–∞—П –≤–Љ–µ—Б—В–Њ —Н—В–Њ–≥–Њ –Є—Б–њ–Њ–ї—М–Ј—Г–µ—В —П—З–µ–є–Ї–Є RAM, –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є—П –≤ –Ї–Њ—В–Њ—А—Л–µ –Ј–∞–≥—А—Г–ґ–∞–µ—В—Б—П —Б–љ–∞—А—Г–ґ–Є –њ—А–Є –≤–Ї–ї—О—З–µ–љ–Є–Є –њ–Є—В–∞–љ–Є—П). –Ґ—А–Є–≥–≥–µ—А –Љ–Њ–ґ–љ–Њ —Б–Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞—В—М –Ї–∞–Ї D-—В—А–Є–≥–≥–µ—А, T-—В—А–Є–≥–≥–µ—А –Є–ї–Є –Ї–∞–Ї –њ—А–Њ–Ј—А–∞—З–љ—Г—О –Ј–∞—Й–µ–ї–Ї—Г. –Ґ–∞–Ї—В–Є—А–Њ–≤–∞–љ–Є–µ –Љ–Њ–ґ–µ—В –Њ—Б—Г—Й–µ—Б—В–≤–ї—П—В—М—Б—П –њ–Њ –ї—О–±–Њ–Љ—Г –њ–µ—А–µ–њ–∞–і—Г, –Є –і–ї—П —Н—В–Њ–≥–Њ –Љ–Њ–ґ–µ—В –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞—В—М—Б—П –Њ—В–і–µ–ї—М–љ—Л–є –Є—Б—В–Њ—З–љ–Є–Ї –Є–ї–Є –Љ–Њ–ґ–µ—В –±—Л—В—М –∞–Ї—В–Є–≤–Є—А–Њ–≤–∞–љ —А–µ–ґ–Є–Љ DualEDGE. –°—Е–µ–Љ—Л —Г—Б—В–∞–љ–Њ–≤–Ї–Є –Є —Б–±—А–Њ—Б–∞ —В—А–Є–≥–≥–µ—А–∞ –Њ—З–µ–љ—М –њ–Њ—Е–Њ–ґ–Є. –£—Б—В–∞–љ–Њ–≤–Ї–∞ –Љ–Њ–ґ–µ—В –±—Л—В—М –≤—Л–±—А–∞–љ–∞ –Є–Ј –≤–∞—А–Є–∞–љ—В–Њ–≤: –Њ—В—Б—Г—В—Б—В–≤–Є–µ —Б–Њ–±—Л—В–Є—П —Г—Б—В–∞–љ–Њ–≤–Ї–Є (GND), —Б–Є–≥–љ–∞–ї —Г—Б—В–∞–љ–Њ–≤–Ї–Є p-term (PTA), Control Term Set (CTS) –Є–ї–Є —Б–Є–≥–љ–∞–ї Global Set/Reset (GSR). –У–ї–Њ–±–∞–ї—М–љ—Л–µ —Б–Є–≥–љ–∞–ї—Л –њ—А–Њ—Е–Њ–і—П—В —З–µ—А–µ–Ј –≤–µ—Б—М —З–Є–њ –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ—Л. –°–Є–≥–љ–∞–ї—Л Control Term –Њ–±—Й–Є–µ –≤ –њ—А–µ–і–µ–ї–∞—Е –Њ–і–љ–Њ–≥–Њ FB. –°–Є–≥–љ–∞–ї—Л Product Term (p-term) –ї–Њ–Ї–∞–ї—М–љ—Л –≤ –њ—А–µ–і–µ–ї–∞—Е –Њ–њ—А–µ–і–µ–ї–µ–љ–љ–Њ–є –Љ–∞–Ї—А–Њ—П—З–µ–є–Ї–Є –≤–љ—Г—В—А–Є FB.

–†–Є—Б. 3. CoolRunner-II CPLD Macrocell.

–° –њ–Њ–Љ–Њ—Й—М—О —А–∞–Ј–і–µ–ї–µ–љ–Є—П –Є –Њ–±—К–µ–і–Є–љ–µ–љ–Є—П –Њ—В–і–µ–ї—М–љ—Л—Е —З–∞—Б—В–µ–є —А–Є—Б—Г–љ–Ї–∞ 3 –і–∞–ї–µ–µ –±—Г–і–µ—В –њ–Њ–Ї–∞–Ј–∞–љ–Њ, –Ї–∞–Ї —Б–Њ–Ј–і–∞–µ—В—Б—П –ї–Њ–≥–Є–Ї–∞ –≤–љ—Г—В—А–Є FB. –Я—А–Є —Н—В–Њ–Љ —А–Є—Б. 3 –±—Г–і–µ—В —Б–ї—Г–ґ–Є—В—М –і–ї—П –љ–∞—Б –Њ–±—Й–µ–є –Њ–њ–Њ—А–љ–Њ–є —В–Њ—З–Ї–Њ–є.

[–Ъ–∞–Ї —А–∞–±–Њ—В–∞–µ—В PLA]

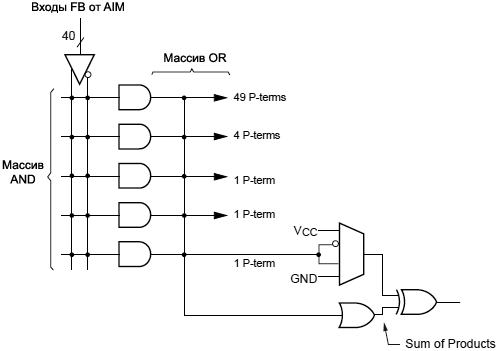

–Я–µ—А–µ–і —В–µ–Љ, –Ї–∞–Ї —А–∞—Б—Б–Љ–Њ—В—А–µ—В—М CoolRunner-II PLA, –і–∞–≤–∞–є—В–µ —Б–љ–∞—З–∞–ї–∞ –Њ–±—Б—Г–і–Є–Љ –Њ—Б–љ–Њ–≤–љ—Л–µ —Д—Г–љ–Ї—Ж–Є–Є PLA. –†–Є—Б. 4 –њ–Њ–Ї–∞–Ј—Л–≤–∞–µ—В —Г—Б—В—А–Њ–є—Б—В–≤–Њ –Њ–і–љ–Њ–є –Є–Ј —В–∞–Ї–Є—Е PLA. –Т —Н—В–Њ–Љ —Б–ї—Г—З–∞–µ –Љ—Л –≤–Є–і–Є–Љ 40 –≤—Е–Њ–і–љ—Л—Е —Б–Є–≥–љ–∞–ї–Њ–≤ –Є—Е –Ї–Њ–Љ–њ–ї–µ–Љ–µ–љ—В–∞—А–љ—Л–µ –±—Г—Д–µ—А—Л. –°–Є–≥–љ–∞–ї—Л –Є –Є—Е –Ї–Њ–Љ–њ–ї–µ–Љ–µ–љ—В (–Є–љ–≤–µ—А—Б–Є—П) –≤—Е–Њ–і—П—В –≤ –њ—А–Њ–≥—А–∞–Љ–Љ–Є—А—Г–µ–Љ—Л–є –Љ–∞—Б—Б–Є–≤ –ї–Њ–≥–Є–Ї–Є "–Ш" (AND).

–†–Є—Б. 4. –С–∞–Ј–Њ–≤–∞—П –∞—А—Е–Є—В–µ–Ї—В—Г—А–∞ PLA.

–Я—А–Њ–≥—А–∞–Љ–Љ–Є—А—Г–µ–Љ—Л–є –Љ–∞—Б—Б–Є–≤ AND –Љ–Њ–ґ–µ—В –њ–Њ–љ–∞—З–∞–ї—Г –≤—Л–≥–ї—П–і–µ—В—М –і–Њ–≤–Њ–ї—М–љ–Њ —Б—В—А–∞–љ–љ—Л–Љ, —Е–Њ—В—П –±—Л –њ–Њ—В–Њ–Љ—Г, —З—В–Њ –µ–≥–Њ –≤–µ–љ—В–Є–ї–Є AND –њ–Њ–Ї–∞–Ј–∞–љ—Л —В–Њ–ї—М–Ї–Њ —Б –Њ–і–љ–Є–Љ –і–ї–Є–љ–љ—Л–Љ –≤—Е–Њ–і–Њ–Љ. –°—Г—В—М –Ј–і–µ—Б—М –≤ —В–Њ–Љ, —З—В–Њ –≤–µ—А—В–Є–Ї–∞–ї—М–љ—Л–µ –ї–Є–љ–Є–Є –Ј–і–µ—Б—М –њ–µ—А–µ—Б–µ–Ї–∞—О—В—Б—П —Б –≥–Њ—А–Є–Ј–Њ–љ—В–∞–ї—М–љ—Л–Љ–Є, –≥–і–µ –Љ–Њ–ґ–µ—В –њ–Њ—В–µ–љ—Ж–Є–∞–ї—М–љ–Њ –±—Л—В—М –Љ–µ—Б—В–Њ —Б–Њ–µ–і–Є–љ–µ–љ–Є—П. –Э–µ –Ј–∞–њ—А–Њ–≥—А–∞–Љ–Љ–Є—А–Њ–≤–∞–љ–љ—Л–µ –Љ–µ—Б—В–∞ –њ–Њ–Ї–∞–Ј–∞–љ—Л –Ї—А–µ—Б—В–Є–Ї–∞–Љ–Є, –∞ –љ–∞ –Ј–∞–њ—А–Њ–≥—А–∞–Љ–Љ–Є—А–Њ–≤–∞–љ–љ—Л—Е –њ–Њ–Ї–∞–Ј–∞–љ –і–Є—Б–Ї. –Т–µ–љ—В–Є–ї–Є AND –љ–∞–Ј—Л–≤–∞—О—В—Б—П –Ј–і–µ—Б—М –Љ–∞—В–µ–Љ–∞—В–Є—З–µ—Б–Ї–Є–Љ –Є–Љ–µ–љ–µ–Љ - product term –Є–ї–Є p-term. –£ CoolRunner-II –Є–Љ–µ–µ—В—Б—П –љ–∞–±–Њ—А –Є–Ј 56 p-term, –њ—А–µ–і—Б—В–∞–≤–ї—П—О—Й–Є—Е –≤–µ–љ—В–Є–ї–Є AND –≤ –Ї–∞–ґ–і–Њ–Љ FB. –Т—Л—Е–Њ–і—Л p-term –љ–∞–њ—А–∞–≤–ї—П—О—В—Б—П –≤–њ—А–∞–≤–Њ, –≥–і–µ –Њ–љ–Є –≤—Е–Њ–і—П—В –≤ –і—А—Г–≥–Њ–є –њ—А–Њ–≥—А–∞–Љ–Љ–Є—А—Г–µ–Љ—Л–є –Љ–∞—Б—Б–Є–≤ "–Ш–Ы–Ш" (–Љ–∞—Б—Б–Є–≤ OR).

–Ч–і–µ—Б—М –Љ—Л —Б–љ–Њ–≤–∞ –≤–Є–і–Є–Љ –≤–µ—А—В–Є–Ї–∞–ї—М–љ—Л–µ –ї–Є–љ–Є–Є, –њ–µ—А–µ—Б–µ–Ї–∞—О—Й–Є–µ –≥–Њ—А–Є–Ј–Њ–љ—В–∞–ї—М–љ—Л–µ, –Є —В–µ –ґ–µ —Б–∞–Љ—Л–µ –Ї—А–µ—Б—В–Є–Ї–Є –Є –і–Є—Б–Ї–Є. –Ґ–∞ –ґ–µ –Є–і–µ—П —А–∞–±–Њ—В–∞–µ—В –Є —Б –Љ–∞—Б—Б–Є–≤–Њ–Љ OR. –Ч–і–µ—Б—М –Ї—А–µ—Б—В–Є–Ї —Н—В–Њ –њ–Њ—В–µ–љ—Ж–Є–∞–ї—М–љ–Њ–µ (–Њ—В—Б—Г—В—Б—В–≤—Г—О—Й–µ–µ) —Б–Њ–µ–і–Є–љ–µ–љ–Є–µ, –Є –і–Є—Б–Ї - —А–µ–∞–ї–Є–Ј–Њ–≤–∞–љ–љ–Њ–µ —Б–Њ–µ–і–Є–љ–µ–љ–Є–µ. –Ъ–ї—О—З–µ–≤–∞—П –Є–і–µ—П –і–ї—П –њ–Њ–љ–Є–Љ–∞–љ–Є—П –Ј–љ–∞—З–µ–љ–Є—П PLA –≤ —В–Њ–Љ, –Ї–∞–Ї —Б–Њ–≤–Љ–µ—Б—В–љ–Њ –Є—Б–њ–Њ–ї—М–Ј—Г—О—В—Б—П p-term. –Ю–±—А–∞—В–Є—В–µ –≤–љ–Є–Љ–∞–љ–Є–µ, —З—В–Њ –≤—Л—Е–Њ–і, –њ–Њ–Љ–µ—З–µ–љ–љ—Л–є –Ї–∞–Ї MC1, –Њ–±—К–µ–і–Є–љ—П–µ—В –Њ–њ–µ—А–∞—Ж–Є–µ–є AND –≤—Е–Њ–і—Л 1 –Є 2 –≤ p-term PT1. –Ш –і–∞–ї–µ–µ MC1 –Њ–њ–µ—А–∞—Ж–Є–µ–є OR –Њ–±—К–µ–і–Є–љ—П–µ—В—Б—П —Б–Њ –≤—Е–Њ–і–Њ–Љ 40. –Т—Л—Е–Њ–і, –њ–Њ–Љ–µ—З–µ–љ–љ—Л–є –Ї–∞–Ї MC2, –њ–Њ–ї—Г—З–∞–µ—В —А–µ–Ј—Г–ї—М—В–∞—В PT1, –Є —Д—Г–љ–Ї—Ж–Є–µ–є OR –Њ–±—К–µ–і–Є–љ—П–µ—В—Б—П –≤ p-term PT3. –Ч–і–µ—Б—М —А–µ–Ј—Г–ї—М—В–∞—В AND PT1 AND –Є—Б–њ–Њ–ї—М–Ј—Г–µ—В—Б—П –і–≤–∞–ґ–і—Л. –Э–µ—В —Б–њ–µ—Ж–Є–∞–ї—М–љ–Њ –≤—Л–і–µ–ї–µ–љ–љ—Л—Е p-term-–Њ–≤ –і–ї—П –ї—О–±–Њ–≥–Њ –Њ–њ—А–µ–і–µ–ї–µ–љ–љ–Њ–≥–Њ –≤—Л—Е–Њ–і–∞ "MC". –Я—А–Њ—Б—В–Њ –і–ї—П –њ–Њ–ї–љ–Њ—В—Л: –љ–∞ —Н—В–Њ–Љ —А–Є—Б. 4 MC56 –≤–Њ–Њ–±—Й–µ –љ–µ –Є—Б–њ–Њ–ї—М–Ј—Г–µ—В—Б—П.

[–Ъ–∞–Ї —А–∞–±–Њ—В–∞–µ—В PLA CoolRunner-II]

–Ґ–µ–њ–µ—А—М –і–∞–≤–∞–є—В–µ –њ–Њ—Б–Љ–Њ—В—А–Є–Љ, –Ї–∞–Ї —Н—В–∞ –Њ–±—Й–∞—П –Є–і–µ—П –њ–Њ–ї—Г—З–∞–µ—В –≤–Њ–њ–ї–Њ—Й–µ–љ–Є–µ –≤ FB –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ—Л CoolRunner-II. –Э–∞ —А–Є—Б. 5 –±–Њ–ї–µ–µ –њ–Њ–і—А–Њ–±–љ–Њ —А–∞—Б—Б–Љ–∞—В—А–Є–≤–∞–µ—В—Б—П –Љ–∞–Ї—А–Њ—П—З–µ–є–Ї—Г –≤ –Ї–Њ–љ—В–µ–Ї—Б—В–µ PLA. –Ю–±—А–∞—В–Є—В–µ –≤–љ–Є–Љ–∞–љ–Є–µ, —З—В–Њ –≤ —Н—В–Њ–є –≤–µ—А—Б–Є–Є –і–Є–∞–≥—А–∞–Љ–Љ—Л –Љ—Л –≤–Є–і–Є–Љ –≤—Б–µ 40 –≤—Е–Њ–і–Њ–≤, —Б–≤–µ—А–љ—Г—В—Л–µ —Б–ї–µ–≤–∞ –≤ –Њ–і–Є–љ –≤—Е–Њ–і–љ–Њ–є –±—Г—Д–µ—А —Б –µ–≥–Њ –Ї–Њ–Љ–њ–ї–µ–Љ–µ–љ—В–∞—А–љ—Л–Љ –і—А–∞–є–≤–µ—А–Њ–Љ. –Т–µ—А—Е–љ–Є–є AND —Н—В–Њ –≤ –і–µ–є—Б—В–≤–Є—В–µ–ї—М–љ–Њ—Б—В–Є 49 –Є–і–µ–љ—В–Є—З–љ—Л—Е –Ї–Њ–њ–Є–є p-term (49 P-terms). –Э–Є–ґ–µ –Є–і—Г—В –µ—Й–µ —З–µ—В—Л—А–µ p-term (4 P-terms), –Ј–∞ –Ї–Њ—В–Њ—А—Л–Љ –Є–і—Г—В –µ—Й–µ —В—А–Є –Њ–і–Є–љ–Њ—З–љ—Л—Е p-term. –Х—Б–ї–Є –њ–Њ—Б–Љ–Њ—В—А–µ—В—М –љ–∞ —А–Є—Б. 3, —В–Њ —З–µ—В—Л—А–µ p-term —Б–Њ–Њ—В–≤–µ—В—Б—В–≤—Г—О—В —Б–Є–≥–љ–∞–ї—Г, –њ–Њ–Љ–µ—З–µ–љ–љ–Њ–Љ—Г –Ї–∞–Ї —З–µ—В—Л—А–µ —Б–Є–≥–љ–∞–ї–∞ CT (Control Terms: CTC, CTR, CTS, CTE). –Ґ—А–Є –Њ—В–і–µ–ї—М–љ—Л—Е p-term –њ–Њ–Љ–µ—З–µ–љ—Л –љ–∞ —А–Є—Б. 3 –Ї–∞–Ї PTA, PTB –Є PTC. –Т—Б–µ–≥–Њ, –µ—Б–ї–Є —Б–ї–Њ–ґ–Є—В—М 49 + 4 + 3, —В–Њ –њ–Њ–ї—Г—З–∞–µ—В—Б—П 56 p-term. –Э–∞ —А–Є—Б. 5 –Љ—Л –Њ–±—Е–Њ–і–Є–Љ—Б—П –±–µ–Ј —Б–Є–Љ–≤–Њ–ї–Њ–≤ –Ї—А–µ—Б—В–Є–Ї–∞ –Є –і–Є—Б–Ї–∞, –Є –њ—А–Њ—Б—В–Њ –њ–Њ–Ї–∞–Ј—Л–≤–∞–µ–Љ –Љ–∞–ї–µ–љ—М–Ї–Є–µ —Б–Є–Љ–≤–Њ–ї—Л –і–Є—Б–Ї–∞ –≤ —В–µ—Е –Љ–µ—Б—В–∞—Е, –Ї–Њ—В–Њ—А—Л–µ –Љ–Њ–≥–ї–Є –±—Л –±—Л—В—М –Ј–∞–њ—А–Њ–≥—А–∞–Љ–Љ–Є—А–Њ–≤–∞–љ–љ—Л–Љ–Є.

–†–Є—Б. 5. –І–∞—Б—В–Є—З–љ–Њ —А–∞–Ј–≤–µ—А–љ—Г—В–∞—П –і–Є–∞–≥—А–∞–Љ–Љ–∞ –Љ–∞–Ї—А–Њ—П—З–µ–є–Ї–Є.

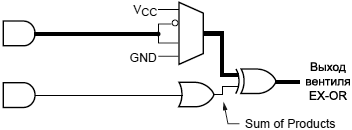

–Т—Л—Е–Њ–і—Л PLA p-term –њ—А–µ–і—Б—В–∞–≤–ї–µ–љ—Л –Ї –Љ–∞—Б—Б–Є–≤—Г OR, –Ї–Њ—В–Њ—А—Л–є –њ–Њ–і–Ї–ї—О—З–∞–µ—В—Б—П –Ї –Њ–і–љ–Њ–Љ—Г –≤—Е–Њ–і—Г –≤–µ–љ—В–Є–ї—П OR, –њ–Њ–Ї–∞–Ј–∞–љ–љ–Њ–≥–Њ –≤–љ–Є–Ј—Г (—Б–Љ. —А–Є—Б. 6). –Ш —Б–љ–Њ–≤–∞, –Љ–∞–ї–µ–љ—М–Ї–Є–µ –і–Є—Б–Ї–Є –њ–Њ–Ї–∞–Ј—Л–≤–∞—О—В –≤–Њ–Ј–Љ–Њ–ґ–љ–Њ—Б—В—М –њ–Њ–і–Ї–ї—О—З–µ–љ–Є—П –Ї OR term, —Б–Њ—Б—В–∞–≤–ї—П—О—Й–µ–Љ—Г –Њ—В–і–µ–ї—М–љ—Л–µ –≤—Е–Њ–і—Л –≤–µ–љ—В–Є–ї—П OR. –Т–љ—Г—В—А–Є FB –µ—Б—В—М –і–Њ 15 –Ї–Њ–њ–Є–є –ї–Њ–≥–Є–Ї–Є –њ—А–∞–≤–Њ–є —З–∞—Б—В–Є —А–Є—Б. 5, –љ–∞—З–Є–љ–∞—П —Б –≤–µ–љ—В–Є–ї—П EX-OR (–Є—Б–Ї–ї—О—З–∞—О—Й–µ–µ –Ш–Ы–Ш). –Ґ–∞–Ї–Є–Љ —Б–њ–Њ—Б–Њ–±–Њ–Љ —В–∞–Ї–Њ–є –ґ–µ –љ–∞–±–Њ—А –Є–Ј 56 p-term –њ–Њ–і–Ї–ї—О—З–∞–µ—В—Б—П —З–µ—А–µ–Ј —Б—В—А—Г–Ї—В—Г—А—Г OR –Є Mux (–Љ—Г–ї—М—В–Є–њ–ї–µ–Ї—Б–Њ—А–∞) –Ї –і—А—Г–≥–Є–Љ 15 –≤–µ–љ—В–Є–ї—П–Љ EX-OR –Љ–∞–Ї—А–Њ—П—З–µ–є–Ї–Є. –Ю–±—А–∞—В–Є—В–µ –≤–љ–Є–Љ–∞–љ–Є–µ, —З—В–Њ —В–Њ—З–Ї–∞ "Sum of Products" —Н—В–Њ –≤—Л—Е–Њ–і OR, –Є —Д–Њ—А–Љ–∞–ї—М–љ–Њ –≤—Л—Е–Њ–і PLA. EX-OR –і–Њ–±–∞–≤–ї–µ–љ –і–ї—П –≥–Є–±–Ї–Њ—Б—В–Є –Є —Г–њ—А–∞–≤–ї–µ–љ–Є—П –њ–Њ–ї—П—А–љ–Њ—Б—В—М—О.

–†–Є—Б. 6. –°—В—А—Г–Ї—В—Г—А–∞ CoolRunner-II PLA.

–Ф–ї—П –і–∞–ї—М–љ–µ–є—И–µ–≥–Њ —А–∞—Б—Б–Љ–Њ—В—А–µ–љ–Є—П —А–Є—Б. 6 –њ–Њ–Ї–∞–Ј—Л–≤–∞–µ—В, –Ї–∞–Ї PLA –њ–µ—А–µ—Е–Њ–і–Є—В –≤ —Б—Е–µ–Љ—Г EX-OR. –Э–∞ —А–Є—Б. 7 –±–Њ–ї–µ–µ –њ–Њ–і—А–Њ–±–љ–Њ –њ–Њ–Ї–∞–Ј–∞–љ –Ї—Г—Б–Њ–Ї —Б—В—А—Г–Ї—В—Г—А—Л Mux/OR/EX-OR, –Ј–і–µ—Б—М –њ–Њ–Ї–∞–Ј–∞–љ –Њ–і–Є–љ p-term, –≤—Е–Њ–і—П—Й–Є–є –≤ OR, –Є –і—А—Г–≥–Њ–є p-term –≤—Е–Њ–і—П—Й–Є–є –≤ Mux. –°–ї–µ–і—Г–µ—В –Њ—В–Љ–µ—В–Є—В—М, —З—В–Њ –Њ–±–∞ p-term-–∞ –≤—Е–Њ–і—П—В –≤ –Љ–∞—Б—Б–Є–≤ OR, –љ–Њ –Ј–і–µ—Б—М –Љ—Л —Д–Њ–Ї—Г—Б–Є—А—Г–µ–Љ—Б—П –љ–∞ —А–∞—Б—Б–Љ–Њ—В—А–µ–љ–Є–Є –ї–Њ–≥–Є—З–µ—Б–Ї–Њ–є —Б—В—А—Г–Ї—В—Г—А—Л, –≥–µ–љ–µ—А–Є—А—Г–µ–Љ–Њ–є –і–≤—Г–Љ—П p-term-–∞–Љ–Є, —А–∞–±–Њ—В–∞—О—Й–Є–Љ–Є –≤ —Б—В—А—Г–Ї—В—Г—А–µ Mux/OR/EX-OR.

–†–Є—Б. 7. –°–µ–Ї—Ж–Є—П OR/EX-OR –Љ–∞–Ї—А–Њ—П—З–µ–є–Ї–Є CoolRunner-II.

–Ь—Г–ї—М—В–Є–њ–ї–µ–Ї—Б–Њ—А —Г–њ—А–∞–≤–ї—П–µ—В –Њ–і–љ–Њ–є –љ–Њ–ґ–Ї–Њ–є –≤–µ–љ—В–Є–ї—П EX-OR, –њ—А–µ–і–Њ—Б—В–∞–≤–ї—П—П –≤—Л–±–Њ—А –Є–ї–Є VCC (–ї–Њ–≥. 1), –Є–ї–Є GND (–ї–Њ–≥. 0), –Є —В–µ–Љ —Б–∞–Љ—Л–Љ –љ–∞–њ—А—П–Љ—Г—О –њ–Њ–і–Ї–ї—О—З–µ–љ –Є–ї–Є –Ї p-term, –ї–Є –Ї –µ–≥–Њ –Ї–Њ–Љ–њ–ї–µ–Љ–µ–љ—В—Г. –°–љ–∞—З–∞–ї–∞ —А–∞—Б—Б–Љ–Њ—В—А–Є–Љ –Њ–њ—Ж–Є–Є VCC –Є GND. –Я–Њ—Б—В–Њ—П–љ–љ–∞—П –µ–і–Є–љ–Є—Ж–∞ –љ–∞ –Њ–і–љ–Њ–є –Є–Ј –љ–Њ–ґ–µ–Ї –≤–µ–љ—В–Є–ї—П EX-OR –і–µ–ї–∞–µ—В –µ–≥–Њ –Є–љ–≤–µ—А—В–Њ—А–Њ–Љ (–Ї–Њ–Љ–њ–ї–µ–Љ–µ–љ—В–Њ–Љ) —Б–Є–≥–љ–∞–ї–∞ –љ–∞ –і—А—Г–≥–Њ–є –љ–Њ–ґ–Ї–µ. –Ш –љ–∞–Њ–±–Њ—А–Њ—В, –њ–Њ—Б—В–Њ—П–љ–љ—Л–є 0 –љ–∞ –Њ–і–љ–Њ–є –Є–Ј –љ–Њ–ґ–µ–Ї –≤–µ–љ—В–Є–ї—П EX-OR –і–µ–ї–∞–µ—В –≤—Л—Е–Њ–і EX-OR —В–µ–Љ –ґ–µ —Б–Є–≥–љ–∞–ї–Њ–Љ, –Ї–Њ—В–Њ—А—Л–є –њ—А–Є—Б—Г—В—Б—В–≤—Г–µ—В –љ–∞ –і—А—Г–≥–Њ–Љ –≤—Е–Њ–і–µ. –Х—Б–ї–Є –њ—А–Њ—Й–µ, —В–Њ VCC –Є–ї–Є GND –љ–∞ —Г–њ—А–∞–≤–ї—П—О—Й–µ–Љ –≤—Е–Њ–і–µ –Љ—Г–ї—М—В–Є–њ–ї–µ–Ї—Б–Њ—А–∞ –і–Є–Ї—В—Г–µ—В, –Ї–∞–Ї –±—Г–і–µ—В –њ—А–Њ—Е–Њ–і–Є—В—М —Б–Є–≥–љ–∞–ї —З–µ—А–µ–Ј –≤–µ–љ—В–Є–ї—М EX-OR - –љ–∞–њ—А—П–Љ—Г—О –Є–ї–Є —Б –Є–љ–≤–µ—А—Б–Є–µ–є (–Њ—А–Є–≥–Є–љ–∞–ї—М–љ—Л–є —Б–Є–≥–љ–∞–ї –Є–ї–Є –µ–≥–Њ –Ї–Њ–Љ–њ–ї–µ–Љ–µ–љ—В).

–Ф–∞–≤–∞–є—В–µ –Њ–±—А–∞—В–Є–Љ –≤–љ–Є–Љ–∞–љ–Є–µ –љ–∞ –њ—Г—В—М —А–∞—Б–њ—А–Њ—Б—В—А–∞–љ–µ–љ–Є—П —Б–Є–≥–љ–∞–ї–∞ —А–Є—Б. 7, –њ–Њ–Ї–∞–Ј–∞–љ–љ—Л–є –ґ–Є—А–љ–Њ–є –ї–Є–љ–Є–µ–є, –≤ –∞—Б–њ–µ–Ї—В–µ VCC/GND –љ–∞ –Љ—Г–ї—М—В–Є–њ–ї–µ–Ї—Б–Њ—А–µ, –Є –Љ—Л —Г–≤–Є–і–Є–Љ —Б–њ–µ—Ж–Є–∞–ї—М–љ—Г—О –≤—Л—Б–Њ–Ї–Њ—Б–Ї–Њ—А–Њ—Б—В–љ—Г—О –Њ–њ—Ж–Є—О. –Ю–і–Є–љ –≤–µ–љ—В–Є–ї—М AND (p-term) –Љ–Њ–ґ–µ—В –љ–∞–њ—А—П–Љ—Г—О –њ—А–Њ—Е–Њ–і–Є—В—М –Љ—Г–ї—М—В–Є–њ–ї–µ–Ї—Б–Њ—А, –≤—Л—Е–Њ–і—П —З–µ—А–µ–Ј EX-OR, –ї–Є –њ–Њ–ї—Г—З–Є—В—М –Ї–Њ–Љ–њ–ї–µ–Љ–µ–љ—В–∞—А–љ—Л–є (NAND) –≤—Л—Е–Њ–і —З–µ—А–µ–Ј EX-OR. –≠—В–Њ—В —Б–Є–≥–љ–∞–ї –Љ–Њ–ґ–µ—В –±—Л—В—М –Ј–∞—В–µ–Љ –ї–Є–±–Њ –њ–Њ–і–Ї–ї—О—З–µ–љ –Ї —В—А–Є–≥–≥–µ—А—Г, –ї–Є–±–Њ –Њ–±–Њ–є—В–Є –µ–≥–Њ –Є –±—Л—В—М –њ–Њ–і–Ї–ї—О—З–µ–љ–љ—Л–Љ –Ї –љ–Њ–ґ–Ї–µ I/O. –Я—Г—В–µ–Љ –Њ–±—Е–Њ–і–∞ PLA OR term –Љ–Њ–ґ–µ—В –±—Л—В—М –њ–Њ–ї—Г—З–µ–љ–Њ —Г—Б–Ї–Њ—А–µ–љ–Є–µ (–Њ–±—Л—З–љ–Њ 0.3 –љ—Б), —З—В–Њ –Љ–Њ–ґ–µ—В –Є–Љ–µ—В—М –Ј–љ–∞—З–µ–љ–Є–µ –і–ї—П –≤—Л—Б–Њ–Ї–Њ—Б–Ї–Њ—А–Њ—Б—В–љ–Њ–≥–Њ –і–µ–Ї–Њ–і–Є—А–Њ–≤–∞–љ–Є—П. –І–∞—Б—В–Њ –і–µ–Ї–Њ–і–Є—А–Њ–≤–∞–љ–Є–µ –∞–і—А–µ—Б–∞ –Љ–Є–Ї—А–Њ–њ—А–Њ—Ж–µ—Б—Б–Њ—А–∞ —В—А–µ–±—Г–µ—В –Љ–∞–Ї—Б–Є–Љ–∞–ї—М–љ–Њ–є —Б–Ї–Њ—А–Њ—Б—В–Є, —З—В–Њ –Љ–Њ–ґ–µ—В –±—Л—В—М —А–µ–∞–ї–Є–Ј–Њ–≤–∞–љ–Њ —В–∞–Ї–Є–Љ —Г—Б–Ї–Њ—А–µ–љ–љ—Л–Љ –њ—А–Њ—Е–Њ–ґ–і–µ–љ–Є–µ–Љ —Б–Є–≥–љ–∞–ї–∞. –Ґ–Њ—В –ґ–µ —Б–∞–Љ—Л–є –±—Л—Б—В—А—Л–є –њ—Г—В—М AND/NAND –Љ–Њ–ґ–µ—В –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞—В—М—Б—П –і–ї—П –њ–Њ—Б—В—А–Њ–µ–љ–Є—П –±—Л—Б—В—А—Л—Е —А–µ–≥–Є—Б—В—А–Њ–≤ —Б–і–≤–Є–≥–∞, —Б—З–µ—В—З–Є–Ї–Њ–≤ –Є –љ–µ–Ї–Њ—В–Њ—А—Л—Е –њ—А–Њ—Б—В—Л—Е –Љ–∞—И–Є–љ —Б–Њ—Б—В–Њ—П–љ–Є–є.

[–Ш—Б–њ–Њ–ї—М–Ј–Њ–≤–∞–љ–Є–µ —А–µ—Б—Г—А—Б–Њ–≤ p-term (Product Term)]

–£—А–µ–Ј–∞–љ–љ–∞—П –≤–µ—А—Б–Є—П —А–Є—Б. 3 –њ–Њ–Ї–∞–Ј–∞–љ–∞ –љ–∞ —А–Є—Б. 8. –≠—В–∞ –≤–µ—А—Б–Є—П –≤–Ј–≥–ї—П–і–∞ –љ–∞ –Љ–∞–Ї—А–Њ—П—З–µ–є–Ї—Г –њ—А–µ–і—Б—В–∞–≤–ї—П–µ—В –≤–Њ–Ј–Љ–Њ–ґ–љ–Њ—Б—В—М –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞—В—М –Њ–і–Є–љ p-term (PTA) –≤ –Ї–∞–Ї —Б–Є–≥–љ–∞–ї —Г—Б—В–∞–љ–Њ–≤–Ї–Є, –Є –і—А—Г–≥–Њ–є p-term (PTC) –Ї–∞–Ї —Б–Є–≥–љ–∞–ї —В–∞–Ї—В–Њ–≤ p-term. –Ю–±—А–∞—В–Є—В–µ –≤–љ–Є–Љ–∞–љ–Є–µ, —З—В–Њ –Я–Ю —А–∞–Ј—А–∞–±–Њ—В–Ї–Є –і–Њ–ї–ґ–љ–Њ —Б–≥–µ–љ–µ—А–Є—А–Њ–≤–∞—В—М –±–Є—В—Л –њ—А–Њ–≥—А–∞–Љ–Љ–Є—А–Њ–≤–∞–љ–Є—П –і–ї—П —Г–њ—А–∞–≤–ї–µ–љ–Є—П –Љ—Г–ї—М—В–Є–њ–ї–µ–Ї—Б–Њ—А–∞–Љ–Є (–њ–Њ–Ї–∞–Ј–∞–љ—Л —В—А–∞–њ–µ—Ж–Є—П–Љ–Є), —З—В–Њ–±—Л –≤—Л–±—А–∞—В—М –љ—Г–ґ–љ–Њ–µ –њ–Њ–і–Ї–ї—О—З–µ–љ–Є–µ. –†–µ—Б—Г—А—Б—Л p-term –і–Њ—Б—В—Г–њ–љ—Л –і–ї—П –Њ–њ—А–µ–і–µ–ї–µ–љ–љ–Њ–є –Љ–∞–Ї—А–Њ—П—З–µ–є–Ї–Є, –љ–Њ –љ–µ –і–ї—П –ї—О–±–Њ–є –і—А—Г–≥–Њ–є –Љ–∞–Ї—А–Њ—П—З–µ–є–Ї–Є. –°–ї–µ–і—Г–µ—В —Г–њ–Њ–Љ—П–љ—Г—В—М, —З—В–Њ PTA –Љ–∞–Ї—А–Њ—П—З–µ–є–Ї–Є вДЦ 1 –Њ—В–ї–Є—З–∞–µ—В—Б—П –≥–µ–љ–µ—А–Є—А—Г–µ—В—Б—П –і—А—Г–≥–Є–Љ p-term, —З–µ–Љ PTA –і–ї—П –Љ–∞–Ї—А–Њ—П—З–µ–є–Ї–Є 2, 3, –Є–ї–Є 16. PTA –і–ї—П –Љ–∞–Ї—А–Њ—П—З–µ–є–Ї–Є 16 –і–Њ–ї–ґ–µ–љ –±—Л—В—М –і—А—Г–≥–Є–Љ –Є–Ј 49 p-term-–Њ–≤, –њ–Њ–Ї–∞–Ј–∞–љ–љ—Л—Е –љ–∞ —А–Є—Б. 8.

–†–Є—Б. 8. –Т–Є–і –љ–∞ –Љ–∞–Ї—А–Њ—П—З–µ–є–Ї—Г, —Г–њ—А–Њ—Й–µ–љ–љ—Л–є –і–ї—П –Њ—В–Њ–±—А–∞–ґ–µ–љ–Є—П —Б–Є–≥–љ–∞–ї–Њ–≤ —Г—Б—В–∞–љ–Њ–≤–Ї–Є p-term (PTA) –Є —В–∞–Ї—В–Њ–≤ p-term (PTC).

[–Ш—Б–њ–Њ–ї—М–Ј–Њ–≤–∞–љ–Є–µ —А–µ—Б—Г—А—Б–Њ–≤ —Г–њ—А–∞–≤–ї–µ–љ–Є—П p-term (Control Term)]

–Ш–љ–Њ–≥–і–∞ –љ–µ—Б–Ї–Њ–ї—М–Ї–Њ –Љ–∞–Ї—А–Њ—П—З–µ–µ–Ї –≤ –њ—А–µ–і–µ–ї–∞—Е –Њ–і–љ–Њ–≥–Њ FB –і–Њ–ї–ґ–љ—Л –Є–Љ–µ—В—М –Њ–і–Є–љ –Є —В–Њ—В –ґ–µ AND, –њ–Њ–ї—Г—З–∞—О—Й–Є–є —Б–Є–≥–љ–∞–ї—Л —В–∞–Ї—В–Њ–≤ (Clock), —Б–±—А–Њ—Б–∞ (Reset), —Г—Б—В–∞–љ–Њ–≤–Ї–Є (Set) –Є–ї–Є —А–∞–Ј—А–µ—И–µ–љ–Є—П –≤—Л—Е–Њ–і–∞ (PTOE). –Т —Н—В–Њ–Љ —Б–ї—Г—З–∞–µ –Я–Ю Fit Xilinx –і–Њ–ї–ґ–љ–Њ –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞—В—М control term –≤–Љ–µ—Б—В–Њ product term. Control term —В–Њ –ґ–µ —Б–∞–Љ–Њ–µ, —З—В–Њ –Є product term —Б —В–µ–Љ –Є—Б–Ї–ї—О—З–µ–љ–Є–µ–Љ, —З—В–Њ –Њ–љ–Є –њ–Њ–і–Ї–ї—О—З–∞—О—В—Б—П –Ї —В–µ–Љ –ґ–µ —Б–Є–≥–љ–∞–ї–∞–Љ –Љ—Г–ї—М—В–Є–Ї—Б–Њ—А–∞ –≤ –Ї–∞–ґ–і–Њ–є –Љ–∞–Ї—А–Њ—П—З–µ–є–Ї–µ –≤ –њ—А–µ–і–µ–ї–∞—Е –Њ–і–љ–Њ–≥–Њ FB. –Ш–Ј-–Ј–∞ —З–∞—Б—В–Њ–≥–Њ –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞–љ–Є—П –≤ –њ—А–Њ–µ–Ї—В–∞—Е, —Н—В–Њ –Њ—З–µ–љ—М –њ–Њ–ї–µ–Ј–љ–Њ –і–ї—П —Н–Ї–Њ–љ–Њ–Љ–Є–Є —Б–Њ–і–µ—А–ґ–Є–Љ–Њ–≥–Њ –Љ–∞—Б—Б–Є–≤–∞ 56 p-term AND. –Т —Б—Г—Й–љ–Њ—Б—В–Є –ґ–µ–ї–∞—В–µ–ї—М–љ–µ–µ –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞—В—М –Њ–і–Є–љ control term –і–∞–ґ–µ —Б –і–≤—Г–Љ—П –љ–µ–Њ–±—Е–Њ–і–Є–Љ—Л–Љ–Є –Љ–∞–Ї—А–Њ—П—З–µ–є–Ї–∞–Љ–Є, —З–µ–Љ —В—А–∞—В–Є—В—М 2 —А–µ—Б—Г—А—Б p-term –≤ –Њ—В–і–µ–ї—М–љ—Л—Е –Љ–∞–Ї—А–Њ—П—З–µ–є–Ї–∞—Е. –†–Є—Б. 9 –њ–Њ–Ї–∞–Ј—Л–≤–∞–µ—В, –Ї–∞–Ї –≤ –Љ–∞–Ї—А–Њ—П—З–µ–є–Ї–µ –Є—Б–њ–Њ–ї—М–Ј—Г—О—В—Б—П —Б–Є–≥–љ–∞–ї—Л control term set –Є control term clock, –Є —В–∞–Ї–ґ–µ —Б—В–∞–љ–Њ–≤—П—В—Б—П –і–Њ—Б—В—Г–њ–љ—Л–Љ–Є –і–ї—П –і—А—Г–≥–Є—Е –Љ–∞–Ї—А–Њ—П—З–µ–µ–Ї.

–†–Є—Б. 9. –Т–Є–і –љ–∞ –Љ–∞–Ї—А–Њ—П—З–µ–є–Ї—Г, —Г–њ—А–Њ—Й–µ–љ–љ—Л–є –і–ї—П –Њ—В–Њ–±—А–∞–ґ–µ–љ–Є—П —Б–Є–≥–љ–∞–ї–Њ–≤ Control Term Set –Є Control Term Clock.

–†–Є—Б. 10 –њ–Њ–Ї–∞–Ј—Л–≤–∞–µ—В, –Ї–∞–Ї control term (CTC) –≤–ї–Є—П–µ—В –љ–∞ –≤—Б–µ –Љ–∞–Ї—А–Њ—П—З–µ–є–Ї–Є –≤ –њ—А–µ–і–µ–ї–∞—Е –Њ–і–љ–Њ–≥–Њ FB. –Х—Б–ї–Є –Њ–і–љ–Є –Є —В–µ –ґ–µ —В–∞–Ї—В—Л –і–Њ–ї–ґ–љ—Л –±—Л–ї–Є –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞—В—М—Б—П –њ–Њ –љ–µ—Б–Ї–Њ–ї—М–Ї–Є–Љ FB, —В–Њ –і–ї—П –Я–Ю –±—Л–ї–Њ –±—Л –ї—Г—З—И–µ –љ–∞–Ј–љ–∞—З–Є—В—М –≥–ї–Њ–±–∞–ї—М–љ—Л–є —А–µ—Б—Г—А—Б (—В–∞–Ї—В—Л, —Г—Б—В–∞–љ–Њ–≤–Ї–∞/—Б–±—А–Њ—Б, —А–∞–Ј—А–µ—И–µ–љ–Є–µ –≤—Л—Е–Њ–і–∞) –≤–Љ–µ—Б—В–Њ —В—А–∞—В—Л p-term-–Њ–≤. –Т –љ–µ–Ї–Њ—В–Њ—А—Л—Е —Б–ї—Г—З–∞—П—Е –Љ–µ–љ—М—И—Г—О –њ–Њ—В—А–µ–±–ї—П–µ–Љ—Г—О –Љ–Њ—Й–љ–Њ—Б—В—М –і–∞—Б—В –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞–љ–Є–µ —А–µ—Б—Г—А—Б–∞ control term –Є–ї–Є product term –њ–Њ —Б—А–∞–≤–љ–µ–љ–Є—О —Б –≥–ї–Њ–±–∞–ї—М–љ—Л–Љ —А–µ—Б—Г—А—Б–Њ–Љ, –Ї–Њ—В–Њ—А—Л–є —В—А–∞—В–Є—В —Н–љ–µ—А–≥–Є—О –љ–∞ –њ–µ—А–µ–Ї–ї—О—З–µ–љ–Є–µ –≥–ї–Њ–±–∞–ї—М–љ–Њ–є —Ж–µ–њ–Є. –Т—Л–±–Њ—А –і–Є–Ї—В—Г–µ—В –Ї–Њ–Љ–њ—А–Њ–Љ–Є—Б—Б –Љ–µ–ґ–і—Г —Б–Ї–Њ—А–Њ—Б—В—М—О –Є –њ–Њ—В—А–µ–±–ї–µ–љ–Є–µ–Љ —В–Њ–Ї–∞.

–†–Є—Б. 10. –Т—Л—Б–Њ–Ї–Њ—Г—А–Њ–≤–љ–µ–≤—Л–є –≤–Є–і –љ–∞ FB, –њ–Њ–Ї–∞–Ј—Л–≤–∞—О—Й–Є–є Control Term C.

[–Ъ–Њ–Љ–±–Є–љ–Є—А–Њ–≤–∞–љ–Є–µ —А–µ—Б—Г—А—Б–Њ–≤ Product Term –Є Control Term]

–†–Є—Б. 11 –њ–Њ–Ї–∞–Ј—Л–≤–∞–µ—В, –Ї–∞–Ї –Љ–Њ–ґ–љ–Њ —Б–Љ–µ—И–Є–≤–∞—В—М –Є —Б–Њ–≤–Љ–µ—Б—В–љ–Њ –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞—В—М —А–µ—Б—Г—А—Б—Л product term –Є control term –≤ –Њ–і–љ–Њ–є –Љ–∞–Ї—А–Њ—П—З–µ–є–Ї–µ. –Т —Н—В–Њ–Љ –њ—А–Є–Љ–µ—А–µ –Љ—Л –≤–Є–і–Є–Љ product term set –Є control term clock. –°–Є–≥–љ–∞–ї control term clock —В–∞–Ї–ґ–µ –і–Њ—Б—В—Г–њ–µ–љ –і–ї—П –і—А—Г–≥–Є—Е –Љ–∞–Ї—А–Њ—П—З–µ–µ–Ї –≤ –њ—А–µ–і–µ–ї–∞—Е –Њ–і–љ–Њ–≥–Њ FB. –Ю–±—Л—З–љ–Њ –Я–Ю —А–∞–Ј—А–∞–±–Њ—В–Ї–Є –±—Г–і–µ—В –і–µ–ї–∞—В—М –≤—Л–±–Њ—А –љ–∞–њ–Њ–і–Њ–±–Є–µ —Н—В–Њ–≥–Њ, –µ—Б–ї–Є –Њ–њ—А–µ–і–µ–ї–µ–љ–љ–∞—П –Љ–∞–Ї—А–Њ—П—З–µ–є–Ї–∞ —В—А–µ–±—Г–µ—В –Њ–±—А–∞–±–Њ—В–Ї–Є —Б–Њ–±—Л—В–Є—П —Г—Б—В–∞–љ–Њ–≤–Ї–Є - —Г–љ–Є–Ї–∞–ї—М–љ–Њ–≥–Њ –і–ї—П –љ–µ—С - –≤ —В–Њ –≤—А–µ–Љ—П –Ї–∞–Ї –µ—С —В–∞–Ї—В–Є—А–Њ–≤–∞–љ–Є–µ –і–Њ–ї–ґ–љ–Њ –±—Л—В—М –Є–і–µ–љ—В–Є—З–љ—Л–Љ –Ї–∞–Ї –Љ–Є–љ–Є–Љ—Г–Љ –µ—Й–µ –Њ–і–љ–Њ–є –і—А—Г–≥–Њ–є –Љ–∞–Ї—А–Њ—П—З–µ–є–Ї–µ –≤ –њ—А–µ–і–µ–ї–∞—Е —В–Њ–≥–Њ –ґ–µ FB. –Ъ–Њ–Љ–њ—А–Њ–Љ–Є—Б—Б –Љ–µ–ґ–і—Г –Ї–∞–Ї–Є–Љ–Є —А–µ—Б—Г—А—Б–∞–Љ–Є –±—Л—В—М –і–µ–Ї–ї–∞—А–Є—А–Њ–≤–∞–љ–љ—Л–Љ–Є –і–ї—П –≥–µ–љ–µ—А–∞—Ж–Є–Є product term, –Є –Ї–∞–Ї–Є–µ –і–ї—П –≥–ї–Њ–±–∞–ї—М–љ—Л—Е —Б–Є–≥–љ–∞–ї–Њ–≤ –Є–ї–Є control term, —А–µ—И–∞–µ—В—Б—П —Б –њ–Њ–Љ–Њ—Й—М—О –Я–Ю —А–∞–Ј—А–∞–±–Њ—В–Ї–Є Fit Xilinx.

–†–Є—Б. 11. –Т–Є–і –љ–∞ –Љ–∞–Ї—А–Њ—П—З–µ–є–Ї—Г, —Г–њ—А–Њ—Й–µ–љ–љ—Л–є –і–ї—П –Њ—В–Њ–±—А–∞–ґ–µ–љ–Є—П –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞–љ–Є—П —Б–Є–≥–љ–∞–ї–Њ–≤ Product Term –Є Control Term.

–Т—Л—Б–Њ–Ї–∞—П —Б–Ї–Њ—А–Њ—Б—В—М –Є –љ–Є–Ј–Ї–Њ–µ –њ–Њ—В—А–µ–±–ї–µ–љ–Є–µ —Н–љ–µ—А–≥–Є–Є —Н—В–Њ —В—А–∞–і–Є—Ж–Є–Њ–љ–љ—Л–є –Ї–Њ–Љ–њ—А–Њ–Љ–Є—Б—Б –њ—А–Є —А–µ–∞–ї–Є–Ј–∞—Ж–Є–Є –Њ–њ—А–µ–і–µ–ї–µ–љ–љ–Њ–≥–Њ –і–Є–Ј–∞–є–љ–∞. –Ю–±—Л—З–љ–Њ –≤—Л—Б–Њ–Ї–Њ—Б–Ї–Њ—А–Њ—Б—В–љ—Л–µ CPLD —В—А–µ–±—Г—О—В –њ–Њ–≤—Л—И–µ–љ–љ–Њ–≥–Њ —В–Њ–Ї–∞ –і–ї—П —А–µ–∞–ї–Є–Ј–∞—Ж–Є–Є –Ї–Њ—А–Њ—В–Ї–Є—Е –Є–љ—В–µ—А–≤–∞–ї–Њ–≤ –њ–µ—А–µ–Ї–ї—О—З–µ–љ–Є—П. CoolRunner-II –њ—А–µ–і–Њ—Б—В–∞–≤–ї—П–µ—В –ї–Њ–≥–Є–Ї—Г, —В—А–µ–±—Г–µ–Љ—Г—О –і–ї—П –≤—Л—Б–Њ–Ї–Њ—Б–Ї–Њ—А–Њ—Б—В–љ—Л—Е –њ—А–Є–ї–Њ–ґ–µ–љ–Є–є –Њ–±—Й–µ–≥–Њ –љ–∞–Ј–љ–∞—З–µ–љ–Є—П –њ—А–Є –∞–±—Б–Њ–ї—О—В–љ–Њ–Љ –Љ–Є–љ–Є–Љ—Г–Љ–µ –њ–Њ—В—А–µ–±–ї—П–µ–Љ–Њ–є –Љ–Њ—Й–љ–Њ—Б—В–Є.

[–°—Б—Л–ї–Ї–Є]

1. XAPP376 Understanding the CoolRunner-II Logic Engine site:xilinx.com.

2. –°–µ–Љ–µ–є—Б—В–≤–Њ CPLD CoolRunner-II.

3. –Ґ–µ—А–Љ–Є–љ—Л –Є —Б–Њ–Ї—А–∞—Й–µ–љ–Є—П, —Б–ї–Њ–≤–∞—А–Є–Ї. |