|

ąÆ čŹč鹊ą╣ čüčéą░čéčīąĄ ą┐čĆąĖą▓ąĄą┤ąĄąĮ ą┐ąĄčĆąĄą▓ąŠą┤ čćą░čüč鹥ą╣ ą┤ąŠą║čāą╝ąĄąĮčéą░čåąĖąĖ [1], ą║ą░čüą░čÄčēąĖčģčüčÅ č鹊ą╗čīą║ąŠ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ Blackfin ADSP-BF53x. ą×ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ čāčéąĖą╗ąĖčéčŗ ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ čäą░ą╣ą╗ą░ ąĘą░ą│čĆčāąĘą║ąĖ - elfloader.exe.

[ąÆą▓ąĄą┤ąĄąĮąĖąĄ: ąŠčüąĮąŠą▓ąĮčŗąĄ ą┐ąŠąĮčÅčéąĖčÅ ąĖ č鹥čĆą╝ąĖąĮčŗ]

ąŁč鹊čé ą┤ąŠą║čāą╝ąĄąĮčé ąŠą┐ąĖčüčŗą▓ą░ąĄčé ą│ą╗ą░ą▓ąĮčŗą╝ ąŠą▒čĆą░ąĘąŠą╝ čäčāąĮą║čåąĖąŠąĮą░ą╗ čāčéąĖą╗ąĖčéčŗ ąĘą░ą│čĆčāąĘą║ąĖ, ą░ čéą░ą║ąČąĄ ą┐čĆąŠčåąĄčüčü loading-ą░ (ąĘą░ą│čĆčāąĘą║ą░) ąĖ splitting-ą░ (čĆą░ąĘą┤ąĄą╗ąĄąĮąĖąĄ ąĖčüą┐ąŠą╗ąĮčÅąĄą╝ąŠą│ąŠ ą║ąŠą┤ą░). ąØąĄą║ąŠč鹊čĆčŗąĄ ąĮąĄą┐ąŠąĮčÅčéąĮčŗąĄ čüąŠą║čĆą░čēąĄąĮąĖčÅ ąĖ č鹥čĆą╝ąĖąĮčŗ čüą╝. ą▓ čĆą░ąĘą┤ąĄą╗ąĄ "ąĪą╗ąŠą▓ą░čĆąĖą║" čüčéą░č鹥ą╣ [3, 4].

ąŚą░ą│čĆčāąĘčćąĖą║ ąĖ ąŻčéąĖą╗ąĖčéą░ ąĘą░ą│čĆčāąĘą║ąĖ. ą¤ąŠą┤ č鹥čĆą╝ąĖąĮąŠą╝ čāčéąĖą╗ąĖčéą░ ąĘą░ą│čĆčāąĘą║ąĖ ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ą░ elfloader.exe (Loader Utility), ą║ąŠč鹊čĆą░čÅ čÅą▓ą╗čÅąĄčéčüčÅ čćą░čüčéčīčÄ ą┐ą░ą║ąĄčéą░ čĆą░ąĘčĆą░ą▒ąŠčéą║ąĖ VisualDSP++. ąŻčéąĖą╗ąĖčéą░ ąĘą░ą│čĆčāąĘą║ąĖ ą▓čŗą┐ąŠą╗ąĮčÅąĄčé ąĘą░ą▓ąĄčĆčłą░čÄčēčāčÄ ąŠą▒čĆą░ą▒ąŠčéą║čā ą┐čĆąŠčåąĄčüčüą░ ą║ąŠą╝ą┐ąĖą╗čÅčåąĖąĖ, ą┐ąŠą╗čāčćą░čÅ ąĮą░ ą▓čģąŠą┤ąĄ ąŠą┤ąĖąĮ ąĖą╗ąĖ ąĮąĄčüą║ąŠą╗čīą║ąŠ ąĖčüą┐ąŠą╗ąĮčÅąĄą╝čŗčģ čäą░ą╣ą╗ąŠą▓ (čü čĆą░čüčłąĖčĆąĄąĮąĖąĄą╝ *.dxe) ąĖ ą│ąĄąĮąĄčĆąĖčĆčāčÅ ąĮą░ ą▓čŗčģąŠą┤ąĄ čäą░ą╣ą╗ ąĘą░ą│čĆčāąĘą║ąĖ (čü čĆą░čüčłąĖčĆąĄąĮąĖąĄą╝ *.ldr). ąÆ ą┐čĆąŠčåąĄčüčüąĄ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ čäą░ą╣ą╗ąŠą▓ *.dxe čāčéąĖą╗ąĖčéą░ ąĘą░ą│čĆčāąĘą║ąĖ čĆą░čüą┐ą░ą║ąŠą▓čŗą▓ą░ąĄčé čüąĄą│ą╝ąĄąĮčéčŗ, ą┤ąĄą║ą╗ą░čĆąĖčĆąŠą▓ą░ąĮąĮčŗąĄ ą║ąŠą╝ą░ąĮą┤ąŠą╣ TYPE(RAM) ą▓ čäą░ą╣ą╗ąĄ Linker Description File (.ldf). ą¤ąŠčüą║ąŠą╗čīą║čā čäą░ą╣ą╗ .dxe čüą╗ąĄą┤čāąĄčé čüčéą░ąĮą┤ą░čĆčéčā Executable and Linkable Format (ELF), čāčéąĖą╗ąĖčéą░ ąĘą░ą│čĆčāąĘą║ąĖ čćą░čüč鹊 ąĮą░ąĘčŗą▓ą░čÄčé čāčéąĖą╗ąĖč鹊ą╣ elfloader. ąĪą╝. čéą░ą║ąČąĄ čĆą░ąĘą┤ąĄą╗ "ąÜą░ą║ čĆą░ą▒ąŠčéą░ąĄčé čāčéąĖą╗ąĖčéą░ ąĘą░ą│čĆčāąĘą║ąĖ".

Splitter Utility. Splitter utility čéą░ą║ąČąĄ čÅą▓ą╗čÅąĄčéčüčÅ čćą░čüčéčīčÄ ą┐ą░ą║ąĄčéą░ VisualDSP++. ąŻčéąĖą╗ąĖčéą░ čüą┐ą╗ąĖčéč鹥čĆą░ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčé ąŠą┤ąĖąĮ ąĖą╗ąĖ ąĮąĄčüą║ąŠą╗čīą║ąŠ čäą░ą╣ą╗ąŠą▓ ąĖčüą┐ąŠą╗ąĮčÅąĄą╝čŗčģ čäą░ą╣ą╗ąŠą▓ (čü čĆą░čüčłąĖčĆąĄąĮąĖąĄą╝ .dxe), čĆą░čüą┐ą░ą║ąŠą▓čŗą▓ą░ąĄčé čüąĄą│ą╝ąĄąĮčéčŗ, ą┤ąĄą║ą╗ą░čĆąĖčĆąŠą▓ą░ąĮąĮčŗąĄ ą║ąŠą╝ą░ąĮą┤ąŠą╣ TYPE(ROM) čäą░ą╣ą╗ą░ Linker Description File (.ldf), ąĖ ą│ąĄąĮąĄčĆąĖčĆčāąĄčé čäą░ą╣ą╗, čüąŠčüč鹊čÅčēąĖą╣ ąĖąĘ ąĖąĮčüčéčĆčāą║čåąĖą╣ (ą║ąŠą╝ą░ąĮą┤) ą┐čĆąŠčåąĄčüčüąŠčĆą░. ąŁč鹊 čäą░ą╣ą╗ ą┐čĆąŠčłąĖą▓ą░ąĄčéčüčÅ ą▓ ą┐ą░ą╝čÅčéčī EPROM ąĖą╗ąĖ flash ą┐čĆąŠčåąĄčüčüąŠčĆą░, ą║ąŠč鹊čĆą░čÅ ą┐ąŠą┤ą║ą╗čÄč湥ąĮą░ ą║ ąĮąĄą╝čā č湥čĆąĄąĘ čüąĖčüč鹥ą╝ąĮčāčÄ čłąĖąĮčā, čéą░ą║ čćč鹊 ą┐čĆąŠčåąĄčüčüąŠčĆ ą╝ąŠąČąĄčé ąĮą░ą┐čĆčÅą╝čāčÄ ą▓čŗą▒ąĖčĆą░čéčī ąŠčéčéčāą┤ą░ ą║ąŠą╝ą░ąĮą┤čŗ ąĖ ą▓čŗą┐ąŠą╗ąĮčÅčéčī ąĖčģ. ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ ą┐čĆąŠ čĆą░ą▒ąŠčéčā Splitter Utility čüą╝. čĆą░ąĘą┤ąĄą╗ "Splitter Utility Operations" čĆčāą║ąŠą▓ąŠą┤čüčéą▓ą░ [1].

ąĀą░ą▒ąŠčéą░ čāčéąĖą╗ąĖčéčŗ čüą┐ą╗ąĖčéč鹥čĆą░ ąĖ čāčéąĖą╗ąĖčéčŗ ąĘą░ą│čĆčāąĘą║ąĖ ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠą▒čĆą░ą▒ąŠčéą░ąĮą░ ą╗ąĖą▒ąŠ ąŠčéą┤ąĄą╗čīąĮčŗą╝ąĖ čāčéąĖą╗ąĖčéą░ą╝ąĖ, ą╗ąĖą▒ąŠ ąŠą┤ąĮąŠą╣ ąĖ č鹊ą╣ ąČąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣ (čüą╝. čĆą░ąĘą┤ąĄą╗ "ąØąĄ ąĘą░ą│čĆčāąČą░ąĄą╝čŗąĄ čäą░ą╣ą╗čŗ (Non-bootable) ąĖ ąĘą░ą│čĆčāąČą░ąĄą╝čŗąĄ (Boot-loadable) - ą▓ č湥ą╝ čĆą░ąĘąĮąĖčåą░?"). ąöą╗čÅ ąĘą░ą│čĆčāąČą░ąĄą╝čŗčģ čäą░ą╣ą╗ąŠą▓ ą▓čŗčģąŠą┤ąĮąŠą╣ čäą░ą╣ą╗ čüąŠą┤ąĄčƹȹĖčé ą║ą░ą║ ąĖąĮčüčéčĆčāą║čåąĖąĖ ą║ąŠą┤ą░, čéą░ą║ ąĖ čüą┐ąĄčåąĖą░ą╗čīąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┐ąŠč鹊ą║ąŠą▓ ąĘą░ą│čĆčāąĘą║ąĖ (ąĘą░ą│ąŠą╗ąŠą▓ą║ąĖ, ąŠą┐ąĖčüčŗą▓ą░čÄčēąĖąĄ čüąĄą║čåąĖąĖ čäą░ą╣ą╗ą░ ąĘą░ą│čĆčāąĘą║ąĖ, čüą╝. [2]).

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: splitter utility ąĮąĄ ąĖą╝ąĄąĄčé ąŠčéąĮąŠčłąĄąĮąĖčÅ ą║ ą┐čĆąŠčåąĄčüčüąŠčĆą░ą╝ Blackfin, ąĖ ą▓ čŹč鹊ą╝ ą┐ąĄčĆąĄą▓ąŠą┤ąĄ ą┤ąŠą║čāą╝ąĄąĮčéą░čåąĖąĖ [1] ąĮąĄ čĆą░čüčüą╝ą░čéčĆąĖą▓ą░ąĄčéčüčÅ.

ążą░ą╣ą╗ ąĘą░ą│čĆčāąĘą║ąĖ. ążą░ą╣ą╗ ąĘą░ą│čĆčāąĘą║ąĖ (loader file) ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ čāčéąĖą╗ąĖč鹊ą╣ ąĘą░ą│čĆčāąĘą║ąĖ. ą×ą▒čŗčćąĮąŠ čŹč鹊čé čäą░ą╣ą╗ ąĖą╝ąĄąĄčé čĆą░čüčłąĖčĆąĄąĮąĖąĄ .ldr, ąĖ ą┐ąŠčŹč鹊ą╝čā čćą░čüč鹊 ąĮą░ąĘčŗą▓ą░ąĄčéčüčÅ čäą░ą╣ą╗ąŠą╝ LDR. ążą░ą╣ą╗čŗ ąĘą░ą│čĆčāąĘą║ąĖ ą╝ąŠą│čāčé čāą┤ąŠą▓ą╗ąĄčéą▓ąŠčĆčÅčéčī ąŠą┤ąĮąŠą╝čā ąĖą╗ąĖ ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ č乊čĆą╝ą░čéą░ą╝. ą×ą▒čēąĖąĄ č乊čĆą╝ą░čéčŗ čüąŠą┤ąĄčƹȹĖą╝ąŠą│ąŠ čäą░ą╣ą╗ą░ ąĘą░ą│čĆčāąĘą║ąĖ: Intel hex-32, binary ąĖą╗ąĖ ASCII (čćą░čēąĄ ą▓čüąĄą│ąŠ ą┐čĆąĖą╝ąĄąĮčÅąĄčéčüčÅ ą┤ą▓ąŠąĖčćąĮčŗą╣ č乊čĆą╝ą░čé, binary). ąØąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé č乊čĆą╝ą░čéą░ čäą░ą╣ą╗ ąĘą░ą│čĆčāąĘą║ąĖ ąŠą┐ąĖčüčŗą▓ą░ąĄčé ąŠą▒čĆą░ąĘ ąĘą░ą│čĆčāąĘą║ąĖ (boot image), ą║ąŠč鹊čĆčŗą╣ ą╝ąŠąČąĮąŠ čāą▓ąĖą┤ąĄčéčī ą▓ ą┤ą▓ąŠąĖčćąĮąŠą╣ (binary) ą▓ąĄčĆčüąĖąĖ čäą░ą╣ą╗ą░ ąĘą░ą│čĆčāąĘą║ąĖ. ąóą░ą║ąČąĄ čüą╝. čĆą░ąĘą┤ąĄą╗ "ąØąĄ ąĘą░ą│čĆčāąČą░ąĄą╝čŗąĄ čäą░ą╣ą╗čŗ (Non-bootable) ąĖ ąĘą░ą│čĆčāąČą░ąĄą╝čŗąĄ (Boot-loadable) - ą▓ č湥ą╝ čĆą░ąĘąĮąĖčåą░?".

ą×ą┐čåąĖąĖ ą║ąŠą╝ą░ąĮą┤ąĮąŠą╣ čüčéčĆąŠą║ąĖ čāčéąĖą╗ąĖčéčŗ ąĘą░ą│čĆčāąĘą║ąĖ. ą¤ąŠą▓ąĄą┤ąĄąĮąĖąĄ čāčéąĖą╗ąĖčéčŗ ąĘą░ą│čĆčāąĘą║ąĖ čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ą╝ąĮąŠą│ąŠčćąĖčüą╗ąĄąĮąĮčŗą╝ąĖ ąŠą┐čåąĖčÅą╝ąĖ ą║ąŠą╝ą░ąĮą┤ąĮąŠą╣ čüčéčĆąŠą║ąĖ, ą║ąŠč鹊čĆčŗąĄ ą▒čāą┤čāčé ą┐ąŠą┤čĆąŠą▒ąĮąŠ čĆą░čüčüą╝ąŠčéčĆąĄąĮčŗ ą┤ą░ą╗ąĄąĄ (ą▓ čŹč鹊ą╝ ą┐ąĄčĆąĄą▓ąŠą┤ąĄ [1] č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ą┐čĆąŠčåąĄčüčüąŠčĆą░ Blackfin). ą×čé ąŠą┐čåąĖą╣ ąĘą░ą▓ąĖčüąĖčé ą│ąĄąĮąĄčĆą░čåąĖčÅ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čäą░ą╣ą╗ą░ ąĘą░ą│čĆčāąĘą║ąĖ *.ldr.

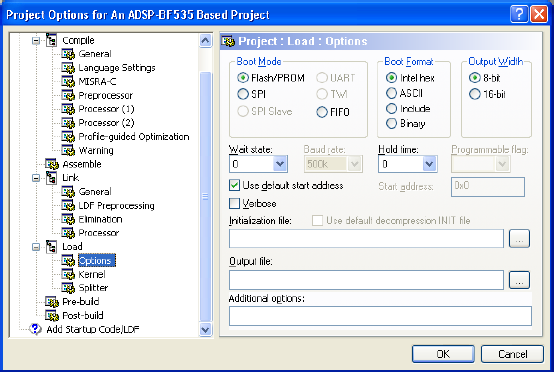

ąĀą░ąĘą┤ąĄą╗ "Load" čüą▓ąŠą╣čüčéą▓ ą┐čĆąŠąĄą║čéą░. ąÆ čüčĆąĄą┤ąĄ VisualDSP++ ą╝ąŠąČąĮąŠ čāą┐čĆą░ą▓ą╗čÅčéčī čüą▓ąŠą╣čüčéą▓ą░ą╝ąĖ ą┐čĆąŠąĄą║čéą░ (Project Options). ąöąĖą░ą╗ąŠą│ čĆąĄą┤ą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ čüą▓ąŠą╣čüčéą▓ ą┐čĆąŠąĄą║čéą░ ąĖą╝ąĄčÄčé čĆą░ąĘą┤ąĄą╗ čüą▓ąŠą╣čüčéą▓ ąĘą░ą│čĆčāąĘą║ąĖ (Load). ąŁč鹊čé ą│čĆą░čäąĖč湥čüą║ąĖą╣ ąĖąĮč鹥čĆč乥ą╣čü ą┐ąŠą╝ąŠą│ą░ąĄčé čüč乊čĆą╝ąĖčĆąŠą▓ą░čéčī ą║ąŠą╝ą░ąĮą┤ąĮčāčÄ čüčéčĆąŠą║čā ą┤ą╗čÅ čāčéąĖą╗ąĖčéčŗ ąĘą░ą│čĆčāąĘą║ąĖ (čāčéąĖą╗ąĖčéą░ elfloader.exe ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą▒čāą┤ąĄčé ąĘą░ą┐čāčēąĄąĮą░ čüčĆąĄą┤ąŠą╣ VisualDSP, ąĄčüą╗ąĖ ą▓čŗą▒čĆą░ąĮą░ ą│ąĄąĮąĄčĆą░čåąĖčÅ čäą░ą╣ą╗ą░ ąĘą░ą│čĆčāąĘą║ąĖ č湥čĆąĄąĘ Project Options -> Project -> čĆą░ąĘą┤ąĄą╗ ąŠą┐čåąĖą╣ Target -> Type: Loader file).

ąĀąĄąČąĖą╝ ąĘą░ą│čĆčāąĘą║ąĖ (Boot Mode). ąæąŠą╗čīčłąĖąĮčüčéą▓ąŠ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé ąĮąĄčüą║ąŠą╗čīą║ąŠ čĆąĄąČąĖą╝ąŠą▓ ąĘą░ą│čĆčāąĘą║ąĖ. ąĀąĄąČąĖą╝ ąĘą░ą│čĆčāąĘą║ąĖ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé čüą┐ąĄčåąĖą░ą╗čīąĮčŗąĄ ą▓čģąŠą┤ąĮčŗąĄ ą▓čŗą▓ąŠą┤čŗ ą┐čĆąŠčåąĄčüčüąŠčĆą░, ą║ąŠč鹊čĆčŗąĄ ąŠą┐čĆą░čłąĖą▓ą░čÄčéčüčÅ ąĖą╝ ą╗ąĖą▒ąŠ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ (reset), ą╗ąĖą▒ąŠ ą┐ąŠčüą╗ąĄ ą▓čŗčģąŠą┤ą░ ąĖąĘ čüąŠčüč鹊čÅąĮąĖčÅ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ (power-down state). ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ ą┐čĆąŠ čĆąĄąČąĖą╝čŗ ąĘą░ą│čĆčāąĘą║ąĖ čüą╝. čĆą░ąĘą┤ąĄą╗ "Boot Modes", ą░ čéą░ą║ąČąĄ čüčéą░čéčīčÄ [2].

Boot Strapping. ą¤čĆąŠčåąĄčüčü ąĘą░ą│čĆčāąĘą║ąĖ čüąŠčüč鹊ąĖčé ąĖąĘ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ čłą░ą│ąŠą▓, čéą░ą║ąĖčģ ą║ą░ą║ ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮą░čÅ ąĘą░ą│čĆčāąĘą║ą░ čÅą┤čĆą░ (boot kernel) ąĖą╗ąĖ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ąĘą░ą│čĆčāąĘčćąĖą║ą░ą╝ąĖ ą▓č鹊čĆąŠą│ąŠ čāčĆąŠą▓ąĮčÅ (second-stage loaders). ąŁčéą░ ą┐čĆąŠčåąĄą┤čāčĆą░ ąĮą░ąĘčŗą▓ą░ąĄčéčüčÅ boot strapping ąĖą╗ąĖ boot ROM.

ąÜąŠą┤ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ (Init Code). ąŁč鹊 čćą░čüčéčī ą┐ąŠč鹊ą║ą░ ąĘą░ą│čĆčāąĘą║ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ Blackfin, ąĖ ąĄčæ ą╝ąŠąČąĮąŠ čĆą░čüčüą╝ą░čéčĆąĖą▓ą░čéčī ą║ą░ą║ čüą┐ąĄčåąĖą░ą╗čīąĮčŗą╣ ą▒ą╗ąŠą║ ąĘą░ą│čĆčāąĘą║ąĖ. ąÆ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ ąŠą▒čŗčćąĮąŠ čüąĮą░čćą░ą╗ą░ ąĘą░ą│čĆčāąČą░čÄčéčüčÅ ą▓čüąĄ ąĘą░ą│čĆčāąČą░ąĄą╝čŗąĄ ą▒ą╗ąŠą║ąĖ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ, ąĖ ąĘą░č鹥ą╝ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą▓ čüą░ą╝ąŠ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ, ą║ąŠą┤ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą▓ąŠ ą▓čĆąĄą╝čÅ ąĘą░ą│čĆčāąĘą║ąĖ - ą║ą░ą║ ą┐ąĄčĆą▓čŗą╣ čłą░ą│ ą▓čüąĄą│ąŠ ą┐čĆąŠčåąĄčüčüą░ ąĘą░ą│čĆčāąĘą║ąĖ. ąóą░ą║ąŠąĄ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé, ą║ąŠą│ą┤ą░ ą║ąŠą┤ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ąĖ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą┐ąĄčĆąĄą┤ ą╗čÄą▒čŗą╝ ą┤čĆčāą│ąĖą╝ ąĘą░ą│čĆčāąČą░ąĄą╝čŗą╝ ą▒ą╗ąŠą║ąŠą╝. ąØąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéčī ąĮą░ą╗ąĖčćąĖčÅ ą║ąŠą┤ą░ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ ąŠą▒čāčüą╗ąŠą▓ą╗ąĄąĮą░ čéą░ą║ąĖą╝ąĖ čüą╗čāčćą░čÅą╝ąĖ, ą║ą░ą║ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéčī ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ ą┐ą░ą╝čÅčéąĖ SDRAM (ąĮą░ą┐čĆąĖą╝ąĄčĆ, ą║ąŠą┤ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ąĖ ą┤ą░ąĮąĮčŗąĄ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĘą░ą│čĆčāąČąĄąĮčŗ ą▓ SDARM), ąĮą░čüčéčĆąŠą╣ą║ą░ ą║ą░ą║ąĖčģ-č鹊 čüą┐ąĄčåąĖčäąĖčćąĮčŗčģ ą░ą┐ą┐ą░čĆą░čéąĮčŗčģ čüčĆąĄą┤čüčéą▓ čüąĖčüč鹥ą╝čŗ, ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖčÅ ą┐čĆąŠčåąĄą┤čāčĆčŗ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ, ąĖą╗ąĖ ą┤ą╗čÅ ąŠą┐čéąĖą╝ąĖąĘą░čåąĖąĖ ą┐čĆąŠčåąĄčüčüą░ ąĘą░ą│čĆčāąĘą║ąĖ ąŠčüąĮąŠą▓ąĮąŠą│ąŠ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ.

Global Header. ąØąĄą║ąŠč鹊čĆčŗąĄ ąĘą░ą│čĆčāąĘčćąĖą║ąĖ čÅą┤čĆą░ (boot kernel) ąŠąČąĖą┤ą░čÄčé ąĮą░ą╗ąĖčćąĖčÅ ą▓ ą┐ąŠč鹊ą║ąĄ ąĘą░ą│čĆčāąĘą║ąĖ čüą┐ąĄčåąĖą░ą╗čīąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ. ąŁč鹊čé č鹥ą│ ąĮą░ąĘčŗą▓ą░ąĄčéčüčÅ ą│ą╗ąŠą▒ą░ą╗čīąĮčŗą╝ ąĘą░ą│ąŠą╗ąŠą▓ą║ąŠą╝ (global header).

Callback Routine. ąØąĄą║ąŠč鹊čĆčŗąĄ ą┐čĆąŠčåąĄčüčüąŠčĆčŗ ąŠą┐čåąĖąŠąĮą░ą╗čīąĮąŠ ą╝ąŠą│čāčé ą▓čŗąĘčŗą▓ą░čéčī ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝čā, ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčāčÄ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╝ - ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ ą║ą░ą║ ą▒ą╗ąŠą║ ąĘą░ą│čĆčāąĘą║ąĖ ąĘą░ą│čĆčāąČąĄąĮ ąĖ ąŠą▒čĆą░ą▒ąŠčéą░ąĮ. ąŁčéą░ ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ąĮą░ąĘčŗą▓ą░ąĄčéčüčÅ callback routine (ą┐čĆąŠčåąĄą┤čāčĆą░ ąŠą▒čĆą░čéąĮąŠą│ąŠ ą▓čŗąĘąŠą▓ą░). ą×ąĮą░ ą╝ąŠąČąĄčé ą┐čĆąĄą┤ąŠčüčéą░ą▓ąĖčéčī čéą░ą║ąĖąĄ čäčāąĮą║čåąĖąĖ, ą║ą░ą║ čĆąĄą░ą╗ąĖąĘą░čåąĖčÅ ą║ąŠąĮčéčĆąŠą╗čīąĮąŠą╣ čüčāą╝ą╝čŗ ą║ąŠą┤ą░, čüčéčĆą░č鹥ą│ąĖąĖ ą┤ąĄą║ąŠą╝ą┐čĆąĄčüčüąĖąĖ.

Slave Boot, Master Boot. ąóąĄčĆą╝ąĖąĮ Slave Boot ąŠčéąĮąŠčüąĖčéčüčÅ ą║ąŠ ą▓čüąĄą╝ čĆąĄąČąĖą╝ą░ą╝ ąĘą░ą│čĆčāąĘą║ąĖ, ą║ąŠą│ą┤ą░ čåąĄą╗ąĄą▓ąŠą╣ ą┐čĆąŠčåąĄčüčüąŠčĆ čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ. Master Boot - ą║ąŠą│ą┤ą░ ą┐čĆąĖ ąĘą░ą│čĆčāąĘą║ąĖ ą▓ąĮąĄčłąĮąĄąĄ čģčĆą░ąĮąĖą╗ąĖčēąĄ ąŠą▒čĆą░ąĘą░ ąĘą░ą│čĆčāąĘą║ąĖ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčéčüčÅ čüą░ą╝ąĖą╝ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą╝ (čé. ąĄ. čģčĆą░ąĮąĖą╗ąĖčēąĄ čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ). ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. [2].

ą£ąĄąĮąĄą┤ąČąĄčĆ ąĘą░ą│čĆčāąĘą║ąĖ (Boot Manager). ą£ąĄąĮąĄą┤ąČąĄčĆ ąĘą░ą│čĆčāąĘą║ąĖ - ą║ąŠą┤ firmware, ą║ąŠč鹊čĆčŗą╣ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé, ą║ą░ą║ąŠąĄ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ąĘą░ą│čĆčāąČąĄąĮąŠ. ą¤čĆąĖą╗ąŠąČąĄąĮąĖąĄ ąŠą▒čŗčćąĮąŠ ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮąŠ ą║ą░ą║ ą┐čĆąŠąĄą║čé čüčĆąĄą┤čŗ VisualDSP++, ąĖ čĆąĄąĘčāą╗čīčéą░čé ą║ąŠą╝ą┐ąĖą╗čÅčåąĖąĖ ą┐čĆąŠąĄą║čéą░ čüąŠčģčĆą░ąĮčÅąĄčéčüčÅ ą▓ ąĖčüą┐ąŠą╗ąĮčÅąĄą╝ąŠą╝ čäą░ą╣ą╗ąĄ čü čĆą░čüčłąĖčĆąĄąĮąĖąĄą╝ *.dxe. ąĪą░ą╝ ą┐ąŠ čüąĄą▒ąĄ ą╝ąĄąĮąĄą┤ąČąĄčĆ ąĘą░ą│čĆčāąĘą║ąĖ ą╝ąŠąČąĄčé ą▒čŗčéčī čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮ ą║ą░ą║ ą▓ čäą░ą╣ą╗ąĄ ąŠčüąĮąŠą▓ąĮąŠą│ąŠ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ *.dxe, čéą░ą║ ąĖ ą▓ ą▓ąĖą┤ąĄ ąŠčéą┤ąĄą╗čīąĮąŠą│ąŠ čäą░ą╣ą╗ą░ *.dxe. ą¦ą░čüč鹊 ą╝ąĄąĮąĄą┤ąČąĄčĆ ąĘą░ą│čĆčāąĘą║ąĖ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą▓ čéą░ą║ ąĮą░ąĘčŗą▓ą░ąĄą╝ąŠą╝ ą║ąŠą┤ąĄ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ (Init Code).

ąÆ čüčåąĄąĮą░čĆąĖčÅčģ ąĘą░ą│čĆčāąĘą║ąĖ slave boot čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ąĘą░ą│čĆčāąĘą║ąŠą╣ ą▓ąŠąĘą╗ą░ą│ą░ąĄčéčüčÅ ąĮą░ ą┐čĆąŠčåąĄčüčüąŠčĆ čģąŠčüčéą░, ąĖ čŹč鹊 ąĮąĄ čéčĆąĄą▒čāąĄčé čüą┐ąĄčåąĖą░ą╗čīąĮąŠą╣ ą┐ąŠą┤ą┤ąĄčƹȹ║ąĖ čüąŠ čüč鹊čĆąŠąĮčŗ VisualDSP++.

Multi-.dxe Boot. ążą░ą╣ą╗ ąĘą░ą│čĆčāąĘą║ąĖ ą╝ąŠąČąĄčé čüąŠą┤ąĄčƹȹ░čéčī ą▓ čüąĄą▒ąĄ ą┤ą░ąĮąĮčŗąĄ čäą░ą╣ą╗ąŠą▓ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ą┐čĆąĖą╗ąŠąČąĄąĮąĖą╣ (*.dxe), ąĄčüą╗ąĖ čāčéąĖą╗ąĖčéą░ elfloader ą▒čŗą╗ą░ ąĘą░ą┐čāčēąĄąĮą░ čü čāą║ą░ąĘą░ąĮąĖąĄą╝ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ą▓čģąŠą┤ąĮčŗčģ čäą░ą╣ą╗ąŠą▓ *.dxe. ąøąĖą▒ąŠ ą╝ąĄąĮąĄą┤ąČąĄčĆ ąĘą░ą│čĆčāąĘą║ąĖ ą┤ąŠą╗ąČąĄąĮ čĆąĄčłąĖčéčī, ą║ą░ą║ąŠąĄ ąĖą╝ąĄąĮąĮąŠ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ ąĖąĘ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ąĘą░ą│čĆčāąČąĄąĮąŠ ąĖ ąĘą░ą┐čāčēąĄąĮąŠ, ą╗ąĖą▒ąŠ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮąŠ ąŠą┤ąĮąŠ ąĘą░ą│čĆčāąČąĄąĮąĮąŠąĄ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ ą╝ąŠąČąĄčé ąŠčüčéą░ąĮąŠą▓ąĖčéčī čüą▓ąŠčÄ čĆą░ą▒ąŠčéčā, ą┐ąŠčüą╗ąĄ č湥ą│ąŠ ąĘą░ą│čĆčāąĘąĖčéčüčÅ čüą╗ąĄą┤čāčÄčēąĄąĄ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ. ąÆ ąĮąĄą║ąŠč鹊čĆčŗčģ čüą╗čāčćą░čÅčģ ąŠą┤ąĮąŠ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ ą╝ąŠąČąĄčé čéą░ą║ąČąĄ čüąŠčüč鹊čÅčéčī ąĖąĘ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ čäą░ą╣ą╗ąŠą▓ *.dxe (čćą░čēąĄ ą▓čüąĄą│ąŠ ąĖąĘ DXE ą┤ą╗čÅ Init Code ąĖ DXE ą┤ą╗čÅ ąŠčüąĮąŠą▓ąĮąŠą│ąŠ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ).

Next .dxe File Pointer. ąĢčüą╗ąĖ čäą░ą╣ą╗ ąĘą░ą│čĆčāąĘą║ąĖ čüąŠčüč鹊ąĖčé ąĖąĘ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ą┐čĆąĖą╗ąŠąČąĄąĮąĖą╣, ąĮąĄą║ąŠč鹊čĆčŗąĄ č乊čĆą╝ą░čéčŗ ą┐ąŠč鹊ą║ą░ ąĘą░ą│čĆčāąĘą║ąĖ ą┐ąŠąĘą▓ąŠą╗čÅčÄčé ąŠčĆą│ą░ąĮąĖąĘąŠą▓ą░čéčī čäą░ą╣ą╗ ąĘą░ą│čĆčāąĘą║ąĖ ą▓ ą▓ąĖą┤ąĄ čüą▓čÅąĘą░ąĮąĮąŠą│ąŠ čüą┐ąĖčüą║ą░. ąŻą║ą░ąĘą░č鹥ą╗čī ąĮą░ čüą╗ąĄą┤čāčÄčēąĖą╣ DXE (next .dxe pointer, NDP) - ą┐čĆąŠčüč鹊 čāą║ą░ąĘą░č鹥ą╗čī ąĮą░ ą╝ąĄčüč鹊, ą│ą┤ąĄ ą▓ ą┐ąŠč鹊ą║ąĄ ąĘą░ą│čĆčāąĘą║ąĖ ąĮą░čģąŠą┤ąĖčéčüčÅ čüą╗ąĄą┤čāčÄčēąĄąĄ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ.

Preboot Routine. ą¤ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝ą░, ą▓čŗą┐ąŠą╗ąĮčÅčÄčēą░čÅčüčÅ ą┐ąĄčĆąĄą┤ ąĘą░ą│čĆčāąĘą║ąŠą╣ (preboot routine), ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮą░ ą▓ čćą░čüčéčÅčģ ą║ąŠą┤ą░ boot ROM ą┐čĆąŠčåąĄčüčüąŠčĆą░ (ąŠą┤ąĮąŠą║čĆą░čéąĮąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝ą░čÅ, OTP ą┐ą░ą╝čÅčéčī, ą║ąŠč鹊čĆą░čÅ ąĘą░ą┐ąĖčüą░ąĮą░ ąĮą░ ąĘą░ą▓ąŠą┤ąĄ). Preboot čćąĖčéą░ąĄčé ą┐ą░ą╝čÅčéčī OTP, ąĖ ąĮą░čüčéčĆą░ąĖą▓ą░ąĄčé ąĮąĄą║ąŠč鹊čĆčŗąĄ čĆąĄą│ąĖčüčéčĆčŗ MMR ąĮą░ ąŠčüąĮąŠą▓ąĄ ąĘą░ą▓ąŠą┤čüą║ąĖčģ ąĖąĮčüčéčĆčāą║čåąĖą╣ ąĖ ąĖąĮčüčéčĆčāą║čåąĖą╣ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ, ą║ą░ą║ čŹč鹊 ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąŠ ą▓ ą┐ą░ą╝čÅčéčī OTP. Preboot routine ąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ ą┤ąŠ ąĘą░ą│čĆčāąĘą║ąĖ čÅą┤čĆą░ (boot kernel).

[ą¦č鹊 čéą░ą║ąŠąĄ Loading, Splitting]

ą¤ąŠčüą╗ąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ čåąĖą║ą╗ą░ ąŠčéą╗ą░ą┤ą║ąĖ, ą░ą┐ą┐ą░čĆą░čéčāčĆą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ąĘą░ą┐čāčēąĄąĮą░ ąŠčéą┤ąĄą╗čīąĮąŠ, ą▓ čüąŠčüčéą░ą▓ąĄ čĆą░ą▒ąŠč湥ą╣ čüąĖčüč鹥ą╝čŗ (ą▒ąĄąĘ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮąŠą│ąŠ ąŠčéą╗ą░ą┤čćąĖą║ą░). ą¤ąŠčüą╗ąĄ ą▓ą║ą╗čÄč湥ąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ ąĮčāąČąĮąŠ ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆąŠą▓ą░čéčī ą▓čüčéčĆąŠąĄąĮąĮčŗąĄ ą▓ čćąĖą┐ ą┐čĆąŠčåąĄčüčüąŠčĆą░, ąĖ ąĮą░čģąŠą┤čÅčēąĖąĄčüčÅ ą▓ąĮąĄ čćąĖą┐ą░ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┐ą░ą╝čÅčéąĖ. ą┐čĆąŠčåąĄčüčü ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ ąŠą▒ą╗ą░čüč鹥ą╣ ą┐ą░ą╝čÅčéąĖ čćą░čüč鹊 ąĮą░ąĘčŗą▓ą░čÄčé ąĘą░ą│čĆčāąĘą║ąŠą╣ (booting). ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝ ą▓čŗčģąŠą┤ąĮąŠą╣ čäą░ą╣ą╗ ą╗ąĖąĮą║ąĄčĆą░ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮ ą▓ č乊čĆą╝ą░čé, ą║ąŠč鹊čĆčŗą╣ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮ ąĘą░ą│čĆčāąĘčćąĖą║ąŠą╝ ą┐čĆąŠčåąĄčüčüąŠčĆą░ (ą║ąŠą┤ąŠą╝ Boot ROM). ąŁč鹊čé ą┐čĆąŠčåąĄčüčü ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčéčüčÅ čāčéąĖą╗ąĖč鹊ą╣ ąĘą░ą│čĆčāąĘčćąĖą║ą░ ąĖ/ąĖą╗ąĖ čüą┐ą╗ąĖčéč鹥čĆą░. ąŻčéąĖą╗ąĖčéą░ loader/splitter ąĖčüą┐ąŠą╗čīąĘčāąĄčé ąŠčéą╗ą░ąČąĄąĮąĮčŗąĄ ąĖ ą┐čĆąŠč鹥čüčéąĖčĆąŠą▓ą░ąĮąĮčŗąĄ ąĮą░ čŹčéą░ą┐ąĄ čĆą░ąĘčĆą░ą▒ąŠčéą║ąĖ ąĖčüą┐ąŠą╗ąĮčÅąĄą╝čŗąĄ čäą░ą╣ą╗čŗ (*.dxe), ą║ą░ą║ ąĖ ąŠą▒čēčāčÄ ą┐ą░ą╝čÅčéčī ąĖ čäą░ą╣ą╗čŗ ąŠą▓ąĄčĆą╗ąĄčÅ ą▓ ą║ą░č湥čüčéą▓ąĄ ą▓čģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ, ąĖ ą│ąĄąĮąĄčĆąĖčĆčāąĄčé čćąĖčéą░ąĄą╝čŗą╣ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą╝ čäą░ą╣ą╗.

ąÆ ą┐ą░ą║ąĄč鹥 čĆą░ąĘčĆą░ą▒ąŠčéą║ąĖ VisualDSP++ 5.0 ą▓ą║ą╗čÄč湥ąĮčŗ čüą╗ąĄą┤čāčÄčēąĖąĄ čāčéąĖą╗ąĖčéčŗ loader ąĖ splitter:

ŌĆó elfloader.exe (čāčéąĖą╗ąĖčéą░ ąĘą░ą│čĆčāąĘą║ąĖ, loader utility) ą┤ą╗čÅ čüąĄą╝ąĄą╣čüčéą▓ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ Blackfin, TigerSHARC ąĖ SHARC. ąŻčéąĖą╗ąĖčéą░ ąĘą░ą│čĆčāąĘą║ąĖ ą┤ą╗čÅ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ Blackfin čĆą░ą▒ąŠčéą░ąĄčé čéą░ą║ąČąĄ ąĖ ą║ą░ą║ čāčéąĖą╗ąĖčéą░ ROM splitter, ą║ąŠą│ą┤ą░ ąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ čü čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╝ąĖ ąŠą┐čåąĖčÅą╝ąĖ ą║ąŠą╝ą░ąĮą┤ąĮąŠą╣ čüčéčĆąŠą║ąĖ.

ŌĆó elfspl21k.exe (čāčéąĖą╗ąĖčéą░ ROM splitter) ą┤ą╗čÅ čüąĄą╝ąĄą╣čüčéą▓ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ TigerSHARC ąĖ SHARC.

ąØą░ ą▓čŗčģąŠą┤ąĄ čāčéąĖą╗ąĖčé loader/splitter ą┐ąŠą╗čāčćą░ąĄčéčüčÅ ą╗ąĖą▒ąŠ ąĘą░ą│čĆčāąČą░ąĄą╝čŗą╣ (boot-loadable), ą╗ąĖą▒ąŠ ąĮąĄ ąĘą░ą│čĆčāąČą░ąĄą╝čŗą╣ (non-bootable) čäą░ą╣ą╗. ą¤ąŠą┤ ą▓čŗčģąŠą┤ąŠą╝ ą┐ąŠąĮąĖą╝ą░čÄčéčüčÅ ą┤ą░ąĮąĮčŗąĄ (ąŠą▒čŗčćąĮąŠ čŹč鹊 čäą░ą╣ą╗ čü čĆą░čüčłąĖčĆąĄąĮąĖąĄą╝ *.ldr), ą┐čĆąŠčłąĖą▓ą░ąĄą╝čŗąĄ ą▓ ą┐ą░ą╝čÅčéčī čåąĄą╗ąĄą▓ąŠą╣ čüąĖčüč鹥ą╝čŗ (čŹč鹊 ą╝ąŠąČąĄčé ą▒čŗčéčī, ąĮą░ą┐čĆąĖą╝ąĄčĆ, FLASH-ą┐ą░ą╝čÅčéčī ąĮą░ ą║čĆąĖčüčéą░ą╗ą╗ąĄ ADSP-BF538, ąĖą╗ąĖ ą┐ą░ą╝čÅčéčī SPI, ąŠčéą║čāą┤ą░ ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┐čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ). ąĢčüčéčī ąĮąĄčüą║ąŠą╗čīą║ąŠ čüą┐ąŠčüąŠą▒ąŠą▓ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą▓čŗčģąŠą┤ą░ čāčéąĖą╗ąĖčé ąĘą░ą│čĆčāąĘą║ąĖ/čüą┐ą╗ąĖčéč鹥čĆą░:

ŌĆó ą¤ą╗ą░ą│ąĖąĮ Flash Programmer. ą×ąĮ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąĘą░ą┐ąĖčüą░čéčī čäą░ą╣ą╗ ąĘą░ą│čĆčāąĘą║ąĖ ą▓ ąŠą▒ą╗ą░čüčéčī PROM ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą┐ą╗ą░čéčŗ čĆą░ąĘčĆą░ą▒ąŠčéčćąĖą║ą░ EZ-KIT Lite┬«. ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. čüą┐čĆą░ą▓ąŠčćąĮčāčÄ čüąĖčüč鹥ą╝čā VisualDSP++, čĆą░ąĘą┤ąĄą╗ Flash Programmer.

ŌĆó ąĪąĖą╝čāą╗čÅč鹊čĆ ąĘą░ą│čĆčāąĘą║ąĖ. ą£ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī VisualDSP++ ą┤ą╗čÅ čüąĖą╝čāą╗ąĖčĆąŠą▓ą░ąĮąĖčÅ ąĘą░ą│čĆčāąĘą║ąĖ ą▓ čüąĄčüčüąĖąĖ čüąĖą╝čāą╗čÅč鹊čĆą░ (ą▓ ąĮą░čüč鹊čÅčēąĄąĄ ą▓čĆąĄą╝čÅ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ą┤ą╗čÅ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ ADSP-21060, ADSP-21061, ADSP-21065L, ADSP-21160 ąĖ ADSP-21161). ąŚą░ą│čĆčāąĘąĖč鹥 čäą░ą╣ą╗ ąĘą░ą│čĆčāąĘą║ąĖ, ąĖ ąĘą░č鹥ą╝ čüą▒čĆąŠčüčīč鹥 ą┐čĆąŠčåąĄčüčüąŠčĆ, čćč鹊ą▒čŗ ąŠčéą╗ą░ą┤ąĖčéčī ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ąĘą░ą│čĆčāąĘą║ąĖ. ąØąĄ čéčĆąĄą▒čāąĄčéčüčÅ ąĮąĖą║ą░ą║ąŠą╣ ą░ą┐ą┐ą░čĆą░čéčāčĆčŗ: ą┐čĆąŠčüč鹊 čāą║ą░ąČąĖč鹥 ąĮą░ ą╝ąĄčüč鹊 ą┐ąŠą╗ąŠąČąĄąĮąĖčÅ čäą░ą╣ą╗ą░ ąĘą░ą│čĆčāąĘą║ąĖ, ąĖ ą┐ąŠąĘą▓ąŠą╗čīč鹥 čüąĖą╝čāą╗čÅč鹊čĆčā ą▓čŗą┐ąŠą╗ąĮąĖčéčī ąŠčüčéą░ą╗čīąĮčāčÄ čĆą░ą▒ąŠčéčā. ąÆčŗ ą╝ąŠąČąĄč鹥 ą┐ąŠ čłą░ą│ą░ą╝ ą▓čŗą┐ąŠą╗ąĮąĖčé ą║ąŠą┤ boot kernel ąĖ ą┐ąŠčüą╝ąŠčéčĆąĄčéčī, ą║ą░ą║ ąŠąĮ ą┐ąĄčĆąĄąĮąŠčüąĖčé ą▓ ą┐ą░ą╝čÅčéčī ąŠčüčéą░ą╗čīąĮąŠą╣ ą║ąŠą┤.

ŌĆó ą£ąĮąŠą│ąŠą┐čĆąŠčåąĄčüčüąŠčĆąĮą░čÅ čüąĖčüč鹥ą╝ą░. ą£ąŠąČąĮąŠ čüąŠčģčĆą░ąĮąĖčéčī čäą░ą╣ą╗ ąĘą░ą│čĆčāąĘą║ąĖ ą▓ ą╝ą░čüčüąĖą▓ ą┤ą╗čÅ ą╝ąĮąŠą│ąŠą┐čĆąŠčåąĄčüčüąŠčĆąĮąŠą╣ čüąĖčüč鹥ą╝čŗ. ąōą╗ą░ą▓ąĮčŗą╣ ą┐čĆąŠčåąĄčüčüąŠčĆ (čģąŠčüčé) čĆą░čüą┐ąŠčĆčÅąČą░ąĄčéčüčÅ čŹčéąĖą╝ ą╝ą░čüčüąĖą▓ąŠą╝ ą┐ą░ą╝čÅčéąĖ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░, ąĖ ąĘą░ą│čĆčāąČą░ąĄčé čäą░ą╣ą╗ ą▓ ą┐ą░ą╝čÅčéčī ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ ą┐čĆąŠčåąĄčüčüąŠčĆą░.

[ąØąĄ ąĘą░ą│čĆčāąČą░ąĄą╝čŗąĄ čäą░ą╣ą╗čŗ (Non-bootable) ąĖ ąĘą░ą│čĆčāąČą░ąĄą╝čŗąĄ (Boot-loadable) - ą▓ č湥ą╝ čĆą░ąĘąĮąĖčåą░?]

ąØąĄ ąĘą░ą│čĆčāąČą░ąĄą╝čŗą╣ čäą░ą╣ą╗ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ąĮą░ą┐čĆčÅą╝čāčÄ ąĖąĘ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ ą┐čĆąŠčåąĄčüčüąŠčĆą░ (ąŠą▒čŗčćąĮąŠ FLASH), ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ ą┤ą░ąĮąĮčŗąĄ ąĘą░ą│čĆčāąČą░ąĄą╝ąŠą│ąŠ čäą░ą╣ą╗ą░ čéčĆą░ąĮčüą┐ąŠčĆčéąĖčĆčāčÄčéčüčÅ ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮčÄčÄ (ąĖ/ąĖą╗ąĖ ąĖąĮąŠą│ą┤ą░ ą▓ąŠ ą▓ąĮąĄčłąĮčÄčÄ ą┐ą░ą╝čÅčéčī SDRAM), ąĖ ą┐ąŠčüą╗ąĄ čŹč鹊ą│ąŠ ąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ ąĮą░ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ. ąŚą░ą│čĆčāąČą░ąĄą╝čŗą╣ čäą░ą╣ą╗ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ ą▓ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ (čŹč鹊 ą╝ąŠąČąĄčé ą▒čŗčéčī SPI EPROM, ąĖą╗ąĖ FLASH) ąÆą░čłąĄą╣ čåąĄą╗ąĄą▓ąŠą╣ čüąĖčüč鹥ą╝čŗ. ąŻčéąĖą╗ąĖčéą░ ąĘą░ą│čĆčāąĘą║ąĖ ą▓čŗą▓ąŠą┤ąĖčé ąĘą░ą│čĆčāąČą░ąĄą╝čŗąĄ čäą░ą╣ą╗čŗ ą▓ č乊čĆą╝ą░čéą░čģ, ą║ąŠč鹊čĆčŗąĄ ą┐ąŠąĮąĖą╝ą░čÄčé ą▒ąŠą╗čīčłąĖąĮčüčéą▓ąŠ ą┐čĆąŠčłąĖą▓ą░ą╗čīčēąĖą║ąŠą▓ EPROM (čéą░ą║ąĖąĄ č乊čĆą╝ą░čéčŗ, ą║ą░ą║ Intel hex-32 ąĖ Motorola S). ąöą╗čÅ ąŠčüąŠą▒čŗčģ čüą╗čāčćą░ąĄą▓ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčéčüčÅ ą┤čĆčāą│ąĖąĄ č乊čĆą╝ą░čéčŗ čäą░ą╣ą╗ą░ ąĖ čĆąĄąČąĖą╝čŗ ąĘą░ą│čĆčāąĘą║ąĖ, čćą░čüč鹊 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čüčŗčĆąŠą╣, ą┤ą▓ąŠąĖčćąĮčŗą╣ č乊čĆą╝ą░čé (ą┐ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. "File Formats" [1]).

ąØąĄ ąĘą░ą│čĆčāąČą░ąĄą╝čŗąĄ ąŠą▒čĆą░ąĘčŗ ą▓čŗą┐ąŠą╗ąĮčÅčÄčéčüčÅ ąĖąĘ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ ą┐čĆąŠčåąĄčüčüąŠčĆą░, čü ą┐čĆąŠą┐čāčüą║ąŠą╝ ą╝ąĄčģą░ąĮąĖąĘą╝ąŠą▓ ąĘą░ą│čĆčāąĘą║ąĖ. ą¤ąŠą┤ą│ąŠč鹊ą▓ą║ą░ ąĮąĄ ąĘą░ą│čĆčāąČą░ąĄą╝ąŠą│ąŠ ąŠą▒čĆą░ąĘą░ EPROM ąĮą░ąĘčŗą▓ą░ąĄčéčüčÅ čüą┐ą╗ąĖčéčéąĖąĮą│ąŠą╝ (splitting). ąÆ ą▒ąŠą╗čīčłąĖąĮčüčéą▓ąĄ čüą╗čāčćą░ąĄą▓ (ąĘą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ Blackfin) čĆą░ąĘčĆą░ą▒ąŠčéčćąĖą║ąĖ, ąĖčüą┐ąŠą╗čīąĘčāčÄčēąĖąĄ ą┐čĆąŠčåąĄčüčüąŠčĆčŗ čü ą┐ą╗ą░ą▓ą░čÄčēąĄą╣ č鹊čćą║ąŠą╣ ąĖą╗ąĖ čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮąŠą╣ č鹊čćą║ąŠą╣, ąĖčüą┐ąŠą╗čīąĘčāčÄčé splitter ą▓ą╝ąĄčüč鹊 čāčéąĖą╗ąĖčéčŗ loader, čćč鹊ą▒čŗ čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ąĮąĄ ąĘą░ą│čĆčāąČą░ąĄą╝čŗą╣ ąŠą▒čĆą░ąĘ ą┐ą░ą╝čÅčéąĖ.

ąÜą░ą║ ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ą┐čĆąŠčåąĄčüčüąŠčĆ ąĖ ą┤ąĖąĘą░ą╣ąĮ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ą┤ąĖą║čéčāčÄčé ą╝ąĄč鹊ą┤, ą║ą░ą║ąĖą╝ ą▒čāą┤ąĄčé ą▓čŗąĘą▓ą░ąĮą░ čāčéąĖą╗ąĖčéą░ loader/splitter, čćč鹊ą▒čŗ ąŠą▒čĆą░ą▒ąŠčéą░čéčī ąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░čéčī ąĖčüą┐ąŠą╗ąĮčÅąĄą╝čŗąĄ čäą░ą╣ą╗čŗ:

ŌĆó ąöą╗čÅ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ Blackfin ąŠą┐ąĄčĆą░čåąĖąĖ loader ąĖ splitter ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░čÄčéčüčÅ ąŠą┤ąĮąŠą╣ čāčéąĖą╗ąĖč鹊ą╣, elfloader.exe. ążčāąĮą║čåąĖčÅ splitter ą▓ąŠą▓ą╗ąĄą║ą░ąĄčéčüčÅ ą┤čĆčāą│ąĖą╝ ąĮą░ą▒ąŠčĆąŠą╝ ąŠą┐čåąĖą╣ ą║ąŠą╝ą░ąĮą┤ąĮąŠą╣ čüčéčĆąŠą║ąĖ, ąŠčéą╗ąĖčćą░čÄčēąĖą╝čüčÅ ąŠčé ąŠą┐čåąĖą╣ čäčāąĮą║čåąĖąĖ loader. ąÆ VisualDSP++ 5.0, ą▓ ą┤ąŠą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ ąŠą┐čåąĖąĖ -readall, čāčéąĖą╗ąĖčéą░ loader ą┤ą╗čÅ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ ADSP-BF51x, BF52x, BF54x Blackfin ą╝ąŠąČąĄčé ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą▓čŗąĘčŗą▓ą░čéčī ą┐čĆąŠą│čĆą░ą╝ą╝čā čüą┐ą╗ąĖčéč鹥čĆą░. ąöą╗čÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ čüą╝. ą▓ [1] ąŠą┐ąĖčüą░ąĮąĖąĄ ąŠą┐čåąĖąĖ -readall.

ŌĆó ąöą╗čÅ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ TigerSHARC ąĖ SHARC ąŠą┐ąĄčĆą░čåąĖąĖ splitter ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░čÄčéčüčÅ ąŠčéą┤ąĄą╗čīąĮąŠą╣ čāčéąĖą╗ąĖč鹊ą╣ čüą┐ą╗ąĖčéč鹥čĆą░ elfspl21k.exe.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▓ąĄąĘą┤ąĄ ą▓ č鹥ą║čüč鹥, ą│ą┤ąĄ ą▓čüčéčĆąĄčćą░ąĄčéčüčÅ ąĮą░ąĖą╝ąĄąĮąŠą▓ą░ąĮąĖąĄ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą▒ąĄąĘ ą┐čĆąĄčäąĖą║čüą░ BF51x, BF52x, BF53x, BF561 ąĖ čé. ą┐., ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčéčüčÅ ą┐čĆąŠčåąĄčüčüąŠčĆ Blackfin čü ą┐čĆąĄčäąĖą║čüąŠą╝ ADSP- (ADSP-BF51x, ADSP-BF52x, ADSP-BF53x, ADSP-BF561 ąĖ čé. ą┐.).

[ąÜą░ą║ čĆą░ą▒ąŠčéą░ąĄčé čāčéąĖą╗ąĖčéą░ ąĘą░ą│čĆčāąĘą║ąĖ]

ą×ą▒čēąĖąĄ ąĘą░ą┤ą░čćąĖ, ą║ąŠč鹊čĆčŗąĄ ą▓čŗą┐ąŠą╗ąĮčÅąĄčé čāčéąĖą╗ąĖčéą░ ąĘą░ą│čĆčāąĘą║ąĖ, ą╝ąŠą│čāčé ą▓ą║ą╗čÄčćą░čéčī čüą╗ąĄą┤čāčÄčēąĄąĄ:

ŌĆó ą×ą▒čĆą░ą▒ąŠčéą║ą░ ąŠą┐čåąĖą╣ loader ą▓ ą║ąŠą╝ą░ąĮą┤ąĮąŠą╣ čüčéčĆąŠą║ąĄ.

ŌĆó ążąŠčĆą╝ą░čéąĖčĆąŠą▓ą░ąĮąĖąĄ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čäą░ą╣ą╗ą░ .ldr ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü čāą║ą░ąĘą░ąĮąĖčÅą╝ąĖ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ. ą¤ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ąĮąĄčüą║ąŠą╗čīą║ąŠ č乊čĆą╝ą░č鹊ą▓ čäą░ą╣ą╗ą░: binary, ASCII, Intel hex-32 ąĖ ąĮąĄą║ąŠč鹊čĆčŗąĄ ą┤čĆčāą│ąĖąĄ, ą┐ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. čĆą░ąĘą┤ąĄą╗ "File Formats" [1].

ŌĆó ąŻą┐ą░ą║ąŠą▓ą║ą░ ą┤ą░ąĮąĮčŗčģ ą║ąŠą┤ą░ ą▓ ą┐ąŠą┤ ąŠčéą┤ąĄą╗čīąĮčŗąĄ č乊čĆą╝ą░čéčŗ ą┤ą░ąĮąĮčŗčģ, ąĘą░ą▓ąĖčüčÅčēąĖąĄ ąŠčé ą┐čĆąŠčåąĄčüčüąŠčĆą░ ąĖ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮąŠą╣ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą┐ą░ą╝čÅčéąĖ: 8-ą▒ąĖčéąĮčŗą╣, 16-ą▒ąĖčéąĮčŗą╣ ąĖą╗ąĖ ą┤ą╗čÅ ąĮąĄą║ąŠč鹊čĆčŗčģ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ 32-ą▒ąĖčéąĮčŗą╣.

ŌĆó ąöąŠą▒ą░ą▓ą╗ąĄąĮąĖąĄ ą║ąŠą┤ą░ ąĖ ą┤ą░ąĮąĮčŗčģ ąĖąĘ čāą║ą░ąĘą░ąĮąĮąŠą│ąŠ čäą░ą╣ą╗ą░ ąĖčüą┐ąŠą╗ąĮčÅąĄą╝ąŠą│ąŠ ą║ąŠą┤ą░ (Init Code DXE), ąĄčüą╗ąĖ čŹč鹊 ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ.

ŌĆó ąöąŠą▒ą░ą▓ą╗ąĄąĮąĖąĄ boot kernel ą┐ąŠą▓ąĄčĆčģ ą║ąŠą┤ą░ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ.

ŌĆó ąĢčüą╗ąĖ čāą║ą░ąĘą░ąĮąŠ, ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮąŠąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ čĆą░ąĘą╝ąĄčēąĄąĮąĖčÅ čäą░ą╣ą╗ą░ .ldr ą▓ čāą║ą░ąĘą░ąĮąĮąŠąĄ ą╝ąĄčüč鹊 PROM.

ŌĆó ąŻą║ą░ąĘą░ąĮąĖąĄ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆąŠą▓ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą┤ą╗čÅ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ čäą░ą╣ą╗ąŠą▓ .dxe ą┤ą╗čÅ ą╝ąĮąŠą│ąŠ ą┐čĆąŠčåąĄčüčüąŠčĆąĮąŠą╣ čüąĖčüč鹥ą╝čŗ, ąĄčüą╗ąĖ čŹč鹊 ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ.

ąÆčŗ ą╝ąŠąČąĄč鹥 ąĘą░ą┐čāčüčéąĖčéčī čāčéąĖą╗ąĖčéčā loader ąĮąĄčÅą▓ąĮąŠ, ą║ąŠą│ą┤ą░ ąĘą░ą┐čāčüą║ą░ąĄč鹥 ą║ąŠą╝ą┐ąĖą╗čÅčåąĖčÄ ą┐čĆąŠąĄą║čéą░ ąĖąĘ čüčĆąĄą┤čŗ čĆą░ąĘčĆą░ą▒ąŠčéą║ąĖ VisualDSP++ (ą║ąŠą│ą┤ą░ ąĘą░ą┤ą░ąĮąŠ ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī čäą░ą╣ą╗ ąĘą░ą│čĆčāąĘą║ąĖ č湥čĆąĄąĘ Project Options -> Project -> čĆą░ąĘą┤ąĄą╗ ąŠą┐čåąĖą╣ Target -> Type: Loader file), ąĖą╗ąĖ ąĖąĘ ą║ąŠą╝ą░ąĮą┤ąĮąŠą╣ čüčéčĆąŠą║ąĖ. ą¦č鹊ą▒čŗ ąĮą░čüčéčĆąŠąĖčéčī ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ čāčéąĖą╗ąĖčéčŗ ą┐čĆąĖ ąĘą░ą┐čāčüą║ąĄ ąĖąĘ VisualDSP++, ąŠčéą║čĆąŠą╣č鹥 čüą▓ąŠą╣čüčéą▓ą░ ą┐čĆąŠąĄą║čéą░ Project Options ą▓ ą╝ąĄąĮčÄ Project, ąĖ ą▓ ą┤ąĖą░ą╗ąŠą│ąĄ ąĮą░čüčéčĆąŠą╣ą║ąĖ čüą▓ąŠą╣čüčéą▓ ą┐čĆąŠąĄą║čéą░ ą┐ąŠą╝ąĄąĮčÅą╣č鹥 Target ąĖąĘ čéąĖą┐ą░ Executable file ą▓ Loader File, ąĖ ąĘą░č鹥ą╝ ąŠčéčĆąĄą┤ą░ą║čéąĖčĆčāą╣č鹥 čĆą░ąĘą┤ąĄą╗ Load čüą▓ąŠą╣čüčéą▓ ą┐čĆąŠąĄą║čéą░.

ąĀą░ą▒ąŠčéą░ čāčéąĖą╗ąĖčéčŗ ąĘą░ą│čĆčāąĘą║ąĖ elfloader.exe ąĘą░ą▓ąĖčüąĖčé ąŠčé čüą▓ąŠą╣čüčéą▓ ąĘą░ą│čĆčāąĘą║ąĖ (čĆą░ąĘą┤ąĄą╗ Load čüą▓ąŠą╣čüčéą▓ ą┐čĆąŠąĄą║čéą░), ą║ąŠč鹊čĆčŗąĄ čāą┐čĆą░ą▓ą╗čÅčÄčé č鹥ą╝, ą║ą░ą║ čāčéąĖą╗ąĖčéą░ ąĘą░ą│čĆčāąĘą║ąĖ ą┐čĆąĄąŠą▒čĆą░ąĘčāąĄčé ąĖčüą┐ąŠą╗ąĮčÅąĄą╝čŗąĄ čäą░ą╣ą╗čŗ ą▓ ąĘą░ą│čĆčāąČą░ąĄą╝čŗąĄ čäą░ą╣ą╗čŗ, ą┐ąŠąĘą▓ąŠą╗čÅčÅ ąÆą░ą╝ ą▓čŗą▒čĆą░čéčī čéą░ą║ąĖąĄ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ, ą║ą░ą║ čÅą┤čĆą░ (kernels), čĆąĄąČąĖą╝čŗ ąĘą░ą│čĆčāąĘą║ąĖ (boot modes) ąĖ ą▓čŗčģąŠą┤ąĮčŗąĄ č乊čĆą╝ą░čéčŗ čäą░ą╣ą╗ą░ (output file formats). ąŁčéąĖ ąŠą┐čåąĖąĖ ąĮą░čüčéčĆą░ąĖą▓ą░čÄčéčüčÅ ą▓ čĆą░ąĘą┤ąĄą╗ąĄ Load čüą▓ąŠą╣čüčéą▓ ą┐čĆąŠąĄą║čéą░ Project Options VisualDSP++, ąĖą╗ąĖ ąĖčģ ą╝ąŠąČąĮąŠ ąĘą░ą┤ą░čéčī ąĖąĘ ą║ąŠą╝ą░ąĮą┤ąĮąŠą╣ čüčéčĆąŠą║ąĖ. ą×ą┐čåąĖąĖ čüčéčĆą░ąĮąĖčå čĆą░ąĘą┤ąĄą╗ą░ Load čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčé ąŠą┐čåąĖčÅą╝ ą║ąŠą╝ą░ąĮą┤ąĮąŠą╣ čüčéčĆąŠą║ąĖ čāčéąĖą╗ąĖčéčŗ elfloader.exe.

[ąĀąĄąČąĖą╝čŗ ąĘą░ą│čĆčāąĘą║ąĖ (Boot Modes)]

ąÜą░ą║ č鹊ą╗čīą║ąŠ ąĖčüą┐ąŠą╗ąĮčÅąĄą╝čŗą╣ čäą░ą╣ą╗ ą┐ąŠą╗ąĮąŠčüčéčīčÄ ąŠčéą╗ą░ąČąĄąĮ, čāčéąĖą╗ąĖčéą░ ąĘą░ą│čĆčāąĘą║ąĖ ą│ąŠč鹊ą▓ą░ ą║ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÄ ąĖčüą┐ąŠą╗ąĮčÅąĄą╝ąŠą│ąŠ čäą░ą╣ą╗ą░ (ąĖą╗ąĖ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ąĖčüą┐ąŠą╗ąĮčÅąĄą╝čŗčģ čäą░ą╣ą╗ąŠą▓) ą▓ ąĘą░ą│čĆčāąČą░ąĄą╝čŗą╣ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą╝ (processor-loadable, ąĖą╗ąĖ boot-loadable) čäą░ą╣ą╗. ąŚą░ą│čĆčāąČą░ąĄą╝čŗą╣ čäą░ą╣ą╗ ą╝ąŠąČąĄčé ą▒čŗčéčī ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąĘą░ą│čĆčāąČąĄąĮ (booted) ą▓ ą┐čĆąŠčåąĄčüčüąŠčĆ ą┐čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ (power-up) ąĖą╗ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čüą▒čĆąŠčüą░ čüąĖčüč鹥ą╝čŗ (software reset). ąĪą┐ąŠčüąŠą▒, ą║ą░ą║ąĖą╝ čāčéąĖą╗ąĖčéą░ ą▒čāą┤ąĄčé čüąŠąĘą┤ą░ą▓ą░čéčī ąĘą░ą│čĆčāąČą░ąĄą╝čŗą╣ čäą░ą╣ą╗, ąĘą░ą▓ąĖčüąĖčé ąŠčé č鹊ą│ąŠ, ą║ą░ą║ ąĘą░ą│čĆčāąČą░ąĄą╝čŗą╣ čäą░ą╣ą╗ ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ą▓ ą┐čĆąŠčåąĄčüčüąŠčĆ (ąĖ ą║ąŠąĮąĄčćąĮąŠ ąČąĄ, čŹč鹊 ąĘą░ą┤ą░ąĄčéčüčÅ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╝ ą▓ čĆą░ąĘą┤ąĄą╗ąĄ Load čüą▓ąŠą╣čüčéą▓ ą┐čĆąŠąĄą║čéą░ ąĖą╗ąĖ č湥čĆąĄąĘ ąŠą┐čåąĖąĖ ą║ąŠą╝ą░ąĮą┤ąĮąŠą╣ čüčéčĆąŠą║ąĖ čāčéąĖą╗ąĖčéčŗ elfloader.exe).

ąĀąĄąČąĖą╝ ąĘą░ą│čĆčāąĘą║ąĖ (boot mode) ą┐čĆąŠčåąĄčüčüąŠčĆą░ [2] ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ąŠą┐čĆąŠčüąŠą╝ ąŠą┤ąĮąŠą│ąŠ ąĖą╗ąĖ ą▒ąŠą╗čīčłąĄą│ąŠ ą║ąŠą╗ąĖč湥čüčéą▓ą░ čüą┐ąĄčåąĖą░ą╗čīąĮčŗčģ ą▓ąĮąĄčłąĮąĖčģ ą▓čŗą▓ąŠą┤ąŠą▓ ą║ąŠčĆą┐čāčüą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░ (ąĮą░ą┐čĆąĖą╝ąĄčĆ, ą┤ą╗čÅ ą┐čĆąŠčåąĄčüčüąŠčĆą░ Blackfin ADSP-BF538 čŹč鹊 ą▓čŗą▓ąŠą┤čŗ BMODE1, BMODE0). ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ąĘą░ą│čĆčāąĘą║ąĖ, ąČąĄčüčéą║ąŠ ąĘą░ą▓ąĖčüčÅčēąĖąĄ čéą░ą║ąČąĄ ąŠčé ą╝ąŠą┤ąĄą╗ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆą░, ą┐ąŠą┤čĆąŠą▒ąĮąŠ ąŠą┐ąĖčüą░ąĮčŗ ą▓ čüą╗ąĄą┤čāčÄčēąĖčģ čĆą░ąĘą┤ąĄą╗ą░čģ.

ą¤čĆąŠčåąĄčüčüąŠčĆčŗ ą║ąŠą╝ą┐ą░ąĮąĖąĖ Analog Devices ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé čĆą░ąĘąĮčŗąĄ ą╝ąĄčģą░ąĮąĖąĘą╝čŗ ąĘą░ą│čĆčāąĘą║ąĖ. ą×ą▒čŗčćąĮąŠ ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ čüą╗ąĄą┤čāčÄčēąĖąĄ čüčģąĄą╝čŗ, čćč鹊ą▒čŗ ą┐čĆąĄą┤ąŠčüčéą░ą▓ąĖčéčī ą┐čĆąŠčåąĄčüčüąŠčĆčā ąĖąĮčüčéčĆčāą║čåąĖąĖ - ą║ą░ą║ ą┤ąĄą╣čüčéą▓ąŠą▓ą░čéčī ą┐čĆąŠčåąĄčüčüąŠčĆčā ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░.

ŌĆó No-Boot Mode

ŌĆó PROM Boot Mode

ŌĆó Host Boot Mode

No-Boot Mode. ą¤ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ąĮą░čćąĖąĮą░ąĄčé ąĮą░ą┐čĆčÅą╝čāčÄ ą▓čŗčćąĖčéčŗą▓ą░čéčī ąĖ ą▓čŗą┐ąŠą╗ąĮčÅčéčī ąĖąĮčüčéčĆčāą║čåąĖąĖ ąĖąĘ čāčüčéčĆąŠą╣čüčéą▓ EPROM/flash (čā ą┐čĆąŠčåąĄčüčüąŠčĆą░ ADSP-BF538F čŹčéą░ ą┐ą░ą╝čÅčéčī ą╝ąŠąČąĄčé ą▒čŗčéčī ą┤ą░ąČąĄ ą▓čüčéčĆąŠąĄąĮą░ ą▓ ą║čĆąĖčüčéą░ą╗ą╗ čćąĖą┐ą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░). ąŁčéą░ čüčģąĄą╝ą░ ąĮąĄ čéčĆąĄą▒čāąĄčé ąĮąĖą║ą░ą║ąĖčģ ą╝ąĄčģą░ąĮąĖąĘą╝ąŠą▓ ąĘą░ą│čĆčāąĘą║ąĖ (čé. ąĄ. ą║ąŠą┤ Boot ROM ąĮąĄ ąĘą░ą┤ąĄą╣čüčéą▓ąŠą▓ą░ąĮ). ąØą░ ą┐čĆąŠą│čĆą░ą╝ą╝čā ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ ą▓ąŠąĘą╗ą░ą│ą░ąĄčéčüčÅ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ čĆą░ą▒ąŠč鹊čüą┐ąŠčüąŠą▒ąĮąŠčüčéąĖ ąĖ čüąŠą┤ąĄčƹȹĖą╝ąŠą│ąŠ 菹ĮąĄčĆą│ąŠąĘą░ą▓ąĖčüąĖą╝ąŠą╣ ą┐ą░ą╝čÅčéąĖ (SRAM L1, SDRAM).

ąŻčéąĖą╗ąĖčéą░ čüą┐ą╗ąĖčéč鹥čĆą░ ą│ąĄąĮąĄčĆąĖčĆčāąĄčé čäą░ą╣ą╗, ą║ąŠč鹊čĆčŗą╣ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąŠčłąĖčé ą▓ ą┐ą░ą╝čÅčéčī PROM.

PROM Boot Mode. ą¤ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ ą┐čĆąŠčåąĄčüčüąŠčĆ ąĮą░čćąĖąĮą░ąĄčé ą▓čŗčćąĖčéčŗą▓ą░čéčī ą┤ą░ąĮąĮčŗąĄ ąĖąĘ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠą│ąŠ ąĖą╗ąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┐ą░ą╝čÅčéąĖ PROM. ą¤ą░ą╝čÅčéčī PROM čģčĆą░ąĮąĖčé čüą┐ąĄčåąĖą░ą╗čīąĮčŗą╝ ąŠą▒čĆą░ąĘąŠą╝ ąŠčéč乊čĆą╝ą░čéąĖčĆąŠą▓ą░ąĮąĮčŗą╣ ą┐ąŠč鹊ą║ ąĘą░ą│čĆčāąĘą║ąĖ (ąĘą░č鹊č湥ąĮąĮčŗą╣ ą┐ąŠą┤ ąŠą▒čĆą░ą▒ąŠčéą║čā ą║ąŠą┤ąŠą╝ Boot ROM, čüą╝. [2]), ą░ ąĮąĄ ą┐čĆąŠčüč鹊 ą║ąŠą┤ ąĖąĮčüčéčĆčāą║čåąĖą╣. ąÆą╝ąĄčüč鹥 čü ą┤ą░ąĮąĮčŗą╝ąĖ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ą┐ąŠč鹊ą║ ąĘą░ą│čĆčāąĘą║ąĖ čüąŠą┤ąĄčƹȹĖčé ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčāčÄ ąĖąĮč乊čĆą╝ą░čåąĖčÄ, čéą░ą║čāčÄ ą║ą░ą║ ą░ą┤čĆąĄčüą░ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ ąĖ čüč湥čéčćąĖą║ąĖ čüą╗ąŠą▓. ą£ą░ą╗ąĄąĮčīą║ą░čÅ ą┐čĆąŠą│čĆą░ą╝ą╝ą░, čéą░ą║ ąĮą░ąĘčŗą▓ą░ąĄą╝čŗą╣ ąĘą░ą│čĆčāąĘčćąĖą║ čÅą┤čĆą░ (ąĖą╗ąĖ ąČąĄ Boot ROM, ą║ą░ą║ čā ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ Blackfin) ą░ąĮą░ą╗ąĖąĘąĖčĆčāąĄčé ą┐ąŠč鹊ą║ ąĘą░ą│čĆčāąĘą║ąĖ ąĖ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü ąĮąĖą╝ ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆčāąĄčé ąŠą▒ą╗ą░čüčéąĖ ą┐ą░ą╝čÅčéąĖ ą┐čĆąŠčåąĄčüčüąŠčĆą░. ąŚą░ą│čĆčāąĘčćąĖą║ čÅą┤čĆą░ (ąĖą╗ąĖ ą║ąŠą┤ Boot ROM) čĆą░ą▒ąŠčéą░ąĄčé ą┐ąŠą┤ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝ čåąĄą╗ąĄą▓ąŠą│ąŠ ą┐čĆąŠčåąĄčüčüąŠčĆą░. ąÆ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą░čĆčģąĖč鹥ą║čéčāčĆčŗ, ąĘą░ą│čĆčāąĘčćąĖą║ čÅą┤čĆą░ ą╝ąŠąČąĄčé ą▓čŗą┐ąŠą╗ąĮčÅčéčīčüčÅ ą╗ąĖą▒ąŠ ąĖąĘ ą▓čüčéčĆąŠąĄąĮąĮąŠą╣ ą▓ čćąĖą┐ ą┐ą░ą╝čÅčéąĖ boot RAM, ąĖą╗ąĖ ąĖąĘ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┐ą░ą╝čÅčéąĖ PROM, ą║ąŠą┐ąĖčĆčāčÅ ą║ąŠą┤ ą▓ SRAM ą┐čĆąŠčåąĄčüčüąŠčĆą░ ąĖ ą▓čŗą┐ąŠą╗ąĮčÅčÅ ąĄą│ąŠ ąŠčéčéčāą┤ą░.

ąŻčéąĖą╗ąĖčéą░ ąĘą░ą│čĆčāąĘą║ąĖ ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ą┤ą░ąĮąĮčŗąĄ ą┐ąŠč鹊ą║ą░ ąĘą░ą│čĆčāąĘą║ąĖ ąĖąĘ ą▓čŗčģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ ą╗ąĖąĮą║ąĄčĆą░ (ąŠą┤ąĖąĮ ąĖą╗ąĖ ąĮąĄčüą║ąŠą╗čīą║ąŠ ąĖčüą┐ąŠą╗ąĮčÅąĄą╝čŗčģ čäą░ą╣ą╗ąŠą▓ *.dxe) ąĖ čüąŠčģčĆą░ąĮčÅąĄčé ą┐ąŠč鹊ą║ ąĘą░ą│čĆčāąĘą║ąĖ ą▓ čäą░ą╣ą╗ (ąŠą▒čŗčćąĮąŠ čŹč鹊 čäą░ą╣ą╗ *.ldr) ą▓ č乊čĆą╝ą░č鹥, ą┐ąŠą┤čģąŠą┤čÅčēąĄą╝ ą┤ą╗čÅ ą┐čĆąŠčłąĖą▓ą║ąĖ ą▓ PROM.

Host Boot Mode. ąÆ čŹč鹊ą╣ čüčģąĄą╝ąĄ čåąĄą╗ąĄą▓ąŠą╣ ą┐čĆąŠčåąĄčüčüąŠčĆ ą▓ąĄą┤ąĄčé čüąĄą▒čÅ ą║ą░ą║ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ, čāą┐čĆą░ą▓ą╗čÅąĄą╝ąŠąĄ čüąĖčüč鹥ą╝ąŠą╣ čģąŠčüčéą░ [2]. ą¤ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ ą┐čĆąŠčåąĄčüčüąŠčĆ ąĘą░ą┤ąĄčƹȹĖą▓ą░ąĄčé ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ, ą┐ąŠą║ą░ ąĮąĄ ą┐ąŠą╗čāčćąĖčé čüąĖą│ąĮą░ą╗ ąŠčé čģąŠčüčé-čüąĖčüč鹥ą╝čŗ, čćč鹊 ą┐čĆąŠčåąĄčüčü ąĘą░ą│čĆčāąĘą║ąĖ ąĘą░ą▓ąĄčĆčłąĄąĮ. ąÆ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą▓ąŠąĘą╝ąŠąČąĮąŠčüč鹥ą╣ ą░ą┐ą┐ą░čĆą░čéčāčĆčŗ, ąĄčüčéčī ą┤ą▓ą░ čĆą░ąĘąĮčŗčģ ą╝ąĄč鹊ą┤ą░ ąĘą░ą│čĆčāąĘą║ąĖ ą┐ąŠą┤ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝ čģąŠčüčéą░. ą¤ąĄčĆą▓čŗą╣ ą╝ąĄč鹊ą┤ - ą║ąŠą│ą┤ą░ čüąĖčüč鹥ą╝ą░ čģąŠčüčéą░ ą┐ąŠą╗čāčćą░ąĄčé ą┐ąŠą╗ąĮąŠąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ąĮą░ą┤ ą▓čüąĄą╝ąĖ ąŠą▒ą╗ą░čüčéčÅą╝ąĖ ą┐ą░ą╝čÅčéąĖ čåąĄą╗ąĄą▓ąŠą╣ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą╣ čüąĖčüč鹥ą╝čŗ. ąźąŠčüčé ą┐čĆąĖąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé čĆą░ą▒ąŠčéčā čåąĄą╗ąĄą▓ąŠą╣ čüąĖčüč鹥ą╝čŗ, ą┐ąŠą║ą░ ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆčāąĄčé ą▓čüąĄ ąŠą▒ą╗ą░čüčéąĖ ą┐ą░ą╝čÅčéąĖ. ą¤ąŠ ą▓č鹊čĆąŠą╝čā ą╝ąĄč鹊ą┤čā čģąŠčüčé ąŠą▒ą╝ąĄąĮąĖą▓ą░ąĄčéčüčÅ čü čåąĄą╗ąĄą▓ąŠą╣ čüąĖčüč鹥ą╝ąŠą╣ čüą┐ąĄčåąĖą░ą╗čīąĮčŗą╝ąĖ čüąĖą│ąĮą░ą╗ą░ą╝ąĖ (čüą╝. [2]), ąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ ą┐ąĄčĆąĄą┤ą░ąĄčé ą┤ą░ąĮąĮčŗąĄ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą╝čā čåąĄą╗ąĄą▓ąŠą╝čā ą┐čĆąŠčåąĄčüčüąŠčĆčā, ąĮą░ ą║ąŠč鹊čĆąŠą╝ čĆą░ą▒ąŠčéą░ąĄčé ąĘą░ą│čĆčāąĘčćąĖą║ čÅą┤čĆą░ (ąĖą╗ąĖ ą║ąŠą┤ Boot ROM). ąÜąŠą┤ ąĘą░ą│čĆčāąĘčćąĖą║ą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮ ąĖąĘ ą▓čüčéčĆąŠąĄąĮąĮąŠą│ąŠ ą▓ čćąĖą┐ Boot ROM, ąĖą╗ąĖ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą│čĆčāąČąĄąĮ ąŠčé čģąŠčüčéą░ ą▓ SRAM ą┐ąŠ ą╗čÄą▒ąŠą╣ ąĖąĘ ą┤čĆčāą│ąĖčģ ą┤ąŠą┐čāčüčéąĖą╝čŗčģ čüčģąĄą╝ ąĘą░ą│čĆčāąĘą║ąĖ.

ąŻčéąĖą╗ąĖčéą░ loader/splitter ą│ąĄąĮąĄčĆąĖčĆčāąĄčé čäą░ą╣ą╗, ą║ąŠč鹊čĆčŗą╣ ąĖčüą┐ąŠą╗čīąĘčāąĄčé čüąĖčüč鹥ą╝ą░ čģąŠčüčéą░. ą×ąĮ ąĘą░ą▓ąĖčüąĖčé ąŠčé ą▓ąŠąĘą╝ąŠąČąĮąŠčüč鹥ą╣ čāčüčéčĆąŠą╣čüčéą▓ą░ čģąŠčüčéą░ ąĖ ąŠčé ą░čĆčģąĖč鹥ą║čéčāčĆčŗ čåąĄą╗ąĄą▓ąŠą╣ čüąĖčüč鹥ą╝čŗ - ąŠąČąĖą┤ą░ąĄčé ą╗ąĖ čģąŠčüčé čüčŗčĆčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ, ąĖą╗ąĖ ąČąĄ ąŠčéč乊čĆą╝ą░čéąĖčĆąŠą▓ą░ąĮąĮčŗą╣ ą┐ąŠč鹊ą║ ąĘą░ą│čĆčāąĘą║ąĖ.

ąÆ čŹč鹊ą╝ ą║ąŠąĮč鹥ą║čüč鹥 ąĘą░ą│čĆčāąČą░ąĄą╝čŗą╣ čäą░ą╣ą╗ ąŠčéą╗ąĖčćą░ąĄčéčüčÅ ąŠčé ąĮąĄ ąĘą░ą│čĆčāąČą░ąĄą╝ąŠą│ąŠ č鹥ą╝, čćč鹊 ąĘą░ą│čĆčāąČą░ąĄą╝čŗą╣ čäą░ą╣ą╗ ą║čĆąŠą╝ąĄ ą║ąŠą┤ą░ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ čüąŠą┤ąĄčƹȹĖčé ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ, ą║ąŠč鹊čĆčŗąĄ ą┤ąŠą╗ąČąĄąĮ ąŠą▒čĆą░ą▒ąŠčéą░čéčī ąĘą░ą│čĆčāąĘčćąĖą║ čÅą┤čĆą░ (ą║ąŠą┤ Boot ROM). ąØąĄ ąĘą░ą│čĆčāąČą░ąĄą╝čŗą╣ čäą░ą╣ą╗ čüąŠą┤ąĄčƹȹĖčé č鹊ą╗čīą║ąŠ čćąĖčüčéčŗą╣ ąĖčüą┐ąŠą╗ąĮčÅąĄą╝čŗą╣ ą║ąŠą┤ ąĖąĮčüčéčĆčāą║čåąĖą╣ (ą║ąŠą╝ą░ąĮą┤) ą┐čĆąŠčåąĄčüčüąŠčĆą░.

[ąŚą░ą│čĆčāąĘą║ą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ADSP-BF53x/BF561]

ą¤čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ ąĖ/ąĖą╗ąĖ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ ą┐čĆąŠčåąĄčüčüąŠčĆ ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī boot mode, ą║ąŠč鹊čĆčŗą╣ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ ą▓ąĮąĄčłąĮąĖą╝ąĖ ą▓čģąŠą┤ąĮčŗą╝ąĖ ą▓čŗą▓ąŠą┤ą░ą╝ąĖ BMODE (čüą╝. [2]). ąŁč鹊 čüą┐ąĄčåąĖą░ą╗čīąĮčŗąĄ, ą▓čŗą┤ąĄą╗ąĄąĮąĮčŗąĄ ą▓čŗą▓ąŠą┤čŗ ą║ąŠčĆą┐čāčüą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░, ą║ąŠč鹊čĆčŗąĄ ąĮąĄ ąŠą▒čüą╗čāąČąĖą▓ą░čÄčé ąĮąĖą║ą░ą║ąĖčģ ą┤čĆčāą│ąĖčģ čäčāąĮą║čåąĖą╣. ąĪąŠčüč鹊čÅąĮąĖąĄ ą▓čŗą▓ąŠą┤ąŠą▓ BMODE ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ ą┐čĆąŠčćąĖčéą░ąĮąŠ č湥čĆąĄąĘ ą▒ąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ čüąĖčüč鹥ą╝čŗ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ (System Reset Configuration Register, SYSCR).

ą¤čĆąŠčåąĄčüčüąŠčĆčŗ Blackfin ą╝ąŠą┤ąĄą╗ąĄą╣ ADSP-BF53x ąĖą╗ąĖ ADSP-BF561 ą╝ąŠą│čāčé ąĘą░ą│čĆčāąČą░čéčīčüčÅ ą╗ąĖą▒ąŠ ąĖąĘ 8-ą▒ąĖčéąĮąŠą╣, ą╗ąĖą▒ąŠ ąĖąĘ 16-ą▒ąĖčéąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ flash/PROM, ąĖą╗ąĖ ąĖąĘ ą░ą┤čĆąĄčüčāąĄą╝ąŠą╣ 8 ą▒ąĖčéą░ą╝ąĖ, 16 ą▒ąĖčéą░ą╝ąĖ ąĖą╗ąĖ 24-ą▒ąĖčéą░ą╝ąĖ ą┐ą░ą╝čÅčéąĖ SPI. ą¤čĆąŠčåąĄčüčüąŠčĆčŗ ADSP-BF561 ąĮąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé ąĘą░ą│čĆčāąĘą║čā č湥čĆąĄąĘ 24-ą▒ąĖčéąĮąŠ ą░ą┤čĆąĄčüčāąĄą╝čāčÄ ą┐ą░ą╝čÅčéčī SPI. ąóą░ą║ąČąĄ ąĖą╝ąĄčÄčéčüčÅ ąŠą┐čåąĖąĖ no-boot (bypass mode, ą┐čĆąŠą┐čāčüą║ ąĘą░ą┐čāčüą║ą░ ą║ąŠą┤ą░ Boot ROM), ą║ąŠą│ą┤ą░ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ čüčĆą░ąĘčā ąĮą░čćąĖąĮą░ąĄčéčüčÅ ąĖąĘ 16-čĆą░ąĘčĆčÅą┤ąĮąŠą╣ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ.

ą×ą┐čåąĖąĖ ąĘą░ą│čĆčāąĘą║ąĖ čéą░ą║ąČąĄ ą╝ąŠą│čāčé ąĘą░ą▓ąĖčüąĄčéčī ąĖ ąŠčé čĆąĄą▓ąĖąĘąĖąĖ ą║čĆąĖčüčéą░ą╗ą╗ą░. ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ ą┐čĆąŠ ą▓ą░čĆąĖą░ąĮčéčŗ ąĘą░ą│čĆčāąĘą║ąĖ Blackfin čüą╝. [2].

ą¤ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ ą┐čĆąŠčåąĄčüčüąŠčĆ ADSP-BF531, BF532, BF533, BF534, BF536, BF537, BF538, BF539 ą┐ąĄčĆąĄą┤ą░ąĄčé čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą▓ąŠ ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ ą▓ ą║čĆąĖčüčéą░ą╗ą╗ ą║ąŠą┤ Boot ROM (ąĄčüą╗ąĖ BMODEx != 00), ąĖą╗ąĖ ą▓ ąŠą▒ą╗ą░čüčéčī ą▓ąĮąĄčłąĮąĄą╣ 16-čĆą░ąĘčĆčÅą┤ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ (ąĄčüą╗ąĖ BMODEx == 00) ą┐ąŠ ą░ą┤čĆąĄčüčā 0x20000000. ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ ą┐čĆąŠ Boot ROM ą┐čĆąŠčåąĄčüčüąŠčĆą░ čüą╝. čĆą░ąĘą┤ąĄą╗ "ADSP-BF531, BF532, BF533, BF534, BF536, BF537, BF538, BF539 On-Chip Boot ROM".

ąÆ čéą░ą▒ą╗ąĖčåąĄ 3-1 čüą▓ąĄą┤ąĄąĮčŗ čĆąĄąČąĖą╝čŗ ąĘą░ą│čĆčāąĘą║ąĖ ąĖ čüčéą░čĆč鹊ą▓čŗąĄ ą░ą┤čĆąĄčüą░ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ ADSP-BF531, ADSP-BF532, ADSP-BF533, ADSP-BF538 ąĖ ADSP-BF539.

ą×čéą║čāą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ąĘą░ą│čĆčāąĘą║ą░

|

BMODE[1:0]

|

ąÉą┤čĆąĄčü ąĮą░čćą░ą╗ą░

ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą║ąŠą┤ą░

|

ADSP-BF531

ADSP-BF532 |

ADSP-BF533

ADSP-BF538

ADSP-BF539 |

| ąÆčŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ąĖąĘ ą▓ąĮąĄčłąĮąĄą╣ 16-ą▒ąĖčéąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮąŠą╣ ą║ ASYNC Bank0 (ą┐čĆąŠą┐čāčüą║ ąĘą░ą┐čāčüą║ą░ ą║ąŠą┤ą░ Boot ROM). |

00 |

0x20000000 |

| ąŚą░ą│čĆčāąĘą║ą░ ąĖąĘ 8/16 ą▒ąĖčéąĮąŠą╣ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠą╣ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ FLASH/PROM. |

01 |

0xFFA08000 |

0xFFA00000 |

| ąŚą░ą│čĆčāąĘą║ą░ č湥čĆąĄąĘ SPI ą▓ čĆąĄąČąĖą╝ąĄ SPI Slave mode (ą┤ą░ąĮąĮčŗąĄ ą┐ąŠčüčéčāą┐ą░čÄčé ąŠčé čģąŠčüčéą░ SPI). |

10 |

| ąŚą░ą│čĆčāąĘą║ą░ ąĖąĘ ą┐ą░ą╝čÅčéąĖ SPI, ą░ą┤čĆąĄčüčāąĄą╝ąŠą╣ 8/16/24 ą▒ąĖčéą░ą╝ąĖ, čü ą┐ąŠą┤ą┤ąĄčƹȹ║ąŠą╣ ą╝ąĖą║čĆąŠčüčģąĄą╝ ą┐ą░ą╝čÅčéąĖ Atmel AT45DB041B, AT45DB081B ąĖ AT45DB161B DataFlash┬« (čģąŠčüč鹊ą╝ SPI ą▓čŗčüčéčāą┐ą░ąĄčé ąĘą░ą│čĆčāąČą░ąĄą╝čŗą╣ ą┐čĆąŠčåąĄčüčüąŠčĆ Blackfin). |

11 |

ŌĆó ąÆčŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ąĖąĘ 16-čĆą░ąĘčĆčÅą┤ąĮąŠą╣ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ ŌĆō ą┐čĆąŠčåąĄčüčüąŠčĆ ąĮą░čćąĖąĮą░ąĄčé ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ąŠą┤ą░ čü ą░ą┤čĆąĄčüą░ 0x20000000 (ą║ąŠą┤ čü 16-čĆą░ąĘčĆčÅą┤ąĮąŠą╣ čāą┐ą░ą║ąŠą▓ą║ąŠą╣). ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ą┐ąĄčĆąĄą┤ą░čćą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą▓ Boot ROM ą┐čĆąŠą┐čāčüą║ą░ąĄčéčüčÅ. ąÆčüąĄ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąŠąĮąĮčŗąĄ ąĮą░čüčéčĆąŠą╣ą║ąĖ ą▓ąĮąĄčłąĮąĄą╣ čłąĖąĮčŗ čüą▒čĆą░čüčŗą▓ą░čÄčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ, čĆą░čüčüčćąĖčéą░ąĮąĮąŠąĄ ąĮą░ čüą░ą╝ąŠąĄ ą╝ąĄą┤ą╗ąĄąĮąĮąŠąĄ ą▓ąĮąĄčłąĮąĄąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐ą░ą╝čÅčéąĖ: 3 čåąĖą║ą╗ą░ ą▓čĆąĄą╝čÅ čāą┤ąĄčƹȹ░ąĮąĖčÅ (hold time), 15 čåąĖą║ą╗ąŠą▓ ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ ąĮą░ čćč鹥ąĮąĖąĄ/ąĘą░ą┐ąĖčüčī, 4 čåąĖą║ą╗ą░ ąĮą░ ą┐čĆąĄą┤čāčüčéą░ąĮąŠą▓ą║čā (setup).

ŌĆó ąŚą░ą│čĆčāąĘą║ą░ ąĖąĘ 8- ąĖą╗ąĖ 16-čĆą░ąĘčĆčÅą┤ąĮąŠą╣ ą▓ąĮąĄčłąĮąĄą╣ flash-ą┐ą░ą╝čÅčéąĖ ŌĆō ą▓ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ąĘą░ą│čĆčāąĘą║ąĖ čĆą░čüą┐ąŠą╗ąŠąČąĄąĮą░ ą▓ ąŠą▒ą╗ą░čüčéąĖ Boot ROM, ąĖ ą┤ą╗čÅ ą┐ąŠč鹊ą║ą░ ąĘą░ą│čĆčāąĘą║ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą░čüąĖąĮčģčĆąŠąĮąĮčŗą╣ ą▒ą░ąĮą║ ą┐ą░ą╝čÅčéąĖ 0. ąÆčüąĄ ąĮą░čüčéčĆąŠą╣ą║ąĖ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ čüą▒čĆą░čüčŗą▓ą░čÄčéčüčÅ ą▓ čĆą░čüč湥č鹥 ąĮą░ čüą░ą╝ąŠąĄ ą╝ąĄą┤ą╗ąĄąĮąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐ą░ą╝čÅčéąĖ: 3 čåąĖą║ą╗ą░ ą▓čĆąĄą╝čÅ čāą┤ąĄčƹȹ░ąĮąĖčÅ (hold time), 15 čåąĖą║ą╗ąŠą▓ ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ ąĮą░ čćč鹥ąĮąĖąĄ/ąĘą░ą┐ąĖčüčī, 4 čåąĖą║ą╗ą░ ąĮą░ ą┐čĆąĄą┤čāčüčéą░ąĮąŠą▓ą║čā (setup). Boot ROM ą░ąĮą░ą╗ąĖąĘąĖčĆčāąĄčé ą┐ąĄčĆą▓čŗą╣ ą▒ą░ą╣čé ą┐ąŠč鹊ą║ą░ ąĘą░ą│čĆčāąĘą║ąĖ ą┐ąŠ ą░ą┤čĆąĄčüčā 0x20000000. ąĢčüą╗ąĖ ąŠąĮ čĆą░ą▓ąĄąĮ 0x40, č鹊 ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ 8-ą▒ąĖčéąĮą░čÅ ąĘą░ą│čĆčāąĘą║ą░. ąĢčüą╗ąĖ ą▒ą░ą╣čé čĆą░ą▓ąĄąĮ 0x60, č鹊 ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčéčüčÅ 16-čĆą░ąĘčĆčÅą┤ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐ą░ą╝čÅčéąĖ ąĖ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ 8-čĆą░ąĘčĆčÅą┤ąĮčŗą╣ DMA. ąæą░ą╣čé 0x20 čéą░ą║ąČąĄ ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčé 16-čĆą░ąĘčĆčÅą┤ąĮčāčÄ ą┐ą░ą╝čÅčéčī, ąĮąŠ ą▓čŗą┐ąŠą╗ąĮčÅąĄčé 16-čĆą░ąĘčĆčÅą┤ąĮčŗą╣ DMA.

ŌĆó ąŚą░ą│čĆčāąĘą║ą░ č湥čĆąĄąĘ SPI ą┐ąŠą┤ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝ čģąŠčüčéą░ ŌĆō ą┐čĆąŠčåąĄčüčüąŠčĆ Blackfin čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ SPI, ąĖ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ ą┤ą╗čÅ ą┐čĆąĖąĄą╝ą░ ą▒ą░ą╣č鹊ą▓ čäą░ą╣ą╗ą░ .ldr ąŠčé čģąŠčüčéą░ (ą╝ą░čüč鹥čĆą░) čłąĖąĮčŗ SPI. ą×ą┐ąĖčüą░ąĮąĖąĄ ą┐čĆąŠčåąĄą┤čāčĆčŗ ąŠą▒ą╝ąĄąĮą░ ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗčģ čüąĖą│ąĮą░ą╗ąŠą▓ čüą╝. ą▓ [2].

ŌĆó ąŚą░ą│čĆčāąĘą║ą░ ąĖąĘ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ SPI (EEPROM ąĖą╗ąĖ flash) ŌĆō ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą┐ą░ą╝čÅčéąĖ čü 8-, 16- ąĖą╗ąĖ 24-čĆą░ąĘčĆčÅą┤ąĮąŠą╣ ą░ą┤čĆąĄčüą░čåąĖąĄą╣, čéą░ą║ąČąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčéčüčÅ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ AT45DB041, AT45DB081, AT45DB161, AT45DB321, AT45DB642 ąĖ AT45DB1282 DataFlash┬« ąŠčé ą║ąŠą╝ą┐ą░ąĮąĖąĖ Atmel. ą×ą┐ąĖčüą░ąĮąĖąĄ ą┐čĆąŠčåąĄą┤čāčĆčŗ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ čéąĖą┐ą░ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ąĖ čüąĖą│ąĮą░ą╗ąŠą▓ ąŠą▒ą╝ąĄąĮą░ čüą╝. ą▓ [2].

ą¤čĆąŠčåąĄčüčüąŠčĆčŗ ADSP-BF534, BF536, BF537 čéą░ą║ąČąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé ąĘą░ą│čĆčāąĘą║čā č湥čĆąĄąĘ ąĖąĮč鹥čĆč乥ą╣čüčŗ TWI ąĖ UART, ą┐ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. [1].

ąæą╗ą░ą│ąŠą┤ą░čĆčÅ ąĮą░ą╗ąĖčćąĖčÄ ą╝ąĄčģą░ąĮąĖąĘą╝ą░ Multi-.dxe Boot ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčüčé ą╝ąŠąČąĄčé čüąŠąĘą┤ą░čéčī čüąŠą▒čüčéą▓ąĄąĮąĮčŗą╣ ąĘą░ą│čĆčāąĘčćąĖą║ ą║ąŠą┤ą░, ą║ąŠč鹊čĆčŗą╣ ą┐ąŠąĘą▓ąŠą╗ąĖčé ąĘą░ą│čĆčāąĘąĖčéčī (ąĖą╗ąĖ ą┤ą░ąČąĄ ąŠą▒ąĮąŠą▓ąĖčéčī) ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ ąĖąĘ ą╗čÄą▒čŗčģ ą┤čĆčāą│ąĖčģ ąĖčüč鹊čćąĮąĖą║ąŠą▓ ąĖą╗ąĖ č湥čĆąĄąĘ ą╗čÄą▒ąŠą╣ ą┤čĆčāą│ąŠą╣ ą┤ąŠčüčéčāą┐ąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü čüą▓čÅąĘąĖ čü ą▓ąĮąĄčłąĮąĖą╝ ą╝ąĖčĆąŠą╝.

[ADSP-BF531, BF532, BF533, BF534, BF536, BF537, BF538, BF539 On-Chip Boot ROM]

ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ ą▓ ą┐čĆąŠčåąĄčüčüąŠčĆ ą║ąŠą┤ ąĘą░ą│čĆčāąĘą║ąĖ (On-Chip Boot ROM) ą┐ąŠą╗čāčćą░ąĄčé čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ, č鹊 ąŠąĮ ą▓čŗą┐ąŠą╗ąĮčÅąĄčé čüą╗ąĄą┤čāčÄčēąĖąĄ ą┤ąĄą╣čüčéą▓ąĖčÅ:

1. ąØą░čüčéčĆą░ąĖą▓ą░ąĄčé čĆąĄąČąĖą╝ čüčāą┐ąĄčĆą▓ąĖąĘąŠčĆą░ (supervisor mode) ą┐čāč鹥ą╝ ą▓čŗčģąŠą┤ą░ ąĖąĘ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ RESET, ąĖ ą┐ąĄčĆąĄčģąŠą┤ą░ ą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čü čüą░ą╝čŗą╝ ąĮąĖąĘą║ąĖą╝ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝ (IVG15).

ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 on-chip boot ROM ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ ADSP-BF534, BF536 ąĖ BF537 ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ąĮą░ čāčĆąŠą▓ąĮąĄ ą┐čĆąĖąŠčĆąĖč鹥čéą░ Reset, ąĮąĄ čüąĮąĖąČą░čÅ čāčĆąŠą▓ąĄąĮčī ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ąĮą░ čüą░ą╝čŗą╣ ąĮąĖąĘą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣.

2. ą¤čĆąŠą▓ąĄčĆčÅąĄčé, ą▒čŗą╗ ą╗ąĖ RESET ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╝ čüą▒čĆąŠčüąŠą╝, ąĖ ąĄčüą╗ąĖ čŹč鹊 čéą░ą║, č鹊 ą╗ąĖą▒ąŠ ą┐čĆąŠą┐čāčüą║ą░ąĄčé ą▓čüčÄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ąĘą░ą│čĆčāąĘą║ąĖ ąĖ ą┤ąĄą╗ą░ąĄčé ą┐ąĄčĆąĄčģąŠą┤ ąĮą░ ąĮą░čćą░ą╗ąŠ ą┐ą░ą╝čÅčéąĖ L1 (ą░ą┤čĆąĄčü 0xFFA00000 ą┤ą╗čÅ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ ADSP-BF533, BF534, BF536, BF537, BF538 ąĖ BF539 processors; ą░ą┤čĆąĄčü 0xFFA08000 ą┤ą╗čÅ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ ADSP-BF531, BF532). ą¤čĆąŠą▓ąĄčĆą║ą░ ą┤ąĄą╗ą░ąĄčéčüčÅ ą║ąŠą┤ąŠą╝ Boot ROM ą┐čāč鹥ą╝ ą░ąĮą░ą╗ąĖąĘą░ ą▒ąĖčéą░ NOBOOT (ą▒ąĖčé 4) čĆąĄą│ąĖčüčéčĆą░ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ čüąĖčüč鹥ą╝čŗ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ (System Reset Configuration Register, SYSCR). ąĢčüą╗ąĖ ą▒ąĖčé 4 ąĮąĄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, č鹊 ą║ąŠą┤ Boot ROM ą▓čŗą┐ąŠą╗ąĮčÅąĄčé ą┐ąŠą╗ąĮčāčÄ ą┐čĆąŠčåąĄą┤čāčĆčā ąĘą░ą│čĆčāąĘą║ąĖ. ąĢčüą╗ąĖ ą▒ąĖčé 4 čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, č鹊 ą║ąŠą┤ Boot ROM ą┐čĆąŠą┐čāčüą║ą░ąĄčé ą┐ąŠą╗ąĮčāčÄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ąĘą░ą│čĆčāąĘą║ąĖ ąĖ čüčĆą░ąĘčā ą┐ąĄčĆąĄą┤ą░ąĄčé čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą▓ ąĮą░čćą░ą╗ąŠ ą┐ą░ą╝čÅčéąĖ L1.

3. ąæąĖčé NOBOOT (ą▒ąĖčé 4 čĆąĄą│ąĖčüčéčĆą░ SYSCR) ąĮąĄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ąĮą░čćąĖąĮą░ąĄčéčüčÅ ą┐ąŠą╗ąĮą░čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ąĘą░ą│čĆčāąĘą║ąĖ (čüą╝. čĆąĖčü. 3-1).

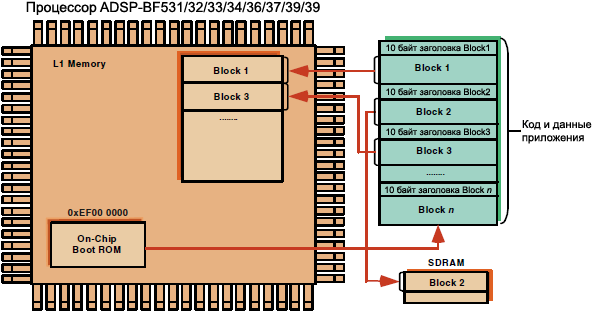

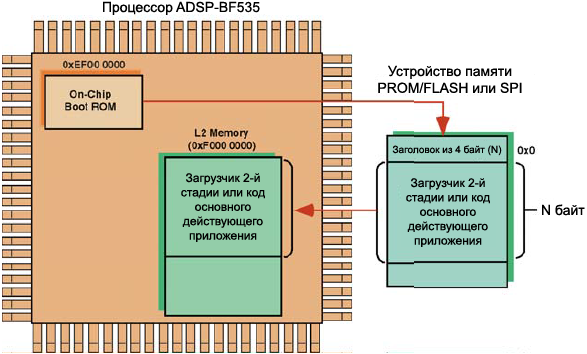

ąĀąĖčü. 3-1. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ąĘą░ą│čĆčāąĘą║ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ ADSP-BF531, BF532, BF533, BF534, BF536, BF537, BF538, BF539.

ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ąĘą░ą│čĆčāąĘą║ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ ADSP-BF531, BF532, BF533, BF534, BF536, BF537, BF538, BF539 ąŠčéą╗ąĖčćą░ąĄčéčüčÅ ąŠčé ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ ADSP-BF535. On-chip boot ROM ą┤ą╗čÅ čŹčéąĖčģ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ ą▓ąĄą┤ąĄčé čüąĄą▒čÅ čéą░ą║ ąČąĄ, ą║ą░ą║ ąĖ ąĘą░ą│čĆčāąĘčćąĖą║ ą▓č鹊čĆąŠą╣ čüčéą░ą┤ąĖąĖ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ADSP-BF535 (ą┐ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. čĆą░ąĘą┤ąĄą╗ "ADSP-BF535 Processor On-Chip Boot ROM"). ąŻ ą║ąŠą┤ą░ Boot ROM ąĄčüčéčī ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░čéčī ą░ą┤čĆąĄčüą░ ąĖ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ą░ą╣čé ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ąĘą░ą│čĆčāąČą░ąĄą╝ąŠą│ąŠ ą▒ą╗ąŠą║ą░ ą┐ąŠč鹊ą║ą░ ąĘą░ą│čĆčāąĘą║ąĖ. ąŁč鹊 čüą╝čÅą│čćą░ąĄčé čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅ ą║ čāčüą╗ąŠą▓ąĖčÅą╝ čĆą░ą▒ąŠčéčŗ ąĘą░ą│čĆčāąĘčćąĖą║ą░ ą▓č鹊čĆąŠą│ąŠ čāčĆąŠą▓ąĮčÅ, ą┐ąŠč鹊ą╝čā čćč鹊 ą┐ąŠą╗ąĮąŠąĄ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą│čĆčāąČąĄąĮąŠ ąĖąĘ čĆą░ąĘą╗ąĖčćąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ą┐ą░ą╝čÅčéąĖ, ą║ąŠą│ą┤ą░ ąĮą░ čüą░ą╝ąŠą╝ ą┐čĆąŠčåąĄčüčüąŠčĆąĄ ąĄčüčéčī č鹊ą╗čīą║ąŠ ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ ą║ąŠą┤ Boot ROM.

ąÜą░ą║ čāąČąĄ čāą┐ąŠą╝ąĖąĮą░ą╗ąŠčüčī, čāčéąĖą╗ąĖčéą░ ąĘą░ą│čĆčāąĘą║ąĖ ą┐čĆąĄąŠą▒čĆą░ąĘčāąĄčé ąĖčüą┐ąŠą╗ąĮčÅąĄą╝ąŠąĄ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ (čäą░ą╣ą╗ .dxe) ą▓ ąĘą░ą│čĆčāąČą░ąĄą╝čŗą╣ čäą░ą╣ą╗, ą░ąĮą░ą╗ąĖąĘąĖčĆčāčÅ ą║ąŠą┤ ąĖ čüąŠąĘą┤ą░ą▓ą░čÅ čäą░ą╣ą╗, ą║ąŠč鹊čĆčŗą╣ čüąŠčüč鹊ąĖčé ąĖąĘ čĆą░ąĘą╗ąĖčćąĮčŗčģ ą▒ą╗ąŠą║ąŠą▓. ąÜą░ąČą┤čŗą╣ ą▒ą╗ąŠą║ čüąĮą░ą▒ąČąĄąĮ 10-ą▒ą░ą╣čéąĮčŗą╝ ąĘą░ą│ąŠą╗ąŠą▓ą║ąŠą╝, ą║ą░ą║ čŹč鹊 ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 3-1, ąĖ ą▒ąŠą╗ąĄąĄ ą┐ąŠą┤čĆąŠą▒ąĮąŠ čĆą░ąĘčŖčÅčüąĮąĄąĮąŠ ą▓ ą┐ąŠčüą╗ąĄą┤čāčÄčēąĖčģ čüąĄą║čåąĖčÅčģ (čéą░ą║ąČąĄ čüą╝. [2]). ąŚą░ą│ąŠą╗ąŠą▓ą║ąĖ, ą▓ čüą▓ąŠčÄ ąŠč湥čĆąĄą┤čī, čćąĖčéą░čÄčéčüčÅ ąĖ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░čÄčéčüčÅ ą║ąŠą┤ąŠą╝ Boot ROM ą▓ąŠ ą▓čĆąĄą╝čÅ ąĘą░ą│čĆčāąĘą║ąĖ.

10-ą▒ą░ą╣čéąĮčŗą╣ ąĘą░ą│ąŠą╗ąŠą▓ąŠą║ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ąĘą░ą│čĆčāąĘčćąĖą║čā (ą║ąŠą┤ Boot ROM) ą▓čüčÄ ąĮąĄąŠą▒čģąŠą┤ąĖą╝čāčÄ ąĖąĮč乊čĆą╝ą░čåąĖčÄ ŌĆö ą║čāą┤ą░ ąĮą░ą┤ąŠ ą┐ąŠą╝ąĄčüčéąĖčéčī ą▒ą╗ąŠą║, čüą║ąŠą╗čīą║ąŠ ą▒ą░ą╣čé ąĘą░ąĮąĖą╝ą░ąĄčé ą▒ą╗ąŠą║, ąĖ čćč鹊 ąĮčāąČąĮąŠ ą┤ąĄą╗ą░čéčī čü čŹčéąĖą╝ ą▒ą╗ąŠą║ąŠą╝.

[ą¤ąŠč鹊ą║ąĖ ąĘą░ą│čĆčāąĘą║ąĖ ADSP-BF531, BF532, BF533, BF534, BF536, BF537, BF538, BF539]

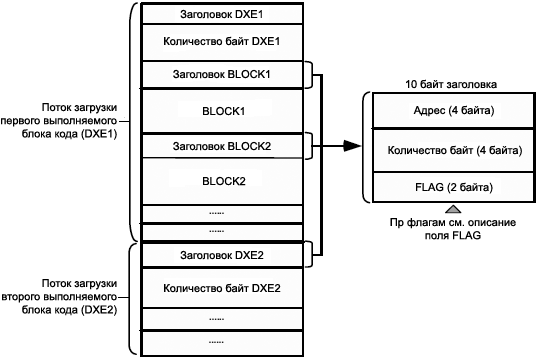

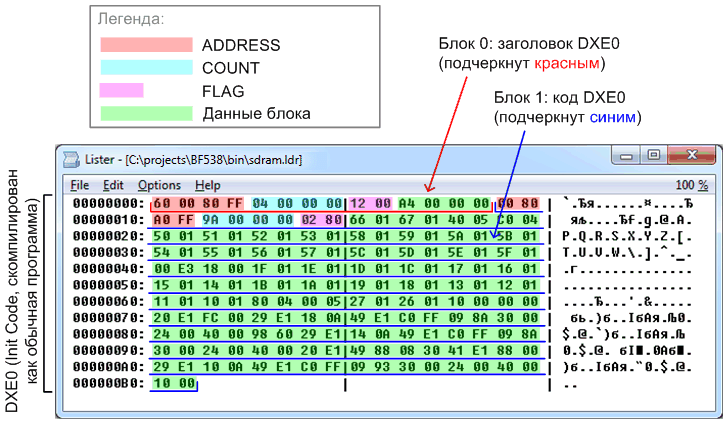

ąöą░ą╗ąĄąĄ ąŠą┐ąĖčüą░ąĮčŗ ą┐ąŠč鹊ą║ ąĘą░ą│čĆčāąĘą║ąĖ, ąĘą░ą│ąŠą╗ąŠą▓ą║ąĖ ąĖ čäą╗ą░ą│ąĖ ą┤ą╗čÅ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ ADSP-BF531, ADSP-BF532, ADSP-BF533, ADSP-BF534, ADSP-BF536, ADSP-BF537, ADSP-BF538 ąĖ ADSP-BF539.

ąÜąŠą│ą┤ą░ čāčéąĖą╗ąĖčéą░ ąĘą░ą│čĆčāąĘą║ąĖ ą┐čĆąĄąŠą▒čĆą░ąĘčāąĄčé ą║ąŠą┤ ąĖąĘ ą▓čģąŠą┤ąĮąŠą│ąŠ čäą░ą╣ą╗ą░ .dxe ą▓ ą▒ą╗ąŠą║ąĖ, ą┐ąŠą╝ąĄčēą░ąĄą╝čŗąĄ ą▓ ą▓čŗčģąŠą┤ąĮąŠą╣ čäą░ą╣ą╗ ąĘą░ą│čĆčāąĘą║ąĖ, ą║ą░ąČą┤čŗą╣ ą▒ą╗ąŠą║ ą┐ąŠą╗čāčćą░ąĄčé 10-ą▒ą░ą╣čéąĮčŗą╣ ąĘą░ą│ąŠą╗ąŠą▓ąŠą║ (ą┐ąŠą║ą░ąĘą░ąĮąĮčŗą╣ ąĮą░ čĆąĖčü. 3-2), ąĘą░ ą║ąŠč鹊čĆčŗą╝ ąĖą┤ąĄčé č鹥ą╗ąŠ ą▒ą╗ąŠą║ą░ (ąĄčüą╗ąĖ čŹč鹊 ąĮąĄ zero-ą▒ą╗ąŠą║) ąĖą╗ąĖ č鹥ą╗ąŠ no-block (ąĄčüą╗ąĖ čŹč鹊 zero-ą▒ą╗ąŠą║). ą×ą┐ąĖčüą░ąĮąĖąĄ čüčéčĆčāą║čéčāčĆčŗ ąĘą░ą│ąŠą╗ąŠą▓ą║ą░ ą┐čĆąĖą▓ąĄą┤ąĄąĮąŠ ą▓ čéą░ą▒ą╗ąĖčåąĄ 3-3.

ąĀąĖčü. 3-2. ą¤čĆąŠčåąĄčüčüąŠčĆčŗ ADSP-BF531, BF532, BF533, BF534, BF536, BF537, BF538, BF539: čüčéčĆčāą║čéčāčĆą░ ą┐ąŠč鹊ą║ą░ ąĘą░ą│čĆčāąĘą║ąĖ.

ąóą░ą▒ą╗ąĖčåą░ 3-3. ąĪčéčĆčāą║čéčāčĆą░ ąĘą░ą│ąŠą╗ąŠą▓ą║ą░ ą▒ą╗ąŠą║ą░ ADSP-BF531, BF532, BF533.

| ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| ADDRESS |

4-ą▒ą░ą╣č鹊ą▓čŗą╣ ą░ą┤čĆąĄčü, čāą║ą░ąĘčŗą▓ą░čÄčēąĖą╣ ąĮą░ ą╝ąĄčüč鹊 čĆą░čüą┐ąŠą╗ąŠąČąĄąĮąĖąĄ ą▒ą╗ąŠą║ą░ ą▓ ą┐ą░ą╝čÅčéąĖ (ą║čāą┤ą░ ą▒ą╗ąŠą║ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ą│čĆčāąČąĄąĮ). |

| COUNT |

4-ą▒ą░ą╣č鹊ą▓ąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ą░ą╣čé ąĘą░ą│čĆčāąČą░ąĄą╝ąŠą│ąŠ ą▒ą╗ąŠą║ą░. |

| FLAG |

2-ą▒ą░ą╣č鹊ą▓ąŠąĄ ą┐ąŠą╗ąĄ, ą▓ ą║ąŠč鹊čĆąŠą╝ čüąŠą┤ąĄčƹȹ░čéčüčÅ čäą╗ą░ą│ąĖ. |

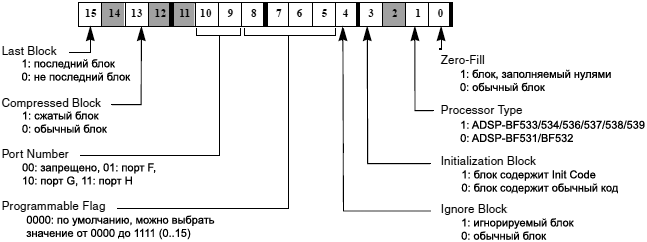

ąØą░ čĆąĖčü. 3-3 ąĖ ą▓ čéą░ą▒ą╗ąĖčåąĄ 3-4 ą┐ąŠčÅčüąĮčÅąĄčéčüčÅ čüčéčĆčāą║čéčāčĆą░ ą▒ąĖč鹊ą▓ čäą╗ą░ą│ąŠą▓.

ąĀąĖčü. 3-3. ąæąĖčéčŗ čäą╗ą░ą│ąŠą▓ ą┤ą╗čÅ 2-ą▒ą░ą╣č鹊ą▓ąŠą│ąŠ ą┐ąŠą╗čÅ čäą╗ą░ą│ąŠą▓ ąĘą░ą│ąŠą╗ąŠą▓ą║ą░.

ąóą░ą▒ą╗ąĖčåą░ 3-4. ąĪčéčĆčāą║čéčāčĆą░ čäą╗ą░ą│ąŠą▓.

| ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| Zero-fill block |

ą¤ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ąĘą░ą│čĆčāąČą░ąĄą╝čŗą╣ ą▒ą╗ąŠą║ čÅą▓ą╗čÅąĄčéčüčÅ ą▒čāč乥čĆąŠą╝ ą▓ ą┐ą░ą╝čÅčéąĖ, ą║ąŠč鹊čĆčŗą╣ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐čĆąŠčüč鹊 ąĘą░ą┐ąŠą╗ąĮąĄąĮ ąĮčāą╗čÅą╝ąĖ. ąóąĄą╗ąŠ čŹč鹊ą│ąŠ ą▒ą╗ąŠą║ą░ ąĮąĄ ą┐čĆąĖčüčāčéčüčéą▓čāąĄčé ą▓ čäą░ą╣ą╗ąĄ ąĘą░ą│čĆčāąĘą║ąĖ (ąĄčüčéčī č鹊ą╗čīą║ąŠ ąĘą░ą│ąŠą╗ąŠą▓ąŠą║). ąÜąŠą│ą┤ą░ čāčéąĖą╗ąĖčéą░ ąĘą░ą│čĆčāąĘą║ąĖ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčé čäą░ą╣ą╗ *.dxe ąĖ ąŠą▒ąĮą░čĆčāąČąĖą▓ą░ąĄčé ą▒ąŠą╗čīčłąĖąĄ ą▒čāč乥čĆčŗ čü ąĮčāą╗čÅą╝ąĖ, č鹊 ąŠąĮą░ čüąŠąĘą┤ą░ąĄčé čéą░ą║ąŠą╣ ą▒ą╗ąŠą║, čćč鹊ą▒čŗ čāą╝ąĄąĮčīčłąĖčéčī čĆą░ąĘą╝ąĄčĆ čäą░ą╣ą╗ą░ ąĘą░ą│čĆčāąĘą║ąĖ ąĖ čüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ ą▓čĆąĄą╝čÅ ąĘą░ą│čĆčāąĘą║ąĖ. ąĢčüą╗ąĖ čŹč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, č鹊 ą┐ąŠčüą╗ąĄ ąĘą░ą│ąŠą╗ąŠą▓ą║ą░ ąĮąĄ ą▒čāą┤ąĄčé č鹥ą╗ą░ ą▒ą╗ąŠą║ą░ čü ą┤ą░ąĮąĮčŗą╝ąĖ. |

| Processor type |

ą¤ąŠą║ą░ąĘčŗą▓ą░ąĄčé čéąĖą┐ ą┐čĆąŠčåąĄčüčüąŠčĆą░ - ą╗ąĖą▒ąŠ ADSP-BF531, BF532, BF538, ą╗ąĖą▒ąŠ ADSP-BF533, BF534, BF536, BF537, BF539. ą¤ąŠčüą╗ąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ąĘą░ą│čĆčāąĘą║ąĖ ą║ąŠą┤ Boot ROM ą▒čāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąŠ ą░ą┤čĆąĄčüčā, ą║ąŠč鹊čĆčŗą╣ ąĘą░ą▓ąĖčüąĖčé ąŠčé čŹč鹊ą│ąŠ ą▒ąĖčéą░ (čüą╝. čéą░ą▒ą╗ąĖčåčā 3-1). ąĢčüą╗ąĖ čŹč鹊čé ą▒ąĖčé čĆą░ą▓ąĄąĮ 1, č鹊 čŹč鹊 ąŠąĘąĮą░čćą░ąĄčé ą┐čĆąŠčåąĄčüčüąŠčĆ BF533, BF534, BF536, BF537, BF538, BF539, ąĄčüą╗ąĖ 0, č鹊 ą┐čĆąŠčåąĄčüčüąŠčĆ BF531, BF532. |

| Initialization block |

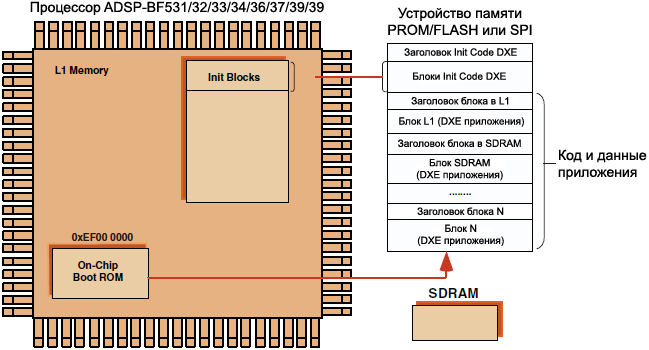

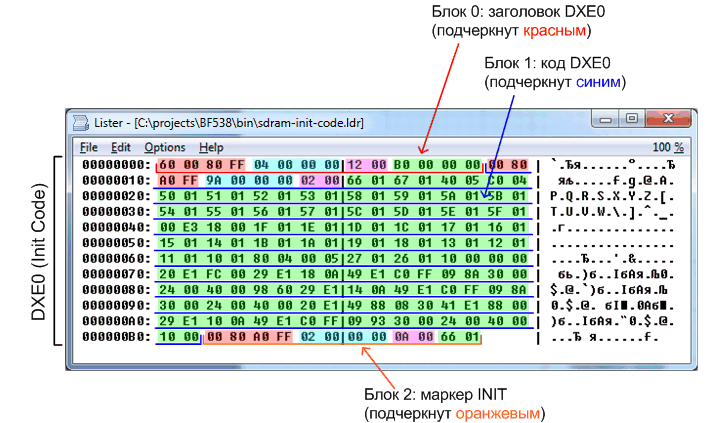

ą¤ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 čŹč鹊čé ą▒ą╗ąŠą║ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮ ą▓ ąĮą░čćą░ą╗ąĄ ąĘą░ą│čĆčāąĘą║ąĖ (ą▒ą╗ąŠą║ čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé Init Code DXE). ążą╗ą░ą│ ąĖąĮą┤ąĖą║ą░č鹊čĆą░ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą║ąŠą┤čā Boot ROM ą▓čŗą┐ąŠą╗ąĮąĖčéčī ąĮąĄą║ąŠč鹊čĆąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ąĖąĮčüčéčĆčāą║čåąĖą╣ ą┤ąŠ ąĘą░ą│čĆčāąĘą║ąĖ ą║ąŠą┤ą░ ą┤ąĄą╣čüčéą▓čāčÄčēąĄą│ąŠ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ. ąÜąŠą│ą┤ą░ ą║ąŠą┤ Boot ROM ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ą╗ ąĮą░ą╗ąĖčćąĖąĄ ą▒ą╗ąŠą║ą░ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ, ąŠąĮ ąĘą░ą│čĆčāąČą░ąĄčé čŹč鹊čé ą▒ą╗ąŠą║ ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮčÄčÄ ą┐ą░ą╝čÅčéčī ą┐čĆąŠčåąĄčüčüąŠčĆą░, ąĖ ą▓čŗą┐ąŠą╗ąĮčÅąĄčé ąĖąĮčüčéčĆčāą║čåąĖčÄ CALL, ą┐ąĄčĆąĄą┤ą░čÄčēčāčÄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą▓ čŹč鹊čé ą▒ą╗ąŠą║ ą║ą░ą║ ą▓ ą┐čĆąŠčåąĄą┤čāčĆčā (čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ Init Code ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čüą║ąŠą╝ą┐ąĖą╗ąĖčĆąŠą▓ą░ąĮ ą║ą░ą║ ą┐čĆąŠčåąĄą┤čāčĆą░, ąŠą║ą░ąĮčćąĖą▓ą░čÄčēą░čÅčüčÅ ąĮą░ ąĖąĮčüčéčĆčāą║čåąĖčÄ RTS). ążčāąĮą║čåąĖčÅ ą║ąŠą┤ą░ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÄ ąĘą░ą┐čāčüčéąĖčéčī čüą┐ąĄčåąĖą░ą╗čīąĮčŗą╣ ą║ąŠą┤, ą║ąŠč鹊čĆčŗą╣ ą╝ąŠąČąĄčé ą┐ąŠą┤ą│ąŠč鹊ą▓ąĖčéčī čüčĆąĄą┤čā ąĘą░ą│čĆčāąĘą║ąĖ ą┤ą╗čÅ ą║ąŠą┤ą░ ąŠčüąĮąŠą▓ąĮąŠą│ąŠ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ (čéą░ą║ąŠąĄ čćą░čüč鹊 čéčĆąĄą▒čāąĄčéčüčÅ, ąĄčüą╗ąĖ ą▓ čüąĖčüč鹥ą╝ąĄ ąĮčāąČąĮąŠ ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮąŠ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī SDRAM). ąØą░ čĆąĖčü. 3-4 ąĖ 3-5 ą┐ąŠą║ą░ąĘą░ąĮ čŹč鹊čé ą┐čĆąŠčåąĄčüčü. ąÜąŠą┤ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┤ąŠą▒ą░ą▓ą╗ąĄąĮ ą▓ čäą░ą╣ą╗ ąĘą░ą│čĆčāąĘą║ąĖ *.ldr čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ ąŠą┐čåąĖąĖ -init ą║ąŠą╝ą░ąĮą┤ąĮąŠą╣ čüčéčĆąŠą║ąĖ čāčéąĖą╗ąĖčéčŗ ąĘą░ą│čĆčāąĘą║ąĖ. ąĪą╝. ąĮąĖąČąĄ ą▓čĆąĄąĘą║čā "ąæą╗ąŠą║ąĖ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ ADSP-BF531, BF532, BF533, BF534, BF536, BF537, BF538, BF539". |

| Ignore block |

ą¤ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 čŹč鹊čé ą▒ą╗ąŠą║ ąĮąĄ ą┤ąŠą╗ąČąĄąĮ ąĘą░ą│čĆčāąČą░čéčīčüčÅ ą▓ ą┐ą░ą╝čÅčéčī. ąŁč鹊čé ą▒ą╗ąŠą║ ą▒čāą┤ąĄčé ą┐čĆąŠą┐čāčēąĄąĮ, ąĖ ąĘą░ą│čĆčāąĘą║ą░ ą┐ąĄčĆąĄą╣ą┤ąĄčé ą║ čüą╗ąĄą┤čāčÄčēąĄą╝čā ą▒ą╗ąŠą║čā. ąÆ ąĮą░čüč鹊čÅčēąĄąĄ ą▓čĆąĄą╝čÅ čŹč鹊 ąĮąĄ čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮąŠ ą┤ą╗čÅ ą║ąŠą┤ą░ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ.

ąŁč鹊čé čäą╗ą░ą│ 菹║ą▓ąĖą▓ą░ą╗ąĄąĮč鹥ąĮ čäą╗ą░ą│čā FIRST ą▓ ą┐ąŠč鹊ą║ą░čģ ąĘą░ą│čĆčāąĘą║ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ ADSP-BF51x, BF52x, BF54x. ąśąĘ-ąĘą░ č鹊ą│ąŠ, čćč鹊 čäą╗ą░ą│ IGNORE ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą┤čĆčāą│ąĖčģ čåąĄą╗ąĄą╣ ąĮą░ ADSP-BF51x, BF52x, BF54x, čäą╗ą░ą│ FIRST ąĖąĘąŠą▒čĆąĄč鹥ąĮ, čćč鹊ą▒čŗ ą┐ąŠą║ą░ąĘą░čéčī ą┐ąĄčĆą▓čŗą╣ ąĘą░ą│ąŠą╗ąŠą▓ąŠą║. |

| Compressed block |

ą¤ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą▒ą╗ąŠą║ čüąŠą┤ąĄčƹȹĖčé čüąČą░čéčŗąĄ ą┤ą░ąĮąĮčŗąĄ (čüąČą░čéčŗą╣ ą▒ą╗ąŠą║). ąĪąČą░čéčŗą╣ ą▒ą╗ąŠą║ ą╝ąŠąČąĄčé ą▓ą║ą╗čÄčćą░čéčī ą▓ čüąĄą▒čÅ ąĮąĄą║ąŠč鹊čĆąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čüąČą░čéčŗčģ čüąŠą▓ą╝ąĄčüčéąĮąŠ ą▒ą╗ąŠą║ąŠą▓, čćč鹊ą▒čŗ čüč乊čĆą╝ąĖčĆąŠą▓ą░čéčī ąŠą┤ąĖąĮ čüąČą░čéčŗą╣ ą▒ą╗ąŠą║. |

| Last block |

ą¤ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 čŹč鹊 ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ą▒ą╗ąŠą║, ąĘą░ą│čĆčāąČą░ąĄą╝čŗą╣ ą▓ ą┐ą░ą╝čÅčéčī. ą¤ąŠčüą╗ąĄ ąĘą░ą│čĆčāąĘą║ąĖ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ ą▒ą╗ąŠą║ą░ ą┐čĆąŠčåąĄčüčüąŠčĆ ą┐ąĄčĆąĄą┤ą░ąĄčé čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą▓ ąĮą░čćą░ą╗ąŠ ą┐ą░ą╝čÅčéąĖ L1, čćč鹊 ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ąĘą░ą┐čāčüą║čā ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ. ąÜąŠą│ą┤ą░ ą┤ąĄą╗ą░ąĄčéčüčÅ ą┐ąĄčĆąĄčģąŠą┤ ą▓ ą┐ą░ą╝čÅčéčī L1 ą┤ą╗čÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą║ąŠą┤ą░ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ, ą┐čĆąŠčåąĄčüčüąŠčĆ ą▓čüąĄ ąĄčēąĄ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ čüčāą┐ąĄčĆą▓ąĖąĘąŠčĆą░ čü čüą░ą╝čŗą╝ ąĮąĖąĘą║ąĖą╝ čāčĆąŠą▓ąĮąĄą╝ ą┐čĆąĖąŠčĆąĖč鹥čéą░ (IVG15). |

ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ą┐čĆąŠčåąĄčüčüąŠčĆčŗ ADSP-BF534, BF536, BF537 ą╝ąŠą│čāčé ąĖą╝ąĄčéčī čüą┐ąĄčåąĖą░ą╗čīąĮčŗą╣ ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ą▒ą╗ąŠą║, ąĄčüą╗ąĖ čĆąĄąČąĖą╝ ąĘą░ą│čĆčāąĘą║ąĖ TWI (Two Wire Interface, I2C, ą┤ą▓čāčģą┐čĆąŠą▓ąŠą┤ąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü). ąŻčéąĖą╗ąĖčéą░ ąĘą░ą│čĆčāąĘą║ąĖ čüąŠčģčĆą░ąĮčÅąĄčé ą▓čüąĄ ą┤ą░ąĮąĮčŗąĄ ąŠčé 0xFF903F00 ą┤ąŠ 0xFF903FFF ąĖ ą┤ąĄą╗ą░ąĄčé ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ą▒ą╗ąŠą║ čü čŹčéąĖą╝ąĖ ą┤ą░ąĮąĮčŗą╝ąĖ. ąŻčéąĖą╗ąĖčéą░ ąĘą░ą│čĆčāąĘą║ąĖ, ąŠą┤ąĮą░ą║ąŠ, čüąŠąĘą┤ą░ąĄčé ąŠą▒čŗčćąĮčŗą╣ ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ą▒ą╗ąŠą║, ąĄčüą╗ąĖ ą▓ čŹč鹊ą╝ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąĮąĄčé ą┤ą░ąĮąĮčŗčģ. ą×ą▒ą╗ą░čüčéčī 0xFF903F00 .. 0xFF903FFF čüąŠčģčĆą░ąĮčÅąĄčéčüčÅ ą┤ą╗čÅ Boot ROM, čćč鹊ą▒čŗ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čŹčéčā ą┐ą░ą╝čÅčéčī ą║ą░ą║ ą▒čāč乥čĆ ą┤ą░ąĮąĮčŗčģ ą┤ą╗čÅ ą┐čĆąŠčåąĄčüčüą░ ąĘą░ą│čĆčāąĘą║ąĖ.

ą×ą┐čåąĖčÅ -init filename ą┤ą░ąĄčé čāą║ą░ąĘą░ąĮąĖąĄ čāčéąĖą╗ąĖč鹥 ąĘą░ą│čĆčāąĘą║ąĖ ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ą▒ą╗ąŠą║ąĖ, ą┐ąŠą╗čāč湥ąĮąĮčŗąĄ ąĖąĘ ą║ąŠą┤ą░ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ (Init Code), ą║ąŠą┤ ą▒ąĄčĆąĄčéčüčÅ ąĖąĘ čäą░ą╣ą╗ą░ filename. ąæą╗ąŠą║ąĖ ą║ąŠą┤ą░ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ ą┐ąŠą╝ąĄčēą░čÄčéčüčÅ ą▓ ąĮą░čćą░ą╗ąŠ čäą░ą╣ą╗ą░ ąĘą░ą│čĆčāąĘą║ąĖ. ą×ąĮąĖ ą▓čŗą┐ąŠą╗ąĮčÅčÄčéčüčÅ ą┤ąŠ č鹊ą│ąŠ, ą║ą░ą║ ąŠčüčéą░ą╗čīąĮą░čÅ čćą░čüčéčī ą║ąŠą┤ą░ ą▓ čäą░ą╣ą╗ąĄ ąĘą░ą│čĆčāąĘą║ąĖ ą▒čāą┤ąĄčé ąĘą░ą│čĆčāąČąĄąĮą░ ą▓ ą┐ą░ą╝čÅčéčī ąĖ ą▓čŗą┐ąŠą╗ąĮąĄąĮą░ (čüą╝. čĆąĖčü. 3-4).

ąĀąĖčü. 3-4. ąÆčŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą▒ą╗ąŠą║ą░ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ (Init Code) ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ ADSP-BF531, BF532, BF533, BF534, BF536, BF537, BF538, BF539.

ą¤ąŠčüą╗ąĄ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą║ąŠą┤ą░ ąĖąĘ ą▒ą╗ąŠą║ąŠą▓ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ, ą┐čĆąŠčåąĄčüčü ąĘą░ą│čĆčāąĘą║ąĖ ą┐čĆąŠą┤ąŠą╗ąČąĖčé ąĘą░ą│čĆčāąČą░čéčī ąŠčüčéą░ą╗čīąĮčŗąĄ ą▒ą╗ąŠą║ąĖ ą┤ą░ąĮąĮčŗčģ, ą┐ąŠą║ą░ ąĮąĄ ą┤ąŠą╣ą┤ąĄčé ą┤ąŠ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ ą▒ą╗ąŠą║ą░ (čüą╝. čĆąĖčü. 3-5). ą¤čĆąĖą╝ąĄčĆ ą║ąŠą┤ą░ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ ą┐ąŠą║ą░ąĘą░ąĮ ą▓ ą╗ąĖčüčéąĖąĮą│ąĄ 3-1.

ąĀąĖčü. 3-5. ąŚą░ą│čĆčāąĘą║ą░ ą║ąŠą┤ą░ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ ADSP-BF531, BF532, BF533, BF534, BF536, BF537, BF538, BF539.

ąøąĖčüčéąĖąĮą│ 3-1. ą¤čĆąĖą╝ąĄčĆ ą▒ą╗ąŠą║ą░ ą║ąŠą┤ą░ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ.

/* ąŁč鹊čé čäą░ą╣ą╗ čüąŠą┤ąĄčƹȹĖčé 3 čüąĄą║čåąĖąĖ: */

/* 1) Pre-Init Section ŌĆō čŹčéą░ čüąĄą║čåąĖčÅ čüąŠčģčĆą░ąĮčÅąĄčé ą▓ čüč鹥ą║ ą▓čüąĄ čĆąĄą│ąĖčüčéčĆčŗ ą┐čĆąŠčåąĄčüčüąŠčĆą░.

2) Init Code Section ŌĆō čŹčéą░ čüąĄą║čåąĖčÅ čüąŠą┤ąĄčƹȹĖčé ą║ąŠą┤ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ, ą║ąŠč鹊čĆčŗą╣

ą╝ąŠąČąĄčé ą▒čŗčéčī ą╝ąŠą┤ąĖčäąĖčåąĖčĆąŠą▓ą░ąĮ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╝. ąÆ ą║ą░č湥čüčéą▓ąĄ ą┐čĆąĖą╝ąĄčĆą░ ąĘą┤ąĄčüčī

ą┐čĆąĖą▓ąĄą┤ąĄąĮ ą║ąŠą┤ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ SDRAM (ąŠą▒čŗčćąĮą░čÅ ąĘą░ą┤ą░čćą░ ą┤ą╗čÅ Init Code).

ąØą░čüčéčĆą░ąĖą▓ą░ąĄčéčüčÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ SDRAM, ą║ą░ą║ čŹč鹊 čéčĆąĄą▒čāąĄčéčüčÅ ą┤ą╗čÅ ąŠčüąĮąŠą▓ąĮčŗčģ čéąĖą┐ąŠą▓

SDRAM. ąĀą░ąĘąĮčŗąĄ čéąĖą┐čŗ SDRAM ą╝ąŠą│čāčé ą┐ąŠčéčĆąĄą▒ąŠą▓ą░čéčī ą┤čĆčāą│ąŠą╣ ą┐čĆąŠčåąĄą┤čāčĆčŗ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ

(ąŠą▒čŗčćąĮąŠ ą┐čĆąŠčüč鹊 ą┤čĆčāą│ąĖčģ ąĘąĮą░č湥ąĮąĖą╣, ąĘą░ą┐ąĖčüą░ąĮąĮčŗčģ ą▓ čĆąĄą│ąĖčüčéčĆčŗ).

3) Post-Init Section ŌĆō čŹčéą░ čüąĄą║čåąĖčÅ ą▓ąŠčüčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ą▓čüąĄ čĆąĄą│ąĖčüčéčĆčŗ ąĖąĘ čüč鹥ą║ą░.

ą¤ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ąĮąĄ ą┤ąŠą╗ąČąĄąĮ ą╝ąĄąĮčÅčéčī čüąĄą║čåąĖąĖ Pre-Init ąĖ Post-Init. ąĪąĄą║čåąĖčÅ

Init Code ą╝ąŠąČąĄčé ą▒čŗčéčī ą╝ąŠą┤ąĖčäąĖčåąĖčĆąŠą▓ą░ąĮą░ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü ąĘą░ą┤ą░čćą░ą╝ąĖ

ąŠčéą┤ąĄą╗čīąĮąŠą│ąŠ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ. */

#include < defBF532.h >

.SECTION program;

/**********************Pre-Init Section************************/

[--SP] = ASTAT; /* Stack Pointer (SP) čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ąĮą░ ą║ąŠąĮąĄčå */

[--SP] = RETS; /* ą┐ą░ą╝čÅčéąĖ scratchpad (0xFFB00FFC) */

[--SP] = (r7:0); /* ą║ąŠą┤ąŠą╝ on-chip Boot ROM */

[--SP] = (p5:0);

[--SP] = I0;[--SP] = I1;[--SP] = I2;[--SP] = I3;

[--SP] = B0;[--SP] = B1;[--SP] = B2;[--SP] = B3;

[--SP] = M0;[--SP] = M1;[--SP] = M2;[--SP] = M3;

[--SP] = L0;[--SP] = L1;[--SP] = L2;[--SP] = L3;

/*******************Init Code Section**************************/

/*****ą¤ąŠąČą░ą╗čāą╣čüčéą░, ą▓čüčéą░ą▓čīč鹥 ą║ąŠą┤ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ ą▓ čŹčéčā čüąĄą║čåąĖčÄ******/

/*********************ąØą░čüčéčĆąŠą╣ą║ą░ SDRAM**************************/

Setup_SDRAM:

P0.L = LO(EBIU_SDRRC);

/* SDRAM Refresh Rate Control Register */

P0.H = HI(EBIU_SDRRC);

R0 = 0x074A(Z);

W[P0] = R0;

SSYNC;

P0.L = LO(EBIU_SDBCTL);

/* SDRAM Memory Bank Control Register */

P0.H = HI(EBIU_SDBCTL);

R0 = 0x0001(Z);

W[P0] = R0;

SSYNC;

P0.L = LO(EBIU_SDGCTL);

/* SDRAM Memory Global Control Register */

P0.H = HI(EBIU_SDGCTL);

R0.L = 0x998D;

R0.H = 0x0091;

[P0] = R0;

SSYNC;

/*********************Post-Init Section************************/

L3 = [SP++]; L2 = [SP++]; L1 = [SP++]; L0 = [SP++];

M3 = [SP++]; M2 = [SP++]; M1 = [SP++]; M0 = [SP++];

B3 = [SP++]; B2 = [SP++]; B1 = [SP++]; B0 = [SP++];

I3 = [SP++]; I2 = [SP++]; I1 = [SP++]; I0 = [SP++];

(p5:0) = [SP++];

(r7:0) = [SP++];

RETS = [SP++];

ASTAT = [SP++];

/************************************************************/

RTS;

ą¤ąŠč鹊ą║ąĖ ąĘą░ą│čĆčāąĘą║ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ADSP-BF531, BF532, BF533, BF534, BF536, BF537, BF538, BF539 ą░ąĮą░ą╗ąŠą│ąĖčćąĮčŗ ą┐ąŠč鹊ą║čā ąĘą░ą│čĆčāąĘą║ąĖ, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ąŠą╝čā ąĘą░ą│čĆčāąĘčćąĖą║ąŠą╝ čÅą┤čĆą░ ą▓č鹊čĆąŠą│ąŠ čāčĆąŠą▓ąĮčÅ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ADSP-BF535 (ą┐ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. čĆą░ąĘą┤ąĄą╗ "ążą░ą╣ą╗čŗ ąĘą░ą│čĆčāąĘą║ąĖ, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ čü ąĘą░ą│čĆčāąĘčćąĖą║ąŠą╝ ą▓č鹊čĆąŠą│ąŠ čāčĆąŠą▓ąĮčÅ"). ą×ą┤ąĮą░ą║ąŠ, ą┐ąŠčüą║ąŠą╗čīą║čā ą┐čĆąĄą┤čŗą┤čāčēąĖąĄ ą┐čĆąŠčåąĄčüčüąŠčĆčŗ ąĮąĄ čĆąĄą░ą╗ąĖąĘąŠą▓ą░ą╗ąĖ ąĘą░ą│čĆčāąĘčćąĖą║ ą▓č鹊čĆąŠą│ąŠ čāčĆąŠą▓ąĮčÅ, ąĖčģ ą┐ąŠč鹊ą║ ąĘą░ą│čĆčāąĘą║ąĖ ąĮąĄ ą▓ą║ą╗čÄčćą░ąĄčé ą▓ čüąĄą▒čÅ ą║ąŠą┤ ą▓č鹊čĆąŠą╣ čüčéą░ą┤ąĖąĖ ąĘą░ą│čĆčāąĘą║ąĖ ąĖ čüą▓čÅąĘą░ąĮąĮčŗą╣ čü ąĮąĖą╝ 4-ą▒ą░ą╣čéąĮčŗą╣ ąĘą░ą│ąŠą╗ąŠą▓ąŠą║, čĆą░čüą┐ąŠą╗ąŠąČąĄąĮąĮčŗą╣ ą┐ąŠą▓ąĄčĆčģ ą║ąŠą┤ą░ čÅą┤čĆą░ (kernel code). ąŚą┤ąĄčüčī čéą░ą║ąČąĄ ąĮąĄčé 4-ą▒ą░ą╣čéąĮąŠą│ąŠ ą│ą╗ąŠą▒ą░ą╗čīąĮąŠą│ąŠ ąĘą░ą│ąŠą╗ąŠą▓ą║ą░ (global header).

ąÉą┐ą┐ą░čĆą░čéąĮą░čÅ čāčüčéą░ąĮąŠą▓ą║ą░ BMODE = 00 ą┤ą╗čÅ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ ADSP-BF531, BF532 ąĖ BF533 ąĖą╗ąĖ BMODE = 000 ą┤ą╗čÅ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ ADSP-BF535 ą▓čŗą▒ąĄčĆąĄčé ąŠą┐čåąĖčÄ ąĘą░ą│čĆčāąĘą║ąĖ no-boot. ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ąŠą┤ą░ ąĘą░ą│čĆčāąĘą║ąĖ, ą▓čüčéčĆąŠąĄąĮąĮąŠą│ąŠ ą▓ ą┐čĆąŠčåąĄčüčüąŠčĆ, ą┐čĆąŠą┐čāčüą║ą░ąĄčéčüčÅ, ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆ ąĮą░čćąĖąĮą░ąĄčé ą▓čŗą▒ąŠčĆą║čā ąĖ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ąĖąĮčüčéčĆčāą║čåąĖą╣ ą┐ąŠ ą░ą┤čĆąĄčüčā 0x20000000 (čŹčéą░ ą┐ą░ą╝čÅčéčī ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą╝ ą▒ą░ąĮą║ąĄ ą┐ą░ą╝čÅčéąĖ 0). ą¤čĆąŠčåąĄčüčüąŠčĆ ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčé ąĮą░ą╗ąĖčćąĖąĄ ą┐ą░ą╝čÅčéąĖ čü čłąĖąĮąŠą╣ 16 ą▒ąĖčé, ą│ą┤ąĄ ąĮą░čģąŠą┤čÅčéčüčÅ ą┤ąŠą┐čāčüčéąĖą╝čŗąĄ ą┤ą╗čÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ąĖąĮčüčéčĆčāą║čåąĖąĖ ą║ąŠą┤ą░ (čé. ąĄ. ą┐ąŠ čŹč鹊ą╝čā ą░ą┤čĆąĄčüčā ą┤ąŠą╗ąČąĄąĮ ąĮą░čģąŠą┤ąĖčéčīčüčÅ čćąĖčüčéčŗą╣ ą║ąŠą┤, ą▒ąĄąĘ čüą╗čāąČąĄą▒ąĮčŗčģ ąĘą░ą│ąŠą╗ąŠą▓ą║ąŠą▓ ąĘą░ą│čĆčāąĘą║ąĖ).

ą¦č鹊ą▒čŗ čüąŠąĘą┤ą░čéčī ą║ąŠčĆčĆąĄą║čéąĮčŗą╣ čäą░ą╣ą╗ .ldr, ą║ąŠč鹊čĆčŗą╣ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮ ą╗ąĖą▒ąŠ ą▓ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮčāčÄ ą┐ą░ą╝čÅčéčī flash, ą╗ąĖą▒ąŠ ą▓ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮčāčÄ ą┐ą░ą╝čÅčéčī EPROM, ąÆčŗ ą┤ąŠą╗ąČąĮčŗ ą╝ąŠą┤ąĖčäąĖčåąĖčĆąŠą▓ą░čéčī čüčéą░ąĮą┤ą░čĆčéąĮčŗą╣ čäą░ą╣ą╗ LDF, čćč鹊ą▒čŗ ą▓ ąĮąĄą╝ ą▒čŗą╗ ą┐čĆą░ą▓ąĖą╗čīąĮąŠ ąĮą░čüčéčĆąŠąĄąĮ ą▓ąĄą║č鹊čĆ čüą▒čĆąŠčüą░. ążčĆą░ą│ą╝ąĄąĮčéčŗ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ ą║ąŠą┤ą░ (ą╗ąĖčüčéąĖąĮą│ 3-6 ąĖ ą╗ąĖčüčéąĖąĮą│ 3-7) ąĖą╗ą╗čÄčüčéčĆąĖčĆčāčÄčé čéčĆąĄą▒čāąĄą╝čŗąĄ ą╝ąŠą┤ąĖčäąĖą║ą░čåąĖąĖ ą▓ čüą╗čāčćą░ąĄ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ADSP-BF533.

ąøąĖčüčéąĖąĮą│ 3-2. ą¤čĆąĖą╝ąĄčĆ ąĮą░ąĘąĮą░č湥ąĮąĖą╣ čüąĄą║čåąĖąĖ (čäą░ą╣ą╗ LDF).

MEMORY

{

/* ą¤ąŠčüč鹊čÅąĮąĮą░čÅ ą┐ą░ą╝čÅčéčī ąĖąĮčüčéčĆčāą║čåąĖą╣ ą▓ (Instruction ROM) ą▓ Async Bank 0,

ąĮą░čģąŠą┤čÅčēąĄą╝čüčÅ ą▓ąĮąĄ čćąĖą┐ą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░ */

MEM_PROGRAM_ROM { TYPE(ROM) START(0x20000000) END(0x2009FFFF) WIDTH(8)

}

MEM_DATA_ROM

{

/* ąöą░ąĮąĮčŗąĄ ą║ąŠąĮčüčéą░ąĮčé ą▓ Async Bank 0, ąĮą░čģąŠą┤čÅčēąĄą╝čüčÅ ą▓ąĮąĄ čćąĖą┐ą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░ */

TYPE(ROM) START(0x200A0000) END(0x200FFFFF) WIDTH(8)

}

MEM_DATA_RAM

{

/* ąöą░ąĮąĮčŗąĄ SRAM (ą┐ą░ą╝čÅčéčī, čäąĖąĘąĖč湥čüą║ąĖ ąĮą░čģąŠą┤čÅčēą░čÅčüčÅ ąĮą░ ą║čĆąĖčüčéą░ą╗ą╗ąĄ ą┐čĆąŠčåąĄčüčüąŠčĆą░),

ąĮąĄ ą▒čāą┤ąĄčé ąĘą░ą│čĆčāąČąĄąĮą░ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ */

TYPE(RAM) START(0xFF903000) END(0xFF907FFF) WIDTH(8)

}

ąøąĖčüčéąĖąĮą│ 3-3. ą¤čĆąĖą╝ąĄčĆ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ čüąĄą│ą╝ąĄąĮčéą░ ROM (čäą░ą╣ą╗ LDF).

PROCESSOR p0

{

OUTPUT( $COMMAND_LINE_OUTPUT_FILE )

SECTIONS

{

program_rom

{

INPUT_SECTION_ALIGN(4)

INPUT_SECTIONS( $OBJECTS(rom_code) )

} >MEM_PROGRAM_ROM

data_rom

{

INPUT_SECTION_ALIGN(4)

INPUT_SECTIONS( $OBJECTS(rom_data) )

} >MEM_DATA_ROM

data_sram

{

INPUT_SECTION_ALIGN(4)

INPUT_SECTIONS( $OBJECTS(ram_data) )

} >MEM_DATA_RAM

ąĪ čäą░ą╣ą╗ąŠą╝ LDF, ą╝ąŠą┤ąĖčäąĖčåąĖčĆąŠą▓ą░ąĮąĮčŗą╝ čéą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, čäą░ą╣ą╗čŗ ąĖčüčģąŠą┤ąĮąŠą│ąŠ ą║ąŠą┤ą░ ą╝ąŠą│čāčé č鹥ą┐ąĄčĆčī ą┐ąŠą╗čāčćąĖčéčī ąĮąŠą▓čŗąĄ ą▓ą▓ąĄą┤ąĄąĮąĮčŗąĄ čüąĄą║čåąĖąĖ, ą║ą░ą║ čŹč鹊 ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▓ ą╗ąĖčüčéąĖąĮą│ąĄ 3-4.

ąøąĖčüčéąĖąĮą│ 3-4. ą¤čĆąĖą╝ąĄčĆ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ čüąĄą║čåąĖą╣ (čäą░ą╣ą╗ ąĖčüčģąŠą┤ąĮąŠą│ąŠ ą║ąŠą┤ą░).

.SECTION rom_code;

_reset_vector:

l0 = 0;

l1 = 0;

l2 = 0;

l3 = 0;

/* ąĘą┤ąĄčüčī ąĮą░čģąŠą┤ąĖčéčüčÅ ą┐čĆąŠą┤ąŠą╗ąČąĄąĮąĖąĄ ąĮą░čüčéčĆąŠą╣ą║ąĖ ąĖ ą║ąŠą┤ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ */

/* . . . */

.SECTION rom_data;

.VAR myconst x = 0xdeadbeef;

/* . . . */

.SECTION ram_data;

.VAR myvar y; /* ąŠą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ą┐ąĄčĆąĄą╝ąĄąĮąĮą░čÅ y ąĮąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆąŠą▓ą░ąĮą░

ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ */

ąÆčüčéčĆąŠąĄąĮąĮčŗą╣ ą▓ ą║čĆąĖčüčéą░ą╗ą╗ ą║ąŠą┤ Boot ROM ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ Blackfin ADSP-BF531, BF532, BF533, BF534, BF536, BF537, BF538, BF539 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąĘą░ą│čĆčāąČą░čéčī čüą╗ąĄą┤čāčÄčēąĖąĄ ą┤ąĖą░ą┐ą░ąĘąŠąĮčŗ ą┐ą░ą╝čÅčéąĖ.

| ą¤ą░ą╝čÅčéčī L1 |

| ADSP-BF531 |

Data bank A SRAM (0xFF80 4000ŌĆō0xFF80 7FFF)

Instruction SRAM (0xFFA0 8000ŌĆō0xFFA0 BFFF) |

| ADSP-BF532 |

Data bank A SRAM (0xFF80 4000ŌĆō0xFF80 7FFF)

Data bank B SRAM (0xFF90 4000ŌĆō0xFF90 7FFF)

Instruction SRAM (0xFFA0 8000ŌĆō0xFFA1 3FFF) |

| ADSP-BF533 |

Data bank A SRAM (0xFF80 0000ŌĆō0xFF80 7FFF)

Data bank B SRAM (0xFF90 000ŌĆō0xFF90 7FFF)

Instruction SRAM (0xFFA0 0000ŌĆō0xFFA1 3FFF) |

| ADSP-BF534 |

Data bank A SRAM (0xFF80 0000ŌĆō0xFF80 7FFF)

Data bank B SRAM (0xFF90 0000ŌĆō0xFF90 7FFF)

Instruction SRAM (0xFFA0 0000ŌĆō0xFFA1 3FFF) |

| ADSP-BF536 |

Data bank A SRAM (0xFF80 4000ŌĆō0xFF80 7FFF)

Data bank B SRAM (0xFF90 4000ŌĆō0xFF90 7FFF)

Instruction SRAM (0xFFA0 0000ŌĆō0xFFA1 3FFF) |

| ADSP-BF537 |

Data bank A SRAM (0xFF80 0000ŌĆō0xFF80 7FFF)

Data bank B SRAM (0xFF90 0000ŌĆō0xFF90 7FFF)

Instruction SRAM (0xFFA0 0000ŌĆō0xFFA1 3FFF) |

| ADSP-BF538 |

Data bank A SRAM (0xFF80 4000ŌĆō0xFF80 7FFF)

Data bank B SRAM (0xFF90 4000ŌĆō0xFF90 7FFF)

Instruction SRAM (0xFFA0 8000ŌĆō0xFFA1 3FFF) |

| ADSP-BF539 |

Data bank A SRAM (0xFF80 0000ŌĆō0xFF80 3FFF)

Data bank B SRAM (0xFF90 2000ŌĆō0xFF90 7FFF)

Instruction SRAM (0xFFA0 0000ŌĆō0xFFA1 3FFF) |

| ą¤ą░ą╝čÅčéčī SDRAM |

| ąÆčüąĄ ą┐čĆąŠčåąĄčüčüąŠčĆčŗ |

Bank 0 (0x0000 0000ŌĆō0x07FF FFFF) |

ąŚą░ą│čĆčāąĘą║ą░ ą▓ ą┐ą░ą╝čÅčéčī scratchpad (0xFFB00000) ąĮąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ.

ąÜąŠą┤ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ ą┤ąŠą╗ąČąĄąĮ ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮąŠ ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆąŠą▓ą░čéčī ą┐ą░ą╝čÅčéčī SDRAM, čćč鹊ą▒čŗ ąĮąĄčæ ą╝ąŠąČąĮąŠ ą▒čŗą╗ąŠ ąĘą░ą│čĆčāąĘąĖčéčī ą║ą░ą║ąĖąĄ-ą╗ąĖą▒ąŠ ą┤ą░ąĮąĮčŗąĄ ąĖą╗ąĖ ą║ąŠą┤.

[ADSP-BF535 On-Chip Boot ROM]

ąĀąĖčü. 3-6. ą¤čĆąŠčåąĄčüčüąŠčĆčŗ ADSP-BF535: On-Chip Boot ROM.

ąÆčüčéčĆąŠąĄąĮąĮčŗą╣ ą▓ ą║čĆąĖčüčéą░ą╗ą╗ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ADSP-BF535 ą║ąŠą┤ Boot ROM ą┤ąĄą╗ą░ąĄčé čüą╗ąĄą┤čāčÄčēąĄąĄ (čüą╝. čĆąĖčü. 3-6):

1. ąØą░čüčéčĆą░ąĖą▓ą░ąĄčé čĆąĄąČąĖą╝ čüčāą┐ąĄčĆą▓ąĖąĘąŠčĆą░ (supervisor mode) ą┐čāč鹥ą╝ ą▓čŗčģąŠą┤ą░ ąĖąĘ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ RESET ąĖ ą┐ąĄčĆąĄčģąŠą┤ąŠą╝ ą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čü čüą░ą╝čŗą╝ ąĮąĖąĘą║ąĖą╝ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝ (IVG15).

2. ą¤čĆąŠą▓ąĄčĆčÅąĄčé, ą▒čŗą╗ ą╗ąĖ čŹč鹊čé RESET ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╝ čüą▒čĆąŠčüąŠą╝, ąĖ ąĄčüą╗ąĖ čŹč鹊 čéą░ą║, č鹊 ą┐čĆąŠą┐čāčüą║ą░ąĄčéčüčÅ ą▓čüčÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ąĘą░ą│čĆčāąĘą║ąĖ ąĖ ą┤ąĄą╗ą░ąĄčéčüčÅ ą┐ąĄčĆąĄčģąŠą┤ ą▓ ąĮą░čćą░ą╗ąŠ ą┐ą░ą╝čÅčéąĖ L2 (0xF0000000) ą┤ą╗čÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ąŠą┤ą░. ąÜąŠą┤ Boot ROM ą▓čŗą┐ąŠą╗ąĮčÅąĄčé čéą░ą║čāčÄ ą┐čĆąŠą▓ąĄčĆą║čā č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖąĄą╝ ą▒ąĖčéą░ 4 čĆąĄą│ąĖčüčéčĆą░ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ čüą▒čĆąŠčüą░ (System Reset Configuration Register, SYSCR). ąĢčüą╗ąĖ ą▒ąĖčé 4 ąĮąĄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, č鹊 ą║ąŠą┤ Boot ROM ą▓čŗą┐ąŠą╗ąĮčÅąĄčé ą┐ąŠą╗ąĮčāčÄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ąĘą░ą│čĆčāąĘą║ąĖ. ąĢčüą╗ąĖ ą▒ąĖčé 4 čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, č鹊 ą║ąŠą┤ Boot ROM ą┐čĆąŠą┐čāčüą║ą░ąĄčé ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ąĘą░ą│čĆčāąĘą║ąĖ, ąĖ ą┐ąĄčĆąĄą┤ą░ąĄčé čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąŠ ą░ą┤čĆąĄčüčā 0xF0000000.

3. ąÆ čüą╗čāčćą░ąĄ ąĘą░ą┐čāčüą║ą░ ą┐ąŠą╗ąĮąŠą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ąĘą░ą│čĆčāąĘą║ąĖ (ąĄčüą╗ąĖ ą▒ąĖčé 4 čĆąĄą│ąĖčüčéčĆą░ SYSCR ąĮąĄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ) ą▒čāą┤čāčé ą▓čŗą┐ąŠą╗ąĮąĄąĮčŗ čüą╗ąĄą┤čāčÄčēąĖąĄ ą┤ąĄą╣čüčéą▓ąĖčÅ:

ŌĆó ą¤čĆąŠą▓ąĄčĆą║ą░ ąĖčüč鹊čćąĮąĖą║ą░ ąĘą░ą│čĆčāąĘą║ąĖ (ą▓ąĮąĄčłąĮąĄąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐ą░ą╝čÅčéąĖ, čŹč鹊 ą╗ąĖą▒ąŠ ą┐ą░ą╝čÅčéčī flash/PROM, ą╗ąĖą▒ąŠ ą┐ą░ą╝čÅčéčī SPI) ą┐čāč鹥ą╝ čćč鹥ąĮąĖčÅ BMODE2ŌĆō0 ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ SYSCR.

ŌĆó ą¦č鹥ąĮąĖąĄ ą┐ąĄčĆą▓čŗčģ 4 ą▒ą░ą╣čé ą┐ąŠ ą░ą┤čĆąĄčüčā 0x0 ą▓ąĮąĄčłąĮąĄą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┐ą░ą╝čÅčéąĖ. ąŁčéąĖ 4 ą▒ą░ą╣čéą░ čüąŠą┤ąĄčƹȹ░čé čüč湥čéčćąĖą║ ą▒ą░ą╣čé (N), ą║ąŠč鹊čĆčŗą╣ ąĘą░ą┤ą░ąĄčé ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ąĘą░ą│čĆčāąČą░ąĄą╝čŗčģ ą▒ą░ą╣čé.

ŌĆó ąŚą░ą│čĆčāąĘą║ą░ N ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮčÄčÄ ą┐ą░ą╝čÅčéčī L2, ąĮą░čćąĖąĮą░čÅ čü ą░ą┤čĆąĄčüą░ 0xF0000000.

ŌĆó ą¤ąĄčĆąĄą┤ą░čćą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą▓ ąĮą░čćą░ą╗ąŠ ą┐ą░ą╝čÅčéąĖ L2 (ąĘą░ą┐čāčüą║ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ąĘą░ą│čĆčāąČąĄąĮąĮąŠą│ąŠ ą║ąŠą┤ą░).

ąÜąŠą┤ on-chip boot ROM ąĘą░ą│čĆčāąČą░ąĄčé N ąĖąĘ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ. ąŁčéąĖ N ą▒ą░ą╣čé ą╝ąŠą│čāčé ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī čĆą░ąĘą╝ąĄčĆ ą║ąŠą┤ą░ ą┤ąĄą╣čüčéą▓čāčÄčēąĄą│ąŠ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ, ąĖą╗ąĖ čŹč鹊 ą╝ąŠąČąĄčé ą▒čŗčéčī ą║ąŠą┤ ąĘą░ą│čĆčāąĘčćąĖą║ą░ ą▓č鹊čĆąŠą│ąŠ čāčĆąŠą▓ąĮčÅ, ą║ąŠč鹊čĆčŗą╣ ąĘą░ą│čĆčāąĘąĖčé ą║ąŠą┤ ą┤ąĄą╣čüčéą▓čāčÄčēąĄą│ąŠ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ.

[ążą░ą╣ą╗čŗ ąĘą░ą│čĆčāąĘą║ąĖ ą▒ąĄąĘ ąĘą░ą│čĆčāąĘčćąĖą║ą░ ą▓č鹊čĆąŠą│ąŠ čāčĆąŠą▓ąĮčÅ]

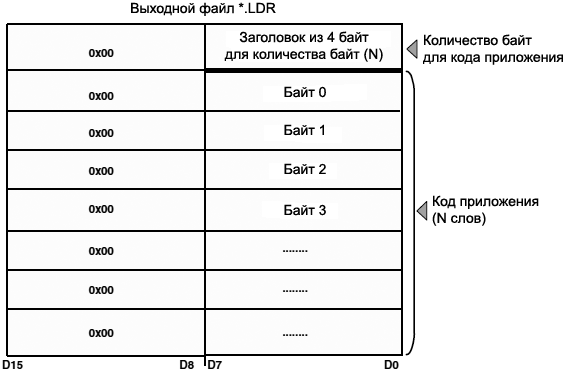

ąØą░ čĆąĖčü. 3-11 ą┐ąŠą║ą░ąĘą░ąĮą░ čüčéčĆčāą║čéčāčĆą░ čäą░ą╣ą╗ą░ ąĘą░ą│čĆčāąĘą║ąĖ ą┤ą╗čÅ 8-ą▒ąĖčéąĮąŠą╣ flash/PROM ąĖą╗ąĖ ą░ą┤čĆąĄčüčāąĄą╝ąŠą╣ 8 ąĖą╗ąĖ 16 ą▒ąĖčéą░ą╝ąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ SPI ą┐čĆąĖ ąĘą░ą│čĆčāąĘą║ąĄ ą▒ąĄąĘ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ąĘą░ą│čĆčāąĘčćąĖą║ą░ ą▓č鹊čĆąŠą│ąŠ čāčĆąŠą▓ąĮčÅ.

ąĀąĖčü. 3-11. ążą░ą╣ą╗ ąĘą░ą│čĆčāąĘą║ąĖ ą┤ą╗čÅ 8-ą▒ąĖčéąĮąŠą╣ Flash/PROM ąĖ SPI ą▒ąĄąĘ ąĘą░ą│čĆčāąĘčćąĖą║ą░ ą▓č鹊čĆąŠą│ąŠ čāčĆąŠą▓ąĮčÅ.

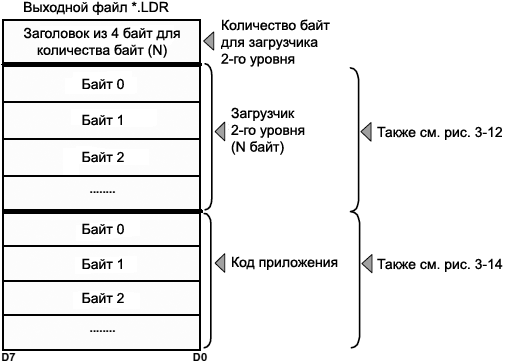

ąØą░ čĆąĖčü. 3-12 ą┐ąŠą║ą░ąĘą░ąĮą░ čüčéčĆčāą║čéčāčĆą░ čäą░ą╣ą╗ą░ ąĘą░ą│čĆčāąĘą║ąĖ ą┤ą╗čÅ 16-ą▒ąĖčéąĮąŠą╣ flash/PROM ą┐čĆąĖ ąĘą░ą│čĆčāąĘą║ąĄ ą▒ąĄąĘ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ąĘą░ą│čĆčāąĘčćąĖą║ą░ ą▓č鹊čĆąŠą│ąŠ čāčĆąŠą▓ąĮčÅ.

ąĀąĖčü. 3-12. ążą░ą╣ą╗ ąĘą░ą│čĆčāąĘą║ąĖ ą┤ą╗čÅ 16-ą▒ąĖčéąĮąŠą╣ Flash/PROM ą▒ąĄąĘ ąĘą░ą│čĆčāąĘčćąĖą║ą░ ą▓č鹊čĆąŠą│ąŠ čāčĆąŠą▓ąĮčÅ.

[ążą░ą╣ą╗čŗ ąĘą░ą│čĆčāąĘą║ąĖ, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ čü ąĘą░ą│čĆčāąĘčćąĖą║ąŠą╝ ą▓č鹊čĆąŠą│ąŠ čāčĆąŠą▓ąĮčÅ]

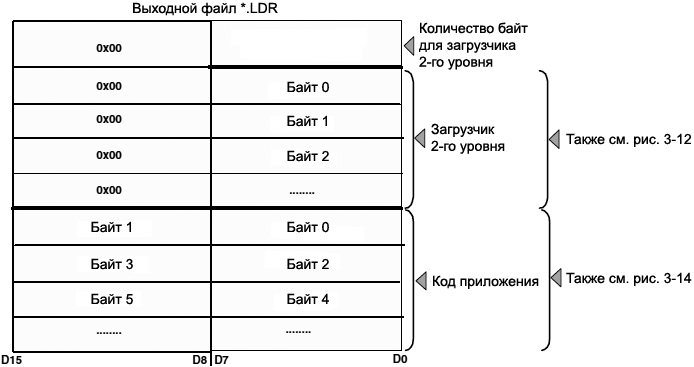

ąØą░ čĆąĖčü. 3-13 ą┐ąŠą║ą░ąĘą░ąĮąŠ ą│čĆą░čäąĖč湥čüą║ąŠąĄ ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮąĖąĄ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čäą░ą╣ą╗ą░ ąĘą░ą│čĆčāąĘą║ąĖ ą┤ą╗čÅ 8-ą▒ąĖčéąĮąŠą╣ ąĘą░ą│čĆčāąĘą║ąĖ ąĖąĘ flash/PROM ąĖ ą░ą┤čĆąĄčüčāąĄą╝ąŠą╣ 8 ąĖą╗ąĖ 16 ą▒ąĖčéą░ą╝ąĖ ąĘą░ą│čĆčāąĘą║ąĖ ąĖąĘ ą┐ą░ą╝čÅčéąĖ SPI ą┐čĆąĖ ąĮą░ą╗ąĖčćąĖąĖ ąĘą░ą│čĆčāąĘčćąĖą║ą░ ą▓č鹊čĆąŠą│ąŠ čāčĆąŠą▓ąĮčÅ.

ąĀąĖčü. 3-13. ążą░ą╣ą╗ ąĘą░ą│čĆčāąĘą║ąĖ ą┤ą╗čÅ 8-ą▒ąĖčéąĮąŠą╣ Flash/PROM ąĖ SPI ą┐čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ ąĘą░ą│čĆčāąĘčćąĖą║ą░ ą▓č鹊čĆąŠą│ąŠ čāčĆąŠą▓ąĮčÅ.

ąØą░ čĆąĖčü. 3-14 ą┐ąŠą║ą░ąĘą░ąĮąŠ ą│čĆą░čäąĖč湥čüą║ąŠąĄ ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮąĖąĄ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čäą░ą╣ą╗ą░ ąĘą░ą│čĆčāąĘą║ąĖ ą┤ą╗čÅ 16-ą▒ąĖčéąĮąŠą╣ ąĘą░ą│čĆčāąĘą║ąĖ ąĖąĘ flash/PROM ą┐čĆąĖ ąĮą░ą╗ąĖčćąĖąĖ ąĘą░ą│čĆčāąĘčćąĖą║ą░ ą▓č鹊čĆąŠą│ąŠ čāčĆąŠą▓ąĮčÅ.

Figure 3-14. ążą░ą╣ą╗ ąĘą░ą│čĆčāąĘą║ąĖ ą┤ą╗čÅ 16-čĆą░ąĘčĆčÅą┤ąĮąŠą╣ Flash/PROM Boot ą┐čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ ąĘą░ą│čĆčāąĘčćąĖą║ą░ ą▓č鹊čĆąŠą│ąŠ čāčĆąŠą▓ąĮčÅ.

[ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ąĘą░ą│čĆčāąĘą║ąŠą╣ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ą┐čĆąĖą╗ąŠąČąĄąĮąĖą╣ (Multi-DXE) ADSP-BF53x ąĖ ADSP-BF561]

ąŁčéą░ čüąĄą║čåąĖčÅ čüčéą░čéčīąĖ ąĮąĄ ąŠčéąĮąŠčüąĖčéčüčÅ ą║ ą┐čĆąŠčåąĄčüčüąŠčĆą░ą╝ ADSP-BF535.

ąŚą┤ąĄčüčī ąŠą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ, ą║ą░ą║ ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī čäą░ą╣ą╗ ąĘą░ą│čĆčāąĘą║ąĖ ąĖ ąĘą░ą│čĆčāąČą░čéčī ąĄą│ąŠ ą┤ą╗čÅ ą▒ąŠą╗ąĄąĄ č湥ą╝ ąŠą┤ąĮąŠą│ąŠ ą▓čģąŠą┤ąĮąŠą│ąŠ čäą░ą╣ą╗ą░ .dxe ą┤ą╗čÅ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ ADSP-BF531, BF532, BF533, BF534, BF536, BF537, BF538, BF539 ąĖ BF561. ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčāčÄ ąĖąĮč乊čĆą╝ą░čåąĖčÄ ą┐ąŠ ą┐čĆąŠčåąĄčüčüąŠčĆą░ą╝ ADSP-BF561 čüą╝. ą▓ čĆą░ąĘą┤ąĄą╗ąĄ "ADSP-BF561 Dual-Core Application Management" [1].

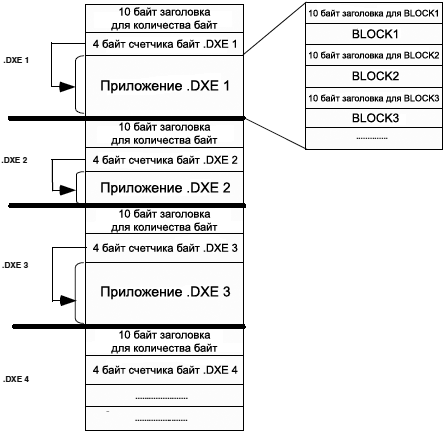

ąĪčéčĆčāą║čéčāčĆą░ čäą░ą╣ą╗ą░ ąĘą░ą│čĆčāąĘą║ąĖ ADSP-BF531, BF532, BF533, BF534, BF536, BF537, BF538, BF539 ąĖ BF561 ąĖ čĆąĄą▓ąĖąĘąĖčÅ ą║čĆąĖčüčéą░ą╗ą╗ą░ (silicon revision) ąŠčé 0.1 ąĖ ą▓čŗčłąĄ ą┐ąŠąĘą▓ąŠą╗čÅčÄčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī čäą░ą╣ą╗ ąĘą░ą│čĆčāąĘą║ąĖ ąĖ ąĘą░ą│čĆčāąČą░čéčī ąĄą│ąŠ ąĖąĘ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ ą┤ą╗čÅ ą▒ąŠą╗čīčłąĄ č湥ą╝ ąŠą┤ąĮąŠą│ąŠ ą▒ą╗ąŠą║ą░ ąĖčüą┐ąŠą╗ąĮčÅąĄą╝ąŠą│ąŠ ą║ąŠą┤ą░ DXE ąĮą░ ąŠą┤ąĖąĮ ą┐čĆąŠčåąĄčüčüąŠčĆ. ąÜą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 3-20, ą║ą░ąČą┤čŗą╣ ą▓čģąŠą┤ąĮąŠą╣ čäą░ą╣ą╗ čü ąĖčüą┐ąŠą╗ąĮčÅąĄą╝čŗą╝ ą║ąŠą┤ąŠą╝ (executable file, čĆą░čüčłąĖčĆąĄąĮąĖąĄ *.DXE) čüąĮą░ą▒ąČą░ąĄčéčüčÅ 4-ą▒ą░ą╣čéąĮčŗą╝ ąĘą░ą│ąŠą╗ąŠą▓ą║ąŠą╝, ą║ ą║ąŠč鹊čĆąŠą╝ čāą║ą░ąĘą░ąĮąŠ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ą░ą╣čé ąĖčüą┐ąŠą╗ąĮčÅąĄą╝ąŠą│ąŠ ą║ąŠą┤ą░, ą▓ą║ą╗čÄčćą░čÅ ąĘą░ą│ąŠą╗ąŠą▓ą║ąĖ. ąŁčéą░ ąĖąĮč乊čĆą╝ą░čåąĖčÅ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ąĘą░ą│čĆčāąĘą║ąĖ ą▓ ą┐čĆąŠčåąĄčüčüąŠčĆ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą│ąŠ, ą▓čŗą▒čĆą░ąĮąĮąŠą│ąŠ ą▒ą╗ąŠą║ą░ DXE ąĖąĘ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ. 4-ą▒ą░ą╣čéąĮčŗą╣ ą▒ą╗ąŠą║, čüąŠą┤ąĄčƹȹ░čēąĖą╣ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ą░ą╣čé, ąĖąĮą║ą░ą┐čüčāą╗ąĖčĆąŠą▓ą░ąĮ ą▓ 10-ą▒ą░ą╣čéąĮčŗą╣ ąĘą░ą│ąŠą╗ąŠą▓ąŠą║, čćč鹊ą▒čŗ čüąŠčģčĆą░ąĮąĖčéčī čüąŠą▓ą╝ąĄčüčéąĖą╝ąŠčüčéčī čü silicon revision 0.0. ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčāčÄ ąĖąĮč乊čĆą╝ą░čåąĖčÄ čüą╝. ą▓ąŠ ą▓čĆąĄąĘą║ąĄ "ąŚą░ą│ąŠą╗ąŠą▓ą║ąĖ ą▒ą╗ąŠą║ąŠą▓ ąĖ čäą╗ą░ą│ąĖ ADSP-BF531, BF532, BF533, BF534, BF536, BF537, BF538, BF539".

ąĀąĖčü. 3-20. ą¤ąŠč鹊ą║ąĖ ąĘą░ą│čĆčāąĘą║ąĖ čü ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅą╝ąĖ ą┤ą╗čÅ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ ADSP-BF531, BF532, BF533, BF534, BF536, BF537, BF538, BF539, BF561.

ąŚą░ą│čĆčāąĘą║ą░ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ąĖčüą┐ąŠą╗ąĮčÅąĄą╝čŗčģ čäą░ą╣ą╗ąŠą▓ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮą░ ą┐ąŠ ąŠą┤ąĮąŠą╝čā ąĖąĘ čüą╗ąĄą┤čāčÄčēąĖčģ ą╝ąĄč鹊ą┤ąŠą▓.

ŌĆó ą£ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┤ą╗čÅ čāčéąĖą╗ąĖčéčŗ ąĘą░ą│čĆčāąĘą║ąĖ ąŠą┐čåąĖčÄ ąĘą░ą│čĆčāąĘčćąĖą║ą░ ą▓č鹊čĆąŠą│ąŠ čāčĆąŠą▓ąĮčÅ (second-stage loader) -l userkernel.dxe. ąŚą┤ąĄčüčī userkernel.dxe - ąĖčüą┐ąŠą╗ąĮčÅąĄą╝čŗą╣ ą║ąŠą┤ DXE ąĘą░ą│čĆčāąĘčćąĖą║ą░ ą▓č鹊čĆąŠą│ąŠ čāčĆąŠą▓ąĮčÅ. ąŁčéą░ ąŠą┐čåąĖčÅ ą┐ąŠąĘą▓ąŠą╗ąĖčé ąÆą░ą╝ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čüą▓ąŠą╣ čüąŠą▒čüčéą▓ąĄąĮąĮčŗą╣ ąĘą░ą│čĆčāąĘčćąĖą║ ą▓č鹊čĆąŠą│ąŠ čāčĆąŠą▓ąĮčÅ.

ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ąĘą░ą│čĆčāąĘčćąĖą║ ą▓č鹊čĆąŠą│ąŠ čāčĆąŠą▓ąĮčÅ ą▒čāą┤ąĄčé ąĘą░ą│čĆčāąČąĄąĮ ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮčÄčÄ ą┐ą░ą╝čÅčéčī č湥čĆąĄąĘ ą┐ąŠą┤ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝ on-chip Boot ROM, čŹč鹊čé ąĘą░ą│čĆčāąĘčćąĖą║ ą▓č鹊čĆąŠą│ąŠ čāčĆąŠą▓ąĮčÅ ą┐ąŠą╗čāčćąĖčé ą┐ąŠą╗ąĮčŗą╣ ą║ąŠąĮčéčĆąŠą╗čī ąĮą░ą┤ ą┐čĆąŠčåąĄčüčüąŠą╝ ąĘą░ą│čĆčāąĘą║ąĖ. ąóąĄą┐ąĄčĆčī ąĘą░ą│čĆčāąĘčćąĖą║ ą▓č鹊čĆąŠą│ąŠ čāčĆąŠą▓ąĮčÅ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čüč湥čéčćąĖą║ąĖ ą▒ą░ą╣čé ą▓ ą▒ą╗ąŠą║ą░čģ DXE, čćč鹊ą▒čŗ ąĘą░ą│čĆčāąĘąĖčéčī ą╗čÄą▒ąŠą╣ ą▓čŗą▒čĆą░ąĮąĮčŗą╣ ą▒ą╗ąŠą║ DXE (ąĖą╗ąĖ ąĮąĄčüą║ąŠą╗čīą║ąŠ DXE ą┤čĆčāą│ ąĘą░ ą┤čĆčāą│ąŠą╝) ąĖąĘ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ.

ŌĆó ą£ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ąŠą┐čåąĖčÄ ą▒ą╗ąŠą║ą░ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ -init filename.dxe, ą│ą┤ąĄ filename.dxe ąĖą╝čÅ ąĖčüą┐ąŠą╗ąĮčÅąĄą╝ąŠą│ąŠ čäą░ą╣ą╗ą░ DXE, ą▓ ą║ąŠč鹊čĆąŠą╝ čüąŠą┤ąĄčƹȹĖčéčüčÅ ą║ąŠą┤ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ (Init Code). ąŁčéą░ ąŠą┐čåąĖčÅ ą┐ąŠąĘą▓ąŠą╗ąĖčé ąÆą░ą╝ ą┐ąŠą╝ąĄąĮčÅčéčī čāą║ą░ąĘą░č鹥ą╗čī ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ, ąĖ ąĘą░ą│čĆčāąĘąĖčéčī ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗą╣ DXE čü ąĘą░ą┤ąĄą╣čüčéą▓ąŠą▓ą░ąĮąĖąĄą╝ Boot ROM. ąöąŠčüč鹊ąĖąĮčüčéą▓ąŠ čŹč鹊ą│ąŠ ą╝ąĄč鹊ą┤ą░ ą▓ č鹊ą╝, čćč鹊 čüą▓ąŠą╣ ąĘą░ą│čĆčāąĘčćąĖą║ ą┐ąĖčüą░čéčī ąĮąĄ ąĮą░ą┤ąŠ, Init Code ą┤ąŠą╗ąČąĄąĮ č鹊ą╗čīą║ąŠ čāą╝ąĄčéčī čćąĖčéą░čéčī čäą░ą╣ą╗ ąĘą░ą│čĆčāąĘą║ąĖ, ą┤ąĄą║ąŠą┤ąĖčĆąŠą▓ą░čéčī ą▓ ąĮąĄą╝ ąĘą░ą│ąŠą╗ąŠą▓ą║ąĖ DXE ąĖ ą┐čĆą░ą▓ąĖą╗čīąĮąŠ ą╝ąĄąĮčÅčéčī čāą║ą░ąĘą░č鹥ą╗čī ąĮą░ ąĮčāąČąĮčŗą╣ ąĘą░ą│čĆčāąČą░ąĄą╝čŗą╣ DXE [2]. ąØą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░čģ ADSP-BF531 ąĖ ADSP-BF561 ą║ąŠą┤ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé čüąŠą▒ąŠą╣ ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝čā, ąĮą░ą┐ąĖčüą░ąĮąĮčāčÄ ąĮą░ ą░čüčüąĄą╝ą▒ą╗ąĄčĆąĄ.

ąØąĖąČąĄ ąĮą░ ą╗ąĖčüčéąĖąĮą│ąĄ 3-5 ą┐čĆąĖą▓ąĄą┤ąĄąĮ ą┐čĆąĖą╝ąĄčĆ ą║ąŠą┤ą░ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ. ąĀąĄą│ąĖčüčéčĆčŗ R0 ąĖ R3 ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą║ą░ą║ čāą║ą░ąĘą░č鹥ą╗ąĖ ąĮą░ ą▓ąĮąĄčłąĮčÄčÄ ą┐ą░ą╝čÅčéčī, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą║ąŠą┤ąŠą╝ on-chip Boot ROM. ąĀąĄą│ąĖčüčéčĆ R0 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ąĘą░ą│čĆčāąĘą║ąĖ ąĖąĘ flash/PROM, ąĖ R3 ą┤ą╗čÅ ąĘą░ą│čĆčāąĘą║ąĖ ąĖąĘ ą┐ą░ą╝čÅčéąĖ SPI. ąÆ ą▒ą╗ąŠą║ąĄ ą║ąŠą┤ą░ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ ąĮčāąČąĮąŠ ąĖąĘą╝ąĄąĮąĖčéčī ąĘąĮą░č湥ąĮąĖąĄ R0 ąĖą╗ąĖ R3 čéą░ą║, čćč鹊ą▒čŗ ąŠąĮąĖ čāą║ą░ąĘčŗą▓ą░ą╗ąĖ ąĮą░ ą╝ąĄčüč鹊 ą▓ąŠ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ, ąŠčéą║čāą┤ą░ ąĮą░čćąĖąĮą░ąĄčéčüčÅ ą║ąŠą┤ ąĮčāąČąĮąŠą│ąŠ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ. ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą┐čĆąŠčåąĄčüčüąŠčĆ ą▓ąĄčĆąĮąĄčé čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ąĖąĘ ą║ąŠą┤ą░ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ ąŠą▒čĆą░čéąĮąŠ ą▓ ą║ąŠą┤ Boot ROM, ą║ąŠą┤ Boot ROM ą┐čĆąŠą┤ąŠą╗ąČąĖčé ąĘą░ą│čĆčāąČą░čéčī ą▒ą░ą╣čéčŗ čü ą╝ąĄčüčéą░, čāą║ą░ąĘą░ąĮąĮąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░ą╝ąĖ R0 ąĖą╗ąĖ R3.

ąøąĖčüčéąĖąĮą│ 3-5. ą¤čĆąĖą╝ąĄčĆ Init Code ą┤ą╗čÅ ąĘą░ą│čĆčāąĘą║ąĖ ą▓ čüčåąĄąĮą░čĆąĖąĖ Multiple .dxe.

#include < defBF532.h >

.SECTION program;

/*******Pre-Init Section***************************************/

[--SP] = ASTAT;

[--SP] = RETS;

[--SP] = (r7:0);

[--SP] = (p5:0);

[--SP] = I0;[--SP] = I1;[--SP] = I2;[--SP] = I3;

[--SP] = B0;[--SP] = B1;[--SP] = B2;[--SP] = B3;

[--SP] = M0;[--SP] = M1;[--SP] = M2;[--SP] = M3;

[--SP] = L0;[--SP] = L1;[--SP] = L2;[--SP] = L3;

/**************************************************************/

/*******Init Code Section**************************************

R0.H = čüčéą░čĆčłą░čÅ čćą░čüčéčī ą░ą┤čĆąĄčüą░ ą╝ąĄčüčéą░ ą┐ąŠą╗ąŠąČąĄąĮąĖčÅ DXE

(R0 ą┤ą╗čÅ flash/PROM boot, R3 ą┤ą╗čÅ SPI boot)

R0.L = ą╝ą╗ą░ą┤čłą░čÅ čćą░čüčéčī ą░ą┤čĆąĄčüą░ ą╝ąĄčüčéą░ ą┐ąŠą╗ąŠąČąĄąĮąĖčÅ DXE

(R0 ą┤ą╗čÅ flash/PROM boot, R3 ą┤ą╗čÅ SPI boot)

***************************************************************/

/*******Post-Init Section**************************************/

L3 = [SP++]; L2 = [SP++]; L1 = [SP++]; L0 = [SP++];

M3 = [SP++]; M2 = [SP++]; M1 = [SP++]; M0 = [SP++];

B3 = [SP++]; B2 = [SP++]; B1 = [SP++]; B0 = [SP++];

I3 = [SP++]; I2 = [SP++]; I1 = [SP++]; I0 = [SP++];

(p5:0) = [SP++];

/* ąŻąæąĢąöąśąóąĢąĪą¼, ą¦ąóą× ąĪąøąŻą¦ąÉąÖąØą× ąØąĢ ąÆą×ąĪąĪąóąÉąØą×ąÆąśąøąś R0 ą┤ą╗čÅ flash/PROM Boot,

ąĖą╗ąĖ R3 ą┤ą╗čÅ SPI Boot */

(r7:0) = [SP++];

RETS = [SP++];

ASTAT = [SP++];

/**************************************************************/

RTS;

[ąĀčāą║ąŠą▓ąŠą┤čüčéą▓ąŠ ą┐ąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÄ ąĘą░ą│čĆčāąĘčćąĖą║ą░ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ ADSP-BF53x/BF561]

ąĀą░ą▒ąŠčéą░ čāčéąĖą╗ąĖčéčŗ ąĘą░ą│čĆčāąĘą║ąĖ elfloader.exe ąĘą░ą▓ąĖčüąĖčé ąŠčé ąŠą┐čåąĖą╣, ą║ąŠč鹊čĆčŗąĄ čāą┐čĆą░ą▓ą╗čÅčÄčé ą┐čĆąŠčåąĄą┤čāčĆąŠą╣ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ąĖčüą┐ąŠą╗ąĮčÅąĄą╝čŗčģ čäą░ą╣ą╗ąŠą▓ DXE. ąÆčŗ ą▓čŗą▒ąĖčĆą░ąĄč鹥 čéą░ą║ąĖąĄ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ, ą║ą░ą║ čĆąĄąČąĖą╝ ąĘą░ą│čĆčāąĘą║ąĖ (boot mode), ąĘą░ą│čĆčāąĘą║ą░ čÅą┤čĆą░ (boot kernel), č乊čĆą╝ą░čé ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čäą░ą╣ą╗ą░ ąĖ čé. ą┤. ą×ą┐čåąĖąĖ čāą║ą░ąĘčŗą▓ą░čÄčéčüčÅ ą┤ą╗čÅ čāčéąĖą╗ąĖčéčŗ ąĘą░ą│čĆčāąĘą║ąĖ č湥čĆąĄąĘ ą║ąŠą╝ą░ąĮą┤ąĮčāčÄ čüčéčĆąŠą║čā, ąĖą╗ąĖ ąŠą┐ąŠčüčĆąĄą┤ąŠą▓ą░ąĮąĮąŠ č湥čĆąĄąĘ ą│čĆą░čäąĖč湥čüą║ąĖą╣ ąĖąĮč鹥čĆč乥ą╣čü ą┤ąĖą░ą╗ąŠą│ą░ čĆąĄą┤ą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ čüą▓ąŠą╣čüčéą▓ ą┐čĆąŠąĄą║čéą░ VisualDSP++ (Project Options -> Load).

ąĀą░ąĘą┤ąĄą╗ Load čüą▓ąŠą╣čüčéą▓ ą┐čĆąŠąĄą║čéą░ čüąŠčüč鹊ąĖčé ąĖąĘ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ą┐ąŠą┤čĆą░ąĘą┤ąĄą╗ąŠą▓. ąÜąŠą│ą┤ą░ ąÆčŗ ą▓čŗą▒čĆą░ą╗ąĖ čĆą░ąĘą┤ąĄą╗ Load, č鹊 ą▓ ąĮąĄą╝ čāąČąĄ ą▒čāą┤čāčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ąĮąĄą║ąŠč鹊čĆčŗąĄ čāčüčéą░ąĮąŠą▓ą║ąĖ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą┤ą╗čÅ ąĘą░ą│čĆčāąĘčćąĖą║ą░ ą▓čŗą▒čĆą░ąĮąĮąŠą│ąŠ ą┐čĆąŠčåąĄčüčüąŠčĆą░.

ąØą░čüčéčĆąŠą╣ą║ąĖ ą▓ čĆą░ąĘą┤ąĄą╗ąĄ Load čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčé ąŠą┐čåąĖčÅą╝, ą║ąŠč鹊čĆčŗąĄ ą▒čāą┤čāčé čāą║ą░ąĘą░ąĮčŗ ą▓ ą║ąŠą╝ą░ąĮą┤ąĮąŠą╣ čüčéčĆąŠą║ąĄ čāčéąĖą╗ąĖčéčŗ ąĘą░ą│čĆčāąĘą║ąĖ elfloader.exe. ą¤ąŠą┤čüą╝ąŠčéčĆąĄčéčī ą┐ąŠą╗ąĮąŠąĄ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ ą║ąŠą╝ą░ąĮą┤ąĮąŠą╣ čüčéčĆąŠą║ąĖ ą╝ąŠąČąĮąŠ ą▓ ą╗ąŠą│-čäą░ą╣ą╗ąĄ ą┐čĆąŠčåąĄčüčüą░ čüą▒ąŠčĆą║ąĖ, čüą╝. ą┐ąŠą┤ą║ą░čéą░ą╗ąŠą│ Release (ąĖą╗ąĖ Debug), čäą░ą╣ą╗ ąĖą╝čÅ_ą┐čĆąŠąĄą║čéą░.log.

ąöą░ą╗ąĄąĄ ą▓ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ čüąĄą║čåąĖčÅčģ ą▒čāą┤ąĄčé ąŠą┐ąĖčüą░ąĮąŠ, ą║ą░ą║ ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ąĘą░ą│čĆčāąČą░ąĄą╝čŗą╣ ąĖ ąĮąĄ ąĘą░ą│čĆčāąČą░ąĄą╝čŗą╣ čäą░ą╣ą╗ ąĘą░ą│čĆčāąĘą║ąĖ:

ŌĆó ąśčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ ą║ąŠą╝ą░ąĮą┤ąĮąŠą╣ čüčéčĆąŠą║ąĖ čāčéąĖą╗ąĖčéčŗ ąĘą░ą│čĆčāąĘą║ąĖ Blackfin.

ŌĆó ąØą░čüčéčĆąŠą╣ą║ą░ ąŠą┐čåąĖą╣ ą│ąĄąĮąĄčĆą░čåąĖąĖ čäą░ą╣ą╗ą░ ąĘą░ą│čĆčāąĘą║ąĖ ą▓ ą┐čĆąŠąĄą║č鹥 VisualDSP++.

ŌĆó Using VisualDSP++ Compression (ąĘą┤ąĄčüčī čŹč鹊čé čĆą░ąĘą┤ąĄą╗ ąĮąĄ čĆą░čüčüą╝ą░čéčĆąĖą▓ą░ąĄčéčüčÅ, čüą╝. [1]).

ŌĆó Using VisualDSP++ Second-Stage Loader for ADSP-BF535 Processors (ąĘą┤ąĄčüčī čŹč鹊čé čĆą░ąĘą┤ąĄą╗ ąĮąĄ čĆą░čüčüą╝ą░čéčĆąĖą▓ą░ąĄčéčüčÅ, čüą╝. [1]).

ŌĆó ąśčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ ROM-čüą┐ą╗ąĖčéč鹥čĆą░ VisualDSP++.

[ąĪąĖąĮčéą░ą║čüąĖčü ą║ąŠą╝ą░ąĮą┤ąĮąŠą╣ čüčéčĆąŠą║ąĖ elfloader.exe]

ąŻčéąĖą╗ąĖčéą░ ąĘą░ą│čĆčāąĘą║ąĖ ADSP-BF5xx Blackfin ąĖčüą┐ąŠą╗čīąĘčāąĄčé loader čüą╗ąĄą┤čāčÄčēąĖą╣ ąŠą▒čēąĖą╣ čüąĖąĮčéą░ą║čüąĖčü ą║ąŠą╝ą░ąĮą┤ąĮąŠą╣ čüčéčĆąŠą║ąĖ. ąöą╗čÅ ąŠą┤ąĮąŠą│ąŠ ą▓čģąŠą┤ąĮąŠą│ąŠ čäą░ą╣ą╗ą░:

elfloader inputfile -proc processor [-ąŠą┐čåąĖčÅ ...]

ąöą╗čÅ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ą▓čģąŠą┤ąĮčŗčģ čäą░ą╣ą╗ąŠą▓:

elfloader inputfile1 inputfile2 ... -proc processor [-ąŠą┐čåąĖčÅ ...]

ąŚą┤ąĄčüčī čāą║ą░ąĘą░ąĮčŗ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ:

inputfile - čŹč鹊 ąĖą╝čÅ čäą░ą╣ą╗ą░ ąĖčüą┐ąŠą╗ąĮčÅąĄą╝ąŠą│ąŠ ą║ąŠą┤ą░ (čü čĆą░čüčłąĖčĆąĄąĮąĖąĄą╝ .dxe), ą║ąŠč鹊čĆčŗą╣ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąŠą▒čĆą░ą▒ąŠčéą░ąĮ, čćč鹊ą▒čŗ ą▓ čĆąĄąĘčāą╗čīčéą░č鹥 ą┐ąŠą╗čāčćąĖą╗čüčÅ ąŠą┤ąĖąĮ ąĘą░ą│čĆčāąČą░ąĄą╝čŗą╣ (boot-loadable) ąĖą╗ąĖ ąĮąĄ ąĘą░ą│čĆčāąČą░ąĄą╝čŗą╣ (non-bootable) čäą░ą╣ą╗. ąśą╝čÅ ą▓čģąŠą┤ąĮąŠą│ąŠ čäą░ą╣ą╗ą░ ą╝ąŠąČąĄčé ą▓ą║ą╗čÄčćą░čéčī ąĖą╝čÅ ą┤ąĖčüą║ą░ (C:, D:, ąĖ čé. ą┐.) ąĖ ą┐ąŠą╗ąĮčŗą╣ ą┐čāčéčī ą┤ąŠ ą║ą░čéą░ą╗ąŠą│ą░, ą│ą┤ąĄ ąĮą░čģąŠą┤ąĖčéčüčÅ čäą░ą╣ą╗ (ą▓ čüąŠčüčéą░ą▓ąĄ ą┐čāčéąĖ ą╝ąŠąČąĮąŠ čéą░ą║ąČąĄ ą┐čĆąĖą╝ąĄąĮčÅčéčī . ąĖ ..). ąöą╗čÅ čüąĖčüč鹥ą╝ čü ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆą░ą╝ąĖ ąĖą╗ąĖ ą▓ čüčåąĄąĮą░čĆąĖąĖ ąĘą░ą│čĆčāąĘą║ąĖ Multi-DXE čāą║ą░ąĘčŗą▓ą░čÄčéčüčÅ ąĮąĄčüą║ąŠą╗čīą║ąŠ ą▓čģąŠą┤ąĮčŗčģ čäą░ą╣ą╗ąŠą▓ .dxe. ąŻą║ą░ąČąĖč鹥 ąĖą╝ąĄąĮą░ ą▓čģąŠą┤ąĮčŗčģ čäą░ą╣ą╗ąŠą▓ ą▓ č鹊ą╝ ą┐ąŠčĆčÅą┤ą║ąĄ, ą▓ ą║ąŠč鹊čĆąŠą╝ ąÆčŗ čģąŠčéąĖč鹥, čćč鹊ą▒čŗ čāčéąĖą╗ąĖčéą░ ąĘą░ą│čĆčāąĘą║ąĖ ąĖčģ ąŠą▒čĆą░ą▒ąŠčéą░ą╗ą░. ąŚą░ą║ą╗čÄčćą░ą╣č鹥 ą┤ą╗ąĖąĮąĮčŗąĄ ąĖą╝ąĄąĮą░ čäą░ą╣ą╗ąŠą▓ (ąĖ ąĖą╝ąĄąĮą░ čäą░ą╣ą╗ąŠą▓ čü ą┐čĆąŠą▒ąĄą╗ą░ą╝ąĖ) ą▓ ą┤ą▓ąŠą╣ąĮčŗąĄ ą║ą░ą▓čŗčćą║ąĖ ("long file name").

-proc processor - ąĘą┤ąĄčüčī čāą║ą░ąĘčŗą▓ą░ąĄčéčüčÅ ą╝ąŠą┤ąĄą╗čī ą┐čĆąŠčåąĄčüčüąŠčĆą░ (ąĮą░ą┐čĆąĖą╝ąĄčĆ, -proc ADSP-BF532), ą┤ą╗čÅ ą║ąŠč鹊čĆąŠą│ąŠ ą▒čāą┤ąĄčé ą┐ąŠčüčéčĆąŠąĄąĮ čäą░ą╣ą╗ ąĘą░ą│čĆčāąĘą║ąĖ. ąĢčüą╗ąĖ ąÆčŗ čĆą░ąĘčĆą░ą▒ą░čéčŗą▓ą░ąĄč鹥 čäą░ą╣ą╗ ąĘą░ą│čĆčāąĘą║ąĖ ą┤ą╗čÅ ą╝ąĮąŠą│ąŠą┐čĆąŠčåąĄčüčüąŠčĆąĮąŠą╣ čüąĖčüč鹥ą╝čŗ, č鹊 ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą▓čģąŠą┤ąĮąŠą│ąŠ čäą░ą╣ą╗ą░ .dxe čāą║ą░ąČąĖč鹥 ą╝ąŠą┤ąĄą╗čī ą┐čĆąŠčåąĄčüčüąŠčĆą░.

-ąŠą┐čåąĖčÅ ... - ąĘą┤ąĄčüčī čāą║ą░ąĘčŗą▓ą░ąĄčéčüčÅ ąŠą┤ąĮą░ ąĖą╗ąĖ ąĮąĄčüą║ąŠą╗čīą║ąŠ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄą╝čŗčģ ąŠą┐čåąĖą╣. ą×ą┐čåąĖąĖ ą▓čŗą▒ąĖčĆą░čÄčé ąŠą┐ąĄčĆą░čåąĖąĖ ąĖ čĆąĄąČąĖą╝čŗ ą┤ą╗čÅ čāčéąĖą╗ąĖčéčŗ ąĘą░ą│čĆčāąĘą║ąĖ.

ą×ą┐čåąĖąĖ ą║ąŠą╝ą░ąĮą┤ąĮąŠą╣ čüčéčĆąŠą║ąĖ ą╝ąŠą│čāčé ą┐ąŠčÅą▓ą╗čÅčéčīčüčÅ ą▓ ą║ąŠą╝ą░ąĮą┤ąĮąŠą╣ čüčéčĆąŠą║ąĄ ą▓ ą╗čÄą▒ąŠą╝ ą┐ąŠčĆčÅą┤ą║ąĄ, ąĘą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ ą┐ąŠčĆčÅą┤ą║ą░ čüą╗ąĄą┤ąŠą▓ą░ąĮąĖčÅ ą▓čģąŠą┤ąĮčŗčģ čäą░ą╣ą╗ąŠą▓ ą┤ą╗čÅ ą╝ąĮąŠą│ąŠą┐čĆąŠčåąĄčüčüąŠčĆąĮąŠą╣ čüąĖčüč鹥ą╝čŗ. ąöą╗čÅ čüąĖčüč鹥ą╝ čüąŠ čüčåąĄąĮą░čĆąĖąĄą╝ ąĘą░ą│čĆčāąĘą║ąĖ Multi-DXE čāčéąĖą╗ąĖčéą░ ąĘą░ą│čĆčāąĘą║ąĖ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčé ą▓čģąŠą┤ąĮčŗąĄ čäą░ą╣ą╗čŗ ą▓ č鹊ą╝ ą┐ąŠčĆčÅą┤ą║ąĄ, ą▓ ą║ą░ą║ąŠą╝ ąŠąĮąĖ ą▒čŗą╗ąĖ čāą║ą░ąĘą░ąĮčŗ ą▓ ą║ąŠą╝ą░ąĮą┤ąĮąŠą╣ čüčéčĆąŠą║ąĄ.

ą¤čāčéąĖ ą┐ąŠąĖčüą║ą░ čäą░ą╣ą╗ąŠą▓. ąŁč鹊 ą▓ą░ąČąĮčŗą╣ čäą░ą║č鹊čĆ ą┤ą╗čÅ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ čäą░ą╣ą╗ą░ ąĘą░ą│čĆčāąĘą║ąĖ. ąŻčéąĖą╗ąĖčéą░ ąĘą░ą│čĆčāąĘą║ąĖ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮčŗąĄ (čé. ąĄ. ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ č鹥ą║čāčēąĄą│ąŠ ą║ą░čéą░ą╗ąŠą│ą░, čé. ąĄ. ą▓ čüąŠčüčéą░ą▓ąĄ ą┐čāčéąĖ ą╝ąŠąČąĮąŠ ą┐čĆąĖą╝ąĄąĮčÅčéčī . ąĖ ..) ąĖ ą░ą▒čüąŠą╗čÄčéąĮčŗąĄ ąĖą╝ąĄąĮą░ ą║ą░čéą░ą╗ąŠą│ąŠą▓, ą║ą░čéą░ą╗ąŠą│ąĖ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ąĖ ą║ą░čéą░ą╗ąŠą│ąĖ, ą▓čŗą▒čĆą░ąĮąĮčŗąĄ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╝. ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ ą┐čĆąŠ ąŠą▒čĆą░ą▒ąŠčéą║čā ą┐čāč鹥ą╣ ą┐ąŠąĖčüą║ą░ čüą╝. [1], čĆą░ąĘą┤ąĄą╗ "File Searches" ąĮą░ čüčéčĆą░ąĮąĖčåąĄ 1-17.

ąĀą░čüčłąĖčĆąĄąĮąĖčÅ čäą░ą╣ą╗ąŠą▓. ąØąĄą║ąŠč鹊čĆčŗąĄ ąŠą┐čåąĖąĖ čāčéąĖą╗ąĖčéčŗ ąĘą░ą│čĆčāąĘą║ąĖ ą┐čĆąĖąĮąĖą╝ą░čÄčé ąĖą╝čÅ čäą░ą╣ą╗ą░ ą▓ ą║ą░č湥čüčéą▓ąĄ ą┐ą░čĆą░ą╝ąĄčéčĆą░ ąŠą┐čåąĖąĖ. ąÆ čéą░ą▒ą╗ąĖčåąĄ 3-9 ą┐ąĄčĆąĄčćąĖčüą╗ąĄąĮčŗ ąŠąČąĖą┤ą░ąĄą╝čŗąĄ čéąĖą┐čŗ čäą░ą╣ą╗ą░, ąĖą╝ąĄąĮą░ ąĖ čĆą░čüčłąĖčĆąĄąĮąĖčÅ čäą░ą╣ą╗ą░.