|

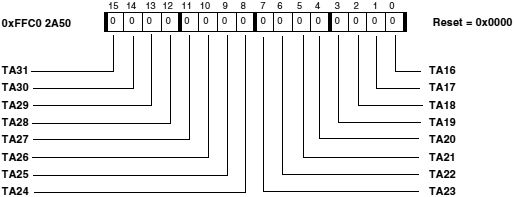

ąŚą┤ąĄčüčī ą┐čĆąĖą▓ąĄą┤ąĄąĮ ą┐ąĄčĆąĄą▓ąŠą┤ čćą░čüčéąĖ ą┤ąŠą║čāą╝ąĄąĮčéą░čåąĖąĖ [1], ą┐ąŠčüą▓čÅčēąĄąĮąĮąŠą╣ ąŠą┐ąĖčüą░ąĮąĖčÄ ą░ą┐ą┐ą░čĆą░čéąĮąŠą│ąŠ ą▒ą╗ąŠą║ą░ čłąĖąĮčŗ CAN, ą┤ąŠčüčéčāą┐ąĮąŠą│ąŠ ą▓ ą┐čĆąŠčåąĄčüčüąŠčĆą░čģ ADSP-BF538, ADSP-BF538F4, ADSP-BF538F8. ą¤čĆąĄą┤ą╗ą░ą│ą░ąĄą╝ąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ ą┐čĆąĄą┤ą┐ąŠą╗ą░ą│ą░ąĄčé, čćč鹊 čćąĖčéą░č鹥ą╗čī ąĘąĮą░ą║ąŠą╝ čüąŠ čüčéą░ąĮą┤ą░čĆč鹊ą╝ CAN (ąŠą▒čĆą░čēą░ą╣č鹥čüčī ą║ čüą┐ąĄčåąĖčäąĖą║ą░čåąĖąĖ Version 2.0 CAN ą║ąŠą╝ą┐ą░ąĮąĖąĖ Robert Bosch GmbH).

ąĢčüą╗ąĖ CAN ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ, č鹊 ą▓čŗą▓ąŠą┤čŗ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖ ą┐čĆąĖąĄą╝ą░ (CANTX ąĖ CANRX) ą╝ąŠąČąĮąŠ ąŠčüą▓ąŠą▒ąŠą┤ąĖčéčī ąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą║ą░ą║ ąĮąŠąČą║ąĖ ą┐ąŠč鹊ą▓ GPIO (CANTX čĆą░ąĘą╝ąĄčēąĄąĮ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ PC0, CANRX ąĮą░ PC1, čüą╝. ąŠą┐ąĖčüą░ąĮąĖąĄ ą┐ąŠčĆč鹊ą▓ ą▓ čüčéą░čéčīąĄ [2]).

ąÆčŗą▓ąŠą┤čŗ CAN ąĮą░ BGA ą║ąŠčĆą┐čāčüąĄ ą┐čĆąŠčåąĄčüčüąŠčĆą░ BC-316:

| ąÆčŗą▓ąŠą┤ |

ą©ą░čĆąĖą║ |

ążčāąĮą║čåąĖčÅ |

| CANTX/PC0 |

B12 |

ąĪąĖą│ąĮą░ą╗ ą┐ąĄčĆąĄą┤ą░čćąĖ CAN (ą▓čŗčģąŠą┤) |

| CANRX/PC1 |

B11 |

ąĪąĖą│ąĮą░ą╗ ą┐čĆąĖąĄą╝ą░ CAN (ą▓čģąŠą┤) |

ą×čüąĮąŠą▓ąĮčŗąĄ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ ąĖ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ ą╝ąŠą┤čāą╗čÅ CAN:

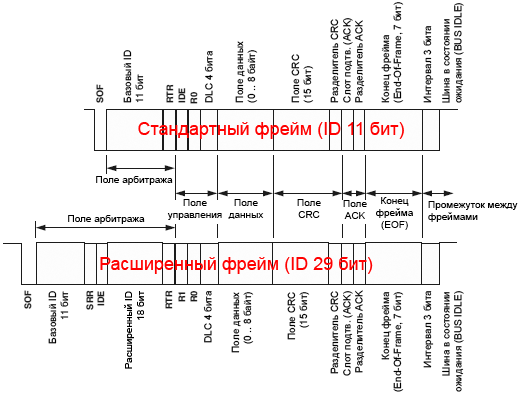

ŌĆó ąŻą┤ąŠą▓ą╗ąĄčéą▓ąŠčĆčÅąĄčé čüčéą░ąĮą┤ą░čĆčéčā CAN 2.0B (ą░ą║čéąĖą▓ąĮą░čÅ ą▓ąĄčĆčüąĖčÅ čüčéą░ąĮą┤ą░čĆčéą░).

ŌĆó ą¤ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé 2 ą▓ąĄčĆčüąĖąĖ CAN-ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆąŠą▓, standard (11 ą▒ąĖčé) ąĖ extended (29 ą▒ąĖčé).

ŌĆó ą¤ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé čüą║ąŠčĆąŠčüčéąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ąŠ 1 ą╝ąĄą│ą░ą▒ąĖčéą░/čüąĄą║.

ŌĆó ąöąŠčüčéčāą┐ąĮąŠ 32 ą┐ąŠčćč鹊ą▓čŗčģ čÅčēąĖą║ą░ (mailbox): 8 ąĮą░ ą┐ąĄčĆąĄą┤ą░čćčā, 8 ąĮą░ ą┐čĆąĖąĄą╝, 16 ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝čŗčģ ąĮą░ ą┐ąĄčĆąĄą┤ą░čćčā ąĖą╗ąĖ ą┐čĆąĖąĄą╝.

ŌĆó ą×čéą┤ąĄą╗čīąĮą░čÅ ą╝ą░čüą║ą░ čäąĖą╗čīčéčĆą░ (acceptance mask) ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ mailbox.

ŌĆó ążąĖą╗čīčéčĆą░čåąĖčÅ ą┐ąŠ ą┤ą░ąĮąĮčŗą╝ (ą┐ąĄčĆą▓čŗą╝ ą┤ą▓čāą╝ ą▒ą░ą╣čéą░ą╝ ą▓ mailbox), čćč鹊 ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┤ą╗čÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ čäąĖą╗čīčéčĆčāčÄčēąĄą╣ ą░ą┤čĆąĄčüą░čåąĖąĖ (acceptance filtering ą▓ čĆąĄąČąĖą╝ąĄ DeviceNetŌäó).

ŌĆó ąĀąĄą│ąĖčüčéčĆčŗ čüąŠčüč鹊čÅąĮąĖčÅ ąŠčłąĖą▒ą║ąĖ (Error status) ąĖ ą┐čĆąĄą┤čāą┐čĆąĄąČą┤ąĄąĮąĖčÅ.

ŌĆó ą£ąŠą┤čāą╗čī čāąĮąĖą▓ąĄčĆčüą░ą╗čīąĮąŠą│ąŠ čüč湥čéčćąĖą║ą░.

ŌĆó ą£ąŠąČąĮąŠ čüčćąĖčéčŗą▓ą░čéčī čāčĆąŠą▓ąĄąĮčī ą▓čŗą▓ąŠą┤ąŠą▓ ą┐čĆąĖąĄą╝ą░ ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ.

ą£ąŠą┤čāą╗čī CAN ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé čüąŠą▒ąŠą╣ ąĮąĖąĘą║ąŠčüą║ąŠčĆąŠčüčéąĮąŠą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü, ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮąĮčŗą╣ ą┤ą╗čÅ ą┐čĆąĖą╗ąŠąČąĄąĮąĖą╣, ą▓ ą║ąŠč鹊čĆčŗčģ čüą║ąŠčĆąŠčüčéčī ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ąĮąĄ ą┐čĆąĄą▓čŗčłą░ąĄčé 1 ą╝ąĄą│ą░ą▒ąĖčé/čüąĄą║. ąÆ ą┐čĆąŠč鹊ą║ąŠą╗ CAN ą▓čüčéčĆąŠąĄąĮą░ ą┐čĆąŠą▓ąĄčĆą║ą░ ą┤ą░ąĮąĮčŗčģ ąĮą░ CRC, čéčĆąĄą║ąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖą╣ ąŠą▒ ąŠčłąĖą▒ą║ą░čģ ąĖ ąŠą│čĆą░ąĮąĖč湥ąĮąĖąĄ čĆą░ą▒ąŠč鹊čüą┐ąŠčüąŠą▒ąĮąŠčüčéąĖ ąŠčéą║ą░ąĘą░ą▓čłąĄą│ąŠ čāąĘą╗ą░ čüąĄčéąĖ (fault node confinement) - ą▓čüąĄ čŹč鹊 ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮąŠ ą┤ą╗čÅ ą┐ąŠą▓čŗčłąĄąĮąĖčÅ ąĮą░ą┤ąĄąČąĮąŠčüčéąĖ čüąĄčéąĖ, čćč鹊ą▒čŗ čāą┤ąŠą▓ą╗ąĄčéą▓ąŠčĆčÅčéčī čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅą╝ ą┐čĆąĖą╗ąŠąČąĄąĮąĖą╣ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ.

ążąĖąĘąĖč湥čüą║ąĖą╣ ąĖąĮč鹥čĆč乥ą╣čü čłąĖąĮčŗ CAN - ą┐čĆąŠčüčéą░čÅ ą┤ą▓čāčģą┐čĆąŠą▓ąŠą┤ąĮą░čÅ ą╗ąĖąĮąĖčÅ. ąØą░ čĆąĖčü. 19-1 ą▓ čüąĖą╝ą▓ąŠą╗ąĖč湥čüą║ąŠą╣ č乊čĆą╝ąĄ ą┐ąŠą║ą░ąĘą░ąĮąŠ čüąŠąĄą┤ąĖąĮąĄąĮąĖąĄ ą┐čĆąŠčåąĄčüčüąŠčĆą░ čü čéčĆą░ąĮčüąĖą▓ąĄčĆąŠą╝ CAN (ąĮą░ą┐čĆąĖą╝ąĄčĆ TJA1041, TJA1050, PCA82C250, MCP2551 ąĖ čé. ą┐., čüą╝. čéą░ą║ąČąĄ [4]). ąÆčŗčģąŠą┤ ąĖ ą▓čģąŠą┤ ą┐čĆąŠčåąĄčüčüąŠčĆą░ Blackfin CANTX ąĖ CANRX ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčéčüčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ ą║ ą▓čŗą▓ąŠą┤ą░ą╝ TX ąĖ RX čéčĆą░ąĮčüąĖą▓ąĄčĆą░ CAN. ąÆčŗą▓ąŠą┤čŗ CANTX ąĖ CANRX čĆą░ą▒ąŠčéą░čÄčé čü čāčĆąŠą▓ąĮčÅą╝ąĖ TTL, ąĖ ą┐ąŠą┤čģąŠą┤čÅčé ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ čü čéčĆą░ąĮčüąĖą▓ąĄčĆą░ą╝ąĖ čłąĖąĮčŗ CAN ą┐ąŠ čüčéą░ąĮą┤ą░čĆčéčā ISO/DIS 11898 ąĖą╗ąĖ ą╝ąŠą┤ąĖčäąĖčåąĖčĆąŠą▓ą░ąĮąĮąŠą╝čā ąĖąĮč鹥čĆč乥ą╣čüčā RS-485 (čüą╝. čéą░ą▒ą╗ąĖčåčā 19-1).

ąĀąĖčü. 19-1. ąĪąŠąĄą┤ąĖąĮąĄąĮąĖąĄ čü č乊čĆą╝ąĖčĆąŠą▓ą░č鹥ą╗ąĄą╝ čäąĖąĘąĖč湥čüą║ąĖčģ čāčĆąŠą▓ąĮąĄą╣ čłąĖąĮčŗ CAN (čéčĆą░ąĮčüąĖą▓ąĄčĆąŠą╝).

ąóą░ą▒ą╗ąĖčåą░ 19-1. ąĀąĄčåąĄčüčüąĖą▓ąĮčŗąĄ ąĖ ą┤ąŠą╝ąĖąĮą░ąĮčéąĮčŗąĄ čāčĆąŠą▓ąĮąĖ čüąĖą│ąĮą░ą╗ąŠą▓ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖ ą┐čĆąĖąĄą╝ą░.

| ąÆčŗą▓ąŠą┤ |

ąŻčĆąŠą▓ąĄąĮčī ąĮą░ ą▓čŗą▓ąŠą┤ąĄ |

ąŚąĮą░č湥ąĮąĖąĄ ąĮą░ čäąĖąĘąĖč湥čüą║ąŠą╣ ą╗ąĖąĮąĖąĖ čłąĖąĮčŗ CAN |

| CANTX |

ąøąŠą│. 0 (GND) |

ąöąŠą╝ąĖąĮą░ąĮčéąĮąŠąĄ |

| ąøąŠą│. 1 (VCCEXT) |

ąĀąĄčåąĄčüčüąĖą▓ąĮąŠąĄ |

| CANRX |

ąøąŠą│. 0 (GND) |

ąöąŠą╝ąĖąĮą░ąĮčéąĮąŠąĄ |

| ąøąŠą│. 1 (VCCEXT) |

ąĀąĄčåąĄčüčüąĖą▓ąĮąŠąĄ |

ą£ąŠą┤čāą╗čī CAN ą┐čĆąŠčåąĄčüčüąŠčĆą░ Blackfin ą╝ąŠąČąĄčé ą┐ąŠą┤ą║ą╗čÄčćą░čéčīčüčÅ ą║ CAN-čéčĆą░ąĮčüąĖą▓ąĄčĆą░ą╝, čĆą░ą▒ąŠčéą░čÄčēąĖą╝ čü ą╗ąŠą│ąĖč湥čüą║ąĖą╝ąĖ čāčĆąŠą▓ąĮčÅą╝ąĖ 3V ąĖą╗ąĖ 5V. ąÆčŗą▓ąŠą┤ CANRX ą┤ąŠą┐čāčüą║ą░ąĄčé ą┐ąŠą┤ą░čćčā TTL-čāčĆąŠą▓ąĮąĄą╣ čü ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄą╝ 5V (5V tolerant), ąĮąĄčüą╝ąŠčéčĆčÅ ąĮą░ č鹊, čćč鹊 ą┐ąŠą┤čüąĖčüč鹥ą╝ą░ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ Blackfin ą┐ąĖčéą░ąĄčéčüčÅ ąŠčé ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ 3.3V (čłąĖąĮą░ ą┐ąĖčéą░ąĮąĖčÅ VDDEXT).

ąĪąŠčüč鹊čÅąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą┤ą╗čÅ ą▓čŗčģąŠą┤ą░ CANTX čĆąĄčåąĄčüčüąĖą▓ąĮąŠąĄ (ą╗ąŠą│. 1). ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 CANTX ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąĖčĆčāąĄčéčüčÅ čü ą▓čŗą▓ąŠą┤ąŠą╝ čüąĖą│ąĮą░ą╗ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ SPORT. ąÆčŗčģąŠą┤ąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ą╗ąŠą│. 0, ąĄčüą╗ąĖ ą▓ą╝ąĄčüč鹊 CAN ą▓čŗą▒čĆą░ąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ SPORT, čćč鹊 ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą┤ą╗čÅ čüąŠčüč鹊čÅąĮąĖčÅ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░. ąÆčģąŠą┤ąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą▓čŗą▓ąŠą┤ą░ CANRX ąĖą│ąĮąŠčĆąĖčĆčāąĄčéčüčÅ.

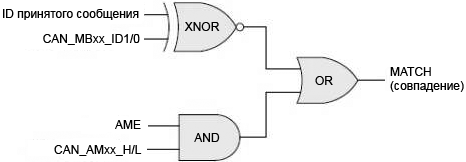

ąÉčĆčģąĖč鹥ą║čéčāčĆą░ ą╝ąŠą┤čāą╗čÅ CAN ąŠčĆą│ą░ąĮąĖąĘąŠą▓ą░ąĮą░ ą▓ąŠą║čĆčāą│ ą░ą┐ą┐ą░čĆą░čéąĮąŠą│ąŠ mailbox RAM ąĮą░ 32 čÅč湥ą╣ą║ąĖ. ąÜ mailbox ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮčŗą╣ ą┤ąŠčüčéčāą┐ č湥čĆąĄąĘ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü CAN, ąĖą╗ąĖ č湥čĆąĄąĘ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ ą┤ąŠčüčéčāą┐ čüąŠ čüč鹊čĆąŠąĮčŗ čÅą┤čĆą░ CPU. ąÜą░ąČą┤čŗą╣ mailbox čüąŠčüč鹊ąĖčé ąĖąĘ ą▓ąŠčüčīą╝ąĖ 16-ą▒ąĖčéąĮčŗčģ čĆąĄą│ąĖčüčéčĆąŠą▓ (čüą╝. ą┤ą░ą╗ąĄąĄ čĆą░ąĘą┤ąĄą╗ "ąźčĆą░ąĮąĖą╗ąĖčēąĄ ą┤ą░ąĮąĮčŗčģ"). ąöą░ąĮąĮčŗąĄ ą▓ čŹčéąĖčģ čĆąĄą│ąĖčüčéčĆą░čģ ą┐ąŠą┤ąĄą╗ąĄąĮčŗ ąĮą░ ą┐ąŠą╗čÅ, ą║ąŠč鹊čĆčŗąĄ ą▓ą║ą╗čÄčćą░čÄčé ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆ čüąŠąŠą▒čēąĄąĮąĖčÅ, ą╝ąĄčéą║čā ą▓čĆąĄą╝ąĄąĮąĖ (time stamp), čüč湥čéčćąĖą║ ą▒ą░ą╣čé, ą┤ąŠ 8 ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ, ą░ čéą░ą║ąČąĄ ąĮąĄčüą║ąŠą╗čīą║ąŠ ą▒ąĖčé čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ. ąÜą░ąČą┤čŗą╣ čāąĘąĄą╗ ąĮą░ čłąĖąĮąĄ CAN ą╝ąŠąĮąĖč鹊čĆąĖčé čüąŠąŠą▒čēąĄąĮąĖčÅ, ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗąĄ ą┐ąŠ čüąĄčéąĖ CAN. ąĢčüą╗ąĖ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆ ą▓ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ąŠą╝ čüąŠąŠą▒čēąĄąĮąĖąĖ čüąŠą▓ą┐ą░ą╗ čü ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆąŠą╝ ą▓ ąŠą┤ąĮąŠą╝ ąĖąĘ mailbox, č鹊 ą╝ąŠą┤čāą╗čī ąĘąĮą░ąĄčé, čćč鹊 čüąŠąŠą▒čēąĄąĮąĖąĄ ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮąŠ ą┤ą╗čÅ ąĮąĄą│ąŠ, ąĖ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčé ą┐čĆąĖąĮčÅčéčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ mailbox, čüąĖą│ąĮą░ą╗ąĖąĘąĖčĆčāčÅ čģąŠčüčéčā ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄą╝ ąŠ čüąŠą▒čŗčéąĖąĖ ą┐ąŠčüčéčāą┐ą╗ąĄąĮąĖčÅ čüąŠąŠą▒čēąĄąĮąĖčÅ.

ąĪąĄčéčī CAN ąĖčüą┐ąŠą╗čīąĘčāąĄčé ąŠą┤ąĮčā ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčāčÄ ą┐ą░čĆčā ą┐čĆąŠą▓ąŠą┤ąŠą▓. ąÆčüąĄ čāąĘą╗čŗ ą┐ąŠą┤ą║ą╗čÄč湥ąĮčŗ ą║ čŹč鹊ą╣ ą┐ą░čĆąĄ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠ, ąĖ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ą┐čĆąŠčüą╗čāčłąĖą▓ą░čÄčé ąĮą░ ąĮąĄą╣ čüąĖą│ąĮą░ą╗. ąÉčüąĖąĮčģčĆąŠąĮąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü CAN ąĮąĄ čéčĆąĄą▒čāąĄčé ąŠčéą┤ąĄą╗čīąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ čéą░ą║č鹊ą▓, ąŠą┤ąĮą░ą║ąŠ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ, čćč鹊ą▒čŗ ąĮą░čüčéčĆąŠą╣ą║ą░ ąĖąĮč鹥čĆą▓ą░ą╗ąŠą▓ čäčĆąĄą╣ą╝ąŠą▓ CAN (čüą║ąŠčĆąŠčüčéąĖ) ą▓čüąĄčģ čāąĘą╗ąŠą▓ čüąĄčéąĖ ą▒čŗą╗ą░ ąĖą┤ąĄąĮčéąĖčćąĮąŠą╣. ąĪąŠąŠą▒čēąĄąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ą▓ ąŠą┤ąĮąŠą╝ ąĖąĘ 4 čüčéą░ąĮą┤ą░čĆčéąĮčŗčģ čéąĖą┐ąŠą▓ čüąŠąŠą▒čēąĄąĮąĖą╣, ąĖą╗ąĖ čäčĆąĄą╣ą╝ąŠą▓. ąĪąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖčÅ ą┤ąŠčüčéąĖą│ą░ąĄčéčüčÅ ą┐ąŠ čéčēą░č鹥ą╗čīąĮąŠ ą┐čĆąŠą┤čāą╝ą░ąĮąĮąŠą╣ čüčģąĄą╝ąĄ, ą▓čŗą┐ąŠą╗ąĮąĄąĮąĮąŠą╣ ą▓ ą║ą░ąČą┤ąŠą╝ ą┐čĆąĖąĄą╝ąĮąĖą║ąĄ CAN. ąÉčĆą▒ąĖčéčĆą░ąČ ąĮą░ čłąĖąĮąĄ čĆąĄą░ą╗ąĖąĘčāąĄčéčüčÅ ą┐ąŠ ą║ą░ąČą┤ąŠą╝čā ą▒ąĖčéčā čäčĆąĄą╣ą╝ą░. ąöą╗čÅ ą▓čüąĄą╣ čüąĄčéąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮą░ ą┤ąŠą╝ąĖąĮą░ąĮčéąĮą░čÅ ą┐ąŠą╗čÅčĆąĮąŠčüčéčī čāčĆąŠą▓ąĮčÅ čüąĖą│ąĮą░ą╗ąŠą▓ ą▓ čüąĄčéąĖ. ąÆčüąĄą╝ čāąĘą╗ą░ą╝ čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī ą▓ ąĮą░čćą░ą╗ąĄ ąŠą┤ąĮąŠą│ąŠ ąĖ č鹊ą│ąŠ ąČąĄ čäčĆąĄą╣ą╝ą░, ąĮą░čćąĖąĮą░čÅ čü ąĖą╝ą┐čāą╗čīčüą░ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ čäčĆąĄą╣ą╝ą░ (frame sync pulse).

ąÜąŠą│ą┤ą░ ą║ą░ąČą┤čŗą╣ čāąĘąĄą╗ ą┐ąĄčĆąĄą┤ą░ąĄčé ą▒ąĖčé, ąŠąĮ ą┐čĆąĖ čŹč鹊ą╝ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ą┐čĆąŠą▓ąĄčĆčÅąĄčé, ąĮą░čģąŠą┤ąĖčéčüčÅ ą╗ąĖ čāčĆąŠą▓ąĄąĮčī ą▒ąĖčéą░ ąĮą░ čłąĖąĮąĄ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗą╝ ąĖą╝ čāčĆąŠą▓ąĮąĄą╝ ą▒ąĖčéą░. ąĢčüą╗ąĖ čŹč鹊 čéą░ą║, č鹊 ą┐ąĄčĆąĄą┤ą░čćą░ ą┐čĆąŠą┤ąŠą╗ąČą░ąĄčéčüčÅ. ąĢčüą╗ąĖ ąČąĄ ąĮąĄčé, č鹊 čŹč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ą┤čĆčāą│ąŠą╣ čāąĘąĄą╗ ą┐ąĄčĆąĄą┤ą░ą╗ ą┤ąŠą╝ąĖąĮą░ąĮčéąĮčŗą╣ ą▒ąĖčé, čéą░ą║ čćč鹊 ą┐ąĄčĆą▓čŗą╣ čāąĘąĄą╗ ą┐ąŠ čŹč鹊ą╝čā čäą░ą║čéčā ąĘąĮą░ąĄčé, čćč鹊 ąŠąĮ ą┐čĆąŠąĖą│čĆą░ą╗ ą░čĆą▒ąĖčéčĆą░ąČ, ąĖ ąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ą┐ąĄčĆąĄą┤ą░čćčā, ąŠčüą▓ąŠą▒ąŠąČą┤ą░čÅ čłąĖąĮčā ą┤ą╗čÅ ą┤čĆčāą│ąŠą│ąŠ čāąĘą╗ą░. ą¤čĆąŠčåąĄčüčü ą░čĆą▒ąĖčéčĆą░ąČą░ ą┐čĆąŠą┤ąŠą╗ąČą░ąĄčéčüčÅ, ą┐ąŠą║ą░ ąĮąĄ ąŠčüčéą░ąĮąĄčéčüčÅ ą┐ąĄčĆąĄą┤ą░čÄčēąĖą╝ č鹊ą╗čīą║ąŠ ąŠą┤ąĖąĮ čāąĘąĄą╗ ąĮą░ čłąĖąĮąĄ (čŹč鹊čé čāąĘąĄą╗ čüčćąĖčéą░ąĄčéčüčÅ ą▓čŗąĖą│čĆą░ą▓čłąĖą╝ ą░čĆą▒ąĖčéčĆą░ąČ čłąĖąĮčŗ CAN).

ąŁą╗ąĄą║čéčĆąĖč湥čüą║ąĖąĄ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ ą║ą░ąČą┤ąŠą╣ ą║ąŠąĮą║čĆąĄčéąĮąŠą╣ čüąĄčéąĖ ą╝ąŠą│čāčé ąĘąĮą░čćąĖč鹥ą╗čīąĮąŠ ąŠčéą╗ąĖčćą░čéčīčüčÅ, ą┐ąŠčŹč鹊ą╝čā ą░ą┐ą┐ą░čĆą░čéčāčĆą░ ąĖąĮč鹥čĆč乥ą╣čüą░ CAN ąŠą▒čŗčćąĮąŠ ą▓čüąĄą│ą┤ą░ ą┤ąĄą╗ąĖčéčüčÅ ąĮą░ 2 čćą░čüčéąĖ: ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ CAN ąĖ čéčĆą░ąĮčüąĖą▓ąĄčĆ CAN (čüą╝. čĆąĖčü. 19-1). ąŁč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąŠą┤ąĮąŠą╝čā ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčā ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čéčī čĆą░ąĘąĮčŗąĄ čéąĖą┐čŗ ą┤čĆą░ą╣ą▓ąĄčĆąŠą▓ ąĖ čüąĄč鹥ą╣ CAN. CAN-ą╝ąŠą┤čāą╗čī ą┐čĆąŠčåąĄčüčüąŠčĆą░ Blackfin ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé č鹊ą╗čīą║ąŠ čćą░čüčéčī ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░. ąĪą░ą╝ ą┐čĆąŠč鹊ą║ąŠą╗ CAN, ąĄą│ąŠ čüčéą░ąĮą┤ą░čĆčéčŗ ąĖ čĆąĄą║ąŠą╝ąĄąĮą┤ą░čåąĖąĖ ą▓ čŹč鹊ą╣ ą┤ąŠą║čāą╝ąĄąĮčéą░čåąĖąĖ ąĮąĄ ą┐čĆąĖą▓ąŠą┤čÅčéčüčÅ ąĖ ąĮąĄ čĆą░čüčüą╝ą░čéčĆąĖą▓ą░čÄčéčüčÅ. ą×ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ č鹊ą╗čīą║ąŠ č鹥 čćą░čüčéąĖ ą┐čĆąŠč鹊ą║ąŠą╗ą░, ą║ąŠč鹊čĆčŗąĄ ąĮąĄą┐ąŠčüčĆąĄą┤čüčéą▓ąĄąĮąĮąŠ čéčĆąĄą▒čāčÄčéčüčÅ ą┤ą╗čÅ ą┐ąŠąĮąĖą╝ą░ąĮąĖčÅ ąĖ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ ą▓ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą╝ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖąĖ, ą║ąŠč鹊čĆąŠąĄ čĆą░ą▒ąŠčéą░ąĄčé čü ą╝ąŠą┤čāą╗ąĄą╝ CAN.

[ążčāąĮą║čåąĖąĖ ą┐ąŠąĮąĖąČąĄąĮąĮąŠą│ąŠ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ]

ą¤čĆąŠčåąĄčüčüąŠčĆ Blackfin ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé čüąŠčüč鹊čÅąĮąĖąĄ hibernate čü ąĮąĖąĘą║ąĖą╝ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄą╝ 菹ĮąĄčĆą│ąĖąĖ [3], ąĖ ą╝ąŠą┤čāą╗čī CAN čĆąĄą░ą╗ąĖąĘčāąĄčé ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ čĆąĄąČąĖą╝ čüąĮą░. ą¤ąŠą▓ąĄą┤ąĄąĮąĖąĄ ą╝ąŠą┤čāą╗čÅ CAN ą▓ čŹčéąĖčģ ą┤ą▓čāčģ čĆąĄąČąĖą╝ą░čģ ąŠą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ ą▓ ą┐ąŠčüą╗ąĄą┤čāčÄčēąĖčģ čüąĄą║čåąĖčÅčģ.

ą¤čĆąŠą▒čāąČą┤ąĄąĮąĖąĄ CAN ąĖąĘ čüąŠčüč鹊čÅąĮąĖčÅ Hibernate. ąÆ čüąŠčüč鹊čÅąĮąĖąĖ hibernate ą┐čĆąŠčåąĄčüčüąŠčĆą░ Blackfin, ą║ąŠą│ą┤ą░ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čĆąĄą│čāą╗čÅč鹊čĆ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ VDDINT ą▓čŗą║ą╗čÄčćą░ąĄčé ą┐ąĖčéą░ąĮąĖąĄ čÅą┤čĆą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░, ąŠčéą║ą╗čÄčćą░čÄčéčüčÅ čéą░ą║čéčŗ čÅą┤čĆą░ ąĖ čüąĖčüč鹥ą╝ąĮąŠą╣ čłąĖąĮčŗ. ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ą║čĆąĖčüčéą░ą╗ą╗ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą┐ąŠčéčĆąĄą▒ą╗čÅąĄčé ąŠč湥ąĮčī ą╝ą░ą╗čŗą╣ č鹊ą║ (ąŠą║ąŠą╗ąŠ 50 ą╝ą║ąÉ). ąŁč鹊čé č鹊ą║ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą┐ąŠą┤ą┤ąĄčƹȹ║ąĖ čüčģąĄą╝čŗ čĆąĄą│čāą╗čÅč鹊čĆą░ ą▓ ąŠąČąĖą┤ą░ąĮąĖąĖ ą┐ąŠčüčéčāą┐ą╗ąĄąĮąĖčÅ čüąĖą│ąĮą░ą╗ąŠą▓ čüąŠą▒čŗčéąĖčÅ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ (hibernate wake-up event). ą×ą┤ąĮąŠ ąĖąĘ čéą░ą║ąĖčģ čüąŠą▒čŗčéąĖą╣ - ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖąĄ ąĖąĘ-ąĘą░ ą░ą║čéąĖą▓ąĮąŠčüčéąĖ ąĮą░ čłąĖąĮąĄ CAN. ą¤ąŠčüą╗ąĄ ą▓čŗčģąŠą┤ą░ ąĖąĘ čüąŠčüč鹊čÅąĮąĖčÅ hibernate ą╝ąŠą┤čāą╗čī CAN ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆąŠą▓ą░ąĮ ą┐ąŠą▓č鹊čĆąĮąŠ.

ąöą╗čÅ čāčüčéčĆąŠą╣čüčéą▓ čü ąĮąĖąĘą║ąĖą╝ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄą╝ ą▓ąĮąĄčłąĮąĖą╣ čéčĆą░ąĮčüąĖą▓ąĄčĆ čłąĖąĮčŗ CAN ąŠą▒čŗčćąĮąŠ ą┐ąĄčĆąĄą▓ąŠą┤ąĖčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ąĖ (standby mode) čü ą┐ąŠą╝ąŠčēčīčÄ ąŠą┤ąĮąŠą│ąŠ ąĖąĘ ą▓ąĮąĄčłąĮąĖčģ ą▓čŗą▓ąŠą┤ąŠą▓ ą┐ąŠčĆč鹊ą▓ GPIO ą┐čĆąŠčåąĄčüčüąŠčĆą░ Blackfin. ąÆ čĆąĄąČąĖą╝ąĄ standby čéčĆą░ąĮčüąĖą▓ąĄčĆ CAN ą┐ąŠčüč鹊čÅąĮąĮąŠ ą▓čŗą┤ą░ąĄčé čĆąĄčåąĄčüčüąĖą▓ąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 1 ąĮą░ ą▓čŗą▓ąŠą┤ CANRX ą╝ąŠą┤čāą╗čÅ CAN ą┐čĆąŠčåąĄčüčüąŠčĆą░. ąĢčüą╗ąĖ čéčĆą░ąĮčüąĖą▓ąĄčĆ ą┐ąŠčćčāą▓čüčéą▓ąŠą▓ą░ą╗ ą░ą║čéąĖą▓ąĮąŠčüčéčī čłąĖąĮčŗ CAN, č鹊 ąŠąĮ ą┐ąĄčĆąĄą▓ąŠą┤ąĖčé ą▓čŗą▓ąŠą┤ CANRX ą▓ ą┤ąŠą╝ąĖąĮą░ąĮčéąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 0. ąŁč鹊 čüąĖą│ąĮą░ą╗ąĖąĘąĖčĆčāąĄčé ą┐čĆąŠčåąĄčüčüąŠčĆčā Blackfin, čćč鹊 ą▒čŗą╗ą░ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮą░ ą░ą║čéąĖą▓ąĮąŠčüčéčī ąĮą░ čłąĖąĮąĄ CAN. ąĢčüą╗ąĖ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čĆąĄą│čāą╗čÅč鹊čĆ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą▒čŗą╗ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ ąĮą░ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖąĄ ą░ą║čéąĖą▓ąĮąŠčüčéąĖ ąĮą░ čłąĖąĮąĄ CAN ą║ą░ą║ čüąŠą▒čŗčéąĖčÅ ą▓čŗčģąŠą┤ą░ ąĖąĘ čüąŠčüč鹊čÅąĮąĖčÅ hibernate, č鹊 ąŠąĮ čĆąĄą░ą│ąĖčĆčāąĄčé čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ (ą▓ą║ą╗čÄčćą░ąĄčéčüčÅ). ąśąĮą░č湥 ą░ą║čéąĖą▓ąĮąŠčüčéčī ąĮą░ ą▓čŗą▓ąŠą┤ąĄ CANRX ąĮąĖą║ą░ą║ ąĮąĄ ą┐ąŠą▓ą╗ąĖčÅąĄčé ąĮą░ čüąŠčüč鹊čÅąĮąĖąĄ ą┐čĆąŠčåąĄčüčüąŠčĆą░.

ą¦č鹊ą▒čŗ čŹč鹊 ą▓čüąĄ čĆą░ą▒ąŠčéą░ą╗ąŠ, čĆąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čĆąĄą│čāą╗čÅč鹊čĆą░ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ (VR_CTL) ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ čü čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╝ ą▒ąĖč鹊ą╝ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ ąŠčé ąĖąĮč鹥čĆč乥ą╣čüą░ CAN (CAN wake-up enable bit). ąÆąŠčé čéąĖą┐ąŠą▓ą░čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī čüąŠą▒čŗčéąĖą╣ ą┤ą╗čÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ čäčāąĮą║čåąĖąĖ CAN wake-up:

1. ąśčüą┐ąŠą╗čīąĘčāą╣č鹥 ą▓čŗą▓ąŠą┤ GPIO ą┐čĆąŠčåąĄčüčüąŠčĆą░, čćč鹊ą▒čŗ ą┐ąĄčĆąĄą▓ąĄčüčéąĖ ą▓ąĮąĄčłąĮąĖą╣ čéčĆą░ąĮčüąĖą▓ąĄčĆ ą▓ čĆąĄąČąĖą╝ standby.

2. ąŚą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāą╣č鹥 čĆąĄą│ąĖčüčéčĆ VR_CTL ąĘąĮą░č湥ąĮąĖąĄą╝, ą│ą┤ąĄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ ąŠčé CAN (CANWE), ąĖ ą┐ąŠą╗ąĄ FREQ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ ą▓ 00.

CAN Sleep Mode. ąŻ ą╝ąŠą┤čāą╗čÅ CAN ąĄčüčéčī ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ čĆąĄąČąĖą╝ čüąĮą░. ąÆ čŹč鹊čé čĆąĄąČąĖą╝ ą╝ąŠą┤čāą╗čī ą▓ą▓ąŠą┤čÅčé čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ SMR ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_CONTROL. ąÜą░ą║ č鹊ą╗čīą║ąŠ ą┐čĆąŠąĖąĘąŠčłąĄą╗ ą▓čģąŠą┤ ą▓ čĆąĄąČąĖą╝ čüąĮą░, ą╝ąĮąŠą│ąĖąĄ ąĖąĘ ą▓ąĮčāčéčĆąĄąĮąĮąĖčģ čéą░ą║č鹊ą▓ ą╝ąŠą┤čāą╗čÅ CAN ą▓čŗą║ą╗čÄčćą░čÄčéčüčÅ, čćč鹊 čüąĮąĖąČą░ąĄčé ąŠą▒čēąĄąĄ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ. ąÜąŠą│ą┤ą░ ą╝ąŠą┤čāą╗čī CAN ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ sleep mode, ą▓čüąĄ ą┐ąŠą┐čŗčéą║ąĖ čćč鹥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆąŠą▓ CAN ą▓ąŠąĘą▓čĆą░čéčÅčé čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ CAN_INTR ą▓ą╝ąĄčüč鹊 ąŠą▒čŗčćąĮąŠą│ąŠ čüąŠą┤ąĄčƹȹ░ąĮąĖčÅ. ąÆčüąĄ ąĘą░ą┐ąĖčüąĖ ą▓ čĆąĄą│ąĖčüčéčĆčŗ, ą║čĆąŠą╝ąĄ čĆąĄą│ąĖčüčéčĆą░ CAN_INTR, ą▓ sleep mode ąĖą│ąĮąŠčĆąĖčĆčāčÄčéčüčÅ.

ąÆ čĆąĄąČąĖą╝ąĄ čüąĮą░ ą╝ą░ą╗ą░čÅ čćą░čüčéčī ą╝ąŠą┤čāą╗čÅ CAN ą┐čĆąŠą┤ąŠą╗ąČą░ąĄčé ą┐ąŠą╗čāčćą░čéčī čéą░ą║čéčŗ, čćč鹊ą▒čŗ ą┐ąŠąĘą▓ąŠą╗ąĖčéčī ą▓čŗčģąŠą┤ ąĖąĘ sleep mode. ąŚą░ą┐ąĖčüčī ą▓ čĆąĄą│ąĖčüčéčĆ CAN_INTR ąĘą░ą▓ąĄčĆčłą░ąĄčé sleep mode. ąĢčüą╗ąĖ ą▒ąĖčé WBA ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_CONTROL ą▒čŗą╗ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą┐ąĄčĆąĄą┤ ą▓čģąŠą┤ąŠą╝ ą▓ sleep mode, č鹊 ą┤ąŠą╝ąĖąĮą░ąĮčéąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī ąĮą░ CANRX ąĘą░ą▓ąĄčĆčłą░ąĄčé sleep mode ą╝ąŠą┤čāą╗čÅ CAN.

[ąĀąĄą│ąĖčüčéčĆčŗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĖ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ CAN]

ąÆ ą│ą╗ą░ą▓ąĮąŠą╝ čāą┐čĆą░ą▓ą╗čÅčÄčēąĄą╝ čĆąĄą│ąĖčüčéčĆąĄ (CAN_CONTROL) čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮąŠ ąĮąĄčüą║ąŠą╗čīą║ąŠ ą│ą╗ąŠą▒ą░ą╗čīąĮčŗčģ ą║ąŠą╝ą░ąĮą┤ąĮčŗčģ ą▒ąĖčé. ąōą╗ąŠą▒ą░ą╗čīąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ čüčéą░čéčāčüą░ (CAN_STATUS) ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé ą▓ąĮčāčéčĆąĄąĮąĮąĖąĄ čüąĖą│ąĮą░ą╗čŗ čüąŠčüč鹊čÅąĮąĖčÅ. ą¤ą░čĆą░ą╝ąĄčéčĆ čéą░ą╣ą╝ąĖąĮą│ą░ ą▒ąĖčé CAN ąĖ čüą┐ąĄčåąĖą░ą╗čīąĮčŗąĄ čĆąĄąČąĖą╝ ą╝ąŠą┤čāą╗čÅ CAN ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮčŗ ą▓ čĆąĄą│ąĖčüčéčĆą░čģ CAN_CLOCK ąĖ CAN_TIMING.

ąÆčüąĄ ąĘąĮą░č湥ąĮąĖčÅ čéą░ą╣ą╝ąĖąĮą│ą░ ą▒ąĖčé ą╝ąŠą│čāčé ą▒čŗčéčī ąĖąĘą╝ąĄąĮąĄąĮčŗ č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ čÅą┤čĆąŠ ą╝ąŠą┤čāą╗čÅ CAN ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ. ą¤čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čüą▒čĆąŠčü (software reset) ąĮąĄ ą╝ąĄąĮčÅąĄčé ąĘąĮą░č湥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆąŠą▓ CAN_CLOCK ąĖ CAN_TIMING. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą▓čŗą┐ąŠą╗ąĮčÅčÄčēą░čÅčüčÅ ą┐ąĄčĆąĄą┤ą░čćą░ ą┐ąŠ čłąĖąĮąĄ CAN ąĮąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠą▓čĆąĄąČą┤ąĄąĮą░ ąĖąĘą╝ąĄąĮąĄąĮąĖąĄą╝ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓ čéą░ą╣ą╝ąĖąĮą│ą░ ą▒ąĖčé ąĖą╗ąĖ ąĖąĮąĖčåąĖąĖčĆąŠą▓ą░ąĮąĖąĄą╝ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čüą▒čĆąŠčüą░ (SRS=1 ą▓ CAN_CONTROL). ąĀąĄą│ąĖčüčéčĆčŗ CAN_CLOCK ąĖ CAN_TIMING ą▒ą╗ąŠą║ąĖčĆčāčÄčéčüčÅ ąĮą░ ąĘą░ą┐ąĖčüčī (ąĖąĘą╝ąĄąĮąĄąĮąĖąĄ ąĖčģ ąĮąĄ čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ), ąĄčüą╗ąĖ CCA=0 ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_STATUS.

ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠ ą╝ąŠą┤čāą╗čī CAN čüąŠą┤ąĄčƹȹĖčé čäčāąĮą║čåąĖčÄ čĆąĄąČąĖą╝ą░ č鹥čüčéą░, ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮąĮčāčÄ ą┤ą╗čÅ ąŠčéą╗ą░ą┤ą║ąĖ ą¤ą× ąĖ čüąĖčüč鹥ą╝čŗ CAN, čćč鹊 ą┤ąŠčüčéčāą┐ąĮąŠ č湥čĆąĄąĘ čĆąĄą│ąĖčüčéčĆ ąŠčéą╗ą░ą┤ą║ąĖ CAN (CAN_DEBUG).

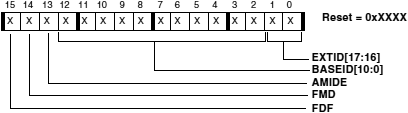

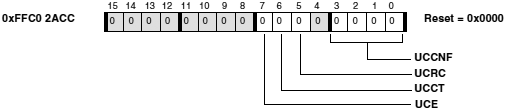

ąØą░ čĆąĖčü. 19-2 ą┐ąŠą║ą░ąĘą░ąĮčŗ ą│ą╗ąŠą▒ą░ą╗čīąĮčŗąĄ ą▒ąĖčéčŗ ą║ąŠą╝ą░ąĮą┤, čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮąĮčŗąĄ ą▓ ą│ą╗ą░ą▓ąĮąŠą╝ čĆąĄą│ąĖčüčéčĆąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ (CAN_CONTROL). ą¤ąŠčüą╗ąĄ ą▓ą║ą╗čÄč湥ąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ, čüą▒čĆąŠčüą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ąĖą╗ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čüą▒čĆąŠčüą░ CAN čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▒ąĖčé CCR, ąĖ ą▓čüąĄ ąĄą│ąŠ ą┤čĆčāą│ąĖąĄ ą▒ąĖčéčŗ ąŠčćąĖčēą░čÄčéčüčÅ. ąÆąŠ ą▓čĆąĄą╝čÅ ą┤ąŠčüčéčāą┐ą░ ąĮą░ ąĘą░ą┐ąĖčüčī ą▓čüąĄ ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąĮčŗąĄ ą▒ąĖčéčŗ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą▓ ą╗ąŠą│. 0.

ąĀąĖčü. 19-2. Master Control Register.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: čāčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖčéą░ CCR ą▓čüąĄą│ąŠ ą╗ąĖčłčī ąŠą▒ąŠąĘąĮą░čćą░ąĄčé ą┐ąŠą┐čŗčéą║čā (ąĘą░ą┐čĆąŠčü) ą▓čģąŠą┤ą░ ą▓ čĆąĄąČąĖą╝ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ, ąŠą┤ąĮą░ą║ąŠ čĆąĄą░ą╗čīąĮąŠ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ CAN ą▒čāą┤ąĄčé ąĮą░čģąŠą┤ąĖčéčīčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ č鹊ą╗čīą║ąŠ č鹊ą│ą┤ą░, ą║ąŠą│ą┤ą░ ą▒čāą┤ąĄčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé CCA (ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖąĄ čĆąĄąČąĖą╝ą░ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ) ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_STATUS. ąśąĮąŠą│ą┤ą░, ą┐ąŠ ąĮąĄą║ąŠč鹊čĆčŗą╝ ąĮąĄ ą▓čŗčÅčüąĮąĄąĮąĮčŗą╝ ą┤ą╗čÅ ą╝ąĄąĮčÅ ą┐čĆąĖčćąĖąĮą░ą╝ (ąĮą░ą┐čĆąĖą╝ąĄčĆ, ą║ąŠą│ą┤ą░ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ CAN ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ąŠčłąĖą▒ą║ąĖ, ąĄčüą╗ąĖ ąĮą░ čłąĖąĮąĄ CAN ą┐čĆąĖčüčāčéčüčéą▓čāčÄčé čüąĖą│ąĮą░ą╗čŗ, ąĮąĄ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ č鹥ą║čāčēąĄą╣ ąĮą░čüčéčĆąŠą╣ą║ąĄ čéą░ą╣ą╝ąĖąĮą│ą░ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ CAN), ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čüą▒čĆąŠčü ąĖąĮč鹥čĆč乥ą╣čüą░ CAN ą┐čĆąĖą▓ąŠą┤ąĖčé č鹊ą╗čīą║ąŠ ą║ čāčüčéą░ąĮąŠą▓ą║ąĄ ą▒ąĖčéą░ CCR, ąĮąŠ ą▒ąĖčé CCA ąĮąĄ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ. ąÆčŗą╣čéąĖ ąĖąĘ čŹč鹊ą╣ čüąĖčéčāą░čåąĖąĖ ą┐ąŠą╗čāčćą░ąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą┐čāč鹥ą╝ čäąĖąĘąĖč湥čüą║ąŠą│ąŠ ąŠčéą║ą╗čÄč湥ąĮąĖčÅ ąŠčé čłąĖąĮčŗ CAN.

ąØąĖąČąĄ ą┐čĆąĖą▓ąĄą┤ąĄąĮąŠ ąŠą┐ąĖčüą░ąĮąĖąĄ ą▒ąĖčé čĆąĄą│ąĖčüčéčĆą░ CAN_CONTROL.

CCR - CAN Configuration Mode Request.

ąĢčüą╗ąĖ ą┐ąŠą╗ąĄ TSEG1 čĆąĄą│ąĖčüčéčĆą░ CAN_TIMING ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąŠ ą▓ 0, č鹊 ą╝ąŠą┤čāą╗čī ąĮąĄ ą┐ąŠą║ąĖą┤ą░ąĄčé čĆąĄąČąĖą╝ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ.

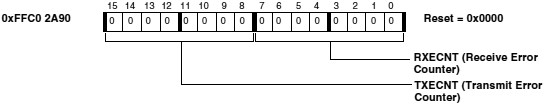

ąĢčüą╗ąĖ čüč湥čéčćąĖą║ ąŠčłąĖą▒ąŠą║ CAN-ą╝ąŠą┤čāą╗čÅ čüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąŠą╗čīčłąĄ ąĖą╗ąĖ čĆą░ą▓ąĄąĮ 256, č鹊 ą╝ąŠą┤čāą╗čī ą▓čģąŠą┤ąĖčé ą▓ čüąŠčüč鹊čÅąĮąĖąĄ "bus-off" (ąŠčéą║ą╗čÄčćą░ąĄčéčüčÅ ąŠčé čłąĖąĮčŗ). ąöą╗čÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ čüą╝. ąŠą┐ąĖčüą░ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ CAN Error Counter (CAN_CEC). ąÆ čŹč鹊ą╝ čüąŠčüč鹊čÅąĮąĖąĖ ą╝ąŠą┤čāą╗čÄ ąĮąĄ ą┤ąŠąĘą▓ąŠą╗čÅąĄčéčüčÅ ąĮąĖą║ą░ą║ ą▓ą╗ąĖčÅčéčī ąĮą░ čüąŠčüč鹊čÅąĮąĖąĄ čłąĖąĮčŗ, čé. ąĄ. ą▓čŗčģąŠą┤ąĮčŗąĄ ą┤čĆą░ą╣ą▓ąĄčĆčŗ ą▓čŗą║ą╗čÄč湥ąĮčŗ.

ąÆąŠ ą▓čĆąĄą╝čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖčÅ ąĖąĘ bus-off ą▒ąĖčé ąĘą░ą┐čĆąŠčüą░ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąŠąĮąĮąŠą│ąŠ čĆąĄąČąĖą╝ą░ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ ą╗ąŠą│ąĖą║ąŠą╣ (CCR = 1), čéą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝ ą╝ąŠą┤čāą╗čī čÅą┤čĆą░ CAN ąĮąĄ ą┐ąŠą┤ą║ą╗čÄčćąĖčéčüčÅ ą║ čłąĖąĮąĄ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ. ąæąĖčé CCR ąĮąĄ ą╝ąŠąČąĄčé čüą▒čĆąŠčüąĖčéčīčüčÅ, ą┐ąŠą║ą░ ąĮąĄ ąĘą░ą▓ąĄčĆčłąĖčéčüčÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖčÅ ąĖąĘ bus-off.

ąæąĖčé CCR čĆą░ą▒ąŠčéą░ąĄčé ą▓ąŠ ą▓ąĘą░ąĖą╝ąŠą┤ąĄą╣čüčéą▓ąĖąĖ čü ą▒ąĖč鹊ą╝ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ čĆąĄąČąĖą╝ą░ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ (ą▒ąĖčé CCA ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_STATUS). ąæąĖčé CCR ąĮąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠčćąĖčēąĄąĮ, ąĄčüą╗ąĖ ąŠąĮ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ąĖ ąŠčćąĖčēąĄąĮ ą▒ąĖčé CCA, ąĖ ą▒ąĖčé CCR ąĮąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ąĄčüą╗ąĖ ąŠąĮ ąŠčćąĖčēąĄąĮ ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé CCA.

1: ąĘą░ą┐čĆąŠčłąĄąĮ čĆąĄąČąĖą╝ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ. ą¤ąŠčüą╗ąĄ ą▓ą║ą╗čÄč湥ąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ čŹč鹊čé čĆąĄąČąĖą╝ ą░ą║čéąĖą▓ąĄąĮ (CCR=1 ąĖ CCA=1). ą¤ą░čĆą░ą╝ąĄčéčĆčŗ čéą░ą╣ą╝ąĖąĮą│ą░ ą▒ąĖčéą░ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮčŗ ą┐ąĄčĆąĄą┤ ą▓čŗčģąŠą┤ąŠą╝ ąĖąĘ čŹč鹊ą│ąŠ čĆąĄąČąĖą╝ą░. ąöąŠčüčéčāą┐ ąĮą░ ąĘą░ą┐ąĖčüčī ą▓ čĆąĄą│ąĖčüčéčĆ ą┐ą░čĆą░ą╝ąĄčéčĆą░ čéą░ą╣ą╝ąĖąĮą│ą░ ą▒ą╗ąŠą║ąĖčĆčāąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą╝ąŠą┤čāą╗čī CAN ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ąĮąŠčĆą╝ą░ą╗čīąĮąŠą╝ čĆą░ą▒ąŠč湥ą╝ čĆąĄąČąĖą╝ąĄ (CCA == 0). ąĢčüą╗ąĖ čÅą┤čĆąŠ ą╝ąŠą┤čāą╗čÅ CAN ą▓ ąĮą░čüč鹊čÅčēąĖą╣ ą╝ąŠą╝ąĄąĮčé ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčé čüąŠąŠą▒čēąĄąĮąĖąĄ ąĮą░ čłąĖąĮąĄ CAN, č鹊 čŹčéą░ ąŠą┐ąĄčĆą░čåąĖčÅ ąĘą░ą▓ąĄčĆčłą░ąĄčéčüčÅ ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ą▒čāą┤ąĄčé ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮ čĆąĄąČąĖą╝ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ (CCA ą▓ ą░ą║čéąĖą▓ąĮąŠą╣ 1). ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą┤ąŠą╗ąČąĄąĮ ąČą┤ą░čéčī čāčüčéą░ąĮąŠą▓ą║ąĖ CCA ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ąŠčüčāčēąĄčüčéą▓ą╗čÅčéčī ą┤ąŠčüčéčāą┐ ą║ ą┐ą░čĆą░ą╝ąĄčéčĆą░ą╝ čéą░ą╣ą╝ąĖąĮą│ą░ ą▒ąĖčé (čĆąĄą│ąĖčüčéčĆčŗ CAN_CLOCK ąĖ CAN_TIMING). ąÆąŠ ą▓čĆąĄą╝čÅ čĆąĄąČąĖą╝ą░ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą╝ąŠą┤čāą╗čī ąĮąĄ ą┐čĆąŠčÅą▓ą╗čÅąĄčé ą░ą║čéąĖą▓ąĮąŠčüčéąĖ ąĮą░ čłąĖąĮąĄ CAN. ąÆčŗčģąŠą┤ CANTX ąŠčüčéą░ąĄčéčüčÅ čĆąĄčåąĄčüčüąĖą▓ąĮčŗą╝, ąĖ ą╝ąŠą┤čāą╗čī ąĮąĄ ą┐čĆąĖąĮąĖą╝ą░ąĄčé ąĖ ąĮąĄ ą┐ąĄčĆąĄą┤ą░ąĄčé čüąŠąŠą▒čēąĄąĮąĖčÅ ąĖą╗ąĖ čäčĆąĄą╣ą╝čŗ ąŠčłąĖą▒ą║ąĖ. ą¤ąŠčüą╗ąĄ ą▓čŗčģąŠą┤ą░ ąĖąĘ čĆąĄąČąĖą╝ą░ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą▓čüąĄ ą▓ąĮčāčéčĆąĄąĮąĮąĖąĄ čĆąĄą│ąĖčüčéčĆčŗ čÅą┤čĆą░ CAN ąĖ čüč湥čéčćąĖą║ąĖ ąŠčłąĖą▒ąŠą║ CAN čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄčéčüčÅ ą▓ čüą▓ąŠąĖ ąĮą░čćą░ą╗čīąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ.

0: ąŠčéą╝ąĄąĮąĄąĮ ąĘą░ą┐čĆąŠčü ąĮą░ čĆąĄąČąĖą╝ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ.

CSR - CAN Suspend Mode Request.

ąæąĖčé CSR čĆą░ą▒ąŠčéą░ąĄčé ą▓ąŠ ą▓ąĘą░ąĖą╝ąŠą┤ąĄą╣čüčéą▓ąĖąĖ čü ą▒ąĖč鹊ą╝ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ čĆąĄąČąĖą╝ą░ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ąĖ (suspend mode acknowledge, CSA ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_STATUS). ąæąĖčé CSR ąĮąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠčćąĖčēąĄąĮ, ąĄčüą╗ąĖ ąŠąĮ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ąĖ ą▒ąĖčé CSA ąŠčćąĖčēąĄąĮ, ąĖ ą▒ąĖčé CSR ąĮąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ąĄčüą╗ąĖ ąŠąĮ ąŠčćąĖčēąĄąĮ ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé CSA.

1: ąĘą░ą┐čĆąŠčłąĄąĮ suspend mode (čĆąĄąČąĖą╝ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ąĖ). ąĢčüą╗ąĖ ą╝ąŠą┤čāą╗čī CAN ą▓ ąĮą░čüč鹊čÅčēąĖą╣ ą╝ąŠą╝ąĄąĮčé ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčé čüąŠąŠą▒čēąĄąĮąĖąĄ ąĮą░ čłąĖąĮąĄ CAN, č鹊 čŹčéą░ ąŠą┐ąĄčĆą░čåąĖčÅ ąĘą░ą▓ąĄčĆčłąĖčéčüčÅ ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ą▒čāą┤ąĄčé ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮ suspend mode (CSA ą▓ ą░ą║čéąĖą▓ąĮąŠą╣ 1). ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą┤ąŠą╗ąČąĄąĮ ąČą┤ą░čéčī čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ CSA. ąÆąŠ ą▓čĆąĄą╝čÅ suspend mode ą╝ąŠą┤čāą╗čī ąĮąĄ ą┐čĆąŠčÅą▓ą╗čÅąĄčé ą░ą║čéąĖą▓ąĮąŠčüčéąĖ ąĮą░ čłąĖąĮąĄ CAN. ąÆčŗčģąŠą┤ CANTX ąŠčüčéą░ąĄčéčüčÅ čĆąĄčåąĄčüčüąĖą▓ąĮčŗą╝, ąĖ ą╝ąŠą┤čāą╗čī ąĮąĄ ą┐čĆąĖąĮąĖą╝ą░ąĄčé ąĖ ąĮąĄ ą┐ąĄčĆąĄą┤ą░ąĄčé čüąŠąŠą▒čēąĄąĮąĖčÅ ąĖą╗ąĖ čäčĆąĄą╣ą╝čŗ ąŠčłąĖą▒ą║ąĖ. ąĪąŠą┤ąĄčƹȹĖą╝ąŠąĄ čüč湥čéčćąĖą║ąŠą▓ ąŠčłąĖą▒ąŠą║ CAN ąŠčüčéą░ąĄčéčüčÅ ąĮąĄąĖąĘą╝ąĄąĮąĮčŗą╝.

0: ąĘą░ą┐čĆąŠčü suspend mode ąŠčéą╝ąĄąĮąĄąĮ.

SMR - Sleep Mode Request.

ąÆ čĆąĄąČąĖą╝ąĄ čüąĮą░ (sleep mode) ąŠčéą║ą╗čÄčćą░ąĄčéčüčÅ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ąĮą░ ą▒ąŠą╗čīčłąĖąĮčüčéą▓ąĄ čĆąĄą│ąĖčüčéčĆąŠą▓ CAN, čćč鹊 čüąĮąĖąČą░ąĄčé ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ č鹊ą║ą░. ą£ąŠą┤čāą╗čī ą╝ąŠąČąĄčé ą┐čĆąŠčüąĮčāčéčīčüčÅ ąŠčé ą░ą║čéąĖą▓ąĮąŠčüčéąĖ ąĮą░ čłąĖąĮąĄ CAN ąĖą╗ąĖ ąŠčé ąĘą░ą┐ąĖčüąĖ ą▓ čĆąĄą│ąĖčüčéčĆ CAN_INTR. ąæąĖčé SMACK ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_INTR ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą░ą║čéąĖą▓ąĄąĮ sleep mode.

ą¦č鹊ą▒čŗ ą┤ąŠčüčéąĖčćčī čüą░ą╝ąŠą│ąŠ ą╗čāčćčłąĄą╣ 菹║ąŠąĮąŠą╝ąĖąĖ 菹ĮąĄčĆą│ąĖąĖ, ąĖčüą┐ąŠą╗čīąĘčāą╣č鹥 čüąŠčüč鹊čÅąĮąĖąĄ hibernate, ąĖ čāčüčéą░ąĮąŠą▓ąĖč鹥 čĆąĄą│čāą╗čÅč鹊čĆ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ąĮą░ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖąĄ ąŠčé ą░ą║čéąĖą▓ąĮąŠčüčéąĖ ąĮą░ čłąĖąĮąĄ CAN. ąöą╗čÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ čüą╝. ą▓čŗčłąĄ "ą¤čĆąŠą▒čāąČą┤ąĄąĮąĖąĄ CAN ąĖąĘ čüąŠčüč鹊čÅąĮąĖčÅ Hibernate".

1: ą╝ąŠą┤čāą╗čī ą▓čģąŠą┤ąĖčé ą▓ sleep mode ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ąĘą░ą▓ąĄčĆčłąĖą╗ą░čüčī ąŠą┐ąĄčĆą░čåąĖčÅ ąĮą░ čłąĖąĮąĄ CAN.

0: ąĮąĄ ą▒čŗą╗ąŠ ąĘą░ą┐čĆąŠčüą░ ąĮą░ ą▓čģąŠą┤ ą▓ sleep mode.

WBA - Wake-Up on CAN Bus Activity.

1: ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖą╣ ą▓čŗčģąŠą┤ ąĖąĘ sleep mode, ąĄčüą╗ąĖ ą▒čŗą╗ą░ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮą░ ą╗čÄą▒ą░čÅ ą░ą║čéąĖą▓ąĮąŠčüčéčī ąĮą░ čłąĖąĮąĄ CAN.

0: ą╝ąŠą┤čāą╗čī ąŠčüčéą░ąĄčéčüčÅ ą▓ sleep mode, ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé čüąŠčüč鹊čÅąĮąĖčÅ čłąĖąĮčŗ CAN, ą┐ąŠą║ą░ čüą▒čĆąŠčłąĄąĮ SMR.

ABO - Auto Bus On.

1: ą┐ąŠčüą╗ąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐čĆąŠčåąĄą┤čāčĆčŗ ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖčÅ ąĖąĘ čüąŠčüč鹊čÅąĮąĖčÅ bus-off ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖą╣ ą▓čģąŠą┤ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ bus active.

0: ą┐ąŠčüą╗ąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐čĆąŠčåąĄą┤čāčĆčŗ ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖčÅ ąĖąĘ čüąŠčüč鹊čÅąĮąĖčÅ bus-off ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą▓čģąŠą┤ ą▓ čĆąĄąČąĖą╝ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ.

DNM - DeviceNet Mode.

ąĢčüą╗ąĖ čĆą░ąĘčĆąĄčłąĄąĮąŠ, č鹊 ąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ čäąĖą╗čīčéčĆą░čåąĖčÅ ą┐čĆąĖąĄą╝ą░ (acceptance filtering) ą┐ąŠčüą╗ąĄ ą┐ąŠą╗čāč湥ąĮąĖčÅ ą┐ąĄčĆą▓ąŠą│ąŠ ą▒ąĖčéą░ CRC, ąĖą╗ąĖ ą┐ąŠčüą╗ąĄ ą┐ąĄčĆą▓ąŠą│ąŠ ą┐čĆąĖąĮčÅč鹊ą│ąŠ ą▒ąĖčéą░ DLC.

1: čĆą░ąĘčĆąĄčłąĄąĮ DeviceNet mode (čäąĖą╗čīčéčĆą░čåąĖčÅ ą┐ąŠ ą▒ą░ą╣čéą░ą╝ ą┤ą░ąĮąĮčŗčģ). ąæąĖčéčŗ FDF ąĖ FMD ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_AMxxH ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčé čäčāąĮą║čåąĖąŠąĮą░ą╗ čĆąĄąČąĖą╝ą░ DeviceNet. ąĪą╝. ą┤ą░ą╗ąĄąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆąŠą▓ CAN Acceptance Mask (CAN_AMxx).

0: čüčéą░ąĮą┤ą░čĆčéąĮą░čÅ čäąĖą╗čīčéčĆą░čåąĖčÅ čüąŠąŠą▒čēąĄąĮąĖą╣ (acceptance filtering), ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄą╝ą░čÅ č鹊ą╗čīą║ąŠ ą┐ąŠ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆčā.

SRS - Software Reset.

ąŁč鹊čé ą▒ąĖčé čĆąĄą│ąĖčüčéčĆą░ ą▓čüąĄą│ą┤ą░ čćąĖčéą░ąĄčéčüčÅ ą║ą░ą║ 0.

1: ąĖąĮąĖčåąĖąĖčĆčāąĄčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čüą▒čĆąŠčü. ąÆčüąĄ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ ą▒ąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ čāčüčéą░ąĮąŠą▓čÅčéčüčÅ ą▓ čüą▓ąŠąĖ ąĮą░čćą░ą╗čīąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ, ąĄčüą╗ąĖ ąĮąĄ čāą║ą░ąĘą░ąĮąŠ čćč鹊-č鹊 ą┤čĆčāą│ąŠąĄ ą▓ ąŠą┐ąĖčüą░ąĮąĖąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ čĆąĄą│ąĖčüčéčĆą░.

0: ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

ąĀąĄą│ąĖčüčéčĆ ą│ą╗ąŠą▒ą░ą╗čīąĮąŠą│ąŠ čüčéą░čéčāčüą░ (CAN_STATUS), ą┐ąŠą║ą░ąĘą░ąĮąĮčŗą╣ ąĮą░ čĆąĖčü. 19-3, ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé čüąĖą│ąĮą░ą╗čŗ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čüąŠčüč鹊čÅąĮąĖčÅ. ąŁč鹊čé čĆąĄą│ąĖčüčéčĆ ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ (RO). ąŚą░ą┐ąĖčüčī ą▓ čĆąĄą│ąĖčüčéčĆ CAN_STATUS ąĮąĄ ą┤ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

ąĀąĖčü. 19-3. Global Status Register (RO, č鹊ą╗čīą║ąŠ čćč鹥ąĮąĖąĄ).

ąØąĖąČąĄ ą┐čĆąĖą▓ąĄą┤ąĄąĮąŠ ąŠą┐ąĖčüą░ąĮąĖąĄ ą▒ąĖčé čĆąĄą│ąĖčüčéčĆą░ CAN_STATUS.

REC - Receive Mode.

1: čÅą┤čĆąŠ ą┐čĆąŠč鹊ą║ąŠą╗ą░ CAN ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ ą┐čĆąĖąĄą╝ą░.

0: čÅą┤čĆąŠ ą┐čĆąŠč鹊ą║ąŠą╗ą░ CAN ąĮąĄ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ ą┐čĆąĖąĄą╝ą░.

RTM - Transmit Mode.

1: čÅą┤čĆąŠ ą┐čĆąŠč鹊ą║ąŠą╗ą░ CAN ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ.

0: čÅą┤čĆąŠ ą┐čĆąŠč鹊ą║ąŠą╗ą░ CAN ąĮąĄ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ.

MBPTR - Mail Box Pointer.

ą¤čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé ąĮąŠą╝ąĄčĆ mailbox č鹥ą║čāčēąĄą│ąŠ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ąŠą│ąŠ čüąŠąŠą▒čēąĄąĮąĖčÅ. ą¤ąŠčüą╗ąĄ čāčüą┐ąĄčłąĮąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ čŹčéąĖ ą▒ąĖčéčŗ ąŠčüčéą░čÄčéčüčÅ ąĮąĄ ąĖąĘą╝ąĄąĮąĄąĮąĮčŗą╝ąĖ.

11111: čüąĄą╣čćą░čü ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčéčüčÅ čüąŠąŠą▒čēąĄąĮąĖąĄ ą▓ mailbox 31.

...

...

00000: čüąĄą╣čćą░čü ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčéčüčÅ čüąŠąŠą▒čēąĄąĮąĖąĄ ą▓ mailbox 0.

CCA - CAN Configuration Mode Acknowledge.

1: čÅą┤čĆąŠ ą┐čĆąŠč鹊ą║ąŠą╗ą░ CAN ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ.

0: čÅą┤čĆąŠ ą┐čĆąŠč鹊ą║ąŠą╗ą░ CAN ąĮąĄ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ.

CSA - CAN Suspend Mode Acknowledge.

1: čÅą┤čĆąŠ ą┐čĆąŠč鹊ą║ąŠą╗ą░ CAN ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ suspend mode.

0: čÅą┤čĆąŠ ą┐čĆąŠč鹊ą║ąŠą╗ą░ CAN ąĮąĄ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ suspend mode.

SMA - Sleep Mode Acknowledge.

ąæąĖčé SMA ą▓čüąĄą│ą┤ą░ čćąĖčéą░ąĄčéčüčÅ ą║ą░ą║ 0. ąĢčüą╗ąĖ ą╝ąŠą┤čāą╗čī CAN ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ sleep mode, čćč鹥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ CAN_STATUS ą▓ąŠąĘą▓čĆą░čéąĖčé čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ čĆąĄą│ąĖčüčéčĆą░ CAN_INTR.

1: ą╝ąŠą┤čāą╗čī ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ sleep mode. ąÆčüąĄ čéą░ą║čéčŗ ą▓čŗą║ą╗čÄč湥ąĮčŗ.

0: ą╝ąŠą┤čāą╗čī ąĮąĄ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ sleep mode.

EBO - CAN Error Bus-Off Mode.

1: čüč湥čéčćąĖą║ ąŠčłąĖą▒ąŠą║ ą┐ąĄčĆąĄą┤ą░čćąĖ TXECNT ą┤ąŠčüčéąĖą│ ą┐čĆąĄą┤ąĄą╗ą░ ąŠčéą║ą╗čÄč湥ąĮąĖčÅ ąŠčé čłąĖąĮčŗ 256 (bus-off limit).

0: ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░ ąŠčłąĖą▒ąŠą║ ą┐ąĄčĆąĄą┤ą░čćąĖ TXECNT ą╝ąĄąĮčīčłąĄ 256.

EP - CAN Error Passive Mode.

1: ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ąŠą┤ąĖąĮ ąĖąĘ čüč湥čéčćąĖą║ąŠą▓ ąŠčłąĖą▒ąŠą║ (RXECNT ąĖ TXECNT) ą┤ąŠčüčéąĖą│ ą┐ą░čüčüąĖą▓ąĮąŠą│ąŠ čāčĆąŠą▓ąĮčÅ ąŠčłąĖą▒ąŠą║ 128.

0: ąĘąĮą░č湥ąĮąĖąĄ ąŠą▒ąŠąĖčģ čüč湥čéčćąĖą║ąŠą▓ ąŠčłąĖą▒ąŠą║ (RXECNT ąĖ TXECNT) ąĮąĖąČąĄ 128.

WR - CAN Receive Warning Flag.

1: ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░ ąŠčłąĖą▒ąŠą║ ą┐čĆąĖąĄą╝ą░ (RXECNT) ą┤ąŠčüčéąĖą│ ą┐čĆąĄą┤ąĄą╗ą░ ą┐čĆąĄą┤čāą┐čĆąĄąČą┤ąĄąĮąĖčÅ (warning limit).

0: ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░ ąŠčłąĖą▒ąŠą║ ą┐čĆąĖąĄą╝ą░ (RXECNT) ąĮąĖąČąĄ ą┐čĆąĄą┤ąĄą╗ą░ ą┐čĆąĄą┤čāą┐čĆąĄąČą┤ąĄąĮąĖčÅ (warning limit).

WT - CAN Transmit Warning Flag.

1: ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░ ąŠčłąĖą▒ąŠą║ ą┐ąĄčĆąĄą┤ą░čćąĖ (TXECNT) ą┤ąŠčüčéąĖą│ ą┐čĆąĄą┤ąĄą╗ą░ ą┐čĆąĄą┤čāą┐čĆąĄąČą┤ąĄąĮąĖčÅ (warning limit).

0: ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░ ąŠčłąĖą▒ąŠą║ ą┐ąĄčĆąĄą┤ą░čćąĖ (TXECNT) ąĮąĖąČąĄ ą┐čĆąĄą┤ąĄą╗ą░ ą┐čĆąĄą┤čāą┐čĆąĄąČą┤ąĄąĮąĖčÅ (warning limit).

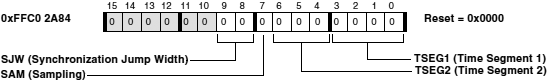

ąĀąĄą│ąĖčüčéčĆ CAN_CLOCK (čĆąĖčü. 19-4) ąĮąĄ ą│ąĄąĮąĄčĆąĖčĆčāąĄčé čüą░ą╝ ą┐ąŠ čüąĄą▒ąĄ ąĖąĮč鹥čĆą▓ą░ą╗čŗ ą▒ąĖčé CAN. ą×ąĮ ąĘą░ą┤ą░ąĄčé ą║ą▓ą░ąĮčé ą▓čĆąĄą╝ąĄąĮąĖ ą▒ąĖčéą░ (time quantum, TQ), č乊čĆą╝ąĖčĆčāąĄą╝čŗą╣ ąĖąĘ čćą░čüč鹊čéčŗ čüąĖčüč鹥ą╝ąĮąŠą╣ čłąĖąĮčŗ (SCLK). ąśąĘ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ą║ą▓ą░ąĮč鹊ą▓ ą▓čĆąĄą╝ąĄąĮąĖ č乊čĆą╝ąĖčĆčāąĄčéčüčÅ ą▒ąĖčé CAN, čćč鹊 čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ čĆąĄą│ąĖčüčéčĆąŠą╝ CAN_TIMING.

ąĀąĖčü. 19-4. CAN Clock Register.

ąÜą▓ą░ąĮčé ą▓čĆąĄą╝ąĄąĮąĖ ą▓čŗčćąĖčüą╗čÅąĄčéčüčÅ ą┐ąŠ č乊čĆą╝čāą╗ąĄ:

TQ = (BRP + 1)/SCLK

BRP. ąźąŠčéčÅ ą┐ąŠą╗ąĄ BRP ą╝ąŠąČąĮąŠ čāčüčéą░ąĮąŠą▓ąĖčéčī ą▓ ą╗čÄą▒ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ, ąŠą┤ąĮą░ą║ąŠ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ, čćč鹊ą▒čŗ ąŠąĮąŠ ą▒čŗą╗ąŠ ą▒ąŠą╗čīčłąĄ ąĖą╗ąĖ čĆą░ą▓ąĮąŠ 4. ąÜąŠą│ą┤ą░ BRP < 4, ąĮą░ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÄ čéą░ą╣ą╝ąĖąĮą│ą░ ą▒ąĖčéą░ ąĮą░ą║ą╗ą░ą┤čŗą▓ą░čÄčéčüčÅ ąŠą│čĆą░ąĮąĖč湥ąĮąĖčÅ.

ąÆčüąĄ čāąĘą╗čŗ čłąĖąĮčŗ CAN ą┤ąŠą╗ąČąĮčŗ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ąŠą┤ąĖąĮą░ą║ąŠą▓čāčÄ čüą║ąŠčĆąŠčüčéčī ą▒ąĖčé (bit rate, ą▒ąĖčéčĆąĄą╣čé).

ąØąĄ ą╝ąŠą┤ąĖčäąĖčåąĖčĆčāą╣č鹥 čĆąĄą│ąĖčüčéčĆ CAN_CLOCK ą▓ąŠ ą▓čĆąĄą╝čÅ ąĮąŠčĆą╝ą░ą╗čīąĮąŠą╣ čĆą░ą▒ąŠčéčŗ ąĖąĮč鹥čĆč乥ą╣čüą░ CAN (CCA == 0). ąöą╗čÅ čŹč鹊ą╣ čåąĄą╗ąĖ ą▓čüąĄą│ą┤ą░ ą▓čģąŠą┤ąĖč鹥 ą▓ čĆąĄąČąĖą╝ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ (CCR == 1, CCA == 1). ąŚą░ą┐ąĖčüąĖ ą▓ čŹč鹊čé čĆąĄą│ąĖčüčéčĆ ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░čÄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░, ą║ąŠą│ą┤ą░ ą╝ąŠą┤čāą╗čī CAN ąĮąĄ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ.

ą¤čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čüą▒čĆąŠčü ąĮąĄ ą▓ą╗ąĖčÅąĄčé ąĮą░ čŹč鹊čé čĆąĄą│ąĖčüčéčĆ (ą┐ąŠčüą╗ąĄ ąĮąĄą│ąŠ ą▓čüąĄ ąĘąĮą░č湥ąĮąĖčÅ ąŠčüčéą░čÄčéčüčÅ ąĮąĄąĖąĘą╝ąĄąĮąĮčŗą╝ąĖ).

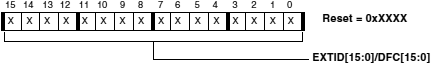

ąØą░ ąŠčüąĮąŠą▓ąĄ ą║ą▓ą░ąĮčéą░ ą▓čĆąĄą╝ąĄąĮąĖ (time quantum, TQ) ą│ąĄąĮąĄčĆąĖčĆčāąĄą╝ąŠą│ąŠ ą┐čĆąĄčüą║ą░ą╗ąĄčĆąŠą╝ BRP ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_CLOCK, čĆąĄą│ąĖčüčéčĆ CAN_TIMING (čĆąĖčü. 19-5) čāą┐čĆą░ą▓ą╗čÅąĄčé ąĮąŠą╝ąĖąĮą░ą╗čīąĮčŗą╝ ą▓čĆąĄą╝ąĄąĮąĄą╝ ą▒ąĖčéą░ ąĖ č鹊čćą║ąŠą╣ ą▓čŗą▒ąŠčĆą║ąĖ ąŠčéą┤ąĄą╗čīąĮčŗčģ ą▒ąĖčé ą▓ ą┐čĆąŠč鹊ą║ąŠą╗ąĄ CAN.

ąĀąĖčü. 19-5. CAN Timing Register (RO, č鹊ą╗čīą║ąŠ čćč鹥ąĮąĖąĄ).

ąĀąĖčü. 19-6 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé 3 čäą░ąĘčŗ ą▒ąĖčéą░ CAN: čüąĄą│ą╝ąĄąĮčé čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ, čüąĄą│ą╝ąĄąĮčé ą┐ąĄčĆąĄą┤ č鹊čćą║ąŠą╣ ą▓čŗą▒ąŠčĆą║ąĖ čāčĆąŠą▓ąĮčÅ (sample point) ąĖ čüąĄą│ą╝ąĄąĮčé ą┐ąŠčüą╗ąĄ č鹊čćą║ąĖ ą▓čŗą▒ąŠčĆą║ąĖ čāčĆąŠą▓ąĮčÅ.

ąĀąĖčü. 19-6. ąóčĆąĖ čäą░ąĘčŗ ą▒ąĖčéą░ CAN.

ąĪąĄą│ą╝ąĄąĮčé čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ąĘą░čäąĖą║čüąĖčĆąŠą▓ą░ąĮ ąĮą░ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéąĖ ąŠą┤ąĮąŠą│ąŠ ą║ą▓ą░ąĮčéą░ TQ. ą×ąĮ čéčĆąĄą▒čāąĄčéčüčÅ ą┤ą╗čÅ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ čāąĘą╗ąŠą▓ ąĮą░ čłąĖąĮąĄ. ąÆčüąĄ ą┐ąĄčĆąĄą┐ą░ą┤čŗ čāčĆąŠą▓ąĮčÅ čüąĖą│ąĮą░ą╗ą░ ąŠąČąĖą┤ą░čÄčéčüčÅ ą▓ ą┐čĆąĄą┤ąĄą╗ą░čģ čŹč鹊ą│ąŠ čüąĄą│ą╝ąĄąĮčéą░.

TSEG1, TSEG2. ą¤ąŠą╗čÅ TSEG1 ąĖ TSEG2 ąĘą░ą┤ą░čÄčé ąĖąĘ čüą║ąŠą╗čīą║ąĖčģ TQ čüąŠčüč鹊ąĖčé ą▒ąĖčé CAN, čćč鹊 ą▓ą╗ąĖčÅąĄčé ąĮą░ čüą║ąŠčĆąŠčüčéčī CAN (bit rate). ąØąŠą╝ąĖąĮą░ą╗čīąĮąŠąĄ ą▓čĆąĄą╝čÅ ą▒ąĖčéą░ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą┐ąŠ č乊čĆą╝čāą╗ąĄ:

tBIT = TQ x (1 + (1 + TSEG1) + (1 + TSEG2))

ąöą╗čÅ ą▒ąĄąĘąŠą┐ą░čüąĮąŠą│ąŠ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĖąĄą╝ą░ ą▓ čäąĖąĘąĖč湥čüą║ąĖčģ čüąĄčéčÅčģ č鹊čćą║ą░ ą▓čŗą▒ąŠčĆą║ąĖ ą┤ą░ąĮąĮčŗčģ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ ą┐ąŠą╗ąĄą╝ TSEG1. ą¤ąŠą╗ąĄ TSEG2 čģčĆą░ąĮąĖčé ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą║ą▓ą░ąĮč鹊ą▓ TQ, ąĮąĄąŠą▒čģąŠą┤ąĖą╝čŗčģ ą┤ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą▓čĆąĄą╝ąĄąĮąĖ ą▒ąĖčéą░. ą¦ą░čüč鹊 čüą░ą╝ą░čÅ ą╗čāčćčłą░čÅ ąĮą░ą┤ąĄąČąĮąŠčüčéčī ą┤ąŠčüčéąĖą│ą░ąĄčéčüčÅ čü č鹊čćą║ą░ą╝ąĖ ą▓čŗą▒ąŠčĆą║ąĖ, ąĮą░čģąŠą┤čÅčēąĖą╝ąĖčüčÅ ą▓ ą▓ąĄčĆčģąĮąĄą╝ 80% ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ą▓čĆąĄą╝ąĄąĮąĖ ą▒ąĖčéą░. ąØąĄ ąĖčüą┐ąŠą╗čīąĘčāą╣č鹥 č鹊čćą║ąĖ ą▓čŗą▒ąŠčĆą║ąĖ ąĮąĖąČąĄ 50%. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, TSEG1 ą▓čüąĄą│ą┤ą░ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą▒ąŠą╗čīčłąĄ ąĖą╗ąĖ čĆą░ą▓ąĮąŠ TSEG2.

ą£ąŠą┤čāą╗čī CAN ą┐čĆąŠčåąĄčüčüąŠčĆą░ Blackfin ąĮąĄ ą┤ąĄą╗ą░ąĄčé čĆą░ąĘą╗ąĖčćąĖą╣ ą╝ąĄąČą┤čā čüąĄą│ą╝ąĄąĮč鹊ą╝ čĆą░čüą┐čĆąŠčüčéčĆą░ąĮąĄąĮąĖčÅ (propagation segment) ąĖ čüąĄą│ą╝ąĄąĮč鹊ą╝ čäą░ąĘčŗ 1 (phase segment 1), ą║ą░ą║ čŹč鹊 ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąŠ čüčéą░ąĮą┤ą░čĆč鹊ą╝. ąŚąĮą░č湥ąĮąĖąĄ TSEG1 ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮąŠ ą┐ąŠą║čĆčŗą▓ą░čéčī ąŠą▒ą░ čŹčéąĖčģ ąĖąĮč鹥čĆą▓ą░ą╗ą░ ą▓čĆąĄą╝ąĄąĮąĖ. ąŚąĮą░č湥ąĮąĖąĄ TSEG2 ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé čüąĄą│ą╝ąĄąĮčé čäą░ąĘčŗ 2 (phase segment 2).

SJW. ąĢčüą╗ąĖ ą╝ąŠą┤čāą╗čī CAN ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ą┐ąĄčĆąĄą┐ą░ą┤ recessive -> dominant ą▓ąĮąĄ čüąĄą│ą╝ąĄąĮčéą░ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ, č鹊 ąŠąĮ ą╝ąŠąČąĄčé ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą┐ąĄčĆąĄą╝ąĄčüčéąĖčéčī č鹊čćą║čā ą▓čŗą▒ąŠčĆą║ąĖ čéą░ą║, čćč鹊ą▒čŗ ą▒ąĖčé CAN ą▓čüąĄ ąĄčēąĄ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ą╗čüčÅ ą┐čĆą░ą▓ąĖą╗čīąĮąŠ. ą¤ąŠą╗ąĄ čüą║ą░čćą║ą░ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ (synchronization jump width, SJW) ąĘą░ą┤ą░ąĄčé ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą║ą▓ą░ąĮč鹊ą▓ TQ, ą┤ąŠą┐čāčüčéąĖą╝ąŠąĄ ą┤ą╗čÅ čéą░ą║ąŠą╣ ą┐ąŠą┐čŗčéą║ąĖ ą┐ąŠą▓č鹊čĆąĮąŠą╣ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ. ąŚąĮą░č湥ąĮąĖąĄ SJW ąĮąĄ ą┤ąŠą╗ąČąĮąŠ ą┐čĆąĄą▓čŗčłą░čéčī TSEG2 ąĖą╗ąĖ TSEG1:

SJW Ōēż TSEG2 Ōēż TSEG1

ąÆ ą┤ąŠą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ čŹč鹊ą╝čā čäčāąĮą┤ą░ą╝ąĄąĮčéą░ą╗čīąĮąŠą╝čā ą┐čĆą░ą▓ąĖą╗čā, ą┐ąŠą╗ąĄ TSEG2 čéą░ą║ąČąĄ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą▒ąŠą╗čīčłąĄ ąĖą╗ąĖ čĆą░ą▓ąĮąŠ ą▓čĆąĄą╝ąĄąĮąĖ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ąĖąĮč乊čĆą╝ą░čåąĖąĖ (information processing time, IPT). ąŁč鹊 ą▓čĆąĄą╝čÅ, čéčĆąĄą▒čāąĄą╝ąŠąĄ ą┤ą╗čÅ ą╗ąŠą│ąĖą║ąĖ, čćč鹊ą▒čŗ čüą┤ąĄą╗ą░čéčī ą▓čŗą▒ąŠčĆą║čā CANRX. ąØą░ ą╝ąŠą┤čāą╗ąĄ CAN ą┐čĆąŠčåąĄčüčüąŠčĆą░ Blackfin čŹč鹊 ą▓čĆąĄą╝čÅ čüąŠčüčéą░ą▓ą╗čÅąĄčé 3 čéą░ą║čéą░ SCLK. ą¤ąŠ čŹč鹊ą╣ ą┐čĆąĖčćąĖąĮąĄ TSEG2 ąĮąĄ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī čĆą░ą▓ąĮąŠ 0. ąĢčüą╗ąĖ ą┐čĆąĄčüą║ą░ą╗ąĄčĆ čéą░ą║č鹊ą▓ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 0, č鹊 TSEG2 ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą▒ąŠą╗čīčłąĄ ąĖą╗ąĖ čĆą░ą▓ąĮąŠ 3. ąĢčüą╗ąĖ ą┐čĆąĄčüą║ą░ą╗ąĄčĆ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1, ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ TSEG2 ą▒čāą┤ąĄčé 2.

SAM. ąĪ ąŠčćąĖčēąĄąĮąĮčŗą╝ ą▒ąĖč鹊ą╝ SAM čāčĆąŠą▓ąĄąĮčī CANRX ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ą┐ąŠčüą╗ąĄ ąĖčüč鹥č湥ąĮąĖčÅ TSEG1. ąĢčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé SAM, č鹊 ą┤ąĄą╗ą░ąĄčéčüčÅ čéčĆąŠą╣ąĮą░čÅ ą▓čŗą▒ąŠčĆą║ą░ ą▓čģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ čü čćą░čüč鹊č鹊ą╣ SCLK. ąĀąĄąĘčāą╗čīčéąĖčĆčāčÄčēąĄąĄ ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčéą░ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą┐ąŠ ą╝ą░ąČąŠčĆąĖčéą░čĆąĮąŠą╝čā ą┐čĆąĖąĮčåąĖą┐čā ąŠčé ąĘąĮą░č湥ąĮąĖą╣ čŹčéąĖčģ čéčĆąĄčģ ą▓čŗą▒ąŠčĆąŠą║. ąÆčüąĄą│ą┤ą░ ąŠčüčéą░ą▓ą╗čÅą╣č鹥 ą▒ąĖčé SAM ąŠčćąĖčēąĄąĮąĮčŗą╝, ąĄčüą╗ąĖ ąĘąĮą░č湥ąĮąĖąĄ BRP ą╝ąĄąĮčīčłąĄ 4.

ąØąĄ ą╝ąŠą┤ąĖčäąĖčåąĖčĆčāą╣č鹥 čŹč鹊čé čĆąĄą│ąĖčüčéčĆ ą▓ąŠ ą▓čĆąĄą╝čÅ ąĮąŠčĆą╝ą░ą╗čīąĮąŠą╣ čĆą░ą▒ąŠčéčŗ ą╝ąŠą┤čāą╗čÅ CAN. ąöą╗čÅ čŹč鹊ą╣ čåąĄą╗ąĖ ą▓čüąĄą│ą┤ą░ ą▓čģąŠą┤ąĖč鹥 ą▓ čĆąĄąČąĖą╝ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ. ąŚą░ą┐ąĖčüčī ą▓ čŹč鹊čé čĆąĄą│ąĖčüčéčĆ ąĮąĄ ą┤ą░ąĄčé čŹčäč乥ą║čéą░, ąĄčüą╗ąĖ ą╝ąŠą┤čāą╗čī CAN ąĮąĄ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ.

ą¤čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čüą▒čĆąŠčü ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą▓ą╗ąĖčÅąĮąĖčÅ ąĮą░ čŹč鹊čé čĆąĄą│ąĖčüčéčĆ (ą┐ąŠčüą╗ąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čüą▒čĆąŠčüą░ ą▓čüąĄ ąĘąĮą░č湥ąĮąĖčÅ ą▓ ąĮąĄą╝ ąŠčüčéą░čÄčéčüčÅ ąĮąĄąĖąĘą╝ąĄąĮąĮčŗą╝ąĖ).

ąØąĖąČąĄ ą┤ą░ąĮ ą┐čĆąĖą╝ąĄčĆ ąĮą░čüčéčĆąŠą╣ą║ąĖ čĆąĄą│ąĖčüčéčĆąŠą▓ CAN_CONTROL ąĖ CAN_TIMING ą┤ą╗čÅ čćą░čüč鹊čéčŗ čłąĖąĮčŗ SCLK=50 ą£ąōčå. ążčāąĮą║čåąĖčÅ Init_CAN_Timing ą┐čĆąĖąĮąĖą╝ą░ąĄčé ą┐ą░čĆą░ą╝ąĄčéčĆ speed, ą│ą┤ąĄ čāą║ą░ąĘą░ąĮą░ čüą║ąŠčĆąŠčüčéčī ą▓ ą║ąĖą╗ąŠą▒ąĖčéą░čģ/čüąĄą║. ąŚąĮą░č湥ąĮąĖąĄ speed ą╝ąŠąČąĄčé ą┐čĆąĖąĮąĖą╝ą░čéčī ąĘąĮą░č湥ąĮąĖąĄ ąĖąĘ čĆčÅą┤ą░ čüą║ą░ąĮą┤ą░čĆčéąĮčŗčģ čüą║ąŠčĆąŠčüč鹥ą╣ 1000, 800, 500, 250, 125, 100, 50, 20, 10 ą║ąĖą╗ąŠą▒ąĖčé/čüąĄą║.

typedef struct

{

u16 speed; // ąĪą║ąŠčĆąŠčüčéčī, ą║ąĖą╗ąŠą▒ąĖčé/čüąĄą║.

u16 can_clock; // ąŚąĮą░č湥ąĮąĖąĄ ą┤ą╗čÅ čĆąĄą│ąĖčüčéčĆą░ CAN_CLOCK.

u16 can_timing; // ąŚąĮą░č湥ąĮąĖąĄ ą┤ą╗čÅ čĆąĄą│ąĖčüčéčĆą░ CAN_TIMING.

}TCanParam;

// ąóą░ą▒ą╗ąĖčåą░ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓ ą┤ą╗čÅ čüčéą░ąĮą┤ą░čĆčéąĮčŗčģ čüą║ąŠčĆąŠčüč鹥ą╣ CAN ąĖ čćą░čüč鹊čéčŗ SCLK = 50 ą£ąōčå,

// ą▓čŗčćąĖčüą╗ąĄąĮąĮą░čÅ ąĮą░ čĆąĄčüčāčĆčüąĄ http://www.bittiming.can-wiki.info/ [5]:

static const TCanParam canparam [] =

{

{1000, 0x0004, 0x0007}, //Sample Point 90%

{ 800, 0, 0},

{ 500, 0x0009, 0x0007}, //Sample Point 90%

{ 250, 0x0013, 0x0007}, //Sample Point 90%

//{ 250, 0x0018, 0x0005}, //Sample Point 87.5%

//{ 125, 0x0018, 0x001C}, //Sample Point 90%

{ 125, 0x0027, 0x0007}, //Sample Point 90%

//{ 125, 0x0031, 0x0005}, //Sample Point 87.5%

{ 100, 0x0031, 0x0007}, //Sample Point 90%

{ 50, 0x0063, 0x0007}, //Sample Point 90%

//{ 50, 0x007C, 0x0005}, //Sample Point 87.5%

//{ 25, 0x007C, 0x001C}, //Sample Point 87.5%

{ 25, 0x00C7, 0x0007}, //Sample Point 90%

//{ 25, 0x00F9, 0x0005}, //Sample Point 87.5%

{ 20, 0x00F9, 0x0007}, //Sample Point 90%

{ 10, 0x01F3, 0x0007}, //Sample Point 90%

//{ 10, 0x0270, 0x0005}, //Sample Point 87.5%

{ 0, 0, 0}

};

/*********************************************************************************

** ążčāąĮą║čåąĖčÅ Init_CAN_Timing - ąĮą░čüčéčĆą░ąĖą▓ą░ąĄčé čĆąĄą│ąĖčüčéčĆčŗ CAN_TIMING ąĖ CAN_CLOCK. **

** ą¤čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮąĮčŗąĄ ą║ąŠą╝ą╝ąĄąĮčéą░čĆąĖąĖ ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčé, ą║ą░ą║ ą▓čŗčćąĖčüą╗ąĖčéčī ą┐ąŠą╗ąĄ BRP ą┐ąŠ ąĖąĘą▓ąĄčüčéąĮąŠą╣ **

** čćą░čüč鹊č鹥 SCLK value (ą┐ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. ą│ą╗ą░ą▓čā CAN ą▓ ą░ą┐ą┐ą░čĆą░čéąĮąŠą╝ čĆčāą║ąŠą▓ąŠą┤čüčéą▓ąĄ). **

** ąÆąĄčĆąĮąĄčé false, ąĄčüą╗ąĖ speed (čāą║ą░ąĘą░ąĮą░ ą▓ ą║ąĖą╗ąŠą▒ąĖčéą░čģ/čüąĄą║) ąĮąĄ ąĮą░ą╣ą┤ąĄąĮą░ ą▓ čéą░ą▒ą╗ąĖčåąĄ **

** čüčéą░ąĮą┤ą░čĆčéąĮčŗčģ čćą░čüč鹊čé canparam. **

*********************************************************************************/

static bool Init_CAN_Timing(u16 speed)

{

// ąÆčģąŠą┤ ą▓ čĆąĄąČąĖą╝ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ CAN (čāčüčéą░ąĮąŠą▓ą║ą░ CCR):

*pCAN_CONTROL = CCR;

while(0 == (*pCAN_STATUS & CCA))

{

// ą”ąĖą║ą╗ ąŠąČąĖą┤ą░ąĮąĖčÅ ą▓čģąŠą┤ą░ ą▓ čĆąĄąČąĖą╝ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ.

ssync();

}

/* ===================================================

* ą¤ą░čĆą░ą╝ąĄčéčĆčŗ ą▓čĆąĄą╝ąĄąĮąĖ ą▒ąĖčéą░, ą┐čĆąĖą╝ąĄčĆ čĆą░čüč湥čéą░:

*

* CAN_TIMING : SJW = 3, TSEG2 = 3, TSEG1 = 4

* SJW <= TSEG2 <= TSEG1

* ===================================================

* CAN_CLOCK : ą┐čĆąĄčüą║ą░ą╗ąĄčĆ (BRP)

* ===================================================

* ąöą╗čÅ 500 ą║ąōčå CAN Clock :: tBIT = 2 ą╝ą║čü

* ===================================================

* tBIT = TQ * (1 + (TSEG1 + 1) + (TSEG2 + 1))

* 2e-6 = TQ * (1 + 5 + 4) * TQ = 2e-7

*

* TQ = (BRP+1) / SCLK

* 2e-7 = (BRP+1) / 112.5e6

* (BRP+1) = 22.5

* BRP = 21.5 = ~22 = CAN_CLOCK

* ==================================================*/

int idx = 0;

bool result = false;

while (canparam[idx].speed)

{

if (canparam[idx].speed == speed)

{

*pCAN_TIMING = canparam[idx].can_timing;

*pCAN_CLOCK = canparam[idx].can_clock;

ssync();

result = true;

break;

}

idx++;

}

// ąÆčŗčģąŠą┤ ąĖąĘ čĆąĄąČąĖą╝ą░ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ CAN (ąŠčćąĖčüčéą║ą░ CCR):

*pCAN_CONTROL = 0;

while(*pCAN_STATUS & CCA)

{

// ą”ąĖą║ą╗ ąŠąČąĖą┤ą░ąĮąĖčÅ ą▓čŗčģąŠą┤ą░ ąĖąĘ čĆąĄąČąĖą╝ą░ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ.

ssync();

}

return result;

}

ą¤ąŠčüą╗ąĄ ą▓čŗąĘąŠą▓ą░ Init_CAN_Timing ąŠčüčéą░ąĮąĄčéčüčÅ ąĮą░čüčéčĆąŠąĖčéčī čÅčēąĖą║ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖ ą┐čĆąĖąĄą╝ą░ ąĖ (ą┐čĆąĖ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéąĖ) ąŠą▒čĆą░ą▒ąŠčéą║čā ąĖčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ (ąŠą▒ čŹč鹊ą╝ ą┤ą░ą╗ąĄąĄ), ąĖ ą╝ąŠą┤čāą╗čī CAN ą┐ąŠą╗ąĮąŠčüčéčīčÄ ą│ąŠč鹊ą▓ ą║ čĆą░ą▒ąŠč鹥.

ąÆ ą╝ąŠą┤čāą╗ąĄ CAN ąĄčüčéčī č鹥čüč鹊ą▓čŗą╣ čĆąĄąČąĖą╝, ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮąĮčŗą╣ ą┤ą╗čÅ ąŠčéą╗ą░ą┤ą║ąĖ ą¤ą× ąĖ čüąĖčüč鹥ą╝čŗ CAN. ąØąĖąČąĄ ą▓ ą╗ąĖčüčéąĖąĮą│ąĄ 19-1 ą┐čĆąĖą▓ąĄą┤ąĄąĮ ą┐čĆąĖą╝ąĄčĆ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ čäčāąĮą║čåąĖąĖ ąŠčéą╗ą░ą┤ą║ąĖ CAN.

ą¤čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ čŹč鹊ą╣ čäčāąĮą║čåąĖąĖ ą╝ąŠą┤čāą╗čī CAN ą╝ąŠąČąĄčé ą▒čŗčéčī ąĮąĄ čüąŠą▓ą╝ąĄčüčéąĖą╝ čüąŠ čüą┐ąĄčåąĖčäąĖą║ą░čåąĖąĄą╣ CAN. ąÆčüąĄ č鹥čüč鹊ą▓čŗąĄ čĆąĄąČąĖą╝čŗ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮčŗ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčēąĄąĮčŗ č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ ą╝ąŠą┤čāą╗čī ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ (CCA=1 ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_STATUS) ąĖą╗ąĖ ą▓ čĆąĄąČąĖą╝ąĄ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ąĖ (suspend mode, CSA = 1 ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_STATUS).

CDE. ąæąĖčé CDE ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ą┤ąŠčüčéčāą┐ą░ ą║ąŠ ą▓čüąĄą╝ čäčāąĮą║čåąĖčÅą╝ ąŠčéą╗ą░ą┤ą║ąĖ. ąŁč鹊čé ą▒ąĖčé ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą┤ą╗čÅ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ č鹥čüč鹊ą▓ąŠą│ąŠ čĆąĄąČąĖą╝ą░, ąĖ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮ ą┐ąĄčĆąĄą┤ ą┐ąŠčüą╗ąĄą┤čāčÄčēąĖą╝ąĖ ąĘą░ą┐ąĖčüčÅą╝ąĖ ą▓ čĆąĄą│ąĖčüčéčĆ CAN_DEBUG. ąÜąŠą│ą┤ą░ ą▒ąĖčé CDE ąŠčćąĖčēąĄąĮ, ą▓čüąĄ čäčāąĮą║čåąĖąĖ ąŠčéą╗ą░ą┤ą║ąĖ ąĘą░ą┐čĆąĄčēąĄąĮčŗ.

ąøąĖčüčéąĖąĮą│ 19-1. ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ čäčāąĮą║čåąĖą╣ ąŠčéą╗ą░ą┤ą║ąĖ (CAN Debug) ąĮą░ čÅąĘčŗą║ąĄ C:

#include < cdefBF538.h>

/* ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ debug mode, CDE ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą┐ąĄčĆąĄą┤ č鹥ą╝,

ą║ą░ą║ ą╝ąŠą│čāčé ą▒čŗčéčī ą╝ąŠą┤ąĖčäąĖčåąĖčĆąŠą▓ą░ąĮčŗ ą┤čĆčāą│ąĖąĄ čäą╗ą░ą│ąĖ ą▓ čĆąĄą│ąĖčüčéčĆąĄ: */

*pCAN_DEBUG |= CDE;

/* ąŻčüčéą░ąĮąŠą▓ą║ą░ čäą╗ą░ą│ąŠą▓ ąŠčéą╗ą░ą┤ą║ąĖ: */

*pCAN_DEBUG &= ~DTO;

*pCAN_DEBUG |= MRB | MAA | DIL;

/* ąŚą░ą┐čāčüą║ ą║ąŠą┤ą░ ą▓ č鹥čüč鹊ą▓ąŠą╝ čĆąĄąČąĖą╝ąĄ: */

...

/* ąŚą░ą┐čĆąĄčé debug mode: */

*pCAN_DEBUG &= ~CDE;

ąÜąŠą│ą┤ą░ ą▒ąĖčé CDE čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, č鹊 čĆą░ąĘčĆąĄčłąĄąĮčŗ ąĘą░ą┐ąĖčüąĖ ą▓ ą┤čĆčāą│ąĖąĄ ą▒ąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ CAN_DEBUG. ąŁč鹊 čéą░ą║ąČąĄ čĆą░ąĘčĆąĄčłą░ąĄčé čäčāąĮą║čåąĖąĖ, ąĮąĄ čüąŠą▓ą╝ąĄčüčéąĖą╝čŗąĄ čüąŠ čüčéą░ąĮą┤ą░čĆč鹊ą╝ CAN:

ŌĆó ąĀąĄą│ąĖčüčéčĆčŗ čéą░ą╣ą╝ąĖąĮą│ą░ ą▒ąĖčé ą╝ąŠąČąĮąŠ ą┐ąŠą╝ąĄąĮčÅčéčī ą▓ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé, ąĮąĄ č鹊ą╗čīą║ąŠ ą▓ čĆąĄąČąĖą╝ąĄ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ. ąŁč鹊 ą▓ą║ą╗čÄčćą░ąĄčé čĆąĄą│ąĖčüčéčĆčŗ CAN_CLOCK ąĖ CAN_TIMING.

ŌĆó ąöąŠą┐čāčüą║ą░ąĄčéčüčÅ ąĘą░ą┐ąĖčüčī ą▓ ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮąĮčŗą╣ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆ ąŠčłąĖą▒ąŠą║ ą┐ąĄčĆąĄą┤ą░čćąĖ/ą┐čĆąĖąĄą╝ą░ CAN_CEC.

MRB. ąæąĖčé ąŠą▒čĆą░čéąĮąŠą│ąŠ čćč鹥ąĮąĖčÅ čĆąĄąČąĖą╝ą░ (mode read back, MRB) ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ read back mode. ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ čüąŠąŠą▒čēąĄąĮąĖąĄ, ą┐ąĄčĆąĄą┤ą░ąĮąĮąŠąĄ ą┐ąŠ čłąĖąĮąĄ CAN (ąĖą╗ąĖ č湥čĆąĄąĘ ą▓ąĮčāčéčĆąĄąĮąĮčÄčÄ ą┐ąĄčéą╗čÄ ąĘą░čåąĖą║ą╗ąĖą▓ą░ąĮąĖčÅ ą▓čŗčģąŠą┤ą░ ąĮą░ ą▓čģąŠą┤, čĆąĄąČąĖą╝ internal loop back) ą┐čĆąĖąĮąĖą╝ą░ąĄčéčüčÅ ąŠą▒čĆą░čéąĮąŠ ąĮą░ą┐čĆčÅą╝čāčÄ ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ ą▒čāč乥čĆ ą┐čĆąĖąĄą╝ą░. ą¤ąŠčüą╗ąĄ ą║ąŠčĆčĆąĄą║čéąĮąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ ą╗ąŠą│ąĖą║ą░ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčé ąĄą│ąŠ ą║ą░ą║ ąĮąŠčĆą╝ą░ą╗čīąĮąŠ ą┐čĆąĖąĮčÅč鹊ąĄ čüąŠąŠą▒čēąĄąĮąĖąĄ. ąŁčéą░ čäčāąĮą║čåąĖčÅ ą┤ą░ąĄčé ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą┐čĆąŠč鹥čüčéąĖčĆąŠą▓ą░čéčī čäčāąĮą║čåąĖąĖ CAN ą▒ąĄąĘ ą▓ąĮąĄčłąĮąĖčģ čāčüčéčĆąŠą╣čüčéą▓ (ą▒ąĄąĘ ą▓ąĮąĄčłąĮąĄą│ąŠ čéčĆą░ąĮčüąĖą▓ąĄčĆą░ ąĖ ą▒ąĄąĘ ą▓ąĮąĄčłąĮąĄą│ąŠ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ą║ čäąĖąĘąĖč湥čüą║ąŠą╣ čüąĄčéąĖ CAN).

MAA. ąæąĖčé čĆąĄąČąĖą╝ą░ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą│ąŠ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ (mode auto acknowledge, MAA) ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą╝ąŠą┤čāą╗čÄ CAN ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī čüąŠą▒čüčéą▓ąĄąĮąĮąŠąĄ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖąĄ ą▓ąŠ ą▓čĆąĄą╝čÅ čüą╗ąŠčéą░ ACK čäčĆąĄą╣ą╝ą░ CAN. ąØąĄ čéčĆąĄą▒čāąĄčéčüčÅ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ą▓ąĮąĄčłąĮąĖčģ čāčüčéčĆąŠą╣čüčéą▓ ąĖą╗ąĖ ą▓ąĮąĄčłąĮąĖčģ čüąŠąĄą┤ąĖąĮąĄąĮąĖą╣, čćč鹊ą▒čŗ ą┐čĆąŠčćąĖčéą░čéčī ąŠą▒čĆą░čéąĮąŠ ą┐ąĄčĆąĄą┤ą░ąĮąĮąŠąĄ čüąŠąŠą▒čēąĄąĮąĖąĄ. ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ čüąŠąŠą▒čēąĄąĮąĖąĄ, ą║ąŠč鹊čĆąŠąĄ ąŠčéą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ, ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ čüąŠčģčĆą░ąĮčÅąĄčéčüčÅ ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ ą▒čāč乥čĆ ą┐čĆąĖąĄą╝ą░. ąÆ čĆąĄąČąĖą╝ąĄ auto acknowledge ą╝ąŠą┤čāą╗čī ą┐ąŠčüčŗą╗ą░ąĄčé ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖąĄ čüą░ą╝ čüąĄą▒ąĄ. ąŁč鹊 ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąŠ ą┐ąŠčÅą▓ą╗čÅčéčīčüčÅ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ CANTX, ąĄčüą╗ąĖ DIL=1 ąĖ DTO=0. ąĢčüą╗ąĖ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖąĄ ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī č鹊ą╗čīą║ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĄ, č鹊 čŹčéąĖ ą▒ąĖčéčŗ č鹥čüč鹊ą▓ąŠą│ąŠ čĆąĄąČąĖą╝ą░ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą▓ ąĘąĮą░č湥ąĮąĖčÅ DIL=0 ąĖ DTO=1.

DIL. ąæąĖčé ąĘą░ą┐čĆąĄčéą░ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ ąŠą▒čĆą░čéąĮąŠą╣ ą┐ąĄčéą╗ąĖ (disable internal loop, DIL) ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ č鹊ą│ąŠ, čćč鹊ą▒čŗ čĆą░ąĘčĆąĄčłąĖčéčī čüąŠąĄą┤ąĖąĮąĖčéčī ą▓ąĮčāčéčĆąĖ ą╝ąŠą┤čāą╗čÅ ą▓čŗčģąŠą┤ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ čüąŠ ą▓čģąŠą┤ąŠą╝ ą┐čĆąĖąĄą╝ąĮąĖą║ą░.

DTO. ąæąĖčé ąĘą░ą┐čĆąĄčéą░ ą▓čŗčģąŠą┤ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ (disable transmit output, DTO) ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ, čćč鹊ą▒čŗ ąĘą░ą┐čĆąĄčéąĖčéčī ą▓čŗčģąŠą┤ CANTX. ąÜąŠą│ą┤ą░ čŹč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ąĮą░ ą▓čŗą▓ąŠą┤ CANTX ą┐ąŠčüč鹊čÅąĮąĮąŠ ą▓čŗą▓ąŠą┤čÅčéčüčÅ čĆąĄčåąĄčüčüąĖą▓ąĮčŗąĄ ą▒ąĖčéčŗ.

DRI. ąæąĖčé ąĘą░ą┐čĆąĄčéą░ ą▓čģąŠą┤ą░ ą┐čĆąĖąĄą╝ą░ (disable receive input, DRI) ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ, čćč鹊ą▒čŗ ąĘą░ą┐čĆąĄčéąĖčéčī ą▓čģąŠą┤ CANRX. ąÜąŠą│ą┤ą░ čŹč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ ą╗ąŠą│ąĖą║ą░ ą┐čĆąĖąĮąĖą╝ą░ąĄčé čĆąĄčåąĄčüčüąĖą▓ąĮčŗąĄ ą▒ąĖčéčŗ, ąĖą╗ąĖ ą┐čĆąĖąĮąĖą╝ą░ąĄčé čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąĮąŠąĄ ą▓ąĮčāčéčĆąĖ ąĘąĮą░č湥ąĮąĖąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▓ čüą╗čāčćą░ąĄ, ą║ąŠą│ą┤ą░ čĆą░ąĘčĆąĄčłąĄąĮąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĄąĄ ąĘą░čåąĖą║ą╗ąĖą▓ą░ąĮąĖąĄ čü ą▓čŗčģąŠą┤ą░ ąĮą░ ą▓čģąŠą┤ (DIL=0). ąÆ ą╗čÄą▒ąŠą╝ čüą╗čāčćą░ąĄ čüąĖą│ąĮą░ą╗čŗ ąĮą░ ą▓čģąŠą┤ąĄ CANRX ąĖą│ąĮąŠčĆąĖčĆčāčÄčéčüčÅ.

DEC. ąæąĖčé ąĘą░ą┐čĆąĄčéą░ čüč湥čéčćąĖą║ąŠą▓ ąŠčłąĖą▒ąŠą║ (disable error counters, DEC) ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ąĘą░ą┐čĆąĄčéą░ čüč湥čéčćąĖą║ąŠą▓ ąŠčłąĖą▒ąŠą║ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖ ą┐čĆąĖąĄą╝ą░ ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_CEC. ąÜąŠą│ą┤ą░ čŹč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, CAN_CEC čģčĆą░ąĮąĖčé čüą▓ąŠąĖ č鹥ą║čāčēąĖąĄ ąĘąĮą░č湥ąĮąĖčÅ, ąĖ ąĮąĄ čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ ąĖąĮą║čĆąĄą╝ąĄąĮčé ąĖą╗ąĖ ą┤ąĄą║čĆąĄą╝ąĄąĮčé čüč湥čéčćąĖą║ąŠą▓ ąŠčłąĖą▒ąŠą║. ąŁč鹊čé čĆąĄąČąĖą╝ ąĮąĄ čāą┤ąŠą▓ą╗ąĄčéą▓ąŠčĆčÅąĄčé čüą┐ąĄčåąĖčäąĖą║ą░čåąĖąĖ CAN.

ąŚą░ą┐ąĖčüąĖ ą▓ čüč湥čéčćąĖą║ąĖ ąŠčłąĖą▒ąŠą║ ą┤ąŠą╗ąČąĮčŗ ąŠčüčāčēąĄčüčéą▓ą╗čÅčéčīčüčÅ č鹊ą╗čīą║ąŠ ą▓ debug mode. ąöąŠčüčéčāą┐ ąĮą░ ąĘą░ą┐ąĖčüčī ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐čĆąĖąĄą╝ą░ ą╝ąŠą│čāčé ą┐čĆąĖą▓ąĄčüčéąĖ ą║ ąĮąĄą┐čĆąĄą┤čüą║ą░ąĘčāąĄą╝čŗą╝ ąĘąĮą░č湥ąĮąĖčÅą╝. ą£ą░ą║čüąĖą╝ą░ą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ, ą║ąŠč鹊čĆąŠąĄ ą╝ąŠąČąĮąŠ ąĘą░ą┐ąĖčüą░čéčī ą▓ čüč湥čéčćąĖą║ąĖ ąŠčłąĖą▒ąŠą║, čĆą░ą▓ąĮąŠ 255. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░ ąŠčłąĖą▒ąŠą║ 256, ą║ąŠč鹊čĆąŠąĄ ą┐čĆąĖąĮčāą┤ąĖč鹥ą╗čīąĮąŠ ą┐ąĄčĆąĄą▓ąĄą┤ąĄčé ą╝ąŠą┤čāą╗čī CAN ą▓ čüąŠčüč鹊čÅąĮąĖąĄ bus-off, ąĮąĄą╗čīąĘčÅ ąĘą░ą┐ąĖčüą░čéčī ą▓ čüč湥čéčćąĖą║ąĖ ąŠčłąĖą▒ąŠą║.

ąóą░ą▒ą╗ąĖčåą░ 19-2 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąŠą▒čēąĖąĄ ą║ąŠą╝ą▒ąĖąĮą░čåąĖąĖ ą▒ąĖčé č鹥čüč鹊ą▓ąŠą│ąŠ čĆąĄąČąĖą╝ą░.

ąóą░ą▒ą╗ąĖčåą░ 19-2. ąóąĄčüč鹊ą▓čŗąĄ čĆąĄąČąĖą╝čŗ ą╝ąŠą┤čāą╗čÅ CAN.

| MRB |

MAA |

DIL |

DTO |

DRI |

CDE |

ążčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ |

| x |

x |

x |

x |

x |

0 |

ąØąŠčĆą╝ą░ą╗čīąĮčŗą╣ čĆąĄąČąĖą╝, ąĮąĄ čĆąĄąČąĖą╝ ąŠčéą╗ą░ą┤ą║ąĖ. |

| 0 |

x |

x |

x |

x |

x |

ąØąĄ čćąĖčéą░čéčī ąŠą▒čĆą░čéąĮąŠ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ąŠąĄ čüąŠąŠą▒čēąĄąĮąĖąĄ. |

| 1 |

0 |

1 |

0 |

0 |

1 |

ąØąŠčĆą╝ą░ą╗čīąĮą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░ ą┐ąŠ čłąĖąĮąĄ CAN. ą×ą▒čĆą░čéąĮąŠąĄ čćč鹥ąĮąĖąĄ. ąóčĆąĄą▒čāąĄčéčüčÅ ą▓ąĮąĄčłąĮąĄąĄ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖąĄ ąŠčé ą▓ąĮąĄčłąĮąĄą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░. |

| 1 |

1 |

1 |

0 |

0 |

1 |

ąØąŠčĆą╝ą░ą╗čīąĮą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░ ą┐ąŠ čłąĖąĮąĄ CAN. ą×ą▒čĆą░čéąĮąŠąĄ čćč鹥ąĮąĖąĄ. ąØąĄ čéčĆąĄą▒čāąĄčéčüčÅ ą▓ąĮąĄčłąĮąĄąĄ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖąĄ ąŠčé ą▓ąĮąĄčłąĮąĄą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░. ą¤ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ąŠąĄ čüąŠąŠą▒čēąĄąĮąĖąĄ ąĖ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖąĄ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą┐ąŠ čłąĖąĮąĄ CAN. ąĀą░ąĘčĆąĄčłąĄąĮ ą▓čģąŠą┤ CANRX. |

| 1 |

1 |

0 |

0 |

0 |

1 |

ąØąŠčĆą╝ą░ą╗čīąĮą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░ ą┐ąŠ čłąĖąĮąĄ CAN. ą×ą▒čĆą░čéąĮąŠąĄ čćč鹥ąĮąĖąĄ. ąØąĄ čéčĆąĄą▒čāąĄčéčüčÅ ą▓ąĮąĄčłąĮąĄąĄ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖąĄ ąŠčé ą▓ąĮąĄčłąĮąĄą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░. ą¤ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ąŠąĄ čüąŠąŠą▒čēąĄąĮąĖąĄ ąĖ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖąĄ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą┐ąŠ čłąĖąĮąĄ CAN. ąÆčģąŠą┤ CANRX ąĖ ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ ą┐ąĄčéą╗čÅ čü ą▓čŗčģąŠą┤ą░ ąĮą░ ą▓čģąŠą┤ čĆą░ąĘčĆąĄčłąĄąĮčŗ (ąŠą┐ąĄčĆą░čåąĖčÅ ąśąøąś ąĮą░ą┤ čüąĖą│ąĮą░ą╗ą░ą╝ąĖ TX ąĖ TX). |

| 1 |

1 |

0 |

0 |

1 |

1 |

ąØąŠčĆą╝ą░ą╗čīąĮą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░ ą┐ąŠ čłąĖąĮąĄ CAN. ą×ą▒čĆą░čéąĮąŠąĄ čćč鹥ąĮąĖąĄ. ąØąĄ čéčĆąĄą▒čāąĄčéčüčÅ ą▓ąĮąĄčłąĮąĄąĄ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖąĄ ąŠčé ą▓ąĮąĄčłąĮąĄą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░. ą¤ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ąŠąĄ čüąŠąŠą▒čēąĄąĮąĖąĄ ąĖ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖąĄ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą┐ąŠ čłąĖąĮąĄ CAN. ąÆčģąŠą┤ CANRX ąĖą│ąĮąŠčĆąĖčĆčāąĄčéčüčÅ. ąÆąĮčāčéčĆąĄąĮąĮčÅčÅ ą┐ąĄčéą╗čÅ čü ą▓čŗčģąŠą┤ą░ ąĮą░ ą▓čģąŠą┤ čĆą░ąĘčĆąĄčłąĄąĮą░. |

| 1 |

1 |

0 |

1 |

1 |

1 |

ąØąĄčé ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐ąŠ čłąĖąĮąĄ CAN. ą×ą▒čĆą░čéąĮąŠąĄ čćč鹥ąĮąĖąĄ. ąØąĄ čéčĆąĄą▒čāąĄčéčüčÅ ą▓ąĮąĄčłąĮąĄąĄ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖąĄ ąŠčé ą▓ąĮąĄčłąĮąĄą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░. ą¤ąŠ čłąĖąĮąĄ CAN ąĮąĄ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ąĮąĖ čüąŠąŠą▒čēąĄąĮąĖąĄ, ąĮąĖ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖąĄ. ąÆčģąŠą┤ CANRX ąĖą│ąĮąŠčĆąĖčĆčāąĄčéčüčÅ. ąÆąĮčāčéčĆąĄąĮąĮčÅčÅ ą┐ąĄčéą╗čÅ čü ą▓čŗčģąŠą┤ą░ ąĮą░ ą▓čģąŠą┤ čĆą░ąĘčĆąĄčłąĄąĮą░. |

[ąźčĆą░ąĮąĖą╗ąĖčēąĄ ą┤ą░ąĮąĮčŗčģ]

ąÆčüąĄ ąŠčéąĮąŠčüčÅčēąĖąĄčüčÅ ą║ CAN ą┤ą░ąĮąĮčŗąĄ čüąŠčģčĆą░ąĮčÅčÄčéčüčÅ ą▓ mailbox RAM. ąŚą┤ąĄčüčī ąĄčüčéčī ą▓ąŠčüąĄą╝čī 16-ą▒ąĖčéąĮčŗčģ čüą╗ąŠą▓ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ąĖąĘ 32 mailbox.

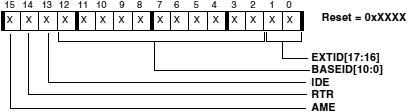

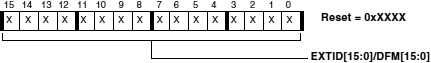

ąŚąĮą░č湥ąĮąĖčÅ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆą░ (ą▒ą░ąĘąŠą▓ą░čÅ ąĖ čĆą░čüčłąĖčĆąĄąĮąĮą░čÅ čćą░čüčéčī), ą▒ąĖčé čĆą░čüčłąĖčĆąĄąĮąĖčÅ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆą░ (identifier extension, IDE), ą▒ąĖčé ąĘą░ą┐čĆąŠčüą░ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ą╗čīąĮąĄą│ąŠ ąŠą║ąŠąĮčćą░ąĮąĖčÅ (remote transmission request, RTR), ą║ąŠą┤ ą┤ą╗ąĖąĮčŗ ą┤ą░ąĮąĮčŗčģ (data length code, DLC) ąĖ ą┐ąŠą╗ąĄ ą┤ą░ąĮąĮčŗčģ ą║ą░ąČą┤ąŠą│ąŠ čüąŠąŠą▒čēąĄąĮąĖčÅ ą╝ąŠąČąĮąŠ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī ą▓ ąŠą▒ą╗ą░čüčéąĖ mailbox (čüą╝. čĆąĖčü. 19-7). ąæąĖčé substitute remote request (SRR, ą▓čüąĄą│ą┤ą░ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą║ą░ą║ čĆąĄčåąĄčüčüąĖą▓ąĮčŗą╣) ąĖ ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąĮčŗąĄ ą▒ąĖčéčŗ R0 ąĖ R1 (ą▓čüąĄą│ą┤ą░ ąŠčéą┐čĆą░ą▓ą╗čÅčÄčéčüčÅ ą║ą░ą║ ą┤ąŠą╝ąĖąĮą░ąĮčéąĮčŗąĄ) ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą│ąĄąĮąĄčĆąĖčĆčāčÄčéčüčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ ą╗ąŠą│ąĖą║ąŠą╣.

ąĀąĖčü. 19-7. ążąŠčĆą╝ą░čéčŗ čüąŠąŠą▒čēąĄąĮąĖčÅ CAN.

[ąĀąĄą│ąĖčüčéčĆčŗ čüą╗ąŠą▓ą░ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆą░ mailbox]

ąÜą░ąČą┤čŗą╣ mailbox čüąŠčüč鹊ąĖčé ąĖąĘ 8 čüą╗ąŠą▓ ąĖ ą▓ą║ą╗čÄčćą░ąĄčé:

ŌĆó 29-ą▒ąĖčéąĮčŗą╣ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆ (ą▒ą░ąĘąŠą▓ą░čÅ čćą░čüčéčī ą┐ą╗čÄčü čĆą░čüčłąĖčĆąĄąĮąĮą░čÅ čćą░čüčéčī).

ŌĆó ąæąĖčé čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą╝ą░čüą║ąĖ čäąĖą╗čīčéčĆą░čåąĖąĖ (acceptance mask enable, AME).

ŌĆó ąæąĖčé ąĘą░ą┐čĆąŠčüą░ ą┐ąĄčĆąĄą┤ą░čćąĖ čü ą┤ą░ą╗čīąĮąĄą│ąŠ ąŠą║ąŠąĮčćą░ąĮąĖčÅ (remote transmission request, RTR).

ŌĆó ąæąĖčé čĆą░čüčłąĖčĆąĄąĮąĖčÅ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆą░ (identifier extension, IDE).

ŌĆó ąÜąŠą┤ ą┤ą╗ąĖąĮčŗ čüąŠąŠą▒čēąĄąĮąĖčÅ (data length code, DLC).

ŌĆó ąöąŠ 8 ą▒ą░ą╣čé ą┤ą╗čÅ ą┐ąŠą╗čÅ ą┤ą░ąĮąĮčŗčģ.

ŌĆó ąöą▓ą░ ą▒ą░ą╣čéą░ ą┤ą╗čÅ ąĘąĮą░č湥ąĮąĖčÅ ą╝ąĄčéą║ąĖ ą▓čĆąĄą╝ąĄąĮąĖ (time stamp value, TSV).

ąĪčéą░čĆčłąĖąĄ 12 ą▒ąĖčé čüą╗ąŠą▓ą░ 4 ą║ą░ąČą┤ąŠą│ąŠ mailbox ą┐ąŠą╝ąĄč湥ąĮčŗ ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąĮčŗą╝ąĖ. ąŁčéąĖ ą▒ąĖčéčŗ ą▓čüąĄą│ą┤ą░ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą▓ 0.

ąĢčüą╗ąĖ čĆą░ąĘčĆąĄčłąĄąĮą░ ąŠą┐čåąĖčÅ čäąĖą╗čīčéčĆą░čåąĖąĖ ą┐ąŠ ą┐ąŠą╗čÄ ą┤ą░ąĮąĮčŗčģ (DNM=1 ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_CONTROL ąĖ FDF=1 čü čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╣ acceptance mask), č鹊 ą▒ąĖčéčŗ [15:0] čüą╗ąŠą▓ą░ 6 (ExtId) ą┐ąŠą▓č鹊čĆąĮąŠ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą║ą░ą║ ą║ąŠą┤ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ (acceptance code, DFC) ą┤ą╗čÅ ą┐ąŠą╗čÅ čäąĖą╗čīčéčĆą░čåąĖąĖ ą┤ą░ąĮąĮčŗčģ.

ąØąĖąČąĄ ą▓ąŠ ą▓čĆąĄąĘą║ą░čģ ą┐čĆąĖą▓ąĄą┤ąĄąĮąŠ ąŠą┐ąĖčüą░ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆąŠą▓ mailbox. ąæčāą║ą▓čŗ xx ąĘą░ą╝ąĄąĮčÅčÄčéčüčÅ ąĮą░ ąĘąĮą░č湥ąĮąĖąĄ ąĮąŠą╝ąĄčĆą░ mailbox ąŠčé 00 ą┤ąŠ 31. ąÆ ąĖą╝ąĄąĮą░čģ ą▒ąĖčé n ąĘą░ą╝ąĄąĮčÅąĄčéčüčÅ ąĮą░ čćąĖčüą╗ąŠ ąŠčé 0 ą┤ąŠ 31.

ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 čĆąĄą│ąĖčüčéčĆčŗ mailbox čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮčŗ ą║ą░ą║ RAM, ąĖ čā ąĮąĖčģ ąĮąĄčé ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░. ą¤ąŠčŹč鹊ą╝čā ą║ą░ąČą┤čŗą╣ mailbox ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čüą▒čĆąŠčłąĄąĮ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ ą┐ąĄčĆąĄą┤ ąĄą│ąŠ čĆą░ąĘčĆąĄčłąĄąĮąĖąĄą╝ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ ą▒ąĖčéą░ ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_MCx.

ąĀąĖčü. 19-8. Mailbox Identifier Word 7 (ą░ą┤čĆąĄčüą░ MMR-čĆąĄą│ąĖčüčéčĆąŠą▓ čüą╝. ą▓ čéą░ą▒ą╗ąĖčåąĄ 19-3).

ąóą░ą▒ą╗ąĖčåą░ 19-3. ąÉą┤čĆąĄčüą░ čĆąĄą│ąĖčüčéčĆąŠą▓ Mailbox Identifier Word 7.

| ąśą╝čÅ čĆąĄą│ąĖčüčéčĆą░ |

MMR-ą░ą┤čĆąĄčü |

ąśą╝čÅ čĆąĄą│ąĖčüčéčĆą░ |

MMR-ą░ą┤čĆąĄčü |

| CAN_MB00_ID1 |

0xFFC0 2C1C |

CAN_MB16_ID1 |

0xFFC0 2E1C |

| CAN_MB01_ID1 |

0xFFC0 2C3C |

CAN_MB17_ID1 |

0xFFC0 2E3C |

| CAN_MB02_ID1 |

0xFFC0 2C5C |

CAN_MB18_ID1 |

0xFFC0 2E5C |

| CAN_MB03_ID1 |

0xFFC0 2C7C |

CAN_MB19_ID1 |

0xFFC0 2E7C |

| CAN_MB04_ID1 |

0xFFC0 2C9C |

CAN_MB20_ID1 |

0xFFC0 2E9C |

| CAN_MB05_ID1 |

0xFFC0 2CBC |

CAN_MB21_ID1 |

0xFFC0 2EBC |

| CAN_MB06_ID1 |

0xFFC0 2CDC |

CAN_MB22_ID1 |

0xFFC0 2EDC |

| CAN_MB07_ID1 |

0xFFC0 2CFC |

CAN_MB23_ID1 |

0xFFC0 2EFC |

| CAN_MB08_ID1 |

0xFFC0 2D1C |

CAN_MB24_ID1 |

0xFFC0 2F1C |

| CAN_MB09_ID1 |

0xFFC0 2D3C |

CAN_MB25_ID1 |

0xFFC0 2F3C |

| CAN_MB10_ID1 |

0xFFC0 2D5C |

CAN_MB26_ID1 |

0xFFC0 2F5C |

| CAN_MB11_ID1 |

0xFFC0 2D7C |

CAN_MB27_ID1 |

0xFFC0 2F7C |

| CAN_MB12_ID1 |

0xFFC0 2D9C |

CAN_MB28_ID1 |

0xFFC0 2F9C |

| CAN_MB13_ID1 |

0xFFC0 2DBC |

CAN_MB29_ID1 |

0xFFC0 2FBC |

| CAN_MB14_ID1 |

0xFFC0 2DDC |

CAN_MB30_ID1 |

0xFFC0 2FDC |

| CAN_MB15_ID1 |

0xFFC0 2DFC |

CAN_MB31_ID1 |

0xFFC0 2FFC |

ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗąĄ ą▒ąĖčéčŗ čĆąĄą│ąĖčüčéčĆąŠą▓ CAN_MBxxID1:

AME - Acceptance Mask Enable.

1: čĆą░ąĘčĆąĄčłą░ąĄčé ą╝ą░čüą║čā čäąĖą╗čīčéčĆą░čåąĖąĖ ą┐ąŠ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆčā ą┤ą╗čÅ ą┐čĆąĖčģąŠą┤čÅčēąĖčģ čüąŠąŠą▒čēąĄąĮąĖą╣ (ą▓ąŠąĘą╝ąŠąČąĄąĮ ą┐čĆąĖąĄą╝ ą┐ąŠ ą│čĆčāą┐ą┐ąĄ ą░ą┤čĆąĄčüąŠą▓).

0: čĆą░ąĘčĆąĄčłą░ąĄčé čäąĖą╗čīčéčĆą░čåąĖčÄ ą┐ąŠ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆčā (ą┐ąŠą╗ąĮąŠąĄ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖąĄ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆą░).

RTR - Remote Transmission Request.

1: čĆą░ąĘčĆąĄčłą░ąĄčé čüąŠąŠą▒čēąĄąĮąĖąĄ ą▓ ą▓ąĖą┤ąĄ čäčĆąĄą╣ą╝ą░ remote.

0: čĆą░ąĘčĆąĄčłą░ąĄčé čüąŠąŠą▒čēąĄąĮąĖąĄ ą▓ ą▓ąĖą┤ąĄ čäčĆąĄą╣ą╝ą░ ą┤ą░ąĮąĮčŗčģ.

IDE - Identifier Extension.

1: čĆą░ąĘčĆąĄčłą░ąĄčé 29-ą▒ąĖčéąĮčŗą╣ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆ.

0: čĆą░ąĘčĆąĄčłą░ąĄčé 11-ą▒ąĖčéąĮčŗą╣ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆ.

ąĀąĖčü. 19-9. Mailbox Identifier Word 6 (ą░ą┤čĆąĄčüą░ MMR-čĆąĄą│ąĖčüčéčĆąŠą▓ čüą╝. ą▓ čéą░ą▒ą╗ąĖčåąĄ 19-4).

EXTID - čŹč鹊 ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗąĄ ą▒ąĖčéčŗ čĆą░čüčłąĖčĆąĄąĮąĮąŠą│ąŠ 29-ą▒ąĖčéąĮąŠą│ąŠ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆą░ čüąŠąŠą▒čēąĄąĮąĖčÅ.

ąóą░ą▒ą╗ąĖčåą░ 19-4. ąÉą┤čĆąĄčüą░ čĆąĄą│ąĖčüčéčĆąŠą▓ Mailbox Identifier Word 6.

| ąśą╝čÅ čĆąĄą│ąĖčüčéčĆą░ |

MMR-ą░ą┤čĆąĄčü |

ąśą╝čÅ čĆąĄą│ąĖčüčéčĆą░ |

MMR-ą░ą┤čĆąĄčü |

| CAN_MB00_ID0 |

0xFFC0 2C18 |

CAN_MB16_ID0 |

0xFFC0 2E18 |

| CAN_MB01_ID0 |

0xFFC0 2C38 |

CAN_MB17_ID0 |

0xFFC0 2E38 |

| CAN_MB02_ID0 |

0xFFC0 2C58 |

CAN_MB18_ID0 |

0xFFC0 2E58 |

| CAN_MB03_ID0 |

0xFFC0 2C78 |

CAN_MB19_ID0 |

0xFFC0 2E78 |

| CAN_MB04_ID0 |

0xFFC0 2C98 |

CAN_MB20_ID0 |

0xFFC0 2E98 |

| CAN_MB05_ID0 |

0xFFC0 2CB8 |

CAN_MB21_ID0 |

0xFFC0 2EB8 |

| CAN_MB06_ID0 |

0xFFC0 2CD8 |

CAN_MB22_ID0 |

0xFFC0 2ED8 |

| CAN_MB07_ID0 |

0xFFC0 2CF8 |

CAN_MB23_ID0 |

0xFFC0 2EF8 |

| CAN_MB08_ID0 |

0xFFC0 2D18 |

CAN_MB24_ID0 |

0xFFC0 2F18 |

| CAN_MB09_ID0 |

0xFFC0 2D38 |

CAN_MB25_ID0 |

0xFFC0 2F38 |

| CAN_MB10_ID0 |

0xFFC0 2D58 |

CAN_MB26_ID0 |

0xFFC0 2F58 |

| CAN_MB11_ID0 |

0xFFC0 2D78 |

CAN_MB27_ID0 |

0xFFC0 2F78 |

| CAN_MB12_ID0 |

0xFFC0 2D98 |

CAN_MB28_ID0 |

0xFFC0 2F98 |

| CAN_MB13_ID0 |

0xFFC0 2DB8 |

CAN_MB29_ID0 |

0xFFC0 2FB8 |

| CAN_MB14_ID0 |

0xFFC0 2DD8 |

CAN_MB30_ID0 |

0xFFC0 2FD8 |

| CAN_MB15_ID0 |

0xFFC0 2DF8 |

CAN_MB31_ID0 |

0xFFC0 2FF8 |

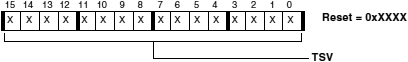

ąĀąĖčü. 19-10. Mailbox Identifier Word 5 (ą░ą┤čĆąĄčüą░ MMR-čĆąĄą│ąĖčüčéčĆąŠą▓ čüą╝. ą▓ čéą░ą▒ą╗ąĖčåąĄ 19-5).

TSV - ą╝ąĄčéą║ą░ ą▓čĆąĄą╝ąĄąĮąĖ čüąŠąŠą▒čēąĄąĮąĖčÅ.

ąóą░ą▒ą╗ąĖčåą░ 19-5. ąÉą┤čĆąĄčüą░ čĆąĄą│ąĖčüčéčĆąŠą▓ Mailbox Identifier Word 5.

| ąśą╝čÅ čĆąĄą│ąĖčüčéčĆą░ |

MMR-ą░ą┤čĆąĄčü |

ąśą╝čÅ čĆąĄą│ąĖčüčéčĆą░ |

MMR-ą░ą┤čĆąĄčü |

| CAN_MB00_TIMESTAMP |

0xFFC0 2C14 |

CAN_MB16_TIMESTAMP |

0xFFC0 2E14 |

| CAN_MB01_TIMESTAMP |

0xFFC0 2C34 |

CAN_MB17_TIMESTAMP |

0xFFC0 2E34 |

| CAN_MB02_TIMESTAMP |

0xFFC0 2C54 |

CAN_MB18_TIMESTAMP |

0xFFC0 2E54 |

| CAN_MB03_TIMESTAMP |

0xFFC0 2C74 |

CAN_MB19_TIMESTAMP |

0xFFC0 2E74 |

| CAN_MB04_TIMESTAMP |

0xFFC0 2C94 |

CAN_MB20_TIMESTAMP |

0xFFC0 2E94 |

| CAN_MB05_TIMESTAMP |

0xFFC0 2CB4 |

CAN_MB21_TIMESTAMP |

0xFFC0 2EB4 |

| CAN_MB06_TIMESTAMP |

0xFFC0 2CD4 |

CAN_MB22_TIMESTAMP |

0xFFC0 2ED4 |

| CAN_MB07_TIMESTAMP |

0xFFC0 2CF4 |

CAN_MB23_TIMESTAMP |

0xFFC0 2EF4 |

| CAN_MB08_TIMESTAMP |

0xFFC0 2D14 |

CAN_MB24_TIMESTAMP |

0xFFC0 2F14 |

| CAN_MB09_TIMESTAMP |

0xFFC0 2D34 |

CAN_MB25_TIMESTAMP |

0xFFC0 2F34 |

| CAN_MB10_TIMESTAMP |

0xFFC0 2D54 |

CAN_MB26_TIMESTAMP |

0xFFC0 2F54 |

| CAN_MB11_TIMESTAMP |

0xFFC0 2D74 |

CAN_MB27_TIMESTAMP |

0xFFC0 2F74 |

| CAN_MB12_TIMESTAMP |

0xFFC0 2D94 |

CAN_MB28_TIMESTAMP |

0xFFC0 2F94 |

| CAN_MB13_TIMESTAMP |

0xFFC0 2DB4 |

CAN_MB29_TIMESTAMP |

0xFFC0 2FB4 |

| CAN_MB14_TIMESTAMP |

0xFFC0 2DD4 |

CAN_MB30_TIMESTAMP |

0xFFC0 2FD4 |

| CAN_MB15_TIMESTAMP |

0xFFC0 2DF4 |

CAN_MB31_TIMESTAMP |

0xFFC0 2FF4 |

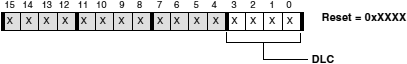

ąøčÄą▒ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ DLC, ą▒ąŠą╗čīčłąĄąĄ 8, ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčéčüčÅ čéą░ą║ ąČąĄ, ą║ą░ą║ ąĘąĮą░č湥ąĮąĖąĄ 8.

ąĀąĖčü. 19-11. Mailbox Identifier Word 4 (ą░ą┤čĆąĄčüą░ MMR-čĆąĄą│ąĖčüčéčĆąŠą▓ čüą╝. ą▓ čéą░ą▒ą╗ąĖčåąĄ 19-6).

DLC - ą┤ą╗ąĖąĮą░ čüąŠąŠą▒čēąĄąĮąĖčÅ ą▓ ą▒ą░ą╣čéą░čģ.

ąóą░ą▒ą╗ąĖčåą░ 19-6. ąÉą┤čĆąĄčüą░ čĆąĄą│ąĖčüčéčĆąŠą▓ Mailbox Identifier Word 4.

| ąśą╝čÅ čĆąĄą│ąĖčüčéčĆą░ |

MMR-ą░ą┤čĆąĄčü |

ąśą╝čÅ čĆąĄą│ąĖčüčéčĆą░ |

MMR-ą░ą┤čĆąĄčü |

| CAN_MB00_LENGTH |

0xFFC0 2C10 |

CAN_MB16_LENGTH |

0xFFC0 2E10 |

| CAN_MB01_LENGTH |

0xFFC0 2C30 |

CAN_MB17_LENGTH |

0xFFC0 2E30 |

| CAN_MB02_LENGTH |

0xFFC0 2C50 |

CAN_MB18_LENGTH |

0xFFC0 2E50 |

| CAN_MB03_LENGTH |

0xFFC0 2C70 |

CAN_MB19_LENGTH |

0xFFC0 2E70 |

| CAN_MB04_LENGTH |

0xFFC0 2C90 |

CAN_MB20_LENGTH |

0xFFC0 2E90 |

| CAN_MB05_LENGTH |

0xFFC0 2CB0 |

CAN_MB21_LENGTH |

0xFFC0 2EB0 |

| CAN_MB06_LENGTH |

0xFFC0 2CD0 |

CAN_MB22_LENGTH |

0xFFC0 2ED0 |

| CAN_MB07_LENGTH |

0xFFC0 2CF0 |

CAN_MB23_LENGTH |

0xFFC0 2EF0 |

| CAN_MB08_LENGTH |

0xFFC0 2D10 |

CAN_MB24_LENGTH |

0xFFC0 2F10 |

| CAN_MB09_LENGTH |

0xFFC0 2D30 |

CAN_MB25_LENGTH |

0xFFC0 2F30 |

| CAN_MB10_LENGTH |

0xFFC0 2D50 |

CAN_MB26_LENGTH |

0xFFC0 2F50 |

| CAN_MB11_LENGTH |

0xFFC0 2D70 |

CAN_MB27_LENGTH |

0xFFC0 2F70 |

| CAN_MB12_LENGTH |

0xFFC0 2D90 |

CAN_MB28_LENGTH |

0xFFC0 2F90 |

| CAN_MB13_LENGTH |

0xFFC0 2DB0 |

CAN_MB29_LENGTH |

0xFFC0 2FB0 |

| CAN_MB14_LENGTH |

0xFFC0 2DD0 |

CAN_MB30_LENGTH |

0xFFC0 2FD0 |

| CAN_MB15_LENGTH |

0xFFC0 2DF0 |

CAN_MB31_LENGTH |

0xFFC0 2FF0 |

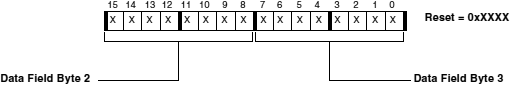

ą¤ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ CAN ąŠą▒ą╝ąĄąĮąĖą▓ą░ąĄčéčüčÅ ą┤ą░ąĮąĮčŗą╝ąĖ čéą░ą║, čćč鹊 čüą░ą╝čŗą╣ "ąĘąĮą░čćą░čēąĖą╣" ą▒ą░ą╣čé (ą║ąŠč鹊čĆčŗą╣ čģčĆą░ąĮąĖčéčüčÅ ą┐ąŠ čüą░ą╝ąŠą╝čā čüčéą░čĆčłąĄą╝čā ą░ą┤čĆąĄčüčā) ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą┐ąĄčĆą▓čŗą╝. ą¤ąŠ čŹč鹊ą╣ ą┐čĆąĖčćąĖąĮąĄ čĆąĄą│ąĖčüčéčĆčŗ CAN_MBxx_DATAx ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ čéą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą║ą░ą║ ąĄčüą╗ąĖ ą▒čŗ čüčéą░čĆčłąĖą╣ ą▒ą░ą╣čé ą▒čŗą╗ ą┐ąĄčĆą▓čŗą╝. ąØą░ą┐čĆąĖą╝ąĄčĆ, ąĄčüą╗ąĖ ą┐ąĄčĆąĄą┤ą░ąĮ ąĖą╗ąĖ ą┐čĆąĖąĮčÅčé č鹊ą╗čīą║ąŠ 1 ą▒ą░ą╣čé (DLC = 1), č鹊 ąŠąĮ čüąŠčģčĆą░ąĮčÅąĄčéčüčÅ ą▓ čüą░ą╝čŗą╣ ąĘąĮą░čćą░čēąĖą╣ ą▒ą░ą╣čé čĆąĄą│ąĖčüčéčĆą░ CAN_MBxx_DATA3. ąĢčüą╗ąĖ ą┐ąĄčĆąĄą┤ą░ąĮčŗ ąĖą╗ąĖ ą┐čĆąĖąĮčÅčéčŗ ą┤ą▓ą░ ą▒ą░ą╣čéą░, č鹊 ąŠąĮąĖ čüąŠčģčĆą░ąĮčÅčÄčéčüčÅ ą▓ čüčéą░čĆčłčāčÄ ąĖ ą╝ą╗ą░ą┤čłčāčÄ ą┐ąŠą╗ąŠą▓ąĖąĮčŗ CAN_MBxx_DATA3. ąĪą╝. čĆąĖčüčāąĮą║ąĖ 19-12, 19-13, 19-14 ąĖ 19-15. ą¤ąŠąĮą░čćą░ą╗čā čŹč鹊 ą▓ąĮąŠčüčéąĖčé ąĖąĘą▓ąĄčüčéąĮčāčÄ ą┐čāčéą░ąĮąĖčåčā, ą▒čāą┤čīč鹥 ą▓ąĮąĖą╝ą░č鹥ą╗čīąĮčŗ!

ąØąĖąČąĄ ą┐ąŠą║ą░ąĘą░ąĮ ą║ąŠą┤, ą║ąŠč鹊čĆčŗą╣ ąŠą▒ąĄčüą┐ąĄčćąĖą▓ą░ąĄčé ą┐čĆąŠą│ąĮąŠąĘąĖčĆčāąĄą╝čŗą╣ ą┐ąŠčĆčÅą┤ąŠą║ čüą╗ąĄą┤ąŠą▓ą░ąĮąĖčÅ ą▒ą░ą╣čé ąĖ ą▓ ą┐ą░ą╝čÅčéąĖ, ąĖ ą┐čĆąĖ ą┐ąĄčĆąĄą┤ą░č湥 - ą┐ąĄčĆą▓čŗą╣ ą▒ą░ą╣čé ą▓ ą┐ą░ą╝čÅčéąĖ (ą┐ąŠ čüą░ą╝ąŠą╝čā ą╝ą╗ą░ą┤čłąĄą╝čā ą░ą┤čĆąĄčüčā) ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą┐ąĄčĆą▓čŗą╝:

// ą×ą▒čŖąĄą┤ąĖąĮąĄąĮąĖąĄ ą┤ą╗čÅ ą┐ąĄčĆąĄčüčéą░ąĮąŠą▓ą║ąĖ ą▒ą░ą╣čé:

typedef union

{

u16 d16;

u8 d8[2];

}TCanDataSwap;

////////////////////////////////////////////////////////////////////

// ążčāąĮą║čåąĖčÅ ąĖčüą┐ąŠą╗čīąĘčāąĄčé ąĮą░ ą┐ąĄčĆąĄą┤ą░čćčā ą▓ąŠčüąĄą╝čī čÅčēąĖą║ąŠą▓ 24..31. ąÆąĄčĆąĮąĄčé true,

// ąĄčüą╗ąĖ ą┐ąĄčĆąĄą┤ą░čćą░ ąĘą░ą▓ąĄčĆčłąĖą╗ą░čüčī čāčüą┐ąĄčłąĮąŠ ąĖ false, ąĄčüą╗ąĖ ą┐ąĄčĆąĄą┤ą░čéčī

// ąĮąĄ čāą┤ą░ą╗ąŠčüčī, ą┐ąŠč鹊ą╝čā čćč鹊 ą▓čüąĄ čŹčéąĖ ą▓ąŠčüąĄą╝čī čÅčēąĖą║ąŠą▓ ąĘą░ąĮčÅčéčŗ ą┐ąĄčĆąĄą┤ą░č湥ą╣.

// ąæą░ą╣čéčŗ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ą▓ č鹊ą╝ ąČąĄ ą┐ąŠčĆčÅą┤ą║ąĄ, ą║ą░ą║ ąŠąĮąĖ ąĮą░čģąŠą┤čÅčéčüčÅ ą▓ ą┐ą░ą╝čÅčéąĖ

// ą┐ąŠ ą░ą┤čĆąĄčüčā data.

bool canTX (u8* data)

{

// ąŻą║ą░ąĘą░č鹥ą╗čī ąĮą░ čĆąĄą│ąĖčüčéčĆ DATA0 ąĮą░ą╣ą┤ąĄąĮąĮąŠą│ąŠ čüą▓ąŠą▒ąŠą┤ąĮąŠą│ąŠ

// ą┐ąĄčĆąĄą┤ą░čÄčēąĄą│ąŠ čÅčēąĖą║ą░ CAN_MBxx:

volatile u16 *pCAN_Ptr;

// ą¤ąŠąĖčüą║ čüą▓ąŠą▒ąŠą┤ąĮąŠą│ąŠ čÅčēąĖą║ą░ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ:

s16 boxnum;

u16 boxmask = 0x0100; // ą╝ą░čüą║ą░ ą▒ąĖčéą░ čÅčēąĖą║ą░ 24 ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_TRS2

u16 boxmaskfinded = 0;

for (boxnum=24; boxnum<32; boxnum++)

{

if (0==(*pCAN_TRS2 & boxmask))

{

boxmaskfinded = boxmask;

break;

}

boxmask <= 1;

}

if (boxmaskfinded)

{

pCAN_Ptr = (u16*)CAN_MB00_DATA0 + (0x10 * boxnum);

TCanDataSwap tmp;

// ąŚą░ą┐ąŠą╗ąĮąĄąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ ą▓ ąĮą░ą╣ą┤ąĄąĮąĮąŠą╝ čÅčēąĖą║ąĄ:

tmp.d8[1] = *data++;

tmp.d8[0] = *data++;

*(pCAN_Ptr + 6) = tmp.d16;

tmp.d8[1] = *data++;

tmp.d8[0] = *data++;

*(pCAN_Ptr + 4) = tmp.d16;

tmp.d8[1] = *data++;

tmp.d8[0] = *data++;

*(pCAN_Ptr + 2) = tmp.d16;

tmp.d8[1] = *data++;

tmp.d8[0] = *data++;

*(pCAN_Ptr + 0) = tmp.d16;

// ąŚą░ą┐čāčüą║ ą┐ąĄčĆąĄą┤ą░čćąĖ:

*pCAN_TRS2 = boxmaskfinded;

}

return (0!=boxmaskfinded);

}

ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 čŹčéą░ čäčāąĮą║čåąĖčÅ ąĮąĄ ąŠą▒ąĄčüą┐ąĄčćąĖą▓ą░ąĄčé ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░ąĮąĮčŗą╣ ą┐ąŠčĆčÅą┤ąŠą║ čüą╗ąĄą┤ąŠą▓ą░ąĮąĖčÅ ą┤čĆčāą│ ąĘą░ ą┤čĆčāą│ąŠą╝ 8-ą▒ą░ą╣čéąĮčŗčģ ą┐ą░ą║ąĄč鹊ą▓ ą▓ č鹊ą╝ čüą╗čāčćą░ąĄ, ąĄčüą╗ąĖ ą┐čĆąĖ ą▓čģąŠą┤ąĄ ą▓ čäčāąĮą║čåąĖčÄ ąĮąĄą║ąŠč鹊čĆčŗąĄ čÅčēąĖą║ąĖ ą▒čŗą╗ąĖ ąĘą░ąĮčÅčéčŗ. ąöą╗čÅ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖčÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą│ąŠ ą┐ąŠčĆčÅą┤ą║ą░ čüą╗ąĄą┤ąŠą▓ą░ąĮąĖčÅ ą┐ą░ą║ąĄč鹊ą▓ ą┤čĆčāą│ ąĘą░ ą┤čĆčāą│ąŠą╝ ąĖčüą┐ąŠą╗čīąĘčāą╣č鹥 ąĮą░ ą┐ąĄčĆąĄą┤ą░čćčā č鹊ą╗čīą║ąŠ ąŠą┤ąĖąĮ ą┐ąĄčĆąĄą┤ą░čÄčēąĖą╣ čÅčēąĖą║.

[CAN_MBxx_DATA3, ą┐ąĄčĆą▓čŗą╣ ąĖ ą▓č鹊čĆąŠą╣ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗąĄ ą▒ą░ą╣čéčŗ]

ąĀąĖčü. 19-12. Mailbox Identifier Word 3 (ą░ą┤čĆąĄčüą░ MMR-čĆąĄą│ąĖčüčéčĆąŠą▓ čüą╝. ą▓ čéą░ą▒ą╗ąĖčåąĄ 19-7).

ąóą░ą▒ą╗ąĖčåą░ 19-7. ąÉą┤čĆąĄčüą░ čĆąĄą│ąĖčüčéčĆąŠą▓ Mailbox Identifier Word 3.

| ąśą╝čÅ čĆąĄą│ąĖčüčéčĆą░ |

MMR-ą░ą┤čĆąĄčü |

ąśą╝čÅ čĆąĄą│ąĖčüčéčĆą░ |

MMR-ą░ą┤čĆąĄčü |

| CAN_MB00_DATA3 |

0xFFC0 2C0C |

CAN_MB16_DATA3 |

0xFFC0 2E0C |

| CAN_MB01_DATA3 |

0xFFC0 2C2C |

CAN_MB17_DATA3 |

0xFFC0 2E2C |

| CAN_MB02_DATA3 |

0xFFC0 2C4C |

CAN_MB18_DATA3 |

0xFFC0 2E4C |

| CAN_MB03_DATA3 |

0xFFC0 2C6C |

CAN_MB19_DATA3 |

0xFFC0 2E6C |

| CAN_MB04_DATA3 |

0xFFC0 2C8C |

CAN_MB20_DATA3 |

0xFFC0 2E8C |

| CAN_MB05_DATA3 |

0xFFC0 2CAC |

CAN_MB21_DATA3 |

0xFFC0 2EAC |

| CAN_MB06_DATA3 |

0xFFC0 2CCC |

CAN_MB22_DATA3 |

0xFFC0 2ECC |

| CAN_MB07_DATA3 |

0xFFC0 2CEC |

CAN_MB23_DATA3 |

0xFFC0 2EEC |

| CAN_MB08_DATA3 |

0xFFC0 2D0C |

CAN_MB24_DATA3 |

0xFFC0 2F0C |

| CAN_MB09_DATA3 |

0xFFC0 2D2C |

CAN_MB25_DATA3 |

0xFFC0 2F2C |

| CAN_MB10_DATA3 |

0xFFC0 2D4C |

CAN_MB26_DATA3 |

0xFFC0 2F4C |

| CAN_MB11_DATA3 |

0xFFC0 2D6C |

CAN_MB27_DATA3 |

0xFFC0 2F6C |

| CAN_MB12_DATA3 |

0xFFC0 2D8C |

CAN_MB28_DATA3 |

0xFFC0 2F8C |

| CAN_MB13_DATA3 |

0xFFC0 2DAC |

CAN_MB29_DATA3 |

0xFFC0 2FAC |

| CAN_MB14_DATA3 |

0xFFC0 2DCC |

CAN_MB30_DATA3 |

0xFFC0 2FCC |

| CAN_MB15_DATA3 |

0xFFC0 2DEC |

CAN_MB31_DATA3 |

0xFFC0 2FEC |

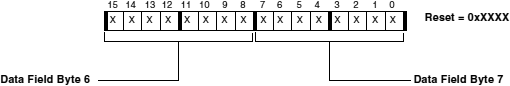

[CAN_MBxx_DATA2, čéčĆąĄčéąĖą╣ ąĖ č湥čéą▓ąĄčĆčéčŗą╣ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗąĄ ą▒ą░ą╣čéčŗ]

ąĀąĖčü. 19-13. Mailbox Identifier Word 2 (ą░ą┤čĆąĄčüą░ MMR-čĆąĄą│ąĖčüčéčĆąŠą▓ čüą╝. ą▓ čéą░ą▒ą╗ąĖčåąĄ 19-8).

ąóą░ą▒ą╗ąĖčåą░ 19-8. ąÉą┤čĆąĄčüą░ čĆąĄą│ąĖčüčéčĆąŠą▓ Mailbox Identifier Word 2.

| ąśą╝čÅ čĆąĄą│ąĖčüčéčĆą░ |

MMR-ą░ą┤čĆąĄčü |

ąśą╝čÅ čĆąĄą│ąĖčüčéčĆą░ |

MMR-ą░ą┤čĆąĄčü |

| CAN_MB00_DATA2 |

0xFFC0 2C08 |

CAN_MB16_DATA2 |

0xFFC0 2E08 |

| CAN_MB01_DATA2 |

0xFFC0 2C28 |

CAN_MB17_DATA2 |

0xFFC0 2E28 |

| CAN_MB02_DATA2 |

0xFFC0 2C48 |

CAN_MB18_DATA2 |

0xFFC0 2E48 |

| CAN_MB03_DATA2 |

0xFFC0 2C68 |

CAN_MB19_DATA2 |

0xFFC0 2E68 |

| CAN_MB04_DATA2 |

0xFFC0 2C88 |

CAN_MB20_DATA2 |

0xFFC0 2E88 |

| CAN_MB05_DATA2 |

0xFFC0 2CA8 |

CAN_MB21_DATA2 |

0xFFC0 2EA8 |

| CAN_MB06_DATA2 |

0xFFC0 2CC8 |

CAN_MB22_DATA2 |

0xFFC0 2EC8 |

| CAN_MB07_DATA2 |

0xFFC0 2CE8 |

CAN_MB23_DATA2 |

0xFFC0 2EE8 |

| CAN_MB08_DATA2 |

0xFFC0 2D08 |

CAN_MB24_DATA2 |

0xFFC0 2F08 |

| CAN_MB09_DATA2 |

0xFFC0 2D28 |

CAN_MB25_DATA2 |

0xFFC0 2F28 |

| CAN_MB10_DATA2 |

0xFFC0 2D48 |

CAN_MB26_DATA2 |

0xFFC0 2F48 |

| CAN_MB11_DATA2 |

0xFFC0 2D68 |

CAN_MB27_DATA2 |

0xFFC0 2F68 |

| CAN_MB12_DATA2 |

0xFFC0 2D88 |

CAN_MB28_DATA2 |

0xFFC0 2F88 |

| CAN_MB13_DATA2 |

0xFFC0 2DA8 |

CAN_MB29_DATA2 |

0xFFC0 2FA8 |

| CAN_MB14_DATA2 |

0xFFC0 2DC8 |

CAN_MB30_DATA2 |

0xFFC0 2FC8 |

| CAN_MB15_DATA2 |

0xFFC0 2DE8 |

CAN_MB31_DATA2 |

0xFFC0 2FE8 |

[CAN_MBxx_DATA1, ą┐čÅčéčŗą╣ ąĖ čłąĄčüč鹊ą╣ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗąĄ ą▒ą░ą╣čéčŗ]

ąĀąĖčü. 19-14. Mailbox Identifier Word 1 (ą░ą┤čĆąĄčüą░ MMR-čĆąĄą│ąĖčüčéčĆąŠą▓ čüą╝. ą▓ čéą░ą▒ą╗ąĖčåąĄ 19-9).

ąóą░ą▒ą╗ąĖčåą░ 19-9. ąÉą┤čĆąĄčüą░ čĆąĄą│ąĖčüčéčĆąŠą▓ Mailbox Identifier Word 1.

| ąśą╝čÅ čĆąĄą│ąĖčüčéčĆą░ |

MMR-ą░ą┤čĆąĄčü |

ąśą╝čÅ čĆąĄą│ąĖčüčéčĆą░ |

MMR-ą░ą┤čĆąĄčü |

| CAN_MB00_DATA1 |

0xFFC0 2C04 |

CAN_MB16_DATA1 |

0xFFC0 2E04 |

| CAN_MB01_DATA1 |

0xFFC0 2C24 |

CAN_MB17_DATA1 |

0xFFC0 2E24 |

| CAN_MB02_DATA1 |

0xFFC0 2C44 |

CAN_MB18_DATA1 |

0xFFC0 2E44 |

| CAN_MB03_DATA1 |

0xFFC0 2C64 |

CAN_MB19_DATA1 |

0xFFC0 2E64 |

| CAN_MB04_DATA1 |

0xFFC0 2C84 |

CAN_MB20_DATA1 |

0xFFC0 2E84 |

| CAN_MB05_DATA1 |

0xFFC0 2CA4 |

CAN_MB21_DATA1 |

0xFFC0 2EA4 |

| CAN_MB06_DATA1 |

0xFFC0 2CC4 |

CAN_MB22_DATA1 |

0xFFC0 2EC4 |

| CAN_MB07_DATA1 |

0xFFC0 2CE4 |

CAN_MB23_DATA1 |

0xFFC0 2EE4 |

| CAN_MB08_DATA1 |

0xFFC0 2D04 |

CAN_MB24_DATA1 |

0xFFC0 2F04 |

| CAN_MB09_DATA1 |

0xFFC0 2D24 |

CAN_MB25_DATA1 |

0xFFC0 2F24 |

| CAN_MB10_DATA1 |

0xFFC0 2D44 |

CAN_MB26_DATA1 |

0xFFC0 2F44 |

| CAN_MB11_DATA1 |

0xFFC0 2D64 |

CAN_MB27_DATA1 |

0xFFC0 2F64 |

| CAN_MB12_DATA1 |

0xFFC0 2D84 |

CAN_MB28_DATA1 |

0xFFC0 2F84 |

| CAN_MB13_DATA1 |

0xFFC0 2DA4 |

CAN_MB29_DATA1 |

0xFFC0 2FA4 |

| CAN_MB14_DATA1 |

0xFFC0 2DC4 |

CAN_MB30_DATA1 |

0xFFC0 2FC4 |

| CAN_MB15_DATA1 |

0xFFC0 2DE4 |

CAN_MB31_DATA1 |

0xFFC0 2FE4 |

[CAN_MBxx_DATA0, čüąĄą┤čīą╝ąŠą╣ ąĖ ą▓ąŠčüčīą╝ąŠą╣ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗąĄ ą▒ą░ą╣čéčŗ]

ąĀąĖčü. 19-15. Mailbox Identifier Word 0 (ą░ą┤čĆąĄčüą░ MMR-čĆąĄą│ąĖčüčéčĆąŠą▓ čüą╝. ą▓ čéą░ą▒ą╗ąĖčåąĄ 19-10).

ąóą░ą▒ą╗ąĖčåą░ 19-10. ąÉą┤čĆąĄčüą░ čĆąĄą│ąĖčüčéčĆąŠą▓ Mailbox Identifier Word 0.

| ąśą╝čÅ čĆąĄą│ąĖčüčéčĆą░ |

MMR-ą░ą┤čĆąĄčü |

ąśą╝čÅ čĆąĄą│ąĖčüčéčĆą░ |

MMR-ą░ą┤čĆąĄčü |

| CAN_MB00_DATA0 |

0xFFC0 2C00 |

CAN_MB16_DATA0 |

0xFFC0 2E00 |

| CAN_MB01_DATA0 |

0xFFC0 2C20 |

CAN_MB17_DATA0 |

0xFFC0 2E20 |

| CAN_MB02_DATA0 |

0xFFC0 2C40 |

CAN_MB18_DATA0 |

0xFFC0 2E40 |

| CAN_MB03_DATA0 |

0xFFC0 2C60 |

CAN_MB19_DATA0 |

0xFFC0 2E60 |

| CAN_MB04_DATA0 |

0xFFC0 2C80 |

CAN_MB20_DATA0 |

0xFFC0 2E80 |

| CAN_MB05_DATA0 |

0xFFC0 2CA0 |

CAN_MB21_DATA0 |

0xFFC0 2EA0 |

| CAN_MB06_DATA0 |

0xFFC0 2CC0 |

CAN_MB22_DATA0 |

0xFFC0 2EC0 |

| CAN_MB07_DATA0 |

0xFFC0 2CE0 |

CAN_MB23_DATA0 |

0xFFC0 2EE0 |

| CAN_MB08_DATA0 |

0xFFC0 2D00 |

CAN_MB24_DATA0 |

0xFFC0 2F00 |

| CAN_MB09_DATA0 |

0xFFC0 2D20 |

CAN_MB25_DATA0 |

0xFFC0 2F20 |

| CAN_MB10_DATA0 |

0xFFC0 2D40 |

CAN_MB26_DATA0 |

0xFFC0 2F40 |

| CAN_MB11_DATA0 |

0xFFC0 2D60 |

CAN_MB27_DATA0 |

0xFFC0 2F60 |

| CAN_MB12_DATA0 |

0xFFC0 2D80 |

CAN_MB28_DATA0 |

0xFFC0 2F80 |

| CAN_MB13_DATA0 |

0xFFC0 2DA0 |

CAN_MB29_DATA0 |

0xFFC0 2FA0 |

| CAN_MB14_DATA0 |

0xFFC0 2DC0 |

CAN_MB30_DATA0 |

0xFFC0 2FC0 |

| CAN_MB15_DATA0 |

0xFFC0 2DE0 |

CAN_MB31_DATA0 |

0xFFC0 2FE0 |

ą¤čĆąĖąĄą╝ąĮčŗąĄ mailbox ąĖčüą┐ąŠą╗čīąĘčāčÄčé ą▓čĆąĄą╝ąĄąĮąĮčŗą╣ ą▒čāč乥čĆ ą┐čĆąĖąĄą╝ą░, ą║ąŠč鹊čĆčŗąĄ ą┐ąĄčĆąĄąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ č鹊ą╗čīą║ąŠ ąĮą░ ąŠčüąĮąŠą▓ąĄ ą║ąŠą┤ą░ DLC čüąŠąŠą▒čēąĄąĮąĖčÅ. ąöą╗čÅ ą║ąŠą┤ąŠą▓ DLC ą╝ąĄąĮčīčłąĄ 8 čüą░ą╝čŗąĄ ą╝ą╗ą░ą┤čłąĖąĄ ą▒ą░ą╣čéčŗ ąĮąĄ ą┐ąĄčĆąĄąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ, ąĖ čüąŠčģčĆą░ąĮčÅčÄčéčüčÅ ą▓ ą┐čĆąĖąĮąĖą╝ą░čÄčēąĄą╝ mailbox. ąæčāą┤čāčé ą┤ąŠą┐čāčüčéąĖą╝čŗ č鹊ą╗čīą║ąŠ ą┤ą░ąĮąĮčŗąĄ, ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą║ąŠč鹊čĆčŗčģ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąŠ ą┐ąŠą╗ąĄą╝ DLC.

ą¤čĆąŠą│čĆą░ą╝ą╝ą░ ą┤ąŠą╗ąČąĮą░ ą┐čĆąŠą▓ąĄčĆčÅčéčī ą║ąŠą┤ DLC ą┐čĆąĖąĮčÅč鹊ą│ąŠ čüąŠąŠą▒čēąĄąĮąĖčÅ, čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī, ą║ą░ą║ąĖąĄ čćąĖčéą░čéčī ą▒ą░ą╣čéčŗ ą▓ čĆąĄą│ąĖčüčéčĆą░čģ CAN_MBxx_DATAx.

[ą×ą▒ą╗ą░čüčéčī mailbox]

ąæąŠą╗čīčłąĖąĮčüčéą▓ąŠ CAN mailbox, ąĮąŠ ąĮąĄ ą▓čüąĄ, ą╝ąŠąČąĮąŠ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī ąĮą░ ą┐ąĄčĆąĄą┤ą░čćčā ąĖą╗ąĖ ą┐čĆąĖąĄą╝. ąŻ ą║ą░ąČą┤ąŠą│ąŠ mailbox ąĄčüčéčī ą╝ą░čüą║ą░ čäąĖą╗čīčéčĆą░čåąĖąĖ ą┐ąŠ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆčā (acceptance mask). Mailbox 31 čŹč鹊 mailbox čüąŠ čüą░ą╝čŗą╝ čüčéą░čĆčłąĖą╝ ąĮąŠą╝ąĄčĆąŠą╝.

ąóąĖą┐čŗ mailbox. Mailbox-čŗ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ ą┐čĆąĖąĄą╝ą░ ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ. 8 mailbox-ąŠą▓ ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮčŗ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ, ąĄčēąĄ 8 č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ą┐čĆąĖąĄą╝ą░, ąĖ ąŠčüčéą░ą╗čīąĮčŗąĄ 16 ą╝ąŠąČąĮąŠ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī ąĮą░ ą┐ąĄčĆąĄą┤ą░čćčā ąĖą╗ąĖ ą┐čĆąĖąĄą╝. ąóąŠą╗čīą║ąŠ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝čŗąĄ mailbox ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé čäčāąĮą║čåąĖčÄ čäčĆąĄą╣ą╝ą░ ąĘą░ą┐čĆąŠčüą░ ą┐ąĄčĆąĄą┤ą░čćąĖ ąŠčé ą┤ą░ą╗čīąĮąĄą│ąŠ ąŠą║ąŠąĮčćą░ąĮąĖčÅ (remote frame-request). ą×ą▒ą╗ą░čüčéčī čĆąĄą│ąĖčüčéčĆąŠą▓ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ mailbox čüąŠčüč鹊ąĖčé ąĖąĘ čĆąĄą│ąĖčüčéčĆąŠą▓:

ŌĆó CAN_MC1 ąĖ CAN_MC2 (čĆąĄą│ąĖčüčéčĆčŗ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ mailbox).

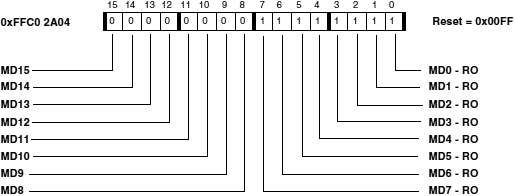

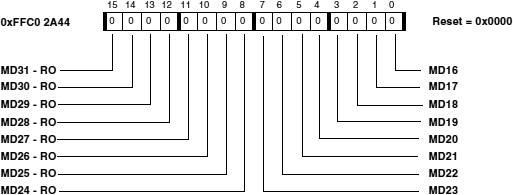

ŌĆó CAN_MD1 ąĖ CAN_MD2 (čĆąĄą│ąĖčüčéčĆčŗ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ mailbox).

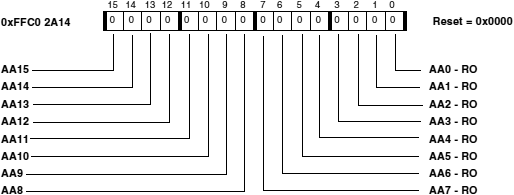

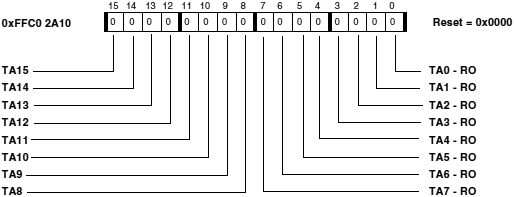

ŌĆó CAN_TA1 ąĖ CAN_TA2 (čĆąĄą│ąĖčüčéčĆčŗ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ).

ŌĆó CAN_AA1 ąĖ CAN_AA2 (čĆąĄą│ąĖčüčéčĆčŗ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ abort).

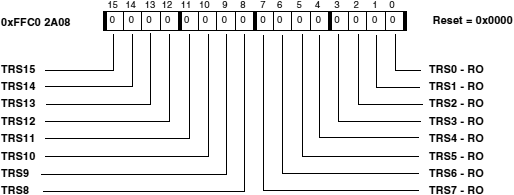

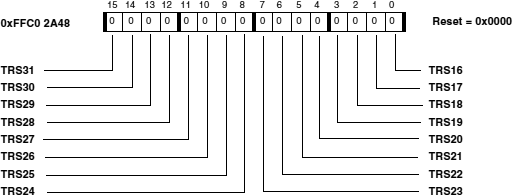

ŌĆó CAN_TRS1 ąĖ CAN_TRS2 (čĆąĄą│ąĖčüčéčĆčŗ čāčüčéą░ąĮąŠą▓ą║ąĖ ąĘą░ą┐čĆąŠčüą░ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ).

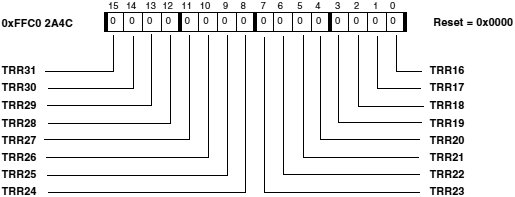

ŌĆó CAN_TRR1 ąĖ CAN_TRR2 (čĆąĄą│ąĖčüčéčĆčŗ čüą▒čĆąŠčüą░ ąĘą░ą┐čĆąŠčüą░ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ).

ŌĆó CAN_RMP1 ąĖ CAN_RMP2 (čĆąĄą│ąĖčüčéčĆčŗ ąŠąČąĖą┤ą░čÄčēąĖčģ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĖąĮčÅčéčŗčģ čüąŠąŠą▒čēąĄąĮąĖą╣).

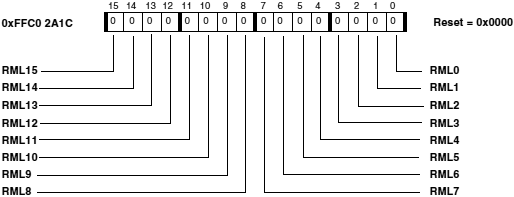

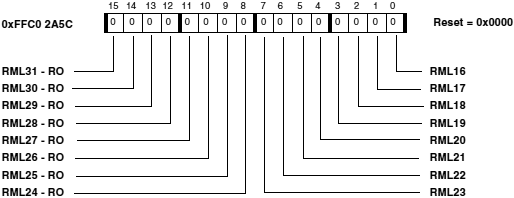

ŌĆó CAN_RML1 ąĖ CAN_RML2 (čĆąĄą│ąĖčüčéčĆčŗ ą┐čĆąĖąĮčÅčéčŗčģ, ąĮąŠ ąĮąĄ ąŠą▒čĆą░ą▒ąŠčéą░ąĮąĮčŗčģ čüąŠąŠą▒čēąĄąĮąĖą╣).

ŌĆó CAN_RFH1 ąĖ CAN_RFH2 (čĆąĄą│ąĖčüčéčĆčŗ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ remote frame).

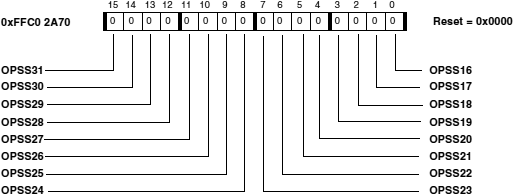

ŌĆó CAN_OPSS1 ąĖ CAN_OPSS2 (čĆąĄą│ąĖčüčéčĆčŗ ąĘą░čēąĖčéčŗ ąŠčé ą┐ąĄčĆąĄąĘą░ą┐ąĖčüąĖ / ąŠą┤ąĖąĮąŠčćąĮąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ).

ŌĆó CAN_MBIM1 ąĖ CAN_MBIM2 (čĆąĄą│ąĖčüčéčĆčŗ ą╝ą░čüą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ mailbox).

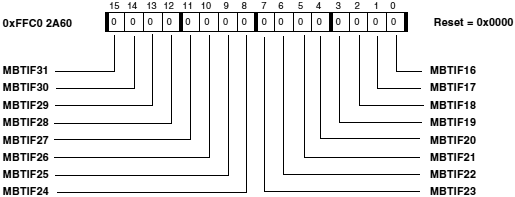

ŌĆó CAN_MBTIF1 and CAN_MBTIF2 (čĆąĄą│ąĖčüčéčĆčŗ čäą╗ą░ą│ąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ mailbox).

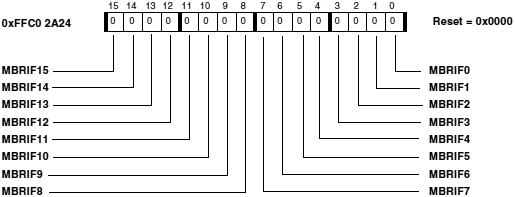

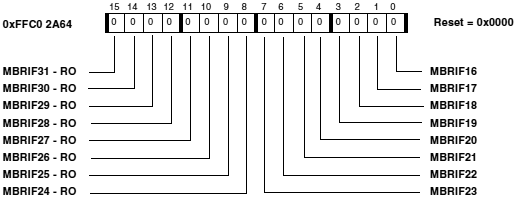

ŌĆó CAN_MBRIF1 and CAN_MBRIF2 (čĆąĄą│ąĖčüčéčĆčŗ čäą╗ą░ą│ąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐čĆąĖąĄą╝ą░ mailbox).

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ mailbox. ąĀąĄą│ąĖčüčéčĆčŗ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ mailbox (CAN_MCx) ąĖ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ mailbox (CAN_MDx) ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāčÄčé ąŠčüąĮąŠą▓ąĮąŠąĄ ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ mailbox-ąŠą▓ CAN. ąÜą░ąČą┤čŗą╣ mailbox ą╝ąŠąČąĄčé ą▒čŗčéčī ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮąŠ čĆą░ąĘčĆąĄčłąĄąĮ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčēąĄąĮ.

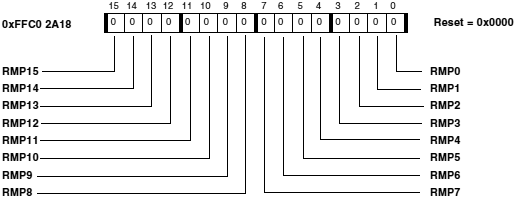

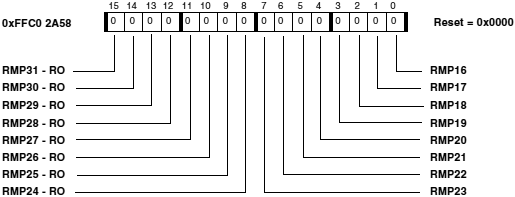

ąĀąĄą│ąĖčüčéčĆčŗ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ mailbox (CAN_MCx) ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčéą░ ą║ą░ąČą┤ąŠą│ąŠ mailbox. ąĀąĄą│ąĖčüčéčĆčŗ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ mailbox (CAN_MDx) ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčé, ą║ą░ą║ąĖąĄ mailbox ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ, ą░ ą║ą░ą║ąĖąĄ ą┤ą╗čÅ ą┐čĆąĖąĄą╝ą░. ąĢčüą╗ąĖ ą▒ąĖčé MCn ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_MCx čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 0, č鹊 čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ mailbox čü ąĮąŠą╝ąĄčĆąŠą╝ n ą▒čāą┤ąĄčé ąĘą░ą┐čĆąĄčēąĄąĮ. Mailbox ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ą┐čĆąĄčēąĄąĮ ą┐ąĄčĆąĄą┤ ąĘą░ą┐ąĖčüčīčÄ ąĄą│ąŠ ą╗čÄą▒ąŠą│ąŠ ą┐ąŠą╗čÅ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆą░. ąĪą╝. čĆąĖčüčāąĮą║ąĖ 19-16 ąĖ Figure 19-17.

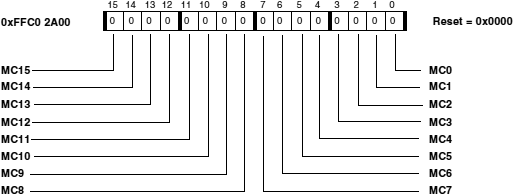

ąĀąĖčü. 19-16. Mailbox Configuration Register 1 (ą┤ą╗čÅ ą▓čüąĄčģ ą▒ąĖčé 0: mailbox ąĘą░ą┐čĆąĄčēąĄąĮ, 1: čĆą░ąĘčĆąĄčłąĄąĮ).

ąĀąĖčü. 19-17. Mailbox Configuration Register 2 (ą┤ą╗čÅ ą▓čüąĄčģ ą▒ąĖčé 0: mailbox ąĘą░ą┐čĆąĄčēąĄąĮ, 1: čĆą░ąĘčĆąĄčłąĄąĮ).

ąØąĄ ąĘą░ą┐ąĖčüčŗą▓ą░ą╣č鹥 ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆ ąŠą▒čŖąĄą║čéą░ čüąŠąŠą▒čēąĄąĮąĖčÅ, ą┐ąŠą║ą░ mailbox čĆą░ąĘčĆąĄčłąĄąĮ ą┤ą╗čÅ ą╝ąŠą┤čāą╗čÅ CAN (ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé CAN_MCx). Mailbox-čŗ, ą║ąŠč鹊čĆčŗąĄ ąĘą░ą┐čĆąĄčēąĄąĮčŗ, ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ CPU ą║ą░ą║ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮą░čÅ ą▒čŗčüčéčĆą░čÅ ą┐ą░ą╝čÅčéčī.

ąĢčüą╗ąĖ mailbox ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ, č鹊 čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé ą▓ čĆąĄą│ąĖčüčéčĆąĄ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ (MCn) ąĖ čĆąĄą│ąĖčüčéčĆąĄ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ (MDn) ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ą▒čāą┤ąĄčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé ąĘą░ą┐čĆąŠčüą░ ąĮą░ ą┐ąĄčĆąĄą┤ą░čćčā (TRSn).

ą¦č鹊ą▒čŗ ąĘą░ą┐čĆąĄčéąĖčéčī ą┐ąĄčĆąĄą┤ą░čÄčēąĖą╣ mailbox, čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé ą▓ čĆąĄą│ąĖčüčéčĆąĄ ąĘą░ą┐čĆąŠčüą░ čüą▒čĆąŠčüą░ ą┐ąĄčĆąĄą┤ą░čćąĖ (CAN_TRRx) ąĖ čĆąĄą│ąĖčüčéčĆą░ čāčüčéą░ąĮąŠą▓ą║ąĖ ąĘą░ą┐čĆąŠčüą░ ą┐ąĄčĆąĄą┤ą░čćąĖ (CAN_TRSx) ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čüąĮą░čćą░ą╗ą░ čüą▒čĆąŠčłąĄąĮčŗ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ ą╗ąŠą│ąĖą║ąŠą╣. ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖčéą░ TRRn čĆąĄą│ąĖčüčéčĆą░ CAN_TRRx ąĖ ą▒ąĖčéą░

TRSn čĆąĄą│ąĖčüčéčĆą░ CAN_TRSx ą░ ąĘą░ą┐čĆąĄčēąĄąĮąĮąŠą╝ mailbox ą╝ąŠąČąĄčé ą┐čĆąĖą▓ąĄčüčéąĖ ą║ ąĮąĄąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą╝čā ą┐ąŠą▓ąĄą┤ąĄąĮąĖčÄ ą╝ąŠą┤čāą╗čÅ CAN.

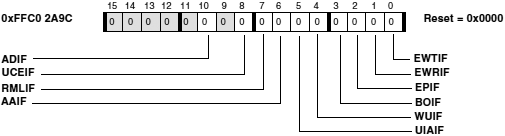

ąĢčüą╗ąĖ mailbox ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą┐čĆąĖąĄą╝ą░ (MDn=1 ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_MDx), ąĖ ąŠąĮ ąĘą░ą┐čĆąĄčēąĄąĮ, č鹊 ą┐čĆąĖąĮąĖą╝ą░ąĄą╝ąŠąĄ ą▓ ąĮą░čüč鹊čÅčēąĖą╣ ą╝ąŠą╝ąĄąĮčé čüąŠąŠą▒čēąĄąĮąĖąĄ ą┤ą╗čÅ čŹč鹊ą│ąŠ čÅčēąĖą║ą░ č鹥čĆčÅąĄčéčüčÅ, ą┤ą░ąČąĄ ąĄčüą╗ąĖ ąĖą╝ąĄąĄčéčüčÅ ą┤čĆčāą│ąŠą╣ mailbox, čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĮčŗą╣ ąĮą░ ą┐čĆąĖąĄą╝ čüąŠąŠą▒čēąĄąĮąĖčÅ čü čéą░ą║ąĖą╝ ąČąĄ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆąŠą╝. ąŁč鹊 ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé, ąĄčüą╗ąĖ mailbox ąĘą░ą┐čĆąĄčēą░ąĄčéčüčÅ (MCn=0 ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_MCx) ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ ą╗ąŠą│ąĖą║ą░ čäąĖą╗čīčéčĆą░čåąĖąĖ (acceptance filtering) ąĘą░ą▓ąĄčĆčłąĖčé ąŠą▒čĆą░ą▒ąŠčéą║čā ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆą░ ąĖ ą┐ąĄčĆąĄą┤ ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĄą╝ ą┐čĆąĖąĄą╝ą░ čŹč鹊ą│ąŠ čüąŠąŠą▒čēąĄąĮąĖčÅ.