ą¤čĆąŠčåąĄčüčüąŠčĆ Blackfin ą┐ąŠą╗ąĮąŠčüčéčīčÄ čüąŠą▓ą╝ąĄčüčéąĖą╝ čüąŠ čüčéą░ąĮą┤ą░čĆč鹊ą╝ IEEE 1149.1, ą║ąŠč鹊čĆčŗą╣ čéą░ą║ąČąĄ ąĖąĘą▓ąĄčüč鹥ąĮ ą║ą░ą║ čüčéą░ąĮą┤ą░čĆčé Joint Test Action Group (JTAG). ąÆ čŹč鹊ą╣ ą▓čĆąĄąĘą║ąĄ ą┐čĆąĖą▓ąĄą┤ąĄąĮą░ ąŠą▒čēą░čÅ čüą┐čĆą░ą▓ą║ą░, ą║čĆą░čéą║ąŠ ąŠą▒čŖčÅčüąĮčÅčÄčēą░čÅ čĆą░ą▒ąŠčéčā ąĖąĮč鹥čĆč乥ą╣čüą░ JTAG ą┐čĆąĖą╝ąĄąĮąĖą╝ąŠ ą║ ą╗čÄą▒ąŠą╣ JTAG-ą╝ąĖą║čĆąŠčüčģąĄą╝ąĄ.

ąĪčéą░ąĮą┤ą░čĆčé JTAG ąŠą▒ąŠąĘąĮą░čćą░ąĄčé ą┐čĆąĖąĮčåąĖą┐čŗ čüčģąĄą╝ąŠč鹥čģąĮąĖą║ąĖ, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ, ąŠą▒čüą╗čāąČąĖą▓ą░ąĮąĖčÅ ąĖ ą┐ąŠą┤ą┤ąĄčƹȹ║ąĖ čüąŠą▒čĆą░ąĮąĮčŗčģ ą┐ąĄčćą░čéąĮčŗčģ ą┐ą╗ą░čé. ąŁčéą░ čüčģąĄą╝ąŠč鹥čģąĮąĖą║ą░ ą▓ą║ą╗čÄčćą░ąĄčé čüčéą░ąĮą┤ą░čĆčéąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü, č湥čĆąĄąĘ ą║ąŠč鹊čĆčŗą╣ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ąĖąĮčüčéčĆčāą║čåąĖąĖ ąĖ ą┤ą░ąĮąĮčŗąĄ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ. ą×ą┐čĆąĄą┤ąĄą╗ąĄąĮ ąĮą░ą▒ąŠčĆ čäčāąĮą║čåąĖą╣ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ, ą▓ą║ą╗čÄčćą░čÅ čĆąĄą│ąĖčüčéčĆ ą┐ąŠą│čĆą░ąĮąĖčćąĮąŠą│ąŠ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ (boundary-scan register), čéą░ą║ čćč鹊 ą║ąŠą╝ą┐ąŠąĮąĄąĮčé ą╝ąŠąČąĄčé ąŠčéą▓ąĄčćą░čéčī ąĮą░ ą╝ąĖąĮąĖą╝ą░ą╗čīąĮčŗą╣ ąĮą░ą▒ąŠčĆ ąĖąĮčüčéčĆčāą║čåąĖą╣, čćč鹊ą▒čŗ ą┐ąŠą╝ąŠčćčī ą┐čĆąŠą▓ąĄčĆąĖčéčī čåąĄą╗ąŠčüčéąĮąŠčüčéčī čåąĄą┐ąĄą╣ ą┐ąĄčćą░čéąĮčŗčģ ą┐ą╗ą░čé.

ąĪčéą░ąĮą┤ą░čĆčé ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ą╗ąŠą│ąĖą║čā č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ, ą║ąŠč鹊čĆą░čÅ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓ą║ą╗čÄč湥ąĮą░ ą▓ čüčģąĄą╝čā, čćč鹊ą▒čŗ ą▓čŗą┐ąŠą╗ąĮąĖčéčī čüą╗ąĄą┤čāčÄčēąĖąĄ č鹥čüčéčŗ:

ŌĆó ą¤čĆąŠą▓ąĄčĆą║ą░ čüąŠąĄą┤ąĖąĮąĄąĮąĖą╣ ą╝ąĄąČą┤čā ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą╝ JTAG (ą▓ ąĮą░čłąĄą╝ čüą╗čāčćą░ąĄ čŹč鹊 ą┐čĆąŠčåąĄčüčüąŠčĆ Blackfin) ąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ą╝ąĖ, ą║ąŠč鹊čĆčŗąĄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ąĮą░ ą┐ąĄčćą░čéąĮčāčÄ ą┐ą╗ą░čéčā.

ŌĆó ąóąĄčüčéąĖčĆąŠą▓ą░ąĮąĖąĄ čüą░ą╝ąŠą│ąŠ ą┐čĆąŠčåąĄčüčüąŠčĆą░ Blackfin.

ŌĆó ą×čéčüą╗ąĄąČąĖą▓ą░ąĮąĖąĄ ąĖą╗ąĖ ą╝ąŠą┤ąĖčäąĖą║ą░čåąĖčÅ ą░ą║čéąĖą▓ąĮąŠčüčéąĖ čüčģąĄą╝čŗ ą▓ąŠ ą▓čĆąĄą╝čÅ ąĮąŠčĆą╝ą░ą╗čīąĮąŠą│ąŠ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖčÅ ą║ąŠą╝ą┐ąŠąĮąĄąĮčéą░ JTAG.

ąøąŠą│ąĖą║ą░ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ ąŠčüąĮąŠą▓ą░ąĮą░ ąĮą░ čĆąĄą│ąĖčüčéčĆąĄ ą┐ąŠą│čĆą░ąĮąĖčćąĮąŠą│ąŠ čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ (boundary-scan register) ąĖ ą┤čĆčāą│ąĖčģ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮčŗčģ ą▒ą╗ąŠą║ą░čģ. ąÜ ą╗ąŠą│ąĖą║ąĄ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą┤ąŠčüčéčāą┐ č湥čĆąĄąĘ ą┐ąŠčĆčé č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ (test access port, TAP).

ą¤ąŠą╗ąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ čüčéą░ąĮą┤ą░čĆčéą░ JTAG ą╝ąŠąČąĮąŠ ąĮą░ą╣čéąĖ ą▓ ą┤ąŠą║čāą╝ąĄąĮčéą░čåąĖąĖ "IEEE Standard Test Access Port and Boundary-Scan Architecture", ISBN 1-55937-350-4 [1].

[ąÉčĆčģąĖč鹥ą║čéčāčĆą░ čüąĖčüč鹥ą╝čŗ ą┐ąŠą│čĆą░ąĮąĖčćąĮąŠą│ąŠ čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ (boundary-scan)]

ąøąŠą│ąĖą║ą░ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ boundary-scan čüąŠčüč鹊ąĖčé ąĖąĘ čüą╗ąĄą┤čāčÄčēąĖčģ čāąĘą╗ąŠą▓:

ŌĆó ąśąĮč鹥čĆč乥ą╣čü TAP, čüąŠčüč鹊čÅčēąĖą╣ ąĖąĘ 5 čüąĖą│ąĮą░ą╗čīąĮčŗčģ ą▓čŗą▓ąŠą┤ąŠą▓ (čüą╝. čéą░ą▒ą╗ąĖčåčā C-1). ąóą░ą║ąČąĄ ą▓ ąĖąĮč鹥čĆč乥ą╣čü ą▓čģąŠą┤ąĖčé ąŠą▒čēąĖą╣ ą┐čĆąŠą▓ąŠą┤ (GND) ąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ čüąĖčüč鹥ą╝čŗ (ą▓ čéą░ą▒ą╗ąĖčåąĄ čŹčéąĖ čüąĖą│ąĮą░ą╗čŗ ąĮąĄ ą┐ąŠą║ą░ąĘą░ąĮčŗ).

ŌĆó ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ TAP, ą║ąŠč鹊čĆčŗą╣ č湥čĆąĄąĘ čĆąĄą│ąĖčüčéčĆčŗ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ čāą┐čĆą░ą▓ą╗čÅąĄčé ą▓čüąĄą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčīčÄ čüąŠą▒čŗčéąĖą╣ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ.

ŌĆó ąĀąĄą│ąĖčüčéčĆ ąĖąĮčüčéčĆčāą║čåąĖą╣ (instruction register, IR), ąĖąĘ ą║ąŠč鹊čĆąŠą│ąŠ 5-čĆą░ąĘčĆčÅą┤ąĮčŗąĄ ą║ąŠą┤čŗ ąĖąĮčüčéčĆčāą║čåąĖąĖ ą▓čŗą▒ąĖčĆą░čÄčé čĆąĄąČąĖą╝ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ, ą║ąŠč鹊čĆčŗą╣ ą▓čŗą┐ąŠą╗ąĮčÅąĄčé ąĮčāąČąĮčāčÄ ąŠą┐ąĄčĆą░čåąĖčÄ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ.

ŌĆó ąØąĄčüą║ąŠą╗čīą║ąŠ čĆąĄą│ąĖčüčéčĆąŠą▓ ą┤ą░ąĮąĮčŗčģ, ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗčģ ą▓ čüčéą░ąĮą┤ą░čĆč鹥 JTAG.

ąóą░ą▒ą╗ąĖčåą░ C-1. ąÆčŗą▓ąŠą┤čŗ ąĖąĮč鹥čĆč乥ą╣čüą░ Test Access Port (TAP).

| ąĪąĖą│ąĮą░ą╗ JTAG |

ąóąĖą┐ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| TDI |

ąÆčģąŠą┤ |

Test Data Input, ą▓čģąŠą┤ ą┤ą░ąĮąĮčŗčģ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ. |

| TMS |

Test Mode Select, ą▓čŗą▒ąŠčĆ čĆąĄąČąĖą╝ą░ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ. |

| TCK |

Test Clock, čéą░ą║čéčŗ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ. |

| ~TRST |

Test Reset, čüą▒čĆąŠčü ą╗ąŠą│ąĖą║ąĖ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ. |

| TDO |

ąÆčŗčģąŠą┤ |

Test Data Out, ą▓čŗčģąŠą┤ ą┤ą░ąĮąĮčŗčģ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ. |

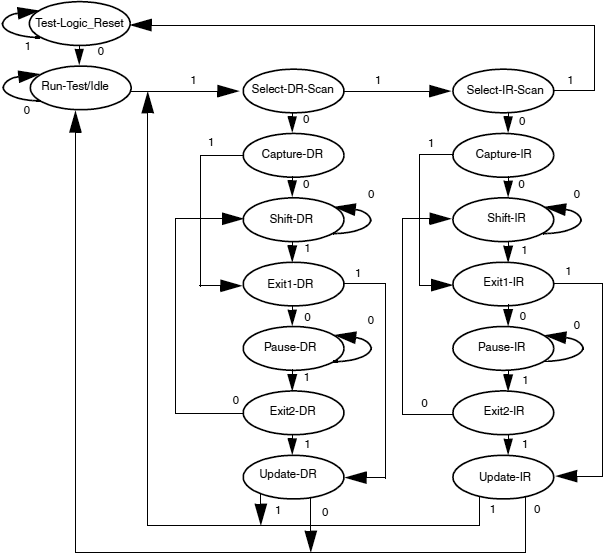

ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ TAP čŹč鹊 čüąĖąĮčģčĆąŠąĮąĮčŗą╣ ą║ąŠąĮąĄčćąĮčŗą╣ ą░ą▓č鹊ą╝ą░čé (finite-state machine) čü 16 čüąŠčüč鹊čÅąĮąĖčÅą╝ąĖ, čāą┐čĆą░ą▓ą╗čÅąĄą╝čŗą╣ ą▓čŗą▓ąŠą┤ą░ą╝ąĖ TCK ąĖ TMS. ą¤ąĄčĆąĄčģąŠą┤čŗ ą╝ąĄąČą┤čā čüąŠčüč鹊čÅąĮąĖčÅą╝ąĖ ą░ą▓č鹊ą╝ą░čéą░ ą┐čĆąŠąĖčüčģąŠą┤čÅčé ą┐ąŠ čäčĆąŠąĮčéčā ąĮą░čĆą░čüčéą░ąĮąĖčÅ ąĖą╝ą┐čāą╗čīčüą░ TCK, ąĖ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮčŗ čüąŠčüč鹊čÅąĮąĖąĄą╝ ą▓čŗą▓ąŠą┤ą░ TMS (ą╝ąŠąČąĄčé ąĮą░čģąŠą┤ąĖčéčīčüčÅ ą╗ąĖą▒ąŠ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą╗ąŠą│. 1, ą╗ąĖą▒ąŠ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą╗ąŠą│. 0). ą¤ąŠą╗ąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ ą┐čĆąŠčåąĄčüčüą░ čĆą░ą▒ąŠčéčŗ čüą╝. ą▓ čüčéą░ąĮą┤ą░čĆč鹥 JTAG. ąØą░ čĆąĖčü. C-1 ą┐ąŠą║ą░ąĘą░ąĮą░ ą┤ąĖą░ą│čĆą░ą╝ą╝ą░ ą┐ąĄčĆąĄčģąŠą┤ą░ čüąŠčüč鹊čÅąĮąĖą╣ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ TAP.

ąĀąĖčü. C-1. ąöąĖą░ą│čĆą░ą╝ą╝ą░ čüąŠčüč鹊čÅąĮąĖą╣ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ TAP.

ą¤ąŠčÅčüąĮąĄąĮąĖčÅ ą║ čĆąĖčü. C-1:

DR Data Register, čĆąĄą│ąĖčüčéčĆ ą┤ą░ąĮąĮčŗčģ.

IR Instruction Register, čĆąĄą│ąĖčüčéčĆ ą║ąŠą╝ą░ąĮą┤čŗ.

Test-Logic_Reset čüąŠčüč鹊čÅąĮąĖąĄ čüą▒čĆąŠčüą░ ą╗ąŠą│ąĖą║ąĖ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ JTAG (ąĖčüčģąŠą┤ąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ).

Run-Test/Idle čüąŠčüč鹊čÅąĮąĖąĄ ąĮą░čćą░ą╗ą░ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ, ąŠąČąĖą┤ą░ąĮąĖąĄ. ą¤ąĄčĆąĄčģąŠą┤ąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą┐čĆąĖ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĖ č鹥čüč鹊ą▓ ąĖą╗ąĖ ąŠąČąĖą┤ą░ąĮąĖąĖ čüą╗ąĄą┤čāčÄčēąĄą╣ ą║ąŠą╝ą░ąĮą┤čŗ.

Select-DR-Scan, Select-IR-Scan čüąŠčüč鹊čÅąĮąĖąĄ, ą┐ąŠčüą╗ąĄ ą║ąŠč鹊čĆąŠą│ąŠ ą▒čāą┤ąĄčé ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖčéčīčüčÅ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖąĄ ą║ąŠą╝ą░ąĮą┤, ą┤ą░ąĮąĮčŗčģ.

Capture-DR, Capture-IR čüąŠčüč鹊čÅąĮąĖąĄ ą┐čĆąĖčæą╝ą░ ą║ąŠą╝ą░ąĮą┤, ą┤ą░ąĮąĮčŗčģ.

Shift-DR, Shift-IR čüąŠčüč鹊čÅąĮąĖąĄ čüą┤ą▓ąĖą│ą░ ą║ąŠą╝ą░ąĮą┤, ą┤ą░ąĮąĮčŗčģ.

Exit1-DR, Exit2-DR ą▓čŗčģąŠą┤ ąĖąĘ čĆąĄąČąĖą╝ą░ čĆą░ą▒ąŠčéčŗ čü ą┤ą░ąĮąĮčŗą╝ąĖ.

Exit1-IR, Exit2-IR ą▓čŗčģąŠą┤ ąĖąĘ čĆąĄąČąĖą╝ą░ čĆą░ą▒ąŠčéčŗ čü ą║ąŠą╝ą░ąĮą┤ą░ą╝ąĖ.

Pause-DR, Pause-IR čüąŠčüč鹊čÅąĮąĖąĄ ą┐ą░čāąĘčŗ.

Update-DR, Update-IR čüąŠčüč鹊čÅąĮąĖąĄ ą┐ąĄčĆąĄąĘą░ą┐ąĖčüąĖ ą┤ą░ąĮąĮčŗčģ ą▓ ą▓čŗčģąŠą┤ąĮčŗąĄ čĆąĄą│ąĖčüčéčĆčŗ ą┤ą░ąĮąĮčŗčģ ąĖ ą║ąŠą╝ą░ąĮą┤ (ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ ąĖ ą║ąŠą╝ą░ąĮą┤).

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ TAP ą▓čģąŠą┤ąĖčé ą▓ čüąŠčüč鹊čÅąĮąĖčÅ čüą▒čĆąŠčüą░ ą╗ąŠą│ąĖą║ąĖ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ (test-logic-reset), ą║ąŠą│ą┤ą░ TMS čāą┤ąĄą╗ąČąĖą▓ą░ąĄčéčüčÅ ą▓ ą╗ąŠą│. 1 ą┐ąŠčüą╗ąĄ 5 čéą░ą║č鹊ą▓ TCK. ąóąŠ ąČąĄ čüą░ą╝ąŠąĄ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé, ą║ąŠą│ą┤ą░ ą░čüąĖąĮčģčĆąŠąĮąĮąŠ ą▓čŗčüčéą░ą▓ą╗ąĄąĮ čüąĖą│ąĮą░ą╗ čüą▒čĆąŠčüą░ TRST. ąÆąĮąĄčłąĮąĖą╣ čüą▒čĆąŠčü čüąĖčüč鹥ą╝čŗ ąĮąĄ ą▓ą╗ąĖčÅąĄčé ąĮą░ čüąŠčüč鹊čÅąĮąĖąĄ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ TAP, ąĖ čüąŠčüč鹊čÅąĮąĖąĄ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ TAP čéą░ą║ąČąĄ ąĮąĄ ą▓ą╗ąĖčÅąĄčé ąĮą░ ą▓ąĮąĄčłąĮąĖą╣ čüąĖčüč鹥ą╝ąĮčŗą╣ čüą▒čĆąŠčü.