|

ąÆ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ATmega32U4, ą║ą░ą║ ąĖ ą┐ąŠčćčéąĖ ą▓ąŠ ą▓čüąĄ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčŗ AVR ATmega, ą▓čüčéčĆąŠąĄąĮ ą░ą┐ą┐ą░čĆą░čéąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü I2C. ą¤ąŠ č鹥čĆą╝ąĖąĮąŠą╗ąŠą│ąĖąĖ Atmel ąŠąĮ ąĮą░ąĘčŗą▓ą░ąĄčéčüčÅ Two Wire Interface, čüąŠą║čĆą░čēąĄąĮąĮąŠ TWI, čéą░ą║ čćč鹊 I2C ąĖ TWI čŹč鹊 ąŠą┤ąĮąŠ ąĖ č鹊 ąČąĄ. ąŁč鹊čé ą░ą┐ą┐ą░čĆą░čéąĮčŗą╣ TWI ąŠą▒ą╗ą░ą┤ą░ąĄčé čüą╗ąĄą┤čāčÄčēąĖą╝ąĖ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčÅą╝ąĖ:

ŌĆó ą¤čĆąŠčüč鹊ą╣, ąĮąŠ ą▓ č鹊 ąČąĄ ą▓čĆąĄą╝čÅ ą╝ąŠčēąĮčŗą╣ ąĖ ą│ąĖą▒ą║ąĖą╣ ą║ąŠą╝ą╝čāąĮąĖą║ą░čåąĖąŠąĮąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü, ą║ąŠč鹊čĆąŠą╝čā ąĮčāąČąĮčŗ č鹊ą╗čīą║ąŠ 2 čüąĖą│ąĮą░ą╗čīąĮčŗčģ ą╗ąĖąĮąĖąĖ.

ŌĆó ą¤ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ čĆą░ą▒ąŠčéą░ ą▓ ąŠą▒ąŠąĖčģ čĆąĄąČąĖą╝ą░čģ čłąĖąĮčŗ I2C (Master ąĖ Slave).

ŌĆó ą£ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ (MCU) ą╝ąŠąČąĄčé čĆą░ą▒ąŠčéą░čéčī ą╗ąĖą▒ąŠ ą║ą░ą║ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║, ą╗ąĖą▒ąŠ ą║ą░ą║ ą┐čĆąĖąĄą╝ąĮąĖą║.

ŌĆó ąĪčéą░ąĮą┤ą░čĆčéąĮąŠąĄ 7-čĆą░ąĘčĆčÅą┤ąĮąŠąĄ ą░ą┤čĆąĄčüąĮąŠąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ čłąĖąĮčŗ I2C ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ą░ą┤čĆąĄčüąŠą▓ą░čéčī (ą┐ąŠą┤ą║ą╗čÄčćąĖčéčī ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠ ą║ čłąĖąĮąĄ) ą┤ąŠ 128 čĆą░ąĘąĮčŗčģ Slave-čāčüčéčĆąŠą╣čüčéą▓.

ŌĆó ą¤ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ą░čĆą▒ąĖčéčĆą░ąČ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ą╝ą░čüč鹥čĆąŠą▓ ąĮą░ ąŠą┤ąĮąŠą╣ čłąĖąĮąĄ (Multi-master Arbitration).

ŌĆó ąĪą║ąŠčĆąŠčüčéčī ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ąŠ 400 ą║ąōčå (400 ą║ąōčå čŹč鹊 čéą░ą║ ąĮą░ąĘčŗą▓ą░ąĄą╝čŗą╣ "ą▒čŗčüčéčĆčŗą╣" čĆąĄąČąĖą╝ I2C).

ŌĆó ąÆčŗčģąŠą┤ąĮčŗąĄ ą┤čĆą░ą╣ą▓ąĄčĆčŗ čü ąŠą│čĆą░ąĮąĖč湥ąĮąĖąĄą╝ čüą║ąŠčĆąŠčüčéąĖ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ (Slew-rate Limited Output Drivers).

ŌĆó ąĪčģąĄą╝ą░ ą┐ąŠą┤ą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąŠą╝ąĄčģ čāą┤ą░ą╗čÅąĄčé ą▓čŗą▒čĆąŠčüčŗ ąĮą░ čüąĖą│ąĮą░ą╗ą░čģ čłąĖąĮčŗ.

ŌĆó ą¤ąŠą╗ąĮąŠčüčéčīčÄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗą╣ ą░ą┤čĆąĄčü Slave-čāčüčéčĆąŠą╣čüčéą▓ą░ čü ą┐ąŠą┤ą┤ąĄčƹȹ║ąŠą╣ čäčāąĮą║čåąĖąĖ ąŠą▒čēąĄą│ąŠ ą▓čŗąĘąŠą▓ą░ (General Call).

ŌĆó ąĀą░čüą┐ąŠąĘąĮą░ą▓ą░ąĮąĖąĄ ą░ą┤čĆąĄčüą░ ą▓čŗą▓ąŠą┤ąĖčé AVR ąĖąĘ čüąĮą░, ą║ąŠą│ą┤ą░ ąŠąĮ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ ą┐ąŠąĮąĖąČąĄąĮąĮąŠą│ąŠ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ (Sleep Mode).

[ąÜčĆą░čéą║ąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ I2C/TWI]

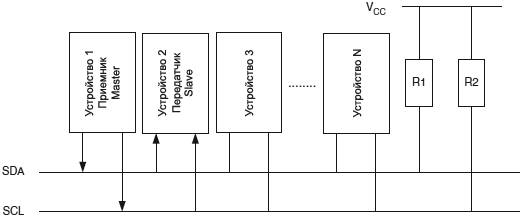

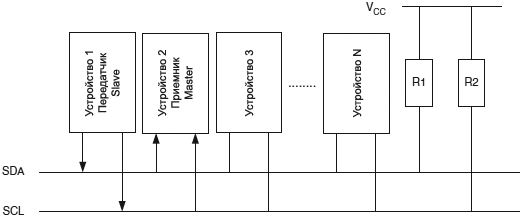

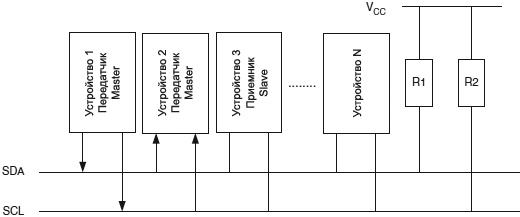

2-wire Serial Interface (TWI) ąĖą┤ąĄą░ą╗čīąĮąŠ ą┐ąŠą┤čģąŠą┤ąĖčé ą┤ą╗čÅ ą┐čĆąĖą╗ąŠąČąĄąĮąĖą╣, ą│ą┤ąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ. ą¤čĆąŠč鹊ą║ąŠą╗ TWI ą┐ąŠąĘą▓ąŠą╗čÅąĄčé čĆą░ąĘčĆą░ą▒ąŠčéčćąĖą║čā čüąĖčüč鹥ą╝čŗ čüąŠąĄą┤ąĖąĮąĖčéčī ą┤čĆčāą│ čü ą┤čĆčāą│ąŠą╝ ą┤ąŠ 128 čĆą░ąĘąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓, ąĖčüą┐ąŠą╗čīąĘčāčÅ č鹊ą╗čīą║ąŠ 2 ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗčģ čüąĖą│ąĮą░ą╗ą░ čłąĖąĮčŗ: čéą░ą║čéčŗ (SCL) ąĖ ą┤ą░ąĮąĮčŗąĄ (SDA). ąöą╗čÅ ąŠčĆą│ą░ąĮąĖąĘą░čåąĖąĖ čłąĖąĮčŗ čéčĆąĄą▒čāąĄčéčüčÅ ą╝ąĖąĮąĖą╝ą░ą╗čīąĮčŗą╣ ą▓ąĮąĄčłąĮąĖą╣ ąŠą▒ą▓ąĄčü - ą▓čüąĄą│ąŠ ą╗ąĖčłčī 2 ą▓ąĄčĆčģąĮąĖčģ ąĮą░ą│čĆčāąĘąŠčćąĮčŗčģ čĆąĄąĘąĖčüč鹊čĆą░ (pull-up), ą┐ąŠ ąŠą┤ąĮąŠą╝čā ąĮą░ ą║ą░ąČą┤čŗą╣ čüąĖą│ąĮą░ą╗ čłąĖąĮčŗ. ąÆčüąĄ čāčüčéčĆąŠą╣čüčéą▓ą░, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗąĄ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠ ą║ ąŠą┤ąĮąŠą╣ čłąĖąĮąĄ, ą┤ąŠą╗ąČąĮčŗ ąĖą╝ąĄčéčī ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮčŗą╣ ą░ą┤čĆąĄčü ąĖ ą╝ąĄčģą░ąĮąĖąĘą╝čŗ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą║ąŠąĮčäą╗ąĖą║čéąĮčŗčģ čüąĖčéčāą░čåąĖą╣ ąĮą░ čłąĖąĮąĄ, čüą▓ąŠą╣čüčéą▓ąĄąĮąĮčŗčģ ą┐čĆąŠč鹊ą║ąŠą╗čā TWI.

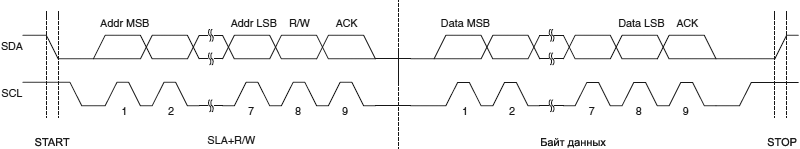

ąĀąĖčü. 20-1. ąĪąŠąĄą┤ąĖąĮąĄąĮąĖčÅ ąĮą░ čłąĖąĮąĄ TWI/I2C.

ąóąĄčĆą╝ąĖąĮąŠą╗ąŠą│ąĖčÅ TWI. ąÆ čŹč鹊ą╣ ą┤ąŠą║čāą╝ąĄąĮčéą░čåąĖąĖ (ą┐ąĄčĆąĄą▓ąŠą┤ ą┤ą░čéą░čłąĖčéą░ [1]) čćą░čüč鹊 ą▓čüčéčĆąĄčćą░čÄčéčüčÅ čüą╗ąĄą┤čāčÄčēąĖąĄ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ:

Master. ąŻčüčéčĆąŠą╣čüčéą▓ąŠ ąĮą░ čłąĖąĮąĄ (ąŠą▒čŗčćąĮąŠ čŹč鹊 MCU), ą║ąŠč鹊čĆąŠąĄ ąĖąĮąĖčåąĖąĖčĆčāąĄčé ąĖ ąĘą░ą▓ąĄčĆčłą░ąĄčé čéčĆą░ąĮąĘą░ą║čåąĖčÄ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ (ą▓ ą╗čÄą▒ąŠą╝ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĖ). Master čéą░ą║ąČąĄ ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ąĖą╝ą┐čāą╗čīčüčŗ čéą░ą║č鹊ą▓ SCL.

Slave. ąŁč鹊 čāčüčéčĆąŠą╣čüčéą▓ąŠ ą░ą┤čĆąĄčüčāąĄčéčüčÅ Master-čāčüčéčĆąŠą╣čüčéą▓ąŠą╝.

ą¤ąĄčĆąĄą┤ą░čéčćąĖą║. ąŻčüčéčĆąŠą╣čüčéą▓ąŠ, ą║ąŠč鹊čĆąŠąĄ ą┐ąŠą╝ąĄčēą░ąĄčé čüą▓ąŠąĖ ą┤ą░ąĮąĮčŗąĄ ąĮą░ čłąĖąĮčā (ą▓čŗą▓ąŠą┤ąĖčé ąĖčģ ąĮą░ čüąĖą│ąĮą░ą╗ SDA).

ą¤čĆąĖąĄą╝ąĮąĖą║. ąŻčüčéčĆąŠą╣čüčéą▓ąŠ, ą║ąŠč鹊čĆąŠąĄ čüčćąĖčéčŗą▓ą░ąĄčé ą┤ą░ąĮąĮčŗąĄ čü čłąĖąĮčŗ (čü čüąĖą│ąĮą░ą╗ą░ SDA).

START. ąĪąĖą│ąĮą░ą╗ ąĮą░čćą░ą╗ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĮą░ čłąĖąĮąĄ (ą┤ą░ą╗ąĄąĄ START), ąĘą░ą┤ą░ą▓ą░ąĄą╝čŗą╣ čüą┐ąĄčåąĖą░ą╗čīąĮąŠą╣ ą║ąŠą╝ą▒ąĖąĮą░čåąĖąĄą╣ čāčĆąŠą▓ąĮąĄą╣ SCL ąĖ SDA.

STOP. ąĪąĖą│ąĮą░ą╗ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĮą░ čłąĖąĮąĄ (ą┤ą░ą╗ąĄąĄ STOP), ąĘą░ą┤ą░ą▓ą░ąĄą╝čŗą╣ čüą┐ąĄčåąĖą░ą╗čīąĮąŠą╣ ą║ąŠą╝ą▒ąĖąĮą░čåąĖąĄą╣ čāčĆąŠą▓ąĮąĄą╣ SCL ąĖ SDA.

ACK. ąĪąĖą│ąĮą░ą╗ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą│ąŠ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ ąŠčé ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░.

NACK. ąĪąĖą│ąĮą░ą╗ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠą│ąŠ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ ąŠčé ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░.

General Call. ążčāąĮą║čåąĖčÅ ąŠą▒čēąĄą│ąŠ ą▓čŗąĘąŠą▓ą░, ąŠąĘąĮą░čćą░čÄčēą░čÅ ą┐ąĄčĆąĄą┤ą░čćčā ą▓čüąĄą╝ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗą╝ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ ąĮą░ čłąĖąĮąĄ (čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąĮąŠą╝čā ą░ą┤čĆąĄčüčā 0).

ąæąĖčé čüąĮąĖąČąĄąĮąĖčÅ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ čŹąĮąĄčĆą│ąĖąĖ TWI (Power Reduction TWI, ą▒ąĖčé PRTWI) ą▓ čĆąĄą│ąĖčüčéčĆąĄ Power Reduction Register 0 - PRR0 [1] ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ ą╗ąŠą│. 0, čćč鹊ą▒čŗ čĆą░ąĘčĆąĄčłąĖčéčī čĆą░ą▒ąŠčéčā TWI.

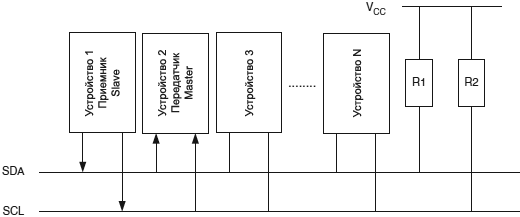

ąŁą╗ąĄą║čéčĆąĖč湥čüą║ąĖąĄ čüąŠąĄą┤ąĖąĮąĄąĮąĖčÅ. ąÜą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčüčāąĮą║ąĄ 20-1 ą▓čŗčłąĄ, ąŠą▒ą░ čüąĖą│ąĮą░ą╗ą░ čłąĖąĮčŗ ą┐ąŠą┤čéčÅąĮčāčéčŗ ą║ ą┐ą╗čÄčüčā ą┐ąĖčéą░ąĮąĖčÅ (VCC) č湥čĆąĄąĘ pull-up čĆąĄąĘąĖčüč鹊čĆčŗ (ąŠą▒čŗčćąĮąŠ ąĖčģ ąĮąŠą╝ąĖąĮą░ą╗ ąŠčé 4.7 ą║ą×ą╝ ą┤ąŠ 10 ą║ą×ą╝, ąĖ ą╝ąŠąČąĄčé ą╝ąĄąĮčÅčéčīčüčÅ ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ąĄą╝ą║ąŠčüčéąĖ čłąĖąĮčŗ ąĖ čüą║ąŠčĆąŠčüčéąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ). ąöčĆą░ą╣ą▓ąĄčĆčŗ čłąĖąĮčŗ TWI-čüąŠą▓ą╝ąĄčüčéąĖą╝čŗčģ čāčüčéčĆąŠą╣čüčéą▓ ą▓čüąĄą│ą┤ą░ ąĖą╝ąĄčÄčé ą▓čŗčģąŠą┤ čü ąŠą▒čēąĖą╝ čüč鹊ą║ąŠą╝ ąĖą╗ąĖ čü ąŠą▒čēąĖą╝ ą║ąŠą╗ą╗ąĄą║č鹊čĆąŠą╝. ąŁčéąĖą╝ čĆąĄą░ą╗ąĖąĘčāąĄčéčüčÅ ą╗ąŠą│ąĖč湥čüą║ą░čÅ čäčāąĮą║čåąĖčÅ "ą┐čĆąŠą▓ąŠą┤ąĮąŠąĄ ąś", ą║ąŠč鹊čĆą░čÅ ą▓ą░ąČąĮą░ ą┤ą╗čÅ ąŠčĆą│ą░ąĮąĖąĘą░čåąĖąĖ čĆą░ą▒ąŠčéčŗ ąĖąĮč鹥čĆč乥ą╣čüą░ I2C. ąØąĖąĘą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī (ą╗ąŠą│. 0) ąĮą░ čłąĖąĮąĄ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ąŠą┤ąĮąŠ ąĖą╗ąĖ ą▒ąŠą╗čīčłąĄąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čāčüčéčĆąŠą╣čüčéą▓ ąĮą░ čłąĖąĮąĄ ą▓čŗą▓ąŠą┤ąĖčé čüąĖą│ąĮą░ą╗ ą╗ąŠą│. 0. ąÆčŗčüąŠą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī ąĮą░ čłąĖąĮąĄ (ą╗ąŠą│. 1) ą┐ąŠčÅą▓ą╗čÅąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą▓čüąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┐ąĄčĆąĄą▓ąŠą┤čÅčé čüą▓ąŠąĖ ą▓čŗčģąŠą┤čŗ ąŠčéą║ą╗čÄč湥ąĮąĮąŠąĄ (čéčĆąĄčéčīąĄ) čüąŠčüč鹊čÅąĮąĖąĄ, ą┐ąŠąĘą▓ąŠą╗čÅčÅ č鹥ą╝ čüą░ą╝čŗą╝ pull-up čĆąĄąĘąĖčüč鹊čĆą░ą╝ ą┐ąŠą┤čéčÅąĮčāčéčī čāčĆąŠą▓ąĄąĮčī ą║ ą╗ąŠą│. 1. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ą▓čüąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗąĄ ą║ čłąĖąĮąĄ TWI čāčüčéčĆąŠą╣čüčéą▓ą░ AVR MCU ą┤ąŠą╗ąČąĮčŗ ą┐ąŠą╗čāčćą░čéčī ą┐ąĖčéą░ąĮąĖąĄ, čćč鹊ą▒čŗ ą▒čŗą╗ą░ ą▓ąŠąĘą╝ąŠąČąĮą░ ą╗čÄą▒ą░čÅ ąŠą┐ąĄčĆą░čåąĖčÅ ąĮą░ čłąĖąĮąĄ.

ąÜąŠą╗ąĖč湥čüčéą▓ąŠ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗčģ ą║ čłąĖąĮąĄ čāčüčéčĆąŠą╣čüčéą▓ ąŠą│čĆą░ąĮąĖčćąĖą▓ą░ąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą┐čĆąĄą┤ąĄą╗ąŠą╝ ąĄą╝ą║ąŠčüčéąĖ čüąĖą│ąĮą░ą╗ąŠą▓ čłąĖąĮčŗ 400 ą┐ąĖą║ąŠčäą░čĆą░ą┤ ąĖ 7-ą▒ąĖčéąĮčŗą╝ ą░ą┤čĆąĄčüąĮčŗą╝ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠą╝ ą┤ą╗čÅ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓. ą¤ąŠą┤čĆąŠą▒ąĮą░čÅ čüą┐ąĄčåąĖčäąĖą║ą░čåąĖčÅ čŹą╗ąĄą║čéčĆąĖč湥čüą║ąĖčģ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ čłąĖąĮčŗ TWI ą┤ą░ąĮą░ ą▓ čüąĄą║čåąĖąĖ "SPI Timing Characteristics" ąĮą░ čüčéčĆą░ąĮąĖčåąĄ 388 ą┤ą░čéą░čłąĖčéą░ [1]. ąŚą┤ąĄčüčī ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮąŠ ą┤ą▓ą░ ąŠčéą╗ąĖčćą░čÄčēąĖčģčüčÅ ąĮą░ą▒ąŠčĆą░ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║, ąŠą┤ąĖąĮ ąŠčéąĮąŠčüąĖčéčüčÅ ą║ čüčéą░ąĮą┤ą░čĆčéąĮąŠą╣ čüą║ąŠčĆąŠčüčéąĖ 100 ą║ąōčå ąĖ ąĮąĖąČąĄ, ąĖ ą┤čĆčāą│ą░čÅ ą║ čüą║ąŠčĆąŠčüčéčÅą╝ ą┤ąŠ 400 ą║ąōčå.

[ą¤ąĄčĆąĄą┤ą░čćą░ ą┤ą░ąĮąĮčŗčģ ąĖ č乊čĆą╝ą░čé čäčĆąĄą╣ą╝ą░]

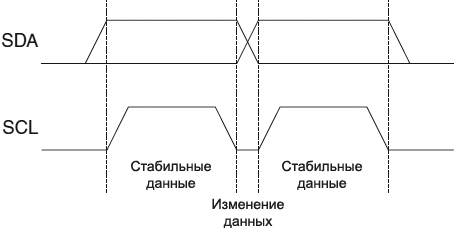

ą¤ąĄčĆąĄą┤ą░čćą░ ą▒ąĖčé. ąÜą░ąČą┤čŗą╣ ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ, ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗą╣ ą┐ąŠ čłąĖąĮąĄ TWI č湥čĆąĄąĘ čüąĖą│ąĮą░ą╗ SDA, čüąŠą┐čĆąŠą▓ąŠąČą┤ą░ąĄčéčüčÅ ąĖą╝ą┐čāą╗čīčüąŠą╝ čéą░ą║č鹊ą▓ ąĮą░ čüąĖą│ąĮą░ą╗ąĄ SCK. ąŻčĆąŠą▓ąĄąĮčī čüąĖą│ąĮą░ą╗ą░ SDA ą┤ąŠą╗ąČąĄąĮ ąŠčüčéą░ą▓ą░čéčīčüčÅ čüčéą░ą▒ąĖą╗čīąĮčŗą╝, ą┐ąŠą║ą░ čüąĖą│ąĮą░ą╗ čéą░ą║č鹊ą▓ SCK ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą╗ąŠą│. 1. ąĢą┤ąĖąĮčüčéą▓ąĄąĮąĮąŠąĄ ąĖčüą║ą╗čÄč湥ąĮąĖąĄ ąĖąĘ čŹč鹊ą│ąŠ ą┐čĆą░ą▓ąĖą╗ą░ ąŠčéąĮąŠčüąĖčéčüčÅ ą║ ą│ąĄąĮąĄčĆą░čåąĖąĖ start condition ąĖ stop condition.

ąĀąĖčü. 20-2. ąöąŠčüč鹊ą▓ąĄčĆąĮąŠčüčéčī ą┤ą░ąĮąĮčŗčģ.

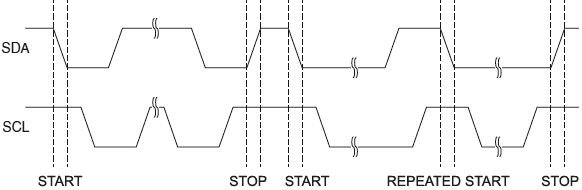

ąĪąĖą│ąĮą░ą╗čŗ START ąĖ STOP. Master ąĖąĮąĖčåąĖąĖčĆčāąĄčé ąĖ ąĘą░ą▓ąĄčĆčłą░ąĄčé ą┐ąĄčĆąĄą┤ą░čćčā ą┤ą░ąĮąĮčŗčģ. ą¤ąĄčĆąĄą┤ą░čćą░ ąĖąĮąĖčåąĖąĖčĆčāąĄčéčüčÅ, ą║ąŠą│ą┤ą░ Master ą▓čŗą┤ą░ąĄčé ąĮą░ čłąĖąĮčā čüąĖą│ąĮą░ą╗ START, ąĖ ą┐ąĄčĆąĄą┤ą░čćą░ ąĘą░ą▓ąĄčĆčłą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ Master ą▓čŗą┤ą░ąĄčé ąĮą░ čłąĖąĮčā čüąĖą│ąĮą░ą╗ STOP. ą£ąĄąČą┤čā čüąĖą│ąĮą░ą╗ą░ą╝ąĖ START ąĖ STOP čłąĖąĮą░ čüčćąĖčéą░ąĄčéčüčÅ ąĘą░ąĮčÅč鹊ą╣, ąĖ ąĮąĖą║ą░ą║ąĖąĄ ą┤čĆčāą│ąĖąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ master ąĮąĄ ą┤ąŠą╗ąČąĮčŗ ą┐čŗčéą░čéčīčüčÅ ą┐ąŠą╗čāčćąĖčéčī čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čłąĖąĮąŠą╣. ąĪą┐ąĄčåąĖą░ą╗čīąĮčŗą╣ čüą╗čāčćą░ą╣, ą║ąŠą│ą┤ą░ ą▓čŗą┤ą░ąĄčéčüčÅ ąĮąŠą▓čŗą╣ čüąĖą│ąĮą░ą╗ START ą╝ąĄąČą┤čā čüąĖą│ąĮą░ą╗ą░ą╝ąĖ START ąĖ STOP. ąŁč鹊 ąĮą░ąĘčŗą▓ą░ąĄčéčüčÅ ą┐ąŠą▓č鹊čĆąĮčŗą╝ čüąĖą│ąĮą░ą╗ąŠą╝ ąĘą░ą┐čāčüą║ą░ (REPEATED START, ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ, ą║ąŠą│ą┤ą░ Master čģąŠč湥čé ąĖąĮąĖčåąĖąĖčĆąŠą▓ą░čéčī ąĮąŠą▓čāčÄ ą┐ąĄčĆąĄą┤ą░čćčā ą▒ąĄąĘ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ čüą▓ąŠąĄą│ąŠ ą║ąŠąĮčéčĆąŠą╗čÅ ąĮą░ą┤ čłąĖąĮąŠą╣. ą¤ąŠčüą╗ąĄ čüąĖą│ąĮą░ą╗ą░ REPEATED START čłąĖąĮą░ čüčćąĖčéą░ąĄčéčüčÅ ąĘą░ąĮčÅč鹊ą╣ ą┤ąŠ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ čüąĖą│ąĮą░ą╗ą░ STOP. ąŁč鹊 ąĖą┤ąĄąĮčéąĖčćąĮąŠ ą┐ąŠą▓ąĄą┤ąĄąĮąĖčÄ čüąĖą│ąĮą░ą╗ą░ START, ąĖ ą┐ąŠčŹč鹊ą╝čā ą┤ą░ą╗ąĄąĄ ą▓ č鹥ą║čüč鹥 ąŠą┐ąĖčüą░ąĮąĖąĄ START ąŠčéąĮąŠčüąĖčéčüčÅ ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠ ąĖ ą║ ąŠą┐ąĖčüą░ąĮąĖčÄ REPEATED START, ąĄčüą╗ąĖ ąĮąĄ čāą║ą░ąĘą░ąĮąŠ ąĮąĄčćč鹊 ąĖąĮąŠąĄ. ąöą░ą╗ąĄąĄ ąŠą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ, čćč鹊 čüąĖą│ąĮą░ą╗čŗ START ąĖ STOP ą│ąĄąĮąĄčĆąĖčĆčāčÄčéčüčÅ ą┐čāč鹥ą╝ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ čāčĆąŠą▓ąĮčÅ SDA, ą║ąŠą│ą┤ą░ SCL ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą╗ąŠą│. 1.

ąĀąĖčü. 20-3. ąĪąĖą│ąĮą░ą╗čŗ START, REPEATED START ąĖ STOP.

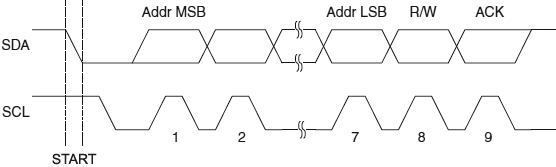

ążąŠčĆą╝ą░čé ą┐ą░ą║ąĄčéą░ ą░ą┤čĆąĄčüą░. ąÆčüąĄ ą┐ą░ą║ąĄčéčŗ ą░ą┤čĆąĄčüą░ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ą┐ąŠ čłąĖąĮąĄ TWI ą┐ąŠčüčŗą╗ą║ą░ą╝ąĖ ąĖąĘ 9 ą▒ąĖčé, ąŠą┤ąĖąĮ ąĖąĘ ą║ąŠč鹊čĆčŗčģ ą▒ąĖčé čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čćč鹥ąĮąĖąĄą╝/ąĘą░ą┐ąĖčüčīčÄ (READ/WRITE bit) ąĖ ąŠą┤ąĖąĮ ą▒ąĖčé ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ (acknowledge bit). ąĢčüą╗ąĖ ą▒ąĖčé READ/WRITE čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, č鹊 ą▒čāą┤ąĄčé ą▓čŗą┐ąŠą╗ąĮąĄąĮą░ ąŠą┐ąĄčĆą░čåąĖčÅ čćč鹥ąĮąĖčÅ, ąĖąĮą░č湥 ą▒čāą┤ąĄčé ą▓čŗą┐ąŠą╗ąĮąĄąĮą░ ąŠą┐ąĄčĆą░čåąĖčÅ ąĘą░ą┐ąĖčüąĖ. ąÜąŠą│ą┤ą░ Slave-čāčüčéčĆąŠą╣čüčéą▓ąŠ čĆą░čüą┐ąŠąĘąĮą░ąĄčé čüą▓ąŠą╣ ą░ą┤čĆąĄčü, ąŠąĮąŠ ą┤ąŠą╗ąČąĮąŠ ą┐ąĄčĆąĄą▓ąĄčüčéąĖ čüą▓ąŠą╣ čüąĖą│ąĮą░ą╗ SDA ą▓ ą╗ąŠą│. 0, ą║ąŠą│ą┤ą░ ą┐ąŠčÅą▓ąĖą╗čüčÅ ą┤ąĄą▓čÅčéčŗą╣ ąĖą╝ą┐čāą╗čīčü SCL, čćč鹊 ąĮą░ąĘčŗą▓ą░ąĄčéčüčÅ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮčŗą╝ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖąĄą╝ (ACK). ąĢčüą╗ąĖ ą░ą┤čĆąĄčüąŠą▓ą░ąĮąĮąŠąĄ Slave-čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĘą░ąĮčÅč鹊, ąĖą╗ąĖ ą┐ąŠ ą║ą░ą║ąŠą╣-č鹊 ą┤čĆčāą│ąŠą╣ ą┐čĆąĖčćąĖąĮąĄ, ąĖą╗ąĖ ąĄčüą╗ąĖ ą░ą┤čĆąĄčüąŠą▓ą░ąĮąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮąĄ ą┐čĆąĖčüčāčéčüčéą▓čāąĄčé ąĮą░ čłąĖąĮąĄ, č鹊 ą▓ ą╝ąŠą╝ąĄąĮčé ą┤ąĄą▓čÅč鹊ą│ąŠ ąĖą╝ą┐čāą╗čīčüą░ SCL čüąĖą│ąĮą░ą╗ SDA ą▒čāą┤ąĄčé ąŠčüčéą░ą▓ą░čéčīčüčÅ ą▓ ą╗ąŠą│. 1, čćč鹊 ąĮą░ąĘčŗą▓ą░ąĄčéčüčÅ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮčŗą╝ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖąĄą╝ (NACK). ą¤ąŠčüą╗ąĄ čŹč鹊ą│ąŠ Master ą╝ąŠąČąĄčé ą▓čŗą┤ą░čéčī čüąĖą│ąĮą░ą╗ STOP ąĖą╗ąĖ čüąĖą│ąĮą░ą╗ REPEATED START, čćč鹊ą▒čŗ ąĖąĮąĖčåąĖąĖčĆąŠą▓ą░čéčī ąĮąŠą▓čāčÄ ą┐ąĄčĆąĄą┤ą░čćčā. ą¤ą░ą║ąĄčé ą░ą┤čĆąĄčüą░, čüąŠčüč鹊čÅčēąĖą╣ ąĖąĘ slave-ą░ą┤čĆąĄčüą░ ąĖ ą▒ąĖčéą░ READ ąĖą╗ąĖ WRITE, ąĮą░ąĘčŗą▓ą░ąĄčéčüčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ SLA+R ąĖą╗ąĖ SLA+W.

ąĪąĮą░čćą░ą╗ą░ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ čüčéą░čĆčłąĖą╣ ą▒ąĖčé (MSB) ą░ą┤čĆąĄčüą░. ąĀą░ąĘčĆą░ą▒ąŠčéčćąĖą║ čüąĖčüč鹥ą╝čŗ čüą▓ąŠą▒ąŠą┤ąĄąĮ ą▓ čĆą░čüą┐čĆąĄą┤ąĄą╗ąĄąĮąĖąĖ ą░ą┤čĆąĄčüąĮąŠą│ąŠ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ą░ čłąĖąĮčŗ (čĆčāą║ąŠą▓ąŠą┤čüčéą▓čāčÅčüčī ą┐čĆąĖ čŹč鹊ą╝ ą┐ą░čĆą░ą╝ąĄčéčĆą░ą╝ąĖ ą░ą┤čĆąĄčüąŠą▓ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓), ąŠą┤ąĮą░ą║ąŠ ą░ą┤čĆąĄčü 0000 000 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮ ą┤ą╗čÅ čäčāąĮą║čåąĖąĖ ąŠą▒čēąĄą│ąŠ ą▓čŗąĘąŠą▓ą░ (general call).

ąÜąŠą│ą┤ą░ ą▓čŗą┤ą░ąĄčéčüčÅ general call, ą▓čüąĄ slave-čāčüčéčĆąŠą╣čüčéą▓ą░ ą┤ąŠą╗ąČąĮčŗ ąŠčéą▓ąĄčéąĖčéčī ą┐ąĄčĆąĄą▓ąŠą┤ąŠą╝ čüąĖą│ąĮą░ą╗ą░ SDA ą▓ ą╗ąŠą│. 0 ąĮą░ čüą╗ąŠč鹥 ą▒ąĖčéą░ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ (čé. ąĄ. ą▓čŗą┤ą░čéčī ACK). ążčāąĮą║čåąĖčÅ general call ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ, ą║ąŠą│ą┤ą░ Master čģąŠč湥čé ą┐ąĄčĆąĄą┤ą░čéčī ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠąĄ čüąŠąŠą▒čēąĄąĮąĖąĄ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ą▓čüąĄą╝ slave-čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ ą▓ čüąĖčüč鹥ą╝ąĄ. ąÜąŠą│ą┤ą░ ąĘą░ ą░ą┤čĆąĄčüąŠą╝ general call ąĖą┤ąĄčé ą▒ąĖčé WRITE, ą▓čüąĄ slave-čāčüčéčĆąŠą╣čüčéą▓ą░, ąĮą░čüčéčĆąŠąĄąĮąĮčŗąĄ ąĮą░ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖąĄ general call, ą▒čāą┤čāčé ą▓čŗą▓ąŠą┤ąĖčéčī ąĮą░ ą╗ąŠą│. 0 ąĮą░ SDA ą▓ ą╝ąŠą╝ąĄąĮčé čåąĖą║ą╗ą░ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ. ą¤ąŠčüą╗ąĄą┤čāčÄčēąĖąĄ ą┐ą░ą║ąĄčéčŗ ą┤ą░ąĮąĮčŗčģ ą▒čāą┤čāčé ą┐čĆąĖąĮčÅčéčŗ ą▓čüąĄą╝ąĖ slave-čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ, ą║ąŠč鹊čĆčŗąĄ ą┐ąŠą┤čéą▓ąĄčĆą┤ąĖą╗ąĖ general call. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ą┐ąĄčĆąĄą┤ą░čćą░ ą░ą┤čĆąĄčüą░ general call, ąĘą░ ą║ąŠč鹊čĆčŗą╝ ąĖą┤ąĄčé ą▒ąĖčéčŗ READ, ą▒čāą┤ąĄčé ą▒ąĄčüčüą╝čŗčüą╗ąĄąĮąĮąŠą╣, ą┐ąŠč鹊ą╝čā čćč鹊 ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ą║ąŠą╗ą╗ąĖąĘąĖąĖ, ąĄčüą╗ąĖ ąĮąĄčüą║ąŠą╗čīą║ąŠ slave-čāčüčéčĆąŠą╣čüčéą▓ ąĮą░čćąĮčāčé ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī čĆą░ąĘąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ.

ąÆčüąĄ ą░ą┤čĆąĄčüą░ č乊čĆą╝ą░čéą░ 1111 xxx ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ ą┤ą╗čÅ ą▒čāą┤čāčēąĄą│ąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ.

ąĀąĖčü. 20-4. ążąŠčĆą╝ą░čé ą┐ą░ą║ąĄčéą░ ą░ą┤čĆąĄčüą░.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: Addr MSB ąŠąĘąĮą░čćą░ąĄčé čüčéą░čĆčłąĖą╣ ą▒ąĖčé ą░ą┤čĆąĄčüą░, Addr LSB ą╝ą╗ą░ą┤čłąĖą╣ ą▒ąĖčé ą░ą┤čĆąĄčüą░.

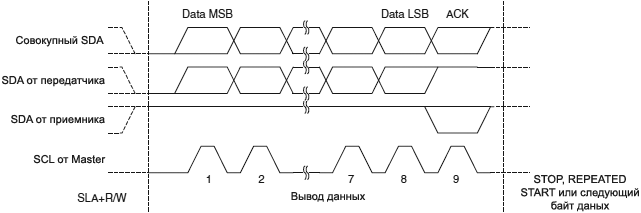

ążąŠčĆą╝ą░čé ą┐ą░ą║ąĄčéą░ ą┤ą░ąĮąĮčŗčģ. ąÆčüąĄ ą┐ą░ą║ąĄčéčŗ, ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗąĄ ą┐ąŠ čłąĖąĮąĄ TWI, ąĖą╝ąĄčÄčé ą┤ą╗ąĖąĮčā 9 ą▒ąĖčé, čüąŠčüč鹊čÅčēąĖąĄ ąĖąĘ ą▒ą░ą╣čéą░ ą┤ą░ąĮąĮčŗčģ (8 ą▒ąĖčé) ąĖ ą▒ąĖčéą░ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ. ąÆąŠ ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ Master ą│ąĄąĮąĄčĆąĖčĆčāąĄčé čüąĖą│ąĮą░ą╗čŗ START ąĖ STOP, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ ą┐čĆąĖąĄą╝ąĮąĖą║ (slave-čāčüčéčĆąŠą╣čüčéą▓ąŠ) ąŠčéą▓ąĄčćą░ąĄčé ąĘą░ ą▓čŗą┤ą░čćčā ą▒ąĖčéą░ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ ą┐čĆąĖąĄą╝ą░. ąÜą░ą║ čāąČąĄ čāą┐ąŠą╝ąĖąĮą░ą╗ąŠčüčī, ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠąĄ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖąĄ (ACK) ą▓čŗą┤ą░ąĄčéčüčÅ ą┐čĆąĖąĄą╝ąĮąĖą║ąŠą╝ ą┐čāč鹥ą╝ ą┐ąĄčĆąĄą▓ąŠą┤ą░ čüąĖą│ąĮą░ą╗ą░ SDA ą▓ ą╗ąŠą│. 0 ą▓ąŠ ą▓čĆąĄą╝čÅ ą┤ąĄą▓čÅč鹊ą│ąŠ ąĖą╝ą┐čāą╗čīčüą░ SCL. ąĢčüą╗ąĖ ą┐čĆąĖąĄą╝ąĮąĖą║ ąŠčüčéą░ą▓ąĖą╗ ą╗ąĖąĮąĖčÄ SDA ą▓ ą╗ąŠą│. 1, č鹊 čŹč鹊 ąŠąĘąĮą░čćą░ąĄčé ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠąĄ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖąĄ (NACK). ąÜąŠą│ą┤ą░ ą┐čĆąĖąĄą╝ąĮąĖą║ ą┐čĆąĖąĮčÅą╗ ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ą▒ą░ą╣čé, ąĖą╗ąĖ ą┐ąŠ ąĮąĄą║ąŠč鹊čĆčŗą╝ ą┐čĆąĖčćąĖąĮą░ą╝ ąĮąĄ ą╝ąŠąČąĄčé ą┐čĆąĖąĮąĖą╝ą░čéčī ą▒ąŠą╗čīčłąĄ ą▒ą░ą╣čéčŗ, ąŠąĮ ą┤ąŠą╗ąČąĄąĮ ąŠą┐ąŠą▓ąĄčüčéąĖčéčī ąŠą▒ čŹč鹊ą╝ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ čüąĖą│ąĮą░ą╗ąŠą╝ NACK ą┐ąŠčüą╗ąĄ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ ą▒ą░ą╣čéą░. ąĪčéą░čĆčłąĖą╣ ą▒ąĖčé (MSB) ą▒ą░ą╣čéą░ ą┤ą░ąĮąĮčŗčģ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą┐ąĄčĆą▓čŗą╝.

ąĀąĖčü. 20-5. ążąŠčĆą╝ą░čé ą┐ą░ą║ąĄčéą░ ą┤ą░ąĮąĮčŗčģ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: Data MSB ąŠąĘąĮą░čćą░ąĄčé čüčéą░čĆčłąĖą╣ ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ, Data LSB ą╝ą╗ą░ą┤čłąĖą╣ ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ.

ąÜąŠą╝ą▒ąĖąĮąĖčĆąŠą▓ą░ąĮąĖąĄ ą▓ ą┐ąĄčĆąĄą┤ą░č湥 ą┐ą░ą║ąĄč鹊ą▓ ą░ą┤čĆąĄčüą░ ąĖ ą┤ą░ąĮąĮčŗčģ. ą¤ąĄčĆąĄą┤ą░čćą░ ąŠą▒čŗčćąĮąŠ čüąŠčüč鹊ąĖčé ąĖąĘ START, SLA+R ąĖą╗ąĖ SLA+W, ąŠą┤ąĮąŠą│ąŠ ąĖą╗ąĖ ą▒ąŠą╗čīčłąĄą│ąŠ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ą┐ą░ą║ąĄč鹊ą▓ ą┤ą░ąĮąĮčŗčģ ąĖ STOP. ą¤čāčüč鹊ąĄ čüąŠąŠą▒čēąĄąĮąĖąĄ, čüąŠčüč鹊čÅčēąĄąĄ ąĖąĘ START, ąĘą░ ą║ąŠč鹊čĆčŗą╝ čüą╗ąĄą┤čāąĄčé čüčĆą░ąĘčā STOP, čÅą▓ą╗čÅąĄčéčüčÅ ąĮąĄąĘą░ą║ąŠąĮąĮčŗą╝. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ą┐čĆąŠą▓ąŠą┤ąĮąŠąĄ ąś ąĮą░ čüąĖą│ąĮą░ą╗ąĄ SCL ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ "čĆčāą║ąŠą┐ąŠąČą░čéąĖčÅ" ą╝ąĄąČą┤čā Master ąĖ Slave. Slave-čāčüčéčĆąŠą╣čüčéą▓ąŠ ą╝ąŠąČąĄčé čĆą░čüčłąĖčĆąĖčéčī ą▓čĆąĄą╝čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ SCL ą┐čāč鹥ą╝ ą┐ąĄčĆąĄą▓ąŠą┤ą░ čüąĖą│ąĮą░ą╗ą░ SCL ą▓ ą╗ąŠą│. 0. ąŁč鹊 ą┐ąŠą╗ąĄąĘąĮąŠ, ąĄčüą╗ąĖ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░, čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮą░čÅ Master, čüą╗ąĖčłą║ąŠą╝ ą▓ąĄą╗ąĖą║ą░ ą┤ą╗čÅ Slave-čāčüčéčĆąŠą╣čüčéą▓ą░, ąĖ ąĄą╝čā čéčĆąĄą▒čāąĄčéčüčÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠąĄ ą▓čĆąĄą╝čÅ ą┤ą╗čÅ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą╝ąĄąČą┤čā ą┐ąĄčĆąĄą┤ą░čćą░ą╝ąĖ ą┤ą░ąĮąĮčŗčģ. ąĀą░čüčłąĖčĆąĄąĮąĖąĄ Slave-čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ ą┐ąĄčĆąĖąŠą┤ą░ ą╗ąŠą│. 0 SCL ąĮąĄ ą┐ąŠą▓ą╗ąĖčÅąĄčé ąĮą░ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī ą┐ąĄčĆąĖąŠą┤ą░ ą╗ąŠą│. 1 SCL, ą║ąŠč鹊čĆą░čÅ ąĘą░ą┤ą░ąĄčéčüčÅ Master. ąÜą░ą║ čüą╗ąĄą┤čüčéą▓ąĖąĄ Slave ą╝ąŠąČąĄčé čüąĮąĖąĘąĖčéčī čüą║ąŠčĆąŠčüčéčī ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ TWI ą┐čāč鹥ą╝ čāą┤ą╗ąĖąĮąĄąĮąĖčÅ čåąĖą║ą╗ą░ SCL.

ąØą░ čĆąĖčü. 20-6 ą┐ąŠą║ą░ąĘą░ąĮčŗ čéąĖą┐ąŠą▓čŗąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ąĮąĄą║ąŠč鹊čĆčŗąĄ ą▒ą░ą╣čéčŗ ą┤ą░ąĮąĮčŗčģ ą╝ąŠą│čāčé ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčīčüčÅ ą╝ąĄąČą┤čā SLA+R (ąĖą╗ąĖ SLA+W) ąĖ STOP, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮąĮąŠą│ąŠ ą░ą╗ą│ąŠčĆąĖčéą╝ą░ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ.

ąĀąĖčü. 20-6. ąöąĖą░ą│čĆą░ą╝ą╝čŗ ą▓čĆąĄą╝ąĄąĮąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ.

ą¤čĆąŠč鹊ą║ąŠą╗ TWI ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąĖą╝ąĄčéčī ąĮą░ čłąĖąĮąĄ ąĮąĄčüą║ąŠą╗čīą║ąŠ master-čāčüčéčĆąŠą╣čüčéą▓ (ąĮąĄčćą░čüč鹊 ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ą░čÅ čüąĖčéčāą░čåąĖčÅ), čŹč鹊 čéą░ą║ ąĮą░ąĘčŗą▓ą░ąĄą╝ą░čÅ čüąĖčüč鹥ą╝ą░ Multi-master. ą¦č鹊ą▒čŗ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī čāčüą┐ąĄčłąĮčāčÄ ą┐ąĄčĆąĄą┤ą░čćčā ą▓ čüąĖčüč鹥ą╝ąĄ Multi-master, čéčĆąĄą▒čāąĄčéčüčÅ čāčćąĖčéčŗą▓ą░čéčī čüą┐ąĄčåąĖą░ą╗čīąĮčŗąĄ čāčüą╗ąŠą▓ąĖčÅ, ą┤ą░ąČąĄ ąĄčüą╗ąĖ ą┤ą▓ą░ ąĖą╗ąĖ ą▒ąŠą╗čīčłąĄąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą╝ą░čüč鹥čĆąŠą▓ ąĮą░čćą░ą╗ąĖ ą┐ąĄčĆąĄą┤ą░čćčā ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ. ąÆ čüąĖčüč鹥ą╝ą░čģ Multi-master ą▓ąŠąĘąĮąĖą║ą░čÄčé ą┤ą▓ąĄ ą┐čĆąŠą▒ą╗ąĄą╝čŗ:

ŌĆó ąöąŠą╗ąČąĄąĮ ą▒čŗčéčī čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮ ą░ą╗ą│ąŠčĆąĖčéą╝, ą┐ąŠąĘą▓ąŠą╗čÅčÄčēąĖą╣ ąŠą┤ąĮąŠą╝čā ąĖąĘ master-čāčüčéčĆąŠą╣čüčéą▓ ąĘą░ą▓ąĄčĆčłąĖčéčī ą┐ąĄčĆąĄą┤ą░čćčā. ąÆčüąĄ ą┤čĆčāą│ąĖąĄ master-čāčüčéčĆąŠą╣čüčéą▓ą░ ą┤ąŠą╗ąČąĮčŗ ą┐čĆąĄą║čĆą░čéąĖčéčī ą┐ąĄčĆąĄą┤ą░čćčā, ą║ąŠą│ą┤ą░ ąŠąĮąĖ ąŠą┐čĆąĄą┤ąĄą╗ąĖą╗ąĖ, čćč鹊 ą┐čĆąŠąĖą│čĆą░ą╗ąĖ ą▓ ą┐čĆąŠčåąĄčüčüąĄ ą▓čŗą▒ąŠčĆą░ ą┐ąĄčĆąĄą┤ą░čÄčēąĄą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░. ąŁč鹊čé ą┐čĆąŠčåąĄčüčü ą▓čŗą▒ąŠčĆą░ ąĮą░ąĘčŗą▓ą░ąĄčéčüčÅ ą░čĆą▒ąĖčéčĆą░ąČąĄą╝. ąÜąŠą│ą┤ą░ ą┐čĆąĄč鹥ąĮą┤čāčÄčēąĖą╣ ąĮą░ čłąĖąĮčā master ąŠą┐čĆąĄą┤ąĄą╗ąĖą╗, čćč鹊 ą┐čĆąŠąĖą│čĆą░ą╗ ą░čĆą▒ąĖčéčĆą░ąČ, ąŠąĮ ą┤ąŠą╗ąČąĄąĮ ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ ą┐ąĄčĆąĄą║ą╗čÄčćąĖčéčīčüčÅ ą▓ čĆąĄąČąĖą╝ Slave, čćč鹊ą▒čŗ ą┐čĆąŠą▓ąĄčĆąĖčéčī, ą▒čŗą╗ ą╗ąĖ ąŠąĮ ą░ą┤čĆąĄčüąŠą▓ą░ąĮ master-čāčüčéčĆąŠą╣čüčéą▓ąŠą╝, ą║ąŠč鹊čĆčŗą╣ ą▓čŗąĖą│čĆą░ą╗ ą░čĆą▒ąĖčéčĆą░ąČ. ążą░ą║čé, čćč鹊 ąĮąĄčüą║ąŠą╗čīą║ąŠ ą╝ą░čüč鹥čĆąŠą▓ ąĮą░čćą░ą╗ąĖ ą┐ąĄčĆąĄą┤ą░čćčā, ąĮąĄ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąŠą▒ąĮą░čĆčāąČąĄąĮ slave-čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ, čé. ąĄ. ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗąĄ ą▓ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ą┤ą░ąĮąĮčŗąĄ ąĮąĄ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą┐ąŠą▓čĆąĄąČą┤ąĄąĮčŗ.

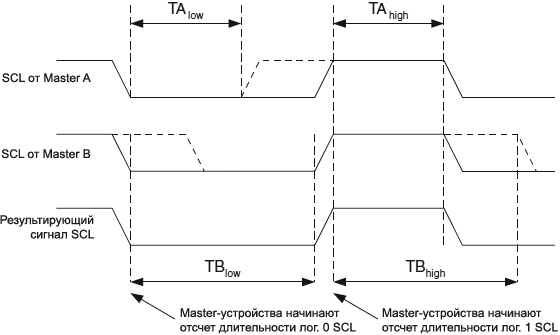

ŌĆó ąĀą░ąĘąĮčŗąĄ master-čāčüčéčĆąŠą╣čüčéą▓ą░ ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čĆą░ąĘąĮčŗąĄ čćą░čüč鹊čéčŗ SCL. ąöąŠą╗ąČąĮą░ ą▒čŗčéčī čĆą░ąĘčĆą░ą▒ąŠčéą░ąĮą░ čüčģąĄą╝ą░ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ čéą░ą║č鹊ą▓ ą▓čüąĄčģ master-čāčüčéčĆąŠą╣čüčéą▓, čćč鹊ą▒čŗ ą┐ąŠąĘą▓ąŠą╗ąĖčéčī ą┐ąĄčĆąĄą┤ą░č湥 ąŠčüčāčēąĄčüčéą▓ąĖčéčīčüčÅ ąČąĄčüčéą║ąŠ čĆąĄą│ą╗ą░ą╝ąĄąĮčéąĖčĆąŠą▓ą░ąĮąĮčŗą╝ čüą┐ąŠčüąŠą▒ąŠą╝. ąŁč鹊 čāą┐čĆąŠčüčéąĖčé ą┐čĆąŠčåąĄčüčü ą░čĆą▒ąĖčéčĆą░ąČą░.

ąöą╗čÅ čĆąĄčłąĄąĮąĖčÅ ąŠą▒ąŠąĖčģ čŹčéąĖčģ ą┐čĆąŠą▒ą╗ąĄą╝ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čüčģąĄą╝ą░ ą┐čĆąŠą▓ąŠą┤ąĮąŠą│ąŠ ąś čüąĖą│ąĮą░ą╗ąŠą▓ čłąĖąĮčŗ. ąĪąĖą│ąĮą░ą╗čŗ čéą░ą║č鹊ą▓ ąŠčé ą▓čüąĄčģ master-čāčüčéčĆąŠą╣čüčéą▓ ąŠą▒čŖąĄą┤ąĖąĮčÅčÄčéčüčÅ čäčāąĮą║čåąĖąĄą╣ ą┐čĆąŠą▓ąŠą┤ąĮąŠą│ąŠ ąś, č鹥ą╝ čüą░ą╝čŗą╝ ą┐ąŠą╗čāčćą░ąĄčéčüčÅ čćą░čüč鹊čéą░ čü ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠą╣ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčīčÄ ą╗ąŠą│. 1, čĆą░ą▓ąĮąŠą╣ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéąĖ čüą░ą╝ąŠą│ąŠ ą║ąŠčĆąŠčéą║ąŠą│ąŠ ą┐ąĄčĆąĖąŠą┤ą░ ą╗ąŠą│. 1 ąŠčé ąŠą┤ąĮąŠą│ąŠ ąĖąĘ Master. ą¤ąĄčĆąĖąŠą┤ ą╗ąŠą│. 0 ą┐ąŠą╗čāčćą░ąĄčéčüčÅ ą║ąŠą╝ą▒ąĖąĮą░čåąĖąĄą╣ ą▓čüąĄčģ čüąĖą│ąĮą░ą╗ąŠą▓ ą┐ąĄčĆąĖąŠą┤ąŠą▓ čāčüčéčĆąŠą╣čüčéą▓ Master, ąĖ ąŠąĮ ą▒čāą┤ąĄčé čĆą░ą▓ąĮčŗą╝ čüą░ą╝ąŠą╝čā ą┤ą╗ąĖąĮąĮąŠą╝čā ą╗ąŠą│. 0 ąŠčé ąŠą┤ąĮąŠą│ąŠ ąĖąĘ Master. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ą▓čüąĄ master-čāčüčéčĆąŠą╣čüčéą▓ą░ ą┐čĆąŠčüą╗čāčłąĖą▓ą░čÄčé čüąĖą│ąĮą░ą╗ SCL, čŹčäč乥ą║čéąĖą▓ąĮąŠ ąŠčéčüčćąĖčéčŗą▓ą░čÅ čüą▓ąŠąĖ ą╗ąŠą│. 1 ąĖ ą╗ąŠą│. 0 ą┐ąĄčĆąĖąŠą┤čŗ čéą░ą╣ą╝ą░čāč鹊ą▓ SCL, ą║ąŠą│ą┤ą░ ą║ąŠą╝ą▒ąĖąĮąĖčĆąŠą▓ą░ąĮąĮčŗą╣ čüąĖą│ąĮą░ą╗ SCL ą┐ąĄčĆąĄčģąŠą┤ąĖčé čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ ą▓ ą╗ąŠą│. 1 ąĖ ą╗ąŠą│. 0.

ąĀąĖčü. 20-7. ąĪąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖčÅ SCL ą╝ąĄąČą┤čā ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ Master-čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ.

ąÉčĆą▒ąĖčéčĆą░ąČ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą▓čüąĄą╝ąĖ master-čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ ą┐čāč鹥ą╝ ą┐ąŠčüč鹊čÅąĮąĮąŠą│ąŠ ą╝ąŠąĮąĖč鹊čĆąĖąĮą│ą░ čüąĖą│ąĮą░ą╗ą░ SDA ą┐ąŠčüą╗ąĄ ą▓čŗą▓ąŠą┤ą░ ą┤ą░ąĮąĮčŗčģ. ąĢčüą╗ąĖ ąĘąĮą░č湥ąĮąĖąĄ, ą┐čĆąŠčćąĖčéą░ąĮąĮąŠąĄ ąĖąĘ SDA, ąĮąĄ čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ą▓čŗą▓ąĄą┤ąĄąĮąĮąŠą╝čā, č鹊 Master č鹥čĆčÅąĄčé ą░čĆą▒ąĖčéčĆą░ąČ. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 Master ą╝ąŠąČąĄčé ą┐ąŠč鹥čĆčÅčéčī ą░čĆą▒ąĖčéčĆą░ąČ č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ ą▓čŗą▓ąŠą┤ąĖčé ąĮą░ SDA ą╗ąŠą│. 1, ąĖ ą▓ čŹč鹊čé ą╝ąŠą╝ąĄąĮčé ą┤čĆčāą│ąŠą╣ Master ą▓čŗą▓ąŠą┤ąĖčé ą╗ąŠą│. 0. ą¤čĆąŠąĖą│čĆą░ą▓čłąĖą╣ ą░čĆą▒ąĖčéčĆą░ąČ Master ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ čĆąĄąČąĖą╝ Slave-čāčüčéčĆąŠą╣čüčéą▓ą░, ą┐čĆąŠą▓ąĄčĆčÅčÅ, ąĮąĄ ą▒čŗą╗ ą╗ąĖ ąŠąĮ ą░ą┤čĆąĄčüąŠą▓ą░ąĮ ą▓čŗąĖą│čĆą░ą▓čłąĖą╝ Master-čāčüčéčĆąŠą╣čüčéą▓ąŠą╝. ąĪąĖą│ąĮą░ą╗ SDA ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąŠčüčéą░ą▓ą╗ąĄąĮ ą┐čĆąŠąĖą│čĆą░ą▓čłąĖą╝ Master ą▓ ą╗ąŠą│. 1, ąŠą┤ąĮą░ą║ąŠ ą┐čĆąŠąĖą│čĆą░ą▓čłąĖąĄ Master-čāčüčéčĆąŠą╣čüčéą▓ą░ ą╝ąŠą│čāčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī čüąĖą│ąĮą░ą╗ čéą░ą║č鹊ą▓ ą┤ąŠ ą║ąŠąĮčåą░ č鹥ą║čāčēąĄą│ąŠ ą┐ą░ą║ąĄčéą░ ą┤ą░ąĮąĮčŗčģ ąĖą╗ąĖ ą░ą┤čĆąĄčüą░. ąÉčĆą▒ąĖčéčĆą░ąČ ą┐čĆąŠą┤ąŠą╗ąČąĖčéčüčÅ ą┤ąŠ č鹊ą│ąŠ ą╝ąŠą╝ąĄąĮčéą░, ą┐ąŠą║ą░ ąŠčüčéą░ąĄčéčüčÅ ąŠą┤ąĖąĮ Master, ąĖ čŹč鹊čé ą┐čĆąŠčåąĄčüčü ą╝ąŠąČąĄčé ą┐čĆąŠąĖąĘąŠą╣čéąĖ ą▓ č鹥č湥ąĮąĖąĄ ą┐čĆąŠčģąŠąČą┤ąĄąĮąĖčÅ ąĮąĄą║ąŠč鹊čĆąŠą│ąŠ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ą▒ąĖčé. ąĢčüą╗ąĖ ąĮąĄčüą║ąŠą╗čīą║ąŠ ą╝ą░čüč鹥čĆąŠą▓ ą┐ąŠą┐čŗčéą░ą╗ąĖčüčī ą░ą┤čĆąĄčüąŠą▓ą░čéčī ąŠą┤ąĮąŠ ąĖ č鹊 ąČąĄ Slave-čāčüčéčĆąŠą╣čüčéą▓ąŠ, ą░čĆą▒ąĖčéčĆą░ąČ ą┐čĆąŠą┤ąŠą╗ąČąĖčéčüčÅ ą┤ąŠ ą┐ą░ą║ąĄčéą░ ą┤ą░ąĮąĮčŗčģ.

ąĀąĖčü. 20-8. ąÉčĆą▒ąĖčéčĆą░ąČ ą╝ąĄąČą┤čā ą┤ą▓čāą╝čÅ Master-čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ.

ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 ą░čĆą▒ąĖčéčĆą░ąČ ąĮąĄ ą┤ąŠąĘą▓ąŠą╗čÅąĄčéčüčÅ ą╝ąĄąČą┤čā:

ŌĆó REPEATED START ąĖ ą▒ąĖč鹊ą╝ ą┤ą░ąĮąĮčŗčģ.

ŌĆó STOP ąĖ ą▒ąĖč鹊ą╝ ą┤ą░ąĮąĮčŗčģ.

ŌĆó REPEATED START ąĖ STOP.

ą¤čĆąŠą│čĆą░ą╝ą╝ą░ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ ąŠčéą▓ąĄčćą░ąĄčé ąĘą░ č鹊, čćč鹊ą▒čŗ ąĮąĖą║ąŠą│ą┤ą░ ąĮąĄ ą┐čĆąŠąĖąĘąŠčłą╗ąĖ čŹčéąĖ čéčĆąĖ ąĮąĄą┤ąŠą┐čāčüčéąĖą╝čŗąĄ čāčüą╗ąŠą▓ąĖčÅ ą░čĆą▒ąĖčéčĆą░ąČą░. ąŁč鹊 ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčé, čćč鹊 ą▓ čüąĖčüč鹥ą╝ą░čģ multi-master ą▓čüąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ą┤ąŠą╗ąČąĮčŗ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ąŠą┤ąĖąĮą░ą║ąŠą▓čāčÄ ą║ąŠą╝ą┐ąŠąĘąĖčåąĖčÄ SLA+R/W ąĖ ą┐ą░ą║ąĄč鹊ą▓ ą┤ą░ąĮąĮčŗčģ. ąöčĆčāą│ąĖą╝ąĖ čüą╗ąŠą▓ą░ą╝ąĖ: ą▓čüąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ąŠą╗ąČąĮčŗ čüąŠą┤ąĄčƹȹ░čéčī ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą┐ą░ą║ąĄč鹊ą▓ ą┤ą░ąĮąĮčŗčģ, ąĖąĮą░č湥 čĆąĄąĘčāą╗čīčéą░čé ą░čĆą▒ąĖčéčĆą░ąČą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĮąĄąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗą╝.

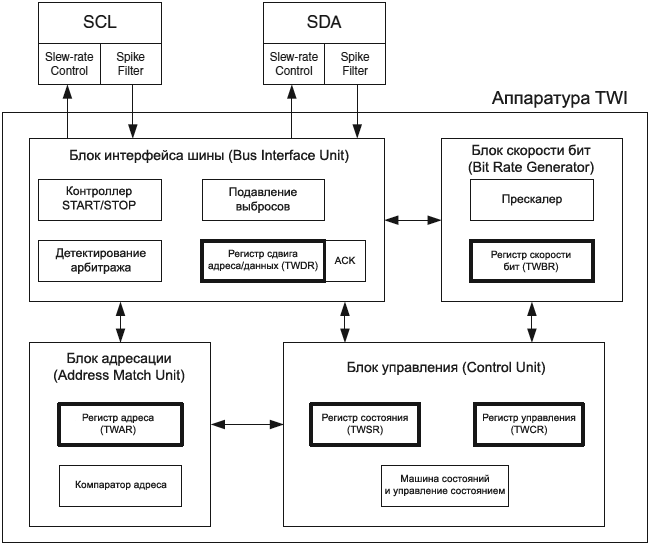

[ą×ą▒ąĘąŠčĆ ą╝ąŠą┤čāą╗čÅ TWI]

ą£ąŠą┤čāą╗čī TWI čüąŠčüč鹊ąĖčé ąĖąĘ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ą▒ą╗ąŠą║ąŠą▓, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 20-9. ąÆčüąĄ čĆąĄą│ąĖčüčéčĆčŗ, ąŠą▒ą▓ąĄą┤ąĄąĮąĮčŗąĄ č鹊ą╗čüč鹊ą╣ ą╗ąĖąĮąĖąĄą╣, ą┤ąŠčüčéčāą┐ąĮčŗ č湥čĆąĄąĘ čłąĖąĮčā ą┤ą░ąĮąĮčŗčģ AVR.

ąĀąĖčü. 20-9. ąĪčéčĆčāą║čéčāčĆąĮą░čÅ čüčģąĄą╝ą░ ą╝ąŠą┤čāą╗čÅ TWI.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: Slew-rate Control ąŠąĘąĮą░čćą░ąĄčé čāąĘąĄą╗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čüą║ąŠčĆąŠčüčéčīčÄ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ ą┤čĆą░ą╣ą▓ąĄčĆą░, Spike Filter ąŠąĘąĮą░čćą░ąĄčé čäąĖą╗čīčéčĆ ą║ąŠčĆąŠčéą║ąĖčģ ąĖą╝ą┐čāą╗čīčüąŠą▓ čüąĖą│ąĮą░ą╗ą░.

ąÆčŗą▓ąŠą┤čŗ čüąĖą│ąĮą░ą╗ąŠą▓ SCL ąĖ SDA. ąŁčéąĖ ąĮąŠąČą║ąĖ ą┐ąŠą┤ą║ą╗čÄčćą░čÄčé AVR TWI ą║ ąŠčüčéą░ą╗čīąĮąŠą╣ čćą░čüčéąĖ ą▓čüąĄą╣ čüąĖčüč鹥ą╝čŗ. ąÆčŗčģąŠą┤ąĮčŗąĄ ą┤čĆą░ą╣ą▓ąĄčĆčŗ čüąŠą┤ąĄčƹȹ░čé ąŠą│čĆą░ąĮąĖčćąĖč鹥ą╗čī čüą║ąŠčĆąŠčüčéąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ (slew-rate limiter), čćč鹊ą▒čŗ čüąĖą│ąĮą░ą╗čŗ čāą┤ąŠą▓ą╗ąĄčéą▓ąŠčĆčÅą╗ąĖ čüą┐ąĄčåąĖčäąĖą║ą░čåąĖąĖ TWI. ąÆčģąŠą┤ąĮčŗąĄ ą║ą░čüą║ą░ą┤čŗ čüąŠą┤ąĄčƹȹ░čé čüčģąĄą╝čā ą┐ąŠą┤ą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąŠą╝ąĄčģ, ą║ąŠč鹊čĆą░čÅ ąŠčéą▒čĆą░čüčŗą▓ą░ąĄčé ąĖą╝ą┐čāą╗čīčüčŗ, ą║ąŠč鹊čĆčŗąĄ ą║ąŠčĆąŠč湥 50 ąĮčü. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ą╝ąŠąČąĮąŠ čĆą░ąĘčĆąĄčłąĖčéčī ą▓ąĮčāčéčĆąĄąĮąĮąĖąĄ ą▓ąĄčĆčģąĮąĖąĄ ą┐ąŠą┤čéčÅą│ąĖą▓ą░čÄčēąĖąĄ čĆąĄąĘąĖčüč鹊čĆčŗ (pull-up) ąĮą░ ąĮąŠąČą║ą░čģ AVR ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖčģ ą▒ąĖčé čĆąĄą│ąĖčüčéčĆą░ PORT (čā ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ATmega32U4 čüąĖą│ąĮą░ą╗ą░ą╝ SCL ąĖ SDA čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčé ąĮąŠąČą║ąĖ ą┐ąŠčĆč鹊ą▓ PD0 ąĖ PD1 čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ, čé. ąĄ. ą┤ą╗čÅ ąĮą░čüčéčĆąŠą╣ą║ąĖ ą▓ąĮčāčéčĆąĄąĮąĮąĖčģ pull-upp ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ čāčüčéą░ąĮąŠą▓ąĖčéčī ą▒ąĖčéčŗ 0 ąĖ 1 čĆąĄą│ąĖčüčéčĆą░ PORTD). ąÆ ąĮąĄą║ąŠč鹊čĆčŗčģ ą┐čĆąŠčüčéčŗčģ čüąĖčüč鹥ą╝ą░čģ čü ą║ąŠčĆąŠčéą║ąŠą╣, ąĮąĄąĘąĮą░čćąĖč鹥ą╗čīąĮąŠ ąĮą░ą│čĆčāąČąĄąĮąĮąŠą╣ čłąĖąĮąŠą╣ I2C ą▓ąĮčāčéčĆąĄąĮąĮąĖąĄ čĆąĄąĘąĖčüč鹊čĆčŗ pull-up ą╝ąŠą│čāčé ąĘą░ą╝ąĄąĮąĖčéčī ą▓ąĮąĄčłąĮąĖąĄ.

ąōąĄąĮąĄčĆą░č鹊čĆ čüą║ąŠčĆąŠčüčéąĖ ą▒ąĖčé. ąŁč鹊čé ą▒ą╗ąŠą║ (Bit Rate Generator Unit) čāą┐čĆą░ą▓ą╗čÅąĄčé ą┐ąĄčĆąĖąŠą┤ąŠą╝ čüąĖą│ąĮą░ą╗ą░ SCL, ą║ąŠą│ą┤ą░ MCU čĆą░ą▒ąŠčéą░ąĄčé ą▓ čĆąĄąČąĖą╝ąĄ Master. ą¤ąĄčĆąĖąŠą┤ SCL čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ąĮą░čüčéčĆąŠą╣ą║ąŠą╣ čĆąĄą│ąĖčüčéčĆą░ TWI Bit Rate Register (TWBR) ąĖ ą▒ąĖčéą░ą╝ąĖ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ (Prescaler) ą▓ čĆąĄą│ąĖčüčéčĆąĄ TWI Status Register (TWSR). Slave-čĆąĄąČąĖą╝ ąĮąĄ ąĘą░ą▓ąĖčüąĖčé ąŠčé ąĮą░čüčéčĆąŠąĄą║ Bit Rate ąĖą╗ąĖ Prescaler, ąŠą┤ąĮą░ą║ąŠ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ CPU ą▓ Slave-čāčüčéčĆąŠą╣čüčéą▓ąĄ MCU ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ą▓ 16 čĆą░ąĘ ą▓čŗčłąĄ čćą░čüč鹊čéčŗ SCL. ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 slave-čāčüčéčĆąŠą╣čüčéą▓ą░ ą╝ąŠą│čāčé čāą▓ąĄą╗ąĖčćąĖą▓ą░čéčī ą┤ą╗ąĖąĮčā ą┐ąĄčĆąĖąŠą┤ą░ ą╗ąŠą│. 0 čüąĖą│ąĮą░ą╗ą░ SCL, čāą▓ąĄą╗ąĖčćąĖą▓ą░čÅ č鹥ą╝ čüą░ą╝čŗą╝ ą┐ąĄčĆąĖąŠą┤ čéą░ą║č鹊ą▓ čłąĖąĮčŗ TWI.

ąōąĄąĮąĄčĆąĖčĆčāąĄą╝ą░čÅ čćą░čüč鹊čéą░ SCL ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą┐ą░čĆą░ą╝ąĄčéčĆą░ą╝ąĖ TWBR ąĖ TWPS.

TWBR = ąĘąĮą░č湥ąĮąĖčÄ TWI Bit Rate Register.

TWPS = ąĘąĮą░č湥ąĮąĖčÄ ą▒ąĖčé ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ ą▓ TWI Status Register.

ążąŠčĆą╝čāą╗ą░ ą┤ą╗čÅ čćą░čüč鹊čéčŗ SCL:

ąóą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ CPU

SQLfreq = ----------------------

16 + 2 ┬Ę (TWBR) ┬Ę 4TWPS

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĘąĮą░č湥ąĮąĖąĄ TWBR ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī 10 ąĖą╗ąĖ ą▒ąŠą╗čīčłąĄ, ąĄčüą╗ąĖ TWI čĆą░ą▒ąŠčéą░ąĄčé ą▓ čĆąĄąČąĖą╝ąĄ Master. ąĢčüą╗ąĖ TWBR ą╝ąĄąĮčīčłąĄ 10, č鹊 Master ą╝ąŠąČąĄčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ąĮąĄą║ąŠčĆčĆąĄą║čéąĮčŗąĄ čüąĖą│ąĮą░ą╗čŗ SDA ąĖ SCL ą┤ą╗čÅ ąĘą░ą▓ąĄčĆčłą░čÄčēąĄą╣ čćą░čüčéąĖ ą▒ą░ą╣čéą░. ą¤čĆąŠą▒ą╗ąĄą╝ą░ ą▓čüčéčĆąĄčćą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą▓ čĆąĄąČąĖą╝ąĄ TWI Master ąŠčéą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ Start + SLA+R (ąĖą╗ąĖ SLA/W) ą▓ Slave-čāčüčéčĆąŠą╣čüčéą▓ąŠ (Slave-čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮąĄ ąŠą▒čÅąĘą░č鹥ą╗čīąĮąŠ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮąŠ ą║ čłąĖąĮąĄ, čćč鹊ą▒čŗ čüą╗čāčćąĖą╗ąŠčüčī ą╗ąŠąČąĮąŠąĄ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖąĄ).

ąæą╗ąŠą║ ąĖąĮč鹥čĆč乥ą╣čüą░ čłąĖąĮčŗ. ąŁč鹊čé ą▒ą╗ąŠą║ (Bus Interface Unit) čüąŠą┤ąĄčƹȹĖčé čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ ą┤ą░ąĮąĮčŗčģ ąĖ ą░ą┤čĆąĄčüą░ (TWDR), ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ START/STOP ąĖ ą░ą┐ą┐ą░čĆą░čéčāčĆčā ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą░čĆą▒ąĖčéčĆą░ąČą░. TWDR čüąŠą┤ąĄčƹȹĖčé ą░ą┤čĆąĄčü ąĖą╗ąĖ ą▒ą░ą╣čéčŗ ą┤ą░ąĮąĮčŗčģ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ, ąĖą╗ąĖ ą┐čĆąĖąĮąĖą╝ą░ąĄą╝čŗąĄ ą░ą┤čĆąĄčü ąĖą╗ąĖ ą▒ą░ą╣čéčŗ ą┤ą░ąĮąĮčŗčģ. ąÆ ą┤ąŠą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ 8-ą▒ąĖčéąĮąŠą╝čā TWDR ą▒ą╗ąŠą║ ąĖąĮč鹥čĆč乥ą╣čüą░ čłąĖąĮčŗ čéą░ą║ąČąĄ čüąŠą┤ąĄčƹȹĖčé čĆąĄą│ąĖčüčéčĆ, čüąŠą┤ąĄčƹȹ░čēąĖą╣ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗą╣ ąĖą╗ąĖ ą┐čĆąĖąĮąĖą╝ą░ąĄą╝čŗą╣ ą▒ąĖčé ACK/NACK, ą║ąŠč鹊čĆčŗą╣ ą║ąŠčüą▓ąĄąĮąĮąŠ ą┤ąŠčüčéčāą┐ąĄąĮ ąĖąĘ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖčÅ. ą×ą┤ąĮą░ą║ąŠ ą║ąŠą│ą┤ą░ ąĖą┤ąĄčé ą┐čĆąĖąĄą╝, čŹč鹊čé ą▒ąĖčé ą╝ąŠąČąĄčé ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ąĖą╗ąĖ ąŠčćąĖčēąĄąĮ ą┐čāč鹥ą╝ ą╝ą░ąĮąĖą┐čāą╗čÅčåąĖąĖ čĆąĄą│ąĖčüčéčĆąŠą╝ TWI Control Register (TWCR). ąÆ čĆąĄąČąĖą╝ąĄ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ ąĘąĮą░č湥ąĮąĖąĄ ą┐čĆąĖąĮčÅč鹊ą│ąŠ ą▒ąĖčéą░ ACK/NACK ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąŠ ąĘąĮą░č湥ąĮąĖąĄą╝ ą▓ čĆąĄą│ąĖčüčéčĆąĄ TWSR.

ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ START/STOP ąŠčéą▓ąĄčćą░ąĄčé ąĘą░ ą│ąĄąĮąĄčĆą░čåąĖčÄ ąĖ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čüąĖą│ąĮą░ą╗ąŠą▓ START, REPEATED START ąĖ STOP. ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ START/STOP ą╝ąŠąČąĄčé ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī čüąĖą│ąĮą░ą╗čŗ START ąĖ STOP, ą┤ą░ąČąĄ ą║ąŠą│ą┤ą░ AVR MCU ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ąŠą┤ąĮąŠą╝ ąĖąĘ čĆąĄąČąĖą╝ąŠą▓ čüąĮą░, čćč鹊 ą┤ą░ąĄčé ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą▓čŗą▓ąĄčüčéąĖ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ MCU ąĖąĘ čĆąĄąČąĖą╝ą░ ą┐ąŠąĮąĖąČąĄąĮąĮąŠą│ąŠ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ, ą║ąŠą│ą┤ą░ ąŠąĮ ą░ą┤čĆąĄčüąŠą▓ą░ąĮ Master-čāčüčéčĆąŠą╣čüčéą▓ąŠą╝.

ąĢčüą╗ąĖ TWI ą▒čŗą╗ ąĖąĮąĖčåąĖąĖčĆąŠą▓ą░ąĮ ąĮą░ ą┐ąĄčĆąĄą┤ą░čćčā ą║ą░ą║ Master, ą░ą┐ą┐ą░čĆą░čéčāčĆą░ Arbitration Detection ą┐ąŠčüč鹊čÅąĮąĮąŠ ą╝ąŠąĮąĖč鹊čĆąĖčé ą┐ąĄčĆąĄą┤ą░čćčā. ąĢčüą╗ąĖ TWI ą┐čĆąŠąĖą│čĆą░ą╗ ą░čĆą▒ąĖčéčĆą░ąČ, č鹊 ąŠą▒ čŹč鹊ą╝ ąĖąĮč乊čĆą╝ąĖčĆčāąĄčéčüčÅ ą▒ą╗ąŠą║ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ (Control Unit). ą¤ąŠčüą╗ąĄ čŹč鹊ą│ąŠ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮą░ ą║ąŠčĆčĆąĄą║čéąĮą░čÅ ąŠą┐ąĄčĆą░čåąĖčÅ ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą│ąĄąĮąĄčĆąĖčĆčāąĄą╝čŗčģ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖčģ ą║ąŠą┤ąŠą▓ čüąŠčüč鹊čÅąĮąĖčÅ.

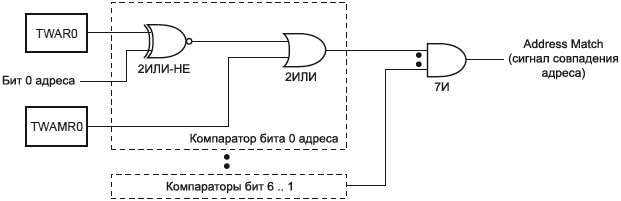

ąæą╗ąŠą║ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ ą░ą┤čĆąĄčüą░. Address Match Unit ą┐čĆąŠą▓ąĄčĆčÅąĄčé, ą▒čŗą╗ąĖ ą╗ąĖ ą┐čĆąĖąĮčÅčéčŗ ą▒ą░ą╣čéčŗ ą░ą┤čĆąĄčüą░, čüąŠą▓ą┐ą░ą┤ą░čÄčēąĖąĄ čü 7-čĆą░ąĘčĆčÅą┤ąĮčŗą╝ ą░ą┤čĆąĄčüąŠą╝ ą▓ TWI Address Register (TWAR). ąĢčüą╗ąĖ ą▒ąĖčé čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ąŠą▒čēąĄą│ąŠ ą▓čŗąĘąŠą▓ą░ (TWI General Call Recognition Enable ą▒ąĖčé, TWGCE) ą▓ čĆąĄą│ąĖčüčéčĆąĄ TWAR čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ ą╗ąŠą│. 1, č鹊 ą▓čüąĄ ą┐čĆąĖčģąŠą┤čÅčēąĖąĄ ą▒ąĖčéčŗ čéą░ą║ąČąĄ čüčĆą░ą▓ąĮąĖą▓ą░čÄčéčüčÅ čü ą░ą┤čĆąĄčüąŠą╝ General Call (čé. ąĄ. čü ąĮčāą╗čÅą╝ąĖ). ą¤čĆąĖ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖąĖ ą░ą┤čĆąĄčüą░ ąŠą▒ čŹč鹊ą╝ ąĖąĮč乊čĆą╝ąĖčĆčāąĄčéčüčÅ Control Unit, ą┐ąŠąĘą▓ąŠą╗čÅčÅ ą▓čŗą┐ąŠą╗ąĮąĖčéčī ą║ąŠčĆčĆąĄą║čéąĮčŗąĄ ą┤ąĄą╣čüčéą▓ąĖčÅ. TWI ą╝ąŠąČąĄčé ą┐ąŠą┤čéą▓ąĄčĆą┤ąĖčéčī (ACK) ąĖą╗ąĖ ąĮąĄ ą┐ąŠą┤čéą▓ąĄčĆą┤ąĖčéčī (NACK), čŹč鹊čé ą░ą┤čĆąĄčü, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ąĮą░čüčéčĆąŠąĄą║ ą▓ TWCR. ąæą╗ąŠą║ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ ą░ą┤čĆąĄčüą░ ą╝ąŠąČąĄčé čüčĆą░ą▓ąĮąĖą▓ą░čéčī ą░ą┤čĆąĄčüą░, ą┤ą░ąČąĄ ą║ąŠą│ą┤ą░ AVR MCU ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ čüąĮą░, čćč鹊 ą┤ą░ąĄčé ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą▓čŗą▓ąĄčüčéąĖ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ MCU ąĖąĘ čĆąĄąČąĖą╝ą░ ą┐ąŠąĮąĖąČąĄąĮąĮąŠą│ąŠ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ, ą║ąŠą│ą┤ą░ ąŠąĮ ą░ą┤čĆąĄčüąŠą▓ą░ąĮ Master-čāčüčéčĆąŠą╣čüčéą▓ąŠą╝. ąĢčüą╗ąĖ ą▓ąŠ ą▓čĆąĄą╝čÅ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ ą░ą┤čĆąĄčüą░ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą┤čĆčāą│ąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ (ąĮą░ą┐čĆąĖą╝ąĄčĆ INT0), ą║ąŠč鹊čĆąŠąĄ čĆą░ąĘą▒čāą┤ąĖčé CPU, č鹊 TWI ąŠą▒ąŠčĆą▓ąĄčé ąŠą┐ąĄčĆą░čåąĖčÄ ąĖ ą▓ąĄčĆąĮąĄčéčüčÅ ą▓ čĆąĄąČąĖą╝ ąŠąČąĖą┤ą░ąĮąĖčÅ. ąĢčüą╗ąĖ čŹč鹊 ą▓čŗąĘčŗą▓ą░ąĄčé ą┐čĆąŠą▒ą╗ąĄą╝čŗ, č鹊 ą│ą░čĆą░ąĮčéąĖčĆčāą╣č鹥, čćč鹊 čĆą░ąĘčĆąĄčłąĄąĮąŠ č鹊ą╗čīą║ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ TWI Address Match, ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą▓čģąŠą┤ ą▓ čĆąĄąČąĖą╝ ą┐ąŠąĮąĖąČąĄąĮąĮąŠą│ąŠ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ/ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ (Power-down).

ąæą╗ąŠą║ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ. Control Unit ą╝ąŠąĮąĖč鹊čĆąĖčé čłąĖąĮčā TWI ąĖ ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ąŠčéą▓ąĄčéąĮčŗąĄ ą┤ąĄą╣čüčéą▓ąĖčÅ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü ąĮą░čüč鹊ą╣ą║ą░ą╝ąĖ ą▓ TWI Control Register (TWCR). ąÜąŠą│ą┤ą░ čüąŠą▒čŗčéąĖąĄ, ą┐čĆąŠąĖąĘąŠčłąĄą┤čłąĄąĄ ąĮą░ čłąĖąĮąĄ, čéčĆąĄą▒čāąĄčé ą▓ąĮąĖą╝ą░ąĮąĖčÅ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ, čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ čäą╗ą░ą│ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ TWI (TWINT). ąØą░ čüą╗ąĄą┤čāčÄčēąĄą╝ čéą░ą║č鹥 čÅą┤čĆą░ čĆąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ TWI Status Register (TWSR) ąŠą▒ąĮąŠą▓ąĖčéčüčÅ ą║ąŠą┤ąŠą╝, ąĖą┤ąĄąĮčéąĖčäąĖčåąĖčĆčāčÄčēąĖą╝ čüąŠą▒čŗčéąĖąĄ. TWSR čüąŠą┤ąĄčƹȹĖčé ą┤ąŠčüč鹊ą▓ąĄčĆąĮčāčÄ ąĖąĮč乊čĆą╝ą░čåąĖčÄ ąŠ čüąŠčüč鹊čÅąĮąĖąĖ č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čäą╗ą░ą│ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ TWI. ąÆąŠ ą▓čüąĄ ą┤čĆčāą│ąĖąĄ ą╝ąŠą╝ąĄąĮčéčŗ TWSR čüąŠą┤ąĄčƹȹĖčé čüą┐ąĄčåąĖą░ą╗čīąĮčŗą╣ ą║ąŠą┤ čüąŠčüč鹊čÅąĮąĖčÅ, ą║ąŠč鹊čĆčŗą╣ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĮąĄą┤ąŠčüčéčāą┐ąĮąŠčüčéčī ąĖąĮč乊čĆą╝ą░čåąĖąĖ ąŠ čüąŠčüč鹊čÅąĮąĖąĖ. ą¤ąŠą║ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čäą╗ą░ą│ TWINT, čüąĖą│ąĮą░ą╗ SCL čāą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ą▓ ą╗ąŠą│. 0. ąŁč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĄ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ąĘą░ą▓ąĄčĆčłąĖčéčī ą▓čüąĄ ąĘą░ą┤ą░čćąĖ ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ą╝ąŠąČąĄčé ą┐čĆąŠą┤ąŠą╗ąČąĖčéčīčüčÅ ą┐ąĄčĆąĄą┤ą░čćą░ TWI.

ążą╗ą░ą│ TWINT čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▓ čüą╗ąĄą┤čāčÄčēąĖčģ čüąĖčéčāą░čåąĖčÅčģ:

ŌĆó ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ TWI ą┐ąĄčĆąĄą┤ą░ą╗ čüąĖą│ąĮą░ą╗ START ąĖą╗ąĖ REPEATED START.

ŌĆó ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ TWI ą┐ąĄčĆąĄą┤ą░ą╗ SLA+R ąĖą╗ąĖ SLA+W.

ŌĆó ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ TWI ą┐ąĄčĆąĄą┤ą░ą╗ ą▒ą░ą╣čé ą░ą┤čĆąĄčüą░.

ŌĆó ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ TWI ą┐čĆąŠąĖą│čĆą░ą╗ ą░čĆą▒ąĖčéčĆą░ąČ.

ŌĆó ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ TWI ą▒čŗą╗ ą░ą┤čĆąĄčüąŠą▓ą░ąĮ čüąŠą▒čüčéą▓ąĄąĮąĮčŗą╝ slave-ą░ą┤čĆąĄčüąŠą╝ ąĖą╗ąĖ čäčāąĮą║čåąĖąĄą╣ general call.

ŌĆó ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ TWI ą┐čĆąĖąĮčÅą╗ ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ.

ŌĆó ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą▒čŗą╗ ą┐čĆąĖąĮčÅčé STOP ąĖą╗ąĖ REPEATED START, ą║ąŠą│ą┤ą░ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąŠčüčéą░ąĄčéčüčÅ ą░ą┤čĆąĄčüąŠą▓ą░ąĮąĮčŗą╝ ą║ą░ą║ Slave-čāčüčéčĆąŠą╣čüčéą▓ąŠ.

ŌĆó ąÜąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ąŠčłąĖą▒ą║ą░ čłąĖąĮčŗ ąĖąĘ-ąĘą░ ąĮąĄą┤ąŠą┐čāčüčéąĖą╝ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ START ąĖą╗ąĖ STOP.

[ąśčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ TWI]

AVR TWI čÅą▓ą╗čÅąĄčéčüčÅ ą▒ą░ą╣čé-ąŠčĆąĖąĄąĮčéąĖčĆąŠą▓ą░ąĮąĮčŗą╝, ąŠčüąĮąŠą▓ą░ąĮąĮčŗą╝ ąĮą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅčģ. ą¤čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čüčĆą░ą▒ą░čéčŗą▓ą░čÄčé ą┐ąŠčüą╗ąĄ ą▓čüąĄčģ čüąŠą▒čŗčéąĖą╣ čłąĖąĮčŗ, ąĮą░ą┐ąŠą┤ąŠą▒ąĖąĄ ą┐čĆąĖąĮčÅčéąĖčÅ ą▒ą░ą╣čéą░ ąĖą╗ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ čüąĖą│ąĮą░ą╗ą░ START. ąśąĘ-ąĘą░ č鹊ą│ąŠ, čćč鹊 TWI ąŠčüąĮąŠą▓ą░ąĮ ąĮą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅčģ, ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ą╝ąŠąČąĄčé čüą▓ąŠą▒ąŠą┤ąĮąŠ ą▓čŗą┐ąŠą╗ąĮčÅčéčī ą┤čĆčāą│ąĖąĄ ąŠą┐ąĄčĆą░čåąĖąĖ ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▒ą░ą╣čéą░ TWI. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ą▒ąĖčé čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ TWI Interrupt Enable (TWIE) ą▓ čĆąĄą│ąĖčüčéčĆąĄ TWCR ą▓ą╝ąĄčüč鹥 čü ą▒ąĖč鹊ą╝ ą│ą╗ąŠą▒ą░ą╗čīąĮąŠą│ąŠ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ Global Interrupt Enable ą▓ čĆąĄą│ąĖčüčéčĆąĄ SREG ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÄ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī, ą┤ąŠą╗ąČąĮą░ ą╗ąĖ čāčüčéą░ąĮąŠą▓ą║ą░ čäą╗ą░ą│ą░ TWINT ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ąĘą░ą┐čĆąŠčü ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ąĢčüą╗ąĖ ą▒ąĖčé TWIE ąŠčćąĖčēąĄąĮ, ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ ą┤ąŠą╗ąČąĮąŠ ąŠą┐čĆą░čłąĖą▓ą░čéčī ą▒ąĖčé TWINT, čćč鹊ą▒čŗ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░čéčī ą┤ąĄą╣čüčéą▓ąĖčÅ ąĮą░ čłąĖąĮąĄ TWI.

ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čäą╗ą░ą│ TWINT, TWI ąĘą░ą▓ąĄčĆčłąĖą╗ ąŠą┐ąĄčĆą░čåąĖčÄ ąĖ ąČą┤ąĄčé ąŠčé ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ą║ą░ą║ąŠą│ąŠ-ą╗ąĖą▒ąŠ ąŠčéą▓ąĄčéą░. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ čĆąĄą│ąĖčüčéčĆ TWI Status Register (TWSR) čüąŠą┤ąĄčƹȹĖčé ąĘąĮą░č湥ąĮąĖąĄ, ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčēąĄąĄ č鹥ą║čāčēąĄąĄ čüąŠčüč鹊čÅąĮąĖąĄ čłąĖąĮčŗ TWI. ą¤čĆąŠą│čĆą░ą╝ą╝ą░ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ą╝ąŠąČąĄčé ą┐čĆąĖąĮčÅčéčī čĆąĄčłąĄąĮąĖąĄ, ą║ą░ą║ TWI ą┤ąŠą╗ąČąĄąĮ ą▓ąĄčüčéąĖ čüąĄą▒čÅ ąĮą░ čüą╗ąĄą┤čāčÄčēąĄą╝ čåąĖą║ą╗ąĄ TWI, ą┐čāč鹥ą╝ ą╝ą░ąĮąĖą┐čāą╗čÅčåąĖąĖ čĆąĄą│ąĖčüčéčĆą░ą╝ąĖ TWCR ąĖ TWDR.

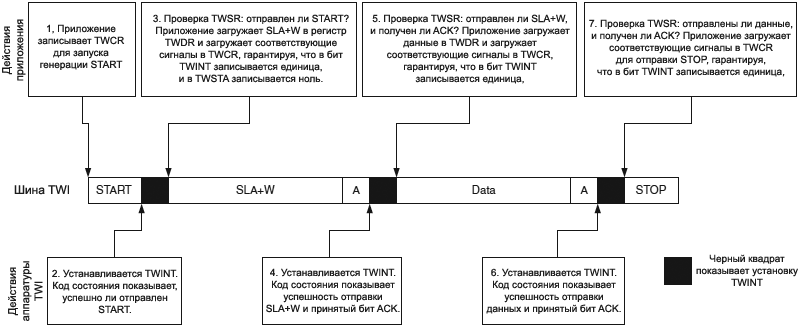

ąĀąĖčü. 20-10 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą┐čĆąŠčüč鹊ą╣ ą┐čĆąĖą╝ąĄčĆ, ą║ą░ą║ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ ą╝ąŠąČąĄčé čĆą░ą▒ąŠčéą░čéčī čü ą░ą┐ą┐ą░čĆą░čéčāčĆąŠą╣ TWI. ąÆ čŹč鹊ą╝ ą┐čĆąĖą╝ąĄčĆąĄ Master čģąŠč湥čé ą┐ąĄčĆąĄą┤ą░čéčī ąŠą┤ąĖąĮ ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ Slave-čāčüčéčĆąŠą╣čüčéą▓čā. ąŁč鹊 ąŠą┐ąĖčüą░ąĮąĖąĄ ą┤ąŠą▓ąŠą╗čīąĮąŠ ą░ą▒čüčéčĆą░ą║čéąĮąŠąĄ, ą▓ čŹč鹊ą╣ čüąĄą║čåąĖąĖ ą▒čāą┤ąĄčé ą┤ą░ąĮąŠ ą▒ąŠą╗ąĄąĄ ą┐ąŠą┤čĆąŠą▒ąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ. ąóą░ą║ąČąĄ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮ ą┐čĆąŠčüč鹊ą╣ ą┐čĆąĖą╝ąĄčĆ ą║ąŠą┤ą░, čĆąĄą░ą╗ąĖąĘčāčÄčēąĖą╣ ąČąĄą╗ą░ąĄą╝ąŠąĄ ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ.

ąĀąĖčü. 20-10. ą¤ąŠą┤ą║ą╗čÄč湥ąĮąĖąĄ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ą║ TWI ą▓ čéąĖą┐ąŠą▓ąŠą╣ ą┐ąĄčĆąĄą┤ą░č湥 ą▒ą░ą╣čéą░.

1. ą¤ąĄčĆą▓čŗą╣ čłą░ą│ ą▓ ą┐ąĄčĆąĄą┤ą░č湥 TWI čüąŠčüč鹊ąĖčé ą▓ ą│ąĄąĮąĄčĆą░čåąĖąĖ START. ąŁč鹊 ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ąĘą░ą┐ąĖčüčīčÄ čüą┐ąĄčåąĖą░ą╗čīąĮąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ ą▓ TWCR, čćč鹊 ąĖąĮčüčéčĆčāą║čéąĖčĆčāąĄčé ą░ą┐ą┐ą░čĆą░čéčāčĆčā TWI ą┐ąĄčĆąĄą┤ą░čéčī čüąĖą│ąĮą░ą╗ START (ą║ą░ą║ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ąĮą░ą┤ąŠ ąĘą░ą┐ąĖčüą░čéčī, ą▒čāą┤ąĄčé ąŠą▒čŖčÅčüąĮąĄąĮąŠ ą┐ąŠąĘąČąĄ). ą×ą┤ąĮą░ą║ąŠ ą▓ą░ąČąĮąŠ, čćč鹊ą▒čŗ ą▓ ąĘą░ą┐ąĖčüą░ąĮąĮąŠą╝ ąĘąĮą░č湥ąĮąĖąĖ ą▒čŗą╗ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé TWINT. ąŚą░ą┐ąĖčüčī ą╗ąŠą│. 1 ą▓ TWINT ąŠčćąĖčēą░ąĄčé čŹč鹊čé čäą╗ą░ą│. TWI ąĮąĄ ąĘą░ą┐čāčüčéąĖčé ą╗čÄą▒čāčÄ ąŠą┐ąĄčĆą░čåąĖčÄ, ą┐ąŠą║ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé TWINT ą▓ čĆąĄą│ąĖčüčéčĆąĄ TWCR. ąĪčĆą░ąĘčā ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ ąŠčćąĖčüčéąĖčé TWINT, ą░ą┐ą┐ą░čĆą░čéčāčĆą░ TWI ąĖąĮąĖčåąĖąĖčĆčāąĄčé ą┐ąĄčĆąĄą┤ą░čćčā čüąĖą│ąĮą░ą╗ą░ START.

2. ąÜąŠą│ą┤ą░ ą┐ąĄčĆąĄą┤ą░ąĮ START, čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ TWINT ą▓ čĆąĄą│ąĖčüčéčĆąĄ TWCR, ąĖ čĆąĄą│ąĖčüčéčĆ TWSR ąŠą▒ąĮąŠą▓ąĖčéčüčÅ ą║ąŠą┤ąŠą╝ čüąŠčüč鹊čÅąĮąĖčÅ, ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčēąĖą╝, čćč鹊 čüąĖą│ąĮą░ą╗ START ą▒čŗą╗ čāčüą┐ąĄčłąĮąŠ ąŠčéą┐čĆą░ą▓ą╗ąĄąĮ.

3. ąóąĄą┐ąĄčĆčī ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ ą┤ąŠą╗ąČąĮąŠ ą┐čĆąŠą▓ąĄčĆąĖčéčī ąĘąĮą░č湥ąĮąĖąĄ TWSR, čćč鹊ą▒čŗ čāą▒ąĄą┤ąĖčéčīčüčÅ, čćč鹊 START ą▒čŗą╗ čāčüą┐ąĄčłąĮąŠ ąŠčéą┐čĆą░ą▓ą╗ąĄąĮ. ąĢčüą╗ąĖ TWSR ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąŠą▒čĆą░čéąĮąŠąĄ, č鹊 ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ ą╝ąŠąČąĄčé ą┐čĆąĄą┤ą┐čĆąĖąĮčÅčéčī ąĮąĄą║ąŠč鹊čĆčŗąĄ čüą┐ąĄčåąĖą░ą╗čīąĮčŗąĄ ą┤ąĄą╣čüčéą▓ąĖčÅ ąĮą░ą┐ąŠą┤ąŠą▒ąĖąĄ ą▓čŗąĘąŠą▓ą░ ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ąŠčłąĖą▒ą║ąĖ. ąĢčüą╗ąĖ ą║ąŠą┤ čüčéą░čéčāčüą░ ąŠą║ą░ąĘą░ą╗čüčÅ ąŠąČąĖą┤ą░ąĄą╝čŗą╝, ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ ą┤ąŠą╗ąČąĮąŠ ąĘą░ą│čĆčāąĘąĖčéčī SLA+W ą▓ čĆąĄą│ąĖčüčéčĆ TWDR. ą¤ąŠą╝ąĮąĖč鹥, čćč鹊 TWDR ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą║ą░ą║ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą░ą┤čĆąĄčüą░, čéą░ą║ ąĖ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ. ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ TWDR ą▒čŗą╗ ąĘą░ą│čĆčāąČąĄąĮ ąČąĄą╗ą░ąĄą╝čŗą╝ ąĘąĮą░č湥ąĮąĖąĄą╝ SLA+W, ą▓ čĆąĄą│ąĖčüčéčĆ TWCR ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮąŠ čüą┐ąĄčåąĖą░ą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ, ąĖąĮčüčéčĆčāą║čéąĖčĆčāčÄčēąĄąĄ ą░ą┐ą┐ą░čĆą░čéčāčĆčā TWI ą┐ąĄčĆąĄą┤ą░čéčī SLA+W, ą┐čĆąĖčüčāčéčüčéą▓čāčÄčēąĄąĄ ą▓ TWDR (čüą┐ąĄčåąĖą░ą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą▒čāą┤ąĄčé ąŠą┐ąĖčüą░ąĮąŠ ą┐ąŠąĘąČąĄ). ą×ą┤ąĮą░ą║ąŠ ą▓ą░ąČąĮąŠ, čćč鹊ą▒čŗ ą▓ ąĘą░ą┐ąĖčüą░ąĮąĮąŠą╝ ąĘąĮą░č湥ąĮąĖąĖ ą▒čŗą╗ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé TWINT. ąŚą░ą┐ąĖčüčī ą╗ąŠą│. 1 ą▓ TWINT ąŠčćąĖčēą░ąĄčé čŹč鹊čé čäą╗ą░ą│. TWI ąĮąĄ ąĘą░ą┐čāčüčéąĖčé ą╗čÄą▒čāčÄ ąŠą┐ąĄčĆą░čåąĖčÄ, ą┐ąŠą║ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé TWINT ą▓ čĆąĄą│ąĖčüčéčĆąĄ TWCR. ąĪčĆą░ąĘčā ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ ąŠčćąĖčüčéąĖčé TWINT, ą░ą┐ą┐ą░čĆą░čéčāčĆą░ TWI ąĖąĮąĖčåąĖąĖčĆčāąĄčé ą┐ąĄčĆąĄą┤ą░čćčā ą┐ą░ą║ąĄčéą░ ą░ą┤čĆąĄčüą░.

4. ąÜąŠą│ą┤ą░ ą┐ą░ą║ąĄčé ą░ą┤čĆąĄčüą░ ą┐ąĄčĆąĄą┤ą░ąĮ, čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ TWINT ą▓ čĆąĄą│ąĖčüčéčĆąĄ TWCR, ąĖ čĆąĄą│ąĖčüčéčĆ TWSR ąŠą▒ąĮąŠą▓ąĖčéčüčÅ ą║ąŠą┤ąŠą╝ čüąŠčüč鹊čÅąĮąĖčÅ, ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčēąĖą╝, čćč鹊 ą┐ą░ą║ąĄčé ą░ą┤čĆąĄčüą░ ą▒čŗčéčī čāčüą┐ąĄčłąĮąŠ ąŠčéą┐čĆą░ą▓ą╗ąĄąĮ. ąŁč鹊čé ą║ąŠą┤ čüąŠčüč鹊čÅąĮąĖčÅ čéą░ą║ąČąĄ čüąŠą┤ąĄčƹȹĖčé ąĖąĮč乊čĆą╝ą░čåąĖčÄ ąŠ č鹊ą╝, ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮ ą╗ąĖ čŹč鹊čé ą░ą┤čĆąĄčü Slave-čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ ąĖą╗ąĖ ąĮąĄčé.

ąØąĄčüą╝ąŠčéčĆčÅ ąĮą░ ą┐čĆąŠčüč鹊čéčā čŹč鹊ą│ąŠ ą┐čĆąĖą╝ąĄčĆą░, ąŠąĮ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąŠčüąĮąŠą▓ąĮčŗąĄ ą┐čĆąĖąĮčåąĖą┐čŗ, ą┤ąĄą╣čüčéą▓čāčÄčēąĖąĄ ą▓ąŠ ą▓čüąĄčģ ą┐ąĄčĆąĄą┤ą░čćą░čģ TWI:

ŌĆó ąÜąŠą│ą┤ą░ TWI ąĘą░ą▓ąĄčĆčłąĖą╗ ąŠą┐ąĄčĆą░čåąĖčÄ ąĖ ąŠąČąĖą┤ą░ąĄčé ąŠčéą▓ąĄčéą░ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ, čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ čäą╗ą░ą│ TWINT. ąĪąĖą│ąĮą░ą╗ SCL ą┐ąŠą┤čéčÅą│ąĖą▓ą░ąĄčéčüčÅ ą║ ą╗ąŠą│. 0, ą┐ąŠą║ą░ ąĮąĄ ą▒čāą┤ąĄčé ąŠčćąĖčēąĄąĮ TWINT.

ŌĆó ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čäą╗ą░ą│ TWINT, ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą┤ąŠą╗ąČąĄąĮ ąŠą▒ąĮąŠą▓ąĖčéčī čĆąĄą│ąĖčüčéčĆčŗ TWI ąĘąĮą░č湥ąĮąĖąĄą╝, ąĮąĄąŠą▒čģąŠą┤ąĖą╝čŗą╝ ą┤ą╗čÅ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ čåąĖą║ą╗ą░ čłąĖąĮčŗ TWI. ąÆ čŹč鹊ą╝ ą┐čĆąĖą╝ąĄčĆąĄ TWDR ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ą│čĆčāąČąĄąĮ ąĘąĮą░č湥ąĮąĖąĄą╝, ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗą╝ ąĮą░ čüą╗ąĄą┤čāčÄčēąĄą╝ čåąĖą║ą╗ąĄ čłąĖąĮčŗ.

ŌĆó ą¤ąŠčüą╗ąĄ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ TWI ąĖ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄą╝ ą┤čĆčāą│ąĖčģ ąŠąČąĖą┤ą░čÄčēąĖčģ ąŠą┐ąĄčĆą░čåąĖą╣, ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ TWCR. ą¤čĆąĖ ąĘą░ą┐ąĖčüąĖ TWCR ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé TWINT. ąÜą░ą║ čāąČąĄ čāą┐ąŠą╝ąĖąĮą░ą╗ąŠčüčī, ąĘą░ą┐ąĖčüčī ąĄą┤ąĖąĮąĖčåčŗ ą▓ TWINT ąŠčćąĖčüčéąĖčé čŹč鹊čé čäą╗ą░ą│. ąóąŠą│ą┤ą░ TWI ąĮą░čćąĮąĄčé ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ąŠą┐ąĄčĆą░čåąĖąĖ čĆą░ą▒ąŠčéčŗ, čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮąŠą╣ ąĮą░čüčéčĆąŠą╣ą║ąŠą╣ TWCR.

ąØąĖąČąĄ ą┐čĆąĖą▓ąĄą┤ąĄąĮą░ ą┐ąŠą┤ą▒ąŠčĆą║ą░ ą║ąŠą┤ą░ ą░čüčüąĄą╝ą▒ą╗ąĄčĆą░ ąĖ C ą┤ą╗čÅ čŹč鹊ą│ąŠ ą┐čĆąĖą╝ąĄčĆą░. ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 ą║ąŠą┤ ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčé ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖąĄ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖčģ ąĘą░ą│ąŠą╗ąŠą▓ąŠčćąĮčŗčģ čäą░ą╣ą╗ąŠą▓ ą┤ąĖčĆąĄą║čéąĖą▓ąŠą╣ #include.

| |

ą¤čĆąĖą╝ąĄčĆ ą║ąŠą┤ą░ ąĮą░ ą░čüčüąĄą╝ą▒ą╗ąĄčĆąĄ |

ą¤čĆąĖą╝ąĄčĆ ą║ąŠą┤ą░ ąĮą░ C |

ąÜąŠą╝ą╝ąĄąĮčéą░čĆąĖąĖ |

| 1 |

ldir16, (1 << TWINT)|(1 << TWSTA)|

(1 << TWEN)

out TWCR, r16

|

TWCR = (1 << TWINT)|(1 << TWSTA)

|(1<<TWEN)

|

ą×čéą┐čĆą░ą▓ą║ą░ START. |

| 2 |

wait1:

in r16,TWCR

sbrs r16,TWINT

rjmp wait1

|

while (!(TWCR & (1 << TWINT)))

|

ą×ąČąĖą┤ą░ąĮąĖąĄ čāčüčéą░ąĮąŠą▓ą║ąĖ čäą╗ą░ą│ą░ TWINT. ąŁč鹊 ą┐ąŠą║ą░ąČąĄčé, čćč鹊 START ą▒čŗą╗ ą┐ąĄčĆąĄą┤ą░ąĮ. |

| 3 |

in r16,TWSR

andi r16, 0xF8

cpi r16, START

brne ERROR

|

if ((TWSR & 0xF8) != START)

ERROR();

|

ą¤čĆąŠą▓ąĄčĆą║ą░ ąĘąĮą░č湥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ čüąŠčüč鹊čÅąĮąĖčÅ TWI čü ą╝ą░čüą║ąĖčĆąŠą▓ą║ąŠą╣ ą▒ąĖčé ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░. ąĢčüą╗ąĖ čüčéą░čéčāčü ąŠčéą╗ąĖčćą░ąĄčéčüčÅ ąŠčé START, č鹊 ą┐ąĄčĆąĄčģąŠą┤ ą║ ąŠą▒čĆą░ą▒ąŠčéą║ąĄ ąŠčłąĖą▒ą║ąĖ. |

ldi r16, SLA_W

out TWDR, r16

ldi r16, (1 << TWINT)|(1 << TWEN)

out TWCR, r16

|

TWDR = SLA_W;

TWCR = (1 << TWINT) | (1 << TWEN);

|

ąŚą░ą│čĆčāąČą░ąĄčé SLA+W ą▓ čĆąĄą│ąĖčüčéčĆ TWDR. ą×čćąĖčēą░ąĄčé ą▒ąĖčé TWINT ą▓ TWCR ą┤ą╗čÅ ąĘą░ą┐čāčüą║ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ ą░ą┤čĆąĄčüą░. |

| 4 |

wait2:

in r16,TWCR

sbrs r16,TWINT

rjmp wait2

|

while (!(TWCR & (1 << TWINT)))

|

ą×ąČąĖą┤ą░ąĮąĖąĄ čāčüčéą░ąĮąŠą▓ą║ąĖ čäą╗ą░ą│ą░ TWINT. ąŁč鹊 ą┐ąŠą║ą░ąČąĄčé, čćč鹊 SLA+W ą▒čŗą╗ ą┐ąĄčĆąĄą┤ą░ąĮ, ąĖ ą▒čāą┤ąĄčé ą┐čĆąĖąĮčÅčé ACK/NACK. |

| 5 |

in r16,TWSR

andi r16, 0xF8

cpi r16, MT_SLA_ACK

brne ERROR

|

if ((TWSR & 0xF8) != MT_SLA_ACK)

ERROR();

|

ą¤čĆąŠą▓ąĄčĆą║ą░ ąĘąĮą░č湥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ čüąŠčüč鹊čÅąĮąĖčÅ TWI čü ą╝ą░čüą║ąĖčĆąŠą▓ą║ąŠą╣ ą▒ąĖčé ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░. ąĢčüą╗ąĖ čüčéą░čéčāčü ąŠčéą╗ąĖčćą░ąĄčéčüčÅ ąŠčé MT_SLA_ACK, č鹊 ą┐ąĄčĆąĄčģąŠą┤ ą║ ąŠą▒čĆą░ą▒ąŠčéą║ąĄ ąŠčłąĖą▒ą║ąĖ ERROR. |

ldi r16, DATA

out TWDR, r16

ldi r16, (1 << TWINT) | (1 << TWEN)

out TWCR, r16

|

TWDR = DATA;

TWCR = (1 << TWINT) | (1 << TWEN);

|

ąŚą░ą│čĆčāąČą░ąĄčé ą┤ą░ąĮąĮčŗąĄ DATA ą▓ čĆąĄą│ąĖčüčéčĆ TWDR. ą×čćąĖčēą░ąĄčé ą▒ąĖčé TWINT ą▓ TWCR ą┤ą╗čÅ ąĘą░ą┐čāčüą║ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ. |

| 6 |

wait3:

in r16,TWCR

sbrs r16,TWINT

rjmp wait3

|

while (!(TWCR & (1 << TWINT)))

|

ą×ąČąĖą┤ą░ąĮąĖąĄ čāčüčéą░ąĮąŠą▓ą║ąĖ čäą╗ą░ą│ą░ TWINT. ąŁč鹊 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 DATA ą▒čŗą╗ąĖ ą┐ąĄčĆąĄą┤ą░ąĮčŗ, ąĖ ą┐čĆąĖąĮčÅčé ACK/NACK. |

| 7 |

in r16,TWSR

andi r16, 0xF8

cpi r16, MT_DATA_ACK

brne ERROR

|

if ((TWSR & 0xF8) != MT_DATA_ACK)

ERROR();

|

ą¤čĆąŠą▓ąĄčĆą║ą░ ąĘąĮą░č湥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ čüąŠčüč鹊čÅąĮąĖčÅ TWI čü ą╝ą░čüą║ąĖčĆąŠą▓ą║ąŠą╣ ą▒ąĖčé ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░. ąĢčüą╗ąĖ čüčéą░čéčāčü ąŠčéą╗ąĖčćą░ąĄčéčüčÅ ąŠčé MT_DATA_ACK, č鹊 ą┐ąĄčĆąĄčģąŠą┤ ą║ ąŠą▒čĆą░ą▒ąŠčéą║ąĄ ąŠčłąĖą▒ą║ąĖ. |

ldi r16, (1 << TWINT)|(1 << TWEN)|

(1 << TWSTO)out TWCR, r16

|

TWCR = (1 << TWINT)|(1 << TWEN)|

(1 << TWSTO);

|

ą¤ąĄčĆąĄą┤ą░čćą░ čüąĖą│ąĮą░ą╗ą░ STOP. |

[ąĀąĄąČąĖą╝čŗ ą┐ąĄčĆąĄą┤ą░čćąĖ]

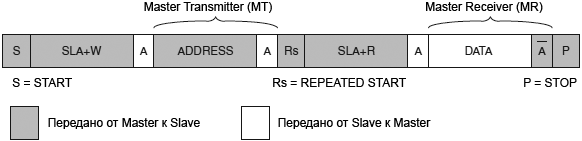

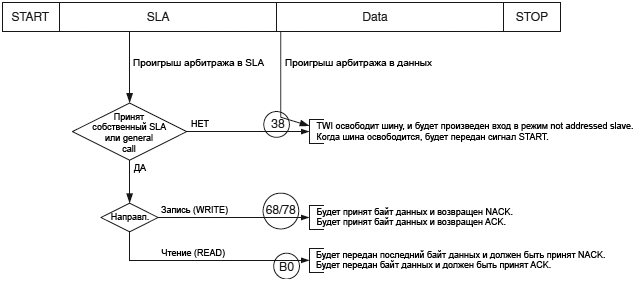

TWI ą╝ąŠąČąĄčé čĆą░ą▒ąŠčéą░čéčī ą▓ ąŠą┤ąĮąŠą╝ ąĖąĘ 4 ąŠčüąĮąŠą▓ąĮčŗčģ čĆąĄąČąĖą╝ąŠą▓. ą×ąĮąĖ ąĮą░ąĘčŗą▓ą░čÄčéčüčÅ Master Transmitter (MT), Master Receiver (MR), Slave Transmitter (ST) ąĖ Slave Receiver (SR). ąØąĄą║ąŠč鹊čĆčŗąĄ ąĖąĘ čŹčéąĖčģ čĆąĄąČąĖą╝ąŠą▓ ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą▓ ąŠą┤ąĮąŠą╝ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĖ. ąØą░ą┐čĆąĖą╝ąĄčĆ, TWI ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čĆąĄąČąĖą╝ MT, čćč鹊ą▒čŗ ąĘą░ą┐ąĖčüą░čéčī ą┤ą░ąĮąĮčŗąĄ ą▓ TWI EEPROM, čĆąĄąČąĖą╝ MR ą┤ą╗čÅ čćč鹥ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ąĖąĘ čŹč鹊ą│ąŠ EEPROM. ąĢčüą╗ąĖ ą▓ čüąĖčüč鹥ą╝ąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤čĆčāą│ąĖąĄ master-čāčüčéčĆąŠą╣čüčéą▓ą░, ąŠąĮąĖ ą╝ąŠą│čāčé ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī ą┤ą░ąĮąĮčŗąĄ ą▓ TWI, ąĖ č鹊ą│ą┤ą░ ą┤ąŠą╗ąČąĄąĮ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ čĆąĄąČąĖą╝ SR. ą¤čĆąŠą│čĆą░ą╝ą╝ą░ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ čĆąĄčłą░ąĄčé, ą║ą░ą║ąŠą╣ ąĖąĘ čĆąĄąČąĖą╝ąŠą▓ ą┐ąŠą┤čģąŠą┤ąĖčé ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą╣ čüąĖčéčāą░čåąĖąĖ.

ąÆ ą┐ąŠčüą╗ąĄą┤čāčÄčēąĖčģ čüąĄą║čåąĖčÅčģ ąŠą┐ąĖčüčŗą▓ą░čÄčéčüčÅ čŹčéąĖ čĆąĄąČąĖą╝čŗ. ąÆąŠąĘą╝ąŠąČąĮčŗąĄ ą║ąŠą┤čŗ čüąŠčüč鹊čÅąĮąĖčÅ ąŠą┐ąĖčüą░ąĮčŗ ą▓ą╝ąĄčüč鹥 čü čĆąĖčüčāąĮą║ą░ą╝ąĖ, ą┐ąŠą┤čĆąŠą▒ąĮąŠ ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčēąĖą╝ąĖ ą┐ąĄčĆąĄą┤ą░čćčā ą┤ą░ąĮąĮčŗčģ ą▓ ą║ą░ąČą┤ąŠą╝ ąĖąĘ čĆąĄąČąĖą╝ąŠą▓. ąŁčéąĖ čĆąĖčüčāąĮą║ąĖ čüąŠą┤ąĄčƹȹ░čé čüą╗ąĄą┤čāčÄčēąĖąĄ ą░ą▒ą▒čĆąĄą▓ąĖą░čéčāčĆčŗ:

S: čüąĖą│ąĮą░ą╗ START

Rs: REPEATED START

R: ą▒ąĖčé čćč鹥ąĮąĖčÅ, Read bit (ą╗ąŠą│. 1 ąĮą░ SDA)

W: ą▒ąĖčé ąĘą░ą┐ąĖčüąĖ, Write bit (ą╗ąŠą│. 0 ąĮą░ SDA)

A: ą▒ąĖčé ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą│ąŠ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ, ACK (ą╗ąŠą│. 0 ąĮą░ SDA)

~A: ą▒ąĖčé ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠą│ąŠ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ, NACK (ą╗ąŠą│. 1 ąĮą░ SDA)

Data: 8-ą▒ąĖčé ą▒ą░ą╣čéą░ ą┤ą░ąĮąĮčŗčģ

P: čüąĖą│ąĮą░ą╗ STOP

SLA: ą░ą┤čĆąĄčü ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░, Slave Address

ąØą░ čĆąĖčüčāąĮą║ą░čģ ąŠčé 20-12 ą┤ąŠ 20-18 ą║čĆčāąČąŠčćą║ąĖ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ čāą║ą░ąĘą░ąĮąĖčÅ čāčüčéą░ąĮąŠą▓ą║ąĖ čäą╗ą░ą│ą░ TWINT. ą¦ąĖčüą╗ą░ ą▓ ą║čĆčāąČąŠčćą║ą░čģ ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčé ą║ąŠą┤ čüąŠčüč鹊čÅąĮąĖčÅ, čüąŠą┤ąĄčƹȹ░čēąĖą╣čüčÅ ą▓ TWSR, čü ą▒ąĖčéą░ą╝ąĖ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░, ąĘą░ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĮčŗą╝ąĖ ąĮčāą╗čÅą╝ąĖ. ąÆ čŹčéąĖčģ č鹊čćą║ą░čģ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ ą┤ąŠą╗ąČąĮąŠ ą┐čĆąĄą┤ą┐čĆąĖąĮčÅčéčī ą║ą░ą║ąĖąĄ-ą╗ąĖą▒ąŠ ą┤ąĄą╣čüčéą▓ąĖčÅ, čćč鹊ą▒čŗ ą┐čĆąŠą┤ąŠą╗ąČąĖčéčī ąĖą╗ąĖ ąĘą░ą▓ąĄčĆčłąĖčéčī ą┐ąĄčĆąĄą┤ą░čćčā TWI. ą¤ąĄčĆąĄą┤ą░čćą░ TWI ą┐čĆąĖąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ, ą┐ąŠą║ą░ čäą╗ą░ą│ TWINT ąĮąĄ ą▒čāą┤ąĄčé ąŠčćąĖčēąĄąĮ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣.

ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čäą╗ą░ą│ TWINT, ą║ąŠą┤ čüąŠčüč鹊čÅąĮąĖčÅ ą▓ TWSR ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ č鹊ą│ąŠ, čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ ą┤ąĄą╣čüčéą▓ąĖąĄ ą┤ą╗čÅ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ. ąöą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą║ąŠą┤ą░ čüąŠčüč鹊čÅąĮąĖčÅ ą▓ čéą░ą▒ą╗ąĖčåą░čģ ąŠčé 20-1 ą┤ąŠ 20-4 ą┤ą░ąĮčŗ čéčĆąĄą▒čāąĄą╝čŗąĄ ą┤ąĄą╣čüčéą▓ąĖčÅ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ąĖ ąŠą┐ąĖčüą░ąĮąĖąĄ ą┐ąŠčüą╗ąĄą┤čāčÄčēąĄą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ. ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 ą▓ čŹčéąĖčģ čéą░ą▒ą╗ąĖčåą░čģ ą▒ąĖčéčŗ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮčŗ ąĮčāą╗čÅą╝ąĖ.

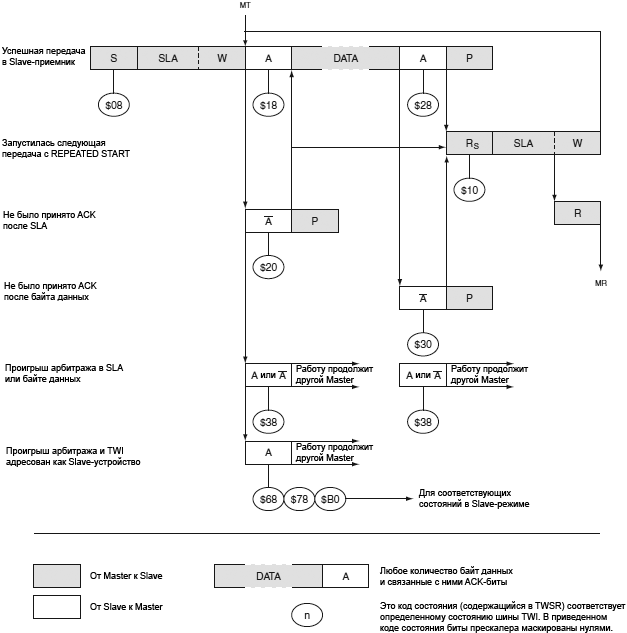

Master Transmitter Mode. ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ąĮąĄą║ąŠč鹊čĆąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą┐čĆąĖąĄą╝ąĮąĖą║čā Slave (čüą╝. čĆąĖčü. 20-11). ą¦č鹊ą▒čŗ ą▓ąŠą╣čéąĖ ą▓ čĆąĄąČąĖą╝ Master, ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąĄčĆąĄą┤ą░ąĮ čüąĖą│ąĮą░ą╗ START. ążąŠčĆą╝ą░čé ą┐ąŠčüą╗ąĄą┤čāčÄčēąĄą│ąŠ ą┐ą░ą║ąĄčéą░ ą░ą┤čĆąĄčüą░ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé, ą▓ ą║ą░ą║ąŠą╣ čĆąĄąČąĖą╝ ąĮčāąČąĮąŠ ą┐ąŠčüą╗ąĄ čŹč鹊ą│ąŠ ą▓ąŠą╣čéąĖ - Master Transmitter ąĖą╗ąĖ Master Receiver. ąĢčüą╗ąĖ ą┐ąĄčĆąĄą┤ą░ąĮ SLA+W, č鹊 ą▓čģąŠą┤čÅčé ą▓ čĆąĄąČąĖą╝ MT, ąĄčüą╗ąĖ ą┐ąĄčĆąĄą┤ą░ąĮ SLA+R, č鹊 ą▓čģąŠą┤čÅčé ą▓ čĆąĄąČąĖą╝ MR. ą¤ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčéčüčÅ, čćč鹊 ą▓ąŠ ą▓čüąĄčģ ą║ąŠą┤ą░čģ čüąŠčüč鹊čÅąĮąĖčÅ, čāą┐ąŠą╝čÅąĮčāčéčŗčģ ą▓ čŹč鹊ą╣ čüąĄą║čåąĖąĖ, ą▒ąĖčéčŗ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ ąĘą░ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮčŗ ąĮčāą╗čÅą╝ąĖ.

ąĀąĖčü. 20-11. ą¤ąĄčĆąĄą┤ą░čćą░ ą┤ą░ąĮąĮčŗčģ ą▓ čĆąĄąČąĖą╝ąĄ MT.

ąĪąĖą│ąĮą░ą╗ START ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ąĘą░ą┐ąĖčüčīčÄ ą▓ TWCR čüą╗ąĄą┤čāčÄčēąĄą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ:

| TWINT |

TWEA |

TWSTA |

TWSTO |

TWWC |

TWEN |

- |

TWIE |

| 1 |

x |

1 |

0 |

x |

1 |

0 |

x |

ąæąĖčé TWEN ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čćč鹊ą▒čŗ čĆą░ąĘčĆąĄčłąĖčéčī TWI, TWSTA ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮ ą▓ ą╗ąŠą│. 1, čćč鹊ą▒čŗ ą┐ąĄčĆąĄą┤ą░čéčī čüąĖą│ąĮą░ą╗ START, ąĖ TWINT ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮ ą▓ ą╗ąŠą│. 1, čćč鹊ą▒čŗ ąŠčćąĖčüčéąĖčéčī čäą╗ą░ą│ TWINTg. ąŚą░č鹥ą╝ TWI ą┐čĆąŠą▓ąĄčĆąĖčé čłąĖąĮčā, čüą▓ąŠą▒ąŠą┤ąĮą░ ą╗ąĖ ąŠąĮą░, ąĖ ą┐ąĄčĆąĄą┤ą░čüčé START, ą║ą░ą║ č鹊ą╗čīą║ąŠ čłąĖąĮą░ ąŠčüą▓ąŠą▒ąŠą┤ąĖčéčüčÅ. ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ START ą▒čŗą╗ ą┐ąĄčĆąĄą┤ą░ąĮ, ą░ą┐ą┐ą░čĆą░čéąĮąŠ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ TWINT, ąĖ ą▓ TWSR ą┐ąŠčÅą▓ąĖčéčüčÅ ą║ąŠą┤ čüąŠčüč鹊čÅąĮąĖčÅ 0x08 (čüą╝. čéą░ą▒ą╗ąĖčåčā 20-1). ą¦č鹊ą▒čŗ ą▓ąŠą╣čéąĖ ą▓ čĆąĄąČąĖą╝ MT, ąĮčāąČąĮąŠ ą┐ąĄčĆąĄą┤ą░čéčī SLA+W. ąŁč鹊 ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ąĘą░ą┐ąĖčüčīčÄ SLA+W ą▓ TWDR. ą¤ąŠčüą╗ąĄ čŹč鹊ą│ąŠ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąŠčćąĖčēąĄąĮ ą▒ąĖčé TWINT (ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ ą▓ ąĮąĄą│ąŠ ą╗ąŠą│. 1), čćč鹊ą▒čŗ ą┐ąĄčĆąĄą┤ą░čćą░ ą┐čĆąŠą┤ąŠą╗ąČąĖą╗ą░čüčī. ąŁč鹊 ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ąĘą░ą┐ąĖčüčīčÄ ą▓ TWCR čüą╗ąĄą┤čāčÄčēąĄą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ:

| TWINT |

TWEA |

TWSTA |

TWSTO |

TWWC |

TWEN |

- |

TWIE |

| 1 |

x |

0 |

0 |

x |

1 |

0 |

x |

ąÜąŠą│ą┤ą░ ą┐ąĄčĆąĄą┤ą░ąĮ SLA+W ąĖ ą┐čĆąĖąĮčÅčé ą▒ąĖčé ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ, TWINT čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čüąĮąŠą▓ą░, ąĖ ą▓ TWSR ą╝ąŠą│čāčé ą┐ąŠčÅą▓ąĖčéčīčüčÅ ąĮąĄą║ąŠč鹊čĆčŗąĄ ą║ąŠą┤čŗ čüąŠčüč鹊čÅąĮąĖčÅ. ąÆąŠąĘą╝ąŠąČąĮčŗąĄ ą║ąŠą┤čŗ čüąŠčüč鹊čÅąĮąĖčÅ ą┤ą╗čÅ čĆąĄąČąĖą╝ą░ Master 0x18, 0x20 ąĖą╗ąĖ 0x38. ąöą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ąĖąĘ čŹčéąĖčģ ą║ąŠą┤ąŠą▓ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą┐čĆąĄą┤ą┐čĆąĖąĮčÅč鹊 čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ ą┤ąĄą╣čüčéą▓ąĖąĄ, čćč鹊 ąŠą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ ą▓ čéą░ą▒ą╗ąĖčåąĄ 20-1.

ąÜąŠą│ą┤ą░ SLA+W ą▒čŗą╗ čāčüą┐ąĄčłąĮąŠ ąŠčéą┐čĆą░ą▓ą╗ąĄąĮ, ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąĄčĆąĄą┤ą░ąĮ ą┐ą░ą║ąĄčé ą┤ą░ąĮąĮčŗčģ. ąŁč鹊 ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ąĘą░ą┐ąĖčüčīčÄ ą▒ą░ą╣čéą░ ą┤ą░ąĮąĮčŗčģ ą▓ TWDR. TWDR ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮ č鹊ą╗čīą║ąŠ č鹊ą│ą┤ą░, ą║ąŠą│ą┤ą░ TWINT ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ą╗ąŠą│. 1. ąĢčüą╗ąĖ čŹč鹊 ąĮąĄ čüąŠą▒ą╗čÄčüčéąĖ, č鹊 ąĘą░ą┐ąĖčüčī ą▒čāą┤ąĄčé ąŠčéą▒čĆąŠčłąĄąĮą░, ąĖ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé ą║ąŠą╗ą╗ąĖąĘąĖąĖ ąĘą░ą┐ąĖčüąĖ Write Collision bit (TWWC) ą▓ čĆąĄą│ąĖčüčéčĆąĄ TWCR. ą¤ąŠčüą╗ąĄ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ TWDR ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąŠčćąĖčēąĄąĮ ą▒ąĖčé TWINT (ąĘą░ą┐ąĖčüčīčÄ ą▓ ąĮąĄą│ąŠ ą╗ąŠą│. 1), čćč鹊ą▒čŗ ą┐ąĄčĆąĄą┤ą░čćą░ ą┐čĆąŠą┤ąŠą╗ąČąĖą╗ą░čüčī. ąŁč鹊 ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ąĘą░ą┐ąĖčüčīčÄ ą▓ TWCR čüą╗ąĄą┤čāčÄčēąĄą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ:

| TWINT |

TWEA |

TWSTA |

TWSTO |

TWWC |

TWEN |

- |

TWIE |

| 1 |

x |

0 |

0 |

x |

1 |

0 |

x |

ąŁčéą░ čüčģąĄą╝ą░ ą┐ąŠą▓č鹊čĆčÅąĄčéčüčÅ, ą┐ąŠą║ą░ ąĮąĄ ą▒čāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ąĮ ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ą▒ą░ą╣čé, ąĖ ą┐ąĄčĆąĄą┤ą░čćą░ ąĘą░ą║ąŠąĮčćąĖčéčüčÅ čüąĖą│ąĮą░ą╗ąŠą╝ STOP ąĖą╗ąĖ ą┐ąŠą▓č鹊čĆąĮąŠą╣ ą▓čŗą┤ą░č湥ą╣ čüąĖą│ąĮą░ą╗ą░ START. STOP ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ąĘą░ą┐ąĖčüčīčÄ ą▓ TWCR čüą╗ąĄą┤čāčÄčēąĄą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ:

| TWINT |

TWEA |

TWSTA |

TWSTO |

TWWC |

TWEN |

- |

TWIE |

| 1 |

x |

0 |

1 |

x |

1 |

0 |

x |

REPEATED START ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ąĘą░ą┐ąĖčüčīčÄ ą▓ TWCR čüą╗ąĄą┤čāčÄčēąĄą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ:

| TWINT |

TWEA |

TWSTA |

TWSTO |

TWWC |

TWEN |

- |

TWIE |

| 1 |

x |

1 |

0 |

x |

1 |

0 |

x |

ą¤ąŠčüą╗ąĄ ą┐ąŠą▓č鹊čĆąĮąŠą│ąŠ START (čüąŠčüč鹊čÅąĮąĖąĄ 0x10) ąĖąĮč鹥čĆč乥ą╣čü TWI čüąĮąŠą▓ą░ ą╝ąŠąČąĄčé ą┐ąŠą╗čāčćąĖčéčī ą┤ąŠčüčéčāą┐ ą║ č鹊ą╝čā ąČąĄ Slave-čāčüčéčĆąŠą╣čüčéą▓čā, ąĖą╗ąĖ ą║ ąĮąŠą▓ąŠą╝čā Slave-čāčüčéčĆąŠą╣čüčéą▓čā ą▒ąĄąĘ ą┐ąĄčĆąĄą┤ą░čćąĖ STOP. ą¤ąŠą▓č鹊čĆąĮąŠ ą▓čŗą┤ą░ąĮąĮčŗą╣ START ą┐ąŠąĘą▓ąŠą╗čÅąĄčé Master-čāčüčéčĆąŠą╣čüčéą▓čā ą┐ąĄčĆąĄą║ą╗čÄčćą░čéčīčüčÅ ą╝ąĄąČą┤čā Slave-čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ, ą╝ąĄąČą┤čā čĆąĄąČąĖą╝ą░ą╝ąĖ MT ąĖ MR ą▒ąĄąĘ ą┐ąŠč鹥čĆąĖ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĮą░ą┤ čłąĖąĮąŠą╣.

ąóą░ą▒ą╗ąĖčåą░ 20-1. ąÜąŠą┤čŗ čüąŠčüč鹊čÅąĮąĖčÅ ą┤ą╗čÅ čĆąĄąČąĖą╝ą░ MT (ą▓ ą┐ąĄčĆą▓ąŠą╝ čüč鹊ą╗ą▒čåąĄ ąĮą░čüčéčĆąŠą╣ą║ą░ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ ąĘą░ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮą░ ąĮčāą╗čÅą╝ąĖ).

| ąÜąŠą┤ čüąŠčüč鹊čÅąĮąĖčÅ (TWSR) |

ąĪąŠčüč鹊čÅąĮąĖąĄ čłąĖąĮčŗ ąĖ ą░ą┐ą┐ą░čĆą░čéčāčĆčŗ TWI |

ą×čéą▓ąĄčé ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ |

ąĪą╗ąĄą┤čāčÄčēąĄąĄ ą┤ąĄą╣čüčéą▓ąĖąĄ, ą┐čĆąĄą┤ą┐čĆąĖąĮąĖą╝ą░ąĄą╝ąŠąĄ ą░ą┐ą┐ą░čĆą░čéčāčĆąŠą╣ TWI |

| ąÆ/ąĖąĘ TWDR |

ąÆ čĆąĄą│ąĖčüčéčĆ TWCR |

| STA |

STO |

TWINT |

TWEA |

| 0x08 |

ą¤ąĄčĆąĄą┤ą░ąĮ čüąĖą│ąĮą░ą╗ START |

ąŚą░ą│čĆčāąĘą║ą░ SLA+W |

0 |

0 |

1 |

x |

ąæčāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ąĮ SLA+W ąĖ ą┐čĆąĖąĮčÅčé ACK ąĖą╗ąĖ NACK |

| 0x10 |

ą¤ąĄčĆąĄą┤ą░ąĮ čüąĖą│ąĮą░ą╗ REPEATED START |

ąŚą░ą│čĆčāąĘą║ą░ SLA+W |

0 |

0 |

1 |

x |

ąæčāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ąĮ SLA+W ąĖ ą┐čĆąĖąĮčÅčé ACK ąĖą╗ąĖ NACK |

| ąŚą░ą│čĆčāąĘą║ą░ SLA+R |

0 |

0 |

1 |

x |

ąæčāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ąĮ SLA+R, ą╗ąŠą│ąĖą║ą░ ą┐ąĄčĆąĄą║ą╗čÄčćąĖčé TWI ą▓ čĆąĄąČąĖą╝ MR |

| 0x18 |

ą¤ąĄčĆąĄą┤ą░ąĮ SLA+W, ą┐čĆąĖąĮčÅčé ACK |

ąŚą░ą│čĆčāąĘą║ą░ ą▒ą░ą╣čéą░ ą┤ą░ąĮąĮčŗčģ |

0 |

0 |

1 |

x |

ąæčāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ąĮ ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ ąĖ ą┐čĆąĖąĮčÅčé ACK ąĖą╗ąĖ NACK |

| ąØąĄčé ą┤ąĄą╣čüčéą▓ąĖčÅ čü TWDR |

1 |

0 |

1 |

x |

ąæčāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ąĮ REPEATED START |

| 0 |

1 |

1 |

x |

ąæčāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ąĮ STOP ąĖ čüą▒čĆąŠčłąĄąĮ čäą╗ą░ą│ TWSTO |

| 1 |

1 |

1 |

x |

ąæčāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ąĮ STOP, ąĘą░ ą║ąŠč鹊čĆčŗą╝ ą┐ąŠčüą╗ąĄą┤čāąĄčé START, ąĖ ą▒čāą┤ąĄčé čüą▒čĆąŠčłąĄąĮ čäą╗ą░ą│ TWSTO |

| 0x20 |

ą¤ąĄčĆąĄą┤ą░ąĮ SLA+W, ą┐čĆąĖąĮčÅčé NACK |

ąŚą░ą│čĆčāąĘą║ą░ ą▒ą░ą╣čéą░ ą┤ą░ąĮąĮčŗčģ |

0 |

0 |

1 |

x |

ąæčāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ąĮ ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ ąĖ ą┐čĆąĖąĮčÅčé ACK ąĖą╗ąĖ NACK |

| ąØąĄčé ą┤ąĄą╣čüčéą▓ąĖčÅ čü TWDR |

1 |

0 |

1 |

x |

ąæčāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ąĮ REPEATED START |

| 0 |

1 |

1 |

x |

ąæčāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ąĮ STOP ąĖ čüą▒čĆąŠčłąĄąĮ čäą╗ą░ą│ TWSTO |

| 1 |

1 |

1 |

x |

ąæčāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ąĮ STOP, ąĘą░ ą║ąŠč鹊čĆčŗą╝ ą┐ąŠčüą╗ąĄą┤čāąĄčé START, ąĖ ą▒čāą┤ąĄčé čüą▒čĆąŠčłąĄąĮ čäą╗ą░ą│ TWSTO |

| 0x28 |

ą¤ąĄčĆąĄą┤ą░ąĮ ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ, ą┐čĆąĖąĮčÅčé ACK |

ąŚą░ą│čĆčāąĘą║ą░ ą▒ą░ą╣čéą░ ą┤ą░ąĮąĮčŗčģ |

0 |

0 |

1 |

x |

ąæčāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ąĮ ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ ąĖ ą┐čĆąĖąĮčÅčé ACK ąĖą╗ąĖ NACK |

| ąØąĄčé ą┤ąĄą╣čüčéą▓ąĖčÅ čü TWDR |

1 |

0 |

1 |

x |

ąæčāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ąĮ REPEATED START |

| 0 |

1 |

1 |

x |

ąæčāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ąĮ STOP ąĖ čüą▒čĆąŠčłąĄąĮ čäą╗ą░ą│ TWSTO |

| 1 |

1 |

1 |

x |

ąæčāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ąĮ STOP, ąĘą░ ą║ąŠč鹊čĆčŗą╝ ą┐ąŠčüą╗ąĄą┤čāąĄčé START, ąĖ ą▒čāą┤ąĄčé čüą▒čĆąŠčłąĄąĮ čäą╗ą░ą│ TWSTO |

| 0x30 |

ą¤ąĄčĆąĄą┤ą░ąĮ ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ, ą┐čĆąĖąĮčÅčé NACK |

ąŚą░ą│čĆčāąĘą║ą░ ą▒ą░ą╣čéą░ ą┤ą░ąĮąĮčŗčģ |

0 |

0 |

1 |

x |

ąæčāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ąĮ ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ ąĖ ą┐čĆąĖąĮčÅčé ACK ąĖą╗ąĖ NACK |

| ąØąĄčé ą┤ąĄą╣čüčéą▓ąĖčÅ čü TWDR |

1 |

0 |

1 |

x |

ąæčāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ąĮ REPEATED START |

| 0 |

1 |

1 |

x |

ąæčāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ąĮ STOP ąĖ čüą▒čĆąŠčłąĄąĮ čäą╗ą░ą│ TWSTO |

| 1 |

1 |

1 |

x |

ąæčāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ąĮ STOP, ąĘą░ ą║ąŠč鹊čĆčŗą╝ ą┐ąŠčüą╗ąĄą┤čāąĄčé START, ąĖ ą▒čāą┤ąĄčé čüą▒čĆąŠčłąĄąĮ čäą╗ą░ą│ TWSTO |

| 0x38 |

ą¤čĆąŠąĖą│čĆą░ąĮ ą░čĆą▒ąĖčéčĆą░ąČ ąĮą░ ą┐ąĄčĆąĄą┤ą░č湥 SLA+W ąĖą╗ąĖ ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ |

ąØąĄčé ą┤ąĄą╣čüčéą▓ąĖčÅ čü TWDR |

0 |

0 |

1 |

x |

ą×čüą▓ąŠą▒ąŠą┤ąĖčéčüčÅ čłąĖąĮą░ I2C, ąĖąĮč鹥čĆč乥ą╣čü TWI ą▓ąŠą╣ą┤ąĄčé ą▓ čĆąĄąČąĖą╝ ąĮąĄ ą░ą┤čĆąĄčüąŠą▓ą░ąĮąĮąŠą│ąŠ Slave-čāčüčéčĆąŠą╣čüčéą▓ą░ |

| 1 |

0 |

1 |

x |

ąÜąŠą│ą┤ą░ čłąĖąĮą░ ąŠčüą▓ąŠą▒ąŠą┤ąĖčéčüčÅ, ą▒čāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ąĮ START |

ąĀąĖčü. 20-12. ążąŠčĆą╝ą░čéčŗ ąĖ ą║ąŠą┤čŗ čüąŠčüč鹊čÅąĮąĖčÅ ą▓ čĆąĄąČąĖą╝ąĄ MT.

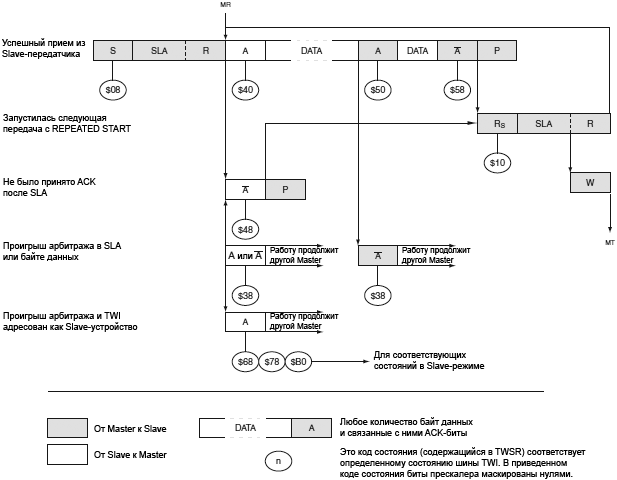

Master Receiver Mode. ąÆ čĆąĄąČąĖą╝ąĄ MR ąĮąĄą║ąŠč鹊čĆąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ą░ą╣čé ą┐čĆąĖąĮąĖą╝ą░ąĄčéčüčÅ ąĖąĘ Slave-ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ (čüą╝. čĆąĖčü. 20-13). ą¦č鹊ą▒čŗ ą▓ąŠą╣čéąĖ ą▓ čĆąĄąČąĖą╝ Master, ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąĄčĆąĄą┤ą░ąĮ čüąĖą│ąĮą░ą╗ START. ążąŠčĆą╝ą░čé ą┐ąŠčüą╗ąĄą┤čāčÄčēąĄą│ąŠ ą┐ą░ą║ąĄčéą░ ą░ą┤čĆąĄčüą░ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé, ą▓ ą║ą░ą║ąŠą╣ čĆąĄąČąĖą╝ ą┐ąŠčüą╗ąĄ čŹč鹊ą│ąŠ ąĮčāąČąĮąŠ ą▓ąŠą╣čéąĖ - Master Transmitter (MT) ąĖą╗ąĖ Master Receiver (MR). ąĢčüą╗ąĖ ą┐ąĄčĆąĄą┤ą░ąĮ SLA+W, č鹊 ą▒čāą┤ąĄčé ąŠčüčāčēąĄčüčéą▓ą╗ąĄąĮ ą▓čģąŠą┤ ą▓ MT, ąĄčüą╗ąĖ ą┐ąĄčĆąĄą┤ą░ąĮ SLA+R, č鹊 ą▒čāą┤ąĄčé ąŠčüčāčēąĄčüčéą▓ą╗ąĄąĮ ą▓čģąŠą┤ ą▓ MR. ąÆčüąĄ ą║ąŠą┤čŗ čüąŠčüč鹊čÅąĮąĖčÅ, čāą┐ąŠą╝čÅąĮčāčéčŗąĄ ą▓ čŹč鹊ą╣ čüąĄą║čåąĖąĖ, ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░čÄčé, čćč鹊 ą▓ ąĮąĖčģ ą▒ąĖčéčŗ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮčŗ ąĮčāą╗čÅą╝ąĖ.

ąĀąĖčü. 20-13. ą¤ąĄčĆąĄą┤ą░čćą░ ą┤ą░ąĮąĮčŗčģ ą▓ čĆąĄąČąĖą╝ąĄ MR.

ąĪąĖą│ąĮą░ą╗ START ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ąĘą░ą┐ąĖčüčīčÄ ą▓ TWCR čüą╗ąĄą┤čāčÄčēąĄą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ:

| TWINT |

TWEA |

TWSTA |

TWSTO |

TWWC |

TWEN |

- |

TWIE |

| 1 |

x |

1 |

0 |

x |

1 |

0 |

x |

ąæąĖčé TWEN ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čćč鹊ą▒čŗ čĆą░ąĘčĆąĄčłąĖčéčī TWI, TWSTA ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮ ą▓ ą╗ąŠą│. 1, čćč鹊ą▒čŗ ą┐ąĄčĆąĄą┤ą░čéčī čüąĖą│ąĮą░ą╗ START, ąĖ TWINT ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮ ą▓ ą╗ąŠą│. 1, čćč鹊ą▒čŗ ąŠčćąĖčüčéąĖčéčī čäą╗ą░ą│ TWINTg. ąŚą░č鹥ą╝ TWI ą┐čĆąŠą▓ąĄčĆąĖčé čłąĖąĮčā, čüą▓ąŠą▒ąŠą┤ąĮą░ ą╗ąĖ ąŠąĮą░, ąĖ ą┐ąĄčĆąĄą┤ą░čüčé START, ą║ą░ą║ č鹊ą╗čīą║ąŠ čłąĖąĮą░ ąŠčüą▓ąŠą▒ąŠą┤ąĖčéčüčÅ. ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ START ą▒čŗą╗ ą┐ąĄčĆąĄą┤ą░ąĮ, ą░ą┐ą┐ą░čĆą░čéąĮąŠ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ TWINT, ąĖ ą▓ TWSR ą┐ąŠčÅą▓ąĖčéčüčÅ ą║ąŠą┤ čüąŠčüč鹊čÅąĮąĖčÅ 0x08 (čüą╝. čéą░ą▒ą╗ąĖčåčā 20-1). ą¦č鹊ą▒čŗ ą▓ąŠą╣čéąĖ ą▓ čĆąĄąČąĖą╝ MR, ąĮčāąČąĮąŠ ą┐ąĄčĆąĄą┤ą░čéčī SLA+R. ąŁč鹊 ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ąĘą░ą┐ąĖčüčīčÄ SLA+R ą▓ TWDR. ą¤ąŠčüą╗ąĄ čŹč鹊ą│ąŠ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąŠčćąĖčēąĄąĮ ą▒ąĖčé TWINT (ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ ą▓ ąĮąĄą│ąŠ ą╗ąŠą│. 1), čćč鹊ą▒čŗ ą┐ąĄčĆąĄą┤ą░čćą░ ą┐čĆąŠą┤ąŠą╗ąČąĖą╗ą░čüčī. ąŁč鹊 ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ąĘą░ą┐ąĖčüčīčÄ ą▓ TWCR čüą╗ąĄą┤čāčÄčēąĄą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ:

| TWINT |

TWEA |

TWSTA |

TWSTO |

TWWC |

TWEN |

- |

TWIE |

| 1 |

x |

0 |

0 |

x |

1 |

0 |

x |

ąÜąŠą│ą┤ą░ ą┐ąĄčĆąĄą┤ą░ąĮ SLA+R, ąĖ ą┐čĆąĖąĮčÅčé ą▒ąĖčé ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ, TWINT čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čüąĮąŠą▓ą░, ąĖ ą▓ TWSR ą╝ąŠą│čāčé ą┐ąŠčÅą▓ąĖčéčīčüčÅ ąĮąĄą║ąŠč鹊čĆčŗąĄ ą║ąŠą┤čŗ čüąŠčüč鹊čÅąĮąĖčÅ. ąÆąŠąĘą╝ąŠąČąĮčŗąĄ ą║ąŠą┤čŗ čüąŠčüč鹊čÅąĮąĖčÅ ą┤ą╗čÅ čĆąĄąČąĖą╝ą░ Master 0x38, 0x40 ąĖą╗ąĖ 0x48. ąöą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ąĖąĘ čŹčéąĖčģ ą║ąŠą┤ąŠą▓ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą┐čĆąĄą┤ą┐čĆąĖąĮčÅč鹊 čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ ą┤ąĄą╣čüčéą▓ąĖąĄ, čćč鹊 ąŠą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ ą▓ čéą░ą▒ą╗ąĖčåąĄ 20-2. ą¤čĆąĖąĮčÅčéčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮčŗ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ TWDR, ą║ąŠą│ą┤ą░ ą▒čāą┤ąĄčé ą░ą┐ą┐ą░čĆą░čéąĮąŠ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čäą╗ą░ą│ TWINT. ąŁčéą░ čüčģąĄą╝ą░ ą┐ąŠą▓č鹊čĆčÅąĄčéčüčÅ ą┤ąŠ č鹥čģ ą┐ąŠčĆ, ą┐ąŠą║ą░ ąĮąĄ ą▒čāą┤ąĄčé ą┐čĆąĖąĮčÅčé ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ą▒ą░ą╣čé. ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ą▒ą░ą╣čé ą▒čŗą╗ ą┐čĆąĖąĮčÅčé, MR ą┤ąŠą╗ąČąĄąĮ ąŠą┐ąŠą▓ąĄčüčéąĖčéčī Slave-ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ ąŠčéą┐čĆą░ą▓ą║ąŠą╣ NACK ą┐ąŠčüą╗ąĄ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ ą┐čĆąĖąĮčÅč鹊ą│ąŠ ą▒ą░ą╣čéą░. ą¤ąĄčĆąĄą┤ą░čćą░ ąĘą░ą║ą░ąĮčćąĖą▓ą░ąĄčéčüčÅ ą│ąĄąĮąĄčĆą░čåąĖąĄą╣ STOP ąĖą╗ąĖ ą┐ąŠą▓č鹊čĆąĮąŠą│ąŠ START. STOP ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ąĘą░ą┐ąĖčüčīčÄ ą▓ TWCR čüą╗ąĄą┤čāčÄčēąĄą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ:

| TWINT |

TWEA |

TWSTA |

TWSTO |

TWWC |

TWEN |

- |

TWIE |

| 1 |

x |

0 |

1 |

x |

1 |

0 |

x |

REPEATED STOP ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ąĘą░ą┐ąĖčüčīčÄ ą▓ TWCR čüą╗ąĄą┤čāčÄčēąĄą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ:

| TWINT |

TWEA |

TWSTA |

TWSTO |

TWWC |

TWEN |

- |

TWIE |

| 1 |

x |

1 |

0 |

x |

1 |

0 |

x |

ą¤ąŠčüą╗ąĄ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą┐ąŠą▓č鹊čĆąĮąŠą│ąŠ START (čüąŠčüč鹊čÅąĮąĖąĄ 0x10) ąĖąĮč鹥čĆč乥ą╣čü TWI ą╝ąŠąČąĄčé čüąĮąŠą▓ą░ ą┐ąŠą╗čāčćąĖčéčī ą┤ąŠčüčéčāą┐ ą║ č鹊ą╝čā ąČąĄ čüą░ą╝ąŠą╝čā Slave-čāčüčéčĆąŠą╣čüčéą▓čā, ąĖą╗ąĖ ą║ ąĮąŠą▓ąŠą╝čā Slave-čāčüčéčĆąŠą╣čüčéą▓čā ą▒ąĄąĘ ą┐ąĄčĆąĄą┤ą░čćąĖ čüąĖą│ąĮą░ą╗ą░ STOP. ą¤ąŠą▓č鹊čĆąĮąŠ ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąĮčŗą╣ START ą┐ąŠąĘą▓ąŠą╗čÅąĄčé Master-čāčüčéčĆąŠą╣čüčéą▓čā ą┐ąĄčĆąĄą║ą╗čÄčćą░čéčīčüčÅ ą╝ąĄąČą┤čā Slave-čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ, ą╝ąĄąČą┤čā čĆąĄąČąĖą╝ą░ą╝ąĖ MT ąĖ MR ą▒ąĄąĘ ą┐ąŠč鹥čĆąĖ ą║ąŠąĮčéčĆąŠą╗čÅ ąĮą░ą┤ čłąĖąĮąŠą╣.

ąóą░ą▒ą╗ąĖčåą░ 20-2. ąÜąŠą┤čŗ čüąŠčüč鹊čÅąĮąĖčÅ ą┤ą╗čÅ čĆąĄąČąĖą╝ą░ MR (ą▓ ą┐ąĄčĆą▓ąŠą╝ čüč鹊ą╗ą▒čåąĄ ąĮą░čüčéčĆąŠą╣ą║ą░ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ ąĘą░ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮą░ ąĮčāą╗čÅą╝ąĖ).

| ąÜąŠą┤ čüąŠčüč鹊čÅąĮąĖčÅ (TWSR) |

ąĪąŠčüč鹊čÅąĮąĖąĄ čłąĖąĮčŗ ąĖ ą░ą┐ą┐ą░čĆą░čéčāčĆčŗ TWI |

ą×čéą▓ąĄčé ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ |

ąĪą╗ąĄą┤čāčÄčēąĄąĄ ą┤ąĄą╣čüčéą▓ąĖąĄ, ą┐čĆąĄą┤ą┐čĆąĖąĮąĖą╝ą░ąĄą╝ąŠąĄ ą░ą┐ą┐ą░čĆą░čéčāčĆąŠą╣ TWI |

| ąÆ/ąĖąĘ TWDR |

ąÆ čĆąĄą│ąĖčüčéčĆ TWCR |

| STA |

STO |

TWINT |

TWEA |

| 0x08 |

ą¤ąĄčĆąĄą┤ą░ąĮ čüąĖą│ąĮą░ą╗ START |

ąŚą░ą│čĆčāąĘą║ą░ SLA+R |

0 |

0 |

1 |

x |

ąæčāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ąĮ SLA+R ąĖ ą┐čĆąĖąĮčÅčé ACK ąĖą╗ąĖ NACK |

| 0x10 |

ą¤ąĄčĆąĄą┤ą░ąĮ čüąĖą│ąĮą░ą╗ REPEATED START |

ąŚą░ą│čĆčāąĘą║ą░ SLA+R |

0 |

0 |

1 |

x |

ąæčāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ąĮ SLA+R ąĖ ą┐čĆąĖąĮčÅčé ACK ąĖą╗ąĖ NACK |

| ąŚą░ą│čĆčāąĘą║ą░ SLA+W |

0 |

0 |

1 |

x |

ąæčāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ąĮ SLA+W, ą╗ąŠą│ąĖą║ą░ ą┐ąĄčĆąĄą║ą╗čÄčćąĖčé TWI ą▓ čĆąĄąČąĖą╝ MT |

| 0x38 |

ą¤čĆąŠąĖą│čĆčŗčł ą░čĆą▒ąĖčéčĆą░ąČą░ ąĮą░ ą┐ąĄčĆąĄą┤ą░č湥 SLA+R ąĖą╗ąĖ ą▒ąĖčéą░ NACK |

ąØąĄčé ą┤ąĄą╣čüčéą▓ąĖčÅ čü TWDR |

0 |

0 |

1 |

x |

ą×čüą▓ąŠą▒ąŠą┤ąĖčéčüčÅ čłąĖąĮą░ I2C, ąĖąĮč鹥čĆč乥ą╣čü TWI ą▓ąŠą╣ą┤ąĄčé ą▓ čĆąĄąČąĖą╝ ąĮąĄ ą░ą┤čĆąĄčüąŠą▓ą░ąĮąĮąŠą│ąŠ Slave-čāčüčéčĆąŠą╣čüčéą▓ą░ |

| 1 |

0 |

1 |

x |

ąÜąŠą│ą┤ą░ čłąĖąĮą░ ąŠčüą▓ąŠą▒ąŠą┤ąĖčéčüčÅ, ą▒čāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ąĮ START |

| 0x40 |

ą¤ąĄčĆąĄą┤ą░ąĮ SLA+R, ą┐čĆąĖąĮčÅčé ACK |

ąØąĄčé ą┤ąĄą╣čüčéą▓ąĖčÅ čü TWDR |

0 |

0 |

1 |

0 |

ąæčāą┤ąĄčé ą┐čĆąĖąĮčÅčé ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ ąĖ ą▓ąŠąĘą▓čĆą░čēąĄąĮ NACK |

| 0 |

0 |

1 |

1 |

ąæčāą┤ąĄčé ą┐čĆąĖąĮčÅčé ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ ąĖ ą▓ąŠąĘą▓čĆą░čēąĄąĮ ACK |

| 0x48 |

ą¤ąĄčĆąĄą┤ą░ąĮ SLA+R, ą┐čĆąĖąĮčÅčé NACK |

ąØąĄčé ą┤ąĄą╣čüčéą▓ąĖčÅ čü TWDR |

1 |

0 |

1 |

x |

ąæčāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ąĮ REPEATED START |

| 0 |

1 |

1 |

x |

ąæčāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ąĮ STOP ąĖ čüą▒čĆąŠčłąĄąĮ čäą╗ą░ą│ TWSTO |

| 1 |

1 |

1 |

x |

ąæčāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ąĮ STOP, ąĘą░ ą║ąŠč鹊čĆčŗą╝ ą┐ąŠčüą╗ąĄą┤čāąĄčé START, ąĖ ą▒čāą┤ąĄčé čüą▒čĆąŠčłąĄąĮ čäą╗ą░ą│ TWSTO |

| 0x50 |

ą¤čĆąĖąĮčÅčé ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ, ą▓ąŠąĘą▓čĆą░čēąĄąĮ ACK |

ą¦č鹥ąĮąĖąĄ ą▒ą░ą╣čéą░ ą┤ą░ąĮąĮčŗčģ |

0 |

0 |

1 |

0 |

ąæčāą┤ąĄčé ą┐čĆąĖąĮčÅčé ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ ąĖ ą▓ąŠąĘą▓čĆą░čēąĄąĮ NACK |

| 0 |

0 |

1 |

1 |

ąæčāą┤ąĄčé ą┐čĆąĖąĮčÅčé ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ ąĖ ą▓ąŠąĘą▓čĆą░čēąĄąĮ ACK |

| 0x58 |

ą¤čĆąĖąĮčÅčé ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ, ą▓ąŠąĘą▓čĆą░čēąĄąĮ NACK |

ą¦č鹥ąĮąĖąĄ ą▒ą░ą╣čéą░ ą┤ą░ąĮąĮčŗčģ |

1 |

0 |

1 |

x |

ąæčāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ąĮ REPEATED START |

| 0 |

1 |

1 |

x |

ąæčāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ąĮ STOP ąĖ čüą▒čĆąŠčłąĄąĮ čäą╗ą░ą│ TWSTO |

| 1 |

1 |

1 |

x |

ąæčāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ąĮ STOP, ąĘą░ ą║ąŠč鹊čĆčŗą╝ ą┐ąŠčüą╗ąĄą┤čāąĄčé START, ąĖ ą▒čāą┤ąĄčé čüą▒čĆąŠčłąĄąĮ čäą╗ą░ą│ TWSTO |

ąĀąĖčü. 20-14. ążąŠčĆą╝ą░čéčŗ ąĖ ą║ąŠą┤čŗ čüąŠčüč鹊čÅąĮąĖčÅ ą▓ čĆąĄąČąĖą╝ąĄ MR.

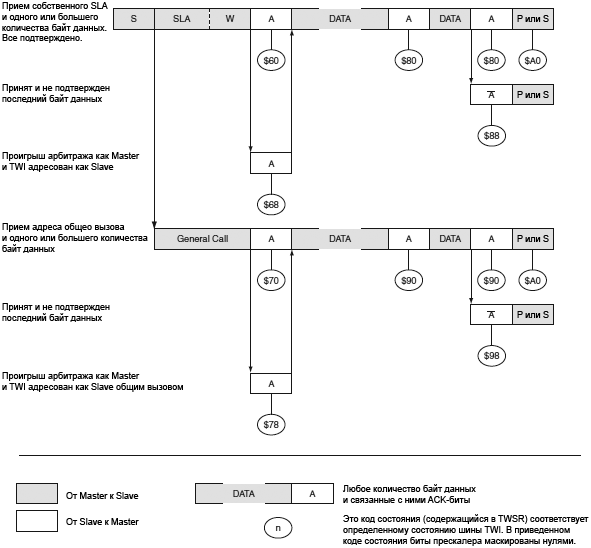

Slave Receiver Mode. ąÆ čĆąĄąČąĖą╝ąĄ SR ąĮąĄą║ąŠč鹊čĆąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ą░ą╣čé ą┐čĆąĖąĮąĖą╝ą░ąĄčéčüčÅ ąŠčé ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ Master (čüą╝. čĆąĖčü. 20-15). ą¤ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčéčüčÅ, čćč鹊 ą▓ąŠ ą▓čüąĄčģ ą║ąŠą┤ą░čģ čüąŠčüč鹊čÅąĮąĖčÅ, čāą┐ąŠą╝čÅąĮčāčéčŗčģ ą▓ čŹč鹊ą╣ čüąĄą║čåąĖąĖ, ą▒ąĖčéčŗ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ ąĘą░ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮčŗ ąĮčāą╗čÅą╝ąĖ.

ąĀąĖčü. 20-15. ą¤ąĄčĆąĄą┤ą░čćą░ ą┤ą░ąĮąĮčŗčģ ą▓ čĆąĄąČąĖą╝ąĄ SR.

ąöą╗čÅ ąĖąĮąĖčåąĖą░čåąĖąĖ čĆąĄąČąĖą╝ą░ SR čĆąĄą│ąĖčüčéčĆčŗ TWAR ąĖ TWCR ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆąŠą▓ą░ąĮčŗ čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝.

ąĀąĄą│ąĖčüčéčĆ TWAR:

| TWA6 |

TWA5 |

TWA4 |

TWA3 |

TWA2 |

TWA1 |

TWA0 |

TWGCE |

| ąĪąŠą▒čüčéą▓ąĄąĮąĮčŗą╣ ą░ą┤čĆąĄčü Slave-čāčüčéčĆąŠą╣čüčéą▓ą░ |

x |

ąĀąĄą│ąĖčüčéčĆ TWCR:

| TWINT |

TWEA |

TWSTA |

TWSTO |

TWWC |

TWEN |

- |

TWIE |

| 0 |

1 |

0 |

0 |

0 |

1 |

0 |

x |

ąĪčéą░čĆčłąĖąĄ 7 ą▒ąĖčé ą▓ TWAR čŹč鹊 ą░ą┤čĆąĄčü, ąĮą░ ą║ąŠč鹊čĆčŗą╣ ąŠčéą▓ąĄčéąĖčé TWI, ą║ąŠą│ą┤ą░ ąŠąĮ ą▒čāą┤ąĄčé ą░ą┤čĆąĄčüąŠą▓ą░ąĮ Master-čāčüčéčĆąŠą╣čüčéą▓ąŠą╝. ąĢčüą╗ąĖ ą▒ąĖčé LSB čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, č鹊 TWI ąŠčéą▓ąĄčéąĖčé ąĮą░ ą░ą┤čĆąĄčü ąŠą▒čēąĄą│ąŠ ą▓čŗąĘąŠą▓ą░ general call (0x00), ąĖąĮą░č湥 čŹč鹊čé ą░ą┤čĆąĄčü ą▒čāą┤ąĄčé ąĖą│ąĮąŠčĆąĖčĆąŠą▓ą░ąĮ.

TWEN ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮ ą▓ ą╗ąŠą│. 1, čćč鹊ą▒čŗ čĆą░ąĘčĆąĄčłąĖčéčī TWI. ąæąĖčé TWEA ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮ ą▓ ą╗ąŠą│. 1, čćč鹊ą▒čŗ čĆą░ąĘčĆąĄčłąĖčéčī ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ čüąŠą▒čüčéą▓ąĄąĮąĮąŠą│ąŠ slave-ą░ą┤čĆąĄčüą░ ąĖą╗ąĖ ą░ą┤čĆąĄčüą░ general call. TWSTA ąĖ TWSTO ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮčŗ ą▓ ą╗ąŠą│. 0.

ąÜąŠą│ą┤ą░ TWAR ąĖ TWCR ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆąŠą▓ą░ąĮčŗ, ąĖąĮč鹥čĆč乥ą╣čü TWI ąČą┤ąĄčé, ą┐ąŠą║ą░ ąĮąĄ ą▒čāą┤ąĄčé ą░ą┤čĆąĄčüąŠą▓ą░ąĮ čüą▓ąŠąĖą╝ čüąŠą▒čüčéą▓ąĄąĮąĮčŗą╝ slave-ą░ą┤čĆąĄčüąŠą╝ (ąĖą╗ąĖ ą░ą┤čĆąĄčüąŠą╝ general call, ąĄčüą╗ąĖ čŹč鹊 čĆą░ąĘčĆąĄčłąĄąĮąŠ), ąĘą░ ą║ąŠč鹊čĆčŗą╝ ąĖą┤ąĄčé ą▒ąĖčé ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ. ąĢčüą╗ąĖ ą▒ąĖčé ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čĆą░ą▓ąĄąĮ 0 (write), č鹊 TWI ą▒čāą┤ąĄčé čĆą░ą▒ąŠčéą░čéčī ą▓ čĆąĄąČąĖą╝ąĄ SR, ąĖąĮą░č湥 ą▒čāą┤ąĄčé ąŠčüčāčēąĄčüčéą▓ą╗ąĄąĮ ą▓čģąŠą┤ ą▓ čĆąĄąČąĖą╝ ST. ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą▒čŗą╗ ą┐čĆąĖąĮčÅčé čüąŠą▒čüčéą▓ąĄąĮąĮčŗą╣ slave-ą░ą┤čĆąĄčü ąĖ ą▒ąĖčé ąĘą░ą┐ąĖčüąĖ, čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé TWINT, ąĖ ą┤ąŠą┐čāčüčéąĖą╝čŗą╣ ą║ąŠą┤ čüąŠčüč鹊čÅąĮąĖčÅ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ TWSR. ąŁč鹊čé ą║ąŠą┤ čüąŠčüč鹊čÅąĮąĖčÅ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ ą┤ąĄą╣čüčéą▓ąĖčÅ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ. ąĪąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ ą┤ąĄą╣čüčéą▓ąĖąĄ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą║ąŠą┤ą░ čüąŠčüč鹊čÅąĮąĖčÅ ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▓ čéą░ą▒ą╗ąĖčåąĄ 20-3. ąÆ čĆąĄąČąĖą╝ SR čéą░ą║ąČąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠčüčāčēąĄčüčéą▓ą╗ąĄąĮ ą▓čģąŠą┤, ąĄčüą╗ąĖ ą▒čŗą╗ ą┐ąŠč鹥čĆčÅąĮ ą░čĆą▒ąĖčéčĆą░ąČ, ą║ąŠą│ą┤ą░ TWI ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ Master (čüą╝. čüąŠčüč鹊čÅąĮąĖčÅ 0x68 ąĖ 0x78).

ąĢčüą╗ąĖ ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▒ąĖčé TWEA čüą▒čĆąŠčłąĄąĮ, č鹊 TWI ą▓ąĄčĆąĮąĄčé NACK (ą╗ąŠą│. 1) ąĮą░ SDA ą┐ąŠčüą╗ąĄ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ ą┐čĆąĖąĮčÅč鹊ą│ąŠ ą▒ą░ą╣čéą░ ą┤ą░ąĮąĮčŗčģ. ąŁč鹊 ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ, čćč鹊ą▒čŗ ą┐ąŠą║ą░ąĘą░čéčī Master-čāčüčéčĆąŠą╣čüčéą▓čā, čćč鹊 Slave ąĮąĄ ą╝ąŠąČąĄčé ą▒ąŠą╗čīčłąĄ ą┐čĆąĖąĮąĖą╝ą░čéčī ą▒ą░ą╣čéčŗ. ąÜąŠą│ą┤ą░ TWEA čĆą░ą▓ąĄąĮ 0, TWI ąĮąĄ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ą░ąĄčé čüąŠą▒čüčéą▓ąĄąĮąĮčŗą╣ slave-ą░ą┤čĆąĄčü. ą×ą┤ąĮą░ą║ąŠ TWI ą▓čüąĄ ąĄčēąĄ ą▒čāą┤ąĄčé ą╝ąŠąĮąĖč鹊čĆąĖčéčī čłąĖąĮčā ąĖ čĆą░čüą┐ąŠąĘąĮą░ą▓ą░ąĮąĖąĄ ą░ą┤čĆąĄčüą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓ąŠąĘąŠą▒ąĮąŠą▓ą╗ąĄąĮąŠ ą▓ ą╗čÄą▒ąŠąĄ ą▓čĆąĄą╝čÅ ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ TWEA. ąŁč鹊 ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčé, čćč鹊 ą▒ąĖčé TWEA ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą▓čĆąĄą╝ąĄąĮąĮąŠą╣ ąĖąĘąŠą╗čÅčåąĖąĖ TWI ąŠčé čłąĖąĮčŗ.

ąÆąŠ ą▓čüąĄčģ čĆąĄąČąĖą╝ą░čģ ą┐ąŠąĮąĖąČąĄąĮąĮąŠą│ąŠ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ, ą║čĆąŠą╝ąĄ Idle mode, čüąĖčüč鹥ą╝ą░ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ TWI ąŠčéą║ą╗čÄčćą░ąĄčéčüčÅ. ąĢčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé TWEA, č鹊 ąĖąĮč鹥čĆč乥ą╣čü ą▓čüąĄ ąĄčēąĄ ą╝ąŠąČąĄčé ą┐ąŠą┤čéą▓ąĄčĆą┤ąĖčéčī čüą▓ąŠą╣ čüąŠą▒čüčéą▓ąĄąĮąĮčŗą╣ slave-ą░ą┤čĆąĄčü ąĖą╗ąĖ ą░ą┤čĆąĄčü general call ą┐čāč鹥ą╝ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ čéą░ą║č鹊ą▓ čłąĖąĮčŗ. ąŚą░č鹥ą╝ MCU ą▒čāą┤ąĄčé ą▓čŗą▓ąĄą┤ąĄąĮ ąĖąĘ čüąĮą░ ąĖ TWI ą▒čāą┤ąĄčé čāą┤ąĄčƹȹĖą▓ą░čéčī SCL ą▓ ą╗ąŠą│. 0 ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ ą┤ąŠ ą╝ąŠą╝ąĄąĮčéą░ ąŠčćąĖčüčéą║ąĖ čäą╗ą░ą│ą░ TWINT (ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ ą▓ ąĮąĄą│ąŠ ą╗ąŠą│. 1). ąæčāą┤čāčēąĖą╣ ą┐čĆąĖąĄą╝ ą┤ą░ąĮąĮčŗčģ ą▒čāą┤ąĄčé ąŠčüčāčēąĄčüčéą▓ą╗čÅčéčīčüčÅ ąĮąŠčĆą╝ą░ą╗čīąĮčŗą╝ ąŠą▒čĆą░ąĘąŠą╝, čü ąŠą▒čŗčćąĮčŗą╝ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄą╝ čéą░ą║čéą░ą╝ąĖ AVR. ąĢčüą╗ąĖ AVR ąĮą░čüčéčĆąŠąĄąĮ ąĮą░ ą┤ąŠą╗ą│ąŠąĄ ą▓čĆąĄą╝čÅ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ (long start-up time), č鹊 čüąĖą│ąĮą░ą╗ SCL ą╝ąŠąČąĄčé čāą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ ą▓ ą╗ąŠą│. 0 ą┤ąŠą╗ą│ąŠąĄ ą▓čĆąĄą╝čÅ, ą▒ą╗ąŠą║ąĖčĆčāčÅ ą┤čĆčāą│ąĖąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ.

ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 čĆąĄą│ąĖčüčéčĆ ą┤ą░ąĮąĮčŗčģ TWDR ąĮąĄ ąŠčéčĆą░ąČą░ąĄčé ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ą▒ą░ą╣čé, ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮąĮčŗą╣ ąĮą░ čłąĖąĮąĄ, ą║ąŠą│ą┤ą░ MCU ą▓čŗčģąŠą┤ąĖčé ąĖąĘ čĆąĄąČąĖą╝ąŠą▓ čüąĮą░.

ąóą░ą▒ą╗ąĖčåą░ 20-3. ąÜąŠą┤čŗ čüąŠčüč鹊čÅąĮąĖčÅ ą▓ čĆąĄąČąĖą╝ąĄ SR (ą▓ ą┐ąĄčĆą▓ąŠą╝ čüč鹊ą╗ą▒čåąĄ ąĮą░čüčéčĆąŠą╣ą║ą░ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ ąĘą░ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮą░ ąĮčāą╗čÅą╝ąĖ).

| ąÜąŠą┤ čüąŠčüč鹊čÅąĮąĖčÅ (TWSR) |

ąĪąŠčüč鹊čÅąĮąĖąĄ čłąĖąĮčŗ ąĖ ą░ą┐ą┐ą░čĆą░čéčāčĆčŗ TWI |

ą×čéą▓ąĄčé ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ |

ąĪą╗ąĄą┤čāčÄčēąĄąĄ ą┤ąĄą╣čüčéą▓ąĖąĄ, ą┐čĆąĄą┤ą┐čĆąĖąĮąĖą╝ą░ąĄą╝ąŠąĄ ą░ą┐ą┐ą░čĆą░čéčāčĆąŠą╣ TWI |

| ąÆ/ąĖąĘ TWDR |

ąÆ čĆąĄą│ąĖčüčéčĆ TWCR |

| STA |

STO |

TWINT |

TWEA |

| 0x60 |

ą¤čĆąĖąĮčÅčé čüą▓ąŠą╣ čüąŠą▒čüčéą▓ąĄąĮąĮčŗą╣ ą░ą┤čĆąĄčü SLA+W, ą▓ąŠąĘą▓čĆą░čēąĄąĮ ACK |

ąØąĄčé ą┤ąĄą╣čüčéą▓ąĖčÅ čü TWDR |

x |

0 |

1 |

0 |

ąæčāą┤ąĄčé ą┐čĆąĖąĮčÅčé ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ ąĖ ą▓ąŠąĘą▓čĆą░čēąĄąĮ NACK |

| x |

0 |

1 |

1 |

ąæčāą┤ąĄčé ą┐čĆąĖąĮčÅčé ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ ąĖ ą▓ąŠąĘą▓čĆą░čēąĄąĮ ACK |

| 0x68 |

ą¤čĆąŠąĖą│čĆčŗčł ą░čĆą▒ąĖčéčĆą░ąČą░ ąĮą░ SLA+R/W, ą┐čĆąĖąĮčÅčé čüąŠą▒čüčéą▓ąĄąĮąĮčŗą╣ SLA+W, ą▓ąŠąĘą▓čĆą░čēąĄąĮ ACK |

ąØąĄčé ą┤ąĄą╣čüčéą▓ąĖčÅ čü TWDR |

x |

0 |

1 |

0 |

ąæčāą┤ąĄčé ą┐čĆąĖąĮčÅčé ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ ąĖ ą▓ąŠąĘą▓čĆą░čēąĄąĮ NACK |

| x |

0 |

1 |

1 |

ąæčāą┤ąĄčé ą┐čĆąĖąĮčÅčé ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ ąĖ ą▓ąŠąĘą▓čĆą░čēąĄąĮ ACK |

| 0x70 |

ą¤čĆąĖąĮčÅčé ą░ą┤čĆąĄčü ąŠą▒čēąĄą│ąŠ ą▓čŗąĘąŠą▓ą░ (general call), ą▓ąŠąĘą▓čĆą░čēąĄąĮ ACK |

ąØąĄčé ą┤ąĄą╣čüčéą▓ąĖčÅ čü TWDR |

x |

0 |

1 |

0 |

ąæčāą┤ąĄčé ą┐čĆąĖąĮčÅčé ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ ąĖ ą▓ąŠąĘą▓čĆą░čēąĄąĮ NACK |

| x |

0 |

1 |

1 |

ąæčāą┤ąĄčé ą┐čĆąĖąĮčÅčé ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ ąĖ ą▓ąŠąĘą▓čĆą░čēąĄąĮ ACK |

| 0x78 |

ą¤čĆąŠąĖą│čĆčŗčł ą░čĆą▒ąĖčéčĆą░ąČą░ ąĮą░ SLA+R/W, ą┐čĆąĖąĮčÅčé ą░ą┤čĆąĄčü ąŠą▒čēąĄą│ąŠ ą▓čŗąĘąŠą▓ą░ (general call), ą▓ąŠąĘą▓čĆą░čēąĄąĮ ACK |

ąØąĄčé ą┤ąĄą╣čüčéą▓ąĖčÅ čü TWDR |

x |

0 |

1 |

0 |

ąæčāą┤ąĄčé ą┐čĆąĖąĮčÅčé ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ ąĖ ą▓ąŠąĘą▓čĆą░čēąĄąĮ NACK |

| x |

0 |

1 |

1 |

ąæčāą┤ąĄčé ą┐čĆąĖąĮčÅčé ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ ąĖ ą▓ąŠąĘą▓čĆą░čēąĄąĮ ACK |

| 0x80 |

ąæčŗą╗ čĆą░ąĮąĄąĄ čāčüą┐ąĄčłąĮąŠ ą░ą┤čĆąĄčüąŠą▓ą░ąĮ čüąŠą▒čüčéą▓ąĄąĮąĮčŗą╝ SLA+W, ą▒čŗą╗ ą┐čĆąĖąĮčÅčé ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ, ą▓ąŠąĘą▓čĆą░čēąĄąĮ ACK |

ą¦č鹥ąĮąĖąĄ ą▒ą░ą╣čéą░ ą┤ą░ąĮąĮčŗčģ |

x |

0 |

1 |

0 |

ąæčāą┤ąĄčé ą┐čĆąĖąĮčÅčé ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ ąĖ ą▓ąŠąĘą▓čĆą░čēąĄąĮ NACK |

| x |

0 |

1 |

1 |

ąæčāą┤ąĄčé ą┐čĆąĖąĮčÅčé ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ ąĖ ą▓ąŠąĘą▓čĆą░čēąĄąĮ ACK |

| 0x88 |

ąæčŗą╗ čĆą░ąĮąĄąĄ čāčüą┐ąĄčłąĮąŠ ą░ą┤čĆąĄčüąŠą▓ą░ąĮ čüąŠą▒čüčéą▓ąĄąĮąĮčŗą╝ SLA+W, ą▒čŗą╗ ą┐čĆąĖąĮčÅčé ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ, ą▓ąŠąĘą▓čĆą░čēąĄąĮ NACK |

ą¦č鹥ąĮąĖąĄ ą▒ą░ą╣čéą░ ą┤ą░ąĮąĮčŗčģ |

0 |

0 |

1 |

0 |

ą¤čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ą▓ čĆąĄąČąĖą╝ not addressed Slave mode; ąĮąĄčé čĆą░čüą┐ąŠąĘąĮą░ą▓ą░ąĮąĖčÅ čüąŠą▒čüčéą▓ąĄąĮąĮąŠą│ąŠ SLA ąĖą╗ąĖ ą░ą┤čĆąĄčüą░ ą│ą╗ąŠą▒ą░ą╗čīąĮąŠą│ąŠ ą▓čŗąĘąŠą▓ą░ |

| 0 |

0 |

1 |

1 |

ą¤čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ą▓ čĆąĄąČąĖą╝ not addressed Slave mode; čüąŠą▒čüčéą▓ąĄąĮąĮčŗą╣ SLA ą▒čāą┤ąĄčé čĆą░čüą┐ąŠąĘąĮą░ąĮ; ą░ą┤čĆąĄčü ą│ą╗ąŠą▒ą░ą╗čīąĮąŠą│ąŠ ą▓čŗąĘąŠą▓ą░ ą▒čāą┤ąĄčé čĆą░čüą┐ąŠąĘąĮą░ąĮ, ąĄčüą╗ąĖ TWGCE=1 |

| 1 |

0 |

1 |

0 |

ą¤čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ą▓ čĆąĄąČąĖą╝ not addressed Slave mode; ąĮąĄčé čĆą░čüą┐ąŠąĘąĮą░ą▓ą░ąĮąĖčÅ čüąŠą▒čüčéą▓ąĄąĮąĮąŠą│ąŠ SLA ąĖą╗ąĖ ą░ą┤čĆąĄčüą░ ą│ą╗ąŠą▒ą░ą╗čīąĮąŠą│ąŠ ą▓čŗąĘąŠą▓ą░; ą║ąŠą│ą┤ą░ čłąĖąĮą░ ąŠčüą▓ąŠą▒ąŠą┤ąĖčéčüčÅ, ą▒čāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ąĮ START |

| 1 |

0 |

1 |

1 |

ą¤čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ą▓ čĆąĄąČąĖą╝ not addressed Slave mode; ą▒čāą┤ąĄčé čĆą░čüą┐ąŠąĘąĮą░ąĮ čüąŠą▒čüčéą▓ąĄąĮąĮčŗą╣ SLA; ą░ą┤čĆąĄčü ą│ą╗ąŠą▒ą░ą╗čīąĮąŠą│ąŠ ą▓čŗąĘąŠą▓ą░ ą▒čāą┤ąĄčé čĆą░čüą┐ąŠąĘąĮą░ąĮ, ąĄčüą╗ąĖ TWGCE=1; ą║ąŠą│ą┤ą░ čłąĖąĮą░ ąŠčüą▓ąŠą▒ąŠą┤ąĖčéčüčÅ, ą▒čāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ąĮ START |

| 0x90 |

ąæčŗą╗ čĆą░ąĮąĄąĄ čāčüą┐ąĄčłąĮąŠ ą░ą┤čĆąĄčüąŠą▓ą░ąĮ ą░ą┤čĆąĄčüąŠą╝ ąŠą▒čēąĄą│ąŠ ą▓čŗąĘąŠą▓ą░, ą▒čŗą╗ ą┐čĆąĖąĮčÅčé ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ, ą▓ąŠąĘą▓čĆą░čēąĄąĮ ACK |

ą¦č鹥ąĮąĖąĄ ą▒ą░ą╣čéą░ ą┤ą░ąĮąĮčŗčģ |

x |

0 |

1 |

0 |

ąæčāą┤ąĄčé ą┐čĆąĖąĮčÅčé ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ ąĖ ą▓ąŠąĘą▓čĆą░čēąĄąĮ NACK |

| x |

0 |

1 |

1 |

ąæčāą┤ąĄčé ą┐čĆąĖąĮčÅčé ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ ąĖ ą▓ąŠąĘą▓čĆą░čēąĄąĮ ACK |

| 0x98 |

ąæčŗą╗ čĆą░ąĮąĄąĄ čāčüą┐ąĄčłąĮąŠ ą░ą┤čĆąĄčüąŠą▓ą░ąĮ ą░ą┤čĆąĄčüąŠą╝ ąŠą▒čēąĄą│ąŠ ą▓čŗąĘąŠą▓ą░, ą▒čŗą╗ ą┐čĆąĖąĮčÅčé ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ, ą▓ąŠąĘą▓čĆą░čēąĄąĮ NACK |

ą¦č鹥ąĮąĖąĄ ą▒ą░ą╣čéą░ ą┤ą░ąĮąĮčŗčģ |

0 |

0 |

1 |

0 |

ą¤čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ą▓ čĆąĄąČąĖą╝ not addressed Slave mode; ąĮąĄčé čĆą░čüą┐ąŠąĘąĮą░ą▓ą░ąĮąĖčÅ čüąŠą▒čüčéą▓ąĄąĮąĮąŠą│ąŠ SLA ąĖą╗ąĖ ą░ą┤čĆąĄčüą░ ą│ą╗ąŠą▒ą░ą╗čīąĮąŠą│ąŠ ą▓čŗąĘąŠą▓ą░ |

| 0 |

0 |

1 |

1 |

ą¤čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ą▓ čĆąĄąČąĖą╝ not addressed Slave mode; čüąŠą▒čüčéą▓ąĄąĮąĮčŗą╣ SLA ą▒čāą┤ąĄčé čĆą░čüą┐ąŠąĘąĮą░ąĮ; ą░ą┤čĆąĄčü ą│ą╗ąŠą▒ą░ą╗čīąĮąŠą│ąŠ ą▓čŗąĘąŠą▓ą░ ą▒čāą┤ąĄčé čĆą░čüą┐ąŠąĘąĮą░ąĮ, ąĄčüą╗ąĖ TWGCE=1 |

| 1 |

0 |

1 |

0 |

ą¤čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ą▓ čĆąĄąČąĖą╝ not addressed Slave mode; ąĮąĄčé čĆą░čüą┐ąŠąĘąĮą░ą▓ą░ąĮąĖčÅ čüąŠą▒čüčéą▓ąĄąĮąĮąŠą│ąŠ SLA ąĖą╗ąĖ ą░ą┤čĆąĄčüą░ ą│ą╗ąŠą▒ą░ą╗čīąĮąŠą│ąŠ ą▓čŗąĘąŠą▓ą░; ą║ąŠą│ą┤ą░ čłąĖąĮą░ ąŠčüą▓ąŠą▒ąŠą┤ąĖčéčüčÅ, ą▒čāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ąĮ START |

| 1 |

0 |

1 |

1 |

ą¤čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ą▓ čĆąĄąČąĖą╝ not addressed Slave mode; ą▒čāą┤ąĄčé čĆą░čüą┐ąŠąĘąĮą░ąĮ čüąŠą▒čüčéą▓ąĄąĮąĮčŗą╣ SLA; ą░ą┤čĆąĄčü ą│ą╗ąŠą▒ą░ą╗čīąĮąŠą│ąŠ ą▓čŗąĘąŠą▓ą░ ą▒čāą┤ąĄčé čĆą░čüą┐ąŠąĘąĮą░ąĮ, ąĄčüą╗ąĖ TWGCE=1; ą║ąŠą│ą┤ą░ čłąĖąĮą░ ąŠčüą▓ąŠą▒ąŠą┤ąĖčéčüčÅ, ą▒čāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ąĮ START |

| 0xA0 |

ąæčŗą╗ ą┐čĆąĖąĮčÅčé čüąĖą│ąĮą░ą╗ STOP ąĖą╗ąĖ REPEATED START, ą║ąŠą│ą┤ą░ TWI ą▓čüąĄ ąĄčēąĄ ą▒čŗą╗ ą░ą┤čĆąĄčüąŠą▓ą░ąĮ ą║ą░ą║ Slave-čāčüčéčĆąŠą╣čüčéą▓ąŠ |

ąØąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ ą┤ąĄą╣čüčéą▓ąĖčÅ |

0 |

0 |

1 |

0 |

ą¤čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ą▓ čĆąĄąČąĖą╝ not addressed Slave mode; ąĮąĄčé čĆą░čüą┐ąŠąĘąĮą░ą▓ą░ąĮąĖčÅ čüąŠą▒čüčéą▓ąĄąĮąĮąŠą│ąŠ SLA ąĖą╗ąĖ ą░ą┤čĆąĄčüą░ ą│ą╗ąŠą▒ą░ą╗čīąĮąŠą│ąŠ ą▓čŗąĘąŠą▓ą░ |

| 0 |

0 |

1 |

1 |

ą¤čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ą▓ čĆąĄąČąĖą╝ not addressed Slave mode; čüąŠą▒čüčéą▓ąĄąĮąĮčŗą╣ SLA ą▒čāą┤ąĄčé čĆą░čüą┐ąŠąĘąĮą░ąĮ; ą░ą┤čĆąĄčü ą│ą╗ąŠą▒ą░ą╗čīąĮąŠą│ąŠ ą▓čŗąĘąŠą▓ą░ ą▒čāą┤ąĄčé čĆą░čüą┐ąŠąĘąĮą░ąĮ, ąĄčüą╗ąĖ TWGCE=1 |

| 1 |

0 |

1 |

0 |

ą¤čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ą▓ čĆąĄąČąĖą╝ not addressed Slave mode; ąĮąĄčé čĆą░čüą┐ąŠąĘąĮą░ą▓ą░ąĮąĖčÅ čüąŠą▒čüčéą▓ąĄąĮąĮąŠą│ąŠ SLA ąĖą╗ąĖ ą░ą┤čĆąĄčüą░ ą│ą╗ąŠą▒ą░ą╗čīąĮąŠą│ąŠ ą▓čŗąĘąŠą▓ą░; ą║ąŠą│ą┤ą░ čłąĖąĮą░ ąŠčüą▓ąŠą▒ąŠą┤ąĖčéčüčÅ, ą▒čāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ąĮ START |

| 1 |

0 |

1 |

1 |

ą¤čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ą▓ čĆąĄąČąĖą╝ not addressed Slave mode; ą▒čāą┤ąĄčé čĆą░čüą┐ąŠąĘąĮą░ąĮ čüąŠą▒čüčéą▓ąĄąĮąĮčŗą╣ SLA; ą░ą┤čĆąĄčü ą│ą╗ąŠą▒ą░ą╗čīąĮąŠą│ąŠ ą▓čŗąĘąŠą▓ą░ ą▒čāą┤ąĄčé čĆą░čüą┐ąŠąĘąĮą░ąĮ, ąĄčüą╗ąĖ TWGCE=1; ą║ąŠą│ą┤ą░ čłąĖąĮą░ ąŠčüą▓ąŠą▒ąŠą┤ąĖčéčüčÅ, ą▒čāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ąĮ START |

ąĀąĖčü. 20-16. ążąŠčĆą╝ą░čéčŗ ąĖ ą║ąŠą┤čŗ čüąŠčüč鹊čÅąĮąĖčÅ čĆąĄąČąĖą╝ą░ SR.

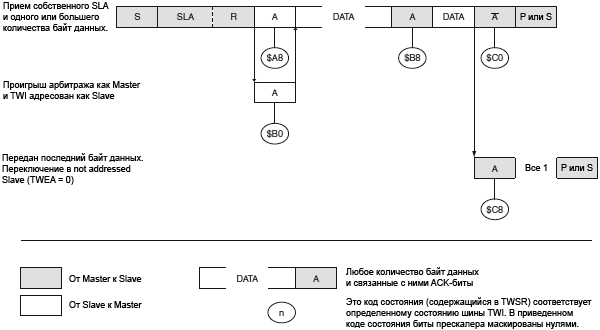

Slave Transmitter Mode. ąÆ čĆąĄąČąĖą╝ąĄ ST ąĮąĄą║ąŠč鹊čĆąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ą░ą╣čé ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą▓ ą┐čĆąĖąĄą╝ąĮąĖą║ Master (čüą╝. čĆąĖčü. 20-17). ą¤ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčéčüčÅ, čćč鹊 ą▓ąŠ ą▓čüąĄčģ ą║ąŠą┤ą░čģ čüąŠčüč鹊čÅąĮąĖčÅ, čāą┐ąŠą╝čÅąĮčāčéčŗčģ ą▓ čŹč鹊ą╣ čüąĄą║čåąĖąĖ, ą▒ąĖčéčŗ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ ąĘą░ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮčŗ ąĮčāą╗čÅą╝ąĖ.

ąĀąĖčü. 20-17. ą¤ąĄčĆąĄą┤ą░čćą░ ą┤ą░ąĮąĮčŗčģ ą▓ čĆąĄąČąĖą╝ąĄ ST.

ąöą╗čÅ ąĖąĮąĖčåąĖą░čåąĖąĖ čĆąĄąČąĖą╝ą░ ST čĆąĄą│ąĖčüčéčĆčŗ TWAR ąĖ TWCR ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆąŠą▓ą░ąĮčŗ čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝.

ąĀąĄą│ąĖčüčéčĆ TWAR:

| TWA6 |

TWA5 |

TWA4 |

TWA3 |

TWA2 |

TWA1 |

TWA0 |

TWGCE |

| ąĪąŠą▒čüčéą▓ąĄąĮąĮčŗą╣ ą░ą┤čĆąĄčü Slave-čāčüčéčĆąŠą╣čüčéą▓ą░ |

x |

ąĀąĄą│ąĖčüčéčĆ TWCR:

| TWINT |

TWEA |

TWSTA |

TWSTO |

TWWC |

TWEN |

- |

TWIE |

| 0 |

1 |

0 |

0 |

0 |

1 |

0 |

x |

ąĪčéą░čĆčłąĖąĄ 7 ą▒ąĖčé ą▓ TWAR čŹč鹊 ą░ą┤čĆąĄčü, ąĮą░ ą║ąŠč鹊čĆčŗą╣ ąŠčéą▓ąĄčéąĖčé TWI, ą║ąŠą│ą┤ą░ ąŠąĮ ą▒čāą┤ąĄčé ą░ą┤čĆąĄčüąŠą▓ą░ąĮ Master-čāčüčéčĆąŠą╣čüčéą▓ąŠą╝. ąĢčüą╗ąĖ ą▒ąĖčé LSB čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, č鹊 TWI ąŠčéą▓ąĄčéąĖčé ąĮą░ ą░ą┤čĆąĄčü ąŠą▒čēąĄą│ąŠ ą▓čŗąĘąŠą▓ą░ general call (0x00), ąĖąĮą░č湥 čŹč鹊čé ą░ą┤čĆąĄčü ą▒čāą┤ąĄčé ąĖą│ąĮąŠčĆąĖčĆąŠą▓ą░ąĮ.

TWEN ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮ ą▓ ą╗ąŠą│. 1, čćč鹊ą▒čŗ čĆą░ąĘčĆąĄčłąĖčéčī TWI. ąæąĖčé TWEA ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮ ą▓ ą╗ąŠą│. 1, čćč鹊ą▒čŗ čĆą░ąĘčĆąĄčłąĖčéčī ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖąĄ čüąŠą▒čüčéą▓ąĄąĮąĮąŠą│ąŠ slave-ą░ą┤čĆąĄčüą░ čāčüčéčĆąŠą╣čüčéą▓ą░ ąĖą╗ąĖ ą░ą┤čĆąĄčüą░ general call. TWSTA ąĖ TWSTO ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮčŗ ą▓ ą╗ąŠą│. 0.

ąÜąŠą│ą┤ą░ TWAR ąĖ TWCR ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆąŠą▓ą░ąĮčŗ, TWI ąČą┤ąĄčé ą╝ąŠą╝ąĄąĮčéą░ ą░ą┤čĆąĄčüą░čåąĖąĖ ą┐ąŠ čüąŠą▒čüčéą▓ąĄąĮąĮąŠą╝čā slave-ą░ą┤čĆąĄčüčā (ąĖą╗ąĖ ą┐ąŠ ą░ą┤čĆąĄčüčā general call, ąĄčüą╗ąĖ čŹč鹊 čĆą░ąĘčĆąĄčłąĄąĮąŠ), ąĘą░ ą║ąŠč鹊čĆčŗą╝ ąĖą┤ąĄčé ą▒ąĖčé ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ. ąĢčüą╗ąĖ ą▒ąĖčé ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čĆą░ą▓ąĄąĮ 1 (read), č鹊 TWI ą▒čāą┤ąĄčé čĆą░ą▒ąŠčéą░čéčī ą▓ čĆąĄąČąĖą╝ąĄ ST, ąĖąĮą░č湥 ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą▓čģąŠą┤ ą▓ čĆąĄąČąĖą╝ SR. ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą▒čŗą╗ ą┐čĆąĖąĮčÅčé čüąŠą▒čüčéą▓ąĄąĮąĮčŗą╣ slave-ą░ą┤čĆąĄčü ąĖ ą▒ąĖčé ąĘą░ą┐ąĖčüąĖ, čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé TWINT, ąĖ ą┤ąŠą┐čāčüčéąĖą╝čŗą╣ ą║ąŠą┤ čüąŠčüč鹊čÅąĮąĖčÅ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ TWSR. ąŁč鹊čé ą║ąŠą┤ čüąŠčüč鹊čÅąĮąĖčÅ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ ą┤ąĄą╣čüčéą▓ąĖčÅ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ. ąĪąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ ą┤ąĄą╣čüčéą▓ąĖąĄ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą║ąŠą┤ą░ čüąŠčüč鹊čÅąĮąĖčÅ ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▓ čéą░ą▒ą╗ąĖčåąĄ 20-4. ąÆ čĆąĄąČąĖą╝ ST čéą░ą║ąČąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠčüčāčēąĄčüčéą▓ą╗ąĄąĮ ą▓čģąŠą┤, ąĄčüą╗ąĖ ą▒čŗą╗ ą┐ąŠč鹥čĆčÅąĮ ą░čĆą▒ąĖčéčĆą░ąČ, ą║ąŠą│ą┤ą░ TWI ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ Master (čüą╝. čüąŠčüč鹊čÅąĮąĖąĄ 0xB0).