|

ąØąĄą║ąŠč鹊čĆčŗąĄ čüąŠą▓čĆąĄą╝ąĄąĮąĮčŗąĄ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčŗ čüąĄčĆąĖąĖ ATmega ą░ą┐ą┐ą░čĆą░čéąĮąŠ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖąĄ ą║ čüčéą░ąĮą┤ą░čĆčéąĮąŠą╣ ą┤ą▓čāčģą┐čĆąŠą▓ąŠą┤ąĮąŠą╣ čłąĖąĮąĄ I2C, ą║ąŠč鹊čĆą░čÅ čćą░čüč鹊 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓ ą┐čĆąĖą▒ąŠčĆą░čģ ąĖ ą▒čŗč鹊ą▓ąŠą╣ č鹥čģąĮąĖą║ąĄ. Atmel ąĮą░ąĘčŗą▓ą░ąĄčé čŹčéčā čłąĖąĮčā two-wire interface, čüąŠą║čĆą░čēąĄąĮąĮąŠ TWI. ąśąĘąĮą░čćą░ą╗čīąĮąŠ čŹčéą░ čłąĖąĮą░ ą┐ąŠą╗čāčćąĖą╗ą░ ąĮą░ąĘą▓ą░ąĮąĖąĄ I2C ąŠčé čäąĖčĆą╝čŗ Philips, ąĮąŠ čŹč鹊 ąĮą░ąĘą▓ą░ąĮąĖąĄ ąĖąĘą▒ąĄą│ą░čÄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą▓ ą┤ąŠą║čāą╝ąĄąĮčéą░čåąĖąĖ Atmel ąĖąĘ-ąĘą░ ą┐ą░č鹥ąĮčéąĮčŗčģ ą┐čĆąŠą▒ą╗ąĄą╝. ą¤ąŠčŹč鹊ą╝čā I2C ąĖ TWI čŹč鹊 ąŠą┤ąĮąŠ ąĖ č鹊 ąČąĄ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą┐ąŠą╗ąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ ą┐čĆąŠč鹊ą║ąŠą╗ą░ I2C čüą╝. ą▓ ą┤ąŠą║čāą╝ąĄąĮč鹥 UM10204.pdf [4].

[ąÆą▓ąĄą┤ąĄąĮąĖąĄ ą▓ TWI]

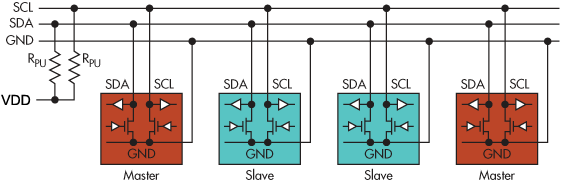

ąöą▓čāčģą┐čĆąŠą▓ąŠą┤ąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü TWI čüąŠčüč鹊ąĖčé ąĖąĘ ą┤ą▓čāčģ čüąĖą│ąĮą░ą╗čīąĮčŗčģ ą┐čĆąŠą▓ąŠą┤ąŠą▓ SDA (serial data, ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ) ąĖ SCL (serial clock, čéą░ą║čéčŗ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ą┤ą░ąĮąĮčŗčģ), ąĖ ą║ąŠąĮąĄčćąĮąŠ ą┐čĆąŠą▓ąŠą┤ ąĘąĄą╝ą╗ąĖ GND. ąÆčüąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ ąĮą░ čłąĖąĮąĄ čüąŠąĄą┤ąĖąĮąĄąĮčŗ ą┤čĆčāą│ čü ą┤čĆčāą│ąŠą╝ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠ, ąĖčüą┐ąŠą╗čīąĘčāčÅ ą┤čĆą░ą╣ą▓ąĄčĆčŗ čü ąŠčéą║čĆčŗčéčŗą╝ čüč鹊ą║ąŠą╝ ą┤ą╗čÅ č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ąĮą░ čłąĖąĮąĄ ą╗ąŠą│ąĖč湥čüą║ąĖčģ čāčĆąŠą▓ąĮąĄą╣ čüąĖą│ąĮą░ą╗ąŠą▓ 0 ąĖ 1. ą¤ąŠ čŹč鹊ą╣ ą┐čĆąĖčćąĖąĮąĄ ąĮą░ čłąĖąĮąĄ ąŠą▒čÅąĘą░č鹥ą╗čīąĮąŠ ą┐čĆąĖčüčāčéčüčéą▓čāčÄčé ą┤ą▓ą░ ą▓ąĄčĆčģąĮąĖčģ ąĮą░ą│čĆčāąĘąŠčćąĮčŗčģ ą┐ąŠą┤čéčÅą│ąĖą▓ą░čÄčēąĖčģ čĆąĄąĘąĖčüč鹊čĆą░ (pull-up, ąĮą░ čĆąĖčüčāąĮą║ąĄ čŹč鹊 čĆąĄąĘąĖčüč鹊čĆčŗ RPU, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗąĄ ą║ ą┐ą╗čÄčüčā ą┐ąĖčéą░ąĮąĖčÅ VDD).

ąØą░ą│čĆčāąĘąŠčćąĮčŗąĄ čĆąĄąĘąĖčüč鹊čĆčŗ ą┤ąŠą╗ąČąĮčŗ ąĖą╝ąĄčéčī ą┤ąŠčüčéą░č鹊čćąĮąŠ ą╝ą░ą╗čŗą╣ ąĮąŠą╝ąĖąĮą░ą╗ ą┤ą╗čÅ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ, čćč鹊ą▒čŗ ą▒čŗčüčéčĆąŠ ąĘą░čĆčÅąČą░čéčī ąĄą╝ą║ąŠčüčéčī čüąĖą│ąĮą░ą╗ąŠą▓ SDA ąĖ SCL ąĖ ą┤ą░ą▓ą░čéčī ą║ąŠčĆąŠčéą║ąĖąĄ čäčĆąŠąĮčéčŗ ąĮą░čĆą░čüčéą░ąĮąĖčÅ čāčĆąŠą▓ąĮčÅ ą╗ąŠą│. 1. ą×ą┤ąĮą░ą║ąŠ čŹčéąĖ čĆąĄąĘąĖčüč鹊čĆčŗ ą┤ąŠą╗ąČąĮčŗ čéą░ą║ąČąĄ ą▒čŗčéčī ą┤ąŠčüčéą░č鹊čćąĮąŠ ą▒ąŠą╗čīčłąĖąĄ, čćč鹊ą▒čŗ ąĮąĄ ą┐ąĄčĆąĄą│čĆčāąČą░čéčī ą▓čŗčģąŠą┤ąĮčŗąĄ čüč鹊ą║ąĖ ą┤čĆą░ą╣ą▓ąĄčĆąŠą▓ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓. ąĀąĄą║ąŠą╝ąĄąĮą┤ą░čåąĖąĖ ą┐ąŠ ą▓čŗą▒ąŠčĆčā ąĮąŠą╝ąĖąĮą░ą╗ąŠą▓ pull-up čĆąĄąĘąĖčüč鹊čĆąŠą▓ ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ č乊čĆą╝čāą╗čŗ ą╝ąŠąČąĮąŠ ąĮą░ą╣čéąĖ ą▓ ą┤ą░čéą░čłąĖč鹥 ąĮą░ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ I2C/TWI (čéąĖą┐ąŠą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ pull-up ąŠą║ąŠą╗ąŠ 4.7 ą║ą×ą╝).

ąŻčüčéčĆąŠą╣čüčéą▓ą░ ąĮą░ čłąĖąĮąĄ ą╝ąŠą│čāčé čĆą░ą▒ąŠčéą░čéčī ą╗ąĖą▒ąŠ ą║ą░ą║ ą╝ą░čüč鹥čĆ (master, čé. ąĄ. ą│ą╗ą░ą▓ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ, ąŠąĮąŠ ąĖąĮąĖčåąĖąĖčĆčāąĄčé ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ą┐ąŠ čłąĖąĮąĄ), ą╗ąĖą▒ąŠ ą║ą░ą║ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ (slave, ąŠąĮąŠ čĆą░ą▒ąŠčéą░ąĄčé čü čłąĖąĮąŠą╣ č鹊ą╗čīą║ąŠ ą┐ąŠ ą▓čŗąĘąŠą▓čā ąŠčé master). ą©ąĖąĮą░ ą╝ąŠąČąĄčé čĆą░ą▒ąŠčéą░čéčī čü ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ ą│ą╗ą░ą▓ąĮčŗą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ (multi-master), ą║ąŠą│ą┤ą░ ą▓ ą║ą░ąČą┤čŗą╣ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé ą▓čĆąĄą╝ąĄąĮąĖ ąĮą░ čłąĖąĮąĄ ą░ą║čéąĖą▓ąĮąŠ č鹊ą╗čīą║ąŠ ąŠą┤ąĮąŠ master-čāčüčéčĆąŠą╣čüčéą▓ąŠ. ą×ą┤ąĮą░ą║ąŠ čćą░čēąĄ ą▓čüąĄą│ąŠ ąĖčüą┐ąŠą╗čīąĘčāčÄčé ą┐čĆąŠčüčéčāčÄ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÄ čłąĖąĮčŗ č鹊ą╗čīą║ąŠ čü ąŠą┤ąĮąĖą╝ master-čāčüčéčĆąŠą╣čüčéą▓ąŠą╝, ą▓čüąĄ ąŠčüčéą░ą╗čīąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ čĆą░ą▒ąŠčéą░čÄčé ą║ą░ą║ slave (ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠą┤ąĮąŠ ąĖą╗ąĖ ąĮąĄčüą║ąŠą╗čīą║ąŠ).

ąöą╗čÅ č鹊ą│ąŠ, čćč鹊ą▒čŗ ąŠčéą╗ąĖčćą░čéčī ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ ąĮą░ čłąĖąĮąĄ, ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ 7-ą▒ąĖčéąĮčŗą╣ ą░ą┤čĆąĄčü (čéą░ą║ ąĖąĘąĮą░čćą░ą╗čīąĮąŠ ąŠą┐čĆąĄą┤ąĄą╗ąĖą╗ą░ ą║ąŠą╝ą┐ą░ąĮąĖčÅ Philips), ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗą╣ ą║ą░ą║ ą┐ąĄčĆą▓čŗą╣ ą▒ą░ą╣čé ą┐ąŠčüą╗ąĄ čüą┐ąĄčåąĖą░ą╗čīąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░, ą║ąŠč鹊čĆčŗą╣ ąĮą░ąĘčŗą▓ą░ąĄčéčüčÅ start condition. ąæąĖčéčŗ ą░ą┤čĆąĄčüą░ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ą▓ čüčéą░čĆčłąĖčģ čüąĄą╝ąĖ ą▒ąĖčéą░čģ ą▒ą░ą╣čéą░, čüčéą░čĆčłąĖą╝ ą▒ąĖč鹊ą╝ (MSB) ą▓ą┐ąĄčĆąĄą┤. ąĪą░ą╝čŗą╣ ą╝ą╗ą░ą┤čłąĖą╣ ą▒ąĖčé (LSB) ą▒ą░ą╣čéą░ ą░ą┤čĆąĄčüą░ ąĖą╝ąĄąĄčé čüą┐ąĄčåąĖą░ą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ R/~W, čé. ąĄ. ąŠąĮ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ą┤ą░ą╗čīąĮąĄą╣čłąĄąĄ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ąĘą░ą┐čĆąŠčüą░ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ - čćč鹥ąĮąĖąĄ (read) ąĖą╗ąĖ ąĘą░ą┐ąĖčüčī (write). ąæčŗą▓ą░čÄčé čéą░ą║ąČąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ čü 10-ą▒ąĖčéąĮčŗą╝ ąĖą╗ąĖ 16-ą▒ąĖčéąĮčŗą╝ ą░ą┤čĆąĄčüąŠą╝ ąĮą░ čłąĖąĮąĄ, ąĮąŠ čŹč鹊čé čüą╗čāčćą░ą╣ ą▓ ąĮą░čłąĄą╝ ą┐čĆąĖą╝ąĄčĆąĄ ąĮąĄ čĆą░čüčüą╝ą░čéčĆąĖą▓ą░ąĄčéčüčÅ.

[ą¤čĆąŠąĄą║čé ą┐čĆąĖą╝ąĄčĆą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ EEPROM č湥čĆąĄąĘ TWI]

ąÉą┐ą┐ą░čĆą░čéčāčĆą░ TWI ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ATmega ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ąŠą▒ą░ čĆąĄąČąĖą╝ą░ čĆą░ą▒ąŠčéčŗ ąĮą░ čłąĖąĮąĄ TWI/I2C: master ąĖ slave. ąÆ čŹč鹊ą╝ ą┐čĆąĖą╝ąĄčĆąĄ ą┤ąĄą╝ąŠąĮčüčéčĆąĖčĆčāąĄčéčüčÅ č鹊ą╗čīą║ąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ AVR ą║ą░ą║ TWI master. ąĀąĄą░ą╗ąĖąĘą░čåąĖčÄ ą┐čĆąĖą╝ąĄčĆą░ ą┐ąŠčüčéą░čĆą░ą╗ąĖčüčī čüą┤ąĄą╗ą░čéčī ą║ą░ą║ ą╝ąŠąČąĮąŠ ą┐čĆąŠčēąĄ, ą║ąŠąĮčåąĄąĮčéčĆąĖčĆčāčÅčüčī ąĮą░ ą┐ąŠčłą░ą│ąŠą▓ąŠą╝ ąŠą▒čēąĄąĮąĖąĖ čü TWI slave, čćč鹊ą▒čŗ ą║ąŠą┤ ą╗ąĄą│ą║ąŠ ą╝ąŠąČąĮąŠ ą▒čŗą╗ąŠ ą░ą┤ą░ą┐čéąĖčĆąŠą▓ą░čéčī ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ čü čĆą░ąĘąĮčŗą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ. ą¤ąŠ č鹊ą╣ ąČąĄ ą┐čĆąĖčćąĖąĮąĄ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čĆąĄąČąĖą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣, ą▓čüčÅ ąŠą▒čĆą░ą▒ąŠčéą║ą░ ąŠą▒ą╝ąĄąĮą░ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ čü ąŠą┐čĆąŠčüąŠą╝ ąŠąČąĖą┤ą░ąĮąĖčÅ ą│ąŠč鹊ą▓ąĮąŠčüčéąĖ (polled-mode), ą║ąŠą│ą┤ą░ ą┐ąĄčĆąĄą┤ ą┐ąĄčĆąĄčģąŠą┤ąŠą╝ ą║ čüą╗ąĄą┤čāčÄčēąĄą╝čā čłą░ą│čā ą┐čĆąŠč鹊ą║ąŠą╗ą░ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ čåąĖą║ą╗čŗ ąŠąČąĖą┤ą░ąĮąĖčÅ, ą┐ąŠą║ą░ ąĮąĄ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé TWINT. ąĢčüą╗ąĖ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ, čćč鹊ą▒čŗ ą║ąŠą╝ą╝čāąĮąĖą║ą░čåąĖąĖ TWI ą┐čĆąŠąĖčüčģąŠą┤ąĖą╗ąĖ ą▓ č乊ąĮąŠą▓ąŠą╝ čĆąĄąČąĖą╝ąĄ, č鹊 čŹč鹊 čüą╗ąĄą┤čāąĄčé čĆąĄą░ą╗ąĖąĘąŠą▓ą░čéčī ąĮą░ ąŠčüąĮąŠą▓ąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣, ą║ąŠą│ą┤ą░ č鹊ą╗čīą║ąŠ ąĘą░ą┐čāčüą║ start condition ąĮčāąČąĮąŠ ąŠčüčāčēąĄčüčéą▓ąĖčéčī ą▓ąĮąĄ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ TWI.

ąÜ čłąĖąĮąĄ TWI ą╝ąŠąČąĮąŠ ą┐ąŠą┤ą║ą╗čÄčćąĖčéčī ą╝ąĮąŠąČąĄčüčéą▓ąŠ čĆą░ąĘą╗ąĖčćąĮčŗčģ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓. ąÆ čŹč鹊ą╝ ą┐čĆąĖą╝ąĄčĆąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐ą░ą╝čÅčéąĖ EEPROM ąĖąĘ čüčéą░ąĮą┤ą░čĆčéąĮąŠą╣ ąĖąĮą┤čāčüčéčĆąĖą░ą╗čīąĮąŠą╣ čüąĄčĆąĖąĖ 24Cxx (ąĘą┤ąĄčüčī xx ą╝ąŠąČąĄčé ą▒čŗčéčī čåąĖčäčĆą░ą╝ąĖ 01, 02, 04, 08 ąĖą╗ąĖ 16). ąóą░ą║ąĖąĄ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ 菹ĮąĄčĆą│ąŠąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠą╣ ą┐ą░ą╝čÅčéąĖ ą┐ąŠčüčéą░ą▓ą╗čÅčÄčéčüčÅ čĆą░ąĘąĮčŗą╝ąĖ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čÅą╝ąĖ. ąÆčŗą▒ąŠčĆ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ąĮąĄ ą║čĆąĖčéąĖč湥ąĮ, ąĮčāąČąĮąŠ ą│ą╗ą░ą▓ąĮčŗą╝ ąŠą▒čĆą░ąĘąŠą╝ ąŠą▒ąĄčüą┐ąĄčćąĖčéčī ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī čĆą░ą▒ąŠčéčŗ ą▓ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ EEPROM ą▓ ąŠą▒ąŠąĖčģ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅčģ (čćč鹥ąĮąĖąĄ ąĖ ąĘą░ą┐ąĖčüčī), ą┐ąŠč鹊ą╝čā čćč鹊 čŹč鹊 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓ ą║ąŠą┤ąĄ ą┐čĆąĖą╝ąĄčĆą░.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: čćą░čēąĄ ą▓čüąĄą│ąŠ ąĮąĄčé ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéąĖ ą┐ąŠą┤ą║ą╗čÄčćą░čéčī ą║ AVR ATmega ąŠčéą┤ąĄą╗čīąĮčāčÄ ą▓ąĮąĄčłąĮčÄčÄ ą╝ąĖą║čĆąŠčüčģąĄą╝čā EEPROM č湥čĆąĄąĘ TWI, ą┐ąŠč鹊ą╝čā čćč鹊 ą┤ą░ąČąĄ čéą░ą║ąŠą╣ ą╝ą╗ą░ą┤čłąĖą╣ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ, ą║ą░ą║ ATmega8, ąĖą╝ąĄąĄčé ą▓čüčéčĆąŠąĄąĮąĮčŗąĄ 512 ą▒ą░ą╣čé EEPROM, čćč鹊 菹║ą▓ąĖą▓ą░ą╗ąĄąĮčéąĮąŠ ąĄą╝ą║ąŠčüčéąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ 24C04. ATmega128 ąĖą╝ąĄąĄčé ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ EEPROM, ą┐ąŠ čĆą░ąĘą╝ąĄčĆčā 菹║ą▓ąĖą▓ą░ą╗ąĄąĮčéąĮčŗą╣ 24C16. ąśčüą║ą╗čÄč湥ąĮąĖąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī, ą║ąŠą│ą┤ą░ čüąĮą░čĆčāąČąĖ ą┐ąŠ ąŠčéąĮąŠčłąĄąĮąĖčÄ ą║ AVR ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ąŠčéą║ą╗čÄčćą░ąĄą╝ąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ EEPROM; ąĮą░ą┐čĆąĖą╝ąĄčĆ ą╝ąŠą┤čāą╗čī ą┐ą░ą╝čÅčéąĖ SDRAM PC ą┐ąŠčüčéą░ą▓ą╗čÅąĄčéčüčÅ čü ą┐ą░ą╝čÅčéčīčÄ TWI EEPROM, ą│ą┤ąĄ ąĘą░ą┐ąĖčüą░ąĮą░ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąŠąĮąĮą░čÅ ąĖąĮč乊čĆą╝ą░čåąĖčÅ ąĖ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ SDRAM.

ąØąĖąČąĄ ą▓ąŠ ą▓čĆąĄąĘą║ąĄ ą┐čĆąĖą▓ąĄą┤ąĄąĮ ąĖčüčģąŠą┤ąĮčŗą╣ ą║ąŠą┤ ą┐čĆąĖą╝ąĄčĆą░ ąĖ ą┐čĆąĖą╝ąĄčćą░ąĮąĖčÅ ą║ ąĮąĄą╝čā. ąöčĆčāą│ąĖąĄ ą┐čĆąĖą╝ąĄčĆčŗ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ I2C ąĮą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░čģ AVR čüą╝. ą┐ąŠ čüčüčŗą╗ą║ą░ą╝ [2, 3].

/*

* ----------------------------------------------------------------------------

* "THE BEER-WARE LICENSE" (Revision 42):

* <joerg@FreeBSD.ORG> ąĮą░ą┐ąĖčüą░ą╗ čŹč鹊čé ą╝ąŠą┤čāą╗čī ą║ąŠą┤ą░. ą¤ąŠą║ą░ ąÆčŗ čüąŠčģčĆą░ąĮčÅąĄč鹥 čŹč鹊čé

* č鹥ą║čüčé, ą╝ąŠąČąĄč鹥 ą┤ąĄą╗ą░čéčī ą▓čüąĄ čćč鹊 čģąŠčéąĖč鹥 čü čŹčéąĖą╝ ą║ąŠą┤ąŠą╝. ąĢčüą╗ąĖ ą╝čŗ ą║ąŠą│ą┤ą░-ąĮąĖą▒čāą┤čī

* ą▓čüčéčĆąĄčéąĖą╝čüčÅ, ąĖ ąĄčüą╗ąĖ ąÆčŗ ą┤čāą╝ą░ąĄč鹥, čćč鹊 čŹč鹊čé ą║ąŠą┤ ą┤ąŠčüčéą░č鹊čćąĮąŠ čģąŠčĆąŠčł, č鹊 ą╝ąŠąČąĄč鹥

* čāą│ąŠčüčéąĖčéčī ą╝ąĄąĮčÅ ą┐ąĖą▓ąŠą╝ ą▓ ąĘąĮą░ą║ ą▒ą╗ą░ą│ąŠą┤ą░čĆąĮąŠčüčéąĖ. Joerg Wunsch

* ----------------------------------------------------------------------------

*/

/*

* ----------------------------------------------------------------------------

* ą×ą▒ąĮąŠą▓ą╗ąĄąĮąŠ ą┤ą╗čÅ ą┐ąŠą┤ą┤ąĄčƹȹ║ąĖ ą▒ąŠą╗ąĄąĄ ą╝ąŠčēąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ą┐ą░ą╝čÅčéąĖ čü 16-ą▒ąĖčéąĮčŗą╝ ą░ą┤čĆąĄčüąĮčŗą╝

* ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠą╝. (2007-09-05) Ruwan Jayanetti

* ----------------------------------------------------------------------------

*/

/* $Id: twitest.c 2244 2011-05-12 03:33:42Z arcanum $ */

/*

* ą¤čĆąŠčüčéą░čÅ ą┤ąĄą╝ąŠąĮčüčéčĆą░čåąĖąŠąĮąĮą░čÅ ą┐čĆąŠą│čĆą░ą╝ą╝ą░, ą║ąŠč鹊čĆą░čÅ ąŠą▒čēą░ąĄčéčüčÅ čü ą╝ąĖą║čĆąŠčüčģąĄą╝ąŠą╣ ą┐ą░ą╝čÅčéąĖ

* 24Cxx IąåC EEPROM, ąĖčüą┐ąŠą╗čīąĘčāčÅ ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ ą░ą┐ą┐ą░čĆą░čéąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü TWI ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░

* ATmega.

*/

#include <inttypes.h>

#include <stdio.h>

#include <stdlib.h>

#include <avr/io.h>

#include <util/twi.h> /* ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ 1 */

#define DEBUG 1

/*

* ąĪąĖčüč鹥ą╝ąĮą░čÅ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░, ąōčå.

*/

#define F_CPU 14745600UL /* ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ 2 */

/*

* ą×ą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ čüąŠą▓ą╝ąĄčüčéąĖą╝ąŠčüčéąĖ. ą×ąĮąĖ ą┤ąŠą╗ąČąĮčŗ čĆą░ą▒ąŠčéą░čéčī čü ATmega8, ATmega16,

* ATmega163, ATmega323 ąĖ ATmega128 (IOW: ąĮą░ ą▓čüąĄčģ čāčüčéčĆąŠą╣čüčéą▓ą░čģ, ą▓ ą║ąŠč鹊čĆčŗčģ

* ąĖą╝ąĄąĄčéčüčÅ ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ ą░ą┐ą┐ą░čĆą░čéąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü TWI (I2C).

*

* ąØą░ ATmega128 ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ USART 1.

*/

#ifndef UCSRB

# ifdef UCSR1A /* ATmega128 */

# define UCSRA UCSR1A

# define UCSRB UCSR1B

# define UBRR UBRR1L

# define UDR UDR1

# else /* ATmega8 */

# define UCSRA USR

# define UCSRB UCR

# endif

#endif

#ifndef UBRR

# define UBRR UBRRL

#endif

/*

* ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ 3

* ąÉą┤čĆąĄčü TWI ą┤ą╗čÅ 24Cxx EEPROM:

*

* 1 0 1 0 E2 E1 E0 R/~W 24C01/24C02

* 1 0 1 0 E2 E1 A8 R/~W 24C04

* 1 0 1 0 E2 A9 A8 R/~W 24C08

* 1 0 1 0 A10 A9 A8 R/~W 24C16

*/

#define TWI_SLA_24CXX 0xa0 /* E2 E1 E0 = 0 0 0 */

/*

* ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ 3a

* ąöą╗ąĖąĮą░ čüą╗ąŠą▓ą░ ą░ą┤čĆąĄčüą░ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┤ą╗čÅ 24Cxx EEPROM

* ąŻčüčéčĆąŠą╣čüčéą▓ą░ EEPROM, čā ą║ąŠč鹊čĆčŗčģ čĆą░ąĘą╝ąĄčĆ ą▒ąŠą╗čīčłąĄ (ąĮą░čćąĖąĮą░čÅ čü 24C32),

* ąĖą╝ąĄčÄčé 16-ą▒ąĖčéąĮčŗą╣ ą░ą┤čĆąĄčü. ą×ą┐čĆąĄą┤ąĄą╗ąĖč鹥 ąĖą╗ąĖ ąĘą░ą║ąŠą╝ą╝ąĄąĮčéąĖčĆčāą╣č鹥 čŹč鹊

* ą╝ą░ą║čĆąŠąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖąĄ ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░.

*/

//#define WORD_ADDRESS_16BIT

/*

* ą£ą░ą║čüąĖą╝ą░ą╗čīąĮąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ąĖč鹥čĆą░čåąĖą╣ ą┤ą╗čÅ ąŠąČąĖą┤ą░ąĮąĖčÅ čāčüčéčĆąŠą╣čüčéą▓ą░, ą║ąŠą│ą┤ą░

* ąŠąĮąŠ ą┤ąŠą╗ąČąĮąŠ ąŠčéą▓ąĄčéąĖčéčī ąĮą░ ąĄą│ąŠ ą▓čŗą▒ąŠčĆ. ąöąŠą╗ąČąĮąŠ ą▒čŗčéčī ą┤ąŠčüčéą░č鹊čćąĮąŠ ą▒ąŠą╗čīčłąĖą╝,

* čćč鹊ą▒čŗ ą┐ąŠąĘą▓ąŠą╗ąĖčéčī ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĄ ąŠąČąĖą┤ą░ąĄą╝ąŠą╣ ąĘą░ą┐ąĖčüąĖ, ąĮąŠ ą┤ąŠčüčéą░č鹊čćąĮąŠ ą╝ą░ą╗čŗą╝,

* čćč鹊ą▒čŗ ąŠą▒ąŠčĆą▓ą░čéčī ą▒ąĄčüą║ąŠąĮąĄčćąĮčŗą╣ čåąĖą║ą╗, ąĄčüą╗ąĖ slave-čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮąĄ ąĖčüą┐čĆą░ą▓ąĮąŠ,

* ą╗ąĖą▒ąŠ ą┐čĆąŠčüč鹊 ąŠčéčüčāčéčüčéą▓čāąĄčé ąĮą░ čłąĖąĮąĄ. ąØą░ čćą░čüč鹊č鹥 ąŠą▒ą╝ąĄąĮą░ 100 ą║ąōčå TWI

* ą┐ąĄčĆąĄą┤ą░čćą░ čüčéą░čĆčéą░ (start condition) ąĖ ą┐ą░ą║ąĄčéą░ SLA+R/W ąĘą░ąĮąĖą╝ą░ąĄčé ąŠą║ąŠą╗ąŠ

* 10 ą╝ą║čü. ą×ąČąĖą┤ą░ąĄčéčüčÅ, čćč鹊 čüą░ą╝čŗą╣ ą┤ąŠą╗ą│ąĖą╣ ą┐ąĄčĆąĖąŠą┤ ąĘą░ą┐ąĖčüąĖ ąĮąĄ ą┐čĆąĄą▓čŗčłą░ąĄčé

* ą┐čĆąĖą╝ąĄčĆąĮąŠ 10 ą╝čü. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ąĮąŠčĆą╝ą░ą╗čīąĮąŠąĄ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĄ

* ąĮąĄ čéčĆąĄą▒čāąĄčé ą▒ąŠą╗čīčłąĄ 100 ąĖč鹥čĆą░čåąĖą╣, čćč鹊ą▒čŗ ą┐ąŠą╗čāčćąĖčéčī ąŠčé čāčüčéčĆąŠą╣čüčéą▓ą░

* ąŠčéą▓ąĄčé ąĮą░ ąĄą│ąŠ ą▓čŗą▒ąŠčĆ.

*/

#define MAX_ITER 200

/*

* ąÜąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ą░ą╣čé, ą║ąŠč鹊čĆąŠąĄ ą╝ąŠąČąĮąŠ ąĘą░ą┐ąĖčüą░čéčī ą▓ čüčéčĆąŠą║ąĄ, čüą╝. ąĮąĖąČąĄ

* ą║ąŠą╝ą╝ąĄąĮčéą░čĆąĖąĖ ą┤ą╗čÅ ee24xx_write_page(). ąØąĄą║ąŠč鹊čĆčŗąĄ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗ąĖ čāčüčéčĆąŠą╣čüčéą▓

* ą╝ąŠą│ą╗ąĖ ą▒čŗ ą┐čĆąĖąĮčÅčéčī 16, ąĮąŠ 8 ą▓čŗą│ą╗čÅą┤ąĖčé ąĮą░ąĖą╝ąĄąĮčīčłąĖą╝ ąŠą▒čēąĖą╝ ąĘąĮą░ą╝ąĄąĮą░č鹥ą╗ąĄą╝.

*

* ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 čĆą░ąĘą╝ąĄčĆ čüčéčĆą░ąĮąĖčåčŗ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čĆą░ą▓ąĄąĮ čüč鹥ą┐ąĄąĮąĖ ą┤ą▓ąŠą╣ą║ąĖ,

* čćč鹊 čāą┐čĆąŠčēą░ąĄčé ą▓čŗčćąĖčüą╗ąĄąĮąĖčÅ ą│čĆą░ąĮąĖčå čüčéčĆą░ąĮąĖčåčŗ.

*/

#define PAGE_SIZE 8

/*

* ąĪąŠčģčĆą░ąĮąĄąĮąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ TWI (čĆąĄą│ąĖčüčéčĆ TWSR), č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čüąŠąŠą▒čēąĄąĮąĖą╣

* ąŠą▒ ąŠčłąĖą▒ą║ą░čģ. ąØą░ą╝ ąĮčāąČąĮąŠ čüąŠčģčĆą░ąĮąĖčéčī ąĄą│ąŠ ą▓ ą┐ąĄčĆąĄą╝ąĄąĮąĮčāčÄ, ą┐ąŠčüą║ąŠą╗čīą║čā ą┤ą░čéą░čłąĖčé

* ą│ą░čĆą░ąĮčéąĖčĆčāąĄčé ą┤ąŠčüč鹊ą▓ąĄčĆąĮąŠąĄ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ čŹč鹊ą│ąŠ čĆąĄą│ąĖčüčéčĆą░ č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░

* čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé TWINT ą▓ čĆąĄą│ąĖčüčéčĆąĄ TWCR.

*/

uint8_t twst;

/*

* ąÆčŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą▓čüąĄčģ ąĮą░čćą░ą╗čīąĮčŗčģ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖą╣ ą┐ąĄčĆąĖč乥čĆąĖąĖ: UART (ą┤ą╗čÅ ąĮą░čłąĄą│ąŠ

* ąŠčéą╗ą░ą┤ąŠčćąĮąŠą│ąŠ ą▓čŗą▓ąŠą┤ą░ ąĖ č鹥čüč鹊ą▓) ąĖ čéą░ą║č鹊ą▓ TWI.

*/

void ioinit(void)

{

#if F_CPU < 1000001UL

/*

* ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ 4

* ąØą░ čŹč鹊ą╣ ąĮąĖąĘą║ąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊č鹥 ą┐čĆąĖą╝ąĄąĮčÅąĄčéčüčÅ ą┤ą▓ąŠą╣ąĮą░čÅ čüą║ąŠčĆąŠčüčéčī UART

* (double Baud), čćč鹊ą▒čŗ čāą╗čāčćčłąĖčéčī čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ą┐ąŠčĆčéą░.

*/

UCSRA = _BV(U2X);

UBRR = (F_CPU / (8 * 9600UL)) - 1; /* 9600 ą▒ąŠą┤ */

#else

UBRR = (F_CPU / (16 * 9600UL)) - 1; /* 9600 ą▒ąŠą┤ */

#endif

UCSRB = _BV(TXEN); /* ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ TX */

/* ąśąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ čéą░ą║č鹊ą▓ TWI: čćą░čüč鹊čéą░ čéą░ą║č鹊ą▓ 100 ą║ąōčå,

TWPS = 0 => ą┐čĆąĄčüą║ą░ą╗ąĄčĆ = 1 */

#if defined(TWPS0)

/* ąĢčüčéčī ą┐čĆąĄčüą║ą░ą╗ąĄčĆ (ATmega128 ąĖ ą▒ąŠą╗ąĄąĄ ąĮąŠą▓čŗąĄ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčŗ) */

TWSR = 0;

#endif

#if F_CPU < 3600000UL

TWBR = 10; /* ąĪą░ą╝ąŠąĄ ą╝ą░ą╗ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ TWBR, čüą╝. ą┐čĆąĖą╝ąĄčćą░ąĮąĖąĄ 5 */

#else

TWBR = (F_CPU / 100000UL - 16) / 2;

#endif

}

/*

* ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ 6

* ą×čéą┐čĆą░ą▓ą║ą░ čüąĖą╝ą▓ąŠą╗ą░ č湥čĆąĄąĘ UART Tx, ąŠąČąĖą┤ą░ąĮąĖąĄ ąŠą┐čāčüč鹊賹ĄąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░

* ą┐ąĄčĆąĄą┤ą░čćąĖ.

*/

int uart_putchar(char c, FILE *unused)

{

if (c == '\n')

uart_putchar('\r', 0);

loop_until_bit_is_set(UCSRA, UDRE);

UDR = c;

return 0;

}

/*

* ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ 7

*

* ążčāąĮą║čåąĖčÅ čćąĖčéą░ąĄčé len ą▒ą░ą╣čé ąĖąĘ EEPROM, ąĮą░čćąĖąĮą░čÅ čü ą░ą┤čĆąĄčüą░ eeaddr,

* ąĖ ą┐ąŠą╝ąĄčēą░ąĄčé ąĖčģ ą▓ ą▒čāč乥čĆ buf.

*

* ąŁčéą░ ąŠą┐ąĄčĆą░čåąĖčÅ čéčĆąĄą▒čāąĄčé ą┤ą▓čāčģ čåąĖą║ą╗ąŠą▓ čłąĖąĮčŗ: ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐ąĄčĆą▓ąŠą│ąŠ čåąĖą║ą╗ą░ čāčüčéčĆąŠą╣čüčéą▓ąŠ

* ą▒čāą┤ąĄčé ą▓čŗą▒čĆą░ąĮąŠ (master transmitter mode) ąĖ ą▒čāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ąĮ ą░ą┤čĆąĄčü.

* ąæąĖčéčŗ ą░ą┤čĆąĄčüą░, ą┐čĆąĄą▓čŗčłą░čÄčēąĄą│ąŠ 256, ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ą▓ ą▒ąĖčéą░čģ E2/E1/E0 (ą▒ąĖčéčŗ

* čüčāą▒ą░ą┤čĆąĄčüą░) čüąĄą╗ąĄą║č鹊čĆą░ čāčüčéčĆąŠą╣čüčéą▓ą░. ąöą╗čÅ čāčüčéčĆąŠą╣čüčéą▓ čü 16-ą▒ąĖčéąĮčŗą╝ ą░ą┤čĆąĄčüąŠą╝

* ą░ą┤čĆąĄčü ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą▓ ą┤ą▓čāčģ ą▓čŗą┤ąĄą╗ąĄąĮąĮčŗčģ 8-ą▒ąĖčéąĮčŗčģ ą┐ąĄčĆąĄą┤ą░čćą░čģ (ąŠčéąĮąŠčüąĖčéčüčÅ

* ą║ ą┤ąŠčüčéą░č鹊čćąĮąŠ ą▒ąŠą╗čīčłąĖą╝ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ EEPROM).

*

* ąÆč鹊čĆąŠą╣ čåąĖą║ą╗ čłąĖąĮčŗ ą▒čāą┤ąĄčé ąĘą░ąĮąŠą▓ąŠ ą▓čŗą▒ąĖčĆą░čéčī čāčüčéčĆąŠą╣čüčéą▓ąŠ (ą┐ąŠą▓č鹊čĆąĖčéčüčÅ start

* condition čü ą┐ąĄčĆąĄčģąŠą┤ąŠą╝ ą▓ master receiver mode), ąĖ ą▒čāą┤čāčé ą┐ąĄčĆąĄą┤ą░ąĮčŗ ą┤ą░ąĮąĮčŗąĄ

* ąĖąĘ čāčüčéčĆąŠą╣čüčéą▓ą░ ą▓ TWI master. ą£ąŠą│čāčé ą▒čŗčéčī ą┐ąĄčĆąĄą┤ą░ąĮčŗ ąĮąĄčüą║ąŠą╗čīą║ąŠ ą▒ą░ą╣čé ą┤čĆčāą│ ąĘą░

* ą┤čĆčāą│ąŠą╝, ąĄčüą╗ąĖ čüąĖą│ąĮą░ą╗ąŠą╝ ACK ą┐ąŠą┤čéą▓ąĄčƹȹ┤ą░ąĄčéčüčÅ ą║ą╗ąĖąĄąĮčéčüą║ą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░.

* ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ą▒ą░ą╣čé ą┐ąŠą╗čāčćą░ąĄčé čüąĖą│ąĮą░ą╗ NACK, čćč鹊 ą┤ą░ąĄčé ąĖąĮą┤ąĖą║ą░čåąĖčÄ ą║ą╗ąĖąĄąĮčéčā,

* čćč鹊 ą┐ąĄčĆąĄą┤ą░čćą░ čćč鹥ąĮąĖčÅ ąĘą░ą▓ąĄčĆčłą░ąĄčéčüčÅ.

*/

int ee24xx_read_bytes(uint16_t eeaddr, int len, uint8_t *buf)

{

uint8_t sla, twcr, n = 0;

int rv = 0;

#ifndef WORD_ADDRESS_16BIT

/* ą¤čāčéčī čüčéą░čĆčłąĖčģ ą▒ąĖčé ą░ą┤čĆąĄčüą░ EEPROM ą▓ SLA */

sla = TWI_SLA_24CXX | (((eeaddr >> 8) & 0x07) << 1);

#else

/* ąŻčüčéčĆąŠą╣čüčéą▓ą░ čü 16-ą▒ąĖčéąĮčŗą╝ ą░ą┤čĆąĄčüąŠą╝ ąĮčāąČą┤ą░čÄčéčüčÅ č鹊ą╗čīą║ąŠ ą▓ ą░ą┤čĆąĄčüąĄ TWI */

sla = TWI_SLA_24CXX;

#endif

/*

* ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ 8

* ą¤ąĄčĆą▓čŗą╣ čåąĖą║ą╗: master transmitter mode

*/

restart:

if (n++ >= MAX_ITER)

return -1;

begin:

TWCR = _BV(TWINT) | _BV(TWSTA) | _BV(TWEN); /* ą┐ąĄčĆąĄą┤ą░čćą░ start condition */

while ((TWCR & _BV(TWINT)) == 0); /* ąŠąČąĖą┤ą░ąĮąĖąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ */

switch ((twst = TW_STATUS))

{

case TW_REP_START: /* OK, ąĮąŠ ąĮąĖč湥ą│ąŠ ąĮąĄ ą┤ąŠą╗ąČąĮąŠ ą┐čĆąŠąĖąĘąŠą╣čéąĖ */

case TW_START:

break;

case TW_MT_ARB_LOST: /* ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ 9 */

goto begin;

default:

return -1; /* ą×čłąĖą▒ą║ą░: ąĮąĄ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ start condition */

/* NB: ąĮąĄ ąĮčāąČąĮąŠ ąŠčéą┐čĆą░ą▓ą╗čÅčéčī stop condition */

}

/* ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ 10 */

/* ą×čéą┐čĆą░ą▓ą║ą░ SLA+W */

TWDR = sla | TW_WRITE;

TWCR = _BV(TWINT) | _BV(TWEN); /* ąŠčćąĖčüčéą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ ąĘą░ą┐čāčüą║ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ */

while ((TWCR & _BV(TWINT)) == 0); /* ąŠąČąĖą┤ą░ąĮąĖąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ */

switch ((twst = TW_STATUS))

{

case TW_MT_SLA_ACK:

break;

case TW_MT_SLA_NACK: /* NACK ą┐čĆąĖ ą▓čŗą▒ąŠčĆąĄ: čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĘą░ąĮčÅč鹊 ąĘą░ą┐ąĖčüčīčÄ */

/* ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ 11 */

goto restart;

case TW_MT_ARB_LOST: /* ą┐ąŠą▓č鹊čĆąĮčŗą╣ ą░čĆą▒ąĖčéčĆą░ąČ */

goto begin;

default:

goto error; /* ąĮčāąČąĮąŠ ąŠčéą┐čĆą░ą▓ąĖčéčī stop condition */

}

#ifdef WORD_ADDRESS_16BIT

TWDR = (eeaddr >> 8); /* ąŻčüčéčĆąŠą╣čüčéą▓ąŠ čü 16-ą▒ąĖčéąĮčŗą╝ čüą╗ąŠą▓ąŠą╝ ą░ą┤čĆąĄčüą░,

ąŠčéą┐čĆą░ą▓ą║ą░ čüčéą░čĆčłąĖčģ 8 ą▒ąĖčé ą░ą┤čĆąĄčüą░ */

TWCR = _BV(TWINT) | _BV(TWEN); /* ąŠčćąĖčüčéą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ ąĘą░ą┐čāčüą║ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ */

while ((TWCR & _BV(TWINT)) == 0) ; /* ąŠąČąĖą┤ą░ąĮąĖąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ */

switch ((twst = TW_STATUS))

{

case TW_MT_DATA_ACK:

break;

case TW_MT_DATA_NACK:

goto quit;

case TW_MT_ARB_LOST:

goto begin;

default:

goto error; /* ąĮčāąČąĮąŠ ąŠčéą┐čĆą░ą▓ąĖčéčī stop condition */

}

#endif

TWDR = eeaddr; /* ą╝ą╗ą░ą┤čłąĖąĄ 8 ą▒ąĖčé ą░ą┤čĆąĄčüą░ */

TWCR = _BV(TWINT) | _BV(TWEN); /* ąŠčćąĖčüčéą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ ąĘą░ą┐čāčüą║ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ */

while ((TWCR & _BV(TWINT)) == 0) ; /* ąŠąČąĖą┤ą░ąĮąĖąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ */

switch ((twst = TW_STATUS))

{

case TW_MT_DATA_ACK:

break;

case TW_MT_DATA_NACK:

goto quit;

case TW_MT_ARB_LOST:

goto begin;

default:

goto error; /* ąĮčāąČąĮąŠ ąŠčéą┐čĆą░ą▓ąĖčéčī stop condition */

}

/*

* ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ 12

* ąĪą╗ąĄą┤čāčÄčēąĖą╣ čåąĖą║ą╗ (ąĖą╗ąĖ čåąĖą║ą╗čŗ): master receiver mode

*/

TWCR = _BV(TWINT) | _BV(TWSTA) | _BV(TWEN); /* send (rep.) start condition */

while ((TWCR & _BV(TWINT)) == 0) ; /* ąŠąČąĖą┤ą░ąĮąĖąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ */

switch ((twst = TW_STATUS))

{

case TW_START: /* OK, ąĮąŠ ąĮąĖč湥ą│ąŠ ąĮąĄ ą┤ąŠą╗ąČąĮąŠ ą┐čĆąŠąĖąĘąŠą╣čéąĖ */

case TW_REP_START:

break;

case TW_MT_ARB_LOST:

goto begin;

default:

goto error;

}

/* ą×čéą┐čĆą░ą▓ą║ą░ SLA+R */

TWDR = sla | TW_READ;

TWCR = _BV(TWINT) | _BV(TWEN); /* ąŠčćąĖčüčéą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ ąĘą░ą┐čāčüą║ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ */

while ((TWCR & _BV(TWINT)) == 0); /* ąŠąČąĖą┤ą░ąĮąĖąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ */

switch ((twst = TW_STATUS))

{

case TW_MR_SLA_ACK:

break;

case TW_MR_SLA_NACK:

goto quit;

case TW_MR_ARB_LOST:

goto begin;

default:

goto error;

}

for (twcr = _BV(TWINT) | _BV(TWEN) | _BV(TWEA) /* ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ 13 */;

len > 0;

len--)

{

if (len == 1)

twcr = _BV(TWINT) | _BV(TWEN); /* ąĮą░ čŹč鹊čé čĆą░ąĘ ąŠčéą┐čĆą░ą▓ą║ą░ NACK */

TWCR = twcr; /* ąŠčćąĖčüčéą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ ąĘą░ą┐čāčüą║ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ */

while ((TWCR & _BV(TWINT)) == 0) ; /* ąŠąČąĖą┤ą░ąĮąĖąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ */

switch ((twst = TW_STATUS))

{

case TW_MR_DATA_NACK:

len = 0; /* ą┐čĆąĖąĮčāą┤ąĖč鹥ą╗čīąĮąŠąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĄ čåąĖą║ą╗ą░ */

/* ąśąöąĢą£ ąöąÉąøą¼ą©ąĢ */

case TW_MR_DATA_ACK:

*buf++ = TWDR;

rv++;

if(twst == TW_MR_DATA_NACK) goto quit;

break;

default:

goto error;

}

}

quit:

/* ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ 14 */

TWCR = _BV(TWINT) | _BV(TWSTO) | _BV(TWEN); /* ąŠčéą┐čĆą░ą▓ą║ą░ stop condition */

return rv;

error:

rv = -1;

goto quit;

}

/*

* ążčāąĮą║čåąĖčÅ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčé len ą▒ą░ą╣čé ą▓ EEPROM, ąĮą░čćąĖąĮą░čÅ čü ą░ą┤čĆąĄčüą░ eeaddr,

* ą▒ą░ą╣čéčŗ ą┤ą╗čÅ ąĘą░ą┐ąĖčüąĖ ą▒ąĄčĆčāčéčüčÅ ąĖąĘ ą▒čāč乥čĆą░ buf.

*

* ąŁčéą░ čäčāąĮą║čåąĖčÅ ąĮąĄą╝ąĮąŠą│ąŠ ą┐čĆąŠčēąĄ, č湥ą╝ ą┐čĆąĄą┤čŗą┤čāčēą░čÅ, ą┐ąŠč鹊ą╝čā čćč鹊 ąŠą▒ąĄ ąŠą┐ąĄčĆą░čåąĖąĖ

* ą┐ąĄčĆąĄą┤ą░čćąĖ ą░ą┤čĆąĄčüą░ ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ čÅą▓ą╗čÅčÄčéčüčÅ ąŠą┐ąĄčĆą░čåąĖčÅą╝ąĖ ąĘą░ą┐ąĖčüąĖ,

* ą┤ą░ąĮąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ą▓ master transmitter mode, čéą░ą║ čćč鹊 ąĮąĄ čéčĆąĄą▒čāąĄčéčüčÅ

* ą┐ąŠą▓č鹊čĆąĮčŗą╣ ą▓čŗą▒ąŠčĆ čāčüčéčĆąŠą╣čüčéą▓ą░. ą×ą┤ąĮą░ą║ąŠ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ EEPROM ą╝ąŠą│čāčé ąĘą░ą┐ąĖčüą░čéčī

* ąĘą░ ąŠą┤ąĖąĮ čĆą░ąĘ č鹊ą╗čīą║ąŠ ąŠą┤ąĮčā čüčéčĆą░ąĮąĖčåčā, ą┐ąŠčŹč鹊ą╝čā ąĮčāąČąĮąŠ ąĘą░ą▒ąŠčéąĖčéčīčüčÅ ąŠ č鹊ą╝,

* čćč鹊ą▒čŗ ąĘą░ ąŠą┤ąĮčā ąŠą┐ąĄčĆą░čåąĖčÄ ąĘą░ą┐ąĖčüąĖ ąĮąĄ ą┐ąĄčĆąĄčüąĄčćčī ą│čĆą░ąĮąĖčåčā čüčéčĆą░ąĮąĖčåčŗ. ąÜąŠą╗ąĖč湥čüčéą▓ąŠ

* ą┤ą░ąĮąĮčŗčģ ąĮą░ čüčéčĆą░ąĮąĖčåąĄ ąĘą░ą▓ąĖčüąĖčé ąŠčé ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čÅ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┐ą░ą╝čÅčéąĖ EEPROM.

* ąØąĄą║ąŠč鹊čĆčŗąĄ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāčÄčé č鹊ą╗čīą║ąŠ 8-ą▒ą░ą╣čéąĮčŗąĄ čüčéčĆą░ąĮąĖčåčŗ ą┤ą╗čÅ

* čāčüčéčĆąŠą╣čüčéą▓ čü ą╝ą░ą╗čŗą╝ ąŠą▒čŖąĄą╝ąŠą╝ ą┐ą░ą╝čÅčéąĖ, ąĖ 16-ą▒ą░ą╣čéąĮčŗąĄ čüčéčĆą░ąĮąĖčåčŗ ą┤ą╗čÅ čāčüčéčĆąŠą╣čüčéą▓

* ą▒ąŠą╗čīčłąĄą│ąŠ ąŠą▒čŖąĄą╝ą░, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ ą┤čĆčāą│ąĖąĄ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāčÄčé č鹊ą╗čīą║ąŠ

* 16-ą▒ą░ą╣čéąĮčŗąĄ čüčéčĆą░ąĮąĖčåčŗ. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą▓ čŹč鹊ą╝ ą║ąŠą┤ąĄ ą╝čŗ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ čüą░ą╝čāčÄ

* ą╝ą░ą╗ąĄąĮčīą║čāčÄ ą┐ąŠčĆčåąĖčÄ ą┤ą░ąĮąĮčŗčģ ąĖąĘ čĆą░čüč湥čéą░ 8 ą▒ą░ą╣čé ąĮą░ čüčéčĆą░ąĮąĖčåčā. ąŁč鹊 ąĘąĮą░č湥ąĮąĖąĄ

* ą┤ąĄą║ą╗ą░čĆąĖčĆčāąĄčéčüčÅ ą▓čŗčłąĄ ą╝ą░ą║čĆąŠčüąŠą╝ PAGE_SIZE.

*

* ąŁčéą░ čäčāąĮą║čåąĖčÅ ą┐čĆąŠčüč鹊 ą┤ąĄą╗ą░ąĄčé ą▓ąŠąĘą▓čĆą░čé ą┐ąŠčüą╗ąĄ ąĘą░ą┐ąĖčüąĖ ąŠą┤ąĮąŠą╣ čüčéčĆą░ąĮąĖčåčŗ,

* ą▓ąŠąĘą▓čĆą░čēą░čÅ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čĆąĄą░ą╗čīąĮąŠ ąĘą░ą┐ąĖčüą░ąĮąĮčŗčģ ą┤ą░ąĮąĮčŗčģ. ąÆčŗąĘčŗą▓ą░čÄčēąĖą╣ ą║ąŠą┤

* ą┤ąŠą╗ąČąĄąĮ ą┐ąŠąĘą░ą▒ąŠčéąĖčéčīčüčÅ ąŠ č鹊ą╝, čćč鹊ą▒čŗ ą┤ąĄą╗ą░čéčī ą┐ąŠą▓č鹊čĆąĮčŗąĄ ą▓čŗąĘąŠą▓čŗ čŹč鹊ą╣ čäčāąĮą║čåąĖąĖ,

* čćč鹊ą▒čŗ ąĘą░ą┐ąĖčüą░čéčī ąŠčüčéą░ą╗čīąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ.

*/

int ee24xx_write_page(uint16_t eeaddr, int len, uint8_t *buf)

{

uint8_t sla, n = 0;

int rv = 0;

uint16_t endaddr;

if (eeaddr + len <= (eeaddr | (PAGE_SIZE - 1)))

endaddr = eeaddr + len;

else

endaddr = (eeaddr | (PAGE_SIZE - 1)) + 1;

len = endaddr - eeaddr;

#ifndef WORD_ADDRESS_16BIT

/* ą┐čāčéčī čüčéą░čĆčłąĖčģ ą▒ąĖčé ą░ą┤čĆąĄčüą░ EEPROM ą▓ SLA */

sla = TWI_SLA_24CXX | (((eeaddr >> 8) & 0x07) << 1);

#else

/* ąŻčüčéčĆąŠą╣čüčéą▓ą░ čü 16-ą▒ąĖčéąĮčŗą╝ ą░ą┤čĆąĄčüąŠą╝ čéčĆąĄą▒čāčÄčé č鹊ą╗čīą║ąŠ ą░ą┤čĆąĄčü TWI-čāčüčéčĆąŠą╣čüčéą▓ą░ */

sla = TWI_SLA_24CXX;

#endif

restart:

if (n++ >= MAX_ITER)

return -1;

begin:

/* ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ 15 */

TWCR = _BV(TWINT) | _BV(TWSTA) | _BV(TWEN); /* ą¤ąĄčĆąĄą┤ą░čćą░ start */

while ((TWCR & _BV(TWINT)) == 0) ; /* ąŠąČąĖą┤ą░ąĮąĖąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ */

switch ((twst = TW_STATUS))

{

case TW_REP_START: /* OK, ąĮąŠ ąĮąĖč湥ą│ąŠ ąĮąĄ ą┤ąŠą╗ąČąĮąŠ ą┐čĆąŠąĖąĘąŠą╣čéąĖ */

case TW_START:

break;

case TW_MT_ARB_LOST:

goto begin;

default:

return -1; /* ąŠčłąĖą▒ą║ą░: ąĮąĄ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ start condition */

/* NB: ąĮąĄ ąĮčāąČąĮąŠ ą┐ąŠčüčŗą╗ą░čéčī stop condition */

}

/* ąŠčéą┐čĆą░ą▓ą║ą░ SLA+W */

TWDR = sla | TW_WRITE;

TWCR = _BV(TWINT) | _BV(TWEN); /* ąŠčćąĖčüčéą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ ąĘą░ą┐čāčüą║ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ */

while ((TWCR & _BV(TWINT)) == 0) ; /* ąŠąČąĖą┤ą░ąĮąĖąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ */

switch ((twst = TW_STATUS))

{

case TW_MT_SLA_ACK:

break;

case TW_MT_SLA_NACK: /* NACK ą▓ąŠ ą▓čĆąĄą╝čÅ ą▓čŗą▒ąŠčĆą░: čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĘą░ąĮčÅč鹊 ąĘą░ą┐ąĖčüčīčÄ */

goto restart;

case TW_MT_ARB_LOST: /* ą┐ąŠą▓č鹊čĆąĮčŗą╣ ą░čĆą▒ąĖčéčĆą░ąČ */

goto begin;

default:

goto error; /* ąĮčāąČąĮąŠ ąŠčéą┐čĆą░ą▓ąĖčéčī stop condition */

}

#ifdef WORD_ADDRESS_16BIT

TWDR = (eeaddr>>8); /* čāčüčéčĆąŠą╣čüčéą▓ąŠ čü 16-ą▒ąĖčéąĮčŗą╝ čüą╗ąŠą▓ąŠą╝ ą░ą┤čĆąĄčüą░, ąŠčéą┐čĆą░ą▓ą║ą░

čüčéą░čĆčłąĖčģ 8 ą▒ąĖčé ą░ą┤čĆąĄčüą░ */

TWCR = _BV(TWINT) | _BV(TWEN); /* ąŠčćąĖčüčéą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ ąĘą░ą┐čāčüą║ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ */

while ((TWCR & _BV(TWINT)) == 0); /* ąŠąČąĖą┤ą░ąĮąĖąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ */

switch ((twst = TW_STATUS))

{

case TW_MT_DATA_ACK:

break;

case TW_MT_DATA_NACK:

goto quit;

case TW_MT_ARB_LOST:

goto begin;

default:

goto error; /* ąĮčāąČąĮąŠ ąŠčéą┐čĆą░ą▓ąĖčéčī stop condition */

}

#endif

TWDR = eeaddr; /* ą╝ą╗ą░ą┤čłąĖąĄ 8 ą▒ąĖčé ą░ą┤čĆąĄčüą░ */

TWCR = _BV(TWINT) | _BV(TWEN); /* ąŠčćąĖčüčéą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ ąĘą░ą┐čāčüą║ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ */

while ((TWCR & _BV(TWINT)) == 0); /* ąŠąČąĖą┤ą░ąĮąĖąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ */

switch ((twst = TW_STATUS))

{

case TW_MT_DATA_ACK:

break;

case TW_MT_DATA_NACK:

goto quit;

case TW_MT_ARB_LOST:

goto begin;

default:

goto error; /* ąĮčāąČąĮąŠ ąŠčéą┐čĆą░ą▓ąĖčéčī stop condition */

}

for (; len > 0; len--)

{

TWDR = *buf++;

TWCR = _BV(TWINT) | _BV(TWEN); /* ąĘą░ą┐čāčüą║ ą┐ąĄčĆąĄą┤ą░čćąĖ */

while ((TWCR & _BV(TWINT)) == 0) ; /* ąŠąČąĖą┤ą░ąĮąĖąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ */

switch ((twst = TW_STATUS))

{

case TW_MT_DATA_NACK:

goto error; /* čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĘą░čēąĖčēąĄąĮąŠ ąŠčé ąĘą░ą┐ąĖčüąĖ - ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ 16 */

case TW_MT_DATA_ACK:

rv++;

break;

default:

goto error;

}

}

quit:

TWCR = _BV(TWINT) | _BV(TWSTO) | _BV(TWEN); /* ąŠčéą┐čĆą░ą▓ą║ą░ stop condition */

return rv;

error:

rv = -1;

goto quit;

}

/*

* ą×ą▒ąĄčĆčéą║ą░ ą▓ąŠą║čĆčāą│ ee24xx_write_page(), ą║ąŠč鹊čĆą░čÅ ą┤ąĄą╗ą░ąĄčé ą┐ąŠą▓č鹊čĆąĮčŗąĄ ą▓čŗąĘąŠą▓čŗ

* čŹč鹊ą╣ čäčāąĮą║čåąĖąĖ ą╗ąĖą▒ąŠ ą┐ąŠą║ą░ ąĮąĄ ą▓ąŠąĘąĮąĖą║ąĮąĄčé ąŠčłąĖą▒ą║ą░, ą╗ąĖą▒ąŠ ąĮąĄ ą▒čāą┤čāčé ąĘą░ą┐ąĖčüą░ąĮčŗ

* ą▓čüąĄ ą▒ą░ą╣čéčŗ.

*/

int ee24xx_write_bytes(uint16_t eeaddr, int len, uint8_t *buf)

{

int rv, total;

total = 0;

do

{

#if DEBUG

printf("Calling ee24xx_write_page(%d, %d, %p)",

eeaddr, len, buf);

#endif

rv = ee24xx_write_page(eeaddr, len, buf);

#if DEBUG

printf(" => %d\n", rv);

#endif

if (rv == -1)

return -1;

eeaddr += rv;

len -= rv;

buf += rv;

total += rv;

}

while (len > 0);

return total;

}

void error(void)

{

printf("error: TWI status %#x\n", twst);

exit(0);

}

FILE mystdout = FDEV_SETUP_STREAM(uart_putchar, NULL, _FDEV_SETUP_WRITE);

void main(void)

{

uint16_t a;

int rv;

uint8_t b[16];

uint8_t x;

ioinit();

stdout = &mystdout;

for (a = 0; a < 256;)

{

printf("%#04x: ", a);

rv = ee24xx_read_bytes(a, 16, b);

if (rv <= 0)

error();

if (rv < 16)

printf("warning: short read %d\n", rv);

a += rv;

for (x = 0; x < rv; x++)

printf("%02x ", b[x]);

putchar('\n');

}

#define EE_WRITE(addr, str) ee24xx_write_bytes(addr, sizeof(str)-1, str)

rv = EE_WRITE(55, "The quick brown fox jumps over the lazy dog.");

if (rv < 0)

error();

printf("Wrote %d bytes.\n", rv);

for (a = 0; a < 256;)

{

printf("%#04x: ", a);

rv = ee24xx_read_bytes(a, 16, b);

if (rv <= 0)

error();

if (rv < 16)

printf("warning: short read %d\n", rv);

a += rv;

for (x = 0; x < rv; x++)

printf("%02x ", b[x]);

putchar('\n');

}

printf("done.\n");

}

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ 1. ąŚą░ą│ąŠą╗ąŠą▓ąŠčćąĮčŗą╣ čäą░ą╣ą╗ util/twi.h čüąŠą┤ąĄčƹȹĖčé ąĮąĄą║ąŠč鹊čĆčŗąĄ ą╝ą░ą║čĆąŠąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ čüąĖą╝ą▓ąŠą╗ąĖč湥čüą║ąĖčģ ą║ąŠąĮčüčéą░ąĮčé, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗčģ ą┤ą╗čÅ ąŠą▒ąŠąĘąĮą░č湥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆąŠą▓ TWI (čéą░ą║ąĖčģ ą║ą░ą║ TWI status register, čĆąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ TWI). ąŁčéąĖ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčé ąĖą╝ąĄąĮą░ą╝ čĆąĄą│ąĖčüčéčĆąŠą▓ ąĖąĘ ą┤ą░čéą░čłąĖčéą░ Atmel ąĘą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ č鹊ą│ąŠ, čćč鹊 ą▓čüąĄ ąĖą╝ąĄąĮą░ ą┐ąŠą╗čāčćą░čÄčé ą┐čĆąĄčäąĖą║čü TW_.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ 2. ąóą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ą░čÅ ą▓ ą▓čŗčćąĖčüą╗ąĄąĮąĖčÅčģ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓ čéą░ą╣ą╝ąĄčĆą░, ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą║ąŠą╝ą┐ąĖą╗čÅč鹊čĆąŠą╝. ąŁč鹊 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ąĮą░čüčéčĆąŠą╣ą║ąĖ čüą║ąŠčĆąŠčüčéąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ UART (baud rate) ąĖ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ TWI.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ 3. ąÉą┤čĆąĄčü, ąĮą░ąĘąĮą░čćą░ąĄą╝čŗą╣ ą┤ą╗čÅ 24Cxx EEPROM, čüąŠčüč鹊ąĖčé ąĖąĘ 1010 ą▓ čüčéą░čĆčłąĖčģ 4 ą▒ąĖčéą░čģ (čĆą░ąĘčĆčÅą┤čŗ 6, 5, 4, 3 ą░ą┤čĆąĄčüą░). ąŚąĮą░č湥ąĮąĖąĄ čüą╗ąĄą┤čāčÄčēąĖčģ čéčĆąĄčģ ą▒ąĖčé (čĆą░ąĘčĆčÅą┤čŗ 2, 1, 0 ą░ą┤čĆąĄčüą░) ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčé sub-ą░ą┤čĆąĄčü slave-čāčüčéčĆąŠą╣čüčéą▓ą░, čćč鹊 ąĘą░ą┤ą░ąĄčéčüčÅ čāčĆąŠą▓ąĮčÅą╝ąĖ A2, A1, A0 ąĮą░ ą▓čŗą▓ąŠą┤ą░čģ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ EEPROM. ąŁč鹊 čüą┤ąĄą╗ą░ąĮąŠ ą┤ą╗čÅ č鹊ą│ąŠ, čćč鹊ą▒čŗ ą║ ąŠą┤ąĮąŠą╣ čłąĖąĮąĄ ą╝ąŠąČąĮąŠ ą▒čŗą╗ąŠ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠ ą┐ąŠą┤ą║ą╗čÄčćąĖčéčī ąĮąĄčüą║ąŠą╗čīą║ąŠ ą╝ąĖą║čĆąŠčüčģąĄą╝, čĆą░ąĘą╗ąĖčćą░čÅ ąĖčģ ą┐ąŠ sub-ą░ą┤čĆąĄčüčā. ą×ą┤ąĮą░ą║ąŠ čüą╗ąĄą┤čāąĄčé ąĖą╝ąĄčéčī ą▓ ą▓ąĖą┤čā, čćč鹊 ą┤ą╗čÅ ąŠą▒čĆą░čēąĄąĮąĖčÅ ą║ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ č鹊ą╗čīą║ąŠ 7-ą▒ąĖčéąĮčŗą╣ ą░ą┤čĆąĄčü, ąĘą░ ą║ąŠč鹊čĆčŗą╝ čüčĆą░ąĘčā ąĖą┤ąĄčé ą┐ą░ą║ąĄčé ą┤ą░ąĮąĮčŗčģ, ąĮąŠ ą╝ąŠąČąĄčé ą▒čŗčéčī čüąĖčéčāą░čåąĖčÅ, ą║ąŠą│ą┤ą░ ą║ čłąĖąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮą░ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ EEPROM, čéčĆąĄą▒čāčÄčēą░čÅ 10-ą▒ąĖčéąĮąŠą│ąŠ ą░ą┤čĆąĄčüą░ (čéą░ą║ą░čÅ ą║ą░ą║ 24C04 ąĖ ą▓čŗčłąĄ). ąóą░ą║ą░čÅ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ čü 10-ą▒ąĖčéąĮčŗą╝ ą░ą┤čĆąĄčüąŠą╝ ą╝ąŠąČąĄčé "čāą║čĆą░čüčéčī" čŹč鹊čé ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ, čüčćąĖčéą░čÅ ąĄą│ąŠ ą▒ą░ą╣č鹊ą╝, ą│ą┤ąĄ ąĮą░čģąŠą┤čÅčéčüčÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗąĄ ą▒ąĖčé. ąŁč鹊čé ą┐čĆąĖą╝ąĄčĆ ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčé, čćč鹊 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą╝ą░ą╗ąĄąĮčīą║ą░čÅ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ čü 7-ą▒ąĖčéąĮčŗą╝ ą░ą┤čĆąĄčüąŠą╝, čā ą║ąŠč鹊čĆąŠą╣ ąĮą░ ąĮąŠąČą║ąĖ A2, A1, A0 ą┐ąŠą┤ą║ą╗čÄč湥ąĮčŗ ą║ ąĘąĄą╝ą╗ąĄ (ą┐ąŠą╗ąĮčŗą╣ 7-ą▒ąĖčéąĮčŗą╣ ą░ą┤čĆąĄčü ą▒čāą┤ąĄčé 1010000).

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ 3a. ą£ąĖą║čĆąŠčüčģąĄą╝čŗ EEPROM čéąĖą┐ą░ 24C32 ąĖ ą▓čŗčłąĄ ąĮąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ą░ą┤čĆąĄčüąŠą▓ą░ąĮčŗ čü ą┐ąŠą╝ąŠčēčīčÄ ą▒ąĖčé sub-ą░ą┤čĆąĄčüą░. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ąŠąĮąĖ čéčĆąĄą▒čāčÄčé, čćč鹊ą▒čŗ čüčéą░čĆčłąĖąĄ ą▒ąĖčéčŗ ą░ą┤čĆąĄčüą░ ą▒čŗą╗ąĖ ą┐ąŠčüą╗ą░ąĮčŗ ą┐ąŠ čłąĖąĮąĄ ąŠčéą┤ąĄą╗čīąĮąŠ ąŠčé ą╝ą╗ą░ą┤čłąĖčģ. ąÜąŠą│ą┤ą░ čĆą░čüą║ąŠą╝ą╝ąĄąĮčéąĖčĆąŠą▓ą░ąĮąŠ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖąĄ WORD_ADDRESS_16BIT, ą░ą╗ą│ąŠčĆąĖčéą╝ čĆąĄą░ą╗ąĖąĘčāąĄčé ą┐ąĄčĆąĄą┤ą░čćčā ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą│ąŠ ą▒ą░ą╣čéą░ ą░ą┤čĆąĄčüą░.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ 4. ąöą╗čÅ ąĮąĖąĘą║ąŠą╣ čćą░čüč鹊čéčŗ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ AVR ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čāą┤ą▓ąŠąĄąĮąĖąĄ čüą║ąŠčĆąŠčüčéąĖ UART (čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ 2 x U[S]ART clock multiplier). ąŁč鹊 ą┐ąŠąĘą▓ąŠą╗ąĖčé ąŠčüčāčēąĄčüčéą▓ąĖčéčī ąŠą▒ą╝ąĄąĮ ą┤ą░ąĮąĮčŗą╝ąĖ ąĮą░ čüą║ąŠčĆąŠčüčéąĖ 9600 ą▒ąŠą┤ ąĮą░ čćą░čüč鹊č鹥 1 ą£ąōčå, ą║ąŠč鹊čĆčāčÄ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé čüčéą░ąĮą┤ą░čĆčéąĮčŗą╣ ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ ą│ąĄąĮąĄčĆą░č鹊čĆ RC AVR (ąŠą▒čŗčćąĮąŠ čŹč鹊 ąĮą░čüčéčĆąŠą╣ą║ą░ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ, ąŠą┐čĆąĄą┤ąĄą╗čÅąĄą╝ą░čÅ čäčīčĹʹ░ą╝ąĖ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ AVR). ą¤ąŠą┤čĆąŠą▒ąĮąŠčüčéąĖ čüą╝. ą▓ čéą░ą▒ą╗ąĖčåą░čģ Baud rate ą┐ąŠčĆčéą░ USART ą┤ą░čéą░čłąĖčéą░ AVR.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ 5. ąÆ ą┤ą░čéą░čłąĖč鹥 ąŠą▒čŖčÅčüąĮčÅąĄčéčüčÅ, ą┐ąŠč湥ą╝čā ą┤ąŠą╗ąČąĮąŠ čüąŠčģčĆą░ąĮčÅčéčīčüčÅ ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ 10 ą┤ą╗čÅ čĆąĄą│ąĖčüčéčĆą░ TWBR, ą║ąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ master mode. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą║ąŠą│ą┤ą░ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ ąĮąĖąČąĄ 3.6 ą£ąōčå, ą╝čŗ ąĮąĄ ą╝ąŠąČąĄą╝ ąĘą░ą┐čāčüčéąĖčéčī čłąĖąĮčā TWI ąĮą░ ąČąĄą╗ą░ąĄą╝ąŠą╣ čćą░čüč鹊č鹥 ąŠą▒ą╝ąĄąĮą░ 100 ą║ąōčå, ą▓ čĆąĄąĘčāą╗čīčéą░č鹥 čĆą░ą▒ąŠčéą░ čłąĖąĮčŗ ą▒čāą┤ąĄčé ą┐čĆąŠąĖčüčģąŠą┤ąĖčéčī ą╝ąĄą┤ą╗ąĄąĮąĮąĄąĄ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ 6. ąŁčéą░ čäčāąĮą║čåąĖčÅ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čüčéą░ąĮą┤ą░čĆčéąĮąŠą│ąŠ ą▓čŗą▓ąŠą┤ą░, čćč鹊 čāą┤ąŠą▒ąĮąŠ ą┤ą╗čÅ ąŠčéą╗ą░ą┤ą║ąĖ ąĖ ą┤ąĄą╝ąŠąĮčüčéčĆą░čåąĖąĖ čĆą░ą▒ąŠčéčŗ ą║ąŠą┤ą░.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ 7. ą¦č鹊ą▒čŗ čāčüą║ąŠčĆąĖčéčī ą┐ąĄčĆąĄą┤ą░čćčā ą┤ą░ąĮąĮčŗčģ ą┐ąŠ čłąĖąĮąĄ TWI, ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ 24Cxx EEPROM ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé ą┐ą░ą║ąĄčéąĮčŗą╣ čĆąĄąČąĖą╝, ą║ąŠą│ą┤ą░ ą▓ ąŠčéą▓ąĄčé ąĮą░ ąŠą┤ąĖąĮ ąĘą░ą┐čĆąŠčü ą┐ąŠ čłąĖąĮąĄ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą┤čĆčāą│ ąĘą░ ą┤čĆčāą│ąŠą╝ ąĮąĄčüą║ąŠą╗čīą║ąŠ ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ. ąŁč鹊 ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ąĘą░ čüč湥čé ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą│ąŠ ąĖąĮą║čĆąĄą╝ąĄąĮčéą░ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čüč湥čéčćąĖą║ą░ ą░ą┤čĆąĄčüą░ ą▒ą░ą╣čéą░ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ (ąĮąĄ ą┐čāčéą░ą╣č鹥 čŹč鹊čé ą░ą┤čĆąĄčü čü TWI-ą░ą┤čĆąĄčüąŠą╝!) ą┐ąŠčüą╗ąĄ čāčüą┐ąĄčłąĮąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ ą║ą░ąČą┤ąŠą│ąŠ ą▒ą░ą╣čéą░. ą¤čĆąĖ čćč鹥ąĮąĖąĖ ą┤ą░ąĮąĮčŗčģ ąĘą░ ąŠą┤ąĖąĮ ąĘą░ą┐čĆąŠčü, ąĄčüą╗ąĖ čŹč鹊 ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ, ą╝ąŠąČąĮąŠ ą┐ąĄčĆąĄą┤ą░čéčī ą▓čüąĄ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ ą┐ą░ą╝čÅčéąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ (ą┐ąŠčüą╗ąĄ ą┤ąŠčüčéąĖąČąĄąĮąĖčÅ ą║ąŠąĮčåą░ ą┐ą░ą╝čÅčéąĖ čüč湥čéčćąĖą║ ą░ą┤čĆąĄčüą░ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĖčéčüčÅ, ąĖ ą▓ąĄčĆąĮąĄčéčüčÅ ą║ ą░ą┤čĆąĄčüčā 0).

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ 8. ą¤čĆąĖ čćč鹥ąĮąĖąĖ EEPROM čüąĮą░čćą░ą╗ą░ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ąĘą░ą┐ąĖčüčī (R/~W čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 0, čćč鹊 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąŠą┐ąĄčĆą░čåąĖčÄ ąĘą░ą┐ąĖčüąĖ), čćč鹊ą▒čŗ ą┐ąĄčĆąĄą┤ą░čéčī ą░ą┤čĆąĄčü EEPROM, ąŠčéą║čāą┤ą░ ą┤ąŠą╗ąČąĮąŠ ąĮą░čćą░čéčīčüčÅ čćč鹥ąĮąĖąĄ. ąŁčéą░ čäą░ąĘą░ ąĮą░ąĘčŗą▓ą░ąĄčéčüčÅ master transmitter mode. ąŚą░ą▓ąĄčĆčłąĄąĮąĖąĄ ą║ą░ąČą┤ąŠą╣ ąŠčéą┤ąĄą╗čīąĮąŠą╣ čäą░ąĘčŗ ąŠą▒ą╝ąĄąĮą░ TWI ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ TWINT ą▓ čĆąĄą│ąĖčüčéčĆąĄ TWCR (ą┐čĆąĖ čŹč鹊ą╝ ą╝ąŠąČąĄčé čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčīčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ąĄčüą╗ąĖ ąŠąĮąŠ čĆą░ąĘčĆąĄčłąĄąĮąŠ. ąÆ ąĮą░čłąĄą╝ ą┐čĆąĖą╝ąĄčĆąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ). ą¤ąŠčüą╗ąĄ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą┤ąĄą╣čüčéą▓ąĖą╣, ą║ąŠč鹊čĆčŗąĄ ąĮčāąČąĮčŗ ą┤ą╗čÅ ą┐ąĄčĆąĄčģąŠą┤ą░ ą║ čüą╗ąĄą┤čāčÄčēąĄą╣ čäą░ąĘąĄ ą║ąŠą╝ą╝čāąĮąĖą║ą░čåąĖąĖ, čäą╗ą░ą│ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąŠčćąĖčēąĄąĮ ą▓čĆčāčćąĮčāčÄ ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ TWINT (ąĮąĄ čāą┤ąĖą▓ą╗čÅą╣č鹥čüčī, ą▒ąĖčé TWINT čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ ąĘą░ą┐ąĖčüčīčÄ ą▓ ąĮąĄą│ąŠ ą╗ąŠą│. 1). ąÆ ąŠčéą╗ąĖčćąĖąĄ ąŠčé ą┤čĆčāą│ąĖčģ ąĖčüč鹊čćąĮąĖą║ąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, čŹč鹊 ąĮčāąČąĮąŠ ą▓čŗą┐ąŠą╗ąĮąĖčéčī ą┤ą░ąČąĄ ą▓ ą║ąŠą┤ąĄ čĆąĄą░ą╗čīąĮąŠą│ąŠ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą┐ąŠčüą║ąŠą╗čīą║čā čüą╗ąĄą┤čāčÄčēą░čÅ čäą░ąĘą░ ąŠą▒ą╝ąĄąĮą░ ąĮąĄ ąĘą░ą┐čāčüčéąĖčéčüčÅ, ą┐ąŠą║ą░ ą▒ąĖčé TWINT ąĮąĄ ą▒čāą┤ąĄčé ąŠčćąĖčēąĄąĮ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ 9. ą¤ąŠčüą║ąŠą╗čīą║čā čłąĖąĮą░ TWI ą╝ąŠąČąĄčé čĆą░ą▒ąŠčéą░čéčī ą▓ čĆąĄąČąĖą╝ąĄ multi-master, ą╝ąŠąČąĄčé ą▒čŗčéčī čüąĖčéčāą░čåąĖčÅ, ą║ąŠą│ą┤ą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ą║ąŠąĮą║čāčĆąĄąĮčåąĖčÅ (ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮčŗą╣ ą┤ąŠčüčéčāą┐ ą║ čłąĖąĮąĄ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ master-čāčüčéčĆąŠą╣čüčéą▓) ą┐čĆąĖ ą┐ąŠą┐čŗčéą║ąĄ ą┤ąŠčüčéčāą┐ą░ ą║ čłąĖąĮąĄ čüąŠ čüč鹊čĆąŠąĮčŗ čāčüčéčĆąŠą╣čüčéą▓ą░ master. ą×ą▒čŗčćąĮąŠ ą░ą┐ą┐ą░čĆą░čéąĮčŗą╣ ą▒ą╗ąŠą║ ąĖąĮč鹥čĆč乥ą╣čüą░ čłąĖąĮčŗ TWI ąŠą┐čĆąĄą┤ąĄą╗ąĖčé čŹčéčā čüąĖčéčāą░čåąĖčÄ, ąĖ ąĮąĄ ą▒čāą┤ąĄčé ąĖąĮąĖčåąĖąĖčĆąŠą▓ą░čéčī ąĘą░ą┐čāčüą║ start condition, ą┐ąŠą║ą░ čłąĖąĮą░ ąĘą░ąĮčÅčéą░. ą×ą┤ąĮą░ą║ąŠ ą▓ čüą╗čāčćą░ąĄ, ą║ąŠą│ą┤ą░ ą┤ą▓ą░ čāčüčéčĆąŠą╣čüčéą▓ą░ master čüčéą░čĆč鹊ą▓ą░ą╗ąĖ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ, čüčĆą░ą▒ąŠčéą░ąĄčé ą░čĆą▒ąĖčéčĆą░ąČ čłąĖąĮčŗ, ą┐čĆąĖ čŹč鹊ą╝ ą▓čüąĄą│ą┤ą░ ąŠą┤ąĖąĮ ąĖąĘ master-čāčüčéčĆąŠą╣čüčéą▓ ą┐čĆąŠąĖą│čĆą░ąĄčé ą░čĆą▒ąĖčéčĆą░ąČ čłąĖąĮčŗ ą▓ąŠ ą▓čĆąĄą╝čÅ ą╗čÄą▒ąŠą╣ ąŠą┐ąĄčĆą░čåąĖąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ. Master, ą║ąŠč鹊čĆčŗą╣ ą┐čĆąŠąĖą│čĆą░ą╗ ą░čĆą▒ąĖčéčĆą░ąČ, ą┐ąŠ ą┐čĆąŠč鹊ą║ąŠą╗čā ą┤ąŠą╗ąČąĄąĮ čüčĆą░ąĘčā ą┐čĆąĄą║čĆą░čéąĖčéčī čüą▓ąŠčÄ ą░ą║čéąĖą▓ąĮąŠčüčéčī ąĮą░ čłąĖąĮąĄ; ą▓ čćą░čüčéąĮąŠčüčéąĖ, ąŠąĮ ąĮąĄ ą┤ąŠą╗ąČąĄąĮ ąĖąĮąĖčåąĖąĖčĆąŠą▓ą░čéčī čüąĖą│ąĮą░ą╗ stop condition, čćč鹊ą▒čŗ ąĮąĄ ą┐ąŠą▓čĆąĄą┤ąĖčéčī ąĖčüčģąŠą┤čÅčēčāčÄ ą┐ąĄčĆąĄą┤ą░čćčā ąŠčé ą┤čĆčāą│ąŠą│ąŠ ą░ą║čéąĖą▓ąĮąŠą│ąŠ master. ąÆ čŹč鹊ą╝ ą┐čĆąĖą╝ąĄčĆąĄ ą┐čĆąĖ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĖ čüąŠą▒čŗčéąĖčÅ ą┐čĆąŠąĖą│čĆčŗčłą░ ą░čĆą▒ąĖčéčĆą░ąČą░, ą▓čüčÅ ą┐ąĄčĆąĄą┤ą░čćą░ ą▒čāą┤ąĄčé ą┐ąĄčĆąĄąĘą░ą┐čāčēąĄąĮą░ ąĘą░ąĮąŠą▓ąŠ. ą¤čĆąĖ čŹč鹊ą╝ ą▒čāą┤ąĄčé ąĖąĮąĖčåąĖąĖčĆąŠą▓ą░ąĮ ąĮąŠą▓čŗą╣ čüąĖą│ąĮą░ą╗ start condition, ą║ąŠč鹊čĆčŗą╣ ą▒čāą┤ąĄčé ąĮąŠčĆą╝ą░ą╗čīąĮąŠ ąĘą░ą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ, ą┐ąŠą║ą░ č鹥ą║čāčēąĖą╣ ą░ą║čéąĖą▓ąĮčŗą╣ ą╝ą░čüč鹥čĆ ąĮąĄ ąŠčüą▓ąŠą▒ąŠą┤ąĖčé čłąĖąĮčā.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ 10. ąöą░ą╗ąĄąĄ slave-čāčüčéčĆąŠą╣čüčéą▓ąŠ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ą┐ąŠą▓č鹊čĆąĮąŠ (čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ čéą░ą║ ąĮą░ąĘčŗą▓ą░ąĄą╝ąŠą│ąŠ ą┐ąŠą▓č鹊čĆąĮąŠą│ąŠ start condition, ą║ąŠč鹊čĆčŗą╣ ą┐čĆąĄą┤ąĮą░ąĘąĮą░čćą░ąĄčéčüčÅ ą┤ą╗čÅ č鹊ą│ąŠ, čćč鹊ą▒čŗ ą░čĆą▒ąĖčéčĆą░ąČ čłąĖąĮčŗ ąŠčüčéą░ą╗čüčÅ čā č鹥ą║čāčēąĄą│ąŠ master), ąĖčüą┐ąŠą╗čīąĘčāčÅ č鹊čé ąČąĄ čüą░ą╝čŗą╣ ą░ą┤čĆąĄčü ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (SLA), ąĮąŠ ąĮą░ čŹč鹊čé čĆą░ąĘ čü čåąĄą╗čīčÄ čćč鹥ąĮąĖčÅ (ą▒ąĖčé R/~W čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ ą╗ąŠą│. 1). ąÆ čĆąĄąĘčāą╗čīčéą░č鹥 ą┐ąŠą╗čāčćąĖčéčüčÅ ąĘą░ą┐čĆąŠčü ą║ slave-čāčüčéčĆąŠą╣čüčéą▓čā, čćč鹊ą▒čŗ ąŠąĮąŠ ą▓ čüą╗ąĄą┤čāčÄčēąĄą╝ ą┐ą░ą║ąĄč鹥 ąĮą░čćą░ą╗ąŠ ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ master.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ 11. ąĢčüą╗ąĖ čāčüčéčĆąŠą╣čüčéą▓ąŠ EEPROM ą▓čüąĄ ąĄčēąĄ ąĘą░ąĮčÅč鹊 ąĘą░ą┐ąĖčüčīčÄ ąŠą┤ąĮąŠą╣ ąĖą╗ąĖ ą▒ąŠą╗čīčłąĄą│ąŠ ą║ąŠą╗ąĖč湥čüčéą▓ą░ čÅč湥ąĄą║, čćč鹊 ą▒čŗą╗ąŠ ąĖąĮąĖčåąĖąĖčĆąŠą▓ą░ąĮąŠ ą┐čĆąĄą┤čŗą┤čāčēąĖą╝ ąĘą░ą┐čĆąŠčüąŠą╝ ąĮą░ ąĘą░ą┐ąĖčüčī, č鹊 ąŠąĮąŠ ą┐čĆąŠčüč鹊 ąŠčüčéą░ą▓ą╗čÅąĄčé čüą▓ąŠąĖ ą┤čĆą░ą╣ą▓ąĄčĆčŗ ąŠčéą║ą╗čÄč湥ąĮąĮčŗą╝ąĖ ąŠčé čłąĖąĮčŗ, ąĖ ąĮąĖą║ą░ą║ ąĮąĄ ąŠčéą▓ąĄčćą░ąĄčé ąĮą░ ą▓čŗą▒ąŠčĆ (ąĘą░ą┐čĆąŠčü) čüąŠ čüč鹊čĆąŠąĮčŗ master. ąŻčüčéčĆąŠą╣čüčéą▓ąŠ master, ą║ąŠč鹊čĆąŠąĄ ą┐ąŠą┐čŗčéą░ą╗ąŠčüčī ą▓čŗą▒čĆą░čéčī čāčüčéčĆąŠą╣čüčéą▓ąŠ slave, ą▓ ąŠčéą▓ąĄčé ąĮą░ čüą▓ąŠą╣ ąĘą░ą┐čĆąŠčü čāą▓ąĖą┤ąĖčé ą╗ąŠą│ąĖč湥čüą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī ąĄą┤ąĖąĮąĖčåčŗ ąĮą░ SDA ą┐ąŠčüą╗ąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐ą░ą║ąĄčéą░ SLA+R/W ą║ą░ą║ čüąĖą│ąĮą░ą╗ NACK. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą┐čĆąŠčåąĄčüčü ą▓čŗą▒ąŠčĆą░ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┐čĆąŠčüč鹊 ą┐ąĄčĆąĄąĘą░ą┐čāčüčéąĖčéčüčÅ (čćč鹊 čŹčäč乥ą║čéąĖą▓ąĮąŠ ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ą┐ąŠą▓č鹊čĆą░ą╝ čüąĖą│ąĮą░ą╗ą░ start condition), ą┐ąŠą║ą░ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮąĄ ąĮą░čćąĮąĄčé čĆąĄą░ą╗čīąĮąŠ ąŠčéą▓ąĄčćą░čéčī. ąŁčéą░ ą┐čĆąŠčåąĄą┤čāčĆą░ ąŠą┐čĆąŠčüą░ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ą▓ ą┤ą░čéą░čłąĖč鹥 24Cxx, čćč鹊ą▒čŗ ą╝ąĖąĮąĖą╝ąĖąĘąĖčĆąŠą▓ą░čéčī ą▓čĆąĄą╝čÅ ąŠąČąĖą┤ą░ąĮąĖčÅ ą┐čĆąĖ ąĘą░ą┐ąĖčüąĖ. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ą▓ čüą╗čāčćą░ąĄ, ą║ąŠą│ą┤ą░ slave-čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐ąŠą▓čĆąĄąČą┤ąĄąĮąŠ ąĖ ąĮąĄ ąŠčéą▓ąĄčćą░ąĄčé ą┐ąŠ čłąĖąĮąĄ (ąĖą╗ąĖ ą┐čĆąŠčüč鹊 ąĮąĄ ą┐čĆąĖčüčāčéčüčéą▓čāąĄčé ąĮą░ čłąĖąĮąĄ), čŹč鹊 ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ą▒ąĄčüą║ąŠąĮąĄčćąĮąŠą╝čā ąĘą░čåąĖą║ą╗ąĖą▓ą░ąĮąĖčÄ (ąĘą░ą▓ąĖčüą░ąĮąĖčÄ). ąöą╗čÅ čāčüčéčĆą░ąĮąĄąĮąĖčÅ čŹč鹊ą╣ ą┐čĆąŠą▒ą╗ąĄą╝čŗ ą▓ą▓ąĄą┤ąĄąĮ ą┐ą░čĆą░ą╝ąĄčéčĆ MAX_ITER ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą│ąŠ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ąĖč鹥čĆą░čåąĖą╣, ą┐ąŠčüą╗ąĄ ą║ąŠč鹊čĆčŗčģ ą▒čāą┤ąĄčé ą▓ąŠąĘą▓čĆą░čēąĄąĮą░ ąŠčłąĖą▒ą║ą░.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ 12. ąŁč鹊 čéą░ą║ ąĮą░ąĘčŗą▓ą░ąĄą╝čŗą╣ čĆąĄąČąĖą╝ ą┐čĆąĖąĄą╝ą░ ą│ą╗ą░ą▓ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (master receiver mode): ą╝ą░čüč鹥čĆ čłąĖąĮčŗ ą▒čāą┤ąĄčé ą┐čĆąŠčüč鹊 ą▓čŗą┤ą░ą▓ą░čéčī ąĖą╝ą┐čāą╗čīčüčŗ čéą░ą║č鹊ą▓ SCL, ąĖ slave-čāčüčéčĆąŠą╣čüčéą▓ąŠ ą▓ ąŠčéą▓ąĄčé ą▒čāą┤ąĄčé čāą┐čĆą░ą▓ą╗čÅčéčī čüąĖą│ąĮą░ą╗ąŠą╝ SDA, ą┐ąĄčĆąĄą┤ą░ą▓ą░čÅ čéčāą┤ą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ ą┤ą░ąĮąĮčŗąĄ. ą¤ąŠčüą╗ąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ 8 ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ master-čāčüčéčĆąŠą╣čüčéą▓ąŠ ąŠčéą▓ąĄčéąĖčé čüąĖą│ąĮą░ą╗ąŠą╝ ACK (ą┐ąĄčĆąĄą▓ąĄą┤čÅ SDA ą▓ ą╗ąŠą│. 0), čćč鹊ą▒čŗ ąĘą░ą┐čĆąŠčüąĖčéčī ą┤čĆčāą│čāčÄ ą┐ąĄčĆąĄą┤ą░čćčā ą┤ą░ąĮąĮčŗčģ ąŠčé slave-čāčüčéčĆąŠą╣čüčéą▓ą░, ąĖą╗ąĖ ą╝ąŠąČąĄčé ąŠčüčéą░ą▓ąĖčéčī čüąĖą│ąĮą░ą╗ SDA ą▓ ą╗ąŠą│. 1 (ą┐ąĄčĆąĄą┤ą░ą▓ą░čÅ č鹥ą╝ čüą░ą╝čŗą╝ čüąĖą│ąĮą░ą╗ NACK), čćč鹊 ą┐ąŠą║ą░ąČąĄčé ą┤ą╗čÅ slave-čāčüčéčĆąŠą╣čüčéą▓ą░, čćč鹊 ąĮčāąČąĮąŠ ąŠčüčéą░ąĮąŠą▓ąĖčéčī ą┐ąĄčĆąĄą┤ą░čćčā. ąÆčŗą┤ą░čćą░ čüąĖą│ąĮą░ą╗ą░ ACK ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ TWEA ą▓ čĆąĄą│ąĖčüčéčĆąĄ TWCR, ą║ąŠą│ą┤ą░ ąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ č鹥ą║čāčēą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ 13. ą×čéą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ čāą┐čĆą░ą▓ą╗čÅčÄčēąĄąĄ čüą╗ąŠą▓ąŠ, čćč鹊ą▒čŗ ąĖąĮąĖčåąĖąĖčĆąŠą▓ą░čéčī ą┐ąĄčĆąĄą┤ą░čćčā čüą╗ąĄą┤čāčÄčēąĄą│ąŠ ą┐ą░ą║ąĄčéą░ ą┤ą░ąĮąĮčŗčģ, ą║ąŠą│ą┤ą░ ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮąŠ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé TWEA. ąÆąŠ ą▓čĆąĄą╝čÅ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╣ ąĖč鹥čĆą░čåąĖąĖ čåąĖą║ą╗ą░ ą▒ąĖčé TWEA čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ, čćč鹊ą▒čŗ slave-čāčüčéčĆąŠą╣čüčéą▓ąŠ ą▒čŗą╗ąŠ ąŠą┐ąŠą▓ąĄčēąĄąĮąŠ, čćč鹊 ą▒ąŠą╗čīčłąĄ ąĮąĄ ąĮčāąČąĮčŗ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ 14. ąÜčĆąŠą╝ąĄ čüą╗čāčćą░čÅ ą┐ąŠč鹥čĆąĖ ą░čĆą▒ąĖčéčĆą░ąČą░, ą▓čüąĄ čéčĆą░ąĮąĘą░ą║čåąĖąĖ ą┐ąŠ čłąĖąĮąĄ ą┤ąŠą╗ąČąĮčŗ ąĘą░ą▓ąĄčĆčłą░čéčīčüčÅ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ master ą┐čāč鹥ą╝ ą▓čŗą┤ą░čćąĖ čüąĖą│ąĮą░ą╗ą░ stop condition.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ 15. ąŚą░ą┐ąĖčüčī ą▓ čāčüčéčĆąŠą╣čüčéą▓ąŠ EEPROM ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą┐čĆąŠčēąĄ, č湥ą╝ čćč鹥ąĮąĖąĄ, ą┐ąŠč鹊ą╝čā čćč鹊 ąĮčāąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī č鹊ą╗čīą║ąŠ ą┐ąĄčĆąĄą┤ą░čćčā master transmitter mode. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ą┐ąĄčĆą▓čŗą╣ ą┐ą░ą║ąĄčé ą┐ąŠčüą╗ąĄ ą┐ą░ą║ąĄčéą░ ą▓čŗą▒ąŠčĆą░ SLA+W ą▓čüąĄą│ą┤ą░ čüčćąĖčéą░ąĄčéčüčÅ TWI-ą░ą┤čĆąĄčüąŠą╝ ą┤ą╗čÅ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ EEPROM, ą║ąŠč鹊čĆčŗą╣ ą▒čāą┤ąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ čüą╗ąĄą┤čāčÄčēąĄą╣ čäą░ąĘčŗ ąŠą▒ą╝ąĄąĮą░ (čŹč鹊čé ą┐ą░ą║ąĄčé č鹊čćąĮąŠ čéą░ą║ąŠą╣ ąČąĄ, ą║ą░ą║ ą▒čŗą╗ ą┐ąŠčüą╗ą░ąĮ ąĮą░ čäą░ąĘąĄ ąĖąĮąĖčåąĖą░čåąĖąĖ ąŠą┐ąĄčĆą░čåąĖąĖ čćč鹥ąĮąĖčÅ). ąÆ čüą╗čāčćą░ąĄ, ą║ąŠą│ą┤ą░ ąŠčüčéą░ąĄčéčüčÅ ą▓ ą┤ąĄą╣čüčéą▓ąĖąĖ master transmitter mode, čüą╗ąĄą┤čāčÄčēąĖąĄ ąŠčéą┐čĆą░ą▓ą╗čÅąĄą╝čŗąĄ ą┐ą░ą║ąĄčéčŗ čüčćąĖčéą░čÄčéčüčÅ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄą╝čŗą╝ąĖ ą▓ EEPROM ą▒ą░ą╣čéą░ą╝ąĖ ą┤ą░ąĮąĮčŗčģ. ąÆąĮčāčéčĆąĄąĮąĮąĖą╣ čüč湥čéčćąĖą║ ą░ą┤čĆąĄčüą░ ą▒čāą┤ąĄčé ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆąŠą▓ą░čéčīčüčÅ ą┐ąŠčüą╗ąĄ ą║ą░ąČą┤ąŠą╣ ąŠą┐ąĄčĆą░čåąĖąĖ ąĘą░ą┐ąĖčüąĖ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ 16. ą£ąĖą║čĆąŠčüčģąĄą╝čŗ ą┐ą░ą╝čÅčéąĖ 24Cxx ą╝ąŠą│čāčé čüčéą░čéčī ąĘą░čēąĖčēąĄąĮąĮčŗą╝ąĖ ąŠčé ąĘą░ą┐ąĖčüąĖ (write-protected) ą┐čāč鹥ą╝ ą┐ąĄčĆąĄą▓ąŠą┤ą░ ąĖčģ ą▓ąĮąĄčłąĮąĄą│ąŠ ą▓čŗą▓ąŠą┤ą░ ~WC ą▓ ą╗ąŠą│. 1 (ąĄčüą╗ąĖ ąŠčüčéą░ą▓ąĖčéčī čŹč鹊čé ą▓čŗą▓ąŠą┤ ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗą╝, č鹊 ąĮą░ ą▓čŗą▓ąŠą┤ąĄ ~WC ą┐ąŠą╗čāčćąĖčéčüčÅ čüąĖą│ąĮą░ą╗ ą╗ąŠą│. 0, čćč鹊 ąŠąĘąĮą░čćą░ąĄčé ąŠčéčüčāčéčüčéą▓ąĖąĄ ąĘą░čēąĖčéčŗ ąŠčé ąĘą░ą┐ąĖčüąĖ). ąÜąŠą│ą┤ą░ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĘą░čēąĖčēąĄąĮąŠ ąŠčé ąĘą░ą┐ąĖčüąĖ, ąĮą░ ą▓čüąĄ ąĘą░ą┐čĆąŠčüčŗ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ąĮą░ ąĘą░ą┐ąĖčüčī ą▒čāą┤čāčé ą┐ąŠčüčŗą╗ą░čéčīčüčÅ čüąĖą│ąĮą░ą╗čŗ NACK. ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 ą▓ ąĮąĄą║ąŠč鹊čĆčŗčģ čāčüčéčĆąŠą╣čüčéą▓ą░čģ čŹč鹊 ą╝ąŠąČąĄčé ą▒čŗčéčī ąĮąĄ čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮąŠ.

[ą¤čĆąĖą╝ąĄčĆ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ Si570 č湥čĆąĄąĘ TWI]

ąŁč鹊 ą┐čĆąŠčüč鹊ą╣ ą┐čĆąĖą╝ąĄčĆ ą║ąŠąĮčüąŠą╗čīąĮąŠą│ąŠ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ, čĆą░ą▒ąŠčéą░čÄčēąĄą│ąŠ č湥čĆąĄąĘ ą▓ąĖčĆčéčāą░ą╗čīąĮčŗą╣ COM-ą┐ąŠčĆčé. ąĪąĖąĮč鹥ąĘą░č鹊čĆ Si570CBC000121G [5] ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą║ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčā ATmega32U4 (ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ą╗ą░čüčī ą╝ą░ą║ąĄčéąĮą░čÅ ą┐ą╗ą░čéą░ AVR-USB32U4 [6]), ą║ąŠč鹊čĆčŗą╣ č湥čĆąĄąĘ TWI ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčé čĆąĄą│ąĖčüčéčĆčŗ Si570 ą┤ą╗čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ ąĮčāąČąĮąŠą╣ čćą░čüč鹊čéčŗ čüąĖąĮč鹥ąĘą░č鹊čĆą░. ą¤ąŠą║ą░ąĘą░ąĮąĮą░čÅ ąĮą░ čĆąĖčüčāąĮą║ąĄ čüčģąĄą╝ą░ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ą╗ą░čüčī ą▓ ą║ą░č湥čüčéą▓ąĄ ą│ąĄč鹥čĆąŠą┤ąĖąĮą░ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ [8].

ąŻčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄą╝ą░čÅ čćą░čüč鹊čéą░ ą▓ą▓ąŠą┤ąĖčéčüčÅ ą▓ ą║ąŠąĮčüąŠą╗ąĖ č鹥ą║čüč鹊ą▓ąŠą╣ ą║ąŠą╝ą░ąĮą┤ąŠą╣ "f čćą░čüč鹊čéą░", ą│ą┤ąĄ čćą░čüč鹊čéą░ čāą║ą░ąĘčŗą▓ą░ąĄčéčüčÅ ą▓ ą£ąōčå, ą▓ ą▓ąĖą┤ąĄ čćąĖčüą╗ą░ čü ą┐ą╗ą░ą▓ą░čÄčēąĄą╣ ąĘą░ą┐čÅč鹊ą╣. ą¤čĆąĖą╝ąĄčĆ ą▓ą▓ąŠą┤ą░ ą║ąŠą╝ą░ąĮą┤čŗ ą┤ą╗čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ čćą░čüč鹊čéčŗ 42.667 ą£ąōčå:

ą£ąŠą┤čāą╗čī ąĖčüčģąŠą┤ąĮąŠą│ąŠ ą║ąŠą┤ą░ Si570.c ą▒čŗą╗ ą┐ąŠčĆčéąĖčĆąŠą▓ą░ąĮ ąĖąĘ ą┤ą░čéą░čłąĖčéą░ AN334 [7] ąĮą░ ą░ą┐ą┐ą░čĆą░čéčāčĆčā TWI ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ AVR.

ąŚą░ą│ąŠą╗ąŠą▓ąŠčćąĮčŗą╣ čäą░ą╣ą╗ Si570.h:

#ifndef __SI570__

#define __SI570__

// ą¦ą░čüč鹊čéą░ ąĘą░ą┐čāčüą║ą░. ąĢčæ ąĮčāąČąĮąŠ ąĘąĮą░čéčī ą┐čĆąĖ ąĘą░ą║ą░ąĘąĄ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ, ąŠą┤ąĮą░ą║ąŠ ąĄčüą╗ąĖ

// čćą░čüč鹊čéą░ ąĮąĄ ąĖąĘą▓ąĄčüčéąĮą░, č鹊 ąĄčæ ą╝ąŠąČąĮąŠ ąĖąĘą╝ąĄąĮąĖčéčī. ąŁč鹊 ąĮčāąČąĮąŠ čüą┤ąĄą╗ą░čéčī č鹊čćąĮąŠ,

// čćč鹊ą▒čŗ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī č鹊čćąĮąŠčüčéčī ą▓čüąĄčģ ą┤čĆčāą│ąĖčģ čćą░čüč鹊čé.

#define FOUT_START_UP 100 // ą£ąōčå

// ąöąĖą░ą┐ą░ąĘąŠąĮ Si57x/598/599's FDCO

// ąŁčéąĖ ąĘąĮą░č湥ąĮąĖčÅ ą╝ąĄąĮčÅčéčī ąĮąĄ čüą╗ąĄą┤čāąĄčé, ąŠą┤ąĮą░ą║ąŠ ąŠąĮąĖ ą╝ąŠą│čāčé ąĘą░ą▓ąĖčüąĄčéčī ąŠčé ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ.

#define FDCO_MIN 4850.0 // float, ą£ąōčå

#define FDCO_MAX 5670.0 // float, ą£ąōčå

void ReadStartUpConfiguration(void);

void RunFreqProg (float freq);

#endif

ąśčüčģąŠą┤ąĮčŗą╣ ą║ąŠą┤ Si570.c:

#include <math.h>

#include "Si570.h"

#include "i2c.h"

// ąŚą┤ąĄčüčī č鹊ą╗čīą║ąŠ ą┤ąŠą┐čāčüčéąĖą╝čŗąĄ ąĘąĮą░č湥ąĮąĖčÅ ą┤ą╗čÅ HSDIV. ą¤ąŠą┤čĆąŠą▒ąĮąŠčüčéąĖ čüą╝. ą▓ ą┤ą░čéą░čłąĖč鹥.

static const HSDIV[6] = {11, 9, 7, 6, 5, 4};

static float FOUT0 = FOUT_START_UP;

//-----------------------------------------------------------------------------

// ąōą╗ąŠą▒ą░ą╗čīąĮčŗąĄ ą┐ąĄčĆąĄą╝ąĄąĮąĮčŗąĄ

//-----------------------------------------------------------------------------

u8 INITIAL_HSDIV; // ąŚąĮą░č湥ąĮąĖąĄ HSDIV, ą┐čĆąŠčćąĖčéą░ąĮąĮąŠąĄ ąĖąĘ Si57x/598/599,

// ą║ąŠą│ą┤ą░ ą▓ą║ą╗čÄčćą░ąĄčéčüčÅ ą┐ąĖčéą░ąĮąĖąĄ

u8 INITIAL_N1; // ąŚąĮą░č湥ąĮąĖąĄ N1, ą┐čĆąŠčćąĖčéą░ąĮąĮąŠąĄ ąĖąĘ Si57x/598/599,

// ą║ąŠą│ą┤ą░ ą▓ą║ą╗čÄčćą░ąĄčéčüčÅ ą┐ąĖčéą░ąĮąĖąĄ

u8 REG[6]; // ą£ą░čüčüąĖą▓ ą▒ąĖčé, čģčĆą░ąĮčÅčēąĖą╣ ąĮą░čćą░ą╗čīąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ,

// ą┐čĆąŠčćąĖčéą░ąĮąĮčŗąĄ ąĖąĘ Si57x/598/599

u32 INITIAL_RFREQ_LONG; // ąŚąĮą░č湥ąĮąĖąĄ RFREQ, ą┐čĆąŠčćąĖčéą░ąĮąĮąŠąĄ ąĖąĘ Si57x/598/599,

// ą║ąŠą│ą┤ą░ ą▓ą║ą╗čÄčćą░ąĄčéčüčÅ ą┐ąĖčéą░ąĮąĖąĄ

float RFREQ; // ąöčĆąŠą▒ąĮčŗą╣ ą╝ąĮąŠąČąĖč鹥ą╗čī, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╣ ą┤ą╗čÅ ą┤ąŠčüčéąĖąČąĄąĮąĖčÅ

// ą║ąŠčĆčĆąĄą║čéąĮąŠą╣ ą▓čŗčģąŠą┤ąĮąŠą╣ čćą░čüč鹊čéčŗ

float FXTAL; // ąźčĆą░ąĮąĖčé ąĘąĮą░č湥ąĮąĖąĄ čćą░čüč鹊čéčŗ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ

// ą║ą▓ą░čĆčåą░

u8* pTWI_DATA_IN; // ąōą╗ąŠą▒ą░ą╗čīąĮčŗą╣ čāą║ą░ąĘą░č鹥ą╗čī ąĮą░ ą┤ą░ąĮąĮčŗąĄ TWI,

// čüčÄą┤ą░ ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ ą▓čüąĄ ą┐čĆąĖąĮąĖą╝ą░ąĄą╝čŗąĄ ą┤ą░ąĮąĮčŗąĄ

u8 TWI_SINGLEBYTE_OUT; // ąōą╗ąŠą▒ą░ą╗čīąĮąŠąĄ čģčĆą░ąĮąĖą╗ąĖčēąĄ ą┤ą╗čÅ ąŠą┤ąĮąŠą│ąŠ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄą╝ąŠą│ąŠ ą▒ą░ą╣čéą░.

u8* pTWI_DATA_OUT; // ąōą╗ąŠą▒ą░ą╗čīąĮčŗą╣ čāą║ą░ąĘą░č鹥ą╗čī ąĮą░ ą┤ą░ąĮąĮčŗąĄ TWI.

// ą×čéčüčÄą┤ą░ ą▒ąĄčĆčāčéčüčÅ ą▓čüąĄ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗąĄ ą┤ą░ąĮąĮčŗąĄ

u8 TWI_DATA_LEN; // ąōą╗ąŠą▒ą░ą╗čīąĮą░čÅ ą┐ąĄčĆąĄą╝ąĄąĮąĮą░čÅ ą┤ą╗čÅ čģčĆą░ąĮąĄąĮąĖčÅ ą║ąŠą╗ąĖč湥čüčéą▓ą░

// ąŠčéą┐čĆą░ą▓ą╗čÅąĄą╝čŗčģ ąĖą╗ąĖ ą┐čĆąĖąĮąĖą╝ą░ąĄą╝čŗčģ ą▒ą░ą╣čé

// č鹥ą║čāčēąĄą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ TWI.

u8 WORD_ADDR; // ąōą╗ąŠą▒ą░ą╗čīąĮą░čÅ ą┐ąĄčĆąĄą╝ąĄąĮąĮą░čÅ ą┤ą╗čÅ čüą╗ąŠą▓ą░ ą░ą┤čĆąĄčüą░ čÅč湥ą╣ą║ąĖ

// ą║ ą║ąŠč鹊čĆąŠą╣ ą▒čāą┤ąĄčé ąŠčüčāčēąĄčüčéą▓ą╗ąĄąĮ ą┤ąŠčüčéčāą┐ ą▓ čüą╗ąĄą┤čāčÄčēąĄą╣ ą┐ąĄčĆąĄą┤ą░č湥

//u32 FRAC_BITS; // ą£ąĄč鹊ą┤ ą▓čŗčćąĖčüą╗ąĄąĮąĖčÅ čü ą┐ą╗ą░ą▓ą░čÄčēąĄą╣ ąĘą░ą┐čÅč鹊ą╣ ą┤ą▓ąŠą╣ąĮąŠą╣ č鹊čćąĮąŠčüčéąĖ.

//-----------------------------------------------------------------------------

// SetBits

//-----------------------------------------------------------------------------

// ąÆąŠąĘą▓čĆą░čēą░ąĄą╝ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ: unsigned char

// ą¤ą░čĆą░ą╝ąĄčéčĆčŗ:

// 1) unsigned char original - ąŠčĆąĖą│ąĖąĮą░ą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą╣, ą║ąŠč鹊čĆą░čÅ ą▒čāą┤ąĄčé

// ąĖąĘą╝ąĄąĮąĄąĮą░

//

// 2) unsigned char reset_mask - čüąŠą┤ąĄčƹȹĖ ą╝ą░čüą║čā ą▒ąĖčé, ą║ąŠč鹊čĆčŗąĄ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čüą▒čĆąŠčłąĄąĮčŗ

// ą▓ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą╣ original.

//

// 3) unsigned char new_val - čüąŠą┤ąĄčƹȹĖčé ą╝ą░čüą║čā ą▒ąĖčé, ą║ąŠč鹊čĆčŗąĄ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ

// ą▓ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą╣ original.

//

// ąŁčéą░ čäčāąĮą║čåąĖčÅ čāčüčéą░ąĮąŠą▓ąĖčé ąĮčāąČąĮčŗąĄ ą▒ąĖčéčŗ ą▓ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą╣ unsigned char.

static u8 SetBits(u8 original, u8 reset_mask, u8 new_val)

{

return (( original & reset_mask ) | new_val );

}

//-----------------------------------------------------------------------------

// ReadStartUpConfig

//-----------------------------------------------------------------------------

// ąÆąŠąĘą▓čĆą░čēą░ąĄą╝ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ: ąĮąĄčé

// ą¤ą░čĆą░ą╝ąĄčéčĆčŗ: ąĮąĄčé

//

// ą¦ąĖčéą░ąĄčé čüčéą░čĆč鹊ą▓ąŠąĄ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ čĆąĄą│ąĖčüčéčĆąŠą▓ RFREQ, HSDIV ąĖ N1, ąĖ ą▓čŗčćąĖčüą╗čÅąĄčé

// čćą░čüč鹊čéčā ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ ą║ą▓ą░čĆčåąĄą▓ąŠą│ąŠ ą│ąĄąĮąĄčĆą░č鹊čĆą░ (FXTAL).

void ReadStartUpConfiguration (void)

{

u8 regval = 0x01;

twi_write_bytes(135, 1, ®val);// ąŚą░ą┐ąĖčüčī 0x01 ą▓ čĆąĄą│ąĖčüčéčĆ 135. ąŁč鹊 ą┐čĆąĖą▓ąĄą┤ąĄčé

// ą║ ą║ąŠą┐ąĖčĆąŠą▓ą░ąĮąĖčÄ ą▒ąĖčé ąĖąĘ NVM ą▓ RAM. ą¤ąŠą┤čĆąŠą▒ąĮąŠčüčéąĖ

// ą┐ąŠ čĆąĄą│ąĖčüčéčĆčā 135 čüą╝. ą▓ ą┤ą░čéą░čłąĖč鹥 Si57x/598/599.

// ą¦č鹥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆąŠą▓ 7..12 čüąĖąĮč鹥ąĘą░č鹊čĆąŠą▓ Si57x/598/599.

// REG[0] čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé čĆąĄą│ąĖčüčéčĆčā 7 čāčüčéčĆąŠą╣čüčéą▓ą░

// REG[5] čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé čĆąĄą│ąĖčüčéčĆčā 12 čāčüčéčĆąŠą╣čüčéą▓ą░

twi_read_bytes(7, 6, REG);

// ą¤ąŠą╗čāč湥ąĮąĖąĄ ąĘąĮą░č湥ąĮąĖčÅ fo INITIAL_HSDIV ąĖąĘ REG[0]:

INITIAL_HSDIV = ((REG[0] & 0xE0) >> 5) + 4;

// ąöąŠą▒ą░ą▓ą╗čÅąĄčéčüčÅ 4, ą┐ąŠč鹊ą╝čā čćč鹊 ą▒ąĖčéčŗ "000" čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčé HSDIV 4, čé. ąĄ. ąĖą╝ąĄąĄčéčüčÅ

// čüą╝ąĄčēąĄąĮąĖąĄ 4. ąĪą╝. ąŠą┐ąĖčüą░ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ 7 ą▓ ą┤ą░čéą░čłąĖč鹥 Si570.

INITIAL_N1 = (( REG[0] & 0x1F ) << 2 ) + (( REG[1] & 0xC0 ) >> 6 );

// ą¤ąŠą╗čāč湥ąĮąĖąĄ ą║ąŠčĆčĆąĄą║čéąĮąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ INITIAL_N1 ą┐čāč鹥ą╝ ą┤ąŠą▒ą░ą▓ą╗ąĄąĮąĖčÅ

//čćą░čüč鹥ą╣ REG[0] ąĖ REG[1]:

if(INITIAL_N1 == 0)

{

INITIAL_N1 = 1; // ąŁč鹊 ą│čĆą░ąĮąĖčćąĮčŗą╣ čüą╗čāčćą░ą╣ ą┤ą╗čÅ N1

}

else if((INITIAL_N1 & 1) != 0)

{

INITIAL_N1 = INITIAL_N1 + 1; // ą¤ąŠ ą┤ą░čéą░čłąĖčéčā ąĮąĄą┤ąŠą┐čāčüčéąĖą╝čŗąĄ ąĮąĄč湥čéąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ

// ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąŠą║čĆčāą│ą╗ąĄąĮčŗ ą▓ą▓ąĄčĆčģ ą┤ąŠ ą┐ąŠą╗čāč湥ąĮąĖčÅ

// ą▒ą╗ąĖąČą░ą╣čłąĄą│ąŠ č湥čéąĮąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ.

}

// ą£ąĄč鹊ą┤ ą▓čŗčćąĖčüą╗ąĄąĮąĖčÅ čü ą┐ą╗ą░ą▓ą░čÄčēąĄą╣ ąĘą░ą┐čÅč鹊ą╣ ą┤ą▓ąŠą╣ąĮąŠą╣ č鹊čćąĮąŠčüčéąĖ.

// ą¤čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ RFREQ: čĆąĄą║ąŠąĮčüčéčĆčāą║čåąĖčÅ ąĖąĘ čĆąĄą│ąĖčüčéčĆąŠą▓ ą┤čĆąŠą▒ąĮąŠą╣ čćą░čüčéąĖ (ą▒ąĖčéčŗ 0..28)

// (ą┤ą╗čÅ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠą╣ č鹊čćąĮąŠčüčéąĖ čŹč鹊čé ą╝ąĄč鹊ą┤ čéčĆąĄą▒čāąĄčé čćąĖčüąĄą╗ čü ą┐ą╗ą░ą▓ą░čÄčēąĄą╣ ąĘą░ą┐čÅč鹊ą╣

// ą┤ą▓ąŠą╣ąĮąŠą╣ č鹊čćąĮąŠčüčéąĖ)

/* FRAC_BITS = (( REG[2] & 0xF ) * POW_2_24 );

FRAC_BITS = FRAC_BITS + (REG[3] * POW_2_16);

FRAC_BITS = FRAC_BITS + (REG[4] * 256);

FRAC_BITS = FRAC_BITS + REG[5];

RFREQ = FRAC_BITS;

RFREQ = RFREQ / POW_2_28;

*/

// ą¦č鹥ąĮąĖąĄ ąĖąĘąĮą░čćą░ą╗čīąĮąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ RFREQ. 34-ą▒ąĖčéąĮąŠąĄ čćąĖčüą╗ąŠ ą┐ąŠą╝ąĄčēą░ąĄčéčüčÅ ą▓ 32 ą▒ąĖčéą░čģ

// ą┐čāč鹥ą╝ ąĖą│ąĮąŠčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą╝ą╗ą░ą┤čłąĖčģ 2 ą▒ąĖčé.

INITIAL_RFREQ_LONG = ( REG[1] & 0x3F );

INITIAL_RFREQ_LONG = (INITIAL_RFREQ_LONG << 8) + ( REG[2] );

INITIAL_RFREQ_LONG = (INITIAL_RFREQ_LONG << 8) + ( REG[3] );

INITIAL_RFREQ_LONG = (INITIAL_RFREQ_LONG << 8) + ( REG[4] );

INITIAL_RFREQ_LONG = (INITIAL_RFREQ_LONG << 6) + ( REG[5] >> 2 );

// ą¤čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ RFREQ: čĆąĄą║ąŠąĮčüčéčĆčāą║čåąĖčÅ ąĖąĘ čĆąĄą│ąĖčüčéčĆąŠą▓ čåąĄą╗ąŠą╣ čćą░čüčéąĖ.

RFREQ = RFREQ + ( (( REG[1] & 0x3F ) << 4 ) + (( REG[2] & 0xF0 ) >> 4 ) );

// ąÆčŗčćąĖčüą╗ąĄąĮąĖąĄ čćą░čüč鹊čéčŗ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ ą║ą▓ą░čĆčåąĄą▓ąŠą│ąŠ ą│ąĄąĮąĄčĆą░č鹊čĆą░ (FXTAL):

FXTAL = (FOUT0 * INITIAL_N1 * INITIAL_HSDIV) / RFREQ; //MHz

}

//-----------------------------------------------------------------------------

// RunFreqProg

//-----------------------------------------------------------------------------

// ąÆąŠąĘą▓čĆą░čēą░ąĄą╝ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ: ąĮąĄčé

// ą¤ą░čĆą░ą╝ąĄčéčĆčŗ: čćą░čüč鹊čéą░ ą▓ ą╝ąĄą│ą░ą│ąĄčĆčåą░čģ

//

// ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ Si570 ą┤ą╗čÅ ą▓čŗą▓ąŠą┤ą░ ąĮčāąČąĮąŠą╣ čćą░čüč鹊čéčŗ.

void RunFreqProg (float freq)

{

u8 i; // ąÆčĆąĄą╝ąĄąĮąĮą░čÅ ą┐ąĄčĆąĄą╝ąĄąĮąĮą░čÅ čüč湥čéčćąĖą║ą░, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ą░čÅ ą▓ čåąĖą║ą╗ą░čģ for.

u8 n1; // ąÆčŗčģąŠą┤ąĮąŠą╣ ą┤ąĄą╗ąĖč鹥ą╗čī, ą║ąŠč鹊čĆčŗą╣ ą╝ąŠą┤ąĖčäąĖčåąĖčĆčāąĄčéčüčÅ ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ

// ą▓ ą▓čŗčćąĖčüą╗ąĄąĮąĖąĖ ąĮąŠą▓ąŠą│ąŠ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéą░ RFREQ

u8 hsdiv; // ąÆčŗčģąŠą┤ąĮąŠą╣ ą┤ąĄą╗ąĖč鹥ą╗čī, ą║ąŠč鹊čĆčŗą╣ ą╝ąŠą┤ąĖčäąĖčåąĖčĆčāąĄčéčüčÅ ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ

// ą▓ ą▓čŗčćąĖčüą╗ąĄąĮąĖąĖ ąĮąŠą▓ąŠą│ąŠ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéą░ RFREQ

bool validCombo; // ążą╗ą░ą│, ą║ąŠč鹊čĆčŗą╣ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▓ 1, ąĄčüą╗ąĖ ą┤ąŠą┐čāčüčéąĖą╝ą░čÅ

// ą║ąŠą╝ą▒ąĖąĮą░čåąĖčÅ N1 ąĖ HSDIV ąĮą░ą╣ą┤ąĄąĮą░

u8 tmpreg;

u16 divider_max; // ą£ą░ą║čüąĖą╝ą░ą╗čīąĮčŗą╣ ą┤ąĄą╗ąĖč鹥ą╗čī ą┤ą╗čÅ ą║ąŠą╝ą▒ąĖąĮą░čåąĖąĖ HSDIV ąĖ N1

u16 curr_div; // ą£ąĖąĮąĖą╝ą░ą╗čīąĮčŗą╣ ą┤ąĄą╗ąĖč鹥ą╗čī ą┤ą╗čÅ ą║ąŠą╝ą▒ąĖąĮą░čåąĖąĖ HSDIV ąĖ N1

// u16 whole; // ąśčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓ ą╝ąĄč鹊ą┤ąĄ čćąĖčüąĄą╗ čü ą┐ą╗ą░ą▓ą░čÄčēąĄą╣ ąĘą░ą┐čÅč鹊ą╣

//ą┤ą▓ąŠą╣ąĮąŠą╣ č鹊čćąĮąŠčüčéąĖ

u32 final_rfreq_long;// ąÜąŠąĮąĄčćąĮčŗą╣ REFREQ, ą║ąŠč鹊čĆčŗą╣ ąŠčéą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ą▓ Si57x/598/599

float curr_n1; // ąśčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą▓čŗčćąĖčüą╗ąĄąĮąĖčÅ ą║ąŠąĮąĄčćąĮąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ N1

float n1_tmp; // ą┤ą╗čÅ ąŠčéą┐čĆą░ą▓ą║ąĖ ą▓ Si570

float ratio = 0; // ąæčāą┤ąĄčé čģčĆą░ąĮąĖčéčī ą║ąŠąĮąĄčćąĮąŠąĄ čüąŠąŠčéąĮąŠčłąĄąĮąĖąĄ ą┤ą╗čÅ čāą╝ąĮąŠąČąĄąĮąĖčÅ

// ąĮą░čćą░ą╗čīąĮąŠą│ąŠ REFREQ ą▓ ą┐čĆąŠčåąĄčüčüąĄ ą┤ąŠčüčéąĖąČąĄąĮąĖčÅ ą║ąŠąĮąĄčćąĮąŠą│ąŠ RFREQ

// ą¤ąŠąĖčüą║ ą┤ąĄą╗ąĖč鹥ą╗ąĄą╣ (ą┐ąŠą╗čāč湥ąĮąĖąĄ max ąĖ min ą┤ąĖą░ą┐ą░ąĘąŠąĮą░ ą┤ąĄą╗ąĖč鹥ą╗čÅ ą┤ą╗čÅ

// ą║ąŠą╝ą▒ąĖąĮą░čåąĖąĖ HSDIV ąĖ N1):

divider_max = floorf(FDCO_MAX / freq);

curr_div = ceil(FDCO_MIN / freq);

validCombo = 0;

while (curr_div <= divider_max)

{

// ą┐čĆąŠą▓ąĄčĆą║ą░ ą▓čüąĄčģ ąĘąĮą░č湥ąĮąĖą╣ HSDIV čüąŠ čüą╗ąĄą┤čāčÄčēąĖą╝ curr_div

for(i=0; i < 6; i++)

{

// ą┐ąŠą╗čāč湥ąĮąĖąĄ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ ą▓ąŠąĘą╝ąŠąČąĮąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ n1

hsdiv = HSDIV[i];

curr_n1 = (float)(curr_div) / (float)(hsdiv);

// ą¤čĆąŠą▓ąĄčĆą║ą░: ąĄčüą╗ąĖ curr_n1 čåąĄą╗ąŠąĄ ąĖ č湥čéąĮąŠąĄ čćąĖčüą╗ąŠ, ąĖą╗ąĖ ąĄą┤ąĖąĮąĖčåą░,

// č鹊 čŹč鹊 ą▒čāą┤ąĄčé ą┤ąŠą┐čāčüčéąĖą╝čŗą╝ ą▓ą░čĆąĖą░ąĮč鹊ą╝ ą┤ąĄą╗ąĖč鹥ą╗čÅ ą┤ą╗čÅ ąĮąŠą▓ąŠą╣ čćą░čüč鹊čéčŗ

n1_tmp = floorf(curr_n1);

n1_tmp = curr_n1 - n1_tmp;

if(n1_tmp == 0.0) // č鹊 curr_n1 čÅą▓ą╗čÅąĄčéčüčÅ čåąĄą╗čŗą╝ čćąĖčüą╗ąŠą╝

{

n1 = (u8) curr_n1;

if( (n1 == 1) || ((n1 & 1) == 0) ) // č鹊 ą▓čŗčćąĖčüą╗ąĄąĮąĮčŗą╣ N1 čÅą▓ą╗čÅąĄčéčüčÅ

{ // ą╗ąĖą▒ąŠ 1, ą╗ąĖą▒ąŠ č湥čéąĮčŗą╝ čćąĖčüą╗ąŠą╝

validCombo = 1;

}

}

if(validCombo == 1) break; // ąöąĄą╗ąĖč鹥ą╗čī ą▒čŗą╗ ąĮą░ą╣ą┤ąĄąĮ, ą▓čŗčģąŠą┤ ąĖąĘ čåąĖą║ą╗ą░

}

if(validCombo == 1) break; // ąöąĄą╗ąĖč鹥ą╗čī ą▒čŗą╗ ąĮą░ą╣ą┤ąĄąĮ, ą▓čŗčģąŠą┤ ąĖąĘ čåąĖą║ą╗ą░

curr_div = curr_div + 1; // ąĢčüą╗ąĖ ą┤ąŠą┐čāčüčéąĖą╝čŗą╣ ą┤ąĄą╗ąĖč鹥ą╗čī ąĮąĄ ąĮą░ą╣ą┤ąĄąĮ,

// č鹊 ąĖąĮą║čĆąĄą╝ąĄąĮčé curr_div ąĖ ą┐ąŠą▓č鹊čĆ č鹥ą╗ą░ čåąĖą║ą╗ą░

}

// ąĢčüą╗ąĖ ą▓ čŹč鹊ą╝ ą╝ąĄčüč鹥 validCombo == 0, č鹊 ąŠčłąĖą▒ą║ą░ ą▓ ą▓čŗčćąĖčüą╗ąĄąĮąĖčÅčģ

// ą¤čĆąŠą▓ąĄčĆčīč鹥, ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÄčé ą╗ąĖ FOUT0 ąĖ FOUT1 ą┤ąŠą┐čāčüčéąĖą╝čŗąĄ

// čćą░čüč鹊čéčŗ.

// ąÆčŗčćąĖčüą╗ąĄąĮąĖąĄ ąĮąŠą▓ąŠą│ąŠ RFREQ

RFREQ = (freq * n1 * hsdiv) / FXTAL;

// RFREQ čāą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ą║ą░ą║ unsigned long, ą▓ čŹč鹊ą╝ č乊čĆą╝ą░č鹥

// ą┤ąŠčüčéčāą┐ąĮąŠ č鹊ą╗čīą║ąŠ 32 ą▒ąĖčéą░. ąÆ čāčüčéčĆąŠą╣čüčéą▓ąĄ čüąĖąĮč鹥ąĘą░č鹊čĆą░

// RFREQ ąĖą╝ąĄąĄčé č鹊čćąĮąŠčüčéčī 34 ą▒ąĖčéą░. ąØčāąČąĮčŗ č鹊ą╗čīą║ąŠ 34 ą▒ąĖčéą░ ąĖąĘ 38,

// ą┐ąŠč鹊ą╝čā čćč鹊 RFREQ ąĮą░čģąŠą┤ąĖčéčüčÅ ą╝ąĄąČą┤čā 42.0 ąĖ 50.0 ą┤ą╗čÅ

// čćą░čüč鹊čéčŗ fxtal = 114.285MHz (ąĮąŠą╝ąĖąĮą░ą╗)

ratio = freq / FOUT0; // ąĪčéą░čĆą░ąĄą╝čüčÅ čāą┤ąĄčƹȹ░čéčī čüąŠąŠčéąĮąŠčłąĄąĮąĖąĄ ąŠą║ąŠą╗ąŠ 1

// ą┤ą╗čÅ čüąŠčģčĆą░ąĮąĄąĮąĖčÅ č鹊čćąĮąŠčüčéąĖ

ratio = ratio * (((float)n1)/((float)INITIAL_N1));

ratio = ratio * (((float)hsdiv)/((float)INITIAL_HSDIV));

final_rfreq_long = ratio * INITIAL_RFREQ_LONG; // ąÆčŗčćąĖčüą╗ąĄąĮąĖąĄ ą║ąŠąĮąĄčćąĮąŠą│ąŠ RFREQ

// ąŚąĮą░č湥ąĮąĖąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ąŠą│ąŠ ąŠčéąĮąŠčłąĄąĮąĖčÅ ą▓čŗčćąĖčüą╗ąĄąĮąŠ ą▓čŗčłąĄ

for(i = 0; i < 6; i++)

{

REG[i] = 0; // ąŠčćąĖčüčéą║ą░ čĆąĄą│ąĖčüčéčĆąŠą▓

}

hsdiv = hsdiv - 4; // ąÆčŗčćč鹥ą╝ 4 ąĖąĘ-ąĘą░ čüą╝ąĄčēąĄąĮąĖčÅ HSDIV.

// ąØą░ą┐čĆąĖą╝ąĄčĆ: "000" ąŠč鹊ą▒čĆą░ąČą░ąĄčéčüčÅ ąĮą░ 4, "001" ąŠč鹊ą▒čĆą░ąČą░ąĄčéčüčÅ ąĮą░ 5

// ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▓ąĄčĆčģąĮąĖčģ 3 ą▒ąĖčé REG[0], ą║ąŠč鹊čĆčŗąĄ ą▒čāą┤čāčé čüąŠąŠčéą▓ąĄčéčüčéą▓ąŠą▓ą░čéčī

// čĆąĄą│ąĖčüčéčĆčā 7 čüąĖąĮč鹥ąĘą░č鹊čĆąŠą▓ Si57x/598/599

REG[0] = (hsdiv << 5);

// ą¤čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ąĮąŠą▓ąŠą│ąŠ N1 ą▓ ą┤ą▓ąŠąĖčćąĮąŠąĄ ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮąĖąĄ

if(n1 == 1)

{

n1 = 0; // ąÜčĆą░ą╣ąĮąĖą╣ čüą╗čāčćą░ą╣ ą┤ą╗čÅ N1. ąĢčüą╗ąĖ N1=1, č鹊 čŹč鹊 ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčéčüčÅ

// ą║ą░ą║ "00000000".

}

else if((n1 & 1) == 0)

{

n1 = n1 - 1; // ąĢčüą╗ąĖ n1 č湥čéąĮąŠąĄ, ąŠą║čĆčāą│ą╗ąĄąĮąĖąĄ ą▓ąĮąĖąĘ ą┤ąŠ ą▒ą╗ąĖąČą░ą╣čłąĄą│ąŠ

// ąĮąĄč湥čéąĮąŠą│ąŠ čćąĖčüą╗ą░. ą¤ąŠą┤čĆąŠą▒ąĮąŠčüčéąĖ čüą╝. ą▓ ą┤ą░čéą░čłąĖč鹥

// čüąĖąĮč鹥ąĘą░č鹊čĆą░ Si57x/598/599.

}

// ąŚą░ą┐ąĖčüčī ąĮąŠą▓čŗčģ ą║ąŠčĆčĆąĄą║čéąĮčŗčģ ąĘąĮą░č湥ąĮąĖą╣ ą▓ REG[0] .. REG[6].

// ą×ąĮąĖ ą▒čāą┤čāčé ąŠčéą┐čĆą░ą▓ą╗ąĄąĮčŗ ą▓ Si57x/598/599, ąĖ ą▒čāą┤ąĄčé ąŠą▒ąĮąŠą▓ą╗ąĄąĮą░

// ą▓čŗčģąŠą┤ąĮą░čÅ čćą░čüč鹊čéą░.

REG[0] = SetBits(REG[0], 0xE0, (n1 >> 2)); // ąŻčüčéą░ąĮąŠą▓ą║ą░ čćą░čüčéąĖ N1 ą▓ REG[0]

REG[1] = (n1 & 3) << 6; // ąŻčüčéą░ąĮąŠą▓ą║ą░ čćą░čüčéąĖ N1 ą▓ REG[1]

// ąŚą░ą┐ąĖčüčī ąĮąŠą▓ąŠą╣ ą▓ąĄčĆčüąĖąĖ RFREQ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ čĆąĄą│ąĖčüčéčĆčŗ

REG[1] = REG[1] | (final_rfreq_long >> 30);

REG[2] = final_rfreq_long >> 22;

REG[3] = final_rfreq_long >> 14;

REG[4] = final_rfreq_long >> 6;

REG[5] = final_rfreq_long << 2;

/*

// ą£ąĄč鹊ą┤ ą┤ą▓ąŠą╣ąĮąŠą╣ č鹊čćąĮąŠčüčéąĖ čćąĖčüą╗ąĄ čü ą┐ą╗ą░ą▓ą░čÄčēąĄą╣ ąĘą░ą┐čÅč鹊ą╣.

// ą¤čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ąĮąŠą▓ąŠą│ąŠ RFREQ ą▓ ą┤ą▓ąŠąĖčćąĮąŠąĄ ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮąĖąĄ.

// ą×čéą┤ąĄą╗ąĄąĮąĖąĄ čåąĄą╗ąŠą╣ čćą░čüčéąĖ.

whole = FLOORF(RFREQ);

// ą¤ąŠą╗čāč湥ąĮąĖąĄ ą┤ą▓ąŠąĖčćąĮąŠą│ąŠ ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮąĖčÅ ą┤čĆąŠą▒ąĮąŠą╣ čćą░čüčéąĖ.

FRAC_BITS = FLOORF((RFREQ - whole) * POW_2_28);

// ąŻčüčéą░ąĮąŠą▓ą║ą░ čĆąĄą│ąĖčüčéčĆąŠą▓ 12..10, ą┤ąĄą╗ą░čÅ frac_bits ą╝ąĄąĮčīčłąĄ

// ą┐čāč鹥ą╝ čüą┤ą▓ąĖą│ą░ ą║ą░ąČą┤čŗą╣ čĆą░ąĘ ą┐ąŠčüą╗ąĄą┤ąĮąĖčģ 8 ą▒ąĖčé

for(i=5; i >=3; i--)

{

REG[i] = FRAC_BITS & 0xFF;

FRAC_BITS = FRAC_BITS >> 8;

}

// ąŻčüčéą░ąĮąŠą▓ą║ą░ ą┐ąŠčüą╗ąĄą┤ąĮąĖčģ 4 ą▒ąĖčé ą┤čĆąŠą▒ąĮąŠą╣ čćą░čüčéąĖ čĆąĄą│ąĖčüčéčĆą░ 9.

REG[2] = SetBits(REG[2], 0xF0, (FRAC_BITS & 0xF));

// ąŻčüčéą░ąĮąŠą▓ą║ą░ čåąĄą╗ąŠą╣ čćą░čüčéąĖ RFREQ ą▓ čĆąĄą│ąĖčüčéčĆą░čģ 8 ąĖ 9

REG[2] = SetBits(REG[2], 0x0F, (whole & 0xF) << 4);

REG[1] = SetBits(REG[1], 0xC0, (whole >> 4) & 0x3F);

*/

twi_read_bytes(137, 1, &tmpreg); // ą¦č鹥ąĮąĖąĄ č鹥ą║čāčēąĄą│ąŠ čüąŠčüč鹊čÅąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ 137

tmpreg |= 0x10; //ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▓ čŹč鹊ą╝ čĆąĄą│ąĖčüčéčĆąĄ ą▒ąĖčéą░ DCO.

twi_write_bytes(137, 1, &tmpreg);// ąŁč鹊 ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī čüą┤ąĄą╗ą░ąĮąŠ, čćč鹊ą▒čŗ ąŠą▒ąĮąŠą▓ąĖčéčī

// čĆąĄą│ąĖčüčéčĆčŗ 7..12 čüąĖąĮč鹥ąĘą░č鹊čĆąŠą▓ Si57x/598/599.

twi_write_bytes(7, 6, REG); // ąŚą░ą┐ąĖčüčī ąĮąŠą▓čŗčģ ąĘąĮą░č湥ąĮąĖą╣ ą▓ čĆąĄą│ąĖčüčéčĆčŗ 7..12.

twi_read_bytes(137, 1, &tmpreg); // ą¦č鹥ąĮąĖąĄ č鹥ą║čāčēąĄą│ąŠ čüąŠčüč鹊čÅąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ 137

tmpreg &= 0xEF; // ą×čćąĖčüčéą║ą░ ą▒ąĖčéą░ DCO.

twi_write_bytes(137, 1, &tmpreg);//

tmpreg = 0x40; // ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖčéą░ NewFreq, čćč鹊ą▒čŗ ąŠą┐ąŠą▓ąĄčüčéąĖčéčī

twi_write_bytes(135, 1, &tmpreg);// čüąĖčüč鹥ą╝čā DPSLL, čćč鹊 ą┐čĆąĖą╝ąĄąĮąĄąĮą░ ąĮąŠą▓ą░čÅ

// ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ čćą░čüč鹊čéčŗ

}

[ąĪą╗ąŠą▓ą░čĆąĖą║]

LSB Least Significant Bit, čüą░ą╝čŗą╣ ą╝ą╗ą░ą┤čłąĖą╣ ąĘąĮą░čćą░čēąĖą╣ ą▒ąĖčé.

MSB Most Significant Bit, čüą░ą╝čŗą╣ čüčéą░čĆčłąĖą╣ ąĘąĮą░čćą░čēąĖą╣ ą▒ąĖčé.

SLA SLave Address, TWI-ą░ą┤čĆąĄčü ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ąĮą░ čłąĖąĮąĄ.

TWI Two Wire Interface, ą┤ą▓čāčģą┐čĆąŠą▓ąŠą┤ąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü. ąóąŠ ąČąĄ čüą░ą╝ąŠąĄ, čćč鹊 ąĖ I2C.

[ąĪčüčŗą╗ą║ąĖ]

1. avr-libc: Example using the two-wire interface (TWI) site:nongnu.org.

2. ą¤ąŠą┤ą║ą╗čÄč湥ąĮąĖąĄ RTC DS1307 ą║ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčā AVR.

3. AVR245: ą║ąŠą┤ąŠą▓čŗą╣ ąĘą░ą╝ąŠą║ čü ą║ą╗ą░ą▓ąĖą░čéčāčĆąŠą╣ 4x4 ąĖ I2C LCD.

4. UM10204 I2C-bus specification and user manual site:nxp.com.

5. Si570, Si571: ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗą╣ č湥čĆąĄąĘ I2C ą│ąĄąĮąĄčĆą░č鹊čĆ XO/VCXO.

6. ą£ą░ą║ąĄčéąĮą░čÅ ą┐ą╗ą░čéą░ AVR-USB32U4.

7. AN334: ą┐čĆąĖą╝ąĄčĆ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ čüąĖąĮč鹥ąĘą░č鹊čĆąŠą▓ Si57X, Si598, Si599.

8. ąøčÄą▒ąĖč鹥ą╗čīčüą║ąĖą╣ ą┐čĆąĖąĄą╝ąĮąĖą║ čŹčéą░ą╗ąŠąĮąĮąŠą╣ čćą░čüč鹊čéčŗ. |