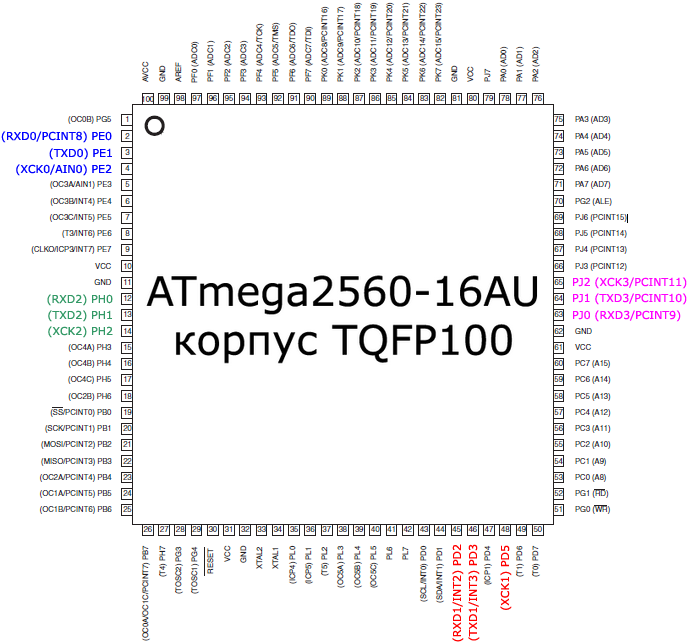

ąÜą░ą║ čāąČąĄ čāą┐ąŠą╝ąĖąĮą░ą╗ąŠčüčī, čā ATmega2560 ąĖą╝ąĄąĄčéčüčÅ 4 ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ą┐ąŠčĆčéą░ USART: USART0, USART1, USART2 ąĖ USART3, ą║ąŠč鹊čĆčŗąĄ čäąĖą║čüąĖčĆąŠą▓ą░ąĮąŠ ą┐čĆąĖą▓čÅąĘą░ąĮčŗ ą║ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗą╝ ąĮąŠąČą║ą░ą╝ ą║ąŠčĆą┐čāčüą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░. ąó. ąĄ. ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗą╣ ą▓čŗą▓ąŠą┤ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą╝ąŠąČąĄčé čĆą░ą▒ąŠčéą░čéčī ą╗ąĖą▒ąŠ ą┐čĆąŠčüč鹊 ą║ą░ą║ ą┐ąŠčĆčé ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░, ą╗ąĖą▒ąŠ ą║ą░ą║ ą░ą┐ą┐ą░čĆą░čéąĮčŗą╣ ą▓čģąŠą┤ ąĖą╗ąĖ ą▓čŗčģąŠą┤ ąĖąĮč鹥čĆč乥ą╣čüą░ USART. ąÆčüąĄ ąĘą░ą▓ąĖčüąĖčé ąŠčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą╣ ąĮą░čüčéčĆąŠą╣ą║ąĖ - ą┤ą░ąĮąĮčŗčģ, ą║ąŠč鹊čĆčŗąĄ ąÆčŗ ąĘą░ą┐ąĖčłąĄč鹥 ą▓ čāą┐čĆą░ą▓ą╗čÅčÄčēąĖąĄ čĆąĄą│ąĖčüčéčĆčŗ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░. ąÆ čéą░ą▒ą╗ąĖčåąĄ ąĖ ąĮą░ ą║ą░čĆčéąĖąĮą║ąĄ ą┐ąŠą║ą░ąĘą░ąĮą░ ą┐čĆąĖą▓čÅąĘą║ą░ ą░ą┐ą┐ą░čĆą░čéčāčĆčŗ USART ą║ ą▓čŗą▓ąŠą┤ą░ą╝ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░.

| ąśą╝čÅ |

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖčÅ |

ąĀąĄą│ąĖčüčéčĆčŗ |

ą¤ąŠčĆčéčŗ RXD, TXD, XCK |

| USART0 |

UDRE0, TXC0, RXC0 |

UDR0, UCSR0A, UCSR0B, UCSR0C, UBRR0L, UBRR0H |

PE0, PE1, PE2 |

| USART1 |

UDRE1, TXC1, RXC1 |

UDR1, UCSR1A, UCSR1B, UCSR1C, UBRR1L, UBRR1H |

PD2, PD3, PD5 |

| USART2 |

UDRE2, TXC2, RXC2 |

UDR2, UCSR2A, UCSR2B, UCSR2C, UBRR2L, UBRR2H |

PH0, PH1, PH2 |

| USART3 |

UDRE3, TXC3, RXC3 |

UDR3, UCSR3A, UCSR3B, UCSR3C, UBRR3L, UBRR3H |

PJ0, PJ1, PJ2 |

ą¤ąŠčĆčéčŗ USART ąŠą▒ą╗ą░ą┤ą░čÄčé čüą╗ąĄą┤čāčÄčēąĖą╝ąĖ ąŠčüąĮąŠą▓ąĮčŗą╝ąĖ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčÅą╝ąĖ:

ŌĆó ą¤ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé ą┐ąŠą╗ąĮčŗą╣ ą┤čāą┐ą╗ąĄą║čü (ąĖą╝ąĄčÄčé ąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗąĄ ą░ą┐ą┐ą░čĆą░čéąĮčŗąĄ ą▒čāč乥čĆčŗ ą┐čĆąĖąĄą╝ą░ ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ).

ŌĆó ą£ąŠą│čāčé čĆą░ą▒ąŠčéą░čéčī ą░čüąĖąĮčģčĆąŠąĮąĮąŠ ąĖ čüąĖąĮčģčĆąŠąĮąĮąŠ.

ŌĆó ąÆ čüąĖąĮčģčĆąŠąĮąĮąŠą╝ čĆąĄąČąĖą╝ąĄ ą╝ąŠą│čāčé ą╗ąĖą▒ąŠ ą▓čŗčĆą░ą▒ą░čéčŗą▓ą░čéčī čéą░ą║čéčŗ, ą╗ąĖą▒ąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą▓ąĮąĄčłąĮąĄąĄ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ (Master or Slave Clocked Synchronous Operation).

ŌĆó ąōąĄąĮąĄčĆą░č鹊čĆ čüą║ąŠčĆąŠčüčéąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ, ąĮą░čüčéčĆą░ąĖą▓ą░ąĄą╝čŗą╣ čü ą▓čŗčüąŠą║ąŠą╣ č鹊čćąĮąŠčüčéčīčÄ (High Resolution Baud Rate Generator).

ŌĆó ą¤ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé čĆą░ąĘą╝ąĄčĆčŗ čäčĆąĄą╣ą╝ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖąĘ 5, 6, 7, 8 ąĖą╗ąĖ 9 ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ ąĖ 1 ąĖą╗ąĖ 2 čüč鹊ą┐ąŠą▓čŗčģ ą▒ąĖčéą░.

ŌĆó ąÉą┐ą┐ą░čĆą░čéąĮą░čÅ ą┐ąŠą┤ą┤ąĄčƹȹ║ą░ ą│ąĄąĮąĄčĆą░čåąĖąĖ ąĖ ą┐čĆąŠą▓ąĄčĆą║ąĖ ąĮą░ ąĮąĄč湥čéąĮąŠčüčéčī ąĖą╗ąĖ č湥čéąĮąŠčüčéčī (Odd or Even Parity).

ŌĆó ąöąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ą┐ąŠč鹥čĆąĖ ą┤ą░ąĮąĮčŗčģ ąĮą░ ą┐čĆąĖąĄą╝ąĄ (Data OverRun Detection).

ŌĆó ąöąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ąŠčłąĖą▒ąŠą║ čäčĆąĄą╣ą╝ą░ (Framing Error Detection).

ŌĆó ążąĖą╗čīčéčĆą░čåąĖčÅ ą┐ąŠą╝ąĄčģ (Noise Filtering) čü ą┐ąŠą╝ąŠčēčīčÄ čåąĖčäčĆąŠą▓ąŠą│ąŠ ążąØą¦, ą▓ą║ą╗čÄčćą░čÄčēą░čÅ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ąŠčłąĖą▒ąŠčćąĮąŠą│ąŠ čüčéą░čĆč鹊ą▓ąŠą│ąŠ ą▒ąĖčéą░.

ŌĆó 3 ąŠčéą┤ąĄą╗čīąĮčŗčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ čüąŠą▒čŗčéąĖčÅą╝ TX Complete, TX Data Register Empty ąĖ RX Complete.

ŌĆó ąĀąĄąČąĖą╝ ąŠą▒ą╝ąĄąĮą░ čü ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆą░ą╝ąĖ (Multi-processor Communication Mode).

ŌĆó ąÉčüąĖąĮčģčĆąŠąĮąĮčŗą╣ čĆąĄąČąĖą╝ čü ą┤ą▓ąŠą╣ąĮąŠą╣ čüą║ąŠčĆąŠčüčéčīčÄ (Double Speed Asynchronous Communication Mode).

ąöą╗čÅ čāą╝ąĄąĮčīčłąĄąĮąĖčÅ ąŠą▒čēąĄą│ąŠ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ ą║čĆąĖčüčéą░ą╗ą╗ą░ ąĮąĄąĮčāąČąĮčŗąĄ USARTn ą╝ąŠą│čāčé ą▒čŗčéčī ą┐ąŠą╗ąĮąŠčüčéčīčÄ ą▓čŗą║ą╗čÄč湥ąĮčŗ čü ą┐ąŠą╝ąŠčēčīčÄ ą▒ąĖč鹊ą▓ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čĆąĄą│ąĖčüčéčĆąŠą▓ PRR0 ąĖ PRR1.

ą¤ąŠčĆčé USART0 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓ ą┐ą╗ą░čéą░čģ Arduino Mega 2560 [2] ą┐ąŠą┤ ą░ą┐ą┐ą░čĆą░čéąĮčŗą╣ ą╝ąŠčüčé USB-UART, čćč鹊ą▒čŗ ąŠą▒ąĄčüą┐ąĄčćąĖčéčī čĆą░ą▒ąŠčéčā ąĘą░ą│čĆčāąĘčćąĖą║ą░ ą║ąŠą┤ą░ ąĖ ą┐ąŠą┤ą┤ąĄčƹȹ║čā ąŠčéą╗ą░ą┤ąŠčćąĮąŠą│ąŠ ą▓čŗą▓ąŠą┤ą░ č湥čĆąĄąĘ Serial Monitor.

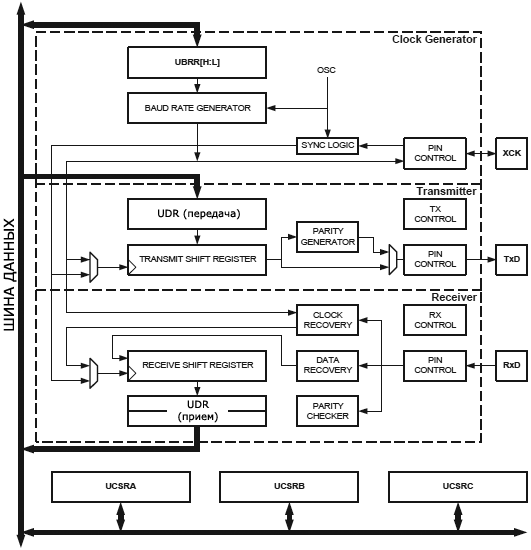

ąĀąĖčü. 22-1. ąæą╗ąŠą║-ą┤ąĖą░ą│čĆą░ą╝ą╝ą░ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ USART.

ąØą░ ą┤ąĖą░ą│čĆą░ą╝ą╝ąĄ ą┐čāąĮą║čéąĖčĆąĮčŗą╝ąĖ ą╗ąĖąĮąĖčÅą╝ąĖ ą▓čŗą┤ąĄą╗ąĄąĮčŗ 3 ąŠčéą┤ąĄą╗čīąĮčŗčģ ą▒ą╗ąŠą║ą░ USART (ą┐ąĄčĆąĄčćąĖčüą╗ąĄąĮąĮčŗąĄ ą┤ą░ą╗ąĄąĄ čüą▓ąĄčĆčģčā ą▓ąĮąĖąĘ): Clock Generator (čéą░ą║č鹊ą▓čŗą╣ ą│ąĄąĮąĄčĆą░č鹊čĆ), Transmitter (ą┐ąĄčĆąĄą┤ą░čéčćąĖą║) ąĖ Receiver (ą┐čĆąĖąĄą╝ąĮąĖą║). ąĀąĄą│ąĖčüčéčĆčŗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąŠą▒čēąĖąĄ ą┤ą╗čÅ ą▓čüąĄčģ čŹčéąĖčģ ą▒ą╗ąŠą║ąŠą▓. ąøąŠą│ąĖą║ą░ Clock Generation čüąŠčüč鹊ąĖčé ąĖąĘ ą╗ąŠą│ąĖą║ąĖ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ą┤ą╗čÅ ą▓ąĮąĄčłąĮąĖčģ čéą░ą║č鹊ą▓ (SYNC LOGIC, ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą╝ čĆąĄąČąĖą╝ąĄ ą┤ą╗čÅ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▒ąĖčé), ąĖ ą│ąĄąĮąĄčĆą░č鹊čĆą░ čüą║ąŠčĆąŠčüčéąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ (BAUD RATE GENERATOR). ąÆčŗą▓ąŠą┤ XCKn (čéą░ą║čéčŗ ą┐ąĄčĆąĄą┤ą░čćąĖ) ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čüąĖąĮčģčĆąŠąĮąĮąŠą│ąŠ čĆąĄąČąĖą╝ą░ čĆą░ą▒ąŠčéčŗ (synchronous transfer mode). ą¤ąĄčĆąĄą┤ą░čéčćąĖą║ čüąŠčüč鹊ąĖčé ąĖąĘ ąŠą┤ąĖąĮąŠčćąĮąŠą│ąŠ ą▒čāč乥čĆą░ ąĘą░ą┐ąĖčüąĖ (UDR), ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░ čüą┤ą▓ąĖą│ą░ (TRANSMIT SHIFT REGISTER), ą│ąĄąĮąĄčĆą░č鹊čĆą░ č湥čéąĮąŠčüčéąĖ (PARITY GENERATOR) ąĖ ą╗ąŠą│ąĖą║ąĖ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ (TX CONTROL) ą┤ą╗čÅ ą┐ąŠą┤ą┤ąĄčƹȹ║ąĖ čĆą░ąĘąĮčŗčģ č乊čĆą╝ą░č鹊ą▓ čäčĆąĄą╣ą╝ą░. ąØą░ą╗ąĖčćąĖąĄ ą░ą┐ą┐ą░čĆą░čéąĮąŠą│ąŠ ą▒čāč乥čĆą░ čäčĆąĄą╣ą╝ą░ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą▓ąĄčüčéąĖ ąĮąĄą┐čĆąĄčĆčŗą▓ąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▒ąĄąĘ ąĘą░ą┤ąĄčƹȹĄą║ ą╝ąĄąČą┤čā ąŠčéą┤ąĄą╗čīąĮčŗą╝ąĖ čäčĆąĄą╣ą╝ą░ą╝ąĖ. ą¤čĆąĖąĄą╝ąĮąĖą║ ąĮą░ąĖą▒ąŠą╗ąĄąĄ čüą╗ąŠąČąĮčŗą╣ čāąĘąĄą╗ USART, ą┐ąŠč鹊ą╝čā čćč鹊 ąŠąĮ ąĖą╝ąĄąĄčé čāąĘą╗čŗ ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖčÅ čéą░ą║č鹊ą▓ (CLOCK RECOVERY) ąĖ ą┤ą░ąĮąĮčŗčģ (DATA RECOVERY), ą║ąŠč鹊čĆčŗąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą│ąŠ ą┐čĆąĖąĄą╝ą░ ą┤ą░ąĮąĮčŗčģ. ąÆ ą┤ąŠą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ čāąĘą╗ą░ą╝ ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖčÅ ą┐čĆąĖąĄą╝ąĮąĖą║ čüąŠą┤ąĄčƹȹĖčé ą▒ą╗ąŠą║ ą┐čĆąŠą▓ąĄčĆą║ąĖ ąĮą░ č湥čéąĮąŠčüčéčī (PARITY CHECKER), ą╗ąŠą│ąĖą║čā čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ (RX CONTROL), čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ ąĖ ą┤ą▓čāčģčāčĆąŠą▓ąĮąĄą▓čŗą╣ ą▒čāč乥čĆ ą┐čĆąĖąĄą╝ą░ (UDR). ą¤čĆąĖąĄą╝ąĮąĖą║ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ąŠą┤ąĖąĮą░ą║ąŠą▓čŗą╣ č乊čĆą╝ą░čé čäčĆąĄą╣ą╝ą░, ą║ąŠč鹊čĆčŗą╣ ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą┐ąĄčĆąĄą┤ą░čéčćąĖą║, ąĖ ą╝ąŠąČąĄčé ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░čéčī ąŠčłąĖą▒ą║čā čäčĆąĄą╣ą╝ą░ (Frame Error), čüąŠą▒čŗčéąĖąĄ ą┐ąŠč鹥čĆąĖ ą┤ą░ąĮąĮčŗčģ ąĮą░ ą┐čĆąĖąĄą╝ąĄ (Data OverRun) ąĖ ąŠčłąĖą▒ą║čā č湥čéąĮąŠčüčéąĖ (Parity Error). ą£ąŠą┤čāą╗čī PIN CONTROL čāą┐čĆą░ą▓ą╗čÅąĄčé ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄą╝ ą┐ąŠčĆčéą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ - ąĖą╗ąĖ čŹč鹊čé ą▓čŗą▓ąŠą┤ čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ąŠą▒čŗčćąĮčŗą╣ ą┐ąŠčĆčé ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ GPIO, ąĖą╗ąĖ ąŠąĮ ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą║ ą░ą┐ą┐ą░čĆą░čéčāčĆąĄ USART ąĖ ą▓čŗą┐ąŠą╗ąĮčÅąĄčé čüą┐ąĄčåąĖą░ą╗čīąĮčāčÄ čäčāąĮą║čåąĖčÄ.

[ąōąĄąĮąĄčĆą░čåąĖčÅ čéą░ą║č鹊ą▓]

ąøąŠą│ąĖą║ą░ ą│ąĄąĮąĄčĆą░čåąĖąĖ čéą░ą║č鹊ą▓ čüąĖąĮč鹥ąĘąĖčĆčāąĄčé ą▒ą░ąĘąŠą▓čāčÄ čćą░čüč鹊čéčā čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ ąĖ ą┐čĆąĖąĄą╝ąĮąĖą║ą░. The USARTn ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé 4 čĆąĄąČąĖą╝ą░ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ: ąĮąŠčĆą╝ą░ą╗čīąĮčŗą╣ ą░čüąĖąĮčģčĆąŠąĮąĮčŗą╣ (Normal asynchronous), ą░čüąĖąĮčģčĆąŠąĮąĮčŗą╣ ą┤ą▓ąŠą╣ąĮąŠą╣ čüą║ąŠčĆąŠčüčéąĖ (Double Speed asynchronous), čüąĖąĮčģčĆąŠąĮąĮčŗą╣ ą│ą╗ą░ą▓ąĮčŗą╣ (Master synchronous) ąĖ čüąĖąĮčģčĆąŠąĮąĮčŗą╣ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗą╣ (Slave synchronous). ąæąĖčé UMSELn ą▓ USART Control and Status Register C (UCSRnC) ą▓čŗą▒ąĖčĆą░ąĄčé ą╝ąĄąČą┤čā ą░čüąĖąĮčģčĆąŠąĮąĮčŗą╝ ąĖ čüąĖąĮčģčĆąŠąĮąĮčŗą╝ čĆąĄąČąĖą╝ą░ą╝ąĖ. ąöą▓ąŠą╣ąĮą░čÅ čüą║ąŠčĆąŠčüčéčī (ą┐čĆąĖą╝ąĄąĮąĖą╝ąŠ č鹊ą╗čīą║ąŠ ą║ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą╝čā čĆąĄąČąĖą╝čā) čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ą▒ąĖč鹊ą╝ U2Xn, ąĮą░čģąŠą┤čÅčēąĄą╝čüčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ UCSRnA. ąÜąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čüąĖąĮčģčĆąŠąĮąĮčŗą╣ čĆąĄąČąĖą╝ (UMSELn = 1), čĆąĄą│ąĖčüčéčĆ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ (Data Direction Register, DDR) ą┤ą╗čÅ ą▓čŗą▓ąŠą┤ą░ XCKn ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé, ą║ą░ą║ąĖą╝ ą▒čāą┤ąĄčé čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ą┤ą╗čÅ čüąĖąĮčģčĆąŠąĮąĮąŠą│ąŠ čĆąĄąČąĖą╝ą░: ą▓ąĮčāčéčĆąĄąĮąĮąĖą╝ (Master mode) ąĖą╗ąĖ ą▓ąĮąĄčłąĮąĖą╝ (Slave mode). ąÆčŗą▓ąŠą┤ XCKn ą░ą║čéąĖą▓ąĄąĮ č鹊ą╗čīą║ąŠ ą▓ ą┐čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ čüąĖąĮčģčĆąŠąĮąĮąŠą│ąŠ čĆąĄąČąĖą╝ą░, ą▓ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą╝ čĆąĄąČąĖą╝ąĄ ąŠąĮ čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą┐čĆąŠčüč鹊ą╣ ą┐ąŠčĆčé GPIO.

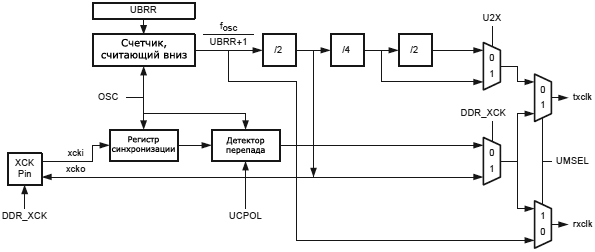

ąĀąĖčü. 22-2. ąæą╗ąŠą║-ą┤ąĖą░ą│čĆą░ą╝ą╝ą░ ą╗ąŠą│ąĖą║ąĖ ą│ąĄąĮąĄčĆą░čåąĖąĖ čéą░ą║č鹊ą▓ USART.

ą×ą┐ąĖčüą░ąĮąĖąĄ čüąĖą│ąĮą░ą╗ąŠą▓:

txclk čéą░ą║čéčŗ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ (ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čüąĖą│ąĮą░ą╗).

rxclk ą▒ą░ąĘąŠą▓čŗąĄ čéą░ą║čéčŗ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ (ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čüąĖą│ąĮą░ą╗).

xcki ą▓ą▓ąŠą┤ ąŠčé ą▓čŗą▓ąŠą┤ą░ XCK (ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čüąĖą│ąĮą░ą╗). ąśčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ ą▓ čüąĖąĮčģčĆąŠąĮąĮąŠą╝ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą╝ čĆąĄąČąĖą╝ąĄ (synchronous slave operation).

xcko ą▓čŗčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ čéą░ą║č鹊ą▓ ą┤ą╗čÅ ą┐ąŠą┤ą░čćąĖ ąĮą░ ą▓čŗą▓ąŠą┤ XCK (ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čüąĖą│ąĮą░ą╗). ąśčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ ą▓ čüąĖąĮčģčĆąŠąĮąĮąŠą╝ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą╝ čĆąĄąČąĖą╝ąĄ (synchronous master operation).

fOSC čćą░čüč鹊čéą░ ą▓čŗą▓ąŠą┤ą░ XTAL (System Clock, čüąĖčüč鹥ą╝ąĮą░čÅ čćą░čüč鹊čéą░).

DDR_XCK čĆą░ąĘčĆčÅą┤ čĆąĄą│ąĖčüčéčĆą░ DDRX, čāą┐čĆą░ą▓ą╗čÅčÄčēąĖą╣ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝ čĆą░ą▒ąŠčéčŗ ąĮąŠąČą║ąĖ ą┐ąŠčĆčéą░ (ą▓čģąŠą┤ ąĖą╗ąĖ ą▓čŗčģąŠą┤).

Baud Rate Generator, ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ ą│ąĄąĮąĄčĆą░čåąĖčÅ čéą░ą║č鹊ą▓. ąōąĄąĮąĄčĆą░čåąĖčÅ čéą░ą║č鹊ą▓ ą▓ąĮčāčéčĆąĖ čćąĖą┐ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą│ąŠ ąĖ čüąĖąĮčģčĆąŠąĮąĮąŠą│ąŠ čĆąĄąČąĖą╝ąŠą▓ čĆą░ą▒ąŠčéčŗ. USART Baud Rate Register (UBRRn) ąĖ čüčćąĖčéą░čÄčēąĖą╣ ą▓ąĮąĖąĘ čüč湥čéčćąĖą║ (Prescaling Down-Counter) ą┐ąŠą┤ą║ą╗čÄč湥ąĮčŗ ą║ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝ąŠą╝čā ą┐čĆąĄčüą║ą░ą╗ąĄčĆčā, ąĖą╗ąĖ ą┤čĆčāą│ąĖą╝ąĖ čüą╗ąŠą▓ą░ą╝ąĖ ą║ ą│ąĄąĮąĄčĆą░č鹊čĆčā čüą║ąŠčĆąŠčüčéąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ (Baud Rate Generator). ą×ą▒čĆą░čéąĮąŠ-čüčćąĖčéą░čÄčēąĖą╣ čüč湥čéčćąĖą║ (down-counter), čĆą░ą▒ąŠčéą░čÄčēąĄą╣ ąĮą░ čüąĖčüč鹥ą╝ąĮąŠą╣ čćą░čüč鹊č鹥 (fOSC), ą║ą░ąČą┤čŗą╣ čĆą░ąĘ ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄą╝ ąĖąĘ UBRRn, ą║ąŠą│ą┤ą░ čüč湥čéčćąĖą║ ą┤ąŠčüčéąĖą│ą░ąĄčé ąĮčāą╗čÅ, ąĖą╗ąĖ ą║ąŠą│ą┤ą░ ąĘą░ą┐ąĖčüą░ąĮ čĆąĄą│ąĖčüčéčĆ UBRRLn. ąÆ čŹč鹊čé ą╝ąŠą╝ąĄąĮčé ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ čéą░ą║č鹊ą▓čŗą╣ ąĖą╝ą┐čāą╗čīčü ą┤ą╗čÅ USART, ą┐ąŠčÅą▓ą╗čÅčÄčēąĖą╣čüčÅ ąĮą░ ą▓čŗčģąŠą┤ąĄ Baud Rate Generator (= fOSC/(UBRRn+1)). ą¤ąĄčĆąĄą┤ą░čéčćąĖą║ ą┤ąĄą╗ąĖčé ą▓čŗčģąŠą┤ąĮčāčÄ čéą░ą║č鹊ą▓čāčÄ čćą░čüč鹊čéčŗ Baud Rate Generator ąĮą░ 2, 8 ąĖą╗ąĖ 16 ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čĆąĄąČąĖą╝ą░. ąÆčŗčģąŠą┤ Baud Rate Generator ąĮą░ą┐čĆčÅą╝čāčÄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ ąĖ čāąĘą╗ąŠą▓ ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ. ą×ą┤ąĮą░ą║ąŠ čāąĘą╗čŗ ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖčÅ ąĖčüą┐ąŠą╗čīąĘčāčÄčé ą╝ą░čłąĖąĮčā čüąŠčüč鹊čÅąĮąĖą╣ ąĖąĘ 2, 8 ąĖą╗ąĖ 16 čüąŠčüč鹊čÅąĮąĖą╣ ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čĆąĄąČąĖą╝ą░, čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮąŠą│ąŠ ą▒ąĖčéą░ą╝ąĖ UMSELn, U2Xn ąĖ DDR_XCKn.

ąóą░ą▒ą╗ąĖčåą░ 22-1 čüąŠą┤ąĄčƹȹĖčé ą▓čŗčĆą░ąČąĄąĮąĖčÅ ą┤ą╗čÅ ą▓čŗčćąĖčüą╗ąĄąĮąĖčÅ čüą║ąŠčĆąŠčüčéąĖ baud rate (ą▓ ą▒ąĖčéą░čģ ąĮą░ čüąĄą║čāąĮą┤čā) ąĖ ą┤ą╗čÅ ą▓čŗčćąĖčüą╗ąĄąĮąĖčÅ ąĘąĮą░č湥ąĮąĖčÅ UBRRn ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ čĆąĄąČąĖą╝ą░ čĆą░ą▒ąŠčéčŗ, ą║ąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą│ąĄąĮąĄčĆąĖčĆčāąĄą╝čŗą╣ ą▓ąĮčāčéčĆąĖ ąĖčüč鹊čćąĮąĖą║ čéą░ą║č鹊ą▓.

ąóą░ą▒ą╗. 22-1. ążąŠčĆą╝čāą╗čŗ ą┤ą╗čÅ čĆą░čüč湥čéą░ čüą║ąŠčĆąŠčüčéąĖ ąĖ ąĮą░čüčéčĆąŠąĄą║ ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čĆąĄąČąĖą╝ą░.

| ąĀąĄąČąĖą╝ |

ąĪą║ąŠčĆąŠčüčéčī(1) |

UBRR |

| ąÉčüąĖąĮčģčĆąŠąĮąĮčŗą╣ ąĮąŠčĆą╝ą░ą╗čīąĮčŗą╣ (U2XN = 0) |

fOSC

BAUD = -----------------------

16 * (UBRRn+1) |

fOSC

UBRRn = ---------------- - 1

16 * BAUD |

| ąÉčüąĖąĮčģčĆąŠąĮąĮčŗą╣ ą┤ą▓ąŠą╣ąĮąŠą╣ čüą║ąŠčĆąŠčüčéąĖ (U2XN = 1) |

fOSC

BAUD = -----------------------

8 * (UBRRn+1) |

fOSC

UBRRn = --------------- - 1

8 * BAUD |

| ąĪąĖąĮčģčĆąŠąĮąĮčŗą╣ ą│ą╗ą░ą▓ąĮčŗą╣ |

fOSC

BAUD = -----------------------

2 * (UBRRn+1) |

fOSC

UBRRn = --------------- - 1

2 * BAUD |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ (1). ąĪą║ąŠčĆąŠčüčéčī ą┐ąĄčĆąĄą┤ą░čćąĖ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮą░ ą║ą░ą║ čüą║ąŠčĆąŠčüčéčī čüą╗ąĄą┤ąŠą▓ą░ąĮąĖčÅ ą▒ąĖčé ą▓ čüąĄą║čāąĮą┤čā (baud rate, bit per second, bps).

BAUD Baud rate (ą▓ ą▒ąĖčéą░čģ/čüąĄą║, bps).

fOSC čüąĖčüč鹥ą╝ąĮą░čÅ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ (System Oscillator clock frequency).

UBRRn čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ čĆąĄą│ąĖčüčéčĆąŠą▓ UBRRHn ąĖ UBRRLn (0-4095).

ąØąĄą║ąŠč鹊čĆčŗąĄ ą┐čĆąĖą╝ąĄčĆčŗ ąĘąĮą░č湥ąĮąĖą╣ UBRRn ą┤ą╗čÅ čĆą░ąĘąĮčŗčģ čéą░ą║č鹊ą▓čŗčģ čćą░čüč鹊čé ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą╝ąŠąČąĮąŠ ąĮą░ą╣čéąĖ ą▓ čéą░ą▒ą╗ąĖčåąĄ 22-9.

Double Speed Operation (U2Xn). ąĪą║ąŠčĆąŠčüčéčī ą┐ąĄčĆąĄą┤ą░čćąĖ ą╝ąŠąČąĄčé ą▒čŗčéčī čāą┤ą▓ąŠąĄąĮą░ (čŹč鹊 ą┐ąŠčłą╗ąŠ ąĄčēąĄ ąŠčé ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ čüąĄčĆąĖąĖ MCS51) ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ U2Xn ą▓ čĆąĄą│ąĖčüčéčĆąĄ UCSRnA. ąŻčüčéą░ąĮąŠą▓ą║ą░ čŹč鹊ą│ąŠ ą▒ąĖčéą░ ą┤ą░ąĄčé čŹčäč乥ą║čé č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą╣ čĆą░ą▒ąŠčéčŗ USART, čüą▒čĆąŠčüčīč鹥 čŹč鹊čé ą▒ąĖčé ą▓ 0 ą┤ą╗čÅ čüąĖąĮčģčĆąŠąĮąĮąŠą│ąŠ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖčÅ.

ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖčéą░ U2Xn čāą╝ąĄąĮčīčłąĖčé ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ą┤ąĄą╗ąĄąĮąĖčÅ čüąĖąĮč鹥ąĘą░č鹊čĆą░ čüą║ąŠčĆąŠčüčéąĖ čü 16 ą┤ąŠ 8, čćč鹊 čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé čāą┤ą▓ąŠąĄąĮąĖčÄ čüą║ąŠčĆąŠčüčéąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖ ą┐čĆąĖąĄą╝ą░ ą┤ą╗čÅ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą│ąŠ čĆąĄąČąĖą╝ą░. ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 ą┐čĆąĖąĄą╝ąĮąĖą║ ą▓ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ą▒čāą┤ąĄčé ą┤ąĄą╗ą░čéčī ą▓ 2 čĆą░ąĘą░ ą╝ąĄąĮčīčłąĄ ą▓čŗą▒ąŠčĆąŠą║ ą┐čĆąĖ ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖąĖ ą┤ą░ąĮąĮčŗčģ ąĖ čéą░ą║č鹊ą▓ (ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▓čŗą▒ąŠčĆąŠą║ čéą░ą║ąČąĄ čāą╝ąĄąĮčīčłąĖčéčīčüčÅ čü 16 ą┤ąŠ 8), čéą░ą║ čćč鹊 ą┤ą╗čÅ čāą┤ą▓ąŠąĄąĮąĖčÅ čüą║ąŠčĆąŠčüčéąĖ čü čüąŠčģčĆą░ąĮąĄąĮąĖąĄą╝ č鹊čćąĮąŠą╣ čāčüčéą░ąĮąŠą▓ą║ąĖ čüą║ąŠčĆąŠčüčéąĖ ą┐ąŠąĮą░ą┤ąŠą▒ąĖčéčüčÅ ą▒ąŠą╗ąĄąĄ č鹊čćąĮąŠ ą▓čŗą┤ąĄčƹȹĖą▓ą░čéčī čüąĖčüč鹥ą╝ąĮčāčÄ čćą░čüč鹊čéčā. ąŁč鹊 ą▓ą░ąČąĮąŠ ą┤ą╗čÅ ą┐čĆąĖąĄą╝ąĮąĖą║ą░, ą░ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ ąĮąĄčé ąĮąĖą║ą░ą║ąĖčģ ą┐čĆąŠą▒ą╗ąĄą╝.

ąÆąĮąĄčłąĮąĄąĄ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ. ąśčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą▓ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą╝ čüąĖąĮčģčĆąŠąĮąĮąŠą╝ čĆąĄąČąĖą╝ąĄ čĆą░ą▒ąŠčéčŗ. ąÆąĮąĄčłąĮąĖąĄ čéą░ą║čéčŗ ą┐ąŠčüčéčāą┐ą░čÄčé ąŠčé ą▓čŗą▓ąŠą┤ą░ XCKn (čüą╝. čĆąĖčü. 22-2), ąĖ ąĖčģ ąĘąĮą░č湥ąĮąĖčÅ ą▓čŗą▒ąĖčĆą░čÄčéčüčÅ čĆąĄą│ąĖčüčéčĆąŠą╝ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ, čćč鹊ą▒čŗ čāą╝ąĄąĮčīčłąĖčéčī čłą░ąĮčüčŗ ąĮąĄčüčéą░ą▒ąĖą╗čīąĮąŠčüčéąĖ. ąÆčŗčģąŠą┤ čĆąĄą│ąĖčüčéčĆą░ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ąĘą░č鹥ą╝ ą┤ąŠą╗ąČąĄąĮ ą┐ąŠčüčéčāą┐ąĖčéčī čüąĮą░čćą░ą╗ą░ ąĮą░ ą┤ąĄč鹥ą║č鹊čĆ ą┐ąĄčĆąĄą┐ą░ą┤ą░, ą┐ąĄčĆąĄą┤ č鹥ą╝ ą║ą░ą║ čüąĖą│ąĮą░ą╗ čéą░ą║č鹊ą▓ ą╝ąŠąČąĮąŠ ą▒čŗą╗ąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą▓ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ąĄ ąĖ ą┐čĆąĖąĄą╝ąĮąĖą║ąĄ. ąŁč鹊čé ą┐čĆąŠčåąĄčüčü ąĘą░ąĮąĖą╝ą░ąĄčé ą┤ą▓ą░ čåąĖą║ą╗ą░ čüąĖčüč鹥ą╝ąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ CPU, čéą░ą║ čćč鹊 čŹčéą░ ąĘą░ą┤ąĄčƹȹ║ą░ ąŠą│čĆą░ąĮąĖčćąĖą▓ą░ąĄčé ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠ ą▓ąŠąĘą╝ąŠąČąĮčāčÄ čéą░ą║č鹊ą▓čāčÄ čćą░čüč鹊čéčā XCKn:

fOSC

fXCK < ------

4

ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 fOSC ąĘą░ą▓ąĖčüąĖčé ąŠčé čüčéą░ą▒ąĖą╗čīąĮąŠčüčéąĖ čćą░čüč鹊čéčŗ ąĖčüč鹊čćąĮąĖą║ą░ čüąĖčüč鹥ą╝ąĮčŗčģ čéą░ą║č鹊ą▓. ąóą░ą║ čćč鹊 čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ą┤ąŠą▒ą░ą▓ąĖčéčī ąĮąĄą║ąŠč鹊čĆčŗą╣ ąĘą░ą┐ą░čü, čćč鹊ą▒čŗ ąĖąĘą▒ąĄąČą░čéčī ą▓ąŠąĘą╝ąŠąČąĮčŗčģ ą┐ąŠč鹥čĆčī ą┤ą░ąĮąĮčŗčģ ąĖąĘ-ąĘą░ ąĮąĄč鹊čćąĮąŠą╣ čāčüčéą░ąĮąŠą▓ą║ąĖ čüąĖčüč鹥ą╝ąĮąŠą╣ čćą░čüč鹊čéčŗ.

ąĪąĖąĮčģčĆąŠąĮąĮčŗą╣ čĆąĄąČąĖą╝ čĆą░ą▒ąŠčéčŗ. ąÜąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čüąĖąĮčģčĆąŠąĮąĮčŗą╣ čĆąĄąČąĖą╝ (UMSELn = 1), ą▓čŗą▓ąŠą┤ XCKn ą▒čāą┤ąĄčé ą░ą┐ą┐ą░čĆą░čéąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą╗ąĖą▒ąŠ ą║ą░ą║ ą▓čģąŠą┤ čéą░ą║č鹊ą▓ (ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ), ą╗ąĖą▒ąŠ ą║ą░ą║ ą▓čŗčģąŠą┤ čéą░ą║č鹊ą▓ (ą│ą╗ą░ą▓ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ). ąŚą░ą▓ąĖčüąĖą╝ąŠčüčéčī ą╝ąĄąČą┤čā ą┐ąĄčĆąĄą┐ą░ą┤ą░ą╝ąĖ čéą░ą║č鹊ą▓ ąĖ ą▓čŗą▒ąŠčĆą║ąŠą╣ ą┤ą░ąĮąĮčŗčģ ąŠčüčéą░ąĄčéčüčÅ č鹊ą╣ ąČąĄ čüą░ą╝ąŠą╣. ąæą░ąĘąŠą▓čŗą╣ ą┐čĆąĖąĮčåąĖą┐ čüąŠčüč鹊ąĖčé ą▓ č鹊ą╝, čćč鹊 ą▓čģąŠą┤ ą┤ą░ąĮąĮčŗčģ (on RxDn) ąŠčåąĖčäčĆąŠą▓čŗą▓ą░ąĄčéčüčÅ ą┐ąŠ ą┐čĆąŠčéąĖą▓ąŠą┐ąŠą╗ąŠąČąĮąŠą╝čā ą┐ąĄčĆąĄą┐ą░ą┤čā XCKn, ą║ąŠą│ą┤ą░ ą╝ąĄąĮčÅąĄčéčüčÅ čüąĖą│ąĮą░ą╗ ąĮą░ ą▓čŗčģąŠą┤ąĄ ą┤ą░ąĮąĮčŗčģ (TxDn).

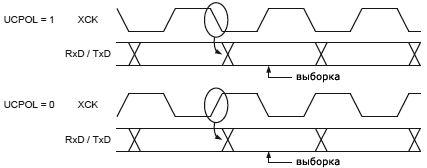

ąĀąĖčü. 22-3. ąÆčĆąĄą╝ąĄąĮąĮčŗąĄ ą┤ąĖą░ą│čĆą░ą╝ą╝čŗ XCKn čüąĖąĮčģčĆąŠąĮąĮąŠą│ąŠ čĆąĄąČąĖą╝ą░.

ąæąĖčé UCRSC čĆąĄą│ąĖčüčéčĆą░ UCPOLn ą▓čŗą▒ąĄčĆąĄčé, ą║ą░ą║ąŠą╣ ąĖąĘ ą┐ąĄčĆąĄą┐ą░ą┤ąŠą▓ XCKn ą▒čāą┤ąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą║ąĖ ą┤ą░ąĮąĮčŗčģ, ą░ ą║ą░ą║ąŠą╣ ą┤ą╗čÅ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ą▓čŗčģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ. ąÜą░ą║ ą▓ąĖą┤ąĮąŠ ąĖąĘ čĆąĖčü. 22-3, ą║ąŠą│ą┤ą░ UCPOLn == 0 ą┤ą░ąĮąĮčŗąĄ ąĖąĘą╝ąĄąĮčÅčÄčéčüčÅ ą┐ąŠ ąĮą░čĆą░čüčéą░ąĮąĖčÄ XCKn ąĖ ą▓čŗą▒ąŠčĆą║ą░ ą┤ąĄą╗ą░ąĄčéčüčÅ ą┐ąŠ čüą┐ą░ą┤čā XCKn. ąś ąĮą░ąŠą▒ąŠčĆąŠčé, ąĄčüą╗ąĖ UCPOLn == 1, č鹊 ą┤ą░ąĮąĮčŗąĄ ąĖąĘą╝ąĄąĮčÅčÄčéčüčÅ ą┐ąŠ čüą┐ą░ą┤čā XCKn, ąĖ ąĖčģ ą▓čŗą▒ąŠčĆą║ą░ ą┤ąĄą╗ą░ąĄčéčüčÅ ą┐ąŠ čäčĆąŠąĮčéčā XCKn.

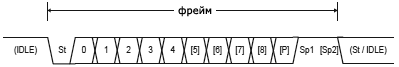

ążąŠčĆą╝ą░čéčŗ čäčĆąĄą╣ą╝ą░. ą¤ąŠą┤ čäčĆąĄą╣ą╝ąŠą╝ ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčéčüčÅ čŹą╗ąĄą╝ąĄąĮčéą░čĆąĮą░čÅ, ąĮąĄą┤ąĄą╗ąĖą╝ą░čÅ ą┐ąŠčüčŗą╗ą║ą░ ąĖąĘ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ą▒ąĖčé. ąÆąŠ čäčĆąĄą╣ą╝ ą▓čģąŠą┤čÅčé ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗą╣ ą║ąŠą┤ čüąĖą╝ą▓ąŠą╗ą░ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą╣ čĆą░ąĘčĆčÅą┤ąĮąŠčüčéąĖ, ą▒ąĖčéčŗ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ (ą▒ąĖčéčŗ start ąĖ stop), ąĖ ąŠą┐čåąĖąŠąĮą░ą╗čīąĮąŠ ą▒ąĖčé č湥čéąĮąŠčüčéąĖ ą┤ą╗čÅ ą┐čĆąŠą▓ąĄčĆą║ąĖ ąĮą░ ąŠčłąĖą▒ą║čā. USART ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąĮą░čüčéčĆąŠąĖčéčī ą▓čüąĄ 30 ą║ąŠą╝ą▒ąĖąĮą░čåąĖą╣ čüą╗ąĄą┤čāčÄčēąĖčģ ą┤ąŠą┐čāčüčéąĖą╝čŗčģ č乊čĆą╝ą░č鹊ą▓ čäčĆąĄą╣ą╝ą░:

ŌĆó 1 start-ą▒ąĖčé

ŌĆó 5, 6, 7, 8 ąĖą╗ąĖ 9 ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ

ŌĆó no, even ąĖą╗ąĖ odd parity bit (ą▒ąĖčé č湥čéąĮąŠčüčéąĖ ąŠčéčüčāčéčüčéą▓čāąĄčé, ąĄčüčéčī ą▒ąĖčé č湥čéąĮąŠčüčéąĖ ąĖą╗ąĖ ąĄčüčéčī ą▒ąĖčé ąĮąĄč湥čéąĮąŠčüčéąĖ)

ŌĆó 1 ąĖą╗ąĖ 2 stop-ą▒ąĖčéą░

ążčĆąĄą╣ą╝ ąĮą░čćąĖąĮą░ąĄčéčüčÅ start-ą▒ąĖč鹊ą╝, ąĘą░ ą║ąŠč鹊čĆčŗą╝ ąĖą┤ąĄčé ąĮą░ąĖą╝ąĄąĮąĄąĄ ąĘąĮą░čćą░čēąĖą╣ ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ (least significant bit, LSB). ąöą░ą╗ąĄąĄ ąĖą┤čāčé ą▒ąĖčéčŗ ą┤ą░ąĮąĮčŗčģ (ą▓čüąĄą│ąŠ ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠčé 5 ą┤ąŠ 9), ąĘą░ą▓ąĄčĆčłą░čÄčēąĖą╣ ą▒ąĖčé čüą░ą╝čŗą╣ čüčéą░čĆčłąĖą╣ (most significant bit, MSB). ąĢčüą╗ąĖ ą║ąŠąĮčéčĆąŠą╗čī č湥čéąĮąŠčüčéąĖ čĆą░ąĘčĆąĄčłąĄąĮ, č鹊 ąĘą░ ą▒ąĖčéą░ą╝ąĖ ą┤ą░ąĮąĮčŗčģ, ą┐ąĄčĆąĄą┤ stop-ą▒ąĖčéą░ą╝ąĖ ą▓čüčéą░ą▓ą╗čÅąĄčéčüčÅ ą▒ąĖčé č湥čéąĮąŠčüčéąĖ. ąÜąŠą│ą┤ą░ ą▓ąĄčüčī čäčĆąĄą╣ą╝ ą┐ąĄčĆąĄą┤ą░ąĮ, č鹊 ąĘą░ ąĮąĖą╝ ą╝ąŠąČąĄčé ą▒ąĄąĘ ąĘą░ą┤ąĄčƹȹ║ąĖ čüą╗ąĄą┤ąŠą▓ą░čéčī čüą╗ąĄą┤čāčÄčēąĖą╣ čäčĆąĄą╣ą╝, ąĖą╗ąĖ ąŠą▒ą╝ąĄąĮ ą╝ąŠąČąĄčé ą┐ąĄčĆąĄą╣čéąĖ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ąŠąČąĖą┤ą░ąĮąĖčÅ idle, ą║ąŠą│ą┤ą░ ąĮą░ ą╗ąĖąĮąĖąĖ ą┤ą░ąĮąĮčŗčģ čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 1. ąØą░ čĆąĖčü. 22-4 ą┐ąŠą║ą░ąĘą░ąĮčŗ ą▓ąŠąĘą╝ąŠąČąĮčŗąĄ ą║ąŠą╝ą▒ąĖąĮą░čåąĖąĖ č乊čĆą╝ą░č鹊ą▓ čäčĆąĄą╣ą╝ą░. ąæąĖčéčŗ ą▓ąĮčāčéčĆąĖ ą║ą▓ą░ą┤čĆą░čéąĮčŗčģ čüą║ąŠą▒ąŠą║ ąŠą┐čåąĖąŠąĮą░ą╗čīąĮčŗ.

ąĀąĖčü. 22-4. ążąŠčĆą╝ą░čéčŗ čäčĆąĄą╣ą╝ą░.

St start-ą▒ąĖčé, ą▓čüąĄą│ą┤ą░ ą╗ąŠą│. 0.

(n) ą▒ąĖčéčŗ ą┤ą░ąĮąĮčŗčģ (ąŠčé 0 ą┤ąŠ 8).

P Parity bit, ą▒ąĖčé č湥čéąĮąŠčüčéąĖ. ą£ąŠąČąĄčé ą▒čŗčéčī ą▒ąĖč鹊ą╝ ąĮąĄč湥čéąĮąŠčüčéąĖ, ąĖą╗ąĖ ą▒ąĖč鹊ą╝ č湥čéąĮąŠčüčéąĖ (odd ąĖą╗ąĖ even, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ąĮą░čüčéčĆąŠą╣ą║ąĖ).

Sp stop-ą▒ąĖčé, ą▓čüąĄą│ą┤ą░ ą╗ąŠą│. 1.

IDLE ąĮąĄčé ą░ą║čéąĖą▓ąĮąŠčüčéąĖ ąĮą░ ą╗ąĖąĮąĖąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ (RxDn ąĖą╗ąĖ TxDn). ąÆ čüąŠčüč鹊čÅąĮąĖąĖ IDLE ąĮą░ ą╗ąĖąĮąĖąĖ ą▓čüąĄą│ą┤ą░ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 1.

ąśčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╣ č乊čĆą╝ą░čé čäčĆąĄą╣ą╝ą░ USART čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▒ąĖčéą░ą╝ąĖ UCSZn2:0, UPMn1:0 ąĖ USBSn ą▓ čĆąĄą│ąĖčüčéčĆą░čģ UCSRnB ąĖ UCSRnC. ą¤čĆąĖąĄą╝ąĮąĖą║ ąĖ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ ąĖčüą┐ąŠą╗čīąĘčāąĄčé ąŠą┤ąĮčā ąĖ čéčā ąČąĄ ąĮą░čüčéčĆąŠą╣ą║čā. ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 ąĖąĘą╝ąĄąĮąĄąĮąĖąĄ ąĮą░čüčéčĆąŠąĄą║ čŹčéąĖčģ ą▒ąĖčé ą▓ąŠ ą▓čĆąĄą╝čÅ ąŠčüčāčēąĄčüčéą▓ą╗ąĄąĮąĖčÅ ą░ą║čéąĖą▓ąĮąŠą│ąŠ ąŠą▒ą╝ąĄąĮą░ ą┐ąŠą▓čĆąĄą┤ąĖčé ą┤ą░ąĮąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ ąĖ ą┐čĆąĖąĄą╝ąĮąĖą║ą░.

ąæąĖčéčŗ čĆą░ąĘą╝ąĄčĆą░ čüąĖą╝ą▓ąŠą╗ą░ USART (UCSZn2:0) ą▓čŗą▒ąĖčĆą░čÄčé ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ ą▓ąŠ čäčĆąĄą╣ą╝ąĄ. ąæąĖčéčŗ čĆąĄąČąĖą╝ą░ č湥čéąĮąŠčüčéąĖ USART Parity mode (UPMn1:0) čĆą░ąĘčĆąĄčłą░čÄčé ąĖ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄčé čéąĖą┐ ą║ąŠąĮčéčĆąŠą╗čÅ č湥čéąĮąŠčüčéąĖ. ąÆčŗą▒ąŠčĆ ą╝ąĄąČą┤čā ąŠą┤ąĮąĖą╝ ąĖą╗ąĖ ą┤ą▓čāą╝čÅ stop-ą▒ąĖčéą░ą╝ąĖ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▒ąĖč鹊ą╝ USART Stop Bit Select (USBSn). ą¤čĆąĖąĄą╝ąĮąĖą║ ąĖą│ąĮąŠčĆąĖčĆčāąĄčé ą▓č鹊čĆąŠą╣ stop-ą▒ąĖčé. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝ FE (Frame Error, ąŠčłąĖą▒ą║ą░ čäčĆąĄą╣ą╝ą░) ą▒čāą┤ąĄčé ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░čéčīčüčÅ ą▓ č鹥čģ čüą╗čāčćą░čÅčģ, ą║ąŠą│ą┤ą░ ą┐ąĄčĆą▓čŗą╣ stop-ą▒ąĖčé čĆą░ą▓ąĄąĮ 0.

ąÆčŗčćąĖčüą╗ąĄąĮąĖąĄ Parity Bit. ąæąĖčé č湥čéąĮąŠčüčéąĖ (parity bit) ą▓čŗčćąĖčüą╗čÅąĄčéčüčÅ čäčāąĮą║čåąĖąĄą╣ ąĖčüą║ą╗čÄčćą░čÄčēąĄąĄ ąśąøąś ąŠčé ą▓čüąĄčģ ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ. ąĢčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą║ąŠąĮčéčĆąŠą╗čī ą┐ąŠ ąĮąĄč湥čéąĮąŠčüčéąĖ (odd parity), č鹊 ą▒ąĄčĆąĄčéčüčÅ čĆąĄąĘčāą╗čīčéą░čé ąĖąĮą▓ąĄčĆčéąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ ąĖčüą║ą╗čÄčćą░čÄčēąĄą│ąŠ ąśąøąś. ąæąĖčé č湥čéąĮąŠčüčéąĖ čĆą░ąĘą╝ąĄčēą░ąĄčéčüčÅ ą╝ąĄąČą┤čā ą┐ąŠčüą╗ąĄą┤ąĮąĖą╝ ą▒ąĖč鹊ą╝ ą┤ą░ąĮąĮčŗčģ ąĖ ą┐ąĄčĆą▓čŗą╝ (ąĖą╗ąĖ ąĄą┤ąĖąĮčüčéą▓ąĄąĮąĮčŗą╝) stop-ą▒ąĖč鹊ą╝ čäčĆąĄą╣ą╝ą░. ąŚą░ą▓ąĖčüąĖą╝ąŠčüčéčī ą╝ąĄąČą┤čā ą▒ąĖč鹊ą╝ č湥čéąĮąŠčüčéąĖ ąĖ ą▒ąĖčéą░ą╝ąĖ ą┤ą░ąĮąĮčŗčģ čüą╗ąĄą┤čāčÄčēą░čÅ:

Peven ą▒ąĖčé č湥čéąĮąŠčüčéąĖ, ą║ąŠą│ą┤ą░ ą┤ą╗čÅ ą║ąŠąĮčéčĆąŠą╗čÅ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ č湥čéąĮąŠčüčéčī (even).

Podd ą▒ąĖčé č湥čéąĮąŠčüčéąĖ, ą║ąŠą│ą┤ą░ ą┤ą╗čÅ ą║ąŠąĮčéčĆąŠą╗čÅ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ąĮąĄč湥čéąĮąŠčüčéčī (odd).

dn ą▒ąĖčéčŗ ą┤ą░ąĮąĮčŗčģ (ą▓ ą║ąŠą╗ąĖč湥čüčéą▓ąĄ n) ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ąŠą│ąŠ čüąĖą╝ą▓ąŠą╗ą░.

[ąśąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ USART]

ą¦č鹊ą▒čŗ ą╝ąŠąČąĮąŠ ą▒čŗą╗ąŠ ąĮą░čćą░čéčī ą║ą░ą║ąŠą╣-ą╗ąĖą▒ąŠ ąŠą▒ą╝ąĄąĮ č湥čĆąĄąĘ USART, ąĄą│ąŠ ąĮą░ą┤ąŠ ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆąŠą▓ą░čéčī. ą¤čĆąŠčåąĄčüčü ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ ąŠą▒čŗčćąĮąŠ čüąŠčüč鹊ąĖčé ąĖąĘ ąĮą░čüčéčĆąŠą╣ą║ąĖ čüą║ąŠčĆąŠčüčéąĖ baud rate, čāčüčéą░ąĮąŠą▓ą║ąĖ č乊čĆą╝ą░čéą░ čäčĆąĄą╣ą╝ą░ ąĖ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ ąĖ/ąĖą╗ąĖ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ. ąöą╗čÅ čĆą░ą▒ąŠčéčŗ čü USART č湥čĆąĄąĘ čüąĖčüč鹥ą╝čā ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ (čüą░ą╝čŗą╣ čŹčäč乥ą║čéąĖą▓ąĮčŗą╣ čüą┐ąŠčüąŠą▒ čĆą░ą▒ąŠčéčŗ čü USART) ą┐ąĄčĆąĄą┤ ąĮą░čüčéčĆąŠą╣ą║ąŠą╣ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čüą▒čĆąŠčłąĄąĮ ą│ą╗ąŠą▒ą░ą╗čīąĮčŗą╣ čäą╗ą░ą│ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ (Global Interrupt Flag, I-čäą╗ą░ą│ ą▓ čĆąĄą│ąĖčüčéčĆąĄ SREG), čćč鹊 ąŠąĘąĮą░čćą░ąĄčé ąĘą░ą┐čĆąĄčé ą▓čüąĄčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣.

ą¤ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ą┤ąĄą╗ą░čéčī ą┐ąŠą▓č鹊čĆąĮčāčÄ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÄ čü čåąĄą╗čīčÄ ą┐ąŠą╝ąĄąĮčÅčéčī baud rate ąĖą╗ąĖ č乊čĆą╝ą░čé čäčĆąĄą╣ą╝ą░ ąĮčāąČąĮąŠ čāą▒ąĄą┤ąĖčéčīčüčÅ, čćč鹊 čüąĄą╣čćą░čü ą░ą║čéąĖą▓ąĮąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▓ ą╝ąŠą╝ąĄąĮčé ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ čĆąĄą│ąĖčüčéčĆąŠą▓. ąöą╗čÅ ą┐čĆąŠą▓ąĄčĆą║ąĖ, čćč鹊 ą┐ąĄčĆąĄą┤ą░čćą░ ąĘą░ą▓ąĄčĆčłąĄąĮą░ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ čäą╗ą░ą│ TXCn, ąĖ čäą╗ą░ą│ RXCn ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ č鹊ą│ąŠ, čćč鹊ą▒čŗ čāąĘąĮą░čéčī, ąĄčüčéčī ą╗ąĖ ąĮąĄ ą┐čĆąŠčćąĖčéą░ąĮąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą▓ ą▒čāč乥čĆąĄ ą┐čĆąĖąĄą╝ą░. ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 čäą╗ą░ą│ TXCn ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąŠčćąĖčēąĄąĮ ą┐ąĄčĆąĄą┤ ą║ą░ąČą┤ąŠą╣ ą┐ąĄčĆąĄą┤ą░č湥ą╣ (ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ čĆąĄą│ąĖčüčéčĆ UDRn), ąĄčüą╗ąĖ ąŠąĮ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čü čéą░ą║ąŠą╣ čåąĄą╗čīčÄ.

ąÆ čüą╗ąĄą┤čāčÄčēąĄą╝ ą┐čĆąŠčüč鹊ą╝ ą┐čĆąĖą╝ąĄčĆąĄ ą║ąŠą┤ą░ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ USART ą┐ąŠą║ą░ąĘą░ąĮ ąŠą┤ąĖąĮ ąĖ č鹊čé ąČąĄ čäčāąĮą║čåąĖąŠąĮą░ą╗ ąĮą░ čÅąĘčŗą║ąĄ ą░čüčüąĄą╝ą▒ą╗ąĄčĆą░ ąĖ ą▓ čäčāąĮą║čåąĖąĖ ąĮą░ čÅąĘčŗą║ąĄ C. ą¤čĆąĖą╝ąĄčĆčŗ ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░čÄčé ą░čüąĖąĮčģčĆąŠąĮąĮčŗą╣ čĆąĄąČąĖą╝ čĆą░ą▒ąŠčéčŗ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ ąŠą┐čĆąŠčüą░ (ą▒ąĄąĘ čĆą░ąĘčĆąĄčłąĄąĮąĮčŗčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣) ąĖ čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ č乊čĆą╝ą░čéą░ čäčĆąĄą╣ą╝ą░. ąĪą║ąŠčĆąŠčüčéčī (baud rate) ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčéčüčÅ ą▓ ą▓ąĖą┤ąĄ ą┐ą░čĆą░ą╝ąĄčéčĆą░ čäčāąĮą║čåąĖąĖ. ąöą╗čÅ ą║ąŠą┤ą░ ąĮą░ ą░čüčüąĄą╝ą▒ą╗ąĄčĆąĄ ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčéčüčÅ, čćč鹊 ą┐ą░čĆą░ą╝ąĄčéčĆ baud rate čüąŠčģčĆą░ąĮąĄąĮ ą▓ čĆąĄą│ąĖčüčéčĆąŠą▓čāčÄ ą┐ą░čĆčā r17:r16.

USART_Init:

; čāčüčéą░ąĮąŠą▓ą║ą░ baud rate

sts UBRRnH, r17

sts UBRRnL, r16

ldi r16, (1 << U2Xn)

sts UCRnA, r16

; čĆą░ąĘčĆąĄčłąĖčéčī ą┐čĆąĖąĄą╝ąĮąĖą║ ąĖ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║

ldi r16, (1 << RXENn)|(1 << TXENn)

sts UCSRnB,r16

; čāčüčéą░ąĮąŠą▓ą║ą░ č乊čĆą╝ą░čéą░ čäčĆąĄą╣ą╝ą░: 8data, 1stop bit

ldi r16, (2 << UMSELn)|(3 << UCSZn0)

sts UCSRnC,r16

ret

#define FOSC 1843200 // čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ čüąĖčüč鹥ą╝čŗ

#define BAUD 9600

#define (MYUBRR FOSC/16/BAUD-1)

void main( void )

{

...

USART_Init ( MYUBRR );

...

}

void USART_Init( unsigned int ubrr)

{

/* ąŻčüčéą░ąĮąŠą▓ą║ą░ baud rate */

UBRRH = (unsigned char)(ubrr >> 8);

UBRRL = (unsigned char)ubrr;

/* ąĀą░ąĘčĆąĄčłąĖčéčī ą┐čĆąĖąĄą╝ąĮąĖą║ ąĖ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ */

UCSRB = (1 << RXEN)|(1 << TXEN);

/* ąŻčüčéą░ąĮąŠą▓ą║ą░ č乊čĆą╝ą░čéą░ čäčĆąĄą╣ą╝ą░: 8data, 2stop bit */

UCSRC = (1 << USBS)|(3 << UCSZ0);

}

ąæąŠą╗ąĄąĄ čüą╗ąŠąČąĮčŗąĄ ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ą╝ąŠą│čāčé ą▒čŗčéčī čüą┤ąĄą╗ą░ąĮčŗ čéą░ą║, čćč鹊 ą▒čāą┤čāčé čāčćąĖčéčŗą▓ą░čéčī č乊čĆą╝ą░čé čäčĆąĄą╣ą╝ą░ ą▓ ą┐ą░čĆą░ą╝ąĄčéčĆą░čģ, ą┤ąĄą╗ą░čéčī ąĘą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą┐čĆąĖ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ ąĖ čé. ą┤. ą×ą┤ąĮą░ą║ąŠ ą▓ąŠ ą╝ąĮąŠą│ąĖčģ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅčģ čćą░čüč鹊 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮą░čÅ ąĮą░čüčéčĆąŠą╣ą║ą░ ą┤ą╗čÅ čĆąĄą│ąĖčüčéčĆąŠą▓ čüą║ąŠčĆąŠčüčéąĖ ąĖ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ, ąĖ ą┤ą╗čÅ ą┐čĆąĖą╗ąŠąČąĄąĮąĖą╣ čéą░ą║ąŠą│ąŠ čéąĖą┐ą░ ą┐ąŠą┤ąŠą▒ąĮčŗą╣ ą║ąŠą┤ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĮą░ą┐čĆčÅą╝čāčÄ ą▓čüčéą░ą▓ą╗ąĄąĮ ą▓ čäčāąĮą║čåąĖčÄ main, ąĖą╗ąĖ čüą║ąŠą╝ą▒ąĖąĮąĖčĆąŠą▓ą░ąĮ čü ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝ą░ą╝ąĖ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ ą┤ą╗čÅ ą┤čĆčāą│ąĖčģ ą╝ąŠą┤čāą╗ąĄą╣ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░.

[ą¤ąĄčĆąĄą┤ą░čćą░ ą┤ą░ąĮąĮčŗčģ ŌĆō USART Transmitter]

ą¤ąĄčĆąĄą┤ą░čéčćąĖą║ USART čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ Transmit Enable (TXEN) ą▓ čĆąĄą│ąĖčüčéčĆąĄ UCSRnB. ąÜąŠą│ą┤ą░ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ čĆą░ąĘčĆąĄčłąĄąĮ, ąĮąŠčĆą╝ą░ą╗čīąĮąŠąĄ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĄ ą┐ąŠčĆčéą░ GPIO ą┤ą╗čÅ ą▓čŗą▓ąŠą┤ą░ TxDn ą┐ąĄčĆąĄąĮą░ąĘąĮą░čćą░ąĄčéčüčÅ ąĮą░ ą░ą┐ą┐ą░čĆą░čéąĮčāčÄ čäčāąĮą║čåąĖčÄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ą▓čŗčģąŠą┤ą░ ą┤ą░ąĮąĮčŗčģ USART. ą¤ą░čĆą░ą╝ąĄčéčĆčŗ baud rate, čĆąĄąČąĖą╝ čĆą░ą▒ąŠčéčŗ ąĖ č乊čĆą╝ą░čé čäčĆąĄą╣ą╝ą░ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĮą░čüčéčĆąŠąĄąĮčŗ ą┐ąĄčĆąĄą┤ ąŠčüčāčēąĄčüčéą▓ą╗ąĄąĮąĖąĄą╝ ą╗čÄą▒čŗčģ ą┐ąĄčĆąĄą┤ą░čć. ąĢčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čüąĖąĮčģčĆąŠąĮąĮčŗą╣ čĆąĄąČąĖą╝ čĆą░ą▒ąŠčéčŗ, č鹊 čéą░ą║čéčŗ ą▓čŗą▓ąŠą┤ą░ XCKn ą┐čĆąĖąĮčāą┤ąĖč鹥ą╗čīąĮąŠ ą▒čāą┤čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ.

ą¤ąĄčĆąĄą┤ą░čćą░ čäčĆąĄą╣ą╝ąŠą▓ čĆą░ąĘą╝ąĄčĆąŠą╝ ąŠčé 5 ą┤ąŠ 8 ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ. ą¤ąĄčĆąĄą┤ą░čćą░ ąĮą░čćąĖąĮą░ąĄčéčüčÅ čü ąĘą░ą│čĆčāąĘą║ąĖ ą▒čāč乥čĆą░ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗą╝ąĖ, ą║ąŠč鹊čĆčŗąĄ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą┐ąĄčĆąĄą┤ą░ąĮčŗ. CPU ą╝ąŠąČąĄčé ąĘą░ą│čĆčāąĘąĖčéčī ą┤ą░ąĮąĮčŗąĄ ą▓ ą▒čāč乥čĆ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ čĆąĄą│ąĖčüčéčĆą░ UDRn ą┐ąŠ ąĄą│ąŠ ą░ą┤čĆąĄčüčā čĆą░ąĘą╝ąĄčēąĄąĮąĖčÅ ą▓ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąĄ I/O. ąöą░ąĮąĮčŗąĄ, ąĮą░čģąŠą┤čÅčēąĖąĄčüčÅ ą▓ ą▒čāč乥čĆąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ, ą┐ąĄčĆąĄą╝ąĄčüčéčÅčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░, ąĖ ą▒čāą┤čāčé ą│ąŠč鹊ą▓čŗ ą║ ąŠčéą┐čĆą░ą▓ą║ąĄ ą▓ ąĮąŠą▓ąŠą╝ čäčĆąĄą╣ą╝ąĄ. ąĀąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ąĮąŠą▓čŗą╝ąĖ ą┤ą░ąĮąĮčŗą╝ąĖ ąĄčüą╗ąĖ USART ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ąŠąČąĖą┤ą░ąĮąĖčÅ idle (ąĮąĄčé ą░ą║čéąĖą▓ąĮąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ) ąĖą╗ąĖ čüčĆą░ąĘčā ą┐ąŠčüą╗ąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ stop-ą▒ąĖčéą░ ą┐čĆąĄą┤čŗą┤čāčēąĄą│ąŠ ą┐ąĄčĆąĄą┤ą░ąĮąĮąŠą│ąŠ čäčĆąĄą╣ą╝ą░. ąÜąŠą│ą┤ą░ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ ąĘą░ą│čĆčāąČąĄąĮ ąĮąŠą▓čŗą╝ąĖ ą┤ą░ąĮąĮčŗą╝ąĖ, ąŠąĮąĖ ą▒čāą┤čāčé ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčīčüčÅ ą▓ ą┐ąŠą╗ąĮąŠą╝ čäčĆąĄą╣ą╝ąĄ čüąŠ čüą║ąŠčĆąŠčüčéčīčÄ, ąĘą░ą┤ą░ąĮąĮąŠą╣ čĆąĄą│ąĖčüčéčĆąŠą╝ Baud Register ąĖ ą▒ąĖč鹊ą╝ U2Xn, ąĖą╗ąĖ ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čĆąĄąČąĖą╝ą░ čĆą░ą▒ąŠčéčŗ čüą║ąŠčĆąŠčüčéčī ą▒čāą┤ąĄčé ąŠą┐čĆąĄą┤ąĄą╗čÅčéčüčÅ čéą░ą║čéą░ą╝ąĖ ąĮą░ XCKn.

ąĪą╗ąĄą┤čāčÄčēąĖąĄ ą┐čĆąĖą╝ąĄčĆčŗ ą║ąŠą┤ą░ ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčé ą┐čĆąŠčüčéčāčÄ čäčāąĮą║čåąĖčÄ ą┐ąĄčĆąĄą┤ą░čćąĖ USART, ąŠčüąĮąŠą▓ą░ąĮąĮčāčÄ ąĮą░ ąŠą┐čĆąŠčüąĄ čäą╗ą░ą│ą░ Data Register Empty (UDREn). ąÜąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ čäčĆąĄą╣ą╝čŗ ą╝ąĄąĮčīčłąĄ 8 ą▒ąĖčé, čüą░ą╝čŗą╣ čüčéą░čĆčłąĖą╣ ą▒ąĖčé, ąĘą░ą┐ąĖčüą░ąĮąĮčŗą╣ ą▓ UDRn, ą▒čāą┤ąĄčé ąĖą│ąĮąŠčĆąĖčĆąŠą▓ą░čéčīčüčÅ. USART ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆąŠą▓ą░ąĮ ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ą╝ąŠąČąĮąŠ ą▒čāą┤ąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čäčāąĮą║čåąĖčÄ ą┐ąĄčĆąĄą┤ą░čćąĖ. ąöą╗čÅ ą║ąŠą┤ą░ ąĮą░ ą░čüčüąĄą╝ą▒ą╗ąĄčĆąĄ ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčéčüčÅ, čćč鹊 ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗąĄ ą┤ą░ąĮąĮčŗčģ čüąŠčģčĆą░ąĮąĄąĮčŗ ą▓ čĆąĄą│ąĖčüčéčĆąĄ R16.

USART_Transmit:

; ą×ąČąĖą┤ą░ąĮąĖąĄ ąŠą┐čāčüč鹊賹ĄąĮąĖčÅ ą▒čāč乥čĆą░ ą┐ąĄčĆąĄą┤ą░čćąĖ

lds r17, UCSRnA

sbrs r17, UDREn

rjmp USART_Transmit

; ą¤ąŠą╝ąĄčüčéąĖčéčī ą┤ą░ąĮąĮčŗąĄ (r16) ą▓ ą▒čāč乥čĆ, ąŠčéą┐čĆą░ą▓ą║ą░ ą┤ą░ąĮąĮčŗčģ

sts UDRn,r16

ret

void USART_Transmit( unsigned char data )

{

/* ą×ąČąĖą┤ą░ąĮąĖąĄ ąŠą┐čāčüč鹊賹ĄąĮąĖčÅ ą▒čāč乥čĆą░ ą┐ąĄčĆąĄą┤ą░čćąĖ */

while ( !( UCSRnA & (1 << UDREn)) )

{

}

/* ą¤ąŠą╝ąĄčüčéąĖčéčī ą┤ą░ąĮąĮčŗąĄ ą▓ ą▒čāč乥čĆ, ąŠčéą┐čĆą░ą▓ą║ą░ ą┤ą░ąĮąĮčŗčģ */

UDRn = data;

}

ążčāąĮą║čåąĖčÅ ą┐čĆąŠčüč鹊 ąČą┤ąĄčé, ą┐ąŠą║ą░ ą▒čāč乥čĆ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĮąĄ ąŠą┐čāčüč鹊賹ĖčéčüčÅ, ą┐čāč鹥ą╝ ą┐ąŠčüč鹊čÅąĮąĮąŠą│ąŠ ąŠą┐čĆąŠčüą░ čäą╗ą░ą│ą░ UDREn, ą┐ąĄčĆąĄą┤ č鹥ą╝ ą║ą░ą║ ąĘą░ą│čĆčāąĘąĖčéčī ąĮąŠą▓čŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ. ąĢčüą╗ąĖ ą▒čŗ ą▒čŗą╗ąŠ ąĘą░ą┤ąĄą╣čüčéą▓ąŠą▓ą░ąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ ąŠą┐čāčüč鹊賹ĄąĮąĖčÄ ą▒čāč乥čĆą░ Data Register Empty, č鹊 ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ čŹč鹊ą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĘą░ą┐ąĖčüą░ą╗ ą▒čŗ ą┤ą░ąĮąĮčŗąĄ ą▓ ą▒čāč乥čĆ ą┐ąĄčĆąĄą┤ą░čćąĖ (ąĖ ą▒čŗą╗ąŠ ą▒čŗ čü菹║ąŠąĮąŠą╝ą╗ąĄąĮąŠ ą▓čĆąĄą╝čÅ ą┐čĆąŠčåąĄčüčüąŠčĆą░, ąĘą░čéčĆą░č湥ąĮąĮąŠąĄ ąĮą░ ą┐čāčüčéčŗąĄ čåąĖą║ą╗čŗ ąŠąČąĖą┤ą░ąĮąĖčÅ ąŠą┐čāčüč鹊賹ĄąĮąĖčÅ ą▒čāč乥čĆą░).

ą¤ąĄčĆąĄą┤ą░čćą░ čäčĆąĄą╣ą╝ąŠą▓ čĆą░ąĘą╝ąĄčĆąŠą╝ 9 ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ. ąĢčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ 9-čĆą░ąĘčĆčÅą┤ąĮčŗąĄ čüąĖą╝ą▓ąŠą╗čŗ (UCSZn = 7), č鹊 čüčéą░čĆčłąĖą╣ ą┤ąĄą▓čÅčéčŗą╣ ą▒ąĖčé ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮ ą▓ ą▒ąĖčé TXB8 čĆąĄą│ąĖčüčéčĆą░ UCSRnB ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ą╝ą╗ą░ą┤čłąĖąĄ 8 ą▒ąĖčé čüąĖą╝ą▓ąŠą╗ą░ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮčŗ ą▓ čĆąĄą│ąĖčüčéčĆ UDRn. ąĪą╗ąĄą┤čāčÄčēąĖąĄ ą┐čĆąĖą╝ąĄčĆčŗ ą║ąŠą┤ą░ ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčé čäčāąĮą║čåąĖčÄ ą┐ąĄčĆąĄą┤ą░čćąĖ, ą║ąŠč鹊čĆą░čÅ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ą┐ąĄčĆąĄą┤ą░čćčā čüąĖą╝ą▓ąŠą╗ąŠą▓ ąĖąĘ 9-ą▒ąĖčé. ąöą╗čÅ ą║ąŠą┤ą░ ą░čüčüąĄą╝ą▒ą╗ąĄčĆą░ ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčéčüčÅ, čćč鹊 ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ ąŠčéą┐čĆą░ą▓ą║ąĖ čüąŠčģčĆą░ąĮąĄąĮčŗ ą▓ čĆąĄą│ąĖčüčéčĆąŠą▓ąŠą╣ ą┐ą░čĆąĄ R17:R16.

USART_Transmit:

; ą×ąČąĖą┤ą░ąĮąĖąĄ ąŠą┐čāčüč鹊賹ĄąĮąĖčÅ ą▒čāč乥čĆą░ ą┐ąĄčĆąĄą┤ą░čćąĖ

sbis UCSRnA,UDREn

rjmp USART_Transmit

; ąÜąŠą┐ąĖčĆąŠą▓ą░ąĮąĖąĄ 9-ą│ąŠ ą▒ąĖčéą░ ąĖąĘ r17 ą▓ TXB8

cbi UCSRnB,TXB8

sbrc r17,0

sbi UCSRnB,TXB8

; ą¤ąŠą╝ąĄčüčéąĖčéčī LSB ą┤ą░ąĮąĮčŗąĄ (r16) ą▓ ą▒čāč乥čĆ, ąŠčéą┐čĆą░ą▓ą║ą░ ą┤ą░ąĮąĮčŗčģ

sts UDRn,r16

ret

void USART_Transmit( unsigned int data )

{

/* ą×ąČąĖą┤ą░ąĮąĖąĄ ąŠą┐čāčüč鹊賹ĄąĮąĖčÅ ą▒čāč乥čĆą░ */

while ( !( UCSRnA & (1 << UDREn))) )

{

}

/* ąÜąŠą┐ąĖčĆąŠą▓ą░ąĮąĖąĄ 9-ą│ąŠ ą▒ąĖčéą░ ą▓ TXB8 */

UCSRnB &= ~(1 << TXB8);

if ( data & 0x0100 )

UCSRnB |= (1 << TXB8);

/* ą¤ąŠą╝ąĄčüčéąĖčéčī ą┤ą░ąĮąĮčŗąĄ ą▓ ą▒čāč乥čĆ, ąŠčéą┐čĆą░ą▓ą║ą░ ą┤ą░ąĮąĮčŗčģ */

UDRn = data;

}

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: čŹčéąĖ čäčāąĮą║čåąĖąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĮą░ą┐ąĖčüą░ąĮčŗ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ą┐čĆąĖą╝ąĄčĆą░. ą×ąĮąĖ ą╝ąŠą│čāčé ą▒čŗčéčī ąŠą┐čéąĖą╝ąĖąĘąĖčĆąŠą▓ą░ąĮčŗ, ąĄčüą╗ąĖ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ UCSRnB čüčéą░čéąĖč湥čüą║ąŠąĄ. ąØą░ą┐čĆąĖą╝ąĄčĆ, ą┐ąŠčüą╗ąĄ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ ą▓ čĆąĄą│ąĖčüčéčĆąĄ UCSRnB ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą▒ąĖčé TXB8.

9-ą╣ ą▒ąĖčé ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ č鹊ą│ąŠ, čćč鹊ą▒čŗ ą┐ąŠą║ą░ąĘą░čéčī ą░ą┤čĆąĄčü čäčĆąĄą╣ą╝ą░ ą▓ čĆąĄąČąĖą╝ąĄ ąŠą▒ą╝ąĄąĮą░ čü ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆą░ą╝ąĖ (multi processor communication mode) ąĖą╗ąĖ ą┤ą╗čÅ ą┤čĆčāą│ąŠą│ąŠ ą┐čĆąŠč鹊ą║ąŠą╗ą░, ąĮą░ą┐čĆąĖą╝ąĄčĆ ą┤ą╗čÅ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ.

ążą╗ą░ą│ąĖ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ąŻ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ USART ąĄčüčéčī 2 čäą╗ą░ą│ą░, ą║ąŠč鹊čĆčŗąĄ ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčé ąĄą│ąŠ čüąŠčüč鹊čÅąĮąĖąĄ: USART Data Register Empty (UDREn) ąĖ Transmit Complete (TXCn). ą×ą▒ą░ čäą╗ą░ą│ą░ ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣.

ążą╗ą░ą│ Data Register Empty (UDREn) ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, ą│ąŠč鹊ą▓ ąĖą╗ąĖ ąĮąĄčé ą▒čāč乥čĆ ą┐ąĄčĆąĄą┤ą░čćąĖ ą║ ąĘą░ą┐ąĖčüąĖ čéčāą┤ą░ ąĮąŠą▓čŗčģ ą┤ą░ąĮąĮčŗčģ. ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą▒čāč乥čĆ ą┐ąĄčĆąĄą┤ą░čćąĖ ąŠą┐čāčüč鹊賹░ąĄčéčüčÅ, ąĖ ąŠčćąĖčēą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą▒čāč乥čĆ ą┐ąĄčĆąĄą┤ą░čćąĖ čüąŠą┤ąĄčƹȹĖčé ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ ąŠčéą┐čĆą░ą▓ą║ąĖ, ą║ąŠč鹊čĆčŗąĄ ąĄčēąĄ ą┐ąŠą║ą░ ąĮąĄ ą┐ąĄčĆąĄą╝ąĄčēąĄąĮčŗ ą▓ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░. ąöą╗čÅ čüąŠą▓ą╝ąĄčüčéąĖą╝ąŠčüčéąĖ čü ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ą╝ąĖ, ą║ąŠč鹊čĆčŗąĄ ą▓ąŠąĘą╝ąŠąČąĮąŠ ą┐ąŠčÅą▓čÅčéčüčÅ ą▓ ą▒čāą┤čāčēąĄą╝, ą▓čüąĄą│ą┤ą░ ąĘą░ą┐ąĖčüčŗą▓ą░ą╣č鹥 čŹč鹊čé ą▒ąĖčé ą▓ 0, ą║ąŠą│ą┤ą░ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄč鹥 čĆąĄą│ąĖčüčéčĆ UCSRnA.

ąÜąŠą│ą┤ą░ ą▓ ą▒ąĖčé Data Register Empty Interrupt Enable (UDRIEn) čĆąĄą│ąĖčüčéčĆą░ UCSRnB ąĘą░ą┐ąĖčüą░ąĮą░ 1, ą▒čāą┤ąĄčé ą▓ąŠąĘą╝ąŠąČąĄąĮ ąĘą░ą┐čāčüą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ USART Data Register Empty, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé UDREn (ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčéčüčÅ, čćč鹊 ą│ą╗ąŠą▒ą░ą╗čīąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čĆą░ąĘčĆąĄčłąĄąĮčŗ).

UDREn ąŠčćąĖčēą░ąĄčéčüčÅ ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ UDRn. ąÜąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┐ąĄčĆąĄą┤ą░čćą░ ą┤ą░ąĮąĮčŗčģ čü čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝ ą┐ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅą╝, ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ Data Register Empty ą┤ąŠą╗ąČąĮą░ ą╗ąĖą▒ąŠ ąĘą░ą┐ąĖčüą░čéčī ąĮąŠą▓čŗąĄ ą┤ą░ąĮąĮčŗąĄ ą▓ UDRn, čćč鹊ą▒čŗ ąŠčćąĖčüčéąĖčéčī UDREn, ą╗ąĖą▒ąŠ ąĘą░ą┐čĆąĄčéąĖčéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ Data Register Empty, ąĖąĮą░č湥 ąĮąŠą▓ąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čāčüčéąĖčéčüčÅ ą┐ąŠčüą╗ąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

ąæąĖčé čäą╗ą░ą│ą░ Transmit Complete (TXCn) čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▓ 1, ą║ąŠą│ą┤ą░ ą▓ąĄčüčī čäčĆąĄą╣ą╝ ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüą┤ą▓ąĖą│ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▒čāą┤ąĄčé ą▓čŗą┤ą▓ąĖąĮčāčé ąĮą░čĆčāąČčā, ąĖ ą▓ ą▒čāč乥čĆąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĮąĄčé ąĮąŠą▓čŗčģ ą┤ą░ąĮąĮčŗčģ. ąæąĖčé čäą╗ą░ą│ą░ TXCn Flag ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąŠčćąĖčēą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ transmit complete, ąĖą╗ąĖ čŹč鹊čé čäą╗ą░ą│ ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠčćąĖčēąĄąĮ ąĘą░ą┐ąĖčüčīčÄ ą▓ ąĮąĄą│ąŠ ą╗ąŠą│. 1. ążą╗ą░ą│ TXCn ą┐ąŠą╗ąĄąĘąĄąĮ ą┐čĆąĖ ą┐ąŠą╗čāą┤čāą┐ą╗ąĄą║čüąĮąŠą╝ ąŠą▒ą╝ąĄąĮąĄ (ąĮą░ą┐ąŠą┤ąŠą▒ąĖąĄ čüčéą░ąĮą┤ą░čĆčéą░ RS-485), ą│ą┤ąĄ ą┐ąĄčĆąĄą┤ą░čÄčēąĄąĄ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ ą┤ąŠą╗ąČąĮąŠ ą▓ąŠą╣čéąĖ ą▓ čĆąĄąČąĖą╝ ą┐čĆąĖąĄą╝ą░ ąĖ ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ ąŠčüą▓ąŠą▒ąŠą┤ąĖčéčī čłąĖąĮčā ąŠą▒ą╝ąĄąĮą░ ą┐ąŠčüą╗ąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ.

ąĢčüą╗ąĖ ą▒ąĖčé Transmit Compete Interrupt Enable (TXCIEn) ą▓ čĆąĄą│ąĖčüčéčĆąĄ UCSRnB čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ąĘą░ą┐čāčüčéąĖčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ USART Transmit Complete, ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ TXCn (ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčéčüčÅ, čćč鹊 ą│ą╗ąŠą▒ą░ą╗čīąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čĆą░ąĘčĆąĄčłąĄąĮčŗ). ąÜąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ transmit complete, ąŠą▒čĆą░ą▒ąŠčéčćąĖą║čā ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĮąĄ ąĮčāąČąĮąŠ ąŠčćąĖčēą░čéčī čäą╗ą░ą│ TXCn, čŹč鹊 ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé, ą║ąŠą│ą┤ą░ čüčĆą░ą▒ąŠčéą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ.

Parity Generator. ąōąĄąĮąĄčĆą░č鹊čĆ č湥čéąĮąŠčüčéąĖ (Parity Generator) ą▓čŗčćąĖčüą╗čÅąĄčé ą▒ąĖčé č湥čéąĮąŠčüčéąĖ ą┤ą╗čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ čäčĆąĄą╣ą╝ą░ ą┤ą░ąĮąĮčŗčģ. ąÜąŠą│ą┤ą░ čĆą░ąĘčĆąĄčłąĄąĮ ą▒ąĖčé č湥čéąĮąŠčüčéąĖ (UPMn1 = 1), ą╗ąŠą│ąĖą║ą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ąŠą╝ ą▓čüčéą░ą▓ą╗čÅąĄčé ą▒ąĖčé č湥čéąĮąŠčüčéąĖ ą╝ąĄąČą┤čā ą┐ąŠčüą╗ąĄą┤ąĮąĖą╝ ą▒ąĖč鹊ą╝ ą┤ą░ąĮąĮčŗčģ ąĖ ą┐ąĄčĆą▓čŗą╝ stop-ą▒ąĖč鹊ą╝ ąŠčéą┐čĆą░ą▓ą╗čÅąĄą╝ąŠą│ąŠ čäčĆąĄą╣ą╝ą░.

ąŚą░ą┐čĆąĄčé ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░. ąŚą░ą┐čĆąĄčé ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ (čüą▒čĆąŠčü TXEN ą▓ 0) ąĮąĄ ą▓čüčéčāą┐ąĖčé ą▓ čüąĖą╗čā, ą┐ąŠą║ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą░ą║čéąĖą▓ąĮą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░, čé. ąĄ. ą┐ąŠą║ą░ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ ąĖ čĆąĄą│ąĖčüčéčĆ ą▒čāč乥čĆą░ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĄčēąĄ čüąŠą┤ąĄčƹȹ░čé ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ. ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ ąĘą░ą┐čĆąĄčēąĄąĮ, ąĮąŠ ą▒ąŠą╗čīčłąĄ ąĮąĄ ą▒čāą┤ąĄčé ą┐ąĄčĆąĄąĮą░ąĘąĮą░čćą░čéčī ą▓čŗą▓ąŠą┤ ą┐ąŠčĆčéą░ TxDn.

[ą¤čĆąĖąĄą╝ ą┤ą░ąĮąĮčŗčģ ŌĆō USART Receiver]

ą¤čĆąĖąĄą╝ąĮąĖą║ USART čĆą░ąĘčĆąĄčłą░čéčüčÅ ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ ą▒ąĖčéą░ Receive Enable (RXENn) čĆąĄą│ąĖčüčéčĆą░ UCSRnB ą▓ 1. ąÜąŠą│ą┤ą░ ą┐čĆąĖąĄą╝ąĮąĖą║ čĆą░ąĘčĆąĄčłąĄąĮ, ąĮąŠčĆą╝ą░ą╗čīąĮą░čÅ čĆą░ą▒ąŠčéą░ ą┐ąŠčĆčéą░ RxDn ą┐ąĄčĆąĄąĮą░ąĘąĮą░čćą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéčāčĆąŠą╣ USART, ąĖ čŹč鹊čé ą┐ąŠčĆčé čüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▓čģąŠą┤ąŠą╝ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ ą┤ą╗čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ą┤ą░ąĮąĮčŗčģ. ą¤ą░čĆą░ą╝ąĄčéčĆčŗ baud rate, čĆąĄąČąĖą╝ą░ čĆą░ą▒ąŠčéčŗ ąĖ č乊čĆą╝ą░čé čäčĆąĄą╣ą╝ą░ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą┤ąŠ č鹊ą│ąŠ, ą║ą░ą║ ą╝ąŠąČąĮąŠ ą▒čāą┤ąĄčé ąŠčüčāčēąĄčüčéą▓ą╗čÅčéčī ą╗čÄą▒ąŠą╣ ą┐čĆąĖąĄą╝. ąĢčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čüąĖąĮčģčĆąŠąĮąĮčŗą╣ čĆąĄąČąĖą╝, č鹊 ą▓čŗą▓ąŠą┤ XCKn ą▒čāą┤ąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą║ą░ą║ čéą░ą║čéčŗ ą┐čĆąĖąĄą╝ą░.

ą¤čĆąĖąĄą╝ čäčĆąĄą╣ą╝ąŠą▓ ą┤ą╗ąĖąĮąŠą╣ ąŠčé 5 ą┤ąŠ 8 ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ. ą¤čĆąĖąĄą╝ąĮąĖą║ ąĮą░čćąĮąĄčé ą┐čĆąĖąĄą╝ ą┤ą░ąĮąĮčŗčģ, ą║ąŠą│ą┤ą░ ą┤ąĄč鹥ą║čéąĖčĆčāąĄčé ą┤ąŠą┐čāčüčéąĖą╝čŗą╣ start-ą▒ąĖčé. ąÜą░ąČą┤čŗą╣ ą▒ąĖčé, ą║ąŠč鹊čĆčŗą╣ čüą╗ąĄą┤čāąĄčé ąĘą░ čüčéą░čĆč鹊ą▓čŗą╝, ą▒čāą┤ąĄčé ąŠčåąĖčäčĆąŠą▓čŗą▓ą░ąĄčéčüčÅ ąĮą░ čüą║ąŠčĆąŠčüčéąĖ baud rate, ąĖą╗ąĖ čü čéą░ą║čéą░ą╝ąĖ XCKn, ąĖ ą▓ą┤ą▓ąĖą│ą░čéčīčüčÅ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░, ą┐ąŠą║ą░ ąĮąĄ ą▒čāą┤ąĄčé ą┐čĆąĖąĮčÅčé ą┐ąĄčĆą▓čŗą╣ stop-ą▒ąĖčé čäčĆąĄą╣ą╝ą░. ąÆč鹊čĆąŠą╣ stop-ą▒ąĖčé ą▒čāą┤ąĄčé ą┐čĆąĖąĄą╝ąĮąĖą║ąŠą╝ ąĖą│ąĮąŠčĆąĖčĆąŠą▓ą░čéčīčüčÅ. ąÜąŠą│ą┤ą░ ą▒čāą┤ąĄčé ą┐čĆąĖąĮčÅčé ą┐ąĄčĆą▓čŗą╣ stop-ą▒ąĖčé, čé. ąĄ. ą║ąŠą│ą┤ą░ ą┐ąŠą╗ąĮčŗą╣ čäčĆąĄą╣ą╝ ą┐čĆąĖčüčāčéčüčéą▓čāąĄčé ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüą┤ą▓ąĖą│ą░, č鹊 čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ čĆąĄą│ąĖčüčéčĆą░ čüą┤ą▓ąĖą│ą░ ą▒čāą┤ąĄčé ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąŠ ą▓ ą▒čāč乥čĆ ą┐čĆąĖąĄą╝ą░. ąæčāč乥čĆ ą┐čĆąĖąĄą╝ą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮ č湥čĆąĄąĘ UDRn.

ąĪą╗ąĄą┤čāčÄčēąĖą╣ ą┐čĆąĖą╝ąĄčĆ ą║ąŠą┤ą░ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą┐čĆąŠčüčéčāčÄ čäčāąĮą║čåąĖčÄ ą┐čĆąĖąĄą╝ą░ USART ąĮą░ ą▒ą░ąĘąĄ ąŠą┐čĆąŠčüą░ čäą╗ą░ą│ą░ Receive Complete (RXCn). ąÜąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ čäčĆąĄą╣ą╝čŗ čĆą░ąĘą╝ąĄčĆąŠą╝ ą╝ąĄąĮčīčłąĄ 8 ą▒ąĖčé, čüą░ą╝čŗą╣ čüčéą░čĆčłąĖą╣ ą▒ąĖčé ą▒ą░ą╣čéą░ ą┤ą░ąĮąĮčŗčģ, ą┐čĆąŠčćąĖčéą░ąĮąĮąŠą│ąŠ ąĖąĘ UDRn, ą▒čāą┤ąĄčé ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮ ąĮčāą╗ąĄą╝. USART ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆąŠą▓ą░ąĮ ą┐ąĄčĆąĄą┤ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ čŹč鹊ą╣ čäčāąĮą║čåąĖąĖ.

USART_Receive:

; ą×ąČąĖą┤ą░ąĮąĖąĄ ą┐ąŠčüčéčāą┐ą╗ąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ

lds r17, UCSRnA

sbrs r17, RXCn

rjmp USART_Receive

; ą¤ąŠą╗čāčćąĖčéčī ąĖ ą▓ąŠąĘą▓čĆą░čéąĖčéčī ą┤ą░ąĮąĮčŗąĄ ąĖąĘ ą▒čāč乥čĆą░

lds r16, UDRn

ret

unsigned char USART_Receive( void )

{

/* ą×ąČąĖą┤ą░ąĮąĖąĄ ą┐ąŠčüčéčāą┐ą╗ąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ */

while ( !(UCSRnA & (1 << RXCn)) )

{

}

/* ą¤ąŠą╗čāčćąĖčéčī ąĖ ą▓ąŠąĘą▓čĆą░čéąĖčéčī ą┤ą░ąĮąĮčŗąĄ ąĖąĘ ą▒čāč乥čĆą░ */

return UDRn;

}

ążčāąĮą║čåąĖčÅ ą┐čĆąŠčüč鹊 ąČą┤ąĄčé ą┐ąŠčÅą▓ą╗ąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ą▓ ą▒čāč乥čĆąĄ ą┐čĆąĖąĄą╝ą░ ą┐čāč鹥ą╝ ą┐čĆąŠą▓ąĄčĆą║ąĖ čäą╗ą░ą│ą░ RXCn ą┐ąĄčĆąĄą┤ čćč鹥ąĮąĖąĄą╝ ą▒čāč乥čĆą░ ąĖ ą▓ąŠąĘą▓čĆą░čéą░ ąĘąĮą░č湥ąĮąĖčÅ. ąŁč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ąŠąĮą░ ą┐ąŠą╗ąĮąŠčüčéčīčÄ ą▒ą╗ąŠą║ąĖčĆčāąĄčé ą┐čĆąŠą│čĆą░ą╝ą╝čā, ąĄčüą╗ąĖ ąĮą░ ą▓čģąŠą┤ USART ąĮąĄ ą┐ąŠčüčéčāą┐ą░čÄčé ą┤ą░ąĮąĮčŗąĄ.

ą¤čĆąĖąĄą╝ čäčĆąĄą╣ą╝ąŠą▓ ą┤ą╗ąĖąĮąŠą╣ 9 ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ. ąĢčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ 9-ą▒ąĖčéąĮčŗąĄ čüąĖą╝ą▓ąŠą╗čŗ (UCSZn=7), č鹊 9-ą╣ ą▒ąĖčé ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮ ąĖąĘ ą▒ąĖčéą░ RXB8n čĆąĄą│ąĖčüčéčĆą░ UCSRnB ą┤ąŠ čćč鹥ąĮąĖčÅ ą╝ą╗ą░ą┤čłąĖčģ 8 ą▒ąĖčé ąĖąĘ UDRn. ąóąŠ ąČąĄ čüą░ą╝ąŠąĄ ą┐čĆą░ą▓ąĖą╗ąŠ ą┤ąĄą╣čüčéą▓čāąĄčé ąĖ ą┤ą╗čÅ čäą╗ą░ą│ąŠą▓ čüąŠčüč鹊čÅąĮąĖčÅ FEn, DORn ąĖ UPEn. ąĪąĮą░čćą░ą╗ą░ ą┐čĆąŠčćąĖčéą░ą╣č鹥 čüąŠčüč鹊čÅąĮąĖąĄ ąĖąĘ UCSRnA, ąĘą░č鹥ą╝ ą┤ą░ąĮąĮčŗąĄ ąĖąĘ UDRn. ą¦č鹥ąĮąĖąĄ UDRn ą┐ąŠ ąĄą│ąŠ ą░ą┤čĆąĄčüčā I/O ą┐ąŠą╝ąĄąĮčÅąĄčé čüąŠčüč鹊čÅąĮąĖąĄ ą┐čĆąĖąĄą╝ąĮąŠą│ąŠ ą▒čāč乥čĆą░ FIFO ąĖ čüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ ą┐ąŠą╝ąĄąĮčÅąĄčéčüčÅ čüąŠčüč鹊čÅąĮąĖąĄ ą▒ąĖč鹊ą▓ TXB8n, FEn, DORn ąĖ UPEn, ą║ąŠč鹊čĆčŗąĄ ą▓čüąĄ čüąŠčģčĆą░ąĮčÅčÄčéčüčÅ ą▓ FIFO.

ąĪą╗ąĄą┤čāčÄčēąĖą╣ ą┐čĆąĖą╝ąĄčĆ ą║ąŠą┤ą░ ą┐ąŠą║ą░ąČąĄčé ą┐čĆąŠčüčéčāčÄ čäčāąĮą║čåąĖčÄ ą┐čĆąĖąĄą╝ą░ USART, ą║ąŠč鹊čĆą░čÅ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčé ą║ą░ą║ 9-ą╣ ą▒ąĖčé, čéą░ą║ ąĖ ą▒ąĖčéčŗ čüčéą░čéčāčüą░.

USART_Receive:

; ą×ąČąĖą┤ą░ąĮąĖąĄ ą┐ąŠčüčéčāą┐ą╗ąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ

lds r17, UCSRnA

sbrs r17, RXCn

rjmp USART_Receive

; ą¤ąŠą╗čāčćąĖčéčī čüąŠčüč鹊čÅąĮąĖąĄ ąĖ 9-ą╣ ą▒ąĖčé, ąĖ ąĘą░č鹥ą╝ ą┤ą░ąĮąĮčŗąĄ ąĖąĘ ą▒čāč乥čĆą░

lds r18, UCSRnA

lds r17, UCSRnB

lds r16, UDRn

; ąĢčüą╗ąĖ ąŠčłąĖą▒ą║ą░, ą▓ąĄčĆąĮčāčéčī -1

andi r18,(1 << FEn)|(1 << DORn)|(1 << UPEn)

breq USART_ReceiveNoError

ldi r17, HIGH(-1)

ldi r16, LOW(-1)USART_ReceiveNoError:

; čäąĖą╗čīčéčĆ 9-ą│ąŠ ą▒ąĖčéą░, ą▓ąĄčĆąĮčāčéčī čüąĖą╝ą▓ąŠą╗

lsr r17

andi r17, 0x01

ret

unsigned int USART_Receive( void )

{

unsigned char status, resh, resl;

/* ą×ąČąĖą┤ą░ąĮąĖąĄ ą┐ąŠčüčéčāą┐ą╗ąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ */

while ( !(UCSRnA & (1 << RXCn)) )

{

}

/* ą¤ąŠą╗čāčćąĖčéčī čüąŠčüč鹊čÅąĮąĖąĄ ąĖ 9-ą╣ ą▒ąĖčé, ąĘą░č鹥ą╝ ą┤ą░ąĮąĮčŗąĄ ąĖąĘ ą▒čāč乥čĆą░ */

status = UCSRnA;

resh = UCSRnB;

resl = UDRn;

/* ąĢčüą╗ąĖ ąŠčłąĖą▒ą║ą░, ą▓ąĄčĆąĮčāčéčī -1 */

if ( status & (1 << FEn)|(1 << DORn)|(1 << UPEn) )

return -1;

/* ążąĖą╗čīčéčĆ 9-ą│ąŠ ą▒ąĖčéą░, ąĖ ą▓ąŠąĘą▓čĆą░čé čüąĖą╝ą▓ąŠą╗ą░ */

resh = (resh >> 1) & 0x01;

return ((resh << 8) | resl);

}

ą¤čĆąĖą╝ąĄčĆ čäčāąĮą║čåąĖąĖ ą┐čĆąĖąĄą╝ą░ čćąĖčéą░ąĄčé ą▓čüąĄ čĆąĄą│ąĖčüčéčĆčŗ I/O ą▓ čĆąĄą│ąĖčüčéčĆąŠą▓čŗą╣ čäą░ą╣ą╗ ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ą▓čŗčćąĖčüą╗ąĄąĮąĖčÅ ąĘą░ą▓ąĄčĆčłą░čéčīčüčÅ. ąŁč鹊 ą┤ą░ąĄčé ąŠą┐čéąĖą╝ą░ą╗čīąĮąŠąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ ą▒čāč乥čĆą░, ą┐ąŠčüą║ąŠą╗čīą║čā čćč鹥ąĮąĖąĄ čÅč湥ąĄą║ ą▒čāč乥čĆą░ ąĮčāąČąĮąŠ ą▓čŗą┐ąŠą╗ąĮąĖčéčī ą║ą░ą║ ą╝ąŠąČąĮąŠ ą▒čŗčüčéčĆąĄąĄ, čćč鹊ą▒čŗ ąŠčüą▓ąŠą▒ąŠą┤ąĖčéčī ąĖčģ čü čåąĄą╗čīčÄ ą┐ąŠą╗čāč湥ąĮąĖčÅ ąĮąŠą▓čŗčģ ą┤ą░ąĮąĮčŗčģ.

ążą╗ą░ą│ ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ Receive Compete. ąŻ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ USART ąĄčüčéčī 1 čäą╗ą░ą│, ą║ąŠč鹊čĆčŗą╣ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüąŠčüč鹊čÅąĮąĖąĄ ą┐čĆąĖąĄą╝ąĮąĖą║ą░. ążą╗ą░ą│ Receive Complete (RXCn) ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą▓ ą▒čāč乥čĆąĄ ą┐čĆąĖąĄą╝ą░ ąĄčüčéčī ąĮąĄ ą┐čĆąŠčćąĖčéą░ąĮąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ. ąŁč鹊čé čäą╗ą░ą│ čĆą░ą▓ąĄąĮ 1, ą║ąŠą│ą┤ą░ ąĮąĄ ą┐čĆąŠčćąĖčéą░ąĮąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ąĄčüčéčī ą▓ ą▒čāč乥čĆąĄ ą┐čĆąĖąĄą╝ą░, ąĖ 0, ą║ąŠą│ą┤ą░ ą▒čāč乥čĆ ą┐čĆąĖąĄą╝ą░ ą┐čāčüčé (čé. ąĄ. ą▓ ąĮąĄą╝ ąĮąĄ čüąŠą┤ąĄčƹȹĖčéčüčÅ ąĮąĖą║ą░ą║ąĖčģ ąĮąĄ ą┐čĆąŠčćąĖčéą░ąĮąĮčŗčģ ą┤ą░ąĮąĮčŗčģ). ąĢčüą╗ąĖ ą┐čĆąĖąĄą╝ąĮąĖą║ ąĘą░ą┐čĆąĄčēąĄąĮ (RXENn = 0), ą▒čāč乥čĆ ą┐čĆąĖąĄą╝ą░ čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ, ąĖ čüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ čäą╗ą░ą│ RXCn ąŠą▒ąĮčāą╗čÅąĄčéčüčÅ.

ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé Receive Complete Interrupt Enable (RXCIEn) ą▓ čĆąĄą│ąĖčüčéčĆąĄ UCSRnB, ą▓čŗą┐ąŠą╗ąĮąĖčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ USART Receive Complete, ą║ąŠą│ą┤ą░ čäą╗ą░ą│ RXCn čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ (ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčéčüčÅ, čćč鹊 ą│ą╗ąŠą▒ą░ą╗čīąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čĆą░ąĘčĆąĄčłąĄąĮčŗ). ąÜąŠą│ą┤ą░ čĆą░ą▒ąŠčéą░ąĄčé ą┐čĆąĖąĄą╝ ą┤ą░ąĮąĮčŗčģ ą┐ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅą╝, č鹊 ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ Receive Complete ą┤ąŠą╗ąČąĮą░ ą┐čĆąŠčćąĖčéą░čéčī ą┐čĆąĖąĮčÅčéčŗąĄ ą┤ą░ąĮąĮčŗąĄ UDRn, čćč鹊ą▒čŗ ąŠčćąĖčüčéąĖčéčī čäą╗ą░ą│ RXCn, ąĖąĮą░č湥 ą┐ąŠčüą╗ąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ čĆą░ą▒ąŠčéčŗ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čüąĮąŠą▓ą░ ąĘą░ą┐čāčüčéąĖčéčīčüčÅ č鹊čé ąČąĄ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

ążą╗ą░ą│ąĖ ąŠčłąĖą▒ąŠą║ ą┐čĆąĖąĄą╝ąĮąĖą║ą░. ąŻ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ USART ąĄčüčéčī 3 čäą╗ą░ą│ą░ ąŠčłąĖą▒ą║ąĖ: Frame Error (FEn), Data OverRun (DORn) ąĖ Parity Error (UPEn). ąÆčüąĄ ą▒ąĖčéčŗ ąŠčłąĖą▒ąŠą║ ą┤ąŠčüčéčāą┐ąĮčŗ č湥čĆąĄąĘ čćč鹥ąĮąĖąĄ UCSRnA. ą×ą▒čēąĖą╝ ą┤ą╗čÅ čäą╗ą░ą│ąŠą▓ ąŠčłąĖą▒ąŠą║ čÅą▓ą╗čÅąĄčéčüčÅ č鹊, čéč湊 ąŠąĮąĖ čĆą░ąĘą╝ąĄčēąĄąĮčŗ ą▓ ą▒čāč乥čĆąĄ ą┐čĆąĖąĄą╝ą░ ą▓ą╝ąĄčüč鹥 čü ą┤ą░ąĮąĮčŗą╝ąĖ čäčĆąĄą╣ą╝ą░, ą┤ą╗čÅ ą║ąŠč鹊čĆąŠą│ąŠ čäą╗ą░ą│ąĖ ąŠčłąĖą▒ąŠą║ ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčé čüąŠčüč鹊čÅąĮąĖąĄ (čé. ąĄ. ą▒čāč乥čĆąĖąĘą░čåąĖčÅ ą┤ą░ąĮąĮčŗčģ čäčĆąĄą╣ą╝ą░ ą┐čĆąĖą▓čÅąĘą░ąĮą░ ą║ ą▒čāč乥čĆąĖąĘą░čåąĖąĖ čäą╗ą░ą│ąŠą▓ ąŠčłąĖą▒ą║ąĖ). ą¤ąŠ čŹč鹊ą╣ ą┐čĆąĖčćąĖąĮąĄ čüąĮą░čćą░ą╗ą░ ąĮčāąČąĮąŠ ą┐čĆąŠčćąĖčéą░čéčī UCSRnA, ąĖ č鹊ą╗čīą║ąŠ ą┐ąŠč鹊ą╝ ą▒čāč乥čĆ ą┤ą░ąĮąĮčŗčģ ą┐čĆąĖąĄą╝ą░ (UDRn), ą┐ąŠčüą║ąŠą╗čīą║čā čćč鹥ąĮąĖąĄ UDRn ą┐ąŠ ąĄą│ąŠ ą╝ąĄčüčéčā čĆą░ąĘą╝ąĄčēąĄąĮąĖčÅ I/O ąŠčüą▓ąŠą▒ąŠą┤ąĖčé ą▒čāč乥čĆ ą┐ąŠą┤ ąĮąŠą▓čŗąĄ ą┤ą░ąĮąĮčŗąĄ. ąĢčēąĄ čäą╗ą░ą│ąĖ ąŠčłąĖą▒ąŠą║ ąŠą▒čŖąĄą┤ąĖąĮčÅąĄčé č鹊, čćč鹊 ąĖčģ ąĮąĄą╗čīąĘčÅ čüą▒čĆąŠčüąĖčéčī ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ ąĘą░ą┐ąĖčüčīčÄ. ą×ą┤ąĮą░ą║ąŠ ą┤ą╗čÅ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖčÅ čüąŠą▓ą╝ąĄčüčéąĖą╝ąŠčüčéąĖ čü ąĖąĘą╝ąĄąĮąĄąĮąĖčÅą╝ąĖ ą▓ USART, ą║ąŠč鹊čĆčŗąĄ ą▓ąŠąĘą╝ąŠąČąĮąŠ ą┐ąŠčÅą▓čÅčéčüčÅ ą▓ ą▒čāą┤čāčēąĄą╝, ą▓čüąĄ čäą╗ą░ą│ąĖ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čüą▒čĆąŠčłąĄąĮčŗ ą▓ 0, ą║ąŠą│ą┤ą░ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ąĘą░ą┐ąĖčüčī UCSRnA. ążą╗ą░ą│ąĖ ąŠčłąĖą▒ą║ąĖ ąĮąĄ ą╝ąŠą│čāčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ.

ążą╗ą░ą│ Frame Error (FEn) ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüąŠčüč鹊čÅąĮąĖąĄ ą┐ąĄčĆą▓ąŠą│ąŠ stop-ą▒ąĖčéą░ ą┐čĆąĖąĮčÅč鹊ą│ąŠ čäčĆąĄą╣ą╝ą░, ąĮą░čģąŠą┤čÅčēąĄą│ąŠčüčÅ ą▓ ą▒čāč乥čĆąĄ ą┐čĆąĖąĄą╝ą░. ążą╗ą░ą│ FEn čĆą░ą▓ąĄąĮ 0, ąĄčüą╗ąĖ stop-ą▒ąĖčé ą▒čŗą╗ ą┐čĆąŠčćąĖčéą░ąĮ ą┐čĆą░ą▓ąĖą╗čīąĮąŠ (ą║ą░ą║ 1), ąĖ čäą╗ą░ą│ FEn ą▒čāą┤ąĄčé ą▓ 1, ą║ąŠą│ą┤ą░ stop-ą▒ąĖčé ąŠčłąĖą▒ąŠč湥ąĮ (čĆą░ą▓ąĄąĮ 0). ąŁč鹊čé čäą╗ą░ą│ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ čüąŠą▒čŗčéąĖą╣ ą▓čŗčģąŠą┤ą░ ąĖąĘ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ, čüąŠą▒čŗčéąĖą╣ ąŠčüčéą░ąĮąŠą▓ą║ąĖ ą┐ąŠč鹊ą║ą░ (break conditions) ąĖ ą┐ąŠą┤ą┤ąĄčƹȹ║ąĖ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąŠč鹊ą║ąŠą╗ą░. ąØą░ čäą╗ą░ą│ FEn ąĮąĄ ą▓ą╗ąĖčÅąĄčé ąĮą░čüčéčĆąŠą╣ą║ą░ ą▒ąĖčéą░ USBSn ą▓ čĆąĄą│ąĖčüčéčĆąĄ UCSRnC, ą┐ąŠčüą║ąŠą╗čīą║čā ą┐čĆąĖąĄą╝ąĮąĖą║ ąĖą│ąĮąŠčĆąĖčĆčāąĄčé ą▓čüąĄ stop-ą▒ąĖčéčŗ, ą║čĆąŠą╝ąĄ ą┐ąĄčĆą▓ąŠą│ąŠ. ąöą╗čÅ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖčÅ čüąŠą▓ą╝ąĄčüčéąĖą╝ąŠčüčéąĖ čü ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ą╝ąĖ, ą║ąŠč鹊čĆčŗą╣ ą▓ąŠąĘą╝ąŠąČąĮąŠ ą┐ąŠčÅą▓čÅčéčüčÅ ą▓ ą▒čāą┤čāčēąĄą╝, ą▓čüąĄą│ą┤ą░ čüą▒čĆą░čüčŗą▓ą░ą╣č鹥 čŹč鹊čé ą▒ąĖčé ą▓ 0, ą║ąŠą│ą┤ą░ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄč鹥 UCSRnA.

ążą╗ą░ą│ Data OverRun (DORn) ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą┐ąŠč鹥čĆčÄ ą┤ą░ąĮąĮčŗčģ, ąĖąĘ-ąĘą░ č鹊ą│ąŠ, čćč鹊 čā ą▒čāč乥čĆąĄ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ ą▒čŗą╗ąĖ ąĮąĄ ą┐čĆąŠčćąĖčéą░ąĮąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ. Data OverRun ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé, ą║ąŠą│ą┤ą░ ą▒čāč乥čĆ ą┐čĆąĖąĄą╝ą░ ąĘą░ą┐ąŠą╗ąĮąĄąĮ (ą▓ ąĮąĄą╝ ąĮą░čģąŠą┤ąĖčéčüčÅ 2 čüąĖą╝ą▓ąŠą╗ą░), ąŠąČąĖą┤ą░ąĄčéčüčÅ ą┐čĆąĖąĄą╝ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ čüąĖą╝ą▓ąŠą╗ą░, ąĖ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮ ąĮąŠą▓čŗą╣ start-ą▒ąĖčé. ąĢčüą╗ąĖ čäą╗ą░ą│ DORn čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, č鹊 ą▒čŗą╗ą░ ą┐ąŠč鹥čĆčÅ ąŠą┤ąĮąŠą│ąŠ ąĖą╗ąĖ ą▒ąŠą╗čīčłąĄą│ąŠ ą║ąŠą╗ąĖč湥čüčéą▓ą░ čäčĆąĄą╣ą╝ąŠą▓ ą╝ąĄąČą┤čā ą┐ąŠčüą╗ąĄą┤ąĮąĖą╝ čćč鹥ąĮąĖąĄą╝ ąĖ čüą╗ąĄą┤čāčÄčēąĖą╝ čćč鹥ąĮąĖąĄą╝ čäčĆąĄą╣ą╝ą░ ąĖąĘ UDRn. ąöą╗čÅ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖčÅ čüąŠą▓ą╝ąĄčüčéąĖą╝ąŠčüčéąĖ čü ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ą╝ąĖ, ą║ąŠč鹊čĆčŗą╣ ą▓ąŠąĘą╝ąŠąČąĮąŠ ą┐ąŠčÅą▓čÅčéčüčÅ ą▓ ą▒čāą┤čāčēąĄą╝, ą▓čüąĄą│ą┤ą░ ąĘą░ą┐ąĖčüčŗą▓ą░ą╣č鹥 čŹč鹊čé ą▒ąĖčé ą▓ 0, ą║ąŠą│ą┤ą░ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄč鹥 UCSRnA. ążą╗ą░ą│ DORn ąŠčćąĖčēą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą┐čĆąĖąĮčÅčéčŗą╣ čäčĆąĄą╣ą╝ čāčüą┐ąĄčłąĮąŠ ą┐ąĄčĆąĄą╝ąĄčēąĄąĮ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ čüą┤ą▓ąĖą│ą░ ą▓ ą▒čāč乥čĆ ą┐čĆąĖąĄą╝ą░.

ążą╗ą░ą│ ąŠčłąĖą▒ą║ąĖ č湥čéąĮąŠčüčéąĖ Parity Error (UPEn) ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 čüą╗ąĄą┤čāčÄčēąĖą╣ čäčĆąĄą╣ą╝, ąĮą░čģąŠą┤čÅčēąĖą╣čüčÅ ą▓ ą▒čāč乥čĆąĄ ą┐čĆąĖąĄą╝ą░, ąĖą╝ąĄąĄčé ąŠčłąĖą▒ą║čā č湥čéąĮąŠčüčéąĖ ąĮą░ ą┐čĆąĖąĄą╝ąĄ. ąĢčüą╗ąĖ ą║ąŠąĮčéčĆąŠą╗čī č湥čéąĮąŠčüčéąĖ ąĮąĄ čĆą░ąĘčĆąĄčłąĄąĮ, č鹊 ą▒ąĖčé UPEn ą▒čāą┤ąĄčé ą▓čüąĄą│ą┤ą░ čćąĖčéą░čéčīčüčÅ ą║ą░ą║ 0. ąöą╗čÅ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖčÅ čüąŠą▓ą╝ąĄčüčéąĖą╝ąŠčüčéąĖ čü ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ą╝ąĖ, ą║ąŠč鹊čĆčŗą╣ ą▓ąŠąĘą╝ąŠąČąĮąŠ ą┐ąŠčÅą▓čÅčéčüčÅ ą▓ ą▒čāą┤čāčēąĄą╝, ą▓čüąĄą│ą┤ą░ čüą▒čĆą░čüčŗą▓ą░ą╣č鹥 čŹč鹊čé ą▒ąĖčé ą▓ 0, ą║ąŠą│ą┤ą░ ą┐ąĖčłąĄč鹥 ą▓ UCSRnA.

ąŻąĘąĄą╗ ą┐čĆąŠą▓ąĄčĆą║ąĖ ą▒ąĖčéą░ č湥čéąĮąŠčüčéąĖ (Parity Checker) ą░ą║čéąĖą▓ąĄąĮ, ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1 ą▒ąĖčé USART Parity mode (UPMn1). ąóąĖą┐ ą▓čŗą┐ąŠą╗ąĮčÅąĄą╝ąŠą╣ ą┐čĆąŠą▓ąĄčĆą║ąĖ ąĮą░ č湥čéąĮąŠčüčéčī (ąĮąĄč湥čéąĮąŠčüčéčī odd ąĖą╗ąĖ č湥čéąĮąŠčüčéčī even) ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ą▒ąĖč鹊ą╝ UPMn0. ąÜąŠą│ą┤ą░ ą┐čĆąŠą▓ąĄčĆą║ą░ č湥čéąĮąŠčüčéąĖ čĆą░ąĘčĆąĄčłąĄąĮą░, Parity Checker ą▓čŗčćąĖčüą╗čÅąĄčé č湥čéąĮąŠčüčéčī ąŠčé ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ ą┐čĆąĖčģąŠą┤čÅčēąĖčģ čäčĆąĄą╣ą╝ąŠą▓, ąĖ čüčĆą░ą▓ąĮąĖą▓ą░ąĄčé čĆąĄąĘčāą╗čīčéą░čé čü ą▒ąĖč鹊ą╝ č湥čéąĮąŠčüčéąĖ ąĖąĘ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ čäčĆąĄą╣ą╝ą░. ąĀąĄąĘčāą╗čīčéą░čé ą┐čĆąŠą▓ąĄčĆą║ąĖ čüąŠčģčĆą░ąĮčÅąĄčéčüčÅ ą▓ ą▒čāč乥čĆąĄ ą┐čĆąĖąĄą╝ą░ ą▓ą╝ąĄčüč鹥 čü ą┐čĆąĖąĮčÅčéčŗą╝ąĖ ą┤ą░ąĮąĮčŗą╝ąĖ ąĖ stop-ą▒ąĖčéą░ą╝ąĖ. ążą╗ą░ą│ Parity Error (UPEn) ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ, čćč鹊ą▒čŗ ą┐čĆąŠą▓ąĄčĆąĖčéčī, ą▒čŗą╗ą░ ą╗ąĖ ą▓ąŠ čäčĆąĄą╣ą╝ąĄ ąŠčłąĖą▒ą║ą░ č湥čéąĮąŠčüčéąĖ.

ąæąĖčé UPEn čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ, ąĄčüą╗ąĖ ą▓ čüą╗ąĄą┤čāčÄčēąĄą╝ čüąĖą╝ą▓ąŠą╗ąĄ, ą║ąŠč鹊čĆčŗą╣ ą╝ąŠąČąĮąŠ ą┐čĆąŠčćąĖčéą░čéčī ąĖąĘ ą▒čāč乥čĆą░ ą┐čĆąĖąĄą╝ą░, ą▒čŗą╗ą░ ąŠčłąĖą▒ą║ą░ č湥čéąĮąŠčüčéąĖ ąĮą░ ą┐čĆąĖąĄą╝ąĄ, ąĖ ą┐čĆąŠą▓ąĄčĆą║ą░ č湥čéąĮąŠčüčéąĖ ą▓ čŹč鹊čé ą╝ąŠą╝ąĄąĮčé ą▒čŗą╗ą░ čĆą░ąĘčĆąĄčłąĄąĮą░ (UPMn1 = 1). ąŁč鹊čé ą▒ąĖčé ą┤ąĄą╣čüčéą▓ąĖč鹥ą╗ąĄąĮ, ą┐ąŠą║ą░ ąĮąĄ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé čćč鹥ąĮąĖąĄ ą▒čāč乥čĆą░ ą┐čĆąĖąĄą╝ą░ (čĆąĄą│ąĖčüčéčĆą░ UDRn).

ąŚą░ą┐čĆąĄčé ą┐čĆąĖąĄą╝ąĮąĖą║ą░. ąÆ ąŠčéą╗ąĖčćąĖąĄ ąŠčé ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░, ąĘą░ą┐čĆąĄčé ą┐čĆąĖąĄą╝ąĮąĖą║ą░ čüčĆą░ą▒ą░čéčŗą▓ą░ąĄčé ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą┐čĆąĖąĮąĖą╝ą░ąĄą╝čŗą╣ ą▓ ąĮą░čüč鹊čÅčēąĖą╣ ą╝ąŠą╝ąĄąĮčé čäčĆąĄą╣ą╝ ą┤ą░ąĮąĮčŗčģ (ąĖ ą║ąŠąĮąĄčćąĮąŠ ą┐ąŠčüą╗ąĄą┤čāčÄčēąĖąĄ ą┐ąŠčüą╗ąĄ ąĘą░ą┐čĆąĄčéą░) ą▒čāą┤čāčé ą┐ąŠč鹥čĆčÅąĮčŗ. ąÜąŠą│ą┤ą░ ą┐čĆąĖąĄą╝ąĮąĖą║ ąĘą░ą┐čĆąĄčēąĄąĮ (čé. ąĄ. RXENn čüą▒čĆąŠčłąĄąĮ ą▓ 0), č鹊 ąŠąĮ ą▒ąŠą╗čīčłąĄ ąĮąĄ ą┐ąĄčĆąĄąĮą░ąĘąĮą░čćą░ąĄčé ąĮąŠčĆą╝ą░ą╗čīąĮčāčÄ čĆą░ą▒ąŠčéčā ą┐ąŠčĆčéą░ RxDn ą║ą░ą║ ąĮąŠąČą║ąĖ GPIO. ą¤čĆąĖ ąĘą░ą┐čĆąĄč鹥 ą┐čĆąĖąĄą╝ąĮąĖą║ą░ ą▒čāč乥čĆ FIFO ą┐čĆąĖąĄą╝ąĮąĖą║ą░ ą▒čāą┤ąĄčé čüą▒čĆąŠčłąĄąĮ, ą▓čüąĄ ąŠčüčéą░ą▓čłąĖąĄčüčÅ ą▓ ąĮąĄą╝ ąĮąĄą┐čĆąŠčćąĖčéą░ąĮąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą▒čāą┤čāčé ą┐ąŠč鹥čĆčÅąĮčŗ.

ąĪą▒čĆąŠčü ą▒čāč乥čĆą░ ą┐čĆąĖąĄą╝ą░. ąæčāč乥čĆ FIFO ą┐čĆąĖąĄą╝ąĮąĖą║ą░ ą▒čāą┤ąĄčé čüą▒čĆąŠčłąĄąĮ, ą║ąŠą│ą┤ą░ ą┐čĆąĖąĄą╝ąĮąĖą║ ąĘą░ą┐čĆąĄčēąĄąĮ, čé. ąĄ. ąĘą░ą┐ąŠą╝ąĮąĄąĮąĮčŗąĄ ą▓ ą▒čāč乥čĆąĄ ą┤ą░ąĮąĮčŗąĄ čāąĮąĖčćč鹊ąČą░čÄčéčüčÅ, ąĮąĄą┐čĆąŠčćąĖčéą░ąĮąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą▒čāą┤čāčé ą┐ąŠč鹥čĆčÅąĮčŗ. ąĢčüą╗ąĖ ąĮčāąČąĮąŠ čüą▒čĆąŠčüąĖčéčī ą▒čāč乥čĆ ą▓ąŠ ą▓čĆąĄą╝čÅ ąĮąŠčĆą╝ą░ą╗čīąĮąŠą╣ čĆą░ą▒ąŠčéčŗ, ąĮą░ą┐čĆąĖą╝ąĄčĆ ą┐ąŠ ą┐čĆąĖčćąĖąĮąĄ čüąŠą▒čŗčéąĖčÅ ąŠčłąĖą▒ą║ąĖ, ą┐čĆąŠčüč鹊 ą┤ąĄą╗ą░ą╣č鹥 čćč鹥ąĮąĖąĄ UDRn, ą┐ąŠą║ą░ čäą╗ą░ą│ RXCn ąĮąĄ ąŠčćąĖčüčéąĖčéčüčÅ. ąÆ čüą╗ąĄą┤čāčÄčēąĄą╝ ą┐čĆąĖą╝ąĄčĆąĄ ą║ąŠą┤ą░ ą┐ąŠą║ą░ąĘą░ąĮą░ ąŠčćąĖčüčéą║ą░ ą▒čāč乥čĆą░ ą┐čĆąĖąĄą╝ą░.

USART_Flush:

sbis UCSRnA, RXCn

ret

in r16, UDRn

rjmp USART_Flush

void USART_Flush( void )

{

unsigned char dummy;

while ( UCSRnA & (1 << RXCn) )

dummy = UDRn;

}

[ąÉčüąĖąĮčģčĆąŠąĮąĮčŗą╣ ą┐čĆąĖąĄą╝ ą┤ą░ąĮąĮčŗčģ]

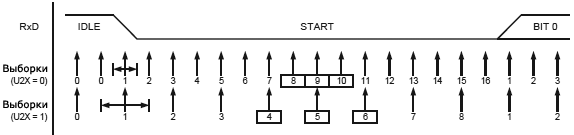

ąÆ čüąŠčüčéą░ą▓ USART ą▓ą║ą╗čÄč湥ąĮčŗ ą▒ą╗ąŠą║ąĖ ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖčÅ čéą░ą║č鹊ą▓ (Asynchronous Clock Recovery) ąĖ ą┤ą░ąĮąĮčŗčģ (Asynchronous Data Recovery), čćč鹊ą▒čŗ ą┐ąŠą┤ą┤ąĄčƹȹ░čéčī ą░čüąĖąĮčģčĆąŠąĮąĮčŗą╣ ą┐čĆąĖąĄą╝ ą┤ą░ąĮąĮčŗčģ. ąøąŠą│ąĖą║ą░ ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖčÅ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ą│ąĄąĮąĄčĆąĖčĆčāąĄą╝čŗčģ ą▓ąĮčāčéčĆąĖ čéą░ą║č鹊ą▓ čüą║ąŠčĆąŠčüčéąĖ (baud rate) ą┤ą╗čÅ ą▓čģąŠą┤čÅčēąĖčģ ą░čüąĖąĮčģčĆąŠąĮąĮčŗčģ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ čäčĆąĄą╣ą╝ąŠą▓ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ RxDn. ąøąŠą│ąĖą║ą░ ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ąŠčåąĖčäčĆąŠą▓čŗą▓ą░ąĄčé ąĖ ą┐čĆąŠą┐čāčüą║ą░ąĄčé č湥čĆąĄąĘ ążąØą¦ ą║ą░ąČą┤čŗą╣ ą▒ąĖčé ą┐čĆąĖčģąŠą┤čÅčēąĖčģ ą┤ą░ąĮąĮčŗčģ, čćč鹊ą▒čŗ čāą╗čāčćčłąĖčéčī čüč鹊ą╣ą║ąŠčüčéčī ą┐čĆąĖąĄą╝ąĮąĖą║ą░ ą║ ą┐ąŠą╝ąĄčģą░ą╝. ąöąĖą░ą┐ą░ąĘąŠąĮ čĆą░ą▒ąŠč鹊čüą┐ąŠčüąŠą▒ąĮąŠčüčéąĖ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą│ąŠ ą┐čĆąĖąĄą╝ą░ ąĘą░ą▓ąĖčüąĖčé ąŠčé č鹊čćąĮąŠčüčéąĖ ą▓ąĮčāčéčĆąĄąĮąĮąĖčģ čéą░ą║č鹊ą▓ čüą║ąŠčĆąŠčüčéąĖ, čüą║ąŠčĆąŠčüčéąĖ ą▓čģąŠą┤čÅčēąĖčģ čäčĆąĄą╣ą╝ąŠą▓, čĆą░ąĘą╝ąĄčĆą░ čäčĆąĄą╣ą╝ą░ ą▓ ą║ąŠą╗ąĖč湥čüčéą▓ąĄ ą▒ąĖčé.

Asynchronous Clock Recovery. ąøąŠą│ąĖą║ą░ ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖčÅ čéą░ą║č鹊ą▓ čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆčāąĄčé ą▓ąĮčāčéčĆąĄąĮąĮąĖąĄ čéą░ą║čéčŗ ą┐ąŠ ą▓čģąŠą┤čÅčēąĖą╝ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╝ čäčĆąĄą╣ą╝ą░ą╝. ąØą░ čĆąĖčü. 22-5 ą┐ąŠą║ą░ąĘą░ąĮ ą┐čĆąŠčåąĄčüčü ąŠčåąĖčäčĆąŠą▓ą║ąĖ čüčéą░čĆč鹊ą▓ąŠą│ąŠ ą▒ąĖčéą░ ą▓čģąŠą┤čÅčēąĄą│ąŠ čäčĆąĄą╣ą╝ą░. ą¦ą░čüč鹊čéą░ ąŠčåąĖčäčĆąŠą▓ą║ąĖ ą▓ 16 čĆą░ąĘ ą▒ąŠą╗čīčłąĄ čćą░čüč鹊čéčŗ ą▒ąĖčé (baud rate) ą┤ą╗čÅ ąĮąŠčĆą╝ą░ą╗čīąĮąŠą│ąŠ čĆąĄąČąĖą╝ą░ (Normal mode), ąĖ ą▓ 8 čĆą░ąĘ ą▒ąŠą╗čīčłąĄ čćą░čüč鹊čéčŗ ą▒ąĖčé ą┤ą╗čÅ čĆąĄąČąĖą╝ą░ ą┤ą▓ąŠą╣ąĮąŠą╣ čüą║ąŠčĆąŠčüčéąĖ (Double Speed mode). ąōąŠčĆąĖąĘąŠąĮčéą░ą╗čīąĮčŗąĄ čüčéčĆąĄą╗ą║ąĖ ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčé ąĖąĮč鹥čĆą▓ą░ą╗čŗ ą┐ąŠą┤čüčéčĆąŠą╣ą║ąĖ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ą▓ ą┐čĆąŠčåąĄčüčüąĄ ąŠčåąĖčäčĆąŠą▓ą║ąĖ. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ ąĮą░ čāą▓ąĄą╗ąĖč湥ąĮąĮčŗąĄ ąĖąĮč鹥čĆą▓ą░ą╗čŗ ą┤ą╗čÅ čĆąĄąČąĖą╝ą░ ą┤ą▓ąŠą╣ąĮąŠą╣ čüą║ąŠčĆąŠčüčéąĖ (Double Speed mode, U2Xn = 1). ąÆčŗą▒ąŠčĆą║ąĖ, ą┐ąŠą╝ąĄč湥ąĮąĮčŗąĄ ąĮčāą╗čÅą╝ąĖ, ąŠąĘąĮą░čćą░čÄčé ą▓čŗą▒ąŠčĆą║ąĖ, ą║ąŠą│ą┤ą░ čüąĖą│ąĮą░ą╗ RxDn ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ąŠąČąĖą┤ą░ąĮąĖčÅ idle (čé. ąĄ. ąĮąĄčé ą░ą║čéąĖą▓ąĮąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ).

ąĀąĖčü. 22-5. ąÆčŗą▒ąŠčĆą║ą░ (ąŠčåąĖčäčĆąŠą▓ą║ą░) start-ą▒ąĖčéą░.

ąÜąŠą│ą┤ą░ ą╗ąŠą│ąĖą║ą░ ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖčÅ čéą░ą║č鹊ą▓ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ą╗ą░ ą┐ąĄčĆąĄčģąŠą┤ ąŠčé ą╗ąŠą│. 1 (idle) ą║ ą╗ąŠą│. 0 (start) ąĮą░ ą╗ąĖąĮąĖąĖ RxDn, ąĖąĮąĖčåąĖąĖčĆčāąĄčéčüčÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ start-ą▒ąĖčéą░. ąÆčŗą▒ąŠčĆą║ą░ 1 ąĮą░ čĆąĖčüčāąĮą║ąĄ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą┐ąĄčĆą▓čāčÄ ąĮčāą╗ąĄą▓čāčÄ ą▓čŗą▒ąŠčĆą║čā. ąŚą░č鹥ą╝ ą╗ąŠą│ąĖą║ą░ ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖčÅ čéą░ą║č鹊ą▓ ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą▓čŗą▒ąŠčĆą║ąĖ 8, 9 ąĖ 10 ą┤ą╗čÅ ąĮąŠčĆą╝ą░ą╗čīąĮąŠą│ąŠ čĆąĄąČąĖą╝ą░, ąĖ ą▓čŗą▒ąŠčĆą║ąĖ 4, 5 ąĖ 6 ą┤ą╗čÅ čĆąĄąČąĖą╝ą░ ą┤ą▓ąŠą╣ąĮąŠą╣ čüą║ąŠčĆąŠčüčéąĖ (čŹčéąĖ čåąĖčäčĆčŗ ą▓čŗą┤ąĄą╗ąĄąĮčŗ ą┐čĆčÅą╝ąŠčāą│ąŠą╗čīąĮąŠą╣ čĆą░ą╝ą║ąŠą╣ ąĮą░ čĆąĖčüčāąĮą║ąĄ), čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī, čćč鹊 ą┤ąĄą╣čüčéą▓ąĖč鹥ą╗čīąĮąŠ ą┐čĆąĖąĮčÅčé ą┤ąŠą┐čāčüčéąĖą╝čŗą╣ start-ą▒ąĖčé. ąĢčüą╗ąĖ 2 ąĖą╗ąĖ ą▒ąŠą╗čīčłąĄąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čŹčéąĖčģ ą▓čŗą▒ąŠčĆąŠą║ ąĖą╝ąĄčÄčé ą╗ąŠą│. 1 (ą┐čĆąĖąĮčåąĖą┐ ą▒ąŠą╗čīčłąĖąĮčüčéą▓ą░), č鹊 start-ą▒ąĖčé ąŠčéą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ ą║ą░ą║ čłčāą╝ąŠą▓ą░čÅ ą┐ąŠą╝ąĄčģą░, ąĖ ą┐čĆąĖąĄą╝ąĮąĖą║ čüąĮąŠą▓ą░ ąĮą░čćąĖąĮą░ąĄčé ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ ą┐ąĄčĆąĄčģąŠą┤ą░ ąŠčé 1 ą║ 0. ą×ą┤ąĮą░ą║ąŠ ąĄčüą╗ąĖ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮ ą┤ąŠą┐čāčüčéąĖą╝čŗą╣ start-ą▒ąĖčé ("ą▒ąŠą╗čīčłąĖąĮčüčéą▓ąŠ" čāą║ą░ąĘčŗą▓ą░ąĄčé ąĮą░ 0), č鹊 ą▓ ą╗ąŠą│ąĖą║ą░ ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖčÅ čéą░ą║č鹊ą▓ čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆčāąĄčéčüčÅ, ąĖ ą╝ąŠąČąĄčé ąĮą░čćą░čéčīčüčÅ ą┐čĆąŠčåąĄčüčü ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ. ą¤čĆąŠčåąĄčüčü čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ą┐ąŠą▓č鹊čĆčÅąĄčéčüčÅ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ start-ą▒ąĖčéą░.

Asynchronous Data Recovery. ąÜąŠą│ą┤ą░ ą┐čĆąŠąĖąĘąŠčłą╗ą░ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖčÅ čéą░ą║č鹊ą▓ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ ą┐ąŠ start-ą▒ąĖčéčā, ą╝ąŠąČąĄčé ąĮą░čćą░čéčī čĆą░ą▒ąŠčéčā ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ. ąæą╗ąŠą║ ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą╝ą░čłąĖąĮčā ąĖąĘ 16 čüąŠčüč鹊čÅąĮąĖą╣ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą▒ąĖčéą░ ą▓ ąĮąŠčĆą╝ą░ą╗čīąĮąŠą╝ čĆąĄąČąĖą╝ąĄ ąĖ ą╝ą░čłąĖąĮčā 8 čüąŠčüč鹊čÅąĮąĖą╣ ą┤ą╗čÅ čĆąĄąČąĖą╝ą░ ą┤ą▓ąŠą╣ąĮąŠą╣ čüą║ąŠčĆąŠčüčéąĖ. ąØą░ čĆąĖčü. 22-6 ą┐ąŠą║ą░ąĘą░ąĮą░ ąŠčåąĖčäčĆąŠą▓ą║ą░ ą▒ąĖč鹊ą▓ ą┤ą░ąĮąĮčŗčģ ąĖ ą▒ąĖčéą░ č湥čéąĮąŠčüčéąĖ (BITn). ąÜą░ąČą┤ą░čÅ ą▓čŗą▒ąŠčĆą║ą░ ą┐ąŠą╝ąĄč湥ąĮą░ čåąĖčäčĆąŠą╣, ą║ąŠč鹊čĆą░čÅ čĆą░ą▓ąĮą░ čüąŠčüč鹊čÅąĮąĖčÄ ą▒ą╗ąŠą║ą░ ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖčÅ.

ąĀąĖčü. 22-6. ąÆčŗą▒ąŠčĆą║ą░ ą┤ą░ąĮąĮčŗčģ ąĖ ą▒ąĖčéą░ č湥čéąĮąŠčüčéąĖ.

ą¤čĆąĖąĮčÅčéąĖąĄ čĆąĄčłąĄąĮąĖčÅ ąŠ ą╗ąŠą│. čāčĆąŠą▓ąĮąĄ ą┐čĆąĖąĮčÅč鹊ą│ąŠ ą▒ąĖčéą░ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą┐ąŠ č鹊ą╝čā ąČąĄ čüą░ą╝ąŠą╝čā "ą┐čĆąĖąĮčåąĖą┐čā ą▒ąŠą╗čīčłąĖąĮčüčéą▓ą░" ąĮą░ 3 ą▓čŗą▒ąŠčĆą║ą░čģ ą┐ąŠčüąĄčĆąĄą┤ąĖąĮąĄ ą┐čĆąĖąĮąĖą╝ą░ąĄą╝ąŠą│ąŠ ą▒ąĖčéą░. ąØąŠą╝ąĄčĆą░ čŹčéąĖčģ ą▓čŗą▒ąŠčĆąŠą║ ą┐ąŠą╝ąĄč湥ąĮčŗ ąĮą░ čĆąĖčüčāąĮą║ąĄ čĆą░ą╝ąŠčćą║ą░ą╝ąĖ. ąĢčüą╗ąĖ 2 ąĖą╗ąĖ ą▒ąŠą╗čīčłąĄąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ąĖąĘ čŹčéąĖčģ 3 ą▓čŗą▒ąŠčĆąŠą║ ą┐čĆąŠčćąĖčéą░ąĮčŗ ą║ą░ą║ 1, č鹊 ą┐čĆąĖąĮčÅčéčŗą╣ ą▒ąĖčé čĆąĄą│ąĖčüčéčĆąĖčĆčāąĄčéčüčÅ ą║ą░ą║ ą╗ąŠą│. 1. ąś ą░ąĮą░ą╗ąŠą│ąĖčćąĮąŠ ąĄčüą╗ąĖ 2 ąĖą╗ąĖ ą▒ąŠą╗čīčłąĄąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ąĖąĘ čŹčéąĖčģ 3 ą▓čŗą▒ąŠčĆąŠą║ ą┐čĆąŠčćąĖčéą░ąĮčŗ ą║ą░ą║ 0, č鹊 ą┐čĆąĖąĮčÅčéčŗą╣ ą▒ąĖčé čĆąĄą│ąĖčüčéčĆąĖčĆčāąĄčéčüčÅ ą║ą░ą║ ą╗ąŠą│. 0. ąŁč鹊čé ą┐čĆąĖąĮčåąĖą┐ čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą┐čĆąŠčüč鹥ą╣čłąĖą╣ čåąĖčäčĆąŠą▓ąŠą╣ ążąØą¦ ą┤ą╗čÅ ą▓čģąŠą┤čÅčēąĄą│ąŠ čüąĖą│ąĮą░ą╗ą░ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ RxDn. ą¤čĆąŠčåąĄčüčü ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ą┐ąŠą▓č鹊čĆčÅąĄčéčüčÅ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą▒ąĖčéą░, ą┐ąŠą║ą░ ąĮąĄ ąĘą░ą▓ąĄčĆčłąĖčéčüčÅ ą┐čĆąĖąĄą╝ ą▓čüąĄą│ąŠ čäčĆąĄą╣ą╝ą░, ą▓ą║ą╗čÄčćą░čÅ ą┐ąĄčĆą▓čŗą╣ stop-ą▒ąĖčé. ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 ą┐čĆąĖąĄą╝ąĮąĖą║ ąĖčüą┐ąŠą╗čīąĘčāąĄčé č鹊ą╗čīą║ąŠ ą┐ąĄčĆą▓čŗą╣ stop-ą▒ąĖčé čäčĆąĄą╣ą╝ą░.

ąØą░ čĆąĖčü. 22-7 ą┐ąŠą║ą░ąĘą░ąĮą░ ąŠčåąĖčäčĆąŠą▓ą║ą░ stop-ą▒ąĖčéą░ ą║ą░ą║ ą╝ąŠąČąĮąŠ čĆą░ąĮčīčłąĄ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ąĮą░čćą░ą╗ą░ start-ą▒ąĖčéą░ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ čäčĆąĄą╣ą╝ą░.

ąĀąĖčü. 22-7. ąÆčŗą▒ąŠčĆą║ą░ čüč鹊ą┐-ą▒ąĖčéą░ ąĖ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ čüčéą░čĆč鹊ą▓ąŠą│ąŠ ą▒ąĖčéą░.

ąöą╗čÅ ąŠčåąĖčäčĆąŠą▓ą║ąĖ (ą┐ąŠą╗čāč湥ąĮąĖčÅ ąĘąĮą░č湥ąĮąĖčÅ) stop-ą▒ąĖčéą░ ą┐čĆąĖą╝ąĄąĮčÅąĄčéčüčÅ č鹊čé ąČąĄ čüą░ą╝čŗą╣ ą╝ą░ąČąŠčĆąĖčéą░čĆąĮčŗą╣ ą┐čĆąĖąĮčåąĖą┐ ą│ąŠą╗ąŠčüąŠą▓ą░ąĮąĖčÅ, ą║ą░ą║ ąĖ ą┤ą╗čÅ ą┤čĆčāą│ąĖčģ ą▒ąĖčé čäčĆąĄą╣ą╝ą░. ąĢčüą╗ąĖ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąŠ, čćč鹊 stop-ą▒ąĖčé čĆą░ą▓ąĄąĮ ą╗ąŠą│. 0, č鹊 čĆąĄą│ąĖčüčéčĆąĖčĆčāąĄčéčüčÅ ąŠčłąĖą▒ą║ą░ čäčĆąĄą╣ą╝ą░, ąĖ ą▒čāą┤ąĄčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čäą╗ą░ą│ Frame Error (FEn).

ąØąŠą▓čŗą╣ ą┐ąĄčĆąĄčģąŠą┤ 1 -> 0 ą┐ąŠą║ą░ąČąĄčé ąĮą░čćą░ą╗ąŠ start-ą▒ąĖčéą░ ąĮąŠą▓ąŠą│ąŠ čäčĆąĄą╣ą╝ą░, ąĖ ąŠąĮ ą╝ąŠąČąĄčé ą┐ąŠčÅą▓ąĖčéčīčüčÅ čüčĆą░ąĘčā ą┐ąŠčüą╗ąĄ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ ą▒ąĖčéą░, ą▓ ą║ąŠč鹊čĆąŠą╝ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ą╗ąŠčüčī ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čāčĆąŠą▓ąĮčÅ ą┐ąŠ ą╝ą░ąČąŠčĆąĖčéą░čĆąĮąŠą╝čā ą┐čĆąĖąĮčåąĖą┐čā. ąöą╗čÅ čĆąĄąČąĖą╝ą░ Normal Speed, ą┐ąĄčĆą▓ą░čÅ ą▓čŗą▒ąŠčĆą║ą░ čü ąĮąĖąĘą║ąĖą╝ čāčĆąŠą▓ąĮąĄą╝ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓ č鹊čćą║ąĄ, ą┐čĆąŠą╝ą░čĆą║ąĖčĆąŠą▓ą░ąĮąĮąŠą╣ ą║ą░ą║ (A) ąĮą░ čĆąĖčü. 22-7. ąöą╗čÅ Double Speed mode ą┐ąĄčĆą▓čŗą╣ ąĮąĖąĘą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ą┤ąĄčƹȹ░ąĮ ą┤ąŠ (B). (C) ą┐ąŠą╝ąĄčćą░ąĄčé stop-ą▒ąĖčé ą┐ąŠą╗ąĮąŠą╣ ą┤ą╗ąĖąĮčŗ. ąĀą░ąĮąĮąĄąĄ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ start-ą▒ąĖčéą░ ą▓ą╗ąĖčÅąĄčé ąĮą░ čĆą░ą▒ąŠčćąĖą╣ ą┤ąĖą░ą┐ą░ąĘąŠąĮ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ (Asynchronous Operational Range).

Asynchronous Operational Range. ąĀą░ą▒ąŠčćąĖą╣ ą┤ąĖą░ą┐ą░ąĘąŠąĮ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ ąĘą░ą▓ąĖčüąĖčé ąŠčé ąĮąĄčüąŠąŠčéą▓ąĄčéčüčéą▓ąĖčÅ čüą║ąŠčĆąŠčüčéąĖ ą┐čĆąĖąĮąĖą╝ą░ąĄą╝čŗčģ ą▒ąĖčé ąĖ ą│ąĄąĮąĄčĆąĖčĆčāąĄą╝ąŠą╣ ą▓ąĮčāčéčĆąĖ čüą║ąŠčĆąŠčüčéąĖ. ąś ą┐ąĄčĆąĄą┤ą░čéčćąĖą║, ąĖ ą┐čĆąĖąĄą╝ąĮąĖą║ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĮą░čüčéčĆąŠąĄąĮčŗ ąĮą░ ąŠą┤ąĮčā ąĖ čéčā ąČąĄ čüą║ąŠčĆąŠčüčéčī, ąĮąŠ ąĖąĘ-ąĘą░ ą┐ąŠą│čĆąĄčłąĮąŠčüčéąĖ čćą░čüč鹊čéčŗ čüąĖčüč鹥ą╝ąĮąŠą│ąŠ čéą░ą║č鹊ą▓ąŠą│ąŠ ą│ąĄąĮąĄčĆą░č鹊čĆą░ čĆąĄą░ą╗čīąĮčŗąĄ čćą░čüč鹊čéčŗ ą╝ąŠą│čāčé ąŠčéą╗ąĖčćą░čéčīčüčÅ. ąĢčüą╗ąĖ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ ą┐ąŠčüčŗą╗ą░ąĄčé čäčĆąĄą╣ą╝čŗ čüąŠ čüą╗ąĖčłą║ąŠą╝ ą▒ąŠą╗čīčłąŠą╣ čćą░čüč鹊č鹊ą╣ ą▒ąĖčé ąĖą╗ąĖ čüą╗ąĖčłą║ąŠą╝ ą╝ą░ą╗ąŠą╣ čćą░čüč鹊č鹊ą╣ ą▒ąĖčé, ąĖą╗ąĖ ąĄčüą╗ąĖ ą│ąĄąĮąĄčĆąĖčĆčāąĄą╝ą░čÅ čćą░čüč鹊čéą░ ą▒ąĖčé ą┐čĆąĖąĄą╝ąĮąĖą║ą░ ąĖą╝ąĄąĄčé ąŠčéą╗ąĖčćą░čÄčēčāčÄčüčÅ ą▒ą░ąĘąŠą▓čāčÄ čćą░čüč鹊čéčā (čüą╝. čéą░ą▒ą╗ąĖčåčā 22-2), č鹊 ą┐čĆąĖąĄą╝ąĮąĖą║ ąĮąĄ čüą╝ąŠąČąĄčé čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆąŠą▓ą░čéčī čäčĆąĄą╣ą╝čŗ ą┐ąŠ start-ą▒ąĖčéčā.

ąĪą╗ąĄą┤čāčÄčēąĖąĄ č乊čĆą╝čāą╗čŗ ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┤ą╗čÅ ą▓čŗčćąĖčüą╗ąĄąĮąĖčÅ čüąŠąŠčéąĮąŠčłąĄąĮąĖčÅ ą╝ąĄąČą┤čā čüą║ąŠčĆąŠčüčéčīčÄ ą┐čĆąĖąĮąĖą╝ą░ąĄą╝čŗčģ ą┤ą░ąĮąĮčŗčģ ąĖ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ čüą║ąŠčĆąŠčüčéčīčÄ ą┐čĆąĖąĄą╝ąĮąĖą║ą░.

(D + 1) * S

Rslow = ----------------------

S - 1 + D*S + SF |

|

|

(D + 2) * S

Rfast = ----------------------

(D + 1) * S + SM |

D čüčāą╝ą╝ą░ čćąĖčüą╗ą░ ą▒ąĖčé čüąĖą╝ą▓ąŠą╗ą░ ąĖ ą▒ąĖčéą░ č湥čéąĮąŠčüčéąĖ (D = 5 .. 10 ą▒ąĖčé).

S ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▓čŗą▒ąŠčĆąŠą║ ąĮą░ ą▒ąĖčé, S = 16 ą┤ą╗čÅ Normal Speed mode ąĖ S = 8 ą┤ą╗čÅ Double Speed mode.

SF ąĮąŠą╝ąĄčĆ ą┐ąĄčĆą▓ąŠą╣ ą▓čŗą▒ąŠčĆą║ąĖ, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ąŠą╣ ą┤ą╗čÅ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ čāčĆąŠą▓ąĮčÅ ą┐ąŠ ą╝ą░ąČąŠčĆąĖčéą░čĆąĮąŠą╝čā ą┐čĆąĖąĮčåąĖą┐čā. SF = 8 ą┤ą╗čÅ Normal Speed mode ąĖ SF = 4 ą┤ą╗čÅ Double Speed mode.

SM ąĮąŠą╝ąĄčĆ čüčĆąĄą┤ąĮąĄą╣ ą▓čŗą▒ąŠčĆą║ąĖ, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ąŠą╣ ą┤ą╗čÅ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ čāčĆąŠą▓ąĮčÅ ą┐ąŠ ą╝ą░ąČąŠčĆąĖčéą░čĆąĮąŠą╝čā ą┐čĆąĖąĮčåąĖą┐čā. SM = 9 ą┤ą╗čÅ Normal Speed mode ąĖ SM = 5 ą┤ą╗čÅ Double Speed mode.

Rslow čüąŠąŠčéąĮąŠčłąĄąĮąĖąĄ ą╝ąĄąČą┤čā čüą░ą╝ąŠą╣ ąĮąĖąĘą║ąŠą╣ ą▓čģąŠą┤ąĮąŠą╣ čüą║ąŠčĆąŠčüčéčīčÄ ąĖ čüąŠą▒čüčéą▓ąĄąĮąĮąŠą╣ čüą║ąŠčĆąŠčüčéčīčÄ ą┐čĆąĖąĄą╝ąĮąĖą║ą░, ą┐čĆąĖ ą║ąŠč鹊čĆąŠą╝ ą┐čĆąĖąĄą╝ąĮąĖą║ ą▓čüąĄ ąĄčēąĄ ą╝ąŠąČąĄčé ą┐čĆąĖąĮąĖą╝ą░čéčī ą┤ą░ąĮąĮčŗąĄ.

Rfast čüąŠąŠčéąĮąŠčłąĄąĮąĖąĄ ą╝ąĄąČą┤čā čüą░ą╝ąŠą╣ ą▓čŗčüąŠą║ąŠą╣ ą▓čģąŠą┤ąĮąŠą╣ čüą║ąŠčĆąŠčüčéčīčÄ ąĖ čüąŠą▒čüčéą▓ąĄąĮąĮąŠą╣ čüą║ąŠčĆąŠčüčéčīčÄ ą┐čĆąĖąĄą╝ąĮąĖą║ą░, ą┐čĆąĖ ą║ąŠč鹊čĆąŠą╝ ą┐čĆąĖąĄą╝ąĮąĖą║ ą▓čüąĄ ąĄčēąĄ ą╝ąŠąČąĄčé ą┐čĆąĖąĮąĖą╝ą░čéčī ą┤ą░ąĮąĮčŗąĄ.

ąóą░ą▒ą╗ąĖčåčŗ 22-2 ąĖ 22-3 ą┤ą░čÄčé čüą┐ąĖčüąŠą║ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠ ą┤ąŠą┐čāčüčéąĖą╝ąŠą╣ ąŠčłąĖą▒ą║ąĖ baud rate ą┐čĆąĖąĄą╝ąĮąĖą║ą░. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ą┤ą╗čÅ Normal Speed mode ą┤ąŠą┐čāčüą║ ą▒ąŠą╗čīčłąĄ.

ąóą░ą▒ą╗. 22-2. ąĀąĄą║ąŠą╝ąĄąĮą┤čāąĄą╝čŗąĄ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮčŗąĄ čüą║ąŠčĆąŠčüčéąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖ ą┐ąŠą│čĆąĄčłąĮąŠčüčéčī ą┐čĆąĖąĄą╝ąĮąĖą║ą░ ą┤ą╗čÅ ąĮąŠčĆą╝ą░ą╗čīąĮąŠą│ąŠ čĆąĄąČąĖą╝ą░ čüą║ąŠčĆąŠčüčéąĖ (U2Xn = 0).

| D (Data + Parity Bit) |

Rslow (%) |

Rfast (%) |

MAX ąŠą▒čēą░čÅ ąŠčłąĖą▒ą║ą░, % |

ąĀąĄą║ąŠą╝ąĄąĮą┤čāąĄą╝ą░čÅ MAX ąŠčłąĖą▒ą║ą░ ą┐čĆąĖąĄą╝ąĮąĖą║ą░, % |

| 5 |

93.20 |

106.67 |

+6.67 / -6.8 |

┬▒3.0 |

| 6 |

94.12 |

105.79 |

+5.79 / -5.88 |

┬▒2.5 |

| 7 |

94.81 |

105.11 |

+5.11 / -5.19 |

┬▒2.0 |

| 8 |

95.36 |

104.58 |

+4.58 / -4.54 |

┬▒2.0 |

| 9 |

95.81 |

104.14 |

+4.14 / -4.19 |

┬▒1.5 |

| 10 |

96.17 |

103.78 |

+3.78 / -3.83 |

┬▒1.5 |

ąóą░ą▒ą╗. 22-3. ąĀąĄą║ąŠą╝ąĄąĮą┤čāąĄą╝čŗąĄ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮčŗąĄ čüą║ąŠčĆąŠčüčéąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖ ą┐ąŠą│čĆąĄčłąĮąŠčüčéčī ą┐čĆąĖąĄą╝ąĮąĖą║ą░ ą┤ą╗čÅ ą┤ą▓ąŠą╣ąĮąŠą╣ čüą║ąŠčĆąŠčüčéąĖ (U2Xn = 1).

| D (Data + Parity Bit) |

Rslow (%) |

Rfast (%) |

MAX ąŠą▒čēą░čÅ ąŠčłąĖą▒ą║ą░, % |

ąĀąĄą║ąŠą╝ąĄąĮą┤čāąĄą╝ą░čÅ MAX ąŠčłąĖą▒ą║ą░ ą┐čĆąĖąĄą╝ąĮąĖą║ą░, % |

| 5 |

94.12 |

105.66 |

+5.66 / -5.88 |

┬▒2.5 |

| 6 |

94.92 |

104.92 |

+4.92 / -5.08 |

┬▒2.0 |

| 7 |

95.52 |

104.35 |

+4.35 / -4.48 |

┬▒1.5 |

| 8 |

96.00 |

103.90 |

+3.90 / -4.00 |

┬▒1.5 |

| 9 |

96.39 |

103.53 |

+3.53 / -3.61 |

┬▒1.5 |

| 10 |

96.70 |

103.23 |

+3.23 / -3.30 |

┬▒1.0 |

ąĀąĄą║ąŠą╝ąĄąĮą┤ą░čåąĖąĖ ą┐ąŠ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą╣ ąŠčłąĖą▒ą║ąĄ baud rate ą┐čĆąĖąĄą╝ąĮąĖą║ą░ ą▒čŗą╗ąĖ čüą┤ąĄą╗ą░ąĮčŗ ąĮą░ ąŠčüąĮąŠą▓ąĄ ą┐čĆąĄą┤ą┐ąŠą╗ąŠąČąĄąĮąĖčÅ, čćč鹊 ąĖ ą┐čĆąĖąĄą╝ąĮąĖą║, ąĖ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ čĆą░ąĘą┤ąĄą╗čÅčÄčé ąŠą┤ąĖąĮą░ą║ąŠą▓čāčÄ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮčāčÄ ą┐ąŠą│čĆąĄčłąĮąŠčüčéčī čćą░čüč鹊čéčŗ.

ąĢčüčéčī 2 ą▓ąŠąĘą╝ąŠąČąĮčŗčģ ąĖčüč鹊čćąĮąĖą║ą░ ąŠčłąĖą▒ąŠą║ baud rate ą┐čĆąĖąĄą╝ąĮąĖą║ą░. ąĪąĖčüč鹥ą╝ąĮą░čÅ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ (XTAL) ą▓čüąĄą│ą┤ą░ ą▒čāą┤ąĄčé ąĮąĄąĘąĮą░čćąĖč鹥ą╗čīąĮąŠ ąĘą░ą▓ąĖčüąĄčéčī ąŠčé ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ ąĖ č鹥ą╝ą┐ąĄčĆą░čéčāčĆčŗ ąŠą║čĆčāąČą░čÄčēąĄą╣ čüčĆąĄą┤čŗ. ąÜąŠą│ą┤ą░ ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ čüąĖčüč鹥ą╝ąĮąŠą╣ čćą░čüč鹊čéčŗ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą║ą▓ą░čĆčå, č鹊 ą▓ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ą┐čĆąŠą▒ą╗ąĄą╝ čćą░čēąĄ ą▓čüąĄą│ąŠ ąĮąĄ ą▒čāą┤ąĄčé. ą×ą┤ąĮą░ą║ąŠ ąĄčüą╗ąĖ ą┐čĆąĖą╝ąĄąĮąĖčéčī ąĮąĄą║ą░č湥čüčéą▓ąĄąĮąĮčŗą╣ čĆąĄąĘąŠąĮą░č鹊čĆ čü ą┤ąŠą┐čāčüą║ąŠą╝ ą▒ąŠą╗ąĄąĄ 2%, č鹊 čŹč鹊 ą╝ąŠąČąĄčé ą┐ąŠčüą╗čāąČąĖčéčī ą┐čĆąĖčćąĖąĮąŠą╣ ąŠčłąĖą▒ąŠą║. ąÆč鹊čĆąŠą╣ ąĖčüč鹊čćąĮąĖą║ ąŠčłąĖą▒ą║ąĖ ą▒ąŠą╗ąĄąĄ čāą┐čĆą░ą▓ą╗čÅąĄą╝čŗą╣. ąōąĄąĮąĄčĆą░č鹊čĆ baud rate ąĮąĄ ą▓čüąĄą│ą┤ą░ ą┤ąĄą╗ą░ąĄčé č鹊čćąĮąŠąĄ ą┤ąĄą╗ąĄąĮąĖąĄ čüąĖčüč鹥ą╝ąĮąŠą╣ čćą░čüč鹊čéčŗ, čćč鹊ą▒čŗ ą┐ąŠą╗čāčćąĖčéčī ąČąĄą╗ą░ąĄą╝ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ baud rate. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ąČąĄą╗ą░č鹥ą╗čīąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī č鹊 ąĘąĮą░č湥ąĮąĖąĄ ą┤ą╗čÅ UBRR, ą║ąŠč鹊čĆąŠąĄ ą┤ą░ąĄčé ąŠčłąĖą▒ą║čā ą║ą░ą║ ą╝ąŠąČąĮąŠ ą╝ąĄąĮčīčłąĄ.

[Multi-processor Communication Mode]

ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖčéą░ Multi-processor Communication mode (MPCMn) ą▓ čĆąĄą│ąĖčüčéčĆąĄ UCSRnA čĆą░ąĘčĆąĄčłą░ąĄčé čäčāąĮą║čåąĖčÄ čäąĖą╗čīčéčĆą░čåąĖąĖ ą▓čģąŠą┤čÅčēąĖčģ čäčĆąĄą╣ą╝ąŠą▓, ą┐ąŠą╗čāč湥ąĮąĮčŗčģ ą┐čĆąĖąĄą╝ąĮąĖą║ąŠą╝ USART. ążčĆąĄą╣ą╝čŗ, ą║ąŠč鹊čĆčŗąĄ ąĮąĄ čüąŠą┤ąĄčƹȹ░čé ąĖąĮč乊čĆą╝ą░čåąĖčÄ ą░ą┤čĆąĄčüą░, ą▒čāą┤čāčé ąĖą│ąĮąŠčĆąĖčĆąŠą▓ą░čéčīčüčÅ ąĖ ąĮąĄ ą┐ąŠą┐ą░ą┤čāčé ą▓ ą▒čāč乥čĆ ą┐čĆąĖąĄą╝ą░. ąŁč鹊 čŹčäč乥ą║čéąĖą▓ąĮąŠ čāą╝ąĄąĮčīčłąĖčé ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▓čģąŠą┤čÅčēąĖčģ čäčĆąĄą╣ą╝ąŠą▓, ą║ąŠč鹊čĆčŗąĄ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ ąŠą▒čĆą░ą▒ąŠčéą░ąĮčŗ CPU ą▓ čüąĖčüč鹥ą╝ąĄ, ą│ą┤ąĄ ąĮąĄčüą║ąŠą╗čīą║ąŠ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ (MCU) ąŠą▒ą╝ąĄąĮąĖą▓ą░čÄčéčüčÅ ą┤ą░ąĮąĮčŗą╝ąĖ ą┐ąŠ ąŠą┤ąĮąŠą╣ ąĖ č鹊ą╣ ąČąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą╣ čłąĖąĮąĄ ą┤ą░ąĮąĮčŗčģ. ąØą░ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ ąĮąĄ ą▓ą╗ąĖčÅąĄčé čāčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖčéą░ MPCMn, ąĮąŠ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ ą┤ąŠą╗ąČąĄąĮ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┐ąŠ-ą┤čĆčāą│ąŠą╝čā, ą║ąŠą│ą┤ą░ ąŠąĮ čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ čćą░čüčéčī čüąĖčüč鹥ą╝čŗ, ąĖčüą┐ąŠą╗čīąĘčāčÄčēąĄą╣ Multi-processor Communication mode.

ąĢčüą╗ąĖ ą┐čĆąĖąĄą╝ąĮąĖą║ ąĮą░čüčéčĆąŠąĄąĮ ą┤ą╗čÅ ą┐čĆąĖąĄą╝ą░ čäčĆąĄą╣ą╝ąŠą▓, čüąŠą┤ąĄčƹȹ░čēąĖčģ ąŠčé 5 ą┤ąŠ 8 ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ, č鹊 ą┐ąĄčĆą▓čŗą╣ stop-ą▒ąĖčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, ąĄčüčéčī ą╗ąĖ ą▓ąŠ čäčĆąĄą╣ą╝ąĄ ąĖąĮč乊čĆą╝ą░čåąĖčÅ ą░ą┤čĆąĄčüą░. ąĢčüą╗ąĖ ą┐čĆąĖąĄą╝ąĮąĖą║ ąĮą░čüčéčĆąŠąĄąĮ ąĮą░ čäčĆąĄą╣ą╝čŗ čü 9 ą▒ąĖčéą░ą╝ąĖ ą┤ą░ąĮąĮčŗčģ, č鹊 9-ą╣ ą▒ąĖčé (RXB8n) ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░čåąĖąĖ čäčĆąĄą╣ą╝ąŠą▓ ą░ą┤čĆąĄčüą░ ąĖ ą┤ą░ąĮąĮčŗčģ. ąÜąŠą│ą┤ą░ ą▒ąĖčé čéąĖą┐ą░ čäčĆąĄą╣ą╝ą░ (čŹč鹊 ą┐ąĄčĆą▓čŗą╣ stop-ą▒ąĖčé ąĖą╗ąĖ 9-ą╣ ą▒ąĖčé) čĆą░ą▓ąĄąĮ 1, č鹊 čäčĆąĄą╣ą╝ čüąŠą┤ąĄčƹȹĖčé ą░ą┤čĆąĄčü. ąÜąŠą│ą┤ą░ ą▒ąĖčé čéąĖą┐ą░ čäčĆąĄą╣ą╝ą░ čĆą░ą▓ąĄąĮ 0, č鹊 čŹč鹊 ą▒čāą┤ąĄčé čäčĆąĄą╣ą╝ ą┤ą░ąĮąĮčŗčģ.

Multi-processor Communication mode čĆą░ąĘčĆąĄčłą░ąĄčé ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗą╝ MCU ą┐čĆąĖąĮąĖą╝ą░čéčī ą┤ą░ąĮąĮčŗąĄ ąŠčé ą│ą╗ą░ą▓ąĮąŠą│ąŠ MCU. ąŁč鹊 ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą┐čāč鹥ą╝ ą┤ąĄą║ąŠą┤ąĖčĆąŠą▓ą░ąĮąĖčÅ čäčĆąĄą╣ą╝ą░ ą░ą┤čĆąĄčüą░, čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī, ą║ą░ą║ąŠą╣ ąĖą╝ąĄąĮąĮąŠ MCU ą░ą┤čĆąĄčüąŠą▓ą░ąĮ ąĮą░ čłąĖąĮąĄ. ąĢčüą╗ąĖ ą░ą┤čĆąĄčüąŠą▓ą░ąĮ ą║ąŠąĮą║čĆąĄčéąĮčŗą╣ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗą╣ MCU, č鹊 ąŠąĮ ą┐čĆąĖą╝ąĄčé čüą╗ąĄą┤čāčÄčēąĖąĄ čäčĆąĄą╣ą╝čŗ ą┤ą░ąĮąĮčŗčģ ą║ą░ą║ ąŠą▒čŗčćąĮąŠ, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą┤čĆčāą│ąĖąĄ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗąĄ MCUs ą▒čāą┤čāčé ąĖą│ąĮąŠčĆąĖčĆąŠą▓ą░čéčī ą┐čĆąĖąĮčÅčéčŗąĄ čäčĆąĄą╣ą╝čŗ, ą┐ąŠą║ą░ ąĮąĄ ą▒čāą┤ąĄčé ą┐čĆąĖąĮčÅčé ą┤čĆčāą│ąŠą╣ ą░ą┤čĆąĄčüąĮčŗą╣ čäčĆąĄą╣ą╝.

ąśčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ MPCMn. ąöą╗čÅ MCU, ą║ąŠč鹊čĆčŗą╣ čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą│ą╗ą░ą▓ąĮčŗą╣ ąĮą░ ąŠą▒čēąĄą╣ čłąĖąĮąĄ, ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī 9-ą▒ąĖčéąĮčŗą╣ č乊čĆą╝ą░čé čäčĆąĄą╣ą╝ą░ (UCSZn = 7). ąöąĄą▓čÅčéčŗą╣ ą▒ąĖčé (TXB8n) ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ą║ąŠą│ą┤ą░ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ čäčĆąĄą╣ą╝ ą░ą┤čĆąĄčüą░ (TXB8n = 1), ąĖą╗ąĖ ąŠčćąĖčēąĄąĮ, ą║ąŠą│ą┤ą░ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ čäčĆąĄą╣ą╝ ą┤ą░ąĮąĮčŗčģ (TXB = 0). ą¤ąŠą┤čćąĖąĮąĄąĮąĮčŗąĄ MCU ą▓ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĮą░čüčéčĆąŠąĄąĮčŗ ą┤ą╗čÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ 9-ą▒ąĖčéąĮąŠą│ąŠ č乊čĆą╝ą░čéą░ čäčĆąĄą╣ą╝ą░.

ąöą╗čÅ ąŠą▒ą╝ąĄąĮą░ ą┤ą░ąĮąĮčŗą╝ąĖ ą▓ Multi-processor Communication mode ą┤ąŠą╗ąČąĮą░ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ čüą╗ąĄą┤čāčÄčēą░čÅ ą┐čĆąŠčåąĄą┤čāčĆą░:

1. ąÆčüąĄ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗąĄ MCU ąĮą░čüčéčĆąŠąĄąĮčŗ ą▓ Multi-processor Communication mode (čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé MPCMn ą▓ čĆąĄą│ąĖčüčéčĆąĄ UCSRnA).

2. ąōą╗ą░ą▓ąĮčŗą╣ MCU ą┐ąŠčüčŗą╗ą░ąĄčé čäčĆąĄą╣ą╝ ą░ą┤čĆąĄčüą░, ąĖ ą▓čüąĄ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┐čĆąĖąĮąĖą╝ą░čÄčé ąĖ čćąĖčéą░čÄčé čŹč鹊čé čäčĆąĄą╣ą╝. ąÆ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗčģ MCU čäą╗ą░ą│ RXCn ą▓ čĆąĄą│ąĖčüčéčĆąĄ UCSRnA ą▒čāą┤ąĄčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą║ą░ą║ ąŠą▒čŗčćąĮąŠ.

3. ąÜą░ąČą┤čŗą╣ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗą╣ MCU čćąĖčéą░ąĄčé čĆąĄą│ąĖčüčéčĆ UDRn, čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī, čćč鹊 ą┤ą╗čÅ ą┐čĆąĖąĄą╝ą░ ą▓čŗą▒čĆą░ąĮ ąĖą╝ąĄąĮąĮąŠ ąŠąĮ (ą┐čĆąŠą▓ąĄčĆčÅąĄčé čüąŠą▓ą┐ą░ą┤ąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░). ąĢčüą╗ąĖ čéą░ą║, č鹊 ąŠąĮ ąŠčćąĖčēą░ąĄčé ą▒ąĖčé MPCMn ą▓ čĆąĄą│ąĖčüčéčĆąĄ UCSRnA, ą▓ ą┐čĆąŠčéąĖą▓ąĮąŠą╝ čüą╗čāčćą░ąĄ ą┐čĆąŠčüč鹊 ąČą┤ąĄčé čüą╗ąĄą┤čāčÄčēąĄą│ąŠ ą░ą┤čĆąĄčüąĮąŠą│ąŠ čäčĆąĄą╣ą╝ą░, čüąŠčģčĆą░ąĮčÅčÅ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╝ ą▒ąĖčé MPCMn.

4. ąÉą┤čĆąĄčüąŠą▓ą░ąĮąĮčŗą╣ MCU ą▒čāą┤ąĄčé ą┐čĆąĖąĮąĖą╝ą░čéčī ą▓čüąĄ čäčĆąĄą╣ą╝čŗ ą┤ą░ąĮąĮčŗčģ, ą┐ąŠą║ą░ ąĮąĄ ą┐ąŠčüčéčāą┐ąĖčé ąĮąŠą▓čŗą╣ čäčĆąĄą╣ą╝ ą░ą┤čĆąĄčüą░. ąöčĆčāą│ąĖąĄ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗąĄ MCUs, čā ą║ąŠč鹊čĆčŗčģ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé MPCMn, ą▒čāą┤čāčé (ą░ą┐ą┐ą░čĆą░čéąĮąŠ) ąĖą│ąĮąŠčĆąĖčĆąŠą▓ą░čéčī čäčĆąĄą╣ą╝čŗ ą┤ą░ąĮąĮčŗčģ.

5. ąÜąŠą│ą┤ą░ ą░ą┤čĆąĄčüąŠą▓ą░ąĮąĮčŗą╣ MCU ą┐čĆąĖą╝ąĄčé ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ čäčĆąĄą╣ą╝ ą┤ą░ąĮąĮčŗčģ, č鹊 ąŠąĮ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ą▒ąĖčé MPCMn ąĖ ąČą┤ąĄčé ąĮąŠą▓čŗą╣ čäčĆąĄą╣ą╝ ą░ą┤čĆąĄčüą░ ąŠčé ą│ą╗ą░ą▓ąĮąŠą│ąŠ MCU. ąŚą░č鹥ą╝ ą┐čĆąŠčåąĄą┤čāčĆą░ ą┐ąŠą▓č鹊čĆčÅąĄčéčüčÅ ąĮą░čćąĖąĮą░čÅ čü čłą░ą│ą░ 2.

ą£ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą╗čÄą▒ąŠą╣ č乊čĆą╝ą░čé čäčĆąĄą╣ą╝ą░ ąŠčé 5 ą┤ąŠ 8 ą▒ąĖčé, ąĮąŠ čŹč鹊 ąĮąĄą┐čĆą░ą║čéąĖčćąĮąŠ, ą┐ąŠč鹊ą╝čā čćč鹊 ą┐čĆąĖąĄą╝ąĮąĖą║ ąĮčāąČąĮąŠ ą┐ąĄčĆąĄą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī ą╝ąĄąČą┤čā ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ n ąĖ n+1 č乊čĆą╝ą░č鹊ą╝ ą▒ąĖčé čäčĆąĄą╣ą╝ą░. ąŁč鹊 ą┤ąĄą╗ą░ąĄčé ą┐ąŠą╗ąĮąŠą┤čāą┐ą╗ąĄą║čüąĮčŗą╣ ąŠą▒ą╝ąĄąĮ čüą╗ąŠąČąĮčŗą╝, ą┐ąŠč鹊ą╝čā čćč鹊 ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ ąĖ ą┐čĆąĖąĄą╝ąĮąĖą║ ąĖčüą┐ąŠą╗čīąĘčāčÄčé ąĮą░čüčéčĆąŠą╣ą║čā ą┤ą╗čÅ ąŠą┤ąĮąŠą│ąŠ ąĖ č鹊ą│ąŠ ąČąĄ čĆą░ąĘą╝ąĄčĆą░ čüąĖą╝ą▓ąŠą╗ą░. ąĢčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ č乊čĆą╝ą░čé čüąĖą╝ą▓ąŠą╗ą░ ąŠčé 5 ą┤ąŠ 8 ą▒ąĖčé, č鹊 ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ąĮą░ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ ą┤ą▓čāčģ stop-ą▒ąĖč鹊ą▓ (USBSn = 1), ą┐ąŠčüą║ąŠą╗čīą║čā ą┐ąĄčĆą▓čŗą╣ stop-ą▒ąĖčé ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čāą║ą░ąĘą░ąĮąĖčÅ čéąĖą┐ą░ čäčĆąĄą╣ą╝ą░ (ą░ą┤čĆąĄčü ąĖą╗ąĖ ą┤ą░ąĮąĮčŗąĄ).

ąØąĄ ąĖčüą┐ąŠą╗čīąĘčāą╣č鹥 ąĖąĮčüčéčĆčāą║čåąĖąĖ ą░čüčüąĄą╝ą▒ą╗ąĄčĆą░ Read-Modify-Write (SBI ąĖ CBI) ą┤ą╗čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ ąĖą╗ąĖ ąŠčćąĖčüčéą║ąĖ ą▒ąĖčéą░ MPCMn. ąæąĖčé MPCMn ąĖčüą┐ąŠą╗čīąĘčāąĄčé č鹊 ąČąĄ čüą░ą╝ąŠąĄ ą╝ąĄčüč鹊 ą▓ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąĄ I/O, ą║ą░ą║ ąĖ čäą╗ą░ą│ TXCn, ąĖ čŹč鹊 ą╝ąŠąČąĄčé čüą╗čāčćą░ą╣ąĮąŠ ąŠčćąĖčüčéąĖčéčī ąĄą│ąŠ ą┐čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ ąĖąĮčüčéčĆčāą║čåąĖą╣ SBI ąĖą╗ąĖ CBI.

ąÜąŠą╝ą╝ąĄąĮčéą░čĆąĖąĖ

microsin: ą┐čĆąŠčćąĖčéą░ą╣č鹥 ą▓ąĮąĖą╝ą░č鹥ą╗čīąĮąŠ čüčéą░čéčīčÄ, ą▓ ąĮąĄą╣ ą▓čüąĄ ąŠą┐ąĖčüą░ąĮąŠ, ą┤ą░ąČąĄ čü ą┐čĆąĖą╝ąĄčĆąŠą╝ ą║ąŠą┤ą░.

RSS ą╗ąĄąĮčéą░ ą║ąŠą╝ą╝ąĄąĮčéą░čĆąĖąĄą▓ čŹč鹊ą╣ ąĘą░ą┐ąĖčüąĖ