|

ąæą░ą╣čéčŗ ąŠą┐čåąĖą╣ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāčÄčéčüčÅ ą║ąŠąĮąĄčćąĮčŗą╝ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╝ ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čéčĆąĄą▒ąŠą▓ą░ąĮąĖą╣ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ. ąóą░ą▒ą╗ąĖčåą░ 14 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąŠčĆą│ą░ąĮąĖąĘą░čåąĖčÄ čŹčéąĖčģ ą▒ą░ą╣čé ą▓ čüąĄą║č鹊čĆąĄ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ (user configuration sector).

ąóą░ą▒ą╗ąĖčåą░ 14. ą×čĆą│ą░ąĮąĖąĘą░čåąĖčÅ ą▒ą░ą╣čé ąŠą┐čåąĖą╣.

| ąÉą┤čĆąĄčü |

ąæąĖčéčŗ [63:16] |

ąæąĖčéčŗ [15:0] |

| 0x1FFFC000 |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ |

ąŚą░čēąĖčéą░ ąŠčé čćč鹥ąĮąĖčÅ ąĖ ą▒ą░ą╣čéčŗ ąŠą┐čåąĖą╣ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ (RDP & USER) |

| 0x1FFFC008 |

SPRMOD ąĖ ą▒ąĖčéčŗ ąĘą░čēąĖčéčŗ ąŠčé ąĘą░ą┐ąĖčüąĖ nWRP ą┤ą╗čÅ čüąĄą║č鹊čĆąŠą▓ 0 .. 11 |

| 0x1FFEC000 |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ |

| 0x1FFEC008 |

SPRMOD ąĖ ą▒ąĖčéčŗ ąĘą░čēąĖčéčŗ ąŠčé ąĘą░ą┐ąĖčüąĖ nWRP ą┤ą╗čÅ čüąĄą║č鹊čĆąŠą▓ 12 .. 23 |

ąóą░ą▒ą╗ąĖčåą░ 15. ą×ą┐ąĖčüą░ąĮąĖąĄ ą▒ą░ą╣čé ąŠą┐čåąĖą╣ STM32F405xx/07xx ąĖ STM32F415xx/17xx.

| ąæą░ą╣čéčŗ ąŠą┐čåąĖą╣ (čüą╗ąŠą▓ąŠ, ą░ą┤čĆąĄčü 0x1FFFC000) |

| RDP: ą▒ą░ą╣čé ąŠą┐čåąĖą╣ ąĘą░čēąĖčéčŗ ąŠčé čćč鹥ąĮąĖčÅ. ąŁč鹊 ąĘą░čēąĖčēą░ąĄčé ąŠčé ąĮąĄąČąĄą╗ą░č鹥ą╗čīąĮąŠą│ąŠ ą┤ąŠčüčéčāą┐ą░ ą║ąŠą┤ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ, čüąŠčģčĆą░ąĮąĄąĮąĮčŗą╣ ą▓ ą┐ą░ą╝čÅčéąĖ Flash. |

| ąæąĖčéčŗ 15:8 |

0xAA: Level 0, ąĘą░čēąĖčéą░ ąŠčéą║ą╗čÄč湥ąĮą░.

0xCC: Level 2, ąĘą░čēąĖčéą░ ą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮą░ (ąĘą░ą┐čĆąĄčēąĄąĮčŗ čäčāąĮą║čåąĖąĖ ąŠčéą╗ą░ą┤ą║ąĖ ąĖ ąĘą░ą│čĆčāąĘą║ąĖ ąĖąĘ RAM).

ąöčĆčāą│ąĖąĄ ąĘąĮą░č湥ąĮąĖčÅ: Level 1, ąĘą░čēąĖčéą░ ąŠčé čćč鹥ąĮąĖčÅ ą┐ą░ą╝čÅčéąĖ (čäčāąĮą║čåąĖąĖ ąŠčéą╗ą░ą┤ą║ąĖ ąŠą│čĆą░ąĮąĖč湥ąĮčŗ). |

USER: ą▒ą░ą╣čé ąŠą┐čåąĖą╣ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ. ąŁč鹊čé ą▒ą░ą╣čé ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ čüą╗ąĄą┤čāčÄčēąĖčģ čäčāąĮą║čåąĖą╣:

ŌĆō ąÆčŗą▒ąŠčĆ čüąŠą▒čŗčéąĖčÅ čüč鹊čĆąŠąČąĄą▓ąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░ (watchdog event): ą░ą┐ą┐ą░čĆą░čéąĮąŠąĄ ąĖą╗ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠąĄ.

ŌĆō ąĪąŠą▒čŗčéąĖąĄ čüą▒čĆąŠčüą░ ą┐čĆąĖ ą▓čģąŠą┤ąĄ ą▓ čĆąĄąČąĖą╝ Stop.

ŌĆō ąĪąŠą▒čŗčéąĖąĄ čüą▒čĆąŠčüą░ ą┐čĆąĖ ą▓čģąŠą┤ąĄ ą▓ čĆąĄąČąĖą╝ Standby. |

| ąæąĖčé 7 |

nRST_STDBY

0: ą┐čĆąĖ ą▓čģąŠą┤ąĄ ą▓ čĆąĄąČąĖą╝ Standby ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ čüą▒čĆąŠčü.

1: čüą▒čĆąŠčü ąĮąĄ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ. |

| ąæąĖčé 6 |

nRST_STOP

0: ą┐čĆąĖ ą▓čģąŠą┤ąĄ ą▓ čĆąĄąČąĖą╝ Stop ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ čüą▒čĆąŠčü.

1: čüą▒čĆąŠčü ąĮąĄ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ. |

| ąæąĖčé 5 |

WDG_SW

0: ą░ą┐ą┐ą░čĆą░čéąĮčŗą╣ ąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗą╣ čüč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ.

1: ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ ąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗą╣ čüč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ. |

| ąæąĖčé 4 |

1: ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ |

| ąæąĖčéčŗ 3:2 |

BOR_LEV: BOR reset Level, čāčĆąŠą▓ąĄąĮčī čüą▒čĆąŠčüą░ ą▒ą╗ąŠą║ą░ ą║ąŠąĮčéčĆąŠą╗čÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ. ąŁčéąĖ ą▒ąĖčéčŗ ąĘą░ą┤ą░čÄčé ą┐ąŠčĆąŠą│ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ, ą║ąŠč鹊čĆčŗą╣ ą░ą║čéąĖą▓ąĖčĆčāąĄčé/čüąĮąĖą╝ą░ąĄčé čüą▒čĆąŠčü. ą×ąĮąĖ ą╝ąŠą│čāčé ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮčŗ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣ ą▓ Flash ą┐ą░ą╝čÅčéąĖ, čćč鹊ą▒čŗ čāčüčéą░ąĮąŠą▓ąĖčéčī ąĮąŠą▓čŗą╣ čāčĆąŠą▓ąĄąĮčī BOR.

00: BOR Level 3 (VBOR3)

01: BOR Level 2 (VBOR2)

10: BOR Level 1 (VBOR1)

11: BOR ąŠčéą║ą╗čÄč湥ąĮ, ą┐čĆąĖą╝ąĄąĮčÅąĄčéčüčÅ ą┐ąŠčĆąŠą│ POR/PDR.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ą┐ąŠą╗ąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ą┐ąŠ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ą░ą╝ BOR čüą╝. čüąĄą║čåąĖčÄ "Electrical characteristics" ą┤ą░čéą░čłąĖčéą░ ąĮą░ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╣ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ. |

| ąæąĖčéčŗ 0:1 |

1: ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ |

| ąæą░ą╣čéčŗ ąŠą┐čåąĖą╣ (čüą╗ąŠą▓ąŠ, ą░ą┤čĆąĄčü 0x1FFFC008) |

| ąæąĖčéčŗ 15:12 |

0xF: ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ |

| nWRP: ą▒ą░ą╣čéčŗ ąŠą┐čåąĖą╣ ąĘą░čēąĖčéčŗ ąŠčé ąĘą░ą┐ąĖčüąĖ čüąĄą║č鹊čĆąŠą▓ 0 .. 11. |

| ąæąĖčéčŗ 11:0 |

nWRPi (0 Ōēż i Ōēż 11)

0: ąĮą░ ą▓čŗą▒čĆą░ąĮąĮąŠą╝ čüąĄą║č鹊čĆąĄ i ą░ą║čéąĖą▓ąĮą░ ąĘą░čēąĖčéą░ ąŠčé ąĘą░ą┐ąĖčüąĖ.

1: ąĮą░ ą▓čŗą▒čĆą░ąĮąĮąŠą╝ čüąĄą║č鹊čĆąĄ i ąĘą░čēąĖčéą░ ąŠčé ąĘą░ą┐ąĖčüąĖ ąĮąĄ ą░ą║čéąĖą▓ąĮą░. |

ąóą░ą▒ą╗ąĖčåą░ 16. ą×ą┐ąĖčüą░ąĮąĖąĄ ą▒ą░ą╣čé ąŠą┐čåąĖą╣ STM32F42xxx ąĖ STM32F43xxx.

| ąæą░ą╣čéčŗ ąŠą┐čåąĖą╣ (čüą╗ąŠą▓ąŠ, ą░ą┤čĆąĄčü 0x1FFFC000) |

| RDP: ą▒ą░ą╣čé ąŠą┐čåąĖą╣ ąĘą░čēąĖčéčŗ ąŠčé čćč鹥ąĮąĖčÅ. ąŁč鹊 ąĘą░čēąĖčēą░ąĄčé ąŠčé ąĮąĄąČąĄą╗ą░č鹥ą╗čīąĮąŠą│ąŠ ą┤ąŠčüčéčāą┐ą░ ą║ąŠą┤ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ, čüąŠčģčĆą░ąĮąĄąĮąĮčŗą╣ ą▓ ą┐ą░ą╝čÅčéąĖ Flash. |

| ąæąĖčéčŗ 15:8 |

0xAA: Level 0, ąĘą░čēąĖčéą░ ąŠčéą║ą╗čÄč湥ąĮą░.

0xCC: Level 2, ąĘą░čēąĖčéą░ ą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮą░ (ąĘą░ą┐čĆąĄčēąĄąĮčŗ čäčāąĮą║čåąĖąĖ ąŠčéą╗ą░ą┤ą║ąĖ ąĖ ąĘą░ą│čĆčāąĘą║ąĖ ąĖąĘ RAM).

ąöčĆčāą│ąĖąĄ ąĘąĮą░č湥ąĮąĖčÅ: Level 1, ąĘą░čēąĖčéą░ ąŠčé čćč鹥ąĮąĖčÅ ą┐ą░ą╝čÅčéąĖ (čäčāąĮą║čåąĖąĖ ąŠčéą╗ą░ą┤ą║ąĖ ąŠą│čĆą░ąĮąĖč湥ąĮčŗ). |

USER: ą▒ą░ą╣čé ąŠą┐čåąĖą╣ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ. ąŁč鹊čé ą▒ą░ą╣čé ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ čüą╗ąĄą┤čāčÄčēąĖčģ čäčāąĮą║čåąĖą╣:

ŌĆō ąÆčŗą▒ąŠčĆ čüąŠą▒čŗčéąĖčÅ čüč鹊čĆąŠąČąĄą▓ąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░ (watchdog event): ą░ą┐ą┐ą░čĆą░čéąĮąŠąĄ ąĖą╗ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠąĄ.

ŌĆō ąĪąŠą▒čŗčéąĖąĄ čüą▒čĆąŠčüą░ ą┐čĆąĖ ą▓čģąŠą┤ąĄ ą▓ čĆąĄąČąĖą╝ Stop.

ŌĆō ąĪąŠą▒čŗčéąĖąĄ čüą▒čĆąŠčüą░ ą┐čĆąĖ ą▓čģąŠą┤ąĄ ą▓ čĆąĄąČąĖą╝ Standby. |

| ąæąĖčé 7 |

nRST_STDBY

0: ą┐čĆąĖ ą▓čģąŠą┤ąĄ ą▓ čĆąĄąČąĖą╝ Standby ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ čüą▒čĆąŠčü.

1: čüą▒čĆąŠčü ąĮąĄ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ. |

| ąæąĖčé 6 |

nRST_STOP

0: ą┐čĆąĖ ą▓čģąŠą┤ąĄ ą▓ čĆąĄąČąĖą╝ Stop ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ čüą▒čĆąŠčü.

1: čüą▒čĆąŠčü ąĮąĄ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ. |

| ąæąĖčé 5 |

WDG_SW

0: ą░ą┐ą┐ą░čĆą░čéąĮčŗą╣ ąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗą╣ čüč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ.

1: ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ ąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗą╣ čüč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ. |

| ąæąĖčé 4 |

BFB2: Dual bank boot

0: ąĘą░ą│čĆčāąĘą║ą░ ąĖąĘ ą▒ą░ąĮą║ą░ 1 ą┐ą░ą╝čÅčéąĖ Flash ąĖą╗ąĖ čüąĖčüč鹥ą╝ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čüąŠčüč鹊čÅąĮąĖčÅ ąĮąŠąČąĄą║ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĘą░ą│čĆčāąĘą║ąŠą╣ (ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ).

1: ąĘą░ą│čĆčāąĘą║ą░ ą▓čüąĄą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ąĖąĘ čüąĖčüč鹥ą╝ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ (Dual bank boot mode). |

| ąæąĖčéčŗ 3:2 |

BOR_LEV: BOR reset Level, čāčĆąŠą▓ąĄąĮčī čüą▒čĆąŠčüą░ ą▒ą╗ąŠą║ą░ ą║ąŠąĮčéčĆąŠą╗čÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ. ąŁčéąĖ ą▒ąĖčéčŗ ąĘą░ą┤ą░čÄčé ą┐ąŠčĆąŠą│ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ, ą║ąŠč鹊čĆčŗą╣ ą░ą║čéąĖą▓ąĖčĆčāąĄčé/čüąĮąĖą╝ą░ąĄčé čüą▒čĆąŠčü. ą×ąĮąĖ ą╝ąŠą│čāčé ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮčŗ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣ ą▓ Flash ą┐ą░ą╝čÅčéąĖ, čćč鹊ą▒čŗ čāčüčéą░ąĮąŠą▓ąĖčéčī ąĮąŠą▓čŗą╣ čāčĆąŠą▓ąĄąĮčī BOR.

00: BOR Level 3 (VBOR3)

01: BOR Level 2 (VBOR2)

10: BOR Level 1 (VBOR1)

11: BOR ąŠčéą║ą╗čÄč湥ąĮ, ą┐čĆąĖą╝ąĄąĮčÅąĄčéčüčÅ ą┐ąŠčĆąŠą│ POR/PDR.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ą┐ąŠą╗ąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ą┐ąŠ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ą░ą╝ BOR čüą╝. čüąĄą║čåąĖčÄ "Electrical characteristics" ą┤ą░čéą░čłąĖčéą░ ąĮą░ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╣ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ. |

| ąæąĖčéčŗ 0:1 |

1: ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ |

| ąæą░ą╣čéčŗ ąŠą┐čåąĖą╣ (čüą╗ąŠą▓ąŠ, ą░ą┤čĆąĄčü 0x1FFFC008) |

| ąæąĖčé 15 |

SPRMOD: ą▓čŗą▒ąŠčĆ čĆąĄąČąĖą╝ą░ ąĘą░čēąĖčéčŗ ą▒ąĖčé nWPRi

0: ą▒ąĖčéčŗ nWPRi ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ ąĘą░čēąĖčéčŗ ąŠčé ąĘą░ą┐ąĖčüąĖ čüąĄą║č鹊čĆą░ i (ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ).

1: ą▒ąĖčéčŗ nWPRi ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ ąĘą░čēąĖčéčŗ PCROP čüąĄą║č鹊čĆą░ i. |

| ąæąĖčé 14 |

DB1M: čāčüčéčĆąŠą╣čüčéą▓ą░ čü Flash-ą┐ą░ą╝čÅčéčīčÄ Dual bank 1 ą╝ąĄą│ą░ą▒ą░ą╣čé

0: ąŠą┤ąĮąŠ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ Flash-ą┐ą░ą╝čÅčéąĖ 1 ą╝ąĄą│ą░ą▒ą░ą╣čé (ąĮąĄą┐čĆąĄčĆčŗą▓ąĮą░čÅ ą░ą┤čĆąĄčüą░čåąĖčÅ ą▓ ą▒ą░ąĮą║ąĄ 1).

1: ą┤ą▓ą░ ą▒ą░ąĮą║ą░ ą┐ą░ą╝čÅčéąĖ Flash ąŠą▒čŖąĄą╝ąŠą╝ 1 ą╝ąĄą│ą░ą▒ą░ą╣čé. ą¤ą░ą╝čÅčéčī Flash ąŠčĆą│ą░ąĮąĖąĘąŠą▓ą░ąĮą░ ą║ą░ą║ 2 ą▒ą░ąĮą║ą░ ą┐ąŠ 512 ą║ąĖą╗ąŠą▒ą░ą╣čé ą║ą░ąČą┤čŗą╣ (čüą╝. čéą░ą▒ą╗ąĖčåčŗ 7 ąĖ 9 ą┤ą░čéą░čłąĖčéą░ [1]). ąöą╗čÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ąŠą┐ąĄčĆą░čåąĖąĖ čüčéąĖčĆą░ąĮąĖčÅ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ ą┐čĆą░ą▓ąĖą╗čīąĮčŗą╣ čüąĄą║č鹊čĆ (čüą╝. čéą░ą▒ą╗ąĖčåčā 7 ą┤ą╗čÅ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ą┐ąŠ čüčģąĄą╝ąĄ ąĮčāą╝ąĄčĆą░čåąĖąĖ čüąĄą║č鹊čĆąŠą▓). |

| ąæąĖčéčŗ 13:12 |

0x2: ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ |

| nWRP: ą▒ą░ą╣čéčŗ ąŠą┐čåąĖą╣ ąĘą░čēąĖčéčŗ ąŠčé ąĘą░ą┐ąĖčüąĖ ą┐ą░ą╝čÅčéąĖ Flash ą┤ą╗čÅ ą▒ą░ąĮą║ą░ 1. ą£ąŠą│čāčé ą▒čŗčéčī ąĘą░čēąĖčēąĄąĮčŗ čüąĄą║č鹊čĆčŗ 0 .. 11. |

| ąæąĖčéčŗ 11:0 |

nWRPi, ąĄčüą╗ąĖ ą▒ąĖčé SPRMOD čüą▒čĆąŠčłąĄąĮ (ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ):

0: ą░ą║čéąĖą▓ąĮą░ ąĘą░čēąĖčéą░ ąŠčé ąĘą░ą┐ąĖčüąĖ čüąĄą║č鹊čĆą░ i.

1: ąĘą░čēąĖčéą░ ąŠčé ąĘą░ą┐ąĖčüąĖ čüąĄą║č鹊čĆą░ i ąĮąĄ ą░ą║čéąĖą▓ąĮą░.

ąĢčüą╗ąĖ ą▒ąĖčé SPRMOD čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ:

0: ąĘą░čēąĖčéą░ PCROP ą┤ą╗čÅ čüąĄą║č鹊čĆą░ i ąĮąĄ ą░ą║čéąĖą▓ąĮą░.

1: ą┤ą╗čÅ čüąĄą║č鹊čĆą░ i ą░ą║čéąĖą▓ąĮą░ ąĘą░čēąĖčéą░ PCROP. |

| ąæą░ą╣čéčŗ ąŠą┐čåąĖą╣ (čüą╗ąŠą▓ąŠ, ą░ą┤čĆąĄčü 0x1FFEC000) |

| ąæąĖčéčŗ 15:0 |

0xFFFF: ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ |

| ąæą░ą╣čéčŗ ąŠą┐čåąĖą╣ (čüą╗ąŠą▓ąŠ, ą░ą┤čĆąĄčü 0x1FFEC008) |

| ąæąĖčéčŗ 15:12 |

0xF: ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ |

| nWRP: ą▒ą░ą╣čéčŗ ąŠą┐čåąĖą╣ ąĘą░čēąĖčéčŗ ąŠčé ąĘą░ą┐ąĖčüąĖ ą┐ą░ą╝čÅčéąĖ Flash ą┤ą╗čÅ ą▒ą░ąĮą║ą░ 2. ą£ąŠą│čāčé ą▒čŗčéčī ąĘą░čēąĖčēąĄąĮčŗ čüąĄą║č鹊čĆčŗ 12 .. 23. |

| ąæąĖčéčŗ 11:0 |

nWRPi, ąĄčüą╗ąĖ ą▒ąĖčé SPRMOD čüą▒čĆąŠčłąĄąĮ (ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ):

0: ą░ą║čéąĖą▓ąĮą░ ąĘą░čēąĖčéą░ ąŠčé ąĘą░ą┐ąĖčüąĖ čüąĄą║č鹊čĆą░ i.

1: ąĘą░čēąĖčéą░ ąŠčé ąĘą░ą┐ąĖčüąĖ čüąĄą║č鹊čĆą░ i ąĮąĄ ą░ą║čéąĖą▓ąĮą░.

ąĢčüą╗ąĖ ą▒ąĖčé SPRMOD čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ:

0: ąĘą░čēąĖčéą░ PCROP ą┤ą╗čÅ čüąĄą║č鹊čĆą░ i ąĮąĄ ą░ą║čéąĖą▓ąĮą░.

1: ą┤ą╗čÅ čüąĄą║č鹊čĆą░ i ą░ą║čéąĖą▓ąĮą░ ąĘą░čēąĖčéą░ PCROP. |

[ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ ą▒ą░ą╣čé ąŠą┐čåąĖą╣]

ą¦č鹊ą▒čŗ ąĘą░ą┐čāčüčéąĖčéčī ą╗čÄą▒čāčÄ ąŠą┐ąĄčĆą░čåąĖčÄ ąĮą░ čŹč鹊ą╝ čüąĄą║č鹊čĆąĄ, ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąŠčćąĖčēąĄąĮ ą▒ąĖčé ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ ąŠą┐čåąĖą╣ (option lock bit, OPTLOCK) ą▓ čĆąĄą│ąĖčüčéčĆąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąŠą┐čåąĖčÅą╝ąĖ Flash (FLASH_OPTCR). ą¦č鹊ą▒čŗ ą╝ąŠąČąĮąŠ ą▒čŗą╗ąŠ ąŠčćąĖčüčéąĖčéčī čŹč鹊čé ą▒ąĖčé, ąÆčŗ ą┤ąŠą╗ąČąĮčŗ ą▓čŗą┐ąŠą╗ąĮąĖčéčī čüą╗ąĄą┤čāčÄčēąĖąĄ ą┤ąĄą╣čüčéą▓ąĖčÅ:

1. ąŚą░ą┐ąĖčüą░čéčī OPTKEY1 = 0x08192A3B ą▓ čĆąĄą│ąĖčüčéčĆ ą║ą╗čÄčćą░ ąŠą┐čåąĖą╣ Flash (FLASH_OPTKEYR).

2. ąŚą░ą┐ąĖčüą░čéčī OPTKEY2 = 0x4C5D6E7F ą▓ čĆąĄą│ąĖčüčéčĆ ą║ą╗čÄčćą░ ąŠą┐čåąĖą╣ Flash (FLASH_OPTKEYR).

ąæą░ą╣čéčŗ ąŠą┐čåąĖą╣ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ ą╝ąŠą│čāčé ą▒čŗčéčī ąĘą░čēąĖčēąĄąĮčŗ ąŠčé ąĮąĄąČąĄą╗ą░č鹥ą╗čīąĮčŗčģ ąŠą┐ąĄčĆą░čåąĖą╣ čüčéąĖčĆą░ąĮąĖčÅ/ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čāč鹥ą╝ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą╣ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ OPTLOCK.

ą£ąŠą┤ąĖčäąĖą║ą░čåąĖčÅ ą▒ą░ą╣čé ąŠą┐čåąĖą╣ STM32F405xx/07xx ąĖ STM32F415xx/17xx. ą¦č鹊ą▒čŗ ą╝ąŠą┤ąĖčäąĖčåąĖčĆąŠą▓ą░čéčī ąĘąĮą░č湥ąĮąĖąĄ ąŠą┐čåąĖąĖ, ą▓čŗą┐ąŠą╗ąĮąĖč鹥 čüą╗ąĄą┤čāčÄčēčāčÄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┤ąĄą╣čüčéą▓ąĖą╣:

1. ą¤čĆąŠą▓ąĄčĆčīč鹥, čćč鹊 ą▓ ąĮą░čüč鹊čÅčēąĖą╣ ą╝ąŠą╝ąĄąĮčé ąĮąĄ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ąŠą┐ąĄčĆą░čåąĖčÅ čü ą┐ą░ą╝čÅčéčīčÄ Flash, ą┐čāč鹥ą╝ ą┐čĆąŠą▓ąĄčĆą║ąĖ ą▒ąĖčéą░ BSY ą▓ čĆąĄą│ąĖčüčéčĆąĄ FLASH_SR.

2. ąŚą░ą┐ąĖčłąĖč鹥 ąČąĄą╗ą░ąĄą╝ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ąŠą┐čåąĖąĖ ą▓ čĆąĄą│ąĖčüčéčĆ FLASH_OPTCR.

3. ąŻčüčéą░ąĮąŠą▓ąĖč鹥 ą▒ąĖčé ąĘą░ą┐čāčüą║ą░ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ąŠą┐čåąĖąĖ (option start bit, OPTSTRT) ą▓ čĆąĄą│ąĖčüčéčĆąĄ FLASH_OPTCR.

4. ą¤ąŠą┤ąŠąČą┤ąĖč鹥 ąŠčćąĖčüčéą║ąĖ ą▒ąĖčéą░ BSY.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĘąĮą░č湥ąĮąĖąĄ ąŠą┐čåąĖąĖ ą╝ąŠą┤ąĖčäąĖčåąĖčĆčāąĄčéčüčÅ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ, ą┐čĆąĖ čŹč鹊ą╝ čüąĮą░čćą░ą╗ą░ čüčéąĖčĆą░ąĄčéčüčÅ čüąĄą║č鹊čĆ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ, ąĖ ąĘą░č鹥ą╝ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāčÄčéčüčÅ ą▓čüąĄ ą▒ą░ą╣čéčŗ ąŠą┐čåąĖą╣ čü ąĘąĮą░č湥ąĮąĖčÅą╝ąĖ, čüąŠą┤ąĄčƹȹ░čēąĖą╝ąĖčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ FLASH_OPTCR.

ą£ąŠą┤ąĖčäąĖą║ą░čåąĖčÅ ą▒ą░ą╣čé ąŠą┐čåąĖą╣ STM32F42xxx ąĖ STM32F43xxx. ąæą░ą╣čéčŗ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ ą┤ą╗čÅ ą▒ą░ąĮą║ą░ 1 ąĖ ą▒ą░ąĮą║ą░ 2 ąĮąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ąĖąĘą╝ąĄąĮąĄąĮčŗ ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ. ą×ąĮąĖ ą┤ąŠą╗ąČąĮčŗ ąŠą▒ąĮąŠą▓ą╗čÅčéčīčüčÅ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ. ą¦č鹊ą▒čŗ ąĖąĘą╝ąĄąĮąĖčéčī ąĘąĮą░č湥ąĮąĖąĄ ą▒ą░ą╣čéą░ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čīčüą║ąŠą╣ ąŠą┐čåąĖąĖ, ą▓čŗą┐ąŠą╗ąĮąĖč鹥 čüą╗ąĄą┤čāčÄčēąĖąĄ ą┤ąĄą╣čüčéą▓ąĖčÅ:

1. ą¤čĆąŠą▓ąĄčĆčīč鹥, čćč鹊 ą▓ ąĮą░čüč鹊čÅčēąĖą╣ ą╝ąŠą╝ąĄąĮčé ąĮąĄ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ąŠą┐ąĄčĆą░čåąĖčÅ čü ą┐ą░ą╝čÅčéčīčÄ Flash, ą┐čāč鹥ą╝ ą┐čĆąŠą▓ąĄčĆą║ąĖ ą▒ąĖčéą░ BSY ą▓ čĆąĄą│ąĖčüčéčĆąĄ FLASH_SR.

2. ąŚą░ą┐ąĖčłąĖč鹥 ąĘąĮą░č湥ąĮąĖąĄ ą▒ą░ą╣čéą░ ąŠą┐čåąĖą╣ ą▒ą░ąĮą║ą░ 2 ą▓ čĆąĄą│ąĖčüčéčĆ FLASH_OPTCR1.

3. ąŚą░ą┐ąĖčłąĖč鹥 ąĘąĮą░č湥ąĮąĖąĄ ą▒ą░ą╣čéą░ ąŠą┐čåąĖą╣ ą▒ą░ąĮą║ą░ 1 ą▓ čĆąĄą│ąĖčüčéčĆ FLASH_OPTCR.

4. ąŻčüčéą░ąĮąŠą▓ąĖč鹥 ą▒ąĖčé ąĘą░ą┐čāčüą║ą░ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ąŠą┐čåąĖąĖ (option start bit, OPTSTRT) ą▓ čĆąĄą│ąĖčüčéčĆąĄ FLASH_OPTCR.

5. ą¤ąŠą┤ąŠąČą┤ąĖč鹥 ąŠčćąĖčüčéą║ąĖ ą▒ąĖčéą░ BSY.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĘąĮą░č湥ąĮąĖąĄ ą▒ą░ą╣čéą░ ąŠą┐čåąĖą╣ ą╝ąŠą┤ąĖčäąĖčåąĖčĆčāąĄčéčüčÅ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ, ą┐čĆąĖ čŹč鹊ą╝ čüąĮą░čćą░ą╗ą░ čüčéąĖčĆą░ąĄčéčüčÅ čüąĄą║č鹊čĆ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ (ą▒ą░ąĮą║ 1 ąĖ ą▒ą░ąĮą║ 2), ąĖ ąĘą░č鹥ą╝ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāčÄčéčüčÅ ą▓čüąĄ ą▒ą░ą╣čéčŗ ąŠą┐čåąĖą╣ čü ąĘąĮą░č湥ąĮąĖčÅą╝ąĖ, čüąŠą┤ąĄčƹȹ░čēąĖą╝ąĖčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆą░čģ FLASH_OPTCR ąĖ FLASH_OPTCR1.

[Read protection (RDP)]

ą¤ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čīčüą║ą░čÅ ąŠą▒ą╗ą░čüčéčī ą▓ ą┐ą░ą╝čÅčéąĖ Flash ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░čēąĖčēąĄąĮą░ ąŠčé ąŠą┐ąĄčĆą░čåąĖą╣ čćč鹥ąĮąĖčÅ čüąŠ čüč鹊čĆąŠąĮčŗ ą┤ąŠą▓ąĄčĆąĄąĮąĮąŠą│ąŠ ą║ąŠą┤ą░. ą×ą┐čĆąĄą┤ąĄą╗ąĄąĮčŗ 3 čāčĆąŠą▓ąĮčÅ ąĘą░čēąĖčéčŗ ąŠčé čćč鹥ąĮąĖčÅ:

ŌĆó Level 0: ąĮąĄčé ąĘą░čēąĖčéčŗ ąŠčé čćč鹥ąĮąĖčÅ

ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čāčĆąŠą▓ąĄąĮčī 0 ąĘą░čēąĖčéčŗ čćč鹥ąĮąĖčÅ ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ 0xAA ą▓ ą▒ą░ą╣čé ąŠą┐čåąĖąĖ ąĘą░čēąĖčéčŗ čćč鹥ąĮąĖčÅ (read protection option byte, RDP), čĆą░ąĘčĆąĄčłąĄąĮčŗ ą▓čüąĄ ąŠą┐ąĄčĆą░čåąĖąĖ čćč鹥ąĮąĖčÅ/ąĘą░ą┐ąĖčüąĖ (ąĄčüą╗ąĖ ąĮąĄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮą░ ąĘą░čēąĖčéą░ ąŠčé ąĘą░ą┐ąĖčüąĖ) ą┐ą░ą╝čÅčéąĖ Flash ąĖą╗ąĖ Backup SRAM ą▓ąŠ ą▓čüąĄčģ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅčģ ąĘą░ą│čĆčāąĘą║ąĖ (Flash user boot, debug or boot from RAM).

ŌĆó Level 1: čĆą░ąĘčĆąĄčłąĄąĮą░ ąĘą░čēąĖčéą░ ąŠčé čćč鹥ąĮąĖčÅ

ąŁč鹊 čāčĆąŠą▓ąĄąĮčī ąĘą░čēąĖčéčŗ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą┐ąŠčüą╗ąĄ čüčéąĖčĆą░ąĮąĖčÅ ą▒ą░ą╣čéą░ ąŠą┐čåąĖą╣. ąŚą░čēąĖčéą░ ąŠčé čćč鹥ąĮąĖčÅ Level 1 ą░ą║čéąĖą▓ąĖčĆčāąĄčéčüčÅ ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ ą╗čÄą▒ąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ (ą║čĆąŠą╝ąĄ 0xAA ąĖ 0xCC, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą┤ą╗čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ čāčĆąŠą▓ąĮąĄą╣ Level 0 ąĖ Level 2 čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ) ą▓ ą▒ą░ą╣čé ąŠą┐čåąĖą╣ RDP. ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮą░ ąĘą░čēąĖčéą░ ąŠčé čćč鹥ąĮąĖčÅ Level 1:

ŌĆō ąØąĄ čĆą░ąĘčĆąĄčłąĄąĮ ą┤ąŠčüčéčāą┐ ą║ ą┐ą░ą╝čÅčéąĖ Flash ąĖą╗ąĖ Backup SRAM (čćč鹥ąĮąĖąĄ, čüčéąĖčĆą░ąĮąĖąĄ, ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ) ą┐čĆąĖ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖąĖ čäčāąĮą║čåąĖąĖ ąŠčéą╗ą░ą┤ą║ąĖ ąĖą╗ąĖ ą┐čĆąĖ ąĘą░ą│čĆčāąĘą║ąĄ ąĖąĘ RAM ąĖą╗ąĖ ąĖąĘ ąĘą░ą│čĆčāąĘčćąĖą║ą░ čüąĖčüč鹥ą╝ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ (system memory bootloader). ąōąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ąŠčłąĖą▒ą║ą░ čłąĖąĮčŗ ą┐čĆąĖ ąĘą░ą┐čĆąŠčüąĄ čćč鹥ąĮąĖčÅ.

ŌĆō ąÜąŠą│ą┤ą░ ą▒čŗą╗ą░ ąĘą░ą│čĆčāąĘą║ą░ ąĖąĘ ą┐ą░ą╝čÅčéąĖ Flash, čĆą░ąĘčĆąĄčłąĄąĮ ą┤ąŠčüčéčāą┐ (čćč鹥ąĮąĖąĄ, čüčéąĖčĆą░ąĮąĖąĄ, ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ) ą║ ą┐ą░ą╝čÅčéąĖ Flash ąĖ Backup SRAM ąĖąĘ ą║ąŠą┤ą░ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ.

ąÜąŠą│ą┤ą░ ą░ą║čéąĖą▓ąĄąĮ čāčĆąŠą▓ąĄąĮčī ąĘą░čēąĖčéčŗ Level 1, ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ ą▒ą░ą╣čéą░ ąŠą┐čåąĖą╣ ąĘą░čēąĖčéčŗ (RDP) ąĮą░ čāčĆąŠą▓ąĄąĮčī Level 0 ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ą┐ąŠą╗ąĮąŠą╝čā čüčéąĖčĆą░ąĮąĖčÄ ą┐ą░ą╝čÅčéąĖ Flash ąĖ Backup SRAM. ąÆ čĆąĄąĘčāą╗čīčéą░č鹥 ą┐ąĄčĆąĄą┤ čüąĮčÅčéąĖąĄą╝ ąĘą░čēąĖčéčŗ ąŠčé čćč鹥ąĮąĖčÅ ą▓čüčÅ ąŠą▒ą╗ą░čüčéčī ą║ąŠą┤ą░ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ čüčéąĖčĆą░ąĄčéčüčÅ. ąŁčéą░ ąŠą┐ąĄčĆą░čåąĖčÅ ą╝ą░čüčüąŠą▓ąŠą╣ ąŠčćąĖčüčéą║ąĖ čüčéąĖčĆą░ąĄčé č鹊ą╗čīą║ąŠ ąŠą▒ą╗ą░čüčéčī ą║ąŠą┤ą░ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ. ąöčĆčāą│ąĖąĄ ą▒ą░ą╣čéčŗ ąŠą┐čåąĖą╣, ą▓ą║ą╗čÄčćą░čÅ ąĘą░čēąĖčéčā ąŠčé ąĘą░ą┐ąĖčüąĖ, ąŠčüčéą░čÄčéčüčÅ ąĮąĄčéčĆąŠąĮčāčéčŗą╝ąĖ. ą×ą▒ą╗ą░čüčéčī OTP čéą░ą║ąČąĄ ąĮąĄ ąĘą░čéčĆą░ą│ąĖą▓ą░ąĄčéčüčÅ čŹč鹊ą╣ ąŠą┐ąĄčĆą░čåąĖąĄą╣ ą╝ą░čüčüąŠą▓ąŠą│ąŠ čüčéąĖčĆą░ąĮąĖčÅ. ą×ą┐ąĄčĆą░čåąĖčÅ ą╝ą░čüčüąŠą▓ąŠą│ąŠ čüčéąĖčĆą░ąĮąĖčÅ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ ą░ą║čéąĖą▓ąĄąĮ čāčĆąŠą▓ąĄąĮčī ąĘą░čēąĖčéčŗ Level 1, ąĖ ąĘą░ą┐čĆąŠčłąĄąĮ čāčĆąŠą▓ąĄąĮčī ąĘą░čēąĖčéčŗ Level 0. ąÜąŠą│ą┤ą░ čāčĆąŠą▓ąĄąĮčī ąĘą░čēąĖčéčŗ čāą▓ąĄą╗ąĖčćąĖą▓ą░ąĄčéčüčÅ (0 -> 1, 1 -> 2, 0 -> 2), ą╝ą░čüčüąŠą▓ąŠąĄ čüčéąĖčĆą░ąĮąĖąĄ ąĮąĄ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ.

ŌĆó Level 2: ąĘą░čēąĖčéą░ ąŠčé ąŠčéą╗ą░ą┤ą║ąĖ / čćč鹥ąĮąĖčÅ čćąĖą┐ą░

ąŻčĆąŠą▓ąĄąĮčī ąĘą░čēąĖčéčŗ ąŠčé čćč鹥ąĮąĖčÅ Level 2 ą░ą║čéąĖą▓ąĖčĆčāąĄčéčüčÅ ąĘą░ą┐ąĖčüčīčÄ 0xCC ą▓ ą▒ą░ą╣čé ąŠą┐čåąĖą╣ RDP. ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čāčĆąŠą▓ąĄąĮčī ąĘą░čēąĖčéčŗ ąŠčé čćč鹥ąĮąĖčÅ Level 2:

ŌĆō ąÉą║čéąĖą▓ąĮčŗ ą▓čüąĄ čäčāąĮą║čåąĖąĖ ąĘą░čēąĖčéčŗ, ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄą╝čŗąĄ Level 1.

ŌĆō ąæąŠą╗čīčłąĄ ąĮąĄ čĆą░ąĘčĆąĄčłąĄąĮą░ ąĘą░ą│čĆčāąĘą║ą░ ąĖąĘ RAM ąĖą╗ąĖ system memory bootloader.

ŌĆō ąŚą░ą┐čĆąĄčēąĄąĮčŗ JTAG, SWV (single-wire viewer), ETM ąĖ čäčāąĮą║čåąĖčÅ ą┐ąŠą│čĆą░ąĮąĖčćąĮąŠą│ąŠ čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ (boundary scan).

ŌĆō ąæąŠą╗čīčłąĄ ąĮąĄą╗čīąĘčÅ ą┐ąŠą╝ąĄąĮčÅčéčī ą▒ą░ą╣čéčŗ ąŠą┐čåąĖą╣ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ.

ŌĆō ą¤čĆąĖ ąĘą░ą│čĆčāąĘą║ąĄ ąĖąĘ ą┐ą░ą╝čÅčéąĖ Flash čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ ą┤ąŠčüčéčāą┐ (čćč鹥ąĮąĖąĄ, čüčéąĖčĆą░ąĮąĖąĄ ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ) ą║ ą┐ą░ą╝čÅčéąĖ Flash ąĖ Backup SRAM ąĖąĘ ą║ąŠą┤ą░ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ.

ąŻčüčéą░ąĮąŠą▓ą║ą░ čāčĆąŠą▓ąĮčÅ ąĘą░čēąĖčéčŗ Level 2 čÅą▓ą╗čÅąĄčéčüčÅ ąĮąĄąŠą▒čĆą░čéąĖą╝ąŠą╣ ąŠą┐ąĄčĆą░čåąĖąĄą╣. ąÜąŠą│ą┤ą░ ą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮ Level 2, čāčĆąŠą▓ąĄąĮčī ąĘą░čēąĖčéčŗ ąĮąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī čāą╝ąĄąĮčīčłąĄąĮ ą┤ąŠ Level 0 ąĖą╗ąĖ Level 1.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą┐čĆąĖ ą░ą║čéąĖą▓ąĮąŠą╝ Level 2 ą┐ąŠčĆčé JTAG ą▒ąĄąĘą▓ąŠąĘą▓čĆą░čéąĮąŠ ąĘą░ą┐čĆąĄčēąĄąĮ (čŹč鹊 čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ čäčīčÄąĘ JTAG). ąÜą░ą║ čüą╗ąĄą┤čüčéą▓ąĖąĄ č鹥čüčéčŗ boundary scan ą▓čŗą┐ąŠą╗ąĮąĖčéčī ąĮąĄą╗čīąĘčÅ. STMicroelectronics ąĮąĄ ą╝ąŠąČąĄčé ą▓čŗą┐ąŠą╗ąĮąĖčéčī ą░ąĮą░ą╗ąĖąĘ ą┤ąĄč乥ą║čéąĮčŗčģ čćąĖą┐ąŠą▓, čā ą║ąŠč鹊čĆčŗčģ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮą░ ąĘą░čēąĖčéą░ Level 2.

ąóą░ą▒ą╗ąĖčåą░ 17. ąŻčĆąŠą▓ąĮąĖ ą┤ąŠčüčéčāą┐ą░ ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮąŠą│ąŠ čāčĆąŠą▓ąĮčÅ ąĘą░čēąĖčéčŗ.

ą×ą▒ą╗ą░čüčéčī ą┐ą░ą╝čÅčéąĖ

|

ąŻčĆąŠą▓ąĄąĮčī ąĘą░čēąĖčéčŗ

|

ążčāąĮą║čåąĖąĖ ąŠčéą╗ą░ą┤ą║ąĖ, ąĘą░ą│čĆčāąĘą║ą░

ąĖąĘ RAM ąĖą╗ąĖ ąĖąĘ ąĘą░ą│čĆčāąĘčćąĖą║ą░ čüąĖčüč鹥ą╝ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ |

ąŚą░ą│čĆčāąĘą║ą░ ąĖąĘ ą┐ą░ą╝čÅčéąĖ FLASH |

| Read |

Write |

Erase |

Read |

Write |

Erase |

| ą×čüąĮąŠą▓ąĮą░čÅ ą┐ą░ą╝čÅčéčī Flash ąĖ Backup SRAM |

Level 1 |

ąĮąĄčé |

ąĮąĄčé(1) |

ąöąÉ |

| Level 2 |

ąĮąĄčé |

ąöąÉ |

| ąæą░ą╣čéčŗ ąŠą┐čåąĖą╣ |

Level 1 |

ąöąÉ |

ąöąÉ |

| Level 2 |

ąĮąĄčé |

ąĮąĄčé |

| OTP |

Level 1 |

ąĮąĄčé |

ąĮąĄą┤ąŠčüčéčāą┐ąĮąŠ |

ąöąÉ |

ąĮąĄą┤ąŠčüčéčāą┐ąĮąŠ |

| Level 2 |

ąĮąĄčé |

ąĮąĄą┤ąŠčüčéčāą┐ąĮąŠ |

ąöąÉ |

ąĮąĄą┤ąŠčüčéčāą┐ąĮąŠ |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ (1): ąŠčüąĮąŠą▓ąĮą░čÅ ą┐ą░ą╝čÅčéčī Flash ąĖ Backup SRAM čüčéąĖčĆą░čÄčéčüčÅ č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ RDP ą╝ąĄąĮčÅąĄčéčüčÅ čü čāčĆąŠą▓ąĮčÅ Level 1 ą║ čāčĆąŠą▓ąĮčÄ Level 0. ą×ą▒ą╗ą░čüčéčī OTP ąŠčüčéą░ąĄčéčüčÅ ąĮąĄąĖąĘą╝ąĄąĮąĄąĮąĮąŠą╣.

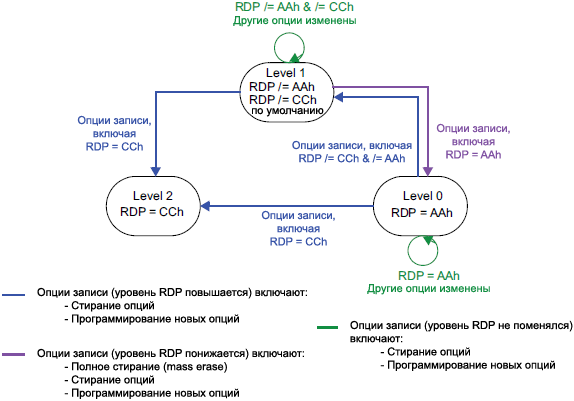

ąØą░ čĆąĖčü. 6 ą┐ąŠą║ą░ąĘą░ąĮąŠ, ą║ą░ą║ ą┐ąĄčĆąĄčģąŠą┤ąĖčéčī ąŠčé ąŠą┤ąĮąŠą│ąŠ čāčĆąŠą▓ąĮčÅ RDP ą║ ą┤čĆčāą│ąŠą╝čā.

ąĀąĖčü. 6. ąŻčĆąŠą▓ąĮąĖ ąĘą░čēąĖčéčŗ RDP.

[ąŚą░čēąĖčéą░ ąŠčé ąĘą░ą┐ąĖčüąĖ]

ą£ąŠąČąĄčé ą▒čŗčéčī ąĘą░čēąĖčēąĄąĮąŠ ą┤ąŠ 24 čüąĄą║č鹊čĆąŠą▓ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ ąŠčé ąĮąĄąČąĄą╗ą░č鹥ą╗čīąĮčŗčģ ąŠą┐ąĄčĆą░čåąĖą╣ ąĘą░ą┐ąĖčüąĖ ąĖąĘ-ąĘą░ čüą▒ąŠąĄą▓ ą▓ ą║ąŠąĮč鹥ą║čüčéą░čģ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ. ąÜąŠą│ą┤ą░ ą▒ąĖčé ąĘą░čēąĖčéčŗ (non-write protection nWRPi, ąĘą┤ąĄčüčī 0 Ōēż i Ōēż 11) ą▓ čĆąĄą│ąĖčüčéčĆą░čģ FLASH_OPTCR ąĖą╗ąĖ FLASH_OPTCR1 čüą▒čĆąŠčłąĄąĮ ą▓ ą╗ąŠą│. 0, čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ čüąĄą║č鹊čĆ ąĮąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī čüč鹥čĆčé ąĖą╗ąĖ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ. ąÜą░ą║ čüą╗ąĄą┤čüčéą▓ąĖąĄ, ąŠą┐ąĄčĆą░čåąĖčÅ ą┐ąŠą╗ąĮąŠą│ąŠ čüčéąĖčĆą░ąĮąĖčÅ (mass erase) ąĮąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮą░, ąĄčüą╗ąĖ čģąŠčéčÅ ą▒čŗ ąŠą┤ąĖąĮ ąĖąĘ čüąĄą║č鹊čĆąŠą▓ ąĘą░čēąĖčēąĄąĮ ąŠčé ąĘą░ą┐ąĖčüąĖ.

ąĢčüą╗ąĖ čüą┤ąĄą╗ą░ąĮą░ ą┐ąŠą┐čŗčéą║ą░ čüčéąĖčĆą░ąĮąĖčÅ/ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ąĮą░ ąĘą░čēąĖčēąĄąĮąĮąŠą╣ čćą░čüčéąĖ ą┐ą░ą╝čÅčéąĖ Flash (ąĮą░ čüąĄą║č鹊čĆąĄ, ąĘą░čēąĖčēąĄąĮąĮąŠą╝ ą▒ąĖč鹊ą╝ ąĘą░čēąĖčéčŗ ąŠčé ąĘą░ą┐ąĖčüąĖ, ąĮą░ ąĘą░ą▒ą╗ąŠą║ąĖčĆąŠą▓ą░ąĮąĮąŠą╣ čćą░čüčéąĖ OTP ąĖą╗ąĖ čćą░čüčéąĖ Flash, ą║ąŠč鹊čĆą░čÅ ąĮąĖą║ąŠą│ą┤ą░ ąĮąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮą░ čéą░ą║, ą║ą░ą║ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ ą┐ą░ą╝čÅčéčī Flash ICP), čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ ąŠčłąĖą▒ą║ąĖ ąĘą░čēąĖčéčŗ ąĘą░ą┐ąĖčüąĖ (write protection error, WRPERR) ą▓ čĆąĄą│ąĖčüčéčĆąĄ FLASH_SR.

ąØą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░čģ STM32F42xxx ąĖ STM32F43xxx, ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čĆąĄąČąĖą╝ PCROP, ą░ą║čéąĖą▓ąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī ą▒ąĖčé nWRPi čüąŠčüčéą░ą▓ą╗čÅąĄčé ą╗ąŠą│. 1, ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ čüąĄą║č鹊čĆ i ąĘą░čēąĖčēąĄąĮ ąŠčé ąĘą░ą┐ąĖčüąĖ, ą║ąŠą│ą┤ą░ nWRPi ą▓ ą╗ąŠą│. 1. ąĪąĄą║č鹊čĆ PCROP ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąĘą░čēąĖčēąĄąĮ ąŠčé ąĘą░ą┐ąĖčüąĖ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą║ąŠą│ą┤ą░ ą▓čŗą▒čĆą░ąĮ čāčĆąŠą▓ąĄąĮčī ąĘą░čēąĖčéčŗ čćč鹥ąĮąĖčÅ ą┐ą░ą╝čÅčéąĖ (čāčĆąŠą▓ąĄąĮčī RDP = 1), ąĮąĄą╗čīąĘčÅ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī ąĖą╗ąĖ čüč鹥čĆąĄčéčī čüąĄą║č鹊čĆ i ą┐ą░ą╝čÅčéąĖ Flash, ąĄčüą╗ąĖ ą┐ąŠą┤ą║ą╗čÄč湥ąĮą░ čäčāąĮą║čåąĖčÅ ąŠčéą╗ą░ą┤ą║ąĖ CPU (JTAG ąĖą╗ąĖ ąŠą┤ąĮąŠą┐čĆąŠą▓ąŠą┤ąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü ąŠčéą╗ą░ą┤ą║ąĖ), ąĖą╗ąĖ ąĖąĘ RAM ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą║ąŠą┤ ąĘą░ą│čĆčāąĘą║ąĖ, ą┤ą░ąČąĄ ąĄčüą╗ąĖ nWRPi = 1.

ążą╗ą░ą│ ąŠčłąĖą▒ą║ąĖ ąĘą░čēąĖčéčŗ ąĘą░ą┐ąĖčüąĖ. ąĢčüą╗ąĖ ą▓čŗą┐ąŠą╗ąĮąĖą╗ą░čüčī ąŠą┐ąĄčĆą░čåąĖčÅ čüčéąĖčĆą░ąĮąĖčÅ/ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓ ąĘą░čēąĖčēąĄąĮąĮčāčÄ ąŠą▒ą╗ą░čüčéčī Flash, čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ ąŠčłąĖą▒ą║ąĖ ąĘą░čēąĖčéčŗ ąĘą░ą┐ąĖčüąĖ (Write Protection Error, WRPERR) ą▓ čĆąĄą│ąĖčüčéčĆąĄ FLASH_SR.

ąĢčüą╗ąĖ ąĘą░ą┐čĆą░čłąĖą▓ą░ąĄčéčüčÅ ąŠą┐ąĄčĆą░čåąĖčÅ čüčéąĖčĆą░ąĮąĖčÅ, č鹊 ą▒ąĖčé WRPERR čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▓ čüą╗ąĄą┤čāčÄčēąĖčģ čüąĖčéčāą░čåąĖčÅčģ:

ŌĆó ąĪą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮą░ ąŠą┐ąĄčĆą░čåąĖčÅ mass erase, bank erase, sector erase (MER ąĖą╗ąĖ MER/MER1 ąĖ SER = 1).

ŌĆó ąŚą░ą┐čĆą░čłąĖą▓ą░ąĄčéčüčÅ ąŠą┐ąĄčĆą░čåąĖčÅ sector erase, ąĖ ąĮąŠą╝ąĄčĆ čüąĄą║č鹊čĆą░ (Sector Number, ą┐ąŠą╗ąĄ SNB) ąĮąĄą┤ąŠą┐čāčüčéąĖą╝čŗą╣.

ŌĆó ąŚą░ą┐čĆąŠčłąĄąĮą░ ąŠą┐ąĄčĆą░čåąĖčÅ mass erase, ą║ąŠą│ą┤ą░ čģąŠčéčÅ ą▒čŗ ąŠą┤ąĖąĮ ąĖąĘ čüąĄą║č鹊čĆąŠą▓ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ ąĘą░čēąĖčēąĄąĮ ąŠčé ąĘą░ą┐ąĖčüąĖ ą▒ąĖč鹊ą╝ ąŠą┐čåąĖą╣ (ą▒ąĖčéčŗ MER ąĖą╗ąĖ MER/MER1 = 1, ąĖ nWRPi = 0, ą│ą┤ąĄ 0 Ōēż i Ōēż 11 ą▓ čĆąĄą│ąĖčüčéčĆąĄ FLASH_OPTCRx).

ŌĆó ąŚą░ą┐čĆąŠčłąĄąĮą░ ąŠą┐ąĄčĆą░čåąĖčÅ čüčéąĖčĆą░ąĮąĖčÅ čüąĄą║č鹊čĆą░ ąĮą░ ąĘą░čēąĖčēąĄąĮąĮąŠą╝ čüąĄą║č鹊čĆąĄ (ą▒ąĖčéčŗ SER = 1, SNB = i ąĖ nWRPi = 0, ą│ą┤ąĄ 0 Ōēż i Ōēż 11 ą▓ čĆąĄą│ąĖčüčéčĆąĄ FLASH_OPTCRx).

ŌĆó ąÉą║čéąĖą▓ąĮą░ ąĘą░čēąĖčéą░ ąŠčé čćč鹥ąĮąĖčÅ ą┐ą░ą╝čÅčéąĖ Flash, ąĖ ą▒čŗą╗ąŠ ąŠą▒ąĮą░čĆčāąČąĄąĮąŠ ą▓č鹊čƹȹĄąĮąĖąĄ.

ąĢčüą╗ąĖ ąĘą░ą┐čĆąŠčłąĄąĮą░ ąŠą┐ąĄčĆą░čåąĖčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ, č鹊 ą▒ąĖčé WRPERR čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▓ čüą╗ąĄą┤čāčÄčēąĖčģ čüąĖčéčāą░čåąĖčÅčģ:

ŌĆó ą×ą┐ąĄčĆą░čåąĖčÅ ąĘą░ą┐ąĖčüąĖ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ąĮą░ čüąĖčüč鹥ą╝ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ (system memory) ąĖą╗ąĖ ą▓ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗą╣ čüąĄą║č鹊čĆ ąĮą░ ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąĮąŠą╣ čćą░čüčéąĖ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ.

ŌĆó ą×ą┐ąĄčĆą░čåąĖčÅ ąĘą░ą┐ąĖčüąĖ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ąĮą░ čüąĄą║č鹊čĆąĄ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ.

ŌĆó ą×ą┐ąĄčĆą░čåąĖčÅ ąĘą░ą┐ąĖčüąĖ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ąĮą░ ąĘą░čēąĖčēąĄąĮąĮąŠą╝ ąŠčé ąĘą░ą┐ąĖčüąĖ čüąĄą║č鹊čĆąĄ (čüąĄą║č鹊čĆ, ąĘą░čēąĖčēąĄąĮąĮčŗą╣ ą▒ąĖč鹊ą╝ ąŠą┐čåąĖą╣ nWRPi).

ŌĆó ą×ą┐ąĄčĆą░čåąĖčÅ ąĘą░ą┐ąĖčüąĖ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ąĮą░ ąŠą▒ą╗ą░čüčéąĖ OTP, ą║ąŠč鹊čĆą░čÅ čāąČąĄ ąĘą░ą▒ą╗ąŠą║ąĖčĆąŠą▓ą░ąĮą░.

ŌĆó ą¤ą░ą╝čÅčéčī Flash ąĘą░čēąĖčēąĄąĮą░ ąŠčé čćč鹥ąĮąĖčÅ, ąĖ ą▒čŗą╗ąŠ ąŠą▒ąĮą░čĆčāąČąĄąĮąŠ ą▓č鹊čƹȹĄąĮąĖąĄ.

[Proprietary code readout protection (PCROP)]

ą¤čĆąŠą┐čĆąĖąĄčéą░čĆąĮą░čÅ ąĘą░čēąĖčéą░ ąŠčé čćč鹥ąĮąĖčÅ (proprietary readout protection, PCROP) ą┤ąŠčüčéčāą┐ąĮą░ č鹊ą╗čīą║ąŠ ąĮą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░čģ STM32F42xxx ąĖ STM32F43xxx.

ąĪąĄą║č鹊čĆą░ ą┐ą░ą╝čÅčéąĖ Flash ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ (ąŠčé 0 ą┤ąŠ 23) ą╝ąŠą│čāčé ą▒čŗčéčī ąĘą░čēąĖčēąĄąĮčŗ ąŠčé čćč鹥ąĮąĖčÅ čüąŠ čüč鹊čĆąŠąĮčŗ D-bus čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ proprietary readout protection (PCROP).

ąŚą░čēąĖčéą░ PCROP ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, č湥čĆąĄąĘ ą▒ąĖčé ąŠą┐čåąĖą╣ SPRMOD ą▓ čĆąĄą│ąĖčüčéčĆąĄ FLASH_OPTCR:

ŌĆó SPRMOD = 0: nWRPi čāą┐čĆą░ą▓ą╗čÅąĄčé ąĘą░čēąĖč鹊ą╣ ąŠčé ąĘą░ą┐ąĖčüąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖčģ čüąĄą║č鹊čĆąŠą▓ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ.

ŌĆó SPRMOD = 1: nWRPi čāą┐čĆą░ą▓ą╗čÅąĄčé ąĘą░čēąĖč鹊ą╣ ąŠčé čćč鹥ąĮąĖčÅ ąĖ ąĘą░ą┐ąĖčüąĖ (PCROP) čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖčģ čüąĄą║č鹊čĆąŠą▓ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ.

ąÜąŠą│ą┤ą░ čüąĄą║č鹊čĆ ąĘą░čēąĖčēąĄąĮ ą░ą║čéąĖą▓ą░čåąĖąĄą╣ čĆąĄąČąĖą╝ą░ PCROP, ą║ ąĮąĄą╝čā ą╝ąŠąČąĮąŠ ą┐ąŠą╗čāčćąĖčéčī ą┤ąŠčüčéčāą┐ ą┤ą╗čÅ ą║ąŠą┤ą░ č鹊ą╗čīą║ąŠ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą║ąĖ ą║ąŠą┤ą░ č湥čĆąĄąĘ čłąĖąĮčā ICODE ą▓ąŠ Flash-ąĖąĮč鹥čĆč乥ą╣čüąĄ:

ŌĆó ąøčÄą▒ą░čÅ ą┐ąŠą┐čŗčéą║ą░ čćč鹥ąĮąĖčÅ, ą▓čŗą┐ąŠą╗ąĮąĄąĮąĮą░čÅ č湥čĆąĄąĘ D-bus, ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ čāčüčéą░ąĮąŠą▓ą║ąĄ čäą╗ą░ą│ą░ ąŠčłąĖą▒ą║ąĖ RDERR.

ŌĆó ąøčÄą▒ą░čÅ ąŠą┐ąĄčĆą░čåąĖčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ/čüčéąĖčĆą░ąĮąĖčÅ ąĮą░ ąĘą░čēąĖčēąĄąĮąĮąŠą╝ PCROP čüąĄą║č鹊čĆąĄ ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ čāčüčéą░ąĮąŠą▓ą║ąĄ čäą╗ą░ą│ą░ ąŠčłąĖą▒ą║ąĖ WRPERR.

ąĀąĖčü. 7. ąŻčĆąŠą▓ąĮąĖ ąĘą░čēąĖčéčŗ PCROP.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ *: "ą┐čĆą░ą▓ąĖą╗čīąĮčŗą╣ nWRPi" ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ąĮąĖ ąŠą┤ąĖąĮ ąĖąĘ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗčģ ą▒ąĖčé nWRP ąĮąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī čüą▒čĆąŠčłąĄąĮ (ą┐ąĄčĆąĄčģąŠą┤ ąŠčé 1 ą║ 0).

ąöąĄą░ą║čéąĖą▓ą░čåąĖčÅ SPRMOD ąĖ/ąĖą╗ąĖ čüąĮčÅčéąĖąĄ ąĘą░čēąĖčéčŗ PCROP čüąĄą║č鹊čĆąŠą▓ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ ą╝ąŠąČąĄčé ą┐čĆąŠąĖčüčģąŠą┤ąĖčéčī č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ čāčĆąŠą▓ąĄąĮčī RDP ą╝ąĄąĮčÅąĄčéčüčÅ čü 1 ąĮą░ 0. ąĢčüą╗ąĖ čŹč鹊 čāčüą╗ąŠą▓ąĖąĄ ąĮąĄ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ, č鹊 ą╝ąŠą┤ąĖčäąĖą║ą░čåąĖčÅ ą▒ą░ą╣čéą░ ąŠą┐čåąĖą╣ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ ąŠčéą╝ąĄąĮčÅąĄčéčüčÅ, ąĖ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ ąŠčłąĖą▒ą║ąĖ ąĘą░ą┐ąĖčüąĖ WRPERR. ą£ąŠą┤ąĖčäąĖą║ą░čåąĖčÅ ą▒ą░ą╣čé ąŠą┐čåąĖą╣ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ (BOR_LEV, RST_STDBY, ..) ą┤ąŠą┐čāčüą║ą░ąĄčéčüčÅ, ą┐ąŠą║ą░ ąĮąĖ ąŠą┤ąĖąĮ ąĖąĘ ą▒ąĖčé nWRPi ąĮąĄ čüą▒čĆąŠčłąĄąĮ, ąĖ ą░ą║čéąĖą▓ąĄąĮ čĆąĄąČąĖą╝ SPRMOD.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą░ą║čéąĖą▓ąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé nWRPi ąĖąĮą▓ąĄčĆčéąĖčĆčāąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą░ą║čéąĖą▓ąĄąĮ čĆąĄąČąĖą╝ PCROP (SPRMOD=1). ąĢčüą╗ąĖ SPRMOD=1 ąĖ nWRPi=1, č鹊 čüąĄą║č鹊čĆ i ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ ą▓ ą▒ą░ąĮą║ąĄ 1, čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ ąĖ ą▓ ą▒ą░ąĮą║ąĄ 2, ąĘą░čēąĖčēąĄąĮ ąŠčé čćč鹥ąĮąĖčÅ/ąĘą░ą┐ąĖčüąĖ (PCROP).

[ą×ą┤ąĮąŠą║čĆą░čéąĮąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗąĄ ą▒ą░ą╣čéčŗ]

ąóą░ą▒ą╗ąĖčåą░ 18 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąŠčĆą│ą░ąĮąĖąĘą░čåąĖčÄ ąŠą┤ąĮąŠą║čĆą░čéąĮąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝ąŠą╣ ąŠą▒ą╗ą░čüčéąĖ (one-time programmable, OTP) ą┐ą░ą╝čÅčéąĖ.

ąóą░ą▒ą╗ąĖčåą░ 18. ą×čĆą│ą░ąĮąĖąĘą░čåąĖčÅ ąŠą▒ą╗ą░čüčéąĖ OTP.

| ąæą╗ąŠą║ |

[128:96] |

[95:64] |

[63:32] |

[31:0] |

ąÉą┤čĆąĄčü ą▒ą░ą╣čéą░ 0 |

| 0 |

OTP0 |

OTP0 |

OTP0 |

OTP0 |

0x1FFF7800 |

| OTP0 |

OTP0 |

OTP0 |

OTP0 |

0x1FFF7810 |

| 1 |

OTP1 |

OTP1 |

OTP1 |

OTP1 |

0x1FFF7820 |

| OTP1 |

OTP1 |

OTP1 |

OTP1 |

0x1FFF7830 |

.

.

. |

.

.

. |

.

.

. |

| 15 |

OTP15 |

OTP15 |

OTP15 |

OTP15 |

0x1FFF79E0 |

| OTP15 |

OTP15 |

OTP15 |

OTP15 |

0x1FFF79F0 |

ąæą╗ąŠą║

ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ |

LOCKB15 ... LOCKB12 |

LOCKB11 ... LOCKB8 |

LOCKB7 ... LOCKB4 |

LOCKB3 ... LOCKB0 |

0x1FFF7A00 |

ą×ą▒ą╗ą░čüčéčī OTP ą┐ąŠą┤ąĄą╗ąĄąĮą░ ąĮą░ 16 ą▒ą╗ąŠą║ąŠą▓ ą┤ą░ąĮąĮčŗčģ OTP ą┐ąŠ 32 ą▒ą░ą╣čéą░ ąĖ ą▒ą╗ąŠą║ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ OTP ąĖąĘ 16 ą▒ą░ą╣čé. ąöą░ąĮąĮčŗąĄ OTP data ąĖ ą▒ą╗ąŠą║ąŠą▓ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ ąĮąĄ ą╝ąŠą│čāčé ą▒čŗčéčī čüč鹥čĆčéčŗ. ąæą╗ąŠą║ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ čüąŠą┤ąĄčƹȹĖčé 16 ą▒ą░ą╣čé LOCKBi (0 Ōēż i Ōēż 15) ą┤ą╗čÅ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖčģ ą▒ą╗ąŠą║ąŠą▓ ą┤ą░ąĮąĮčŗčģ OTP (ą▒ą╗ąŠą║ąĖ ąŠčé 0 ą┤ąŠ 15). ąÜą░ąČą┤čŗą╣ ą▒ą╗ąŠą║ ą┤ą░ąĮąĮčŗčģ OTP ą╝ąŠąČąĄčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčīčüčÅ, ą┐ąŠą║ą░ ąĮąĄ ą▒čāą┤ąĄčé ąĘą░ą┐ąĖčüą░ąĮąŠ ąĘąĮą░č湥ąĮąĖąĄ 0x00 ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ą░ą╣čé ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ OTP. ąæą░ą╣čéčŗ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ ą┤ąŠą╗ąČąĮčŗ čüąŠą┤ąĄčƹȹ░čéčī č鹊ą╗čīą║ąŠ ąĘąĮą░č湥ąĮąĖčÅ 0x00 ąĖ 0xFF, ąĖąĮą░č湥 ą▒ą░ą╣čéčŗ OTP ą╝ąŠą│čāčé čāčćąĖčéčŗą▓ą░čéčīčüčÅ ąĮąĄą┐čĆą░ą▓ąĖą╗čīąĮąŠ.

[ąĪčüčŗą╗ą║ąĖ]

1. RM0090 Reference manual STM32F405/415, STM32F407/417, STM32F427/437 and STM32F429/439 advanced Arm®-based 32-bit MCUs site:st.com.

2. ąśąĮč鹥čĆč乥ą╣čü ą┐ą░ą╝čÅčéąĖ Flash STM32F4.

3. STM32F4xx: ą┐ą░ą╝čÅčéčī ąĖ ą░čĆčģąĖč鹥ą║čéčāčĆą░ čłąĖąĮ. |