|

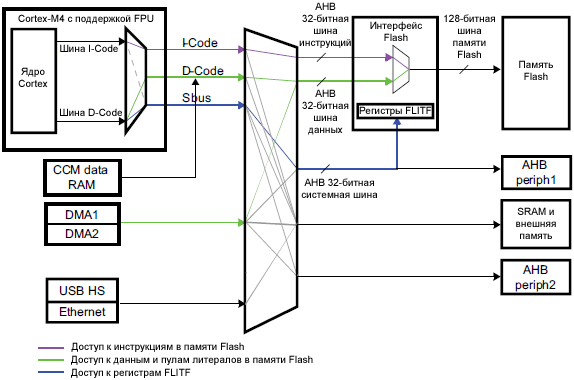

ąśąĮč鹥čĆč乥ą╣čü ą┐ą░ą╝čÅčéąĖ Flash ąŠą▒čüą╗čāąČąĖą▓ą░ąĄčé ąŠą┐ąĄčĆą░čåąĖąĖ ą┤ąŠčüčéčāą┐ą░ CPU AHB I-Code ąĖ D-Code ą║ ą┐ą░ą╝čÅčéąĖ Flash. ąÆ čŹč鹊ą╝ ąĖąĮč鹥čĆč乥ą╣čüąĄ čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮčŗ ąŠą┐ąĄčĆą░čåąĖąĖ čüčéąĖčĆą░ąĮąĖčÅ ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ Flash, ą░ čéą░ą║ąČąĄ ą╝ąĄčģą░ąĮąĖąĘą╝čŗ ąĘą░čēąĖčéčŗ ąŠčé čćč鹥ąĮąĖčÅ ąĖ ąŠčé ąĘą░ą┐ąĖčüąĖ.

ąśąĮč鹥čĆč乥ą╣čü ą┐ą░ą╝čÅčéąĖ Flash čāčüą║ąŠčĆčÅąĄčé ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ąŠą┤ą░ čü ą┐ąŠą╝ąŠčēčīčÄ čüąĖčüč鹥ą╝čŗ ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮąŠą╣ ą▓čŗą▒ąŠčĆą║ąĖ ąĖąĮčüčéčĆčāą║čåąĖą╣ (instruction prefetch) ąĖ čüčéčĆąŠą║ ą║čŹčłą░.

ą×čüąĮąŠą▓ąĮčŗąĄ čäčāąĮą║čåąĖąĖ ąĖąĮč鹥čĆč乥ą╣čüą░ ą┐ą░ą╝čÅčéąĖ Flash:

ŌĆó ą×ą┐ąĄčĆą░čåąĖąĖ čćč鹥ąĮąĖčÅ Flash.

ŌĆó ą×ą┐ąĄčĆą░čåąĖąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ/čüčéąĖčĆą░ąĮąĖčÅ Flash.

ŌĆó ąÆą░čĆąĖą░ąĮčéčŗ ąĘą░čēąĖčé ąŠčé čćč鹥ąĮąĖčÅ ąĖ ąĘą░ą┐ąĖčüąĖ.

ŌĆó ą¤čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮą░čÅ ą▓čŗą▒ąŠčĆą║ą░ I-Code.

ŌĆó 64 čüčéčĆąŠą║ ą║čŹčłą░ 128 ą▒ąĖčé ąĮą░ I-Code.

ŌĆó 8 čüčéčĆąŠą║ ą║čŹčłą░ 128 ą▒ąĖčé ąĮą░ D-Code.

ąĀąĖčü. 3 ąĖ 4 ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčé čüąŠąĄą┤ąĖąĮąĄąĮąĖčÅ ąĖąĮč鹥čĆč乥ą╣čüą░ ą┐ą░ą╝čÅčéąĖ Flash ą▓ąĮčāčéčĆąĖ čüąĖčüč鹥ą╝ąĮąŠą╣ ą░čĆčģąĖč鹥ą║čéčāčĆčŗ MCU STM32F4.

ąĀąĖčü. 3. ąĪąŠąĄą┤ąĖąĮąĄąĮąĖčÅ ąĖąĮč鹥čĆč乥ą╣čüą░ ą┐ą░ą╝čÅčéąĖ Flash ą▓ čüąĖčüč鹥ą╝ąĮąŠą╣ ą░čĆčģąĖč鹥ą║čéčāčĆąĄ STM32F405xx/07xx ąĖ STM32F415xx/17xx.

ąĀąĖčü. 4. ąĪąŠąĄą┤ąĖąĮąĄąĮąĖčÅ ąĖąĮč鹥čĆč乥ą╣čüą░ ą┐ą░ą╝čÅčéąĖ Flash ą▓ čüąĖčüč鹥ą╝ąĮąŠą╣ ą░čĆčģąĖč鹥ą║čéčāčĆąĄ STM32F42xxx ąĖ STM32F43xxx.

[Flash STM32F405xx/07xx ąĖ STM32F415xx/17xx]

ŌĆó ąĢą╝ą║ąŠčüčéčī ą┐ą░ą╝čÅčéąĖ ą┤ąŠ 1 ą╝ąĄą│ą░ą▒ą░ą╣čéą░.

ŌĆó 128-čĆą░ąĘčĆčÅą┤ąĮąŠąĄ čćč鹥ąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ.

ŌĆó ąŚą░ą┐ąĖčüčī ą▒ą░ą╣čéą░ (8 ą▒ąĖčé), ą┐ąŠą╗ąŠą▓ąĖąĮčŗ čüą╗ąŠą▓ą░ (16 ą▒ąĖčé), čüą╗ąŠą▓ą░ (32 ą▒ąĖčéą░) ąĖ ą┤ą▓ąŠą╣ąĮąŠą│ąŠ čüą╗ąŠą▓ą░ (64 ą▒ąĖčéą░).

ŌĆó ąĪčéąĖčĆą░ąĮąĖąĄ čüąĄą║č鹊čĆą░ ąĖ ą┐ąŠą╗ąĮąŠąĄ čüčéąĖčĆą░ąĮąĖąĄ (mass erase).

ŌĆó ąĀąĄąČąĖą╝čŗ ą┐ąŠąĮąĖąČąĄąĮąĮąŠą│ąŠ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ, ą┐ąŠą┤čĆąŠą▒ąĮąŠčüčéąĖ čüą╝. ą▓ čüąĄą║čåąĖąĖ Power control (PWR) čĆčāą║ąŠą▓ąŠą┤čüčéą▓ą░.

ą¤ą░ą╝čÅčéčī Flash ąŠčĆą│ą░ąĮąĖąĘąŠą▓ą░ąĮą░ čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝:

ŌĆō ą×čüąĮąŠą▓ąĮąŠą╣ ą▒ą╗ąŠą║ ą┐ą░ą╝čÅčéąĖ ą┐ąŠą┤ąĄą╗ąĄąĮ ąĮą░ 4 čüąĄą║č鹊čĆą░ ą┐ąŠ 16 ą║ąĖą╗ąŠą▒ą░ą╣čé, 1 čüąĄą║č鹊čĆ ąĮą░ 64 ą║ąĖą╗ąŠą▒ą░ą╣čéą░ ąĖ 7 čüąĄą║č鹊čĆąŠą▓ ą┐ąŠ 128 ą║ąĖą╗ąŠą▒ą░ą╣čé.

ŌĆō ąĪąĖčüč鹥ą╝ąĮą░čÅ ą┐ą░ą╝čÅčéčī, ąĖąĘ ą║ąŠč鹊čĆąŠą╣ MCU ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ ąĘą░ą│čĆčāąĘą║ąĖ System memory boot.

ŌĆō 512 ąŠą┤ąĮąŠą║čĆą░čéąĮąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗčģ ą▒ą░ą╣čé OTP (one-time programmable) ą┤ą╗čÅ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čīčüą║ąĖčģ ą┤ą░ąĮąĮčŗčģ. ą×ą▒ą╗ą░čüčéčī OTP čüąŠą┤ąĄčƹȹĖčé 16 ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗčģ ą▒ą░ą╣čé, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗčģ ą┤ą╗čÅ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╣ ąŠą▒ą╗ą░čüčéąĖ ą┤ą░ąĮąĮčŗčģ OTP.

ŌĆō ąæą░ą╣čéčŗ ąŠą┐čåąĖą╣ ą┤ą╗čÅ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ąĘą░čēąĖčé ąŠčé čćč鹥ąĮąĖčÅ ąĖ ąŠčé ąĘą░ą┐ąĖčüąĖ, čāčĆąŠą▓ąĄąĮčī BOR, watchdog software/hardware ąĖ čüą▒čĆąŠčüą░, ą║ąŠą│ą┤ą░ MCU ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ Standby ąĖą╗ąĖ Stop.

ąóą░ą▒ą╗ąĖčåą░ 5. ą×čĆą│ą░ąĮąĖąĘą░čåąĖčÅ ą╝ąŠą┤čāą╗čÅ Flash STM32F40x ąĖ STM32F41x.

| ą×ą▒ą╗ą░čüčéčī ą┐ą░ą╝čÅčéąĖ |

ąśą╝čÅ |

ąöąĖą░ą┐ą░ąĘąŠąĮ ą░ą┤čĆąĄčüąŠą▓ |

ąĀą░ąĘą╝ąĄčĆ |

| ą×čüąĮąŠą▓ąĮą░čÅ ą┐ą░ą╝čÅčéčī |

ąĪąĄą║č鹊čĆ 0 |

0x08000000 - 0x08003FFF |

16 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| ąĪąĄą║č鹊čĆ 1 |

0x08004000 - 0x08007FFF |

| ąĪąĄą║č鹊čĆ 2 |

0x08008000 - 0x0800BFFF |

| ąĪąĄą║č鹊čĆ 3 |

0x0800C000 - 0x0800FFFF |

| ąĪąĄą║č鹊čĆ 4 |

0x08010000 - 0x0801FFFF |

64 ą║ąĖą╗ąŠą▒ą░ą╣čéą░ |

| ąĪąĄą║č鹊čĆ 5 |

0x08020000 - 0x0803FFFF |

128 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| ąĪąĄą║č鹊čĆ 6 |

0x08040000 - 0x0805FFFF |

128 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| . . . |

. . . |

. . . |

| ąĪąĄą║č鹊čĆ 11 |

0x080E0000 - 0x080FFFFF |

128 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| ąĪąĖčüč鹥ą╝ąĮą░čÅ ą┐ą░ą╝čÅčéčī |

0x1FFF0000 - 0x1FFF77FF |

30 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| OTP |

0x1FFF7800 - 0x1FFF7A0F |

528 ą▒ą░ą╣čé |

| ąæą░ą╣čéčŗ ąŠą┐čåąĖą╣ |

0x1FFFC000 - 0x1FFFC00F |

16 ą▒ą░ą╣čé |

[Flash STM32F42xxx ąĖ STM32F43xxx]

ŌĆó ąĢą╝ą║ąŠčüčéčī ą┤ąŠ 2 ą╝ąĄą│ą░ą▒ą░ą╣čé ąĮą░ 2 ą▒ą░ąĮą║ą░čģ, čü ą┐ąŠą┤ą┤ąĄčƹȹ║ąŠą╣ čäčāąĮą║čåąĖąĖ čćč鹥ąĮąĖąĄ-ą┐čĆąĖ-ąĘą░ą┐ąĖčüąĖ (read-while-write, RWW).

ŌĆó 128-čĆą░ąĘčĆčÅą┤ąĮąŠąĄ čćč鹥ąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ.

ŌĆó ąŚą░ą┐ąĖčüčī ą▒ą░ą╣čéą░ (8 ą▒ąĖčé), ą┐ąŠą╗ąŠą▓ąĖąĮčŗ čüą╗ąŠą▓ą░ (16 ą▒ąĖčé), čüą╗ąŠą▓ą░ (32 ą▒ąĖčéą░) ąĖ ą┤ą▓ąŠą╣ąĮąŠą│ąŠ čüą╗ąŠą▓ą░ (64 ą▒ąĖčéą░).

ŌĆó ą×ą┐ąĄčĆą░čåąĖąĖ čüčéąĖčĆą░ąĮąĖčÅ čüąĄą║č鹊čĆą░, ą▒ą░ąĮą║ą░ ąĖ ą┐ąŠą╗ąĮąŠą│ąŠ čüčéąĖčĆą░ąĮąĖčÅ (ąŠą▒ąŠąĖčģ ą▒ą░ąĮą║ąŠą▓).

ąöą▓ą░ ą▒ą░ąĮą║ą░ Flash ąŠčĆą│ą░ąĮąĖąĘąŠą▓ą░ąĮčŗ čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝:

ŌĆō ąöą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą▒ą░ąĮą║ą░ ąŠčüąĮąŠą▓ąĮąŠą╣ ą▒ą╗ąŠą║ ą┐ą░ą╝čÅčéąĖ (1 ą╝ąĄą│ą░ą▒ą░ą╣čé) ą┐ąŠą┤ąĄą╗ąĄąĮ ąĮą░ 4 čüąĄą║č鹊čĆą░ ą┐ąŠ 16 ą║ąĖą╗ąŠą▒ą░ą╣čé, 1 čüąĄą║č鹊čĆ ąĮą░ 64 ą║ąĖą╗ąŠą▒ą░ą╣čéą░ ąĖ 7 čüąĄą║č鹊čĆąŠą▓ ą┐ąŠ 128 ą║ąĖą╗ąŠą▒ą░ą╣čé.

ŌĆō ąĪąĖčüč鹥ą╝ąĮą░čÅ ą┐ą░ą╝čÅčéčī, ąŠčéą║čāą┤ą░ MCU ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ System memory boot.

ŌĆō 512 ą▒ą░ą╣čé OTP ą┤ą╗čÅ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čīčüą║ąĖčģ ą┤ą░ąĮąĮčŗčģ. ą×ą▒ą╗ą░čüčéčī OTP čüąŠą┤ąĄčƹȹĖčé 16 ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗčģ ą▒ą░ą╣čé, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗčģ ą┤ą╗čÅ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╣ ąŠą▒ą╗ą░čüčéąĖ ą┤ą░ąĮąĮčŗčģ OTP.

ŌĆō ąæą░ą╣čéčŗ ąŠą┐čåąĖą╣ ą┤ą╗čÅ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ąĘą░čēąĖčé ąŠčé čćč鹥ąĮąĖčÅ ąĖ ąŠčé ąĘą░ą┐ąĖčüąĖ, čāčĆąŠą▓ąĮčÅ BOR, watchdog, čĆąĄąČąĖą╝ą░ dual bank boot, čäčāąĮą║čåąĖąĖ dual bank, software/hardware ąĖ čüą▒čĆąŠčüą░, ą║ąŠą│ą┤ą░ MCU ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ Standby ąĖą╗ąĖ Stop.

ąöą▓ą░ ą▒ą░ąĮą║ą░ Flash ąĮą░ MCU čü 1 ą╝ąĄą│ą░ą▒ą░ą╣č鹊ą╝ ąŠčĆą│ą░ąĮąĖąĘąŠą▓ą░ąĮčŗ čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝. ążčāąĮą║čåąĖčÅ ą┤ą▓čāčģ ą▒ą░ąĮą║ąŠą▓ čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ ąŠą┐čåąĖą╣ DB1M. ąöą╗čÅ ą┤ąŠčüčéąĖąČąĄąĮąĖčÅ čüčéčĆčāą║čéčāčĆčŗ ą┤ą▓čāčģ ą▒ą░ąĮą║ąŠą▓ ą┐ąŠčüą╗ąĄą┤ąĮąĖąĄ 512 ą║ąĖą╗ąŠą▒ą░ą╣čé ąŠą┤ąĮąŠą│ąŠ ą▒ą░ąĮą║ą░ (čüąĄą║č鹊čĆčŗ [8:11]) čĆąĄčüčéčĆčāą║čéčāčĆąĖčĆčāčéčüčÅ čéą░ą║ ąČąĄ, ą║ą░ą║ ąĖ ą┐ąĄčĆą▓čŗąĄ 512 ą║ąĖą╗ąŠą▒ą░ą╣čé. ąØčāą╝ąĄčĆą░čåąĖčÅ čüąĄą║č鹊čĆąŠą▓ čü ą┤ą▓čāą╝čÅ ą▒ą░ąĮą║ą░ą╝ąĖ ąŠčéą╗ąĖčćą░ąĄčéčüčÅ ąŠčé ąĮčāą╝ąĄčĆą░čåąĖąĖ čü ąŠą┤ąĮąĖą╝ ą▒ą░ąĮą║ąŠą╝: ą┐čĆąĖ ąŠą┤ąĮąŠą╝ ą▒ą░ąĮą║ąĄ ąŠąĮ čüąŠą┤ąĄčƹȹĖčé 12 čüąĄą║č鹊čĆąŠą▓, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ čü ą┤ą▓čāą╝čÅ ą▒ą░ąĮą║ą░ą╝ąĖ ąĖą╝ąĄąĄčéčüčÅ 16 čüąĄą║č鹊čĆąŠą▓ (čüą╝. čéą░ą▒ą╗ąĖčåčā 7).

ąöą╗čÅ ąŠą┐ąĄčĆą░čåąĖąĖ čüčéąĖčĆą░ąĮąĖčÅ ą┤ąŠą╗ąČąĮą░ čāčćąĖčéčŗą▓ą░čéčīčüčÅ ą┐čĆą░ą▓ąĖą╗čīąĮą░čÅ ąĮčāą╝ąĄčĆą░čåąĖčÅ čüąĄą║č鹊čĆąŠą▓, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą▒ąĖčéą░ DB1M:

ŌĆō ąÜąŠą│ą┤ą░ DB1M = 0, ąŠą┐ąĄčĆą░čåąĖčÅ čüčéąĖčĆą░ąĮąĖčÅ ą┤ąŠą╗ąČąĮą░ ą▓čŗą┐ąŠą╗ąĮčÅčéčīčüčÅ ąĮą░ ąĮąŠą╝ąĄčĆą░čģ čüąĄą║č鹊čĆąŠą▓ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ.

ŌĆō ąÜąŠą│ą┤ą░ DB1M = 1, ą┤ą╗čÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ąŠą┐ąĄčĆą░čåąĖąĖ čüčéąĖčĆą░ąĮąĖčÅ ą▒ą░ąĮą║ą░ 2 ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ ąĮąŠą╝ąĄčĆ čüąĄą║č鹊čĆą░ (ąŠčé 12 ą┤ąŠ 19). ąĪą╝. čĆąĄą│ąĖčüčéčĆ FLASH_CR ą┤ą╗čÅ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą┐ąŠą╗čÅ ąĮąŠą╝ąĄčĆą░ čüąĄą║č鹊čĆą░ SNB (Sector number).

ą¤ąŠą┤čĆąŠą▒ąĮąŠčüčéąĖ ą┐ąŠ ąŠčĆą│ą░ąĮąĖąĘą░čåąĖąĖ 1 ą╝ąĄą│ą░ą▒ą░ą╣čé ąĮą░ ąŠą┤ąĮąŠą╝ ą▒ą░ąĮą║ąĄ ąĖ ąĮą░ ą┤ą▓čāčģ ą▒ą░ąĮą║ą░čģ čüą╝. ą▓ čéą░ą▒ą╗ąĖčåą░čģ 8 ąĖ 9.

ąóą░ą▒ą╗ąĖčåą░ 6. ąöą▓čāčģą▒ą░ąĮą║ąŠą▓ą░čÅ ąŠčĆą│ą░ąĮąĖąĘą░čåąĖčÅ 2 ą╝ąĄą│ą░ą▒ą░ą╣čé Flash STM32F42xxx ąĖ STM32F43xxx.

| ą×ą▒ą╗ą░čüčéčī ą┐ą░ą╝čÅčéąĖ |

ąæą░ąĮą║ |

ąśą╝čÅ |

ąöąĖą░ą┐ą░ąĘąŠąĮ ą░ą┤čĆąĄčüąŠą▓ |

ąĀą░ąĘą╝ąĄčĆ |

| ą×čüąĮąŠą▓ąĮą░čÅ ą┐ą░ą╝čÅčéčī |

ąæą░ąĮą║ 1 |

ąĪąĄą║č鹊čĆ 0 |

0x08000000 - 0x08003FFF |

16 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| ąĪąĄą║č鹊čĆ 1 |

0x08004000 - 0x08007FFF |

16 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| ąĪąĄą║č鹊čĆ 2 |

0x08008000 - 0x0800BFFF |

16 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| ąĪąĄą║č鹊čĆ 3 |

0x0800C000 - 0x0800FFFF |

16 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| ąĪąĄą║č鹊čĆ 4 |

0x08010000 - 0x0801FFFF |

64 ą║ąĖą╗ąŠą▒ą░ą╣čéą░ |

| ąĪąĄą║č鹊čĆ 5 |

0x08020000 - 0x0803FFFF |

128 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| ąĪąĄą║č鹊čĆ 6 |

0x08040000 - 0x0805FFFF |

128 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| . . . |

. . . |

. . . |

| ąĪąĄą║č鹊čĆ 11 |

0x080E0000 - 0x080FFFFF |

128 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| ąæą░ąĮą║ 2 |

ąĪąĄą║č鹊čĆ 12 |

0x08100000 - 0x08103FFF |

16 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| ąĪąĄą║č鹊čĆ 13 |

0x08104000 - 0x08107FFF |

16 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| ąĪąĄą║č鹊čĆ 14 |

0x08108000 - 0x0810BFFF |

16 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| ąĪąĄą║č鹊čĆ 15 |

0x0810C000 - 0x0810FFFF |

16 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| ąĪąĄą║č鹊čĆ 16 |

0x08110000 - 0x0811FFFF |

64 ą║ąĖą╗ąŠą▒ą░ą╣čéą░ |

| ąĪąĄą║č鹊čĆ 17 |

0x08120000 - 0x0813FFFF |

128 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| ąĪąĄą║č鹊čĆ 18 |

0x08140000 - 0x0815FFFF |

128 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| . . . |

. . . |

. . . |

| ąĪąĄą║č鹊čĆ 23 |

0x081E0000 - 0x081FFFFF |

128 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| ąĪąĖčüč鹥ą╝ąĮą░čÅ ą┐ą░ą╝čÅčéčī |

0x1FFF0000 - 0x1FFF77FF |

30 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| OTP |

0x1FFF7800 - 0x1FFF7A0F |

528 ą▒ą░ą╣čé |

| ąæą░ą╣čéčŗ ąŠą┐čåąĖą╣ |

ąæą░ąĮą║ 1 |

|

0x1FFFC000 - 0x1FFFC00F |

16 ą▒ą░ą╣čé |

| ąæą░ąĮą║ 2 |

|

0x1FFEC000 - 0x1FFEC00F |

16 ą▒ą░ą╣čé |

ąóą░ą▒ą╗ąĖčåą░ 7. 1 ą╝ąĄą│ą░ą▒ą░ą╣čé Flash ąĮą░ ąŠą┤ąĮąŠą╝ ąĖ ąĮą░ ą┤ą▓čāčģ ą▒ą░ąĮą║ą░čģ STM32F42xxx ąĖ STM32F43xxx.

| 1 ą╝ąĄą│ą░ą▒ą░ą╣čé ą▓ ąŠą┤ąĮąŠą╝ ą▒ą░ąĮą║ąĄ Flash (ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ) |

1 ą╝ąĄą│ą░ą▒ą░ą╣čé ą▓ ą┤ą▓čāčģ ą▒ą░ąĮą║ą░čģ Flash |

| DB1M = 0 |

DB1M = 1 |

| ą×čüąĮąŠą▓ąĮą░čÅ ą┐ą░ą╝čÅčéčī |

Ōä¢ čüąĄą║č鹊čĆą░ |

ąĀą░ąĘą╝ąĄčĆ |

ą×čüąĮąŠą▓ąĮą░čÅ ą┐ą░ą╝čÅčéčī |

Ōä¢ čüąĄą║č鹊čĆą░ |

ąĀą░ąĘą╝ąĄčĆ |

| 1 ą╝ąĄą│ą░ą▒ą░ą╣čé |

ąĪąĄą║č鹊čĆ 0 |

16 ą║ąĖą╗ąŠą▒ą░ą╣čé |

ąæą░ąĮą║ 1, 512 ą║ąĖą╗ąŠą▒ą░ą╣čé |

ąĪąĄą║č鹊čĆ 0 |

16 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| ąĪąĄą║č鹊čĆ 1 |

16 ą║ąĖą╗ąŠą▒ą░ą╣čé |

ąĪąĄą║č鹊čĆ 1 |

16 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| ąĪąĄą║č鹊čĆ 2 |

16 ą║ąĖą╗ąŠą▒ą░ą╣čé |

ąĪąĄą║č鹊čĆ 2 |

16 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| ąĪąĄą║č鹊čĆ 3 |

16 ą║ąĖą╗ąŠą▒ą░ą╣čé |

ąĪąĄą║č鹊čĆ 3 |

16 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| ąĪąĄą║č鹊čĆ 4 |

64 ą║ąĖą╗ąŠą▒ą░ą╣čéą░ |

ąĪąĄą║č鹊čĆ 4 |

64 ą║ąĖą╗ąŠą▒ą░ą╣čéą░ |

| ąĪąĄą║č鹊čĆ 5 |

128 ą║ąĖą╗ąŠą▒ą░ą╣čé |

ąĪąĄą║č鹊čĆ 5 |

128 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| ąĪąĄą║č鹊čĆ 6 |

128 ą║ąĖą╗ąŠą▒ą░ą╣čé |

ąĪąĄą║č鹊čĆ 6 |

128 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| ąĪąĄą║č鹊čĆ 7 |

128 ą║ąĖą╗ąŠą▒ą░ą╣čé |

ąĪąĄą║č鹊čĆ 7 |

128 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| ąĪąĄą║č鹊čĆ 8 |

128 ą║ąĖą╗ąŠą▒ą░ą╣čé |

ąæą░ąĮą║ 2, 512 ą║ąĖą╗ąŠą▒ą░ą╣čé |

ąĪąĄą║č鹊čĆ 12 |

16 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| ąĪąĄą║č鹊čĆ 9 |

128 ą║ąĖą╗ąŠą▒ą░ą╣čé |

ąĪąĄą║č鹊čĆ 13 |

16 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| ąĪąĄą║č鹊čĆ 10 |

128 ą║ąĖą╗ąŠą▒ą░ą╣čé |

ąĪąĄą║č鹊čĆ 14 |

16 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| ąĪąĄą║č鹊čĆ 11 |

128 ą║ąĖą╗ąŠą▒ą░ą╣čé |

ąĪąĄą║č鹊čĆ 15 |

16 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| - |

- |

ąĪąĄą║č鹊čĆ 16 |

64 ą║ąĖą╗ąŠą▒ą░ą╣čéą░ |

| - |

- |

ąĪąĄą║č鹊čĆ 17 |

128 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| - |

- |

ąĪąĄą║č鹊čĆ 18 |

128 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| - |

- |

ąĪąĄą║č鹊čĆ 19 |

128 ą║ąĖą╗ąŠą▒ą░ą╣čé |

ąóą░ą▒ą╗ąĖčåą░ 8. 1 ą╝ąĄą│ą░ą▒ą░ą╣čé Flash ąĮą░ ąŠą┤ąĮąŠą╝ ą▒ą░ąĮą║ąĄ STM32F42xxx ąĖ STM32F43xxx.

| ą×ą▒ą╗ą░čüčéčī ą┐ą░ą╝čÅčéąĖ |

ąæą░ąĮą║ |

ąśą╝čÅ |

ąöąĖą░ą┐ą░ąĘąŠąĮ ą░ą┤čĆąĄčüąŠą▓ |

ąĀą░ąĘą╝ąĄčĆ |

| ą×čüąĮąŠą▓ąĮą░čÅ ą┐ą░ą╝čÅčéčī |

ą×ą┤ąĖąĮ ą▒ą░ąĮą║ |

ąĪąĄą║č鹊čĆ 0 |

0x08000000 - 0x08003FFF |

16 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| ąĪąĄą║č鹊čĆ 1 |

0x08004000 - 0x08007FFF |

16 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| ąĪąĄą║č鹊čĆ 2 |

0x08008000 - 0x0800BFFF |

16 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| ąĪąĄą║č鹊čĆ 3 |

0x0800C000 - 0x0800FFFF |

16 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| ąĪąĄą║č鹊čĆ 4 |

0x08010000 - 0x0801FFFF |

64 ą║ąĖą╗ąŠą▒ą░ą╣čéą░ |

| ąĪąĄą║č鹊čĆ 5 |

0x08020000 - 0x0803FFFF |

128 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| ąĪąĄą║č鹊čĆ 6 |

0x08040000 - 0x0805FFFF |

128 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| ąĪąĄą║č鹊čĆ 7 |

0x08060000 - 0x0807FFFF |

128 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| ąĪąĄą║č鹊čĆ 8 |

0x08080000 - 0x0809FFFF |

128 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| ąĪąĄą║č鹊čĆ 9 |

0x080A0000 - 0x080BFFFF |

128 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| ąĪąĄą║č鹊čĆ 10 |

0x080C0000 - 0x080DFFFF |

128 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| ąĪąĄą║č鹊čĆ 11 |

0x080E0000 - 0x080FFFFF |

128 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| ąĪąĖčüč鹥ą╝ąĮą░čÅ ą┐ą░ą╝čÅčéčī |

0x1FFF0000 - 0x1FFF77FF |

30 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| OTP |

0x1FFF7800 - 0x1FFF7A0F |

528 ą▒ą░ą╣čé |

| ąæą░ą╣čéčŗ ąŠą┐čåąĖą╣ |

0x1FFFC000 - 0x1FFFC00F |

16 ą▒ą░ą╣čé |

| 0x1FFEC000 - 0x1FFEC00F |

16 ą▒ą░ą╣čé |

ąóą░ą▒ą╗ąĖčåą░ 9. 1 ą╝ąĄą│ą░ą▒ą░ą╣čé Flash ąĮą░ ą┤ą▓čāčģ ą▒ą░ąĮą║ą░čģ (STM32F42xxx ąĖ STM32F43xxx).

| ą×ą▒ą╗ą░čüčéčī ą┐ą░ą╝čÅčéąĖ |

ąæą░ąĮą║ |

ąśą╝čÅ |

ąöąĖą░ą┐ą░ąĘąŠąĮ ą░ą┤čĆąĄčüąŠą▓ |

ąĀą░ąĘą╝ąĄčĆ |

| ą×čüąĮąŠą▓ąĮą░čÅ ą┐ą░ą╝čÅčéčī |

ąæą░ąĮą║ 1 |

ąĪąĄą║č鹊čĆ 0 |

0x08000000 - 0x08003FFF |

16 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| ąĪąĄą║č鹊čĆ 1 |

0x08004000 - 0x08007FFF |

16 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| ąĪąĄą║č鹊čĆ 2 |

0x08008000 - 0x0800BFFF |

16 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| ąĪąĄą║č鹊čĆ 3 |

0x0800C000 - 0x0800FFFF |

16 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| ąĪąĄą║č鹊čĆ 4 |

0x08010000 - 0x0801FFFF |

64 ą║ąĖą╗ąŠą▒ą░ą╣čéą░ |

| ąĪąĄą║č鹊čĆ 5 |

0x08020000 - 0x0803FFFF |

128 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| ąĪąĄą║č鹊čĆ 6 |

0x08040000 - 0x0805FFFF |

128 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| ąĪąĄą║č鹊čĆ 7 |

0x08060000 - 0x0807FFFF |

128 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| ąæą░ąĮą║ 2 |

ąĪąĄą║č鹊čĆ 12 |

0x08100000 - 0x08103FFF |

16 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| ąĪąĄą║č鹊čĆ 13 |

0x08104000 - 0x08107FFF |

16 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| ąĪąĄą║č鹊čĆ 14 |

0x08108000 - 0x0810BFFF |

16 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| ąĪąĄą║č鹊čĆ 15 |

0x0810C000 - 0x0810FFFF |

16 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| ąĪąĄą║č鹊čĆ 16 |

0x08110000 - 0x0811FFFF |

64 ą║ąĖą╗ąŠą▒ą░ą╣čéą░ |

| ąĪąĄą║č鹊čĆ 17 |

0x08120000 - 0x0813FFFF |

128 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| ąĪąĄą║č鹊čĆ 18 |

0x08140000 - 0x0815FFFF |

128 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| ąĪąĄą║č鹊čĆ 19 |

0x080E0000 - 0x080FFFFF |

128 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| ąĪąĖčüč鹥ą╝ąĮą░čÅ ą┐ą░ą╝čÅčéčī |

0x1FFF0000 - 0x1FFF77FF |

30 ą║ąĖą╗ąŠą▒ą░ą╣čé |

| OTP |

0x1FFF7800 - 0x1FFF7A0F |

528 ą▒ą░ą╣čé |

| ąæą░ą╣čéčŗ ąŠą┐čåąĖą╣ |

ąæą░ąĮą║ 1 |

|

0x1FFFC000 - 0x1FFFC00F |

16 ą▒ą░ą╣čé |

| ąæą░ąĮą║ 2 |

|

0x1FFEC000 - 0x1FFEC00F |

16 ą▒ą░ą╣čé |

[ąśąĮč鹥čĆč乥ą╣čü čćč鹥ąĮąĖčÅ]

ą¦ą░čüč鹊čéą░ čéą░ą║č鹊ą▓ CPU ąĖ ą▓čĆąĄą╝čÅ čćč鹥ąĮąĖčÅ Flash. ąöą╗čÅ ą║ąŠčĆčĆąĄą║čéąĮąŠą│ąŠ čćč鹥ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ąĖąĘ Flash ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąŠ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ ąĘąĮą░č湥ąĮąĖąĄ ą║ąŠą╗ąĖč湥čüčéą▓ą░ čåąĖą║ą╗ąŠą▓ ąŠąČąĖą┤ą░ąĮąĖčÅ wait states (LATENCY) ą▓ čĆąĄą│ąĖčüčéčĆąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┤ąŠčüčéčāą┐ąŠą╝ ą║ Flash (FLASH_ACR). ąŁč鹊 ąĘąĮą░č湥ąĮąĖąĄ ąĘą░ą▓ąĖčüąĖčé ąŠčé čćą░čüč鹊čéčŗ čéą░ą║č鹊ą▓ CPU (HCLK) ąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ.

ąæčāč乥čĆ ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮąŠą╣ ą▓čŗą▒ąŠčĆą║ąĖ (prefetch) ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ą┐čĆąĄčēąĄąĮ, ą║ąŠą│ą┤ą░ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ ąĮąĖąČąĄ 2.1V. ąĪąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĄ ą╝ąĄąČą┤čā ą║ąŠą╗ąĖč湥čüčéą▓ąŠą╝ wait states ąĖ čćą░čüč鹊č鹊ą╣ CPU ą┐čĆąĖą▓ąĄą┤ąĄąĮą░ ą▓ čéą░ą▒ą╗ąĖčåą░čģ 10 ąĖ 11.

ąØą░ STM32F405xx/07xx ąĖ STM32F415xx/17xx:

- ąÜąŠą│ą┤ą░ VOS = 0, ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮą░čÅ čćą░čüč鹊čéą░ fHCLK = 144 ą£ąōčå.

- ąÜąŠą│ą┤ą░ VOS = 1, ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮą░čÅ čćą░čüč鹊čéą░ fHCLK = 168 ą£ąōčå.

ąØą░ STM32F42xxx ąĖ STM32F43xxx:

- ąÜąŠą│ą┤ą░ VOS[1:0] = 0x01, ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ fHCLK 120 ą£ąōčå.

- ąÜąŠą│ą┤ą░ VOS[1:0] = 0x10, ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ fHCLK 144 ą£ąōčå. ą£ą░ą║čüąĖą╝ą░ą╗čīąĮą░čÅ čćą░čüč鹊čéą░ ą╝ąŠąČąĄčé ą▒čŗčéčī čāą▓ąĄą╗ąĖč湥ąĮą░ ą┤ąŠ 168 ą£ąōčå ą░ą║čéąĖą▓ą░čåąĖąĄą╣ čĆąĄąČąĖą╝ą░ over-drive.

- ąÜąŠą│ą┤ą░ VOS[1:0] = 0x11, ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ fHCLK 168 ą£ąōčå. ą£ą░ą║čüąĖą╝ą░ą╗čīąĮą░čÅ čćą░čüč鹊čéą░ ą╝ąŠąČąĄčé ą▒čŗčéčī čāą▓ąĄą╗ąĖč湥ąĮą░ ą┤ąŠ 180 ą£ąōčå ą░ą║čéąĖą▓ą░čåąĖąĄą╣ čĆąĄąČąĖą╝ą░ over-drive.

- ąĀąĄąČąĖą╝ over-drive ąĮąĄą┤ąŠčüčéčāą┐ąĄąĮ ą┤ą╗čÅ VDD ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąŠčé 1.8V ą┤ąŠ 2.1 V.

ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ ąŠ č鹊ą╝, ą║ą░ą║ ą░ą║čéąĖą▓ąĖčĆąŠą▓ą░čéčī čĆąĄąČąĖą╝ over-drive čüą╝. čĆą░ąĘą┤ąĄą╗ 5.1.4: Voltage regulator for STM32F42xxx and STM32F43xxx ą┤ą░čéą░čłąĖčéą░ [1].

ąóą░ą▒ą╗ąĖčåą░ 10. ąÜąŠą╗ąĖč湥čüčéą▓ąŠ wait states, čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊č鹥 CPU (HCLK) ąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÄ ą┐ąĖčéą░ąĮąĖčÅ ą┤ą╗čÅ STM32F405xx/07xx ąĖ STM32F415xx/17xx.

ąÜąŠą╗ąĖč湥čüčéą▓ąŠ

čéą░ą║č鹊ą▓ ąŠąČąĖą┤ą░ąĮąĖčÅ

WS (LATENCY)

|

HCLK (ą£ąōčå) |

| 2.7V - 3.6V |

2.4V - 2.7V |

2.1V - 2.4V |

1.8V - 2.1V

Prefetch OFF |

| 0 WS (1 čéą░ą║čé CPU) |

0 < HCLK Ōēż 30 |

0 < HCLK Ōēż 24 |

0 < HCLK Ōēż 22 |

0 < HCLK Ōēż 20 |

| 1 WS (2 čéą░ą║č鹊ą▓ CPU) |

30 < HCLK Ōēż 60 |

24 < HCLK Ōēż 48 |

22 < HCLK Ōēż 44 |

20 < HCLK Ōēż 40 |

| 2 WS (3 čéą░ą║čéą░ CPU) |

60 < HCLK Ōēż 90 |

48 < HCLK Ōēż 72 |

44 < HCLK Ōēż 66 |

40 < HCLK Ōēż 60 |

| 3 WS (4 čéą░ą║čéą░ CPU) |

90 < HCLK Ōēż 120 |

72 < HCLK Ōēż 96 |

66 < HCLK Ōēż 88 |

60 < HCLK Ōēż 80 |

| 4 WS (5 čéą░ą║č鹊ą▓ CPU) |

120 < HCLK Ōēż 150 |

96 < HCLK Ōēż 120 |

88 < HCLK Ōēż 110 |

80 < HCLK Ōēż 100 |

| 5 WS (6 čéą░ą║č鹊ą▓ CPU) |

150 < HCLK Ōēż 168 |

120 < HCLK Ōēż 144 |

110 < HCLK Ōēż 132 |

100 < HCLK Ōēż 120 |

| 6 WS (7 čéą░č鹊ą▓ CPU) |

|

144 < HCLK Ōēż 168 |

132 < HCLK Ōēż 154 |

120 < HCLK Ōēż 140 |

| 7 WS (8 čéą░ą║č鹊ą▓ CPU) |

|

|

154 < HCLK Ōēż 168 |

140 < HCLK Ōēż 160 |

ąóą░ą▒ą╗ąĖčåą░ 11. ąÜąŠą╗ąĖč湥čüčéą▓ąŠ wait states, čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊č鹥 CPU (HCLK) ą┤ą╗čÅ STM32F42xxx ąĖ STM32F43xxx.

ąÜąŠą╗ąĖč湥čüčéą▓ąŠ

čéą░ą║č鹊ą▓ ąŠąČąĖą┤ą░ąĮąĖčÅ

WS (LATENCY)

|

HCLK (ą£ąōčå) |

| 2.7V - 3.6V |

2.4V - 2.7V |

2.1V - 2.4V |

1.8V - 2.1V

Prefetch OFF |

| 0 WS (1 čéą░ą║čé CPU) |

0 < HCLK Ōēż 30 |

0 < HCLK Ōēż 24 |

0 < HCLK Ōēż 22 |

0 < HCLK Ōēż 20 |

| 1 WS (2 čéą░ą║č鹊ą▓ CPU) |

30 < HCLK Ōēż 60 |

24 < HCLK Ōēż 48 |

22 < HCLK Ōēż 44 |

20 < HCLK Ōēż 40 |

| 2 WS (3 čéą░ą║čéą░ CPU) |

60 < HCLK Ōēż 90 |

48 < HCLK Ōēż 72 |

44 < HCLK Ōēż 66 |

40 < HCLK Ōēż 60 |

| 3 WS (4 čéą░ą║čéą░ CPU) |

90 < HCLK Ōēż 120 |

72 < HCLK Ōēż 96 |

66 < HCLK Ōēż 88 |

60 < HCLK Ōēż 80 |

| 4 WS (5 čéą░ą║č鹊ą▓ CPU) |

120 < HCLK Ōēż 150 |

96 < HCLK Ōēż 120 |

88 < HCLK Ōēż 110 |

80 < HCLK Ōēż 100 |

| 5 WS (6 čéą░ą║č鹊ą▓ CPU) |

150 < HCLK Ōēż 180 |

120 < HCLK Ōēż 144 |

110 < HCLK Ōēż 132 |

100 < HCLK Ōēż 120 |

| 6 WS (7 čéą░č鹊ą▓ CPU) |

|

144 < HCLK Ōēż 168 |

132 < HCLK Ōēż 154 |

120 < HCLK Ōēż 140 |

| 7 WS (8 čéą░ą║č鹊ą▓ CPU) |

|

168 |

154 < HCLK Ōēż 176 |

140 < HCLK Ōēż 160 |

| 8 WS (9 čéą░ą║č鹊ą▓ CPU) |

|

|

176 < HCLK Ōēż 180 |

160 < HCLK Ōēż 168 |

ą¤ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ CPU čĆą░ą▓ąĮą░ 16 ą£ąōčå (čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ąŠčé ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ RC-ą│ąĄąĮąĄčĆą░č鹊čĆą░ HSI), ąĖ ą▓ čĆąĄą│ąĖčüčéčĆąĄ FLASH_ACR čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąŠ 0 wait state (WS).

ąØą░čüč鹊čÅč鹥ą╗čīąĮąŠ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ą┐čĆąĖą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ čüą╗ąĄą┤čāčÄčēąĄą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ čłą░ą│ąŠą▓ ą▓ ą┐čĆąŠą│čĆą░ą╝ą╝ąĄ, čćč鹊ą▒čŗ ą┐ąŠą┤čüčéčĆąŠąĖčéčī ą║ąŠą╗ąĖč湥čüčéą▓ąŠ wait states, ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠąĄ ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ ą║ ą┐ą░ą╝čÅčéąĖ Flash, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čćą░čüč鹊čéčŗ CPU.

ąŻą▓ąĄą╗ąĖč湥ąĮąĖąĄ čćą░čüč鹊čéčŗ CPU:

1. ąŚą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāą╣č鹥 ąĮąŠą▓ąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ wait states ą▓ ą▒ąĖčéčŗ LATENCY čĆąĄą│ąĖčüčéčĆą░ FLASH_ACR.

2. ą¤čĆąŠą▓ąĄčĆčīč鹥, čćč鹊 ąĮąŠą▓ąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ wait states ą▓čüčéčāą┐ąĖą╗ąŠ ą▓ ą┤ąĄą╣čüčéą▓ąĖąĄ ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ ą║ ą┐ą░ą╝čÅčéąĖ Flash, ą┐čāč鹥ą╝ čćč鹥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ FLASH_ACR.

3. ąśąĘą╝ąĄąĮąĖč鹥 ąĖčüč鹊čćąĮąĖą║ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ CPU ąĘą░ą┐ąĖčüčīčÄ ą▒ąĖčé SW ą▓ čĆąĄą│ąĖčüčéčĆąĄ RCC_CFGR.

4. ąĢčüą╗ąĖ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ, ąĖąĘą╝ąĄąĮąĖč鹥 ą┐čĆąĄčüą║ą░ą╗ąĄčĆ čéą░ą║č鹊ą▓ CPU ąĘą░ą┐ąĖčüčīčÄ ą▒ąĖčé HPRE ą▓ čĆąĄą│ąĖčüčéčĆąĄ RCC_CFGR.

5. ą¤čĆąŠą▓ąĄčĆčīč鹥, čćč鹊 ąĮąŠą▓čŗą╣ ąĖčüč鹊čćąĮąĖą║ čéą░ą║č鹊ą▓ CPU ąĖ/ąĖą╗ąĖ ąĮąŠą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ čéą░ą║č鹊ą▓ CPU ą▓čüčéčāą┐ąĖą╗ąĖ ą▓ ą┤ąĄą╣čüčéą▓ąĖąĄ ą┐čāč鹥ą╝ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ čćč鹥ąĮąĖčÅ čüčéą░čéčāčüą░ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ (ą▒ąĖčéčŗ SWS) ąĖ/ąĖą╗ąĖ ąĘąĮą░č湥ąĮąĖčÅ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ AHB (ą▒ąĖčéčŗ HPRE) ą▓ čĆąĄą│ąĖčüčéčĆąĄ RCC_CFGR.

ąŻą╝ąĄąĮčīčłąĄąĮąĖąĄ čćą░čüč鹊čéčŗ CPU:

1. ąśąĘą╝ąĄąĮąĖč鹥 ąĖčüč鹊čćąĮąĖą║ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ CPU ąĘą░ą┐ąĖčüčīčÄ ą▒ąĖčé SW ą▓ čĆąĄą│ąĖčüčéčĆąĄ RCC_CFGR.

2. ąĢčüą╗ąĖ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ, ąĖąĘą╝ąĄąĮąĖč鹥 ą┐čĆąĄčüą║ą░ą╗ąĄčĆ čéą░ą║č鹊ą▓ CPU ąĘą░ą┐ąĖčüčīčÄ ą▒ąĖčé HPRE ą▓ čĆąĄą│ąĖčüčéčĆąĄ RCC_CFGR.

3. ą¤čĆąŠą▓ąĄčĆčīč鹥, čćč鹊 ąĮąŠą▓čŗą╣ ąĖčüč鹊čćąĮąĖą║ čéą░ą║č鹊ą▓ CPU ąĖ/ąĖą╗ąĖ ąĮąŠą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ čéą░ą║č鹊ą▓ CPU ą▓čüčéčāą┐ąĖą╗ąĖ ą▓ ą┤ąĄą╣čüčéą▓ąĖąĄ ą┐čāč鹥ą╝ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ čćč鹥ąĮąĖčÅ čüčéą░čéčāčüą░ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ (ą▒ąĖčéčŗ SWS) ąĖ/ąĖą╗ąĖ ąĘąĮą░č湥ąĮąĖčÅ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ AHB (ą▒ąĖčéčŗ HPRE) ą▓ čĆąĄą│ąĖčüčéčĆąĄ RCC_CFGR.

4. ąŚą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāą╣č鹥 ąĮąŠą▓ąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ wait states ą▓ ą▒ąĖčéčŗ LATENCY čĆąĄą│ąĖčüčéčĆą░ FLASH_ACR.

5. ą¤čĆąŠą▓ąĄčĆčīč鹥, čćč鹊 ąĮąŠą▓ąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ wait states ą▓čüčéčāą┐ąĖą╗ąŠ ą▓ ą┤ąĄą╣čüčéą▓ąĖąĄ ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ ą║ ą┐ą░ą╝čÅčéąĖ Flash, ą┐čāč鹥ą╝ čćč鹥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ FLASH_ACR.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĖąĘą╝ąĄąĮąĄąĮąĖąĄ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ CPU ąĖą╗ąĖ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ wait state (WS) ą╝ąŠąČąĄčé ąĮąĄ ą▓čüčéčāą┐ąĖčéčī ą▓ čüąĖą╗čā čüčĆą░ąĘčā ąČąĄ. ąöą╗čÅ ą┐čĆąŠą▓ąĄčĆą║ąĖ, čćč鹊 č鹥ą║čāčēą░čÅ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ CPU čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊č鹥, ą╝ąŠąČąĮąŠ ą┐čĆąŠą▓ąĄčĆąĖčéčī ąĘąĮą░č湥ąĮąĖčÅ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéą░ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ AHB ąĖ ą▒ąĖčéčŗ čüčéą░čéčāčüą░ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓. ąöą╗čÅ ą┐čĆąŠą▓ąĄčĆą║ąĖ, čćč鹊 ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮčŗčģ WS ą▓čüčéčāą┐ąĖą╗ąŠ ą▓ ą┤ąĄą╣čüčéą▓ąĖąĄ, ą╝ąŠąČąĮąŠ ą┐čĆąĖčćąĖčéą░čéčī čĆąĄą│ąĖčüčéčĆ FLASH_ACR.

[ART AcceleratorŌäó]

ą¤čĆąŠą┐čĆąĖąĄčéą░čĆąĮčŗą╣ ą░ą┤ą░ą┐čéąĖą▓ąĮčŗą╣ čāčüą║ąŠčĆąĖč鹥ą╗čī ą┐ą░ą╝čÅčéąĖ, čĆą░ą▒ąŠčéą░čÄčēąĖą╣ ą▓ čĆąĄąČąĖą╝ąĄ čĆąĄą░ą╗čīąĮąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ (Adaptive real-time memory accelerator, ART) ąŠą┐čéąĖą╝ąĖąĘąĖčĆąŠą▓ą░ąĮ čā STM32 ą┤ą╗čÅ ąĖąĮą┤čāčüčéčĆąĖą░ą╗čīąĮąŠą│ąŠ čüčéą░ąĮą┤ą░čĆčéą░ Arm┬« Cortex┬«-M4 čü FPU. ą×ąĮ ą▒ą░ą╗ą░ąĮčüąĖčĆčāąĄčé ą┤ąŠčüč鹊ąĖąĮčüčéą▓ą░ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéąĖ Arm┬« Cortex┬«-M4 čü FPU ą▓ą╝ąĄčüč鹥 čü č鹥čģąĮąŠą╗ąŠą│ąĖčÅą╝ąĖ ą┐ą░ą╝čÅčéąĖ Flash, ą║ąŠą│ą┤ą░ ąŠą▒čŗčćąĮąŠ ąŠčé ą┐čĆąŠčåąĄčüčüąŠčĆą░ čéčĆąĄą▒čāąĄčéčüčÅ ąŠąČąĖą┤ą░ąĮąĖąĄ ą╝ąĄą┤ą╗ąĄąĮąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ Flash ąĮą░ ą▒ąŠą╗ąĄąĄ ą▓čŗčüąŠą║ąĖčģ čĆą░ą▒ąŠčćąĖčģ čćą░čüč鹊čéą░čģ CPU.

ą¦č鹊ą▒čŗ ą┐čĆąŠčåąĄčüčüąŠčĆ ą┐ąŠą║ą░ąĘčŗą▓ą░ą╗ ą┐ąŠą╗ąĮčāčÄ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéčī, ART čĆąĄą░ą╗ąĖąĘčāąĄčé ąŠč湥čĆąĄą┤čī ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮąŠą╣ ą▓čŗą▒ąŠčĆą║ąĖ ąĖąĮčüčéčĆčāą║čåąĖą╣ (instruction prefetch queue) ąĖ ą║čŹčł ą▓ąĄčéą▓ą╗ąĄąĮąĖą╣, čćč鹊 čāą▓ąĄą╗ąĖčćąĖą▓ą░ąĄčé ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ąĖąĘ 128-čĆą░ąĘčĆčÅą┤ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ Flash. ą¤ąŠ č鹥čüčéčā CoreMark čü ą┐ąŠą╝ąŠčēčīčÄ čāčüą║ąŠčĆąĖč鹥ą╗čÅ ART ą┤ąŠčüčéąĖą│ą░ąĄčéčüčÅ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéčī, 菹║ą▓ąĖą▓ą░ą╗ąĄąĮčéąĮą░čÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÄ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ąĖąĘ Flash čü ąĮčāą╗ąĄą▓čŗą╝ąĖ čéą░ą║čéą░ą╝ąĖ ąŠąČąĖą┤ą░ąĮąĖčÅ (0 wait state) ą┐čĆąĖ čćą░čüč鹊č鹥 čéą░ą║č鹊ą▓ CPU ą┤ąŠ 180 ą£ąōčå.

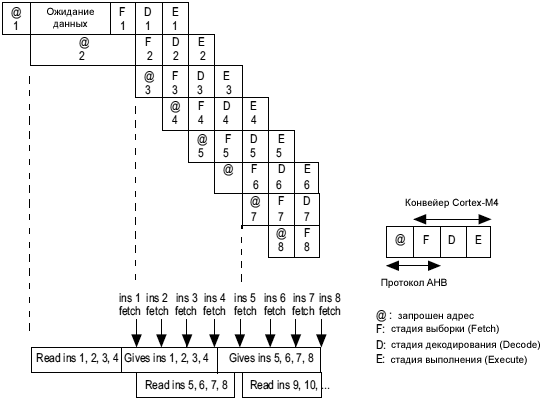

ą¤čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮą░čÅ ą▓čŗą▒ąŠčĆą║ą░ ąĖąĮčüčéčĆčāą║čåąĖą╣. ąÜą░ąČą┤ą░čÅ ąŠą┐ąĄčĆą░čåąĖčÅ čćč鹥ąĮąĖčÅ ą┐ą░ą╝čÅčéąĖ Flash ą┐čĆąĖ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĖ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé 128 ą▒ąĖčé ą╗ąĖą▒ąŠ ą┤ą╗čÅ č湥čéčŗčĆąĄčģ 32-ą▒ąĖčéąĮčŗčģ ąĖąĮčüčéčĆčāą║čåąĖą╣, ą╗ąĖą▒ąŠ ą▓ąŠčüčīą╝ąĖ 16-ą▒ąĖčéąĮčŗčģ ąĖąĮčüčéčĆčāą║čåąĖą╣. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą┐čĆąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą╝ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĖ ą║ąŠą┤ą░ čéčĆąĄą▒čāąĄčéčüčÅ ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ 4 čéą░ą║čéą░ CPU ą┤ą╗čÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ čĆą░ąĮąĄąĄ ą┐čĆąŠčćąĖčéą░ąĮąĮąŠą╣ čüčéčĆąŠą║ąĖ ąĖąĮčüčéčĆčāą║čåąĖą╣. ą£ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮą░čÅ ą▓čŗą▒ąŠčĆą║ą░ ąĮą░ čłąĖąĮąĄ ą║ąŠą┤ą░ (prefetch on I-Code bus) ą┤ą╗čÅ čćč鹥ąĮąĖčÅ čüą╗ąĄą┤čāčÄčēąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą╣ ą╗ąĖąĮąĖąĖ ąĖąĮčüčéčĆčāą║čåąĖą╣ ąĖąĘ ą┐ą░ą╝čÅčéąĖ Flash, ą┐ąŠą║ą░ č鹥ą║čāčēą░čÅ ąĖąĮčüčéčĆčāą║čåąĖčÅ ąĘą░ą┐čĆą░čłąĖą▓ą░ąĄčéčüčÅ CPU. ą¤čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮą░čÅ ą▓čŗą▒ąŠčĆą║ą░ ąĖąĮčüčéčĆčāą║čåąĖą╣ čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ PRFTEN ą▓ čĆąĄą│ąĖčüčéčĆąĄ FLASH_ACR. ąŁčéą░ čäčāąĮą║čåąĖčÅ ą┐ąŠą╗ąĄąĘąĮą░, ąĄčüą╗ąĖ ąĮčāąČąĄąĮ čģąŠčéčÅ ą▒čŗ ąŠą┤ąĖąĮ wait state ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ ą║ ą┐ą░ą╝čÅčéąĖ Flash.

ąĀąĖčü. 5a ąĖ 5b ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčé ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ čüą╗ąĄą┤čāčÄčēąĖčģ ą┤čĆčāą│ ąĘą░ ą┤čĆčāą│ąŠą╝ 32-čĆą░ąĘčĆčÅą┤ąĮčŗčģ ąĖąĮčüčéčĆčāą║čåąĖą╣ čü ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮąŠą╣ ą▓čŗą▒ąŠčĆą║ąŠą╣ ąĖ ą▒ąĄąĘ ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮąŠą╣ ą▓čŗą▒ąŠčĆą║ąĖ, ą║ąŠą│ą┤ą░ čéčĆąĄą▒čāąĄčéčüčÅ čéčĆąĖ čéą░ą║čéą░ ąŠąČąĖą┤ą░ąĮąĖčÅ (3 WS) ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ ą║ ą┐ą░ą╝čÅčéąĖ Flash.

ąĀąĖčü. 5a. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ 32-ą▒ąĖčéąĮčŗčģ ąĖąĮčüčéčĆčāą║čåąĖą╣ ą▒ąĄąĘ ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮąŠą╣ ą▓čŗą▒ąŠčĆą║ąĖ ąĖąĮčüčéčĆčāą║čåąĖą╣.

ąĀąĖčü. 5b. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ 32-ą▒ąĖčéąĮčŗčģ ąĖąĮčüčéčĆčāą║čåąĖą╣ čü ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮąŠą╣ ą▓čŗą▒ąŠčĆą║ąŠą╣ ąĖąĮčüčéčĆčāą║čåąĖą╣ (prefetch).

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ ą║ čĆąĖčü. 5a ąĖ 5b: ins fetch ąŠąĘąĮą░čćą░ąĄčé ą▓čŗą▒ąŠčĆą║ą░ ąĖąĮčüčéčĆčāą║čåąĖąĖ, Read ins čćč鹥ąĮąĖąĄ ąĖąĮčüčéčĆčāą║čåąĖąĖ, Gives ins ą▓čŗą┤ą░čćą░ ąĖąĮčüčéčĆčāą║čåąĖąĖ.

ąÜąŠą│ą┤ą░ ą║ąŠą┤ ąĮąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ (ąĖą╝ąĄąĄčé ą▓ąĄčéą▓ą╗ąĄąĮąĖčÅ ąĖą╗ąĖ ą┐ąĄčĆąĄčģąŠą┤čŗ), ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ą░čÅ ą▓ ąĮą░čüč鹊čÅčēąĖą╣ ą╝ąŠą╝ąĄąĮčé ąĖąĮčüčéčĆčāą║čåąĖčÅ ą╝ąŠąČąĄčé ąĮąĄ ą┐čĆąĖčüčāčéčüčéą▓ąŠą▓ą░čéčī ą▓ čüčéčĆąŠą║ąĄ ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮąŠą╣ ą▓čŗą▒ąŠčĆą║ąĖ. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą┐čĆąŠą╝ą░čģ ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮąŠą╣ ą▓čŗą▒ąŠčĆą║ąĖ, ąĖ ą▓čüčéą░ą▓ą╗čÅąĄčéčüčÅ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ą░čÅ ąĘą░ą┤ąĄčƹȹ║ą░ ą┤ąŠčüčéčāą┐ą░ ą║ Flash, čĆą░ą▓ąĮą░čÅ ą║ąŠą╗ąĖč湥čüčéą▓čā ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮčŗčģ čéą░ą║č鹊ą▓ ąŠąČąĖą┤ą░ąĮąĖčÅ (wait states, WS).

ąÜčŹčł ą┐ą░ą╝čÅčéąĖ ąĖąĮčüčéčĆčāą║čåąĖą╣. ą¦č鹊ą▒čŗ ąŠą│čĆą░ąĮąĖčćąĖčéčī ą┐ąŠč鹥čĆąĖ ą▓čĆąĄą╝ąĄąĮąĖ ąĖąĘ-ąĘą░ ą┐ąĄčĆąĄčģąŠą┤ąŠą▓, ą▓ ą║čŹčłąĄ ą┐ą░ą╝čÅčéąĖ ąĖąĮčüčéčĆčāą║čåąĖą╣ ą╝ąŠąČąĮąŠ čģčĆą░ąĮąĖčéčī ą┤ąŠ 64 čüčéčĆąŠą║ąĖ ą┐ąŠ 128 ą▒ąĖčé. ąŁčéą░ čäčāąĮą║čåąĖčÅ ą╝ąŠąČąĄčé ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮą░ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą║čŹčłą░ ąĖąĮčüčéčĆčāą║čåąĖą╣ (instruction cache enable, ICEN) ą▓ čĆąĄą│ąĖčüčéčĆąĄ FLASH_ACR. ąÜą░ąČą┤čŗą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą┐čĆąŠą╝ą░čģ (ąĘą░ą┐čĆą░čłąĖą▓ą░ąĄą╝čŗąĄ ą┤ą░ąĮąĮčŗąĄ ąĮąĄ ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮčŗ ą▓ č鹥ą║čāčēąĄą╣ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ąŠą╣ ąĖąĮčüčéčĆčāą║čåąĖąĖ, ą▓ ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮąŠ ą▓čŗą▒čĆą░ąĮąĮąŠą╣ čüčéčĆąŠą║ąĄ ąĖąĮčüčéčĆčāą║čåąĖą╣ ąĖą╗ąĖ ą▓ ą┐ą░ą╝čÅčéąĖ ą║čŹčłą░ ąĖąĮčüčéčĆčāą║čåąĖą╣), ą┐čĆąŠčćąĖčéą░ąĮąĮą░čÅ čüčéčĆąŠą║ą░ ą║ąŠą┐ąĖčĆčāąĄčéčüčÅ ą▓ ą┐ą░ą╝čÅčéčī ą║čŹčłą░ ąĖąĮčüčéčĆčāą║čåąĖą╣. ąĢčüą╗ąĖ CPU ąĘą░ą┐čĆą░čłąĖą▓ą░ąĄčé ą┤ą░ąĮąĮčŗąĄ, ą║ąŠč鹊čĆčŗąĄ čüąŠą┤ąĄčƹȹ░čéčüčÅ ą▓ ą║čŹčłąĄ ąĖąĮčüčéčĆčāą║čåąĖą╣, č鹊 ąŠąĮąĖ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÄčéčüčÅ ą▒ąĄąĘ ąĘą░ą┤ąĄčƹȹ║ąĖ. ąÜąŠą│ą┤ą░ ą▓ąĄčüčī ą║čŹčł ąĖąĮčüčéčĆčāą║čåąĖą╣ ąĘą░ą┐ąŠą╗ąĮąĄąĮ, ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┐ąŠą╗ąĖčéąĖą║ą░ "ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĮčŗą╣" (least recently used, LRU), čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī čüčéčĆąŠą║čā, ą║ąŠč鹊čĆą░čÅ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ąĘą░ą╝ąĄąĮąĄąĮą░ ą▓ ą║čŹčłąĄ ąĖąĮčüčéčĆčāą║čåąĖą╣. ąŁčéą░ čäčāąĮą║čåąĖčÅ ą▓ čćą░čüčéąĮąŠčüčéąĖ ą┐ąŠą╗ąĄąĘąĮą░ ą┤ą╗čÅ ą║ąŠą┤ą░, čüąŠą┤ąĄčƹȹ░čēąĄą│ąŠ čåąĖą║ą╗čŗ.

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┤ą░ąĮąĮčŗą╝ąĖ. ą¤čāą╗čŗ ą╗ąĖč鹥čĆą░ą╗ąŠą▓ ąĖąĘą▓ą╗ąĄą║ą░čÄčéčüčÅ ąĖąĘ Flash-ą┐ą░ą╝čÅčéąĖ ą┐ąŠ čłąĖąĮąĄ D-Code ąĮą░ čŹčéą░ą┐ąĄ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą║ąŠąĮą▓ąĄą╣ąĄčĆą░ CPU. ąĪą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ, ą║ąŠąĮą▓ąĄą╣ąĄčĆ CPU ą┐čĆąĖąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ, ą┐ąŠą║ą░ ąĮąĄ ą▒čāą┤ąĄčé ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮ ąĘą░ą┐čĆąŠčłąĄąĮąĮčŗą╣ ą┐čāą╗ ą╗ąĖč鹥čĆą░ą╗ąŠą▓. ą¦č鹊ą▒čŗ ąŠą│čĆą░ąĮąĖčćąĖčéčī ą┐ąŠč鹥čĆąĖ ą▓čĆąĄą╝ąĄąĮąĖ ąĖąĘ-ąĘą░ ą┐čāą╗ąŠą▓ ą╗ąĖč鹥čĆą░ą╗ąŠą▓, ąŠą┐ąĄčĆą░čåąĖąĖ ą┤ąŠčüčéčāą┐ą░ čłąĖąĮčŗ ą┤ą░ąĮąĮčŗčģ AHB D-Code ąĖą╝ąĄčÄčé ą┐čĆąĖąŠčĆąĖč鹥čé ąĮą░ą┤ ąŠą┐ąĄčĆą░čåąĖčÅą╝ąĖ ą┤ąŠčüčéčāą┐ą░ č湥čĆąĄąĘ čłąĖąĮčā ąĖąĮčüčéčĆčāą║čåąĖą╣ AHB I-Code.

ąĢčüą╗ąĖ ąĮąĄą║ąŠč鹊čĆčŗąĄ ą┐čāą╗čŗ ą╗ąĖč鹥čĆą░ą╗ąŠą▓ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ čćą░čüč鹊, ą╝ąŠąČąĄčé ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮ ą║čŹčł ą┤ą░ąĮąĮčŗčģ ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ (DCEN) ą▓ čĆąĄą│ąĖčüčéčĆąĄ FLASH_ACR. ąŁčéą░ čäčāąĮą║čåąĖčÅ čĆą░ą▒ąŠčéą░ąĄčé ą┐ąŠą┤ąŠą▒ąĮąŠ ą║čŹčłčā ąĖąĮčüčéčĆčāą║čåąĖą╣, ąĮąŠ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čüąŠčģčĆą░ąĮąĄąĮąĮčŗčģ ą┤ą░ąĮąĮčŗčģ ą▓ ą║čŹčłąĄ ąŠą│čĆą░ąĮąĖč湥ąĮąŠ 8 čüčéčĆąŠą║ą░ą╝ąĖ ą┐ąŠ 128 ą▒ąĖčé.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą┤ą░ąĮąĮčŗąĄ ą▓ čüąĄą║č鹊čĆąĄ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ ąĮąĄ ą║čŹčłąĖčĆčāčÄčéčüčÅ.

[ąĪčéąĖčĆą░ąĮąĖąĄ ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ]

ąöą╗čÅ ą╗čÄą▒ąŠą╣ ąŠą┐ąĄčĆą░čåąĖąĖ ąĮą░ą┤ ą┐ą░ą╝čÅčéčīčÄ ą┐čĆąŠą│čĆą░ą╝ą╝ Flash (čüčéąĖčĆą░ąĮąĖąĄ ąĖą╗ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ), čćą░čüč鹊čéą░ čéą░ą║č鹊ą▓ CPU (HCLK) ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ 1 ą£ąōčå. ąĪąŠą┤ąĄčƹȹĖą╝ąŠąĄ ą┐ą░ą╝čÅčéąĖ Flash ąĮąĄ ą│ą░čĆą░ąĮčéąĖčĆčāąĄčéčüčÅ, ąĄčüą╗ąĖ ą┐čĆąŠąĖąĘąŠčłąĄą╗ čüą▒čĆąŠčü čāčüčéčĆąŠą╣čüčéą▓ą░ ą▓ąŠ ą▓čĆąĄą╝čÅ ąŠą┐ąĄčĆą░čåąĖąĖ čü Flash.

ąøčÄą▒ą░čÅ ą┐ąŠą┐čŗčéą║ą░ čćč鹥ąĮąĖčÅ ą┐ą░ą╝čÅčéąĖ Flash STM32F4xx, ą║ąŠą│ą┤ą░ ąŠąĮą░ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ ąĖą╗ąĖ čüčéąĖčĆą░ąĄčéčüčÅ, ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ąĄ čłąĖąĮčŗ. ą×ą┐ąĄčĆą░čåąĖąĖ čćč鹥ąĮąĖčÅ ą║ąŠčĆčĆąĄą║čéąĮąŠ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░čÄčéčüčÅ, ą║ąŠą│ą┤ą░ ąŠą┐ąĄčĆą░čåąĖčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ąĘą░ą▓ąĄčĆčłąĄąĮą░. ąŁč鹊 ąĘąĮą░čćąĖčé, čćč鹊 ą▓čŗą▒ąŠčĆą║ąĖ ą║ąŠą┤ą░ ąĖą╗ąĖ ą┤ą░ąĮąĮčŗčģ ąĮąĄ ą╝ąŠą│čāčé ą▓čŗą┐ąŠą╗ąĮčÅčéčīčüčÅ, ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ąŠą┐ąĄčĆą░čåąĖčÅ ąĘą░ą┐ąĖčüąĖ/čüčéąĖčĆą░ąĮąĖčÅ.

ąØą░ STM32F42xxx ąĖ STM32F43xxx ą┤ąŠčüčéčāą┐ąĮčŗ 2 ą▒ą░ąĮą║ą░, ą┐čĆąĖ čŹč鹊ą╝ ą┤ąŠą┐čāčüą║ą░ąĄčéčüčÅ čćč鹥ąĮąĖąĄ ąŠą┤ąĮąŠą│ąŠ ą▒ą░ąĮą║ą░, ą║ąŠą│ą┤ą░ ąĮą░ ą┤čĆčāą│ąŠą╝ ą▒ą░ąĮą║ąĄ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ąŠą┐ąĄčĆą░čåąĖčÅ ąĘą░ą┐ąĖčüąĖ/čüčéąĖčĆą░ąĮąĖčÅ.

ąĀą░ąĘą▒ą╗ąŠą║ąĖčĆąŠą▓ą░ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ Flash. ą¤ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ ąĮąĄ čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ ąĘą░ą┐ąĖčüčī ą▓ čĆąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ Flash (FLASH_CR), čćč鹊ą▒čŗ ąĘą░čēąĖčéąĖčéčī Flash ąŠčé ą▓ąŠąĘą╝ąŠąČąĮčŗčģ ąĮąĄą┐čĆą░ą▓ąĖą╗čīąĮčŗčģ ąŠą┐ąĄčĆą░čåąĖą╣, ąĮą░ą┐čĆąĖą╝čĆ ąĖąĘ-ąĘą░ 菹╗ąĄą║čéčĆąĖč湥čüą║ąĖčģ ą┐ąŠą╝ąĄčģ. ąöą╗čÅ čĆą░ąĘą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ čĆąĄą│ąĖčüčéčĆą░ FLASH_CR ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čüą╗ąĄą┤čāčÄčēą░čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┤ąĄą╣čüčéą▓ąĖą╣:

1. ąŚą░ą┐ąĖčüčī KEY1 = 0x45670123 ą▓ čĆąĄą│ąĖčüčéčĆ ą║ą╗čÄčćą░ Flash (FLASH_KEYR).

2. ąŚą░ą┐ąĖčüčī KEY2 = 0xCDEF89AB ą▓ čĆąĄą│ąĖčüčéčĆ ą║ą╗čÄčćą░ Flash (FLASH_KEYR).

ąøčÄą▒ąŠąĄ ąĮąĄčüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĄ ą▓ čŹč鹊ą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ąŠčłąĖą▒ą║ąĄ čłąĖąĮčŗ ąĖ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĄ čĆąĄą│ąĖčüčéčĆą░ FLASH_CR ą┤ąŠ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ čüą▒čĆąŠčüą░.

ąĀąĄą│ąĖčüčéčĆ FLASH_CR ą╝ąŠąČąĄčé ą▒čŗčéčī čüąĮąŠą▓ą░ ąĘą░ą▒ą╗ąŠą║ąĖčĆąŠą▓ą░ąĮ ą┐čĆąŠą│čĆą░ą╝ą╝ąŠą╣ ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ LOCK ą▓ čĆąĄą│ąĖčüčéčĆąĄ FLASH_CR.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: čĆąĄą│ąĖčüčéčĆ FLASH_CR ąĮąĄą┤ąŠčüčéčāą┐ąĄąĮ ą▓ čĆąĄąČąĖą╝ąĄ ąĘą░ą┐ąĖčüąĖ, ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé BSY ą▓ čĆąĄą│ąĖčüčéčĆąĄ FLASH_SR. ąøčÄą▒ą░čÅ ą┐ąŠą┐čŗčéą║ą░ ąĘą░ą┐ąĖčüąĖ ą▓ ąĮąĄą│ąŠ, ą║ąŠą│ą┤ą░ ą▒ąĖčé BSY čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ą┐čĆąĖą▓ąĄą┤ąĄąĮ ą║ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ąĄ čłąĖąĮčŗ AHB ą┤ąŠ ąŠčćąĖčüčéą║ąĖ ą▒ąĖčéą░ BSY.

ą¤ą░čĆą░ą╗ą╗ąĄą╗ąĖąĘą╝ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ/čüčéąĖčĆą░ąĮąĖčÅ. ąĀą░ąĘą╝ąĄčĆ ą┐ą░čĆą░ą╗ą╗ąĄą╗ąĖąĘą╝ą░ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ ą┐ąŠą╗ąĄą╝ PSIZE ą▓ čĆąĄą│ąĖčüčéčĆąĄ FLASH_CR. ąŁč鹊 ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ą░ą╣čé ą┤ą╗čÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą║ą░ąČą┤čŗą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ąŠą┐ąĄčĆą░čåąĖčÅ ąĘą░ą┐ąĖčüąĖ ą▓ ą┐ą░ą╝čÅčéčī Flash. PSIZE ąŠą│čĆą░ąĮąĖčćąĖą▓ą░ąĄčéčüčÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄą╝ ą┐ąĖčéą░ąĮąĖčÅ ąĖ čäą░ą║č鹊ą╝, ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą╗ąĖ ą▓ąĮąĄčłąĮąĄąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ VPP, ąĖą╗ąĖ ąĮąĄčé. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, čŹč鹊 ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą║ąŠčĆčĆąĄą║čéąĮąŠ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąŠ ą▓ čĆąĄą│ąĖčüčéčĆąĄ FLASH_CR ą┐ąĄčĆąĄą┤ ą╗čÄą▒ąŠą╣ ąŠą┐ąĄčĆą░čåąĖąĄą╣ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ/čüčéąĖčĆą░ąĮąĖčÅ.

ą×ą┐ąĄčĆą░čåąĖčÅ čüčéąĖčĆą░ąĮąĖčÅ Flash ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮą░ č鹊ą╗čīą║ąŠ ąĮą░ą┤ čüąĄą║č鹊čĆąŠą╝, ąĮą░ą┤ ą▒ą░ąĮą║ąŠą╝ ąĖą╗ąĖ ąĮą░ą┤ ą▓čüąĄą╣ ą┐ą░ą╝čÅčéčīčÄ Flash (mass erase). ąÆčĆąĄą╝čÅ čüčéąĖčĆą░ąĮąĖčÅ ąĘą░ą▓ąĖčüąĖčé ąŠčé ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ PSIZE. ąæąŠą╗ąĄąĄ ą┐ąŠą┤čĆąŠą▒ąĮąŠ ą┐čĆąŠ ą▓čĆąĄą╝čÅ čüčéąĖčĆą░ąĮąĖčÅ čüą╝. čüąĄą║čåąĖčÄ čŹą╗ąĄą║čéčĆąĖč湥čüą║ąĖčģ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ ąĮą░ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╣ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ.

ąóą░ą▒ą╗ąĖčåą░ 12 ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą║ąŠčĆčĆąĄą║čéąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ PSIZE.

ąóą░ą▒ą╗ąĖčåą░ 12. ą¤ą░čĆą░ą╗ą╗ąĄą╗ąĖąĘą╝ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ/čüčéąĖčĆą░ąĮąĖčÅ.

| |

2.7V - 3.6V,

čü ą▓ąĮąĄčłąĮąĖą╝ VPP |

2.7V - 3.6V |

2.4V - 2.7V |

2.1V - 2.4V |

1.8V - 2.1V |

| ąĀą░ąĘą╝ąĄčĆ ą┐ą░čĆą░ą╗ą╗ąĄą╗ąĖąĘą╝ą░ |

x64 |

x32 |

x16 |

x8 |

| PSIZE(1:0) |

11 |

10 |

01 |

00 |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą╗čÄą▒ą░čÅ ąŠą┐ąĄčĆą░čåąĖčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖą╗ąĖ čüčéąĖčĆą░ąĮąĖčÅ, ąĮą░čćą░čéą░čÅ čü ąĮąĄą┐čĆą░ą▓ąĖą╗čīąĮąŠ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮčŗą╝ąĖ ąĮą░čüčéčĆąŠą║ą░ą╝ąĖ ą┤ąĖą░ą┐ą░ąĘąŠąĮą░ ą┐ą░čĆą░ą╗ą╗ąĄą╗ąĖąĘą╝ą░/ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ, ą╝ąŠąČąĄčé ą┐čĆąĖą▓ąĄčüčéąĖ ą║ ąĮąĄą┐čĆąĄą┤čüą║ą░ąĘčāąĄą╝čŗą╝ čĆąĄąĘčāą╗čīčéą░čéą░ą╝. ąöą░ąČąĄ ąĄčüą╗ąĖ ą┐ąŠčüą╗ąĄą┤čāčÄčēą░čÅ ąŠą┐ąĄčĆą░čåąĖčÅ čćč鹥ąĮąĖčÅ ą┐ąŠą║ą░ąĘąĄčé, čćč鹊 ą╗ąŠą│ąĖč湥čüą║ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą▒čŗą╗ąŠ čŹčäč乥ą║čéąĖą▓ąĮąŠ ąĘą░ą┐ąĖčüą░ąĮąŠ ą▓ ą┐ą░ą╝čÅčéčī, čŹč鹊 ąĘąĮą░č湥ąĮąĖąĄ ą╝ąŠąČąĄčé ąĮą░ čüą░ą╝ąŠą╝ ą┤ąĄą╗ąĄ ąĮąĄ čüąŠčģčĆą░ąĮąĖčéčīčüčÅ. ąöą╗čÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ VPP ąĮą░ ąĮąŠąČą║čā VPP ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą┐ąŠą┤ą░ąĮąŠ ą▓ąĮąĄčłąĮąĄąĄ ą▓čŗčüąŠą║ąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ (ą╝ąĄąČą┤čā 8V ąĖ 9V). ąŁč鹊 ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┤ąŠą╗ąČąĮąŠ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čéčī čüą▓ąŠą╣ čāčĆąŠą▓ąĄąĮčī, ą┤ą░ąČąĄ ąĄčüą╗ąĖ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ ą┐ąŠčüč鹊čÅąĮąĮąŠą│ąŠ č鹊ą║ą░ ą┐čĆąĄą▓čŗčüąĖčé 10 ą╝ąÉ. ąĀąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ąŠą│čĆą░ąĮąĖčćąĖčéčī ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ VPP ąĮą░čćą░ą╗čīąĮčŗą╝ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄą╝ ąĮą░ ą┐čĆąŠąĖąĘą▓ąŠą┤čüčéą▓ąĄ. ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ VPP ąĮąĄ ą┤ąŠą╗ąČąĮąŠ ą┐čĆąĖą║ą╗ą░ą┤čŗą▓ą░čéčīčüčÅ ą▒ąŠą╗čīčłąĄ čćą░čüą░, ąĖąĮą░č湥 ą┐ą░ą╝čÅčéčī Flash ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠą▓čĆąĄąČą┤ąĄąĮą░.

[ąĪčéąĖčĆą░ąĮąĖąĄ (Erase)]

ą×ą┐ąĄčĆą░čåąĖčÅ čüčéąĖčĆą░ąĮąĖčÅ ą┐ą░ą╝čÅčéąĖ Flash ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮą░ ąĮą░ čāčĆąŠą▓ąĮąĄ čüąĄą║č鹊čĆą░, ąĖą╗ąĖ ąĮą░ ą▓čüąĄą╣ ą┐ą░ą╝čÅčéąĖ Flash (Mass Erase). Mass Erase ąĮąĄ ą▓ą╗ąĖčÅąĄčé ąĮą░ čüąĄą║č鹊čĆ OTP ąĖą╗ąĖ ąĮą░ čüąĄą║č鹊čĆ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ.

ąĪčéąĖčĆą░ąĮąĖąĄ čüąĄą║č鹊čĆą░. ąöą╗čÅ čüčéąĖčĆą░ąĮąĖčÅ čüąĄą║č鹊čĆą░ ą▓čŗą┐ąŠą╗ąĮąĖč鹥 čüą╗ąĄą┤čāčÄčēąĄąĄ:

1. ą¤čĆąŠą▓ąĄčĆčīč鹥, čćč鹊 ą▓ ąĮą░čüč鹊čÅčēąĖą╣ ą╝ąŠą╝ąĄąĮčé ąĮąĄ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą╗čÄą▒ą░čÅ ąŠą┐ąĄčĆą░čåąĖčÅ čü ą┐ą░ą╝čÅčéčīčÄ Flash ą┐čāč鹥ą╝ ą┐čĆąŠą▓ąĄčĆą║ąĖ ą▒ąĖčéą░ BSY ą▓ čĆąĄą│ąĖčüčéčĆąĄ FLASH_SR. ąĢčüą╗ąĖ BSY = 0, č鹊 Flash ąĮąĄ ąĘą░ąĮčÅčéą░, ąĖ ą╝ąŠąČąĮąŠ ą┐ąĄčĆąĄą╣čéąĖ ą║ čłą░ą│čā 2.

2. ąŻčüčéą░ąĮąŠą▓ąĖč鹥 ą▒ąĖčé SER, ąĖ ą▓čŗą▒ąĄčĆąĖč鹥 ąŠą┤ąĖąĮ ąĖąĘ 12 čüąĄą║č鹊čĆąŠą▓ ą┤ą╗čÅ STM32F405xx/07xx ąĖ STM32F415xx/17xx, ąĖ ąŠą┤ąĖąĮ ąĖąĘ 24 čüąĄą║č鹊čĆąŠą▓ ą┤ą╗čÅ STM32F42xxx ąĖ STM32F43xxx ą▓ ąŠčüąĮąŠą▓ąĮąŠą╝ ą▒ą╗ąŠą║ąĄ ą┐ą░ą╝čÅčéąĖ, ą║ąŠč鹊čĆčŗą╣ ąĮčāąČąĮąŠ čüč鹥čĆąĄčéčī. ąØąŠą╝ąĄčĆ čüąĄą║č鹊čĆą░ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ą┐ąŠą╗ąĄą╝ SNB ą▓ čĆąĄą│ąĖčüčéčĆąĄ FLASH_CR.

3. ąŻčüčéą░ąĮąŠą▓ąĖč鹥 ą▒ąĖčé STRT ą▓ čĆąĄą│ąĖčüčéčĆąĄ FLASH_CR.

4. ą¤ąŠą┤ąŠąČą┤ąĖč鹥, ą┐ąŠą║ą░ ąĮąĄ ąŠčćąĖčüčéąĖčéčüčÅ ą▒ąĖčé BSY. BSY = 0 ąŠąĘąĮą░čćą░ąĄčé ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĄ ąŠą┐ąĄčĆą░čåąĖąĖ čüčéąĖčĆą░ąĮąĖčÅ.

ąĪčéąĖčĆą░ąĮąĖąĄ ą▒ą░ąĮą║ą░ ą▓ STM32F42xxx ąĖ STM32F43xxx. ą¦č鹊ą▒čŗ čüč鹥čĆąĄčéčī ą▒ą░ąĮą║ 1 ąĖą╗ąĖ ą▒ą░ąĮą║ 2, čüą╗ąĄą┤čāą╣č鹥 čüą╗ąĄą┤čāčÄčēąĄą╣ ą┐čĆąŠčåąĄą┤čāčĆąĄ:

1. ą¤čĆąŠą▓ąĄčĆčīč鹥, čćč鹊 ą▓ ąĮą░čüč鹊čÅčēąĖą╣ ą╝ąŠą╝ąĄąĮčé ąĮąĄ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą╗čÄą▒ą░čÅ ąŠą┐ąĄčĆą░čåąĖčÅ čü ą┐ą░ą╝čÅčéčīčÄ Flash ą┐čāč鹥ą╝ ą┐čĆąŠą▓ąĄčĆą║ąĖ ą▒ąĖčéą░ BSY ą▓ čĆąĄą│ąĖčüčéčĆąĄ FLASH_SR.

2. ąŻčüčéą░ąĮąŠą▓ąĖč鹥 čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ą░ąĮą║čā ą▒ąĖčé MER ąĖą╗ąĖ MER1 ą▓ čĆąĄą│ąĖčüčéčĆąĄ FLASH_CR.

3. ąŻčüčéą░ąĮąŠą▓ąĖč鹥 ą▒ąĖčé STRT ą▓ čĆąĄą│ąĖčüčéčĆąĄ FLASH_CR.

4. ą¤ąŠą┤ąŠąČą┤ąĖč鹥, ą┐ąŠą║ą░ ąĮąĄ ąŠčćąĖčüčéąĖčéčüčÅ ą▒ąĖčé BSY.

Mass Erase. ąöą╗čÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą┐ąŠą╗ąĮąŠą│ąŠ čüčéąĖčĆą░ąĮąĖčÅ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ čüą╗ąĄą┤čāčÄčēą░čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┤ąĄą╣čüčéą▓ąĖą╣:

1. ą¤čĆąŠą▓ąĄčĆčīč鹥, čćč鹊 ą▓ ąĮą░čüč鹊čÅčēąĖą╣ ą╝ąŠą╝ąĄąĮčé ąĮąĄ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą╗čÄą▒ą░čÅ ąŠą┐ąĄčĆą░čåąĖčÅ čü ą┐ą░ą╝čÅčéčīčÄ Flash ą┐čāč鹥ą╝ ą┐čĆąŠą▓ąĄčĆą║ąĖ ą▒ąĖčéą░ BSY ą▓ čĆąĄą│ąĖčüčéčĆąĄ FLASH_SR.

2. ąŻčüčéą░ąĮąŠą▓ąĖč鹥 ą▒ąĖčé MER ą▓ čĆąĄą│ąĖčüčéčĆąĄ FLASH_CR ą┤ą╗čÅ STM32F405xx/07xx ąĖ STM32F415xx/17xx, ąĖą╗ąĖ ąŠą▒ą░ ą▒ąĖčéą░ MER ąĖ MER1 ą┤ą╗čÅ STM32F42xxx ąĖ STM32F43xxx.

3. ąŻčüčéą░ąĮąŠą▓ąĖč鹥 ą▒ąĖčé STRT ą▓ čĆąĄą│ąĖčüčéčĆąĄ FLASH_CR.

4. ą¤ąŠą┤ąŠąČą┤ąĖč鹥, ą┐ąŠą║ą░ ąĮąĄ ąŠčćąĖčüčéąĖčéčüčÅ ą▒ąĖčé BSY.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĄčüą╗ąĖ ą▓ čĆąĄą│ąĖčüčéčĆąĄ FLASH_CR čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ąŠą▒ą░ ą▒ąĖčéą░ MERx ąĖ SER, č鹊 ą▒čāą┤ąĄčé ą▓čŗą┐ąŠą╗ąĮąĄąĮąŠ ą┐ąŠą╗ąĮąŠąĄ čüčéąĖčĆą░ąĮąĖąĄ (mass erase). ąĢčüą╗ąĖ ąŠą▒ą░ ą▒ąĖčéą░ MERx ąĖ SER čüą▒čĆąŠčłąĄąĮčŗ ąĖ ą▒ąĖčé STRT čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, č鹊 ą╝ąŠąČąĄčé ą┐čĆąŠąĖąĘąŠą╣čéąĖ ąĮąĄą┐čĆąĄą┤čüą║ą░ąĘčāąĄą╝ąŠąĄ ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ čü ą│ąĄąĮąĄčĆą░čåąĖąĄą╣ ą╗čÄą▒ąŠą│ąŠ čäą╗ą░ą│ą░ ąŠčłąĖą▒ą║ąĖ. ąØąĄ ą┤ąŠą╗ąČąĮąŠ ą┤ąŠą┐čāčüą║ą░čéčīčüčÅ čéą░ą║ąŠąĄ ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ.

[ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ]

ąĪčéą░ąĮą┤ą░čĆčéąĮąŠąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ. ąöą╗čÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐ą░ą╝čÅčéąĖ Flash ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┤ąĄą╣čüčéą▓ąĖą╣ čüą╗ąĄą┤čāčÄčēą░čÅ:

1. ą¤čĆąŠą▓ąĄčĆčīč鹥, čćč鹊 ą▓ ąĮą░čüč鹊čÅčēąĖą╣ ą╝ąŠą╝ąĄąĮčé ąĮąĄ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą╗čÄą▒ą░čÅ ąŠą┐ąĄčĆą░čåąĖčÅ čü ą┐ą░ą╝čÅčéčīčÄ Flash ą┐čāč鹥ą╝ ą┐čĆąŠą▓ąĄčĆą║ąĖ ą▒ąĖčéą░ BSY ą▓ čĆąĄą│ąĖčüčéčĆąĄ FLASH_SR.

2. ąŻčüčéą░ąĮąŠą▓ąĖč鹥 ą▒ąĖčé PG ą▓ čĆąĄą│ąĖčüčéčĆąĄ FLASH_CR.

3. ąÆčŗą┐ąŠą╗ąĮąĖč鹥 ąŠą┐ąĄčĆą░čåąĖčÄ (ąĖą╗ąĖ ąĮąĄčüą║ąŠą╗čīą║ąŠ ąŠą┐ąĄčĆą░čåąĖą╣) ąĘą░ą┐ąĖčüąĖ ą┐ąŠ ąČąĄą╗ą░ąĄą╝ąŠą╝čā ą░ą┤čĆąĄčüčā ą▓ ą┐ą░ą╝čÅčéąĖ (ą▓ ą┐čĆąĄą┤ąĄą╗ą░čģ ąŠčüąĮąŠą▓ąĮąŠą│ąŠ ą▒ą╗ąŠą║ą░ ą┐ą░ą╝čÅčéąĖ ąĖą╗ąĖ ąŠą▒ą╗ą░čüčéąĖ OTP):

ŌĆō ą¤čĆąĖ ą┐ą░čĆą░ą╗ą╗ąĄą╗ąĖąĘą╝ąĄ x8 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▒ą░ą╣č鹊ą▓čŗą╣ ą┤ąŠčüčéčāą┐.

ŌĆō ą¤čĆąĖ ą┐ą░čĆą░ą╗ą╗ąĄą╗ąĖąĘą╝ąĄ x16 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ąŠčüčéčāą┐ ąĮą░ ą┐ąŠą╗ąŠą▓ąĖąĮčā čüą╗ąŠą▓ą░.

ŌĆō ą¤čĆąĖ ą┐ą░čĆą░ą╗ą╗ąĄą╗ąĖąĘą╝ąĄ x32 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ąŠčüčéčāą┐ ą║ čüą╗ąŠą▓čā.

ŌĆō ą¤čĆąĖ ą┐ą░čĆą░ą╗ą╗ąĄą╗ąĖąĘą╝ąĄ x64 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ąŠčüčéčāą┐ ą║ ą┤ą▓ąŠą╣ąĮąŠą╝čā čüą╗ąŠą▓čā.

4. ą¤ąŠą┤ąŠąČą┤ąĖč鹥, ą┐ąŠą║ą░ ąĮąĄ ąŠčćąĖčüčéąĖčéčüčÅ ą▒ąĖčé BSY.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: čāčüą┐ąĄčłąĮą░čÅ ąŠą┐ąĄčĆą░čåąĖčÅ ąĘą░ą┐ąĖčüąĖ ą╝ąŠąČąĄčé ą┐čĆąŠąĖąĘąŠą╣čéąĖ ą▒ąĄąĘ ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮąŠą╣ ąŠą┐ąĄčĆą░čåąĖąĖ čüčéąĖčĆą░ąĮąĖčÅ, ą║ąŠą│ą┤ą░ ąĘąĮą░č湥ąĮąĖčÅ ą▒ąĖčé ą▓ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄą╝čŗčģ ą┤ą░ąĮąĮčŗčģ ą╝ąĄąĮčÅčÄčéčüčÅ čü 1 ąĮą░ 0. ąŚą░ą┐ąĖčüčī 1 ą▓ čÅč湥ą╣ą║čā Flash, ą│ą┤ąĄ čāąČąĄ ąĘą░ą┐ąĖčüą░ąĮ 0, čéčĆąĄą▒čāąĄčé ąŠą┐ąĄčĆą░čåąĖąĖ čüčéąĖčĆą░ąĮąĖčÅ. ąĢčüą╗ąĖ ąŠą┐ąĄčĆą░čåąĖčÅ čüčéąĖčĆą░ąĮąĖčÅ ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ąĘą░ą┐čĆąŠčłąĄąĮčŗ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ, č鹊 čüąĮą░čćą░ą╗ą░ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ čüčéąĖčĆą░ąĮąĖąĄ.

ą×čłąĖą▒ą║ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ. ąØąĄ čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī ą┤ą░ąĮąĮčŗąĄ ą▓ ą┐ą░ą╝čÅčéčī Flash, ą║ąŠą│ą┤ą░ ąŠąĮąĖ ą┐ąĄčĆąĄčüąĄą║ą░čÄčé 128-ą▒ąĖčéąĮčāčÄ ą│čĆą░ąĮąĖčåčā čüčéčĆąŠą║ąĖ. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ąŠą┐ąĄčĆą░čåąĖčÅ ąĘą░ą┐ąĖčüąĖ ąĮąĄ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ, ąĖ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ ąŠčłąĖą▒ą║ąĖ ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖčÅ (program alignment error, PGAERR) ą▓ čĆąĄą│ąĖčüčéčĆąĄ FLASH_SR.

ąóąĖą┐ ą┤ąŠčüčéčāą┐ą░ ąĮą░ ąĘą░ą┐ąĖčüčī (byte, half-word, word ąĖą╗ąĖ double word) ą┤ąŠą╗ąČąĄąĮ čüąŠąŠčéą▓ąĄčéčüčéą▓ąŠą▓ą░čéčī ą▓čŗą▒čĆą░ąĮąĮąŠą╝čā čéąĖą┐čā ą┐ą░čĆą░ą╗ą╗ąĄą╗ąĖąĘą╝ą░ (x8, x16, x32 ąĖą╗ąĖ x64). ąĢčüą╗ąĖ čŹč鹊 ąĮąĄ čéą░ą║, č鹊 ąŠą┐ąĄčĆą░čåąĖčÅ ąĘą░ą┐ąĖčüąĖ ąĮąĄ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ, ąĖ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ ąŠčłąĖą▒ą║ąĖ ą┐ą░čĆą░ą╗ą╗ąĄą╗ąĖąĘą╝ą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ (program parallelism error, PGPERR) ą▓ čĆąĄą│ąĖčüčéčĆąĄ FLASH_SR.

ąĢčüą╗ąĖ ąĮąĄ čüąŠą▒ą╗čÄą┤ą░ąĄčéčüčÅ čüčéą░ąĮą┤ą░čĆčéąĮą░čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┐čĆąŠą│čĆą░ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ (ąĮą░ą┐čĆąĖą╝ąĄčĆ, ąĄčüą╗ąĖ čüą┤ąĄą╗ą░ąĮą░ ą┐ąŠą┐čŗčéą║ą░ ąĘą░ą┐ąĖčüąĖ ą┐ąŠ ą░ą┤čĆąĄčüčā ą┐ą░ą╝čÅčéąĖ Flash, ą║ąŠą│ą┤ą░ ąĮąĄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé PG), č鹊 ąŠą┐ąĄčĆą░čåąĖčÅ ąĘą░ą┐ąĖčüąĖ ą▒čāą┤ąĄčé ąŠą▒ąŠčĆą▓ą░ąĮą░, ąĖ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ ąŠčłąĖą▒ą║ąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ (program sequence error, PGSERR) ą▓ čĆąĄą│ąĖčüčéčĆąĄ FLASH_SR.

ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ ąĖ ą║čŹčłąĖčĆąŠą▓ą░ąĮąĖąĄ. ąĢčüą╗ąĖ ą┤ąŠčüčéčāą┐ ąĮą░ ąĘą░ą┐ąĖčüčī ą▓ąŠ Flash ą║ą░čüą░ąĄčéčüčÅ ąĮąĄą║ąŠč鹊čĆčŗčģ ą┤ą░ąĮąĮčŗčģ ą▓ ą║čŹčłąĄ ą┤ą░ąĮąĮčŗčģ, č鹊 ą┤ąŠčüčéčāą┐ ąĮą░ ąĘą░ą┐ąĖčüčī Flash ąĖąĘą╝ąĄąĮąĖčé ą┤ą░ąĮąĮčŗąĄ ą▓ ą┐ą░ą╝čÅčéąĖ Flash ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ ą┤ą░ąĮąĮčŗčģ ą▓ ą║čŹčłąĄ.

ąĢčüą╗ąĖ ąŠą┐ąĄčĆą░čåąĖčÅ čüčéąĖčĆą░ąĮąĖčÅ ą▓ ą┐ą░ą╝čÅčéąĖ Flash čéą░ą║ąČąĄ ą║ą░čüą░ąĄčéčüčÅ ą┤ą░ąĮąĮčŗčģ, ąĮą░čģąŠą┤čÅčēąĖčģčüčÅ ą▓ ą║čŹčłąĄ ą┤ą░ąĮąĮčŗčģ ąĖą╗ąĖ ą║čŹčłąĄ ąĖąĮčüčéčĆčāą║čåąĖą╣, č鹊 ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ čāą▒ąĄą┤ąĖčéčīčüčÅ, čćč鹊 čŹčéąĖ ą┤ą░ąĮąĮčŗąĄ ą┐ąĄčĆąĄąĘą░ą┐ąĖčüą░ąĮčŗ ą┤ąŠ ąŠą▒čĆą░čēąĄąĮąĖčÅ ą║ ąĮąĖą╝ ą▓ąŠ ą▓čĆąĄą╝čÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą║ąŠą┤ą░. ąĢčüą╗ąĖ čŹč鹊 ąĮąĄą╗čīąĘčÅ čüą┤ąĄą╗ą░čéčī ą▒ąĄąĘąŠą┐ą░čüąĮčŗą╝ čüą┐ąŠčüąŠą▒ąŠą╝, č鹊 čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ čüą▒čĆąŠčüąĖčéčī (flush) ą║čŹčłąĖ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčé DCRST ąĖ ICRST ą▓ čĆąĄą│ąĖčüčéčĆąĄ FLASH_CR.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą║čŹčł ąĖąĮčüčéčĆčāą║čåąĖą╣/ą┤ą░ąĮąĮčŗčģ (I/D cache) ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čüą▒čĆąŠčłąĄąĮ č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ ą║čŹčł ąĘą░ą┐čĆąĄčēąĄąĮ (I/DCEN = 0).

[Read-while-write (RWW)]

ąŻ MCU STM32F42xxx ąĖ STM32F43xxx ą┐ą░ą╝čÅčéčī Flash ą┐ąŠą┤ąĄą╗ąĄąĮą░ ąĮą░ 2 ą▒ą░ąĮą║ą░, čćč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą▓čŗą┐ąŠą╗ąĮčÅčéčī ąŠą┐ąĄčĆą░čåąĖąĖ čćč鹥ąĮąĖąĄ-ą┐čĆąĖ-ąĘą░ą┐ąĖčüąĖ (read-while-write, RWW). ąŁčéą░ čäčāąĮą║čåąĖčÅ ą┐ąŠąĘą▓ąŠą╗ąĖčé ą▓čŗą┐ąŠą╗ąĮąĖčéčī ąŠą┐ąĄčĆą░čåąĖčÄ čćč鹥ąĮąĖčÅ ąĖąĘ ąŠą┤ąĮąŠą│ąŠ ą▒ą░ąĮą║ą░, ą║ąŠą│ą┤ą░ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ąŠą┐ąĄčĆą░čåąĖčÅ čüčéąĖčĆą░ąĮąĖčÅ ąĖą╗ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą┤čĆčāą│ąŠą│ąŠ ą▒ą░ąĮą║ą░.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąŠą┐ąĄčĆą░čåąĖąĖ write-while-write (ąĘą░ą┐ąĖčüčī-ą┐čĆąĖ-ąĘą░ą┐ąĖčüąĖ) ąĮąĄ ą┤ąŠą┐čāčüą║ą░čÄčéčüčÅ. ąØą░ą┐čĆąĖą╝ąĄčĆ, ąĮąĄą╗čīąĘčÅ ą▓čŗą┐ąŠą╗ąĮąĖčéčī čüčéąĖčĆą░ąĮąĖąĄ ą▓ ąŠą┤ąĮąŠą╝ ą▒ą░ąĮą║ąĄ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ čü ąŠą┐ąĄčĆą░čåąĖąĄą╣ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓ ą┤čĆčāą│ąŠą╝ ą▒ą░ąĮą║ąĄ.

ą¦č鹥ąĮąĖąĄ ą▒ą░ąĮą║ą░ 1 ą┐čĆąĖ čüčéąĖčĆą░ąĮąĖąĖ ą▓ ą▒ą░ąĮą║ąĄ 2. ąÜąŠą│ą┤ą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ ą║ąŠą┤ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ąĖąĘ ą▒ą░ąĮą║ą░ 1, č鹊 ą╝ąŠąČąĮąŠ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖčéčī čüčéąĖčĆą░ąĮąĖąĄ ą▓ ą▒ą░ąĮą║ąĄ 2 (ąĖ ąĮą░ąŠą▒ąŠčĆąŠčé). ąöą╗čÅ čŹč鹊ą│ąŠ ą▓čŗą┐ąŠą╗ąĮąĖč鹥 čüą╗ąĄą┤čāčÄčēčāčÄ ą┐čĆąŠčåąĄą┤čāčĆčā:

1. ą¤čĆąŠą▓ąĄčĆčīč鹥, čćč鹊 ąĮąĄ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ąŠą┐ąĄčĆą░čåąĖčÅ čü ą┐ą░ą╝čÅčéčīčÄ Flash ą┐čāč鹥ą╝ ą┐čĆąŠą▓ąĄčĆą║ąĖ ąĮą░ 0 ą▒ąĖčéą░ BSY ą▓ čĆąĄą│ąĖčüčéčĆąĄ FLASH_SR (BSY = 1, ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ąŠą┐ąĄčĆą░čåąĖčÅ čüčéąĖčĆą░ąĮąĖčÅ ąĖą╗ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓ ą▒ą░ąĮą║ąĄ 1 ąĖą╗ąĖ 2).

2. ąŻčüčéą░ąĮąŠą▓ąĖč鹥 ą▒ąĖčé MER ąĖą╗ąĖ MER1 ą▓ čĆąĄą│ąĖčüčéčĆąĄ FLASH_CR.

3. ąŻčüčéą░ąĮąŠą▓ąĖč鹥 ą▒ąĖčé STRT ą▓ čĆąĄą│ąĖčüčéčĆąĄ FLASH_CR.

4. ą¤ąŠą┤ąŠąČą┤ąĖč鹥, ą┐ąŠą║ą░ ąĮąĄ ąŠčćąĖčüčéąĖčéčüčÅ ą▒ąĖčé BSY (ąĖą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāą╣č鹥 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠą║ąŠąĮčćą░ąĮąĖčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ EOP).

ą¦č鹥ąĮąĖąĄ ąĖąĘ ą▒ą░ąĮą║ą░ 1 ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą▒ą░ąĮą║ą░ 2. ą¤čĆąĖ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĖ ą║ąŠą┤ą░ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ (ą║ąŠą│ą┤ą░ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ čćč鹥ąĮąĖąĄ ąĖąĮčüčéčĆčāą║čåąĖą╣ ą┐ąŠ čłąĖąĮąĄ I-Code) ąĖąĘ ą▒ą░ąĮą║ą░ 1 ą╝ąŠąČąĮąŠ ą▓čŗą┐ąŠą╗ąĮąĖčéčī ąŠą┐ąĄčĆą░čåąĖčÄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓ ą▒ą░ąĮą║ąĄ 2 (ąĖ ąĮą░ąŠą▒ąŠčĆąŠčé). ąöą╗čÅ čŹč鹊ą│ąŠ ą▓čŗą┐ąŠą╗ąĮąĖč鹥 čüą╗ąĄą┤čāčÄčēčāčÄ ą┐čĆąŠčåąĄą┤čāčĆčā:

1. ą¤čĆąŠą▓ąĄčĆčīč鹥, čćč鹊 ąĮąĄ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ąŠą┐ąĄčĆą░čåąĖčÅ čü ą┐ą░ą╝čÅčéčīčÄ Flash ą┐čāč鹥ą╝ ą┐čĆąŠą▓ąĄčĆą║ąĖ ąĮą░ 0 ą▒ąĖčéą░ BSY ą▓ čĆąĄą│ąĖčüčéčĆąĄ FLASH_SR (BSY = 1, ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ąŠą┐ąĄčĆą░čåąĖčÅ čüčéąĖčĆą░ąĮąĖčÅ ąĖą╗ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓ ą▒ą░ąĮą║ąĄ 1 ąĖą╗ąĖ 2).

2. ąŻčüčéą░ąĮąŠą▓ąĖč鹥 ą▒ąĖčé PG ą▓ čĆąĄą│ąĖčüčéčĆąĄ FLASH_CR.

3. ąÆčŗą┐ąŠą╗ąĮąĖč鹥 ąŠą┐ąĄčĆą░čåąĖčÄ (ąĖą╗ąĖ ąŠą┐ąĄčĆą░čåąĖąĖ) ąĘą░ą┐ąĖčüąĖ ą┤ą░ąĮąĮčŗčģ ą┐ąŠ ąČąĄą╗ą░ąĄą╝ąŠą╝čā ą░ą┤čĆąĄčüčā ą┐ą░ą╝čÅčéąĖ ą▓ ą┐čĆąĄą┤ąĄą╗ą░čģ ąŠčüąĮąŠą▓ąĮąŠą╣ ąŠą▒ą╗ą░čüčéąĖ ą┐ą░ą╝čÅčéąĖ ąĖą╗ąĖ ąŠą▒ą╗ą░čüčéąĖ OTP.

4. ą¤ąŠą┤ąŠąČą┤ąĖč鹥, ą┐ąŠą║ą░ ąĮąĄ ąŠčćąĖčüčéąĖčéčüčÅ ą▒ąĖčé BSY.

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖčéą░ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ąŠą║ąŠąĮčćą░ąĮąĖčÅ ąŠą┐ąĄčĆą░čåąĖąĖ (end of operation interrupt enable, (EOPIE) ą▓ čĆąĄą│ąĖčüčéčĆąĄ FLASH_CR čĆą░ąĘčĆąĄčłąĖčé ą│ąĄąĮąĄčĆą░čåąĖčÄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą║ąŠą│ą┤ą░ ąĘą░ą║ąŠąĮčćąĖčéčüčÅ čüčéąĖčĆą░ąĮąĖąĄ ąĖą╗ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ Flash, čé. ąĄ. ą║ąŠą│ą┤ą░ ąŠčćąĖčüčéąĖčéčüčÅ ą▒ąĖčé ąĘą░ąĮčÅč鹊čüčéąĖ (BSY) ą▓ čĆąĄą│ąĖčüčéčĆąĄ FLASH_SR (čŹč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ąŠą┐ąĄčĆą░čåąĖčÅ ąĘą░ą▓ąĄčĆčłąĖą╗ą░čüčī, ą║ąŠčĆčĆąĄą║čéąĮąŠ ąĖą╗ąĖ ąĮąĄčé). ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ąŠą┐ąĄčĆą░čåąĖąĖ (end of operation, EOP) ą▓ čĆąĄą│ąĖčüčéčĆąĄ FLASH_SR.

ąĢčüą╗ąĖ ą┐čĆąŠąĖąĘąŠčłą╗ą░ ąŠčłąĖą▒ą║ą░ ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ, čüčéąĖčĆą░ąĮąĖčÅ ąĖą╗ąĖ ą┐čĆąĖ ąĘą░ą┐čĆąŠčüąĄ ąŠą┐ąĄčĆą░čåąĖąĖ čćč鹥ąĮąĖčÅ, č鹊 ą▓ čĆąĄą│ąĖčüčéčĆąĄ FLASH_SR čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ąŠą┤ąĖąĮ ąĖąĘ čüą╗ąĄą┤čāčÄčēąĖčģ čäą╗ą░ą│ąŠą▓ ąŠčłąĖą▒ą║ąĖ:

ŌĆó PGAERR, PGPERR, PGSERR (čäą╗ą░ą│ąĖ ąŠčłąĖą▒ą║ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ).

ŌĆó WRPERR (čäą╗ą░ą│ ąŠčłąĖą▒ą║ąĖ ąĘą░čēąĖčéčŗ ąŠčé ąĘą░ą┐ąĖčüąĖ).

ŌĆó RDERR (čäą╗ą░ą│ ąŠčłąĖą▒ą║ąĖ ąĘą░čēąĖčéčŗ ąŠčé čćč鹥ąĮąĖčÅ) - č鹊ą╗čīą║ąŠ ą┤ą╗čÅ STM32F42xxx ąĖ STM32F43xxx.

ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠčłąĖą▒ą║ąĖ (error interrupt enable, ERRIE) ą▓ čĆąĄą│ąĖčüčéčĆąĄ FLASH_CR, č鹊 ą▒čāą┤ąĄčé čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ąĖ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé ąŠčłąĖą▒ą║ąĖ ąŠą┐ąĄčĆą░čåąĖąĖ (operation error, OPERR) ą▓ čĆąĄą│ąĖčüčéčĆąĄ FLASH_SR.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą┐čĆąĖ ąŠą▒ąĮą░čĆčāąČąĄąĮąĖąĖ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ąŠčłąĖą▒ąŠą║ (ąĮą░ą┐čĆąĖą╝ąĄčĆ, ą▓ čüą╗čāčćą░ąĄ čéčĆą░ąĮąĘą░ą║čåąĖąĖ DMA ą▓ ą┐ą░ą╝čÅčéčī Flash), čäą╗ą░ą│ąĖ ąŠčłąĖą▒ą║ąĖ ąĮąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ąŠčćąĖčēąĄąĮčŗ ą┤ąŠ ąŠą║ąŠąĮčćą░ąĮąĖčÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ąĘą░ą┐čĆąŠčüąŠą▓ ąĮą░ ąĘą░ą┐ąĖčüčī.

ąóą░ą▒ą╗ąĖčåą░ 13. ąŚą░ą┐čĆąŠčüčŗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ Flash.

| ąĪąŠą▒čŗčéąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ |

ążą╗ą░ą│ čüąŠą▒čŗčéąĖčÅ |

ąæąĖčé čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ |

| End of operation (ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĄ ąŠą┐ąĄčĆą░čåąĖąĖ) |

EOP |

EOPIE |

| Write protection error (ąŠčłąĖą▒ą║ą░ ąĘą░čēąĖčéčŗ ąŠčé ąĘą░ą┐ąĖčüąĖ) |

WRPERR |

ERRIE |

| Programming error (ąŠčłąĖą▒ą║ą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ) |

PGAERR, PGPERR, PGSERR |

| Read protection error (ąŠčłąĖą▒ą║ą░ ąĘą░čēąĖčéčŗ ąŠčé čćč鹥ąĮąĖčÅ) |

RDERR |

[ąæą░ą╣čéčŗ ąŠą┐čåąĖą╣ STM32F4, ąŠą┤ąĮąŠą║čĆą░čéąĮąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗąĄ ą┤ą░ąĮąĮčŗąĄ]

ąæą░ą╣čéčŗ ąŠą┐čåąĖą╣ (user option bytes) ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ STM32F4 ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāčÄčéčüčÅ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╝ ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čéčĆąĄą▒ąŠą▓ą░ąĮąĖą╣ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ. ą×ąĮąĖ ąĮą░čüčéčĆą░ąĖą▓ą░čÄčé ąĘą░čēąĖčéčā ąŠčé čćč鹥ąĮąĖčÅ ąĖ ąĘą░ą┐ąĖčüąĖ, ąĘą░ą│čĆčāąĘą║čā ąĖ ą┤čĆčāą│ąĖąĄ ąŠą┐čåąĖąĖ MCU. ąóą░ą║ąČąĄ ąĖą╝ąĄčÄčéčüčÅ ąŠą┤ąĮąŠą║čĆą░čéąĮąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗąĄ ą┤ą░ąĮąĮčŗąĄ OTP. ą¤ąŠą┤čĆąŠą▒ąĮąŠ ą┐čĆąŠ ąĮą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ą░ą╣čé ąŠą┐čåąĖą╣, ą▒ą░ą╣čé OTP, ąĖčģ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ čüą╝. čüčéą░čéčīčÄ [3].

[ąĀąĄą│ąĖčüčéčĆčŗ ąĖąĮč鹥čĆč乥ą╣čüą░ Flash]

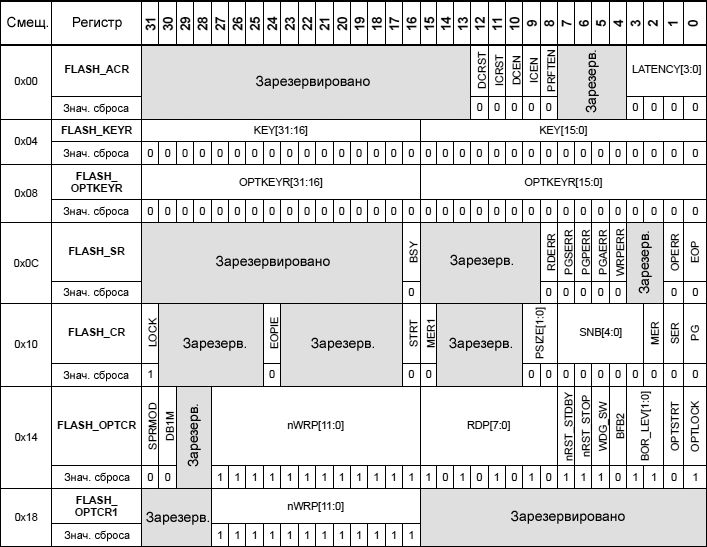

ąóą░ą▒ą╗ąĖčåą░ 19. ąÜą░čĆčéą░ ą┐ą░ą╝čÅčéąĖ čĆąĄą│ąĖčüčéčĆąŠą▓ ąĖ ąĘąĮą░č湥ąĮąĖčÅ čüą▒čĆąŠčüą░ ą┤ą╗čÅ STM32F405xx/07xx ąĖ STM32F415xx/17xx.

ąóą░ą▒ą╗ąĖčåą░ 20. ąÜą░čĆčéą░ ą┐ą░ą╝čÅčéąĖ čĆąĄą│ąĖčüčéčĆąŠą▓ ąĖ ąĘąĮą░č湥ąĮąĖčÅ čüą▒čĆąŠčüą░ ą┤ą╗čÅ STM32F42xxx ąĖ STM32F43xxx.

ąĀąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┤ąŠčüčéčāą┐ąŠą╝ ą║ Flash FLASH_ACR ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ/ąĘą░ą┐čĆąĄčéą░ čäčāąĮą║čåąĖąĖ čāčüą║ąŠčĆąĄąĮąĖčÅ ąĖ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┤ąŠčüčéčāą┐ąŠą╝ ą║ Flash ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü čćą░čüč鹊č鹊ą╣ čéą░ą║č鹊ą▓ CPU.

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x00.

ąŚąĮą░č湥ąĮąĖąĄ čüą▒čĆąŠčüą░: 0x00000000.

ąöąŠčüčéčāą┐: ą▒ąĄąĘ čéą░ą║č鹊ą▓ ąŠąČąĖą┤ą░ąĮąĖčÅ, ą║ą░ą║ ą║ čüą╗ąŠą▓čā, ą┐ąŠą╗ąŠą▓ąĖąĮąĄ čüą╗ąŠą▓ą░ ąĖą╗ąĖ ą▒ą░ą╣čéčā.

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ

|

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

ąĘą░čĆąĄčĆąĄąĘą▓ąĖčĆąŠą▓ą░ąĮąŠ

|

DCRST

rw |

ICRST

w |

DCEN

rw |

ICEN

rw |

PRFTEN

rw |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

LATENCY[2:0]

rw |

ąæąĖčéčŗ 31:11 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ, ąĖ ą┤ąŠą╗ąČąĮčŗ čüąŠčģčĆą░ąĮčÅčéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (ą▓čüąĄ ąĮčāą╗ąĖ).

DCRST (ą▒ąĖčé 12): Data cache reset, čüą▒čĆąŠčü ą║čŹčłą░ ą┤ą░ąĮąĮčŗčģ.

0 ą║čŹčł ą┤ą░ąĮąĮčŗčģ ąĮąĄ čüą▒čĆąŠčłąĄąĮ.

1 ą║čŹčł ą┤ą░ąĮąĮčŗčģ čüą▒čĆąŠčłąĄąĮ.

ąŁč鹊čé ą▒ąĖčé ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮ č鹊ą╗čīą║ąŠ ą║ąŠą┤ą░ D-ą║čŹčł ąĘą░ą┐čĆąĄčēąĄąĮ (DCEN = 0).

ICRST (ą▒ąĖčé 11): Instruction cache reset, čüą▒čĆąŠčü ą║čŹčłą░ ąĖąĮčüčéčĆčāą║čåąĖą╣.

0 ą║čŹčł ąĖąĮčüčéčĆčāą║čåąĖą╣ ąĮąĄ čüą▒čĆąŠčłąĄąĮ.

1 ą║čŹčł ąĖąĮčüčéčĆčāą║čåąĖą╣ čüą▒čĆąŠčłąĄąĮ.

ąŁč鹊čé ą▒ąĖčé ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮ č鹊ą╗čīą║ąŠ ą║ąŠą┤ą░ I-ą║čŹčł ąĘą░ą┐čĆąĄčēąĄąĮ (ICEN = 0).

DCEN (ą▒ąĖčé 10): Data cache enable, čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ą║čŹčłą░ ą┤ą░ąĮąĮčŗčģ.

0 ą║čŹčł ą┤ą░ąĮąĮčŗčģ ąĘą░ą┐čĆąĄčēąĄąĮ.

1 ą║čŹčł ą┤ą░ąĮąĮčŗčģ čĆą░ąĘčĆąĄčłąĄąĮ.

ICEN (ą▒ąĖčé 9): Instruction cache enable, čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ą║čŹčłą░ ąĖąĮčüčéčĆčāą║čåąĖą╣.

0 ą║čŹčł ąĖąĮčüčéčĆčāą║čåąĖą╣ ąĘą░ą┐čĆąĄčēąĄąĮ.

1 ą║čŹčł ąĖąĮčüčéčĆčāą║čåąĖą╣ čĆą░ąĘčĆąĄčłąĄąĮ.

PRFTEN (ą▒ąĖčé 8): Prefetch enable, čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮąŠą╣ ą▓čŗą▒ąŠčĆą║ąĖ ąĖąĮčüčéčĆčāą║čåąĖą╣.

0 ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮą░čÅ ą▓čŗą▒ąŠčĆą║ą░ ąĘą░ą┐čĆąĄčēąĄąĮą░.

1 ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮą░čÅ ą▓čŗą▒ąŠčĆą║ą░ čĆą░ąĘčĆąĄčłąĄąĮą░.

ąæąĖčéčŗ 7:3 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ, ąĖ ą┤ąŠą╗ąČąĮčŗ čüąŠčģčĆą░ąĮčÅčéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (ą▓čüąĄ ąĮčāą╗ąĖ).

LATENCY[2:0] (ą▒ąĖčéčŗ 2:0): Latency, ą╗ą░č鹥ąĮčéąĮąŠčüčéčī. ąŁčéąĖ ą▒ąĖčéčŗ ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅčÄčé čüąŠąŠčéąĮąŠčłąĄąĮąĖąĄ ą╝ąĄąČą┤čā ą┐ąĄčĆąĖąŠą┤ąŠą╝ čéą░ą║č鹊ą▓ CPU ąĖ ą▓čĆąĄą╝ąĄąĮąĄą╝ ą┤ąŠčüčéčāą┐ą░ ą║ ą┐ą░ą╝čÅčéąĖ Flash (ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čåąĖą║ą╗ąŠą▓ ąŠąČąĖą┤ą░ąĮąĖčÅ wait state).

000: ąĮąŠą╗čī čåąĖą║ą╗ąŠą▓ ąŠąČąĖą┤ą░ąĮąĖčÅ.

001: 1 čåąĖą║ą╗ ąŠąČąĖą┤ą░ąĮąĖčÅ.

010: 2 čåąĖą║ą╗ą░ ąŠąČąĖą┤ą░ąĮąĖčÅ.

011: 3 čåąĖą║ą╗ą░ ąŠąČąĖą┤ą░ąĮąĖčÅ.

100: 4 čåąĖą║ą╗ą░ ąŠąČąĖą┤ą░ąĮąĖčÅ.

101: 5 čåąĖą║ą╗ąŠą▓ ąŠąČąĖą┤ą░ąĮąĖčÅ.

110: 6 čåąĖą║ą╗ąŠą▓ ąŠąČąĖą┤ą░ąĮąĖčÅ.

111: 7 čåąĖą║ą╗ąŠą▓ ąŠąČąĖą┤ą░ąĮąĖčÅ.

ąĀąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┤ąŠčüčéčāą┐ąŠą╝ ą║ Flash FLASH_ACR ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ/ąĘą░ą┐čĆąĄčéą░ čäčāąĮą║čåąĖąĖ čāčüą║ąŠčĆąĄąĮąĖčÅ ąĖ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┤ąŠčüčéčāą┐ąŠą╝ ą║ Flash ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü čćą░čüč鹊č鹊ą╣ čéą░ą║č鹊ą▓ CPU.

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x00.

ąŚąĮą░č湥ąĮąĖąĄ čüą▒čĆąŠčüą░: 0x00000000.

ąöąŠčüčéčāą┐: ą▒ąĄąĘ čéą░ą║č鹊ą▓ ąŠąČąĖą┤ą░ąĮąĖčÅ, ą║ą░ą║ ą║ čüą╗ąŠą▓čā, ą┐ąŠą╗ąŠą▓ąĖąĮąĄ čüą╗ąŠą▓ą░ ąĖą╗ąĖ ą▒ą░ą╣čéčā.

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ

|

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ

|

DCRST

rw |

ICRST

w |

DCEN

rw |

ICEN

rw |

PRFTEN

rw |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ

|

LATENCY[3:0]

rw

|

ąæąĖčéčŗ 31:11 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ, ąĖ ą┤ąŠą╗ąČąĮčŗ čüąŠčģčĆą░ąĮčÅčéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (ą▓čüąĄ ąĮčāą╗ąĖ).

DCRST (ą▒ąĖčé 12): Data cache reset, čüą▒čĆąŠčü ą║čŹčłą░ ą┤ą░ąĮąĮčŗčģ.

0 ą║čŹčł ą┤ą░ąĮąĮčŗčģ ąĮąĄ čüą▒čĆąŠčłąĄąĮ.

1 ą║čŹčł ą┤ą░ąĮąĮčŗčģ čüą▒čĆąŠčłąĄąĮ.

ąŁč鹊čé ą▒ąĖčé ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮ č鹊ą╗čīą║ąŠ ą║ąŠą┤ą░ D-ą║čŹčł ąĘą░ą┐čĆąĄčēąĄąĮ (DCEN = 0).

ICRST (ą▒ąĖčé 11): Instruction cache reset, čüą▒čĆąŠčü ą║čŹčłą░ ąĖąĮčüčéčĆčāą║čåąĖą╣.

0 ą║čŹčł ąĖąĮčüčéčĆčāą║čåąĖą╣ ąĮąĄ čüą▒čĆąŠčłąĄąĮ.

1 ą║čŹčł ąĖąĮčüčéčĆčāą║čåąĖą╣ čüą▒čĆąŠčłąĄąĮ.

ąŁč鹊čé ą▒ąĖčé ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮ č鹊ą╗čīą║ąŠ ą║ąŠą┤ą░ I-ą║čŹčł ąĘą░ą┐čĆąĄčēąĄąĮ (ICEN = 0).

DCEN (ą▒ąĖčé 10): Data cache enable, čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ą║čŹčłą░ ą┤ą░ąĮąĮčŗčģ.

0 ą║čŹčł ą┤ą░ąĮąĮčŗčģ ąĘą░ą┐čĆąĄčēąĄąĮ.

1 ą║čŹčł ą┤ą░ąĮąĮčŗčģ čĆą░ąĘčĆąĄčłąĄąĮ.

ICEN (ą▒ąĖčé 9): Instruction cache enable, čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ą║čŹčłą░ ąĖąĮčüčéčĆčāą║čåąĖą╣.

0 ą║čŹčł ąĖąĮčüčéčĆčāą║čåąĖą╣ ąĘą░ą┐čĆąĄčēąĄąĮ.

1 ą║čŹčł ąĖąĮčüčéčĆčāą║čåąĖą╣ čĆą░ąĘčĆąĄčłąĄąĮ.

PRFTEN (ą▒ąĖčé 8): Prefetch enable, čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮąŠą╣ ą▓čŗą▒ąŠčĆą║ąĖ ąĖąĮčüčéčĆčāą║čåąĖą╣.

0 ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮą░čÅ ą▓čŗą▒ąŠčĆą║ą░ ąĘą░ą┐čĆąĄčēąĄąĮą░.

1 ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮą░čÅ ą▓čŗą▒ąŠčĆą║ą░ čĆą░ąĘčĆąĄčłąĄąĮą░.

ąæąĖčéčŗ 7:4 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ, ąĖ ą┤ąŠą╗ąČąĮčŗ čüąŠčģčĆą░ąĮčÅčéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (ą▓čüąĄ ąĮčāą╗ąĖ).

LATENCY[3:0] (ą▒ąĖčéčŗ 3:0): Latency, ą╗ą░č鹥ąĮčéąĮąŠčüčéčī. ąŁčéąĖ ą▒ąĖčéčŗ ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅčÄčé čüąŠąŠčéąĮąŠčłąĄąĮąĖąĄ ą╝ąĄąČą┤čā ą┐ąĄčĆąĖąŠą┤ąŠą╝ čéą░ą║č鹊ą▓ CPU ąĖ ą▓čĆąĄą╝ąĄąĮąĄą╝ ą┤ąŠčüčéčāą┐ą░ ą║ ą┐ą░ą╝čÅčéąĖ Flash (ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čåąĖą║ą╗ąŠą▓ ąŠąČąĖą┤ą░ąĮąĖčÅ wait state).

0000: ąĮąŠą╗čī čåąĖą║ą╗ąŠą▓ ąŠąČąĖą┤ą░ąĮąĖčÅ.

0001: 1 čåąĖą║ą╗ ąŠąČąĖą┤ą░ąĮąĖčÅ.

0010: 2 čåąĖą║ą╗ą░ ąŠąČąĖą┤ą░ąĮąĖčÅ.

..

1110: 14 čåąĖą║ą╗ąŠą▓ ąŠąČąĖą┤ą░ąĮąĖčÅ.

1111: 15 čåąĖą║ą╗ąŠą▓ ąŠąČąĖą┤ą░ąĮąĖčÅ.

ąĀąĄą│ąĖčüčéčĆ ą║ą╗čÄčćą░ Flash ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┤ąŠčüčéčāą┐ą░ ą║ čĆąĄą│ąĖčüčéčĆčā čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ Flash, čćč鹊ą▒čŗ ą╝ąŠąČąĮąŠ ą▒čŗą╗ąŠ ą▓čŗą┐ąŠą╗ąĮčÅčéčī ąŠą┐ąĄčĆą░čåąĖąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖ čüčéąĖčĆą░ąĮąĖčÅ.

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x04.

ąŚąĮą░č湥ąĮąĖąĄ čüą▒čĆąŠčüą░: 0x00000000.

ąöąŠčüčéčāą┐: ą▒ąĄąĘ čéą░ą║č鹊ą▓ ąŠąČąĖą┤ą░ąĮąĖčÅ, ą║ą░ą║ ą║ čüą╗ąŠą▓čā.

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| KEY[31:16] |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

KEY[15:0]

|

FKEYR[31:0]: FPEC key. ąĪą╗ąĄą┤čāčÄčēąĖąĄ ąĘąĮą░č湥ąĮąĖčÅ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮčŗ ą▓ čŹč鹊čé čĆąĄą│ąĖčüčéčĆ, čćč鹊ą▒čŗ čĆą░ąĘą▒ą╗ąŠą║ąĖčĆąŠą▓ą░čéčī ą┤ąŠčüčéčāą┐ ą║ čĆąĄą│ąĖčüčéčĆčā FLASH_CR:

a) KEY1 = 0x45670123

b) KEY2 = 0xCDEF89AB

ąĀąĄą│ąĖčüčéčĆ ą║ą╗čÄčćą░ ąŠą┐čåąĖą╣ Flash ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ąŠą┐ąĄčĆą░čåąĖą╣ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖ čüčéąĖčĆą░ąĮąĖčÅ čüąĄą║č鹊čĆą░ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ (ą▒ą░ą╣čéčŗ ąŠą┐čåąĖą╣).

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x08.

ąŚąĮą░č湥ąĮąĖąĄ čüą▒čĆąŠčüą░: 0x00000000.

ąöąŠčüčéčāą┐: ą▒ąĄąĘ čéą░ą║č鹊ą▓ ąŠąČąĖą┤ą░ąĮąĖčÅ, ą║ą░ą║ ą║ čüą╗ąŠą▓čā.

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

| OPTKEYR[31:16] |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

OPTKEYR[15:0]

|

OPTKEYR[31:0]: OPTKEYR key. ąĪą╗ąĄą┤čāčÄčēąĖąĄ ąĘąĮą░č湥ąĮąĖčÅ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮčŗ ą▓ čŹč鹊čé čĆąĄą│ąĖčüčéčĆ, čćč鹊ą▒čŗ čĆą░ąĘą▒ą╗ąŠą║ąĖčĆąŠą▓ą░čéčī ą┤ąŠčüčéčāą┐ čüąĄą║č鹊čĆčā ąŠą┐čåąĖą╣:

a) OPTKEY1 = 0x08192A3B

b) OPTKEY2 = 0x4C5D6E7F

ąĀąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ Flash ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ąĖąĮč乊čĆą╝ą░čåąĖčÄ ąŠ č鹊ą╝, ą║ą░ą║ ą┐čĆąŠąĖčüčģąŠą┤čÅčé ąŠą┐ąĄčĆą░čåąĖąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖ čüčéąĖčĆą░ąĮąĖčÅ.

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x0C.

ąŚąĮą░č湥ąĮąĖąĄ čüą▒čĆąŠčüą░: 0x00000000.

ąöąŠčüčéčāą┐: ą▒ąĄąĘ čéą░ą║č鹊ą▓ ąŠąČąĖą┤ą░ąĮąĖčÅ, ą║ą░ą║ ą║ čüą╗ąŠą▓čā, ą┐ąŠą╗ąŠą▓ąĖąĮąĄ čüą╗ąŠą▓ą░ ąĖą╗ąĖ ą▒ą░ą╣čéčā.

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ

|

BSY

r |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ

|

PGSERR

rc_w1 |

PGPERR

rc_w1 |

PGAERR

rc_w1 |

WRPERR

rc_w1 |

ąĘą░čĆąĄąĘčĆą▓. |

OPERR

rc_w1 |

EOP

rc_w1 |

ąæąĖčéčŗ 31:17 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ, ąĖ ą┤ąŠą╗ąČąĮčŗ čüąŠčģčĆą░ąĮčÅčéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (ą▓čüąĄ ąĮčāą╗ąĖ).

BSY (ą▒ąĖčé 16): Busy, ąĘą░ąĮčÅč鹊čüčéčī Flash. ąŁč鹊čé ą▒ąĖčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą╗ąĖ ą▓ ąĮą░čüč鹊čÅčēąĖą╣ ą╝ąŠą╝ąĄąĮčé ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ ąŠą┐ąĄčĆą░čåąĖčÅ čü ą┐ą░ą╝čÅčéčīčÄ Flash. BSY čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▓ ąĮą░čćą░ą╗ąĄ ąŠą┐ąĄčĆą░čåąĖąĖ, ąĖ ąŠčćąĖčēą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ąŠą┐ąĄčĆą░čåąĖčÅ ąĘą░ą▓ąĄčĆčłąĖą╗ą░čüčī, ąĖą╗ąĖ ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖąĘąŠčłą╗ą░ ąŠčłąĖą▒ą║ą░.

0 ą▓ ąĮą░čüč鹊čÅčēąĖą╣ ą╝ąŠą╝ąĄąĮčé ąĮąĄ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ąŠą┐ąĄčĆą░čåąĖčÅ čü ą┐ą░ą╝čÅčéčīčÄ Flash.

1 ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ ąŠą┐ąĄčĆą░čåąĖčÅ Flash.

ąæąĖčéčŗ 15:8 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ, ąĖ ą┤ąŠą╗ąČąĮčŗ čüąŠčģčĆą░ąĮčÅčéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (ą▓čüąĄ ąĮčāą╗ąĖ).

PGSERR (ą▒ąĖčé 7): Programming sequence error, ąŠčłąĖą▒ą║ą░ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ. ąŻčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą║ąŠą│ą┤ą░ ą║ąŠą┤ ą┐ąŠą┐čŗčéą░ą╗čüčÅ ąŠčüčāčēąĄčüčéą▓ąĖčéčī ąĘą░ą┐ąĖčüčī ą▓ąŠ Flash, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ čĆąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĮąĄ ą▒čŗą╗ ą║ąŠčĆčĆąĄą║čéąĮąŠ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ. ąæąĖčé PGSERR ąŠčćąĖčēą░ąĄčéčüčÅ ąĘą░ą┐ąĖčüčīčÄ ą▓ ąĮąĄą│ąŠ ą╗ąŠą│. 1.

PGPERR (ą▒ąĖčé 6): Programming parallelism error, ąŠčłąĖą▒ą║ą░ ą┐ą░čĆą░ą╗ą╗ąĄą╗ąĖąĘą╝ą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ. ąŻčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą║ąŠą│ą┤ą░ čĆą░ąĘą╝ąĄčĆ ą┤ąŠčüčéčāą┐ą░ (byte, half-word, word, double word) ą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ąĮąĄ čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ą┐ąŠą╗čÄ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą┐ą░čĆą░ą╗ą╗ąĄą╗ąĖąĘą╝ą░ PSIZE (x8, x16, x32, x64). ąæąĖčé PGPERR ąŠčćąĖčēą░ąĄčéčüčÅ ąĘą░ą┐ąĖčüčīčÄ ą▓ ąĮąĄą│ąŠ ą╗ąŠą│. 1.

PGAERR (ą▒ąĖčé 5): Programming alignment error, ąŠčłąĖą▒ą║ą░ ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ. ąŻčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą║ąŠą│ą┤ą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗąĄ ą┤ą░ąĮąĮčŗąĄ ąĮąĄ ą╝ąŠą│čāčé čüąŠą┤ąĄčƹȹ░čéčīčüčÅ ą▓ ą┐čĆąĄą┤ąĄą╗ą░čģ ąŠą┤ąĮąŠą│ąŠ 128-ą▒ąĖčéąĮąŠą│ąŠ ą▒ą╗ąŠą║ą░ čüčéčĆąŠą║ąĖ Flash. ąæąĖčé PGAERR ąŠčćąĖčēą░ąĄčéčüčÅ ąĘą░ą┐ąĖčüčīčÄ ą▓ ąĮąĄą│ąŠ ą╗ąŠą│. 1.

WRPERR (ą▒ąĖčé 4): Write protection error, ąŠčłąĖą▒ą║ą░ ąĘą░čēąĖčéčŗ ąŠčé ąĘą░ą┐ąĖčüąĖ. ąŻčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą║ąŠą│ą┤ą░ ą░ą┤čĆąĄčü ą┤ą╗čÅ čüčéąĖčĆą░ąĮąĖčÅ/ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĖąĮą░ą┤ą╗ąĄąČąĖčé ąĘą░čēąĖčēąĄąĮąĮąŠą╣ ąŠą▒ą╗ą░čüčéąĖ ą┐ą░ą╝čÅčéąĖ Flash. ąæąĖčé WRPERR ąŠčćąĖčēą░ąĄčéčüčÅ ąĘą░ą┐ąĖčüčīčÄ ą▓ ąĮąĄą│ąŠ ą╗ąŠą│. 1.

ąæąĖčéčŗ 3:2 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ, ąĖ ą┤ąŠą╗ąČąĮčŗ čüąŠčģčĆą░ąĮčÅčéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (ą▓čüąĄ ąĮčāą╗ąĖ).

OPERR (ą▒ąĖčé 1): Operation error, ąŠčłąĖą▒ą║ą░ ąŠą┐ąĄčĆą░čåąĖąĖ. ąŻčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą║ąŠą│ą┤ą░ ąŠą▒ąĮą░čĆčāąČąĄąĮ ąĘą░ą┐čĆąŠčü ąŠą┐ąĄčĆą░čåąĖąĖ ąĮą░ą┤ Flash (programming/erase/read), ąĖ čŹč鹊čé ąĘą░ą┐čĆąŠčü ąĮąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čāčēąĄąĮ ąĖąĘ-ąĘą░ ąŠčłąĖą▒ą║ąĖ ą┐ą░čĆą░ą╗ą╗ąĄą╗ąĖąĘą╝ą░, ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖčÅ ąĖą╗ąĖ ąĘą░čēąĖčéčŗ ąŠčé ąĘą░ą┐ąĖčüąĖ. ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ č鹊ą╗čīą║ąŠ ąĄčüą╗ąĖ čĆą░ąĘčĆąĄčłąĄąĮčŗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠčłąĖą▒ą║ąĖ (ERRIE = 1).

EOP (ą▒ąĖčé 0): End of operation, ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĄ ąŠą┐ąĄčĆą░čåąĖąĖ. ąŻčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą║ąŠą│ą┤ą░ ąŠą┤ąĮą░ ąŠą┐ąĄčĆą░čåąĖčÅ (ąĖą╗ąĖ ąĮąĄčüą║ąŠą╗čīą║ąŠ ąŠą┐ąĄčĆą░čåąĖą╣) ąĮą░ą┤ ą┐ą░ą╝čÅčéčīčÄ Flash (program/erase) ąĘą░ą▓ąĄčĆčłąĖą╗ą░čüčī čāčüą┐ąĄčłąĮąŠ. ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ č鹊ą╗čīą║ąŠ ąĄčüą╗ąĖ čĆą░ąĘčĆąĄčłąĄąĮčŗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ąŠą┐ąĄčĆą░čåąĖąĖ (EOPIE = 1). ąæąĖčé EOP ąŠčćąĖčēą░ąĄčéčüčÅ ąĘą░ą┐ąĖčüčīčÄ ą▓ ąĮąĄą│ąŠ ą╗ąŠą│. 1.

ąĀąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ Flash ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ąĖąĮč乊čĆą╝ą░čåąĖčÄ ąŠ č鹊ą╝, ą║ą░ą║ ą┐čĆąŠąĖčüčģąŠą┤čÅčé ąŠą┐ąĄčĆą░čåąĖąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖ čüčéąĖčĆą░ąĮąĖčÅ.

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x0C.

ąŚąĮą░č湥ąĮąĖąĄ čüą▒čĆąŠčüą░: 0x00000000.

ąöąŠčüčéčāą┐: ą▒ąĄąĘ čéą░ą║č鹊ą▓ ąŠąČąĖą┤ą░ąĮąĖčÅ, ą║ą░ą║ ą║ čüą╗ąŠą▓čā, ą┐ąŠą╗ąŠą▓ąĖąĮąĄ čüą╗ąŠą▓ą░ ąĖą╗ąĖ ą▒ą░ą╣čéčā.

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ

|

BSY

r |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ

|

RDERR

rc_w1 |

PGSERR

rc_w1 |

PGPERR

rc_w1 |

PGAERR

rc_w1 |

WRPERR

rc_w1 |

ąĘą░čĆąĄąĘąĄčĆą▓. |

OPERR

rc_w1 |

EOP

rc_w1

|

ąæąĖčéčŗ 31:17 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ, ąĖ ą┤ąŠą╗ąČąĮčŗ čüąŠčģčĆą░ąĮčÅčéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (ą▓čüąĄ ąĮčāą╗ąĖ).

BSY (ą▒ąĖčé 16): Busy, ąĘą░ąĮčÅč鹊čüčéčī Flash. ąŁč鹊čé ą▒ąĖčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą╗ąĖ ą▓ ąĮą░čüč鹊čÅčēąĖą╣ ą╝ąŠą╝ąĄąĮčé ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ ąŠą┐ąĄčĆą░čåąĖčÅ čü ą┐ą░ą╝čÅčéčīčÄ Flash. BSY čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▓ ąĮą░čćą░ą╗ąĄ ąŠą┐ąĄčĆą░čåąĖąĖ, ąĖ ąŠčćąĖčēą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ąŠą┐ąĄčĆą░čåąĖčÅ ąĘą░ą▓ąĄčĆčłąĖą╗ą░čüčī, ąĖą╗ąĖ ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖąĘąŠčłą╗ą░ ąŠčłąĖą▒ą║ą░.

0 ą▓ ąĮą░čüč鹊čÅčēąĖą╣ ą╝ąŠą╝ąĄąĮčé ąĮąĄ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ąŠą┐ąĄčĆą░čåąĖčÅ čü ą┐ą░ą╝čÅčéčīčÄ Flash.

1 ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ ąŠą┐ąĄčĆą░čåąĖčÅ Flash.

ąæąĖčéčŗ 15:9 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ, ąĖ ą┤ąŠą╗ąČąĮčŗ čüąŠčģčĆą░ąĮčÅčéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (ą▓čüąĄ ąĮčāą╗ąĖ).

RDERR (ą▒ąĖčé 8): Proprietary readout protection (PCROP) error, ąŠčłąĖą▒ą║ą░ ąĘą░čēąĖčéčŗ ąŠčé čćč鹥ąĮąĖčÅ ą┐čĆąŠą┐čĆąĖąĄčéą░čĆąĮąŠą│ąŠ ą║ąŠą┤ą░. ąŻčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą║ąŠą│ą┤ą░ ą▓čŗą┐ąŠą╗ąĮąĄąĮ ą┤ąŠčüčéčāą┐ ąĮą░ čćč鹥ąĮąĖąĄ ą┐ąŠ D-čłąĖąĮąĄ, ąĖ ą░ą┤čĆąĄčü ą┤ąŠčüčéčāą┐ą░ ą┐čĆąĖąĮą░ą┤ą╗ąĄąČąĖčé čüąĄą║č鹊čĆčā Flash, ąĮą░ ą║ąŠč鹊čĆčŗą╣ ą┐čĆąĖą╝ąĄąĮąĄąĮą░ ąĘą░čēąĖčéą░ ą┐čĆąŠą┐čĆąĖąĄčéą░čĆąĮąŠą│ąŠ ą║ąŠą┤ą░. ąæąĖčé RDERR ąŠčćąĖčēą░ąĄčéčüčÅ ąĘą░ą┐ąĖčüčīčÄ ą▓ ąĮąĄą│ąŠ ą╗ąŠą│. 1.

PGSERR (ą▒ąĖčé 7): Programming sequence error, ąŠčłąĖą▒ą║ą░ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ. ąŻčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą║ąŠą│ą┤ą░ ą║ąŠą┤ ą┐ąŠą┐čŗčéą░ą╗čüčÅ ąŠčüčāčēąĄčüčéą▓ąĖčéčī ąĘą░ą┐ąĖčüčī ą▓ąŠ Flash, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ čĆąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĮąĄ ą▒čŗą╗ ą║ąŠčĆčĆąĄą║čéąĮąŠ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ. ąæąĖčé PGSERR ąŠčćąĖčēą░ąĄčéčüčÅ ąĘą░ą┐ąĖčüčīčÄ ą▓ ąĮąĄą│ąŠ ą╗ąŠą│. 1.

PGPERR (ą▒ąĖčé 6): Programming parallelism error, ąŠčłąĖą▒ą║ą░ ą┐ą░čĆą░ą╗ą╗ąĄą╗ąĖąĘą╝ą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ. ąŻčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą║ąŠą│ą┤ą░ čĆą░ąĘą╝ąĄčĆ ą┤ąŠčüčéčāą┐ą░ (byte, half-word, word, double word) ą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ąĮąĄ čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ą┐ąŠą╗čÄ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą┐ą░čĆą░ą╗ą╗ąĄą╗ąĖąĘą╝ą░ PSIZE (x8, x16, x32, x64). ąæąĖčé PGPERR ąŠčćąĖčēą░ąĄčéčüčÅ ąĘą░ą┐ąĖčüčīčÄ ą▓ ąĮąĄą│ąŠ ą╗ąŠą│. 1.

PGAERR (ą▒ąĖčé 5): Programming alignment error, ąŠčłąĖą▒ą║ą░ ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ. ąŻčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą║ąŠą│ą┤ą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗąĄ ą┤ą░ąĮąĮčŗąĄ ąĮąĄ ą╝ąŠą│čāčé čüąŠą┤ąĄčƹȹ░čéčīčüčÅ ą▓ ą┐čĆąĄą┤ąĄą╗ą░čģ ąŠą┤ąĮąŠą│ąŠ 128-ą▒ąĖčéąĮąŠą│ąŠ ą▒ą╗ąŠą║ą░ čüčéčĆąŠą║ąĖ Flash. ąæąĖčé PGAERR ąŠčćąĖčēą░ąĄčéčüčÅ ąĘą░ą┐ąĖčüčīčÄ ą▓ ąĮąĄą│ąŠ ą╗ąŠą│. 1.

WRPERR (ą▒ąĖčé 4): Write protection error, ąŠčłąĖą▒ą║ą░ ąĘą░čēąĖčéčŗ ąŠčé ąĘą░ą┐ąĖčüąĖ. ąŻčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą║ąŠą│ą┤ą░ ą░ą┤čĆąĄčü ą┤ą╗čÅ čüčéąĖčĆą░ąĮąĖčÅ/ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĖąĮą░ą┤ą╗ąĄąČąĖčé ąĘą░čēąĖčēąĄąĮąĮąŠą╣ ąŠą▒ą╗ą░čüčéąĖ ą┐ą░ą╝čÅčéąĖ Flash. ąæąĖčé WRPERR ąŠčćąĖčēą░ąĄčéčüčÅ ąĘą░ą┐ąĖčüčīčÄ ą▓ ąĮąĄą│ąŠ ą╗ąŠą│. 1.

ąæąĖčéčŗ 3:2 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ, ąĖ ą┤ąŠą╗ąČąĮčŗ čüąŠčģčĆą░ąĮčÅčéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (ą▓čüąĄ ąĮčāą╗ąĖ).

OPERR (ą▒ąĖčé 1): Operation error, ąŠčłąĖą▒ą║ą░ ąŠą┐ąĄčĆą░čåąĖąĖ. ąŻčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą║ąŠą│ą┤ą░ ąŠą▒ąĮą░čĆčāąČąĄąĮ ąĘą░ą┐čĆąŠčü ąŠą┐ąĄčĆą░čåąĖąĖ ąĮą░ą┤ Flash (programming/erase/read), ąĖ čŹč鹊čé ąĘą░ą┐čĆąŠčü ąĮąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čāčēąĄąĮ ąĖąĘ-ąĘą░ ąŠčłąĖą▒ą║ąĖ ą┐ą░čĆą░ą╗ą╗ąĄą╗ąĖąĘą╝ą░, ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖčÅ ąĖą╗ąĖ ąĘą░čēąĖčéčŗ ąŠčé ąĘą░ą┐ąĖčüąĖ. ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ č鹊ą╗čīą║ąŠ ąĄčüą╗ąĖ čĆą░ąĘčĆąĄčłąĄąĮčŗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠčłąĖą▒ą║ąĖ (ERRIE = 1).

EOP (ą▒ąĖčé 0): End of operation, ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĄ ąŠą┐ąĄčĆą░čåąĖąĖ. ąŻčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą║ąŠą│ą┤ą░ ąŠą┤ąĮą░ ąŠą┐ąĄčĆą░čåąĖčÅ (ąĖą╗ąĖ ąĮąĄčüą║ąŠą╗čīą║ąŠ ąŠą┐ąĄčĆą░čåąĖą╣) ąĮą░ą┤ ą┐ą░ą╝čÅčéčīčÄ Flash (program/erase) ąĘą░ą▓ąĄčĆčłąĖą╗ą░čüčī čāčüą┐ąĄčłąĮąŠ. ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ č鹊ą╗čīą║ąŠ ąĄčüą╗ąĖ čĆą░ąĘčĆąĄčłąĄąĮčŗ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ąŠą┐ąĄčĆą░čåąĖąĖ (EOPIE = 1). ąæąĖčé EOP ąŠčćąĖčēą░ąĄčéčüčÅ ąĘą░ą┐ąĖčüčīčÄ ą▓ ąĮąĄą│ąŠ ą╗ąŠą│. 1.

ąĀąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ Flash FLASH_CR ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖ ąĘą░ą┐čāčüą║ą░ ąŠą┐ąĄčĆą░čåąĖąĖ čü ą┐ą░ą╝čÅčéčīčÄ Flash.

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x10.

ąŚąĮą░č湥ąĮąĖąĄ čüą▒čĆąŠčüą░: 0x80000000.

ąöąŠčüčéčāą┐: ą▒ąĄąĘ čéą░ą║č鹊ą▓ ąŠąČąĖą┤ą░ąĮąĖčÅ, ą║ąŠą│ą┤ą░ ąĮąĄčé ąŠą┐ąĄčĆą░čåąĖąĖ čü Flash. ąöąŠčüčéčāą┐ ą▓ąŠąĘą╝ąŠąČąĄąĮ ą║ą░ą║ ą║ čüą╗ąŠą▓čā, ą┐ąŠą╗ąŠą▓ąĖąĮąĄ čüą╗ąŠą▓ą░ ąĖą╗ąĖ ą▒ą░ą╣čéčā.

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

LOCK

rs |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ERRIE

rw |

EOPIE

rw |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

STRT

rs |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ

|

PSIZE[1:0]

rw |

ąĘą░čĆąĄąĘ. |

SNB[3:0]

rw |

MER

rw |

SER

rw |

PG

rw

|

LOCK (ą▒ąĖčé 31): Lock, ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ą░. ąŚą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą▓ ą╗ąŠą│. 1. ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊čé ą▒ąĖčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 čĆąĄą│ąĖčüčéčĆ FLASH_CR ąĘą░ą▒ą╗ąŠą║ąĖčĆąŠą▓ą░ąĮ. ąæąĖčé LOCK ąŠčćąĖčēą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ ą┐ąŠčüą╗ąĄ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ čüą┐ąĄčåąĖą░ą╗čīąĮąŠą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą┤ąĄą╣čüčéą▓ąĖą╣ ą┐ąŠ čĆą░ąĘą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĄ. ą¤ąŠčüą╗ąĄ ąĮąĄčāą┤ą░čćąĮąŠą╣ ąŠą┐ąĄčĆą░čåąĖąĖ čĆą░ąĘą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ čŹč鹊čé ą▒ąĖčé ąŠčüčéą░ąĮąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╝ ą┤ąŠ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ čüą▒čĆąŠčüą░ (čé. ąĄ. FLASH_CR ąĮąĄą╗čīąĘčÅ čĆą░ąĘą▒ą╗ąŠą║ąĖčĆąŠą▓ą░čéčī, ą┐ąŠą║ą░ ąĮąĄ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé čüą▒čĆąŠčü).

ąæąĖčéčŗ 30:26 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ, ąĖ ą┤ąŠą╗ąČąĮčŗ čüąŠčģčĆą░ąĮčÅčéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (ą▓čüąĄ ąĮčāą╗ąĖ).

ERRIE (ą▒ąĖčé 25): Error interrupt enable, čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠčłąĖą▒ą║ąĖ. ąŁč鹊čé ą▒ąĖčé čĆą░ąĘčĆąĄčłą░ąĄčé ą│ąĄąĮąĄčĆą░čåąĖčÄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▓ 1 ą▒ąĖčé OPERR ą▓ čĆąĄą│ąĖčüčéčĆąĄ FLASH_SR.

0 ą│ąĄąĮąĄčĆą░čåąĖčÅ ąŠčłąĖą▒ą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĘą░ą┐čĆąĄčēąĄąĮą░.

1 ą│ąĄąĮąĄčĆą░čåąĖčÅ ąŠčłąĖą▒ą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čĆą░ąĘčĆąĄčłąĄąĮą░.

EOPIE (ą▒ąĖčé 24): End of operation interrupt enable, čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖčÄ ąŠą┐ąĄčĆą░čåąĖąĖ. ąŁč鹊čé ą▒ąĖčé čĆą░ąĘčĆąĄčłą░ąĄčé ą│ąĄąĮąĄčĆą░čåąĖčÄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą║ąŠą│ą┤ą░ ą┐ąĄčĆąĄą╣ą┤ąĄčé ą▓ 1 ą▒ąĖčé EOP čĆąĄą│ąĖčüčéčĆą░ FLASH_SR.

0 ą│ąĄąĮąĄčĆą░čåąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĘą░ą┐čĆąĄčēąĄąĮą░.

1 ą│ąĄąĮąĄčĆą░čåąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čĆą░ąĘčĆąĄčłąĄąĮą░.

ąæąĖčéčŗ 23:17 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ, ąĖ ą┤ąŠą╗ąČąĮčŗ čüąŠčģčĆą░ąĮčÅčéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (ą▓čüąĄ ąĮčāą╗ąĖ).

STRT (ą▒ąĖčé 16): Start. ąæčāą┤čāčćąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╝, čŹč鹊čé ą▒ąĖčé ąĘą░ą┐čāčüą║ą░ąĄčé ąŠą┐ąĄčĆą░čåąĖčÄ čüčéąĖčĆą░ąĮąĖčÅ. ąæąĖčé STRT čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ, ąĖ ąŠčćąĖčüčéąĖčéčüčÅ ą▓ ą╝ąŠą╝ąĄąĮčé ąŠčćąĖčüčéą║ąĖ ą▒ąĖčéą░ BSY.

ąæąĖčéčŗ 15:19 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ, ąĖ ą┤ąŠą╗ąČąĮčŗ čüąŠčģčĆą░ąĮčÅčéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (ą▓čüąĄ ąĮčāą╗ąĖ).

PSIZE[1:0] (ą▒ąĖčéčŗ 9:8): Program size, čĆą░ąĘą╝ąĄčĆ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝ąŠą╣ ą┐ąŠčĆčåąĖąĖ ą┤ą░ąĮąĮčŗčģ. ąŁčéąĖ ą▒ąĖčéčŗ ą▓čŗą▒ąĖčĆą░čÄčé ą┐ą░čĆą░ą╗ą╗ąĄą╗ąĖąĘą╝ ąŠą┐ąĄčĆą░čåąĖąĖ ąĘą░ą┐ąĖčüąĖ.

00: x8 (ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ ą▒ą░ą╣čé).

01: x16 (ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ ą┐ąŠą╗ąŠą▓ąĖąĮą░ čüą╗ąŠą▓ą░).

10: x32 (ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ čüą╗ąŠą▓ąŠ).

11: x64 (ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ ą┤ą▓ąŠą╣ąĮąŠąĄ čüą╗ąŠą▓ąŠ).

ąæąĖčé 7 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮ, ąĖ ą┤ąŠą╗ąČąĄąĮ čüąŠčģčĆą░ąĮčÅčéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (0).

SNB[3:0] (ą▒ąĖčéčŗ 6:3): Sector number, ąĮąŠą╝ąĄčĆ čüąĄą║č鹊čĆą░. ąŁč鹊 ą┐ąŠą╗ąĄ ą▒ąĖčé ą▓čŗą▒ąĖčĆą░ąĄčé ąĮąŠą╝ąĄčĆ čüąĄą║č鹊čĆą░ ą┤ą╗čÅ čüčéąĖčĆą░ąĮąĖčÅ.

0000: čüąĄą║č鹊čĆ 0.

0001: čüąĄą║č鹊čĆ 1.

..

1011: čüąĄą║č鹊čĆ 11.

ąöčĆčāą│ąĖąĄ ąĘąĮą░č湥ąĮąĖčÅ ąĮąĄ ą┤ąŠą┐čāčüą║ą░čÄčéčüčÅ.

MER (ą▒ąĖčé 2): Mass Erase, ą┐ąŠą╗ąĮą░čÅ ąŠčćąĖčüčéą║ą░ Flash. ąŚą░ą┐ąĖčüčī ą╗ąŠą│. 1 ą▓ čŹč鹊čé ą▒ąĖčé ą░ą║čéąĖą▓ąĖčĆčāąĄčé čüčéąĖčĆą░ąĮąĖąĄ ą▓čüąĄčģ čüąĄą║č鹊čĆąŠą▓ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ (ą║čĆąŠą╝ąĄ čüąĄą║č鹊čĆą░ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ąĖ ą▒ą░ą╣čé OTP).

SER (ą▒ąĖčé 1): Sector Erase, čüčéąĖčĆą░ąĮąĖąĄ čüąĄą║č鹊čĆą░. ąŚą░ą┐ąĖčüčī ą╗ąŠą│. 1 ą▓ čŹč鹊čé ą▒ąĖčé ą░ą║čéąĖą▓ąĖčĆčāąĄčé čüčéąĖčĆą░ąĮąĖąĄ ą▓čŗą▒čĆą░ąĮąĮąŠą│ąŠ čüąĄą║č鹊čĆą░.

PG (ą▒ąĖčé 0): Programming, ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ. ąŚą░ą┐ąĖčüčī ą╗ąŠą│. 1 ą▓ čŹč鹊čé ą▒ąĖčé ą░ą║čéąĖą▓ąĖčĆčāąĄčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ Flash.

ąĀąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ Flash FLASH_CR ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖ ąĘą░ą┐čāčüą║ą░ ąŠą┐ąĄčĆą░čåąĖąĖ čü ą┐ą░ą╝čÅčéčīčÄ Flash.

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x10.

ąŚąĮą░č湥ąĮąĖąĄ čüą▒čĆąŠčüą░: 0x80000000.

ąöąŠčüčéčāą┐: ą▒ąĄąĘ čéą░ą║č鹊ą▓ ąŠąČąĖą┤ą░ąĮąĖčÅ, ą║ąŠą│ą┤ą░ ąĮąĄčé ąŠą┐ąĄčĆą░čåąĖąĖ čü Flash. ąöąŠčüčéčāą┐ ą▓ąŠąĘą╝ąŠąČąĄąĮ ą║ą░ą║ ą║ čüą╗ąŠą▓čā, ą┐ąŠą╗ąŠą▓ąĖąĮąĄ čüą╗ąŠą▓ą░ ąĖą╗ąĖ ą▒ą░ą╣čéčā.

| 31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

LOCK

rs |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ERRIE

rw |

EOPIE

rw |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

STRT

rs |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

MER1

rw |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

PSIZE[1:0]

rw |

SNB[3:0]

rw

|

MER

rw |

SER

rw |

PG

rw

|

LOCK (ą▒ąĖčé 31): Lock, ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ą░. ąŚą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą▓ ą╗ąŠą│. 1. ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊čé ą▒ąĖčé ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 čĆąĄą│ąĖčüčéčĆ FLASH_CR ąĘą░ą▒ą╗ąŠą║ąĖčĆąŠą▓ą░ąĮ. ąæąĖčé LOCK ąŠčćąĖčēą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ ą┐ąŠčüą╗ąĄ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ čüą┐ąĄčåąĖą░ą╗čīąĮąŠą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą┤ąĄą╣čüčéą▓ąĖą╣ ą┐ąŠ čĆą░ąĘą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĄ. ą¤ąŠčüą╗ąĄ ąĮąĄčāą┤ą░čćąĮąŠą╣ ąŠą┐ąĄčĆą░čåąĖąĖ čĆą░ąĘą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ čŹč鹊čé ą▒ąĖčé ąŠčüčéą░ąĮąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╝ ą┤ąŠ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ čüą▒čĆąŠčüą░ (čé. ąĄ. FLASH_CR ąĮąĄą╗čīąĘčÅ čĆą░ąĘą▒ą╗ąŠą║ąĖčĆąŠą▓ą░čéčī, ą┐ąŠą║ą░ ąĮąĄ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé čüą▒čĆąŠčü).

ąæąĖčéčŗ 30:26 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ, ąĖ ą┤ąŠą╗ąČąĮčŗ čüąŠčģčĆą░ąĮčÅčéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (ą▓čüąĄ ąĮčāą╗ąĖ).

ERRIE (ą▒ąĖčé 25): Error interrupt enable, čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠčłąĖą▒ą║ąĖ. ąŁč鹊čé ą▒ąĖčé čĆą░ąĘčĆąĄčłą░ąĄčé ą│ąĄąĮąĄčĆą░čåąĖčÄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▓ 1 ą▒ąĖčé OPERR ą▓ čĆąĄą│ąĖčüčéčĆąĄ FLASH_SR.

0 ą│ąĄąĮąĄčĆą░čåąĖčÅ ąŠčłąĖą▒ą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĘą░ą┐čĆąĄčēąĄąĮą░.

1 ą│ąĄąĮąĄčĆą░čåąĖčÅ ąŠčłąĖą▒ą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čĆą░ąĘčĆąĄčłąĄąĮą░.

EOPIE (ą▒ąĖčé 24): End of operation interrupt enable, čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖčÄ ąŠą┐ąĄčĆą░čåąĖąĖ. ąŁč鹊čé ą▒ąĖčé čĆą░ąĘčĆąĄčłą░ąĄčé ą│ąĄąĮąĄčĆą░čåąĖčÄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą║ąŠą│ą┤ą░ ą┐ąĄčĆąĄą╣ą┤ąĄčé ą▓ 1 ą▒ąĖčé EOP čĆąĄą│ąĖčüčéčĆą░ FLASH_SR.

0 ą│ąĄąĮąĄčĆą░čåąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĘą░ą┐čĆąĄčēąĄąĮą░.

1 ą│ąĄąĮąĄčĆą░čåąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čĆą░ąĘčĆąĄčłąĄąĮą░.

ąæąĖčéčŗ 23:17 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ, ąĖ ą┤ąŠą╗ąČąĮčŗ čüąŠčģčĆą░ąĮčÅčéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (ą▓čüąĄ ąĮčāą╗ąĖ).

STRT (ą▒ąĖčé 16): Start. ąæčāą┤čāčćąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╝, čŹč鹊čé ą▒ąĖčé ąĘą░ą┐čāčüą║ą░ąĄčé ąŠą┐ąĄčĆą░čåąĖčÄ čüčéąĖčĆą░ąĮąĖčÅ. ąæąĖčé STRT čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ, ąĖ ąŠčćąĖčüčéąĖčéčüčÅ ą▓ ą╝ąŠą╝ąĄąĮčé ąŠčćąĖčüčéą║ąĖ ą▒ąĖčéą░ BSY.

MER1 (ą▒ąĖčé 15): Mass Erase of bank 2 sectors, ą┐ąŠą╗ąĮąŠąĄ čüčéąĖčĆą░ąĮąĖąĄ čüąĄą║č鹊čĆąŠą▓ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ ą▒ą░ąĮą║ą░ 2 (čüąĄą║č鹊čĆą░ ąŠčé 12 ą┤ąŠ 23).

ąæąĖčéčŗ 14:19 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ, ąĖ ą┤ąŠą╗ąČąĮčŗ čüąŠčģčĆą░ąĮčÅčéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ čüą▒čĆąŠčüą░ (ą▓čüąĄ ąĮčāą╗ąĖ).

PSIZE[1:0] (ą▒ąĖčéčŗ 9:8): Program size, čĆą░ąĘą╝ąĄčĆ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝ąŠą╣ ą┐ąŠčĆčåąĖąĖ ą┤ą░ąĮąĮčŗčģ. ąŁčéąĖ ą▒ąĖčéčŗ ą▓čŗą▒ąĖčĆą░čÄčé ą┐ą░čĆą░ą╗ą╗ąĄą╗ąĖąĘą╝ ąŠą┐ąĄčĆą░čåąĖąĖ ąĘą░ą┐ąĖčüąĖ.

00: x8 (ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ ą▒ą░ą╣čé).

01: x16 (ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ ą┐ąŠą╗ąŠą▓ąĖąĮą░ čüą╗ąŠą▓ą░).

10: x32 (ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ čüą╗ąŠą▓ąŠ).

11: x64 (ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ ą┤ą▓ąŠą╣ąĮąŠąĄ čüą╗ąŠą▓ąŠ).

SNB[4:0] (ą▒ąĖčéčŗ 7:3): Sector number, ąĮąŠą╝ąĄčĆ čüąĄą║č鹊čĆą░. ąŁč鹊 ą┐ąŠą╗ąĄ ą▒ąĖčé ą▓čŗą▒ąĖčĆą░ąĄčé ąĮąŠą╝ąĄčĆ čüąĄą║č鹊čĆą░ ą┤ą╗čÅ čüčéąĖčĆą░ąĮąĖčÅ.

00000: čüąĄą║č鹊čĆ 0.

00001: čüąĄą║č鹊čĆ 1.

..

01011: čüąĄą║č鹊čĆ 11.

01100: ąĮąĄ ą┤ąŠą┐čāčüą║ą░ąĄčéčüčÅ.

01101: ąĮąĄ ą┤ąŠą┐čāčüą║ą░ąĄčéčüčÅ.

01110: ąĮąĄ ą┤ąŠą┐čāčüą║ą░ąĄčéčüčÅ.

01111: ąĮąĄ ą┤ąŠą┐čāčüą║ą░ąĄčéčüčÅ.

10000: čüąĄą║č鹊čĆ 12.

10001: čüąĄą║č鹊čĆ 13.

...

11011: čüąĄą║č鹊čĆ 23.

11100: ąĮąĄ ą┤ąŠą┐čāčüą║ą░ąĄčéčüčÅ.

11101: ąĮąĄ ą┤ąŠą┐čāčüą║ą░ąĄčéčüčÅ.

11110: ąĮąĄ ą┤ąŠą┐čāčüą║ą░ąĄčéčüčÅ.

11111: ąĮąĄ ą┤ąŠą┐čāčüą║ą░ąĄčéčüčÅ.

MER (ą▒ąĖčé 2): Mass Erase of bank 1 sectors, ą┐ąŠą╗ąĮą░čÅ ąŠčćąĖčüčéą║ą░ čüąĄą║č鹊čĆąŠą▓ ą▒ą░ąĮą║ą░ 1 Flash (čüąĄą║č鹊čĆą░ ąŠčé 0 ą┤ąŠ 11).

SER (ą▒ąĖčé 1): Sector Erase, čüčéąĖčĆą░ąĮąĖąĄ čüąĄą║č鹊čĆą░. ąŚą░ą┐ąĖčüčī ą╗ąŠą│. 1 ą▓ čŹč鹊čé ą▒ąĖčé ą░ą║čéąĖą▓ąĖčĆčāąĄčé čüčéąĖčĆą░ąĮąĖąĄ ą▓čŗą▒čĆą░ąĮąĮąŠą│ąŠ čüąĄą║č鹊čĆą░.

PG (ą▒ąĖčé 0): Programming, ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ. ąŚą░ą┐ąĖčüčī ą╗ąŠą│. 1 ą▓ čŹč鹊čé ą▒ąĖčé ą░ą║čéąĖą▓ąĖčĆčāąĄčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ Flash.