|

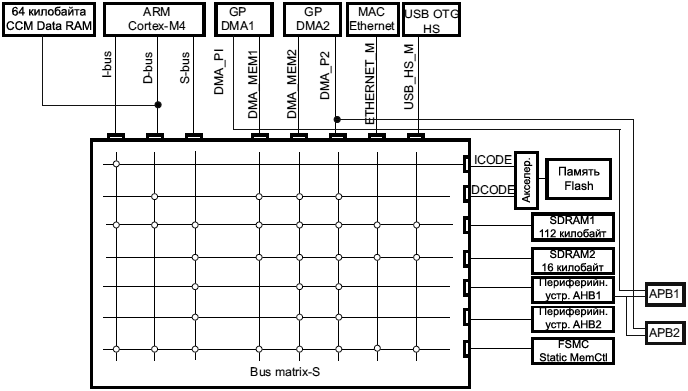

ąÆ čŹč鹊ą╣ čüčéą░čéčīąĄ ą┤ą░ąĮ ąŠą▒ąĘąŠčĆ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ čüąĖčüč鹥ą╝čŗ čłąĖąĮ ąĖ ą┐ą░ą╝čÅčéąĖ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ STM32F4 (ą┐ąĄčĆąĄą▓ąŠą┤ čĆą░ąĘą┤ąĄą╗ą░ "2 Memory and bus architecture" ą┤ą░čéą░čłąĖčéą░ [1]). ąÆčüąĄ ąĮąĄą┐ąŠąĮčÅčéąĮčŗąĄ č鹥čĆą╝ąĖąĮčŗ ąĖ čüąŠą║čĆą░čēąĄąĮąĖčÅ čüą╝. ą▓ ąĪą╗ąŠą▓ą░čĆąĖą║ąĄ [7].

[ąÉčĆčģąĖč鹥ą║čéčāčĆą░ čüąĖčüč鹥ą╝čŗ]

STM32F405xx/07xx ąĖ STM32F415xx/17xx. ą×čüąĮąŠą▓ąĮą░čÅ ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ čüąĖčüč鹥ą╝ą░ ąŠčüąĮąŠą▓ą░ąĮą░ ąĮą░ 32-čĆą░ąĘčĆčÅą┤ąĮąŠą╣ ą╝ąĮąŠą│ąŠčüą╗ąŠą╣ąĮąŠą╣ ą╝ą░čéčĆąĖčåąĄ čłąĖąĮ AHB, ą║ąŠč鹊čĆą░čÅ čüąŠąĄą┤ąĖąĮčÅąĄčé:

ŌĆó 8 ą│ą╗ą░ą▓ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ (master):

ŌĆō Cortex┬«-M4 čÅą┤čĆąŠ čü FPU I-bus, D-bus ąĖ S-bus

ŌĆō čłąĖąĮą░ ą┐ą░ą╝čÅčéąĖ DMA1

ŌĆō čłąĖąĮą░ ą┐ą░ą╝čÅčéąĖ DMA2

ŌĆō čłąĖąĮą░ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ DMA2

ŌĆō čłąĖąĮą░ Ethernet DMA

ŌĆō čłąĖąĮą░ USB OTG HS DMA

ŌĆó 7 ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ (slave):

ŌĆō čłąĖąĮą░ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ Flash ICode

ŌĆō čłąĖąĮą░ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ Flash DCode

ŌĆō ąŠčüąĮąŠą▓ąĮą░čÅ ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ ą┐ą░ą╝čÅčéčī SRAM1 (112 ą║ąĖą╗ąŠą▒ą░ą╣čé)

ŌĆō ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮą░čÅ ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ ą┐ą░ą╝čÅčéčī SRAM2 (16 ą║ąĖą╗ąŠą▒ą░ą╣čé)

ŌĆō ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ AHB1, ą▓ą║ą╗čÄčćą░čÅ ą╝ąŠčüčéčŗ AHB - APB ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ APB

ŌĆō ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ AHB2

ŌĆō FSMC

ą£ą░čéčĆąĖčåą░ čłąĖąĮ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą┤ąŠčüčéčāą┐ ąŠčé master ą║ slave, ą┐ąŠąĘą▓ąŠą╗čÅčÅ čĆąĄą░ą╗ąĖąĘąŠą▓ą░čéčī ą║ąŠąĮą║čāčĆąĄąĮčéąĮčŗą╣ ą┤ąŠčüčéčāą┐ ąĖ čŹčäč乥ą║čéąĖą▓ąĮčāčÄ čĆą░ą▒ąŠčéčā ą┤ą░ąČąĄ ą║ąŠą│ą┤ą░ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ čĆą░ą▒ąŠčéą░čÄčé ąĮąĄčüą║ąŠą╗čīą║ąŠ ą▓čŗčüąŠą║ąŠčüą║ąŠčĆąŠčüčéąĮčŗčģ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓. 64-ą║ąĖą╗ąŠą▒ą░ą╣čéąĮą░čÅ ą┐ą░ą╝čÅčéčī ą┤ą░ąĮąĮčŗčģ CCM (Core Coupled Memory) ąĮąĄ čÅą▓ą╗čÅąĄčéčüčÅ čćą░čüčéčīčÄ ą╝ą░čéčĆąĖčåčŗ čłąĖąĮ, ąĖ ą║ ąĮąĄą╣ ą╝ąŠąČąĮąŠ ąŠčüčāčēąĄčüčéą▓ą╗čÅčéčī ą┤ąŠčüčéčāą┐ č鹊ą╗čīą║ąŠ č湥čĆąĄąĘ čÅą┤čĆąŠ CPU. ąŁčéą░ ą░čĆčģąĖč鹥ą║čéčāčĆą░ ą┐ąŠą║ą░ąĘą░ąĮą░ ąĮą░ čĆąĖčü. 1.

ąĀąĖčü. 1. ąÉčĆčģąĖč鹥ą║čéčāčĆą░ čüąĖčüč鹥ą╝čŗ MCU STM32F405xx/07xx ąĖ STM32F415xx/17xx.

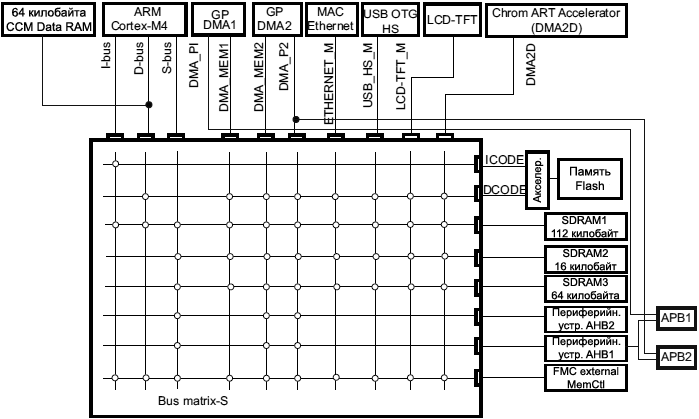

STM32F42xx ąĖ STM32F43xx. ą×čüąĮąŠą▓ąĮą░čÅ ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ čüąĖčüč鹥ą╝ą░ ąŠčüąĮąŠą▓ą░ąĮą░ ąĮą░ 32-čĆą░ąĘčĆčÅą┤ąĮąŠą╣ ą╝ąĮąŠą│ąŠčüą╗ąŠą╣ąĮąŠą╣ ą╝ą░čéčĆąĖčåąĄ čłąĖąĮ AHB, ą║ąŠč鹊čĆą░čÅ čüąŠąĄą┤ąĖąĮčÅąĄčé:

ŌĆó 10 ą│ą╗ą░ą▓ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ (master):

ŌĆō Cortex┬«-M4 čÅą┤čĆąŠ čü FPU I-bus, D-bus ąĖ S-bus

ŌĆō čłąĖąĮą░ ą┐ą░ą╝čÅčéąĖ DMA1

ŌĆō čłąĖąĮą░ ą┐ą░ą╝čÅčéąĖ DMA2

ŌĆō čłąĖąĮą░ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ DMA2

ŌĆō čłąĖąĮą░ Ethernet DMA

ŌĆō čłąĖąĮą░ USB OTG HS DMA

ŌĆō čłąĖąĮą░ DMA ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ LCD [5]

ŌĆō čłąĖąĮą░ ą┐ą░ą╝čÅčéąĖ DMA2D (Chrom-Art AcceleratorŌäó)

ŌĆó 8 ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ (slave):

ŌĆō čłąĖąĮą░ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ Flash ICode ŌĆō čłąĖąĮą░ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ Flash DCode

ŌĆō ąŠčüąĮąŠą▓ąĮą░čÅ ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ ą┐ą░ą╝čÅčéčī SRAM1 (112 ą║ąĖą╗ąŠą▒ą░ą╣čé)

ŌĆō ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮą░čÅ ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ ą┐ą░ą╝čÅčéčī SRAM2 (16 ą║ąĖą╗ąŠą▒ą░ą╣čé)

ŌĆō ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮą░čÅ ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ ą┐ą░ą╝čÅčéčī SRAM3 (64 ą║ąĖą╗ąŠą▒ą░ą╣čéą░)

ŌĆō ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ AHB1, ą▓ą║ą╗čÄčćą░čÅ ą╝ąŠčüčéčŗ AHB - APB ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ APB

ŌĆō ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ AHB2

ŌĆō FSMC

ą£ą░čéčĆąĖčåą░ čłąĖąĮ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą┤ąŠčüčéčāą┐ ąŠčé master ą║ slave, ą┐ąŠąĘą▓ąŠą╗čÅčÅ čĆąĄą░ą╗ąĖąĘąŠą▓ą░čéčī ą║ąŠąĮą║čāčĆąĄąĮčéąĮčŗą╣ ą┤ąŠčüčéčāą┐ ąĖ čŹčäč乥ą║čéąĖą▓ąĮčāčÄ čĆą░ą▒ąŠčéčā ą┤ą░ąČąĄ ą║ąŠą│ą┤ą░ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ čĆą░ą▒ąŠčéą░čÄčé ąĮąĄčüą║ąŠą╗čīą║ąŠ ą▓čŗčüąŠą║ąŠčüą║ąŠčĆąŠčüčéąĮčŗčģ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓. 64-ą║ąĖą╗ąŠą▒ą░ą╣čéąĮą░čÅ ą┐ą░ą╝čÅčéčī ą┤ą░ąĮąĮčŗčģ CCM (Core Coupled Memory) ąĮąĄ čÅą▓ą╗čÅąĄčéčüčÅ čćą░čüčéčīčÄ ą╝ą░čéčĆąĖčåčŗ čłąĖąĮ, ąĖ ą║ ąĮąĄą╣ ą╝ąŠąČąĮąŠ ąŠčüčāčēąĄčüčéą▓ą╗čÅčéčī ą┤ąŠčüčéčāą┐ č鹊ą╗čīą║ąŠ č湥čĆąĄąĘ čÅą┤čĆąŠ CPU. ąŁčéą░ ą░čĆčģąĖč鹥ą║čéčāčĆą░ ą┐ąŠą║ą░ąĘą░ąĮą░ ąĮą░ čĆąĖčü. 2.

ąĀąĖčü. 2. ąÉčĆčģąĖč鹥ą║čéčāčĆą░ čüąĖčüč鹥ą╝čŗ MCU STM32F42xxx ąĖ STM32F43xxx.

I-bus. ąŁčéą░ čłąĖąĮą░ čüąŠąĄą┤ąĖąĮčÅąĄčé čü ą╝ą░čéčĆąĖčåąĄą╣ čłąĖąĮ čłąĖąĮčā ąĖąĮčüčéčĆčāą║čåąĖą╣ čÅą┤čĆą░ Cortex┬«-M4. ą©ąĖąĮą░ I-bus ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čÅą┤čĆąŠą╝ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą║ąĖ ąĖąĮčüčéčĆčāą║čåąĖą╣. ąŁčéą░ čłąĖąĮą░ čĆą░ą▒ąŠčéą░ąĄčé čü ą┐ą░ą╝čÅčéčīčÄ, ą│ą┤ąĄ ąĮą░čģąŠą┤ąĖčéčüčÅ ą║ąŠą┤ (ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ ą┐ą░ą╝čÅčéčī Flash/SRAM ąĖą╗ąĖ ą▓ąĮąĄčłąĮąĖąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┐ą░ą╝čÅčéąĖ, ą┤ąŠčüčéčāą┐ąĮčŗąĄ č湥čĆąĄąĘ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ FSMC/FMC).

D-bus. ąŁčéą░ čłąĖąĮą░ čüąŠąĄą┤ąĖąĮčÅąĄčé ą┐ą░ą╝čÅčéčī ą┤ą░ąĮąĮčŗčģ 64-ą║ąĖą╗ąŠą▒ą░ą╣čé CCM čü čłąĖąĮąŠą╣ ą┤ą░ąĮąĮčŗčģ čÅą┤čĆą░ Cortex┬«-M4 č湥čĆąĄąĘ ą╝ą░čéčĆąĖčåčā čłąĖąĮ (BusMatrix). ą©ąĖąĮą░ D-bus ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čÅą┤čĆąŠą╝ ą┤ą╗čÅ ąĘą░ą│čĆčāąĘą║ąĖ ą┤ą░ąĮąĮčŗčģ ąĖ ą┤ąŠčüčéčāą┐ą░ ą║ ąŠčéą╗ą░ą┤ą║ąĄ. ąŁčéą░ čłąĖąĮą░ čĆą░ą▒ąŠčéą░ąĄčé čü ą┐ą░ą╝čÅčéčīčÄ, ą│ą┤ąĄ čüąŠą┤ąĄčƹȹĖčéčüčÅ ą║ąŠą┤ ąĖą╗ąĖ ą┤ą░ąĮąĮčŗąĄ (ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ ą┐ą░ą╝čÅčéčī Flash ąĖą╗ąĖ ą▓ąĮąĄčłąĮąĖąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┐ą░ą╝čÅčéąĖ, ą┤ąŠčüčéčāą┐ąĮčŗąĄ č湥čĆąĄąĘ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ FSMC/FMC).

S-bus. ąŁčéą░ čłąĖąĮą░ čüąŠąĄą┤ąĖąĮčÅąĄčé čüąĖčüč鹥ą╝ąĮčāčÄ čłąĖąĮčā čÅą┤čĆą░ Cortex┬«-M4 čü BusMatrix. ą©ąĖąĮą░ S-bus ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ ą║ ą┐ą░ą╝čÅčéąĖ, ąĮą░čģąŠą┤čÅčēąĄą╣čüčÅ ą▓ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą╝ čāčüčéčĆąŠą╣čüčéą▓ąĄ ąĖą╗ąĖ ą▓ SRAM. ą¦ąĄčĆąĄąĘ čŹčéčā čłąĖąĮčā ą╝ąŠąČąĄčé čéą░ą║ąČąĄ ąŠčüčāčēąĄčüčéą▓ą╗čÅčéčīčüčÅ ą▓čŗą▒ąŠčĆą║ą░ ąĖąĮčüčéčĆčāą║čåąĖą╣ (čü ą╝ąĄąĮčīčłąĄą╣ čŹčäč乥ą║čéąĖą▓ąĮąŠčüčéčīčÄ ą┐ąŠ čüčĆą░ą▓ąĮąĄąĮąĖčÄ čü ICode). ą©ąĖąĮą░ S-bus čĆą░ą▒ąŠčéą░ąĄčé čü ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ ą┐ą░ą╝čÅčéčīčÄ SRAM1, SRAM2 ąĖ SRAM3, ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ AHB1, ą▓ą║ą╗čÄčćą░čÅ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ APB, ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ AHB2 ąĖ ą▓ąĮąĄčłąĮąĖąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┐ą░ą╝čÅčéąĖ, ą┤ąŠčüčéčāą┐ąĮčŗąĄ č湥čĆąĄąĘ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ FSMC/FMC.

ą©ąĖąĮą░ ą┐ą░ą╝čÅčéąĖ DMA. ąŁčéą░ čłąĖąĮą░ čüąŠąĄą┤ąĖąĮčÅąĄčé ą╝ą░čüč鹥čĆą░ čłąĖąĮčŗ ą┐ą░ą╝čÅčéąĖ DMA čü BusMatrix. ą©ąĖąĮą░ ą┐ą░ą╝čÅčéąĖ DMA ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▒ą╗ąŠą║ąŠą╝ DMA ą┤ą╗čÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ą╝ąĄąČą┤čā ąŠą▒ą╗ą░čüčéčÅą╝ąĖ ą┐ą░ą╝čÅčéąĖ. ąŁčéą░ čłąĖąĮą░ čĆą░ą▒ąŠčéą░ąĄčé čüąŠ čüą╗ąĄą┤čāčÄčēąĖą╝ąĖ ąŠą▒ą╗ą░čüčéčÅą╝ąĖ ą┤ą░ąĮąĮčŗčģ: ą▓ąĮčāčéčĆąĄąĮąĮąĖąĄ ą▒ą░ąĮą║ąĖ SRAM (SRAM1, SRAM2 ąĖ SRAM3) ąĖ ą▓ąĮąĄčłąĮąĖąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┐ą░ą╝čÅčéąĖ, ą┤ąŠčüčéčāą┐ąĮčŗąĄ č湥čĆąĄąĘ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ FSMC/FMC.

ą©ąĖąĮą░ DMA ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓. ąŁčéą░ čłąĖąĮą░ čüąŠąĄą┤ąĖąĮčÅąĄčé ąĖąĮč鹥čĆč乥ą╣čü ą╝ą░čüč鹥čĆą░ DMA ą┐ąĄčĆąĖč乥čĆąĖąĖ čü BusMatrix. ą©ąĖąĮą░ DMA ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▒ą╗ąŠą║ąŠą╝ DMA ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ ą║ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ AHB, ąĖą╗ąĖ ą┤ą╗čÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖą╣ ą┤ą░ąĮąĮčŗčģ ą╝ąĄąČą┤čā ąŠą▒ą╗ą░čüčéčÅą╝ąĖ ą┐ą░ą╝čÅčéąĖ. ąŁčéą░ čłąĖąĮą░ čĆą░ą▒ąŠčéą░ąĄčé čü ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ AHB ąĖ APB ą┐ą╗čÄčü čü ą┐ą░ą╝čÅčéčīčÄ ą┤ą░ąĮąĮčŗčģ: ą▓ąĮčāčéčĆąĄąĮąĮąĖąĄ ą▒ą░ąĮą║ąĖ SRAM (SRAM1, SRAM2 ąĖ SRAM3) ąĖ ą▓ąĮąĄčłąĮąĖąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┐ą░ą╝čÅčéąĖ, ą┤ąŠčüčéčāą┐ąĮčŗąĄ č湥čĆąĄąĘ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ FSMC/FMC.

ą©ąĖąĮą░ Ethernet DMA. ąŁčéą░ čłąĖąĮą░ čüąŠąĄą┤ąĖąĮčÅąĄčé ąĖąĮč鹥čĆč乥ą╣čü ą╝ą░čüč鹥čĆą░ Ethernet DMA čü BusMatrix. ą©ąĖąĮą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▒ą╗ąŠą║ąŠą╝ Ethernet DMA ą┤ą╗čÅ ąŠą▒ą╝ąĄąĮą░ ą┤ą░ąĮąĮčŗą╝ąĖ čü ą┐ą░ą╝čÅčéčīčÄ. ą©ąĖąĮą░ Ethernet DMA čĆą░ą▒ąŠčéą░ąĄčé čü ą┐ą░ą╝čÅčéčīčÄ ą┤ą░ąĮąĮčŗčģ: ą▓ąĮčāčéčĆąĄąĮąĮąĖąĄ ą▒ą░ąĮą║ąĖ SRAM (SRAM1, SRAM2 ąĖ SRAM3), ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ ą┐ą░ą╝čÅčéčī Flash ąĖ ą▓ąĮąĄčłąĮąĖąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┐ą░ą╝čÅčéąĖ, ą┤ąŠčüčéčāą┐ąĮčŗąĄ č湥čĆąĄąĘ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ FSMC/FMC.

ą©ąĖąĮą░ USB OTG HS DMA. ąŁčéą░ čłąĖąĮą░ čüąŠąĄą┤ąĖąĮčÅąĄčé ąĖąĮč鹥čĆč乥ą╣čü ą╝ą░čüč鹥čĆą░ USB OTG HS DMA čü BusMatrix. ą©ąĖąĮą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▒ą╗ąŠą║ąŠą╝ USB OTG HS DMA ą┤ą╗čÅ ąŠą▒ą╝ąĄąĮą░ ą┤ą░ąĮąĮčŗą╝ąĖ čü ą┐ą░ą╝čÅčéčīčÄ. ą©ąĖąĮą░ USB OTG HS DMA čĆą░ą▒ąŠčéą░ąĄčé čü ą┐ą░ą╝čÅčéčīčÄ ą┤ą░ąĮąĮčŗčģ: ą▓ąĮčāčéčĆąĄąĮąĮąĖąĄ ą▒ą░ąĮą║ąĖ SRAM (SRAM1, SRAM2 ąĖ SRAM3), ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ ą┐ą░ą╝čÅčéčī Flash ąĖ ą▓ąĮąĄčłąĮąĖąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┐ą░ą╝čÅčéąĖ, ą┤ąŠčüčéčāą┐ąĮčŗąĄ č湥čĆąĄąĘ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ FSMC/FMC.

ą©ąĖąĮą░ DMA ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ LCD-TFT. ąŁčéą░ čłąĖąĮą░ čüąŠąĄą┤ąĖąĮčÅąĄčé ąĖąĮč鹥čĆč乥ą╣čü ą╝ą░čüč鹥čĆą░ DMA ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ LCD [5] čü BusMatrix. ą©ąĖąĮą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▒ą╗ąŠą║ąŠą╝ LCD-TFT DMA ą┤ą╗čÅ ąŠą▒ą╝ąĄąĮą░ ą┤ą░ąĮąĮčŗą╝ąĖ čü ą┐ą░ą╝čÅčéčīčÄ. ą©ąĖąĮą░ DMA ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ LCD-TFT čĆą░ą▒ąŠčéą░ąĄčé čü ą┐ą░ą╝čÅčéčīčÄ ą┤ą░ąĮąĮčŗčģ: ą▓ąĮčāčéčĆąĄąĮąĮąĖąĄ ą▒ą░ąĮą║ąĖ SRAM (SRAM1, SRAM2 ąĖ SRAM3), ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ ą┐ą░ą╝čÅčéčī Flash ąĖ ą▓ąĮąĄčłąĮąĖąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┐ą░ą╝čÅčéąĖ, ą┤ąŠčüčéčāą┐ąĮčŗąĄ č湥čĆąĄąĘ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ FMC.

ą©ąĖąĮą░ DMA2D. ąŁčéą░ čłąĖąĮą░ čüąŠąĄą┤ąĖąĮčÅąĄčé ąĖąĮč鹥čĆč乥ą╣čü ą╝ą░čüč鹥čĆą░ DMA2D čü BusMatrix. ą©ąĖąĮą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▒ą╗ąŠą║ąŠą╝ ą│čĆą░čäąĖč湥čüą║ąŠą│ąŠ čāčüą║ąŠčĆąĖč鹥ą╗čÅ DMA2D ą┤ą╗čÅ ąŠą▒ą╝ąĄąĮą░ ą┤ą░ąĮąĮčŗą╝ąĖ čü ą┐ą░ą╝čÅčéčīčÄ. ą©ąĖąĮą░ DMA2D čĆą░ą▒ąŠčéą░ąĄčé čü ą┐ą░ą╝čÅčéčīčÄ ą┤ą░ąĮąĮčŗčģ: ą▓ąĮčāčéčĆąĄąĮąĮąĖąĄ ą▒ą░ąĮą║ąĖ SRAM (SRAM1, SRAM2 ąĖ SRAM3), ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ ą┐ą░ą╝čÅčéčī Flash ąĖ ą▓ąĮąĄčłąĮąĖąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┐ą░ą╝čÅčéąĖ, ą┤ąŠčüčéčāą┐ąĮčŗąĄ č湥čĆąĄąĘ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ FMC.

BusMatrix. ą£ą░čéčĆąĖčåą░ čłąĖąĮ čāą┐čĆą░ą▓ą╗čÅąĄčé ą░čĆą▒ąĖčéčĆą░ąČąĄą╝ ą╝ąĄąČą┤čā ą╝ą░čüč鹥čĆą░ą╝ąĖ. ąÉčĆą▒ąĖčéčĆą░ąČ ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą░ą╗ą│ąŠčĆąĖčéą╝ round-robin (čåąĖą║ą╗ąĖč湥čüą║ą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░ ą┐čĆąĖąŠčĆąĖč鹥čéą░).

ą£ąŠčüčéčŗ AHB/APB. ąöą▓ą░ ą╝ąŠčüčéą░ AHB/APB, APB1 ąĖ APB2, ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÄčé ą┐ąŠą╗ąĮąŠąĄ čüąĖąĮčģčĆąŠąĮąĮąŠąĄ čüąŠąĄą┤ąĖąĮąĄąĮąĖąĄ ą╝ąĄąČą┤čā čłąĖąĮąŠą╣ AHB ąĖ ą┤ą▓čāą╝čÅ čłąĖąĮą░ą╝ąĖ APB, čćč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą│ąĖą▒ą║ąŠ ą▓čŗą▒ąĖčĆą░čéčī čćą░čüč鹊čéčā čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓. ąöą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ą┐ąŠą┤čĆąŠą▒ąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ą┐ąŠ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮčŗą╝ čćą░čüč鹊čéą░ą╝ čłąĖąĮ APB1 ąĖ APB2 čüą╝. ą┤ą░čéą░čłąĖčé ąĮą░ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╣ MCU. ąÆ čéą░ą▒ą╗ąĖčåąĄ 1 ą┐ąŠą║ą░ąĘą░ąĮąŠ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖąĄ ą░ą┤čĆąĄčüąŠą▓ AHB ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ APB.

ą¤ąŠčüą╗ąĄ ą║ą░ąČą┤ąŠą│ąŠ čüą▒čĆąŠčüą░ MCU čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ą▓čüąĄčģ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ąĘą░ą┐čĆąĄčēąĄąĮąŠ (ą║čĆąŠą╝ąĄ ąĖąĮč鹥čĆč乥ą╣čüą░ ą┐ą░ą╝čÅčéąĖ SRAM ąĖ Flash). ą¤ąŠčŹč鹊ą╝čā ą┐ąĄčĆąĄą┤ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ čĆą░ąĘčĆąĄčłąĖčéčī ąĄą│ąŠ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄą╝ čĆąĄą│ąĖčüčéčĆąŠą▓ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ RCC (RCC_AHBxENR ąĖą╗ąĖ RCC_APBxENR).

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą║ąŠą│ą┤ą░ ą║ čĆąĄą│ąĖčüčéčĆčā APB ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ 16-ą▒ąĖčéąĮčŗą╣ ąĖą╗ąĖ 8-ą▒ąĖčéąĮčŗą╣ ą┤ąŠčüčéčāą┐, čŹč鹊čé ą┤ąŠčüčéčāą┐ ą┐čĆąĄąŠą▒čĆą░ąĘčāąĄčéčüčÅ ą▓ 32-ą▒ąĖčéąĮčŗą╣: ą╝ąŠčüčé ą┤čāą▒ą╗ąĖčĆčāąĄčé 16-ą▒ąĖčéąĮčŗąĄ ąĖą╗ąĖ 8-ą▒ąĖčéąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ ą┐ąŠą┤ą░čćąĖ 32-ą▒ąĖčéąĮąŠą│ąŠ ą▓ąĄą║č鹊čĆą░.

[ą×čĆą│ą░ąĮąĖąĘą░čåąĖčÅ ą┐ą░ą╝čÅčéąĖ]

ą¤ą░ą╝čÅčéčī ą┐čĆąŠą│čĆą░ą╝ą╝čŗ, ą┐ą░ą╝čÅčéčī ą┤ą░ąĮąĮčŗčģ, čĆąĄą│ąĖčüčéčĆčŗ ąĖ ą┐ąŠčĆčéčŗ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ ąŠčĆą│ą░ąĮąĖąĘąŠą▓ą░ąĮčŗ ą▓ ąŠą┤ąĮąŠą╝ ąŠą▒čēąĄą╝, ą╗ąĖąĮąĄą╣ąĮąŠą╝ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąĄ ą░ą┤čĆąĄčüąŠą▓ ąŠą▒čŖąĄą╝ąŠą╝ 4 ą│ąĖą│ą░ą▒ą░ą╣čéą░.

ąöą░ąĮąĮčŗąĄ čģčĆą░ąĮčÅčéčüčÅ ą▓ ą┐ą░ą╝čÅčéąĖ ą▓ č乊čĆą╝ą░č鹥 little endian [6]. ąæą░ą╣čé čü ąĮą░ąĖą╝ąĄąĮčīčłąĖą╝ ąĮąŠą╝ąĄčĆąŠą╝ ą▓ čüą╗ąŠą▓ąĄ (čü čüą░ą╝čŗą╝ ą╝ą░ą╗čŗą╝ ą░ą┤čĆąĄčüąŠą╝) čüčćąĖčéą░ąĄčéčüčÅ čüą░ą╝čŗą╝ ą╝ą╗ą░ą┤čłąĖą╝ ąĘąĮą░čćą░čēąĖą╝ ą▒ą░ą╣č鹊ą╝ čŹč鹊ą│ąŠ čüą╗ąŠą▓ą░. ąś ąĮą░ąŠą▒ąŠčĆąŠčé, ą▒ą░ą╣čé čü čüą░ą╝čŗą╝ ą▒ąŠą╗čīčłąĖą╝ ąĮąŠą╝ąĄčĆąŠą╝ (čü čüą░ą╝čŗą╝ ą▒ąŠą╗čīčłąĖą╝ ą░ą┤čĆąĄčüąŠą╝) čüčćąĖčéą░ąĄčéčüčÅ čüą░ą╝čŗą╝ ąĘąĮą░čćą░čēąĖą╝ ą▒ą░ą╣č鹊ą╝ čüą╗ąŠą▓ą░.

ą¤ąŠą┤čĆąŠą▒ąĮčāčÄ ąĖąĮč乊čĆą╝ą░čåąĖčÄ ą┐ąŠ ą░ą┤čĆąĄčüą░ą╝ čĆąĄą│ąĖčüčéčĆąŠą▓ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ čüą╝. čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ čĆą░ąĘą┤ąĄą╗čŗ ą┤ą░čéą░čłąĖčéą░ [1].

ąÉą┤čĆąĄčüčāąĄą╝ąŠąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ ą┐ą░ą╝čÅčéąĖ ą┐ąŠą┤ąĄą╗ąĄąĮąŠ ąĮą░ 8 ąŠčüąĮąŠą▓ąĮčŗčģ ą▒ą╗ąŠą║ąŠą▓, ą║ą░ąČą┤čŗą╣ ą┐ąŠ 512 ą╝ąĄą│ą░ą▒ą░ą╣čé. ąÆčüąĄ ąŠą▒ą╗ą░čüčéąĖ ą┐ą░ą╝čÅčéąĖ, ą║ąŠč鹊čĆčŗąĄ ąĮąĄ ą┐čĆąĖąĮą░ą┤ą╗ąĄąČą░čé ą▓čüčéčĆąŠąĄąĮąĮčŗą╝ ą▓ čćąĖą┐ ąŠą▒ą╗ą░čüčéčÅą╝ ą┐ą░ą╝čÅčéąĖ ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ čüčćąĖčéą░čÄčéčüčÅ ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąĮčŗą╝ąĖ. ąĪą╝. ą║ą░čĆčéčā ą┐ą░ą╝čÅčéąĖ ą▓ ą┤ą░čéą░čłąĖč鹥 ąĮą░ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╣ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ.

[ąÜą░čĆčéą░ ą┐ą░ą╝čÅčéąĖ]

ą¤ąŠą┤čĆąŠą▒ąĮčāčÄ čüčģąĄą╝čā ą║ą░čĆčéčŗ ą┐ą░ą╝čÅčéąĖ čüą╝. ą▓ čéą░ą▒ą╗ąĖčåąĄ, čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╣ ą▓ą░čłąĄą╝čā ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ąŠą╝čā MCU ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą╝čā čāčüčéčĆąŠą╣čüčéą▓čā. ąóą░ą▒ą╗ąĖčåą░ 1 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą│čĆą░ąĮąĖčåčŗ ą░ą┤čĆąĄčüąŠą▓ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓, ąĖą╝ąĄčÄčēąĖčģčüčÅ ą▓ąŠ ą▓čüąĄčģ MCU STM32F4xx.

ąóą░ą▒ą╗ąĖčåą░ 1. ą×ą▒ą╗ą░čüčéąĖ ą░ą┤čĆąĄčüąŠą▓ čĆąĄą│ąĖčüčéčĆąŠą▓ STM32F4xx.

| ąōčĆą░ąĮąĖčåčŗ ą░ą┤čĆąĄčüąŠą▓ |

ą¤ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ |

ą©ąĖąĮą░ |

ąÜą░čĆčéą░ čĆąĄą│ąĖčüčéčĆąŠą▓ (ą▓ ą┤ą░čéą░čłąĖč鹥 [1]) |

| 0xA0000000 - 0xA0000FFF |

FSMC control register (STM32F405xx/07xx ąĖ STM32F415xx/17xx) /

FMC control register (STM32F42xxx ąĖ STM32F43xxx) |

AHB3 |

"36.6.9: FSMC register map", čüčéčĆ. 1600

"37.8: FMC register map", čüčéčĆ. 1680 |

| 0x50060800 - 0x50060BFF |

RNG |

AHB2 |

"24.4.4: RNG register map", čüčéčĆ. 771 |

| 0x50060400 - 0x500607FF |

HASH |

"25.4.9: HASH register map", čüčéčĆ. 795 |

| 0x50060000 - 0x500603FF |

CRYP |

"23.6.13: CRYP register map", čüčéčĆ. 763 |

| 0x50050000 - 0x500503FF |

DCMI |

"15.8.12: DCMI register map", čüčéčĆ. 478 |

| 0x50000000 - 0x5003FFFF |

USB OTG FS |

"34.16.6: OTG_FS register map", čüčéčĆ. 1326 |

| 0x40040000 - 0x4007FFFF |

USB OTG HS |

AHB1 |

"5.12.6: OTG_HS register map", čüčéčĆ. 1472 |

| 0x4002B000 - 0x4002BBFF |

DMA2D |

"11.5: DMA2D registers", čüčéčĆ. 352 |

| 0x40028000 - 0x400293FF |

ETHERNET MAC |

"33.8.5: Ethernet register maps", čüčéčĆ. 1236 |

| 0x40026400 - 0x400267FF |

DMA2 |

"10.5.11: DMA register map", čüčéčĆ. 335 |

| 0x40026000 - 0x400263FF |

DMA1 |

| 0x40024000 - 0x40024FFF |

BKPSRAM |

|

| 0x40023C00 - 0x40023FFF |

ąĀąĄą│ąĖčüčéčĆčŗ ąĖąĮč鹥čĆč乥ą╣čüą░ Flash |

"3.9: Flash interface registers" |

| 0x40023800 - 0x40023BFF |

RCC |

"7.3.24: RCC register map", čüčéčĆ. 265 |

| 0x40023000 - 0x400233FF |

CRC |

"4.4.4: CRC register map", čüčéčĆ. 115 |

| 0x40022800 - 0x40022BFF |

GPIOK |

"8.4.11: GPIO register map", čüčéčĆ. 287 |

| 0x40022400 - 0x400227FF |

GPIOJ |

| 0x40022000 - 0x400223FF |

GPIOI |

"8.4.11: GPIO register map", čüčéčĆ. 287 |

| 0x40021C00 - 0x40021FFF |

GPIOH |

| 0x40021800 - 0x40021BFF |

GPIOG |

| 0x40021400 - 0x400217FF |

GPIOF |

| 0x40021000 - 0x400213FF |

GPIOE |

| 0x40020C00 - 0x40020FFF |

GPIOD |

| 0x40020800 - 0x40020BFF |

GPIOC |

| 0x40020400 - 0x400207FF |

GPIOB |

| 0x40020000 - 0x400203FF |

GPIOA |

| 0x40016800 - 0x40016BFF |

LCD-TFT |

APB2 |

"16.7.26: LTDC register map", čüčéčĆ. 512 |

| 0x40015800 - 0x40015BFF |

SAI1 |

"29.17.9: SAI register map", čüčéčĆ. 963 |

| 0x40015400 - 0x400157FF |

SPI6 |

"28.5.10: SPI register map", čüčéčĆ. 925 |

| 0x40015000 - 0x400153FF |

SPI5 |

| 0x40014800 - 0x40014BFF |

TIM11 |

"19.5.12: TIM10/11/13/14 register map", čüčéčĆ. 694 |

| 0x40014400 - 0x400147FF |

TIM10 |

| 0x40014000 - 0x400143FF |

TIM9 |

"19.4.13: TIM9/12 register map", čüčéčĆ. 684 |

| 0x40013C00 - 0x40013FFF |

EXTI |

"12.3.7: EXTI register map", čüčéčĆ. 387 |

| 0x40013800 - 0x40013BFF |

SYSCFG |

"9.2.8: SYSCFG register map" ą┤ą╗čÅ STM32F405xx/07xx ąĖ STM32F415xx/17xx čüčéčĆ. 294

"9.3.8: SYSCFG register map" ą┤ą╗čÅ STM32F42xxx ąĖ STM32F43xxx čüčéčĆ. 301 |

| 0x40013400 - 0x400137FF |

SPI4 |

"28.5.10: SPI register map", čüčéčĆ. 925 |

| 0x40013000 - 0x400133FF |

SPI1 |

| 0x40012C00 - 0x40012FFF |

SDIO |

"31.9.16: SDIO register map", čüčéčĆ. 1074 |

| 0x40012000 - 0x400123FF |

ADC1, ADC2, ADC3 |

"13.13.18: ADC register map", čüčéčĆ. 430 |

| 0x40011400 - 0x400117FF |

USART6 |

"30.6.8: USART register map", čüčéčĆ. 1018 |

| 0x40011000 - 0x400113FF |

USART1 |

| 0x40010400 - 0x400107FF |

TIM8 |

"17.4.21: TIM1 and TIM8 register map", čüčéčĆ. 587 |

| 0x40010000 - 0x400103FF |

TIM1 |

| 0x40007C00 - 0x40007FFF |

UART8 |

APB1 |

"30.6.8: USART register map", čüčéčĆ. 1018 |

| 0x40007800 - 0x40007BFF |

UART7 |

| 0x40007400 - 0x400077FF |

DAC |

"14.5.15: DAC register map", čüčéčĆ. 453 |

| 0x40007000 - 0x400073FF |

PWR |

"5.6: PWR register map", čüčéčĆ. 149 |

| 0x40006800 - 0x40006BFF |

CAN2 |

"32.9.5: bxCAN register map", čüčéčĆ. 1118 |

| 0x40006400 - 0x400067FF |

CAN1 |

| 0x40005C00 - 0x40005FFF |

I2C3 |

"27.6.11: I2C register map", čüčéčĆ. 872 |

| 0x40005800 - 0x40005BFF |

I2C2 |

| 0x40005400 - 0x400057FF |

I2C1 |

| 0x40005000 - 0x400053FF |

UART5 |

"30.6.8: USART register map", čüčéčĆ. 1018 |

| 0x40004C00 - 0x40004FFF |

UART4 |

| 0x40004800 - 0x40004BFF |

USART3 |

| 0x40004400 - 0x400047FF |

USART2 |

| 0x40004000 - 0x400043FF |

I2S3ext |

"28.5.10: SPI register map", čüčéčĆ. 925 |

| 0x40003C00 - 0x40003FFF |

SPI3 / I2S3 |

| 0x40003800 - 0x40003BFF |

SPI2 / I2S2 |

| 0x40003400 - 0x400037FF |

I2S2ext |

| 0x40003000 - 0x400033FF |

IWDG |

"21.4.5: IWDG register map", čüčéčĆ. 712 |

| 0x40002C00 - 0x40002FFF |

WWDG |

"22.6.4: WWDG register map", čüčéčĆ. 719 |

| 0x40002800 - 0x40002BFF |

ąĀąĄą│ąĖčüčéčĆčŗ RTC ąĖ BKP |

"26.6.21: RTC register map", čüčéčĆ. 836 |

| 0x40002000 - 0x400023FF |

TIM14 |

"19.5.12: TIM10/11/13/14 register map", čüčéčĆ. 694 |

| 0x40001C00 - 0x40001FFF |

TIM13 |

| 0x40001800 - 0x40001BFF |

TIM12 |

"19.4.13: TIM9/12 register map", čüčéčĆ. 684 |

| 0x40001400 - 0x400017FF |

TIM7 |

"20.4.9: TIM6 and TIM7 register map", čüčéčĆ. 707 |

| 0x40001000 - 0x400013FF |

TIM6 |

| 0x40000C00 - 0x40000FFF |

TIM5 |

"18.4.21: TIMx register map", čüčéčĆ. 648 |

| 0x40000800 - 0x40000BFF |

TIM4 |

| 0x40000400 - 0x400007FF |

TIM3 |

| 0x40000000 - 0x400003FF |

TIM2 |

ąÆčüčéčĆąŠąĄąĮąĮą░čÅ SRAM. ąÆ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░čģ STM32F405xx/07xx ąĖ STM32F415xx/17xx ąĖą╝ąĄąĄčéčüčÅ 4 ą║ąĖą╗ąŠą▒ą░ą╣čéą░ Backup SRAM ąĖ 192 ą║ąĖą╗ąŠą▒ą░ą╣čéą░ čüąĖčüč鹥ą╝ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ SRAM. ąÆ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░čģ STM32F42xxx ąĖ STM32F43xxx ąĖą╝ąĄąĄčéčüčÅ 4 ą║ąĖą╗ąŠą▒ą░ą╣čéą░ Backup SRAM ąĖ 192 ą║ąĖą╗ąŠą▒ą░ą╣čéą░ čüąĖčüč鹥ą╝ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ SRAM. ą×ą┐ąĖčüą░ąĮąĖąĄ Backup SRAM čüą╝. ą▓ čüąĄą║čåąĖąĖ "5.1.2: Battery backup domain" ą┤ą░čéą░čłąĖčéą░ [1].

ąÜ ą▓čüčéčĆąŠąĄąĮąĮąŠą╣ SRAM ą╝ąŠąČąĮąŠ ąŠą▒čĆą░čēą░čéčīčüčÅ ą║ą░ą║ ą║ ą▒ą░ą╣čéą░ą╝, ą┐ąŠą╗ąŠą▓ąĖąĮą║ą░ą╝ čüą╗ąŠą▓ (16 ą▒ąĖčé) ąĖą╗ąĖ ą║ ą┐ąŠą╗ąĮčŗą╝ čüą╗ąŠą▓ą░ą╝ (32 ą▒ąĖčéą░). ą×ą┐ąĄčĆą░čåąĖąĖ čćč鹥ąĮąĖčÅ ąĖ ąĘą░ą┐ąĖčüąĖ ą▓čŗą┐ąŠą╗ąĮčÅčÄčéčüčÅ ąĮą░ ą┐ąŠą╗ąĮąŠą╣ čüą║ąŠčĆąŠčüčéąĖ CPU ą▒ąĄąĘ čåąĖą║ą╗ąŠą▓ ąĘą░ą┤ąĄčƹȹĄą║ ąĮą░ ąŠąČąĖą┤ą░ąĮąĖąĄ (0 wait state). ąÆčüčéčĆąŠąĄąĮąĮą░čÅ SRAM ą┐ąŠą┤ąĄą╗ąĄąĮą░ ąĮą░ 3 ą▒ą╗ąŠą║ą░:

ŌĆó SRAM1 ąĖ SRAM2, ąŠč鹊ą▒čĆą░ąČąĄąĮąĮą░čÅ ąĮą░ ą░ą┤čĆąĄčü 0x20000000, ąĖ ą┤ąŠčüčéčāą┐ąĮą░čÅ ą┤ą╗čÅ ą▓čüąĄčģ ą╝ą░čüč鹥čĆąŠą▓ AHB.

ŌĆó SRAM3 (ąĖą╝ąĄąĄčéčüčÅ čā STM32F42xxx ąĖ STM32F43xxx), ąŠč鹊ą▒čĆą░ąČąĄąĮąĮą░čÅ ąĮą░ ą░ą┤čĆąĄčü 0x20020000, ąĖ ą┤ąŠčüčéčāą┐ąĮą░čÅ ą┤ą╗čÅ ą▓čüąĄčģ ą╝ą░čüč鹥čĆąŠą▓ AHB.

ŌĆó CCM (Core Coupled Memory), ąŠč鹊ą▒čĆą░ąČąĄąĮąĮą░čÅ ąĮą░ ą░ą┤čĆąĄčü 0x10000000, ąĖ ą┤ąŠčüčéčāą┐ąĮą░čÅ ą┤ą╗čÅ CPU č湥čĆąĄąĘ D-bus.

ą£ą░čüč鹥čĆą░ AHB ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé ą║ąŠąĮą║čāčĆąĄąĮčéąĮčŗąĄ ą┐ąŠą┐čŗčéą║ąĖ ą┤ąŠčüčéčāą┐ą░ ą║ SRAM (ąŠčé Ethernet ąĖą╗ąĖ USB OTG HS): ąĮą░ą┐čĆąĖą╝ąĄčĆ, Ethernet MAC ą╝ąŠąČąĄčé čćąĖčéą░čéčī/ąĘą░ą┐ąĖčüčŗą▓ą░čéčī SRAM2, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ CPU čćąĖčéą░ąĄčé/ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčé SRAM1 ąĖą╗ąĖ SRAM3.

CPU ą╝ąŠąČąĄčé ąŠą▒čĆą░čēą░čéčīčüčÅ ą║ SRAM1, SRAM2 ąĖ SRAM3 č湥čĆąĄąĘ čüąĖčüč鹥ą╝ąĮčāčÄ čłąĖąĮčā (System Bus) ąĖą╗ąĖ č湥čĆąĄąĘ čłąĖąĮčŗ I-Code/D-Code, ą║ąŠą│ą┤ą░ ą▓čŗą▒čĆą░ąĮą░ ąĘą░ą│čĆčāąĘą║ą░ (boot) ąĖąĘ SRAM, ąĖą╗ąĖ ą║ąŠą│ą┤ą░ ą▓čŗą▒čĆą░ąĮąŠ čäąĖąĘąĖč湥čüą║ąŠąĄ ą┐ąĄčĆąĄąĮą░ąĘąĮą░č湥ąĮąĖąĄ ą║ą░čĆčéčŗ ą┐ą░ą╝čÅčéąĖ (physical remap, čüą╝. čüąĄą║čåąĖčÄ "9.2.1: SYSCFG memory remap register (SYSCFG_MEMRMP)" ąŠą┐ąĖčüą░ąĮąĖčÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ SYSCFG ą┤ą░čéą░čłąĖčéą░ [1]). ą¦č鹊ą▒čŗ ą┐ąŠą╗čāčćąĖčéčī ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮčāčÄ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą║ąŠą┤ą░ ąĖąĘ SRAM, ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮąŠ physical remap (ą▓čŗą▒ąŠčĆ ą║ąŠą┤ą░ boot ąĖą╗ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ).

ą¤ą░ą╝čÅčéčī Flash. ąśąĮč鹥čĆč乥ą╣čü ą┐ą░ą╝čÅčéąĖ Flash ąŠą▒čüą╗čāąČąĖą▓ą░ąĄčé ą┤ąŠčüčéčāą┐ čłąĖąĮ CPU AHB I-Code ąĖ D-Code ą║ ą┐ą░ą╝čÅčéąĖ Flash. ą×ąĮ čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮ ą┤ą╗čÅ ąŠą┐ąĄčĆą░čåąĖą╣ čüčéąĖčĆą░ąĮąĖčÅ ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐ą░ą╝čÅčéąĖ Flash, ąĖ ą┤ą╗čÅ ą╝ąĄčģą░ąĮąĖąĘą╝ąŠą▓ ąĘą░čēąĖčéčŗ ąŠčé čćč鹥ąĮąĖčÅ ąĖ ąĘą░ą┐ąĖčüąĖ. ąśąĮč鹥čĆč乥ą╣čü čāčüą║ąŠčĆčÅąĄčé ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ąŠą┤ą░ čü ą┐ąŠą╝ąŠčēčīčÄ ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮąŠą╣ ą▓čŗą▒ąŠčĆą║ąĖ ąĖąĮčüčéčĆčāą║čåąĖąĖ ąĖ ą╗ąĖąĮąĄąĄą║ ą║ąĄčłą░.

ą¤ą░ą╝čÅčéčī Flash ąŠčĆą│ą░ąĮąĖąĘąŠą▓ą░ąĮą░ čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝:

ŌĆó ą×čüąĮąŠą▓ąĮąŠą╣ ą▒ą╗ąŠą║ ą┐ą░ą╝čÅčéąĖ ą┐ąŠą┤ąĄą╗ąĄąĮ ąĮą░ čüąĄą║č鹊čĆčŗ.

ŌĆó ąĪąĖčüč鹥ą╝ąĮą░čÅ ą┐ą░ą╝čÅčéčī, ąĖąĘ ą║ąŠč鹊čĆąŠą╣ ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ čüąĖčüč鹥ą╝ą░ ą▓ čĆąĄąČąĖą╝ąĄ ąĘą░ą│čĆčāąĘą║ąĖ System memory boot mode.

ŌĆó 512 ą▒ą░ą╣čé OTP (ąŠą┤ąĮąŠą║čĆą░čéąĮąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝ą░čÅ ą┐ą░ą╝čÅčéčī) ą┤ą╗čÅ ą┤ą░ąĮąĮčŗčģ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╣.

ŌĆó ąæą░ą╣čéčŗ ąŠą┐čåąĖą╣, ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮąĮčŗąĄ ą┤ą╗čÅ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ąĘą░čēąĖčéčŗ čćč鹥ąĮąĖčÅ ąĖ ąĘą░ą┐ąĖčüąĖ, čāčĆąŠą▓ąĮčÅ ą┤ąĄč鹥ą║č鹊čĆą░ ą┐čĆąŠą┐ą░ą┤ą░ąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ ą┤ą╗čÅ čüą▒čĆąŠčüą░ (BOR), ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ/ą░ą┐ą┐ą░čĆą░čéąĮąŠą│ąŠ čüč鹊čĆąŠąČąĄą▓ąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░ ąĖ čüą▒čĆąŠčüą░, ą║ąŠą│ą┤ą░ MCU ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ Standby ąĖą╗ąĖ Stop.

ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. čüąĄą║čåąĖčÄ "3: Embedded Flash memory interface" ą▓ ą┤ą░čéą░čłąĖč鹥 [1].

ąæąĖč鹊ą▓čŗąĄ ąŠą┐ąĄčĆą░čåąĖąĖ (bit banding). ąÜą░čĆčéą░ ą┐ą░ą╝čÅčéąĖ Cortex┬«-M4 čü FPU ą▓ą║ą╗čÄčćą░ąĄčé ą┤ą▓ąĄ ą│čĆčāą┐ą┐čŗ ą▒ąĖčé (bit-band). ąŁčéąĖ čĆąĄą│ąĖąŠąĮčŗ ąŠč鹊ą▒čĆą░ąČą░čÄčé ą║ą░ąČą┤ąŠąĄ čüą╗ąŠą▓ąŠ čüčüčŗą╗ąŠčćąĮąŠą│ąŠ čĆąĄą│ąĖąŠąĮą░ ą┐ą░ą╝čÅčéąĖ ąĮą░ ą▒ąĖčé ą▓ ą│čĆčāą┐ą┐ąĄ (bit-band) ą┐ą░ą╝čÅčéąĖ. ąŚą░ą┐ąĖčüčī čüą╗ąŠą▓ą░ čüčüčŗą╗ąŠčćąĮąŠą│ąŠ čĆąĄą│ąĖąŠąĮą░ ą┤ą░ąĄčé č鹊čé ąČąĄ čŹčäč乥ą║čé, čćč鹊 ąĖ ąŠą┐ąĄčĆą░čåąĖčÅ read-modify-write (čćč鹥ąĮąĖąĄ-ą╝ąŠą┤ąĖčäąĖą║ą░čåąĖčÅ-ąĘą░ą┐ąĖčüčī) čåąĄą╗ąĄą▓ąŠą│ąŠ ą▒ąĖčéą░ ą│čĆčāą┐ą┐čŗ bit-band.

ąÆ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░čģ STM32F4xx ą║ą░ą║ čĆąĄą│ąĖčüčéčĆčŗ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓, čéą░ą║ ąĖ SRAM, ąŠč鹊ą▒čĆą░ąČąĄąĮčŗ ąĮą░ ąŠą▒ą╗ą░čüčéčī bitband, ą┐ąŠčŹč鹊ą╝čā ą┤ąŠąĘą▓ąŠą╗čÅčÄčéčüčÅ ąŠą┤ąĖąĮąŠčćąĮčŗąĄ ąŠą┐ąĄčĆą░čåąĖąĖ bit-band ąĘą░ą┐ąĖčüąĖ ąĖ čćč鹥ąĮąĖčÅ. ąŁčéąĖ ąŠą┐ąĄčĆą░čåąĖąĖ ą┤ąŠčüčéčāą┐ąĮčŗ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ Cortex┬«-M4 čü FPU, ąĮąŠ ąĮąĄ ąŠčé ą┤čĆčāą│ąĖčģ ą╝ą░čüč鹥čĆąŠą▓ čłąĖąĮčŗ (ąĮą░ą┐čĆąĖą╝ąĄčĆ DMA).

ążąŠčĆą╝čāą╗ą░ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖčÅ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, ą║ą░ą║ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ čüčüčŗą╗ą║ą░ ąĮą░ ą║ą░ąČą┤ąŠąĄ čüą╗ąŠą▓ąŠ ą▓ ą░ą╗ąĖą░čü-čĆąĄą│ąĖąŠąĮąĄ ąĮą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé ą│čĆčāą┐ą┐čŗ ą▓ čĆąĄą│ąĖąŠąĮąĄ bit-band:

bit_word_addr = bit_band_base + (byte_offset x 32) + (bit_number x 4)

ąĘą┤ąĄčüčī:

bit_word_addr - ą░ą┤čĆąĄčü čüą╗ąŠą▓ą░ ą▓ ą░ą╗ąĖą░čü-čĆąĄą│ąĖąŠąĮąĄ ą┐ą░ą╝čÅčéąĖ, ą║ąŠč鹊čĆą░čÅ ąŠč鹊ą▒čĆą░ąČą░ąĄčéčüčÅ ąĮą░ čåąĄą╗ąĄą▓ąŠą╣ ą▒ąĖčé.

bit_band_base - ąĮą░čćą░ą╗čīąĮčŗą╣ ą░ą┤čĆąĄčü ą░ą╗ąĖą░čü-čĆąĄą│ąĖąŠąĮą░.

byte_offset - ąĮąŠą╝ąĄčĆ ą▒ą░ą╣čéą░ ą▓ čĆąĄą│ąĖąŠąĮąĄ bit-band, ą║ąŠč鹊čĆčŗą╣ čüąŠą┤ąĄčƹȹĖčé čåąĄą╗ąĄą▓ąŠą╣ ą▒ąĖčé.

bit_number - ą┐ąŠąĘąĖčåąĖčÅ (0 .. 7) čåąĄą╗ąĄą▓ąŠą│ąŠ ą▒ąĖčéą░.

ąĪą╗ąĄą┤čāčÄčēąĖą╣ ą┐čĆąĖą╝ąĄčĆ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, ą║ą░ą║ ąŠč鹊ą▒čĆą░ąČą░ąĄčéčüčÅ ą▒ąĖčé 2 ą▒ą░ą╣čéą░, ąĮą░čģąŠą┤čÅčēąĄą│ąŠčüčÅ ą▓ SRAM ą┐ąŠ ą░ą┤čĆąĄčüčā 0x20000300, ąĮą░ ą░ą╗ąĖą░čü-čĆąĄą│ąĖąŠąĮ:

0x22006008 = 0x22000000 + (0x300*32) + (2*4)

ąŚą░ą┐ąĖčüčī ą┐ąŠ ą░ą┤čĆąĄčüčā 0x22006008 ą┤ą░ąĄčé č鹊čé ąČąĄ čŹčäč乥ą║čé, čćč鹊 ąĖ ąŠą┐ąĄčĆą░čåąĖčÅ read-modify-write ą▒ąĖčéą░ 2 ą▒ą░ą╣čéą░ SRAM ą┐ąŠ ą░ą┤čĆąĄčüčā 0x20000300.

ą¦č鹥ąĮąĖąĄ ą░ą┤čĆąĄčüą░ 0x22006008 ą▓ąŠąĘą▓čĆą░čéąĖčé ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčéą░ 2 (0x01 ąĖą╗ąĖ 0x00) ą▒ą░ą╣čéą░ ą┐ąŠ ą░ą┤čĆąĄčüčā 0x20000300 (0x01 ą▒ąĖčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, 0x00 ą▒ąĖčé čüą▒čĆąŠčłąĄąĮ).

ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ ą┐čĆąŠ bit-banding čüą╝. čĆčāą║ąŠą▓ąŠą┤čüčéą▓ąŠ ą┐ąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÄ PM0214 [3].

[ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ąĘą░ą│čĆčāąĘą║ąĖ]

ąśąĘ-ąĘą░ čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮąŠą╣ ą║ą░čĆčéčŗ ą┐ą░ą╝čÅčéąĖ ąŠą▒ą╗ą░čüčéčī ą║ąŠą┤ą░ (ą┐čĆąŠą│čĆą░ą╝ą╝ą░) ąĮą░čćąĖąĮą░ąĄčéčüčÅ čü ą░ą┤čĆąĄčüą░ 0x00000000 (čŹčéą░ ąŠą▒ą╗ą░čüčéčī ą┐ą░ą╝čÅčéąĖ ą┤ąŠčüčéčāą┐ąĮą░ č湥čĆąĄąĘ čłąĖąĮčŗ ICode/DCode), ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ ąŠą▒ą╗ą░čüčéčī ą┤ą░ąĮąĮčŗčģ (SRAM) ąĮą░čćąĖąĮą░ąĄčéčüčÅ čü ą░ą┤čĆąĄčüą░ 0x20000000 (čŹčéą░ ąŠą▒ą╗ą░čüčéčī ą┤ąŠčüčéčāą┐ąĮą░ č湥čĆąĄąĘ čüąĖčüč鹥ą╝ąĮčāčÄ čłąĖąĮčā). CPU Cortex┬«-M4 ą▓čüąĄą│ą┤ą░ ą┤ąĄą╗ą░ąĄčé ą▓čŗą▒ąŠčĆą║čā ąĖąĮčüčéčĆčāą║čåąĖąĖ ą┐ąŠ ą▓ąĄą║č鹊čĆčā čüą▒čĆąŠčüą░ ąĮą░ čłąĖąĮąĄ ICode. ąŁč鹊 ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčé, čćč鹊 ąŠą▒ą╗ą░čüčéčī ąĘą░ą│čĆčāąĘą║ąĖ ą┤ąŠčüčéčāą┐ąĮą░ č鹊ą╗čīą║ąŠ ą▓ ąŠą▒ą╗ą░čüčéąĖ ą║ąŠą┤ą░ (ąŠą▒čŗčćąĮąŠ ą┐ą░ą╝čÅčéčī Flash). ą£ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčŗ STM32F4xx čĆąĄą░ą╗ąĖąĘčāčÄčé čüą┐ąĄčåąĖą░ą╗čīąĮčŗą╣ ą╝ąĄčģą░ąĮąĖąĘą╝, ą┐ąŠąĘą▓ąŠą╗čÅčÄčēąĖą╣ ąĘą░ą│čĆčāąĘąĖčéčīčüčÅ ąĖąĘ ą┤čĆčāą│ąĖčģ ąŠą▒ą╗ą░čüč鹥ą╣ ą┐ą░ą╝čÅčéąĖ (ąĮą░ą┐ąŠą┤ąŠą▒ąĖąĄ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ SRAM).

ąÆ STM32F4xx ąĄčüčéčī 3 čĆą░ąĘąĮčŗčģ čĆąĄąČąĖą╝ą░ ąĘą░ą│čĆčāąĘą║ąĖ, ą▓čŗą▒ąĖčĆą░ąĄą╝čŗąĄ ąĮąŠąČą║ą░ą╝ąĖ ą║ąŠčĆą┐čāčüą░ BOOT[1:0], čćč鹊 ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▓ čéą░ą▒ą╗ąĖčåąĄ 2.

ąóą░ą▒ą╗ąĖčåą░ 2. ąĀąĄąČąĖą╝čŗ ąĘą░ą│čĆčāąĘą║ąĖ.

| ąÆčŗą▓ąŠą┤čŗ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą░ čĆąĄąČąĖą╝ą░ ąĘą░ą│čĆčāąĘą║ąĖ |

ąĀąĄąČąĖą╝ ąĘą░ą│čĆčāąĘą║ąĖ

|

ąØą░ čćč鹊 ą┐čĆąŠąĖčüčģąŠą┤ąĖčé čüčüčŗą╗ą║ą░

|

| BOOT1 |

BOOT0 |

| x |

0 |

ą×čüąĮąŠą▓ąĮą░čÅ ą┐ą░ą╝čÅčéčī Flash |

ąÆ ą║ą░č湥čüčéą▓ąĄ ąŠą▒ą╗ą░čüčéąĖ ąĘą░ą│čĆčāąĘą║ąĖ ą▓čŗą▒čĆą░ąĮą░ ąŠčüąĮąŠą▓ąĮą░čÅ ą┐ą░ą╝čÅčéčī Flash. |

| 0 |

1 |

ąĪąĖčüč鹥ą╝ąĮą░čÅ ą┐ą░ą╝čÅčéčī |

ąÆ ą║ą░č湥čüčéą▓ąĄ ąŠą▒ą╗ą░čüčéąĖ ąĘą░ą│čĆčāąĘą║ąĖ ą▓čŗą▒čĆą░ąĮą░ System Memory. |

| 1 |

1 |

ąÆčüčéčĆąŠąĄąĮąĮą░čÅ SRAM |

ąÆ ą║ą░č湥čüčéą▓ąĄ ąŠą▒ą╗ą░čüčéąĖ ąĘą░ą│čĆčāąĘą║ąĖ ą▓čŗą▒čĆą░ąĮą░ ą▓čüčéčĆąŠąĄąĮąĮą░čÅ SRAM. |

ąŚąĮą░č湥ąĮąĖčÅ ąĮą░ ą▓čŗą▓ąŠą┤ą░čģ BOOTx ąĘą░čēąĄą╗ą║ąĖą▓ą░čÄčéčüčÅ ąĮą░ 4-ąŠą╝ čäčĆąŠąĮč鹥 ąĮą░čĆą░čüčéą░ąĮąĖčÅ čāčĆąŠą▓ąĮčÅ čéą░ą║č鹊ą▓ SYSCLK ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░. ą¤ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą┤ąŠą╗ąČąĄąĮ čāčüčéą░ąĮąŠą▓ąĖčéčī ą╗ąŠą│ąĖč湥čüą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī ąĮąŠąČąĄą║ ą║ąŠčĆą┐čāčüą░ BOOT1 ąĖ BOOT0, čćč鹊ą▒čŗ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ ą▒čŗą╗ ą▓čŗą▒čĆą░ąĮ ąĮąĄąŠą▒čģąŠą┤ąĖą╝čŗą╣ čĆąĄąČąĖą╝ ąĘą░ą│čĆčāąĘą║ąĖ.

ąöą╗čÅ čäčāąĮą║čåąĖąĖ BOOT0 ą▓čŗą┤ąĄą╗ąĄąĮą░ čüą┐ąĄčåąĖą░ą╗čīąĮą░čÅ ąĮąŠąČą║ą░ ą║ąŠčĆą┐čāčüą░, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ čäčāąĮą║čåąĖčÅ BOOT1 čüąŠą▓ą╝ąĄčēąĄąĮą░ čü ąĮąŠąČą║ąŠą╣ ą┐ąŠčĆčéą░ GPIO. ąÜą░ą║ č鹊ą╗čīą║ąŠ čāčĆąŠą▓ąĄąĮčī BOOT1 ą▒čŗą╗ ą┐čĆąŠčćąĖčéą░ąĮ, čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēą░čÅ ąĮąŠąČą║ą░ GPIO ąŠčüą▓ąŠą▒ąŠąČą┤ą░ąĄčéčüčÅ, ąĖ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą┤čĆčāą│ąĖčģ čåąĄą╗ąĄą╣.

ąŻčĆąŠą▓ąĮąĖ ąĮą░ ąĮąŠąČą║ą░čģ BOOT čéą░ą║ąČąĄ ą░ąĮą░ą╗ąĖąĘąĖčĆčāčÄčéčüčÅ, ą║ąŠą│ą┤ą░ MCU ą▓čŗčģąŠą┤ąĖčé ąĖąĘ čĆąĄąČąĖą╝ą░ Standby. ąĪą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ, ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ čüąŠčģčĆą░ąĮąĖčéčī čéčĆąĄą▒čāąĄą╝čāčÄ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÄ čĆąĄąČąĖą╝ą░ ąĘą░ą│čĆčāąĘą║ąĖ, ą║ąŠą│ą┤ą░ MCU ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ Standby. ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ąĘą░ą┤ąĄčƹȹ║ą░ startup ąĘą░ą║ąŠąĮčćąĖčéčüčÅ, CPU ą┤ąĄą╗ą░ąĄčé ą▓čŗą▒ąŠčĆą║čā ąĘąĮą░č湥ąĮąĖąĄ ą▓ąĄčĆčłąĖąĮčŗ čüč鹥ą║ą░ ą┐ąŠ ą░ą┤čĆąĄčüčā 0x00000000, ąĖ ąĘą░č鹥ą╝ ąĮą░čćąĖąĮą░ąĄčé ą▓čŗą┐ąŠą╗ąĮčÅčéčī ą║ąŠą┤ ąĖąĘ ą┐ą░ą╝čÅčéąĖ ąĘą░ą│čĆčāąĘą║ąĖ (boot memory), ąĮą░čćąĖąĮą░čÅ čü 0x00000004.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą║ąŠą│ą┤ą░ MCU ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ąĖąĘ SRAM, ą▓ ą║ąŠą┤ąĄ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ą┐ąĄčĆąĄčĆą░ąĘą╝ąĄčüčéąĖčéčī čéą░ą▒ą╗ąĖčåčā ą▓ąĄą║č鹊čĆąŠą▓ ą▓ SRAM, ąĖčüą┐ąŠą╗čīąĘčāčÅ čéą░ą▒ą╗ąĖčåčā ąĖčüą║ą╗čÄč湥ąĮąĖą╣ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ (NVIC exception table) ąĖ čĆąĄą│ąĖčüčéčĆ čüą╝ąĄčēąĄąĮąĖčÅ.

ąÆ čüą╗čāčćą░ąĄ, ą║ąŠą│ą┤ą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčŗ STM32F42xxx ąĖ STM32F43xxx ąĘą░ą│čĆčāąČą░čÄčéčüčÅ ąĖąĘ ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ Flash, ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ą╝ąŠąČąĄčé ąĘą░ą│čĆčāąĘąĖčéčīčüčÅ ą╗ąĖą▒ąŠ ąĖąĘ ą▒ą░ąĮą║ą░ 1, ą╗ąĖą▒ąŠ ąĖąĘ ą▒ą░ąĮą║ą░ 2. ą¤ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą▓čŗą▒čĆą░ąĮ ą▒ą░ąĮą║ 1.

ąöą╗čÅ ą▓čŗą▒ąŠčĆą░ ąĘą░ą│čĆčāąĘą║ąĖ ąĖąĘ ą▒ą░ąĮą║ą░ 2 ą┐ą░ą╝čÅčéąĖ Flash čāčüčéą░ąĮąŠą▓ąĖč鹥 ą▒ąĖčé BFB2 ą▓ ą▒ą░ą╣čéą░čģ ąŠą┐čåąĖą╣ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ. ąÜąŠą│ą┤ą░ čŹč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ąĖ ąĮąŠąČą║ąĖ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĘą░ą│čĆčāąĘą║ąŠą╣ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ąĮą░ ąĘą░ą│čĆčāąĘą║čā ąĖąĘ ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ Flash, čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ąĖąĘ čüąĖčüč鹥ą╝ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ, ąĖ ąĘą░ą│čĆčāąĘčćąĖą║ ą┤ąĄą╗ą░ąĄčé ą▒ąĄąĘčāčüą╗ąŠą▓ąĮčŗą╣ ą┐ąĄčĆąĄčģąŠą┤ ąĮą░ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ, ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ ą▓ ą▒ą░ąĮą║ąĄ 2 ą┐ą░ą╝čÅčéąĖ Flash. ąöą╗čÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ čüą╝. ą░ą┐ąĮąŠčāčé AN2606 (ą┤ą╗čÅ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ STM32F42xxx ąĖ STM32F43xxx čüą╝. čüčéą░čéčīčÄ [4]).

ąÆčüčéčĆąŠąĄąĮąĮčŗą╣ ąĘą░ą│čĆčāąĘčćąĖą║. ąĀąĄąČąĖą╝ ą▓čüčéčĆąŠąĄąĮąĮąŠą│ąŠ ąĘą░ą│čĆčāąĘčćąĖą║ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą┐ąĄčĆąĄą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐ą░ą╝čÅčéąĖ Flash, ąĖčüą┐ąŠą╗čīąĘčāčÅ ąŠą┤ąĖąĮ ąĖąĘ čüą╗ąĄą┤čāčÄčēąĖčģ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ąĖąĮč鹥čĆč乥ą╣čüąŠą▓:

ŌĆó USART1 (ąĮąŠąČą║ąĖ ą┐ąŠčĆč鹊ą▓ PA9/PA10)

ŌĆó USART3 (ąĮąŠąČą║ąĖ ą┐ąŠčĆč鹊ą▓ PB10/PB11 ąĖ PC10/PC11)

ŌĆó CAN2 (ąĮąŠąČą║ąĖ ą┐ąŠč鹊ą▓ PB5 ąĖ PB13)

ŌĆó USB OTG FS (ąĮąŠąČą║ąĖ ą┐ąŠčĆč鹊ą▓ PA11/PA12) ą▓ čĆąĄąČąĖą╝ąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ USB (čŹč鹊čé ąĖąĮč鹥čĆč乥ą╣čü ąŠą▒ąŠąĘąĮą░čćą░ąĄčéčüčÅ ą░ą▒ą▒čĆąĄą▓ąĖą░čéčāčĆąŠą╣ DFU: device firmware upgrade, ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ ą¤ą× čāčüčéčĆąŠą╣čüčéą▓ą░).

ą¤ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ USART čĆą░ą▒ąŠčéą░čÄčé ąŠčé ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ ą▓čŗčüąŠą║ąŠčüą║ąŠčĆąŠčüčéąĮąŠą│ąŠ RC-ą│ąĄąĮąĄčĆą░č鹊čĆą░ 16 ą£ąōčå (HSI), ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ CAN ąĖ USB OTG FS čéčĆąĄą▒čāčÄčé ą▓ąĮąĄčłąĮąĄą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓ (ąŠą▒čŗčćąĮąŠ čŹč鹊 ą║ą▓ą░čĆčå, ą│ąĄąĮąĄčĆą░č鹊čĆ HSE) čü čćą░čüč鹊ą╣, ąĮą░čåąĄą╗ąŠ ą┤ąĄą╗čÅčēąĄą╣čüčÅ ąĮą░ 1 ą£ąōčå (ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąŠčé 4 ą┤ąŠ 26 ą£ąōčå).

ąÆčüčéčĆąŠąĄąĮąĮčŗą╣ ąĘą░ą│čĆčāąĘčćąĖą║ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čüąĖčüč鹥ą╝ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ, ąŠąĮ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ ą║ąŠą╝ą┐ą░ąĮąĖąĄą╣ ST ą▓ ą┐čĆąŠčåąĄčüčüąĄ ą┐čĆąŠąĖąĘą▓ąŠą┤čüčéą▓ą░. ąöą╗čÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ čüą╝. ą░ą┐ąĮąŠčāčé AN2606 (ą┤ą╗čÅ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ STM32F42xxx ąĖ STM32F43xxx čüą╝. čüčéą░čéčīčÄ [4]).

Physical remap STM32F405xx/07xx ąĖ STM32F415xx/17xx. ąÜą░ą║ č鹊ą╗čīą║ąŠ ą▓čŗą▒čĆą░ąĮąŠ čüąŠčüč鹊čÅąĮąĖąĄ ą▓čŗą▓ąŠą┤ąŠą▓ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĘą░ą│čĆčāąĘą║ąŠą╣, ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ą╝ąŠąČąĄčé ąĖąĘą╝ąĄąĮąĖčéčī ą┐ą░ą╝čÅčéčī, ą┤ąŠčüčéčāą┐ąĮčāčÄ ą▓ ąŠą▒ą╗ą░čüčéąĖ ą║ąŠą┤ą░ (čéą░ą║ąĖą╝ čüą┐ąŠčüąŠą▒ąŠą╝ ą║ąŠą┤ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮ č湥čĆąĄąĘ čłąĖąĮčā ICode ą▓ą╝ąĄčüč鹊 č鹊ą│ąŠ, čćč鹊ą▒čŗ ą▓čŗą┐ąŠą╗ąĮčÅčéčīčüčÅ č湥čĆąĄąĘ čüąĖčüč鹥ą╝ąĮčāčÄ čłąĖąĮčā). ąŁčéą░ ą╝ąŠą┤ąĖčäąĖą║ą░čåąĖčÅ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄą╝ čĆąĄą│ąĖčüčéčĆą░ ą┐ąĄčĆąĄąĮą░ąĘąĮą░č湥ąĮąĖčÅ ą┐ą░ą╝čÅčéąĖ (SYSCFG memory remap register, SYSCFG_MEMRMP) ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ SYSCFG, čüą╝. [1].

ą¤ąĄčĆąĄąĮą░ąĘąĮą░č湥ąĮąĖąĄ (remap) ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąĖą╝ąĄąĮąĄąĮąŠ ą║ čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒ą╗ą░čüčéčÅą╝ ą┐ą░ą╝čÅčéąĖ:

ŌĆó ą×čüąĮąŠą▓ąĮą░čÅ ą┐ą░ą╝čÅčéčī Flash

ŌĆó ąĪąĖčüč鹥ą╝ąĮą░čÅ ą┐ą░ą╝čÅčéčī

ŌĆó ąÆčüčéčĆąŠąĄąĮąĮą░čÅ SRAM1 (112 ą║ąĖą╗ąŠą▒ą░ą╣čé)

ŌĆó FSMC bank 1 (NOR/PSRAM 1 ąĖ 2)

ąóą░ą▒ą╗ąĖčåą░ 3. ą×č鹊ą▒čĆą░ąČąĄąĮąĖąĄ ą┐ą░ą╝čÅčéąĖ ą┐čĆąĖ Boot mode/physical remap ą┤ą╗čÅ STM32F405xx/07xx ąĖ STM32F415xx/17xx.

| ąÉą┤čĆąĄčüą░ |

Boot/Remap

ą▓ ąŠčüąĮąŠą▓ąĮčāčÄ Flash |

Boot/Remap

ą▓ąŠ ą▓čüčéčĆąŠąĄąĮąĮčāčÄ SRAM |

Boot/Remap

ą▓ System Memory |

Remap ą▓ FSMC |

| 0x2001C000 - 0x2001FFFF |

SRAM2 (16 KB) |

SRAM2 (16 KB) |

SRAM2 (16 KB) |

SRAM2 (16 KB) |

| 0x20000000 - 0x2001BFFF |

SRAM1 (112 KB) |

SRAM1 (112 KB) |

SRAM1 (112 KB) |

SRAM1 (112 KB) |

| 0x1FFF0000 - 0x1FFF77FF |

System Memory |

System Memory |

System Memory |

System Memory |

| 0x08100000 - 0x0FFFFFFF |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

| 0x08000000 - 0x080FFFFF |

ą¤ą░ą╝čÅčéčī Flash |

ą¤ą░ą╝čÅčéčī Flash |

ą¤ą░ą╝čÅčéčī Flash |

ą¤ą░ą╝čÅčéčī Flash |

| 0x04000000 - 0x07FFFFFF |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

| 0x00000000 - 0x000FFFFF(1)(2) |

ąĪčüčŗą╗ą║ą░ ąĮą░ Flash (1 MB) |

ąĪčüčŗą╗ą║ą░ ąĮą░ SRAM1 (112 KB) |

ąĪčüčŗą╗ą║ą░ ąĮą░ System

Memory (30 KB) |

ąĪčüčŗą╗ą║ą░ ąĮą░ FSMC bank 1 NOR

/PSRAM 1 (128 MB) |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

(1) ąÜąŠą│ą┤ą░ FSMC ą┐ąĄčĆąĄąĮą░ąĘąĮą░č湥ąĮ ąĮą░ ą░ą┤čĆąĄčü 0x00000000, ą╝ąŠą│čāčé ą▒čŗčéčī ą┐ąĄčĆąĄąĮą░ąĘąĮą░č湥ąĮčŗ č鹊ą╗čīą║ąŠ ą┐ąĄčĆą▓čŗąĄ 2 čĆąĄą│ąĖąŠąĮą░ ą▒ą░ąĮą║ą░ 1 ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą┐ą░ą╝čÅčéąĖ (bank 1 NOR/PSRAM 1 ąĖ NOR/PSRAM 2). ąÆ čĆąĄąČąĖą╝ąĄ ą┐ąĄčĆąĄąĮą░ąĘąĮą░č湥ąĮąĖčÅ (remap mode), CPU ą╝ąŠąČąĄčé ą┐ąŠą╗čāčćąĖčéčī ą┤ąŠčüčéčāą┐ ą║ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ č湥čĆąĄąĘ čłąĖąĮčā ICode ą▓ą╝ąĄčüč鹊 čüąĖčüč鹥ą╝ąĮąŠą╣ čłąĖąĮčŗ, čćč鹊 čāą╗čāčćčłą░ąĄčé ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéčī.

(2) ąöą░ąČąĄ ą║ąŠą│ą┤ą░ ą┐ą░ą╝čÅčéčī čüčüčŗą╗ąŠčćąĮąŠ ąŠč鹊ą▒čĆą░ąČąĄąĮą░ ąĮą░ ąŠą▒ą╗ą░čüčéčī ąĘą░ą│čĆčāąĘą║ąĖ (boot memory space), čŹčéą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēą░čÅ ą┐ą░ą╝čÅčéčī ą▓čüąĄ ąĄčēąĄ ą┤ąŠčüčéčāą┐ąĮą░ ą┐ąŠ čüą▓ąŠąĖą╝ ąŠčĆąĖą│ąĖąĮą░ą╗čīąĮčŗą╝ ą░ą┤čĆąĄčüą░ą╝ ąĮą░ ą║ą░čĆč鹥 ą┐ą░ą╝čÅčéąĖ.

Physical remap STM32F42xxx ąĖ STM32F43xxx. ąÜą░ą║ č鹊ą╗čīą║ąŠ ą▓čŗą▒čĆą░ąĮąŠ čüąŠčüč鹊čÅąĮąĖąĄ ą▓čŗą▓ąŠą┤ąŠą▓ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĘą░ą│čĆčāąĘą║ąŠą╣, ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ą╝ąŠąČąĄčé ąĖąĘą╝ąĄąĮąĖčéčī ą┐ą░ą╝čÅčéčī, ą┤ąŠčüčéčāą┐ąĮčāčÄ ą▓ ąŠą▒ą╗ą░čüčéąĖ ą║ąŠą┤ą░ (čéą░ą║ąĖą╝ čüą┐ąŠčüąŠą▒ąŠą╝ ą║ąŠą┤ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮ č湥čĆąĄąĘ čłąĖąĮčā ICode ą▓ą╝ąĄčüč鹊 č鹊ą│ąŠ, čćč鹊ą▒čŗ ą▓čŗą┐ąŠą╗ąĮčÅčéčīčüčÅ č湥čĆąĄąĘ čüąĖčüč鹥ą╝ąĮčāčÄ čłąĖąĮčā). ąŁčéą░ ą╝ąŠą┤ąĖčäąĖą║ą░čåąĖčÅ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄą╝ čĆąĄą│ąĖčüčéčĆą░ ą┐ąĄčĆąĄąĮą░ąĘąĮą░č湥ąĮąĖčÅ ą┐ą░ą╝čÅčéąĖ (SYSCFG memory remap register, SYSCFG_MEMRMP) ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ SYSCFG, čüą╝. [1].

ą¤ąĄčĆąĄąĮą░ąĘąĮą░č湥ąĮąĖąĄ (remap) ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąĖą╝ąĄąĮąĄąĮąŠ ą║ čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒ą╗ą░čüčéčÅą╝ ą┐ą░ą╝čÅčéąĖ:

ŌĆó ą×čüąĮąŠą▓ąĮą░čÅ ą┐ą░ą╝čÅčéčī Flash

ŌĆó ąĪąĖčüč鹥ą╝ąĮą░čÅ ą┐ą░ą╝čÅčéčī

ŌĆó ąÆčüčéčĆąŠąĄąĮąĮą░čÅ SRAM1 (112 ą║ąĖą╗ąŠą▒ą░ą╣čé)

ŌĆó FSMC bank 1 (NOR/PSRAM 1 ąĖ 2)

ŌĆó FMC SDRAM bank 1

ąóą░ą▒ą╗ąĖčåą░ 4. ą×č鹊ą▒čĆą░ąČąĄąĮąĖąĄ ą┐ą░ą╝čÅčéąĖ ą┐čĆąĖ Boot mode/physical remap ą┤ą╗čÅ STM32F42xxx ąĖ STM32F43xxx.

| ąÉą┤čĆąĄčüą░ |

Boot/Remap

ą▓ ąŠčüąĮąŠą▓ąĮčāčÄ Flash |

Boot/Remap

ą▓ąŠ ą▓čüčéčĆąŠąĄąĮąĮčāčÄ SRAM |

Boot/Remap

ą▓ System Memory |

Remap ą▓ FMC |

| 0x20020000 - 0x2002FFFF |

SRAM3 (64 KB) |

SRAM3 (64 KB) |

SRAM3 (64 KB) |

SRAM3 (64 KB) |

| 0x2001C000 - 0x2001FFFF |

SRAM2 (16 KB) |

SRAM2 (16 KB) |

SRAM2 (16 KB) |

SRAM2 (16 KB) |

| 0x20000000 - 0x2001BFFF |

SRAM1 (112 KB) |

SRAM1 (112 KB) |

SRAM1 (112 KB) |

SRAM1 (112 KB) |

| 0x1FFF0000 - 0x1FFF77FF |

System Memory |

System Memory |

System Memory |

System Memory |

| 0x08100000 - 0x0FFFFFFF |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

| 0x08000000 - 0x080FFFFF |

ą¤ą░ą╝čÅčéčī Flash |

ą¤ą░ą╝čÅčéčī Flash |

ą¤ą░ą╝čÅčéčī Flash |

ą¤ą░ą╝čÅčéčī Flash |

| 0x04000000 - 0x07FFFFFF |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąĪčüčŗą╗ą║ą░ ąĮą░ FMC bank 1 NOR

/PSRAM 2 (128 MB) |

| 0x00000000 - 0x001FFFFF(1)(2) |

ąĪčüčŗą╗ą║ą░ ąĮą░ Flash (2 MB) |

ąĪčüčŗą╗ą║ą░ ąĮą░ SRAM1 (112 KB) |

ąĪčüčŗą╗ą║ą░ ąĮą░ System

Memory (30 KB) |

ąĪčüčŗą╗ą║ą░ ąĮą░ FMC bank 1 NOR

/PSRAM 1 (128 MB),

ąĖą╗ąĖ čüčüčŗą╗ą║ą░ ąĮą░ FMC SDRAM

bank 1 (128 MB) |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

(1) ąÜąŠą│ą┤ą░ FSMC ą┐ąĄčĆąĄąĮą░ąĘąĮą░č湥ąĮ ąĮą░ ą░ą┤čĆąĄčü 0x00000000, ą╝ąŠą│čāčé ą▒čŗčéčī ą┐ąĄčĆąĄąĮą░ąĘąĮą░č湥ąĮčŗ č鹊ą╗čīą║ąŠ ą┐ąĄčĆą▓čŗąĄ 2 čĆąĄą│ąĖąŠąĮą░ ą▒ą░ąĮą║ą░ 1 ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą┐ą░ą╝čÅčéąĖ (bank 1 NOR/PSRAM 1 ąĖ NOR/PSRAM 2) ąĖą╗ąĖ SDRAM bank 1. ąÆ čĆąĄąČąĖą╝ąĄ ą┐ąĄčĆąĄąĮą░ąĘąĮą░č湥ąĮąĖčÅ (remap mode), CPU ą╝ąŠąČąĄčé ą┐ąŠą╗čāčćąĖčéčī ą┤ąŠčüčéčāą┐ ą║ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ č湥čĆąĄąĘ čłąĖąĮčā ICode ą▓ą╝ąĄčüč鹊 čüąĖčüč鹥ą╝ąĮąŠą╣ čłąĖąĮčŗ, čćč鹊 čāą╗čāčćčłą░ąĄčé ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéčī.

(2) ąöą░ąČąĄ ą║ąŠą│ą┤ą░ ą┐ą░ą╝čÅčéčī čüčüčŗą╗ąŠčćąĮąŠ ąŠč鹊ą▒čĆą░ąČąĄąĮą░ ąĮą░ ąŠą▒ą╗ą░čüčéčī ąĘą░ą│čĆčāąĘą║ąĖ (boot memory space), čŹčéą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēą░čÅ ą┐ą░ą╝čÅčéčī ą▓čüąĄ ąĄčēąĄ ą┤ąŠčüčéčāą┐ąĮą░ ą┐ąŠ čüą▓ąŠąĖą╝ ąŠčĆąĖą│ąĖąĮą░ą╗čīąĮčŗą╝ ą░ą┤čĆąĄčüą░ą╝ ąĮą░ ą║ą░čĆč鹥 ą┐ą░ą╝čÅčéąĖ.

[ąĪčüčŗą╗ą║ąĖ]

1. RM0090 Reference manual STM32F405/415, STM32F407/417, STM32F427/437 and STM32F429/439 advanced Arm®-based 32-bit MCUs site:st.com.

2. STM32: ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ ą┐ą░ą╝čÅčéąĖ CCM ą▓ ą┐čĆąŠąĄą║čéą░čģ GCC.

3. STM32F3xx/F4xxx Cortex®-M4 with FPU programming manual (PM0214).

4. ąŚą░ą│čĆčāąĘčćąĖą║ STM32F42xxx ąĖ STM32F43xxx.

5. STM32: ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ LCD-TFT (LTDC).

6. ą¤ąŠčĆčÅą┤ąŠą║ čüą╗ąĄą┤ąŠą▓ą░ąĮąĖčÅ ą▒ą░ą╣čé (endianness).

7. STM32: ą░ą▒ą▒čĆąĄą▓ąĖą░čéčāčĆčŗ ąĖ č鹥čĆą╝ąĖąĮčŗ.

8. ąśąĮč鹥čĆč乥ą╣čü ą┐ą░ą╝čÅčéąĖ Flash STM32F4.

9. STM32F4xx: ą▒ą░ą╣čéčŗ ąŠą┐čåąĖą╣. |