|

ą£ąĖą║čĆąŠčüčģąĄą╝ą░ RTC6715 ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé čüąŠą▒ąŠą╣ ąĖąĮč鹥ą│čĆą░ą╗čīąĮčŗą╣ čĆą░ą┤ąĖąŠą┐čĆąĖąĄą╝ąĮąĖą║ FM, ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮąĮčŗą╣ ą┤ą╗čÅ ą┤ąĄą╝ąŠą┤čāą╗čÅčåąĖąĖ čćą░čüč鹊čéąĮąŠ-ą╝ąŠą┤čāą╗ąĖčĆąŠą▓ą░ąĮąĮčŗčģ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗčģ čüąĖą│ąĮą░ą╗ąŠą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮą░ 5.8 ąōąōčå. ą¦ąĖą┐ ą▓ą║ą╗čÄčćą░ąĄčé ą▓ čüąĄą▒čÅ ą╝ą░ą╗ąŠčłčāą╝čÅčēąĖą╣ čāčüąĖą╗ąĖč鹥ą╗čī (low noise amplifier, čüą╝ąĄčüąĖč鹥ą╗čī, čāčüąĖą╗ąĖč鹥ą╗čī ą┐čĆąŠą╝ąĄąČčāč鹊čćąĮąŠą╣ čćą░čüč鹊čéčŗ (IF amplifier), ą┤ąĄą╝ąŠą┤čāą╗čÅč鹊čĆ FM, čüąĖčüč鹥ą╝čā ąÉąĀąŻ (AGC), ą┤ąĄą╝ąŠą┤čāą╗čÅč鹊čĆčŗ ąĘą▓čāą║ą░, ąŻąØą¦ ąĖ čłčāą╝ąŠą┐ąŠą┤ą░ą▓ąĖč鹥ą╗čī. ąØą░ ą▓čŗą▓ąŠą┤ąĄ RSSI ą┐ąŠ čāčĆąŠą▓ąĮčÄ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą╝ąŠąČąĮąŠ ąĮąĄą┐ąŠčüčĆąĄą┤čüčéą▓ąĄąĮąĮąŠ ą║ąŠąĮčéčĆąŠą╗ąĖčĆąŠą▓ą░čéčī čāčĆąŠą▓ąĄąĮčī čĆą░ą┤ąĖąŠčüąĖą│ąĮą░ą╗ą░. RTC6715 ą╝ąŠąČąĄčé ą┤ąĄą╝ąŠą┤čāą╗ąĖčĆąŠą▓ą░čéčī ą▓ąĖą┤ąĄąŠčüąĖą│ąĮą░ą╗, ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗą╣ čü ą╝ąŠą┤čāą╗čÅčåąĖąĄą╣ FM, ą░ čéą░ą║ąČąĄ čüč鹥čĆąĄąŠąĘą▓čāą║, ą┐ąŠčüčéą░ą▓ą╗čÅąĄą╝čŗą╣ RTC6705, ąĖ čĆą░ąĘą┤ąĄą╗čÅčéčī ąČąĄą╗ą░ąĄą╝čŗąĄ čüąĖą│ąĮą░ą╗čŗ ąĮą░ ą▓čŗą┤ąĄą╗ąĄąĮąĮčŗčģ ą▓ąĮąĄčłąĮąĖčģ ą▓čŗčģąŠą┤ą░čģ. ą¤ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčéčüčÅ čĆąĄąČąĖą╝čŗ Stereo ąĖ Mono ą░čāą┤ąĖąŠ.

ąĀą░ą▒ąŠčćą░čÅ čćą░čüč鹊čéą░ ą┐čĆąĖąĄą╝ą░ RTC6715 ą╝ąŠąČąĄčé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čéčīčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄą╝ č湥čĆąĄąĘ SPI, ąĖą╗ąĖ čü ą┐ąŠą╝ąŠčēčīčÄ ą▓čŗą▒ąŠčĆą░ čāčĆąŠą▓ąĮąĄą╣ ąĮą░ 6 ą▓čŗą┤ąĄą╗ąĄąĮąĮčŗčģ ą▓čŗą▓ąŠą┤ą░čģ. ąĀąĄą│čāą╗čÅč鹊čĆąĮčŗąĄ čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅ čüčéą░ąĮą┤ą░čĆč鹊ą▓ CE ąĖ FCC ą╗ąĄą│ą║ąŠ čüąŠą▒ą╗čÄą┤ą░čÄčéčüčÅ ą┐čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ RTC6715 ą▓ čüčģąĄą╝ąĄ, ą│ą┤ąĄ ą┐ąĄčćą░čéą░ąĮą░čÅ ą┐ą╗ą░čéą░ čāčüčéčĆąŠą╣čüčéą▓ą░ ąĘą░ą║čĆčŗčéą░ 菹║čĆą░ąĮąŠą╝.

ą×čüąĮąŠą▓ąĮčŗąĄ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮčŗąĄ ąŠčüąŠą▒ąĄąĮąĮąŠčüčéąĖ RTC6715:

ŌĆó ą×ą┤ąĮąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ 3.3V

ŌĆó ąöąĄą╝ąŠą┤čāą╗čÅč鹊čĆ FM ą┤ąĖą░ą┐ą░ąĘąŠąĮą░ 5.8 ąōąōčå čü ą┤ą▓čāą╝čÅ ą┤ąĄą╝ąŠą┤čāą╗čÅč鹊čĆą░ą╝ąĖ ą┐ąŠą┤ąĮąĄčüčāčēąĖčģ ąĮą░ 6 ą£ąōčå / 6.5 ą£ąōčå

ŌĆó ąÆčŗčüąŠą║ą░čÅ čćčāą▓čüčéą▓ąĖč鹥ą╗čīąĮąŠčüčéčī: -85dBm

ŌĆó ą¤čĆąŠčüč鹊ą╣ ą▓čŗą▒ąŠčĆ 24 čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮčŗčģ ą║ą░ąĮą░ą╗ąŠą▓ čü ą┐ąŠą╝ąŠčēčīčÄ 6 čåąĖčäčĆąŠą▓čŗčģ ą▓čģąŠą┤ąŠą▓, č湥ą╝ čāčüčéčĆą░ąĮčÅąĄčéčüčÅ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ą▓ąĮąĄčłąĮąĄą│ąŠ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░

ŌĆó ąśąĮą┤ąĖą║ą░č鹊čĆ čāčĆąŠą▓ąĮčÅ čĆą░ą┤ąĖąŠčüąĖą│ąĮą░ą╗ą░ (Radio Signal Strength Indicator, RSSI)

ŌĆó ą¤čĆąĖą│ą╗čāčłąĄąĮąĖčÅ ąĘą▓čāą║ą░ (hard mute) čü ą┐ąŠą╝ąŠčēčīčÄ čłčāą╝ąŠą┐ąŠą┤ą░ą▓ąĖč鹥ą╗čÅ

ŌĆó ą¦ąĖą┐ ąĖąĘą│ąŠč鹊ą▓ą╗ąĄąĮ ą┐ąŠ č鹥čģąĮąŠą╗ąŠą│ąĖąĖ CMOS čü ąĖąĮč鹥ą│čĆąĖčĆąŠą▓ą░ąĮąĮčŗą╝ ą│ąĄąĮąĄčĆą░č鹊čĆąŠą╝, čāą┐čĆą░ą▓ą╗čÅąĄą╝čŗą╝ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄą╝ (VCO) ąĖ ążąÉą¤ą¦ (PLL)

ŌĆó 48-ą▓čŗą▓ąŠą┤ąĮčŗą╣ ąĮąĄ čüąŠą┤ąĄčƹȹ░čēąĖą╣ čüą▓ąĖąĮąĄčå ą║ąŠčĆą┐čāčü QFN, čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅą╝ RoHS

ą×ą▒ą╗ą░čüčéąĖ ą┐čĆąĖą╝ąĄąĮąĄąĮąĖčÅ:

ŌĆó ą¤ąĄčĆąĄą┤ą░čćą░ ą┐ąŠ čĆą░ą┤ąĖąŠ ąĘą▓čāą║ą░ ąĖ ą▓ąĖą┤ąĄąŠ (AV Sender)

ŌĆó ąĪąĖčüč鹥ą╝čŗ FPV ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┤čĆąŠąĮą░ą╝ąĖ

ŌĆó ąÆąĖą┤ąĄąŠąĮą░ą▒ą╗čÄą┤ąĄąĮąĖąĄ

ŌĆó ą£ąŠąĮąĖč鹊čĆąĖąĮą│ ą┤ąĄč鹥ą╣

ŌĆó ąæąĄčüą┐čĆąŠą▓ąŠą┤ąĮą░čÅ ą║ą░ą╝ąĄčĆą░

ŌĆó ąæąĄčüą┐čĆąŠą▓ąŠą┤ąĮą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░ ąĘą▓čāą║ą░

ŌĆó ąæąĄčüą┐čĆąŠą▓ąŠą┤ąĮčŗąĄ ą│ąŠą╗ąŠą▓ąĮčŗąĄ ąĮą░čāčłąĮąĖą║ąĖ

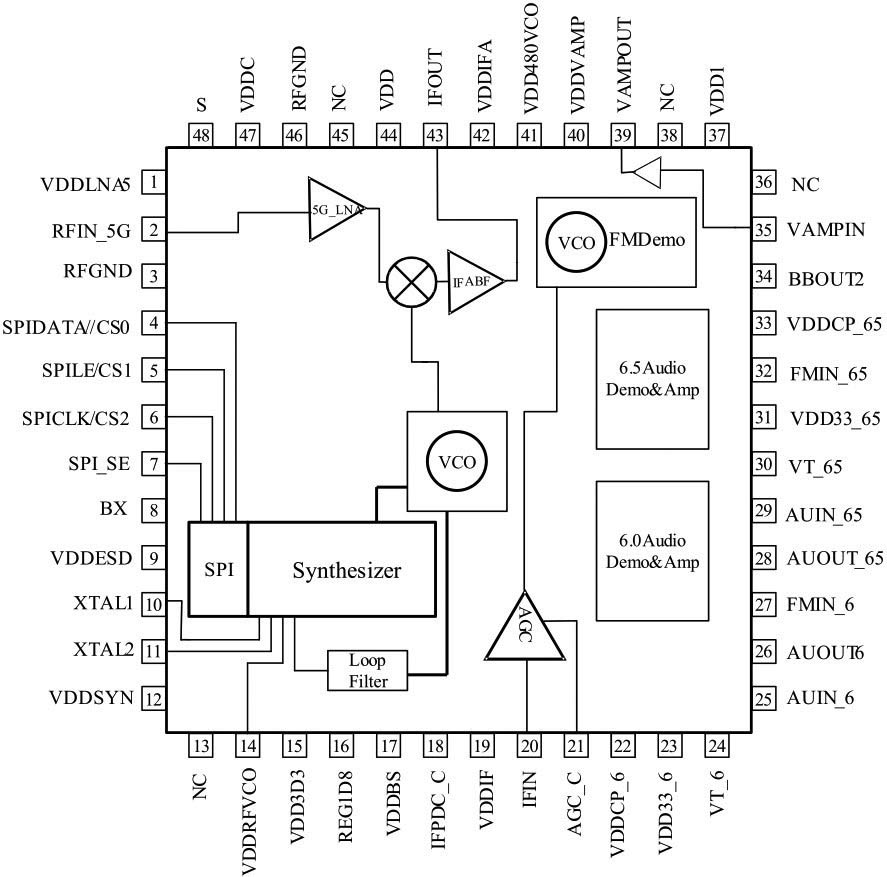

ąĀąĖčü. 1. ą”ąŠą║ąŠą╗ąĄą▓ą║ą░ ą║ąŠčĆą┐čāčüą░ ąĖ čāą┐čĆąŠčēąĄąĮąĮą░čÅ ą▒ą╗ąŠą║-čüčģąĄą╝ą░ RTC6715.

ąóą░ą▒ą╗ąĖčåą░ 1. ą×ą┐ąĖčüą░ąĮąĖąĄ ą▓čŗą▓ąŠą┤ąŠą▓.

| Ōä¢ |

ąśą╝čÅ |

I/O |

ążčāąĮą║čåąĖčÅ |

| 1 |

VDDLNA5 |

ą¤ąĖčéą░ąĮąĖąĄ |

+3.3V RX LNA5G |

| 2 |

RFIN_5G |

ąÉąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ą▓čģąŠą┤ |

ąÆčģąŠą┤ RF čüąĖą│ąĮą░ą╗ą░ 5 ąōąōčå LNA |

| 3 |

RFGND |

Analog GND |

ąŚąĄą╝ą╗čÅ RF |

| 4 |

CS0 |

ą”ąĖčäčĆąŠą▓ąŠą╣ ą▓čģąŠą┤ |

ąŻą┐čĆąŠčēąĄąĮąĮčŗą╣ ą▓čŗą▒ąŠčĆ ą║ą░ąĮą░ą╗ą░ (čü ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ ą▓ąĄčĆčģąĮąĄą╣ ą┐ąŠą┤čéčÅąČą║ąŠą╣(1)) |

| SPIDATA |

ą”ąĖčäčĆąŠą▓ąŠą╣ ą▓čģąŠą┤ |

ąÆčģąŠą┤ ą┤ą░ąĮąĮčŗčģ SPI(1) |

| 5 |

CS1 |

ą”ąĖčäčĆąŠą▓ąŠą╣ ą▓čģąŠą┤ |

ąŻą┐čĆąŠčēąĄąĮąĮčŗą╣ ą▓čŗą▒ąŠčĆ ą║ą░ąĮą░ą╗ą░ (čü ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ ą▓ąĄčĆčģąĮąĄą╣ ą┐ąŠą┤čéčÅąČą║ąŠą╣(1)) |

| SPILE |

ą”ąĖčäčĆąŠą▓ąŠą╣ ą▓čģąŠą┤ |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ čĆą░ą▒ąŠčéčŗ čłąĖąĮčŗ SPI (SPI bus latch enable input(1)) |

| 6 |

CS2 |

ą”ąĖčäčĆąŠą▓ąŠą╣ ą▓čģąŠą┤ |

ąŻą┐čĆąŠčēąĄąĮąĮčŗą╣ ą▓čŗą▒ąŠčĆ ą║ą░ąĮą░ą╗ą░ (čü ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ ą▓ąĄčĆčģąĮąĄą╣ ą┐ąŠą┤čéčÅąČą║ąŠą╣(1)) |

| SPICLK |

ą”ąĖčäčĆąŠą▓ąŠą╣ ą▓čģąŠą┤ |

ąĪąĖą│ąĮą░ą╗ čéą░ą║č鹊ą▓ SPI |

| 7 |

SPI_SE |

ą”ąĖčäčĆąŠą▓ąŠą╣ ą▓čģąŠą┤ |

ąÆčŗą▒ąŠčĆ čĆąĄąČąĖą╝ą░ ą▓čŗą▓ąŠą┤ąŠą▓ CSx: čāą┐čĆąŠčēąĄąĮąĮčŗą╣ ą▓čŗą▒ąŠčĆ ą║ą░ąĮą░ą╗ą░ ąĖą╗ąĖ SPI |

| 8 |

BX |

ą”ąĖčäčĆąŠą▓ąŠą╣ ą▓čģąŠą┤ |

ąÆ čĆąĄąČąĖą╝ąĄ čāą┐čĆąŠčēąĄąĮąĮąŠą│ąŠ ą▓čŗą▒ąŠčĆą░ ą║ą░ąĮą░ą╗ą░ BX ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą░ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮąŠą│ąŠ ą┤ąĖą░ą┐ą░ąĘąŠąĮą░(1). ąÆ čĆąĄąČąĖą╝ąĄ SPI ą▓čŗą▓ąŠą┤ BX ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ. |

| 9 |

VDDESD |

ą¤ąĖčéą░ąĮąĖąĄ |

+3.3V |

| 10 |

XTAL1 |

ąÉąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ą▓čģąŠą┤ |

ą¤ąŠą┤ą║ą╗čÄč湥ąĮąĖąĄ ą▓ąĮąĄčłąĮąĄą│ąŠ ą║ą▓ą░čĆčåąĄą▓ąŠą│ąŠ čĆąĄąĘąŠąĮą░č鹊čĆą░ |

| 11 |

XTAL2 |

ąÉąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ą▓čģąŠą┤ |

ą¤ąŠą┤ą║ą╗čÄč湥ąĮąĖąĄ ą▓ąĮąĄčłąĮąĄą│ąŠ ą║ą▓ą░čĆčåąĄą▓ąŠą│ąŠ čĆąĄąĘąŠąĮą░č鹊čĆą░ |

| 12 |

VDDSYN |

ą”ąĖčäčĆąŠą▓ą░čÅ ąĘąĄą╝ą╗čÅ |

+3.3V ą┤ą╗čÅ čüąĖąĮč鹥ąĘą░č鹊čĆą░ čćą░čüč鹊čéčŗ RF |

| 13 |

NC |

|

ąØąĖą║čāą┤ą░ ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąŠ |

| 14 |

VDDRFVCO |

ą¤ąĖčéą░ąĮąĖąĄ |

+3.3V ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░č鹊čĆą░, čāą┐čĆą░ą▓ą╗čÅąĄą╝ąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄą╝ (5GHz VCO) |

| 15 |

VDD3D3 |

ą¤ąĖčéą░ąĮąĖąĄ |

+3.3V ą┤ą╗čÅ čåąĖčäčĆąŠą▓ąŠą│ąŠ čĆąĄą│čāą╗čÅč鹊čĆą░ +1.8V |

| 16 |

REG1D8 |

ąÉąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ą▓čŗčģąŠą┤ |

ąĀąĄą│čāą╗čÅč鹊čĆ +1.8V ą┤ą╗čÅ ą┐ąĖčéą░ąĮąĖčÅ čåąĖčäčĆąŠą▓ąŠą│ąŠ ą▒ą╗ąŠą║ą░ |

| 17 |

VDDBS |

ą¤ąĖčéą░ąĮąĖąĄ |

+3.3V ą┤ą╗čÅ čüą╝ąĄčēąĄąĮąĖčÅ |

| 18 |

IFPDC_C |

ąÉąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ą▓čŗčģąŠą┤ |

ąśąĮą┤ąĖą║ą░č鹊čĆ čāčĆąŠą▓ąĮčÅ ą┐čĆąĖąĮąĖą╝ą░ąĄą╝ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ (RSSI) |

| 19 |

VDDIF |

ą¤ąĖčéą░ąĮąĖąĄ |

+3.3V ą┤ą╗čÅ IFAAF |

| 20 |

IFIN |

ąÉąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ą▓čģąŠą┤ |

ąÆčģąŠą┤čŗ IFA_AF |

| 21 |

AGC_C |

ąÉąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ą▓čģąŠą┤/ą▓čŗčģąŠą┤ |

ąÆčŗčģąŠą┤ ą▓čŗą┐čĆčÅą╝ąĖč鹥ą╗čÅ ąÉąĀąŻ (AGC) |

| 22 |

VDDCP_6 |

ą¤ąĖčéą░ąĮąĖąĄ |

+3.3V ą┤ą╗čÅ 6 ą£ąōčå charge pump ąĖ VCO |

| 23 |

VDD33_6 |

ą¤ąĖčéą░ąĮąĖąĄ |

+3.3V ą┤ą╗čÅ 6 ą£ąōčå čāčüąĖą╗ąĖč鹥ą╗čÅ ąĘą▓čāą║ą░ |

| 24 |

VT_6 |

ąÉąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ą▓čŗčģąŠą┤ |

Audio demo out ą┤ą╗čÅ 6 ą£ąōčå VCO |

| 25 |

AUIN_6 |

ąÉąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ą▓čģąŠą┤ |

ąÆčģąŠą┤ čāčüąĖą╗ąĖč鹥ą╗čÅ ąĘą▓čāą║ą░ ą┤ą╗čÅ čåąĄą┐ąĖ 6 ą£ąōčå |

| 26 |

AUOUT6 |

ąÉąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ą▓čŗčģąŠą┤ |

ąÆčŗčģąŠą┤ čāčüąĖą╗ąĖč鹥ą╗čÅ ąĘą▓čāą║ą░ ą┤ą╗čÅ čåąĄą┐ąĖ 6 ą£ąōčå |

| 27 |

FMIN_6 |

ąÉąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ą▓čģąŠą┤ |

ąÆčģąŠą┤ ąĘą▓čāą║ą░ 6 ą£ąōčå FM |

| 28 |

AUOUT_65 |

ąÉąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ą▓čŗčģąŠą┤ |

ąÆčŗčģąŠą┤ čāčüąĖą╗ąĖč鹥ą╗čÅ ąĘą▓čāą║ą░ ą┤ą╗čÅ čåąĄą┐ąĖ 6.5 ą£ąōčå |

| 29 |

AUIN_65 |

ąÉąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ą▓čģąŠą┤ |

ąÆčģąŠą┤ čāčüąĖą╗ąĖč鹥ą╗čÅ ąĘą▓čāą║ą░ ą┤ą╗čÅ čåąĄą┐ąĖ 6.5 ą£ąōčå |

| 30 |

VT_65 |

ąÉąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ą▓čŗčģąŠą┤ |

Audio demo out ą┤ą╗čÅ 6.5 ą£ąōčå VCO |

| 31 |

VDD33_65 |

ą¤ąĖčéą░ąĮąĖąĄ |

+3.3V ą┤ą╗čÅ čāčüąĖą╗ąĖč鹥ą╗čÅ ąĘą▓čāą║ą░ 6.5 ą£ąōčå |

| 32 |

FMIN_65 |

ąÉąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ą▓čģąŠą┤ |

ąÆčģąŠą┤ ąĘą▓čāą║ą░ 6.5 ą£ąōčå FM |

| 33 |

VDDCP_65 |

ą”ąĖčäčĆąŠą▓ąŠą╣ ą▓čģąŠą┤ |

+3.3V ą┤ą╗čÅ 6.5 ą£ąōčå charge pump ąĖ VCO |

| 34 |

BBOUT2 |

ąÉąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ą▓čŗčģąŠą┤ |

ąÆčŗčģąŠą┤ ą▒čāč乥čĆą░ ą┤ąĄą╝ąŠą┤čāą╗čÅč鹊čĆą░ FM (FMDeMod) |

| 35 |

VAMPIN |

ąÉąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ą▓čģąŠą┤ |

ąÆčģąŠą┤ ą▓ąĖą┤ąĄąŠčāčüąĖą╗ąĖč鹥ą╗čÅ (Video Amp) |

| 36 |

NC |

|

ąØąĖą║čāą┤ą░ ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąŠ |

| 37 |

VDD1 |

ą¤ąĖčéą░ąĮąĖąĄ |

+3.3V |

| 38 |

NC |

|

ąØąĖą║čāą┤ą░ ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąŠ |

| 39 |

VAMPOUT |

ąÉąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ą▓čŗčģąŠą┤ |

ąÆčŗčģąŠą┤ ą▓ąĖą┤ąĄąŠčāčüąĖą╗ąĖč鹥ą╗čÅ |

| 40 |

VDDVAMP |

ą¤ąĖčéą░ąĮąĖąĄ |

+3.3V ą┤ą╗čÅ ą▓ąĖą┤ąĄąŠčāčüąĖą╗ąĖč鹥ą╗čÅ |

| 41 |

VDD480VCO |

ą¤ąĖčéą░ąĮąĖąĄ |

+3.3V ą┤ą╗čÅ VCO ą┤ąĄą╝ąŠą┤čāą╗čÅč鹊čĆą░ FM |

| 42 |

VDDIFA |

ą¤ąĖčéą░ąĮąĖąĄ |

+3.3V ą┤ą╗čÅ RX IFA |

| 43 |

IFOUT |

ąÉąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ą▓čŗčģąŠą┤ |

ąÆčŗčģąŠą┤ ąŻą¤ą¦ |

| 44 |

VDD |

ą¤ąĖčéą░ąĮąĖąĄ |

+3.3V VDD |

| 45 |

NC |

|

ąØąĖą║čāą┤ą░ ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąŠ |

| 46 |

RFGND |

ąÉąĮą░ą╗ąŠą│ąŠą▓ą░čÅ ąĘąĄą╝ą╗čÅ |

ąŚąĄą╝ą╗čÅ RF |

| 47 |

NC |

|

ąØąĖą║čāą┤ą░ ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąŠ |

| 48 |

S |

ą”ąĖčäčĆąŠą▓ąŠą╣ ą▓čģąŠą┤ |

ąÆčŗą▒ąŠčĆ ą┤ąĖą░ą┐ą░ąĘąŠąĮą░ A/B (1). 0: ą┤ąĖą░ą┐ą░ąĘąŠąĮ A, 1: ą┤ąĖą░ą┐ą░ąĘąŠąĮ B. |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ (1): čåąĖčäčĆąŠą▓čŗąĄ ą▓čŗą▓ąŠą┤čŗ, BX, SPI_SE ąĖ SPIDATA/CS0, SPILE/CS1 ąĖ SPICLK/CS2 ąĖą╝ąĄčÄčé ą▓čüčéčĆąŠąĄąĮąĮčāčÄ ą▓ ą║čĆąĖčüčéą░ą╗ą╗ ą▓ąĄčĆčģąĮčÄčÄ ą┐ąŠą┤čéčÅąČą║čā (pull-high).

ąóą░ą▒ą╗ąĖčåą░ 2. ą¤čĆąĄą┤ąĄą╗čīąĮčŗąĄ ą┤ąŠą┐čāčüčéąĖą╝čŗąĄ ąĘąĮą░č湥ąĮąĖčÅ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓.

| ąĪąĖą╝ą▓. |

ą¤ą░čĆą░ą╝ąĄčéčĆ |

ąŚąĮą░č湥ąĮąĖčÅ |

ąĢą┤. |

| Tstr |

ąöąĖą░ą┐ą░ąĘąŠąĮ č鹥ą╝ą┐ąĄčĆą░čéčāčĆ čģčĆą░ąĮąĄąĮąĖčÅ |

-65 .. +150 |

┬░C |

| Totr |

ąöąĖą░ą┐ą░ąĘąŠąĮ čĆą░ą▒ąŠčćąĖčģ č鹥ą╝ą┐ąĄčĆą░čéčāčĆ |

-40 .. +85 |

| Vdd |

ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ |

-0.5 .. +5 |

V |

| Vlog |

ąŻčĆąŠą▓ąĄąĮčī ą╗ąŠą│ąĖą║ąĖ čāą┐čĆą░ą▓ą╗čÅčÄčēąĖčģ čüąĖą│ąĮą░ą╗ąŠą▓ |

-0.5 .. +5 |

| VRX |

ąÆčģąŠą┤ RX |

-2 .. +2 |

ą£ą░ą║čüąĖą╝ą░ą╗čīąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ, ą┐čĆąĖą▓ąĄą┤ąĄąĮąĮčŗąĄ ą▓ čéą░ą▒ą╗ąĖčåąĄ 2, ąĮąĖą║ąŠą│ą┤ą░ ąĮąĄ ą┤ąŠą╗ąČąĮčŗ ą┐čĆąĄą▓čŗčłą░čéčīčüčÅ. ąØąĄ ą┤ąŠą┐čāčüą║ą░ąĄčéčüčÅ čĆą░ą▒ąŠčéą░ čāčüčéčĆąŠą╣čüčéą▓ą░ ą▓ čāčüą╗ąŠą▓ąĖčÅčģ ą┐čĆąĄą▓čŗčłąĄąĮąĖčÅ čŹčéąĖčģ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓.

ąóą░ą▒ą╗ąĖčåą░ 3. ąŁą╗ąĄą║čéčĆąĖč湥čüą║ąĖąĄ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ.

| ąĪąĖą╝ą▓. |

ą¤ą░čĆą░ą╝ąĄčéčĆ |

ąŻčüą╗ąŠą▓ąĖčÅ |

min |

typ |

MAX |

ąĢą┤. |

| Tj |

ąöąĖą░ą┐ą░ąĘąŠąĮ č鹥ą╝ą┐ąĄčĆą░čéčāčĆ |

|

-40 |

25 |

85 |

┬░C |

| VDD33 |

ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ |

|

3.1 |

3.3 |

3.5 |

V |

| I_module |

ą¤ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ č鹊ą║ą░ ą▓ č鹥čüč鹊ą▓ąŠą╣ čüčģąĄą╝ąĄ ą┐čĆąĖ ą┐ąĄčĆąĄą┤ą░č湥 čüąĖą│ąĮą░ą╗ą░ čåą▓ąĄčéąĮčŗčģ ą┐ąŠą╗ąŠčü |

TT 25┬░C, 3.3V |

|

195 |

|

mA |

| Icc |

ą¤ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ č鹊ą║ą░ |

|

146 |

|

| Fref |

ąĀą░ą▒ąŠčćą░čÅ čćą░čüč鹊čéą░ ą│ąĄąĮąĄčĆą░č鹊čĆą░ |

|

|

8 |

|

ą£ąōčå |

| V_IH |

ąŻčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 1 ą┤ą╗čÅ ą▓čģąŠą┤ąĮčŗčģ čüąĖą│ąĮą░ą╗ąŠą▓ čåąĖčäčĆąŠą▓ąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ |

V_IO=3V |

0.7 x V_IO |

|

V_IO + 0.3 |

V |

| V_IL |

ąŻčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 0 ą┤ą╗čÅ ą▓čģąŠą┤ąĮčŗčģ čüąĖą│ąĮą░ą╗ąŠą▓ čåąĖčäčĆąŠą▓ąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ |

|

-0.3 |

|

0.3 x V_IO |

ąóą░ą▒ą╗ąĖčåą░ 4. ą¤ą░čĆą░ą╝ąĄčéčĆčŗ FM ą┐čĆąĖąĄą╝ąĮąĖą║ą░ ą┤ąĖą░ą┐ą░ąĘąŠąĮą░ 5 ąōąōčå (VDD = +3.3V, 25Ōäā).

| ąĪąĖą╝ą▓. |

ą¤ą░čĆą░ą╝ąĄčéčĆ |

ąŻčüą╗ąŠą▓ąĖčÅ |

min |

typ |

MAX |

ąĢą┤. |

| RF_Freq |

ą¦ą░čüč鹊čéą░ ąĮą░ ą▓čģąŠą┤ąĄ RF |

|

5725 |

|

5865 |

ą£ąōčå |

| IF_Freq |

ą¦ą░čüč鹊čéą░ ąĮą░ ą▓čŗčģąŠą┤ąĄ ąŻą¤ą¦ |

|

479 |

480 |

|

| S11 |

ą¤ąŠč鹥čĆąĖ ąĮą░ ą▓čģąŠą┤ąĄ RF ą▓ č鹥čüč鹊ą▓ąŠą╣ čüčģąĄą╝ąĄ |

ąśą╝ą┐ąĄą┤ą░ąĮčü ą▓ąĮąĄčłąĮąĄą╣ čåąĄą┐ąĖ 50 ą×ą╝ |

|

-10 |

|

dB |

| Si |

ą¦čāą▓čüčéą▓ąĖč鹥ą╗čīąĮąŠčüčéčī ą┐ąŠ ą▓čģąŠą┤čā ą▓ č鹥čüč鹊ą▓ąŠą╣ čüčģąĄą╝ąĄ |

SNR 43dB

Fmod = 15 ą║ąōčå

ąöąĄą▓ąĖą░čåąĖčÅ čćą░čüč鹊čéčŗ: ┬▒2.5 ą£ąōčå

ą¤ąŠą╗ąŠčüą░ ążąØą¦: 20 ą║ąōčå |

|

-85 |

|

dBm |

| ążą░ąĘąŠą▓čŗą╣ čłčāą╝ |

LO: 5246 ą£ąōčå |

ąĪą╝ąĄčēąĄąĮąĖąĄ 100 ą║ąōčå |

|

-90 |

|

dBc/ąōčå |

| ąĪą╝ąĄčēąĄąĮąĖąĄ 1 ą£ąōčå |

|

-112 |

|

| VRSSI |

ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮą░ ą▓čŗčģąŠą┤ąĄ RSSI |

-91dBm .. 5dBm |

|

0.5 ~ 1.1 |

|

V |

| Z22_IFout |

ąśą╝ą┐ąĄą┤ą░ąĮčü ą▓čŗčģąŠą┤ą░ ąŻą¤ą¦ (IF) 480 ą£ąōčå |

SE |

|

50 |

|

╬® |

| Z22_IFin |

ąśą╝ą┐ąĄą┤ą░ąĮčü ą▓čģąŠą┤ą░ ąŻą¤ą¦ (IF) 480 ą£ąōčå |

|

60 |

|

| ąÆąĖą┤ąĄąŠ |

| V_pp |

ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ ąŠčé ą┐ąĖą║ą░ ą┤ąŠ ą┐ąĖą║ą░ ą┐ąŠčüą╗ąĄ čäąĖą║čüą░čåąĖąĖ ą▓ąĖą┤ąĄąŠčüąĖą│ąĮą░ą╗ą░ |

ąØą░ą│čĆčāąĘą║ą░ 75 ╬® |

|

1 |

|

V |

| ąÉčāą┤ąĖąŠ |

| Carrier_Freq |

ą¦ą░čüč鹊čéą░ ąĮąĄčüčāčēąĄą╣ ąĘą▓čāą║ą░ |

|

|

6/6.5 |

|

ą£ąōčå |

| ąŻčĆąŠą▓ąĄąĮčī ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ |

ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ ąŠčé ą┐ąĖą║ą░ ą┤ąŠ ą┐ąĖą║ą░ ą┐ąŠčüą╗ąĄ čāčüąĖą╗ąĖč鹥ą╗čÅ ąĘą▓čāą║ą░ |

Fmod: č鹊ąĮ 1 ą║ąōčå

ąöąĄą▓ąĖą░čåąĖčÅ čćą░čüč鹊čéčŗ: ┬▒25 ą║ąōčå

ąØą░ą│čĆčāąĘą║ą░: > 1 ą║ą×ą╝ |

|

1 |

|

V |

| Max_App |

ą£ą░ą║čüąĖą╝ą░ą╗čīąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąŠčé ą┐ąĖą║ą░ ą┤ąŠ ą┐ąĖą║ą░ ąĮą░ ą▓čŗčģąŠą┤ąĄ čāčüąĖą╗ąĖč鹥ą╗čÅ ąĘą▓čāą║ą░ ą┐čĆąĖ ą║ąŠčŹčäčäąĖčåąĖąĄąĮč鹥 ąĖčüą║ą░ąČąĄąĮąĖą╣ < 1% |

Fmod: č鹊ąĮ 1 ą║ąōčå

ąöąĄą▓ąĖą░čåąĖčÅ čćą░čüč鹊čéčŗ: ┬▒50 ą║ąōčå

ąØą░ą│čĆčāąĘą║ą░: > 1 ą║ą×ą╝ |

|

2 |

|

| THD |

ą×ą▒čēąĖąĄ ą│ą░čĆą╝ąŠąĮąĖč湥čüą║ąĖąĄ ąĖčüą║ą░ąČąĄąĮąĖčÅ, ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮą░ ą▓čŗčģąŠą┤ąĄ 1V ąŠčé ą┐ąĖą║ą░ ą┤ąŠ ą┐ąĖą║ą░ |

Fmod: č鹊ąĮ 1 ą║ąōčå

ąöąĄą▓ąĖą░čåąĖčÅ čćą░čüč鹊čéčŗ: ┬▒25 ą║ąōčå

ąØą░ą│čĆčāąĘą║ą░: > 1 ą║ą×ą╝ |

|

1 |

|

% |

| S/N |

Audio SNR (čüąŠąŠčéąĮąŠčłąĄąĮąĖąĄ čüąĖą│ąĮą░ą╗/čłčāą╝ ąŠą▒čĆą░ąĘčåąŠą▓ąŠą│ąŠ ą┤ąĖąĘą░ą╣ąĮą░) čü ą┐čĆąĖą╝ąĄąĮąĄąĮąĖąĄą╝ pre-emphasis/de-emphasis |

Fmod: č鹊ąĮ 1 ą║ąōčå, ąĮą░ ą▓čŗčģąŠą┤ąĄ ąĘą▓čāą║ą░ 2V ąŠčé ą┐ąĖą║ą░ ą┤ąŠ ą┐ąĖą║ą░

ąØą░ą│čĆčāąĘą║ą░: > 1 ą║ą×ą╝ |

|

56 |

|

dB |

[ąśąĮč鹥čĆč乥ą╣čü SPI]

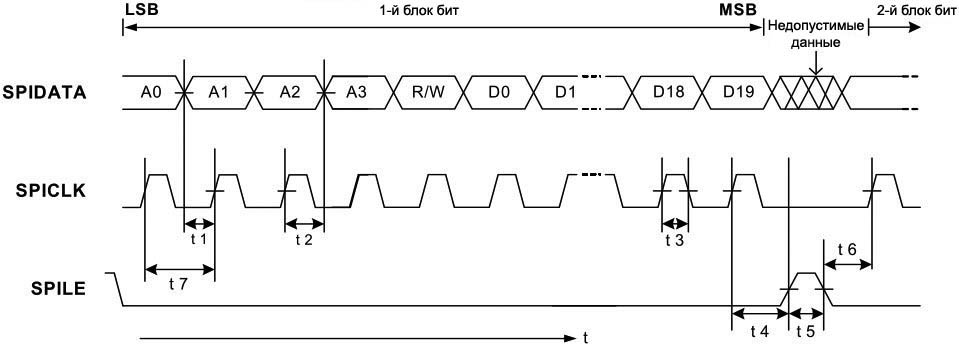

ąÆ čĆąĄąČąĖą╝ąĄ SPI (SPI_SE = 1) ą┤ą╗čÅ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ čćą░čüč鹊čéčŗ ąĖ ą▓ąĮčāčéčĆąĄąĮąĮąĖčģ čĆąĄą│ąĖčüčéčĆąŠą▓ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ 3-ą┐čĆąŠą▓ąŠą┤ąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü SPI. ą¤ąŠč鹊ą║ ą┤ą░ąĮąĮčŗčģ čüąŠčüč鹊ąĖčé ąĖąĘ 25 ą▒ąĖčé, ą▓ ą║ąŠč鹊čĆčŗąĄ ą▓čģąŠą┤čÅčé 4 ą▒ąĖčéą░ ą░ą┤čĆąĄčüą░, 1 čāą┐čĆą░ą▓ą╗čÅčÄčēąĖą╣ ą▒ąĖčé ą┤ą╗čÅ čćč鹥ąĮąĖčÅ/ąĘą░ą┐ąĖčüąĖ ąĖ 20 ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ. ąöą░ąĮąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ą╝ą╗ą░ą┤čłąĖą╝ ą▒ąĖč鹊ą╝ (LSB) ą▓ą┐ąĄčĆąĄą┤.

ąÆąŠ ą▓čĆąĄą╝čÅ čåąĖą║ą╗ą░ ąĘą░ą┐ąĖčüąĖ (R/W = 1) čćąĖą┐ ą░ąĮą░ą╗ąĖąĘąĖčĆčāąĄčé čüąĖą│ąĮą░ą╗ ą┤ą░ąĮąĮčŗčģ SPIDATA ą┐ąŠ čäčĆąŠąĮčéčā ąĮą░čĆą░čüčéą░ąĮąĖčÅ čāčĆąŠą▓ąĮčÅ SPICLK. ąĪčćąĖčéą░ąĮąĮčŗąĄ čćąĖą┐ąŠą╝ ą┤ą░ąĮąĮčŗąĄ ą▓čĆąĄą╝ąĄąĮąĮąŠ čüąŠčģčĆą░ąĮčÅčÄčéčüčÅ ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╝ čĆąĄą│ąĖčüčéčĆąĄ čüą┤ą▓ąĖą│ą░. ą¤ąŠ čäčĆąŠąĮčéčā ąĮą░čĆą░čüčéą░ąĮąĖčÅ čāčĆąŠą▓ąĮčÅ SPILE ą┤ą░ąĮąĮčŗąĄ čĆąĄą│ąĖčüčéčĆą░ čüą┤ą▓ąĖą│ą░ ąĘą░čēąĄą╗ą║ąĖą▓ą░čÄčéčüčÅ ą▓ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ, čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą┐ąĄčĆąĄą┤ą░ąĮąĮąŠą╝čā ą░ą┤čĆąĄčüčā.

ąÆąŠ ą▓čĆąĄą╝čÅ čåąĖą║ą╗ą░ čćč鹥ąĮąĖčÅ (R/W = 0) ą░ą┤čĆąĄčü ąĖ ą▒ąĖčé čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čćč鹥ąĮąĖąĄą╝/ąĘą░ą┐ąĖčüčīčÄ ą░ąĮą░ą╗ąĖąĘąĖčĆčāčÄčéčüčÅ ą┐ąŠ čäčĆąŠąĮčéčā ąĮą░čĆą░čüčéą░ąĮąĖčÅ čāčĆąŠą▓ąĮčÅ SPICLK, ąŠą┤ąĮą░ą║ąŠ ą▒ąĖčéčŗ ą┤ą░ąĮąĮčŗąĄ ą┐ąŠčüčŗą╗ą░čÄčéčüčÅ ą┐ąŠ čüą┐ą░ą┤čā čāčĆąŠą▓ąĮčÅ SPICLK.

ąĀąĖčü. 2. ąöąĖą░ą│čĆą░ą╝ą╝ą░ ą║ą░ą┤čĆą░ čüąĖą│ąĮą░ą╗ąŠą▓ 3-ą┐čĆąŠą▓ąŠą┤ąĮąŠą│ąŠ SPI.

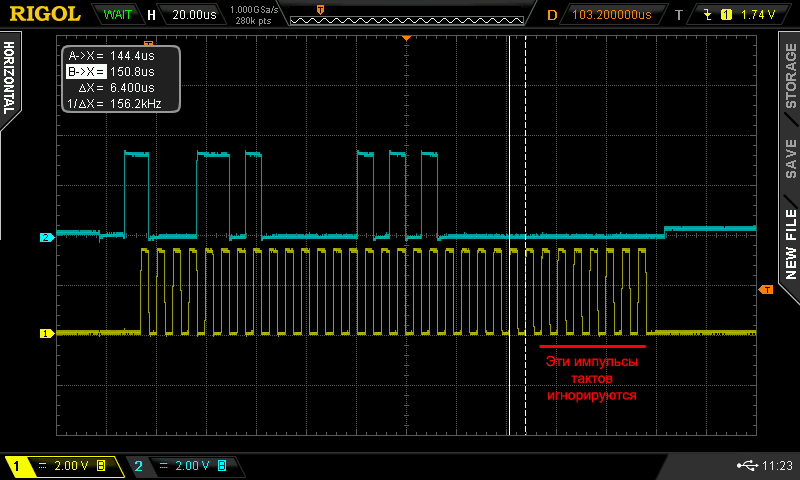

ąśą╝ą┐čāą╗čīčüčŗ SPICLK ą╝ąŠą│čāčé ą┐čĆąŠą┤ąŠą╗ąČą░čéčīčüčÅ ąĖ ą┐ąŠčüą╗ąĄ ą▒ąĖčéą░ ą┤ą░ąĮąĮčŗčģ D19, ąŠąĮąĖ ą▒čāą┤čāčé ą┐čĆąŠčüč鹊 ąĖą│ąĮąŠčĆąĖčĆąŠą▓ą░čéčīčüčÅ čćąĖą┐ąŠą╝ RTC6715. ą¤ąŠčŹč鹊ą╝čā ą╝ąŠąČąĮąŠ ą┤ą╗čÅ ąŠčéą┐čĆą░ą▓ą║ąĖ ą┤ą░ąĮąĮčŗčģ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą░ą┐ą┐ą░čĆą░čéąĮčŗą╣ SPI, ą║ąŠč鹊čĆčŗą╣ ą╝ąŠąČąĄčé ą┐ąŠčüčŗą╗ą░čéčī č鹊ą╗čīą║ąŠ ą▒ą░ą╣čéčŗ ąĖ 16-ą▒ąĖčéąĮčŗąĄ ąĖą╗ąĖ 32-ą▒ąĖčéąĮčŗąĄ čüą╗ąŠą▓ą░.

ąØą░ čüą╗ąĄą┤čāčÄčēąĄą╣ ąŠčüčåąĖą╗ą╗ąŠą│čĆą░ą╝ą╝ąĄ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ čüčéą░ąĮą┤ą░čĆčéąĮčŗą╣ ą║ą░ą┤čĆ SPI ąĖąĘ 32 ą▒ąĖčé, ą│ą┤ąĄ ą┐ąŠą╗ąĄąĘąĮčŗą╝ąĖ čÅą▓ą╗čÅčÄčéčüčÅ č鹊ą╗čīą║ąŠ ą┐ąĄčĆą▓čŗąĄ 25, ą║ąŠč鹊čĆčŗąĄ čĆąĄą░ą╗čīąĮąŠ ą▓ąŠčüą┐čĆąĖąĮąĖą╝ą░čÄčéčüčÅ čćąĖą┐ąŠą╝ RTC6715. ą×čüčéą░ą╗čīąĮčŗąĄ 7 ąĖą╝ą┐čāą╗čīčüąŠą▓ čéą░ą║č鹊ą▓ ąĖą│ąĮąŠčĆąĖčĆčāčÄčéčüčÅ.

ąöą╗čÅ čćč鹥ąĮąĖčÅ čéą░ą║ąŠą╣ ą┐ąŠą┤čģąŠą┤ čāąČąĄ ąĮąĄ čüčĆą░ą▒ąŠčéą░ąĄčé, ą┐ąŠčŹč鹊ą╝čā ą┐čĆąĖą┤ąĄčéčüčÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą╝ąĄč鹊ą┤ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąŠčĆčéą░ą╝ąĖ GPIO (bitbang) ą┤ą╗čÅ č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą║ą░ą┤čĆą░ čćč鹥ąĮąĖčÅ.

ąóą░ą▒ą╗ąĖčåą░ 5. ąśąĮč鹥čĆą▓ą░ą╗čŗ ą▓čĆąĄą╝ąĄąĮąĖ 3-ą┐čĆąŠą▓ąŠą┤ąĮąŠą│ąŠ SPI.

| ą¤ą░čĆą░ą╝ąĄčéčĆ |

min |

typ |

MAX |

ąĢą┤. |

| t1 |

20 |

- |

- |

ąĮčü |

| t2 |

20 |

- |

- |

| t3 |

30 |

- |

- |

| t4 |

30 |

- |

- |

| t5 |

100 |

- |

- |

| t6 |

20 |

- |

- |

| t7 |

100 |

- |

- |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą┐ąŠ čäčĆąŠąĮčéčā ąĮą░čĆą░čüčéą░ąĮąĖčÅ SPICLK ąŠą┤ąĖąĮ ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ ą┐ąĄčĆąĄčüčŗą╗ą░ąĄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░. ąŻčĆąŠą▓ąĄąĮčī SPILE ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą╗ąŠą│. 0, ą║ąŠą│ą┤ą░ ą┤ą░ąĮąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░.

[ąĀąĄąČąĖą╝ čāą┐čĆąŠčēąĄąĮąĮąŠą│ąŠ ą▓čŗą▒ąŠčĆą░ ą║ą░ąĮą░ą╗ą░]

ąÜąŠą│ą┤ą░ ą▓čŗą▓ąŠą┤ 7 (SPI_SE) čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ ą╗ąŠą│. 0, čćąĖą┐ čĆą░ą▒ąŠčéą░ąĄčé ą▓ čĆąĄąČąĖą╝ąĄ čāą┐čĆąŠčēąĄąĮąĮąŠą│ąŠ ą▓čŗą▒ąŠčĆą░ ą║ą░ąĮą░ą╗ą░, ą┐čĆąĖ čŹč鹊ą╝ čāčĆąŠą▓ąĮąĖ ą╗ąŠą│ąĖą║ąĖ ąĮą░ ą▓čŗą▓ąŠą┤ą░čģ ą║ąŠčĆą┐čāčüą░ 4 (SPIDATA/CS0), 5 (SPILE/CS1), 6 (SPICLK/CS2)’╝ī48 (S) ąĖ 8 (BX) ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą░ ą║ą░ąĮą░ą╗ą░ (čüą╝. čéą░ą▒ą╗ąĖčåčā 6).

ąóą░ą▒ą╗ąĖčåą░ 6. ąÆčŗą▒ąŠčĆ ą║ą░ąĮą░ą╗ą░ čü ą┐ąŠą╝ąŠčēčīčÄ čüąĖą│ąĮą░ą╗ąŠą▓ CX0, CX1, CX2, S ąĖ BX.

5GHz

Band |

SPI_SE |

Band

|

BX

|

S

|

CS[2:0] |

| 000 |

001 |

010 |

011 |

100 |

101 |

110 |

111 |

| 0 |

A |

0 |

0 |

5865M |

5845M |

5825M |

5805M |

5785M |

5765M |

5745M |

5725M |

| 0 |

B |

0 |

1 |

5733M |

5752M |

5771M |

5790M |

5809M |

5828M |

5847M |

5866M |

| 0 |

E |

1 |

X |

5705M |

5685M |

5665M |

5645M |

5885M |

5905M |

5925M |

5945M |

| 1 |

SPI |

X |

X |

ąŻą┐čĆą░ą▓ą╗čÅčÄčēąĖąĄ čüąĖą│ąĮą░ą╗čŗ 3-ą┐čĆąŠą▓ąŠą┤ąĮąŠą│ąŠ SPI |

[ąĀąĄąČąĖą╝ SPI]

ąÜąŠą│ą┤ą░ ą▓čŗą▓ąŠą┤ 7 (SPI_SE) čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ ą╗ąŠą│. 1 (+3.3V), čćąĖą┐ čĆą░ą▒ąŠčéą░ąĄčé ą▓ čĆąĄąČąĖą╝ąĄ SPI, ąĖ ą▓čŗą▓ąŠą┤čŗ ą║ąŠčĆą┐čāčüą░ 4 (SPIDATA/CS0), 5 (SPILE/CS1) ąĖ 6 (SPICLK/CS2) ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą║ą░ą║ čüąĖą│ąĮą░ą╗čŗ 3-ą┐čĆąŠą▓ąŠą┤ąĮąŠą│ąŠ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ.

ąÉą┤čĆąĄčü 0x00: Synthesizer Register A

| ąæąĖčéčŗ |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| ąśą╝čÅ |

- |

SYN_RF_R_REG[14:0] |

| 5G Default |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

SYN_RF_R_REG [14:0]: ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 5.8 ąōąōčå (0010H). R-counter divider ratio control ą┤ą╗čÅ RF-čüąĖąĮč鹥ąĘą░č鹊čĆą░.

ąöą╗čÅ 5.8 ąōąōčå ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ: 00008H. ą¦ą░čüč鹊čéą░ čéą░ą║č鹊ą▓ ą║ą▓ą░čĆčåą░ (Fosc) = 8 ą£ąōčå. ą×ą┐ąŠčĆąĮą░čÅ čćą░čüč鹊čéą░ = čćą░čüč鹊č鹥 ą║ą▓ą░čĆčåą░ / R-counter = 8 ą£ąōčå / 8 = 1 ą£ąōčå.

ąÉą┤čĆąĄčü 0x01: Synthesizer Register B

| ąæąĖčéčŗ |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| ąśą╝čÅ |

SYN_RF_N_REG[12:0] |

SYN_RF_A_REG[6:0] |

| 5G Default |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

ąŚąĮą░č湥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą┤ą╗čÅ 5865 ą£ąōčå: 0x02A05.

ąÉą╗ą│ąŠčĆąĖčéą╝ čĆą░čüč湥čéą░ (čāą┐čĆąŠčēąĄąĮąĮčŗą╣, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╣ ą▓ ą┐čĆąŠčłąĖą▓ą║ą░čģ):

ąöą╗čÅ ąĮą░čüčéčĆąŠą╣ą║ąĖ čüąĖąĮč鹥ąĘą░č鹊čĆą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┐čĆčÅą╝ąŠąĄ čåąĖčäčĆąŠą▓ąŠąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ą┐ąŠ č乊čĆą╝čāą╗ąĄ:

ąŚąĮą░č湥ąĮąĖąĄ_čĆąĄą│ąĖčüčéčĆą░ = ( (ą¦ą░čüč鹊čéą░ - 479) / 2 )

ą©ą░ą│ąĖ čĆą░čüč湥čéą░ ą┤ą╗čÅ 5865 ą£ąōčå:

1. ąĀą░čüčüčćąĖčéčŗą▓ą░ąĄą╝ ąĘąĮą░č湥ąĮąĖąĄ ą│ąĄč鹥čĆąŠą┤ąĖąĮą░ čü čāč湥č鹊ą╝ ą┐čĆąŠą╝ąĄąČčāč鹊čćąĮąŠą╣ čćą░čüč鹊čéčŗ:

F_lo = ą¦ą░čüč鹊čéą░ - 479 = 5865 - 479 = 5386 ą£ąōčå

ąöąĄą╗ąĖą╝ čĆąĄąĘčāą╗čīčéą░čé ąĮą░ 2:

F_lo_half = 5386 / 2 = 2693

2. ąĀą░ąĘą▒ąĖą▓ą░ąĄą╝ ą┐ąŠą╗čāč湥ąĮąĮąŠąĄ čćąĖčüą╗ąŠ ąĮą░ ą║ąŠą╝ą┐ąŠąĮąĄąĮčéčŗ N ąĖ A:

N = F_lo_half / 32 (čåąĄą╗ąŠčćąĖčüą╗ąĄąĮąĮąŠąĄ ą┤ąĄą╗ąĄąĮąĖąĄ)

A = F_lo_half % 32 (ąŠčüčéą░č鹊ą║ ąŠčé ą┤ąĄą╗ąĄąĮąĖčÅ)

N = 2693 / 32 = 84 (čéą░ą║ ą║ą░ą║ 84 * 32 = 2688)

A = 2693 % 32 = 5 (čéą░ą║ ą║ą░ą║ 2688 + 5 = 2693)

3. ążąŠčĆą╝ąĖčĆčāąĄą╝ ąĘąĮą░č湥ąĮąĖąĄ ą┤ą╗čÅ čĆąĄą│ąĖčüčéčĆą░ Synthesizer B (ąĘ

ąĮą░č湥ąĮąĖąĄ ą║ąŠą┤ąĖčĆčāąĄčéčüčÅ ą┐ąŠ č乊čĆą╝čāą╗ąĄ: (N << 7) | A):

N = 84 ŌåÆ ą▓ ą┤ą▓ąŠąĖčćąĮąŠą╝ ą▓ąĖą┤ąĄ 1010100

A = 5 ŌåÆ ą▓ ą┤ą▓ąŠąĖčćąĮąŠą╝ ą▓ąĖą┤ąĄ 0000101

(84 << 7) = 10101000000000 (čüą┤ą▓ąĖą│ ąĮą░ 7 ą▒ąĖčé ą▓ą╗ąĄą▓ąŠ)

(84 << 7) | 5 = 10101000000000 | 0000101 = 10101000000101

10101000000101 ą▓ ą┤ą▓ąŠąĖčćąĮąŠą╣ = 0x2A05 ą▓ čłąĄčüčéąĮą░ą┤čåą░č鹥čĆąĖčćąĮąŠą╣

ąśč鹊ą│: ąöą╗čÅ ąĮą░čüčéčĆąŠą╣ą║ąĖ ąĮą░ čćą░čüč鹊čéčā 5865 ą£ąōčå ą▓ čĆąĄą│ąĖčüčéčĆ 0x01 (Synthesizer Register B) ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ąĘą░ą┐ąĖčüą░čéčī ąĘąĮą░č湥ąĮąĖąĄ 0x02A05.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ ąŠ čäąĖąĘąĖč湥čüą║ąŠą╣ č乊čĆą╝čāą╗ąĄ čüąĖąĮč鹥ąĘą░č鹊čĆą░:

ąśčüčģąŠą┤ąĮąŠąĄ čāą┐ąŠą╝ąĖąĮą░ąĮąĖąĄ č乊čĆą╝čāą╗čŗ FLO = 2*(N*32+A)*(Fosc/R) ą▓ąĄčĆąĮąŠ ą┤ą╗čÅ ąŠą┐ąĖčüą░ąĮąĖčÅ čäąĖąĘąĖč湥čüą║ąŠą│ąŠ ą┐čĆąĖąĮčåąĖą┐ą░ čĆą░ą▒ąŠčéčŗ PLL-čüąĖąĮč鹥ąĘą░č鹊čĆą░ RTC6715, ą│ą┤ąĄ:

Fosc ŌĆö čćą░čüč鹊čéą░ ą║ą▓ą░čĆčåą░ (ąŠą▒čŗčćąĮąŠ 8 ą£ąōčå ąĖą╗ąĖ 12 ą£ąōčå)

R ŌĆö ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ą┤ąĄą╗ąĄąĮąĖčÅ ąŠą┐ąŠčĆąĮąŠą╣ čćą░čüč鹊čéčŗ

ą×ą┤ąĮą░ą║ąŠ ąĮą░ ą┐čĆą░ą║čéąĖą║ąĄ ą┤ą╗čÅ čāą┐čĆąŠčēąĄąĮąĖčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┐čĆąĖą▓ąĄą┤ąĄąĮąĮčŗą╣ ą▓čŗčłąĄ ą░ą╗ą│ąŠčĆąĖčéą╝ čü ą╝ą░ą│ąĖč湥čüą║ąĖą╝ čćąĖčüą╗ąŠą╝ 479, ą║ąŠč鹊čĆčŗą╣ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ čāčćąĖčéčŗą▓ą░ąĄčé ąĖ čćą░čüč鹊čéčā ą║ą▓ą░čĆčåą░, ąĖ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé čāą╝ąĮąŠąČąĄąĮąĖčÅ, ąĖ ąĘąĮą░č湥ąĮąĖąĄ R, ąĖąĘą▒ą░ą▓ą╗čÅčÅ čĆą░ąĘčĆą░ą▒ąŠčéčćąĖą║ą░ ąŠčé čüą╗ąŠąČąĮčŗčģ čĆą░čüč湥č鹊ą▓.

ąÉą┤čĆąĄčü 0x02: Synthesizer Register C

| ąæąĖčéčŗ |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| ąśą╝čÅ |

AGC_6M[2:0] |

AGC_6M5[2:0] |

CC_VCO[1:0] |

CP_5GLO[2:0] |

CP_FT[2:0] |

SC_CTL |

MOUT[1:0] |

PRES_FT[2:0] |

| Default |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

ąŚąĮą░č湥ąĮąĖčÅ ą┐ąŠą╗ąĄą╣:

| Default: FFE44H |

| AGC_6M[2:0] |

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ąÉąĀąŻ ą┤ąĄą╝ąŠą┤čāą╗čÅč鹊čĆą░ ąĘą▓čāą║ą░ 6M |

| AGC_6M5[2:0] |

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ąÉąĀąŻ ą┤ąĄą╝ąŠą┤čāą╗čÅč鹊čĆą░ ąĘą▓čāą║ą░ 6M5 |

| CC_VCO[1:0] |

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ č鹊ą║ąŠą╝ VCO |

| CP_5GLO[2:0] |

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ č鹊ą║ąŠą╝ ą▒čāč乥čĆą░ 5G VCO |

| CP_FT[2:0] |

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ č鹊ą║ąŠą╝ charge pump (ąŠčé 50uA ą┤ąŠ 6mA, default=100uA) |

| SC_CTL |

CP current test control |

| MOUT[1:0] |

ą£ąĮąŠą│ąŠčäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮčŗą╣ ą▓čŗą▒ąŠčĆ ą▓čŗčģąŠą┤ą░ (ą▓čŗčģąŠą┤ ą┤ąĄą╗ąĖč鹥ą╗čÅ RF R, ą▓čŗčģąŠą┤ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ RF, lock in detect) |

| PRES_FT [2:0] |

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ č鹊ą║ąŠą╝ tail ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ (20 ~ 140uA) |

ąÉą┤čĆąĄčü 0x03: Synthesizer Register D

| ąæąĖčéčŗ |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| ąśą╝čÅ |

- |

SYN_C3[2:0] |

SYN_CZ[2:0] |

SYN_RZ[7:0] |

| Default |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąŚąĮą░č湥ąĮąĖčÅ ą┐ąŠą╗ąĄą╣:

| Default: 03980H |

| SYN_C3[2:0] |

Loop filter C3 control |

| SYN_CZ[2:0] |

Loop filter CZ control |

| SYN_RZ[7:0] |

Loop filter RZ control |

ąÉą┤čĆąĄčü 0x04: VCO Switch-Cap Control Register

| ąæąĖčéčŗ |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| ąśą╝čÅ |

RFVCO_EX_CAP[4:0] |

VCO480_EX_CAP[4:0] |

VCO6M_EX_CAP[4:0] |

VCO6M5_EX_CAP[4:0] |

| Default |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

ąŚąĮą░č湥ąĮąĖčÅ ą┐ąŠą╗ąĄą╣:

| Default: 7ABEFH |

| RFVCO_EX_CAP[4:0] |

ąöą╗čÅ ą┐ąŠą┤čüčéčĆąŠą╣ą║ąĖ RF VCO |

| 480VCO_EX_CAP[4:0] |

ąöą╗čÅ ą┐ąŠą┤čüčéčĆąŠą╣ą║ąĖ IF VCO |

| 6MVCO_EX_CAP[4:0] |

ąöą╗čÅ ą┐ąŠą┤čüčéčĆąŠą╣ą║ąĖ 6M VCO |

| 6M5VCO_EX_CAP[4:0] |

ąöą╗čÅ ą┐ąŠą┤čüčéčĆąŠą╣ą║ąĖ 6M5 VCO |

ąÉą┤čĆąĄčü 0x05: DFC Control Register

| ąæąĖčéčŗ |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| ąśą╝čÅ |

EN_RECAL |

R[5:0] |

OK_RF |

OK_IF |

OK_6M |

OK_6M5 |

VCODFC_OVP[2:0] |

DFC480_OVP[2:0] |

AUDFC_OVP[2:0] |

| Default |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

ąŚąĮą░č湥ąĮąĖčÅ ą┐ąŠą╗ąĄą╣:

| Default: 7E1D2H |

| EN_RECAL |

|

| R[5:0] |

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ąŠą┐ąŠčĆąĮąŠą╣ čćą░čüč鹊č鹊ą╣ DFC, čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 63 |

| OK_RF |

ąóąŠčćąĮą░čÅ ąĮą░čüčéčĆąŠą╣ą║ą░ RF VCO |

| OK_IF |

ąóąŠčćąĮą░čÅ ąĮą░čüčéčĆąŠą╣ą║ą░ IF VCO |

| OK_6M |

ąóąŠčćąĮą░čÅ ąĮą░čüčéčĆąŠą╣ą║ą░ 6M VCO |

| OK_6M5 |

ąóąŠčćąĮą░čÅ ąĮą░čüčéčĆąŠą╣ą║ą░ 6M5 VCO |

| VCODFC_OVP[2:0] |

ąŻčüčéą░ąĮąŠą▓ą║ą░ RF VCO |

| DFC480_OVP[2:0] |

ąŻčüčéą░ąĮąŠą▓ą║ą░ IF VCO |

| AUDFC_OVP[2:0] |

ąŻčüčéą░ąĮąŠą▓ą║ą░ 6M/6M5 VCO |

ąÉą┤čĆąĄčü 0x06: 6M Audio Demodulator Control Register

| ąæąĖčéčŗ |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| ąśą╝čÅ |

6M_ICP[5:0] |

6M_C3[2:0] |

6M_CZ [2:0] |

6M_RZ[7:0] |

| Default |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

ąŚąĮą░č湥ąĮąĖčÅ ą┐ąŠą╗ąĄą╣:

| Default: 82408H |

| 6M_ICP[5:0] |

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ č鹊ą║ąŠą╝ 6M Charge-Pump |

| 6M_C3[2:0] |

ą¤ąŠą┤čüčéčĆąŠą╣ą║ą░ 6M Loop Filter |

| 6M_CZ[2:0] |

| 6M_RZ[7:0] |

ąÉą┤čĆąĄčü 0x07: 6M5 Audio Demodulator Control Register

| ąæąĖčéčŗ |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| ąśą╝čÅ |

6M5_ICP[5:0] |

6M5_C3[2:0] |

6M5_CZ [2:0] |

6M5_RZ[7:0] |

| Default |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

ąŚąĮą░č湥ąĮąĖčÅ ą┐ąŠą╗ąĄą╣:

| Default: 82408H |

| 6M5_ICP[5:0] |

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ č鹊ą║ąŠą╝ 6M5 Charge-Pump |

| 6M5_C3[2:0] |

ą¤ąŠą┤čüčéčĆąŠą╣ą║ą░ 6M5 Loop Filter |

| 6M5_CZ[2:0] |

| 6M5_RZ[7:0] |

ąÉą┤čĆąĄčü 0x08: Receiver Control Register 1

| ąæąĖčéčŗ |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| ąśą╝čÅ |

- |

ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

CP_MIXER[2:0] |

IFA_GN[2:0] |

VAMP_GN[7:0] |

| Default |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

ąŚąĮą░č湥ąĮąĖčÅ ą┐ąŠą╗ąĄą╣:

| Default: 0FF80H |

| CP_MIXER[2:0] |

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ č鹊ą║ąŠą╝ čüą╝ąĄčüąĖč鹥ą╗čÅ RF |

| IFA_GN[2:0] |

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čāčüąĖą╗ąĄąĮąĖąĄą╝ IFABF |

| VAMP_GN[7:0] |

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čāčüąĖą╗ąĄąĮąĖąĄą╝ 2 ą▓ąĖą┤ąĄąŠ |

ąÉą┤čĆąĄčü 0x09: Receiver Control Register 2

| ąæąĖčéčŗ |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| ąśą╝čÅ |

IFAF_GN[2:0] |

REGBS_VADJ[2:0] |

REGIF_VADJ[2:0] |

BC[2:0] |

RSSI_SQUELCH_D[7:0] |

| Default |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

ąŚąĮą░č湥ąĮąĖčÅ ą┐ąŠą╗ąĄą╣:

| Default: B2007H |

| IFAF_GN[2:0] |

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čāčüąĖą╗ąĄąĮąĖąĄą╝ IFAAF |

| REGBS_VADJ[2:0] |

ą¤ąŠą┤čüčéčĆąŠą╣ą║ą░ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ čĆąĄą│čāą╗čÅč鹊čĆą░ BS |

| REGIF_VADJ[2:0] |

ą¤ąŠą┤čüčéčĆąŠą╣ą║ą░ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ čĆąĄą│čāą╗čÅč鹊čĆą░ IF |

| BC[2:0] |

ą¤ąŠą┤čüčéčĆąŠą╣ą║ą░ BC |

| RSSI_SQUELCH_D[7:0] |

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ RSSI ąĖ čłčāą╝ąŠą┐ąŠą┤ą░ą▓ąĖč鹥ą╗čÅ |

ąÉą┤čĆąĄčü 0x0A: Power Down Control Register

| ąæąĖčéčŗ |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

| ąśą╝čÅ |

PD_VCLAMP |

PD_VAMP |

PD_IF_DEMOD |

PD_IFAF |

PD_RSSI_SQUELCH |

PD_REGBS |

PD_REGIF |

PD_BC |

PD_DIV4 |

PD_5GVCO |

| 5G Default |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

| ąæąĖčéčŗ |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| ąśą╝čÅ |

PD_SYN |

PD_AU6M |

PD_6M |

PD_AU6M5 |

PD_6M5 |

PD_REG1D8 |

PD_IFABF |

PD_MIXER |

PD_DIV80 |

PD_PLL1D8 |

| 5G Default |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

ąŚąĮą░č湥ąĮąĖčÅ ą┐ąŠą╗ąĄą╣:

| 5GHz Default: 10C13H |

| PD_VCLAMP |

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą▓čŗą║ą╗čÄč湥ąĮąĖąĄą╝ ą┐ąĖčéą░ąĮąĖčÅ Video clamp |

| PD_VAMP |

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą▓čŗą║ą╗čÄč湥ąĮąĖąĄą╝ ą┐ąĖčéą░ąĮąĖčÅ ą▓ąĖą┤ąĄąŠčāčüąĖą╗ąĖč鹥ą╗čÅ |

| PD_IF_DEMOD |

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą▓čŗą║ą╗čÄč湥ąĮąĖąĄą╝ ą┐ąĖčéą░ąĮąĖčÅ ą┤ąĄą╝ąŠą┤čāą╗čÅč鹊čĆą░ ą¤ą¦ |

| PD_IFAF |

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą▓čŗą║ą╗čÄč湥ąĮąĖąĄą╝ ą┐ąĖčéą░ąĮąĖčÅ IFAF |

| PD_RSSI_SQUELCH |

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą▓čŗą║ą╗čÄč湥ąĮąĖąĄą╝ ą┐ąĖčéą░ąĮąĖčÅ RSSI ąĖ čłčāą╝ąŠą┐ąŠą┤ą░ą▓ąĖč鹥ą╗čÅ |

| PD_REGBS |

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą▓čŗą║ą╗čÄč湥ąĮąĖąĄą╝ ą┐ąĖčéą░ąĮąĖčÅ BS |

| PD_REGIF |

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą▓čŗą║ą╗čÄč湥ąĮąĖąĄą╝ ą┐ąĖčéą░ąĮąĖčÅ čĆąĄą│čāą╗čÅč鹊čĆą░ IF |

| PD_BC |

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą▓čŗą║ą╗čÄč湥ąĮąĖąĄą╝ ą┐ąĖčéą░ąĮąĖčÅ BC |

| PD_DIV4 |

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą▓čŗą║ą╗čÄč湥ąĮąĖąĄą╝ ą┐ąĖčéą░ąĮąĖčÅ ą┤ąĄą╗ąĖč鹥ą╗čÅ ąĮą░ 4 |

| PD_5GVCO |

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą▓čŗą║ą╗čÄč湥ąĮąĖąĄą╝ ą┐ąĖčéą░ąĮąĖčÅ 5G VCO |

| PD_SYN |

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą▓čŗą║ą╗čÄč湥ąĮąĖąĄą╝ ą┐ąĖčéą░ąĮąĖčÅ SYN |

| PD_AU6M |

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą▓čŗą║ą╗čÄč湥ąĮąĖąĄą╝ ą┐ąĖčéą░ąĮąĖčÅ 6M ą╝ąŠą┤čāą╗čÅč鹊čĆą░ ąĘą▓čāą║ą░ |

| PD_6M |

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą▓čŗą║ą╗čÄč湥ąĮąĖąĄą╝ ą┐ąĖčéą░ąĮąĖčÅ 6M |

| PD_AU6M5 |

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą▓čŗą║ą╗čÄč湥ąĮąĖąĄą╝ ą┐ąĖčéą░ąĮąĖčÅ 6M5 ą╝ąŠą┤čāą╗čÅč鹊čĆą░ ąĘą▓čāą║ą░ |

| PD_6M5 |

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą▓čŗą║ą╗čÄč湥ąĮąĖąĄą╝ ą┐ąĖčéą░ąĮąĖčÅ 6M5 |

| PD_REG1D8 |

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą▓čŗą║ą╗čÄč湥ąĮąĖąĄą╝ ą┐ąĖčéą░ąĮąĖčÅ čĆąĄą│čāą╗čÅč鹊čĆą░ 1.8V |

| PD_IFABF |

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą▓čŗą║ą╗čÄč湥ąĮąĖąĄą╝ ą┐ąĖčéą░ąĮąĖčÅ IFABF |

| PD_MIXER |

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą▓čŗą║ą╗čÄč湥ąĮąĖąĄą╝ ą┐ąĖčéą░ąĮąĖčÅ čüą╝ąĄčüąĖč鹥ą╗čÅ RF |

| PD_DIV80 |

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą▓čŗą║ą╗čÄč湥ąĮąĖąĄą╝ ą┐ąĖčéą░ąĮąĖčÅ ą┤ąĄą╗ąĖč鹥ą╗čÅ ąĮą░ 80 |

| PD_PLL1D8 |

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą▓čŗą║ą╗čÄč湥ąĮąĖąĄą╝ ą┐ąĖčéą░ąĮąĖčÅ čĆąĄą│čāą╗čÅč鹊čĆą░ PLL 1.8V |

ąÉą┤čĆąĄčüą░ 0x0B .. 0x0E: ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ

ąÉą┤čĆąĄčü 0x0F: State Register

| ąæąĖčéčŗ |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| ąśą╝čÅ |

- |

STATE[2:0] |

| Default |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąĪąŠčüč鹊čÅąĮąĖčÅ:

| STATE[2:0] |

ąśą╝čÅ čüąŠčüč鹊čÅąĮąĖčÅ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| 000 |

RESET |

ąĪąŠčüč鹊čÅąĮąĖąĄ čüą▒čĆąŠčüą░ |

| 001 |

PWRON_CAL |

ąĪąŠčüč鹊čÅąĮąĖąĄ ą▓ą║ą╗čÄč湥ąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ |

| 010 |

STBY |

ąĪąŠčüč鹊čÅąĮąĖąĄ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ąĖ (standby) |

| 011 |

VCO_CAL |

ąĪąŠčüč鹊čÅąĮąĖąĄ VCO |

| 100 .. 111 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

|

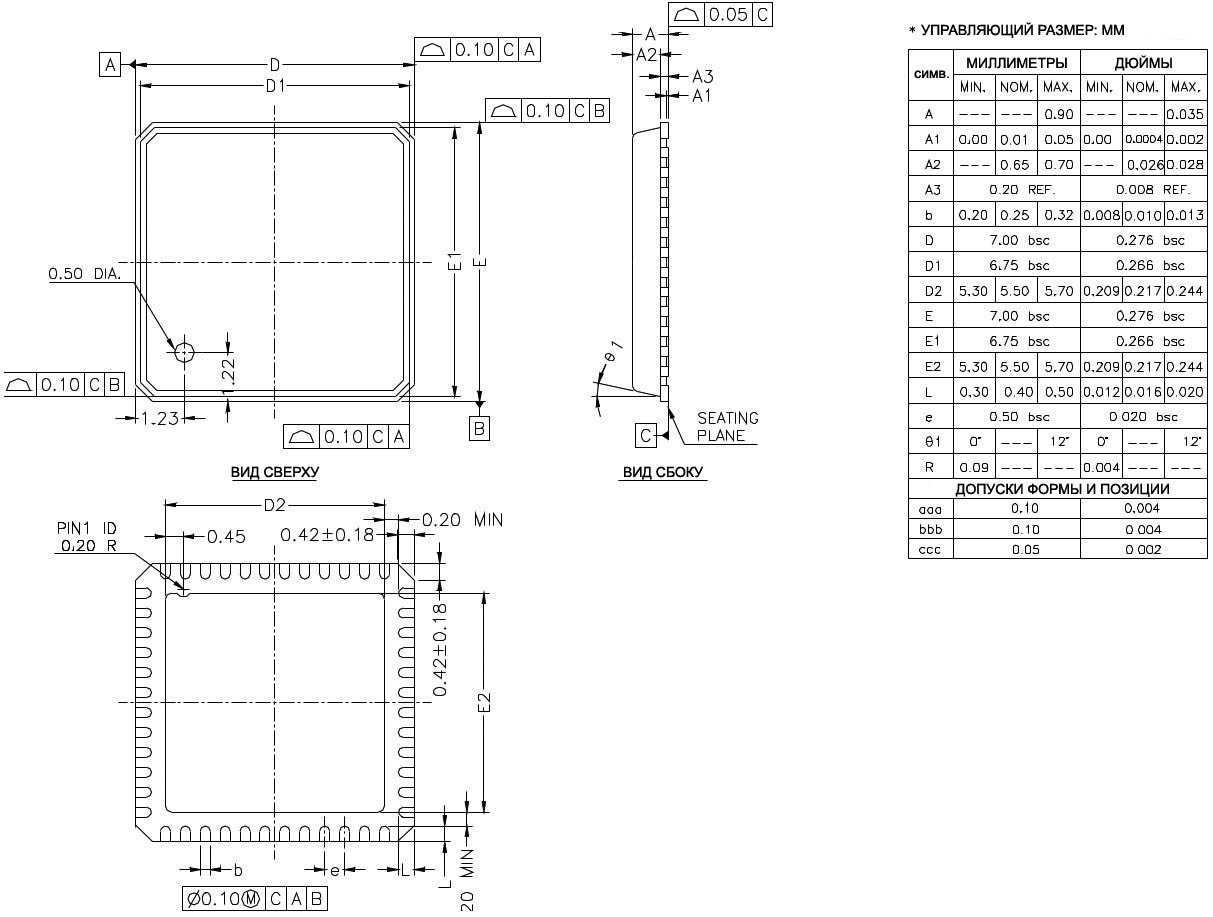

ąĀąĖčü. 3. ąÜąŠčĆą┐čāčü QFN 7X7 ą╝ą╝, 48 ą▓čŗą▓ąŠą┤ąŠą▓.

[ąØą░čüčéčĆąŠą╣ą║ą░ ąĮą░ ą┐čĆąŠąĖąĘą▓ąŠą╗čīąĮčāčÄ čćą░čüč鹊čéčā]

ąÆ ą┐čĆąŠąĄą║č鹥 [2] ąĄčüčéčī čäčāąĮą║čåąĖčÅ prog_freg, ąŠąĮą░ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī RTC6715 ąĮą░ ą╗čÄą▒čāčÄ čćą░čüč鹊čéčā ą┤ąĖą░ą┐ą░ąĘąŠąĮą░ 5.8 ąōąōčå. ąØą░ ą▓čģąŠą┤ąĄ čäčāąĮą║čåąĖčÅ ą┐čĆąĖąĮąĖą╝ą░ąĄčé ąĘąĮą░č湥ąĮąĖąĄ ą▓ ą£ąōčå.

[ąĪčüčŗą╗ą║ąĖ]

1. ąØą░čüčéčĆąŠą╣ą║ą░ ATOMRC Tx2500 5.8G VTX.

2. ą¤čĆąŠą┤ą▓ąĖąĮčāčéčŗą╣ ą┐čĆąĖąĄą╝ąĮąĖą║ ąĮą░ 5.8ąōąōčå ąĖą╗ąĖ AVR + RX5808 site:kt-315.livejournal.com. |