|

ą¤ąŠ ą╝ąĄčĆąĄ čĆąŠčüčéą░ ąĘą░ą┐čĆąŠčüąŠą▓ ą║ ą▓čŗčüąŠą║ąŠčüą║ąŠčĆąŠčüčéąĮąŠą╣ ą┐ąĄčĆąĄą┤ą░č湥 ą┤ą░ąĮąĮčŗčģ ąĖąĮč鹥čĆč乥ą╣čü ą╝ąĄąČą┤čā ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ą╝ąĖ čüčéą░ą╗ ą║čĆąĖčéąĖč湥čüą║ąĖą╝ ą┐čĆąĖ ą┤ąŠčüčéąĖąČąĄąĮąĖąĖ ą┐čĆąŠčéąĖą▓ąŠčĆąĄčćąĖą▓čŗčģ čéčĆąĄą▒ąŠą▓ą░ąĮąĖą╣ ą▓čŗčüąŠą║ąŠą╣ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéąĖ, ąĮąĖąĘą║ąŠą│ąŠ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ čŹąĮąĄčĆą│ąĖąĖ ąĖ čāčüč鹊ą╣čćąĖą▓ąŠčüčéąĖ ą║ ą┐ąŠą╝ąĄčģą░ą╝. ą¦ą░čēąĄ ą▓čüąĄą│ąŠ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ čéčĆąĖ ąĖąĮč鹥čĆč乥ą╣čüą░: PECL (positive-referenced emitter-coupled logic), LVDS (low-voltage differential signals) ąĖ CML (current mode logic). ą¤čĆąĖ čĆą░ąĘčĆą░ą▒ąŠčéą║ąĄ ą▓čŗčüąŠą║ąŠčüą║ąŠčĆąŠčüčéąĮčŗčģ čüąĖčüč鹥ą╝ ą╗čÄą┤ąĖ čćą░čüč鹊 ą▓čüčéčĆąĄčćą░čÄčéčüčÅ čü ą┐čĆąŠą▒ą╗ąĄą╝ąŠą╣ čüąŠąĄą┤ąĖąĮąĄąĮąĖčÅ čĆą░ąĘą╗ąĖčćąĮčŗčģ ą╝ąĖą║čĆąŠčüčģąĄą╝ čü čĆą░ąĘąĮčŗą╝ąĖ ąĖąĮč鹥čĆč乥ą╣čüą░ą╝ąĖ. ą¦č鹊ą▒čŗ čĆąĄčłąĖčéčī čŹčéčā ą┐čĆąŠą▒ą╗ąĄą╝čā, ą▓ą░ąČąĮąŠ ą┐ąŠąĮąĖą╝ą░čéčī ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ čüčģąĄą╝ ą▓čģąŠą┤ąŠą▓ ąĖ ą▓čŗčģąŠą┤ąŠą▓ ą║ą░ąČą┤ąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░, čćč鹊ą▒čŗ ąŠčĆą│ą░ąĮąĖąĘąŠą▓ą░čéčī ą┐čĆą░ą▓ąĖą╗čīąĮąŠąĄ čüą╝ąĄčēąĄąĮąĖąĄ čāčĆąŠą▓ąĮąĄą╣ ąĖ č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖąĄ. ąÆ čŹč鹊ą╝ ą┤ąŠą║čāą╝ąĄąĮč鹥 (ą┐ąĄčĆąĄą▓ąŠą┤ ą┤ąŠą║čāą╝ąĄąĮčéą░čåąĖąĖ [1, 2]) ąŠą┐ąĖčüčŗą▓ą░čÄčéčüčÅ čĆą░ąĘą╗ąĖčćąĮčŗąĄ čüąŠąĄą┤ąĖąĮąĄąĮąĖčÅ ą╝ąĄąČą┤čā PECL, CML ąĖ LVDS ą┤ą╗čÅ ą▓čŗčüąŠą║ąŠčüą║ąŠčĆąŠčüčéąĮčŗčģ čüąĖčüč鹥ą╝ ąŠą▒ą╝ąĄąĮą░ ą┤ą░ąĮąĮčŗą╝ąĖ. ąÆ ą┐čĆąĖą╝ąĄčĆą░čģ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą║ąŠą╝ą┐ą░ąĮąĖą╣ Maxim Integrated ąĖ Texas Instruments.

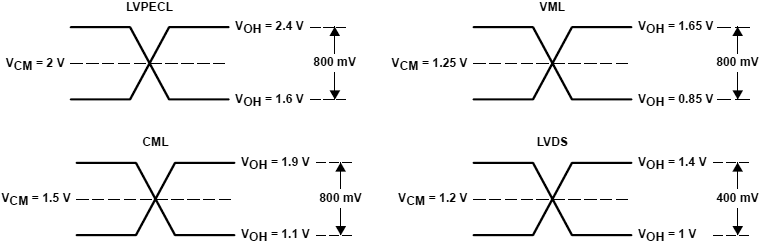

ąÆ čéą░ą▒ą╗ąĖčåąĄ ąĮąĖąČąĄ ą┐ąŠą║ą░ąĘą░ąĮčŗ ą▓ čüčĆą░ą▓ąĮąĄąĮąĖąĖ ąŠą▒čēąĖąĄ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ ą▓čŗčüąŠą║ąŠčüą║ąŠčĆąŠčüčéąĮčŗčģ ąĖąĮč鹥čĆč乥ą╣čüąŠą▓ LVPECL, CML, VML ąĖ LVDS.

| ą¤ą░čĆą░ą╝ąĄčéčĆ |

LVPECL |

CML |

VML |

LVDS |

| VOH (ą╗ąŠą│. 1) |

2.4 V |

1.9 V |

1.65 V |

1.4 V |

| VOL (ą╗ąŠą│. 0) |

1.6 V |

1.1 V |

0.85 V |

1 V |

| ąĀą░ąĘąĮąĖčåą░ ą╝ąĄąČą┤čā ą╗ąŠą│. 0 ąĖ ą╗ąŠą│. 1 (ą▓čŗčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗) |

800 mV |

400 mV |

| VCM (čüčĆąĄą┤ąĮąĄąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ąĘąĄą╝ą╗ąĖ) |

2 V |

1.5 V |

1.25 V |

1.2 V |

ąÆ čéą░ą▒ą╗ąĖčåąĄ ąĮąĖąČąĄ ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮčŗ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą╗ąŠą│ąĖą║ąĖ SERDES ą║ąŠą╝ą┐ą░ąĮąĖąĖ Texas Instruments čü ąĖąĮč鹥čĆč乥ą╣čüą░ą╝ąĖ LVPECL, CML, VML, LVDS. ąÆ ąĮąĄą║ąŠč鹊čĆčŗčģ ąĖąĘ ąĮąĖčģ ąĖą╝ąĄąĄčéčüčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĄąĄ č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖąĄ ąĖ ąŠčĆą│ą░ąĮąĖąĘą░čåąĖčÅ čüą╝ąĄčēąĄąĮąĖčÅ (čüč鹊ą╗ą▒čåčŗ ąóąĄčĆą╝. ąĖ ąĪą╝ąĄčē.).

| ą£ąĖą║čĆąŠčüčģąĄą╝ą░ |

LVPECL |

CML |

VML |

LVDS |

ąóąĄčĆą╝. |

ąĪą╝ąĄčē. |

| TNETE2201B |

ŌłÜ |

|

|

|

|

|

| TLK1501 |

|

ŌłÜ |

|

|

|

|

| TLK2501 |

|

ŌłÜ |

|

|

|

|

| TLK2701 |

|

ŌłÜ |

|

|

|

|

| TLK2711 |

|

|

ŌłÜ |

|

ŌłÜ |

ŌłÜ |

| TLK3101 |

|

|

ŌłÜ |

|

ŌłÜ |

ŌłÜ |

| TLK1201 |

|

|

ŌłÜ |

|

|

ŌłÜ |

| TLK2201 |

|

|

ŌłÜ |

|

|

ŌłÜ |

| TLK2208 |

|

|

ŌłÜ |

|

ŌłÜ |

ŌłÜ |

| TLK31x4 |

|

|

ŌłÜ |

|

ŌłÜ |

ŌłÜ |

| TLK4015 |

|

ŌłÜ |

|

|

|

|

| SLK25x1 |

|

|

ŌłÜ |

|

ŌłÜ |

ŌłÜ |

| SLK27x1 |

|

|

ŌłÜ |

|

ŌłÜ |

ŌłÜ |

| SLK2504 |

|

|

ŌłÜ |

|

ŌłÜ |

ŌłÜ |

| SN65LVDS9x |

|

|

|

ŌłÜ |

|

|

| SN65LV1021/1212 |

|

|

|

ŌłÜ |

|

|

| SN65LV1023/1224 |

|

|

|

ŌłÜ |

|

|

[ąśąĮč鹥čĆč乥ą╣čü PECL]

PECL ą┐čĆąŠąĖąĘąŠčłąĄą╗ ąŠčé ECL, ąĮąŠ ą▓ ąŠčéą╗ąĖčćąĖąĄ ąŠčé ECL ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ. ą×čéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ąĮąĄą▒ąŠą╗čīčłąŠą╣ ą┐ąĄčĆąĄą┐ą░ą┤ čüąĖą│ąĮą░ą╗ą░ PECL ą┤ąĄą╗ą░ąĄčé čŹčéčā ą╗ąŠą│ąĖą║čā ą┐ąŠą┤čģąŠą┤čÅčēąĄą╣ ą┤ą╗čÅ ą▓čŗčüąŠą║ąŠčüą║ąŠčĆąŠčüčéąĮčŗčģ ą╗ąĖąĮą║ąŠą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą╣ ąĖ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ. ąśąĘąĮą░čćą░ą╗čīąĮąŠ čĆą░ąĘčĆą░ą▒ąŠčéą░ąĮąĮčŗą╣ Motorola, čüčéą░ąĮą┤ą░čĆčé PECL čāąČąĄ ą┤ą░ą▓ąĮąŠ ąĘą░ą▓ąŠąĄą▓ą░ą╗ ą┐ąŠą┐čāą╗čÅčĆąĮąŠčüčéčī čā ąŠčüčéą░ą╗čīąĮčŗčģ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗ąĄą╣ 菹╗ąĄą║čéčĆąŠąĮąĖą║ąĖ.

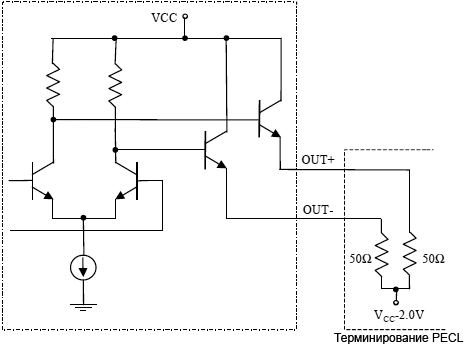

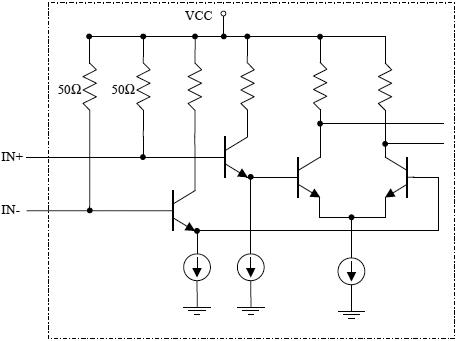

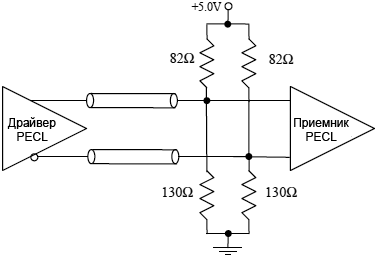

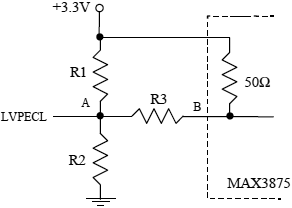

ąĪčéčĆčāą║čéčāčĆą░ ą▓čŗčģąŠą┤ą░ PECL. ą×čĆą│ą░ąĮąĖąĘą░čåąĖčÅ ą▓čŗčģąŠą┤ą░ PECL ą┐ąŠą║ą░ąĘą░ąĮą░ ąĮą░ čĆąĖčü. 1. ą×ąĮą░ čüąŠčüč鹊ąĖčé ąĖąĘ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą╣ ą┐ą░čĆčŗ, ą║ąŠč鹊čĆą░čÅ čāą┐čĆą░ą▓ą╗čÅąĄčé ą┐ą░čĆąŠą╣ 菹╝ąĖčéč鹥čĆąĮčŗčģ ą┐ąŠą▓č鹊čĆąĖč鹥ą╗ąĄą╣. ąÆčŗčģąŠą┤ 菹╝ąĖčéč鹥čĆąĮčŗčģ ą┐ąŠą▓č鹊čĆąĖč鹥ą╗ąĄą╣ ą┤ąŠą╗ąČąĄąĮ čĆą░ą▒ąŠčéą░čéčī ą▓ ą░ą║čéąĖą▓ąĮąŠą╝ čĆąĄą│ąĖąŠąĮąĄ, čü č鹥ą║čāčēąĖą╝ ąĮąĄą┐čĆąĄčĆčŗą▓ąĮąŠ ą┐ąŠčüč鹊čÅąĮąĮčŗą╝ č鹊ą║ąŠą╝ (čéčĆą░ąĮąĘąĖčüč鹊čĆčŗ ą┐ąŠčüč鹊čÅąĮąĮąŠ ąĮą░čģąŠą┤čÅčéčüčÅ ąĮą░ ą░ą║čéąĖą▓ąĮąŠą╝ čāčćą░čüčéą║ąĄ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ, ąĮąĄ ą▓čģąŠą┤čÅ ą▓ ąĮą░čüčŗčēąĄąĮąĖąĄ ąĖą╗ąĖ ąŠčéčüąĄčćą║čā). ąŁč鹊 ą┐ąŠą▓čŗčłą░ąĄčé čüą║ąŠčĆąŠčüčéčī ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ, ąĖ ą┐ąŠą╝ąŠą│ą░ąĄčé čüąĮąĖąĘąĖčéčī ą▓čĆąĄą╝čÅ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ čéčĆą░ąĮąĘąĖčüč鹊čĆąŠą▓. ąöą╗čÅ ą▓čŗčģąŠą┤ą░ PECL ą┐čĆą░ą▓ąĖą╗čīąĮąŠąĄ č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖąĄ čüąŠčüčéą░ą▓ą╗čÅąĄčé 50 ╬® ą┤ą╗čÅ (VCCŌĆō2V). ą¤čĆąĖ čéą░ą║ąŠą╝ č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖąĖ ąŠą▒ą░ ą▓čŗčģąŠą┤ą░ OUT+ ąĖ OUT- ą▒čāą┤čāčé ąŠą▒čŗčćąĮąŠ ąĮą░ čāčĆąŠą▓ąĮąĄ (VCC-1.3V), ą▓ čĆąĄąĘčāą╗čīčéą░č鹥 č湥ą│ąŠ ą┐ąŠčüč鹊čÅąĮąĮčŗą╣ ą▓čŗčģąŠą┤ąĮąŠą╣ č鹊ą║ čüąŠčüčéą░ą▓ąĖčé ą┐čĆąĖą╝ąĄčĆąĮąŠ 14 mA. ąÆčŗčģąŠą┤ąĮąŠąĄ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ ą▓čŗčģąŠą┤ą░ PECL ąĮąĖąĘą║ąŠąĄ, ąŠą▒čŗčćąĮąŠ ą┐ąŠčĆčÅą┤ą║ą░ 4 .. 5 ╬®, čćč鹊 ą┤ą░ąĄčé ąŠčéą╗ąĖčćąĮčāčÄ čāą┐čĆą░ą▓ą╗čÅąĄą╝ąŠčüčéčī ą┐ąŠ ą▓čŗčģąŠą┤čā. ąÜąŠą│ą┤ą░ ą▓čŗčģąŠą┤čŗ PECL čāą┐čĆą░ą▓ą╗čÅčÄčé ą╗ąĖąĮąĖąĄą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ, čŹč鹊 ąĮąĖąĘą║ąŠąĄ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ, ą║ąŠč鹊čĆąŠąĄ ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ąĮąĄą┐čĆą░ą▓ąĖą╗čīąĮąŠąĄ ąŠą▒čĆą░čéąĮąŠąĄ č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖąĄ, ą╝ąŠąČąĄčé ą┐čĆąĖą▓ąĄčüčéąĖ ą║ ą▓čŗčüąŠą║ąŠčćą░čüč鹊čéąĮčŗą╝ ąĖčüą║ą░ąČąĄąĮąĖčÅą╝.

ąĀąĖčü. 1. ąĪčéčĆčāą║čéčāčĆą░ ą▓čŗčģąŠą┤ą░ PECL.

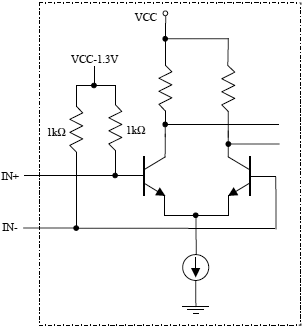

ąĪčéčĆčāą║čéčāčĆą░ ą▓čģąŠą┤ą░ PECL. ą×čĆą│ą░ąĮąĖąĘą░čåąĖčÅ ą▓čģąŠą┤ą░ PECL ą┐ąŠą║ą░ąĘą░ąĮą░ ąĮą░ čĆąĖčü. 2. ąŁč鹊 ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣ ą║ą░čüą║ą░ą┤, ą┐ąĄčĆąĄą║ą╗čÄčćą░ąĄą╝čŗą╣ č鹊ą║ąŠą╝, čü ą▓čŗčüąŠą║ąĖą╝ ą▓čģąŠą┤ąĮčŗą╝ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄą╝. ąöą╗čÅ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖčÅ čĆą░ą▒ąŠč湥ą│ąŠ čĆąĄąČąĖą╝ą░ čüčĆąĄą┤ąĮąĄąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ąĘąĄą╝ą╗ąĖ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ąŠą║ąŠą╗ąŠ (VCC-1.3V). ąÆčŗčüąŠą║ąŠčćą░čüč鹊čéąĮčŗąĄ (HF) ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ Maxim ą▒čŗą▓ą░čÄčé ą┤ą▓čāčģ čéąĖą┐ąŠą▓ ąŠčĆą│ą░ąĮąĖąĘą░čåąĖąĖ ą▓čģąŠą┤ą░ PECL. ą×ą┤ąĖąĮ čüąŠ ą▓čüčéčĆąŠąĄąĮąĮčŗą╝ čüą╝ąĄčēąĄąĮąĖąĄą╝ (ąĮą░ą┐čĆąĖą╝ąĄčĆ MAX3885), ą┤čĆčāą│ąŠą╣ ą▒ąĄąĘ ą▓čüčéčĆąŠąĄąĮąĮąŠą│ąŠ čüą╝ąĄčēąĄąĮąĖčÅ (ąĮą░ą┐čĆąĖą╝ąĄčĆ MAX3867, MAX3675). ąÆ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╝ čüą╗čāčćą░ąĄ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠąĄ ą▓ąĮąĄčłąĮąĄąĄ čüą╝ąĄčēąĄąĮąĖąĄ ą┐ąŠ ą┐ąŠčüč鹊čÅąĮąĮąŠą╝čā č鹊ą║čā ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮąŠ čüąĮą░čĆčāąČąĖ.

|

|

(a) ąĪąŠ ą▓čüčéčĆąŠąĄąĮąĮąŠą╣ ą▓ čćąĖą┐ čüčģąĄą╝ąŠą╣

ą▓čŗčüąŠą║ąŠąŠą╝ąĮąŠą│ąŠ čüą╝ąĄčēąĄąĮąĖčÅ |

(b) ąæąĄąĘ ą▓čüčéčĆąŠąĄąĮąĮąŠą│ąŠ čüą╝ąĄčēąĄąĮąĖčÅ |

ąĀąĖčü 2. ąĪčéčĆčāą║čéčāčĆą░ ą▓čģąŠą┤ą░ PECL.

ąÆ čéą░ą▒ą╗ąĖčåąĄ I ą┤ą░ąĮčŗ čüą┐ąĄčåąĖčäąĖą║ą░čåąĖąĖ ą▓čģąŠą┤ąŠą▓ ąĖ ą▓čŗčģąŠą┤ąŠą▓ PECL ą║ąŠą╝ą┐ą░ąĮąĖąĖ Maxim.

ąóą░ą▒ą╗ąĖčåą░ I. ą¤ą░čĆą░ą╝ąĄčéčĆčŗ ą▓čģąŠą┤ąŠą▓ ąĖ ą▓čŗčģąŠą┤ąŠą▓ PECL.

| ą¤ą░čĆą░ą╝ąĄčéčĆ |

ąŻčüą╗ąŠą▓ąĖčÅ |

min |

MAX |

ąĢą┤. |

| ąÆčŗčģąŠą┤ąĮą░čÅ ą╗ąŠą│. 1 |

TA = 0┬░C .. +85┬░C |

VCC ŌĆō 1.025 |

VCC ŌĆō 0.88 |

V |

| TA = ŌĆō40┬░C |

VCC ŌĆō 1.085 |

| ąÆčŗčģąŠą┤ąĮąŠą╣ ą╗ąŠą│. 0 |

TA = 0┬░C .. +85┬░C |

VCC ŌĆō 1.81 |

VCC ŌĆō 1.62 |

| TA = ŌĆō40┬░C |

VCC ŌĆō 1.83 |

VCC ŌĆō 1.55 |

| ąÆčģąŠą┤ąĮą░čÅ ą╗ąŠą│. 1 |

|

VCC ŌĆō 1.16 |

VCC ŌĆō 0.88 |

| ąÆčģąŠą┤ąĮąŠą╣ ą╗ąŠą│. 0 |

|

VCC ŌĆō 1.81 |

VCC ŌĆō 1.48 |

ąśąĮč鹥čĆč乥ą╣čü PECL ą┐ąŠą┤čģąŠą┤ąĖčé ą║ą░ą║ ą┤ą╗čÅ +5.0V, čéą░ą║ ąĖ ą┤ą╗čÅ +3.3V ąĮą░ą┐čĆčÅąČąĄąĮąĖą╣ ą┐ąĖčéą░ąĮąĖčÅ. ąÜąŠą│ą┤ą░ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ +3.3V, čéą░ą║ąŠą╣ ąĖąĮč鹥čĆč乥ą╣čü ąŠą▒čŗčćąĮąŠ ąĮą░ąĘčŗą▓ą░čÄčé ąĮąĖąĘą║ąŠą▓ąŠą╗čīčéąĮčŗą╝ PECL (low-voltage PECL, čüąŠą║čĆą░čēąĄąĮąĮąŠ LVPECL).

ąĪą╗ąĄą┤čāąĄčé čāą┤ąĄą╗ąĖčéčī ąŠčüąŠą▒ąŠąĄ ą▓ąĮąĖą╝ą░ąĮąĖąĄ čĆą░ąĘą▓čÅąĘą║ąĄ ą┐ąŠ ą┐ąĖčéą░ąĮąĖčÄ, čćč鹊ą▒čŗ ąŠą▒ąĄčüą┐ąĄčćąĖčéčī ąŠčéčüčāčéčüčéą▓ąĖąĄ ą┐ąŠą╝ąĄčģ ąĖ čłčāą╝ą░ ąĮą░ čłąĖąĮąĄ ą┐ąĖčéą░ąĮąĖčÅ. ąóą░ą║ąČąĄ čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅ ą┐ąŠ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą╝čā č鹊ą║čā (AC) ąĖ ą┐ąŠčüč鹊čÅąĮąĮąŠą╝čā č鹊ą║čā (DC) ąĮą░ą║ą╗ą░ą┤čŗą▓ą░čÄčé ąĮą░ ą▓čŗčģąŠą┤čŗ PECL ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗąĄ ąŠą│čĆą░ąĮąĖč湥ąĮąĖčÅ ą┐ąŠ č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖčÄ čåąĄą┐ąĄą╣.

[ąśąĮč鹥čĆč乥ą╣čü CML]

CML čÅą▓ą╗čÅąĄčéčüčÅ ąŠą┤ąĮąĖą╝ ąĖąĘ ą┐čĆąŠčüč鹥ą╣čłąĖčģ ą┐čĆąŠč鹊ą║ąŠą╗ąŠą▓ ą┤ą╗čÅ ą▓čŗčüąŠą║ąŠčüą║ąŠčĆąŠčüčéąĮąŠą│ąŠ ą▓ąĘą░ąĖą╝ąŠą┤ąĄą╣čüčéą▓ąĖčÅ. ąÆčüčéčĆąŠąĄąĮąĮčŗąĄ č鹥čĆą╝ąĖąĮą░č鹊čĆčŗ ą┐ąŠ ą▓čģąŠą┤čā ąĖ ą▓čŗčģąŠą┤čā ą╝ąĖąĮąĖą╝ąĖąĘąĖčĆčāčÄčé ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▓ąĮąĄčłąĮąĖčģ ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓, čéčĆąĄą▒čāąĄą╝čŗčģ ą┤ą╗čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ čĆą░ą▒ąŠčćąĖčģ čāčüą╗ąŠą▓ąĖą╣. ą¤ąĄčĆąĄą┐ą░ą┤ čüąĖą│ąĮą░ą╗ą░ ąĮą░ ą▓čŗčģąŠą┤ąĄ CML ąĮąĄą▒ąŠą╗čīčłąŠą╣, ą▒ą╗ą░ą│ąŠą┤ą░čĆčÅ č湥ą╝čā ą┤ąŠčüčéąĖą│ą░ąĄčéčüčÅ ąĮąĖąĘą║ąŠąĄ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ 菹ĮąĄčĆą│ąĖąĖ. ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠ 50 ╬® ąŠą▒čĆą░čéąĮąŠąĄ č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖąĄ ą╝ąĖąĮąĖą╝ąĖąĘąĖčĆčāąĄčé ąŠčéčĆą░ąČąĄąĮąĖąĄ čüąĖą│ąĮą░ą╗ą░, č鹥ą╝ čüą░ą╝čŗą╝ čüąĮąĖąČą░čÅ ą▓čŗčüąŠą║ąŠčćą░čüč鹊čéąĮčŗąĄ ąĖčüą║ą░ąČąĄąĮąĖčÅ.

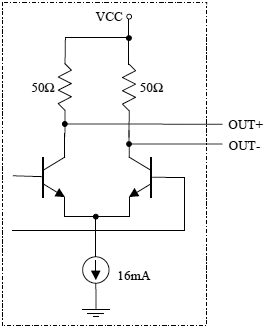

ąĪčéčĆčāą║čéčāčĆą░ ą▓čŗčģąŠą┤ą░ CML. ąÆčŗčģąŠą┤ CML čüąŠčüč鹊ąĖčé ąĖąĘ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą╣ ą┐ą░čĆčŗ čü 50 ╬® čĆąĄąĘąĖčüč鹊čĆą░ą╝ąĖ ą▓ ą║ąŠą╗ą╗ąĄą║č鹊čĆąĄ, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 3.

ąĀąĖčü. 3. ąĪčéčĆčāą║čéčāčĆą░ ą▓čŗčģąŠą┤ą░ CML.

ą¤ąĄčĆąĄą┐ą░ą┤ čüąĖą│ąĮą░ą╗ą░ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄą╝ č鹊ą║ą░ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą╣ ą┐ą░čĆčŗ čéčĆą░ąĮąĘąĖčüč鹊čĆąŠą▓ čü ąŠą▒čēąĖą╝ 菹╝ąĖčéč鹥čĆąŠą╝. ąĢčüą╗ąĖ ą┐čĆąĄą┤ą┐ąŠą╗ąŠąČąĖčéčī, čćč鹊 ą▓ čéąĖą┐ąŠą▓ąŠą╝ ą┐čĆąĖą╝ąĄąĮąĄąĮąĖąĖ ąĖčüč鹊čćąĮąĖą║ č鹊ą║ą░ ą▓ 菹╝ąĖčéč鹥čĆą░čģ 16mA, ąĖ ą▓čŗčģąŠą┤ CML ąĮą░ą│čĆčāąČąĄąĮ 50 ╬® ą▓ąĄčĆčģąĮąĖą╝ąĖ čĆąĄąĘąĖčüč鹊čĆą░ą╝ąĖ (pullup) ąĮą░ VCC, č鹊 ą┐ąĄčĆąĄą┐ą░ą┤ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ąĮą░ ą▓čŗčģąŠą┤ąĄ CML čüąŠčüčéą░ą▓ąĖčé ąŠčé VCC ą┤ąŠ (VCC-0.4V). ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣ čüąĖą│ąĮą░ą╗ ąĮą░ ą▓čŗčģąŠą┤ąĄ CML čüąŠčüčéą░ą▓ąĖčé 800mV, ąĖ čüčĆąĄą┤ąĮąĄąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ąĘąĄą╝ą╗ąĖ ą▒čāą┤ąĄčé (VCC ŌĆō 0.2V). ąöą╗čÅ ąŠą┤ąĮąŠ ąĖ č鹊ą│ąŠ ąČąĄ ąĖčüč鹊čćąĮąĖą║ą░ č鹊ą║ą░, ąĄčüą╗ąĖ ą▓čŗčģąŠą┤ ą┐ąŠ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą╝čā č鹊ą║čā ąĮą░ą│čĆčāąČąĄąĮ ąĮą░ 50 ╬®, č鹊 čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ ą┐ąŠ ą┐ąŠčüč鹊čÅąĮąĮąŠą╝čā č鹊ą║čā č鹥ą┐ąĄčĆčī čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą║ąŠą╗ą╗ąĄą║č鹊čĆąĮčŗą╝ čĆąĄąĘąĖčüč鹊čĆąŠą╝ 50 ╬®. ąÆčŗčģąŠą┤ąĮąŠąĄ čüčĆąĄą┤ąĮąĄąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ąĘąĄą╝ą╗ąĖ CML č鹥ą┐ąĄčĆčī (VCC - 0,4 ąÆ), ąĖ čĆą░ąĘąĮąŠčüčéąĮčŗą╣ ą┐ąĄčĆąĄą┐ą░ą┤ čüąĖą│ąĮą░ą╗ą░ 800 mV ąŠčé ą┐ąĖą║ą░ ą┤ąŠ ą┐ąĖą║ą░. ąÆčŗčģąŠą┤ąĮčŗąĄ čüąĖą│ąĮą░ą╗čŗ ą┤ą╗čÅ AC- ąĖ DC-čüą▓čÅąĘąĖ ą┐ąŠą║ą░ąĘą░ąĮčŗ ąĮą░ čĆąĖčü. 4.

|

|

| (a) DC-coupled, 50 ╬® ąĮą░ VCC |

(b) AC-coupled, čü č鹥čĆą╝ąĖąĮą░č鹊čĆąŠą╝ 50 ╬® |

ąĀąĖčü. 4. ąÆčŗčģąŠą┤ąĮčŗąĄ CML-čüąĖą│ąĮą░ą╗čŗ ą┤ą╗čÅ čüą▓čÅąĘąĖ ą┐ąŠ ą┐ąŠčüč鹊čÅąĮąĮąŠą╝čā č鹊ą║čā (DC-coupled) ąĖ ą┐ąŠ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą╝čā č鹊ą║čā (AC-coupled).

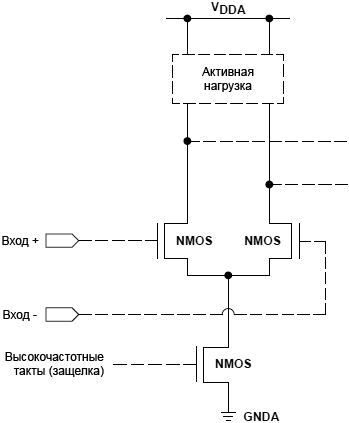

ąĪčéčĆčāą║čéčāčĆą░ ą▓čģąŠą┤ą░ CML. ąĪčéčĆčāą║čéčāčĆą░ ą▓čģąŠą┤ą░ CML ąĖą╝ąĄąĄčé ąĮąĄčüą║ąŠą╗čīą║ąŠ ąŠčüąŠą▒ąĄąĮąĮąŠčüč鹥ą╣, ą║ąŠč鹊čĆčŗąĄ ą┤ąĄą╗ą░čÄčé ąĄąĄ ą┐ąŠą┐čāą╗čÅčĆąĮčŗą╝ ą▓čŗą▒ąŠčĆąŠą╝ ą┤ą╗čÅ ą▓čŗčüąŠą║ąŠčüą║ąŠčĆąŠčüčéąĮčŗčģ ąŠą┐ąĄčĆą░čåąĖą╣. ąÜą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 5, ą▓čģąŠą┤ąĮą░čÅ čüčéčĆčāą║čéčāčĆą░ CML ą║ąŠą╝ą┐ą░ąĮąĖąĖ Maxim ąĖą╝ąĄąĄčé ą▓čģąŠą┤ąĮąŠąĄ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ 50 ╬® ą┤ą╗čÅ čāą┐čĆąŠčēąĄąĮąĖčÅ č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖčÅ. ąÆčģąŠą┤ąĮčŗąĄ čéčĆą░ąĮąĘąĖčüč鹊čĆčŗ ą▓ą║ą╗čÄč湥ąĮčŗ ą║ą░ą║ 菹╝ąĖčéč鹥čĆąĮčŗąĄ ą┐ąŠą▓č鹊čĆąĖč鹥ą╗ąĖ ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ą░čĆąŠą╣ čéčĆą░ąĮąĘąĖčüč鹊čĆąŠą▓ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą│ąŠ čāčüąĖą╗ąĖč鹥ą╗čÅ.

ąĀąĖčü. 5. ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą▓čģąŠą┤ąĮąŠą╣ čåąĄą┐ąĖ CML.

ąÆ čéą░ą▒ą╗ąĖčåąĄ II ą┐ąĄčĆąĄčćąĖčüą╗ąĄąĮčŗ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ ą▓čŗčģąŠą┤ą░ ąĖ ą▓čģąŠą┤ą░ CML ą┤ą╗čÅ MAX3831/MAX3832.

ąóą░ą▒ą╗ąĖčåą░ II. ą¤ą░čĆą░ą╝ąĄčéčĆčŗ ą▓čģąŠą┤ą░ ąĖ ą▓čŗčģąŠą┤ą░ CML (ąĮą░ą│čĆčāąĘą║ą░ = 50 ╬® ąĮą░ VCC).

| ą¤ą░čĆą░ą╝ąĄčéčĆ |

ąĪąĖą╝ą▓. |

min |

typ |

MAX |

ąĢą┤. |

| ąöąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠąĄ ą▓čŗčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ |

|

640 |

800 |

1000 |

mVP-P |

| ąĪčĆąĄą┤ąĮąĄąĄ ą▓čŗčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ąĘąĄą╝ą╗ąĖ |

|

VCC ŌĆō 1.085 |

VCC - 0.2 |

|

V |

| ąöąĖą░ą┐ą░ąĘąŠąĮ ąĮąĄ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą│ąŠ ą▓čģąŠą┤ąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ |

VIS |

VCC ŌĆō 0.6 |

|

VCC + 0.2 |

V |

| ąĀą░ąĘą╝ą░čģ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą│ąŠ ą▓čģąŠą┤ąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ |

|

400 |

|

1200 |

mVP-P |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: čĆą░ąĘą╗ąĖčćąĮčŗąĄ čéąĖą┐čŗ ą╝ąĖą║čĆąŠčüčģąĄą╝ Maxim ąĖą╝ąĄčÄčé čĆą░ąĘąĮčāčÄ čćčāą▓čüčéą▓ąĖč鹥ą╗čīąĮąŠčüčéčī ą┐ąŠ ą▓čģąŠą┤čā CML (ąĮą░ą┐čĆąĖą╝ąĄčĆ MAX3875, MAX3876).

[ąśąĮč鹥čĆč乥ą╣čü VML]

VML čĆą░čüčłąĖčäčĆąŠą▓čŗą▓ą░ąĄčéčüčÅ ą║ą░ą║ voltage-mode logic. ąöčĆą░ą╣ą▓ąĄčĆčŗ VML ą║ąŠą╝ą┐ą░ąĮąĖąĖ Texas Instruments ą┐ąŠ čāčĆąŠą▓ąĮčÅą╝ čüąŠą▓ą╝ąĄčüčéąĖą╝čŗ čü LVPECL. ąÜą░ą║ ąĖ CML, čŹčéąĖ ą┤čĆą░ą╣ą▓ąĄčĆčŗ čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮčŗ ą┐ąŠ č鹥čģąĮąŠą╗ąŠą│ąĖąĖ CMOS, ąĮąŠ ąĖą╝ąĄčÄčé ą┤ąŠčüč鹊ąĖąĮčüčéą▓ąŠ ą▓ č鹊ą╝, čćč鹊 ąĮąĄ čéčĆąĄą▒čāčÄčé ą▓ąĮąĄčłąĮąĖčģ ą▓ąĄčĆčģąĮąĖčģ ąĮą░ą│čĆčāąĘąŠčćąĮčŗčģ čĆąĄąĘąĖčüč鹊čĆąŠą▓ (pullup), ą┐ąŠč鹊ą╝čā čćč鹊 ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĖąĄ čéčĆą░ąĮąĘąĖčüč鹊čĆčŗ NMOS ąĖ PMOS, čćč鹊ą▒čŗ ąŠą▒ąĄčüą┐ąĄčćąĖčéčī ą│ąĄąĮąĄčĆą░čåąĖčÄ ą┐ąĄčĆąĄą┐ą░ą┤ąŠą▓ čüą┐ą░ą┤ą░ ąĖ ąĮą░čĆą░čüčéą░ąĮąĖčÅ čāčĆąŠą▓ąĮčÅ. ąØąĄčüą╝ąŠčéčĆčÅ ąĮą░ č鹊, čćč鹊 VML ą┐ąŠą║ą░ ąĮąĄ čéą░ą║ čłąĖčĆąŠą║ąŠ čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮčŗ, ą║ą░ą║ ą┤čĆčāą│ąĖąĄ ą┤čĆą░ą╣ą▓ąĄčĆčŗ, VML ą▓čüąĄ ąĄčēąĄ ąŠčüčéą░ąĄčéčüčÅ čüąŠą▓ą╝ąĄčüčéąĖą╝čŗą╝ ą┐ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÄ čü čāčĆąŠą▓ąĮčÅą╝ąĖ čüąĖą│ąĮą░ą╗ą░ LVPECL, ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓ąŠ ą╝ąĮąŠą│ąĖčģ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖą╝čŗčģ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░čģ Texas Instruments. ąĀąĄčłąĄąĮąĖčÅ ą┤ą╗čÅ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖčÅ ą│ąĖą│ą░ą▒ąĖčéąĮčŗčģ čüą║ąŠčĆąŠčüč鹥ą╣ čüąŠą┤ąĄčƹȹ░čé ą▓ čüąĄą▒ąĄ ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ ą┤čĆą░ą╣ą▓ąĄčĆ VML. ąóąĄčģąĮąŠą╗ąŠą│ąĖčÅ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░čģ TLK2711, TLK3101, TLK1201, TLK2201, TLK2208, TLK3104SA, TLK3114SA, TLK3104SC, TLK4010, SLK2501, SLK2511, SLK2701, SLK2721 ąĖ SLK2504.

ąĪčéčĆčāą║čéčāčĆą░ ą▓čŗčģąŠą┤ą░ VML. ąØą░ čĆąĖčüčāąĮą║ąĄ ąĮąĖąČąĄ ą┐ąŠą║ą░ąĘą░ąĮą░ ąŠčĆą│ą░ąĮąĖąĘą░čåąĖčÅ ą▓čŗčģąŠą┤ą░ ą┤čĆą░ą╣ą▓ąĄčĆąŠą▓ VML. ąØą░ą┐čĆčÅąČąĄąĮąĖčÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čéčĆą░ąĮąĘąĖčüč鹊čĆą░ą╝ąĖ PMOS ąĖ NMOS ąĖčüą┐ąŠą╗čīąĘčāčÄčé čāčĆąŠą▓ąĮąĖ VOH ąĖ VOL ą┤čĆą░ą╣ą▓ąĄčĆą░, ąĖ ą▓čŗčģąŠą┤ąĮąŠą╣ čéčĆą░ąĮąĘąĖčüč鹊čĆ ą┐čĆąŠčüč鹊 ą┐ąĄčĆąĄą║ą╗čÄčćą░ąĄčéčüčÅ ą╝ąĄąČą┤čā čŹčéąĖą╝ąĖ čāčĆąŠą▓ąĮčÅą╝ąĖ. ąĀą░ąĘą╝ą░čģ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ąĮą░ ą▓čŗčģąŠą┤ąĄ ąĖąĮč鹥čĆč乥ą╣čüąŠą▓ VML ąĮąĄ ąĘą░ą▓ąĖčüąĖčé ąŠčé ąĖą╝ą┐ąĄą┤ą░ąĮčüą░ ąĮą░ą│čĆčāąĘą║ąĖ.

ą×čĆą│ą░ąĮąĖąĘą░čåąĖčÅ ą▓čģąŠą┤ą░ VML. ąÉąĮą░ą╗ąŠą│ąĖčćąĮąŠ ą┐čĆąĖčæą╝ąĮąĖą║čā CML, ą▓čģąŠą┤ąĮąŠą╣ ą║ą░čüą║ą░ą┤ ą┤ą╗čÅ čāčüčéčĆąŠą╣čüčéą▓, čéčĆąĄą▒čāčÄčēąĖčģ čāčĆąŠą▓ąĮąĄą╣ čüąĖą│ąĮą░ą╗ąĖąĘą░čåąĖąĖ VML, čüąŠčüč鹊ąĖčé ąĖąĘ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą╣ ą┐ą░čĆčŗ, ąĖčüą┐ąŠą╗čīąĘčāčÄčēąĄą╣ NMOS-čéčĆą░ąĮąĘąĖčüč鹊čĆčŗ ąĖ ą▓čģąŠą┤čŗ (+ ąĖ -), ą┤ą╗čÅ ą║ąŠč鹊čĆčŗčģ ąĮčāąČąĮčŗ ą▓ąĄčĆčģąĮąĖąĄ ą┐ąŠą┤čéčÅą│ąĖą▓ą░čÄčēąĖąĄ čĆąĄąĘąĖčüč鹊čĆčŗ (pullup) ą┤ą╗čÅ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖčÅ čāčĆąŠą▓ąĮčÅ čüą╝ąĄčēąĄąĮąĖčÅ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ąĘąĄą╝ą╗ąĖ (ą┐ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. [2]).

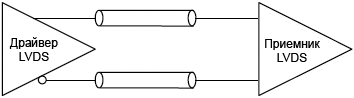

[ąśąĮč鹥čĆč乥ą╣čü LVDS]

LVDS ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĮąĖąĘą║ąŠą▓ąŠą╗čīčéąĮąŠą│ąŠ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ą▓ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ č鹊čćą║ą░-č鹊čćą║ą░ (ąŠčé ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ ą║ ą┐čĆąĖąĄą╝ąĮąĖą║čā). LVDS ąŠą▒ą╗ą░ą┤ą░ąĄčé ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ ą┐čĆąĖą▓ą╗ąĄą║ą░č鹥ą╗čīąĮčŗą╝ąĖ ą┐čĆąĄąĖą╝čāčēąĄčüčéą▓ą░ą╝ąĖ. ąØąĄą▒ąŠą╗čīčłąŠą╣ čĆą░ąĘą╝ą░čģ čüąĖą│ąĮą░ą╗ą░ ą┐čĆąĖą▓ąŠą┤ąĖčé ą║ ąĮąĖąĘą║ąŠą╝čā 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÄ, čüą░ą╝ąŠąĄ ą▒ąŠą╗čīčłąĄąĄ 4mA, ą┐ąŠčüčŗą╗ą░ąĄą╝čŗąĄ č湥čĆąĄąĘ č鹥čĆą╝ąĖąĮąĖčĆčāčÄčēąĖą╣ čĆąĄąĘąĖčüč鹊čĆ 100 ╬®. ąŁč鹊 ą┤ąĄą╗ą░ąĄčé LVDS ą┐čĆąĄą┤ą┐ąŠčćčéąĖč鹥ą╗čīąĮčŗą╝ ą┤ą╗čÅ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠą│ąŠ ą╗ąĖąĮą║ą░ ą┐čĆąĖ ą┐ąĄčĆąĄą┤ą░č湥 ą┤ą░ąĮąĮčŗčģ. ąŻčĆąŠą▓ąĮąĖ čüąĖą│ąĮą░ą╗ąŠą▓ ą┤ąŠčüčéą░č鹊čćąĮąŠ ą╝ą░ą╗čŗ, čćč鹊ą▒čŗ ą╝ąŠąČąĮąŠ ą▒čŗą╗ąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ 2.5V ąĖ ąĮąĖąČąĄ. ą¤ąŠčüą║ąŠą╗čīą║čā ą┤ąĖą░ą┐ą░ąĘąŠąĮ ą▓čģąŠą┤ąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ąŠčé 0V ą┤ąŠ 2.4V, ąĖ ą┐ąĄčĆąĄą┐ą░ą┤ čüąĖą│ąĮą░ą╗ą░ 400 mV, ą▓čģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ąĘąĄą╝ą╗ąĖ ą▒čāą┤ąĄčé ąŠčé 0.2V ą┤ąŠ 2.2V. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝ LVDS ą╝ąŠąČąĄčé ą▓čŗą┤ąĄčƹȹĖą▓ą░čéčī čĆą░ąĘąĮąŠčüčéčī ą┐ąŠč鹥ąĮčåąĖą░ą╗ąŠą▓ ąĘąĄą╝ą╗ąĖ ┬▒1V ą╝ąĄąČą┤čā ą┤čĆą░ą╣ą▓ąĄčĆąŠą╝ (ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ąŠą╝) ąĖ ą┐čĆąĖąĄą╝ąĮąĖą║ąŠą╝ LVDS.

ąĪčéčĆčāą║čéčāčĆą░ ą▓čŗčģąŠą┤ą░ LVDS. ą×čĆą│ą░ąĮąĖąĘą░čåąĖčÅ ą▓čŗčģąŠą┤ą░ LVDS ąŠčé ą║ąŠą╝ą┐ą░ąĮąĖąĖ Maxim ąŠą┐čéąĖą╝ąĖąĘąĖčĆąŠą▓ą░ąĮą░ ą┤ą╗čÅ ąĮąĖąĘą║ąŠą│ąŠ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ čŹąĮąĄčĆą│ąĖąĖ ąĖ ą▓čŗčüąŠą║ąŠą╣ čüą║ąŠčĆąŠčüčéąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ. ąĪčģąĄą╝ą░ ą┐ąŠą║ą░ąĘą░ąĮą░ ąĮą░ čĆąĖčü. 6. ąóąĖą┐ąŠą▓ąŠą╣ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣ ą▓čŗčģąŠą┤ąĮąŠą╣ ąĖą╝ą┐ąĄą┤ą░ąĮčü čüąŠčüčéą░ą▓ą╗čÅąĄčé 100 ╬®. ąĪą╝. čéą░ą▒ą╗ąĖčåčā III ą┤ą╗čÅ ą┤čĆčāą│ąĖčģ ą▓čŗčģąŠą┤ąĮčŗčģ čüą┐ąĄčåąĖčäąĖą║ą░čåąĖą╣.

ąĀąĖčü. 6. ąĪčéčĆčāą║čéčāčĆą░ ą▓čŗčģąŠą┤ą░ LVDS.

ąĪčéčĆčāą║čéčāčĆą░ ą▓čģąŠą┤ą░ LVDS. ą×čĆą│ą░ąĮąĖąĘą░čåąĖčÅ ą▓čģąŠą┤ą░ LVDS, ą┐ąŠą║ą░ąĘą░ąĮąĮą░čÅ ąĮą░ čĆąĖčü. 7, ąĖą╝ąĄąĄčé ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣ ąĖą╝ą┐ąĄą┤ą░ąĮčü 100 ╬® ą╝ąĄąČą┤čā IN+ ąĖ IN-. ąöą╗čÅ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖčÅ čłąĖčĆąŠą║ąŠą│ąŠ ą┤ąĖą░ą┐ą░ąĘąŠąĮą░ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ąĘąĄą╝ą╗ąĖ ą░ą┤ą░ą┐čéąĖą▓ąĮą░čÅ čüčģąĄą╝ą░ čüą┤ą▓ąĖą│ą░ čāčĆąŠą▓ąĮčÅ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé čüčĆąĄą┤ąĮąĄąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ąĘąĄą╝ą╗ąĖ ą▓ ą┐ąŠčüč鹊čÅąĮąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ąĮą░ ą▓čģąŠą┤ąĄ čéčĆąĖą│ą│ąĄčĆą░ ą©ą╝ąĖčéčéą░. ąóčĆąĖą│ą│ąĄčĆ ą©ą╝ąĖčéčéą░ ąŠą▒ąĄčüą┐ąĄčćąĖą▓ą░ąĄčé ą│ąĖčüč鹥čĆąĄąĘąĖčü ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ą▓čģąŠą┤ąĮąŠą│ąŠ ą┐ąŠčĆąŠą│ą░. ąŁč鹊čé čüąĖą│ąĮą░ą╗ ąĘą░č鹥ą╝ ą┐ąŠą┤ą░ąĄčéčüčÅ ąĮą░ čüą╗ąĄą┤čāčÄčēąĖą╣ ą║ą░čüą║ą░ą┤ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą│ąŠ čāčüąĖą╗ąĖč鹥ą╗čÅ.

ąĀąĖčü. 7. ąĪčéčĆčāą║čéčāčĆą░ ą▓čģąŠą┤ą░ LVDS.

ąÆ čéą░ą▒ą╗ąĖčåąĄ III čüčāą╝ą╝ą░čĆąĮąŠ ą┤ą░ąĮčŗ čüą┐ąĄčåąĖčäąĖą║ą░čåąĖąĖ ą▓čģąŠą┤ą░ ąĖ ą▓čŗčģąŠą┤ą░ LVDS (ą┐čĆąĖą╝ąĄąĮąĖą╝ąŠ ą║ MAX3831, MAX3832 ąĖ MAX3890).

ąóą░ą▒ą╗ąĖčåą░ III. ąÆčģąŠą┤ąĮčŗąĄ ąĖ ą▓čŗčģąŠą┤ąĮčŗąĄ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ LVDS.

| ą¤ą░čĆą░ą╝ąĄčéčĆ |

ąĪąĖą╝ą▓. |

ąŻčüą╗ąŠą▓ąĖčÅ |

min |

typ |

MAX |

ąĢą┤. |

| ąÆčŗčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą╗ąŠą│. 1 |

VOH |

|

|

|

1.475 |

V |

| ąÆčŗčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą╗ąŠą│. 0 |

VOL |

|

0.925 |

|

|

V |

| ąöąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠąĄ ą▓čŗčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ |

|Vod| |

|

250 |

|

400 |

mV |

| ąśąĘą╝ąĄąĮąĄąĮąĖąĄ ą░ą╝ą┐ą╗ąĖčéčāą┤čŗ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą│ąŠ ą▓čŗčģąŠą┤ą░ ą┤ą╗čÅ ą║ąŠą╝ą┐ą╗ąĄą╝ąĄąĮčéą░čĆąĮčŗčģ čüąŠčüč鹊čÅąĮąĖą╣ |

Δ|Vod| |

|

|

|

25 |

mV |

| ąÆčŗčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ čüą╝ąĄčēąĄąĮąĖčÅ |

|

|

1.125 |

|

1.275 |

V |

| ąśąĘą╝ąĄąĮąĄąĮąĖąĄ ą░ą╝ą┐ą╗ąĖčéčāą┤čŗ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą│ąŠ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čüą╝ąĄčēąĄąĮąĖčÅ ą┤ą╗čÅ ą║ąŠą╝ą┐ą╗ąĄą╝ąĄąĮčéą░čĆąĮčŗčģ čüąŠčüč鹊čÅąĮąĖą╣ |

Δ|Vos| |

|

|

|

25 |

mV

|

| ąöąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣ ą▓čŗčģąŠą┤ąĮąŠą╣ ąĖą╝ą┐ąĄą┤ą░ąĮčü |

|

|

80 |

|

120 |

╬® |

| ąÆčŗčģąŠą┤ąĮąŠą╣ č鹊ą║ |

|

ąŚą░ą╝čŗą║ą░ąĮąĖąĄ ą┤čĆčāą│ ąĮą░ ą┤čĆčāą│ą░ |

|

|

12 |

mA |

| |

ąŚą░ą╝čŗą║ą░ąĮąĖąĄ ąĮą░ GND |

|

|

40 |

mA |

| ąöąĖą░ą┐ą░ąĘąŠąĮ ą▓čģąŠą┤ąĮčŗčģ ąĮą░ą┐čĆčÅąČąĄąĮąĖą╣ |

Vi |

|

0 |

|

2.4 |

V |

| ąöąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠąĄ ą▓čģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ |

|Vid| |

|

100 |

|

|

mV |

| ąÆčģąŠą┤ąĮąŠą╣ ąĮąĄ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣ č鹊ą║ |

|

ąÆčģąŠą┤ LVDS VOS = 1.2V |

|

350 |

|

╬╝A |

| ą¤ąŠčĆąŠą│ ą│ąĖčüč鹥čĆąĄąĘąĖčüą░ |

|

|

|

70 |

|

mV |

| ąöąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣ ą▓čģąŠą┤ąĮąŠą╣ ąĖą╝ą┐ąĄą┤ą░ąĮčü |

Rin |

|

85 |

100 |

115 |

╬® |

[ąĪąŠąĄą┤ąĖąĮąĄąĮąĖąĄ ą╝ąĄąČą┤čā ąĖąĮč鹥čĆč乥ą╣čüą░ą╝ąĖ]

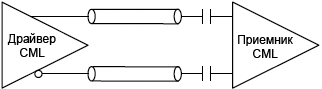

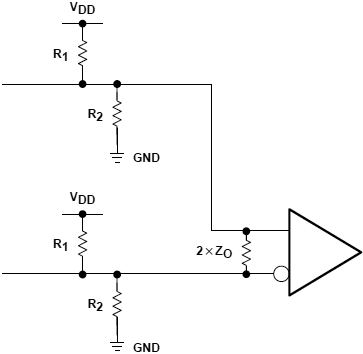

CML-CML. ąĢčüą╗ąĖ ą┐čĆąĖąĄą╝ąĮąĖą║ ąĖ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ ąĖčüą┐ąŠą╗čīąĘčāčÄčé ąŠą▒čēąĄąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ ą┤ą╗čÅ VCC, č鹊 ą▓čŗčģąŠą┤ ą┤čĆą░ą╣ą▓ąĄčĆą░ CML ą╝ąŠąČąĄčé ą▒čŗčéčī ąĮą░ą┐čĆčÅą╝čāčÄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą┐ąŠ ą┐ąŠčüč鹊čÅąĮąĮąŠą╝čā č鹊ą║čā (DC-coupling) ą║ąŠ ą▓čģąŠą┤čā ą┐čĆąĖąĄą╝ąĮąĖą║ą░ CML ą▒ąĄąĘ ą▓čüčÅą║ąĖčģ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗčģ ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓. ąĪąŠąĄą┤ąĖąĮąĄąĮąĖąĄ ą┐ąŠ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą╝čā č鹊ą║čā (AC-coupling) ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ čüąĖčüč鹥ą╝, ą▓ ą║ąŠč鹊čĆčŗčģ ą┐čĆąĖąĄą╝ąĮąĖą║ ąĖ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ čĆą░ą▒ąŠčéą░čÄčé ąŠčé čĆą░ąĘąĮčŗčģ ąĮą░ą┐čĆčÅąČąĄąĮąĖą╣ ą┐ąĖčéą░ąĮąĖčÅ. ąöą╗čÅ AC-coupling čüąŠąĄą┤ąĖąĮčÅčÄčēąĖą╣ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┤ąŠčüčéą░č鹊čćąĮąŠ ą▒ąŠą╗čīčłąĖą╝, čćč鹊ą▒čŗ ąĖąĘą▒ąĄąČą░čéčī čćčĆąĄąĘą╝ąĄčĆąĮąŠą│ąŠ ą┐ą░ą┤ąĄąĮąĖčÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┤ą╗čÅ ąĮąĖąĘą║ąŠčćą░čüč鹊čéąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░, ą║ąŠą│ą┤ą░ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗąĄ ą┤ą░ąĮąĮčŗąĄ čüąŠą┤ąĄčƹȹ░čé ą┤ą╗ąĖąĮąĮčŗąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ąŠą┤ąĖąĮą░ą║ąŠą▓čŗčģ čāčĆąŠą▓ąĮąĄą╣ (čüą╝. ą░ą┐ąĮąŠčāčé HFAN-1.1 [1]). ąĪąŠąĄą┤ąĖąĮąĄąĮąĖąĄ CML-CML ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 8.

|

|

| (a) DC-coupling CML - CML |

(b) AC-coupling CML - CML |

ąĀąĖčü. 8. ąśąĮč鹥čĆč乥ą╣čü CML-CML.

PECL-PECL, DC-coupling: 菹║ą▓ąĖą▓ą░ą╗ąĄąĮčé ąóąĄą▓ąĄąĮąĖąĮą░ 50 ╬® ą┤ą╗čÅ (VCC-2V). ąÆčŗčģąŠą┤ PECL čĆą░ąĘčĆą░ą▒ąŠčéą░ąĮ ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ 50 ╬® ąĮą░ą│čĆčāąĘą║ąŠą╣ ą┤ą╗čÅ (VCC ŌĆō 2V). ąśąĘ-ąĘą░ č鹊ą│ąŠ, čćč鹊 ą┐ąŠč鹥ąĮčåąĖą░ą╗ (VCC ŌĆō 2V) ąŠą▒čŗčćąĮąŠ ąĮąĄą┤ąŠčüčéčāą┐ąĄąĮ ą┤ą╗čÅ čåąĄą┐ąĄą╣ čü č鹥čĆą╝ąĖąĮą░č鹊čĆąŠą╝, čćą░čüč鹊 ą┐čĆąĄą┤ą┐ąŠčćčéąĖč鹥ą╗čīąĮąĄąĄ ąĮą░ą╣čéąĖ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮčāčÄ ą║ąŠą╝ą▒ąĖąĮą░čåąĖčÄ čĆąĄąĘąĖčüč鹊čĆąŠą▓, ą┐čĆąĖą▓ąŠą┤čÅčēčāčÄ ą║ čåąĄą┐ąĖ, 菹║ą▓ąĖą▓ą░ą╗ąĄąĮčéąĮąŠą╣ ąóąĄą▓ąĄąĮąĖąĮčā. ąĀąĖčü. 9 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čĆąĄąĘčāą╗čīčéą░čé čéčĆą░ąĮčüč乊čĆą╝ą░čåąĖąĖ ąóąĄą▓ąĄąĮąĖąĮą░. ąóčĆąĄą▒ąŠą▓ą░ąĮąĖčÅ č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖčÅ 50 ╬® ą┤ą╗čÅ (VCC ŌĆō 2V) ąĮą░ą╗ą░ą│ą░čÄčé čāčüą╗ąŠą▓ąĖčÅ:

(VCC - 2V) = VCC (R2 / (R1 + R2)) ąĖ (R1// R2) = 50 ╬®

ąĀąĄčłąĄąĮąĖąĄ ą┤ą╗čÅ R1 ąĖ R2 ą┤ą░ąĄčé čüą╗ąĄą┤čāčÄčēąĄąĄ:

R1 = 50 * VCC / (VCC - 2V) ąĖ R2 = 25 * VCC

ąĀąĖčü. 9. ąŁą║ą▓ąĖą▓ą░ą╗ąĄąĮčéąĮąŠąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ąóąĄą▓ąĄąĮąĖąĮą░.

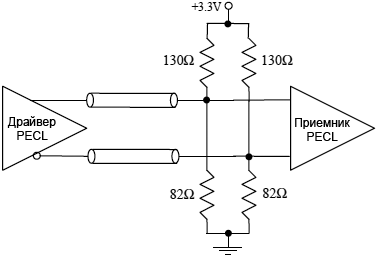

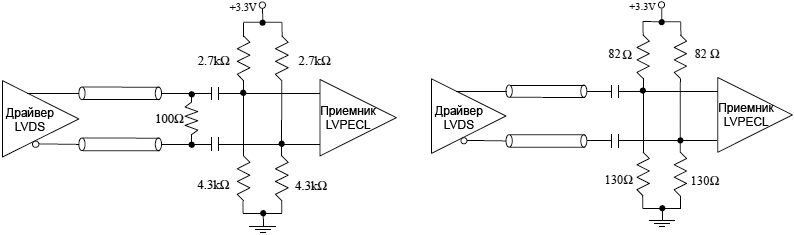

ą¤čĆąĖ +3.3V čüčéą░ąĮą┤ą░čĆčéąĮčŗąĄ 5% ąĘąĮą░č湥ąĮąĖčÅ čĆąĄąĘąĖčüč鹊čĆą░ ą▒čāą┤čāčé R1 = 130 ╬® ąĖ R2 = 82 ╬®. ą¤čĆąĖ + 5.0V ą┐ąŠą╗čāč湥ąĮąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ ą▒čāą┤čāčé R1 = 82 ╬® ąĖ R2 = 130 ╬®. ąĀąĖčü. 10 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé 菹║ą▓ąĖą▓ą░ą╗ąĄąĮčéąĮąŠąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ąóąĄą▓ąĄąĮąĖąĮą░ čåąĄą┐ąĖ č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖčÅ ą┤ą╗čÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖą╣ ą┐ąĖčéą░ąĮąĖčÅ +3.3V ąĖ +5.0V.

|

|

| (a) ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ +3.3V |

(b) ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ 5.0V |

ąĀąĖčü. 10. DC-coupling PECL-PECL.

ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą▓čŗčģąŠą┤ą░ PECL čüąŠą┤ąĄčƹȹ░čé ąŠčéą║čĆčŗčéčŗą╣ 菹╝ąĖčéč鹥čĆ ą▒ąĄąĘ ąŠą▒čĆą░čéąĮąŠą│ąŠ č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖčÅ (čüą╝. čĆąĖčü. 1).

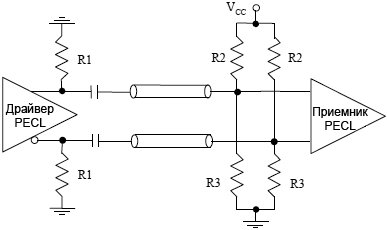

PECL-PECL, AC-coupling. ąÜąŠą│ą┤ą░ ą▓čŗčģąŠą┤čŗ PECL ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĮą░ą│čĆčāąČąĄąĮčŗ ą┐ąŠ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą╝čā č鹊ą║čā ąĮą░ č鹥čĆą╝ąĖąĮą░č鹊čĆ 50 ╬®, ą┤ąŠą╗ąČąĄąĮ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ čĆąĄąĘąĖčüč鹊čĆ ąĮą░ ąĘąĄą╝ą╗čÄ ą┤ą╗čÅ ąŠčĆą│ą░ąĮąĖąĘą░čåąĖąĖ čüą╝ąĄčēąĄąĮąĖčÅ ą┐ąŠ ą┐ąŠčüč鹊čÅąĮąĮąŠą╝čā č鹊ą║čā ą▓čŗčģąŠą┤ą░ PECL ą┐ąĄčĆąĄą┤ AC-coupling ą┤ą╗čÅ ą╗ąĖąĮąĖąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 11.

ąöą╗čÅ č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓čģąŠą┤ą░ PECL ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą▓čŗą▒čĆą░ąĮčŗ R2 ąĖ R3 čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝: (1) čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮąŠąĄ čüą╝ąĄčēąĄąĮąĖąĄ ą┐ąŠčüč鹊čÅąĮąĮąŠą╝čā č鹊ą║čā ą▓čģąŠą┤ąŠą▓ PECL (VCC-1.3V); (2) čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĄ ąĖą╝ą┐ąĄą┤ą░ąĮčüą░ ą╗ąĖąĮąĖąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ; (3) 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ; ąĖ (4) ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▓ąĮąĄčłąĮąĖčģ ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓. ąĀąĖčü. 11(a) ąŠą┐čéąĖą╝ąĖąĘąĖčĆčāąĄčé čüčģąĄą╝čā ą┤ą╗čÅ čüąĮąĖąČąĄąĮąĖčÅ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ R2 ąĖ R3 ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčéčüčÅ ą┐ąŠ čāčüą╗ąŠą▓ąĖčÅą╝ (R3 * VCC) / (R2 + R3) = VCC - 1.3V, ąĖ R2 // R3 = 50 ╬®. ąŁč鹊 ą┤ą░ąĄčé čüą╗ąĄą┤čāčÄčēąĄąĄ: R2 = 82 ╬® ąĖ R3 = 130 ╬® ą┤ą╗čÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ +3.3V ąĖ R2 = 68 ╬® ąĖ R3 = 180 ╬® ą┤ą╗čÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ +5.0V.

|

|

| (a) |

(b) |

ąĀąĖčü. 11. AC-coupling PECL-PECL.

ąØąĄą┤ąŠčüčéą░č鹊ą║ čüčģąĄą╝čŗ čĆąĖčü. 11(a) ą▓ č鹊ą╝, čćč鹊 ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ 菹ĮąĄčĆą│ąĖąĖ čåąĄą┐čīčÄ č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖčÅ čüą╗ąĖčłą║ąŠą╝ ą▓čŗčüąŠą║ąŠąĄ. ąöą╗čÅ čüąĖčüč鹥ą╝, ą│ą┤ąĄ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ ą▓ą░ąČąĮčŗą╣ ą╝ąŠą╝ąĄąĮčé, ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ čüčģąĄą╝ą░ čĆąĖčü. 11(b). ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ąĮą░ą╝ ąĮčāąČąĮąŠ ąŠą▒ąĄčüą┐ąĄčćąĖčéčī (R3 * VCC) / (R2 + R3) = VCC - 1.3V ąĖ R2 // R3 // 50 ╬® = 50 ╬®. ą×ą┤ąĮąŠ ąĖąĘ čĆąĄčłąĄąĮąĖą╣ R2 = 2.7 ą║╬® ąĖ R3 = 4.3 ą║╬® ą┤ą╗čÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ +3.3V ąĖ R2 = 2.7 ą║╬® ąĖ R3 = 7.8 ą║╬® ą┤ą╗čÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ +5.0V.

ąśąĘ-ąĘą░ č鹊ą│ąŠ, čćč鹊 ą▓čŗčģąŠą┤ąĮąŠąĄ čüčĆąĄą┤ąĮąĄąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ąĘąĄą╝ą╗ąĖ PECL čäąĖą║čüąĖčĆąŠą▓ą░ąĮąŠ ąĮą░ (VCC-1.3V), čĆąĄąĘąĖčüč鹊čĆ ą┐ąŠčüč鹊čÅąĮąĮąŠą│ąŠ čüą╝ąĄčēąĄąĮąĖčÅ (R1) ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą▒čĆą░ąĮ ąĖąĘ ą┐čĆąĄą┤ą┐ąŠą╗ąŠąČąĄąĮąĖčÅ ą┐ąŠčüč鹊čÅąĮąĮąŠą│ąŠ č鹊ą║ą░ 14mA. ą¤ąĄčĆą▓ąŠąĮą░čćą░ą╗čīąĮčŗą╝ čĆą░čüč湥č鹊ą╝ ą▒čāą┤ąĄčé R1 = (VCC - 1.3V) / 14mA, čćč鹊 ą▓ čĆąĄąĘčāą╗čīčéą░č鹥 ą┤ą░ąĄčé R1 = 142 ╬® ą┤ą╗čÅ ą┐ąĖčéą░ąĮąĖčÅ +3.3V ąĖ R1 = 270 ╬® ą┤ą╗čÅ ą┐ąĖčéą░ąĮąĖčÅ +5.0V. ą×ą┤ąĮą░ą║ąŠ čŹč鹊 ą▓čŗčćąĖčüą╗ąĄąĮąĖąĄ ą┤ą░ąĄčé čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐ąŠ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą╝čā č鹊ą║čā ą╝ąĄąĮčīčłąĄ 50 ╬®, ą║ąŠč鹊čĆąŠąĄ ą╝ąŠąČąĮąŠ čāą▓ąĖą┤ąĄčéčī ąĮą░ ą▓čŗčģąŠą┤ąĄ PECL. ąÆ čĆąĄą░ą╗čīąĮčŗčģ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅčģ ą┤ą╗čÅ ą▒ą░ą╗ą░ąĮčü ą╝ąĄąČą┤čā AC ąĖ DC čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅą╝ąĖ R1 ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą▒čĆą░ąĮ ą╝ąĄąČą┤čā 142 ╬® ąĖ 200 ╬® ą┤ą╗čÅ ą┐ąĖčéą░ąĮąĖčÅ +3.3V ąĖ ą╝ąĄąČą┤čā 270 ╬® ąĖ 350 ╬® ą┤ą╗čÅ ą┐ąĖčéą░ąĮąĖčÅ +5.0V.

ąöą░ą╗čīąĮąĄą╣čłąĄąĄ čāą╗čāčćčłąĄąĮąĖąĄ č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖą╣ ą▓ PECL ą╝ąŠąČąĄčé ą▒čŗčéčī ą┤ąŠčüčéąĖą│ąĮčāč鹊 ą┤ą▓čāą╝čÅ čüą┐ąŠčüąŠą▒ą░ą╝ąĖ: (1) ą┤ąŠą▒ą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ čĆąĄąĘąĖčüč鹊čĆą░ čü ąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆą░, čćč鹊ą▒čŗ ąĖą╝ą┐ąĄą┤ą░ąĮčü AC ą┤ą╗čÅ ą┤čĆą░ą╣ą▓ąĄčĆą░ PECL ą▒čŗą╗ ą▒ą╗ąĖąĘąŠą║ ą║ 50 ╬®, (2) ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą╣ ąĖąĮą┤čāą║čéąĖą▓ąĮąŠčüčéąĖ ą║ R1. ąŁč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąŠą▒ąĄčüą┐ąĄčćąĖą▓ą░čéčī ą┤ąŠą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖą╝ą┐ąĄą┤ą░ąĮčüą░ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą│ąŠ č鹊ą║ą░ ą┐ąŠ ą┐čĆąĖąĄą╝ąĮąĖą║čā, ą░ ąĮąĄ ą┐ąŠ R1.

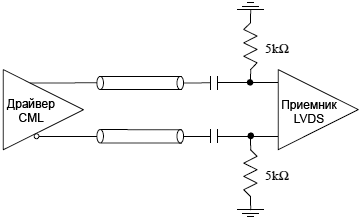

LVDS-LVDS. ąśąĘ-ąĘą░ č鹊ą│ąŠ, čćč鹊 ą▓čģąŠą┤čŗ LVDS ąĖą╝ąĄčÄčé ą▓čüčéčĆąŠąĄąĮąĮąŠąĄ č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖąĄ, ąĖąĮč鹥čĆč乥ą╣čü ą╝ąĄąČą┤čā ą┤čĆą░ą╣ą▓ąĄčĆąŠą╝ LVDS ąĖ ą┐čĆąĖąĄą╝ąĮąĖą║ąŠą╝ LVDS čāą┐čĆąŠčēą░ąĄčéčüčÅ ą┤ą╗čÅ ą┐čĆčÅą╝ąŠą│ąŠ čüąŠąĄą┤ąĖąĮąĄąĮąĖčÅ, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 12.

ąĀąĖčü. 12. ąśąĮč鹥čĆč乥ą╣čü LVDS-LVDS.

[ąśąĮč鹥čĆč乥ą╣čü ą╝ąĄąČą┤čā LVDS, PECL ąĖ CML]

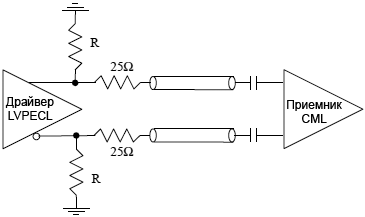

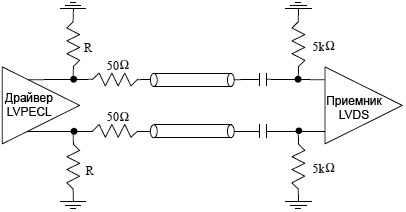

ąŚą┤ąĄčüčī ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčéčüčÅ +3.3V PECL. LVPECL - CML čüąŠąĄą┤ąĖąĮąĄąĮąĖąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮąŠ ą┐ąŠ ą┐ąŠčüč鹊čÅąĮąĮąŠą╝čā (DC-Coupling) ąĖ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą╝čā č鹊ą║čā (AC-Coupling).

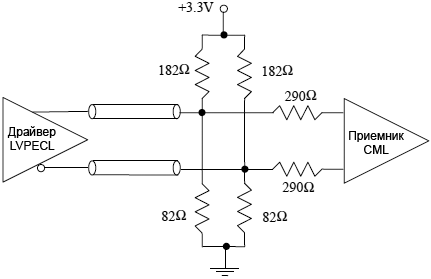

LVPECL-CML, AC-Coupling. ą×ą┤ąĖąĮ ąĖąĘ čüą┐ąŠčüąŠą▒ąŠą▓ čüąŠąĄą┤ąĖąĮąĄąĮąĖčÅ ą┐ąŠ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą╝čā ą┤ąŠą║čā ą╝ąĄąČą┤čā ą┤čĆą░ą╣ą▓ąĄčĆąŠą╝ LVPECL ąĖ ą┐čĆąĖąĄą╝ąĮąĖą║ąŠą╝ CML ą┐ąŠą║ą░ąĘą░ąĮ ąĮą░ čĆąĖčü. 13. ąÜą░ąČą┤čŗą╣ ąĖąĘ ą▓čŗčģąŠą┤ąŠą▓ LVPECL ąĮą░ą│čĆčāąČąĄąĮ ąĮą░ čĆąĄąĘąĖčüč鹊čĆ R (142 ╬® .. 200 ╬®), čüąŠąĄą┤ąĖąĮąĄąĮąĮčŗą╣ čü ąĘąĄą╝ą╗ąĄą╣ ą┤ą╗čÅ ą┐čĆą░ą▓ąĖą╗čīąĮąŠą│ąŠ čüą╝ąĄčēąĄąĮąĖčÅ ą┐ąŠ ą┐ąŠčüč鹊čÅąĮąĮąŠą╝čā č鹊ą║čā. ąĢčüą╗ąĖ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣ ą┐ąĄčĆąĄą┐ą░ą┤ čüąĖą│ąĮą░ą╗ą░ LVPECL ą▒ąŠą╗čīčłąĄ, č湥ą╝ ą╝ąŠąČąĄčé ąŠą▒čĆą░ą▒ąŠčéą░čéčī ą┐čĆąĖąĄą╝ąĮąĖą║ CML, č鹊 ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ čĆąĄąĘąĖčüč鹊čĆ 25 ╬®, čćč鹊ą▒čŗ čāą╝ąĄąĮčīčłąĖčéčī ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ čü ą║ąŠčŹčäčäąĖčåąĖąĄąĮč鹊ą╝ 0.67.

ąĀąĖčü. 13. AC-coupling LVPECL-CML.

LVPECL-CML, DC-Coupling. ąöą╗čÅ čüąŠąĄą┤ąĖąĮąĄąĮąĖčÅ ą┐ąŠ ą┐ąŠčüč鹊čÅąĮąĮąŠą╝čā č鹊ą║čā ą╝ąĄąČą┤čā LVPECL ąĖ CML ąĮčāąČąĮą░ čåąĄą┐ąŠčćą║ą░ čüą┤ą▓ąĖą│ą░ čāčĆąŠą▓ąĮčÅ, čćč鹊ą▒čŗ ą┐čĆąĖą▓ąĄčüčéąĖ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĄ čāčĆąŠą▓ąĮąĖ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ąĘąĄą╝ą╗ąĖ ą▓čŗčģąŠą┤ą░ LVPECL ąĖ ą▓čģąŠą┤ą░ CML. ą¤ąŠąĮąĖąČąĄąĮąĖąĄ čāčĆąŠą▓ąĮčÅ čüąĖą│ąĮą░ą╗ą░, ą║ąŠč鹊čĆąŠąĄ ą▓ą▓ąŠą┤ąĖčéčüčÅ čŹčéąĖą╝ąĖ čåąĄą┐čÅą╝ąĖ čüą┤ą▓ąĖą│ą░ čāčĆąŠą▓ąĮčÅ, ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą┤ąŠčüčéą░č鹊čćąĮąŠ ą╝ą░ą╗čŗą╝, čćč鹊ą▒čŗ čĆą░ąĘą╝ą░čģ čüąĖą│ąĮą░ą╗ą░ ąĮą░ ą▓čģąŠą┤ąĄ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ CML ą┐čĆąĄą▓čŗčłą░ą╗ ąĄą│ąŠ čćčāą▓čüčéą▓ąĖč鹥ą╗čīąĮąŠčüčéčī. ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠ ąŠą▒čēąĖą╣ ąĖą╝ą┐ąĄą┤ą░ąĮčü ąĮą░ ą▓čŗčģąŠą┤ąĄ LVPECL ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čüąŠčģčĆą░ąĮąĄąĮ ą▒ą╗ąĖąĘą║ąĖą╝ ą║ 50 ╬®, čćč鹊ą▒čŗ ąŠą▒ąĄčüą┐ąĄčćąĖčéčī čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĄ ąĖą╝ą┐ąĄą┤ą░ąĮčüą░. ąĪą╗ąĄą┤čāčÄčēąĖą╣ ą┐čĆąĖą╝ąĄčĆ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, ą║ą░ą║ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą▓čŗčģąŠą┤ LVPECL ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą▓čģąŠą┤ąŠą╝ CML ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ MAX3875. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ čåąĄą┐ąŠčćą║ą░ čüą┤ą▓ąĖą│ą░ čāčĆąŠą▓ąĮčÅ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠčüčéčĆąŠąĄąĮą░ ą┐ąŠ čüčģąĄą╝ąĄ čĆąĖčü. 14.

ąĀąĖčü. 14. ąĀąĄąĘąĖčüč鹊čĆąĮą░čÅ čåąĄą┐ąŠčćą║ą░ ą╝ąĄąČą┤čā LVPECL ąĖ CML (MAX3875).

ąöąŠą╗ąČąĮčŗ ą▓čŗą┐ąŠą╗ąĮčÅčéčīčüčÅ čüą╗ąĄą┤čāčÄčēąĖąĄ čāčüą╗ąŠą▓ąĖčÅ:

R2 * VCC

VA = VCC - 2.0V = --------------------- (1) [ąŁą║ą▓. ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ąŠčéą║čĆčŗč鹊ą╣ čüčģąĄą╝čŗ ąóąĄą▓ąĄąĮąĖąĮą░]

R2 + R1 // (R3 + 50 ╬®)

Zin = R1 // R2 //(R3 + 50W) = 50 ╬® (2) [ąŁą║ą▓. čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ ąóąĄą▓ąĄąĮąĖąĮą░]

VCC * R3 + 50 ╬® * (VCC - 1.3V)

VB = VCC - 0.2V = -------------------------------- (3) [ąÆ ą┐čĆąĄą┤ą┐ąŠą╗ąŠąČąĄąĮąĖąĖ VA = VPECL-CM = (VCC-1.3V)]

(50 ╬® + R3)

Gain (čāčüąĖą╗ąĄąĮąĖąĄ) = 50 / (R3 + 50) Ōēź 0.042 (4)

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĄčüą╗ąĖ ą┐čĆąĄą┤ą┐ąŠą╗ąŠąČąĖčéčī, čćč鹊 ą╝ąĖąĮąĖą╝ą░ą╗čīąĮčŗą╣ ą┐ąĄčĆąĄą┐ą░ą┤ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ąĮą░ ą▓čŗčģąŠą┤ąĄ LVPECL 1200 mV, ąĖ čā MAX3875 ą▓čģąŠą┤ąĮą░čÅ čćčāą▓čüčéą▓ąĖč鹥ą╗čīąĮąŠčüčéčī 50 mV, č鹊 čāčüąĖą╗ąĄąĮąĖąĄ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą▒ąŠą╗čīčłąĄ 50mV/1200mV = 0.042.

ą¤ąŠ č乊čĆą╝čāą╗ą░ą╝, ą┐čĆąĖą▓ąĄą┤ąĄąĮąĮčŗą╝ ą▓čŗčłąĄ, ą╝čŗ ą┐ąŠą╗čāčćąĖą╝ R1 = 182 ╬®, R2 = 82.5 ╬® ąĖ R3 = 294 ╬® (čüčéą░ąĮą┤ą░čĆčéąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ čü č鹊čćąĮąŠčüčéčīčÄ 1%). ąÆ čĆąĄąĘčāą╗čīčéą░č鹥 ą┐ąŠą╗čāčćąĖčéčüčÅ VA = 1.35V, VB = 3.11V, čāčüąĖą╗ąĄąĮąĖąĄ = 0.147 ąĖ Zin = 49 ╬®. ąÜąŠą│ą┤ą░ ą▓čŗčģąŠą┤čŗ LVPECL čüąŠąĄą┤ąĖąĮčÅčÄčéčüčÅ čüąŠ ą▓čģąŠą┤ą░ą╝ąĖ MAX3875 č湥čĆąĄąĘ čŹčéčā čåąĄą┐ąŠčćą║čā, ąĖąĘą╝ąĄčĆąĄąĮąĮąŠąĄ VA = 2.0V ąĖ VB = 3.13V.

ąĪą▓čÅąĘčī ą┐ąŠ ą┐ąŠčüč鹊čÅąĮąĮąŠą╝čā č鹊ą║čā ą╝ąĄąČą┤čā ą▓čŗčģąŠą┤ą░ą╝ąĖ LVPECL ąĖ ą▓čģąŠą┤ą░ą╝ąĖ MAX3875 ą┐ąŠą║ą░ąĘą░ąĮą░ ąĮą░ čĆąĖčü. 15. ąöą╗čÅ ą┤čĆčāą│ąĖčģ ą▓čģąŠą┤ąŠą▓ CML ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ąĘąĄą╝ą╗ąĖ ą╝ąŠąČąĄčé ąŠčéą╗ąĖčćą░čéčīčüčÅ; čéą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą╝ąŠąČąĄčé ą▓čŗčćąĖčüą╗ąĖčéčī ą┤čĆčāą│ąĖąĄ ąĘąĮą░č湥ąĮąĖčÅ čĆąĄąĘąĖčüč鹊čĆąŠą▓ ąĮą░ ąŠčüąĮąŠą▓ąĄ ą▓čŗčłąĄčāą║ą░ąĘą░ąĮąĮčŗčģ čüąŠąŠą▒čĆą░ąČąĄąĮąĖą╣.

ąĀąĖčü. 15. DC-coupling ą╝ąĄąČą┤čā LVPECL ąĖ CML (MAX3875).

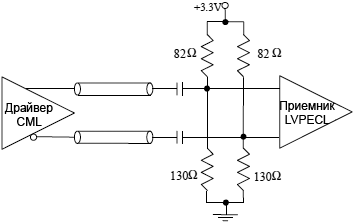

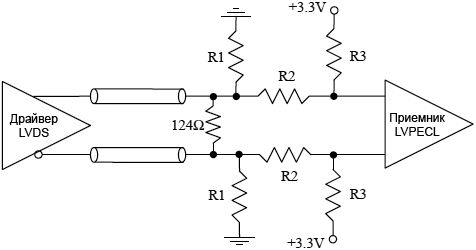

CML-LVPECL. ąöą╗čÅ ąĖąĮč鹥čĆč乥ą╣čüą░ ą╝ąĄąČą┤čā CML ąĖ LVPECL ąĮąĄąŠą▒čģąŠą┤ąĖą╝ą░ čüą▓čÅąĘčī ą┐ąŠ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą╝čā č鹊ą║čā AC-coupling (čüą╝. čĆąĖčü. 16).

|

| (a) |

|

| (b) |

|

| (c) LVPECL čüąŠ ą▓čüčéčĆąŠąĄąĮąĮčŗą╝ ą▓čŗčüąŠą║ąŠąŠą╝ąĮčŗą╝ čüą╝ąĄčēąĄąĮąĖąĄą╝ |

ąĀąĖčü. 16. AC-coupling ą╝ąĄąČą┤čā CML ąĖ LVPECL.

LVPECL-LVDS, DC-Coupling. ąöą╗čÅ čüąŠąĄą┤ąĖąĮąĄąĮąĖčÅ ą╝ąĄąČą┤čā LVPECL ąĖ LVDS ą┐ąŠ ą┐ąŠčüč鹊čÅąĮąĮąŠą╝čā č鹊ą║čā (DC-coupling) čéčĆąĄą▒čāąĄčéčüčÅ čåąĄą┐ąŠčćą║ą░ čüą┤ą▓ąĖą│ą░ ąĖ ą┐ąŠą┤čüčéčĆąŠą╣ą║ąĖ čāčĆąŠą▓ąĮčÅ, ą┐ąŠą║ą░ąĘą░ąĮąĮą░čÅ ąĮą░ čĆąĖčü. 17.

|

|

| (a) ąØąĄą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮą░čÅ čŹą║ą▓ąĖą▓ą░ą╗ąĄąĮčéąĮą░čÅ čüčģąĄą╝ą░ |

(b) ąśąĮč鹥čĆč乥ą╣čü LVPECL - LVDS |

ąĀąĖčü. 17. DC-coupling LVPECL - LVDS.

ąĪą╗ąĄą┤čāąĄčé čāčćąĖčéčŗą▓ą░čéčī ąĮąĄčüą║ąŠą╗čīą║ąŠ ą╝ąŠą╝ąĄąĮč鹊ą▓. ąÆąŠ-ą┐ąĄčĆą▓čŗčģ, ą▓čŗčģąŠą┤ LVPECL ąŠą┐čéąĖą╝ąĖąĘąĖčĆąŠą▓ą░ąĮ ą┤ą╗čÅ 50 ╬® ąĮą░ą│čĆčāąĘą║ąĖ (VCC-2V). ąÆąŠ-ą▓č鹊čĆčŗčģ, ą┐ąŠą┤čüčéčĆąŠą╣ą║ą░ čåąĄą┐ąĖ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī čéą░ą║ąŠą╣, čćč鹊ą▒čŗ ą▓čŗčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ LVPECL ą┐ąŠčüą╗ąĄ ą┐ąŠą┤čüčéčĆąŠą╣ą║ąĖ ąĮą░čģąŠą┤ąĖą╗čüčÅ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ą▓čģąŠą┤ąĮčŗčģ čāčĆąŠą▓ąĮąĄą╣ LVDS. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣ ą▓čģąŠą┤ąĮąŠą╣ ąĖą╝ą┐ąĄą┤ą░ąĮčü LVDS čüąŠčüčéą░ą▓ą╗čÅąĄčé 100 ╬®, ąĖą╗ąĖ 50 ╬® ą┤ą╗čÅ ą▓ąĖčĆčéčāą░ą╗čīąĮąŠą╣ ąĘąĄą╝ą╗ąĖ ąĮą░ ą║ą░ąČą┤ąŠą╣ ą╗ąĖąĮąĖąĖ čüąĖą│ąĮą░ą╗ą░ (čĆąĖčü. 7). ąŁč鹊 ąĮąĄ ąŠčéąĮąŠčüąĖčéčüčÅ ą║ č鹥čĆą╝ąĖąĮąĖčĆčāčÄčēąĄą╝čā ąĖą╝ą┐ąĄą┤ą░ąĮčüčā ą┐ąŠ ą┐ąŠčüč鹊čÅąĮąĮąŠą╝čā č鹊ą║čā (DC), ąĮąŠ ą▓ą░ąČąĮąŠ ą┤ą╗čÅ ąĖą╝ą┐ąĄą┤ą░ąĮčüą░ č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐ąŠ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą╝čā č鹊ą║čā (AC). ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ąĖą╝ą┐ąĄą┤ą░ąĮčü AC ąĖ DC ą▒čāą┤ąĄčé ą▓čüąĄą│ą┤ą░ ąŠčéą╗ąĖčćą░čéčīčüčÅ, ąĖ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ čåąĄą┐ąĄą╣ ą┤ąŠą╗ąČąĮčŗ čāą┤ąŠą▓ą╗ąĄčéą▓ąŠčĆčÅčéčī čüą╗ąĄą┤čāčÄčēąĖą╝ čāčĆą░ą▓ąĮąĄąĮąĖčÅą╝:

R2 + R3

VA = VCC - 2.0V = VCC * --------------------- (1)

R1 + R2 + R3

RAC = R1//R2 + (R3// 50W) = 50W (2)

RDC = R1//(R2 + R3) = 50W (3)

R3//50 ╬®

Gain (čāčüąĖą╗ąĄąĮąĖąĄ) = ---------------- Ōēź 0.17 (4)

R2 + (R3//50 ╬®)

ą¤čĆąĖ VCC = +3.3V ąĖ čĆąĄčłąĄąĮąĖąĖ čŹčéąĖčģ čāčĆą░ą▓ąĮąĄąĮąĖą╣ ą╝čŗ ą┐ąŠą╗čāčćąĖą╝ R1 = 182 ╬®, R2 = 47.5 ╬® ąĖ R3 = 47.5 ╬®. ąÆčŗčćąĖčüą╗ąĄąĮąĮąŠąĄ VA = 1.13V, RAC = 51.5 ╬®, RDC = 62.4 ╬® ąĖ čāčüąĖą╗ąĄąĮąĖąĄ = 0.337. ąÜąŠą│ą┤ą░ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ čüąŠąĄą┤ąĖąĮąĄąĮąĖąĄ ą▓čŗčģąŠą┤ą░ LVPECL č湥čĆąĄąĘ čŹčéčā č鹥čĆą╝ąĖąĮąĖčĆčāčÄčēčāčÄ čåąĄą┐ąŠčćą║čā, ąĖąĘą╝ąĄčĆąĄąĮąĮčŗąĄ čāčĆąŠą▓ąĮąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ąĘąĄą╝ą╗ąĖ VA = 2.1V ąĖ VB = 1.06V. ąĢčüą╗ąĖ ą┐čĆąĄą┤ą┐ąŠą╗ąŠąČąĖčéčī, čćč鹊 ą╝ąĖąĮąĖą╝ą░ą╗čīąĮčŗą╣ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣ čüąĖą│ąĮą░ą╗ ąĮą░ ą▓čŗčģąŠą┤ąĄ LVPECL 930 mV, č鹊 ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ, ą┐ąŠčüčéčāą┐ą░čÄčēąĄąĄ ąĮą░ ą▓čģąŠą┤ LVDS ą┐ąŠą╗čāčćąĖčéčüčÅ 313 mV, čćč鹊 čāą┤ąŠą▓ą╗ąĄčéą▓ąŠčĆčÅąĄčé čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÄ čćčāą▓čüčéą▓ąĖč鹥ą╗čīąĮąŠčüčéąĖ ą▓čģąŠą┤ą░ LVDS. ąĪ ą┤čĆčāą│ąŠą╣ čüč鹊čĆąŠąĮčŗ, ąĄčüą╗ąĖ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠąĄ ą▓čŗčģąŠą┤ąĮąŠąĄ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ LVPECL 1.9V, č鹊 ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮčŗą╣ čüąĖą│ąĮą░ą╗ ąĮą░ ą▓čģąŠą┤ąĄ LVDS ą┐ąŠą╗čāčćąĖčéčüčÅ 640 mV, čćč鹊 čéą░ą║ąČąĄ čāą┤ąŠą▓ą╗ąĄčéą▓ąŠčĆčÅąĄčé čüą┐ąĄčåąĖčäąĖą║ą░čåąĖąĖ ą▓čģąŠą┤ąŠą▓ LVDS.

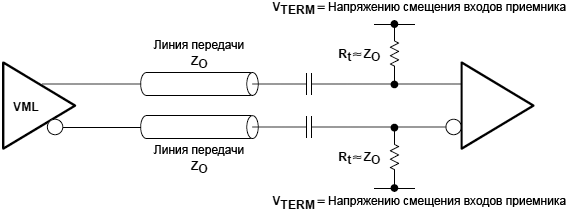

LVPECL-LVDS, AC-Coupling. ąĀąĄčłąĄąĮąĖąĄ čüąŠąĄą┤ąĖąĮąĄąĮąĖčÅ ą┐ąŠ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą╝čā č鹊ą║čā (AC-coupling) ą╝ąĄąČą┤čā LVPECL ąĖ LVDS ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 18. ąÆčŗčģąŠą┤ LVPECL čüą╝ąĄčēąĄąĮ ą┐ąŠ ą┐ąŠčüč鹊čÅąĮąĮąŠą╝čā č鹊ą║čā čĆąĄąĘąĖčüč鹊čĆąŠą╝ R (ąŠčé 142 ╬® ą┤ąŠ 200 ╬®), čüąŠąĄą┤ąĖąĮąĄąĮąĮčŗą╝ ąĮą░ ąĘąĄą╝ą╗čÄ. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ čĆąĄąĘąĖčüč鹊čĆ 50 ╬® ąĮčāąČąĄąĮ ą┤ą╗čÅ ą┐ąŠą┤čüčéčĆąŠą╣ą║ąĖ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ LVPECL, čćč鹊ą▒čŗ čāą┤ąŠą▓ą╗ąĄčéą▓ąŠčĆąĖčéčī čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅą╝ ą▓čģąŠą┤ą░ LVDS. ąØą░ ą▓čģąŠą┤ąĄ LVDS čĆąĄąĘąĖčüč鹊čĆ 5.0 ą║╬® ąĮą░ ąĘąĄą╝ą╗čÄ ąĮą░ ą║ą░ąČą┤ąŠą╣ čüč鹊čĆąŠąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čüą╝ąĄčēąĄąĮąĖčÅ ą┐ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÄ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ąĘąĄą╝ą╗ąĖ.

ąĀąĖčü. 18. AC-coupling ą╝ąĄąČą┤čā LVPECL ąĖ LVDS.

LVDS-LVPECL. ąöą╗čÅ čĆąĄą░ą╗ąĖąĘą░čåąĖą╣ čéą░ą║ąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ čéą░ą║ąČąĄ ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čüąŠąĄą┤ąĖąĮąĄąĮąĖčÅ ą┐ąŠ ą┐ąŠčüč鹊čÅąĮąĮąŠą╝čā (DC-coupling) ąĖ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą╝čā č鹊ą║čā (AC-coupling).

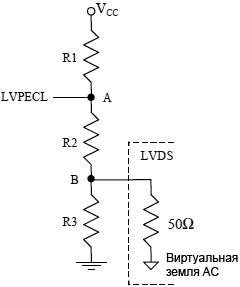

LVDS-LVPECL, DC-coupling. ą¤čĆąĖ čüąŠąĄą┤ąĖąĮąĄąĮąĖąĖ ą┐ąŠ ą┐ąŠčüč鹊čÅąĮąĮąŠą╝čā č鹊ą║čā ą╝ąĄąČą┤čā LVDS ąĖ LVPECL ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čĆąĄąĘąĖčüč鹊čĆąĮą░čÅ čåąĄą┐ąŠčćą║ą░, ą┐ąŠą║ą░ąĘą░ąĮąĮą░čÅ ąĮą░ čĆąĖčü. 19. ąŁčéą░ čåąĄą┐ąŠčćą║ą░ čüą┤ą▓ąĖą│ą░ąĄčé čāčĆąŠą▓ąĄąĮčī DC ąŠčé ą▓čŗčģąŠą┤ą░ LVDS (1.2V) ą┤ąŠ ą▓čģąŠą┤ą░ LVPECL (VCC-1.3V). ąśąĘ-ąĘą░ č鹊ą│ąŠ, čćč鹊 ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮą░ ą▓čŗčģąŠą┤ąĄ LVDS ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ąĘąĄą╝ą╗ąĖ, ąĖ ą▓čģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ LVPECL ą░ąĮą░ą╗ąĖąĘąĖčĆčāąĄčéčüčÅ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ VCC, čŹčéą░ čåąĄą┐ąŠčćą║ą░ čüą┤ą▓ąĖą│ą░ čāčĆąŠą▓ąĮčÅ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą┐ąŠčüčéčĆąŠąĄąĮą░ čéą░ą║, čćč鹊ą▒čŗ ąĮą░ ą▓čŗčģąŠą┤ LVDS ąĮąĄ ą▓ą╗ąĖčÅą╗ąĖ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ.

ąöčĆčāą│ąŠą╣ ą▓ą░ąČąĮčŗą╣ ą╝ąŠą╝ąĄąĮčé - ą▓čŗą▒ąŠčĆ ą║ąŠą╝ą┐čĆąŠą╝ąĖčüčüą░ ą╝ąĄąČą┤čā 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄą╝ ąĖ čüą║ąŠčĆąŠčüčéčīčÄ. ąĢčüą╗ąĖ ą╝čŗ ą▓čŗą▒ąĄčĆąĄą╝ ą╝ą░ą╗čŗąĄ ąĘąĮą░č湥ąĮąĖčÅ čĆąĄąĘąĖčüč鹊čĆąŠą▓ ą┤ą╗čÅ R1, R2, R3, č鹊 ą┐ąŠčüč鹊čÅąĮąĮą░čÅ ą▓čĆąĄą╝ąĄąĮąĖ čŹč鹊ą╣ čĆąĄąĘąĖčüč鹊čĆąĮąŠą╣ čåąĄą┐ąĖ ąĖ ą┐ą░čĆą░ąĘąĖčéąĮąŠą╣ ąĄą╝ą║ąŠčüčéąĖ ą▓čģąŠą┤ą░ LVPECL ą┐ąŠą╗čāčćąĖčéčüčÅ ąĮąĖąĘą║ąŠą╣, čćč鹊 ą┐ąŠąĘą▓ąŠą╗ąĖčé ą┐ąŠą▓čŗčüąĖčéčī čüą║ąŠčĆąŠčüčéčī ą┐ąĄčĆąĄą┤ą░čćąĖ. ąĪ ą┤čĆčāą│ąŠą╣ čüč鹊čĆąŠąĮčŗ, čŹč鹊 čāą▓ąĄą╗ąĖčćąĖčé č鹊ą║, ą║ąŠč鹊čĆčŗą╣ ą┐čĆąŠč鹥ą║ą░ąĄčé č湥čĆąĄąĘ čŹčéąĖ čĆąĄąĘąĖčüč鹊čĆčŗ. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ąĮą░ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéčī ą▓čŗčģąŠą┤ą░ LVDS ą╝ąŠąČąĄčé ą┐ąŠą▓ą╗ąĖčÅčéčī ąĖąĘą╝ąĄąĮąĄąĮąĖąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ. ąś ąŠą┐čÅčéčī-čéą░ą║ąĖ ąĮčāąČąĮąŠ čāčćąĖčéčŗą▓ą░čéčī čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĄ ąĖą╝ą┐ąĄą┤ą░ąĮčüą░ ą▓čģąŠą┤ą░ ąĖ ą▓čŗčģąŠą┤ą░.

ąŚąĮą░č湥ąĮąĖčÅ čĆąĄąĘąĖčüč鹊čĆąŠą▓ ą╝ąŠąČąĮąŠ ą▓čŗčćąĖčüą╗ąĖčéčī ą┐ąŠ čüą╗ąĄą┤čāčÄčēąĖą╝ č乊čĆą╝čāą╗ą░ą╝:

R1

VA = VCC * -------------- = 1.2V (1)

R1 + R2 + R3

R1 + R2

VB = VCC * -------------- = VCC - 1.3V (2)

R1 + R2 + R3

R3 * (R1 + R2)

RIN = ---------------- // 62 ╬® = 50 ╬® (3)

R3 + (R1 + R2)

R3

Gain (čāčüąĖą╗ąĄąĮąĖąĄ) = ----------- (4)

(R2 + R3)

ą¤čĆąĖ VCC = +3.3V ą┐ąŠčüą╗ąĄ ą▓čŗčćąĖčüą╗ąĄąĮąĖčÅ ą┐ąŠą║ą░ąĘą░ąĮąĮčŗčģ ą▓čŗčłąĄ č乊čĆą╝čāą╗ ą╝čŗ ą▓čŗą▒ąĄčĆąĄą╝ R1 = 374 ╬®, R2 = 249 ╬® ąĖ R3 = 402 ╬®. ąŁč鹊 ą┤ą░čüčé VA = 1.2V, VB = 2.0V, RIN = 49 ╬® ąĖ čāčüąĖą╗ąĄąĮąĖąĄ = 0.62. ąśąĘ-ąĘą░ č鹊ą│ąŠ, čćč鹊 ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠąĄ ą▓čŗčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ čüąĖą│ąĮą░ą╗ą░ ą▓čŗčģąŠą┤ą░ LVDS čüąŠčüčéą░ą▓ąĖčé 500 mV ąŠčé ą┐ąĖą║ą░ ą┤ąŠ ą┐ąĖą║ą░, čĆą░ąĘą╝ą░čģ čüąĖą│ąĮą░ą╗ą░ ąĮą░ ą▓čģąŠą┤ąĄ LVPECL ą┐ąŠą╗čāčćąĖčéčüčÅ 310 mV ąŠčé ą┐ąĖą║ą░ ą┤ąŠ ą┐ąĖą║ą░. ąŁč鹊 ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ą╝ą░ą╗ąĄąĮčīą║ąĖą╝ ą┤ą╗čÅ čüčéą░ąĮą┤ą░čĆčéąĮąŠą│ąŠ ą▓čģąŠą┤ą░ PECL, ąĮąŠ ą▒ąŠą╗čīčłąĖąĮčüčéą▓ąŠ ą▓čģąŠą┤ąŠą▓ Maxim LVPECL ą╝ąŠąČąĄčé ą┐čĆąĖąĮčÅčéčī čéą░ą║ąŠą╣ ą┐ąĄčĆąĄą┐ą░ą┤ čüąĖą│ąĮą░ą╗ą░ ąĖąĘ-ąĘą░ ąĮą░ą╗ąĖčćąĖčÅ ą▒ąŠą╗čīčłąŠą│ąŠ čāčüąĖą╗ąĄąĮąĖčÅ ą┐ąŠ ą▓čģąŠą┤čā. ąÆ čĆąĄą░ą╗čīąĮąŠą╝ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĖ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÄ ąĮčāąČąĮąŠ ą┐čĆąĖąĮčÅčéčī čĆąĄčłąĄąĮąĖąĄ ąĮą░ ąŠčüąĮąŠą▓ąĄ čéčĆąĄą▒ąŠą▓ą░ąĮąĖą╣ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéąĖ.

|

|

| (a) ąśąĮč鹥čĆč乥ą╣čü LVDS-LVPECL |

(b) ąØąĄą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮą░čÅ

菹║ą▓ąĖą▓ą░ą╗ąĄąĮčéąĮą░čÅ čüčģąĄą╝ą░ |

ąĀąĖčü. 19. DC-coupling ą╝ąĄąČą┤čā LVDS ąĖ LVPECL.

LVDS-LVPECL, AC-Coupling. ąĪąŠąĄą┤ąĖąĮąĄąĮąĖąĄ ą┐ąŠ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą╝čā č鹊ą║čā ą╝ąĄąČą┤čā LVDS ąĖ LVPECL ą┐čĆąŠčüč鹊ąĄ, ąĮą░ čĆąĖčü. 20 ą┐ąŠą║ą░ąĘą░ąĮčŗ ą┤ą▓ą░ ą┐čĆąĖą╝ąĄčĆą░.

|

| (a) LVPECL čüąŠ ą▓čüčéčĆąŠąĄąĮąĮčŗą╝ ą▓ čćąĖą┐ č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖąĄą╝ (MAX3885) |

|

| (b) LVPECL ą▒ąĄąĘ ą▓čüčéčĆąŠąĄąĮąĮąŠą│ąŠ č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖčÅ (MAX3867) |

ąĀąĖčü. 20. AC-coupling ą╝ąĄąČą┤čā LVDS ąĖ LVPECL.

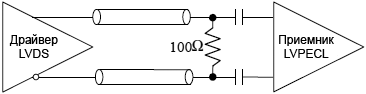

ąśąĮč鹥čĆč乥ą╣čü CML-LVDS. ąØą░ čĆąĖčü. 21 ą┐ąŠą║ą░ąĘą░ąĮąŠ čüąŠąĄą┤ąĖąĮąĄąĮąĖąĄ ą┐ąŠ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą╝čā č鹊ą║čā ą╝ąĄąČą┤čā CML ąĖ LVDS. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ą┐ąĄčĆąĄą┐ą░ą┤ čüąĖą│ąĮą░ą╗ą░ ąĮą░ ą▓čŗčģąŠą┤ąĄ CML ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ, ą║ąŠč鹊čĆčŗą╣ ą╝ąŠąČąĄčé ąŠą▒čĆą░ą▒ąŠčéą░čéčī ą▓čģąŠą┤ LVDS.

ąĀąĖčü. 21. AC-coupling ą╝ąĄąČą┤čā CML ąĖ LVDS.

ąĢčüą╗ąĖ ą┤čĆą░ą╣ą▓ąĄčĆ LVDS ą┤ąŠą╗ąČąĄąĮ ą┐ąŠą┤ą░ą▓ą░čéčī čüąĖą│ąĮą░ą╗ ąĮą░ ą┐čĆąĖąĄą╝ąĮąĖą║ CML, ą┐čĆąĖą╝ąĄčĆ čĆąĄčłąĄąĮąĖčÅ ą┐ąŠą║ą░ąĘą░ąĮ ąĮą░ čĆąĖčü. 22.

ąĀąĖčü. 22. AC-coupling ą╝ąĄąČą┤čā LVDS ąĖ CML.

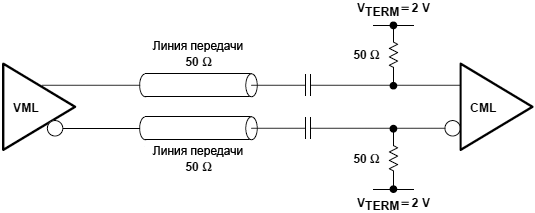

VML-VML, DC-coupled. ąöąŠčüč鹊ąĖąĮčüčéą▓ąŠ ą┤čĆą░ą╣ą▓ąĄčĆąŠą▓ VML ą▓ č鹊ą╝, čćč鹊 ąĖą╝ ąĮąĄ ąĮčāąČąĮčŗ ą▓ąĄčĆčģąĮąĖąĄ (pullup) ąĖą╗ąĖ ąĮąĖąČąĮąĖąĄ (pulldown) ąĮą░ą│čĆčāąĘąŠčćąĮčŗąĄ čĆąĄąĘąĖčüč鹊čĆčŗ, ą┐ąŠč鹊ą╝čā čćč鹊 ą▓ ąĖčģ ą▓čŗčģąŠą┤ąĮčŗčģ čüčéčĆčāą║čéčāčĆą░čģ ą▓čüčéčĆąŠąĄąĮčŗ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗąĄ čéčĆą░ąĮąĘąĖčüč鹊čĆčŗ PMOS ąĖ NMOS, ą║ąŠč鹊čĆčŗąĄ č乊čĆą╝ąĖčĆčāčÄčé ą┐ąĄčĆąĄą┐ą░ą┤čŗ čüą┐ą░ą┤ą░ ąĖ ąĮą░čĆą░čüčéą░ąĮąĖčÅ čāčĆąŠą▓ąĮčÅ. ąŁč鹊 čāą┐čĆąŠčēą░ąĄčé čĆą░ąĘą▓ąŠą┤ą║čā ą┐ąĄčćą░čéąĮąŠą╣ ą┐ą╗ą░čéčŗ. ąĢą┤ąĖąĮčüčéą▓ąĄąĮąĮąŠąĄ čéčĆąĄą▒ąŠą▓ą░ąĮąĖąĄ - ąŠą▒ąĄčüą┐ąĄčćąĖčéčī č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖąĄ ą╗ąĖąĮąĖąĖ ąĮą░ čüč鹊čĆąŠąĮąĄ ą┐čĆąĖąĄą╝ąĮąĖą║ą░.

ąĀąĖčü. 23. ąöčĆą░ą╣ą▓ąĄčĆ VML ą┤ą╗čÅ čüąŠąĄą┤ąĖąĮąĄąĮąĖčÅ ą┐ąŠ ą┐ąŠčüč鹊čÅąĮąĮąŠą╝čā č鹊ą║čā (DC-coupled).

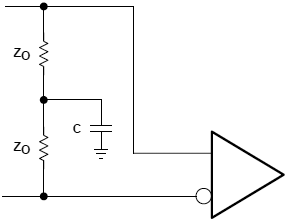

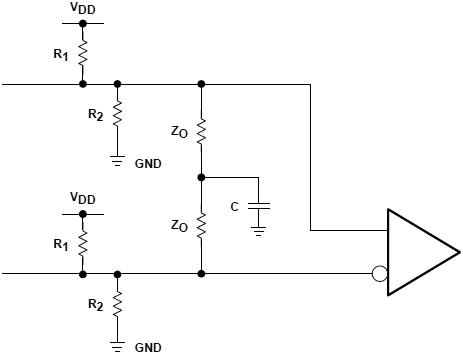

ąŁčéą░ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖčÅ čĆą░ą▒ąŠčéą░ąĄčé čģąŠčĆąŠčłąŠ, ąĄčüą╗ąĖ ąĮąĄčé ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą│ąŠ ą┐ąĄčĆąĄą║ąŠčüą░ ąĖą╗ąĖ čłčāą╝ą░ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ąĘąĄą╝ą╗ąĖ. ą×ą┤ąĮą░ą║ąŠ ą▓ ą▒ąŠą╗čīčłąĖąĮčüčéą▓ąĄ čüąĖčéčāą░čåąĖą╣ ąĄčüčéčī ąĮąĄą║ąŠč鹊čĆąŠąĄ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠąĄ čüą╝ąĄčēąĄąĮąĖąĄ ąĖą╗ąĖ čłčāą╝ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ąŠą▒čēąĄą│ąŠ ą┐čĆąŠą▓ąŠą┤ą░, ą┐ąŠčŹč鹊ą╝čā ą╝ąŠąČąĄčé ą▒čŗčéčī ą▒ąŠą╗ąĄąĄ ą┐ąŠą┤čģąŠą┤čÅčēąĖą╝ čüą╗ąĄą┤čāčÄčēąĄąĄ č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖąĄ, ą┐ąŠą║ą░ąĘą░ąĮąĮąŠąĄ ąĮą░ čĆąĖčü. 15. ąŚą┤ąĄčüčī čĆąĄąĘąĖčüč鹊čĆčŗ č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖčÅ ZO ąĖ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ čāčüčéčĆą░ąĮčÅčÄčé ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣ ą┐ąĄčĆąĄą║ąŠčü ąĖ čłčāą╝ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ąĘąĄą╝ą╗ąĖ.

ąĀąĖčü. 24. ąĀą░ąĘą┤ąĄą╗ąĄąĮąĖąĄ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą│ąŠ č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖčÅ čü ą┐ąŠą╝ąŠčēčīčÄ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆą░.

VML-VML, AC-coupled. ąÆ čüą╗čāčćą░ąĄ čüą▓čÅąĘąĖ ą┐ąŠ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą╝čā č鹊ą║čā (AC-coupling), č鹥čĆą╝ąĖąĮąĖčĆčāčÄčēąĖąĄ čĆąĄąĘąĖčüč鹊čĆčŗ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮčŗ ą║ čłąĖąĮąĄ, č乊čĆą╝ąĖčĆčāčÄčēąĄą╣ čüą╝ąĄčēąĄąĮąĖąĄ ą▓čģąŠą┤ąŠą▓ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ ą┐ąŠ ą┐ąŠčüč鹊čÅąĮąĮąŠą╝čā č鹊ą║čā ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ąĘąĄą╝ą╗ąĖ. ąś čüąĮąŠą▓ą░, ą┤ąŠčüč鹊ąĖąĮčüčéą▓ąŠ ą┤čĆą░ą╣ą▓ąĄčĆąŠą▓ VML ą▓ č鹊ą╝, čćč鹊 ą┤ą░ąČąĄ ą┐čĆąĖ čüą▓čÅąĘąĖ ą┐ąŠ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą╝čā č鹊ą║čā ąĮąĄ ąĮčāąČąĮčŗ čĆąĄąĘąĖčüč鹊čĆčŗ pullup ąĖą╗ąĖ pulldown.

ąĀąĖčü. 25. ąöčĆą░ą╣ą▓ąĄčĆ VML ą┤ą╗čÅ čüąŠąĄą┤ąĖąĮąĄąĮąĖčÅ ą┐ąŠ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą╝čā č鹊ą║čā (AC-coupled).

ąĪąŠąĄą┤ąĖąĮąĄąĮąĖąĄ VML-CML. ąĀą░čüčüą╝ąŠčéčĆąĖą╝ čüą╗čāčćą░ą╣ ą┤čĆą░ą╣ą▓ąĄčĆą░ VML ąĖ CML-ą┐čĆąĖąĄą╝ąĮąĖą║ą░ TLK2501, ą║ąŠč鹊čĆčŗą╣ čéčĆąĄą▒čāąĄčé ąĮą░ ą▓čģąŠą┤ą░čģ čāčĆąŠą▓ąĮąĄą╣ CML. ąźą░čĆą░ą║č鹥čĆąĖčüčéąĖč湥čüą║ąĖą╣ ąĖą╝ą┐ąĄą┤ą░ąĮčü ą╗ąĖąĮąĖąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ 50 ą×ą╝ ąĖ VDD 2.5V. ąÆčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ąĘąĄą╝ą╗ąĖ ą┤ą╗čÅ TLK2501 ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ąŠčé 1.5V ą┤ąŠ VDD ŌĆō VID/2. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ąĘąĮą░č湥ąĮąĖąĄ 2.0V ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą▒čĆą░ąĮąŠ ą▓ ą║ą░č湥čüčéą▓ąĄ ą┐ąŠą┤čģąŠą┤čÅčēąĄą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ ą┤ą╗čÅ čüą╝ąĄčēąĄąĮąĖčÅ.

ąĪą░ą╝čŗą╣ ą┐čĆąŠčüč鹊ą╣ čüą┐ąŠčüąŠą▒ čüąŠąĘą┤ą░ąĮąĖčÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ čüą╝ąĄčēąĄąĮąĖčÅ - ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čĆąĄąĘąĖčüč鹊čĆąĮčāčÄ čåąĄą┐ąŠčćą║čā, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 26.

ąĀąĖčü. 26. ą¤čĆąŠčüčéą░čÅ čĆąĄąĘąĖčüč鹊čĆąĮą░čÅ čåąĄą┐ąŠčćą║ą░ ą┤ą╗čÅ čüąŠąĘą┤ą░ąĮąĖčÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ čüą╝ąĄčēąĄąĮąĖčÅ č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖčÅ VTERM.

ąĀąĖčü. 27. ą¤čĆąĖą╝ąĄčĆ čüąŠąĄą┤ąĖąĮąĄąĮąĖčÅ ą┤čĆą░ą╣ą▓ąĄčĆą░ VML ąĖ ą┐čĆąĖąĄą╝ąĮąĖą║ą░, čéčĆąĄą▒čāčÄčēąĄą│ąŠ čāčĆąŠą▓ąĮąĄą╣ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ CML.

ąÆčŗčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ąĮąŠą╝ąĖąĮą░ą╗ą░ą╝ąĖ čĆąĄąĘąĖčüč鹊čĆąŠą▓ ą┤ąĄą╗ąĖč鹥ą╗čÅ:

R2

VOUT = VIN * --------- (1)

R1 + R2

ąŁčéčā č乊čĆą╝čāą╗čā ą╝ąŠąČąĮąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░čéčī ą┤ą╗čÅ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéą░ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ.

VOUT R2

------ = -------- (2)

VIN R1 + R2

ąöą╗čÅ ą┐čĆąĖą╝ąĄčĆą░ čĆąĖčü. 27 ą┐ąŠą┤čüčéą░ąĮąŠą▓ą║ą░ ąĘąĮą░č湥ąĮąĖą╣ VDD ąĖ VTERM ą▓ č乊čĆą╝čāą╗čā 2 ą┤ą░čüčé čüą╗ąĄą┤čāčÄčēąĄąĄ:

R2

------- = 0.8

R1 + R2

ąóąĖą┐ąĖčćąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ ą┤ą╗čÅ R1 ąĖ R2 ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĮąĄčüą║ąŠą╗čīą║ąŠ čüąŠč鹥ąĮ ą×ą╝, čćč鹊ą▒čŗ ąŠą▒ąĄčüą┐ąĄčćąĖčéčī ą┤ąŠčüčéą░č鹊čćąĮčŗą╣ č鹊ą║ ą┤ą╗čÅ čüąŠąĘą┤ą░ąĮąĖčÅ č鹊čćą║ąĖ čüą╝ąĄčēąĄąĮąĖčÅ ąĮą░ čéčĆąĄą▒čāąĄą╝ąŠą╝ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĖ ąĖ ą┐čĆąĖ čŹč鹊ą╝ ąĮąĄ ą┐ąŠą▓ą╗ąĖčÅčéčī ąĮą░ č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖąĄ čüąĖą│ąĮą░ą╗ąŠą▓.

ąØą░ ąŠčéą╗ą░ą┤ąŠčćąĮąŠą╝ ą╝ąŠą┤čāą╗ąĄ TLK2501 ą║ąŠą╝ą┐ą░ąĮąĖąĖ Texas Instruments ąĘąĮą░č湥ąĮąĖčÅ čĆąĄąĘąĖčüč鹊čĆąŠą▓ R1 ąĖ R2 ą▒čŗą╗ąĖ ą▓čŗą▒čĆą░ąĮčŗ R1 = 200 ą×ą╝ ąĖ R2 = 825 ą×ą╝, čćč鹊 ą┤ą░ąĄčé ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖčÅ 2.01V.

ąĢčüčéčī ąĖ ą┤čĆčāą│ąĖąĄ, ą▒ąŠą╗ąĄąĄ 菹╗ąĄą│ą░ąĮčéąĮčŗąĄ čüą┐ąŠčüąŠą▒čŗ čüąŠąĘą┤ą░ąĮąĖčÅ č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖ čüą╝ąĄčēąĄąĮąĖčÅ, čüą╝. ą▓čĆąĄąĘą║čā "ąĪčģąĄą╝čŗ č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖ čüą╝ąĄčēąĄąĮąĖčÅ".

ąĪčāčēąĄčüčéą▓čāąĄčé č湥čéčŗčĆąĄ čéąĖą┐ąŠą▓čŗčģ čüą┐ąŠčüąŠą▒ą░ č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖ čüą╝ąĄčēąĄąĮąĖčÅ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗčģ ą╗ąĖąĮąĖą╣ čüą▓čÅąĘąĖ. ąŻ ą║ą░ąČą┤ąŠą╣ ąĄčüčéčī čüą▓ąŠąĖ ą┤ąŠčüč鹊ąĖąĮčüčéą▓ą░ ąĖ ąĮąĄą┤ąŠčüčéą░čéą║ąĖ.

ąöąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮą░čÅ čüčģąĄą╝ą░. ąŁč鹊 ąĮą░ą▓ąĄčĆąĮąŠąĄ čüą░ą╝ą░čÅ ą┐čĆąŠčüčéą░čÅ ąĖąĘ ą▓čüąĄčģ čüčģąĄą╝ č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖ čüą╝ąĄčēąĄąĮąĖčÅ. R1 ąĖ R2 ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ ą┤ąĄą╗ąĖč鹥ą╗čÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ. ąśąĘ ąĘąĮą░č湥ąĮąĖčÅ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ą║ąĖą╗ąŠąŠą╝ą░, ąĖ ąĖą╝ąĖ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą║ąŠčĆčĆąĄą║čéąĮąŠąĄ ą┤ą╗čÅ ą▓čģąŠą┤ąŠą▓ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ ąĘąĮą░č湥ąĮąĖąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ąĘąĄą╝ą╗ąĖ. ąöąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠąĄ č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖąĄ ą┐čĆąŠčüč鹊 ą▓ 2 čĆą░ąĘą░ ą┐čĆąĄą▓čŗčłą░ąĄčé čģą░čĆą░ą║č鹥čĆąĖčüčéąĖč湥čüą║ąĖą╣ ąĖą╝ą┐ąĄą┤ą░ąĮčü.

ąĀąĖčü. 28. ąöąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠąĄ č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖąĄ čüąŠ čüą╝ąĄčēąĄąĮąĖąĄą╝.

ą×čüąĮąŠą▓ąĮąŠą╣ ąĮąĄą┤ąŠčüčéą░č鹊ą║ čéą░ą║ąŠą╣ čüčģąĄą╝čŗ - ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓ ąĖ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ č鹊ą║ą░ čåąĄą┐ąŠčćą║ąŠą╣ ą┤ąĄą╗ąĖč鹥ą╗čÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ. ą×ą┤ąĮą░ą║ąŠ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī čüąĮąĖąČąĄąĮąŠ ą▓čŗą▒ąŠčĆąŠą╝ ą▒ąŠą╗ąĄąĄ ą▓čŗčüąŠą║ąĖčģ ąĘąĮą░č湥ąĮąĖą╣ R1 ąĖ R2.

ąöąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮą░čÅ čüčģąĄą╝ą░ čü čĆą░ąĘą▓čÅąĘčŗą▓ą░čÄčēąĖą╝ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆąŠą╝. ąÆč鹊čĆąŠą╣ ą▓ą░čĆąĖą░ąĮčé čüčģąĄą╝čŗ č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐ąŠą║ą░ąĘą░ąĮ ąĮą░ čĆąĖčü. 29, ąĮą░ čŹč鹊čé čĆą░ąĘ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣ č鹥čĆą╝ąĖąĮąĖčĆčāčÄčēąĖą╣ čĆąĄąĘąĖčüč鹊čĆ čĆą░ąĘą┤ąĄą╗ąĄąĮ ąĮą░ ą┤ą▓ąĄ ą┐ąŠą╗ąŠą▓ąĖąĮą║ąĖ ą┐ąŠ 50 ą×ą╝ (ZO), čüąŠąĄą┤ąĖąĮąĄąĮąĮčŗąĄ ą┤ą╗čÅ čüąĖą│ąĮą░ą╗ą░ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ. ąĪčĆąĄą┤ąĮčÅčÅ č鹊čćą║ą░ čüąŠąĄą┤ąĖąĮąĄąĮąĖčÅ čŹčéąĖčģ čĆąĄąĘąĖčüč鹊čĆąŠą▓ čüąŠąĄą┤ąĖąĮąĄąĮą░ č湥čĆąĄąĘ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ C ą░ ąĘąĄą╝ą╗čÄ.

ąĀąĖčü. 29. ąöąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠąĄ č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖąĄ ąĖ čüą╝ąĄčēąĄąĮąĖąĄ čü čĆą░ąĘą▓čÅąĘčŗą▓ą░čÄčēąĖą╝ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆąŠą╝.

ąÜą░ą║ ąĖ ą▓ ą┐čĆąĄą┤čŗą┤čāčēąĄą╣ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą╣ čüčģąĄą╝ąĄ čĆąĖčü. 28, ąŠčüąĮąŠą▓ąĮąŠą╣ ąĮąĄą┤ąŠčüčéą░č鹊ą║ čüčģąĄą╝čŗ čĆąĖčü. 29 ą▓ ą║ąŠą╗ąĖč湥čüčéą▓ąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗčģ ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓ ąĖ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ čåąĄą┐ąŠč湥ą║ ą┤ąĄą╗ąĖč鹥ą╗ąĄą╣. ąŁąĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ čéą░ą║ąČąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī čüąĮąĖąČąĄąĮąŠ čāą▓ąĄą╗ąĖč湥ąĮąĖąĄą╝ ąĮąŠą╝ąĖąĮą░ą╗ąŠą▓ R1 ąĖd R2. ą×ą┤ąĮą░ą║ąŠ ą┤ąŠčüč鹊ąĖąĮčüčéą▓ąŠ čüčģąĄą╝čŗ ą▓ č鹊ą╝, čćč鹊 ąŠąĮą░ ą▒ą░ą╗ą░ąĮčüąĖčĆčāąĄčé čāčĆąŠą▓ąĮąĖ čüąĖą│ąĮą░ą╗ąŠą▓ ąĮą░ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗčģ ą▓čģąŠą┤ąŠą▓ ąĘą░ čüč湥čé ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆą░ C, ą║ąŠč鹊čĆčŗą╣ ą┤ą╗čÅ ą▓čŗčüąŠą║ąĖčģ čćą░čüč鹊čé čüąĖą│ąĮą░ą╗ą░ čüąŠčüčéą░ą▓ą╗čÅąĄčé ą║ąŠčĆąŠčéą║ąŠąĄ ąĘą░ą╝čŗą║ą░ąĮąĖąĄ ąĮą░ ąĘąĄą╝ą╗čÄ.

ąöąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮą░čÅ čüčģąĄą╝ą░ čü čāą╝ąĄąĮčīčłąĄąĮąĮčŗą╝ ą║ąŠą╗ąĖč湥čüčéą▓ąŠą╝ čĆąĄąĘąĖčüč鹊čĆąŠą▓. ąóčĆąĄčéąĖą╣ ą▓ą░čĆąĖą░ąĮčé č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖ čüą╝ąĄčēąĄąĮąĖčÅ ą┐ąŠą║ą░ąĘą░ąĮ ąĮą░ čĆąĖčü. 30. ąŚą┤ąĄčüčī ą║ąŠą╝ą▒ąĖąĮąĖčĆčāąĄčéčüčÅ č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖąĄ čü čåąĄą┐ąŠčćą║ąŠą╣ ą┤ąĄą╗ąĖč鹥ą╗čÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ.

ąĀąĖčü. 30. ąöąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮą░čÅ čüčģąĄą╝ą░ č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖ čüą╝ąĄčēąĄąĮąĖčÅ čü čāą╝ąĄąĮčīčłąĄąĮąĮčŗą╝ ą║ąŠą╗ąĖč湥čüčéą▓ąŠą╝ čĆąĄąĘąĖčüč鹊čĆąŠą▓.

ąśą┤ąĄčÅ čüąŠčüč鹊ąĖčé ą▓ č鹊ą╝, čćč鹊ą▒čŗ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠąĄ ą┐ąŠ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą╝čā č鹊ą║čā ą▓ą║ą╗čÄč湥ąĮąĖąĄ čĆąĄąĘąĖčüč鹊čĆąŠą▓ R1 ąĖ R2 ą▒čŗą╗ąŠ čĆą░ą▓ąĮąŠ ZO ą┤ą╗čÅ ą╗ąĖąĮąĖąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ. ą×ą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ čŹčéąĖ čĆąĄąĘąĖčüč鹊čĆčŗ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čĆą░čüčüčćąĖčéą░ąĮčŗ čéą░ą║, čćč鹊ą▒čŗ čüąŠąĘą┤ą░ą▓ą░čéčī ą║ąŠčĆčĆąĄą║čéąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ čüą╝ąĄčēąĄąĮąĖčÅ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ąĘąĄą╝ą╗ąĖ ą┤ą╗čÅ ą▓čģąŠą┤ąŠą▓ ą┐čĆąĖąĄą╝ąĮąĖą║ą░.

ąöą╗čÅ čĆą░čüč湥čéą░ ą┐čĆąĖą╝ąĄčĆą░ ą▓ąŠąĘčīą╝ąĄą╝ ą┤čĆą░ą╣ą▓ąĄčĆ VML ąĖ CML-ą┐čĆąĖąĄą╝ąĮąĖą║ TLK2501. ąźą░čĆą░ą║č鹥čĆąĖčüčéąĖč湥čüą║ąĖą╣ ąĖą╝ą┐ąĄą┤ą░ąĮčü ą╗ąĖąĮąĖąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ 50 ą×ą╝, ąĖ VDD = 2.5V. ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ čüą╝ąĄčēąĄąĮąĖčÅ ąĮą░ ą▓čģąŠą┤ą░čģ TLK2501 ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąŠčé 1.5V ą┤ąŠ VDD ŌĆō VID/2. ąÆ ąĮą░čłąĄą╝ čüą╗čāčćą░ąĄ 2.0V ą▒čāą┤ąĄčé ą┐ąŠą┤čģąŠą┤čÅčēąĖą╝ ą▓čŗą▒ąŠčĆąŠą╝ ą┤ą╗čÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ čüą╝ąĄčēąĄąĮąĖčÅ.

ąĀąĖčü. 31. ą¤čĆąĖą╝ąĄčĆ čüąŠąĄą┤ąĖąĮąĄąĮąĖčÅ ą┤čĆą░ą╣ą▓ąĄčĆą░ VML ąĖ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ CML.

ąöą▓ą░ ąŠčüąĮąŠą▓ąĮčŗčģ ą║čĆąĖč鹥čĆąĖčÅ ą┤ą╗čÅ čŹč鹊ą╣ čüčģąĄą╝čŗ č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖčÅ čüą╗ąĄą┤čāčÄčēąĖąĄ:

1. R1 || R2 = ZO.

2. ą”ąĄą┐ąŠčćą║ą░ ą┤ąĄą╗ąĖč鹥ą╗čÅ R1 ąĖ R2 ą┤ąŠą╗ąČąĮą░ čāčüčéą░ąĮąŠą▓ąĖčéčī VTERM = 2.0V.

ąśąĘą▓ąĄčüčéąĮą░čÅ č乊čĆą╝čāą╗ą░ ą┤ą╗čÅ ą▓čŗčćąĖčüą╗ąĄąĮąĖčÅ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖčÅ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠ ą▓ą║ą╗čÄč湥ąĮąĮčŗčģ čĆąĄąĘąĖčüč鹊čĆąŠą▓ (R1 ąĖ R2 ą┤ą╗čÅ čüąĖą│ąĮą░ą╗ą░ čüąŠąĄą┤ąĖąĮąĄąĮčŗ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠ, ąĖ ąĖčģ čĆąĄąĘčāą╗čīčéąĖčĆčāčÄčēąĄąĄ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ ą┤ąŠą╗ąČąĮąŠ čüąŠčüčéą░ą▓ą╗čÅčéčī 50 ą×ą╝):

1 1 1 1

--- + --- = --- = -------

R1 R2 ZO 50 ą×ą╝

ąŁčéčā č乊čĆą╝čāą╗čā ą╝ąŠąČąĮąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░čéčī čéą░ą║:

R1 * R2

------- = 50 ą×ą╝

R1 + R2

ąĢčēąĄ ąŠą┤ąĮąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ:

R1 * R2

(R1 + R2) = --------- (3)

50 ą×ą╝

ążąŠčĆą╝čāą╗ą░ ą┤ą╗čÅ ą▓čŗčćąĖčüą╗ąĄąĮąĖčÅ ą┤ąĄą╗ąĖč鹥ą╗čÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ:

R2 VDD

------- = -------

R1 + R2 VTERM

ąŁčéčā č乊čĆą╝čāą╗čā ą╝ąŠąČąĮąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░čéčī čéą░ą║:

R2 * VDD

(R1 + R2) = ----------

VTERM

ąĢčēąĄ ąŠą┤ąĮąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ:

(R1 + R2) = 1.25 R2 (4)

ą¤čĆąĖ ą┐ąŠą┤čüčéą░ąĮąŠą▓ą║ąĄ č乊čĆą╝čāą╗čŗ 4 ą▓ č乊čĆą╝čāą╗čā 3 ą┐ąŠą╗čāčćąĖą╝:

R1 * R2

1.25 R2 = --------- (5)

50 ą×ą╝

R1 = 1.25 * 50 ą×ą╝ R1 = 62.5 ą×ą╝

R2 = R1 / 0.2 R2 = 250 ą×ą╝

ą×č湥ą▓ąĖą┤ąĮąŠ, čćč鹊 ą┤ą╗čÅ čŹč鹊ą╣ čüčģąĄą╝čŗ ąĘąĮą░č湥ąĮąĖčÅ čĆąĄąĘąĖčüč鹊čĆąŠą▓ R1 ąĖ R2 ą╝ąĄąĮčīčłąĄ, čćč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé čüąĮąĖąĘąĖčéčī ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓, ąŠą┤ąĮą░ą║ąŠ čŹč鹊 ą┤ąŠčüčéąĖą│ą░ąĄčéčüčÅ čåąĄąĮąŠą╣ čāą▓ąĄą╗ąĖč湥ąĮąĖčÅ čŹąĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ.

ąöąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮą░čÅ čüčģąĄą╝ą░ čü ąŠą┤ąĮąŠą╣ čåąĄą┐ąŠčćą║ąŠą╣ čüąŠąĘą┤ą░ąĮąĖčÅ čüą╝ąĄčēąĄąĮąĖčÅ. ą¤ąŠčüą╗ąĄą┤ąĮąĖą╣ ą▓ą░čĆąĖą░ąĮčé čüčģąĄą╝čŗ ąĮą░ čĆąĖčü. 32 ą║ąŠą╝ą▒ąĖąĮąĖčĆčāąĄčé č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖąĄ čü čåąĄą┐ąŠčćą║ąŠą╣ ą┤ąĄą╗ąĖč鹥ą╗čÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ.

ąĀąĖčü. 32. ąöąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠąĄ č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖąĄ čü ąŠą┤ąĮąŠą╣ čåąĄą┐ąŠčćą║ąŠą╣ čüąŠąĘą┤ą░ąĮąĖčÅ čüą╝ąĄčēąĄąĮąĖčÅ.

ąŁč鹊 ąŠč湥ąĮčī ąŠą┐čéąĖą╝ą░ą╗čīąĮą░čÅ čüčģąĄą╝ą░, ą┐ąŠč鹊ą╝čā čćč鹊 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ č鹊ą╗čīą║ąŠ ąŠą┤ąĖąĮ ą┤ąĄą╗ąĖč鹥ą╗čī ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┤ą╗čÅ čüąŠąĘą┤ą░ąĮąĖčÅ čüą╝ąĄčēąĄąĮąĖčÅ, čćč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé čāą╝ąĄąĮčīčłąĖčéčī ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ č鹊ą║ą░. ąĀą░ąĘą▓čÅąĘčŗą▓ą░čÄčēąĖą╣ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ C ąĖ ą┤ą▓ą░ čĆąĄąĘąĖčüč鹊čĆą░ č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖčÅ čüąĮąĖąČą░čÄčé čüąĖąĮčäą░ąĘąĮčŗą╣ čłčāą╝ ąĮą░ ą▓čģąŠą┤ąĄ ą┐čĆąĖąĄą╝ąĮąĖą║ą░. ąŁč鹊 ąŠą┤ąĮą░ ąĖąĘ ą╗čāčćčłąĖčģ čüčģąĄą╝ č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖ čüą╝ąĄčēąĄąĮąĖčÅ ą┤ą╗čÅ ą╝ąĖą║čĆąŠčüčģąĄą╝ ą┐čĆąĖąĄą╝ąĮąĖą║ąŠą▓, ą▓ ą║ąŠč鹊čĆčŗčģ ąĮąĄčé ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čüą╝ąĄčēąĄąĮąĖčÅ ą▓čģąŠą┤ąŠą▓.

R1 ąĖ R2 ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą┐ąŠčĆčÅą┤ą║ą░ ą║ąĖą╗ąŠąŠą╝, ąĖ čĆąĄąĘąĖčüč鹊čĆčŗ č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖčÅ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ čĆą░ą▓ąĮčŗą╝ąĖ ZO.

ąŁčéą░ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé čāčüčéą░ąĮąŠą▓ąĖčéčī čĆąĄąĘąĖčüč鹊čĆčŗ č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖčÅ čĆčÅą┤ąŠą╝ čü ą┐čĆąĖąĄą╝ąĮąĖą║ąŠą╝, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ čüčģąĄą╝ą░ čüąŠąĘą┤ą░ąĮąĖčÅ čüą╝ąĄčēąĄąĮąĖčÅ ą╝ąŠąČąĄčé ą▒čŗčéčī čĆą░ąĘą╝ąĄčēąĄąĮą░ ąĮą░ ąĮąĄą║ąŠč鹊čĆąŠą╝ čĆą░čüčüč鹊čÅąĮąĖąĖ ąŠčé ą┐čĆąĖąĄą╝ąĮąĖą║ą░. ą×ą┤ąĮą░ą║ąŠ ąĖą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ C ą┤ąŠą╗ąČąĄąĮ ąĮą░čģąŠą┤ąĖčéčīčüčÅ ą║ą░ą║ ą╝ąŠąČąĮąŠ ą▒ą╗ąĖąČąĄ ą║ąŠ ą▓čģąŠą┤ą░ą╝ ą┐čĆąĖąĄą╝ąĮąĖą║ą░.

[ąĪčüčŗą╗ą║ąĖ]

1. HFAN-1.0 Introduction to LVDS, PECL, and CML site:maximintegrated.com.

2. Interfacing Between LVPECL, VML, CML, and LVDS Levels site:ti.com. |

ąÜąŠą╝ą╝ąĄąĮčéą░čĆąĖąĖ

RSS ą╗ąĄąĮčéą░ ą║ąŠą╝ą╝ąĄąĮčéą░čĆąĖąĄą▓ čŹč鹊ą╣ ąĘą░ą┐ąĖčüąĖ