|

ą£ąĖą║čĆąŠčüčģąĄą╝ą░ L3G4200D ą║ąŠą╝ą┐ą░ąĮąĖąĖ STMicroelectronics (ST) ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé čüąŠą▒ąŠą╣ ą╝ąĖąĮąĖą░čéčÄčĆąĮčŗą╣ čüą▓ąĄčĆčģčüčéą░ą▒ąĖą╗čīąĮčŗą╣ ą┤ą░čéčćąĖą║ ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖą╣ ą▓ 3D ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąĄ, ąĖąĘą│ąŠč鹊ą▓ą╗ąĄąĮąĮčŗą╣ ą┐ąŠ MEMS č鹥čģąĮąŠą╗ąŠą│ąĖąĖ. ą×ąĮ ą╝ąŠąČąĄčé čĆą░ą▒ąŠčéą░čéčī ą║ą░ą║ ą│ąĖčĆąŠčüą║ąŠą┐ ą▓ ą░ą▓ąĖąŠąĮąĖą║ąĄ, ą░ą▓č鹊ą╝ąŠą▒ąĖą╗čīąĮąŠą╣ ą┐čĆąŠą╝čŗčłą╗ąĄąĮąĮąŠčüčéąĖ ąĖ ą┤čĆčāą│ąĖčģ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅčģ, ą║ąŠč鹊čĆčŗąĄ čéčĆąĄą▒čāčÄčé ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ ą┐ąŠą╗ąŠąČąĄąĮąĖčÅ ąŠą▒čŖąĄą║čéą░ ą▓ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąĄ. ąöą░ą╗ąĄąĄ ą┐čĆąĖą▓ąĄą┤ąĄąĮ ą┐ąĄčĆąĄą▓ąŠą┤ ą┤ą░čéą░čłąĖčéą░ L3G4200D, ąĮąĄą┐ąŠąĮčÅčéąĮčŗąĄ č鹥čĆą╝ąĖąĮčŗ ąĖ čüąŠą║čĆą░čēąĄąĮąĖčÅ čüą╝. ą▓ čĆą░ąĘą┤ąĄą╗ąĄ ąĪą╗ąŠą▓ą░čĆąĖą║, ą▓ ą║ąŠąĮčåąĄ čüčéą░čéčīąĖ.

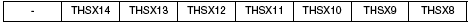

[ą×čüąĮąŠą▓ąĮčŗąĄ ąŠčüąŠą▒ąĄąĮąĮąŠčüčéąĖ čüąĄąĮčüąŠčĆą░ L3G4200D]

ŌĆó ąóčĆąĖ ą▓čŗą▒ąĖčĆą░ąĄą╝čŗąĄ ą┐ąŠą╗ąĮčŗąĄ čłą║ą░ą╗čŗ (250/500/2000 dps).

ŌĆó ą”ąĖčäčĆąŠą▓čŗąĄ ą▓čŗčģąŠą┤ąĮčŗąĄ ąĖąĮč鹥čĆč乥ą╣čüčŗ I2C ąĖ SPI.

ŌĆó 16-ą▒ąĖčéąĮčŗąĄ ą▓čŗčģąŠą┤ąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ.

ŌĆó ąÆčüčéčĆąŠąĄąĮąĮčŗą╣ čüąĄąĮčüąŠčĆ č鹥ą╝ą┐ąĄčĆą░čéčāčĆčŗ, čü ą║ąŠč鹊čĆąŠą│ąŠ ą╝ąŠąČąĮąŠ čüčćąĖčéą░čéčī 8-ą▒ąĖčéąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ.

ŌĆó ąöą▓ą░ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗčģ ą▓čŗčģąŠą┤ąĮčŗčģ čüąĖą│ąĮą░ą╗ą░ (ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĖ ą│ąŠč鹊ą▓ąĮąŠčüčéčī ą┤ą░ąĮąĮčŗčģ).

ŌĆó ąÆčüčéčĆąŠąĄąĮąĮčŗąĄ čäąĖą╗čīčéčĆčŗ ążąØą¦ ąĖ ążąÆą¦, ą┐ąŠą╗ąŠčüčā ą┐čĆąŠą┐čāčüą║ą░ąĮąĖčÅ ą║ąŠč鹊čĆčŗčģ ą╝ąŠąČąĮąŠ ą▓čŗą▒čĆą░čéčī.

ŌĆó ą¦čĆąĄąĘą▓čŗčćą░ą╣ąĮąŠ ą▓čŗčüąŠą║ą░čÅ čüčéą░ą▒ąĖą╗čīąĮąŠčüčéčī ą┐ąŠą║ą░ąĘą░ąĮąĖą╣ ą┐ąŠ č鹥ą╝ą┐ąĄčĆą░čéčāčĆąĄ ąĖ ą▓čĆąĄą╝ąĄąĮąĖ.

ŌĆó ą©ąĖčĆąŠą║ąĖą╣ ą┤ąĖą░ą┐ą░ąĘąŠąĮ ą┐ąĖčéą░čÄčēąĖčģ ąĮą░ą┐čĆčÅąČąĄąĮąĖą╣ 2.4V .. 3.6V.

ŌĆó ąÆčģąŠą┤čŗ ąĖ ą▓čŗčģąŠą┤čŗ (IO), čüąŠą▓ą╝ąĄčüčéąĖą╝čŗąĄ čü ąĮąĖąĘą║ąŠą▓ąŠą╗čīčéąĮąŠą╣ ą╗ąŠą│ąĖą║ąŠą╣ (1.8V).

ŌĆó ąÆčüčéčĆąŠąĄąĮąĮčŗąĄ čĆąĄąČąĖą╝čŗ ąŠčéą║ą╗čÄč湥ąĮąĖčÅ (power-down) ąĖ čüąĮą░ (sleep).

ŌĆó ąÆčüčéčĆąŠąĄąĮąĮčŗą╣ FIFO.

ŌĆó ąÆčŗčüąŠą║ą░čÅ čāčüč鹊ą╣čćąĖą▓ąŠčüčéčī ą║ čāą┤ą░čĆą░ą╝ ąĖ ą▓ąĖą▒čĆą░čåąĖčÅą╝.

ŌĆó ąĀą░čüčłąĖčĆąĄąĮąĮčŗą╣ čĆą░ą▒ąŠčćąĖą╣ č鹥ą╝ą┐ąĄčĆą░čéčāčĆąĮčŗą╣ ą┤ąĖą░ą┐ą░ąĘąŠąĮ (-40┬░C .. +85┬░C).

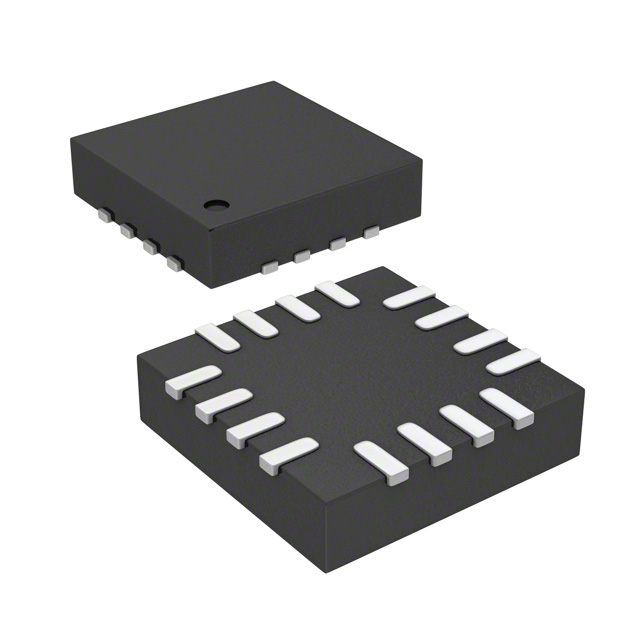

ŌĆó ą£ąĖąĮąĖą░čéčÄčĆąĮčŗą╣ ą┐ą╗ą░čüčéą╝ą░čüčüąŠą▓čŗą╣ ą║ąŠčĆą┐čāčü LGA-16 (4x4x1.1 mm).

ŌĆó ąŻą┐ą░ą║ąŠą▓ą║ą░ čüąŠą▓ą╝ąĄčüčéąĖą╝ą░ čüąŠ čüčéą░ąĮą┤ą░čĆčéą░ą╝ąĖ ECOPACK┬« RoHS ąĖ "Green".

ą×ą▒ą╗ą░čüčéąĖ ą┐čĆąĖą╝ąĄąĮąĄąĮąĖčÅ L3G4200D:

ŌĆó ąśą│čĆčŗ ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ ą▓ą▓ąŠą┤ą░ ą┤ą╗čÅ čüąĖčüč鹥ą╝ ą▓ąĖčĆčéčāą░ą╗čīąĮąŠą╣ čĆąĄą░ą╗čīąĮąŠčüčéąĖ.

ŌĆó ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┤ą▓ąĖąČąĄąĮąĖąĄą╝, ąĖąĮč鹥čĆč乥ą╣čüčŗ MMI.

ŌĆó ąĪąĖčüč鹥ą╝čŗ ąĮą░ą▓ąĖą│ą░čåąĖąĖ GPS.

ŌĆó ą¤čĆąĖą▒ąŠčĆčŗ ąĖ čĆąŠą▒ąŠč鹊č鹥čģąĮąĖą║ą░.

[ą×ą▒čēąĄąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ L3G4200D]

L3G4200D čÅą▓ą╗čÅąĄčéčüčÅ čéčĆąĄčģąŠčüąĄą▓čŗą╝ ą┤ą░čéčćąĖą║ąŠą╝ čāą│ą╗ąŠą▓čŗčģ ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖą╣ čü ąĮąĖąĘą║ąĖą╝ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄą╝, ąŠą▒ą╗ą░ą┤ą░čÄčēąĖą╝ čéą░ą║ąČąĄ čćčĆąĄąĘą▓čŗčćą░ą╣ąĮąŠą╣ čüčéą░ą▒ąĖą╗čīąĮąŠčüčéčīčÄ ąĮčāą╗ąĄą▓ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ ąĖ ą▓čŗčüąŠą║ąŠą╣ č鹊čćąĮąŠčüčéčīčÄ ą┐ąŠą║ą░ąĘą░ąĮąĖą╣, ą║ąŠč鹊čĆą░čÅ čüąŠčģčĆą░ąĮčÅąĄčéčüčÅ ą┐čĆąĖ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅčģ č鹥ą╝ą┐ąĄčĆą░čéčāčĆčŗ ąĖ ą┤ą╗ąĖč鹥ą╗čīąĮąŠą╣ čĆą░ą▒ąŠč鹥 ą┤ą░čéčćąĖą║ą░. ąÆ ą╝ąĖą║čĆąŠčüčģąĄą╝čā, ą║čĆąŠą╝ąĄ čćčāą▓čüčéą▓ąĖč鹥ą╗čīąĮąŠą│ąŠ 菹╗ąĄą╝ąĄąĮčéą░, ą▓čüčéčĆąŠąĄąĮ ąĖąĮč鹥čĆč乥ą╣čü I2C/SPI, č湥čĆąĄąĘ ą║ąŠč鹊čĆčŗą╣ ą╝ąŠąČąĮąŠ ą┐ąĄčĆąĄą┤ą░čéčī ą▓ąŠ ą▓ąĮąĄčłąĮąĖą╣ ą╝ąĖčĆ čüą║ąŠčĆąŠčüčéčī ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ čāą│ą╗ą░ ą┐ąŠ čéčĆąĄą╝ ąŠčüčÅą╝ (čŹč鹊čé ąĖąĮč鹥čĆč乥ą╣čü ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ą║ ą▓ąĮąĄčłąĮąĄą╝čā ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčā). ą¦čāą▓čüčéą▓ąĖč鹥ą╗čīąĮčŗą╣ 菹╗ąĄą╝ąĄąĮčé ą┤ą░čéčćąĖą║ą░ ąĖąĘą│ąŠč鹊ą▓ą╗ąĄąĮ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ čüą┐ąĄčåąĖą░ą╗čīąĮąŠą╣ ą╝ąĖą║čĆąŠą╝ąĄčģą░ąĮąĖč湥čüą║ąŠą╣ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ, čĆą░ąĘčĆą░ą▒ąŠčéą░ąĮąĮąŠą╣ STMicroelectronics, čćč鹊ą▒čŗ ą▓čŗą┐ąŠą╗ąĮąĖčéčī ąĖąĮąĄčĆčåąĖąŠąĮąĮčŗąĄ čüąĄąĮčüąŠčĆčŗ ąĖ ą░ą║čéčāą░č鹊čĆčŗ ąĮą░ ą║čĆąĄą╝ąĮąĖąĄą▓čŗčģ ą┐ą╗ą░čüčéąĖąĮą░čģ. ąÆąĮąĄčłąĮąĖą╣ čåąĖčäčĆąŠą▓ąŠą╣ ąĖąĮč鹥čĆč乥ą╣čü čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮ ą┐ąŠ CMOS-č鹥čģąĮąŠą╗ąŠą│ąĖąĖ, ą┐ąŠąĘą▓ąŠą╗čÅčÄčēąĄą╣ čüąŠąĘą┤ą░čéčī ą▓čŗčüąŠą║ąŠąĖąĮč鹥ą│čĆąĖčĆąŠą▓ą░ąĮąĮčŗą╣ ą┤ąĖąĘą░ą╣ąĮ, ąĮą░ąĖą╗čāčćčłąĖą╝ ąŠą▒čĆą░ąĘąŠą╝ ą┐ąŠą┤čüčéčĆąŠąĄąĮąĮčŗą╣ ą┐ąŠą┤ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ čćčāą▓čüčéą▓ąĖč鹥ą╗čīąĮąŠą│ąŠ 菹╗ąĄą╝ąĄąĮčéą░ ą┤ą░čéčćąĖą║ą░. L3G4200D ąĖą╝ąĄąĄčé ą┐ąŠą╗ąĮčŗąĄ čłą║ą░ą╗čŗ ┬▒250/┬▒500/┬▒2000 dps, ąĖ ą╝ąŠąČąĄčé ąĖąĘą╝ąĄčĆčÅčéčī čüą║ąŠčĆąŠčüčéčī ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ čāą│ą╗ą░ ą▓ ą▓čŗą▒čĆą░ąĮąĮąŠą╣ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╝ ą┐ąŠą╗ąŠčüąĄ čćą░čüč鹊čé. L3G4200D ą▓čŗą┐čāčüą║ą░ąĄčéčüčÅ ą▓ ą┐ą╗ą░čüčéą╝ą░čüčüąŠą▓ąŠą╝ ą║ąŠčĆą┐čāčüąĄ land grid array (LGA) ąĖ ą╝ąŠąČąĄčé čĆą░ą▒ąŠčéą░čéčī ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ č鹥ą╝ą┐ąĄčĆą░čéčāčĆ -40┬░C .. +85┬░C.

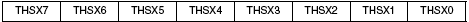

ąóą░ą▒ą╗ąĖčåą░ 1. ąÆą░čĆąĖą░ąĮčéčŗ ą┐ąŠčüčéą░ą▓ą║ąĖ L3G4200D.

| ąÜąŠą┤ ąĘą░ą║čāą┐ą║ąĖ |

ąóąĄą╝ą┐ąĄčĆą░čéčāčĆąĮčŗą╣

ą┤ąĖą░ą┐ą░ąĘąŠąĮ (oC) |

ąÜąŠčĆą┐čāčü |

ąŻą┐ą░ą║ąŠą▓ą║ą░ |

| L3G4200D |

-40 .. +85 |

LGA-16 (4x4x1.1 mm) |

ąøąŠč鹊ą║ (tray) |

| L3G4200DTR |

-40 .. +85 |

LGA-16 (4x4x1.1 mm) |

ąøąĄąĮčéą░ ąĖ ą╗ąĖąĮąĄą╣ą║ąĖ (tape and reel) |

[1. ąæą╗ąŠą║-čüčģąĄą╝ą░ ąĖ ąŠą┐ąĖčüą░ąĮąĖąĄ ą▓čŗą▓ąŠą┤ąŠą▓ L3G4200D]

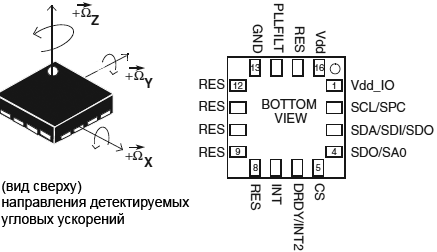

ąĀąĖčü.1. ąæą╗ąŠą║-čüčģąĄą╝ą░ L3G4200D

ą¤ąŠčÅčüąĮąĄąĮąĖčÅ ą║ ą▒ą╗ąŠą║-čüčģąĄą╝ąĄ:

MUX ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąŠčĆ čüąĖą│ąĮą░ą╗ąŠą▓.

CHARGE AMP čāčüąĖą╗ąĖč鹥ą╗čī ąĘą░čĆčÅą┤ą░.

MIXER čüą╝ąĄčüąĖč鹥ą╗čī.

LOW-PASS FILTER čäąĖą╗čīčéčĆ ąĮąĖąĘą║ąŠą╣ čćą░čüč鹊čéčŗ, ążąØą¦.

ADC1 ą░ąĮą░ą╗ąŠą│ąŠ-čåąĖčäčĆąŠą▓ąŠą╣ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░č鹥ą╗čī (ąÉą”ą¤) ą┤ą╗čÅ čüąĖą│ąĮą░ą╗ąŠą▓ čü ą┤ą░čéčćąĖą║ąŠą▓ čāą│ą╗ąŠą▓ąŠą│ąŠ čāčüą║ąŠčĆąĄąĮąĖčÅ.

DIGITAL FILTERING ą▒ą╗ąŠą║ čåąĖčäčĆąŠą▓ąŠą╣ čäąĖą╗čīčéčĆą░čåąĖąĖ.

I2C, SPI ą▒ą╗ąŠą║ ą▓ąĮąĄčłąĮąĖčģ ąĖąĮč鹥čĆč乥ą╣čüąŠą▓.

CS, SCL/SPC, SDA/SDO/SDI, SDO ą▓ąĮąĄčłąĮąĖąĄ čüąĖą│ąĮą░ą╗čīąĮčŗąĄ ą╗ąĖąĮąĖąĖ čåąĖčäčĆąŠą▓čŗčģ ąĖąĮč鹥čĆč乥ą╣čüąŠą▓.

DRIVING MASS čćčāą▓čüčéą▓ąĖč鹥ą╗čīąĮą░čÅ ą║ čāčüą║ąŠčĆąĄąĮąĖčÅą╝ ą╝ą░čüčüą░.

Feedback loop ą┐ąĄčéą╗čÅ ąŠą▒čĆą░čéąĮąŠą╣ čüą▓čÅąĘąĖ.

TEMPERATURE SENSOR č鹥čĆą╝ąŠą┤ą░čéčćąĖą║.

ADC2 ą░ąĮą░ą╗ąŠą│ąŠ-čåąĖčäčĆąŠą▓ąŠą╣ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░č鹥ą╗čī (ąÉą”ą¤) ą┤ą╗čÅ čüąĖą│ąĮą░ą╗ą░ čü č鹥čĆą╝ąŠą┤ą░čéčćąĖą║ą░.

REFERENCE ąĖčüč鹊čćąĮąĖą║ ąŠą┐ąŠčĆąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░.

TRIMMING CIRCUITS čāąĘą╗čŗ ą┐ąŠą┤čüčéčĆąŠą╣ą║ąĖ.

FIFO ą▒čāč乥čĆ ą▓čŗčģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ čü ą┤ą░čéčćąĖą║ą░ čāą│ą╗ąŠą▓čŗčģ čāčüą║ąŠčĆąĄąĮąĖą╣.

CLOCK & PHASE GENERATOR ą│ąĄąĮąĄčĆą░č鹊čĆ čéą░ą║č鹊ą▓ ąĖ čäą░ąĘ.

CONTROL LOGIC & INTERRUPT GEN čāą┐čĆą░ą▓ą╗čÅčÄčēą░čÅ ą╗ąŠą│ąĖą║ą░ ąĖ ą│ąĄąĮąĄčĆą░čåąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣.

INT1, DRDY/INT2 ą▓ąĮąĄčłąĮąĖąĄ ą▓čŗčģąŠą┤ąĮčŗąĄ čüąĖą│ąĮą░ą╗čŗ, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ąĘą░ą▓ąĄą┤ąĄąĮčŗ ąĮą░ čģąŠčüčé (čāą┐čĆą░ą▓ą╗čÅčÄčēąĖą╣ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ) ą┤ą╗čÅ ą▓čŗą┤ą░čćąĖ ą░ą┐ą┐ą░čĆą░čéąĮčŗčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ąĖą╗ąĖ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ.

ąÆąĖą▒čĆą░čåąĖčÅ ąĖąĘą╝ąĄčĆąĖč鹥ą╗čīąĮąŠą╣ čüčéčĆčāą║čéčāčĆčŗ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčéčüčÅ čüčģąĄą╝ąŠą╣ ą┤čĆą░ą╣ą▓ąĄčĆą░ ą▓ čåąĖą║ą╗ąĄ ąŠą▒čĆą░čéąĮąŠą╣ čüą▓čÅąĘąĖ. ąśąĘą╝ąĄčĆčÅąĄą╝čŗą╣ čüąĖą│ąĮą░ą╗ čäąĖą╗čīčéčĆčāąĄčéčüčÅ ąĖ ą┐ąŠčÅą▓ą╗čÅąĄčéčüčÅ ąĮą░ ą▓čŗčģąŠą┤ąĄ ą║ą░ą║ čåąĖčäčĆąŠą▓čŗąĄ ą┤ą░ąĮąĮčŗąĄ.

1.1. ą×ą┐ąĖčüą░ąĮąĖąĄ ą▓čŗą▓ąŠą┤ąŠą▓

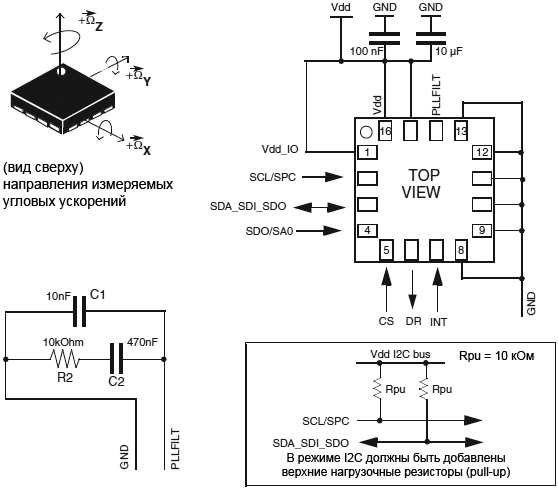

ąĀąĖčü. 2. ą¤ąŠą┤ą║ą╗čÄč湥ąĮąĖąĄ ą▓ ą▓ąĮąĄčłąĮąĖą╝ ą▓čŗą▓ąŠą┤ą░ą╝ ą║ąŠčĆą┐čāčüą░.

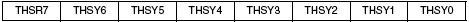

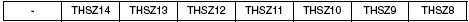

ąóą░ą▒ą╗ąĖčåą░ 2. ą×ą┐ąĖčüą░ąĮąĖąĄ ą▓čŗą▓ąŠą┤ąŠą▓.

| Ōä¢ ą▓čŗą▓. |

ąśą╝čÅ |

ąóąĖą┐ |

ążčāąĮą║čåąĖčÅ |

| 1 |

Vdd_IO |

PWR |

ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĖčüč鹊čćąĮąĖą║ą░ ą┐ąĖčéą░ąĮąĖčÅ ą┤ą╗čÅ ą┐ąŠčĆč鹊ą▓ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░. |

| 2 |

SCL

SPC |

I

I |

ąóą░ą║čéčŗ I2C.

ąóą░ą║čéčŗ SPI. |

| 3 |

SDA

SDI

SDO |

I/O

I

O |

ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ I2C.

ąÆčģąŠą┤ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ą┤ą░ąĮąĮčŗčģ SPI.

ąÆčŗčģąŠą┤ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ą┤ą░ąĮąĮčŗčģ SPI ą▓ 3-ą┐čĆąŠą▓ąŠą┤ąĮąŠą╝ čĆąĄąČąĖą╝ąĄ. |

| 4 |

SDO

SA0 |

O

I |

ąÆčŗčģąŠą┤ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ą┤ą░ąĮąĮčŗčģ SPI.

LSB-ą▒ąĖčé ą░ą┤čĆąĄčüą░ čāčüčéčĆąŠą╣čüčéą▓ą░ I2C. |

| 5 |

CS |

I |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ čĆą░ą▒ąŠčéčŗ SPI, ą▓čŗą▒ąŠčĆ čĆąĄąČąĖą╝ą░ ąĖąĮč鹥čĆč乥ą╣čüą░ (I2C/SPI) ą┐čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ (ąŠą┐ąĖčüą░ąĮąĖąĄ čüą╝. ą┤ą░ą╗ąĄąĄ). |

| 6 |

DRDY/INT2 |

O |

ąĪąĖą│ąĮą░ą╗ ą│ąŠč鹊ą▓ąĮąŠčüčéąĖ ą┤ą░ąĮąĮčŗčģ (Data Ready)/ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠčé FIFO. |

| 7 |

INT1 |

O |

ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝ąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ. |

| 8 |

Reserved |

|

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ, ą┐ąŠą┤ą║ą╗čÄčćąĖč鹥 ą║ GND. |

| 9 |

Reserved |

|

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ, ą┐ąŠą┤ą║ą╗čÄčćąĖč鹥 ą║ GND. |

| 10 |

Reserved |

|

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ, ą┐ąŠą┤ą║ą╗čÄčćąĖč鹥 ą║ GND. |

| 11 |

Reserved |

|

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ, ą┐ąŠą┤ą║ą╗čÄčćąĖč鹥 ą║ GND. |

| 12 |

Reserved |

|

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ, ą┐ąŠą┤ą║ą╗čÄčćąĖč鹥 ą║ GND. |

| 13 |

GND |

PWR |

ą×ą▒čēąĖą╣ ą┐čĆąŠą▓ąŠą┤ ą┤ą╗čÅ ą▓čüąĄčģ čüąĖą│ąĮą░ą╗ąŠą▓, 0V ą┐ąĖčéą░ąĮąĖčÅ. |

| 14 |

PLLFILT |

A |

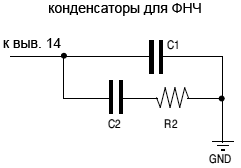

ąÆąĮąĄčłąĮąĖąĄ ą║ąŠą╝ą┐ąŠąĮąĄąĮčéčŗ ą┤ą╗čÅ čäąĖą╗čīčéčĆą░ PLL (čüą╝. čĆąĖčü. 3). |

| 15 |

Reserved |

|

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ, ą┐ąŠą┤ą║ą╗čÄčćąĖč鹥 ą║ Vdd. |

| 16 |

Vdd |

PWR |

ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĖčüč鹊čćąĮąĖą║ą░ ą┐ąĖčéą░ąĮąĖčÅ. |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ ą║ čéą░ą▒ą╗ąĖčåąĄ:

I čåąĖčäčĆąŠą▓ąŠą╣ ą▓čģąŠą┤.

O čåąĖčäčĆąŠą▓ąŠą╣ ą▓čŗčģąŠą┤.

I/O ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╣ čåąĖčäčĆąŠą▓ąŠą╣ čüąĖą│ąĮą░ą╗ (čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą▓čģąŠą┤, čéą░ą║ ąĖ ą║ą░ą║ ą▓čŗčģąŠą┤).

PWR čłąĖąĮą░ ą┐ąĖčéą░ąĮąĖčÅ.

A ą░ąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ą▓čŗą▓ąŠą┤ (ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖąĄ ą▓ąĮąĄčłąĮąĖčģ ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓ ą┤ą╗čÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠą│ąŠ ążąØą¦).

ąĀąĖčü. 3. ąĪčģąĄą╝ą░ ą▓ąĮąĄčłąĮąĄą│ąŠ ążąØą¦

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠ ą┤ąŠą┐čāčüčéąĖą╝ąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ 14 PLLFILT čĆą░ą▓ąĮąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÄ ą┐ąĖčéą░ąĮąĖčÅ Vdd.

ąóą░ą▒ą╗ąĖčåą░ 3. ąØąŠą╝ąĖąĮą░ą╗čŗ ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓ ą┤ą╗čÅ ążąØą¦

| ąÜąŠą╝ą┐ąŠąĮąĄąĮčé |

ąØąŠą╝ąĖąĮą░ą╗ |

| C1 |

10 nF ┬▒ 10 % |

| ąĪ2 |

470 nF ┬▒ 10 % |

| R2 |

10 ą║ą×ą╝ ┬▒ 10 % |

[2. ą£ąĄčģą░ąĮąĖč湥čüą║ąĖąĄ ąĖ 菹╗ąĄą║čéčĆąĖč湥čüą║ąĖąĄ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ]

2.1 ą£ąĄčģą░ąĮąĖč湥čüą║ąĖąĄ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ

ąóą░ą▒ą╗ąĖčåą░ 4. ą£ąĄčģą░ąĮąĖč湥čüą║ąĖąĄ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ, ą┐čĆąĖą▓ąĄą┤ąĄąĮąĮčŗąĄ ą┤ą╗čÅ Vdd=3V ąĖ T=25┬░C, ąĄčüą╗ąĖ ąĮąĄ čāą║ą░ąĘą░ąĮąŠ čćč鹊-č鹊 ą┤čĆčāą│ąŠąĄ(1).

| ą£ąĮąĄą╝ąŠąĮąĖą║ą░ |

ą¤ą░čĆą░ą╝ąĄčéčĆ |

ąŻčüą╗ąŠą▓ąĖčÅ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ |

Min. |

Typ.(2) |

ą£ą░čģ. |

ąĢą┤ąĖąĮąĖčåčŗ |

| FS |

ąöąĖą░ą┐ą░ąĘąŠąĮ ąĖąĘą╝ąĄčĆąĄąĮąĖčÅ |

ąÆčŗą▒ąĖčĆą░ąĄčéčüčÅ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╝ |

|

┬▒250

┬▒500

┬▒2000 |

|

dps |

| So |

ą¦čāą▓čüčéą▓ąĖč鹥ą╗čīąĮąŠčüčéčī |

FS = 250 dps

FS = 500 dps

FS = 2000 dps |

|

8.75

17.5

70 |

|

mdps/digit |

| SoDr |

ąśąĘą╝ąĄąĮąĄąĮąĖąĄ čćčāą▓čüčéą▓ąĖč鹥ą╗čīąĮąŠčüčéąĖ ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé č鹥ą╝ą┐ąĄčĆą░čéčāčĆčŗ |

-40oC .. +85oC |

|

┬▒2 |

|

% |

| DVoff |

ą”ąĖčäčĆąŠą▓ąŠą╣ čāčĆąŠą▓ąĄąĮčī ąĮčāą╗čÅ |

FS = 250 dps

FS = 500 dps

FS = 2000 dps |

|

┬▒10

┬▒15

┬▒75 |

|

dps |

| OffDr |

ąśąĘą╝ąĄąĮąĄąĮąĖąĄ čāčĆąŠą▓ąĮčÅ ąĮčāą╗čÅ ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé č鹥ą╝ą┐ąĄčĆą░čéčāčĆčŗ(3) |

FS = 250 dps

FS = 2000 dps |

|

┬▒0.03

┬▒0.04 |

|

dps/oC |

| NL |

ąØąĄą╗ąĖąĮąĄą╣ąĮąŠčüčéčī(4) |

ąÉą┐ą┐čĆąŠą║čüąĖą╝ą░čåąĖčÅ ą║ ą┐čĆčÅą╝ąŠą╣ ą╗ąĖąĮąĖąĖ |

|

0.2 |

|

% FS |

| DST |

ąśąĘą╝ąĄąĮąĄąĮąĖąĄ ą▓čŗčģąŠą┤ą░ ą┐čĆąĖ čüą░ą╝ąŠč鹥čüčéąĖčĆąŠą▓ą░ąĮąĖąĖ |

FS = 250 dps

FS = 500 dps

FS = 2000 dps |

|

130

200

530 |

|

dps |

| Rn |

ąŻčĆąŠą▓ąĄąĮčī čłčāą╝ą░ (rate noise density) |

BW = 50 ąōčå |

|

0.03 |

|

dps/sqrt(ąōčå) |

| ODR |

ąĪą║ąŠčĆąŠčüčéčī ąŠčåąĖčäčĆąŠą▓ą║ąĖ (digital output data rate) |

|

|

100/200/

400/800 |

|

ąōčå |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

1. ąöą░čéčćąĖą║ ą║ą░ą╗ąĖą▒čĆąŠą▓ą░ą╗čüčÅ ąĮą░ ąĘą░ą▓ąŠą┤ąĄ ą┐čĆąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ Vdd=3V. ąĀą░ą▒ąŠčćąĖą╣ ą┤ąĖą░ą┐ą░ąĘąŠąĮ ą┐ąĖčéą░čÄčēąĖčģ ąĮą░ą┐čĆčÅąČąĄąĮąĖą╣ čāą║ą░ąĘą░ąĮ ą▓ čéą░ą▒ą╗ąĖčåąĄ 5.

2. ąóąĖą┐ąĖčćąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ (Typ.) ąĮąĄ ą│ą░čĆą░ąĮčéąĖčĆčāčÄčéčüčÅ.

3. ą£ąĖąĮąĖą╝ą░ą╗čīąĮčŗąĄ ąĖ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ (Min. ąĖ Max.) ą▒čŗą╗ąĖ ą▓čŗčćąĖčüą╗ąĄąĮčŗ ąĮą░ ąŠčüąĮąŠą▓ą░ąĮąĖąĖ ąĖąĘą╝ąĄčĆąĄąĮąĖą╣ ąĮą░ ą│ąĖčĆąŠčüą║ąŠą┐ą░čģ, ąĮą░čģąŠą┤čÅčēąĖčģčüčÅ ą▓ č鹥ą║čāčēąĄą╝ ą┐čĆąŠąĖąĘą▓ąŠą┤čüčéą▓ąĄ.

4. ąōą░čĆą░ąĮčéąĖčĆčāąĄčéčüčÅ čĆą░ąĘčĆą░ą▒ąŠčéą║ąŠą╣ ą┤ą░čéčćąĖą║ą░.

2.2. ąŁą╗ąĄą║čéčĆąĖč湥čüą║ąĖąĄ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ

ąóą░ą▒ą╗ąĖčåą░ 5. ąŁą╗ąĄą║čéčĆąĖč湥čüą║ąĖąĄ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ, ą┐čĆąĖą▓ąĄą┤ąĄąĮąĮčŗąĄ ą┤ą╗čÅ Vdd=3V ąĖ T=25┬░C, ąĄčüą╗ąĖ ąĮąĄ čāą║ą░ąĘą░ąĮąŠ čćč鹊-č鹊 ą┤čĆčāą│ąŠąĄ(1).

| ą£ąĮąĄą╝ąŠąĮąĖą║ą░ |

ą¤ą░čĆą░ą╝ąĄčéčĆ |

ąŻčüą╗ąŠą▓ąĖčÅ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ |

Min. |

Typ.(2) |

ą£ą░čģ. |

ąĢą┤ąĖąĮąĖčåčŗ |

| Vdd |

ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ |

|

2.4 |

3.0 |

3.6 |

V |

| Vdd_IO |

ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ ą┐ąŠčĆč鹊ą▓ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░(3) |

|

1.71 |

|

Vdd+0.1 |

V |

| Idd |

ąóąŠą║ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ |

|

|

6.1 |

|

mA |

| IddSL |

ąóąŠą║ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ ą▓ čĆąĄąČąĖą╝ąĄ čüąĮą░ (SLeep mode)(4) |

ąÆčŗą▒ąĖčĆą░ąĄčéčüčÅ č湥čĆąĄąĘ čåąĖčäčĆąŠą▓ąŠą╣ ąĖąĮč鹥čĆč乥ą╣čü |

|

1.5 |

|

mA |

| IddPdn |

ąóąŠą║ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ ą▓ čĆąĄąČąĖą╝ąĄ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ (Power DowN mode) |

ąÆčŗą▒ąĖčĆą░ąĄčéčüčÅ č湥čĆąĄąĘ čåąĖčäčĆąŠą▓ąŠą╣ ąĖąĮč鹥čĆč乥ą╣čü |

|

0.005 |

|

mA |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

1. ąöą░čéčćąĖą║ ą║ą░ą╗ąĖą▒čĆąŠą▓ą░ą╗čüčÅ ąĮą░ ąĘą░ą▓ąŠą┤ąĄ ą┐čĆąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ Vdd=3V.

2. ąóąĖą┐ąĖčćąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ (Typ.) ąĮąĄ ą│ą░čĆą░ąĮčéąĖčĆčāčÄčéčüčÅ.

3. ą£ąŠąČąĮąŠ ąŠčéą║ą╗čÄčćąĖčéčī ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ Vdd čü čüąŠčģčĆą░ąĮąĄąĮąĖąĄą╝ Vdd_IO, ą┐čĆąĖ čŹč鹊ą╝ ąĮąĄ ą▒čāą┤ąĄčé ą▒ą╗ąŠą║ąĖčĆąŠą▓ą░ąĮčŗ čłąĖąĮčŗ ąŠą▒ą╝ąĄąĮą░. ą¤čĆąĖ čŹč鹊ą╝ ąĖąĘą╝ąĄčĆąĖč鹥ą╗čīąĮą░čÅ čćą░čüčéčī ą▒čāą┤ąĄčé ąŠčéą║ą╗čÄč湥ąĮą░.

4. ąśąĘ čĆąĄąČąĖą╝ą░ čüąĮą░ (Sleep mode) ą╝ąŠąČąĮąŠ ą▒čŗčüčéčĆąĄąĄ ą┐ąĄčĆąĄą╣čéąĖ ą▓ čĆą░ą▒ąŠčćąĖą╣ čĆąĄąČąĖą╝, č湥ą╝ ąĖąĘ čĆąĄąČąĖą╝ą░ ąŠčéą║ą╗čÄč湥ąĮąĖčÅ (power-down mode).

2.3. ąóąĄą╝ą┐ąĄčĆą░čéčāčĆąĮčŗąĄ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ čüąĄąĮčüąŠčĆą░

ąóą░ą▒ą╗ąĖčåą░ 6. ąóąĄą╝ą┐ąĄčĆą░čéčāčĆąĮčŗąĄ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ, ą┐čĆąĖą▓ąĄą┤ąĄąĮąĮčŗąĄ ą┤ą╗čÅ Vdd=3V ąĖ T=25┬░C, ąĄčüą╗ąĖ ąĮąĄ čāą║ą░ąĘą░ąĮąŠ čćč鹊-č鹊 ą┤čĆčāą│ąŠąĄ(1).

| ą£ąĮąĄą╝ąŠąĮąĖą║ą░ |

ą¤ą░čĆą░ą╝ąĄčéčĆ |

ąŻčüą╗ąŠą▓ąĖčÅ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ |

Min. |

Typ.(2) |

ą£ą░čģ. |

ąĢą┤ąĖąĮąĖčåčŗ |

| TSDr |

ąŻčģąŠą┤ ąĘąĮą░č湥ąĮąĖčÅ ą▓čŗčģąŠą┤ą░ čü ą┤ą░čéčćąĖą║ą░ č鹥ą╝ą┐ąĄčĆą░čéčāčĆčŗ ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé č鹥ą╝ą┐ąĄčĆą░čéčāčĆčŗ. |

|

|

-1 |

|

oC/digit |

| TODr |

ąĪą║ąŠčĆąŠčüčéčī ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ č鹥ą╝ą┐ąĄčĆą░čéčāčĆčŗ |

|

|

1 |

|

ąōčå |

| Top |

ąĀą░ą▒ąŠčćąĖą╣ ą┤ąĖą░ą┐ą░ąĘąŠąĮ č鹥ą╝ą┐ąĄčĆą░čéčāčĆ |

|

-40 |

|

+85 |

oC |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

1. ąöą░čéčćąĖą║ ą║ą░ą╗ąĖą▒čĆąŠą▓ą░ą╗čüčÅ ąĮą░ ąĘą░ą▓ąŠą┤ąĄ ą┐čĆąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ Vdd=3V.

2. ąóąĖą┐ąĖčćąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ (Typ.) ąĮąĄ ą│ą░čĆą░ąĮčéąĖčĆčāčÄčéčüčÅ.

2.4. ąźą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ ąĖąĮč鹥čĆč乥ą╣čüą░ ąŠą▒ą╝ąĄąĮą░ ą┤ą░ąĮąĮčŗą╝ąĖ

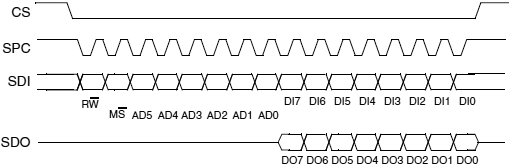

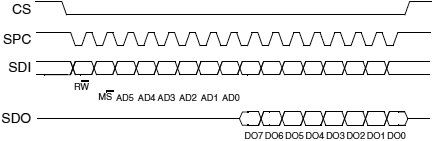

2.4.1. SPI - serial peripheral interface

ą¤čĆąĖą▓ąĄą┤ąĄąĮčŗ ąŠą▒čŗčćąĮčŗąĄ čĆą░ą▒ąŠčćąĖąĄ ąĘąĮą░č湥ąĮąĖčÅ ą┤ą╗čÅ Vdd ąĖ Top. ąØą░ čłąĖąĮąĄ SPI ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ L3G4200D čÅą▓ą╗čÅąĄčéčüčÅ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗą╝ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ (SPI slave).

ąóą░ą▒ą╗ąĖčåą░ 7. ąśąĮč鹥čĆą▓ą░ą╗čŗ ą▓čĆąĄą╝ąĄąĮąĖ ą┤ą╗čÅ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ SPI

| ą£ąĮąĄą╝ąŠąĮąĖą║ą░ |

ą¤ą░čĆą░ą╝ąĄčéčĆ |

ąŚąĮą░č湥ąĮąĖąĄ |

ąĢą┤ąĖąĮąĖčåčŗ |

| Min. |

Max. |

| tc(SPC) |

ąöą╗ąĖč鹥ą╗čīąĮąŠčüčéčī čåąĖą║ą╗ą░ čéą░ą║č鹊ą▓ SPI |

100 |

|

ąĮąĪ |

| fc(SPC) |

ą¦ą░čüč鹊čéą░ čéą░ą║č鹊ą▓ SPI |

|

10 |

ą£ąōčå |

tsu(CS)

th(CS)

tsu(SI)

th(SI)

tv(SO)

th(SO)

tdis(SO) |

ąÆčĆąĄą╝čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ CS (setup time)

ąÆčĆąĄą╝čÅ čāą┤ąĄčƹȹ░ąĮąĖčÅ CS (hold time)

ąÆčĆąĄą╝čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▓čģąŠą┤ą░ SDI (setuh time)

ąÆčĆąĄą╝čÅ čāą┤ąĄčƹȹ░ąĮąĖčÅ ą▓čģąŠą┤ą░ SDI (hold time)

ąÆčĆąĄą╝čÅ ą┤ąŠčüč鹊ą▓ąĄčĆąĮąŠą│ąŠ ą▓čŗčģąŠą┤ą░ SDO (valid output)

ąÆčĆąĄą╝čÅ čāą┤ąĄčƹȹ░ąĮąĖčÅ ą▓čŗčģąŠą┤ą░ SDO (hold time)

ąÆčĆąĄą╝čÅ ąĘą░ą┐čĆąĄčéą░ ą▓čŗčģąŠą┤ą░ SDO (disable time) |

5

8

5

15

6

|

50

50 |

ąĮąĪ |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ 1: ąĘąĮą░č湥ąĮąĖčÅ ą│ą░čĆą░ąĮčéąĖčĆčāčÄčéčüčÅ ąĮą░ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊č鹥 SPI 10 ą£ąōčå čü 4 ąĖ 3 čüąĖą│ąĮą░ą╗ą░ą╝ąĖ ąĮą░ ąŠčüąĮąŠą▓ą░ąĮąĖąĖ čĆąĄąĘčāą╗čīčéą░č鹊ą▓ čĆą░čüč湥č鹊ą▓. ąÆ ą┐čĆąŠąĖąĘą▓ąŠą┤čüčéą▓ąĄ ąĘąĮą░č湥ąĮąĖčÅ ąĮąĄ ą┐čĆąŠą▓ąĄčĆčÅčÄčéčüčÅ.

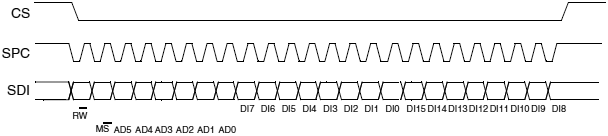

ąĀąĖčü. 4. ąÆčĆąĄą╝ąĄąĮąĮčŗąĄ ą┤ąĖą░ą│čĆą░ą╝ą╝čŗ SPI slave

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĖąĘą╝ąĄčĆąĄąĮąĖčÅ ą▒čŗą╗ąĖ čüą┤ąĄą╗ą░ąĮčŗ ą▓ č鹊čćą║ą░čģ 0.2 ąĖ 0.8 ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ Vdd_IO, ą║ą░ą║ ą┤ą╗čÅ ą▓čģąŠą┤ąŠą▓, čéą░ą║ ąĖ ą┤ą╗čÅ ą▓čŗčģąŠą┤ąŠą▓.

2.4.2. I2C ąĖąĮč鹥čĆč乥ą╣čü

ą¤čĆąĖą▓ąĄą┤ąĄąĮčŗ ąŠą▒čŗčćąĮčŗąĄ čĆą░ą▒ąŠčćąĖąĄ ąĘąĮą░č湥ąĮąĖčÅ ą┤ą╗čÅ Vdd ąĖ Top. ąØą░ čłąĖąĮąĄ I2C ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ L3G4200D čÅą▓ą╗čÅąĄčéčüčÅ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗą╝ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ (slave).

ąóą░ą▒ą╗ąĖčåą░ 8. ąśąĮč鹥čĆą▓ą░ą╗čŗ ą▓čĆąĄą╝ąĄąĮąĖ ą┤ą╗čÅ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ I2C

| ą£ąĮąĄą╝ąŠąĮąĖą║ą░ |

ą¤ą░čĆą░ą╝ąĄčéčĆ |

I2C standard mode(1) |

I2C fast mode(1) |

ąĢą┤ąĖąĮąĖčåčŗ |

| Min |

Max |

Min |

Max |

| f(SCL) |

ąóą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ SCL |

0 |

100 |

0 |

400 |

ą║ąōčå |

tW(SCLL)

tW(SCLH) |

ąÆčĆąĄą╝čÅ ą╗ąŠą│. 0 SCL

ąÆčĆąĄą╝čÅ ą╗ąŠą│. 1 SCL |

4.7

4.0 |

|

1.3

0.6 |

|

ą╝ą║ąĪ |

| tSU(SDA) |

ąÆčĆąĄą╝čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ SDA (setup time) |

250 |

|

100 |

|

ąĮąĪ |

| th(SDA) |

ąÆčĆąĄą╝čÅ čāą┤ąĄčƹȹ░ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ SDA (hold time) |

0 |

3.45 |

0 |

0.9 |

ą╝ą║ąĪ |

tr(SDA), tr(SCL)

tf(SDA), tf(SCL) |

ąÆčĆąĄą╝čÅ ąĮą░čĆą░čüčéą░ąĮąĖčÅ SDA ąĖ SCL

ąÆčĆąĄą╝čÅ čüą┐ą░ą┤ą░ SDA ąĖ SCL |

|

1000

300 |

20+0.1Cb(2) |

300 |

ąĮąĪ |

th(ST)

tSU(SR)

tSU(SP) |

ąÆčĆąĄą╝čÅ čāą┤ąĄčƹȹ░ąĮąĖčÅ čüąŠą▒čŗčéąĖčÅ START

ąÆčĆąĄą╝čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ ą┐ąŠą▓č鹊čĆąĮąŠą│ąŠ čüąŠą▒čŗčéąĖčÅ START

ąÆčĆąĄą╝čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ čüąŠą▒čŗčéąĖčÅ STOP |

4

4.7

4 |

|

0.6 |

|

ą╝ą║ąĪ |

| tW(SP:SR) |

ąÆčĆąĄą╝čÅ čüą▓ąŠą▒ąŠą┤ąĮąŠą│ąŠ čüąŠčüč鹊čÅąĮąĖčÅ čłąĖąĮčŗ ą╝ąĄąČą┤čā čüąŠą▒čŗčéąĖčÅą╝ąĖ START ąĖ STOP |

4.7 |

|

1.3 |

|

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

1. I2C standard mode - čüčéą░ąĮą┤ą░čĆčéąĮčŗą╣ čüą║ąŠčĆąŠčüčéąĮąŠą╣ čĆąĄąČąĖą╝ I2C, fast mode - čāčüą║ąŠčĆąĄąĮąĮčŗą╣ čĆąĄąČąĖą╝. ąöą░ąĮąĮčŗąĄ ąŠčüąĮąŠą▓ą░ąĮčŗ ąĮą░ čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅčģ čüčéą░ąĮą┤ą░čĆčéą░ ą┐čĆąŠč鹊ą║ąŠą╗ą░ I2C, ąĖ ąŠąĮąĖ ąĮąĄ č鹥čüčéąĖčĆčāčÄčéčüčÅ ą▓ ą┐čĆąŠąĖąĘą▓ąŠą┤čüčéą▓ąĄ.

2. Cb = ą┐ąŠą╗ąĮą░čÅ ąĄą╝ą║ąŠčüčéčī ąŠą┤ąĮąŠą│ąŠ ą┐čĆąŠą▓ąŠą┤ą░ čłąĖąĮčŗ ą▓ ą┐ąĖą║ąŠčäą░čĆą░ą┤ą░čģ (pF).

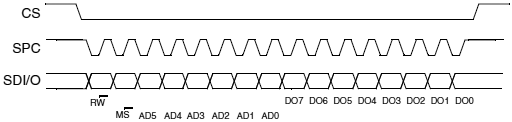

ąĀąĖčü. 5. ąÆčĆąĄą╝ąĄąĮąĮčŗąĄ ą┤ąĖą░ą│čĆą░ą╝ą╝čŗ I2C slave

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĖąĘą╝ąĄčĆąĄąĮąĖčÅ ą┤ą╗čÅ čüąĖą│ąĮą░ą╗ąŠą▓ SDA ąĖ SDC ą▒čŗą╗ąĖ čüą┤ąĄą╗ą░ąĮčŗ ą▓ č鹊čćą║ą░čģ 0.2 ąĖ 0.8 ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ Vdd_IO.

2.5. ą¤čĆąĄą┤ąĄą╗čīąĮčŗąĄ ą░ą▒čüąŠą╗čÄčéąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓ (Absolute maximum ratings)

ąĪčéčĆąĄčüčüąŠą▓čŗąĄ ąĘąĮą░č湥ąĮąĖčÅ, ą║ąŠč鹊čĆčŗąĄ ą┐čĆąĄą▓čŗčłą░čÄčé ąĘąĮą░č湥ąĮąĖčÅ ą▓ čéą░ą▒ą╗ąĖčåąĄ "Absolute maximum ratings" ą╝ąŠą│čāčé ą┐čĆąĖą▓ąĄčüčéąĖ ą║ ąĮąĄąŠą▒čĆą░čéąĖą╝ąŠą╝čā ą┐ąŠą▓čĆąĄąČą┤ąĄąĮąĖčÄ čāčüčéčĆąŠą╣čüčéą▓ą░. ą¤čĆąĄą┤ąĄą╗čīąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓ ą┐čĆąĖą▓ąĄą┤ąĄąĮčŗ č鹊ą╗čīą║ąŠ ą▓ ą║ą░č湥čüčéą▓ąĄ čĆąĄą╣čéąĖąĮą│ą░, ąĖ ąĮąĄ ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčéčüčÅ čĆą░ą▒ąŠčéą░ čāčüčéčĆąŠą╣čüčéą▓ą░ čü čéą░ą║ąĖą╝ąĖ ąĘąĮą░č湥ąĮąĖčÅą╝ąĖ. ąĀą░ą▒ąŠčéą░ ą▓ čāčüą╗ąŠą▓ąĖčÅčģ ą┐čĆąĄą┤ąĄą╗čīąĮčŗčģ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮčŗčģ ąĘąĮą░č湥ąĮąĖą╣ ą╝ąŠąČąĄčé ą┐ąŠą▓ą╗ąĖčÅčéčī ąĮą░ ąĮą░ą┤ąĄąČąĮąŠčüčéčī čāčüčéčĆąŠą╣čüčéą▓ą░.

ąóą░ą▒ą╗ąĖčåą░ 9. Absolute maximum ratings

| ą£ąĮąĄą╝ąŠąĮąĖą║ą░ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

ą£ą░ą║čüąĖą╝ą░ą╗čīąĮąŠąĄ

ąĘąĮą░č湥ąĮąĖąĄ |

ąĢą┤ąĖąĮąĖčåčŗ |

| Vdd |

ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ |

-0.3 .. 4.8 |

V |

| TSTG |

ąöąĖą░ą┐ą░ąĘąŠąĮ č鹥ą╝ą┐ąĄčĆą░čéčāčĆ ą┐čĆąĖ čģčĆą░ąĮąĄąĮąĖąĖ |

-40 .. +125 |

oC |

| Sg |

ąŻčüą║ąŠčĆąĄąĮąĖąĄ g ą┤ą╗čÅ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéąĖ 0.1 ą╝ąĪ |

10,000 |

g |

| ESD |

ąŚą░čēąĖčéą░ ąŠčé čüčéą░čéąĖč湥čüą║ąŠą│ąŠ 菹╗ąĄą║čéčĆąĖč湥čüčéą▓ą░ |

2 (HBM) |

kV |

|

ąŁč鹊 čāčüčéčĆąŠą╣čüčéą▓ąŠ čćčāą▓čüčéą▓ąĖč鹥ą╗čīąĮąŠ ą║ čāą┤ą░čĆą░ą╝, ąĖ ąĮąĄą┐čĆą░ą▓ąĖą╗čīąĮąŠąĄ ąŠą▒čĆą░čēąĄąĮąĖąĄ ą╝ąŠąČąĄčé ą┐čĆąĖą▓ąĄčüčéąĖ ą║ ą┐ąŠą▓čĆąĄąČą┤ąĄąĮąĖčÅą╝ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ |

|

ąŁč鹊 čāčüčéčĆąŠą╣čüčéą▓ąŠ čćčāą▓čüčéą▓ąĖč鹥ą╗čīąĮąŠ ą║ ESD, ąĖ ąĮąĄą┐čĆą░ą▓ąĖą╗čīąĮąŠąĄ ąŠą▒čĆą░čēąĄąĮąĖąĄ ą╝ąŠąČąĄčé ą┐čĆąĖą▓ąĄčüčéąĖ ą║ ą┐ąŠą▓čĆąĄąČą┤ąĄąĮąĖčÅą╝ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ |

2.6. ąśčüą┐ąŠą╗čīąĘčāąĄą╝ą░čÅ č鹥čĆą╝ąĖąĮąŠą╗ąŠą│ąĖčÅ

2.6.1. ą¦čāą▓čüčéą▓ąĖč鹥ą╗čīąĮąŠčüčéčī

ąōąĖčĆąŠčüą║ąŠą┐ ą┐ąŠ čüą║ąŠčĆąŠčüčéąĖ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ čāą│ą╗ą░ čÅą▓ą╗čÅąĄčéčüčÅ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝, ą║ąŠč鹊čĆąŠąĄ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮčŗąĄ ą▓čŗčģąŠą┤ąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ ą┤ą╗čÅ ą┐ąŠą▓ąŠčĆąŠčéą░ ą┐čĆąŠčéąĖą▓ čćą░čüąŠą▓ąŠą╣ čüčéčĆąĄą╗ą║ąĖ ą▓ąŠą║čĆčāą│ ąĖąĘą╝ąĄčĆčÅąĄą╝čŗčģ ąŠčüąĄą╣. ą¦čāą▓čüčéą▓ąĖč鹥ą╗čīąĮąŠčüčéčī ąŠą┐ąĖčüčŗą▓ą░ąĄčé čāčüąĖą╗ąĄąĮąĖąĄ čüąĄąĮčüąŠčĆą░ ąĖ ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮą░ ąĘą░ą┤ą░ąĮąĖąĄą╝ čāčüą║ąŠčĆąĄąĮąĖčÅ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ąĮą░ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗą╣ čāą│ąŠą╗. ą£ąĖą║čĆąŠčüčģąĄą╝ą░ čüą┐čĆąŠąĄą║čéąĖčĆąŠą▓ą░ąĮą░ čéą░ą║, čćč鹊 ąĖąĘą╝ąĄčĆčÅąĄą╝čŗąĄ ąĘąĮą░č湥ąĮąĖčÅ ąĖąĘą╝ąĄąĮčÅčÄčéčüčÅ ąŠč湥ąĮčī ąĮąĄąĘąĮą░čćąĖč鹥ą╗čīąĮąŠ čü č鹥č湥ąĮąĖąĄą╝ ą▓čĆąĄą╝ąĄąĮąĖ ąĖ ą┐ąŠą┤ ą▓ąŠąĘą┤ąĄą╣čüčéą▓ąĖąĄą╝ ąĖąĘą╝ąĄąĮąĄąĮąĖą╣ č鹥ą╝ą┐ąĄčĆą░čéčāčĆčŗ.

2.6.2. ąØčāą╗ąĄą▓ąŠą╣ čāčĆąŠą▓ąĄąĮčī (Zero-rate level)

ąØčāą╗ąĄą▓ąŠą╣ čāčĆąŠą▓ąĄąĮčī ąŠą┐ąĖčüčŗą▓ą░ąĄčé čĆąĄą░ą╗čīąĮčŗąĄ ą▓čŗčģąŠą┤ąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ, ą║ąŠą│ą┤ą░ ąĮąĄčé čāą│ą╗ąŠą▓čŗčģ ąĖąĘą╝ąĄąĮąĄąĮąĖą╣. ąŻčĆąŠą▓ąĄąĮčī ąĮčāą╗čÅ ą┤ą╗čÅ č鹊čćąĮčŗčģ MEMS-čüąĄąĮčüąŠčĆąŠą▓ ą▓ ąĮąĄą║ąŠč鹊čĆčŗčģ čüą╗čāčćą░čÅčģ čÅą▓ą╗čÅąĄčéčüčÅ čĆąĄąĘčāą╗čīčéą░č鹊ą╝ čüčéčĆąĄčüčüąŠą▓čŗčģ ąĮą░ą│čĆčāąĘąŠą║ ąĮą░ čüąĄąĮčüąŠčĆ ąĖ, čéą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, čāčĆąŠą▓ąĄąĮčī ąĮčāą╗čÅ ą╝ąŠąČąĄčé ąĘąĮą░čćąĖč鹥ą╗čīąĮąŠ ąĖąĘą╝ąĄąĮčÅčéčīčüčÅ ą┐ąŠčüą╗ąĄ ą╝ąŠąĮčéą░ąČą░ čüąĄąĮčüąŠčĆą░ ąĮą░ ą┐ąĄčćą░čéąĮčāčÄ ą┐ą╗ą░čéčā ąĖą╗ąĖ ą┐ąŠčüą╗ąĄ ą▓ąŠąĘą┤ąĄą╣čüčéą▓ąĖčÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗčģ ą╝ąĄčģą░ąĮąĖč湥čüą║ąĖčģ ąĮą░ą│čĆčāąĘąŠą║. ąÜą░ą║ ąĖ čćčāą▓čüčéą▓ąĖč鹥ą╗čīąĮąŠčüčéčī, čāčĆąŠą▓ąĄąĮčī ąĮčāą╗čÅ čéą░ą║ąČąĄ ąŠč湥ąĮčī ą╝ą░ą╗ąŠ ąĘą░ą▓ąĖčüąĖčé ąŠčé ą▓čĆąĄą╝ąĄąĮąĖ čĆą░ą▒ąŠčéčŗ ąĖ č鹥ą╝ą┐ąĄčĆą░čéčāčĆčŗ.

2.6.3. ąĪčéą░ą▒ąĖą╗čīąĮąŠčüčéčī ą┐ąŠ ą▓čĆąĄą╝ąĄąĮąĖ ąĖ č鹥ą╝ą┐ąĄčĆą░čéčāčĆąĄ

ąæą╗ą░ą│ąŠą┤ą░čĆčÅ čāąĮąĖą║ą░ą╗čīąĮąŠą╣ č鹥čģąĮąŠą╗ąŠą│ąĖąĖ ąĖ ąŠą┐čéąĖą╝ąĖąĘąĖčĆąŠą▓ą░ąĮąĮąŠą╝čā ą┤ąĖąĘą░ą╣ąĮčā ą│ąĖčĆąŠčüą║ąŠą┐čŗ ą║ąŠą╝ą┐ą░ąĮąĖąĖ ST ą╝ąŠą│čāčé ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī ą┐čĆąĄą▓ąŠčüčģąŠą┤ąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ ą┤ą╗čÅ ą╝ąĄčģą░ąĮąĖč湥čüą║ąŠą╣ ą╝ą░čüčüčŗ MEMS ąĖ ą║ą░č湥čüčéą▓ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ ASIC, čćč鹊 čĆą░čüą┐čĆąŠčüčéčĆą░ąĮčÅąĄčéčüčÅ ąĮą░ ą▒ąĄčüą┐čĆąĄčåąĄą┤ąĄąĮčéąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī čüčéą░ą▒ąĖą╗čīąĮąŠčüčéąĖ ą▓ čĆą░ą▒ąŠč鹥 ą┐ąŠ č鹥ą╝ą┐ąĄčĆą░čéčāčĆąĄ ąĖ ą▓čĆąĄą╝ąĄąĮąĖ.

ą¤ąŠ ą┐ą░čĆą░ą╝ąĄčéčĆą░ą╝ čāčģąŠą┤ą░ čćčāą▓čüčéą▓ąĖč鹥ą╗čīąĮąŠčüčéąĖ ąĖ ąĮčāą╗ąĄą▓ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ L3G4200D ą┐čĆąĄą▓ąŠčüčģąŠą┤ąĖčé ąĖą╝ąĄčÄčēąĖąĄčüčÅ ąĮą░ čĆčŗąĮą║ąĄ ą░ąĮą░ą╗ąŠą│ąĖ ą▓ ą┤ąĄčüčÅčéą║ąĖ čĆą░ąĘ. ąŁč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÄ čāčüčéčĆą░ąĮąĖčéčī ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéčī ą▓ ą┐ąŠčüą╗ąĄą┤čāčÄčēąĖčģ ą║ąŠą╝ą┐ąĄąĮčüą░čåąĖčÅčģ ąĖ ą║ą░ą╗ąĖą▒čĆąŠą▓ą║ąĄ ąĖ ą╝ąŠąČąĄčé čāčüą║ąŠčĆąĖčéčī ą▓čŗčģąŠą┤ ąĮą░ čĆčŗąĮąŠą║ ą│ąŠč鹊ą▓ąŠą╣ ą┐čĆąŠą┤čāą║čåąĖąĖ, čāą┐čĆąŠčüčéąĖčéčī čĆą░ąĘčĆą░ą▒ąŠčéą║čā, ą┐ąŠą╗čāčćąĖčéčī ą▓čŗčüąŠą║ąĖąĄ 菹║čüą┐ą╗čāą░čéą░čåąĖąŠąĮąĮčŗąĄ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ ąĖ ą▓ ą║ąŠąĮąĄčćąĮąŠą╝ čüč湥č鹥 čüąŠčģčĆą░ąĮąĖčéčī ą┤ąĄąĮčīą│ąĖ.

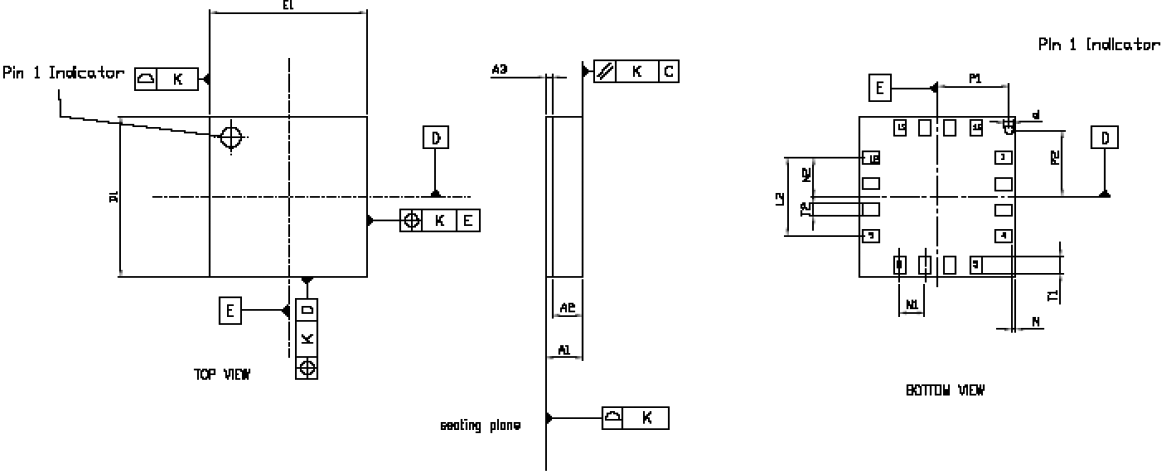

2.7. ąśąĮč乊čĆą╝ą░čåąĖčÅ ą┐ąŠ ą┐ą░ą╣ą║ąĄ

ąÜąŠčĆą┐čāčü LGA čüąŠą▓ą╝ąĄčüčéąĖą╝ čüąŠ čüčéą░ąĮą┤ą░čĆčéą░ą╝ąĖ ECOPACK┬«, RoHS ąĖ "Green". ą×ąĮ ą║ą▓ą░ą╗ąĖčäąĖčåąĖčĆąŠą▓ą░ąĮ ą┐ąŠ č鹥ą┐ą╗ąŠą▓ąŠą╝čā čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖčÄ ą┤ą╗čÅ ą┐ą░ą╣ą║ąĖ ą┐ąŠ čüčéą░ąĮą┤ą░čĆčéčā JEDEC J-STD-020.

ą¤čĆąĖ ą┐ą░ą╣ą║ąĄ ąŠčüčéą░ą▓čīč鹥 ą▓čŗą▓ąŠą┤ "pin 1 Indicator" ąĮąĄą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗą╝.

ą¤ąŠčüą░ą┤ąŠčćąĮąŠąĄ ą╝ąĄčüč鹊 (Land pattern) ąĖ čĆąĄą║ąŠą╝ąĄąĮą┤ą░čåąĖąĖ ą┐ąŠ ą┐ą░ą╣ą║ąĄ ą╝ąŠąČąĮąŠ ą┐ąŠą╗čāčćąĖčéčī ąĮą░ čüą░ą╣č鹥 www.st.com [1].

[3. ą×čüąĮąŠą▓ąĮčŗąĄ čåąĖčäčĆąŠą▓čŗąĄ ą▒ą╗ąŠą║ąĖ L3G4200D]

3.1. ąæą╗ąŠą║-čüčģąĄą╝ą░

ąĀąĖčü. 6. ąæą╗ąŠą║-čüčģąĄą╝ą░ L3G4200D

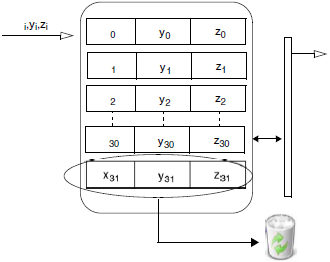

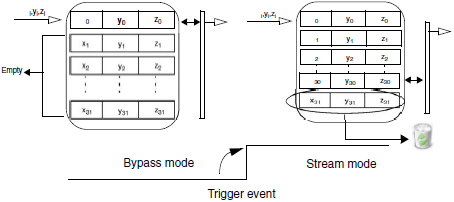

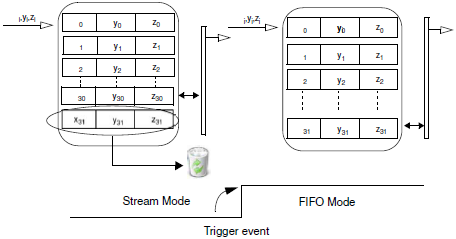

3.2. ąæčāč乥čĆ FIFO

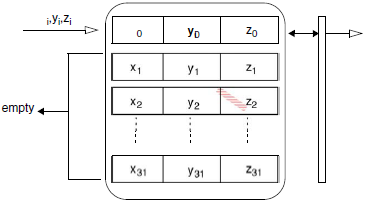

ąÆ ą╝ąĖą║čĆąŠčüčģąĄą╝ąĄ L3G4200D ąĖą╝ąĄąĄčéčüčÅ ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ 32-čüą╗ąŠč鹊ą▓čŗą╣, 16-ą▒ąĖčéąĮčŗą╣ ą▒čāč乥čĆ ą┤ą░ąĮąĮčŗčģ FIFO ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ąĖąĘ čéčĆąĄčģ ą▓čŗčģąŠą┤ąĮčŗčģ ą║ą░ąĮą░ą╗ąŠą▓: čāą║ą╗ąŠąĮąĄąĮąĖąĄ (yaw), ą┐ąŠą┤ą░čćą░ (pitch) ąĖ čüą║ą░čé (roll). ąŁč鹊čé ą▒čāč乥čĆ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé 菹║ąŠąĮąŠą╝ąĖčéčī ąĮą░ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĖ ą▓ čüąĖčüč鹥ą╝ąĄ, čéą░ą║ ą║ą░ą║ čģąŠčüčéčā (čāą┐čĆą░ą▓ą╗čÅčÄčēąĄą╝čā ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčā) ąĮąĄ ąĮčāąČąĮąŠ ą┐ąŠčüč鹊čÅąĮąĮąŠ ąŠą┐čĆą░čłąĖą▓ą░čéčī čüąĄąĮčüąŠčĆ ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ. ąÆą╝ąĄčüč鹊 čŹč鹊ą│ąŠ čģąŠčüčé ą╝ąŠąČąĄčé ą┐čĆąĖ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéąĖ ą▓čŗą▓ąŠą┤ąĖčéčīčüčÅ ąĖąĘ čüąĮą░ ąĖ ą▒čŗčüčéčĆąŠ čüčćąĖčéčŗą▓ą░čéčī ąĘąĮą░čćąĖą╝čŗąĄ ą┤ą░ąĮąĮčŗąĄ ąĖąĘ FIFO. ąŁč鹊čé ą▒čāč乥čĆ ą╝ąŠąČąĄčé čĆą░ą▒ąŠčéą░čéčī ą▓ 5 čĆą░ąĘą╗ąĖčćąĮčŗčģ čĆąĄąČąĖą╝ą░čģ. ąÜą░ąČą┤čŗą╣ čĆąĄąČąĖą╝ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ą▒ąĖčéą░ą╝ąĖ FIFO_MODE ą▓ čĆąĄą│ąĖčüčéčĆąĄ FIFO_CTRL_REG. ą£ąŠą│čāčé ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮčŗ čüąŠą▒čŗčéąĖčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĖčÅ ą▒čāč乥čĆą░ (watermark level), FIFO_empty ąĖą╗ąĖ FIFO_Full, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠą│čāčé ą▓čŗą┤ą░ą▓ą░čéčī čüąĖą│ąĮą░ą╗ ąĮą░ ą▓čŗą▓ąŠą┤ DRDY/INT2 (ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ č湥čĆąĄąĘ CTRL_REG3), ąĖ ąĖąĮč乊čĆą╝ą░čåąĖčÅ ąŠ čüąŠą▒čŗčéąĖąĖ ą┤ąŠčüčéčāą┐ąĮą░ ą▓ FIFO_SRC_REG. ąĪąĖą│ąĮą░ą╗ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ąĖą╗ąĖ ą▓čŗą▓ąŠą┤ą░ ąĄą│ąŠ ąĖąĘ čüąĮą░. ąŻčĆąŠą▓ąĄąĮčī ąĘą░ą┐ąŠą╗ąĮąĄąĮąĖčÅ ą▒čāč乥čĆą░ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ ą▒ąĖčéą░ą╝ąĖ WTM4:0 ą▓ čĆąĄą│ąĖčüčéčĆąĄ FIFO_CTRL_REG.

3.2.1. Bypass mode

ąÆ čĆąĄąČąĖą╝ąĄ ą▒ą░ą╣ą┐ą░čü ą▒čāč乥čĆ FIFO ąĮąĄ čĆą░ą▒ąŠčéą░ąĄčé, ąĖ ą┐ąŠ čŹč鹊ą╣ ą┐čĆąĖčćąĖąĮąĄ ąŠčüčéą░ąĄčéčüčÅ ą┐čāčüčéčŗą╝. ąÜą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 7, ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą║ą░ąĮą░ą╗ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą┐ąĄčĆą▓čŗą╣ ą░ą┤čĆąĄčü. ą×čüčéą░ą╗čīąĮčŗąĄ čüą╗ąŠčéčŗ FIFO ą┐čāčüčéčŗ (empty). ąÜąŠą│ą┤ą░ ą┐ąŠčüčéčāą┐čÅčé ąĮąŠą▓čŗąĄ ą┤ą░ąĮąĮčŗąĄ, č鹊 čüčéą░čĆčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą▒čāą┤čāčé ą┐ąĄčĆąĄąĘą░ą┐ąĖčüą░ąĮčŗ.

ąĀąĖčü. 7. ąĀą░ą▒ąŠčéą░ FIFO ą▓ čĆąĄąČąĖą╝ąĄ Bypass

3.2.2. FIFO mode

ąÆ čĆąĄąČąĖą╝ąĄ FIFO ą┤ą░ąĮąĮčŗąĄ ą▓čüąĄčģ 3 ą║ą░ąĮą░ą╗ąŠą▓ čüąŠčģčĆą░ąĮčÅčÄčéčüčÅ ą▓ FIFO. ą£ąŠąČąĄčé ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ (ą▒ąĖč鹊ą╝ I2_WMK ą▓ čĆąĄą│ąĖčüčéčĆąĄ CTRL_REG3) ą┐ąŠ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĖčÄ ą▒čāč乥čĆą░ ą┤ąŠ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą│ąŠ čāčĆąŠą▓ąĮčÅ (watermark interrupt). ąŻčĆąŠą▓ąĄąĮčī ąĘą░ą┐ąŠą╗ąĮąĄąĮąĖčÅ čāą║ą░ąĘčŗą▓ą░ąĄčéčüčÅ ą▓ ą▒ąĖčéą░čģ WTM 4:0 čĆąĄą│ąĖčüčéčĆą░ FIFO_CTRL_REG. FIFO ą┐čĆąŠą┤ąŠą╗ąČąĖčé ąĘą░ą┐ąŠą╗ąĮąĄąĮąĖąĄ, ą┐ąŠą║ą░ ąĮąĄ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĖčéčüčÅ (32 čüą╗ąŠčéą░ 16-ą▒ąĖčéąĮčŗčģ ą┤ą░ąĮąĮčŗčģ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ąŠą▓ yaw, pitch ąĖ roll). ąÜąŠą│ą┤ą░ FIFO ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĖčéčüčÅ, ą┤ąŠ čüą▒ąŠčĆ ą┤ą░ąĮąĮčŗčģ čü ą▓čģąŠą┤ąĮčŗčģ ą║ą░ąĮą░ą╗ąŠą▓ ąŠčüčéą░ąĮąŠą▓ąĖčéčüčÅ. ą¦č鹊ą▒čŗ ą▓ąŠąĘąŠą▒ąĮąŠą▓ąĖčéčī čüą▒ąŠčĆ ą┤ą░ąĮąĮčŗčģ, ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ąĘą░ą┐ąĖčüą░čéčī čĆąĄą│ąĖčüčéčĆ FIFO_CTRL_REG ąĖ ą┐ąĄčĆąĄą▓ąĄčüčéąĖ FIFO ą▓ čĆąĄąČąĖą╝ bypass. ąĀą░ą▒ąŠčéą░ čĆąĄąČąĖą╝ą░ FIFO ą┐ąŠą║ą░ąĘą░ąĮą░ ąĮą░ čĆąĖčü. 8.

ąĀąĖčü. 8. ąĀą░ą▒ąŠčéą░ čĆąĄąČąĖą╝ą░ FIFO

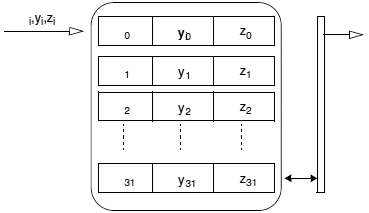

3.2.3. ą¤ąŠč鹊ą║ąŠą▓čŗą╣ čĆąĄąČąĖą╝ (Stream mode)

ąŁč鹊čé čĆąĄąČąĖą╝ čĆą░ą▒ąŠčéą░ąĄčé čéą░ą║ ąČąĄ, ą║ą░ą║ ąĖ čĆąĄąČąĖą╝ FIFO, ąŠčéą╗ąĖčćąĖąĄ č鹊ą╗čīą║ąŠ ą▓ č鹊ą╝, čćč鹊 ą┐ąŠ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĖąĖ FIFO (32 čüą╗ąŠčéą░ 16-ą▒ąĖčéąĮčŗčģ ą┤ą░ąĮąĮčŗčģ ą║ą░ąĮą░ą╗ąŠą▓ yaw, pitch ąĖ roll) čüčéą░čĆčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą▒čāą┤čāčé ąŠčéą▒čĆą░čüčŗą▓ą░čéčīčüčÅ ą┐ąŠ ą╝ąĄčĆąĄ ą┐ąŠčüčéčāą┐ą╗ąĄąĮąĖčÅ ąĮąŠą▓čŗčģ ą┤ą░ąĮąĮčŗčģ. ąÜą░ą║ ąĖ ą▓ čĆąĄąČąĖą╝ąĄ FIFO, ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮčŗ čüąŠą▒čŗčéąĖčÅ watermark level ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ čüąĖą│ąĮą░ą╗ąŠą╝ ąĮą░ ąĮąŠąČą║ąĄ DRDY/INT2 (ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ č湥čĆąĄąĘ CTRL_REG3). Stream mode ą┐ąŠą║ą░ąĘą░ąĮ ąĮą░ čĆąĖčü. 9.

ąĀąĖčü. 9. ąĀą░ą▒ąŠčéą░ čĆąĄąČąĖą╝ą░ Stream mode

3.2.4. Bypass-to-stream mode

ąÆ čĆąĄąČąĖą╝ąĄ bypass-to-stream FIFO ąĮą░čćąĖąĮą░ąĄčé čĆą░ą▒ąŠčéčā ą▓ čĆąĄąČąĖą╝ąĄ bypass, ąĖ ą║ą░ą║ č鹊ą╗čīą║ąŠ ąĮą░čüčéčāą┐ąĖčé čüąŠą▒čŗčéąĖąĄ (ąŠčéąĮąŠčüčÅčēąĄąĄčüčÅ ą║ čüąŠą▒čŗčéąĖčÅą╝, ąĘą░ą┤ą░ąĮąĮčŗą╝ ą▓ čĆąĄą│ąĖčüčéčĆąĄ INT1_CFG), FIFO ąĮą░čćąĮąĄčé čĆą░ą▒ąŠčéą░čéčī ą▓ stream mode (čüą╝. čĆąĖčü. 10).

ąĀąĖčü. 10. ąĀą░ą▒ąŠčéą░ čĆąĄąČąĖą╝ą░ Bypass-to-stream

ą¤ąŠčÅčüąĮąĄąĮąĖąĄ ą║ čĆąĖčüčāąĮą║čā: Trigger event ąŠąĘąĮą░čćą░ąĄčé čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĄ čüąŠą▒čŗčéąĖčÅ, ą║ąŠč鹊čĆąŠąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĮą░čüčéčĆąŠąĄąĮąŠ ąĮą░ ą│ąĄąĮąĄčĆą░čåąĖčÄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čģąŠčüčéą░.

3.2.5. Stream-to-FIFO mode

ąÆ čĆąĄąČąĖą╝ąĄ Stream-to-FIFO ą┤ą░ąĮąĮčŗąĄ ąĖąĘą╝ąĄčĆąĄąĮąĖą╣ ą║ą░ąĮą░ą╗ąŠą▓ yaw, pitch ąĖ roll čüąŠčģčĆą░ąĮčÅčÄčéčüčÅ ą▓ FIFO. ąĪąŠą▒čŗčéąĖąĄ watermark interrupt ą╝ąŠąČąĄčé ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮąŠ ąĮą░ ąĮąŠąČą║ąĄ DRDY/INT2 ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ I2_WTM ą▓ čĆąĄą│ąĖčüčéčĆąĄ CTRL_REG3. ąÜą░ą║ ąĖ ą▓ ą┤čĆčāą│ąĖčģ čĆąĄąČąĖą╝ą░čģ, čŹč鹊 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čüčĆą░ą▒ąŠčéą░ąĄčé, ą║ąŠą│ą┤ą░ FIFO ąĘą░ą┐ąŠą╗ąĮąĖčéčüčÅ ą┤ąŠ čāčĆąŠą▓ąĮčÅ, ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ ą▒ąĖčéą░ą╝ąĖ WTM4:0 ą▓ čĆąĄą│ąĖčüčéčĆąĄ FIFO_CTRL_REG. FIFO ą┐čĆąŠą┤ąŠą╗ąČąĖčé ąĘą░ą┐ąŠą╗ąĮčÅčéčī čüą▓ąŠąĖ čÅč湥ą╣ą║ąĖ (32 čüą╗ąŠčéą░ 16-ą▒ąĖčéąĮčŗčģ ą┤ą░ąĮąĮčŗčģ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ąŠą▓ yaw, pitch ąĖ roll) ą┤ąŠ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ. ąÜąŠą│ą┤ą░ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĄ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé, FIFO ąŠčéą▒čĆąŠčüąĖčé čüčéą░čĆčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┐čĆąĖ ą┐ąŠčüčéčāą┐ą╗ąĄąĮąĖąĖ ąĮąŠą▓čŗčģ ą┤ą░ąĮąĮčŗčģ. ą¤čĆąĖ ąĮą░čüčéčāą┐ą╗ąĄąĮąĖąĖ čüąŠą▒čŗčéąĖą╣ (čüą▓čÅąĘą░ąĮąĮčŗčģ čü čĆąĄą│ąĖčüčéčĆąŠą╝ INT1_CFG) FIFO ąĮą░čćąĮąĄčé čĆą░ą▒ąŠčéą░čéčī ą▓ čĆąĄąČąĖą╝ąĄ FIFO (čüą╝. čĆąĖčü. 11).

ąĀąĖčü. 11. ąĀą░ą▒ąŠčéą░ čĆąĄąČąĖą╝ą░ Stream-to-FIFO

3.2.6. ą¤ąŠą╗čāč湥ąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ ąĖąĘ FIFO

ąöą░ąĮąĮčŗąĄ FIFO čüčćąĖčéčŗą▓ą░čÄčéčüčÅ ąĖąĘ čĆąĄą│ąĖčüčéčĆąŠą▓ OUT_X, OUT_Y ąĖ OUT_Z. ąÜąŠą│ą┤ą░ FIFO ą▓ ą┐ąŠč鹊ą║ąŠą▓ąŠą╝ čĆąĄąČąĖą╝ąĄ (stream), ą▓ čĆąĄąČąĖą╝ąĄ čéčĆąĖą│ą│ąĄčĆą░ ąĖą╗ąĖ FIFO, ąŠą┐ąĄčĆą░čåąĖčÅ čćč鹥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆąŠą▓ OUT_X, OUT_Y ąĖą╗ąĖ OUT_Z ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą┤ą░ąĮąĮčŗąĄ, čüąŠčģčĆą░ąĮąĄąĮąĮčŗąĄ ą▓ FIFO. ąÜą░ąČą┤čŗą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ ą┤ą░ąĮąĮčŗąĄ ą┐čĆąŠčćąĖčéą░ąĮčŗ ąĖąĘ FIFO, čüą░ą╝čŗąĄ čüčéą░čĆčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą║ą░ąĮą░ą╗ąŠą▓ pitch, roll ąĖ yaw ą┐ąŠą╝ąĄčēą░čÄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆčŗ OUT_X, OUT_Y ąĖ OUT_Z, ąĖ ą╝ąŠą│čāčé ą▒čŗčéčī ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮčŗ ąŠą▒ąĄ ąŠą┐ąĄčĆą░čåąĖąĖ čćč鹥ąĮąĖčÅ - ąŠą┤ąĖąĮąŠčćąĮąŠąĄ čćč鹥ąĮąĖąĄ (single read) ąĖ čāčüą║ąŠčĆąĄąĮąĮąŠąĄ čćč鹥ąĮąĖąĄ (read_burst, X,Y ąĖ Z čü ą░ą▓č鹊ąĖąĮą║čĆąĄą╝ąĄąĮč鹊ą╝ ą░ą┤čĆąĄčüą░). ąÆ čĆąĄąČąĖą╝ąĄ read_burst, ą║ąŠą│ą┤ą░ ą┤ą░ąĮąĮčŗąĄ ą┐čĆąŠčćąĖčéą░ąĮčŗ ąĖąĘ OUT_Z_H, čüąĖčüč鹥ą╝ą░ čüąĮąŠą▓ą░ ąĮą░čćąĮąĄčé čćč鹥ąĮąĖąĄ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ą┐ąŠ ą░ą┤čĆąĄčüčā OUT_X_L.

[4. ąŻą║ą░ąĘą░ąĮąĖčÅ ą┐ąŠ ą┐čĆąĖą╝ąĄąĮąĄąĮąĖčÄ]

ąĀąĖčü. 12. ąŁą╗ąĄą║čéčĆąĖč湥čüą║ąĖąĄ čüąŠąĄą┤ąĖąĮąĄąĮąĖčÅ L3G4200D ąĖ ąĮąŠą╝ąĖąĮą░ą╗čŗ ą▓ąĮąĄčłąĮąĖčģ ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓

ąĀą░ąĘą▓čÅąĘčŗą▓ą░čÄčēąĖąĄ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆčŗ ą┐ąŠ ą┐ąĖčéą░ąĮąĖčÄ (ą║ąĄčĆą░ą╝ąĖč湥čüą║ąĖąĄ ąĮą░ 100 nF ąĖą╗ąĖ ą┐ąŠą╗ąĖčŹčüč鹥čĆąŠą▓čŗąĄ 10 uF) ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čĆą░ąĘą╝ąĄčēąĄąĮčŗ ą║ą░ą║ ą╝ąŠąČąĮąŠ ą▒ą╗ąĖąČąĄ ą║ čāčüčéčĆąŠą╣čüčéą▓čā (ą║ą░ą║ ąĖ ą┤ąĄą╗ą░čÄčé ąŠą▒čŗčćąĮąŠ ąĮą░ ą┐čĆą░ą║čéąĖą║ąĄ). ąĢčüą╗ąĖ čłąĖąĮčŗ ą┐ąĖčéą░ąĮąĖčÅ Vdd ąĖ Vdd_IO ąĮąĄ čüąŠąĄą┤ąĖąĮąĄąĮčŗ ą┤čĆčāą│ čü ą┤čĆčāą│ąŠą╝, č鹊 ąŠčéą┤ąĄą╗čīąĮčŗąĄ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆčŗ ą╝ąĄąČą┤čā Vdd - ąĘąĄą╝ą╗čÅ ąĖ Vdd_IO - ąĘąĄą╝ą╗čÅ (čü čéą░ą║ąĖą╝ąĖ ąČąĄ ąĮąŠą╝ąĖąĮą░ą╗ą░ą╝ąĖ) čéą░ą║ąČąĄ ą┤ąŠą╗ąČąĮčŗ čĆą░ąĘą╝ąĄčēą░čéčīčüčÅ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠ ą▒ą╗ąĖąĘą║ąŠ ą║ čāčüčéčĆąŠą╣čüčéą▓čā.

ąÆ ą╝ąĖą║čĆąŠčüčģąĄą╝ąĄ L3G4200D ąĖą╝ąĄąĄčéčüčÅ čāąĘąĄą╗ PLL (phase locked loop) ą┤ą╗čÅ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ąĖąĮč鹥čĆč乥ą╣čüąŠą▓ (ą▓ąĮąĄčłąĮąĄą│ąŠ ąĖ čćčāą▓čüčéą▓ąĖč鹥ą╗čīąĮąŠą│ąŠ ą┤ą░čéčćąĖą║ą░). ąöą╗čÅ čŹč鹊ą│ąŠ ąĮą░ ąĮąŠąČą║čā PLLFILT ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą┤ąŠą▒ą░ą▓ą╗ąĄąĮčŗ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆčŗ ąĖ čĆąĄąĘąĖčüč鹊čĆčŗ (ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 12) - čćč鹊ą▒čŗ čĆąĄą░ą╗ąĖąĘąŠą▓ą░čéčī ążąØą¦ ą▓č鹊čĆąŠą│ąŠ ą┐ąŠčĆčÅą┤ą║ą░ ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ PLL. ąÆ čéą░ą▒ą╗ąĖčåąĄ 3 ą┐čĆąĖą▓ąĄą┤ąĄąĮčŗ ąĮąŠą╝ąĖąĮą░ą╗čŗ ą┤ąĄčéą░ą╗ąĄą╣ ążąØą¦ PLL.

[5. ą”ąĖčäčĆąŠą▓čŗąĄ ąĖąĮč鹥čĆč乥ą╣čüčŗ]

ąÆčüčéčĆąŠąĄąĮąĮčŗąĄ ą▓ L3G4200D čĆąĄą│ąĖčüčéčĆčŗ ą┤ąŠčüčéčāą┐ąĮčŗ ą║ą░ą║ č湥čĆąĄąĘ ąĖąĮč鹥čĆč乥ą╣čü I2C, čéą░ą║ ąĖ č湥čĆąĄąĘ ąĖąĮč鹥čĆč乥ą╣čü SPI - ą┐ąŠ ą▓čŗą▒ąŠčĆčā ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ. ą¤ąŠčüą╗ąĄą┤ąĮąĖą╣ ą╝ąŠąČąĄčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ ą▓ 3- ąĖą╗ąĖ 4-ą┐čĆąŠą▓ąŠą┤ąĮąŠą╝ čĆąĄąČąĖą╝ąĄ.

ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗąĄ ąĖąĮč鹥čĆč乥ą╣čüčŗ ą┐čĆąĖą▓čÅąĘą░ąĮčŗ ą║ ąŠą┤ąĮąĖą╝ ąĖ č鹥ą╝ ąČąĄ ąĮąŠąČą║ą░ą╝ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ. ą¦č鹊ą▒čŗ ą▓čŗą▒čĆą░čéčī ą▓ą░čĆąĖą░ąĮčé čĆą░ą▒ąŠčéčŗ čü ąĖąĮč鹥čĆč乥ą╣čüąŠą╝ I2C, ąĮą░ ą▓čŗą▓ąŠą┤ CS ąĮčāąČąĮąŠ ą┐ąŠą┤ą░čéčī ą╗ąŠą│. 1 (ąĮą░ą┐čĆąĖą╝ąĄčĆ, CS ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą║ čłąĖąĮąĄ ą┐ąĖčéą░ąĮąĖčÅ Vdd_IO).

ąóą░ą▒ą╗ąĖčåą░ 11. ą×ą┐ąĖčüą░ąĮąĖąĄ ą▓čŗą▓ąŠą┤ąŠą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░

| Ōä¢ ą▓čŗą▓. |

ąśą╝čÅ |

ąóąĖą┐ |

ą×ą┐ąĖčüą░ąĮąĖąĄ ą▓čŗą▓ąŠą┤ą░ |

| 2 |

SCL

SPC |

I

I |

ąóą░ą║čéčŗ I2C.

ąóą░ą║čéčŗ SPI. |

| 3 |

SDA

SDI

SDO |

I/O

I

O |

ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ I2C.

ąÆčģąŠą┤ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ą┤ą░ąĮąĮčŗčģ SPI.

ąÆčŗčģąŠą┤ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ą┤ą░ąĮąĮčŗčģ SPI ą▓ 3-ą┐čĆąŠą▓ąŠą┤ąĮąŠą╝ čĆąĄąČąĖą╝ąĄ. |

| 4 |

SDO

SA0 |

O

I |

ąÆčŗčģąŠą┤ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ą┤ą░ąĮąĮčŗčģ SPI.

LSB-ą▒ąĖčé ą░ą┤čĆąĄčüą░ čāčüčéčĆąŠą╣čüčéą▓ą░ I2C. |

| 5 |

CS |

I |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ čĆą░ą▒ąŠčéčŗ SPI (SPI enable), ą▓čŗą▒ąŠčĆ čĆąĄąČąĖą╝ą░ ąĖąĮč鹥čĆč乥ą╣čüą░ (I2C/SPI) ą┐čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ (1: čĆąĄąČąĖą╝ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ąĖ SPI, čĆą░ąĘčĆąĄčłąĄąĮą░ čĆą░ą▒ąŠčéą░ I2C; 0: čĆąĄąČąĖą╝ ąŠą▒ą╝ąĄąĮą░ SPI, I2C ąĘą░ą┐čĆąĄčēąĄąĮ). |

5.1. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü I2C

ą£ąĖą║čĆąŠčüčģąĄą╝ą░ L3G4200D ąĮą░ čłąĖąĮąĄ I2C čÅą▓ą╗čÅąĄčéčüčÅ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗą╝ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ (slave). I2C čāčüčéčĆąŠąĄąĮą░ čéą░ą║, čćč鹊 ą╝ąŠąČąĄčé ąĘą░ą┐ąĖčüčŗą▓ą░čéčī ą┤ą░ąĮąĮčŗąĄ ą▓ čĆąĄą│ąĖčüčéčĆčŗ, čćčīąĄ čüąŠą┤ąĄčƹȹ░ąĮąĖąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī čéą░ą║ąČąĄ ą┐čĆąŠčćąĖčéą░ąĮąŠ ąŠą▒čĆą░čéąĮąŠ. ąĪąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēą░čÅ č鹥čĆą╝ąĖąĮąŠą╗ąŠą│ąĖčÅ I2C ą┐čĆąĖą▓ąĄą┤ąĄąĮą░ ą▓ čéą░ą▒ą╗ąĖčåąĄ ąĮąĖąČąĄ.

ąóą░ą▒ą╗ąĖčåą░ 12. ąóąĄčĆą╝ąĖąĮčŗ I2C

| ąóąĄčĆą╝ąĖąĮ |

ążčāąĮą║čåąĖčÅ |

| Transmitter (čéčĆą░ąĮčüą╝ąĖčéč鹥čĆ, ą┐ąĄčĆąĄą┤ą░čéčćąĖą║) |

ąŻčüčéčĆąŠą╣čüčéą▓ąŠ, ą║ąŠč鹊čĆąŠąĄ ą┐ąĄčĆąĄą┤ą░ąĄčé ą┤ą░ąĮąĮčŗąĄ ą┐ąŠ čłąĖąĮąĄ. |

| Receiver (ą┐čĆąĖąĄą╝ąĮąĖą║) |

ąŻčüčéčĆąŠą╣čüčéą▓ąŠ, ą║ąŠč鹊čĆąŠąĄ ą┐čĆąĖąĮąĖą╝ą░ąĄčé ą┤ą░ąĮąĮčŗąĄ ą┐ąŠ čłąĖąĮąĄ. |

| Master (ą╝ą░čüč鹥čĆ, čģąŠčüčé) |

ąōą╗ą░ą▓ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮą░ čłąĖąĮąĄ, ą║ąŠč鹊čĆąŠąĄ ąĮą░čćąĖąĮą░ąĄčé ą┐ąĄčĆąĄą┤ą░čćčā, ą│ąĄąĮąĄčĆąĖčĆčāąĄčé čéą░ą║č鹊ą▓čŗąĄ čüąĖą│ąĮą░ą╗čŗ ąĖ ąĘą░ą▓ąĄčĆčłą░ąĄčé ą┐čĆąŠčåąĄčüčü ą┐ąĄčĆąĄą┤ą░čćąĖ. |

| Slave (ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ) |

ąŻčüčéčĆąŠą╣čüčéą▓ąŠ, ą░ą┤čĆąĄčüąŠą▓ą░ąĮąĮąŠąĄ ą╝ą░čüč鹥čĆąŠą╝ ą┤ą╗čÅ ąŠą▒ą╝ąĄąĮą░ ą┤ą░ąĮąĮčŗą╝ąĖ. |

ąśą╝ąĄąĄčéčüčÅ ą┤ą▓ą░ čüąĖą│ąĮą░ą╗ą░, čüą▓čÅąĘą░ąĮąĮčŗąĄ čü čłąĖąĮąŠą╣ I2C: ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗąĄ čéą░ą║čéčŗ (serial clock line, SCL) ąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ (serial data line, SDA). ąĪąĖą│ąĮą░ą╗ SDA čÅą▓ą╗čÅąĄčéčüčÅ ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╝, ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ąŠčéą┐čĆą░ą▓ą║ąĖ ąĖ ą┐čĆąĖąĄą╝ą░ ą┤ą░ąĮąĮčŗčģ č湥čĆąĄąĘ ąĖąĮč鹥čĆč乥ą╣čü. ą×ą▒ą░ čüąĖą│ąĮą░ą╗ą░ SDA ąĖ SCL ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą┐ąŠą┤čéčÅąĮčāčéčŗ ą║ čłąĖąĮąĄ Vdd_IO č湥čĆąĄąĘ ą▓ąĮąĄčłąĮąĖąĄ ąĮą░ą│čĆčāąĘąŠčćąĮčŗąĄ čĆąĄąĘąĖčüč鹊čĆčŗ (pull-up). ąÜąŠą│ą┤ą░ čłąĖąĮą░ čüą▓ąŠą▒ąŠą┤ąĮą░, č鹊 ąŠą▒ą░ čüąĖą│ąĮą░ą╗ą░ ąĮą░čģąŠą┤čÅčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą╗ąŠą│. 1.

ąśąĮč鹥čĆč乥ą╣čü I2C čüąŠą▓ą╝ąĄčüčéąĖą╝ čüąŠ čüčéą░ąĮą┤ą░čĆčéą░ą╝ąĖ ą▒čŗčüčéčĆąŠą│ąŠ čĆąĄąČąĖą╝ą░ (fast mode, čćą░čüč鹊čéą░ čéą░ą║č鹊ą▓ 400 ą║ąōčå) ąĖ ąĮąŠčĆą╝ą░ą╗čīąĮąŠą│ąŠ čĆąĄąČąĖą╝ą░.

5.1.1. ąÜą░ą║ čĆą░ą▒ąŠčéą░ąĄčé I2C

ąóčĆą░ąĮąĘą░ą║čåąĖąĖ ąĮą░ čłąĖąĮąĄ ąĮą░čćąĖąĮą░čÄčéčüčÅ čü čüąĖą│ąĮą░ą╗ą░ START (ST). ąĪąŠą▒čŗčéąĖąĄ START ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąŠ ą║ą░ą║ ą┐ąĄčĆąĄčģąŠą┤ SDA ąŠčé čüąŠčüč鹊čÅąĮąĖčÅ HIGH ą║ čüąŠčüč鹊čÅąĮąĖčÄ LOW (ą┐ąŠą┤ HIGH ąĖ LOW ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░čÄčéčüčÅ čüąŠčüč鹊čÅąĮąĖčÅ ą╗ąŠą│. 1 ąĖ ą╗ąŠą│. 0 čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ), ą║ąŠą│ą┤ą░ SCL ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ HIGH. ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ START ą▒čŗą╗ ąĖąĮąĖčåąĖąĖčĆąŠą▓ą░ąĮ ą╝ą░čüč鹥čĆąŠą╝ čłąĖąĮčŗ, čłąĖąĮą░ čüčćąĖčéą░ąĄčéčüčÅ ąĘą░ąĮčÅč鹊ą╣. ąĪą╗ąĄą┤čāčÄčēąĖą╣ ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą┐ąŠčüą╗ąĄ čüąŠą▒čŗčéąĖčÅ START, ąĖ ąŠąĮ čüąŠą┤ąĄčƹȹĖčé ą░ą┤čĆąĄčü ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ą▓ ą┐ąĄčĆą▓čŗčģ 7 ą▒ąĖčéą░čģ, ąĖ 8 ą▒ąĖčé ą│ąŠą▓ąŠčĆąĖčé, ą▒čāą┤ąĄčé ą╝ą░čüč鹥čĆ ą┐ąŠą╗čāčćą░čéčī ą┤ą░ąĮąĮčŗąĄ ąŠčé ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ąĖą╗ąĖ ąČąĄ ą┤ą░ąĮąĮčŗąĄ ą▒čāą┤čāčé ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčīčüčÅ ą▓ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ. ąÜąŠą│ą┤ą░ ą░ą┤čĆąĄčü ą┐ąĄčĆąĄą┤ą░ąĮ, č鹊 ą║ą░ąČą┤ąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮąŠąĄ ą║ čŹč鹊ą╣ čłąĖąĮąĄ ą▓ čüąĖčüč鹥ą╝ąĄ, čüčĆą░ą▓ąĮąĖą▓ą░ąĄčé ą┐ąĄčĆą▓čŗąĄ 7 ą▒ąĖčé ą┐ąŠčüą╗ąĄ čüąŠą▒čŗčéąĖčÅ START čüąŠ čüą▓ąŠąĖą╝ čüąŠą▒čüčéą▓ąĄąĮąĮčŗą╝ ą░ą┤čĆąĄčüąŠą╝. ąĢčüą╗ąĖ ą░ą┤čĆąĄčüą░ čüąŠą▓ą┐ą░ą╗ąĖ, č鹊 čāčüčéčĆąŠą╣čüčéą▓ąŠ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé, čćč鹊 ąĖą╝ąĄąĮąĮąŠ čü ąĮąĖą╝ ą▒čāą┤ąĄčé čĆą░ą▒ąŠčéą░čéčī ą╝ą░čüč鹥čĆ (čéą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ąĮą░ ąŠą┤ąĮąŠą╣ čłąĖąĮąĄ I2C ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮąŠ ą┤ąŠ 8 čāčüčéčĆąŠą╣čüčéą▓ čü čĆą░ąĘąĮčŗą╝ ą░ą┤čĆąĄčüąŠą╝).

ąÉą┤čĆąĄčü ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (slave address, SAD), čüą▓čÅąĘą░ąĮąĮčŗą╣ čü L3G4200D, čĆą░ą▓ąĄąĮ 110100xb. ąØąŠąČą║ą░ SDO ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ č鹊ą│ąŠ, čćč鹊ą▒čŗ ąĘą░ą┤ą░čéčī ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ LSB ą▒ąĖčé (ą║ąŠč鹊čĆčŗą╣ ą┐ąŠą╝ąĄč湥ąĮ x) ą░ą┤čĆąĄčüą░ čāčüčéčĆąŠą╣čüčéą▓ą░. ąĢčüą╗ąĖ ąĮą░ SDO ą╗ąŠą│. 1 (ąĮą░ą┐čĆąĖą╝ąĄčĆ, SDO ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą║ čłąĖąĮąĄ ą┐ąĖčéą░ąĮąĖčÅ), č鹊 ą▒ąĖčé LSB ą░ą┤čĆąĄčüą░ 1, ąĖ ą░ą┤čĆąĄčü ą▒čāą┤ąĄčé 1101001b. ąś ąĮą░ąŠą▒ąŠčĆąŠčé, ąĄčüą╗ąĖ ąĮą░ SDO ą┐ąŠą┤ą░ąĮ ą╗ąŠą│. 0 (ąŠąĮ ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą║ ąĘąĄą╝ą╗ąĄ), č鹊 LSB ą▒čāą┤ąĄčé čĆą░ą▓ąĄąĮ 0, ą░ą┤čĆąĄčü ą▒čāą┤ąĄčé 1101000b. ąŁč鹊čé ą╝ąĄč鹊ą┤ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐ąŠą┤ą║ą╗čÄčćąĖčéčī ąĮą░ ąŠą┤ąĮčā čłąĖąĮčā I2C ą┤ą▓ą░ čĆą░ąĘąĮčŗčģ ą│ąĖčĆąŠčüą║ąŠą┐ą░ L3G4200D.

ą¤ąĄčĆąĄą┤ą░čćą░ ą┤ą░ąĮąĮčŗčģ ą┐ąŠ čłąĖąĮąĄ I2C čéčĆąĄą▒čāąĄčé ąŠą▒čÅąĘą░č鹥ą╗čīąĮąŠą│ąŠ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ (acknowledge). ąöą╗čÅ čŹč鹊ą│ąŠ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ ą┤ąŠą╗ąČąĄąĮ ąŠčüą▓ąŠą▒ąŠą┤ąĖčéčī ą╗ąĖąĮąĖčÄ SDA ą▓ąŠ ą▓čĆąĄą╝čÅ ąĖą╝ą┐čāą╗čīčüą░ acknowledge. ą¤čĆąĖąĄą╝ąĮąĖą║ ą┤ąŠą╗ąČąĄąĮ ą┐ąĄčĆąĄą▓ąĄčüčéąĖ SDA ą▓ čüąŠčüč鹊čÅąĮąĖąĄ LOW, ąĖ čāą┤ąĄčƹȹĖą▓ą░čéčī ąĄčæ ą▓ čéą░ą║ąŠą╝ čüąŠčüč鹊čÅąĮąĖąĖ ą┐ąŠ ą▓čĆąĄą╝čÅ HIGH čüąŠčüč鹊čÅąĮąĖčÅ ąĖą╝ą┐čāą╗čīčüą░ čéą░ą║čéą░ ą┤ą╗čÅ ą▒ąĖčéą░ acknowledge. ą¤čĆąĖąĄą╝ąĮąĖą║, ą║ąŠč鹊čĆčŗą╣ ą▒čŗą╗ ą░ą┤čĆąĄčüąŠą▓ą░ąĮ, ą┤ąŠą╗ąČąĄąĮ ąŠą▒čÅąĘą░č鹥ą╗čīąĮąŠ ą▓čŗą┤ą░ą▓ą░čéčī čéą░ą║ąŠąĄ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ ą┐ąŠčüą╗ąĄ ą║ą░ąČą┤ąŠą│ąŠ ą┐čĆąĖąĮčÅč鹊ą│ąŠ ą▒ą░ą╣čéą░ ą┤ą░ąĮąĮčŗčģ.

I2C, ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ ą▓ L3G4200D, ą▓ąĄą┤ąĄčé čüąĄą▒čÅ ą║ą░ą║ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ, čéą░ą║ čćč鹊 L3G4200D ą┤ąŠą╗ąČąĮąŠ ą┐čĆąĖą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ čéą░ą║ąŠą│ąŠ ąČąĄ ą┐čĆąŠč鹊ą║ąŠą╗ą░. ą¤ąŠčüą╗ąĄ čüąŠą▒čŗčéąĖčÅ START (ST), ą╝ą░čüč鹥čĆąŠą╝ ąŠčéą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ą░ą┤čĆąĄčü ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░. ąÜą░ą║ č鹊ą╗čīą║ąŠ ą▒čŗą╗ ą▓ąŠąĘą▓čĆą░čēąĄąĮ čüąĖą│ąĮą░ą╗ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ ąŠčé ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (slave acknowledge, SAK), 8-ą▒ąĖčéąĮą░čÅ čćą░čüčéčī ą░ą┤čĆąĄčüą░ čüčćąĖčéą░ąĄčéčüčÅ ą┐ąĄčĆąĄą┤ą░ąĮąĮąŠą╣. ąæąĖčé 7 LSB ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé čĆąĄą░ą╗čīąĮčŗą╣ ą░ą┤čĆąĄčü čĆąĄą│ąĖčüčéčĆą░, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ MSB čĆą░ąĘčĆąĄčłą░ąĄčé ą░ą▓č鹊ąĖąĮą║čĆąĄą╝ąĄąĮčé ą░ą┤čĆąĄčüą░. ąĢčüą╗ąĖ MSB ą▓ ą┐ąŠą╗ąĄ SUB čĆą░ą▓ąĄąĮ 1, č鹊 SUB (ą░ą┤čĆąĄčü čĆąĄą│ąĖčüčéčĆą░) ą▒čāą┤ąĄčé ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆąŠą▓ą░čéčīčüčÅ, čćč鹊ą▒čŗ ą┐ąŠąĘą▓ąŠą╗ąĖčéčī ą┐čĆąŠčćąĖčéą░čéčī/ąĘą░ą┐ąĖčüą░čéčī ąĮąĄčüą║ąŠą╗čīą║ąŠ ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ.

ąÜą░ą║ čāąČąĄ ą▒čŗą╗ąŠ čāą┐ąŠą╝čÅąĮčāč鹊, ą░ą┤čĆąĄčü ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ąĘą░ą▓ąĄčĆčłą░ąĄčéčüčÅ ą▒ąĖč鹊ą╝ čćč鹥ąĮąĖčÅ/ąĘą░ą┐ąĖčüąĖ (read/write bit). ąĢčüą╗ąĖ čŹč鹊čé ą▒ąĖčé 1, (čćč鹥ąĮąĖąĄ, read), ą┐ąŠą▓č鹊čĆčÅčÄčēąĄąĄčüčÅ čüąŠą▒čŗčéąĖąĄ čüčéą░čĆčéą░ (REPEATED START, SR) ą┤ąŠą╗ąČąĮąŠ ą▓čŗą┤ą░ą▓ą░čéčīčüčÅ ą┐ąŠčüą╗ąĄ ą┤ą▓čāčģ ą▒ą░ą╣čé čüčāą▒ą░ą┤čĆąĄčüą░; ąĄčüą╗ąĖ čŹč鹊čé ą▒ąĖčé 0 (ąĘą░ą┐ąĖčüčī, write), č鹊 ą╝ą░čüč鹥čĆ ą┐ąĄčĆąĄą┤ą░ąĄčé ą┤ą░ąĮąĮčŗąĄ ą║ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą╝čā čāčüčéčĆąŠą╣čüčéą▓čā ą▓ ąĮąĄąĖąĘą╝ąĄąĮąĮąŠą╝ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĖ. ąóą░ą▒ą╗ąĖčåą░ 13 ąŠą┐ąĖčüčŗą▓ą░ąĄčé, ą║ą░ą║ čüąŠčüčéą░ą▓ą╗čÅčÄčéčüčÅ ą┐ą░čéč鹥čĆąĮčŗ SAD+read/write bit, ą┐ąĄčĆąĄčćąĖčüą╗ąĄąĮčŗ ą▓čüąĄ ą▓ąŠąĘą╝ąŠąČąĮčŗąĄ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ.

ąóą░ą▒ą╗ąĖčåą░ 13. ą¤ą░čéč鹥čĆąĮčŗ (ą┤ą░ąĮąĮčŗąĄ) SAD+read/write (čćč鹥ąĮąĖąĄ/ąĘą░ą┐ąĖčüčī)

| ąÜąŠą╝ą░ąĮą┤ą░ |

SAD[6:1] |

SAD[0]=SDO |

R/W |

SAD+R/W |

| Read |

110100 |

0 |

1 |

11010001 (D1h) |

| Write |

110100 |

0 |

0 |

11010000 (D0h) |

| Read |

110100 |

1 |

1 |

11010011 (D3h) |

| Write |

110100 |

1 |

0 |

11010010 (D2h) |

ąóą░ą▒ą╗ąĖčåą░ 14. ą¤ąĄčĆąĄą┤ą░čćą░, ą║ąŠą│ą┤ą░ ą╝ą░čüč鹥čĆ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčé ąŠą┤ąĖąĮ ą▒ą░ą╣čé ą▓ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ

| Master |

ST |

SAD + W |

|

SUB |

|

DATA |

|

SP |

| Slave |

|

|

SAK |

|

SAK |

|

SAK |

|

ąóą░ą▒ą╗ąĖčåą░ 15. ą¤ąĄčĆąĄą┤ą░čćą░, ą║ąŠą│ą┤ą░ ą╝ą░čüč鹥čĆ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčé ąĮąĄčüą║ąŠą╗čīą║ąŠ ą▒ą░ą╣čé ą▓ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ

| Master |

ST |

SAD + W |

|

SUB |

|

DATA |

|

DATA |

|

SP |

| Slave |

|

|

SAK |

|

SAK |

|

SAK |

|

SAK |

|

ąóą░ą▒ą╗ąĖčåą░ 16. ą¤ąĄčĆąĄą┤ą░čćą░, ą║ąŠą│ą┤ą░ ą╝ą░čüč鹥čĆ ą┐ąŠą╗čāčćą░ąĄčé (čćąĖčéą░ąĄčé) ąŠą┤ąĖąĮ ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ ąĖąĘ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░

| Master |

ST |

SAD + W |

|

SUB |

|

SR |

SAD+R |

|

|

NMAK |

SP |

| Slave |

|

|

SAK |

|

SAK |

|

|

SAK |

DATA |

|

|

ąóą░ą▒ą╗ąĖčåą░ 17. ą¤ąĄčĆąĄą┤ą░čćą░, ą║ąŠą│ą┤ą░ ą╝ą░čüč鹥čĆ ą┐ąŠą╗čāčćą░ąĄčé (čćąĖčéą░ąĄčé) ąĮąĄčüą║ąŠą╗čīą║ąŠ ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ ąĖąĘ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░

| Master |

ST |

SAD + W |

|

SUB |

|

SR |

SAD+R |

|

|

MAK |

|

MAK |

|

NMAK |

SP |

| Slave |

|

|

SAK |

|

SAK |

|

|

SAK |

DATA |

|

DATA |

|

DATA |

|

|

ąöą░ąĮąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ą┐ąŠą▒ą░ą╣čéąĮąŠ (DATA). ąÜą░ąČą┤ą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░ ą┤ą░ąĮąĮčŗčģ čüąŠą┤ąĄčƹȹĖčé 8 ą▒ąĖčé. ąŚą░ ąŠą┤ąĖąĮ čéčĆą░ąĮčüč乥čĆ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąĄčĆąĄą┤ą░ąĮąŠ ą▒ąĄčüą║ąŠąĮąĄčćąĮąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ą░ą╣čé. ąöą░ąĮąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ čüčéą░čĆčłąĖą╝ ą▒ąĖč鹊ą╝ (MSB) ą▓ą┐ąĄčĆąĄą┤. ąĢčüą╗ąĖ ą┐čĆąĖąĄą╝ąĮąĖą║ ąĮąĄ ą╝ąŠąČąĄčé ą┐čĆąĖąĮčÅčéčī ą┤čĆčāą│ąŠą╣ ą┐ąŠą╗ąĮčŗą╣ ą▒ą░ą╣čé, ą┐ąŠą║ą░ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą▓ ą┐čĆąĖąĄą╝ąĮąĖą║ąĄ ą║ą░ą║ą░čÅ-č鹊 ą┤čĆčāą│ą░čÅ čäčāąĮą║čåąĖčÅ, č鹊 ą┐čĆąĖąĄą╝ąĮąĖą║ ą┤ąŠą╗ąČąĄąĮ čāą┤ąĄčƹȹ░čéčī čéą░ą║č鹊ą▓čāčÄ ą╗ąĖąĮąĖčÄ SCL ą▓ čüąŠčüč鹊čÅąĮąĖąĖ LOW, čćč鹊ą▒čŗ ą┐čĆąĖąĮčāą┤ąĖč鹥ą╗čīąĮąŠ ą┐ąĄčĆąĄą▓ąĄčüčéąĖ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ąŠąČąĖą┤ą░ąĮąĖčÅ. ą¤ąĄčĆąĄą┤ą░čćą░ ą┤ą░ąĮąĮčŗčģ ą┐čĆąŠą┤ąŠą╗ąČąĖčéčüčÅ č鹊ą╗čīą║ąŠ č鹊ą│ą┤ą░, ą║ąŠą│ą┤ą░ ą┐čĆąĖąĄą╝ąĮąĖą║ ą▒čāą┤ąĄčé ą│ąŠč鹊ą▓ ą║ ą┤čĆčāą│ąŠą╝čā ą▒ą░ą╣čéčā ąĖ ąŠčüą▓ąŠą▒ąŠą┤ąĖčé ą╗ąĖąĮąĖčÄ ą┤ą░ąĮąĮčŗčģ. ąĢčüą╗ąĖ ą┐čĆąĖąĄą╝ąĮąĖą║ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ąĮąĄ ą┐ąŠą┤čéą▓ąĄčĆą┤ąĖą╗ slave address (ą║ ą┐čĆąĖą╝ąĄčĆčā, ą┐čĆąĖąĄą╝ąĮąĖą║ ą┐ąŠą║ą░ ąĮąĄ ą╝ąŠąČąĄčé ą┐čĆąĖąĮčÅčéčī ą┐ąŠ ą┐čĆąĖčćąĖąĮąĄ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą║ą░ą║ąĖčģ-č鹊 ą▓ąĮčāčéčĆąĄąĮąĮąĖčģ čäčāąĮą║čåąĖą╣ ą▓ čĆąĄą░ą╗čīąĮąŠą╝ ą▓čĆąĄą╝ąĄąĮąĖ) ą╗ąĖąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ SDA ą┤ąŠą╗ąČąĮą░ ąŠčüčéą░ą▓ą░čéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ HIGH, ąŠčéą┐čāčēąĄąĮąĮąŠą╣ ą┐ąŠą┤čćąĖąĮąĄąĮąĮčŗą╝ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝. ą£ą░čüč鹥čĆ ą╝ąŠąČąĄčé ąŠą▒ąŠčĆą▓ą░čéčī ą┐ąĄčĆąĄą┤ą░čćčā. ą¤ąĄčĆąĄčģąŠą┤ ąŠčé LOW ą║ HIGH ąĮą░ ą╗ąĖąĮąĖąĖ SDA, ą║ąŠą│ą┤ą░ SCL ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ HIGH, ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮ ą║ą░ą║ čüąŠą▒čŗčéąĖąĄ STOP. ąÜą░ąČą┤ą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░ ą┤ą░ąĮąĮčŗčģ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ąĘą░ą▓ąĄčĆčłąĄąĮą░ čüąŠą▒čŗčéąĖąĄą╝ STOP (SP).

ą¦č鹊ą▒čŗ ą┐čĆąŠčćąĖčéą░čéčī ąĮąĄčüą║ąŠą╗čīą║ąŠ ą▒ą░ą╣č鹊ą▓, ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ąĘą░ą┐ąŠą╗ąĮąĖčéčī MSB ą┐ąŠą╗čÅ čüčāą▒ą░ą┤čĆąĄčüą░. ąöčĆčāą│ąĖą╝ąĖ čüą╗ąŠą▓ą░ą╝ąĖ, ą┐ąŠą╗ąĄ SUB(7) ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī čĆą░ą▓ąĮąŠ 1, ą┐čĆąĖ čŹč鹊ą╝ SUB(6-0) ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅčÄčé ą░ą┤čĆąĄčü ą┐ąĄčĆą▓ąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░, ą║ąŠč鹊čĆčŗą╣ ą▒čāą┤ąĄčé ą┐čĆąŠčćąĖčéą░ąĮ.

ąÆ ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮąĮąŠą╝ č乊čĆą╝ą░č鹥 ąŠą▒ą╝ąĄąĮą░ MAK ąŠąĘąĮą░čćą░ąĄčé "master acknowledge" (ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖąĄ ą┤ą╗čÅ ą╝ą░čüč鹥čĆą░) NMAK ąŠąĘąĮą░čćą░ąĄčé "no master acknowledge" (ąĮąĄčé ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ ą┤ą╗čÅ ą╝ą░čüč鹥čĆą░).

5.2. ą©ąĖąĮą░ ąĖąĮč鹥čĆč乥ą╣čüą░ SPI

L3G4200D čĆą░ą▒ąŠčéą░ąĄčé ąĮą░ čłąĖąĮąĄ SPI čéą░ą║ąČąĄ ą║ą░ą║ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ. SPI ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąĘą░ą┐ąĖčüčŗą▓ą░čéčī ąĖ čćąĖčéą░čéčī čĆąĄą│ąĖčüčéčĆčŗ čāčüčéčĆąŠą╣čüčéą▓ą░. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü SPI ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąŠą▒ą╝ąĄąĮąĖą▓ą░čéčīčüčÅ ą┤ą░ąĮąĮčŗą╝ąĖ čü ą▓ąĮąĄčłąĮąĖą╝ ą╝ąĖčĆąŠą╝ č湥čĆąĄąĘ 4 ą┐čĆąŠą▓ąŠą┤ą░: CS, SPC, SDI ąĖ SDO.

ąĀąĖčü. 13. ą¤čĆąŠč鹊ą║ąŠą╗ čćč鹥ąĮąĖčÅ ąĖ ąĘą░ą┐ąĖčüąĖ SPI

CS čÅą▓ą╗čÅąĄčéčüčÅ čüąĖą│ąĮą░ą╗ąŠą╝ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ čĆą░ą▒ąŠčéčŗ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ą┐ąŠčĆčéą░, ąĖ ąŠąĮ čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ą╝ą░čüč鹥čĆąŠą╝ SPI. ą×ąĮ ą┐ąĄčĆąĄčģąŠą┤ąĖčé ąĮą░ čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 0 ą▓ ąĮą░čćą░ą╗ąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ, ąĖ ą▓ąŠąĘą▓čĆą░čēą░ąĄčéčüčÅ ą║ ą╗ąŠą│. 1 ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ. SPC čŹč鹊 čüąĖą│ąĮą░ą╗ čéą░ą║č鹊ą▓, ąĖ ąŠąĮ čéą░ą║ąČąĄ ą▓čŗą┤ą░ąĄčéčüčÅ ą╝ą░čüč鹥čĆąŠą╝ SPI. ąóą░ą║čéčŗ ą┐ąĄčĆąĄčüčéą░čÄčé ą▓čŗą┤ą░ą▓ą░čéčīčüčÅ, ą║ąŠą│ą┤ą░ CS ą▓ ą╗ąŠą│. 1, (ą┐ąĄčĆąĄą┤ą░čćąĖ ąĮąĄčé). ąĪąĖą│ąĮą░ą╗čŗ SDI ąĖ SDO čÅą▓ą╗čÅčÄčéčüčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ ą▓čģąŠą┤ąŠą╝ ąĖ ą▓čŗčģąŠą┤ąŠą╝ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ą┤ą░ąĮąĮčŗčģ. ąŁčéąĖ čüąĖą│ąĮą░ą╗čŗ ą┤ą░ąĮąĮčŗčģ ą╝ąĄąĮčÅčÄčé čüą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠ čüą┐ą░ą┤čā čāčĆąŠą▓ąĮčÅ (ą┐ąĄčĆąĄčģąŠą┤čā ąŠčé ą╗ąŠą│. 1 ą║ ą╗ąŠą│. 0) čéą░ą║č鹊ą▓ SPC, ąĖ ą┤ąŠą╗ąČąĮčŗ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░čéčīčüčÅ ą┐ąŠ čäčĆąŠąĮčéčā (ą┐ąĄčĆąĄčģąŠą┤čā ąŠčé ą╗ąŠą│. 0 ą║ ą╗ąŠą│. 1) čéą░ą║č鹊ą▓ SPC.

ą×ą▒ąĄ ą║ąŠą╝ą░ąĮą┤čŗ, ą║ą░ą║ čćč鹥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ čéą░ą║ ąĖ ąĘą░ą┐ąĖčüąĖ čĆąĄą│ąĖčüčéčĆą░ ąĘą░ą▓ąĄčĆčłą░čÄčéčüčÅ ąĘą░ 16 ąĖą╝ą┐čāą╗čīčüąŠą▓ čéą░ą║č鹊ą▓ SPC, ąĖą╗ąĖ ąĘą░ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ą░ą╣čé čāą╝ąĮąŠąČąĄąĮąĮąŠąĄ ąĮą░ 8 ą▓ čüą╗čāčćą░ąĄ čćč鹥ąĮąĖčÅ/ąĘą░ą┐ąĖčüąĖ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ą▒ą░ą╣čé. ąöą╗ąĖč鹥ą╗čīąĮąŠčüčéčī ą▒ąĖčéą░ čĆą░ą▓ąĮą░ ą▓čĆąĄą╝ąĄąĮąĖ ą╝ąĄąČą┤čā ą┤ą▓čāą╝čÅ čüą┐ą░ą┤ą░ą╝ąĖ čüąĖą│ąĮą░ą╗ą░ SPC. ą¤ąĄčĆą▓čŗą╣ ą▒ąĖčé (ą▒ąĖčé 0) ąĮą░čćąĖąĮą░ąĄčéčüčÅ ą┐ąŠ ą┐ąĄčĆą▓ąŠą╝čā čüą┐ą░ą┤čā SPC ą┐ąŠčüą╗ąĄ čüą┐ą░ą┤ą░ CS, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ą▒ąĖčé (ą▒ąĖčé 15, ą▒ąĖčé 23 ąĖ čé. ą┤.), ąĮą░čćąĖąĮą░ąĄčéčüčÅ ą┐ąŠ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╝čā čüą┐ą░ą┤čā SPC čüčĆą░ąĘčā ą┐ąĄčĆąĄą┤ ąĮą░čĆą░čüčéą░ąĮąĖąĄą╝ čāčĆąŠą▓ąĮčÅ CS.

Bit 0: ą▒ąĖčé čćč鹥ąĮąĖčÅ/ąĘą░ą┐ąĖčüąĖ (RW bit). ąÜąŠą│ą┤ą░ 0, ą┤ą░ąĮąĮčŗąĄ DI(7:0) ą▒čāą┤čāčé ąĘą░ą┐ąĖčüą░ąĮčŗ ą▓ čāčüčéčĆąŠą╣čüčéą▓ąŠ. ąÜąŠą│ą┤ą░ 1, ą┤ą░ąĮąĮčŗąĄ DO(7:0) ą▒čāą┤čāčé ą┐čĆąŠčćąĖčéą░ąĮčŗ ąĖąĘ čāčüčéčĆąŠą╣čüčéą▓ą░. ąÆ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╝ čüą╗čāčćą░ąĄ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ čāą┐čĆą░ą▓ą╗čÅąĄčé ą▓čŗčģąŠą┤ąŠą╝ SDO ą┐čĆąĖ ąĮą░čćą░ą╗ąĄ ą▒ąĖčéą░ 8.

Bit 1: MS bit (Multiple Send). ąÜąŠą│ą┤ą░ 0, č鹊 ą░ą┤čĆąĄčü ąŠčüčéą░ąĄčéčüčÅ ąĮąĄąĖąĘą╝ąĄąĮąĮčŗą╝ ą┐čĆąĖ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ą║ąŠą╝ą░ąĮą┤ą░čģ čćč鹥ąĮąĖčÅ/ąĘą░ą┐ąĖčüąĖ. ąÜąŠą│ą┤ą░ 1, č鹊 ą░ą┤čĆąĄčü ą▒čāą┤ąĄčé ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆąŠą▓ą░čéčīčüčÅ ą┐čĆąĖ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ą║ąŠą╝ą░ąĮą┤ą░čģ čćč鹥ąĮąĖčÅ/ąĘą░ą┐ąĖčüąĖ.

Bit 2-7: ą░ą┤čĆąĄčü AD(5:0). ąŁč鹊 ą┐ąŠą╗ąĄ ą░ą┤čĆąĄčüą░ ąĖąĮą┤ąĄą║čüąĖčĆčāąĄą╝ąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░.

Bit 8-15: ą┤ą░ąĮąĮčŗąĄ DI(7:0) (čĆąĄąČąĖą╝ ąĘą░ą┐ąĖčüąĖ). ąŁč鹊 ą┤ą░ąĮąĮčŗąĄ, ą║ąŠč鹊čĆčŗąĄ ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ ą▓ čāčüčéčĆąŠą╣čüčéą▓ąŠ (MSB ąĖą┤ąĄčé ą┐ąĄčĆą▓čŗą╝).

Bit 8-15: ą┤ą░ąĮąĮčŗąĄ DO(7:0) (čĆąĄąČąĖą╝ čćč鹥ąĮąĖčÅ). ąŁč鹊 ą┤ą░ąĮąĮčŗąĄ, ą║ąŠč鹊čĆčŗąĄ čćąĖčéą░čÄčéčüčÅ ąĖąĘ čāčüčéčĆąŠą╣čüčéą▓ą░ (MSB ąĖą┤ąĄčé ą┐ąĄčĆą▓čŗą╝).

ą¤čĆąĖ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ą║ąŠą╝ą░ąĮą┤ą░čģ čćč鹥ąĮąĖčÅ/ąĘą░ą┐ąĖčüąĖ, ą┤ąŠą▒ą░ą▓ą╗čÅčÄčéčüčÅ ą┐ąŠčüą╗ąĄą┤čāčÄčēąĖąĄ ą▒ą╗ąŠą║ąĖ ą┐ąŠ 8 ą┐ąĄčĆąĖąŠą┤ąŠą▓ čéą░ą║č鹊ą▓. ąÜąŠą│ą┤ą░ MS bit čĆą░ą▓ąĄąĮ 0, č鹊 ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╣ ą░ą┤čĆąĄčü ąŠčüčéą░ąĄčéčüčÅ č鹊čé ąČąĄ čüą░ą╝čŗą╣ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą▒ą╗ąŠą║ą░. ąÜąŠą│ą┤ą░ MS bit čĆą░ą▓ąĄąĮ 1, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╣ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ/ąĘą░ą┐ąĖčüąĖ ą░ą┤čĆąĄčü ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ čü ą║ą░ąČą┤čŗą╝ ąĮąŠą▓čŗą╝ ą▒ą╗ąŠą║ąŠą╝.

ążčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĄ ąĖ ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ čüąĖą│ąĮą░ą╗ąŠą▓ SDI ąĖ SDO ąŠčüčéą░čÄčéčüčÅ ąĮąĄąĖąĘą╝ąĄąĮąĮčŗą╝ąĖ.

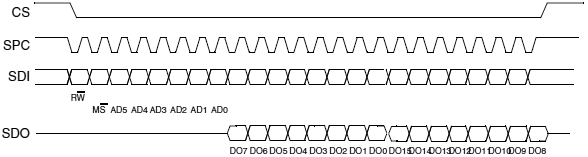

5.2.1. SPI read (čćč鹥ąĮąĖąĄ)

ąĀąĖčü. 14. ą¤čĆąŠč鹊ą║ąŠą╗ čćč鹥ąĮąĖčÅ SPI

ąÜąŠą╝ą░ąĮą┤ą░ SPI read ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮą░ ąĘą░ 16 čéą░ą║č鹊ą▓čŗčģ ąĖą╝ą┐čāą╗čīčüąŠą▓. ąÜąŠą╝ą░ąĮą┤ą░ čćč鹥ąĮąĖčÅ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ą▒ą░ą╣čé ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą┐čāč鹥ą╝ ą┤ąŠą▒ą░ą▓ą╗ąĄąĮąĖčÅ ą▒ą╗ąŠą║ąŠą▓ ą┐ąŠ 8 čéą░ą║č鹊ą▓čŗčģ ąĖą╝ą┐čāą╗čīčüąŠą▓ ą║ ą┐čĆąĄą┤čŗą┤čāčēąĖą╝ ą▒ą╗ąŠą║ą░ą╝.

Bit 0: READ bit, čĆą░ą▓ąĮčŗą╣ 1.

Bit 1: MS bit. ąÜąŠą│ą┤ą░ 0, č鹊 ą░ą┤čĆąĄčü ąĮąĄ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ; ą║ąŠą│ą┤ą░ 1, č鹊 ą┐čĆąĖ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ čćč鹥ąĮąĖčÅčģ ą░ą┤čĆąĄčü ą▒čāą┤ąĄčé ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆąŠą▓ą░čéčīčüčÅ.

Bit 2-7: ą░ą┤čĆąĄčü AD(5:0). ąŁč鹊 ą┐ąŠą╗ąĄ ą░ą┤čĆąĄčüą░ ąĖąĮą┤ąĄą║čüąĖčĆčāąĄą╝ąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░.

Bit 8-15: ą┤ą░ąĮąĮčŗąĄ DO(7:0) (čĆąĄąČąĖą╝ čćč鹥ąĮąĖčÅ). ąŁč鹊 ą┤ą░ąĮąĮčŗąĄ, ą║ąŠč鹊čĆčŗąĄ čćąĖčéą░čÄčéčüčÅ ąĖąĘ čāčüčéčĆąŠą╣čüčéą▓ą░ (MSB ąĖą┤ąĄčé ą┐ąĄčĆą▓čŗą╝).

Bit 16-... : ą┤ą░ąĮąĮčŗąĄ DO(...-8). ą¤ąŠčüą╗ąĄą┤čāčÄčēąĖąĄ ą▒ą░ą╣čéčŗ ą┤ą░ąĮąĮčŗčģ ą┐čĆąĖ čćč鹥ąĮąĖąĖ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ą▒ą░ą╣čé.

ąĀąĖčü. 15. ą¤čĆąŠč鹊ą║ąŠą╗ čćč鹥ąĮąĖčÅ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ą▒ą░ą╣čé SPI (ą┐čĆąĖą╝ąĄčĆ ą┤ą╗čÅ 2 ą▒ą░ą╣čé)

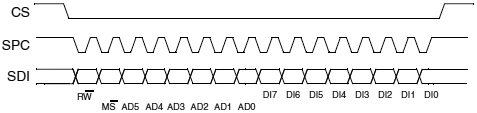

5.2.2. SPI write (ąĘą░ą┐ąĖčüčī)

ąĀąĖčü. 16. ą¤čĆąŠč鹊ą║ąŠą╗ ąĘą░ą┐ąĖčüąĖ SPI

ąÜąŠą╝ą░ąĮą┤ą░ SPI write ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮą░ ąĘą░ 16 čéą░ą║č鹊ą▓čŗčģ ąĖą╝ą┐čāą╗čīčüąŠą▓. ąÜąŠą╝ą░ąĮą┤ą░ ąĘą░ą┐ąĖčüąĖ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ą▒ą░ą╣čé ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą┐čāč鹥ą╝ ą┤ąŠą▒ą░ą▓ą╗ąĄąĮąĖčÅ ą▒ą╗ąŠą║ąŠą▓ ą┐ąŠ 8 čéą░ą║č鹊ą▓čŗčģ ąĖą╝ą┐čāą╗čīčüąŠą▓ ą║ ą┐čĆąĄą┤čŗą┤čāčēąĖą╝ ą▒ą╗ąŠą║ą░ą╝.

Bit 0: WRITE bit, čĆą░ą▓ąĮčŗą╣ 0.

Bit 1: MS bit. ąÜąŠą│ą┤ą░ 0, č鹊 ą░ą┤čĆąĄčü ąĮąĄ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ; ą║ąŠą│ą┤ą░ 1, č鹊 ą┐čĆąĖ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ąĘą░ą┐ąĖčüčÅčģ ą░ą┤čĆąĄčü ą▒čāą┤ąĄčé ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆąŠą▓ą░čéčīčüčÅ.

Bit 2-7: ą░ą┤čĆąĄčü AD(5:0). This is the address field of the indexed register.

Bit 8-15: ą┤ą░ąĮąĮčŗąĄ DI(7:0) (čĆąĄąČąĖą╝ ąĘą░ą┐ąĖčüąĖ). ąŁč鹊 ą┤ą░ąĮąĮčŗąĄ, ą║ąŠč鹊čĆčŗąĄ ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ ą▓ čāčüčéčĆąŠą╣čüčéą▓ąŠ (MSB ąĖą┤ąĄčé ą┐ąĄčĆą▓čŗą╝).

Bit 16-... : ą┤ą░ąĮąĮčŗąĄ DI(...-8). ą¤ąŠčüą╗ąĄą┤čāčÄčēąĖąĄ ą┤ą░ąĮąĮčŗąĄ ą┐čĆąĖ ąĘą░ą┐ąĖčüąĖ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ą▒ą░ą╣čé.

ąĀąĖčü. 17. ą¤čĆąŠč鹊ą║ąŠą╗ ąĘą░ą┐ąĖčüąĖ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ą▒ą░ą╣čé SPI (ą┐čĆąĖą╝ąĄčĆ ą┤ą╗čÅ 2 ą▒ą░ą╣čé)

5.2.3. SPI read ą▓ 3-ą┐čĆąŠą▓ąŠą┤ąĮąŠą╝ čĆąĄąČąĖą╝ąĄ

ąÆ čéčĆąĄčģą┐čĆąŠą▓ąŠą┤ąĮčŗą╣ čĆąĄąČąĖą╝ (3-wire mode) ą╝ąŠąČąĮąŠ ą▓ąŠą╣čéąĖ, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ąĖčéčī ą▓ čĆąĄą│ąĖčüčéčĆąĄ CTRL_REG2 ą▒ąĖčé SIM (SPI serial interface mode selection, ą▓čŗą▒ąŠčĆ čĆąĄąČąĖą╝ą░ čĆą░ą▒ąŠčéčŗ ąĖąĮč鹥čĆč乥ą╣čüą░ SPI) ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ą╗ąŠą│. 1.

ąĀąĖčü. 18. ą¤čĆąŠč鹊ą║ąŠą╗ čćč鹥ąĮąĖčÅ SPI ą▓ 3-ą┐čĆąŠą▓ąŠą┤ąĮąŠą╝ čĆąĄąČąĖą╝ąĄ

ąÜąŠą╝ą░ąĮą┤ą░ SPI read ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮą░ ąĘą░ 16 čéą░ą║č鹊ą▓čŗčģ ąĖą╝ą┐čāą╗čīčüąŠą▓:

Bit 0: READ bit, čĆą░ą▓ąĮčŗą╣ 1.

Bit 1: MS bit. ąÜąŠą│ą┤ą░ 0, č鹊 ą░ą┤čĆąĄčü ąĮąĄ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ; ą║ąŠą│ą┤ą░ 1, č鹊 ą┐čĆąĖ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ čćč鹥ąĮąĖčÅčģ ą░ą┤čĆąĄčü ą▒čāą┤ąĄčé ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆąŠą▓ą░čéčīčüčÅ.

Bit 2-7: ą░ą┤čĆąĄčü AD(5:0). ąŁč鹊 ą┐ąŠą╗ąĄ ą░ą┤čĆąĄčüą░ ąĖąĮą┤ąĄą║čüąĖčĆčāąĄą╝ąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░.

Bit 8-15: ą┤ą░ąĮąĮčŗąĄ DO(7:0) (čĆąĄąČąĖą╝ čćč鹥ąĮąĖčÅ). ąŁč鹊 ą┤ą░ąĮąĮčŗąĄ, ą║ąŠč鹊čĆčŗąĄ čćąĖčéą░čÄčéčüčÅ ąĖąĘ čāčüčéčĆąŠą╣čüčéą▓ą░ (MSB ąĖą┤ąĄčé ą┐ąĄčĆą▓čŗą╝).

ąÆ 3-ą┐čĆąŠą▓ąŠą┤ąĮąŠą╝ čĆąĄąČąĖą╝ąĄ ą┤ąŠčüčéčāą┐ąĮą░ čéą░ą║ąČąĄ ą║ąŠą╝ą░ąĮą┤ą░ čćč鹥ąĮąĖčÅ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ą▒ą░ą╣čé (multiple read command).

[6. ąÜą░čĆčéą░ čĆąĄą│ąĖčüčéčĆąŠą▓ L3G4200D (Output register mapping)]

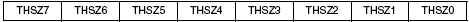

ąóą░ą▒ą╗ąĖčåą░ ąĮąĖąČąĄ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé čüą┐ąĖčüąŠą║ 8-ą▒ąĖčéąĮčŗčģ čĆąĄą│ąĖčüčéčĆąŠą▓, ą▓čüčéčĆąŠąĄąĮąĮčŗčģ ą▓ L3G4200D, ą▓ą╝ąĄčüč鹥 čü ąĖčģ ą░ą┤čĆąĄčüą░ą╝ąĖ.

ąóą░ą▒ą╗ąĖčåą░ 18. ąÜą░čĆčéą░ ą┐ą░ą╝čÅčéąĖ čĆąĄą│ąĖčüčéčĆąŠą▓

| ąśą╝čÅ |

ąóąĖą┐ |

ąÉą┤čĆąĄčü čĆąĄą│ąĖčüčéčĆą░ |

ąŚąĮą░č湥ąĮąĖąĄ

ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ |

| Hex |

Binary |

| ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

- |

00-0E |

- |

- |

| WHO_AM_I |

r |

0F |

0001111 |

11010011 |

| ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

- |

10-1F |

- |

- |

| CTRL_REG1 |

rw |

20 |

0100000 |

00000111 |

| CTRL_REG2 |

rw |

21 |

0100001 |

00000000 |

| CTRL_REG3 |

rw |

22 |

0100010 |

00000000 |

| CTRL_REG4 |

rw |

23 |

0100011 |

00000000 |

| CTRL_REG5 |

rw |

24 |

0100100 |

00000000 |

| REFERENCE |

rw |

25 |

0100101 |

00000000 |

| OUT_TEMP |

r |

26 |

0100110 |

output |

| STATUS_REG |

r |

27 |

0100111 |

output |

| OUT_X_L |

r |

28 |

0101000 |

output |

| OUT_X_H |

r |

29 |

0101001 |

output |

| OUT_Y_L |

r |

2A |

0101010 |

output |

| OUT_Y_H |

r |

2B |

0101011 |

output |

| OUT_Z_L |

r |

2C |

0101100 |

output |

| OUT_Z_H |

r |

2D |

0101101 |

output |

| FIFO_CTRL_REG |

rw |

2E |

0101110 |

00000000 |

| FIFO_SRC_REG |

r |

2F |

0101111 |

output |

| INT1_CFG |

rw |

30 |

0110000 |

00000000 |

| INT1_SRC |

r |

31 |

0110001 |

output |

| INT1_TSH_XH |

rw |

32 |

0110010 |

00000000 |

| INT1_TSH_XL |

rw |

33 |

0110011 |

00000000 |

| INT1_TSH_YH |

rw |

34 |

0110100 |

00000000 |

| INT1_TSH_YL |

rw |

35 |

0110101 |

00000000 |

| INT1_TSH_ZH |

rw |

36 |

0110110 |

00000000 |

| INT1_TSH_ZL |

rw |

37 |

0110111 |

00000000 |

| INT1_DURATION |

rw |

38 |

0111000 |

00000000 |

ąĀąĄą│ąĖčüčéčĆčŗ, ą┐ąŠą╝ąĄč湥ąĮąĮčŗąĄ ą║ą░ą║ ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ, ąĮąĄą╗čīąĘčÅ ąĖąĘą╝ąĄąĮčÅčéčī. ąŚą░ą┐ąĖčüčī ą▓ čŹčéąĖ čĆąĄą│ąĖčüčéčĆčŗ ą╝ąŠąČąĄčé ą┐čĆąĖą▓ąĄčüčéąĖ ą║ ąĮąĄąŠą▒čĆą░čéąĖą╝ąŠą╝čā ą┐ąŠą▓čĆąĄąČą┤ąĄąĮąĖčÄ čāčüčéčĆąŠą╣čüčéą▓ą░.

ąĪąŠą┤ąĄčƹȹĖą╝ąŠąĄ čĆąĄą│ąĖčüčéčĆąŠą▓, ą║ąŠč鹊čĆąŠąĄ ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ą┐čĆąĖ čüčéą░čĆč鹥 čüąĖčüč鹥ą╝čŗ, ąĮąĄ ą┤ąŠą╗ąČąĮąŠ ąĖąĘą╝ąĄąĮčÅčéčīčüčÅ. ą×ąĮąĖ čüąŠą┤ąĄčƹȹ░čéčī ąĘąĮą░č湥ąĮąĖčÅ, ąŠčéą║ą░ą╗ąĖą▒čĆąŠą▓ą░ąĮąĮčŗąĄ ąĮą░ ąĘą░ą▓ąŠą┤ąĄ. ąśčģ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ ą▒čāą┤ąĄčé ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ ą┐čĆąĖ ą┐ąŠą┤ą░č湥 ą┐ąĖčéą░ąĮąĖčÅ ąĮą░ čāčüčéčĆąŠą╣čüčéą▓ąŠ.

[7. ą×ą┐ąĖčüą░ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆąŠą▓]

ąŻčüčéčĆąŠą╣čüčéą▓ąŠ čüąŠą┤ąĄčƹȹĖčé ąĮą░ą▒ąŠčĆ čĆąĄą│ąĖčüčéčĆąŠą▓, ą║ąŠč鹊čĆčŗąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĄą│ąŠ ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄą╝ ąĖ ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ čāčüą║ąŠčĆąĄąĮąĖčÅ. ąÉą┤čĆąĄčüą░ čĆąĄą│ąĖčüčéčĆąŠą▓, čüąŠčüč鹊čÅčēąĖąĄ ąĖąĘ 7 ą▒ąĖč鹊ą▓, ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░čåąĖąĖ ąĖčģ ąĖ ąĘą░ą┐ąĖčüąĖ ą┤ą░ąĮąĮčŗčģ č湥čĆąĄąĘ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü.

7.1. WHO_AM_I (0Fh)

ąóą░ą▒ą╗ąĖčåą░ 19. ąĀąĄą│ąĖčüčéčĆ WHO_AM_I (ą║č鹊 čÅ)

ąŁč鹊 čĆąĄą│ąĖčüčéčĆ, ą║ąŠč鹊čĆčŗą╣ ąĖą┤ąĄąĮčéąĖčäąĖčåąĖčĆčāąĄčé čüą░ą╝ąŠ čāčüčéčĆąŠą╣čüčéą▓ąŠ L3G4200D.

7.2. CTRL_REG1 (20h)

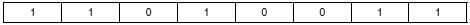

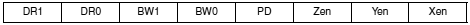

ąóą░ą▒ą╗ąĖčåą░ 20. ąĀąĄą│ąĖčüčéčĆ CTRL_REG1

ąóą░ą▒ą╗ąĖčåą░ 21. ą×ą┐ąĖčüą░ąĮąĖąĄ ą▒ąĖč鹊ą▓ čĆąĄą│ąĖčüčéčĆą░ CTRL_REG1

DR1-DR0 ąÆčŗą▒ąŠčĆ čüą║ąŠčĆąŠčüčéąĖ ą▓čŗčģąŠą┤ąĮąŠą╣ ąŠčåąĖčäčĆąŠą▓ą║ąĖ čüąĖą│ąĮą░ą╗ą░ (Output Data Rate, ODR). ąĪą╝. čéą░ą▒ą╗ąĖčåčā 22.

BW1-BW0 ąÆčŗą▒ąŠčĆ ą┐ąŠą╗ąŠčüčŗ ą┐čĆąŠą┐čāčüą║ą░ąĮąĖčÅ. ąĪą╝. čéą░ą▒ą╗ąĖčåčā 22.

PD ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ čĆąĄąČąĖą╝ą░ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ (Power Down). ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 0 (0: čĆąĄąČąĖą╝ power down, 1: ąĮąŠčĆą╝ą░ą╗čīąĮčŗą╣ čĆąĄąČąĖą╝ ąĖą╗ąĖ čĆąĄąČąĖą╝ čüąĮą░).

Zen ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ čĆą░ą▒ąŠčéčŗ ąŠčüąĖ Z. ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 1 (0: ąŠčüčī Z ąĘą░ą┐čĆąĄčēąĄąĮą░, 1: čĆą░ąĘčĆąĄčłąĄąĮą░).

Yen ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ čĆą░ą▒ąŠčéčŗ ąŠčüąĖ Y. ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 1 (0: ąŠčüčī Y ąĘą░ą┐čĆąĄčēąĄąĮą░, 1: čĆą░ąĘčĆąĄčłąĄąĮą░).

Xen ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ čĆą░ą▒ąŠčéčŗ ąŠčüąĖ X. ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 1 (0: ąŠčüčī X ąĘą░ą┐čĆąĄčēąĄąĮą░, 1: čĆą░ąĘčĆąĄčłąĄąĮą░).

DR < 1:0 > ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▓čŗą▒ąŠčĆą░ ODR (čüą║ąŠčĆąŠčüčéčī ą▓čŗčģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ). BW < 1:0 > ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą░ ą┐ąŠą╗ąŠčüčŗ ą┐čĆąŠą┐čāčüą║ą░ąĮąĖčÅ (Cut-Off, čćą░čüč鹊čéą░ čüčĆąĄąĘą░ čåąĖčäčĆąŠą▓ąŠą│ąŠ čäąĖą╗čīčéčĆą░). ąÆ čüą╗ąĄą┤čāčÄčēąĄą╣ čéą░ą▒ą╗ąĖčåąĄ ą┐ąŠą║ą░ąĘą░ąĮčŗ ą▓čüąĄ čĆąĄąĘčāą╗čīčéąĖčĆčāčÄčēąĖąĄ čćą░čüč鹊čéčŗ ą▓ ą║ąŠą╝ą▒ąĖąĮą░čåąĖąĖ ą▒ąĖč鹊ą▓ DR ąĖ BW.

ąóą░ą▒ą╗ąĖčåą░ 22. ąÜąŠąĮčäąĖą│čāčĆą░čåąĖąŠąĮąĮčŗąĄ čāčüčéą░ąĮąŠą▓ą║ąĖ DR ąĖ BW

| DR1DR0 |

BW1BW0 |

ODR (ąōčå) |

Cut-Off |

| 00 |

00 |

100 |

12.5 |

| 01 |

25 |

| 10 |

| 11 |

| 01 |

00 |

200 |

12.5 |

| 01 |

25 |

| 10 |

50 |

| 11 |

70 |

| 10 |

00 |

400 |

20 |

| 01 |

25 |

| 10 |

50 |

| 11 |

110 |

| 11 |

00 |

800 |

30 |

| 01 |

35 |

| 10 |

50 |

| 11 |

110 |

ąÜąŠą╝ą▒ąĖąĮą░čåąĖąĖ PD, Zen, Yen, Xen ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ ą▓ čĆą░ąĘąĮčŗąĄ čĆąĄąČąĖą╝čŗ (power down, ą▓čŗą║ą╗čÄč湥ąĮąĖąĄ / normal, čĆą░ą▒ąŠčćąĖą╣ čĆąĄąČąĖą╝ / sleep mode, čĆąĄąČąĖą╝ čüąĮą░) ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čüąŠ čüą╗ąĄą┤čāčÄčēąĄą╣ čéą░ą▒ą╗ąĖčåąĄą╣.

ąóą░ą▒ą╗ąĖčåą░ 23. ąÆčŗą▒ąŠčĆ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ čĆąĄąČąĖą╝ą░ ą┐ąĖčéą░ąĮąĖčÅ

| ąĀąĄąČąĖą╝ |

PD |

Zen |

Yen |

Xen |

| Power down (ą┐ąĖčéą░ąĮąĖąĄ ą▓čŗą║ą╗čÄč湥ąĮąŠ) |

0 |

- |

- |

- |

| Sleep (čĆąĄąČąĖą╝ čüąĮą░) |

1 |

0 |

0 |

0 |

| ąØąŠčĆą╝ą░ą╗čīąĮčŗą╣ čĆą░ą▒ąŠčćąĖą╣ čĆąĄąČąĖą╝ |

1 |

- |

- |

- |

7.3. CTRL_REG2 (21h)

ąóą░ą▒ą╗ąĖčåą░ 24. ąĀąĄą│ąĖčüčéčĆ CTRL_REG2

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ 1: ąĘąĮą░č湥ąĮąĖąĄ ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ą┐čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ, ąĖ ą┤ą░ą╗ąĄąĄ ąĮąĄ ą┤ąŠą╗ąČąĮąŠ ąĖąĘą╝ąĄąĮčÅčéčīčüčÅ.

ąóą░ą▒ą╗ąĖčåą░ 25. ą×ą┐ąĖčüą░ąĮąĖąĄ ą▒ąĖč鹊ą▓ čĆąĄą│ąĖčüčéčĆą░ CTRL_REG2

HPM1-HPM0 ąÆčŗą▒ąŠčĆ čĆąĄąČąĖą╝ą░ čĆą░ą▒ąŠčéčŗ ążąÆą¦. ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 00, čüą╝. čéą░ą║ąČąĄ čéą░ą▒ą╗ąĖčåčā 26.

HPCF3-HPCF0 ąÆčŗą▒ąŠčĆ čćą░čüč鹊čéčŗ čüčĆąĄąĘą░ ążąÆą¦, čüą╝. čéą░ą▒ą╗ąĖčåčā 27.

ąóą░ą▒ą╗ąĖčåą░ 26. ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ čĆąĄąČąĖą╝ą░ ążąÆą¦

| HPM1 |

HPM0 |

ąĀąĄąČąĖą╝ ążąÆą¦ |

| 0 |

0 |

ąØąŠčĆą╝ą░ą╗čīąĮčŗą╣ čĆąĄąČąĖą╝ (čüą▒čĆąŠčü čćč鹥ąĮąĖąĄą╝ HP_RESET_FILTER) |

| 0 |

1 |

ąöą╗čÅ čäąĖą╗čīčéčĆą░čåąĖąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ąŠą▒čĆą░ąĘčåąŠą▓čŗą╣ čüąĖą│ąĮą░ą╗ (reference signal) |

| 1 |

0 |

ąØąŠčĆą╝ą░ą╗čīąĮčŗą╣ čĆąĄąČąĖą╝ |

| 1 |

1 |

ąÉą▓č鹊čüą▒čĆąŠčü ą┐ąŠ čüąŠą▒čŗčéąĖčÄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ |

ąóą░ą▒ą╗ąĖčåą░ 27. ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ čćą░čüč鹊čéčŗ čüčĆąĄąĘą░ ążąÆą¦ (ąōčå)

| HPCF3..0 |

ODR = 100 ąōčå |

ODR = 200 ąōčå |

ODR = 400 ąōčå |

ODR = 800 ąōčå |

| 0000 |

8 |

15 |

30 |

56 |

| 0001 |

4 |

8 |

15 |

30 |

| 0010 |

2 |

4 |

8 |

15 |

| 0011 |

1 |

2 |

4 |

8 |

| 0100 |

0.5 |

1 |

2 |

4 |

| 0101 |

0.2 |

0.5 |

1 |

2 |

| 0110 |

0.1 |

0.2 |

0.5 |

1 |

| 0111 |

0.05 |

0.1 |

0.2 |

0.5 |

| 1000 |

0.02 |

0.05 |

0.1 |

0.2 |

| 1001 |

0.01 |

0.02 |

0.05 |

0.1 |

7.4. CTRL_REG3 (22h)

ąóą░ą▒ą╗ąĖčåą░ 28. ąĀąĄą│ąĖčüčéčĆ CTRL_REG3

ąóą░ą▒ą╗ąĖčåą░ 29. ą×ą┐ąĖčüą░ąĮąĖąĄ ą▒ąĖč鹊ą▓ čĆąĄą│ąĖčüčéčĆą░ CTRL_REG3

I1_Int1 ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ INT1. ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 0 (0: ąĘą░ą┐čĆąĄčēąĄąĮąŠ; 1: čĆą░ąĘčĆąĄčłąĄąĮąŠ).

I1_Boot ąĪčéą░čéčāčü ąĘą░ą│čĆčāąĘą║ąĖ ą┤ąŠčüčéčāą┐ąĄąĮ ąĮą░ INT1. ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 0 (0: ąĘą░ą┐čĆąĄčēąĄąĮąŠ; 1: čĆą░ąĘčĆąĄčłąĄąĮąŠ).

H_Lactive ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą░ą║čéąĖą▓ąĮąŠą│ąŠ čüąŠčüč鹊čÅąĮąĖčÅ INT1. ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 0 (0: ą╗ąŠą│. 1; 1: ą╗ąŠą│. 0).

PP_OD ąÆčŗą▒ąŠčĆ čĆąĄąČąĖą╝ą░ čĆą░ą▒ąŠčéčŗ ą▓čŗčģąŠą┤ą░ Push-Pull (ą┤ą▓čāčģčéą░ą║čéąĮčŗą╣ ą║ą╗čÄčć) / Open drain (ąŠčéą║čĆčŗčéčŗą╣ čüč鹊ą║). ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 0 (0: Push-Pull; 1: Open drain).

I2_DRDY ąÆčŗą▓ąŠą┤ čüąŠčüč鹊čÅąĮąĖčÅ Data Ready ąĮą░ DRDY/INT2. ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 0 (0: ąĘą░ą┐čĆąĄčēąĄąĮąŠ; 1: čĆą░ąĘčĆąĄčłąĄąĮąŠ).

I2_WTM ąÆčŗą▓ąŠą┤ čüąŠą▒čŗčéąĖčÅ FIFO Watermark interrupt (ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĖčÄ ąĘą░ą┤ą░ąĮąĮąŠą│ąŠ čāčĆąŠą▓ąĮčÅ FIFO) ąĮą░ DRDY/INT2. ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 0 (0: ąĘą░ą┐čĆąĄčēąĄąĮąŠ; 1: čĆą░ąĘčĆąĄčłąĄąĮąŠ).

I2_ORun ąÆčŗą▓ąŠą┤ čüąŠą▒čŗčéąĖčÅ FIFO Overrun interrupt (ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐čĆąĖ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĖ ą▒čāč乥čĆą░ FIFO) ąĮą░ DRDY/INT2. ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 0 (0: ąĘą░ą┐čĆąĄčēąĄąĮąŠ; 1: čĆą░ąĘčĆąĄčłąĄąĮąŠ).

I2_Empty ąÆčŗą▓ąŠą┤ čüąŠą▒čŗčéąĖčÅ FIFO Empty interrupt (ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ą║ąŠą│ą┤ą░ FIFO ąŠą┐čāčüč鹥ą╗) ąĮą░ DRDY/INT2. ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 0 (0: ąĘą░ą┐čĆąĄčēąĄąĮąŠ; 1: čĆą░ąĘčĆąĄčłąĄąĮąŠ).

7.5. CTRL_REG4 (23h)

ąóą░ą▒ą╗ąĖčåą░ 30. ąĀąĄą│ąĖčüčéčĆ CTRL_REG4

ąóą░ą▒ą╗ąĖčåą░ 31. ą×ą┐ąĖčüą░ąĮąĖąĄ ą▒ąĖč鹊ą▓ čĆąĄą│ąĖčüčéčĆą░ CTRL_REG4

BDU Block Data Update (ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ ą▒ą╗ąŠą║ą░ ą┤ą░ąĮąĮčŗčģ). ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 0 (0: ąĮąĄą┐čĆąĄčĆčŗą▓ąĮąŠąĄ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ; 1: ą▓čŗčģąŠą┤ąĮčŗąĄ čĆąĄą│ąĖčüčéčĆčŗ ąĮąĄ ą▒čāą┤čāčé ąŠą▒ąĮąŠą▓ą╗ąĄąĮčŗ, ą┐ąŠą║ą░ ąĮąĄ ą▒čāą┤čāčé ą┐čĆąŠčćąĖčéą░ąĮčŗ čüčéą░čĆčłąĖą╣ ąĖ ą╝ą╗ą░ą┤čłąĖą╣ ą▒ą░ą╣čéčŗ).

BLE ąÆčŗą▒ąŠčĆ č乊čĆą╝ą░čéą░ ą┤ą░ąĮąĮčŗčģ Big/Little Endian. ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 0 (0: ą┤ą░ąĮąĮčŗąĄ ą╝ą╗ą░ą┤čłąĖą╣ ą▒ą░ą╣čé ą┐ąŠ ą╝ąĄąĮčīčłąĄą╝čā ą░ą┤čĆąĄčüčā; 1: ą┤ą░ąĮąĮčŗąĄ čüčéą░čĆčłąĖą╣ ą▒ą░ą╣čé ą┐ąŠ ą╝ąĄąĮčīčłąĄą╝čā ą░ą┤čĆąĄčüčā).

FS1-FS0 ąÆčŗą▒ąŠčĆ ą┐ąŠą╗ąĮąŠą╣ čłą║ą░ą╗čŗ. ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 00 (00: 250 dps; 01: 500 dps; 10: 2000 dps; 11: 2000 dps).

ST1-ST0 ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ čĆąĄąČąĖą╝ą░ čüą░ą╝ąŠč鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ. ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 00 (00: čüą░ą╝ąŠč鹥čüčéąĖčĆąŠą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ, ą┤čĆčāą│ąĖąĄ ąĘąĮą░č湥ąĮąĖčÅ čüą╝. ą▓ čéą░ą▒ą╗ąĖčåąĄ 32).

SIM ąÆčŗą▒ąŠčĆ čĆąĄąČąĖą╝ą░ čĆą░ą▒ąŠčéčŗ SPI. ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 0 (0: 4-ą┐čĆąŠą▓ąŠą┤ąĮčŗą╣ čĆąĄąČąĖą╝, 1: 3-ą┐čĆąŠą▓ąŠą┤ąĮčŗą╣ čĆąĄąČąĖą╝).

ąóą░ą▒ą╗ąĖčåą░ 32. ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ čĆąĄąČąĖą╝ą░ čüą░ą╝ąŠč鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ

| ST1 |

ST0 |

ąĀąĄąČąĖą╝ čüą░ą╝ąŠč鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ |

| 0 |

0 |

ąØąŠčĆą╝ą░ą╗čīąĮčŗą╣ čĆąĄąČąĖą╝ čĆą░ą▒ąŠčéčŗ (čüą░ą╝ąŠč鹥čüčéąĖčĆąŠą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ) |

| 0 |

1 |

ąĪą░ą╝ąŠč鹥čüčéąĖčĆąŠą▓ą░ąĮąĖąĄ 0 (+)(1) |

| 1 |

0 |

-- |

| 1 |

1 |

ąĪą░ą╝ąŠč鹥čüčéąĖčĆąŠą▓ą░ąĮąĖąĄ 1 (-)(1) |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ 1: ąĘąĮą░ą║ DST (ą░ą▒čüąŠą╗čÄčéąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą▓ čéą░ą▒ą╗ąĖčåąĄ 4).

7.6. CTRL_REG5 (24h)

ąóą░ą▒ą╗ąĖčåą░ 33. ąĀąĄą│ąĖčüčéčĆ CTRL_REG5

ąóą░ą▒ą╗ąĖčåą░ 34. ą×ą┐ąĖčüą░ąĮąĖąĄ ą▒ąĖč鹊ą▓ čĆąĄą│ąĖčüčéčĆą░ CTRL_REG5

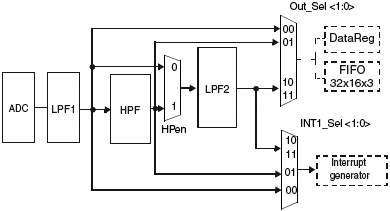

BOOT ą¤ąĄčĆąĄąĘą░ą│čĆčāąĘąĖčéčī čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ ą┐ą░ą╝čÅčéąĖ. ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 0 (0: ąĮąŠčĆą╝ą░ą╗čīąĮčŗą╣ čĆąĄąČąĖą╝, 1: ą┐ąĄčĆąĄąĘą░ą│čĆčāąĘąĖčéčī ą┐ą░ą╝čÅčéčī).

FIFO_EN ąĀą░ąĘčĆąĄčłąĖčéčī FIFO. ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 0 (0: FIFO ąĘą░ą┐čĆąĄčēąĄąĮ, 1: FIFO čĆą░ąĘčĆąĄčłąĄąĮ).

HPen ąĀą░ąĘčĆąĄčłąĖčéčī ążąÆą¦. (0: HPF ąĘą░ą┐čĆąĄčēąĄąĮ, 1: HPF čĆą░ąĘčĆąĄčłąĄąĮ).

INT1_Sel1-INT1_Sel0 ąÆčŗą▒ąŠčĆ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ INT1. ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 0 (čüą╝. čĆąĖčü. 19).

Out_Sel1-Out_Sel0 ąÆčŗą▒ąŠčĆ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą▓čŗčģąŠą┤ą░. ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 0 (čüą╝. čĆąĖčü. 19).

ąĀąĖčü. 19. ąæą╗ąŠą║-čüčģąĄą╝ą░ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ INT1_Sel ąĖ Out_Sel

ąóą░ą▒ą╗ąĖčåą░ 35. ąŻčüčéą░ąĮąŠą▓ą║ą░ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ Out_Sel

| Hpen |

OUT_SEL1 |

OUT_SEL0 |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| x |

0 |

0 |

ąöą░ąĮąĮčŗąĄ ą▓ DataReg ąĖ FIFO ąĮąĄ ą┐čĆąŠčģąŠą┤čÅčé č湥čĆąĄąĘ ążąÆą¦ (ąĮąĄ čäąĖą╗čīčéčĆčāčÄčéčüčÅ).

|

| x |

0 |

1 |

ąöą░ąĮąĮčŗąĄ ą▓ DataReg ąĖ FIFO čäąĖą╗čīčéčĆčāčÄčéčüčÅ č湥čĆąĄąĘ ążąÆą¦. |

| 0 |

1 |

x |

ąöą░ąĮąĮčŗąĄ ą▓ DataReg ąĖ FIFO čäąĖą╗čīčéčĆčāčÄčéčüčÅ ążąØą¦ LPF2.

|

| 1 |

1 |

x |

ąöą░ąĮąĮčŗąĄ ą▓ DataReg ąĖ FIFO čäąĖą╗čīčéčĆčāčÄčéčüčÅ ążąÆą¦ ąĖ ążąØą¦ LPF2. |

ąóą░ą▒ą╗ąĖčåą░ 36. ąŻčüčéą░ąĮąŠą▓ą║ą░ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ INT_SEL

| Hpen |

INT_SEL1 |

INT_SEL0 |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| x |

0 |

0 |

ąöą╗čÅ ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ąĮąĄčäąĖą╗čīčéčĆąŠą▓ą░ąĮąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ.

|

| x |

0 |

1 |

ąöą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą░ąĮąĮčŗąĄ, ą┐čĆąŠčłąĄą┤čłąĖąĄ č湥čĆąĄąĘ ążąÆą¦. |

| 0 |

1 |

x |

ąöą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą░ąĮąĮčŗąĄ, ą┐čĆąŠčłąĄą┤čłąĖąĄ č湥čĆąĄąĘ ążąØą¦.

|

| 1 |

1 |

x |

ąöą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą░ąĮąĮčŗąĄ, ą┐čĆąŠčłąĄą┤čłąĖąĄ č湥čĆąĄąĘ ążąÆą¦ ąĖ ążąØą¦. |

7.7. REFERENCE/DATACAPTURE (25h)

ąóą░ą▒ą╗ąĖčåą░ 37. ąĀąĄą│ąĖčüčéčĆ REFERENCE

ąóą░ą▒ą╗ąĖčåą░ 38. ą×ą┐ąĖčüą░ąĮąĖąĄ ą▒ąĖč鹊ą▓ čĆąĄą│ąĖčüčéčĆą░ REFERENCE

Ref7-Ref0 ą×ą▒čĆą░ąĘčåąŠą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┤ą╗čÅ ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 0.

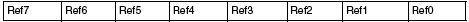

7.8. OUT_TEMP (26h)

ąóą░ą▒ą╗ąĖčåą░ 39. ąĀąĄą│ąĖčüčéčĆ OUT_TEMP

ąóą░ą▒ą╗ąĖčåą░ 40. ą×ą┐ąĖčüą░ąĮąĖąĄ ą▒ąĖč鹊ą▓ čĆąĄą│ąĖčüčéčĆą░ OUT_TEMP

Temp7-Temp0 ąöą░ąĮąĮčŗąĄ č鹥ą╝ą┐ąĄčĆą░čéčāčĆčŗ.

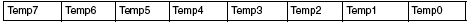

7.9. STATUS_REG (27h)

ąóą░ą▒ą╗ąĖčåą░ 41. ąĀąĄą│ąĖčüčéčĆ STATUS_REG

ąóą░ą▒ą╗ąĖčåą░ 42. ą×ą┐ąĖčüą░ąĮąĖąĄ ą▒ąĖč鹊ą▓ čĆąĄą│ąĖčüčéčĆą░ STATUS_REG

ZYXOR ą¤ąŠč鹥čĆčÅ (ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĄ) ą┤ą░ąĮąĮčŗčģ (data overrun) ą┐ąŠ ąŠčüčÅą╝ X, Y, Z. ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 0 (0: ąĮąĄ ą▒čŗą╗ąŠ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ, 1: ąĮąŠą▓čŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┐ąĄčĆąĄąĘą░ą┐ąĖčüą░ą╗ąĖ čüčéą░čĆčŗąĄ, ą┐čĆąĖč湥ą╝ čüčéą░čĆčŗąĄ ą┤ą░ąĮąĮčŗąĄ ąĄčēąĄ ąĮąĄ ą▒čŗą╗ąĖ čüčćąĖčéą░ąĮčŗ).

ZOR ą¤ąŠč鹥čĆčÅ (ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĄ) ą┤ą░ąĮąĮčŗčģ (data overrun) ą┐ąŠ ąŠčüąĖ Z. ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 0 (0: ąĮąĄ ą▒čŗą╗ąŠ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ, 1: ąĮąŠą▓čŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┐ąĄčĆąĄąĘą░ą┐ąĖčüą░ą╗ąĖ čüčéą░čĆčŗąĄ, ą┐čĆąĖč湥ą╝ čüčéą░čĆčŗąĄ ą┤ą░ąĮąĮčŗąĄ ąĄčēąĄ ąĮąĄ ą▒čŗą╗ąĖ čüčćąĖčéą░ąĮčŗ).

YOR ą¤ąŠč鹥čĆčÅ (ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĄ) ą┤ą░ąĮąĮčŗčģ (data overrun) ą┐ąŠ ąŠčüąĖ Y. ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 0 (0: ąĮąĄ ą▒čŗą╗ąŠ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ, 1: ąĮąŠą▓čŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┐ąĄčĆąĄąĘą░ą┐ąĖčüą░ą╗ąĖ čüčéą░čĆčŗąĄ, ą┐čĆąĖč湥ą╝ čüčéą░čĆčŗąĄ ą┤ą░ąĮąĮčŗąĄ ąĄčēąĄ ąĮąĄ ą▒čŗą╗ąĖ čüčćąĖčéą░ąĮčŗ).

XOR ą¤ąŠč鹥čĆčÅ (ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĄ) ą┤ą░ąĮąĮčŗčģ (data overrun) ą┐ąŠ ąŠčüąĖ X. ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 0 (0: ąĮąĄ ą▒čŗą╗ąŠ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ, 1: ąĮąŠą▓čŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┐ąĄčĆąĄąĘą░ą┐ąĖčüą░ą╗ąĖ čüčéą░čĆčŗąĄ, ą┐čĆąĖč湥ą╝ čüčéą░čĆčŗąĄ ą┤ą░ąĮąĮčŗąĄ ąĄčēąĄ ąĮąĄ ą▒čŗą╗ąĖ čüčćąĖčéą░ąĮčŗ).

ZYXDA ąöąŠčüčéčāą┐ąĮčŗ ąĮąŠą▓čŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┐ąŠ ąŠčüčÅą╝ X, Y, Z. ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 0 (0: ąĮąŠą▓čŗčģ ą┤ą░ąĮąĮčŗčģ ą┐ąŠą║ą░ ąĮąĄčé, 1: ą┤ąŠčüčéčāą┐ąĮčŗ ąĮąŠą▓čŗąĄ ą┤ą░ąĮąĮčŗąĄ).

ZDA ąöąŠčüčéčāą┐ąĮčŗ ąĮąŠą▓čŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┐ąŠ ąŠčüąĖ Z. ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 0 (0: ąĮąŠą▓čŗčģ ą┤ą░ąĮąĮčŗčģ ą┐ąŠą║ą░ ąĮąĄčé, 1: ą┤ąŠčüčéčāą┐ąĮčŗ ąĮąŠą▓čŗąĄ ą┤ą░ąĮąĮčŗąĄ).

YDA ąöąŠčüčéčāą┐ąĮčŗ ąĮąŠą▓čŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┐ąŠ ąŠčüąĖ Y. ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 0 (0: ąĮąŠą▓čŗčģ ą┤ą░ąĮąĮčŗčģ ą┐ąŠą║ą░ ąĮąĄčé, 1: ą┤ąŠčüčéčāą┐ąĮčŗ ąĮąŠą▓čŗąĄ ą┤ą░ąĮąĮčŗąĄ).

XDA ąöąŠčüčéčāą┐ąĮčŗ ąĮąŠą▓čŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┐ąŠ ąŠčüąĖ X. ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 0 (0: ąĮąŠą▓čŗčģ ą┤ą░ąĮąĮčŗčģ ą┐ąŠą║ą░ ąĮąĄčé, 1: ą┤ąŠčüčéčāą┐ąĮčŗ ąĮąŠą▓čŗąĄ ą┤ą░ąĮąĮčŗąĄ).

7.10. OUT_X_L (28h), OUT_X_H (29h)

ąŻą│ą╗ąŠą▓čŗąĄ ą┤ą░ąĮąĮčŗąĄ čāčüą║ąŠčĆąĄąĮąĖčÅ ą┐ąŠ ąŠčüąĖ X. ąŚąĮą░č湥ąĮąĖąĄ ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮąŠ ą║ą░ą║ čćąĖčüą╗ąŠ čüąŠ ąĘąĮą░ą║ąŠą╝ ą▓ č乊čĆą╝ą░č鹥 ą┤ąŠą┐ąŠą╗ąĮąĄąĮąĖčÅ ą┤ąŠ 2.

7.11. OUT_Y_L (2Ah), OUT_Y_H (2Bh)

ąŻą│ą╗ąŠą▓čŗąĄ ą┤ą░ąĮąĮčŗąĄ čāčüą║ąŠčĆąĄąĮąĖčÅ ą┐ąŠ ąŠčüąĖ Y. ąŚąĮą░č湥ąĮąĖąĄ ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮąŠ ą║ą░ą║ čćąĖčüą╗ąŠ čüąŠ ąĘąĮą░ą║ąŠą╝ ą▓ č乊čĆą╝ą░č鹥 ą┤ąŠą┐ąŠą╗ąĮąĄąĮąĖčÅ ą┤ąŠ 2.

7.12. OUT_Z_L (2Ch), OUT_Z_H (2Dh)

ąŻą│ą╗ąŠą▓čŗąĄ ą┤ą░ąĮąĮčŗąĄ čāčüą║ąŠčĆąĄąĮąĖčÅ ą┐ąŠ ąŠčüąĖ Z. ąŚąĮą░č湥ąĮąĖąĄ ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮąŠ ą║ą░ą║ čćąĖčüą╗ąŠ čüąŠ ąĘąĮą░ą║ąŠą╝ ą▓ č乊čĆą╝ą░č鹥 ą┤ąŠą┐ąŠą╗ąĮąĄąĮąĖčÅ ą┤ąŠ 2.

7.13. FIFO_CTRL_REG (2Eh)

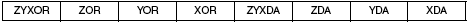

ąóą░ą▒ą╗ąĖčåą░ 43. ąĀąĄą│ąĖčüčéčĆ FIFO_CTRL_REG

ąóą░ą▒ą╗ąĖčåą░ 44. ą×ą┐ąĖčüą░ąĮąĖąĄ ą▒ąĖč鹊ą▓ čĆąĄą│ąĖčüčéčĆą░ FIFO_CTRL_REG

FM2-FM0 ąÆčŗą▒ąŠčĆ čĆąĄąČąĖą╝ą░ čĆą░ą▒ąŠčéčŗ FIFO. ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 00 (čüą╝. čéą░ą▒ą╗ąĖčåčā 45).

WTM4-WTM0 ą¤ąŠčĆąŠą│ čāčĆąŠą▓ąĮčÅ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĖčÅ FIFO (watermark).

ąóą░ą▒ą╗ąĖčåą░ 45. ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ čĆąĄąČąĖą╝ą░ FIFO

| FM2 |

FM1 |

FM0 |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| 0 |

0 |

0 |

ąĀąĄąČąĖą╝ bypass (ą▒ąĄąĘ FIFO).

|

| 0 |

0 |

1 |

ąĀąĄąČąĖą╝ FIFO. |

| 0 |

1 |

0 |

ą¤ąŠč鹊ą║ąŠą▓čŗą╣ čĆąĄąČąĖą╝ (stream mode).

|

| 0 |

1 |

1 |

ąĀąĄąČąĖą╝ Stream-to-FIFO. |

| 1 |

0 |

0 |

ąĀąĄąČąĖą╝ Bypass-to-Stream. |

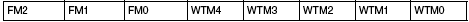

7.14. FIFO_SRC_REG (2Fh)

ąóą░ą▒ą╗ąĖčåą░ 46. ąĀąĄą│ąĖčüčéčĆ FIFO_SRC_REG

ąóą░ą▒ą╗ąĖčåą░ 47. ą×ą┐ąĖčüą░ąĮąĖąĄ ą▒ąĖč鹊ą▓ čĆąĄą│ąĖčüčéčĆą░ FIFO_SRC_REG

WTM ąĪčéą░čéčāčü čāčĆąŠą▓ąĮčÅ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĖčÅ (0: FIFO ąĘą░ą┐ąŠą╗ąĮąĄąĮ ą╝ąĄąĮčīčłąĄ, č湥ą╝ čāčĆąŠą▓ąĄąĮčī WTM, 1: čāčĆąŠą▓ąĄąĮčī ąĘą░ą┐ąŠą╗ąĮąĄąĮąĖčÅ čĆą░ą▓ąĄąĮ ąĖą╗ąĖ ą▓čŗčłąĄ WTM).

OVRN ąæąĖčé čüąŠčüč鹊čÅąĮąĖčÅ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ (overrun, 0: FIFO ąĮąĄ ą┐ąŠą╗ąĮąŠčüčéčīčÄ ąĘą░ą┐ąŠą╗ąĮąĄąĮ, 1: FIFO ąĘą░ą┐ąŠą╗ąĮąĄąĮ ą┐ąŠą╗ąĮąŠčüčéčīčÄ).

EMPTY ąæąĖčé, ąŠąĘąĮą░čćą░čÄčēąĖą╣ ą┐čāčüč鹊čéčā FIFO (0: FIFO ąĮąĄ ą┐čāčüčé, 1: FIFO ą┐čāčüčé).

FSS4-FSS1 ąĪąŠčģčĆą░ąĮąĄąĮąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī ą┤ą░ąĮąĮčŗčģ FIFO.

7.15. INT1_CFG (30h)

ąóą░ą▒ą╗ąĖčåą░ 48. ąĀąĄą│ąĖčüčéčĆ INT1_CFG

ąóą░ą▒ą╗ąĖčåą░ 49. ą×ą┐ąĖčüą░ąĮąĖąĄ ą▒ąĖč鹊ą▓ čĆąĄą│ąĖčüčéčĆą░ INT1_CFG

AND/OR ąÆčŗą▒ąŠčĆ ą║ąŠą╝ą▒ąĖąĮą░čåąĖąĖ ąś/ąśąøąś ą┤ą╗čÅ čüąŠą▒čŗčéąĖą╣ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 0 (0: ą┤ą╗čÅ čüąŠą▒čŗčéąĖą╣ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą║ąŠą╝ą▒ąĖąĮą░čåąĖčÅ ąśąøąś, OR; 1: ą┤ą╗čÅ čüąŠą▒čŗčéąĖą╣ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą║ąŠą╝ą▒ąĖąĮą░čåąĖčÅ ąś, AND).

LIR ąŚą░čēąĄą╗ą║ąĖą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąŠčüą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (Latch Interrupt Request). ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 0 (0: ąĘą░ą┐čĆąŠčü ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĮąĄ ąĘą░ą┐ąŠą╝ąĖąĮą░ąĄčéčüčÅ, 1: ąĘą░ą┐čĆąŠčü ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĘą░ą┐ąŠą╝ąĖąĮą░ąĄčéčüčÅ). ą×čćąĖčēą░ąĄčéčüčÅ čćč鹥ąĮąĖąĄą╝ čĆąĄą│ąĖčüčéčĆą░ INT1_SRC.

ZHIE ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐čĆąĖ čüąŠą▒čŗčéąĖąĖ Z high. ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 0 (0: ąĘą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, 1: čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą║ąŠą│ą┤ą░ ąĖąĘą╝ąĄčĆąĄąĮąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī čāčüą║ąŠčĆąĄąĮąĖčÅ ą▓čŗčłąĄ, č湥ą╝ ą┐čĆąĄą┤čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╣ ą┐ąŠčĆąŠą│).

ZLIE ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐čĆąĖ čüąŠą▒čŗčéąĖąĖ Z low. ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 0 (0: ąĘą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, 1: čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą║ąŠą│ą┤ą░ ąĖąĘą╝ąĄčĆąĄąĮąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī čāčüą║ąŠčĆąĄąĮąĖčÅ ą╝ąĄąĮčīčłąĄ, č湥ą╝ ą┐čĆąĄą┤čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╣ ą┐ąŠčĆąŠą│).

YHIE ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐čĆąĖ čüąŠą▒čŗčéąĖąĖ Y high. ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 0 (0: ąĘą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, 1: čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą║ąŠą│ą┤ą░ ąĖąĘą╝ąĄčĆąĄąĮąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī čāčüą║ąŠčĆąĄąĮąĖčÅ ą▓čŗčłąĄ, č湥ą╝ ą┐čĆąĄą┤čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╣ ą┐ąŠčĆąŠą│).

YLIE ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐čĆąĖ čüąŠą▒čŗčéąĖąĖ Y low. ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 0 (0: ąĘą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, 1: čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą║ąŠą│ą┤ą░ ąĖąĘą╝ąĄčĆąĄąĮąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī čāčüą║ąŠčĆąĄąĮąĖčÅ ą╝ąĄąĮčīčłąĄ, č湥ą╝ ą┐čĆąĄą┤čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╣ ą┐ąŠčĆąŠą│).

XHIE ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐čĆąĖ čüąŠą▒čŗčéąĖąĖ X high. ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 0 (0: ąĘą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, 1: čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą║ąŠą│ą┤ą░ ąĖąĘą╝ąĄčĆąĄąĮąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī čāčüą║ąŠčĆąĄąĮąĖčÅ ą▓čŗčłąĄ, č湥ą╝ ą┐čĆąĄą┤čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╣ ą┐ąŠčĆąŠą│).

XLIE ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐čĆąĖ čüąŠą▒čŗčéąĖąĖ X low. ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 0 (0: ąĘą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, 1: čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą║ąŠą│ą┤ą░ ąĖąĘą╝ąĄčĆąĄąĮąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī čāčüą║ąŠčĆąĄąĮąĖčÅ ą╝ąĄąĮčīčłąĄ, č湥ą╝ ą┐čĆąĄą┤čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╣ ą┐ąŠčĆąŠą│).

7.16. INT1_SRC (31h)

ąÜąŠąĮčäąĖą│čāčĆą░čåąĖąŠąĮąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ ą┤ą╗čÅ ąĖčüč鹊čćąĮąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

ąóą░ą▒ą╗ąĖčåą░ 50. ąĀąĄą│ąĖčüčéčĆ INT1_SRC

ąóą░ą▒ą╗ąĖčåą░ 51. ą×ą┐ąĖčüą░ąĮąĖąĄ ą▒ąĖč鹊ą▓ čĆąĄą│ąĖčüčéčĆą░ INT1_SRC

IA ąÉą║čéąĖą▓ąĮąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ (Interrupt Active). ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 0 (0: ąĮąĄ ą▒čŗą╗ąŠ čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, 1: čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąŠ ąŠą┤ąĮąŠ ąĖą╗ąĖ ą▒ąŠą╗čīčłąĄąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣).

ZH Z high. ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 0 (0: ąĮąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, 1: ą┐čĆąŠąĖąĘąŠčłą╗ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠčé ą▓čŗčüąŠą║ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ čāčüą║ąŠčĆąĄąĮąĖčÅ ą┐ąŠ ąŠčüąĖ Z).

ZL Z low. ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 0 (0: ąĮąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, 1: ą┐čĆąŠąĖąĘąŠčłą╗ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠčé ąĮąĖąĘą║ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ čāčüą║ąŠčĆąĄąĮąĖčÅ ą┐ąŠ ąŠčüąĖ Z).

YH Y high. ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 0 (0: ąĮąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, 1: ą┐čĆąŠąĖąĘąŠčłą╗ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠčé ą▓čŗčüąŠą║ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ čāčüą║ąŠčĆąĄąĮąĖčÅ ą┐ąŠ ąŠčüąĖ Y).

YL Y low. ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 0 (0: ąĮąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, 1: ą┐čĆąŠąĖąĘąŠčłą╗ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠčé ąĮąĖąĘą║ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ čāčüą║ąŠčĆąĄąĮąĖčÅ ą┐ąŠ ąŠčüąĖ Y).

XH X high. ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 0 (0: ąĮąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, 1: ą┐čĆąŠąĖąĘąŠčłą╗ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠčé ą▓čŗčüąŠą║ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ čāčüą║ąŠčĆąĄąĮąĖčÅ ą┐ąŠ ąŠčüąĖ X).

XL X low. ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 0 (0: ąĮąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, 1: ą┐čĆąŠąĖąĘąŠčłą╗ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠčé ąĮąĖąĘą║ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ čāčüą║ąŠčĆąĄąĮąĖčÅ ą┐ąŠ ąŠčüąĖ X).

ąĀąĄą│ąĖčüčéčĆ, ąŠą▒ąŠąĘąĮą░čćą░čÄčēąĖą╣ ąĖčüč鹊čćąĮąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ. ą¦č鹥ąĮąĖąĄ ą┐ąŠ čŹč鹊ą╝čā ą░ą┤čĆąĄčüčā ąŠčćąĖčēą░ąĄčé ą▒ąĖčé IA čĆąĄą│ąĖčüčéčĆą░ INT1_SRC (čéą░ą║ąČąĄ čüą▒čĆą░čüčŗą▓ą░ąĄčé ą▓ąŠąĘąĮąĖą║ą░čÄčēąĖą╣ ą┐ąŠ čüąŠą▒čŗčéąĖčÄ čüąĖą│ąĮą░ą╗ ąĮą░ ąĮąŠąČą║ąĄ INT1), ąĖ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąŠą▒ąĮąŠą▓ąĖčéčī ą┤ą░ąĮąĮčŗąĄ ą▓ čĆąĄą│ąĖčüčéčĆąĄ INT1_SRC, ąĄčüą╗ąĖ ą▓čŗą▒čĆą░ąĮą░ ąŠą┐čåąĖčÅ čü ąĘą░čēąĄą╗ą║ąĖą▓ą░ąĮąĖąĄą╝ ą┤ą░ąĮąĮčŗčģ.