|

ąÆ čüčéą░čéčīąĄ ąŠą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ čüąŠą▓čĆąĄą╝ąĄąĮąĮčŗą╣ ą▓čŗčüąŠą║ąŠčüą║ąŠčĆąŠčüčéąĮąŠą╣ čćąĖą┐ FTDI - FT2232H, Hi-Speed USB 2.0 - Dual UART/FIFO Converter (USB 2.0 High Speed ąĖ Full Speed, FT2232HL-xxxx 64 Pin LQFP). ą×čüąĮąŠą▓ąŠą╣ ą┤ą╗čÅ ą╝ą░č鹥čĆąĖą░ą╗ą░ čüčéą░čéčīąĖ ą┐ąŠčüą╗čāąČąĖą╗ ą┐ąĄčĆąĄą▓ąŠą┤ ą┤ą░čéą░čłąĖčéą░ ąĮą░ FT2232H (ą▓ ą┤ą░čéą░čłąĖč鹥, ą║čüčéą░čéąĖ ą│ąŠą▓ąŠčĆčÅ, ąĖą╝ąĄčÄčéčüčÅ ąŠą┐ąĄčćą░čéą║ąĖ, ą║ąŠč鹊čĆčŗąĄ ą┐ąŠ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ ąĖčüą┐čĆą░ą▓ą╗ąĄąĮčŗ ą▓ čŹč鹊ą╝ č鹥ą║čüč鹥).

ą£ąĮąŠą│ąĖąĄ čĆą░ą┤ąĖąŠą╗čÄą▒ąĖč鹥ą╗ąĖ čģąŠčĆąŠčłąŠ ąĘąĮą░čÄčé ąĖ čāčüą┐ąĄčłąĮąŠ ą┐čĆąĖą╝ąĄąĮčÅčÄčé ą▓ čüą▓ąŠąĖčģ ą║ąŠąĮčüčéčĆčāą║čåąĖčÅčģ čćąĖą┐ FT232 (FT232R, FT232BL, FT232BQ, FT232BM) - ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░č鹥ą╗čī USB < -- > ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ą┐ąŠčĆčé RS232 (COM-ą┐ąŠčĆčé). ą¦ąĖą┐ FT232 čģąŠčĆąŠčł č鹥ą╝, čćč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąĮąĄ ąĘą░ą▒ąŠčéąĖčéčīčüčÅ ąĮąĖ ąŠ ą┤čĆą░ą╣ą▓ąĄčĆą░čģ, ąĮąĖ ąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą╝ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖąĖ ąĮą░ ą║ąŠą╝ą┐čīčÄč鹥čĆąĄ - USB-čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮą░ čćąĖą┐ąĄ FT232 čĆą░ą▒ąŠčéą░ąĄčé ą▓ čüčéą░ąĮą┤ą░čĆčéąĮąŠą╝ ą║ą╗ą░čüčüąĄ CDC, ąĖ ąŠą▒čĆą░ąĘčāąĄčé ąĮą░ ą║ąŠą╝ą┐čīčÄč鹥čĆąĄ ą▓ąĖčĆčéčāą░ą╗čīąĮčŗą╣ COM-ą┐ąŠčĆčé, čü ą║ąŠč鹊čĆčŗą╝ čāą┤ąŠą▒ąĮąŠ čĆą░ą▒ąŠčéą░čéčī ą║ą░ą║ č湥čĆąĄąĘ ą╝ąĮąŠąČąĄčüčéą▓ąŠ ą│ąŠč鹊ą▓čŗčģ ą┐čĆąŠą│čĆą░ą╝ą╝ (SecureCRT, terraterm, putty), čéą░ą║ ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ č湥čĆąĄąĘ ą┐čĆąŠčüč鹊ąĄ API ą▓ ąŠą┐ąĄčĆą░čåąĖąŠąĮąĮčŗčģ čüąĖčüč鹥ą╝ą░čģ Windows ąĖ Linux. ą£ąĮąŠą│ąĖąĄ čĆą░ą┤ąĖąŠą╗čÄą▒ąĖč鹥ą╗ąĖ čģąŠčĆąŠčłąŠ ąĘąĮą░čÄčé ąĖ čāčüą┐ąĄčłąĮąŠ ą┐čĆąĖą╝ąĄąĮčÅčÄčé ą▓ čüą▓ąŠąĖčģ ą║ąŠąĮčüčéčĆčāą║čåąĖčÅčģ čćąĖą┐ FT232 (FT232R, FT232BL, FT232BQ, FT232BM) - ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░č鹥ą╗čī USB < -- > ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ą┐ąŠčĆčé RS232 (COM-ą┐ąŠčĆčé). ą¦ąĖą┐ FT232 čģąŠčĆąŠčł č鹥ą╝, čćč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąĮąĄ ąĘą░ą▒ąŠčéąĖčéčīčüčÅ ąĮąĖ ąŠ ą┤čĆą░ą╣ą▓ąĄčĆą░čģ, ąĮąĖ ąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą╝ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖąĖ ąĮą░ ą║ąŠą╝ą┐čīčÄč鹥čĆąĄ - USB-čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮą░ čćąĖą┐ąĄ FT232 čĆą░ą▒ąŠčéą░ąĄčé ą▓ čüčéą░ąĮą┤ą░čĆčéąĮąŠą╝ ą║ą╗ą░čüčüąĄ CDC, ąĖ ąŠą▒čĆą░ąĘčāąĄčé ąĮą░ ą║ąŠą╝ą┐čīčÄč鹥čĆąĄ ą▓ąĖčĆčéčāą░ą╗čīąĮčŗą╣ COM-ą┐ąŠčĆčé, čü ą║ąŠč鹊čĆčŗą╝ čāą┤ąŠą▒ąĮąŠ čĆą░ą▒ąŠčéą░čéčī ą║ą░ą║ č湥čĆąĄąĘ ą╝ąĮąŠąČąĄčüčéą▓ąŠ ą│ąŠč鹊ą▓čŗčģ ą┐čĆąŠą│čĆą░ą╝ą╝ (SecureCRT, terraterm, putty), čéą░ą║ ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ č湥čĆąĄąĘ ą┐čĆąŠčüč鹊ąĄ API ą▓ ąŠą┐ąĄčĆą░čåąĖąŠąĮąĮčŗčģ čüąĖčüč鹥ą╝ą░čģ Windows ąĖ Linux.

ąØąĄą┤ąŠčüčéą░č鹊ą║ čéą░ą║ąŠą│ąŠ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ąĘą░ą║ą╗čÄčćą░ąĄčéčüčÅ ą▓ č鹊ą╝, čćč鹊 ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ą┤ąŠčüčéčāą┐ąĮčŗ ąĮąĖąĘą║ąĖąĄ čüą║ąŠčĆąŠčüčéąĖ (ą╝ą░ą║čüąĖą╝čāą╝ 3 ą╝ąĄą│ą░ą▒ąĖčéą░ ą▓ čüąĄą║čāąĮą┤čā) ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ą║ą░ąĮą░ą╗ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ, ąĖ č鹊ą╗čīą║ąŠ ąŠą┤ąĖąĮ ą║ą░ąĮą░ą╗ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ. ąĀąĄąČąĖą╝čŗ USB 2.0 Full Speed ąĖ USB 2.0 High Speed čüą┐ąŠčüąŠą▒ąĮčŗ ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī ą┤ą░ąĮąĮčŗąĄ ąĮą░ ą│ąŠčĆą░ąĘą┤ąŠ ą▒ą×ą╗čīčłąĖčģ čüą║ąŠčĆąŠčüčéčÅčģ - 12 ą╝ąĄą│ą░ą▒ąĖčé ą▓ čüąĄą║čāąĮą┤čā ąĖ 480 ą╝ąĄą│ą░ą▒ąĖčé ą▓ čüąĄą║čāąĮą┤čā čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ. ąöą╗čÅ čŹč鹊ą│ąŠ ą║ąŠą╝ą┐ą░ąĮąĖąĄą╣ FTDI ą▒čŗą╗ąĖ čĆą░ąĘčĆą░ą▒ąŠčéą░ąĮčŗ ą┤ą▓ąĄ ąĮąŠą▓čŗąĄ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ - FT2232H ąĖ FT4232H. ąśą╝ąĄąĄčéčüčÅ čéą░ą║ąČąĄ ą┐ąŠą╗ąĮąŠčüą║ąŠčĆąŠčüčéąĮąŠą╣ (Full Speed USB), ą▒ąŠą╗ąĄąĄ ą┤ąĄčłąĄą▓čŗą╣ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮčŗą╣ ą░ąĮą░ą╗ąŠą│ FT2232D, čā ą║ąŠč鹊čĆąŠą│ąŠ ą╝ąĄąĮčīčłąĄ ą▓čŗą▓ąŠą┤ąŠą▓ (ą║ąŠčĆą┐čāčü LQFP48). ąÆ čŹč鹊ą╣ čüčéą░čéčīąĄ ą┐ąŠą┤čĆąŠą▒ąĮąŠ čĆą░čüčüą╝ą░čéčĆąĖą▓ą░ąĄčéčüčÅ čćąĖą┐ FT2232H.

ą£ąĖą║čĆąŠčüčģąĄą╝ą░ FT2232H ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮą░ ą┤ą╗čÅ "ą┐čĆąĖąĘąĄą╝ą╗ąĄąĮąĖčÅ" USB-ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ čĆą░ąĘą╗ąĖčćąĮčŗą╝ąĖ čüą┐ąŠčüąŠą▒ą░ą╝ąĖ - ą▓ ą║ą░č湥čüčéą▓ąĄ čüą║ąŠčĆąŠčüčéąĮčŗčģ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ąĖąĮč鹥čĆč乥ą╣čüąŠą▓ UART, JTAG, I2C, SPI, ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮčŗčģ ąĖąĮč鹥čĆč乥ą╣čüąŠą▓ FIFO, bit-bang, ąĖ ą┤ą░ąČąĄ ą║ą░ą║ ąŠą▒čŗčćąĮčŗąĄ ą┐ąŠčĆčéčŗ ą┐čĆčÅą╝ąŠą│ąŠ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ (GPIO). ą¦ąĖą┐ FT2232H ą▓čŗą┐čāčüą║ą░ąĄčéčüčÅ ą▓ 64-ą▓čŗą▓ąŠą┤ąĮčŗčģ ą║ąŠčĆą┐čāčüą░čģ LQFP ąĖą╗ąĖ QFN, čĆą░čüčüčćąĖčéą░ąĮ ąĮą░ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ 3.3 ą▓ąŠą╗čīčé, ąĖ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ čü ą┐ąŠą╝ąŠčēčīčÄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ą▓ąĮąĄčłąĮąĄą╣ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ EEPROM 93ąĪ46 (ąĖą╗ąĖ ą░ąĮą░ą╗ąŠą│ąĖčćąĮąŠą╣). ą¤čĆąĖą╝ąĄąĮąĄąĮąĖąĄ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ FT2232H ą┤ą░ąĄčé čĆą░ąĘčĆą░ą▒ąŠčéčćąĖą║čā ą┐čĆąŠčüč鹊ą╣ čüą┐ąŠčüąŠą▒ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ ą▓čŗčüąŠą║ąŠčüą║ąŠčĆąŠčüčéąĮąŠą│ąŠ ą╝ąŠčüčéą░ ą╝ąĄąČą┤čā USB ąĖ čĆą░ąĘą╗ąĖčćąĮčŗą╝ąĖ čéąĖą┐ą░ą╝ąĖ ą┤ąŠčüčéčāą┐ąĮčŗčģ ąĖąĮč鹥čĆč乥ą╣čüąŠą▓, ą▓ ą║ąŠč鹊čĆčŗąĄ ą╝ąŠąČąĮąŠ ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī (ąĖ ąŠčéą║čāą┤ą░ ą╝ąŠąČąĮąŠ ą┐čĆąĖąĮąĖą╝ą░čéčī) ą┤ą░ąĮąĮčŗąĄ č湥čĆąĄąĘ USB. ą£ąĖą║čĆąŠčüčģąĄą╝ą░ FT4232H ąŠčéą╗ąĖčćą░ąĄčéčüčÅ ąŠčé FT2232H ąĮą░ą▒ąŠčĆąŠą╝ ąĖąĮč鹥čĆč乥ą╣čüąŠą▓ ąĖ čłąĖąĮ. ąæą╗ą░ą│ąŠą┤ą░čĆčÅ ąĮą░ą╗ąĖčćąĖčÄ ą┤ą▓čāčģ ą╝ąĖą║čĆąŠčüčģąĄą╝ FT2232H ąĖ FT4232H čĆą░ąĘčĆą░ą▒ąŠčéčćąĖą║ ą┐ąŠą╗čāčćą░ąĄčé čłąĖčĆąŠą║ąĖąĄ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ ą┐ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÄ ąĖąĮč鹥čĆč乥ą╣čüą░ USB ą▓ ąĮąĄąŠą▒čģąŠą┤ąĖą╝čŗąĄ ąĄą╝čā čłąĖąĮčŗ (čüą╝. ą┤ą░ą╗ąĄąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ čĆąĄąČąĖą╝ąŠą▓ ąĖ čłąĖąĮ).

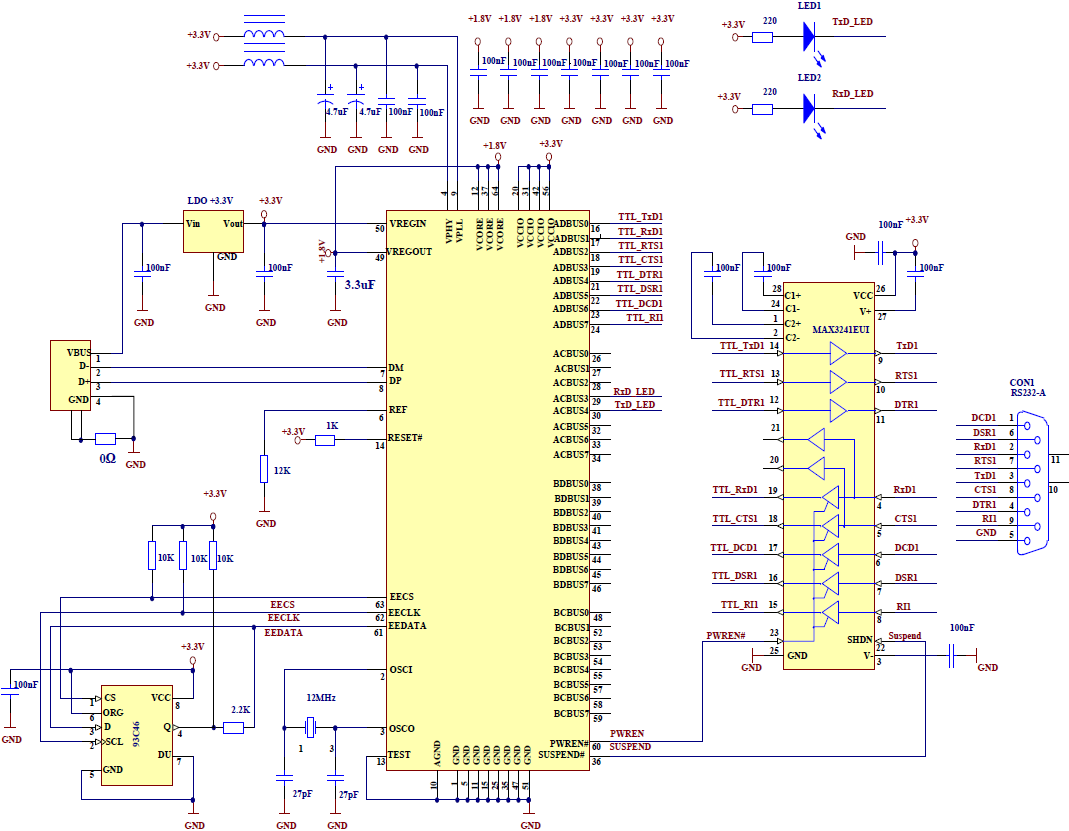

[ą×čüąĮąŠą▓ąĮčŗąĄ ąŠčüąŠą▒ąĄąĮąĮąŠčüčéąĖ FT2232H]

ą£ąĖą║čĆąŠčüčģąĄą╝ą░ FT2232H (ą┐čĆąĖąĮą░ą┤ą╗ąĄąČą░čēą░čÅ 5 ą┐ąŠą║ąŠą╗ąĄąĮąĖčÄ USB čāčüčéčĆąŠą╣čüčéą▓ FTDI) - ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░č鹥ą╗čī ąĖąĮč鹥čĆč乥ą╣čüą░ USB 2.0 High Speed 480 ą╝ąĄą│ą░ą▒ąĖčé/čüąĄą║ (ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ čüąŠą▓ą╝ąĄčüčéąĖą╝ąŠčüčéčī čü USB 2.0 High Speed 480 ą╝ąĄą│ą░ą▒ąĖčé/čüąĄą║ ąĖ Full Speed 12 ą╝ąĄą│ą░ą▒ąĖčé/čüąĄą║) ą▓ ąĖąĮč鹥čĆč乥ą╣čüčŗ UART/FIFO čü ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčīčÄ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓ čĆą░ąĘą╗ąĖčćąĮčŗąĄ čüčéą░ąĮą┤ą░čĆčéąĮčŗąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗąĄ ąĖą╗ąĖ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮčŗąĄ ąĖąĮč鹥čĆč乥ą╣čüčŗ. ą¤čĆąŠč鹊ą║ąŠą╗ USB ą┐ąŠą╗ąĮąŠčüčéčīčÄ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčéčüčÅ ą▓ąĮčāčéčĆąĖ čćąĖą┐ą░, ąĮąĄ čéčĆąĄą▒čāąĄčéčüčÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠąĄ firmware. ąśą╝ąĄčÄčéčüčÅ čüą╗ąĄą┤čāčÄčēąĖąĄ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ:

- ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ąŠą┤ąĮąŠą│ąŠ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ USB ą▓ ą┤ą▓ą░ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ąĖą╗ąĖ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮčŗčģ ą┐ąŠčĆčéą░ ą▓ čĆą░ąĘą╗ąĖčćąĮčŗčģ ą║ąŠą╝ą▒ąĖąĮą░čåąĖčÅčģ.

- ą┤ą▓ąĄ čüąĖčüč鹥ą╝čŗ Multi-Protocol Synchronous Serial Engine (MPSSE) čāą┐čĆąŠčēą░čÄčé čĆą░ąĘčĆą░ą▒ąŠčéą║čā čü ą┐ąŠą┤ą┤ąĄčƹȹ║ąŠą╣ čüąĖąĮčģčĆąŠąĮąĮčŗčģ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ą┐čĆąŠč鹊ą║ąŠą╗ąŠą▓ (ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ USB ą▓ ąĖąĮč鹥čĆč乥ą╣čüčŗ JTAG, I2C, SPI ąĖą╗ąĖ bit-bang).

- ą┤ą▓ą░ ąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗčģ UART ąĖą╗ąĖ FIFO, ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝čŗčģ č湥čĆąĄąĘ MPSSE.

- ąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗąĄ ą│ąĄąĮąĄčĆą░č鹊čĆčŗ čüą║ąŠčĆąŠčüčéąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ (Baud rate generators).

- čüą║ąŠčĆąŠčüčéčī RS232/RS422/RS485 UART ą┤ąŠ 12 ą╝ąĄą│ą░ą▒ąŠą┤ (ą╝ąĄą│ą░ą▒ąĖčé/čü). ąĪą║ąŠčĆąŠčüčéčī RS232 ąŠą│čĆą░ąĮąĖč湥ąĮą░ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčÅą╝ąĖ ą▓ąĮąĄčłąĮąĄą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░č鹥ą╗čÅ čāčĆąŠą▓ąĮčÅ.

- čüą║ąŠčĆąŠčüčéčī USB < -- > ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮą░čÅ čłąĖąĮą░ FIFO ą┤ąŠ 8 ą╝ąĄą│ą░ą▒ą░ą╣čé/čüąĄą║ (ąŠą║ąŠą╗ąŠ 64 ą╝ąĄą│ą░ą▒ąĖčé/čüąĄą║).

- čĆąĄąČąĖą╝ ąŠą┤ąĮąŠą║ą░ąĮą░ą╗čīąĮąŠą│ąŠ čüąĖąĮčģčĆąŠąĮąĮąŠą│ąŠ FIFO čüąŠ čüą║ąŠčĆąŠčüčéčīčÄ ą┤ąŠ ą┤ąŠ 25 ą╝ąĄą│ą░ą▒ą░ą╣čé/čüąĄą║ (ąŠą║ąŠą╗ąŠ 200 ą╝ąĄą│ą░ą▒ąĖčé/čüąĄą║).

- čĆąĄąČąĖą╝ FIFO ą▓ čüčéąĖą╗ąĄ ąĖąĮč鹥čĆč乥ą╣čüą░ CPU (ąĮą░ą┐ąŠą┤ąŠą▒ąĖąĄ čłąĖąĮčŗ Intel).

- čĆąĄąČąĖą╝ 菹╝čāą╗čÅčåąĖąĖ ą╝ąĖą║čĆąŠą┐čĆąŠčåąĄčüčüąŠčĆąĮąŠą╣ čłąĖąĮčŗ MCU.

- čĆąĄąČąĖą╝ ą▒čŗčüčéčĆąŠą│ąŠ ąŠą┐č鹊ąĖąĘąŠą╗ąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ (fast opto-isolated serial interface mode).

- ą▒ąĄčüą┐ą╗ą░čéąĮčŗąĄ ą┤ą╗čÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą┤čĆą░ą╣ą▓ąĄčĆą░ ąŠčé FTDI - ą┤ą╗čÅ Virtual Com Port (VCP) ąĖ Direct (D2XX), ą║ąŠč鹊čĆčŗąĄ ą▓ ą▒ąŠą╗čīčłąĖąĮčüčéą▓ąĄ čüą╗čāčćą░ąĄą▓ čāčüčéčĆą░ąĮčÅčÄčé ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéčī ą▓ čĆą░ąĘčĆą░ą▒ąŠčéą║ąĄ ą┤čĆą░ą╣ą▓ąĄčĆą░ USB ą┤ą╗čÅ ąŠą┐ąĄčĆą░čåąĖąŠąĮąĮąŠą╣ čüąĖčüč鹥ą╝čŗ.

- ąĮą░čüčéčĆą░ąĖą▓ą░ąĄą╝čŗą╣ čéą░ą╣ą╝ą░čāčé ą┐čĆąĖąĄą╝ąĮąŠą│ąŠ ą▒čāč乥čĆą░.

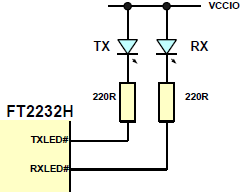

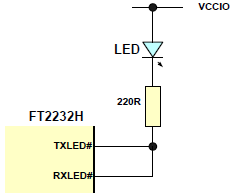

- ąŠą┐čåąĖčÅ ą┤ą╗čÅ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ čüą▓ąĄč鹊ą┤ąĖąŠą┤ąŠą▓ LED, čüąĖą│ąĮą░ą╗ąĖąĘąĖčĆčāčÄčēąĖčģ ąŠ ą┐čĆąĖąĄą╝ąĄ ąĖ ą┐ąĄčĆąĄą┤ą░č湥.

- čĆą░čüčłąĖčĆąĄąĮąĮčŗą╣ čĆąĄąČąĖą╝ ąĖąĮč鹥čĆč乥ą╣čüą░ bit-bang čüąŠ čüčéčĆąŠą▒ą░ą╝ąĖ ~RD ąĖ ~WR.

- čĆąĄąČąĖą╝ ąĖąĮč鹥čĆč乥ą╣čüą░ FIFO ą▓ čüčéąĖą╗ąĄ FT245B čü ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮąŠą╣ čłąĖąĮąŠą╣ ąĖ 4-ą┐čĆąŠą▓ąŠą┤ąĮčŗą╝ ąĖąĮč鹥čĆč乥ą╣čüąŠą╝ ą║ą▓ąĖčéąĖčĆąŠą▓ą░ąĮąĖčÅ (handshake).

- ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ čüčéą░ą▒ąĖą╗ąĖąĘą░č鹊čĆ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ +1.8V LDO (Low Dropout, čĆąĄą│čāą╗čÅč鹊čĆ čü ą╝ą░ą╗čŗą╝ ą┐ą░ą┤ąĄąĮąĖąĄą╝ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ), čäčāąĮą║čåąĖčÅ čüą▒čĆąŠčüą░ ą┐ąŠ ą┐ąĖčéą░ąĮąĖčÄ (Power-On Reset, POR), čāą╝ąĮąŠąČąĖč鹥ą╗čī čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ ążąÉą¤ą¦ (clock multiplier PLL) 12 ą£ąōčå ŌĆō 480 ą£ąōčå.

- čĆąĄąČąĖą╝ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ UART čü ą┐ąŠą╗ąĮąŠą╣ ą░ą┐ą┐ą░čĆą░čéąĮąŠą╣ čłąĖąĮąŠą╣ ą║ą▓ąĖčéąĖčĆąŠą▓ą░ąĮąĖčÅ (hardware handshaking) ąĖ ą▓čüąĄą╝ąĖ čüąĖą│ąĮą░ą╗ą░ą╝ąĖ ąĖąĮč鹥čĆč乥ą╣čüą░ čü ą╝ąŠą┤ąĄą╝ąŠą╝.

- ą░ą┐ą┐ą░čĆą░čéąĮčŗąĄ čüčĆąĄą┤čüčéą▓ą░, ą║ąŠč鹊čĆčŗąĄ ą┐ąŠą╗ąĮąŠčüčéčīčÄ ą┐ąŠą╝ąŠą│ą░čÄčé ą░ą┐ą┐ą░čĆą░čéąĮąŠą╝čā ąĖą╗ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą╝čā (X-On/X-Off) ą║ą▓ąĖčéąĖčĆąŠą▓ą░ąĮąĖčÄ.

- ąĖąĮč鹥čĆč乥ą╣čü UART ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ą▓čüąĄ čüčéą░ąĮą┤ą░čĆčéąĮčŗąĄ čĆąĄąČąĖą╝čŗ 7 ąĖą╗ąĖ 8 ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ, 1 ąĖą╗ąĖ 2 čüč鹊ą┐-ą▒ąĖčéą░, ąĖ čĆąĄąČąĖą╝čŗ Odd/Even/Mark/Space/No Parity.

- čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą╣ ą┐ąĄčĆąĄą┤ą░č湥ą╣ ą┤ą╗čÅ ą┐čĆąĖą╗ąŠąČąĄąĮąĖą╣.

- čĆąĄąČąĖą╝ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ č湥čĆąĄąĘ USB, ą║ąŠč鹊čĆčŗą╣ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąĘą░ą┤ą░čéčī čüčéčĆąŠą║ąŠą▓čŗąĄ ąŠą┐ąĖčüą░č鹥ą╗ąĖ ą┤ą╗čÅ USB ąĖ čüąŠčģčĆą░ąĮąĖčéčī ąĖčģ ą▓ąŠ ą▓ąĮąĄčłąĮąĄą╝ EEPROM 93ąĪ46.

- ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝ą░čÅ ąĮą░ą│čĆčāąĘąŠčćąĮą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī ą▓ą▓ąŠą┤ą░-ą▓čŗą▓ąŠą┤ą░ (4, 8, 12 ąĖą╗ąĖ 16 ą╝ąÉ) ąĖ čüą║ąŠčĆąŠčüčéčī ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ (slew rate).

- ąĮąĖąĘą║ąŠąĄ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ ą▓ čĆą░ą▒ąŠč湥ą╝ čĆąĄąČąĖą╝ąĄ ąĖ čĆąĄąČąĖą╝ąĄ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ąĖ (USB suspend).

- ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčéčüčÅ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ USB čü ą┐ąĖčéą░ąĮąĖąĄą╝ ąŠčé čłąĖąĮčŗ USB (bus powered), čü čüąŠą▒čüčéą▓ąĄąĮąĮčŗą╝ ą┐ąĖčéą░ąĮąĖąĄą╝ (self powered) ąĖ čü ą┐ąĖčéą░ąĮąĖąĄą╝ ąŠčé čłąĖąĮčŗ USB čü ą┐ąŠą▓čŗčłąĄąĮąĮčŗą╝ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄą╝ (high-power bus powered).

- ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ čüąŠą▓ą╝ąĄčüčéąĖą╝ąŠčüčéčī čü čģąŠčüč鹊ą╝ ą┐ąŠ čüčéą░ąĮą┤ą░čĆčéą░ą╝ UHCI/OHCI/EHCI.

- čĆąĄąČąĖą╝ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ USB Bulk (ą┐ą░ą║ąĄčéčŗ ą┐ąŠ 512 ą▒ą░ą╣čé ą▓ čĆąĄąČąĖą╝ąĄ High Speed).

- ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ čÅą┤čĆą░ (chip core) +1.8 ą▓ąŠą╗čīčé ąĖ ąĖąĮč鹥čĆč乥ą╣čü ą▓ą▓ąŠą┤ą░-ą▓čŗą▓ąŠą┤ą░ +3.3 ą▓ąŠą╗čīčé (čüąŠą▓ą╝ąĄčüčéąĖą╝čŗą╣ čü +5 ą▓ąŠą╗čīčé).

- č鹥ą╝ą┐ąĄčĆą░čéčāčĆąĮčŗą╣ ą┤ąĖą░ą┐ą░ąĘąŠąĮ -40..+85 ą│čĆą░ą┤.

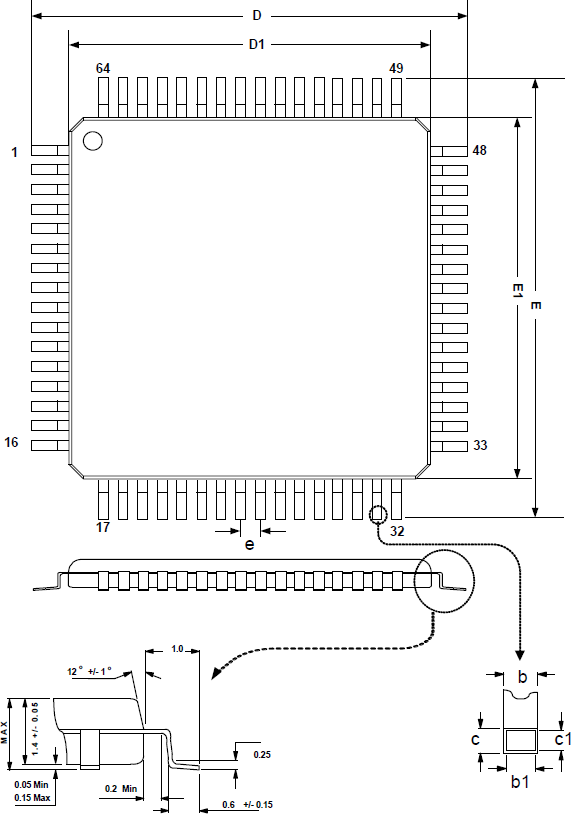

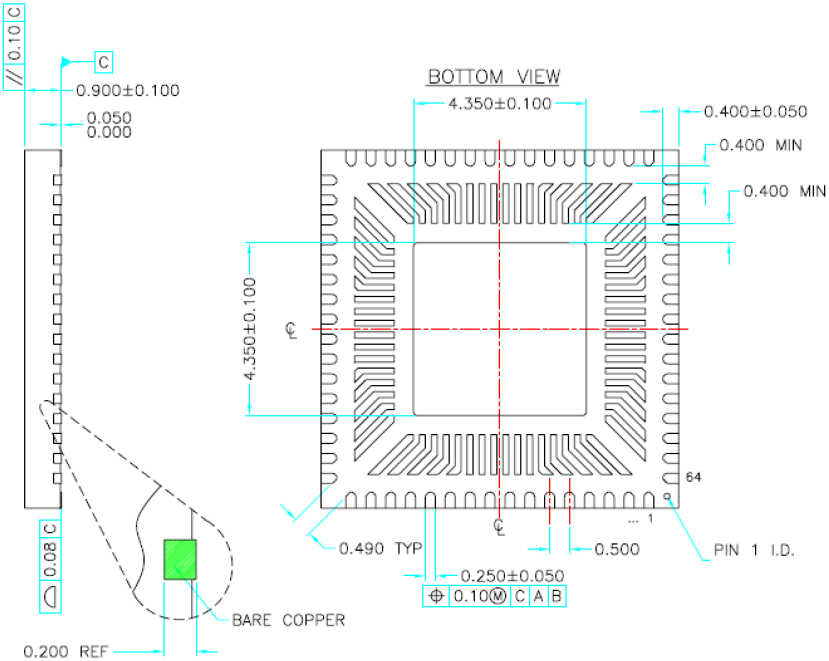

- ą╝ą░ą╗ąŠą│ą░ą▒ą░čĆąĖčéąĮčŗą╣ 64-ą▓čŗą▓ąŠą┤ąĮčŗą╣ ą║ąŠčĆą┐čāčü LQFP ąĖą╗ąĖ QFN.

- ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ ą┤ąŠčüčéą░č鹊čćąĮąŠ ąŠą┤ąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ +3.3 ą▓ąŠą╗čīčé.

- ąĮą░ ą┐ąŠčĆčéą░čģ I/O ą┐čĆąĄą┤čāčüą╝ąŠčéčĆąĄąĮą░ ąĘą░čēąĖčéą░ ąŠčé čüčéą░čéąĖč湥čüą║ąŠą│ąŠ 菹╗ąĄą║čéčĆąĖč湥čüčéą▓ą░ (ESD protection).

ą£ąĖą║čĆąŠčüčģąĄą╝ą░ FT2232H ą▓čŗą┐čāčüą║ą░ąĄčéčüčÅ ą▓ ą┤ą▓čāčģ ą▓ąĖą┤ą░čģ ą║ąŠčĆą┐čāčüąŠą▓ - 64 Pin LQFP ąĖ 64 Pin QFN.

|

|

|

| FT2232HL-xxxx 64 Pin LQFP |

|

FT2232HQ-xxxx 64 Pin QFN |

ąŚą┤ąĄčüčī xxxx ąĘą░ą║ąŠą┤ąĖčĆąŠą▓ą░ąĮ čüą┐ąŠčüąŠą▒ ą┐ąŠčüčéą░ą▓ą║ąĖ čü ąĘą░ą▓ąŠą┤ą░, Reel ąĖą╗ąĖ Tray.

Reel: Taped and Reel (ą╗ąĄąĮčéą░ ąĖ ą╗ąĖąĮąĄą╣ą║ą░), LQFP = 1000 čłčéčāą║ ąĮą░ ą╗ąĖąĮąĄą╣ą║čā, QFN = 4000 čłčéčāą║ ąĮą░ ą╗ąĖąĮąĄą╣ą║čā.

Tray: Tray packing (čāą┐ą░ą║ąŠą▓ą║ą░ ą▓ ą▓ąĖą┤ąĄ ą┐ąŠą┤ą┤ąŠąĮą░) LQFP = 160 čłčéčāą║ ąĮą░ čāą┐ą░ą║ąŠą▓ą║čā, QFN = 260 čłčéčāą║ ąĮą░ čāą┐ą░ą║ąŠą▓ą║čā.

ąæąŠą╗ąĄąĄ ą┐ąŠą┤čĆąŠą▒ąĮąŠ ą┐ąŠ čéąĖą┐ą░ą╝ ą║ąŠčĆą┐čāčüą░ ąĖ čāą┐ą░ą║ąŠą▓ą║ąĖ čüą╝. ą┤ą░čéą░čłąĖčé ąĮą░ ą╝ąĖą║čĆąŠčüčģąĄą╝čā FT2232HL (ą╗ąĖą▒ąŠ ą┐ąŠ čüčüčŗą╗ą║ąĄ [5], ą╗ąĖą▒ąŠ ąĮą░ čüą░ą╣č鹥 ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čÅ).

1 ąóąĖą┐ąĖčćąĮčŗąĄ ą┐čĆąĖą╝ąĄąĮąĄąĮąĖčÅ FT2232H

- ą╝ąŠčüčé USB < -- > 2 ą║ą░ąĮą░ą╗ą░ UART (RS232, RS422 ąĖą╗ąĖ RS485)

- ą╝ąŠčüčé USB < -- > 2 ą║ą░ąĮą░ą╗ą░ FIFO

- ą╝ąŠčüčé USB < -- > 2 ą║ą░ąĮą░ą╗ą░ JTAG

- ą╝ąŠčüčé USB < -- > 2 ą║ą░ąĮą░ą╗ą░ SPI

- ą╝ąŠčüčé USB < -- > 2 ą║ą░ąĮą░ą╗ą░ I2C

- ą╝ąŠčüčé USB < -- > 2 ą║ą░ąĮą░ą╗ą░ Bit-Bang

- ą╝ąŠčüčé USB < -- > ą║ąŠą╝ą▒ąĖąĮą░čåąĖčÅ ąĖąĘ ą▓čŗčłąĄą┐ąĄčĆąĄčćąĖčüą╗ąĄąĮąĮčŗčģ ąĖąĮč鹥čĆč乥ą╣čüąŠą▓

- ą╝ąŠčüčé USB < -- > ą▒čŗčüčéčĆčŗą╣ ąŠą┐čéąĖč湥čüą║ąĖą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü (Fast Serial Optic Interface)

- ą╝ąŠčüčé USB < -- > ą┤ą▓ąŠą╣ąĮąŠą╣, ąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗą╣ ąĖąĮč鹥čĆč乥ą╣čü CPU (ą▓ ą║ą░č湥čüčéą▓ąĄ ą┐ą░ą╝čÅčéąĖ)

- ą╝ąŠčüčé USB < -- > 菹╝čāą╗čÅčåąĖčÅ Host Bus (ą▓ ą║ą░č湥čüčéą▓ąĄ CPU)

- ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖąĄ PDA ą║ USB

- čĆąĖą┤ąĄčĆčŗ ą┤ą╗čÅ čüą╝ą░čĆčé-ą║ą░čĆčé, ą┐ąŠą┤ą║ą╗čÄčćą░ąĄą╝čŗąĄ ą┐ąŠ USB

- ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖąĄ ą┐ą╗ąĄąĄčĆąŠą▓ mp3 ą║ USB

- ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ čłąĖąĮčŗ USB ą┤ą╗čÅ ą┐čĆąŠą╝čŗčłą╗ąĄąĮąĮąŠą│ąŠ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĖ ąĖąĮčüčéčĆčāą╝ąĄąĮčéą░ą╗čīąĮąŠąĄ ą┐čĆąĖą╝ąĄąĮąĄąĮąĖąĄ USB

- čĆąĖą┤ąĄčĆčŗ ą┤ą╗čÅ FLASH-ą║ą░čĆčé, ą┐ąŠą┤ą║ą╗čÄčćą░ąĄą╝čŗąĄ ą┐ąŠ USB

- ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖąĄ čåąĖčäčĆąŠą▓čŗčģ ą▓ąĖą┤ąĄąŠą║ą░ą╝ąĄčĆ ą║ USB

- čĆąĖą┤ąĄčĆčŗ ą┤ą╗čÅ ą▒ą░čĆą║ąŠą┤ą░ (čłčéčĆąĖčģąŠą▓ąŠą╣ ą║ąŠą┤), ą┐ąŠą┤ą║ą╗čÄčćą░ąĄą╝čŗąĄ ą┐ąŠ USB

1.1 ąöčĆą░ą╣ą▓ąĄčĆ ą┤ą╗čÅ čĆą░ąĘą╗ąĖčćąĮčŗčģ ąŠą┐ąĄčĆą░čåąĖąŠąĮąĮčŗčģ čüąĖčüč鹥ą╝

ąöą╗čÅ čĆą░ą▒ąŠčéčŗ FT2232H ąĮčāąČąĮčŗ ą┤čĆą░ą╣ą▓ąĄčĆčŗ (ą┐ąĄčĆąĄčćąĖčüą╗ąĄąĮąĮčŗąĄ ąĮąĖąČąĄ), ą║ąŠč鹊čĆčŗąĄ ą╝ąŠąČąĮąŠ čüą▓ąŠą▒ąŠą┤ąĮąŠ čüą║ą░čćą░čéčī (ąĖ ąĘą░č鹥ą╝ ą▒ąĄčüą┐ą╗ą░čéąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī) čü čüą░ą╣čéą░ FTDI (čüą╝. čüčüčŗą╗ą║ąĖ [1, 2]). ąöčĆą░ą╣ą▓ąĄčĆ ą┤ą╗čÅ FT2232H ą▒čŗą▓ą░ąĄčé ą┤ą▓čāčģ ą▓ąĖą┤ąŠą▓. ą¤ąĄčĆą▓čŗą╣ ą┤ą╗čÅ č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓ąĖčĆčéčāą░ą╗čīąĮąŠą│ąŠ COM-ą┐ąŠčĆčéą░ (virtual COM port, VCP), čćč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé č湥čĆąĄąĘ USB 菹╝čāą╗ąĖčĆąŠą▓ą░čéčī čüčéą░ąĮą┤ą░čĆčéąĮčŗą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ą┐ąŠčĆčé PC (ąĮą░ą┐čĆąĖą╝ąĄčĆ TTX). ąöčĆčāą│ąŠą╣ ą┤čĆą░ą╣ą▓ąĄčĆ USB ąŠčé ą║ąŠą╝ą┐ą░ąĮąĖąĖ FTDI, čéą░ą║ ąĮą░ąĘčŗą▓ą░ąĄą╝čŗą╣ D2XX, ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╝ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖąĄą╝ čģąŠčüčéą░ ą┤ą╗čÅ ą┐čĆčÅą╝ąŠą│ąŠ ą┤ąŠčüčéčāą┐ą░ ą║ FT2232H č湥čĆąĄąĘ ą▒ąĖą▒ą╗ąĖąŠč鹥ą║čā DLL.

Royalty free VIRTUAL COM PORT (VCP) DRIVERS ą┤ą╗čÅ:

- Windows 2000, Server 2003, Server 2008

- Windows XP ąĖ XP 64-bit

- Windows Vista ąĖ Vista 64-bit

- Windows XP Embedded Windows CE 4.2, 5.0, 5.2 ąĖ 6.0

- Mac OS-X

- Linux (2.6.9 ąĖą╗ąĖ ą▒ąŠą╗ąĄąĄ čüą▓ąĄąČą░čÅ)

- Windows 7 ąĖ Windows 7 64-bit

Royalty free D2XX Direct Drivers (USB Drivers + DLL S/W Interface) ą┤ą╗čÅ:

- Windows 2000, Server 2003, Server 2008

- Windows XP ąĖ XP 64-bit

- Windows Vista ąĖ Vista 64-bit

- Windows XP Embedded Windows CE 4.2, 5.0, 5.2 ąĖ 6.0

- Linux (2.4 ąĖą╗ąĖ ą▒ąŠą╗ąĄąĄ čüą▓ąĄąČą░čÅ) ąĖ Linux x86_64

- Windows 7 and Windows 7 64-bit

ąöą╗čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ ą┤čĆą░ą╣ą▓ąĄčĆą░ ąĖą╝ąĄčÄčéčüčÅ ą░ą┐ąĮąŠčāčéčŗ AN_103, AN_104, AN_107, AN_119, ą░ čéą░ą║ąČąĄ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮą░čÅ ąĖąĮč乊čĆą╝ą░čåąĖčÅ ą┐ąŠ čāčüčéą░ąĮąŠą▓ą║ąĄ ąĖ ą┐čĆąĖą╝ąĄąĮąĄąĮąĖčÄ - ą░ą┐ąĮąŠčāčéčŗ AN_113, AN_109, AN_110, AN_111, AN_113, AN114, AN135, AN108, TN_104 (čüą╝. čüčüčŗą╗ą║ąĖ [4, 5]).

1.2 ąśą╝ąĄąĮąŠą▓ą░ąĮąĖąĄ čćąĖą┐ąŠą▓ (part numbers)

| Part Number |

Package (ą║ąŠčĆą┐čāčü) |

| FT2232HL-xxxx |

64 Pin LQFP (LQFP64) |

| FT2232HQ-xxxx |

64 Pin QFN (QFN64) |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą║ąŠą┤ čāą┐ą░ą║ąŠą▓ą║ąĖ ą▓ xxxx čüą╗ąĄą┤čāčÄčēąĖą╣:

- Reel: ą▓ ą╗ąĄąĮč鹥 ąĖ ą║ą░čéčāčłą║ąĄ (LQFP =1000 čłčéčāą║ ąĮą░ ą║ą░čéčāčłą║čā, QFN =4000 čłčéčāą║ ąĮą░ ą║ą░čéčāčłą║čā).

- Tray: ą▓ ą╗ąŠčéą║ąĄ (LQFP =160 čłčéčāą║ ąĮą░ ą╗ąŠč鹊ą║, QFN =260 čłčéčāą║ ąĮą░ ą╗ąŠč鹊ą║).

ąĪą╝. čüąĄą║čåąĖčÄ 8 ą┐ąŠ ą╝ąĄčģą░ąĮąĖč湥čüą║ąĖą╝ ą┐ą░čĆą░ą╝ąĄčéčĆą░ą╝ ą▓čüąĄčģ ą║ąŠčĆą┐čāčüąŠą▓.

1.3 ąĪąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĄ čüčéą░ąĮą┤ą░čĆčéčā USB

ą£ąŠčüčé FT2232H ą┐ąŠą╗ąĮąŠčüčéčīčÄ čüąŠą▓ą╝ąĄčüčéąĖą╝ čüąŠ čüčéą░ąĮą┤ą░čĆč鹊ą╝ USB 2.0, ąĖ ą┐ąŠą╗čāčćąĖą╗ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ USB-IF Test-ID (TID) 40720019.

ą¤ą░čĆą░ą╝ąĄčéčĆčŗ ą▓čĆąĄą╝ąĄąĮąĖ ąĮą░čĆą░čüčéą░ąĮąĖčÅ ąĖ čüą┐ą░ą┤ą░ čüąĖą│ąĮą░ą╗ąŠą▓ USB ąĮąĄ č鹊ą╗čīą║ąŠ ąĘą░ą▓ąĖčüčÅčé ąŠčé ą┤čĆą░ą╣ą▓ąĄčĆąŠą▓ čüąĖą│ąĮą░ą╗ąŠą▓ USB, ąĮąŠ čéą░ą║ąČąĄ ąĘą░ą▓ąĖčüčÅčé ąŠčé čüąĖčüč鹥ą╝čŗ ąĖ čäą░ą║č鹊čĆąŠą▓ čĆą░ąĘą▓ąŠą┤ą║ąĖ PCB (ą┐ąĄčćą░čéąĮąŠą╣ ą┐ą╗ą░čéčŗ), ą▓ąĮąĄčłąĮąĖčģ ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓ ąĖ ąĘą░čēąĖčéčŗ ąŠčé ą┐ąĄčĆąĄą┐ą░ą┤ąŠą▓, ąĖą╝ąĄčÄčēąĖčģčüčÅ ąĮą░ čüąĖą│ąĮą░ą╗ą░čģ USB. ąöą╗čÅ čüąŠą▓ą╝ąĄčüčéąĖą╝ąŠčüčéąĖ čü USB ą╝ąŠąČąĄčé ą┐ąŠčéčĆąĄą▒ąŠą▓ą░čéčīčüčÅ ąŠč湥ąĮčī ąĮąĄąĘąĮą░čćąĖč鹥ą╗čīąĮą░čÅ ą┐ąŠą┤čüčéčĆąŠą╣ą║ą░. ą¤ą░čĆą░ą╝ąĄčéčĆčŗ ą▓čĆąĄą╝ąĄąĮąĖ ą╝ąŠą│čāčé ą▒čŗčéčī ąĖąĘą╝ąĄąĮąĄąĮčŗ č湥čĆąĄąĘ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗąĄ čāčüčéą░ąĮąŠą▓ą║ąĖ, čüąŠčģčĆą░ąĮčÅąĄą╝čŗąĄ ą▓ č鹊ą╝ ąČąĄ čüą░ą╝ąŠą╝ EEPROM, ą║ąŠč鹊čĆąŠąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čüąŠčģčĆą░ąĮąĄąĮąĖčÅ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą▓ USB. ąÜčĆąŠą╝ąĄ č鹊ą│ąŠ, ą╝ąŠąČąĮąŠ ą┐čĆąĖą╝ąĄąĮąĖčéčī ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗąĄ ą┐ą░čüčüąĖą▓ąĮčŗąĄ ą║ąŠą╝ą┐ąŠąĮąĄąĮčéčŗ, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗąĄ ą║ čäąĖąĘąĖč湥čüą║ąĖą╝ čüąĖą│ąĮą░ą╗ą░ą╝ USB.

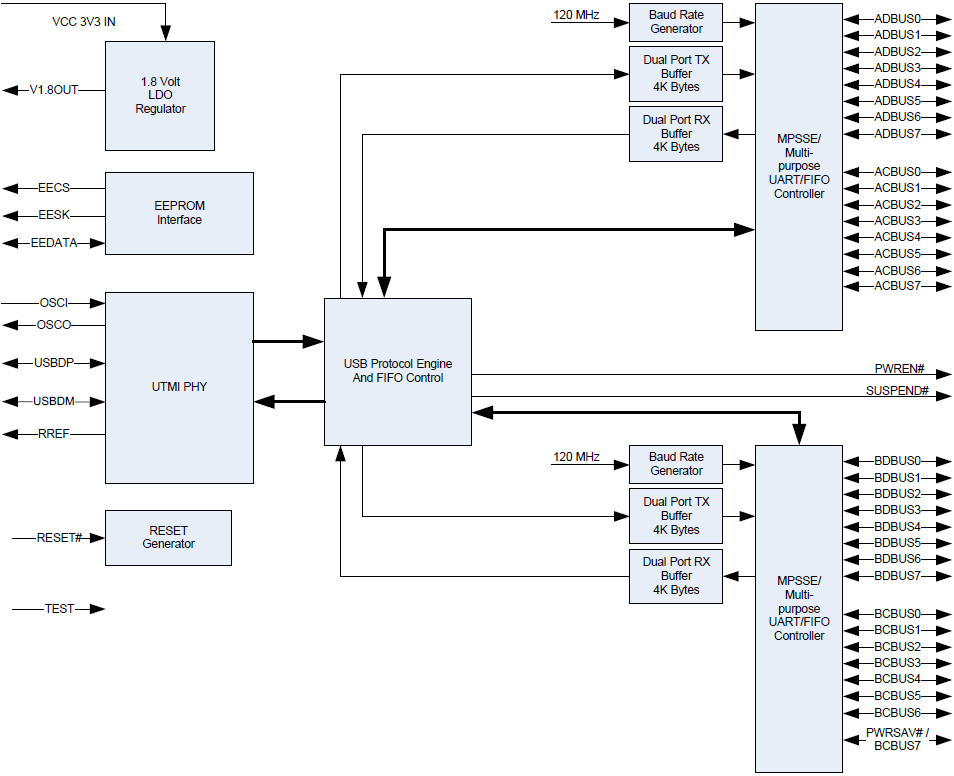

2 FT2232H Block Diagram (čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮą░čÅ ą▒ą╗ąŠčćąĮą░čÅ ą┤ąĖą░ą│čĆą░ą╝ą╝ą░)

ą×ą┐ąĖčüą░ąĮąĖąĄ čäčāąĮą║čåąĖąĖ ą║ą░ąČą┤ąŠą│ąŠ ą▒ą╗ąŠą║ą░ čüą╝. ą▓ čüąĄą║čåąĖąĖ 4.

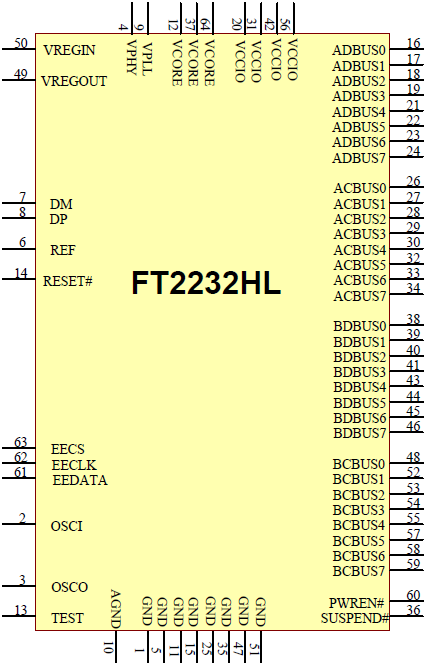

[3 ą”ąŠą║ąŠą╗ąĄą▓ą║ą░ ąĖ ąŠą┐ąĖčüą░ąĮąĖąĄ ą▓čŗą▓ąŠą┤ąŠą▓ FT2232H]

ąÜąŠčĆą┐čāčüą░ 64-pin LQFP ąĖ 64-pin QFN ąĖą╝ąĄčÄčé ąŠą┤ąĖąĮą░ą║ąŠą▓čāčÄ ąĮčāą╝ąĄčĆą░čåąĖčÄ ąĮąŠąČąĄą║ ą┐ąŠ čüą▓ąŠąĖą╝ ą▓čŗą┐ąŠą╗ąĮčÅąĄą╝čŗą╝ čäčāąĮą║čåąĖčÅą╝.

3.2 ą×ą┐ąĖčüą░ąĮąĖąĄ ą▓čŗą▓ąŠą┤ąŠą▓ (ąĮąŠąČąĄą║) ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ FT2232H

ążčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĄ ą╝ąĮąŠą│ąĖčģ ąĮąŠąČąĄą║ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą▓čŗą▒čĆą░ąĮąĮąŠą╣ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĄą╣ FT2232H. ąÆ čéą░ą▒ą╗ąĖčåąĄ ąĮąĖąČąĄ ą┐ąŠą┤čĆąŠą▒ąĮąŠ ąŠą┐ąĖčüą░ąĮąŠ ąĮą░ąĘąĮą░č湥ąĮąĖąĄ ą║ą░ąČą┤ąŠą╣ ąĮąŠąČą║ąĖ ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ąĖąĮč鹥čĆč乥ą╣čüą░ (ą┤ą╗čÅ čüąĖą│ąĮą░ą╗ąŠą▓ ąĖą╝ąĄčÄčēąĖčģ ąĮąĖąĘą║ąĖą╣ ą░ą║čéąĖą▓ąĮčŗą╣ ą╗ąŠą│ąĖč湥čüą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī, ą▓ ą║ąŠąĮčåąĄ ąĖą╝ąĄąĮąĖ čāą║ą░ąĘą░ąĮ čüąĖą╝ą▓ąŠą╗ #). ąØąŠąČą║ąĖ, ą┐ąŠą╝ąĄč湥ąĮąĮčŗąĄ **, ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ čĆą░ą▒ąŠčéą░čÄčé ą║ą░ą║ ą▓čģąŠą┤čŗ čü čéčĆąĄčéčīąĖą╝ čüąŠčüč鹊čÅąĮąĖąĄą╝, čü ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗą╝ąĖ pull-up čĆąĄąĘąĖčüč鹊čĆą░ą╝ąĖ ąĮąŠą╝ąĖąĮą░ą╗ąŠą╝ (ą┐čĆąĖą▒ą╗ąĖąĘąĖč鹥ą╗čīąĮąŠ) 75 ą║ą×ą╝ ąĮą░ čłąĖąĮčā VCCIO.

| ąóą░ą▒ą╗ąĖčåą░ ąĮąŠąČąĄą║ FT2232H, čäčāąĮą║čåąĖąĖ ą║ąŠč鹊čĆčŗčģ ąĘą░ą▓ąĖčüąĖčé ąŠčé ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ |

| ąÆčŗą▓ąŠą┤ |

ążčāąĮą║čåąĖąĖ ą▓čŗą▓ąŠą┤ąŠą▓ (ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ EEPROM) |

| Ōä¢ |

ąĖą╝čÅ |

ASYNC

Serial

(RS232) |

245 FIFO

SYNC |

245 FIFO |

ASYNC

Bit-bang |

SYNC

Bit-bang |

MPSSE |

Fast

Serial

interface |

CPU

Style

FIFO |

Host Bus

Emulation |

| ąÜą░ąĮą░ą╗ A |

| 16 |

ADBUS0 |

TXD |

D0 |

D0 |

D0 |

D0 |

TCK/SK |

ąśčüą┐ąŠą╗čīąĘčāąĄčé

ą║ą░ąĮą░ą╗ B |

D0 |

AD0 |

| 17 |

ADBUS1 |

RXD |

D1 |

D1 |

D1 |

D1 |

TDI/DO |

D1 |

AD1 |

| 18 |

ADBUS2 |

RTS# |

D2 |

D2 |

D2 |

D2 |

TDO/DI |

D2 |

AD2 |

| 19 |

ADBUS3 |

CTS# |

D3 |

D3 |

D3 |

D3 |

TMS/CS |

D3 |

AD3 |

| 21 |

ADBUS4 |

DTR# |

D4 |

D4 |

D4 |

D4 |

GPIOL0 |

|

D4 |

AD4 |

| 22 |

ADBUS5 |

DSR# |

D5 |

D5 |

D5 |

D5 |

GPIOL1 |

|

D5 |

AD5 |

| 23 |

ADBUS6 |

DCD# |

D6 |

D6 |

D6 |

D6 |

GPIOL2 |

|

D6 |

AD6 |

| 24 |

ADBUS7 |

RI# |

D7 |

D7 |

D7 |

D7 |

GPIOL3 |

|

D7 |

AD7 |

| 26 |

ACBUS0 |

TXDEN |

RXF# |

RXF# |

** |

** |

GPIOH0 |

|

CS# |

A8 |

| 27 |

ACBUS1 |

** |

TXE# |

TXE# |

WRSTB# |

WRSTB# |

GPIOH1 |

|

A0 |

A9 |

| 28 |

ACBUS2 |

** |

RD# |

RD# |

RDSTB# |

RDSTB# |

GPIOH2 |

|

RD# |

A10 |

| 29 |

ACBUS3 |

RXLED# |

WR# |

WR# |

** |

** |

GPIOH3 |

|

WR# |

A11 |

| 30 |

ACBUS4 |

TXLED# |

SIWUA |

SIWUA |

SIWUA |

SIWUA |

GPIOH4 |

|

SIWUA |

A12 |

| 32 |

ACBUS5 |

** |

CLKOUT |

** |

** |

** |

GPIOH5 |

|

** |

A13 |

| 33 |

ACBUS6 |

** |

OE# |

** |

** |

** |

GPIOH6 |

|

** |

A14 |

| 34 |

ACBUS7 |

** |

** |

** |

** |

** |

GPIOH7 |

|

** |

A15 |

| ąÜą░ąĮą░ą╗ B |

| 38 |

BDBUS0 |

TXD |

|

D0 |

D0 |

D0 |

TCK/SK |

FSDI |

D0 |

CS# |

| 39 |

BDBUS1 |

RXD |

|

D1 |

D1 |

D1 |

TDI/DO |

FSCLK |

D1 |

ALE |

| 40 |

BDBUS2 |

RTS# |

|

D2 |

D2 |

D2 |

TDO/DI |

FSDO |

D2 |

RD# |

| 41 |

BDBUS3 |

CTS# |

|

D3 |

D3 |

D3 |

TMS/CS |

FSCTS |

D3 |

WR# |

| 43 |

BDBUS4 |

DTR# |

|

D4 |

D4 |

D4 |

GPIOL0 |

|

D4 |

IORDY |

| 44 |

BDBUS5 |

DSR# |

|

D5 |

D5 |

D5 |

GPIOL1 |

|

D5 |

CLKOUT |

| 45 |

BDBUS6 |

DCD# |

|

D6 |

D6 |

D6 |

GPIOL2 |

|

D6 |

I/O0 |

| 46 |

BDBUS7 |

RI# |

|

D7 |

D7 |

D7 |

GPIOL3 |

|

D7 |

I/O1 |

| 48 |

BCBUS0 |

TXDEN |

|

RXF# |

** |

** |

GPIOH0 |

|

CS# |

** |

| 52 |

BCBUS1 |

** |

|

TXE# |

WRSTB# |

WRSTB# |

GPIOH1 |

|

A0 |

** |

| 53 |

BCBUS2 |

** |

|

RD# |

RDSTB# |

RDSTB# |

GPIOH2 |

|

RD# |

** |

| 54 |

BCBUS3 |

RXLED# |

|

WR# |

** |

** |

GPIOH3 |

|

WR# |

** |

| 55 |

BCBUS4 |

TXLED# |

|

SIWUB |

SIWUB |

SIWUB |

GPIOH4 |

SIWUB |

SIWUB |

** |

| 57 |

BCBUS5 |

** |

|

** |

** |

** |

GPIOH5 |

|

** |

** |

| 58 |

BCBUS6 |

** |

|

** |

** |

** |

GPIOH6 |

|

** |

** |

| 59 |

BCBUS7 |

PWRSAW# |

PWRSAW# |

PWRSAW# |

PWRSAW# |

PWRSAW# |

GPIOH7 |

PWRSAW# |

PWRSAW# |

PWRSAW# |

| 60 |

PWREN# |

PWREN# |

PWREN# |

PWREN# |

PWREN# |

PWREN# |

PWREN# |

PWREN# |

PWREN# |

PWREN# |

| 36 |

SUSPEND# |

SUSPEND# |

SUSPEND# |

SUSPEND# |

SUSPEND# |

SUSPEND# |

SUSPEND# |

SUSPEND# |

SUSPEND# |

SUSPEND# |

ąśąĮč鹥čĆč乥ą╣čü ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąŠąĮąĮąŠą╣ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ (EEPROM), čäčāąĮą║čåąĖčÅ čŹčéąĖčģ ą▓čŗą▓ąŠą┤ąŠą▓ ąĮąĄ ąĘą░ą▓ąĖčüąĖčé ąŠčé ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ

|

| 63 |

EECS |

I/O (ą▓čģąŠą┤/ą▓čŗčģąŠą┤), Chip Select, ą▓čŗą▒ąŠčĆą║ą░ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ. ąØą░čģąŠą┤ąĖčéčüčÅ ą▓ čéčĆąĄčéčīąĄą╝ čüąŠčüč鹊čÅąĮąĖąĖ ą┐čĆąĖ čüą▒čĆąŠčüąĄ FT2232H. |

| 62 |

EECLK |

Output (ą▓čŗčģąŠą┤), čéą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗ ą┤ą░ąĮąĮčŗčģ ą┤ą╗čÅ EEPROM. ąØą░čģąŠą┤ąĖčéčüčÅ ą▓ čéčĆąĄčéčīąĄą╝ čüąŠčüč鹊čÅąĮąĖąĖ ą┐čĆąĖ čüą▒čĆąŠčüąĄ FT2232H. |

| 61 |

EEDATA |

I/O (ą▓čģąŠą┤/ą▓čŗčģąŠą┤), čüąĖą│ąĮą░ą╗ ą┤ą░ąĮąĮčŗčģ, ąĮą░ą┐čĆčÅą╝čāčÄ ą┐ąŠą┤ą║ą╗čÄčćą░ąĄą╝čŗą╣ ą║ ą▓čģąŠą┤čā ą┤ą░ąĮąĮčŗčģ EEPROM (Data-In) ąĖ ą║ ą▓čŗčģąŠą┤čā EEPROM (Data-Out) č湥čĆąĄąĘ čĆąĄąĘąĖčüč鹊čĆ 2.2 ą║ą×ą╝. ąóą░ą║ąČąĄ ą┤ą╗čÅ ą║ąŠčĆčĆąĄą║čéąĮąŠą╣ čĆą░ą▒ąŠčéčŗ ąĮčāąČąĄąĮ ą▓ąĄčĆčģąĮąĖą╣ ąĮą░ą│čĆčāąĘąŠčćąĮčŗą╣ čĆąĄąĘąĖčüč鹊čĆ (pullup) ąĮąŠą╝ąĖąĮą░ą╗ąŠą╝ 10 ą║ą×ą╝. ąØą░čģąŠą┤ąĖčéčüčÅ ą▓ čéčĆąĄčéčīąĄą╝ čüąŠčüč鹊čÅąĮąĖąĖ ą┐čĆąĖ čüą▒čĆąŠčüąĄ FT2232H. |

ąóą░ą▒ą╗ąĖčåą░ ąĮąŠąČąĄą║ FT2232H, čäčāąĮą║čåąĖąĖ ą║ąŠč鹊čĆčŗčģ ąĮąĄ ąĘą░ą▓ąĖčüąĖčé ąŠčé ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ (ą┐ąĖčéą░ąĮąĖąĄ ąĖ ąĘąĄą╝ą╗čÅ)

|

| Pin Ōä¢ |

ąśą╝čÅ |

ąóąĖą┐ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| 12,37,64 |

VCORE |

ąÆčģąŠą┤ ą┐ąĖčéą░ąĮąĖčÅ (POWER Input) |

ąÆčģąŠą┤ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ +1.8V ą┤ą╗čÅ ą┐ąĖčéą░ąĮąĖčÅ čÅą┤čĆą░. |

| 20,31,42,56 |

VCCIO |

ąÆčģąŠą┤ ą┐ąĖčéą░ąĮąĖčÅ (POWER Input) |

ąÆčģąŠą┤ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ +3.3V, ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮąĮąŠą│ąŠ ą┤ą╗čÅ ą┐ąĖčéą░ąĮąĖčÅ ąĖąĮč鹥čĆč乥ą╣čüą░ I/O. ą×čłąĖą▒ąŠčćąĮąŠąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖąĄ ą▓čüąĄčģ ąĮąŠąČąĄą║ VCCIO ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ąĮąĄą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖčÅ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ. |

| 9 |

VPLL |

ąÆčģąŠą┤ ą┐ąĖčéą░ąĮąĖčÅ (POWER Input) |

ąÆčģąŠą┤ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ +3.3V, ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮąĮąŠą│ąŠ ą┤ą╗čÅ ą┐ąĖčéą░ąĮąĖčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čāąĘą╗ą░ PHY PLL (čüąĖčüč鹥ą╝ą░ ążąÉą¤ą¦). ąĀąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ čŹč鹊čé ąĖčüč鹊čćąĮąĖą║ ą┐ąĖčéą░ąĮąĖčÅ čäąĖą╗čīčéčĆąŠą▓ą░čéčī čü ą┐ąŠą╝ąŠčēčīčÄ LC-čäąĖą╗čīčéčĆą░. |

| 4 |

VPHY |

ąÆčģąŠą┤ ą┐ąĖčéą░ąĮąĖčÅ (POWER Input) |

ąÆčģąŠą┤ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ +3.3V, ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮąĮąŠą│ąŠ ą┤ą╗čÅ ą┐ąĖčéą░ąĮąĖčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čāąĘą╗ą░ USB PHY. ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 čŹč鹊čé ą▓čģąŠą┤ ąĮąĄą╗čīąĘčÅ čüąŠąĄą┤ąĖąĮčÅčéčī ąĮą░ą┐čĆčÅą╝čāčÄ ą║ ą┐ąĖčéą░ąĮąĖčÄ USB (čłąĖąĮą░ VBUS), ą┤ąŠą╗ąČąĄąĮ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą▓ąĮąĄčłąĮąĖą╣ čĆąĄą│čāą╗čÅč鹊čĆ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ąĮą░ +3.3V. ąĀąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ čŹč鹊čé ąĖčüč鹊čćąĮąĖą║ ą┐ąĖčéą░ąĮąĖčÅ čäąĖą╗čīčéčĆąŠą▓ą░čéčī čü ą┐ąŠą╝ąŠčēčīčÄ LC-čäąĖą╗čīčéčĆą░. |

| 50 |

VREGIN |

ąÆčģąŠą┤ ą┐ąĖčéą░ąĮąĖčÅ (POWER Input) |

ąÆčģąŠą┤ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ +3.3V. ą¤ąŠą┤ą║ą╗čÄč湥ąĮ ą║ ą▓čģąŠą┤čā ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čĆąĄą│čāą╗čÅč鹊čĆą░ 1.8V ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ. |

| 49 |

VREGOUT |

ąÆčŗčģąŠą┤ ą┐ąĖčéą░ąĮąĖčÅ (POWER Output) |

ąÆčŗčģąŠą┤ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ +1.8V. ą¤ąŠą┤ą║ą╗čÄč湥ąĮ ą║ ą▓čŗčģąŠą┤čā ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čĆąĄą│čāą╗čÅč鹊čĆą░ 1.8V ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ. ąĪąŠąĄą┤ąĖąĮąĖč鹥 VREGOUT ąĖ VCORE, ąĖ ą┐ąŠą┤ą║ą╗čÄčćąĖč鹥 čüčÄą┤ą░ čäąĖą╗čīčéčĆčāčÄčēąĖą╣ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ ąĮą░ 3.3 ą╝ą║ąż. |

| 10 |

AGND |

ąÆčģąŠą┤ ą┐ąĖčéą░ąĮąĖčÅ (POWER Input) |

0V, ą░ąĮą░ą╗ąŠą│ąŠą▓ą░čÅ ąĘąĄą╝ą╗čÅ (Analog ground). |

1,5,11,15,

25,35,47,51 |

GND |

ąÆčģąŠą┤ ą┐ąĖčéą░ąĮąĖčÅ (POWER Input) |

0V, ąĘąĄą╝ą╗čÅ, ąŠą▒čēąĖą╣ ą┐čĆąŠą▓ąŠą┤ (Ground input). |

ąóą░ą▒ą╗ąĖčåą░ ąŠą▒čēąĖčģ ąĮąŠąČąĄą║ FT2232H, čäčāąĮą║čåąĖčÅ ą║ąŠč鹊čĆčŗčģ ąĮąĄ ąĘą░ą▓ąĖčüąĖčé ąŠčé ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ

|

| Pin Ōä¢ |

ąśą╝čÅ |

ąóąĖą┐ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| 2 |

OSCI |

ąÆčģąŠą┤ |

ąÆčģąŠą┤ ą│ąĄąĮąĄčĆą░č鹊čĆą░ (ąŠą▒čŗčćąĮąŠ ą┐ąŠą┤ą║ą╗čÄčćą░čÄčé ą║ ą║ą▓ą░čĆčåąĄą▓ąŠą╝čā čĆąĄąĘąŠąĮą░č鹊čĆčā). |

| 3 |

OSCO |

ąÆčŗčģąŠą┤ |

ąÆčŗčģąŠą┤ ą│ąĄąĮąĄčĆą░č鹊čĆą░ (ąŠą▒čŗčćąĮąŠ ą┐ąŠą┤ą║ą╗čÄčćą░čÄčé ą║ ą║ą▓ą░čĆčåąĄą▓ąŠą╝čā čĆąĄąĘąŠąĮą░č鹊čĆčā). |

| 6 |

REF |

ąÆčģąŠą┤ |

ąŁčéą░ą╗ąŠąĮąĮčŗą╣ ąĖčüč鹊čćąĮąĖą║ č鹊ą║ą░ - ą╝ąĄąČą┤čā ą▓čŗą▓ąŠą┤ąŠą╝ REF ąĖ GND ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮ čĆąĄąĘąĖčüč鹊čĆ ąĮą░ 12 ą║ą×ą╝ čü č鹊čćąĮąŠčüčéčīčÄ 1%. |

| 7 |

DM |

ąÆčģąŠą┤ |

ąĪąĖą│ąĮą░ą╗ USB D- (Data Minus). |

| 8 |

DP |

ąÆčģąŠą┤ |

ąĪąĖą│ąĮą░ą╗ USB D+ (Data Plus). |

| 13 |

TEST |

ąÆčģąŠą┤ |

ąÆčģąŠą┤ ą┤ą╗čÅ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ. ąöą╗čÅ ąĮąŠčĆą╝ą░ą╗čīąĮąŠą│ąŠ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖčÅ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą║ GND. |

| 14 |

RESET# |

ąÆčģąŠą┤ |

ąÆčģąŠą┤ čüą▒čĆąŠčüą░ (ą░ą║čéąĖą▓ąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 0). |

| 60 |

PWREN# |

ąÆčŗčģąŠą┤ |

ąÆčŗčģąŠą┤ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ, ą░ą║čéąĖą▓ąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 0. ąÜąŠą│ą┤ą░ PWREN# = 0, č鹊 čŹč鹊 ąŠąĘąĮą░čćą░ąĄčé ąĮąŠčĆą╝ą░ą╗čīąĮąŠąĄ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĄ, ą░ ą║ąŠą│ą┤ą░ PWREN# = 1, č鹊 čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ USB SUSPEND (ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ą░ USB), ąĖą╗ąĖ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮąĄ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąŠ. ąŁč鹊čé ą▓čŗčģąŠą┤ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮ ą▓ąĮąĄčłąĮąĖą╝ąĖ čüčģąĄą╝ą░ą╝ąĖ ą┤ą╗čÅ ą╗ąŠą│ąĖą║ąĖ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ, ą║ąŠą│ą┤ą░ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ąĖ USB, ąĖą╗ąĖ ąĮąĄ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąŠ. |

| 36 |

SUSPEND# |

ąÆčŗčģąŠą┤ |

ąÉą║čéąĖą▓ąĮčŗą╣ čüąĖą│ąĮą░ą╗ ą╗ąŠą│. 0 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ (čāčüčéčĆąŠą╣čüčéą▓ąŠ USB) ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ suspend (ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ). |

| 59 |

PWRSAV# |

ąÆčģąŠą┤ |

ąÆčģąŠą┤ ą┤ą╗čÅ ą▓ą║ą╗čÄč湥ąĮąĖčÅ čĆąĄąČąĖą╝ą░ ą┐ąŠąĮąĖąČąĄąĮąĮąŠą│ąŠ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ (Power Save). ąŁčéą░ ąŠą┐čåąĖčÅ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ ą▓ EEPROM. ąśčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ, ą║ąŠą│ą┤ą░ FT2232H čĆą░ą▒ąŠčéą░ąĄčé ą▓ čĆąĄąČąĖą╝ąĄ čü čüąŠą▒čüčéą▓ąĄąĮąĮčŗą╝ ąĖčüč鹊čćąĮąĖą║ąŠą╝ ą┐ąĖčéą░ąĮąĖčÅ (self powered mode) ą┤ą╗čÅ ą┐čĆąĄą┤ąŠčéą▓čĆą░čēąĄąĮąĖčÅ čüč鹥ą║ą░ąĮąĖčÅ č鹊ą║ą░ čüąĖą│ąĮą░ą╗ąŠą▓ USB, ą║ąŠą│ą┤ą░ čģąŠčüčé ąĖą╗ąĖ čģą░ą▒ ą▓čŗą║ą╗čÄčćą░čÄčéčüčÅ.

PWRSAW# = 1: ąĮąŠčĆą╝ą░ą╗čīąĮčŗą╣ čĆąĄąČąĖą╝ čĆą░ą▒ąŠčéčŗ.

PWRSAW# = 0: FT2232H ą┐čĆąĖąĮčāą┤ąĖč鹥ą╗čīąĮąŠ ą┐ąĄčĆąĄą▓ąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ SUSPEND.

PWRSAW# ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą║ GND (č湥čĆąĄąĘ čĆąĄąĘąĖčüč鹊čĆ 10 ą║ą×ą╝) ąĖ ą║ ą┤čĆčāą│ąŠą╝čā čĆąĄąĘąĖčüč鹊čĆčā (ąĮą░ą┐čĆąĖą╝ąĄčĆ 4.7 ą║ą×ą╝), ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮąŠą╝čā ą║ čłąĖąĮąĄ VBUS ą║ąŠąĮąĮąĄą║č鹊čĆą░ USB. ąÜąŠą│ą┤ą░ ąĮą░ čŹč鹊ą╝ ą▓čģąŠą┤ąĄ ą╗ąŠą│. 1, č鹊 čŹč鹊 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 FT2232H ą┐ąŠą┤ą║ą╗čÄč湥ąĮą░ ą║ čģąŠčüčéčā PC. ąÜąŠą│ą┤ą░ čģąŠčüčé PC ąĖą╗ąĖ čģą░ą▒ ą▓čŗą║ą╗čÄčćą░ąĄčéčüčÅ, č鹊 FT2232H ą▒čāą┤ąĄčé čāą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ SUSPEND (ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ą░). |

3.4 ąÜąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝čŗąĄ ą▓čŗą▓ąŠą┤čŗ FT2232H

ą¤ąŠčüą╗ąĄą┤čāčÄčēąĖąĄ čüąĄą║čåąĖąĖ ąŠą┐ąĖčüčŗą▓ą░čÄčé čäčāąĮą║čåąĖčÄ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝čŗčģ ą▓čŗą▓ąŠą┤ąŠą▓, ą║ąŠč鹊čĆčŗąĄ čāą║ą░ąĘą░ąĮčŗ ą▓ čéą░ą▒ą╗ąĖčåąĄ čüąĄą║čåąĖąĖ 3.2. ąśčģ čäčāąĮą║čåąĖčÅ ąĘą░ą▓ąĖčüąĖčé ąŠčé č鹊ą│ąŠ, ą║ą░ą║ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮą░ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ FT2232H (ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąŠąĮąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ čüčćąĖčéčŗą▓ą░čÄčéčüčÅ ąĖąĘ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮąŠą╣ ą▓ąĮąĄčłąĮąĄą╣ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ EEPROM).

3.4.1 ą×ą┐ąĖčüą░ąĮąĖąĄ ąĮąŠąČąĄą║, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗčģ ą▓ ąĖąĮč鹥čĆč乥ą╣čüąĄ RS232

ąÜą░ąĮą░ą╗ A ąĖą╗ąĖ ą║ą░ąĮą░ą╗ B ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ FT2232H ą╝ąŠąČąĄčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą║ą░ą║ ąĖąĮč鹥čĆč乥ą╣čü RS232. ąÆ čéą░ą▒ą╗ąĖčåąĄ čāą║ą░ąĘą░ąĮčŗ ąĮąŠąČą║ąĖ, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą▓ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ, ąĖ ą┐čĆąĖą▓ąĄą┤ąĄąĮąŠ ąĖčģ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ.

ąÜą░ąĮą░ą╗ A

Pin Ōä¢ |

ąÜą░ąĮą░ą╗ B

Pin Ōä¢ |

ąśą╝čÅ |

ąóąĖą┐ |

ą×ą┐ąĖčüą░ąĮąĖąĄ čüąĖą│ąĮą░ą╗ąŠą▓ RS232 |

| 16 |

38 |

TXD |

ąÆčŗčģąŠą┤ |

ąÆčŗčģąŠą┤ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ |

| 17 |

39 |

RXD |

ąÆčģąŠą┤ |

ąÆčģąŠą┤ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ |

| 18 |

40 |

RTS# |

ąÆčŗčģąŠą┤ |

ąÆčŗčģąŠą┤ ą║ą▓ąĖčéąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐ąŠč鹊ą║ą░ ą┤ą░ąĮąĮčŗčģ (handshake) Ready To Send (ą│ąŠč鹊ą▓ ą║ ą┐ąĄčĆąĄą┤ą░č湥) |

| 19 |

41 |

CTS# |

ąÆčģąŠą┤ |

ąÆčģąŠą┤ ą║ą▓ąĖčéąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐ąŠč鹊ą║ą░ ą┤ą░ąĮąĮčŗčģ (handshake) Clear To Send (ąŠčćąĖčēąĄąĮąŠ ą┤ą╗čÅ ą║ ą┐ąĄčĆąĄą┤ą░čćąĖ) |

| 21 |

43 |

DTR# |

ąÆčŗčģąŠą┤ |

ąøąĖąĮąĖčÅ čüąĖą│ąĮą░ą╗ąĖąĘą░čåąĖąĖ ą┤ą╗čÅ ą╝ąŠą┤ąĄą╝ą░ Data Transmit Ready (ą│ąŠč鹊ą▓ ą║ ą┐ąĄčĆąĄą┤ą░č湥 ą┤ą░ąĮąĮčŗčģ) |

| 22 |

44 |

DSR# |

ąÆčģąŠą┤ |

ąøąĖąĮąĖčÅ čüąĖą│ąĮą░ą╗ąĖąĘą░čåąĖąĖ ąŠčé ą╝ąŠą┤ąĄą╝ą░ Data Set Ready (ą│ąŠč鹊ą▓ ą║ ąĮą░ą▒ąŠčĆčā ą┤ą░ąĮąĮčŗčģ) |

| 23 |

45 |

DCD# |

ąÆčģąŠą┤ |

ąøąĖąĮąĖčÅ čüąĖą│ąĮą░ą╗ąĖąĘą░čåąĖąĖ ąŠčé ą╝ąŠą┤ąĄą╝ą░ Data Carrier Detect (ąŠą▒ąĮą░čĆčāąČąĄąĮą░ ąĮąĄčüčāčēą░čÅ ą┤ą░ąĮąĮčŗčģ) |

| 24 |

46 |

RI# |

ąÆčģąŠą┤ |

ąŻą┐čĆą░ą▓ą╗čÅčÄčēąĖą╣ ą▓čģąŠą┤ ąĖąĮą┤ąĖą║ą░čåąĖąĖ ąĘą▓ąŠąĮą║ą░ (Ring Indicator). ąÜąŠą│ą┤ą░ ąŠą┐čåąĖčÅ čāą┤ą░ą╗ąĄąĮąĮąŠą│ąŠ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ (Remote Wake up) čĆą░ąĘčĆąĄčłąĄąĮą░ ą▓ EEPROM, ą▓čŗčüčéą░ą▓ą╗ąĄąĮąĖąĄ RI# ą▓ čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 0 ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą▓ąŠąĘąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ čĆą░ą▒ąŠčéčŗ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ USB čģąŠčüčéą░ PC (ą▓čŗčģąŠą┤ą░ ąĄą│ąŠ ąĖąĘ čĆąĄąČąĖą╝ą░ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ąĖ suspend). ąóą░ą║ąČąĄ čüą╝. ą┐čĆąĖą╝ąĄčćą░ąĮąĖčÅ 1, 2, 3 ą▓ čüąĄą║čåąĖąĖ 4.12. |

| 26 |

48 |

TXDEN |

ąÆčŗčģąŠą┤ |

ąöą╗čÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ čü ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░č鹥ą╗čÅą╝ąĖ čāčĆąŠą▓ąĮčÅ RS485. |

| 29 |

54 |

RXLED# |

ąÆčŗčģąŠą┤ |

ąÆčŗčģąŠą┤, čüąĖą│ąĮą░ą╗ąĖąĘąĖčĆčāčÄčēąĖą╣ ąŠ ą┐čĆąĖąĄą╝ąĄ ą┤ą░ąĮąĮčŗčģ. ąŚą┤ąĄčüčī ą┐ąŠčÅą▓ą╗čÅčÄčéčüčÅ ąĖą╝ą┐čāą╗čīčüčŗ ą╗ąŠą│. 0, ą║ąŠą│ą┤ą░ ą┐čĆąĖąĮąĖą╝ą░čÄčéčüčÅ ą┤ą░ąĮąĮčŗąĄ č湥čĆąĄąĘ USB. ąŁč鹊čé ą▓čŗčģąŠą┤ ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮ ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čüą▓ąĄč鹊ą┤ąĖąŠą┤ąŠą╝. |

| 30 |

55 |

TXLED# |

ąÆčŗčģąŠą┤ |

ąÆčŗčģąŠą┤, čüąĖą│ąĮą░ą╗ąĖąĘąĖčĆčāčÄčēąĖą╣ ąŠ ą┐ąĄčĆąĄą┤ą░č湥 ą┤ą░ąĮąĮčŗčģ. ąŚą┤ąĄčüčī ą┐ąŠčÅą▓ą╗čÅčÄčéčüčÅ ąĖą╝ą┐čāą╗čīčüčŗ ą╗ąŠą│. 0, ą║ąŠą│ą┤ą░ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ą┤ą░ąĮąĮčŗąĄ č湥čĆąĄąĘ USB. ąŁč鹊čé ą▓čŗčģąŠą┤ ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮ ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čüą▓ąĄč鹊ą┤ąĖąŠą┤ąŠą╝. |

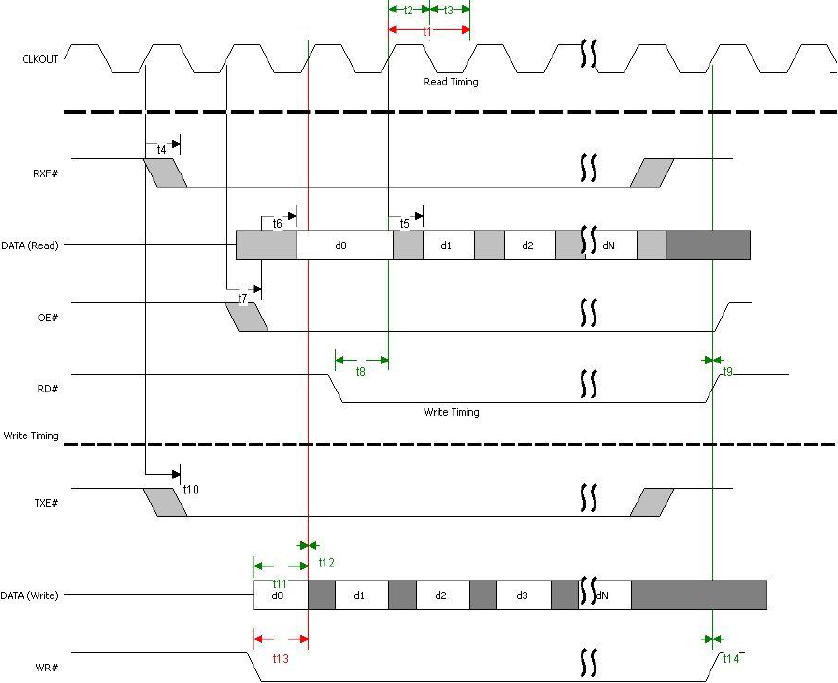

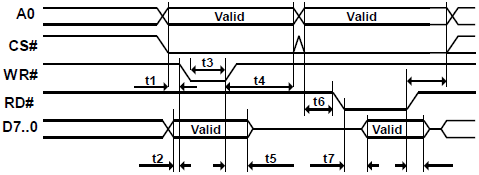

3.4.2 ą×ą┐ąĖčüą░ąĮąĖąĄ ąĮąŠąČąĄą║, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗčģ ą▓ ąĖąĮč鹥čĆč乥ą╣čüąĄ FT245 Style Synchronous FIFO

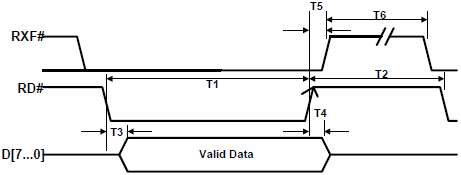

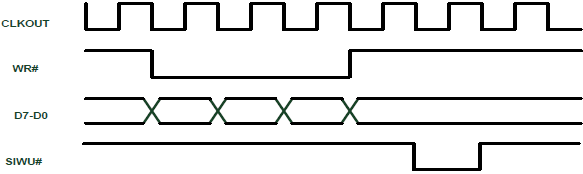

ąóąŠą╗čīą║ąŠ ą║ą░ąĮą░ą╗ A ą╝ąŠąČąĄčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą▓ ą║ą░č湥čüčéą▓ąĄ čüąĖąĮčģčĆąŠąĮąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ FIFO ą▓ čüčéąĖą╗ąĄ FT245. ąÆ čéą░ą▒ą╗ąĖčåąĄ čāą║ą░ąĘą░ąĮčŗ ąĮąŠąČą║ąĖ, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą▓ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ, ąĖ ą┐čĆąĖą▓ąĄą┤ąĄąĮąŠ ąĖčģ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ. ąöą╗čÅ ą▓čģąŠą┤ą░ ą▓ čŹč鹊čé čĆąĄąČąĖą╝ ą▓ąĮąĄčłąĮąĄąĄ EEPROM ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąŠ ą┤ą╗čÅ ą┐ąĄčĆąĄą▓ąŠą┤ą░ ą┐ąŠčĆčéą░ A ą▓ čĆąĄąČąĖą╝ 245 (port A 245 mode). ąöčĆą░ą╣ą▓ąĄčĆčā FTDI ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą┐ąŠčüą╗ą░ąĮą░ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄą╝ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮą░čÅ ą║ąŠą╝ą░ąĮą┤ą░ (Set Bit Mode option, čāčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖč鹊ą▓ąŠą│ąŠ čĆąĄąČąĖą╝ą░), ą║ąŠč鹊čĆą░čÅ ą┐ąĄčĆąĄą▓ąŠą┤ąĖčé čćąĖą┐ ą▓ čĆąĄąČąĖą╝ ąŠą┤ąĮąŠą║ą░ąĮą░ą╗čīąĮąŠą│ąŠ čüąĖąĮčģčĆąŠąĮąĮąŠą│ąŠ FIFO. ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ą║ą░ąĮą░ą╗ B ąĮąĄ ą┤ąŠčüčéčāą┐ąĄąĮ, ąĖ ą▓čüąĄ čĆąĄčüčāčĆčüčŗ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą┐ąĄčĆąĄą║ą╗čÄčćą░čÄčéčüčÅ ąĮą░ ąŠą▒čüą╗čāąČąĖą▓ą░ąĮąĖąĄ ą║ą░ąĮą░ą╗ą░ A. ąöą░ąĮąĮčŗąĄ ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ ąĖą╗ąĖ čüčćąĖčéčŗą▓ą░čÄčéčüčÅ ą┐ąŠ čäčĆąŠąĮčéčā ąĮą░čĆą░čüčéą░ąĮąĖčÅ čüąĖą│ąĮą░ą╗ą░ CLKOUT.

ąÜą░ąĮą░ą╗ A

Pin Ōä¢ |

ąśą╝čÅ |

ąóąĖą┐ |

ą×ą┐ąĖčüą░ąĮąĖąĄ čüąĖą│ąĮą░ą╗ąŠą▓ FT245 |

24,23,22,21,

19,18,17,16 |

ADBUS[7:0] |

I/O |

ąöą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮą░čÅ čłąĖąĮą░ ą┤ą░ąĮąĮčŗčģ FIFO, čüąĖą│ąĮą░ą╗čŗ D7 .. D0. ąŁčéą░ čłąĖąĮą░ ą▓ ąĮąŠčĆą╝ą░ą╗čīąĮąŠą╝ čüąŠčüč鹊čÅąĮąĖąĖ čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą▓čģąŠą┤čŗ, ąĘą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ čüąĖčéčāą░čåąĖąĖ, ą║ąŠą│ą┤ą░ OE# ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą╗ąŠą│. 0. |

| 26 |

RXF# |

ąÆčŗčģąŠą┤ |

ąÜąŠą│ą┤ą░ ą╗ąŠą│. 1, ąĮąĄ čćąĖčéą░ą╣č鹥 ą┤ą░ąĮąĮčŗąĄ ąĖąĘ FIFO. ąÜąŠą│ą┤ą░ ą╗ąŠą│. 0, č鹊 ą┤ą░ąĮąĮčŗąĄ ą┤ąŠčüčéčāą┐ąĮčŗ ą▓ FIFO, ąĖ ąŠąĮąĖ ą╝ąŠą│čāčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮčŗ ą┐čĆąĖ ą┐ąĄčĆąĄą▓ąŠą┤ąĄ čüąĖą│ąĮą░ą╗ą░ RD# ą▓ ą╗ąŠą│. 0. ąÆ čüąĖąĮčģčĆąŠąĮąĮąŠą╝ čĆąĄąČąĖą╝ąĄ ą┤ą░ąĮąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ą┐ąŠ ą║ą░ąČą┤ąŠą╝čā čéą░ą║čéčā, ą║ąŠą│ą┤ą░ ąŠą▒ą░ čüąĖą│ąĮą░ą╗ą░ RXF# ąĖ RD# ąĮą░čģąŠą┤čÅčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą╗ąŠą│. 0. ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 ą▓čŗą▓ąŠą┤ OE# ą┤ąŠą╗ąČąĄąĮ čāą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ ą▓ ą╗ąŠą│. 0 ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ 1 čéą░ą║č鹊ą▓čŗą╣ ą┐ąĄčĆąĖąŠą┤ ą┐ąĄčĆąĄą┤ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ asserting RD# ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ą╗ąŠą│. 0. |

| 27 |

TXE# |

ąÆčŗčģąŠą┤ |

ąÜąŠą│ą┤ą░ ą╗ąŠą│. 1, ąĮąĄ ąĘą░ą┐ąĖčüčŗą▓ą░ą╣č鹥 ą┤ą░ąĮąĮčŗąĄ ą▓ FIFO. ąÜąŠą│ą┤ą░ ą╗ąŠą│. 0, ą┤ą░ąĮąĮčŗąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮčŗ ą▓ FIFO ą┐čĆąĖ ą┐ąĄčĆąĄą▓ąŠą┤ąĄ čüąĖą│ąĮą░ą╗ą░ WR# ą▓ ą╗ąŠą│. 0. ąÆ čüąĖąĮčģčĆąŠąĮąĮąŠą╝ čĆąĄąČąĖą╝ąĄ ą┤ą░ąĮąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ą┐ąŠ ą║ą░ąČą┤ąŠą╝čā čéą░ą║čéčā, ą║ąŠą│ą┤ą░ ąŠą▒ą░ čüąĖą│ąĮą░ą╗ą░ TXE# ąĖ WR# ąĮą░čģąŠą┤čÅčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą╗ąŠą│. 0. |

| 28 |

RD# |

ąÆčģąŠą┤ |

ąĀą░ąĘčĆąĄčłą░ąĄčéčüčÅ ą▓čŗčüčéą░ą▓ą╗ąĄąĮąĖąĄ ąĮą░ D0...D7 č鹥ą║čāčēąĄą│ąŠ ą▒ą░ą╣čéą░ ą┤ą░ąĮąĮčŗčģ FIFO, ą║ąŠą│ą┤ą░ čüąĖą│ąĮą░ą╗ RD# ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ ą╗ąŠą│. 0. ąĪą╗ąĄą┤čāčÄčēąĖą╣ ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ FIFO (ąĄčüą╗ąĖ ąŠąĮ ą┤ąŠčüčéčāą┐ąĄąĮ) ą┐ąŠčüčéčāą┐ą░ąĄčé ąĖąĘ ą┐čĆąĖąĄą╝ąĮąŠą│ąŠ ą▒čāč乥čĆą░ FIFO ą┐ąŠ ą║ą░ąČą┤ąŠą╝čā čåąĖą║ą╗čā CLKOUT, ą┐ąŠą║ą░ RD# ąĮąĄ ą┐ąĄčĆąĄą╣ą┤ąĄčé ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ą╗ąŠą│. 1. |

| 29 |

WR# |

ąÆčģąŠą┤ |

ąĀą░ąĘčĆąĄčłą░ąĄčéčüčÅ ąĘą░ą┐ąĖčüčī ą▒ą░ą╣čéą░ ą┤ą░ąĮąĮčŗčģ čü ąĮąŠąČąĄą║ D0...D7 ą▓ ą┐ąĄčĆąĄą┤ą░čÄčēąĖą╣ ą▒čāč乥čĆ FIFO, ą║ąŠą│ą┤ą░ čüąĖą│ąĮą░ą╗ WR# ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą╗ąŠą│. 0. ąĪą╗ąĄą┤čāčÄčēąĖą╣ ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ FIFO ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ ą▓ ą┐ąĄčĆąĄą┤ą░čÄčēąĖą╣ ą▒čāč乥čĆ FIFO ą┐ąŠ ą║ą░ąČą┤ąŠą╝čā čåąĖą║ą╗čā CLKOUT, ą┐ąŠą║ą░ WR# ąĮąĄ ą┐ąĄčĆąĄą╣ą┤ąĄčé ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ą╗ąŠą│. 1. |

| 32 |

CLKOUT |

ąÆčŗčģąŠą┤ |

ąóą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ 60 ą£ąōčå, ą║ąŠč鹊čĆą░čÅ ą▓čŗčģąŠą┤ąĖčé ąĖąĘ FT2232H. ąÆčüąĄ čüąĖą│ąĮą░ą╗čŗ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆąŠą▓ą░ąĮčŗ čü čŹč鹊ą╣ čćą░čüč鹊č鹊ą╣. |

| 33 |

OE# |

ąÆčģąŠą┤ |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą▓čŗčģąŠą┤ą░, ą║ąŠą│ą┤ą░ ąĮą░ OE# ą╗ąŠą│. 0, č鹊 ą┤ą░ąĮąĮčŗąĄ ą▓čŗą▓ąŠą┤čÅčéčüčÅ ąĮą░ D0 .. D7. ąĪąĖą│ąĮą░ą╗ OE# ą┤ąŠą╗ąČąĄąĮ ą┐ąĄčĆąĄą▓ąŠą┤ąĖčéčīčüčÅ ą▓ 0 ąĮą░ ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ 1 čéą░ą║č鹊ą▓čŗą╣ ą┐ąĄčĆąĖąŠą┤ ą┐ąĄčĆąĄą┤ ą┐ąĄčĆąĄą▓ąŠą┤ąŠą╝ RD# ą▓ ą╗ąŠą│. 0, čćč鹊ą▒čŗ ąŠą▒ąĄčüą┐ąĄčćąĖčéčī ąĮąŠčĆą╝ą░ą╗čīąĮąŠąĄ ąŠą▒čĆą░čēąĄąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ ą▓ ą▒čāč乥čĆąĄ. |

| 30 |

SIWU |

ąÆčģąŠą┤ |

ąĪąĖą│ąĮą░ą╗ SIWU (Send Immediate / WakeUp, ąŠčéą┐čĆą░ą▓ąĖčéčī ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ / ą┐čĆąŠą▒čāą┤ąĖčéčī) ą║ąŠą╝ą▒ąĖąĮąĖčĆčāąĄčé ą┤ą▓ąĄ čäčāąĮą║čåąĖąĖ ąĮą░ ąŠą┤ąĮąŠą╝ ą▓čŗą▓ąŠą┤ąĄ. ąĢčüą╗ąĖ USB ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ąĖ (suspend mode, PWREN# = 1) ąĖ čĆą░ąĘčĆąĄčłąĄąĮąŠ čāą┤ą░ą╗ąĄąĮąĮąŠąĄ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖąĄ (remote wakeup) č湥čĆąĄąĘ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ EEPROM, č鹊 čüčéčĆąŠą▒ąĖčĆąŠą▓ą░ąĮąĖąĄ čŹč鹊ą╣ ąĮąŠąČą║ąĖ ą▓ ą╗ąŠą│. 0 ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ č鹊ą╝čā, čćč鹊 čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĘą░ą┐čĆąŠčüąĖčé ą▓ąŠąĘąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ (resume, ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖąĄ) ą┐ąŠ čłąĖąĮąĄ USB. ą×ą▒čŗčćąĮąŠ čŹč鹊 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ čģąŠčüčéą░ PC.

ąÆąŠ ą▓čĆąĄą╝čÅ ąĮąŠčĆą╝ą░ą╗čīąĮąŠą╣ čĆą░ą▒ąŠčéčŗ (PWREN# = 0) ąĄčüą╗ąĖ čŹčéą░ ąĮąŠąČą║ą░ čüčéčĆąŠą▒ąĖčĆčāąĄčéčüčÅ ą▓ ą╗ąŠą│. 0, č鹊 ą╗čÄą▒čŗąĄ ą┤ą░ąĮąĮčŗąĄ ą▓ ą▒čāč乥čĆąĄ TX čāčüčéčĆąŠą╣čüčéą▓ą░ ą▒čāą┤čāčé ąŠčéą┐čĆą░ą▓ą╗ąĄąĮčŗ ą┐ąŠ USB ą▓ čüą╗ąĄą┤čāčÄčēąĄą╝ ąĘą░ą┐čĆąŠčüąĄ Bulk-IN ąŠčé ą┤čĆą░ą╣ą▓ąĄčĆą░, ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé čĆą░ąĘą╝ąĄčĆą░ ąŠąČąĖą┤ą░čÄčēąĄą│ąŠ ą┐ą░ą║ąĄčéą░. ąŁč鹊 ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ąŠą┐čéąĖą╝ąĖąĘą░čåąĖąĖ čüą║ąŠčĆąŠčüčéąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ USB ą▓ ąĮąĄą║ąŠč鹊čĆčŗčģ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅčģ. ą¤ąŠą┤ą║ą╗čÄčćąĖč鹥 čŹčéčā ąĮąŠąČą║čā ą║ VCCIO, ąĄčüą╗ąĖ ąĄčæ ąĮąĄ ąĮčāąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī. ąĪą╝. čéą░ą║ąČąĄ ą┐čĆąĖą╝ąĄčćą░ąĮąĖčÅ 1, 2, 3 ą▓ čüąĄą║čåąĖąĖ 4.12. |

ążčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ FT245 Synchronous FIFO Interface Mode čüą╝. ą▓ čüąĄą║čåąĖąĖ 4.4.

3.4.3 ą×ą┐ąĖčüą░ąĮąĖąĄ ąĮąŠąČąĄą║, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗčģ ą▓ ąĖąĮč鹥čĆč乥ą╣čüąĄ FT245 Style Asynchronous FIFO

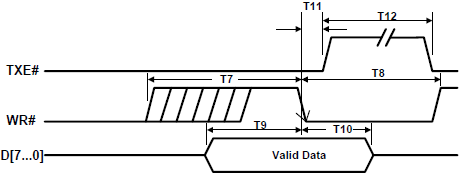

ąóąŠą╗čīą║ąŠ ą║ą░ąĮą░ą╗ A ąĖą╗ąĖ ą║ą░ąĮą░ą╗ B ą╝ąŠąČąĄčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą▓ ą║ą░č湥čüčéą▓ąĄ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ FIFO FT245. ąÆ čéą░ą▒ą╗ąĖčåąĄ čāą║ą░ąĘą░ąĮčŗ ąĮąŠąČą║ąĖ, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą▓ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ, ąĖ ą┐čĆąĖą▓ąĄą┤ąĄąĮąŠ ąĖčģ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ. ąöą╗čÅ ą▓čģąŠą┤ą░ ą▓ čŹč鹊čé čĆąĄąČąĖą╝ ą▓ąĮąĄčłąĮąĄąĄ EEPROM ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąŠ ą┤ą╗čÅ ą┐ąĄčĆąĄą▓ąŠą┤ą░ ą┐ąŠčĆčéą░ A, ąĖą╗ąĖ ą┐ąŠčĆčéą░ B, ąĖą╗ąĖ čüčĆą░ąĘčā ą┤ą▓čāčģ ą┐ąŠčĆč鹊ą▓ ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ ą▓ čĆąĄąČąĖą╝ąĄ 245 (245 mode). ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ą┤ą░ąĮąĮčŗąĄ ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ ąĖą╗ąĖ čüčćąĖčéčŗą▓ą░čÄčéčüčÅ ą┐ąŠ čüą┐ą░ą┤čā čüąĖą│ąĮą░ą╗ą░ WR# ąĖą╗ąĖ RD# čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ.

ąÜą░ąĮą░ą╗ A

Pin Ōä¢ |

ąÜą░ąĮą░ą╗ B

Pin Ōä¢ |

ąśą╝čÅ |

ąóąĖą┐ |

ą×ą┐ąĖčüą░ąĮąĖąĄ čüąĖą│ąĮą░ą╗ąŠą▓ FT245 |

24,23,22,21,

19,18,17,16 |

46,45,44,43,

41,40,39,38 |

ąÜą░ąĮą░ą╗ A =

ADBUS[7:0]

ąÜą░ąĮą░ą╗ B =

BDBUS[7:0] |

I/O |

ąöą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮą░čÅ čłąĖąĮą░ ą┤ą░ąĮąĮčŗčģ FIFO, čüąĖą│ąĮą░ą╗čŗ ą▒ąĖčé D7..D0. ąŁčéą░ čłąĖąĮą░ ąĮąŠčĆą╝ą░ą╗čīąĮąŠ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą▓čģąŠą┤ą░, ąĘą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ č鹊ą│ąŠ čüą╗čāčćą░čÅ, ąĄčüą╗ąĖ RD# ą▓ ą╗ąŠą│. 0. |

| 26 |

48 |

RXF# |

ąÆčŗčģąŠą┤ |

ąÜąŠą│ą┤ą░ ą╗ąŠą│. 1, č鹊 ąĮąĄ čćąĖčéą░ą╣č鹥 ą┤ą░ąĮąĮčŗąĄ ąĖąĘ FIFO. ąÜąŠą│ą┤ą░ ą╗ąŠą│. 0, č鹊 ą┤ą░ąĮąĮčŗąĄ ą┤ąŠčüčéčāą┐ąĮčŗ ą▓ FIFO, ąĖ ąĖčģ ą╝ąŠąČąĮąŠ ą┐čĆąŠčćąĖčéą░čéčī ą┐čāč鹥ą╝ ą┐ąĄčĆąĄą▓ąŠą┤ą░ RD# ą▓ ą╗ąŠą│. 0. ąÜąŠą│ą┤ą░ RD# čüąĮąŠą▓ą░ ą┐ąŠą╗čāčćą░ąĄčé čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 1, č鹊ą│ą┤ą░ RXF# ą▓čüąĄą│ą┤ą░ ą┐ąĄčĆąĄčģąŠą┤ąĖčé ąĮą░ čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 1, ąĖ čüąĮąŠą▓ą░ ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ ą╗ąŠą│. 0 č鹊ą╗čīą║ąŠ č鹊ą│ą┤ą░, ą║ąŠą│ą┤ą░ ąĄčüą╗ąĖ ąĖą╝ąĄąĄčéčüčÅ ą▓ FIFO ą┤čĆčāą│ąŠą╣ ą▒ą░ą╣čé ą┤ą╗čÅ čćč鹥ąĮąĖčÅ. ąÆąŠ ą▓čĆąĄą╝čÅ čüą▒čĆąŠčüą░ čŹčéą░ čüąĖą│ąĮą░ą╗čīąĮą░čÅ ąĮąŠąČą║ą░ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čéčĆąĄčéčīąĄą╝ čüąŠčüč鹊čÅąĮąĖąĖ, ąĮąŠ ą║ ąĮąĄą╣ ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ ą▓ąĄčĆčģąĮąĖą╣ ąĮą░ą│čĆčāąĘąŠčćąĮčŗą╣ čĆąĄąĘąĖčüč鹊čĆ (pullup) ąĮąŠą╝ąĖąĮą░ą╗ąŠą╝ 200 ą║ą×ą╝ (ą▓č鹊čĆąŠą╣ ą║ąŠąĮąĄčå čĆąĄąĘąĖčüč鹊čĆą░ ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą║ VCCIO). |

| 27 |

52 |

TXE# |

ąÆčŗčģąŠą┤ |

ąÜąŠą│ą┤ą░ ą╗ąŠą│. 1, č鹊 ąĮąĄ ąĘą░ą┐ąĖčüčŗą▓ą░ą╣č鹥 ą┤ą░ąĮąĮčŗąĄ ą▓ FIFO. ąÜąŠą│ą┤ą░ ą╗ąŠą│. 0, č鹊 ą┤ą░ąĮąĮčŗąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮčŗ ą▓ FIFO ą┐čāč鹥ą╝ čüčéčĆąŠą▒ąĖčĆąŠą▓ą░ąĮąĖčÅ WR# čüąĮą░čćą░ą╗ą░ ą▓ ą╗ąŠą│. 1, ąĘą░č鹥ą╝ ą▓ ą╗ąŠą│. 0. ąÆąŠ ą▓čĆąĄą╝čÅ čüą▒čĆąŠčüą░ čŹčéą░ čüąĖą│ąĮą░ą╗čīąĮą░čÅ ąĮąŠąČą║ą░ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čéčĆąĄčéčīąĄą╝ čüąŠčüč鹊čÅąĮąĖąĖ, ąĮąŠ ą║ ąĮąĄą╣ ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ ą▓ąĄčĆčģąĮąĖą╣ ąĮą░ą│čĆčāąĘąŠčćąĮčŗą╣ čĆąĄąĘąĖčüč鹊čĆ (pullup) ąĮąŠą╝ąĖąĮą░ą╗ąŠą╝ 200 ą║ą×ą╝ (ą▓č鹊čĆąŠą╣ ą║ąŠąĮąĄčå čĆąĄąĘąĖčüč鹊čĆą░ ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą║ VCCIO). |

| 28 |

53 |

RD# |

ąÆčģąŠą┤ |

ąĀą░ąĘčĆąĄčłą░ąĄčéčüčÅ ą┐ąĄčĆąĄą┤ą░čćą░ ąĮą░ čłąĖąĮčā ą┤ą░ąĮąĮčŗčģ D7..D0 č鹥ą║čāčēąĄą│ąŠ ą▒ą░ą╣čéą░ ą┤ą░ąĮąĮčŗčģ ąĖąĘ FIFO, ą║ąŠą│ą┤ą░ RD# ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ ą╗ąŠą│. 0. ąśąĘ FIFO ą┐čĆąĖąĄą╝ą░ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ąĮąŠą▓čŗą╣ ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ, ąĄčüą╗ąĖ ąŠąĮ ą┤ąŠčüčéčāą┐ąĄąĮ, ą║ąŠą│ą┤ą░ RD# ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ ą╗ąŠą│. 1. |

| 29 |

54 |

WR# |

ąÆčģąŠą┤ |

ąŚą░ą┐ąĖčüčŗą▓ą░ąĄčé ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ čü ąĮąŠąČąĄą║ D7..D0 ą▓ ą┐ąĄčĆąĄą┤ą░čÄčēąĖą╣ ą▒čāč乥čĆ FIFO, ą║ąŠą│ą┤ą░ WR ą┐ąĄčĆąĄčģąŠą┤ąĖčé ąĖąĘ ą╗ąŠą│. 1 ą▓ ą╗ąŠą│. 0. |

| 30 |

55 |

SIWU |

ąÆčģąŠą┤ |

ąĪąĖą│ąĮą░ą╗ SIWU (Send Immediate / WakeUp, ąŠčéą┐čĆą░ą▓ąĖčéčī ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ / ą┐čĆąŠą▒čāą┤ąĖčéčī) ą║ąŠą╝ą▒ąĖąĮąĖčĆčāąĄčé ą┤ą▓ąĄ čäčāąĮą║čåąĖąĖ ąĮą░ ąŠą┤ąĮąŠą╝ ą▓čŗą▓ąŠą┤ąĄ. ąĢčüą╗ąĖ USB ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ąĖ (suspend mode, PWREN# = 1) ąĖ čĆą░ąĘčĆąĄčłąĄąĮąŠ čāą┤ą░ą╗ąĄąĮąĮąŠąĄ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖąĄ (remote wakeup) č湥čĆąĄąĘ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ EEPROM, č鹊 čüčéčĆąŠą▒ąĖčĆąŠą▓ą░ąĮąĖąĄ čŹč鹊ą╣ ąĮąŠąČą║ąĖ ą▓ ą╗ąŠą│. 0 ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ č鹊ą╝čā, čćč鹊 čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĘą░ą┐čĆąŠčüąĖčé ą▓ąŠąĘąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ (resume, ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖąĄ) ą┐ąŠ čłąĖąĮąĄ USB. ą×ą▒čŗčćąĮąŠ čŹč鹊 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ čģąŠčüčéą░ PC.

ąÆąŠ ą▓čĆąĄą╝čÅ ąĮąŠčĆą╝ą░ą╗čīąĮąŠą╣ čĆą░ą▒ąŠčéčŗ (PWREN# = 0) ąĄčüą╗ąĖ čŹčéą░ ąĮąŠąČą║ą░ čüčéčĆąŠą▒ąĖčĆčāąĄčéčüčÅ ą▓ ą╗ąŠą│. 0, č鹊 ą╗čÄą▒čŗąĄ ą┤ą░ąĮąĮčŗąĄ ą▓ ą▒čāč乥čĆąĄ TX čāčüčéčĆąŠą╣čüčéą▓ą░ ą▒čāą┤čāčé ąŠčéą┐čĆą░ą▓ą╗ąĄąĮčŗ ą┐ąŠ USB ą▓ čüą╗ąĄą┤čāčÄčēąĄą╝ ąĘą░ą┐čĆąŠčüąĄ Bulk-IN ąŠčé ą┤čĆą░ą╣ą▓ąĄčĆą░, ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé čĆą░ąĘą╝ąĄčĆą░ ąŠąČąĖą┤ą░čÄčēąĄą│ąŠ ą┐ą░ą║ąĄčéą░. ąŁč鹊 ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ąŠą┐čéąĖą╝ąĖąĘą░čåąĖąĖ čüą║ąŠčĆąŠčüčéąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ USB ą▓ ąĮąĄą║ąŠč鹊čĆčŗčģ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅčģ. ą¤ąŠą┤ą║ą╗čÄčćąĖč鹥 čŹčéčā ąĮąŠąČą║čā ą║ VCCIO, ąĄčüą╗ąĖ ąĄčæ ąĮąĄ ąĮčāąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī. ąĪą╝. čéą░ą║ąČąĄ ą┐čĆąĖą╝ąĄčćą░ąĮąĖčÅ 1, 2, 3 ą▓ čüąĄą║čåąĖąĖ 4.12. |

ążčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ FT245 Asynchronous FIFO Interface Mode čüą╝. ą▓ čüąĄą║čåąĖąĖ 4.5.

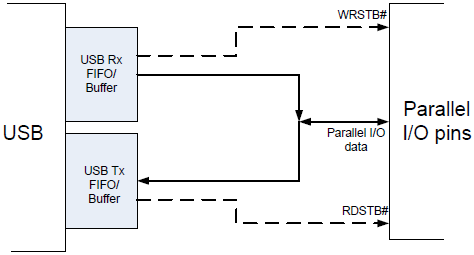

3.4.4 ą×ą┐ąĖčüą░ąĮąĖąĄ ąĮąŠąČąĄą║, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗčģ ą▓ čüąĖąĮčģčĆąŠąĮąĮąŠą╝ ąĖą╗ąĖ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą╝ ąĖąĮč鹥čĆč乥ą╣čüąĄ Bit-Bang

ąÆ čćąĖą┐ąĄ FT2232H ą║ą░ąĮą░ą╗ A ąĖą╗ąĖ ą║ą░ąĮą░ą╗ B ą╝ąŠąČąĄčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą║ą░ą║ čüąĖąĮčģčĆąŠąĮąĮčŗą╣ ąĖą╗ąĖ ą░čüąĖąĮčģčĆąŠąĮąĮčŗą╣ bit-bang ąĖąĮč鹥čĆč乥ą╣čü. ąŁč鹊 čüą┐ąĄčåąĖą░ą╗čīąĮčŗą╣ čĆąĄąČąĖą╝, ą▓ ą║ąŠč鹊čĆąŠą╝ 8 ą╗ąĖąĮąĖą╣ IO ą║ą░ąĮą░ą╗ą░ A ąĖą╗ąĖ B (ąĖą╗ąĖ ąŠą▒ąŠąĖčģ ą║ą░ąĮą░ą╗ąŠą▓ čüčĆą░ąĘčā) čĆą░ą▒ąŠčéą░čÄčé ą║ą░ą║ 8-ą▒ąĖčéąĮą░čÅ ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮą░čÅ čłąĖąĮą░ ą┤ą░ąĮąĮčŗčģ. ąśą╝ąĄąĄčéčüčÅ ą┤ą▓ąĄ čĆą░ąĘąĮąŠą▓ąĖą┤ąĮąŠčüčéąĖ čĆąĄąČąĖą╝ą░ bit-bang: čüąĖąĮčģčĆąŠąĮąĮčŗą╣ ąĖ ą░čüąĖąĮčģčĆąŠąĮąĮčŗą╣. ąÆ čéą░ą▒ą╗ąĖčåąĄ čāą║ą░ąĘą░ąĮčŗ ąĮąŠąČą║ąĖ, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą▓ ą╗čÄą▒ąŠą╝ ąĖąĘ ą▓ą░čĆąĖą░ąĮč鹊ą▓ čĆąĄąČąĖą╝ą░ bit-bang, ąĖ ą┐čĆąĖą▓ąĄą┤ąĄąĮąŠ ąĖčģ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ.

ąÜą░ąĮą░ą╗ A

Pin Ōä¢ |

ąÜą░ąĮą░ą╗ B

Pin Ōä¢ |

ąśą╝čÅ |

ąóąĖą┐ |

ą×ą┐ąĖčüą░ąĮąĖąĄ čüąĖą│ąĮą░ą╗ąŠą▓ ą▓ čĆąĄąČąĖą╝ąĄ Bit-Bang

|

24,23,22,21,

19,18,17,16 |

46,45,44,43,

41,40,39,38 |

ąÜą░ąĮą░ą╗ A =

ADBUS[7:0]

ąÜą░ąĮą░ą╗ B =

BDBUS[7:0] |

I/O |

ąöą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮą░čÅ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮą░čÅ čłąĖąĮą░ ą┤ą░ąĮąĮčŗčģ. |

| 27 |

52 |

WRSTB# |

ąÆčŗčģąŠą┤ |

ąĪčéčĆąŠą▒ ąĘą░ą┐ąĖčüąĖ, ą╗ąŠą│. 0 ąĮą░ čŹč鹊ą╝ ą▓čŗčģąŠą┤ąĄ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ąĮąŠą▓čŗąĄ ą┤ą░ąĮąĮčŗąĄ ą▒čŗą╗ąĖ ąĘą░ą┐ąĖčüą░ąĮčŗ ą▓ ąĮąŠąČą║ąĖ I/O ąŠčé čģąŠčüčéą░ PC (ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ ą┐čĆąĖčłąĄą╗ č湥čĆąĄąĘ ąĖąĮč鹥čĆč乥ą╣čü USB). |

| 28 |

53 |

RDSTB# |

ąÆčŗčģąŠą┤ |

ąĪčéčĆąŠą▒ čćč鹥ąĮąĖčÅ, čüčĆąĄąĘ ąĮą░čĆą░čüčéą░ąĮąĖčÅ (ą┐ąĄčĆąĄčģąŠą┤ ąĖąĘ ą╗ąŠą│. 0 ą▓ ą╗ąŠą│. 1) ąĮą░ čŹč鹊ą╝ ą▓čŗčģąŠą┤ąĄ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą┤ą░ąĮąĮčŗąĄ ą▒čŗą╗ąĖ ą┐čĆąŠčćąĖčéą░ąĮčŗ ąĖąĘ ąĮąŠąČąĄą║ I/O ąĖ ą┐ąĄčĆąĄą┤ą░ąĮčŗ čģąŠčüčéčā PC (č湥čĆąĄąĘ ąĖąĮč鹥čĆč乥ą╣čü USB). |

| 30 |

55 |

SIWU |

ąÆčģąŠą┤ |

ąĪąĖą│ąĮą░ą╗ SIWU (Send Immediate / WakeUp, ąŠčéą┐čĆą░ą▓ąĖčéčī ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ / ą┐čĆąŠą▒čāą┤ąĖčéčī) ą║ąŠą╝ą▒ąĖąĮąĖčĆčāąĄčé ą┤ą▓ąĄ čäčāąĮą║čåąĖąĖ ąĮą░ ąŠą┤ąĮąŠą╝ ą▓čŗą▓ąŠą┤ąĄ. ąĢčüą╗ąĖ USB ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ąĖ (suspend mode, PWREN# = 1) ąĖ čĆą░ąĘčĆąĄčłąĄąĮąŠ čāą┤ą░ą╗ąĄąĮąĮąŠąĄ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖąĄ (remote wakeup) č湥čĆąĄąĘ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ EEPROM, č鹊 čüčéčĆąŠą▒ąĖčĆąŠą▓ą░ąĮąĖąĄ čŹč鹊ą╣ ąĮąŠąČą║ąĖ ą▓ ą╗ąŠą│. 0 ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ č鹊ą╝čā, čćč鹊 čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĘą░ą┐čĆąŠčüąĖčé ą▓ąŠąĘąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ (resume, ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖąĄ) ą┐ąŠ čłąĖąĮąĄ USB. ą×ą▒čŗčćąĮąŠ čŹč鹊 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ čģąŠčüčéą░ PC.

ąÆąŠ ą▓čĆąĄą╝čÅ ąĮąŠčĆą╝ą░ą╗čīąĮąŠą╣ čĆą░ą▒ąŠčéčŗ (PWREN# = 0) ąĄčüą╗ąĖ čŹčéą░ ąĮąŠąČą║ą░ čüčéčĆąŠą▒ąĖčĆčāąĄčéčüčÅ ą▓ ą╗ąŠą│. 0, č鹊 ą╗čÄą▒čŗąĄ ą┤ą░ąĮąĮčŗąĄ ą▓ ą▒čāč乥čĆąĄ TX čāčüčéčĆąŠą╣čüčéą▓ą░ ą▒čāą┤čāčé ąŠčéą┐čĆą░ą▓ą╗ąĄąĮčŗ ą┐ąŠ USB ą▓ čüą╗ąĄą┤čāčÄčēąĄą╝ ąĘą░ą┐čĆąŠčüąĄ Bulk-IN ąŠčé ą┤čĆą░ą╣ą▓ąĄčĆą░, ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé čĆą░ąĘą╝ąĄčĆą░ ąŠąČąĖą┤ą░čÄčēąĄą│ąŠ ą┐ą░ą║ąĄčéą░. ąŁč鹊 ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ąŠą┐čéąĖą╝ąĖąĘą░čåąĖąĖ čüą║ąŠčĆąŠčüčéąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ USB ą▓ ąĮąĄą║ąŠč鹊čĆčŗčģ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅčģ. ą¤ąŠą┤ą║ą╗čÄčćąĖč鹥 čŹčéčā ąĮąŠąČą║čā ą║ VCCIO, ąĄčüą╗ąĖ ąĄčæ ąĮąĄ ąĮčāąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī. ąĪą╝. čéą░ą║ąČąĄ ą┐čĆąĖą╝ąĄčćą░ąĮąĖčÅ 1, 2, 3 ą▓ čüąĄą║čåąĖąĖ 4.12. |

ążčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ čüąĖąĮčģčĆąŠąĮąĮąŠą│ąŠ ąĖ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą│ąŠ čĆąĄąČąĖą╝ą░ bit-bang čüą╝. ą▓ čüąĄą║čåąĖąĖ 4.10.

3.4.5 ą×ą┐ąĖčüą░ąĮąĖąĄ ąĮąŠąČąĄą║, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗčģ ą▓ MPSSE

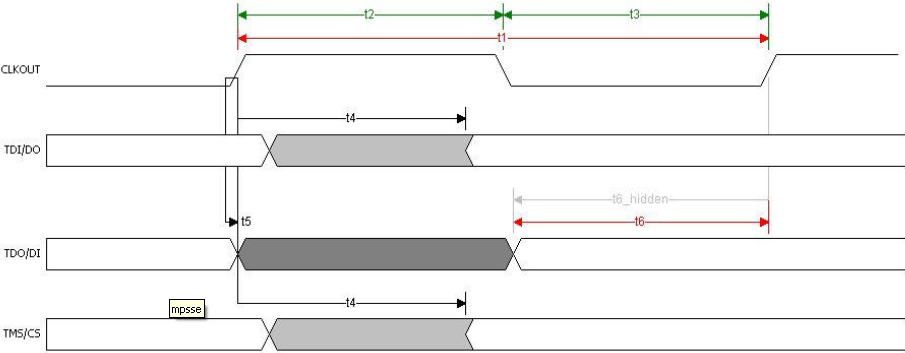

ąÜą░ąČą┤čŗą╣ ąĖąĘ ą║ą░ąĮą░ą╗ąŠą▓ (A ąĖ B) čćąĖą┐ą░ FT2232H ąĖą╝ąĄčÄčé čäčāąĮą║čåąĖčÄ Multi-Protocol Synchronous Serial Engine (MPSSE). ąÜą░ąČą┤čŗą╣ MPSSE ą╝ąŠąČąĄčé ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčīčüčÅ ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ą▓ ąŠą┤ąĖąĮ ąĖąĘ ą┐ąŠą┐čāą╗čÅčĆąĮčŗčģ čüčéą░ąĮą┤ą░čĆčéąĮčŗčģ ą┐čĆąŠč鹊ą║ąŠą╗ąŠą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ąĖąĮč鹥čĆč乥ą╣čüąŠą▓ čéąĖą┐ą░ JTAG, I2C ąĖą╗ąĖ SPI, ąĖą╗ąĖ čéą░ą║ąČąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą┤ą╗čÅ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ ą┐čĆąŠą┐čĆąĖąĄčéą░čĆąĮąŠą│ąŠ ą┐čĆąŠč鹊ą║ąŠą╗ą░ čłąĖąĮčŗ. ąØą░ą┐čĆąĖą╝ąĄčĆ, ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ąŠą┤ąĖąĮ ą║ą░ąĮą░ą╗ ą┤ą╗čÅ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ą║ FPGA (ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝ąŠą╣ č湥čĆąĄąĘ SRAM) čäąĖčĆą╝ Altera ąĖą╗ąĖ Xilinx. ą¦ąĖą┐ FPGA ą┐čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ ąŠą▒čŗčćąĮąŠ ąĮąĄ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ (čé. ąĄ. ą▓ ąĮąĄą╝ ąĮąĄ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮčŗ ąĮąĖą║ą░ą║ąĖąĄ ą╗ąŠą│ąĖč湥čüą║ąĖąĄ čäčāąĮą║čåąĖąĖ). ą¤čĆąĖą╗ąŠąČąĄąĮąĖąĄ (ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ąĮą░ PC) ą╝ąŠąČąĄčé ą┐čĆąĖą╝ąĄąĮąĖčéčī MPSSE ą┤ą╗čÅ ąĘą░ą│čĆčāąĘą║ąĖ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąŠąĮąĮčŗčģ ą┤ą░ąĮąĮčŗčģ ą▓ čćąĖą┐ FPGA č湥čĆąĄąĘ USB. ąŁčéąĖ ą┤ą░ąĮąĮčŗąĄ ą▒čāą┤čāčé ąŠą┐čĆąĄą┤ąĄą╗čÅčéčī ą┐čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ, ą║ą░ą║ąĖąĄ ą░ą┐ą┐ą░čĆą░čéąĮčŗąĄ ą╗ąŠą│ąĖč湥čüą║ąĖąĄ čäčāąĮą║čåąĖąĖ ą▒čāą┤čāčé čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮčŗ ą▓ čćąĖą┐ąĄ FPGA. ąöčĆčāą│ąŠą╣ ą║ą░ąĮą░ą╗ FT2232H ą▒čāą┤ąĄčé ą┤ąŠčüčéčāą┐ąĄąĮ ą┤ą╗čÅ ą┤čĆčāą│ąŠą╣ čäčāąĮą║čåąĖąĖ. ąÉą╗čīč鹥čĆąĮą░čéąĖą▓ąĮąŠ ą║ą░ąČą┤čŗą╣ MPSSE ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĮąĄą║ąŠč鹊čĆčŗą╝ ą║ąŠą╗ąĖč湥čüčéą▓ąŠą╝ ąĮąŠąČąĄą║ GPIO (General Purpose IO, ąŠą▒čŗčćąĮčŗąĄ ą┐ąŠčĆčéčŗ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░). ąÆ čéą░ą▒ą╗ąĖčåąĄ čāą║ą░ąĘą░ąĮčŗ ąĮąŠąČą║ąĖ, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą▓ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ, ąĖ ą┐čĆąĖą▓ąĄą┤ąĄąĮąŠ ąĖčģ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ.

ąÜą░ąĮą░ą╗ A

Pin Ōä¢ |

ąÜą░ąĮą░ą╗ B

Pin Ōä¢ |

ąśą╝čÅ |

ąóąĖą┐ |

ą×ą┐ąĖčüą░ąĮąĖąĄ čüąĖą│ąĮą░ą╗ąŠą▓ MPSSE |

| 16 |

38 |

TCK/SK |

ąÆčŗčģąŠą┤ |

ąĪąĖą│ąĮą░ą╗ čéą░ą║č鹊ą▓. ąØą░ą┐čĆąĖą╝ąĄčĆ:

JTAG - TCK, Test interface clock

SPI - SK, Serial Clock |

| 17 |

39 |

TDI/DO |

ąÆčŗčģąŠą┤ |

ąÆčŗčģąŠą┤ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ą║ą░ąĮą░ą╗ą░ ą┤ą░ąĮąĮčŗčģ. ąØą░ą┐čĆąĖą╝ąĄčĆ:

JTAG - TDI, Test Data Input

SPI - DO, Data Output |

| 18 |

40 |

TDO/DI |

ąÆčģąŠą┤ |

ąÆčģąŠą┤ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ą║ą░ąĮą░ą╗ą░ ą┤ą░ąĮąĮčŗčģ. ąØą░ą┐čĆąĖą╝ąĄčĆ:

JTAG - TDO, Test Data Output

SPI - DI, Data Intput |

| 19 |

41 |

TMS/CS |

ąÆčŗčģąŠą┤ |

ąĪąĖą│ąĮą░ą╗ ą▓čŗą▒ąŠčĆą║ąĖ. ąØą░ą┐čĆąĖą╝ąĄčĆ:

JTAG - TMS, Test Mode Select

SPI - CS, Chip Select |

21,22,23,24

|

43,44,45,46 |

GPIOL0..3 |

I/O |

ą¤ąŠčĆčé ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ ąŠą▒čēąĄą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ (GPIO) |

26,27,28,29,

30,32,33,34

|

48,52,53,54,

55,57,58,59 |

GPIOH0..7 |

I/O |

ą¤ąŠčĆčé ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ ąŠą▒čēąĄą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ (GPIO) |

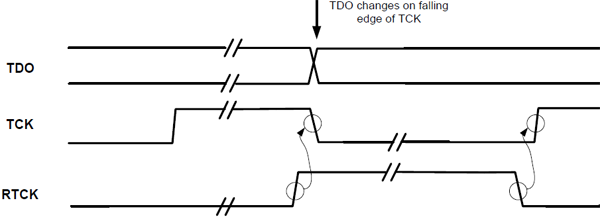

ążčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ čŹč鹊ą│ąŠ čĆąĄąČąĖą╝ą░ čüą╝. ą▓ čüąĄą║čåąĖąĖ 4.6.

3.4.6 ą×ą┐ąĖčüą░ąĮąĖąĄ ąĮąŠąČąĄą║, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗčģ ą▓ ą▒čŗčüčéčĆąŠą╝ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą╝ ąĖąĮč鹥čĆč乥ą╣čüąĄ (Fast Serial Interface)

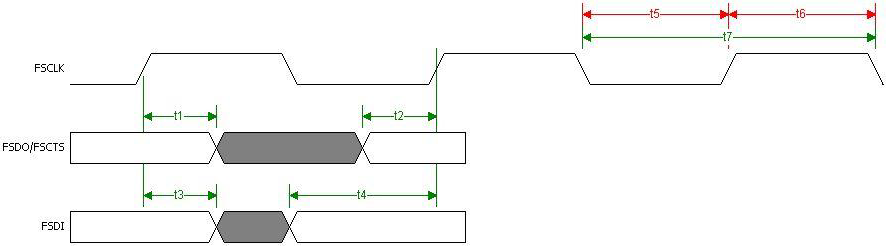

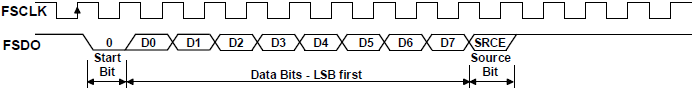

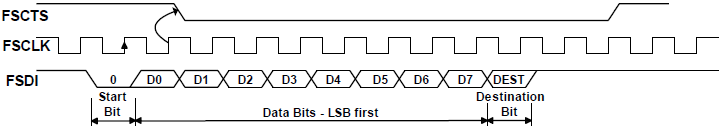

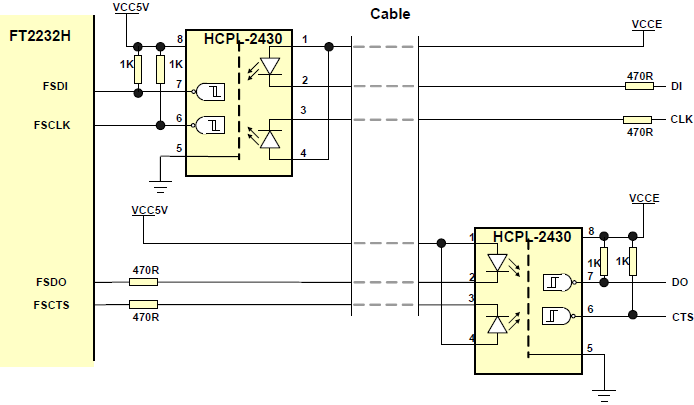

ąÜą░ąĮą░ą╗ B čćąĖą┐ą░ FT2232H ą╝ąŠąČąĄčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą┤ą╗čÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą▓čŗčüąŠą║ąŠčüą║ąŠčĆąŠčüčéąĮąŠą╣, ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮąŠą╣ ąŠą┐č鹊ąĖąĘąŠą╗ąĖčĆąŠą▓ą░ąĮąĮąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ: Fast Serial Interface. ąöą╗čÅ ą║ą░ąĮą░ą╗ą░ A čŹčéą░ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ąĮąĄą┤ąŠčüčéčāą┐ąĮą░. ą¤čĆąŠą┐čĆąĖąĄčéą░čĆąĮčŗą╣ ą┐čĆąŠč鹊ą║ąŠą╗ FTDI čĆą░ąĘčĆą░ą▒ąŠčéą░ąĮ ą┤ą╗čÅ č鹊ą│ąŠ, čćč鹊ą▒čŗ ą│ą░ą╗čīą▓ą░ąĮąĖč湥čüą║ąĖ ąĖąĘąŠą╗ąĖčĆąŠą▓ą░ąĮąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ ą╝ąŠą│ą╗ąĖ čüąĖąĮčģčĆąŠąĮąĮąŠ ąŠą▒ą╝ąĄąĮąĖą▓ą░čéčīčüčÅ ą┤ą░ąĮąĮčŗą╝ąĖ č湥čĆąĄąĘ čćąĖą┐ FT2232H, ąĖčüą┐ąŠą╗čīąĘčāčÅ č鹊ą╗čīą║ąŠ 4 čüąĖą│ąĮą░ą╗čīąĮčŗąĄ ąĮąŠąČą║ąĖ (č湥čĆąĄąĘ ą┤ą▓ą░ ą┤ą▓ąŠą╣ąĮčŗčģ ąŠą┐čéąĖč湥čüą║ąĖčģ ąĖąĘąŠą╗čÅč鹊čĆą░) ąĖ ą┤ą▓ąĄ ą╗ąĖąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ. ą¤ąĄčĆąĖč乥čĆąĖą╣ąĮą░čÅ čüčģąĄą╝ą░ čāą┐čĆą░ą▓ą╗čÅąĄčé čüą║ąŠčĆąŠčüčéčīčÄ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ą▓ ąŠą▒ąŠąĖčģ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅčģ ą┐čĆąĖ ą┐ąŠą┤ą┤ąĄčƹȹ░ąĮąĖąĖ ą┐ąŠą╗ąĮąŠą╣ čåąĄą╗ąŠčüčéąĮąŠčüčéąĖ ą┤ą░ąĮąĮčŗčģ. ą£ąŠąČąĄčé ą▒čŗčéčī ą┤ąŠčüčéąĖą│ąĮčāčéą░ čüą║ąŠčĆąŠčüčéčī ą┐ąĄčĆąĄą┤ą░čćąĖ, ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮą░čÅ ą┤ą╗čÅ ąĖąĮč鹥čĆč乥ą╣čüą░ USB. ąĢčüą╗ąĖ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ, ąŠą▒ą░ ą║ą░ąĮą░ą╗ą░ A ąĖ B, ą╝ąŠą│čāčé ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī ą┤ą░ąĮąĮčŗąĄ č湥čĆąĄąĘ ąŠą┤ąĖąĮ ąĖ č鹊čé ąČąĄ 4-ą┐čĆąŠą▓ąŠą┤ąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü. ąÆ čéą░ą▒ą╗ąĖčåąĄ čāą║ą░ąĘą░ąĮčŗ ąĮąŠąČą║ąĖ, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą▓ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ, ąĖ ą┐čĆąĖą▓ąĄą┤ąĄąĮąŠ ąĖčģ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ.

ąÜą░ąĮą░ą╗ B

Pin Ōä¢ |

ąśą╝čÅ |

ąóąĖą┐ |

ą×ą┐ąĖčüą░ąĮąĖąĄ čüąĖą│ąĮą░ą╗ąŠą▓ Fast Serial Interface |

| 38 |

FSDI |

ąÆčģąŠą┤ |

ąÆčģąŠą┤ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ą┤ą░ąĮąĮčŗčģ ąĖąĮč鹥čĆč乥ą╣čüą░ Fast Serial. |

| 39 |

FSCLK |

ąÆčģąŠą┤ |

ąÆčģąŠą┤ čéą░ą║č鹊ą▓ ąĖąĮč鹥čĆč乥ą╣čüą░ Fast Serial. ąÆčģąŠą┤ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ FT2232H ą┤ą╗čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ą▓ą▓ąŠą┤ą░ ąĖ ą▓čŗą▓ąŠą┤ą░ ą┤ą░ąĮąĮčŗčģ. |

| 40 |

FSDO |

ąÆčŗčģąŠą┤ |

ąÆčŗčģąŠą┤ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ą┤ą░ąĮąĮčŗčģ ąĖąĮč鹥čĆč乥ą╣čüą░ Fast Serial. |

| 41 |

FSCTS |

ąÆčŗčģąŠą┤ |

ąÆčŗčģąŠą┤ čüąĖą│ąĮą░ą╗ą░ Clear To Send (ąŠčćąĖčēąĄąĮąŠ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ) ąĖąĮč鹥čĆč乥ą╣čüą░ Fast Serial. ąøąŠą│. 0 ąĮą░ čŹč鹊ą╝ čüąĖą│ąĮą░ą╗ąĄ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ ą│ąŠč鹊ą▓ą░ ą║ ą┐ąĄčĆąĄą┤ą░č湥 ą┤ą░ąĮąĮčŗčģ. |

ążčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ čŹč鹊ą│ąŠ čĆąĄąČąĖą╝ą░ čüą╝. ą▓ čüąĄą║čåąĖąĖ 4.8.

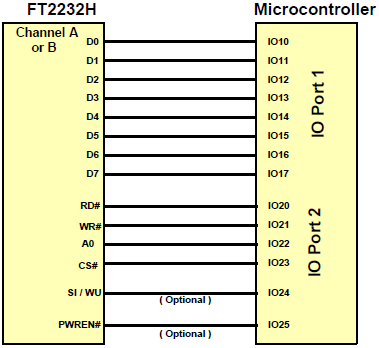

3.4.7 ą×ą┐ąĖčüą░ąĮąĖąĄ ąĮąŠąČąĄą║, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗčģ ą▓ FIFO ąĖąĮč鹥čĆč乥ą╣čüąĄ čüčéąĖą╗čÅ CPU

ąÜą░ąĮą░ą╗ A ąĖą╗ąĖ B ą╝ąŠąČąĄčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą▓ čĆąĄąČąĖą╝ąĄ ąĖąĮč鹥čĆč乥ą╣čüą░ CPU-style FIFO, ą║ąŠč鹊čĆčŗą╣ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐čĆąŠčåąĄčüčüąŠčĆčā (CPU) ąŠą▒ą╝ąĄąĮąĖą▓ą░čéčīčüčÅ ą┤ą░ąĮąĮčŗą╝ąĖ ą┐ąŠ USB č湥čĆąĄąĘ čćąĖą┐ FT2232H. ąŁč鹊čé čĆąĄąČąĖą╝ ą▓ą║ą╗čÄčćą░ąĄčéčüčÅ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄą╝ ą▓ąĮąĄčłąĮąĄą│ąŠ EEPROM. ąÆ čéą░ą▒ą╗ąĖčåąĄ čāą║ą░ąĘą░ąĮčŗ ąĮąŠąČą║ąĖ, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą▓ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ, ąĖ ą┐čĆąĖą▓ąĄą┤ąĄąĮąŠ ąĖčģ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ.

ąÜą░ąĮą░ą╗ A

Pin Ōä¢ |

ąÜą░ąĮą░ą╗ B

Pin Ōä¢ |

ąśą╝čÅ |

ąóąĖą┐ |

ą×ą┐ąĖčüą░ąĮąĖąĄ čüąĖą│ąĮą░ą╗ąŠą▓ ą▓ čĆąĄąČąĖą╝ąĄ CPU-style FIFO Interface

|

24,23,22,21,

19,18,17,16 |

46,45,44,43,

41,40,39,38 |

ąÜą░ąĮą░ą╗ A =

ADBUS[7:0]

ąÜą░ąĮą░ą╗ B =

BDBUS[7:0] |

I/O |

ąöą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮą░čÅ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮą░čÅ čłąĖąĮą░ ą┤ą░ąĮąĮčŗčģ. |

| 26 |

48 |

CS# |

ąÆčģąŠą┤ |

ąÆčģąŠą┤ ą▓čŗą▒ąŠčĆą║ąĖ čćąĖą┐ą░, ą░ą║čéąĖą▓ąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 0. |

| 27 |

52 |

A0 |

ąÆčģąŠą┤ |

ąæąĖčé ą░ą┤čĆąĄčüą░ A0. |

| 28 |

53 |

RD# |

ąÆčģąŠą┤ |

ąÆčģąŠą┤ čüąĖą│ąĮą░ą╗ą░ čćč鹥ąĮąĖčÅ FIFO (FIFO Read), ą░ą║čéąĖą▓ąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 0. |

| 29 |

54 |

WR# |

ąÆčģąŠą┤ |

ąÆčģąŠą┤ čüąĖą│ąĮą░ą╗ą░ ąĘą░ą┐ąĖčüąĖ FIFO (FIFO Write), ą░ą║čéąĖą▓ąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 0. |

ążčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ čŹč鹊ą│ąŠ čĆąĄąČąĖą╝ą░ čüą╝. ą▓ čüąĄą║čåąĖąĖ 4.9 - CPU-style FIFO Interface Mode.

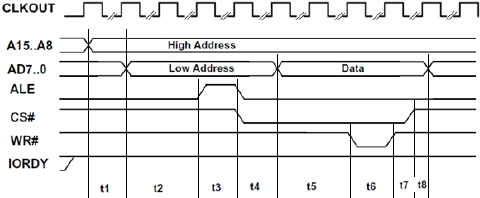

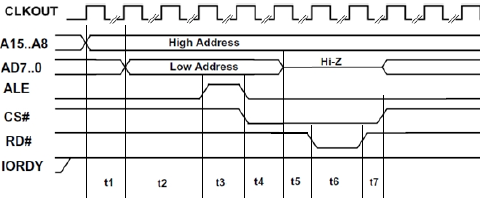

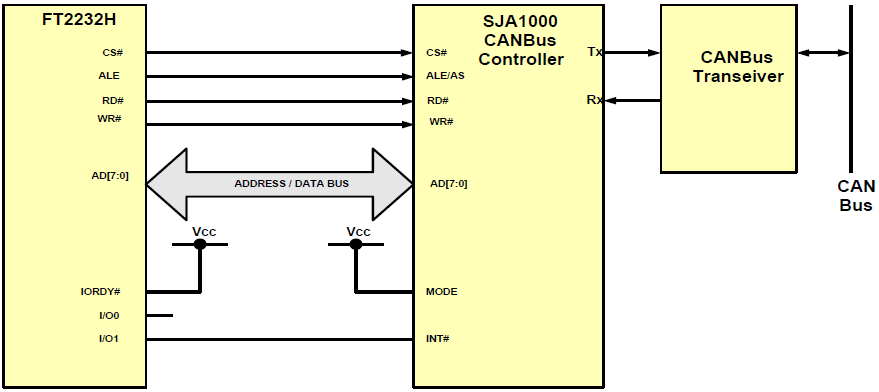

3.4.8 ą×ą┐ąĖčüą░ąĮąĖąĄ ąĮąŠąČąĄą║, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗčģ ą▓ ąĖąĮč鹥čĆč乥ą╣čüąĄ 菹╝čāą╗čÅčåąĖąĖ čłąĖąĮčŗ čģąŠčüčéą░ (Host Bus Emulation Interface)

ąÜąŠą╝ą▒ąĖąĮą░čåąĖčÅ ą║ą░ąĮą░ą╗ąŠą▓ A ąĖ B ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮą░ ą┤ą╗čÅ čĆąĄąČąĖą╝ą░ 菹╝čāą╗čÅčåąĖąĖ čłąĖąĮčŗ ą┤ą░ąĮąĮčŗčģ čģąŠčüčéą░ čüčéą░ąĮą┤ą░čĆčéą░ 8048 ąĖą╗ąĖ 8051 MCU (ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąĮą░čÅ čłąĖąĮą░ ą░ą┤čĆąĄčüą░ ąĖ ą┤ą░ąĮąĮčŗčģ ą┐čĆąŠčåąĄčüčüąŠčĆą░). ąÆ čéą░ą▒ą╗ąĖčåąĄ čāą║ą░ąĘą░ąĮčŗ ąĮąŠąČą║ąĖ, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą▓ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ, ąĖ ą┐čĆąĖą▓ąĄą┤ąĄąĮąŠ ąĖčģ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ.

| Pin Ōä¢ |

ąśą╝čÅ |

ąóąĖą┐ |

ą×ą┐ąĖčüą░ąĮąĖąĄ čüąĖą│ąĮą░ą╗ąŠą▓ Host Bus Emulation Interface |

24,23,22,21,

19,18,17,16 |

ADBUS[7:0] |

I/O |

ą£čāą╗čīčéąĖą┐ą╗ąĄą║čüąĖčĆąŠą▓ą░ąĮąĮą░čÅ čłąĖąĮą░ ą┤ą░ąĮąĮčŗčģ ąĖ ą░ą┤čĆąĄčüą░ AD7 .. AD0 |

34,33,32,30,

29,28,27,26 |

A[15:8] |

ąÆčŗčģąŠą┤ |

ąĪčéą░čĆčłąĖą╣ ą▒ą░ą╣čé ą░ą┤čĆąĄčüą░ (extended address, čĆą░čüčłąĖčĆąĄąĮąĮčŗą╣ ą░ą┤čĆąĄčü) A15 .. A8 |

| 38 |

CS# |

ąÆčŗčģąŠą┤ |

ąĪąĖą│ąĮą░ą╗ ą▓čŗą▒ąŠčĆą║ąĖ čćąĖą┐ą░, ą░ą║čéąĖą▓ąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 0 ą▓ąŠ ą▓čĆąĄą╝čÅ ąŠą┐ąĄčĆą░čåąĖą╣ Read (čćč鹥ąĮąĖąĄ) ąĖą╗ąĖ Write (ąĘą░ą┐ąĖčüčī). |

| 39 |

ALE |

ąÆčŗčģąŠą┤ |

ą¤ąŠą╗ąŠąČąĖč鹥ą╗čīąĮčŗą╣ ąĖą╝ą┐čāą╗čīčü ą┤ą╗čÅ ąĘą░čēąĄą╗ą║ąĖą▓ą░ąĮąĖčÅ ą░ą┤čĆąĄčüą░ A7 .. A0 (ąĖąĘ ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąĖčĆąŠą▓ą░ąĮąĮąŠą╣ čłąĖąĮčŗ ADBUS[7:0]). |

| 40 |

RD# |

ąÆčŗčģąŠą┤ |

ąÆčŗčģąŠą┤ čüąĖą│ąĮą░ą╗ą░ čćč鹥ąĮąĖčÅ, ą░ą║čéąĖą▓ąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 0. |

| 41 |

WR# |

ąÆčŗčģąŠą┤ |

ąÆčŗčģąŠą┤ čüąĖą│ąĮą░ą╗ą░ ąĘą░ą┐ąĖčüąĖ, ą░ą║čéąĖą▓ąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 0 (ą┤ą░ąĮąĮčŗąĄ ąĮą░ čłąĖąĮąĄ ADBUS[7:0] ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ, ą║ąŠą│ą┤ą░ WR# ą┐ąĄčĆąĄčłąĄą╗ ą▓ ą╗ąŠą│. 0, ąĖ ą┤ąŠą╗ąČąĮčŗ čāą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĄčģąŠą┤ą░ WR# ą▓ ą╗ąŠą│. 1). |

| 43 |

IORDY |

ąÆčģąŠą┤ |

ąĀą░čüčéčÅą│ąĖą▓ą░ąĄčé ą▓čĆąĄą╝čÅ, ą▓čŗą┤ąĄą╗čÅąĄą╝ąŠąĄ ąĮą░ ąŠą┐ąĄčĆą░čåąĖąĖ Read ąĖą╗ąĖ Write, ąĄčüą╗ąĖ IORDY čāą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ą▓ ą╗ąŠą│. 0. ąĪąŠąĄą┤ąĖąĮąĖč鹥 čüąĖą│ąĮą░ą╗ IORDY čü ą┐čĆąŠą▓ąŠą┤ąŠą╝ VCORE, ąĄčüą╗ąĖ IORDY ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ. |

| 44 |

CLKOUT |

ąÆčŗčģąŠą┤ |

ąōą╗ą░ą▓ąĮčŗą╣ ą▓čŗčģąŠą┤ čéą░ą║č鹊ą▓. ąÆčŗą▓ąŠą┤ąĖčé čéą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╣ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĮčŗą╝ ąĖąĮč鹥čĆč乥ą╣čüąŠą╝. |

| 45 |

I/O0 |

I/O |

ąĪ čŹčéąĖą╝ ą▓čŗą▓ąŠą┤ąŠą╝ ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ąĖąĮčüčéčĆčāą║čåąĖąĖ čĆąĄąČąĖą╝ą░ MPSSE ą┤ą╗čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ / ąŠčćąĖčüčéą║ąĖ ąĖą╗ąĖ čćč鹥ąĮąĖąĄ čüčéą░čĆčłąĄą│ąŠ ą▒ą░ą╣čéą░ ą┤ą░ąĮąĮčŗčģ. ą¤ąŠą┤čĆąŠą▒ąĮąŠčüčéąĖ čäčāąĮą║čåąĖąĖ čŹčéąĖčģ ąĖąĮčüčéčĆčāą║čåąĖą╣ čćąĖčéą░ą╣č鹥 ą▓ ą░ą┐ąĮąŠčāč鹥 AN_108. |

| 46 |

I/O1 |

I/O |

ąĪ čŹčéąĖą╝ ą▓čŗą▓ąŠą┤ąŠą╝ ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ąĖąĮčüčéčĆčāą║čåąĖąĖ čĆąĄąČąĖą╝ą░ MPSSE ą┤ą╗čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ / ąŠčćąĖčüčéą║ąĖ ąĖą╗ąĖ čćč鹥ąĮąĖąĄ čüčéą░čĆčłąĄą│ąŠ ą▒ą░ą╣čéą░ ą┤ą░ąĮąĮčŗčģ. ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠ čŹč鹊čé ą▓čŗą▓ąŠą┤ ąĖą╝ąĄąĄčé ąĖąĮčüčéčĆčāą║čåąĖąĖ, ą║ąŠč鹊čĆčŗąĄ ą┐ąĄčĆąĄą▓ąŠą┤čÅčé ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą▓ ąŠąČąĖą┤ą░ąĮąĖąĄ ą┐ąŠą║ą░ ą▓čŗą▓ąŠą┤ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą╗ąŠą│. 1, ąĖą╗ąĖ ą▓ ąŠąČąĖą┤ą░ąĮąĖąĖ, ą┐ąŠą║ą░ ąŠąĮ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą╗ąŠą│. 0. ąŁč鹊 ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ą║ ąĮąŠąČą║ąĄ IRQ čćąĖą┐ą░ ą┐ąĄčĆąĖč乥čĆąĖąĖ. ą£ąĖą║čĆąŠčüčģąĄą╝ą░ FT2232H ą▒čāą┤ąĄčé ąŠąČąĖą┤ą░čéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ąĖ ą┐ąŠčüą╗ąĄ čŹč鹊ą│ąŠ ą┐čĆąŠčćąĖčéą░ąĄčé čāčüčéčĆąŠą╣čüčéą▓ąŠ, ąĖ ą┐ąĄčĆąĄą┤ą░čüčé ąŠčéą▓ąĄčé ąŠą▒čĆą░čéąĮąŠ čģąŠčüčéčā PC. ąÆčŗą▓ąŠą┤ I/O1 ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāą┤ąĄčƹȹ░ąĮ ą▓ čĆąĄąČąĖą╝ąĄ ą▓čģąŠą┤ą░, ąĄčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čŹčéą░ ąŠą┐čåąĖčÅ. ą¤ąŠą┤čĆąŠą▒ąĮąŠčüčéąĖ čäčāąĮą║čåąĖąĖ čŹčéąĖčģ ąĖąĮčüčéčĆčāą║čåąĖą╣ čćąĖčéą░ą╣č鹥 ą▓ ą░ą┐ąĮąŠčāč鹥 AN_108. |

ąóą░ą▒ą╗ąĖčåą░ 3.11. ą×ą┐ąĖčüą░ąĮąĖąĄ ą▓čŗą▓ąŠą┤ąŠą▓ ą║ą░ąĮą░ą╗ą░ A ąĖ ą║ą░ąĮą░ą╗ą░ B, čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĮčŗčģ ą▓ čĆąĄąČąĖą╝ąĄ ąĖąĮč鹥čĆč乥ą╣čüą░ Host Bus Emulation

ążčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ čŹč鹊ą│ąŠ čĆąĄąČąĖą╝ą░ čüą╝. ą▓ čüąĄą║čåąĖąĖ 4.7 MCU Host Bus Emulation Mode.

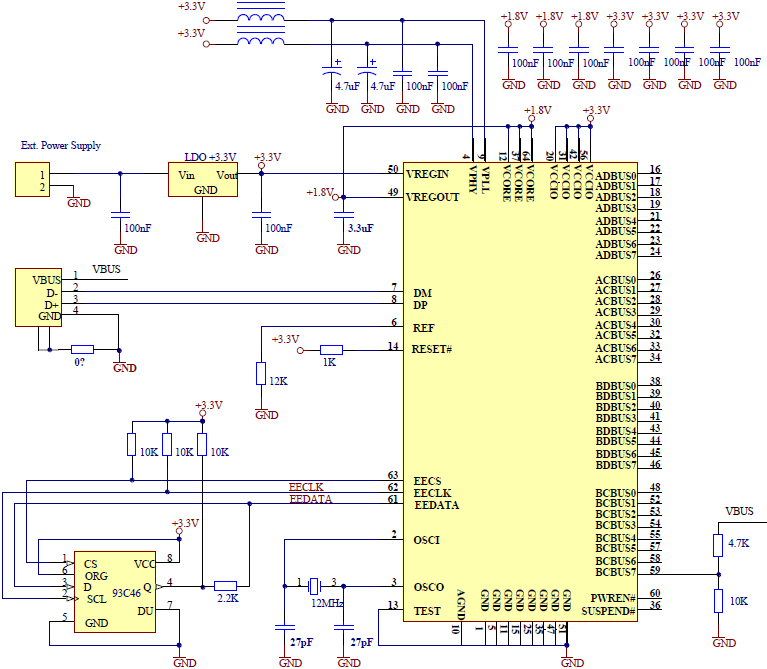

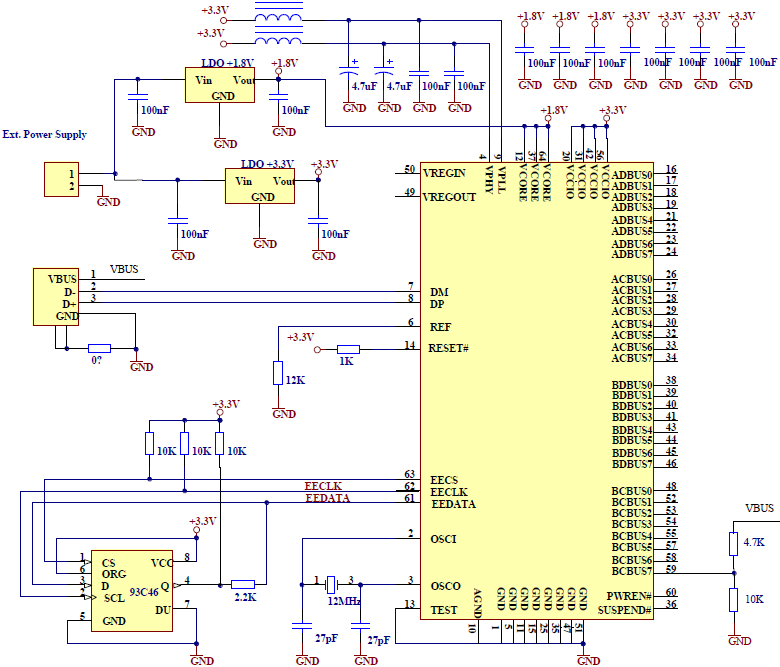

[4 ążčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ FT2232H]

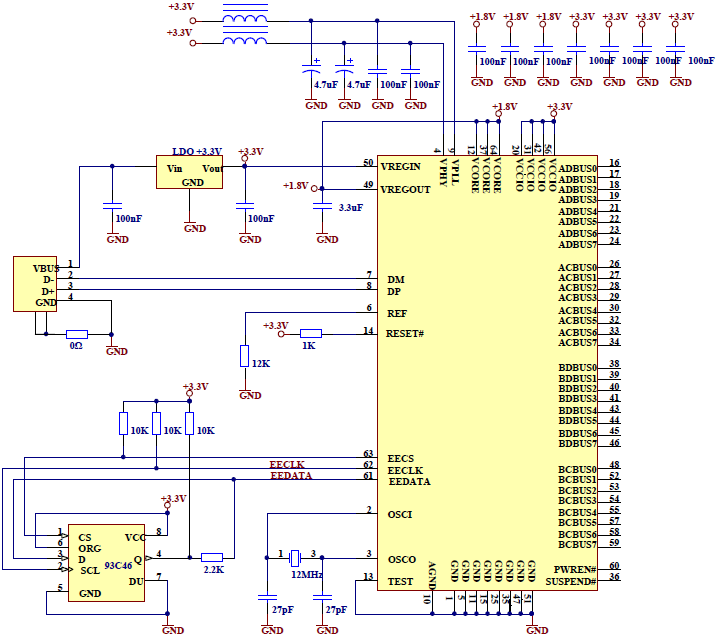

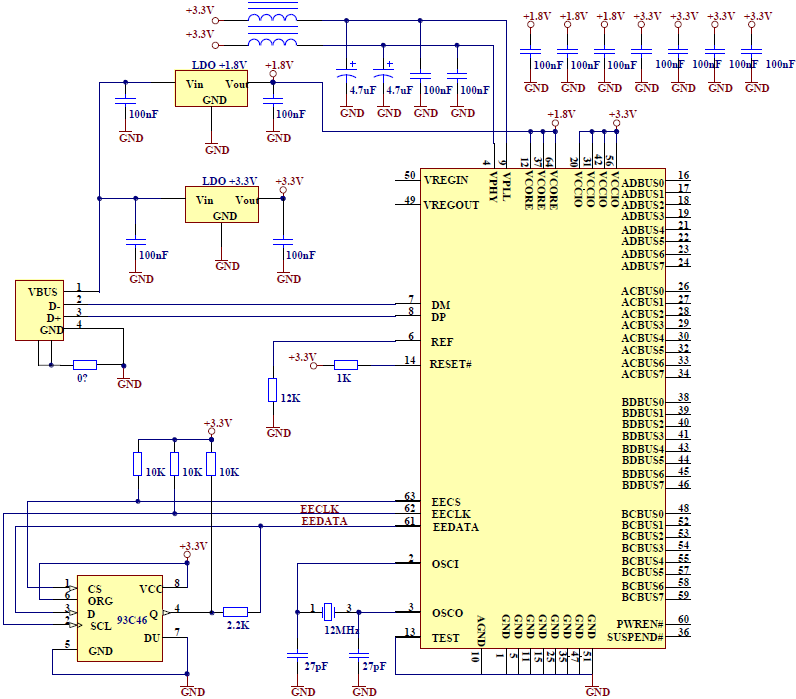

ąÆ ą╝ąĖą║čĆąŠčüčģąĄą╝ąĄ FT2232H ąĖą╝ąĄąĄčéčüčÅ ą┤ą▓ą░ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝čŗčģ ą║ą░ąĮą░ą╗ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ (ąĖąĮč鹥čĆč乥ą╣čüą░). ąŁčéąĖ ą║ą░ąĮą░ą╗čŗ ą╝ąŠąČąĮąŠ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ą╝ąĄąČą┤čā ąŠą┤ąĮąĖą╝ ąĖąĮč鹥čĆč乥ą╣čüąŠą╝ USB (USB 2.0 High Speed 480 ą╝ą▒ąĖčé/čüąĄą║) ąĖ ą┤ą▓čāą╝čÅ ą┤čĆčāą│ąĖą╝ąĖ ąĖąĮč鹥čĆč乥ą╣čüą░ą╝ąĖ, ąĄčüą╗ąĖ ąŠąĮąĖ čĆą░ą▒ąŠčéą░čÄčé ą▓ ąŠą┤ąĮąŠą╝ ąĖąĘ čüą╗ąĄą┤čāčÄčēąĖčģ čĆąĄąČąĖą╝ąŠą▓ - UART, FIFO, JTAG, SPI, I2C ąĖą╗ąĖ bit-bang. ą¤čĆąĖč湥ą╝ čüą║ąŠčĆąŠčüčéčī ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖ čĆąĄąČąĖą╝ ą║ą░ąČą┤ąŠą│ąŠ ą║ą░ąĮą░ą╗ą░ ą▓ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ąĮą░čüčéčĆą░ąĖą▓ą░ąĄčéčüčÅ ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé ą┤čĆčāą│ąŠą│ąŠ ą║ą░ąĮą░ą╗ą░. ąÆ ą┤ąŠą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ čĆąĄąČąĖą╝ą░ą╝ UART, FIFO, JTAG, SPI, I2C ąĖą╗ąĖ bit-bang ąĖą╝ąĄčÄčéčüčÅ čéą░ą║ąČąĄ čĆąĄąČąĖą╝čŗ, ą│ą┤ąĄ ąĘą░ą┤ąĄą╣čüčéą▓ąŠą▓ą░ąĮčŗ čüčĆą░ąĘčā ą┤ą▓ą░ ą║ą░ąĮą░ą╗ą░ - čŹč鹊 čĆąĄąČąĖą╝čŗ 菹╝čāą╗čÅčåąĖąĖ čłąĖąĮčŗ čģąŠčüčéą░ (host bus emulation), čĆąĄąČąĖą╝ FIFO ą▓ čüčéąĖą╗ąĄ CPU (CPU-Style FIFO mode) ąĖ čĆąĄąČąĖą╝ ą▒čŗčüčéčĆąŠą│ąŠ ąŠą┐č鹊ąĖąĘąŠą╗ąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░.

4.1 ąÜą╗čÄč湥ą▓čŗąĄ ąŠčüąŠą▒ąĄąĮąĮąŠčüčéąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ FT2232H

USB High Speed to Dual Interface. ąÜą░ą║ čāąČąĄ čāą┐ąŠą╝ąĖąĮą░ą╗ąŠčüčī, ą▓ ą╝ąĖą║čĆąŠčüčģąĄą╝ąĄ FT2232H čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮ ą▓čŗčüąŠą║ąŠčüą║ąŠčĆąŠčüčéąĮąŠą╣ USB 2.0 High Speed (480Mbits/s) ąĖąĮč鹥čĆč乥ą╣čü, ą║ąŠč鹊čĆčŗą╣ ą┐čĆąĄąŠą▒čĆą░ąĘčāąĄčéčüčÅ čäąĖąĘąĖč湥čüą║ąĖ ą▓ ą┤ą▓ą░ ąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗčģ ąĖ ą│ąĖą▒ą║ąŠ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝čŗčģ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮčŗčģ/ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ąĖąĮč鹥čĆč乥ą╣čüą░.

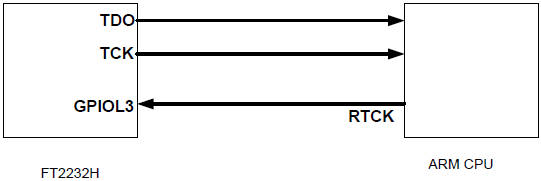

ąōą╗čāą▒ąŠą║ą░čÅ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮą░čÅ ąĖąĮč鹥ą│čĆą░čåąĖčÅ. ą£ąĖą║čĆąŠčüčģąĄą╝ą░ FT2232H ąĖąĮč鹥ą│čĆąĖčĆčāąĄčé ą▓ čüąĄą▒ąĄ USB ą▓ą╝ąĄčüč鹥 čü ąĖąĮč鹥čĆč乥ą╣čüąŠą╝ UTMI (Universal Transceiver Macrocell Interface), ąĖ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčé ą┐ąĄčĆąĄą┤ą░čćčā ą┤ą░ąĮąĮčŗčģ ąĮą░ čüą║ąŠčĆąŠčüčéąĖ ą┐čĆąŠč鹊ą║ąŠą╗ą░ USB 2.0 High Speed. FT2232H čéą░ą║ąČąĄ ąĖą╝ąĄąĄčé ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ čüčéą░ą▒ąĖą╗ąĖąĘą░č鹊čĆ +1.8 ą▓ąŠą╗čīčé čü ą╝ą░ą╗ąĄąĮčīą║ąĖą╝ ą┐ą░ą┤ąĄąĮąĖąĄą╝ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ąĮą░ čĆąĄą│čāą╗ąĖčĆčāčÄčēąĄą╝ 菹╗ąĄą╝ąĄąĮč鹥 (Low Drop-Out (LDO) regulator), ąĖ čāąĘąĄą╗ ążąÉą¤ą¦ (PLL) ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ 480 ą£ąōčå ąĖąĘ čćą░čüč鹊čéčŗ ą║ą▓ą░čĆčåą░ 12 ą£ąōčå.

MPSSE. ąĪąĖčüč鹥ą╝čŗ MPSSE (2 čłčé.) ą┐ąŠąĘą▓ąŠą╗čÅčÄčé ą┐čĆąĖą╝ąĄąĮčÅčéčī čüąĖąĮčģčĆąŠąĮąĮčŗąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗąĄ ąĖąĮč鹥čĆč乥ą╣čüčŗ ą▓ čĆą░ąĘą╗ąĖčćąĮčŗčģ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅčģ, ąĮą░ čüą║ąŠčĆąŠčüčéčÅčģ ą┤ąŠ 30 ą╝ą▒ąĖčé/čü.

Data Transfer rate. ą£ąĖą║čĆąŠčüčģąĄą╝ą░ FT2232H ą▓ čĆąĄąČąĖą╝ąĄ RS232/RS422/RS485 UART ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé čüą║ąŠčĆąŠčüčéčī ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ąŠ 12 ą╝ąĄą│ą░ą▒ąĖčé, ąĖ ą▓ čĆąĄąČąĖą╝ąĄ čüąĖąĮčģčĆąŠąĮąĮąŠą│ąŠ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠą│ąŠ FIFO čüą▓čŗčłąĄ 25 ą╝ąĄą│ą░ą▒ą░ą╣čé/čü. ąÆąĮąĖą╝ą░ąĮąĖąĄ - ąĮąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčéčüčÅ čüą║ąŠčĆąŠčüčéąĖ 7, 9, 10 ąĖ 11 ą╝ąĄą│ą░ą▒ąŠą┤.

Latency Timer. ąÆčüčéčĆąŠąĄąĮąĮčŗą╣ čéą░ą╣ą╝ąĄčĆ ąĘą░ą┤ąĄčƹȹ║ąĖ (Latency Timer) ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┤čĆą░ą╣ą▓ąĄčĆčā ąĘą░ą┤ą░ą▓ą░čéčī ą║ąŠčĆąŠčéą║ąĖąĄ čéą░ą╣ą╝ą░čāčéčŗ ą┤ą╗čÅ čüą▒čĆąŠčüą░ ą║ąŠčĆąŠčéą║ąĖčģ ą┐ą░ą║ąĄč鹊ą▓ ą┤ą░ąĮąĮčŗčģ ąŠą▒čĆą░čéąĮąŠ ąĮą░ ą║ąŠą╝ą┐čīčÄč鹥čĆ. ą¤ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ čéą░ą╣ą╝ąĄčĆ ąĮą░čüčéčĆąŠąĄąĮ ąĮą░ 16 ą╝čü, ąĮąŠ ąĄą│ąŠ ą╝ąŠąČąĮąŠ ąĮą░čüčéčĆąŠąĖčéčī ąĮą░ ąĖąĮč鹥čĆą▓ą░ą╗ 0..256 ą╝čü. ą¤čĆąĖ ąĘą░ą┤ąĄčƹȹ║ąĄ 0 ą╝čü ą┐ąŠą╗čāčćą░ąĄčéčüčÅ ą┐ąĄčĆąĄą┤ą░čćą░ ą┐ą░ą║ąĄč鹊ą▓ ą▓ ą║ą░ąČą┤ąŠą╝ ą▓čŗčüąŠą║ąŠčüą║ąŠčĆąŠčüčéąĮąŠą╝ ą╝ąĖą║čĆąŠčäčĆąĄą╣ą╝ąĄ.

4.2 ą×ą┐ąĖčüą░ąĮąĖąĄ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮčŗčģ ą▒ą╗ąŠą║ąŠą▓

Dual Multi-Purpose UART/FIFO Controllers. ąöą▓ąŠą╣ąĮčŗąĄ ą╝ąĮąŠą│ąŠčåąĄą╗ąĄą▓čŗąĄ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčŗ UART/FIFO (Dual Multi-Purpose UART/FIFO Controllers). FT2232H ąĖą╝ąĄąĄčé ą┤ą▓ą░ ąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗčģ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ UART/FIFO. ą×ąĮąĖ ą╝ąŠą│čāčé čāą┐čĆą░ą▓ą╗čÅčéčī ą┤ą░ąĮąĮčŗą╝ąĖ UART, ą┤ą░ąĮąĮčŗą╝ąĖ 245 fifo, ąĖąĮč鹥čĆč乥ą╣čüąŠą╝ čü ąŠą┐č鹊ąĖąĘąŠą╗čÅčåąĖąĄą╣ (Fast Serial), ąĖą╗ąĖ čĆą░ą▒ąŠčéą░čéčī ą▓ čĆąĄąČąĖą╝ąĄ Bit-Bang, ąĄčüą╗ąĖ čŹč鹊 ą▓ą║ą╗čÄč湥ąĮąŠ ą║ąŠą╝ą░ąĮą┤ąŠą╣ SETUP. ąÜą░ąČą┤čŗą╣ ąĖąĘ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ čéą░ą║ąČąĄ ą▓ čüąĄą▒ąĄ čüąŠą┤ąĄčƹȹĖčé čüąĖčüč鹥ą╝čā MPSSE (Multi Protocol Synchronous Serial Engine), ą║ąŠč鹊čĆą░čÅ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą▓ ą║ą░ąČą┤ąŠą╝ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąĄ ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé ą┤čĆčāą│ąŠą│ąŠ. ąĪ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ MPSSE ą╝ąĮąŠą│ąŠčäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮčŗą╣ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ UART/FIFO ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ 1 MPSSE + 1 UART / 245 FIFO (ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ UART / 245 ą╝ąŠąČąĄčé ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čĆąĄąČąĖą╝ Bit Bang ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ą┐čĆąĖ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéąĖ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗčģ ą┐ąŠčĆč鹊ą▓ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ I/O), ąĖą╗ąĖ 2 MPSSE.

USB Protocol Engine and FIFO control. ąĪąĖčüč鹥ą╝ą░ ą┐ąŠą┤ą┤ąĄčƹȹ║ąĖ ą┐čĆąŠč鹊ą║ąŠą╗ą░ USB ąĖ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ FIFO (USB Protocol Engine and FIFO control). ąöą▓ąĖąČąŠą║ ą┐čĆąŠč鹊ą║ąŠą╗ą░ USB ąŠą▒čüą╗čāąČąĖą▓ą░ąĄčé ą▓ ą╝ąĖą║čĆąŠčüčģąĄą╝ąĄ ąĖąĮč鹥čĆč乥ą╣čü ą╝ąĄąČą┤čā UTMI PHY čüč鹥ą║ą░ą╝ąĖ FIFO. ą×ąĮ čéą░ą║ąČąĄ ąŠą▒čüą╗čāąČąĖą▓ą░ąĄčé čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖąĄą╝ ąĖ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé čüčéą░ąĮą┤ą░čĆčé ą┐čĆąŠč鹊ą║ąŠą╗ą░ USB.

Dual Port FIFO TX Buffer (4Kbytes per interface). ąöą▓ąŠą╣ąĮąŠą╣ ą▒čāč乥čĆ ą┐ąĄčĆąĄą┤ą░čćąĖ FIFO (Dual Port FIFO TX Buffer), 4 ą║ąĖą╗ąŠą▒ą░ą╣čéą░ ąĮą░ ąĖąĮč鹥čĆč乥ą╣čü. ąöą░ąĮąĮčŗąĄ ąŠčé čģąŠčüčéą░ PC čüąŠčģčĆą░ąĮčÅčÄčéčüčÅ ą▓ čŹčéąĖčģ ą▒čāč乥čĆą░čģ, ą┤ą╗čÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą▓ą╝ąĄčüč鹥 čü ą╝ąĮąŠą│ąŠčäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮčŗą╝ąĖ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ą╝ąĖ UART/FIFO. ąŁč鹊 čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ą┐ąŠą┤čüąĖčüč鹥ą╝ąŠą╣ ą┐čĆąŠč鹊ą║ąŠą╗ą░ USB ąĖ ą▒ą╗ąŠą║ąŠą╝ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ FIFO.

Dual Port FIFO RX Buffer (4Kbytes per interface). ąöą▓ąŠą╣ąĮąŠą╣ ą▒čāč乥čĆ ą┐čĆąĖąĄą╝ą░ FIFO (Dual Port FIFO RX Buffer), 4 ą║ąĖą╗ąŠą▒ą░ą╣čéą░ ąĮą░ ąĖąĮč鹥čĆč乥ą╣čü. ąöą░ąĮąĮčŗąĄ ąŠčé ą╝ąĮąŠą│ąŠčäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮčŗčģ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ UART/FIFO čüąŠčģčĆą░ąĮčÅčÄčéčüčÅ ą▓ čŹčéąĖčģ ą▒ą╗ąŠą║ą░čģ ą┤ą╗čÅ ąŠčéą┐čĆą░ą▓ą║ąĖ ąĖčģ ą▓ą┐ąŠčüą╗ąĄą┤čüčéą▓ąĖąĖ ąŠą▒čĆą░čéąĮąŠ ąĮą░ ą║ąŠą╝ą┐čīčÄč鹥čĆ čģąŠčüčéą░ (ą┐ąŠ ąĄą│ąŠ ąĘą░ą┐čĆąŠčüčā). ąŁč鹊 čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ą┐ąŠą┤čüąĖčüč鹥ą╝ąŠą╣ ą┐čĆąŠč鹊ą║ąŠą╗ą░ USB ąĖ ą▒ą╗ąŠą║ąŠą╝ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ FIFO.

RESET Generator. ąōąĄąĮąĄčĆą░č鹊čĆ čüąĖą│ąĮą░ą╗ą░ ąĪąæąĀą×ąĪ (RESET Generator) ŌĆō ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ ą│ąĄąĮąĄčĆą░č鹊čĆ čüą▒čĆąŠčüą░ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ąĮą░ą┤ąĄąČąĮčŗą╣ čüą▒čĆąŠčü ą▓čüąĄčģ ą▓ąĮčāčéčĆąĄąĮąĮąĖčģ čāąĘą╗ąŠą▓ ą┐čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ (power-on reset) čāčüčéčĆąŠą╣čüčéą▓ą░. ąÆčģąŠą┤ąĮąŠą╣ ą▓čŗą▓ąŠą┤ RESET# ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą▓ąĮąĄčłąĮąĖą╝ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ čüą▒čĆą░čüčŗą▓ą░čéčī FT2232H. RESET# ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąŠą┤čéčÅąĮčāčé ą║ VCCIO (+3.3 ą▓ąŠą╗čīčé), ąĄčüą╗ąĖ ą▓ąĮąĄčłąĮąĖą╣ čüą▒čĆąŠčü ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ.

Independent Baud Rate Generators. ąØąĄąĘą░ą▓ąĖčüąĖą╝čŗąĄ ą│ąĄąĮąĄčĆą░č鹊čĆčŗ čüą║ąŠčĆąŠčüč鹥ą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ (Independent Baud Rate Generators) ŌĆō ą│ąĄąĮąĄčĆą░č鹊čĆčŗ čüą║ąŠčĆąŠčüč鹥ą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÄčé x16 ąĖą╗ąĖ x10 čéą░ą║č鹊ą▓čŗąĄ ą▓čģąŠą┤čŗ ą┤ą╗čÅ UART-ąŠą▓ ąŠčé ąŠą┐ąŠčĆąĮąŠą╣ čćą░čüč鹊čéčŗ 120 ą£ąōčå, ąĖ čüąŠčüč鹊ąĖčé ąĖąĘ 14-ą▒ąĖčéąĮąŠą│ąŠ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ ąĖ 4-ą▒ąĖčéąĮąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░, ą║ąŠč鹊čĆčŗąĄ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÄčé č鹊ąĮą║čāčÄ ąĮą░čüčéčĆąŠą╣ą║čā čüą║ąŠčĆąŠčüčéąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ/ą┐čĆąĖąĄą╝ą░ (ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ ą┤ąĄą╗ąĄąĮąĖčÅ ąĮą░ čåąĄą╗ąŠąĄ čćąĖčüą╗ąŠ ą┐ą╗čÄčü ą┤čĆąŠą▒čī). ąŁč鹊 ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé čüą║ąŠčĆąŠčüčéąĖ UART, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮčŗ ąŠčé 183 ą▒ąŠą┤ ą┤ąŠ 12 ą╝ąĖą╗ą╗ąĖąŠąĮąŠą▓ ą▒ąŠą┤. FT2232H ąĮąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé čüą║ąŠčĆąŠčüčéąĖ 7, 9, 10 ąĖ 11 ą╝ąĄą│ą░ą▒ąŠą┤.

+1.8V LDO Regulator. ąĪčéą░ą▒ąĖą╗ąĖąĘą░č鹊čĆ +1.8V čü ąĮąĖąĘą║ąĖą╝ ą┐ą░ą┤ąĄąĮąĖąĄą╝ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ (LDO Regulator). ąōąĄąĮąĄčĆąĖčĆčāąĄčé +1.8 ą▓ąŠą╗čīčé ą┤ą╗čÅ ą┐ąĖčéą░ąĮąĖčÅ čÅą┤čĆą░ ąĖ ą┐čĆąĖąĄą╝ąŠą┐ąĄčĆąĄą┤ą░čéčćąĖą║ąŠą▓ USB. ąÆčģąŠą┤ čüčéą░ą▒ąĖą╗ąĖąĘą░č鹊čĆą░ (VREGIN) ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą║ ą▓ąĮąĄčłąĮąĄą╝čā ąĖčüč鹊čćąĮąĖą║čā ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ +3.3V. ąĀąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ čéą░ą║ąČąĄ ą┤ąŠą▒ą░ą▓ąĖčéčī ą▓ąĮąĄčłąĮąĖą╣ čäąĖą╗čīčéčĆčāčÄčēąĖą╣ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ ąĮą░ ąĮąŠąČą║čā VREGIN. ąØąĄ čüčāčēąĄčüčéą▓čāąĄčé ą┐čĆčÅą╝ąŠą│ąŠ čüąŠąĄą┤ąĖąĮąĄąĮąĖčÅ ąŠčé ą▓čŗčģąŠą┤ą░ +1.8V (VREGOUT) ą║ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╝ ą┐ąŠčéčĆąĄą▒ąĖč鹥ą╗čÅą╝ čćąĖą┐ą░ FT2232H. ą¤ąĄčćą░čéąĮą░čÅ ą┐ą╗ą░čéą░ ą┤ąŠą╗ąČąĮą░ čüąŠąĄą┤ąĖąĮčÅčéčī VREGOUT čü čåąĄą┐čīčÄ +1.8V VREGIN.

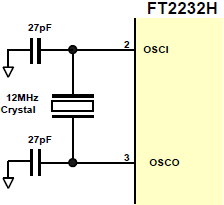

UTMI PHY. ąśąĮč鹥čĆč乥ą╣čü UTMI (Universal Transceiver Macrocell Interface) - čŹč鹊čé ą▒ą╗ąŠą║ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé Full speed / High Speed čäčāąĮą║čåąĖčÄ SERDES (serialise ŌĆō deserialise) ą┤ą╗čÅ ą┤ą░ąĮąĮčŗčģ USB TX/RX data. ą×ąĮ čéą░ą║ąČąĄ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé čéą░ą║čéčŗ ą┤ą╗čÅ ąŠčüčéą░ą╗čīąĮąŠą╣ čćą░čüčéąĖ čćąĖą┐ą░. ąÜą▓ą░čĆčå 12 ą£ąōčå ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą║ ąĮąŠąČą║ą░ą╝ OSCI ąĖ OSCO. ąĀąĄąĘąĖčüč鹊čĆ 12 ąÜą×ą╝ (č鹊čćąĮąŠčüčéčī 1%) ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ąĮą░ ą┐ąĄčćą░čéąĮąŠą╣ ą┐ą╗ą░č鹥 ą╝ąĄąČą┤čā ąĮąŠąČą║ąŠą╣ REF ąĖ GND. ążčāąĮą║čåąĖąĖ UTMI PHY ą▓ą║ą╗čÄčćą░čÄčé ą▓ čüąĄą▒čÅ:

- ą┐ąŠą┤ą┤ąĄčƹȹ║čā čüą║ąŠčĆąŠčüčéąĖ 480 ą£ą▒ąĖčé/čüąĄą║ "High Speed" (HS), 12 ą£ą▒ąĖčé/čüąĄą║ "Full Speed" (FS), FS Only ąĖ "Low Speed" (LS).

- ą│ąĄąĮąĄčĆą░čåąĖčÄ ąĖ ą┐čĆąŠą▓ąĄčĆą║čā SYNC/EOP.

- ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ ąĖ čéą░ą║č鹊ą▓ ąĖąĘ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ą┐ąŠč鹊ą║ą░ čüąĖą│ąĮą░ą╗ą░ USB.

- ą▓čüčéą░ą▓ą║ą░/čāą┤ą░ą╗ąĄąĮąĖąĄ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗčģ ą▒ąĖčé (Bit-stuffing/unstuffing), ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ąŠčłąĖą▒ąŠą║ ą▒ąĖčéčüčéą░čäčäąĖąĮą│ą░ (bit stuff error detection).

- ą┐ąŠą┤ą┤ąĄčƹȹ║ą░ čäčāąĮą║čåąĖą╣ USB: ą▓ąŠąĘąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ (Resume), ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖąĄ (Wake Up) ąĖ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ą░ (Suspend).

- ąŠą┤ąĖąĮąŠčćąĮčŗą╣ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮčŗą╣ ą▓čŗčģąŠą┤ čéą░ą║č鹊ą▓ ą┤ą░ąĮąĮčŗčģ čüąŠ ą▓čüčéčĆąŠąĄąĮąĮąŠą│ąŠ PLL - ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ čéą░ą║č鹊ą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ą┤ą░ąĮąĮčŗčģ ąĮą░ ą▓čŗčüąŠą║ąĖčģ čüą║ąŠčĆąŠčüčéčÅčģ.

ąśąĮč鹥čĆč乥ą╣čü EEPROM. ąÜąŠą│ą┤ą░ ą▓ąĮąĄčłąĮąĄąĄ EEPROM ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ (ąŠčéčüčāčéčüčéą▓čāąĄčé), čćąĖą┐ FT2232H ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą┤ą▓ąŠą╣ąĮąŠą╣ ą░čüąĖąĮčģčĆąŠąĮąĮčŗą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ą┐ąŠčĆčé. ąöąŠą▒ą░ą▓ą╗ąĄąĮąĖąĄ ą▓ąĮąĄčłąĮąĄą╣ 93C46 (93C56 ąĖą╗ąĖ 93C66) EEPROM ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą║ą░ąČą┤ąŠą╝čā ąĖąĘ ą║ą░ąĮą░ą╗ąŠą▓ čćąĖą┐ą░ ą▒čŗčéčī ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĮčŗą╝ ą║ą░ą║ serial UART (čĆąĄąČąĖą╝ RS232), čĆąĄąČąĖą╝ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠą│ąŠ FIFO (245) ąĖą╗ąĖ čĆąĄąČąĖą╝ ą▒čŗčüčéčĆąŠą│ąŠ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ fast serial (čü ąŠą┐č鹊ąĖąĘąŠą╗čÅčåąĖąĄą╣). ąÆąĮąĄčłąĮąĄąĄ EEPROM ą╝ąŠąČąĄčé ą▒čŗčéčī ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąŠ ą┤ą╗čÅ ąĘą░ą┤ą░ąĮąĖčÅ USB ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆąŠą▓ VID, PID, čüąĄčĆąĖą╣ąĮąŠą│ąŠ ąĮąŠą╝ąĄčĆą░, čüčéčĆąŠą║ąŠą▓čŗčģ ąŠą┐ąĖčüą░č鹥ą╗ąĄą╣ ą┐čĆąŠą┤čāą║čéą░ (Product Description Strings) ąĖ ąĘąĮą░č湥ąĮąĖčÅ č鹊ą║ą░ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ (Power Descriptor value) čćąĖą┐ą░ FT2232H - ą┤ą╗čÅ ą┐čĆąĖą╗ąŠąČąĄąĮąĖą╣ OEM. ą¦ąĄčĆąĄąĘ EEPROM ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāčÄčéčüčÅ ą┤čĆčāą│ąĖąĄ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ, ą▓ą║ą╗čÄčćą░čÅ Remote Wake Up (čäčāąĮą║čåąĖčÅ čāą┤ą░ą╗ąĄąĮąĮąŠą│ąŠ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ), Soft Pull Down on Power-Off ąĖ ąĮą░ą│čĆčāąĘąŠčćąĮą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī ąĮąŠąČąĄą║ I/O.

ą£ąĖą║čĆąŠčüčģąĄą╝ą░ EEPROM ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī 16-ą▒ąĖčéąĮąŠą╣ ąĮą░ą┐ąŠą┤ąŠą▒ąĖąĄ Microchip 93LC46B ąĖą╗ąĖ ą░ąĮą░ą╗ąŠą│ąĖčćąĮą░čÅ, ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčēąĄą╣ čüą║ąŠčĆąŠčüčéčī čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ 1 ą╝ąĄą│ą░ą▒ąĖčé/čüąĄą║ ą┐čĆąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ VCC ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ +3.00 .. +3.6V. ąöą░ąĮąĮčŗąĄ ą▓ EEPROM ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāčÄčéčüčÅ ą┐čĆčÅą╝ąŠ ą▓ čüčģąĄą╝ąĄ č湥čĆąĄąĘ USB, ą┐čĆąĖ ą┐ąŠą╝ąŠčēąĖ čüą┐ąĄčåąĖą░ą╗čīąĮąŠą╣ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ MPROG, ą┤ąŠčüčéčāą┐ąĮąŠą╣ ąĮą░ čüą░ą╣č鹥 FTDI www.ftdichip.com (čüą╝. čüčüčŗą╗ą║čā [3]). ąŁč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąĮą░ą┐ą░čÅčéčī ąĮą░ ą┐ąĄčćą░čéąĮčāčÄ ą┐ą╗ą░čéčā čüčĆą░ąĘčā čćąĖčüčéčāčÄ ą╝ąĖą║čĆąŠčüčģąĄą╝čā EEPROM, ąĖ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī ąĄčæ ą▓ ą┐čĆąŠčåąĄčüčüąĄ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĖ ą┐čĆąŠąĖąĘą▓ąŠą┤čüčéą▓ąĄ ą│ąŠč鹊ą▓čŗčģ čāčüčéčĆąŠą╣čüčéą▓. ąĢčüą╗ąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ EEPROM ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮą░ (ąĖą╗ąĖ EEPROM ą┐ąŠą╗ąĮąŠčüčéčīčÄ čćąĖčüčéą░čÅ), čćąĖą┐ FT2232H ą▒čāą┤ąĄčé ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ čĆą░ą▒ąŠčéą░čéčī ą║ą░ą║ ą┤ą▓ą░ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ą┐ąŠčĆčéą░. ąŻčüčéčĆąŠą╣čüčéą▓ąŠ ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą▓ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ą▓čüčéčĆąŠąĄąĮąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ - VID (0x0403) ąĖ PID (0x6010), ąŠą┐ąĖčüą░ąĮąĖąĄ ą┐čĆąŠą┤čāą║čéą░ ąĖ ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠčéčĆąĄą▒ą╗čÅąĄą╝ąŠą╣ ą╝ąŠčēąĮąŠčüčéąĖ. ąóą░ą║ąČąĄ ą▒čāą┤ąĄčé ąŠčéčüčāčéčüčéą▓ąŠą▓ą░čéčī čüąĄčĆąĖą╣ąĮčŗą╣ ąĮąŠą╝ąĄčĆ ą║ą░ą║ čćą░čüčéčī ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ USB.

4.3 ą×ą┐ąĖčüą░ąĮąĖąĄ čĆąĄąČąĖą╝ą░ ą┤ą▓ąŠą╣ąĮąŠą│ąŠ ą┐ąŠčĆčéą░ UART (FT232 Interface Mode)

FT2232H ą╝ąŠąČąĄčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą▓ čĆąĄąČąĖą╝ą░čģ, ą║ąŠč鹊čĆčŗąĄ ą▒čŗą╗ąĖ ą▓ čāąČąĄ ąĖąĘą▓ąĄčüčéąĮčŗčģ čćąĖą┐ą░čģ FT232 ą║ąŠą╝ą┐ą░ąĮąĖąĖ FTDI. ąÆ čüą╗ąĄą┤čāčÄčēąĄą╝ ą┐čĆąĖą╝ąĄčĆąĄ ą┐ąŠą║ą░ąĘą░ąĮąŠ, ą║ą░ą║ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī FT2232H ą┤ą╗čÅ ą┐ąŠą┤ą┤ąĄčƹȹ║ąĖ ąĖąĮč鹥čĆč乥ą╣čüąŠą▓ RS232, RS422 ąĖą╗ąĖ RS485. FT2232H ą╝ąŠąČąĄčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą║ą░ą║ čüą╝ąĄčüčī čŹčéąĖčģ ąĖąĮč鹥čĆč乥ą╣čüąŠą▓.

4.3.1 ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą┤ą▓ąŠą╣ąĮąŠą│ąŠ ą┐ąŠčĆčéą░ RS232

ąØą░ čĆąĖčüčāąĮą║ąĄ ą┐ąŠą║ą░ąĘą░ąĮąŠ, ą║ą░ą║ FT2232H ą╝ąŠąČąĄčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą┤ą╗čÅ ą┐ąŠą┤ą┤ąĄčƹȹ║ąĖ ąĖąĮč鹥čĆč乥ą╣čüą░ RS232 UART. ąŁč鹊 ą▓ą║ą╗čÄč湥ąĮąĖąĄ ą╝ąŠąČąĮąŠ ą┐ąŠą▓č鹊čĆąĖčéčī ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ B ąĖ ą┐ąŠą╗čāčćąĖčéčī ą┤ą▓ą░ ąĖąĮč鹥čĆč乥ą╣čüą░ RS232 (ą┤ą╗čÅ čāą┐čĆąŠčēąĄąĮąĖčÅ ąĮą░ čüčģąĄą╝ąĄ ą▓č鹊čĆąŠą╣ ąĖąĮč鹥čĆč乥ą╣čü ąĮąĄ ą┐ąŠą║ą░ąĘą░ąĮ).

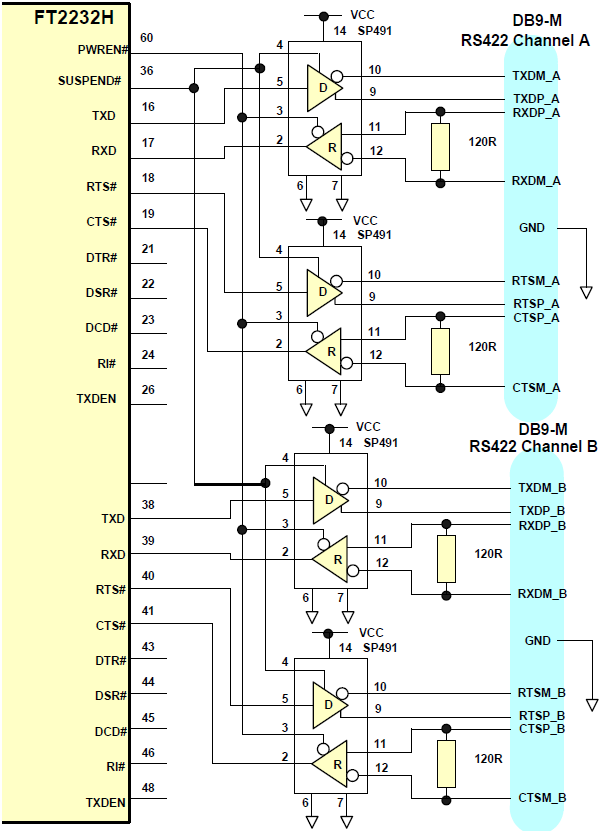

4.3.2 ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą┤ą▓ąŠą╣ąĮąŠą│ąŠ ą┐ąŠčĆčéą░ RS422

ąØą░ čĆąĖčüčāąĮą║ąĄ ą┐ąŠą║ą░ąĘą░ąĮąŠ, ą║ą░ą║ FT2232H ą╝ąŠąČąĄčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą┤ą╗čÅ ą┐ąŠą┤ą┤ąĄčƹȹ║ąĖ ą┤ą▓ąŠą╣ąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ RS422.

ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ąŠą▒ą░ ą║ą░ąĮą░ą╗ą░ A ąĖ B čĆą░ą▒ąŠčéą░čÄčé ą║ą░ą║ UART ąĮą░ čāčĆąŠą▓ąĮčÅčģ čüąĖą│ąĮą░ą╗ą░ TTL. ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮą░čÅ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ Sipex SP491 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą║ą░ą║ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░č鹥ą╗čī čāčĆąŠą▓ąĮąĄą╣, ą║ąŠč鹊čĆą░čÅ ą┐čĆąĄąŠą▒čĆą░ąĘčāąĄčé čüąĖą│ąĮą░ą╗čŗ TTL FT2232H ą▓ čāčĆąŠą▓ąĮąĖ ąĖąĮč鹥čĆč乥ą╣čüą░ RS422. ąĪąĖą│ąĮą░ą╗ PWREN# ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ ą╝ąĖą║čĆąŠčüčģąĄą╝ SP491 - ą┐ąĄčĆąĄą▓ąŠą┤ą░ ąĖčģ ą▓ čĆąĄąČąĖą╝ ą┐ąŠąĮąĖąČąĄąĮąĮąŠą│ąŠ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ, ą║ąŠą│ą┤ą░ ąĖąĮč鹥čĆč乥ą╣čü USB ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮąŠą╝ čüąŠčüč鹊čÅąĮąĖąĖ (suspend mode).

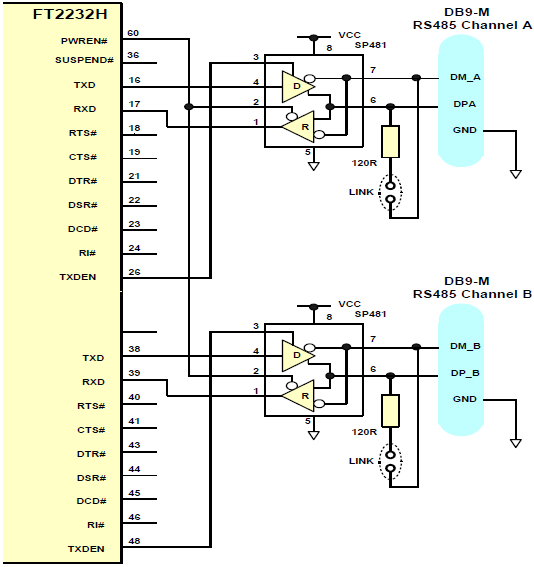

4.3.3 ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą┤ą▓ąŠą╣ąĮąŠą│ąŠ ą┐ąŠčĆčéą░ RS485

ąØą░ čĆąĖčüčāąĮą║ąĄ ą┐ąŠą║ą░ąĘą░ąĮąŠ, ą║ą░ą║ FT2232H ą╝ąŠąČąĄčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą┤ą╗čÅ ą┐ąŠą┤ą┤ąĄčƹȹ║ąĖ ą┤ą▓ąŠą╣ąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ RS485.

ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ąŠą▒ą░ ą║ą░ąĮą░ą╗ą░ A ąĖ B čĆą░ą▒ąŠčéą░čÄčé ą║ą░ą║ RS485 ąĮą░ čāčĆąŠą▓ąĮčÅčģ čüąĖą│ąĮą░ą╗ą░ TTL. ąÆ ą┐čĆąĖą╝ąĄčĆąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą▓ąĄ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ Sipex SP491, ąŠą┤ąĮą░ą║ąŠ ąĖą╝ąĄčÄčéčüčÅ ą░ąĮą░ą╗ąŠą│ąĖčćąĮčŗąĄ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ čäąĖčĆą╝ Maxim, Analog Devices ąĖ ą╝ąĮąŠą│ąĖčģ ą┤čĆčāą│ąĖčģ. SP491 čÅą▓ą╗čÅąĄčéčüčÅ čćąĖą┐ąŠą╝ ąĖąĮč鹥čĆč乥ą╣čüą░ RS485 ą▓ ą║ąŠą╝ą┐ą░ą║čéąĮąŠą╝ 8-ą▓čŗą▓ąŠą┤ąĮąŠą╝ ą║ąŠčĆą┐čāčüąĄ SOP. ą×ąĮ ąĖą╝ąĄąĄčé ąŠčéą┤ąĄą╗čīąĮčŗąĄ ą▓čģąŠą┤čŗ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ ąĖ ą┐čĆąĖąĄą╝ąĮąĖą║ą░. ąĪ ąĖąĮč鹥čĆč乥ą╣čüąŠą╝ RS485 ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą▓ ą╝ąŠą╝ąĄąĮčé ą┐ąĄčĆąĄą┤ą░čćąĖ čüąĖą╝ą▓ąŠą╗ą░ č湥čĆąĄąĘ UART. ąĪąĖą│ąĮą░ą╗čŗ TXDEN čćąĖą┐ą░ FT2232H čüą┐ąĄčåąĖą░ą╗čīąĮąŠ ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮčŗ ą┤ą╗čÅ čŹč鹊ą╣ čåąĄą╗ąĖ, ąĖ ą║ ąĮąĖą╝ ą┐ąŠą┤ą║ą╗čÄč湥ąĮčŗ ą▓čŗą▓ąŠą┤čŗ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░. ąĪąĖą│ąĮą░ą╗ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ ąĖą╝ąĄąĄčé ą░ą║čéąĖą▓ąĮčŗą╣ ą╗ąŠą│ąĖč湥čüą║ąĖą╣ 0, ąĖ ąŠąĮ čĆą░ąĘą▓ąĄą┤ąĄąĮ ąĮą░ ąĮąŠąČą║čā PWREN# - čćč鹊ą▒čŗ ąĘą░ą┐čĆąĄčéąĖčéčī ą┐čĆąĖąĄą╝ąĮąĖą║, ą║ąŠą│ą┤ą░ USB ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ suspend mode.

RS485 čÅą▓ą╗čÅąĄčéčüčÅ čüąĄčéčīčÄ čéąĖą┐ą░ multi-drop network ŌĆō čé. ąĄ. ą╝ąĮąŠą│ąŠčćąĖčüą╗ąĄąĮąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ ą╝ąŠą│čāčé čüąŠąĄą┤ąĖąĮčÅčéčīčüčÅ ą┤čĆčāą│ čü ą┤čĆčāą│ąŠą╝ č湥čĆąĄąĘ ąŠą┤ąĖąĮąŠčćąĮčŗą╣ ą┤ą▓čāčģą┐čĆąŠą▓ąŠą┤ąĮčŗą╣ ą║ą░ą▒ąĄą╗čī. ąÜą░ą▒ąĄą╗čī RS485 čéčĆąĄą▒čāąĄčé čüą┐ąĄčåąĖą░ą╗čīąĮąŠą╣ ąĮą░ą│čĆčāąĘą║ąĖ-č鹥čĆą╝ąĖąĮą░č鹊čĆą░ ąĮą░ ą║ą░ąČą┤ąŠą╝ ą║ąŠąĮčåąĄ ą╗ąĖąĮąĖąĖ ą║ą░ą▒ąĄą╗čÅ. ą¤ąĄčĆąĄą╝čŗčćą║ą░ LINK ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮą░ ą┤ą╗čÅ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ č鹥čĆą╝ąĖąĮą░č鹊čĆą░, ąĄčüą╗ąĖ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮą░čģąŠą┤ąĖčéčüčÅ ąĮą░ ąŠą┤ąĮąŠą╝ ąĖąĘ ą║ąŠąĮčåąŠą▓ ą║ą░ą▒ąĄą╗čÅ.

ąÆ čŹč鹊ą╝ ą┐čĆąĖą╝ąĄčĆąĄ ą┤ą░ąĮąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ čćąĖą┐ąŠą╝ FT2232H, ąĖ ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ čüčĆą░ąĘčā ą┐čĆąĖąĮąĖą╝ą░čÄčéčüčÅ čŹčéąĖą╝ ąČąĄ čćąĖą┐ąŠą╝. ąŁč鹊 čÅą▓ą╗čÅąĄčéčüčÅ ąŠčüąĮąŠą▓ąĮąŠą╣ ąŠčüąŠą▒ąĄąĮąĮąŠčüčéčīčÄ RS485, ą║ąŠč鹊čĆčŗą╣ ąŠą▒čŗčćąĮąŠ čéčĆąĄą▒čāąĄčé čāą┤ą░ą╗ąĄąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗčģ ą┤ą░ąĮąĮčŗčģ ąĖąĘ ą┐ąŠč鹊ą║ą░ ą║ą░ąĮą░ą╗ą░ ą┐čĆąĖąĄą╝ą░ (čŹčéčā čäčāąĮą║čåąĖčÄ ą┤ąŠą╗ąČąĮąŠ ą▓čŗą┐ąŠą╗ąĮčÅčéčī ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠąĄ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ, čĆą░ą▒ąŠčéą░čÄčēąĄąĄ čü ą║ą░ąĮą░ą╗ąŠą╝ RS485). ąĪ ą╝ąĖą║čĆąŠčüčģąĄą╝ąŠą╣ FT2232H ą╝ąŠąČąĮąŠ čĆąĄą░ą╗ąĖąĘąŠą▓ą░čéčī čŹčéčā čäčāąĮą║čåąĖčÄ ą┐ąŠą╗ąĮąŠčüčéčīčÄ ą░ą┐ą┐ą░čĆą░čéąĮąŠ - ąĄčüą╗ąĖ ą╝ąŠą┤ąĖčäąĖčåąĖčĆąŠą▓ą░čéčī čüčģąĄą╝čā čéą░ą║, čćč鹊ą▒čŗ čüąĖą│ąĮą░ą╗ RXD FT2232H ą▒čŗą╗ ą┐ąŠą╗čāč湥ąĮ ąŠą┐ąĄčĆą░čåąĖąĄą╣ OR (ą╗ąŠą│ąĖč湥čüą║ąŠąĄ ąśąøąś) ą▓čŗčģąŠą┤ą░ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ SP481 ąĖ čüąĖą│ąĮą░ą╗ą░ TXDEN. ąöą╗čÅ čŹč鹊ą│ąŠ ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ąŠą▒čŗčćąĮčŗą╣ ą╗ąŠą│ąĖč湥čüą║ąĖą╣ 菹╗ąĄą╝ąĄąĮčé ąĖąĘ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ HC32 (ąĮą░ą┐čĆąĖą╝ąĄčĆ ą╝ąĖą║čĆąŠčüčģąĄą╝čā MM74HC32, ą▓ ą║ąŠč鹊čĆąŠą╝ 4 čéą░ą║ąĖčģ ą╗ąŠą│ąĖč湥čüą║ąĖčģ 菹╗ąĄą╝ąĄąĮčéą░).

4.4 ą×ą┐ąĖčüą░ąĮąĖąĄ čĆąĄąČąĖą╝ą░ ąĖąĮč鹥čĆč乥ą╣čüą░ čüąĖąĮčģčĆąŠąĮąĮąŠą│ąŠ FIFO FT245