|

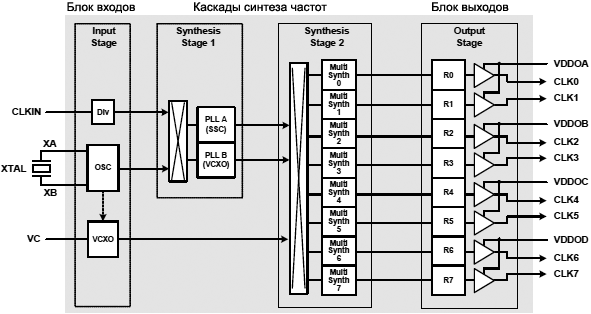

ą£ąĖą║čĆąŠčüčģąĄą╝ą░ Si5351 ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé čüąŠą▒ąŠą╣ ąŠč湥ąĮčī ą│ąĖą▒ą║ąŠ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝čŗą╣ ą│ąĄąĮąĄčĆą░č鹊čĆ čéą░ą║č鹊ą▓ ąĖ VCXO (čüą╝. čĆąĖčü. 1). ąÜąŠą╝ą┐ą░ąĮąĖčÅ Silicon Labs ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé čüą┐ąĄčåąĖą░ą╗čīąĮčāčÄ čāčéąĖą╗ąĖčéčā ClockBuilder Desktop [3], ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮąĮčāčÄ ą┤ą╗čÅ čāą┐čĆąŠčēąĄąĮąĖčÅ čüąŠąĘą┤ą░ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ą┤ą╗čÅ čĆąĄą│ąĖčüčéčĆąŠą▓ Si5351 ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ąĮčāąČąĮąŠą╣ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ. ą¤ąŠčüą║ąŠą╗čīą║čā ClockBuilder Desktop ąĮąĄ ą▓čüąĄą│ą┤ą░ ą╝ąŠąČąĄčé čāą┤ąŠą▓ą╗ąĄčéą▓ąŠčĆčÅčéčī ą▓čüąĄą╝ čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅą╝ čĆą░ąĘčĆą░ą▒ąŠčéčćąĖą║ąŠą▓ (ą▓ čćą░čüčéąĮąŠčüčéąĖ, ąĮąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ čüąĖąĮč鹥ąĘ ą│ąĄąĮąĄčĆą░čåąĖąĖ ąĮąĖąĘą║ąĖčģ čćą░čüč鹊čé ąŠčé 2.5 ą║ąōčå ą┤ąŠ 500 ą║ąōčå), ą▓ čŹč鹊ą╝ ą┤ąŠą║čāą╝ąĄąĮč鹥 ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮčŗ ą┐čĆąŠčåąĄą┤čāčĆčŗ ąĖ č乊čĆą╝čāą╗čŗ ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ ą┐ąŠą╗ąĮąŠą│ąŠ ąĮą░ą▒ąŠčĆą░ čĆąĄą│ąĖčüčéčĆąŠą▓ ąĖąĘ ąĘą░ą┐ą╗ą░ąĮąĖčĆąŠą▓ą░ąĮąĮčŗčģ č乊čĆą╝ąĖčĆčāąĄą╝čŗčģ čćą░čüč鹊čé (ą┐ąĄčĆąĄą▓ąŠą┤ ą┤ą░čéą░čłąĖčéą░ [1]). ąĀą░ąĘą┤ąĄą╗ 2 ą┤ą░ąĄčé ąŠą▒čēąĖą╣ ąŠą▒ąĘąŠčĆ ą░ą╗ą│ąŠčĆąĖčéą╝ą░ čćą░čüč鹊čéąĮąŠą│ąŠ ą┐ą╗ą░ąĮą░, ąĖ čüąĄą║čåąĖąĖ čĆą░ąĘą┤ąĄą╗ą░ 3 ą▒ąŠą╗ąĄąĄ ą┐ąŠą┤čĆąŠą▒ąĮąŠ ąŠą┐ąĖčüčŗą▓ą░čÄčé ą▓čüąĄ ą▓čŗčćąĖčüą╗ąĄąĮąĖčÅ ą┤ą╗čÅ čüąŠąĘą┤ą░ąĮąĖčÅ ąĘąĮą░č湥ąĮąĖą╣ čĆąĄą│ąĖčüčéčĆąŠą▓.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▓čüąĄ ąĮąĄą┐ąŠąĮčÅčéąĮčŗąĄ č鹥čĆą╝ąĖąĮčŗ ąĖ čüąŠą║čĆą░čēąĄąĮąĖčÅ čüą╝. ą▓ čĆą░ąĘą┤ąĄą╗ąĄ "ąĪą╗ąŠą▓ą░čĆąĖą║" čüčéą░čéčīąĖ [2].

ąĀąĖčü. 1. ą×ą▒čēą░čÅ ą▒ą╗ąŠą║-ą┤ąĖą░ą│čĆą░ą╝ą╝ą░ Si5351.

Si5351 ą┤ąŠčüčéčāą┐ąĮą░ ą▓ 3 ą▓ą░čĆąĖą░ąĮčéą░čģ ąĖčüą┐ąŠą╗ąĮąĄąĮąĖčÅ [2]:

Si5351A: čĆą░ą▒ąŠčéą░ąĄčé č鹊ą╗čīą║ąŠ ąŠčé ą║ą▓ą░čĆčåą░ (XTAL only).

Si5351B: XTAL + VCXO.

Si5351C: XTAL + CLKIN.

ąĢčüą╗ąĖ ą▓ą║ą╗čÄč湥ąĮą░ čäčāąĮą║čåąĖčÅ čĆą░čüčłąĖčĆąĄąĮąĖčÅ čüą┐ąĄą║čéčĆą░, č鹊 čŹč鹊 ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ą▒ą╗ąŠą║ąŠą╝ ążąÉą¤ą¦ PLLA. ążčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠčüčéčī VCXO (ą┤ąŠčüčéčāą┐ąĮą░ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čāčüčéčĆąŠą╣čüčéą▓ Si5351B) ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ą▒ą╗ąŠą║ąŠą╝ ążąÉą¤ą¦ PLLB.

[2. ąÜąŠąĮčåąĄą┐čåąĖčÅ ą┐ą╗ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ čćą░čüč鹊čé]

ąŻčüčéčĆąŠą╣čüčéą▓ąŠ čüąŠą┤ąĄčƹȹĖčé 2 ą▒ą╗ąŠą║ą░ PLL (ążąÉą¤ą¦) - PLLA ąĖ PLLB. ąÜą░ąČą┤čŗą╣ PLL čüąŠą┤ąĄčƹȹĖčé čüąĖčüč鹥ą╝čā Feedback Multisynth, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čāčÄ ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ ą┐čĆąŠą╝ąĄąČčāč鹊čćąĮąŠą╣ čćą░čüč鹊čéčŗ VCO ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąŠčé 600 ą┤ąŠ 900 ą£ąōčå. ąøčÄą▒ą░čÅ ąĖąĘ čŹčéąĖčģ čćą░čüč鹊čé VCO ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠą┤ąĄą╗ąĄąĮą░ ąŠčéą┤ąĄą╗čīąĮčŗą╝ąĖ ą▓čŗčģąŠą┤ąĮčŗą╝ąĖ ą┤ąĄą╗ąĖč鹥ą╗čÅą╝ąĖ Multisynth, čćč鹊ą▒čŗ ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī čćą░čüč鹊čéčā Multisynth ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąŠčé 500 ą║ąōčå ą┤ąŠ 200 ą£ąōčå. ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠ ą╝ąŠą│čāčé ą▒čŗčéčī ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮčŗ ą▓čŗčģąŠą┤ąĮčŗąĄ ą┤ąĄą╗ąĖč鹥ą╗ąĖ R, čćč鹊ą▒čŗ ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ąĮąĖąĘą║ąĖąĄ čćą░čüč鹊čéčŗ ą┤ąŠ 2.5 ą║ąōčå. ąÆąĘą░ąĖą╝ąŠčüą▓čÅąĘčī ą╝ąĄąČą┤čā čćą░čüč鹊č鹊ą╣ VCO ąĖ ą▓čŗčģąŠą┤ąĮčŗą╝ąĖ čćą░čüč鹊čéą░ą╝ąĖ ą▓čŗčĆą░ąČą░ąĄčéčüčÅ č乊čĆą╝čāą╗ąŠą╣:

fVCO

foutx = ------------------

Multisynthx ┬Ę Rx

ąśčüą┐ąŠą╗čīąĘčāą╣č鹥 ąŠą┐ąĖčüą░ąĮąĮčŗąĄ ąĮąĖąČąĄ čłą░ą│ąĖ, čćč鹊ą▒čŗ čüąŠčüčéą░ą▓ąĖčéčī ą┐ą╗ą░ąĮ čüąĖąĮč鹥ąĘą░ čćą░čüč鹊čé.

2.1. ąÆčŗą▒ąŠčĆ PLL

ąĢčüą╗ąĖ čäčāąĮą║čåąĖčÅ čĆą░čüčłąĖčĆąĄąĮąĖčÅ čüą┐ąĄą║čéčĆą░ (Spread Spectrum) ąĮąĄ čĆą░ąĘčĆąĄčłąĄąĮą░, č鹊 ą╗čÄą▒ą░čÅ ąĖąĘ PLLA ąĖą╗ąĖ PLLB ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖčüč鹊čćąĮąĖą║ą░ č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ čćą░čüč鹊čéčŗ ą┤ą╗čÅ ą╗čÄą▒čŗčģ ą▓čŗčģąŠą┤ąŠą▓ Si5351A. ąĢčüą╗ąĖ ąČąĄ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą│ąĄąĮąĄčĆą░čåąĖčÅ ąĖ ąŠčé XTAL, ąĖ ąŠčé ą▓čģąŠą┤ą░ CLKIN (ą▓ąŠąĘą╝ąŠąČąĮąŠ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ Si5351C), č鹊 ąŠą┤ąĖąĮ ąĖąĘ čŹčéąĖčģ PLL ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮ ą┤ą╗čÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ čü CLKIN, ąĖ ą┤čĆčāą│ąŠą╣ ą┤ą╗čÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ čü XTAL.

ąŚą░ą╝ąĄčćą░ąĮąĖąĄ: PLLA ą┤ąŠą╗ąČąĄąĮ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą╗čÄą▒čŗčģ ą▓čŗčģąŠą┤ąŠą▓, ąĮą░ ą║ąŠč鹊čĆčŗčģ čĆą░ąĘčĆąĄčłąĄąĮą░ čäčāąĮą║čåąĖčÅ čĆą░čüčłąĖčĆąĄąĮąĖčÅ čüą┐ąĄą║čéčĆą░. PLLB ą┤ąŠą╗ąČąĄąĮ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą╗čÄą▒čŗčģ ą▓čŗčģąŠą┤ąŠą▓ VCXO.

2.1.1. ąÆčŗą▒ąŠčĆ ą┐čĆą░ą▓ąĖą╗čīąĮąŠą│ąŠ čüąŠąŠčéąĮąŠčłąĄąĮąĖčÅ čćą░čüč鹊čé VCO ąĖ ą║ąŠčŹčäčäąĖčåąĖąĄąĮč鹊ą▓ ą┤ąĄą╗ąĄąĮąĖčÅ

ąØąĖąČąĄ ą┐čĆąĖą▓ąĄą┤ąĄąĮ ąŠčüąĮąŠą▓ąĮčŗąĄ ą║čĆąĖč鹥čĆąĖąĖ ą┤ą╗čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ čćą░čüč鹊čé VCO. ąŁč鹊 ąŠą▒čēą░čÅ ą╝ąŠą┤ąĄą╗čī, ąĖ ąŠčéą┤ąĄą╗čīąĮčŗąĄ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ą╝ąŠą│čāčé ą┐ąŠčéčĆąĄą▒ąŠą▓ą░čéčī ąĮąĄą║ąŠč鹊čĆčŗąĄ ą╝ąŠą┤ąĖčäąĖą║ą░čåąĖąĖ.

1. ąöąŠą┐čāčüčéąĖą╝čŗąĄ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéčŗ ą┤ąĄą╗ąĄąĮąĖčÅ Multisynth 4, 6, 8, ąĖ ą╗čÄą▒ąŠąĄ ą┤čĆąŠą▒ąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą╝ąĄąČą┤čā 8 + 1/1048575 ąĖ 900 + 0/1. ąŁč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ąĄčüą╗ąĖ čćą░čüč鹊čéą░ ąĮą░ ą╗čÄą▒ąŠą╝ ą▓čŗčģąŠą┤ąĄ ą▒ąŠą╗čīčłąĄ 112.5 ą£ąōčå (900 ą£ąōčå / 8), č鹊 čŹčéą░ ą▓čŗčģąŠą┤ąĮą░čÅ čćą░čüč鹊čé čāčüčéą░ąĮąŠą▓ąĖčé ąŠą┤ąĮčā ąĖąĘ čćą░čüč鹊čé VCO.

2. ąöą╗čÅ čćą░čüč鹊čé, čā ą║ąŠč鹊čĆčŗčģ ą▓ą░ąČąĄąĮ ą╝ąĖąĮąĖą╝ą░ą╗čīąĮčŗą╣ ą┤ąČąĖčéč鹥čĆ, ą▓čŗą▒ąĖčĆą░ą╣č鹥 čåąĄą╗čŗąĄ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéčŗ ą┤ąĄą╗ąĄąĮąĖčÅ Multisynth. ąĢčüą╗ąĖ ą▓ąŠąĘą╝ąŠąČąĮąŠ, ą▓čŗą▒ąĖčĆą░ą╣č鹥 čåąĄą╗čŗąĄ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéčŗ ą┤ą╗čÅ ą▓čŗčģąŠą┤ą░ ąĖ ąŠą▒čĆą░čéąĮąŠą╣ čüą▓čÅąĘąĖ (output ąĖ feedback Multisynth ratio).

3. ąÜąŠą│ą┤ą░ čāą┤ąŠą▓ą╗ąĄčéą▓ąŠčĆčÅčÄčéčüčÅ ą║čĆąĖč鹥čĆąĖąĖ 1 ąĖ 2, ą┐ąŠą┐čĆąŠą▒čāą╣č鹥 ą║ą░ą║ ą╝ąŠąČąĮąŠ ą▒ąŠą╗čīčłąĄ ą▓čŗą▒čĆą░čéčī čåąĄą╗ąŠčćąĖčüą╗ąĄąĮąĮčŗčģ ą║ąŠčŹčäčäąĖčåąĖąĄąĮč鹊ą▓ output Multisynth.

ąŚą░ą╝ąĄčćą░ąĮąĖąĄ: ą┤ą╗čÅ ą┤ąĄą╗ąĖč鹥ą╗ąĄą╣ Multisynth CLK6 ąĖ CLK7 ą┤ąŠą┐čāčüčéąĖą╝čŗ č鹊ą╗čīą║ąŠ čåąĄą╗čŗąĄ čćąĖčüą╗ą░ ą╝ąĄąČą┤čā 6 ąĖ 254 ą▓ą║ą╗čÄčćąĖč鹥ą╗čīąĮąŠ. ąŁč鹊 ą╝ąŠąČąĄčé ąŠą│čĆą░ąĮąĖčćąĖčéčī ą┤ą▓ąĄ čćą░čüč鹊čéčŗ VCO, ąĄčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą▓čüąĄ 8 ą▓čŗčģąŠą┤ąŠą▓ ą│ąĄąĮąĄčĆą░čåąĖąĖ čéą░ą║č鹊ą▓.

2.2. ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▓čŗčģąŠą┤ąĮčŗčģ ą▓čŗą▓ąŠą┤ąŠą▓ ą│ąĄąĮąĄčĆą░čåąĖąĖ čéą░ą║č鹊ą▓ (ąŠą┐čåąĖąŠąĮą░ą╗čīąĮąŠ)

ąØąĄą║ąŠč鹊čĆčŗą╝ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅą╝ ą╝ąŠąČąĄčé ą┐ąŠąĮą░ą┤ąŠą▒ąĖčéčīčüčÅ ą┐ąŠą╗ąĮąŠąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ąĮą░ąĘąĮą░č湥ąĮąĖąĄą╝ ą▓čŗčģąŠą┤ąĮčŗčģ ą▓čŗą▓ąŠą┤ąŠą▓ čéą░ą║č鹊ą▓. ąöą╗čÅ čŹč鹊ą╣ čåąĄą╗ąĖ ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čüą╗ąĄą┤čāčÄčēąĖąĄ čĆąĄą║ąŠą╝ąĄąĮą┤ą░čåąĖąĖ.

1. ą×ą┤ąĖąĮą░ą║ąŠą▓čŗąĄ ą▓čŗčģąŠą┤ąĮčŗąĄ čćą░čüč鹊čéčŗ ą┤ąŠą╗ąČąĮčŗ ą┐ąŠ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ąŠą▒čēąĖą╣ ą▒ą░ąĮą║ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ VDDO (ąĮą░ą┐čĆąĖą╝ąĄčĆ CLK0 ąĖ CLK1, CLK2 ąĖ CLK3, ąĖ čé. ą┐.), čćč鹊ą▒čŗ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī ą╝ąĖąĮąĖą╝ą░ą╗čīąĮčŗą╣ ą┤ąČąĖčéč鹥čĆ ąĖąĘ-ąĘą░ ą┐ą░čĆą░ąĘąĖčéąĮčŗčģ ą┐ąĄčĆąĄą║čĆąĄčüčéąĮčŗčģ čüą▓čÅąĘąĄą╣ ąĮą░ ą┐ąĄčćą░čéąĮąŠą╣ ą┐ą╗ą░č鹥 (PCB crosstalk).

2. ąĢčüą╗ąĖ čŹč鹊 ą▓ąŠąĘą╝ąŠąČąĮąŠ, ąĖąĘąŠą╗ąĖčĆčāą╣č鹥 čāąĮąĖą║ą░ą╗čīąĮčŗąĄ ą▓čŗčģąŠą┤ąĮčŗąĄ čćą░čüč鹊čéčŗ ąĮą░ ąŠčéą┤ąĄą╗čīąĮąŠą╝ ą▒ą░ąĮą║ąĄ VDDO. ąØą░ą┐čĆąĖą╝ąĄčĆ, ąĄčüą╗ąĖ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ čüąĖąĮč鹥ąĘąĖčĆąŠą▓ą░čéčī čćą░čüč鹊čéčŗ 25 ą£ąōčå, 25 ą£ąōčå, 27 ą£ąōčå ąĖ 74.25 ą£ąōčå, č鹊 ą┐ąŠą╝ąĄčüčéąĖč鹥 ąĖčģ ąĮą░ ą▓čŗčģąŠą┤ą░čģ CLK0, CLK1, CLK2 ąĖ CLK4 čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ.

3. ąśąĮą░č湥 ąĖčüą┐ąŠą╗čīąĘčāą╣č鹥 ą▓čüąĄ ąĮąĄąŠą▒čģąŠą┤ąĖą╝čŗąĄ ą║ą░ąĮą░ą╗čŗ CLK, ą▒ą░ąĘąĖčĆčāčÅčüčī ąĮą░ čéčĆąĄą▒čāąĄą╝ąŠą╝ ą┐ą╗ą░ąĮąĄ čćą░čüč鹊čé.

ąŚą░ą╝ąĄčćą░ąĮąĖąĄ: ą┤ą╗čÅ ą┤ąĄą╗ąĖč鹥ą╗ąĄą╣ Multisynth CLK6 ąĖ CLK7 ą┤ąŠą┐čāčüčéąĖą╝čŗ č鹊ą╗čīą║ąŠ čåąĄą╗čŗąĄ čćąĖčüą╗ą░ ą╝ąĄąČą┤čā 6 ąĖ 254 ą▓ą║ą╗čÄčćąĖč鹥ą╗čīąĮąŠ. ąŁč鹊 ą╝ąŠąČąĄčé ąŠą│čĆą░ąĮąĖčćąĖčéčī ą┤ą▓ąĄ čćą░čüč鹊čéčŗ VCO, ąĄčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą▓čüąĄ 8 ą▓čŗčģąŠą┤ąŠą▓ ą│ąĄąĮąĄčĆą░čåąĖąĖ čéą░ą║č鹊ą▓.

[3. ąÜąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆąŠą▓ ą▓čģąŠą┤ą░ ąĖ PLL (ą┐ąĄčĆą▓čŗą╣ ą║ą░čüą║ą░ą┤ čüąĖąĮč鹥ąĘą░)]

ąÆ čŹč鹊ą╝ čĆą░ąĘą┤ąĄą╗ąĄ ąŠą┐ąĖčüą░ąĮčŗ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ čĆąĄą│ąĖčüčéčĆąŠą▓, čüą▓čÅąĘą░ąĮąĮčŗąĄ čü ą▓čģąŠą┤ąĮąŠą╣ ąŠą┐ąŠčĆąĮąŠą╣ čćą░čüč鹊č鹊ą╣ ąĖ ą┤ą▓čāą╝čÅ ą▒ą╗ąŠą║ą░ą╝ąĖ PLL (ążąÉą¤ą¦).

3.1. ąśčüč鹊čćąĮąĖą║ čéą░ą║č鹊ą▓ ą┤ą╗čÅ ążąÉą¤ą¦ (PLL Input Source)

ąöą╗čÅ ą║ą░ąČą┤ąŠą╣ PLL ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą▓čŗą▒čĆą░ąĮ ąĖčüč鹊čćąĮąĖą║ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ. ąöą╗čÅ čāčüčéčĆąŠą╣čüčéą▓ Si5351A ąĖ Si5351B ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī č鹊ą╗čīą║ąŠ XTAL (ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ ą│ąĄąĮąĄčĆą░č鹊čĆ, čüčéą░ą▒ąĖą╗ąĖąĘąĖčĆąŠą▓ą░ąĮąĮčŗą╣ ą║ą▓ą░čĆčåąĄą╝, ąĖą╗ąĖ ą▓čģąŠą┤ XA), ąĮąŠ ą┤ą╗čÅ Si5351C ą║ą░ąČą┤čŗą╣ ąĖąĘ PLLA ąĖ PLLB ą╝ąŠąČąĄčé čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆąŠą▓ą░čéčīčüčÅ ą╗ąĖą▒ąŠ ąŠčé XTAL, ą╗ąĖą▒ąŠ ąŠčé čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ čāčĆąŠą▓ąĮąĄą╣ CMOS, ą┐ąŠą┤ą░ąĮąĮąŠą╣ ąĮą░ ą▓čŗą▓ąŠą┤ CLKIN.

3.1.1. ąóą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ąŠčé XTAL

ąĢčüą╗ąĖ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ PLL ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ąŠčé ą║ą▓ą░čĆčåą░, ą▓ čĆąĄą│ąĖčüčéčĆąĄ 15 ą▒ąĖčé PLLx_SRC ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 0. ąæąĖčéčŗ XTAL_CL[1:0] čéą░ą║ąČąĄ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čéčĆąĄą▒čāąĄą╝ąŠą╣ ąĮą░ą│čĆčāąĘąŠčćąĮąŠą╣ ąĄą╝ą║ąŠčüčéąĖ ą║ą▓ą░čĆčåąĄą▓ (čüą╝. čĆąĄą│ąĖčüčéčĆ 183).

3.1.2. ąóą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čāčĆąŠą▓ąĮčÅą╝ąĖ CMOS

ąĢčüą╗ąĖ PLL ąĮčāąČąĮąŠ čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆąŠą▓ą░čéčī čü čéą░ą║čéą░ą╝ąĖ CMOS, ą▒ąĖčé PLLx_SRC ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1. ąÆčģąŠą┤ąĮąŠą╣ ą┤ąĖą░ą┐ą░ąĘąŠąĮ PLL čüąŠčüčéą░ą▓ą╗čÅąĄčé 10..40 ą£ąōčå. ąĢčüą╗ąĖ CLKIN > 40 ą£ąōčå, č鹊 ąĮčāąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą▓čģąŠą┤ąĮąŠą╣ ą┤ąĄą╗ąĖč鹥ą╗čīthe CLKIN, čćč鹊ą▒čŗ ą┐čĆąĖą▓ąĄčüčéąĖ čćą░čüč鹊čéčā ąĮą░ ą▓čģąŠą┤ąĄ PLL ą║ ą┤ąĖą░ą┐ą░ąĘąŠąĮčā 10..40 ą£ąōčå. ąĪą╝. ą▒ąĖčéčŗ CLKIN_DIV[1:0] čĆąĄą│ąĖčüčéčĆą░ 15 (ą▒ąĖčéčŗ [7:6]).

3.2. ążąŠčĆą╝čāą╗čŗ ą┤ąĄą╗ąĖč鹥ą╗ąĄą╣ ąŠą▒čĆą░čéąĮąŠą╣ čüą▓čÅąĘąĖ (Feedback Multisynth Divider)

ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮą░ ą▓čģąŠą┤ąĮą░čÅ čćą░čüč鹊čéą░ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą╣ PLL, ąĖ (ąĄčüą╗ąĖ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ) ąĘąĮą░č湥ąĮąĖąĄ CLKIN_DIV, ą┤ą▓ąĄ ą▓čŗą▒čĆą░ąĮąĮčŗąĄ ą▓čŗčłąĄ ą▓ čüąĄą║čåąĖąĖ 2 čćą░čüč鹊čéčŗ VCO ą╝ąŠą│čāčé ą▒čŗčéčī čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮčŗ, ąĖčüą┐ąŠą╗čīąĘčāčÅ čüą╗ąĄą┤čāčÄčēąĖąĄ č乊čĆą╝čāą╗čŗ. ąÜą░ąČą┤čŗą╣ ą┤ąĄą╗ąĖč鹥ą╗čī ąŠą▒čĆą░čéąĮąŠą╣ čüą▓čÅąĘąĖ ą┐ąŠ čüčāčéąĖ čāą╝ąĮąŠąČą░ąĄčé ą▓čģąŠą┤ąĮčāčÄ čćą░čüč鹊čéčā čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝:

fVCO = fXTAL ┬Ę (a + b/c)

ąĖ/ąĖą╗ąĖ:

fVCO = (fCLKIN/CLKIN_DIV)┬Ę (a + b/c)

ąöąŠą┐čāčüčéąĖą╝čŗą╣ ą┤ąĖą░ą┐ą░ąĘąŠąĮ ą┤ą╗čÅ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéą░ a + b/c čüąŠčüčéą░ą▓ą╗čÅąĄčé ąŠčé 15 + 0/1048575 ą┤ąŠ 90 +0/1048575. ąŁč鹊čé ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ ą▓ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ čĆąĄą│ąĖčüčéčĆąŠą▓ Si5351 ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čüąŠ čüą╗ąĄą┤čāčÄčēąĖą╝ąĖ č乊čĆą╝čāą╗ą░ą╝ąĖ:

MSNx_P1[17:0] = (128 ┬Ę a) + Floor(128 ┬Ę b/c) - 512

MSNx_P2[19:0] = (128 ┬Ę b) - (c ┬Ę Floor(128 ┬Ę b/c))

MSNx_P3[19:0] = c

ąŁčéąĖčģ ą▓čŗčĆą░ąČąĄąĮąĖčÅčģ x ąĘą░ą╝ąĄąĮčÅąĄčéčüčÅ ąĮą░ A ąĖą╗ąĖ B (MSNA, MSNB) ą┤ą╗čÅ ąŠą▒ąŠąĘąĮą░č湥ąĮąĖčÅ ą┤ąĄą╗ąĖč鹥ą╗ąĄą╣ Multisynth ą▒ą╗ąŠą║ąŠą▓ ążąÉą¤ą¦ PLLA ąĖ PLLB čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ. ąŁčéąĖ ąČąĄ ą▓čŗčĆą░ąČąĄąĮąĖčÅ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą┐ąŠą▓č鹊čĆąĄąĮčŗ ą┤ą╗čÅ Multisynths NA ąĖ NB. ąÜą░ą║ čāą┐ąŠą╝ąĖąĮą░ą╗ąŠčüčī čĆą░ąĮąĄąĄ ą▓ čüąĄą║čåąĖąĖ "2.1. ąÆčŗą▒ąŠčĆ PLL", čäčāąĮą║čåąĖčÅ čĆą░čüčłąĖčĆąĄąĮąĖčÅ čüą┐ąĄą║čéčĆą░ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ č鹊ą╗čīą║ąŠ PLLA, ąĖ čäčāąĮą║čåąĖąŠąĮą░ą╗ VCXO ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ č鹊ą╗čīą║ąŠ PLLB. ąÜąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ VCXO čāčüčéą░ąĮąŠą▓ąĖč鹥 ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ą┤ąĄą╗ąĄąĮąĖčÅ MSNB a + b/c čéą░ą║, čćč鹊ą▒čŗ c = 106. ąŁč鹊 ą┤ąŠą╗ąČąĮąŠ čāčćąĖčéčŗą▓ą░čéčīčüčÅ, ą║ąŠą│ą┤ą░ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ ą┐ą╗ą░ąĮ čćą░čüč鹊čé.

3.2.1. ą”ąĄą╗čŗąĄ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéčŗ ą┤ąĄą╗ąĄąĮąĖčÅ (FBx_INT)

ąĢčüą╗ąĖ čćąĖčüą╗ a + b/c čåąĄą╗ąŠąĄ ąĖ č湥čéąĮąŠąĄ, č鹊 ą┤ą╗čÅ PLLA ąĖą╗ąĖ PLLB ą╝ąŠąČąĄčé ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮ čåąĄą╗ąŠčćąĖčüą╗ąĄąĮąĮčŗą╣ čĆąĄąČąĖą╝ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą┐ą░čĆą░ą╝ąĄčéčĆą░ FBA_INT ąĖą╗ąĖ FBB_INT čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ. ąÆ ą▒ąŠą╗čīčłąĖąĮčüčéą▓ąĄ čüą╗čāčćą░ąĄą▓ čāčüčéą░ąĮąŠą▓ą║ą░ čŹč鹊ą│ąŠ ą▒ąĖčéą░ čüąĮąĖąĘąĖčé ą┤ąČąĖčéč鹥čĆ, ą║ąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ čåąĄą╗čŗąĄ ąĖ č湥čéąĮčŗąĄ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéčŗ ą┤ąĄą╗ąĄąĮąĖčÅ. ąÆčüčÅą║ąĖą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ ą▓ą║ą╗čÄč湥ąĮą░ čäčāąĮą║čåąĖčÅ čĆą░čüčłąĖčĆąĄąĮąĖčÅ čüą┐ąĄą║čéčĆą░, FBA_INT ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čüą▒čĆąŠčłąĄąĮ ą▓ 0.

3.3. ąöčĆčāą│ąĖąĄ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ PLL

PLLA_CL=2

PLLB_CL=2

[4. ą¤ą░čĆą░ą╝ąĄčéčĆčŗ ą▓čŗčģąŠą┤ąŠą▓]

ąÆ čŹč鹊ą╝ čĆą░ąĘą┤ąĄą╗ąĄ ąŠą┐ąĖčüą░ąĮčŗ ąĮą░čüčéčĆąŠą╣ą║ąĖ Multisynth ąĖ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ ą┤čĆą░ą╣ą▓ąĄčĆą░, ąĮąĄąŠą▒čģąŠą┤ąĖą╝čŗąĄ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą▓čŗčģąŠą┤ą░. ąÜą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 2, ąŠą┤ąĮą░ ąĖąĘ ą┤ą▓čāčģ čćą░čüč鹊čé VCO ą┤ąĄą╗ąĖčéčüčÅ ą║ą░ąČą┤čŗą╝ ą┤ąĄą╗ąĖč鹥ą╗ąĄą╝ Multisynth. ąŁč鹊 čüąŠą┐čĆąŠą▓ąŠąČą┤ą░ąĄčéčüčÅ ą▓čŗčģąŠą┤ąĮčŗą╝ čüąŠčüč鹊čÅąĮąĖąĄą╝ ą┤čĆą░ą╣ą▓ąĄčĆą░. ąĪą╝. "4.2. Output Driver Settings".

ąĀąĖčü. 2. ą¤ąŠą┤čĆąŠą▒ąĮą░čÅ ą▒ą╗ąŠą║-čüčģąĄą╝ą░ ą┤ąĄą╗ąĖč鹥ą╗ąĄą╣ ąĖ ą▓čŗčģąŠą┤ąĮčŗčģ ą┤čĆą░ą╣ą▓ąĄčĆąŠą▓.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ *: ąÜąŠčŹčäčäąĖčåąĖąĄąĮčéčŗ ą┤ąĄą╗ąĄąĮąĖčÅ Multisynth6 ąĖ Multisynth7 ą╝ąŠą│čāčé ą▒čŗčéčī č鹊ą╗čīą║ąŠ čåąĄą╗čŗą╝ąĖ č湥čéąĮčŗą╝ąĖ ąĘąĮą░č湥ąĮąĖčÅą╝ąĖ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ą╝ąĄąČą┤čā 6 ąĖ 254 ą▓ą║ą╗čÄčćąĖč鹥ą╗čīąĮąŠ.

4.1. ąØą░čüč鹊ą╣ą║ąĖ ą▓čŗčģąŠą┤ą░ Multisynth (ą▓č鹊čĆąŠą╣ ą║ą░čüą║ą░ą┤ čüąĖąĮč鹥ąĘą░)

ąŁčéą░ čüąĄą║čåąĖčÅ ąŠą┐ąĖčüčŗą▓ą░ąĄčé ąĮą░čüčéčĆąŠą╣ą║ąĖ, čüą▓čÅąĘą░ąĮąĮčŗąĄ čü ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮčŗą╝ąĖ ą▒ą╗ąŠą║ą░ą╝ąĖ Multisynth. ąÆ Si5351 ąĖą╝ąĄąĄčéčüčÅ 6 ą┤čĆąŠą▒ąĮčŗčģ ą┤ąĄą╗ąĖč鹥ą╗ąĄą╣ Multisynth (MS0..MS5) ąĖ č湥čéąĮčŗąĄ čåąĄą╗čŗąĄ ą┤ąĄą╗ąĖč鹥ą╗ąĖ (MS6 ąĖ MS7).

4.1.1. ąśčüč鹊čćąĮąĖą║ ą┤ą╗čÅ Multisynth (MSx_SRC)

ąÜą░ąČą┤čŗą╣ ąĖąĘ čŹčéąĖčģ ą┤ąĄą╗ąĖč鹥ą╗ąĄą╣ ą╝ąŠąČąĄčé ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą┤ą╗čÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą▓čŗčģąŠą┤ąĮąŠą╣ čćą░čüč鹊čéčŗ PLLA ąĖą╗ąĖ PLLB, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ MSx_SRC ą▓ 0 ąĖą╗ąĖ 1 čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ. ąĪą╝. ąŠą┐ąĖčüą░ąĮąĖąĄ ą▒ąĖčéą░ 5 čĆąĄą│ąĖčüčéčĆąŠą▓ 16..23.

4.1.2. ążąŠčĆą╝čāą╗čŗ ą▓čŗčģąŠą┤ąĮčŗčģ ą┤ąĄą╗ąĖč鹥ą╗ąĄą╣ Multisynth ą┤ą╗čÅ Fout Ōēż 150 ą£ąōčå

ąÜą░ą║ č鹊ą╗čīą║ąŠ ą▓čŗą▒čĆą░ąĮ ąĖčüč鹊čćąĮąĖą║ PLL ą┤ą╗čÅ ąŠčéą┤ąĄą╗čīąĮčŗčģ Multisynth, ą┤ą╗čÅ ąĮąĖčģ ą╝ąŠąČąĄčé ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ą┤ąĄą╗ąĄąĮąĖčÅ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü ą▓čŗčĆą░ąČąĄąĮąĖčÅą╝ąĖ, ą┐ąŠą║ą░ąĘą░ąĮąĮčŗą╝ąĖ ąĮąĖąČąĄ. ąöąĄą╗ąĄąĮąĖąĄ ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮąŠ ą┤čĆąŠą▒ąĮčŗą╝ čćąĖčüą╗ąŠą╝:

a + b/c

ąŁč鹊 čćąĖčüą╗ąŠ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ą╝ąĄąČą┤čā 6 ąĖ 1800.

MSx_P1[17:0] = (128 ┬Ę a) + Floor(128 ┬Ę b/c) - 512

MSx_P2[19:0] = (128 ┬Ę b) - (c ┬Ę Floor(128 ┬Ę b/c))

MSx_P3[19:0] = c

ąŁčéąĖčģ ą▓čŗčĆą░ąČąĄąĮąĖčÅčģ x ąŠą▒ąŠąĘąĮą░čćą░ąĄčé ą▒ą╗ąŠą║ Multisynth 0, 1, ..., 5. ąÜą░ą║ čāąČąĄ ą▒čŗą╗ąŠ ąŠčéą╝ąĄč湥ąĮąŠ, MS6 ąĖ MS7 ą╝ąŠąČąĄčé ąĖą╝ąĄčéčī č鹊ą╗čīą║ąŠ čåąĄą╗čŗąĄ č湥čéąĮčŗąĄ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéčŗ ą┤ąĄą╗ąĄąĮąĖčÅ, čé. ąĄ. ą┤ąŠą┐čāčüčéąĖą╝čŗą╣ ą┤ąĖą░ą┐ą░ąĘąŠąĮ ąĘąĮą░č湥ąĮąĖą╣ ą┤ą╗čÅ čŹčéąĖčģ ą┤ąĄą╗ąĖč鹥ą╗ąĄą╣ - ą▓čüąĄ čåąĄą╗čŗąĄ čćąĖčüą╗ą░ ą╝ąĄąČą┤čā 6 ąĖ 254 ą▓ą║ą╗čÄčćąĖč鹥ą╗čīąĮąŠ (6, 8, 10, ..., 252, 254). ąöą╗čÅ MS6 ąĖ MS7 čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ MSx_P1 ąĮą░ą┐čĆčÅą╝čāčÄ (čé. ąĄ. MSx_P1 čĆą░ą▓ąĄąĮ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéčā ą┤ąĄą╗ąĄąĮąĖčÅ).

4.1.2.1. ą”ąĄą╗ąŠčćąĖčüą╗ąĄąĮąĮčŗąĄ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéčŗ ą┤ąĄą╗ąĄąĮąĖčÅ (MSx_INT)

ąĢčüą╗ąĖ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ą╗čÄą▒ąŠą│ąŠ ąĖąĘ MS0..MS5 čĆą░ą▓ąĄąĮ čåąĄą╗ąŠą╝čā č湥čéąĮąŠą╝čā ąĘąĮą░č湥ąĮąĖčÄ, č鹊 ą╝ąŠąČąĄčé ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮ čĆąĄąČąĖą╝ čåąĄą╗ąŠčćąĖčüą╗ąĄąĮąĮąŠą│ąŠ ą┤ąĄą╗ąĄąĮąĖčÅ (Multisynth integer mode) čāčüčéą░ąĮąŠą▓ą║ąŠą╣ MSx_INT=1 (čüą╝. ą▒ąĖčé 6 čĆąĄą│ąĖčüčéčĆąŠą▓ 16-21). ąÆ ą▒ąŠą╗čīčłąĖąĮčüčéą▓ąĄ čüą╗čāčćą░ąĄą▓ čāčüčéą░ąĮąŠą▓ą║ą░ čŹč鹊ą│ąŠ ą▒ąĖčéą░ čāą╝ąĄąĮčīčłąĖčé ą┤ąČąĖčéč鹥čĆ č乊čĆą╝ąĖčĆčāąĄą╝ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ čéą░ą║č鹊ą▓, ą║ąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ čåąĄą╗čŗąĄ ąĖ č湥čéąĮčŗąĄ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéčŗ ą┤ąĄą╗ąĄąĮąĖčÅ. Multisynth6 ąĖ Multisynth7 ąĖąĘąĮą░čćą░ą╗čīąĮąŠ čĆą░ą▒ąŠčéą░čÄčé ą▓ integer mode, čéą░ą║ čćč鹊 ąĮąĄčé čĆąĄą│ąĖčüčéčĆą░ ą┤ą╗čÅ ą▓ą║ą╗čÄč湥ąĮąĖčÅ ąĖą╗ąĖ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ čåąĄą╗ąŠčćąĖčüą╗ąĄąĮąĮąŠą│ąŠ čĆąĄąČąĖą╝ą░.

4.1.3. ążąŠčĆą╝čāą╗čŗ ą▓čŗčģąŠą┤ąĮčŗčģ ą┤ąĄą╗ąĖč鹥ą╗ąĄą╣ Multisynth ą┤ą╗čÅ 150 ą£ąōčå < Fout Ōēż 200 ą£ąōčå

ąÆčŗčģąŠą┤ąĮčŗąĄ čćą░čüč鹊čéčŗ ą▓čŗčłąĄ 150 ą£ąōčå ą╝ąŠąČąĮąŠ ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ąĮą░ Multisynth 0..5. ąöą╗čÅ čŹč鹊ą│ąŠ čćą░čüč鹊čéąĮąŠą│ąŠ ą┤ąĖą░ą┐ą░ąĘąŠąĮą░ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ą┤ąĄą╗ąĄąĮąĖčÅ čüą╗ąĄą┤čāčÄčēąĖą╝ąĖ ąĮą░čüčéčĆąŠą╣ą║ą░ą╝ąĖ:

MSx_P1=0

MSx_P2=0

MSx_P3=1

MSx_INT=1

MSx_DIVBY4[1:0]=11b

ąŁč鹊 ąĮą░čüčéčĆąŠąĖčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēčāčÄ ąŠą▒čĆą░čéąĮčāčÄ čüą▓čÅąĘčī Multisynth ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ fVCO = Fout*4.

4.2. ąØą░čüčéčĆąŠą╣ą║ąĖ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ ą┤čĆą░ą╣ą▓ąĄčĆą░

ąÜą░ą║ č鹊ą╗čīą║ąŠ čüąŠą▒čĆą░ąĮčŗ čĆąĄą│ąĖčüčéčĆčŗ Multisynth, ą╝ąŠą│čāčé ą▒čŗčéčī ą╝ąŠą┤ąĖčäąĖčåąĖčĆąŠą▓ą░ąĮčŗ ąĮą░čüčéčĆąŠą╣ą║ąĖ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ ą┤čĆą░ą╣ą▓ąĄčĆą░ ą┐ąŠ čĆąĄą║ąŠą╝ąĄąĮą┤ą░čåąĖčÅą╝ ą▓ čŹč鹊ą╣ čüąĄą║čåąĖąĖ.

4.2.1. ąśčüč鹊čćąĮąĖą║ čéą░ą║č鹊ą▓ (CLKx_SRC)

ą×ą▒čŗčćąĮąŠ Multisynth x ą┤ąŠą╗ąČąĄąĮ ą▓čŗą▓ąŠą┤ąĖčéčī čćą░čüč鹊čéčā ąĮą░ ą▓čŗčģąŠą┤ąĄ CLKx, ąŠą┤ąĮą░ą║ąŠ XO, CLKIN ąĖą╗ąĖ ą┐ąŠą┤ąĄą╗ąĄąĮąĮą░čÅ čćą░čüč鹊čéą░ (čüą╝. čüąĄą║čåąĖčÄ 4.2.2 čü ąŠą┐ąĖčüą░ąĮąĖąĄą╝ ą┤ąĄą╗ąĖč鹥ą╗ąĄą╣ R) ą╝ąŠąČąĄčé čéą░ą║ąČąĄ ą▒čŗčéčī ą▓čŗą▓ąĄą┤ąĄąĮą░ ąĮą░ ą▓čŗą▓ąŠą┤čŗ CLKx. ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠ MS0 (ą┐ąŠą┤ąĄą╗ąĄąĮąĮą░čÅ čćą░čüč鹊čéą░ MS0) ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą▓ąĄą┤ąĄąĮą░ ąĮą░ CLK0..CLK3, ąĖ MS4 (ąĖą╗ąĖ ą┐ąŠą┤ąĄą╗ąĄąĮąĮą░čÅ čćą░čüč鹊čéą░ MS4) ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą▓ąĄą┤ąĄąĮą░ ąĮą░ CLK4..CLK7. ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. ąŠą┐ąĖčüą░ąĮąĖąĄ CLKx_SRC.

4.2.2. ąöąĄą╗ąĖč鹥ą╗ąĖ R

ąöąĄą╗ąĖč鹥ą╗ąĖ R ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ čćą░čüč鹊čé ąĮąĖąČąĄ 500 ą║ąōčå. ąÜą░ąČą┤čŗą╣ ąŠčéą┤ąĄą╗čīąĮčŗą╣ ą┤ąĄą╗ąĖč鹥ą╗čī ą▓čŗčģąŠą┤ąĮąŠą╣ čćą░čüč鹊čéčŗ R ą╝ąŠąČąĄčé ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1, 2, 4, 8, ..., 128 ąĘą░ą┐ąĖčüčīčÄ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╣ ąĮą░čüčéčĆąŠą╣ą║ąĖ ą▓ Rx_DIV. ąŻčüčéą░ąĮąŠą▓ą║ą░ čŹč鹊ą│ąŠ ą┐ą░čĆą░ą╝ąĄčéčĆą░ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī čćą░čüč鹊čéčŗ ą┤ąŠ 8 ą║ąōčå.

4.2.3. ąśąĮą▓ąĄčĆčüąĖčÅ (CLKx_INV)

ąÆ ąĮąĄą║ąŠč鹊čĆčŗčģ čüą╗čāčćą░čÅčģ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÄ čéą░ą║ąČąĄ ą╝ąŠąČąĄčé ą┐ąŠąĮą░ą┤ąŠą▒ąĖčéčīčüčÅ ąĖąĮą▓ąĄčĆčéąĖčĆąŠą▓ą░čéčī ą┐ąŠą╗čÅčĆąĮąŠčüčéčī (čé. ąĄ. ą┐ąŠą▓ąĄčĆąĮčāčéčī čäą░ąĘčā ąĮą░ 180┬░) ąŠą┤ąĮąŠą│ąŠ ąĖą╗ąĖ ą▒ąŠą╗čīčłąĄą│ąŠ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ą▓čŗčģąŠą┤ąŠą▓ ą┐ąŠ ąŠčéąĮąŠčłąĄąĮąĖčÄ ą║ ą┤čĆčāą│ąĖą╝ ą▓čŗčģąŠą┤ą░ą╝ąĖ. ąŁč鹊 ą┤ąŠčüčéąĖąČąĖą╝ąŠ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ CLKx_INV=1.

4.2.4. ąŚą░ą┐čĆąĄčēąĄąĮąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ ą▓čŗčģąŠą┤ą░ (CLKx_DIS_STATE)

ąÜąŠą│ą┤ą░ ą▓čŗčģąŠą┤ąĮą░čÅ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ ąĘą░ą┐čĆąĄčēąĄąĮą░ ą╗ąĖą▒ąŠ čāčĆąŠą▓ąĮąĄą╝ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ OEB, ą╗ąĖą▒ąŠ č湥čĆąĄąĘ čĆąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ OEB (čüą╝. čĆąĄą│ąĖčüčéčĆ 3), ąĮą░ ą▓čŗčģąŠą┤ąĄ ą┤čĆą░ą╣ą▓ąĄčĆą░ ą╝ąŠąČąĄčé ą┐čĆąĖčüčāčéčüčéą▓ąŠą▓ą░čéčī ą╗ąĖą▒ąŠ ą╗ąŠą│ąĖč湥čüą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī 0, ą╗ąŠą│ąĖč湥čüą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī 1 ąĖą╗ąĖ ą▓čŗčüąŠą║ąŠąĄ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ (Hi-Z, čéčĆąĄčéčīąĄ čüąŠčüč鹊čÅąĮąĖąĄ). ą¤ąŠą┤čĆąŠą▒ąĮąŠčüčéąĖ čüą╝. ą▓ ąŠą┐ąĖčüą░ąĮąĖąĖ CLKx_DIS_STATE.

4.2.5. ąØąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą▓čŗčģąŠą┤čŗ čéą░ą║č鹊ą▓

ąøčÄą▒čŗąĄ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą▓čŗčģąŠą┤čŗ ą╝ąŠą│čāčé ą▒čŗčéčī ą▓čŗą║ą╗čÄč湥ąĮčŗ ą┤ą╗čÅ čāą╝ąĄąĮčīčłąĄąĮąĖčÅ č鹊ą║ą░ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ IDDO. ąŁč鹊 ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ CLKx_PDN=1, čćč鹊 ą▓čŗą║ą╗čÄčćą░ąĄčé ą▓čŗčģąŠą┤ąĮąŠą╣ ą┤čĆą░ą╣ą▓ąĄčĆ.

[5. ą¤ą░čĆą░ą╝ąĄčéčĆčŗ Spread Spectrum]

ąöą╗čÅ ą╗čÄą▒ąŠą│ąŠ ą▓čŗčģąŠą┤ą░ Multisynth, ą║ąŠč鹊čĆčŗą╣ ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą▓ ą║ą░č湥čüčéą▓ąĄ ą▓čģąŠą┤ąĮąŠą╣ čćą░čüč鹊čéčŗ PLLA, ą╝ąŠąČąĄčé ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮą░ čäčāąĮą║čåąĖčÅ čĆą░čüčłąĖčĆąĄąĮąĖčÅ čüą┐ąĄą║čéčĆą░ (Spread Spectrum). ąöąŠą┐čāčüčéąĖą╝čŗąĄ ą┤ąĖą░ą┐ą░ąĘąŠąĮčŗ čĆą░čüčłąĖčĆąĄąĮąĖčÅ ą▓ą║ą╗čÄčćą░čÄčé ŌĆō0.1% .. ŌĆō2.5% ą┐čĆąĖ čĆą░čüčłąĖčĆąĄąĮąĖąĖ čüą┐ąĄą║čéčĆą░ ą▓ čüč鹊čĆąŠąĮčā ąĮąĖąĘą║ąĖčģ čćą░čüč鹊čé ąĖ ą┤ąŠ ┬▒1.5% ą┐čĆąĖ čĆą░čüčłąĖčĆąĄąĮąĖąĖ čüą┐ąĄą║čéčĆą░ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ čåąĄąĮčéčĆą░ą╗čīąĮąŠą╣ čćą░čüč鹊čéčŗ. ą¦ą░čüč鹊čéą░ ą╝ąŠą┤čāą╗čÅčåąĖąĖ čäąĖą║čüąĖčĆąŠą▓ą░ąĮą░ ą┐čĆąĖą╝ąĄčĆąĮąŠ ąĮą░ 31.5 ą║ąōčå.

ąöą╗čÅ ą┐čĆą░ą▓ąĖą╗čīąĮąŠą╣ čāčüčéą░ąĮąŠą▓ą║ąĖ čĆą░čüčłąĖčĆąĄąĮąĖčÅ čüą┐ąĄą║čéčĆą░ čüą╗ąĄą┤čāąĄčé ąĘąĮą░čéčī čüą╗ąĄą┤čāčÄčēąĖąĄ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ:

fPFD(A), ą▓čģąŠą┤ąĮą░čÅ čćą░čüč鹊čéą░ PLLA (ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą▓čŗčłąĄ ą▓ čĆą░ąĘą┤ąĄą╗ąĄ "2. ąÜąŠąĮčåąĄą┐čåąĖčÅ ą┐ą╗ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ čćą░čüč鹊čé", ąĖ ąŠčéąĮąŠčüąĖčéčüčÅ čéą░ą║ąČąĄ ą║ čüąĄą║čåąĖąĖ "3.1.2. ąóą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ čāčĆąŠą▓ąĮčÅą╝ąĖ CMOS"). ąŁč鹊 čéą░ą║ąČąĄ ą┐ąĄčĆąĄčćąĖčüą╗ąĄąĮąŠ ą▓ čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąĮąŠą╣ čāčéąĖą╗ąĖč鹊ą╣ ClockBuilder Desktop ą║ą░čĆč鹥 čĆąĄą│ąĖčüčéčĆąŠą▓ ą║ą░ą║ "#PFD(MHz)=...".

a + b/c, ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé čāą╝ąĮąŠąČąĄąĮąĖčÅ PLLA Multisynth (ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą▓čŗčłąĄ ą▓ čĆą░ąĘą┤ąĄą╗ąĄ "2. ąÜąŠąĮčåąĄą┐čåąĖčÅ ą┐ą╗ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ čćą░čüč鹊čé"). ąŁč鹊 čéą░ą║ąČąĄ ą┐ąĄčĆąĄčćąĖčüą╗ąĄąĮąŠ ą▓ čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąĮąŠą╣ čāčéąĖą╗ąĖč鹊ą╣ ClockBuilder Desktop ą║ą░čĆč鹥 čĆąĄą│ąĖčüčéčĆąŠą▓ ą║ą░ą║ "#Feedback Divider=...".

sscAMP, ą░ą╝ą┐ą╗ąĖčéčāą┤ą░ čüą┐ąĄą║čéčĆą░ (ąĮą░ą┐čĆąĖą╝ąĄčĆ, ą┤ą╗čÅ 1% čüą╝ąĄčēąĄąĮąĖčÅ čüą┐ąĄą║čéčĆą░ ą▓ąĮąĖąĘ ąĖą╗ąĖ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ čåąĄąĮčéčĆą░ą╗čīąĮąŠą╣ čćą░čüč鹊čéčŗ sscAmp = 0.01).

ąöą╗čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ ąĮčāąČąĮąŠą│ąŠ ą┐čĆąŠčäąĖą╗čÅ čüą┐ąĄą║čéčĆą░ ąĖčüą┐ąŠą╗čīąĘčāą╣č鹥 ą▓čŗčĆą░ąČąĄąĮąĖčÅ ąĮąĖąČąĄ.

ąŚą░ą╝ąĄčćą░ąĮąĖąĄ: ą┐čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ čäčāąĮą║čåąĖąĖ čĆą░čüčłąĖčĆąĄąĮąĖčÅ čüą┐ąĄą║čéčĆą░ čāą▒ąĄą┤ąĖč鹥čüčī, čćč鹊 MSNA čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ ą┤čĆąŠą▒ąĮčŗą╣ čĆąĄąČąĖą╝. ąĪą╝. ą┐ą░čĆą░ą╝ąĄčéčĆ FBA_INT ą▓ čĆąĄą│ąĖčüčéčĆąĄ 22.

5.1. ąĀą░čüčłąĖčĆąĄąĮąĖąĄ čüą┐ąĄą║čéčĆą░ ą▓ąĮąĖąĘ (Down Spread)

ąöą╗čÅ čĆą░čüčłąĖčĆąĄąĮąĖčÅ čüą┐ąĄą║čéčĆą░ ą▓ąĮąĖąĘ ąĮčāąČąĮąŠ ąĘą░ą┐ąĖčüą░čéčī 4 ą┐ą░čĆą░ą╝ąĄčéčĆą░: SSUDP[11:0], SSDN_P1[11:0], SSDN_P2[14:0] ąĖ SSDN_P3[14:0]. ą¤ą░čĆą░ą╝ąĄčéčĆ Up/Down:

fPFD

SSUDP[11:0] = Floor(-----------)

4 ┬Ę 31500

ą¤čĆąŠą╝ąĄąČčāč鹊čćąĮąŠąĄ ą▓čŗčĆą░ąČąĄąĮąĖąĄ (ąĮąĄ ą┤ą╗čÅ ąĘą░ą┐ąĖčüąĖ ą▓ čĆąĄą│ąĖčüčéčĆčŗ):

b sscAmp

SSDN = 64 ┬Ę (a + -) ┬Ę --------------------

c (1 + sscAmp) ┬Ę SSUDP

ą¤ą░čĆą░ą╝ąĄčéčĆčŗ Down-Spread:

SSDN_P1[11:0] = Floor(SSDN)

SSDN_P2[14:0] = 32767 ┬Ę (SSDN - SSDN_P1)

SSDN_P3[14:0] = 32767 = 0x7FFF

ą¤ą░čĆą░ą╝ąĄčéčĆčŗ Up-Spread:

SSUP_P1 = 0

SSUP_P2 = 0

SSUP_P3 = 1

5.2. ąĀą░čüčłąĖčĆąĄąĮąĖąĄ čüą┐ąĄą║čéčĆą░ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ čåąĄąĮčéčĆą░ą╗čīąĮąŠą╣ čćą░čüč鹊čéčŗ

ąöą╗čÅ čĆą░čüčłąĖčĆąĄąĮąĖčÅ čüą┐ąĄą║čéčĆą░ ą┐ąŠčüąĄčĆąĄą┤ąĖąĮąĄ ąĮčāąČąĮąŠ ąĘą░ą┐ąĖčüą░čéčī 7 ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓: SSUDP[11:0], SSDN_P1[11:0], SSDN_P2[14:0], SSDN_P3[14:0], SSUP_P1[11:0], SSUP_P2[14:0] ąĖ SSUP_P3[14:0]. ą¤ą░čĆą░ą╝ąĄčéčĆ Up/Down:

fPFD

SSUDP[11:0] = Floor(-----------)

4 ┬Ę 31500

ą¤čĆąŠą╝ąĄąČčāč鹊čćąĮčŗąĄ ą▓čŗčĆą░ąČąĄąĮąĖčÅ (ąĮąĄ ą┤ą╗čÅ ąĘą░ą┐ąĖčüąĖ ą▓ čĆąĄą│ąĖčüčéčĆčŗ):

b sscAmp

SSUP = 128 ┬Ę (a + -) ┬Ę --------------------

c (1 - sscAmp) ┬Ę SSUDP

b sscAmp

SSDN = 128 ┬Ę (a + -) ┬Ę --------------------

c (1 + sscAmp) ┬Ę SSUDP

ą¤ą░čĆą░ą╝ąĄčéčĆčŗ Up-Spread:

SSUP_P1[11:0] = Floor(SSUP)

SSUP_P2[14:0] = 32767 ┬Ę (SSUP - SSUP_P1)

SSUP_P3[14:0] = 32767 = 0x7FFF

ą¤ą░čĆą░ą╝ąĄčéčĆčŗ Down-Spread:

SSDN_P1[11:0] = Floor(SSDN)

SSDN_P2[14:0] = 32767 ┬Ę (SSDN - SSDN_P1)

SSDN_P3[14:0] = 32767 = 0x7FFF

5.3. ąÆčŗą▓ąŠą┤ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ Spread Spectrum (SSEN)

ąÆ čāčüčéčĆąŠą╣čüčéą▓ą░čģ Si5351A ąĖ Si5351B (ą▓ąĄčĆčüąĖąĖ ą║ąŠčĆą┐čāčüą░ QFN20) ąĖą╝ąĄąĄčéčüčÅ ą▓čŗą▓ąŠą┤ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą▓čŗą▓ąŠą┤ Spread Spectrum Enable. ążčāąĮą║čåąĖčÅ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ čüą┐ąĄą║čéčĆą░ čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ ą╗ąŠą│ąĖč湥čüą║ąĖą╝ ąśąøąś čāčĆąŠą▓ąĮčÅ SSEN ąĖ ą▒ąĖčéą░ SSC_EN čĆąĄą│ąĖčüčéčĆą░, čéą░ą║ čćč鹊ą▒čŗ ą▓čŗą▓ąŠą┤ SSEN čĆą░ą▒ąŠčéą░ą╗ ą┐čĆą░ą▓ąĖą╗čīąĮąŠ, ą▒ąĖčé čĆąĄą│ąĖčüčéčĆą░ SSC_EN ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čüą▒čĆąŠčłąĄąĮ ą▓ 0.

[6. ąÜąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ čüą╝ąĄčēąĄąĮąĖčÅ čäą░ąĘčŗ]

ąÆčŗčģąŠą┤čŗ 0-5 ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ Si5351 ą╝ąŠąČąĮąŠ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī ąĮą░ ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠąĄ čüą╝ąĄčēąĄąĮąĖąĄ ąĮą░čćą░ą╗čīąĮąŠą╣ čäą░ąĘčŗ. ą¤ą░čĆą░ą╝ąĄčéčĆ čüą╝ąĄčēąĄąĮąĖčÅ čäą░ąĘčŗ čŹč鹊 čåąĄą╗ąŠąĄ čćąĖčüą╗ąŠ ą▒ąĄąĘ ąĘąĮą░ą║ą░, ą│ą┤ąĄ ą║ą░ąČą┤čŗą╣ LSB ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé čĆą░ąĘąĮąĖčåčā čäą░ąĘčŗ č湥čéą▓ąĄčĆčéąĖ ą┐ąĄčĆąĖąŠą┤ą░ VCO, TVCO/4. ąöą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ ąĘąĮą░č湥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ ąĖčüą┐ąŠą╗čīąĘčāą╣č鹥 čüą╗ąĄą┤čāčÄčēčāčÄ č乊čĆą╝čāą╗čā:

CLKx_PHOFF[4:0] = Round(DesiredOffset(sec) ┬Ę 4 ┬Ę fVCO)

[7. ą¤ą░čĆą░ą╝ąĄčéčĆčŗ VCXO (č鹊ą╗čīą║ąŠ Si5351B)]

ą£ąĖą║čĆąŠčüčģąĄą╝ą░ Si5351B ą║ąŠą╝ą▒ąĖąĮąĖčĆčāąĄčé ą▓ ąŠą┤ąĮąŠą╝ ą║ąŠčĆą┐čāčüąĄ ąĮąĄąĘą░ą▓ąĖčüąĖą╝čāčÄ ą│ąĄąĮąĄčĆą░čåąĖčÄ čéą░ą║č鹊ą▓ (free-running clock) ąĖ VCXO. ąÉčĆčģąĖč鹥ą║čéčāčĆą░ VCXO Si5350B čāčüčéčĆą░ąĮčÅąĄčé ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéčī ą▓ąŠ ą▓ąĮąĄčłąĮąĄą╝ čāą┐čĆą░ą▓ą╗čÅąĄą╝ąŠą╝ ą║ą▓ą░čĆčåąĄą▓ąŠą╝ ą│ąĄąĮąĄčĆą░č鹊čĆąĄ. ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čćą░čüč鹊č鹊ą╣ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą▒ą╗ąŠą║ąŠą╝ PLLB. ąöą╗čÅ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĖą╝ąĄąĮčÅąĄčéčüčÅ ąĮąĄą┤ąŠčĆąŠą│ąŠą╣, čüčéą░ąĮą┤ą░čĆčéąĮčŗą╣ ą║ą▓ą░čĆčå čü AT-čüčĆąĄąĘąŠą╝ ąĮą░ čćą░čüč鹊čéčā 25 ąĖą╗ąĖ 27 ą£ąōčå ą┤ą╗čÅ ąŠą▒ąŠąĖčģ ą▒ą╗ąŠą║ąŠą▓ ążąÉą¤ą¦ PLLA ąĖ PLLB.

PLLB ą┤ąŠą╗ąČąĄąĮ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓ ą┤ą╗čÅ ą╗čÄą▒ąŠą╣ ą▓čŗčģąŠą┤ąĮąŠą╣ č乊čĆą╝ąĖčĆčāąĄą╝ąŠą╣ ąŠčé VCXO čćą░čüč鹊čéčŗ. ąÜąŠčŹčäčäąĖčåąĖąĄąĮčé Feedback B Multisynth ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čéą░ą║, čćč鹊ą▒čŗ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé c ąĘąĮą░ą╝ąĄąĮą░č鹥ą╗čÅ č乊čĆą╝čāą╗čŗ a + b/c ą▒čŗą╗ ąĘą░čäąĖą║čüąĖčĆąŠą▓ą░ąĮ ąĮą░ ąĘąĮą░č湥ąĮąĖąĖ 106. ąŻčüčéą░ąĮąŠą▓ąĖč鹥 ąĘąĮą░č湥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ VCXO_Param ą┐ąŠ č乊čĆą╝čāą╗ąĄ ąĮąĖąČąĄ. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 1.03 ąŠą│čĆą░ąĮąĖčćąĖą▓ą░čÄčēąĖą╣ čäą░ą║č鹊čĆ, čćč鹊ą▒čŗ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī ą┤ąŠčüčéąĖąČąĄąĮąĖąĄ ą┐ąŠą╗ąĮąŠą│ąŠ ąČąĄą╗ą░ąĄą╝ąŠą│ąŠ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ čćą░čüč鹊čéčŗ. ąöą╗čÅ ąČąĄą╗ą░ąĄą╝ąŠą│ąŠ ą┤ąĖą░ą┐ą░ąĘąŠąĮą░ ą┐ąŠą┤čüčéčĆąŠą╣ą║ąĖ (pull-range) +/ŌĆō30 ppm ąĘąĮą░č湥ąĮąĖąĄ APR ą▓ č乊čĆą╝čāą╗ąĄ ąĮąĖąČąĄ čĆą░ą▓ąĮąŠ 30, ą┤ą╗čÅ +/ŌĆō60 ppm APR čĆą░ą▓ąĮąŠ 60, ąĖ čéą░ą║ ą┤ą░ą╗ąĄąĄ.

b

VCXO_Param[21:0] = 1.03 ┬Ę (128a + ---) ┬Ę APR

106

[8. ąĀąĄą│ąĖčüčéčĆčŗ Si5351]

ąŚą┤ąĄčüčī ą┐čĆąĖą▓ąĄą┤ąĄąĮąŠ ąŠą┐ąĖčüą░ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆąŠą▓ ąĖ ą┐ąŠą┤čĆąŠą▒ąĮąŠąĄ ąĖčģ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ. ąŚąĮą░č湥ąĮąĖčÅ čŹčéąĖčģ čĆąĄą│ąĖčüčéčĆąŠą▓ ą╝ąŠąČąĮąŠ čāą┐čĆąŠčēąĄąĮąĮąŠ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī čāčéąĖą╗ąĖč鹊ą╣ ClockBuilder Desktop (čüą╝. čüąĄą║čåąĖčÄ "3.1.1 ClockbuilderTM Desktop Software" ą▓ ą┤ą░čéą░čłąĖč鹥 Si5338). ąóą░ą║ąČąĄ čüą╝. ą░ą┐ąĮąŠčāčé AN428 ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ čĆą░ą▒ąŠč湥ą│ąŠ ą┐čĆąĖą╝ąĄčĆą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ čü ą┐ąŠą╝ąŠčēčīčÄ F301 MCU ą║ąŠą╝ą┐ą░ąĮąĖąĖ Silicon Labs.

8.1. ąÜą░čĆčéą░ ą┐ą░ą╝čÅčéąĖ čĆąĄą│ąĖčüčéčĆąŠą▓

ąÆ čüą╗ąĄą┤čāčÄčēąĄą╣ čéą░ą▒ą╗ąĖčåąĄ ą┐ąŠą║ą░ąĘą░ąĮą░ ąŠą▒čēą░čÅ ą║ą░čĆčéą░ ą░ą┤čĆąĄčüąŠą▓ čĆąĄą│ąĖčüčéčĆąŠą▓, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗčģ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ čüąŠčüč鹊čÅąĮąĖčÅ, čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĖ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ Si5351.

| Reg.

|

7

|

6

|

5

|

4

|

3

|

2

|

1

|

0

|

| 0 |

SYS_INIT |

LOL_B |

LOL_A |

LOS |

čĆąĄąĘąĄčĆą▓

|

REVID[1:0] |

| 1 |

SYS_INIT_STKY |

LOS_B_STKY |

LOS_A_STKY |

čĆąĄąĘąĄčĆą▓

|

| 2 |

SYS_INIT_MASK |

LOS_B_MASK |

LOS_A_MASK |

čĆąĄąĘąĄčĆą▓

|

| 3 |

CLK7_EN |

CLK6_EN |

CLK5_EN |

CLK4_EN |

CLK3_EN |

CLK2_EN |

CLK1_EN |

CLK0_EN |

| 4..8 |

čĆąĄąĘąĄčĆą▓

|

| 9 |

OEB_MASK7 |

OEB_MASK6 |

OEB_MASK5 |

OEB_MASK4 |

OEB_MASK3 |

OEB_MASK2 |

OEB_MASK1 |

OEB_MASK0 |

| 10..14 |

čĆąĄąĘąĄčĆą▓

|

| 15 |

CLKIN_DIV[2:0] |

0 |

0 |

PLLB_SRC |

PLLA_SRC |

0 |

0 |

| 16 |

CLK0_PDN |

MS0_INT |

MS0_SRC |

CLK0_INV |

CLK0_SRC[1:0] |

CLK0_IDRV[1:0] |

| 17 |

CLK1_PDN |

MS1_INT |

MS1_SRC |

CLK1_INV |

CLK1_SRC[1:0] |

CLK1_IDRV[1:0] |

| 18 |

CLK2_PDN |

MS2_INT |

MS2_SRC |

CLK2_INV |

CLK2_SRC[1:0] |

CLK2_IDRV[1:0] |

| 19 |

CLK3_PDN |

MS3_INT |

MS3_SRC |

CLK3_INV |

CLK3_SRC[1:0] |

CLK3_IDRV[1:0] |

| 20 |

CLK4_PDN |

MS4_INT |

MS4_SRC |

CLK4_INV |

CLK4_SRC[1:0] |

CLK4_IDRV[1:0] |

| 21 |

CLK5_PDN |

MS5_INT |

MS5_SRC |

CLK5_INV |

CLK5_SRC[1:0] |

CLK5_IDRV[1:0] |

| 22 |

CLK6_PDN |

FBA_INT |

MS6_SRC |

CLK6_INV |

CLK6_SRC[1:0] |

CLK6_IDRV[1:0] |

| 23 |

CLK7_PDN |

FBB_INT |

MS7_SRC |

CLK7_INV |

CLK7_SRC[1:0] |

CLK7_IDRV[1:0] |

| 24 |

CLK3_DIS_STATE |

CLK2_DIS_STATE |

CLK1_DIS_STATE |

CLK0_DIS_STATE |

| 25 |

CLK7_DIS_STATE |

CLK6_DIS_STATE |

CLK5_DIS_STATE |

CLK4_DIS_STATE |

| 26 |

MSNA_P3[15:8] |

| 27 |

MSNA_P3[7:0] |

| 28 |

čĆąĄąĘąĄčĆą▓

|

MSNA_P1[17:16] |

| 29 |

MSNA_P1[15:8] |

| 30 |

MSNA_P1[7:0] |

| 31 |

MSNA_P3[19:16] |

MSNA_P2[19:16] |

| 32 |

MSNA_P2[15:8] |

| 33 |

MSNA_P2[7:0] |

| 34 |

MSNB_P3[15:8] |

| 35 |

MSNB_P3[7:0] |

| 36 |

MSNB_P2[17:16] |

čĆąĄąĘąĄčĆą▓

|

| 37 |

MSNB_P1[15:8] |

| 38 |

MSNB_P1[7:0] |

| 39 |

MSNB_P3[19:16] |

MSNB_P2[19:16] |

| 40 |

MSNB_P2[15:8] |

| 41 |

MSNB_P2[7:0] |

| 42 |

MS0_P3[15:8] |

| 43 |

MS0_P3[7:0] |

| 44 |

čĆąĄąĘąĄčĆą▓

|

R0_DIV[2:0] |

MS0_DIVBY4[1:0] |

MS0_P1[17:16] |

| 45 |

MS0_P1[15:8] |

| 46 |

MS0_P1[7:0] |

| 47 |

MS0_P3[19:16] |

MS0_P2[19:16] |

| 48 |

MS0_P2[15:8] |

| 49 |

MS0_P2[7:0] |

| 50 |

MS1_P3[15:8] |

| 51 |

MS1_P3[7:0] |

| 52 |

|

R1_DIV[2:0] |

MS1_DIVBY4[1:0] |

MS1_P1[17:16] |

| 53 |

MS1_P1[15:8] |

| 54 |

MS1_P1[7:0] |

| 55 |

MS1_P3[19:16] |

MS1_P2[19:16] |

| 56 |

MS1_P2[15:8] |

| 57 |

MS1_P2[7:0] |

| 58 |

MS2_P3[15:8] |

| 59 |

MS2_P3[7:0] |

| 60 |

|

R2_DIV[2:0] |

MS2_DIVBY4[1:0] |

MS2_P1[17:16] |

| 61 |

MS2_P1[15:8] |

| 62 |

MS2_P1[7:0] |

| 63 |

MS2_P3[19:16] |

MS2_P2[19:16] |

| 64 |

MS2_P2[15:8] |

| 65 |

MS2_P2[7:0] |

| 66 |

MS3_P3[15:8] |

| 67 |

MS3_P3[7:0] |

| 68 |

|

R3_DIV[2:0] |

MS3_DIVBY4[1:0] |

MS3_P1[17:16] |

| 69 |

MS3_P1[15:8] |

| 70 |

MS3_P1[7:0] |

| 71 |

MS3_P3[19:16] |

MS3_P2[19:16] |

| 72 |

MS3_P2[15:8] |

| 73 |

MS3_P2[7:0] |

| 74 |

MS4_P3[15:8] |

| 75 |

MS4_P3[7:0] |

| 76 |

|

R4_DIV[2:0] |

MS4_DIVBY4[1:0] |

MS4_P1[17:16] |

| 77 |

MS4_P1[15:8] |

| 78 |

MS4_P1[7:0] |

| 79 |

MS4_P3[19:16] |

MS4_P2[19:16] |

| 80 |

MS4_P2[15:8] |

| 81 |

MS4_P2[7:0] |

| 82 |

MS5_P3[15:8] |

| 83 |

MS5_P3[7:0] |

| 84 |

|

R5_DIV[2:0] |

MS5_DIVBY4[1:0] |

MS5_P1[17:16] |

| 85 |

MS5_P1[15:8] |

| 86 |

MS5_P1[7:0] |

| 87 |

MS5_P3[19:16] |

MS5_P2[19:16] |

| 88 |

MS5_P2[15:8] |

| 89 |

MS5_P2[7:0] |

| 90 |

MS6_P1[7:0] |

| 91 |

MS7_P1[7:0] |

| 92 |

|

R7_DIV[2:0] |

|

R6_DIV[2:0] |

| 93..148 |

čĆąĄąĘąĄčĆą▓

|

| 149 |

SSC_EN |

SSDN_P2[14:8] |

| 150 |

SSDN_P2[7:0] |

| 151 |

SSC_MODE |

SSDN_P3[14:8] |

| 152 |

SSDN_P3[7:0] |

| 153 |

SSDN_P1[7:0] |

| 154 |

SSUDP[11:8] |

SSDN_P1[11:8] |

| 155 |

SSUDP[7:0] |

| 156 |

SSUP_P2[14:8] |

| 157 |

SSUP_P2[7:0] |

| 158 |

SSUP_P3[14:8] |

| 159 |

SSUP_P3[7:0] |

| 160 |

SSUP_P1[7:0] |

| 161 |

SS_NCLK[3:0] |

SSUP_P1[11:8] |

| 162 |

VCXO_Param[7:0] |

| 163 |

VCXO_Param[15:8] |

| 164 |

čĆąĄąĘąĄčĆą▓

|

VCXO_Param[21:16] |

| 165 |

čĆąĄąĘąĄčĆą▓

|

CLK0_PHOFF[6:0] |

| 166 |

čĆąĄąĘąĄčĆą▓

|

CLK1_PHOFF[6:0] |

| 167 |

čĆąĄąĘąĄčĆą▓

|

CLK2_PHOFF[6:0] |

| 168 |

čĆąĄąĘąĄčĆą▓

|

CLK3_PHOFF[6:0] |

| 169 |

čĆąĄąĘąĄčĆą▓

|

CLK4_PHOFF[6:0] |

| 170 |

čĆąĄąĘąĄčĆą▓

|

CLK5_PHOFF[6:0] |

| 171..176 |

čĆąĄąĘąĄčĆą▓

|

| 177 |

PLLB_RST |

čĆąĄąĘąĄčĆą▓

|

PLLA_RST |

čĆąĄąĘąĄčĆą▓

|

| 178..182 |

čĆąĄąĘąĄčĆą▓

|

| 183 |

XTAL_CL |

čĆąĄąĘąĄčĆą▓

|

| 184..186 |

čĆąĄąĘąĄčĆą▓

|

| 187 |

CLKIN_FANOUT_EN |

XO_FANOUT_EN |

čĆąĄąĘąĄčĆą▓

|

MS_FANOUT_EN |

čĆąĄąĘąĄčĆą▓

|

| 188..255 |

čĆąĄąĘąĄčĆą▓

|

[9. ą×ą┐ąĖčüą░ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆąŠą▓]

| Ōä¢ čĆą░ąĘčĆčÅą┤ąŠą▓ |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| ąśą╝ąĄąĮą░ ą▒ąĖčé

|

SYS_INIT

|

LOL_B

|

LOL_A

|

LOS

|

-

|

-

|

REVID[1:0]

|

| ą¦č鹥ąĮąĖąĄ/ąĘą░ą┐ąĖčüčī |

R |

R |

R |

R |

R |

R |

R |

R |

| ąØą░čć. ąĘąĮą░č湥ąĮąĖąĄ |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

| ąæąĖčé

|

ąśą╝čÅ

|

ą×ą┐ąĖčüą░ąĮąĖąĄ

|

| 7 |

SYS_INIT

|

System Initialization Status. ą¤čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą║ąŠą┐ąĖčĆčāąĄčé čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ NVM (NonVolatile Memory, 菹ĮąĄčĆą│ąŠąĮąĄąĘą░ą▓ąĖčüąĖą╝ą░čÅ ą┐ą░ą╝čÅčéčī) ą▓ RAM, ąĖ ą▓čŗą┐ąŠą╗ąĮčÅąĄčé ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÄ čüą▓ąŠąĄą╣ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ čüąĖčüč鹥ą╝čŗ. ąŻčüčéčĆąŠą╣čüčéą▓ąŠ ąĮąĄ čĆą░ą▒ąŠčéą░ąĄčé, ą┐ąŠą║ą░ čŹčéą░ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ ąĮąĄ ąĘą░ą▓ąĄčĆčłąĖčéčüčÅ. ąØąĄ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ čćąĖčéą░čéčī ąĖą╗ąĖ ąĘą░ą┐ąĖčüčŗą▓ą░čéčī čĆąĄą│ąĖčüčéčĆčŗ ą▓ RAM č湥čĆąĄąĘ ąĖąĮč鹥čĆč乥ą╣čü I2C, ą┐ąŠą║ą░ ąĮąĄ ąĘą░ą▓ąĄčĆčłąĖčéčüčÅ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ. ąĪčĆą░ą▒ąŠčéą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ (INTR pin = 0, č鹊ą╗čīą║ąŠ Si5351C) ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĖąŠą┤ą░ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ čüąĖčüč鹥ą╝čŗ.

0: ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ čüąĖčüč鹥ą╝čŗ ąĘą░ą▓ąĄčĆčłąĄąĮą░, čāčüčéčĆąŠą╣čüčéą▓ąŠ ą│ąŠč鹊ą▓ąŠ ą║ čĆą░ą▒ąŠč鹥.

1: čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ. |

| 6 |

LOL_B

|

PLLB Loss Of Lock Status. ą×čéąĮąŠčüąĖčéčüčÅ č鹊ą╗čīą║ąŠ ą║ Si5351A ąĖ Si5351C. PLLB ą▒čāą┤ąĄčé čĆą░ą▒ąŠčéą░čéčī ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ąĘą░čģą▓ą░čéą░, ą║ąŠą│ą┤ą░ ą┐ąŠą╗čāčćą░ąĄčé ąĮąŠčĆą╝ą░ą╗čīąĮčŗąĄ čéą░ą║čéčŗ ąŠčé CLKIN ąĖą╗ąĖ XTAL. ą¤čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą┐ąŠč鹥čĆčÅ ąĘą░čģą▓ą░čéą░, ąĄčüą╗ąĖ čćą░čüč鹊čéą░ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓ ą▓čŗąĮčāą┤ąĖčé PLL čĆą░ą▒ąŠčéą░čéčī ą▓ąĮąĄ ą┤ąŠą┐čāčüčéąĖą╝ąŠą│ąŠ ą┤ąĖą░ą┐ą░ąĘąŠąĮą░ čćą░čüč鹊čé, ąĖą╗ąĖ ąĄčüą╗ąĖ ąŠą┐ąŠčĆąĮčŗąĄ čéą░ą║čéčŗ ąĮąĄ čāą┤ąŠą▓ą╗ąĄčéą▓ąŠčĆčÅčÄčé ą╝ąĖąĮąĖą╝ą░ą╗čīąĮčŗą╝ čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅą╝ ą┤ąŠą┐čāčüčéąĖą╝ąŠčüčéąĖ ą▓čģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░, ą║ą░ą║ čŹč鹊 čāą║ą░ąĘą░ąĮąŠ ą▓ ą┤ą░čéą░čłąĖč鹥 Si5351 [2]. ąĪčĆą░ą▒ąŠčéą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ (ą▓čŗą▓ąŠą┤ INTR = 0, č鹊ą╗čīą║ąŠ Si5351C) ą┐čĆąĖ ąĮą░čüčéčāą┐ą╗ąĄąĮąĖąĖ čüąŠą▒čŗčéąĖčÅ LOL.

0: PLLB ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ąĘą░čģą▓ą░čéą░.

1: ąĮąĄčé ąĘą░čģą▓ą░čéą░ čćą░čüč鹊čéčŗ PLLB. ąÜąŠą│ą┤ą░ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐ąŠą┐ą░ą┤ą░ąĄčé ą▓ čŹč鹊 čüąŠčüč鹊čÅąĮąĖąĄ, č鹊 čŹč鹊 ą▓čŗąĘąŠą▓ąĄčé ą│ąĄąĮąĄčĆą░čåąĖčÄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čü ą┐ąĄčĆąĄčģąŠą┤ąŠą╝ INTR ą▓ ą╗ąŠą│. 0 (č鹊ą╗čīą║ąŠ Si5351C). |

| 5 |

LOL_A

|

PLLA Loss Of Lock Status. ąóąŠ ąČąĄ čüą░ą╝ąŠąĄ, čćč鹊 ąĖ LOL_B, č鹊ą╗čīą║ąŠ ąŠčéąĮąŠčüąĖčéčüčÅ ą║ PLLA. |

| 4 |

LOS |

CLKIN Loss Of Signal (č鹊ą╗čīą║ąŠ Si5351C). ąĪąĖą│ąĮą░ą╗ čüąŠčüč鹊čÅąĮąĖčÅ ą┐ąŠč鹥čĆąĖ čüąĖą│ąĮą░ą╗ą░ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ąŠą┐ąŠčĆąĮą░čÅ čćą░čüč鹊čéą░ ąĮąĄ čāą┤ąŠą▓ą╗ąĄčéą▓ąŠčĆčÅąĄčé ą╝ąĖąĮąĖą╝ą░ą╗čīąĮčŗą╝ čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅą╝ ą║ ą▓čģąŠą┤ąĮąŠą╝čā čüąĖą│ąĮą░ą╗čā, čāą║ą░ąĘą░ąĮąĮčŗą╝ ą▓ ą┤ą░čéą░čłąĖč鹥 Si5351 [2]. ą¤čĆąĖ ą▓ąŠąĘąĮąĖą║ąĮąŠą▓ąĄąĮąĖąĖ čüąŠą▒čŗčéąĖčÅ LOS ą▒čāą┤ąĄčé čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ (ą▓čŗą▓ąŠą┤ INTR = 0, č鹊ą╗čīą║ąŠ Si5351C). 0: ąöąŠą┐čāčüčéąĖą╝čŗą╣ čüąĖą│ąĮą░ą╗ čéą░ą║č鹊ą▓ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ CLKIN. 1: ą×ą▒ąĮą░čĆčāąČąĄąĮą░ ą┐ąŠč鹥čĆčÅ čüąĖą│ąĮą░ą╗ą░ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ CLKIN. |

| 3:0

|

-

|

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ.

|

| Ōä¢ čĆą░ąĘčĆčÅą┤ąŠą▓ |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| ąśą╝ąĄąĮą░ ą▒ąĖčé

|

SYS_INIT_STKY

|

LOL_B_STKY

|

LOL_A_STKY

|

LOS_STKY

|

-

|

-

|

-

|

-

|

| ą¦č鹥ąĮąĖąĄ/ąĘą░ą┐ąĖčüčī |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

| ąØą░čć. ąĘąĮą░č湥ąĮąĖąĄ |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

| ąæąĖčé

|

ąśą╝čÅ

|

ą×ą┐ąĖčüą░ąĮąĖąĄ

|

| 7 |

SYS_INIT_STKY

|

System Calibration Status Sticky Bit. ąæąĖčé SYS_INIT_STKY ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ ą╗ąŠą│. 1, ą║ąŠą│ą┤ą░ ą▒ąĖčé SYS_INIT (reg. 0, bit 7) ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ ą╗ąŠą│. 1. ąæąĖčé ąŠčüčéą░ąĄčéčüčÅ ą▓ ą╗ąŠą│. 1, ą┐ąŠą║ą░ ąĮąĄ ą▒čāą┤ąĄčé ąŠčćąĖčēąĄąĮ. ąŚą░ą┐ąĖčüčī 0 ą▓ čŹč鹊čé ą▒ąĖčé čĆąĄą│ąĖčüčéčĆą░ ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ąĄą│ąŠ ąŠčćąĖčüčéą║ąĄ.

0: ąĮąĄ ą▒čŗą╗ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ SYS_INIT ą┐ąŠčüą╗ąĄ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╣ ąŠčćąĖčüčéą║ąĖ.

1: ą┐čĆąŠąĖąĘąŠčłą╗ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ SYS_INIT ą┐ąŠčüą╗ąĄ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╣ ąŠčćąĖčüčéą║ąĖ. |

| 6 |

LOL_B_STKY

|

PLLB Loss Of Lock Status Sticky Bit. ąæąĖčé LOL_B_STKY ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ ą╗ąŠą│. 1, ą║ąŠą│ą┤ą░ ą▒ąĖčé LOL_B (reg. 0, bit 6) ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ ą╗ąŠą│. 1. ąæąĖčé ąŠčüčéą░ąĄčéčüčÅ ą▓ ą╗ąŠą│. 1, ą┐ąŠą║ą░ ąĮąĄ ą▒čāą┤ąĄčé ąŠčćąĖčēąĄąĮ. ąŚą░ą┐ąĖčüčī 0 ą▓ čŹč鹊čé ą▒ąĖčé čĆąĄą│ąĖčüčéčĆą░ ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ąĄą│ąŠ ąŠčćąĖčüčéą║ąĄ.

0: ąĮąĄ ą▒čŗą╗ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ PLLB ą┐ąŠčüą╗ąĄ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╣ ąŠčćąĖčüčéą║ąĖ.

1: ą┐čĆąŠąĖąĘąŠčłą╗ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ PLLB ą┐ąŠčüą╗ąĄ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╣ ąŠčćąĖčüčéą║ąĖ. |

| 5 |

LOL_A_STKY

|

PLLA Loss Of Lock Status Sticky Bit. ąóąŠ ąČąĄ čüą░ą╝ąŠąĄ, čćč鹊 ąĖ LOL_B_STKY, č鹊ą╗čīą║ąŠ ąŠčéąĮąŠčüąĖčéčüčÅ ą║ PLLA. |

| 4 |

LOS_STKY

|

CLKIN Loss Of Signal Sticky Bit (č鹊ą╗čīą║ąŠ Si5351C). ąæąĖčé LOL_STKY ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ ą╗ąŠą│. 1, ą║ąŠą│ą┤ą░ ą▒ąĖčé LOS (reg. 0, bit 4) ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ ą╗ąŠą│. 1. ąæąĖčé ąŠčüčéą░ąĄčéčüčÅ ą▓ ą╗ąŠą│. 1, ą┐ąŠą║ą░ ąĮąĄ ą▒čāą┤ąĄčé ąŠčćąĖčēąĄąĮ. ąŚą░ą┐ąĖčüčī 0 ą▓ čŹč鹊čé ą▒ąĖčé čĆąĄą│ąĖčüčéčĆą░ ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ąĄą│ąŠ ąŠčćąĖčüčéą║ąĄ.

0: ąĮąĄ ą▒čŗą╗ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ LOS ą┐ąŠčüą╗ąĄ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╣ ąŠčćąĖčüčéą║ąĖ.

1: ą┐čĆąŠąĖąĘąŠčłą╗ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ LOS ą┐ąŠčüą╗ąĄ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╣ ąŠčćąĖčüčéą║ąĖ. |

| 3:0

|

-

|

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ.

|

| Ōä¢ čĆą░ąĘčĆčÅą┤ąŠą▓ |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| ąśą╝ąĄąĮą░ ą▒ąĖčé

|

SYS_INIT_MASK

|

LOL_B_MASK

|

LOL_A_MASK

|

LOS_MASK

|

-

|

-

|

-

|

-

|

| ą¦č鹥ąĮąĖąĄ/ąĘą░ą┐ąĖčüčī |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

| ąØą░čć. ąĘąĮą░č湥ąĮąĖąĄ |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

| ąæąĖčé

|

ąśą╝čÅ

|

ą×ą┐ąĖčüą░ąĮąĖąĄ

|

| 7 |

SYS_INIT_MASK

|

System Initialization Status Mask. ąśčüą┐ąŠą╗čīąĘčāą╣č鹥 čŹč鹊čé ą▒ąĖčé ą┤ą╗čÅ ą╝ą░čüą║ąĖčĆąŠą▓ą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čüąĖą│ąĮą░ą╗ąŠą╝ ą┐ąĄčĆąĄčģąŠą┤ą░ INTR ą▓ ą╗ąŠą│. 0 (č鹊ą╗čīą║ąŠ Si5351C), ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé SYS_INIT.

0: ąĮąĄ ą╝ą░čüą║ąĖčĆąŠą▓ą░čéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ SYS_INIT.

1: ą╝ą░čüą║ąĖčĆąŠą▓ą░čéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ SYS_INIT. |

| 6 |

LOL_B_MASK

|

PLLB Loss Of Lock Status Mask. ąóąŠ ąČąĄ čüą░ą╝ąŠąĄ, č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ LOL_B. |

| 5 |

LOL_A_MASK

|

PLL A Loss Of Lock Status Mask. ąóąŠ ąČąĄ čüą░ą╝ąŠąĄ, č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ LOL_A. |

| 4 |

LOS_MASK

|

CLKIN Loss Of Signal Mask (č鹊ą╗čīą║ąŠ Si5351C). ąóąŠ ąČąĄ čüą░ą╝ąŠąĄ, č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ LOS. |

| 3:0

|

-

|

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ.

|

| Ōä¢ čĆą░ąĘčĆčÅą┤ąŠą▓ |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| ąśą╝ąĄąĮą░ ą▒ąĖčé

|

CLK7_OEB

|

CLK6_OEB

|

CLK5_OEB

|

CLK4_OEB

|

CLK3_OEB

|

CLK2_OEB

|

CLK1_OEB

|

CLK0_OEB

|

| ą¦č鹥ąĮąĖąĄ/ąĘą░ą┐ąĖčüčī |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

| ąØą░čć. ąĘąĮą░č湥ąĮąĖąĄ |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

| ąæąĖčé

|

ąśą╝čÅ

|

ą×ą┐ąĖčüą░ąĮąĖąĄ

|

| 7:0 |

CLKx_OEB

|

Output Disable for CLKx. ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ąĘą░ą┐čĆąĄč鹊ą╝ čĆą░ą▒ąŠčéčŗ ą▓čŗčģąŠą┤ąŠą▓ CLKx (x = 0..7).

0: čĆą░ąĘčĆąĄčłąĖčéčī čĆą░ą▒ąŠčéčā CLKx.

1: ąĘą░ą┐čĆąĄčéąĖčéčī čĆą░ą▒ąŠčéčā CLKx. |

| Ōä¢ čĆą░ąĘčĆčÅą┤ąŠą▓ |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| ąśą╝ąĄąĮą░ ą▒ąĖčé

|

OEB_MASK7

|

OEB_MASK6

|

OEB_MASK5

|

OEB_MASK4

|

OEB_MASK3

|

OEB_MASK2

|

OEB_MASK1

|

OEB_MASK0

|

| ą¦č鹥ąĮąĖąĄ/ąĘą░ą┐ąĖčüčī |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

| ąØą░čć. ąĘąĮą░č湥ąĮąĖąĄ |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

| ąæąĖčé

|

ąśą╝čÅ

|

ą×ą┐ąĖčüą░ąĮąĖąĄ

|

| 7:0 |

OEB_CLKx

|

OEB pin enable control of CLKx. ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą▓čŗą▓ąŠą┤ąŠą╝ OEB ą┤ą╗čÅ ą▓čŗčģąŠą┤ąŠą▓ CLKx (x = 0..7).

0: ą▓čŗą▓ąŠą┤ OEB čāą┐čĆą░ą▓ą╗čÅąĄčé čüąŠčüč鹊čÅąĮąĖąĄą╝ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ/ąĘą░ą┐čĆąĄčéą░ CLKx.

1: ą▓čŗą▓ąŠą┤ OEB ąĮąĄ čāą┐čĆą░ą▓ą╗čÅąĄčé čüąŠčüč鹊čÅąĮąĖąĄą╝ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ/ąĘą░ą┐čĆąĄčéą░ CLKx. |

| Ōä¢ čĆą░ąĘčĆčÅą┤ąŠą▓ |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| ąśą╝ąĄąĮą░ ą▒ąĖčé

|

CLKIN_DIV[1:0]

|

-

|

-

|

PLLB_SRC

|

PLLA_SRC

|

-

|

-

|

| ą¦č鹥ąĮąĖąĄ/ąĘą░ą┐ąĖčüčī |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

| ąØą░čć. ąĘąĮą░č湥ąĮąĖąĄ |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

| ąæąĖčé

|

ąśą╝čÅ

|

ą×ą┐ąĖčüą░ąĮąĖąĄ

|

| 7:6 |

CLKIN_DIV[1:0]

|

CLKIN Input Divider. ąÆčģąŠą┤ąĮąŠą╣ ą┤ąĄą╗ąĖč鹥ą╗čī ą┤ą╗čÅ ą▓čŗą▓ąŠą┤ą░ CLKIN. ąöąŠą┐čāčüčéąĖą╝ą░čÅ čćą░čüč鹊čéą░ ąĮą░ ą▓čģąŠą┤ąĄ PLL ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ 10..40 ą£ąōčå. ąĢčüą╗ąĖ čćą░čüč鹊čéą░ ąĮąĄ čāą║ą╗ą░ą┤čŗą▓ą░ąĄčéčüčÅ ą▓ čŹčéąĖ ą┐čĆąĄą┤ąĄą╗čŗ, č鹊 ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąŠą┤ąŠą▒čĆą░ąĮ ą┐čĆą░ą▓ąĖą╗čīąĮčŗą╣ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ą┤ąĄą╗ąĄąĮąĖčÅ čćą░čüč鹊čéčŗ ąĮą░ ą▓čģąŠą┤ąĄ PLL.

00: ąŠčéčüčāčéčüčéą▓ąĖąĄ ą┤ąĄą╗ąĄąĮąĖčÅ (ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ą┤ąĄą╗ąĄąĮąĖčÅ 1).

01: ą┤ąĄą╗ąĄąĮąĖąĄ ąĮą░ 2.

10: ą┤ąĄą╗ąĄąĮąĖąĄ ąĮą░ 4.

11: ą┤ąĄą╗ąĄąĮąĖąĄ ąĮą░ 8.

|

| 5:4

|

-

|

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ. ą×čüčéą░ą▓ąĖčéčī ąĘąĮą░č湥ąĮąĖčÅ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ.

|

| 3 |

PLLB_SRC

|

Input Source Select for PLLB.

0: ą▓ ą║ą░č湥čüčéą▓ąĄ ąŠą┐ąŠčĆąĮąŠą╣ čćą░čüč鹊čéčŗ ą┤ą╗čÅ PLLA ą▓čŗą▒čĆą░ąĮ ą▓čģąŠą┤ XTAL.

1: ą▓ ą║ą░č湥čüčéą▓ąĄ ąŠą┐ąŠčĆąĮąŠą╣ čćą░čüč鹊čéčŗ PLLA ą▓čŗą▒čĆą░ąĮ ą▓čģąŠą┤ CLKIN (č鹊ą╗čīą║ąŠ ą┤ą╗čÅ Si5351C).

|

| 2 |

PLLA_SRC

|

Input Source Select for PLLA. ąóąŠ ąČąĄ čüą░ą╝ąŠąĄ, čćč鹊 ąĖ PLLB_SRC, č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ą▒ą╗ąŠą║ą░ PLLA.

|

| 1:0

|

-

|

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ. ą×čüčéą░ą▓ąĖčéčī ąĘąĮą░č湥ąĮąĖčÅ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ.

|

16. ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ CLK0

| Ōä¢ čĆą░ąĘčĆčÅą┤ąŠą▓ |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| ąśą╝ąĄąĮą░ ą▒ąĖčé

|

CLK0_PDN

|

MS0_INT

|

MS0_SRC

|

CLK0_INV

|

CLK0_SRC[1:0]

|

CLK0_IDRV[1:0]

|

| ą¦č鹥ąĮąĖąĄ/ąĘą░ą┐ąĖčüčī |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

| ąØą░čć. ąĘąĮą░č湥ąĮąĖąĄ |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

| ąæąĖčé

|

ąśą╝čÅ

|

ą×ą┐ąĖčüą░ąĮąĖąĄ

|

| 7 |

CLK0_PDN

|

Clock 0 Power Down. ąæąĖčé ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą▓čŗą║ą╗čÄčćąĖčéčī ą┐ąĖčéą░ąĮąĖąĄ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ ą┤čĆą░ą╣ą▓ąĄčĆą░ CLK0, ą║ąŠą│ą┤ą░ čŹč鹊čé ą▓čŗčģąŠą┤ čéą░ą║č鹊ą▓ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ.

0: CLK0 čĆą░ą▒ąŠčéą░ąĄčé.

1: CLK0 ą▓čŗą║ą╗čÄč湥ąĮ.

|

| 6 |

MS0_INT

|

MultiSynth 0 Integer Mode. ąŁč鹊čé ą▒ąĖčé ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą┐čĆąĖąĮčāą┤ąĖč鹥ą╗čīąĮąŠą│ąŠ ą┐ąĄčĆąĄą▓ąŠą┤ą░ MS0 ą▓ čåąĄą╗ąŠčćąĖčüą╗ąĄąĮąĮčŗą╣ čĆąĄąČąĖą╝ ą┤ąĄą╗ąĖč鹥ą╗ąĄą╣, čćč鹊ą▒čŗ čāą╗čāčćčłąĖčéčī ą┐ą░čĆą░ą╝ąĄčéčĆčŗ ą┐ąŠ ą┤ąČąĖčéč鹥čĆčā. ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┤čĆąŠą▒ąĮčŗą╣ čĆąĄąČąĖą╝ ą┤ąĄą╗ąĖč鹥ą╗ąĄą╣ (fractional mode), ą║ąŠą│ą┤ą░ ą┤ą╗čÅ CLK0 čāą║ą░ąĘą░ąĮąŠ čüą╝ąĄčēąĄąĮąĖąĄ ąĘą░ą┤ąĄčƹȹ║ąĖ.

0: MS0 čĆą░ą▒ąŠčéą░ąĄčé čü čĆąĄąČąĖą╝ąĄ čü ą┤čĆąŠą▒ąĮčŗą╝ąĖ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéą░ą╝ąĖ ą┤ąĄą╗ąĄąĮąĖčÅ.

1: MS0 čĆą░ą▒ąŠčéą░ąĄčé ą▓ čĆąĄąČąĖą╝ąĄ čü čåąĄą╗ąŠčćąĖčüą╗ąĄąĮąĮčŗą╝ąĖ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéą░ą╝ąĖ ą┤ąĄą╗ąĄąĮąĖčÅ.

|

| 5 |

MS0_SRC

|

MultiSynth Source Select for CLK0.

0: MS0 čéą░ą║čéąĖčĆčāąĄčéčüčÅ ąŠčé PLLA.

1: MS0 čéą░ą║čéąĖčĆčāąĄčéčüčÅ ąŠčé PLLB (č鹊ą╗čīą║ąŠ Si5351A ąĖ Si5351C) ąĖą╗ąĖ ąŠčé VCXO (č鹊ą╗čīą║ąŠ Si5351B).

|

| 4 |

CLK0_INV

|

Output Clock 0 Invert.

0: ąĮąĄčé ąĖąĮą▓ąĄčĆčüąĖąĖ ąĮą░ ą▓čŗčģąŠą┤ąĄ CLK0.

1: CLK0 ą▓čŗą▓ąŠą┤ąĖčéčüčÅ čü ąĖąĮą▓ąĄčĆčüąĖąĄą╣.

|

| 3:2 |

CLK0_SRC[1:0]

|

Output Clock 0 Input Source. ąŁčéąĖ ą▒ąĖčéčŗ ą▓čŗą▒ąĖčĆą░čÄčé ąĖčüč鹊čćąĮąĖą║ čéą░ą║č鹊ą▓ ą┤ą╗čÅ CLK0.

00: ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓ ą▓čŗą▒čĆą░ąĮ XTAL. ąŁčéą░ ąŠą┐čåąĖčÅ ą┐čĆąŠą┐čāčüą║ą░ąĄčé ąŠą▒ą░ ą║ą░čüą║ą░ą┤ą░ čüąĖąĮč鹥ąĘą░ (PLL/VCXO ąĖ MultiSynth), ąĖ ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčé CLK0 ąĮą░ą┐čĆčÅą╝čāčÄ ą║ ą│ąĄąĮąĄčĆą░č鹊čĆčā, ą║ąŠč鹊čĆčŗą╣ č乊čĆą╝ąĖčĆčāąĄčé ą▓čŗčģąŠą┤ąĮčāčÄ čćą░čüč鹊čéčā, ąŠą┐čĆąĄą┤ąĄą╗čÅąĄą╝čāčÄ čćą░čüč鹊č鹊ą╣ XTAL.

01: ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓ ą▓čŗą▒čĆą░ąĮ CLKIN. ąŁčéą░ ąŠą┐čåąĖčÅ ą┐čĆąŠą┐čāčüą║ą░ąĄčé ąŠą▒ą░ ą║ą░čüą║ą░ą┤ą░ čüąĖąĮč鹥ąĘą░ (PLL/VCXO ąĖ MultiSynth), ąĖ ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčé CLK0 ąĮą░ą┐čĆčÅą╝čāčÄ ą║ąŠ ą▓čģąŠą┤čā CLKIN. ąÆ čüčāčēąĮąŠčüčéąĖ čŹč鹊 ą┐čĆąŠčüč鹊 čüąŠąĘą┤ą░ąĄčé ą▒čāč乥čĆ ą┤ą╗čÅ ą▓čģąŠą┤ą░ CLKIN.

10: ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ, ąĮąĄ ą▓čŗą▒ąĖčĆą░ą╣č鹥 čŹč鹊čé ą▓ą░čĆąĖą░ąĮčé.

11: ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓ ą▓čŗą▒čĆą░ąĮ MultiSynth 0. ąÆčŗą▒ąĄčĆąĖč鹥 čŹčéčā ąŠą┐čåąĖčÄ, ą║ąŠą│ą┤ą░ čģąŠčéąĖč鹥 ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī Si5351 ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ č乊čĆą╝ąĖčĆčāąĄą╝čŗčģ (free-running) ąĖą╗ąĖ čüąĖąĮčģčĆąŠąĮąĮčŗčģ čéą░ą║č鹊ą▓čŗčģ čüąĖą│ąĮą░ą╗ąŠą▓.

|

| 1:0 |

CLK0_IDRV[1:0]

|

CLK0 Output Rise and Fall time / Drive Strength Control. ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ąĮą░ą│čĆčāąĘąŠčćąĮąŠą╣ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčīčÄ ą▓čŗčģąŠą┤ą░ CLK0.

00: 2 ą╝ąÉ.

01: 4 ą╝ąÉ.

10: 6 ą╝ąÉ.

11: 8 ą╝ąÉ.

|

17. ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ CLK1

| Ōä¢ čĆą░ąĘčĆčÅą┤ąŠą▓ |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| ąśą╝ąĄąĮą░ ą▒ąĖčé

|

CLK1_PDN

|

MS1_INT

|

MS1_SRC

|

CLK1_INV

|

CLK1_SRC[1:0]

|

CLK1_IDRV[1:0]

|

| ą¦č鹥ąĮąĖąĄ/ąĘą░ą┐ąĖčüčī |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

| ąØą░čć. ąĘąĮą░č湥ąĮąĖąĄ |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

| ąæąĖčé

|

ąśą╝čÅ

|

ą×ą┐ąĖčüą░ąĮąĖąĄ

|

| 7 |

CLK1_PDN

|

Clock 1 Power Down. ąæąĖčé ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą▓čŗą║ą╗čÄčćąĖčéčī ą┐ąĖčéą░ąĮąĖąĄ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ ą┤čĆą░ą╣ą▓ąĄčĆą░ CLK1, ą║ąŠą│ą┤ą░ čŹč鹊čé ą▓čŗčģąŠą┤ čéą░ą║č鹊ą▓ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ.

0: CLK1 čĆą░ą▒ąŠčéą░ąĄčé.

1: CLK1 ą▓čŗą║ą╗čÄč湥ąĮ.

|

| 6 |

MS1_INT

|

MultiSynth 1 Integer Mode. ąŁč鹊čé ą▒ąĖčé ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą┐čĆąĖąĮčāą┤ąĖč鹥ą╗čīąĮąŠą│ąŠ ą┐ąĄčĆąĄą▓ąŠą┤ą░ MS1 ą▓ čåąĄą╗ąŠčćąĖčüą╗ąĄąĮąĮčŗą╣ čĆąĄąČąĖą╝ ą┤ąĄą╗ąĖč鹥ą╗ąĄą╣, čćč鹊ą▒čŗ čāą╗čāčćčłąĖčéčī ą┐ą░čĆą░ą╝ąĄčéčĆčŗ ą┐ąŠ ą┤ąČąĖčéč鹥čĆčā. ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┤čĆąŠą▒ąĮčŗą╣ čĆąĄąČąĖą╝ ą┤ąĄą╗ąĖč鹥ą╗ąĄą╣ (fractional mode), ą║ąŠą│ą┤ą░ ą┤ą╗čÅ CLK1 čāą║ą░ąĘą░ąĮąŠ čüą╝ąĄčēąĄąĮąĖąĄ ąĘą░ą┤ąĄčƹȹ║ąĖ.

0: MS1 čĆą░ą▒ąŠčéą░ąĄčé čü čĆąĄąČąĖą╝ąĄ čü ą┤čĆąŠą▒ąĮčŗą╝ąĖ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéą░ą╝ąĖ ą┤ąĄą╗ąĄąĮąĖčÅ.

1: MS1 čĆą░ą▒ąŠčéą░ąĄčé ą▓ čĆąĄąČąĖą╝ąĄ čü čåąĄą╗ąŠčćąĖčüą╗ąĄąĮąĮčŗą╝ąĖ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéą░ą╝ąĖ ą┤ąĄą╗ąĄąĮąĖčÅ.

|

| 5 |

MS1_SRC

|

MultiSynth Source Select for CLK1.

0: MS1 čéą░ą║čéąĖčĆčāąĄčéčüčÅ ąŠčé PLLA.

1: MS1 čéą░ą║čéąĖčĆčāąĄčéčüčÅ ąŠčé PLLB (č鹊ą╗čīą║ąŠ Si5351A ąĖ Si5351C) ąĖą╗ąĖ ąŠčé VCXO (č鹊ą╗čīą║ąŠ Si5351B).

|

| 4 |

CLK1_INV

|

Output Clock 1 Invert.

0: ąĮąĄčé ąĖąĮą▓ąĄčĆčüąĖąĖ ąĮą░ ą▓čŗčģąŠą┤ąĄ CLK1.

1: CLK1 ą▓čŗą▓ąŠą┤ąĖčéčüčÅ čü ąĖąĮą▓ąĄčĆčüąĖąĄą╣.

|

| 3:2 |

CLK1_SRC[1:0]

|

Output Clock 1 Input Source. ąŁčéąĖ ą▒ąĖčéčŗ ą▓čŗą▒ąĖčĆą░čÄčé ąĖčüč鹊čćąĮąĖą║ čéą░ą║č鹊ą▓ ą┤ą╗čÅ CLK1.

00: ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓ ą▓čŗą▒čĆą░ąĮ XTAL. ąŁčéą░ ąŠą┐čåąĖčÅ ą┐čĆąŠą┐čāčüą║ą░ąĄčé ąŠą▒ą░ ą║ą░čüą║ą░ą┤ą░ čüąĖąĮč鹥ąĘą░ (PLL/VCXO ąĖ MultiSynth), ąĖ ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčé CLK1 ąĮą░ą┐čĆčÅą╝čāčÄ ą║ ą│ąĄąĮąĄčĆą░č鹊čĆčā, ą║ąŠč鹊čĆčŗą╣ č乊čĆą╝ąĖčĆčāąĄčé ą▓čŗčģąŠą┤ąĮčāčÄ čćą░čüč鹊čéčā, ąŠą┐čĆąĄą┤ąĄą╗čÅąĄą╝čāčÄ čćą░čüč鹊č鹊ą╣ XTAL.

01: ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓ ą▓čŗą▒čĆą░ąĮ CLKIN. ąŁčéą░ ąŠą┐čåąĖčÅ ą┐čĆąŠą┐čāčüą║ą░ąĄčé ąŠą▒ą░ ą║ą░čüą║ą░ą┤ą░ čüąĖąĮč鹥ąĘą░ (PLL/VCXO ąĖ MultiSynth), ąĖ ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčé CLK1 ąĮą░ą┐čĆčÅą╝čāčÄ ą║ąŠ ą▓čģąŠą┤čā CLKIN. ąÆ čüčāčēąĮąŠčüčéąĖ čŹč鹊 ą┐čĆąŠčüč鹊 čüąŠąĘą┤ą░ąĄčé ą▒čāč乥čĆ ą┤ą╗čÅ ą▓čģąŠą┤ą░ CLKIN.

10: ą▓čŗą▒ąĖčĆą░ąĄčé Multisynth 0 ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓.

11: ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓ ą▓čŗą▒čĆą░ąĮ MultiSynth 1. ąÆčŗą▒ąĄčĆąĖč鹥 čŹčéčā ąŠą┐čåąĖčÄ, ą║ąŠą│ą┤ą░ čģąŠčéąĖč鹥 ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī Si5351 ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ č乊čĆą╝ąĖčĆčāąĄą╝čŗčģ (free-running) ąĖą╗ąĖ čüąĖąĮčģčĆąŠąĮąĮčŗčģ čéą░ą║č鹊ą▓čŗčģ čüąĖą│ąĮą░ą╗ąŠą▓.

|

| 1:0 |

CLK1_IDRV[1:0]

|

CLK1 Output Rise and Fall time / Drive Strength Control. ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ąĮą░ą│čĆčāąĘąŠčćąĮąŠą╣ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčīčÄ ą▓čŗčģąŠą┤ą░ CLK1.

00: 2 ą╝ąÉ.

01: 4 ą╝ąÉ.

10: 6 ą╝ąÉ.

11: 8 ą╝ąÉ.

|

18. ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ CLK2

| Ōä¢ čĆą░ąĘčĆčÅą┤ąŠą▓ |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| ąśą╝ąĄąĮą░ ą▒ąĖčé

|

CLK2_PDN

|

MS2_INT

|

MS2_SRC

|

CLK2_INV

|

CLK2_SRC[1:0]

|

CLK2_IDRV[1:0]

|

| ą¦č鹥ąĮąĖąĄ/ąĘą░ą┐ąĖčüčī |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

| ąØą░čć. ąĘąĮą░č湥ąĮąĖąĄ |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

| ąæąĖčé

|

ąśą╝čÅ

|

ą×ą┐ąĖčüą░ąĮąĖąĄ

|

| 7 |

CLK2_PDN

|

Clock 2 Power Down. ąæąĖčé ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą▓čŗą║ą╗čÄčćąĖčéčī ą┐ąĖčéą░ąĮąĖąĄ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ ą┤čĆą░ą╣ą▓ąĄčĆą░ CLK2, ą║ąŠą│ą┤ą░ čŹč鹊čé ą▓čŗčģąŠą┤ čéą░ą║č鹊ą▓ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ.

0: CLK2 čĆą░ą▒ąŠčéą░ąĄčé.

1: CLK2 ą▓čŗą║ą╗čÄč湥ąĮ.

|

| 6 |

MS2_INT

|

MultiSynth 2 Integer Mode. ąŁč鹊čé ą▒ąĖčé ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą┐čĆąĖąĮčāą┤ąĖč鹥ą╗čīąĮąŠą│ąŠ ą┐ąĄčĆąĄą▓ąŠą┤ą░ MS2 ą▓ čåąĄą╗ąŠčćąĖčüą╗ąĄąĮąĮčŗą╣ čĆąĄąČąĖą╝ ą┤ąĄą╗ąĖč鹥ą╗ąĄą╣, čćč鹊ą▒čŗ čāą╗čāčćčłąĖčéčī ą┐ą░čĆą░ą╝ąĄčéčĆčŗ ą┐ąŠ ą┤ąČąĖčéč鹥čĆčā. ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┤čĆąŠą▒ąĮčŗą╣ čĆąĄąČąĖą╝ ą┤ąĄą╗ąĖč鹥ą╗ąĄą╣ (fractional mode), ą║ąŠą│ą┤ą░ ą┤ą╗čÅ CLK2 čāą║ą░ąĘą░ąĮąŠ čüą╝ąĄčēąĄąĮąĖąĄ ąĘą░ą┤ąĄčƹȹ║ąĖ.

0: MS2 čĆą░ą▒ąŠčéą░ąĄčé čü čĆąĄąČąĖą╝ąĄ čü ą┤čĆąŠą▒ąĮčŗą╝ąĖ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéą░ą╝ąĖ ą┤ąĄą╗ąĄąĮąĖčÅ.

1: MS2 čĆą░ą▒ąŠčéą░ąĄčé ą▓ čĆąĄąČąĖą╝ąĄ čü čåąĄą╗ąŠčćąĖčüą╗ąĄąĮąĮčŗą╝ąĖ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéą░ą╝ąĖ ą┤ąĄą╗ąĄąĮąĖčÅ.

|

| 5 |

MS2_SRC

|

MultiSynth Source Select for CLK2.

0: MS2 čéą░ą║čéąĖčĆčāąĄčéčüčÅ ąŠčé PLLA.

1: MS2 čéą░ą║čéąĖčĆčāąĄčéčüčÅ ąŠčé PLLB (č鹊ą╗čīą║ąŠ Si5351A ąĖ Si5351C) ąĖą╗ąĖ ąŠčé VCXO (č鹊ą╗čīą║ąŠ Si5351B).

|

| 4 |

CLK2_INV

|

Output Clock 2 Invert.

0: ąĮąĄčé ąĖąĮą▓ąĄčĆčüąĖąĖ ąĮą░ ą▓čŗčģąŠą┤ąĄ CLK2.

1: CLK2 ą▓čŗą▓ąŠą┤ąĖčéčüčÅ čü ąĖąĮą▓ąĄčĆčüąĖąĄą╣.

|

| 3:2 |

CLK2_SRC[1:0]

|

Output Clock 2 Input Source. ąŁčéąĖ ą▒ąĖčéčŗ ą▓čŗą▒ąĖčĆą░čÄčé ąĖčüč鹊čćąĮąĖą║ čéą░ą║č鹊ą▓ ą┤ą╗čÅ CLK2.

00: ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓ ą▓čŗą▒čĆą░ąĮ XTAL. ąŁčéą░ ąŠą┐čåąĖčÅ ą┐čĆąŠą┐čāčüą║ą░ąĄčé ąŠą▒ą░ ą║ą░čüą║ą░ą┤ą░ čüąĖąĮč鹥ąĘą░ (PLL/VCXO ąĖ MultiSynth), ąĖ ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčé CLK2 ąĮą░ą┐čĆčÅą╝čāčÄ ą║ ą│ąĄąĮąĄčĆą░č鹊čĆčā, ą║ąŠč鹊čĆčŗą╣ č乊čĆą╝ąĖčĆčāąĄčé ą▓čŗčģąŠą┤ąĮčāčÄ čćą░čüč鹊čéčā, ąŠą┐čĆąĄą┤ąĄą╗čÅąĄą╝čāčÄ čćą░čüč鹊č鹊ą╣ XTAL.

01: ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓ ą▓čŗą▒čĆą░ąĮ CLKIN. ąŁčéą░ ąŠą┐čåąĖčÅ ą┐čĆąŠą┐čāčüą║ą░ąĄčé ąŠą▒ą░ ą║ą░čüą║ą░ą┤ą░ čüąĖąĮč鹥ąĘą░ (PLL/VCXO ąĖ MultiSynth), ąĖ ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčé CLK2 ąĮą░ą┐čĆčÅą╝čāčÄ ą║ąŠ ą▓čģąŠą┤čā CLKIN. ąÆ čüčāčēąĮąŠčüčéąĖ čŹč鹊 ą┐čĆąŠčüč鹊 čüąŠąĘą┤ą░ąĄčé ą▒čāč乥čĆ ą┤ą╗čÅ ą▓čģąŠą┤ą░ CLKIN.

10: ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓ ą▓čŗą▒čĆą░ąĮ MultiSynth 0.

11: ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓ ą▓čŗą▒čĆą░ąĮ MultiSynth 2. ąÆčŗą▒ąĄčĆąĖč鹥 čŹčéčā ąŠą┐čåąĖčÄ, ą║ąŠą│ą┤ą░ čģąŠčéąĖč鹥 ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī Si5351 ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ č乊čĆą╝ąĖčĆčāąĄą╝čŗčģ (free-running) ąĖą╗ąĖ čüąĖąĮčģčĆąŠąĮąĮčŗčģ čéą░ą║č鹊ą▓čŗčģ čüąĖą│ąĮą░ą╗ąŠą▓.

|

| 1:0 |

CLK2_IDRV[1:0]

|

CLK2 Output Rise and Fall time / Drive Strength Control. ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ąĮą░ą│čĆčāąĘąŠčćąĮąŠą╣ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčīčÄ ą▓čŗčģąŠą┤ą░ CLK2.

00: 2 ą╝ąÉ.

01: 4 ą╝ąÉ.

10: 6 ą╝ąÉ.

11: 8 ą╝ąÉ.

|

19. ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ CLK3

| Ōä¢ čĆą░ąĘčĆčÅą┤ąŠą▓ |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| ąśą╝ąĄąĮą░ ą▒ąĖčé

|

CLK3_PDN

|

MS3_INT

|

MS3_SRC

|

CLK3_INV

|

CLK3_SRC[1:0]

|

CLK3_IDRV[1:0]

|

| ą¦č鹥ąĮąĖąĄ/ąĘą░ą┐ąĖčüčī |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

| ąØą░čć. ąĘąĮą░č湥ąĮąĖąĄ |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

| ąæąĖčé

|

ąśą╝čÅ

|

ą×ą┐ąĖčüą░ąĮąĖąĄ

|

| 7 |

CLK3_PDN

|

Clock 3 Power Down. ąæąĖčé ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą▓čŗą║ą╗čÄčćąĖčéčī ą┐ąĖčéą░ąĮąĖąĄ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ ą┤čĆą░ą╣ą▓ąĄčĆą░ CLK3, ą║ąŠą│ą┤ą░ čŹč鹊čé ą▓čŗčģąŠą┤ čéą░ą║č鹊ą▓ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ.

0: CLK3 čĆą░ą▒ąŠčéą░ąĄčé.

1: CLK3 ą▓čŗą║ą╗čÄč湥ąĮ.

|

| 6 |

MS3_INT

|

MultiSynth 3 Integer Mode. ąŁč鹊čé ą▒ąĖčé ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą┐čĆąĖąĮčāą┤ąĖč鹥ą╗čīąĮąŠą│ąŠ ą┐ąĄčĆąĄą▓ąŠą┤ą░ MS3 ą▓ čåąĄą╗ąŠčćąĖčüą╗ąĄąĮąĮčŗą╣ čĆąĄąČąĖą╝ ą┤ąĄą╗ąĖč鹥ą╗ąĄą╣, čćč鹊ą▒čŗ čāą╗čāčćčłąĖčéčī ą┐ą░čĆą░ą╝ąĄčéčĆčŗ ą┐ąŠ ą┤ąČąĖčéč鹥čĆčā. ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┤čĆąŠą▒ąĮčŗą╣ čĆąĄąČąĖą╝ ą┤ąĄą╗ąĖč鹥ą╗ąĄą╣ (fractional mode), ą║ąŠą│ą┤ą░ ą┤ą╗čÅ CLK3 čāą║ą░ąĘą░ąĮąŠ čüą╝ąĄčēąĄąĮąĖąĄ ąĘą░ą┤ąĄčƹȹ║ąĖ.

0: MS3 čĆą░ą▒ąŠčéą░ąĄčé čü čĆąĄąČąĖą╝ąĄ čü ą┤čĆąŠą▒ąĮčŗą╝ąĖ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéą░ą╝ąĖ ą┤ąĄą╗ąĄąĮąĖčÅ.

1: MS3 čĆą░ą▒ąŠčéą░ąĄčé ą▓ čĆąĄąČąĖą╝ąĄ čü čåąĄą╗ąŠčćąĖčüą╗ąĄąĮąĮčŗą╝ąĖ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéą░ą╝ąĖ ą┤ąĄą╗ąĄąĮąĖčÅ.

|

| 5 |

MS3_SRC

|

MultiSynth Source Select for CLK3.

0: MS3 čéą░ą║čéąĖčĆčāąĄčéčüčÅ ąŠčé PLLA.

1: MS3 čéą░ą║čéąĖčĆčāąĄčéčüčÅ ąŠčé PLLB (č鹊ą╗čīą║ąŠ Si5351A ąĖ Si5351C) ąĖą╗ąĖ ąŠčé VCXO (č鹊ą╗čīą║ąŠ Si5351B).

|

| 4 |

CLK3_INV

|

Output Clock 3 Invert.

0: ąĮąĄčé ąĖąĮą▓ąĄčĆčüąĖąĖ ąĮą░ ą▓čŗčģąŠą┤ąĄ CLK3.

1: CLK3 ą▓čŗą▓ąŠą┤ąĖčéčüčÅ čü ąĖąĮą▓ąĄčĆčüąĖąĄą╣.

|

| 3:2 |

CLK3_SRC[1:0]

|

Output Clock 3 Input Source. ąŁčéąĖ ą▒ąĖčéčŗ ą▓čŗą▒ąĖčĆą░čÄčé ąĖčüč鹊čćąĮąĖą║ čéą░ą║č鹊ą▓ ą┤ą╗čÅ CLK3.

00: ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓ ą▓čŗą▒čĆą░ąĮ XTAL. ąŁčéą░ ąŠą┐čåąĖčÅ ą┐čĆąŠą┐čāčüą║ą░ąĄčé ąŠą▒ą░ ą║ą░čüą║ą░ą┤ą░ čüąĖąĮč鹥ąĘą░ (PLL/VCXO ąĖ MultiSynth), ąĖ ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčé CLK3 ąĮą░ą┐čĆčÅą╝čāčÄ ą║ ą│ąĄąĮąĄčĆą░č鹊čĆčā, ą║ąŠč鹊čĆčŗą╣ č乊čĆą╝ąĖčĆčāąĄčé ą▓čŗčģąŠą┤ąĮčāčÄ čćą░čüč鹊čéčā, ąŠą┐čĆąĄą┤ąĄą╗čÅąĄą╝čāčÄ čćą░čüč鹊č鹊ą╣ XTAL.

01: ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓ ą▓čŗą▒čĆą░ąĮ CLKIN. ąŁčéą░ ąŠą┐čåąĖčÅ ą┐čĆąŠą┐čāčüą║ą░ąĄčé ąŠą▒ą░ ą║ą░čüą║ą░ą┤ą░ čüąĖąĮč鹥ąĘą░ (PLL/VCXO ąĖ MultiSynth), ąĖ ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčé CLK3 ąĮą░ą┐čĆčÅą╝čāčÄ ą║ąŠ ą▓čģąŠą┤čā CLKIN. ąÆ čüčāčēąĮąŠčüčéąĖ čŹč鹊 ą┐čĆąŠčüč鹊 čüąŠąĘą┤ą░ąĄčé ą▒čāč乥čĆ ą┤ą╗čÅ ą▓čģąŠą┤ą░ CLKIN.

10: ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓ ą▓čŗą▒čĆą░ąĮ MultiSynth 0.

11: ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓ ą▓čŗą▒čĆą░ąĮ MultiSynth 3. ąÆčŗą▒ąĄčĆąĖč鹥 čŹčéčā ąŠą┐čåąĖčÄ, ą║ąŠą│ą┤ą░ čģąŠčéąĖč鹥 ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī Si5351 ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ č乊čĆą╝ąĖčĆčāąĄą╝čŗčģ (free-running) ąĖą╗ąĖ čüąĖąĮčģčĆąŠąĮąĮčŗčģ čéą░ą║č鹊ą▓čŗčģ čüąĖą│ąĮą░ą╗ąŠą▓.

|

| 1:0 |

CLK3_IDRV[1:0]

|

CLK3 Output Rise and Fall time / Drive Strength Control. ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ąĮą░ą│čĆčāąĘąŠčćąĮąŠą╣ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčīčÄ ą▓čŗčģąŠą┤ą░ CLK3.

00: 2 ą╝ąÉ.

01: 4 ą╝ąÉ.

10: 6 ą╝ąÉ.

11: 8 ą╝ąÉ.

|

20. ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ CLK4

| Ōä¢ čĆą░ąĘčĆčÅą┤ąŠą▓ |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| ąśą╝ąĄąĮą░ ą▒ąĖčé

|

CLK4_PDN

|

MS4_INT

|

MS4_SRC

|

CLK4_INV

|

CLK4_SRC[1:0]

|

CLK4_IDRV[1:0]

|

| ą¦č鹥ąĮąĖąĄ/ąĘą░ą┐ąĖčüčī |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

| ąØą░čć. ąĘąĮą░č湥ąĮąĖąĄ |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

| ąæąĖčé

|

ąśą╝čÅ

|

ą×ą┐ąĖčüą░ąĮąĖąĄ

|

| 7 |

CLK4_PDN

|

Clock 4 Power Down. ąæąĖčé ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą▓čŗą║ą╗čÄčćąĖčéčī ą┐ąĖčéą░ąĮąĖąĄ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ ą┤čĆą░ą╣ą▓ąĄčĆą░ CLK4, ą║ąŠą│ą┤ą░ čŹč鹊čé ą▓čŗčģąŠą┤ čéą░ą║č鹊ą▓ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ.

0: CLK4 čĆą░ą▒ąŠčéą░ąĄčé.

1: CLK4 ą▓čŗą║ą╗čÄč湥ąĮ.

|

| 6 |

MS4_INT

|

MultiSynth 4 Integer Mode. ąŁč鹊čé ą▒ąĖčé ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą┐čĆąĖąĮčāą┤ąĖč鹥ą╗čīąĮąŠą│ąŠ ą┐ąĄčĆąĄą▓ąŠą┤ą░ MS4 ą▓ čåąĄą╗ąŠčćąĖčüą╗ąĄąĮąĮčŗą╣ čĆąĄąČąĖą╝ ą┤ąĄą╗ąĖč鹥ą╗ąĄą╣, čćč鹊ą▒čŗ čāą╗čāčćčłąĖčéčī ą┐ą░čĆą░ą╝ąĄčéčĆčŗ ą┐ąŠ ą┤ąČąĖčéč鹥čĆčā. ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┤čĆąŠą▒ąĮčŗą╣ čĆąĄąČąĖą╝ ą┤ąĄą╗ąĖč鹥ą╗ąĄą╣ (fractional mode), ą║ąŠą│ą┤ą░ ą┤ą╗čÅ CLK4 čāą║ą░ąĘą░ąĮąŠ čüą╝ąĄčēąĄąĮąĖąĄ ąĘą░ą┤ąĄčƹȹ║ąĖ.

0: MS4 čĆą░ą▒ąŠčéą░ąĄčé čü čĆąĄąČąĖą╝ąĄ čü ą┤čĆąŠą▒ąĮčŗą╝ąĖ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéą░ą╝ąĖ ą┤ąĄą╗ąĄąĮąĖčÅ.

1: MS4 čĆą░ą▒ąŠčéą░ąĄčé ą▓ čĆąĄąČąĖą╝ąĄ čü čåąĄą╗ąŠčćąĖčüą╗ąĄąĮąĮčŗą╝ąĖ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéą░ą╝ąĖ ą┤ąĄą╗ąĄąĮąĖčÅ.

|

| 5 |

MS4_SRC

|

MultiSynth Source Select for CLK4.

0: MS4 čéą░ą║čéąĖčĆčāąĄčéčüčÅ ąŠčé PLLA.

1: MS4 čéą░ą║čéąĖčĆčāąĄčéčüčÅ ąŠčé PLLB (č鹊ą╗čīą║ąŠ Si5351A ąĖ Si5351C) ąĖą╗ąĖ ąŠčé VCXO (č鹊ą╗čīą║ąŠ Si5351B).

|

| 4 |

CLK4_INV

|

Output Clock 4 Invert.

0: ąĮąĄčé ąĖąĮą▓ąĄčĆčüąĖąĖ ąĮą░ ą▓čŗčģąŠą┤ąĄ CLK4.

1: CLK4 ą▓čŗą▓ąŠą┤ąĖčéčüčÅ čü ąĖąĮą▓ąĄčĆčüąĖąĄą╣.

|

| 3:2 |

CLK4_SRC[1:0]

|

Output Clock 4 Input Source. ąŁčéąĖ ą▒ąĖčéčŗ ą▓čŗą▒ąĖčĆą░čÄčé ąĖčüč鹊čćąĮąĖą║ čéą░ą║č鹊ą▓ ą┤ą╗čÅ CLK4.

00: ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓ ą▓čŗą▒čĆą░ąĮ XTAL. ąŁčéą░ ąŠą┐čåąĖčÅ ą┐čĆąŠą┐čāčüą║ą░ąĄčé ąŠą▒ą░ ą║ą░čüą║ą░ą┤ą░ čüąĖąĮč鹥ąĘą░ (PLL/VCXO ąĖ MultiSynth), ąĖ ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčé CLK4 ąĮą░ą┐čĆčÅą╝čāčÄ ą║ ą│ąĄąĮąĄčĆą░č鹊čĆčā, ą║ąŠč鹊čĆčŗą╣ č乊čĆą╝ąĖčĆčāąĄčé ą▓čŗčģąŠą┤ąĮčāčÄ čćą░čüč鹊čéčā, ąŠą┐čĆąĄą┤ąĄą╗čÅąĄą╝čāčÄ čćą░čüč鹊č鹊ą╣ XTAL.

01: ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓ ą▓čŗą▒čĆą░ąĮ CLKIN. ąŁčéą░ ąŠą┐čåąĖčÅ ą┐čĆąŠą┐čāčüą║ą░ąĄčé ąŠą▒ą░ ą║ą░čüą║ą░ą┤ą░ čüąĖąĮč鹥ąĘą░ (PLL/VCXO ąĖ MultiSynth), ąĖ ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčé CLK4 ąĮą░ą┐čĆčÅą╝čāčÄ ą║ąŠ ą▓čģąŠą┤čā CLKIN. ąÆ čüčāčēąĮąŠčüčéąĖ čŹč鹊 ą┐čĆąŠčüč鹊 čüąŠąĘą┤ą░ąĄčé ą▒čāč乥čĆ ą┤ą╗čÅ ą▓čģąŠą┤ą░ CLKIN.

10: ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ, ąĮąĄ ą▓čŗą▒ąĖčĆą░ą╣č鹥 čŹč鹊čé ą▓ą░čĆąĖą░ąĮčé.

11: ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓ ą▓čŗą▒čĆą░ąĮ MultiSynth 4. ąÆčŗą▒ąĄčĆąĖč鹥 čŹčéčā ąŠą┐čåąĖčÄ, ą║ąŠą│ą┤ą░ čģąŠčéąĖč鹥 ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī Si5351 ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ č乊čĆą╝ąĖčĆčāąĄą╝čŗčģ (free-running) ąĖą╗ąĖ čüąĖąĮčģčĆąŠąĮąĮčŗčģ čéą░ą║č鹊ą▓čŗčģ čüąĖą│ąĮą░ą╗ąŠą▓.

|

| 1:0 |

CLK4_IDRV[1:0]

|

CLK4 Output Rise and Fall time / Drive Strength Control. ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ąĮą░ą│čĆčāąĘąŠčćąĮąŠą╣ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčīčÄ ą▓čŗčģąŠą┤ą░ CLK4.

00: 2 ą╝ąÉ.

01: 4 ą╝ąÉ.

10: 6 ą╝ąÉ.

11: 8 ą╝ąÉ.

|

21. ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ CLK5

| Ōä¢ čĆą░ąĘčĆčÅą┤ąŠą▓ |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| ąśą╝ąĄąĮą░ ą▒ąĖčé

|

CLK5_PDN

|

MS5_INT

|

MS5_SRC

|

CLK5_INV

|

CLK5_SRC[1:0]

|

CLK5_IDRV[1:0]

|

| ą¦č鹥ąĮąĖąĄ/ąĘą░ą┐ąĖčüčī |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

| ąØą░čć. ąĘąĮą░č湥ąĮąĖąĄ |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

| ąæąĖčé

|

ąśą╝čÅ

|

ą×ą┐ąĖčüą░ąĮąĖąĄ

|

| 7 |

CLK5_PDN

|

Clock 5 Power Down. ąæąĖčé ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą▓čŗą║ą╗čÄčćąĖčéčī ą┐ąĖčéą░ąĮąĖąĄ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ ą┤čĆą░ą╣ą▓ąĄčĆą░ CLK5, ą║ąŠą│ą┤ą░ čŹč鹊čé ą▓čŗčģąŠą┤ čéą░ą║č鹊ą▓ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ.

0: CLK5 čĆą░ą▒ąŠčéą░ąĄčé.

1: CLK5 ą▓čŗą║ą╗čÄč湥ąĮ.

|

| 6 |

MS5_INT

|

MultiSynth 5 Integer Mode. ąŁč鹊čé ą▒ąĖčé ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą┐čĆąĖąĮčāą┤ąĖč鹥ą╗čīąĮąŠą│ąŠ ą┐ąĄčĆąĄą▓ąŠą┤ą░ MS5 ą▓ čåąĄą╗ąŠčćąĖčüą╗ąĄąĮąĮčŗą╣ čĆąĄąČąĖą╝ ą┤ąĄą╗ąĖč鹥ą╗ąĄą╣, čćč鹊ą▒čŗ čāą╗čāčćčłąĖčéčī ą┐ą░čĆą░ą╝ąĄčéčĆčŗ ą┐ąŠ ą┤ąČąĖčéč鹥čĆčā. ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┤čĆąŠą▒ąĮčŗą╣ čĆąĄąČąĖą╝ ą┤ąĄą╗ąĖč鹥ą╗ąĄą╣ (fractional mode), ą║ąŠą│ą┤ą░ ą┤ą╗čÅ CLK5 čāą║ą░ąĘą░ąĮąŠ čüą╝ąĄčēąĄąĮąĖąĄ ąĘą░ą┤ąĄčƹȹ║ąĖ.

0: MS5 čĆą░ą▒ąŠčéą░ąĄčé čü čĆąĄąČąĖą╝ąĄ čü ą┤čĆąŠą▒ąĮčŗą╝ąĖ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéą░ą╝ąĖ ą┤ąĄą╗ąĄąĮąĖčÅ.

1: MS5 čĆą░ą▒ąŠčéą░ąĄčé ą▓ čĆąĄąČąĖą╝ąĄ čü čåąĄą╗ąŠčćąĖčüą╗ąĄąĮąĮčŗą╝ąĖ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéą░ą╝ąĖ ą┤ąĄą╗ąĄąĮąĖčÅ.

|

| 5 |

MS5_SRC

|

MultiSynth Source Select for CLK5.

0: MS5 čéą░ą║čéąĖčĆčāąĄčéčüčÅ ąŠčé PLLA.

1: MS5 čéą░ą║čéąĖčĆčāąĄčéčüčÅ ąŠčé PLLB (č鹊ą╗čīą║ąŠ Si5351A ąĖ Si5351C) ąĖą╗ąĖ ąŠčé VCXO (č鹊ą╗čīą║ąŠ Si5351B).

|

| 4 |

CLK5_INV

|

Output Clock 5 Invert.

0: ąĮąĄčé ąĖąĮą▓ąĄčĆčüąĖąĖ ąĮą░ ą▓čŗčģąŠą┤ąĄ CLK5.

1: CLK5 ą▓čŗą▓ąŠą┤ąĖčéčüčÅ čü ąĖąĮą▓ąĄčĆčüąĖąĄą╣.

|

| 3:2 |

CLK5_SRC[1:0]

|

Output Clock 5 Input Source. ąŁčéąĖ ą▒ąĖčéčŗ ą▓čŗą▒ąĖčĆą░čÄčé ąĖčüč鹊čćąĮąĖą║ čéą░ą║č鹊ą▓ ą┤ą╗čÅ CLK5.

00: ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓ ą▓čŗą▒čĆą░ąĮ XTAL. ąŁčéą░ ąŠą┐čåąĖčÅ ą┐čĆąŠą┐čāčüą║ą░ąĄčé ąŠą▒ą░ ą║ą░čüą║ą░ą┤ą░ čüąĖąĮč鹥ąĘą░ (PLL/VCXO ąĖ MultiSynth), ąĖ ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčé CLK5 ąĮą░ą┐čĆčÅą╝čāčÄ ą║ ą│ąĄąĮąĄčĆą░č鹊čĆčā, ą║ąŠč鹊čĆčŗą╣ č乊čĆą╝ąĖčĆčāąĄčé ą▓čŗčģąŠą┤ąĮčāčÄ čćą░čüč鹊čéčā, ąŠą┐čĆąĄą┤ąĄą╗čÅąĄą╝čāčÄ čćą░čüč鹊č鹊ą╣ XTAL.

01: ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓ ą▓čŗą▒čĆą░ąĮ CLKIN. ąŁčéą░ ąŠą┐čåąĖčÅ ą┐čĆąŠą┐čāčüą║ą░ąĄčé ąŠą▒ą░ ą║ą░čüą║ą░ą┤ą░ čüąĖąĮč鹥ąĘą░ (PLL/VCXO ąĖ MultiSynth), ąĖ ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčé CLK5 ąĮą░ą┐čĆčÅą╝čāčÄ ą║ąŠ ą▓čģąŠą┤čā CLKIN. ąÆ čüčāčēąĮąŠčüčéąĖ čŹč鹊 ą┐čĆąŠčüč鹊 čüąŠąĘą┤ą░ąĄčé ą▒čāč乥čĆ ą┤ą╗čÅ ą▓čģąŠą┤ą░ CLKIN.

10: ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓ ą▓čŗą▒čĆą░ąĮ MultiSynth 4.

11: ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓ ą▓čŗą▒čĆą░ąĮ MultiSynth 5. ąÆčŗą▒ąĄčĆąĖč鹥 čŹčéčā ąŠą┐čåąĖčÄ, ą║ąŠą│ą┤ą░ čģąŠčéąĖč鹥 ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī Si5351 ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ č乊čĆą╝ąĖčĆčāąĄą╝čŗčģ (free-running) ąĖą╗ąĖ čüąĖąĮčģčĆąŠąĮąĮčŗčģ čéą░ą║č鹊ą▓čŗčģ čüąĖą│ąĮą░ą╗ąŠą▓.

|

| 1:0 |

CLK5_IDRV[1:0]

|

CLK5 Output Rise and Fall time / Drive Strength Control. ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ąĮą░ą│čĆčāąĘąŠčćąĮąŠą╣ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčīčÄ ą▓čŗčģąŠą┤ą░ CLK5.

00: 2 ą╝ąÉ.

01: 4 ą╝ąÉ.

10: 6 ą╝ąÉ.

11: 8 ą╝ąÉ.

|

22. ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ CLK6

| Ōä¢ čĆą░ąĘčĆčÅą┤ąŠą▓ |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| ąśą╝ąĄąĮą░ ą▒ąĖčé

|

CLK6_PDN

|

MS6_INT

|

MS6_SRC

|

CLK6_INV

|

CLK6_SRC[1:0]

|

CLK6_IDRV[1:0]

|

| ą¦č鹥ąĮąĖąĄ/ąĘą░ą┐ąĖčüčī |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

| ąØą░čć. ąĘąĮą░č湥ąĮąĖąĄ |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

| ąæąĖčé

|

ąśą╝čÅ

|

ą×ą┐ąĖčüą░ąĮąĖąĄ

|

| 7 |

CLK6_PDN

|

Clock 6 Power Down. ąæąĖčé ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą▓čŗą║ą╗čÄčćąĖčéčī ą┐ąĖčéą░ąĮąĖąĄ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ ą┤čĆą░ą╣ą▓ąĄčĆą░ CLK6, ą║ąŠą│ą┤ą░ čŹč鹊čé ą▓čŗčģąŠą┤ čéą░ą║č鹊ą▓ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ.

0: CLK6 čĆą░ą▒ąŠčéą░ąĄčé.

1: CLK6 ą▓čŗą║ą╗čÄč湥ąĮ.

|

| 6 |

MS6_INT

|

MultiSynth 6 Integer Mode. ąŁč鹊čé ą▒ąĖčé ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą┐čĆąĖąĮčāą┤ąĖč鹥ą╗čīąĮąŠą│ąŠ ą┐ąĄčĆąĄą▓ąŠą┤ą░ MS6 ą▓ čåąĄą╗ąŠčćąĖčüą╗ąĄąĮąĮčŗą╣ čĆąĄąČąĖą╝ ą┤ąĄą╗ąĖč鹥ą╗ąĄą╣, čćč鹊ą▒čŗ čāą╗čāčćčłąĖčéčī ą┐ą░čĆą░ą╝ąĄčéčĆčŗ ą┐ąŠ ą┤ąČąĖčéč鹥čĆčā. ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┤čĆąŠą▒ąĮčŗą╣ čĆąĄąČąĖą╝ ą┤ąĄą╗ąĖč鹥ą╗ąĄą╣ (fractional mode), ą║ąŠą│ą┤ą░ ą┤ą╗čÅ CLK6 čāą║ą░ąĘą░ąĮąŠ čüą╝ąĄčēąĄąĮąĖąĄ ąĘą░ą┤ąĄčƹȹ║ąĖ.

0: MS6 čĆą░ą▒ąŠčéą░ąĄčé čü čĆąĄąČąĖą╝ąĄ čü ą┤čĆąŠą▒ąĮčŗą╝ąĖ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéą░ą╝ąĖ ą┤ąĄą╗ąĄąĮąĖčÅ.

1: MS6 čĆą░ą▒ąŠčéą░ąĄčé ą▓ čĆąĄąČąĖą╝ąĄ čü čåąĄą╗ąŠčćąĖčüą╗ąĄąĮąĮčŗą╝ąĖ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéą░ą╝ąĖ ą┤ąĄą╗ąĄąĮąĖčÅ.

|

| 5 |

MS6_SRC

|

MultiSynth Source Select for CLK6.

0: MS6 čéą░ą║čéąĖčĆčāąĄčéčüčÅ ąŠčé PLLA.

1: MS6 čéą░ą║čéąĖčĆčāąĄčéčüčÅ ąŠčé PLLB (č鹊ą╗čīą║ąŠ Si5351A ąĖ Si5351C) ąĖą╗ąĖ ąŠčé VCXO (č鹊ą╗čīą║ąŠ Si5351B).

|

| 4 |

CLK6_INV

|

Output Clock 6 Invert.

0: ąĮąĄčé ąĖąĮą▓ąĄčĆčüąĖąĖ ąĮą░ ą▓čŗčģąŠą┤ąĄ CLK6.

1: CLK6 ą▓čŗą▓ąŠą┤ąĖčéčüčÅ čü ąĖąĮą▓ąĄčĆčüąĖąĄą╣.

|

| 3:2 |

CLK6_SRC[1:0]

|

Output Clock 6 Input Source. ąŁčéąĖ ą▒ąĖčéčŗ ą▓čŗą▒ąĖčĆą░čÄčé ąĖčüč鹊čćąĮąĖą║ čéą░ą║č鹊ą▓ ą┤ą╗čÅ CLK6.

00: ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓ ą▓čŗą▒čĆą░ąĮ XTAL. ąŁčéą░ ąŠą┐čåąĖčÅ ą┐čĆąŠą┐čāčüą║ą░ąĄčé ąŠą▒ą░ ą║ą░čüą║ą░ą┤ą░ čüąĖąĮč鹥ąĘą░ (PLL/VCXO ąĖ MultiSynth), ąĖ ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčé CLK6 ąĮą░ą┐čĆčÅą╝čāčÄ ą║ ą│ąĄąĮąĄčĆą░č鹊čĆčā, ą║ąŠč鹊čĆčŗą╣ č乊čĆą╝ąĖčĆčāąĄčé ą▓čŗčģąŠą┤ąĮčāčÄ čćą░čüč鹊čéčā, ąŠą┐čĆąĄą┤ąĄą╗čÅąĄą╝čāčÄ čćą░čüč鹊č鹊ą╣ XTAL.

01: ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓ ą▓čŗą▒čĆą░ąĮ CLKIN. ąŁčéą░ ąŠą┐čåąĖčÅ ą┐čĆąŠą┐čāčüą║ą░ąĄčé ąŠą▒ą░ ą║ą░čüą║ą░ą┤ą░ čüąĖąĮč鹥ąĘą░ (PLL/VCXO ąĖ MultiSynth), ąĖ ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčé CLK6 ąĮą░ą┐čĆčÅą╝čāčÄ ą║ąŠ ą▓čģąŠą┤čā CLKIN. ąÆ čüčāčēąĮąŠčüčéąĖ čŹč鹊 ą┐čĆąŠčüč鹊 čüąŠąĘą┤ą░ąĄčé ą▒čāč乥čĆ ą┤ą╗čÅ ą▓čģąŠą┤ą░ CLKIN.

10: ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓ ą▓čŗą▒čĆą░ąĮ MultiSynth 4.

11: ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓ ą▓čŗą▒čĆą░ąĮ MultiSynth 6. ąÆčŗą▒ąĄčĆąĖč鹥 čŹčéčā ąŠą┐čåąĖčÄ, ą║ąŠą│ą┤ą░ čģąŠčéąĖč鹥 ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī Si5351 ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ č乊čĆą╝ąĖčĆčāąĄą╝čŗčģ (free-running) ąĖą╗ąĖ čüąĖąĮčģčĆąŠąĮąĮčŗčģ čéą░ą║č鹊ą▓čŗčģ čüąĖą│ąĮą░ą╗ąŠą▓.

|

| 1:0 |

CLK6_IDRV[1:0]

|

CLK6 Output Rise and Fall time / Drive Strength Control. ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ąĮą░ą│čĆčāąĘąŠčćąĮąŠą╣ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčīčÄ ą▓čŗčģąŠą┤ą░ CLK6.

00: 2 ą╝ąÉ.

01: 4 ą╝ąÉ.

10: 6 ą╝ąÉ.

11: 8 ą╝ąÉ.

|

23. ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ CLK7

| Ōä¢ čĆą░ąĘčĆčÅą┤ąŠą▓ |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| ąśą╝ąĄąĮą░ ą▒ąĖčé

|

CLK7_PDN

|

MS7_INT

|

MS7_SRC

|

CLK7_INV

|

CLK7_SRC[1:0]

|

CLK7_IDRV[1:0]

|

| ą¦č鹥ąĮąĖąĄ/ąĘą░ą┐ąĖčüčī |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

| ąØą░čć. ąĘąĮą░č湥ąĮąĖąĄ |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

| ąæąĖčé

|

ąśą╝čÅ

|

ą×ą┐ąĖčüą░ąĮąĖąĄ

|

| 7 |

CLK7_PDN

|

Clock 7 Power Down. ąæąĖčé ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą▓čŗą║ą╗čÄčćąĖčéčī ą┐ąĖčéą░ąĮąĖąĄ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ ą┤čĆą░ą╣ą▓ąĄčĆą░ CLK7, ą║ąŠą│ą┤ą░ čŹč鹊čé ą▓čŗčģąŠą┤ čéą░ą║č鹊ą▓ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ.

0: CLK7 čĆą░ą▒ąŠčéą░ąĄčé.

1: CLK7 ą▓čŗą║ą╗čÄč湥ąĮ.

|

| 6 |

MS7_INT

|

MultiSynth 7 Integer Mode. ąŁč鹊čé ą▒ąĖčé ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ą┐čĆąĖąĮčāą┤ąĖč鹥ą╗čīąĮąŠą│ąŠ ą┐ąĄčĆąĄą▓ąŠą┤ą░ MS7 ą▓ čåąĄą╗ąŠčćąĖčüą╗ąĄąĮąĮčŗą╣ čĆąĄąČąĖą╝ ą┤ąĄą╗ąĖč鹥ą╗ąĄą╣, čćč鹊ą▒čŗ čāą╗čāčćčłąĖčéčī ą┐ą░čĆą░ą╝ąĄčéčĆčŗ ą┐ąŠ ą┤ąČąĖčéč鹥čĆčā. ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┤čĆąŠą▒ąĮčŗą╣ čĆąĄąČąĖą╝ ą┤ąĄą╗ąĖč鹥ą╗ąĄą╣ (fractional mode), ą║ąŠą│ą┤ą░ ą┤ą╗čÅ CLK7 čāą║ą░ąĘą░ąĮąŠ čüą╝ąĄčēąĄąĮąĖąĄ ąĘą░ą┤ąĄčƹȹ║ąĖ.

0: MS7 čĆą░ą▒ąŠčéą░ąĄčé čü čĆąĄąČąĖą╝ąĄ čü ą┤čĆąŠą▒ąĮčŗą╝ąĖ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéą░ą╝ąĖ ą┤ąĄą╗ąĄąĮąĖčÅ.

1: MS7 čĆą░ą▒ąŠčéą░ąĄčé ą▓ čĆąĄąČąĖą╝ąĄ čü čåąĄą╗ąŠčćąĖčüą╗ąĄąĮąĮčŗą╝ąĖ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéą░ą╝ąĖ ą┤ąĄą╗ąĄąĮąĖčÅ.

|

| 5 |

MS7_SRC

|

MultiSynth Source Select for CLK7.

0: MS7 čéą░ą║čéąĖčĆčāąĄčéčüčÅ ąŠčé PLLA.

1: MS7 čéą░ą║čéąĖčĆčāąĄčéčüčÅ ąŠčé PLLB (č鹊ą╗čīą║ąŠ Si5351A ąĖ Si5351C) ąĖą╗ąĖ ąŠčé VCXO (č鹊ą╗čīą║ąŠ Si5351B).

|

| 4 |

CLK7_INV

|

Output Clock 7 Invert.

0: ąĮąĄčé ąĖąĮą▓ąĄčĆčüąĖąĖ ąĮą░ ą▓čŗčģąŠą┤ąĄ CLK7.

1: CLK7 ą▓čŗą▓ąŠą┤ąĖčéčüčÅ čü ąĖąĮą▓ąĄčĆčüąĖąĄą╣.

|

| 3:2 |

CLK7_SRC[1:0]

|

Output Clock 7 Input Source. ąŁčéąĖ ą▒ąĖčéčŗ ą▓čŗą▒ąĖčĆą░čÄčé ąĖčüč鹊čćąĮąĖą║ čéą░ą║č鹊ą▓ ą┤ą╗čÅ CLK7.

00: ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓ ą▓čŗą▒čĆą░ąĮ XTAL. ąŁčéą░ ąŠą┐čåąĖčÅ ą┐čĆąŠą┐čāčüą║ą░ąĄčé ąŠą▒ą░ ą║ą░čüą║ą░ą┤ą░ čüąĖąĮč鹥ąĘą░ (PLL/VCXO ąĖ MultiSynth), ąĖ ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčé CLK7 ąĮą░ą┐čĆčÅą╝čāčÄ ą║ ą│ąĄąĮąĄčĆą░č鹊čĆčā, ą║ąŠč鹊čĆčŗą╣ č乊čĆą╝ąĖčĆčāąĄčé ą▓čŗčģąŠą┤ąĮčāčÄ čćą░čüč鹊čéčā, ąŠą┐čĆąĄą┤ąĄą╗čÅąĄą╝čāčÄ čćą░čüč鹊č鹊ą╣ XTAL.

01: ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓ ą▓čŗą▒čĆą░ąĮ CLKIN. ąŁčéą░ ąŠą┐čåąĖčÅ ą┐čĆąŠą┐čāčüą║ą░ąĄčé ąŠą▒ą░ ą║ą░čüą║ą░ą┤ą░ čüąĖąĮč鹥ąĘą░ (PLL/VCXO ąĖ MultiSynth), ąĖ ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčé CLK7 ąĮą░ą┐čĆčÅą╝čāčÄ ą║ąŠ ą▓čģąŠą┤čā CLKIN. ąÆ čüčāčēąĮąŠčüčéąĖ čŹč鹊 ą┐čĆąŠčüč鹊 čüąŠąĘą┤ą░ąĄčé ą▒čāč乥čĆ ą┤ą╗čÅ ą▓čģąŠą┤ą░ CLKIN.

10: ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓ ą▓čŗą▒čĆą░ąĮ MultiSynth 4.

11: ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║č鹊ą▓ ą▓čŗą▒čĆą░ąĮ MultiSynth 7. ąÆčŗą▒ąĄčĆąĖč鹥 čŹčéčā ąŠą┐čåąĖčÄ, ą║ąŠą│ą┤ą░ čģąŠčéąĖč鹥 ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī Si5351 ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ č乊čĆą╝ąĖčĆčāąĄą╝čŗčģ (free-running) ąĖą╗ąĖ čüąĖąĮčģčĆąŠąĮąĮčŗčģ čéą░ą║č鹊ą▓čŗčģ čüąĖą│ąĮą░ą╗ąŠą▓.

|

| 1:0 |

CLK7_IDRV[1:0]

|

CLK7 Output Rise and Fall time / Drive Strength Control. ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ąĮą░ą│čĆčāąĘąŠčćąĮąŠą╣ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčīčÄ ą▓čŗčģąŠą┤ą░ CLK7.

00: 2 ą╝ąÉ.

01: 4 ą╝ąÉ.

10: 6 ą╝ąÉ.

11: 8 ą╝ąÉ.

|

| Ōä¢ čĆą░ąĘčĆčÅą┤ąŠą▓ |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| ąśą╝ąĄąĮą░ ą▒ąĖčé

|

CLK3_DIS_STATE

|

CLK2_DIS_STATE

|

CLK1_DIS_STATE

|

CLK0_DIS_STATE

|

| ą¦č鹥ąĮąĖąĄ/ąĘą░ą┐ąĖčüčī |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

| ąØą░čć. ąĘąĮą░č湥ąĮąĖąĄ |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

| ąæąĖčé

|

ąśą╝čÅ

|

ą×ą┐ąĖčüą░ąĮąĖąĄ

|

| 7:0 |

CLKx_DIS_STATE

|

CLKx Disable State. ąŁčéąĖ 2 ą▒ąĖčéą░ ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčé čüąŠčüč鹊čÅąĮąĖąĄ ą▓čŗčģąŠą┤ą░ CLKx (x = 0..3), ą║ąŠą│ą┤ą░ ą▓čŗčģąŠą┤ ąĘą░ą┐čĆąĄčēąĄąĮ. ą×čéą┤ąĄą╗čīąĮčŗąĄ čéą░ą║č鹊ą▓čŗąĄ ą▓čŗčģąŠą┤čŗ ą╝ąŠą│čāčé ą▒čŗčéčī ąĘą░ą┐čĆąĄčēąĄąĮčŗ čü ą┐ąŠą╝ąŠčēčīčÄ čĆąĄą│ąĖčüčéčĆą░ čü ą░ą┤čĆąĄčüąŠą╝ 3 (Output Enable Control). ąóą░ą║ąČąĄ ą▓čŗčģąŠą┤čŗ ą╝ąŠą│čāčé ą▒čŗčéčī ąĘą░ą┐čĆąĄčēąĄąĮčŗ čü ą┐ąŠą╝ąŠčēčīčÄ ą▓čŗą▓ąŠą┤ą░ OEB.

00: ą║ąŠą│ą┤ą░ ą▓čŗčģąŠą┤ čéą░ą║č鹊ą▓ ąĘą░ą┐čĆąĄčēąĄąĮ, ąŠąĮ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą╗ąŠą│. 0.

01: ą║ąŠą│ą┤ą░ ą▓čŗčģąŠą┤ čéą░ą║č鹊ą▓ ąĘą░ą┐čĆąĄčēąĄąĮ, ąŠąĮ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą╗ąŠą│. 1.

10: ą║ąŠą│ą┤ą░ ą▓čŗčģąŠą┤ čéą░ą║č鹊ą▓ ąĘą░ą┐čĆąĄčēąĄąĮ, ąŠąĮ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ąŠčéą║ą╗čÄč湥ąĮąĮąŠą╝ čüąŠčüč鹊čÅąĮąĖąĖ (čéčĆąĄčéčīąĄ čüąŠčüč鹊čÅąĮąĖąĄ, čüąŠčüč鹊čÅąĮąĖąĄ ą▓čŗčüąŠą║ąŠą│ąŠ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖčÅ, Hi-Z).

11: ą▓čŗčģąŠą┤ čéą░ą║č鹊ą▓ ąĮąĖą║ąŠą│ą┤ą░ ąĮąĄ ąĘą░ą┐čĆąĄčēą░ąĄčéčüčÅ.

|

| Ōä¢ čĆą░ąĘčĆčÅą┤ąŠą▓ |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| ąśą╝ąĄąĮą░ ą▒ąĖčé

|

CLK7_DIS_STATE

|

CLK6_DIS_STATE

|

CLK5_DIS_STATE

|

CLK4_DIS_STATE

|

| ą¦č鹥ąĮąĖąĄ/ąĘą░ą┐ąĖčüčī |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

| ąØą░čć. ąĘąĮą░č湥ąĮąĖąĄ |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

| ąæąĖčé

|

ąśą╝čÅ

|

ą×ą┐ąĖčüą░ąĮąĖąĄ

|

| 7:0 |

CLKx_DIS_STATE

|

CLKx Disable State. ąŁčéąĖ 2 ą▒ąĖčéą░ ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčé čüąŠčüč鹊čÅąĮąĖąĄ ą▓čŗčģąŠą┤ą░ CLKx (x = 4..7), ą║ąŠą│ą┤ą░ ą▓čŗčģąŠą┤ ąĘą░ą┐čĆąĄčēąĄąĮ. ą×čéą┤ąĄą╗čīąĮčŗąĄ čéą░ą║č鹊ą▓čŗąĄ ą▓čŗčģąŠą┤čŗ ą╝ąŠą│čāčé ą▒čŗčéčī ąĘą░ą┐čĆąĄčēąĄąĮčŗ čü ą┐ąŠą╝ąŠčēčīčÄ čĆąĄą│ąĖčüčéčĆą░ čü ą░ą┤čĆąĄčüąŠą╝ 3 (Output Enable Control). ąóą░ą║ąČąĄ ą▓čŗčģąŠą┤čŗ ą╝ąŠą│čāčé ą▒čŗčéčī ąĘą░ą┐čĆąĄčēąĄąĮčŗ čü ą┐ąŠą╝ąŠčēčīčÄ ą▓čŗą▓ąŠą┤ą░ OEB.

00: ą║ąŠą│ą┤ą░ ą▓čŗčģąŠą┤ čéą░ą║č鹊ą▓ ąĘą░ą┐čĆąĄčēąĄąĮ, ąŠąĮ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą╗ąŠą│. 0.

01: ą║ąŠą│ą┤ą░ ą▓čŗčģąŠą┤ čéą░ą║č鹊ą▓ ąĘą░ą┐čĆąĄčēąĄąĮ, ąŠąĮ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą╗ąŠą│. 1.

10: ą║ąŠą│ą┤ą░ ą▓čŗčģąŠą┤ čéą░ą║č鹊ą▓ ąĘą░ą┐čĆąĄčēąĄąĮ, ąŠąĮ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ąŠčéą║ą╗čÄč湥ąĮąĮąŠą╝ čüąŠčüč鹊čÅąĮąĖąĖ (čéčĆąĄčéčīąĄ čüąŠčüč鹊čÅąĮąĖąĄ, čüąŠčüč鹊čÅąĮąĖąĄ ą▓čŗčüąŠą║ąŠą│ąŠ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖčÅ, Hi-Z).

11: ą▓čŗčģąŠą┤ čéą░ą║č鹊ą▓ ąĮąĖą║ąŠą│ą┤ą░ ąĮąĄ ąĘą░ą┐čĆąĄčēą░ąĄčéčüčÅ.

|

26. MSNA_P3[15:8]

| Ōä¢ čĆą░ąĘčĆčÅą┤ąŠą▓ |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| ąśą╝ąĄąĮą░ ą▒ąĖčé

|

MSNA_P3[15:8]

|

| ą¦č鹥ąĮąĖąĄ/ąĘą░ą┐ąĖčüčī |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

| ąØą░čć. ąĘąĮą░č湥ąĮąĖąĄ |

x |

x |

x |

x |

x |

x |

x |

x |

| ąæąĖčé

|

ąśą╝čÅ

|

ą×ą┐ąĖčüą░ąĮąĖąĄ

|

| 7:0 |

MSNA_P3[15:8]

|

Multisynth NA Parameter 3. ą¦ą░čüčéčī 20-ą▒ąĖčéąĮąŠą│ąŠ čćąĖčüą╗ą░, ą║ąŠą┤ąĖčĆčāčÄčēąĄą│ąŠ ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮąĖąĄ ąĘąĮą░ą╝ąĄąĮą░č鹥ą╗čÅ ą┤čĆąŠą▒ąĮąŠą╣ čćą░čüčéąĖ ą┤ąĄą╗ąĖč鹥ą╗čÅ čćą░čüč鹊čéčŗ ąŠą▒čĆą░čéąĮąŠą╣ čüą▓čÅąĘąĖ PLLA (Feedback Multisynth Divider).

|

27. MSNA_P3[7:0]

| Ōä¢ čĆą░ąĘčĆčÅą┤ąŠą▓ |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| ąśą╝ąĄąĮą░ ą▒ąĖčé

|

MSNA_P3[7:0]

|

| ą¦č鹥ąĮąĖąĄ/ąĘą░ą┐ąĖčüčī |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

| ąØą░čć. ąĘąĮą░č湥ąĮąĖąĄ |

x |

x |

x |

x |

x |

x |

x |

x |

| ąæąĖčé

|

ąśą╝čÅ

|

ą×ą┐ąĖčüą░ąĮąĖąĄ

|

| 7:0 |

MSNA_P3[7:0]