|

ą£ąĖą║čĆąŠčüčģąĄą╝ą░ ą░ąĮą░ą╗ąŠą│ąŠ-čåąĖčäčĆąŠą▓ąŠą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░č鹥ą╗čÅ AD7680 ą║ąŠą╝ą┐ą░ąĮąĖąĖ Analog Devices ąŠą▒ą╗ą░ą┤ą░ąĄčé čüą╗ąĄą┤čāčÄčēąĖą╝ąĖ ąŠčüąĮąŠą▓ąĮčŗą╝ąĖ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčÅą╝ąĖ:

ŌĆó ąĪą║ąŠčĆąŠčüčéčī ąŠčåąĖčäčĆąŠą▓ą║ąĖ 100 kSPS (100 čéčŗčüčÅčć ą▓čŗą▒ąŠčĆąŠą║/čüąĄą║), 16 ą▒ąĖčé ąĮą░ ą▓čŗą▒ąŠčĆą║čā

ŌĆó ą£ąŠąČąĄčé čĆą░ą▒ąŠčéą░čéčī ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖą╣ ą┐ąĖčéą░ąĮąĖčÅ VDD ąŠčé 2.5V ą┤ąŠ 5.5V

ŌĆó ą¤ąŠčéčĆąĄą▒ą╗čÅąĄčé ąĮąĄą▒ąŠą╗čīčłąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ 菹ĮąĄčĆą│ąĖąĖ:

3 ą╝ąÆčé ąĮą░ čćą░čüč鹊č鹥 ąŠą┐čĆąŠčüą░ 100 kSPS ąĖ ą┐ąĖčéą░ąĮąĖąĖ 2.5V

3.9 ą╝ąÆčé ąĮą░ čćą░čüč鹊č鹥 ąŠą┐čĆąŠčüą░ 100 kSPS ąĖ ą┐ąĖčéą░ąĮąĖąĖ 3V

16.7 ą╝ąÆčé ąĮą░ čćą░čüč鹊č鹥 ąŠą┐čĆąŠčüą░ 100 kSPS ąĖ ą┐ąĖčéą░ąĮąĖąĖ 5V

ąÆ čĆąĄąČąĖą╝ąĄ Standby ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠąĄ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ 0.5╬╝A

ŌĆó ą©ąĖčĆąŠą║ą░čÅ ą▓čģąŠą┤ąĮą░čÅ ą┐ąŠą╗ąŠčüą░ čćą░čüč鹊čé: ąŠčéąĮąŠčłąĄąĮąĖąĄ čüąĖą│ąĮą░ą╗/čłčāą╝ (SNR) 86 dB ąĮą░ ą▓čģąŠą┤ąĮąŠą╣ čćą░čüč鹊č鹥 10 ą║ąōčå

ŌĆó ąōąĖą▒ą║ąŠąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖąĄą╝ / čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊č鹊ą╣

ŌĆó ą×čéčüčāčéčüčéą▓ąĖąĄ ąĘą░ą┤ąĄčƹȹ║ąĖ ą║ąŠąĮą▓ąĄą╣ąĄčĆąĖąĘą░čåąĖąĖ

ŌĆó ąÆčŗčüąŠą║ąŠčüą║ąŠčĆąŠčüčéąĮąŠą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü (čüąŠą▓ą╝ąĄčüčéąĖą╝čŗą╣ čü SPI┬«/QSPIŌäó/╬╝Wire/DSP)

ŌĆó ą¤ąŠčüčéą░ą▓ą╗čÅąĄčéčüčÅ ą▓ 6-ą▓čŗą▓ąŠą┤ąĮąŠą╝ ą║ąŠčĆą┐čāčüąĄ SOT-23 ąĖ 8-ą▓čŗą▓ąŠą┤ąĮąŠą╝ ą║ąŠčĆą┐čāčüąĄ MSOP

ą×čüąĮąŠą▓ąĮąŠąĄ ą┐čĆąĖą╝ąĄąĮąĄąĮąĖąĄ:

ŌĆó ąĪąĖčüč鹥ą╝čŗ čü ą┐ąĖčéą░ąĮąĖąĄą╝ ąŠčé ą▒ą░čéą░čĆąĄąĖ (ą╝ąĄą┤ąĖčåąĖąĮą░, ą╝ąŠą▒ąĖą╗čīąĮčŗąĄ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ąĖ čé. ą┐.)

ŌĆó ąĪąĖčüč鹥ą╝čŗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĖ ą║ąŠąĮčéčĆąŠą╗čÅ ą▓ ą┐čĆąŠą╝čŗčłą╗ąĄąĮąĮąŠčüčéąĖ

ŌĆó ąĪąĖčüč鹥ą╝čŗ čāą┤ą░ą╗ąĄąĮąĮąŠą│ąŠ čüą▒ąŠčĆą░ ą┤ą░ąĮąĮčŗčģ

ŌĆó ąÆčŗčüąŠą║ąŠčüą║ąŠčĆąŠčüčéąĮčŗąĄ ą╝ąŠą┤ąĄą╝čŗ

ŌĆó ą×ą┐čéąĖč湥čüą║ąĖąĄ čüąĄąĮčüąŠčĆčŗ

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: čŹč鹊 ą┐ąĄčĆąĄą▓ąŠą┤ ą┤ą░čéą░čłąĖčéą░ [1]. ąÆčüąĄ ąĮąĄąĘąĮą░ą║ąŠą╝čŗąĄ č鹥čĆą╝ąĖąĮčŗ ąĖ čüąŠą║čĆą░čēąĄąĮąĖčÅ čüą╝. ą▓ąŠ ą▓čĆąĄąĘą║ąĄ "ąóąĄčĆą╝ąĖąĮąŠą╗ąŠą│ąĖčÅ" ąĖ čĆą░ąĘą┤ąĄą╗ąĄ "ąĪą╗ąŠą▓ą░čĆąĖą║" ą▓ ą║ąŠąĮčåąĄ čüčéą░čéčīąĖ.

[ą×ą▒čēąĄąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ]

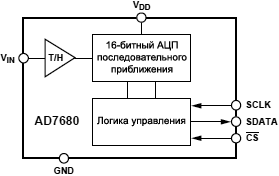

AD7680 čÅą▓ą╗čÅąĄčéčüčÅ ą▒čŗčüčéčĆčŗą╝, 菹║ąŠąĮąŠą╝ąĖčćąĮčŗą╝, 16-ą▒ąĖčéąĮčŗą╝ ąÉą”ą¤, ą┐ąŠčüčéčĆąŠąĄąĮąĮčŗą╝ ą┐ąŠ ą┐čĆąĖąĮčåąĖą┐čā ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ą┐čĆąĖą▒ą╗ąĖąČąĄąĮąĖčÅ (successive approximation ADC). ąŻčüčéčĆąŠą╣čüčéą▓ąŠ čĆą░ą▒ąŠčéą░ąĄčé ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖą╣ ą┐ąĖčéą░ąĮąĖčÅ 2.5V .. 5.5V, ąĖ ą╝ąŠąČąĄčé ąŠčåąĖčäčĆąŠą▓čŗą▓ą░čéčī čüąŠ čüą║ąŠčĆąŠčüčéčīčÄ ą┤ąŠ 100 kSPS (ą║ąĖą╗ąŠą▓čŗą▒ąŠčĆąŠą║/čüąĄą║). ąśą╝ąĄąĄčéčüčÅ ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ ą╝ą░ą╗ąŠčłčāą╝čÅčēąĖą╣ ąĖ čłąĖčĆąŠą║ąŠą┐ąŠą╗ąŠčüąĮčŗą╣ čāčüąĖą╗ąĖč鹥ą╗čī čüąŠ čüčģąĄą╝ąŠą╣ ą▓čŗą▒ąŠčĆą║ąĖ/čģčĆą░ąĮąĄąĮąĖčÅ, ą║ąŠč鹊čĆčŗą╣ ą╝ąŠąČąĄčé ąŠą▒čĆą░ą▒ąŠčéą░čéčī ą▓čģąŠą┤ąĮčŗąĄ čćą░čüč鹊čéčŗ čüą▓čŗčłąĄ 7 ą£ąōčå.

ą¤čĆąŠčåąĄčüčü ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ąĖ ąŠčåąĖčäčĆąŠą▓ą║ą░ ą┤ą░ąĮąĮčŗčģ čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ čü ą┐ąŠą╝ąŠčēčīčÄ čüąĖą│ąĮą░ą╗ą░ ą▓čŗą▒ąŠčĆą║ąĖ ~CS ąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ čéą░ą║č鹊ą▓ SCLK, čćč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą╗ąĄą│ą║ąŠ ą┐ąŠą┤ą║ą╗čÄčćąĖčéčī ąÉą”ą¤ ą║ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčā ąĖą╗ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆčā DSP. ąÆčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ ąĘą░čēąĄą╗ą║ąĖą▓ą░ąĄčéčüčÅ ą┐ąŠ čüą┐ą░ą┤čā čüąĖą│ąĮą░ą╗ą░ ~CS, ąĖ ą▓ čŹč鹊čé ą╝ąŠą╝ąĄąĮčé ąĮą░čćąĖąĮą░ąĄčéčüčÅ ą┐čĆąŠčåąĄčüčü ą║ąŠąĮą▓ąĄčĆčüąĖąĖ. ąÆ ą╝ąĖą║čĆąŠčüčģąĄą╝ąĄ ąĮąĄčé ąĮąĖą║ą░ą║ąĖčģ ąĘą░ą┤ąĄčƹȹĄą║ ą║ąŠąĮą▓ąĄą╣ąĄčĆąĖąĘą░čåąĖąĖ.

AD7680 ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą┐čĆąŠą┤ą▓ąĖąĮčāčéčŗą╣ ą┤ąĖąĘą░ą╣ąĮ, čćč鹊ą▒čŗ ą┤ąŠčüčéąĖčćčī ąŠč湥ąĮčī ąĮąĖąĘą║ąŠą╣ čĆą░čüčüąĄąĖą▓ą░ąĄą╝ąŠą╣ ą╝ąŠčēąĮąŠčüčéąĖ ąĮą░ ą▓čŗčüąŠą║ąĖčģ čüą║ąŠčĆąŠčüčéčÅčģ ąŠą▒ą╝ąĄąĮą░. ą×ą┐ąŠčĆąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą▒ąĄčĆąĄčéčüčÅ čü ą▓čŗą▓ąŠą┤ą░ ą┐ąĖčéą░ąĮąĖčÅ VDD. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą▓čģąŠą┤ąĮąŠą╣ ą┤ąĖą░ą┐ą░ąĘąŠąĮ ąŠčåąĖčäčĆąŠą▓čŗą▓ą░ąĄą╝čŗčģ ąĮą░ą┐čĆčÅąČąĄąĮąĖą╣ čüąŠčüčéą░ą▓ą╗čÅąĄčé 0 .. VDD ą▓ąŠą╗čīčé. ąĪą║ąŠčĆąŠčüčéčī ąŠčåąĖčäčĆąŠą▓ą║ąĖ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊č鹊ą╣ SCLK. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą▓čĆąĄą╝čÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą╝ąŠąČąĮąŠ čāą╝ąĄąĮčīčłąĖčéčī, ąĄčüą╗ąĖ čāą▓ąĄą╗ąĖčćąĖčéčī čüą║ąŠčĆąŠčüčéčī čéą░ą║č鹊ą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░. ąŻą╝ąĄąĮčīčłąĄąĮąĖąĄ ą▓čĆąĄą╝ąĄąĮąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé čüąĮąĖąĘąĖčéčī čüčĆąĄą┤ąĮąĄąĄ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ ąÉą”ą¤, ą║ąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čĆąĄąČąĖą╝ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ (power-down mode). ąśą╝ąĄąĄčéčüčÅ čéą░ą║ąČąĄ čĆąĄąČąĖą╝ shutdown, ą┐ąŠąĘą▓ąŠą╗čÅčÄčēąĖą╣ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠ čāą▓ąĄą╗ąĖčćąĖčéčī čŹčäč乥ą║čéąĖą▓ąĮąŠčüčéčī ą▓ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĖ 菹ĮąĄčĆą│ąĖąĖ ąĮą░ ąĮąĖąĘą║ąĖčģ čüą║ąŠčĆąŠčüčéčÅčģ ąŠą▒ą╝ąĄąĮą░.

ąĀąĖčü. 1. ążčāąĮą║čåąĖąŠąĮą░ą╗čīąĮą░čÅ ą▒ą╗ąŠą║-čüčģąĄą╝ą░ AD7680.

ąóą░ą▒ą╗ąĖčåą░ 1. ąØąĄą║ąŠč鹊čĆčŗąĄ čéąĖą┐čŗ ąÉą”ą¤ PulSAR ą▓ ą║ąŠčĆą┐čāčüą░čģ MSOP/SOT-23.

| ąóąĖą┐ |

100 kSPS |

250 kSPS |

500 kSPS |

| ą¤ąŠą╗ąĮąŠą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗąĄ ą▓čģąŠą┤čŗ |

AD7684 |

AD7687 |

AD7688 |

| ą¤čüąĄą▓ą┤ąŠą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗąĄ ą▓čģąŠą┤čŗ |

AD7683 |

AD7685 |

AD7686 |

| ą×ą┤ąĮąŠą┐ąŠą╗čÅčĆąĮčŗą╣ ą▓čģąŠą┤ |

AD7680 |

|

|

ąóą░ą▒ą╗ąĖčåą░ 2. VDD=4.5..5.5V, fSCLK=2.5 ą£ąōčå, fSAMPLE=100kSPS, ąĄčüą╗ąĖ ąĮąĄ čāą║ą░ąĘą░ąĮąŠ ąĮąĄčćč鹊 ąĖąĮąŠąĄ. TA = TMIN..TMAX, ąĄčüą╗ąĖ ąĮąĄ čāą║ą░ąĘą░ąĮąŠ ąĮąĄčćč鹊 ąĖąĮąŠąĄ.

| ą¤ą░čĆą░ą╝ąĄčéčĆ |

ąÆąĄčĆčüąĖąĖ A, B1 |

ąĢą┤. |

ąŻčüą╗ąŠą▓ąĖčÅ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ, ą║ąŠą╝ą╝ąĄąĮčéą░čĆąĖąĖ |

ąöąĖąĮą░ą╝ąĖč湥čüą║ąĖąĄ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ

SINAD2

SNR2

THD2

SFDR2

IMD2 ą▓č鹊čĆąŠą│ąŠ ą┐ąŠčĆčÅą┤ą║ą░

IMD2 čéčĆąĄčéčīąĄą│ąŠ ą┐ąŠčĆčÅą┤ą║ą░

ąŚą░ą┤ąĄčƹȹ║ą░ ą░ą┐ąĄčĆčéčāčĆčŗ

ąöąČąĖčéč鹥čĆ ą░ą┐ąĄčĆčéčāčĆčŗ

ą¤ąŠą╗ąĮą░čÅ ą┐ąŠą╗ąŠčüą░ ą┐čĆąŠą┐čāčüą║ą░ąĮąĖčÅ

|

83

85

84

86

-97

-95

-94

-100

20

30

8

2.2 |

dB, min

dB, typ

dB, min

dB, typ

dB, typ

dB, typ

dB, typ

dB, typ

nS, max

ps, max

ą£ąōčå, typ

ą£ąōčå, typ |

fIN = 10 ą║ąōčå, čüąĖąĮčāčü

@ -3 dB

@ -0.1 dB |

ąóąŠčćąĮąŠčüčéčī ą┐ąŠ ą┐ąŠčüč鹊čÅąĮąĮąŠą╝čā ąĮą░ą┐čĆčÅąČąĄąĮąĖčÄ

ąĀą░ąĘčĆčÅą┤ąŠą▓ ą▒ąĄąĘ ą┐čĆąŠą┐čāčüą║ą░ ą║ąŠą┤ą░

ąśąĮč鹥ą│čĆą░ą╗čīąĮą░čÅ ąĮąĄą╗ąĖąĮąĄą╣ąĮąŠčüčéčī (INL)2

ą×čłąĖą▒ą║ą░ čüą╝ąĄčēąĄąĮąĖčÅ2

ą×čłąĖą▒ą║ą░ čāčüąĖą╗ąĄąĮąĖčÅ2 |

15

┬▒4

┬▒1.68

┬▒0.038 |

ą▒ąĖčé, typ

LSB, typ

mV, max

% FS max |

|

ąÉąĮą░ą╗ąŠą│ąŠą▓čŗąĄ ą▓čģąŠą┤čŗ

ąöąĖą░ą┐ą░ąĘąŠąĮ ą▓čģąŠą┤ąĮčŗčģ ąĮą░ą┐čĆčÅąČąĄąĮąĖą╣

ą¤ąŠčüč鹊čÅąĮąĮčŗą╣ č鹊ą║ čāč鹥čćą║ąĖ

ąÆčģąŠą┤ąĮąŠąĄ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ |

0..VDD

┬▒0.3

30 |

V

╬╝A, max

pF, typ |

|

ą”ąĖčäčĆąŠą▓čŗąĄ ą▓čģąŠą┤čŗ

ąŻčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 1, VINH

ąŻčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 0, VINL

ąÆčģąŠą┤ąĮąŠą╣ č鹊ą║, IIN

ąÆčģąŠą┤ąĮą░čÅ ąĄą╝ą║ąŠčüčéčī, CIN2, 3 |

2.8

0.4

┬▒0.3

10 |

V, min

V, max

╬╝A, max

pF, max |

ą×ą▒čŗčćąĮąŠ IIN=10 nA ą┐čĆąĖ VIN=0 ąĖą╗ąĖ VDD. |

ą”ąĖčäčĆąŠą▓čŗąĄ ą▓čŗčģąŠą┤čŗ

ąŻčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 1, V0H

ąŻčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 0, V0L

ąóąŠą║ čāč鹥čćą║ąĖ 3-ą│ąŠ čüąŠčüč鹊čÅąĮąĖčÅ

ąÆčŗčģąŠą┤ąĮą░čÅ ąĄą╝ą║ąŠčüčéčī 3-ą│ąŠ čüąŠčüč鹊čÅąĮąĖčÅ2, 3 |

VDD-0.2

0.4

┬▒0.3

10 |

V, min

V, max

╬╝A, max

pF, max |

ISOURCE=200╬╝A

ISINK=200╬╝A

|

ąĪą║ąŠčĆąŠčüčéčī ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ

ąÆčĆąĄą╝čÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ

ąÆčĆąĄą╝čÅ ąĘą░čģą▓ą░čéą░ čüčģąĄą╝čŗ ą▓čŗą▒ąŠčĆą║ąĖ-čģčĆą░ąĮąĄąĮąĖčÅ

ą¤čĆąŠą┐čāčüą║ąĮą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī |

8

9.6

1.5

400

100 |

╬╝s, max

╬╝s, max

╬╝s, max

ns, max

kSPS |

20 čéą░ą║č鹊ą▓ SCLK=2.5ą£ąōčå

24 čéą░ą║čéą░ SCLK=2.5ą£ąōčå

ąĮą░ ą▓čģąŠą┤ąĄ čüąĖąĮčāčü Ōēż 10ą║ąōčå

čüą╝. "ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü" |

ąóčĆąĄą▒ąŠą▓ą░ąĮąĖčÅ ą║ ą┐ąĖčéą░ąĮąĖčÄ

VDD

IDD

ąĀąĄąČąĖą╝ Normal (čüčéą░čéąĖčćąĮčŗą╣)

ąĀąĄąČąĖą╝ Normal (čĆą░ą▒ąŠčćąĖą╣)

ą¤ąŠą╗ąĮąŠčüčéčīčÄ ą▓čŗą║ą╗. (Power-Down)

ąĀą░čüčüąĄąĖą▓ą░ąĄą╝ą░čÅ ą╝ąŠčēąĮąŠčüčéčī4

ąĀąĄąČąĖą╝ Normal (čĆą░ą▒ąŠčćąĖą╣)

ą¤ąŠą╗ąĮąŠčüčéčīčÄ ą▓čŗą║ą╗. (Power-Down) |

4.5..5.5

5.2

4.8

0.5

26.4

2.75 |

V, min..max

mA, max

mA, max

╬╝A, max

mW, max

╬╝W, max |

ąśąĘą╝ąĄąĮąĄąĮąĖčÅ ą▓čģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ 0..VDD

SCLK ą▓ ą╗ąŠą│. 0 ąĖą╗ąĖ ą╗ąŠą│. 1, VDD=5.5V

fSAMPLE=100kSPS, VDD=5.5V; 3.3mA typ

SCLK ą▓ ą╗ąŠą│. 0 ąĖą╗ąĖ ą╗ąŠą│. 1, VDD=5.5V

VDD=5.5V

fSAMPLE=100kSPS

|

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

1 ąóąĄą╝ą┐ąĄčĆą░čéčāčĆąĮčŗą╣ ą┤ąĖą░ą┐ą░ąĘąŠąĮ ą┤ą╗čÅ ą▓ąĄčĆčüąĖą╣ A, B: -40..+85 ┬░C.

2 ąĪą╝. ą▓čĆąĄąĘą║čā "ąóąĄčĆą╝ąĖąĮąŠą╗ąŠą│ąĖčÅ".

3 ąÆčŗą▒ąŠčĆą║ą░ č鹥čüčéąĖčĆąŠą▓ą░ą╗ą░čüčī ą▓ąŠ ą▓čĆąĄą╝čÅ ąĮą░čćą░ą╗čīąĮąŠą│ąŠ čĆąĄą╗ąĖąĘą░, čćč鹊ą▒čŗ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī čüąŠą▓ą╝ąĄčüčéąĖą╝ąŠčüčéčī.

4 ąĪą╝. čĆą░ąĘą┤ąĄą╗ "ąĪąŠąŠčéąĮąŠčłąĄąĮąĖąĄ ą┐ąŠčéčĆąĄą▒ą╗čÅąĄą╝ąŠą╣ ą╝ąŠčēąĮąŠčüčéąĖ ąĖ čüą║ąŠčĆąŠčüčéąĖ ąŠčåąĖčäčĆąŠą▓ą║ąĖ".

ąóą░ą▒ą╗ąĖčåą░ 3. VDD=2.5..4.096V, fSCLK=2.5 ą£ąōčå, fSAMPLE=100kSPS, ąĄčüą╗ąĖ ąĮąĄ čāą║ą░ąĘą░ąĮąŠ ąĮąĄčćč鹊 ąĖąĮąŠąĄ. TA = TMIN..TMAX, ąĄčüą╗ąĖ ąĮąĄ čāą║ą░ąĘą░ąĮąŠ ąĮąĄčćč鹊 ąĖąĮąŠąĄ.

| ą¤ą░čĆą░ą╝ąĄčéčĆ |

ąÆąĄčĆčüąĖčÅ A1 |

ąÆąĄčĆčüąĖčÅ B1 |

ąĢą┤. |

ąŻčüą╗ąŠą▓ąĖčÅ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ, ą║ąŠą╝ą╝ąĄąĮčéą░čĆąĖąĖ |

ąöąĖąĮą░ą╝ąĖč湥čüą║ąĖąĄ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ

SINAD2

SNR2

THD2

SFDR2

IMD2 ą▓č鹊čĆąŠą│ąŠ ą┐ąŠčĆčÅą┤ą║ą░

IMD2 čéčĆąĄčéčīąĄą│ąŠ ą┐ąŠčĆčÅą┤ą║ą░

ąŚą░ą┤ąĄčƹȹ║ą░ ą░ą┐ąĄčĆčéčāčĆčŗ

ąöąČąĖčéč鹥čĆ ą░ą┐ąĄčĆčéčāčĆčŗ

ą¤ąŠą╗ąĮą░čÅ ą┐ąŠą╗ąŠčüą░ ą┐čĆąŠą┐čāčüą║ą░ąĮąĖčÅ

|

83

82

86

84

83

86

-98

-95

-94

-100

20

30

7

5

2

1.6 |

83

82

86

84

83

86

-98

-99

-94

-100

10

30

7

5

2

1.6 |

dB, min

dB, min

dB, typ

dB, min

dB, min

dB, typ

dB, typ

dB, typ

dB, typ

dB, typ

nS, max

ps, typ

ą£ąōčå, typ

ą£ąōčå, typ

ą£ąōčå, typ

ą£ąōčå, typ

|

fIN = 10 ą║ąōčå, čüąĖąĮčāčü

VDD=4.096V

VDD=2.5..3.6V

VDD=4.096V

VDD=2.5..3.6V

@ -3 dB; VDD=4.096V

@ -3 dB; VDD=2.5..3.6V

@ -0.1 dB; VDD=4.096V

@ -0.1 dB; VDD=2.5..3.6V |

ąóąŠčćąĮąŠčüčéčī ą┐ąŠ ą┐ąŠčüč鹊čÅąĮąĮąŠą╝čā ąĮą░ą┐čĆčÅąČąĄąĮąĖčÄ

ąĀą░ąĘčĆčÅą┤ąŠą▓ ą▒ąĄąĘ ą┐čĆąŠą┐čāčüą║ą░ ą║ąŠą┤ą░

ąśąĮč鹥ą│čĆą░ą╗čīąĮą░čÅ ąĮąĄą╗ąĖąĮąĄą╣ąĮąŠčüčéčī (INL)2

ą×čłąĖą▒ą║ą░ čüą╝ąĄčēąĄąĮąĖčÅ2

ą×čłąĖą▒ą║ą░ čāčüąĖą╗ąĄąĮąĖčÅ2 |

14

┬▒3.5

┬▒3

┬▒1.25

┬▒1.098

┬▒0.038

|

15

┬▒3.5

┬▒3

┬▒1.25

┬▒1.098

┬▒0.038 |

ą▒ąĖčé, min

LSB, max

LSB, max

mV, max

mV, max

% FS max |

VDD=4.096V

VDD=2.5..3.6V

VDD=4.096V

VDD=2.5..3.6V

|

ąÉąĮą░ą╗ąŠą│ąŠą▓čŗąĄ ą▓čģąŠą┤čŗ

ąöąĖą░ą┐ą░ąĘąŠąĮ ą▓čģąŠą┤ąĮčŗčģ ąĮą░ą┐čĆčÅąČąĄąĮąĖą╣

ą¤ąŠčüč鹊čÅąĮąĮčŗą╣ č鹊ą║ čāč鹥čćą║ąĖ

ąÆčģąŠą┤ąĮąŠąĄ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ |

0..VDD

┬▒0.3

30 |

0..VDD

┬▒0.3

30 |

V

╬╝A, max

pF, typ |

|

ą”ąĖčäčĆąŠą▓čŗąĄ ą▓čģąŠą┤čŗ

ąŻčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 1, VINH

ąŻčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 0, VINL

ąÆčģąŠą┤ąĮąŠą╣ č鹊ą║, IIN

ąÆčģąŠą┤ąĮą░čÅ ąĄą╝ą║ąŠčüčéčī, CIN2, 3 |

2.4

0.4

┬▒0.3

10 |

2.4

0.4

┬▒0.3

10 |

V, min

V, max

╬╝A, max

pF, max |

ą×ą▒čŗčćąĮąŠ IIN=10 nA ą┐čĆąĖ VIN=0 ąĖą╗ąĖ VDD. |

ą”ąĖčäčĆąŠą▓čŗąĄ ą▓čŗčģąŠą┤čŗ

ąŻčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 1, V0H

ąŻčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 0, V0L

ąóąŠą║ čāč鹥čćą║ąĖ 3-ą│ąŠ čüąŠčüč鹊čÅąĮąĖčÅ

ąÆčŗčģąŠą┤ąĮą░čÅ ąĄą╝ą║ąŠčüčéčī 3-ą│ąŠ čüąŠčüč鹊čÅąĮąĖčÅ2, 3 |

VDD-0.2

0.4

┬▒0.3

10 |

VDD-0.2

0.4

┬▒0.3

10 |

V, min

V, max

╬╝A, max

pF, max |

ISOURCE=200╬╝A

ISINK=200╬╝A

|

ąĪą║ąŠčĆąŠčüčéčī ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ

ąÆčĆąĄą╝čÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ

ąÆčĆąĄą╝čÅ ąĘą░čģą▓ą░čéą░ čüčģąĄą╝čŗ ą▓čŗą▒ąŠčĆą║ąĖ-čģčĆą░ąĮąĄąĮąĖčÅ

ą¤čĆąŠą┐čāčüą║ąĮą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī |

8

9.6

1.5

400

100 |

8

9.6

1.5

400

100 |

╬╝s, max

╬╝s, max

╬╝s, max

ns, max

kSPS |

20 čéą░ą║č鹊ą▓ SCLK=2.5ą£ąōčå

24 čéą░ą║čéą░ SCLK=2.5ą£ąōčå

ąĮą░ ą▓čģąŠą┤ąĄ čüąĖąĮčāčü Ōēż 10ą║ąōčå

čüą╝. "ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü" |

ąóčĆąĄą▒ąŠą▓ą░ąĮąĖčÅ ą║ ą┐ąĖčéą░ąĮąĖčÄ

VDD

IDD

ąĀąĄąČąĖą╝ Normal (čüčéą░čéąĖčćąĮčŗą╣)

ąĀąĄąČąĖą╝ Normal (čĆą░ą▒ąŠčćąĖą╣)

ą¤ąŠą╗ąĮąŠčüčéčīčÄ ą▓čŗą║ą╗. (Power-Down)

ąĀą░čüčüąĄąĖą▓ą░ąĄą╝ą░čÅ ą╝ąŠčēąĮąŠčüčéčī4

ąĀąĄąČąĖą╝ Normal (čĆą░ą▒ąŠčćąĖą╣)

ą¤ąŠą╗ąĮąŠčüčéčīčÄ ą▓čŗą║ą╗. (Power-Down)

|

2.5..4.096

2.8

2

2.6

1.9

0.3

10.65

6.84

3

1.23

1.08 |

2.5..4.096

2.8

2

2.6

1.9

0.3

10.65

6.84

3

1.23

1.08 |

V, min..max

mA, max

mA, max

mA, max

mA, max

╬╝A, max

mW, max

mW, max

mW, typ

╬╝W, max

╬╝W, max |

ąśąĘą╝ąĄąĮąĄąĮąĖčÅ ą▓čģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ 0..VDD

SCLK ą▓ ą╗ąŠą│. 0 ąĖą╗ąĖ ą╗ąŠą│. 1, VDD=4.096V

SCLK ą▓ ą╗ąŠą│. 0 ąĖą╗ąĖ ą╗ąŠą│. 1, VDD=3.6V

fSAMPLE=100kSPS, VDD=4.096V; 1.75mA typ

fSAMPLE=100kSPS, VDD=3.6V; 1.29mA typ

SCLK ą▓ ą╗ąŠą│. 0 ąĖą╗ąĖ ą╗ąŠą│. 1

fSAMPLE=100kSPS, VDD=4.096V

fSAMPLE=100kSPS, VDD=3.6V

VDD=2.5V

VDD=4.096V

VDD=3.6V |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

1 ąóąĄą╝ą┐ąĄčĆą░čéčāčĆąĮčŗą╣ ą┤ąĖą░ą┐ą░ąĘąŠąĮ ą┤ą╗čÅ ą▓ąĄčĆčüąĖą╣ A, B: -40..+85 ┬░C.

2 ąĪą╝. ą▓čĆąĄąĘą║čā "ąóąĄčĆą╝ąĖąĮąŠą╗ąŠą│ąĖčÅ".

3 ąÆčŗą▒ąŠčĆą║ą░ č鹥čüčéąĖčĆąŠą▓ą░ą╗ą░čüčī ą▓ąŠ ą▓čĆąĄą╝čÅ ąĮą░čćą░ą╗čīąĮąŠą│ąŠ čĆąĄą╗ąĖąĘą░, čćč鹊ą▒čŗ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī čüąŠą▓ą╝ąĄčüčéąĖą╝ąŠčüčéčī.

4 ąĪą╝. čĆą░ąĘą┤ąĄą╗ "ąĪąŠąŠčéąĮąŠčłąĄąĮąĖąĄ ą┐ąŠčéčĆąĄą▒ą╗čÅąĄą╝ąŠą╣ ą╝ąŠčēąĮąŠčüčéąĖ ąĖ čüą║ąŠčĆąŠčüčéąĖ ąŠčåąĖčäčĆąŠą▓ą║ąĖ".

ąóą░ą▒ą╗ąĖčåą░ 4. VDD=2.5..5.5V; TA=TMIN..TMAX, ąĄčüą╗ąĖ ąĮąĄ čāą║ą░ąĘą░ąĮąŠ ąĮąĄčćč鹊 ąĖąĮąŠąĄ.

ą¤ą░čĆą░ą╝ąĄčéčĆ

|

ą¤čĆąĄą┤ąĄą╗ ą┐čĆąĖ TMIN, TMAX

|

ąĢą┤.

|

ą×ą┐ąĖčüą░ąĮąĖąĄ

|

| 3V |

5V |

fSCLK2

tCONVERT

tQUET

t1

t2

t33

t43

t5

t6

t7

t84

tPOWER-UP5 |

250

2.5

20 x tSCLK

100

10

10

48

120

0.4 tSCLK

0.4 tSCLK

10

45

1 |

250

2.5

20 x tSCLK

100

10

10

35

80

0.4 tSCLK

0.4 tSCLK

10

35

1 |

ą║ąōčå, min

ą£ąōčå, max

min

ns, min

ns, min

ns, min

ns, max

ns, max

ns, min

ns, min

ns, min

ns, max

╬╝S, typ |

ą£ąĖąĮ. ą▓čĆąĄą╝čÅ čéąĖčłąĖąĮčŗ ą╝ąĄąČą┤čā ąŠčüčéą░ą▓ą╗ąĄąĮąĖąĄą╝ čłąĖąĮčŗ ąĖ ąĮą░čćą░ą╗ąŠą╝ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ

ą£ąĖąĮ. čłąĖčĆąĖąĮą░ ąĖą╝ą┐čāą╗čīčüą░ ~CS

ąÆčĆąĄą╝čÅ ą┐ąĄčĆąĄčģąŠą┤ą░ ąŠčé ~CS ą║ SCLK

ąŚą░ą┤ąĄčƹȹ║ą░ ąŠčé ~CS ą┤ąŠ ą▓čŗčģąŠą┤ą░ SDATA ąĖąĘ ąĮąĄą░ą║čéąĖą▓ąĮąŠą│ąŠ čüąŠčüč鹊čÅąĮąĖčÅ

ąÆčĆąĄą╝čÅ ą┤ąŠčüčéčāą┐ą░ ą┐ąŠčüą╗ąĄ čüą┐ą░ą┤ą░ SCLK

ąöą╗ąĖč鹥ą╗čīąĮąŠčüčéčī ą╗ąŠą│. 0 SCLK

ąöą╗ąĖč鹥ą╗čīąĮąŠčüčéčī ą╗ąŠą│. 1 SCLK

ąÆčĆąĄą╝čÅ čāą┤ąĄčƹȹ░ąĮąĖčÅ SCLK ą┤ąŠ ą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗčģ ą┤ą░ąĮąĮčŗčģ

ąÆčĆąĄą╝čÅ ąŠčé čüą┐ą░ą┤ą░ SCLK ą┤ąŠ ą┐ąĄčĆąĄčģąŠą┤ą░ SDATA ą▓ čéčĆąĄčéčīąĄ čüąŠčüč鹊čÅąĮąĖąĄ

ąÆčĆąĄą╝čÅ ą▓čŗčģąŠą┤ą░ ąĖąĘ čĆąĄąČąĖą╝ą░ ą┐ąŠą╗ąĮąŠą│ąŠ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ (power down) |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

1 ąÆčŗą▒ąŠčĆą║ą░ č鹥čüčéąĖčĆąŠą▓ą░ą╗ą░čüčī ą▓ąŠ ą▓čĆąĄą╝čÅ ąĮą░čćą░ą╗čīąĮąŠą│ąŠ čĆąĄą╗ąĖąĘą░ ą┤ą╗čÅ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░ąĮąĖčÅ čüąŠą▓ą╝ąĄčüčéąĖą╝ąŠčüčéąĖ. ąÆčüąĄ ą▓čģąŠą┤ąĮčŗąĄ čüąĖą│ąĮą░ą╗čŗ čāą║ą░ąĘą░ąĮčŗ ą┤ą╗čÅ tr = tf = 5 ns (ą┐ąĄčĆąĄčģąŠą┤ čāčĆąŠą▓ąĮčÅ ąŠčé 10% ą┤ąŠ 90% VDD) ąĖ ąŠčåąĄąĮąĖą▓ą░ą╗ąĖčüčī ą┐čĆąĖ čāčĆąŠą▓ąĮąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ 1.6V.

2 ąĪąŠąŠčéąĮąŠčłąĄąĮąĖąĄ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüč鹥ą╣ ą╗ąŠą│. 0 ąĖ ą╗ąŠą│. 1 ąŠčé 40/60 ą┤ąŠ 60/40.

3 ąśąĘą╝ąĄčĆąĄąĮąŠ ą┤ą╗čÅ ąĮą░ą│čĆčāąĘąŠčćąĮąŠą╣ čüčģąĄą╝čŗ ąĮą░ čĆąĖčü. 2, ąĖ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąŠ ą║ą░ą║ ą▓čĆąĄą╝čÅ, čéčĆąĄą▒čāąĄą╝ąŠąĄ ą┤ą╗čÅ ą┐ąĄčĆąĄčģąŠą┤ą░ ą▓čŗčģąŠą┤ą░ ąŠčé čāčĆąŠą▓ąĮčÅ 0.8V ą║ čāčĆąŠą▓ąĮčÄ 2.0V.

4 t8 ą▓čŗčćąĖčüą╗ąĄąĮąĮą░čÅ č乊čĆą╝ą░ ąĖąĘą╝ąĄčĆąĄąĮąĮąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ, ą▓ąĘčÅč鹊ą│ąŠ ąŠčé ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ą▓čŗčģąŠą┤ą░ 0.5V, ą║ąŠą│ą┤ą░ čüčģąĄą╝ą░ ąĮą░ą│čĆčāąČąĄąĮą░ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü čĆąĖčü. 2. ąśąĘą╝ąĄčĆąĄąĮąĮąŠąĄ čćąĖčüą╗ąŠ ąĘą░č鹥ą╝ ą▒čŗą╗ąŠ 菹║čüčéčĆą░ą┐ąŠą╗ąĖčĆąŠą▓ą░ąĮąŠ ąŠą▒čĆą░čéąĮąŠ, čćč鹊ą▒čŗ čāčüčéčĆą░ąĮąĖčéčī čŹčäč乥ą║čéčŗ ąĘą░čĆčÅą┤ą░ ąĖą╗ąĖ čĆą░ąĘčĆčÅą┤ą░ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆą░ 50 pF. ąŁč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ą▓čĆąĄą╝čÅ t8 čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ą░ą╝ ą▓čĆąĄą╝ąĄąĮąĖ čĆąĄą░ą╗čīąĮąŠą│ąŠ ąŠčüą▓ąŠą▒ąŠąČą┤ąĄąĮąĖčÅ čłąĖąĮčŗ ą╝ąĖą║čĆąŠčüčģąĄą╝ąŠą╣, ąĖ ąĮąĄ ąĘą░ą▓ąĖčüąĖčé ąŠčé ąĮą░ą│čĆčāąČąĄąĮąĮąŠčüčéąĖ čłąĖąĮčŗ.

5 ąĪą╝. čĆą░ąĘą┤ąĄą╗ "ąĪąŠąŠčéąĮąŠčłąĄąĮąĖąĄ ą┐ąŠčéčĆąĄą▒ą╗čÅąĄą╝ąŠą╣ ą╝ąŠčēąĮąŠčüčéąĖ ąĖ čüą║ąŠčĆąŠčüčéąĖ ąŠčåąĖčäčĆąŠą▓ą║ąĖ".

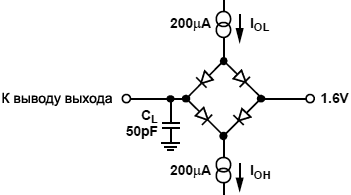

ąĀąĖčü. 2. ąØą░ą│čĆčāąĘąŠčćąĮą░čÅ čüčģąĄą╝ą░ ą┤ą╗čÅ čüą┐ąĄčåąĖčäąĖą║ą░čåąĖąĖ ą▓čĆąĄą╝ąĄąĮąĮčŗčģ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ čåąĖčäčĆąŠą▓ąŠą│ąŠ ą▓čŗčģąŠą┤ą░.

ąĪčéčĆąĄčüčüąŠą▓čŗąĄ čāčüą╗ąŠą▓ąĖčÅ, čāą║ą░ąĘą░ąĮąĮčŗąĄ ą▓ čéą░ą▒ą╗ąĖčåąĄ, ąĖą╗ąĖ ąĖčģ ąĘąĮą░č湥ąĮąĖčÅ, ą║ąŠč鹊čĆčŗąĄ ą▒ąŠą╗čīčłąĄ č湥ą╝ ą▓ čéą░ą▒ą╗ąĖčåąĄ, ą╝ąŠą│čāčé ąĮąĄąŠą▒čĆą░čéąĖą╝ąŠ ą┐ąŠą▓čĆąĄą┤ąĖčéčī čāčüčéčĆąŠą╣čüčéą▓ąŠ. ą¤ąŠčŹč鹊ą╝čā ą┐ą░čĆą░ą╝ąĄčéčĆčŗ čāą║ą░ąĘą░ąĮčŗ č鹊ą╗čīą║ąŠ ą▓ ą║ą░č湥čüčéą▓ąĄ čüčéčĆąĄčüčüąŠą▓ąŠą│ąŠ čĆąĄą╣čéąĖąĮą│ą░; ąĮąĄ ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčéčüčÅ čĆą░ą▒ąŠčéą░ čāčüčéčĆąŠą╣čüčéą▓ą░ ą▓ čŹčéąĖčģ čāčüą╗ąŠą▓ąĖčÅčģ ąĖą╗ąĖ ą▓ čāčüą╗ąŠą▓ąĖčÅčģ čü ą┐čĆąĄą▓čŗčłąĄąĮąĖąĄą╝ čŹčéąĖčģ ąĘąĮą░č湥ąĮąĖą╣ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓. ąĀą░ą▒ąŠčéą░ ą▓ąŠąĘą╗ąĄ čŹčéąĖčģ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮčŗčģ čĆą░ą▒ąŠčćąĖčģ čāčüą╗ąŠą▓ąĖą╣ ą▓ č鹥č湥ąĮąĖąĄ ą┤ą╗ąĖč鹥ą╗čīąĮąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ ą╝ąŠąČąĄčé ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠ ą┐ąŠą▓ą╗ąĖčÅčéčī ąĮą░ ąĮą░ą┤ąĄąČąĮąŠčüčéčī čāčüčéčĆąŠą╣čüčéą▓ą░.

ąóą░ą▒ą╗ąĖčåą░ 5. TA = 25┬░C, ąĄčüą╗ąĖ ąĮąĄ čāą║ą░ąĘą░ąĮąŠ ąĮąĄčćč鹊 ąĖąĮąŠąĄ.

| ą¤ą░čĆą░ą╝ąĄčéčĆ |

ą¤čĆąĄą┤ąĄą╗čīąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ |

ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ VDD ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ GND

ąÉąĮą░ą╗ąŠą│ąŠą▓ąŠąĄ ą▓čģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ GND

ą”ąĖčäčĆąŠą▓ąŠąĄ ą▓čģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ GND

ą”ąĖčäčĆąŠą▓ąŠąĄ ą▓čŗčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ GND

ąÆčģąŠą┤ąĮąŠą╣ č鹊ą║ č湥čĆąĄąĘ ą╗čÄą▒ąŠą╣ ą▓čŗą▓ąŠą┤, ą║čĆąŠą╝ąĄ ą▓čŗą▓ąŠą┤ąŠą▓ ą┐ąĖčéą░ąĮąĖčÅ1

ąöąĖą░ą┐ą░ąĘąŠąĮ č鹥ą╝ą┐ąĄčĆą░čéčāčĆ:

čĆą░ą▒ąŠčćąĖą╣ ą┤ą╗čÅ ą║ąŠą╝ą╝ąĄčĆč湥čüą║ąŠą╣ ą▓ąĄčĆčüąĖąĖ (ą▓ąĄčĆčüąĖčÅ B)

ą┤ą╗čÅ čģčĆą░ąĮąĄąĮąĖčÅ

ąóąĄą╝ą┐ąĄčĆą░čéčāčĆą░ ą║čĆąĖčüčéą░ą╗ą╗ą░

ąĀą░čüčüąĄąĖą▓ą░ąĄą╝ą░čÅ ą╝ąŠčēąĮąŠčüčéčī ą┤ą╗čÅ ą║ąŠčĆą┐čāčüą░ SOT-23

ąóąĄčĆą╝ąŠčüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ ╬śJA

ąóąĄčĆą╝ąŠčüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ ╬śJC

ąĀą░čüčüąĄąĖą▓ą░ąĄą╝ą░čÅ ą╝ąŠčēąĮąŠčüčéčī ą┤ą╗čÅ ą║ąŠčĆą┐čāčüą░ MSOP

ąóąĄčĆą╝ąŠčüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ ╬śJA

ąóąĄčĆą╝ąŠčüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ ╬śJC

ąóąĄą╝ą┐ąĄčĆą░čéčāčĆą░ ą┐ą░ą╣ą║ąĖ ą▓čŗą▓ąŠą┤ąŠą▓

ążą░ąĘą░ ą║ąŠąĮą┤ąĄąĮčüą░čåąĖąĖ (60 čüąĄą║)

ążą░ąĘą░ ąĖąĮčäčĆą░ą║čĆą░čüąĮąŠą│ąŠ ą┐čĆąŠą│čĆąĄą▓ą░ (15 čüąĄą║)

ESD |

-0.3V .. +7V

-0.3V .. VDD+0.3V

-0.3V .. +7V

-0.3V .. VDD+0.3V

┬▒10 mA

-40┬░C .. +85┬░C

-65┬░C .. +150┬░C

150┬░C

450 mW

229.6┬░C/W

91.99┬░C/W

450 mW

205.9┬░C/W

43.74┬░C/W

215┬░C

220┬░C

2 kV |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ 1: ą┐ąĄčĆąĄčģąŠą┤ąĮčŗąĄ č鹊ą║ąĖ ą┤ąŠ 100 mA ąĮąĄ ą┐čĆąĖą▓ąŠą┤čÅčé ą║ ąĘą░čēąĄą╗ą║ąĖą▓ą░ąĮąĖčÄ SCR.

[ąĪčéą░čéąĖč湥čüą║ąŠąĄ 菹╗ąĄą║čéčĆąĖč湥čüčéą▓ąŠ]

ą£ąĖą║čĆąŠčüčģąĄą╝ą░ čćčāą▓čüčéą▓ąĖč鹥ą╗čīąĮą░ ą║ čüčéą░čéąĖč湥čüą║ąŠą╝čā 菹╗ąĄą║čéčĆąĖč湥čüčéą▓čā, ESD (electrostatic discharge). ąŁą╗ąĄą║čéčĆąŠčüčéą░čéąĖč湥čüą║ąĖąĄ ąĘą░čĆčÅą┤čŗ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄą╝ ą┐ąŠčĆčÅą┤ą║ą░ 4000V ą╝ąŠą│čāčé ąĮą░ą║ą░ą┐ą╗ąĖą▓ą░čéčīčüčÅ ąĮą░ č鹥ą╗ąĄ č湥ą╗ąŠą▓ąĄą║ą░ ąĖ ąĮą░ č鹥čüč鹊ą▓ąŠą╝ ąŠą▒ąŠčĆčāą┤ąŠą▓ą░ąĮąĖąĖ, ą┐ąŠčüą╗ąĄ č湥ą│ąŠ ą╝ąŠą│čāčé ąĮąĄąĘą░ą╝ąĄčéąĮąŠ čĆą░ąĘčĆčÅą┤ąĖčéčīčüčÅ č湥čĆąĄąĘ ą▓čŗą▓ąŠą┤čŗ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ (ąĄčüą╗ąĖ ąĮąĄ ą┐čĆąĖąĮčÅčéčī ą╝ąĄčĆčŗ ą┐čĆąĄą┤ąŠčüč鹊čĆąŠąČąĮąŠčüčéąĖ). ąźąŠčéčÅ čŹčéą░ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ čüąĮą░ą▒ąČąĄąĮą░ ąĮąĄą║ąŠč鹊čĆčŗą╝ąĖ ą┐čĆąŠą┐čĆąĖąĄčéą░čĆąĮčŗą╝ąĖ čüčģąĄą╝ą░ą╝ąĖ ąĘą░čēąĖčéčŗ ąŠčé ESD, 菹╗ąĄą║čéčĆąŠčüčéą░čéąĖč湥čüą║ąĖą╣ čĆą░ąĘčĆčÅą┤ čü ą▓čŗčüąŠą║ąŠą╣ 菹ĮąĄčĆą│ąĖąĄą╣ ą╝ąŠąČąĄčé ąĮąĄąŠą▒čĆą░čéąĖą╝ąŠ ą┐ąŠą▓čĆąĄą┤ąĖčéčī ą╝ąĖą║čĆąŠčüčģąĄą╝čā. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ą┐čĆąĄą┤ą┐čĆąĖąĮąĖą╝ą░čéčī ą╝ąĄčĆčŗ ąĘą░čēąĖčéčŗ ąŠčé ESD, čćč鹊ą▒čŗ ąĖąĘą▒ąĄąČą░čéčī ą┐ąŠč鹥čĆčī ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéąĖ ąĖą╗ąĖ ą▓čŗčģąŠą┤ą░ ąĖąĘ čüčéčĆąŠčÅ ą╝ąĖą║čĆąŠčüčģąĄą╝.

[ą”ąŠą║ąŠą╗ąĄą▓ą║ą░ ą║ąŠčĆą┐čāčüą░ ąĖ ąŠą┐ąĖčüą░ąĮąĖąĄ ą▓čŗą▓ąŠą┤ąŠą▓ AD7680]

ąĀąĖčü. 3. ąÜąŠčĆą┐čāčü SOT-23.

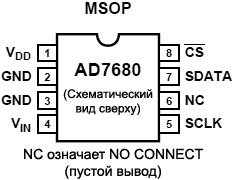

ąĀąĖčü. 4. ąÜąŠčĆą┐čāčü MSOP.

ąóą░ą▒ą╗ąĖčåą░ 6. ążčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ ą▓čŗą▓ąŠą┤ąŠą▓.

| Ōä¢ ą▓čŗą▓ąŠą┤ą░ |

ą£ąĮąĄą╝ąŠąĮąĖą║ą░

|

ążčāąĮą║čåąĖčÅ

|

| SOT-23 |

MSOP |

| 1 |

1 |

VDD |

ąÆčģąŠą┤ ą┤ą╗čÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ ąĖ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ. ąöąĖą░ą┐ą░ąĘąŠąĮ ą┤ą╗čÅ VDD ą┤ąŠą┐čāčüą║ą░ąĄčéčüčÅ ąŠčé 2.5V ą┤ąŠ 5.5V. |

| 2 |

2, 3 |

GND |

ąÉąĮą░ą╗ąŠą│ąŠą▓ą░čÅ ąĘąĄą╝ą╗čÅ. ą×ą┐ąŠčĆąĮą░čÅ č鹊čćą║ą░ ą┤ą╗čÅ ą▓čüąĄčģ čüčģąĄą╝ AD7680. ąÆčüąĄ čüąĖą│ąĮą░ą╗čŗ ą┤ąŠą╗ąČąĮčŗ ą┐ąŠčüčéčāą┐ą░čéčī ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ čłąĖąĮčŗ GND. |

| 3 |

4 |

VIN |

ąÉąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ą▓čģąŠą┤. ą×ą┤ąĮąŠą┐ąŠą╗čÅčĆąĮčŗą╣ ą▓čģąŠą┤ ąÉą”ą¤. ąöąĖą░ą┐ą░ąĘąŠąĮ ąŠčåąĖčäčĆąŠą▓čŗą▓ą░ąĄą╝ąŠą│ąŠ ą▓čģąŠą┤ąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ą┐čĆąĄą┤ąĄą╗ą░čģ ąŠčé 0 ą┤ąŠ VDD. |

| 4 |

5 |

SCLK |

ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗąĄ čéą░ą║čéčŗ, ą╗ąŠą│ąĖč湥čüą║ąĖą╣ čåąĖčäčĆąŠą▓ąŠą╣ ą▓čģąŠą┤. ąŁčéąĖ čéą░ą║čéčŗ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÄčéčüčÅ čģąŠčüč鹊ą╝ ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ ą║ čĆąĄąĘčāą╗čīčéą░čéą░ą╝ ąŠčåąĖčäčĆąŠą▓ą║ąĖ ąÉą”ą¤. ąóą░ą║ąČąĄ čüąĖą│ąĮą░ą╗ SCLK ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą║ą░ą║ čéą░ą║č鹊ą▓čŗą╣ ą▓čģąŠą┤ ą┤ą╗čÅ ą┐čĆąŠčåąĄčüčüą░ ąŠčåąĖčäčĆąŠą▓ą║ąĖ AD7680. |

| 5 |

7 |

SDATA |

ąæąĖčéčŗ ą┤ą░ąĮąĮčŗčģ ą▓čŗą┤ą▓ąĖą│ą░čÄčéčüčÅ ąĖąĘ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą┐ąŠ čüą┐ą░ą┤čā ą╗ąŠą│ąĖč湥čüą║ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ SCLK. ą¤ąŠč鹊ą║ ą┤ą░ąĮąĮčŗčģ čüąŠčüč鹊ąĖčé ąĖąĘ 4 ąĮą░čćą░ą╗čīąĮčŗčģ ąĮčāą╗ąĄą╣, ąĘą░ ą║ąŠč鹊čĆčŗą╝ąĖ ąĖą┤čāčé 16 ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ, ą▓ ą┐ąŠč鹊ą║ąĄ ą▒ąĖčé MSB ąĖą┤ąĄčé ą┐ąĄčĆą▓čŗą╝. ąŚą░ 16 ą▒ąĖčéą░ą╝ąĖ ą┤ą░ąĮąĮčŗčģ ą╝ąŠą│čāčé čüą╗ąĄą┤ąŠą▓ą░čéčī 4 ąĘą░ą▓ąĄčĆčłą░čÄčēąĖčģ ąĮčāą╗čÅ, ąĄčüą╗ąĖ ~CS čāą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą╗ąŠą│. 0 ąĮą░ ą▓čĆąĄą╝čÅ ą┤ąĄą╣čüčéą▓ąĖčÅ 24 čéą░ą║č鹊ą▓čŗčģ ą┐ąĄčĆąĄą┐ą░ą┤ąŠą▓ SCLK. ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. čĆą░ąĘą┤ąĄą╗ "ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü". |

| 6 |

8 |

~CS |

ąĪąĖą│ąĮą░ą╗ chip select (ą▓čŗą▒ąŠčĆą║ą░ ą║čĆąĖčüčéą░ą╗ą╗ą░). ąÉą║čéąĖą▓ąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 0. ąŁč鹊čé ą▓čģąŠą┤ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą┤ą▓ąŠą╣ąĮčāčÄ čäčāąĮą║čåąĖčÄ - ąĘą░ą┐čāčüą║ą░ąĄčé ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ąĖ čāą┐čĆą░ą▓ą╗čÅąĄčé čäčĆąĄą╣ą╝ąŠą╝ ą┐ąŠč鹊ą║ą░ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ą┤ą░ąĮąĮčŗčģ. |

| - |

6 |

NC |

No Connect. ąŁč鹊čé ą▓čŗą▓ąŠą┤ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąŠčüčéą░ą▓ą╗ąĄąĮ ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗą╝. |

Integral Nonlinearity, INL (ąĖąĮč鹥ą│čĆą░ą╗čīąĮą░čÅ ąĮąĄą╗ąĖąĮąĄą╣ąĮąŠčüčéčī). ąŁč鹊 ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠąĄ ąŠčéą║ą╗ąŠąĮąĄąĮąĖąĄ ąŠčé ą┐čĆčÅą╝ąŠą╣ ą╗ąĖąĮąĖąĖ, ą┐čĆąŠčģąŠą┤čÅčēąĄą╣ č湥čĆąĄąĘ ą║čĆą░ą╣ąĮąĖąĄ č鹊čćą║ąĖ čäčāąĮą║čåąĖąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ąÉą”ą¤. ąÜąŠąĮąĄčćąĮčŗąĄ č鹊čćą║ąĖ ąĮą░čģąŠą┤čÅčéčüčÅ ąĮą░ ąĮčāą╗ąĄą▓ąŠą╣ čłą║ą░ą╗ąĄ, č鹊čćą║ą░ ąĮą░ 1/2 LSB ąĮąĖąČąĄ ą┐ąĄčĆą▓ąŠą│ąŠ ą┐ąĄčĆąĄčģąŠą┤ą░ ą║ąŠą┤ą░, ąĖ ąĮą░ ą┐ąŠą╗ąĮąŠą╣ čłą║ą░ą╗ąĄ, ąĮą░ 1/2 LSB ą▓čŗčłąĄ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ ą┐ąĄčĆąĄčģąŠą┤ą░ ą║ąŠą┤ą░.

Differential Nonlinearity, DNL (ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮą░čÅ ąĮąĄą╗ąĖąĮąĄą╣ąĮąŠčüčéčī). ąŁč鹊 čĆą░ąĘąĮąĖčåą░ ą╝ąĄąČą┤čā ąĖąĘą╝ąĄčĆąĄąĮąĮčŗą╝ ąĖ ąĖą┤ąĄą░ą╗čīąĮčŗą╝ ąĖąĘą╝ąĄąĮąĄąĮąĖąĄą╝ 1 LSB ą╝ąĄąČą┤čā ą┤ą▓čāą╝čÅ čüąŠčüąĄą┤ąĮąĖą╝ąĖ ą▓čŗčģąŠą┤ąĮčŗą╝ąĖ ą║ąŠą┤ą░ą╝ąĖ ADC.

Offset Error (ąŠčłąĖą▒ą║ą░ čüą╝ąĄčēąĄąĮąĖčÅ). ąŁč鹊 ąŠčéą║ą╗ąŠąĮąĄąĮąĖąĄ ąŠčé ą┐ąĄčĆą▓ąŠą│ąŠ ą┐ąĄčĆąĄčģąŠą┤ą░ ą║ąŠą┤ą░ (00...000) ą║ (00...001) ąŠčé ąĖą┤ąĄą░ą╗čīąĮąŠą│ąŠ, ąĮą░ą┐čĆąĖą╝ąĄčĆ AGND + 1 LSB.

Gain Error (ąŠčłąĖą▒ą║ą░ čāčüąĖą╗ąĄąĮąĖčÅ). ąŁč鹊 ąŠčéą║ą╗ąŠąĮąĄąĮąĖąĄ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ ą┐ąĄčĆąĄčģąŠą┤ą░ ą║ąŠą┤ą░ (111 ... 110) ą║ (111...111) ąŠčé ąĖą┤ąĄą░ą╗čīąĮąŠą│ąŠ (ąĮą░ą┐čĆąĖą╝ąĄčĆ, VREF ŌłÆ 1 LSB) ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ ą║ą░ą║ ąŠčłąĖą▒ą║ą░ čüą╝ąĄčēąĄąĮąĖčÅ ą▒čŗą╗ą░ čüą║ąŠčĆčĆąĄą║čéąĖčĆąŠą▓ą░ąĮą░.

Track-and-Hold Acquisition Time (ą▓čĆąĄą╝čÅ ąĘą░čģą▓ą░čéą░ čüčģąĄą╝čŗ ą▓čŗą▒ąŠčĆą║ąĖ-čģčĆą░ąĮąĄąĮąĖčÅ). ąŻčüąĖą╗ąĖč鹥ą╗čī čüčģąĄą╝čŗ ą▓čŗą▒ąŠčĆą║ąĖ-čģčĆą░ąĮąĄąĮąĖčÅ ą▓ąŠąĘą▓čĆą░čēą░ąĄčéčüčÅ ą▓ čĆąĄąČąĖą╝ ąŠčéčüą╗ąĄąČąĖą▓ą░ąĮąĖčÅ čüąĖą│ąĮą░ą╗ą░ ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ. ąÆčĆąĄą╝čÅ ąĘą░čģą▓ą░čéą░ čüčģąĄą╝čŗ ą▓čŗą▒ąŠčĆą║ąĖ-čģčĆą░ąĮąĄąĮąĖčÅ čŹč鹊 ą▓čĆąĄą╝čÅ, ą║ąŠč鹊čĆąŠąĄ čéčĆąĄą▒čāąĄčéčüčÅ, čćč鹊ą▒čŗ ą▓čŗčģąŠą┤ čāčüąĖą╗ąĖč鹥ą╗čÅ čüčģąĄą╝čŗ ą▓čŗą▒ąŠčĆą║ąĖ-čģčĆą░ąĮąĄąĮąĖčÅ ą┤ąŠčüčéąĖą│ ą║ąŠąĮąĄčćąĮąŠą╣ ą▓ąĄą╗ąĖčćąĖąĮčŗ, ą▓ ą┐čĆąĄą┤ąĄą╗ą░čģ ┬▒1 LSB ą┐ąŠčüą╗ąĄ ąŠą║ąŠąĮčćą░ąĮąĖčÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ. ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. čĆą░ąĘą┤ąĄą╗ "ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü".

Signal-to-(Noise + Distortion) Ratio (SNR, SINAD). ąśąĘą╝ąĄčĆąĄąĮąĮąŠąĄ čüąŠąŠčéąĮąŠčłąĄąĮąĖąĄ čüąĖą│ąĮą░ą╗/čłčāą╝ (čŹč鹊 SNR) ąĖą╗ąĖ čüąĖą│ąĮą░ą╗/(čłčāą╝+ąĖčüą║ą░ąČąĄąĮąĖčÅ) (čŹč鹊 SINAD) ąĮą░ ą▓čŗčģąŠą┤ąĄ ąÉą”ą¤. ąĪąĖą│ąĮą░ą╗ čŹč鹊 čüčĆąĄą┤ąĮąĄą║ą▓ą░ą┤čĆą░čéąĖč湥čüą║ą░čÅ ą░ą╝ą┐ą╗ąĖčéčāą┤ą░ (RMS, root mean square) ąŠčüąĮąŠą▓ąĮąŠą╣ ąĖąĘą╝ąĄčĆčÅąĄą╝ąŠą╣ ą▓ąĄą╗ąĖčćąĖąĮčŗ. ą©čāą╝ čŹč鹊 čüčāą╝ą╝ą░ ą▓čüąĄčģ ąĮąĄ ąŠčüąĮąŠą▓ąĮčŗčģ čüąĖą│ąĮą░ą╗ąŠą▓, čćą░čüč鹊čéą░ ą║ąŠč鹊čĆčŗčģ ą╝ąĄąĮčīčłąĄ ą┐ąŠą╗ąŠą▓ąĖąĮčŗ čćą░čüč鹊čéčŗ ą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ (fS/2, ąĖčüą║ą╗čÄčćą░čÅ ą┐ąŠčüč鹊čÅąĮąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ). ąĪąŠąŠčéąĮąŠčłąĄąĮąĖąĄ ąĘą░ą▓ąĖčüąĖčé ąŠčé ą║ąŠą╗ąĖč湥čüčéą▓ą░ čāčĆąŠą▓ąĮąĄą╣ ą║ą▓ą░ąĮč鹊ą▓ą░ąĮąĖčÅ ą▓ ą┐čĆąŠčåąĄčüčüąĄ ąŠčåąĖčäčĆąŠą▓ą║ąĖ čüąĖą│ąĮą░ą╗ą░; č湥ą╝ ą▒ąŠą╗čīčłąĄ čāčĆąŠą▓ąĮąĄą╣, č鹥ą╝ ą╝ąĄąĮčīčłąĄ čłčāą╝ ą║ą▓ą░ąĮč鹊ą▓ą░ąĮąĖčÅ. ąóąĄąŠčĆąĄčéąĖč湥čüą║ąŠąĄ čüąŠąŠčéąĮąŠčłąĄąĮąĖąĄ SNR (SINAD) ą┤ą╗čÅ ąĖą┤ąĄą░ą╗čīąĮąŠą│ąŠ N-čĆą░ąĘčĆčÅą┤ąĮąŠą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░č鹥ą╗čÅ ą▓čŗčćąĖčüą╗čÅąĄčéčüčÅ ą┐ąŠ č乊čĆą╝čāą╗ąĄ

Signal-to-(Noise + Distortion) = (6.02 N + 1.76) dB

ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą┤ą╗čÅ 16-ą▒ąĖčéąĮąŠą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░č鹥ą╗čÅ čŹč鹊čé ą┐ą░čĆą░ą╝ąĄčéčĆ čĆą░ą▓ąĄąĮ 98 dB.

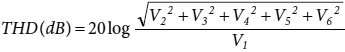

Total Harmonic Distortion, THD (ąŠą▒čēąĖąĄ ą│ą░čĆą╝ąŠąĮąĖč湥čüą║ąĖąĄ ąĖčüą║ą░ąČąĄąĮąĖčÅ). THD čŹč鹊 čüąŠąŠčéąĮąŠčłąĄąĮąĖąĄ čüčāą╝ą╝čŗ rms ą│ą░čĆą╝ąŠąĮąĖą║ ą║ ąŠčüąĮąŠą▓ąĮąŠą╝čā čüąĖą│ąĮą░ą╗čā. ąöą╗čÅ AD7680 ąŠąĮąŠ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąŠ ą║ą░ą║

ą│ą┤ąĄ V1 čŹč鹊 ą░ą╝ą┐ą╗ąĖčéčāą┤ą░ rms ąŠčüąĮąŠą▓ąĮąŠą╣ čćą░čüč鹊čéčŗ ąĖ V2, V3, V4, V5 ąĖ V6 čŹč鹊 ą░ą╝ą┐ą╗ąĖčéčāą┤čŗ rms ą│ą░čĆą╝ąŠąĮąĖą║ ąŠčé ą▓č鹊čĆąŠą╣ ą┤ąŠ čłąĄčüč鹊ą╣.

Peak Harmonic or Spurious Noise (ą┐ąĖą║ąŠą▓ą░čÅ ą│ą░čĆą╝ąŠąĮąĖą║ą░ ąĖą╗ąĖ čüą╗čāčćą░ą╣ąĮčŗą╣ čłčāą╝). ąĪąŠąŠčéąĮąŠčłąĄąĮąĖąĄ ąĘąĮą░č湥ąĮąĖčÅ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ ąĮą░ąĖą▒ąŠą╗čīčłąĄą│ąŠ ą║ąŠą╝ą┐ąŠąĮąĄąĮčéą░ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą▓ ą▓čŗčģąŠą┤ąĮąŠą╝ čüą┐ąĄą║čéčĆąĄ (ą┤ąŠ fS/2, ąĖčüą║ą╗čÄčćą░čÅ ą┐ąŠčüč鹊čÅąĮąĮčāčÄ čüąŠčüčéą░ą▓ą╗čÅčÄčēčāčÄ) ą║ ąĘąĮą░č湥ąĮąĖčÄ rms ąŠčüąĮąŠą▓ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░. ą×ą▒čŗčćąĮąŠ čŹč鹊 ąĘąĮą░č湥ąĮąĖąĄ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą┐ąŠ čüą░ą╝ąŠą╣ ą▒ąŠą╗čīčłąŠą╣ ą│ą░čĆą╝ąŠąĮąĖą║ąĄ ą▓ čüą┐ąĄą║čéčĆąĄ, ąĮąŠ ą┤ą╗čÅ ąÉą”ą¤, ą│ą┤ąĄ ą│ą░čĆą╝ąŠąĮąĖą║ą░ ą┐ąŠčģąŠčĆąŠąĮąĄąĮą░ ąĮą░ č乊ąĮąĄ čłčāą╝ąŠą▓, čŹč鹊 ą▒čāą┤ąĄčé ą┐ąĖą║ąŠą▓čŗą╣ čłčāą╝.

Intermodulation Distortion, IMD (ąĖąĮč鹥čĆą╝ąŠą┤čāą╗čÅčåąĖąŠąĮąĮčŗąĄ ąĖčüą║ą░ąČąĄąĮąĖčÅ). ąÜąŠą│ą┤ą░ ąĮą░ ą▓čģąŠą┤ąĄ ą┐čĆąĖčüčāčéčüčéą▓čāčÄčé 2 čüąĖąĮčāčüąŠąĖą┤ą░ą╗čīąĮčŗčģ čüąĖą│ąĮą░ą╗ą░ čü 2 čćą░čüč鹊čéą░ą╝ąĖ fa ąĖ fb, č鹊 ą╗čÄą▒ąŠąĄ ą░ą║čéąĖą▓ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ, čā ą║ąŠč鹊čĆąŠą│ąŠ ąĄčüčéčī ąĮąĄą╗ąĖąĮąĄą╣ąĮąŠčüčéčī, čüąŠąĘą┤ą░ąĄčé ąĖčüą║ą░ąČąĄąĮąĖčÅ ą║ą░ą║ čüčāą╝ą╝čā ąĖ čĆą░ąĘąĮąŠčüčéčī čćą░čüč鹊čé mfa ┬▒ nfb, ą│ą┤ąĄ m, n = 0, 1, 2, 3. ąŻčüą╗ąŠą▓ąĖčÅ ąĖąĮč鹥čĆą╝ąŠą┤čāą╗čÅčåąĖąŠąĮąĮčŗčģ ąĖčüą║ą░ąČąĄąĮąĖą╣ - ą║ąŠą│ą┤ą░ ąĮąĖ m, ąĮąĖ n ąĮąĄ čĆą░ą▓ąĮčŗ 0. ąØą░ą┐čĆąĖą╝ąĄčĆ, čāčüą╗ąŠą▓ąĖčÅ ą▓č鹊čĆąŠą│ąŠ ą┐ąŠčĆčÅą┤ą║ą░ ą▓ą║ą╗čÄčćą░čÄčé (fa + fb) ąĖ (fa ŌłÆ fb), č鹊ą│ą┤ą░ ą║ą░ą║ čāčüą╗ąŠą▓ąĖčÅ čéčĆąĄčéčīąĄą│ąŠ ą┐ąŠčĆčÅą┤ą║ą░ ą▓ą║ą╗čÄčćą░čÄčé (2fa + fb), (2fa ŌłÆ fb), (fa + 2fb) ąĖ (fa ŌłÆ2fb).

AD7680 ą▒čŗą╗ ą┐čĆąŠč鹥čüčéąĖčĆąŠą▓ą░ąĮ ą┐ąŠ čüčéą░ąĮą┤ą░čĆčéčā CCIF, ą│ą┤ąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ą╗ąĖčüčī ą┤ą▓ąĄ ą▓čģąŠą┤ąĮčŗąĄ čćą░čüč鹊čéčŗ, ą▒ą╗ąĖąĘą║ąĖąĄ ą║ ą║ąŠąĮčåčā ą┐ąŠą╗ąŠčüčŗ ą┐čĆąŠą┐čāčüą║ą░ąĮąĖčÅ ą┐ąŠ ą▓čģąŠą┤čā. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ čāčüą╗ąŠą▓ąĖąĄ ą▓č鹊čĆąŠą│ąŠ ą┐ąŠčĆčÅą┤ą║ą░ ąŠą▒čŗčćąĮąŠ ąĮą░čģąŠą┤ąĖčéčüčÅ ąĮą░ čĆą░čüčüč鹊čÅąĮąĖąĖ ąŠčé ąŠčĆąĖą│ąĖąĮą░ą╗čīąĮčŗčģ ą▓čģąŠą┤ąĮčŗčģ čćą░čüč鹊čé, ąĖ čāčüą╗ąŠą▓ąĖąĄ čéčĆąĄčéčīąĄą│ąŠ ą┐ąŠčĆčÅą┤ą║ą░ ąŠą▒čŗčćąĮąŠ ą┐ąŠ čćą░čüč鹊č鹥 ą▒ą╗ąĖąĘą║ąŠ ą║ ą▓čģąŠą┤ąĮčŗą╝ čćą░čüč鹊čéą░ą╝. ąÆ čĆąĄąĘčāą╗čīčéą░č鹥 čāčüą╗ąŠą▓ąĖčÅ ą▓č鹊čĆąŠą│ąŠ ąĖ čéčĆąĄčéčīąĄą│ąŠ ą┐ąŠčĆčÅą┤ą║ą░ čāą║ą░ąĘą░ąĮčŗ ąŠčéą┤ąĄą╗čīąĮąŠ. ąÆčŗčćąĖčüą╗ąĄąĮąĖąĄ ąĖąĮč鹥čĆą╝ąŠą┤čāą╗čÅčåąĖąŠąĮąĮąŠą│ąŠ ąĖčüą║ą░ąČąĄąĮąĖčÅ čüą┤ąĄą╗ą░ąĮąŠ ą║ą░ą║ ą▓ čüą┐ąĄčåąĖčäąĖą║ą░čåąĖąĖ THD, ą│ą┤ąĄ čŹč鹊 čüąŠąŠčéąĮąŠčłąĄąĮąĖąĄ čüčāą╝ą╝čŗ rms ą┐čĆąŠą┤čāą║č鹊ą▓ ąĖčüą║ą░ąČąĄąĮąĖą╣ ą║ čüčāą╝ą╝ąĄ ą░ą╝ą┐ą╗ąĖčéčāą┤ rms ąŠčüąĮąŠą▓ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░, ą▓čŗčĆą░ąČąĄąĮąĮąŠąĄ ą▓ dB (ą┤ąĄčåąĖą▒ąĄą╗čŗ).

Spurious-Free Dynamic Range, SFDR. ąĪąŠąŠčéąĮąŠčłąĄąĮąĖąĄ ąŠčüąĮąŠą▓ąĮąŠą│ąŠ ą┐ąŠą╗ąĄąĘąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ą║ čüą░ą╝ąŠą╝čā čüąĖą╗čīąĮąŠą╝ ą┐ąŠą▒ąŠčćąĮąŠą╝čā (ą┐ąŠą╝ąĄčģą░). ą×ą┐čĆąĄą┤ąĄą╗čÅąĄčé čĆą░ą▒ąŠčćąĖą╣ ą┤ąĖą░ą┐ą░ąĘąŠąĮ ąÉą”ą¤.

[ąóąĖą┐ąŠą▓čŗąĄ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ, čüą▓čÅąĘą░ąĮąĮčŗąĄ čü ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéčīčÄ]

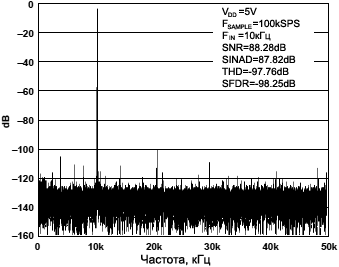

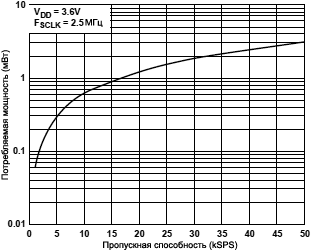

ąØą░ čĆąĖčü. 5 ą┐ąŠą║ą░ąĘą░ąĮ čéąĖą┐ąĖčćąĮčŗą╣ ą│čĆą░čäąĖą║ FFT (ą▒čŗčüčéčĆąŠąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ążčāčĆčīąĄ) ą┤ą╗čÅ AD7680 ąĮą░ čüą║ąŠčĆąŠčüčéąĖ ąŠčåąĖčäčĆąŠą▓ą║ąĖ 100 kSPS ąĖ ą▓čģąŠą┤ąĮąŠą╣ čćą░čüč鹊č鹥 10 ą║ąōčå. ąĀąĖčü. 6 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéčī čüąŠąŠčéąĮąŠčłąĄąĮąĖčÅ čüąĖą│ąĮą░ą╗/čłčāą╝ (signal-to-noise, SNR) ąĖ čüąĖą│ąĮą░ą╗/ąĖčüą║ą░ąČąĄąĮąĖčÅ (signal-to-distortion, SND) ąŠčé ą▓čģąŠą┤ąĮąŠą╣ čćą░čüč鹊čéčŗ ą┤ą╗čÅ čĆą░ąĘąĮčŗčģ ąĮą░ą┐čĆčÅąČąĄąĮąĖą╣ ą┐ąĖčéą░ąĮąĖčÅ ą┐čĆąĖ čüą║ąŠčĆąŠčüčéąĖ ąŠčåąĖčäčĆąŠą▓ą║ąĖ 100 kSPS ąĖ čćą░čüč鹊č鹥 čéą░ą║č鹊ą▓ SCLK 2.5 ą£ąōčå.

ąĀąĖčü. 5. ąöąĖąĮą░ą╝ąĖč湥čüą║ą░čÅ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ą░ AD7680 ąĮą░ čüą║ąŠčĆąŠčüčéąĖ ąŠčåąĖčäčĆąŠą▓ą║ąĖ 100 kSPS.

ąĀąĖčü. 6. AD7680 SINAD ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą╣ ą▓čģąŠą┤ąĮąŠą╣ čćą░čüč鹊čéčŗ ą┤ą╗čÅ čĆą░ąĘą╗ąĖčćąĮčŗčģ ąĮą░ą┐čĆčÅąČąĄąĮąĖą╣ ą┐ąĖčéą░ąĮąĖčÅ ąĖ čüą║ąŠčĆąŠčüčéąĖ ąŠčåąĖčäčĆąŠą▓ą║ąĖ 100 kSPS.

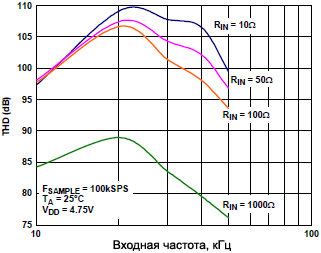

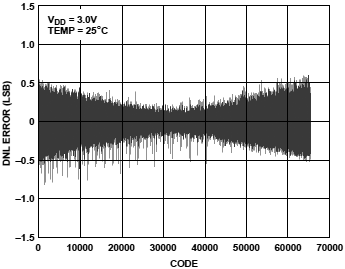

ąØą░ čĆąĖčü. 7 ą┐ąŠą║ą░ąĘą░ąĮ ą│čĆą░čä ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠą▒čēąĖčģ ą│ą░čĆą╝ąŠąĮąĖč湥čüą║ąĖčģ ąĖčüą║ą░ąČąĄąĮąĖą╣ ąŠčé ą▓čģąŠą┤ąĮąŠą╣ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą╣ čćą░čüč鹊čéčŗ ą┤ą╗čÅ čĆą░ąĘą╗ąĖčćąĮčŗčģ ąĮą░ą┐čĆčÅąČąĄąĮąĖą╣ ą┐ąĖčéą░ąĮąĖčÅ. ąĀąĖčü. 8 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą│čĆą░čä ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠą▒čēąĖčģ ą│ą░čĆą╝ąŠąĮąĖč湥čüą║ąĖčģ ąĖčüą║ą░ąČąĄąĮąĖą╣ ąŠčé ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą╣ ą▓čģąŠą┤ąĮąŠą╣ čćą░čüč鹊čéčŗ ą┤ą╗čÅ čĆą░ąĘą╗ąĖčćąĮčŗčģ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖą╣ ąĖčüč鹊čćąĮąĖą║ą░ čüąĖą│ąĮą░ą╗ą░ (čüą╝. čĆą░ąĘą┤ąĄą╗ "ąÉąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ą▓čģąŠą┤"). ąĀąĖčü. 9 ąĖ 10 ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčé čéąĖą┐ąĖčćąĮčŗąĄ ą│čĆą░čäąĖą║ąĖ INL ąĖ DNL ą┤ą╗čÅ ąÉą”ą¤ AD7680.

ąĀąĖčü. 7. ąŚą░ą▓ąĖčüąĖą╝ąŠčüčéčī AD7680 THD ąŠčé ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą╣ ą▓čģąŠą┤ąĮąŠą╣ čćą░čüč鹊čéčŗ ą┤ą╗čÅ čĆą░ąĘą╗ąĖčćąĮčŗčģ ąĮą░ą┐čĆčÅąČąĄąĮąĖą╣ ą┐ąĖčéą░ąĮąĖčÅ ąĖ čüą║ąŠčĆąŠčüčéąĖ ąŠčåąĖčäčĆąŠą▓ą║ąĖ 100 kSPS.

ąĀąĖčü. 8. ąŚą░ą▓ąĖčüąĖą╝ąŠčüčéčī AD7680 THD ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą╣ ą▓čģąŠą┤ąĮąŠą╣ čćą░čüč鹊čéčŗ ą┤ą╗čÅ čĆą░ąĘą╗ąĖčćąĮčŗčģ ą▓čŗčģąŠą┤ąĮčŗčģ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖą╣ ąĖčüč鹊čćąĮąĖą║ą░ čüąĖą│ąĮą░ą╗ą░.

ąĀąĖčü. 9. ąóąĖą┐ąĖčćąĮčŗą╣ INL ą┤ą╗čÅ AD7680.

ąĀąĖčü. 10. ąóąĖą┐ąĖčćąĮčŗą╣ DNL ą┤ą╗čÅ AD7680.

[ąÆąĮčāčéčĆąĄąĮąĮčÅčÅ čüčģąĄą╝ąŠč鹥čģąĮąĖą║ą░]

AD7680 čÅą▓ą╗čÅąĄčéčüčÅ ą▒čŗčüčéčĆčŗą╝, ą╝ą░ą╗ąŠą┐ąŠčéčĆąĄą▒ą╗čÅčÄčēąĖą╝ 16-ą▒ąĖčéąĮčŗą╝ ADC čü ąŠą┤ąĖąĮąŠčćąĮčŗą╝ ą┐ąĖčéą░ąĮąĖąĄą╝. ą£ąĖą║čĆąŠčüčģąĄą╝ą░ ą╝ąŠąČąĄčé čĆą░ą▒ąŠčéą░čéčī ąŠčé ąĖčüč鹊čćąĮąĖą║ą░ ą┐ąĖčéą░ąĮąĖčÅ čü ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄą╝ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ 2.5V .. 5.5V, ąĖ ą╝ąŠąČąĄčé ą┐čĆąĖ čŹč鹊ą╝ ąŠą▒ąĄčüą┐ąĄčćąĖčéčī čüą║ąŠčĆąŠčüčéčī ąŠčåąĖčäčĆąŠą▓ą║ąĖ 100 kSPS ąĮą░ čćą░čüč鹊č鹥 čéą░ą║č鹊ą▓ ąĖąĮč鹥čĆč乥ą╣čüą░ 2.5 ą£ąōčå.

AD7680 ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą▓čüčéčĆąŠąĄąĮąĮčāčÄ ą▓ ą║čĆąĖčüčéą░ą╗ą╗ ą┐ąĄčĆąĄą┤ ąÉą”ą¤ čüčģąĄą╝čā ą▓čŗą▒ąŠčĆą║ąĖ-čģčĆą░ąĮąĄąĮąĖčÅ ąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü - ąĖ ą▓čüąĄ čŹč鹊 ą▓ ą╝ą░ą╗ąĄąĮčīą║ąŠą╝ 6-ą▓čŗą▓ąŠą┤ąĮąŠą╝ ą║ąŠčĆą┐čāčüąĄ SOT-23 ąĖą╗ąĖ 8-ą▓čŗą▓ąŠą┤ąĮąŠą╝ ą║ąŠčĆą┐čāčüąĄ MSOP, čćč鹊 ą┤ą░ąĄčé ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÄ ą┐čĆąĄąĖą╝čāčēąĄčüčéą▓ąŠ ą┐čĆąĖ čĆą░ąĘčĆą░ą▒ąŠčéą║ąĄ ą┐ąĄčćą░čéąĮąŠą╣ ą┐ą╗ą░čéčŗ ą▓ čüčĆą░ą▓ąĮąĄąĮąĖąĖ čü ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčŗą╝ąĖ čĆąĄčłąĄąĮąĖčÅą╝ąĖ. ąÆčģąŠą┤ ą┤ą╗čÅ čéą░ą║č鹊ą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ SCLK ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé čéą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗ ą┤ą╗čÅ čüčģąĄą╝čŗ ąÉą”ą¤ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ą┐čĆąĖą▒ą╗ąĖąČąĄąĮąĖčÅ. ąöąĖą░ą┐ą░ąĘąŠąĮ ą▓čģąŠą┤ąĮčŗčģ ąŠčåąĖčäčĆąŠą▓čŗą▓ą░ąĄą╝čŗčģ ąĮą░ą┐čĆčÅąČąĄąĮąĖą╣ ą┤ą╗čÅ AD7680 ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ą┐čĆąĄą┤ąĄą╗ą░čģ ąŠčé 0V ą┤ąŠ VDD. ąÆąĮąĄčłąĮąĄąĄ ąŠčéą┤ąĄą╗čīąĮąŠąĄ ąŠą┐ąŠčĆąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮąĄ čéčĆąĄą▒čāąĄčéčüčÅ, ą┐ąŠčüą║ąŠą╗čīą║čā ąŠąĮąŠ ą▒ąĄčĆąĄčéčüčÅ ąŠčé ą▓čŗą▓ąŠą┤ą░ ą┐ąŠą┤ą░čćąĖ ą┐ąĖčéą░ąĮąĖčÅ VDD.

AD7680 čéą░ą║ąČąĄ ąĖą╝ąĄąĄčé ąŠą┐čåąĖčÄ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ (power-down), ą┐ąŠąĘą▓ąŠą╗čÅčÄčēčāčÄ čŹą║ąŠąĮąŠą╝ąĖčéčī 菹ĮąĄčĆą│ąĖčÄ ąĖčüč鹊čćąĮąĖą║ą░ ą┐ąĖčéą░ąĮąĖčÅ ą╝ąĄąČą┤čā ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅą╝ąĖ. ąŁčéą░ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮą░ ąĮą░ ąŠčüąĮąŠą▓ąĄ čüčéą░ąĮą┤ą░čĆčéąĮąŠą│ąŠ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░, ąĖ ą┐ąŠą┤čĆąŠą▒ąĮąĄąĄ ąŠą┐ąĖčüą░ąĮą░ ą▓ čĆą░ąĘą┤ąĄą╗ąĄ "ąĀąĄąČąĖą╝čŗ čĆą░ą▒ąŠčéčŗ".

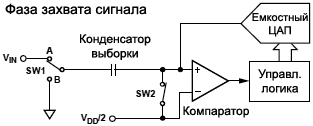

ąÜą░ą║ čĆą░ą▒ąŠčéą░ąĄčé ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ąÉą”ą¤. AD7680 čÅą▓ą╗čÅąĄčéčüčÅ 16-ą▒ąĖčéąĮčŗą╝ ąÉą”ą¤, čĆą░ą▒ąŠčéą░čÄčēąĖą╝ ą┐ąŠ ą┐čĆąĖąĮčåąĖą┐čā ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ą┐čĆąĖą▒ą╗ąĖąČąĄąĮąĖčÅ ąĮą░ ą▒ą░ąĘąĄ ą”ąÉą¤ ąĮą░ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆą░čģ (capacitive DAC). AD7680 ą╝ąŠąČąĄčé ąŠčåąĖčäčĆąŠą▓čŗą▓ą░čéčī ą░ąĮą░ą╗ąŠą│ąŠą▓čŗąĄ ą▓čģąŠą┤ąĮčŗąĄ čüąĖą│ąĮą░ą╗čŗ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąŠčé 0V ą┤ąŠ VDD. ąĀąĖčü. 11 ąĖ 12 čāą┐čĆąŠčēąĄąĮąĮąŠ ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčé čüčģąĄą╝ąŠč鹥čģąĮąĖą║čā ąÉą”ą¤. ąÆ ąĮąĄčæ ą▓čģąŠą┤ąĖčé čāą┐čĆą░ą▓ą╗čÅčÄčēą░čÅ ą╗ąŠą│ąĖą║ą░, SAR ąĖ ąĄą╝ą║ąŠčüčéąĮąŠą╣ DAC. ąĀąĖčü. 11 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ADC ą▓ čäą░ąĘąĄ ąĘą░čģą▓ą░čéą░ ą▓čģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ (acquisition). SW2 ąĘą░ą╝ą║ąĮčāčé, ąĖ SW1 ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ą┐ąŠą╗ąŠąČąĄąĮąĖąĖ A. ąÜąŠą╝ą┐ą░čĆą░č鹊čĆ čāą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ą▓ čüą▒ą░ą╗ą░ąĮčüąĖčĆąŠą▓ą░ąĮąĮąŠą╝ čüąŠčüč鹊čÅąĮąĖąĖ ąĖ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ ą┤ą╗čÅ čģčĆą░ąĮąĄąĮąĖčÅ ą▓čŗą▒ąŠčĆą║ąĖ čüąĖą│ąĮą░ą╗ą░ ąĘą░čģą▓ą░čéčŗą▓ą░ąĄčé čāčĆąŠą▓ąĄąĮčī ąĮą░ ą▓čģąŠą┤ąĄ VIN.

ąĀąĖčü. 11. ążą░ąĘą░ ąĘą░čģą▓ą░čéą░ ą▓čģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ąÉą”ą¤ (ADC Acquisition Phase).

ąÜąŠą│ą┤ą░ ADC ąĮą░čćąĖąĮą░ąĄčé ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ, ą║ą╗čÄčć SW2 ąŠčéą║čĆčŗą▓ą░ąĄčéčüčÅ ąĖ SW1 ą┐ąĄčĆąĄą║ą╗čÄčćą░ąĄčéčüčÅ ą▓ ą┐ąŠą╗ąŠąČąĄąĮąĖąĄ B, čćč鹊 ą┐čĆąĖą▓ąŠą┤ąĖčé ą║ čĆą░ąĘą▒ą░ą╗ą░ąĮčüąĖčĆąŠą▓ą║ąĄ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ (čĆąĖčü. 12). ąøąŠą│ąĖą║ą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĖ čæą╝ą║ąŠčüčéąĮčŗą╣ DAC ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ ą┐čĆąĖą▒ą░ą▓ą╗ąĄąĮąĖčÅ ąĖ ą▓čŗčćąĖčéą░ąĮąĖčÅ čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ąĘą░čĆčÅą┤ ąĖąĘ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆą░ ąĘą░čģą▓ą░čéą░, ą┐čŗčéą░čÅčüčī ą┐ąĄčĆąĄą▓ąĄčüčéąĖ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ą▒ą░ą╗ą░ąĮčüą░. ąÜąŠą│ą┤ą░ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆ ą┐čĆąŠčģąŠą┤ąĖčé ą▓čüąĄ čüčéą░ą┤ąĖąĖ ą▒ą░ą╗ą░ąĮčüąĖčĆąŠą▓ą║ąĖ, ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ čüčćąĖčéą░ąĄčéčüčÅ ąĘą░ą▓ąĄčĆčłąĄąĮąĮąŠą╣. ąŻą┐čĆą░ą▓ą╗čÅčÄčēą░čÅ ą╗ąŠą│ąĖą║ą░ ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ą▓čŗčģąŠą┤ąĮąŠą╣ ą║ąŠą┤ ADC (čüą╝. čĆą░ąĘą┤ąĄą╗ "ą¤ąĄčĆąĄą┤ą░č鹊čćąĮą░čÅ čäčāąĮą║čåąĖčÅ ąÉą”ą¤").

ąĀąĖčü. 12. ążą░ąĘą░ ąŠčåąĖčäčĆąŠą▓ą║ąĖ čüąĖą│ąĮą░ą╗ą░ ąÉą”ą¤ (ADC Conversion Phase).

[ąÉąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ą▓čģąŠą┤]

ąØą░ čĆąĖčü. 13 ą┐ąŠą║ą░ąĘą░ąĮą░ 菹║ą▓ąĖą▓ą░ą╗ąĄąĮčéąĮą░čÅ čüčģąĄą╝ą░ čüčéčĆčāą║čéčāčĆčŗ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ą▓čģąŠą┤ą░ AD7680. ąöą▓ą░ ą┤ąĖąŠą┤ą░ D1 ąĖ D2 ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÄčé ąĘą░čēąĖčéčā ESD ą┤ą╗čÅ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ą▓čģąŠą┤ą░. ąĪą╗ąĄą┤čāąĄčé ąĘą░ą▒ąŠčéąĖčéčīčüčÅ ąŠ č鹊ą╝, čćč鹊ą▒čŗ čāčĆąŠą▓ąĄąĮčī ą▓čģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ąĮąĄ ą▓čŗčģąŠą┤ąĖą╗ ąĘą░ ą┐čĆąĄą┤ąĄą╗čŗ ą┤ąĖą░ą┐ą░ąĘąŠąĮą░ GND-0.3V .. VCC+0.3V. ą¤čĆąĖčćąĖąĮą░ ą┐ąŠąĮčÅčéąĮą░ - ą▓ąĮąĄ čŹč鹊ą│ąŠ ą┤ąĖą░ą┐ą░ąĘąŠąĮą░ ą┤ąĖąŠą┤čŗ ąŠčéą║čĆčŗą▓ą░čÄčéčüčÅ, ąĖ č湥čĆąĄąĘ ąĮąĖčģ ą┐ąŠč鹥č湥čé ą▓čģąŠą┤ąĮąŠą╣ č鹊ą║. ą£ą░ą║čüąĖą╝ą░ą╗čīąĮčŗą╣ ą┤ąŠą┐čāčüčéąĖą╝čŗą╣ č鹊ą║, ą┐ąŠčüą╗ąĄ ą║ąŠč鹊čĆąŠą│ąŠ ąŠąĮąĖ ą╝ąŠą│čāčé ą┐ąŠą▓čĆąĄą┤ąĖčéčīčüčÅ, čüąŠčüčéą░ą▓ą╗čÅąĄčé 10 ą╝ąÉ. ąÜąŠąĮą┤ąĄąĮčüą░č鹊čĆ C1 ąĮą░ čĆąĖčü. 13 ąĖą╝ąĄąĄčé ąŠą▒čŗčćąĮąŠ ąĄą╝ą║ąŠčüčéčī ąŠą║ąŠą╗ąŠ 5 ą┐ąż, ąĖ ąŠąĮ ąŠčéčĆą░ąČą░ąĄčé ąĄą╝ą║ąŠčüčéčī ą▓čŗą▓ąŠą┤ą░ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ. ąĀąĄąĘąĖčüč鹊čĆ R1 čÅą▓ą╗čÅąĄčéčüčÅ čüąŠčüčéą░ą▓ąĮčŗą╝ ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą╝, ą▓ ą║ąŠč鹊čĆčŗą╣ ą▓čģąŠą┤ąĖčé ą▓čģąŠą┤ąĮąŠąĄ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ ą║ą╗čÄčćą░ čüčģąĄą╝čŗ ą▓čŗą▒ąŠčĆą║ąĖ/čģčĆą░ąĮąĄąĮąĖčÅ (čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ čŹč鹊ą│ąŠ čĆąĄąĘąĖčüč鹊čĆą░ ąŠą║ąŠą╗ąŠ 25╬®). ąĢą╝ą║ąŠčüčéčī C2 čŹč鹊 ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ ą▓čŗą▒ąŠčĆą║ąĖ ADC, ąĖ čā ąĮąĄą│ąŠ čéąĖą┐ąĖčćąĮą░čÅ ąĄą╝ą║ąŠčüčéčī ą┐ąŠčĆčÅą┤ą║ą░ 25 ą┐ąż. ąöą╗čÅ ą┐čĆąĖą╗ąŠąČąĄąĮąĖą╣, ą│ą┤ąĄ ąĮčāąČąĮą░ ąŠčåąĖčäčĆąŠą▓ą║ą░ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ, čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ą▓čŗčĆąĄąĘą░čéčī ą▓čŗčüąŠą║ąŠčćą░čüč鹊čéąĮčāčÄ čüąŠčüčéą░ą▓ą╗čÅčÄčēčāčÄ ąĖąĘ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ą▓čģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░, ąĖčüą┐ąŠą╗čīąĘčāčÅ ążąØą¦ ąĮą░ čĆąĄąĘąĖčüč鹊čĆą░čģ ąĖ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆą░čģ (RC low-pass filter), ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗą╣ ą║ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą╝čā ą▓čģąŠą┤čā. ąÆ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅčģ, ą│ą┤ąĄ ą║čĆąĖčéąĖčćąĮčŗ ą│ą░čĆą╝ąŠąĮąĖč湥čüą║ąĖąĄ ąĖčüą║ą░ąČąĄąĮąĖčÅ ąĖ čüąŠąŠčéąĮąŠčłąĄąĮąĖąĄ čüąĖą│ąĮą░ą╗/čłčāą╝, ą░ąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ą▓čģąŠą┤ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą║ ąĖčüč鹊čćąĮąĖą║čā čüąĖą│ąĮą░ą╗ą░ čü ąĮąĖąĘą║ąĖą╝ ą▓čŗčģąŠą┤ąĮčŗą╝ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄą╝. ąæąŠą╗čīčłąŠąĄ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ ąĖčüč鹊čćąĮąĖą║ą░ čüąĖą│ąĮą░ą╗ą░ ąĘąĮą░čćąĖč鹥ą╗čīąĮąŠ ą▓ą╗ąĖčÅąĄčé ąĮą░ ą║ą░č湥čüčéą▓ąŠ ąŠčåąĖčäčĆąŠą▓ą║ąĖ ą▓čģąŠą┤ąĮąŠą│ąŠ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ADC. ąöą╗čÅ čŹč鹊ą│ąŠ ą╝ąŠąČąĄčé ą┐ąŠčéčĆąĄą▒ąŠą▓ą░čéčīčüčÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą▓čģąŠą┤ąĮąŠą╣ ą▒čāč乥čĆąĮčŗą╣ čāčüąĖą╗ąĖč鹥ą╗čī. ąÆčŗą▒ąŠčĆ ąŠą┐ąĄčĆą░čåąĖąŠąĮąĮąŠą│ąŠ čāčüąĖą╗ąĖč鹥ą╗čÅ ąĘą░ą▓ąĖčüąĖčé ąŠčé ą║ąŠąĮą║čĆąĄčéąĮąŠą│ąŠ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ. ąÜąŠą│ą┤ą░ čāčüąĖą╗ąĖč鹥ą╗čī ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ, ą▓čŗčģąŠą┤ąĮąŠąĄ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ ąĖčüč鹊čćąĮąĖą║ą░ čüąĖą│ąĮą░ą╗ą░ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ąĮąĖąĘą║ąĖą╝. ą£ą░ą║čüąĖą╝ą░ą╗čīąĮąŠąĄ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ ąĖčüč鹊čćąĮąĖą║ą░ čüąĖą│ąĮą░ą╗ą░ ąĘą░ą▓ąĖčüąĖčé ąŠčé ą┤ąŠą┐čāčüčéąĖą╝ąŠą╣ ą▓ąĄą╗ąĖčćąĖąĮčŗ ąŠą▒čēąĖčģ ą│ą░čĆą╝ąŠąĮąĖč湥čüą║ąĖčģ ąĖčüą║ą░ąČąĄąĮąĖą╣ (total harmonic distortion, THD). THD čāą▓ąĄą╗ąĖčćąĖą▓ą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ čāą▓ąĄą╗ąĖčćąĖą▓ą░ąĄčéčüčÅ ą▓čŗčģąŠą┤ąĮąŠąĄ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ ąĖčüč鹊čćąĮąĖą║ą░ čüąĖą│ąĮą░ą╗ą░, ąĖ čāčģčāą┤čłą░ąĄčéčüčÅ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéčī ąÉą”ą¤ (čüą╝. čĆąĖčü. 8).

ąĀąĖčü. 13. ąŁą║ą▓ąĖą▓ą░ą╗ąĄąĮčéąĮą░čÅ čüčģąĄą╝ą░ čåąĄą┐ąĖ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ą▓čģąŠą┤ą░.

[ą¤ąĄčĆąĄą┤ą░č鹊čćąĮą░čÅ čäčāąĮą║čåąĖčÅ ąÉą”ą¤]

ąÆčŗčģąŠą┤ąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą║ąŠą┤ą░ AD7680 ąĖą╝ąĄąĄčé ąŠą▒čŗčćąĮčŗą╣ ą┐čĆčÅą╝ąŠą╣ ą┤ą▓ąŠąĖčćąĮčŗą╣ č乊čĆą╝ą░čé. ą¤ąĄčĆąĄčģąŠą┤čŗ ą║ąŠą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤čÅčé ą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ čåąĄą╗ąŠčćąĖčüą╗ąĄąĮąĮčŗčģ ąĘąĮą░č湥ąĮąĖčÅčģ LSB, čé. ąĄ., 1 LSB, 2 LSB. ąÆąĄčü ą╝ą╗ą░ą┤čłąĄą│ąŠ čĆą░ąĘčĆčÅą┤ą░ čüąŠčüčéą░ą▓ą╗čÅąĄčé VDD/65536. ąśą┤ąĄą░ą╗čīąĮą░čÅ ą┐ąĄčĆąĄčģąŠą┤ąĮą░čÅ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ą░ ą┤ą╗čÅ AD7680 ą┐ąŠą║ą░ąĘą░ąĮą░ ąĮą░ čĆąĖčü. 14.

ąĀąĖčü. 14. ąźą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ą░ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ AD7680.

[ąóąĖą┐ąŠą▓ą░čÅ čüčģąĄą╝ą░ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ]

ąĀąĖčü. 15. ą×ą▒čŗčćąĮą░čÅ čüčģąĄą╝ą░ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ AD7680.

ą×ą┐ąŠčĆąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┤ą╗čÅ ąÉą”ą¤ VREF ą▒ąĄčĆąĄčéčüčÅ ąŠčé ą▓čŗą▓ąŠą┤ą░ ą┐ąĖčéą░ąĮąĖčÅ VDD, čéą░ą║ čćč鹊 ąŠąĮąŠ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī čģąŠčĆąŠčłąŠ čĆą░ąĘą▓čÅąĘą░ąĮąŠ ąŠčé ą┐ąŠą╝ąĄčģ. ąĀąĄąĘčāą╗čīčéą░čé ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ąĮą░ ą▓čŗčģąŠą┤ąĄ ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮ ą║ą░ą║ 24-ą▒ąĖčéąĮąŠąĄ čüą╗ąŠą▓ąŠ, ąĖą╗ąĖ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮąŠ ą▓čüąĄ 16 ą▒ąĖčé ą║ąŠąĮą▓ąĄčĆčüąĖąĖ čĆąĄąĘčāą╗čīčéą░čéą░ ą╝ąŠą│čāčé ą▒čŗčéčī ą┐ąŠą╗čāč湥ąĮčŗ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ ą╝ąĖąĮąĖą╝čāą╝ 20 čéą░ą║č鹊ą▓ SCLK. ąŁč鹊čé 20-/24-ą▒ąĖčéąĮčŗą╣ ą┐ąŠč鹊ą║ ą┤ą░ąĮąĮčŗčģ čüąŠčüč鹊ąĖčé ąĖąĘ 4 ąĮą░čćą░ą╗čīąĮčŗčģ ąĮčāą╗ąĄą╣, ąĘą░ ą║ąŠč鹊čĆčŗą╝ąĖ ąĖą┤čāčé 16 ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ, ąĘą░ ą║ąŠč鹊čĆčŗą╝ąĖ ąĖą┤čāčé ąĄčēąĄ 4 ąĘą░ą▓ąĄčĆčłą░čÄčēąĖčģ ąĮčāą╗čÅ, ąĄčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┐ą░čćą║ą░ ąĖąĘ 24 čéą░ą║č鹊ą▓ SCLK. ąöą╗čÅ ą┐čĆąĖą╗ąŠąČąĄąĮąĖą╣, ą│ą┤ąĄ ą▓ą░ąČąĮą░ 菹║ąŠąĮąŠą╝ąĖčÅ ą▓ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĖ 菹ĮąĄčĆą│ąĖąĖ, ą┤ąŠą╗ąČąĄąĮ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ čĆąĄąČąĖą╝ power-down ą╝ąĄąČą┤čā ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅą╝ąĖ, ąĖą╗ąĖ ą╝ąĄąČą┤čā ą┐ą░čćą║ą░ą╝ąĖ ąĖąĘ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖą╣ (čüą╝. čĆą░ąĘą┤ąĄą╗ "ąĀąĄąČąĖą╝čŗ čĆą░ą▒ąŠčéčŗ").

ążą░ą║čéąĖč湥čüą║ąĖ, ą┐ąŠčüą║ąŠą╗čīą║čā čéčĆąĄą▒čāąĄą╝čŗą╣ č鹊ą║ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ AD7680 ą╝ą░ą╗, ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖčüč鹊čćąĮąĖą║ą░ ą┐ąĖčéą░ąĮąĖčÅ ą┤ą╗čÅ VDD ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī č鹊čćąĮčŗą╣ ąĖčüč鹊čćąĮąĖą║ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ. ąØą░ą┐čĆąĖą╝ąĄčĆ, ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą╝ąĖą║čĆąŠčüčģąĄą╝čā ą│ąĄąĮąĄčĆą░č鹊čĆą░ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ REF19x (REF195 ą┤ą╗čÅ 5V ąĖą╗ąĖ REF193 ą┤ą╗čÅ 3 V) ąĖą╗ąĖ AD780, čćč鹊ą▒čŗ ą┐ąŠą┤ą░čéčī čéčĆąĄą▒čāąĄą╝ąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮą░ ADC (čüą╝. čĆąĖčü. 15). ąóą░ą║ą░čÅ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ąŠčüąŠą▒ąĄąĮąĮąŠ ą┐ąŠą╗ąĄąĘąĮą░, ą║ąŠą│ą┤ą░ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ čüą╗ąĖčłą║ąŠą╝ ąĘą░čłčāą╝ą╗ąĄąĮąŠ, ąĖą╗ąĖ ąĄčüą╗ąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ ą▓ čüąĖčüč鹥ą╝ąĄ čüąĖą╗čīąĮąŠ ąŠčéą╗ąĖčćą░čÄčéčüčÅ ąŠčé čĆą░ą▒ąŠč湥ą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ AD7680, ąĮą░ą┐čĆąĖą╝ąĄčĆ ąĄčüčéčī ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ 15V. ąÆčŗčģąŠą┤ REF19x ąĖą╗ąĖ AD780 ą▓ą┐ąŠą╗ąĮąĄ ą┐ąŠą┤čģąŠą┤ąĖčé ą┤ą╗čÅ VDD AD7680. ąöą╗čÅ čäąĖą╗čīčéčĆą░čåąĖąĖ VDD čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čĆą░ąĘą▓čÅąĘčŗą▓ą░čÄčēąĖąĄ ą║ąĄčĆą░ą╝ąĖč湥čüą║ąĖąĄ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆčŗ ąĄą╝ą║ąŠčüčéčīčÄ ą┐ąŠčĆčÅą┤ą║ą░ 100 ąĮąż čü ąĮąĖąĘą║ąĖą╝ ESR (Farnell 335-1816) ąĖ 10╬╝F čéą░ąĮčéą░ą╗ąŠą▓čŗą╣ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ čü ąĮąĖąĘą║ąĖą╝ ESR (Farnell 197-130).

ą”ąĖčäčĆąŠą▓čŗąĄ ą▓čŗą▓ąŠą┤čŗ. ąöą╗čÅ čåąĖčäčĆąŠą▓čŗčģ ą▓čģąŠą┤ąŠą▓ AD7680 ą┤ąĄą╣čüčéą▓čāčÄčé čüąŠą▓čüąĄą╝ ą┤čĆčāą│ąĖąĄ ąŠą│čĆą░ąĮąĖč湥ąĮąĖčÅ, ąŠčéą╗ąĖčćą░čÄčēąĖąĄčüčÅ ąŠčé ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ą▓čģąŠą┤ą░. ąØą░ čåąĖčäčĆąŠą▓ąŠą╣ ą▓čģąŠą┤ ą╝ąŠąČąĮąŠ ą┐ąŠą┤ą░čéčī čāčĆąŠą▓ąĄąĮčī ą┤ąŠ 7V, čé. ąĄ. ąĘą┤ąĄčüčī ąĮąĄčé ąŠą│čĆą░ąĮąĖč湥ąĮąĖčÅ VDD+0.3V, ą║ą░ą║ąŠąĄ ą┤ąĄą╣čüčéą▓čāąĄčé ą┤ą╗čÅ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ą▓čģąŠą┤ą░ inputs. ąØą░ą┐čĆąĖą╝ąĄčĆ, ąĄčüą╗ąĖ AD7680 čĆą░ą▒ąŠčéą░ąĄčé čü VDD=3V, ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čåąĖčäčĆąŠą▓čŗąĄ ą╗ąŠą│ąĖč湥čüą║ąĖąĄ čāčĆąŠą▓ąĮąĖ 5V. ą×ą┤ąĮą░ą║ąŠ čüą╗ąĄą┤čāąĄčé ą┐ąŠą╝ąĮąĖčéčī, čćč鹊 ąĮą░ ą▓čŗčģąŠą┤ąĄ SDATA ą▒čāą┤ąĄčé ą▓čüąĄ ąĄčēąĄ čāčĆąŠą▓ąĄąĮčī 3V ą┤ą╗čÅ ą╗ąŠą│. 1, ą║ąŠą│ą┤ą░ VDD=3V.

ąöčĆčāą│ąŠąĄ ą┐čĆąĄąĖą╝čāčēąĄčüčéą▓ąŠ čéą░ą║ąŠą╣ ąŠčĆą│ą░ąĮąĖąĘą░čåąĖąĖ čåąĖčäčĆąŠą▓čŗčģ ą▓čģąŠą┤ąŠą▓ SCLK ~CS (čāčĆąŠą▓ąĮąĖ ąĮą░ ąĮąĖčģ ąĮąĄ ąŠą│čĆą░ąĮąĖč湥ąĮčŗ VDD+0.3V) čüąŠčüč鹊ąĖčé ą▓ č鹊ą╝, čćč鹊 ą╝ąŠąČąĮąŠ ąĖąĘą▒ąĄąČą░čéčī ą┐čĆąŠą▒ą╗ąĄą╝, čüą▓čÅąĘą░ąĮąĮčŗčģ čü ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčīčÄ ą┐ąŠą┤ą░čćąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖą╣ ą┐ąĖčéą░ąĮąĖčÅ ą┐čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ. ąĢčüą╗ąĖ čāčĆąŠą▓ąĄąĮčī ąĮą░ čŹčéąĖčģ čåąĖčäčĆąŠą▓čŗčģ ą▓čģąŠą┤ą░čģ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čĆą░ąĮčīčłąĄ, č湥ą╝ ą┐ąŠčÅą▓ąĖčéčüčÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ VDD, ąĮąĄčé čĆąĖčüą║ą░ ą┐ąŠą▓čĆąĄąČą┤ąĄąĮąĖčÅ čåąĖčäčĆąŠą▓čŗčģ ą▓čģąŠą┤ąŠą▓ ąĖąĘ-ąĘą░ ąĘą░čēąĄą╗ą║ąĖą▓ą░ąĮąĖčÅ ą┐ąŠą╗čāą┐čĆąŠą▓ąŠą┤ąĮąĖą║ąŠą▓čŗčģ čüčéčĆčāą║čéčāčĆ, ą║ą░ą║ ą╝ąŠą│ą╗ąŠ ą▒čŗ ą┐čĆąŠąĖąĘąŠą╣čéąĖ čü ą░ąĮą░ą╗ąŠą│ąŠą▓čŗą╝ ą▓čģąŠą┤ąŠą╝, ąĄčüą╗ąĖ ą▒čŗ ą║ ąĮąĄą╝čā ą▒čŗą╗ąŠ ą┐čĆąĖą╗ąŠąČąĄąĮąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ čāčĆąŠą▓ąĮąĄą╝ ąĮą░ 0.3V ą▓čŗčłąĄ, č湥ą╝ ą┐ąŠą┤ą░ąĮąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮą░ VDD.

[ąĀąĄąČąĖą╝čŗ čĆą░ą▒ąŠčéčŗ]

ąĀąĄąČąĖą╝ čĆą░ą▒ąŠčéčŗ AD7680 ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝ ą╗ąŠą│ąĖč湥čüą║ąĖą╝ čüąŠčüč鹊čÅąĮąĖąĄą╝ čüąĖą│ąĮą░ą╗ą░ CS ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ. ą£ąŠąČąĄčé ą▒čŗčéčī 2 ą▓ąŠąĘą╝ąŠąČąĮčŗčģ čĆąĄąČąĖą╝ą░ čĆą░ą▒ąŠčéčŗ, normal ąĖ power-down. ą£ąŠą╝ąĄąĮčé, ą▓ ą║ąŠč鹊čĆąŠą╝ ~CS ą┐ąĄčĆąĄą▓ąŠą┤ąĖčéčüčÅ ą▓ ą╗ąŠą│. 1 ą┐ąŠčüą╗ąĄ ąĖąĮąĖčåąĖąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ, ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé, ą▓ąŠą╣ą┤ąĄčé ąĖą╗ąĖ ąĮąĄčé AD7680 ą▓ čĆąĄąČąĖą╝ power-down. ą¤ąŠą┤ąŠą▒ąĮčŗą╝ ąŠą▒čĆą░ąĘąŠą╝, ąĄčüą╗ąĖ AD7680 čāąČąĄ ą▓ čĆąĄąČąĖą╝ąĄ power-down, ~CS ą╝ąŠąČąĄčé čāą┐čĆą░ą▓ą╗čÅčéčī, ą▓ąĄčĆąĮąĄčéčüčÅ ą╗ąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ ą▓ čĆąĄąČąĖą╝ normal, ąĖą╗ąĖ ąŠčüčéą░ąĮąĄčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ power-down. ąŁčéąĖ čĆąĄąČąĖą╝čŗ čĆą░ą▒ąŠčéčŗ čĆą░ąĘčĆą░ą▒ąŠčéą░ąĮčŗ čü čåąĄą╗čīčÄ ą┐čĆąĄą┤ąŠčüčéą░ą▓ąĖčéčī ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą│ąĖą▒ą║ąŠą│ąŠ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čŹąĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄą╝. ąóą░ą║ą░čÅ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąŠą┐čéąĖą╝ąĖąĘąĖčĆąŠą▓ą░čéčī čüąŠąŠčéąĮąŠčłąĄąĮąĖąĄ čĆą░čüčüąĄąĖą▓ą░ąĄą╝ą░čÅ ą╝ąŠčēąĮąŠčüčéčī / čüą║ąŠčĆąŠčüčéčī ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čĆą░ąĘą╗ąĖčćąĮčŗčģ čéčĆąĄą▒ąŠą▓ą░ąĮąĖą╣ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ.

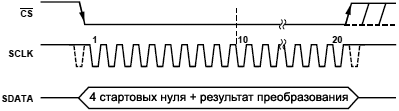

ąĀąĄąČąĖą╝ normal. ąŁč鹊čé čĆąĄąČąĖą╝ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé čüą░ą╝čāčÄ ą▒ąŠą╗čīčłčāčÄ ą┐čĆąŠą┐čāčüą║ąĮčāčÄ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī, ą┐ąŠčüą║ąŠą╗čīą║čā ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ąĮąĄ ą▒ąĄčüą┐ąŠą║ąŠąĖčéčüčÅ ą┐ąŠ ą┐ąŠą▓ąŠą┤čā ąĖąĮč鹥čĆą▓ą░ą╗ąŠą▓ ą▓čĆąĄą╝ąĄąĮąĖ power-up, AD7680 ą▓čüąĄą│ą┤ą░ ąŠčüčéą░ąĄčéčüčÅ ą▓ ą░ą║čéąĖą▓ąĮąŠą╝ čĆąĄąČąĖą╝ąĄ. ąĀąĖčü. 16 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąŠčüąĮąŠą▓ąĮčāčÄ ą┤ąĖą░ą│čĆą░ą╝ą╝čā čĆą░ą▒ąŠčéčŗ AD7680 ą▓ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ.

ąĀąĖčü. 16. ąØąŠčĆą╝ą░ą╗čīąĮčŗą╣ čĆąĄąČąĖą╝ čĆą░ą▒ąŠčéčŗ (Normal).

ą¤čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ąĖąĮąĖčåąĖąĖčĆčāąĄčéčüčÅ čüą┐ą░ą┤ąŠą╝ čāčĆąŠą▓ąĮčÅ ąĮą░ ą▓čģąŠą┤ąĄ ~CS. ą¦č鹊ą▒čŗ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī, čćč鹊 ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ ąŠčüčéą░ąĮąĄčéčüčÅ ą▓čüąĄą│ą┤ą░ ą┐ąŠą╗ąĮąŠčüčéčīčÄ ąĘą░ą┐ąĖčéą░ąĮąĮąŠą╣, ą▓čŗą▓ąŠą┤ ą▓čŗą▒ąŠčĆą║ąĖ ~CS ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ ą┤ąŠą╗ąČąĄąĮ ąŠčüčéą░ą▓ą░čéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą╗ąŠą│. 0 ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ čüą┐ą░ą┤ąŠą▓ 10 SCLK, ą║ąŠč鹊čĆčŗąĄ ą┤ąŠą╗ąČąĮčŗ ą┐čĆąŠą╣čéąĖ ą┐ąŠčüą╗ąĄ čüą┐ą░ą┤ą░ ą▓ ą╗ąŠą│. 0 čāčĆąŠą▓ąĮčÅ ~CS. ąĢčüą╗ąĖ ~CS ą┐ąĄčĆąĄą╣ą┤ąĄčé ą▓ ą╗ąŠą│. 1 ą▓ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé ą┐ąŠčüą╗ąĄ ą┐čĆąŠčģąŠąČą┤ąĄąĮąĖčÅ 10-č鹊ą│ąŠ čüą┐ą░ą┤ą░ SCLK, ąĮąŠ ą┐ąĄčĆąĄą┤ 20-čéčŗą╝ čüą┐ą░ą┤ąŠą╝ SCLK, ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ ąŠčüčéą░ąĮąĄčéčüčÅ ąĘą░ą┐ąĖčéą░ąĮąĮąŠą╣, ąĮąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ą▒čāą┤ąĄčé ą┐čĆąĄčĆą▓ą░ąĮąŠ ąĖ ą▓čŗčģąŠą┤ SDATA ą▓ąĄčĆąĮąĄčéčüčÅ ąŠą▒čĆą░čéąĮąŠ ą▓ čéčĆąĄčéčīąĄ (ąŠčéą║ą╗čÄč湥ąĮąĮąŠąĄ) čüąŠčüč鹊čÅąĮąĖąĄ. ąóčĆąĄą▒čāąĄčéčüčÅ ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ 20 čéą░ą║č鹊ą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ SCLK, čćč鹊ą▒čŗ ą▓čŗą┐ąŠą╗ąĮąĖčéčī ą┐ąŠą╗ąĮąŠąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ąĖ ą┐ąŠą╗čāčćąĖčéčī ą┐ąŠą╗ąĮčŗą╣ čĆąĄąĘčāą╗čīčéą░čé. ąĢčüą╗ąĖ ą▒čāą┤ąĄčé ą▓čŗą┤ą░ąĮčŗ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠ čéą░ą║č鹊ą▓čŗąĄ ąĖą╝ą┐čāą╗čīčüčŗ ą┤ąŠ ąŠą▒čēąĄą│ąŠ ą║ąŠą╗ąĖč湥čüčéą▓ą░ 24 čéą░ą║č鹊ą▓ SCLK, č鹊 č湥čĆąĄąĘ SDATA ą▒čāą┤čāčé ą┐ąĄčĆąĄą┤ą░ąĮčŗ 4 ąĘą░ą▓ąĄčĆčłą░čÄčēąĖčģ ąĮčāą╗čÅ. ~CS ą╝ąŠąČąĄčé ąŠčüčéą░ą▓ą░čéčīčüčÅ ą▓ ą╗ąŠą│. 1 ą┤ąŠ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ, ąĖą╗ąĖ ą╝ąŠąČąĄčé ąŠčüčéą░ą▓ą░čéčīčüčÅ ą▓ ą╗ąŠą│. 0 ą┤ąŠ ą╝ąŠą╝ąĄąĮčéą░, ą║ąŠą│ą┤ą░ ~CS ą▓ąĄčĆąĮąĄčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ą╗ąŠą│. 1 ą┐ąĄčĆąĄą┤ čüą╗ąĄą┤čāčÄčēąĖą╝ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄą╝.

ąÜą░ą║ č鹊ą╗čīą║ąŠ ąĘą░ą▓ąĄčĆčłąĖčéčüčÅ ą┐ąĄčĆąĄą┤ą░čćą░ ą┤ą░ąĮąĮčŗčģ (ą▓čŗčģąŠą┤ SDATA ą▓ąĄčĆąĮčāą╗čüčÅ ą▓ čéčĆąĄčéčīąĄ čüąŠčüč鹊čÅąĮąĖąĄ), ą╝ąŠąČąĄčé ą▒čŗčéčī ąĖąĮąĖčåąĖąĖčĆąŠą▓ą░ąĮąŠ ą┤čĆčāą│ąŠąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ą┐ąŠčüą╗ąĄ "ą▓čĆąĄą╝ąĄąĮąĖ čéąĖčłąĖąĮčŗ" tQUIET, ą┐čāč鹥ą╝ ą┐ąŠą▓č鹊čĆąĮąŠą│ąŠ ą┐ąĄčĆąĄą▓ąŠą┤ą░ čüąĖą│ąĮą░ą╗ą░ ~CS ą▓ ą╗ąŠą│. 0.

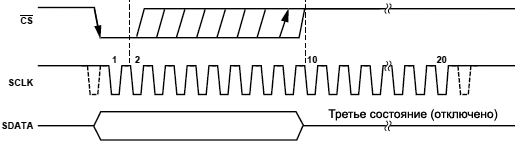

ąĀąĄąČąĖą╝ power-down. ąŁč鹊čé čĆąĄąČąĖą╝ ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮ ą┤ą╗čÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą▓ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅčģ, ą│ą┤ąĄ ą╝ąŠąČąĮąŠ čüąĮąĖąĘąĖčéčī čüą║ąŠčĆąŠčüčéčī ą┐ąŠč鹊ą║ą░ ą┤ą░ąĮąĮčŗčģ. ąøąĖą▒ąŠ ADC ą▓čŗą║ą╗čÄčćą░ąĄčéčüčÅ ą╝ąĄąČą┤čā ą║ą░ąČą┤čŗą╝ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄą╝, ą╗ąĖą▒ąŠ ą┤ąĄą╗ą░ąĄčéčüčÅ ą┐ą░čćą║ą░ ąĖąĘ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖą╣ čü ą▓čŗčüąŠą║ąŠą╣ čüą║ąŠčĆąŠčüčéčīčÄ, ą┐ąŠčüą╗ąĄ č湥ą│ąŠ ADC ą▓čŗą║ą╗čÄčćą░ąĄčéčüčÅ ąĮą░ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ą▒ąŠą╗čīčłąŠą╣ ąĖąĮč鹥čĆą▓ą░ą╗ ą▓čĆąĄą╝ąĄąĮąĖ ą╝ąĄąČą┤čā čŹčéąĖą╝ąĖ ą┐ą░ą║ąĄčéąĮčŗą╝ąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅą╝ąĖ. ąÜąŠą│ą┤ą░ AD7680 ą▓ ąŠčéą║ą╗čÄč湥ąĮąĮąŠą╝ čĆąĄąČąĖą╝ąĄ (power-down), ą▓čüąĄ ąĄą│ąŠ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗąĄ čüčģąĄą╝čŗ ą▓čŗą║ą╗čÄčćą░čÄčéčüčÅ.

ąöą╗čÅ ą▓čģąŠą┤ą░ ą▓ čĆąĄąČąĖą╝ power-down, ą┐čĆąŠčåąĄčüčü ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐čĆąĄčĆą▓ą░ąĮ ą┐čāč鹥ą╝ ą┐ąĄčĆąĄą▓ąŠą┤ą░ ~CS ą▓ ą╗ąŠą│. 1 ą┐ąŠčüą╗ąĄ 2-ą│ąŠ čüą┐ą░ą┤ą░ ąĮą░ SCLK ąĖ ą┐ąĄčĆąĄą┤ 10-čŗą╝ čüą┐ą░ą┤ąŠą╝ SCLK, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 17. ąÜą░ą║ č鹊ą╗čīą║ąŠ ~CS ą┐ąĄčĆąĄą╣ą┤ąĄčé ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ą╗ąŠą│. 1 ą▓ čŹč鹊ą╝ ąŠą║ąĮąĄ čéą░ą║č鹊ą▓čŗčģ ąĖą╝ą┐čāą╗čīčüąŠą▓ SCLK, ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ ą┐ąĄčĆąĄą╣ą┤ąĄčé ą▓ čĆąĄąČąĖą╝ power-down, ąĖąĮąĖčåąĖąĖčĆąŠą▓ą░ąĮąĮąŠąĄ čüą┐ą░ą┤ąŠą╝ ~CS ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ą▒čāą┤ąĄčé ą┐čĆąĄčĆą▓ą░ąĮąŠ, ąĖ ą▓čŗčģąŠą┤ SDATA ą┐ąĄčĆąĄą╣ą┤ąĄčé ąŠą▒čĆą░čéąĮąŠ ą▓ čéčĆąĄčéčīąĄ čüąŠčüč鹊čÅąĮąĖąĄ. ąĢčüą╗ąĖ CS ą┐ąĄčĆąĄą╣ą┤ąĄčé ą▓ ą╗ąŠą│. 1 ą┐ąĄčĆąĄą┤ ą▓č鹊čĆčŗą╝ čüą┐ą░ą┤ąŠą╝ SCLK, ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ ąŠčüčéą░ąĮąĄčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ normal ąĖ ąĮąĄ ą▓čŗą║ą╗čÄčćąĖčéčüčÅ. ąŁč鹊 ą┐čĆąĄą┤ąŠčéą▓čĆą░čéąĖčé čüą╗čāčćą░ą╣ąĮčŗąĄ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ąĖąĘ-ąĘą░ ą▓ąŠąĘą╝ąŠąČąĮčŗčģ ąĖą╝ą┐čāą╗čīčüąŠą▓ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ ~CS.

ąĀąĖčü. 17. ąÆčģąŠą┤ ą▓ čĆąĄąČąĖą╝ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ (Power-Down).

ą¦č鹊ą▒čŗ ą▓čŗą╣čéąĖ ąĖąĘ čŹč鹊ą│ąŠ čĆąĄąČąĖą╝ą░ čĆą░ą▒ąŠčéčŗ ąĖ čüąĮąŠą▓ą░ ąĘą░ą┐ąĖčéą░čéčī AD7680, ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮą░ ą┐čāčüčéą░čÅ ąŠą┐ąĄčĆą░čåąĖčÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ (dummy conversion). ą¤ąŠ čüą┐ą░ą┤čā ~CS čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮą░čćąĮąĄčé ą▓ą║ą╗čÄčćą░čéčīčüčÅ, ąĖ ąŠčüčéą░ąĮąĄčéčüčÅ ą▓ą║ą╗čÄč湥ąĮąĮčŗą╝, ą┐ąŠą║ą░ ~CS čāą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ą▓ ą╗ąŠą│. 0 ą┤ąŠ 10-ą│ąŠ čüą┐ą░ą┤ą░ SCLK. ą£ąĖą║čĆąŠčüčģąĄą╝ą░ ą┐ąŠą╗ąĮąŠčüčéčīčÄ ą▓ą║ą╗čÄčćą░ąĄčéčüčÅ, ą║ą░ą║ č鹊ą╗čīą║ąŠ ą┐čĆąŠą╣ą┤čāčé ą╝ąĖąĮąĖą╝čāą╝ 16 čéą░ą║č鹊ą▓ SCLK (ąĖą╗ąĖ ą┐čĆąĖą╝ąĄčĆąĮąŠ 6 ╬╝s), ąĖ ą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ąŠčåąĖčäčĆąŠą▓ą║ąĖ ą╝ąŠą│čāčé ą▒čŗčéčī ą┐ąŠą╗čāč湥ąĮčŗ ą┐čĆąĖ čüą╗ąĄą┤čāčÄčēąĄą╝ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĖ, ą║ą░ą║ čŹč鹊 ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 18. ąĢčüą╗ąĖ ~CS ą┐ąĄčĆąĄą╣ą┤ąĄčé ą▓ ą╗ąŠą│. 1 ą┐ąĄčĆąĄą┤ 10-čŗą╝ čüą┐ą░ą┤ąŠą╝ čāčĆąŠą▓ąĮčÅ SCLK, ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé čćą░čüč鹊čéčŗ SCLK, AD7680 čüąĮąŠą▓ą░ ą▓ąĄčĆąĮąĄčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ power-down. ąŁč鹊 ą┐ąŠąĘą▓ąŠą╗ąĖčé ąĖąĘą▒ąĄąČą░čéčī čüą╗čāčćą░ą╣ąĮąŠą│ąŠ ą▓ą║ą╗čÄč湥ąĮąĖčÅ ąĖąĘ-ąĘą░ ąĖą╝ą┐čāą╗čīčüąŠą▓ ą┐ąŠą╝ąĄčģ ąĮą░ čüąĖą│ąĮą░ą╗ąĄ ~CS, ąĖą╗ąĖ ąĮąĄą┐čĆąĄą┤ąĮą░ą╝ąĄčĆąĄąĮąĮąŠą│ąŠ ą┐ą░ą║ąĄčéą░ ąĖąĘ 8 čéą░ą║č鹊ą▓čŗčģ ą┐ąĄčĆąĄą┐ą░ą┤ąŠą▓ SCLK, ą┐ąŠą║ą░ ~CS ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ą╗ąŠą│. 0. ąóą░ą║ čćč鹊 čģąŠčéčÅ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą╝ąŠąČąĄčé ąĮą░čćą░čéčī ą▓ą║ą╗čÄč湥ąĮąĖąĄ ą┐ąŠčüą╗ąĄ čüą┐ą░ą┤ą░ ąĮą░ ~CS, ąŠąĮąŠ čüąĮąŠą▓ą░ ą▓čŗą║ą╗čÄčćąĖčéčüčÅ ą┐ąŠ čäčĆąŠąĮčéčā ąĮą░čĆą░čüčéą░ąĮąĖčÅ ~CS, ą║ą░ą║ čŹč鹊 ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą┐ąĄčĆąĄą┤ 10-čŗą╝ čüą┐ą░ą┤ąŠą╝ SCLK.

Figure 18. ąÆčŗčģąŠą┤ ąĖąĘ čĆąĄąČąĖą╝ą░ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ (Power-Down).

[ąĪąŠąŠčéąĮąŠčłąĄąĮąĖąĄ ą┐ąŠčéčĆąĄą▒ą╗čÅąĄą╝ąŠą╣ ą╝ąŠčēąĮąŠčüčéąĖ ąĖ čüą║ąŠčĆąŠčüčéąĖ ąŠčåąĖčäčĆąŠą▓ą║ąĖ]

ąĢčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čĆąĄąČąĖą╝ power-down, ą║ąŠą│ą┤ą░ AD7680 ąĮąĄ ąŠčåąĖčäčĆąŠą▓čŗą▓ą░ąĄčé čüąĖą│ąĮą░ą╗, ą╝ąŠąČąĮąŠ čāą╝ąĄąĮčīčłąĖčéčī čüčĆąĄą┤ąĮąĄąĄ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ ADC, ą║ąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ąĮąĖąĘą║ąĖąĄ čüą║ąŠčĆąŠčüčéąĖ ąŠčåąĖčäčĆąŠą▓ą║ąĖ. ąĀąĖčü. 19 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, ą║ą░ą║ čāą╝ąĄąĮčīčłą░ąĄčéčüčÅ čüą║ąŠčĆąŠčüčéčī ąŠčåąĖčäčĆąŠą▓ą║ąĖ, ąĖ ą┐čĆąŠą┐ąŠčĆčåąĖąŠąĮą░ą╗čīąĮąŠ čāą▓ąĄą╗ąĖč湥ąĮąĖčÄ ą▓čĆąĄą╝ąĄąĮąĖ, ą║ąŠą│ą┤ą░ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ ADC ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ą▓čŗą║ą╗čÄč湥ąĮąĮąŠą╝ čüąŠčüč鹊čÅąĮąĖąĖ, čüąĮąĖąČą░ąĄčéčüčÅ čüčĆąĄą┤ąĮąĄąĄ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ.

ąØą░ą┐čĆąĖą╝ąĄčĆ, ąĄčüą╗ąĖ AD7680 čĆą░ą▒ąŠčéą░ąĄčé ą▓ čĆąĄąČąĖą╝ąĄ ą┐ąŠčüč鹊čÅąĮąĮąŠą╣ ąŠčåąĖčäčĆąŠą▓ą║ąĖ, ąŠčåąĖčäčĆąŠą▓čŗą▓ą░čÅ ą┤ą░ąĮąĮčŗąĄ čü čćą░čüč鹊č鹊ą╣ 10 kSPS ąĖ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊č鹊ą╣ SCLK 2.5 ą£ąōčå (ą┐čĆąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ VDD=3.6V), ąĖ ą╝ąĄąČą┤čā ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅą╝ąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ ą┐ąŠą╝ąĄčēą░ąĄčéčüčÅ ą▓ čĆąĄąČąĖą╝ power-down, 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ ą▓čŗčćąĖčüą╗čÅąĄčéčüčÅ čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝. ą£ą░ą║čüąĖą╝ą░ą╗čīąĮąŠąĄ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ ą▓ čĆąĄąČąĖą╝ąĄ normal čüąŠčüčéą░ą▓ą╗čÅąĄčé 6.84 ą╝ąÆčé (ą┐čĆąĖ VDD=3.6V). ąĢčüą╗ąĖ ą▓čĆąĄą╝čÅ ą▓ą║ą╗čÄč湥ąĮąĖčÅ (ą▓čĆąĄą╝čÅ ą▓čŗčģąŠą┤ą░ ąĖąĘ čüąŠčüč鹊čÅąĮąĖčÅ power-down) čĆą░ą▓ąĮąŠ 1 ╬╝s, ąĖ ąŠčüčéą░ą▓čłąĄąĄčüčÅ ą▓čĆąĄą╝čÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ čüąŠčüčéą░ą▓ą╗čÅąĄčé 8 ╬╝s (ą┐čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ čü 20 čéą░ą║čéą░ą╝ąĖ SCLK), č鹊 AD7680 ą╝ąŠąČąĄčé čĆą░čüčüąĄąĖą▓ą░čéčī 6.84 mW ą┤ą╗čÅ 9 ╬╝s ą▓ąŠ ą▓čĆąĄą╝čÅ ą║ą░ąČą┤ąŠą│ąŠ čåąĖą║ą╗ą░ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ. ąØą░ čüą║ąŠčĆąŠčüčéąĖ ąŠčåąĖčäčĆąŠą▓ą║ąĖ 10 kSPS ą▓čĆąĄą╝čÅ čåąĖą║ą╗ą░ čüąŠčüčéą░ą▓ąĖčé 100 ╬╝s.

ąØą░ ąŠčüčéą░ą▓čłąĄąĄčüčÅ ąŠčé ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖą╣ ą▓čĆąĄą╝čÅ 91 ╬╝s ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ ąŠčüčéą░ąĄčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ power-down. AD7680 ą╝ąŠąČąĄčé ą┐ąŠčéčĆąĄą▒ą╗čÅčéčī 1.08 ╬╝W ąĘą░ čŹčéąĖ 91 ╬╝s ą╝ąĄąČą┤čā čåąĖą║ą╗ą░ą╝ąĖ ąŠčåąĖčäčĆąŠą▓ą║ąĖ. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą┐čĆąĖ čüą║ąŠčĆąŠčüčéąĖ ąŠčåąĖčäčĆąŠą▓ą║ąĖ 10 kSPS čüčĆąĄą┤ąĮčÅčÅ čĆą░čüčüąĄąĖą▓ą░ąĄą╝ą░čÅ ą╝ąŠčēąĮąŠčüčéčī čüąŠčüčéą░ą▓ąĖčé ą▓ ą║ą░ąČą┤ąŠą╝ čåąĖą║ą╗ąĄ:

(9/100) x (6.84 mW) + (91/100) x (1.08 ╬╝W) = 0.62 mW

ąĀąĖčü. 19. ąŚą░ą▓ąĖčüąĖą╝ąŠčüčéčī 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ ąŠčé čüą║ąŠčĆąŠčüčéąĖ ąŠčåąĖčäčĆąŠą▓ą║ąĖ čü ą┐ąĄčĆąĄčģąŠą┤ą░ą╝ąĖ ą▓ Power-Down ą╝ąĄąČą┤čā ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅą╝ąĖ (ą┐ąĄčĆąĄą┤ą░čćą░ 20 SCLK, ą┐ąĖčéą░ąĮąĖąĄ VDD=3.6V).

[ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü]

ąĀąĖčü. 20 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą┐ąŠą┤čĆąŠą▒ąĮčāčÄ ą┤ąĖą░ą│čĆą░ą╝ą╝čā ą▓čĆąĄą╝ąĄąĮąĖ ą┤ą╗čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ AD7680. ąóą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé čéą░ą║čéčŗ ą┤ą╗čÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ, ąĖ čéą░ą║ąČąĄ čāą┐čĆą░ą▓ą╗čÅąĄčé ą┐ąĄčĆąĄą┤ą░č湥ą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ąŠčé AD7680 ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ.

ąÜą░ą║ čāąČąĄ čāą┐ąŠą╝ąĖąĮą░ą╗ąŠčüčī, čüąĖą│ąĮą░ą╗ ~CS ąĖąĮąĖčåąĖąĖčĆčāąĄčé ą┐ąĄčĆąĄą┤ą░čćčā ą┤ą░ąĮąĮčŗčģ ąĖ ą┐čĆąŠčåąĄčüčü ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ. ąĪą┐ą░ą┤ ~CS ą┐ąĄčĆąĄą▓ąŠą┤ąĖčé čāąĘąĄą╗ ą▓čŗą▒ąŠčĆą║ąĖ/čģčĆą░ąĮąĄąĮąĖčÅ ą▓ čĆąĄąČąĖą╝ čāą┤ąĄčƹȹ░ąĮąĖčÅ, ą▓čŗą▓ąŠą┤ąĖčé ą▓čŗčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ ąĖąĘ čéčĆąĄčéčīąĄą│ąŠ čüąŠčüč鹊čÅąĮąĖčÅ, ąĖ ą┤ąĄą╗ą░ąĄčé ą▓čŗą▒ąŠčĆą║čā čüąĖą│ąĮą░ą╗ą░ čü ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ą▓čģąŠą┤ą░. ąÆ čŹč鹊čé ą╝ąŠą╝ąĄąĮčé čéą░ą║ąČąĄ ąĮą░čćąĖąĮą░ąĄčéčüčÅ ą┐čĆąŠčåąĄčüčü ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ, ąĖ čéčĆąĄą▒čāąĄčéčüčÅ ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ 20 čéą░ą║č鹊ą▓ SCLK ą┤ą╗čÅ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ. ąÜą░ą║ č鹊ą╗čīą║ąŠ ą┐čĆąŠą╣ą┤ąĄčé 17-ą╣ ąĖą╝ą┐čāą╗čīčü čüą┐ą░ą┤ą░ SCLK, čüčģąĄą╝ą░ ą▓čŗą▒ąŠčĆą║ąĖ/čģčĆą░ąĮąĄąĮąĖčÅ ą┐ąĄčĆąĄą╣ą┤ąĄčé ąŠą▒čĆą░čéąĮąŠ ą▓ čĆąĄąČąĖą╝ ąŠčéčüą╗ąĄąČąĖą▓ą░ąĮąĖčÅ čüąĖą│ąĮą░ą╗ą░ ąĮą░ čüą╗ąĄą┤čāčÄčēąĄą╝ ąĖą╝ą┐čāą╗čīčüąĄ ąĮą░čĆą░čüčéą░ąĮąĖčÅ SCLK. ąØą░ čĆąĖčü. 20 ą┐ąŠą║ą░ąĘą░ąĮą░ ą┐ąĄčĆąĄą┤ą░čćą░ ąĮą░ 24 ąĖą╝ą┐čāą╗čīčüą░čģ SCLK, ą║ąŠč鹊čĆą░čÅ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┤ąŠčüčéąĖčćčī čüą║ąŠčĆąŠčüčéąĖ ąŠčåąĖčäčĆąŠą▓ą║ąĖ 100 kSPS. ąØą░ 24-č鹊ą╝ čüą┐ą░ą┤ąĄ SCLK, ą▓čŗčģąŠą┤ SDATA ąĮąĄ ą▓ąŠąĘą▓čĆą░čēą░ąĄčéčüčÅ ą▓ čéčĆąĄčéčīąĄ čüąŠčüč鹊čÅąĮąĖąĄ. ąĢčüą╗ąĖ čäčĆąŠąĮčé ąĮą░čĆą░čüčéą░ąĮąĖčÅ ~CS ą┐čĆąŠąĖąĘąŠčłąĄą╗ ą┐ąĄčĆąĄą┤ ą┐čĆąŠčģąŠąČą┤ąĄąĮąĖąĄą╝ 24 čéą░ą║č鹊ą▓ SCLK, ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ą▒čāą┤ąĄčé ą┐čĆąĄčĆą▓ą░ąĮąŠ ąĖ ą▓čŗčģąŠą┤ SDATA ą┐ąĄčĆąĄą╣ą┤ąĄčé ąŠą▒čĆą░čéąĮąŠ ą▓ čéčĆąĄčéčīąĄ čüąŠčüč鹊čÅąĮąĖąĄ; ąĖąĮą░č湥 SDATA ą┐ąĄčĆąĄą╣ą┤ąĄčé ą▓ čéčĆąĄčéčīąĄ čüąŠčüč鹊čÅąĮąĖąĄ ąĮą░ 24-č鹊ą╝ čüą┐ą░ą┤ąĄ SCLK, ą║ą░ą║ čŹč鹊 ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 20.

ąĀąĖčü. 20. ąöąĖą░ą│čĆą░ą╝ą╝ą░ ą▓čĆąĄą╝ąĄąĮąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ AD7680 ą┐čĆąĖ ą┐ąĄčĆąĄą┤ą░č湥, čāą┐čĆą░ą▓ą╗čÅąĄą╝ąŠą╣ 24 čéą░ą║čéą░ą╝ąĖ SCLK.

ąóčĆąĄą▒čāąĄčéčüčÅ ą╝ąĖąĮąĖą╝čāą╝ 20 čéą░ą║č鹊ą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░, čćč鹊ą▒čŗ ą▓čŗą┐ąŠą╗ąĮąĖčéčī ą┐čĆąŠčåąĄčüčü ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ąĖ ą┐ąŠą╗čāčćąĖčéčī ą┤ą░ąĮąĮčŗąĄ ąŠčé AD7680. ąÆ ą╝ąŠą╝ąĄąĮčé ą┐ąĄčĆąĄčģąŠą┤ą░ ~CS ą▓ ą╗ąŠą│. 0 ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčéčüčÅ ą┐ąĄčĆą▓čŗą╣ ąĮą░čćą░ą╗čīąĮčŗą╣ 0 ą┤ą╗čÅ čćč鹥ąĮąĖčÅ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ ąĖą╗ąĖ DSP. ą×čüčéą░ą╗čīąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą▓čŗą┤ą▓ąĖą│ą░čÄčéčüčÅ ą┐ąŠčüą╗ąĄą┤čāčÄčēąĖą╝ąĖ čüą┐ą░ą┤ą░ą╝ąĖ čüąĖą│ąĮą░ą╗ą░ SCLK, ąĮą░čćąĖąĮą░čÅ čüąŠ ą▓č鹊čĆąŠą│ąŠ ąĮą░čćą░ą╗čīąĮąŠą│ąŠ ąĮčāą╗čÅ; čéą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą┐ąĄčĆą▓čŗą╣ čüą┐ą░ą┤ čéą░ą║č鹊ą▓ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą┐ąĄčĆą▓čŗą╣ ąĮą░čćą░ą╗čīąĮčŗą╣ 0, ąĖ čéą░ą║ąČąĄ ą▓čŗą┤ą▓ąĖą│ą░ąĄčé ą▓č鹊čĆąŠą╣ ąĮą░čćą░ą╗čīąĮčŗą╣ 0. ąĢčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┐ąĄčĆąĄą┤ą░čćą░ čü 24 čéą░ą║čéą░ą╝ąĖ SCLK, ą║ą░ą║ čŹč鹊 ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 20, ą┐ąĄčĆąĄą┤ą░čćą░ ą┤ą░ąĮąĮčŗčģ čüąŠčüč鹊ąĖčé ąĖąĘ 4 ąĮą░čćą░ą╗čīąĮčŗčģ ąĮčāą╗ąĄą╣, ąĘą░ ą║ąŠč鹊čĆčŗą╝ąĖ ąĖą┤čāčé 16 ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ, ąĘą░ą▓ąĄčĆčłą░ąĄą╝čŗąĄ 4-ą╝čÅ ąĘą░ą▓ąĄčĆčłą░čÄčēąĖą╝ąĖ ąĮčāą╗čÅą╝ąĖ. ą¤ąŠčüą╗ąĄą┤ąĮąĖą╣ ą▒ąĖčé (č湥čéą▓ąĄčĆčéčŗą╣ ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ 0) ą▓ ą┐ąĄčĆąĄą┤ą░č湥 ą┤ą░ąĮąĮčŗčģ ą▒čāą┤ąĄčé ą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗą╝ ąĮą░ 24-č鹊ą╝ čüą┐ą░ą┤ąĄ SCLK, ąŠąĮ ą▒čŗą╗ ą▓čŗą┤ą▓ąĖąĮčāčé ą┐čĆąĄą┤čŗą┤čāčēąĖą╝ (23-ąĖą╝) čüą┐ą░ą┤ąŠą╝ SCLK. ąĢčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┐ąĄčĆąĄą┤ą░čćą░ ąĖąĘ 20 ąĖą╝ą┐čāą╗čīčüąŠą▓ SCLK, ą║ą░ą║ čŹč鹊 ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 21, ą▓čŗčģąŠą┤ąĮąŠą╣ ą┐ąŠč鹊ą║ ą┤ą░ąĮąĮčŗčģ čüąŠčüč鹊ąĖčé č鹊ą╗čīą║ąŠ ąĖąĘ 4 ąĮą░čćą░ą╗čīąĮčŗčģ ąĮčāą╗ąĄą╣, ąĘą░ ą║ąŠč鹊čĆčŗą╝ąĖ ąĖą┤čāčé 16 ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ, ą│ą┤ąĄ ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ą▒ąĖčé ą▒čāą┤ąĄčé ą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗą╝ ąĮą░ 20-č鹊ą╝ čüą┐ą░ą┤ąĄ SCLK. ą¤ąĄčĆąĄą┤ą░čćą░ čü 20 SCLK ą┐ąŠąĘą▓ąŠą╗čÅąĄčé čāą╝ąĄąĮčīčłąĖčéčī ą▓čĆąĄą╝čÅ ą┐ąŠą╗ąĮąŠą│ąŠ čåąĖą║ą╗ą░, ąĖ čéą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝ ą┤ąŠčüčéąĖčćčī ą▒ąŠą╗ąĄąĄ ą▓čŗčüąŠą║ąŠą╣ čüą║ąŠčĆąŠčüčéąĖ ąŠčåąĖčäčĆąŠą▓ą║ąĖ.

ąĀąĖčü. 21. ąöąĖą░ą│čĆą░ą╝ą╝ą░ ą▓čĆąĄą╝ąĄąĮąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ AD7680 ą┐čĆąĖ ą┐ąĄčĆąĄą┤ą░č湥, čāą┐čĆą░ą▓ą╗čÅąĄą╝ąŠą╣ 20 čéą░ą║čéą░ą╝ąĖ SCLK.

ą£ąŠąČąĮąŠ čéą░ą║ąČąĄ ą┐ąŠą╗čāčćąĖčéčī ą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ąĮą░ ą║ą░ąČą┤ąŠą╝ čäčĆąŠąĮč鹥 ąĮą░čĆą░čüčéą░ąĮąĖčÅ SCLK, ą░ ąĮąĄ ąĮą░ čüą┐ą░ą┤ą░čģ SCLK, ą┐ąŠčüą║ąŠą╗čīą║čā ą▓čĆąĄą╝čÅ čåąĖą║ą╗ą░ SCLK ą┤ąŠčüčéą░č鹊čćąĮąŠ ą┐čĆąŠą┤ąŠą╗ąČąĖč鹥ą╗čīąĮąŠąĄ, čćč鹊ą▒čŗ ą┤ą░ąĮąĮčŗąĄ ą▒čŗą╗ąĖ ą▓ ą│ąŠč鹊ą▓ąĮąŠčüčéąĖ ąĮą░ čäčĆąŠąĮč鹥 ąĮą░čĆą░čüčéą░ąĮąĖčÅ SCLK. ą×ą┤ąĮą░ą║ąŠ ą┐ąĄčĆą▓čŗą╣ ąĮą░čćą░ą╗čīąĮčŗą╣ 0 ą▒čāą┤ąĄčé ą▓čüąĄ ąĄčēąĄ ą┤ąŠčüčéčāą┐ąĄąĮ ą┐ąŠ čüą┐ą░ą┤čā ~CS, čéą░ą║ čćč鹊 ąĄą│ąŠ ą╝ąŠąČąĮąŠ ą┐ąŠą╗čāčćąĖčéčī č鹊ą╗čīą║ąŠ ą┐ąŠ ą┐ąĄčĆą▓ąŠą╝čā čüą┐ą░ą┤čā čüąĖą│ąĮą░ą╗ą░ SCLK. ąŁč鹊 ą╝ąŠąČąĮąŠ ąĖą│ąĮąŠčĆąĖčĆąŠą▓ą░čéčī, ąĖ ą┐ąĄčĆą▓čŗą╣ ąĖą╝ą┐čāą╗čīčü ąĮą░čĆą░čüčéą░ąĮąĖčÅ SCLK ą┐ąŠčüą╗ąĄ čüą┐ą░ą┤ą░ ~CS ą┤ą░čüčé čćč鹥ąĮąĖąĄ ą▓č鹊čĆąŠą│ąŠ ąĮą░čćą░ą╗čīąĮąŠą│ąŠ 0, ąĖ 23-ąĖą╣ čäčĆąŠąĮčé ąĮą░čĆą░čüčéą░ąĮąĖčÅ SCLK ą┤ą░čüčé ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ąĘą░ą▓ąĄčĆčłą░čÄčēąĖą╣ 0. ąŁč鹊čé ą╝ąĄč鹊ą┤ ą╝ąŠąČąĄčé ąĮąĄ čĆą░ą▒ąŠčéą░čéčī čü ą▒ąŠą╗čīčłąĖąĮčüčéą▓ąŠą╝ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓/DSP, ąĮąŠ ąĄą│ąŠ ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čüąŠą▓ą╝ąĄčüčéąĮąŠ čü ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ą╝ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝ąŠą╣ ą╗ąŠą│ąĖą║ąĖ FPGA ąĖ ASIC.

ąĪąĄą╝ąĄą╣čüčéą▓ąŠ ADSP-218x ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ DSP ą╝ąŠąČąĄčé ą▒čŗčéčī ąĮą░ą┐čĆčÅą╝čāčÄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąŠ ą║ AD7680 ą▒ąĄąĘ ą║ą░ą║ąĖčģ-ą╗ąĖą▒ąŠ ą┐čĆąŠą╝ąĄąČčāč鹊čćąĮčŗčģ ą╗ąŠą│ąĖč湥čüą║ąĖčģ čüčģąĄą╝. ąĀąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ SPORT ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĮą░čüčéčĆąŠąĄąĮ čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝:

TFSW = RFSW = 1, Alternate Framing (ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčŗą╣ č乊čĆą╝ą░čé čäčĆąĄą╣ą╝ą░)

INVRFS = INVTFS = 1, Active Low Frame Signal (ą┤ą╗čÅ čüąĖą│ąĮą░ą╗ą░ čäčĆąĄą╣ą╝ą░ ą░ą║čéąĖą▓ąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 0)

DTYPE = 00, Right Justify Data (ą┐čĆą░ą▓ąŠąĄ ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ)

SLEN = 0111, 8-Bit Data-Words (8-ą▒ąĖčéąĮčŗąĄ čüą╗ąŠą▓ą░ ą┤ą░ąĮąĮčŗčģ)

ISCLK = 1, Internal Serial Clock (ą▓ąĮčāčéčĆąĄąĮąĮąĖąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗąĄ čéą░ą║čéčŗ)

TFSR = RFSR = 0, Frame First Word (čäčĆąĄą╣ą╝ ą┐ąĄčĆą▓ąŠą│ąŠ čüą╗ąŠą▓ą░)

IRFS = 0

ITFS = 1

ąöą╗čÅ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ čĆąĄąČąĖą╝ą░ power-down ą┐ąŠą╗ąĄ SLEN ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ ą▓ ąĘąĮą░č湥ąĮąĖąĄ 0111, čćč鹊ą▒čŗ ą▓čŗą┤ą░čéčī ą┐ą░ą║ąĄčé 8-ą▒ąĖčé SCLK. ąĪčģąĄą╝ą░ čüąŠąĄą┤ąĖąĮąĄąĮąĖą╣ ą┐ąŠą║ą░ąĘą░ąĮą░ ąĮą░ čĆąĖčü. 22. ąĪąĖą│ąĮą░ą╗čŗ TFS ąĖ RFS ą┐ąŠčĆčéą░ SPORT ą┐čĆąŠčåąĄčüčüąŠčĆą░ ADSP-218x čüąŠąĄą┤ąĖąĮąĄąĮčŗ ą┤čĆčāą│ čü ą┤čĆčāą│ąŠą╝, ąĖ TFS ąĮą░čüčéčĆąŠąĄąĮ ą║ą░ą║ ą▓čŗčģąŠą┤ ąĖ RFS ąĮą░čüčéčĆąŠąĄąĮ ą║ą░ą║ ą▓čģąŠą┤. DSP čĆą░ą▒ąŠčéą░ąĄčé ą▓ čĆąĄąČąĖą╝ąĄ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮąŠą│ąŠ čäčĆąĄą╣ą╝ą░, ąĖ čĆąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ SPORT ąĮą░čüčéčĆąŠąĄąĮ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▓čŗčłąĄ. ąśčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą░ą▓č鹊ą▒čāč乥čĆąĖąĘą░čåąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖ ą┐čĆąĖąĄą╝ą░, čćč鹊ą▒čŗ ą┐ąŠą╗čāčćąĖčéčī ą┐ąĄčĆąĄą┤ą░čćčā ąĖąĘ 24 ąĖą╝ą┐čāą╗čīčüąŠą▓ SCLK. ąÜą░ąČą┤čŗą╣ ą▒čāč乥čĆ čüąŠą┤ąĄčƹȹĖčé čéčĆąĖ 8-ą▒ąĖčéąĮčŗčģ čüą╗ąŠą▓ą░. ąĪąĖą│ąĮą░ą╗ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ čäčĆąĄą╣ą╝ą░ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ąĮą░ TFS, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮąŠą╝ ą║ ~CS, ąĖ ą║ą░ą║ čéčĆąĄą▒čāąĄčéčüčÅ ą▓ąŠ ą▓čüąĄčģ čüąĖčüč鹥ą╝ą░čģ čåąĖčäčĆąŠą▓ąŠą╣ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ čüąĖą│ąĮą░ą╗ą░, ą┤ą╗čÅ ąŠčåąĖčäčĆąŠą▓ą║ąĖ ąĮčāąČąĮą░ ą▓čŗą▒ąŠčĆą║ą░ čü čĆąĄą│čāą╗čÅčĆąĮčŗą╝ąĖ ąĖąĮč鹥čĆą▓ą░ą╗ą░ą╝ąĖ. ąÆ čŹč鹊ą╝ ą┐čĆąĖą╝ąĄčĆąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čéą░ą╣ą╝ąĄčĆą░, čćč鹊ą▒čŗ čāą┐čĆą░ą▓ą╗čÅčéčī čćą░čüč鹊č鹊ą╣ ąŠą┐čĆąŠčüą░ ADC.

ąĀąĖčü. 22. ą¤čĆąĖą╝ąĄčĆ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ą║ ADSP-218x.

ąĀąĄą│ąĖčüčéčĆ čéą░ą╣ą╝ąĄčĆą░ ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄą╝, ą║ąŠč鹊čĆąŠąĄ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĮą░ čéčĆąĄą▒čāąĄą╝ąŠą╝ ąĖąĮč鹥čĆą▓ą░ą╗ąĄ ą╝ąĄąČą┤čā ą▓čŗą▒ąŠčĆą║ą░ą╝ąĖ. ąÜąŠą│ą┤ą░ ą┐čĆąŠąĖąĘąŠčłą╗ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ąĘąĮą░č湥ąĮąĖčÅ ą▓ ą░ą▓č鹊ą▒čāč乥čĆąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĮą░čćąĖąĮą░čÄčé ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčīčüčÅ, ąĖ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ čüąĖą│ąĮą░ą╗ TFS. TFS ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ RFS, ąĖ čéą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ čćč鹥ąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ. ąöą░ąĮąĮčŗąĄ čüąŠčģčĆą░ąĮčÅčÄčéčüčÅ ą▓ ą░ą▓č鹊ą▒čāč乥čĆąĄ ą┐čĆąĖąĄą╝ą░ ą┤ą╗čÅ ą┐ąŠčüą╗ąĄą┤čāčÄčēąĄą╣ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ. ą¦ą░čüč鹊čéą░ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ čéą░ą║č鹊ą▓ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ SCLKDIV. ąÜąŠą│ą┤ą░ ą▓čŗą┤ą░ąĄčéčüčÅ ąĖąĮčüčéčĆčāą║čåąĖčÅ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ čü TFS, ąĮą░ą┐čĆąĖą╝ąĄčĆ TX0 = AX0, ą┐čĆąŠą▓ąĄčĆčÅąĄčéčüčÅ čüąŠčüč鹊čÅąĮąĖąĄ SCLK. DSP ąČą┤ąĄčé, ą┐ąŠą║ą░ SCLK ąĮąĄ ą┐ąĄčĆąĄą╣ą┤ąĄčé ą▓ ą╗ąŠą│. 1, ą╗ąŠą│. 0, ąĖ čüąĮąŠą▓ą░ ą▓ ą╗ąŠą│. 1 ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ ąĮą░čćąĮąĄčéčüčÅ ą┐ąĄčĆąĄą┤ą░čćą░. ąĢčüą╗ąĖ čéą░ą╣ą╝ąĄčĆ ąĖ ąĘąĮą░č湥ąĮąĖčÅ SCLK ą▓čŗą▒čĆą░ąĮčŗ čéą░ą║, čćč鹊 ąĖąĮčüčéčĆčāą║čåąĖčÅ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą▒ą╗ąĖąĘą║ąŠ ą║ čäčĆąŠąĮčéčā ąĮą░čĆą░čüčéą░ąĮąĖčÅ SCLK, ą┤ą░ąĮąĮčŗąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ą┐ąĄčĆąĄą┤ą░ąĮčŗ ąĖą╗ąĖ ą╝ąŠą│čāčé ąŠąČąĖą┤ą░čéčī čüą╗ąĄą┤čāčÄčēąĄą│ąŠ ą┐ąĄčĆąĄą┐ą░ą┤ą░ čéą░ą║č鹊ą▓.

ąÆ čŹč鹊ą╝ ą┐čĆąĖą╝ąĄčĆąĄ ą┐čĆąŠčåąĄčüčüąŠčĆ Blackfin ADSP-BF538 ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą║ ąÉą”ą¤ AD7680 č湥čĆąĄąĘ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ą┐ąŠčĆčé SPI2 (ą┐ąŠą┤čĆąŠą▒ąĮąĄąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ ą┐ąŠčĆčéą░ SPI čüą╝. ą▓ [3]). ąĀąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ SPI2_CTL ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĮą░čüčéčĆąŠąĄąĮ čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝:

SPE = 1, čĆą░ąĘčĆąĄčłąĖčéčī čĆą░ą▒ąŠčéčā SPI

WOM = 0, ąŠą▒čŗčćąĮčŗą╣ ą┤ą▓čāčģčéą░ą║čéąĮčŗą╣ ą▒čāč乥čĆ

MSTR = 1, Blackfin čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą│ą╗ą░ą▓ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮą░ čłąĖąĮąĄ SPI

SPOL = 1, ąĮą░čüčéčĆąŠą╣ą║ą░ ą┐ąŠą╗čÅčĆąĮąŠčüčéąĖ čüąĖą│ąĮą░ą╗ą░ čéą░ą║č鹊ą▓ SCK

CPHA = 0, čäą░ąĘą░ čüąĖą│ąĮą░ą╗ą░ čéą░ą║č鹊ą▓ SCK

SIZE = 1, ą▓čŗą▒ąĖčĆą░ąĄčé 16-ą▒ąĖčéąĮčŗą╣ č乊čĆą╝ą░čé čäčĆąĄą╣ą╝ą░

EMISO = 0, ą▓čŗčģąŠą┤ MISO ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą║ą░ą║ ą▓čģąŠą┤

PSSE = 0, ą░ą┐ą┐ą░čĆą░čéąĮčŗą╣ ą▓čŗčģąŠą┤ ą▓čŗą▒ąŠčĆą║ąĖ ~SPI2SS ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ

GM = 0, ą▓ čüą╗čāčćą░ąĄ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ ą┐čĆąĖąĄą╝ą░ ą┤ą░ąĮąĮčŗąĄ ą▒čāą┤čāčé ąŠčéą▒čĆą░čüčŗą▓ą░čéčīčüčÅ

TIMOD = 01, čéčĆą░ąĮąĘą░ą║čåąĖčÅ ą┐ąŠčĆčéą░ SPI ąĮą░čćąĖąĮą░ąĄčéčüčÅ ąĘą░ą┐ąĖčüčīčÄ ą▓ čĆąĄą│ąĖčüčéčĆ ą┐ąĄčĆąĄą┤ą░čćąĖ SPI2_TDBR

*pSPI2_CTL = SPE|MSTR|CPOL|SIZE|TDBR_CORE;

ą¤čĆąĖą╝ąĄčĆ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ą║ ADSP-BF538.

ą¤ąŠčĆčé SPI Blackfin ą╝ąŠąČąĄčé ąĘą░ ąŠą┤ąĖąĮ čäčĆąĄą╣ą╝ ą░ą┐ą┐ą░čĆą░čéąĮąŠ čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ą╗ąĖą▒ąŠ 8, ą╗ąĖą▒ąŠ 16 čéą░ą║č鹊ą▓čŗčģ ąĖą╝ą┐čāą╗čīčüąŠą▓ (ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą▓čŗą▒čĆą░ąĮąĮąŠą╣ čłąĖčĆąĖąĮčŗ čäčĆąĄą╣ą╝ą░ 8 ąĖą╗ąĖ 16 ą▒ąĖčé). ąØąŠ ą┤ą╗čÅ ąŠą┐čĆąŠčüą░ AD7680 ąĮčāąČąĮąŠ čüč乊čĆą╝ąĖčĆąŠą▓ą░čéčī ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ 20 čéą░ą║č鹊ą▓čŗčģ ą┐ąĄčĆąĄą┐ą░ą┤ąŠą▓. ą£ąŠąČąĮąŠ ą┐čĆąĖą╝ąĄąĮąĖčéčī 2 ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčŗčģ čĆąĄčłąĄąĮąĖčÅ:

1. ąŚą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī ą┐čĆąĖąĄą╝ DMA ąĮą░ čéčĆąĖ 8-ą▒ąĖčéąĮčŗčģ čäčĆąĄą╣ą╝ą░ ą┐ąŠą┤čĆčÅą┤, ą▓ čĆąĄąĘčāą╗čīčéą░č鹥 ą┐ąŠą╗čāčćąĖčéčüčÅ 24 čéą░ą║č鹊ą▓čŗčģ ą┐ąĄčĆąĄą┐ą░ą┤ą░ SCLK. ą¤čĆąĖąĮčÅč鹊ąĄ 24-ą▒ąĖčéąĮąŠąĄ čćąĖčüą╗ąŠ čüą┤ą▓ąĖąĮčāčéčī ą▓ą┐čĆą░ą▓ąŠ ąĮą░ 4 čĆą░ąĘčĆčÅą┤ą░, ą┐ąŠą╗čāčćąĖčéčüčÅ čĆąĄąĘčāą╗čīčéą░čé ąŠčåąĖčäčĆąŠą▓ą║ąĖ.

2. ąÆčŗą┐ąŠą╗ąĮąĖčéčī ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠąĄ č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ ą┐ąĄčĆą▓čŗčģ 4 čéą░ą║č鹊ą▓čŗčģ ą┐ąĄčĆąĄą┐ą░ą┤ą░ SCLK (ą┤ąĄčĆą│ą░čÅ ąĮąŠąČą║ąŠą╣ SCK2 ą║ą░ą║ ą┐ąŠčĆč鹊ą╝ GPIO). ąŚą░č鹥ą╝ ą┐ąĄčĆąĄą║ą╗čÄčćąĖčéčī ąĮąŠąČą║čā SCK2 ąĮą░ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ SPI2, ąĖ ąĘą░ą┐čāčüčéąĖčéčī čéčĆą░ąĮąĘą░ą║čåąĖčÄ SPI ąĮą░ čłąĖčĆąĖąĮčā čäčĆąĄą╣ą╝ą░ 16 ą▒ąĖčé. ąÆ čĆąĄąĘčāą╗čīčéą░č鹥 ą┐ąŠą╗čāčćąĖą╝ ąĮčāąČąĮčŗąĄ 20 čéą░ą║č鹊ą▓čŗčģ ą┐ąĄčĆąĄą┐ą░ą┤ąŠą▓ čüąĖą│ąĮą░ą╗ą░ SCLK, ąĖ ą▓ čĆąĄą│ąĖčüčéčĆąĄ ą┐čĆąĖąĄą╝ą░ SPI2_RDBR ą╝ąŠąČąĮąŠ ą┐čĆąŠčćąĖčéą░čéčī ą│ąŠč鹊ą▓čŗą╣ čĆąĄąĘčāą╗čīčéą░čé ąŠčåąĖčäčĆąŠą▓ą║ąĖ.

ąÆ ąŠą▒ąŠąĖčģ čüą╗čāčćą░čÅčģ ą▓čŗą▒ąŠčĆą║ąŠą╣ ąÉą”ą¤ (čüąĖą│ąĮą░ą╗ąŠą╝ ~CS) ą╝ąŠąČąĮąŠ čāą┐čĆą░ą▓ą╗čÅčéčī ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ.

ąÆ čĆąĄąĘčāą╗čīčéą░č鹥 ą▒čŗą╗ ą▓čŗą▒čĆą░ąĮ 2 ą▓ą░čĆąĖą░ąĮčé. ąØą░ čüą║čĆąĖąĮčłąŠč鹥 ąŠčüčåąĖą╗ą╗ąŠą│čĆą░čäą░ Tektronix MSO 2014 ą╝ąŠąČąĮąŠ ą┐ąŠčüą╝ąŠčéčĆąĄčéčī, ą║ą░ą║ąĖąĄ ą┐ąŠą╗čāčćąĖą╗ąĖčüčī ą┤ąĖą░ą│čĆą░ą╝ą╝čŗ čüąĖą│ąĮą░ą╗ąŠą▓ ąĖąĮč鹥čĆč乥ą╣čüą░:

ąÜą░ą║ ą╝ąŠąČąĮąŠ čāą▓ąĖą┤ąĄčéčī ąĖąĘ ąŠčåąĖą╗ą╗ąŠą│čĆą░ą╝ą╝čŗ, SPI ąĘą░ą┐čāčēąĄąĮ ąĮą░ čćą░čüč鹊č鹥 čéą░ą║č鹊ą▓ 5.4 ą£ąōčå, čģąŠčéčÅ ą┐ąŠ ą┤ą░čéą░čłąĖčéčā ą┐čĆąĄą┤ąĄą╗čīąĮąŠ ą┤ąŠą┐čāčüčéąĖą╝ą░čÅ čćą░čüč鹊čéą░ 2.5 ą£ąōčå. ąØąĄčüą╝ąŠčéčĆčÅ ąĮą░ ą┐ąŠą▓čŗčłąĄąĮąĮčāčÄ čćą░čüč鹊čéčā, ąÉą”ą¤ AD7680 ą▓čüąĄ čĆą░ą▓ąĮąŠ ą┐ąŠą║ą░ąĘą░ą╗ ąĮąŠčĆą╝ą░ą╗čīąĮčŗą╣ čĆąĄąĘčāą╗čīčéą░čé čĆą░ą▒ąŠčéčŗ. ąÜčĆąŠą╝ąĄ č鹊ą│ąŠ, ąĮąĄ ą┐ąŠą╗čāčćąĖą╗ąŠčüčī čüč乊čĆą╝ąĖčĆąŠą▓ą░čéčī čüčéą░ą▒ąĖą╗čīąĮčāčÄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ąĖąĘ 20 ą┐ąĄčĆąĄą┐ą░ą┤ąŠą▓ SCLK. ą×ą┤ąĮą░ą║ąŠ ąĮąĄčĆą░ą▓ąĮąŠą╝ąĄčĆąĮąŠčüčéčī ą┐ąĄčĆąĖąŠą┤ąŠą▓ čéą░ą║č鹊ą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ąĖ ąĄą│ąŠ ą┐ąŠą▓čŗčłąĄąĮąĮą░čÅ čćą░čüč鹊čéą░ ąĮąĄ ą┐ąŠą▓ą╗ąĖčÅą╗ąĖ ąĮą░ ą║ąŠčĆčĆąĄą║čéąĮąŠčüčéčī ąŠčåąĖčäčĆąŠą▓ą║ąĖ ąĖ čćč鹥ąĮąĖčÅ čĆą░ąĘčāą╗čīčéą░č鹊ą▓ ąĖąĘ ąÉą”ą¤.

ąØąĖąČąĄ ą┐čĆąĖą▓ąĄą┤ąĄąĮ ą║ąŠą┤ ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝ ąĮą░čüčéčĆąŠą╣ą║ąĖ SPI2 ąĖ čćč鹥ąĮąĖčÅ čĆąĄąĘčāą╗čīčéą░čéą░ ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ čü ąÉą”ą¤ AD7680.

ąŚą░ą│ąŠą╗ąŠą▓ąŠčćąĮčŗą╣ čäą░ą╣ą╗ AD7680.h:

#ifndef __AD7680__

#define __AD7680__

//ą×ą┐ąŠčĆąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ 3.3V:

#define AD7680_REF 3.3

//16-ą▒ąĖčéąĮčŗą╣ čĆąĄąĘčāą╗čīčéą░čé ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ:

extern u16 accvoltage16;

//ążčāąĮą║čåąĖčÅ ąĮą░čüčéčĆąŠą╣ą║ąĖ ą┐ąŠčĆčéą░ SPI2, ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą▓čŗąĘą▓ą░ąĮą░

// 1 čĆą░ąĘ ą┐ąĄčĆąĄą┤ ą▓čģąŠą┤ąŠą╝ ą▓ ą│ą╗ą░ą▓ąĮčŗą╣ čåąĖą║ą╗ main:

void AD7680_InitCom (void);

//ąØąĄ ą▒ą╗ąŠą║ąĖčĆčāčÄčēą░čÅ čäčāąĮą║čåąĖčÅ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ čćč鹥ąĮąĖčÅ ąÉą”ą¤, ąĄčæ ą▓čŗąĘąŠą▓

// ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą▓čüčéą░ą▓ą╗ąĄąĮ ą▓ č鹥ą╗ąŠ čåąĖą║ą╗ą░ main:

void AD7680handler (void);

#endif //__AD7680__

ą£ąŠą┤čāą╗čī AD7680.cpp:

#include "pins.h"

#include "delay.h"

#include "uart/BfDebugger.h"

#include "AD7680.h"

u16 accvoltage16;

void AD7680_InitCom (void)

{

//ąØą░čüčéčĆąŠą╣ą║ą░ ąĮąŠąČą║ąĖ ą▓čŗą▒ąŠčĆą║ąĖ:

*pPORTDIO_FER |= portCSpwr;

*pPORTDIO_DIR |= portCSpwr;

*pPORTDIO_SET = portCSpwr;

//ąØą░čüčéčĆąŠą╣ą║ąĖ ąĮąŠąČą║ąĖ ą┤ą╗čÅ čéą░ą║č鹊ą▓:

*pPORTDIO_FER |= portSCKpwr;

*pPORTDIO_DIR |= portSCKpwr;

*pPORTDIO_SET = portSCKpwr;

*pSPI2_BAUD = 3; //ąØą░čüčéčĆąŠą╣ą║ą░ SPI1 ąĮą░ 5.4 ą£ąōčå.

//ąØą░čüčéčĆąŠą╣ą║ą░ ą┐ąŠčĆčéą░ SPI2. ą¦č鹊 čéčāčé ąĮą░čüčéčĆąŠąĄąĮąŠ:

// SPE čĆą░ąĘčĆąĄčłąĖčéčī SPE

// MSTR ą│ą╗ą░ą▓ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ

// CPOL ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ą┐ąŠą╗čÅčĆąĮąŠčüčéčī SCK

// CPHA ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé čäą░ąĘčā SCK

// LSBF = 0, čüčéą░čĆčłąĖą╣ ą▒ąĖčé ąĖą┤ąĄčé ą┐ąĄčĆą▓čŗą╝

// SIZE ą▓čŗą▒ąĖčĆą░ąĄčé 16-ą▒ąĖčéąĮčŗą╣ č乊čĆą╝ą░čé čćąĖčéą░ąĄą╝ąŠą│ąŠ čüą╗ąŠą▓ą░

// TDBR_CORE ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé, čćč鹊 ą┐ąĄčĆąĄą┤ą░čćą░ ąĮą░čćąĖąĮą░ąĄčéčüčÅ ąĘą░ą┐ąĖčüčīčÄ SPI2_TDBR

// čüąŠ čüč鹊čĆąŠąĮčŗ čÅą┤čĆą░ (ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠą╗čÅ TIMOD).

*pSPI2_CTL = SPE|MSTR|CPOL/*|CPHA*/|SIZE|TDBR_CORE;

}

static void AD7680_StartConversion (void)

{

//ąÆčŗą▒čĆą░čéčī ąÉą”ą¤:

*pPORTDIO_FER |= portSCKpwr; //ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ąĮąŠąČą║ąĖ SCLK ą▓ čĆąĄąČąĖą╝ GPIO

*pPORTDIO_CLEAR = portCSpwr; //~CS=0 (ą░ą║čéąĖą▓ąĮą░čÅ ą▓čŗą▒ąŠčĆą║ą░ AD7680)

//4 čĆą░ąĘą░ ą┤ąĄčĆąĮčāčéčī ąĮąŠąČą║ąŠą╣ SCK ą┤ą╗čÅ ą┐čĆąŠčģąŠąČą┤ąĄąĮąĖčÅ 4 ąĮčāą╗ąĄą╣:

for (u8 bitcnt=0; bitcnt<4; bitcnt++)

{

*pPORTDIO_CLEAR = portSCKpwr;

ssync();

csync();

*pPORTDIO_SET = portSCKpwr;

ssync();

csync();

}

//ą¤ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ąĮąŠąČą║ąĖ SCLK ą▓ ą░ą┐ą┐ą░čĆą░čéąĮčŗą╣ čĆąĄąČąĖą╝:

*pPORTDIO_FER &= ~portSCKpwr;

//ąŚą░ą┐čāčüą║ ą┐ąĄčĆąĄą┤ą░čćąĖ (ąĖ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ą┐čĆąĖąĄą╝ą░) SPI.

*pSPI2_TDBR = 0;

}

static bool AD7680_Read (u16 *value)

{

if (*pSPI2_STAT & RXS)

{

*value = *pSPI2_RDBR;

*pPORTDIO_SET = portCSpwr; //~CS=1 (ą▓čŗą▒ąŠčĆą║ą░ AD7680 ąĮąĄ ą░ą║čéąĖą▓ąĮą░)

return true;

}

else

return false;

}

#define AD7680_START 0

#define AD7680_READ 1

#define AD7680_WAIT 2

void AD7680handler (void)

{

static u8 state = AD7680_START;

static clock_t waittimeout = 0;

switch (state)

{

case AD7680_START:

AD7680_StartConversion();

state = AD7680_READ;

break;

case AD7680_READ:

if (AD7680_Read(&accvoltage16))

{

waittimeout = clock() + 100*MS_TICKS;

DEBUG(1, "%0.2f ", AD7680_REF * accvoltage16 / 65535);

state = AD7680_WAIT;

}

break;

case AD7680_WAIT:

if(waittimeout < clock())

state = AD7680_START;

break;

}

}

ą¦č鹊ą▒čŗ ąĖąĘą▒ąĄąČą░čéčī ą╗ąĖčłąĮąĄą│ąŠ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą░ąĮąĖčÅ ąŠčüąĮąŠą▓ąĮąŠą│ąŠ čåąĖą║ą╗ą░ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ, ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī čćč鹥ąĮąĖčÅ čĆą░ąĘą┤ąĄą╗ąĄąĮą░ ąĮą░ 3 čäą░ąĘčŗ: čäą░ąĘą░ ąĘą░ą┐čāčüą║ą░ ąŠčåąĖčäčĆąŠą▓ą║ąĖ (AD7680_START), čäą░ąĘą░ čćč鹥ąĮąĖčÅ (AD7680_READ) ąĖ čäą░ąĘą░ ą┐ą░čāąĘčŗ ą╝ąĄąČą┤čā ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅą╝ąĖ (AD7680_WAIT).

ąØą░ čäą░ąĘąĄ ąĘą░ą┐čāčüą║ą░ ąŠčåąĖčäčĆąŠą▓ą║ąĖ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ čüą┐ą░ą┤ ą▓ ą╗ąŠą│. 0 čüąĖą│ąĮą░ą╗ą░ ą▓čŗą▒ąŠčĆą║ąĖ ~CS, ąĘą░č鹥ą╝ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ č乊čĆą╝ąĖčĆčāčÄčéčüčÅ 4 čéą░ą║č鹊ą▓čŗčģ ą┐ąĄčĆąĄą┐ą░ą┤ą░ SCLK, ąĮąŠąČą║ą░ čéą░ą║č鹊ą▓ ą┐ąĄčĆąĄą║ą╗čÄčćą░ąĄčéčüčÅ ą▓ ą░ą┐ą┐ą░čĆą░čéąĮčŗą╣ čĆąĄąČąĖą╝, ą┐ąŠčüą╗ąĄ č湥ą│ąŠ ąĘą░ą┐ąĖčüčīčÄ ą▒čāč乥čĆą░ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ čéčĆą░ąĮąĘą░ą║čåąĖčÅ ą┐čĆąĖąĄą╝ą░/ą┐ąĄčĆąĄą┤ą░čćąĖ čäčĆąĄą╣ą╝ą░ SPI. ąÆčüąĄ čŹč鹊 ą┤ąĄą╗ą░ąĄčé čäčāąĮą║čåąĖčÅ AD7680_StartConversion.

ąØą░ čäą░ąĘąĄ čćč鹥ąĮąĖčÅ ąŠąČąĖą┤ą░ąĄčéčüčÅ ą┐ąŠčÅą▓ą╗ąĄąĮąĖąĄ čäą╗ą░ą│ą░ RXS, čüąĖą│ąĮą░ą╗ąĖąĘąĖčĆčāčÄčēąĄą│ąŠ ąŠ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĖąĖ ą▒čāč乥čĆą░ ą┐čĆąĖąĄą╝ą░. ąÜą░ą║ č鹊ą╗čīą║ąŠ čäą╗ą░ą│ RXS ą▓ąĘą▓ąĄą┤ąĄąĮ, čĆąĄąĘčāą╗čīčéą░čé ąŠčåąĖčäčĆąŠą▓ą║ąĖ ą▓čŗčćąĖčéčŗą▓ą░ąĄčéčüčÅ ąĖąĘ ą▒čāč乥čĆą░ ą┐čĆąĖąĄą╝ą░ ąĖ ą┐ąŠą╝ąĄčēą░ąĄčéčüčÅ ą▓ ą│ą╗ąŠą▒ą░ą╗čīąĮčāčÄ ą┐ąĄčĆąĄą╝ąĄąĮąĮčāčÄ accvoltage16. ą¦č鹥ąĮąĖąĄ čĆąĄąĘčāą╗čīčéą░čéą░ ą▓čŗą┐ąŠą╗ąĮčÅąĄčé čäčāąĮą║čåąĖčÅ AD7680_Read. ą¤ąŠčüą╗ąĄ čŹč鹊ą│ąŠ ąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ ąŠčéčüč湥čé čéą░ą╣ą╝ą░čāčéą░ ą┐ą░čāąĘčŗ (ą▓ ą┤ą░ąĮąĮąŠą╝ ą┐čĆąĖą╝ąĄčĆąĄ ą╝ąĄąČą┤čā ąŠčåąĖčäčĆąŠą▓ą║ą░ą╝ąĖ ą▓čŗą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ą┐ą░čāąĘą░ ą▓ 100 ą╝čü).

ąØą░ čäą░ąĘąĄ ąŠąČąĖą┤ą░ąĮąĖčÅ ąĮąĄ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ąĮąĖą║ą░ą║ąĖčģ ą┤ąĄą╣čüčéą▓ąĖą╣, ą║čĆąŠą╝ąĄ ąŠčéčüą╗ąĄąČąĖą▓ą░ąĮąĖčÅ ąĖčüč鹥č湥ąĮąĖčÅ čéą░ą╣ą╝ą░čāčéą░. ąÜą░ą║ č鹊ą╗čīą║ąŠ čéą░ą╣ą╝ą░čāčé ąĖčüč鹥ą║, čüąĮąŠą▓ą░ ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆčāąĄčéčüčÅ ą┐ąĄčĆąĄčģąŠą┤ ą▓ čäą░ąĘčā ąĘą░ą┐čāčüą║ą░ ąŠčåąĖčäčĆąŠą▓ą║ąĖ.

[ąĪąŠą▓ąĄčéčŗ ą┐ąŠ ą┐čĆąĖą╝ąĄąĮąĄąĮąĖčÄ]

ąŚą░ąĘąĄą╝ą╗ąĄąĮąĖąĄ ąĖ čĆą░ąĘą▓ąŠą┤ą║ą░ ą┐ą╗ą░čéčŗ. ą¤ąĄčćą░čéąĮą░čÅ ą┐ą╗ą░čéą░ ą┐čĆąĖą▒ąŠčĆą░, ąĮą░ ą║ąŠč鹊čĆąŠą╣ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮą░ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ AD7680, ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī čĆą░ąĘčĆą░ą▒ąŠčéą░ąĮą░ čéą░ą║, čćč鹊ą▒čŗ čåąĄą┐ąĖ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗčģ ąĖ čåąĖčäčĆąŠą▓čŗčģ čüąĖą│ąĮą░ą╗ąŠą▓ ą▒čŗą╗ąĖ čĆą░ąĘą┤ąĄą╗ąĄąĮčŗ, ąĖ ąŠą│čĆą░ąĮąĖč湥ąĮčŗ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗą╝ąĖ ąŠą▒ą╗ą░čüčéčÅą╝ąĖ ą┐ą╗ą░čéčŗ. ąŁč鹊 čāą┐čĆąŠčēą░ąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ ą┐ą╗ąŠčüą║ąŠčüč鹥ą╣ ąĘąĄą╝ą╗ąĖ, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠąČąĮąŠ čĆą░ąĘą┤ąĄą╗ąĖčéčī ą┐čĆąĖ čĆą░ąĘą▓ąŠą┤ą║ąĄ. ąśčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠą│ąŠ ąĘą░ąĘąŠčĆą░ čéčĆą░ą▓ą╗ąĄąĮąĖčÅ ą┤ą╗čÅ ąĘą░ą╗ąĖą▓ąŠą║ ąĘąĄą╝ą╗ąĖ ą┤ą░čüčé čüą░ą╝čŗą╣ ą╗čāčćčłąĖą╣ čĆąĄąĘčāą╗čīčéą░čé, ą┐ąŠčüą║ąŠą╗čīą║čā ą┐čĆąĖ čŹč鹊ą╝ ą┐ąŠą╗čāčćą░ąĄčéčüčÅ čüą░ą╝ąŠąĄ ą╗čāčćčłąĄąĄ 菹║čĆą░ąĮąĖčĆąŠą▓ą░ąĮąĖąĄ. ąŚą░ą╗ąĖą▓ą║ąĖ ąĘąĄą╝ą╗ąĖ čåąĖčäčĆąŠą▓čŗčģ čåąĄą┐ąĄą╣ ąĖ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗčģ čåąĄą┐ąĄą╣ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čüąŠąĄą┤ąĖąĮąĄąĮčŗ ą┤čĆčāą│ čü ą┤čĆčāą│ąŠą╝ č鹊ą╗čīą║ąŠ ą▓ ąŠą┤ąĮąŠą╝ ą╝ąĄčüč鹥. ąĢčüą╗ąĖ AD7680 ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čüąĖčüč鹥ą╝ąĄ, ą│ą┤ąĄ ąĮąĄčüą║ąŠą╗čīą║ąŠ čāčüčéčĆąŠą╣čüčéą▓ čéčĆąĄą▒čāčÄčé ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ AGND ą║ DGND, čüąŠąĄą┤ąĖąĮąĄąĮąĖąĄ ą▓čüąĄ čĆą░ą▓ąĮąŠ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī čüą┤ąĄą╗ą░ąĮąŠ č鹊ą╗čīą║ąŠ ą▓ ąŠą┤ąĮąŠą╣ č鹊čćą║ąĄ, ąĖ č鹊čćą║ą░ čüąŠąĄą┤ąĖąĮąĄąĮąĖą╣ ąĘą▓ąĄąĘą┤čŗ ą┤ąŠą╗ąČąĮčŗ ąĮą░čģąŠą┤ąĖčéčīčüčÅ ą║ą░ą║ ą╝ąŠąČąĮąŠ ą▒ą╗ąĖąČąĄ ą║ AD7680.

ąśąĘą▒ąĄą│ą░ą╣č鹥 ą┐čĆąŠą║ą╗ą░ą┤ą║ąĖ čåąĖčäčĆąŠą▓čŗčģ čüąĖą│ąĮą░ą╗čīąĮčŗčģ ą╗ąĖąĮąĖą╣ ą┐ąŠą┤ ą║ąŠčĆą┐čāčüąŠą╝ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ, ą┐ąŠč鹊ą╝čā čćč鹊 čŹč鹊 ą╝ąŠąČąĄčé ą┐ąŠčĆąŠąČą┤ą░čéčī ą┐ą░čĆą░ąĘąĖčéąĮčŗąĄ ąĮą░ą▓ąŠą┤ą║ąĖ. ąÉąĮą░ą╗ąŠą│ąŠą▓ą░čÅ ąĘąĄą╝ą╗čÅ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī čĆą░ąĘą╝ąĄčēąĄąĮą░ ą┐ąŠą┤ AD7680, čćč鹊ą▒čŗ čāą╝ąĄąĮčīčłąĖčéčī čłčāą╝ąŠą▓čŗąĄ ąĮą░ą▓ąŠą┤ą║ąĖ. ą”ąĄą┐ąĖ ą┐ąĖčéą░ąĮąĖčÅ AD7680 ą┤ąŠą╗ąČąĮčŗ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą║ą░ą║ ą╝ąŠąČąĮąŠ ą▒ąŠą╗ąĄąĄ č鹊ą╗čüčéčŗąĄ ą┐čĆąŠą▓ąŠą┤ąĮąĖą║ąĖ, čćč鹊ą▒čŗ čāą╝ąĄąĮčīčłąĖčéčī ąĖčģ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ ąĖ ąĖąĮą┤čāą║čéąĖą▓ąĮąŠčüčéčī, ąĖ č鹥ą╝ čüą░ą╝čŗą╝ čāą╝ąĄąĮčīčłąĖčéčī ą▓ą╗ąĖčÅąĮąĖąĄ ąĖą╝ą┐čāą╗čīčüąŠą▓ ą▓čŗą▒čĆąŠčüąŠą▓ ą┐ąŠ ą┐ąĖčéą░ąĮąĖčÄ. ąĪąĖą│ąĮą░ą╗čŗ, ą┐ąĄčĆąĄą║ą╗čÄčćą░čÄčēąĖąĄčüčÅ čü ą▓čŗčüąŠą║ąŠą╣ čćą░čüč鹊č鹊ą╣, čéą░ą║ąĖąĄ ą║ą░ą║ čéą░ą║č鹊ą▓čŗąĄ, ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī 菹║čĆą░ąĮąĖčĆąŠą▓ą░ąĮčŗ čåąĖčäčĆąŠą▓ąŠą╣ ąĘąĄą╝ą╗ąĄą╣, čćč鹊ą▒čŗ ąĖąĘą▒ąĄąČą░čéčī ąĮą░ą▓ąŠą┤ąŠą║ ą░ ą┤čĆčāą│ąĖąĄ čüąĄą║čåąĖąĖ ą┐ą╗ą░čéčŗ, ąĖ čéą░ą║č鹊ą▓čŗąĄ čüąĖą│ąĮą░ą╗čŗ ąĮąĄ ą┤ąŠą╗ąČąĮčŗ ą┐čĆąŠčģąŠą┤ąĖčéčī čĆčÅą┤ąŠą╝ čü ą░ąĮą░ą╗ąŠą│ąŠą▓čŗą╝ąĖ ą▓čģąŠą┤ą░ą╝ąĖ. ąśąĘą▒ąĄą│ą░ą╣č鹥 ą┐ąĄčĆąĄčüąĄč湥ąĮąĖčÅ čåąĖčäčĆąŠą▓čŗčģ ąĖ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗčģ čüąĖą│ąĮą░ą╗ąŠą▓. ąóčĆą░čüčüčŗ ąĮą░ ą┐čĆąŠčéąĖą▓ąŠą┐ąŠą╗ąŠąČąĮčŗčģ čüč鹊čĆąŠąĮą░čģ ą┐ą╗ą░čéčŗ ą┤ąŠą╗ąČąĮčŗ ą┐čĆąŠčģąŠą┤ąĖčéčī ą┤čĆčāą│ ą║ ą┤čĆčāą│čā ą┐ąŠą┤ ą┐čĆčÅą╝čŗą╝ čāą│ą╗ąŠą╝, čŹč鹊 čāą╝ąĄąĮčīčłąĖčé čŹčäč乥ą║čé ą▓ąĘą░ąĖą╝ąĮąŠą│ąŠ ą▓ą╗ąĖčÅąĮąĖčÅ čüąĖą│ąĮą░ą╗ąŠą▓ ąĮą░ ą┐ą╗ą░č鹥. ąóąĄčģąĮąĖą║ą░ microstrip čüą║ąŠčĆąĄąĄ ą▓čüąĄą│ąŠ ą▒čāą┤ąĄčé ą╗čāčćčłąĄą╣, ąĮąŠ ąĄčæ ąĮąĄ ą▓čüąĄą│ą┤ą░ ą╝ąŠąČąĮąŠ ąŠčüčāčēąĄčüčéą▓ąĖčéčī ą┤ą╗čÅ ą┤ą▓čāčģčüą╗ąŠą╣ąĮąŠą╣ ą┐ą╗ą░čéčŗ. ą¤ąŠ čŹč鹊ą╣ č鹥čģąĮąĖą║ąĄ čüč鹊čĆąŠąĮą░ ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓ ą┐ą╗ą░čéčŗ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čŹą║čĆą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ (ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠ ąĘą░ą╗ąĖčéą░ ą┐čĆąŠą▓ąŠą┤ąĮąĖą║ąŠą╝ ąĘąĄą╝ą╗ąĖ), ą░ čĆą░ąĘą▓ąŠą┤ą║ą░ ą▓čüąĄčģ čåąĄą┐ąĄą╣ čüąĖą│ąĮą░ą╗ąŠą▓ ą▓čŗą┐ąŠą╗ąĮąĄąĮą░ ąĮą░ ąŠą▒čĆą░čéąĮąŠą╣ čüč鹊čĆąŠąĮąĄ ą┐ą╗ą░čéčŗ (čéą░ą║ ąĮą░ąĘčŗą▓ą░ąĄą╝ą░čÅ ąĮąĖąČąĮčÅčÅ čüč鹊čĆąŠąĮą░, ąĖą╗ąĖ "čüč鹊čĆąŠąĮą░ ą┐ą░ą╣ą║ąĖ", ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ č鹥čĆą╝ąĖąĮ ąĮąĄ ą▓čüąĄą│ą┤ą░ ąŠą┐čĆą░ą▓ą┤čŗą▓ą░ąĄčé čüą▓ąŠąĄ ąĮą░ąĘą▓ą░ąĮąĖąĄ ą▓ čüą╗čāčćą░ąĄ ą┐čĆąĖą╝ąĄąĮąĄąĮąĖčÅ ą┐ąŠą▓ąĄčĆčģąĮąŠčüčéąĮąŠą│ąŠ ą╝ąŠąĮčéą░ąČą░).

ąźąŠčĆąŠčłą░čÅ čĆą░ąĘą▓čÅąĘą║ą░ ą┐ąĖčéą░ąĮąĖčÅ čéą░ą║ąČąĄ ąŠč湥ąĮčī ą▓ą░ąČąĮą░. ąÆčüąĄ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗąĄ čåąĄą┐ąĖ ą┐ąĖčéą░ąĮąĖčÅ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čĆą░ąĘą▓čÅąĘą░ąĮčŗ čéą░ąĮčéą░ą╗ąŠą▓čŗą╝ąĖ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆą░ą╝ąĖ 10 ╬╝F ąĖ ą▓ą║ą╗čÄč湥ąĮąĮčŗą╝ąĖ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠ ąĖą╝ ą║ąĄčĆą░ą╝ąĖč湥čüą║ąĖą╝ąĖ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆą░ą╝ąĖ 0.1 ╬╝F ąĮą░ AGND, ą║ą░ą║ čŹč鹊 ąŠą▒čüčāąČą┤ą░ą╗ąŠčüčī ą▓ čĆą░ąĘą┤ąĄą╗ąĄ "ąóąĖą┐ąŠą▓ą░čÅ čüčģąĄą╝ą░ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ". ą¦č鹊ą▒čŗ ą┤ąŠčüčéąĖčćčī ąĮą░ąĖą╗čāčćčłąĄą╣ čŹčäč乥ą║čéąĖą▓ąĮąŠčüčéąĖ ąŠčé ą┐čĆąĖą╝ąĄąĮąĄąĮąĖčÅ čĆą░ąĘą▓čÅąĘčŗą▓ą░čÄčēąĖčģ ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓, ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą┤ąŠą╗ąČąĄąĮ ą┐ąŠčüčéą░čĆą░čéčīčüčÅ ą▓čŗą┤ąĄčƹȹĖą▓ą░čéčī ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠąĄ čĆą░čüčüč鹊čÅąĮąĖąĄ ą╝ąĄąČą┤čā ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆą░ą╝ąĖ čĆą░ąĘą▓čÅąĘą║ąĖ ąĖ ą▓čŗą▓ąŠą┤ą░ą╝ąĖ VDD ąĖ GND, čü ą┐čĆąĖą╝ąĄąĮąĄąĮąĖąĄą╝ ą║ą░ą║ ą╝ąŠąČąĮąŠ ą║ąŠčĆąŠčéą║ąĖčģ ą┐čĆąŠą▓ąŠą┤ąĮąĖą║ąŠą▓ ą┤ą╗čÅ čüąŠąĄą┤ąĖąĮąĄąĮąĖčÅ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆąŠą▓ čü čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╝ąĖ ą▓čŗą▓ąŠą┤ą░ą╝ąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ.

-package.png)

ąĀąĖčü. 23. ąĀą░ąĘą╝ąĄčĆčŗ 6-ą▓čŗą▓ąŠą┤ąĮąŠą│ąŠ ą║ąŠčĆą┐čāčüą░ Small Outline Transistor Package, SOT-23 (RJ-6), čāą║ą░ąĘą░ąĮąĮčŗąĄ ą▓ ą╝ąĖą╗ą╗ąĖą╝ąĄčéčĆą░čģ.

-package.png)

ąĀąĖčü. 24. ąĀą░ąĘą╝ąĄčĆčŗ 8-ą▓čŗą▓ąŠą┤ąĮąŠą│ąŠ ą║ąŠčĆą┐čāčüą░ Micro Small Outline Package, MSOP (RM-8), čāą║ą░ąĘą░ąĮąĮčŗąĄ ą▓ ą╝ąĖą╗ą╗ąĖą╝ąĄčéčĆą░čģ.

[ąöąŠčüčéčāą┐ąĮčŗąĄ ą┤ą╗čÅ ą┐ąŠą║čāą┐ą║ąĖ ą▓ą░čĆąĖą░ąĮčéčŗ AD7680]

| ą£ąŠą┤ąĄą╗čī1 |

ąöąĖą░ą┐ą░ąĘąŠąĮ č鹥ą╝ą┐ąĄčĆą░čéčāčĆ |

ą×čłąĖą▒ą║ą░ ą╗ąĖąĮąĄą╣ąĮąŠčüčéąĖ (LSB)2

|

ą×ą┐ąĖčüą░ąĮąĖąĄ ą║ąŠčĆą┐čāčüą░

|

ą×ą┐čåąĖčÅ ą║ąŠčĆą┐čāčüą░ |

ą£ą░čĆą║ąĖčĆąŠą▓ą║ą░ |

| AD7680ARJZ-REEL7 |

ŌłÆ40┬░C .. +85┬░C |

14 ą▒ąĖčé min |

6-ą▓čŗą▓ąŠą┤ąĮčŗą╣ SOT-23 |

RJ-6 |

C40 |

| AD7680ARM |

ŌłÆ40┬░C .. +85┬░C |

14 ą▒ąĖčé min |

8-ą▓čŗą▓ąŠą┤ąĮčŗą╣ MSOP |

RM-8 |

CQA |

| AD7680ARM-REEL |

ŌłÆ40┬░C .. +85┬░C |

14 ą▒ąĖčé min |

8-ą▓čŗą▓ąŠą┤ąĮčŗą╣ MSOP |

RM-8 |

CQA |

| AD7680ARM-REEL7 |

ŌłÆ40┬░C .. +85┬░C |

14 ą▒ąĖčé min |

8-ą▓čŗą▓ąŠą┤ąĮčŗą╣ MSOP |

RM-8 |

CQA |

| AD7680ARMZ |

ŌłÆ40┬░C .. +85┬░C |

14 ą▒ąĖčé min |