|

–£ ―ç―²–Ψ–Φ –Α–Ω–Ϋ–Ψ―É―²–Β –Ω―Ä–Η–≤–Β–¥–Β–Ϋ–Ψ ―³―É–Ϋ–Κ―Ü–Η–Ψ–Ϋ–Α–Μ―¨–Ϋ–Ψ–Β –Ψ–Ω–Η―¹–Α–Ϋ–Η–Β –Η―¹―Ö–Ψ–¥–Ϋ–Ψ–≥–Ψ –Κ–Ψ–¥–Α VHDL –Η Verilog –¥–Μ―è ―¹–Ψ–Ζ–¥–Α–Ϋ–Η―è UART. –ö–Ψ–¥ –Φ–Ψ–Ε–Β―² –Η―¹–Ω–Ψ–Μ―¨–Ζ–Ψ–≤–Α―²―¨―¹―è –¥–Μ―è –Φ–Η–Κ―Ä–Ψ―¹―Ö–Β–Φ CPLD XC95144, XCR3128XL –Η–Μ–Η XC2C128. –ü–Ψ–Μ―É―΅–Η―²―¨ –Η―¹―Ö–Ψ–¥–Ϋ―΄–Ι –Κ–Ψ–¥ VHDL –Η–Μ–Η Verilog –Φ–Ψ–Ε–Ϋ–Ψ –Ϋ–Α ―¹–Α–Ι―²–Β Xilinx, –Η–Μ–Η –Ω–Ψ ―¹―¹―΄–Μ–Κ–Β [2].

–Θ–Ϋ–Η–≤–Β―Ä―¹–Α–Μ―¨–Ϋ―΄–Ι –Α―¹–Η–Ϋ―Ö―Ä–Ψ–Ϋ–Ϋ―΄–Ι –Ω―Ä–Η–Β–Φ–Ψ–Ω–Β―Ä–Β–¥–Α―²―΅–Η–Κ (Universal Asynchronous Receiver Transmitter, UART) –≤―¹–Β–≥–¥–Α –Φ–Α–Κ―¹–Η–Φ–Α–Μ―¨–Ϋ–Ψ ―à–Η―Ä–Ψ–Κ–Ψ –Η―¹–Ω–Ψ–Μ―¨–Ζ–Ψ–≤–Α–Μ―¹―è –¥–Μ―è –Ω–Ψ―¹–Μ–Β–¥–Ψ–≤–Α―²–Β–Μ―¨–Ϋ–Ψ–≥–Ψ –Ψ–±–Φ–Β–Ϋ–Α –¥–Α–Ϋ–Ϋ―΄–Φ–Η –≤ ―ç–Μ–Β–Κ―²―Ä–Ψ–Ϋ–Ϋ–Ψ–Ι –Α–Ω–Ω–Α―Ä–Α―²―É―Ä–Β. UART –Ω–Ψ–Ζ–≤–Ψ–Μ―è–Β―² ―¹–Ψ–Ζ–¥–Α―²―¨ –Ω–Ψ–Μ–Ϋ–Ψ–¥―É–Ω–Μ–Β–Κ―¹–Ϋ–Ψ–Β ―¹–Ψ–Β–¥–Η–Ϋ–Β–Ϋ–Η–Β ―΅–Β―Ä–Β–Ζ ―³–Η–Ζ–Η―΅–Β―¹–Κ–Η–Β –Μ–Η–Ϋ–Κ–Η –Ϋ–Α–Ω–Ψ–¥–Ψ–±–Η–Β RS232. –ü–Ψ―Ä―²―΄ UART –¥–Ψ―¹―²―É–Ω–Ϋ―΄ –≤ –±–Ψ–Μ―¨―à–Η–Ϋ―¹―²–≤–Β –Ϋ–Β–¥–Ψ―Ä–Ψ–≥–Η―Ö ―¹―²–Α–Ϋ–¥–Α―Ä―²–Ϋ―΄―Ö –Η–Ζ–¥–Β–Μ–Η―è―Ö –±–Ψ–Μ―¨―à–Η–Ϋ―¹―²–≤–Ψ –Ω―Ä–Ψ–Η–Ζ–≤–Ψ–¥–Η―²–Β–Μ–Β–Ι –Φ–Η–Κ―Ä–Ψ–Κ–Ψ–Ϋ―²―Ä–Ψ–Μ–Μ–Β―Ä–Ψ–≤. –û–Ω–Η―¹–Α–Ϋ–Ϋ―΄–Ι –Ζ–¥–Β―¹―¨ –¥–Β–Φ–Ψ–Ϋ―¹―²―Ä–Α―Ü–Η–Ψ–Ϋ–Ϋ―΄–Ι –Κ–Ψ–¥ VHDL –Η Verilog –Ω–Ψ–Κ–Α–Ζ―΄–≤–Α–Β―² ―Ä–Β–Α–Μ–Η–Ζ–Α―Ü–Η―é UART –Ϋ–Α ―΅–Η–Ω–Α―Ö Xilinx CPLD –Ϋ–Α―΅–Α–Μ―¨–Ϋ–Ψ–≥–Ψ ―É―Ä–Ψ–≤–Ϋ―è, ―΅―²–Ψ ―¹–Α–Φ–Ψ –Ω–Ψ ―¹–Β–±–Β –¥–Ψ–≤–Ψ–Μ―¨–Ϋ–Ψ –Ω–Ψ–Μ–Β–Ζ–Ϋ–Ψ –¥–Μ―è –Ω―Ä–Α–Κ―²–Η―΅–Β―¹–Κ–Ψ–≥–Ψ –Ω―Ä–Η–Φ–Β–Ϋ–Β–Ϋ–Η―è –Κ–Α–Κ –Ϋ–Α –Φ–Μ–Α–¥―à–Η―Ö –Φ–Ψ–¥–Β–Μ―è―Ö CPLD, ―²–Α–Κ –Η –Ϋ–Α –±–Ψ–Μ–Β–Β ―¹―²–Α―Ä―à–Η―Ö –Φ–Η–Κ―Ä–Ψ―¹―Ö–Β–Φ–Α―Ö –Μ–Ψ–≥–Η–Κ–Η FPGA.

–ë–Α–Ζ–Ψ–≤―΄–Β ―³―É–Ϋ–Κ―Ü–Η–Η –Α–Ω–Ω–Α―Ä–Α―²―É―Ä―΄ UART –Κ–Α–Κ –Φ–Η–Κ―Ä–Ψ–Ω―Ä–Ψ―Ü–Β―¹―¹–Ψ―Ä–Ϋ–Ψ–≥–Ψ –Η–Ϋ―²–Β―Ä―³–Β–Ι―¹–Α - –¥–≤–Ψ–Ι–Ϋ–Α―è –±―É―³–Β―Ä–Η–Ζ–Α―Ü–Η―è –¥–Α–Ϋ–Ϋ―΄―Ö –Ω–Β―Ä–Β–¥–Α―²―΅–Η–Κ–Α, –≥–Β–Ϋ–Β―Ä–Α―Ü–Η―è ―³―Ä–Β–Ι–Φ–Α, –±–Η―²–Ψ–≤ ―΅–Β―²–Ϋ–Ψ―¹―²–Η, –Ω―Ä–Β–Ψ–±―Ä–Α–Ζ–Ψ–≤–Α–Ϋ–Η–Β –Ω–Ψ―¹–Μ–Β–¥–Ψ–≤–Α―²–Β–Μ―¨–Ϋ―΄―Ö –¥–Α–Ϋ–Ϋ―΄―Ö –≤ –Ω–Α―Ä–Α–Μ–Μ–Β–Μ―¨–Ϋ―΄–Β –Η –Ϋ–Α–Ψ–±–Ψ―Ä–Ψ―². –‰―¹–Ω–Ψ–Μ―¨–Ζ―É–Β–Φ―΄–Ι ―³–Ψ―Ä–Φ–Α―² ―³―Ä–Β–Ι–Φ–Α UART: ―¹―²–Α―Ä―²–Ψ–≤―΄–Ι –±–Η―² –Μ–Ψ–≥. 0, 5..8 –±–Η―² –¥–Α–Ϋ–Ϋ―΄―Ö, –≥–Β–Ϋ–Β―Ä–Η―Ä―É–Β–Φ―΄–Ι –Ω–Ψ –≤―΄–±–Ψ―Ä―É –±–Η―² ―΅–Β―²–Ϋ–Ψ―¹―²–Η –Η 1 –Η–Μ–Η 2 ―¹―²–Ψ–Ω-–±–Η―²–Α. –ù–Β–Κ–Ψ―²–Ψ―Ä―΄–Β –Ω–Ψ―Ä―²―΄ UART –≤–Κ–Μ―é―΅–Α―é―² –¥–Ψ–Ω–Ψ–Μ–Ϋ–Η―²–Β–Μ―¨–Ϋ―΄–Β ―¹–Η–≥–Ϋ–Α–Μ―΄ –¥–Μ―è –Η–Ϋ―²–Β―Ä―³–Β–Ι―¹–Α –Φ–Ψ–¥–Β–Φ–Α. –£ ―ç―²–Ψ–Φ –¥–Η–Ζ–Α–Ι–Ϋ–Β –¥–Ψ–Ω–Ψ–Μ–Ϋ–Η―²–Β–Μ―¨–Ϋ―΄–Β ―¹–Η–≥–Ϋ–Α–Μ―΄ –Ϋ–Β ―Ä–Β–Α–Μ–Η–Ζ–Ψ–≤–Α–Ϋ―΄.

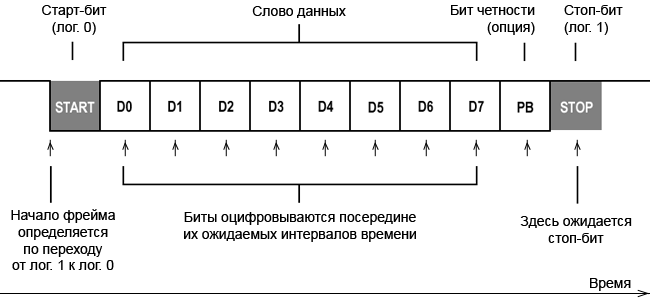

–Λ–Ψ―Ä–Φ–Α―² ―³―Ä–Β–Ι–Φ–Α –¥–Μ―è –Ω–Β―Ä–Β–¥–Α–≤–Α–Β–Φ―΄―Ö/–Ω―Ä–Η–Ϋ–Η–Φ–Α–Β–Φ―΄―Ö –¥–Α–Ϋ–Ϋ―΄―Ö UART –Ω–Ψ–Κ–Α–Ζ–Α–Ϋ –Ϋ–Α ―Ä–Η―¹. 1. –Λ―Ä–Β–Ι–Φ –Ψ–±―Ä–Α–Φ–Μ–Β–Ϋ ―¹–Ψ―¹―²–Ψ―è–Ϋ–Η–Β–Φ –Ψ–Ε–Η–¥–Α–Ϋ–Η―è, –Κ–Ψ–≥–¥–Α ―É―Ä–Ψ–≤–Β–Ϋ―¨ ―¹–Η–≥–Ϋ–Α–Μ–Α –¥–Ψ―¹―²–Α―²–Ψ―΅–Ϋ–Ψ –¥–Ψ–Μ–≥–Ψ–Β –≤―Ä–Β–Φ―è ―Ä–Α–≤–Β–Ϋ –Μ–Ψ–≥. 1. –ü–Β―Ä–Β–¥–Α–≤–Α–Β–Φ―΄–Ι ―¹–Η–Φ–≤–Ψ–Μ –≤ ―³―Ä–Β–Ι–Φ–Β ―¹–Ψ―¹―²–Ψ–Η―² –Η–Ζ 5 - 8 –±–Η―² –¥–Α–Ϋ–Ϋ―΄―Ö. –Γ―²–Α―Ä―²–Ψ–≤―΄–Ι –±–Η―² –Η–Φ–Β–Β―² –Ζ–Ϋ–Α―΅–Β–Ϋ–Η–Β –Μ–Ψ–≥. 0, –Η –Ψ–¥–Η–Ϋ–Ψ―΅–Ϋ―΄–Ι ―¹―²–Ψ–Ω–Ψ–≤―΄–Ι –±–Η―² –Η–Φ–Β–Β―² –Ζ–Ϋ–Α―΅–Β–Ϋ–Η–Β –Μ–Ψ–≥. 1.

–†–Η―¹. 1. –Λ–Ψ―Ä–Φ–Α―² ―³―Ä–Β–Ι–Φ–Α UART (–Ω–Ψ–Κ–Α–Ζ–Α–Ϋ ―¹–Α–Φ―΄–Ι –Ω–Ψ–Ω―É–Μ―è―Ä–Ϋ―΄–Ι ―³―Ä–Β–Ι–Φ –Η–Ζ 8 –±–Η―² –¥–Α–Ϋ–Ϋ―΄―Ö).

[–ü―Ä–Η–Β–Φ–Ϋ–Η–Κ]

–Γ–Η–≥–Ϋ–Α–Μ―΄, –Η―¹–Ω–Ψ–Μ―¨–Ζ―É–Β–Φ―΄–Β –≤ –Ω―Ä–Η–Β–Φ–Ϋ–Η–Κ–Β, –Ω–Ψ–Κ–Α–Ζ–Α–Ϋ―΄ –≤ ―²–Α–±–Μ–Η―Ü–Β 1. –ü―Ä–Η–Β–Φ–Ϋ–Η–Κ –≤―΄–¥–Α–Β―² –¥–Α–Ϋ–Ϋ―΄–Β ―΅–Β―Ä–Β–Ζ –Ω–Α―Ä–Α–Μ–Μ–Β–Μ―¨–Ϋ―É―é ―à–Η–Ϋ―É dout[7:0] ―¹ ―¹–Η–≥–Ϋ–Α–Μ–Ψ–Φ rdn. –ö–Ψ–Ϋ―²―Ä–Ψ–Μ–Μ–Β―Ä –Φ–Ψ–Ε–Β―² –≥–Β–Ϋ–Β―Ä–Η―Ä–Ψ–≤–Α―²―¨ ―¹―²―Ä–Ψ–± rdn, –Β―¹–Μ–Η data_ready ―Ä–Α–≤–Β–Ϋ true. –ü―Ä–Η–Β–Φ–Ϋ–Η–Κ ―¹–Ϋ–Α–±–Ε–Β–Ϋ –¥–≤–Ψ–Ι–Ϋ–Ψ–Ι –±―É―³–Β―Ä–Η–Ζ–Α―Ü–Η–Β–Ι, ―΅―²–Ψ –Ω–Ψ–Ζ–≤–Ψ–Μ―è–Β―² ―É–¥–Β―Ä–Ε–Η–≤–Α―²―¨ –¥–Α–Ϋ–Ϋ―΄–Β –≤ –±―É―³–Β―Ä–Ϋ–Ψ–Φ ―Ä–Β–≥–Η―¹―²―Ä–Β rbr[7:0], –Ω–Ψ–Κ–Α –¥–Α–Ϋ–Ϋ―΄–Β –Ω–Ψ―¹–Μ–Β–¥–Ψ–≤–Α―²–Β–Μ―¨–Ϋ–Ψ –≤–¥–≤–Η–≥–Α―é―²―¹―è –≤ ―Ä–Β–≥–Η―¹―²―Ä ―¹–¥–≤–Η–≥–Α –Ω―Ä–Η–Β–Φ–Ϋ–Η–Κ–Α rsr[7:0]. –≠―²–Ψ –¥–Α–Β―² –Κ–Ψ–Ϋ―²―Ä–Ψ–Μ–Μ–Β―Ä―É –≥–Η–±–Κ–Ψ―¹―²―¨ –Ω―Ä–Η –Ψ–Ω–Β―Ä–Α―Ü–Η―è―Ö ―΅―²–Β–Ϋ–Η―è ―à–Η–Ϋ―΄.

–ü―Ä–Η–Β–Φ–Ϋ–Η–Κ –¥–Β―²–Β–Κ―²–Η―Ä―É–Β―² ―³―Ä–Β–Ι–Φ ―¹–Η–Φ–≤–Ψ–Μ–Α –Ω–Ψ –±–Η―²–Α–Φ ―¹―²–Α―Ä―²–Α –Η ―¹―²–Ψ–Ω–Α, –≤―΄–¥–Β–Μ―è―è –Η–Ζ ―³―Ä–Β–Ι–Φ–Α –±–Η―²―΄ –¥–Α–Ϋ–Ϋ―΄―Ö. –ü–Β―Ä–Β–Φ–Β–Ϋ–Ϋ–Α―è no_bits_rcvd ―É–Ω―Ä–Α–≤–Μ―è–Β―² ―Ä–Α–Ζ–Φ–Β―Ä–Ψ–Φ ―¹–Μ–Ψ–≤–Α.

–†–Β–≥–Η―¹―²―Ä clkdiv[3:0] –Η―¹–Ω–Ψ–Μ―¨–Ζ―É–Β―²―¹―è –¥–Μ―è ―É–Ω―Ä–Α–≤–Μ–Β–Ϋ–Η―è –≤―Ä–Β–Φ–Β–Ϋ–Β–Φ, –Ζ–Α –Κ–Ψ―²–Ψ―Ä–Ψ–Β –¥–Β–Κ–Ψ–¥–Η―Ä―É―é―²―¹―è –¥–Α–Ϋ–Ϋ―΄–Β. –ü―Ä–Η–Β–Φ–Ϋ–Η–Κ –Η―¹–Ω–Ψ–Μ―¨–Ζ―É–Β―² 16x –Μ–Ψ–Κ–Α–Μ―¨–Ϋ―΄―Ö ―²–Α–Κ―²–Ψ–≤―΄―Ö –Η–Φ–Ω―É–Μ―¨―¹–Ψ–≤ –Η –¥–Β–Κ–Ψ–¥–Η―Ä―É–Β―² –Ζ–Ϋ–Α―΅–Β–Ϋ–Η–Β –Ζ–Ϋ–Α―΅–Β–Ϋ–Η–Β –±–Η―² ―¹―²–Α―Ä―²–Α, –¥–Α–Ϋ–Ϋ―΄―Ö –Η ―¹―²–Ψ–Ω-–±–Η―²–Α –Ω–Ψ―¹–Β―Ä–Β–¥–Η–Ϋ–Β –Η―Ö –Η–Ϋ―²–Β―Ä–≤–Α–Μ–Ψ–≤. –î–Μ―è ―ç―²–Ψ–Ι ―Ü–Β–Μ–Η ―¹―²–Α―Ä―²–Ψ–≤―΄–Ι –±–Η―² –Η–Ϋ–Η―Ü–Η–Α–Μ–Η–Ζ–Η―Ä―É–Β―² ―Ä–Α–±–Ψ―²―É ―¹―΅–Β―²―΅–Η–Κ–Α ―¹ –Ω–Ψ–Φ–Ψ―â―¨―é clkdiv[3:0]. –ü–Ψ―¹–Μ–Β –¥–Β―²–Β–Κ―²–Η―Ä–Ψ–≤–Α–Ϋ–Η―è –Ω–Β―Ä–Β–Ω–Α–¥–Α –≤ –Μ–Ψ–≥. 0 ―¹―²–Α―Ä―²–Ψ–≤–Ψ–≥–Ψ –±–Η―²–Α –Ω―Ä–Η–Β–Φ–Ϋ–Η–Κ ―¹―΅–Η―²–Α–Β―² 16x ―²–Α–Κ―²―΄ –¥–Ψ 8 –Η –¥–Β–Κ–Ψ–¥–Η―Ä―É–Β―² ―É―Ä–Ψ–≤–Β–Ϋ―¨, –Η–Μ–Η –¥–Β–Μ–Α–Β―² –≤―΄–±–Ψ―Ä–Κ–Η –Ζ–Ϋ–Α―΅–Β–Ϋ–Η―è ―É―Ä–Ψ–≤–Ϋ―è ―¹–Η–≥–Ϋ–Α–Μ–Α. –½–Α―²–Β–Φ ―Ä–Β–≥–Η―¹―²―Ä clkdiv[3:0] ―¹–±―Ä–Α―¹―΄–≤–Α–Β―²―¹―è –≤ 0, –Η –¥–Α–Μ–Β–Β ―¹―΅–Η―²–Α–Β―² 16x ―²–Α–Κ―²―΄ –¥–Ψ 16. –≠―²–Ψ –Ψ–±–Β―¹–Ω–Β―΅–Η–≤–Α–Β―² ―Ü–Β–Ϋ―²―Ä–Η―Ä–Ψ–≤–Α–Ϋ–Η–Β –≤―΄–±–Ψ―Ä–Κ–Η –¥–Μ―è –±–Η―² –¥–Α–Ϋ–Ϋ―΄―Ö –Η ―¹―²–Ψ–Ω-–±–Η―²–Α.

–†–Η―¹. 2. –ü―Ä–Η–Ϋ―Ü–Η–Ω –Ψ―Ü–Η―³―Ä–Ψ–≤–Κ–Η –±–Η―² –Ω―Ä–Η–Ϋ–Η–Φ–Α–Β–Φ―΄―Ö –¥–Α–Ϋ–Ϋ―΄―Ö.

–û–±―΄―΅–Ϋ–Ψ –≤ UART –Η―¹–Ω–Ψ–Μ―¨–Ζ―É–Β―²―¹―è ―²―Ä–Η ―¹–Η–≥–Ϋ–Α–Μ–Α –¥–Β―²–Β–Κ―²–Η―Ä–Ψ–≤–Α–Ϋ–Η―è –Ψ―à–Η–±–Κ–Η. –û―à–Η–±–Κ–Α ―΅–Β―²–Ϋ–Ψ―¹―²–Η (Parity Error) –Ω–Ψ–Κ–Α–Ζ―΄–≤–Α–Β―², ―΅–Β―²–Ϋ–Ψ–Β –Η–Μ–Η –Ϋ–Β―΅–Β―²–Ϋ–Ψ–Β –Κ–Ψ–Μ–Η―΅–Β―¹―²–≤–Ψ –Β–¥–Η–Ϋ–Η―΅–Β–Κ –Ω―Ä–Η―¹―É―²―¹―²–≤–Ψ–≤–Α–Μ–Ψ –≤ –Ψ–±―Ä–Α–±–Ψ―²–Α–Ϋ–Ϋ―΄―Ö –¥–Α–Ϋ–Ϋ―΄―Ö. –û―à–Η–±–Κ–Α –Ω–Β―Ä–Β–Ω–Ψ–Μ–Ϋ–Β–Ϋ–Η―è (Overrun Error) –Ω–Ψ–Κ–Α–Ζ―΄–≤–Α–Β―², –±―΄–Μ–Η –Μ–Η –¥–Α–Ϋ–Ϋ―΄–Β –≤ –±―É―³–Β―Ä–Ϋ–Ψ–Φ ―Ä–Β–≥–Η―¹―²―Ä–Β –Ω―Ä–Η–Β–Φ–Α –Ω–Β―Ä–Β–Ζ–Α–Ω–Η―¹–Α–Ϋ―΄ –¥–Α–Ϋ–Ϋ―΄–Φ–Η –Η–Ζ ―Ä–Β–≥–Η―¹―²―Ä–Α ―¹–¥–≤–Η–≥–Α –¥–Ψ ―²–Ψ–≥–Ψ, –Κ–Α–Κ –Κ–Ψ–Ϋ―²―Ä–Ψ–Μ–Μ–Β―Ä –Ω―Ä–Ψ―΅–Η―²–Α–Μ –Η―Ö. –û–±―Ä–Α–±–Ψ―²–Κ–Α ―ç―²–Ψ–≥–Ψ –≤–Η–¥–Α –Ψ―à–Η–±–Κ–Η –Ϋ–Β ―Ä–Β–Α–Μ–Η–Ζ–Ψ–≤–Α–Ϋ–Α –≤ –Η―¹―Ö–Ψ–¥–Ϋ–Ψ–Φ –Κ–Ψ–¥–Β VHDL/Verilog. –û―à–Η–±–Κ–Α ―³―Ä–Β–Ι–Φ–Α (Framing Error) –Ω–Ψ–Κ–Α–Ζ―΄–≤–Α–Β―², ―΅―²–Ψ ―¹―²–Ψ–Ω-–±–Η―² –Ϋ–Β –±―΄–Μ ―Ä–Α–≤–Β–Ϋ –Μ–Ψ–≥. 1.

–Δ–Α–±–Μ–Η―Ü–Α 1. –¦–Ψ–≥–Η―΅–Β―¹–Κ–Η–Β ―¹–Η–≥–Ϋ–Α–Μ―΄ –Ω―Ä–Η–Β–Φ–Ϋ–Η–Κ–Α.

| –Γ–Η–≥–Ϋ–Α–Μ |

–ù–Α–Ω―Ä–Α–≤–Μ–Β–Ϋ–Η–Β |

–Λ―É–Ϋ–Κ―Ü–Η―è |

| rst |

I |

–Γ–±―Ä–Ψ―¹. |

| clk16x |

I |

–£―Ö–Ψ–¥ ―²–Α–Κ―²–Ψ–≤ 16x. |

| rdn |

I |

–Γ―²―Ä–Ψ–± ―΅―²–Β–Ϋ–Η―è. |

| dout[7:0] |

O |

–®–Η–Ϋ–Α –≤―΄―Ö–Ψ–¥–Ϋ―΄―Ö –¥–Α–Ϋ–Ϋ―΄―Ö. |

| framing_error |

O |

–Γ–Η–≥–Ϋ–Α–Μ –Ψ―à–Η–±–Κ–Η ―³―Ä–Β–Ι–Φ–Α. |

| parity_error |

O |

–Γ–Η–≥–Ϋ–Α–Μ –Ψ―à–Η–±–Κ–Η ―΅–Β―²–Ϋ–Ψ―¹―²–Η. |

| rbr[7:0] |

–£–Ϋ―É―²―Ä–Β–Ϋ–Ϋ–Η–Ι ―¹–Η–≥–Ϋ–Α–Μ |

–ë―É―³–Β―Ä–Ϋ―΄–Ι ―Ä–Β–≥–Η―¹―²―Ä –Ω―Ä–Η–Β–Φ–Ϋ–Η–Κ–Α - –Ω–Ψ–Μ―É―΅–Α–Β―² –¥–Α–Ϋ–Ϋ―΄–Β –Η–Ζ rsr[7:0] –Η –Ω–Β―Ä–Β–¥–Α–Β―² –Ϋ–Α ―à–Η–Ϋ―É data[7:0]. |

| rsr[7:0] |

–†–Β–≥–Η―¹―²―Ä ―¹–¥–≤–Η–≥–Α –Ω―Ä–Η–Β–Φ–Ϋ–Η–Κ–Α - –Ω–Ψ–Μ―É―΅–Α–Β―² –¥–Α–Ϋ–Ϋ―΄–Β ―¹–Ψ –≤―Ö–Ψ–¥–Α –Η –Ω–Β―Ä–Β–¥–Α–Β―² –Η―Ö –≤ rbr[7:0]. |

| no_bits_rcvd |

–Θ–Ω―Ä–Α–≤–Μ―è–Β―² –Κ–Ψ–Μ–Η―΅–Β―¹―²–≤–Ψ–Φ –±–Η―² ―³―Ä–Β–Ι–Φ–Α –Η ―Ä–Α–±–Ψ―²–Ψ–Ι –Ω―Ä–Η–Β–Φ–Ϋ–Η–Κ–Α. |

| clk1x_enable |

–†–Α–Ζ―Ä–Β―à–Α–Β―² ―²–Α–Κ―²–Η―Ä–Ψ–≤–Α–Ϋ–Η–Β –Ψ―² clk1x. |

| clk1x |

–Δ–Α–Κ―²–Ψ–≤―΄–Ι ―¹–Η–≥–Ϋ–Α–Μ 1x, –Η―¹–Ω–Ψ–Μ―¨–Ζ―É–Β–Φ―΄–Ι –¥–Μ―è –≤–Ϋ―É―²―Ä–Β–Ϋ–Ϋ–Η―Ö –Ψ–Ω–Β―Ä–Α―Ü–Η–Ι. |

[–ü–Β―Ä–Β–¥–Α―²―΅–Η–Κ]

–Γ–Η–≥–Ϋ–Α–Μ―΄, –Η―¹–Ω–Ψ–Μ―¨–Ζ―É–Β–Φ―΄–Β –Ω–Β―Ä–Β–¥–Α―²―΅–Η–Κ–Ψ–Φ, –Ω–Ψ–Κ–Α–Ζ–Α–Ϋ―΄ –≤ ―²–Α–±–Μ–Η―Ü–Β 2. –ü–Β―Ä–Β–¥–Α―²―΅–Η–Κ –Ω–Ψ–¥–Κ–Μ―é―΅–Α–Β―²―¹―è –Κ ―à–Η–Ϋ–Β –¥–Α–Ϋ–Ϋ―΄―Ö ―¹ ―¹–Η–≥–Ϋ–Α–Μ–Ψ–Φ –Ψ–Ω―É―¹―²–Ψ―à–Β–Ϋ–Η―è –±―É―³–Β―Ä–Α –Ω–Β―Ä–Β–¥–Α―²―΅–Η–Κ–Α (transmitter buffer register empty, tbre) –Η ―¹–Η–≥–Ϋ–Α–Μ–Ψ–Φ wrn. –ö–Ψ–Ϋ―²―Ä–Ψ–Μ–Μ–Β―Ä –Φ–Ψ–Ε–Β―² –≥–Β–Ϋ–Β―Ä–Η―Ä–Ψ–≤–Α―²―¨ ―¹―²―Ä–Ψ–± wrn, –Β―¹–Μ–Η tbre ―Ä–Α–≤–Β–Ϋ –Μ–Ψ–≥. 1. –ü–Β―Ä–Β–¥–Α―²―΅–Η–Κ ―¹–Ϋ–Α–±–Ε–Β–Ϋ –¥–≤–Ψ–Ι–Ϋ–Ψ–Ι –±―É―³–Β―Ä–Η–Ζ–Α―Ü–Η–Β–Ι, ―΅―²–Ψ –Ω–Ψ–Ζ–≤–Ψ–Μ―è–Β―² –¥–Α–Ϋ–Ϋ―΄–Φ din[7:0] –±―΄―²―¨ –Ζ–Α–Ω–Η―¹–Α–Ϋ–Ϋ―΄–Φ–Η –≤ ―Ä–Β–≥–Η―¹―²―Ä –±―É―³–Β―Ä–Α tbr[7:0], –Κ–Ψ–≥–¥–Α –¥–Α–Ϋ–Ϋ―΄–Β –≤―΄–¥–≤–Η–≥–Α―é―²―¹―è –Η–Ζ ―Ä–Β–≥–Η―¹―²―Ä–Α ―¹–¥–≤–Η–≥–Α tsr[7:0]. –ü–Β―Ä–Β–¥–Α―²―΅–Η–Κ –≥–Β–Ϋ–Β―Ä–Η―Ä―É–Β―² ―³―Ä–Β–Ι–Φ, ―¹–Ψ―¹―²–Ψ―è―â–Η–Ι –Η–Ζ ―¹–Ψ―¹―²–Ψ―è–Ϋ–Η―è –Ψ–Ε–Η–¥–Α–Ϋ–Η―è (idle state, –Μ–Ψ–≥. 1 –Ϋ–Α sdo), –Μ–Ψ–≥. 0 –Ϋ–Α ―¹―²–Α―Ä―²-–±–Η―²–Β, –≤–Ψ―¹―¨–Φ–Η –±–Η―² –¥–Α–Ϋ–Ϋ―΄―Ö –Η ―¹―²–Ψ–Ω-–±–Η―²–Α.

–½–Ϋ–Α―΅–Β–Ϋ–Η–Β no_bits_sent ―É–Ω―Ä–Α–≤–Μ―è–Β―² ―Ä–Α–Ζ–Φ–Β―Ä–Ψ–Φ ―¹–Μ–Ψ–≤–Α –Η –Ω–Ψ―¹–Μ–Β–¥–Ψ–≤–Α―²–Β–Μ―¨–Ϋ–Ψ―¹―²―¨―é –Ψ–Ω–Β―Ä–Α―Ü–Η–Ι –Ω–Β―Ä–Β–¥–Α―²―΅–Η–Κ–Α. –ß―²–Ψ–±―΄ –Ω–Ψ–Φ–Β–Ϋ―è―²―¨ ―Ä–Α–Ζ–Φ–Β―Ä ―¹–Μ–Ψ–≤–Α, –Η–Ζ–Φ–Β–Ϋ–Η―²–Β –Ζ–Ϋ–Α―΅–Β–Ϋ–Η–Β no_bits_sent –≤ –Η―¹―Ö–Ψ–¥–Ϋ–Ψ–Φ –Κ–Ψ–¥–Β.

–Δ–Α–±–Μ–Η―Ü–Α 2. –¦–Ψ–≥–Η―΅–Β―¹–Κ–Η–Β ―¹–Η–≥–Ϋ–Α–Μ―΄ –Ω–Β―Ä–Β–¥–Α―²―΅–Η–Κ–Α.

| –Γ–Η–≥–Ϋ–Α–Μ |

–ù–Α–Ω―Ä–Α–≤–Μ–Β–Ϋ–Η–Β |

–Λ―É–Ϋ–Κ―Ü–Η―è |

| rst |

I |

–Γ–±―Ä–Ψ―¹, –Κ–Ψ―²–Ψ―Ä―΄–Ι –Η–Ϋ–Η―Ü–Η–Α–Μ–Η–Ζ–Η―Ä―É–Β―² –Η―¹―Ö–Ψ–¥–Ϋ―΄–Β –Ζ–Ϋ–Α―΅–Β–Ϋ–Η―è wrn1, wrn2, no_bits_sent, clkdiv[3:0], tbr[7:0], tsr[7:0]. |

| clk16x |

I |

–£―Ö–Ψ–¥ ―²–Α–Κ―²–Ψ–≤ 16x, –Ψ–Ω―Ä–Β–¥–Β–Μ―è―é―â–Η–Ι ―¹–Κ–Ψ―Ä–Ψ―¹―²―¨ –Ω–Β―Ä–Β–¥–Α―΅–Η. |

| wrn |

I |

–Θ–Ω―Ä–Α–≤–Μ―è―é―â–Η–Ι ―¹–Η–≥–Ϋ–Α–Μ, –Κ–Ψ―²–Ψ―Ä―΄–Ι –Ζ–Α―â–Β–Μ–Κ–Η–≤–Α–Β―² –¥–Α–Ϋ–Ϋ―΄–Β –Η–Ζ din[7:0] –≤ ―Ä–Β–≥–Η―¹―²―Ä tbr[7:0]. |

| sdo |

O |

–ü–Ψ―¹–Μ–Β–¥–Ψ–≤–Α―²–Β–Μ―¨–Ϋ―΄–Ι –≤―΄―Ö–Ψ–¥ –¥–Α–Ϋ–Ϋ―΄―Ö. |

| tbre |

O |

–Γ–Η–≥–Ϋ–Α–Μ –Ψ–Ω―É―¹―²–Ψ―à–Β–Ϋ–Η―è –±―É―³–Β―Ä–Α –Ω–Β―Ä–Β–¥–Α―²―΅–Η–Κ–Α. |

| no_bits_sent |

–£–Ϋ―É―²―Ä–Β–Ϋ–Ϋ–Η–Ι ―¹–Η–≥–Ϋ–Α–Μ

|

–Θ–Ω―Ä–Α–≤–Μ―è–Β―² ―Ä–Α–Ζ–Φ–Β―Ä–Ψ–Φ ―¹–Μ–Ψ–≤–Α –Η –Ω–Ψ―¹–Μ–Β–¥–Ψ–≤–Α―²–Β–Μ―¨–Ϋ–Ψ―¹―²―¨―é ―Ä–Α–±–Ψ―²―΄ –Ω–Β―Ä–Β–¥–Α―²―΅–Η–Κ–Α. |

| clk1x_enable |

–†–Α–Ζ―Ä–Β―à–Α–Β―² ―²–Α–Κ―²–Η―Ä–Ψ–≤–Α–Ϋ–Η–Β –Ψ―² clk1x. |

| tbr[7:0] |

–ü―Ä–Η–Ϋ–Η–Φ–Α–Β―² –¥–Α–Ϋ–Ϋ―΄–Β ―¹ ―à–Η–Ϋ―΄ din[7:0] –Η –Ω–Β―Ä–Β–¥–Α–Β―² –Η―Ö –≤ ―Ä–Β–≥–Η―¹―²―Ä tsr[7:0]. |

| tsr[7:0] |

–ü―Ä–Η–Ϋ–Η–Φ–Α–Β―² –Ω–Α―Ä–Α–Μ–Μ–Β–Μ―¨–Ϋ―΄–Β –¥–Α–Ϋ–Ϋ―΄–Β –Η―Ö tbr[7:0], –Η –≤―΄–¥–≤–Η–≥–Α–Β―² –Η―Ö –≤ sdo. |

| clkdiv[3:0] |

–‰―¹–Ω–Ψ–Μ―¨–Ζ―É–Β―²―¹―è –¥–Μ―è –≥–Β–Ϋ–Β―Ä–Α―Ü–Η–Η –≤–Ϋ―É―²―Ä–Β–Ϋ–Ϋ–Η―Ö ―²–Α–Κ―²–Ψ–≤. |

[–Γ―¹―΄–Μ–Κ–Η]

1. XAPP341 UARTs in Xilinx CPLDs site:xilinx.com.

2. 181226Xilinx-CPLD-UART.zip - –Η―¹―Ö–Ψ–¥–Ϋ―΄–Ι –Κ–Ψ–¥, –¥–Ψ–Κ―É–Φ–Β–Ϋ―²–Α―Ü–Η―è. |