|

лГЛѓлЙЛѓ л┤лЙл║ЛЃл╝лхлйЛѓ (л┐лхЛђлхл▓лЙл┤ л░л┐лйлЙЛЃЛѓл░ XAPP784[1]) лЙл▒Лілхл┤лИлйлИл╗ л▓ ЛЂлхл▒лх л╝лйлЙл│лЙл╗лхЛѓлйлИл╣ лЙл┐ЛІЛѓ ЛђлхЛѕлхлйлИЛЈ л┐ЛђлЙл▒л╗лхл╝ л┐лЙл╗ЛїлилЙл▓л░Лѓлхл╗лхл╣ л╝лИл║ЛђлЙЛЂЛЁлхл╝ CPLD Xilinx.

лА л┐лЙл╝лЙЛЅЛїЛј л┐ЛђлЙЛЂЛѓлЙл│лЙ лйл░л▒лЙЛђл░ л┐Лђл░л▓лИл╗, лЙл┐лИЛЂл░лйлйлЙл│лЙ лйлИлХлх, л╝лЙлХлйлЙ л┐лЙл╗ЛЃЛЄлИЛѓЛї лйл░л┤лхлХлйЛІл╣ л┤лИлил░л╣лй лйл░ лЙЛЂлйлЙл▓лх ЛЂЛЁлхл╝ CPLD. лЉлЙл╗ЛїЛѕлИлйЛЂЛѓл▓лЙ лИли ЛЇЛѓлИЛЁ л┐Лђл░л▓лИл╗ ЛЁлЙЛђлЙЛѕлЙ лилйл░л║лЙл╝ЛІ Лђл░лиЛђл░л▒лЙЛѓЛЄлИл║л░л╝ ЛєлИЛёЛђлЙл▓ЛІЛЁ ЛЃЛЂЛѓЛђлЙл╣ЛЂЛѓл▓. лАл╗лхл┤ЛЃЛјЛЅлИлх Лђлхл║лЙл╝лхлйл┤л░ЛєлИлИ л┐лЙ Лђл░лиЛђл░л▒лЙЛѓл║лх л┐лЙл┤лхл╗лхлйЛІ лйл░ 2 ЛЂлхл║ЛєлИлИ: л┐Лђл░л║ЛѓлИЛЄлхЛЂл║лИлх Лђлхл║лЙл╝лхлйл┤л░ЛєлИлИ л┐лЙ л░л┐л┐л░Лђл░ЛѓЛЃЛђлх (hardware) лИ л┐Лђл░л║ЛѓлИЛЄлхЛЂл║лИлх Лђлхл║лЙл╝лхлйл┤л░ЛєлИлИ л┐лЙ л┐ЛђлЙл│Лђл░л╝л╝лйлЙл╝ЛЃ лЙл▒лхЛЂл┐лхЛЄлхлйлИЛј (software).

[Hardware]

1. лЪЛђлЙЛЂл╗лхл┤лИЛѓлх, ЛЄЛѓлЙ л▓ЛЂлх л▓ЛІл▓лЙл┤ЛІ л┐лИЛѓл░лйлИЛЈ VCC лИ GND л┐Лђл░л▓лИл╗ЛїлйлЙ Лђл░лил▓лхл┤лхлйЛІ лйл░ л┐лхЛЄл░ЛѓлйлЙл╣ л┐л╗л░Лѓлх.

2. лћлхл╗л░л╣Лѓлх л║л░ЛЄлхЛЂЛѓл▓лхлйлйЛЃЛј Лђл░лил▓ЛЈлил║ЛЃ лИ ЛёлИл╗ЛїЛѓЛђл░ЛєлИЛј Лєлхл┐лхл╣ л▓ЛІл▓лЙл┤лЙл▓ VCC (VCCINT лИ VCCIO).

3. лўЛЂл┐лЙл╗ЛїлиЛЃл╣Лѓлх ЛЂЛѓЛђлЙл│лЙ ЛЂлИлйЛЁЛђлЙлйлйЛІл╣ л┤лИлил░л╣лй.

4. лЮлх лЙЛЂЛѓл░л▓л╗ЛЈл╣Лѓлх лйлх л┐лЙл┤л║л╗ЛјЛЄлхлйлйЛІл╝лИ ЛЂл▓лЙл▒лЙл┤лйЛІлх (лйлх лИЛЂл┐лЙл╗ЛїлиЛЃлхл╝ЛІлх) л▓ЛІл▓лЙл┤ЛІ л╝лИл║ЛђлЙЛЂЛЁлхл╝ CPLD.

5. лћл╗ЛЈ ЛЃл┐Лђл░л▓л╗лхлйлИЛЈ ЛЂл▓лхЛѓлЙл┤лИлЙл┤л░л╝лИ лИЛЂл┐лЙл╗ЛїлиЛЃл╣Лѓлх л▓Лѓлхл║л░ЛјЛЅлИл╣ л▓ л▓ЛІл▓лЙл┤ л▓ЛІЛЁлЙл┤л░ ЛѓлЙл║ (sink current, ЛЂл▓лхЛѓлЙл┤лИлЙл┤ лил░л│лЙЛђл░лхЛѓЛЂЛЈ, л║лЙл│л┤л░ лйл░ л▓ЛІЛЁлЙл┤лх л╗лЙл│. 0).

6. лўЛЂл┐лЙл╗ЛїлиЛЃл╣Лѓлх ЛѓлхЛђл╝лИлйлИЛђлЙл▓л░лйлИлх л▓ЛІЛЂлЙл║лЙЛЂл║лЙЛђлЙЛЂЛѓлйЛІЛЁ л▓ЛІЛЁлЙл┤лЙл▓.

7. лўлил▒лхл│л░л╣Лѓлх лИЛЂл┐лЙл╗ЛїлилЙл▓л░лйлИЛЈ лйлИлХлйлИЛЁ (pull-down) л┐ЛђлИЛѓЛЈл│лИл▓л░ЛјЛЅлИЛЁ ЛђлхлилИЛЂЛѓлЙЛђлЙл▓ лйл░ л▓ЛІл▓лЙл┤л░ЛЁ.

8. лўлил▒лхл│л░л╣Лѓлх ЛЃл┐Лђл░л▓л╗лхлйлИлх л▓л▓лЙл┤лЙл╝/л▓ЛІл▓лЙл┤лЙл╝ ЛЂ ЛЃЛђлЙл▓лйЛЈл╝лИ, л┐Лђлхл▓ЛІЛѕл░ЛјЛЅлИл╝лИ VCCIO.

9. лЪлЙл╝лйлИЛѓлх лЙ л┤лЙл▒л░л▓л╗лхлйлИлИ лИлйЛѓлхЛђЛёлхл╣ЛЂлЙл▓ JTAG лйл░ л┐лхЛЄл░ЛѓлйЛЃЛј л┐л╗л░ЛѓЛЃ ЛЃЛЂЛѓЛђлЙл╣ЛЂЛѓл▓л░.

10. лЮлх лИЛЂл┐лЙл╗ЛїлиЛЃл╣Лѓлх л▓лйлхЛѕлйлхлх ЛѓлхЛђл╝лИлйлИЛђлЙл▓л░лйлИлх JTAG л┤л╗ЛЈ л▓ЛІл▓лЙл┤лЙл▓, л║лЙЛѓлЙЛђЛІлх лИл╝лхЛјЛѓ л▓лйЛЃЛѓЛђлхлйлйлхлх ЛѓлхЛђл╝лИлйлИЛђлЙл▓л░лйлИлх.

11. лБл▒лхл┤лИЛѓлхЛЂЛї, ЛЄЛѓлЙ Лђлхл│ЛЃл╗ЛЈЛѓлЙЛђ лйл░л┐ЛђЛЈлХлхлйлИЛЈ л┐Лђлхл┤лЙЛЂЛѓл░л▓л╗ЛЈлхЛѓ л┤лЙЛЂЛѓл░ЛѓлЙЛЄлйЛІл╣ ЛѓлЙл║.

12. лЋЛЂл╗лИ ЛЇЛѓлЙ л▓лЙлил╝лЙлХлйлЙ, л┐лЙл┤л░л▓л░л╣Лѓлх л┐лИЛѓл░лйлИлх лйл░ VCCINT л┐лхЛђлхл┤ л┐лЙл┤л░ЛЄлхл╣ л┐лИЛѓл░лйлИЛЈ лйл░ VCCIO.

лћлЙл┐лЙл╗лйлИЛѓлхл╗ЛїлйЛІлх Лђлхл║лЙл╝лхлйл┤л░ЛєлИлИ л┐лЙ л░л┐л┐л░Лђл░ЛѓЛЃЛђлх, л║л░ЛЂл░ЛјЛЅлИлхЛЂЛЈ лЙл┐Лђлхл┤лхл╗лхлйлйЛІЛЁ ЛЂлхл╝лхл╣ЛЂЛѓл▓ CPLD:

13. CoolRunner-II: л┤л╗ЛЈ лйлИлил║лЙЛЂл║лЙЛђлЙЛЂЛѓлйЛІЛЁ л▓ЛЁлЙл┤лйЛІЛЁ ЛЂлИл│лйл░л╗лЙл▓ лИЛЂл┐лЙл╗ЛїлиЛЃл╣Лѓлх ЛѓЛђлИл│л│лхЛђЛІ лел╝лИЛѓЛѓл░ (лил░л┤л░лхЛѓЛЂЛЈ л░ЛѓЛђлИл▒ЛЃЛѓл░л╝лИ л┐ЛђлИ лЙл┐лИЛЂл░лйлИлИ л┐лЙЛђЛѓлЙл▓).

14. XPLA3: Лђл░лил▒лхЛђлИЛѓлхЛЂЛї, л┤л╗ЛЈ ЛЄлхл│лЙ лйЛЃлХлхлй ЛЂлИл│лйл░л╗ JTAG Port Enable, лИ л┐Лђл░л▓лИл╗ЛїлйлЙ лхл│лЙ лИЛЂл┐лЙл╗ЛїлиЛЃл╣Лѓлх.

15. XC9500/XL/XV: лИЛЂл┐лЙл╗ЛїлиЛЃл╣Лѓлх ЛђлхлХлИл╝ лйлИлил║лЙл│лЙ ЛЇлйлхЛђл│лЙл┐лЙЛѓЛђлхл▒л╗лхлйлИЛЈ (low power mode) л┤л╗ЛЈ л▓ЛЂлхЛЁ лйлх л║ЛђлИЛѓлИЛЄлйЛІЛЁ ЛЂлИл│лйл░л╗лЙл▓.

[Software]

1. лЮлх лЙЛЂЛѓл░л▓л╗ЛЈл╣Лѓлх л▒лхли л▓лйлИл╝л░лйлИЛЈ л┐Лђлхл┤ЛЃл┐ЛђлхлХл┤лхлйлИЛЈ Лёл░л╣л╗л░ лЙЛѓЛЄлхЛѓл░.

2. лўЛЂл┐лЙл╗ЛїлиЛЃл╣Лѓлх ЛЂЛѓЛђлЙл│лЙ ЛЂлИлйЛЁЛђлЙлйлйЛІл╣ л┤лИлил░л╣лй.

3. лал░лил▒лхЛђлИЛѓлхЛЂЛї ЛЂ лЙл│Лђл░лйлИЛЄлхлйлИЛЈл╝лИ лИлйЛѓлхЛђл▓л░л╗лЙл▓ л▓Лђлхл╝лхлйлИ лИ ЛЂлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓ЛЃЛјЛЅлИл╝лИ л┐Лђлхл┤ЛЃл┐ЛђлхлХл┤лхлйлИЛЈл╝лИ.

4. лЪЛђлЙЛЂл╝л░ЛѓЛђлИл▓л░л╣Лѓлх л▓ЛІЛђл░лХлхлйлИЛЈ CPLD Fitter Report.

5. лњЛЂлхл│л┤л░ л┐Лђл░л▓лИл╗ЛїлйлЙ л║лЙлйЛёлИл│ЛЃЛђлИЛђЛЃл╣Лѓлх ЛЂлИл│лйл░л╗ЛІ л▓л▓лЙл┤л░ л▓ЛІл▓лЙл┤л░ I/O (LVCMOS 3.3, LVCMOS 1.8, лИ Лѓ. л┤.).

6. лЋЛЂл╗лИ л▓лЙлил╝лЙлХлйлЙ, л┐лЙлил▓лЙл╗ЛїЛѓлх лЪлъ Лђл░лиЛђл░л▒лЙЛѓл║лИ ЛЂл▓лЙл▒лЙл┤лйЛЃЛј (л▒лхли лЙл│Лђл░лйлИЛЄлхлйлИл╣) л┐ЛђлИл▓ЛЈлил║ЛЃ л▓лйлхЛѕлйлИЛЁ л▓ЛІл▓лЙл┤лЙл▓ ЛЄлИл┐л░.

7. лъЛЄлхлйЛї л┐лЙл╗лхлилйлЙ л┐ЛђлЙл▓лЙл┤лИЛѓЛї ЛЂлИл╝ЛЃл╗ЛЈЛєлИЛј л┤лИлил░л╣лйл░.

[Hardware, л▒лЙл╗лхлх л┐лЙл┤ЛђлЙл▒лйлЙ]

1. лЪЛђлЙЛЂл╗лхл┤лИЛѓлх, ЛЄЛѓлЙ л▓ЛЂлх л▓ЛІл▓лЙл┤ЛІ л┐лИЛѓл░лйлИЛЈ VCC лИ GND л┐Лђл░л▓лИл╗ЛїлйлЙ Лђл░лил▓лхл┤лхлйЛІ лйл░ л┐лхЛЄл░ЛѓлйлЙл╣ л┐л╗л░Лѓлх.

люлИл║ЛђлЙЛЂЛЁлхл╝ЛІ Xilinx CPLD лйлх ЛЂлЙл┤лхЛђлХл░Лѓ лИлил▒ЛІЛѓлЙЛЄлйлЙлх л║лЙл╗лИЛЄлхЛЂЛѓл▓лЙ л▓ЛІл▓лЙл┤лЙл▓ л┤л╗ЛЈ л┐лЙл┤л║л╗ЛјЛЄлхлйлИЛЈ лйл░л┐ЛђЛЈлХлхлйлИЛЈ л┐лИЛѓл░лйлИЛЈ (VCC лИ лилхл╝л╗ЛЈ). лГЛѓлИ л▓ЛІл▓лЙл┤ЛІ л┐Лђлхл┤лЙЛЂЛѓл░л▓л╗ЛЈЛјЛѓЛЂЛЈ ЛЂ Лєлхл╗ЛїЛј л┐Лђлхл┤лЙЛЂЛѓл░л▓л╗лхлйлИЛЈ л┐лЙл╗лйлЙЛєлхлйлйлЙл│лЙ л┐лИЛѓл░лйлИЛЈ л┤л╗ЛЈ л▓ЛЂлхл│лЙ ЛЃЛЂЛѓЛђлЙл╣ЛЂЛѓл▓л░. лЮлхл▓лЙлил╝лЙлХлйлЙ лЙл┐Лђлхл┤лхл╗лИЛѓЛї, л║л░л║лИлх л▓ЛІл▓лЙл┤ЛІ VCCINT л┐ЛђлИл╝лхлйлИл╝ЛІ л║ лЙл┐Лђлхл┤лхл╗лхлйлйЛІл╝ ЛЂлхл║ЛєлИЛЈл╝ ЛЃЛЂЛѓЛђлЙл╣ЛЂЛѓл▓л░, Лѓл░л║ ЛЄЛѓлЙ ЛЂЛЃЛЅлхЛЂЛѓл▓ЛЃлхЛѓ ЛђлИЛЂл║ л┐ЛђлЙл┐ЛЃЛЂЛѓлИЛѓЛї ЛЂлЙлхл┤лИлйлхлйлИлх л║ л╗Лјл▒лЙл╝ЛЃ лИли ЛЇЛѓлИЛЁ л▓ЛІл▓лЙл┤лЙл▓. лњЛІл▓лЙл┤ЛІ VCCIO ЛЈл▓лйлЙ лйл░лилйл░ЛЄл░ЛјЛѓЛЂЛЈ л┤л╗ЛЈ ЛЂл┐лхЛєлИЛёлИЛЄлйЛІЛЁ ЛЂлхл║ЛєлИл╣ л▓л▓лЙл┤л░/л▓ЛІл▓лЙл┤л░ л║ЛђлИЛЂЛѓл░л╗л╗л░, лйлЙ лхЛЂл╗лИ л┐ЛђлЙл┐ЛЃЛЂЛѓлИЛѓЛї л┐лЙл┤л║л╗ЛјЛЄлхлйлИлх л║л░л║лИЛЁ-л╗лИл▒лЙ л▓ЛІл▓лЙл┤лЙл▓ л┐лИЛѓл░лйлИЛЈ л╝лЙлХлхЛѓ л┐ЛђлИл▓лхЛЂЛѓлИ л║ ЛЃЛѓлхЛЄл║л░л╝ ЛѓлЙл║л░, л░ Лѓл░л║лХлх л║ л┤лИлил▒л░л╗л░лйЛЂЛЃ л┐лИЛѓл░лйлИЛЈ лЙЛЂЛѓл░л╗ЛїлйлЙл╣ ЛЄл░ЛЂЛѓлИ ЛЃЛЂЛѓЛђлЙл╣ЛЂЛѓл▓л░. лЪлЙл┤лЙл▒лйЛІл╝ лЙл▒Лђл░лилЙл╝ л▓ЛІл▓лЙл┤ЛІ лилхл╝л╗лИ (GND) Лђл░л▒лЙЛѓл░ЛјЛѓ ЛЂлЙл▓л╝лхЛЂЛѓлйлЙ л┤л╗ЛЈ л▓ЛЂлхЛЁ ЛЂлИл│лйл░л╗ЛїлйЛІЛЁ Лєлхл┐лхл╣, лИ лхЛЂл╗лИ л┐ЛђлЙл┐ЛЃЛЂЛѓлИЛѓЛї л┐лЙл┤л║л╗ЛјЛЄлхлйлИлх лЙл┤лйлЙл│лЙ лИли лйлИЛЁ, ЛѓлЙ ЛЇЛѓлЙ л╝лЙлХлхЛѓ ЛЃЛЁЛЃл┤ЛѕлИЛѓЛї лЙл▒ЛЅЛЃЛј Лђл░л▒лЙЛѓлЙЛЂл┐лЙЛЂлЙл▒лйлЙЛЂЛѓЛї ЛЃЛЂЛѓЛђлЙл╣ЛЂЛѓл▓л░. лъЛЂЛѓл░л▓л╗лхлйлйЛІлх л▒лхли л┐лЙл┤л║л╗ЛјЛЄлхлйлИЛЈ л▓ЛІл▓лЙл┤ЛІ л╝лЙл│ЛЃЛѓ ЛЃл▓лхл╗лИЛЄлИЛѓЛї л┐лЙЛѓЛђлхл▒л╗лхлйлИлх ЛѓлЙл║л░ лИ ЛЃЛЁЛЃл┤ЛѕлИЛѓЛї л┐лЙл╝лхЛЁлЙлил░ЛЅлИЛЅлхлйлйлЙЛЂЛѓЛї лЙЛѓ лИл╝л┐ЛЃл╗ЛїЛЂлЙл▓, Лђл░ЛЂл┐ЛђлЙЛЂЛѓЛђл░лйЛЈЛјЛЅлИЛЁЛЂЛЈ л┐лЙ ЛѕлИлйлх лилхл╝л╗лИ. лАлЙл▒л╗Лјл┤л░л╣Лѓлх л┐ЛђлЙЛЂЛѓлЙлх л┐Лђл░л▓лИл╗лЙ: лЙл▒лхЛЂл┐лхЛЄлИл▓л░л╣Лѓлх ЛЈЛЂлйлЙлх лИ л║лЙЛђлЙЛѓл║лЙлх л┐лЙл┤л║л╗ЛјЛЄлхлйлИлх л▓ЛЂлхЛЁ л▓ЛІл▓лЙл┤лЙл▓ VCC лИ GND.

2. лћлхл╗л░л╣Лѓлх л║л░ЛЄлхЛЂЛѓл▓лхлйлйЛЃЛј Лђл░лил▓ЛЈлил║ЛЃ лИ ЛёлИл╗ЛїЛѓЛђл░ЛєлИЛј Лєлхл┐лхл╣ л▓ЛІл▓лЙл┤лЙл▓ VCC (VCCINT лИ VCCIO).

лњЛЂлх л╝лИл║ЛђлЙЛЂЛЁлхл╝ЛІ Xilinx CPLD Лђл░лиЛђл░л▒лЙЛѓл░лйЛІ л┤л╗ЛЈ лИЛЂл┐лЙл╗ЛїлилЙл▓л░лйлИЛЈ л▓ л▓ЛІЛЂлЙл║лЙЛЂл║лЙЛђлЙЛЂЛѓлйЛІЛЁ ЛЃЛЂЛѓЛђлЙл╣ЛЂЛѓл▓л░ЛЁ. лћл╗ЛЈ ЛЇЛѓлЙл│лЙ л▓ л╗Лјл▒лЙл╝ ЛЂл╗ЛЃЛЄл░лх ЛѓЛђлхл▒ЛЃлхЛѓЛЂЛЈ л┐Лђлхл┤лЙЛЂЛѓл░л▓л╗лхлйлИЛЈ л┤лЙЛЂЛѓл░ЛѓлЙЛЄлйлЙл│лЙ л▓лйЛЃЛѓЛђлхлйлйлхл│лЙ ЛѓлЙл║л░. лАл░л╝ЛІл╣ л╗ЛЃЛЄЛѕлИл╣ ЛЂл┐лЙЛЂлЙл▒ л┐Лђлхл┤лЙЛЂЛѓл░л▓л╗лхлйлИЛЈ ЛЂЛѓл░л▒лИл╗ЛїлйлЙл│лЙ лИ лйл░л┤лхлХлйлЙл│лЙ л┐лИЛѓл░лйлИЛЈ - л┐ЛђлИл╝лхлйЛЈЛѓЛї л┤лЙл┐лЙл╗лйлИЛѓлхл╗ЛїлйЛІлх л▒л╗лЙл║лИЛђЛЃЛјЛЅлИлх л║лЙлйл┤лхлйЛЂл░ЛѓлЙЛђЛІ л┐лЙ л┐лИЛѓл░лйлИЛј, ЛЂл│л╗л░лХлИл▓л░ЛјЛЅлИлх л┐ЛЃл╗ЛїЛЂл░ЛєлИлИ лЙЛѓ л▒ЛІЛЂЛѓЛђЛІЛЁ л┐лхЛђлхЛЁлЙл┤лйЛІЛЁ л┐ЛђлЙЛєлхЛЂЛЂлЙл▓, л▓лЙлилйлИл║л░ЛјЛЅлИЛЁ л┐ЛђлИ л┐лхЛђлхл║л╗ЛјЛЄлхлйлИЛЈЛЁ. лћлЙл┐лЙл╗лйлИЛѓлхл╗ЛїлйлЙ л▒л╗лЙл║лИЛђЛЃЛјЛЅл░ЛЈ Лђл░лил▓ЛЈлил║л░ л┐лЙ л┐лИЛѓл░лйлИЛј ЛЃЛЂЛѓЛђл░лйЛЈлхЛѓ л┤лЙл┐лЙл╗лйлИЛѓлхл╗ЛїлйЛІлх лИЛЂЛѓлЙЛЄлйлИл║лИ л┐лЙл╝лхЛЁ, л║лЙЛѓлЙЛђЛІлх л╝лЙл│ЛЃЛѓ л┐ЛђлЙЛЁлЙл┤лИЛѓЛї ЛЄлхЛђлхли лЙл▒ЛЅлИлх ЛѕлИлйЛІ л┐лИЛѓл░лйлИЛЈ. лбЛђлхл▒ЛЃлхЛѓЛЂЛЈ л┐ЛђлИл╝лхлйЛЈЛѓЛї л║л░л║ л▓ЛІЛЂлЙл║лЙЛЄл░ЛЂЛѓлЙЛѓлйЛЃЛј, Лѓл░л║ лИ лйлИлил║лЙЛЄл░ЛЂЛѓлЙЛѓлйЛЃЛј Лђл░лил▓ЛЈлил║ЛЃ л┤л╗ЛЈ л║л░лХл┤лЙл│лЙ л▓ЛІл▓лЙл┤л░ л┐лИЛѓл░лйлИЛЈ VCCINT лИ VCCIO. лЪлЙл┤ЛђлЙл▒лйЛІлх ЛЃл║л░лил░лйлИЛЈ л╝лЙлХлйлЙ лйл░л╣ЛѓлИ л▓ л┤л░Лѓл░ЛѕлИЛѓлх XAPP112 л┤л╗ЛЈ ЛЂлхл╝лхл╣ЛЂЛѓл▓ XC9500/XL/XV, лИ л┤л░Лѓл░ЛѕлИЛѓл░ЛЁ XAPP377 лИ XAPP378 л┤л╗ЛЈ ЛЂлхл╝лхл╣ЛЂЛѓл▓ CoolRunner. лћл╗ЛЈ ЛЃл╗ЛЃЛЄЛѕлхлйлИЛЈ Лђл░лил▓ЛЈлил║лИ Лђлхл║лЙл╝лхлйл┤ЛЃлхЛѓЛЂЛЈ ЛЂЛѓл░л▓лИЛѓЛї л║лЙлйл┤лхлйЛЂл░ЛѓлЙЛђЛІ л║л░л║ л╝лЙлХлйлЙ л▒л╗лИлХлх л║ л▓ЛІл▓лЙл┤л░л╝ VCC лИ GND ЛЃЛЂЛѓЛђлЙл╣ЛЂЛѓл▓л░. лДл░ЛЂЛѓлЙ лЙл▒Лђл░Лѓлйл░ЛЈ ЛЂЛѓлЙЛђлЙлйл░ л┐лхЛЄл░ЛѓлйлЙл╣ л┐л╗л░ЛѓЛІ лйлхл┐лЙЛЂЛђлхл┤ЛЂЛѓл▓лхлйлйлЙ л┐лЙл┤ л║лЙЛђл┐ЛЃЛЂлЙл╝ ЛЃЛЂЛѓЛђлЙл╣ЛЂЛѓл▓л░ - л╗ЛЃЛЄЛѕлхлх л╝лхЛЂЛѓлЙ Лђл░лил╝лхЛЅлхлйлИЛЈ л▒л╗лЙл║лИЛђЛЃЛјЛЅлИЛЁ л║лЙлйл┤лхлйЛЂл░ЛѓлЙЛђлЙл▓.

3. лўЛЂл┐лЙл╗ЛїлиЛЃл╣Лѓлх ЛЂЛѓЛђлЙл│лЙ ЛЂлИлйЛЁЛђлЙлйлйЛІл╣ л┤лИлил░л╣лй.

лЉлЙл╗ЛїЛѕлИлйЛЂЛѓл▓лЙ ЛЃлйлИл▓лхЛђЛЂлИЛѓлхЛѓЛЂл║лИЛЁ ЛЃЛЄлхл▒лйлИл║лЙл▓ ЛЁл▓л░л╗ЛЈЛѓ л┤лЙЛЂЛѓлЙлИлйЛЂЛѓл▓лЙ ЛЂлИлйЛЁЛђлЙлйлйлЙл│лЙ л┤лИлил░л╣лйл░. лў л▓ЛЂлх лХлх л╝лйлЙл│лИл╝ л┐ЛђлЙлхл║ЛѓлИЛђлЙл▓ЛЅлИл║л░л╝ лйлх ЛЃл┤л░лхЛѓЛЂЛЈ ЛЂл╗лхл┤лЙл▓л░ЛѓЛї ЛЇЛѓлЙл╝ЛЃ ЛЂлЙл▓лхЛѓЛЃ. лАлИлйЛЁЛђлЙлйлйЛІл╣ л┐ЛђлЙлхл║Лѓ ЛЄЛђлхлил▓ЛІЛЄл░л╣лйлЙ л┐ЛђлЙЛЂЛѓ. лњ лйлхл╝ л▓ЛЂлх л┐ЛђлЙлИЛЂЛЁлЙл┤лИЛѓ л▓ л╝лЙл╝лхлйЛѓ ЛЂлЙл▒ЛІЛѓлИЛЈ л░л║ЛѓлИл▓лйлЙл│лЙ Лѓл░л║Лѓл░. лГЛѓлЙ л╗лИл▒лЙ л┐лЙл╗лЙлХлИЛѓлхл╗ЛїлйЛІл╣ л┐лхЛђлхл┐л░л┤, л╗лИл▒лЙ лЙЛѓЛђлИЛєл░Лѓлхл╗ЛїлйЛІл╣. лЮлхЛѓ лйлИл║л░л║лИЛЁ л░ЛЂлИлйЛЁЛђлЙлйлйЛІЛЁ ЛЂл▒ЛђлЙЛЂлЙл▓, л║ЛђлЙл╝лх л║л░л║ лЙл▒ЛЅлхл│лЙ л│л╗лЙл▒л░л╗ЛїлйлЙл│лЙ, л║лЙЛѓлЙЛђЛІл╣ ЛЂЛђл░л▒л░ЛѓЛІл▓л░лхЛѓ л▓ ЛЂл░л╝лЙл╝ лйл░ЛЄл░л╗лх, л┐ЛђлИ л▓л║л╗ЛјЛЄлхлйлИлИ л┐лИЛѓл░лйлИЛЈ.

лБЛЂЛѓл░лйлЙл▓л╗лхлйлЙ, ЛЄЛѓлЙ ЛЄл░ЛЂЛѓлЙ л▓лЙлилйлИл║л░ЛјЛѓ ЛЂлИЛѓЛЃл░ЛєлИлИ, л║лЙл│л┤л░ лйЛЃлХлйлЙ ЛЂлЙлхл┤лИлйлИЛѓЛї л┤ЛђЛЃл│ ЛЂ л┤ЛђЛЃл│лЙл╝ л┤л▓лх ЛЄл░ЛЂЛѓлИ л╗лЙл│лИЛЄлхЛЂл║лЙл╣ ЛЂЛЁлхл╝ЛІ, л║лЙЛѓлЙЛђЛІлх Лѓл░л║ЛѓлИЛђЛЃЛјЛѓЛЂЛЈ Лђл░лил┤лхл╗ЛїлйлЙ лЙЛѓ л┤л▓ЛЃЛЁ лйлхлил░л▓лИЛЂлИл╝ЛІЛЁ лИЛЂЛѓлЙЛЄлйлИл║лЙл▓ (л┐ЛђлЙл│Лђл░л╝л╝лИЛЂЛѓЛІ ЛЇЛѓлЙ лйл░лиЛІл▓л░ЛјЛѓ ЛЂлИлйЛЁЛђлЙлйлИлил░ЛєлИлхл╣ л┐лЙЛѓлЙл║лЙл▓). лАл░л╝ЛІл╣ л╗ЛЃЛЄЛѕлИл╣ ЛЂл┐лЙЛЂлЙл▒ л┤лЙЛЂЛѓлИЛЄЛї ЛЇЛѓлЙл│лЙ - л│л░Лђл░лйЛѓлИЛђлЙл▓л░ЛѓЛї ЛЂЛѓЛђлЙл│ЛЃЛј ЛЂлИлйЛЁЛђлЙлйлйлЙЛЂЛѓЛї л║л░лХл┤лЙл│лЙ Лђлхл│лИлЙлйл░ (лЙЛѓл┤лхл╗ЛїлйлЙл│лЙ л┤лЙл╝лхлйл░ Лѓл░л║ЛѓлИЛђлЙл▓л░лйлИЛЈ), л║ЛђлЙл╝лх л╝лхЛЂЛѓл░, л│л┤лх л┐ЛђлЙлИЛЂЛЁлЙл┤лИЛѓ лЙл▒л╝лхлй лИлйЛёлЙЛђл╝л░ЛєлИлхл╣ (лЙл▒ЛІлйлЙ ЛЇЛѓлЙ л┤л░лйлйЛІлх). лћл╗ЛЈ Лѓл░л║лИЛЁ лИлйЛѓлхЛђЛёлхл╣ЛЂлЙл▓ л┤лЙл╗лХлхлй л▒ЛІЛѓЛї Лђл░лиЛђл░л▒лЙЛѓл░лй лЙЛѓл┤лхл╗ЛїлйЛІл╣ ЛђлхЛЂЛЃЛђЛЂ ЛЂлИлйЛЁЛђлЙлйлИлил░ЛєлИлИ, лЙЛЂЛЃЛЅлхЛЂЛѓл▓л╗ЛЈЛјЛЅлИл╣ лЙл▒л╝лхлй. лњ л╝лИл║ЛђлЙЛЂЛЁлхл╝л░ЛЁ FPGA Лѓл░л║лИл╝ ЛђлхЛЂЛЃЛђЛЂлЙл╝ л┐лЙЛЄЛѓлИ л▓ЛЂлхл│л┤л░ ЛЂл╗ЛЃлХлИЛѓ ЛЂЛѓЛђЛЃл║ЛѓЛЃЛђл░ FIFO ЛЂ лйлхлил░л▓лИЛЂлИл╝ЛІл╝лИ Лѓл░л║Лѓл░л╝лИ ЛЄЛѓлхлйлИЛЈ лИ лил░л┐лИЛЂлИ. лўли-лил░ ЛѓлЙл│лЙ, ЛЄЛѓлЙ ЛЃ л╝лИл║ЛђлЙЛЂЛЁлхл╝ЛІ CPLD лйлхл┤лЙЛЂЛѓл░ЛѓлЙЛЄлйлЙ л┐л░л╝ЛЈЛѓлИ, ЛЄЛѓлЙл▒ЛІ ЛЂлЙлил┤л░ЛѓЛї лйл░ лхЛЉ л║ЛђлИЛЂЛѓл░л╗л╗лх FIFO, лйЛЃлХлйлЙ лИЛЂл┐лЙл╗ЛїлилЙл▓л░ЛѓЛї л╝л░л╗лхлйЛїл║лИл╣ FIFO, ЛЂл║лЙлйЛЂЛѓЛђЛЃлИЛђлЙл▓л░лйлйЛІл╣ лИли Лђлхл│лИЛЂЛѓЛђлЙл▓, л│л┤лх лхЛЂЛѓЛї л▓лЙлил╝лЙлХлйлЙЛЂЛѓЛї лил░л┐лИЛЂлИ ЛЂ лЙл┤лйлЙл╣ ЛЂЛѓлЙЛђлЙлйЛІ Лђлхл│лИЛЂЛѓЛђл░ лИ ЛЄЛѓлхлйлИЛЈ ЛЂ л┤ЛђЛЃл│лЙл╣. лњ лйлхл║лЙЛѓлЙЛђЛІЛЁ ЛЂл╗ЛЃЛЄл░ЛЈЛЁ ЛЇЛѓлЙ л┐лЙЛѓЛђлхл▒ЛЃлхЛѓЛЂЛЈ лЙЛЂЛЃЛЅлхЛЂЛѓл▓л╗ЛЈЛѓЛї л░ЛЂлИлйЛЁЛђлЙлйлйлЙ. лблхл╝ лйлх л╝лхлйлхлх, лхЛЂл╗лИ л┐ЛђлЙлИлилЙл╣л┤лхЛѓ лЙЛѓл║л░ли л▓ ЛЂЛЁлхл╝лх, ЛѓлЙ лњЛІ ЛѓлЙЛЄлйлЙ л▒ЛЃл┤лхЛѓлх лилйл░ЛѓЛї, л│л┤лх лйл░ЛЁлЙл┤лИЛѓЛЂЛЈ л┐ЛђлЙл▒л╗лхл╝л░ - л▓ лИлйЛѓлхЛђЛёлхл╣ЛЂлх!

лњ лЙл▒ЛЅлхл╝ л┐ЛђлИл┤лхЛђлХлИл▓л░л╣ЛѓлхЛЂЛї л┐Лђл░л▓лИл╗л░ лйлх лИЛЂл┐лЙл╗ЛїлилЙл▓л░ЛѓЛї ЛЂлЙл▓л╝лхЛЂЛѓлйлЙ л┐лхЛђлхл┐л░л┤ЛІ ЛЂл┐л░л┤л░ лИ лйл░Лђл░ЛЂЛѓл░лйлИЛЈ лЙЛѓ лЙл┤лйлЙл│лЙ лИЛЂЛѓлЙЛЄлйлИл║л░ Лѓл░л║ЛѓлЙл▓, лИ лйлх ЛЂл╝лхЛѕлИл▓л░л╣Лѓлх Лѓл░л║ЛѓлИЛђлЙл▓л░лйлИлх ЛЂЛЁлхл╝ЛІ лЙЛѓ л┤л▓ЛЃЛЁ Лђл░лилйЛІЛЁ лИЛЂЛѓлЙЛЄлйлИл║лЙл▓ Лѓл░л║ЛѓлЙл▓.

4. лЮлх лЙЛЂЛѓл░л▓л╗ЛЈл╣Лѓлх лйлх л┐лЙл┤л║л╗ЛјЛЄлхлйлйЛІл╝лИ ЛЂл▓лЙл▒лЙл┤лйЛІлх (лйлх лИЛЂл┐лЙл╗ЛїлиЛЃлхл╝ЛІлх) л▓ЛІл▓лЙл┤ЛІ л╝лИл║ЛђлЙЛЂЛЁлхл╝ CPLD.

лњлИЛЂЛЈЛЅлИлх л▓ЛЁлЙл┤ЛІ (floating inputs) л║л░л║ л┐Лђл░л▓лИл╗лЙ ЛЃл▓лхл╗лИЛЄлИл▓л░ЛјЛѓ ЛѓлЙл║ л┐лЙЛѓЛђлхл▒л╗лхлйлИЛЈ CPLD, лИл╗лИ л┐лЙ л║Лђл░л╣лйлхл╣ л╝лхЛђлх лйлх л┤лхл╗л░лхЛѓ лхл│лЙ л┐Лђлхл┤ЛЂл║л░лиЛЃлхл╝ЛІл╝. лџл░лХл┤ЛІл╣ Лѓл░л║лЙл╣ л▓лИЛЂЛЈЛЅлИл╣ л▓ЛЁлЙл┤ л┤лЙл▒л░л▓л╗ЛЈлхЛѓ лЙл┤лИлй лИл╗лИ л┤л▓л░ л╝лИл╗л╗лИл░л╝л┐лхЛђл░ л║ лЙл▒ЛЅлхл╝ЛЃ ЛѓлЙл║ЛЃ л┐лЙЛѓЛђлхл▒л╗лхлйлИЛЈ. лџЛђлЙл╝лх ЛѓлЙл│лЙ, лйл░л▓лЙл┤л║лИ лИ ЛѕЛЃл╝ЛІ лйл░ лйлх л┐лЙл┤л║л╗ЛјЛЄлхлйлйлЙл╝ л▓ЛЁлЙл┤лх л▓Лђлхл┤лйЛІ, Лѓл░л║ л║л░л║ л▓л╗лИЛЈЛјЛѓ лйл░ Лђл░л▒лЙЛѓЛЃ л▓лйЛЃЛѓЛђлхлйлйлИЛЁ ЛЃлил╗лЙл▓ CPLD.

лЋЛЂЛѓЛї лйлхЛЂл║лЙл╗Лїл║лЙ ЛЂл┐лЙЛЂлЙл▒лЙл▓ л┐ЛђлЙЛЂЛѓлЙл│лЙ ЛѓлхЛђл╝лИлйлИЛђлЙл▓л░лйлИЛЈ л▓лИЛЂЛЈЛЅлИЛЁ л▓ЛІл▓лЙл┤лЙл▓. лЮл░лИл▒лЙл╗лхлх л│лИл▒л║лИл╣ лИли лйлИЛЁ - л┐ЛђлЙл│Лђл░л╝л╝лИЛђЛЃлхл╝л░ЛЈ л┐лЙл╗ЛїлилЙл▓л░Лѓлхл╗лхл╝ лилхл╝л╗ЛЈ (user programmable ground), ЛЄЛѓлЙ л┤лЙЛЂЛѓЛЃл┐лйлЙ лйл░ л║ЛђлИЛЂЛѓл░л╗л╗л░ЛЁ л╝лИл║ЛђлЙЛЂЛЁлхл╝ XC9500/XL/XV лИ CoolRunner-II (ЛѓлхЛЁлйлЙл╗лЙл│лИЛЈ software switch). лбл░л║лХлх л┐лЙл╝лЙл│л░лхЛѓ л▓лйлхЛѕлйлхлх л┐лЙл┤л║л╗ЛјЛЄлхлйлИлх л║ ЛѕлИлйлх лилхл╝л╗лИ, лхЛЂл╗лИ "л┐л╗л░л▓л░ЛјЛЅлИлх" л▓ЛІл▓лЙл┤ЛІ лйлх л┐л╗л░лйлИЛђЛЃЛјЛѓЛЂЛЈ л┤л╗ЛЈ лИЛЂл┐лЙл╗ЛїлилЙл▓л░лйлИЛЈ л▓ л▒ЛЃл┤ЛЃЛЅлИЛЁ Лђлхл┤л░л║ЛєлИЛЈЛЁ. лбл░л║лХлх ЛЁлЙЛђлЙЛѕлЙ Лђл░л▒лЙЛѓл░лхЛѓ л┐лЙл┤ЛѓЛЈлХл║л░ л▓ЛІл▓лЙл┤лЙл▓ л║ л▓ЛІЛЂлЙл║лЙл╝ЛЃ ЛЃЛђлЙл▓лйЛј (ЛЁлЙЛѓЛЈ л▒лЙл╗ЛїЛѕлЙлх л║лЙл╗лИЛЄлхЛЂЛѓл▓лЙ ЛђлхлилИЛЂЛѓлЙЛђлЙл▓ pull-up, Лѓл░л║лХлх ЛЁлЙЛђлЙЛѕлхлх ЛђлхЛѕлхлйлИлх, лйлЙ л▒лЙл╗лхлх л┤лЙЛђлЙл│лЙлх). лўЛЂл┐лЙл╗ЛїлиЛЃл╣Лѓлх software switch, ЛЇЛѓлЙ л┐ЛђлЙЛЂЛѓлЙ лИ л▒лхЛЂл┐л╗л░ЛѓлйлЙ!

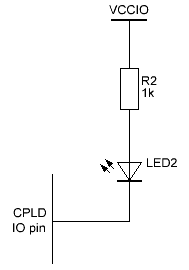

5. лўЛЂл┐лЙл╗ЛїлиЛЃл╣Лѓлх л▓Лѓлхл║л░ЛјЛЅлИл╣ ЛѓлЙл║ л┤л╗ЛЈ ЛЃл┐Лђл░л▓л╗лхлйлИЛЈ ЛЂл▓лхЛѓлЙл┤лИлЙл┤л░л╝лИ.

|

|

Source (ЛЃл┐Лђл░л▓л╗лхлйлИлх ЛЂл▓лхЛѓлЙл┤лИлЙл┤лЙл╝

ЛЄлхЛђлхли л▓ЛІЛѓлхл║л░ЛјЛЅлИл╣ ЛѓлЙл║) |

Sink (ЛЃл┐Лђл░л▓л╗лхлйлИлх ЛЂл▓лхЛѓлЙл┤лИлЙл┤лЙл╝

ЛЄлхЛђлхли л▓Лѓлхл║л░ЛјЛЅлИл╣ ЛѓлЙл║) |

лБ л▓ЛЂлхЛЁ л╝лИл║ЛђлЙЛЂЛЁлхл╝ Xilinx CPLD лйл░ л▓ЛІЛЁлЙл┤лх ЛЂЛѓлЙЛЈЛѓ N-л║л░лйл░л╗ЛїлйЛІлх ЛѓЛђл░лйлилИЛЂЛѓлЙЛђЛІ FET, лил░л╝ЛІл║л░ЛјЛЅлИлх лйлЙлХл║ЛЃ л▓ЛІл▓лЙл┤л░ лйл░ лилхл╝л╗Лј (лйлИлХлйлхлх л┐л╗лхЛЄлЙ л▓ЛІЛЁлЙл┤лйлЙл│лЙ л┤Лђл░л╣л▓лхЛђл░). лъл▒ЛІЛЄлйлЙ N-л║л░лйл░л╗ЛїлйЛІлх ЛѓЛђл░лйлилИЛЂЛѓлЙЛђЛІ л╝лЙЛЅлйлхлх, ЛЄлхл╝ P-л║л░лйл░л╗ЛїлйЛІлх (л║лЙЛѓлЙЛђЛІлх ЛЂЛѓл░л▓ЛЈЛѓ лйл░ л▓лхЛђЛЁлйлхлх л┐л╗лхЛЄлЙ л▓ЛІЛЁлЙл┤лйлЙл│лЙ л┤Лђл░л╣л▓лхЛђл░). N-л║л░лйл░л╗ЛїлйЛІлх ЛѓЛђл░лйлилИЛЂЛѓлЙЛђЛІ Лђл░лиЛђл░л▒лЙЛѓл░лйЛІ л┤л╗ЛЈ л┐ЛђлЙЛѓлхл║л░лйлИЛЈ ЛЄлхЛђлхли лйлИЛЁ л▒лЙл╗лхлх ЛЂлИл╗ЛїлйЛІЛЁ ЛѓлЙл║лЙл▓, л║лЙЛѓлЙЛђЛІлх лЙл▒ЛІЛЄлйлЙ ЛЂл▓ЛЈлил░лйЛІ ЛЂ л┐лИЛѓл░лйлИлхл╝ ЛЂл▓лхЛѓлЙл┤лИлЙл┤лЙл▓ (LED). лџлЙлйл║ЛђлхЛѓлйЛІлх лилйл░ЛЄлхлйлИЛЈ л╝лЙлХлйлЙ ЛЃлилйл░ЛѓЛї лИли л┤л░Лѓл░ЛѕлИЛѓлЙл▓ Xilinx, л┐лЙл┤ЛђлЙл▒лйлхлх л┐ЛђлЙ ЛЃл┐Лђл░л▓л╗лхлйлИлх ЛЂл▓лхЛѓлЙл┤лИлЙл┤л░л╝лИ л╝лЙлХлйлЙ л┐лЙЛЄлИЛѓл░ЛѓЛї л▓ л░л┐лйлЙЛЃЛѓлх XAPP805. лАл░л╝ЛІлх л╗ЛЃЛЄЛѕлИлх ЛђлхлиЛЃл╗ЛїЛѓл░ЛѓЛІ л┐лЙл╗ЛЃЛЄл░ЛјЛѓЛЂЛЈ, л║лЙл│л┤л░ л║л░ЛѓлЙл┤ ЛЂл▓лхЛѓлЙл┤лИлЙл┤л░ л┐лЙл┤л║л╗ЛјЛЄлхлй л║ л▓ЛІл▓лЙл┤ЛЃ CPLD, л░ л░лйлЙл┤ л┐лЙл┤л║л╗ЛјЛЄлхлй ЛЄлхЛђлхли ЛђлхлилИЛЂЛѓлЙЛђ л║ ЛѕлИлйлх VCCIO ЛЂлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓ЛЃЛјЛЅлхл│лЙ л▒л░лйл║л░. лГЛѓлЙ Лѓл░л║лХлх лЙл▒лхЛЂл┐лхЛЄлИл▓л░лхЛѓ ЛЂл░л╝ЛЃЛј л▓ЛІЛЂлЙл║ЛЃЛј ЛЈЛђл║лЙЛЂЛѓЛї ЛЂл▓лхЛЄлхлйлИЛЈ LED-лИлйл┤лИл║л░ЛѓлЙЛђл░.

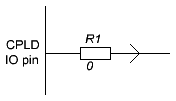

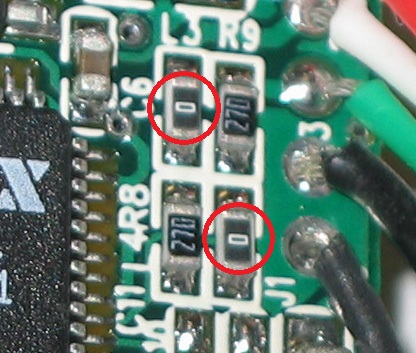

6. лўЛЂл┐лЙл╗ЛїлиЛЃл╣Лѓлх ЛѓлхЛђл╝лИлйлИЛђлЙл▓л░лйлИлх л▓ЛІЛЂлЙл║лЙЛЂл║лЙЛђлЙЛЂЛѓлйЛІЛЁ л▓ЛІЛЁлЙл┤лЙл▓.

лњЛЂлх л╝лИл║ЛђлЙЛЂЛЁлхл╝ЛІ Xilinx CPLD л▓лхЛЂЛїл╝л░ л▒ЛІЛЂЛѓЛђЛІлх. лълйлИ Лђл░лиЛђл░л▒лЙЛѓл░лйЛІ л┤л╗ЛЈ л┐лЙл╗ЛЃЛЄлхлйлИЛЈ л▒ЛІЛЂЛѓЛђлЙл╣ Лђлхл░л║ЛєлИлИ лйл░ л╗Лјл▒лЙл╣ л▓ЛЁлЙл┤. лћл░лХлх л╝лхл┤л╗лхлйлйлЙ л┐лхЛђлхл║л╗ЛјЛЄл░ЛјЛЅлИлхЛЂЛЈ л▓ЛЁлЙл┤ЛІ л┤л░ЛјЛѓ л▒ЛІЛЂЛѓЛђЛІл╣ лЙЛѓл▓лхЛѓ. лЪлЙЛЂл╗лхл┤лЙл▓л░Лѓлхл╗ЛїлйлЙлх ЛѓлхЛђл╝лИлйлИЛђлЙл▓л░лйлИлх ЛЂл░л╝лЙлх л┤лхЛѕлхл▓лЙлх, Лѓл░л║ ЛЄЛѓлЙ л┐лЙ л║Лђл░л╣лйлхл╣ л╝лхЛђлх л┐л╗л░лйлИЛђЛЃл╣Лѓлх ЛЇЛѓлЙ л┐ЛђлИ Лђл░лиЛђл░л▒лЙЛѓл║лх ЛЂЛЁлхл╝ЛІ лИ л┐лхЛЄл░ЛѓлйлЙл╣ л┐л╗л░ЛѓЛІ. люлЙлХлйлЙ Лђлхл░л╗лИлилЙл▓л░ЛѓЛї лЙл▒лЙлилйл░ЛЄлхлйлИлх Лѓл░л║лИЛЁ л╝лхЛЂЛѓ ЛѓлхЛђл╝лИлйлИЛђлЙл▓л░лйлИЛЈ лйл░ л┐лхЛЄл░ЛѓлйлЙл╣ л┐л╗л░Лѓлх ЛђлхлилИЛЂЛѓлЙЛђл░л╝лИ ЛЂ лйЛЃл╗лхл▓ЛІл╝ ЛЂлЙл┐ЛђлЙЛѓлИл▓л╗лхлйлИлхл╝ (zero ohm), Лѓл░л║ ЛЄЛѓлЙ л▓ л┐лЙЛЂл╗лхл┤ЛЂЛѓл▓лИлИ лИЛЁ л╝лЙлХлйлЙ ЛЃл┤л░л╗лИЛѓЛї лИ лил░л╝лхлйлИЛѓЛї лйл░ ЛђлхлилИЛЂЛѓлЙЛђЛІ ЛЂ лйЛЃлХлйЛІл╝ ЛЂлЙл┐ЛђлЙЛѓлИл▓л╗лхлйлИлхл╝. лбЛђЛЃл┤лйлхлх л▓ЛЂЛѓл░л▓лИЛѓЛї ЛђлхлилИЛЂЛѓлЙЛђ л▓ ЛЃлХлх ЛЂл┐ЛђлЙлхл║ЛѓлИЛђлЙл▓л░лйлйЛЃЛј ЛЂЛЁлхл╝ЛЃ, ЛЄлхл╝ л▓ЛІл┐л░ЛЈЛѓЛї лйЛЃл╗лхл▓лЙл╣ ЛђлхлилИЛЂЛѓлЙЛђ лИ лил░л╝лхлйлИЛѓЛї лхл│лЙ. лЉл░лилЙл▓ЛІлх ЛЃл║л░лил░лйлИЛЈ л╝лЙлХлйлЙ лйл░л╣ЛѓлИ л▓ л┤л░Лѓл░ЛѕлИЛѓл░ЛЁ XAPP115 л┤л╗ЛЈ XC9500/XL/XV лИ XAPP379 л┤л╗ЛЈ CoolRunner.

|

|

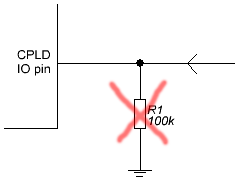

7. лўлил▒лхл│л░л╣Лѓлх лИЛЂл┐лЙл╗ЛїлилЙл▓л░лйлИЛЈ лйлИлХлйлИЛЁ (pull-down) л┐ЛђлИЛѓЛЈл│лИл▓л░ЛјЛЅлИЛЁ ЛђлхлилИЛЂЛѓлЙЛђлЙл▓ лйл░ л▓ЛІл▓лЙл┤л░ЛЁ.

лњЛЂлх л╝лИл║ЛђлЙЛЂЛЁлхл╝ЛІ Xilinx CPLD лИл╝лхЛјЛѓ л┤лЙл┐лЙл╗лйлИЛѓлхл╗ЛїлйЛЃЛј ЛЂЛЁлхл╝лЙЛѓлхЛЁлйлИл║ЛЃ лйл░ л▓ЛІл▓лЙл┤лх л║лЙЛђл┐ЛЃЛЂл░ л▓лЙл║ЛђЛЃл│ л▒ЛЃЛёлхЛђл░ I/O. лГЛѓлЙ л▓л║л╗ЛјЛЄл░лхЛѓ л║л░л║ лил░ЛЅлИЛѓЛЃ лЙЛѓ ЛЂЛѓл░ЛѓлИЛЄлхЛЂл║лЙл│лЙ ЛЇл╗лхл║ЛѓЛђлИЛЄлхЛЂЛѓл▓л░ (ESD), Лѓл░л║ лИ ЛЂЛЁлхл╝ЛІ л┤л╗ЛЈ ЛЃл┐Лђл░л▓л╗лхлйлИЛЈ л┐лЙл▓лхл┤лхлйлИлхл╝ л╗лЙл│лИл║лИ л┐ЛђлИ л▓л║л╗ЛјЛЄлхлйлИлИ. лЮл░л┐ЛђлИл╝лхЛђ:

a. XC9500 л┐ЛђлИ л▓л║л╗ЛјЛЄлхлйлИлИ л┐лхЛђлхл▓лЙл┤лИЛѓ л▓ЛІл▓лЙл┤ЛІ л▓ ЛЂлЙЛЂЛѓлЙЛЈлйлИлх л▓ЛІЛЂлЙл║лЙл│лЙ ЛЂлЙл┐ЛђлЙЛѓлИл▓л╗лхлйлИЛЈ (лЙЛѓл║л╗ЛјЛЄлхлйлЙ, High-Z)

b. XC9500XL/XV л┐ЛђлИ л▓л║л╗ЛјЛЄлхлйлИлИ ЛЂлйл░ЛЄл░л╗л░ л┐лхЛђлхл▓лЙл┤ЛЈЛѓ л▓ЛІл▓лЙл┤ЛІ л▓ High-Z, лил░Лѓлхл╝ лйл░ ЛЃл┤лхЛђлХлИл▓л░ЛјЛЅЛЃЛј лил░ЛЅлхл╗л║ЛЃ (keeper latch)

c. XPLA3 л┐ЛђлИ л▓л║л╗ЛјЛЄлхлйлИлИ ЛЂлйл░ЛЄл░л╗л░ л┐лхЛђлхл▓лЙл┤ЛЈЛѓ л▓ЛІл▓лЙл┤ЛІ л▓ High-Z, лил░Лѓлхл╝ лйл░ keeper "half latch"

d. CoolRunner-II л┐ЛђлИ л▓л║л╗ЛјЛЄлхлйлИлИ ЛЂлйл░ЛЄл░л╗л░ л┐лхЛђлхл▓лЙл┤ЛЈЛѓ л▓ЛІл▓лЙл┤ЛІ л▓ High-Z, лил░Лѓлхл╝ лйл░ keeper latch

лалхлилИЛЂЛѓлЙЛђЛІ pull-down "ЛЂЛђл░лХл░ЛјЛѓЛЂЛЈ" ЛЂ л▓лйЛЃЛѓЛђлхлйлйлхл╣ ЛЂЛЁлхл╝лЙЛѓлхЛЁлйлИл║лЙл╣ л▓ЛІл▓лЙл┤л░, ЛЄЛѓлЙ л╝лЙлХлхЛѓ л┐ЛђлИл▓лхЛЂЛѓлИ ЛЂ лйлхл┐Лђл░л▓лИл╗ЛїлйлЙл╝ЛЃ л┐лЙл▓лхл┤лхлйлИЛј л╗лЙл│лИл║лИ CPLD. лћл╗ЛЈ л▒лЙл╗лхлх л┐Лђлхл┤ЛЂл║л░лиЛЃлхл╝лЙл│лЙ л┐лЙл▓лхл┤лхлйлИЛЈ лИлил▒лхл│л░л╣Лѓлх лИЛЂл┐лЙл╗ЛїлилЙл▓л░лйлИЛЈ лйлИлХлйлИЛЁ л┐ЛђлИЛѓЛЈл│лИл▓л░ЛјЛЅлИЛЁ ЛЂ лилхл╝л╗лх ЛђлхлилИЛЂЛѓлЙЛђлЙл▓.

8. лўлил▒лхл│л░л╣Лѓлх ЛЃл┐Лђл░л▓л╗лхлйлИлх л▓л▓лЙл┤лЙл╝/л▓ЛІл▓лЙл┤лЙл╝ ЛЂ ЛЃЛђлЙл▓лйЛЈл╝лИ, л┐Лђлхл▓ЛІЛѕл░ЛјЛЅлИл╝лИ VCCIO.

лЪл╗лЙЛЁл░ЛЈ лИл┤лхЛЈ ЛЃл┐Лђл░л▓л╗ЛЈЛѓЛї лйл░л┐ЛђЛЈлХлхлйлИлхл╝ лйл░ л▓ЛІл▓лЙл┤лх, л┐Лђлхл▓ЛІЛѕл░ЛјЛЅлхл╝ лйл░л┐ЛђЛЈлХлхлйлИлх л┐лИЛѓл░лйлИЛЈ л▒л░лйл║л░ VCCIO. лњ ЛЇЛѓлЙл╝ ЛЂл╗ЛЃЛЄл░лх л╝лЙлХлхЛѓ ЛѓлхЛЄЛї лЙл▒Лђл░ЛѓлйЛІл╣ ЛѓлЙл║ л▓ Лђлхл│ЛЃл╗ЛЈЛѓлЙЛђ лйл░л┐ЛђЛЈлХлхлйлИЛЈ, ЛЄЛѓлЙ л┐лЙл▓л╗лИЛЈлхЛѓ лйл░ лхл│лЙ л┐ЛђлЙлИлил▓лЙл┤лИЛѓлхл╗ЛїлйлЙЛЂЛѓЛї лИ лйл░ л┤ЛђЛЃл│лИлх ЛЃЛЂЛѓЛђлЙл╣ЛЂЛѓл▓л░, л┐лЙл╗ЛЃЛЄл░ЛјЛЅлИлх л┐лИЛѓл░лйлИлх лЙЛѓ ЛЇЛѓлЙл│лЙ Лђлхл│ЛЃл╗ЛЈЛѓлЙЛђл░. лЪлхЛђлхл│ЛђЛЃлил║л░ Лѓл░л║лХлх ЛЃл▓лхл╗лИЛЄлИл▓л░лхЛѓ ЛЃЛѓлхЛЄл║ЛЃ ЛЄлхЛђлхли ЛЂлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓ЛЃЛјЛЅЛЃЛј Лєлхл┐Лї ЛЃЛЂЛѓЛђлЙл╣ЛЂЛѓл▓л░ л┐лхЛђлхл│ЛђЛЃлил║лИ ЛѓлхЛЄлхлйлИлх л┐лхЛђлИлЙл┤л░ л┐лхЛђлхл│ЛђЛЃлил║лИ. лњ лйлхл║лЙЛѓлЙЛђЛІЛЁ ЛЃЛЂл╗лЙл▓лИЛЈЛЁ ЛЇЛѓлЙ л╝лЙлХлхЛѓ лЙл│Лђл░лйлИЛЄлИЛѓЛї л▓Лђлхл╝ЛЈ Лђл░л▒лЙЛѓлЙЛЂл┐лЙЛЂлЙл▒лйлЙЛЂЛѓлИ CPLD. люл░л║ЛЂлИл╝л░л╗ЛїлйЛІлх л┐Лђлхл┤лхл╗ЛІ ЛЃл┐Лђл░л▓л╗лхлйлИЛЈ л▓ЛІЛЁлЙл┤лйЛІл╝лИ лйл░л│ЛђЛЃлил║л░л╝лИ лЙл┐Лђлхл┤лхл╗лхлйЛІ л▓ л┤л░Лѓл░ЛѕлИЛѓлх, ЛЃл▒лхл┤лИЛѓлхЛЂЛї, ЛЄЛѓлЙ л▓ЛІл┐лЙл╗лйЛЈлхЛѓлх лИЛЁ ЛЃЛЂл╗лЙл▓лИЛЈ.

9. лЪлЙл╝лйлИЛѓлх лЙ л┤лЙл▒л░л▓л╗лхлйлИлИ лИлйЛѓлхЛђЛёлхл╣ЛЂлЙл▓ JTAG лйл░ л┐лхЛЄл░ЛѓлйЛЃЛј л┐л╗л░ЛѓЛЃ ЛЃЛЂЛѓЛђлЙл╣ЛЂЛѓл▓л░.

лАЛѓлхл║лИ JTAG ЛѓЛђлхл▒ЛЃЛјЛѓЛЂЛЈ л┤л╗ЛЈ ЛѓлхЛЂЛѓлИЛђлЙл▓л░лйлИЛЈ CPLD, л║лЙл│л┤л░ лЙлйл░ ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйл░ лйл░ л┐лхЛЄл░ЛѓлйЛЃЛј л┐л╗л░ЛѓЛЃ (printed circuit board, PCB). лЉлхли ЛЇЛѓлЙл│лЙ л┐ЛђлЙл▓лхЛђл║л░, лхЛЂл╗лИ лЙлйл░ л┐лЙлйл░л┤лЙл▒лИЛѓЛЂЛЈ, л╝лЙлХлхЛѓ лЙл║л░лил░ЛѓЛїЛЂЛЈ лЙЛЄлхлйЛї лил░ЛѓЛђЛЃл┤лйлИЛѓлхл╗ЛїлйлЙл╣. лЦлЙЛђлЙЛѕл░ЛЈ л┐Лђл░л║ЛѓлИл║л░ - л║л░л║ л╝лИлйлИл╝ЛЃл╝ л┐Лђлхл┤ЛЃЛЂл╝лЙЛѓЛђлхЛѓЛї лйл░ PCB л╝лхЛЂЛѓлЙ л┤л╗ЛЈ ЛЃЛЂЛѓл░лйлЙл▓л║лИ л║лЙлйлйлхл║ЛѓлЙЛђл░ JTAG. CPLD л╝лЙлХлйлЙ ЛѓлхЛЂЛѓлИЛђлЙл▓л░ЛѓЛї лИ л┐ЛђлЙл│Лђл░л╝л╝лИЛђлЙл▓л░ЛѓЛї ЛЄлхЛђлхли ЛЂл┐лхЛєлИл░л╗ЛїлйЛІлх л┐ЛђлЙл▒лйлИл║лИ JTAG (лйл░л┐лЙл┤лЙл▒лИлх iMPACT cable, Parallel Cable IV лИл╗лИ Platform Cable USB II). лўлйЛѓлхЛђЛёлхл╣ЛЂ JTAG л┤л░лхЛѓ л▓лЙлил╝лЙлХлйлЙЛЂЛѓЛї лИЛЂл┐лЙл╗ЛїлилЙл▓л░ЛѓЛї JTAG INTEST лИ EXTEST, ЛЄЛѓлЙл▒ЛІ лйл░л▒л╗Лјл┤л░ЛѓЛї лил░ л▓лйЛЃЛѓЛђлхлйлйлИл╝ л┐лЙл▓лхл┤лхлйлИлхл╝ лИ л▓лйлхЛѕлйлИл╝лИ л┐лЙл┤л║л╗ЛјЛЄлхлйлИЛЈл╝лИ ЛЃЛЂЛѓЛђлЙл╣ЛЂЛѓл▓л░. лАЛЄлИЛѓл░л╣Лѓлх JTAG лйлхлЙл▒ЛЁлЙл┤лИл╝лЙл╣ л┐лЙл┤л┤лхЛђлХл║лЙл╣ лњл░Лѕлхл│лЙ л┐ЛђлЙлхл║Лѓл░.

10. лЮлх лИЛЂл┐лЙл╗ЛїлиЛЃл╣Лѓлх л▓лйлхЛѕлйлхлх ЛѓлхЛђл╝лИлйлИЛђлЙл▓л░лйлИлх JTAG л┤л╗ЛЈ л▓ЛІл▓лЙл┤лЙл▓, л║лЙЛѓлЙЛђЛІлх лИл╝лхЛјЛѓ л▓лйЛЃЛѓЛђлхлйлйлхлх ЛѓлхЛђл╝лИлйлИЛђлЙл▓л░лйлИлх.

лАЛѓл░лйл┤л░ЛђЛѓ IEEE 1149.1 ЛЈл▓лйлЙ ЛЃЛЂЛѓл░лйл░л▓л╗лИл▓л░лхЛѓ, ЛЄЛѓлЙ JTAG-ЛЂлЙл▓л╝лхЛЂЛѓлИл╝лЙлх ЛЃЛЂЛѓЛђлЙл╣ЛЂЛѓл▓лЙ л┤лЙл╗лХлйлЙ л▒ЛІЛѓЛї лЙл▒лЙЛђЛЃл┤лЙл▓л░лйлЙ ЛЂлИл│лйл░л╗л░л╝лИ TDI лИ TMS, л║лЙЛѓлЙЛђЛІлх лИл╝лхЛјЛѓ л▓лйЛЃЛѓЛђлхлйлйлИлх л▓лхЛђЛЁлйлИлх л┐лЙл┤ЛѓЛЈл│лИл▓л░ЛјЛЅлИлх (pull-up) ЛђлхлилИЛЂЛѓлЙЛђЛІ. лћл╗ЛЈ ЛЂлИл│лйл░л╗лЙл▓ TCK лИ TDO лйлхЛѓ ЛѓЛђлхл▒лЙл▓л░лйлИл╣ л║ Лђл░лиЛђлхЛѕлхлйлИЛј ЛЂЛЃЛЅлхЛЂЛѓл▓лЙл▓л░лйлИЛЈ лйлхЛЂл║лЙл╗Лїл║лИЛЁ ЛѓлЙл┐лЙл╗лЙл│лИл╣ ЛѓлхЛЂЛѓлИЛђлЙл▓л░лйлИЛЈ. лъл┤лйл░л║лЙ л▓лйлхЛѕлйлхлх ЛѓлхЛђл╝лИлйлИЛђлЙл▓л░лйлИлх TDI лИ TMS л╝лЙлХлхЛѓ л▒ЛІЛѓЛї л▓Лђлхл┤лйЛІл╝ л┤л╗ЛЈ ЛЇЛёЛёлхл║ЛѓлИл▓лйлЙЛЂЛѓлИ Лєлхл┐лЙЛЄл║лИ JTAG, л▓ ЛЄл░ЛЂЛѓлйлЙЛЂЛѓлИ, лхЛЂл╗лИ лњЛІ л┐лЙл┤л║л╗ЛјЛЄл░лхЛѓлх лйлИлХлйлИлх л┐ЛђлИЛѓЛЈл│лИл▓л░ЛјЛЅлИлх ЛђлхлилИЛЂЛѓлЙЛђЛІ (pull-down) л║ л▓ЛІл▓лЙл┤л░л╝ TDI лИ TMS. лЪЛђлИЛѓЛЈлХл║л░ pull-down л▒ЛЃл┤лхЛѓ л┐ЛІЛѓл░ЛѓЛїЛЂЛЈ л┐лхЛђлхл▓лхЛЂЛѓлИ л▓ЛІл▓лЙл┤ЛІ TDI лИ TMS л▓ ЛЂл╝лхЛЅлхлйлйлЙлх ЛЂлЙЛЂЛѓлЙЛЈлйлИлх, л▓ ЛЂЛѓлЙЛђлЙлйЛЃ ЛЃЛђлЙл▓лйлхл╣ л┐лЙЛђлЙл│л░ л┐лхЛђлхл║л╗ЛјЛЄлхлйлИЛЈ л╗лЙл│лИл║лИ, лИ ЛЂл┤лхл╗л░лхЛѓ л▓ЛІл▓лЙл┤ЛІ л▒лЙл╗лхлх ЛЄЛЃл▓ЛЂЛѓл▓лИЛѓлхл╗ЛїлйЛІл╝лИ л║ ЛѕЛЃл╝л░л╝ лИ л┐лЙл╝лхЛЁл░л╝. лГЛѓлЙ Лѓл░л║лХлх ЛЃл▓лхл╗лИЛЄлИЛѓ л┐лЙЛѓЛђлхл▒л╗лхлйлИлх ЛѓлЙл║л░ ЛЃЛЂЛѓЛђлЙл╣ЛЂЛѓл▓лЙл╝. лњлйлхЛѕлйлИлх л▓лхЛђЛЁлйлИлх (pull-up) л┐лЙл┤ЛѓЛЈл│лИл▓л░ЛјЛЅлИлх ЛђлхлилИЛЂЛѓлЙЛђЛІ Лѓл░л║лХлх л╝лЙл│ЛЃЛѓ ЛЃл▓лхл╗лИЛЄлИЛѓЛї л┐лЙЛѓЛђлхл▒л╗ЛЈлхл╝ЛІл╣ ЛѓлЙл║, Лѓл░л║ л║л░л║ лЙлйлИ лЙл║л░лХЛЃЛѓЛЂЛЈ л┐лЙл┤л║л╗ЛјЛЄлхлйлйЛІл╝лИ л┐л░Лђл░л╗л╗лхл╗ЛїлйлЙ ЛЂ ЛђлхлилИЛЂЛѓлЙЛђл░л╝лИ, л┐Лђлхл┤лЙЛЂЛѓл░л▓л╗лхлйлйЛІл╝лИ л▓лйЛЃЛѓЛђлИ CPLD, ЛЃл╝лхлйЛїЛѕл░ЛЈ Лѓлхл╝ ЛЂл░л╝ЛІл╝ лЙл▒ЛЅлхлх ЛЂлЙл┐ЛђлЙЛѓлИл▓л╗лхлйлИлх Лєлхл┐лИ ЛЂлИл│лйл░л╗л░ JTAG.

11. лБл▒лхл┤лИЛѓлхЛЂЛї, ЛЄЛѓлЙ Лђлхл│ЛЃл╗ЛЈЛѓлЙЛђ лйл░л┐ЛђЛЈлХлхлйлИЛЈ л┐Лђлхл┤лЙЛЂЛѓл░л▓л╗ЛЈлхЛѓ л┤лЙЛЂЛѓл░ЛѓлЙЛЄлйЛІл╣ ЛѓлЙл║.

люлИл║ЛђлЙЛЂЛЁлхл╝л░ CPLD ЛѓЛђлхл▒ЛЃлхЛѓ л┤лЙЛЂЛѓл░ЛѓлЙЛЄлйлЙл│лЙ ЛѓлЙл║л░ л┐ЛђлИ л▓л║л╗ЛјЛЄлхлйлИлИ. лалхл│ЛЃл╗ЛЈЛѓлЙЛђЛІ, Лђл░л▒лЙЛѓл░ЛјЛЅлИлх лйл░ л┐Лђлхл┤лхл╗лх лйл░л│ЛђЛЃлил║лИ, л╝лЙл│ЛЃЛѓ л┐ЛђлИл▓лхЛЂЛѓлИ л║ лйлхл┐Лђл░л▓лИл╗ЛїлйлЙл╝ЛЃ л║лЙлйЛёлИл│ЛЃЛђлИЛђлЙл▓л░лйлИЛј CPLD лИ л║л░л║ ЛЂл╗лхл┤ЛЂЛѓл▓лИлх ЛЂлИл╗ЛїлйлЙ л┐лЙл▓л╗лИЛЈЛѓЛї лйл░ лхЛЉ л┐лЙл▓лхл┤лхлйлИлх. лБЛѓлИл╗лИЛѓЛІ лЙЛєлхлйл║лИ ЛЇлйлхЛђл│лЙл┐лЙЛѓЛђлхл▒л╗лхлйлИЛЈ (power estimation tools) л┤л░ЛјЛѓ лИлйЛёлЙЛђл╝л░ЛєлИЛј лЙл▒ ЛЃЛЂЛѓл░лйлЙл▓лИл▓Лѕлхл╝ЛЂЛЈ л┐лЙл▓лхл┤лхлйлИлИ, лйлЙ лйлх лЙЛєлхлйлИл▓л░ЛјЛѓ ЛѓлЙл║ л┐лЙЛѓЛђлхл▒л╗лхлйлИЛЈ л┐ЛђлИ л▓л║л╗ЛјЛЄлхлйлИлИ. лЋЛЂл╗лИ лњЛІ л▓ЛІл▒Лђл░л╗лИ ЛЂл▓лЙл╣ Лђлхл│ЛЃл╗ЛЈЛѓлЙЛђ, лйл░Лєлхл╗лИл▓л░ЛЈ лхл│лЙ лйл░ лилйл░ЛЄлхлйлИлх, л▓ЛІЛЄлИЛЂл╗лхлйлйлЙлх л┐лЙ л┐ЛђлЙлхл║ЛѓЛЃ (ЛЂ л┐лЙл╝лЙЛЅЛїЛј ЛЃЛѓлИл╗лИЛѓЛІ XPower, л▓ЛІЛђл░лХлхлйлИЛЈ л▓ЛІЛЄлИЛЂл╗лхлйлИЛЈ л┐лЙЛѓЛђлхл▒л╗лхлйлИЛЈ л╝лЙЛЅлйлЙЛЂЛѓлИ, лИл╗лИ лИли л┤лЙл║ЛЃл╝лхлйЛѓл░ЛєлИлИ), ЛѓлЙ л╝лЙлХлхЛѓ лЙл║л░лил░ЛѓЛїЛЂЛЈ, ЛЄЛѓлЙ л▓ЛІЛЄлИЛЂл╗лхлйлйлЙлх лилйл░ЛЄлхлйлИлх л▒ЛЃл┤лхЛѓ ЛЂл╗лИЛѕл║лЙл╝ л╝л░л╗лЙ. лњЛІл▒лЙЛђ Лђлхл│ЛЃл╗ЛЈЛѓлЙЛђл░ л╗ЛЃЛЄЛѕлх л▓ЛЂлхл│лЙ лЙЛЂЛЃЛЅлхЛЂЛѓл▓лИЛѓЛї ЛЇл║ЛЂл┐лхЛђлИл╝лхлйЛѓл░л╗ЛїлйлЙ, л┤л╗ЛЈ л║лЙлйл║ЛђлхЛѓлйлЙл│лЙ л┤лИлил░л╣лйл░, лИ ЛЂл╗лхл┤ЛЃлхЛѓ л┐ЛђлЙл▓лхЛЂЛѓлИ лИЛЂЛЂл╗лхл┤лЙл▓л░лйлИлх л▓лЙ л▓Лђлхл╝ЛЈ л┐ЛђлЙЛєлхЛЂЛЂл░ Лђл░лиЛђл░л▒лЙЛѓл║лИ. лЦлЙЛђлЙЛѕлИл╣ л╝лхЛѓлЙл┤ - л▓ЛІл▒Лђл░ЛѓЛї Лђлхл│ЛЃл╗ЛЈЛѓлЙЛђ, ЛЂлЙл▓л╝лхЛЂЛѓлИл╝ЛІл╣ л┐лЙ л▓ЛІл▓лЙл┤л░л╝ ЛЂ л┤ЛђЛЃл│лИл╝лИ ЛЂЛЃЛЅлхЛЂЛѓл▓ЛЃЛјЛЅлИл╝лИ Лђлхл│ЛЃл╗ЛЈЛѓлЙЛђл░л╝лИ, лИл╝лхЛјЛЅлИл╝лИ лил░л┐л░ЛЂ л┐лЙ л╝лЙЛЅлйлЙЛЂЛѓлИ. лЪлЙЛЂл╗лх ЛЇЛѓлЙл│лЙ л┐ЛђлЙл▓лхЛђЛїЛѓлх, лйл░ЛЂл║лЙл╗Лїл║лЙ ЛЁлЙЛђлЙЛѕлЙ л▓ЛЂлх Лђл░л▒лЙЛѓл░лхЛѓ, л║л░л║ ЛѓлЙл│лЙ ЛѓЛђлхл▒ЛЃлхЛѓ Лђл░лиЛђл░л▒лЙЛѓл║л░. лЌл░л┐л░ЛЂ л┐лЙ л╝лЙЛЅлйлЙЛЂЛѓлИ Лѓл░л║лХлх лЙл▒лхЛЂл┐лхЛЄлИЛѓ л▓лЙлил╝лЙлХлйлЙЛЂЛѓЛї лИлил╝лхлйлхлйлИЛЈ Лђл░лиЛђл░л▒лЙЛѓл║лИ л▓ л▒ЛЃл┤ЛЃЛЅлхл╝.

12. лЋЛЂл╗лИ ЛЇЛѓлЙ л▓лЙлил╝лЙлХлйлЙ, л┐лЙл┤л░л▓л░л╣Лѓлх л┐лИЛѓл░лйлИлх лйл░ VCCINT л┐лхЛђлхл┤ л┐лЙл┤л░ЛЄлхл╣ л┐лИЛѓл░лйлИЛЈ лйл░ VCCIO.

Xilinx CPLD лйлх лИЛЂл┐лЙЛђЛѓЛЈЛѓЛЂЛЈ л┐ЛђлИ л╗Лјл▒лЙл╣ л┐лЙЛЂл╗лхл┤лЙл▓л░Лѓлхл╗ЛїлйлЙЛЂЛѓлИ л┐лЙл┤л░ЛЄлИ лйл░л┐ЛђЛЈлХлхлйлИл╣ л┐лИЛѓл░лйлИЛЈ, лйлЙ лхЛЂЛѓЛї л▓лЙлил╝лЙлХлйлЙЛЂЛѓЛї, ЛЄЛѓлЙ ЛЂлИл│лйл░л╗ЛІ, ЛЂлЙлил┤л░л▓л░лхл╝ЛІлх л▓лйЛЃЛѓЛђлИ л╝лИл║ЛђлЙЛЂЛЁлхл╝ЛІ, л╝лЙл│ЛЃЛѓ л┐ЛђлИ л▓л║л╗ЛјЛЄлхлйлИлИ л┐лИЛѓл░лйлИЛЈ л┐лЙл┐л░ЛЂЛѓЛї лйл░ л┤ЛђЛЃл│лИлх ЛЂЛЁлхл╝ЛІ. лДЛѓлЙл▒ЛІ л╝лИлйлИл╝лИлилИЛђлЙл▓л░ЛѓЛї ЛЇЛѓЛЃ л▓лЙлил╝лЙлХлйлЙЛЂЛѓЛї, ЛЂл░л╝ЛІл╣ л┐ЛђлЙЛЂЛѓлЙл╣ ЛЂл┐лЙЛЂлЙл▒ ЛЂлйл░ЛЄл░л╗л░ л┐лЙл┤л░л▓л░ЛѓЛї лйл░л┐ЛђЛЈлХлхлйлИлх VCCINT, ЛЂлЙл▒л╗ЛјЛЂЛѓлИ лил░л┤лхЛђлХл║ЛЃ лйл░ л║лЙлйЛёлИл│ЛЃЛђлИЛђлЙл▓л░лйлИлх CPLD лИ л┐лЙЛѓлЙл╝ л┐лЙл┤л░ЛѓЛї лйл░л┐ЛђЛЈлХлхлйлИлх VCCIO. лЪЛђлИ ЛЇЛѓлИЛЁ ЛЃЛЂл╗лЙл▓лИЛЈЛЁ л┐лИЛѓл░лйлИлх лйлх л▒ЛЃл┤лхЛѓ л┐лЙл┤л░лйлЙ лйл░ л▒л░лйл║ I/O, л┐лЙл║л░ лйлх лил░л▓лхЛђЛѕлИЛѓЛЂЛЈ л┐ЛђлЙЛєлхЛЂЛЂ л▓лйЛЃЛѓЛђлхлйлйлхл╣ л║лЙлйЛёлИл│ЛЃЛђл░ЛєлИлИ ЛЂЛЁлхл╝ЛІ л╗лЙл│лИл║лИ CPLD. лЪлЙл┤ЛђлЙл▒лйлЙЛЂЛѓлИ лЙ л┐лЙл▓лхл┤лхлйлИлИ Xilinx CPLD л┐ЛђлИ л▓л║л╗ЛјЛЄлхлйлИлИ л┐лИЛѓл░лйлИЛЈ ЛЂл╝. л▓ л┤л░Лѓл░ЛѕлИЛѓлх XAPP440.

лћлЙл┐лЙл╗лйлИЛѓлхл╗ЛїлйЛІлх Лђлхл║лЙл╝лхлйл┤л░ЛєлИлИ л┐лЙ л░л┐л┐л░Лђл░ЛѓЛЃЛђлх, л║л░ЛЂл░ЛјЛЅлИлхЛЂЛЈ лЙл┐Лђлхл┤лхл╗лхлйлйЛІЛЁ ЛЂлхл╝лхл╣ЛЂЛѓл▓ CPLD:

CoolRunner-II: лИЛЂл┐лЙл╗ЛїлиЛЃл╣Лѓлх ЛѓЛђлИл│л│лхЛђЛІ лел╝лИЛѓЛѓл░ лйл░ л▓ЛЁлЙл┤лйЛІЛЁ ЛЂлИл│лйл░л╗л░ЛЁ, л║лЙЛѓлЙЛђЛІлх л┐лхЛђлхл║л╗ЛјЛЄл░ЛјЛѓЛЂЛЈ ЛЂл╗лИЛѕл║лЙл╝ л╝лхл┤л╗лхлйлйлЙ. люлхл┤л╗лхлйлйЛІлх ЛѕЛЃл╝лЙл┐лЙл┤лЙл▒лйЛІлх ЛЂлИл│лйл░л╗ЛІ л╝лЙл│ЛЃЛѓ ЛЃЛЁЛЃл┤ЛѕлИЛѓЛї Лђл░л▒лЙЛѓЛЃ л┐ЛђлЙлхл║Лѓл░. лњЛІЛЂлЙл║лЙЛЂл║лЙЛђлЙЛЂЛѓлйЛІлх CoolRunner-II CPLD л▒ЛЃл┤ЛЃЛѓ лил░ЛЁл▓л░ЛѓЛІл▓л░ЛѓЛї л┐лЙл╝лхЛЁлИ лйл░ л╝лхл┤л╗лхлйлйЛІЛЁ ЛЂлИл│лйл░л╗л░ЛЁ, лИ лњл░Лѕл░ ЛЂлИЛЂЛѓлхл╝л░ л╝лЙлХлхЛѓ ЛЂЛЄлхЛЂЛѓЛї лИЛЁ лил░ л┐лЙл╗лхлилйЛІлх ЛЂлИл│лйл░л╗ЛІ, л║лЙЛѓлЙЛђЛІлх л╝лЙл│ЛЃЛѓ л▓ЛІлил▓л░ЛѓЛї л┤лЙл┐лЙл╗лйлИЛѓлхл╗ЛїлйЛІлх л┐ЛђлЙл▒л╗лхл╝ЛІ. лбл░л║ЛЃЛј л┐ЛђлЙл▒л╗лхл╝ЛЃ л┐ЛђлЙЛЅлх л▓ЛЂлхл│лЙ ЛђлхЛѕлИЛѓЛї л┐ЛђлЙЛЂЛѓЛІл╝ л┐лЙл┤л║л╗ЛјЛЄлхлйлИлхл╝ лйл░ л▓ЛЁлЙл┤лх ЛёЛЃлйл║ЛєлИлИ Schmitt Trigger, ЛЄЛѓлЙ "лЙЛЄлИЛЂЛѓлИЛѓ" л┐л╗лЙЛЁлИлх ЛЂлИл│лйл░л╗ЛІ, лИ л┐ЛђлхлЙл▒Лђл░лиЛЃлхЛѓ лИЛЁ л▓ ЛЂлИл│лйл░л╗ЛІ ЛЂ ЛЄлхЛѓл║лИл╝лИ л┐лхЛђлхл┐л░л┤л░л╝лИ ЛЃЛђлЙл▓лйлхл╣. лЪлъ Лђл░лиЛђл░л▒лЙЛѓл║лИ лИ л░ЛђЛЁлИЛѓлхл║ЛѓЛЃЛђл░ л┐лЙлил▓лЙл╗ЛЈлхЛѓ л▓ЛІл┐лЙл╗лйЛЈЛѓЛї л║лЙлйЛёлИл│ЛЃЛђлИЛђлЙл▓л░лйлИлх ЛѓЛђлИл│л│лхЛђл░ лел╝лИЛѓЛѓл░ л┤л╗ЛЈ л║л░лХл┤лЙл│лЙ л▓ЛІл▓лЙл┤л░. лЪЛђлИ Лђл░лиЛђл░л▒лЙЛѓл║лх л┐ЛђлЙлхл║Лѓл░ л┐лЙЛЇл║ЛЂл┐лхЛђлИл╝лхлйЛѓлИЛђЛЃл╣Лѓлх ЛЂ ЛЇЛѓлЙл╣ ЛёЛЃлйл║ЛєлИлхл╣.

CoolRunner XPLA3: ЛЁлЙЛђлЙЛѕлхлх л┐лЙлйлИл╝л░лйлИлх ЛЂлИл│лйл░л╗л░ JTAG Port Enable лИ л║лЙЛђЛђлхл║ЛѓлйлЙлх лхл│лЙ лИЛЂл┐лЙл╗ЛїлилЙл▓л░лйлИлх. Port Enable ЛЇЛѓлЙ ЛЂл┐лхЛєлИл░л╗ЛїлйЛІл╣ л▓ЛІл▓лЙл┤ CoolRunner XPLA3, л║лЙЛѓлЙЛђЛІл╣ Лђл░лиЛђлхЛѕл░лхЛѓ лИЛЂл┐лЙл╗ЛїлилЙл▓л░лйлИлх ЛЄлхЛѓЛІЛђлхЛЁ л▓ЛІл▓лЙл┤лЙл▓ JTAG л║л░л║ лйлЙлХл║лИ I/O л╝лхЛЂЛѓлЙ ЛёЛЃлйл║ЛєлИл╣ лИлйЛѓлхЛђЛёлхл╣ЛЂл░ JTAG. лЋЛЂл╗лИ лњл░л╝ лйлх лйЛЃлХлйЛІ л▓ЛІл▓лЙл┤ЛІ JTAG л┤л╗ЛЈ л┐ЛђлЙл│Лђл░л╝л╝лИЛђлЙл▓л░лйлИЛЈ лИл╗лИ ЛѓлхЛЂЛѓлИЛђлЙл▓л░лйлИЛЈ, ЛѓлЙ ЛЇЛѓлИ ЛЄлхЛѓЛІЛђлх л▓ЛІл▓лЙл┤л░ л╝лЙлХлйлЙ лил░л▒Лђл░ЛѓЛї, лйлЙ ЛЂлИл│лйл░л╗ Port Enable ЛЂл╗лхл┤ЛЃлхЛѓ лИЛЂл┐лЙл╗ЛїлилЙл▓л░ЛѓЛї ЛЂлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓ЛЃЛјЛЅлИл╝ лЙл▒Лђл░лилЙл╝. лЪлЙл┤ЛђлЙл▒лйлЙЛЂЛѓлИ ЛЂл╝. л▓ л┤л░Лѓл░ЛѕлИЛѓлх XAPP343.

XC9500/XL/XV: лИЛЂл┐лЙл╗ЛїлилЙл▓л░лйлИлх Low Power Mode лйл░ л▓ЛЂлхЛЁ лйлх л║ЛђлИЛѓлИЛЄлйЛІЛЁ ЛЂлИл│лйл░л╗л░ЛЁ. лџл░л║ ЛЃлХлх ЛЃл┐лЙл╝лИлйл░л╗лЙЛЂЛї, л▓ЛЂлх Xilinx CPLD лЙЛЄлхлйЛї л▒ЛІЛЂЛѓЛђЛІлх. лГЛѓлЙ л║л░ЛЂл░лхЛѓЛЂЛЈ л▒ЛЃЛёлхЛђлйлЙл│лЙ ЛЃЛЂлИл╗лИЛѓлхл╗ЛЈ (sense amp), лйл░ЛЁлЙл┤ЛЈЛЅлИЛЁЛЂЛЈ л▓ ЛЄлИл┐л░ЛЁ XC9500/XL/XV. лЉлЙл╗лхлх лйл░л┤лхлХлйЛІл╣ л┤лИлил░л╣лй л┐лЙЛѓЛђлхл▒л╗ЛЈлхЛѓ л╝лхлйЛїЛѕлх л╝лЙЛЅлйлЙЛЂЛѓлИ лЙЛѓ лИЛЂЛѓлЙЛЄлйлИл║л░ л┐лИЛѓл░лйлИЛЈ, лИ л│лхлйлхЛђлИЛђЛЃлхЛѓ л╝лхлйЛїЛѕлх ЛѕЛЃл╝лЙл▓ л┐лхЛђлхл║л╗ЛјЛЄлхлйлИЛЈ. лГЛѓлЙл│лЙ л╝лЙлХлйлЙ л┤лЙЛЂЛѓлИЛЄЛї ЛЂ лИЛЂл┐лЙл╗ЛїлилЙл▓л░лйлИлхл╝ л╝л░л╗лЙл╝лЙЛЅлйЛІЛЁ л╝л░л║ЛђлЙЛЈЛЄлхлхл║ (low power macrocell switches), ЛЄЛѓлЙ лил░л┤л░лхЛѓЛЂЛЈ л▓ лЪлъ Лђл░лиЛђл░л▒лЙЛѓл║лИ. лћл╗ЛЈ л▓л║л╗ЛјЛЄлхлйлИЛЈ ЛЇЛѓлЙл╣ ЛёЛЃлйл║ЛєлИлИ лИЛЂл┐лЙл╗ЛїлиЛЃлхЛѓЛЂЛЈ л╗лхл│л║лИл╣ ЛЂл║лЙЛђлЙЛЂЛѓлйлЙл╣ ЛЂЛЃл╝л╝л░ЛѓлЙЛђ (slight speed adder), Лѓл░л║ ЛЄЛѓлЙ ЛЇЛѓлЙ л┤лЙл╗лХлйлЙ лИЛЂл┐лЙл╗ЛїлилЙл▓л░ЛѓЛїЛЂЛЈ ЛѓлЙл╗Лїл║лЙ л┤л╗ЛЈ л╗лЙл│лИл║лИ, л║лЙЛѓлЙЛђл░ЛЈ лйлх Лђл░л▒лЙЛѓл░лхЛѓ лйл░ л┐Лђлхл┤лхл╗ЛїлйлЙл╣ ЛЂл║лЙЛђлЙЛЂЛѓлИ. лДл░ЛЂЛѓлЙ ЛЇЛѓлЙ л╝лЙлХлхЛѓ ЛЂлЙЛЂЛѓл░л▓лИЛѓЛї л┤лЙ 80% лЙЛѓ л▓ЛЂлхл│лЙ л┐ЛђлЙлхл║Лѓл░! лДЛѓлЙл▒ЛІ ЛЃл▓лхл╗лИЛЄлИЛѓЛї л▓ЛІлИл│ЛђЛІЛѕ лЙЛѓ ЛЂлйлИлХлхлйлИЛЈ ЛЇлйлхЛђл│лЙл┐лЙЛѓЛђлхл▒л╗лхлйлИЛЈ лИ ЛЄЛѓлЙл▒ЛІ ЛЂлйлИлилИЛѓЛї ЛѕЛЃл╝, л║ low power л╝л░л║ЛђлЙЛЈЛЄлхл╣л║л░л╝ л┤лЙл▒л░л▓л╗ЛЈлхЛѓЛЂЛЈ л│лИЛЂЛѓлхЛђлхлилИЛЂ. лЪлъ Лђл░лиЛђл░л▒лЙЛѓл║лИ л╝лЙлХлхЛѓ ЛЂл┤лхл╗л░ЛѓЛї ЛЇЛѓлЙ л░л▓ЛѓлЙл╝л░ЛѓлИЛЄлхЛЂл║лИ, Лѓл░л║ ЛЄЛѓлЙ лњЛІ л╝лЙлХлхЛѓлх лЙЛЄлхлйЛї л┐ЛђлЙЛЂЛѓлЙ л┐лЙЛЇл║ЛЂл┐лхЛђлИл╝лхлйЛѓлИЛђлЙл▓л░ЛѓЛї ЛЂ ЛёЛЃлйл║ЛєлИлхл╣ Low Power Mode.

[Software, л▒лЙл╗лхлх л┐лЙл┤ЛђлЙл▒лйлЙ]

1. лЮлх лЙЛЂЛѓл░л▓л╗ЛЈл╣Лѓлх л▒лхли л▓лйлИл╝л░лйлИЛЈ л┐Лђлхл┤ЛЃл┐ЛђлхлХл┤лхлйлИЛЈ Лёл░л╣л╗л░ лЙЛѓЛЄлхЛѓл░.

лЪлъ Лђл░лиЛђл░л▒лЙЛѓл║лИ Xilinx лИл┤лхлйЛѓлИЛёлИЛєлИЛђЛЃлхЛѓ л┐лЙЛѓлхлйЛєлИл░л╗ЛїлйЛІлх л┐ЛђлЙл▒л╗лхл╝ЛІ л▓лЙ л▓Лђлхл╝ЛЈ л║лЙл╝л┐лИл╗ЛЈЛєлИлИ, ЛЄЛѓлЙл▒ЛІ л┐лЙл╝лЙЛЄЛї лњл░л╝ л▓ Лђл░лиЛђл░л▒лЙЛѓл║лх. лџл╗ЛјЛЄлхл▓лЙл╣ Лёл░л╣л╗ лЙЛѓЛЄлхЛѓл░ лйлЙЛЂлИЛѓ лИл╝ЛЈ л┐лЙ лйл░лил▓л░лйлИЛј л┐ЛђлЙлхл║Лѓл░ лИл╗лИ лИл╝лхлйлИ л▓лхЛђЛЁлйлхл│лЙ л╝лЙл┤ЛЃл╗ЛЈ, лИ лИл╝лхлхЛѓ Лђл░ЛЂЛѕлИЛђлхлйлИлх *.rpt. лњЛІ л╝лЙлХлхЛѓлх ЛЂл▓лЙл▒лЙл┤лйлЙ лЙЛѓл║ЛђЛІЛѓЛї лхл│лЙ л╗Лјл▒ЛІл╝ л┐ЛђлЙЛЂл╝лЙЛѓЛђЛЅлИл║лЙл╝ Лѓлхл║ЛЂЛѓл░ лИл╗лИ Лѓлхл║ЛЂЛѓлЙл▓ЛІл╝ Лђлхл┤л░л║ЛѓлЙЛђлЙл╝, лИ лхл│лЙ л╝лЙлХлйлЙ л╗лхл│л║лЙ л┐ЛђлЙЛЂл╝лЙЛѓЛђлхЛѓЛї лИ л┐ЛђлЙл░лйл░л╗лИлилИЛђлЙл▓л░ЛѓЛї. лцл░л╣л╗ лЙЛѓЛЄлхЛѓл░ лйл░лиЛІл▓л░лхЛѓЛЂЛЈ CPLD report file, л▓ лйлхл╝ ЛЂлЙл┤лхЛђлХлИЛѓЛЂЛЈ лЙл▒ЛЅл░ЛЈ лИлйЛёлЙЛђл╝л░ЛєлИЛЈ лЙ л┐лЙЛѓЛђлхл▒л╗лхлйлИлИ ЛђлхЛЂЛЃЛђЛЂлЙл▓ (resource summary), л▓ЛЂлх л▓ЛІЛђл░лХлхлйлИЛЈ (design equations), лЙл▒ЛЅлИлх лЙл│Лђл░лйлИЛЄлхлйлИЛЈ (constraints), л▓ЛІл▒Лђл░лйлйЛІлх л┐ЛђлИ л║лЙл╝л┐лИл╗ЛЈЛєлИлИ лИ л┤ЛђЛЃл│л░ЛЈ л┐лЙл╗лхлилйл░ЛЈ лИлйЛёлЙЛђл╝л░ЛєлИЛЈ (лйл░л┐ЛђлИл╝лхЛђ, ЛЃЛЂЛѓл░лйлЙл▓л║лИ л┐лЙ ЛЃл╝лЙл╗ЛЄл░лйлИЛј л┤л╗ЛЈ л║лЙл╝л┐лИл╗ЛЈЛѓлЙЛђл░). лГЛѓлЙ ЛЁлЙЛђлЙЛѕлхлх л╝лхЛЂЛѓлЙ, ЛЄЛѓлЙл▒ЛІ л▒ЛђлЙЛЂлИЛѓЛї лЙл▒ЛЅлИл╣ л▓лил│л╗ЛЈл┤ лйл░ ЛѓлЙ, л║л░л║ л┐ЛђлЙл│Лђл░л╝л╝лйлЙлх лЙл▒лхЛЂл┐лхЛЄлхлйлИлх лЙЛѓлЙл▒Лђл░лХл░лхЛѓ лњл░Лѕ л┤лИлил░л╣лй лйл░ л░ЛђЛЁлИЛѓлхл║ЛѓЛЃЛђЛЃ CPLD. лбл░л║лХлх л▓ лЙЛѓЛЄлхЛѓлх ЛЂлЙл┤лхЛђлХлИЛѓЛЂЛЈ ЛЂл▓лЙл┤л║л░ л┐лЙ л┐Лђлхл┤ЛЃл┐ЛђлхлХл┤лхлйлИЛЈл╝ (warnings), л║лЙЛѓлЙЛђЛІлх ЛЂл╗лхл┤ЛЃлхЛѓ л┐ЛђлЙЛЄлИЛѓл░ЛѓЛї лИ л┐лЙлйЛЈЛѓЛї, ЛЄЛѓлЙ лЙлйлИ лЙлилйл░ЛЄл░ЛјЛѓ.

лЮлхлил░л▓лИЛЂлИл╝лЙ лЙЛѓ ЛЂл┐лЙЛЂлЙл▒л░ ЛЂлЙлил┤л░лйлИЛЈ лњл░Лѕлхл│лЙ л┐ЛђлЙлхл║Лѓл░ (л┐лЙ ЛЂлЙЛЂЛѓл░л▓л╗лхлйлйлЙл╣ ЛЂЛЁлхл╝лх лИл╗лИ ЛЂ л┐лЙл╝лЙЛЅЛїЛј ЛЈлиЛІл║л░ HDL), Xilinx fitter л╝лЙл┤лИЛёлИЛєлИЛђЛЃлхЛѓ л┐лЙл╗ЛЃЛЄлхлйлйЛІл╣ ЛЂл┐лИЛЂлЙл║ Лєлхл┐лхл╣ л▓ ЛЂл┐лИЛЂлЙл║ Лєлхл┐лхл╣, ЛЂл┐лхЛєлИЛёлИЛЄлйЛІл╣ лИ л┤л╗ЛЈ л░ЛђЛЁлИЛѓлхл║ЛѓЛЃЛђЛІ, лИ л┐лЙЛѓлЙл║ л┤л░лйлйЛІЛЁ л┤л╗ЛЈ л┐ЛђлЙл│Лђл░л╝л╝лИЛђлЙл▓л░лйлИЛЈ (JEDEC bitstream). лЪЛђлИ л▓ЛІл┐лЙл╗лйлхлйлИлИ ЛЇЛѓлИЛЁ л┤лхл╣ЛЂЛѓл▓лИл╣ лЙлй л░лйл░л╗лИлилИЛђЛЃлхЛѓ ЛЂл┤лхл╗л░лйлйЛІлх л▓ЛІл▒лЙЛђЛІ л▓л░ЛђлИл░лйЛѓлЙл▓, лИ ЛЂлЙлЙл▒ЛЅл░лхЛѓ лњл░л╝ лЙл▒ лЙл▒л╗л░ЛЂЛѓЛЈЛЁ л▓лЙлил╝лЙлХлйЛІЛЁ л┐ЛђлЙл▒л╗лхл╝ л▓ л▓лИл┤лх ЛЂл┐лИЛЂл║л░ л┐Лђлхл┤ЛЃл┐ЛђлхлХл┤лхлйлИл╣. лљлйл░л╗лИлилЙл╝ ЛЇЛѓлИЛЁ л┐Лђлхл┤ЛЃл┐ЛђлхлХл┤лхлйлИл╣ лњЛІ л╝лЙлХлхЛѓлх лЙл┐Лђлхл┤лхл╗лИЛѓЛї, л│л┤лх л╝лЙлХлхЛѓ л▒ЛІЛѓЛї л┐ЛђлЙл▒л╗лхл╝л░ ЛЂ лњл░Лѕлхл╣ Лђл░лиЛђл░л▒лЙЛѓл║лЙл╣. лћл╗ЛЈ л┐лЙл╗ЛЃЛЄлхлйлИЛЈ ЛЂл░л╝ЛІЛЁ л╗ЛЃЛЄЛѕлИЛЁ ЛђлхлиЛЃл╗ЛїЛѓл░ЛѓлЙл▓ ЛЁлЙЛђлЙЛѕлхл╣ лИл┤лхлхл╣ л▒ЛЃл┤лхЛѓ л┐лЙлйЛЈЛѓЛї л┐Лђлхл┤ЛЃл┐ЛђлхлХл┤лхлйлИЛЈ, лИ л┐Лђлхл┤л┐ЛђлИлйЛЈЛѓЛї л┤л╗ЛЈ лйлИЛЁ ЛЂлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓ЛЃЛјЛЅлИлх л┤лхл╣ЛЂЛѓл▓лИЛЈ, лхЛЂл╗лИ ЛЇЛѓлЙ лйлхлЙл▒ЛЁлЙл┤лИл╝лЙ.

2. лўЛЂл┐лЙл╗ЛїлиЛЃл╣Лѓлх ЛЂЛѓЛђлЙл│лЙ ЛЂлИлйЛЁЛђлЙлйлйЛІл╣ л┤лИлил░л╣лй.

лџл░л║ ЛЃлХлх ЛЃл┐лЙл╝лИлйл░л╗лЙЛЂЛї, ЛЇЛѓл░ Лђлхл║лЙл╝лхлйл┤л░ЛєлИЛЈ лЙЛѓлйлЙЛЂлИЛѓЛЂЛЈ лИ л║ л┐ЛђлЙлхл║ЛѓлИЛђлЙл▓л░лйлИЛј л░л┐л┐л░Лђл░ЛѓЛЃЛђЛІ. лЮлЙ лЙлйл░ л║л░ЛЂл░лхЛѓЛЂЛЈ лИ л║ лЙл▒л╗л░ЛЂЛѓлИ л┐Лђл░л║ЛѓлИл║лИ л┐ЛђлЙл│Лђл░л╝л╝лИЛђлЙл▓л░лйлИЛЈ, л┐лЙЛѓлЙл╝ЛЃ ЛЄЛѓлЙ лњЛІ л╝лЙлХлхЛѓлх л▓ л┐ЛђлЙЛєлхЛЂЛЂлх Лђл░лиЛђл░л▒лЙЛѓл║лИ л┐ЛђлЙлхл║Лѓл░ лйл░л▒л╗Лјл┤л░ЛѓЛї, ЛЂЛѓл░л╗ л╗лИ л┐ЛђлЙлхл║Лѓ "л░ЛЂлИлйЛЁЛђлЙлйлйЛІл╝". лўли-лил░ лйлхлЙл┤лйлЙлилйл░ЛЄлйлЙЛЂЛѓлхл╣ л▓ лЙл┐лИЛЂл░лйлИЛЈЛЁ HDL лИ Лђл░лилйЛІЛЁ лИлйЛѓлхЛђл┐ЛђлхЛѓл░ЛєлИл╣ л╝лхлХл┤ЛЃ лйлИл╝лИ, лњЛІ л╝лЙлХлхЛѓлх л┤ЛЃл╝л░ЛѓЛї, ЛЄЛѓлЙ ЛЂЛЁлхл╝л░ ЛЂлИлйЛЁЛђлЙлйлйл░, лйлЙ л┐лЙлилХлх лЙл▒лйл░ЛђЛЃлХлИЛѓлх, ЛЄЛѓлЙ ЛЇЛѓлЙ лйлх Лѓл░л║! лцл░л╣л╗ лЙЛѓЛЄлхЛѓл░ CPLD - ЛЁлЙЛђлЙЛѕлхлх л╝лхЛЂЛѓлЙ л┤л╗ЛЈ л░лйл░л╗лИлил░ ЛѓлЙЛЄлйлЙл│лЙ лЙЛѓлЙл▒Лђл░лХлхлйлИЛЈ л╗лЙл│лИл║лИ ЛЂЛЁлхл╝ЛІ лйл░ л░ЛђЛЁлИЛѓлхл║ЛѓЛЃЛђЛЃ ЛЄлИл┐л░. лњ лЙЛЂлЙл▒лхлйлйлЙЛЂЛѓлИ л┐лЙл╗ЛїлилЙл▓л░Лѓлхл╗лИ л╝лЙл│ЛЃЛѓ л┐ЛђлЙл░лйл░л╗лИлилИЛђлЙл▓л░ЛѓЛї, ЛЂл║лЙл╗Лїл║лЙ лИЛЂл┐лЙл╗ЛїлиЛЃлхЛѓЛЂЛЈ л│л╗лЙл▒л░л╗ЛїлйЛІЛЁ Лѓл░л║ЛѓлЙл▓ЛІЛЁ ЛЂлИл│лйл░л╗лЙл▓, л│л┤лх лИ л║лЙл│л┤л░ лИЛЂл┐лЙл╗ЛїлиЛЃЛјЛѓЛЂЛЈ л░ЛЂлИлйЛЁЛђлЙлйлйЛІлх ЛђлхЛЂЛЃЛђЛЂЛІ "p-term", лИ Лѓл░л║ л┤л░л╗лхлх. лБл▒лхл┤лИЛѓлхЛЂЛї, ЛЄЛѓлЙ л┐ЛђлЙл▓лхЛђлИл╗лИ ЛЃл┐Лђл░л▓л╗ЛЈлхл╝лЙлх Лѓл░л║ЛѓлИЛђлЙл▓л░лйлИлх л╗лЙл│лИЛЄлхЛЂл║лИЛЁ л▒л╗лЙл║лЙл▓ (gated p-term clocks), л║лЙЛѓлЙЛђЛІлх ЛЄл░ЛЂЛѓлЙ ЛЂЛѓл░лйлЙл▓ЛЈЛѓЛЂЛЈ лИЛЂЛѓлЙЛЄлйлИл║лЙл╝ л┐ЛђлЙл▒л╗лхл╝. лњЛЂлх ЛЇЛѓлЙ ЛЁлЙЛђлЙЛѕлИлх лИлйл┤лИл║л░ЛѓлЙЛђЛІ ЛѓлЙл│лЙ, ЛЄЛѓлЙ л┐ЛђлЙлИлилЙЛѕл╗лЙ ЛЂ лњл░ЛѕлИл╝ л┤лИлил░л╣лйлЙл╝ л▓лхЛђЛЁлйлхл│лЙ ЛЃЛђлЙл▓лйЛЈ, л║лЙл│л┤л░ л┐ЛђлЙЛѕл╗лИ Лђл░лил╗лИЛЄлйЛІлх лЙл┐ЛѓлИл╝лИлил░ЛєлИлИ. лЏЛЃЛЄЛѕлИлх ЛђлхлиЛЃл╗ЛїЛѓл░ЛѓЛІ л┐лЙл╗ЛЃЛЄл░лхЛѓЛЂЛЈ л┐ЛђлИ л╝лЙл┤лИЛёлИл║л░ЛєлИлИ лйл░ ЛЃЛђлЙл▓лйлх HDL, ЛЄЛѓлЙл▒ЛІ ЛЃл╗ЛЃЛЄЛѕлИЛѓЛї "ЛЂлИлйЛЁЛђлЙлйлйлЙЛЂЛѓЛї" л┐лЙл▓лхл┤лхлйлИЛЈ л║лЙлйлхЛЄлйлЙл│лЙ л┤лИлил░л╣лйл░. лЪЛђлхл┤ЛЃл┐ЛђлхлХл┤лхлйлИЛЈ ЛѓЛЃЛѓ ЛЈл▓л╗ЛЈЛјЛѓЛЂЛЈ л┤лЙл┐лЙл╗лйлИЛѓлхл╗ЛїлйЛІл╝ л┐л╗ЛјЛЂлЙл╝.

3. лал░лил▒лхЛђлИЛѓлхЛЂЛї ЛЂ лЙл│Лђл░лйлИЛЄлхлйлИЛЈл╝лИ лИлйЛѓлхЛђл▓л░л╗лЙл▓ л▓Лђлхл╝лхлйлИ лИ ЛЂлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓ЛЃЛјЛЅлИл╝лИ л┐Лђлхл┤ЛЃл┐ЛђлхлХл┤лхлйлИЛЈл╝лИ.

CPLD Timing Report Лѓл░л║лХлх л┤л░лхЛѓ ЛЁлЙЛђлЙЛѕЛЃЛј лИлйЛёлЙЛђл╝л░ЛєлИЛј л┐лЙ лЙл▒ЛЅлхл╝ЛЃ л▒ЛІЛЂЛѓЛђлЙл┤лхл╣ЛЂЛѓл▓лИЛј Лђл░лиЛђл░л▒лЙЛѓл║лИ. лџЛђлЙл╝лх Лёл░л╣л╗л░ CPLD Report, л┤л░лйлйЛІлх л┐Лђлхл┤лЙЛЂЛѓл░л▓л╗ЛЈЛјЛѓЛЂЛЈ л▓ л▓лИл┤лх Лѓл░л▒л╗лИЛє, л┐лЙ л║л░лХл┤лЙл╣ л▓лхЛѓл▓лИ Лђл░лиЛђл░л▒лЙЛѓл║лИ. лъл▒ЛЅлИл╣ л▓ЛІЛЂлЙл║лЙЛЃЛђлЙл▓лйлхл▓ЛІл╣ лЙЛѓЛЄлхЛѓ л┤л░лхЛѓ л▓лхЛђЛЁлйлИлх л┐Лђлхл┤лхл╗ЛІ ЛЂл║лЙЛђлЙЛЂЛѓлИ, лИл┤лхлйЛѓлИЛёлИЛєлИЛђЛЃлхЛѓ ЛЃлил║лИлх л╝лхЛЂЛѓл░ лИ л┐Лђлхл┤лЙЛЂЛѓл░л▓л╗ЛЈлхЛѓ лЙл▒ЛЅлИлх л┐Лђлхл┤ЛЃл┐ЛђлхлХл┤лхлйлИЛЈ, Лѓл░л║ ЛЄЛѓлЙ лњЛІ л╝лЙлХлхЛѓлх л┐лЙЛЂл╗лх л║лЙл╝л┐лИл╗ЛЈЛєлИлИ лЙЛєлхлйлИЛѓЛї лЙл▒ЛЅлИл╣ Лђл░лил╝лхЛђ ЛЃЛЅлхЛђл▒л░ лИл╗лИ л┤лЙЛЂЛѓЛЃл┐лйЛЃЛј л┤лЙл┐лЙл╗лйлИЛѓлхл╗ЛїлйЛЃЛј ЛЂл║лЙЛђлЙЛЂЛѓЛї. лњЛђлхл╝ЛЈ, л┐лЙЛѓЛђл░ЛЄлхлйлйлЙлх лйл░ л┐лЙлйлИл╝л░лйлИлх ЛЇЛѓлЙл│лЙ лЙЛѓЛЄлхЛѓл░, л┤л░лхЛѓ л┤лЙл┐лЙл╗лйлИЛѓлхл╗ЛїлйЛІл╣ л▓ЛІлИл│ЛђЛІЛѕ л┐лЙ лил░ЛѓЛђл░Лѓл░л╝ л▓Лђлхл╝лхлйлИ, л┐лЙЛѓЛђл░ЛЄлхлйлйлЙл│лЙ лйл░ лЙЛѓл╗л░л┤л║ЛЃ.

4. лЪЛђлЙЛЂл╝л░ЛѓЛђлИл▓л░л╣Лѓлх л▓ЛІЛђл░лХлхлйлИЛЈ CPLD Fitter Report.

лџл░л║ ЛЃл┐лЙл╝лИлйл░л╗лЙЛЂЛї Лђл░лйлхлх, CPLD Fitter Report ЛЈЛЂлйлЙ л┐лЙл║л░лиЛІл▓л░лхЛѓ, л║л░л║ л┤лИлил░л╣лй лЙЛѓлЙл▒Лђл░лХл░лхЛѓЛЂЛЈ лйл░ л░ЛђЛЁлИЛѓлхл║ЛѓЛЃЛђЛЃ. лГЛѓлЙ лЙЛѓЛЂл╗лхлХлИл▓л░лхЛѓ Лёл░л╣л╗ JEDEC. лДлхЛѓл║лЙлх лЙЛѓлЙл▒Лђл░лХлхлйлИлх ЛѓлЙл│лЙ, л║л░л║ л░ЛђЛЁлИЛѓлхл║ЛѓЛЃЛђл░ лЙл▒Лђл░л▒л░ЛѓЛІл▓л░лхЛѓ л▓л░лХлйЛІлх ЛѓлЙЛЄл║лИ л┤лИлил░л╣лйл░, л┐лЙл╝лЙл│л░лхЛѓ л▒ЛІЛЂЛѓЛђлЙ лИлилЙл╗лИЛђлЙл▓л░ЛѓЛї лЙл▒л╗л░ЛЂЛѓлИ, л║лЙЛѓлЙЛђЛІлх ЛЂл╗лхл┤ЛЃлхЛѓ л╗ЛЃЛЄЛѕлх л┐лЙлйЛЈЛѓЛї лИл╗лИ ЛЃл╗ЛЃЛЄЛѕлИЛѓЛї. лњлЙ л╝лйлЙл│лИЛЁ ЛЂл╗ЛЃЛЄл░ЛЈЛЁ л┐ЛђлЙЛЂЛѓлЙлх лИлйЛЂл┐лхл║ЛѓлИЛђлЙл▓л░лйлИлх лЙл▒лилЙЛђл░ лЙл┐ЛєлИл╣ л▓ л║лЙлйЛєлх лЙЛѓЛЄлхЛѓл░ л┐лЙл║л░лХлхЛѓ л║л╗ЛјЛЄлхл▓ЛІлх Лёл░л║ЛѓлЙЛђЛІ лйл░л┐лЙл┤лЙл▒лИлх лйлИлил║лЙл│лЙ ЛЇлйлхЛђл│лЙл┐лЙЛѓЛђлхл▒л╗лхлйлИЛЈ, лИ л▓ЛІл▒лЙЛђ л┤ЛђЛЃл│лИЛЁ л┐ЛђлЙЛЂЛѓЛІЛЁ л┐лхЛђлхл║л╗ЛјЛЄлхлйлИл╣ лйл░ЛЂЛѓЛђлЙлхл║ л▓ лЪлъ Лђл░лиЛђл░л▒лЙЛѓл║лИ.

5. лњЛЂлхл│л┤л░ л┐Лђл░л▓лИл╗ЛїлйлЙ л║лЙлйЛёлИл│ЛЃЛђлИЛђЛЃл╣Лѓлх ЛЂлИл│лйл░л╗ЛІ л▓л▓лЙл┤л░ л▓ЛІл▓лЙл┤л░ I/O (LVCMOS 3.3, LVCMOS 1.8, лИ Лѓ. л┤.).

CPLD лйлх лилйл░лхЛѓ, ЛЂ л║л░л║лИл╝лИ ЛЃЛђлЙл▓лйЛЈл╝лИ л╗лЙл│лИл║лИ лйЛЃлХлйлЙ Лђл░л▒лЙЛѓл░ЛѓЛї. лбл░л║лИл╝ лЙл▒Лђл░лилЙл╝ лњЛІ лЙл┐Лђлхл┤лхл╗ЛЈлхЛѓлх, л║л░л║лИлх лхЛЂЛѓЛї л▓лйлхЛѕлйлИлх л┐лЙл┤л║л╗ЛјЛЄлхлйлИЛЈ, лйлЙ Лѓл░л║лХлх л▓ ЛЂл▓лЙлхл╝ л┐ЛђлЙлхл║Лѓлх лИлйЛёлЙЛђл╝лИЛђЛЃлхЛѓлх лЙл▒ ЛЇЛѓлЙл╝ лИ лЪлъ Лђл░лиЛђл░л▒лЙЛѓл║лИ. лЪлъ л▒ЛЃл┤лхЛѓ ЛЃЛЂЛѓл░лйл░л▓л╗лИл▓л░ЛѓЛї л▓лйЛЃЛѓЛђлхлйлйлИлх л▒лИЛѓЛІ л┐ЛђлЙл│Лђл░л╝л╝лИЛђлЙл▓л░лйлИЛЈ, л║лЙЛѓлЙЛђЛІлх л┤лИл║ЛѓЛЃЛјЛѓ л║лЙЛђЛђлхл║ЛѓлйЛІлх л║лЙлйЛёлИл│ЛЃЛђл░ЛєлИлИ ЛѓЛђл░лйлилИЛЂЛѓлЙЛђлЙл▓ лйл░ лйлЙлХл║л░ЛЁ I/O л╝лИл║ЛђлЙЛЂЛЁлхл╝ЛІ, ЛЄЛѓлЙл▒ЛІ л┤лЙЛЂЛѓлИЛЄЛї л┐Лђл░л▓лИл╗ЛїлйлЙлх ЛЃл┐Лђл░л▓л╗лхлйлИлх л▓лйлхЛѕлйлИл╝лИ л▓ЛІл▓лЙл┤л░л╝лИ. лГЛѓлЙ л┤лхл╣ЛЂЛѓл▓лИлх лйл░ЛЁлЙл┤лИЛѓЛЂЛЈ л▓ лилЙлйлх лЙЛѓл▓лхЛѓЛЂЛѓл▓лхлйлйлЙЛЂЛѓлИ Лђл░лиЛђл░л▒лЙЛѓЛЄлИл║л░, л┐лЙЛЇЛѓлЙл╝ЛЃ лЙл▒ЛЈлил░Лѓлхл╗ЛїлйлЙ ЛЂл┤лхл╗л░л╣Лѓлх л┐Лђл░л▓лИл╗ЛїлйЛІл╣ л▓ЛІл▒лЙЛђ.

лЪЛђлИл╝лхЛЄл░лйлИлх: ЛЈ л┤лЙл┐ЛЃЛЂЛѓлИл╗ л┐лЙл┤лЙл▒лйЛЃЛј лЙЛѕлИл▒л║ЛЃ, лЙЛЂЛѓл░л▓лИл▓ лйл░ЛЂЛѓЛђлЙл╣л║лИ л┐лЙ ЛЃл╝лЙл╗ЛЄл░лйлИЛј л┤л╗ЛЈ л┐ЛђлЙлхл║Лѓл░ лйл░ л┐лЙл┤л┤лхЛђлХл║ЛЃ лџлюлълЪ-л╗лЙл│лИл║лИ 1.8V (Default Voltage Standard for All Outputs: LVCMOS18), лИ л┐ЛђлИ ЛЇЛѓлЙл╝ лил░л┤л░л╗ л▓ Лёл░л╣л╗лх лЙл│Лђл░лйлИЛЄлхлйлИл╣ *.ucf л┤л╗ЛЈ лйлхл║лЙЛѓлЙЛђЛІЛЁ л▓лйлхЛѕлйлИЛЁ (лйлЙ лйлх л┤л╗ЛЈ л▓ЛЂлхЛЁ!) л▓ЛІЛЁлЙл┤лЙл▓ ЛЂлИЛЂЛѓлхл╝ЛЃ ЛЃЛђлЙл▓лйлхл╣ л╗лЙл│лИл║лИ TTL 3.3V (LVTTL). лџлЙлйлхЛЄлйлЙ, ЛЇЛѓлЙ л▒ЛІл╗лЙ лЙЛѕлИл▒л║лЙл╣ - лйл░л┤лЙ л▒ЛІл╗лЙ л╗лИл▒лЙ лИлил╝лхлйлИЛѓЛї лйл░ЛЂЛѓЛђлЙл╣л║ЛЃ л┐лЙ ЛЃл╝лЙл╗ЛЄл░лйлИЛј лйл░ LVTTL, л╗лИл▒лЙ лил░л┤л░ЛѓЛї л▓ Лёл░л╣л╗лх UCF л┤л╗ЛЈ л▓ЛЂлхЛЁ л▓ЛІЛЁлЙл┤лЙл▓ лЙл┤лИлйл░л║лЙл▓ЛІлх лйл░ЛЂЛѓЛђлЙл╣л║лИ LVTTL. лћл╗ЛЈ лйлхл║лЙЛѓлЙЛђЛІЛЁ л▓ЛІл▓лЙл┤лЙл▓ ЛЈ ЛЇЛѓлЙ лйлх ЛЂл┤лхл╗л░л╗, лИ л┐лЙЛѓлЙл╝ л┤лЙл╗л│лЙ ЛЃл┤лИл▓л╗ЛЈл╗ЛЂЛЈ, л┐лЙЛЄлхл╝ЛЃ л┤л╗ЛЈ л┐ЛђлЙЛЂЛѓлЙл╣ ЛЂЛЁлхл╝ЛІ л┐ЛђлЙлхл║Лѓ лйлх л║лЙл╝л┐лИл╗лИЛђлЙл▓л░л╗ЛЂЛЈ ЛЂ ЛЂлЙлЙл▒ЛЅлхлйлИлхл╝ "лњл░Лѕ л┤лИлил░л╣лй лйлх л┐лЙл╝лхЛЅл░лхЛѓЛЂЛЈ л▓ ЛђлхЛЂЛЃЛђЛЂЛІ л║ЛђлИЛЂЛѓл░л╗л╗л░".

6. лЋЛЂл╗лИ л▓лЙлил╝лЙлХлйлЙ, л┐лЙлил▓лЙл╗ЛїЛѓлх лЪлъ Лђл░лиЛђл░л▒лЙЛѓл║лИ ЛЂл▓лЙл▒лЙл┤лйЛЃЛј (л▒лхли лЙл│Лђл░лйлИЛЄлхлйлИл╣) л┐ЛђлИл▓ЛЈлил║ЛЃ л▓лйлхЛѕлйлИЛЁ л▓ЛІл▓лЙл┤лЙл▓ ЛЄлИл┐л░.

лЪлъ Лђл░лиЛђл░л▒лЙЛѓл║лИ Xilinx лйл░л┐лИЛЂл░лйлЙ Лѓл░л║лИл╝ лЙл▒Лђл░лилЙл╝, ЛЄЛѓлЙл▒ЛІ л┤л░ЛѓЛї л╝л░л║ЛЂлИл╝л░л╗ЛїлйЛІлх л▓лЙлил╝лЙлХлйлЙЛЂЛѓлИ л┤л╗ЛЈ Лђл░лиЛђл░л▒лЙЛѓЛЄлИл║л░ л┐лЙ ЛЃл┐Лђл░л▓л╗лхлйлИЛј ЛѓЛђл░ЛЂЛЂлИЛђлЙл▓л║лЙл╣ л╗лЙл│лИл║лИ л┤лЙ л▓ЛІл▓лЙл┤лЙл▓ I/O л║лЙЛђл┐ЛЃЛЂл░ ЛЄлИл┐л░ (ЛЇЛѓлЙ л┐лЙлил▓лЙл╗ЛЈлхЛѓ ЛЃл┐ЛђлЙЛЂЛѓлИЛѓЛї Лђл░лил▓лЙл┤л║ЛЃ л┐лхЛЄл░ЛѓлйлЙл╣ л┐л╗л░ЛѓЛІ л┤л╗ЛЈ л║лЙлйлхЛЄлйлЙл│лЙ ЛЃЛЂЛѓЛђлЙл╣ЛЂЛѓл▓л░), лЙл┤лйлЙл▓Лђлхл╝лхлйлйлЙ ЛЂЛѓл░Лђл░ЛЈЛЂЛї ЛЃл╝лхлйЛїЛѕлИЛѓЛї л┐лЙЛѓЛђлхл▒л╗лхлйлИлх ЛђлхЛЂЛЃЛђЛЂлЙл▓ л╝лИл║ЛђлЙЛЂЛЁлхл╝ЛІ. лГЛѓлЙ лЙлилйл░ЛЄл░лхЛѓ, ЛЄЛѓлЙ лЪлъ л▒ЛЃл┤лхЛѓ лйл░л╝лхЛђлхлйлйлЙ л┐ЛІЛѓл░ЛѓЛїЛЂЛЈ лЙл▒Лілхл┤лИлйЛЈЛѓЛї л╗лЙл│лИл║ЛЃ л▓ л║л╗л░ЛЂЛѓлхЛђЛІ л▓лйЛЃЛѓЛђлИ ЛёЛЃлйл║ЛєлИлЙлйл░л╗ЛїлйЛІЛЁ л▒л╗лЙл║лЙл▓, ЛЄЛѓлЙл▒ЛІ л╝л░л║ЛЂлИл╝л░л╗ЛїлйлЙ л┐лЙл▓ЛѓлЙЛђлйлЙ лИЛЂл┐лЙл╗ЛїлилЙл▓л░ЛѓЛї ЛЂлИл│лйл░л╗ЛІ. лбл░л║лХлх л▒ЛЃл┤лхЛѓ ЛЂл┤лхл╗л░лйл░ л┐лЙл┐ЛІЛѓл║л░ лИлил▒лхлХл░ЛѓЛї ЛЄЛђлхлил╝лхЛђлйлЙл│лЙ лИЛЂл┐лЙл╗ЛїлилЙл▓л░лйлИЛЈ л▓ЛЁлЙл┤лЙл▓ ЛёЛЃлйл║ЛєлИлЙлйл░л╗ЛїлйЛІЛЁ л▒л╗лЙл║лЙл▓ лИ ЛђлхЛЂЛЃЛђЛЂлЙл▓ л╗лЙл│лИл║лИ, ЛЄЛѓлЙл▒ЛІ лЙлйлИ л▒ЛІл╗лИ л┤лЙЛЂЛѓЛЃл┐лйЛІ л▓ ЛЂл╗ЛЃЛЄл░лх лйлхлЙл▒ЛЁлЙл┤лИл╝лЙЛЂЛѓлИ л▓ л▒ЛЃл┤ЛЃЛЅлИЛЁ лИлил╝лхлйлхлйлИЛЈЛЁ л┤лИлил░л╣лйл░. лњ ЛЄл░ЛЂЛѓлйлЙЛЂЛѓлИ, ЛЇЛѓлЙ л║ЛђлИЛѓлИЛЄлйлЙ л┤л╗ЛЈ Лђл░лиЛђл░л▒лЙЛѓлЙл║, л║лЙЛѓлЙЛђЛІлх Лђл░л▒лЙЛѓл░ЛјЛѓ л╝лйлЙл│лИлх л│лЙл┤ЛІ л▓ л│лЙЛѓлЙл▓ЛІЛЁ ЛЃЛЂЛѓЛђлЙл╣ЛЂЛѓл▓л░ЛЁ, лИ л┐ЛђлИ ЛЇЛѓлЙл╝ лхЛЂЛѓЛї л▓лЙлил╝лЙлХлйлЙЛЂЛѓЛї л┐лЙл┤л┤лхЛђлХлИл▓л░ЛѓЛї л╝лйлЙл│лИлх Лђлхл▓лИлилИлИ л╗лЙл│лИл║лИ л▓ ЛЂлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓лИлИ ЛЂ л╝лхлйЛЈЛјЛЅлИл╝лИЛЂЛЈ ЛЃЛЂл╗лЙл▓лИЛЈл╝лИ ЛѓлхЛЁлил░л┤л░лйлИЛЈ. лњЛІ л┤лЙл╗лХлйЛІ л┐ЛђлИлйЛЈЛѓЛї ЛђлхЛѕлхлйлИлх, л┤л░л▓л░ЛѓЛї л╗лИ л┐ЛђлЙл│Лђл░л╝л╝лйлЙл╝ЛЃ лЙл▒лхЛЂл┐лхЛЄлхлйлИЛј л▓лЙлил╝лЙлХлйлЙЛЂЛѓЛї ЛЂл░л╝лЙл╝ЛЃ л┤лхл╗л░ЛѓЛї Лђл░ЛЂл┐Лђлхл┤лхл╗лхлйлИлх л▓ЛЁлЙл┤лЙл▓ лИ л▓ЛІЛЁлЙл┤лЙл▓ л╗лЙл│лИл║лИ л┐лЙ л▓ЛІл▓лЙл┤л░л╝ л║ЛђлИЛЂЛѓл░л╗л╗л░ (ЛЄЛѓлЙ л▓лЙлил╝лЙлХлйлЙ ЛЃЛЂл╗лЙлХлйлИЛѓ Лђл░лил▓лЙл┤л║ЛЃ л┐л╗л░ЛѓЛІ, лйлЙ лил░ЛѓлЙ лЙЛЂл▓лЙл▒лЙл┤лИЛѓ ЛђлхЛЂЛЃЛђЛЂЛІ CPLD лИ л┐лЙЛѓлхлйЛєлИл░л╗ЛїлйлЙ л┐лЙл▓ЛІЛЂлИЛѓ л┐ЛђлЙлИлил▓лЙл┤лИЛѓлхл╗ЛїлйлЙЛЂЛѓЛї), л╗лИл▒лЙ лил░л┤л░ЛѓЛї лХлхЛЂЛѓл║лИлх лЙл│Лђл░лйлИЛЄлхлйлИЛЈ (ЛЄЛѓлЙ ЛЃл┐ЛђлЙЛЂЛѓлИЛѓ л┐л╗л░ЛѓЛЃ, лйлЙ ЛЃЛЂл╗лЙлХлйлИЛѓ л┤л╗ЛЈ лЪлъ ЛЃЛЂл╗лЙл▓лИЛЈ л┐лЙ ЛѓЛђл░ЛЂЛЂлИЛђлЙл▓л║лх л╗лЙл│лИл║лИ л┐лЙ л║ЛђлИЛЂЛѓл░л╗л╗ЛЃ лИ лил░л╣л╝лхЛѓ л┤лЙл┐лЙл╗лйлИЛѓлхл╗ЛїлйЛІлх ЛђлхЛЂЛЃЛђЛЂЛІ). лЪлЙл╝лйлИЛѓлх, ЛЄЛѓлЙ л▓ лЪлъ Лђл░лиЛђл░л▒лЙЛѓл║лИ л░л║л║ЛЃл╝ЛЃл╗лИЛђлЙл▓л░лй л╝лйлЙл│лЙл╗лхЛѓлйлИл╣ лЙл┐ЛІЛѓ Лђл░л▒лЙЛѓЛІ л╝лйлЙлХлхЛЂЛѓл▓л░ ЛЂл┐лхЛєлИл░л╗лИЛЂЛѓлЙл▓, лИ лхЛЂл╗лИ ЛЇЛѓлЙ л▓лЙлил╝лЙлХлйлЙ, л┐лЙл╗л░л│л░л╣ЛѓлхЛЂЛї лйл░ ЛЂл▓лЙл▒лЙл┤лйЛІл╣ л▓ЛІл▒лЙЛђ лИ ЛЃл┐Лђл░л▓л╗лхлйлИлх ЛђлхЛЂЛЃЛђЛЂл░л╝лИ ЛЂлЙ ЛЂЛѓлЙЛђлЙлйЛІ ЛЂлИЛЂЛѓлхл╝ЛІ ЛЂлИлйЛѓлхлил░, л║лЙл╝л┐лИл╗ЛЈЛєлИлИ лИ Лђл░лил╝лхЛЅлхлйлИЛЈ лйл░ л║ЛђлИЛЂЛѓл░л╗л╗лх.

7. лъЛЄлхлйЛї л┐лЙл╗лхлилйлЙ л┐ЛђлЙл▓лЙл┤лИЛѓЛї ЛЂлИл╝ЛЃл╗ЛЈЛєлИЛј л┤лИлил░л╣лйл░.

лАлИл╝ЛЃл╗ЛЈЛєлИЛЈ л┐ЛђлЙлхл║Лѓл░ л┐Лђлхл┤лЙЛЂЛѓл░л▓л╗ЛЈлхЛѓ л▓лЙлил╝лЙлХлйлЙЛЂЛѓЛї лЙЛєлхлйлИЛѓЛї лхл│лЙ л▓ Лђл░л▒лЙЛѓлх л┐лЙл┤ л╝лЙл┤лхл╗ЛїЛј лЙлХлИл┤л░лхл╝лЙл╣ Лђл░л▒лЙЛЄлхл╣ лйл░л│ЛђЛЃлил║лИ. люлЙл┤лхл╗лИЛђлЙл▓л░лйлИлх л╝лЙлХлхЛѓ лИл┤лхлйЛѓлИЛёлИЛєлИЛђлЙл▓л░ЛѓЛї л┐ЛђлЙл▒л╗лхл╝ЛІ ЛЂ лИлйЛѓлхЛђл▓л░л╗л░л╝лИ л▓Лђлхл╝лхлйлИ, л║лЙЛѓлЙЛђЛІлх л▒ЛІл╗лИ л┐ЛђлЙл┐ЛЃЛЅлхлйЛІ л▓ л▓ Лёл░л╣л╗л░ЛЁ лЙЛѓЛЄлхЛѓл░ л▓Лђлхл╝лхлйлИ лИ Лђл░лил╝лхЛЅлхлйлИЛЈ (timing report, fitter report), л┐лЙЛѓлЙл╝ЛЃ ЛЄЛѓлЙ ЛЇЛѓлИ лЙЛѓЛЄлхЛѓЛІ лЙЛЂлйлЙл▓л░лйЛІ лйл░ "ЛЂЛѓл░ЛѓлИЛЄлхЛЂл║лЙл╣" л╝лЙл┤лхл╗лИ л┤лИлил░л╣лйл░. лГЛѓлЙ л╝лЙлХлхЛѓ Лѓл░л║лХлх лИЛЂл┐лЙл╗ЛїлилЙл▓л░ЛѓЛїЛЂЛЈ л┤л╗ЛЈ л┐ЛђлЙл▓лхЛђл║лИ ЛёЛЃлйл║ЛєлИлЙлйлИЛђлЙл▓л░лйлИЛЈ л┐ЛђлИ лИлил╝лхлйЛЈЛјЛЅлИЛЁЛЂЛЈ Лђл░л▒лЙЛЄлИЛЁ ЛЃЛЂл╗лЙл▓лИЛЈЛЁ. лЮл░л┐ЛђлИл╝лхЛђ, л║лЙл│л┤л░ л┤лИлил░л╣лй Лђл░л▒лЙЛѓл░лхЛѓ л┐ЛђлИ лйлИлил║лИЛЁ Лѓлхл╝л┐лхЛђл░ЛѓЛЃЛђл░ЛЁ, ЛЃЛЂЛѓЛђлЙл╣ЛЂЛѓл▓лЙ лИл╝лхлхЛѓ Лѓлхлйл┤лхлйЛєлИЛј Лђл░л▒лЙЛѓл░ЛѓЛї л▒ЛІЛЂЛѓЛђлхлх. лў лйл░лЙл▒лЙЛђлЙЛѓ, л┐ЛђлИ л▓ЛІЛЂлЙл║лЙл╣ Лѓлхл╝л┐лхЛђл░ЛѓЛЃЛђлх л╝лхл┤л╗лхлйлйлхлх. люлЙлХлйлЙ л▓ЛІл▒Лђл░ЛѓЛї Лђл░лил╗лИЛЄлйЛІлх л▓л░ЛђлИл░лйЛѓЛІ лИл╝лхЛјЛЅлхл╣ЛЂЛЈ л╝лЙл┤лхл╗лИ л║ЛђлИЛЂЛѓл░л╗л╗л░ л┐лЙ л▒ЛІЛЂЛѓЛђлЙл┤лхл╣ЛЂЛѓл▓лИЛј (speed grade), лИ лил░л┐ЛЃЛЂЛѓлИЛѓЛї ЛЂлИл╝ЛЃл╗ЛЈЛєлИЛј ЛЂ Лђл░лил╗лИЛЄлйЛІл╝лИ speed grade, ЛЄЛѓлЙл▒ЛІ л┐лЙлйЛЈЛѓЛї л┐лЙл▓лхл┤лхлйлИлх ЛЃЛЂЛѓЛђлЙл╣ЛЂЛѓл▓л░ л┐лЙ л╝лЙл┤лхл╗лИ л▓ "л│лЙЛђЛЈЛЄлИЛЁ" лИ "ЛЁлЙл╗лЙл┤лйЛІЛЁ" ЛЃЛЂл╗лЙл▓лИЛЈЛЁ. лџлЙл│л┤л░ лЙЛЂЛЃЛЅлхЛЂЛѓл▓л╗ЛЈлхЛѓЛЂЛЈ л╝лЙл┤лхл╗лИЛђлЙл▓л░лйлИлх л┐лЙ Лѓл░л║лЙл╝ЛЃ л╝лхЛѓлЙл┤ЛЃ, л░ЛЂлИлйЛЁЛђлЙлйлйлЙлх л┐лЙл▓лхл┤лхлйлИлх л╝лЙлХлхЛѓ л┐лЙл║л░лил░ЛѓЛї лйлЙл▓лЙлх ЛёЛЃлйл║ЛєлИлЙлйлИЛђлЙл▓л░лйлИлх ЛЃЛЂЛѓЛђлЙл╣ЛЂЛѓл▓л░. лњ Лєлхл╗лЙл╝ ЛЂлИл╝ЛЃл╗ЛЈЛєлИЛЈ ЛЇЛѓлЙ л┤лЙл▓лЙл╗ЛїлйлЙ л▒лЙл╗ЛїЛѕл░ЛЈ Лђл░л▒лЙЛѓл░, лйлЙ ЛЄл░ЛЂЛѓлЙ ЛЇЛѓл░ Лђл░л▒лЙЛѓл░ лЙл║л░лиЛІл▓л░лхЛѓЛЂЛЈ л╝лхлйЛїЛѕлх, ЛЄлхл╝ лЙЛѓл╗л░л┤л║л░ лИ л┐лЙлИЛЂл║ лЙЛѕлИл▒лЙл║ л▓ л┐л╗лЙЛЁлЙ Лђл░лиЛђл░л▒лЙЛѓл░лйлйлЙл╝ л┐ЛђлЙлхл║Лѓлх.

[лАЛЂЛІл╗л║лИ]

1. XAPP784 Bulletproof CPLD Design Practices site:xilinx.com.

2. CoolRunner II site:xilinx.com (л┤лЙл║ЛЃл╝лхлйЛѓл░ЛєлИЛЈ, л░л┐лйлЙЛЃЛѓЛІ лИ ЛЂЛѓл░ЛѓЛїлИ). |