|

ąøčÄą▒ąŠą╣ ą┤ąĖąĘą░ą╣ąĮ VHDL FPGA ą╝ąŠąČąĄčé ąĖą╝ąĄčéčī ą▓ ą║ąŠą┤ąĄ ąĮąĄčüą║ąŠą╗čīą║ąŠ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗčģ čéąĖą┐ąŠą▓ VHDL. ąæąŠą╗čīčłąĖąĮčüčéą▓ąŠ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗčģ čéąĖą┐ąŠą▓ ą▓ čüąĖąĮč鹥ąĘąĖčĆčāąĄą╝ąŠą╝ ą║ąŠą┤ąĄ VHDL čŹč鹊 std_logic, std_logic_vector, signed, unsigned ąĖ integer. ą¤ąŠčüą║ąŠą╗čīą║čā VHDL čŹč鹊 čÅąĘčŗą║ čüąŠ čüčéčĆąŠą│ąĖą╝ ą║ąŠąĮčéčĆąŠą╗ąĄą╝ čéąĖą┐ąŠą▓, ąŠč湥ąĮčī čćą░čüč鹊 ąŠčéą╗ąĖčćą░čÄčēąĖąĄčüčÅ čéąĖą┐čŗ ąĮąĄ ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą▓ ąŠą┤ąĮąŠą╝ ą▓čŗčĆą░ąČąĄąĮąĖąĖ. ąÜčĆąŠą╝ąĄ č鹊ą│ąŠ, ą║ąŠą│ą┤ą░ ąÆčŗ ą╝ąŠąČąĄč鹥 ą┐čĆčÅą╝ąŠ ą║ąŠą╝ą▒ąĖąĮąĖčĆąŠą▓ą░čéčī ą┤ą▓ą░ čéąĖą┐ą░ ą▓ ąŠą┤ąĮąŠą╝ ą▓čŗčĆą░ąČąĄąĮąĖąĖ, č鹊 ąĮą░ čüą░ą╝ąŠą╝ ą┤ąĄą╗ąĄ ąŠčüčéą░ą▓ą╗čÅąĄč鹥 ąĮą░ ą▓ąŠą╗čÄ ą║ąŠą╝ą┐ąĖą╗čÅč鹊čĆą░ ąĖą╗ąĖ ąĖąĮčüčéčĆčāą╝ąĄąĮčéą░ čüąĖąĮč鹥ąĘą░ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī, ą║ą░ą║ ą┤ąŠą╗ąČąĮąŠ čüąĄą▒čÅ ą▓ąĄčüčéąĖ čŹč鹊 ą▓čŗčĆą░ąČąĄąĮąĖąĄ, čćč鹊 ą┤ąŠą▓ąŠą╗čīąĮąŠ ąŠą┐ą░čüąĮą░čÅ ą▓ąĄčēčī.

ąÆ čŹč鹊ą╣ čüčéą░čéčīąĄ (ą┐ąĄčĆąĄą▓ąŠą┤ [1]) ąŠą▒čüčāąČą┤ą░čÄčéčüčÅ čüą╗ąĄą┤čāčÄčēąĖąĄ č鹥ą╝čŗ:

1. ą¤čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ čéąĖą┐ąŠą▓ (type cast) ąĖ čäčāąĮą║čåąĖąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ.

2. ąÆ č湥ą╝ ą▓ą░ąČąĮąŠčüčéčī ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą┐ąŠą┤čģąŠą┤čÅčēąĄą│ąŠ čéąĖą┐ą░.

3. ą×ą▒čŗčćąĮąŠąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖą╣ čéąĖą┐ąŠą▓ ąĖ ą┐čĆąĖą╝ąĄčĆčŗ.

[ą¤čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ čéąĖą┐ąŠą▓ (type cast) ąĖ čäčāąĮą║čåąĖąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ąĮą░ VHDL]

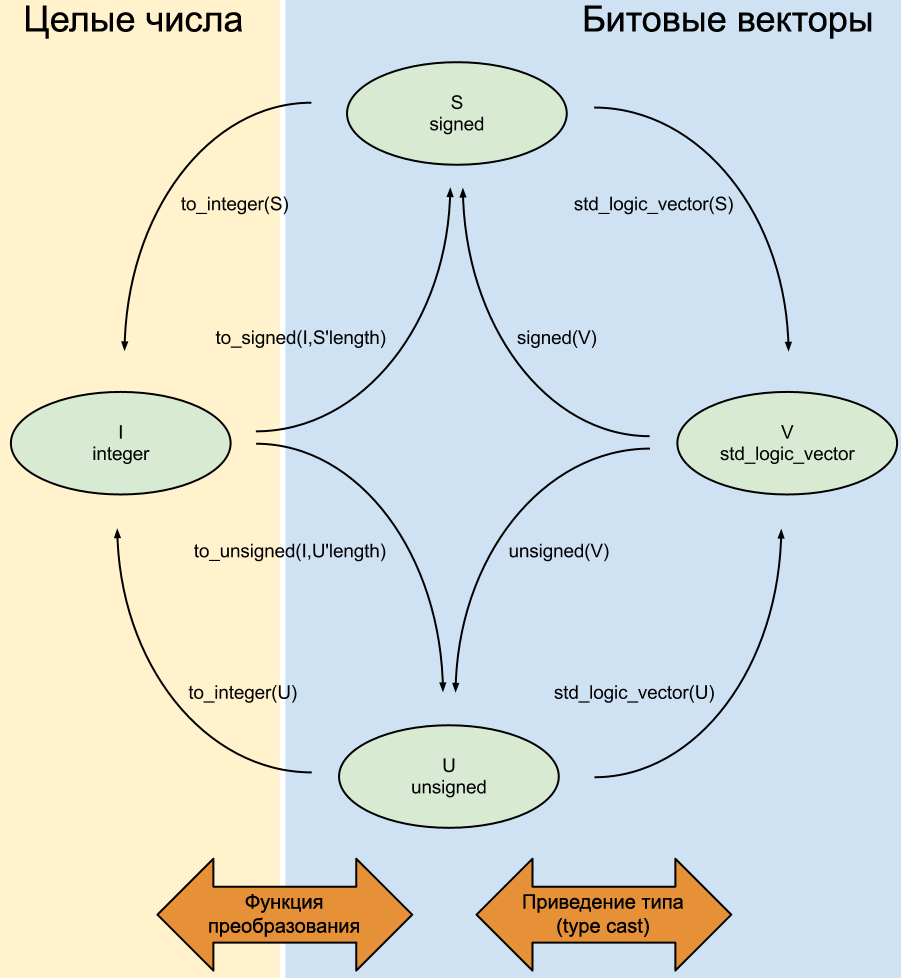

ąØą░ ą║ą░čĆčéąĖąĮą║ąĄ ąĮąĖąČąĄ ą┐ąŠą║ą░ąĘą░ąĮąŠ, ą║ą░ą║ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░čéčī ą▒ąŠą╗čīčłąĖąĮčüčéą▓ąŠ čéąĖą┐ąŠą▓ VHDL.

ą¤čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ čéąĖą┐ąŠą▓ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą┐ąĄčĆąĄčģąŠą┤ą░ ąŠčé čéąĖą┐ą░ std_logic_vector ą║ čéąĖą┐ą░ą╝ signed ąĖ unsigned.

-- ą×ą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ čüąĖą│ąĮą░ą╗ąŠą▓:

signal slv : std_logic_vector(7 downto 0);

signal s : signed(7 downto 0);

signal us : unsigned(7 downto 0);

-- ą¤čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ąĖąĘ std_logic_vector ą▓ signed/unsigned:

sgn <= signed(slv);

usgn <= unsigned(slv);

-- ą¤čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ąĖąĘ signed/unsigned ą▓ std_logic_vector:

svl <= std_logic_vector(sgn);

svl <= std_logic_vector(usgn);

ąöą╗čÅ ą┐ąĄčĆąĄčģąŠą┤ą░ ą╝ąĄąČą┤čā čéąĖą┐ą░ą╝ąĖ signed/unsigned ąĖ integer ąĖčüą┐ąŠą╗čīąĘčāčÄčé čäčāąĮą║čåąĖąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ.

-- ą×ą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ čüąĖą│ąĮą░ą╗ąŠą▓:

signal i : integer;

signal sgn : signed(7 downto 0);

signal usgn : unsigned(7 downto 0);

-- ą¤čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ąĖąĘ integer ą▓ signed/unsigned:

sgn <= to_signed(i,8);

usgn <= to_unsigned(i,8);

-- ą¤čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ąĖąĘ signed/unsigned ą▓ integer:

i <= to_integer(sgn);

i <= to_integer(usgn);

ą¤čĆąŠčüč鹊ą╣ čüą┐ąŠčüąŠą▒ ąĘą░ą┐ąŠą╝ąĮąĖčéčī, ą║ąŠą│ą┤ą░ ąĮą░ą┤ąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čäčāąĮą║čåąĖčÄ, ą░ ą║ąŠą│ą┤ą░ type cast, čüąŠčüč鹊ąĖčé ą▓ č鹊ą╝, čćč鹊 ąŠą▒ą░ čéąĖą┐ą░ std_logic_vector ąĖ signed/unsigned ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčéčüčÅ čüąŠ čüą┐ąĄčåąĖčäąĖčćąĮąŠą╣ čłąĖčĆąĖąĮąŠą╣ ą▓ ą▒ąĖčéą░čģ, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ čćąĖčüą╗ą░ integer ąĮąĄ ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčé čĆą░ąĘčĆčÅą┤ąĮąŠčüčéčī.

Type cast ą╝ąĄąČą┤čā std_logic_vector ąĖ signed/unsigned ą╝ąŠąČąĄčé ą▒čŗčéčī ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąŠ, ą┐ąŠą║ą░ ąĖčüč鹊čćąĮąĖą║ ąĖ ą╝ąĄčüč鹊 ąĮą░ąĘąĮą░č湥ąĮąĖčÅ čüąĖą│ąĮą░ą╗ą░ ąĖą╝ąĄčÄčé ąŠą┤ąĖąĮą░ą║ąŠą▓čāčÄ čĆą░ąĘčĆčÅą┤ąĮąŠčüčéčī. ą¦ąĖčüą╗ą░ integer ąĮąĄ ąĖą╝ąĄčÄčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčāčÄ čĆą░ąĘčĆčÅą┤ąĮąŠčüčéčī, ą┐ąŠ čŹč鹊ą╣ ą┐čĆąĖčćąĖąĮąĄ čäčāąĮą║čåąĖčÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ąŠčé integer ą║ signed/unsigned ą▓ą║ą╗čÄčćą░ąĄčé čüą┐ąĄčåąĖčäąĖą║ą░čåąĖčÄ ąĮčāąČąĮąŠą╣ čĆą░ąĘčĆčÅą┤ąĮąŠčüčéąĖ.

ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠąĄ ąĘą░ą╝ąĄčćą░ąĮąĖąĄ ą┐ąŠ integer: čüą╗ąĄą┤čāąĄčé ąŠą▒čĆą░čéąĖčéčī ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ąĮąĄčé ą┐čĆčÅą╝ąŠą│ąŠ ą┐čāčéąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą╝ąĄąČą┤čā čéąĖą┐ąŠą╝ std_logic_vector ąĖ čéąĖą┐ąŠą╝ integer. ąóąĖą┐čŗ integer ąĮąĄ ąĖą╝ąĄčÄčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮąŠą╣ čłąĖčĆąĖąĮčŗ ą▓ ą▒ąĖčéą░čģ, ą▓ ąŠčéą╗ąĖčćąĖąĄ ąŠčé čéąĖą┐ąŠą▓ signed, unsigned ąĖ std_logic_vector. ą¦č鹊ą▒čŗ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░čéčī ąĘąĮą░č湥ąĮąĖčÅ ą╝ąĄąČą┤čā čéąĖą┐ą░ą╝ąĖ integer ąĖ std_logic_vector, ąÆčŗ ą┤ąŠą╗ąČąĮčŗ čüąĮą░čćą░ą╗ą░ čüą┤ąĄą╗ą░čéčī ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ąĘąĮą░č湥ąĮąĖčÅ ą▓ signed ąĖą╗ąĖ unsigned.

ąĢčüą╗ąĖ ąĮąĄčé ąŠą│čĆą░ąĮąĖč湥ąĮąĖčÅ ą┐ąŠ ą┤ąĖą░ą┐ą░ąĘąŠąĮčā ąĘąĮą░č湥ąĮąĖą╣, ą║ąŠą│ą┤ą░ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ integer, č鹊 ą║ąŠą╝ą┐ąĖą╗čÅč鹊čĆ ą▒čāą┤ąĄčé ą┐čĆąĄą┤ą┐ąŠą╗ą░ą│ą░čéčī čĆą░ąĘčĆčÅą┤ąĮąŠčüčéčī 32 ą▒ąĖčéą░. ąÆ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ąÆą░čłąĄą│ąŠ ąĖąĮčüčéčĆčāą╝ąĄąĮčéą░ čüąĖąĮč鹥ąĘą░ ąĖ ąĄą│ąŠ ąĮą░čüčéčĆąŠąĄą║, čĆą░ąĘčĆčÅą┤ąĮąŠčüčéčī ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 32 ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠą┐čéąĖą╝ąĖąĘąĖčĆąŠą▓ą░ąĮą░ ąĖą╗ąĖ ąĮąĄčé ą║ ą┐ąŠą┤čģąŠą┤čÅčēąĄą╣ čĆą░ąĘčĆčÅą┤ąĮąŠčüčéąĖ.

[ąśčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ ą║ąŠčĆčĆąĄą║čéąĮąŠą│ąŠ čéąĖą┐ą░ ąĮą░ VHDL]

ąźąŠčéčÅ ą╝ąŠąČąĮąŠ ą▓čŗą┐ąŠą╗ąĮąĖčéčī ą╝ąĮąŠąČąĄčüčéą▓ąŠ ą╝ą░č鹥ą╝ą░čéąĖč湥čüą║ąĖčģ čäčāąĮą║čåąĖą╣ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ čéąĖą┐ą░ std_logic_vector, ą┐ąŠčüčéčāą┐ą░čéčī čéą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝ ąŠąĘąĮą░čćą░ąĄčé ą┤ąŠą▒ą░ą▓ą╗čÅčéčī ąĮąĄąĮčāąČąĮčāčÄ čüą╗ąŠąČąĮąŠčüčéčī ą┐čĆąĖ ą┐čĆąŠąĄą║čéąĖčĆąŠą▓ą░ąĮąĖąĖ čåąĖčäčĆąŠą▓ąŠą╣ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ čüąĖą│ąĮą░ą╗ąŠą▓ (DSP). ąśčüą┐ąŠą╗čīąĘčāą╣č鹥 čéąĖą┐čŗ signed ąĖ unsigned, čćč鹊ą▒čŗ ąŠčéčüą╗ąĄąČąĖą▓ą░čéčī č鹊čćąĮąŠčüčéčī ąĖ čéąĖą┐ ąĘąĮą░ą║ą░. ąÆ ą║ąŠąĮčåąĄ ą║ąŠąĮčåąŠą▓, ą┐ąŠč湥ą╝čā ąÆčŗ ą┐čĆąĖą╝ąĄąĮčÅąĄč鹥 VHDL, ąĄčüą╗ąĖ ąĮąĄ čüąŠą▒ąĖčĆą░ąĄč鹥čüčī ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ąĄą│ąŠ čüąĖą╗čā čüčéčĆąŠą│ąŠą│ąŠ ą║ąŠąĮčéčĆąŠą╗čÅ čéąĖą┐ąŠą▓?

ąØąĖą║ąŠą│ą┤ą░ ąĮąĄ ą┤ą░ą▓ą░ą╣č鹥 ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ ą║ąŠą╝ą┐ąĖą╗čÅč鹊čĆčā ąĖą╗ąĖ ąĖąĮčüčéčĆčāą╝ąĄąĮčéčā čüąĖąĮč鹥ąĘą░ čĆąĄčłą░čéčī, ą║ą░ą║čāčÄ čĆą░ą▒ąŠčéčā ąÆčŗ čģąŠčéąĖč鹥 ą▓čŗą┐ąŠą╗ąĮąĖčéčī, ąĖą╗ąĖ ą║ą░ą║ąŠą╣ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čĆąĄąĘčāą╗čīčéą░čé ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą▓čŗčĆą░ąČąĄąĮąĖčÅ! ąÆ čŹč鹊ą╝ ą┐ą╗ą░ąĮąĄ ą▓ą░ąČąĮąŠ ąŠą▒čĆą░čēą░čéčī ąŠčüąŠą▒ąŠąĄ ą▓ąĮąĖą╝ą░ąĮąĖąĄ ąĮą░ ą┐čĆąĄą┤čāą┐čĆąĄąČą┤ąĄąĮąĖčÅ ą║ąŠą╝ą┐ąĖą╗čÅč鹊čĆą░, ą║ąŠč鹊čĆčŗąĄ čÅą║ąŠą▒čŗ ąĮąĄ ą║čĆąĖčéąĖč湥čüą║ąĖąĄ.

[ą×ą▒čēąĄąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ, ą┐čĆąĖą╝ąĄčĆčŗ]

ą×ą▒čŗčćąĮčŗ čüąĖčéčāą░čåąĖąĖ, ą║ąŠą│ą┤ą░ ąĮčāąČąĮąŠ ą┐čĆąĖą╝ąĄąĮąĖčéčī type cast ąĖą╗ąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ą▓ ą╝ą░č鹥ą╝ą░čéąĖč湥čüą║ąĖčģ ą▓čŗčĆą░ąČąĄąĮąĖčÅčģ. ąöčĆčāą│ąŠą╣ ąŠą▒čŗčćąĮčŗą╣ čüą╗čāčćą░ą╣, ą║ąŠą│ą┤ą░ ąÆčŗ čģąŠčéąĖč鹥 ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░ ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖąĮą┤ąĄą║čüą░ ą▓ ą╝ą░čüčüąĖą▓ąĄ. ą£ąŠąČąĄčé ą▒čŗčéčī ą╝ąĮąŠąČąĄčüčéą▓ąŠ ą┤čĆčāą│ąĖčģ ą┐čĆąĖą╝ąĄąĮąĄąĮąĖą╣ ą║ąŠąĮą▓ąĄčĆčüąĖąĖ, ąĮąŠ čĆą░čüčüą╝ąŠčéčĆąĖą╝ č鹊ą╗čīą║ąŠ čŹčéąĖ ą┤ą▓ą░.

ąÆąŠčé čćč鹊 ą┐čĆąŠąĖčüčģąŠą┤ąĖčé, ą║ąŠą│ą┤ą░ ą▓čŗčćąĖčéą░čÄčéčüčÅ ą┤čĆčāą│ ąĖąĘ ą┤čĆčāą│ą░ ą┤ą▓ą░ čćąĖčüą╗ą░ unsigned:

signal sum_u : unsigned(11 downto 0);

signal sum_s : signed(11 downto 0);

constant a : unsigned(3 downto 0) := X"A";

sum_u <= counter_fr + (X"00" & a);

sum_s <= signed(counter_fr) + signed(X"00" & a);

ąÆ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé č鹊ą│ąŠ, ą║ą░ą║ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮ čĆąĄąĘčāą╗čīčéą░čé ąŠą┐ąĄčĆą░čåąĖąĖ, signed ąĖą╗ąĖ unsigned, čĆąĄąĘčāą╗čīčéą░čéčŗ ą┐ąŠą╗čāčćą░čéčüčÅ ą░ą▒čüąŠą╗čÄčéąĮąŠ čĆą░ąĘąĮčŗąĄ. ąÜąŠą│ą┤ą░ čüč湥čéčćąĖą║ counter_fr čüąŠą┤ąĄčƹȹĖčé ą┤ą▓ąŠąĖčćąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ 1000 (binary), sum_u=18 ąĖ sum_s=2. ą¤čĆąĖčćąĖąĮą░ ą▓ č鹊ą╝, čćč鹊 ą┤ą▓ąŠąĖčćąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ 1000 čŹč鹊 ą┤ąĄčüčÅčéąĖčćąĮąŠąĄ 8, ąĖ -8 čŹč鹊 čćąĖčüą╗ąŠ čüąŠ ąĘąĮą░ą║ąŠą╝, ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮąĮąŠąĄ ą▓ čüčéą░ąĮą┤ą░čĆčéąĮąŠą╝ č乊čĆą╝ą░č鹥 ą┤ąŠą┐ąŠą╗ąĮąĄąĮąĖčÅ ą┤ąŠ 2 (twoŌĆÖs complement signed).

ąöčĆčāą│ąŠąĄ ąŠą▒čŗčćąĮąŠąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ - ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ čéąĖą┐ą░ std_logic_vector ąĖą╗ąĖ unsigned ą▓ čéąĖą┐ integer čéą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, čćč鹊ą▒čŗ integer ą╝ąŠąČąĮąŠ ą▒čŗą╗ąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖąĮą┤ąĄą║čüą░ ą╝ą░čüčüąĖą▓ą░. ąÜ čüąŠą┤ąĄčƹȹĖą╝ąŠą╝čā ą╝ą░čüčüąĖą▓ą░ ą╝ąŠąČąĮąŠ ą┐ąŠą╗čāčćąĖčéčī ą┤ąŠčüčéčāą┐ č鹊ą╗čīą║ąŠ č湥čĆąĄąĘ ąĖąĮą┤ąĄą║čüčŗ, ą║ąŠč鹊čĆčŗąĄ ąĖą╝ąĄčÄčé čéąĖą┐ integer. ąØąĄ čüą┐čĆą░čłąĖą▓ą░ą╣č鹥 ą╝ąĄąĮčÅ, ą┐ąŠč湥ą╝čā.

constant vec : std_logic_vector(15 downto 0);

signal count : std_logic_vector(3 downto 0);

signal element : std_logic_vector(0 downto 0);

...

element <= vec(to_integer(unsigned(count),4));

[ąĪčüčŗą╗ą║ąĖ]

1. VHDL Type Conversion site:bitweenie.com.

2. VHDL Shift Register site:bitweenie.com.

3. VHDL Counter site:bitweenie.com.

4. Verilog vs. VHDL site:bitweenie.com. |