|

ąŁč鹊čé ą┤ąŠą║čāą╝ąĄąĮčé (ą┐ąĄčĆąĄą▓ąŠą┤ [1]) ąŠą┐ąĖčüčŗą▓ą░ąĄčé ą▒ą╗ąŠą║ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą┐ą░ą╝čÅčéąĖ Spartan┬«-6 FPGA (memory controller block, MCB). ąöą╗čÅ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ ąĖąĮč鹥čĆč乥ą╣čüą░ čü ą┐ą░ą╝čÅčéčīčÄ ąĮą░ ąŠčüąĮąŠą▓ąĄ MCB ą┤ąŠą╗ąČąĮčŗ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ąŠą┤ąĖąĮ ąĖąĘ ą┤ą▓čāčģ ąĖąĮčüčéčĆčāą╝ąĄąĮč鹊ą▓:

1. Memory Interface Generator (MIG). ąöą╗čÅ čéčĆą░ą┤ąĖčåąĖąŠąĮąĮčŗčģ ą┤ąĖąĘą░ą╣ąĮąŠą▓ FPGA (ą▒ąĄąĘ ą▓čüčéčĆąŠąĄąĮąĮčŗčģ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓, non-embedded) čüą╝. čĆčāą║ąŠą▓ąŠą┤čüčéą▓ąŠ UG416 [2], ą│ą┤ąĄ ąĮą░čģąŠą┤ąĖčéčüčÅ ąĖąĮč乊čĆą╝ą░čåąĖčÅ ą┐ąŠ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ ąĖąĮč鹥čĆč乥ą╣čüą░ čü ą┐ą░ą╝čÅčéčīčÄ čü ą┐ąŠą╝ąŠčēčīčÄ čāčéąĖą╗ąĖčéčŗ MIG ą▓ čüąŠčüčéą░ą▓ąĄ ą¤ą× CORE GeneratorŌäó. ąŁč鹊čé ą┤ąŠą║čāą╝ąĄąĮčé čéą░ą║ąČąĄ čüąŠą┤ąĄčƹȹĖčé ąĖąĮč乊čĆą╝ą░čåąĖčÄ ą┐ąŠ ąŠčéą╗ą░ą┤ą║ąĄ ąĖąĮč鹥čĆč乥ą╣čüąŠą▓ MCB.

2. Embedded Development Kit (EDK). ąöą╗čÅ embedded-ą┤ąĖąĘą░ą╣ąĮąŠą▓ čüą╝. DS643 [3], ą│ą┤ąĄ ąŠą┐ąĖčüą░ąĮąŠ, ą║ą░ą║ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ MCB ą┤ą╗čÅ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ MPMC ą▓ čüčĆąĄą┤ąĄ EDK.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: čāčéąĖą╗ąĖčéą░ MIG ą┤ą╗čÅ ąŠčĆą│ą░ąĮąĖąĘą░čåąĖąĖ ą┤ąŠčüčéčāą┐ą░ ą║ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčā SDRAM ą┤ąŠčüčéčāą┐ąĮą░ ą▓ čüčĆąĄą┤ąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ Xilinx ISE [10] č湥čĆąĄąĘ ą╝ąĄąĮčÄ Tools -> Core Generator... -> IP Catalog -> View by Function -> Memories & Storage Elements -> Memory Interface Generators -> MIG Virtex-6 and Spartan-6.

ąĀčāą║ąŠą▓ąŠą┤čüčéą▓ąŠ čüąŠą┤ąĄčƹȹĖčé ą│ą╗ą░ą▓čŗ:

1. ą×ą▒ąĘąŠčĆ MCB, ą▓ą▓ąŠą┤ąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ Spartan-6 FPGA MCB.

2. ążčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ MCB. ą×ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ ą░čĆčģąĖč鹥ą║čéčāčĆą░, čüąĖą│ąĮą░ą╗čīąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü, ą▓ąŠąĘą╝ąŠąČąĮčŗąĄ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ MCB.

3. ąĀą░ąĘčĆą░ą▒ąŠčéą║ą░ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ MCB, ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÄčéčüčÅ ą┐ąŠą┤čĆąŠą▒ąĮąŠčüčéąĖ ą┐čĆąĖą╝ąĄąĮąĄąĮąĖčÅ MCB ą▓ ą┤ąĖąĘą░ą╣ąĮąĄ ąĮą░ Spartan-6, čüąŠ čüą┐ąĄčåąĖčäąĖą║ąŠą╣ ąĮą░čüčéčĆąŠą╣ą║ąĖ ą▒ą╗ąŠą║ą░ ą┤ą╗čÅ ąĖą╝ąĄčÄčēąĄą│ąŠčüčÅ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ.

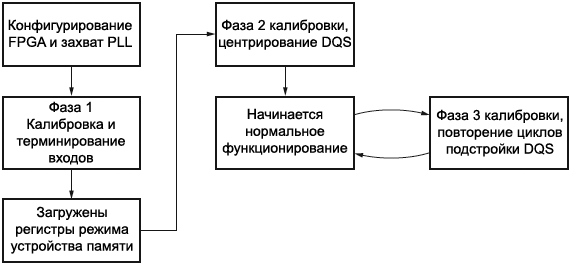

4. ąĀą░ą▒ąŠčéą░ MCB, ąŠą▒čŖčÅčüąĮąĄąĮąĖąĄ čäčāąĮą║čåąĖą╣ MCB ą▓ čĆą░ąĘą╗ąĖčćąĮčŗčģ čĆą░ą▒ąŠčćąĖčģ čĆąĄąČąĖą╝ą░čģ: ąĘą░ą┐čāčüą║ (startup), ą║ą░ą╗ąĖą▒čĆąŠą▓ą║ą░ (calibration), ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ čÅč湥ąĄą║ SDRAM (refresh), ą┐čĆąĄą┤ąĘą░čĆčÅą┤ (precharge), čüčéą░ąĮą┤ą░čĆčéąĮčŗąĄ čéčĆą░ąĮąĘą░ą║čåąĖąĖ čćč鹥ąĮąĖčÅ/ąĘą░ą┐ąĖčüąĖ ąĖ čé. ą┤.

ą¤čĆąĖą╗ąŠąČąĄąĮąĖąĄ A, čüčüčŗą╗ą║ąĖ ąĮą░ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčāčÄ ą┤ąŠą║čāą╝ąĄąĮčéą░čåąĖčÄ, ą║ą░čüą░čÄčēčāčÄčüčÅ čĆą░ąĘčĆą░ą▒ąŠčéą║ąĖ ąĖąĮč鹥čĆč乥ą╣čüą░ ą┐ą░ą╝čÅčéąĖ.

ąĪą╗ąĄą┤čāčÄčēąĖąĄ ą┤ąŠą║čāą╝ąĄąĮčéčŗ čéą░ą║ąČąĄ ą┤ąŠčüčéčāą┐ąĮčŗ ą┤ą╗čÅ ąĘą░ą│čĆčāąĘą║ąĖ ąĮą░ čüą░ą╣č鹥 xilinx.com.

ŌĆó Spartan-6 Family Overview. ąŁč鹊čé ąŠą▒ąĘąŠčĆ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čäčāąĮą║čåąĖąĖ ąĖ ą▓ą░čĆąĖą░ąĮčéčŗ ą▓čŗą▒ąŠčĆą░ ą┐čĆąŠą┤čāą║čåąĖąĖ čüąĄą╝ąĄą╣čüčéą▓ą░ Spartan-6.

ŌĆó Spartan-6 FPGA Data Sheet: DC and Switching Characteristics. ąŁč鹊čé ą┤ą░čéą░čłąĖčé čüąŠą┤ąĄčƹȹĖčé čüą┐ąĄčåąĖčäąĖą║ą░čåąĖąĖ ą┐ąŠčüč鹊čÅąĮąĮąŠą│ąŠ č鹊ą║ą░ (DC) ąĖ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ ą┤ą╗čÅ čüąĄą╝ąĄą╣čüčéą▓ą░ Spartan-6.

ŌĆó Spartan-6 FPGA Packaging and Pinouts Product Specification. ąŁčéą░ čüą┐ąĄčåąĖčäąĖą║ą░čåąĖčÅ ą▓ą║ą╗čÄčćą░ąĄčé čéą░ą▒ą╗ąĖčåčŗ ą┤ą╗čÅ ą║ąŠą╝ą▒ąĖąĮą░čåąĖą╣ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░/ą║ąŠčĆą┐čāčü ąĖ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą│ąŠ ą║ąŠą╗ąĖč湥čüčéą▓ą░ I/O, ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ ą▓čŗą▓ąŠą┤ąŠą▓, čéą░ą▒ą╗ąĖčå čĆą░ąĘą▓ąŠą┤ą║ąĖ ą▓čŗą▓ąŠą┤ąŠą▓, ą┤ąĖą░ą│čĆą░ą╝ą╝ ą▓čŗą▓ąŠą┤ąŠą▓, ą╝ąĄčģą░ąĮąĖč湥čüą║ąĖąĄ č湥čĆč鹥ąČąĖ ą║ąŠčĆą┐čāčüąŠą▓, čüą┐ąĄčåąĖčäąĖą║ą░čåąĖą╣ č鹥ą╝ą┐ąĄčĆą░čéčāčĆąĮčŗčģ čéčĆąĄą▒ąŠą▓ą░ąĮąĖą╣.

ŌĆó Spartan-6 FPGA Configuration User Guide. ąŁč鹊 ą▓čüąĄąŠą▒čŖąĄą╝ą╗čÄčēąĄąĄ čĆčāą║ąŠą▓ąŠą┤čüčéą▓ąŠ ą┐ąŠ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÄ ą▓ą║ą╗čÄčćą░ąĄčé ą│ą╗ą░ą▓čŗ ą┐ąŠ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ąĖąĮč鹥čĆč乥ą╣čüąŠą▓ (ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ąĖ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮčŗčģ), čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÄ ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ ą┐ąŠč鹊ą║ą░ą╝ąĖ ą▒ąĖčé, čłąĖčäčĆąŠą▓ą░ąĮąĖčÄ ą┐ąŠč鹊ą║ą░ ą▒ąĖčé, č鹥čģąĮąŠą╗ąŠą│ąĖąĖ boundary-scan ąĖ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ JTAG ąĖ č鹥čģąĮąĖą║ą░ą╝ ą┐ąĄčĆąĄą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ.

ŌĆó Spartan-6 FPGA SelectIO Resources User Guide. ąŁč鹊 čĆčāą║ąŠą▓ąŠą┤čüčéą▓ąŠ ąŠą┐ąĖčüčŗą▓ą░ąĄčé čĆąĄčüčāčĆčüčŗ SelectIOŌäó, ą┤ąŠčüčéčāą┐ąĮčŗąĄ ą▓ąŠ ą▓čüąĄčģ čāčüčéčĆąŠą╣čüčéą▓ Spartan-6.

ŌĆó Spartan-6 FPGA Clocking Resources User Guide. ąŁč鹊 čĆčāą║ąŠą▓ąŠą┤čüčéą▓ąŠ ąŠą┐ąĖčüčŗą▓ą░ąĄčé čĆąĄčüčāčĆčüčŗ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ, ą┤ąŠčüčéčāą┐ąĮčŗąĄ ą▓ąŠ ą▓čüąĄčģ čāčüčéčĆąŠą╣čüčéą▓ą░čģ Spartan-6, ą▓ą║ą╗čÄčćą░čÅ ą▒ą╗ąŠą║ąĖ DCM ąĖ PLL.

ŌĆó Spartan-6 FPGA Block RAM Resources User Guide. ąŁč鹊 čĆčāą║ąŠą▓ąŠą┤čüčéą▓ąŠ ąŠą┐ąĖčüčŗą▓ą░ąĄčé ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ ą▒ą╗ąŠą║ą░ RAM čāčüčéčĆąŠą╣čüčéą▓ą░ Spartan-6.

ŌĆó Spartan-6 FPGA Configurable Logic Block User Guide. ąŁč鹊 čĆčāą║ąŠą▓ąŠą┤čüčéą▓ąŠ ąŠą┐ąĖčüčŗą▓ą░ąĄčé ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ ą▒ą╗ąŠą║ąŠą▓ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝ąŠą╣ ą╗ąŠą│ąĖą║ąĖ (configurable logic blocks, CLB), ą┤ąŠčüčéčāą┐ąĮčŗčģ ą▓ąŠ ą▓čüąĄčģ čāčüčéčĆąŠą╣čüčéą▓ą░čģ Spartan-6.

ŌĆó Spartan-6 FPGA GTP Transceivers User Guide. ąŁč鹊 čĆčāą║ąŠą▓ąŠą┤čüčéą▓ąŠ ąŠą┐ąĖčüčŗą▓ą░ąĄčé čéčĆą░ąĮčüąĖą▓ąĄčĆčŗ GTP, ą┤ąŠčüčéčāą┐ąĮčŗąĄ ą▓ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░čģ Spartan-6 LXT FPGA.

ŌĆó Spartan-6 FPGA DSP48A1 Slice User Guide. ąŁč鹊 čĆčāą║ąŠą▓ąŠą┤čüčéą▓ąŠ ąŠą┐ąĖčüčŗą▓ą░ąĄčé ą░čĆčģąĖč鹥ą║čéčāčĆčā čüą╗ą░ą╣čüą░ DSP48A1 ą▓ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░čģ Spartan-6 FPGA, ąĖ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą┐čĆąĖą╝ąĄčĆčŗ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ.

ŌĆó Spartan-6 FPGA PCB and Pin Planning Design Guide. ąŁč鹊 čĆčāą║ąŠą▓ąŠą┤čüčéą▓ąŠ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ąĖąĮč乊čĆą╝ą░čåąĖčÄ ą┐ąŠ ą┤ąĖąĘą░ą╣ąĮčā ą┐ąĄčćą░čéąĮąŠą╣ ą┐ą╗ą░čéčŗ čü čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ Spartan-6, čü č乊ą║čāčüąŠą╝ ąĮą░ čüčéčĆą░č鹥ą│ąĖąĖ ą┤ą╗čÅ ą┐čĆąĖąĮčÅčéąĖčÅ čĆąĄčłąĄąĮąĖą╣ ą┐ąŠ ą┤ąĖąĘą░ą╣ąĮčā ąĮą░ čāčĆąŠą▓ąĮąĄ ą┐ąĄčćą░čéąĮąŠą╣ ą┐ą╗ą░čéčŗ ąĖ ąĖąĮč鹥čĆč乥ą╣čüą░.

ŌĆó Spartan-6 FPGA Power Management User Guide. ąŁč鹊 čĆčāą║ąŠą▓ąŠą┤čüčéą▓ąŠ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ąĖąĮč乊čĆą╝ą░čåąĖčÄ ą┐ąŠ čĆą░ąĘą╗ąĖčćąĮčŗą╝ ą░ą┐ą┐ą░čĆą░čéąĮčŗą╝ ą╝ąĄč鹊ą┤ą░ą╝ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖąĄą╝ čāčüčéčĆąŠą╣čüčéą▓ Spartan-6 devices, č乊ą║čāčüąĖčĆčāčÅčüčī ą│ą╗ą░ą▓ąĮčŗą╝ ąŠą▒čĆą░ąĘąŠą╝ ąĮą░ čĆąĄąČąĖą╝ąĄ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ąĖ (suspend mode).

[1. ą×ą▒ąĘąŠčĆ MCB]

MCB čŹč鹊 čüą┐ąĄčåąĖą░ą╗čīąĮčŗą╣ ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ ą▒ą╗ąŠą║ ą╝ąĮąŠą│ąŠą┐ąŠčĆč鹊ą▓ąŠą│ąŠ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░, ą║ąŠč鹊čĆčŗą╣ ąĘąĮą░čćąĖč鹥ą╗čīąĮąŠ čāą┐čĆąŠčēą░ąĄčé ąĘą░ą┤ą░čćčā ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ čāčüčéčĆąŠą╣čüčéą▓ Spartan-6 ą║ ą▒ąŠą╗čīčłąĖąĮčüčéą▓čā čüčéą░ąĮą┤ą░čĆč鹊ą▓ ą┐ą░ą╝čÅčéąĖ. MCB ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą▓čŗčüąŠą║ąŠąĄ ą▒čŗčüčéčĆąŠą┤ąĄą╣čüčéą▓ąĖąĄ, ą┐ąŠąĮąĖąČąĄąĮąĮąŠąĄ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ ąĖ ą▒čŗčüčéčĆčāčÄ čĆą░ąĘčĆą░ą▒ąŠčéą║čā - ą▓čüąĄ čŹč鹊 ą▒ąŠą╗ąĄąĄ ą▓čŗčüąŠą║ąŠą│ąŠ ą║ą░č湥čüčéą▓ą░, č湥ą╝ ą▒ąŠą╗čīčłąĖąĮčüčéą▓ąŠ 菹║ą▓ąĖą▓ą░ą╗ąĄąĮčéąĮčŗčģ čĆąĄą░ą╗ąĖąĘą░čåąĖą╣ IP. ąÆčüčéčĆąŠąĄąĮąĮą░čÅ čĆąĄą░ą╗ąĖąĘą░čåąĖčÅ MCB čüąŠčģčĆą░ąĮčÅąĄčé ąĘąĮą░čćąĖą╝čŗąĄ čĆąĄčüčāčĆčüčŗ FPGA, ąĖ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÄ čüč乊ą║čāčüąĖčĆąŠą▓ą░čéčīčüčÅ ąĮą░ ą▒ąŠą╗ąĄąĄ čāąĮąĖą║ą░ą╗čīąĮčŗčģ čäčāąĮą║čåąĖčÅčģ ą┤ąĖąĘą░ą╣ąĮą░ FPGA.

MCB ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé čüą╗ąĄą┤čāčÄčēąĖąĄ čäčāąĮą║čåąĖąĖ ąĖ ą┐čĆąĄąĖą╝čāčēąĄčüčéą▓ą░ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą┐ą░ą╝čÅčéąĖ Spartan-6 FPGA:

ŌĆó ą¤ąŠą┤ą┤ąĄčƹȹ║ą░ čüčéą░ąĮą┤ą░čĆč鹊ą▓ ą┐ą░ą╝čÅčéąĖ DDR, DDR2, DDR3 ąĖ LPDDR (Mobile DDR)

ŌĆó ą¤čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéčī ą┤ąŠ 800 Mb/s (400 ą£ąōčå double data rate)

ŌĆó ąöąŠ 4 čÅą┤ąĄčĆ MCB ą▓ ąŠą┤ąĮąŠą╝ čāčüčéčĆąŠą╣čüčéą▓ąĄ Spartan-6. ąÜą░ąČą┤ąŠąĄ čÅą┤čĆąŠ MCB čüąŠą┤ąĄčƹȹĖčé:

- 4-, 8- ąĖą╗ąĖ 16-čĆą░ąĘčĆčÅą┤ąĮčŗą╣ ąŠą┤ąĖąĮąŠčćąĮčŗą╣ ą║ąŠą╝ą┐ąŠąĮąĄąĮčé ąĖąĮč鹥čĆč乥ą╣čüą░ ą┐ą░ą╝čÅčéąĖ

- ą¤ą╗ąŠčéąĮąŠčüčéčī ą┐ą░ą╝čÅčéąĖ ą┤ąŠ 4 Gb

- ąÉą│čĆąĄą│ą░čéąĮčāčÄ ą┐ąŠą╗ąŠčüčā ą┐čĆąŠą┐čāčüą║ą░ąĮąĖčÅ ą┤ąŠ 12.8 Gb/s

ŌĆó ąÜąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝čŗą╣ ą▓čŗą┤ąĄą╗ąĄąĮąĮčŗą╣ ą╝ąĮąŠą│ąŠą┐ąŠčĆč鹊ą▓čŗą╣ ąĖąĮč鹥čĆč乥ą╣čü ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ ą┤ą╗čÅ ą╗ąŠą│ąĖą║ąĖ FPGA

- ą×čé 1 ą┤ąŠ 6 ą┐ąŠčĆč鹊ą▓ ąĮą░ MCB ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ

- 32-, 64- ąĖą╗ąĖ 128-ą▒ąĖčéąĮą░čÅ čłąĖąĮą░ ą┤ą░ąĮąĮčŗčģ

- ąöą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╣ (R/W) ąĖą╗ąĖ ąŠą┤ąĮąŠąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╣ (č鹊ą╗čīą║ąŠ W ąĖą╗ąĖ č鹊ą╗čīą║ąŠ R) ą┐ąŠčĆčé.

ŌĆó ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą▒ą░ąĮą║ą░ą╝ąĖ ą┐ą░ą╝čÅčéąĖ

- ąöąŠ 8 ą▒ą░ąĮą║ąŠą▓ ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠčéą║čĆčŗč鹊 ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ą┤ą╗čÅ ą┐ąŠą▓čŗčłąĄąĮąĖčÅ čŹčäč乥ą║čéąĖą▓ąĮąŠčüčéąĖ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░

ŌĆó ąÆčüčéčĆąŠąĄąĮąĮčŗą╣ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ąĖ čäąĖąĘąĖč湥čüą║ąĖą╣ ąĖąĮč鹥čĆč乥ą╣čü (PHY), ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÄčēąĖą╣:

- ą¤čĆąĄą┤čüą║ą░ąĘčāąĄą╝čŗąĄ ąĖąĮč鹥čĆą▓ą░ą╗čŗ ą▓čĆąĄą╝ąĄąĮąĖ

- ąØąĖąĘą║ąŠąĄ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ

- ąōą░čĆą░ąĮčéąĖčĆčāąĄą╝ą░čÅ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéčī

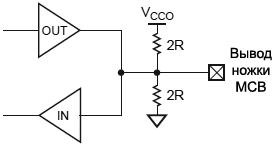

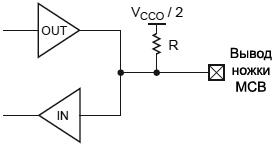

ŌĆó ąŚą░čĆą░ąĮąĄąĄ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮą░čÅ čĆą░ąĘą▓ąŠą┤ą║ą░ ą▓ąĮąĄčłąĮąĖčģ ą▓čŗą▓ąŠą┤ąŠą▓ (ą╝ąĄčüčéą░ I/O ąĮą░ ą║ąŠčĆą┐čāčüąĄ) ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ MCB

- ąŻą┐čĆąŠčēąĄąĮąĮčŗą╣ ą┤ąĖąĘą░ą╣ąĮ ą┐ąĄčćą░čéąĮąŠą╣ ą┐ą╗ą░čéčŗ

- ąØąŠąČą║ąĖ I/O, ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāą╝čŗąĄ ą▓ ąĖąĮč鹥čĆč乥ą╣čüą░ MCB, čüčéą░ąĮąŠą▓čÅčéčüčÅ ąŠą▒čŗčćąĮčŗą╝ąĖ ą▓čŗą▓ąŠą┤ą░ą╝ąĖ I/O ( ą┐ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. ąŠą┐ąĖčüą░ąĮąĖąĄ ąĖąĮč鹥čĆč乥ą╣čüą░ ą┐ą░ą╝čÅčéąĖ ąĖ čéą░ą▒ą╗ąĖčåčā 2-0).

ŌĆó ą¤ąŠą┤ą┤ąĄčƹȹ║ą░ ąŠą▒čēąĖčģ ąŠą┐čåąĖą╣ ąĖ ą░čéčĆąĖą▒čāč鹊ą▓ ą╝ąĖą║čĆąŠčüčģąĄą╝ ą┐ą░ą╝čÅčéąĖ

- ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝ą░čÅ ąĮą░ą│čĆčāąĘąŠčćąĮą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī

- On-Die Termination (ODT)

- CAS latency (ąĘą░ą┤ąĄčƹȹ║ą░ čüąĖą│ąĮą░ą╗ą░ ą▓čŗą▒ąŠčĆą║ąĖ čüč鹊ą╗ą▒čåą░)

- Self refresh (čüą░ą╝ąŠąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ, ą▓ą║ą╗čÄčćą░čÅ čćą░čüčéčī ą╝ą░čüčüąĖą▓ą░)

- ąśąĮč鹥čĆą▓ą░ą╗ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ

- Write recovery time (ą▓čĆąĄą╝čÅ ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖčÅ ąĘą░ą┐ąĖčüąĖ)

ŌĆó ąÉą▓č鹊ą╝ą░čéąĖč湥čüą║ą░čÅ ą║ą░ą╗ąĖą▒čĆąŠą▓ą║ą░ ąĘą░ą┤ąĄčƹȹ║ąĖ čüčéčĆąŠą▒ą░ ą┐ą░ą╝čÅčéąĖ ąĖ čćč鹥ąĮąĖčÅ ą▓čģąŠą┤ąŠą▓ ą┤ą░ąĮąĮčŗčģ

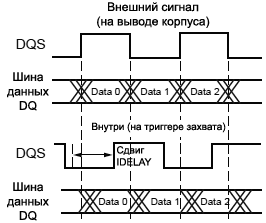

- ą¤ąŠą┤čüčéčĆąŠą╣ą║ą░ ą▓ąĘą░ąĖą╝ąŠčüą▓čÅąĘąĖ DQS (čüčéčĆąŠą▒) ąĖ DQ (ą┤ą░ąĮąĮčŗąĄ) ą┤ą╗čÅ ąŠą┐čéąĖą╝ą░ą╗čīąĮąŠą╣ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéąĖ čćč鹥ąĮąĖčÅ

ŌĆó ą×ą┐čåąĖąŠąĮą░ą╗čīąĮą░čÅ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ą░čÅ ą║ą░ą╗ąĖą▒čĆąŠą▓ą║ą░ ą▓čüčéčĆąŠąĄąĮąĮąŠą│ąŠ ą▓ ą║čĆąĖčüčéą░ą╗ą╗ FPGA č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓čģąŠą┤ąŠą▓ ą┤ą╗čÅ ąŠą┐čéąĖą╝ą░ą╗čīąĮąŠą│ąŠ ą║ą░č湥čüčéą▓ą░ čüąĖą│ąĮą░ą╗ąŠą▓

ŌĆó ą¤ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄą╝čŗą╣ Xilinx┬« ąĖąĮčüčéčĆčāą╝ąĄąĮčéą░čĆąĖą╣ čĆą░ąĘčĆą░ą▒ąŠčéą║ąĖ CORE GeneratorŌäó ąĖ Embedded Development Kit (EDK):

- ąŻčéąĖą╗ąĖčéą░ Memory Interface Generator (MIG), ą▓čģąŠą┤čÅčēą░čÅ ą▓ čüąŠčüčéą░ą▓ ą¤ą× CORE Generator, čāą┐čĆąŠčēą░ąĄčé čĆą░ąĘčĆą░ą▒ąŠčéą║čā čü ą┐čĆąĖą╝ąĄąĮąĄąĮąĖąĄą╝ MCB

- ąöąĖąĘą░ą╣ąĮčŗ čüąŠ ą▓čüčéčĆąŠąĄąĮąĮčŗą╝ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą╝ čéą░ą║ąČąĄ ą┐ąŠą╗čāčćą░čÄčé ą┤ąŠčüčéčāą┐ ą║ MCB č湥čĆąĄąĘ ą╝ąĮąŠą│ąŠą┐ąŠčĆč鹊ą▓čŗą╣ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą┐ą░ą╝čÅčéąĖ (multi-port memory controller, MPMC), ą║ąŠč鹊čĆčŗą╣ ą┤ąŠčüčéčāą┐ąĄąĮ ą▓ EDK ą║ą░ą║ IP.

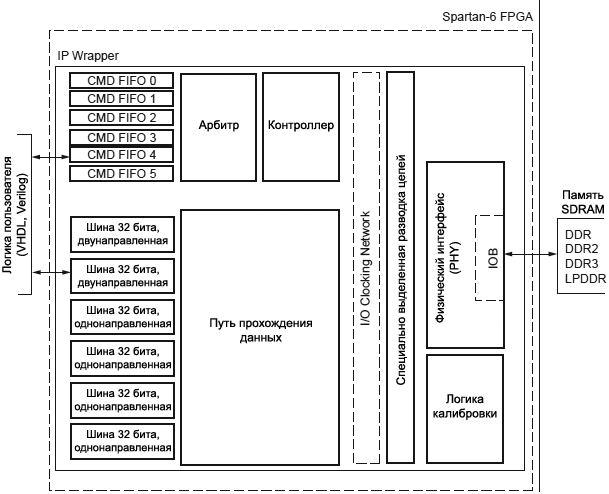

ąæą╗ąŠą║-čüčģąĄą╝ą░ ąĮą░ čĆąĖčü. 1-1 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą│ą╗ą░ą▓ąĮčŗąĄ ą║ąŠą╝ą┐ąŠąĮąĄąĮčéčŗ ą░čĆčģąĖč鹥ą║čéčāčĆčŗ čÅą┤čĆą░ MCB. ąÆčüčÄą┤čā ą▓ čŹč鹊ą╝ ąŠą┐ąĖčüą░ąĮąĖąĖ MCB ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮ čéą░ą║ ąČąĄ, ą║ą░ą║ ąĖ ą▓ memory IP tools ą¤ą× CORE Generator ąĖą╗ąĖ čĆą░ą▒ąŠč湥ą╣ čüčĆąĄą┤ąĄ EDK. ąŁčéąĖ ąĖąĮčüčéčĆčāą╝ąĄąĮčéčŗ ąŠą▒čŗčćąĮąŠ ą│ąĄąĮąĄčĆąĖčĆčāčÄčé čäą░ą╣ą╗čŗ ą▓čŗčüąŠą║ąŠčāčĆąŠą▓ąĮąĄą▓ąŠą╣ ąŠą▒ąĄčĆčéą║ąĖ (IP Wrapper), ą║ąŠč鹊čĆčŗąĄ čĆąĄą░ą╗ąĖąĘčāčÄčé ą┐čĆąĖą╝ąĖčéąĖą▓ ą▓čüčéčĆąŠąĄąĮąĮąŠą│ąŠ ą▒ą╗ąŠą║ą░ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą┐ą░ą╝čÅčéąĖ ąĖ ąĮąĄąŠą▒čģąŠą┤ąĖą╝čāčÄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčāčÄ ą╗ąŠą│ąĖą║čā ą▓ą╝ąĄčüč鹥 čü ąŠč鹊ą▒čĆą░ąČąĄąĮąĖąĄą╝ ą┐ąŠčĆč鹊ą▓, ąĮąĄąŠą▒čģąŠą┤ąĖą╝čŗąĄ ą┤ą╗čÅ ą┐ąŠą╗ąĮąŠą│ąŠ čĆąĄčłąĄąĮąĖčÅ. ąØą░ą┐čĆąĖą╝ąĄčĆ, ąĮą░ čĆąĖčü. 1-1 čäąĖąĘąĖč湥čüą║ąĖą╣ ąĖąĮč鹥čĆč乥ą╣čü MCB ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ ąŠčüąĮąŠą▓ąĮąŠą│ąŠ ą▒ą╗ąŠą║ą░ ą▓ą▓ąŠą┤ą░ ą▓čŗą▓ąŠą┤ą░ (I/O block, IOB) ą┤ą╗čÅ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ ą▓ąĮąĄčłąĮąĄą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ čü ą┐ą░ą╝čÅčéčīčÄ. ąóą░ą║ąČąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ čĆąĄčüčāčĆčüčŗ čåąĄą┐ąĄą╣ ąŠą▒čēąĄą│ąŠ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ (I/O clock network).

ąĀąĖčü. 1-1. ąæą╗ąŠą║ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą┐ą░ą╝čÅčéąĖ (MCB) Spartan-6 FPGA (ą▓ąĖą┤ ąĮą░ IP Wrapper).

ąśąĮč鹥čĆč乥ą╣čü ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ MCB ąĮą░ ąŠą▒čŗčćąĮąŠą╣ čüą║ąŠčĆąŠčüčéąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ (single data rate, SDR) ą▓ąĮčāčéčĆąĖ FPGA ą╝ąŠąČąĄčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ č湥čĆąĄąĘ ą┐ąŠčĆčéčŗ, ąŠčé 1 ą┤ąŠ 6. ąŻ ą║ą░ąČą┤ąŠą│ąŠ čéą░ą║ąŠą│ąŠ ą┐ąŠčĆčéą░ ąĄčüčéčī ąĖąĮč鹥čĆč乥ą╣čü ą║ąŠą╝ą░ąĮą┤ ąĖ ąĖąĮč鹥čĆč乥ą╣čü čćč鹥ąĮąĖčÅ ąĖ/ąĖą╗ąĖ ąĘą░ą┐ąĖčüąĖ ą┤ą░ąĮąĮčŗčģ. ąöą▓ą░ ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗčģ 32-ą▒ąĖčéąĮčŗčģ ąĖ č湥čéčŗčĆąĄ ąŠą┤ąĮąŠąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗčģ 32-ą▒ąĖčéąĮčŗčģ ą░ą┐ą┐ą░čĆą░čéąĮčŗčģ ą┐ąŠčĆčéą░ ą▓ MCB ą╝ąŠą│čāčé ą▒čŗčéčī čüą│čĆčāą┐ą┐ąĖčĆąŠą▓ą░ąĮčŗ ą┤ą╗čÅ čüąŠąĘą┤ą░ąĮąĖčÅ ą┐čÅčéąĖ čĆą░ąĘą╗ąĖčćąĮčŗčģ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖą╣ ą┐ąŠčĆč鹊ą▓.

ąöčĆčāą│ąĖąĄ ąŠčüąĮąŠą▓ąĮčŗąĄ ą║ąŠą╝ą┐ąŠąĮąĄąĮčéčŗ MCB:

ŌĆó ąÉčĆą▒ąĖčéčĆ: ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé, ą║ą░ą║ąŠą╣ ą┐ąŠčĆčé čüąĄą╣čćą░čü ąĖą╝ąĄąĄčé ą┐čĆąĖąŠčĆąĖč鹥čé ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ ą║ ą╝ąĖą║čĆąŠčüčģąĄą╝ąĄ ą┐ą░ą╝čÅčéąĖ.

ŌĆó ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ: ą│ą╗ą░ą▓ąĮčŗą╣ ą▒ą╗ąŠą║ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ, ą║ąŠč鹊čĆčŗą╣ ą┐čĆąĄąŠą▒čĆą░ąĘčāąĄčé ą┐čĆąŠčüčéčŗąĄ ąĘą░ą┐čĆąŠčüčŗ, ą┐ąŠčüą╗ą░ąĮąĮčŗąĄ č湥čĆąĄąĘ ąĖąĮč鹥čĆč乥ą╣čü ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ, ą▓ ąĮąĄąŠą▒čģąŠą┤ąĖą╝čŗąĄ ąĖąĮčüčéčĆčāą║čåąĖąĖ ąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ, ąĮąĄąŠą▒čģąŠą┤ąĖą╝čŗąĄ ą┤ą╗čÅ ą║ąŠą╝ą╝čāąĮąĖą║ą░čåąĖąĖ čü ą╝ąĖą║čĆąŠčüčģąĄą╝ąŠą╣ ą┐ą░ą╝čÅčéąĖ.

ŌĆó ą¤čāčéčī ą┐čĆąŠčģąŠąČą┤ąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ (Datapath): ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčé ą┐ąŠč鹊ą║ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄą╝čŗčģ ąĖ čćąĖčéą░ąĄą╝čŗčģ ą┤ą░ąĮąĮčŗčģ ą╝ąĄąČą┤čā ą╝ąĖą║čĆąŠčüčģąĄą╝ąŠą╣ ą┐ą░ą╝čÅčéąĖ ąĖ ą╗ąŠą│ąĖą║ąŠą╣ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ.

ŌĆó ążąĖąĘąĖč湥čüą║ąĖą╣ ąĖąĮč鹥čĆč乥ą╣čü (Physical Interface, PHY): ą┐čĆąĄąŠą▒čĆą░ąĘčāąĄčé ąĖąĮčüčéčĆčāą║čåąĖąĖ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą▓ čĆąĄą░ą╗čīąĮčŗąĄ ą┤ąĖą░ą│čĆą░ą╝ą╝čŗ ą▓čĆąĄą╝ąĄąĮąĖ ąĖ čüąĖą│ąĮą░ą╗čŗ DDR, ąĮąĄąŠą▒čģąŠą┤ąĖą╝čŗąĄ ą┤ą╗čÅ ą║ąŠą╝ą╝čāąĮąĖą║ą░čåąĖąĖ čü ą╝ąĖą║čĆąŠčüčģąĄą╝ąŠą╣ ą┐ą░ą╝čÅčéąĖ.

ŌĆó ąøąŠą│ąĖą║ą░ ą║ą░ą╗ąĖą▒čĆąŠą▓ą║ąĖ: ą║ą░ą╗ąĖą▒čĆčāąĄčé PHY ą┤ą╗čÅ ąŠą┐čéąĖą╝ą░ą╗čīąĮąŠą╣ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéąĖ ąĖ ąĮą░ą┤ąĄąČąĮąŠčüčéąĖ.

ąÆčŗą┤ąĄą╗ąĄąĮąĮčŗąĄ čÅą┤čĆą░ MCB ą▓ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░čģ Spartan-6 ą┐ąŠąĘą▓ąŠą╗čÅčÄčé čĆąĄą░ą╗ąĖąĘąŠą▓ą░čéčī čāčĆąŠą▓ąĮąĖ ą▒čŗčüčéčĆąŠą┤ąĄą╣čüčéą▓ąĖčÅ ą▓čŗčłąĄ, č湥ą╝ 菹║ą▓ąĖą▓ą░ą╗ąĄąĮčéąĮčŗąĄ čĆąĄčłąĄąĮąĖčÅ IP, čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮąĮčŗąĄ ąĮą░ ą╗ąŠą│ąĖą║ąĄ FPGA. ąśąĘ-ąĘą░ č鹊ą│ąŠ, čćč鹊 čćą░čēąĄ ą▓čüąĄą│ąŠ ą┐ąŠą╗ąŠčüą░ ą┐čĆąŠą┐čāčüą║ą░ąĮąĖčÅ ą║ą░ąĮą░ą╗ą░ ą┐ą░ą╝čÅčéąĖ čÅą▓ą╗čÅąĄčéčüčÅ čāąĘą║ąĖą╝ ą╝ąĄčüč鹊ą╝ ą┤ą╗čÅ ąŠą▒čēąĄą╣ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéąĖ čüąĖčüč鹥ą╝čŗ, čÅą┤čĆą░ MCB čüą┐ąĄčåąĖą░ą╗čīąĮąŠ čĆą░ąĘčĆą░ą▒ąŠčéą░ąĮą░ ą┤ą╗čÅ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╣, ą║ąŠč鹊čĆčŗąĄ ąŠąČąĖą┤ą░čÄčé ą┐ąŠą╗čāčćąĖčéčī ą╝ą░ą║čüąĖą╝čāą╝ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéąĖ ą┤ą╗čÅ ąĮąĄą┤ąŠčĆąŠą│ąŠą│ąŠ, ą╝ą░ą╗ąŠą┐ąŠčéčĆąĄą▒ą╗čÅčÄčēąĄą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ FPGA.

ąÜą░ąČą┤ąŠąĄ čÅą┤čĆąŠ MCB ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ąĖąĮč鹥čĆč乥ą╣čü ą┐ą░ą╝čÅčéąĖ čüąŠ čüą║ąŠčĆąŠčüčéčÅą╝ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ, ą┐ąŠą║ą░ąĘą░ąĮąĮčŗą╝ąĖ ą▓ čéą░ą▒ą╗ąĖčåąĄ 1-1. ą¤ąĖą║ąŠą▓ą░čÅ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéčī ąŠą┤ąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ ą┐ą░ą╝čÅčéąĖ MCB ą▓čŗčćąĖčüą╗čÅąĄčéčüčÅ ą┤ą╗čÅ čéčĆąĄčģ ą┤ąŠčüčéčāą┐ąĮčŗčģ ą▓ą░čĆąĖą░ąĮč鹊ą▓ ą┐ąŠą╗ąŠčüčŗ ą┐čĆąŠą┐čāčüą║ą░ąĮąĖčÅ ąĖąĮč鹥čĆč乥ą╣čüą░.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: MCB ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé čüčéą░ąĮą┤ą░čĆčéąĮčŗą╣ (Standard) ąĖ čĆą░čüčłąĖčĆąĄąĮąĮčŗą╣ (Extended) čĆąĄąČąĖą╝čŗ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéąĖ, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą▓čŗą▒čĆą░ąĮąĮčŗčģ čĆą░ą▒ąŠčćąĖčģ čāčüą╗ąŠą▓ąĖą╣ VCCINT. ą¤ąĖą║ąŠą▓čŗąĄ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéąĖ, ą┐ąŠą║ą░ąĘą░ąĮąĮčŗąĄ ą▓ čéą░ą▒ą╗ąĖčåąĄ 1-1, ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅčÄčé ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮčāčÄ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéčī, ą║ąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ąĖą░ą┐ą░ąĘąŠąĮ VCCINT ą▓ čĆą░čüčłąĖčĆąĄąĮąĮąŠą╝ čĆąĄąČąĖą╝ąĄ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéąĖ. ą×ą▒čĆą░čéąĖč鹥čüčī ą║ čéą░ą▒ą╗ąĖčåąĄ 2 (Recommended Operating Conditions, čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄą╝čŗąĄ čĆą░ą▒ąŠčćąĖąĄ čāčüą╗ąŠą▓ąĖčÅ) ąĖ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéąĖ (Performance Characteristics) ą▓ čüąĄą║čåąĖąĖ DS162, Spartan-6 FPGA Data Sheet: DC and Switching Characteristics ą┤ą╗čÅ čĆą░ą▒ąŠčćąĖčģ čāčüą╗ąŠą▓ąĖą╣ VCCINT ąĖ čüą┐ąĄčåąĖčäąĖą║ą░čåąĖą╣ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéąĖ ą┤ą╗čÅ čĆąĄąČąĖą╝ąŠą▓ Standard ąĖ Extended.

ąóą░ą▒ą╗ąĖčåą░ 1-1. ąĪą║ąŠčĆąŠčüčéąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ąĖ ą┐ąĖą║ąŠą▓ą░čÅ ą┐ąŠą╗ąŠčüą░ ą┐čĆąŠą┐čāčüą║ą░ąĮąĖčÅ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ MCB.

ąóąĖą┐ ą┐ą░ą╝čÅčéąĖ

|

ąĪą║ąŠčĆąŠčüčéčī (Data Rate) Mb/čüąĄą║ DDR (čéą░ą║čéčŗ ą▓ ą£ąōčå)

|

ą¤ąĖą║ąŠą▓ą░čÅ ą┐ąŠą╗ąŠčüą░ ąĮą░ ąĖąĮč鹥čĆč乥ą╣čü MCB (Gb/čüąĄą║)

|

| Min |

Max(1) |

4 ą▒ąĖčéą░ |

8 ą▒ąĖčé |

16 ą▒ąĖčé |

| DDR |

167 Mb/čüąĄą║(2)

(83.3 ą£ąōčå) |

400 Mb/čüąĄą║

(200 ą£ąōčå) |

1.6 Gb/čüąĄą║ |

3.2Gb/čüąĄą║ |

6.4 Gb/čüąĄą║ |

| DDR2 |

250 Mb/čüąĄą║(2)

(125 ą£ąōčå) |

800 Mb/čüąĄą║

(400 ą£ąōčå) |

3.2 Gb/čüąĄą║ |

6.4Gb/čüąĄą║ |

12.8 Gb/čüąĄą║ |

| DDR3 |

606 Mb/čüąĄą║(2)

(303 ą£ąōčå) |

800 Mb/čüąĄą║

(400 ą£ąōčå) |

3.2 Gb/čüąĄą║ |

6.4Gb/čüąĄą║ |

12.8 Gb/čüąĄą║ |

| LPDDR |

60 Mb/čüąĄą║(2)

(30 ą£ąōčå) |

400 Mb/čüąĄą║

(200 ą£ąōčå) |

1.6 Gb/čüąĄą║ |

3.2Gb/čüąĄą║ |

6.4 Gb/čüąĄą║ |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

1. ą¤ąŠą║ą░ąĘą░ąĮ ą╝ą░ą║čüąĖą╝čāą╝ čüą║ąŠčĆąŠčüčéąĖ ą┤ą░ąĮąĮčŗčģ MCB, ą║ąŠč鹊čĆčŗą╣ ąĮąĄ ąŠčéąĮąŠčüąĖčéčüčÅ ą║ąŠ ą▓čüąĄą╝ ą║ą╗ą░čüčüą░ą╝ čüą║ąŠčĆąŠčüč鹥ą╣ (speed grade) FPGA. ąĪą╝. DS162, Spartan-6 FPGA Data Sheet: DC and Switching Characteristics, ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéąĖ ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé speed grade. ąŻčüčéčĆąŠą╣čüčéą▓ą░ -3N speed-grade ąĮąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé MCB.

2. ą£ąĖąĮąĖą╝ą░ą╗čīąĮčŗąĄ čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅ ą║ čćą░čüč鹊č鹥 MCB ą┤ąĖą║čéčāčÄčéčüčÅ ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠą╣ čüą┐ąĄčåąĖčäąĖą║ą░čåąĖąĄą╣ čćą░čüč鹊čéčŗ ą┤ą╗čÅ čüčéą░ąĮą┤ą░čĆčéą░ ą┐ą░ą╝čÅčéąĖ. ąĪą╝. čüčéą░ąĮą┤ą░čĆčéčŗ ą┐ą░ą╝čÅčéąĖ ą▓ ą¤čĆąĖą╗ąŠąČąĄąĮąĖąĖ A, ą│ą┤ąĄ ą┤ą░ąĮčŗ čüčüčŗą╗ą║ąĖ ąĮą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ čüą┐ąĄčåąĖčäąĖą║ą░čåąĖąĖ JEDEC.

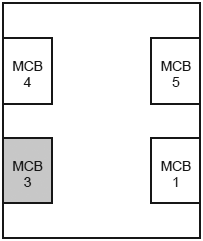

ąÜąŠą╗ąĖč湥čüčéą▓ąŠ ą┤ąŠčüčéčāą┐ąĮčŗčģ MCB ą▓ ąĖą╝ąĄčÄčēąĄą╝čüčÅ čāčüčéčĆąŠą╣čüčéą▓ąĄ Spartan-6 ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą┐ąŠ ą┤ąĖą░ą┐ą░ąĘąŠąĮčā ą┐ą╗ąŠčéąĮąŠčüčéąĖ ą╗ąŠą│ąĖą║ąĖ, ą▓ ą║ąŠč鹊čĆčŗą╣ ą┐ąŠą┐ą░ą┤ą░ąĄčé čāčüčéčĆąŠą╣čüčéą▓ąŠ. ąĪą░ą╝ąŠąĄ ą╝ą░ą╗ąĄąĮčīą║ąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ (XC6SLX4) ąĮąĄ čüąŠą┤ąĄčƹȹĖčé MCB, čüčĆąĄą┤ąĮąĖąĄ ą┐ąŠ ą┐ą╗ąŠčéąĮąŠčüčéąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ čüąŠą┤ąĄčƹȹ░čé ą┤ą▓ą░ MCB, ąĖ ą▒ąŠą╗ąĄąĄ ą║čĆčāą┐ąĮčŗąĄ ą┐ąŠ ą┐ą╗ąŠčéąĮąŠčüčéąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ čüąŠą┤ąĄčƹȹ░čé č湥čéčŗčĆąĄ MCB. ąóą░ą▒ą╗ąĖčåą░ 1-2 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄą╝čŗčģ MCB ą┤ą╗čÅ ą║ą░ąČą┤ąŠą╣ ą║ąŠą╝ą▒ąĖąĮą░čåąĖąĖ čāčüčéčĆąŠą╣čüčéą▓ąŠ/ą║ąŠčĆą┐čāčü.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: MCB čĆą░ąĘčĆą░ą▒ąŠčéą░ąĮ ą┤ą╗čÅ ąŠą┤ąĮąŠą│ąŠ ą║ąŠą╝ą┐ąŠąĮąĄąĮčéą░ ą┐ą░ą╝čÅčéąĖ x4, x8 ąĖą╗ąĖ x16. ąśąĮč鹥čĆč乥ą╣čüčŗ čü ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ ą║ąŠą╝ą┐ąŠąĮąĄąĮčéą░ą╝ąĖ ą▓ ąŠą┤ąĮąŠą╝ MCB (ąĮą░ą┐čĆąĖą╝ąĄčĆ, ą┤ą▓ąĄ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą┐ą░ą╝čÅčéąĖ x8, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗąĄ ą║ MCB ą▓ čĆąĄąČąĖą╝ąĄ x16) ąĮąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčéčüčÅ.

ąóą░ą▒ą╗ąĖčåą░ 1-2. ą¤ąŠą┤ą┤ąĄčƹȹ║ą░ MCB ą▓ čĆą░ąĘąĮčŗčģ ą║ąŠą╝ą▒ąĖąĮą░čåąĖčÅčģ čāčüčéčĆąŠą╣čüčéą▓ąŠ/ą║ąŠčĆą┐čāčü.

ąŻčüčéčĆąŠą╣čüčéą▓ąŠ

|

ąÜąŠčĆą┐čāčü |

| TQG144 |

CPG196 |

CSG225 |

FT(G)256 |

CSG324 |

FG(G)484 |

CSG484 |

FG(G)676 |

FG(G)900 |

| XC6SLX4 |

0 |

0 |

0 |

|

|

|

|

|

|

| XC6SLX9 |

0 |

0 |

2(1) |

2 |

2 |

|

|

|

|

| XC6SLX16 |

|

0 |

2(1) |

2 |

2 |

|

|

|

|

| XC6SLX25 |

|

|

|

2 |

2 |

2 |

|

|

|

| XC6SLX45 |

|

|

|

|

2 |

2 |

2 |

2 |

|

| XC6SLX75 |

|

|

|

|

|

2(2) |

2(2) |

4 |

|

| XC6SLX100 |

|

|

|

|

|

2(2) |

2(2) |

4 |

|

| XC6SLX150 |

|

|

|

|

|

2(2) |

2(2) |

4 |

4 |

| XC6SLX25T |

|

|

|

|

2 |

2 |

|

|

|

| XC6SLX45T |

|

|

|

|

2 |

2 |

2 |

|

|

| XC6SLX75T |

|

|

|

|

|

2(2) |

2(2) |

4 |

|

| XC6SLX100T |

|

|

|

|

|

2(2) |

2(2) |

4 |

|

| XC6SLX150T |

|

|

|

|

|

2(2) |

2(2) |

4 |

4 |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

1. ąöą╗čÅ čāčüčéčĆąŠą╣čüčéą▓ ą▓ ą║ąŠčĆą┐čāčüąĄ CSG225 ą▒ą╗ąŠą║ąĖ MCB ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčéčüčÅ č鹊ą╗čīą║ąŠ ą▓ ąŠą┐čåąĖčÅčģ ąĖąĮč鹥čĆč乥ą╣čüą░ ą┐ą░ą╝čÅčéąĖ x4 ąĖ x8, čé. ąĄ. čāčüčéčĆąŠą╣čüčéą▓ą░ LPDDR ąĮąĄ ą╝ąŠą│čāčé ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ. ąÜčĆąŠą╝ąĄ č鹊ą│ąŠ, ą▓ čŹč鹊ą╝ ą║ąŠčĆą┐čāčüąĄ ą┤ąŠčüčéčāą┐ąĮąŠ č鹊ą╗čīą║ąŠ 13 ą▒ąĖčé ą░ą┤čĆąĄčüą░ MCB, čćč鹊 ąŠą│čĆą░ąĮąĖčćąĖą▓ą░ąĄčé ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮčāčÄ ą┐ą╗ąŠčéąĮąŠčüčéąĖ ą┐ą░ą╝čÅčéąĖ ą┤ąŠ 256 Mb ą┤ą╗čÅ DDR2 ąĖ 512 Mb ą┤ą╗čÅ DDR ąĖ DDR3.

2. ąöą╗čÅ čāčüčéčĆąŠą╣čüčéą▓ čü č湥čéčŗčĆčīą╝čÅ MCB č鹊ą╗čīą║ąŠ ą┤ą▓ą░ MCB ą┐čĆąĖą▓čÅąĘą░ąĮčŗ ą║ ąĮąŠąČą║ą░ą╝ ą║ąŠčĆą┐čāčüąŠą▓ FGG484 ąĖ CSG484.

Spartan-6 FPGA MCB ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé čłąĖčĆąŠą║ąĖą╣ ą┤ąĖą░ą┐ą░ąĘąŠąĮ čéąĖą┐ąŠą▓ ą┐ą░ą╝čÅčéąĖ, ą║ąŠąĮčäąĖą│čāčĆą░čåąĖą╣ ąĖ ą┐ą╗ąŠčéąĮąŠčüč鹥ą╣, čćč鹊 ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▓ čéą░ą▒ą╗ąĖčåąĄ 1-3.

ąóą░ą▒ą╗ąĖčåą░ 1-3. ą¤ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄą╝čŗąĄ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą┐ą░ą╝čÅčéąĖ.

ą¤ą╗ąŠčéąĮąŠčüčéčī ą┐ą░ą╝čÅčéąĖ

(ą▓ ą▒ąĖčéą░čģ) |

ąĀą░ąĘčĆčÅą┤ąĮąŠčüčéčī

(ą▒ąĖčé DQ)

|

ąóąĖą┐ ą┐ą░ą╝čÅčéąĖ

|

| LPDDR |

DDR |

DDR2 |

DDR3 |

| 128 Mb |

x16 |

X |

X |

|

|

| x8 |

|

X |

|

|

| x4 |

|

X |

|

|

| 256 Mb |

x16 |

X |

X |

X |

|

| x8 |

|

X |

X |

|

| x4 |

|

X |

X |

|

| 512 Mb |

x16 |

X |

X |

X |

X |

| x8 |

|

X |

X |

X |

| x4 |

|

X |

X |

X |

| 1 Gb |

x16 |

X |

X |

X |

X |

| x8 |

|

X |

X |

X |

| x4 |

|

X |

X |

X |

| 2 Gb |

x16 |

|

|

X |

X |

| x8 |

|

|

X |

X |

| x4 |

|

|

X |

X |

| 4 Gb(1) |

x16 |

|

|

|

X |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

1. MCB ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé single-die 4 Gb ą║ąŠą╝ą┐ąŠąĮąĄąĮčéčŗ ą┐ą░ą╝čÅčéąĖ (ą║ąŠą│ą┤ą░ ąŠąĮąĖ ą┤ąŠčüčéčāą┐ąĮčŗ ąŠčé ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗ąĄą╣ ą┐ą░ą╝čÅčéąĖ) ąĮąŠ ąĮąĄ dual-die 4 Gb.

Spartan-6 FPGA MCB ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ čüčéą░ąĮą┤ą░čĆčéąĮčŗą╝ ą¤ą× ąĖ ąĖąĮčüčéčĆčāą╝ąĄąĮčéą░ą╝ąĖ, ą║ą░ą║ ąĖ ą┤čĆčāą│ąŠą╣ čüąŠčäčé ąĖ ą▓čüčéčĆą░ąĖą▓ą░ąĄą╝čŗąĄ ą▒ą╗ąŠą║ąĖ IP, ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄą╝čŗąĄ ą║ąŠą╝ą┐ą░ąĮąĖąĄą╣ Xilinx. ąöą╗čÅ ąŠą▒čŗčćąĮčŗčģ (čé. ąĄ. ą▒ąĄąĘ ą▓čüčéčĆąŠąĄąĮąĮčŗčģ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓, non-embedded) ą┤ąĖąĘą░ą╣ąĮąŠą▓ FPGA ą▒ą╗ąŠą║ąĖ MCB ą╝ąŠą│čāčé ą▒čŗčéčī ąĖąĮč鹥ą│čĆąĖčĆąŠą▓ą░ąĮčŗ ą▓ ą┤ąĖąĘą░ą╣ąĮ čü ą┐ąŠą╝ąŠčēčīčÄ čāčéąĖą╗ąĖčéčŗ Memory Interface Generator (MIG), ą┤ąŠčüčéčāą┐ąĮąŠą╣ ą▓ ąĖąĮčüčéčĆčāą╝ąĄąĮč鹥 CORE Generator.

ąŻčéąĖą╗ąĖčéą░ MIG ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ąĖąĮč鹥čĆč乥ą╣čüąŠą▓ ą┐ą░ą╝čÅčéąĖ ą┤ą╗čÅ ą▓čüąĄčģ Xilinx FPGA. ą×ąĮą░ ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ąĮąĄąŠą▒čģąŠą┤ąĖą╝čŗąĄ čäą░ą╣ą╗čŗ RTL ą┤ąĖąĘą░ą╣ąĮą░, čäą░ą╣ą╗čŗ ąŠą│čĆą░ąĮąĖč湥ąĮąĖą╣ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ (user constraints files, UCF) ąĖ čäą░ą╣ą╗čŗ čüą║čĆąĖą┐č鹊ą▓ ą┤ą╗čÅ čüąĖą╝čāą╗čÅčåąĖąĖ ąĖ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ čĆąĄčłąĄąĮąĖą╣ ą┐ą░ą╝čÅčéąĖ, ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮąĮčŗčģ Xilinx. ąÆ ą│ą╗ą░ą▓ąĄ Getting Started čĆčāą║ąŠą▓ąŠą┤čüčéą▓ą░ UG416 [2] čüąŠą┤ąĄčƹȹ░čéčüčÅ ą┐ąŠą┤čĆąŠą▒ąĮčŗąĄ ą┐ąŠčłą░ą│ąŠą▓čŗąĄ ąĖąĮčüčéčĆčāą║čåąĖąĖ ąŠ č鹊ą╝, ą║ą░ą║ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čāčéąĖą╗ąĖčéčā MIG ą┤ą╗čÅ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ ąĖąĮč鹥čĆč乥ą╣čüąŠą▓ ą┐ą░ą╝čÅčéąĖ ąĮą░ ąŠčüąĮąŠą▓ąĄ MCB.

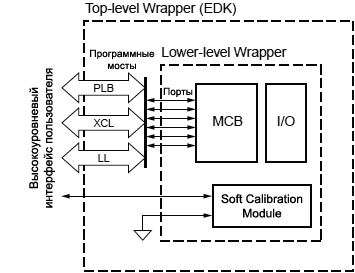

ąöą╗čÅ embedded-ą┤ąĖąĘą░ą╣ąĮąŠą▓ (ąĮą░ą┐čĆąĖą╝ąĄčĆ, čü čÅą┤čĆąŠą╝ ą┐čĆąŠčåąĄčüčüąŠčĆą░ MicroBlazeŌäó), GUI ą║ąŠąĮčäąĖą│čāčĆą░č鹊čĆ IP ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ąĖąĮčüčéčĆčāą╝ąĄąĮčéą░čĆąĖąĖ Xilinx Platform Studio ąĖąĘ čüąŠčüčéą░ą▓ą░ čĆą░ą▒ąŠč湥ą╣ čüčĆąĄą┤čŗ EDK, ą║ąŠč鹊čĆčŗą╣ ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┤ą╗čÅ čāą║ą░ąĘą░ąĮąĖčÅ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ ąĖąĮč鹥čĆč乥ą╣čüą░ ą┐ą░ą╝čÅčéąĖ. ąÆ čéą░ą║ąŠą╝ ą┐čĆąŠčåąĄčüčüąĄ čĆą░ąĘčĆą░ą▒ąŠčéą║ąĖ MCB čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ąĮąĖąČąĄą╗ąĄąČą░čēą░čÅ ą░ą┐ą┐ą░čĆą░čéąĮą░čÅ čĆąĄą░ą╗ąĖąĘą░čåąĖčÅ ą▒ą╗ąŠą║ą░ MPMC IP, ą║ąŠč鹊čĆčŗą╣ ą┤ąŠčüčéčāą┐ąĄąĮ ą▓ ą▒ąĖą▒ą╗ąĖąŠč鹥ą║ąĄ EDK. ąÆ ą┤ąŠą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ ąĮą░čüčéčĆąŠą╣ą║ąĄ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ąĖ ą░čéčĆąĖą▒čāč鹊ą▓ ąĖąĮč鹥čĆč乥ą╣čüą░ ą┐ą░ą╝čÅčéąĖ ąĖąĮčüčéčĆčāą╝ąĄąĮčéą░čĆąĖą╣ ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ąĮąĄąŠą▒čģąŠą┤ąĖą╝čŗąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗąĄ ą╝ąŠčüčéčŗ ą║ čłąĖąĮąĄ PLB, Xilinx Cache Link (XCL), LocalLink (LL) ąĖą╗ąĖ ą┤čĆčāą│ąĖą╝ čāą║ą░ąĘą░ąĮąĮčŗą╝ ąĖąĮč鹥čĆč乥ą╣čüą░ą╝ ą┤ą╗čÅ čüąŠąĄą┤ąĖąĮąĄąĮąĖčÅ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ EDK čü ą║ąŠąĮąĄčćąĮčŗą╝ąĖ ą┐ąŠčĆčéą░ą╝ąĖ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą┐ą░ą╝čÅčéąĖ.

[2. ążčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ MCB]

MCB ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą┐čĆąŠčüč鹊ą╣, ąĮą░ą┤ąĄąČąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü ą┤ą╗čÅ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ą║ ą┐ą░ą╝čÅčéąĖ ąĖąĘ ąŠą┤ąĮąŠą│ąŠ ą║ąŠą╝ą┐ąŠąĮąĄąĮčéą░ (ąŠą┤ąĮąŠą╣ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ SDRAM). ąśąĮč鹥čĆč乥ą╣čü ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ (MCB User Interface) čāčüčéčĆą░ąĮčÅąĄčé čüą╗ąŠąČąĮąŠčüčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ DDR, čéą░ą║ čćč鹊 ą▒ąŠą╗čīčłąĄ čĆąĄčüčāčĆčüąŠą▓ FPGA ą╝ąŠąČąĄčé ą▒čŗčéčī ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąŠ ąĮą░ čāąĮąĖą║ą░ą╗čīąĮčŗąĄ ą░čüą┐ąĄą║čéčŗ ą┤ąĖąĘą░ą╣ąĮą░.

MCB ą╝ąŠąČąĄčé čĆą░ą▒ąŠčéą░čéčī ąĮą░ čüą║ąŠčĆąŠčüčéčÅčģ, ą║ąŠč鹊čĆčŗąĄ ą▓čŗčłąĄ čüčĆą░ą▓ąĮąĖą╝čŗčģ ą┐ąŠ čäčāąĮą║čåąĖąŠąĮą░ą╗čā "soft"-čĆąĄčłąĄąĮąĖą╣, čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮąĮčŗčģ ąĮą░ ą╗ąŠą│ąĖą║ąĄ FPGA. ąĪąŠ čüą║ąŠčĆąŠčüčéčÅą╝ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ą┤ąŠ 800 Mb/s ą▒ą╗ąŠą║ MCB ą▒ąŠą╗ąĄąĄ č湥ą╝ ą▓ą┤ą▓ąŠąĄ ą┐ąŠą▓čŗčłą░ąĄčé ą▒čŗčüčéčĆąŠą┤ąĄą╣čüčéą▓ąĖąĄ ą┐ąŠ čüčĆą░ą▓ąĮąĄąĮąĖčÄ čü ą┐čĆąĄą┤čŗą┤čāčēąĖą╝ąĖ ąĮąĄą┤ąŠčĆąŠą│ąĖą╝ąĖ čĆąĄčłąĄąĮąĖčÅą╝ąĖ ąĖąĮč鹥čĆč乥ą╣čüą░ ą┐ą░ą╝čÅčéąĖ FPGA, ą┐ąŠą▓čŗčłą░čÅ čāčĆąŠą▓ąĄąĮčī ą┐ąŠą╗ąŠčüčŗ ą┐čĆąŠą┐čāčüą║ą░ąĮąĖčÅ ąĖ/ąĖą╗ąĖ čĆą░čüčłąĖčĆčÅčÅ čĆą░ąĘčĆčÅą┤ąĮąŠčüčéčī čłąĖąĮ ą┐ą░ą╝čÅčéąĖ. ąÆ čĆąĄąĘčāą╗čīčéą░č鹥 菹║ąŠąĮąŠą╝čÅčéčüčÅ čĆąĄčüčāčĆčüčŗ ą╗ąŠą│ąĖą║ąĖ FPGA ąĖ čĆąĄčüčāčĆčüčŗ I/O, ą║ąŠč鹊čĆčŗąĄ ąĖąĮą░č湥 ą┐ąŠčéčĆąĄą▒ąŠą▓ą░ą╗ąĖčüčī ą▒čŗ ą┤ą╗čÅ ą║ąŠą╝ą╝čāąĮąĖą║ą░čåąĖąĖ čü ą╝ąĖą║čĆąŠčüčģąĄą╝ąŠą╣ ą┐ą░ą╝čÅčéąĖ.

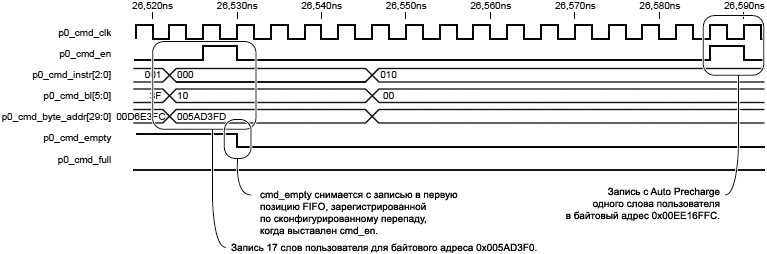

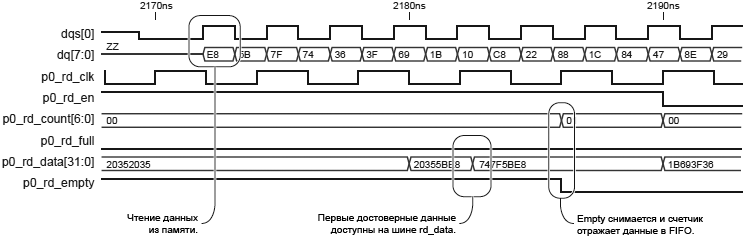

ąĀąĖčü. 2-1 čĆą░čüčłąĖčĆčÅąĄčé ą▒ą╗ąŠą║-ą┤ąĖą░ą│čĆą░ą╝ą╝čā MCB, ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮąĮčāčÄ ą▓ ąōą╗ą░ą▓ąĄ 1, čćč鹊ą▒čŗ ą┐ąŠą║ą░ąĘą░čéčī ąŠčüąĮąŠą▓ąĮčŗąĄ čüąĖą│ąĮą░ą╗čŗ, čüą▓čÅąĘą░ąĮąĮčŗąĄ čü ą▓ąĮčāčéčĆąĄąĮąĮąĖą╝ ąĖąĮč鹥čĆč乥ą╣čüąŠą╝ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ (User Interface) ą▓ FPGA, ą░ čéą░ą║ąČąĄ čüąĖą│ąĮą░ą╗čŗ I/O, ą┐ąŠą┤ą║ą╗čÄčćą░ąĄą╝čŗąĄ ą║ ą▓ąĮąĄčłąĮąĄą╝čā čāčüčéčĆąŠą╣čüčéą▓čā ą┐ą░ą╝čÅčéąĖ. ąźąŠčéčÅ User Interface ą╝ąŠąČąĄčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą┤ą╗čÅ ą┐ąŠą┤ą┤ąĄčƹȹ║ąĖ ą┤ąŠ 6 ą┐ąŠčĆč鹊ą▓, ą┤ą╗čÅ čāą┐čĆąŠčēąĄąĮąĖčÅ čĆąĖčü. 2-1 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüąĖą│ąĮą░ą╗čŗ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ąŠą┤ąĮąŠą│ąŠ ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮąŠą│ąŠ ą┐ąŠčĆčéą░.

ąĀąĖčü. 2-1. ąÉčĆčģąĖč鹥ą║čéčāčĆą░ MCB čü ąŠčüąĮąŠą▓ąĮčŗą╝ąĖ ą▓ąĮąĄčłąĮąĖą╝ąĖ (I/O) ąĖ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╝ąĖ čüąĖą│ąĮą░ą╗ą░ą╝ąĖ.

ąśą╝ąĄąĄčéčüčÅ 3 ą▒ą░ąĘąŠą▓čŗčģ čéąĖą┐ą░ ą┐ąŠčĆč鹊ą▓, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠą│čāčé ą▒čŗčéčī čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮčŗ ą▓ User Interface:

ŌĆó ą¤ąŠčĆčé čćč鹥ąĮąĖčÅ (Read port, ąŠą┤ąĮąŠąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╣)

ŌĆó ą¤ąŠčĆčé ąĘą░ą┐ąĖčüąĖ (Write port ąŠą┤ąĮąŠąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╣)

ŌĆó ą¤ąŠčĆčé čćč鹥ąĮąĖčÅ ąĖ ąĘą░ą┐ąĖčüąĖ (Read and Write port, ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╣)

ąÜą░ąČą┤čŗą╣ ą┐ąŠčĆčé čüąŠą┤ąĄčƹȹĖčé ą┐čāčéčī ą┤ą╗čÅ ą║ąŠą╝ą░ąĮą┤čŗ (command path) ąĖ ą┐čāčéčī ą┤ą╗čÅ ą┤ą░ąĮąĮčŗčģ (datapath). ąöą╗čÅ ąŠą┤ąĮąŠąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮąŠą│ąŠ ą┐ąŠčĆčéą░ command path čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮ ą▓ ą┐ą░čĆąĄ čü read-only ąĖą╗ąĖ ąŠą┤ąĖąĮąŠčćąĮčŗą╝ write-only datapath. ą×ą┤ąĮą░ą║ąŠ ą┤ą╗čÅ ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮąŠą│ąŠ ą┐ąŠčĆčéą░ ąŠą┤ąĖąĮąŠčćąĮčŗą╣ command čüą┤ąĄą╗ą░ąĮ ąŠą▒čēąĖą╝ ą┤ą╗čÅ ąŠą▒ąŠąĖčģ ą┐čāč鹥ą╣ datapath read ąĖ write ą┤ą╗čÅ čŹč鹊ą│ąŠ ą┐ąŠčĆčéą░. ąØą░ User Interface ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ čüč鹥ą║ąĖ FIFO ą┤ą╗čÅ command path ąĖ datapath, čćč鹊ą▒čŗ ąŠčĆą│ą░ąĮąĖąĘąŠą▓ą░čéčī ąŠč湥čĆąĄą┤čī ąĘą░ą┐čĆąŠčüąŠą▓ ą║ ą┐ą░ą╝čÅčéąĖ ąĖ čāą┐čĆą░ą▓ą╗čÅčéčī ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖčÅą╝ąĖ ą┤ą░ąĮąĮčŗčģ ąĖąĘ ą┤ąŠą╝ąĄąĮą░ čéą░ą║č鹊ą▓ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ ą▓ ą┤ąŠą╝ąĄąĮ čéą░ą║č鹊ą▓ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą┐ą░ą╝čÅčéąĖ.

ąĪąĖą│ąĮą░ą╗čŗ command path ą┤ą╗čÅ ą┐ąŠčĆčéą░ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┐čĆąĖ ą▓čŗą┤ą░č湥 ąĘą░ą┐čĆąŠčüąŠą▓ ą║ čüč鹥ą║ą░ą╝ FIFO ą║ąŠą╝ą░ąĮą┤. ąŻ čüč鹥ą║ą░ command FIFO ą│ą╗čāą▒ąĖąĮą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╝ ą┤ąŠ 4 čÅč湥ąĄą║. ąÆ ąĮąĄą╝ čüąŠčģčĆą░ąĮčÅąĄčéčüčÅ čéąĖą┐ ąĖąĮčüčéčĆčāą║čåąĖąĖ (read, write, refresh ąĖ čé. ą┤.), ą░ą┤čĆąĄčü ąĖ ą┤ą╗ąĖąĮą░ ą┐ą░ą║ąĄčéą░ (burst length) čüą▓čÅąĘą░ąĮąĮčŗąĄ čü ąĘą░ą┐čĆąŠčłąĄąĮąĮąŠą╣ čéčĆą░ąĮąĘą░ą║čåąĖąĄą╣ ą┐ą░ą╝čÅčéąĖ. ą¤čāčéčī ą║ąŠą╝ą░ąĮą┤čŗ (command path) čéą░ą║ąČąĄ ą▓ą║ą╗čÄčćą░ąĄčé čäą╗ą░ą│ąĖ čüčéą░čéčāčüą░ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĮąŠčüčéąĖ ąĖ ąŠą┐čāčüč鹊賹ĄąĮąĖčÅ (full ąĖ empty), ą▓čŗčģąŠą┤čÅčēąĖąĄ ąĖąĘ čüč鹥ą║ą░ command FIFO, ąŠąĮąĖ ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčé, ą╝ąŠą│čāčé ą╗ąĖ ą▒čŗčéčī ą┐čĆąĖąĮčÅčéčŗ ąĮąŠą▓čŗąĄ ąĘą░ą┐čĆąŠčüčŗ. ąśą╝ąĄąĄčéčüčÅ 6 command FIFO, ą┤ąŠčüčéčāą┐ąĮčŗčģ ą░ą┐ą┐ą░čĆą░čéąĮąŠ; ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą┐ąŠčĆč鹊ą▓ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé, čćč鹊 ą┤ąŠčüčéčāą┐ąĮąŠ ą┤ą╗čÅ User Interface (čüą╝. "ąÜąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą┐ąŠčĆčéą░"). ąöą╗čÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ą┐ąŠ čüąĖą│ąĮą░ą╗ą░ą╝ command path čüą╝. "ą¤ąŠą┤čĆąŠą▒ąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ ąĖąĮč鹥čĆč乥ą╣čüą░".

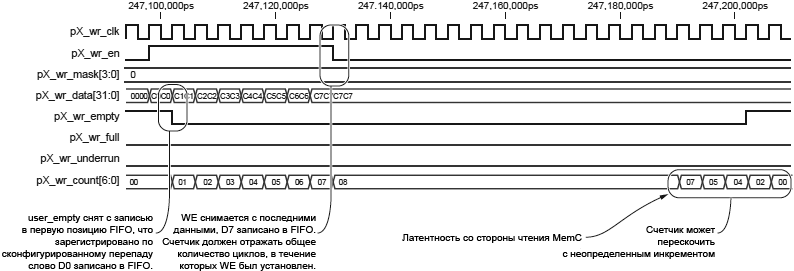

ąØą░ datapath ąĮąĖąČąĄą╗ąĄąČą░čēą░čÅ ą░ą┐ą┐ą░čĆą░čéčāčĆą░ čüąŠą┤ąĄčƹȹĖčé 6 ą┐ąŠčĆč鹊ą▓ čĆą░ąĘčĆčÅą┤ąĮąŠčüčéčīčÄ 32-ą▒ąĖčéą░, ą┤ą▓ą░ ąĖąĘ ą║ąŠč鹊čĆčŗčģ ąĖąĘąĮą░čćą░ą╗čīąĮąŠ ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗąĄ. ąöčĆčāą│ąĖąĄ č湥čéčŗčĆąĄ ą┐ąŠčĆčéą░ ąĖąĘąĮą░čćą░ą╗čīąĮąŠ ąŠą┤ąĮąŠąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗąĄ, ąĮąŠ ąŠąĮąĖ ą╝ąŠą│čāčé čéą░ą║ąČąĄ ą║ąŠą╝ą▒ąĖąĮąĖčĆąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ čüąŠąĘą┤ą░ąĮąĖčÅ ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗčģ ą┐ąŠčĆč鹊ą▓. ąÆčüąĄą│ąŠ ą▓ąŠąĘą╝ąŠąČąĮąŠ čüąŠąĘą┤ą░čéčī 5 ą║ąŠąĮčäąĖą│čāčĆą░čåąĖą╣ ą┐ąŠčĆč鹊ą▓ ą┐čāč鹥ą╝ čĆą░ąĘą╗ąĖčćąĮčŗčģ ą║ąŠą╝ą▒ąĖąĮą░čåąĖą╣ čŹčéąĖčģ čłąĄčüčéąĖ ą░ą┐ą┐ą░čĆą░čéąĮčŗčģ ą┐ąŠčĆč鹊ą▓ ą┤ą╗čÅ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ ąČąĄą╗ą░ąĄą╝ąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ (User Interface, čüą╝. "ąÜąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą┐ąŠčĆčéą░"). ą©ąĖčĆąĖąĮą░ ą┐ąŠą╗ąĄą╣ čüą╗ąŠą▓ą░ ą┤ą░ąĮąĮčŗčģ čćč鹥ąĮąĖčÅ ąĖ ąĘą░ą┐ąĖčüąĖ ąĖąĮč鹥čĆč乥ą╣čüą░ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ ąĄčüč鹥čüčéą▓ąĄąĮąĮąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāčÄčéčüčÅ ą┐čāč鹥ą╝ ą▓čŗą▒ąŠčĆą░ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ.

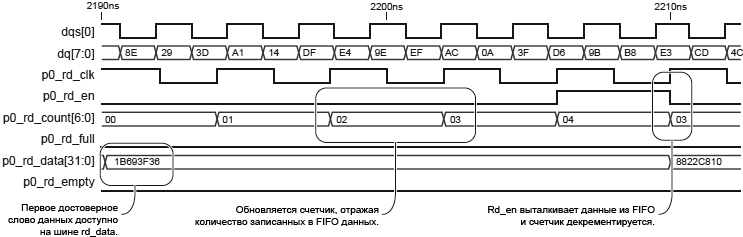

ąĪč鹥ą║ąĖ FIFO datapath ąĖą╝ąĄčÄčé ą│ą╗čāą▒ąĖąĮčā 64 čÅč湥ą╣ą║ąĖ, ą┐ąŠąĘą▓ąŠą╗čÅčÅ ą┐ą░ą║ąĄčéąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą╗ąĖąĮąŠą╣ ą┤ąŠ 64 čüą╗ąŠą▓ ą┤ą░ąĮąĮčŗčģ ąŠčé čāą║ą░ąĘą░ąĮąĮąŠą│ąŠ ąĮą░čćą░ą╗čīąĮąŠą│ąŠ ą░ą┤čĆąĄčüą░. ąÆ ą┤ąŠą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ ą┐ąŠą╗čÄ čüą╗ąŠą▓ą░ ą┤ą░ąĮąĮčŗčģ čüč鹥ą║ąĖ FIFO ą┐čāčéąĖ ąĘą░ą┐ąĖčüąĖ čüąŠą┤ąĄčƹȹ░čé ą┐ąŠą╗čÅ ą▒ąĖčé ą╝ą░čüą║ąĖ, ą║ąŠč鹊čĆčŗąĄ ą┐ąŠąĘą▓ąŠą╗čÅčÄčé ąŠą┐čåąĖąŠąĮą░ą╗čīąĮąŠ ą╝ą░čüą║ąĖčĆąŠą▓ą░čéčī ąĘą░ą┐ąĖčüčŗą▓ą░ąĄą╝čŗąĄ ą┤ą░ąĮąĮčŗąĄ ąĮą░ ą▒ą░ąĘąĄ ą▒ą░ą╣čéą░. ąÆčŗčģąŠą┤čŗ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĮąŠčüčéąĖ (full), ąŠą┐čāčüč鹊賹ĄąĮąĖčÅ (empty), ąĮąĄą┤ąŠą│čĆčāąĘą║ąĖ (underrun), čüč湥čéčćąĖą║ą░ ą║ąŠą╗ąĖč湥čüčéą▓ą░ (count) ąĖ ąŠčłąĖą▒ą║ąĖ ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčé č鹥ą║čāčēąĄąĄ čüąŠčüč鹊čÅąĮąĖąĄ čüč鹥ą║ąŠą▓ FIFO ąĘą░ą┐ąĖčüčŗą▓ą░ąĄą╝čŗčģ ą┤ą░ąĮąĮčŗčģ. ąĪč鹥ą║ąĖ FIFO ą┤ą░ąĮąĮčŗčģ čćč鹥ąĮąĖčÅ ąĖą╝ąĄčÄčé ą┐ąŠą┤ąŠą▒ąĮčŗą╣ ąĮą░ą▒ąŠčĆ ą▓čŗčģąŠą┤ąŠą▓ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ąŠ čüąŠčüč鹊čÅąĮąĖąĖ. ąæąŠą╗ąĄąĄ ą┐ąŠą┤čĆąŠą▒ąĮąŠ ą┐čĆąŠ čüąĖą│ąĮą░ą╗čŗ read ąĖ write datapath čüą╝. "ą¤ąŠą┤čĆąŠą▒ąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ ąĖąĮč鹥čĆč乥ą╣čüą░".

ąÉčĆą▒ąĖčéčĆ ą▓ąĮčāčéčĆąĖ MCB ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą╝ąĄčģą░ąĮąĖąĘą╝ ą░čĆą▒ąĖčéčĆą░ąČą░ ąĮą░ ąŠčüąĮąŠą▓ąĄ čüą╗ąŠč鹊ą▓ ą▓čĆąĄą╝ąĄąĮąĖ, čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ąŠčé ąŠą┤ąĮąŠą│ąŠ ą┤ąŠ čłąĄčüčéąĖ ą┐ąŠčĆč鹊ą▓ User Interface, ą║ąŠč鹊čĆčŗąĄ ą▓ ąĮą░čüč鹊čÅčēąĄąĄ ą▓čĆąĄą╝čÅ ąĖą╝ąĄčÄčé ą┤ąŠčüčéčāą┐ ą║ ą┐ą░ą╝čÅčéąĖ. ąĢčüčéčī čéą░ą║ąČąĄ ą╝ąĄč鹊ą┤čŗ, ą║ąŠč鹊čĆčŗąĄ ą┐ąŠąĘą▓ąŠą╗čÅčÄčé ąĮąĄą║ąŠč鹊čĆčŗą╝ ą┐ąŠčĆčéą░ą╝ ą┤ą░čéčī ą┐ąŠą▓čŗčłąĄąĮąĮčŗą╣ ą┐čĆąĖąŠčĆąĖč鹥čé, čéą░ą║ čćč鹊 ąŠąĮąĖ ą╝ąŠą│čāčé čćą░čēąĄ ą┐ąŠą╗čāčćąĖčéčī ą┤ąŠčüčéčāą┐ ą║ ą┐ą░ą╝čÅčéąĖ. ąŁč鹊 ąŠą▒čüčāąČą┤ą░ąĄčéčüčÅ ą▓ čĆą░ąĘą┤ąĄą╗ąĄ "ąÉčĆą▒ąĖčéčĆą░ąČ".

ąøąŠą│ąĖą║ą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą▒ą░ąĮą║ąŠą╝ ą▓ MCB ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąŠčéą║čĆčŗčéčī ą┤ąŠ 8 ą▒ą░ąĮą║ąŠą▓ ą┐ą░ą╝čÅčéąĖ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ, čćč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčā ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čéčī ą▓čŗčüąŠą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī čŹčäč乥ą║čéąĖą▓ąĮąŠčüčéąĖ ą┤ąŠčüčéčāą┐ą░ ą║ ą┤ą░ąĮąĮčŗą╝ ą┐ąŠ ą▓čüąĄą╝ ą▒ą░ąĮą║ą░ą╝. ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠ ąĘą░ą┐čĆąŠčüčŗ čćč鹥ąĮąĖčÅ ąĖ ąĘą░ą┐ąĖčüąĖ ą┐ą░ą╝čÅčéąĖ ą╝ąŠą│čāčé ą▓ą║ą╗čÄčćą░čéčī ąŠą┐čåąĖąŠąĮą░ą╗čīąĮčŗą╣ ą░ą▓č鹊-ą┐čĆąĄą┤ąĘą░čĆčÅą┤ (auto-precharge), čćč鹊ą▒čŗ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąĘą░ą║čĆčŗčéčī ą▒ą░ąĮą║ ą┐ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĖ čéčĆą░ąĮąĘą░ą║čåąĖąĖ. ąŁč鹊 ą┐ąŠą▓čŗčłą░ąĄčé čŹčäč乥ą║čéąĖą▓ąĮąŠčüčéčī ą┐čĆąŠąĖąĘą▓ąŠą╗čīąĮąŠą│ąŠ ą┤ąŠčüčéčāą┐ą░ ą║ ą┤ą░ąĮąĮčŗą╝ ą▓ ą┐čĆąĄą┤ąĄą╗ą░čģ ą▒ą░ąĮą║ą░. MCB ąĮąĄ ą▓čŗą┐ąŠą╗ąĮčÅąĄčé ą╗čÄą▒ąŠąĄ ą┐ąĄčĆąĄčāą┐ąŠčĆčÅą┤ąŠčćąĖą▓ą░ąĮąĖąĄ čéčĆą░ąĮąĘą░ą║čåąĖą╣.

ąÜąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą┐ąŠčĆčéą░. 5 ą▓ąŠąĘą╝ąŠąČąĮčŗčģ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖą╣ ą┐ąŠčĆčéą░ ą┤ą╗čÅ ąĖąĮč鹥čĆč乥ą╣čüą░ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ (User Interface) ą┐ąŠą║ą░ąĘą░ąĮčŗ ąĮą░ čĆąĖčü. 2-2. ąÆ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ 1, ą┐ąŠčĆčéčŗ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ ą▓ ą┤ąĄą╣čüčéą▓ąĖč鹥ą╗čīąĮąŠčüčéąĖ ąĮą░ą┐čĆčÅą╝čāčÄ ąŠč鹊ą▒čĆą░ąČą░čÄčéčüčÅ ąĮą░ 6 ąĮąĖąČąĄą╗ąĄąČą░čēąĖčģ čäąĖąĘąĖč湥čüą║ąĖčģ ą░ą┐ą┐ą░čĆą░čéąĮčŗčģ ą┐ąŠčĆč鹊ą▓. ąöą╗čÅ ą┤čĆčāą│ąĖčģ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖą╣ ą┤ąĖą░ą│čĆą░ą╝ą╝ą░ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, ą║ą░ą║ čäąĖąĘąĖč湥čüą║ąĖąĄ ą┐ąŠčĆčéčŗ čüąŠąĄą┤ąĖąĮčÅčÄčéčüčÅ ą┤ą╗čÅ čüąŠąĘą┤ą░ąĮąĖčÅ čĆą░ąĘą╗ąĖčćąĮčŗčģ ą║ąŠą╝ą▒ąĖąĮą░čåąĖą╣ ą┐ąŠčĆč鹊ą▓ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ. ąÜą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 2-2, čāčéąĖą╗ąĖčéą░ MIG ą▓čüąĄą│ą┤ą░ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ ąĮčāą╝ąĄčĆčāąĄčé ą┐ąŠčĆčéčŗ ą┤ą╗čÅ User Interface ąĮą░čćąĖąĮą░čÅ čü 0, ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé ąĮąĖąČąĄą╗ąĄąČą░čēąĖčģ ąĮąŠą╝ąĄčĆąŠą▓ čäąĖąĘąĖč湥čüą║ąĖčģ ą┐ąŠčĆč鹊ą▓.

ąÆąŠ ą▓čüąĄčģ ą┐čÅčéąĖ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖą╣ ą┐ąŠčĆč鹊ą▓ command path, write datapath ąĖ read datapath ą▓ ąĖą╝ąĄčÄčēąĄą╝čüčÅ ą┐ąŠčĆč鹥 ą▓čüąĄą│ą┤ą░ ąĖą╝ąĄčÄčé ąŠčéą┤ąĄą╗čīąĮąŠąĄ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ, ąĖ ą┐ąŠčŹč鹊ą╝čā ą╝ąŠą│čāčé ą▒čŗčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮčŗ ą║ ąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗą╝ ą┤čĆčāą│ ąŠčé ą┤čĆčāą│ą░ ą┤ąŠą╝ąĄąĮą░ą╝ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ. ą×ą┤ąĮą░ą║ąŠ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ, čćč鹊ą▒čŗ ą▓čüąĄ ą┐čāčéąĖ, čüą▓čÅąĘą░ąĮąĮčŗąĄ čü ąĖą╝ąĄčÄčēąĖą╝čüčÅ ą┐ąŠčĆč鹊ą╝, čāą┤ąĄčƹȹĖą▓ą░ą╗ąĖčüčī ą▓ ąŠą┤ąĮąŠą╝ ą┤ąŠą╝ąĄąĮąĄ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ, čćč鹊ą▒čŗ čāą┐čĆąŠčüčéąĖčéčī čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅ ą║ ąĖąĮč鹥čĆč乥ą╣čüčā.

ąĀąĖčü. 2-2. ąÆąŠąĘą╝ąŠąČąĮčŗąĄ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą┐ąŠčĆčéą░ ą┤ą╗čÅ ąĖąĮč鹥čĆč乥ą╣čüą░ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ.

ąŻčéąĖą╗ąĖčéą░ MIG ą▓ ąĖąĮčüčéčĆčāą╝ąĄąĮčéą░čĆąĖąĖ CORE GeneratorŌäó ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą┐čĆąŠčüč鹊ą╣ ą│čĆą░čäąĖč湥čüą║ąĖą╣ ąĖąĮč鹥čĆč乥ą╣čü ą┤ą╗čÅ ąĮą░čüčéčĆąŠą╣ą║ąĖ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ąĖ čéąĖą┐ą░ ą┐ąŠčĆč鹊ą▓, čéčĆąĄą▒čāąĄą╝čŗčģ ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą│ąŠ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ. ąöą╗čÅ ą┤ąĖąĘą░ą╣ąĮąŠą▓, ą║ąŠč鹊čĆčŗąĄ čéčĆąĄą▒čāčÄčé ą╝ąĄąĮčīčłčāčÄ čłąĖčĆąĖąĮčā čłąĖąĮ, č湥ą╝ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮą░čÅ, ąĖą╗ąĖ ą╝ąĄąĮčīčłčāčÄ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠčüčéčī User Interface, ąĮąĄąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą┐ąŠčĆčéčŗ ą╝ąŠą│čāčé ą▒čŗčéčī ą┐čĆąŠčüč鹊 ąĘą░ą┐čĆąĄčēąĄąĮčŗ č湥čĆąĄąĘ ąĖąĮč鹥čĆč乥ą╣čü MIG. ąÆ čüą╗čāčćą░ąĄ, ą║ąŠą│ą┤ą░ čéčĆąĄą▒čāčÄčéčüčÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗąĄ ą┐ąŠčĆčéčŗ ą▓ąĮąĄ čŹčéąĖčģ 6 ą┐ąŠčĆč鹊ą▓, ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮąĮčŗčģ ą▓ MCB, ą▓ ą╗ąŠą│ąĖą║ąĄ FPGA ą╝ąŠą│čāčé ą▒čŗčéčī čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮčŗ ą╝ąŠčüčéčŗ ą┐ąŠčĆč鹊ą▓ čü ą┤ąŠą▒ą░ą▓ąŠčćąĮčŗą╝ąĖ ą╝ąĄčģą░ąĮąĖąĘą╝ą░ą╝ąĖ ą░čĆą▒ąĖčéčĆą░ąČą░, čćč鹊ą▒čŗ čĆą░čüčłąĖčĆąĖčéčī ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ ą┐ąŠčĆčéą░ MCB.

ąÉčĆą▒ąĖčéčĆą░ąČ. ąÉčĆą▒ąĖčéčĆ ą▓ąĮčāčéčĆąĖ MCB ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą╝ąĄčģą░ąĮąĖąĘą╝ ą░čĆą▒ąĖčéčĆą░ąČą░ ąĮą░ ąŠčüąĮąŠą▓ąĄ čüą╗ąŠč鹊ą▓ ą▓čĆąĄą╝ąĄąĮąĖ, čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī, ą║ą░ą║ąŠą╣ ą┐ąŠčĆčé User Interface ą▓ ąĮą░čüč鹊čÅčēąĖą╣ ą╝ąŠą╝ąĄąĮčé ą╝ąŠąČąĄčé ą┐ąŠą╗čāčćąĖčéčī ą┤ąŠčüčéčāą┐ ą║ ą┐ą░ą╝čÅčéąĖ. ąśą╝ąĄąĄčéčüčÅ 12 čéą░ą╣ą╝-čüą╗ąŠč鹊ą▓ ą▓ čéą░ą▒ą╗ąĖčåąĄ ą░čĆą▒ąĖčéčĆą░ąČą░, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▓ čéą░ą▒ą╗ąĖčåąĄ 2-1. ąÜą░ąČą┤čŗą╣ čéą░ą╣ą╝-čüą╗ąŠčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ąŠą┤ąĮąŠą╝čā ą┐ąĄčĆąĖąŠą┤čā čéą░ą║čéą░ ą┐ą░ą╝čÅčéąĖ. ą¤ąŠčĆčÅą┤ąŠą║ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┐ąŠčĆčéą░ ą▓ ąĖą╝ąĄčÄčēąĄą╝čüčÅ čéą░ą╣ą╝-čüą╗ąŠč鹥 ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą┐ąŠ ąĮąŠą╝ąĄčĆą░ą╝ ą┐ąŠčĆč鹊ą▓, ą▓ą▓ąĄą┤ąĄąĮąĮčŗą╝ ą▓ čüč鹊ą╗ą▒čåčŗ ąŠčé Priority 1 ą┤ąŠ 6 čü ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖąĄą╝ čüą╗ąĄą▓ą░ ąĮą░ą┐čĆą░ą▓ąŠ ą┐ąŠ čéą░ą▒ą╗ąĖčåąĄ.

ąóą░ą▒ą╗ąĖčåą░ 2-1. ąóą░ą▒ą╗ąĖčåą░ ą░čĆą▒ąĖčéčĆą░ąČą░ MCB čü ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĄą╣ Round Robin.

| ąóą░ą╣ą╝-čüą╗ąŠčé |

ą¤čĆąĖąŠčĆąĖč鹥čé 1 |

ą¤čĆąĖąŠčĆąĖč鹥čé 2 |

ą¤čĆąĖąŠčĆąĖč鹥čé 3 |

ą¤čĆąĖąŠčĆąĖč鹥čé 4 |

ą¤čĆąĖąŠčĆąĖč鹥čé 5 |

ą¤čĆąĖąŠčĆąĖč鹥čé 6 |

| 0 |

0 |

1 |

2 |

3 |

4 |

5 |

| 1 |

1 |

2 |

3 |

4 |

5 |

0 |

| 2 |

2 |

3 |

4 |

5 |

0 |

1 |

| 3 |

3 |

4 |

5 |

0 |

1 |

2 |

| 4 |

4 |

5 |

0 |

1 |

2 |

3 |

| 5 |

5 |

0 |

1 |

2 |

3 |

4 |

| 6 |

0 |

1 |

2 |

3 |

4 |

5 |

| 7 |

1 |

2 |

3 |

4 |

5 |

0 |

| 8 |

2 |

3 |

4 |

5 |

0 |

1 |

| 9 |

3 |

4 |

5 |

0 |

1 |

2 |

| 10 |

4 |

5 |

0 |

1 |

2 |

3 |

| 11 |

5 |

0 |

1 |

2 |

3 |

4 |

ąóą░ą▒ą╗ąĖčåą░ 2-1 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüą╗čāčćą░ą╣, ą│ą┤ąĄ User Interface ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ ąĮą░ ą╝ą░ą║čüąĖą╝čāą╝ 6 ą┐ąŠčĆč鹊ą▓. ąĢčüą╗ąĖ MCB čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ąĮą░ ą╝ąĄąĮčīčłąĄ, č湥ą╝ 6 ą┐ąŠčĆč鹊ą▓, čéą░ą▒ą╗ąĖčåą░ ą░čĆą▒ąĖčéčĆą░ąČą░ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą┐ąŠą┤čüčéčĆą░ąĖą▓ą░ąĄčéčüčÅ, čćč鹊ą▒čŗ ą▒čŗą╗ąĖ č鹊ą╗čīą║ąŠ čüč鹊ą╗ą▒čåčŗ ą┐čĆąĖąŠčĆąĖč鹥čéą░ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ą▓čŗą▒čĆą░ąĮąĮąŠą│ąŠ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ą┐ąŠčĆč鹊ą▓.

ąÆąŠ ą▓čĆąĄą╝čÅ ąĖą╝ąĄčÄčēąĄą│ąŠčüčÅ ą┐ąĄčĆąĖąŠą┤ą░ čéą░ą║č鹊ą▓ ą░čĆą▒ąĖčéčĆ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé, ą║ą░ą║ąŠą╣ ą┐ąŠčĆčé ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčéčüčÅ ą▓ ą║ą░ą║ąŠą╝ čéą░ą╣ą╝-čüą╗ąŠč鹥. ą¤ąŠąĘąĖčåąĖčÅ ą┐ąĄčĆąĄą╝ąĄčēą░ąĄčéčüčÅ čüą╗ąĄą▓ą░ ąĮą░ą┐čĆą░ą▓ąŠ ą┐ąŠ čüč鹊ą╗ą▒čåą░ą╝ ą┐čĆąĖąŠčĆąĖč鹥čéą░, čćč鹊ą▒čŗ ąĮą░ą╣čéąĖ ą┐ąĄčĆą▓čŗą╣ ą┐ąŠčĆčé ą▓ č鹊ą╣ čüčéčĆąŠą║ąĄ, čā ą║ąŠč鹊čĆąŠą╣ ąĄčüčéčī ą║ąŠą╝ą░ąĮą┤ą░, ąŠąČąĖą┤ą░čÄčēą░čÅ ą▓ ąĄą│ąŠ command FIFO. ąŁč鹊čé ą┐ąŠčĆčé č鹊ą│ą┤ą░ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčéčüčÅ čü ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄą╝ ąŠąČąĖą┤ą░čÄčēąĄą╣ ą║ąŠą╝ą░ąĮą┤čŗ, ąĖ ą░čĆą▒ąĖčéčĆ ą┐ąĄčĆąĄą╝ąĄčēą░ąĄčéčüčÅ ą║ čüą╗ąĄą┤čāčÄčēąĄą╝čā čéą░ą╣ą╝-čüą╗ąŠčéčā ąĮą░ čüą╗ąĄą┤čāčÄčēąĄą╝ čéą░ą║č鹥. ąĢčüą╗ąĖ ąĮąĄčé ą┐ąŠčĆčéą░ čü ą║ąŠą╝ą░ąĮą┤ąŠą╣ ą▓ čéą░ą║ąŠą╝ čüč鹊ą╗ą▒čåąĄ, č鹊 ą▓ čŹč鹊ą╝ čéą░ą╣ą╝-čüą╗ąŠč鹥 ąĮąĖą║ą░ą║ąĖčģ ą┤ąĄą╣čüčéą▓ąĖą╣ ąĮąĄ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖčéčüčÅ, ąĖ čéą░ą║čé č鹥čĆčÅąĄčéčüčÅ.

ą¤ąŠčĆčÅą┤ąŠą║ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą▓ ą┐ąŠčĆčéą░ ą▓ čéą░ą▒ą╗ąĖčåąĄ ą░čĆą▒ąĖčéčĆą░ąČą░ ą┐ąŠą╗ąĮąŠčüčéčīčÄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ. ąŻčéąĖą╗ąĖčéą░ MIG ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé čüčģąĄą╝čā ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą▓ round-robin, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▓ čéą░ą▒ą╗ąĖčåąĄ 2-1, ą│ą┤ąĄ ą▓čüąĄą╝ ą┐ąŠčĆčéą░ą╝ ą┤ą░ąĄčéčüčÅ čüą░ą╝čŗą╣ ą▓čŗčüąŠą║ąĖą╣ ą┐čĆąĖąŠčĆąĖč鹥čé ą▓ 2 ąĖąĘ 12 ą┤ąŠčüčéčāą┐ąĮčŗčģ čéą░ą╣ą╝-čüą╗ąŠč鹊ą▓. ą×ą┤ąĮą░ą║ąŠ čāčéąĖą╗ąĖčéą░ MIG čéą░ą║ąČąĄ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ąĮą░čüčéčĆą░ąĖą▓ą░ąĄą╝čāčÄ ąŠą┐čåąĖčÄ, ą│ą┤ąĄ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą╝ąŠąČąĄčé ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ą╗čÄą▒čāčÄ čéą░ą▒ą╗ąĖčåčā ą░čĆą▒ąĖčéčĆą░ąČą░. ąŁč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┤ą╗čÅ ąĮąĄą║ąŠč鹊čĆčŗčģ ą┐ąŠčĆč鹊ą▓ ą┐ąŠą╗čāčćąĖčéčī čāą╗čāčćčłąĄąĮąĮčŗą╣ ą┤ąŠčüčéčāą┐ ą║ čāčüčéčĆąŠą╣čüčéą▓čā ą┐ą░ą╝čÅčéąĖ. ą×ą┤ąĮą░ą║ąŠ čŹčéčā ąŠą┐čåąĖčÄ čüą╗ąĄą┤čāąĄčé ą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ čü ąŠčüč鹊čĆąŠąČąĮąŠčüčéčīčÄ, čćč鹊ą▒čŗ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī, čćč鹊 ą▓čüąĄ ą┐čĆąĖčüą▓ąŠąĄąĮąĮčŗąĄ ą┐čĆąĖąŠčĆąĖč鹥čéčŗ ąĮąĄ ą┐čĆąĄą┤ąŠčéą▓čĆą░čēą░čÄčé ą┤ąŠčüčéčāą┐ ą║ čāčüčéčĆąŠą╣čüčéą▓čā ą┐ą░ą╝čÅčéąĖ ą╗čÄą▒čŗčģ ą░ą║čéąĖą▓ąĮčŗčģ ą┐ąŠčĆč鹊ą▓.

ą£ąŠąČąĮąŠ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī User Interface ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ 5 ą┐ąŠčĆč鹊ą▓ (ą┤ą▓čāčģ 32-ą▒ąĖčéąĮčŗčģ ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗčģ ąĖ čéčĆąĄčģ 32-ą▒ąĖčéąĮčŗčģ ąŠą┤ąĮąŠąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗčģ, čü ąŠą┤ąĮąĖą╝ ąĘą░ą┐čĆąĄčēąĄąĮąĮčŗą╝ 32-ą▒ąĖčéąĮčŗą╝ ąŠą┤ąĮąŠąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╝ ą┐ąŠčĆč鹊ą╝). ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ čéą░ą▒ą╗ąĖčåą░ ą░čĆą▒ąĖčéčĆą░ąČą░ čāą╝ąĄąĮčīčłą░ąĄčéčüčÅ ą┤ąŠ 10 čéą░ą╣ą╝-čüą╗ąŠč鹊ą▓. ąÜąŠą│ą┤ą░ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čéą░ą╣ą╝-čüą╗ąŠč鹊ą▓ čüą╗čāčćą░ą╣ąĮąŠ ą┤ąĄą╗ąĖčéčüčÅ ąĮą░ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą┐ąŠčĆč鹊ą▓, č鹊 ą│ą░čĆą░ąĮčéąĖčĆčāąĄčéčüčÅ, čćč鹊 ą║ą░ąČą┤čŗą╣ ą┐ąŠčĆčé ą┐ąŠą╗čāčćąĖčé 菹║ą▓ąĖą▓ą░ą╗ąĄąĮčéąĮčŗą╣ ą┤ąŠčüčéčāą┐ ą║ čāčüčéčĆąŠą╣čüčéą▓čā ą┐ą░ą╝čÅčéąĖ, ąĄčüą╗ąĖ čŹč鹊 ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ.

ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ. MCB ą│ą╗čāą▒ąŠą║ąŠ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāčéčüčÅ č湥čĆąĄąĘ ąĮą░ą▒ąŠčĆ ą░čéčĆąĖą▒čāč鹊ą▓ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┐ą░ą╝čÅčéąĖ ąĖ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░, ą┐ąŠąĘą▓ąŠą╗čÅčÅ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čéčī ąĮąĄčüą║ąŠą╗čīą║ąŠ čüčéą░ąĮą┤ą░čĆč鹊ą▓ ąĖ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖą╣ ą┐ą░ą╝čÅčéąĖ. ąŻčéąĖą╗ąĖčéą░ MIG ąĖąĘ ąĖąĮčüčéčĆčāą╝ąĄąĮčéą░čĆąĖčÅ CORE Generator ąĖ IP Configurator ą▓ čüčĆąĄą┤ąĄ čĆą░ąĘčĆą░ą▒ąŠčéą║ąĖ Xilinx Platform Studio čü ąĮą░ą╗ąĖčćąĖąĄą╝ EDK ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÄčé ą┐čĆąŠčüč鹊ą╣ čüą┐ąŠčüąŠą▒ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą░čéčĆąĖą▒čāč鹊ą▓ MCB ą┤ą╗čÅ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ ąČąĄą╗ą░ąĄą╝ąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ ą┐ą░ą╝čÅčéąĖ (ąĮą░ą┐čĆąĖą╝ąĄčĆ, čüą╝. ą│ą╗ą░ą▓čā "Getting Started" ąĖąĘ [2]).

ąóą░ą▒ą╗ąĖčåčŗ 2-2 ąĖ 2-3 ą┐ąĄčĆąĄčćąĖčüą╗čÅčÄčé čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ ą░čéčĆąĖą▒čāčéčŗ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┐ą░ą╝čÅčéąĖ ąĖ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░, ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄą╝čŗąĄ MCB. ą¤čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮčŗ čüą┐ąĄčåąĖčäąĖč湥čüą║ąĖąĄ ą┤ą╗čÅ HDL ąĖą╝ąĄąĮą░ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓, ą▓ąŠąĘą╝ąŠąČąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ ąĖ ąŠą┐ąĖčüą░ąĮąĖčÅ, čüą▓čÅąĘą░ąĮąĮčŗąĄ čü ą║ą░ąČą┤čŗą╝ ą░čéčĆąĖą▒čāč鹊ą╝. ąōą╗ą░ą▓ąĮčŗą╝ ąŠą▒čĆą░ąĘąŠą╝ čāčéąĖą╗ąĖčéą░ MIG ąĖą╗ąĖ ąĖąĮčüčéčĆčāą╝ąĄąĮčéčŗ IP Configurator ąŠčéą▓ąĄčćą░čÄčé ąĘą░ čāčüčéą░ąĮąŠą▓ą║čā ąĘąĮą░č湥ąĮąĖą╣ ą▓čüąĄčģ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓, čéą░ą║ čćč鹊 ąĖčģ ąĘąĮą░č湥ąĮąĖčÅ ąĮąĄ ą┤ąŠą╗ąČąĮčŗ ą╝ąŠą┤ąĖčäąĖčåąĖčĆąŠą▓ą░čéčīčüčÅ ąĮą░ą┐čĆčÅą╝čāčÄ.

| ąÉčéčĆąĖą▒čāčé |

ąśą╝čÅ ą┐ą░čĆą░ą╝ąĄčéčĆą░ |

ą×ą┐ąĖčüą░ąĮąĖąĄ / ą▓ąŠąĘą╝ąŠąČąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ |

| ąóąĖą┐ ą┐ą░ą╝čÅčéąĖ |

C_MEM_TYPE |

ąŁč鹊čé ą░čéčĆąĖą▒čāčé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé čüčéą░ąĮą┤ą░čĆčé ą┐ą░ą╝čÅčéąĖ, čĆąĄą░ą╗ąĖąĘčāąĄą╝čŗą╣ MCB. ąÆąŠąĘą╝ąŠąČąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ: DDR, DDR2, DDR3, LPDDR. |

| ą©ąĖčĆąĖąĮą░ čłąĖąĮčŗ ą┤ą░ąĮąĮčŗčģ ą┐ą░ą╝čÅčéąĖ |

C_NUM_DQ_PINS |

ąÉčéčĆąĖą▒čāčé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé čĆą░ąĘčĆčÅą┤ąĮąŠčüčéčī čłąĖąĮčŗ DQ. ąÆąŠąĘą╝ąŠąČąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ "4", "8", "16". |

| ą©ąĖčĆąĖąĮą░ čłąĖąĮčŗ ą░ą┤čĆąĄčüą░ ą┐ą░ą╝čÅčéąĖ |

C_MEM_ADDR_WIDTH |

ąÉčéčĆąĖą▒čāčé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé čĆą░ąĘčĆčÅą┤ąĮąŠčüčéčī čłąĖąĮčŗ ą░ą┤čĆąĄčüą░ (ąŠą▒čēąĄąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ąĖčé ą░ą┤čĆąĄčüą░). ąÆąŠąĘą╝ąŠąČąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ ąĘą░ą▓ąĖčüčÅčé ąŠčé ą▓čŗą▒ąŠčĆą░ čāčüčéčĆąŠą╣čüčéą▓ą░ ą▓ čāčéąĖą╗ąĖč鹥 MIG. |

| ą©ąĖčĆąĖąĮą░ čłąĖąĮčŗ ą░ą┤čĆąĄčüą░ ą▒ą░ąĮą║ą░ |

C_MEM_BANKADDR_WIDTH |

ąÉčéčĆąĖą▒čāčé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ąĖčé ą░ą┤čĆąĄčüą░ ą▓čŗą▒ąŠčĆą░ ą▒ą░ąĮą║ą░. ąÆąŠąĘą╝ąŠąČąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ ąĘą░ą▓ąĖčüčÅčé ąŠčé ą▓čŗą▒ąŠčĆą░ čāčüčéčĆąŠą╣čüčéą▓ą░ ą▓ čāčéąĖą╗ąĖč鹥 MIG. |

| ą©ąĖčĆąĖąĮą░ čłąĖąĮčŗ ą░ą┤čĆąĄčüą░ čüč鹊ą╗ą▒čåą░ |

C_MEM_NUM_COL_BITS |

ąÉčéčĆąĖą▒čāčé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ąĖčé ą░ą┤čĆąĄčüą░ čüč鹊ą╗ą▒čåą░. ąÆąŠąĘą╝ąŠąČąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ ąĘą░ą▓ąĖčüčÅčé ąŠčé ą▓čŗą▒ąŠčĆą░ čāčüčéčĆąŠą╣čüčéą▓ą░ ą▓ čāčéąĖą╗ąĖč鹥 MIG. |

| ą©ąĖčĆąĖąĮą░ ą┐ą░ą║ąĄčéą░ (Memory Burst Length) |

C_MEM_BURST_LEN |

ąÉčéčĆąĖą▒čāčé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ą┤ą╗ąĖąĮą░ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ąŠą│ąŠ ą┐ą░ą║ąĄčéą░. ąŻčéąĖą╗ąĖčéą░ MIG ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé čŹč鹊 ąĘąĮą░č湥ąĮąĖąĄ, ąŠčüąĮąŠą▓čŗą▓ą░čÅčüčī ąĮą░ čüčéą░ąĮą┤ą░čĆč鹥 ą┐ą░ą╝čÅčéąĖ, ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą┐ąŠčĆčéą░ ąĖ čłąĖčĆąĖąĮąĄ ąĖąĮč鹥čĆč乥ą╣čüą░. ąöą╗čÅ DDR3 ą▓čüąĄą│ą┤ą░ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ 8. ąÆąŠąĘą╝ąŠąČąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ: "4", "8". |

| ąŚą░ą┤ąĄčƹȹ║ą░ CAS (Memory CAS Latency) |

ąöą╗čÅ DDR, DDR2, LPDDR: C_MEM_CAS_LATENCY

ąöą╗čÅ DDR3: C_MEM_DDR3_CAS_LATENCY,

C_MEM_DDR3_CAS_WR_LATENCY |

ąÉčéčĆąĖą▒čāčé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ąĘą░ą┤ąĄčƹȹ║čā čüąĖą│ąĮą░ą╗ą░ ą▓čŗą▒ąŠčĆą║ąĖ čüč鹊ą╗ą▒čåą░ CAS (ąĘą░ą┤ąĄčƹȹ║ą░ ą▓ ą┐ąĄčĆąĖąŠą┤ąŠą▓ čéą░ą║č鹊ą▓ ą╝ąĄąČą┤čā ą║ąŠą╝ą░ąĮą┤ąŠą╣ READ ąĖ ą┐ąĄčĆą▓čŗą╝ąĖ ą▓čŗčģąŠą┤čÅčēąĖą╝ąĖ ą┤ą░ąĮąĮčŗą╝ąĖ) ą┤ą╗čÅ ą┐ą░ą╝čÅčéąĖ. ąŻ DDR3 ąŠčéą┤ąĄą╗čīąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ ąĘą░ą┤čƹȹ║ąĖ CAS ą┤ą╗čÅ Read ąĖ Write. ąÆąŠąĘą╝ąŠąČąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čéąĖą┐ą░ ą┐ą░ą╝čÅčéąĖ: 2, 3, 4, 5, 6, 7, 8, 9, 10. |

| Partial Array Self-Refresh Size |

C_MEM_MOBILE_PA_SR |

ąöą╗čÅ LPDDR: čŹč鹊čé ą░čéčĆąĖą▒čāčé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé čĆą░ąĘą╝ąĄčĆ ą╝ą░čüčüąĖą▓ą░ ą┤ą╗čÅ ąŠą┐ąĄčĆą░čåąĖąĖ čüą░ą╝ąŠąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ. ąÆąŠąĘą╝ąŠąČąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ: Full, Half. |

| Memory Drive Strength |

DDR, DDR2: C_MEM_DDR1_2_ODS

DDR3: C_MEM_DDR3_ODS

LPDDR: C_MEM_MDDR_ODS |

ąÉčéčĆąĖą▒čāčé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ąĮą░ą│čĆčāąĘąŠčćąĮčāčÄ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī ą▓čŗčģąŠą┤ą░ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┐ą░ą╝čÅčéąĖ. ąÆąŠąĘą╝ąŠąČąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ:

DDR/DDR2: FULL, REDUCED

DDR3: DIV6 (RZQ/6), DIV7 (RZQ/7)

LPDDR: FULL, THREEQUARTERS, HALF, QUARTER |

| Memory Termination Value (ODT) |

DDR2: C_MEM_DDR2_RTT

DDR3: C_MEM_DDR3_RTT |

ąŻčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ on-die termination čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐ą░ą╝čÅčéąĖ. ąÆąŠąĘą╝ąŠąČąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ:

DDR2: OFF, 50OHMS, 75OHMS, 150OHMS

DDR3: OFF, DIV2 (RZQ/2), DIV4, (RZQ/4), DIV6 (RZQ/6), DIV8 (RZQ/8), DIV12 (RZQ/12)

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: RZQ=240╬® |

| Memory Differential DQS Enable |

C_MEM_DDR2_DIFF_DQS_EN |

ąĀą░ąĘčĆąĄčłą░ąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą│ąŠ čüčéčĆąŠą▒ą░ DQS. ąŁč鹊čé ą░čéčĆąĖą▒čāčé ą▓čüąĄą│ą┤ą░ čĆą░ąĘčĆąĄčłąĄąĮ ą┤ą╗čÅ DDR3; ąŠąĮ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ąĮą░ YES ą┤ą╗čÅ DDR2 ąĮą░ čćą░čüč鹊č鹥 ą▓čŗčłąĄ 200 ą£ąōčå. ąÆąŠąĘą╝ąŠąČąĮčŗąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┤ą╗čÅ DDR2: YES, NO |

| Memory Auto Self Refresh |

C_MEM_DDR3_AUTO_SR |

ąóąŠą╗čīą║ąŠ ą┤ą╗čÅ DDR3: auto self-refresh ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐ą░ą╝čÅčéąĖ ąŠą┐čĆąĄą┤ąĄą╗čÅčéčī ą╗čāčćčłąĖą╣ ąĖąĮč鹥čĆą▓ą░ą╗ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ, ąŠčüąĮąŠą▓čŗą▓ą░čÅčüčī ąĮą░ č鹥ą╝ą┐ąĄčĆą░čéčāčĆąĄ čāčüčéčĆąŠą╣čüčéą▓ą░. ąĢčüą╗ąĖ ą░ą▓č鹊ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ, čĆą░ą▒ąŠčćąĖą╣ ą┤ąĖą░ą┐ą░ąĘąŠąĮ č鹥ą╝ą┐ąĄčĆą░čéčāčĆ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąŠą║ą░ąĘą░ąĮ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ čĆąĄą│ąĖčüčéčĆą░ ą▓čŗčüąŠą║ąŠą╣ č鹥ą╝ą┐ąĄčĆą░čéčāčĆčŗ čüą░ą╝ąŠąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ. ąÆąŠąĘą╝ąŠąČąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ: ENABLED, MANUAL. |

| Memory High Temperature Self Refresh |

C_MEM_DDR2_3_HIGH_TEMP_SR |

ąöą╗čÅ DDR2 ąĖ DDR3: ą┐ą░ą╝čÅčéčī ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąĄčĆąĄą▓ąĄą┤ąĄąĮą░ ą▓ čĆąĄąČąĖą╝ čüą░ą╝ąŠąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ ą▓čŗčüąŠą║ąŠą╣ č鹥ą╝ą┐ąĄčĆą░čéčāčĆčŗ, čćč鹊ą▒čŗ čāą╝ąĄąĮčīčłąĖčéčī ąĖąĮč鹥čĆą▓ą░ą╗ ą▓čĆąĄą╝ąĄąĮąĖ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ. ąÆąŠąĘą╝ąŠąČąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ DDR2/DDR3: NORMAL (0ŌĆō85┬░C), EXTENDED (> 85┬░C). |

| Memory Dynamic Output Driver Termination |

C_MEM_DDR3_DYN_WRT_ODT |

ąöą╗čÅ DDR3: ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ąĘąĮą░č湥ąĮąĖąĄ ą┤ąĖąĮą░ą╝ąĖč湥čüą║ąŠą│ąŠ č鹥čĆą╝ąĖąĮąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓čŗčģąŠą┤ą░ ą┤čĆą░ą╣ą▓ąĄčĆą░. ąÆąŠąĘą╝ąŠąČąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ: DDR3: OFF, DIV2 (RZQ/2), DIV4 (RZQ/4). |

| ąŚąĮą░č湥ąĮąĖąĄ tRAS ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą┐ą░ą╝čÅčéąĖ |

C_MEM_TRAS |

ą£ąĖąĮąĖą╝ą░ą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┐ąĄčĆąĖąŠą┤ą░ ąŠčé čüąŠčüč鹊čÅąĮąĖčÅ Active ą┤ąŠ čüąŠčüč鹊čÅąĮąĖčÅ Precharge. ąÆąŠąĘą╝ąŠąČąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ (ą▓ ą┐ąĖą║ąŠčüąĄą║čāąĮą┤ą░čģ) čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄčéčüčÅ ąĮą░ ą▒ą░ąĘąĄ ą▓čŗą▒čĆą░ąĮąĮąŠą╣ ą▓ čāčéąĖą╗ąĖč鹥 MIG ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą┐ą░ą╝čÅčéąĖ. |

| ąŚąĮą░č湥ąĮąĖąĄ tRCD ą┤ą╗čÅ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą┐ą░ą╝čÅčéąĖ |

C_MEM_TRCD |

ą£ąĖąĮąĖą╝ą░ą╗čīąĮą░čÅ ąĘą░ą┤ąĄčƹȹ║ą░ ąŠčé čüąŠčüč鹊čÅąĮąĖčÅ Active ą┤ąŠ ą║ąŠą╝ą░ąĮą┤čŗ Read ąĖą╗ąĖ Write. ąÆąŠąĘą╝ąŠąČąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ (ą▓ ą┐ąĖą║ąŠčüąĄą║čāąĮą┤ą░čģ) čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄčéčüčÅ ąĮą░ ą▒ą░ąĘąĄ ą▓čŗą▒čĆą░ąĮąĮąŠą╣ ą▓ čāčéąĖą╗ąĖč鹥 MIG ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą┐ą░ą╝čÅčéąĖ. |

| ąŚąĮą░č湥ąĮąĖąĄ tREFI ą┤ą╗čÅ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą┐ą░ą╝čÅčéąĖ |

C_MEM_TREFI |

ąĪčĆąĄą┤ąĮąĖą╣ ą┐ąĄčĆąĖąŠą┤ąĖč湥čüą║ąĖą╣ ąĖąĮč鹥čĆą▓ą░ą╗ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ ą┤ą╗čÅ ą┐ą░ą╝čÅčéąĖ. ąŁč鹊čé ą░čéčĆąĖą▒čāčé ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé čćą░čüč鹊čéčā, čü ą║ąŠč鹊čĆąŠą╣ MCB ąŠą▒ąĮąŠą▓ą╗čÅąĄčé ą┐ą░ą╝čÅčéčī, ą░ ąĮąĄ ąĖąĮč鹥čĆą▓ą░ą╗ self-refresh. ąÆąŠąĘą╝ąŠąČąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ (ą▓ ą┐ąĖą║ąŠčüąĄą║čāąĮą┤ą░čģ) čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄčéčüčÅ ąĮą░ ą▒ą░ąĘąĄ ą▓čŗą▒čĆą░ąĮąĮąŠą╣ ą▓ čāčéąĖą╗ąĖč鹥 MIG ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą┐ą░ą╝čÅčéąĖ. |

| ąŚąĮą░č湥ąĮąĖąĄ tRFC ą┤ą╗čÅ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą┐ą░ą╝čÅčéąĖ |

C_MEM_TRFC |

ą£ąĖąĮąĖą╝ą░ą╗čīąĮčŗą╣ ąĖąĮč鹥čĆą▓ą░ą╗ ąŠčé Auto-Refresh ą┤ąŠ čüąŠčüč鹊čÅąĮąĖčÅ Active, ąĖą╗ąĖ ą┐ąĄčĆąĖąŠą┤ ą║ąŠą╝ą░ąĮą┤čŗ Auto-Refresh. ąÆąŠąĘą╝ąŠąČąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ (ą▓ ą┐ąĖą║ąŠčüąĄą║čāąĮą┤ą░čģ) čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄčéčüčÅ ąĮą░ ą▒ą░ąĘąĄ ą▓čŗą▒čĆą░ąĮąĮąŠą╣ ą▓ čāčéąĖą╗ąĖč鹥 MIG ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą┐ą░ą╝čÅčéąĖ. |

| ąŚąĮą░č湥ąĮąĖąĄ tRP ą┤ą╗čÅ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą┐ą░ą╝čÅčéąĖ |

C_MEM_TRP |

ą£ąĖąĮąĖą╝ą░ą╗čīąĮčŗą╣ ą┐ąĄčĆąĖąŠą┤ ą║ąŠą╝ą░ąĮą┤čŗ Precharge. ąÆąŠąĘą╝ąŠąČąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ (ą▓ ą┐ąĖą║ąŠčüąĄą║čāąĮą┤ą░čģ) čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄčéčüčÅ ąĮą░ ą▒ą░ąĘąĄ ą▓čŗą▒čĆą░ąĮąĮąŠą╣ ą▓ čāčéąĖą╗ąĖč鹥 MIG ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą┐ą░ą╝čÅčéąĖ. |

| ąŚąĮą░č湥ąĮąĖąĄ tWR ą┤ą╗čÅ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą┐ą░ą╝čÅčéąĖ |

C_MEM_TWR |

ą£ąĖąĮąĖą╝ą░ą╗čīąĮąŠąĄ ą▓čĆąĄą╝čÅ ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖčÅ ąĘą░ą┐ąĖčüąĖ (Write Recovery) ą┤ą╗čÅ ą┐ą░ą╝čÅčéąĖ. ąÆąŠąĘą╝ąŠąČąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ (ą▓ ą┐ąĖą║ąŠčüąĄą║čāąĮą┤ą░čģ) čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄčéčüčÅ ąĮą░ ą▒ą░ąĘąĄ ą▓čŗą▒čĆą░ąĮąĮąŠą╣ ą▓ čāčéąĖą╗ąĖč鹥 MIG ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą┐ą░ą╝čÅčéąĖ. |

| ąŚąĮą░č湥ąĮąĖąĄ tRTP ą┤ą╗čÅ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą┐ą░ą╝čÅčéąĖ |

C_MEM_TRTP |

ą£ąĖąĮąĖą╝ą░ą╗čīąĮą░čÅ ąĘą░ą┤ąĄčƹȹ║ą░ ą╝ąĄąČą┤čā ą║ąŠą╝ą░ąĮą┤ąŠą╣ Read ą┤ąŠ ą║ąŠą╝ą░ąĮą┤čŗ Precharge. ą×ą▒čŗčćąĮąŠ čŹč鹊čé ą┐ą░čĆą░ą╝ąĄčéčĆ ą╝ąŠąČąĮąŠ ąĮą░ą╣čéąĖ č鹊ą╗čīą║ąŠ ąĮą░ čāčüčéčĆąŠą╣čüčéą▓ą░čģ DDR2 ąĖ DDR3. ąÆąŠąĘą╝ąŠąČąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ (ą▓ ą┐ąĖą║ąŠčüąĄą║čāąĮą┤ą░čģ) čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄčéčüčÅ ąĮą░ ą▒ą░ąĘąĄ ą▓čŗą▒čĆą░ąĮąĮąŠą╣ ą▓ čāčéąĖą╗ąĖč鹥 MIG ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą┐ą░ą╝čÅčéąĖ. |

| ąŚąĮą░č湥ąĮąĖąĄ tWTR ą┤ą╗čÅ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą┐ą░ą╝čÅčéąĖ |

C_MEM_TWTR |

ą£ąĖąĮąĖą╝ą░ą╗čīąĮą░čÅ ąĘą░ą┤ąĄčƹȹ║ą░ ąŠčé ą║ąŠą╝ą░ąĮą┤čŗ Write ą┤ąŠ ą║ąŠą╝ą░ąĮą┤čŗ Read. ąÆąŠąĘą╝ąŠąČąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ (ą▓ ą┐ąĖą║ąŠčüąĄą║čāąĮą┤ą░čģ) čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄčéčüčÅ ąĮą░ ą▒ą░ąĘąĄ ą▓čŗą▒čĆą░ąĮąĮąŠą╣ ą▓ čāčéąĖą╗ąĖč鹥 MIG ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą┐ą░ą╝čÅčéąĖ. |

| ąÉčéčĆąĖą▒čāčé |

ąśą╝čÅ ą┐ą░čĆą░ą╝ąĄčéčĆą░ |

ą×ą┐ąĖčüą░ąĮąĖąĄ / ą▓ąŠąĘą╝ąŠąČąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ |

| ą¤ąĄčĆąĖąŠą┤ čéą░ą║č鹊ą▓ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ |

C_MEMCLK_PERIOD |

ąŁč鹊čé ą░čéčĆąĖą▒čāčé ą║ąŠąĮą▓ąĄčĆčéąĖčĆčāąĄčé ą┐ą░čĆą░ą╝ąĄčéčĆčŗ ą▓čĆąĄą╝ąĄąĮąĖ ą┐ą░ą╝čÅčéąĖ ą╝ąĄąČą┤čā čåąĖą║ą╗ą░ą╝ąĖ čéą░ą║č鹊ą▓ ąĖ ą┐ąĖą║ąŠčüąĄą║čāąĮą┤ą░ą╝ąĖ. ąÆąŠąĘą╝ąŠąČąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ (ą▓ ą┐ąĖą║ąŠčüąĄą║čāąĮą┤ą░čģ) čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄčéčüčÅ ąĮą░ ą▒ą░ąĘąĄ ą▓čŗą▒čĆą░ąĮąĮąŠą╣ ą▓ čāčéąĖą╗ąĖč鹥 MIG ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą┐ą░ą╝čÅčéąĖ. |

| ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą┐ąŠčĆčéą░ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ |

C_PORT_CONFIG |

ąŁč鹊čé ą░čéčĆąĖą▒čāčé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÄ ą┐ąŠčĆčéą░ User Interface. ą×ąĮ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąŠčĆčéą░ (B = Bidirectional, W = Unidirectional Write, R = Unidirectional Read) ąĖ čłąĖčĆąĖąĮčā čłąĖąĮčŗ ą┤ą░ąĮąĮčŗčģ (32, 64 ąĖą╗ąĖ 128 ą▒ąĖčé). ąÆąŠąĘą╝ąŠąČąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ:

B32_B32_W32_W32_W32_W32

B32_B32_W32_W32_W32_R32

B32_B32_W32_W32_R32_W32

B32_B32_W32_W32_R32_R32

B32_B32_W32_R32_W32_W32

B32_B32_W32_R32_W32_R32

B32_B32_W32_R32_R32_W32

B32_B32_W32_R32_R32_R32

B32_B32_R32_W32_W32_W32

B32_B32_R32_W32_W32_R32

B32_B32_R32_W32_R32_W32

B32_B32_R32_W32_R32_R32

B32_B32_R32_R32_W32_W32

B32_B32_R32_R32_W32_R32

B32_B32_R32_R32_R32_W32

B32_B32_R32_R32_R32_R32

B32_B32_B32_B32

B64_B32_B32

B64_B64

B128 |

| ą©ąĖčĆąĖąĮą░ čłąĖąĮčŗ ą┤ą░ąĮąĮčŗčģ ą┐ąŠčĆčéą░ (ą┐ąŠčĆčéčŗ 0 ąĖ 1) |

C_P0_DATA_PORT_SIZE C_P1_DATA_PORT_SIZE |

ą¤ąŠčĆčéčŗ 0 ąĖ 1 User Interface ą╝ąŠą│čāčé ą╝ąĄąĮčÅčéčī čłąĖčĆąĖąĮčā čłąĖąĮčŗ ą┤ą░ąĮąĮčŗčģ ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą▓čŗą▒čĆą░ąĮąĮąŠą╣ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą┐ąŠčĆčéą░ (ą┐ąŠčĆčéčŗ ąŠčé 3 ą┤ąŠ 5, ąĄčüą╗ąĖ ą┤ąŠčüčéčāą┐ąĮčŗ, ąĖą╝ąĄčÄčé ą▓čüąĄą│ą┤ą░ čĆą░ąĘčĆčÅą┤ąĮąŠčüčéčī 32 ą▒ąĖčéą░). ąŁčéąĖ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄčé čłąĖčĆąĖąĮčā ą┤ą░ąĮąĮčŗčģ ą┐ąŠčĆčéą░ 0 ąĖ 1. ąÆąŠąĘą╝ąŠąČąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ: 32, 64, 128. |

| ą©ąĖčĆąĖąĮą░ ą╝ą░čüą║ąĖ ą┤ą░ąĮąĮčŗčģ (ą┐ąŠčĆčéčŗ 0 ąĖ 1) |

C_P0_MASK_SIZE

C_P1_MASK_SIZE |

ąŁč鹊čé ą░čéčĆąĖą▒čāčé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ąĖčé ą╝ą░čüą║ąĖ ą┤ą╗čÅ ą┐ąŠčĆč鹊ą▓ 0 ąĖ 1, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čłąĖčĆąĖąĮčŗ čłąĖąĮčŗ ą┤ą░ąĮąĮčŗčģ, ą║ą░ą║ čŹč鹊 ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąŠ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĄą╣ ą┐ąŠčĆčéą░. ąÆąŠąĘą╝ąŠąČąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ: 4, 8, 16. |

| ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐ąŠčĆčéą░ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ |

C_PORT_ENABLE |

ąŁč鹊 6-ą▒ąĖčéąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé, ą║ą░ą║ąŠą╣ ąĖąĘ ąĮąĖąČąĄą╗ąĄąČą░čēąĖčģ čłąĄčüčéąĖ ą░ą┐ą┐ą░čĆą░čéąĮčŗčģ 32-ą▒ąĖčéąĮčŗčģ ą┐ąŠčĆčéą░ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą▓ ąĖą╝ąĄčÄčēąĄą╣čüčÅ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą┐ąŠčĆčéą░. ąÆąŠąĘą╝ąŠąČąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ: ąĮą░ą┐čĆąĖą╝ąĄčĆ, b001111 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 čĆą░ąĘčĆąĄčłąĄąĮčŗ ą┐ąŠčĆčéčŗ ąŠčé 0 ą┤ąŠ 3. |

| ą¤ąŠčĆčÅą┤ąŠą║ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖčÅ ą░ą┤čĆąĄčüąŠą▓ |

C_MEM_ADDR_ORDER |

ąŁč鹊čé ą░čéčĆąĖą▒čāčé ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé, ą║ą░ą║ ą░ą┤čĆąĄčü ą▒ą░ą╣čéą░, ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮąĮčŗą╣ ą┤ą╗čÅ User Interface, ąŠč鹊ą▒čĆą░ąČą░ąĄčéčüčÅ ąĮą░ ą▒ąĖčéčŗ ą░ą┤čĆąĄčüą░ čäąĖąĘąĖč湥čüą║ąŠą│ąŠ ą▒ą░ąĮą║ą░ ą┐ą░ą╝čÅčéąĖ, čüčéčĆąŠą║ąĖ, ąĖ čüč鹊ą╗ą▒čåą░. ąŁč鹊čé ą░čéčĆąĖą▒čāčé ąŠčüąĮąŠą▓čŗą▓ą░ąĄčéčüčÅ ąĮą░ čüčģąĄą╝ąĄ čüąĖčüč鹥ą╝ąĮąŠą╣ ą░ą┤čĆąĄčüą░čåąĖąĖ. ąŁč鹊 ąĘąĮą░č湥ąĮąĖąĄ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ąĮą░ąĖą▒ąŠą╗čīčłąĄą│ąŠ ą┐čĆąĄąĖą╝čāčēąĄčüčéą▓ą░ MCB ą┐čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ ą▓ąŠąĘą╝ąŠąČąĮąŠčüč鹥ą╣ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąŠčéą║čĆčŗčéčŗą╝ ą▒ą░ąĮą║ąŠą╝. ąÆąŠąĘą╝ąŠąČąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ: BANK_ROW_COLUMN, ROW_BANK_COLUMN. |

| Arbitration Time Slot Count |

C_ARB_NUM_TIME_SLOTS |

ąÉčéčĆąĖą▒čāčé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čéą░ą╣ą╝-čüą╗ąŠč鹊ą▓ ą▓ čéą░ą▒ą╗ąĖčåąĄ ą░čĆą▒ąĖčéčĆą░ąČą░. ąæąŠą╗čīčłąĖąĮčüčéą▓ąŠ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖą╣ ą┐ąŠčĆčéą░ ąĖą╝ąĄčÄčé 12 čéą░ą╣ą╝-čüą╗ąŠč鹊ą▓, ąĮąŠ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą┐ąŠčĆčéą░ čü 5 ą░ą║čéąĖą▓ąĮčŗą╝ąĖ ą┐ąŠčĆčéą░ą╝ąĖ ąĖą╝ąĄčÄčé 10 čéą░ą╣ą╝-čüą╗ąŠč鹊ą▓ ą▓ čéą░ą▒ą╗ąĖčåąĄ ą░čĆą▒ąĖčéčĆą░ąČą░, čćč鹊ą▒čŗ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī ąŠą┤ąĖąĮą░ą║ąŠą▓čŗą╣ ą░čĆą▒ąĖčéčĆą░ąČ. ąÆąŠąĘą╝ąŠąČąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ: 12, 10. |

| Arbitration Time Slot Values |

C_ARB_TIME_SLOT[0:11] |

ąŁčéąĖ ą▓ąŠčüčīą╝ąĄčĆąĖčćąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ ąĖąĘ 6 čåąĖčäčĆ (18 ą▒ąĖčé) čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄčé ąĘąĮą░č湥ąĮąĖčÅ ą┐čĆąĖąŠčĆąĖč鹥čéą░ ą┐ąŠčĆčéą░ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ čéą░ą╣ą╝-čüą╗ąŠčéą░. ąÆąŠąĘą╝ąŠąČąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ: ąĮą░ą┐čĆąĖą╝ąĄčĆ, C_ARB_TIME_SLOT0 = 18'o012345 (čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ą┐ąŠčĆčé 0 čü ąĮą░ąĖą▓čŗčüčłąĖą╝ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝ ą┤ąŠ ą┐ąŠčĆčéą░ 5 čü čüą░ą╝čŗą╝ ąĮąĖąĘą║ąĖą╝ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝). |

| ą¤čĆąŠą┐čāčüą║ ą║ą░ą╗ąĖą▒čĆąŠą▓ą║ąĖ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ (čüąĖą╝čāą╗čÅčåąĖčÅ) |

C_MC_CALIB_BYPASS |

ąŻą║ą░ąĘčŗą▓ą░ąĄčé čāčéąĖą╗ąĖč鹥 MIG čāčüčéą░ąĮąŠą▓ąĖčéčī čäą░ą╣ą╗čŗ čüąĖą╝čāą╗čÅčåąĖąĖ ą┤ą╗čÅ ą┐čĆąŠą┐čāčüą║ą░ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą║ą░ą╗ąĖą▒čĆąŠą▓ą║ąĖ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░, čćč鹊ą▒čŗ čāčüą║ąŠčĆąĖčéčī čüąĖą╝čāą╗čÅčåąĖčÄ. ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: čŹč鹊čé ą┐ą░čĆą░ą╝ąĄčéčĆ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čüąĖą╝čāą╗čÅčåąĖąĖ. ąÆąŠąĘą╝ąŠąČąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ: YES, NO. |

| Reserved Calibration Address Space |

C_MC_CALIBRATION_RA C_MC_CALIBRATION_BA C_MC_CALIBRATION_CA |

ą×ą┐čĆąĄą┤ąĄą╗čÅąĄčé ąĮą░čćą░ą╗čīąĮčŗąĄ ą░ą┤čĆąĄčüą░ čüčéčĆąŠą║ąĖ, ą▒ą░ąĮą║ą░ ąĖ čüč鹊ą╗ą▒čåą░, ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąĮčŗąĄ ą┤ą╗čÅ ą║ą░ą╗ąĖą▒čĆąŠą▓ą║ąĖ. ąŁč鹊čé ą░čéčĆąĖą▒čāčé ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čéčĆąĄąĮąĖčĆąŠą▓ą║ąĖ čłą░ą▒ą╗ąŠąĮą░ą╝ąĖ ą┤ą░ąĮąĮčŗčģ ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĄą║ą░ą╗ąĖą▒čĆąŠą▓ą║ąĖ, čćč鹊ą▒čŗ ąĖąĘą▒ąĄąČą░čéčī ą┐ąĄčĆąĄąĘą░ą┐ąĖčüąĖ ą┤ą░ąĮąĮčŗčģ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ. ąÆąŠąĘą╝ąŠąČąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ (ą▓ąŠąĘą╝ąŠąČąĄąĮ ą╗čÄą▒ąŠą╣ ą┤ąŠą┐čāčüčéąĖą╝čŗą╣ ą░ą┤čĆąĄčü), ą┐čĆąĖą╝ąĄčĆčŗ:

C_MC_CALIBRATION_RA = 15'h0000

C_MC_CALIBRATION_BA = 3'h0

C_MC_CALIBRATION_CA = 12'h000 |

| ąĀąĄąČąĖą╝ ą║ą░ą╗ąĖą▒čĆąŠą▓ą║ąĖ |

C_MC_CALIBRATION_MODE |

ąŁč鹊čé ą░čéčĆąĖą▒čāčé ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé, ą▓čŗą┐ąŠą╗ąĮąĖčé ą╗ąĖ MCB č鹊čćąĮąŠąĄ ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖąĄ ąĖ ą║ąŠą╝ą┐ąĄąĮčüą░čåąĖčÄ ą▓ čĆąĄą░ą╗čīąĮąŠą╝ ą▓čĆąĄą╝ąĄąĮąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ/č鹥ą╝ą┐ąĄčĆą░čéčāčĆčŗ ą┤ą╗čÅ čüčéčĆąŠą▒ą░ DQS (čćč鹊 čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ) ąĖą╗ąĖ ą▒čāą┤ąĄčé ą┐čĆąŠčüč鹊 ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮąŠąĄ čüąŠąŠčéąĮąŠčłąĄąĮąĖčÅ ą┐ąĄčĆąĖąŠą┤ą░ ą▒ąĖčéą░ ą║ čüą╝ąĄčēąĄąĮąĖčÄ DQS ą▓ ąŠą║ąĮąĄ ą┤ą░ąĮąĮčŗčģ. ąÆąŠąĘą╝ąŠąČąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ: CALIBRATION (č鹊čćąĮąŠąĄ ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖąĄ DQS čü ą║ąŠą╝ą┐ąĄąĮčüą░čåąĖąĄą╣ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ/č鹥ą╝ą┐ąĄčĆą░čéčāčĆčŗ), NOCALIBRATION (čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮą░čÅ ąĘą░ą┤ąĄčƹȹ║ą░ čüą╝ąĄčēąĄąĮąĖčÅ DQS). |

| ąŚąĮą░č湥ąĮąĖąĄ ąĘą░ą┤ąĄčƹȹ║ąĖ čüą╝ąĄčēąĄąĮąĖčÅ DQS |

C_MC_CALIBRATION_DELAY |

ąŁč鹊čé ą░čéčĆąĖą▒čāčé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮčāčÄ ąĘą░ą┤ąĄčƹȹ║čā čüą╝ąĄčēąĄąĮąĖčÅ DQS ą║ą░ą║ čüąŠąŠčéąĮąŠčłąĄąĮąĖąĄ ą┐ąĄčĆąĖąŠą┤ą░ ą▒ąĖčéą░, ą║ąŠą│ą┤ą░ C_MC_CALIBRATION_MODE = NOCALIBRATION. ąÆąŠąĘą╝ąŠąČąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ: QUARTER, HALF, THREEQUARTER, FULL. |

ą¤ą░čĆą░ą╝ąĄčéčĆčŗ ąĖąĮč鹥čĆą▓ą░ą╗ąŠą▓ ą▓čĆąĄą╝ąĄąĮąĖ ą┐ą░ą╝čÅčéąĖ ą▒ąĄčĆčāčéčüčÅ ąĖąĘ ą┤ą░čéą░čłąĖč鹊ą▓ ą▓ąĄąĮą┤ąŠčĆąŠą▓, ąĖ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąĮą░ąĘąĮą░čćą░čÄčéčüčÅ ąĖąĮčüčéčĆčāą╝ąĄąĮčéą░ą╝ąĖ, ą║ąŠą│ą┤ą░ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄą╝ąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ. ą¤ą░čĆą░ą╝ąĄčéčĆčŗ ąĖąĮč鹥čĆą▓ą░ą╗ąŠą▓ ą▓čĆąĄą╝ąĄąĮąĖ ą╝ąŠą│čāčé ą▒čŗčéčī čāą║ą░ąĘą░ąĮčŗ ą┐čĆąĖ čüąŠąĘą┤ą░ąĮąĖąĖ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čīčüą║ąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ (čüą╝. "Setting Controller Options" ą▓ [2]).

ą¤ąŠą┤čĆąŠą▒ąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ ąĖąĮč鹥čĆč乥ą╣čüą░. ąÜą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▓ ą▒ą╗ąŠą║-čüčģąĄą╝ąĄ ą░čĆčģąĖč鹥ą║čéčāčĆčŗ ąĮą░ čĆąĖčü. 2-1, čā MCB ąĄčüčéčī 2 ą▒ą░ąĘąŠą▓čŗčģ ąĖąĮč鹥čĆč乥ą╣čüą░: ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ User Interface ą┤ą╗čÅ ą╗ąŠą│ąĖą║ąĖ FPGA, ąĖ ą▓ąĮąĄčłąĮąĖą╣ ąĖąĮč鹥čĆč乥ą╣čü ą║ čāčüčéčĆąŠą╣čüčéą▓čā ą┐ą░ą╝čÅčéąĖ čü ą┐čĆąĄą┤ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗą╝ąĖ ąĮąŠąČą║ą░ą╝ąĖ ą▓čŗą▓ąŠą┤ąŠą▓ I/O. ąÆ čüą╗ąĄą┤čāčÄčēąĖčģ ą┐ąŠą┤čüąĄą║čåąĖčÅ ąŠą▒čüčāąČą┤ą░čÄčéčüčÅ ą▓čüąĄ čüąĖą│ąĮą░ą╗čŗ, čüą▓čÅąĘą░ąĮąĮčŗąĄ čü čŹčéąĖą╝ąĖ ą┤ą▓čāą╝čÅ ąĖąĮč鹥čĆč乥ą╣čüą░ą╝ąĖ. ąÆ ąŠčüčéą░ą╗čīąĮąŠą╣ čćą░čüčéąĖ čŹč鹊ą│ąŠ ą┤ąŠą║čāą╝ąĄąĮčéą░ ą▓čüąĄ ąŠą┐ąĖčüą░ąĮąĖčÅ čüčüčŗą╗ą░čÄčéčüčÅ ąĮą░ ąĖąĮč鹥čĆč乥ą╣čü IP wrapper, ą┐ąŠą╗čāč湥ąĮąĮčŗą╣ ąŠčé CORE Generator ąĖą╗ąĖ ąĖąĮčüčéčĆčāą╝ąĄąĮčéą░čĆąĖčÅ EDK, ąĮąŠ ąĮąĄ ą║ ąĖąĮč鹥čĆč乥ą╣čüčā ą┐čĆąĖą╝ąĖčéąĖą▓ą░ ąĮąĖąČąĄą╗ąĄąČą░čēąĄą│ąŠ ą▒ą╗ąŠą║ą░ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą┐ą░ą╝čÅčéąĖ.

ąśąĮč鹥čĆč乥ą╣čü ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ (čüč鹊čĆąŠąĮą░ čäą░ą▒čĆąĖą║ąĖ ą║čĆąĖčüčéą░ą╗ą╗ą░). User Interface čüąŠą┤ąĄčƹȹĖčé ą▓čüąĄ ąĮąĄąŠą▒čģąŠą┤ąĖą╝čŗąĄ čüąĖą│ąĮą░ą╗čŗ ą┤ą╗čÅ ą╗ąŠą│ąĖą║ąĖ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ ą▓ FPGA, čćč鹊ą▒čŗ ą▓ąĘą░ąĖą╝ąŠą┤ąĄą╣čüčéą▓ąŠą▓ą░čéčī čü command path ąĖ datapath ą┐ąŠčĆč鹊ą▓ MCB. ą×ąĮ čéą░ą║ąČąĄ ą▓ą║ą╗čÄčćą░ąĄčé čüąĖą│ąĮą░ą╗čŗ ąŠčüąĮąŠą▓ąĮąŠą│ąŠ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖ čüą▒čĆąŠčüą░ MCB, ą║ą░ą║ ąĖ čüąĖą│ąĮą░ą╗čŗ, ąŠčéąĮąŠčüčÅčēąĖąĄčüčÅ ą║ ąŠą┐ąĄčĆą░čåąĖčÅą╝ ą║ą░ą╗ąĖą▒čĆąŠą▓ą║ąĖ, ąŠčéą╗ą░ą┤ą║ąĖ ąĖ čüą░ą╝ąŠąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ. User Interface ą╝ąŠąČąĄčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ąĮą░ ą╗čÄą▒ąŠą╣ ąŠą┤ąĖąĮ ąĖąĘ 6 ą┐ąŠčĆč鹊ą▓, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▓ čĆą░ąĘą┤ąĄą╗ąĄ "ąÜąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą┐ąŠčĆčéą░".

ąĪąĖą│ąĮą░ą╗čŗ čéą░ą║č鹊ą▓, čüą▒čĆąŠčüą░, ą║ą░ą╗ąĖą▒čĆąŠą▓ą║ąĖ. ąóą░ą▒ą╗ąĖčåą░ 2-4 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüąĖą│ąĮą░ą╗čŗ, čüą▓čÅąĘą░ąĮąĮčŗąĄ čü čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄą╝, čüą▒čĆąŠčüąŠą╝ ąĖ ą║ą░ą╗ąĖą▒čĆąŠą▓ą║ąŠą╣ MCB User Interface.

ąóą░ą▒ą╗ąĖčåą░ 2-4. ąĪąĖą│ąĮą░ą╗čŗ Clock, Reset ąĖ Calbration.

| ąśą╝čÅ čüąĖą│ąĮą░ą╗ą░ |

ąØą░ą┐čĆ. |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| async_rst |

ąÆčģąŠą┤ |

ąōą╗ą░ą▓ąĮčŗą╣ čüąĖčüč鹥ą╝ąĮčŗą╣ čüą▒čĆąŠčü ą┤ą╗čÅ MCB. |

| calib_done |

ąÆčŗčģąŠą┤ |

ąŁč鹊čé čüąĖą│ąĮą░ą╗ čü ą░ą║čéąĖą▓ąĮčŗą╝ čāčĆąŠą▓ąĮąĄą╝ ą╗ąŠą│. 1 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĄ ą▓čüąĄčģ čäą░ąĘ ą║ą░ą╗ąĖą▒čĆąŠą▓ą║ąĖ ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ąĘą░ą┐čāčüą║ą░ (start-up) MCB. ąóčĆą░ąĮąĘą░ą║čåąĖąĖ ąĮąĄ ą┤ąŠą╗ąČąĮčŗ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ą░čéčīčüčÅ ą┤ą╗čÅ MCB, ą┐ąŠą║ą░ čŹč鹊čé čüąĖą│ąĮą░ą╗ ąĮąĄ ą┐ąĄčĆąĄą╣ą┤ąĄčé ą▓ ą╗ąŠą│. 1, čćč鹊ą▒čŗ ą┐ąŠą║ą░ąĘą░čéčī ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĄ ą║ą░ą╗ąĖą▒čĆąŠą▓ą║ąĖ. ąĪą╝. čĆą░ąĘą┤ąĄą╗ "ąÜą░ą╗ąĖą▒čĆąŠą▓ą║ą░" ą▓ ąōą╗ą░ą▓ąĄ 4 ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ. |

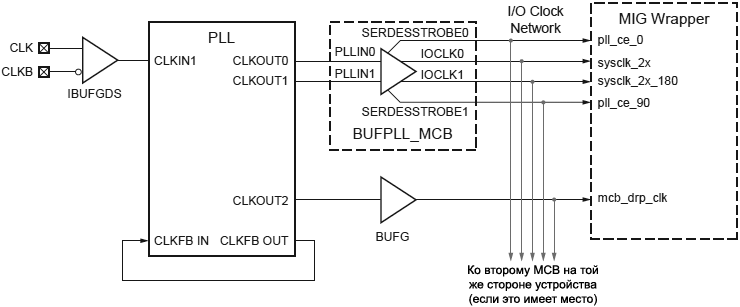

| mcb_drp_clk |

ąÆčģąŠą┤ |

ąŁč鹊čé čéą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗ čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆčāąĄčé ą╝ąŠą┤čāą╗čī ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą╣ ą║ą░ą╗ąĖą▒čĆąŠą▓ą║ąĖ (soft calibration module) čü ą┤ąŠą╝ąĄąĮąŠą╝ čéą░ą║č鹊ą▓ sysclk_2x. ąŁč鹊čé čéą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮ č鹊ą╣ ąČąĄ PLL, čćč鹊 ąĖ sysclk_2x, čćč鹊ą▒čŗ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī čüąĖąĮčģčĆąŠąĮąĮąŠčüčéčī čäą░ąĘčŗ čéą░ą║č鹊ą▓ čü čŹčéąĖą╝ ą┤ąŠą╝ąĄąĮąŠą╝. ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. "ąóą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ" ą▓ ąōą╗ą░ą▓ąĄ 3. |

| pll_ce_0 |

ąÆčģąŠą┤ |

ąĪčéčĆąŠą▒ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ (I/O clock enable) ąŠčé BUFPLL_MCB. ąŁč鹊čé čüąĖą│ąĮą░ą╗ ą▓čŗą┤ą░ąĄčé ąĖą╝ą┐čāą╗čīčü ą╗ąŠą│. 1 ąĮą░ ą║ą░ąČą┤ąŠą╝ ą┤čĆčāą│ąŠą╝ ą┐ąĄčĆąĖąŠą┤ąĄ čéą░ą║č鹊ą▓ sysclk_2x. ą×ąĮ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čāą┤ą▓ąŠąĄąĮąĖčÅ čüą║ąŠčĆąŠčüčéąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ą▓ ą▒ą╗ąŠą║ą░čģ I/O. |

| pll_ce_90 |

ąÆčģąŠą┤ |

ąĪčéčĆąŠą▒ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ (I/O clock enable) ąŠčé BUFPLL_MCB. ąŁč鹊čé čüąĖą│ąĮą░ą╗ ą▓čŗą┤ą░ąĄčé ąĖą╝ą┐čāą╗čīčü ą╗ąŠą│. 1 ąĮą░ ą║ą░ąČą┤ąŠą╝ ą┤čĆčāą│ąŠą╝ ą┐ąĄčĆąĖąŠą┤ąĄ čéą░ą║č鹊ą▓ sysclk_2x_180. ą×ąĮ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čāą┤ą▓ąŠąĄąĮąĖčÅ čüą║ąŠčĆąŠčüčéąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ą▓ ą▒ą╗ąŠą║ą░čģ I/O. |

| pll_lock |

ąÆčģąŠą┤ |

ąĪąĖą│ąĮą░ą╗ ąĘą░čģą▓ą░čéą░ PLL ąŠčé ą▒ą╗ąŠą║ą░ BUFPLL_MCB. |

| sysclk_2x |

ąÆčģąŠą┤ |

ąōą╗ą░ą▓ąĮą░čÅ čüąĖčüč鹥ą╝ąĮą░čÅ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ ą┤ą╗čÅ MCB. ąŁč鹊čé čüąĖą│ąĮą░ą╗ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą▒ą╗ąŠą║ąŠą╝ PLL Spartan-6 FPGA, ąĖ ą┐ąŠą▓č鹊čĆąĮąŠ ą▒čāč乥čĆąĖąĘąĖčĆčāąĄčéčüčÅ ą┤čĆą░ą╣ą▓ąĄčĆąŠą╝ BUFPLL_MCB ą┤ą╗čÅ čåąĄą┐ąĖ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ (I/O clock network). ą×ąĮ čĆą░ą▒ąŠčéą░ąĄčé ąĮą░ ą┤ą▓ąŠą╣ąĮąŠą╣ čćą░čüč鹊č鹥 čéą░ą║č鹊ą▓ ą┐ą░ą╝čÅčéąĖ (ąĮą░ą┐čĆąĖą╝ąĄčĆ 667 ą£ąōčå ą┤ą╗čÅ 333 ą£ąōčå ąĮą░ ąĖąĮč鹥čĆč乥ą╣čüąĄ ą┐ą░ą╝čÅčéąĖ). |

| sysclk_2x_180 |

ąÆčģąŠą┤ |

ąŁč鹊 ą▓čģąŠą┤ čüąĖą│ąĮą░ą╗ą░ ą┤ą╗čÅ čüą┤ą▓ąĖąĮčāčéčŗčģ ą┐ąŠ čäą░ąĘąĄ čéą░ą║č鹊ą▓ čü č鹊ą╣ ąČąĄ čćą░čüč鹊č鹊ą╣, čćč鹊 ąĖ sysclk_2x. ąŁč鹊čé čüąĖą│ąĮą░ą╗ čéą░ą║č鹊ą▓ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ č鹥ą╝ąĖ ąČąĄ čĆąĄčüčāčĆčüą░ą╝ąĖ PLL/BUFPLL_MCB. |

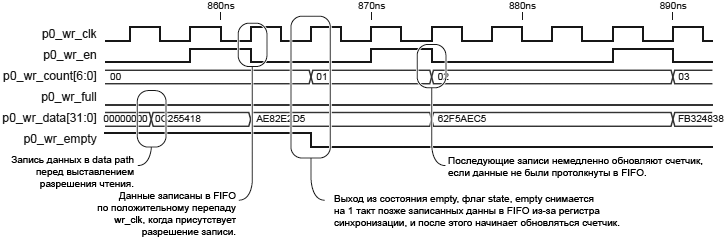

Command Path. ąóą░ą▒ą╗ąĖčåą░ 2-5 ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé čüąĖą│ąĮą░ą╗čŗ, čüą▓čÅąĘą░ąĮąĮčŗąĄ čü ą┐čāč鹥ą╝ ą║ąŠą╝ą░ąĮą┤ MCB User Interface. ąÆčüąĄ ąĖą╝ąĄąĮą░ čüąĖą│ąĮą░ą╗ąŠą▓ ą┐ąŠčĆčéą░ ąĖą╝ąĄčÄčé ą┐čĆąĄčäąĖą║čü pX, ą│ą┤ąĄ X ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé ąĮąŠą╝ąĄčĆ ą┐ąŠčĆčéą░ (ąĮą░ą┐čĆąĖą╝ąĄčĆ čüąĖą│ąĮą░ą╗čŗ ą┐ąŠčĆčéą░ 0 ąĖą╝ąĄčÄčé ą┐čĆąĄčäąĖą║čü p0, ą┐ąŠčĆčé 1 ą┐čĆąĄčäąĖą║čü p1, ąĖ čéą░ą║ ą┤ą░ą╗ąĄąĄ).

ąóą░ą▒ą╗ąĖčåą░ 2-5. ąĪąĖą│ąĮą░ą╗čŗ Command Path.

| ąśą╝čÅ čüąĖą│ąĮą░ą╗ą░ |

ąØą░ą┐čĆ. |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| pX_cmd_addr[29:0] |

ąÆčģąŠą┤ |

ąæą░ą╣č鹊ą▓čŗą╣ ąĮą░čćą░ą╗čīąĮčŗą╣ ą░ą┤čĆąĄčü ą┤ą╗čÅ č鹥ą║čāčēąĄą╣ čéčĆą░ąĮąĘą░ą║čåąĖąĖ. ąÉą┤čĆąĄčü ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą▓čŗčĆąŠą▓ąĮąĄąĮ ą┐ąŠ čĆą░ąĘą╝ąĄčĆčā ą┐ąŠčĆčéą░: ą┤ą╗čÅ 32-ą▒ąĖčéąĮčŗčģ ą┐ąŠčĆč鹊ą▓ ą╝ą╗ą░ą┤čłąĖąĄ 2 ą▒ąĖčéą░ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĮčāą╗čÅą╝ąĖ, ą┤ą╗čÅ 64-ą▒ąĖčéąĮčŗčģ ą┐ąŠčĆč鹊ą▓ ą╝ą╗ą░ą┤čłąĖąĄ 3 ą▒ąĖčéą░ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĮčāą╗čÅą╝ąĖ, ąĖ ą┤ą╗čÅ 128-ą▒ąĖčéąĮčŗčģ ą┐ąŠčĆč鹊ą▓ ą╝ą╗ą░ą┤čłą░čÅ č鹥čéčĆą░ą┤ą░ ą░ą┤čĆąĄčüą░ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ąŠą▒ąĮčāą╗ąĄąĮą░. |

| pX_cmd_bl[5:0] |

ąÆčģąŠą┤ |

ąöą╗ąĖąĮą░ ą┐ą░ą║ąĄčéą░ (Burst Length) ą▓ ą║ąŠą╗ąĖč湥čüčéą▓ąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗčģ čüą╗ąŠą▓ ą┤ą╗čÅ č鹥ą║čāčēąĄą╣ čéčĆą░ąĮąĘą░ą║čåąĖąĖ. Burst Length ą║ąŠą┤ąĖčĆčāąĄčéčüčÅ čćąĖčüą╗ą░ą╝ąĖ ąŠčé 0 ą┤ąŠ 63, ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅčÅ čŹčéąĖą╝ ąŠčé 1 ą┤ąŠ 64 čüą╗ąŠą▓ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ (ąĮą░ą┐čĆąĖą╝ąĄčĆ, b00011 ąŠąĘąĮą░čćą░ąĄčé ą┤ą╗ąĖąĮčā ą┐ą░ą║ąĄčéą░ čéčĆą░ąĮąĘą░ą║čåąĖąĖ 4). ą©ąĖčĆąĖąĮą░ čüą╗ąŠą▓ą░ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ čĆą░ą▓ąĮą░ čĆą░ąĘčĆčÅą┤ąĮąŠčüčéąĖ ą┐ąŠčĆčéą░ (ąĮą░ą┐čĆąĖą╝ąĄčĆ, burst length 3 ąĮą░ 64-ą▒ąĖčéąĮąŠą╝ ą┐ąŠčĆčéčā ą┐ąĄčĆąĄą┤ą░ąĄčé 3 x 64-ą▒ąĖčéąĮčŗčģ čüą╗ąŠą▓ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ, čćč鹊 ą▓čüąĄą│ąŠ čĆą░ą▓ąĮąŠ 192 ą▒ąĖčéą░ą╝). |

| pX_cmd_clk |

ąÆčģąŠą┤ |

ąóą░ą║čéčŗ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ ą┤ą╗čÅ Command FIFO. ąĪąĖą│ąĮą░ą╗čŗ FIFO ąĘą░čģą▓ą░čéčŗą▓ą░čÄčéčüčÅ ąĮą░ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą╝ ą┐ąĄčĆąĄą┐ą░ą┤ąĄ čŹčéąĖčģ čéą░ą║č鹊ą▓. |

| pX_cmd_empty |

ąÆčŗčģąŠą┤ |

ąŁč鹊 čäą╗ą░ą│ čü ą░ą║čéąĖą▓ąĮčŗą╝ čāčĆąŠą▓ąĮąĄą╝ ą╗ąŠą│. 1 ą┤ą╗čÅ Command FIFO, ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčēąĖą╣, čćč鹊 ąĮąĄčé ą║ąŠą╝ą░ąĮą┤, ą┐ąŠčüčéą░ą▓ą╗ąĄąĮąĮčŗčģ ą▓ ąŠč湥čĆąĄą┤čī FIFO, čģąŠčéčÅ ą▓ čŹč鹊čé ą╝ąŠą╝ąĄąĮčé ą╝ąŠą│čāčé ą▒čŗčéčī ą║ąŠą╝ą░ąĮą┤čŗ ą▓ ąŠą▒čĆą░ą▒ąŠčéą║ąĄ. |

| pX_cmd_en |

ąÆčģąŠą┤ |

ąŁč鹊 čüąĖą│ąĮą░ą╗, ą░ą║čéąĖą▓ąĮčŗą╣ ą┐ąŠ ą╗ąŠą│. 1, ą┤ą╗čÅ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ąĘą░ą┐ąĖčüąĖ (write-enable) ą┤ą╗čÅ Command FIFO. ąŁč鹊čé čüąĖą│ąĮą░ą╗ ą▒ąŠą╗ąĄąĄ ą┐ąŠą┤čĆąŠą▒ąĮąŠ ąŠą┐ąĖčüą░ąĮ ą▓ ąōą╗ą░ą▓ąĄ 4. |

| pX_cmd_error |

ąÆčŗčģąŠą┤ |

ąŁč鹊čé ą▓čŗčģąŠą┤ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą┐čĆąŠąĖąĘąŠčłą╗ą░ ąŠčłąĖą▒ą║ą░ ą┐ąŠčĆčéą░ ą║ąŠą╝ą░ąĮą┤čŗ (Command Port), ą┐ąŠč鹊ą╝čā čćč鹊 čāą║ą░ąĘą░č鹥ą╗ąĖ FIFO ąĮąĄ čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆąŠą▓ą░ą╗ąĖčüčī. ąóčĆąĄą▒čāąĄčéčüčÅ čüą▒čĆąŠčü MCB ą┤ą╗čÅ ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖčÅ ąĖąĘ čŹč鹊ą╣ čüąĖčéčāą░čåąĖąĖ. |

| pX_cmd_full |

ąÆčŗčģąŠą┤ |

ąŁč鹊 ą▓čŗčģąŠą┤ čü ą░ą║čéąĖą▓ąĮčŗą╝ ą╗ąŠą│. 1, ą║ąŠč鹊čĆčŗą╣ čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ čäą╗ą░ą│ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĖčÅ Command FIFO. ą×ąĮ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 FIFO ąĮąĄ ą╝ąŠąČąĄčé ą┐čĆąĖąĮčÅčéčī ą▒ąŠą╗čīčłąĄ ą║ąŠą╝ą░ąĮą┤ ąĖ ąĘą░ą┐ąĖčüąĄą╣ ą▒ą╗ąŠą║ąŠą▓ ą▓ Command FIFO. |

| pX_cmd_instr[2:0] |

ąÆčģąŠą┤ |

ąÜąŠą┤ ą║ąŠą╝ą░ąĮą┤čŗ ą┤ą╗čÅ č鹥ą║čāčēąĄą╣ ąĖąĮčüčéčĆčāą║čåąĖąĖ. ąæąĖčé 0 ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé ą▓čŗą▒ąŠčĆ READ/WRITE, ą▒ąĖčé 1 čŹč鹊 čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ Auto Precharge, ąĖ ą▒ąĖčé 2 ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé Refresh, ą║ąŠč鹊čĆčŗą╣ ą▓čüąĄą│ą┤ą░ ą┐ąŠą╗čāčćą░ąĄčé ą┐čĆąĖąŠčĆąĖč鹥čé:

Write: 3'b000

Read: 3'b001

Write with Auto Precharge: 3'b010

Read with Auto Precharge: 3'b011

Refresh: 3'b1xx

ąæąŠą╗ąĄąĄ ą┐ąŠą┤čĆąŠą▒ąĮąŠ čŹč鹊čé čüąĖą│ąĮą░ą╗ ąŠą┐ąĖčüą░ąĮ ą▓ ąōą╗ą░ą▓ąĄ 4. |

Write Datapath. ąóą░ą▒ą╗ąĖčåą░ 2-6 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą▓čüąĄ čüąĖą│ąĮą░ą╗čŗ, čüą▓čÅąĘą░ąĮąĮčŗąĄ čü ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ MCB User Interface. ąÆčüąĄ ąĖą╝ąĄąĮą░ čüąĖą│ąĮą░ą╗ąŠą▓ ą┐ąŠčĆčéą░ ąĖą╝ąĄčÄčé ą┐čĆąĄčäąĖą║čü pX, ą│ą┤ąĄ X ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé ąĮąŠą╝ąĄčĆ ą┐ąŠčĆčéą░ (ąĮą░ą┐čĆąĖą╝ąĄčĆ čüąĖą│ąĮą░ą╗čŗ ą┐ąŠčĆčéą░ 0 ąĖą╝ąĄčÄčé ą┐čĆąĄčäąĖą║čü p0, ą┐ąŠčĆčé 1 ą┐čĆąĄčäąĖą║čü p1, ąĖ čéą░ą║ ą┤ą░ą╗ąĄąĄ).

ąóą░ą▒ą╗ąĖčåą░ 2-6. ąĪąĖą│ąĮą░ą╗čŗ Write Datapath.

| ąśą╝čÅ čüąĖą│ąĮą░ą╗ą░ |

ąØą░ą┐čĆ. |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| pX_wr_clk |

ąÆčģąŠą┤ |

ąŁč鹊 čüąĖą│ąĮą░ą╗ čéą░ą║č鹊ą▓ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ ą┤ą╗čÅ Write Data FIFO. |

| pX_wr_count[6:0] |

ąÆčŗčģąŠą┤ |

ąŚąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░ ą┤ą╗čÅ Write Data FIFO. ąŁč鹊čé ą▓čŗčģąŠą┤ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čüą║ąŠą╗čīą║ąŠ čüą╗ąŠą▓ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ FIFO (ąŠčé 1 ą┤ąŠ 64). ąŚąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░ 0 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 FIFO ą┐čāčüčé. ąŁč鹊čé čüąĖą│ąĮą░ą╗ ąĖą╝ąĄąĄčé ą╗ą░č鹥ąĮčéąĮąŠčüčéčī ą▒ąŠą╗čīčłąĄ, č湥ą╝ čäą╗ą░ą│ pX_wr_empty. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, FIFO ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čāčüčéčŗą╝ ąĖą╗ąĖ ąĖčüą┐čŗčéčŗą▓ą░čéčī ąĮąĄą┤ąŠą│čĆčāąĘą║čā, ą┤ą░ąČąĄ ą║ąŠą│ą┤ą░ čüč湥čéčćąĖą║ ąĮąĄ čĆą░ą▓ąĄąĮ 0. |

| pX_wr_data[PX_SIZE-1:0] |

ąÆčģąŠą┤ |

ąŚąĮą░č湥ąĮąĖąĄ Write Data ą┤ą╗čÅ ąĘą░ą│čĆčāąĘą║ąĖ ą▓ Write Data FIFO ąĖ ąŠčéą┐čĆą░ą▓ą║ąĖ ą▓ ą┐ą░ą╝čÅčéčī. PX_SIZE ą╝ąŠąČąĄčé ą▒čŗčéčī 32, 64 ąĖą╗ąĖ 128 ą▒ąĖčé, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ. |

| pX_wr_empty |

ąÆčŗčģąŠą┤ |

ąŁč鹊 čüąĖą│ąĮą░ą╗, ą░ą║čéąĖą▓ąĮčŗą╣ ą┐ąŠ ą╗ąŠą│. 1, čÅą▓ą╗čÅąĄčéčüčÅ čäą╗ą░ą│ąŠą╝ ąŠą┐čāčüč鹊賹ĄąĮąĖčÅ Write Data FIFO. ą×ąĮ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą▓ FIFO ąĮąĄčé ą┤ą░ąĮąĮčŗčģ ą┤ą╗čÅ ąĘą░ą┐ąĖčüąĖ ą▓ ą┐ą░ą╝čÅčéčī. |

| pX_wr_en |

ąÆčģąŠą┤ |

ąŁč鹊 čüąĖą│ąĮą░ą╗, ą░ą║čéąĖą▓ąĮčŗą╣ ą┐ąŠ ą╗ąŠą│. 1, čÅą▓ą╗čÅąĄčéčüčÅ čüąĖą│ąĮą░ą╗ąŠą╝ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ąĘą░ą┐ąĖčüąĖ ą┤ą╗čÅ Write Data FIFO. ą×ąĮ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ąĘąĮą░č湥ąĮąĖąĄ pX_wr_data ą┤ąŠą┐čāčüčéąĖą╝ąŠ ą┤ą╗čÅ ąĘą░ą│čĆčāąĘą║ąĖ ą▓ FIFO. ąöą░ąĮąĮčŗąĄ ąĘą░ą│čĆčāąČą░čÄčéčüčÅ ą┐ąŠ čäčĆąŠąĮčéčā ąĮą░čĆą░čüčéą░ąĮąĖčÅ pX_wr_clk, ą║ąŠą│ą┤ą░ pX_wr_en = 1 ąĖ pX_wr_full = 0. |

| pX_wr_error |

ąÆčŗčģąŠą┤ |

ąŁč鹊čé čüąĖą│ąĮą░ą╗ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą┐čĆąŠąĖąĘąŠčłą╗ą░ ąŠčłąĖą▒ą║ą░ Write Data FIFO, ąĖąĘ-ąĘą░ č鹊ą│ąŠ, čćč鹊 čāą║ą░ąĘą░č鹥ą╗ąĖ FIFO čĆą░čüčüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆąŠą▓ą░ą╗ąĖčüčī. ąöą╗čÅ ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖčÅ ąĖąĘ čŹč鹊ą│ąŠ čüąŠčüč鹊čÅąĮąĖčÅ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐čĆąŠąĖąĘą▓ąĄą┤ąĄąĮ čüą▒čĆąŠčü MCB. |

| pX_wr_full |

ąÆčŗčģąŠą┤ |

ąŁč鹊čé čüąĖą│ąĮą░ą╗ čü ą░ą║čéąĖą▓ąĮčŗą╝ ą╗ąŠą│. 1 čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ čäą╗ą░ą│ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĮąŠčüčéąĖ Write Data FIFO. ąÜąŠą│ą┤ą░ čŹč鹊čé čüąĖą│ąĮą░ą╗ ą▓ ą╗ąŠą│. 1, č鹊 ą┐čĆąĄą┤ąŠčéą▓čĆą░čēą░ąĄčéčüčÅ ąĘą░ą│čĆčāąĘą║ą░ ą┤ą░ąĮąĮčŗčģ ą▓ FIFO. |

| pX_wr_mask[PX_MASKSIZE-1:0] |

ąÆčģąŠą┤ |

ąæąĖčéčŗ ą╝ą░čüą║ąĖ ą┤ą░ąĮąĮčŗčģ ą┤ą╗čÅ Write Data. ąŁčéą░ ą╝ą░čüą║ą░ ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ą▓ FIFO čü čüąŠą▓ą┐ą░ą┤ąĄąĮąĖąĄą╝ čüąŠ čüą▓čÅąĘą░ąĮąĮčŗą╝ąĖ Write Data (pX_wr_data). ą×ą┤ąĖąĮ ą▒ąĖčé ą╝ą░čüą║ąĖ čüą▓čÅąĘą░ąĮ čü ą║ą░ąČą┤čŗą╝ ą▒ą░ą╣č鹊ą╝ ą┤ą░ąĮąĮčŗčģ. ąÜąŠą│ą┤ą░ ą▒ąĖčé pX_wr_mask bit ą▓ ą╗ąŠą│. 1, čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ ą╝ą░čüą║ąĖčĆčāąĄčéčüčÅ (čé. ąĄ. ąĮąĄ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ ą▓ ą┐ą░ą╝čÅčéčī). |

| pX_wr_underrun |

ąÆčŗčģąŠą┤ |

ąŁč鹊čé čüąĖą│ąĮą░ą╗ čü ą░ą║čéąĖą▓ąĮčŗą╝ ą╗ąŠą│. 1 čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ čäą╗ą░ą│ ąĮąĄą┤ąŠą│čĆčāąĘą║ąĖ. ą×ąĮ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ąĮąĄą┤ąŠčüčéą░č鹊čćąĮąŠ ą┤ą░ąĮąĮčŗčģ ą▓ Write Data FIFO ą┤ą╗čÅ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ čéčĆą░ąĮąĘą░ą║čåąĖąĖ. ą¤ąŠčüą╗ąĄą┤ąĮąĄąĄ ą┤ąŠčüč鹊ą▓ąĄčĆąĮąŠąĄ čüą╗ąŠą▓ąŠ ą┤ą░ąĮąĮčŗčģ ą▒čāą┤ąĄčé ąĘą░ą┐ąĖčüą░ąĮąŠ ą┤ą╗čÅ ą┐čĆąŠą┤ąŠą╗ąČąĄąĮąĖčÅ ąĖ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐ą░ą║ąĄčéą░. ą¦č鹊ą▒čŗ ą┐čĆąĄą┤ąŠčéą▓čĆą░čéąĖčéčī ąĮąĄą┤ąŠą│čĆčāąĘą║čā, ą│ą░čĆą░ąĮčéąĖčĆčāą╣č鹥, čćč鹊 ą▓ FIFO ą┤ąŠčüčéą░č鹊čćąĮąŠ ą┤ą░ąĮąĮčŗčģ, ą║ąŠą│ą┤ą░ ą▓čŗą┤ą░ąĄč鹥 ąĖąĮčüčéčĆčāą║čåąĖčÄ Write ą┤ą╗čÅ Command FIFO. ąöąŠą╗ąČąĄąĮ ą▒čŗčéčī ą▓čŗčüčéą░ą▓ą╗ąĄąĮ čüąĖą│ąĮą░ą╗ sys_rst ą┤ą╗čÅ čüą▒čĆąŠčüą░ čŹč鹊ą│ąŠ čäą╗ą░ą│ą░ ąĖ ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖčÅ ąĖąĘ čŹč鹊ą╣ čüąĖčéčāą░čåąĖąĖ. |

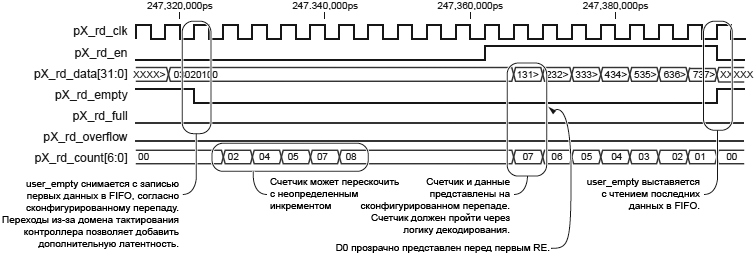

Read Datapath. ąóą░ą▒ą╗ąĖčåą░ 2-7 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą▓čüąĄ čüąĖą│ąĮą░ą╗čŗ, čüą▓čÅąĘą░ąĮąĮčŗąĄ čü ą┐čāč鹥ą╝ čćč鹥ąĮąĖčÅ MCB User Interface. ąÆčüąĄ ąĖą╝ąĄąĮą░ čüąĖą│ąĮą░ą╗ąŠą▓ ą┐ąŠčĆčéą░ ąĖą╝ąĄčÄčé ą┐čĆąĄčäąĖą║čü pX, ą│ą┤ąĄ X ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé ąĮąŠą╝ąĄčĆ ą┐ąŠčĆčéą░ (ąĮą░ą┐čĆąĖą╝ąĄčĆ čüąĖą│ąĮą░ą╗čŗ ą┐ąŠčĆčéą░ 0 ąĖą╝ąĄčÄčé ą┐čĆąĄčäąĖą║čü p0, ą┐ąŠčĆčé 1 ą┐čĆąĄčäąĖą║čü p1, ąĖ čéą░ą║ ą┤ą░ą╗ąĄąĄ).

ąóą░ą▒ą╗ąĖčåą░ 2-7. ąĪąĖą│ąĮą░ą╗čŗ Read Datapath.

| ąśą╝čÅ čüąĖą│ąĮą░ą╗ą░ |

ąØą░ą┐čĆ. |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| pX_rr_clk |

ąÆčģąŠą┤ |

ąØą░ čŹč鹊čé ą▓čģąŠą┤ ą┐ąŠą┤ą░čÄčéčüčÅ čéą░ą║čéčŗ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ ą┤ą╗čÅ Read Data FIFO. |

| pX_rd_en |

ąÆčģąŠą┤ |

ąŁč鹊 čüąĖą│ąĮą░ą╗, ą░ą║čéąĖą▓ąĮčŗą╣ ą┐ąŠ ą╗ąŠą│. 1, čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ čćč鹥ąĮąĖčÅ ą┤ą╗čÅ Read Data FIFO. ą¦ąĖčéą░ąĄą╝čŗąĄ ą┤ą░ąĮąĮčŗąĄ čéą░ą║čéąĖčĆčāčÄčéčüčÅ ą┤ą╗čÅ ą▓čŗą▓ąŠą┤ą░ ąĖąĘ FIFO ą┐ąŠ čäčĆąŠąĮčéčā ąĮą░čĆą░čüčéą░ąĮąĖčÅ pX_rd_clk, ą║ąŠą│ą┤ą░ pX_rd_en = 1 ąĖ pX_rd_empty = 0. |

| pX_rd_data[PX_SIZE-1:0] |

ąÆčŗčģąŠą┤ |

ąŚąĮą░č湥ąĮąĖąĄ Read Data, ą▓ąŠąĘą▓čĆą░čēą░ąĄą╝ąŠąĄ ąĖąĘ ą┐ą░ą╝čÅčéąĖ. ąŁč鹊čé čüąĖą│ąĮą░ą╗ čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ą▓čŗčģąŠą┤ąŠą╝ Read Data FIFO ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▓ ą╗ąŠą│ąĖą║čā FPGA. PX_SIZE ą╝ąŠąČąĄčé ą▒čŗčéčī 32, 64 ąĖą╗ąĖ 128 ą▒ąĖčéą░, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą┐ąŠčĆčéą░. |

| pX_rd_full |

ąÆčŗčģąŠą┤ |

ąŁč鹊 čüąĖą│ąĮą░ą╗ čü ą░ą║čéąĖą▓ąĮčŗą╝ čāčĆąŠą▓ąĮąĄą╝ ą╗ąŠą│. 1 ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé čäą╗ą░ą│ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĮąŠčüčéąĖ Read Data FIFO. ąÜąŠą│ą┤ą░ čüąĖą│ąĮą░ą╗ ą▓ ą╗ąŠą│. 1, ąŠąĮ ą┐čĆąĄą┤ąŠčéą▓čĆą░čēą░ąĄčé ą▓ąŠąĘą▓čĆą░čé ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗčģ ą┤ą░ąĮąĮčŗčģ ąĖąĘ ą┐ą░ą╝čÅčéąĖ (ą┤ą░ąĮąĮčŗąĄ ąĮąĄ ą▒čāą┤čāčé ą┐ąŠą┐ą░ą┤ą░čéčī ą▓ FIFO). |

| pX_rd_empty |

ąÆčŗčģąŠą┤ |

ąŁč鹊čé čüąĖą│ąĮą░ą╗, ą░ą║čéąĖą▓ąĮčŗą╣ ą┐ąŠ ą╗ąŠą│. 1, čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ čäą╗ą░ą│ ąŠą┐čāčüč鹊賹ĄąĮąĖčÅ Read Data FIFO. ą×ąĮ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ąĮąĄčé ą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗčģ ą┤ą░ąĮąĮčŗčģ ą▓ FIFO. |

| pX_rd_count[6:0] |

ąÆčŗčģąŠą┤ |

ąŚąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░ ą┤ą╗čÅ Read Data FIFO. ąŁč鹊čé čüąĖą│ąĮą░ą╗ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čüą║ąŠą╗čīą║ąŠ čüą╗ąŠą▓ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ FIFO (ąŠčé 1 ą┤ąŠ 64). ąŚąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░ 0 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 FIFO ą┐čāčüčé. ąŁč鹊čé čüąĖą│ąĮą░ą╗ ąĖą╝ąĄąĄčé ąĘą░ą┤ąĄčƹȹ║čā ą▒ąŠą╗čīčłąĄ, č湥ą╝ čäą╗ą░ą│ pX_rd_full. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, FIFO ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠą╗ąĮčŗą╝ ąĖą╗ąĖ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĄ, ą┤ą░ąČąĄ ąĄčüą╗ąĖ ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéčćąĖą║ą░ ą╝ąĄąĮčīčłąĄ 64. |

| pX_rd_overflow |

ąÆčŗčģąŠą┤ |

ąĪąĖą│ąĮą░ą╗ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ čü ą░ą║čéąĖą▓ąĮčŗą╝ ą╗ąŠą│. 1. ą×ąĮ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą┤ą░ąĮąĮčŗąĄ ą▒čŗą╗ąĖ ą┐ąŠč鹥čĆčÅąĮčŗ ąĖąĘ-ąĘą░ č鹊ą│ąŠ, čćč鹊 Read Data ą┐čĆąŠą┤ąŠą╗ąČą░ą╗ą░ ą▓ąŠąĘą▓čĆą░čēą░čéčī ą┤ą░ąĮąĮčŗąĄ ąĖąĘ ą┐ą░ą╝čÅčéąĖ ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ Read Data FIFO ąĘą░ą┐ąŠą╗ąĮąĖą╗čüčÅ. ą¦č鹊ą▒čŗ ą┐čĆąĄą┤ąŠčéą▓čĆą░čéąĖčéčī ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĄ:

ŌĆó ąŻą▒ąĄą┤ąĖč鹥čüčī, čćč鹊 ą┤ąŠčüčéą░č鹊čćąĮąŠ ą┐ą░ą╝čÅčéąĖ ą┤ą╗čÅ čüąŠčģčĆą░ąĮąĄąĮąĖčÅ ąĘą░ą┐čĆąŠčłąĄąĮąĮčŗčģ Read Data ą▓ FIFO ą┐ąĄčĆąĄą┤ ą▓čŗą┤ą░č湥ą╣ ąĖąĮčüčéčĆčāą║čåąĖąĖ Read ą▓ Command FIFO.

ŌĆó ąŻą▒ąĄą┤ąĖč鹥čüčī, čćč鹊 čāčćč鹥ąĮčŗ ą▓čüąĄ ą▓čŗą┐ąŠą╗ąĮčÅčÄčēąĖąĄčüčÅ čéčĆą░ąĮąĘą░ą║čåąĖąĖ. ąöąŠą╗ąČąĄąĮ ą▒čŗčéčī ą▓čŗčüčéą░ą▓ą╗ąĄąĮ čüąĖą│ąĮą░ą╗ sys_rst ą┤ą╗čÅ čüą▒čĆąŠčüą░ čŹč鹊ą│ąŠ čäą╗ą░ą│ą░ ąĖ ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖčÅ ąĖąĘ čŹč鹊ą╣ čüąĖčéčāą░čåąĖąĖ. |

| pX_rd_error |

ąÆčŗčģąŠą┤ |

ąŁč鹊čé čüąĖą│ąĮą░ą╗ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą┐čĆąŠąĖąĘąŠčłą╗ą░ ąŠčłąĖą▒ą║ą░ Read Data FIFO, ą┐ąŠč鹊ą╝čā čćč鹊 čĆą░čüčüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆąŠą▓ą░ą╗ąĖčüčī čāą║ą░ąĘą░č鹥ą╗ąĖ FIFO. ąöą╗čÅ ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖčÅ ąĖąĘ čŹč鹊ą╣ čüąĖčéčāą░čåąĖąĖ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą▓čŗčüčéą░ą▓ą╗ąĄąĮ čüą▒čĆąŠčü MCB. |

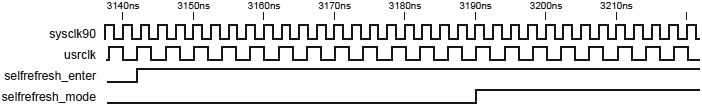

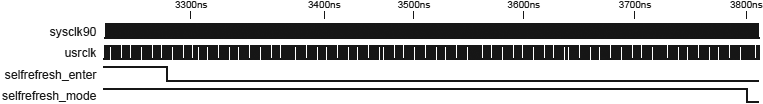

ąĪąĖą│ąĮą░ą╗čŗ čüą░ą╝ąŠąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ. ąóą░ą▒ą╗ąĖčåą░ 2-8 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüąĖą│ąĮą░ą╗čŗ self-refresh, ą┤ąŠčüčéčāą┐ąĮčŗąĄ č湥čĆąĄąĘ ąĖąĮč鹥čĆč乥ą╣čü ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ. ąĪą░ą╝ąŠąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ ą┐ąŠą┤čĆąŠą▒ąĮąĄąĄ čĆą░čüčüą╝ą░čéčĆąĖą▓ą░ąĄčéčüčÅ ą▓ ąōą╗ą░ą▓ąĄ 4.

ąóą░ą▒ą╗ąĖčåą░ 2-8. ąĪąĖą│ąĮą░ą╗čŗ Self-Refresh.

| ąśą╝čÅ čüąĖą│ąĮą░ą╗ą░ |

ąØą░ą┐čĆ. |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| selfrefresh_enter |

ąÆčģąŠą┤ |

ąŁč鹊čé ą▓čģąŠą┤ čüčĆą░ą▒ą░čéčŗą▓ą░ąĄčé ą┐ąŠ ą┐ąĄčĆąĄą┐ą░ą┤čā ąĮą░čĆą░čüčéą░ąĮąĖčÅ čāčĆąŠą▓ąĮčÅ. ąÜąŠą│ą┤ą░ ąŠąĮ ą▓čŗčüčéą░ą▓ą╗ąĄąĮ, MCB ąĘą░ą┐čĆą░čłąĖą▓ą░ąĄčé čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐ą░ą╝čÅčéąĖ ą▓čģąŠą┤ ą▓ čĆąĄąČąĖą╝ čüą░ą╝ąŠąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ (self-refresh mode). ąŁč鹊čé čüąĖą│ąĮą░ą╗ ą┤ąŠą╗ąČąĄąĮ ąŠčüčéą░ą▓ą░čéčīčüčÅ ą▓čŗčüčéą░ą▓ą╗ąĄąĮąĮčŗą╝, ą┐ąŠą║ą░ ąĮąĄ čüčéą░ąĮąĄčé ą░ą║čéąĖą▓ąĮčŗą╝ čüąĖą│ąĮą░ą╗ selfrefresh_mode. |

| selfrefresh_mode |

ąÆčŗčģąŠą┤ |

ąÉą║čéąĖą▓ąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 1 čŹč鹊ą│ąŠ čüąĖą│ąĮą░ą╗ą░ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐ą░ą╝čÅčéąĖ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ čüą░ą╝ąŠąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ. |

ąśąĮč鹥čĆč乥ą╣čü čāčüčéčĆąŠą╣čüčéą▓ą░ ą┐ą░ą╝čÅčéąĖ. Memory Device Interface čüąŠą┤ąĄčƹȹĖčé ą▓čüąĄ ąĮąĄąŠą▒čģąŠą┤ąĖą╝čŗąĄ čüąĖą│ąĮą░ą╗čŗ ą┤ą╗čÅ ąŠą▒ą╝ąĄąĮą░ čü ą▓ąĮąĄčłąĮąĖą╝ čāčüčéčĆąŠą╣čüčéą▓ąŠą╝ ą┐ą░ą╝čÅčéąĖ. ąÆčüąĄ čŹčéąĖ čüąĖą│ąĮą░ą╗čŗ (čéą░ą▒ą╗ąĖčåą░ 2-9) ą▓ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░čģ ą╗ąŠą│ąĖą║ąĖ Spartan-6 ą▓čŗą▓ąĄą┤ąĄąĮčŗ ąĮą░ ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮąŠ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗąĄ ą▓čŗą▓ąŠą┤čŗ ą║ąŠčĆą┐čāčüą░. ąĪą╝. See UG385 [4] ą┤ą╗čÅ ą┐ąŠą┤čĆąŠą▒ąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ą┐ąŠ čĆą░ąĘą▓ąŠą┤ą║ąĄ ą▓čŗą▓ąŠą┤ąŠą▓ MCB ą║ą░ąČą┤ąŠą╣ ą║ąŠą╝ą▒ąĖąĮą░čåąĖąĖ čāčüčéčĆąŠą╣čüčéą▓ąŠ/ą║ąŠčĆą┐čāčü. ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ ą╝ąŠą┤čāą╗čī ą║ą░ą╗ąĖą▒čĆąŠą▓ą║ąĖ (soft calibration module), čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąĮčŗą╣ MIG, čéčĆąĄą▒čāąĄčé ą▓čŗą┤ąĄą╗ąĄąĮąĖąĄ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą│ąŠ ą▓čŗą▓ąŠą┤ą░ (RZQ) ą┤ą╗čÅ ą▓čüąĄčģ ą┤ąĖąĘą░ą╣ąĮąŠą▓ MCB. RZQ čéčĆąĄą▒čāąĄą╝čŗą╣ ą▓čŗą▓ąŠą┤, ąŠą┤ąĮą░ą║ąŠ ąĄą│ąŠ ą╝ąĄčüč鹊ąĮą░čģąŠąČą┤ąĄąĮąĖąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąŠ ą▓ ą┐čĆąĄą┤ąĄą╗ą░čģ ą▒ą░ąĮą║ą░ MCB. ąÜąŠą│ą┤ą░ ą║ą░ą╗ąĖą▒čĆąŠą▓ą░ąĮąĮčŗą╣ ą▓čģąŠą┤ ąŠčüčéą░ąĮąŠą▓ą║ąĖ (Calibrated Input Termination) ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ čāčéąĖą╗ąĖč鹊ą╣ MIG, ą▓čŗą▓ąŠą┤ ZIO čéą░ą║ąČąĄ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą┤ą╗čÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą▓ ą╝ąŠą┤čāą╗ąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą╣ ą║ą░ą╗ąĖą▒čĆąŠą▓ą║ąĖ. ą£ąĄčüč鹊 ą▓čŗą▓ąŠą┤ą░ ZIO ą╝ąŠąČąĄčé ą▒čŗčéčī čéą░ą║ąČąĄ ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąŠ, ąĮąŠ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī čĆą░ąĘą╝ąĄčēąĄąĮąŠ ąĮą░ čüą▓čÅąĘą░ąĮąĮąŠą╝ I/O (čé. ąĄ. ąĮą░ ą┤ąŠą┐čāčüčéąĖą╝ąŠą╝ ą▓čŗą▓ąŠą┤ąĄ ą║ąŠčĆą┐čāčüą░) ą▓ ą┐čĆąĄą┤ąĄą╗ą░čģ ą▒ą░ąĮą║ą░ MCB. ąĪą╝. čüąĄą║čåąĖčÄ "Setting FPGA Options" ą▓ UG416 [2] ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ą┐ąŠ ą▓čŗą▓ąŠą┤ą░ą╝ RZQ ąĖ ZIO.