|

–ù–∞–ø–∏—Å–∞–Ω–∏–µ –∫–æ–¥–∞ –Ω–∞ Verilog –ø–æ–∑–≤–æ–ª—è–µ—Ç –Ω–∞–º —Å—Ñ–æ–∫—É—Å–∏—Ä–æ–≤–∞—Ç—å—Å—è –Ω–∞ –ø–æ–≤–µ–¥–µ–Ω–∏–∏ –∞–ø–ø–∞—Ä–∞—Ç—É—Ä—ã —Å —Ç–æ—á–∫–∏ –∑—Ä–µ–Ω–∏—è –≤—ã—Å–æ–∫–æ–≥–æ —É—Ä–æ–≤–Ω—è –≤–º–µ—Å—Ç–æ —Ç–æ–≥–æ, —á—Ç–æ–±—ã –æ–ø–∏—Å—ã–≤–∞—Ç—å —Å—Ö–µ–º—É –Ω–∞ –Ω–∏–∑–∫–æ–º —É—Ä–æ–≤–Ω–µ —Å –ø–æ–º–æ—â—å—é –Ω–∏–∑–∫–æ—É—Ä–æ–≤–Ω–µ–≤—ã—Ö —ç–ª–µ–º–µ–Ω—Ç–æ–≤ –ª–æ–≥–∏–∫–∏. –°—É—â–µ—Å—Ç–≤—É–µ—Ç –º–Ω–æ–∂–µ—Å—Ç–≤–æ –∫–∞—á–µ—Å—Ç–≤–µ–Ω–Ω–æ–π –ª–∏—Ç–µ—Ä–∞—Ç—É—Ä—ã –ø–æ –ø—Ä–æ–≥—Ä–∞–º–º–∏—Ä–æ–≤–∞–Ω–∏—é –Ω–∞ HDL-—è–∑—ã–∫–∞—Ö Verilog –∏ VHDL. –û–¥–Ω–∞–∫–æ, –∫ —Å–æ–∂–∞–ª–µ–Ω–∏—é, —á–∞—Å—Ç–æ —Ç–∞–∫–∏–µ –∫–Ω–∏–∂–∫–∏ –≤–µ–ª–∏–∫–∏ –ø–æ –æ–±—ä–µ–º—É –∏ –¥–æ–≤–æ–ª—å–Ω–æ —Ç—Ä—É–¥–Ω—ã –¥–ª—è –æ—Å–≤–æ–µ–Ω–∏—è –∏ –ø–æ–Ω–∏–º–∞–Ω–∏—è. –≠—Ç–æ —Ä—É–∫–æ–≤–æ–¥—Å—Ç–≤–æ (–ø–µ—Ä–µ–≤–æ–¥ [1]) –¥–µ–ª–∞–µ—Ç –ø–æ–ø—ã—Ç–∫—É —É—Å–∫–æ—Ä–µ–Ω–Ω–æ–≥–æ –∑–Ω–∞–∫–æ–º—Å—Ç–≤–∞ —Å Verilog –¥–ª—è —Ç–µ—Ö, –∫—Ç–æ —Ö–æ—á–µ—Ç –±—ã—Å—Ç—Ä–æ –Ω–∞—á–∞—Ç—å –ø—Ä–æ–≥—Ä–∞–º–º–∏—Ä–æ–≤–∞—Ç—å –Ω–∞ –ø—Ä–∞–∫—Ç–∏–∫–µ.

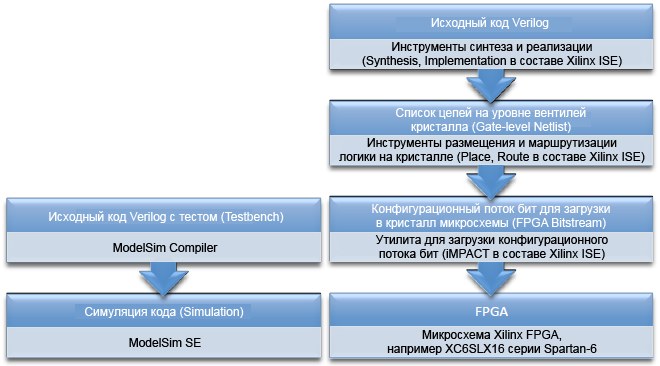

–Ý–∞–∑—Ä–∞–±–æ—Ç–∫–∞ —Ü–∏—Ñ—Ä–æ–≤–æ–π —Å—Ö–µ–º—ã –Ω–∞ Verilog –æ–±—ã—á–Ω–æ –≤–∫–ª—é—á–∞–µ—Ç –≤ —Å–µ–±—è –¥–≤–∞ –æ—Å–Ω–æ–≤–Ω—ã—Ö –ø—Ä–æ—Ü–µ—Å—Å–∞ - —Ç–µ—Å—Ç –Ω–∞ –æ—Å–Ω–æ–≤–µ —Å–∏–º—É–ª—è—Ü–∏–∏ –∏ —Ä–µ–∞–ª–∏–∑–∞—Ü–∏—è —Ä–∞–±–æ—á–µ–≥–æ –∫–æ–¥–∞. –ù–∞ —Ä–∏—Å—É–Ω–∫–µ –Ω–∏–∂–µ –ø–æ–∫–∞–∑–∞–Ω—ã —ç—Ç–∏ –ø—Ä–æ—Ü–µ—Å—Å—ã. –°–Ω–∞—á–∞–ª–∞ –Ω—É–∂–Ω–æ –ø–µ—Ä–µ–¥–∞—Ç—å –∏—Å—Ö–æ–¥–Ω—ã–µ —Ñ–∞–π–ª—ã Verilog –≤ –∏–Ω—Å—Ç—Ä—É–º–µ–Ω—Ç–∞—Ä–∏–π —Å–∏–º—É–ª—è—Ü–∏–∏, —á—Ç–æ –ø–æ–∫–∞–∑–∞–Ω–æ –Ω–∞ —Ä–∏—Å—É–Ω–∫–µ —Å–ª–µ–≤–∞. –ò–Ω—Å—Ç—Ä—É–º–µ–Ω—Ç —Å–∏–º—É–ª—è—Ü–∏–∏ –ø—Ä–æ–≥—Ä–∞–º–º–Ω–æ —ç–º—É–ª–∏—Ä—É–µ—Ç —Ä–µ–∞–ª—å–Ω–æ–µ –ø–æ–≤–µ–¥–µ–Ω–∏–µ –∞–ø–ø–∞—Ä–∞—Ç—É—Ä—ã —Å—Ö–µ–º—ã –¥–ª—è –æ–ø—Ä–µ–¥–µ–ª–µ–Ω–Ω—ã—Ö –≤—Ö–æ–¥–Ω—ã—Ö –≤–æ–∑–¥–µ–π—Å—Ç–≤–∏–π, —á—Ç–æ –æ–ø–∏—Å—ã–≤–∞–µ—Ç—Å—è –≤ —Å–ø–µ—Ü–∏–∞–ª—å–Ω–æ –Ω–∞–ø–∏—Å–∞–Ω–Ω–æ–º —Ç–µ—Å—Ç–µ (testbench). –ü–æ—Å–∫–æ–ª—å–∫—É –∫–æ–º–ø–∏–ª—è—Ü–∏—è –Ω–∞—à–µ–≥–æ –∫–æ–¥–∞ Verilog –¥–ª—è –∏–Ω—Å—Ç—Ä—É–º–µ–Ω—Ç–∞ —Å–∏–º—É–ª—è—Ü–∏–∏ –æ—Å—É—â–µ—Å—Ç–≤–ª—è–µ—Ç—Å—è –æ—Ç–Ω–æ—Å–∏—Ç–µ–ª—å–Ω–æ –±—ã—Å—Ç—Ä–æ, —Ç–æ —ç—Ç–æ—Ç —à–∞–≥ –∏—Å–ø–æ–ª—å–∑—É–µ—Ç—Å—è –≥–ª–∞–≤–Ω—ã–º –æ–±—Ä–∞–∑–æ–º –¥–ª—è –æ—Ü–µ–Ω–∫–∏ –æ–±—â–µ–π —Ä–∞–±–æ—Ç–æ—Å–ø–æ—Å–æ–±–Ω–æ—Å—Ç–∏ –¥–∏–∑–∞–π–Ω–∞.

–ü—Ä–∏–º–µ—á–∞–Ω–∏–µ: –Ω–∞ —Ä–∏—Å—É–Ω–∫–µ —Å–ª–µ–≤–∞ –ø–æ–∫–∞–∑–∞–Ω–∞ —Å–∏–º—É–ª—è—Ü–∏—è —Å –ø–æ–º–æ—â—å—é –ø–∞–∫–µ—Ç–∞ ModelSim, –æ–¥–Ω–∞–∫–æ —Å–∏–º—É–ª—è—Ü–∏—é –º–æ–∂–Ω–æ —Ä–µ–∞–ª–∏–∑–æ–≤–∞—Ç—å –∏ —Å –ø–æ–º–æ—â—å—é –±–µ—Å–ø–ª–∞—Ç–Ω–æ–≥–æ —Å–∏–º—É–ª—è—Ç–æ—Ä–∞ iSIM, –≤—Ö–æ–¥—è—â–µ–≥–æ –≤ –ø–∞–∫–µ—Ç —Ä–∞–∑—Ä–∞–±–æ—Ç–∫–∏ Xilinx ISE Webpack. –ü—Ä–æ—Ü–µ—Å—Å —É—Å—Ç–∞–Ω–æ–≤–∫–∏ —ç—Ç–æ–≥–æ –ø–∞–∫–µ—Ç–∞ –∏ –æ–ø–∏—Å–∞–Ω–∏–µ —Å–∏–º—É–ª—è—Ü–∏–∏ –≤ iSIM –ø–æ–∫–∞–∑–∞–Ω—ã –≤ —Å—Ç–∞—Ç—å–µ [3].

–ù–∞ —Ä–∏—Å—É–Ω–∫–µ —Å–ø—Ä–∞–≤–∞ —É–ø—Ä–æ—â–µ–Ω–Ω–æ –ø–æ–∫–∞–∑–∞–Ω –ø—Ä–æ—Ü–µ—Å—Å —Ä–µ–∞–ª–∏–∑–∞—Ü–∏–∏ –ø—Ä–æ–µ–∫—Ç–∞ –ø–æ—Å–ª–µ —É—Å–ø–µ—à–Ω–æ–≥–æ –ø—Ä–æ–≥–æ–Ω–∞ —Ç–µ—Å—Ç–∞ –≤ —Å–∏–º—É–ª—è—Ç–æ—Ä–µ. –ü–æ—Å–ª–µ —Ç–æ–≥–æ, –∫–∞–∫ –º—ã —É–¥–æ—Å—Ç–æ–≤–µ—Ä–∏–ª–∏—Å—å –≤ –∫–æ—Ä—Ä–µ–∫—Ç–Ω–æ—Å—Ç–∏ –≤—ã—Å–æ–∫–æ—É—Ä–æ–≤–Ω–µ–≤–æ–≥–æ –∏—Å—Ö–æ–¥–Ω–æ–≥–æ –∫–æ–¥–∞ Verilog, –º—ã –∏—Å–ø–æ–ª—å–∑—É–µ–º –∏–Ω—Å—Ç—Ä—É–º–µ–Ω—Ç–∞—Ä–∏–π —Å–∏–Ω—Ç–µ–∑–∞ –¥–ª—è –ø—Ä–µ–≤—Ä–∞—â–µ–Ω–∏—è —ç—Ç–æ–≥–æ –∫–æ–¥–∞ –≤ –Ω–∏–∑–∫–æ—É—Ä–æ–≤–Ω–µ–≤—ã–π —Å–ø–∏—Å–æ–∫ –ª–æ–≥–∏—á–µ—Å–∫–∏—Ö –≤–µ–Ω—Ç–∏–ª–µ–π (gate netlist). –ó–∞—Ç–µ–º —É—Ç–∏–ª–∏—Ç–∞ –æ—Ç–æ–±—Ä–∞–∂–µ–Ω–∏—è (mapping tool) –ø—Ä–∏–≤—è–∑—ã–≤–∞–µ—Ç netlist –∫ —Å–æ–æ—Ç–≤–µ—Ç—Å—Ç–≤—É—é—â–∏–º —Ä–µ—Å—É—Ä—Å–∞–º –∏—Å–ø–æ–ª—å–∑—É–µ–º–æ–≥–æ –∫—Ä–∏—Å—Ç–∞–ª–ª–∞ –ª–æ–≥–∏–∫–∏ (–º–∏–∫—Ä–æ—Å—Ö–µ–º–∞ CPLD –∏–ª–∏ FPGA). –ù–∞ –∑–∞–∫–ª—é—á–∏—Ç–µ–ª—å–Ω–æ–º —à–∞–≥–µ –º—ã –∑–∞–≥—Ä—É–∂–∞–µ–º –∫–æ–Ω—Ñ–∏–≥—É—Ä–∞—Ü–∏–æ–Ω–Ω—ã–π –ø–æ—Ç–æ–∫ –¥–∞–Ω–Ω—ã—Ö (bitstream) –≤ –≤—ã–±—Ä–∞–Ω–Ω—É—é –º–∏–∫—Ä–æ—Å—Ö–µ–º—É –ª–æ–≥–∏–∫–∏ (—ç—Ç–æ –¥–µ–ª–∞–µ—Ç—Å—è —Å –ø–æ–º–æ—â—å—é –∫–∞–±–µ–ª—è JTAG). –í —Ä–µ–∑—É–ª—å—Ç–∞—Ç–µ –ø–æ–ª—É—á–∞–µ—Ç—Å—è –≥–æ—Ç–æ–≤–∞—è —Å—Ö–µ–º–∞, –≤—ã–ø–æ–ª–Ω—è—é—â–∞—è –Ω—É–∂–Ω—ã–µ –ª–æ–≥–∏—á–µ—Å–∫–∏–µ —Ñ—É–Ω–∫—Ü–∏–∏.

[–§–∏–ª–æ—Å–æ—Ñ–∏—è Verilog]

–£ Verilog —Å–∏–Ω—Ç–∞–∫—Å–∏—Å –ø–æ—Ö–æ–∂ –Ω–∞ —è–∑—ã–∫ C. –û–¥–Ω–∞–∫–æ –∫–æ–Ω—Ü–µ–ø—Ç—É–∞–ª—å–Ω–æ Verilog –æ—Ç–ª–∏—á–∞–µ—Ç—Å—è –æ—Ç –±–æ–ª—å—à–∏–Ω—Å—Ç–≤–∞ —è–∑—ã–∫–æ–≤ –ø—Ä–æ–≥—Ä–∞–º–º–∏—Ä–æ–≤–∞–Ω–∏—è, –ø–æ—Å–∫–æ–ª—å–∫—É Verilog –æ–ø–∏—Å—ã–≤–∞–µ—Ç –∞–ø–ø–∞—Ä–∞—Ç—É—Ä—É, –∞ –Ω–µ –ø—Ä–æ–≥—Ä–∞–º–º—É. –í —á–∞—Å—Ç–Ω–æ—Å—Ç–∏:

• Операторы Verilog по своей природе изначально конкурентны (они выполняются в реальном времени параллельно). Это означает, что кроме кода, который появляется между ограничителями блока begin и end, нет заранее определенного порядка, в каком выполняются операторы. Такое поведение отличается от большинства языков программирования наподобие C, в которых подразумевается, что операторы выполняются последовательно, друг за другом. Первая строка в функции main() будет выполнена первой, затем вторая строка, и так далее.

• Синтезируемый код Verilog в конечном счете отображается (map) на реальные аппаратные вентили логики. С другой стороны, компилируемый код C отображается на некие биты в памяти, которые CPU будет или не будет интерпретировать как команды и/или данные при выполнении программы.

[–°–∏–Ω—Ç–∞–∫—Å–∏—Å —Å–∏–Ω—Ç–µ–∑–∏—Ä—É–µ–º–æ–π –∫–æ–º–±–∏–Ω–∞—Ç–æ—Ä–Ω–æ–π –ª–æ–≥–∏–∫–∏ Verilog]

–ú–æ–¥—É–ª–∏. –ë–∞–∑–æ–≤—ã–π –±–ª–æ–∫ –ø—Ä–æ–≥—Ä–∞–º–º—ã Verilog —ç—Ç–æ –æ–ø–µ—Ä–∞—Ç–æ—Ä module. –û–Ω –≤ —á–µ–º-—Ç–æ —è–≤–ª—è–µ—Ç—Å—è –∞–Ω–∞–ª–æ–≥–æ–º –æ–ø—Ä–µ–¥–µ–ª–µ–Ω–∏—è —Ñ—É–Ω–∫—Ü–∏–∏ –Ω–∞ —è–∑—ã–∫–µ C:

module < –∏–º—è–º–æ–¥—É–ª—è >(< —Å–ø–∏—Å–æ–∫_–≤—Ö–æ–¥–æ–≤_–∏_–≤—ã—Ö–æ–¥–æ–≤ >[, ..., ...]);

// –°–ø–∏—Å–æ–∫ –≤—Ö–æ–¥–æ–≤ –∏ –≤—ã—Ö–æ–¥–æ–≤:

input < –∏–º—è–≤—Ö–æ–¥–∞ >;

output < –∏–º—è–≤—ã—Ö–æ–¥–∞ >;

// –î–∞–ª–µ–µ –∏–¥–µ—Ç —Å–ø–∏—Å–æ–∫ –ø–µ—Ä–µ–º–µ–Ω–Ω—ã—Ö, –µ—Å–ª–∏ –æ–Ω –µ—Å—Ç—å, –∏ –∫–æ–¥ –º–æ–¥—É–ª—è:

...

endmodule

–ù–∏–∂–µ –≤ –∫–∞—á–µ—Å—Ç–≤–µ –ø—Ä–∏–º–µ—Ä–∞ –ø—Ä–∏–≤–µ–¥–µ–Ω –º–æ–¥—É–ª—å, —É –∫–æ—Ç–æ—Ä–æ–≥–æ 3 –≤—Ö–æ–¥–∞: –¥–≤–∞ 5-—Ä–∞–∑—Ä—è–¥–Ω—ã—Ö –æ–ø–µ—Ä–∞–Ω–¥–∞ a –∏ b, –≤—Ö–æ–¥ —Ä–∞–∑—Ä–µ—à–µ–Ω–∏—è —Ä–∞–±–æ—Ç—ã en, –∏ —Ç–∞–∫–∂–µ –µ—Å—Ç—å –≤—ã—Ö–æ–¥ a_gt_b. –ú–æ–¥—É–ª—å –Ω–∞–∑—ã–≤–∞–µ—Ç—Å—è comparator (–¥–ª—è –ø—Ä–æ—Å—Ç–æ—Ç—ã –∫–æ–¥ –ª–æ–≥–∏–∫–∏ –º–æ–¥—É–ª—è –Ω–µ –ø—Ä–∏–≤–µ–¥–µ–Ω).

module comparator(a, b, en, a_gt_b);

input [4:0] a, b;

input en;

output a_gt_b;

endmodule

–í —Ç–∞–∫–æ–º —Å–æ—Å—Ç–æ—è–Ω–∏–∏ –∫–æ–¥ –º–æ–¥—É–ª—è –Ω–µ –ø—Ä–æ–∏–∑–≤–æ–¥–∏—Ç –Ω–∏–∫–∞–∫–∏—Ö –¥–µ–π—Å—Ç–≤–∏–π - –ø–æ –¥–≤—É–º –ø—Ä–∏—á–∏–Ω–∞–º. –í–æ-–ø–µ—Ä–≤—ã—Ö, –≤ —Ç–µ–ª–µ –º–æ–¥—É–ª—è –Ω–µ—Ç –æ–ø–∏—Å–∞–Ω–∏—è –ª–æ–≥–∏–∫–∏ –¥–ª—è –¥–µ–π—Å—Ç–≤–∏–π, –∫–æ—Ç–æ—Ä—ã–µ –∏–∑ –≤—Ö–æ–¥–Ω—ã—Ö —Å–∏–≥–Ω–∞–ª–æ–≤ –≥–µ–Ω–µ—Ä–∏—Ä–æ–≤–∞–ª–∏ –±—ã —Å–∏–≥–Ω–∞–ª –Ω–∞ –≤—ã—Ö–æ–¥–µ. –í–æ-–≤—Ç–æ—Ä—ã—Ö, –æ–ø—Ä–µ–¥–µ–ª–µ–Ω–∏–µ –º–æ–¥—É–ª—è —Å–∞–º–æ –ø–æ —Å–µ–±–µ –Ω–µ–¥–æ—Å—Ç–∞—Ç–æ—á–Ω–æ –¥–ª—è —Ä–µ–∞–ª–∏–∑–∞—Ü–∏–∏ —Ä–∞–±–æ—Ç—ã –ª–æ–≥–∏–∫–∏ (–∫—Ä–æ–º–µ —Å–ª—É—á–∞—è —Ç–∞–∫ –Ω–∞–∑—ã–≤–∞–µ–º–æ–≥–æ –º–æ–¥—É–ª—è –≤–µ—Ä—Ö–Ω–µ–≥–æ —É—Ä–æ–≤–Ω—è), –∏ –Ω–∞–º –Ω—É–∂–Ω–æ —Å–¥–µ–ª–∞—Ç—å —Ç–∞–∫ –Ω–∞–∑—ã–≤–∞–µ–º—É—é –∏–Ω—Å—Ç–∞–Ω—Ü–∏–∞—Ü–∏—é –º–æ–¥—É–ª—è, —Ç. –µ. –Ω—É–∂–Ω–æ —Å–æ–∑–¥–∞—Ç—å —ç–∫–∑–µ–º–ø–ª—è—Ä –º–æ–¥—É–ª—è, –∫–æ—Ç–æ—Ä—ã–π –±—É–¥–µ—Ç –¥–µ–ª–∞—Ç—å —Ä–µ–∞–ª—å–Ω—É—é —Ä–∞–±–æ—Ç—É.

–ò–Ω—Å—Ç–∞–Ω—Ü–∏–∞—Ü–∏—è –º–æ–¥—É–ª–µ–π. –î–ª—è —Å–æ–∑–¥–∞–Ω–∏—è —ç–∫–∑–µ–º–ø–ª—è—Ä–∞ –º–æ–¥—É–ª—è –≤ –∫–æ–¥–µ –¥—Ä—É–≥–æ–≥–æ –º–æ–¥—É–ª—è –∏—Å–ø–æ–ª—å–∑—É–µ—Ç—Å—è —Å–ª–µ–¥—É—é—â–∏–π —Å–∏–Ω—Ç–∞–∫—Å–∏—Å:

< –∏–º—è–º–æ–¥—É–ª—è > < –∏–º—è—ç–∫–∑–µ–º–ø–ª—è—Ä–∞ >(< —Å–ø–∏—Å–æ–∫–ø–æ—Ä—Ç–æ–≤ >);

–ü–æ—Ä—Ç–∞–º–∏ –Ω–∞–∑—ã–≤–∞—é—Ç—Å—è —Å–∏–≥–Ω–∞–ª—ã, —Å –∫–æ—Ç–æ—Ä—ã–º–∏ —Ä–∞–±–æ—Ç–∞–µ—Ç –º–æ–¥—É–ª—å. –ù–∞–ø—Ä–∏–º–µ—Ä, –¥–ª—è –∏–Ω—Å—Ç–∞–Ω—Ü–∏–∞—Ü–∏–∏ –º–æ–¥—É–ª—è –∫–æ–º–ø–∞—Ä–∞—Ç–æ—Ä–∞ —Å –∏–º–µ–Ω–µ–º —ç–∫–∑–µ–º–ø–ª—è—Ä–∞ comparator1, –≤—Ö–æ–¥–Ω—ã–º–∏ —Å–∏–≥–Ω–∞–ª–∞–º–∏ in1, in2 –∏ en, –∏ –≤—ã—Ö–æ–¥–æ–º gt (–æ–Ω–∏ –±—É–¥—É—Ç —Å–æ—Å—Ç–∞–≤–ª—è—Ç—å —Å–ø–∏—Å–æ–∫–ø–æ—Ä—Ç–æ–≤), –º—ã –¥–æ–ª–∂–Ω—ã –Ω–∞–ø–∏—Å–∞—Ç—å —Å–ª–µ–¥—É—é—â–∏–π –∫–æ–¥:

comparator comparator1(in1, in2, en, gt);

–≠—Ç–∞ –∏–Ω—Å—Ç–∞–Ω—Ü–∏–∞—Ü–∏—è –∑–∞–≤–∏—Å–∏—Ç –æ—Ç –ø–æ—Ä—è–¥–∫–∞ —Å–ª–µ–¥–æ–≤–∞–Ω–∏—è –ø–æ—Ä—Ç–æ–≤ –≤ —Å–ø–∏—Å–∫–µ –∞—Ä–≥—É–º–µ–Ω—Ç–æ–≤ –º–æ–¥—É–ª—è comparator. –¢–∞–∫–∂–µ –µ—Å—Ç—å –∞–ª—å—Ç–µ—Ä–Ω–∞—Ç–∏–≤–Ω—ã–π —Å–∏–Ω—Ç–∞–∫—Å–∏—Å –∏–Ω—Å—Ç–∞–Ω—Ü–∏–∞—Ü–∏–∏ –º–æ–¥—É–ª–µ–π, –Ω–µ –∑–∞–≤–∏—Å—è—â–∏–π –æ—Ç –ø–æ—Ä—è–¥–∫–∞ —Å–ª–µ–¥–æ–≤–∞–Ω–∏—è –ø–æ—Ä—Ç–æ–≤, —á–∞—Å—Ç–æ –∏—Å–ø–æ–ª—å–∑—É—é—â–∏–π—Å—è –ø–æ —ç—Ç–æ–π –ø—Ä–∏—á–∏–Ω–µ:

< –∏–º—è–º–æ–¥—É–ª—è > < –∏–º—è—ç–∫–∑–µ–º–ø–ª—è—Ä–∞ >(.< –∏–º—è–ø–æ—Ä—Ç–∞ >(ioname), ...);

–î–ª—è –ø—Ä–µ–¥—ã–¥—É—â–µ–≥–æ –ø—Ä–∏–º–µ—Ä–∞ –ø–æ–ª—É—á–∏—Ç—Å—è —Å–ª–µ–¥—É—é—â–∏–π –∫–æ–¥:

comparator comparator1(.b(in2), .a(in1), .en(en), .a_gt_b(gt));

–û–±—Ä–∞—Ç–∏—Ç–µ –≤–Ω–∏–º–∞–Ω–∏–µ, —á—Ç–æ –Ω–µ—Å–º–æ—Ç—Ä—è –Ω–∞ —Ç–æ, —á—Ç–æ –ø–æ—Ä—è–¥–æ–∫ —Å–ª–µ–¥–æ–≤–∞–Ω–∏—è –ø–æ—Ä—Ç–æ–≤ –≤ –∞—Ä–≥—É–º–µ–Ω—Ç–∞—Ö –º–æ–¥—É–ª—è –∏–∑–º–µ–Ω–µ–Ω (b —Ç–µ–ø–µ—Ä—å –∏–¥–µ—Ç –ø–µ—Ä–µ–¥ a), —ç—Ç–∞ –∏–Ω—Å—Ç–∞–Ω—Ü–∏–∞—Ü–∏—è —Ç–µ–ø–µ—Ä—å –≤—Å–µ –µ—â–µ –±—É–¥–µ—Ç —Ä–∞–±–æ—Ç–∞—Ç—å –∫–æ—Ä—Ä–µ–∫—Ç–Ω–æ, –ø–æ—Ç–æ–º—É —á—Ç–æ –¥–æ–ø–æ–ª–Ω–∏—Ç–µ–ª—å–Ω–æ —É–∫–∞–∑–∞–Ω—ã –∫–æ–Ω–∫—Ä–µ—Ç–Ω—ã–µ —Å–∏–≥–Ω–∞–ª—ã, –∫ –∫–æ—Ç–æ—Ä—ã–º –ø–æ–¥–∫–ª—é—á–∞—é—Ç—Å—è –ø–æ—Ä—Ç—ã.

–ö–æ–º–º–µ–Ω—Ç–∞—Ä–∏–∏. –ö–æ–º–º–µ–Ω—Ç–∞—Ä–∏–∏ Verilog –¥–æ–±–∞–≤–ª—è—é—Ç—Å—è –ø–æ —Ç–∞–∫–∏–º –∂–µ –ø—Ä–∞–≤–∏–ª–∞–º, —á—Ç–æ –∏ –Ω–∞ —è–∑—ã–∫–µ C.

// –≠—Ç–æ –æ–¥–Ω–æ—Å—Ç—Ä–æ—á–Ω—ã–π –∫–æ–º–º–µ–Ω—Ç–∞—Ä–∏–π.

/* –ö–æ–º–º–µ–Ω—Ç–∞—Ä–∏–π, —Å–æ—Å—Ç–æ—è—â–∏–π

–∏–∑ –Ω–µ—Å–∫–æ–ª—å–∫–∏—Ö —Å—Ç—Ä–æ–∫. */

–ß–∏—Å–ª–æ–≤—ã–µ –ª–∏—Ç–µ—Ä–∞–ª—ã. –ú–Ω–æ–≥–∏–µ –º–æ–¥—É–ª–∏ –±—É–¥—É—Ç —Å–æ–¥–µ—Ä–∂–∞—Ç—å –≤ –∫–æ–¥–µ —á–∏—Å–ª–æ–≤—ã–µ –ª–∏—Ç–µ—Ä–∞–ª—ã. –ü–æ —É–º–æ–ª—á–∞–Ω–∏—é –Ω–∞ Verilog —á–∏—Å–ª–æ–≤—ã–µ –ª–∏—Ç–µ—Ä–∞–ª—ã –æ–±—Ä–∞–±–∞—Ç—ã–≤–∞—é—Ç—Å—è –∫–∞–∫ 32-–±–∏—Ç–Ω—ã–µ —á–∏—Å–ª–∞ –±–µ–∑ –∑–Ω–∞–∫–∞, –æ–¥–Ω–∞–∫–æ —Å–ª–µ–¥—É–µ—Ç –≤—ã—Ä–∞–±–æ—Ç–∞—Ç—å –≤ —Å–µ–±–µ –ø—Ä–∏–≤—ã—á–∫—É –¥–µ–∫–ª–∞—Ä–∏—Ä–æ–≤–∞—Ç—å —à–∏—Ä–∏–Ω—É (—Ä–∞–∑—Ä—è–¥–Ω–æ—Å—Ç—å) –∫–∞–∂–¥–æ–≥–æ —Ç–∞–∫–æ–≥–æ —á–∏—Å–ª–æ–≤–æ–≥–æ –ª–∏—Ç–µ—Ä–∞–ª–∞. –≠—Ç–æ –ø—Ä–∏–≤–µ–¥–µ—Ç –∫ –º–µ–Ω—å—à–µ–º—É –∫–æ–ª–∏—á–µ—Å—Ç–≤—É –¥–æ–≥–∞–¥–æ–∫, –∫–∞–∫–∏–º –æ–±—Ä–∞–∑–æ–º –Ω—É–∂–Ω–æ —Å–≤—è–∑—ã–≤–∞—Ç—å —Å–∏–≥–Ω–∞–ª (wire) –∏ —á–∏—Å–ª–æ–≤–æ–π –ª–∏—Ç–µ—Ä–∞–ª (—á—Ç–æ –ø–æ–∫–∞–∑–∞–Ω–æ –Ω–∏–∂–µ).

–ü—Ä–∏–º–µ—Ä—ã —á–∏—Å–ª–æ–≤—ã—Ö –ª–∏—Ç–µ—Ä–∞–ª–æ–≤:

/* –û–±—â–∏–π —Å–∏–Ω—Ç–∞–∫—Å–∏—Å:

< –∫–æ–ª–∏—á–µ—Å—Ç–≤–æ–±–∏—Ç >'< —Å–∏—Å—Ç–µ–º–∞—Å—á–∏—Å–ª–µ–Ω–∏—è >< —á–∏—Å–ª–æ >

–ó–¥–µ—Å—å —Å–∏—Å—Ç–µ–º–∞—Å—á–∏—Å–ª–µ–Ω–∏—è —É–∫–∞–∑—ã–≤–∞–µ—Ç—Å—è —Å–∏–º–≤–æ–ª–∞–º–∏:

b –¥–≤–æ—á–∏–Ω–∞—è (binary

d –¥–µ—Å—è—Ç–∏—á–Ω–∞—è (decimal)

h —à–µ—Å—Ç–Ω–∞–¥—Ü–∞—Ç–∏—Ä–∏—á–Ω–∞—è (hexadecimal) */

wire [2:0] a = 3'b111; // 3-—Ä–∞–∑—Ä—è–¥–Ω–æ–µ –¥–≤–æ–∏—á–Ω–æ–µ —á–∏—Å–ª–æ, –≤ –∫–æ—Ç–æ—Ä–æ–º –≤—Å–µ —Ä–∞–∑—Ä—è–¥—ã –≤ –ª–æ–≥. 1

wire [4:0] b = 5'd31; // 5-—Ä–∞–∑—Ä—è–¥–Ω–æ–µ –¥–µ—Å—è—Ç–∏—á–Ω–æ–µ —á–∏—Å–ª–æ 31

wire [31:0] c = 32'hdeadbeef; // 32-–±–∏—Ç–Ω–æ–µ —à–µ—Å—Ç–Ω–∞–¥—Ü–∞—Ç–µ—Ä–∏—á–Ω–æ–µ —á–∏—Å–ª–æ 0xdeadbeef

–ú—ã –ø–æ–∫–∞ –Ω–µ –æ–ø—Ä–µ–¥–µ–ª–∏–ª–∏, —á—Ç–æ —á—Ç–æ —Ç–∞–∫–æ–µ —Å–∏–≥–Ω–∞–ª (wire), —Å–¥–µ–ª–∞–µ–º —ç—Ç–æ –ø–æ–∑–∂–µ.

–ö–æ–Ω—Å—Ç–∞–Ω—Ç—ã. –ú—ã –º–æ–∂–µ–º –∏—Å–ø–æ–ª—å–∑–æ–≤–∞—Ç—å –æ–ø–µ—Ä–∞—Ç–æ—Ä `define, —á—Ç–æ–±—ã –æ–ø—Ä–µ–¥–µ–ª–∏—Ç—å –≥–ª–æ–±–∞–ª—å–Ω—ã–µ –∫–æ–Ω—Å—Ç–∞–Ω—Ç—ã –≤ –∫–æ–¥–µ, –Ω–∞–ø–æ–¥–æ–±–∏–µ –¥–∏—Ä–µ–∫—Ç–∏–≤—ã –ø—Ä–µ–ø—Ä–æ—Ü–µ—Å—Å–æ—Ä–∞ #define –Ω–∞ —è–∑—ã–∫–µ C. –û–±—Ä–∞—Ç–∏—Ç–µ –≤–Ω–∏–º–∞–Ω–∏–µ, —á—Ç–æ –≤ –æ—Ç–ª–∏—á–∏–µ –æ—Ç —è–∑—ã–∫–∞ C, –∫–æ–≥–¥–∞ –æ—Å—É—â–µ—Å—Ç–≤–ª—è–µ—Ç—Å—è —Å—Å—ã–ª–∫–∞ –Ω–∞ –∫–æ–Ω—Å—Ç–∞–Ω—Ç—É, –Ω–∞–º –Ω—É–∂–Ω–æ –¥–æ–±–∞–≤–∏—Ç—å —Å–∏–º–≤–æ–ª –æ–±—Ä–∞—Ç–Ω–æ–π –∫–∞–≤—ã—á–∫–∏ (backtick) –ø–µ—Ä–µ–¥ –∫–æ–Ω—Å—Ç–∞–Ω—Ç–æ–π: –Ω–∞–ø—Ä–∏–º–µ—Ä, –≤ –Ω–∞—à–µ–º —Å–ª—É—á–∞–µ –º—ã –¥–æ–ª–∂–Ω—ã –∏—Å–ø–æ–ª—å–∑–æ–≤–∞—Ç—å `FRI –≤–º–µ—Å—Ç–æ FRI. –¢–∞–∫–∂–µ (–∫–∞–∫ –∏ –Ω–∞ C) –Ω–µ –¥–æ–±–∞–≤–ª—è–π—Ç–µ —Ç–æ—á–∫—É —Å –∑–∞–ø—è—Ç–æ–π –∫ –∫ –æ–ø–µ—Ä–∞—Ç–æ—Ä—É `define.

`define RED 2'b00 // –≤ –æ–ø–µ—Ä–∞—Ç–æ—Ä `define —Ç–æ—á–∫—É —Å –∑–∞–ø—è—Ç–æ–π –¥–æ–±–∞–≤–ª—è—Ç—å –Ω–µ –Ω—É–∂–Ω–æ,

`define WHITE 2'b01 // –∫–∞–∫ –∏ –≤ –æ–ø–µ—Ä–∞—Ç–æ—Ä–µ #define –Ω–∞ —è–∑—ã–∫–µ C

`define BLUE 2'b10

wire [1:0] color1 = `RED;

wire [1:0] color2 = `WHITE;

wire [1:0] color3 = `BLUE;

–°–∏–≥–Ω–∞–ª—ã (wire). –î–ª—è –Ω–∞—á–∞–ª–∞ —Ä–∞–∑–±–µ—Ä–µ–º—Å—è, –∫–∞–∫ –¥–µ–∫–ª–∞—Ä–∏—Ä–æ–≤–∞—Ç—å 2 —Ç–∏–ø–∞ –¥–∞–Ω–Ω—ã—Ö –≤ –Ω–∞—à–∏—Ö –º–æ–¥—É–ª—è—Ö: —Å–∏–≥–Ω–∞–ª—ã (wire) –∏ —Ä–µ–≥–∏—Å—Ç—Ä—ã (reg). –í—ã –º–æ–∂–µ—Ç–µ –¥—É–º–∞—Ç—å –æ —Å–∏–≥–Ω–∞–ª–∞—Ö –∫–∞–∫ –æ —Ñ–∏–∑–∏—á–µ—Å–∫–∏—Ö –ø—Ä–æ–≤–æ–¥–∞—Ö - –∏—Ö –º–æ–∂–Ω–æ –ø–æ–¥–∫–ª—é—á–∞—Ç—å –ª–∏–±–æ –∫ –¥—Ä—É–≥–æ–º—É wire, –∫ –≤—Ö–æ–¥–Ω–æ–º—É –∏–ª–∏ –≤—ã—Ö–æ–¥–Ω–æ–º—É –ø–æ—Ä—Ç—É, –∏–ª–∏ –∫ –ª–æ–≥–∏—á–µ—Å–∫–æ–º—É –∑–Ω–∞—á–µ–Ω–∏—é –∫–æ–Ω—Å—Ç–∞–Ω—Ç—ã. –ß—Ç–æ–±—ã –¥–µ–∫–ª–∞—Ä–∏—Ä–æ–≤–∞—Ç—å —Å–∏–≥–Ω–∞–ª, –º—ã –∏—Å–ø–æ–ª—å–∑—É–µ–º –æ–ø–µ—Ä–∞—Ç–æ—Ä wire:

wire a_wire;

wire [1:0] two_bit_wire;

wire [4:0] five_bit_wire;

–î–ª—è –ø–æ–¥–∫–ª—é—á–µ–Ω–∏—è —Å–∏–≥–Ω–∞–ª–∞ –∫ —á–µ–º—É-–Ω–∏–±—É–¥—å –º—ã –∏—Å–ø–æ–ª—å–∑—É–µ–º –æ–ø–µ—Ä–∞—Ç–æ—Ä assign. –ü—Ä–µ–¥–ø–æ–ª–æ–∂–∏–º, —á—Ç–æ —É –Ω–∞—à –º–æ–¥—É–ª—å –ø—Ä–∏–Ω–∏–º–∞–µ—Ç –¥–≤—É—Ö–±–∏—Ç–Ω—ã–π —Å–∏–≥–Ω–∞–ª –∏ –∏–º–µ–Ω–µ–º two_bit_input, —Ç–æ–≥–¥–∞ –Ω–∞–º –Ω—É–∂–Ω–æ —Å–¥–µ–ª–∞—Ç—å —Å–ª–µ–¥—É—é—â–µ–µ:

assign two_bit_wire = two_bit_input;

// –ü–æ–¥–∫–ª—é—á–∏–º —Å–∏–≥–Ω–∞–ª a_wire –∫ –º–ª–∞–¥—à–µ–º—É –±–∏—Ç—É two_bit_wire:

assign a_wire = two_bit_wire[0];

/* {} –æ–±–æ–∑–Ω–∞—á–∞–µ—Ç –∫–æ–Ω–∫–∞—Ç–µ–Ω–∞—Ü–∏—é - –≤ 3 —Å—Ç–∞—Ä—à–∏—Ö –±–∏—Ç–∞—Ö –±—É–¥–µ—Ç –∑–Ω–∞—á–µ–Ω–∏–µ 101,

–∞ 2 –º–ª–∞–¥—à–∏—Ö –±–∏—Ç–∞ –±—É–¥—É—Ç –ø–æ–¥–∫–ª—é—á–µ–Ω—ã –∫ two_bit_wire */

assign five_bit_wire = {3'b101, two_bit_wire};

// –≠—Ç–∞ —Å—Ç—Ä–æ–∫–∞ –ø—Ä–∏–≤–µ–¥–µ—Ç –∫ –æ—à–∏–±–∫–µ, –ø–æ—Ç–æ–º—É —á—Ç–æ –Ω–µ–ª—å–∑—è –ø—Ä–∏–º–µ–Ω—è—Ç—å assign

// –¥–≤–∞–∂–¥—ã –∫ –æ–¥–Ω–æ–º—É –∏ —Ç–æ–º—É –∂–µ wire:

// assign a_wire = 1’b1;

–û–±—Ä–∞—Ç–∏—Ç–µ –≤–Ω–∏–º–∞–Ω–∏–µ, —á—Ç–æ assign –≤—ã–ø–æ–ª–Ω—è–µ—Ç –ù–ï–ü–Ý–ï–Ý–´–í–ù–û–ï (continuous) –ø—Ä–∏—Å–≤–∞–∏–≤–∞–Ω–∏–µ. –≠—Ç–æ –æ–∑–Ω–∞—á–∞–µ—Ç –≤ –ø—Ä–µ–¥—ã–¥—É—â–µ–º –ø—Ä–∏–º–µ—Ä–µ, —á—Ç–æ –≤—Å–µ–≥–¥–∞, –∫–æ–≥–¥–∞ –º–µ–Ω—è–µ—Ç—Å—è –≤—Ö–æ–¥–Ω–æ–π —Å–∏–≥–Ω–∞–ª two_bit_input, —Ç–æ —Ç–∞–∫–∂–µ –ø–æ–º–µ–Ω—è–µ—Ç—Å—è –∑–Ω–∞—á–µ–Ω–∏–µ two_bit_wire, a_wire –∏ five_bit_wire. –ù–µ—Ç –Ω–∏–∫–∞–∫–æ–≥–æ –ø–æ—Ä—è–¥–∫–∞ –æ—á–µ—Ä–µ–¥–Ω–æ—Å—Ç–∏ –¥–ª—è —ç—Ç–∏—Ö –∏–∑–º–µ–Ω–µ–Ω–∏–π —Å–∏–≥–Ω–∞–ª–æ–≤ - –≤—Å–µ –æ–Ω–∏ –ø—Ä–æ–∏—Å—Ö–æ–¥—è—Ç –æ–¥–Ω–æ–≤—Ä–µ–º–µ–Ω–Ω–æ. –ò–º–µ–Ω–Ω–æ –ø–æ —ç—Ç–æ–π –ø—Ä–∏—á–∏–Ω–µ –Ω–µ–ª—å–∑—è –Ω–µ—Å–∫–æ–ª—å–∫–æ —Ä–∞–∑ –ø—Ä–∏–º–µ–Ω—è—Ç—å assign –∫ –æ–¥–Ω–æ–º—É –∏ —Ç–æ–º—É –∂–µ wire - —Å–∏–≥–Ω–∞–ª wire –Ω–µ –º–æ–∂–µ—Ç —É–ø—Ä–∞–≤–ª—è—Ç—å—Å—è —Ä–∞–∑–Ω—ã–º–∏ –≤—ã—Ö–æ–¥–∞–º–∏ –æ–¥–Ω–æ–≤—Ä–µ–º–µ–Ω–Ω–æ. –û–¥–Ω–æ–≤—Ä–µ–º–µ–Ω–Ω–æ–µ –¥–µ–π—Å—Ç–≤–∏–µ –æ–ø–µ—Ä–∞—Ç–æ—Ä–æ–≤ assign —ç—Ç–æ –∏–º–µ–Ω–Ω–æ —Ç–æ, —á—Ç–æ –º—ã –ø–æ–¥—Ä–∞–∑—É–º–µ–≤–∞–µ–º, –≥–æ–≤–æ—Ä—è –æ Verilog, —á—Ç–æ –æ–Ω "–∏–∑–Ω–∞—á–∞–ª—å–Ω–æ –ø–∞—Ä–∞–ª–ª–µ–ª–µ–Ω".

–í –∑–∞–∫–ª—é—á–µ–Ω–∏–µ —Ä–∞—Å—Å–º–æ—Ç—Ä–∏–º –∫—Ä–∞—Ç–∫–æ–µ –≤—ã—Ä–∞–∂–µ–Ω–∏–µ, –∫–æ—Ç–æ—Ä–æ–µ –∏–Ω–æ–≥–¥–∞ –∏—Å–ø–æ–ª—å–∑—É–µ—Ç—Å—è –¥–ª—è –¥–µ–∫–ª–∞—Ä–∏—Ä–æ–≤–∞–Ω–∏—è –∏ –Ω–∞–∑–Ω–∞—á–µ–Ω–∏—è –∑–∞ –æ–¥–∏–Ω —Ä–∞–∑:

// –î–µ–∫–ª–∞—Ä–∏—Ä—É–µ—Ç—Å—è —Å–∏–≥–Ω–∞–ª gnd –∏ –æ–¥–Ω–æ–≤—Ä–µ–º–µ–Ω–Ω–æ –Ω–∞–∑–Ω–∞—á–∞–µ—Ç—Å—è –µ–º—É –∑–Ω–∞—á–µ–Ω–∏–µ 0:

wire gnd = 1'b0;

–Ý–µ–≥–∏—Å—Ç—Ä—ã. –ï—â–µ –æ–¥–∏–Ω —Ç–∏–ø –¥–∞–Ω–Ω—ã—Ö, –∫–æ—Ç–æ—Ä—ã–π –º—ã –±—É–¥–µ–º –∏—Å–ø–æ–ª—å–∑–æ–≤–∞—Ç—å, —ç—Ç–æ —Ä–µ–≥–∏—Å—Ç—Ä. –ù–µ—Å–º–æ—Ç—Ä—è –Ω–∞ –∏–º—è —Ç–∏–ø–∞, —Ä–µ–≥–∏—Å—Ç—Ä—ã –Ω–µ –ø–æ–¥—Ä–∞–∑—É–º–µ–≤–∞—é—Ç, —á—Ç–æ —ç—Ç–æ –ø–∞–º—è—Ç—å. –≠—Ç–æ –ø—Ä–æ—Å—Ç–æ –∫–æ–Ω—Å—Ç—Ä—É–∫—Ü–∏—è —è–∑—ã–∫–∞, –æ–±–æ–∑–Ω–∞—á–∞—é—â–∞—è –ø–µ—Ä–µ–º–µ–Ω–Ω—ã–µ, –∫–æ—Ç–æ—Ä—ã–µ –º–æ–≥—É—Ç –ø–æ—è–≤–ª—è—Ç—å—Å—è –Ω–∞ –ª–µ–≤–æ–π —Å—Ç–æ—Ä–æ–Ω–µ –±–ª–æ–∫–∞ always (–∏ –≤ –∫–æ–¥–µ —Å–∏–º—É–ª—è—Ü–∏–∏ –≤ –±–ª–æ–∫–∞—Ö initial –∏ forever). –í—ã –¥–µ–∫–ª–∞—Ä–∏—Ä—É–µ—Ç–µ —Ä–µ–≥–∏—Å—Ç—Ä—ã –Ω–∞–ø–æ–¥–æ–±–∏–µ —Å–∏–≥–Ω–∞–ª–æ–≤ wire, –Ω–∞ –≤–µ—Ä—Ö–Ω–µ–º —É—Ä–æ–≤–Ω–µ –º–æ–¥—É–ª—è, –∏ –í—ã –Ω–µ –º–æ–∂–µ—Ç–µ –¥–µ–ª–∞—Ç—å –Ω–∞–∑–Ω–∞—á–µ–Ω–∏–µ (assign) –¥–ª—è —Å–∏–≥–Ω–∞–ª–æ–≤ (wire) –≤–Ω—É—Ç—Ä–∏ –±–ª–æ–∫–∞ always.

–ë–ª–æ–∫–∏ always. –≠—Ç–æ –±–ª–æ–∫–∏, –º–æ–¥–µ–ª–∏—Ä—É—é—â–∏–µ –ø–æ–≤–µ–¥–µ–Ω–∏–µ, –∫–æ—Ç–æ—Ä—ã–µ –≤—ã–ø–æ–ª–Ω—è—é—Ç—Å—è —Å –ø–æ–≤—Ç–æ—Ä–µ–Ω–∏—è–º–∏, —Å–ª—É—á–∞—é—â–∏–º–∏—Å—è –≤ —Å–æ–æ—Ç–≤–µ—Ç—Å—Ç–≤–∏–∏ —Å —Å–æ–±—ã—Ç–∏—è–º–∏, –æ–ø—Ä–µ–¥–µ–ª—è–µ–º—ã–º–∏ —Å–ø–∏—Å–∫–æ–º —á—É–≤—Å—Ç–≤–∏—Ç–µ–ª—å–Ω–æ—Å—Ç–∏. –°–ø–∏—Å–æ–∫ —á—É–≤—Å—Ç–≤–∏—Ç–µ–ª—å–Ω–æ—Å—Ç–∏ –∑–∞–¥–∞–µ—Ç—Å—è –≤ –∫—Ä—É–≥–ª—ã—Ö —Å–∫–æ–±–∫–∞—Ö –±–ª–æ–∫–∞ always. –í—Å—è–∫–∏–π —Ä–∞–∑, –∫–æ–≥–¥–∞ —Å–∏–≥–Ω–∞–ª –≤ —ç—Ç–æ–º —Å–ø–∏—Å–∫–µ –º–µ–Ω—è–µ—Ç —Å–≤–æ–µ –∑–Ω–∞—á–µ–Ω–∏–µ, –æ–ø–µ—Ä–∞—Ç–æ—Ä—ã –≤ –±–ª–æ–∫–µ always –±—É–¥—É—Ç –≤—ã–ø–æ–ª–Ω—è—Ç—å—Å—è –ø–æ—Å–ª–µ–¥–æ–≤–∞—Ç–µ–ª—å–Ω–æ –¥—Ä—É–≥ –∑–∞ –¥—Ä—É–≥–æ–º, —á—Ç–æ –º–æ–∂–Ω–æ —É–≤–∏–¥–µ—Ç—å –≤ —Å–∏–º—É–ª—è—Ç–æ—Ä–µ. –í –∫–æ–Ω—Ç–µ–∫—Å—Ç–µ —Ä–µ–∞–ª—å–Ω–æ–π –∞–ø–ø–∞—Ä–∞—Ç—É—Ä—ã –∏–Ω—Å—Ç—Ä—É–º–µ–Ω—Ç —Å–∏–Ω—Ç–µ–∑–∞ —Å–≥–µ–Ω–µ—Ä–∏—Ä—É–µ—Ç —Å—Ö–µ–º—É, –∫–æ—Ç–æ—Ä–∞—è –±—É–¥–µ—Ç —ç–∫–≤–∏–≤–∞–ª–µ–Ω—Ç–Ω–∞ –æ–ø–µ—Ä–∞—Ç–æ—Ä–∞–º –≤ –±–ª–æ–∫–µ always.

–í –ø—Ä–æ—Å—Ç–µ–π—à–µ–º —Å–ª—É—á–∞–µ —Ä–µ–≥–∏—Å—Ç—Ä –≤ –æ–ø–µ—Ä–∞—Ç–æ—Ä–µ always —Ä–∞–±–æ—Ç–∞–µ—Ç –Ω–∞–ø–æ–¥–æ–±–∏–µ —Ç–∏–ø–∞ –¥–∞–Ω–Ω—ã—Ö wire, –∫–∞–∫ –≤ —ç—Ç–æ–º –ø—Ä–æ—Å—Ç–æ–º –º–æ–¥—É–ª–µ:

module bitwise_not(a_in, a_out);

input [1:0] a_in;

output [1:0] a_out;

// –î–µ–∫–ª–∞—Ä–∏—Ä—É–µ—Ç—Å—è 2-–±–∏—Ç–Ω—ã–π –≤—ã—Ö–æ–¥ a_out –∫–∞–∫ —Ä–µ–≥–∏—Å—Ç—Ä, –ø–æ—Å–∫–æ–ª—å–∫—É

// –æ–Ω –∏—Å–ø–æ–ª—å–∑—É–µ—Ç—Å—è –≤ –ª–µ–≤–æ–π —á–∞—Å—Ç–∏ –≤—ã—Ä–∞–∂–µ–Ω–∏—è –±–ª–æ–∫–∞ always:

reg [1:0] a_out;

// –ó–¥–µ—Å—å –ª—É—á—à–µ –±—ã–ª–æ –±—ã –∏—Å–ø–æ–ª—å–∑–æ–≤–∞—Ç—å @*, —Å–º. —Å–ª–µ–¥—É—é—â–∏–π –ø—Ä–∏–º–µ—Ä:

always @(a_in)

begin

a_out = ~a_in; // out = –ø–æ–±–∏—Ç–Ω–∞—è –∏–Ω–≤–µ—Ä—Å–∏—è –≤—Ö–æ–¥–∞ a_in

end

endmodule

–í —ç—Ç–æ–º –º–æ–¥—É–ª–µ –æ–ø–∏—Å—ã–≤–∞–µ—Ç—Å—è, —á—Ç–æ –≤—Å–µ–≥–¥–∞, –∫–æ–≥–¥–∞ –º–µ–Ω—è–µ—Ç—Å—è –≤—Ö–æ–¥–Ω–æ–π —Å–∏–≥–Ω–∞–ª a_in, –±—É–¥–µ—Ç –æ–±—Ä–∞–±–∞—Ç—ã–≤–∞—Ç—å—Å—è –±–ª–æ–∫ always, –≤ —Ä–µ–∑—É–ª—å—Ç–∞—Ç–µ —á–µ–≥–æ a_out –ø–æ–ª—É—á–∞–µ—Ç –∑–Ω–∞—á–µ–Ω–∏–µ, –≤—ã—á–∏—Å–ª–µ–Ω–Ω–æ–µ –∏–∑ –∑–Ω–∞—á–µ–Ω–∏—è a_in. –≠—Ç–æ –∫–∞–∫ –±—ã –µ—Å–ª–∏ –º—ã –¥–µ–∫–ª–∞—Ä–∏—Ä–æ–≤–∞–ª–∏ a_out –∫–∞–∫ wire, –∏ –Ω–∞–∑–Ω–∞—á–∏–ª–∏ –µ–º—É –∑–Ω–∞—á–µ–Ω–∏–µ –ø–æ–±–∏—Ç–Ω–æ–π –∏–Ω–≤–µ—Ä—Å–∏–∏ a_in.

–û–ø–µ—Ä–∞—Ç–æ—Ä—ã if –∏ case. –ï—â–µ –±–æ–ª–µ–µ –∏–Ω—Ç–µ—Ä–µ—Å–Ω–æ, —á—Ç–æ –º—ã –º–æ–∂–µ–º –ø–æ–º–µ—Å—Ç–∏—Ç—å –æ–ø–µ—Ä–∞—Ç–æ—Ä—ã case –∏ if –≤–Ω—É—Ç—Ä—å –±–ª–æ–∫–æ–≤ always. –û–± –æ–ø–µ—Ä–∞—Ç–æ—Ä–∞—Ö case –∏ if –º—ã –º–æ–∂–µ–º –¥—É–º–∞—Ç—å, —á—Ç–æ –æ–Ω–∏ —Å–∏–Ω—Ç–µ–∑–∏—Ä—É—é—Ç—Å—è –≤ –Ω–µ–∫–∏–π –≤–∏–¥ –º—É–ª—å—Ç–∏–ø–ª–µ–∫—Å–æ—Ä–∞. –í —Å—É—â–Ω–æ—Å—Ç–∏ if –∏ case —Ä–∞–±–æ—Ç–∞—é—Ç –æ–¥–∏–Ω–∞–∫–æ–≤–æ, –æ–¥–Ω–∞–∫–æ –æ–Ω–∏ —Å—É—â–µ—Å—Ç–≤—É—é—Ç –æ—Ç–¥–µ–ª—å–Ω–æ –≤ –æ—Å–Ω–æ–≤–Ω–æ–º —Ç–æ–ª—å–∫–æ –¥–ª—è —Ç–æ–≥–æ, —á—Ç–æ–±—ã —Å–¥–µ–ª–∞—Ç—å –∫–æ–¥ –±–æ–ª–µ–µ —É–¥–æ–±–æ—á–∏—Ç–∞–µ–º—ã–º.

–ù–∏–∂–µ –ø–æ–∫–∞–∑–∞–Ω–∞ –ø—Ä–æ—Å—Ç–∞—è —Å—Ö–µ–º–∞, –∏—Å–ø–æ–ª—å–∑—É—é—â–∞—è –æ–ø–µ—Ä–∞—Ç–æ—Ä case –≤–Ω—É—Ç—Ä–∏ –æ–ø–µ—Ä–∞—Ç–æ—Ä–∞ if:

module alarm_clock(day_i, hour_o, minute_o);

input [2:0] day_i;

output [4:0] hour_o;

output [5:0] minute_o;

wire [2:0] day_i;

/* –î–µ–∫–ª–∞—Ä–∏—Ä—É—é—Ç—Å—è —Ä–µ–≥–∏—Å—Ç—Ä—ã hour_o –∏ minute_o, –ø–æ—Å–∫–æ–ª—å–∫—É –æ–Ω–∏

* –∏—Å–ø–æ–ª—å–∑—É—é—Ç—Å—è –≤ –ª–µ–≤–æ–π —á–∞—Å—Ç–∏ –≤—ã—Ä–∞–∂–µ–Ω–∏—è –±–ª–æ–∫–∞ always */

reg [4:0] hour_o;

reg [5:0] minute_o;

// –°–∏–≥–Ω–∞–ª is_weekday –ø–æ–ª—É—á–∞–µ—Ç –∑–Ω–∞—á–µ–Ω–∏–µ –∫–æ–º–ø–∞—Ä–∞—Ç–æ—Ä–∞:

wire is_weekday;

assign is_weekday = (day_i <= `FRI);

always @* begin

if (is_weekday) begin

hour_o = 5'd8;

minute_o = 6'd30;

end

else begin

case (day_i)

`SAT: {hour_o, minute_o} = {5'd11, 6'd15};

`SUN: {hour_o, minute_o} = {5'd12, 6'd45};

default: {hour_o, minute_o} = 11'd0;

endcase

end

end

endmodule

–í —á–∞—Å—Ç–Ω–æ—Å—Ç–∏, –∏–º–µ–π—Ç–µ –≤ –≤–∏–¥—É:

• Операторы case и if должны размещаться в блоке always.

• По поводу использования always @*: это новая конструкция Verilog-2001, которая автоматически заполняет список чувствительности всеми переменными, перечисленными в правой части выражений блока always. Если специально не указано нечто другое, Вы должны всегда использовать always @* для списков чувствительности блоков always, что может экономить многие часы отладки.

• Операторы begin end используются для обозначения блоков из нескольких строк (то же самое, для чего используют фигурные скобки {} на языке C). Можно опустить конструкцию begin/end, если присваивания в операторах case или if состоят только из одной строки.

• Фактически каждый оператор case имеет оператор default, и каждый оператор if имеет соответствующий else. Не забывайте об этом, или Вы сгенерируете защелки (latch)!

–ü–∞—Ä–∞–º–µ—Ç—Ä—ã. –ß–∞—Å—Ç–æ –º—ã —Ö–æ—Ç–∏–º —Å–æ–∑–¥–∞—Ç—å —Å—Ç–∞–Ω–¥–∞—Ä—Ç–Ω—ã–π –º–æ–¥—É–ª—å, –∫–æ—Ç–æ—Ä—ã–π –º–æ–∂–Ω–æ –Ω–∞—Å—Ç—Ä–æ–∏—Ç—å –Ω–µ—Å–∫–æ–ª—å–∫–∏–º–∏ –ø–∞—Ä–∞–º–µ—Ç—Ä–∞–º–∏, –∫–æ–≥–¥–∞ –¥–ª—è —ç—Ç–æ–≥–æ –º–æ–¥—É–ª—è —Å–æ–∑–¥–∞–µ—Ç—Å—è —ç–∫–∑–µ–º–ø–ª—è—Ä (–∏–Ω—Å—Ç–∞–Ω—Ü–∏–∞—Ü–∏—è –º–æ–¥—É–ª—è). –≠—Ç–æ —Ç–æ –º–µ—Å—Ç–æ, –≥–¥–µ –ø–æ—è–≤–ª—è–µ—Ç—Å—è –æ–ø–µ—Ä–∞—Ç–æ—Ä parameter. –ù–∏–∂–µ –ø–æ–∫–∞–∑–∞–Ω –ø—Ä–∏–º–µ—Ä –ø–∞—Ä–∞–º–µ—Ç—Ä–∏–∑–æ–≤–∞–Ω–Ω–æ–≥–æ ALU, –∫–æ—Ç–æ—Ä—ã–π –ø–æ —É–º–æ–ª—á–∞–Ω–∏—é 32-—Ä–∞–∑—Ä—è–¥–Ω—ã–π, –µ—Å–ª–∏ –ø—Ä–∏ –∏–Ω—Å—Ç–∞–Ω—Ü–∏–∞—Ü–∏–∏ –º–æ–¥—É–ª—è –Ω–µ –±—ã–ª –ø—Ä–µ–¥–æ—Å—Ç–∞–≤–ª–µ–Ω –ø–∞—Ä–∞–º–µ—Ç—Ä:

`define ADD 3'd0

`define LESS 3'd1

`define EQ 3'd2

`define OR 3'd3

`define AND 3'd4

`define NOT 3'd5

module ALU(opcode, op_a, op_b, result);

parameter N = 32;

input [2:0] opcode;

input [N-1:0] op_a, op_b;

output [N-1:0] result;

// result –∏—Å–ø–æ–ª—å–∑—É–µ—Ç—Å—è –≤ –ª–µ–≤–æ–π —á–∞—Å—Ç–∏ –±–ª–æ–∫–∞ always, —Å–ª–µ–¥–æ–≤–∞—Ç–µ–ª—å–Ω–æ

// –æ–Ω –¥–æ–ª–∂–µ–Ω –±—ã—Ç—å –æ–ø—Ä–µ–¥–µ–ª–µ–Ω –∫–∞–∫ —Ä–µ–≥–∏—Å—Ç—Ä:

reg [N-1:0] result;

always @* begin

case (opcode)

`ADD: result = op_a + op_b;

`LESS: result = op_a < op_b;

`EQ: result = op_a == op_b;

`OR: result = op_a | op_b;

`AND: result = op_a & op_b;

`NOT: result = ~op_a;

default: result = 0;

endcase

end

endmodule

–¢–æ–≥–¥–∞ –¥–ª—è –∏–Ω—Å—Ç–∞–Ω—Ü–∏–∞—Ü–∏–∏ ALU –≤–Ω—É—Ç—Ä–∏ –¥—Ä—É–≥–æ–≥–æ –º–æ–¥—É–ª—è –º–æ–∂–Ω–æ –∏—Å–ø–æ–ª—å–∑–æ–≤–∞—Ç—å —Å–∏–º–≤–æ–ª—ã #() –≤ —Å—Ç—Ä–æ–∫–µ –∏–Ω—Å—Ç–∞–Ω—Ü–∏–∞—Ü–∏–∏, —á—Ç–æ–±—ã –ø—Ä–∏–º–µ–Ω–∏—Ç—å –ø–∞—Ä–∞–º–µ—Ç—Ä. –î–ª—è –Ω–∞—à–µ–≥–æ –ø—Ä–∏–º–µ—Ä–∞, –≤–æ—Ç —Ç–∞–∫ –Ω—É–∂–Ω–æ –∏–Ω—Å—Ç–∞–Ω—Ü–∏–∏—Ä–æ–≤–∞—Ç—å 16-–±–∏—Ç–Ω–æ–µ ALU:

[–°–∏–º—É–ª—è—Ü–∏—è, —Ç–µ—Å—Ç–∏—Ä–æ–≤–∞–Ω–∏–µ –∫–æ–¥–∞]

–ö–æ–¥ –¥–ª—è –ø–æ–¥–¥–µ—Ä–∂–∫–∏ —Ç–µ—Å—Ç–∏—Ä–æ–≤–∞–Ω–∏—è (testbench). –î–æ –Ω–∞—Å—Ç–æ—è—â–µ–≥–æ –º–æ–º–µ–Ω—Ç–∞ –º—ã –ø–∏—Å–∞–ª–∏ —Ç–æ–ª—å–∫–æ —Å–∏–Ω—Ç–µ–∑–∏—Ä—É–µ–º—ã–π –∫–æ–¥ Verilog, —Ç. –µ. —Ç–æ—Ç –∫–æ–¥, –∫–æ—Ç–æ—Ä—ã–π —Å–∏–Ω—Ç–µ–∑–∏—Ä—É–µ—Ç—Å—è, —Ç—Ä–∞–Ω—Å–ª–∏—Ä—É–µ—Ç—Å—è –∏ –æ—Ç–æ–±—Ä–∞–∂–∞–µ—Ç—Å—è –≤ —Ä–µ–∞–ª—å–Ω—É—é –∞–ø–ø–∞—Ä–∞—Ç—É—Ä—É (–Ω–∞–ø—Ä–∏–º–µ—Ä –≤ –≤–µ–Ω—Ç–∏–ª–∏ FPGA). –û–¥–Ω–∞–∫–æ –ø–µ—Ä–µ–¥ —Ç–µ–º, –∫–∞–∫ –ø—Ä–æ–±–æ–≤–∞—Ç—å –Ω–∞—à—É –ª–æ–≥–∏–∫—É –Ω–∞ —Ä–µ–∞–ª—å–Ω–æ–º —É—Å—Ç—Ä–æ–π—Å—Ç–≤–µ, –Ω–∞–º —Å–ª–µ–¥—É–µ—Ç —É–¥–æ—Å—Ç–æ–≤–µ—Ä–∏—Ç—å—Å—è, —á—Ç–æ –æ–Ω–∞ —Ñ—É–Ω–∫—Ü–∏–æ–Ω–∏—Ä—É–µ—Ç –∫–æ—Ä—Ä–µ–∫—Ç–Ω–æ. –ü—Ä–æ–≤–µ—Ä–∫–∞ –¥–µ–ª–∞–µ—Ç—Å—è —Å –ø–æ–º–æ—â—å—é –Ω–∞–ø–∏—Å–∞–Ω–∏—è –Ω–∞ Verilog –∫–æ–¥–∞ —Ç–µ—Å—Ç–∞ (testbench) –∏ –ø—Ä–∏–º–µ–Ω–µ–Ω–∏—è –ø—Ä–æ–≥—Ä–∞–º–º–Ω–æ–≥–æ –æ–±–µ—Å–ø–µ—á–µ–Ω–∏—è —Å–∏–º—É–ª—è—Ü–∏–∏, —á—Ç–æ–±—ã –∑–∞–ø—É—Å—Ç–∏—Ç—å —Ç–µ—Å—Ç.

Verilog testbench —ç—Ç–æ —Å–ø–µ—Ü–∏–∞–ª—å–Ω—ã–π —Ñ–∞–π–ª, –∫–æ—Ç–æ—Ä—ã–π –∏–Ω—Å—Ç–∞–Ω—Ü–∏–∏—Ä—É–µ—Ç –º–æ–¥—É–ª—å (–∏–ª–∏ –º–æ–¥—É–ª–∏), –∫–æ—Ç–æ—Ä—ã–µ –Ω–∞–º –Ω—É–∂–Ω—ã –¥–ª—è –ø—Ä–æ–≥–æ–Ω–∞ —Ç–µ—Å—Ç–∞. –≠—Ç–æ—Ç testbench –Ω–µ —Å–∏–Ω—Ç–µ–∑–∏—Ä—É–µ—Ç—Å—è –≤ –∞–ø–ø–∞—Ä–∞—Ç—É—Ä—É. –í–º–µ—Å—Ç–æ —ç—Ç–æ–≥–æ –æ–Ω –ø—Ä–µ–¥–æ—Å—Ç–∞–≤–ª—è–µ—Ç –≤—Ö–æ–¥–Ω—ã–µ —Å–∏–≥–Ω–∞–ª—ã (—Å—Ç–∏–º—É–ª) –≤ –∏–Ω—Å—Ç–∞–Ω—Ü–∏–∏—Ä–æ–≤–∞–Ω–Ω—ã—Ö –º–æ–¥—É–ª—è—Ö, –±–ª–∞–≥–æ–¥–∞—Ä—è —á–µ–º—É –º—ã –º–æ–∂–µ–º –∑–∞–ø—É—Å—Ç–∏—Ç—å testbench –≤ –ø—Ä–æ–≥—Ä–∞–º–º–Ω–æ–º —Å–∏–º—É–ª—è—Ç–æ—Ä–µ –Ω–∞—à–µ–≥–æ –ø—Ä–æ–µ–∫—Ç–∏—Ä—É–µ–º–æ–≥–æ –¥–∏–∑–∞–π–Ω–∞ –ª–æ–≥–∏–∫–∏. –ò–∑-–∑–∞ —Ç–æ–≥–æ, —á—Ç–æ —ç—Ç–æ—Ç –∫–æ–¥ testbench –Ω–µ —Å–∏–Ω—Ç–µ–∑–∏—Ä—É–µ—Ç—Å—è, –æ–Ω –º–æ–∂–µ—Ç –±—ã—Ç—å –Ω–∞–ø–∏—Å–∞–Ω –≤ –¥—Ä—É–≥–æ–º —Å—Ç–∏–ª–µ, –æ—Ç–ª–∏—á–∞—é—â–µ–º—Å—è –æ—Ç –æ–±—ã—á–Ω–æ–≥–æ —Å–∏–Ω—Ç–µ–∑–∏—Ä—É–µ–º–æ–≥–æ –º–æ–¥—É–ª—è Verilog.

–û–ø–µ—Ä–∞—Ç–æ—Ä—ã –∑–∞–¥–µ—Ä–∂–∫–∏. –°–∏–º—É–ª—è—Ü–∏—è –∞–ø–ø–∞—Ä–∞—Ç—É—Ä—ã –ø—Ä–æ–∏—Å—Ö–æ–¥–∏—Ç –≤ –¥–∏—Å–∫—Ä–µ—Ç–Ω—ã–µ –º–æ–º–µ–Ω—Ç—ã –≤—Ä–µ–º–µ–Ω–∏. –ß—Ç–æ–±—ã –≤—ã–ø–æ–ª–Ω–∏—Ç—å –¥–µ–π—Å—Ç–≤–∏—è –≤ —Å–∏–º—É–ª—è—Ü–∏–∏ –≤ –æ–ø—Ä–µ–¥–µ–ª–µ–Ω–Ω–æ–º –ø–æ—Ä—è–¥–∫–µ, –Ω–∞–º —á–∞—Å—Ç–æ —Ç—Ä–µ–±—É–µ—Ç—Å—è –ø—Ä–µ–¥—Å—Ç–∞–≤–∏—Ç—å –≥–µ–Ω–µ—Ä–∏—Ä—É–µ–º—ã–µ –≤—Ö–æ–¥–Ω—ã–µ —Å—Ç–∏–º—É–ª—ã —Ä–∞–∑–Ω—ã–º–∏ –≤ —Ä–∞–∑–Ω—ã–µ –º–æ–º–µ–Ω—Ç—ã –≤—Ä–µ–º–µ–Ω–∏, –≤–º–µ—Å—Ç–æ —Ç–æ–≥–æ, —á—Ç–æ–±—ã –ø—Ä–æ–∏–∑–≤–æ–¥–∏—Ç—å –∏—Ö –æ–¥–Ω–æ–≤—Ä–µ–º–µ–Ω–Ω–æ. –î–ª—è —ç—Ç–æ–≥–æ –º—ã –∏—Å–ø–æ–ª—å–∑—É–µ–º –æ–ø–µ—Ä–∞—Ç–æ—Ä—ã –∑–∞–¥–µ—Ä–∂–∫–∏:

// –û–±—â–∏–π —Å–∏–Ω—Ç–∞–∫—Å–∏—Å –æ–ø–µ—Ä–∞—Ç–æ—Ä–∞: #< n >, –∑–¥–µ—Å—å n –∑–∞–¥–∞–µ—Ç –∑–∞–¥–µ—Ä–∂–∫—É –≤ –µ–¥–∏–Ω–∏—Ü–∞—Ö –≤—Ä–µ–º–µ–Ω–∏.

#5; // –∑–∞–¥–µ—Ä–∂–∫–∞ –≤ 5 –µ–¥–∏–Ω–∏—Ü –≤—Ä–µ–º–µ–Ω–∏

#100; // –∑–∞–¥–µ—Ä–∂–∫–∞ –≤ 100 –µ–¥–∏–Ω–∏—Ü –≤—Ä–µ–º–µ–Ω–∏

// –¢–∞–∫–∂–µ –æ–ø–µ—Ä–∞—Ç–æ—Ä –∑–∞–¥–µ—Ä–∂–∫–∏ –º–æ–∂–Ω–æ —Å–∫–æ–º–ø–æ–Ω–æ–≤–∞—Ç—å —Å –¥—Ä—É–≥–∏–º –æ–ø–µ—Ä–∞—Ç–æ—Ä–æ–º,

// —á—Ç–æ–±—ã –∑–∞–¥–µ—Ä–∂–∞—Ç—å –µ–≥–æ –≤—ã–ø–æ–ª–Ω–µ–Ω–∏–µ:

#3 $display("hi"); // –ø–æ–¥–æ–∂–¥–∞—Ç—å 3 –µ–¥–∏–Ω–∏—Ü—ã –≤—Ä–µ–º–µ–Ω–∏, –∑–∞—Ç–µ–º –æ—Ç–æ–±—Ä–∞–∑–∏—Ç—å "hi"

–ï–¥–∏–Ω–∏—Ü–∞ –≤—Ä–µ–º–µ–Ω–∏ –∑–∞–¥–∞–µ—Ç—Å—è –≤ –Ω–∞—á–∞–ª–µ —Ñ–∞–π–ª–∞ Verilog —Å—Ç—Ä–æ–∫–æ–π –≤–∏–¥–∞:

1ns –æ–∑–Ω–∞—á–∞–µ—Ç —à–∫–∞–ª—É –≤—Ä–µ–º–µ–Ω–∏ –¥–ª—è —Å–∏–º—É–ª—è—Ç–æ—Ä–∞, –∞ 1ps –æ–∑–Ω–∞—á–∞–µ—Ç —Ç–æ—á–Ω–æ—Å—Ç—å —É—á–µ—Ç–∞ –≤—Ä–µ–º–µ–Ω–∏ –¥–ª—è –Ω–µ–≥–æ. –ï–¥–∏–Ω–∏—Ü—ã –≤—Ä–µ–º–µ–Ω–∏, —É–∫–∞–∑–∞–Ω–Ω—ã–µ –∑–¥–µ—Å—å, –ø—Ä–∏–º–µ–Ω—è—é—Ç—Å—è –ø—Ä–∏ —Å–æ–∑–¥–∞–Ω–∏–∏ —Ç–µ—Å—Ç–æ–≤—ã—Ö —Å–∏–≥–Ω–∞–ª–æ–≤, –ø–æ–¥–∞–≤–∞–µ–º—ã—Ö –Ω–∞ –≤—Ö–æ–¥ —Ç–µ—Å—Ç–∏—Ä—É–µ–º–æ–π –≤ —Å–∏–º—É–ª—è—Ç–æ—Ä–µ —Å—Ö–µ–º—ã.

–ë–ª–æ–∫–∏ initial. –ë–ª–æ–∫–∏ initial –∏ forever –ø–æ–¥–æ–±–Ω—ã –±–ª–æ–∫–∞–º always, –∫–æ—Ç–æ—Ä—ã–µ –≤—ã–ø–æ–ª–Ω—è—é—Ç—Å—è –≤ –æ–ø—Ä–µ–¥–µ–ª–µ–Ω–Ω–æ–º –ø–æ—Ä—è–¥–∫–µ, –∫–æ–≥–¥–∞ –∑–∞–¥–∞–Ω–æ –∏—Ö —Å—Ä–∞–±–∞—Ç—ã–≤–∞–Ω–∏–µ. –¢–æ—á–Ω–æ —Ç–∞–∫ –∂–µ –≤ –ª–µ–≤–æ–π —á–∞—Å—Ç–∏ —ç—Ç–∏—Ö –±–ª–æ–∫–æ–≤ –º–æ–∂–Ω–æ –∏—Å–ø–æ–ª—å–∑–æ–≤–∞—Ç—å —Ç–æ–ª—å–∫–æ —Ä–µ–≥–∏—Å—Ç—Ä—ã. –û–¥–Ω–∞–∫–æ –≤ –æ—Ç–ª–∏—á–∏–µ –æ—Ç –±–ª–æ–∫–æ–≤ always, –∫–æ—Ç–æ—Ä—ã–µ —Å—Ä–∞–±–∞—Ç—ã–≤–∞—é—Ç –≤—Å—è–∫–∏–π —Ä–∞–∑, –∫–æ–≥–¥–∞ –∏—Å—Ç–∏–Ω–Ω–æ —É—Å–ª–æ–≤–∏–µ —Å–ø–∏—Å–∫–∞ —á—É–≤—Å—Ç–≤–∏—Ç–µ–ª—å–Ω–æ—Å—Ç–∏, –±–ª–æ–∫ initial –≤—ã–ø–æ–ª–Ω—è–µ—Ç—Å—è —Ç–æ–ª—å–∫–æ –æ–¥–∏–Ω —Ä–∞–∑ –≤ –Ω–∞—á–∞–ª–µ –ø—Ä–æ–≥—Ä–∞–º–º—ã. –ë–ª–æ–∫ forever, —Å—É–¥—è –ø–æ —Å–≤–æ–µ–º—É –Ω–∞–∑–≤–∞–Ω–∏—é, –ø—Ä–µ–¥–Ω–∞–∑–Ω–∞—á–µ–Ω –¥–ª—è —Å–æ–∑–¥–∞–Ω–∏—è –±–µ—Å–∫–æ–Ω–µ—á–Ω–æ–≥–æ –∑–∞—Ü–∏–∫–ª–∏–≤–∞–Ω–∏—è –∫—É—Å–∫–∞ –∫–æ–¥–∞.

–°–ª–µ–¥—É—é—â–∏–π –∫–æ–¥ —É—Å—Ç–∞–Ω–∞–≤–ª–∏–≤–∞–µ—Ç —Ä–µ–≥–∏—Å—Ç—Ä—ã opcode, op_a –∏ op_b –≤ –∑–Ω–∞—á–µ–Ω–∏—è 0, 10 –∏ 20 —Å–æ–æ—Ç–≤–µ—Ç—Å—Ç–≤–µ–Ω–Ω–æ –≤ –º–æ–º–µ–Ω—Ç –≤—Ä–µ–º–µ–Ω–∏ —Å–∏–º—É–ª—è—Ü–∏–∏ t=0, –∏ –∑–∞—Ç–µ–º —á–µ—Ä–µ–∑ –∑–∞–¥–µ—Ä–∂–∫—É 5 –∏—Ö –Ω–∞–∑–Ω–∞—á–µ–Ω–∏—è –º–µ–Ω—è—é—Ç—Å—è –Ω–∞ 2, 10 –∏ 20 —Å–æ–æ—Ç–≤–µ—Ç—Å—Ç–≤–µ–Ω–Ω–æ (–º–æ–º–µ–Ω—Ç –≤—Ä–µ–º–µ–Ω–∏ —Å–∏–º—É–ª—è—Ü–∏–∏ t=5):

reg [2:0] opcode;

reg [4:0] op_a, op_b;

initial begin

opcode = 3'b000;

op_a = 5'd10;

op_b = 5'd20;

#5 opcode = 3'b010;

op_a = 5'd10;

op_b = 5'd20;

end

–û–ø–µ—Ä–∞—Ç–æ—Ä display. –ò—Å–ø–æ–ª—å–∑—É–µ—Ç—Å—è –¥–ª—è –æ—Ç–æ–±—Ä–∞–∂–µ–Ω–∏—è –∑–Ω–∞—á–µ–Ω–∏—è –ø–µ—Ä–µ–º–µ–Ω–Ω–æ–π, –¥–ª—è —Ñ–æ—Ä–º–∞—Ç–∏—Ä–æ–≤–∞–Ω–∏—è —Ä–µ–∑—É–ª—å—Ç–∞—Ç–∞ –∏—Å–ø–æ–ª—å–∑—É–µ—Ç—Å—è printf-–ø–æ–¥–æ–±–Ω—ã–π —Å–∏–Ω—Ç–∞–∫—Å–∏—Å. –ü—Ä–∏ –≤—ã–≤–æ–¥–µ –æ–ø–µ—Ä–∞—Ç–æ—Ä –∞–≤—Ç–æ–º–∞—Ç–∏—á–µ—Å–∫–∏ –¥–æ–±–∞–≤–ª—è–µ—Ç –≤ –∫–æ–Ω–µ—Ü —Å—Ç—Ä–æ–∫–∏ –ø–µ—Ä–µ—Ö–æ–¥ –Ω–∞ –Ω–æ–≤—É—é —Å—Ç—Ä–æ–∫—É.

wire [3:0] ten = 4'd10;

$display("10 in hex: %h, dec: %d, bin: %b", ten, ten, ten);

[–ü—Ä–∏–º–µ—Ä testbench]

–ò—Å–ø–æ–ª—å–∑—É—è —ç—Ç–∏ –æ–ø–µ—Ä–∞—Ç–æ—Ä—ã, –º—ã –º–æ–∂–µ–º —Å–æ–∑–¥–∞—Ç—å –æ—á–µ–Ω—å —Å—ã—Ä–æ–π —Ç–µ—Å—Ç –¥–ª—è –º–æ–¥—É–ª—è ALU.

module ALU_test;

/* –î–µ–∫–ª–∞—Ä–∞—Ü–∏—è —Ä–µ–≥–∏—Å—Ç—Ä–æ–≤, –ø–æ—Å–∫–æ–ª—å–∫—É –º—ã –º–µ–Ω—è–µ–º —ç—Ç–∏ –∑–Ω–∞—á–µ–Ω–∏—è

–≤ –±–ª–æ–∫–∞—Ö always */

reg [2:0] opcode;

reg [15:0] op_a, op_b;

wire [15:0] result; // –ø—Ä–æ—Å—Ç–æ –ø–æ–¥–∫–ª—é—á–µ–Ω–æ –∫ –º–æ–¥—É–ª—é

// –ò–Ω—Å—Ç–∞–Ω—Ü–∏–∞—Ü–∏—è –º–æ–¥—É–ª—è ALU

ALU #(16) alu(.opcode(opcode), .op_a(op_a),

.op_b(op_b), .result(result));

initial begin

opcode = `ADD;

{op_a, op_b} = {16'd32, 16'd5};

// –û–∂–∏–¥–∞–Ω–∏–µ 1 –µ–¥–∏–Ω–∏—Ü—É –≤—Ä–µ–º–µ–Ω–∏ –¥–ª—è –æ—Ç–æ–±—Ä–∞–∂–µ–Ω–∏—è —É—Å—Ç–∞–Ω–æ–≤–∫–∏ result:

#1 $display("%b + %b = %b", op_a, op_b, result);

#5;

opcode = `OR;

{op_a, op_b} = {16'd8, 16'd7};

#1 $display("%b | %b = %b", op_a, op_b, result);

// –∏ —Ç. –¥.

end

endmodule

/* –í—ã–≤–æ–¥ –≤ —Å–∏–º—É–ª—è—Ç–æ—Ä–µ:

# 0000000000100000 + 0000000000000101 = 0000000000100101

# 0000000000001000 | 0000000000000111 = 0000000000001111 */

–≠—Ç–æ—Ç —Ç–µ—Å—Ç –¥–∞–ª–µ–∫ –æ—Ç –∑–∞–≤–µ—Ä—à–µ–Ω–∏—è. –ó–¥–µ—Å—å –º—ã –ø—Ä–æ—Ç–µ—Å—Ç–∏—Ä–æ–≤–∞–ª–∏ —Ç–æ–ª—å–∫–æ —É—Å—Ç–∞–Ω–æ–≤–∫—É –≤—Ö–æ–¥–æ–≤ —Ç–æ–ª—å–∫–æ –¥–ª—è –¥–≤—É—Ö —Ñ—É–Ω–∫—Ü–∏–π —É—Å—Ç—Ä–æ–π—Å—Ç–≤–∞. –¢–∞–∫–∂–µ –Ω—É–∂–Ω–æ –ø—Ä–æ–≤–µ—Ä–∏—Ç—å –±–æ–ª—å—à–µ —Å–ª—É—á–∞–µ–≤, –æ—Å–æ–±–µ–Ω–Ω–æ –∫—Ä–∞–π–Ω–∏–µ. –¢–∞–∫–∂–µ –∞–≤—Ç–æ–º–∞—Ç–∏–∑–∏—Ä–æ–≤–∞–Ω–Ω—ã–π —Ç–µ—Å—Ç –ª—É—á—à–µ, —á–µ–º —Ä—É—á–Ω–æ–π —Ç–µ—Å—Ç –Ω–∞–ø–æ–¥–æ–±–∏–µ —ç—Ç–æ–≥–æ. –û–¥–Ω–∞–∫–æ –ø—Ä–∏–≤–µ–¥–µ–Ω–Ω—ã–π –ø—Ä–∏–º–µ—Ä –ø—Ä–æ—Å—Ç–æ –ø–æ–∫–∞–∑—ã–≤–∞–µ—Ç –Ω–∞—á–∞–ª—å–Ω—É—é —Ç–æ—á–∫—É, –æ—Ç –∫–æ—Ç–æ—Ä–æ–π –í—ã –º–æ–∂–µ—Ç–µ –Ω–∞—á–∞—Ç—å –ø–∏—Å–∞—Ç—å –ø—Ä–æ–≥—Ä–∞–º–º—É –±–æ–ª–µ–µ —Å–ª–æ–∂–Ω–æ–≥–æ —Ç–µ—Å—Ç–∞.

[–°—Å—ã–ª–∫–∏]

1. Introduction to Verilog site:cva.stanford.edu.

2. Introduction to Verilog site:lsi.upc.edu.

3. WebPack ISE: –±—ã—Å—Ç—Ä—ã–π —Å—Ç–∞—Ä—Ç. |