|

ąŁč鹊čé ą┤ą░čéą░čłąĖčé ąŠą┐ąĖčüčŗą▓ą░ąĄčé ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčŗ TUSB3410, TUSB3410I ą║ąŠą╝ą┐ą░ąĮąĖąĖ Texas Instruments (ą┐ąĄčĆąĄą▓ąŠą┤ ąŠčĆąĖą│ąĖąĮą░ą╗čīąĮąŠą│ąŠ ą┤ą░čéą░čłąĖčéą░ [1]). ąÆčüąĄ ąĮąĄąĘąĮą░ą║ąŠą╝čŗąĄ č鹥čĆą╝ąĖąĮčŗ ąĖ ą░ą▒ą▒čĆąĄą▓ąĖą░čéčāčĆčŗ čüą╝ąŠčéčĆąĖč鹥 ą▓ čüą╗ąŠą▓ą░čĆąĖą║ąĄ, ą▓ ą║ąŠąĮčåąĄ čüčéą░čéčīąĖ.

[1. ąÆą▓ąĄą┤ąĄąĮąĖąĄ]

1.1. ą×ą▒čēąĄąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ TUSB3410

TUSB3410 ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą╝ąŠčüč鹊ą▓ąŠąĄ čüąŠąĄą┤ąĖąĮąĄąĮąĖąĄ ą╝ąĄąČą┤čā ą┐ąŠčĆč鹊ą╝ USB ąĖ čĆą░čüčłąĖčĆąĄąĮąĮčŗą╝ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╝ ą┐ąŠčĆč鹊ą╝ UART. TUSB3410 čüąŠą┤ąĄčƹȹĖčé ą▓čüčÄ ąĮąĄąŠą▒čģąŠą┤ąĖą╝čāčÄ ą╗ąŠą│ąĖą║čā ą┤ą╗čÅ ąŠą▒ą╝ąĄąĮą░ ą┤ą░ąĮąĮčŗą╝ąĖ čü čģąŠčüč鹊ą╝ (ą║ąŠą╝ą┐čīčÄč鹥čĆąŠą╝) čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ čłąĖąĮčŗ USB. ąÆąĮčāčéčĆąĖ - čÅą┤čĆąŠ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ 8052 (MCU) čü 16 ą║ą▒ą░ą╣čé RAM, ą┐čĆąĖč湥ą╝ čŹčéą░ RAM ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą│čĆčāąČąĄąĮą░ ą╗ąĖą▒ąŠ ąĖąĘ čģąŠčüčéą░ PC č湥čĆąĄąĘ USB, ą╗ąĖą▒ąŠ ąĖąĘ ą▓ąĮąĄčłąĮąĄą╣ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮąŠą╣ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą┐ą░ą╝čÅčéąĖ ą┐ąŠ čłąĖąĮąĄ I2C. ąÆ TUSB3410 čéą░ą║ąČąĄ čüąŠą┤ąĄčƹȹĖčéčüčÅ 10 ą║ą▒ą░ą╣čé ROM, ą║ąŠč鹊čĆą░čÅ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī ą┐ąŠčĆčé USB ą┐čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ ąĖ ąĘą░ą│čĆčāąĘą║ąĄ (boot time). ąÜąŠą┤ ROM čüąŠą┤ąĄčƹȹĖčé ą▓ čüąĄą▒ąĄ ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ ą▒čāčéą╗ąŠą░ą┤ąĄčĆ I2C. ąÆąĄčüčī čäčāąĮą║čåąĖąŠąĮą░ą╗ čāčüčéčĆąŠą╣čüčéą▓ą░, čéą░ą║ąŠą╣ ą║ą░ą║ ą┤ąĄą║ąŠą┤ąĖčĆąŠą▓ą░ąĮąĖąĄ ą║ąŠą╝ą░ąĮą┤, ąĮą░čüčéčĆąŠą╣ą║ą░ UART, čüąŠąŠą▒čēąĄąĮąĖąĄ ąŠą▒ ąŠčłąĖą▒ą║ą░čģ - ąĘą░ą╗ąŠąČąĄąĮ ą▓ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą╝ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖąĖ firmware MCU. ąŁč鹊 firmware čĆą░ą▒ąŠčéą░ąĄčé ą┐ąŠą┤ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝ čģąŠčüčéą░ PC.

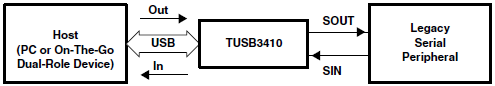

ą£ąĖą║čĆąŠčüčģąĄą╝ą░ TUSB3410 ą╝ąŠąČąĄčé ą▒čŗčéčī ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮą░ ą║ą░ą║ ąĖąĮč鹥čĆč乥ą╣čü ą╝ąĄąČą┤čā čü ą║ą░ą║ąĖą╝-ąĮąĖą▒čāą┤čī čāčüčéčĆąŠą╣čüčéą▓ąŠą╝, ąĖą╝ąĄčÄčēąĖą╝ čéčĆą░ą┤ąĖčåąĖąŠąĮąĮčŗą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ą┐ąŠčĆčé, ąĖ ą║ąŠą╝ą┐čīčÄč鹥čĆąŠą╝ PC čü ą┐ąŠčĆčéą░ą╝ąĖ USB. ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ TUSB3410 čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮą░, ą┐ąŠč鹊ą║ ą┤ą░ąĮąĮčŗčģ ąŠčé čģąŠčüčéą░ ą┤ąŠ TUSB3410 č湥čĆąĄąĘ ą║ąŠą╝ą░ąĮą┤čŗ USB OUT ą▓čŗčģąŠą┤ąĖčé ąĘą░č鹥ą╝ č湥čĆąĄąĘ čüąĖą│ąĮą░ą╗čīąĮčāčÄ ą╗ąĖąĮąĖčÄ SOUT čćąĖą┐ą░ TUSB3410. ąÆ ąŠą▒čĆą░čéąĮąŠą╝ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĖ ą┐ąŠč鹊ą║ ą┤ą░ąĮąĮčŗčģ ą▓čģąŠą┤ąĖčé ą▓ TUSB3410 č湥čĆąĄąĘ ą╗ąĖąĮąĖčÄ SIN, ąĖ ąĘą░č鹥ą╝ ą┐ąŠčüčéčāą┐ą░ąĄčé ą▓ čģąŠčüčé č湥čĆąĄąĘ ą║ąŠą╝ą░ąĮą┤čŗ USB IN.

ąĀąĖčü. 1-1. ąÜą░ą║ ą┐čĆąŠčģąŠą┤čÅčé ą┐ąŠč鹊ą║ąĖ ą┤ą░ąĮąĮčŗčģ ą▓ čćąĖą┐ąĄ TUSB3410.

ą¤ąŠčÅčüąĮąĄąĮąĖčÅ ą║ čĆąĖčü. 1-1:

Host čģąŠčüčé, ą║ąŠą╝ą┐čīčÄč鹥čĆ ąĖą╗ąĖ čāčüčéčĆąŠą╣čüčéą▓ąŠ On-The-Go, ą║ąŠč鹊čĆąŠąĄ ą╝ąŠąČąĄčé čĆą░ą▒ąŠčéą░čéčī ąĖ ą║ą░ą║ čģąŠčüčé, ąĖ ą║ą░ą║ čāčüčéčĆąŠą╣čüčéą▓ąŠ USB.

In, Out ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ą┐ąŠ čłąĖąĮąĄ USB. ąĪ čŹčéąĖą╝ąĖ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅą╝ąĖ čüą▓čÅąĘą░ąĮčŗ ąŠą┤ąĮąŠąĖą╝ąĄąĮąĮčŗąĄ ą║ąŠąĮąĄčćąĮčŗąĄ č鹊čćą║ąĖ ąĖ ąĮą░ąĘą▓ą░ąĮąĖčÅ čéčĆą░ąĮąĘą░ą║čåąĖą╣ ąĖ ą┐ą░ą║ąĄč鹊ą▓.

SOUT, SIN čüąĖą│ąĮą░ą╗čŗ TTL ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ą┐ąŠčĆčéą░, čĆą░ą▒ąŠčéą░čÄčēąĄą│ąŠ ą┐ąŠ čüčéą░ąĮą┤ą░čĆčéčā RS-232.

Legacy Serial Peripheral čüčéą░ąĮą┤ą░čĆčéąĮąŠąĄ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ, ąĖą╝ąĄčÄčēąĄąĄ ą░ą┐ą┐ą░čĆą░čéąĮčŗą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ą┐ąŠčĆčé RS-232. ąŁč鹊 ą╝ąŠąČąĄčé ą▒čŗčéčī, ą║ ą┐čĆąĖą╝ąĄčĆčā, ą║ą░ą║ąŠą╣-ąĮąĖą▒čāą┤čī ą▓ąĮąĄčłąĮąĖą╣ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ.

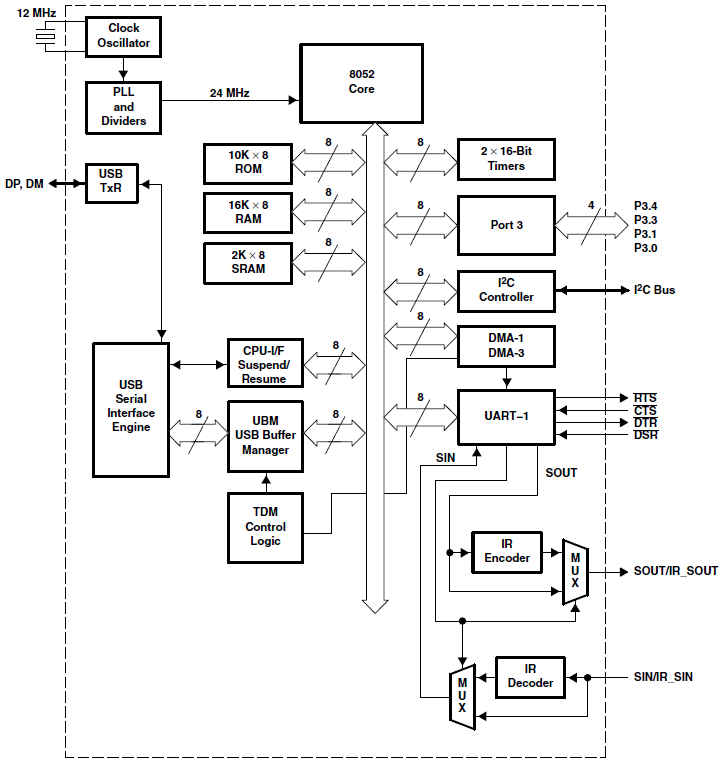

ąĀąĖčü. 1-2. ąæą╗ąŠčćąĮą░čÅ ą┤ąĖą░ą│čĆą░ą╝ą╝ą░ TUSB3410.

ą¤ąŠčÅčüąĮąĄąĮąĖčÅ ą║ čĆąĖčü. 1-2:

Clock Oscillator čéą░ą║č鹊ą▓čŗą╣ ą│ąĄąĮąĄčĆą░č鹊čĆ, čĆą░ą▒ąŠčéą░čÄčēąĖą╣ ąŠčé ą▓ąĮąĄčłąĮąĄą│ąŠ ą║ą▓ą░čĆčåąĄą▓ąŠą│ąŠ čĆąĄąĘąŠąĮą░č鹊čĆą░ 12 ą£ąōčå.

PLL and Dividers čāąĘąĄą╗ ążąÉą¤ą¦ ąĖ ą┤ąĄą╗ąĖč鹥ą╗čÅ, ą║ąŠč鹊čĆčŗą╣ ą▓čŗčĆą░ą▒ą░čéčŗą▓ą░ąĄčé ą▓ąĮčāčéčĆąĄąĮąĮčÄčÄ čéą░ą║č鹊ą▓čāčÄ čćą░čüč鹊čéčā 24 ą£ąōčå.

DP, DM čäąĖąĘąĖč湥čüą║ąĖąĄ čüąĖą│ąĮą░ą╗čŗ ą┤ą░ąĮąĮčŗčģ čłąĖąĮčŗ USB D+ ąĖ D-.

USB TxR čāąĘąĄą╗ čéčĆą░ąĮčüąĖą▓ąĄčĆą░ čäąĖąĘąĖč湥čüą║ąĖčģ čüąĖą│ąĮą░ą╗ąŠą▓ čłąĖąĮčŗ USB.

USB Serial Interface Engine ą░ą┐ą┐ą░čĆą░čéąĮčŗą╣ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░č鹥ą╗čī ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ čüąĖą│ąĮą░ą╗ąŠą▓ čłąĖąĮčŗ USB ą▓ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮčŗą╣ ą║ąŠą┤.

10K x 8 ROM ą┐ą░ą╝čÅčéčī ROM (ą¤ąŚąŻ) 10 ą║ąĖą╗ąŠą▒ą░ą╣čé, ą▓ ą║ąŠč鹊čĆąŠą╣ ąĘą░ą┐ąĖčüą░ąĮ ą║ąŠą┤ ąĘą░ą│čĆčāąĘą║ąĖ (bootcode, ą▒čāčéą╗ąŠą░ą┤ąĄčĆ).

16K x 8 RAM ą┐ą░ą╝čÅčéčī RAM (ą×ąŚąŻ) 16 ą║ąĖą╗ąŠą▒ą░ą╣čé, ą║ąŠč鹊čĆą░čÅ ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮą░ ą┤ą╗čÅ ąĘą░ą│čĆčāąĘą║ąĖ ą▓ ąĮąĄčæ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ firmware (ą║ąŠą┤ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ą┤ą╗čÅ MCU 8052).

2K x 8 SRAM ą┐ą░ą╝čÅčéčī ą×ąŚąŻ 2 ą║ąĖą╗ąŠą▒ą░ą╣čéą░, ą║ąŠč鹊čĆą░čÅ čĆą░čüą┐ąŠą╗ąŠąČąĄąĮą░ ą▓ ąŠą▒ą╗ą░čüčéąĖ XDATA ą░čĆčģąĖč鹥ą║čéčāčĆčŗ 8052 ąĖ ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮą░ ą┤ą╗čÅ čģčĆą░ąĮąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ firmware.

CPU-I/F Suspend/Resume čāąĘąĄą╗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ąŠą╣ ąĖ ą▓ąŠąĘąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄą╝ čĆą░ą▒ąŠčéčŗ CPU.

UBM USB Buffer Manager ą╝ąĄąĮąĄą┤ąČąĄčĆ ą▒čāč乥čĆąŠą▓ USB.

TDM Control Logic ą╗ąŠą│ąĖą║ą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąŠč鹊ą║ą░ą╝ąĖ ą┤ą░ąĮąĮčŗčģ DMA.

2 x 16-Bit Timers ą┤ą▓ą░ čéą░ą╣ą╝ąĄčĆą░, čüčéą░ąĮą┤ą░čĆčéąĮčŗčģ ą┤ą╗čÅ ą░čĆčģąĖč鹥ą║čéčāčĆčŗ 8052.

Port 3 ą┐ąŠčĆčé ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ P3 (GPIO), čéą░ą║ąČąĄ čüčéą░ąĮą┤ą░čĆčéąĮčŗą╣ ą┤ą╗čÅ ą░čĆčģąĖč鹥ą║čéčāčĆčŗ 8052.

P3.0, P3.1, P3.3, P3.4 ą▓čŗą▓ąŠą┤čŗ ą┐ąŠčĆčéą░ P3.

I2C Controller ą░ą┐ą┐ą░čĆą░čéąĮčŗą╣ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ čłąĖąĮčŗ I2C.

DMA-1, DMA-3 ą║ą░ąĮą░ą╗čŗ ą┐čĆčÅą╝ąŠą│ąŠ ą┤ąŠčüčéčāą┐ą░ ą║ ą┐ą░ą╝čÅčéąĖ.

UART-1 ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ą┐ąŠčĆčé.

SIN, SOUT čüąĖą│ąĮą░ą╗čŗ ą┤ą░ąĮąĮčŗčģ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ą┐ąŠčĆčéą░.

~RTS, ~CTS, ~DTS, ~DSR čüčéą░ąĮą┤ą░čĆčéąĮčŗąĄ čüąĖą│ąĮą░ą╗čŗ ąĖąĮč鹥čĆč乥ą╣čüą░ RS-232. ąóąĖą╗čīą┤ą░ ą▓ ąĮą░čćą░ą╗ąĄ ąĖą╝ąĄąĮąĖ ąŠąĘąĮą░čćą░ąĄčé ą╗ąŠą│ąĖč湥čüą║čāčÄ ąĖąĮą▓ąĄčĆčüąĖčÄ.

IR Encoder ą║ąŠą┤ąĄčĆ ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ čüąĖą│ąĮą░ą╗ąŠą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ą║ą░ąĮą░ą╗ą░ ąĖąĮčäčĆą░ą║čĆą░čüąĮąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ.

IR Decoder ą┤ąĄą║ąŠą┤ąĄčĆ ą┤ą╗čÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ čüąĖą│ąĮą░ą╗ą░ ąĖąĮčäčĆą░ą║čĆą░čüąĮąŠą│ąŠ ą║ą░ąĮą░ą╗ą░ ą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ą║ąŠą┤.

SOUT/IR_SOUT ą▓čŗčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ą┐ąŠčĆčéą░.

SIN/IR_SIN ą▓čģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ą┐ąŠčĆčéą░.

[2. ą×čüąĮąŠą▓ąĮčŗąĄ ąŠčüąŠą▒ąĄąĮąĮąŠčüčéąĖ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ TUSB3410]

2.1. USB

ŌĆó ą¤ąŠą╗ąĮąŠčüčéčīčÄ čüąŠą▓ą╝ąĄčüčéąĖą╝ čüąŠ čüčéą░ąĮą┤ą░čĆč鹊ą╝ USB 2.0: TID #40340262.

ŌĆó ą¤ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé čüą║ąŠčĆąŠčüčéčī ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ USB ą┤ąŠ 12 ą╝ąĄą│ą░ą▒ąĖčé/čüąĄą║ (full speed).

ŌĆó ą¤ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║čā čĆą░ą▒ąŠčéčŗ USB (USB suspend), ą▓ąŠąĘąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ čĆą░ą▒ąŠčéčŗ (USB resume), ąĖ čäčāąĮą║čåąĖčÄ čāą┤ą░ą╗ąĄąĮąĮąŠą│ąŠ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ (remote wakeup).

ŌĆó ą¤ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ą┤ą▓ą░ čĆąĄąČąĖą╝ą░ ą┐ąĖčéą░ąĮąĖčÅ:

- ą┐ąĖčéą░ąĮąĖąĄ ąŠčé čłąĖąĮčŗ USB (Bus-powered mode)

- ą┐ąĖčéą░ąĮąĖąĄ ąŠčé čüąŠą▒čüčéą▓ąĄąĮąĮąŠą│ąŠ ąŠčéą┤ąĄą╗čīąĮąŠą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ ą┐ąĖčéą░ąĮąĖčÅ (Self-powered mode)

ŌĆó ą£ąŠąČąĄčé ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čéčī ą┤ąŠ čéčĆąĄčģ ą▓čģąŠą┤ąĮčŗčģ (IN endpoint) ąĖ ą┤ąŠ čéčĆąĄčģ ą▓čŗčģąŠą┤ąĮčŗčģ (OUT endpoint) ą║ąŠąĮąĄčćąĮčŗčģ č鹊č湥ą║ (čĆą░ą▒ąŠčéą░čÄčēąĖčģ ą▓ čĆąĄąČąĖą╝ą░čģ interrupt, bulk).

2.2. ą×čüąĮąŠą▓ąĮčŗąĄ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ

ŌĆó ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ąŠčüąĮąŠą▓ą░ąĮ ąĮą░ ą▓čüčéčĆąŠąĄąĮąĮąŠą╝ čÅą┤čĆąĄ 8052, ą║ąŠč鹊čĆąŠąĄ čüąŠą┤ąĄčƹȹĖčé:

- 256 ą║ąĖą╗ąŠą▒ą░ą╣čé RAM ą┤ą╗čÅ ą▓ąĮčāčéčĆąĄąĮąĮąĖčģ ą┤ą░ąĮąĮčŗčģ (IDATA ą░čĆčģąĖč鹥ą║čéčāčĆčŗ 8052).

- 10 ą║ąĖą╗ąŠą▒ą░ą╣čé ROM (ą▓ ą║ąŠč鹊čĆąŠą╝ ąĘą░ą┐ąĖčüą░ąĮčŗ ąĮąĄčüčéąĖčĆą░ąĄą╝čŗą╣ ą▒čāčéą╗ąŠą░ą┤ąĄčĆ USB ąĖ I2C).

- 16K ą║ąĖą╗ąŠą▒ą░ą╣čé RAM ą┤ą╗čÅ ą║ąŠą┤ą░ firmware, ą║ąŠč鹊čĆčŗą╣ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą│čĆčāąČąĄąĮ čü čģąŠčüčéą░ ąĖą╗ąĖ č湥čĆąĄąĘ ą┐ąŠčĆčé I2C.

- 2 ą║ąĖą╗ąŠą▒ą░ą╣čéą░ ąŠą▒čēąĄą╣ RAM, ą║ąŠč鹊čĆą░čÅ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą║ą░ą║ ą▒čāč乥čĆąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ąĖ ą▒ą╗ąŠą║ąĖ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą▓ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ (endpoint descriptor blocks, EDB).

- 4 ąĮąŠąČą║ąĖ GPIO, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗąĄ ą║ ą┐ąŠčĆčéčā 3 (P3) ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ 8052.

- ą│ą╗ą░ą▓ąĮčŗą╣ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ I2C ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ ą║ ą╝ąĖą║čĆąŠčüčģąĄą╝ąĄ EEPROM.

- MCU čĆą░ą▒ąŠčéą░ąĄčé ąĮą░ čćą░čüč鹊č鹥 24 ą£ąōčå čüąŠ čüą║ąŠčĆąŠčüčéčīčÄ 2 MIPS.

- čüč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ 128 ą╝čü (watchdog timer).

ŌĆó ąöą▓ą░ ą▓čüčéčĆąŠąĄąĮąĮčŗčģ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ DMA ą┤ą╗čÅ ąŠą┐ąĄčĆą░čåąĖą╣ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ I/O č湥čĆąĄąĘ ą┐ąŠčĆčéčŗ USB/UART.

ŌĆó ąĀą░ą▒ąŠčéą░ąĄčé ąŠčé ą║ą▓ą░čĆčåą░ 12 ą£ąōčå.

ŌĆó ą¤ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ąĘą░čüčŗą┐ą░ąĮąĖąĄ ąĖ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖąĄ USB (suspend ąĖ resume).

ŌĆó ą¤ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ą┐čĆąŠčåąĄą┤čāčĆčā ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ čģąŠčüčéą░ (remote wake-up).

ŌĆó ąśą╝ąĄąĄčé 32-ą▓čŗą▓ąŠą┤ąĮčŗą╣ ą║ąŠčĆą┐čāčü LQFP.

ŌĆó ąśčüą┐ąŠą╗čīąĘčāąĄčé ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ 3.3V ąĖ ąĖą╝ąĄąĄčé ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ čĆąĄą│čāą╗čÅč鹊čĆ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ 1.8V, ą║ąŠč鹊čĆčŗą╣ ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┤ą╗čÅ ą┐ąĖčéą░ąĮąĖčÅ čÅą┤čĆą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░.

2.3. ą¤ąŠčĆčé UART čü čĆą░čüčłąĖčĆąĄąĮąĮčŗą╝ąĖ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčÅą╝ąĖ

ŌĆó ą¤čĆąŠą│čĆą░ą╝ą╝ąĮąŠ/ą░ą┐ą┐ą░čĆą░čéąĮąŠąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąŠč鹊ą║ąŠą╝ ą┤ą░ąĮąĮčŗčģ (Software/hardware flow control):

- ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗąĄ čüąĖą╝ą▓ąŠą╗čŗ Xon/Xoff.

- ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗąĄ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ čĆą░ą▒ąŠčéą░čÄčēąĖąĄ čüąĖą│ąĮą░ą╗čŗ ~RTS/~DTR ąĖ ~CTS/~DSR.

ŌĆó ąÉą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐čĆąĖąĄą╝ąŠą┐ąĄčĆąĄą┤ą░čéčćąĖą║ąŠą╝ čłąĖąĮčŗ RS-485, čü ą▓ą║ą╗čÄč湥ąĮąĮčŗą╝ ąĖ ą▓čŗą║ą╗čÄč湥ąĮąĮčŗą╝ čŹčģąŠ.

ŌĆó ąÆčŗą▒ąĖčĆą░ąĄą╝čŗą╣ čĆąĄąČąĖą╝ IrDA, čĆą░ą▒ąŠčéą░čÄčēąĖą╣ ąĮą░ čüą║ąŠčĆąŠčüčéąĖ ą┤ąŠ 115.2 ą║ąĖą╗ąŠą▒ąĖčé/čüąĄą║ (kbps).

ŌĆó ą¤čĆąŠą│čĆą░ą╝ą╝ąĮąŠ ąĘą░ą┤ą░ą▓ą░ąĄą╝ą░čÅ čüą║ąŠčĆąŠčüčéčī ą┐ąĄčĆąĄą┤ą░čćąĖ UART (baud rate) ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąŠčé 50 ą┤ąŠ 921.6 ą║ąĖą╗ąŠą▒ąŠą┤.

ŌĆó ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗąĄ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ UART:

- ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ąĖčé ą▓ čüąĖą╝ą▓ąŠą╗ąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą▒čĆą░ąĮąŠ 5, 6, 7, ąĖą╗ąĖ 8.

- ą▓čŗą▒ąŠčĆ ą│ąĄąĮąĄčĆą░čåąĖąĖ ąĖ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą▒ąĖčéą░ č湥čéąĮąŠčüčéąĖ Even (č湥čéąĮąŠ), odd (ąĮąĄč湥čéąĮąŠ), ąĖą╗ąĖ no parity (ą▒ąĄąĘ ą▒ąĖčéą░ č湥čéąĮąŠčüčéąĖ).

- ą▓čŗą▒ąŠčĆ ą║ąŠą╗ąĖč湥čüčéą▓ą░ čüč鹊ą┐ąŠą▓čŗčģ ą▒ąĖčé 1, 1.5, ąĖą╗ąĖ 2 (stop bit).

ŌĆó ąōąĄąĮąĄčĆą░čåąĖčÅ ąĖ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ čüąĖą│ąĮą░ą╗ą░ ąŠčüčéą░ąĮąŠą▓ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ (Line break).

ŌĆó ąÆčüčéčĆąŠąĄąĮąĮčŗą╣ č鹥čüčé ąĖ ąĘą░ą╝čŗą║ą░ąĮąĖąĄ čüąŠ ą▓čģąŠą┤ą░ ąĮą░ ą▓čŗčģąŠą┤ (loop-back).

ŌĆó ążčāąĮą║čåąĖąĖ ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą╝ąŠą┤ąĄą╝ąŠą╝ (čüąĖą│ąĮą░ą╗čŗ ~CTS, ~RTS, ~DSR, ~DTR, ~RI ąĖ ~DCD).

ŌĆó ąÆąĮčāčéčĆąĄąĮąĮčÅčÅ ą┤ąĖą░ą│ąĮąŠčüčéąĖą║ą░:

- čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ Loopback (čüąŠąĄą┤ąĖąĮąĄąĮąĖąĄ ą▓čģąŠą┤ą░ čü ą▓čŗčģąŠą┤ąŠą╝ ą┤ą╗čÅ ą┐čĆąŠą▓ąĄčĆą║ąĖ), ą┤ą╗čÅ ą║ąŠą╝ą╝čāąĮąĖą║ą░čåąĖą╣ ą┐čĆąĖ ą┐ąŠč鹥čĆąĖ čüą▓čÅąĘąĄą╣.

- čüąĖą╝čāą╗čÅčåąĖčÅ čüąŠą▒čŗčéąĖą╣ ąĖ ąŠčłąĖą▒ąŠą║ Break, parity, overrun, framing-error.

2.4. ą”ąŠą║ąŠą╗ąĄą▓ą║ą░ ą║ąŠčĆą┐čāčüą░ (čĆą░čüą┐ąŠą╗ąŠąČąĄąĮąĖąĄ ą▓čŗą▓ąŠą┤ąŠą▓, ą▓ąĖą┤ čüą▓ąĄčĆčģčā)

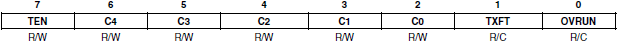

|

|

| ąÜąŠčĆą┐čāčü VF, ą▓ąĖą┤ čüą▓ąĄčĆčģčā |

ąÜąŠčĆą┐čāčü RHB, ą▓ąĖą┤ čüąĮąĖąĘčā |

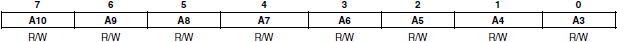

ąóą░ą▒ą╗ąĖčåą░ 2-1. ąØą░ąĘąĮą░č湥ąĮąĖąĄ ąĖ ąĮčāą╝ąĄčĆą░čåąĖčÅ ą▓čŗą▓ąŠą┤ąŠą▓ TUSB3410

| ąśą╝čÅ |

Ōä¢ ą▓čŗą▓. |

I/O |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| CLKOUT |

22 |

O |

ąÆčŗčģąŠą┤ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ (čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ą▒ąĖč鹊ą╝ 2 CLKOUTEN ąĖ ą▒ąĖč鹊ą╝ 3 CLKSLCT čĆąĄą│ąĖčüčéčĆą░ MODECNFG), čüą╝. čüąĄą║čåąĖčÄ 5.5 ąĖ ą┐čĆąĖą╝ąĄčćą░ąĮąĖąĄ 1. |

| ~CTS |

13 |

I |

UART: čüąĖą│ąĮą░ą╗ Clear to send, ąŠčćąĖčēąĄąĮąŠ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ (čüą╝. ą┐čĆąĖą╝ąĄčćą░ąĮąĖąĄ 4). |

| ~DCD |

15 |

I |

UART: čüąĖą│ąĮą░ą╗ Data carrier detect, ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ąĮąĄčüčāčēąĄą╣ (čüą╝. ą┐čĆąĖą╝ąĄčćą░ąĮąĖąĄ 4). |

| DM |

7 |

I/O |

ążąĖąĘąĖč湥čüą║ąĖą╣ čüąĖą│ąĮą░ą╗ ą┤ą░ąĮąĮčŗčģ D- čłąĖąĮčŗ USB. |

| DP |

6 |

I/O |

ążąĖąĘąĖč湥čüą║ąĖą╣ čüąĖą│ąĮą░ą╗ ą┤ą░ąĮąĮčŗčģ D+ čłąĖąĮčŗ USB. |

| ~DSR |

14 |

I |

UART: čüąĖą│ąĮą░ą╗ Data set ready, ąĮą░ą▒ąŠčĆ ą┤ą░ąĮąĮčŗčģ ą│ąŠč鹊ą▓ (čüą╝. ą┐čĆąĖą╝ąĄčćą░ąĮąĖąĄ 4). |

| ~DTR |

21 |

O |

UART: čüąĖą│ąĮą░ą╗ Data terminal ready (čüą╝. ą┐čĆąĖą╝ąĄčćą░ąĮąĖąĄ 1). |

| GND |

8, 18, 28 |

|

ą”ąĖčäčĆąŠą▓ą░čÅ ąĘąĄą╝ą╗čÅ ąĖ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮčŗą╣ ą┐čĆąŠą▓ąŠą┤ ą┐ąĖčéą░ąĮąĖčÅ. |

| P3.0 |

32 |

I/O |

ąæąĖčé 0 GPIO ą┐ąŠčĆčéą░ 3 (čüą╝. ą┐čĆąĖą╝ąĄčćą░ąĮąĖčÅ 3, 5 ąĖ 8). |

| P3.1 |

31 |

I/O |

ąæąĖčé 1 GPIO ą┐ąŠčĆčéą░ 3 (čüą╝. ą┐čĆąĖą╝ąĄčćą░ąĮąĖčÅ 3, 5 ąĖ 8). |

| P3.3 |

30 |

I/O |

ąæąĖčé 3 GPIO ą┐ąŠčĆčéą░ 3 (čüą╝. ą┐čĆąĖą╝ąĄčćą░ąĮąĖčÅ 3, 5 ąĖ 8). |

| P3.4 |

29 |

I/O |

ąæąĖčé 4 GPIO ą┐ąŠčĆčéą░ 3 (čüą╝. ą┐čĆąĖą╝ąĄčćą░ąĮąĖčÅ 3, 5 ąĖ 8). |

| PUR |

5 |

O |

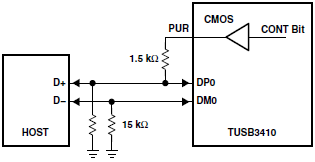

ą¤ąŠą┤ą║ą╗čÄč湥ąĮąĖąĄ ąĮą░ą│čĆčāąĘąŠčćąĮąŠą│ąŠ čĆąĄąĘąĖčüč鹊čĆą░ (pull-up) ą┤ą╗čÅ čłąĖąĮčŗ USB (čüą╝. ą┐čĆąĖą╝ąĄčćą░ąĮąĖąĄ 2). |

| ~RESET |

9 |

I |

ąōą╗ą░ą▓ąĮčŗą╣ ą▓čģąŠą┤ čüą▒čĆąŠčüą░ (čüą╝. ą┐čĆąĖą╝ąĄčćą░ąĮąĖąĄ 4). |

| ~RI/CP |

16 |

I |

UART: čüąĖą│ąĮą░ą╗ Ring indicator, ąĮą░ą╗ąĖčćąĖąĄ ą▓čŗąĘąŠą▓ą░ (čüą╝. ą┐čĆąĖą╝ąĄčćą░ąĮąĖąĄ 4). |

| ~RTS |

20 |

O |

UART: čüąĖą│ąĮą░ą╗ Request to send, ąĘą░ą┐čĆąŠčü ąĮą░ ą┐ąĄčĆąĄą┤ą░čćčā (čüą╝. ą┐čĆąĖą╝ąĄčćą░ąĮąĖąĄ 4). |

| SCL |

11 |

O |

ąĪąĖą│ąĮą░ą╗ čéą░ą║č鹊ą▓ ą╝ą░čüč鹥čĆą░ čłąĖąĮčŗ I2C, čüčÄą┤ą░ ąŠą▒čŗčćąĮąŠ ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčéčüčÅ ą▓ąĮąĄčłąĮčÅčÅ ą┐ą░ą╝čÅčéčī EEPROM ą┤ą╗čÅ ąĘą░ą│čĆčāąĘą║ąĖ (čüą╝. ą┐čĆąĖą╝ąĄčćą░ąĮąĖąĄ 1). |

| SDA |

10 |

I/O |

ąĪąĖą│ąĮą░ą╗ ą┤ą░ąĮąĮčŗčģ ą╝ą░čüč鹥čĆą░ čłąĖąĮčŗ I2C, čüčÄą┤ą░ ąŠą▒čŗčćąĮąŠ ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčéčüčÅ ą▓ąĮąĄčłąĮčÅčÅ ą┐ą░ą╝čÅčéčī EEPROM ą┤ą╗čÅ ąĘą░ą│čĆčāąĘą║ąĖ (čüą╝. ą┐čĆąĖą╝ąĄčćą░ąĮąĖąĄ 1 ąĖ 5). |

| SIN/IR_SIN |

17 |

I |

UART: ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗąĄ ą▓čģąŠą┤ąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ / ą▓čģąŠą┤ ą┤ą░ąĮąĮčŗčģ ą║ą░ąĮą░ą╗ą░ IR (čüą╝. ą┐čĆąĖą╝ąĄčćą░ąĮąĖąĄ 6). |

| SOUT/IR_SOUT |

19 |

O |

UART: ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗąĄ ą▓čŗčģąŠą┤ąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ / ą▓čŗčģąŠą┤ ą┤ą░ąĮąĮčŗčģ ą║ą░ąĮą░ą╗ą░ IR (čüą╝. ą┐čĆąĖą╝ąĄčćą░ąĮąĖąĄ 7). |

| SUSPEND |

2 |

O |

ąÆčŗą▓ąŠą┤ ąĖąĮą┤ąĖą║ą░čåąĖąĖ čĆąĄąČąĖą╝ą░ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ąĖ (čüą╝. ą┐čĆąĖą╝ąĄčćą░ąĮąĖąĄ 3). ąÜąŠą│ą┤ą░ ąĮą░ čŹč鹊ą╝ ą▓čŗą▓ąŠą┤ąĄ ą╗ąŠą│. 1, čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ąĖ (suspend mode). |

| TEST0 |

23 |

I |

ąóąĄčüč鹊ą▓čŗą╣ ą▓čģąŠą┤, ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮąĮčŗą╣ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ąĘą░ą▓ąŠą┤čüą║ąŠą│ąŠ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ (čüą╝. ą┐čĆąĖą╝ąĄčćą░ąĮąĖąĄ 5). ąŁč鹊čé ą▓čŗą▓ąŠą┤ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąŠą┤čéčÅąĮčāčé ą║ VCC č湥čĆąĄąĘ čĆąĄąĘąĖčüč鹊čĆ 10 ą║ą×ą╝. |

| TEST1 |

24 |

I |

ąóąĄčüč鹊ą▓čŗą╣ ą▓čģąŠą┤, ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮąĮčŗą╣ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ąĘą░ą▓ąŠą┤čüą║ąŠą│ąŠ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ (čüą╝. ą┐čĆąĖą╝ąĄčćą░ąĮąĖąĄ 5). ąŁč鹊čé ą▓čŗą▓ąŠą┤ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąŠą┤čéčÅąĮčāčé ą║ VCC č湥čĆąĄąĘ čĆąĄąĘąĖčüč鹊čĆ 10 ą║ą×ą╝. |

| VCC |

3, 25 |

PWR |

3.3V, ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ. |

| VDD18 |

4 |

PWR |

ąÆčŗčģąŠą┤ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čĆąĄą│čāą╗čÅč鹊čĆą░ ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ 1.8V. ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą▓čŗą▓ąŠą┤ ~VREGEN ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą╗ąŠą│. 0. ąÜąŠą│ą┤ą░ ~VREGEN ą▓ ą╗ąŠą│. 1, ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ 1.8V (ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą┐ąĖčéą░ąĮąĖčÅ čÅą┤čĆą░ MCU) ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮąŠ ąŠčé ą▓ąĮąĄčłąĮąĄą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ ą┐ąĖčéą░ąĮąĖčÅ. |

| ~VREGEN |

1 |

I |

ąÆčģąŠą┤, ą░ą║čéąĖą▓ąĮčŗą╣ ą║ ąĮąĖąĘą║ąŠą╝čā čāčĆąŠą▓ąĮčÄ, ą┤ą╗čÅ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ čĆą░ą▒ąŠčéčŗ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čüčéą░ą▒ąĖą╗ąĖąĘą░č鹊čĆą░ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ (ąĖąĘ 3.3V ą┐ąŠą╗čāčćą░ąĄčé 1.8V). |

| ~WAKEUP |

12 |

I |

ąÆčŗą▓ąŠą┤ ą┤ą╗čÅ ąĘą░ą┐čĆąŠčüą░ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ čģąŠčüčéą░ (wake-up request). ąÜąŠą│ą┤ą░ ą╗ąŠą│. 0, ą▓čŗą▓ąŠą┤ąĖčé ąĖąĘ čüą┐čÅčćą║ąĖ ąŠą┐ąĄčĆą░čåąĖąŠąĮąĮčāčÄ čüąĖčüč鹥ą╝čā ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮąŠą│ąŠ ą║ąŠą╝ą┐čīčÄč鹥čĆą░ (čüą╝. ą┐čĆąĖą╝ąĄčćą░ąĮąĖąĄ 5). |

| X1/CLKI |

27 |

I |

ąÆčŗą▓ąŠą┤ ą┤ą╗čÅ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ą║čĆąĖčüčéą░ą╗ą╗ą░ (ą▓čģąŠą┤) 12 ą£ąōčå ąĖą╗ąĖ ą▓čģąŠą┤ ą▓ąĮąĄčłąĮąĖčģ čéą░ą║č鹊ą▓. |

| X2 |

26 |

O |

ąÆčŗą▓ąŠą┤ ą┤ą╗čÅ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ą║čĆąĖčüčéą░ą╗ą╗ą░ (ą▓čŗčģąŠą┤) 12 ą£ąōčå. |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ ą║ čéą░ą▒ą╗ąĖčåąĄ 2-1 (čéąĖą╗čīą┤ą░ ~ ą▓ ąĖą╝ąĄąĮą░čģ čüąĖą│ąĮą░ą╗ąŠą▓ ąŠąĘąĮą░čćą░ąĄčé ą╗ąŠą│ąĖč湥čüą║čāčÄ ąĖąĮą▓ąĄčĆčüąĖčÄ):

1. ąÆčŗčģąŠą┤ ą▒čāč乥čĆą░ CMOS čü čéčĆąĄą╝čÅ čüąŠčüč鹊čÅąĮąĖčÅą╝ąĖ ą▓čŗčģąŠą┤ą░ (ąĮą░ą│čĆčāąĘąŠčćąĮą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī +- 4 mA).

2. ąÆčŗčģąŠą┤ ą▒čāč乥čĆą░ CMOS čü čéčĆąĄą╝čÅ čüąŠčüč鹊čÅąĮąĖčÅą╝ąĖ ą▓čŗčģąŠą┤ą░ (ąĮą░ą│čĆčāąĘąŠčćąĮą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī +- 8 mA).

3. ąÆčŗčģąŠą┤ ą▒čāč乥čĆą░ CMOS čü čéčĆąĄą╝čÅ čüąŠčüč鹊čÅąĮąĖčÅą╝ąĖ ą▓čŗčģąŠą┤ą░ (ąĮą░ą│čĆčāąĘąŠčćąĮą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī +- 12 mA).

4. ąÆčģąŠą┤ čüąŠą▓ą╝ąĄčüčéąĖą╝čŗą╣ čü TTL, čü ą│ąĖčüč鹥čĆąĄąĘąĖčüąŠą╝.

5. ąÆčģąŠą┤ čüąŠą▓ą╝ąĄčüčéąĖą╝čŗą╣ čü TTL, čü ą│ąĖčüč鹥čĆąĄąĘąĖčüąŠą╝, čü ą▓ąĮčāčéčĆąĄąĮąĮąĖą╝ ą░ą║čéąĖą▓ąĮčŗą╝ ą▓ąĄčĆčģąĮąĖą╝ (pullup) ąĮą░ą│čĆčāąĘąŠčćąĮčŗą╝ čĆąĄąĘąĖčüč鹊čĆąŠą╝ ąĮą░ 100 mkA.

6. ąÆčģąŠą┤ čüąŠą▓ą╝ąĄčüčéąĖą╝čŗą╣ čü TTL, ą▒ąĄąĘ ą│ąĖčüč鹥čĆąĄąĘąĖčüą░, čü ą▓ąĮčāčéčĆąĄąĮąĮąĖą╝ ą░ą║čéąĖą▓ąĮčŗą╝ ą▓ąĄčĆčģąĮąĖą╝ (pullup) ąĮą░ą│čĆčāąĘąŠčćąĮčŗą╝ čĆąĄąĘąĖčüč鹊čĆąŠą╝ ąĮą░ 100 mkA.

7. ąØąŠčĆą╝ą░ą╗čīąĮčŗą╣ čĆąĄąČąĖą╝ ąĖą╗ąĖ IR-čĆąĄąČąĖą╝: ą▓čŗčģąŠą┤ ą▒čāč乥čĆą░ CMOS čü čéčĆąĄą╝čÅ čüąŠčüč鹊čÅąĮąĖčÅą╝ąĖ ą▓čŗčģąŠą┤ą░ (ąĮą░ą│čĆčāąĘąŠčćąĮą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī +- 4 mA).

8. MCU čĆą░ą▒ąŠčéą░ąĄčé čü ą▓čŗčģąŠą┤ą░ą╝ąĖ ą║ą░ą║ čü ąŠčéą║čĆčŗčéčŗą╝ čüč鹊ą║ąŠą╝ čéą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, čćč鹊 ąĮąĖąĘą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī ą╝ąŠąČąĄčé čāą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ ąĮą░ ą▓čŗčģąŠą┤ąĄ ą┐čĆąŠą┤ąŠą╗ąČąĖč鹥ą╗čīąĮąŠąĄ ą▓čĆąĄą╝čÅ, ą░ ą▓čŗčüąŠą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī ą┐ąŠčÅą▓ą╗čÅąĄčéčüčÅ ąĮą░ ą▓čŗčģąŠą┤ąĄ č鹊ą╗čīą║ąŠ ąĮą░ 2 čéą░ą║čéą░ CPU, ą┐ąŠčüą╗ąĄ č湥ą│ąŠ ą▓čŗčģąŠą┤ ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ą▓čŗčüąŠą║ąŠą│ąŠ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖčÅ (čéčĆąĄčéčīąĄ čüąŠčüč鹊čÅąĮąĖąĄ).

[3. ą¤ąŠą┤čĆąŠą▒ąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ TUSB3410]

3.1. ąĀą░ą▒ąŠčćąĖąĄ čĆąĄąČąĖą╝čŗ

TUSB3410 čāą┐čĆą░ą▓ą╗čÅąĄčé ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄą╝ ąĖąĮč鹥čĆč乥ą╣čüą░ ą▓ ąŠčéą▓ąĄčé ąĮą░ ą║ąŠą╝ą░ąĮą┤čŗ USB, ąĖ čŹč鹊 čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĄ ąĘą░ą▓ąĖčüąĖčé ąŠčé ą▓čŗą▒čĆą░ąĮąĮąŠą│ąŠ čĆąĄąČąĖą╝ą░ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ą┐ąŠčĆčéą░. ąĪ ą┤čĆčāą│ąŠą╣ čüč鹊čĆąŠąĮčŗ, ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ą┐ąŠčĆčé ą╝ąŠąČąĄčé ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčīčüčÅ ą▓ čéčĆąĄčģ čĆą░ąĘą╗ąĖčćąĮčŗčģ čĆąĄąČąĖą╝ą░čģ.

ąÜą░ą║ ąĖ ą▓ ą╗čÄą▒ąŠą╝ ąĖąĮč鹥čĆč乥ą╣čüąĮąŠą╝ čāčüčéčĆąŠą╣čüčéą▓ąĄ, ą┐ąĄčĆąĄą┤ą░čćą░ ą┤ą░ąĮąĮčŗčģ čÅą▓ą╗čÅąĄčéčüčÅ ąŠčüąĮąŠą▓ąĮąŠą╣ čäčāąĮą║čåąĖąĄą╣ TUSB3410, ąĮąŠ ąŠą▒čŗčćąĮąŠ ąĮą░čćą░ą╗čīąĮąŠąĄ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ ąĖ ąŠą▒čĆą░ą▒ąŠčéą║ą░ ąŠčłąĖą▒ąŠą║ čéčĆąĄą▒čāąĄčé ąĮąĄą║ąŠč鹊čĆąŠą╣ ą┐ąŠą┤ą┤ąĄčƹȹ║ąĖ ą▓ ą║ąŠą┤ąĄ firmware. ąÆ ą┐ąŠčüą╗ąĄą┤čāčÄčēąĖčģ čüąĄą║čåąĖčÅčģ ą▒čāą┤ąĄčé ąŠą┐ąĖčüą░ąĮčŗ čĆą░ąĘą╗ąĖčćąĮčŗąĄ čĆąĄąČąĖą╝čŗ, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮčŗ ą┤ą╗čÅ čāčüčéčĆąŠą╣čüčéą▓ą░, čćč鹊 ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé ąĖąĘ čüąĄą▒čÅ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ ą▓ ą┤ą░ąĮąĮčŗčģ čĆąĄąČąĖą╝ą░čģ.

3.2. ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ąĖąĮč鹥čĆč乥ą╣čüą░ USB

TUSB3410 čüąŠą┤ąĄčƹȹĖčé ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ ą╝ąĖą║čĆąŠą║ąŠą┤, ą║ąŠč鹊čĆčŗą╣ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé MCU ąĮą░čüčéčĆąŠąĖčéčī USB, čćč鹊ą▒čŗ ąŠąĮąŠ čāčüą┐ąĄčłąĮąŠ ą┐čĆąŠčłą╗ąŠ ą┐čĆąŠčåąĄą┤čāčĆčā 菹Įčāą╝ąĄčĆą░čåąĖąĖ ąĮą░ čģąŠčüč鹥. ą£ąĖą║čĆąŠą║ąŠą┤ ROM ą╝ąŠąČąĄčé čéą░ą║ąČąĄ ąĘą░ą│čĆčāąĘąĖčéčī ą║ąŠą┤ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ (application code) ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮčÄčÄ ą┐ą░ą╝čÅčéčī RAM ąĖąĘ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ č湥čĆąĄąĘ čłąĖąĮčā I2C (čéą░ą║čāčÄ čłąĖąĮčā ąĖą╝ąĄčÄčé ą╝ąĮąŠą│ąĖąĄ ą┐ąŠą┐čāą╗čÅčĆąĮčŗąĄ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ EEPROM čü ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╝ ąĖąĮč鹥čĆč乥ą╣čüąŠą╝) ąĖą╗ąĖ ąŠčé čģąŠčüčéą░, ą┐čĆčÅą╝ąŠ č湥čĆąĄąĘ ąĖąĮč鹥čĆč乥ą╣čü USB.

3.2.1. ąŚą░ą│čĆčāąĘą║ą░ ą║ąŠą┤ą░ ąĖąĘ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮąŠą╣ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ

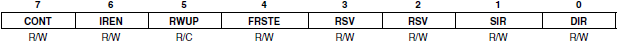

ą¤ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ (ąĖą╗ąĖ ą▓ą║ą╗čÄč湥ąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ) TUSB3410 ąŠčéą║ą╗čÄčćą░ąĄčéčüčÅ ąŠčé USB (čüąĖą│ąĮą░ą╗čŗ ą┐čĆąĖą▓ąŠą┤čÅčéčüčÅ ą▓ čéą░ą║ąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ, čćč鹊 čģąŠčüčé ą▓ąĖą┤ąĖčé čāčüčéčĆąŠą╣čüčéą▓ąŠ ąŠčéą║ą╗čÄč湥ąĮąĮčŗą╝, ą┤ą░ąČąĄ ąĄčüą╗ąĖ ąŠąĮąŠ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąŠ ą║ ą┐ąŠčĆčéčā USB). ąæąĖčé 7 (CONT) čĆąĄą│ąĖčüčéčĆą░ USBCTL (čüą╝. čüąĄą║čåąĖčÄ 5.4) ąŠčćąĖčēą░ąĄčéčüčÅ. TUSB3410 ą┐čĆąŠą▓ąĄčĆčÅąĄčé ą┐ąŠčĆčé I2C ąĮą░ ąĮą░ą╗ąĖčćąĖąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮąŠą╣ ą▓ąĮąĄčłąĮąĄą╣ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą┐ą░ą╝čÅčéąĖ (ąĮą░ą┐čĆąĖą╝ąĄčĆ, čŹč鹊 ą╝ąŠąČąĄčé ą▒čŗčéčī ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ 24C512), ąĖ ąĮą░ą╗ąĖčćąĖąĄ ą▓ ąĮąĄą╣ ą┤ąŠą┐čāčüčéąĖą╝ąŠą│ąŠ ą┐čĆąŠčłąĖč鹊ą│ąŠ ą║ąŠą┤ą░; ąĄčüą╗ąĖ ą▓ą░ą╗ąĖą┤ąĮčŗą╣ ą║ąŠą┤ ąĮą░ą╣ą┤ąĄąĮ, č鹊 čŹč鹊čé ą║ąŠą┤ čüčćąĖčéčŗą▓ą░ąĄčéčüčÅ ąĖąĘ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą┐ą░ą╝čÅčéąĖ ąĖ ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮčÄčÄ RAM, ą║ąŠč鹊čĆą░čÅ ą▓ą║ą╗čÄč湥ąĮą░ ą▓ ąŠą▒ą╗ą░čüčéčī ą┐ą░ą╝čÅčéčī ą┐čĆąŠą│čĆą░ą╝ą╝. ąÜą░ą║ č鹊ą╗čīą║ąŠ ą║ąŠą┤ ąĘą░ą│čĆčāąČąĄąĮ, TUSB3410 ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčéčüčÅ ą║ USB čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ CONT, ąĖ ąĘą░č鹥ą╝ ą┐čĆąŠąĖčüčģąŠą┤čÅčé čüčéą░ąĮą┤ą░čĆčéąĮčŗąĄ ą┐čĆąŠčåąĄčüčüčŗ 菹Įčāą╝ąĄčĆą░čåąĖąĖ ąĖ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ. ąóą░ą║ąŠą╣ ą▓ą░čĆąĖą░ąĮčé ąĘą░ą│čĆčāąĘą║ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ąĮą░ąĖą▒ąŠą╗ąĄąĄ čćą░čüč鹊.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą┤ą╗čÅ ą┐ąŠą┤ą│ąŠč鹊ą▓ą║ąĖ ą┤ą░ą╝ą┐ą░ ą║ąŠą┤ą░ (čćč鹊ą▒čŗ ąŠąĮ čüčéą░ą╗ ą┤ąŠą┐čāčüčéąĖą╝čŗą╝ ą┤ą╗čÅ ąĘą░ą│čĆčāąĘą║ąĖ TUSB3410) ąĖ ą┐čĆąŠčłąĖą▓ą║ąĖ ąĄą│ąŠ ą▓ ą┐ą░ą╝čÅčéčī EEPROM čäąĖčĆą╝ą░ Texas Instruments ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé čüą┐ąĄčåąĖą░ą╗čīąĮčāčÄ čāčéąĖą╗ąĖčéčā ą┐ąŠą┤ą│ąŠč鹊ą▓ą║ąĖ ąŠą▒čĆą░ąĘą░ ą┤ą╗čÅ EEPROM Header.exe, čüą╝. [2].

3.2.2. ąŚą░ą│čĆčāąĘą║ą░ ą║ąŠą┤ą░ ąĖąĘ čģąŠčüčéą░ PC

ąĢčüą╗ąĖ ą┐ąŠ čłąĖąĮąĄ I2C ąĮąĄ čāą┤ą░ą╗ąŠčüčī ąĮą░ą╣čéąĖ ąĖ čüčćąĖčéą░čéčī ą┤ąŠą┐čāčüčéąĖą╝čŗą╣ ą║ąŠą┤, č鹊 TUSB3410 čüą░ą╝ą░ ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčéčüčÅ ą║ USB (ą▒čāčéą╗ąŠą░ą┤ąĄčĆ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ą▒ąĖčé 7 CONT čĆąĄą│ąĖčüčéčĆąĄ USBCTL, čüą╝. čüąĄą║čåąĖčÄ 5.4), ąĖ ąĘą░č鹥ą╝ ą┐čĆąŠčģąŠą┤ąĖčé ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ ąĖ čüčéą░ąĮą┤ą░čĆčéąĮčāčÄ čŹąĮčāą╝ąĄčĆą░čåąĖčÄ ąĮą░ čģąŠčüč鹥. ą¤ąŠčüą╗ąĄ čŹč鹊ą│ąŠ ą║ąŠą┤ ą╝ąŠąČąĄčé ąĘą░ą│čĆčāąĘąĖčéčī ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗą╣ ą║ąŠą┤ ą▓ RAM, čŹč鹊čé ą║ąŠą┤ ą╝ąŠąČąĄčé čüąŠą┤ąĄčƹȹ░čéčī ą▓ čüąĄą▒ąĄ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ. ą¤ąŠčüą╗ąĄ ąĘą░ą│čĆčāąĘą║ąĖ ą║ąŠą┤ą░ MCU ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą┤ąĄą╗ą░ąĄčé ą┐ąĄčĆąĄą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖąĄ ą║ USB čü ą┐ąŠą╝ąŠčēčīčÄ čüą▒čĆąŠčüą░ ąĖ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ CONT, čćč鹊 ą┐čĆąĖą▓ąŠą┤ąĖčé ą║ ą┐ąŠą▓č鹊čĆąĮąŠą╣ 菹Įčāą╝ąĄčĆą░čåąĖąĖ ąĮą░ čģąŠčüč鹥, ąĮąŠ č鹥ą┐ąĄčĆčī čāąČąĄ ą┐ąŠą┤ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝ ą║ąŠą┤ą░, ąĘą░ą│čĆčāąČąĄąĮąĮąŠą│ąŠ ą▓ RAM. ąóąĄą┐ąĄčĆčī ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ čāčüčéčĆąŠą╣čüčéą▓ą░ USB ą╝ąŠąČąĄčé ą▒čŗčéčī čüąŠą▓čüąĄą╝ ą┤čĆčāą│ąŠą╣, ą┐ąŠą╗ąĮąŠčüčéčīčÄ ąĘą░ą▓ąĖčüčÅčēąĄą╣ ąŠčé ąĘą░ą│čĆčāąČąĄąĮąĮąŠą│ąŠ ą▓ RAM ą║ąŠą┤ą░ firmware.

ąöą╗čÅ č鹊ą│ąŠ, čćč鹊ą▒čŗ ąĘą░ą│čĆčāąĘą║ą░ č湥čĆąĄąĘ USB čĆą░ą▒ąŠčéą░ą╗ą░, ąĮąĄąŠą▒čģąŠą┤ąĖą╝ą░ čāčüčéą░ąĮąŠą▓ą║ą░ ą┤čĆą░ą╣ą▓ąĄčĆą░ USB TI WDF USBUART Single Driver, čüą╝. [2].

3.3. ą¤ąĄčĆąĄą┤ą░čćą░ ą┤ą░ąĮąĮčŗčģ ą┐ąŠ USB

ą¤ąŠ čüčéą░ąĮą┤ą░čĆčéčā USB ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ TUSB3410 ą▓ąĖą┤ąĖčéčüčÅ ąĮą░ čģąŠčüč鹥 ą║ą░ą║ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ USB. ąÜą░ą║ ąĖ ą▓čüąĄ čéą░ą║ąĖąĄ čāčüčéčĆąŠą╣čüčéą▓ą░, ąŠąĮąŠ ąĖčüą┐ąŠą╗čīąĘčāąĄčé endpoint 0 ą║ą░ą║ ą║ąŠąĮąĄčćąĮčāčÄ č鹊čćą║čā čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ (control endpoint). ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠ ą╝ąŠą│čāčé čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ ą┤ąŠ 3 ą▓čģąŠą┤ąĮčŗčģ ą║ąŠąĮąĄčćąĮčŗčģ č鹊č湥ą║ (input endpoint) ąĖ ą▓čŗčģąŠą┤ąĮčŗčģ (output endpoint). ąæąŠą╗čīčłąĖąĮčüčéą▓ąŠ ą┐čĆąĖą╗ąŠąČąĄąĮąĖą╣ ąĖčüą┐ąŠą╗čīąĘčāčÄčé ąŠą┤ąĮčā bulk input endpoint ą┤ą╗čÅ ą▓ą▓ąŠą┤ą░ ą┤ą░ąĮąĮčŗčģ ą▓ čģąŠčüčé (data in) ąĖ ąŠą┤ąĮčā bulk output endpoint ą┤ą╗čÅ ą▓čŗą▓ąŠą┤ą░ ą┤ą░ąĮąĮčŗčģ ąĖąĘ čģąŠčüčéą░ (data out), ąĖ ąŠą┤ąĮčā interrupt endpoint ą┤ą╗čÅ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ čüčéą░čéčāčüą░ čāčüčéčĆąŠą╣čüčéą▓ą░. ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ USB ą╝ąŠąČąĄčé ąŠčüčéą░ą▓ą░čéčīčüčÅ ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠą╣ ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ą┐ąŠčĆčéą░.

ą¦ą░čēąĄ ą▓čüąĄą│ąŠ ą┤ą░ąĮąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ čüąŠ čüč鹊čĆąŠąĮčŗ USB ąĮą░ čüč鹊čĆąŠąĮčā UART (ąĖ ą▓ ąŠą▒čĆą░čéąĮąŠą╝ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĖ) čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ ą▓čüčéčĆąŠąĄąĮąĮąŠą│ąŠ ą▓ čćąĖą┐ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ DMA. ąÆ ąĮąĄą║ąŠč鹊čĆčŗčģ ąŠčüąŠą▒čŗčģ čüą╗čāčćą░čÅčģ (ąĮą░ą┐čĆąĖą╝ąĄčĆ, ąĄčüą╗ąĖ ąĮčāąČąĮąŠ čĆąĄą░ą╗ąĖąĘąŠą▓ą░čéčī čāčüčéčĆąŠą╣čüčéą▓ąŠ ą║ą╗ą░čüčüą░ USB HID) čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖąĄą╝ ą┤ą░ąĮąĮčŗčģ ą╝ąŠąČąĄčé ąŠčüčāčēąĄčüčéą▓ą╗čÅčéčīčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ čü ą┐ąŠą╝ąŠčēčīčÄ ą║ąŠą┤ą░ firmware MCU.

3.4. ąØą░čüčéčĆąŠą╣ą║ą░ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ą┐ąŠčĆčéą░

ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ą┐ąŠčĆčé čéčĆąĄą▒čāąĄčé ąĮąĄą║ąŠč鹊čĆąŠą╣ ąĮą░čüčéčĆąŠą╣ą║ąĖ čāą┐čĆą░ą▓ą╗čÅčÄčēąĖčģ čĆąĄą│ąĖčüčéčĆąŠą▓, ą║ąŠč鹊čĆčŗąĄ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮčŗ ą┤ą╗čÅ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐ąŠčĆčéą░. ąŁčéą░ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠą╣ ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ąŠą│ąŠ čüą┐ąŠčüąŠą▒ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ. ąŁčéąĖ čĆąĄą│ąĖčüčéčĆčŗ ą▓ą║ą╗čÄčćą░čÄčé ą▓ čüąĄą▒čÅ čĆąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą╗ąĖąĮąĖąĄą╣ (line control register), ą║ąŠč鹊čĆčŗą╣ čāą┐čĆą░ą▓ą╗čÅąĄčé č乊čĆą╝ą░č鹊ą╝ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ąŠą│ąŠ čüą╗ąŠą▓ą░ ąĖ čĆąĄą│ąĖčüčéčĆčŗ ą┤ąĄą╗ąĖč鹥ą╗čÅ, ą║ąŠč鹊čĆčŗąĄ ąĘą░ą┤ą░čÄčé čüą║ąŠčĆąŠčüčéčī ą┐ąĄčĆąĄą┤ą░čćąĖ (baud rate).

ąŁčéąĖ čĆąĄą│ąĖčüčéčĆčŗ ąŠą▒čŗčćąĮąŠ čāą┐čĆą░ą▓ą╗čÅčÄčéčüčÅ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄą╝ čģąŠčüčéą░.

3.5. ąĀąĄąČąĖą╝čŗ ą┤ą░ąĮąĮčŗčģ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ą┐ąŠčĆčéą░

ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ą┐ąŠčĆčé ą╝ąŠąČąĄčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą▓ čéčĆąĄčģ čĆą░ąĘą╗ąĖčćąĮčŗčģ (ąŠą┤ąĮą░ą║ąŠ ą┐ąŠčģąŠąČąĖčģ ą┤čĆčāą│ ąĮą░ ą┤čĆčāą│ą░ ą▓ čĆą░ą▒ąŠč鹥) čĆąĄąČąĖą╝ą░čģ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ (data mode): RS-232 data mode, RS-485 data mode ąĖ IrDA data mode. ąÜą░ą║ ąĖ čĆąĄąČąĖą╝ USB čĆąĄąČąĖą╝ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ą┐ąŠčĆčéą░ ąŠą▒čŗčćąĮąŠ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ ąŠą┤ąĮąŠą║čĆą░čéąĮąŠ (ą┐čĆąĖ čüą▒čĆąŠčüąĄ/ąĘą░ą│čĆčāąĘą║ąĄ ąĖą╗ąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ) ąĖ ą┤ą░ą╗čīčłąĄ ą▓ ą┐čĆąŠčåąĄčüčüąĄ čĆą░ą▒ąŠčéčŗ ąĮąĄ ą╝ąĄąĮčÅąĄčéčüčÅ. ąĀą░ąĘą╗ąĖčćąĖąĄ ą╝ąĄąČą┤čā čĆąĄąČąĖą╝ą░ą╝ąĖ ąĘą░ą║ą╗čÄčćą░ąĄčéčüčÅ ą▓ ąĖąĮč鹥čĆą▓ą░ą╗ą░čģ ą▓čĆąĄą╝ąĄąĮąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ą▓ą▓ąŠą┤ą░ ąĖ ą▓čŗą▓ąŠą┤ą░ ąĖą╗ąĖ ą▓ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗčģ čāą┐čĆą░ą▓ą╗čÅčÄčēąĖčģ čüąĖą│ąĮą░ą╗ąŠą▓. ą×ą┤ąĮą░ą║ąŠ ą▒ą░ąĘąŠą▓čŗą╣ ą┐čĆąŠčåąĄčüčü ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ą║ąŠą┤ą░ USB ą▓ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮčŗą╣ ąĖ ąĘą░č鹥ą╝ ąĖąĘ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠą│ąŠ čüąĮąŠą▓ą░ ą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ (ąĖ ąŠą▒čĆą░čéąĮąŠ) ąŠą┤ąĖąĮą░ą║ąŠą▓čŗą╣ ą┤ą╗čÅ ą▓čüąĄčģ čĆąĄąČąĖą╝ąŠą▓. ąØąĄą║ąŠč鹊čĆčŗąĄ ąŠą┐čåąĖąĖ ąĮą░čüčéčĆąŠą╣ą║ąĖ ą┤ąŠčüčéčāą┐ąĮčŗ ą┤ą╗čÅ ą▓čüąĄčģ čĆąĄąČąĖą╝ąŠą▓, ą░ ąĮąĄą║ąŠč鹊čĆčŗąĄ ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗčģ čĆąĄąČąĖą╝ąŠą▓. ąØą░ą┐čĆąĖą╝ąĄčĆ, ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąŠč鹊ą║ąŠą╝ (software flow control) čü ą┐ąŠą╝ąŠčēčīčÄ čüąĖą╝ą▓ąŠą╗ąŠą▓ Xoff/Xon ą╝ąŠąČąĄčé ą▒čŗčéčī ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąŠ ą▓ąŠ ą▓čüąĄčģ čĆąĄąČąĖą╝ą░čģ, ąĮąŠ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ č鹊ą╗čīą║ąŠ ą▓ čĆąĄąČąĖą╝ą░čģ RS-232 ąĖą╗ąĖ IrDA, ą┐ąŠč鹊ą╝čā čćč鹊 čĆąĄąČąĖą╝ RS-485 čĆą░ą▒ąŠčéą░ąĄčé ą▓ ą┐ąŠą╗čāą┤čāą┐ą╗ąĄą║čüąĄ. ąóąŠčćąĮąŠ čéą░ą║ ąČąĄ ą░ą┐ą┐ą░čĆą░čéąĮąŠąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąŠč鹊ą║ąŠą╝ (hardware flow control) ąĖ ą┐čĆąŠčåąĄą┤čāčĆą░ čāčüčéą░ąĮąŠą▓ą║ąĖ čüą▓čÅąĘąĖ (handshaking) čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ čüąĖą│ąĮą░ą╗ąŠą▓ ~RTS/~CTS (ąĖą╗ąĖ ~DTR/~DSR) ą┤ąŠčüčéčāą┐ąĮą░ ą▓ čĆąĄąČąĖą╝ą░čģ RS-232 ąĖą╗ąĖ IrDA. ą×ą┤ąĮą░ą║ąŠ ą▓ čĆąĄą░ą╗čīąĮąŠčüčéąĖ čŹčéą░ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ č鹊ą╗čīą║ąŠ ą▓ čĆąĄąČąĖą╝ąĄ RS-232 mode, ą┐ąŠč鹊ą╝čā čćč鹊 čĆąĄąČąĖą╝ IrDA ąĖą╝ąĄąĄčé č鹊ą╗čīą║ąŠ čüąĖą│ąĮą░ą╗čŗ SIN ąĖ SOUT, ą│ą░ą╗čīą▓ą░ąĮąĖč湥čüą║ąĖ čĆą░ąĘą▓čÅąĘą░ąĮąĮčŗąĄ ąŠą┐čéąĖą║ąŠą╣ (ąŠą▒čŗčćąĮąŠ ąŠą┐čéčĆąŠąĮą░ą╝ąĖ).

3.5.1. RS-232 Data Mode

ąĀąĄąČąĖą╝ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ąĮą░ąĘčŗą▓ą░ąĄčéčüčÅ RS-232 mode, ąŠąĮ ąŠą▒čŗčćąĮąŠ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą┐ąŠą╗ąĮąŠą┤čāą┐ą╗ąĄą║čüąĮąŠą│ąŠ (full duplex) ąŠą▒ą╝ąĄąĮą░ ą┤ą░ąĮąĮčŗą╝ąĖ č湥čĆąĄąĘ čüąĖą│ąĮą░ą╗čŗ SOUT ąĖ SIN. ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ą▓čŗčģąŠą┤čŗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą╝ąŠą┤ąĄą╝ąŠą╝ (~RTS ąĖ ~DTR) čüąŠąĄą┤ąĖąĮąĄąĮčŗ čü ą╝ąŠą┤ąĄą╝ąŠą╝ ąĖ ąŠą▒čŗčćąĮąŠ ąĮą░čüčéčĆąŠąĄąĮčŗ ą║ą░ą║ čåąĖčäčĆąŠą▓čŗąĄ ą▓čŗčģąŠą┤čŗ. ąÆčģąŠą┤čŗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą╝ąŠą┤ąĄą╝ąŠą╝ (~CTS, ~DSR, ~DCD ąĖ ~RI/CP) čéą░ą║ąČąĄ ąŠą▒čŗčćąĮąŠ čüąŠąĄą┤ąĖąĮąĄąĮčŗ čü ą╝ąŠą┤ąĄą╝ąŠą╝ ąĖ ąĮą░čüčéčĆąŠąĄąĮčŗ ą║ą░ą║ čåąĖčäčĆąŠą▓čŗąĄ ą▓čģąŠą┤čŗ. ąÉą╗čīč鹥čĆąĮą░čéąĖą▓ąĮąŠ ~RTS ąĖ ~CTS (ąĖą╗ąĖ ~DTR ąĖ ~DSR) ą╝ąŠą│čāčé čĆąĄą│čāą╗ąĖčĆąŠą▓ą░čéčī ą┐ąŠč鹊ą║ ą┤ą░ąĮąĮčŗčģ č湥čĆąĄąĘ SOUT ąĖ SIN ą┤ą╗čÅ ą┐čĆąĄą┤ąŠčéą▓čĆą░čēąĄąĮąĖčÅ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ ą┐čĆąĖąĄą╝ąĮąŠą│ąŠ FIFO. ąś ąĮą░ą║ąŠąĮąĄčå, čü č鹊ą╣ ąČąĄ čåąĄą╗čīčÄ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąŠč鹊ą║ąŠą╝ (software flow control) č湥čĆąĄąĘ čüąĖą╝ą▓ąŠą╗čŗ Xoff/Xon.

ąĀąĄąČąĖą╝ RS-232 ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮ ą▓ąŠ ą╝ąĮąŠą│ąĖčģ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅčģ, ąĖ ą┤čĆčāą│ąĖąĄ čĆąĄąČąĖą╝čŗ čÅą▓ą╗čÅčÄčéčüčÅ ą┐ąŠą┤ą╝ąĮąŠąČąĄčüčéą▓ąŠą╝ čŹč鹊ą│ąŠ čĆąĄąČąĖą╝ą░.

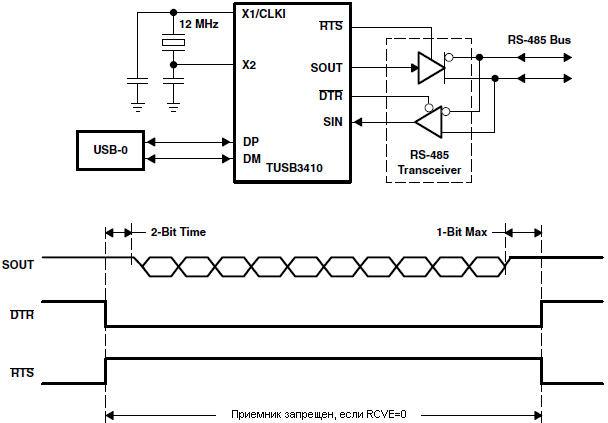

3.5.2. RS-485 Data Mode

ąĀąĄąČąĖą╝ RS-485 ąŠč湥ąĮčī ą┐ąŠčģąŠąČ ąĮą░ čĆąĄąČąĖą╝ RS-232 č鹥ą╝, čćč鹊 ąĮą░ąĘąĮą░č湥ąĮąĖąĄ ą╗ąĖąĮąĖą╣ SOUT, SIN ąĖ č乊čĆą╝ą░čé čüąĖą│ąĮą░ą╗ą░ ąĮą░ ąĮąĖčģ ąŠčüčéą░ą╗ąĖčüčī čéą░ą║ąĖą╝ąĖ ąČąĄ. ą¤ąŠčüą║ąŠą╗čīą║čā RS-485 ąĖą╝ąĄąĄčé čłąĖąĮąĮčāčÄ ą░čĆčģąĖč鹥ą║čéčāčĆčā čü ąĮąĄąŠčéčŖąĄą╝ą╗ąĄą╝čŗą╝ čüą▓ąŠą╣čüčéą▓ąŠą╝ čüąĖčüč鹥ą╝čŗ ąŠą▒ą╝ąĄąĮą░ čü ąŠą┤ąĖąĮąŠčćąĮčŗą╝ ą┤čāą┐ą╗ąĄą║čüąŠą╝. ąÆ čĆąĄąČąĖą╝ąĄ RS-485 ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ TUSB3410 čāą┐čĆą░ą▓ą╗čÅąĄčé čüąĖą│ąĮą░ą╗ą░ą╝ąĖ ~RTS ąĖ ~DTR, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠą│čāčé čĆą░ąĘčĆąĄčłąĖčéčī ą╗ąĖą▒ąŠ ą┤čĆą░ą╣ą▓ąĄčĆ RS-485 (ą┐ąĄčĆąĄą┤ą░čéčćąĖą║), ą╗ąĖą▒ąŠ ą┐čĆąĖąĄą╝ąĮąĖą║ RS-485. ąÆ čĆąĄąČąĖą╝ąĄ RS-485 čĆą░ąĘčĆąĄčłą░čÄčēąĖąĄ čüąĖą│ąĮą░ą╗čŗ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą▓čŗčüčéą░ą▓ą╗čÅčÄčéčüčÅ ą▓čüčÅą║ąĖą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ DMA ąĮą░čüčéčĆąŠąĄąĮ ąĮą░ ą▓čŗą┤ą░čćčā ą┤ą░ąĮąĮčŗčģ. ą¤čĆąĖąĄą╝ąĮąĖą║ ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠčüčéą░ą▓ą╗ąĄąĮ čĆą░ąĘčĆąĄčłąĄąĮąĮčŗą╝ ą┐čĆąĖ čĆą░ąĘčĆąĄčłąĄąĮąĮąŠą╝ ą┤čĆą░ą╣ą▓ąĄčĆąĄ (ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ąĄ), čćč鹊ą▒čŗ ą┐ąŠąĘą▓ąŠą╗ąĖčéčī ą┐čĆąĖ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéąĖ ą┐čĆąĖąĮąĖą╝ą░čéčī čŹčģąŠ, ąĮąŠ ą║ąŠą│ą┤ą░ ąŠąČąĖą┤ą░čÄčéčüčÅ čĆąĄą░ą╗čīąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ąĖąĘ ą║ą░ąĮą░ą╗ą░ RS-485, č鹊 ą┐čĆąĖ ą┐čĆąĖąĄą╝ąĄ ą┤čĆą░ą╣ą▓ąĄčĆ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ą┐čĆąĄčēąĄąĮ. ąŚą░ą╝ąĄčéčīč鹥, čćč鹊 čŹč鹊 čāčüčéčĆą░ąĮčÅąĄčé ą░ą┐ą┐ą░čĆą░čéąĮąŠąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąŠč鹊ą║ąŠą╝ (hardware flow control), ą┐ąŠčüą║ąŠą╗čīą║čā čĆą░ą▒ąŠčéą░ ą┐ąŠ ą┐ąĄčĆąĄą┤ą░č湥 ą┤ą░ąĮąĮčŗčģ ąĖą┤ąĄčé ą▓ ą┐ąŠą╗čāą┤čāą┐ą╗ąĄą║čüąĄ (č鹊 ą▓ ąŠą┤ąĮąŠą╝ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĖ, č鹊 ą▓ ą┤čĆčāą│ąŠą╝, ąĖ ąĮąĖą║ąŠą│ą┤ą░ ą▓ ąŠą▒ąŠąĖčģ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅčģ čüčĆą░ąĘčā), ąĖ ą░ą┐ą┐ą░čĆą░čéąĮąŠąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąŠč鹊ą║ąŠą╝ ąĮąĄ čŹčäč乥ą║čéąĖą▓ąĮąŠ. ą¤čĆąŠą│čĆą░ą╝ą╝ąĮąŠąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąŠč鹊ą║ąŠą╝ (software flow control) čéą░ą║ąČąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ, ąĮąŠ ąŠąĮąŠ ą╝ąŠąČąĄčé ąĖą╝ąĄčéčī ąŠą│čĆą░ąĮąĖč湥ąĮąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ.

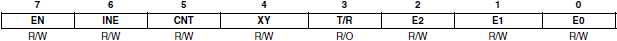

ąĀąĄąČąĖą╝ RS-485 čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ 7 (485E) ą▓ čĆąĄą│ąĖčüčéčĆąĄ FCRL (čüą╝. čüąĄą║čåąĖčÄ 7.1.4), ąĖ ą▒ąĖčéą░ 1 (RCVE) ą▓ čĆąĄą│ąĖčüčéčĆąĄ MCR (čüą╝. čüąĄą║čåąĖčÄ 7.1.6), čćč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐čĆąĖąĄą╝ąĮąĖą║čā ą┐ąŠą┤čüą╗čāčłąĖą▓ą░čéčī ą▓ čĆąĄąČąĖą╝ąĄ RS-485.

3.5.3. IrDA Data Mode

ąÆ čĆąĄąČąĖą╝ąĄ IrDA čüąĖą│ąĮą░ą╗ SOUT ą║ąŠą┤ąĖčĆčāąĄčéčüčÅ ąĖ SIN ą┤ąĄą║ąŠą┤ąĖčĆčāąĄčéčüčÅ ą┐ąŠ čüčéą░ąĮą┤ą░čĆčéčā IrDA, ąĖ ą┤ą░ąĮąĮčŗąĄ ą╝ąŠą│čāčé ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčīčüčÅ čüąŠ čüą║ąŠčĆąŠčüčéčīčÄ ą┤ąŠ 115.2 ą║ąĖą╗ąŠą▒ąĖčé/čüąĄą║ (kbps). ą¤čĆąĖ čŹč鹊ą╝ čéčĆąĄą▒čāąĄčéčüčÅ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖąĄ ą║ ą▓ąĮąĄčłąĮąĄą╝čā čéčĆą░ąĮčüąĖą▓ąĄčĆčā IrDA. ą×ą▒ą╝ąĄąĮ ą┤ą░ąĮąĮčŗą╝ąĖ ąŠą▒čŗčćąĮąŠ ąĖą┤ąĄčé ą▓ ą┐ąŠą╗ąĮąŠą╝ ą┤čāą┐ą╗ąĄą║čüąĄ (full duplex), čé. ąĄ. čüčĆą░ąĘčā ą▓ ą┤ą▓čāčģ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅčģ. ą×ą▒čŗčćąĮąŠ ą▓ čüąĖčüč鹥ą╝ąĄ IrDA č鹊ą╗čīą║ąŠ čüąĖą│ąĮą░ą╗čŗ SOUT ąĖ SIN ą┐ąŠą┤ą║ą╗čÄč湥ąĮčŗ ą║ ą░ą┐ą┐ą░čĆą░čéčāčĆąĄ, čéą░ą║ čćč鹊 ą░ą┐ą┐ą░čĆą░čéąĮąŠąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąŠč鹊ą║ąŠą╝ (hardware flow control) ąĮąĄ ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░ąĄčéčüčÅ. ąóą░ą║ąČąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąŠč鹊ą║ąŠą╝ (software flow control).

ąĀąĄąČąĖą╝ IrDA čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ 6 (IREN) ą▓ čĆąĄą│ąĖčüčéčĆąĄ USBCTL (čüą╝. čüąĄą║čåąĖčÄ 5.4).

ąĪčģąĄą╝čŗ ą║ąŠą┤ąĄčĆą░ ąĖ ą┤ąĄą║ąŠą┤ąĄčĆą░ IR čĆą░ą▒ąŠčéą░čÄčé čüąŠą▓ą╝ąĄčüčéąĮąŠ čü UART, čćč鹊ą▒čŗ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░čéčī ą┐ąŠč鹊ą║ ą▒ąĖčé ą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ąĖą╝ą┐čāą╗čīčüąŠą▓, ąĖ ąŠą▒čĆą░čéąĮąŠ. ąöą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ąĮčāą╗ąĄą▓ąŠą│ąŠ ą▒ąĖčéą░ ą▓ąŠ ą▓čģąŠą┤ąĮąŠą╝ ą┐ąŠč鹊ą║ąĄ ą┤ą░ąĮąĮčŗčģ ą║ąŠą┤ąĄčĆ ą▓čŗčĆą░ą▒ą░čéčŗą▓ą░ąĄčé ąĖ ąŠčéą┐čĆą░ą▓ą╗čÅąĄčé ąĖą╝ą┐čāą╗čīčü 0 -> 1 -> 0 čü ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčīčÄ 3/16 ąŠčé ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéąĖ čäčĆąĄą╣ą╝ą░ ą▒ąĖčéą░, ą┐ąŠčüąĄčĆąĄą┤ąĖąĮąĄ ą▓čĆąĄą╝ąĄąĮąĖ ą▒ąĖčéą░. ąöą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ąĄą┤ąĖąĮąĖčćąĮąŠą│ąŠ ą▒ąĖčéą░ ą▓ ą┐ąŠč鹊ą║ąĄ ą┤ą░ąĮąĮčŗčģ ą▓čŗčģąŠą┤ ą║ąŠą┤ąĄčĆą░ ąŠčüčéą░ąĄčéčüčÅ ą▓ ą╗ąŠą│. 0 ąĮą░ ą▓čüąĄ ą▓čĆąĄą╝čÅ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéąĖ ą▒ąĖčéą░.

ą¤čĆąŠčåąĄčüčü ą┤ąĄą║ąŠą┤ąĖčĆąŠą▓ą░ąĮąĖčÅ čüąŠčüč鹊ąĖčé ąĖąĘ ą┐čĆąĖąĄą╝ą░ čüąĖą│ąĮą░ą╗ą░ ąŠčé ą┐čĆąĖąĄą╝ąĮąĖą║ą░ IrDA ąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ąĄą│ąŠ ąŠą▒čĆą░čéąĮąŠ ą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ąĮąŠą╗ąĖą║ąŠą▓ ąĖ ąĄą┤ąĖąĮąĖč湥ą║. ąÆ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄą╝ ą║ąŠą┤ąĄčĆą░, ą┤ąĄą║ąŠą┤ąĄčĆ ą┐čĆąĄąŠą▒čĆą░ąĘčāąĄčé ąĖą╝ą┐čāą╗čīčü ą▓ ą▒ąĖčé ąĮčāą╗čÅ ąĖ ąŠčéčüčāčéčüčéą▓ąĖąĄ ąĖą╝ą┐čāą╗čīčüą░ ą▓ ą▒ąĖčé ąĄą┤ąĖąĮąĖčåčŗ.

ąĀąĖčü. 3-1. ąÆčŗą▒ąŠčĆ čĆąĄąČąĖą╝ą░ RS-232 ąĖ IR

ą¤ąŠčÅčüąĮąĄąĮąĖčÅ ą║ čĆąĖčüčāąĮą║čā 3-1:

From UART, SOUT čüąĖą│ąĮą░ą╗ ą┤ą░ąĮąĮčŗčģ čü ą▓čŗčģąŠą┤ą░ UART.

IREN ą▒ąĖčé ą▓ čĆąĄą│ąĖčüčéčĆąĄ USBCTL, ą║ąŠč鹊čĆčŗą╣ čĆą░ąĘčĆąĄčłą░ąĄčé čĆą░ą▒ąŠčéčā IR.

UART BaudOut Clock čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ ą┤ą╗čÅ UART, ąŠčé ą║ąŠč鹊čĆąŠą╣ ąĘą░ą▓ąĖčüąĖčé čüą║ąŠčĆąŠčüčéčī ą┐ąĄčĆąĄą┤ą░čćąĖ.

TXCNTL ą▒ąĖčé ą▓ čĆąĄą│ąĖčüčéčĆąĄ MODECNFG, čāą┐čĆą░ą▓ą╗čÅčÄčēąĖą╣ čĆąĄąČąĖą╝ąŠą╝ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░č湥ą╣ (čüą╝. čüąĄą║čåąĖčÄ 5.5).

SOFTSW ą▒ąĖčé ą▓ čĆąĄą│ąĖčüčéčĆąĄ MODECNFG, ą┐ąŠąĘą▓ąŠą╗čÅčÄčēąĖą╣ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ čĆą░ąĘčĆąĄčłą░čéčī čĆą░ą▒ąŠčéčā ą▓čŗčģąŠą┤ą░ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░(čüą╝. čüąĄą║čåąĖčÄ 5.5).

CLKSLKT ą▒ąĖčé ą▓ čĆąĄą│ąĖčüčéčĆąĄ MODECNFG, čāą┐čĆą░ą▓ą╗čÅčÄčēąĖą╣ ą▓čŗą▒ąŠčĆąŠą╝ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ, ą┐ąŠčÅą▓ą╗čÅčÄčēąĄą╣čüčÅ ąĮą░ ą▓čŗčģąŠą┤ąĄ CLKOUT.

To UART Receiver, SIN čüąĖą│ąĮą░ą╗ ą┤ą░ąĮąĮčŗčģ, ą┐ąŠčüčéčāą┐ą░čÄčēąĖą╣ ąĮą░ ą▓čģąŠą┤ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ UART.

SOUT/IR_SOUT ą▓čŗčģąŠą┤ąĮąŠą╣ ą┐ąŠčĆčé (ą▓ąĮąĄčłąĮąĖą╣ ą▓čŗą▓ąŠą┤) ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ UART/IR.

SIN/IR_SIN ą▓čģąŠą┤ąĮąŠą╣ ą┐ąŠčĆčé (ą▓ąĮąĄčłąĮąĖą╣ ą▓čŗą▓ąŠą┤) ą┐čĆąĖąĄą╝ąĮąĖą║ą░ UART/IR.

CLKOUT ą▓čŗčģąŠą┤ąĮąŠą╣ ą┐ąŠčĆčé (ą▓ąĮąĄčłąĮąĖą╣ ą▓čŗą▓ąŠą┤), ąĮą░ ą║ąŠč鹊čĆčŗą╣ ą▓čŗą▓ąŠą┤ąĖčéčüčÅ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░.

ąĀąĖčü. 3-2. ąĀąĄą░ą╗ąĖąĘą░čåąĖčÅ ąĖąĮč鹥čĆč乥ą╣čüą░ USB < -- > Serial (RS-232)

ąĀąĖčü. 3-3. ąĀąĄą░ą╗ąĖąĘą░čåąĖčÅ ąĖąĮč鹥čĆč乥ą╣čüą░ USB < -- > RS-485

[4. ąÜą░čĆčéą░ ą┐ą░ą╝čÅčéąĖ (Memory Map) MCU]

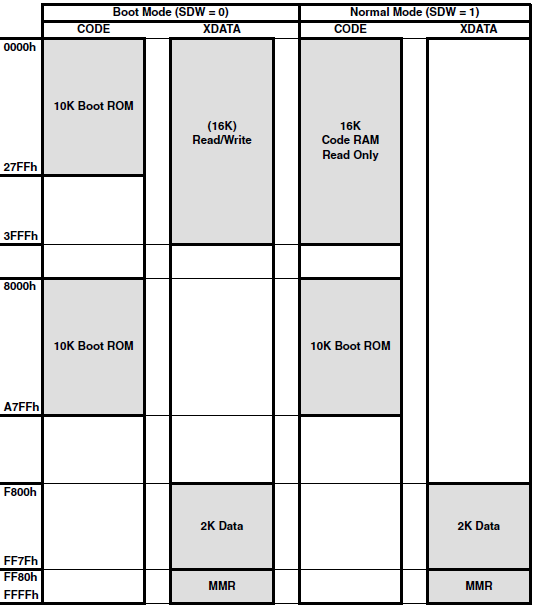

ąØą░ čĆąĖčüčāąĮą║ąĄ 4-1 ą┐ąŠą║ą░ąĘą░ąĮą░ ą║ą░čĆčéą░ ą┐ą░ą╝čÅčéąĖ (ą░ą┤čĆąĄčüąĮąŠąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ) ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą▓ ą┤ą▓čāčģ čĆąĄąČąĖą╝ą░čģ - ąĘą░ą│čĆčāąĘą║ą░ ą┐ąŠą┤ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝ ą▒čāčéą╗ąŠą░ą┤ąĄčĆą░ (boot) ąĖ čĆąĄąČąĖą╝ ąĮąŠčĆą╝ą░ą╗čīąĮąŠą╣ čĆą░ą▒ąŠčéčŗ (normal operation, ą║ąŠą│ą┤ą░ ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÅ ąĘą░ą│čĆčāąČąĄąĮą░ ą▓ ą┐ą░ą╝čÅčéčī RAM).

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĮą░ čĆąĖčü. 4-1 ąĮąĄ ą┐ąŠą║ą░ąĘą░ąĮą░ ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ čüčéą░ąĮą┤ą░čĆčéąĮą░čÅ ą┤ą╗čÅ ą░čĆčģąĖč鹥ą║čéčāčĆčŗ MCS-51 ą┐ą░ą╝čÅčéčī RAM (DATA 256 ą▒ą░ą╣čé, ą║ąŠč鹊čĆčŗąĄ ąĮą░čģąŠą┤čÅčéčüčÅ ą▓ ąŠčéą┤ąĄą╗čīąĮąŠą╝ ą░ą┤čĆąĄčüąĮąŠą╝ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąĄ čÅą┤čĆą░ 8052 - ą░ą┤čĆąĄčüą░ ąŠčé 0000h ą┤ąŠ 00FFh). ąŚą░č鹥ąĮąĄąĮąĮčŗąĄ ąŠą▒ą╗ą░čüčéąĖ ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮčŗ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╝ ROM/RAM.

ŌĆó ąÜąŠą│ą┤ą░ ą▒ąĖčé 0 (SDW) čĆąĄą│ąĖčüčéčĆą░ ROMS čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 0 (boot mode)

ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ 10 ą║ąĖą╗ąŠą▒ą░ą╣čé ROM ąŠč鹊ą▒čĆą░ąČąĄąĮčŗ ąĮą░ ąĮą░čćą░ą╗čīąĮčŗąĄ ą░ą┤čĆąĄčüą░ CODE 0x0000 .. 0x27FF, ąĖ čŹčéą░ ąŠą▒ą╗ą░čüčéčī ąĘą░ą┤čāą▒ą╗ąĖčĆąŠą▓ą░ąĮą░ čéą░ą║ąČąĄ ą┐ąŠ ą░ą┤čĆąĄčüą░ą╝ CODE 0x8000 .. 0xA7FF. ąÆąĮčāčéčĆąĄąĮąĮčÅčÅ ą┐ą░ą╝čÅčéčī 16 ą║ąĖą╗ąŠą▒ą░ą╣čé RAM ąŠč鹊ą▒čĆą░ąČąĄąĮą░ ąĮą░ ą░ą┤čĆąĄčüą░ XDATA 0x0000 .. 0x3FFF. ąæčāč乥čĆčŗ, MMR ąĖ I/O ąŠč鹊ą▒čĆą░ąČąĄąĮčŗ ąĮą░ ą┤ąĖą░ą┐ą░ąĘąŠąĮ XDATA 0xF800 .. 0xFFFF.

ŌĆó ąÜąŠą│ą┤ą░ ą▒ąĖčé 0 (SDW) čĆąĄą│ąĖčüčéčĆą░ ROMS čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 0 (normal mode)

10 ą║ąĖą╗ąŠą▒ą░ą╣čé ROM ąŠč鹊ą▒čĆą░ąČąĄąĮ ąĮą░ CODE 0x8000 .. 0xA7FF. ąÆąĮčāčéčĆąĄąĮąĮąĖąĄ 16 ą║ąĖą╗ąŠą▒ą░ą╣čé RAM ąŠč鹊ą▒čĆą░ąČąĄąĮčŗ ąĮą░ CODE 0x0000 .. 0x3FFF. ąæčāč乥čĆčŗ, MMR ąĖ I/O ąŠč鹊ą▒čĆą░ąČąĄąĮčŗ ąĮą░ ą┤ąĖą░ą┐ą░ąĘąŠąĮ XDATA 0xF800 .. 0xFFFF, ąĮą░ č鹊 ąČąĄ čüą░ą╝ąŠąĄ ą╝ąĄčüč鹊.

ąĀąĖčü. 4-1. ąÜą░čĆčéą░ ą┐ą░ą╝čÅčéąĖ MCU

4.1. ąĀą░ąĘą╗ąĖčćąĮčŗąĄ čĆąĄą│ąĖčüčéčĆčŗ

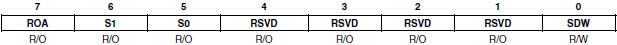

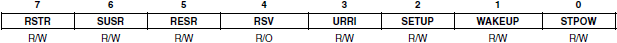

4.1.1. ROMS: ROM Shadow Configuration Register (ą░ą┤čĆąĄčü FF90h) - čĆąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ąĘą░č鹥ąĮąĄąĮąĖčÅ

ąŁč鹊čé čĆąĄą│ąĖčüčéčĆ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ MCU ą┤ą╗čÅ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ ąĖąĘ čĆąĄąČąĖą╝ą░ ąĘą░ą│čĆčāąĘą║ąĖ (boot mode) ą▓ ąŠą▒čŗčćąĮčŗą╣ čĆąĄąČąĖą╝ (normal operation mode), ą┐čĆąĖč湥ą╝ boot mode čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą┐ąŠ čüą▒čĆąŠčüčā ą┐čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ. ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠ čŹč鹊čé čĆąĄą│ąĖčüčéčĆ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ąĮąŠą╝ąĄčĆ čĆąĄą▓ąĖąĘąĖąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ ąĖ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÄ ROM/RAM.

| Ōä¢ ą▒ąĖčéą░ |

ąśą╝čÅ |

RESET |

ą×ą┐ąĖčüą░ąĮąĖąĄ ą▒ąĖčé |

| 0 |

SDW |

0 |

ąŁč鹊čé ą▒ąĖčé čĆą░ąĘčĆąĄčłą░ąĄčé/ąĘą░ą┐čĆąĄčēą░ąĄčé boot ROM (čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ąĘą░č鹥ąĮąĄąĮąĖąĄą╝ ROM).

SDW=0: ą║ąŠą│ą┤ą░ ą▒ąĖčé SDW ąŠčćąĖčēąĄąĮ, č鹊 MCU ą▓čŗą┐ąŠą╗ąĮčÅąĄčé ą║ąŠą┤ ąĖąĘ 10 ą║ąĖą╗ąŠą▒ą░ą╣čéąĮąŠą│ąŠ boot ROM (čéčāą┤ą░ ąĘą░ą┐ąĖčüą░ąĮ ą║ąŠą┤ ąĘą░ą│čĆčāąĘą║ąĖ, ą▒čāčéą╗ąŠą░ą┤ąĄčĆ, ąĘą░ą│čĆčāąĘčćąĖą║). ROM ą┐ąŠčÅą▓ą╗čÅąĄčéčüčÅ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ą▓ 2 ą╝ąĄčüčéą░čģ - ą┐ąŠ ą░ą┤čĆąĄčüčā 0000h ąĖ ą┐ąŠ ą░ą┤čĆąĄčüčā 8000h. 16 ą║ąĖą╗ąŠą▒ą░ą╣čé RAM ąŠč鹊ą▒čĆą░ąČąĄąĮčŗ ąĮą░ ą░ą┤čĆąĄčüąĮąŠąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ XDATA, čéą░ą║ čćč鹊 čÅą┤čĆąŠ MCU ą╝ąŠąČąĄčé čćąĖčéą░čéčī ąĖ ąĘą░ą┐ąĖčüčŗą▓ą░čéčī ą▓ ąĮąĄą│ąŠ ą┤ą░ąĮąĮčŗąĄ. ąæąĖčé SDW čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą║ąŠą┤ ąĘą░ą│čĆčāąĘą║ąĖ ąĘą░ą▓ąĄčĆčłąĖą╗ ąĘą░ą│čĆčāąĘą║čā ą▓ RAM ą┐čĆąŠą│čĆą░ą╝ą╝čŗ firmware. ą»ą┤čĆąŠ MCU ąĮąĄ ą╝ąŠąČąĄčé ąŠčćąĖčüčéąĖčéčī čŹč鹊čé ą▒ąĖčé, ąŠąĮ ąŠčćąĖčēą░ąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą┐čĆąĖ čüą▒čĆąŠčüąĄ ą▓ ą╝ąŠą╝ąĄąĮčé ą┐ąŠą┤ą░čćąĖ ą┐ąĖčéą░ąĮąĖčÅ, ą┐ąŠą┤ą░č湥 čüąĖą│ąĮą░ą╗ą░ čüą▒čĆąŠčüą░ ąĖą╗ąĖ ą┐čĆąĖ čüą▒čĆąŠčüąĄ ąŠčé ąĖčüč鹥č湥ąĮąĖčÅ čéą░ą╣ą╝ą░čāčéą░ čüč鹊čĆąŠąČąĄą▓ąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░.

SDW=1: ą║ąŠą│ą┤ą░ ą▒ąĖčé SDW čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, č鹊 boot ROM ąŠč鹊ą▒čĆą░ąČąĄąĮąŠ ąĮą░ ą░ą┤čĆąĄčü 8000h, ąĖ RAM ąŠč鹊ą▒čĆą░ąČąĄąĮąŠ ąĮą░ ą░ą┤čĆąĄčüąĮąŠąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ CODE ą┐ąŠ ą░ą┤čĆąĄčüčā 0000h. ą¤čĆąĖ čŹč鹊ą╝ MCU ąĮą░čćąĖąĮą░ąĄčé ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ąĖąĘ RAM, ą┐čĆąĖ čŹč鹊ą╝ ąĘą░ą┐ąĖčüčī ą▓ RAM ąĮąĄą▓ąŠąĘą╝ąŠąČąĮą░, čéą░ą║ ą║ą░ą║ ąŠąĮą░ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ąŠą▒ą╗ą░čüčéąĖ ą┐ą░ą╝čÅčéąĖ ą┐čĆąŠą│čĆą░ą╝ą╝. |

| 4-1 |

RSVD |

ąĮąĄ ą▓ą╗ąĖčÅąĄčé |

ąŁčéąĖ ą▒ąĖčéčŗ ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ, ąĖ ą▓čüąĄą│ą┤ą░ čćąĖčéą░čÄčéčüčÅ ą║ą░ą║ ąĮčāą╗ąĖ. |

| 6-5 |

S[1:0] |

ąĮąĄ ą▓ą╗ąĖčÅąĄčé |

ąĀą░ąĘą╝ąĄčĆ ą░ą┤čĆąĄčüąĮąŠą│ąŠ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ą░ ą║ąŠą┤ą░. ą¤ąŠ čŹčéąĖą╝ ą▒ąĖčéą░ą╝ ą╝ąŠąČąĮąŠ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ ą║ąŠą┤ą░ ROM ąĖą╗ąĖ RAM (ą▒ąĖčé 7 ROA ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ROM ąĖą╗ąĖ RAM). ąŁčéąĖ ą▒ąĖčéčŗ ą┐ąŠčüč鹊čÅąĮąĮąŠ ąĮą░čģąŠą┤čÅčéčüčÅ ą▓ ąĘąĮą░č湥ąĮąĖąĖ 10b, čćč鹊 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą║ąŠą┤ąŠą▓ąŠąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ 16 ą║ą▒ą░ą╣čé, ąĖ ąĮą░ čüąŠčüč鹊čÅąĮąĖąĄ čŹčéąĖčģ ą▒ąĖčé čüą▒čĆąŠčü ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ ą▓ą╗ąĖčÅąĮąĖčÅ.

00 = 4 ą║ąĖą╗ąŠą▒ą░ą╣čéą░ ą┐ąŠą┤ ą║ąŠą┤

01 = 8 ą║ąĖą╗ąŠą▒ą░ą╣čé ą┐ąŠą┤ ą║ąŠą┤

10 = 16 ą║ąĖą╗ąŠą▒ą░ą╣čé ą┐ąŠą┤ ą║ąŠą┤

11 = 32 ą║ąĖą╗ąŠą▒ą░ą╣čéą░ ą┐ąŠą┤ ą║ąŠą┤

|

| 7 |

ROA |

ąĮąĄ ą▓ą╗ąĖčÅąĄčé |

ą¤ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą▓ąĄčĆčüąĖčÄ ROM ąĖą╗ąĖ RAM, ąĮą░ č湥ą╝ ąŠčüąĮąŠą▓čŗą▓ą░ąĄčéčüčÅ ą░ą┤čĆąĄčüąĮąŠąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ CODE (ą║ąŠą┤ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ). ąŁč鹊čé ą▒ąĖčé ą▓čüąĄą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1 (čćč鹊 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĮą░ ą║ąŠą┤ąŠą▓ąŠąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ ąĮą░ ąŠčüąĮąŠą▓ąĄ RAM), ąĖ čüą▒čĆąŠčü ąĮą░ ąĮąĄą│ąŠ ąĮąĄ ą▓ą╗ąĖčÅąĄčé.

ROA = 0: ą║ąŠą┤ąŠą▓ąŠąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ ROM

ROA = 1: ą║ąŠą┤ąŠą▓ąŠąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ RAM

|

ąóą░ą▒ą╗ąĖčåą░ 4-1. ą×ą┐čĆąĄą┤ąĄą╗ąĄąĮąĖąĄ čĆą░ąĘą╝ąĄčĆą░ ROM/RAM

| ąĀąĄą│ąĖčüčéčĆ ROMS |

BOOT ROM |

RAM CODE |

ROM CODE |

| ROA |

S1 |

S0 |

| 0 |

0 |

0 |

ąĮąĄčé |

ąĮąĄčé |

4K |

| 0 |

0 |

1 |

ąĮąĄčé |

ąĮąĄčé |

8K |

| 0 |

1 |

0 |

ąĮąĄčé |

ąĮąĄčé |

16K (ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ) |

| 0 |

1 |

1 |

ąĮąĄčé |

ąĮąĄčé |

32K (ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ) |

| 1 |

0 |

0 |

10K |

4K |

ąĮąĄčé |

| 1 |

0 |

1 |

10K |

8K |

ąĮąĄčé |

| 1* |

1* |

0* |

10K* |

16K* |

ąĮąĄčé* |

| 1 |

1 |

1 |

10K |

32K (ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ) |

ąĮąĄčé |

* čüąĄą╣čćą░čü ąČąĄčüčéą║ąŠ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ č鹊ą╗čīą║ąŠ čŹč鹊čé ą▓ą░čĆąĖą░ąĮčé.

4.1.2. ąĀą░ą▒ąŠčéą░ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ Boot (ąĘą░ą│čĆčāąĘą║ą░ MCU firmware ą▓ ą┐ą░ą╝čÅčéčī CODE RAM)

ą¤ąŠčüą║ąŠą╗čīą║čā ą║ąŠą┤ąŠą▓ąŠąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ firmware ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ CODE RAM (ąĖčüą║ą╗čÄčćą░čÅ boot ROM), č鹊 firmware ą┤ą╗čÅ TUSB3410 ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ąĘą░ą│čĆčāąČąĄąĮąŠ ąĖąĘ ą║ą░ą║ąŠą╣-č鹊 ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ. ąÜą░ą║ čāąČąĄ čāą┐ąŠą╝ąĖąĮą░ą╗ąŠčüčī, čéą░ą║ąĖčģ ąĖčüč鹊čćąĮąĖą║ąŠą▓ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ ą┤ą▓ą░: ąŠą┤ąĖąĮ čŹč鹊 ą▓ąĮąĄčłąĮčÅčÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮą░čÅ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ EEPROM čü ąĖąĮč鹥čĆč乥ą╣čüąŠą╝ I2C, ąĖ ą┤čĆčāą│ąŠą╣ čŹč鹊 čģąŠčüčé, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗą╣ č湥čĆąĄąĘ USB. ąÜąŠą│ą┤ą░ čāčüčéčĆąŠą╣čüčéą▓ąŠ čüą▒čĆąŠčłąĄąĮąŠ, ą▒ąĖčé 0 (SDW) ą▓ čĆąĄą│ąĖčüčéčĆąĄ ROMS (čüą╝. čüąĄą║čåąĖčÄ 4.1.1) ąĖ ą▒ąĖčé 7 (CONT) ą▓ čĆąĄą│ąĖčüčéčĆąĄ USBCTL (čüą╝. čüąĄą║čåąĖčÄ 5.4) ąŠčćąĖčēąĄąĮčŗ. ąŁč鹊 ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčé ą║ą░čĆčéčā ą┐ą░ą╝čÅčéąĖ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ boot mode (čüą╝. čéą░ą▒ą╗ąĖčåčā 4-3) ąĖ čāą┤ąĄčƹȹĖą▓ą░ąĄčé čāčüčéčĆąŠą╣čüčéą▓ąŠ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ąŠčéą║ą╗čÄč湥ąĮąĖčÅ ąŠčé čģąŠčüčéą░. ą¤ąĄčĆą▓ą░čÅ ąĖąĮčüčéčĆčāą║čåąĖčÅ ą║ąŠą┤ą░ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ą┐ąŠ ą░ą┤čĆąĄčüčā CODE 0000h (čüąĄą╣čćą░čü ą▓ čŹč鹊 ą╝ąĄčüč鹊 ąŠč鹊ą▒čĆą░ąČąĄąĮčŗ 10 ą║ąĖą╗ąŠą▒ą░ą╣čé ROM). 16 ą║ąĖą╗ąŠą▒ą░ą╣čé RAM ąŠč鹊ą▒čĆą░ąČąĄąĮčŗ ą▓ ąŠą▒ą╗ą░čüčéčī XDATA (ąĮą░čćąĖąĮą░čÅ čü ą░ą┤čĆąĄčüą░ 0000h). MCU ą┐ąŠą┤ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝ ą▒čāčéą╗ąŠą░ą┤ąĄčĆą░ ROM čćąĖčéą░ąĄčé ą▓ąĮąĄčłąĮčÄčÄ ą┐ą░ą╝čÅčéčī EEPROM ąĖ ą┐čĆąŠą▓ąĄčĆčÅąĄčé ą┤ą░ąĮąĮčŗąĄ ą▓ ąĮąĄą╣ ąĮą░ ąĮą░ą╗ąĖčćąĖąĄ ą║ąŠą┤ą░ (ą┐ąŠ čüą┐ąĄčåąĖą░ą╗čīąĮąŠą╣ čüąĖą│ąĮą░čéčāčĆąĄ ąĘą░ą│čĆčāąĘą║ąĖ). ąĢčüą╗ąĖ ą▓ EEPROM čüąŠą┤ąĄčƹȹĖčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą┤ąŠą┐čāčüčéąĖą╝čŗą╣ ą║ąŠą┤ (ą┐čĆą░ą▓ąĖą╗čīąĮčāčÄ čüąĖą│ąĮą░čéčāčĆčā), č鹊 MCU čćąĖčéą░ąĄčé ą║ąŠą┤ firmware ąĖąĘ EEPROM ąĖ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčé ąĄą│ąŠ ą▓ 16 ą║ąĖą╗ąŠą▒ą░ą╣čé XDATA RAM. ąĢčüą╗ąĖ ą║ąŠą┤ (čüąĖą│ąĮą░čéčāčĆą░) ąĮąĄ ąĮą░ą╣ą┤ąĄąĮ, č鹊 MCU ą▓čŗą┐ąŠą╗ąĮčÅąĄčé ąĘą░ą│čĆčāąĘą║čā ąĖąĘ USB.

ąÜą░ą║ č鹊ą╗čīą║ąŠ ą║ąŠą┤ ąĘą░ą│čĆčāąČąĄąĮ, MCU čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ą▒ąĖčé SDW čĆąĄą│ąĖčüčéčĆą░ ROMS ą▓ 1. ąŁč鹊 ą┐ąĄčĆąĄą║ą╗čÄčćą░ąĄčé ą║ą░čĆčéčā ą┐ą░ą╝čÅčéąĖ ą▓ normal mode; ą║ą░ą║ č鹊ą╗čīą║ąŠ čŹč鹊 čüą┤ąĄą╗ą░ąĮąŠ, 16 ą║ąĖą╗ąŠą▒ą░ą╣čé RAM ą▒čāą┤čāčé ąŠč鹊ą▒čĆą░ąČąĄąĮčŗ ąĮą░ ą░ą┤čĆąĄčüąĮąŠąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ CODE (ąĮą░čćąĖąĮą░čÅ čü ą░ą┤čĆąĄčüą░ 0000h), ąĖ MCU ąĮą░čćąĮąĄčé ąŠčéčéčāą┤ą░ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ. ąÜąŠą┤ čüąĮąŠą▓ą░ ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆčāąĄčé USB ąĖ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐čĆąŠčģąŠą┤ąĖčé ąŠą▒čŗčćąĮčāčÄ ą┐čĆąŠčåąĄą┤čāčĆčā 菹Įčāą╝ąĄčĆą░čåąĖąĖ ąĮą░ čģąŠčüč鹥.

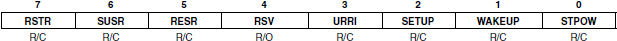

4.1.3. WDCSR: Watchdog Timer, Control, and Status Register (ą░ą┤čĆąĄčü FF93h) - čĆąĄą│ąĖčüčéčĆ čüč鹊čĆąŠąČąĄą▓ąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░, čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĖ čüčéą░čéčāčüą░

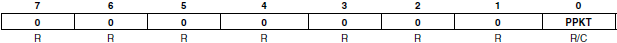

ąÆ TUSB3410 ąĖą╝ąĄąĄčéčüčÅ čüč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ (WDT, WatchDog Timer) čü ą┤ąĖčüą║čĆąĄčéąĮąŠčüčéčīčÄ 1 ą╝čü. ąĢčüą╗ąĖ ą║ čŹč鹊ą╝čā čĆąĄą│ąĖčüčéčĆčā ąĮąĄ ą▒čŗą╗ąŠ ąŠą▒čĆą░čēąĄąĮąĖčÅ ą▓ č鹥č湥ąĮąĖąĄ 128 ą╝čü, č鹊 čüč湥čéčćąĖą║ WDT čüą▒čĆą░čüčŗą▓ą░ąĄčé MCU (čüą╝. čĆąĖčü. 5-1). ąĪč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ čĆą░ąĘčĆąĄčłąĄąĮ, ąĖ ąĄą│ąŠ ą╝ąŠąČąĮąŠ ąĘą░ą┐čĆąĄčéąĖčéčī, ąĄčüą╗ąĖ ąĘą░ą┐ąĖčüą░čéčī čüąĖą│ąĮą░čéčāčĆčā 101010b ą▓ ą▒ąĖčéčŗ WDD[5:0] čĆąĄą│ąĖčüčéčĆą░. ąóą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗ čü ą┐ąĄčĆąĖąŠą┤ąŠą╝ 1 ą╝čü ą┤ą╗čÅ WDT ą┐ąŠčüčéčāą┐ą░ąĄčé ąŠčé ąĖą╝ą┐čāą╗čīčüąŠą▓ SOF. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, čćč鹊ą▒čŗ čéą░ą╣ą╝ąĄčĆ WDT čüčćąĖčéą░ą╗, ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé 7 (CONT) ą▓ čĆąĄą│ąĖčüčéčĆąĄ USBCTL (čüą╝. čüąĄą║čåąĖčÄ 5.4).

| Ōä¢ ą▒ąĖčéą░ |

ąśą╝čÅ |

RESET |

ą×ą┐ąĖčüą░ąĮąĖąĄ ą▒ąĖčé |

| 0 |

WDT |

0 |

MCU firmware ą┤ąŠą╗ąČąĮąŠ ąĘą░ą┐ąĖčüčŗą▓ą░čéčī 1 ą▓ čŹč鹊čé ą▒ąĖčé, čćč鹊ą▒čŗ ą┐čĆąĄą┤ąŠčéą▓čĆą░čéąĖčéčī ą┐ąĄčĆąĄąĘą░ą│čĆčāąĘą║čā, ą║ąŠč鹊čĆčāčÄ ą╝ąŠąČąĄčé ą▓čŗąĘą▓ą░čéčī ąĖčüč鹥č湥ąĮąĖąĄ čéą░ą╣ą╝ą░čāčéą░ čüč鹊čĆąŠąČąĄą▓ąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░ (watchdog). ąĢčüą╗ąĖ MCU ąĮąĄ ąĘą░ą┐ąĖčüą░ą╗ ą▓ čŹč鹊čé ą▒ąĖčé 1 ą▓ č鹥č湥ąĮąĖąĄ ą▓čĆąĄą╝ąĄąĮąĖ 128 ą╝čü, č鹊 watchdog ą┐ąĄčĆąĄąĘą░ą│čĆčāąĘąĖčé ą╝ąĖą║čĆąŠčüčģąĄą╝čā. ąŚą░ą┐ąĖčüčī 0 ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ ą▓ąŠąĘą┤ąĄą╣čüčéą▓ąĖčÅ ąĮą░ watchdog. ąóą░ą╣ą╝ąĄčĆ watchdog ąĖą╝ąĄąĄčé 7 čĆą░ąĘčĆčÅą┤ąŠą▓, ąĖ ąĮą░ ąĮąĄą│ąŠ ą┐ąŠą┤ą░ąĄčéčüčÅ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ čü ą┐ąĄčĆąĖąŠą┤ąŠą╝ 1 ą╝čü (ąŠčé ąĖą╝ą┐čāą╗čīčüąŠą▓ SOF). ą¦ąĖčéą░ąĄčéčüčÅ ą▒ąĖčé WDT ą▓čüąĄą│ą┤ą░ ą║ą░ą║ 0.

|

| 5-1 |

WDD[5:1] |

00000 |

ąŁčéąĖ ą▒ąĖčéčŗ ą┐ąŠąĘą▓ąŠą╗čÅčÄčé ąĘą░ą┐čĆąĄčéąĖčéčī watchdog. ą¦č鹊ą▒čŗ ąĘą░ą┐čĆąĄčéąĖčéčī čüč鹊čĆąŠąČąĄą▓ąŠą╣ čéą░ą╣ą╝ąĄčĆ, ą▓ čŹčéąĖ ą▒ąĖčéčŗ ąĮą░ą┤ąŠ ąĘą░ą┐ąĖčüą░čéčī 10101b ąĖ ą▒ąĖčé 7 WDD0 čéą░ą║ąČąĄ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čüą▒čĆąŠčłąĄąĮ ą▓ 0. ąŚą░ą┐ąĖčüčī ą┤čĆčāą│ąĖčģ ąĘąĮą░č湥ąĮąĖą╣ ąĮąĄ ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ąĘą░ą┐čĆąĄčéčā watchdog. |

| 6 |

WDR |

0 |

ąæąĖčé, ą║ąŠč鹊čĆčŗą╣ čāą║ą░ąĘčŗą▓ą░ąĄčé ąĮą░ čüą▒čĆąŠčü ą┐ąŠ čüč鹊čĆąŠąČąĄą▓ąŠą╝čā čéą░ą╣ą╝ąĄčĆčā ąĖą╗ąĖ ąĮą░ čüą▒čĆąŠčü ą┐čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ.

WDR=0: ą┐čĆąŠąĖąĘąŠčłąĄą╗ čüą▒čĆąŠčü ą┐čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ.

WDR=1: ą┐čĆąŠąĖąĘąŠčłąĄą╗ čüą▒čĆąŠčü ąŠčé watchdog. ą¦č鹊ą▒čŗ ąŠčćąĖčüčéąĖčéčī čŹč鹊čé ą▒ąĖčé, MCU ą┤ąŠą╗ąČąĄąĮ ąĘą░ą┐ąĖčüą░čéčī čüčÄą┤ą░ 1, ąĘą░ą┐ąĖčüčī 0 ąĮąĄ ą┤ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░.

|

| 7 |

WDD0 |

1 |

ąŁč鹊 ąŠą┤ąĖąĮ ąĖąĘ 6 ą▒ąĖčé, ą║ąŠč鹊čĆčŗą╣ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąĘą░ą┐čĆąĄčéąĖčéčī watchdog. ąöą╗čÅ ąĘą░ą┐čĆąĄčéą░ watchdog čŹč鹊čé ą▒ąĖčé ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąŠčćąĖčēąĄąĮ.

|

4.2. ąæčāč乥čĆčŗ ąĖ ą║ą░čĆčéą░ ą┐ą░ą╝čÅčéąĖ ą▓ą▓ąŠą┤ą░ ą▓čŗą▓ąŠą┤ą░ (I/O)

ąÉą┤čĆąĄčüąĮąŠąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ XDATA ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąŠčé F800h ą┤ąŠ FFFFh (2 ą║ąĖą╗ąŠą▒ą░ą╣čéą░) ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ ą┤ą╗čÅ ą▒čāč乥čĆąŠą▓ ą┤ą░ąĮąĮčŗčģ, ą┐ą░ą║ąĄčéą░ ąĮą░čüčéčĆąŠą╣ą║ąĖ USB (setup packet), ą▒ą╗ąŠą║ąŠą▓ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą▓ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ (endpoint descriptors block, EDB), ąĖ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ (I/O). ąŚą┤ąĄčüčī 128 čÅč湥ąĄą║ ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ ą┤ą╗čÅ čĆąĄą│ąĖčüčéčĆąŠą▓ MMR. ąÆ čéą░ą▒ą╗ąĖčåąĄ 4-2 ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮąŠ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ XDATA ąĖ ąŠą│čĆą░ąĮąĖč湥ąĮąĖąĄ ą┤ąŠčüčéčāą┐ą░ ą║ ąĮąĄą╝čā č湥čĆąĄąĘ DMA, ą╝ąĄąĮąĄą┤ąČąĄčĆ ą▒čāč乥čĆą░ USB (USB buffer manager, UBM) ąĖ MCU.

ąóą░ą▒ą╗ąĖčåą░ 4-2. ąÉą┤čĆąĄčüąĮąŠąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ XDATA

| ą×ą┐ąĖčüą░ąĮąĖąĄ |

ąöąĖą░ą┐ą░ąĘąŠąĮ ą░ą┤čĆąĄčüąŠą▓ |

ąöąŠčüčéčāą┐ ą┤ą╗čÅ UBM |

ąöąŠčüčéčāą┐ ą┤ą╗čÅ DMA |

ąöąŠčüčéčāą┐ ą┤ą╗čÅ MCU |

| ąÆąĮčāčéčĆąĄąĮąĮąĖąĄ MMR |

FFFFh .. FF80h |

ąĮąĄčé (č鹊ą╗čīą║ąŠ EDB-0) |

ąĮąĄčé (č鹊ą╗čīą║ąŠ čĆąĄą│ąĖčüčéčĆ ą┤ą░ąĮąĮčŗčģ ąĖ EDB-0) |

ąöąÉ |

| EDB |

FF7Fh .. FF08h |

ąóąŠą╗čīą║ąŠ ą┤ą╗čÅ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ EDB |

ąóąŠą╗čīą║ąŠ ą┤ą╗čÅ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ EDB |

ąöąÉ |

| Setup Paket |

FF07h .. FF00h |

ąöąÉ |

ąĮąĄčé |

ąöąÉ |

| ąæčāč乥čĆ Input endpoint-0 |

FEFFh .. FEF8h |

ąöąÉ |

ąöąÉ |

ąöąÉ |

| ąæčāč乥čĆ Output endpoint-0 |

FEF7h .. FEF0h |

ąöąÉ |

ąöąÉ |

ąöąÉ |

| ąæčāč乥čĆčŗ ą┤ą░ąĮąĮčŗčģ |

FEEFh .. F800h |

ąöąÉ |

ąöąÉ |

ąöąÉ |

ąóą░ą▒ą╗ąĖčåą░ 4-3. ąÉą┤čĆąĄčüąĮąŠąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ XDATA ą┤ą╗čÅ čĆąĄą│ąĖčüčéčĆąŠą▓ MMR (ą░ą┤čĆąĄčüą░ FF80h .. FFFFh)

| ąÉą┤čĆąĄčü |

ąĀąĄą│ąĖčüčéčĆ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| FFFFh |

FUNADR |

Function address register - čĆąĄą│ąĖčüčéčĆ ą░ą┤čĆąĄčüą░ čäčāąĮą║čåąĖąĖ. |

| FFFEh |

USBSTA |

USB status register - čĆąĄą│ąĖčüčéčĆ čüčéą░čéčāčüą░ USB. |

| FFFDh |

USBMSK |

USB interrupt mask register - čĆąĄą│ąĖčüčéčĆ ą╝ą░čüą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ USB. |

| FFFCh |

USBCTL |

USB control register - čĆąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ USB. |

| FFFBh |

MODECNFG |

ąĀąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ čĆąĄąČąĖą╝ą░. |

| FFFAh .. FFF4h |

- |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ. |

| FFF3h |

I2CADR |

ąĀąĄą│ąĖčüčéčĆ ą░ą┤čĆąĄčüą░ ą┐ąŠčĆčéą░ I2C. |

| FFF2h |

I2CDATI |

ąĀąĄą│ąĖčüčéčĆ ą▓čģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ ą┐ąŠčĆčéą░ I2C. |

| FFF1h |

I2CDATO |

ąĀąĄą│ąĖčüčéčĆ ą▓čŗčģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ ą┐ąŠčĆčéą░ I2C. |

| FFF0h |

I2CSTA |

ąĀąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ ą┐ąŠčĆčéą░ I2C. |

| FFEFh .. FFE8h |

SERNUM7 .. SERNUM0 |

ąĀąĄą│ąĖčüčéčĆčŗ čüąĄčĆąĖą╣ąĮąŠą│ąŠ ąĮąŠą╝ąĄčĆą░. |

| FFE7h .. FFE6h |

- |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ. |

| FFE5h |

DMACSR3 |

DMA-3: čĆąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĖ čüčéą░čéčāčüą░. |

| FFE4h |

DMACDR3 |

DMA-3: čĆąĄą│ąĖčüčéčĆ čāą║ą░ąĘą░ąĮąĖčÅ ą║ą░ąĮą░ą╗ą░. |

| FFE3h .. FFE2h |

- |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ. |

| FFE1h |

DMACRS1 |

DMA-1: čĆąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĖ čüčéą░čéčāčüą░. |

| FFE0h |

DMACDR1 |

DMA-1: čĆąĄą│ąĖčüčéčĆ čāą║ą░ąĘą░ąĮąĖčÅ ą║ą░ąĮą░ą╗ą░. |

| FFDFh .. FFACh |

- |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ. |

| FFABh |

MASK |

UART: čĆąĄą│ąĖčüčéčĆ ą╝ą░čüą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. |

| FFAAh |

XOFF |

UART: čĆąĄą│ąĖčüčéčĆ Xoff. |

| FFA9h |

XON |

UART: čĆąĄą│ąĖčüčéčĆ Xon. |

| FFA8h |

DLH |

UART: čüčéą░čĆčłąĖą╣ ą▒ą░ą╣čé ą┤ąĄą╗ąĖč鹥ą╗čÅ. |

| FFA7h |

DLL |

UART: ą╝ą╗ą░ą┤čłąĖą╣ ą▒ą░ą╣čé ą┤ąĄą╗ąĖč鹥ą╗čÅ. |

| FFA6h |

MSR |

UART: Modem status register, čĆąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ ą╝ąŠą┤ąĄą╝ą░. |

| FFA5h |

LSR |

UART: Line status register, čĆąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ ą╗ąĖąĮąĖąĖ. |

| FFA4h |

MCR |

UART: Modem control register, čĆąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą╝ąŠą┤ąĄą╝ąŠą╝. |

| FFA3h |

FCRL |

UART: Flow control register, čĆąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąŠč鹊ą║ąŠą╝. |

| FFA2h |

LCR |

UART: Line control register, čĆąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą╗ąĖąĮąĖąĄą╣. |

| FFA1h |

TDR |

UART: čĆąĄą│ąĖčüčéčĆ ą┤ą░ąĮąĮčŗčģ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░. |

| FFA0h |

RDR |

UART: čĆąĄą│ąĖčüčéčĆ ą┤ą░ąĮąĮčŗčģ ą┐čĆąĖąĄą╝ąĮąĖą║ą░. |

| FF9Eh |

PUR_3 |

GPIO: čĆąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╝ ąĮą░ą│čĆčāąĘąŠčćąĮčŗą╝ čĆąĄąĘąĖčüč鹊čĆąŠą╝ (pullup) ą┤ą╗čÅ ą┐ąŠčĆčéą░ 3 (P3). |

| FF9Dh .. FF94h |

- |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ. |

| FF93h |

WDCSR |

ąĀąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĖ čüčéą░čéčāčüą░ čüč鹊čĆąŠąČąĄą▓ąŠą│ąŠ čéą░ą╣ą╝ąĄčĆą░ (watchdog). |

| FF92h |

VECINT |

Vector interrupt register, čĆąĄą│ąĖčüčéčĆ ą▓ąĄą║č鹊čĆą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. |

| FF91h |

- |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ. |

| FF90h |

ROMS |

ąĀąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĄą╣ ąĘą░č鹥ąĮąĄąĮąĖčÅ ROM. |

| FF8Fh .. FF84h |

- |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ. |

| FF83h |

OEPBCNT_0 |

Output endpoint_0: čĆąĄą│ąĖčüčéčĆ čüč湥čéčćąĖą║ą░ ą▒ą░ą╣čé. |

| FF82h |

OEPCNFG_0 |

Output endpoint_0: čĆąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ. |

| FF81h |

IEPBCNT_0 |

Input endpoint_0: čĆąĄą│ąĖčüčéčĆ čüč湥čéčćąĖą║ą░ ą▒ą░ą╣čé. |

| FF80h |

IEPCNFG_0 |

Input endpoint_0: čĆąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ. |

ąóą░ą▒ą╗ąĖčåą░ 4-4. ąÉą┤čĆąĄčüąĮąŠąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ XDATA ą┤ą╗čÅ čÅč湥ąĄą║ EDB

| ąÉą┤čĆąĄčü |

ąĀąĄą│ąĖčüčéčĆ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| FF7Fh .. FF60h |

- |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ. |

| FF5Fh |

IEPSIZXY_3 |

Input endpoint_3: čĆą░ąĘą╝ąĄčĆ ą▒čāč乥čĆą░ X-Y. |

| FF5Eh |

IEPBCTY_3 |

Input endpoint_3: čüč湥čéčćąĖą║ ą▒ą░ą╣čé Y. |

| FF5Dh |

IEPBBAY_3 |

Input endpoint_3: ą▒ą░ąĘąŠą▓čŗą╣ ą░ą┤čĆąĄčü ą▒čāč乥čĆą░ Y. |

| FF5Ch, FF5Bh |

- |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ. |

| FF5Ah |

IEPBCTX_3 |

Input endpoint_3: čüč湥čéčćąĖą║ ą▒ą░ą╣čé X. |

| FF59h |

IEPBBAX_3 |

Input endpoint_3: ą▒ą░ąĘąŠą▓čŗą╣ ą░ą┤čĆąĄčü ą▒čāč乥čĆą░ Y. |

| FF58h |

IEPCNF_3 |

Input endpoint_3: ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ. |

| FF57h |

IEPSIZXY_2 |

Input endpoint_2: čĆą░ąĘą╝ąĄčĆ ą▒čāč乥čĆą░ X-Y. |

| FF56h |

IEPBCTY_2 |

Input endpoint_2: čüč湥čéčćąĖą║ ą▒ą░ą╣čé Y. |

| FF55h |

IEPBBAY_2 |

Input endpoint_2: ą▒ą░ąĘąŠą▓čŗą╣ ą░ą┤čĆąĄčü ą▒čāč乥čĆą░ Y. |

| FF54h, FF53h |

- |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ. |

| FF52h |

IEPBCTX_2 |

Input endpoint_2: čüč湥čéčćąĖą║ ą▒ą░ą╣čé X. |

| FF51h |

IEPBBAX_2 |

Input endpoint_2: ą▒ą░ąĘąŠą▓čŗą╣ ą░ą┤čĆąĄčü ą▒čāč乥čĆą░ Y. |

| FF50h |

IEPCNF_2 |

Input endpoint_2: ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ. |

| FF4Fh |

IEPSIZXY_1 |

Input endpoint_1: čĆą░ąĘą╝ąĄčĆ ą▒čāč乥čĆą░ X-Y. |

| FF4Eh |

IEPBCTY_1 |

Input endpoint_1: čüč湥čéčćąĖą║ ą▒ą░ą╣čé Y. |

| FF4Dh |

IEPBBAY_1 |

Input endpoint_1: ą▒ą░ąĘąŠą▓čŗą╣ ą░ą┤čĆąĄčü ą▒čāč乥čĆą░ Y. |

| FF4Ch, FF4Bh |

- |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ. |

| FF4Ah |

IEPBCTX_1 |

Input endpoint_1: čüč湥čéčćąĖą║ ą▒ą░ą╣čé X. |

| FF49h |

IEPBBAX_1 |

Input endpoint_1: ą▒ą░ąĘąŠą▓čŗą╣ ą░ą┤čĆąĄčü ą▒čāč乥čĆą░ Y. |

| FF48h |

IEPCNF_1 |

Input endpoint_1: ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ. |

| FF47h .. FF20h |

- |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ. |

| FF1Fh |

OEPSIZXY_3 |

Output endpoint_3: čĆą░ąĘą╝ąĄčĆ ą▒čāč乥čĆą░ X-Y. |

| FF1Eh |

OEPBCTY_3 |

Output endpoint_3: čüč湥čéčćąĖą║ ą▒ą░ą╣čé Y. |

| FF1Dh |

OEPBBAY_3 |

Output endpoint_3: ą▒ą░ąĘąŠą▓čŗą╣ ą░ą┤čĆąĄčü ą▒čāč乥čĆą░ Y. |

| FF1Ch, FF1Bh |

- |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ. |

| FF1Ah |

OEPBCTX_3 |

Output endpoint_3: čüč湥čéčćąĖą║ ą▒ą░ą╣čé X. |

| FF19h |

OEPBBAX_3 |

Output endpoint_3: ą▒ą░ąĘąŠą▓čŗą╣ ą░ą┤čĆąĄčü ą▒čāč乥čĆą░ X. |

| FF18h |

OEPCNF_3 |

Output endpoint_3: ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ. |

| FF17h |

OEPSIZXY_2 |

Output endpoint_2: čĆą░ąĘą╝ąĄčĆ ą▒čāč乥čĆą░ X-Y. |

| FF16h |

OEPBCTY_2 |

Output endpoint_2: čüč湥čéčćąĖą║ ą▒ą░ą╣čé Y. |

| FF15h |

OEPBBAY_2 |

Output endpoint_2: ą▒ą░ąĘąŠą▓čŗą╣ ą░ą┤čĆąĄčü ą▒čāč乥čĆą░ Y. |

| FF14h, FF13h |

- |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ. |

| FF12h |

OEPBCTX_2 |

Output endpoint_2: čüč湥čéčćąĖą║ ą▒ą░ą╣čé X. |

| FF11h |

OEPBBAX_2 |

Output endpoint_2: ą▒ą░ąĘąŠą▓čŗą╣ ą░ą┤čĆąĄčü ą▒čāč乥čĆą░ X. |

| FF10h |

OEPCNF_2 |

Output endpoint_2: ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ. |

| FF0Fh |

OEPSIZXY_1 |

Output endpoint_1: čĆą░ąĘą╝ąĄčĆ ą▒čāč乥čĆą░ X-Y. |

| FF0Eh |

OEPBCTY_1 |

Output endpoint_1: čüč湥čéčćąĖą║ ą▒ą░ą╣čé Y. |

| FF0Dh |

OEPBBAY_1 |

Output endpoint_1: ą▒ą░ąĘąŠą▓čŗą╣ ą░ą┤čĆąĄčü ą▒čāč乥čĆą░ Y. |

| FF0Ch, FF0Bh |

- |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ. |

| FF0Ah |

OEPBCTX_1 |

Output endpoint_1: čüč湥čéčćąĖą║ ą▒ą░ą╣čé X. |

| FF09h |

OEPBBAX_1 |

Output endpoint_1: ą▒ą░ąĘąŠą▓čŗą╣ ą░ą┤čĆąĄčü ą▒čāč乥čĆą░ X. |

| FF08h |

OEPCNF_1 |

Output endpoint_1: ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ. |

| FF07h .. FF00h |

8 ą▒ą░ą╣čé |

ąæą╗ąŠą║ ą┐ą░ą║ąĄčéą░ ąĮą░čüčéčĆąŠą╣ą║ąĖ (Setup Packet). |

| FEFFh .. FEF8h |

8 ą▒ą░ą╣čé |

ąæčāč乥čĆ Input endpoint_0. |

| FEF7h .. FEF0h |

8 ą▒ą░ą╣čé |

ąæčāč乥čĆ Output endpoint_0. |

| FEEFh .. F800h |

TOPBUFF .. STABUFF |

ą¤čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ, ą▓čŗą┤ąĄą╗ąĄąĮąĮąŠąĄ ą┐ąŠą┤ ą▒čāč乥čĆčŗ ą┤ą░ąĮąĮčŗčģ. |

4.3. Endpoint Descriptor Block (ąŠčé EDB-1 ą┤ąŠ EDB-3)

ą¤ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ č湥čĆąĄąĘ ą╝ąĄąČą┤čā USB, MCU ąĖ ą▓ąĮąĄčłąĮąĖą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮčŗ ą▓ endpoint descriptor block (EDB). ąśą╝ąĄąĄčéčüčÅ čéčĆąĖ input EDB ąĖ čéčĆąĖ output EDB. ąŚą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ EDB-0 (I/O endpoint-0), ą▓čüąĄ EDB čĆą░ąĘą╝ąĄčēąĄąĮčŗ ą▓ SRAM, ą║ą░ą║ ąŠą┐ąĖčüą░ąĮąŠ ą▓ čéą░ą▒ą╗ąĖčåąĄ 4-3. ąÜą░ąČą┤čŗą╣ EDB čüąŠą┤ąĄčƹȹĖčé ąĖąĮč乊čĆą╝ą░čåąĖčÄ, ąŠą┐ąĖčüčŗą▓ą░čÄčēčāčÄ X- ąĖ Y- ą▒čāč乥čĆčŗ. ąÆ ą┤ąŠą┐ąŠą╗ąĮąĄąĮąĖąĄ, ą║ą░ąČą┤čŗą╣ EDB ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ąŠą▒čēčāčÄ ąĖąĮč乊čĆą╝ą░čåąĖčÄ čüčéą░čéčāčüą░.

ąÆ čéą░ą▒ą╗ąĖčåąĄ 4-5 ą┐ąŠą║ą░ąĘą░ąĮčŗ ąĘą░ą┐ąĖčüąĖ ą┤ą╗čÅ ą▒ą╗ąŠą║ąŠą▓ EDB ąŠčé EDB-1 ą┤ąŠ EDB-3. ąĀąĄą│ąĖčüčéčĆčŗ EDB-0 ąŠą┐ąĖčüą░ąĮčŗ ą▓ čéą░ą▒ą╗ąĖčåąĄ 4-6.

ąóą░ą▒ą╗ąĖčåą░ 4-5. ąĀąĄą│ąĖčüčéčĆčŗ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ ąĖ čüą╝ąĄčēąĄąĮąĖčÅ ą▓ RAM (n = 1 .. 3)

| ąĪą╝ąĄčēąĄąĮąĖąĄ |

ąśą╝čÅ ąĘą░ą┐ąĖčüąĖ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| 07 |

EPSIZXY_n |

I/O endpoint_n: čĆą░ąĘą╝ąĄčĆ ą▒čāč乥čĆą░ X/Y. |

| 06 |

EPBCTY_n |

I/O endpoint_n: čüč湥čéčćąĖą║ ą▒ą░ą╣čé Y. |

| 05 |

EPBBAY_n |

I/O endpoint_n: ą▒ą░ąĘąŠą▓čŗą╣ ą░ą┤čĆąĄčü ą▒čāč乥čĆą░ Y. |

| 04, 03 |

SPARE |

ąØąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ. |

| 02 |

EPBCTX_n |

I/O endpoint_n: čüč湥čéčćąĖą║ ą▒ą░ą╣čé X. |

| 01 |

EPBBAX_n |

I/O endpoint_n: ą▒ą░ąĘąŠą▓čŗą╣ ą░ą┤čĆąĄčü ą▒čāč乥čĆą░ X. |

| 00 |

EPCNF_n |

I/O endpoint_n: ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ. |

ąóą░ą▒ą╗ąĖčåą░ 4-6. ąæą░ąĘąŠą▓čŗąĄ ą░ą┤čĆąĄčüą░ čĆąĄą│ąĖčüčéčĆąŠą▓ ą║ąŠąĮąĄčćąĮąŠą╣ č鹊čćą║ąĖ

| ąæą░ąĘąŠą▓čŗą╣ ą░ą┤čĆąĄčü |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| FF08h |

Output endpoint 1 |

| FF10h |

Output endpoint 2 |

| FF18h |

Output endpoint 3 |

| FF48h |

Input endpoint 1 |

| FF50h |

Input endpoint 2 |

| FF58h |

Input endpoint 3 |

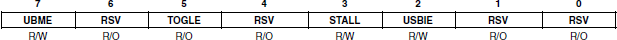

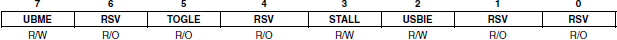

4.3.1. OEPCNF_n: Output Endpoint Configuration (n = 1 .. 3) (ą▒ą░ąĘąŠą▓čŗąĄ ą░ą┤čĆąĄčüą░: FF08h, FF10h, FF18h) - ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ Output Endpoint

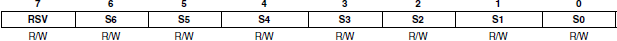

| Ōä¢ ą▒ąĖčéą░ |

ąśą╝čÅ |

RESET |

ą×ą┐ąĖčüą░ąĮąĖąĄ ą▒ąĖčé |

| 1-0 |

RSV |

x |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ, čĆą░ą▓ąĮąŠ 0.

|

| 2 |

USBIE |

x |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÄ čéčĆą░ąĮąĘą░ą║čåąĖąĖ USB. ąŻčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ąĖ čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ MCU.

USBIE=0: ą┐ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÄ čéčĆą░ąĮąĘą░ą║čåąĖąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĮąĄ čüčĆą░ą▒ąŠčéą░ąĄčé.

USBIE=1: ą┐ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÄ čéčĆą░ąĮąĘą░ą║čåąĖąĖ čüčĆą░ą▒ąŠčéą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ.

|

| 3 |

STALL |

0 |

ą¤ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüąŠą▒čŗčéąĖąĄ stall. ąŻčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ąĖ čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ MCU.

STALL=0: ąĮąĄčé čüąŠą▒čŗčéąĖčÅ stall.

STALL=1: ą┐čĆąŠąĖąĘąŠčłą╗ąŠ čüąŠą▒čŗčéąĖąĄ stall. ąĢčüą╗ąĖ čŹč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ MCU, č鹊 ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆčāąĄčéčüčÅ STALL čĆčāą║ąŠą┐ąŠąČą░čéąĖąĄ (handshake) ąĖ ą▒ąĖčé ąŠčćąĖčēą░ąĄčéčüčÅ MCU.

|

| 4 |

DBUF |

x |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┤ą▓ąŠą╣ąĮąŠą│ąŠ ą▒čāč乥čĆą░ (X ąĖ Y). ąŻčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ąĖ čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ MCU.

DBUF=0: ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą│ą╗ą░ą▓ąĮčŗą╣ ą▒čāč乥čĆ (č鹊ą╗čīą║ąŠ ą▒čāč乥čĆ X).

DBUF=1: ą▓ ą▓čŗą▒ąŠčĆąĄ ą▒čāč乥čĆą░ čāčćą░čüčéą▓čāąĄčé TOGLE - ą▒ąĖčé ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ ą▒čāč乥čĆą░ (čĆą░ą▒ąŠčéą░ąĄčé ą┤ą▓ąŠą╣ąĮąŠąĄ ą▒čāč乥čĆąĖąĘąĖčĆąŠą▓ą░ąĮąĖąĄ).

|

| 5 |

TOGLE |

x |

ąæąĖčé ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ ą▒čāč乥čĆą░ USB, ąŠčéčĆą░ąČą░čÄčēąĖą╣ čüąŠčüč鹊čÅąĮąĖąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ DATA0, DATA1.

|

| 6 |

ISO |

x |

ISO=0 ąŠąĘąĮą░čćą░ąĄčé ąĮąĄąĖąĘąŠčģčĆąŠąĮąĮčŗą╣ čéčĆą░ąĮčüč乥čĆ ą┤ą░ąĮąĮčŗčģ. ąŁč鹊čé ą▒ąĖčé ąŠą▒čÅąĘą░č鹥ą╗čīąĮąŠ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąŠčćąĖčēąĄąĮ MCU, ą┐ąŠčüą║ąŠą╗čīą║čā ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčéčüčÅ č鹊ą╗čīą║ąŠ ąĮąĄąĖąĘąŠčģčĆąŠąĮąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ.

|

| 7 |

UBME |

x |

ąæąĖčé čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ UBM. ąŻčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ąĖ čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ MCU.

UBME=0: UBM ąĮąĄ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čŹčéčā ą║ąŠąĮąĄčćąĮčāčÄ č鹊čćą║čā.

UBME=1: UBM ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čŹčéčā ą║ąŠąĮąĄčćąĮčāčÄ č鹊čćą║čā.

|

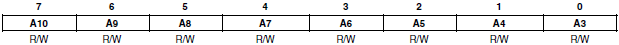

4.3.2. OEPBBAX_n: Output Endpoint X-Buffer Base Address (n = 1 .. 3) (čüą╝ąĄčēąĄąĮąĖąĄ 1) - ą▒ą░ąĘąŠą▓čŗą╣ ą░ą┤čĆąĄčü X-ą▒čāč乥čĆą░ Output Endpoint

| Ōä¢ ą▒ąĖčéą░ |

ąśą╝čÅ |

RESET |

ą×ą┐ąĖčüą░ąĮąĖąĄ ą▒ąĖčé |

| 7-0 |

A[10:3] |

x |

ąæąĖčéčŗ 10..3 ą▒ą░ąĘąŠą▓ąŠą│ąŠ ą░ą┤čĆąĄčüą░ ą▒čāč乥čĆą░ X, ą┤ąŠą┐ąŠą╗ąĮąĄąĮąĮčŗąĄ čüą┐čĆą░ą▓ą░ 3 ąĮčāą╗ąĄą▓čŗą╝ąĖ ą╝ą╗ą░ą┤čłąĖą╝ąĖ ą▒ąĖčéą░ą╝ąĖ ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ 11-ą▒ąĖčéąĮąŠą│ąŠ ą░ą┤čĆąĄčüą░. ąŚąĮą░č湥ąĮąĖąĄ čŹč鹊ą│ąŠ čĆąĄą│ąĖčüčéčĆą░ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ MCU. UBM ąĖą╗ąĖ DMA ąĖčüą┐ąŠą╗čīąĘčāčÄčé čŹč鹊 ąĘąĮą░č湥ąĮąĖąĄ ą║ą░ą║ ąĮą░čćą░ą╗čīąĮčŗą╣ ą░ą┤čĆąĄčü ą┤ą╗čÅ čāą║ą░ąĘą░ąĮąĮąŠą╣ čéčĆą░ąĮąĘą░ą║čåąĖąĖ. ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 UBM ąĖą╗ąĖ DMA ąĮąĄ ą╝ąĄąĮčÅčÄčé čŹč鹊 ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ čéčĆą░ąĮąĘą░ą║čåąĖąĖ.

|

ąÆ čĆąĄą│ąĖčüčéčĆąĄ OEPBBAX_n ąĘą░ą┤ą░ąĮąŠ čüą╝ąĄčēąĄąĮąĖąĄ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ą░ą┤čĆąĄčüą░ 0xF800 ą▓ ąŠą▒ą╗ą░čüčéąĖ ą┤ą░ąĮąĮčŗčģ XDATA. ąó. ąĄ. čĆąĄą░ą╗čīąĮčŗą╣ ą░ą▒čüąŠą╗čÄčéąĮčŗą╣ ą░ą┤čĆąĄčü ą▒čāč乥čĆą░, ą▓ ą║ąŠč鹊čĆčŗą╣ ą▒čāą┤ąĄčé ą║ą╗ą░čüčéčī ą┤ą░ąĮąĮčŗąĄ UBM, ą▓čŗčćąĖčüą╗čÅąĄčéčüčÅ čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝:

OUT_BUFFERXn_ADDRESS = 0xF800 + (OEPBBAX_n << 3)

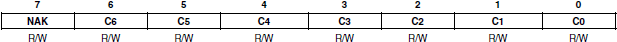

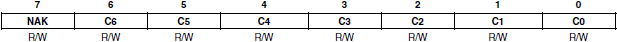

4.3.3. OEPBCTX_n: Output Endpoint X Byte Count (n = 1 .. 3) (čüą╝ąĄčēąĄąĮąĖąĄ 2) - čüč湥čéčćąĖą║ ą▒ą░ą╣čé X-ą▒čāč乥čĆą░ Output Endpoint

| Ōä¢ ą▒ąĖčéą░ |

ąśą╝čÅ |

RESET |

ą×ą┐ąĖčüą░ąĮąĖąĄ ą▒ąĖčé |

| 6-0 |

C[6:0] |

x |

ąĪč湥čéčćąĖą║ ą▒ą░ą╣čé ą▒čāč乥čĆą░ X, ą║ąŠč鹊čĆčŗą╣ čüčćąĖčéą░ąĄčé ą┤ąŠ 64 (1000000b). ąøčÄą▒ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą▒ąŠą╗čīčłąĄ 64 ą╝ąŠąČąĄčé ą┐čĆąĖą▓ąĄčüčéąĖ ą║ ąĮąĄą┐čĆąĄą┤čüą║ą░ąĘčāąĄą╝čŗą╝ čĆąĄąĘčāą╗čīčéą░čéą░ą╝.

|

| 7 |

NAK |

x |

NAK=0: ą▓ ą▒čāč乥čĆąĄ ąĮąĄčé ą┤ąŠą┐čāčüčéąĖą╝čŗčģ ą┤ą░ąĮąĮčŗčģ. ąōąŠč鹊ą▓ąĮąŠčüčéčī ą║ OUT čģąŠčüčéą░.

NAK=1: ą▒čāč乥čĆ čüąŠą┤ąĄčƹȹĖčé ą┤ąŠą┐čāčüčéąĖą╝čŗą╣ ą┐ą░ą║ąĄčé ąŠčé čģąŠčüčéą░ (ą▓čŗą┤ą░ąĄčé ąŠčéą▓ąĄčé NAK ąĮą░ ąĘą░ą┐čĆąŠčü čģąŠčüčéą░ OUT).

|

4.3.4. OEPBBAY_n: Output Endpoint Y-Buffer Base Address (n = 1 .. 3) (čüą╝ąĄčēąĄąĮąĖąĄ 5) - ą▒ą░ąĘąŠą▓čŗą╣ ą░ą┤čĆąĄčü Y-ą▒čāč乥čĆą░ Output Endpoint

| Ōä¢ ą▒ąĖčéą░ |

ąśą╝čÅ |

RESET |

ą×ą┐ąĖčüą░ąĮąĖąĄ ą▒ąĖčé |

| 7-0 |

A[10:3] |

x |

ąæąĖčéčŗ 10..3 ą▒ą░ąĘąŠą▓ąŠą│ąŠ ą░ą┤čĆąĄčüą░ ą▒čāč乥čĆą░ Y, ą┤ąŠą┐ąŠą╗ąĮąĄąĮąĮčŗąĄ čüą┐čĆą░ą▓ą░ 3 ąĮčāą╗ąĄą▓čŗą╝ąĖ ą╝ą╗ą░ą┤čłąĖą╝ąĖ ą▒ąĖčéą░ą╝ąĖ ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ 11-ą▒ąĖčéąĮąŠą│ąŠ ą░ą┤čĆąĄčüą░. ąŚąĮą░č湥ąĮąĖąĄ čŹč鹊ą│ąŠ čĆąĄą│ąĖčüčéčĆą░ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ MCU. UBM ąĖą╗ąĖ DMA ąĖčüą┐ąŠą╗čīąĘčāčÄčé čŹč鹊 ąĘąĮą░č湥ąĮąĖąĄ ą║ą░ą║ ąĮą░čćą░ą╗čīąĮčŗą╣ ą░ą┤čĆąĄčü ą┤ą╗čÅ čāą║ą░ąĘą░ąĮąĮąŠą╣ čéčĆą░ąĮąĘą░ą║čåąĖąĖ. ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 UBM ąĖą╗ąĖ DMA ąĮąĄ ą╝ąĄąĮčÅčÄčé čŹč鹊 ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ čéčĆą░ąĮąĘą░ą║čåąĖąĖ.

|

ąÆ čĆąĄą│ąĖčüčéčĆąĄ OEPBBAY_n ąĘą░ą┤ą░ąĮąŠ čüą╝ąĄčēąĄąĮąĖąĄ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ą░ą┤čĆąĄčüą░ 0xF800 ą▓ ąŠą▒ą╗ą░čüčéąĖ ą┤ą░ąĮąĮčŗčģ XDATA. ąó. ąĄ. čĆąĄą░ą╗čīąĮčŗą╣ ą░ą▒čüąŠą╗čÄčéąĮčŗą╣ ą░ą┤čĆąĄčü ą▒čāč乥čĆą░, ą▓ ą║ąŠč鹊čĆčŗą╣ ą▒čāą┤ąĄčé ą║ą╗ą░čüčéčī ą┤ą░ąĮąĮčŗąĄ UBM, ą▓čŗčćąĖčüą╗čÅąĄčéčüčÅ čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝:

OUT_BUFFERYn_ADDRESS = 0xF800 + (OEPBBAY_n << 3)

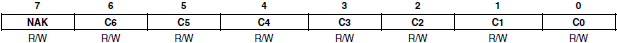

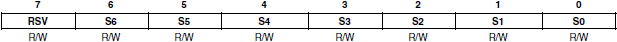

4.3.5. OEPBCTY_n: Output Endpoint Y Byte Count (n = 1 .. 3) (čüą╝ąĄčēąĄąĮąĖąĄ 6) - čüč湥čéčćąĖą║ ą▒ą░ą╣čé Y-ą▒čāč乥čĆą░ Output Endpoint

| Ōä¢ ą▒ąĖčéą░ |

ąśą╝čÅ |

RESET |

ą×ą┐ąĖčüą░ąĮąĖąĄ ą▒ąĖčé |

| 6-0 |

C[6:0] |

x |

ąĪč湥čéčćąĖą║ ą▒ą░ą╣čé ą▒čāč乥čĆą░ Y, ą║ąŠč鹊čĆčŗą╣ čüčćąĖčéą░ąĄčé ą┤ąŠ 64 (1000000b). ąøčÄą▒ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą▒ąŠą╗čīčłąĄ 64 ą╝ąŠąČąĄčé ą┐čĆąĖą▓ąĄčüčéąĖ ą║ ąĮąĄą┐čĆąĄą┤čüą║ą░ąĘčāąĄą╝čŗą╝ čĆąĄąĘčāą╗čīčéą░čéą░ą╝.

|

| 7 |

NAK |

x |

NAK=0: ą▓ ą▒čāč乥čĆąĄ ąĮąĄčé ą┤ąŠą┐čāčüčéąĖą╝čŗčģ ą┤ą░ąĮąĮčŗčģ. ąōąŠč鹊ą▓ąĮąŠčüčéčī ą║ OUT čģąŠčüčéą░.

NAK=1: ą▒čāč乥čĆ čüąŠą┤ąĄčƹȹĖčé ą┤ąŠą┐čāčüčéąĖą╝čŗą╣ ą┐ą░ą║ąĄčé ąŠčé čģąŠčüčéą░ (ą▓čŗą┤ą░ąĄčé ąŠčéą▓ąĄčé NAK ąĮą░ ąĘą░ą┐čĆąŠčü čģąŠčüčéą░ OUT).

|

4.3.6. OEPSIZXY_n: Output Endpoint X-/Y-Buffer Size (n = 1 .. 3) (čüą╝ąĄčēąĄąĮąĖąĄ 7) - čĆą░ąĘą╝ąĄčĆ ą▒čāč乥čĆąŠą▓ X ąĖ Y Output Endpoint

| Ōä¢ ą▒ąĖčéą░ |

ąśą╝čÅ |

RESET |

ą×ą┐ąĖčüą░ąĮąĖąĄ ą▒ąĖčé |

| 6-0 |

S[6:0] |

x |

ąĀą░ąĘą╝ąĄčĆ ą▒čāč乥čĆą░ X ąĖ ą▒čāč乥čĆą░ Y, ąŠčé 0 (0000000b) ą┤ąŠ 64 (1000000b). ąøčÄą▒ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą▒ąŠą╗čīčłąĄ 64 ą╝ąŠąČąĄčé ą┐čĆąĖą▓ąĄčüčéąĖ ą║ ąĮąĄą┐čĆąĄą┤čüą║ą░ąĘčāąĄą╝čŗą╝ čĆąĄąĘčāą╗čīčéą░čéą░ą╝.

|

| 7 |

RSV |

x |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ, čĆą░ą▓ąĮąŠ 0.

|

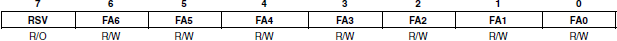

4.3.7. IEPCNF_n: Input Endpoint Configuration (n = 1 .. 3) (ą▒ą░ąĘąŠą▓čŗą╣ ą░ą┤čĆąĄčü: FF48h, FF50h, FF58h) - ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ Input Endpoint

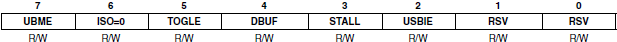

| Ōä¢ ą▒ąĖčéą░ |

ąśą╝čÅ |

RESET |

ą×ą┐ąĖčüą░ąĮąĖąĄ ą▒ąĖčé |

| 1-0 |

RSV |

x |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ, čĆą░ą▓ąĮąŠ 0.

|

| 2 |

USBIE |

x |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÄ čéčĆą░ąĮąĘą░ą║čåąĖąĖ USB. ąŻčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ąĖ čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ MCU.

USBIE=0: ą┐ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÄ čéčĆą░ąĮąĘą░ą║čåąĖąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĮąĄ čüčĆą░ą▒ąŠčéą░ąĄčé.

USBIE=1: ą┐ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÄ čéčĆą░ąĮąĘą░ą║čåąĖąĖ čüčĆą░ą▒ąŠčéą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ.

|

| 3 |

STALL |

0 |

ą¤ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüąŠą▒čŗčéąĖąĄ stall. ąŻčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ UBM, ąĮąŠ ą╝ąŠąČąĄčé ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ / čüą▒čĆąŠčłąĄąĮ MCU.

STALL=0: ąĮąĄčé čüąŠą▒čŗčéąĖčÅ stall.

STALL=1: ą┐čĆąŠąĖąĘąŠčłą╗ąŠ čüąŠą▒čŗčéąĖąĄ stall. ąĢčüą╗ąĖ čŹč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ MCU, č鹊 ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆčāąĄčéčüčÅ STALL čĆčāą║ąŠą┐ąŠąČą░čéąĖąĄ (handshake) ąĖ ą▒ąĖčé ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąŠčćąĖčēą░ąĄčéčüčÅ.

|

| 4 |

DBUF |

x |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┤ą▓ąŠą╣ąĮąŠą│ąŠ ą▒čāč乥čĆą░ (X ąĖ Y). ąŻčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ąĖ čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ MCU.

DBUF=0: ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą│ą╗ą░ą▓ąĮčŗą╣ ą▒čāč乥čĆ (č鹊ą╗čīą║ąŠ ą▒čāč乥čĆ X).

DBUF=1: ą▓ ą▓čŗą▒ąŠčĆąĄ ą▒čāč乥čĆą░ čāčćą░čüčéą▓čāąĄčé TOGLE - ą▒ąĖčé ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ ą▒čāč乥čĆą░ (čĆą░ą▒ąŠčéą░ąĄčé ą┤ą▓ąŠą╣ąĮąŠąĄ ą▒čāč乥čĆąĖąĘąĖčĆąŠą▓ą░ąĮąĖąĄ).

|

| 5 |

TOGLE |

x |

ąæąĖčé ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ ą▒čāč乥čĆą░ USB, ąŠčéčĆą░ąČą░čÄčēąĖą╣ čüąŠčüč鹊čÅąĮąĖąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ DATA0, DATA1.

|

| 6 |

ISO |

x |

ISO=0 ąŠąĘąĮą░čćą░ąĄčé ąĮąĄąĖąĘąŠčģčĆąŠąĮąĮčŗą╣ čéčĆą░ąĮčüč乥čĆ ą┤ą░ąĮąĮčŗčģ. ąŁč鹊čé ą▒ąĖčé ąŠą▒čÅąĘą░č鹥ą╗čīąĮąŠ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąŠčćąĖčēąĄąĮ MCU, ą┐ąŠčüą║ąŠą╗čīą║čā ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčéčüčÅ č鹊ą╗čīą║ąŠ ąĮąĄąĖąĘąŠčģčĆąŠąĮąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ.

|

| 7 |

UBME |

x |

ąæąĖčé čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ UBM. ąŻčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ąĖ čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ MCU.

UBME=0: UBM ąĮąĄ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čŹčéčā ą║ąŠąĮąĄčćąĮčāčÄ č鹊čćą║čā.

UBME=1: UBM ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čŹčéčā ą║ąŠąĮąĄčćąĮčāčÄ č鹊čćą║čā.

|

4.3.8. IEPBBAX_n: Input Endpoint X-Buffer Base Address (n = 1 .. 3) (čüą╝ąĄčēąĄąĮąĖąĄ 1) - ą▒ą░ąĘąŠą▓čŗą╣ ą░ą┤čĆąĄčü X-ą▒čāč乥čĆą░ Input Endpoint

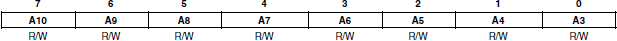

| Ōä¢ ą▒ąĖčéą░ |

ąśą╝čÅ |

RESET |

ą×ą┐ąĖčüą░ąĮąĖąĄ ą▒ąĖčé |

| 7-0 |

A[10:3] |

x |

ąæąĖčéčŗ 10..3 ą▒ą░ąĘąŠą▓ąŠą│ąŠ ą░ą┤čĆąĄčüą░ ą▒čāč乥čĆą░ X, ą┤ąŠą┐ąŠą╗ąĮąĄąĮąĮčŗąĄ čüą┐čĆą░ą▓ą░ 3 ąĮčāą╗ąĄą▓čŗą╝ąĖ ą╝ą╗ą░ą┤čłąĖą╝ąĖ ą▒ąĖčéą░ą╝ąĖ ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ 11-ą▒ąĖčéąĮąŠą│ąŠ ą░ą┤čĆąĄčüą░. ąŚąĮą░č湥ąĮąĖąĄ čŹč鹊ą│ąŠ čĆąĄą│ąĖčüčéčĆą░ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ MCU. UBM ąĖą╗ąĖ DMA ąĖčüą┐ąŠą╗čīąĘčāčÄčé čŹč鹊 ąĘąĮą░č湥ąĮąĖąĄ ą║ą░ą║ ąĮą░čćą░ą╗čīąĮčŗą╣ ą░ą┤čĆąĄčü ą┤ą╗čÅ čāą║ą░ąĘą░ąĮąĮąŠą╣ čéčĆą░ąĮąĘą░ą║čåąĖąĖ. ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 UBM ąĖą╗ąĖ DMA ąĮąĄ ą╝ąĄąĮčÅčÄčé čŹč鹊 ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ čéčĆą░ąĮąĘą░ą║čåąĖąĖ.

|

ąÆ čĆąĄą│ąĖčüčéčĆąĄ IEPBBAX_n ąĘą░ą┤ą░ąĮąŠ čüą╝ąĄčēąĄąĮąĖąĄ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ą░ą┤čĆąĄčüą░ 0xF800 ą▓ ąŠą▒ą╗ą░čüčéąĖ ą┤ą░ąĮąĮčŗčģ XDATA. ąó. ąĄ. čĆąĄą░ą╗čīąĮčŗą╣ ą░ą▒čüąŠą╗čÄčéąĮčŗą╣ ą░ą┤čĆąĄčü ą▒čāč乥čĆą░, ąĖąĘ ą║ąŠč鹊čĆąŠą│ąŠ UBM ą▒čāą┤ąĄčé ą▒čĆą░čéčī ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ ąŠčéą┐čĆą░ą▓ą║ąĖ čģąŠčüčéčā, ą▓čŗčćąĖčüą╗čÅąĄčéčüčÅ čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝:

IN_BUFFERXn_ADDRESS = 0xF800 + (IEPBBAX_n << 3)

4.3.9. IEPBCTX_n: Input Endpoint X-Byte Count (n = 1 .. 3) (čüą╝ąĄčēąĄąĮąĖąĄ 2) - čüč湥čéčćąĖą║ ą▒ą░ą╣čé X-ą▒čāč乥čĆą░ Input Endpoint

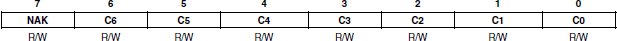

| Ōä¢ ą▒ąĖčéą░ |

ąśą╝čÅ |

RESET |

ą×ą┐ąĖčüą░ąĮąĖąĄ ą▒ąĖčé |

| 6-0 |

C[6:0] |

x |

ąĪč湥čéčćąĖą║ ą▒ą░ą╣čé ą▒čāč乥čĆą░ X, ą║ąŠč鹊čĆčŗą╣ čüčćąĖčéą░ąĄčé ą┤ąŠ 64 (1000000b). ąøčÄą▒ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą▒ąŠą╗čīčłąĄ 64 ą╝ąŠąČąĄčé ą┐čĆąĖą▓ąĄčüčéąĖ ą║ ąĮąĄą┐čĆąĄą┤čüą║ą░ąĘčāąĄą╝čŗą╝ čĆąĄąĘčāą╗čīčéą░čéą░ą╝.

|

| 7 |

NAK |

x |

NAK=0: ą▒čāč乥čĆ čüąŠą┤ąĄčƹȹĖčé ą┤ąŠą┐čāčüčéąĖą╝čŗą╣ ą┐ą░ą║ąĄčé ą┤ą╗čÅ IN-čéčĆą░ąĮąĘą░ą║čåąĖąĖ čģąŠčüčéą░.

NAK=1: ą▒čāč乥čĆ ą┐čāčüčé (ą▓čŗą┤ą░ąĄčé ąŠčéą▓ąĄčé NAK ąĮą░ ąĘą░ą┐čĆąŠčü čģąŠčüčéą░ IN).

|

4.3.10. IEPBBAY_n: Input Endpoint Y-Buffer Base Address (n = 1 .. 3) (čüą╝ąĄčēąĄąĮąĖąĄ 5) - ą▒ą░ąĘąŠą▓čŗą╣ ą░ą┤čĆąĄčü Y-ą▒čāč乥čĆą░ Input Endpoint

| Ōä¢ ą▒ąĖčéą░ |

ąśą╝čÅ |

RESET |

ą×ą┐ąĖčüą░ąĮąĖąĄ ą▒ąĖčé |

| 7-0 |

A[10:3] |

x |

ąæąĖčéčŗ 10..3 ą▒ą░ąĘąŠą▓ąŠą│ąŠ ą░ą┤čĆąĄčüą░ ą▒čāč乥čĆą░ Y, ą┤ąŠą┐ąŠą╗ąĮąĄąĮąĮčŗąĄ čüą┐čĆą░ą▓ą░ 3 ąĮčāą╗ąĄą▓čŗą╝ąĖ ą╝ą╗ą░ą┤čłąĖą╝ąĖ ą▒ąĖčéą░ą╝ąĖ ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ 11-ą▒ąĖčéąĮąŠą│ąŠ ą░ą┤čĆąĄčüą░. ąŚąĮą░č湥ąĮąĖąĄ čŹč鹊ą│ąŠ čĆąĄą│ąĖčüčéčĆą░ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ MCU. UBM ąĖą╗ąĖ DMA ąĖčüą┐ąŠą╗čīąĘčāčÄčé čŹč鹊 ąĘąĮą░č湥ąĮąĖąĄ ą║ą░ą║ ąĮą░čćą░ą╗čīąĮčŗą╣ ą░ą┤čĆąĄčü ą┤ą╗čÅ čāą║ą░ąĘą░ąĮąĮąŠą╣ čéčĆą░ąĮąĘą░ą║čåąĖąĖ. ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 UBM ąĖą╗ąĖ DMA ąĮąĄ ą╝ąĄąĮčÅčÄčé čŹč鹊 ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ čéčĆą░ąĮąĘą░ą║čåąĖąĖ.

|

ąÆ čĆąĄą│ąĖčüčéčĆąĄ IEPBBAY_n ąĘą░ą┤ą░ąĮąŠ čüą╝ąĄčēąĄąĮąĖąĄ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ą░ą┤čĆąĄčüą░ 0xF800 ą▓ ąŠą▒ą╗ą░čüčéąĖ ą┤ą░ąĮąĮčŗčģ XDATA. ąó. ąĄ. čĆąĄą░ą╗čīąĮčŗą╣ ą░ą▒čüąŠą╗čÄčéąĮčŗą╣ ą░ą┤čĆąĄčü ą▒čāč乥čĆą░, ąĖąĘ ą║ąŠč鹊čĆąŠą│ąŠ UBM ą▒čāą┤ąĄčé ą▒čĆą░čéčī ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ ąŠčéą┐čĆą░ą▓ą║ąĖ čģąŠčüčéčā, ą▓čŗčćąĖčüą╗čÅąĄčéčüčÅ čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝:

IN_BUFFERYn_ADDRESS = 0xF800 + (IEPBBAY_n << 3)

4.3.11. IEPBCTY_n: Input Endpoint Y-Byte Count (n = 1 .. 3) (čüą╝ąĄčēąĄąĮąĖąĄ 6) - čüč湥čéčćąĖą║ ą▒ą░ą╣čé Y-ą▒čāč乥čĆą░ Input Endpoint

| Ōä¢ ą▒ąĖčéą░ |

ąśą╝čÅ |

RESET |

ą×ą┐ąĖčüą░ąĮąĖąĄ ą▒ąĖčé |

| 6-0 |

C[6:0] |

x |

ąĪč湥čéčćąĖą║ ą▒ą░ą╣čé ą▒čāč乥čĆą░ Y, ą║ąŠč鹊čĆčŗą╣ čüčćąĖčéą░ąĄčé ą┤ąŠ 64 (1000000b). ąøčÄą▒ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą▒ąŠą╗čīčłąĄ 64 ą╝ąŠąČąĄčé ą┐čĆąĖą▓ąĄčüčéąĖ ą║ ąĮąĄą┐čĆąĄą┤čüą║ą░ąĘčāąĄą╝čŗą╝ čĆąĄąĘčāą╗čīčéą░čéą░ą╝.

|

| 7 |

NAK |

x |

NAK=0: ą▒čāč乥čĆ čüąŠą┤ąĄčƹȹĖčé ą┤ąŠą┐čāčüčéąĖą╝čŗą╣ ą┐ą░ą║ąĄčé ą┤ą╗čÅ IN-čéčĆą░ąĮąĘą░ą║čåąĖąĖ čģąŠčüčéą░.

NAK=1: ą▒čāč乥čĆ ą┐čāčüčé (ą▓čŗą┤ą░ąĄčé ąŠčéą▓ąĄčé NAK ąĮą░ ąĘą░ą┐čĆąŠčü čģąŠčüčéą░ IN).

|

4.3.12. IEPSIZXY_n: Input Endpoint X-/Y-Buffer Size (n = 1 .. 3) (čüą╝ąĄčēąĄąĮąĖąĄ 7) - čĆą░ąĘą╝ąĄčĆ ą▒čāč乥čĆąŠą▓ X ąĖ Y Input Endpoint

| Ōä¢ ą▒ąĖčéą░ |

ąśą╝čÅ |

RESET |

ą×ą┐ąĖčüą░ąĮąĖąĄ ą▒ąĖčé |

| 6-0 |

S[6:0] |

x |

ąĀą░ąĘą╝ąĄčĆ ą▒čāč乥čĆą░ X ąĖ ą▒čāč乥čĆą░ Y, ąŠčé 0 (0000000b) ą┤ąŠ 64 (1000000b). ąøčÄą▒ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą▒ąŠą╗čīčłąĄ 64 ą╝ąŠąČąĄčé ą┐čĆąĖą▓ąĄčüčéąĖ ą║ ąĮąĄą┐čĆąĄą┤čüą║ą░ąĘčāąĄą╝čŗą╝ čĆąĄąĘčāą╗čīčéą░čéą░ą╝.

|

| 7 |

RSV |

x |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ, čĆą░ą▓ąĮąŠ 0.

|

4.4. ąĀąĄą│ąĖčüčéčĆčŗ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ Endpoint-0

ąÆ ąŠčéą╗ąĖčćąĖąĄ ąŠčé čĆąĄą│ąĖčüčéčĆąŠą▓ EDB-1 .. EDB-3, ą║ąŠč鹊čĆčŗąĄ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮčŗ ą║ą░ą║ čÅč湥ą╣ą║ąĖ ą┐ą░ą╝čÅčéąĖ SRAM, endpoint-0 ąŠą┐ąĖčüą░ąĮą░ ąĮą░ą▒ąŠčĆąŠą╝ 4 čĆąĄą│ąĖčüčéčĆąŠą▓ (ą┤ą▓ą░ ą┤ą╗čÅ ą▓čŗą▓ąŠą┤ą░ ąĖ ą┤ą▓ą░ ą┤ą╗čÅ ą▓ą▓ąŠą┤ą░). ąĀąĄą│ąĖčüčéčĆčŗ ą┤ąĄčüą║čĆąĖą┐č鹊čĆą░ EDB-0 ąĖ ąĖčģ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ ą░ą┤čĆąĄčüą░ čāą║ą░ąĘą░ąĮčŗ ą▓ čéą░ą▒ą╗ąĖčåąĄ 4-7. ąŻ EDB-0 ąĮąĄčé čĆąĄą│ąĖčüčéčĆą░ ą▒ą░ąĘąŠą▓ąŠą│ąŠ ą░ą┤čĆąĄčüą░ ą▒čāč乥čĆą░, ą┐ąŠčüą║ąŠą╗čīą║čā čŹčéąĖ ą░ą┤čĆąĄčüą░ ąČąĄčüčéą║ąŠ ąĮą░ąĘąĮą░č湥ąĮčŗ ąĮą░ čÅč湥ą╣ą║ąĖ FEF8h ąĖ FEF0h. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ą┐ąŠąĘąĖčåąĖąĖ ą▒ąĖčé čüąŠčģčĆą░ąĮąĄąĮčŗ, čćč鹊ą▒čŗ čüąŠąŠčéą▓ąĄčéčüčéą▓ąŠą▓ą░čéčī EDB-n (n = 1 .. 3).

ąóą░ą▒ą╗ąĖčåą░ 4-7. ąĀąĄą│ąĖčüčéčĆčŗ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ EDB-0

| ąÉą┤čĆąĄčü |

ąśą╝čÅ čĆąĄą│ąĖčüčéčĆą░ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

ąæą░ąĘąŠą▓čŗą╣ ą░ą┤čĆąĄčü ą▒čāč乥čĆą░ |

FF83h

FF82h |

OEPBCNT_0

OEPCNFG_0 |

Output endpoint_0: čĆąĄą│ąĖčüčéčĆ čüč湥čéčćąĖą║ą░ ą▒ą░ą╣čé

Output endpoint_0: čĆąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ |

FEF0h |

FF81h

FF80h |

IEPBCNT_0

IEPCNFG_0 |

Input endpoint_0: čĆąĄą│ąĖčüčéčĆ čüč湥čéčćąĖą║ą░ ą▒ą░ą╣čé

Input endpoint_0: čĆąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ |

FEF8h |

4.4.1. IEPCNFG_0: Input Endpoint-0 Configuration Register (ą░ą┤čĆąĄčü FF80h) - čĆąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ Input Endpoint-0

| Ōä¢ ą▒ąĖčéą░ |

ąśą╝čÅ |

RESET |

ą×ą┐ąĖčüą░ąĮąĖąĄ ą▒ąĖčé |

| 1-0 |

RSV |

0 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ, čĆą░ą▓ąĮąŠ 0.

|

| 2 |

USBIE |

0 |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÄ čéčĆą░ąĮąĘą░ą║čåąĖąĖ USB. ąŻčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ąĖ čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ MCU.

USBIE=0: ą┐ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÄ čéčĆą░ąĮąĘą░ą║čåąĖąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĮąĄ čüčĆą░ą▒ąŠčéą░ąĄčé.

USBIE=1: ą┐ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÄ čéčĆą░ąĮąĘą░ą║čåąĖąĖ čüčĆą░ą▒ąŠčéą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ.

|

| 3 |

STALL |

0 |

ą¤ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüąŠą▒čŗčéąĖąĄ stall. ąŻčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ąĖ čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ MCU.

STALL=0: ąĮąĄčé čüąŠą▒čŗčéąĖčÅ stall.

STALL=1: ą┐čĆąŠąĖąĘąŠčłą╗ąŠ čüąŠą▒čŗčéąĖąĄ stall. ąĢčüą╗ąĖ čŹč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ MCU, č鹊 ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆčāąĄčéčüčÅ STALL čĆčāą║ąŠą┐ąŠąČą░čéąĖąĄ (handshake) ąĖ ą▒ąĖčé ąŠčćąĖčēą░ąĄčéčüčÅ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą┐čĆąĖ čüą╗ąĄą┤čāčÄčēąĄą╣ čéčĆą░ąĮąĘą░ą║čåąĖąĖ ąĮą░čüčéčĆąŠą╣ą║ąĖ (setup).

|

| 4 |

RSV |

0 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ, čĆą░ą▓ąĮąŠ 0.

|

| 5 |

TOGLE |

0 |

ąæąĖčé ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ ą▒čāč乥čĆą░ USB, ąŠčéčĆą░ąČą░čÄčēąĖą╣ čüąŠčüč鹊čÅąĮąĖąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ DATA0, DATA1.

|

| 6 |

RSV |

0 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ, čĆą░ą▓ąĮąŠ 0.

|

| 7 |

UBME |

0 |

ąæąĖčé čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ UBM. ąŻčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ąĖ čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ MCU.

UBME=0: UBM ąĮąĄ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čŹčéčā ą║ąŠąĮąĄčćąĮčāčÄ č鹊čćą║čā.

UBME=1: UBM ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čŹčéčā ą║ąŠąĮąĄčćąĮčāčÄ č鹊čćą║čā.

|

4.4.2. IEPBCNT_0: Input Endpoint-0 Byte Count Register (ą░ą┤čĆąĄčü FF81h) - čĆąĄą│ąĖčüčéčĆ čüč湥čéčćąĖą║ą░ ą▒ą░ą╣čé Input Endpoint-0

| Ōä¢ ą▒ąĖčéą░ |

ąśą╝čÅ |

RESET |

ą×ą┐ąĖčüą░ąĮąĖąĄ ą▒ąĖčé |

| 3-0 |

C[3:0] |

0000 |

ąĪč湥čéčćąĖą║ ą▒ą░ą╣čé, ą║ąŠč鹊čĆčŗą╣ čüčćąĖčéą░ąĄčé ą┤ąŠ 8 (1000b). ąøčÄą▒ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą▒ąŠą╗čīčłąĄ 8 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ (ąĄčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ, č鹊 ą▓čüąĄ čĆą░ą▓ąĮąŠ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 8).

|

| 6-4 |

RSV |

000 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ, čĆą░ą▓ąĮąŠ 0.

|

| 7 |

NAK |

1 |

NAK=0: ą▒čāč乥čĆ čüąŠą┤ąĄčƹȹĖčé ą┤ąŠą┐čāčüčéąĖą╝čŗą╣ ą┐ą░ą║ąĄčé ą┤ą╗čÅ IN-čéčĆą░ąĮąĘą░ą║čåąĖąĖ čģąŠčüčéą░.

NAK=1: ą▒čāč乥čĆ ą┐čāčüčé (ą▓čŗą┤ą░ąĄčé ąŠčéą▓ąĄčé NAK ąĮą░ ąĘą░ą┐čĆąŠčü čģąŠčüčéą░ IN).

|

4.4.3. OEPCNFG_0: Output Endpoint-0 Configuration Register (ą░ą┤čĆąĄčü FF82h) - čĆąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ Output Endpoint-0

| Ōä¢ ą▒ąĖčéą░ |

ąśą╝čÅ |

RESET |

ą×ą┐ąĖčüą░ąĮąĖąĄ ą▒ąĖčé |

| 1-0 |

RSV |

0 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ, čĆą░ą▓ąĮąŠ 0.

|

| 2 |

USBIE |

0 |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÄ čéčĆą░ąĮąĘą░ą║čåąĖąĖ USB. ąŻčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ąĖ čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ MCU.

USBIE=0: ą┐ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÄ čéčĆą░ąĮąĘą░ą║čåąĖąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĮąĄ čüčĆą░ą▒ąŠčéą░ąĄčé.

USBIE=1: ą┐ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÄ čéčĆą░ąĮąĘą░ą║čåąĖąĖ čüčĆą░ą▒ąŠčéą░ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ.

|

| 3 |

STALL |

0 |

ą¤ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüąŠą▒čŗčéąĖąĄ stall. ąŻčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ąĖ čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ MCU.

STALL=0: ąĮąĄčé čüąŠą▒čŗčéąĖčÅ stall.

STALL=1: ą┐čĆąŠąĖąĘąŠčłą╗ąŠ čüąŠą▒čŗčéąĖąĄ stall. ąĢčüą╗ąĖ čŹč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ MCU, č鹊 ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆčāąĄčéčüčÅ STALL čĆčāą║ąŠą┐ąŠąČą░čéąĖąĄ (handshake) ąĖ ą▒ąĖčé ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąŠčćąĖčēą░ąĄčéčüčÅ.

|

| 4 |

RSV |

0 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ, čĆą░ą▓ąĮąŠ 0.

|

| 5 |

TOGLE |

0 |

ąæąĖčé ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ ą▒čāč乥čĆą░ USB, ąŠčéčĆą░ąČą░čÄčēąĖą╣ čüąŠčüč鹊čÅąĮąĖąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ DATA0, DATA1.

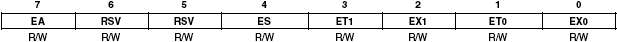

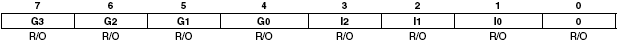

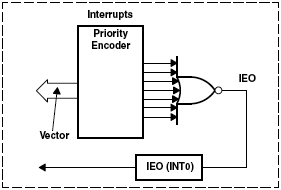

|