|

ą×ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ ą┐čĆąĖą╝ąĄčĆ čćč鹥ąĮąĖčÅ 18-ą▒ąĖčéąĮąŠą│ąŠ ąÉą”ą¤ čü ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╝ ąĖąĮč鹥čĆč乥ą╣čüąŠą╝ AD7691 č湥čĆąĄąĘ ą┐ąŠčĆčé SPORT3 ą┐čĆąŠčåąĄčüčüąŠčĆą░ Blackfin ADSP-BF538. ąÆ ą┤ą░ąĮąĮąŠą╝ ą┐čĆąĖą╝ąĄčĆąĄ ąŠčéą┤ąĄą╗čīąĮčŗąĄ ą▓čŗą▒ąŠčĆą║ąĖ ą▓čŗčćąĖčéčŗą▓ą░čÄčéčüčÅ ąĖąĘ ąÉą”ą¤ ą░ą▒čüąŠą╗čÄčéąĮąŠ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ, čü ą┐ąŠą╝ąŠčēčīčÄ ą░ą┐ą┐ą░čĆą░čéčāčĆčŗ DMA, čĆą░ąĘą│čĆčāąČą░čÅ ą┐čĆąŠčåąĄčüčüąŠčĆ ą┤ą╗čÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ čŹčäč乥ą║čéąĖą▓ąĮčŗčģ č乊ąĮąŠą▓čŗčģ ą▓čŗčćąĖčüą╗ąĄąĮąĖą╣.

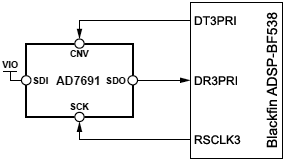

ąĀąĖčü. 1. ąĪčģąĄą╝ą░ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ AD7691 ą║ SPORT3 ADSP-BF538.

ąÉą”ą¤ AD7691 ą┐ąŠą┤ą║ą╗čÄč湥ąĮ čüą╗ąĄą┤čāčÄčēąĖą╝ąĖ čüąĖą│ąĮą░ą╗ą░ą╝ąĖ:

VIO: čŹčéą░ ąĮąŠąČą║ą░ (ą▓čģąŠą┤) ąĖą╝ąĄąĄčé ą╝ąĮąŠą│ąŠčäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠąĄ ąĮą░ąĘąĮą░č湥ąĮąĖąĄ ą▓ ą┐čĆąŠą┐čĆąĖąĄčéą░čĆąĮąŠą╝ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą╝ ąĖąĮč鹥čĆč乥ą╣čüąĄ ąÉą”ą¤. ąÆ ą┤ą░ąĮąĮąŠą╝ čüą╗čāčćą░ąĄ ąĮą░ ąĮąĄčæ ąČąĄčüčéą║ąŠ ą┐ąŠą┤ą░ąĮ + ą┐ąĖčéą░ąĮąĖčÅ, č湥ą╝ ą▓čŗą▒čĆą░ąĮ 3-ą┐čĆąŠą▓ąŠą┤ąĮčŗą╣ čĆąĄąČąĖą╝ ąĖąĮč鹥čĆč乥ą╣čüą░, ą▒ąĄąĘ ą│ąĄąĮąĄčĆą░čåąĖąĖ čüąĖą│ąĮą░ą╗ą░ ąĘą░ąĮčÅč鹊čüčéąĖ [1].

CNV: čŹčéą░ ąĮąŠąČą║ą░ (ą▓čģąŠą┤) ą▓čŗą┐ąŠą╗ąĮčÅąĄčé čüčĆą░ąĘčā 2 čäčāąĮą║čåąĖąĖ - ą▓ąŠ-ą┐ąĄčĆą▓čŗčģ, ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮčŗą╣ ą┐ąĄčĆąĄą┐ą░ą┤ ąĮą░ ąĮąĄą╣ ąĘą░ą┤ą░ąĄčé ą╝ąŠą╝ąĄąĮčé ąĮą░čćą░ą╗ą░ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ conv. ąÆąŠ-ą▓č鹊čĆčŗčģ, ąĮą░ čŹčéčā ąČąĄ ąĮąŠąČą║čā ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąŠą┤ą░ąĮ čüąĖą│ąĮą░ą╗ ą▓čŗą▒ąŠčĆą║ąĖ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ą┤ą░ąĮąĮčŗčģ č湥čĆąĄąĘ ą▓čŗčģąŠą┤ SDO, ąĖąĮč鹥čĆą▓ą░ą╗ ą╗ąŠą│. 0 ą╝ąĄąČą┤čā ą╝ąŠą╝ąĄąĮčéą░ą╝ąĖ ą▓čĆąĄą╝ąĄąĮąĖ select ąĖ deselect (čüą╝. čĆąĖčü. 3).

SDO: ą▓čŗčģąŠą┤ ą┤ą░ąĮąĮčŗčģ, ą║ąŠč鹊čĆčŗąĄ ą▓čŗą┤ą▓ąĖą│ą░čÄčéčüčÅ ąĖąĘ ąÉą”ą¤ ą┐ąŠ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮčŗą╝ ą┐ąĄčĆąĄą┐ą░ą┤ą░ą╝ čüąĖą│ąĮą░ą╗ą░ SCK.

SCK: čéą░ą║č鹊ą▓čŗą╣ ą▓čģąŠą┤, ąĖą╝ą┐čāą╗čīčüą░ą╝ąĖ ąĮą░ ą║ąŠč鹊čĆąŠą╝ ą╝ą░čüč鹥čĆ čłąĖąĮčŗ (ą▓ ąĮą░čłąĄą╝ ą┐čĆąĖą╝ąĄčĆąĄ čŹč鹊 ą┐čĆąŠčåąĄčüčüąŠčĆ Blackfin ADSP-BF538) čāą┐čĆą░ą▓ą╗čÅąĄčé čćč鹥ąĮąĖąĄą╝ ą┤ą░ąĮąĮčŗčģ č湥čĆąĄąĘ čüąĖą│ąĮą░ą╗ SDO. ą¤ąŠ čäčĆąŠąĮčéą░ą╝ SCK (ą┐ąĄčĆąĄčģąŠą┤ 0->1) ą┤ą░ąĮąĮčŗąĄ ą▓čŗčćąĖčéčŗą▓ą░čÄčéčüčÅ, ą░ ą┐ąŠ čüą┐ą░ą┤ą░ą╝ (1->0) ą┐ąĄčĆąĄą║ą╗čÄčćą░čÄčéčüčÅ ąĮą░ čüą╗ąĄą┤čāčÄčēąĖą╣ ą▒ąĖčé (čüą╝. čĆąĖčü. 2 ąĖ 3).

ąÜą░ą║ čāąČąĄ čāą┐ąŠą╝ąĖąĮą░ą╗ąŠčüčī, ąÉą”ą¤ ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą┐ąŠ 3-ą┐čĆąŠą▓ąŠą┤ąĮąŠą╣ čüčģąĄą╝ąĄ ą▒ąĄąĘ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ čüąĖą│ąĮą░ą╗ą░ ąĘą░ąĮčÅč鹊čüčéąĖ (ą┐ąŠą┤čĆąŠą▒ąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ čĆą░ąĘą╗ąĖčćąĮčŗčģ čĆąĄąČąĖą╝ąŠą▓ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ čüą╝. ą▓ [1]). ąöą╗čÅ čĆą░ą▒ąŠčéčŗ čŹč鹊ą│ąŠ čĆąĄąČąĖą╝ą░ ąĮą░ ą▓čģąŠą┤ ąĘą░ą┐čāčüą║ą░ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ CNV čéčĆąĄą▒čāąĄčéčüčÅ ą┐ąŠą┤ą░čéčī čüąĖą│ąĮą░ą╗ ąŠčüąŠą▒ąŠą╣ č乊čĆą╝čŗ, ą║ąŠč鹊čĆčŗą╣ ą▒čāą┤ąĄčé ąĘą░ą┐čāčüą║ą░čéčī ąŠčåąĖčäčĆąŠą▓ą║čā čüąĖą│ąĮą░ą╗ą░, ąĖ čéą░ą║ąČąĄ ą▒čāą┤ąĄčé čüą╗čāąČąĖčéčī čüąĖą│ąĮą░ą╗ąŠą╝ ą▓čŗą▒ąŠčĆą║ąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░, ą┐ąŠ ą║ąŠč鹊čĆąŠą╝čā ąÉą”ą¤ ą▒čāą┤ąĄčé ą▓čŗą┤ą▓ąĖą│ą░čéčī ą┤ą░ąĮąĮčŗąĄ ąĮą░ ą┐čĆąŠą▓ąŠą┤ SDO ą┐ąŠ čéą░ą║č鹊ą▓ąŠą╝čā čüąĖą│ąĮą░ą╗čā SCK.

ąĪąĖą│ąĮą░ą╗ ą┤ą░ąĮąĮčŗčģ SDO ąŠčé ąÉą”ą¤ ą┐čĆąĖčģąŠą┤ąĖčé ąĮą░ ą▓čģąŠą┤ ą┤ą░ąĮąĮčŗčģ DR3PRI ą┐ąŠčĆčéą░ SPORT3, ąĖ čüąĖą│ąĮą░ą╗ čéą░ą║č鹊ą▓ ą┤ą╗čÅ ąÉą”ą¤ č乊čĆą╝ąĖčĆčāąĄčéčüčÅ ą▓čŗčģąŠą┤ąĮčŗą╝ąĖ čéą░ą║čéą░ą╝ąĖ RSCLK3 ąŠčé SPORT3. ą¤čĆąĖ čŹč鹊ą╝ ą┤ą░ąĮąĮčŗąĄ ą▓čŗčćąĖčéčŗą▓ą░čÄčéčüčÅ ąĖąĘ SDO ą░ą┐ą┐ą░čĆą░čéąĮąŠ čü ą┐ąŠą╝ąŠčēčīčÄ ą┤ą▓ąŠą╣ąĮąŠą│ąŠ ą▒čāč乥čĆąĖąĘąĖčĆąŠą▓ą░ąĮąĖčÅ, ąŠčĆą│ą░ąĮąĖąĘąŠą▓ą░ąĮąĮąŠą│ąŠ ąĮą░ ąŠčüąĮąŠą▓ąĄ 2D DMA [3]. ą×ą▒čĆą░ą▒ąŠčéą║ą░ čüąŠ čüč鹊čĆąŠąĮčŗ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą▓čŗąĘčŗą▓ą░ąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą▓ ą╝ąŠą╝ąĄąĮčé ąĘą░ą┐ąŠą╗ąĮąĄąĮąĖčÅ ąŠą┤ąĮąŠą│ąŠ ąĖąĘ ą┤ą▓čāčģ ą▒čāč乥čĆąŠą▓ ą┐ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÄ. ąÜą░ąĮą░ą╗ ą┐čĆąĖąĄą╝ą░ SPORT ąĮą░čüčéčĆąŠąĄąĮ ą┤ą╗čÅ 18 ą▒ąĖčé ąĮą░ čäčĆąĄą╣ą╝, čü ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčīčÄ čäčĆąĄą╣ą╝ą░ 32 ą▒ąĖčéą░. ąśąĘ čŹčéąĖčģ 32 ą▒ąĖčé ą┐čĆąĖčģąŠą┤ąĖčéčüčÅ 18 ąĮą░ ą▓čŗčćąĖčéčŗą▓ą░ąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ, ą░ ąŠčüčéą░ą╗čīąĮą░čÅ čćą░čüčéčī ąĖąĘ 12 ą▒ąĖčé - ąĮą░ ąĖąĮč鹥čĆą▓ą░ą╗ ąĘą░ą┐čāčüą║ą░ ąŠčåąĖčäčĆąŠą▓ą║ąĖ ąĖ ąŠąČąĖą┤ą░ąĮąĖąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ąÉą”ą¤.

ąĪąĖą│ąĮą░ą╗ CNV, ą┐ąŠčüą║ąŠą╗čīą║čā ąŠčé ąĮąĄą│ąŠ čéčĆąĄą▒čāąĄčéčüčÅ čüą┐ąĄčåąĖą░ą╗čīąĮą░čÅ č乊čĆą╝ą░, čüąĖąĮč鹥ąĘąĖčĆčāąĄčéčüčÅ čü ą┐ąŠą╝ąŠčēčīčÄ čüąĖą│ąĮą░ą╗ą░ ą┤ą░ąĮąĮčŗčģ ą┐ąĄčĆąĄą┤ą░čćąĖ DT3PRI č鹊ą│ąŠ ąČąĄ SPORT3, čüąĖąĮčģčĆąŠąĮąĮąŠ čü čĆą░ą▒ąŠč鹊ą╣ ą║ą░ąĮą░ą╗ą░ ą┐čĆąĖąĄą╝ą░. ąĪąĖąĮčģčĆąŠąĮąĮą░čÅ čĆą░ą▒ąŠčéą░ ą║ą░ąĮą░ą╗ąŠą▓ ą┐čĆąĖąĄą╝ą░ ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▓ąŠąĘą╝ąŠąČąĮą░ ą┐ąŠ č鹊ą╣ ą┐čĆąĖčćąĖąĮąĄ, čćč鹊 ąŠą▒ą░ čŹčéąĖčģ ą║ą░ąĮą░ą╗ą░ čéą░ą║čéąĖčĆčāčÄčéčüčÅ ąŠčé ąŠą┤ąĮąŠą│ąŠ ąĖ č鹊ą│ąŠ ąČąĄ ąĖčüč鹊čćąĮąĖą║ą░ - čüąĖą│ąĮą░ą╗ SCLK čüąĖčüč鹥ą╝ąĮąŠą╣ čłąĖąĮčŗ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ADSP-BF538.

ąöą╗čÅ ą║ą░ąĮą░ą╗ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ čéą░ą║ąČąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ DMA, ąĮąŠ ą▓ ą┤čĆčāą│ąŠą╝ čĆąĄąČąĖą╝ąĄ - ą┐čĆąŠčüč鹊ą╣ ąŠą┤ąĮąŠą╝ąĄčĆąĮčŗą╣ ą░ą▓č鹊ą▒čāč乥čĆ ąĮą░ 4 čüą╗ąŠą▓ą░. ą¦ą░čüč鹊čéą░ ą▒ąĖčé ąĮą░ ą┐ąĄčĆąĄą┤ą░čćčā ą▓čŗą▒čĆą░ąĮą░ ą▓ 4 čĆą░ąĘą░ ą▓čŗčłąĄ čü č鹊ą╣ čåąĄą╗čīčÄ, čćč鹊ą▒čŗ ą╝ąŠąČąĮąŠ ą▒čŗą╗ąŠ č鹊čćąĮąĄąĄ ą┐ąŠą┤ąŠą▒čĆą░čéčī č乊čĆą╝čā čüąĖą│ąĮą░ą╗ą░ CNV. ąŁč鹊 ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓ą░ąČąĮčŗą╝ ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ ąĮą░ ą▓čŗčüąŠą║ąĖčģ čćą░čüč鹊čéą░čģ, ą║ąŠą│ą┤ą░ ą╝ąĄąČą┤čā ąÉą”ą¤ ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą╝ čüč鹊čÅčé ą│ą░ą╗čīą▓ą░ąĮąĖč湥čüą║ąĖąĄ ąĖąĘąŠą╗čÅč鹊čĆčŗ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ čüąĖą│ąĮą░ą╗ąŠą▓ (ąŠąĮąĖ ą▓ąĮąŠčüčÅčé ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗąĄ ąĘą░ą┤ąĄčƹȹ║ąĖ, ą║ąŠč鹊čĆčŗąĄ ąČąĄą╗ą░č鹥ą╗čīąĮąŠ ą║ąŠą╝ą┐ąĄąĮčüąĖčĆąŠą▓ą░čéčī).

ąĀąĖčü. 2. ąöąĖą░ą│čĆą░ą╝ą╝ą░ ąŠą┐čĆąŠčüą░ ąÉą”ą¤ čü ą┐ąŠą╝ąŠčēčīčÄ čüąĖą│ąĮą░ą╗ąŠą▓ SPORT3.

[ą¤čĆąĖą╝ąĄčĆ ą║ąŠą┤ą░ ąĮą░čüčéčĆąŠą╣ą║ąĖ 2D DMA ą┤ą╗čÅ čćč鹥ąĮąĖčÅ ąÉą”ą¤]

ąÜąŠą┤ ąĮą░čüčéčĆąŠą╣ą║ąĖ SPORT:

////////////////////////////////////////////////////////////////////////////

// sport.h

#ifndef __SPORT__

#define __SPORT__

#include "system.h"

/* ąöą╗čÅ ą║ąŠčĆčĆąĄą║čéąĮąŠą╣ čĆą░ą▒ąŠčéčŗ čćč鹥ąĮąĖčÅ ąÉą”ą¤ ąĮčāąČąĮąŠ ą▓čŗą▒čĆą░čéčī ą┐čĆą░ą▓ąĖą╗čīąĮąŠąĄ čüąŠąŠčéąĮąŠčłąĄąĮąĖąĄ ą╝ąĄąČą┤čā

čćą░čüč鹊č鹊ą╣ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ čéą░ą╣ą╝ąĄčĆą░, ą║ąŠč鹊čĆčŗą╣ ą│ąĄąĮąĄčĆąĖčé čüąĖą│ąĮą░ą╗ ą║ąŠąĮą▓ąĄčĆčüąĖąĖ (ą║ąŠčĆąŠčéą║ąĖąĄ ąĖą╝ą┐čāą╗čīčüčŗ

ą╗ąŠą│. 0 č乊čĆą╝ąĖčĆčāčÄčé čüąĖą│ąĮą░ą╗čŗ ą║ąŠąĮą▓ąĄčĆčüąĖąĖ CNV ą┤ą╗čÅ ąÉą”ą¤, čüąĄą╣čćą░čü ąĖčģ čćą░čüč鹊čéą░ 32768 ąōčå).

ą¤čāčüčéčī čćą░čüč鹊čéą░ CNV ąĮą░ąĘčŗą▓ą░ąĄčéčüčÅ Fcnv.

ą¦ą░čüč鹊čéą░ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ąÉą”ą¤ RSCLK_frequency ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ čéą░ą║, čćč鹊ą▒čŗ čüąŠąŠčéąĮąŠčłąĄąĮąĖąĄ

RSCLK_frequency / Fcnv ą▒čŗą╗ąŠ čü ąĘą░ą┐ą░čüąŠą╝ ą▒ąŠą╗čīčłąĄ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ą▒ąĖčé (18). ąŚą┤ąĄčüčī ą▓čŗą▒čĆą░ąĮąŠ

RSCLK_frequency / Fcnv = 1024 / 32 = 32, čé. ąĄ. 32 čéą░ą║čéą░ SCK ą┤ą╗čÅ ąÉą”ą¤ ą▓ą╗ąĄąĘą░čÄčé

ą▓ ą┐ąĄčĆąĖąŠą┤ ą╝ąĄąČą┤čā ąŠą┐čĆąŠčüą░ą╝ąĖ ąÉą”ą¤.

ą×čéčüčÄą┤ą░ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ RFSDIV, ą║ąŠč鹊čĆąŠąĄ čĆą░ą▓ąĮąŠ (RSCLK_frequency / Fcnv)-1 = 31.*/

//Peripheral Interrupt ID:

#define DMA10_SPORT3_RX_Peripheral 35

//ą×ą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą▓:

#define ADC_double_buffer_DMA_IVG ik_ivg11 //ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĖčÅ ą▒čāč乥čĆą░ ąÉą”ą¤

//////////////////////////////////////////////////////////////////////////

// ą¤ą░čĆą░ą╝ąĄčéčĆčŗ ąĮą░čüčéčĆąŠą╣ą║ąĖ ą║ą░ąĮą░ą╗ą░ ą┐čĆąĖąĄą╝ą░ SPORT3, ą║ą░ąĮą░ą╗ ą┐čĆąĖąĄą╝ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ

// ą┤ą╗čÅ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą│ąŠ (č湥čĆąĄąĘ 2D DMA) čćč鹥ąĮąĖčÅ ąÉą”ą¤ AD7691.

#define SCLK 32768 //čćą░čüč鹊čéą░ čüąĖčüč鹥ą╝ąĮąŠą╣ čłąĖąĮčŗ, ą║ąōčå

#define RSCLK_frequency (128*32) // 4096 ą║ąōčå, ą┤ą╗čÅ čćą░čüč鹊čéčŗ ąŠčåąĖčäčĆąŠą▓ą║ąĖ 128 ą║ąōčå

#define SPORT_RCLKDIV (SCLK/RSCLK_frequency/2-1)

#define DTYPE_SIGN 0x0004

#define RCR1 (LARFS | LRFS | RFSR | IRFS | DTYPE_SIGN | IRCLK)

#define RCR2 17 //18 ą▒ąĖčé ąĮą░ čäčĆąĄą╣ą╝, ą┐ąŠč鹊ą╝čā čćč鹊 ąÉą”ą¤ ą▓čŗą┤ą░ąĄčé 18 ą▒ąĖčé

#define RFSDIV 31 //ą┐ąĄčĆąĖąŠą┤ RFS čüąŠčüčéą░ą▓ąĖčé 32 ą▒ąĖčéą░.

#define SPORT3RX_U32_WORDS 256

//////////////////////////////////////////////////////////////////////////

// ą¤ą░čĆą░ą╝ąĄčéčĆčŗ ąĮą░čüčéčĆąŠą╣ą║ąĖ ą║ą░ąĮą░ą╗ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ SPORT3, ą║ą░ąĮą░ą╗ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ

// ą┤ą╗čÅ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą│ąŠ (č湥čĆąĄąĘ 1D DMA) č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ čüąĖą│ąĮą░ą╗ą░ ą║ąŠąĮą▓ąĄčĆčüąĖąĖ

// ąĖ ą▓čŗą▒ąŠčĆą║ąĖ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ ąÉą”ą¤ AD7691.

#define TSCLK_frequency (RSCLK_frequency*4) // 16384 ą║ąōčå

#define SPORT_TCLKDIV (SCLK/TSCLK_frequency/2-1)

#define TCR1 (TCKFE | LATFS | LTFS | TFSR | ITFS | ITCLK)

#define TCR2 31 //32 ą▒ąĖčéą░ ąĮą░ čäčĆąĄą╣ą╝

#define SPORT3TX_U32_WORDS 4

extern int adcdatarx[2][SPORT3RX_U32_WORDS];

void SportInit(void);

void SportInitDMA(void);

void SportRun(void);

void SportStop(void);

#endif //__SPORT__

ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ ąĮą░ ą╝ą░čüą║čā ą┤ą╗čÅ čäą╗ą░ąČą║ą░ DTYPE_SIGN, ą║ąŠč鹊čĆą░čÅ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čüąŠąĘą┤ą░ąĮąĖčÅ ą║ąŠąĮčüčéą░ąĮčéčŗ ąĮą░čüčéčĆąŠą╣ą║ąĖ RCR1. ąŻčüčéą░ąĮąŠą▓ą║ąŠą╣ ą┐ąŠą╗čÅ RDTYPE ą▓ ąĘąĮą░č湥ąĮąĖąĄ 01 ą×ąĮą░ ą▓ą║ą╗čÄčćą░ąĄčé čäčāąĮą║čåąĖčÄ čĆą░čüčłąĖčĆąĄąĮąĖčÅ ąĘąĮą░ą║ąŠą╝ (Sign-Extended, čüą╝. ąŠą┐ąĖčüą░ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ SPORTx_RCR1 ą▓ [2]) ą┤ą╗čÅ ą┐čĆąĖąĮąĖą╝ą░ąĄą╝čŗčģ ą┤ą░ąĮąĮčŗčģ č湥čĆąĄąĘ SPORT3. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ąĄčüą╗ąĖ čäčāąĮą║čåąĖčÅ čĆą░čüčłąĖčĆąĄąĮąĖčÅ ąĘąĮą░ą║ąŠą╝ ą▓ą║ą╗čÄč湥ąĮą░, č鹊 ą┐čĆąĖąĮčÅč鹊ąĄ 18-ą▒ąĖčéąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ čüąŠ ąĘąĮą░ą║ąŠą╝ ą▓ čüčéą░čĆčłąĄą╝ čĆą░ąĘčĆčÅą┤ąĄ D17 čĆą░čüą┐čĆąŠčüčéčĆą░ąĮąĖčéčüčÅ ąĮą░ ą▓čüąĄ ąŠčüčéą░ą╗čīąĮčŗąĄ čüčéą░čĆčłąĖąĄ čĆą░ąĘčĆčÅą┤čŗ D31..D17, ąĖ ą▓ ą▒čāč乥čĆąĄ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą┐ąŠą╗čāčćą░čéčüčÅ 32-ą▒ąĖčéąĮčŗąĄ čćąĖčüą╗ą░ čüąŠ ąĘąĮą░ą║ąŠą╝.

////////////////////////////////////////////////////////////////////////////

// sport.c

#include "settings.h"

#include "SPORT.h"

//ą£ą░čüčüąĖą▓ ą┤ą╗čÅ č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ čüąĖą│ąĮą░ą╗ą░ SDI (ą▓čŗą▒ąŠčĆą║ą░) ąÉą”ą¤ AD7691 (ą░ą▓č鹊ą▒čāč乥čĆ 1D):

static int adcdatatx[SPORT3TX_U32_WORDS];

//ą£ą░čüčüąĖą▓ ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ čü ąÉą”ą¤ AD7691 č湥čĆąĄąĘ čüąĖą│ąĮą░ą╗ SDO (ą░ą▓č鹊ą▒čāč乥čĆ 2D):

int adcdatarx[2][SPORT3RX_U32_WORDS];

void SportInit (void)

{

//ąØą░čüčéčĆąŠą╣ą║ą░ ą║ą░ąĮą░ą╗ą░ ą┐čĆąĖąĄą╝ą░, ą▓ ąĮąĄą│ąŠ ą▒čāą┤čāčé ą┐ąŠčüčéčāą┐ą░čéčī ą┤ą░ąĮąĮčŗąĄ ąÉą”ą¤:

*pSPORT3_RCLKDIV=SPORT_RCLKDIV;

*pSPORT3_RCR1 = RCR1;

*pSPORT3_RCR2 = RCR2;

*pSPORT3_RFSDIV = RFSDIV;

ssync();

//ąØą░čüčéčĆąŠą╣ą║ą░ ą║ą░ąĮą░ą╗ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ, ąŠąĮ ą┤ąŠą╗ąČąĄąĮ č乊čĆą╝ąĖčĆąŠą▓ą░čéčī ą▓čŗą▒ąŠčĆą║ąĖ SDI ą┤ą╗čÅ ąÉą”ą¤:

*pSPORT3_TCLKDIV=SPORT_TCLKDIV;

*pSPORT3_TCR1 = TCR1;

*pSPORT3_TCR2 = TCR2;

*pSPORT3_TFSDIV = RFSDIV;

ssync();

}

void SportInitDMA(void)

{

///////////////////////////////////////////////////

// ąÜą░ąĮą░ą╗ ą┐čĆąĖąĄą╝ą░ ą▒čāą┤ąĄčé ą┐ąŠą╗čāčćą░čéčī ą┤ą░ąĮąĮčŗąĄ ąŠčé ąÉą”ą¤:

*pDMA10_PERIPHERAL_MAP = 0x2000; // ąÜą░ąĮą░ą╗ DMA ą┤ą╗čÅ ą┐čĆąĖąĄą╝ą░ č湥čĆąĄąĘ SPORT3

//FLOW_AUTO: ą░ą▓č鹊ąĘą░ą┐ąŠą╗ąĮąĄąĮąĖąĄ ą▒čāč乥čĆą░ ą┐ąŠ ą║čĆčāą│čā |

//DI_EN: čĆąĄąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÄ ą▒čāč乥čĆą░ |

//DI_SEL: ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ ą║ą░ąČą┤ąŠą╝čā ą▒čāč乥čĆčā

//DMA2D: ą┤ą▓čāčģą╝ąĄčĆąĮčŗą╣ (ą┤ą▓ąŠą╣ąĮąŠą╣) ą▒čāč乥čĆ |

//WDSIZE_32: ą┐ąĄčĆąĄą┤ą░čćąĖ 32-ą▒ąĖčéąĮčŗąĄ |

//WNR: ąĘą░ą┐ąĖčüčī ą▓ ą┐ą░ą╝čÅčéčī čüąŠ čüč鹊čĆąŠąĮčŗ DMA

*pDMA10_CONFIG = FLOW_AUTO | DI_EN | DI_SEL | DMA2D | WDSIZE_32 | WNR;

*pDMA10_START_ADDR = (void *)&adcdatarx;

*pDMA10_X_COUNT = SPORT3RX_U32_WORDS;

*pDMA10_X_MODIFY = 4; //sizeof(int)

*pDMA10_Y_COUNT = 2; // 2 ą▒čāč乥čĆą░

*pDMA10_Y_MODIFY = 4; //sizeof(int)

ssync();

///////////////////////////////////////////////////

// ąÜą░ąĮą░ą╗ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▒čāą┤ąĄčé č乊čĆą╝ąĖčĆąŠą▓ą░čéčī čüąĖą│ąĮą░ą╗ ą▓čŗą▒ąŠčĆą║ąĖ SDI ą┤ą╗čÅ ąÉą”ą¤:

//ąÆą░čĆąĖą░ąĮčé ą┤ą╗čÅ TCLK==RCLK*4:

adcdatatx[0] = 0x00000000; // 0000 0000 0000 0000 0000 0000 0000 0000

adcdatatx[0] = 0x007FFE1F; // 0000 0000 0111 1111 1111 1110 0001 1111

adcdatatx[0] = 0xFFFFFFFF; // 1111 1111 1111 1111 1111 1111 1111 1111

adcdatatx[0] = 0x80000000; // 1000 0000 0000 0000 0000 0000 0000 0000

*pDMA11_PERIPHERAL_MAP = 0x3000; // ąÜą░ąĮą░ą╗ DMA ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ č湥čĆąĄąĘ SPORT3

//ąÜą░ąĮą░ą╗ ą┐ąĄčĆąĄą┤ą░čćąĖ | 32-ą▒ąĖčéąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ | ą░ą▓č鹊ą┐ąĄčĆąĄą┤ą░čćą░ ą▒čāč乥čĆą░ ą┐ąŠ ą║čĆčāą│čā.

*pDMA11_CONFIG = WDSIZE_32 | FLOW_AUTO;

*pDMA11_START_ADDR = (void *)&adcdatatx;

*pDMA11_X_COUNT = 4;

*pDMA11_X_MODIFY = 4; //sizeof(int)

ssync();

}

void SportRun(void)

{

*pDMA10_CONFIG |= DMAEN;

*pSPORT3_RCR1 |= RSPEN;

ssync();

*pDMA11_CONFIG |= DMAEN;

*pSPORT3_TCR1 |= TSPEN;

ssync();

}

void SportStop (void)

{

*pSPORT3_RCR1 &= ~RSPEN;

*pDMA10_CONFIG &= ~DMAEN;

}

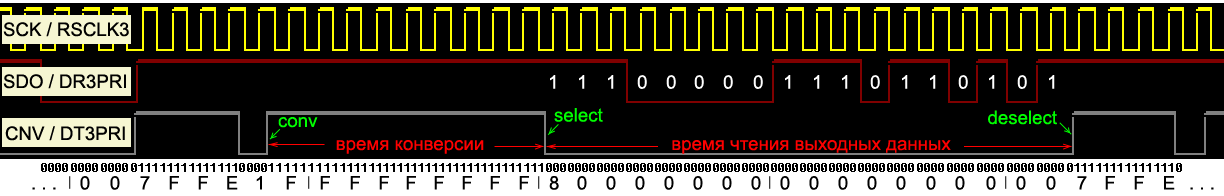

ąĀąĖčü. 3. ą¤ąŠčÅčüąĮąĄąĮąĖąĄ čüąĖąĮč鹥ąĘą░ čüąĖą│ąĮą░ą╗ą░ CNV ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĘą░ą┐čāčüą║ąŠą╝ ą║ąŠąĮą▓ąĄčĆčüąĖąĖ ąĖ čćč鹥ąĮąĖčÅ ąÉą”ą¤ AD7691.

ąĪ ą┐ąŠą╝ąŠčēčīčÄ čüąĖą│ąĮą░ą╗ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ DT3PRI ą┐ąŠčĆčéą░ SPORT3 č乊čĆą╝ąĖčĆčāąĄčéčüčÅ čüąĖą│ąĮą░ą╗ CNV ą┤ą╗čÅ ąŠą┐čĆąŠčüą░ ąÉą”ą¤. ą£ąŠą╝ąĄąĮčé conv čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ąĘą░ą┐čāčüą║čā ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ (ą║ąŠąĮą▓ąĄčĆčüąĖčÅ, ą║ąŠą│ą┤ą░ ąĘą░čĆčÅąČą░čÄčéčüčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĖąĄ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆčŗ čüčģąĄą╝čŗ ą▓čŗą▒ąŠčĆą║ąĖ/čģčĆą░ąĮąĄąĮąĖčÅ ąÉą”ą¤). ą£ąŠą╝ąĄąĮčé select čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ąĮą░čćą░ą╗čā čüąĖą│ąĮą░ą╗ą░ ą▓čŗą▒ąŠčĆą║ąĖ, ą║ąŠą│ą┤ą░ ąĮą░čćąĖąĮą░ąĄčéčüčÅ čćč鹥ąĮąĖąĄ ą╗ąĖąĮąĖąĖ SDO ą┐ąŠ čéą░ą║čéą░ą╝ SCK. ą£ąĄąČą┤čā ą╝ąŠą╝ąĄąĮč鹊ą╝ conv ąĖ select ą┤ąŠą╗ąČąĮąŠ ą┐čĆąŠą╣čéąĖ ąĮąĄ ą╝ąĄąĮčīčłąĄ 2.2 ą╝ą║čü, čŹč鹊 ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠ ą▓ąŠąĘą╝ąŠąČąĮąŠąĄ ą┐ą░čüą┐ąŠčĆčéąĮąŠąĄ ą▓čĆąĄą╝čÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ąÉą”ą¤ (čüą╝. ą┐ą░čĆą░ą╝ąĄčéčĆ tCONV ąĖąĘ čéą░ą▒ą╗ąĖčåčŗ 4 ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓ ąĖąĮč鹥čĆą▓ą░ą╗ąŠą▓ ą▓čĆąĄą╝ąĄąĮąĖ ąĖąĘ [1]). ą£ąŠą╝ąĄąĮčé deselect čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ąŠą║ąŠąĮčćą░ąĮąĖčÄ čćč鹥ąĮąĖčÅ ąÉą”ą¤, ą║ąŠą│ą┤ą░ ą▓čŗą┤ą▓ąĖąĮčāčéčŗ ą▓čüąĄ 18 čĆą░ąĘčĆčÅą┤ąŠą▓ ą┤ą░ąĮąĮčŗčģ.

ąÜąŠą┤ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĖčÅ ą┐ąŠą╗ąŠą▓ąĖąĮą║ąĖ ą▒čāč乥čĆą░ (ADC_data_ISR) ąĖ ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ąĮą░čüčéčĆąŠą╣ą║ąĖ ąĘą░ą┐čāčüą║ą░ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (ADC_Init):

////////////////////////////////////////////////////////////////////////////

// AD7691.h

#ifndef __AD7691__

#define __AD7691__

#include "SPORT.h"

#define REF198_VOLTAGE 4.096

#define ONE_BIT_VOLTAGE (REF198_VOLTAGE/131071)

void ADC_Init (void);

#endif //__AD7691__

////////////////////////////////////////////////////////////////////////////

// AD7691.c

#include "pins.h"

#include "AD7691.h"

EX_REENTRANT_HANDLER(ADC_data_ISR)

{

*pDMA10_IRQ_STATUS |= 0x0001;

TOGGLEVD10();

}

void ADC_Init (void)

{

//ąśąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĖčÅ ą┐ąŠą╗ąŠą▓ąĖąĮą║ąĖ ą▒čāč乥čĆą░ 2D DMA

// ą┤ą╗čÅ čćč鹥ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ąĖąĘ ąÉą”ą¤.

// (ID ą┐ąĄčĆąĖč乥čĆąĖąĖ, ą┐čĆąĖąŠčĆąĖč鹥čé )

*pSIC_IAR4 |= PX_IVG(DMA10_SPORT3_RX_Peripheral, ADC_double_buffer_DMA_IVG);

// (ą┐čĆąĖąŠčĆąĖč鹥čé, ISR )

register_handler(ADC_double_buffer_DMA_IVG, ADC_data_ISR);

*pSIC_IMASK1 |= DMA10_IRQ; // čāčüčéą░ąĮąŠą▓ą║ą░ ą╝ą░čüą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ

}

[ąĪčüčŗą╗ą║ąĖ]

1. ąÉą”ą¤ AD7691.

2. ADSP-BF538: ąĖąĮč鹥čĆč乥ą╣čü SPORT.

3. ADSP-BF538: DMA.

4. Blackfin: ąĮą░čüčéčĆąŠą╣ą║ą░ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. |