|

ą£ąĖą║čĆąŠčüčģąĄą╝čŗ AD5627R/AD5647R/AD5667R ą║ąŠą╝ą┐ą░ąĮąĖąĖ Analog Devices čŹč鹊 12-/14-/16-bit DAC (ą”ąÉą¤) čüąŠ ą▓čüčéčĆąŠąĄąĮąĮčŗą╝ ąŠą┐ąŠčĆąĮčŗą╝ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄą╝ 1.25V/2.5V, ąŠą▒ą╗ą░ą┤ą░čÄčēąĖą╝ čüčéą░ą▒ąĖą╗čīąĮąŠčüčéčīčÄ 5 ppm/┬░C. ą£ąĖą║čĆąŠčüčģąĄą╝čŗ AD5627/AD5667 (ą▒ąĄąĘ ą▒čāą║ą▓čŗ R) ąŠčéą╗ąĖčćą░čÄčéčüčÅ č鹥ą╝, čćč鹊 ąĖą╝ąĄčÄčé čĆą░ąĘčĆčÅą┤ąĮąŠčüčéčī 12-/16-bit, ąĖ čĆą░ą▒ąŠčéą░čÄčé č鹊ą╗čīą║ąŠ ąŠčé ą▓ąĮąĄčłąĮąĄą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ.

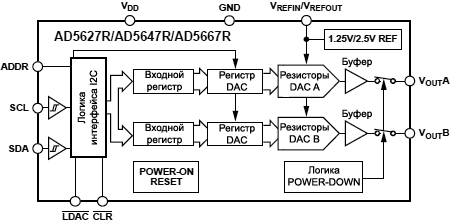

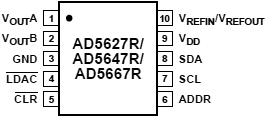

ąĀąĖčü. 1. AD5627R/AD5647R/AD5667R.

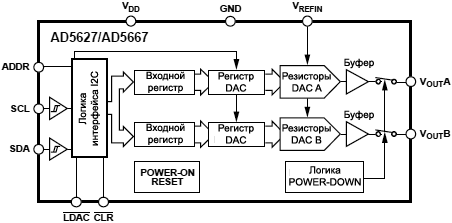

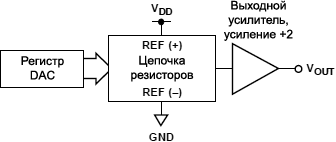

ąĀąĖčü. 2. AD5627/AD5667.

ą£ąĖą║čĆąŠčüčģąĄą╝čŗ ą▓čŗą┐čāčüą║ą░čÄčéčüčÅ ą▓ ą╝ąĖąĮąĖą░čéčÄčĆąĮčŗčģ ą║ąŠčĆą┐čāčüą░čģ: 3x3 ą╝ą╝ LFCSP ąĖ 10-ą▓čŗą▓ąŠą┤ąĮąŠą╝ MSOP. ąĢčüčéčī ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ čüą▒čĆąŠčü ą┐čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ, ą▓ąŠąĘą▓čĆą░čēą░čÄčēąĖą╣ DAC ą║ ąĮčāą╗ąĄą▓ąŠą╣ čłą║ą░ą╗ąĄ, ą║ą░ąČą┤čŗą╣ ą║ą░ąĮą░ą╗ ąĖą╝ąĄąĄčé čäčāąĮą║čåąĖčÄ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ. ąÉą┐ą┐ą░čĆą░čéąĮčŗąĄ čüąĖą│ąĮą░ą╗čŗ ~LDAC ąĖ ~CLR čüą╗čāąČą░čé ą┤ą╗čÅ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ą┐čĆąŠčåąĄčüčüą░ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▓čŗčģąŠą┤ą░. I2C-čüąŠą▓ą╝ąĄčüčéąĖą╝čŗą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé čĆąĄąČąĖą╝čŗ čüčéą░ąĮą┤ą░čĆčéąĮąŠą╣ čüą║ąŠčĆąŠčüčéąĖ (standard speed 100 ą║ąōčå), ą┐ąŠą▓čŗčłąĄąĮąĮąŠą╣ čüą║ąŠčĆąŠčüčéąĖ (fast speed 400 ą║ąōčå) ąĖ high speed (3.4 ą£ąōčå).

[ą×ą▒čēąĄąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ]

ą£ąŠą┤ąĄą╗ąĖ AD5627R/AD5647R/AD5667R, AD5627/AD5667 ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅčÄčé čüąĄą╝ąĄą╣čüčéą▓ąŠ nanoDAC - ą”ąÉą¤ čü ąĮąĖąĘą║ąĖą╝ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄą╝, ą┤ą▓čāčģą║ą░ąĮą░ą╗čīąĮčŗą╣, čĆą░ąĘčĆčÅą┤ąĮąŠčüčéčīčÄ 12, 14, 16 ą▒ąĖčé čü ą▒čāč乥čĆąĖąĘą░čåąĖąĄą╣, čüąŠ ą▓čüčéčĆąŠąĄąĮąĮčŗą╝ ąĖčüč鹊čćąĮąĖą║ąŠą╝ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ (AD5627/AD5667 čĆą░ą▒ąŠčéą░čÄčé ąŠčé ą▓ąĮąĄčłąĮąĄą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ). ąÆčüąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ ą╝ąŠą│čāčé čĆą░ą▒ąŠčéą░čéčī ąŠčé ąŠą┤ąĮąŠą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ 2.7V .. 5.5V.

ąŻ ą╝ąŠą┤ąĄą╗ąĄą╣ AD5627R/AD5647R/AD5667R ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ ąĖčüč鹊čćąĮąĖą║ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ. ą£ąŠą┤ąĄą╗čī AD56x7RBCPZ ąĖą╝ąĄąĄčé ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ ąĖčüč鹊čćąĮąĖą║ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ 1.25V, ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčēąĖą╣ č鹥ą╝ą┐ąĄčĆą░čéčāčĆąĮčŗą╣ čāčģąŠą┤ 5ppm/┬░C, čćč鹊 ąŠą▒ąĄčüą┐ąĄčćąĖą▓ą░čéčī ą┤ąĖą░ą┐ą░ąĘąŠąĮ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ 2.5V; ą╝ąŠą┤ąĄą╗čī AD56x7RBRMZ čüąĮą░ą▒ąČąĄąĮą░ ąŠą┐ąŠčĆąĮčŗą╝ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄą╝ 2.5 V, č鹊čćąĮąŠčüčéčī 5ppm/┬░C, ąĖ ą┤ą░ąĄčé ą┤ąĖą░ą┐ą░ąĘąŠąĮ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ąĮą░ ą▓čŗčģąŠą┤ąĄ 5V. ą¤čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ ąĖčüč鹊čćąĮąĖą║ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą▓čŗą║ą╗čÄč湥ąĮ, čćč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą▓ąĮąĄčłąĮąĖą╣ ąĖčüč鹊čćąĮąĖą║ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ. ąÆąĮčāčéčĆąĄąĮąĮąĖą╣ ąĖčüč鹊čćąĮąĖą║ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą╣ ąĘą░ą┐ąĖčüčīčÄ. ą£ąŠą┤ąĄą╗ąĖ AD5667 ąĖ AD5627 čéčĆąĄą▒čāčÄčé ą▓ąĮąĄčłąĮąĖą╣ ąĖčüč鹊čćąĮąĖą║ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┤ą╗čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ ą┤ąĖą░ą┐ą░ąĘąŠąĮą░ DAC.

ąÆ AD56x7R/AD56x7 ą▓čüčéčĆąŠąĄąĮą░ čüčģąĄą╝ą░ čüą▒čĆąŠčüą░ ą┐čĆąĖ ą┐ąŠą┤ą░č湥 ą┐ąĖčéą░ąĮąĖčÅ (power-on reset circuit), čćč鹊 ą│ą░čĆą░ąĮčéąĖčĆčāąĄčé ą┐ąŠčÅą▓ą╗ąĄąĮąĖąĄ 0V ąĮą░ ą▓čŗčģąŠą┤ąĄ DAC ą┐čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ, ąĖ čŹč鹊 čüąŠčüč鹊čÅąĮąĖąĄ čüąŠčģčĆą░ąĮčÅąĄčéčüčÅ, ą┐ąŠą║ą░ ąĮąĄ ą▒čāą┤ąĄčé ą▓čŗą┐ąŠą╗ąĮąĄąĮą░ ą┐čĆą░ą▓ąĖą╗čīąĮą░čÅ ąŠą┐ąĄčĆą░čåąĖčÅ ąĘą░ą┐ąĖčüąĖ. ążčāąĮą║čåąĖčÅ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ ą║ą░ąĮą░ą╗ąŠą▓ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé čüąĮąĖąČą░čéčī ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ 菹ĮąĄčĆą│ąĖąĖ ą┤ąŠ 480 nA ąŠčé 5V, ąĖ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ ą▓čŗą▒ąĖčĆą░ąĄą╝čāčÄ ą▓čŗčģąŠą┤ąĮčāčÄ ąĮą░ą│čĆčāąĘą║čā ą▓ čĆąĄąČąĖą╝ąĄ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ (power-down mode). ąØąĖąĘą║ąŠąĄ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ ą┤ąĄą╗ą░ąĄčé ą╝ąĖą║čĆąŠčüčģąĄą╝čā ąĖą┤ąĄą░ą╗čīąĮąŠ ą┐ąŠą┤čģąŠą┤čÅčēąĄą╣ ą┤ą╗čÅ čāčüčéčĆąŠą╣čüčéą▓ čü ą┐ąĖčéą░ąĮąĖąĄą╝ ąŠčé ą▒ą░čéą░čĆąĄąĖ. ąÆčüčéčĆąŠąĄąĮąĮčŗą╣ č鹊čćąĮčŗą╣ ą▓čŗčģąŠą┤ąĮąŠą╣ čāčüąĖą╗ąĖč鹥ą╗čī ąŠą▒ąĄčüą┐ąĄčćąĖą▓ą░ąĄčé ąĖąĘą╝ąĄąĮąĄąĮąĖąĄ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą▓ąŠ ą▓čüąĄą╝ čĆą░ą▒ąŠč湥ą╝ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ (rail-to-rail output swing).

ąóą░ą▒ą╗ąĖčåą░ 1. ąÆą░čĆąĖą░ąĮčéčŗ ą╝ąŠą┤ąĄą╗ąĄą╣ DAC ąŠčé Analog Devices.

| ą£ąŠą┤ąĄą╗čī DAC |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| AD5663 |

ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ 2.7V .. 5.5V, ą┤ą▓ą░ 16-ą▒ąĖčéąĮčŗčģ DAC, ą▓ąĮąĄčłąĮąĄąĄ ąŠą┐ąŠčĆąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ, ąĖąĮč鹥čĆč乥ą╣čü SPI |

| AD5623R/AD5643R/AD5663R |

ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ 2.7V .. 5.5V, ą┤ą▓ą░ DAC ąĮą░ 12/14/16 ą▒ąĖčé, ą▓ąĮčāčéčĆąĄąĮąĮąĄąĄ ąŠą┐ąŠčĆąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ, ąĖąĮč鹥čĆč乥ą╣čü SPI |

| AD5625R/AD5645R/AD5665R, AD5625/AD5665 |

ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ 2.7V .. 5.5V, č湥čéčŗčĆąĄ DAC ąĮą░ 12/14/16 ą▒ąĖčé, ą▓ąĮčāčéčĆąĄąĮąĮąĄąĄ ą╗ąĖą▒ąŠ ą▓ąĮąĄčłąĮąĄąĄ ąŠą┐ąŠčĆąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ, ąĖąĮč鹥čĆč乥ą╣čü I2C |

| AD5627R/AD5647R/AD5667R, AD5627/AD5667 |

ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ 2.7V .. 5.5V, ą┤ą▓ą░ DAC ąĮą░ 12/14/16 ą▒ąĖčé, ą▓ąĮčāčéčĆąĄąĮąĮąĄąĄ ą╗ąĖą▒ąŠ ą▓ąĮąĄčłąĮąĄąĄ ąŠą┐ąŠčĆąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ, ąĖąĮč鹥čĆč乥ą╣čü I2C |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: 菹╗ąĄą║čéčĆąĖč湥čüą║ąĖąĄ ąĖ ą┤čĆčāą│ąĖąĄ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ, ą┐ą░čĆą░ą╝ąĄčéčĆąĖč湥čüą║ąĖąĄ ą│čĆą░čäąĖą║ąĖ čüą╝. ą▓ ąŠčĆąĖą│ąĖąĮą░ą╗ąĄ ą┤ą░čéą░čłąĖčéą░ [1], ą▓ čŹč鹊ą╝ ą┐ąĄčĆąĄą▓ąŠą┤ąĄ ą┐čĆąĖą▓ąĄą┤ąĄąĮą░ č鹊ą╗čīą║ąŠ ąŠčüąĮąŠą▓ąĮą░čÅ ąĖąĮč乊čĆą╝ą░čåąĖčÅ ą┐ąŠ ą┐čĆąĖą╝ąĄąĮąĄąĮąĖčÄ ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÄ ą╝ąĖą║čĆąŠčüčģąĄą╝ DAC.

[ąśčüą┐ąŠą╗čīąĘčāąĄą╝ą░čÅ č鹥čĆą╝ąĖąĮąŠą╗ąŠą│ąĖčÅ]

Relative Accuracy or Integral Nonlinearity (INL). ą×čéąĮąŠčüąĖč鹥ą╗čīąĮą░čÅ č鹊čćąĮąŠčüčéčī ąĖą╗ąĖ ąĖąĮč鹥ą│čĆą░ą╗čīąĮą░čÅ ąĮąĄą╗ąĖąĮąĄą╣ąĮąŠčüčéčī - ą┤ą╗čÅ DAC čŹč鹊čé ą┐ą░čĆą░ą╝ąĄčéčĆ ąŠčåąĄąĮąĖą▓ą░ąĄčé ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮčāčÄ ą┤ąĄą▓ąĖą░čåąĖčÄ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čāčĆąŠą▓ąĮčÅ ą▓ ąĄą┤ąĖąĮąĖčåą░čģ ą╝ą╗ą░ą┤čłąĖčģ čĆą░ąĘčĆčÅą┤ąŠą▓ LSB ąŠčé ą┐čĆčÅą╝ąŠą╣ ą╗ąĖąĮąĖąĖ ą┐ąĄčĆąĄą┤ą░č鹊čćąĮąŠą╣ čäčāąĮą║čåąĖąĖ DAC (ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ą▓čģąŠą┤ąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ - ą▓čŗčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ).

Differential Nonlinearity (DNL). ąöąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮą░čÅ ąĮąĄą╗ąĖąĮąĄą╣ąĮąŠčüčéčī - čĆą░ąĘąĮąĖčåą░ ą╝ąĄąČą┤čā ąĖąĘą╝ąĄčĆąĄąĮąĮčŗą╝ ąĖąĘą╝ąĄąĮąĄąĮąĖąĄą╝ ąĖ ąĖą┤ąĄą░ą╗čīąĮčŗą╝ ąĖąĘą╝ąĄąĮąĄąĮąĖąĄą╝ ą┐čĆąĖ čüą╝ąĄąĮąĄ ą▓čģąŠą┤ąĮąŠą│ąŠ ą║ąŠą┤ą░ ąĮą░ 1 LSB, ą║ąŠą│ą┤ą░ ąĖąĘą╝ąĄąĮąĄąĮąĖąĄ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą╝ąĄąČą┤čā ą┤ą▓čāą╝čÅ čüąŠčüąĄą┤ąĮąĖą╝ąĖ ą▓čģąŠą┤ąĮčŗą╝ąĖ ą║ąŠą┤ą░ą╝ąĖ. ąŻą║ą░ąĘą░ąĮąĮą░čÅ DNL, čĆą░ą▓ąĮą░čÅ ┬▒1 LSB ą╝ą░ą║čüąĖą╝čāą╝, ą│ą░čĆą░ąĮčéąĖčĆčāąĄčé ą╝ąŠąĮąŠč鹊ąĮąĮąŠčüčéčī ą┐ąĄčĆąĄą┤ą░č鹊čćąĮąŠą╣ čäčāąĮą║čåąĖąĖ DAC. ąöąĖąĘą░ą╣ąĮ čŹč鹊ą╣ čüąĄčĆąĖąĖ DAC ąŠą▒ąĄčüą┐ąĄčćąĖą▓ą░ąĄčé ą╝ąŠąĮąŠč鹊ąĮąĮąŠčüčéčī ą┐ąĄčĆąĄą┤ą░č鹊čćąĮąŠą╣ čäčāąĮą║čåąĖąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ą║ąŠą┤ - ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ.

Zero-Code Error. ą×čłąĖą▒ą║ą░ ąĮčāą╗čÅ - ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąŠčéą║ą╗ąŠąĮąĄąĮąĖąĄ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čāčĆąŠą▓ąĮčÅ ąŠčé 0V, ą║ąŠą│ą┤ą░ ą▓ čĆąĄą│ąĖčüčéčĆ ą┤ą░ąĮąĮčŗčģ DAC ąĘą░ą┐ąĖčüą░ąĮąŠ 0x0000. ąÆ ąĖą┤ąĄą░ą╗čīąĮąŠą╣ čüąĖčéčāą░čåąĖąĖ ąĮą░ ą▓čŗčģąŠą┤ąĄ ą┐čĆąĖ čŹč鹊ą╝ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī 0V. ą×čłąĖą▒ą║ą░ ąĮčāą╗čÅ AD5667R ą▓čüąĄą│ą┤ą░ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮą░čÅ, ą┐ąŠč鹊ą╝čā čćč鹊 čāčĆąŠą▓ąĄąĮčī ąĮą░ ą▓čŗčģąŠą┤ąĄ ąĮąĄ ą╝ąŠąČąĄčé ąŠą┐čāčüčéąĖčéčīčüčÅ ąĮąĖąČąĄ 0V ąĖąĘ-ąĘą░ ą║ąŠą╝ą▒ąĖąĮą░čåąĖąĖ ąŠčłąĖą▒ąŠą║ čüą╝ąĄčēąĄąĮąĖčÅ DAC ąĖ čüčģąĄą╝čŗ ą┐ąŠčüčéčĆąŠąĄąĮąĖčÅ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čāčüąĖą╗ąĖč鹥ą╗čÅ. ą×čłąĖą▒ą║ą░ ąĮčāą╗čÅ ą▓čŗčĆą░ąČą░ąĄčéčüčÅ ą▓ mV.

Full-Scale Range, FSR. ą¤ąŠą╗ąĮčŗą╣ ą┤ąĖą░ą┐ą░ąĘąŠąĮ ą▓čģąŠą┤ąĮčŗčģ ą║ąŠą┤ąŠą▓ ąĖ ą▓čŗčģąŠą┤ąĮčŗčģ ąĮą░ą┐čĆčÅąČąĄąĮąĖą╣, čü ą║ąŠč鹊čĆčŗą╝ąĖ čĆą░ą▒ąŠčéą░ąĄčé ą”ąÉą¤.

Full-Scale Error. ą×čłąĖą▒ą║ą░ ą┐ąŠą╗ąĮąŠą╣ čłą║ą░ą╗čŗ - ąŠčéą║ą╗ąŠąĮąĄąĮąĖąĄ čāčĆąŠą▓ąĮčÅ ąŠčé ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą│ąŠ ąŠąČąĖą┤ą░ąĄą╝ąŠą│ąŠ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ, ą║ąŠą│ą┤ą░ ą▓ąŠ ą▓čģąŠą┤ąĮąŠą╣ čĆąĄą│ąĖčüčéčĆ DAC ąĘą░ą│čĆčāąČąĄąĮ ą║ąŠą┤ ą┐ąŠą╗ąĮąŠą╣ čłą║ą░ą╗čŗ (0xFFFF). ąöą╗čÅ ąĖą┤ąĄą░ą╗čīąĮąŠą│ąŠ čüą╗čāčćą░čÅ ąĮą░ ą▓čŗčģąŠą┤ąĄ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐čĆąĖ čŹč鹊ą╝ čāčĆąŠą▓ąĄąĮčī VDD ą╝ąĖąĮčāčü ą▓ąĄčü 1 LSB. ą×čłąĖą▒ą║ą░ ą┐ąŠą╗ąĮąŠą╣ čłą║ą░ą╗čŗ ą▓čŗčĆą░ąČą░ąĄčéčüčÅ ą▓ % ąŠčé ą┐ąŠą╗ąĮąŠą│ąŠ ą┤ąĖą░ą┐ą░ąĘąŠąĮą░ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ (full-scale range, FSR).

Gain Error. ą×čłąĖą▒ą║ą░ čāčüąĖą╗ąĄąĮąĖčÅ DAC. ą¤ą░čĆą░ą╝ąĄčéčĆ ąŠčåąĄąĮąĖą▓ą░ąĄčé čāčĆąŠą▓ąĄąĮčī ąŠčéą║ą╗ąŠąĮąĄąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░č鹊čćąĮąŠą╣ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ DAC ąŠčé ąĖą┤ąĄą░ą╗čīąĮąŠą╣, ą▓čŗčĆą░ąČąĄąĮąĮčŗą╣ ą▓ % ąŠčé FSR.

Zero-Code Error Drift. ą×čåąĄąĮąĖą▓ą░ąĄčé ąĖąĘą╝ąĄąĮąĄąĮąĖąĄ ąŠčłąĖą▒ą║ąĖ ąĮčāą╗čÅ ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ č鹥ą╝ą┐ąĄčĆą░čéčāčĆčŗ. ąÆčŗčĆą░ąČą░ąĄčéčüčÅ ą▓ mkV/┬░C.

Gain Temperature Coefficient. ąóąĄą╝ą┐ąĄčĆą░čéčāčĆąĮčŗą╣ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ čāčüąĖą╗ąĄąĮąĖčÅ ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ č鹥ą╝ą┐ąĄčĆą░čéčāčĆčŗ. ąÆčŗčĆą░ąČą░ąĄčéčüčÅ ą▓ ppm ąŠčé FSR/┬░C.

Offset Error. ą×čłąĖą▒ą║ą░ čüą╝ąĄčēąĄąĮąĖčÅ ąŠčåąĄąĮąĖą▓ą░ąĄčé čĆą░ąĘąĮąĖčåčā ąĮą░ ą▓čŗčģąŠą┤ąĄ ą╝ąĄąČą┤čā VOUT čĆąĄą░ą╗čīąĮąŠą│ąŠ ąŠčé VOUT ąĖą┤ąĄą░ą╗čīąĮąŠą│ąŠ DAC, ą▓čŗčĆą░ąČąĄąĮąĮčāčÄ ą▓ mV. ąśąĘą╝ąĄčĆąĄąĮąĖąĄ čĆą░ąĘąĮąĖčåčŗ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖčéčüčÅ ą┐ąŠčüąĄčĆąĄą┤ąĖąĮąĄ ą╗ąĖąĮąĄą╣ąĮąŠą│ąŠ čāčćą░čüčéą║ą░ ą┐ąĄčĆąĄą┤ą░č鹊čćąĮąŠą╣ čäčāąĮą║čåąĖąĖ DAC. ą×čłąĖą▒ą║ą░ čüą╝ąĄčēąĄąĮąĖčÅ AD5667R ąŠčåąĄąĮąĖą▓ą░ąĄčéčüčÅ ą┐čĆąĖ ąĘą░ą│čĆčāąĘą║ąĄ ą║ąŠą┤ą░ 512 ą▓ čĆąĄą│ąĖčüčéčĆ DAC, ąŠąĮą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą╣ ąĖą╗ąĖ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠą╣.

DC Power Supply Rejection Ratio (PSRR). ąÜąŠčŹčäčäąĖčåąĖąĄąĮčé ą┐ąŠą┤ą░ą▓ą╗ąĄąĮąĖčÅ ą▓ą╗ąĖčÅąĮąĖčÅ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ - ą┐ą░čĆą░ą╝ąĄčéčĆ ąŠčåąĄąĮąĖą▓ą░ąĄčé, ą║ą░ą║ ąĮą░ ą▓čŗčģąŠą┤ DAC ą▓ą╗ąĖčÅąĄčé čāčĆąŠą▓ąĄąĮčī ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ. PSRR čŹč鹊 ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ VOUT ą║ ąĖąĘą╝ąĄąĮąĄąĮąĖčÄ VDD ą┤ą╗čÅ full-scale output DAC, ąĖąĘą╝ąĄčĆčÅąĄčéčüčÅ ą▓ dB. VREF čāą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ąĮą░ čāčĆąŠą▓ąĮąĄ 2V ąĖ VDD ąĖąĘą╝ąĄąĮčÅąĄčéčüčÅ ą▓ ą┐čĆąĄą┤ąĄą╗ą░čģ ┬▒10%.

Output Voltage Settling Time. ąÆčĆąĄą╝čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ - ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▓čĆąĄą╝ąĄąĮąĖ, ąĘą░ ą║ąŠč鹊čĆąŠąĄ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé čāčüčéą░ąĮąŠą▓ą║ą░ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čāčĆąŠą▓ąĮčÅ DAC ą╝ąĄąČą┤čā ąĖąĘą╝ąĄąĮąĄąĮąĖąĄą╝ ąŠčé 1/4 ą┤ąŠ 3/4 FSR. ąŁč鹊 ą▓čĆąĄą╝čÅ ąĖąĘą╝ąĄčĆčÅąĄčéčüčÅ ąŠčé čäčĆąŠąĮčéą░ ąĮą░čĆą░čüčéą░ąĮąĖčÅ čüąŠą▒čŗčéąĖčÅ STOP čłąĖąĮčŗ I2C.

Digital-to-Analog Glitch Impulse. ąśą╝ą┐čāą╗čīčü ą┐ąŠą╝ąĄčģąĖ, ąĖąĮąČąĄą║čéąĖčĆčāąĄą╝čŗą╣ ąĮą░ ą▓čŗčģąŠą┤ DAC, ą║ąŠą│ą┤ą░ ą╝ąĄąĮčÅąĄčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄ ą▓čģąŠą┤ąĮąŠą│ąŠ ą║ąŠą┤ą░ ą▓ čĆąĄą│ąĖčüčéčĆąĄ DAC. ą×ą▒čŗčćąĮąŠ čāą║ą░ąĘčŗą▓ą░ąĄčéčüčÅ ą║ą░ą║ ąŠą▒ą╗ą░čüčéčī čāčĆąŠą▓ąĮčÅ ą┐ąŠą╝ąĄčģąĖ ą▓ nV, ąĖ ąĖąĘą╝ąĄčĆčÅąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą▓čģąŠą┤ąĮąŠą╣ ą║ąŠą┤ ą╝ąĄąĮčÅąĄčéčüčÅ ąĮą░ 1 LSB ą┐čĆąĖ ą┐ąĄčĆąĄčģąŠą┤ąĄ ąŠčé 0x7FFF ą║ 0x8000 (čüą╝. čĆąĖčü. 42 ąĖąĘ ą┤ą░čéą░čłąĖčéą░ [1]).

Digital Feedthrough. ąØą░ą▓ąŠą┤ą║ą░ čåąĖčäčĆąŠą▓ąŠą╣ ą┐ąŠą╝ąĄčģąĖ - ąĖąĘą╝ąĄčĆąĄąĮąĮčŗą╣ ąĖą╝ą┐čāą╗čīčü ąĮą░ ą▓čŗčģąŠą┤ąĄ, ąĖąĮąČąĄą║čéąĖčĆčāąĄą╝čŗą╣ ąĮą░ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ą▓čŗčģąŠą┤ DAC, ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ąĖąĘą╝ąĄąĮąĄąĮąĖąĄ čāčĆąŠą▓ąĮčÅ ąĮą░ čåąĖčäčĆąŠą▓čŗčģ ą▓čģąŠą┤ą░čģ, ąŠą┤ąĮą░ą║ąŠ čŹč鹊 ąĖąĘą╝ąĄčĆąĄąĮąĖąĄ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖčéčüčÅ, ą║ąŠą│ą┤ą░ ą▓čŗčģąŠą┤ DAC ąĮąĄ ąŠą▒ąĮąŠą▓ą╗čÅąĄčéčüčÅ. ą¤ą░čĆą░ą╝ąĄčéčĆ čāą║ą░ąĘčŗą▓ą░ąĄčéčüčÅ ą▓ nV, ąĖ ąĖąĘą╝ąĄčĆčÅąĄčéčüčÅ ą┐čĆąĖ ąĖąĘą╝ąĄąĮąĄąĮąĖąĄ ą▓čģąŠą┤ąĮąŠą│ąŠ ą║ąŠą┤ą░ ą┐ąŠ ą▓čüąĄą╣ čłą║ą░ą╗ąĄ, čé. ąĄ. ąŠčé ą▓čüąĄčģ ąĮčāą╗ąĄą╣ ą┤ąŠ ą▓čüąĄčģ ąĄą┤ąĖąĮąĖč湥ą║, ąĖ ąĮą░ąŠą▒ąŠčĆąŠčé.

Reference Feedthrough. ąØą░ą▓ąŠą┤ą║ą░ ą┐ąŠą╝ąĄčģąĖ ąĮą░ ąŠą┐ąŠčĆąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ - čüąŠąŠčéąĮąŠčłąĄąĮąĖąĄ ą░ą╝ą┐ą╗ąĖčéčāą┤čŗ čüąĖą│ąĮą░ą╗ą░ ąĮą░ ą▓čŗčģąŠą┤ąĄ DAC ą║ąŠ ą▓čģąŠą┤čā ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ, ą║ąŠą│ą┤ą░ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮą░ ą▓čŗčģąŠą┤ąĄ DAC ąĮąĄ ąŠą▒ąĮąŠą▓ą╗čÅąĄčéčüčÅ. ą¤ą░čĆą░ą╝ąĄčéčĆ ą▓čŗčĆą░ąČą░ąĄčéčüčÅ ą▓ dB.

Output Noise Spectral Density. ąĪą┐ąĄą║čéčĆą░ą╗čīąĮą░čÅ ą┐ą╗ąŠčéąĮąŠčüčéčī čłčāą╝ą░ ąĮą░ ą▓čŗčģąŠą┤ąĄ - ą┐ą░čĆą░ą╝ąĄčéčĆ ąŠčåąĄąĮąĖą▓ą░ąĄčé čāčĆąŠą▓ąĄąĮčī čłčāą╝ą░, ą│ąĄąĮąĄčĆąĖčĆčāąĄą╝ąŠą│ąŠ ą▓ąĮčāčéčĆąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ. ąĪą╗čāčćą░ą╣ąĮčŗą╣ čłčāą╝ čģą░čĆą░ą║č鹥čĆąĖąĘčāąĄčéčüčÅ čüą┐ąĄą║čéčĆą░ą╗čīąĮąŠą╣ ą┐ą╗ąŠčéąĮąŠčüčéčīčÄ. ąśąĘą╝ąĄčĆčÅąĄčéčüčÅ ąĮą░ ą▓čŗčģąŠą┤ąĄ ą┐čĆąĖ ąĘą░ą│čĆčāąĘą║ąĄ ą▓ DAC čüčĆąĄą┤ąĮąĄą│ąŠ čāčĆąŠą▓ąĮčÅ, ąĄą┤ąĖąĮąĖčåčŗ nV / ą║ąŠčĆąĄąĮčī ąōčå. ąōčĆą░čäąĖą║ čüą┐ąĄą║čéčĆą░ą╗čīąĮąŠą╣ ą┐ą╗ąŠčéąĮąŠčüčéąĖ ą╝ąŠąČąĮąŠ čāą▓ąĖą┤ąĄčéčī ąĮą░ čĆąĖčü. 48 ą┤ą░čéą░čłąĖčéą░ [1].

DC Crosstalk. ą¤ą░čĆą░ą╝ąĄčéčĆ ąŠčåąĄąĮąĖą▓ą░ąĄčé ą┐ąĄčĆąĄą║čĆąĄčüčéąĮčŗąĄ ą┐ąŠą╝ąĄčģąĖ ą╝ąĄąČą┤čā ą║ą░ąĮą░ą╗ą░ą╝ąĖ DAC. ąśąĘą╝ąĄčĆčÅąĄčéčüčÅ ą┐čĆąĖ ąĖąĘą╝ąĄąĮąĄąĮąĖąĖ ą┐ąŠ ą┐ąŠą╗ąĮąŠą╣ čłą║ą░ą╗ąĄ ąĮą░ ą▓čŗčģąŠą┤ąĄ ąŠą┤ąĮąŠą│ąŠ DAC (ąĖą╗ąĖ ą┐čĆąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą╝ ą▓čŗą║ą╗čÄč湥ąĮąĖąĖ ąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ), ą║ąŠą│ą┤ą░ ąĮą░ ą▓čŗčģąŠą┤ąĄ ą┤čĆčāą│ąŠą│ąŠ ą║ą░ąĮą░ą╗ą░ čāą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ čüčĆąĄą┤ąĮąĖą╣ čāčĆąŠą▓ąĄąĮčī FSR. ąÆčŗčĆą░ąČą░ąĄčéčüčÅ ą▓ mkV.

DC crosstalk ąĖąĘ-ąĘą░ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ č鹊ą║ą░ ąĮą░ą│čĆčāąĘą║ąĖ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą▓ą╗ąĖčÅąĮąĖąĄ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ č鹊ą║ą░ ąĮą░ą│čĆčāąĘą║ąĖ ąŠą┤ąĮąŠą│ąŠ ą║ą░ąĮą░ą╗ą░ DAC, ą║ąŠą│ą┤ą░ ąĮą░ ą▓čŗčģąŠą┤ąĄ ą┤čĆčāą│ąŠą│ąŠ ą║ą░ąĮą░ą╗ą░ čāą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ čüčĆąĄą┤ąĮąĖą╣ čāčĆąŠą▓ąĄąĮčī FSR. ąÆčŗčĆą░ąČą░ąĄčéčüčÅ ą▓ mkV/mA.

Digital Crosstalk. ą×čåąĄąĮąĖą▓ą░ąĄčé ąĖą╝ą┐čāą╗čīčü ą┐ąŠą╝ąĄčģąĖ, ą║ąŠč鹊čĆčŗą╣ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ąĮą░ ą▓čŗčģąŠą┤ ąŠą┤ąĮąŠą│ąŠ ąĖąĘ ą║ą░ąĮą░ą╗ąŠą▓ DAC, ą║ąŠą│ą┤ą░ ąĮą░ ąĄą│ąŠ ą▓čŗčģąŠą┤ąĄ čüčĆąĄą┤ąĮąĖą╣ čāčĆąŠą▓ąĄąĮčī, ąŠčé ą┤čĆčāą│ąŠą│ąŠ ą║ą░ąĮą░ą╗ą░ DAC, ą║ąŠą│ą┤ą░ ąĄą│ąŠ ą▓čģąŠą┤ąĮąŠą╣ ą║ąŠą┤ ą╝ąĄąĮčÅąĄčéčüčÅ ąŠčé ą▓čüąĄčģ ąĮčāą╗ąĄą╣ ą┤ąŠ ą▓čüąĄčģ ąĄą┤ąĖąĮąĖčå ąĖ ąĮą░ąŠą▒ąŠčĆąŠčé. ąśąĘą╝ąĄčĆčÅčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ standalone ąĖ ą▓čŗčĆą░ąČą░ąĄčéčüčÅ ą▓ nV.

Analog Crosstalk. ąÉąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ąĖą╝ą┐čāą╗čīčü ą┐ąŠą╝ąĄčģąĖ, ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗą╣ ąĮą░ ą▓čŗčģąŠą┤ ąŠą┤ąĮąŠą│ąŠ DAC ą┐čĆąĖ ąĖąĘą╝ąĄąĮąĄąĮąĖąĖ čāčĆąŠą▓ąĮčÅ ąĮą░ ą┤čĆčāą│ąŠą╝ DAC. ąśąĘą╝ąĄčĆčÅąĄčéčüčÅ ąĘą░ą│čĆčāąĘą║ąŠą╣ ąŠą┤ąĮąŠą│ąŠ ąĖąĘ ą▓čģąŠą┤ąĮčŗčģ čĆąĄą│ąĖčüčéčĆąŠą▓ ąĖąĘą╝ąĄąĮąĄąĮąĖąĄą╝ ą║ąŠą┤ą░ ą┐ąŠ ą▓čüąĄą╣ čłą║ą░ą╗ąĄ (ąŠčé ą▓čüąĄčģ ąĮčāą╗ąĄą╣ ą┤ąŠ ą▓čüąĄčģ ąĄą┤ąĖąĮąĖčå ąĖ ąŠą▒čĆą░čéąĮąŠ), ąĘą░č鹥ą╝ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄą╝ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ ~LDAC ąĖ ą╝ąŠąĮąĖč鹊čĆąĖąĮą│ąŠą╝ ą▓čŗčģąŠą┤ą░ DAC, ą║ąŠą│ą┤ą░ čåąĖčäčĆąŠą▓ąŠą╣ ą║ąŠą┤ ąĮąĄ ą╝ąĄąĮčÅąĄčéčüčÅ. ąöąĖą░ą┐ą░ąĘąŠąĮ ą┐ąŠą╝ąĄčģąĖ ą▓čŗčĆą░ąČą░ąĄčéčüčÅ ą▓ nV.

DAC-to-DAC Crosstalk. ąÉąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ąĖą╝ą┐čāą╗čīčü ą┐ąŠą╝ąĄčģąĖ, ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗą╣ ąĮą░ ą▓čŗčģąŠą┤ ąŠą┤ąĮąŠą│ąŠ DAC ą┐čĆąĖ ąĖąĘą╝ąĄąĮąĄąĮąĖąĖ čåąĖčäčĆąŠą▓ąŠą│ąŠ ą║ąŠą┤ą░ ąĖ ą┐ąŠčüą╗ąĄą┤čāčÄčēąĄą│ąŠ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ čāčĆąŠą▓ąĮčÅ ąĮą░ ą┤čĆčāą│ąŠą╝ DAC. ąśąĘą╝ąĄčĆčÅąĄčéčüčÅ ą┐čĆąĖ ąĖąĘą╝ąĄąĮąĄąĮąĖąĖ ąĮą░ą▓ąŠą┤čÅčēąĄą│ąŠ ą┐ąŠą╝ąĄčģčā ą║ą░ąĮą░ą╗ą░ ą┐ąŠ ą┐ąŠą╗ąĮąŠą╣ čłą║ą░ą╗ąĄ (ąŠčé ą▓čüąĄčģ ąĮčāą╗ąĄą╣ ą┤ąŠ ą▓čüąĄčģ ąĄą┤ąĖąĮąĖčå ąĖ ąŠą▒čĆą░čéąĮąŠ) ą┐čĆąĖ čāčĆąŠą▓ąĮąĄ ą╗ąŠą│. 0 ąĮą░ ~LDAC ą┐čāč鹥ą╝ ą╝ąŠąĮąĖč鹊čĆąĖąĮą│ą░ ą▓čŗčģąŠą┤ą░ ąĮą░ ą┤čĆčāą│ąŠą╝ ą║ą░ąĮą░ą╗ąĄ, ąĮą░ ą▓čŗčģąŠą┤ąĄ ą║ąŠč鹊čĆąŠą│ąŠ čāčĆąŠą▓ąĄąĮčī ą┐ąŠą╗ąŠą▓ąĖąĮčŗ čłą║ą░ą╗čŗ. ąŁąĮąĄčĆą│ąĖčÅ ą┐ąŠą╝ąĄčģąĖ ą▓čŗčĆą░ąČą░ąĄčéčüčÅ ą▓ nV.

Multiplying Bandwidth. ą×čåąĄąĮą║ą░ ą║ąŠąĮąĄčćąĮąŠą╣ ą┐ąŠą╗ąŠčüčŗ ą┐čĆąŠą┐čāčüą║ą░ąĮąĖčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĖčģ čāčüąĖą╗ąĖč鹥ą╗ąĄą╣ DAC. ąĪąĖąĮčāčüąŠąĖą┤ą░ą╗čīąĮčŗą╣ čüąĖą│ąĮą░ą╗ ąĮą░ ąŠą┐ąŠčĆąĮąŠą╝ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĖ (čü ą║ąŠą┤ąŠą╝ FSR, ąĘą░ą│čĆčāąČąĄąĮąĮąŠą╝ ą▓ DAC) ą┐ąŠčÅą▓ąĖčéčüčÅ ąĮą░ ą▓čŗčģąŠą┤ąĄ. Multiplying Bandwidth čŹč鹊 čćą░čüč鹊čéą░, čü ą║ąŠč鹊čĆąŠą╣ ą░ą╝ą┐ą╗ąĖčéčāą┤ą░ ą▓čŗčģąŠą┤ą░ ą┐ą░ą┤ą░ąĄčé ąĮą░ 3dB ąĮąĖąČąĄ ą░ą╝ą┐ą╗ąĖčéčāą┤čŗ ą▓čģąŠą┤ą░.

Total Harmonic Distortion (THD). ą×ą▒čēąĖą╣ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ą│ą░čĆą╝ąŠąĮąĖč湥čüą║ąĖčģ ąĖčüą║ą░ąČąĄąĮąĖą╣ - ąŠčåąĄąĮąĖą▓ą░ąĄčé čĆą░ąĘąĮąĖčåčā ą╝ąĄąČą┤čā ąĖą┤ąĄą░ą╗čīąĮąŠą╣ čüąĖąĮčāčüąŠąĖą┤ąŠą╣ ąĖ ąĄčæ ą▓ąĄčĆčüąĖąĄą╣, ą┐ąŠą╗čāč湥ąĮąĮąŠą╣ čü ą┐ąŠą╝ąŠčēčīčÄ DAC. ąĪąĖąĮčāčüąŠąĖą┤ą░ą╗čīąĮčŗą╣ čüąĖą│ąĮą░ą╗ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą║ą░ą║ ąŠą┐ąŠčĆąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┤ą╗čÅ DAC, ąĖ THD ąĖąĘą╝ąĄčĆčÅąĄčé ą│ą░čĆą╝ąŠąĮąĖą║ąĖ, ą┐čĆąĖčüčāčéčüčéą▓čāčÄčēąĖąĄ ąĮą░ ą▓čŗčģąŠą┤ąĄ DAC. ąśąĘą╝ąĄčĆčÅąĄčéčüčÅ ą▓ dB.

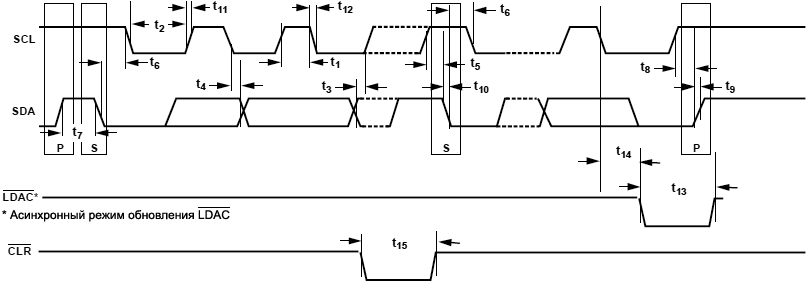

ąóą░ą▒ą╗ąĖčåą░ 4. ą¤ą░čĆą░ą╝ąĄčéčĆčŗ čāą║ą░ąĘą░ąĮčŗ ą┤ą╗čÅ VDD = 2.7V .. 5.5V, č鹥ą╝ą┐ąĄčĆą░čéčāčĆą░ ą╝ąĄąČą┤čā TMIN ąĖ TMAX, fSCL = 3.4 ą£ąōčå, ąĄčüą╗ąĖ ąĮąĄ čāą║ą░ąĘą░ąĮąŠ ąĮąĄčćč鹊 ą┤čĆčāą│ąŠąĄ1.

| ą¤ą░čĆą░ą╝. |

ąŻčüą╗ąŠą▓ąĖčÅ2 |

MIN |

MAX |

ąĢą┤. |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| fSCL3 |

Standard mode |

|

100 |

ą║ąōčå |

ą¦ą░čüč鹊čéą░ čéą░ą║č鹊ą▓ I2C |

| Fast mode |

|

400 |

| High speed mode, CB = 100 ą┐ąż |

|

3.4 |

ą£ąōčå |

| High speed mode, CB = 400 ą┐ąż |

|

1.7 |

t1

|

Standard mode |

4 |

|

ą╝ą║čü |

tHIGH, ą▓čĆąĄą╝čÅ ąĮą░čģąŠąČą┤ąĄąĮąĖčÅ SCL ą▓ ą╗ąŠą│. 1 |

| Fast mode |

0.6 |

|

| High speed mode, CB = 100 ą┐ąż |

60 |

|

ąĮčü |

| High speed mode, CB = 400 ą┐ąż |

120 |

|

t2

|

Standard mode |

4.7 |

|

ą╝ą║čü |

tLOW, ą▓čĆąĄą╝čÅ ąĮą░čģąŠąČą┤ąĄąĮąĖčÅ SCL ą▓ ą╗ąŠą│. 0 |

| Fast mode |

1.3 |

|

| High speed mode, CB = 100 ą┐ąż |

160 |

|

ąĮčü |

| High speed mode, CB = 400 ą┐ąż |

320 |

|

t3

|

Standard mode |

250 |

|

ąĮčü |

tSU;DAT, data setup time (ą▓čĆąĄą╝čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ ą┤ą░ąĮąĮčŗčģ) |

| Fast mode |

100 |

|

| High speed mode |

10 |

|

t4

|

Standard mode |

0 |

3.45 |

ą╝ą║čü |

tHD;DAT, data hold time (ą▓čĆąĄą╝čÅ čāą┤ąĄčƹȹ░ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ) |

| Fast mode |

0 |

0.9 |

| High speed mode, CB = 100 ą┐ąż |

0 |

70 |

ąĮčü |

| High speed mode, CB = 400 ą┐ąż |

0 |

150 |

t5

|

Standard mode |

4.7 |

|

ą╝ą║čü |

tSU;STA, setup time (ą▓čĆąĄą╝čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ) ą┤ą╗čÅ repeated START |

| Fast mode |

0.6 |

|

| High speed mode |

160 |

|

ąĮčü |

t6

|

Standard mode |

4 |

|

ą╝ą║čü |

tHD;STA, hold time, ą▓čĆąĄą╝čÅ čāą┤ąĄčƹȹ░ąĮąĖčÅ ą┤ą╗čÅ (repeated) START |

| Fast mode |

0.6 |

|

| High speed mode |

160 |

|

ąĮčü |

t7

|

Standard mode |

4.7 |

|

ą╝ą║čü |

tBUF, ą▓čĆąĄą╝čÅ čüą▓ąŠą▒ąŠą┤ąĮąŠą│ąŠ čüąŠčüč鹊čÅąĮąĖčÅ čłąĖąĮčŗ ą╝ąĄąČą┤čā STOP ąĖ START |

| Fast mode |

1.3 |

|

t8

|

Standard mode |

4 |

|

ą╝ą║čü |

tSU;STO, setup time (ą▓čĆąĄą╝čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ) ą┤ą╗čÅ STOP |

| Fast mode |

0.6 |

|

| High speed mode |

160 |

|

ąĮčü |

t9

|

Standard mode |

|

1000 |

ąĮčü |

tRDA, rise time SDA, ą▓čĆąĄą╝čÅ ąĮą░čĆą░čüčéą░ąĮąĖčÅ čüąĖą│ąĮą░ą╗ą░ ą┤ą░ąĮąĮčŗčģ |

| Fast mode |

|

300 |

| High speed mode, CB = 100 ą┐ąż |

10 |

80 |

| High speed mode, CB = 400 ą┐ąż |

20 |

160 |

t10

|

Standard mode |

|

300 |

ąĮčü |

tFDA, fall time SDA, ą▓čĆąĄą╝čÅ čüą┐ą░ą┤ą░ čüąĖą│ąĮą░ą╗ą░ ą┤ą░ąĮąĮčŗčģ |

| Fast mode |

|

300 |

| High speed mode, CB = 100 ą┐ąż |

10 |

80 |

| High speed mode, CB = 400 ą┐ąż |

20 |

160 |

t11

|

Standard mode |

|

1000 |

ąĮčü |

tRCL, rise time SCL, ą▓čĆąĄą╝čÅ ąĮą░čĆą░čüčéą░ąĮąĖčÅ čüąĖą│ąĮą░ą╗ą░ čéą░ą║č鹊ą▓ |

| Fast mode |

|

300 |

| High speed mode, CB = 100 ą┐ąż |

10 |

40 |

| High speed mode, CB = 400 ą┐ąż |

20 |

80 |

t11A

|

Standard mode |

|

1000 |

ąĮčü |

tRCL1, rise time SCL, ą▓čĆąĄą╝čÅ ąĮą░čĆą░čüčéą░ąĮąĖčÅ čüąĖą│ąĮą░ą╗ą░ čéą░ą║č鹊ą▓ ą┐ąŠčüą╗ąĄ repeated START ąĖ ą┐ąŠčüą╗ąĄ ą▒ąĖčéą░ ACK/NACK |

| Fast mode |

|

300 |

| High speed mode, CB = 100 ą┐ąż |

10 |

80 |

| High speed mode, CB = 400 ą┐ąż |

20 |

160 |

t12

|

Standard mode |

|

300 |

ąĮčü |

tFCL, fall time SCL, ą▓čĆąĄą╝čÅ čüą┐ą░ą┤ą░ čüąĖą│ąĮą░ą╗ą░ čéą░ą║č鹊ą▓ |

| Fast mode |

|

300 |

| High speed mode, CB = 100 ą┐ąż |

10 |

40 |

| High speed mode, CB = 400 ą┐ąż |

20 |

80 |

t13

|

Standard mode |

10 |

|

ąĮčü |

ąÆčĆąĄą╝čÅ ą╗ąŠą│. 0 ą┤ą╗čÅ ąĖą╝ą┐čāą╗čīčüą░ ~LDAC |

| Fast mode |

10 |

|

| High speed mode |

10 |

|

t14

|

Standard mode |

300 |

|

ąĮčü |

ąÆčĆąĄą╝čÅ čüą┐ą░ą┤ą░ 9-ą│ąŠ ąĖą╝ą┐čāą╗čīčüą░ SCL ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ ą▒ą░ą╣čéą░ ą┐čĆą░ą▓ąĖą╗čīąĮąŠą╣ ąĘą░ą┐ąĖčüąĖ |

| Fast mode |

300 |

|

| High speed mode |

30 |

|

t15

|

Standard mode |

20 |

|

ąĮčü |

ąÆčĆąĄą╝čÅ ą╗ąŠą│. 0 ą┤ą╗čÅ ąĖą╝ą┐čāą╗čīčüą░ ~CLR |

| Fast mode |

20 |

|

| High speed mode |

20 |

|

| tSP4 |

Fast mode |

0 |

50 |

ąĮčü |

ą©ąĖčĆąĖąĮą░ ą┐ąŠą┤ą░ą▓ą╗ąĄąĮąĮčŗčģ ąĖą╝ą┐čāą╗čīčüąŠą▓ ą┐ąŠą╝ąĄčģ |

| High speed mode |

0 |

10 |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

1. ąĪą╝. čĆąĖčü. 3. ą¤ą░čĆą░ą╝ąĄčéčĆčŗ čĆąĄąČąĖą╝ą░ high speed ą┐čĆąĖą╝ąĄąĮąĖą╝čŗ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ą╝ąĖą║čĆąŠčüčģąĄą╝ AD5627RBRMZ-2/AD5627BRMZ-2REEL7 ąĖ AD5667RBRMZ-2/AD5667BRMZ-2REEL7.

2. CB ąŠą▒ąŠąĘąĮą░čćą░ąĄčé ąĄą╝ą║ąŠčüčéčī čüąĖą│ąĮą░ą╗ą░ čłąĖąĮčŗ (capacitance bus).

3. ąśąĮč鹥čĆą▓ą░ą╗čŗ ą▓čĆąĄą╝ąĄąĮąĖ SDA ąĖ SCL ąĖąĘą╝ąĄčĆąĄąĮčŗ čü čĆą░ąĘčĆąĄčłąĄąĮąĖąĄą╝ ą▓čģąŠą┤ąĮčŗčģ čäąĖą╗čīčéčĆąŠą▓. ąÆčŗą║ą╗čÄč湥ąĮąĖąĄ ą▓čģąŠą┤ąĮčŗčģ čäąĖą╗čīčéčĆąŠą▓ čāą▓ąĄą╗ąĖčćąĖą▓ą░ąĄčé čüą║ąŠčĆąŠčüčéąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ, ąŠą┤ąĮą░ą║ąŠ ąĮąĄą│ą░čéąĖą▓ąĮąŠ ą▓ą╗ąĖčÅąĄčé ąĮą░ EMC-ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ.

4. ąÆčģąŠą┤ąĮą░čÅ čäąĖą╗čīčéčĆą░čåąĖčÅ SCL ąĖ SDA ą┐ąŠą┤ą░ą▓ą╗čÅąĄčé ą▓čŗą▒čĆąŠčüčŗ ą┐ąŠą╝ąĄčģ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčīčÄ ą╝ąĄąĮčīčłąĄ 50 ąĮčü ą┤ą╗čÅ fast mode ąĖą╗ąĖ 10 ąĮčü ą┤ą╗čÅ high speed mode.

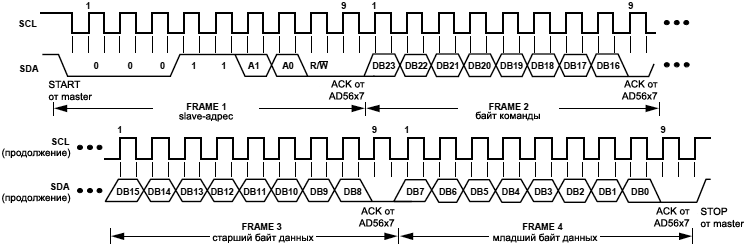

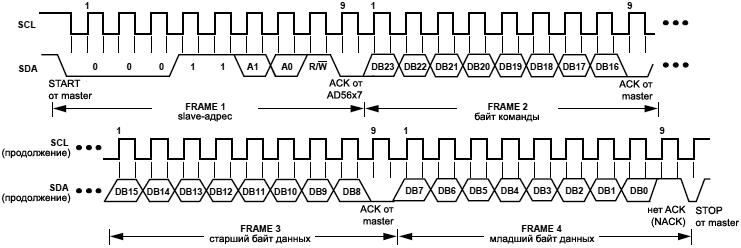

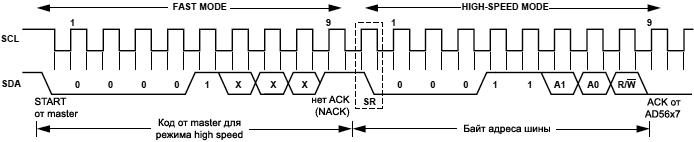

ąĀąĖčü. 3. ąöąĖą░ą│čĆą░ą╝ą╝ą░ ą▓čĆąĄą╝ąĄąĮąĖ čüąĖą│ąĮą░ą╗ąŠą▓ 2-ą┐čĆąŠą▓ąŠą┤ąĮąŠą╣ čłąĖąĮčŗ I2C.

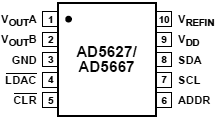

ąĀąĖčü. 4. ą”ąŠą║ąŠą╗ąĄą▓ą║ą░ AD5627/AD5667, ą▓ąĖą┤ čüą▓ąĄčĆčģčā.

ąĀąĖčü. 5. ą”ąŠą║ąŠą╗ąĄą▓ą║ą░ AD5627R/AD5647R/AD5667R, ą▓ąĖą┤ čüą▓ąĄčĆčģčā.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĮąĖąČąĮčÅčÅ ą╝ąĄčéą░ą╗ą╗ąĖč湥čüą║ą░čÅ ą┐ą╗ąŠčēą░ą┤ą║ą░ ą║ąŠčĆą┐čāčüą░ LFCSP ąĮą░ą║ąŠčĆąŠčéą║ąŠ čüąŠąĄą┤ąĖąĮčÅąĄčéčüčÅ čü GND.

ąóą░ą▒ą╗ąĖčåą░ 6. ążčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ ą▓čŗą▓ąŠą┤ąŠą▓.

| Ōä¢ |

ą£ąĮąĄą╝. |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| 1 |

VOUTA |

ąÉąĮą░ą╗ąŠą│ąŠą▓ąŠąĄ ą▓čŗčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą║ą░ąĮą░ą╗ą░ A. ąÆčŗčģąŠą┤ čāčüąĖą╗ąĖč鹥ą╗čÅ čĆą░ą▒ąŠčéą░ąĄčé ą┐ąŠ čāčĆąŠą▓ąĮčÅą╝ ą║ą░ą║ rail-to-rail. |

| 2 |

VOUTB |

ąÉąĮą░ą╗ąŠą│ąŠą▓ąŠąĄ ą▓čŗčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą║ą░ąĮą░ą╗ą░ B. ąÆčŗčģąŠą┤ čāčüąĖą╗ąĖč鹥ą╗čÅ čĆą░ą▒ąŠčéą░ąĄčé ą┐ąŠ čāčĆąŠą▓ąĮčÅą╝ ą║ą░ą║ rail-to-rail. |

| 3 |

GND |

ąŚąĄą╝ą╗čÅ ą┤ą╗čÅ ą▓čüąĄčģ čüąĖą│ąĮą░ą╗ąŠą▓, ą╝ąĖąĮčāčü ą┐ąĖčéą░ąĮąĖčÅ. |

| 4 |

~LDAC |

ą¤ąŠą┤ą░čćą░ ąĖą╝ą┐čāą╗čīčüą░ ą╗ąŠą│. 0 ąĮą░ čŹč鹊čé ą▓čŗą▓ąŠą┤ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą╗čÄą▒ąŠą╝čā čĆąĄą│ąĖčüčéčĆčā DAC ąĖą╗ąĖ ą▓čüąĄą╝ čĆąĄą│ąĖčüčéčĆą░ą╝ DAC ąŠą▒ąĮąŠą▓ąĖčéčīčüčÅ, ąĄčüą╗ąĖ ąĮą░ ą▓čģąŠą┤ ą┐ąŠčüčéčāą┐ąĖą╗ąĖ ąĮąŠą▓čŗąĄ ą┤ą░ąĮąĮčŗąĄ. ąŁč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ąŠą▒ąĮąŠą▓ąĖčéčī ą▓čüąĄ ą▓čŗčģąŠą┤čŗ DAC. ąÉą╗čīč鹥čĆąĮą░čéąĖą▓ąĮąŠ čŹč鹊čé ą▓čŗą▓ąŠą┤ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠčüč鹊čÅąĮąĮąŠ ą▓ ą╗ąŠą│. 0. |

| 5 |

~CLR |

ąÉčüąĖąĮčģčĆąŠąĮąĮčŗą╣ ą▓čģąŠą┤ ąŠčćąĖčüčéą║ąĖ. ąÆčģąŠą┤ ~CLR čüčĆą░ą▒ą░čéčŗą▓ą░ąĄčé ą┐ąŠ čüą┐ą░ą┤čā čāčĆąŠą▓ąĮčÅ. ąÜąŠą│ą┤ą░ ~CLR ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ą╗ąŠą│. 0, ą▓čüąĄ ąĖą╝ą┐čāą╗čīčüčŗ ~LDAC ąĖą│ąĮąŠčĆąĖčĆčāčÄčéčüčÅ. ąÜąŠą│ą┤ą░ ~CLR ą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮ, ą▓ąŠ ą▓čüąĄ ą▓čģąŠą┤ąĮčŗąĄ čĆąĄą│ąĖčüčéčĆčŗ ąĖ čĆąĄą│ąĖčüčéčĆčŗ DAC ąĘą░ą│čĆčāąČą░čÄčéčüčÅ ąĮčāą╗ąĖ, čćč鹊 ą┐čĆąĖą▓ąŠą┤ąĖčé ą║ ą┐ąŠčÅą▓ą╗ąĄąĮąĖčÄ ąĮą░ ą▓čŗčģąŠą┤ąĄ 0V. ą£ąĖą║čĆąŠčüčģąĄą╝ą░ ą▓čŗą╣ą┤ąĄčé ąĖąĘ čĆąĄąČąĖą╝ą░ ąŠčćąĖčüčéą║ąĖ ą┐ąŠ čüą┐ą░ą┤čā 9-ą│ąŠ čéą░ą║č鹊ą▓ąŠą│ąŠ ąĖą╝ą┐čāą╗čīčüą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ ą▒ą░ą╣čéą░ ą┐čĆą░ą▓ąĖą╗čīąĮąŠą╣ ąŠą┐ąĄčĆą░čåąĖąĖ ąĘą░ą┐ąĖčüąĖ. ąĢčüą╗ąĖ ~CLR ą▒čŗą╗ ą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮ ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ąĘą░ą┐ąĖčüąĖ, č鹊 čŹčéą░ ąĘą░ą┐ąĖčüčī ąŠą▒čĆčŗą▓ą░ąĄčéčüčÅ. ąĢčüą╗ąĖ ~CLR ą▒čŗą╗ ą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮ ą▓ čĆąĄąČąĖą╝ąĄ high speed, č鹊 ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ ą▓čŗą╣ą┤ąĄčé ąĖąĘ čĆąĄąČąĖą╝ą░ high speed. |

| 6 |

ADDR |

ąÆčģąŠą┤, čćčāą▓čüčéą▓ąĖč鹥ą╗čīąĮčŗą╣ ą║ čéčĆąĄą╝ čüąŠčüč鹊čÅąĮąĖčÅą╝. ąĢą│ąŠ čüąŠčüč鹊čÅąĮąĖąĄ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ą┤ą▓ą░ ą╝ą╗ą░ą┤čłąĖčģ ą▒ąĖčéą░ (A1, A0) 7-ą▒ąĖčéąĮąŠą│ąŠ slave-ą░ą┤čĆąĄčüą░. |

| 7 |

SCL |

Serial Clock Line, čéą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗ I2C. ąśčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓ą╝ąĄčüč鹥 čü SDA ą┤ą╗čÅ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ą▓ 24-ą▒ąĖčéąĮčŗą╣ ą▓čģąŠą┤ąĮąŠą╣ čĆąĄą│ąĖčüčéčĆ ąĖ ąĖąĘ ąĮąĄą│ąŠ. |

| 8 |

SDA |

Serial Data Line, čüąĖą│ąĮą░ą╗ ą┤ą░ąĮąĮčŗčģ I2C. ąśčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓ą╝ąĄčüč鹥 čü SCL ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ą▓ 24-ą▒ąĖčéąĮčŗą╣ ą▓čģąŠą┤ąĮąŠą╣ čĆąĄą│ąĖčüčéčĆ ąĖ ąĖąĘ ąĮąĄą│ąŠ. ąŁč鹊 ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╣ čüąĖą│ąĮą░ą╗ čü ąŠčéą║čĆčŗčéčŗą╝ čüč鹊ą║ąŠą╝, ą║ąŠč鹊čĆčŗą╣ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐ąŠą┤čéčÅąĮčāčé ą▓ąĄčĆčģąĮąĖą╝ ą┐ąŠą┤čéčÅą│ąĖą▓ą░čÄčēąĖą╝ čĆąĄąĘąĖčüč鹊čĆąŠą╝ (pull-up) ą║ VDD. |

| 9 |

VDD |

ąÆčģąŠą┤ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ. ąŁčéąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą╝ąŠą│čāčé čĆą░ą▒ąŠčéą░čéčī ąŠčé ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąŠčé 2.7V ą┤ąŠ 5.5V, ąĖ ą┐ąĖčéą░ąĮąĖąĄ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ąŠčéčäąĖą╗čīčéčĆąŠą▓ą░ąĮąŠ ąĮą░ GND ą┤ą▓čāą╝čÅ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠ čüąŠąĄą┤ąĖąĮąĄąĮąĮčŗą╝ąĖ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆą░ą╝ąĖ 10 ą╝ą║ąż ąĖ 0.1 ą╝ą║ąż. |

| 10 |

VREFIN/VREFOUT |

AD56x7R ąĖą╝ąĄčÄčé ąŠą▒čēąĖą╣ ą▓čŗą▓ąŠą┤ ą┤ą╗čÅ ą▓čģąŠą┤ą░ ąĖ ą▓čŗčģąŠą┤ą░ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ. ąÜąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ ąĖčüč鹊čćąĮąĖą║ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ, č鹊 čŹč鹊 ą▓čŗčģąŠą┤. ąÜąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓ąĮąĄčłąĮąĖą╣ ąĖčüč鹊čćąĮąĖą║ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ, č鹊 čŹč鹊 ą▓čģąŠą┤. ą¤ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ čŹč鹊čé ą▓čŗą▓ąŠą┤ čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą▓čģąŠą┤ ą┤ą╗čÅ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ. ąÆčģąŠą┤ ąĖ ą▓čŗčģąŠą┤ ą╝ąŠąČąĄčé ą▒čŗčéčī č鹊ą╗čīą║ąŠ ą▓ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░čģ čü čüčāčäčäąĖą║čüąŠą╝ R. ą£ąĖą║čĆąŠčüčģąĄą╝čŗ AD56x7 ąĖčüą┐ąŠą╗čīąĘčāčÄčé čŹč鹊čé ą▓čŗą▓ąŠą┤ č鹊ą╗čīą║ąŠ ą║ą░ą║ ą▓čģąŠą┤. |

[ą¤čĆąĖąĮčåąĖą┐ čĆą░ą▒ąŠčéčŗ]

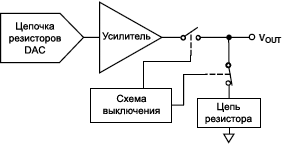

ąĪčģąĄą╝ą░ čåąĖčäčĆąŠ-ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ. AD56x7R/AD56x7 DAC ą┐čĆąŠąĖąĘą▓ąŠą┤čÅčéčüčÅ ą┐ąŠ č鹥čģą┐čĆąŠčåąĄčüčüčā CMOS. ąĪčģąĄą╝ą░ ą┐ąŠčüčéčĆąŠąĄąĮą░ ąĮą░ ąŠčüąĮąŠą▓ąĄ ą╗ąĖąĮąĄą╣ą║ąĖ čĆąĄąĘąĖčüč鹊čĆąŠą▓ ąĖ ą║ą╗čÄč湥ą╣, ąĘą░ ą║ąŠč鹊čĆčŗą╝ ąĖą┤ąĄčé ą▒čāč乥čĆąĮčŗą╣ čāčüąĖą╗ąĖč鹥ą╗čī.

ąĀąĖčü. 52. ąæą╗ąŠą║-čüčģąĄą╝ą░ ą░čĆčģąĖč鹥ą║čéčāčĆčŗ DAC.

ąĀąĖčü. 53. ą”ąĄą┐ąŠčćą║ą░ čĆąĄąĘąĖčüč鹊čĆąŠą▓ DAC, ą▓čŗą┐ąŠą╗ąĮčÅčÄčēą░čÅ čåąĖčäčĆąŠ-ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ.

ąÆčŗčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĖą┤ąĄą░ą╗čīąĮąŠą│ąŠ DAC ą┐čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ ą▓ąĮąĄčłąĮąĄą│ąŠ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą▓čŗčćąĖčüą╗čÅąĄčéčüčÅ ą┐ąŠ č乊čĆą╝čāą╗ąĄ (VOUT ą▓čŗčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ, VREFIN ąŠą┐ąŠčĆąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ, D čŹč鹊 ą▓čģąŠą┤ąĮąŠą╣ čåąĖčäčĆąŠą▓ąŠą╣ ą║ąŠą┤, N čŹč鹊 čĆą░ąĘčĆčÅą┤ąĮąŠčüčéčī DAC):

VOUT = VREFIN x (D / 2N)

ąÆčŗčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĖą┤ąĄą░ą╗čīąĮąŠą│ąŠ DAC ą┐čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą▓čŗčćąĖčüą╗čÅąĄčéčüčÅ ą┐ąŠ č乊čĆą╝čāą╗ąĄ (VOUT ą▓čŗčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ, VREFOUT ąŠą┐ąŠčĆąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ, D čŹč鹊 ą▓čģąŠą┤ąĮąŠą╣ čåąĖčäčĆąŠą▓ąŠą╣ ą║ąŠą┤, N čŹč鹊 čĆą░ąĘčĆčÅą┤ąĮąŠčüčéčī DAC):

VOUT = 2 x VREFOUT x (D / 2N)

ąŚąĮą░č湥ąĮąĖąĄ ą║ąŠą┤ą░ D ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąŠčé 0 ą┤ąŠ 4095 ą┤ą╗čÅ AD5627R/AD5627 (12-bit DAC), ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąŠčé 0 ą┤ąŠ 16383 ą┤ą╗čÅ AD5647R (14-bit DAC) ąĖ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ 0 .. 65535 ą┤ą╗čÅ AD5667R/AD5667 (16-bit DAC).

ąÆčŗčģąŠą┤ąĮąŠą╣ čāčüąĖą╗ąĖč鹥ą╗čī. ąÆčŗčģąŠą┤ąĮąŠą╣ ą▒čāč乥čĆąĮčŗą╣ čāčüąĖą╗ąĖč鹥ą╗čī ą╝ąŠąČąĄčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ą▓čŗčģąŠą┤ąĮąŠą╣ čāčĆąŠą▓ąĄąĮčī ą▓ąŠ ą▓čüąĄą╝ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖą╣ (rail-to-rail voltages), ąŠčé 0V ą┤ąŠ VDD. ą×ąĮ ą╝ąŠąČąĄčé ą▓čŗą┤ą░ą▓ą░čéčī čüąĖą│ąĮą░ą╗ ąĮą░ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠ čüąŠąĄą┤ąĖąĮąĄąĮąĮčāčÄ čåąĄą┐ąŠčćą║čā ąĖąĘ 2 ą║ą×ą╝ čĆąĄąĘąĖčüč鹊čĆą░ ąĖ 1000 pF ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆą░ (ąŠą┤ąĖąĮ ą║ąŠąĮąĄčå čåąĄą┐ąŠčćą║ąĖ ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą║ ą▓čŗčģąŠą┤čā čāčüąĖą╗ąĖč鹥ą╗čÅ, ą▓č鹊čĆąŠą╣ ą║ GND). ąÆąŠąĘą╝ąŠąČąĮąŠčüčéąĖ ą┐ąŠ ą▓č鹥ą║ą░čÄčēąĄą╝čā ąĖ ą▓čŗč鹥ą║ą░čÄčēąĄą╝čā č鹊ą║čā ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čāčüąĖą╗ąĖč鹥ą╗čÅ ą┐ąŠą║ą░ąĘą░ąĮčŗ ąĮą░ čĆąĖčüčāąĮą║ą░čģ 33 ąĖ 34 (čüą╝. ą┤ą░čéą░čłąĖčé [1]). ąĪą║ąŠčĆąŠčüčéčī ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ čüąŠčüčéą░ą▓ą╗čÅąĄčé 1.8V/ą╝ą║čü čü ą▓čĆąĄą╝ąĄąĮąĄą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ 7 ą╝ą║čü ą┐čĆąĖ ąĖąĘą╝ąĄąĮąĄąĮąĖąĖ čāčĆąŠą▓ąĮčÅ ąĮą░ ą▓čŗčģąŠą┤ąĄ ąŠčé 1/4 ą┤ąŠ 3/4 FSR.

ąÆąĮčāčéčĆąĄąĮąĮąĄąĄ ąŠą┐ąŠčĆąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ. AD5627R/AD5647R/AD5667R čüąĮą░ą▒ąČąĄąĮčŗ ą▓čüčéčĆąŠąĄąĮąĮčŗą╝ ąĖčüč鹊čćąĮąĖą║ąŠą╝ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ. ąÆąĄčĆčüąĖąĖ ą▒ąĄąĘ čüčāčäčäąĖą║čüą░ R čéčĆąĄą▒čāčÄčé ą▓ąĮąĄčłąĮąĄą│ąŠ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ. ąÆčüčéčĆąŠąĄąĮąĮąŠąĄ ąŠą┐ąŠčĆąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą▓čŗą║ą╗čÄč湥ąĮąŠ ą┐čĆąĖ ą┐ąŠą┤ą░č湥 ą┐ąĖčéą░ąĮąĖčÅ, ąĖ ą▓ą║ą╗čÄčćą░ąĄčéčüčÅ čüą┐ąĄčåąĖą░ą╗čīąĮąŠą╣ ą║ąŠą╝ą░ąĮą┤ąŠą╣ ąĘą░ą┐ąĖčüąĖ ą▓ čĆąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ (ą┐ąŠą┤čĆąŠą▒ąĮąŠčüčéąĖ čüą╝. ą┤ą░ą╗ąĄąĄ ą▓ čüąĄą║čåąĖąĖ "ąØą░čüčéčĆąŠą╣ą║ą░ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ").

ąÆąĄčĆčüąĖąĖ ą▓ 10-ą▓čŗą▓ąŠą┤ąĮčŗčģ ą║ąŠčĆą┐čāčüą░čģ LFCSP ąĖą╝ąĄčÄčé ąŠą┐ąŠčĆąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ 1.25V, čćč鹊 ą┤ą░ąĄčé ą▓čŗčģąŠą┤ FSR 2.5V. ąŁčéąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą╝ąŠą│čāčé čĆą░ą▒ąŠčéą░čéčī ą┐čĆąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąŠčé 2.7V ą┤ąŠ 5.5V. ąÆąĄčĆčüąĖąĖ ą▓ 10-ą▓čŗą▓ąŠą┤ąĮąŠą╝ ą║ąŠčĆą┐čāčüąĄ MSOP ąĖą╝ąĄčÄčé ąŠą┐ąŠčĆąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ 2.5V, čćč鹊 ą┤ą░ąĄčé ą▓čŗčģąŠą┤ FSR 5V. ąŁčéąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮčŗ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖą╣ ą┐ąĖčéą░ąĮąĖčÅ ąŠčé 2.7V ą┤ąŠ 5.5V, ąŠą┤ąĮą░ą║ąŠ ą║ąŠą│ą┤ą░ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ VDD čüčéą░ąĮąŠą▓ąĖčéčüčÅ ą╝ąĄąĮčīčłąĄ 5V, čāčĆąŠą▓ąĄąĮčī ąĮą░ ą▓čŗčģąŠą┤ąĄ ąŠą▒čĆąĄąĘą░ąĄčéčüčÅ ą┤ąŠ čāčĆąŠą▓ąĮčÅ VDD. ą¤ąŠą╗ąĮčŗą╣ čüą┐ąĖčüąŠą║ ą╝ąŠą┤ąĄą╗ąĄą╣ ą╝ąĖą║čĆąŠčüčģąĄą╝ čüą╝. čĆą░ąĘą┤ąĄą╗ąĄ "Ordering Guide" ą┤ą░čéą░čłąĖčéą░ [1]. ąŻčĆąŠą▓ąĄąĮčī ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą▓čŗą▓ąŠą┤ąĖčéčüčÅ ąĮą░ ąĮąŠąČą║čā VREFOUT ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ. ąĢčüą╗ąĖ ąĮą░ čŹč鹊čé čüąĖą│ąĮą░ą╗ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮą░ ą▓ąĮąĄčłąĮčÅčÅ ąĮą░ą│čĆčāąĘą║ą░, č鹊 ą┤ą╗čÅ ąĮąĄčæ čéčĆąĄą▒čāąĄčéčüčÅ ą▒čāč乥čĆąĮčŗą╣ čāčüąĖą╗ąĖč鹥ą╗čī. ą¤čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą▒ą╗ąŠą║ąĖčĆčāčÄčēąĖą╣ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ 100 nF ą╝ąĄąČą┤čā ą▓čŗą▓ąŠą┤ąŠą╝ VREFOUT ąĖ GND.

ąÆąĮąĄčłąĮąĄąĄ ąŠą┐ąŠčĆąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ. AD5627/AD5667 čéčĆąĄą▒čāčÄčé ą▓ąĮąĄčłąĮąĄą│ąŠ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ, ą┐ąŠą┤ą░ąĮąĮąŠą│ąŠ ąĮą░ ą▓čŗą▓ąŠą┤ VREFIN. ąÆčŗą▓ąŠą┤ VREFIN ą╝ąĖą║čĆąŠčüčģąĄą╝ AD56x7R ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą▓ąĮąĄčłąĮąĄąĄ ąŠą┐ąŠčĆąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ, ąĄčüą╗ąĖ č鹊ą│ąŠ čéčĆąĄą▒čāąĄčé ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ. ą¤ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą┐čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ ąĖčüč鹊čćąĮąĖą║ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą▓čŗą║ą╗čÄč湥ąĮ. ąÆčüąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ ą╝ąŠą│čāčé čĆą░ą▒ąŠčéą░čéčī ąŠčé ąŠą┤ąĮąŠą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąŠčé 2.7V ą┤ąŠ 5.5V.

[ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü]

AD56x7R/AD56x7 čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą┐ąŠą┤čćąĖąĮąĄąĮąĮąŠąĄ (slave) I2C-čāčüčéčĆąŠą╣čüčéą▓ąŠ. ą¤ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčéčüčÅ čüą║ąŠčĆąŠčüčéąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ standard (100 ą║ąōčå), fast (400 ą║ąōčå) ąĖ high speed (3.4 ą£ąōčå). ąĀąĄąČąĖą╝ high speed ą┤ąŠčüčéčāą┐ąĄąĮ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗčģ ą╝ąŠą┤ąĄą╗ąĄą╣ (čüą╝. "Ordering Guide" ą┤ą░čéą░čłąĖčéą░ [1]). ąØąĄ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčéčüčÅ ą┐ąŠą┤ą┤ąĄčƹȹ║ą░ ą┤ą╗čÅ 10-ą▒ąĖčéąĮąŠą╣ ą░ą┤čĆąĄčüą░čåąĖąĖ ąĖ ą░ą┤čĆąĄčüą░čåąĖąĖ general call (ąŠčéą┤ąĄą╗čīąĮčŗąĄ čäčāąĮą║čåąĖąĖ ą┐čĆąŠč鹊ą║ąŠą╗ą░ I2C/TWI).

ąÜą░ąČą┤ą░čÅ AD56x7R/AD56x7 ąĖą╝ąĄąĄčé 7-ą▒ąĖčéąĮčŗą╣ slave-ą░ą┤čĆąĄčü. 5 čüčéą░čĆčłąĖčģ ą▒ąĖčé 00011, ąĖ ą┤ą▓ą░ ą╝ą╗ą░ą┤čłąĖčģ (A1, A0) ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčéčüčÅ čüąŠčüč鹊čÅąĮąĖąĄą╝ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ą▓čŗą▓ąŠą┤ą░ ADDR, čćč鹊 ą┤ą░ąĄčé ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą┐ąŠą┤ą║ą╗čÄčćąĖčéčī ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠ ąĮą░ ąŠą┤ąĮčā čłąĖąĮčā I2C ą┤ąŠ čéčĆąĄčģ ą╝ąĖą║čĆąŠčüčģąĄą╝. ąŚąĮą░č湥ąĮąĖąĄ ą▒ąĖčé ą░ą┤čĆąĄčüą░ A1 ąĖ A0 ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čüąŠčüč鹊čÅąĮąĖčÅ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ą▓čŗą▓ąŠą┤ą░ ADDR ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▓ čéą░ą▒ą╗ąĖčåąĄ 7.

ąóą░ą▒ą╗ąĖčåą░ 7. ąÆčŗą▒ąŠčĆ ą░ą┤čĆąĄčüą░ ą┤ą╗čÅ A1 ąĖ A0.

| ą¤ąŠą┤ą║ą╗čÄč湥ąĮąĖąĄ ą▓čŗą▓ąŠą┤ą░ ADDR |

A1 |

A0 |

| VDD |

0 |

0 |

| ąØąĖą║čāą┤ą░ ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮ |

1 |

0 |

| GND |

1 |

1 |

2-ą┐čĆąŠą▓ąŠą┤ąĮčŗą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ą┐čĆąŠč鹊ą║ąŠą╗ čłąĖąĮčŗ I2C/TWI čĆą░ą▒ąŠčéą░ąĄčé čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝:

1. Master ąĖąĮąĖčåąĖąĖčĆčāąĄčé ą┐ąĄčĆąĄą┤ą░čćčā ą┤ą░ąĮąĮčŗčģ čüąŠą▒čŗčéąĖąĄą╝ START, ą║ąŠą│ą┤ą░ SDA ą┐ąĄčĆąĄčģąŠą┤ąĖčé 1 -> 0 ą┐čĆąĖ čāčĆąŠą▓ąĮąĄ 1 ąĮą░ SCL. ąŚą░č鹥ą╝ ąĖą┤ąĄčé ą▒ą░ą╣čé ą░ą┤čĆąĄčüą░, ą▓ ą║ąŠč鹊čĆąŠą╝ ąĮą░čģąŠą┤ąĖčéčüčÅ 7-ą▒ąĖčéąĮčŗą╣ slave-ą░ą┤čĆąĄčü čāčüčéčĆąŠą╣čüčéą▓ą░. Slave-čāčüčéčĆąŠą╣čüčéą▓ąŠ, čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ ą┐ąĄčĆąĄą┤ą░ąĮąĮąŠą╝čā ą░ą┤čĆąĄčüčā, ąŠčéą▓ąĄčćą░ąĄčé ą┐ąŠą┤čéčÅąČą║ąŠą╣ SDA ą║ ą╗ąŠą│. 0 ą▓ąŠ ą▓čĆąĄą╝čÅ 9-ą│ąŠ čéą░ą║č鹊ą▓ąŠą│ąŠ ąĖą╝ą┐čāą╗čīčüą░ (čŹč鹊 čéą░ą║ ąĮą░ąĘčŗą▓ą░ąĄą╝čŗą╣ ą▒ąĖčé ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ, acknowledge bit, čüąŠą║čĆą░čēąĄąĮąĮąŠ ACK). ąØą░ čŹč鹊ą╣ čüčéą░ą┤ąĖąĖ ą▓čüąĄ ą┤čĆčāą│ąĖąĄ čāčüčéčĆąŠą╣čüčéą▓ą░, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗąĄ ą║ čłąĖąĮąĄ (ąĄčüą╗ąĖ ąŠąĮąĖ ąĄčüčéčī), ąŠčüčéą░čÄčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ąĮąĄ ą░ą║čéąĖą▓ąĮąŠčüčéąĖ ą┐ąŠ čłąĖąĮąĄ, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ ą░ą┤čĆąĄčüąŠą▓ą░ąĮąĮąŠąĄ slave-čāčüčéčĆąŠą╣čüčéą▓ąŠ ąČą┤ąĄčé ą┐ąŠčüčéčāą┐ą╗ąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ą┤ą╗čÅ ąĘą░ą┐ąĖčüąĖ ą▓ ąĮąĄą│ąŠ ąĖą╗ąĖ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ ąĖąĘ ąĮąĄą│ąŠ.

2. ąöą░ąĮąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ą┐ąŠ čłąĖąĮąĄ ą┤čĆčāą│ ąĘą░ ą┤čĆčāą│ąŠą╝, ą┐čĆąĖ ą┐čĆąŠčģąŠąČą┤ąĄąĮąĖąĖ 9 čéą░ą║č鹊ą▓čŗčģ ąĖą╝ą┐čāą╗čīčüąŠą▓ (8 ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ, ąĘą░ ą║ąŠč鹊čĆčŗą╝ ąĖą┤ąĄčé ą▒ąĖčé ACK). ąśąĘą╝ąĄąĮąĄąĮąĖčÅ čāčĆąŠą▓ąĮčÅ ąĮą░ SDA ą┤ąŠą╗ąČąĮčŗ ą┐čĆąŠąĖčüčģąŠą┤ąĖčéčī, ą║ąŠą│ą┤ą░ ąĮą░ SCL ą┐čĆąĖčüčāčéčüčéą▓čāąĄčé čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 0, ąĖ ąĮą░ SDA ą┤ąŠą╗ąČąĄąĮ ąŠčüčéą░ą▓ą░čéčīčüčÅ čüčéą░ą▒ąĖą╗čīąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī, ą║ąŠą│ą┤ą░ ąĮą░ SCL ą┐čĆąĖčüčāčéčüčéą▓čāąĄčé ą╗ąŠą│. 1.

3. ąÜąŠą│ą┤ą░ ą▓čüąĄ ą▒ąĖčéčŗ ą┤ą░ąĮąĮčŗčģ ą▒čŗą╗ąĖ ąĘą░ą┐ąĖčüą░ąĮčŗ ąĖą╗ąĖ ą┐čĆąŠčćąĖčéą░ąĮčŗ, ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ čüąĖą│ąĮą░ą╗ STOP. ąöą╗čÅ čŹč鹊ą╣ čåąĄą╗ąĖ ą▓ čĆąĄąČąĖą╝ąĄ ąĘą░ą┐ąĖčüąĖ master ą┐ąŠą┤čéčÅą│ąĖą▓ą░ąĄčé SDA ą║ ą╗ąŠą│. 1 ą▓ąŠ ą▓čĆąĄą╝čÅ 10-č鹊 čéą░ą║č鹊ą▓ąŠą│ąŠ ąĖą╝ą┐čāą╗čīčüą░. ąÆ čĆąĄąČąĖą╝ąĄ čćč鹥ąĮąĖčÅ master ą▓čŗą┤ą░ąĄčé no acknowledge (NACK) ą▓ąŠ ą▓čĆąĄą╝čÅ 9-ą│ąŠ čéą░ą║č鹊ą▓ąŠą│ąŠ ąĖą╝ą┐čāą╗čīčüą░ (čé. ąĄ. SDA ąŠčüčéą░ąĄčéčüčÅ ą▓ ą╗ąŠą│. 1). ąŚą░č鹥ą╝ master ą┐ąĄčĆąĄą▓ąŠą┤ąĖčé SDA ą▓ ą╗ąŠą│. 0 ą▓ąŠ ą▓čĆąĄą╝čÅ 10-ą│ąŠ čéą░ą║č鹊ą▓ąŠą│ąŠ ąĖą╝ą┐čāą╗čīčüą░, čćč鹊ą▒čŗ ą▓čŗą┤ą░čéčī čüąĖą│ąĮą░ą╗ STOP.

ą×ą┐ąĄčĆą░čåąĖčÅ ąĘą░ą┐ąĖčüąĖ (WRITE). ą¤čĆąĖ ąĘą░ą┐ąĖčüąĖ ą▓ AD56x7R/AD56x7 master ą┤ąŠą╗ąČąĄąĮ ą▓čŗą┤ą░čéčī START, ąĘą░ ą║ąŠč鹊čĆčŗą╝ ąĖą┤ąĄčé ą▒ą░ą╣čé ą░ą┤čĆąĄčüą░ čü ą▒ąĖč鹊ą╝ R/W čĆą░ą▓ąĮčŗą╝ 0, ą┐ąŠčüą╗ąĄ č湥ą│ąŠ DAC ą┐ąŠą┤čéą▓ąĄčƹȹ┤ą░ąĄčé, čćč鹊 ą│ąŠč鹊ą▓ ą┐čĆąĖąĮąĖą╝ą░čéčī ą┤ą░ąĮąĮčŗąĄ, ą┐čāč鹥ą╝ ą┐ąŠą┤čéčÅąČą║ąĖ SDA ą║ ą╗ąŠą│. 0. AD56x7R/AD56x7 čéčĆąĄą▒čāąĄčé ą┤ą▓čāčģ ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ ą┤ą╗čÅ DAC ąĖ ą▒ą░ą╣čéą░ ą║ąŠą╝ą░ąĮą┤čŗ, ą║ąŠč鹊čĆčŗą╣ čāą┐čĆą░ą▓ą╗čÅąĄčé čĆą░ąĘą╗ąĖčćąĮčŗą╝ąĖ čäčāąĮą║čåąĖčÅą╝ąĖ DAC. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą▓ DAC ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮčŗ 3 ą▒ą░ą╣čéą░: ą▒ą░ą╣čé ą║ąŠą╝ą░ąĮą┤čŗ, ąĘą░ ą║ąŠč鹊čĆčŗą╝ ąĖą┤ąĄčé čüčéą░čĆčłąĖą╣ ą▒ą░ą╣čé, ąĖ ąĘą░č鹥ą╝ ąĖą┤ąĄčé ą╝ą╗ą░ą┤čłąĖą╣ ą▒ą░ą╣čé, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 54. ąÆčüąĄ čŹčéąĖ ą▒ą░ą╣čéčŗ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ą░čÄčéčüčÅ AD56x7R/AD56x7. ąŚą░č鹥ą╝ ąĖą┤ąĄčé čüąĖą│ąĮą░ą╗ STOP.

ąĀąĖčü. 54. ą×ą┐ąĄčĆą░čåąĖčÅ ąĘą░ą┐ąĖčüąĖ I2C.

ą×ą┐ąĄčĆą░čåąĖčÅ čćč鹥ąĮąĖčÅ (READ). ąÜąŠą│ą┤ą░ ą┤ą░ąĮąĮčŗąĄ ą▓čŗčćąĖčéčŗą▓ą░čÄčéčüčÅ ąŠą▒čĆą░čéąĮąŠ ąĖąĘ AD56x7R/AD56x7, ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą▓čŗą┤ą░ąĄčé START, ąĘą░ ą║ąŠč鹊čĆčŗą╝ ąĖą┤ąĄčé ą▒ą░ą╣čé ą░ą┤čĆąĄčüą░ čü ą▒ąĖč鹊ą╝ R/W = 1, ą┐ąŠčüą╗ąĄ č湥ą│ąŠ DAC ą┐ąŠą┤čéą▓ąĄčƹȹ┤ą░ąĄčé, čćč鹊 ą│ąŠč鹊ą▓ ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī ą┤ą░ąĮąĮčŗąĄ ą┐čāč鹥ą╝ ą┐ąŠą┤čéčÅąČą║ąĖ SDA ą║ ą╗ąŠą│. 0. ąŚą░č鹥ą╝ ąĖąĘ DAC ą▓čŗčćąĖčéčŗą▓ą░čÄčéčüčÅ 3 ą▒ą░ą╣čéą░, ą║ąŠč鹊čĆčŗąĄ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ą░čÄčéčüčÅ master, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 55. ąŚą░č鹥ą╝ ąĖą┤ąĄčé čüąĖą│ąĮą░ą╗ STOP.

ąĀąĖčü. 55. ą×ą┐ąĄčĆą░čåąĖčÅ čćč鹥ąĮąĖčÅ I2C.

HIGH SPEED MODE. AD5627RBRMZ b AD5667RBRMZ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÄčé čĆąĄąČąĖą╝ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ąŠą▒ą╝ąĄąĮą░ čü čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊č鹊ą╣ 3.4 ą£ąōčå (čüą╝. čĆą░ąĘą┤ąĄą╗ "Ordering Guide" ą┤ą░čéą░čłąĖčéą░ [1]).

ąĀąĄąČąĖą╝ ąŠą▒ą╝ąĄąĮą░ high speed ąĮą░čćąĖąĮą░ąĄčéčüčÅ ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ master ą░ą┤čĆąĄčüčāąĄčé ą▓čüąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗąĄ ą║ čłąĖąĮąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ ą║ąŠą┤ąŠą╝ 00001XXX, čćč鹊ą▒čŗ ą┐ąŠą║ą░ąĘą░čéčī ąĮą░čćą░ą╗ąŠ ą▓čŗčüąŠą║ąŠčüą║ąŠčĆąŠčüčéąĮąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ (čüą╝. čĆąĖčü. 56). ąŁč鹊čé ą║ąŠą┤ ąĮąĄ čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ą░čéčī ąĮąĖ ąŠą┤ąĮąŠą╝čā čāčüčéčĆąŠą╣čüčéą▓čā, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮąŠą╝čā ą║ čłąĖąĮąĄ, ą┐ąŠčŹč鹊ą╝čā ą▓ ąŠčéą▓ąĄčé ąĮą░ čŹč鹊čé ą║ąŠą┤ ą┐čĆąĖą┤ąĄčé NACK. ąŚą░č鹥ą╝ master ą┤ąŠą╗ąČąĄąĮ ą▓čŗą┤ą░čéčī ą┐ąŠą▓č鹊čĆąĮčŗą╣ START (repeated START), ąĘą░ ą║ąŠč鹊čĆčŗą╝ ąĖą┤ąĄčé ą░ą┤čĆąĄčü čāčüčéčĆąŠą╣čüčéą▓ą░. ąÆčŗą▒čĆą░ąĮąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐ąŠą┤čéą▓ąĄčĆą┤ąĖčé čŹč鹊čé ą░ą┤čĆąĄčü.

ąĀąĖčü. 56. ą¤ąĄčĆąĄą▓ąŠą┤ AD5627RBRMZ-2/AD5667RBRMZ-2 ą▓ High Speed Mode.

ąÆčüąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┐čĆąŠą┤ąŠą╗ąČą░čé čĆą░ą▒ąŠčéą░čéčī ą▓ čĆąĄąČąĖą╝ąĄ high speed ą┤ąŠ č鹥čģ ą┐ąŠčĆ, ą┐ąŠą║ą░ master ąĮąĄ ą▓čŗą┤ą░čüčé čüąĖą│ąĮą░ą╗ STOP. ąÜąŠą┤ą░ ą▒čāą┤ąĄčé ą▓čŗą┤ą░ąĮ čüąĖą│ąĮą░ą╗ STOP, ą▓čüąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ ą▓ąĄčĆąĮčāčéčüčÅ ą▓ čĆąĄąČąĖą╝ standard/fast. ą£ąĖą║čĆąŠčüčģąĄą╝ą░ čéą░ą║ąČąĄ ą▓ąĄčĆąĮąĄčéčüčÅ ą▓ čĆąĄąČąĖą╝ standard/fast, ą║ąŠą│ą┤ą░ ą░ą║čéąĖą▓ąĖčĆčāąĄčéčüčÅ čüąĖą│ąĮą░ą╗ ~CLR, ą║ąŠą│ą┤ą░ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ high speed.

ąÆčģąŠą┤ąĮąŠą╣ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░. ąŁč鹊čé čĆąĄą│ąĖčüčéčĆ ąĖą╝ąĄąĄčé čłąĖčĆąĖąĮčā 24 ą▒ąĖčéą░. ąöą░ąĮąĮčŗąĄ ąĘą░ą│čĆčāąČą░čÄčéčüčÅ ą▓ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą║ą░ą║ 24-ą▒ąĖčéąĮąŠąĄ čüą╗ąŠą▓ąŠ ą┐ąŠą┤ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝ čüąĖą│ąĮą░ą╗ą░ čéą░ą║č鹊ą▓ SCL. ążąĖąĘąĖč湥čüą║ą░čÅ ą┤ąĖą░ą│čĆą░ą╝ą╝ą░ ą▓čĆąĄą╝ąĄąĮąĖ čŹč鹊ą╣ ąŠą┐ąĄčĆą░čåąĖąĖ ąĖ ąĄčæ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ ą┐ąŠą║ą░ąĘą░ąĮčŗ ą▓ąŠ ą▓čĆąĄąĘą║ąĄ "ą¤ą░čĆą░ą╝ąĄčéčĆčŗ I2C" ą▓čŗčłąĄ (čéą░ą▒ą╗ąĖčåą░ 4 ąĖ čĆąĖčü. 3). ąĪčéą░čĆčłąĖąĄ 8 ą▒ąĖčé čŹč鹊ą│ąŠ čĆąĄą│ąĖčüčéčĆą░ čŹč鹊 ą▒ą░ą╣čé ą║ąŠą╝ą░ąĮą┤čŗ. ąæąĖčé DB23 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮ, ąĖ ą▓čüąĄą│ą┤ą░ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 0, ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ąĘą░ą┐ąĖčüčī ą▓ čāčüčéčĆąŠą╣čüčéą▓ąŠ. ąæąĖčé DB22 (S) ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą░ ą╝ąĮąŠą│ąŠą▒ą░ą╣čéąĮąŠą│ąŠ čĆąĄąČąĖą╝ą░ čĆą░ą▒ąŠčéčŗ (Multiple Block Write). ąĪą╗ąĄą┤čāčÄčēąĖąĄ 3 ą▒ąĖčéą░ čŹč鹊 ą▒ąĖčéčŗ ą║ąŠą╝ą░ąĮą┤čŗ C2C1C0, ą║ąŠč鹊čĆčŗąĄ čāą┐čĆą░ą▓ą╗čÅčÄčé čĆąĄąČąĖą╝ąŠą╝ čĆą░ą▒ąŠčéčŗ čāčüčéčĆąŠą╣čüčéą▓ą░ (čüą╝. čéą░ą▒ą╗ąĖčåčā 8). ą¤ąŠčüą╗ąĄą┤ąĮąĖąĄ 3 ą▒ąĖčéą░ ą┐ąĄčĆą▓ąŠą│ąŠ ą▒ą░ą╣čéą░ čŹč鹊 ą▒ąĖčéčŗ ą░ą┤čĆąĄčüą░ A2A1A0 ą▓čŗą▒ąŠčĆą░ ą║ą░ąĮą░ą╗ą░ A ąĖ/ąĖą╗ąĖ B (čüą╝. čéą░ą▒ą╗ąĖčåčā 9). ą×čüčéą░ą▓čłąĖąĄčüčÅ ą┤ą░ąĮąĮčŗąĄ čŹč鹊 čüą╗ąŠą▓ą░ąŠ ą┤ą░ąĮąĮčŗčģ (2 ą▒ą░ą╣čéą░), ą▓ ą║ąŠč鹊čĆčŗčģ ąĘąĮą░čćąĖą╝čŗą╝ąĖ (ą┐ąŠą╗ąĄąĘąĮčŗą╝ąĖ) ą▒čāą┤čāčé 16, 14 ąĖą╗ąĖ 12 ą▒ąĖčé (ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą╝ąŠą┤ąĄą╗ąĖ DAC). ą¤ąŠą╗ąĄąĘąĮčŗąĄ ą▒ąĖčéčŗ ą▓čüąĄą│ą┤ą░ ąĖą┤čāčé ą┐ąĄčĆą▓čŗą╝ąĖ, ąĮą░čćąĖąĮą░čÅ čü čüą░ą╝ąŠą│ąŠ ąĘąĮą░čćą░čēąĄą│ąŠ ą▒ąĖčéą░, ąĖ ą┐ąŠčüą╗ąĄą┤ąĮąĖąĄ 2 ąĖą╗ąĖ 4 ą▒ąĖčéą░ ąĖąĘ 16 ą▒ąĖčé ą╝ąŠą│čāčé ą▒čŗčéčī ąĮąĖč湥ą│ąŠ ąĮąĄ ąĘąĮą░čćą░čēąĖą╝ąĖ ą▓ čüą╗čāčćą░ąĄ 14-ą▒ąĖčéąĮąŠą│ąŠ ąĖą╗ąĖ 12-ą▒ąĖčéąĮąŠą│ąŠ DAC čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ (čé. ąĄ. čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ ą┤ą╗čÅ AD5647R ąĖ ą┤ą╗čÅ AD5627R/AD5627, čüą╝. čĆąĖčüčāąĮą║ąĖ 59 .. 61, ąĮąĖč湥ą│ąŠ ąĮąĄ ąĘąĮą░čćą░čēąĖąĄ ą╝ą╗ą░ą┤čłąĖąĄ ą▒ąĖčéčŗ ą┤ą░ąĮąĮčŗčģ ą┐ąŠą║ą░ąĘą░ąĮčŗ ą║čĆąĄčüčéąĖą║ą░ą╝ąĖ X).

ąóą░ą▒ą╗ąĖčåą░ 8. ą×ą┐čĆąĄą┤ąĄą╗ąĄąĮąĖąĄ ą║ąŠą╝ą░ąĮą┤.

| C2 |

C1 |

C0 |

ąÜąŠą╝ą░ąĮą┤ą░ |

| 0 |

0 |

0 |

ąŚą░ą┐ąĖčüčī ą▓ąŠ ą▓čģąŠą┤ąĮąŠą╣ čĆąĄą│ąĖčüčéčĆ n. |

| 0 |

0 |

1 |

ą×ą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ DAC n. |

| 0 |

1 |

0 |

ąŚą░ą┐ąĖčüčī ą▓ąŠ ą▓čģąŠą┤ąĮąŠą╣ čĆąĄą│ąĖčüčéčĆ n, ąŠą▒ąĮąŠą▓ąĖčéčī ą▓čüąĄ (ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ ~LDAC). |

| 0 |

1 |

1 |

ąŚą░ą┐ąĖčüčī ąĖ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ DAC ą║ą░ąĮą░ą╗ą░ n. |

| 1 |

0 |

0 |

ąÆą║ą╗čÄč湥ąĮąĖąĄ/ą▓čŗą║ą╗čÄč湥ąĮąĖąĄ. |

| 1 |

0 |

1 |

ąĪą▒čĆąŠčü. |

| 1 |

1 |

0 |

ąØą░čüčéčĆąŠą╣ą║ą░ čĆąĄą│ąĖčüčéčĆą░ ~LDAC. |

| 1 |

1 |

1 |

ąØą░čüčéčĆąŠą╣ą║ą░ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ (ą▓ą║ą╗čÄč湥ąĮąĖąĄ/ą▓čŗą║ą╗čÄč湥ąĮąĖąĄ). |

ąóą░ą▒ą╗ąĖčåą░ 9. ąÜąŠą╝ą░ąĮą┤ą░ ą░ą┤čĆąĄčüą░ DAC.

| A2 |

A1 |

A0 |

ąÉą┤čĆąĄčü (n) |

| 0 |

0 |

0 |

DAC A |

| 0 |

0 |

1 |

DAC B |

| 1 |

1 |

1 |

ąÉą┤čĆąĄčüąŠą▓ą░ąĮčŗ ąŠą▒ą░ DAC-ą░ |

Multiple Block Write. ąŁč鹊čé čĆąĄąČąĖą╝ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ AD56x7R/AD56x7, ąŠąĮ ą┐ąŠą╗ąĄąĘąĄąĮ ą┤ą╗čÅ ą┐čĆąĖą╗ąŠąČąĄąĮąĖą╣, čéčĆąĄą▒čāčÄčēąĖčģ ą▒čŗčüčéčĆąŠą│ąŠ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ DAC, ą║ąŠą│ą┤ą░ ąĮąĄ ąĮą░ą┤ąŠ ą╝ąĄąĮčÅčéčī ą▒ą░ą╣čé ą║ąŠą╝ą░ąĮą┤čŗ. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ą║ą░ąČą┤ą░čÅ ą▓čŗą▒ąŠčĆą║ą░ ą┤ą░ąĮąĮčŗčģ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą┤ą▓čāą╝čÅ ą▒ą░ą╣čéą░ą╝ąĖ, ą▒ąĄąĘ ą▓čŗą┤ą░čćąĖ čüąĖą│ąĮą░ą╗ą░ STOP ą┐ąŠčüą╗ąĄ ą║ą░ąČą┤ąŠą╣ ą┐ąĄčĆąĄą┤ą░ąĮąĮąŠą╣ ą┐ą░čĆčŗ ą▒ą░ą╣čé. ąæąĖčé S (DB22) ą▓ ą▒ą░ą╣č鹥 ą║ąŠą╝ą░ąĮą┤čŗ ą┤ą╗čÅ ą╝ąĮąŠą│ąŠą▒ą░ą╣čéąĮąŠą│ąŠ čĆąĄąČąĖą╝ą░ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1 (čüą╝. čĆąĖčü. 57). ąöą╗čÅ čüčéą░ąĮą┤ą░čĆčéąĮčŗčģ čĆąĄąČąĖą╝ąŠą▓ 3-ą▒ą░ą╣čéąĮąŠą│ąŠ ąĖ 4-ą▒ą░ą╣čéąĮąŠą│ąŠ ą▒ąĖčé S (DB22) ą▓ ą▒ą░ą╣č鹥 ą║ąŠą╝ą░ąĮą┤čŗ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 0 (čüą╝. čĆąĖčü. 58).

-fig57.png)

ąĀąĖčü. 57. Multiple Block Write č鹊ą╗čīą║ąŠ čü ąĮą░čćą░ą╗čīąĮčŗą╝ ą▒ą░ą╣č鹊ą╝ ą║ąŠą╝ą░ąĮą┤čŗ (S = 1).

-fig58.png)

ąĀąĖčü. 58. Multiple Block Write c ą▒ą░ą╣č鹊ą╝ ą║ąŠą╝ą░ąĮą┤čŗ ą▓ ą║ą░ąČą┤ąŠą╝ ą▒ą╗ąŠą║ąĄ (S = 0).

-fig59.png)

ąĀąĖčü. 59. ąÆčģąŠą┤ąĮąŠą╣ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ ą╝ąĖą║čĆąŠčüčģąĄą╝ AD5667R/AD5667 (16-ą▒ąĖčéąĮčŗą╣ DAC).

-fig60.png)

ąĀąĖčü. 60. ąÆčģąŠą┤ąĮąŠą╣ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ ą╝ąĖą║čĆąŠčüčģąĄą╝ AD5647R (14-ą▒ąĖčéąĮčŗą╣ DAC).

-fig61.png)

ąĀąĖčü. 61. ąÆčģąŠą┤ąĮąŠą╣ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ ą╝ąĖą║čĆąŠčüčģąĄą╝ AD5627R/AD5627 (12-ą▒ąĖčéąĮčŗą╣ DAC).

ąĪąĖąĮčģčĆąŠąĮąĮčŗą╣ ~LDAC. ąĀąĄą│ąĖčüčéčĆčŗ DAC ąŠą▒ąĮąŠą▓ą╗čÅčÄčéčüčÅ ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą▒čŗą╗ąĖ ą▓ą▓ąĄą┤ąĄąĮčŗ ąĮąŠą▓čŗąĄ ą┤ą░ąĮąĮčŗąĄ. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ~LDAC ą╝ąŠąČąĄčé ąĮą░čģąŠą┤ąĖčéčīčüčÅ ą┐ąŠčüč鹊čÅąĮąĮąŠ ą▓ ą╗ąŠą│. 0 ąĖą╗ąĖ ąĮą░ ąĮąĄą│ąŠ ą╝ąŠą│čāčé ą┐čĆąĖčģąŠą┤ąĖčéčī ąĖą╝ą┐čāą╗čīčüčŗ.

ąÉčüąĖąĮčģčĆąŠąĮąĮčŗą╣ ~LDAC. ąÆčŗčģąŠą┤čŗ ąĮąĄ ąŠą▒ąĮąŠą▓ą╗čÅčÄčéčüčÅ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ čü ąĘą░ą┐ąĖčüčīčÄ ą▓čģąŠą┤ąĮčŗčģ čĆąĄą│ąĖčüčéčĆąŠą▓. ąÜąŠą│ą┤ą░ ~LDAC ą┐ąĄčĆąĄčģąŠą┤ąĖčé ą▓ ą╗ąŠą│. 0, čĆąĄą│ąĖčüčéčĆčŗ DAC ąŠą▒ąĮąŠą▓ą╗čÅčÄčéčüčÅ čüąŠą┤ąĄčƹȹĖą╝čŗą╝ ą▓čģąŠą┤ąĮąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░.

ąĀąĄą│ąĖčüčéčĆ ~LDAC ą┤ą░ąĄčé ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÄ ą┐ąŠą╗ąĮčāčÄ ą│ąĖą▒ą║ąŠčüčéčī ąĖ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ č湥čĆąĄąĘ ą░ą┐ą┐ą░čĆą░čéąĮčŗą╣ ą▓čŗą▓ąŠą┤ ~LDAC. ąŁč鹊čé čĆąĄą│ąĖčüčéčĆ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą▓čŗą▒čĆą░čéčī, ą║ą░ą║ą░čÅ ą║ąŠą╝ą▒ąĖąĮą░čåąĖčÅ ą║ą░ąĮą░ą╗ąŠą▓ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ąŠą▒ąĮąŠą▓ą╗čÅąĄčéčüčÅ, ą║ąŠą│ą┤ą░ čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮčŗą╣ ą▓čŗą▓ąŠą┤ ~LDAC. ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▓ 0 ą▒ąĖčéą░ ~LDAC čĆąĄą│ąĖčüčéčĆą░ ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ čŹč鹊ą│ąŠ ą║ą░ąĮą░ą╗ą░ čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ą▓čŗą▓ąŠą┤ąŠą╝ ~LDAC. ąĢčüą╗ąĖ čŹč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1, č鹊 čŹč鹊čé ą║ą░ąĮą░ą╗ ąŠą▒ąĮąŠą▓ą╗čÅąĄčéčüčÅ čüąĖąĮčģčĆąŠąĮąĮąŠ, čé. ąĄ. čĆąĄą│ąĖčüčéčĆ DAC ąŠą▒ąĮąŠą▓ą╗čÅąĄčéčüčÅ ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą▒čāą┤čāčé ą▓ą▓ąĄą┤ąĄąĮčŗ ąĮąŠą▓čŗąĄ ą┤ą░ąĮąĮčŗąĄ, ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé čüąŠčüč鹊čÅąĮąĖčÅ ą▓čŗą▓ąŠą┤ą░ ~LDAC. ąŁč鹊 ą▓čŗą│ą╗čÅą┤ąĖčé čéą░ą║, ą║ą░ą║ ąĄčüą╗ąĖ ą▒čŗ ą▓čŗą▓ąŠą┤ ~LDAC ą▒čŗą╗ ą▒čŗ ą┐ąŠą┤čéčÅąĮčāčé ą║ ą╗ąŠą│. 0. ąĪą╝. čéą░ą▒ą╗ąĖčåčā 10 ą┤ą╗čÅ čĆąĄąČąĖą╝ą░ čĆą░ą▒ąŠčéčŗ čĆąĄą│ąĖčüčéčĆą░ ~LDAC. ąŁčéą░ ą│ąĖą▒ą║ąŠčüčéčī ą┐ąŠą╗ąĄąĘąĮą░ ą▓ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅčģ, ą║ąŠą│ą┤ą░ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī čģąŠč湥čé ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ąŠą▒ąĮąŠą▓ąĖčéčī ą║ą░ąĮą░ą╗čŗ, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ ąŠčüčéą░ą╗čīąĮą░čÅ čćą░čüčéčī ą║ą░ąĮą░ą╗ąŠą▓ čüąĖąĮčģčĆąŠąĮąĮąŠ ąŠą▒ąĮąŠą▓ą╗čÅąĄčéčüčÅ.

ąóą░ą▒ą╗ąĖčåą░ 10. ąĀąĄąČąĖą╝ čĆą░ą▒ąŠčéčŗ čĆąĄą│ąĖčüčéčĆą░ ~LDAC: ąĘą░ą│čĆčāąĘą║ą░ čĆąĄą│ąĖčüčéčĆą░ ~LDAC.

| ąæąĖčéčŗ ~LDAC (DB1, DB0) |

ąÆčŗą▓ąŠą┤ ~LDAC |

ąĀą░ą▒ąŠčéą░ ~LDAC |

| 0 |

1/0 |

ą×ą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą▓čŗą▓ąŠą┤ąŠą╝ ~LDAC |

| 1 |

x - čāčĆąŠą▓ąĄąĮčī ąĮąĄ ąĖą╝ąĄąĄčé ąĘąĮą░č湥ąĮąĖčÅ |

ąĀąĄą│ąĖčüčéčĆčŗ DAC ąŠą▒ąĮąŠą▓ą╗čÅčÄčéčüčÅ čüčĆą░ąĘčā ą┐ąŠčüą╗ąĄ ą┐ąŠčüčéčāą┐ą╗ąĄąĮąĖčÅ ąĮąŠą▓čŗčģ ą┤ą░ąĮąĮčŗčģ |

ąŚą░ą┐ąĖčüčī ą▓ DAC ą║ąŠą╝ą░ąĮą┤čŗ 110 ąĘą░ą│čĆčāąĘąĖčé 2-ą▒ąĖčéąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ LDAC [DB1:DB0]. ą¤ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą║ą░ąĮą░ą╗ą░ čéčāčé 0, čé. ąĄ. ą▓čŗą▓ąŠą┤ ~LDAC čĆą░ą▒ąŠčéą░ąĄčé ą▓ ąĮąŠčĆą╝ą░ą╗čīąĮąŠą╝ čĆąĄąČąĖą╝ąĄ. ąŻčüčéą░ąĮąŠą▓ą║ą░ čŹčéąĖčģ ą▒ąĖčé ą▓ 1 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 čĆąĄą│ąĖčüčéčĆ DAC ąŠą▒ąĮąŠą▓ą╗čÅąĄčéčüčÅ ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé čüąŠčüč鹊čÅąĮąĖčÅ ą▓čŗą▓ąŠą┤ą░ ~LDAC. ąĪą╝. čĆąĖčü. 63 ą┤ą╗čÅ čüąŠą┤ąĄčƹȹĖą╝ąŠą│ąŠ ą▓čģąŠą┤ąĮąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░ čüą┤ą▓ąĖą│ą░ ą▓ąŠ ą▓čĆąĄą╝čÅ ą║ąŠą╝ą░ąĮą┤čŗ ąĮą░čüčéčĆąŠą╣ą║ąĖ čĆąĄą│ąĖčüčéčĆą░ ~LDAC.

ąĀąĖčü. 63. ~LDAC Setup Command.

ąÜąŠą╝ą░ąĮą┤ą░ 100 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮą░ ą┤ą╗čÅ čäčāąĮą║čåąĖąĖ power-up/down (ą▓ą║ą╗čÄč湥ąĮąĖąĄ/ą▓čŗą║ą╗čÄč湥ąĮąĖąĄ). ąĀąĄąČąĖą╝čŗ power-up/down ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāčÄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčé DB5 ąĖ DB4. ąŁč鹊 ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ą▓čŗčģąŠą┤ąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ čāčüąĖą╗ąĖč鹥ą╗čÅ DAC, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▓ čéą░ą▒ą╗ąĖčåąĄ 11.

ąóą░ą▒ą╗ąĖčåą░ 11. ąĀąĄąČąĖą╝čŗ čĆą░ą▒ąŠčéčŗ AD56x7R/AD56x7.

| DB5 |

DB4 |

ąĀąĄąČąĖą╝ čĆą░ą▒ąŠčéčŗ |

| 0 |

0 |

ąØąŠčĆą╝ą░ą╗čīąĮą░čÅ čĆą░ą▒ąŠčéą░ |

| ąĀąĄąČąĖą╝čŗ power-down: |

| 0 |

1 |

ą£ąĄąČą┤čā GND ąĖ ą▓čŗčģąŠą┤ąŠą╝ ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčéčüčÅ čĆąĄąĘąĖčüč鹊čĆ 1 ą║ą×ą╝ |

| 1 |

0 |

ą£ąĄąČą┤čā GND ąĖ ą▓čŗčģąŠą┤ąŠą╝ ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčéčüčÅ čĆąĄąĘąĖčüč鹊čĆ 100 ą║ą×ą╝ |

| 1 |

1 |

ąÆčŗčģąŠą┤ ą▓ čéčĆąĄčéčīąĄą╝ čüąŠčüč鹊čÅąĮąĖąĖ, ąŠčéą║ą╗čÄč湥ąĮ (ą▓čŗčüąŠą║ąŠąĄ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ) |

ąæąĖčéčŗ DB1 ąĖ DB0 ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčé, ą║ą░ą║ąŠą╝čā DAC ąĖą╗ąĖ ą║ą░ą║ąĖą╝ DAC ą┐čĆąĖą╝ąĄąĮčÅąĄčéčüčÅ ą║ąŠą╝ą░ąĮą┤ą░ power-up/down. ąŻčüčéą░ąĮąŠą▓ą║ą░ ąŠą┤ąĮąŠą│ąŠ ąĖąĘ čŹčéąĖčģ ą▒ąĖčé ą▓ 1 ą┐čĆąĖą╝ąĄąĮčÅąĄčé čüąŠčüč鹊čÅąĮąĖąĄ power-up/down, ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠąĄ ą▒ąĖčéą░ą╝ąĖ DB5 ąĖ DB4 ą┤ą╗čÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ DAC. ąĢčüą╗ąĖ čŹč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 0, č鹊 čüąŠčüč鹊čÅąĮąĖąĄ DAC ąĮąĄ ąĖąĘą╝ąĄąĮąĖčéčüčÅ. ąĀąĖčü. 65 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ ą▓čģąŠą┤ąĮąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░ čüą┤ą▓ąĖą│ą░ ą┤ą╗čÅ ą║ąŠą╝ą░ąĮą┤čŗ power up/down.

ąĀąĖčü. 65. Power Up/Down Command.

ąÜąŠą│ą┤ą░ ą▒ąĖčé DB5 ąĖ ą▒ąĖčé DB4 čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą▓ 0, ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ čĆą░ą▒ąŠčéą░ąĄčé ą▓ ąĮąŠčĆą╝ą░ą╗čīąĮąŠą╝ čĆąĄąČąĖą╝ąĄ, ą┐ąŠčéčĆąĄą▒ą╗čÅčÅ č鹊ą║ 0.4 mA ąŠčé 5V. ą×ą┤ąĮą░ą║ąŠ ą┤ą╗čÅ čéčĆąĄčģ čĆąĄąČąĖą╝ąŠą▓ power-down č鹊ą║ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ ą┐ą░ą┤ą░ąĄčé ą┤ąŠ 480 nA ą┐čĆąĖ 5V. ą¤ą░ą┤ą░ąĄčé ąĮąĄ č鹊ą╗čīą║ąŠ č鹊ą║ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ, ąĮąŠ ąĄčēąĄ ą▓čŗčģąŠą┤ąĮąŠą╣ ą║ą░čüą║ą░ą┤ ą▓ąĮčāčéčĆąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą┐ąĄčĆąĄą║ą╗čÄčćą░ąĄčé ą▓čŗčģąŠą┤ čāčüąĖą╗ąĖč鹥ą╗čÅ ąĮą░ čĆąĄąĘąĖčüč鹊čĆąĮčāčÄ čåąĄą┐čī čü ąĖąĘą▓ąĄčüčéąĮčŗą╝ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄą╝. ąŁč鹊 ą┤ą░ąĄčé ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ąĘąĮą░čéčī ą▓čŗčģąŠą┤ąĮąŠąĄ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ, ą║ąŠą│ą┤ą░ ąĄčæ ą║ą░ąĮą░ą╗ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ power-down. ąÆčŗčģąŠą┤čŗ ą╝ąŠą│čāčé ą▒čŗčéčī ą╗ąĖą▒ąŠ ą┐ąŠą┤ą║ą╗čÄč湥ąĮčŗ ą▓ąĮčāčéčĆąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą║ GND č湥čĆąĄąĘ čĆąĄąĘąĖčüč鹊čĆ 1 ą║ą×ą╝ ąĖą╗ąĖ 100 ą║ą×ą╝, ąĖą╗ąĖ ąČąĄ ą╝ąŠą│čāčé ąŠčüčéą░čéčīčüčÅ ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗą╝ąĖ (čéčĆąĄčéčīąĄ čüąŠčüč鹊čÅąĮąĖąĄ), ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 62.

ąĀąĖčü. 62. ąĪąŠčüč鹊čÅąĮąĖąĄ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ ą║ą░čüą║ą░ą┤ą░ ą▓ąŠ ą▓čĆąĄą╝čÅ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ (power-down).

ąÜąŠą│ą┤ą░ ą░ą║čéąĖą▓ąĖčĆčāąĄčéčüčÅ čĆąĄąČąĖą╝ power-down, ą▓čŗą║ą╗čÄčćą░čÄčéčüčÅ ą│ąĄąĮąĄčĆą░č鹊čĆ čüą╝ąĄčēąĄąĮąĖčÅ (bias generator), ą▓čŗčģąŠą┤ąĮąŠą╣ čāčüąĖą╗ąĖč鹥ą╗čī, čåąĄą┐ąŠčćą║ą░ čĆąĄąĘąĖčüč鹊čĆąŠą▓ DAC ąĖ ą┤čĆčāą│ąĖąĄ ą╗ąĖąĮąĄą╣ąĮčŗąĄ čüčģąĄą╝čŗ, ą║ąŠč鹊čĆčŗąĄ ą▓ čĆą░ą▒ąŠč湥ą╝ čĆąĄąČąĖą╝ąĄ ą┐ąŠčéčĆąĄą▒ą╗čÅą╗ąĖ č鹊ą║. ą×ą┤ąĮą░ą║ąŠ ą▓čŗą║ą╗čÄč湥ąĮąĖąĄ ąĮąĄ ą▓ą╗ąĖčÅąĄčé ąĮą░ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ čĆąĄą│ąĖčüčéčĆą░ DAC. ąÆčĆąĄą╝čÅ ą▓čŗčģąŠą┤čÅ ąĖąĘ power-down ąŠą▒čŗčćąĮąŠ čüąŠčüčéą░ą▓ą╗čÅąĄčé 4 ą╝ą║čü ą┤ą╗čÅ VDD = 5V.

Power-on reset ąĖ software reset. AD56x7R/AD56x7 čüąŠą┤ąĄčƹȹĖčé čüčģąĄą╝čā čüą▒čĆąŠčüą░ ą┐čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ (power-on reset), ą║ąŠč鹊čĆą░čÅ čāą┐čĆą░ą▓ą╗čÅąĄčé ą▓čŗčģąŠą┤ąĮčŗą╝ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄą╝ ą▓ ą╝ąŠą╝ąĄąĮčé ą┐ąŠą┤ą░čćąĖ ąĮą░ ą╝ąĖą║čĆąŠčüčģąĄą╝čā ą┐ąĖčéą░ąĮąĖčÅ. ąŁč鹊 ąŠą▒ąĄčüą┐ąĄčćąĖą▓ą░ąĄčé ą┐ąŠčÅą▓ą╗ąĄąĮąĖąĄ ąĮą░ ą▓čŗčģąŠą┤ąĄ 0V ą┐čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ, ąĖ ą▓čŗčģąŠą┤ ąŠčüčéą░ąĄčéčüčÅ ą▓ čéą░ą║ąŠą╝ čüąŠčüč鹊čÅąĮąĖąĖ ą┤ąŠ č鹥čģ ą┐ąŠčĆ, ą┐ąŠą║ą░ ąĮąĄ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą┐čĆą░ą▓ąĖą╗čīąĮą░čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ąĘą░ą┐ąĖčüąĖ ą┤ą░ąĮąĮčŗčģ ą▓ DAC. ąŁč鹊 ą┐ąŠą╗ąĄąĘąĮąŠ ą▓ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅčģ, ą│ą┤ąĄ ą▓ą░ąČąĮąŠ ąĘąĮą░čéčī čüąŠčüč鹊čÅąĮąĖąĄ ą▓čŗčģąŠą┤ą░ DAC, ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą▓ą║ą╗čÄč湥ąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ. ąøčÄą▒čŗąĄ čüąŠą▒čŗčéąĖčÅ ąĮą░ čüąĖą│ąĮą░ą╗ą░čģ ~LDAC ąĖą╗ąĖ ~CLR ąĖą│ąĮąŠčĆąĖčĆčāčÄčéčüčÅ ą▓ąŠ ą▓čĆąĄą╝čÅ power-on reset.

ąóą░ą║ąČąĄ ąĄčüčéčī čäčāąĮą║čåąĖčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čüą▒čĆąŠčüą░ (software reset), ą▓čŗą┐ąŠą╗ąĮčÅąĄą╝ą░čÅ ą║ąŠą╝ą░ąĮą┤ąŠą╣ 101. ąŁčéą░ ą║ąŠą╝ą░ąĮą┤ą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čüą▒čĆąŠčüą░ ąĖą╝ąĄąĄčé 2 čĆąĄąČąĖą╝ą░ čüą▒čĆąŠčüą░, ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗčģ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ DB0 ą▓ąŠ ą▓čģąŠą┤ąĮąŠą╝ čĆąĄą│ąĖčüčéčĆąĄ čüą┤ą▓ąĖą│ą░.

ąóą░ą▒ą╗ąĖčåą░ 12 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüąŠčüč鹊čÅąĮąĖčÅ ą▒ąĖčéą░ ąĖ čĆą░ą▒ąŠčéčā čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖčģ čĆąĄąČąĖą╝ąŠą▓ čüą▒čĆąŠčüą░ čāčüčéčĆąŠą╣čüčéą▓ą░. ąĀąĖčü. 64 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ ą▓čģąŠą┤ąĮąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░ čüą┤ą▓ąĖą│ą░ ą▓ąŠ ą▓čĆąĄą╝čÅ čĆąĄąČąĖą╝ą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čüą▒čĆąŠčüą░.

ąóą░ą▒ą╗ąĖčåą░ 12. ąĀąĄąČąĖą╝čŗ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čüą▒čĆąŠčüą░ AD56x7R/AD56x7.

| DB0 |

ąĀąĄą│ąĖčüčéčĆčŗ, čüą▒čĆą░čüčŗą▓ą░ąĄą╝čŗąĄ ą▓ 0 |

| 0 |

ąĀąĄą│ąĖčüčéčĆ DAC.

ąÆčģąŠą┤ąĮąŠą╣ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░. |

| 1 (Power-On Reset) |

ąĀąĄą│ąĖčüčéčĆ DAC.

ąÆčģąŠą┤ąĮąŠą╣ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░.

ąĀąĄą│ąĖčüčéčĆ ~LDAC.

ąĀąĄą│ąĖčüčéčĆ Power-Down.

ąĀąĄą│ąĖčüčéčĆ ąĮą░čüčéčĆąŠą╣ą║ąĖ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ. |

ąĀąĖčü. 64. Software Reset Command.

ąÆčģąŠą┤ ąŠčćąĖčüčéą║ąĖ ~CLR. ąŻ AD56x7R/AD56x7 ąĄčüčéčī ą░čüąĖąĮčģčĆąŠąĮąĮčŗą╣ ą▓čģąŠą┤ čüą▒čĆąŠčüą░ ~CLR. ąöą╗čÅ čŹč鹊ą│ąŠ ą▓čģąŠą┤ą░ ą╝ąŠą╝ąĄąĮč鹊ą╝ ą░ą║čéąĖą▓ą░čåąĖąĖ čÅą▓ą╗čÅąĄčéčüčÅ čüą┐ą░ą┤ čāčĆąŠą▓ąĮčÅ (ą┐ąĄčĆąĄčģąŠą┤ 1 -> 0). ąÜąŠą│ą┤ą░ ~CLR ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ą╗ąŠą│. 0, ą▓čüąĄ ąĖą╝ą┐čāą╗čīčüčŗ ąĮą░ ~LDAC ąĖą│ąĮąŠčĆąĖčĆčāčÄčéčüčÅ. ąÜąŠą│ą┤ą░ ~CLR ą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮ, ą▓ąŠ ą▓čüąĄ ą▓čģąŠą┤ąĮčŗąĄ čĆąĄą│ąĖčüčéčĆčŗ ąĖ čĆąĄą│ąĖčüčéčĆčŗ DAC ąĘą░ą│čĆčāąČą░čÄčéčüčÅ ąĮčāą╗ąĖ, čŹč鹊 ą┐ąĄčĆąĄą▓ąŠą┤ąĖčé ą▓čŗčģąŠą┤ ą▓ čāčĆąŠą▓ąĄąĮčī 0V. ą£ąĖą║čĆąŠčüčģąĄą╝ą░ ą▓čŗčģąŠą┤ąĖčé ąĖąĘ čĆąĄąČąĖą╝ą░ ąŠčćąĖčüčéą║ąĖ ą┐ąŠ čüą┐ą░ą┤čā čāčĆąŠą▓ąĮčÅ 9-ą│ąŠ čéą░ą║č鹊ą▓ąŠą│ąŠ ąĖą╝ą┐čāą╗čīčüą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ ą▒ą░ą╣čéą░ ą┐čĆą░ą▓ąĖą╗čīąĮąŠą╣ ąĘą░ą┐ąĖčüąĖ. ąĢčüą╗ąĖ ~CLR ą▒čŗą╗ ą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮ ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ąĘą░ą┐ąĖčüąĖ, č鹊 ąĘą░ą┐ąĖčüčī ą▒čāą┤ąĄčé ąŠą▒ąŠčĆą▓ą░ąĮą░. ąĢčüą╗ąĖ ~CLR ą▒čŗą╗ ą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮ ą▓ąŠ ą▓čĆąĄą╝čÅ čĆąĄąČąĖą╝ą░ high speed, č鹊 ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ ą▓čŗą╣ą┤ąĄčé ąĖąĘ čĆąĄąČąĖą╝ą░ high speed, ą┐ąĄčĆąĄą╣ą┤čÅ ą▓ ąĮąŠčĆą╝ą░ą╗čīąĮčŗą╣ čĆąĄąČąĖą╝ čüą║ąŠčĆąŠčüčéąĖ (standard/fast speed mode).

ąØą░čüčéčĆąŠą╣ą║ą░ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ. ąŁčéą░ ąĮą░čüčéčĆąŠą╣ą║ą░ ą┐čĆąĖą╝ąĄąĮąĖą╝ą░ č鹊ą╗čīą║ąŠ ą║ ą▓ąĄčĆčüąĖčÅą╝ R ą╝ąĖą║čĆąŠčüčģąĄą╝. ą¤ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą┐čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ ąĖčüč鹊čćąĮąĖą║ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą▓čŗą║ą╗čÄč湥ąĮ. ą×ąĮ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓ą║ą╗čÄč湥ąĮ ą║ąŠą╝ą░ąĮą┤ąŠą╣ ąĮą░čüčéčĆąŠą╣ą║ąĖ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ 111 (reference setup command) ąĖ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ DB0 ą▓ąŠ ą▓čģąŠą┤ąĮąŠą╝ čĆąĄą│ąĖčüčéčĆąĄ čüą┤ą▓ąĖą│ą░. ąóą░ą▒ą╗ąĖčåą░ 13 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüąŠčüč鹊čÅąĮąĖčÅ ą▒ąĖčéą░ ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ čĆąĄąČąĖą╝čŗ čĆą░ą▒ąŠčéčŗ. ąĀąĖčü. 66 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ čĆąĄą│ąĖčüčéčĆą░ čüą┤ą▓ąĖą│ą░ ą▓ąŠ ą▓čĆąĄą╝čÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą║ąŠą╝ą░ąĮą┤čŗ ąĮą░čüčéčĆąŠą╣ą║ąĖ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ.

ąóą░ą▒ą╗ąĖčåą░ 13. Reference Setup Command.

| DB0 |

ąöąĄą╣čüčéą▓ąĖąĄ |

| 0 |

ąÆąĮčāčéčĆąĄąĮąĮąĖą╣ ąĖčüč鹊čćąĮąĖą║ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą▓čŗą║ą╗čÄč湥ąĮ (ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ). |

| 1 |

ąÆąĮčāčéčĆąĄąĮąĮąĖą╣ ąĖčüč鹊čćąĮąĖą║ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą▓ą║ą╗čÄč湥ąĮ. |

ąĀąĖčü. 66. Reference Setup Command.

[ąśąĮč乊čĆą╝ą░čåąĖčÅ ą┐ąŠ ą┐čĆąĖą╝ąĄąĮąĄąĮąĖčÄ]

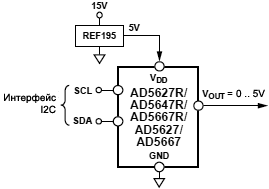

ąśčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ ą▓ ą║ą░č湥čüčéą▓ąĄ ą┐ąĖčéą░ąĮąĖčÅ ąĖčüč鹊čćąĮąĖą║ą░ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ. ąśąĘ-ąĘą░ č鹊ą│ąŠ, čćč鹊 č鹊ą║ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ AD56x7R/AD56x7 čćčĆąĄąĘą▓čŗčćą░ą╣ąĮąŠ ą╝ą░ą╗, č鹊 ą║ą░ą║ ą▓ą░čĆąĖą░ąĮčé ą┤ą╗čÅ ąĄą│ąŠ ą┐ąĖčéą░ąĮąĖčÅ ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą╝ąĖą║čĆąŠčüčģąĄą╝čā ąĖčüč鹊čćąĮąĖą║ą░ čŹčéą░ą╗ąŠąĮąĮąŠą│ąŠ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ (čüą╝. čĆąĖčü. 67).

ąĀąĖčü. 67. ą¤čĆąĖą╝ąĄąĮąĄąĮąĖąĄ REF195 ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖčüč鹊čćąĮąĖą║ą░ ą┐ąĖčéą░ąĮąĖčÅ ą┤ą╗čÅ AD56x7R/AD56x7.

ąŁč鹊 ąŠčüąŠą▒ąĄąĮąĮąŠ ą┐ąŠą╗ąĄąĘąĮąŠ, ąĄčüą╗ąĖ ąŠčüąĮąŠą▓ąĮąŠą╣ ąĖčüč鹊čćąĮąĖą║ ą┐ąĖčéą░ąĮąĖčÅ ą┤ąŠą▓ąŠą╗čīąĮąŠ ąĘą░čłčāą╝ą╗ąĄąĮąĮčŗą╣, ąĖą╗ąĖ ąĄčüą╗ąĖ čüąĖčüč鹥ą╝ąĮčŗąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ ąĖą╝ąĄčÄčé ąĘąĮą░č湥ąĮąĖčÅ, ąŠčéą╗ąĖčćą░čÄčēąĖąĄčüčÅ ąŠčé 5V ąĖą╗ąĖ 3V, ąĮą░ą┐čĆąĖą╝ąĄčĆ 15V. ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┤ą░čüčé čüčéą░ą▒ąĖą╗čīąĮąŠąĄ ą┐ąĖčéą░ąĮąĖąĄ ą┤ą╗čÅ AD56x7R/AD56x7. ąĢčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ low dropout REF195, č鹊 ąŠąĮą░ ą┤ąŠą╗ąČąĮą░ ą┐čĆąĄą┤ąŠčüčéą░ą▓ąĖčéčī ą┤ą╗čÅ AD56x7R/AD56x7 č鹊ą║ ą┐ąŠčĆčÅą┤ą║ą░ 0.45 mA, ą║ąŠą│ą┤ą░ ąĮą░ ą▓čŗčģąŠą┤ąĄ DAC ąĮąĄčé ąĮą░ą│čĆčāąĘą║ąĖ. ąÜąŠą│ą┤ą░ ąĮą░ ą▓čŗčģąŠą┤ąĄ DAC ąĄčüčéčī ąĮą░ą│čĆčāąĘą║ą░, č鹊 ąŠčé REF195 ą▒čāą┤ąĄčé ą┐ąŠčéčĆąĄą▒ą╗čÅčéčīčüčÅ ą▒ąŠą╗čīčłąĄ č鹊ą║ą░. ą×ą▒čēąĖą╣ čéčĆąĄą▒čāąĄą╝čŗą╣ č鹊ą║ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ čü ąĮą░ą│čĆčāąĘą║ąŠą╣ 5 ą║ą×ą╝ ąĮą░ ą▓čŗčģąŠą┤ąĄ DAC ą▓čŗčćąĖčüą╗čÅąĄčéčüčÅ ą┐ąŠ č乊čĆą╝čāą╗ąĄ:

450 ą╝ą║ąÉ + (5 V/5 ą║ą×ą╝) = 1.45 ą╝ąÉ

ąźą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ą░ čĆąĄą│čāą╗ąĖčĆąŠą▓ą░ąĮąĖčÅ REF195 ąŠą▒čŗčćąĮąŠ čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé 2 ppm/mA, čćč鹊 ą┤ą░ąĄčé ąŠčłąĖą▒ą║čā 2.9 ppm (14.5 mkV) ą┤ą╗čÅ č鹊ą║ą░ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ 1.45 ą╝ąÉ. ąŁč鹊 čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ąŠčłąĖą▒ą║ąĄ 0.191 LSB.

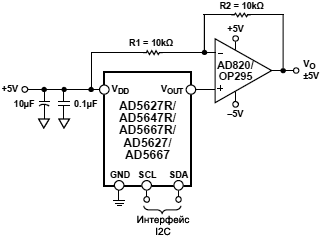

ąæąĖą┐ąŠą╗čÅčĆąĮąŠąĄ ą▓ą║ą╗čÄč湥ąĮąĖąĄ. AD56x7R/AD56x7 ą▒čŗą╗ą░ čĆą░ąĘčĆą░ą▒ąŠčéą░ąĮą░ ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ ą▓ ąŠą┤ąĮąŠą┐ąŠą╗čÅčĆąĮąŠą╝ ą▓ą║ą╗čÄč湥ąĮąĖąĖ, ąŠą┤ąĮą░ą║ąŠ ą╝ąŠąČąĮąŠ čéą░ą║ąČąĄ čĆąĄą░ą╗ąĖąĘąŠą▓ą░čéčī ą▒ąĖą┐ąŠą╗čÅčĆąĮčŗą╣ čĆąĄąČąĖą╝ čĆą░ą▒ąŠčéčŗ ą▓čŗčģąŠą┤ą░ ą┐ąŠ čüčģąĄą╝ąĄ ąĮą░ čĆąĖčü. 68. ąŁčéą░ čüčģąĄą╝ą░ ą┤ą░ąĄčé ą▓čŗčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ┬▒5 V. ąĀą░ą▒ąŠčéą░ rail-to-rail ąĮą░ ą▓čŗčģąŠą┤ąĄ ą┤ąŠčüčéąĖą│ą░ąĄčéčüčÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ ąŠą┐ąĄčĆą░čåąĖąŠąĮąĮąŠą│ąŠ čāčüąĖą╗ąĖč鹥ą╗čÅ AD820 ąĖą╗ąĖ OP295 ą▓ ą║ą░č湥čüčéą▓ąĄ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čāčüąĖą╗ąĖč鹥ą╗čÅ.

ąĀąĖčü. 68. ąĀą░ą▒ąŠčéą░ AD56x7R/AD56x7 ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą▒ąĖą┐ąŠą╗čÅčĆąĮąŠą│ąŠ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ.

ąÆčŗčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┤ą╗čÅ ą╗čÄą▒ąŠą│ąŠ ą▓čģąŠą┤ąĮąŠą│ąŠ ą║ąŠą┤ą░ ą╝ąŠąČąĮąŠ ą▓čŗčćąĖčüą╗ąĖčéčī ą┐ąŠ č乊čĆą╝čāą╗ąĄ:

VO = [VDD x (D / 65536) x ((R1+R2)/R1) - VDD x (R2/R1)]

ąŚą┤ąĄčüčī D čŹč鹊 ą▓čģąŠą┤ąĮąŠą╣ ą║ąŠą┤ (ą▓ ą┤ąĄčüčÅčéąĖčćąĮąŠą╣ č乊čĆą╝ąĄ 0 .. 65535, ą▓ HEX-č乊čĆą╝ąĄ 0x0000 .. 0xFFFF). ą¤čĆąĖ VDD = 5V, R1 = R2 = 10 ą║ą×ą╝ ą▓čŗčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ čüąŠčüčéą░ą▓ąĖčé:

VO = ( 10 x D / 65536 ) - 5V

ąŁč鹊 ą┤ą░ąĄčé ą┤ąĖą░ą┐ą░ąĘąŠąĮ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ąĮą░ ą▓čŗčģąŠą┤ąĄ ┬▒5 V, ą║ąŠą│ą┤ą░ D = 0x0000 čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé -5V ąĮą░ ą▓čŗčģąŠą┤ąĄ, ąĖ D = 0xFFFF čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé +5V ąĮą░ ą▓čŗčģąŠą┤ąĄ.

ążąĖą╗čīčéčĆą░čåąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ ąĖ ąĘą░ąĘąĄą╝ą╗ąĄąĮąĖąĄ. ąÜąŠą│ą┤ą░ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ą┤ąŠčüčéąĖčćčī ą▓čŗčüąŠą║ąŠą╣ č鹊čćąĮąŠčüčéąĖ DAC, ąĮą░ ą┐ąĄčćą░čéąĮąŠą╣ ą┐ą╗ą░č鹥 čüą╗ąĄą┤čāąĄčé čéčēą░č鹥ą╗čīąĮąŠ čĆąĄą░ą╗ąĖąĘąŠą▓ą░čéčī čĆą░ąĘą▓ąŠą┤ą║čā ą┐ąĖčéą░ąĮąĖčÅ ąĖ ąĘąĄą╝ą╗ąĖ. ą¤ąĄčćą░čéąĮą░čÅ ą┐ą╗ą░čéą░, ą│ą┤ąĄ ą┐čĆąĖą╝ąĄąĮčÅąĄčéčüčÅ AD56x7R/AD56x7, ą┤ąŠą╗ąČąĮą░ ąĖą╝ąĄčéčī čĆą░ąĘą┤ąĄą╗čīąĮčŗąĄ čüąĄą║čåąĖąĖ čåąĖčäčĆąŠą▓čŗčģ ąĖ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗčģ čåąĄą┐ąĄą╣, ą║ą░ąČą┤ą░čÅ ąĖąĘ ą║ąŠč鹊čĆčŗčģ ąĘą░ąĮąĖą╝ą░čÄčé ąŠčéą┤ąĄą╗čīąĮčŗąĄ ąŠą▒ą╗ą░čüčéčī ąĮą░ ą┐ą╗ą░č鹥. ąĢčüą╗ąĖ AD56x7R/AD56x7 ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čüąĖčüč鹥ą╝ąĄ, ą│ą┤ąĄ ą┤čĆčāą│ąĖąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ čéą░ą║ąČąĄ čéčĆąĄą▒čāčÄčé čüąŠąĄą┤ąĖąĮąĄąĮąĖčÅ čåąĄą┐ąĄą╣ AGND ąĖ DGND, č鹊 čŹč鹊 čüąŠąĄą┤ąĖąĮąĄąĮąĖąĄ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮąŠ č鹊ą╗čīą║ąŠ ą▓ ąŠą┤ąĮąŠą╣ č鹊čćą║ąĄ. ąŁčéą░ č鹊čćą║ą░ ąĘą░ąĘąĄą╝ą╗ąĄąĮąĖčÅ ą┤ąŠą╗ąČąĮą░ ąĮą░čģąŠą┤ąĖčéčīčüčÅ ą║ą░ą║ ą╝ąŠąČąĮąŠ ą▒ą╗ąĖąČąĄ ą║ AD56x7R/AD56x7.

ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ AD56x7R/AD56x7 ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ąŠčéčäąĖą╗čīčéčĆąŠą▓ą░ąĮąŠ ą▒ą╗ąŠą║ąĖčĆąŠą▓ąŠčćąĮčŗą╝ąĖ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆąŠą╝ 10 ą╝ą║čä, ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠ ą║ąŠč鹊čĆąŠą╝čā čüč鹊ąĖčé ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ 0.1 ą╝ą║čä. ąŁčéąĖ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆčŗ ą┤ąŠą╗ąČąĮčŗ ąĮą░čģąŠą┤ąĖčéčīčüčÅ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠ ą▒ą╗ąĖąĘą║ąŠ ą║ ą╝ąĖą║čĆąŠčüčģąĄą╝ąĄ, ąĖą┤ąĄą░ą╗čīąĮčŗą╣ ą▓ą░čĆąĖą░ąĮčé - ą║ąŠą│ą┤ą░ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ 0.1 ą╝ą║čä čüč鹊ąĖčé ą▓ ąĮąĄą┐ąŠčüčĆąĄą┤čüčéą▓ąĄąĮąĮąŠą╣ ą▒ą╗ąĖąĘąŠčüčéąĖ čü čāčüčéčĆąŠą╣čüčéą▓ąŠą╝. ąÜąŠąĮą┤ąĄąĮčüą░č鹊čĆ 10 ą╝ą║čä ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čéą░ąĮčéą░ą╗ąŠą▓čŗą╝. ąÆą░ąČąĮąŠ, čćč鹊ą▒čŗ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ 0.1 ą╝ą║čä ąĖą╝ąĄą╗ ąĮąĖąĘą║ąŠąĄ čŹčäč乥ą║čéąĖą▓ąĮąŠąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠąĄ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ (effective series resistance, ESR) ąĖ čŹčäč乥ą║čéąĖą▓ąĮčāčÄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčāčÄ ąĖąĮą┤čāą║čéąĖą▓ąĮąŠčüčéčī (effective series inductance, ESI), ąĮą░ą┐čĆąĖą╝ąĄčĆ čŹč鹊 ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą║ą░č湥čüčéą▓ąĄąĮąĮčŗą╣ ą║ąĄčĆą░ą╝ąĖč湥čüą║ąĖą╣ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ SMD. ąóą░ą║ąŠą╣ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ ą┐čĆąĄą┤ąŠčüčéą░ą▓ąĖčé ąĮąĖąĘą║ąŠąĄ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ ą┤ą╗čÅ ąĘą░ą╝čŗą║ą░ąĮąĖčÅ ąĮą░ ąĘąĄą╝ą╗čÄ č鹊ą║ąŠą▓ ą┐čāą╗čīčüą░čåąĖą╣, ą│ąĄąĮąĄčĆąĖčĆčāąĄą╝čŗčģ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅą╝ąĖ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ ą╗ąŠą│ąĖą║ąĖ.

ą©ąĖąĮą░ ą┐ąĖčéą░ąĮąĖčÅ ą┤ąŠą╗ąČąĮą░ ąĖą╝ąĄčéčī ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠ ą▓ąŠąĘą╝ąŠąČąĮčāčÄ čłąĖčĆąĖąĮčā, čćč鹊ą▒čŗ ąŠą▒ąĄčüą┐ąĄčćąĖčéčī ąĮąĖąĘą║ąŠąĄ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ čåąĄą┐ąĖ ą┐ąĖčéą░ąĮąĖčÅ ąĖ čüąĮąĖąĘąĖčéčī ąĖą╝ą┐čāą╗čīčüčŗ ą┐čĆąŠą▓ą░ą╗ąŠą▓ ą┐ąŠ ą┐ąĖčéą░ąĮąĖčÄ. ąóą░ą║čéčŗ ąĖ ą┤čĆčāą│ąĖąĄ ą▒čŗčüčéčĆąŠ ą┐ąĄčĆąĄą║ą╗čÄčćą░čÄčēąĖąĄčüčÅ čåąĖčäčĆąŠą▓čŗąĄ čüąĖą│ąĮą░ą╗čŗ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī 菹║čĆą░ąĮąĖčĆąŠą▓ą░ąĮčŗ čåąĖčäčĆąŠą▓ąŠą╣ ąĘąĄą╝ą╗ąĄą╣ DGND ąŠčé ą┤čĆčāą│ąĖčģ čćą░čüč鹥ą╣ ą┐ąĄčćą░čéąĮąŠą╣ ą┐ą╗ą░čéčŗ. ą¤ąŠ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ ąĖąĘą▒ąĄą│ą░ą╣č鹥 ą┐ąĄčĆąĄčüąĄč湥ąĮąĖčÅ ąĖ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠą│ąŠ ą┐čĆąŠą╗ąĄą│ą░ąĮąĖčÅ čåąĖčäčĆąŠą▓čŗčģ ąĖ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗčģ čüąĖą│ąĮą░ą╗ąŠą▓ ąĮą░ ą┐ą╗ą░č鹥. ąÜąŠą│ą┤ą░ ą┐čĆąŠą▓ąŠą┤ąĮąĖą║ąĖ ą┐čĆąŠčģąŠą┤čÅčé ą┐ąŠ ą┐čĆąŠčéąĖą▓ąŠą┐ąŠą╗ąŠąČąĮčŗą╝ čüč鹊čĆąŠąĮą░ą╝ ą┐ąĄčćą░čéąĮąŠą╣ ą┐ą╗ą░čéčŗ, ą┐ąŠčüčéą░čĆą░ą╣č鹥čüčī ąŠą▒ąĄčüą┐ąĄčćąĖčéčī ąĖčģ ąŠčĆąĖąĄąĮčéąĖčĆąŠą▓ą║čā ą┐ąŠą┤ ą┐čĆčÅą╝čŗą╝ čāą│ą╗ąŠą╝ ą┤čĆčāą│ ą║ ą┤čĆčāą│čā, čŹč鹊 čüąĮąĖąĘąĖčé ą┐ąĄčĆąĄą║čĆąĄčüčéąĮčŗąĄ ąĮą░ą▓ąŠą┤ą║ąĖ ą╝ąĄąČą┤čā čüąĖą│ąĮą░ą╗ą░ą╝ąĖ. ąøčāčćčłą░čÅ č鹥čģąĮąĖą║ą░ čĆą░ąĘą▓ąŠą┤ą║ąĖ - microstrip, ą║ąŠą│ą┤ą░ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą╣ čüč鹊čĆąŠąĮčŗ ą▓čŗą┤ąĄą╗ąĄąĮ ąŠčéą┤ąĄą╗čīąĮčŗą╣ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čüą╗ąŠą╣ ąĘąĄą╝ą╗ąĖ, ąĖ čüąĖą│ąĮą░ą╗čīąĮčŗąĄ ą┐čĆąŠą▓ąŠą┤ąĮąĖą║ąĖ ą┐čĆąŠčģąŠą┤čÅčé ą┐ąŠ ą▓ąĄčĆčģąĮąĄą╣ čüč鹊čĆąŠąĮąĄ ą┐ą╗ą░čéčŗ. ą×ą┤ąĮą░ą║ąŠ čŹč鹊 ąĮąĄ ą▓čüąĄą│ą┤ą░ ą▓ąŠąĘą╝ąŠąČąĮąŠ ą┤ą╗čÅ ą┤ą▓čāčģčüą╗ąŠą╣ąĮčŗčģ ą┐ą╗ą░čé. ą¤čĆąĖą╝ąĄąĮčÅą╣č鹥 ąĘą░ą╗ąĖą▓ą║čā ą╝ąĄą┤čīčÄ ąĘąĄą╝ą╗ąĖ ą┤ą╗čÅ ą▓čüąĄčģ čüą▓ąŠą▒ąŠą┤ąĮčŗčģ ąŠčé čåąĄą┐ąĄą╣ čāčćą░čüčéą║ąŠą▓ ą┐ąĄčćą░čéąĮąŠą╣ ą┐ą╗ą░čéčŗ.

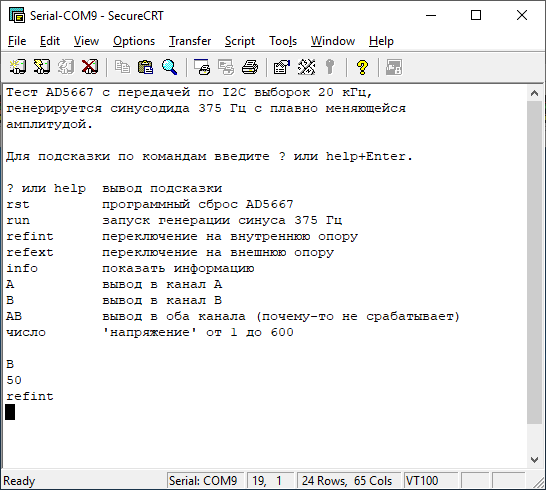

[ą¤čĆąĖą╝ąĄčĆ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ AD5667]

ąØąĖąČąĄ ąŠą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ ą▒ąĖą▒ą╗ąĖąŠč鹥ą║ą░ Blackfin ąĖ ą┐čĆąĖą╝ąĄčĆ ąĄčæ ą┐čĆąĖą╝ąĄąĮąĄąĮąĖčÅ - č鹥čüč鹊ą▓ą░čÅ ą┐čĆąŠą│čĆą░ą╝ą╝ą░, ą║ąŠč鹊čĆą░čÅ č乊čĆą╝ąĖčĆčāąĄčé čüąĖąĮčāčüąŠąĖą┤ą░ą╗čīąĮčŗą╣ čüąĖą│ąĮą░ą╗ ąĮą░ ą▓čŗčģąŠą┤ąĄ ą”ąÉą¤. ąÜąŠą┤ ąĘą░ą┐čāčüą║ą░ą╗čüčÅ ąĮą░ ą╝ą░ą║ąĄčéąĮąŠą╣ ą┐ą╗ą░č鹥 Simple Blackfin ADSP-BF538 Board [3]. ą”ąÉą¤ ą┐ąŠą┤ą║ą╗čÄčćą░ą╗čüčÅ ą║ ą║ąŠąĮąĮąĄą║č鹊čĆčā J11 I2C1. ąÆ ą┐čĆąĖą╝ąĄčĆąĄ ąĄčüčéčī č鹊ą╗čīą║ąŠ ąŠą┤ąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ - ąŠčé čéą░ą╣ą╝ąĄčĆą░, čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą░ą┐ą┐ą░čĆą░čéčāčĆąŠą╣ I2C/TWI ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą▒ąĄąĘ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣.

ąöą╗čÅ čāą┐čĆąŠčēąĄąĮąĖčÅ ą┐ąŠąĮąĖą╝ą░ąĮąĖčÅ čĆą░ą▒ąŠčéčŗ ą║ąŠą┤ą░ č鹥ą║čüčé ąĘą░ą│ąŠą╗ąŠą▓ąŠčćąĮčŗčģ čäą░ą╣ą╗ąŠą▓ ąŠą┐čāčēąĄąĮ. ą¤ąŠą╗ąĮčŗą╣ ąĖčüčģąŠą┤ąĮčŗą╣ ą║ąŠą┤ (ą┐čĆąŠąĄą║čé VisualDSP) ą╝ąŠąČąĮąŠ čüą║ą░čćą░čéčī ą┐ąŠ čüčüčŗą╗ą║ąĄ [4].

ą£ąŠą┤čāą╗čī twi.c:

/****************************************************

ą¤ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ čü TWI ąĮą░ ąĮąĖąĘą║ąŠą╝ čāčĆąŠą▓ąĮąĄ.

*****************************************************/

#include "init_platform.h"#include "TWI.h"

static void twi_clear_all_stat (void)

{

/* ą×čćąĖčēą░ąĄčé ą▓čüąĄ ą▒ąĖčéčŗ čüąŠčüč鹊čÅąĮąĖčÅ */

//*pTWI_MASTER_STAT = ( BUFWRERR | BUFRDERR | DNAK | ANAK | LOSTARB);

*pTWI_MASTER_STAT = *pTWI_MASTER_STAT;

ssync();

/* ą×čćąĖčēą░ąĄčé ą▓čüąĄ čäą╗ą░ą│ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣, ąŠąČąĖą┤ą░čÄčēąĖčģ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ */

//*pTWI_INT_STAT = ( SINIT | SCOMP | SERR | SOVF | MCOMP | MERR | XMTSERV | RCVSERV );

*pTWI_INT_STAT = *pTWI_INT_STAT;

ssync();

/* ąĪą▒čĆąŠčü ą▒čāč乥čĆąŠą▓ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖ ą┐čĆąĖąĄą╝ą░ */

*pTWI_FIFO_CTRL = ( XMTFLUSH | RCVFLUSH );

ssync();

}

// ą¤čĆąŠčåąĄą┤čāčĆą░ čüą▒čĆą░čüčŗą▓ą░ąĄčé ąĖąĮč鹥čĆč乥ą╣čü TWI.

void twi_reset(void)

{

/* ąĪą▒čĆąŠčü ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ TWI */

*pTWI_CONTROL = TWI_RESET_VAL;

ssync();

twi_clear_all_stat();

}

ą£ąŠą┤čāą╗čī AD5667.c:

#include "AD5667.h"

#include "TWI.h"

#include "timer.h"

// ą¤ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą”ąÉą¤ AD5667. ąĀąĄą░ą╗ąĖąĘąŠą▓ą░ąĮčŗ č鹊ą╗čīą║ąŠ

// čäčāąĮą║čåąĖąĖ ąĘą░ą┐ąĖčüąĖ. ąÜą░ąČą┤ą░čÅ čäčāąĮą║čåąĖčÅ (ą║čĆąŠą╝ąĄ DAC_multiple_start

// ąĖ DAC_multiple_stop) ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčé ąŠą┤ąĖąĮąŠčćąĮčāčÄ ąĘą░ą┐ąĖčüčī

// ą┐ąŠ čüą╗ąĄą┤čāčÄčēąĄą╝čā ą░ą╗ą│ąŠčĆąĖčéą╝čā:

// ą×čéą┐čĆą░ą▓ą║ą░ čüąĖą│ąĮą░ą╗ą░ START

// ą¤ąĄčĆąĄą┤ą░čćą░ 7-ą▒ąĖčéąĮąŠą│ąŠ ą░ą┤čĆąĄčüą░ ąĖ ą▒ąĖčéą░ W

// ą¤ąĄčĆąĄą┤ą░čćą░ ą▒ą░ą╣čéą░ ą║ąŠą╝ą░ąĮą┤čŗ

// ą¤ąĄčĆąĄą┤ą░čćą░ 2 ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ

// ą×čéą┐čĆą░ą▓ą║ą░ čüąĖą│ąĮą░ą╗ą░ STOP.

volatile u8 twistate = TWI_IDLE;

u8 channelDAC = DAC_A;

static inline void START (u8 stop_or_not)

{

// ą×čćąĖčüčéą║ą░ ą▒ąĖčé ą▓čĆčāčćąĮčāčÄ:

*pTWI_FIFO_CTRL = 0;

// ąØą░čüčéčĆąŠą╣ą║ą░ čüą║ąŠčĆąŠčüčéąĖ:

*pTWI_CONTROL = ( TWI_ENA | PRESCALE_VALUE );

// CLKDIV = (1/SCL)/(1/10MHz):

*pTWI_CLKDIV = ( ((CLKDIV_HI) << 8) | (CLKDIV_LO) );

// ą”ąĄą╗ąĄą▓ąŠą╣ ą░ą┤čĆąĄčü čāčüčéčĆąŠą╣čüčéą▓ą░ (7-ą▒ąĖčéąĮčŗą╣ ą░ą┤čĆąĄčü ą▒ąĄąĘ ą▒ąĖčéą░ R/~W):

*pTWI_MASTER_ADDR = AD5667_I2C_ADDR;

// ąĢčüą╗ąĖ stop_or_not == 0xFF, č鹊 ą│ąĄąĮąĄčĆą░čåąĖąĖ STOP ą┐ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÄ

// ą┐ąĄčĆąĄą┤ą░čćąĖ ąĮąĄ ą▒čāą┤ąĄčé:

*pTWI_MASTER_CTRL = (stop_or_not << 6) | MEN;

ssync();

}

void DAC_init (void)

{

// ąĪą▒čĆąŠčü ąČąĄą╗ąĄąĘą░ I2C:

//twi_reset();

}

// ąŚą░ą┐ąĖčüčŗą▓ą░ąĄčé čüą╗ąŠą▓ąŠ ą▓ čĆąĄą│ąĖčüčéčĆ ą┤ą░ąĮąĮčŗčģ (0 .. 65535), čćč鹊ą▒čŗ

// ąĮą░ ą▓čŗčģąŠą┤ąĄ ą”ąÉą¤ ą┐ąŠčÅą▓ąĖą╗ąŠčüčī čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ.

void DAC_write_value (u16 data)

{

if (TWI_IDLE == twistate)

{

twi_reset();

// ą¤ąŠčüą╗ąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ ą░ą┤čĆąĄčüą░ ąĖ 3 ą▒ą░ą╣čé ą▒čāą┤ąĄčé čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮ STOP:

START(GENERATE_STOP);

// ą¤ąĄčĆąĄą┤ą░čćą░ ą║ąŠą╝ą░ąĮą┤čŗ ąĖ ąĮąŠą╝ąĄčĆą░ ą║ą░ąĮą░ą╗ą░:

*pTWI_XMT_DATA8 = CMD_WRITE_AND_UPDATE_CHNL | channelDAC;

ssync();

// ą¤ąĄčĆąĄą┤ą░čćą░ ą┤ą░ąĮąĮčŗčģ ą▓čŗą▒ąŠčĆą║ąĖ:

while (*pTWI_FIFO_STAT != XMT_EMPTY) { ssync(); }

*pTWI_XMT_DATA16 = (data << 8) | (data >> 8);

ssync();

// ą×ąČąĖą┤ą░ąĮąĖąĄ ąŠą║ąŠąĮčćą░ąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ:

*pTWI_INT_STAT = *pTWI_INT_STAT;

while (0==(*pTWI_INT_STAT & MCOMP)) { ssync(); }

}

}

// ąŻčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ą╗ąĖą▒ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĄąĄ, ą╗ąĖą▒ąŠ ą▓ąĮąĄčłąĮąĄąĄ

// ąŠą┐ąŠčĆąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą”ąÉą¤. ą¤ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ, ą┐ąŠčüą╗ąĄ

// ą▓ą║ą╗čÄč湥ąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ, ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓ąĮąĄčłąĮąĖą╣ ąĖčüč鹊čćąĮąĖą║

// ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ.

void DAC_set_reference (u8 ref)

{

if (TWI_IDLE == twistate)

{

twi_reset();

START(GENERATE_STOP);

// ą¤ąĄčĆąĄą┤ą░čćą░ ą║ąŠą╝ą░ąĮą┤čŗ čāčüčéą░ąĮąŠą▓ą║ąĖ ąĖčüč鹊čćąĮąĖą║ą░ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ:

*pTWI_XMT_DATA8 = CMD_REFERENCE;

ssync();

while (*pTWI_FIFO_STAT != XMT_EMPTY) { ssync(); }

// ą¤ąĄčĆąĄą┤ą░čćą░ ąĮą░čüčéčĆąŠą╣ą║ąĖ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣/ą▓ąĮąĄčłąĮąĖą╣ ąĖčüč鹊čćąĮąĖą║ ąŠą┐ąŠčĆčŗ:

*pTWI_XMT_DATA16 = ref << 8;

ssync();

// ą×ąČąĖą┤ą░ąĮąĖąĄ ąŠą║ąŠąĮčćą░ąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ:

*pTWI_INT_STAT = *pTWI_INT_STAT;

while (0==(*pTWI_INT_STAT & MCOMP)) { ssync(); }

}

}

// ą¤čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čüą▒čĆąŠčü AD5667

void DAC_softreset (void)

{

// ą×čüčéą░ąĮąŠą▓ą║ą░ ą╝ąĮąŠą│ąŠčüą╗ąŠą▓ąĮąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ, ąĄčüą╗ąĖ ąŠąĮą░ ą░ą║čéąĖą▓ąĮą░:

DAC_multiple_stop();

twi_reset();

START(GENERATE_STOP);

// ą¤ąĄčĆąĄą┤ą░čćą░ ą║ąŠą╝ą░ąĮą┤čŗ čüą▒čĆąŠčüą░:

*pTWI_XMT_DATA8 = CMD_RESET;

ssync();

while (*pTWI_FIFO_STAT != XMT_EMPTY) { ssync(); }

// ą¤ąĄčĆąĄą┤ą░čćą░ ą┤ą░ąĮąĮčŗčģ, ą║ąŠč鹊čĆčŗąĄ ąĮąĖč湥ą│ąŠ ąĮąĄ ąĘąĮą░čćą░čé:

*pTWI_XMT_DATA16 = 0;

ssync();

// ą×ąČąĖą┤ą░ąĮąĖąĄ ąŠą║ąŠąĮčćą░ąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ:

*pTWI_INT_STAT = *pTWI_INT_STAT;

while (0==(*pTWI_INT_STAT & MCOMP)) { ssync(); }

}

// ąŚą░ą┐čāčüą║ "ą╝ąĮąŠą│ąŠą▒ą░ą╣čéąĮąŠą╣" ą┐ąĄčĆąĄą┤ą░čćąĖ (multuple block write).

void DAC_multiple_start (void)

{

if (TWI_IDLE == twistate)

{

// ąŚą░ą┐ąĖčüčī ąĮą░ ą▓čŗčģąŠą┤ ą”ąÉą¤ čüčĆąĄą┤ąĮąĄą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ:

DAC_write_value(SHIFT);

// ą¤ąŠą┤ą░čćą░ ą║ąŠą╝ą░ąĮą┤čŗ Multiple Block Write, ą┐ąŠčüą╗ąĄ ą║ąŠč鹊čĆąŠą╣

// ą║ą░ąČą┤ą░čÅ 16-ą▒ąĖčéąĮą░čÅ ą▓čŗą▒ąŠčĆą║ą░ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą┤ą▓čāą╝čÅ ą▒ą░ą╣čéą░ą╝ąĖ

// ą▒ąĄčüą║ąŠąĮąĄčćąĮąŠ ą▓ čåąĖą║ą╗ąĄ, ą▒ąĄąĘ ą│ąĄąĮąĄčĆą░čåąĖąĖ STOP:

START(WITHOUT_STOP);

*pTWI_XMT_DATA8 = S_MULTIBYTE | CMD_WRITE_AND_UPDATE_CHNL | channelDAC;

ssync();

// ą×ąČąĖą┤ą░ąĮąĖąĄ ąŠą┐čāčüč鹊賹ĄąĮąĖčÅ FIFO ą┐ąĄčĆąĄą┤ą░čćąĖ:

while (*pTWI_FIFO_STAT != XMT_EMPTY) { ssync(); }

twistate = TWI_RUNNING;

// ąŚą░ą┐čāčüą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ čéą░ą╣ą╝ąĄčĆą░:

Timer0init();

}

}

// ą×čüčéą░ąĮąŠą▓ą║ą░ "ą╝ąĮąŠą│ąŠą▒ą░ą╣čéąĮąŠą╣" ą┐ąĄčĆąĄą┤ą░čćąĖ.

void DAC_multiple_stop (void)

{

if (TWI_RUNNING == twistate)

{

// ą¤ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ą║ąŠąĮąĄčćąĮąŠą│ąŠ ą░ą▓č鹊ą╝ą░čéą░ čéą░ą╣ą╝ąĄčĆą░

// ąĮą░ ąŠčüčéą░ąĮąŠą▓ą║čā:

twistate = TWI_STOP;

// ą×ąČąĖą┤ą░ąĮąĖąĄ ąŠčüčéą░ąĮąŠą▓ą║ąĖ čéą░ą╣ą╝ąĄčĆą░:

while (twistate != TWI_IDLE){}

}

}

// ąŻčüčéą░ąĮąŠą▓ą║ą░ č鹥ą║čāčēąĄą│ąŠ ą║ą░ąĮą░ą╗ą░ ą”ąÉą¤, A ąĖą╗ąĖ B.

void DAC_set_channel (u8 channel)

{

if (TWI_RUNNING == twistate)

{

// ąĢčüą╗ąĖ čéą░ą╣ą╝ąĄčĆ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ ą╝ąĮąŠą│ąŠą▒ą░ą╣čéąĮąŠą╣

// ą┐ąĄčĆąĄą┤ą░čćąĖ, č鹊 čéčĆąĄą▒čāąĄčéčüčÅ ąĄą│ąŠ ąŠčüčéą░ąĮąŠą▓ą║ą░.

DAC_multiple_stop();

channelDAC = channel;

DAC_multiple_start();

}

else

channelDAC = channel;

}

ą£ąŠą┤čāą╗čī timer.c, ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▓čŗą▒ąŠčĆąŠą║ ą▓ ą”ąÉą¤ čü čćą░čüč鹊č鹊ą╣ ą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ 20 ą║ąōčå ą┤ą╗čÅ č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░:

#include < sys/exception.h >

#include "pins.h"

#include "timer.h"

#include "TWI.h"

#include "AD5667.h"

u8 ampl256 = MAX;

u16 voltage = 600;

// ą×čüčéą░ąĮąŠą▓ą║ą░ čéą░ą╣ą╝ąĄčĆą░:

static void Timer0stop (void)

{

// ąŚą░ą┐čĆąĄčé čĆą░ą▒ąŠčéčŗ čéą░ą╣ą╝ąĄčĆą░:

*pTIMER_DISABLE = TIMEN0;

// ą¤ąĄčĆąĄą┤ą░čćą░ ąĘą░ą▓ąĄčĆčłą░čÄčēąĄą╣ ą▓čŗą▒ąŠčĆą║ąĖ čü ą│ąĄąĮąĄčĆą░čåąĖąĄą╣ STOP:

*pTWI_MASTER_CTRL = (2 << 6) | MEN;

u16 val16 = SHIFT;

*pTWI_XMT_DATA16 = (val16 >> 8)|(val16 << 8);

// ą×ąČąĖą┤ą░ąĮąĖąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ I2C:

*pTWI_INT_STAT = *pTWI_INT_STAT;

while (0==(*pTWI_INT_STAT & MCOMP)) { ssync(); }

twistate = TWI_IDLE;

}

// ą×ą▒čĆą░ą▒ąŠčéčćąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čéą░ą╣ą╝ąĄčĆą░ 0, ą║ąŠč鹊čĆčŗą╣ čüčĆą░ą▒ą░čéčŗą▓ą░ąĄčé

// čü čćą░čüč鹊č鹊ą╣ 20 ą║ąōčå (ąĘą░ą▓ąĖčüąĖčé ąŠčé SAMPLERATE). ą¤čĆąĖ ą║ą░ąČą┤ąŠą╝

// čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čéą░ą╣ą╝ąĄčĆą░ ą▓ ą”ąÉą¤ AD5667R ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ

// ąŠą┤ąĮą░ 16-ą▒ąĖčéąĮą░čÅ ą▓čŗą▒ąŠčĆą║ą░ ą┤ą░ąĮąĮčŗčģ. ą¤čĆąĖ čćą░čüč鹊č鹥 čéą░ą║č鹊ą▓ I2C

// 400 ą║ąōčå ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮą░čÅ čćą░čüč鹊čéą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ čéą░ą╣ą╝ąĄčĆą░

// ąŠą│čĆą░ąĮąĖč湥ąĮą░ 20 ą║ąōčå.

EX_INTERRUPT_HANDLER(Timer0ISR)

{

*pTIMER_STATUS = TIMIL0;

// ąĪč湥čéčćąĖą║ čäą░ąĘčŗ:

static float phase = 0;

// ąŻą║ą░ąĘą░č鹥ą╗čī ąĮą░ čéą░ą▒ą╗ąĖčåčā čüąĖąĮčāčüą░ ą▓ SDRAM:

s16 *ptr = 0;

u16 val16phase;

u16 val16;

switch (twistate)

{

case TWI_IDLE:

break;

case TWI_RUNNING:

LED(1);

// ąŚą░ą┐ąĖčüčī ąŠą┤ąĮąŠą╣ ą▓čŗą▒ąŠčĆą║ąĖ:

val16phase = (u16)phase;

val16 = SHIFT + (ptr[val16phase] * (float)ampl256/600)*voltage;

*pTWI_XMT_DATA16 = (val16 >> 8)|(val16 << 8);

// ąśąĮą║čĆąĄą╝ąĄąĮčé čäą░ąĘčŗ ą┤ą╗čÅ 375 ąōčå:

phase += 512.0/((float)SAMPLERATE/375);

if (phase > 512.0)

phase = phase - 512.0;

LED(0);

break;

case TWI_STOP:

Timer0stop();

break;

}

}

// ąØą░čüčéčĆąŠą╣ą║ą░ ąĖ ąĘą░ą┐čāčüą║ čéą░ą╣ą╝ąĄčĆą░.

void Timer0init (void)

{

// ąØą░čüčéčĆąŠą╣ą║ą░ čéą░ą╣ą╝ąĄčĆą░ ąĮą░ čćą░čüč鹊čéčā 20 ą║ąōčå:

*pTIMER0_PERIOD = T0PERIOD;

*pTIMER0_WIDTH = T0WIDTH;

*pTIMER0_CONFIG = PWM_OUT | PULSE_HI | PERIOD_CNT | IRQ_ENA;

// ą¤čĆąĖą▓čÅąĘą║ą░ ą┐ąĄčĆąĖč乥čĆąĖąĖ ą║ IVG:

*pSIC_IAR2 |= PX_IVG(TIMER0_PERIPH_INT_ID, ik_ivg7);

// ąĀąĄą│ąĖčüčéčĆą░čåąĖčÅ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ:

register_handler_ex(ik_ivg7, Timer0ISR, EX_INT_ENABLE);

// ąŻčüčéą░ąĮąŠą▓ą║ą░ ą╝ą░čüą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣:

*pSIC_IMASK0 |= TIMER0_IRQ;

// ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ čĆą░ą▒ąŠčéčŗ čéą░ą╣ą╝ąĄčĆą░:

*pTIMER_ENABLE = TIMEN0;

}

ą¤čĆąĖą╝ąĄčĆ ą┐čĆąĖą╝ąĄąĮąĄąĮąĖčÅ ą▒ąĖą▒ą╗ąĖąŠč鹥ą║ąĖ (čäčĆą░ą│ą╝ąĄąĮčé ą╝ąŠą┤čāą╗čÅ main.c):

void main (void)

{

...

// ąĪąŠąĘą┤ą░ąĮąĖąĄ čéą░ą▒ą╗ąĖčåčŗ čüąĖąĮčāčüą░ ą▓ SDRAM:

GenSinusTable();

// ąŚą░ą┐čāčüą║ ą”ąÉą¤ AD5667R:

DAC_init();

TPT();

DAC_set_reference(REF_EXTERNAL);

DAC_multiple_start();

// ąōą╗ą░ą▓ąĮčŗą╣ čåąĖą║ą╗ ąĮąĖč湥ą│ąŠ ąĮąĄ ą┤ąĄą╗ą░ąĄčé, č鹊ą╗čīą║ąŠ ą╝ąĄąĮčÅąĄčé ą░ą╝ą┐ą╗ąĖčéčāą┤čā ampl256

// ąŠčé 0 ą┤ąŠ 255 ąĖ ąŠą▒čĆą░čéąĮąŠ. ąŁčéą░ ą░ą╝ą┐ą╗ąĖčéčāą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čĆąĄą│čāą╗ąĖčĆąŠą▓ą░ąĮąĖčÅ

// čüąĖąĮčāčüą░, ą┤ą░ąĮąĮčŗąĄ ą║ąŠč鹊čĆąŠą│ąŠ ą┐ąŠčüčŗą╗ą░čÄčéčüčÅ ą▓ ą”ąÉą¤ AD5667R ą▓ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ąĄ

// ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ EX_INTERRUPT_HANDLER(Timer0ISR).

while(true)

{

delay_ms(10);

ChangeAmplitude();

UARTconsolePoll();

}

}

ąóąĄčüčé-ą┐čĆąŠą│čĆą░ą╝ą╝ą░ čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ą║ąŠą╝ą░ąĮą┤ą░ą╝ąĖ ą║ąŠąĮčüąŠą╗ąĖ UART:

[ąĪčüčŗą╗ą║ąĖ]

1. Dual, 12-/14-/16-Bit nanoDACs® with 5 ppm/°C On-Chip Reference, I2C® Interface site:analog.com.

2. ADSP-BF538: ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčŗ ąĖąĮč鹥čĆč乥ą╣čüą░ TWI (I2C).

3. Simple Blackfin ADSP-BF538 Board.

4. 191011TestAD5667.zip - ą▒ąĖą▒ą╗ąĖąŠč鹥ą║ą░ AD5667 ąĖ ąĖčüčģąŠą┤ąĮčŗą╣ ą║ąŠą┤ ą┐čĆąĖą╝ąĄčĆą░ (ą┐čĆąŠąĄą║čé VisualDSP). |