|

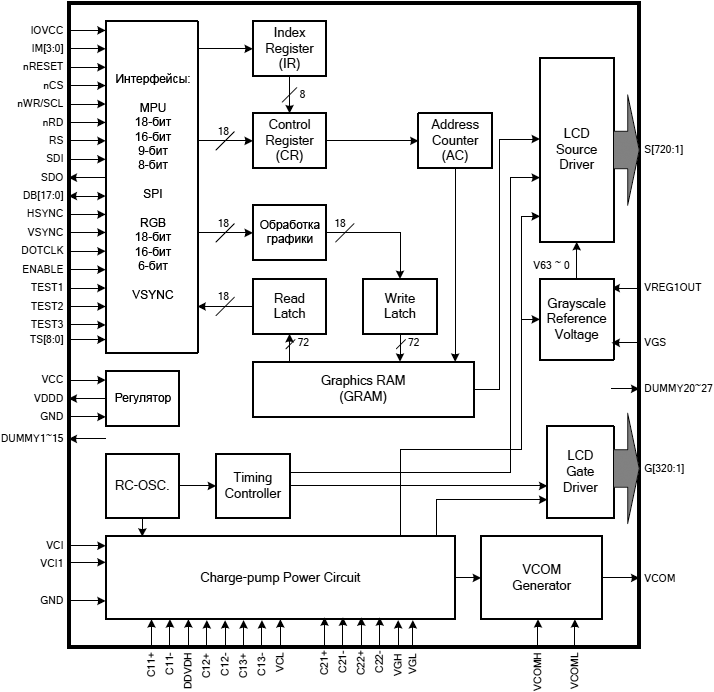

ILI9325 čŹč鹊 ąŠą┤ąĮąŠą║čĆąĖčüčéą░ą╗čīąĮčŗą╣ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ/ą┤čĆą░ą╣ą▓ąĄčĆ (System-on-Chip, SoC) ą┤ą╗čÅ TFT LCD ą┤ąĖčüą┐ą╗ąĄčÅ čĆą░ąĘčĆąĄčłąĄąĮąĖąĄą╝ 240x320 č鹊č湥ą║, čü ą┐ąŠą┤ą┤ąĄčƹȹ║ąŠą╣ RGB ą┐ą░ą╗ąĖčéčĆčŗ 262144 čåą▓ąĄč鹊ą▓. ą×ąĮ čüąŠčüč鹊ąĖčé ąĖąĘ 720-ą║ą░ąĮą░ą╗čīąĮąŠą│ąŠ ą┤čĆą░ą╣ą▓ąĄčĆą░ ąĖčüč鹊čćąĮąĖą║ą░ č鹊ą║ą░, 320-ą║ą░ąĮą░ą╗ąŠą▓ čāą┐čĆą░ą▓ą╗čÅčÄčēąĖčģ ą║ą╗čÄč湥ą╣, 172800 ą▒ą░ą╣čé ą┤ą╗čÅ ą┤ą░ąĮąĮčŗčģ ą│čĆą░čäąĖą║ąĖ 240RGBx320 č鹊č湥ą║ ąĖ čüčģąĄą╝čŗ ą┐ąĖčéą░ąĮąĖčÅ.

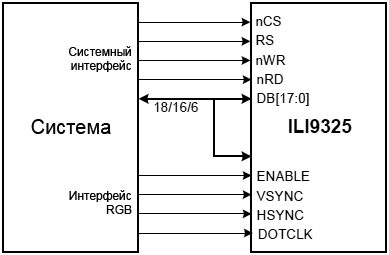

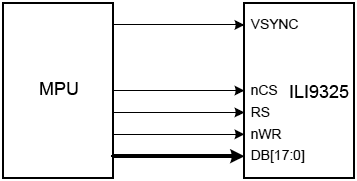

ąöą╗čÅ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ą║ čāą┐čĆą░ą▓ą╗čÅčÄčēąĄą╝čā ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčā čā ILI9325 ąĄčüčéčī 4 ą▓ąĖą┤ą░ čüąĖčüč鹥ą╝ąĮčŗčģ ąĖąĮč鹥čĆč乥ą╣čüąŠą▓. ąŁč鹊 ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü čüčéąĖą╗čÅ i80 MPU (čü čłąĖčĆąĖąĮąŠą╣ čłąĖąĮčŗ ą┤ą░ąĮąĮčŗčģ 8, 9, 16, 18 ą▒ąĖčé), ąĖąĮč鹥čĆč乥ą╣čü VSYNC (čüąĖčüč鹥ą╝ąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü + VSYNC, ą▓ąĮčāčéčĆąĄąĮąĮąĖąĄ čéą░ą║čéčŗ, DB[17:0]), ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü SPI ąĖ RGB 6-, 16-, 18-čĆą░ąĘčĆčÅą┤ąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü (DOTCLK, VSYNC, HSYNC, ENABLE, DB[17:0]).

ąÆ čĆąĄąČąĖą╝ąĄ ąĖąĮč鹥čĆč乥ą╣čüą░ RGB ąĖ ąĖąĮč鹥čĆč乥ą╣čüą░ VSYNC ą║ąŠą╝ą▒ąĖąĮąĖčĆąŠą▓ą░ąĮąĮąŠąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ čäčāąĮą║čåąĖąĖ ąĘą░ą┐ąĖčüąĖ ą▓ ą▓čŗčüąŠą║ąŠčüą║ąŠčĆąŠčüčéąĮąŠąĄ RAM ąĖ čäčāąĮą║čåąĖąĖ ą░ą┤čĆąĄčüą░čåąĖąĖ ąŠą║ąĮą░ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┤ąĖčüą┐ą╗ąĄčÄ čüą┤ą▓ąĖąĮčāčéčī ą║ą░čĆčéąĖąĮą║čā ą▓ ą┐ąŠąĘąĖčåąĖčÄ, čāą║ą░ąĘą░ąĮąĮčāčÄ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╝, ąĖ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ąŠč鹊ą▒čĆą░ąČą░čéčī ą║ą░čĆčéąĖąĮą║čā ą▓ ą┤čĆčāą│ąĖčģ ąŠą▒ą╗ą░čüčéčÅčģ 菹║čĆą░ąĮą░. ąŁč鹊 ą┤ą░ąĄčé ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ąŠą┐čéąĖą╝ąĖąĘąĖčĆąŠą▓ą░čéčī ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ą┐ąŠ čłąĖąĮąĄ ąĖ čüąĮąĖąĘąĖčéčī 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ.

ąÆ čĆąĄąČąĖą╝ąĄ ąĖąĮč鹥čĆč乥ą╣čüą░ VSYNC čĆą░ą▒ąŠčéą░ 菹║čĆą░ąĮą░ čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆąŠą▓ą░ąĮą░ čü ą▓ąĮąĄčłąĮąĖą╝ąĖ čéą░ą║čéą░ą╝ąĖ, ą║čĆąŠą╝ąĄ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ą║ą░ą┤čĆą░ (frame), ą║ąŠą│ą┤ą░ čĆą░ą▒ąŠčéą░ čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆčāąĄčéčüčÅ čüąĖą│ąĮą░ą╗ąŠą╝ VSYNC. ą×č鹊ą▒čĆą░ąČą░ąĄą╝čŗąĄ ą┤ą░ąĮąĮčŗąĄ ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĄąĄ GRAM č湥čĆąĄąĘ čüąĖčüč鹥ą╝ąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ąĄčüčéčī ąŠą│čĆą░ąĮąĖč湥ąĮąĖčÅ ąĮą░ čüą║ąŠčĆąŠčüčéčī ąĖ ą╝ąĄč鹊ą┤ ąĘą░ą┐ąĖčüąĖ ą┤ą░ąĮąĮčŗčģ ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĄąĄ ą×ąŚąŻ (čüą╝. ą┤ą░ą╗ąĄąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ čĆąĄąČąĖą╝ą░ VSYNC). ILI9325 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐ąĄčĆąĄą║ą╗čÄčćą░čéčīčüčÅ ą╝ąĄąČą┤čā ą▓ąĮąĄčłąĮąĖą╝ ąĖąĮč鹥čĆč乥ą╣čüąŠą╝ 菹║čĆą░ąĮą░ ąĖ čüąĖčüč鹥ą╝ąĮčŗą╝ ąĖąĮč鹥čĆč乥ą╣čüąŠą╝ čüą┐ąĄčåąĖą░ą╗čīąĮąŠą╣ ąĖąĮčüčéčĆčāą║čåąĖąĄą╣, čćč鹊ą▒čŗ ą▓čŗą▒čĆą░čéčī ąŠą┐čéąĖą╝ą░ą╗čīąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą│ąŠ ą▓ąĖą┤ą░ ąŠč鹊ą▒čĆą░ąČą░ąĄą╝ąŠą╣ ą║ą░čĆčéąĖąĮą║ąĖ (ąĖ/ąĖą╗ąĖ ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖčÅ ą│čĆą░čäąĖą║ąĖ ąĮą░ 菹║čĆą░ąĮąĄ). ąśąĮč鹥čĆč乥ą╣čü RGB, ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ ą▓čüąĄčģ ąŠč鹊ą▒čĆą░ąČą░ąĄą╝čŗčģ ą┤ą░ąĮąĮčŗčģ ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĄąĄ ą×ąŚąŻ, ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐ąĄčĆąĄą╝ąĄčēą░čéčī ą┤ą░ąĮąĮčŗąĄ ąĮą░ 菹║čĆą░ąĮ č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ ąŠą▒ąĮąŠą▓ą╗čÅąĄčéčüčÅ ą║ą░ą┤čĆ ąĖąĘą╝ąĄąĮčÅčÄčēąĄą│ąŠčüčÅ ąĖąĘąŠą▒čĆą░ąČąĄąĮąĖčÅ, ą┐ąŠąĘą▓ąŠą╗čÅčÅ čüąĮąĖąĘąĖčéčī 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ ą┐čĆąĖ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖąĖ ą▓ąĖą┤ąĄąŠ.

ILI9325 ą╝ąŠąČąĄčé čĆą░ą▒ąŠčéą░čéčī čü čāčĆąŠą▓ąĮčÅą╝ąĖ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ 1.65V, ąĖ čüąŠą┤ąĄčƹȹĖčé ą▓čüčéčĆąŠąĄąĮąĮčāčÄ čüčģąĄą╝čā č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ čāčĆąŠą▓ąĮąĄą╣ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą╝ą░čéčĆąĖčåąĄą╣ LCD. ILI9325 čéą░ą║ąČąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé čäčāąĮą║čåąĖčÄ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖčÅ ą║ą░čĆčéąĖąĮą║ąĖ ą▓ 8 čåą▓ąĄčéą░čģ ąĖ čĆąĄąČąĖą╝ čüąĮą░ (sleep mode), ą┤ą░ą▓ą░čÅ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī č鹊čćąĮąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ čāą┐čĆą░ą▓ą╗čÅčéčī ą┐ąŠčéčĆąĄą▒ą╗čÅąĄą╝ąŠą╣ ą╝ąŠčēąĮąŠčüčéčīčÄ, ąĖ čŹčéąĖ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ ą┤ąĄą╗ą░čÄčé ą┤čĆą░ą╣ą▓ąĄčĆ ILI9325 ąĖą┤ąĄą░ą╗čīąĮčŗą╝ čĆąĄčłąĄąĮąĖąĄą╝ ą┤ą╗čÅ ą┐ąŠčĆčéą░čéąĖą▓ąĮčŗčģ 菹╗ąĄą║čéčĆąŠąĮąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓, čéą░ą║ąĖčģ ą║ą░ą║ čüąŠč鹊ą▓čŗąĄ č鹥ą╗ąĄč乊ąĮčŗ, čüą╝ą░čĆčéč乊ąĮčŗ, PDA, PMP, ą│ą┤ąĄ ąŠč湥ąĮčī ą▓ą░ąČąĮčŗ čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅ ą║ čāą▓ąĄą╗ąĖč湥ąĮąĖčÄ ą▓čĆąĄą╝ąĄąĮąĖ čĆą░ą▒ąŠčéčŗ ąŠčé ą▒ą░čéą░čĆąĄąĖ.

ą×čüąĮąŠą▓ąĮčŗąĄ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ ąĖ čäčāąĮą║čåąĖąĖ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░:

ŌĆó ą×ą┤ąĮąŠą║čĆąĖčüčéą░ą╗čīąĮąŠąĄ čĆąĄčłąĄąĮąĖąĄ ą┤ą╗čÅ ą┤ąĖčüą┐ą╗ąĄčÅ QVGA TFT LCD.

ŌĆó ąĀą░ąĘčĆąĄčłą░čÄčēą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī 240RGBx320 č鹊č湥ą║ čü ąŠč鹊ą▒čĆą░ąČąĄąĮąĖąĄą╝ 262144 čåą▓ąĄč鹊ą▓.

ŌĆó ą¤ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé MVA (Multi-domain Vertical Alignment).

ŌĆó ąÆčüčéčĆąŠąĄąĮąĮčŗą╣ 720-ą║ą░ąĮą░ą╗čīąĮčŗą╣ ą┤čĆą░ą╣ą▓ąĄčĆ ąĖčüč鹊čćąĮąĖą║ą░ č鹊ą║ą░ (Source/VCOM) ąĖ 320-ą║ą░ąĮą░ą╗čīąĮčŗą╣ ą┤čĆą░ą╣ą▓ąĄčĆ ą║ą╗čÄč湥ą╣.

ŌĆó ąÆčüčéčĆąŠąĄąĮąĮąŠąĄ ą│čĆą░čäąĖč湥čüą║ąŠąĄ ą×ąŚąŻ ąĖąĘ 172800 ą▒ą░ą╣čé (GRAM).

ŌĆó ąÆčŗčüąŠą║ąŠčüą║ąŠčĆąŠčüčéąĮą░čÅ čäčāąĮą║čåąĖčÅ ą┐ą░ą║ąĄčéąĮąŠą╣ ąĘą░ą┐ąĖčüąĖ ą▓ ą×ąŚąŻ (High-speed RAM burst write).

ŌĆó ąĪąĖčüč鹥ą╝ąĮčŗąĄ ąĖąĮč鹥čĆč乥ą╣čüčŗ:

- i80 čü čłąĖčĆąĖąĮąŠą╣ čłąĖąĮčŗ 8, 9, 16, 18 ą▒ąĖčé.

- Serial Peripheral Interface (SPI).

- RGB čü čłąĖčĆąĖąĮąŠą╣ čłąĖąĮčŗ 6, 16, 18 ą▒ąĖčé (VSYNC, HSYNC, DOTCLK, ENABLE, DB[17:0]).

- VSYNC (System interface + VSYNC).

ŌĆó ąÆąĮčāčéčĆąĄąĮąĮąĖą╣ ą│ąĄąĮąĄčĆą░č鹊čĆ ąĖ ą░ą┐ą┐ą░čĆą░čéąĮčŗą╣ čüą▒čĆąŠčü.

ŌĆó ążčāąĮą║čåąĖčÅ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ čĆą░ąĘą╝ąĄčĆą░ (x1/2, x1/4).

ŌĆó ąśąĘą╝ąĄąĮčÅąĄą╝ąŠąĄ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čüą┤ą▓ąĖą│ą░ ą┤čĆą░ą╣ą▓ąĄčĆąŠą▓ č鹊ą║ą░/ą║ą╗čÄč湥ą╣.

ŌĆó ążčāąĮą║čåąĖčÅ ą░ą┤čĆąĄčüą░čåąĖąĖ ąŠą║ąĮą░, čćč鹊ą▒čŗ čāą║ą░ąĘą░čéčī ą┐čĆčÅą╝ąŠčāą│ąŠą╗čīąĮčāčÄ ąŠą▒ą╗ą░čüčéčī ą┐čĆąĖ ą┤ąŠčüčéčāą┐ąĄ ą║ GRAM.

ŌĆó ąæąŠą│ą░čéčŗą╣ ąĮą░ą▒ąŠčĆ čäčāąĮą║čåąĖą╣ ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čåą▓ąĄč鹊ą▓čŗą╝ 菹║čĆą░ąĮąŠą╝.

ŌĆó ążčāąĮą║čåąĖčÅ ą│ą░ą╝ą╝ą░-ą║ąŠčĆčĆąĄą║čåąĖąĖ, ą┐ąŠąĘą▓ąŠą╗čÅčÄčēą░čÅ ąŠč鹊ą▒čĆą░ąČą░čéčī 262144 čåą▓ąĄč鹊ą▓.

ŌĆó ążčāąĮą║čåąĖčÅ ą╗ąĖąĮąĄą╣ąĮąŠą╣ ą▓ąĄčĆčéąĖą║ą░ą╗čīąĮąŠą╣ ą┐čĆąŠą║čĆčāčéą║ąĖ.

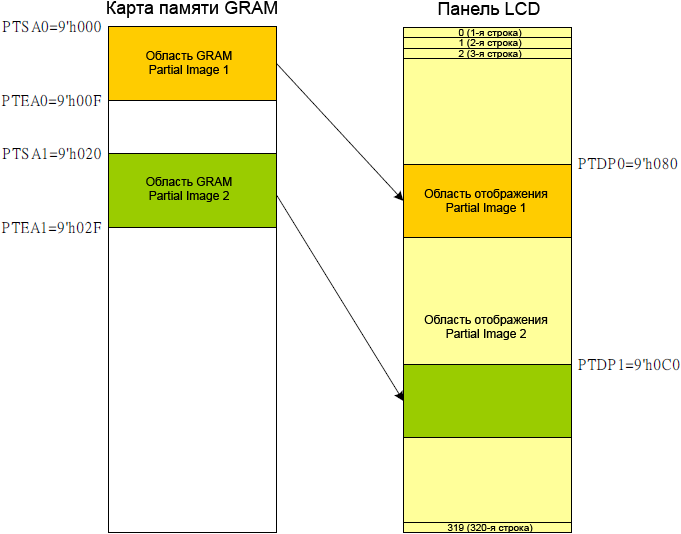

ŌĆó ążčāąĮą║čåąĖčÅ čćą░čüčéąĖčćąĮąŠą│ąŠ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ, ą┐ąŠąĘą▓ąŠą╗čÅčÄčēą░čÅ čāą┐čĆą░ą▓ą╗čÅčéčī čćą░čüčéčīčÄ ą┐ą░ąĮąĄą╗ąĖ LCD ą▓ ą┐ąŠąĘąĖčåąĖąĖ, čāą║ą░ąĘą░ąĮąĮąŠą╣ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╝.

ŌĆó ąÆčüčéčĆąŠąĄąĮąĮą░čÅ čüčģąĄą╝ą░ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą┐ąŠą▓čŗčłąĄąĮąĮčŗčģ ąĮą░ą┐čĆčÅąČąĄąĮąĖą╣ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ LCD (ą┐ąŠą▓čŗčłąĄąĮąĖąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą║čĆą░čéąĮąŠčüčéąĖ ą┤ąŠ 6 čĆą░ąĘ).

ŌĆó ążčāąĮą║čåąĖąĖ 菹║ąŠąĮąŠą╝ąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ:

- ąĀąĄąČąĖą╝ 8 čåą▓ąĄč鹊ą▓.

- ąĀąĄąČąĖą╝ ą┐čĆąĖąŠčüčéą░ąĮąŠą▓ą║ąĖ (standby mode).

- ąĀąĄąČąĖą╝ čüąĮą░ (sleep mode).

ŌĆó ąÉčĆčģąĖč鹥ą║čéčāčĆą░, čüą┐čĆąŠąĄą║čéąĖčĆąŠą▓ą░ąĮąĮą░čÅ ąĮą░ ą┐ąĖčéą░ąĮąĖąĄ ąŠčé ąĖčüč鹊čćąĮąĖą║ąŠą▓ ąĮąĖąĘą║ąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ:

IOVcc = 1.65V .. 3.3 V (ąĖąĮč鹥čĆč乥ą╣čü ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░, I/O).

Vci = 2.5V .. 3.3 V (ą░ąĮą░ą╗ąŠą│ąŠą▓čŗąĄ čüčģąĄą╝čŗ).

ąØą░ą┐čĆčÅąČąĄąĮąĖčÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ LCD:

ŌĆó ą¤ąĖčéą░ąĮąĖąĄ Source/VCOM

DDVDH - GND = 4.5V .. 6.0V

VCL ŌĆō GND = -2.0V .. -3.0V

VCI ŌĆō VCL Ōēż 6.0V

ŌĆó ą¤ąĖčéą░ąĮąĖąĄ ą┤čĆą░ą╣ą▓ąĄčĆąŠą▓ ą▓čŗčģąŠą┤ąĮčŗčģ ą║ą╗čÄč湥ą╣

VGH - GND = 10V .. 20V

VGL ŌĆō GND = -5V .. -15V

VGH ŌĆō VGL Ōēż 32V

ŌĆó ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ ą▓čŗčģąŠą┤ą░ ą┤čĆą░ą╣ą▓ąĄčĆą░ VCOM

VCOMH = 3.0V .. (DDVDH-0.2)V

VCOML = (VCL+0.5)V .. 0V

VCOMH-VCOML Ōēż 6.0V

ąæą╗ąŠą║-čüčģąĄą╝ą░ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░:

| ą£ąĮąĄą╝. |

I/O |

ąóąĖą┐ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| ąśąĮč鹥čĆč乥ą╣čü ą▓ą▓ąŠą┤ą░ |

| IM3, IM2, IM1, IM0/ID |

I |

IOVcc |

ąÆčŗą▒ąĖčĆą░ąĄčé čéąĖą┐ ąĖąĮč鹥čĆč乥ą╣čüą░ čü čāą┐čĆą░ą▓ą╗čÅčÄčēąĖą╝ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą╝ (čüą╝. čéą░ą▒ą╗ąĖčåčā ąĮąĖąČąĄ ą┤ą╗čÅ ąŠą┐ąĖčüą░ąĮąĖčÅ čüąŠčüč鹊čÅąĮąĖą╣ ą▓čŗą▓ąŠą┤ąŠą▓ IM3, IM2, IM1, IM0). ąÜąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ąĖąĮč鹥čĆč乥ą╣čü SPI, čüąĖą│ąĮą░ą╗ IM0 čüą╗čāąČąĖčé ą▓ ą║ą░č湥čüčéą▓ąĄ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆą░ čāčüčéčĆąŠą╣čüčéą▓ą░ (ID). |

| nCS |

I |

MPU IOVcc |

ąĪąĖą│ąĮą░ą╗ ą▓čŗą▒ąŠčĆą║ąĖ (chip select). 0: ILI9325 ą▓čŗą▒čĆą░ąĮ ąĖ ą┤ąŠčüčéčāą┐ąĄąĮ ą┤ą╗čÅ ąŠą▒ą╝ąĄąĮą░, 1: ILI9325 ąĮąĄ ą▓čŗą▒čĆą░ąĮ ąĖ ąĮąĄą┤ąŠčüčéčāą┐ąĄąĮ. ąÜąŠą│ą┤ą░ čŹč鹊čé čüąĖą│ąĮą░ą╗ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ, ąŠąĮ ąĮą░ą┐čĆčÅą╝čāčÄ ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčéčüčÅ ą║ GND. |

| RS |

I |

MPU IOVcc |

ąĪąĖą│ąĮą░ą╗ ą▓čŗą▒ąŠčĆą░ čĆąĄą│ąĖčüčéčĆą░ (register select). 0: ą▓čŗą▒ąĖčĆą░ąĄčé čĆąĄą│ąĖčüčéčĆ ąĖąĮą┤ąĄą║čüą░ ąĖą╗ąĖ čĆąĄą│ąĖčüčéčĆ čüčéą░čéčāčüą░, 1: ą▓čŗą▒ąĖčĆą░ąĄčé čĆąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ. ąÜąŠą│ą┤ą░ čŹč鹊čé čüąĖą│ąĮą░ą╗ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ, ąŠąĮ ąĮą░ą┐čĆčÅą╝čāčÄ ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčéčüčÅ ą║ IOVcc ąĖą╗ąĖ GND. |

| nWR/SCL |

I |

MPU IOVcc |

ąĪąĖą│ąĮą░ą╗ čüčéčĆąŠą▒ą░ ąĖ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ąĘą░ą┐ąĖčüąĖ. ąöą░ąĮąĮčŗąĄ ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ, ą║ąŠą│ą┤ą░ čŹč鹊čé čüąĖą│ąĮą░ą╗ ą▓ ą╗ąŠą│. 0. ążąĖą║čüąĖčĆčāąĄčéčüčÅ ąĮą░ čāčĆąŠą▓ąĄąĮčī ą╗ąĖą▒ąŠ IOVcc, ą╗ąĖą▒ąŠ GND, ą║ąŠą│ą┤ą░ čŹč鹊čé čüąĖą│ąĮą░ą╗ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ. ąÆ čĆąĄąČąĖą╝ąĄ SPI: čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆčāčÄčēąĖą╣ čüąĖą│ąĮą░ą╗ čéą░ą║č鹊ą▓. |

| nRD |

I |

MPU IOVcc |

ąĪąĖą│ąĮą░ą╗ čüčéčĆąŠą▒ą░ ąĖ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ čćč鹥ąĮąĖčÅ. ąöą░ąĮąĮčŗąĄ čüčćąĖčéčŗą▓ą░čÄčéčüčÅ, ą║ąŠą│ą┤ą░ čŹč鹊čé čüąĖą│ąĮą░ą╗ ą▓ ą╗ąŠą│. 0. ążąĖą║čüąĖčĆčāąĄčéčüčÅ ąĮą░ čāčĆąŠą▓ąĄąĮčī ą╗ąĖą▒ąŠ IOVcc, ą╗ąĖą▒ąŠ GND, ą║ąŠą│ą┤ą░ čŹč鹊čé čüąĖą│ąĮą░ą╗ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ. |

| nRESET |

I |

MPU IOVcc |

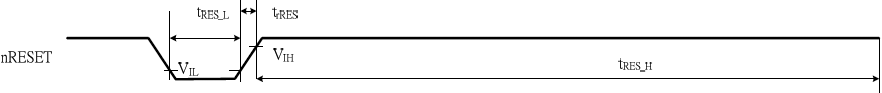

ąĪąĖą│ąĮą░ą╗ čüą▒čĆąŠčüą░, ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆčāąĄčé ILI9325 ą┐čĆąĖ ą┐ąŠą┤ą░č湥 ą╗ąŠą│. 0. ą×ą▒ąĄčüą┐ąĄčćčīč鹥 čüą▒čĆąŠčü ą┐ąŠčüą╗ąĄ ą┐ąŠą┤ą░čćąĖ ą┐ąĖčéą░ąĮąĖčÅ. |

| SDI |

I |

MPU IOVcc |

ąĪąĖą│ąĮą░ą╗ ą▓ą▓ąŠą┤ą░ ą┤ą░ąĮąĮčŗčģ SPI. ąæąĖčéčŗ ą┤ą░ąĮąĮčŗčģ ąĘą░čēąĄą╗ą║ąĖą▓ą░čÄčéčüčÅ ą┐ąŠ čäčĆąŠąĮčéčā ąĮą░čĆą░čüčéą░ąĮąĖčÅ čāčĆąŠą▓ąĮčÅ čüąĖą│ąĮą░ą╗ą░ SCL. |

| SDO |

O |

MPU IOVcc |

ąĪąĖą│ąĮą░ą╗ ą▓čŗą▓ąŠą┤ą░ ą┤ą░ąĮąĮčŗčģ SPI. ąæąĖčéčŗ ą┤ą░ąĮąĮčŗčģ ąĘą░čēąĄą╗ą║ąĖą▓ą░čÄčéčüčÅ ą┐ąŠ čüą┐ą░ą┤čā čāčĆąŠą▓ąĮčÅ čüąĖą│ąĮą░ą╗ą░ SCL. ąĢčüą╗ąĖ čüąĖą│ąĮą░ą╗ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ, ąŠčüčéą░ą▓čīč鹥 ąĄą│ąŠ ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗą╝ |

| DB[17:0] |

I/O |

MPU IOVcc |

ą¤ą░čĆą░ą╗ą╗ąĄą╗čīąĮą░čÅ 18-čĆą░ąĘčĆčÅą┤ąĮą░čÅ, ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮą░čÅ čłąĖąĮą░ ą┤ą░ąĮąĮčŗčģ ą┤ą╗čÅ ąŠą▒ą╝ąĄąĮą░ čü čāą┐čĆą░ą▓ą╗čÅčÄčēąĖą╝ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą╝. ąśčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ čĆą░ąĘčĆčÅą┤čŗ:

8-ą▒ąĖčéąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü: ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ čĆą░ąĘčĆčÅą┤čŗ DB[17:10].

9-ą▒ąĖčéąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü: ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ čĆą░ąĘčĆčÅą┤čŗ DB[17:9].

16-ą▒ąĖčéąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü: ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ čĆą░ąĘčĆčÅą┤čŗ DB[17:10] ąĖ DB[8:1].

18-ą▒ąĖčéąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü: ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą▓čüąĄ čĆą░ąĘčĆčÅą┤čŗ DB[17:0].

18-ą▒ąĖčéąĮą░čÅ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮą░čÅ ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮą░čÅ čłąĖąĮą░ ą┤ą░ąĮąĮčŗčģ ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ ąĖąĮč鹥čĆč乥ą╣čüą░ RGB:

6-ą▒ąĖčéąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü RGB: ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ čĆą░ąĘčĆčÅą┤čŗ DB[17:12].

16-ą▒ąĖčéąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü RGB: ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ čĆą░ąĘčĆčÅą┤čŗ DB[17:13] ąĖ DB[11:1].

18-ą▒ąĖčéąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü RGB: ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ čĆą░ąĘčĆčÅą┤čŗ DB[17:0].

ąØąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą▓čŗą▓ąŠą┤čŗ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮčŗ ą║ GND. |

| ENABLE |

I |

MPU IOVcc |

ąĪąĖą│ąĮą░ą╗ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ ąĖąĮč鹥čĆč乥ą╣čüą░ RGB. 0: ą▓čŗą▒čĆą░ąĮąŠ (ą┤ąŠčüčéčāą┐ čĆą░ąĘčĆąĄčłąĄąĮ), 1: ąĮąĄ ą▓čŗą▒čĆą░ąĮąŠ (ą┤ąŠčüčéčāą┐ ąĘą░ą┐čĆąĄčēąĄąĮ). ąæąĖčé EPL ąĖąĮą▓ąĄčĆčéąĖčĆčāąĄčé ą┐ąŠą╗čÅčĆąĮąŠčüčéčī čüąĖą│ąĮą░ą╗ą░ ENABLE. ąÜąŠą│ą┤ą░ ENABLE ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ, ąŠąĮ čäąĖą║čüąĖčĆąŠą▓ą░ąĮąŠ ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčéčüčÅ ą║ IOVcc ąĖą╗ąĖ GND. |

| DOTCLK |

I |

MPU IOVcc |

ąĪąĖą│ąĮą░ą╗ čéą░ą║č鹊ą▓ č鹊č湥ą║ ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ ąĖąĮč鹥čĆč乥ą╣čüą░ RGB. DPL = 0: ą▓ą▓ąŠą┤ ą┤ą░ąĮąĮčŗčģ ą┐ąŠ čäčĆąŠąĮčéčā ąĮą░čĆą░čüčéą░ąĮąĖčÅ čāčĆąŠą▓ąĮčÅ DOTCLK, DPL = 1: ą▓ą▓ąŠą┤ ą┤ą░ąĮąĮčŗčģ ą┐ąŠ čüą┐ą░ą┤čā čāčĆąŠą▓ąĮčÅ DOTCLK. ąĢčüą╗ąĖ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ, č鹊 čäąĖą║čüąĖčĆąŠą▓ą░ąĮąŠ ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčéčüčÅ ą║ GND. |

| VSYNC |

I |

MPU IOVcc |

ąĪąĖą│ąĮą░ą╗ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ą║ą░ą┤čĆą░ ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ ąĖąĮč鹥čĆč乥ą╣čüą░ RGB. VSPL = 0: VSYNC ą░ą║čéąĖą▓ąĄąĮ ą┐čĆąĖ ą╗ąŠą│. 0, VSPL = 1: čüąĖą│ąĮą░ą╗ VSYNC ą░ą║čéąĖą▓ąĄąĮ ą┐čĆąĖ ą╗ąŠą│. 1. ąĢčüą╗ąĖ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ, č鹊 čäąĖą║čüąĖčĆąŠą▓ą░ąĮąŠ ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčéčüčÅ ą║ GND. |

| HSYNC |

I |

MPU IOVcc |

ąĪąĖą│ąĮą░ą╗ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ čüčéčĆąŠą║ąĖ ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ ąĖąĮč鹥čĆč乥ą╣čüą░ RGB. HSPL = 0: HSYNC ą░ą║čéąĖą▓ąĄąĮ ą┐čĆąĖ ą╗ąŠą│. 0, HSPL = 1: čüąĖą│ąĮą░ą╗ HSYNC ą░ą║čéąĖą▓ąĄąĮ ą┐čĆąĖ ą╗ąŠą│. 1. ąĢčüą╗ąĖ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ, č鹊 čäąĖą║čüąĖčĆąŠą▓ą░ąĮąŠ ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčéčüčÅ ą║ GND. |

| FMARK |

O |

MPU IOVcc |

ąÆčŗčģąŠą┤ čüąĖą│ąĮą░ą╗ą░ ąĮą░čćą░ą╗ą░ čäčĆąĄą╣ą╝ą░ (frame head pulse). ąĪąĖą│ąĮą░ą╗ FMARK ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ąĘą░ą┐ąĖčüčī ą┤ą░ąĮąĮčŗčģ ą▓ ą×ąŚąŻ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆčāąĄčéčüčÅ čü ą║ą░ą┤čĆąŠą╝. ąĢčüą╗ąĖ čŹč鹊čé čüąĖą│ąĮą░ą╗ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ, ąŠčüčéą░ą▓čīč鹥 ąĄą│ąŠ ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗą╝. |

| ąĪąĖą│ąĮą░ą╗čŗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čüąĄą│ą╝ąĄąĮčéą░ą╝ąĖ ą┐ą░ąĮąĄą╗ąĖ LCD |

S720

..

S1 |

O |

LCD |

ąÆčŗčģąŠą┤čŗ čüąĖą│ąĮą░ą╗ąŠą▓ č鹊ą║ą░, ą┐ąŠą┤ą░ą▓ą░ąĄą╝čŗąĄ ąĮą░ č鹊čćą║ąĖ ąČąĖą┤ą║ąĖčģ ą║čĆąĖčüčéą░ą╗ą╗ąŠą▓ (LCD). ąöą╗čÅ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čüą┤ą▓ąĖą│ą░ ą▓čŗčģąŠą┤ąŠą▓ čüąĖą│ąĮą░ą╗ąŠą▓ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▒ąĖčé SS. ą¤čĆąĖ SS = 0 ą┤ą░ąĮąĮčŗąĄ ą×ąŚąŻ ą┐ąŠ ą░ą┤čĆąĄčüčā 00000h ą▓čŗą▓ąŠą┤čÅčéčüčÅ ąĖąĘ S1. ą¤čĆąĖ SS = 1, ą┤ą░ąĮąĮčŗąĄ ą×ąŚąŻ ą┐ąŠ ą░ą┤čĆąĄčüčā 00000h ą▓čŗą▓ąŠą┤čÅčéčüčÅ ąĖąĘ S720. S1, S4, S7, ... ąŠč鹊ą▒čĆą░ąČą░čÄčé ą║čĆą░čüąĮčŗą╣ (red, R), S2, S5, S8, ... ąŠč鹊ą▒čĆą░ąČą░čÄčé ąĘąĄą╗ąĄąĮčŗą╣ (green, G), ąĖ S3, S6, S9, ... ąŠč鹊ą▒čĆą░ąČą░čÄčé čüąĖąĮąĖą╣ (blue, B) (ą┐čĆąĖ SS = 0). |

G320

..

G1 |

O |

LCD |

ąÆčŗčģąŠą┤čŗ čüąĖą│ąĮą░ą╗ąŠą▓ ą┤čĆą░ą╣ą▓ąĄčĆąŠą▓. VGH: čāčĆąŠą▓ąĄąĮčī ą▓čŗą▒ąŠčĆą░ čüčéčĆąŠą║, VGL: čāčĆąŠą▓ąĄąĮčī ąŠčéčüčāčéčüčéą▓ąĖčÅ ą▓čŗą▒ąŠčĆą░ čüčéčĆąŠą║. |

| VCOM |

O |

TFT, ąŠą▒čēąĖą╣ 菹╗ąĄą║čéčĆąŠą┤ |

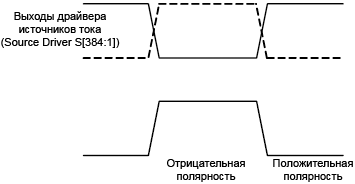

ą×ą▒čēąĖą╣ ą┐čĆąŠą▓ąŠą┤ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ ą┐ą░ąĮąĄą╗ąĖ TFT. VCOM čŹč鹊 AC-čüąĖą│ąĮą░ą╗ čü ąĖąĘą╝ąĄąĮčÅčÄčēąĖą╝ąĖčüčÅ čāčĆąŠą▓ąĮčÅą╝ąĖ ą╝ąĄąČą┤čā VCOMH ąĖ VCOML. |

| VCOMH |

O |

ążąĖą╗čīčéčĆčāčÄčēąĖą╣ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ |

ąÆčŗčüąŠą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī ą┤ą╗čÅ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ VCOM. ą¤ąŠą┤ą║ą╗čÄčćą░ąĄčéčüčÅ ą║ čäąĖą╗čīčéčĆčāčÄčēąĄą╝čā ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆčā. |

| VCOML |

O |

ążąĖą╗čīčéčĆčāčÄčēąĖą╣ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ |

ąØąĖąĘą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī ą┤ą╗čÅ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ VCOM. ą¤ąŠą┤ą║ą╗čÄčćą░ąĄčéčüčÅ ą║ čäąĖą╗čīčéčĆčāčÄčēąĄą╝čā ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆčā. |

| VGS |

I |

GND ąĖą╗ąĖ ą▓ąĮąĄčłąĮąĖą╣ čĆąĄąĘąĖčüč鹊čĆ |

ą×ą┐ąŠčĆąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī ą┤ą╗čÅ čüčģąĄą╝čŗ ą│ąĄąĮąĄčĆą░čåąĖąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ čāčĆąŠą▓ąĮčÅ čüąĄčĆąŠą│ąŠ. ąŻčĆąŠą▓ąĄąĮčī VGS ą╝ąŠąČąĄčé ą▒čŗčéčī ąĖąĘą╝ąĄąĮąĄąĮ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖąĄą╝ ą▓ąĮąĄčłąĮąĄą│ąŠ čĆąĄąĘąĖčüč鹊čĆą░. |

| ąĪčģąĄą╝čŗ ąĮą░ą║ą░čćą║ąĖ (charge-pump) ąĖ čĆąĄą│čāą╗ąĖčĆąŠą▓ą░ąĮąĖčÅ |

| Vci |

I |

ąśčüč鹊čćąĮąĖą║ ą┐ąĖčéą░ąĮąĖčÅ |

ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ ą┤ą╗čÅ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą╣ čüčģąĄą╝čŗ. ą¤ąŠą┤ą║ą╗čÄčćą░ąĄčéčüčÅ ą║ ą▓ąĮąĄčłąĮąĄą╝čā ąĖčüč鹊čćąĮąĖą║čā ą┐ąĖčéą░ąĮąĖčÅ 2.5 .. 3.3V. |

| GND |

I |

ąśčüč鹊čćąĮąĖą║ ą┐ąĖčéą░ąĮąĖčÅ |

ąŚąĄą╝ą╗čÅ, ąŠą▒čēąĖą╣ ą┐čĆąŠą▓ąŠą┤ ą┤ą╗čÅ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗčģ ąĖ čåąĖčäčĆąŠą▓čŗčģ čüčģąĄą╝. ąÆ čüą╗čāčćą░ąĄ COG (chip-on-glass, ą║čĆąĖčüčéą░ą╗ą╗ ąĮą░ čüč鹥ą║ą╗ąĄ) ą┤ą╗čÅ ą┐čĆąĄą┤ąŠčéą▓čĆą░čēąĄąĮąĖčÅ čłčāą╝ą░ ą┐ąŠą┤ą║ą╗čÄčćąĖč鹥 ą║ FPC (Flex Panel Connector, ą│ąĖą▒ą║ąĖą╣ čłą╗ąĄą╣čä ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ). |

| Vci1 |

O |

ążąĖą╗čīčéčĆčāčÄčēąĖą╣ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ |

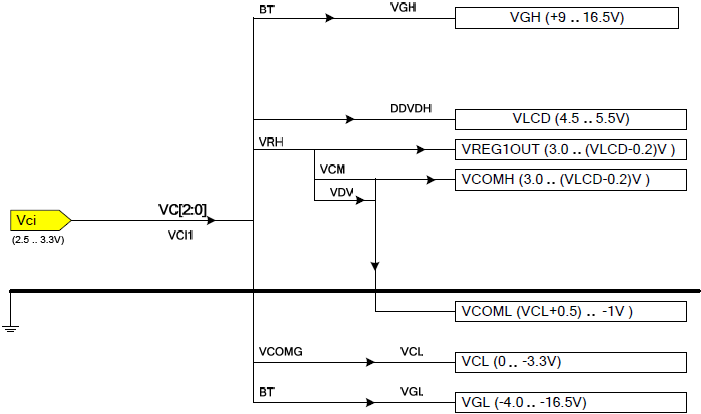

ąÆąĮčāčéčĆąĄąĮąĮąĄąĄ ąŠą┐ąŠčĆąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┤ą╗čÅ čüčģąĄą╝čŗ ą┐ąŠą▓čŗčłąĄąĮąĖčÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ (step-up circuit1). ąÉą╝ą┐ą╗ąĖčéčāą┤ą░ ą╝ąĄąČą┤čā Vci ąĖ GND ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą▒ąĖčéą░ą╝ąĖ VC[2:0]. ąōą░čĆą░ąĮčéąĖčĆčāą╣č鹥 čāčüčéą░ąĮąŠą▓ą║čā ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ Vci1 čéą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, čćč鹊ą▒čŗ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ DDVDH, VGH ąĖ VGL ą▒čŗą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čüąŠ čüą┐ąĄčåąĖčäąĖą║ą░čåąĖąĄą╣. |

| DDVDH |

O |

ążąĖą╗čīčéčĆčāčÄčēąĖą╣ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ |

ąśčüč鹊čćąĮąĖą║ ą┐ąĖčéą░ąĮąĖčÅ ą┤ą╗čÅ ą┤čĆą░ą╣ą▓ąĄčĆą░ č鹊ą║ą░ ąĖ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ Vcom. |

| VGH |

O |

ążąĖą╗čīčéčĆčāčÄčēąĖą╣ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ |

ą¤ąĖčéą░ąĮąĖąĄ ą┤ą╗čÅ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ ą┤čĆą░ą╣ą▓ąĄčĆą░. |

| VGL |

O |

ążąĖą╗čīčéčĆčāčÄčēąĖą╣ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ |

ą¤ąĖčéą░ąĮąĖąĄ ą┤ą╗čÅ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ ą┤čĆą░ą╣ą▓ąĄčĆą░. |

| VCL |

O |

ążąĖą╗čīčéčĆčāčÄčēąĖą╣ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ |

ą¤ąĖčéą░ąĮąĖąĄ ą┤čĆą░ą╣ą▓ąĄčĆą░ VcomL. VCL = 0.5 .. ŌĆōVCI. ąÜąŠąĮą┤ąĄąĮčüą░č鹊čĆ ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčéčüčÅ ą╝ąĄąČą┤čā VCL ąĖ GND. |

| C11+ C11- C12+ C12- |

I/O |

ąÜąŠąĮą┤ąĄąĮčüą░č鹊čĆčŗ ą┐ąŠą▓čŗčłą░čÄčēąĄą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░č鹥ą╗čÅ |

ąÆčŗą▓ąŠą┤čŗ ą┤ą╗čÅ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆąŠą▓ čüčģąĄą╝čŗ čāą╝ąĮąŠąČąĖč鹥ą╗čÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ 1 (step-up circuit 1). |

| C13+ C13- C21+ C21- C22+ C22- |

I/O |

ąÜąŠąĮą┤ąĄąĮčüą░č鹊čĆčŗ ą┐ąŠą▓čŗčłą░čÄčēąĄą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░č鹥ą╗čÅ |

ąÆčŗą▓ąŠą┤čŗ ą┤ą╗čÅ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆąŠą▓ čüčģąĄą╝čŗ čāą╝ąĮąŠąČąĖč鹥ą╗čÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ 2 (step-up circuit 2). |

| VREG1OUT |

I/O |

ążąĖą╗čīčéčĆčāčÄčēąĖą╣ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ |

ąÆčŗčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ, čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąĮąŠąĄ ąĖąĘ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ. ąŻčĆąŠą▓ąĄąĮčī ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▒ąĖčéą░ą╝ąĖ VRH. VREG1OUT čŹč鹊 ąĖčüč鹊čćąĮąĖą║ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą│ąĄąĮąĄčĆą░č鹊čĆą░ čāčĆąŠą▓ąĮčÅ čüąĄčĆąŠą│ąŠ (1), čāčĆąŠą▓ąĮčÅ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ VcomH (2) ąĖ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ Vcom (3). VREG1OUT = 3.0V .. (DDVDH ŌĆō 0.2)V. |

| ąÜąŠąĮčéą░ą║čéčŗ ą┐ąĖčéą░ąĮąĖčÅ |

| IOVcc |

I |

ąśčüč鹊čćąĮąĖą║ ą┐ąĖčéą░ąĮąĖčÅ |

ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ ą┤ą╗čÅ ą▓čŗą▓ąŠą┤ąŠą▓ ąĖąĮč鹥čĆč乥ą╣čüą░: IM[3:0], nRESET, nCS, nWR, nRD, RS, DB[17:0], VSYNC, HSYNC, DOTCLK, ENABLE, SCL, SDI, SDO. IOVcc = 1.65V .. 3.3V ąĖ Vcc Ōē¦ IOVcc. ąÆ čüą╗čāčćą░ąĄ COG ą┤ą╗čÅ ą┐čĆąĄą┤ąŠčéą▓čĆą░čēąĄąĮąĖčÅ čłčāą╝ą░ ą┐ąŠą┤ą║ą╗čÄčćąĖč鹥 Vcc ą║ FPC, ąĄčüą╗ąĖ IOVcc = Vcc. |

| VDDD |

O |

ą¤ąĖčéą░ąĮąĖąĄ |

ąØąŠąČą║ą░ ą┐ąĖčéą░ąĮąĖčÅ čåąĖčäčĆąŠą▓ąŠą╣ čüčģąĄą╝čŗ. ą¤ąŠą┤ą║ą╗čÄčćąĖč鹥 čŹčéąĖ ą▓čŗą▓ąŠą┤čŗ ą║ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆčā 1uF. |

| GND |

I |

ąśčüč鹊čćąĮąĖą║ ą┐ąĖčéą░ąĮąĖčÅ |

GND = 0V |

| ąÜąŠąĮčéą░ą║čéčŗ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ |

| DUMMY1..15 DUMMY20..27 |

- |

- |

ą¤čāčüčéčŗąĄ ą║ąŠąĮčéą░ą║čéąĮčŗąĄ ą┐ą╗ąŠčēą░ą┤ą║ąĖ. ą×čüčéą░ą▓čīč鹥 ąĖčģ ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗą╝ąĖ. |

| IOGNDDUM |

O |

GND |

ąÆčŗą▓ąŠą┤ ąŠą▒čēąĄą│ąŠ ą┐čĆąŠą▓ąŠą┤ą░. |

| TESTO1..16 |

O |

Open |

ąÆčŗą▓ąŠą┤čŗ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ. ą×čüčéą░ą▓čīč鹥 ąĖčģ ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗą╝ąĖ. |

| TEST1, 2, 3 |

I |

IOGND |

ąÆčŗą▓ąŠą┤čŗ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ (čü ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ ą┐ąŠą┤čéčÅąČą║ąŠą╣ ą║ ą╗ąŠą│. 0). ą¤ąŠą┤ą║ą╗čÄčćąĖč鹥 ąĖčģ ą║ GND ąĖą╗ąĖ ąŠčüčéą░ą▓čīč鹥 ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗą╝ąĖ. |

| TS0..8 |

I |

Open |

ąÆčŗą▓ąŠą┤čŗ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ (čü ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ ą┐ąŠą┤čéčÅąČą║ąŠą╣ ą║ ą╗ąŠą│. 0). ą×čüčéą░ą▓čīč鹥 ąĖčģ ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗą╝ąĖ. |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▓ čüč鹊ą╗ą▒čåąĄ I/O ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čüąĖą│ąĮą░ą╗ą░: I ą▓čģąŠą┤, O ą▓čŗčģąŠą┤, I/O ą┤ą▓čāąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĮčŗą╣ čüąĖą│ąĮą░ą╗.

ąóą░ą▒ą╗ąĖčåą░ 1. ąĪą┐ąĄčåąĖčäąĖą║ą░čåąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ LCD.

| ą¤ą░čĆą░ą╝ąĄčéčĆ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| ąöčĆą░ą╣ą▓ąĄčĆ č鹊ą║ą░ ą┐ą░ąĮąĄą╗ąĖ (TFT Source Driver) |

720 ą▓čŗą▓ąŠą┤ąŠą▓ (240 x RGB) |

| ąöčĆą░ą╣ą▓ąĄčĆ ą▓čŗčģąŠą┤ąŠą▓ (TFT Gate Driver) |

320 ą▓čŗą▓ąŠą┤ąŠą▓ |

| ąĪčéčĆčāą║čéčāčĆą░ ąĄą╝ą║ąŠčüč鹥ą╣ 菹║čĆą░ąĮą░ (TFT Display Capacitor Structure) |

ą×ą▒čēąĖą╣ VCOM |

| ąÆčŗčģąŠą┤čŗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ LCD |

S1 .. S720 |

ąŻčĆąŠą▓ąĮąĖ čüąĄčĆąŠą│ąŠ V0 .. V63 |

| G1 .. G320 |

VGH - VGL |

| VCOM |

VCOMH - VCOML |

| ąÆčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ |

IOVcc |

1.65V .. 3.30V |

| Vci |

2.50V .. 3.30V |

| ąØą░ą┐čĆčÅąČąĄąĮąĖčÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ LCD |

DDVDH |

4.5V .. 6.0V |

| VGH |

10V .. 20V |

| VGL |

-5V .. -15V |

| VCL |

-2.0V .. -3.0V |

| VGH - VGL |

Max. 32V |

| Vci - VCL |

Max. 6.0V |

| ąÆąĮčāčéčĆąĄąĮąĮąĖąĄ čüčģąĄą╝čŗ ą┐ąŠą▓čŗčłąĄąĮąĖčÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ (Step-up Circuits) |

DDVDH |

Vci1 x2 |

| VGH |

Vci1 x4, x5, x6 |

| VGL |

Vci1 x-3, x-4, x-5 |

| VCL |

Vci1 x-1 |

[ąĪąĖčüč鹥ą╝ąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü ILI9325]

ILI9325 ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ą▓čŗčüąŠą║ąŠčüą║ąŠčĆąŠčüčéąĮčŗąĄ ąĖąĮč鹥čĆč乥ą╣čüčŗ: čüčéąĖą╗čÅ i80 (ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮą░ čłąĖąĮą░ 8, 9, 16, 18 ą▒ąĖčé) ąĖ SPI. ąĀąĄąČąĖą╝ ąĖąĮč鹥čĆč乥ą╣čüą░ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ą┐čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ čü ą┐ąŠą╝ąŠčēčīčÄ ą▓čŗą▓ąŠą┤ąŠą▓ IM[3:0].

ąóą░ą▒ą╗ąĖčåą░ čüąŠčüč鹊čÅąĮąĖčÅ ą▓čŗą▓ąŠą┤ąŠą▓ IM3, IM2, IM1, IM0 ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ čĆąĄąČąĖą╝čŗ ąĖąĮč鹥čĆč乥ą╣čüą░:

| IM3 |

IM2 |

IM1 |

IM0 |

ąĀąĄąČąĖą╝ ąĖąĮč鹥čĆč乥ą╣čüą░ MPU |

ąĪąĖą│ąĮą░ą╗čŗ ą┤ą░ąĮąĮčŗčģ |

| 0 |

0 |

0 |

0 |

ąØąĄą┤ąŠą┐čāčüčéąĖą╝ą░čÅ ą║ąŠą╝ą▒ąĖąĮą░čåąĖčÅ |

- |

| 0 |

0 |

0 |

1 |

| 0 |

0 |

1 |

0 |

i80 čüąĖčüč鹥ą╝ąĮčŗą╣ 16-ą▒ąĖčéąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü |

DB[17:10], DB[8:1] |

| 0 |

0 |

1 |

1 |

i80 čüąĖčüč鹥ą╝ąĮčŗą╣ 8-ą▒ąĖčéąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü |

DB[17:10] |

| 0 |

1 |

0 |

ID |

ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü SPI |

SDI, SDO |

| 0 |

1 |

1 |

* |

ąØąĄą┤ąŠą┐čāčüčéąĖą╝ą░čÅ ą║ąŠą╝ą▒ąĖąĮą░čåąĖčÅ |

- |

| 1 |

0 |

0 |

0 |

| 1 |

0 |

0 |

1 |

| 1 |

0 |

1 |

0 |

i80 čüąĖčüč鹥ą╝ąĮčŗą╣ 18-ą▒ąĖčéąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü |

DB[17:0] |

| 1 |

0 |

1 |

1 |

i80 čüąĖčüč鹥ą╝ąĮčŗą╣ 9-ą▒ąĖčéąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü |

DB[17:9] |

| 1 |

1 |

* |

* |

ąØąĄą┤ąŠą┐čāčüčéąĖą╝ą░čÅ ą║ąŠą╝ą▒ąĖąĮą░čåąĖčÅ |

- |

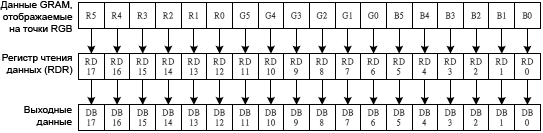

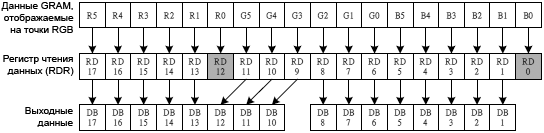

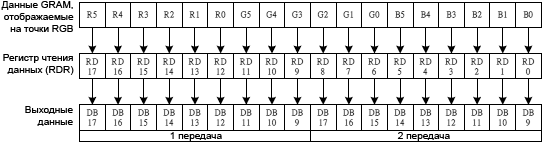

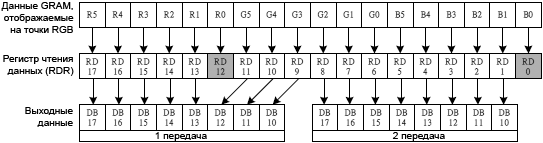

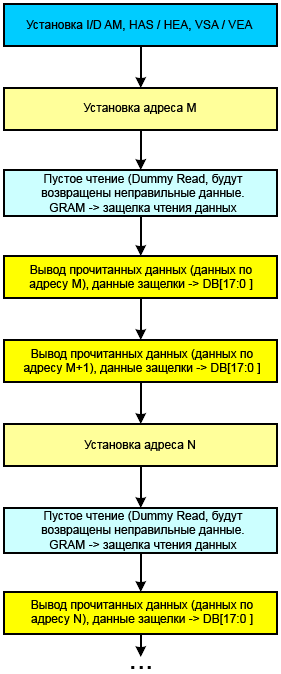

ąŻ ILI9325 ąĄčüčéčī 16-ą▒ąĖčéąĮčŗą╣ ąĖąĮą┤ąĄą║čüąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ (IR), 18-ą▒ąĖčéąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ ąĘą░ą┐ąĖčüąĖ ą┤ą░ąĮąĮčŗčģ (WDR) ąĖ 18 ą▒ąĖčéąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ čćč鹥ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ (RDR). ąĀąĄą│ąĖčüčéčĆ IR ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮ ą┤ą╗čÅ čüąŠčģčĆą░ąĮąĄąĮąĖčÅ ąĖąĮą┤ąĄą║čüąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ąĖąĘ čĆąĄą│ąĖčüčéčĆąŠą▓ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĖ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ ą×ąŚąŻ (GRAM). ąĀąĄą│ąĖčüčéčĆ WDR ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮ ą┤ą╗čÅ ą▓čĆąĄą╝ąĄąĮąĮąŠą│ąŠ čüąŠčģčĆą░ąĮąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ą┤ą╗čÅ ąĘą░ą┐ąĖčüąĖ ą▓ čĆąĄą│ąĖčüčéčĆčŗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĖ ą▓ąĮčāčéčĆąĄąĮąĮąĄąĄ GRAM. ąĀąĄą│ąĖčüčéčĆ RDR čüą╗čāąČąĖčé ą▓čĆąĄą╝ąĄąĮąĮčŗą╝ čģčĆą░ąĮąĖą╗ąĖčēąĄą╝ ą┤ą╗čÅ ą┤ą░ąĮąĮčŗčģ, ą┐čĆąŠčćąĖčéą░ąĮąĮčŗčģ ąĖąĘ GRAM. ąŚą░ą┐ąĖčüčŗą▓ą░ąĄą╝čŗąĄ ą┤ą░ąĮąĮčŗąĄ ąĖąĘ čāą┐čĆą░ą▓ą╗čÅčÄčēąĄą│ąŠ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ (MPU), ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮąĮčŗąĄ ą┤ą╗čÅ ąĘą░ą┐ąĖčüąĖ ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĄąĄ GRAM, čüąĮą░čćą░ą╗ą░ ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ ą▓ WDR, ąĖ ąĘą░č鹥ą╝ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ, ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ ąŠą┐ąĄčĆą░čåąĖąĄą╣ ą┐ąĄčĆąĄąĮąŠčüčÅčéčüčÅ ą▓ GRAM. ąöą░čéą░ ąĖąĘ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ GRAM čćąĖčéą░čÄčéčüčÅ č湥čĆąĄąĘ RDR. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą┐čĆąĖ ą┐ąĄčĆą▓ąŠą╝ čćč鹥ąĮąĖąĖ ą┤ą░ąĮąĮčŗčģ ąĖąĘ ILI9325 GRAM ą▒čāą┤čāčé ą┐čĆąŠčćąĖčéą░ąĮčŗ ąĮąĄą┐čĆą░ą▓ąĖą╗čīąĮčŗąĄ ą┤ą░ąĮąĮčŗčģ. ąöąŠčüč鹊ą▓ąĄčĆąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą▒čāą┤čāčé ą┐čĆąŠčćąĖčéą░ąĮčŗ ą┐ąŠčüą╗ąĄ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą▓č鹊čĆąŠą╣ ąŠą┐ąĄčĆą░čåąĖąĖ čćč鹥ąĮąĖčÅ ILI9325.

ąĀąĄą│ąĖčüčéčĆčŗ ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ, ą┐ąŠ ą╝ąĄčĆąĄ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą║ąŠą╝ą░ąĮą┤.

ąĪąĖčüč鹥ą╝ą░ ą▓čŗą▒ąŠčĆą░ čĆąĄą│ąĖčüčéčĆąŠą▓ ąĖąĮč鹥čĆč乥ą╣čüą░ i80 čü ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠą╣ čłąĖąĮąŠą╣ 8, 9, 16, 18 ą▒ąĖčé:

| ążčāąĮą║čåąĖčÅ |

RS |

nWR |

nRD |

| ąŚą░ą┐ąĖčüčī ąĖąĮą┤ąĄą║čüą░ ą▓ čĆąĄą│ąĖčüčéčĆ IR |

0 |

0 |

1 |

| ą¦č鹥ąĮąĖąĄ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čüčéą░čéčāčüą░ |

0 |

1 |

0 |

| ąŚą░ą┐ąĖčüčī ą▓ čĆąĄą│ąĖčüčéčĆčŗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĖą╗ąĖ ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĄąĄ GRAM č湥čĆąĄąĘ čĆąĄą│ąĖčüčéčĆ WDR |

1 |

0 |

1 |

| ą¦č鹥ąĮąĖąĄ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ ąĖą╗ąĖ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ GRAM č湥čĆąĄąĘ čĆąĄą│ąĖčüčéčĆ RDR |

1 |

1 |

0 |

ąĪąĖčüč鹥ą╝ą░ ą▓čŗą▒ąŠčĆą░ čĆąĄą│ąĖčüčéčĆąŠą▓ ąĖąĮč鹥čĆč乥ą╣čüą░ SPI:

| ążčāąĮą║čåąĖčÅ |

R/W |

RS |

| ąŚą░ą┐ąĖčüčī ąĖąĮą┤ąĄą║čüą░ ą▓ čĆąĄą│ąĖčüčéčĆ IR |

0 |

0 |

| ą¦č鹥ąĮąĖąĄ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čüčéą░čéčāčüą░ |

1 |

0 |

| ąŚą░ą┐ąĖčüčī ą▓ čĆąĄą│ąĖčüčéčĆčŗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĖą╗ąĖ ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĄąĄ GRAM č湥čĆąĄąĘ čĆąĄą│ąĖčüčéčĆ WDR |

0 |

1 |

| ą¦č鹥ąĮąĖąĄ ąĖąĘ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ GRAM č湥čĆąĄąĘ čĆąĄą│ąĖčüčéčĆ RDR |

1 |

1 |

ąĪąĖčüč鹥ą╝ąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü ILI9325 ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ / ąĘą░ą┐ąĖčüąĖ čĆąĄą│ąĖčüčéčĆąŠą▓ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĖ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ą▓ (GRAM), ąĖ ąĖąĮč鹥čĆč乥ą╣čü RGB ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮ ą┤ą╗čÅ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖčÅ ą▓ąĖą┤ąĄąŠ. ą¤ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą╝ąŠąČąĄčé ą▓čŗą▒čĆą░čéčī ąŠą┐čéąĖą╝ą░ą╗čīąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü ą┤ą╗čÅ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖčÅ ąĖąĘą╝ąĄąĮčÅčÄčēąĄą╣čüčÅ ąĖą╗ąĖ ą┐ąŠčüč鹊čÅąĮąĮąŠą╣ ą║ą░čĆčéąĖąĮą║ąĖ ą┤ą╗čÅ čŹčäč乥ą║čéąĖą▓ąĮąŠą│ąŠ ąŠą▒ą╝ąĄąĮą░ ą┤ą░ąĮąĮčŗą╝ąĖ. ąÆčüąĄ ąŠč鹊ą▒čĆą░ąČą░ąĄą╝čŗąĄ ą┤ą░ąĮąĮčŗąĄ čüąŠčģčĆą░ąĮčÅčÄčéčüčÅ ą▓ GRAM, čćč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé čāą╝ąĄąĮčīčłąĖčéčī ąĘą░čéčĆą░čéčŗ ąĮą░ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ ąĖąĘąŠą▒čĆą░ąČąĄąĮąĖčÅ - ą╝ąŠąČąĮąŠ ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī č鹊ą╗čīą║ąŠ č鹥 ą┤ą░ąĮąĮčŗąĄ, čćč鹊 ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąŠą▒ąĮąŠą▓ą╗ąĄąĮčŗ. ą¤ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą╝ąŠąČąĄčé ąŠą▒ąĮąŠą▓ą╗čÅčéčī č鹊ą╗čīą║ąŠ ąŠą▒ą╗ą░čüčéąĖ GRAM bčü ą┐ąŠą╝ąŠčēčīčÄ čäčāąĮą║čåąĖąĖ ą░ą┤čĆąĄčüą░čåąĖąĖ ąŠą║ąĮą░.

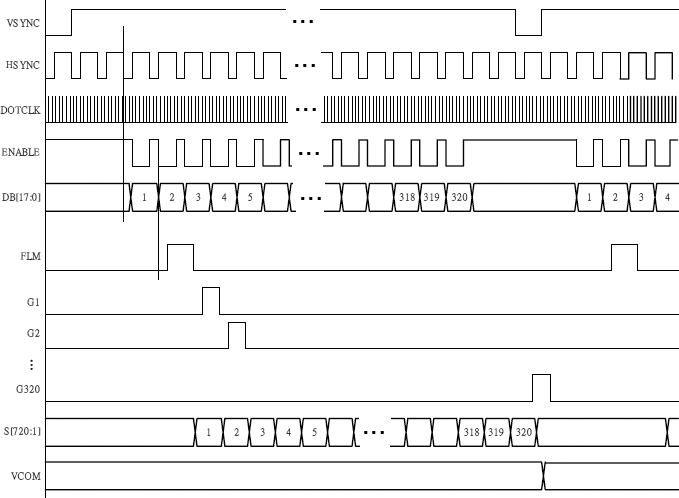

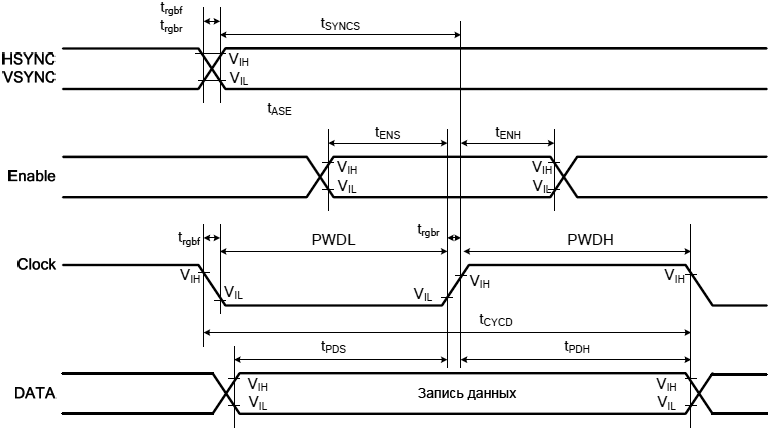

ąóą░ą║ąČąĄ čā ILI9325 ąĄčüčéčī RGB-ąĖąĮč鹥čĆč乥ą╣čü ąĖ VSYNC-ąĖąĮč鹥čĆč乥ą╣čü ą┤ą╗čÅ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖčÅ ą┤ą▓ąĖąČčāčēąĄą╣čüčÅ ą║ą░čĆčéąĖąĮą║ąĖ ą▒ąĄąĘ ą╝ąĄčĆčåą░ąĮąĖčÅ čŹą║čĆą░ąĮą░. ąÆ čĆąĄąČąĖą╝ąĄ RGB-ąĖąĮč鹥čĆč乥ą╣čüą░ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖąĄ ąĘą░ą┐ąĖčüą░ąĮąĮčŗčģ ą▓ GRAM ą┤ą░ąĮąĮčŗčģ čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ čüąĖą│ąĮą░ą╗ą░ą╝ ENABLE, VSYNC, HSYNC, DOTCLK ąĖ čłąĖąĮąŠą╣ ą┤ą░ąĮąĮčŗčģ DB[17:0].

[ą¤ą░čĆą░ą╗ą╗ąĄą╗čīąĮčŗą╣ RGB-ąĖąĮč鹥čĆč乥ą╣čü]

ILI9325 ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ąĖąĮč鹥čĆč乥ą╣čü RGB ąĖ ąĖąĮč鹥čĆč乥ą╣čü VSYNC ą▓ ą║ą░č湥čüčéą▓ąĄ ą▓ąĮąĄčłąĮąĄą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ ą┤ą╗čÅ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖčÅ ąĖ ą┐ąĄčĆąĄą╝ąĄčēąĄąĮąĖčÅ ą║ą░čĆčéąĖąĮą║ąĖ. ąÜąŠą│ą┤ą░ ą▓čŗą▒čĆą░ąĮ ąĖąĮč鹥čĆč乥ą╣čü RGB, čĆą░ą▒ąŠčéą░ ą┤ąĖčüą┐ą╗ąĄčÅ čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆčāąĄčéčüčÅ čü ą▓ąĮąĄčłąĮąĖą╝ąĖ čüąĖą│ąĮą░ą╗ą░ą╝ąĖ VSYNC, HSYNC ąĖ DOTCLK. ąÆ čĆąĄąČąĖą╝ąĄ ąĖąĮč鹥čĆč乥ą╣čüą░ RGB ą┤ą░ąĮąĮčŗąĄ (DB17-0) ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ čüąĖąĮčģčĆąŠąĮąĮąŠ čü čŹčéąĖą╝ąĖ čüąĖą│ąĮą░ą╗ą░ą╝ąĖ, ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü ą┐ąŠą╗čÅčĆąĮąŠčüčéčīčÄ čüąĖą│ąĮą░ą╗ą░ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ (ENABLE), čćč鹊ą▒čŗ ąĖąĘą▒ąĄąČą░čéčī ąĖčüą║ą░ąČąĄąĮąĖčÅ ą║ą░čĆčéąĖąĮą║ąĖ ąĖ ą╝ąĄčĆčåą░ąĮąĖčÅ ą┐čĆąĖ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĖ ą┤ą░ąĮąĮčŗčģ 菹║čĆą░ąĮą░.

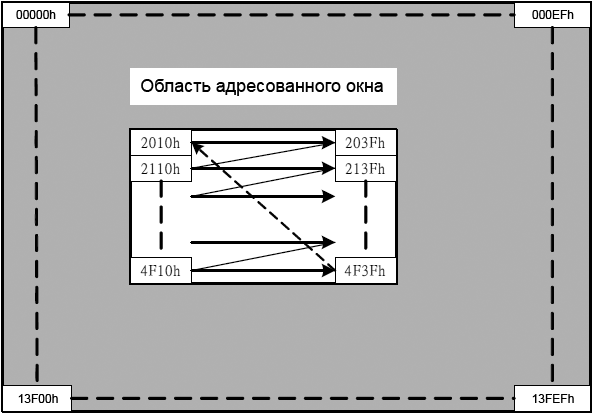

ąĪč湥čéčćąĖą║ ą░ą┤čĆąĄčüą░ (AC). ąŁč鹊 čĆąĄą│ąĖčüčéčĆ, ą║ąŠč鹊čĆčŗą╣ ą┤ą░ąĄčé ą░ą┤čĆąĄčü ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ GRAM. ąÜąŠą│ą┤ą░ ą▓ IR ąĘą░ą┐ąĖčüą░ąĮ ąĖąĮą┤ąĄą║čü ą┤ą╗čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ ą░ą┤čĆąĄčüą░ ą×ąŚąŻ, čŹčéą░ ąĖąĮč乊čĆą╝ą░čåąĖčÅ ą░ą┤čĆąĄčüą░ ąŠčéą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ąĖąĘ IR ą▓ AC. ą¤ąŠ ą╝ąĄčĆąĄ ąĘą░ą┐ąĖčüąĖ ą┤ą░ąĮąĮčŗčģ ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĄąĄ GRAM, ą░ą┤čĆąĄčü ą▓ AC ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąŠą▒ąĮąŠą▓ą╗čÅąĄčéčüčÅ ą┐čāč鹥ą╝ ą┤ąŠą▒ą░ą▓ą╗ąĄąĮąĖčÅ ąĖą╗ąĖ ą▓čŗčćąĖčéą░ąĮąĖčÅ 1. ążčāąĮą║čåąĖčÅ ą░ą┤čĆąĄčüą░čåąĖąĖ ąŠą║ąĮą░ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąĘą░ą┐ąĖčüčŗą▓ą░čéčī ą┤ą░ąĮąĮčŗąĄ č鹊ą╗čīą║ąŠ ą▓ ą┐čĆčÅą╝ąŠčāą│ąŠą╗čīąĮčāčÄ ąŠą▒ą╗ą░čüčéčī GRAM, ą║ąŠč鹊čĆčāčÄ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą▓čŗą▒ąĖčĆą░ąĄčé ą┐čĆąŠąĖąĘą▓ąŠą╗čīąĮąŠ.

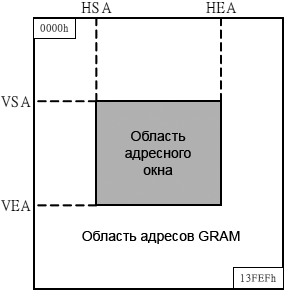

ąōčĆą░čäąĖč湥čüą║ąŠąĄ ą×ąŚąŻ (Graphics RAM, GRAM). ąŁč鹊 ąŠą┐ąĄčĆą░čéąĖą▓ąĮą░čÅ ą┐ą░ą╝čÅčéčī ąĖąĘ 172820 ą▒ą░ą╣čé (240 x 320 x 18 / 8), ą║ąŠč鹊čĆą░čÅ čģčĆą░ąĮąĖčé čĆą░čüčéčĆ ą║ą░čĆčéąĖąĮą║ąĖ 菹║čĆą░ąĮą░. ą”ą▓ąĄč鹊ą▓ąŠąĄ čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ čüąŠčüčéą░ą▓ą╗čÅąĄčé 18 ą▒ąĖčé ąĮą░ č鹊čćą║čā.

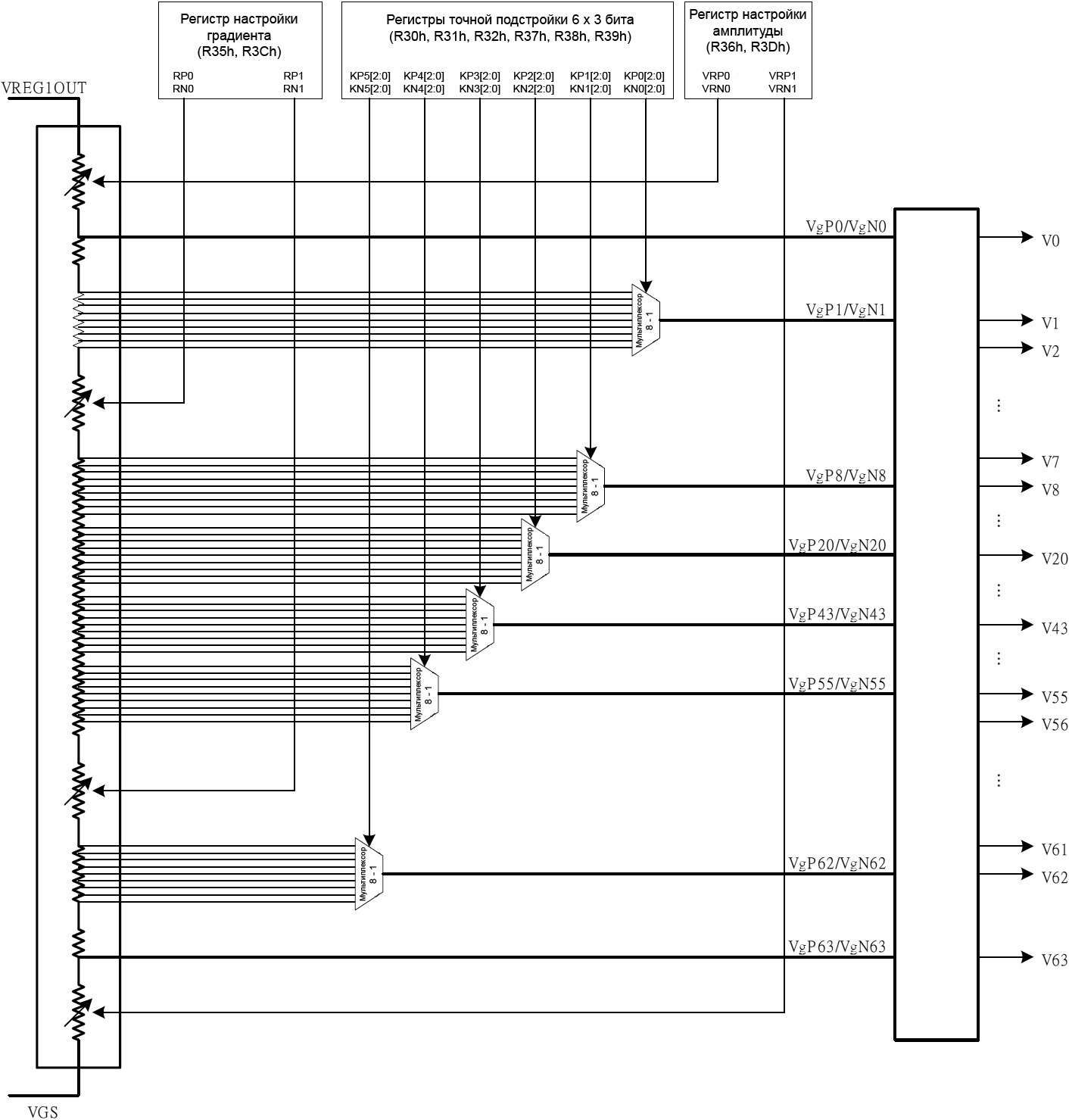

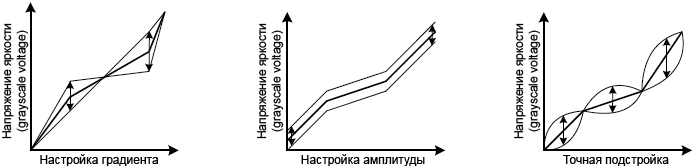

ąōąĄąĮąĄčĆą░č鹊čĆ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čÅčĆą║ąŠčüčéčīčÄ. ąöą╗čÅ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖčÅ 262144 čåą▓ąĄč鹊ą▓ čŹč鹊čé ą▒ą╗ąŠą║ č乊čĆą╝ąĖčĆčāąĄčé ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą┤ą╗čÅ LCD ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü ą┤ą░ąĮąĮčŗą╝ąĖ čāčĆąŠą▓ąĮčÅ čüąĄčĆąŠą│ąŠ, čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╝ąĖ ą▓ čĆąĄą│ąĖčüčéčĆąĄ ą│ą░ą╝ą╝ą░-ą║ąŠčĆčĆąĄą║čåąĖąĖ.

ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ąĖąĮč鹥čĆą▓ą░ą╗ąŠą▓ ą▓čĆąĄą╝ąĄąĮąĖ. ąŁč鹊čé ą▒ą╗ąŠą║ č乊čĆą╝ąĖčĆčāąĄčé čüąĖą│ąĮą░ą╗čŗ ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ ą▓ąĮčāčéčĆąĄąĮąĮąĖčģ čüčģąĄą╝. ąśąĮč鹥čĆą▓ą░ą╗čŗ ą▓čĆąĄą╝ąĄąĮąĖ ąŠą┐ąĄčĆą░čåąĖą╣ čü 菹║čĆą░ąĮąŠą╝, čéą░ą║ąĖčģ ą║ą░ą║ čćč鹥ąĮąĖąĄ GRAM, č乊čĆą╝ąĖčĆčāčÄčéčüčÅ čéą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, čćč鹊ą▒čŗ ąĮą░ ąĮąĖčģ ąĮąĄ ą▓ą╗ąĖčÅą╗ąĖ ąŠą┐ąĄčĆą░čåąĖąĖ ą┤ąŠčüčéčāą┐ą░ čüąŠ čüč鹊čĆąŠąĮčŗ ą▓ąĮąĄčłąĮąĄą│ąŠ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░.

ąōąĄąĮąĄčĆą░č鹊čĆ čéą░ą║č鹊ą▓ (OSC). ąÆ ILI9325 ąĄčüčéčī ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ RC-ą│ąĄąĮąĄčĆą░č鹊čĆ. ą¦ą░čüč鹊čéą░ ą║ą░ą┤čĆąŠą▓ (frame rate) ąĮą░čüčéčĆą░ąĖą▓ą░ąĄčéčüčÅ čü ą┐ąŠą╝ąŠčēčīčÄ čāčüčéą░ąĮąŠą▓ą║ąĖ čüą┐ąĄčåąĖą░ą╗čīąĮąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░.

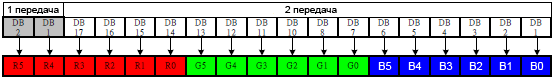

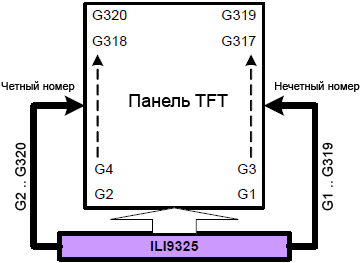

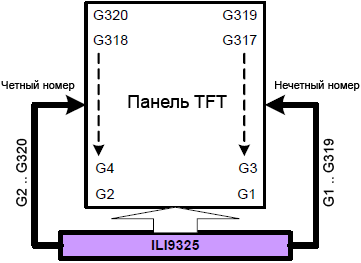

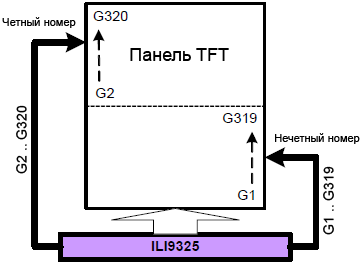

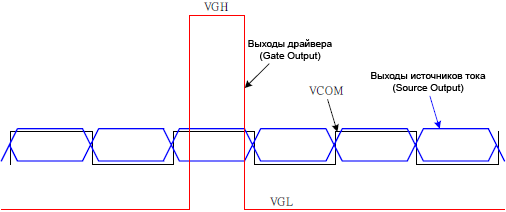

ąöčĆą░ą╣ą▓ąĄčĆ LCD. ąĪčģąĄą╝ą░ ą┤čĆą░ą╣ą▓ąĄčĆą░ LCD ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ILI9325 čüąŠčüč鹊ąĖčé ąĖąĘ 720-ą║ą░ąĮą░ą╗čīąĮąŠą│ąŠ ą┤čĆą░ą╣ą▓ąĄčĆą░ č鹊ą║ą░ (S1 .. S720) ąĖ 320-ą║ą░ąĮą░ą╗čīąĮąŠą│ąŠ ą┤čĆą░ą╣ą▓ąĄčĆą░ ą║ą╗čÄč湥ą╣ (G1 .. G320). ąóąŠčćą║ą░ 菹║čĆą░ąĮą░ čäąĖą║čüąĖčĆčāčÄčéčüčÅ ą┐čĆąĖ ą▓ą▓ąŠą┤ąĄ 720-ą│ąŠ ą▒ąĖčéą░ ą┤ą░ąĮąĮčŗčģ. ąŚą░čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ čāą┐čĆą░ą▓ą╗čÅčÄčé ą┤čĆą░ą╣ą▓ąĄčĆąŠą╝ č鹊ą║ą░ ąĖ ą│ąĄąĮąĄčĆąĖčĆčāčÄčé č乊čĆą╝čā čüąĖą│ąĮą░ą╗ą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ. ąöčĆą░ą╣ą▓ąĄčĆ ą║ą╗čÄč湥ą╣ ą┤ą╗čÅ čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓čŗą▓ąŠą┤ąĖčé čāčĆąŠą▓ąĮąĖ ą╗ąĖą▒ąŠ VGH, ą╗ąĖą▒ąŠ VGL. ąØą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čüą┤ą▓ąĖą│ą░ 720 ą▓čŗčģąŠą┤ąŠą▓ ą┤čĆą░ą╣ą▓ąĄčĆą░ č鹊ą║ą░ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▒ąĖč鹊ą╝ SS ąĖ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čüą┤ą▓ąĖą│ą░ ą▓čŗčģąŠą┤ąŠą▓ ą║ą╗čÄč湥ą╣ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▒ąĖč鹊ą╝ GS. ąĀąĄąČąĖą╝ čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ ą┤čĆą░ą╣ą▓ąĄčĆą░ ą║ą╗čÄč湥ą╣ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▒ąĖč鹊ą╝ SM. ąŁčéąĖ ą▒ąĖčéčŗ ą┐ąŠąĘą▓ąŠą╗čÅčÄčé čāčüčéą░ąĮąŠą▓ąĖčéčī ą┐ąŠą┤čģąŠą┤čÅčēąĖą╣ ą┤ą╗čÅ LCD ą╝ąĄč鹊ą┤ čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ.

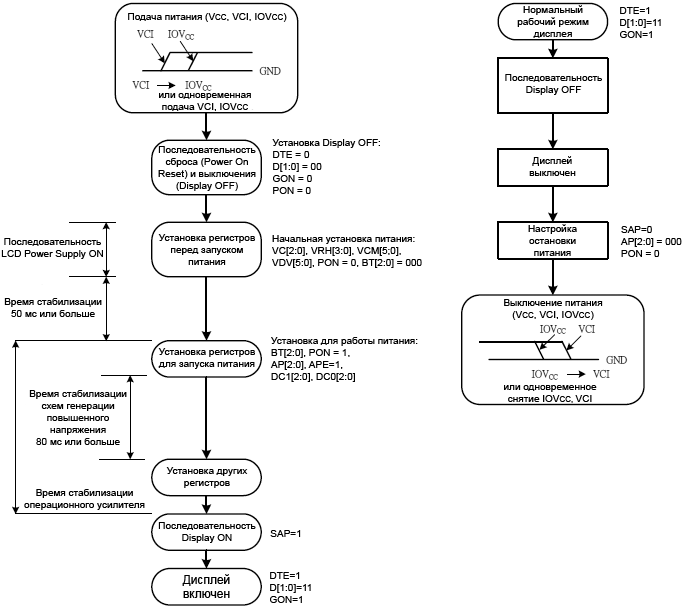

ąĪčģąĄą╝ą░ ą┐ąĖčéą░ąĮąĖčÅ ą┤čĆą░ą╣ą▓ąĄčĆą░ LCD. ąŁč鹊čé čāąĘąĄą╗ č乊čĆą╝ąĖčĆčāąĄčé čāčĆąŠą▓ąĮąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ VREG1OUT, VGH, VGL ąĖ Vcom ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ LCD.

ILI9325 čĆą░ą▒ąŠčéą░ąĄčé ą▓ ąŠą┤ąĮąŠą╝ ąĖąĘ 4 čĆąĄąČąĖą╝ąŠą▓. ąĀąĄąČąĖą╝ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖčÅ ą╝ąŠąČąĮąŠ ą┐ąĄčĆąĄą║ą╗čÄčćąĖčéčī č湥čĆąĄąĘ čĆąĄą│ąĖčüčéčĆ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ. ą¤čĆąĖ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĖ ąĖąĘ ąŠą┤ąĮąŠą│ąŠ čĆąĄąČąĖą╝ą░ ą▓ ą┤čĆčāą│ąŠą╣ čüą╗ąĄą┤čāą╣č鹥 ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ, ąŠą┐ąĖčüą░ąĮąĮąŠą╣ ą▓ čüąĄą║čåąĖčÅčģ ąĖąĮč鹥čĆč乥ą╣čüąŠą▓ RGB ąĖ VSYNC.

| ąĀą░ą▒ąŠčćąĖą╣ čĆąĄąČąĖą╝ |

ąŻčüčéą░ąĮąŠą▓ą║ą░ ą┤ąŠčüčéčāą┐ą░ ą║ ą×ąŚąŻ (RM) |

ąĀąĄąČąĖą╝ čĆą░ą▒ąŠčéčŗ ą┤ąĖčüą┐ą╗ąĄčÅ |

| ąĀą░ą▒ąŠčéą░ č鹊ą╗čīą║ąŠ ąŠčé ą▓ąĮčāčéčĆąĄąĮąĮąĖčģ čéą░ą║č鹊ą▓ (ąŠč鹊ą▒čĆą░ąČąĄąĮąĖąĄ čüčéą░čéąĖč湥čüą║ąĖčģ ą║ą░čĆčéąĖąĮąŠą║) |

ąĪąĖčüč鹥ą╝ąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü (RM = 0) |

ąĀą░ą▒ąŠčéą░ ąŠčé ą▓ąĮčāčéčĆąĄąĮąĮąĖčģ čéą░ą║č鹊ą▓ (DM[1:0] = 00) |

| ąśąĮč鹥čĆč乥ą╣čü RGB(1) (ąŠč鹊ą▒čĆą░ąČąĄąĮąĖąĄ ąĖąĘą╝ąĄąĮčÅčÄčēąĖčģčüčÅ ą║ą░čĆčéąĖąĮąŠą║) |

ąśąĮč鹥čĆč乥ą╣čü RGB (RM = 1) |

ąśąĮč鹥čĆč乥ą╣čü RGB (DM[1:0] = 01) |

| ąśąĮč鹥čĆč乥ą╣čü RGB(2) (ą┐ąĄčĆąĄąĘą░ą┐ąĖčüčī čüčéą░čéąĖč湥čüą║ąĖčģ ą║ą░čĆčéąĖąĮąŠą║ ą┐čĆąĖ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖąĖ ąĖąĘą╝ąĄąĮčÅčÄčēąĖčģčüčÅ ą║ą░čĆčéąĖąĮąŠą║) |

ąĪąĖčüč鹥ą╝ąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü (RM = 0) |

ąśąĮč鹥čĆč乥ą╣čü RGB (DM[1:0] = 01) |

| ąśąĮč鹥čĆč乥ą╣čü VSYNC (ąŠč鹊ą▒čĆą░ąČąĄąĮąĖąĄ ąĖąĘą╝ąĄąĮčÅčÄčēąĖčģčüčÅ ą║ą░čĆčéąĖąĮąŠą║) |

ąĪąĖčüč鹥ą╝ąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü (RM = 0) |

ąśąĮč鹥čĆč乥ą╣čü VSYNC (DM[1:0] = 01) |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

(1) ąĀąĄą│ąĖčüčéčĆčŗ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄčéčüčÅ č鹊ą╗čīą║ąŠ č湥čĆąĄąĘ čüąĖčüč鹥ą╝ąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü ąĖą╗ąĖ SPI.

(2) ąśąĮč鹥čĆč乥ą╣čüčŗ RGB ąĖ VSYNC ąĮąĄ ą┤ąŠčüčéčāą┐ąĮčŗ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ.

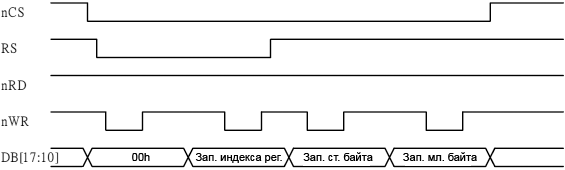

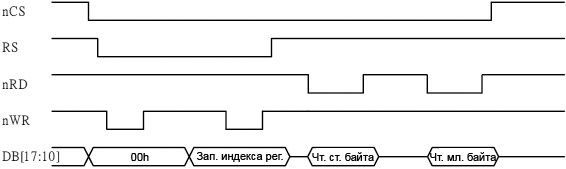

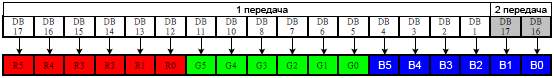

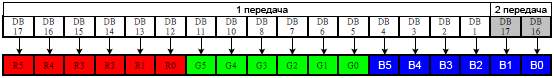

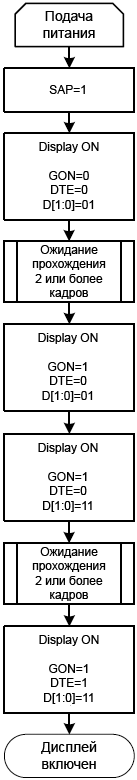

ąĀąĖčü. 1. ąĪąŠąĄą┤ąĖąĮąĄąĮąĖčÅ č湥čĆąĄąĘ čüąĖčüč鹥ą╝ąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü ąĖ RGB-ąĖąĮč鹥čĆč乥ą╣čü.

ąśąĮč鹥čĆč乥ą╣čü ą▓ą▓ąŠą┤ą░. ąØąĖąČąĄ ą┐ąŠą║ą░ąĘą░ąĮčŗ čüąĖčüč鹥ą╝ąĮčŗąĄ ąĖąĮč鹥čĆč乥ą╣čüčŗ, ą┤ąŠčüčéčāą┐ąĮčŗąĄ ą┤ą╗čÅ ILI9325. ąśąĮč鹥čĆč乥ą╣čü ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▓čŗą▓ąŠą┤ąŠą▓ IM[3:0] (čüą╝. ą▓čŗčłąĄ čéą░ą▒ą╗ąĖčåčā čüąŠčüč鹊čÅąĮąĖčÅ ą▓čŗą▓ąŠą┤ąŠą▓ IM3, IM2, IM1, IM0). ąĪąĖčüč鹥ą╝ąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ čĆąĄą│ąĖčüčéčĆąŠą▓ ąĖ ą┤ąŠčüčéčāą┐ą░ ą║ GRAM.

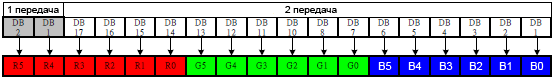

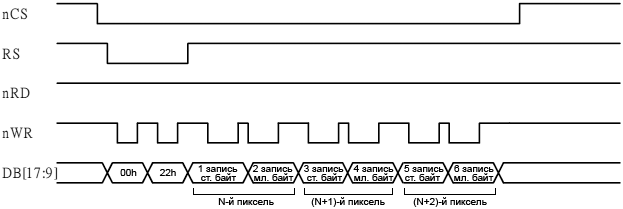

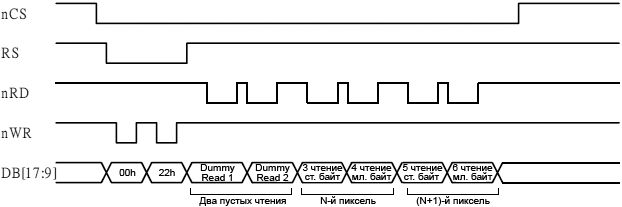

ąĪąĖčüč鹥ą╝ąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü i80/18-ą▒ąĖčé. ąŁč鹊čé čéąĖą┐ ąĖąĮč鹥čĆč乥ą╣čüą░ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ 1010 čüąĖą│ąĮą░ą╗ąŠą▓ IM[3:0].

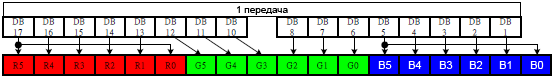

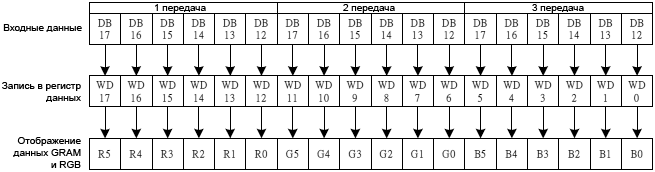

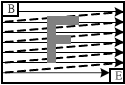

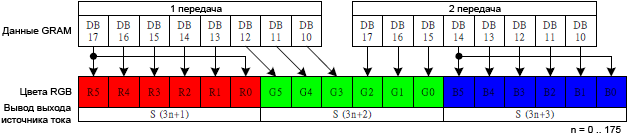

ąĀąĖčü. 2. ążąŠčĆą╝ą░čé ą┤ą░ąĮąĮčŗčģ 18-ą▒ąĖčéąĮąŠą│ąŠ čüąĖčüč鹥ą╝ąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░.

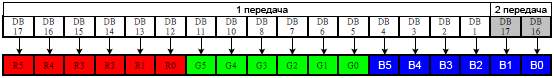

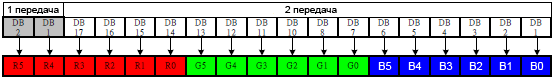

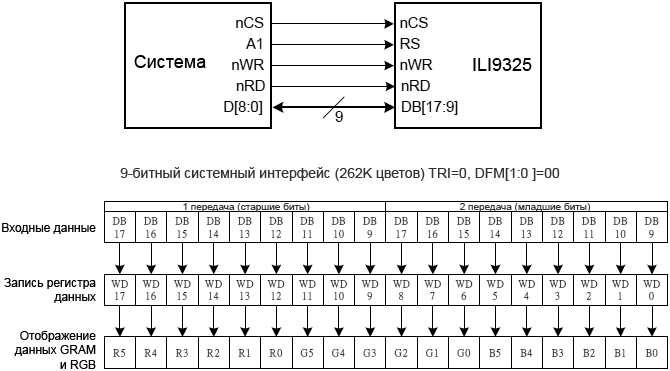

ąĪąĖčüč鹥ą╝ąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü i80/16-ą▒ąĖčé. ąŁč鹊čé čéąĖą┐ ąĖąĮč鹥čĆč乥ą╣čüą░ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ 0010 čüąĖą│ąĮą░ą╗ąŠą▓ IM[3:0]. 262K ąĖą╗ąĖ 65K čåą▓ąĄč鹊ą▓ ą╝ąŠąČąĮąŠ ąŠč鹊ą▒čĆą░ąČą░čéčī č湥čĆąĄąĘ 16-ą▒ąĖčéąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü MPU. ąÜąŠą│ą┤ą░ ąŠč鹊ą▒čĆą░ąČą░čÄčéčüčÅ 262K čåą▓ąĄč鹊ą▓, ą┤ą╗čÅ 16-ą▒ąĖčéąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ ąĮčāąČąĮąŠ ąŠčüčāčēąĄčüčéą▓ą╗čÅčéčī ą┤ą▓ąĄ ą┐ąĄčĆąĄčüčŗą╗ą║ąĖ (1-čÅ ą┐ąĄčĆąĄą┤ą░ąĄčé 2 ą▒ąĖčéą░ ąĖ 2-čÅ 16 ą▒ąĖčé, ąĖą╗ąĖ 1-čÅ 16 ą▒ąĖčé ąĖ ą▓č鹊čĆą░čÅ 2 ą▒ąĖčéą░).

| TRI |

DFM |

ążąŠčĆą╝ą░čé ą┤ą░ąĮąĮčŗčģ 16-ą▒ąĖčéąĮąŠą│ąŠ čüąĖčüč鹥ą╝ąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ MPU |

| 0 |

* |

ąĪąĖčüč鹥ą╝ąĮčŗą╣ 16-ą▒ąĖčéąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü 65536 čåą▓ąĄč鹊ą▓ (1 ą┐ąĄčĆąĄą┤ą░čćą░ ąĮą░ č鹊čćą║čā)

|

| 1 |

0 |

ąĪąĖčüč鹥ą╝ąĮčŗą╣ 16-ą▒ąĖčéąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü 262144 čåą▓ąĄč鹊ą▓ (2 ą┐ąĄčĆąĄą┤ą░čćąĖ ąĮą░ č鹊čćą║čā)

|

| 1 |

1 |

ąĪąĖčüč鹥ą╝ąĮčŗą╣ 16-ą▒ąĖčéąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü 262144 čåą▓ąĄč鹊ą▓ (2 ą┐ąĄčĆąĄą┤ą░čćąĖ ąĮą░ č鹊čćą║čā)

|

ąĀąĖčü. 3. ążąŠčĆą╝ą░čé ą┤ą░ąĮąĮčŗčģ 16-ą▒ąĖčéąĮąŠą│ąŠ čüąĖčüč鹥ą╝ąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ i80.

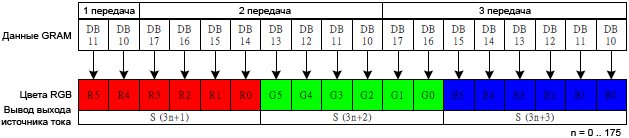

ąĪąĖčüč鹥ą╝ąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü i80/9-ą▒ąĖčé. ąŁč鹊čé čéąĖą┐ ąĖąĮč鹥čĆč乥ą╣čüą░ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ 1011 čüąĖą│ąĮą░ą╗ąŠą▓ IM[3:0], ąĖ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą▓čŗą▓ąŠą┤čŗ DB17..DB9. ąÜąŠą│ą┤ą░ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ 16-ą▒ąĖčéąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ, ą┤ą░ąĮąĮčŗąĄ ą┤ąĄą╗čÅčéčüčÅ ąĮą░ čüčéą░čĆčłąĖą╣ ą▒ą░ą╣čé (ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗą╣ č湥čĆąĄąĘ 8 ą▒ąĖčé, ą╝ą╗ą░ą┤čłąĖą╣ ą▒ąĖčé ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ) ąĖ ą╝ą╗ą░ą┤čłąĖą╣ ą▒ą░ą╣čé, čüčéą░čĆčłąĖą╣ ą▒ą░ą╣čé ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą┐ąĄčĆą▓čŗą╝. ą×č鹊ą▒čĆą░ąČą░ąĄą╝čŗąĄ ą┤ą░ąĮąĮčŗąĄ čéą░ą║ąČąĄ ą┤ąĄą╗čÅčéčüčÅ ąĮą░ čüčéą░čĆčłąĖą╣ ą▒ą░ą╣čé (9 ą▒ąĖčé) ąĖ ą╝ą╗ą░ą┤čłąĖą╣ ą▒ą░ą╣čé, čüčéą░čĆčłąĖą╣ ą▒ą░ą╣čé čéą░ą║ąČąĄ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą┐ąĄčĆą▓čŗą╝. ąØąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą▓čŗą▓ąŠą┤čŗ DB[8:0] ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą┐ąŠą┤čéčÅąĮčāčéčŗ ą║ GND.

ąĀąĖčü. 4. ążąŠčĆą╝ą░čé ą┤ą░ąĮąĮčŗčģ 9-ą▒ąĖčéąĮąŠą│ąŠ čüąĖčüč鹥ą╝ąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░.

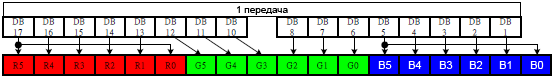

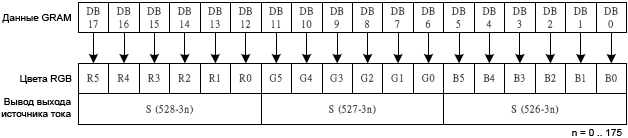

ąĪąĖčüč鹥ą╝ąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü i80/8-ą▒ąĖčé. ąŁč鹊čé čéąĖą┐ ąĖąĮč鹥čĆč乥ą╣čüą░ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ 0011 čüąĖą│ąĮą░ą╗ąŠą▓ IM[3:0], ąĖ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą▓čŗą▓ąŠą┤čŗ DB17..DB10. ąÜąŠą│ą┤ą░ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ 16-ą▒ąĖčéąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ, ą┤ą░ąĮąĮčŗąĄ ą┤ąĄą╗čÅčéčüčÅ ąĮą░ čüčéą░čĆčłąĖą╣ ą▒ą░ą╣čé ąĖ ą╝ą╗ą░ą┤čłąĖą╣ ą▒ą░ą╣čé, čüčéą░čĆčłąĖą╣ ą▒ą░ą╣čé ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą┐ąĄčĆą▓čŗą╝. ą×č鹊ą▒čĆą░ąČą░ąĄą╝čŗąĄ ą┤ą░ąĮąĮčŗąĄ čéą░ą║ąČąĄ ą┤ąĄą╗čÅčéčüčÅ ąĮą░ čüčéą░čĆčłąĖą╣ ą▒ą░ą╣čé (8 ą▒ąĖčé) ąĖ ą╝ą╗ą░ą┤čłąĖą╣ ą▒ą░ą╣čé, čüčéą░čĆčłąĖą╣ ą▒ą░ą╣čé čéą░ą║ąČąĄ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą┐ąĄčĆą▓čŗą╝. ąØąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą▓čŗą▓ąŠą┤čŗ DB[9:0] ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą┐ąŠą┤čéčÅąĮčāčéčŗ ą║ GND.

| TRI |

DFM |

ążąŠčĆą╝ą░čé ą┤ą░ąĮąĮčŗčģ 8-ą▒ąĖčéąĮąŠą│ąŠ čüąĖčüč鹥ą╝ąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ MPU |

| 0 |

* |

ąĪąĖčüč鹥ą╝ąĮčŗą╣ 8-ą▒ąĖčéąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü 65536 čåą▓ąĄč鹊ą▓ (2 ą┐ąĄčĆąĄą┤ą░čćąĖ ąĮą░ č鹊čćą║čā)

|

| 1 |

0 |

ąĪąĖčüč鹥ą╝ąĮčŗą╣ 8-ą▒ąĖčéąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü 262144 čåą▓ąĄč鹊ą▓ (3 ą┐ąĄčĆąĄą┤ą░čćąĖ ąĮą░ č鹊čćą║čā)

|

| 1 |

1 |

ąĪąĖčüč鹥ą╝ąĮčŗą╣ 8-ą▒ąĖčéąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü 262144 čåą▓ąĄč鹊ą▓ (3 ą┐ąĄčĆąĄą┤ą░čćąĖ ąĮą░ č鹊čćą║čā)

|

ąĀąĖčü. 5. ążąŠčĆą╝ą░čé ą┤ą░ąĮąĮčŗčģ 8-ą▒ąĖčéąĮąŠą│ąŠ čüąĖčüč鹥ą╝ąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ i80.

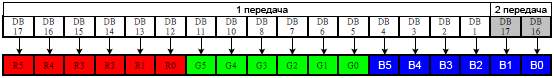

ąĪąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ą▓ čĆąĄąČąĖą╝ąĄ 8/9-ą▒ąĖčéąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░. ILI9325 ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé čäčāąĮą║čåąĖčÄ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ą┤ą╗čÅ čüą▒čĆąŠčüą░ ą▓ąĄčĆčģąĮąĄą│ąŠ ąĖ ąĮąĖąČąĮąĄą│ąŠ čüč湥čéčćąĖą║ąŠą▓, ą║ąŠč鹊čĆčŗąĄ čüčćąĖčéą░čÄčé ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą┐ąĄčĆąĄą┤ą░čć čüčéą░čĆčłąĄą│ąŠ ąĖ ą╝ą╗ą░ą┤čłąĄą│ąŠ ą▒ą░ą╣čé ą▓ čĆąĄąČąĖą╝ąĄ 8/9-ą▒ąĖčé ąĖąĮč鹥čĆč乥ą╣čüą░. ąĢčüą╗ąĖ ą┐čĆąŠąĖąĘąŠčłą╗ąŠ čĆą░čüčģąŠąČą┤ąĄąĮąĖąĄ ą▓ ą║ąŠą╗ąĖč湥čüčéą▓ąĄ ą┐ąĄčĆąĄą┤ą░čć čüčéą░čĆčłąĄą│ąŠ ąĖ ą╝ą╗ą░ą┤čłąĄą│ąŠ ą▒ą░ą╣čé ąĖąĘ-ąĘą░ čłčāą╝ą░ ąĖ ą┤čĆčāą│ąĖčģ ą┐čĆąĖčćąĖąĮ, čĆąĄą│ąĖčüčéčĆ 00h ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ 4 čĆą░ąĘą░, čćč鹊ą▒čŗ čüą▒čĆąŠčüąĖčéčī ą▓ąĄčĆčģąĮąĖą╣ ąĖ ąĮąĖąČąĮąĖą╣ čüč湥čéčćąĖą║ąĖ, ąĖ ą┐ąĄčĆąĄą┤ą░čćą░ ą┤ą░ąĮąĮčŗčģ ą┐ąĄčĆąĄąĘą░ą┐čāčüčéąĖčéčüčÅ čüąŠ čüčéą░čĆčłąĄą│ąŠ ą▒ą░ą╣čéą░. ąŁčéą░ čäčāąĮą║čåąĖčÅ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ čŹčäč乥ą║čéąĖą▓ąĮąŠ ą┐čĆąĄą┤ąŠčéą▓čĆą░čēą░ąĄčé ąŠčłąĖą▒ą║čā ąŠč鹊ą▒čĆą░ąČąĄąĮąĖčÅ, ąĄčüą╗ąĖ ą┐ąĄčĆąĖąŠą┤ąĖč湥čüą║ąĖ čüą▒čĆą░čüčŗą▓ą░čéčī ą▓ąĄčĆčģąĮąĖą╣ ąĖ ąĮąĖąČąĮąĖą╣ čüč湥čéčćąĖą║ąĖ.

ąĀąĖčü. 6. ąĪąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ą┤ą╗čÅ čüąĖčüč鹥ą╝ąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ 8/9-ą▒ąĖčé.

[ąśąĮč鹥čĆč乥ą╣čü SPI]

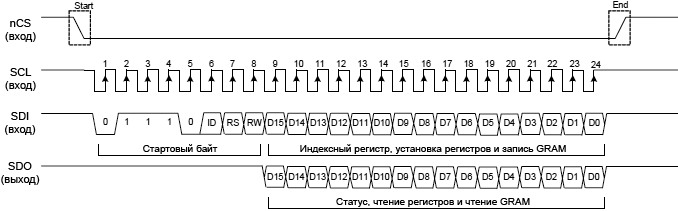

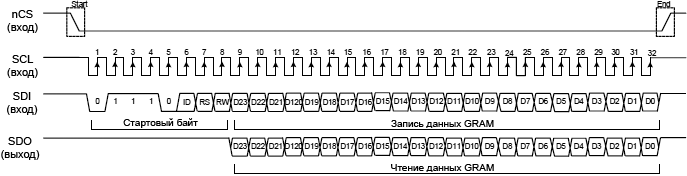

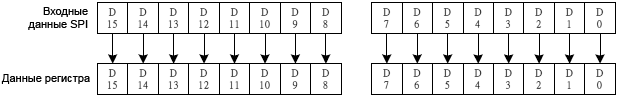

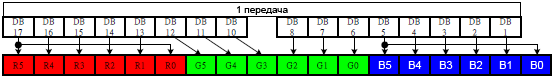

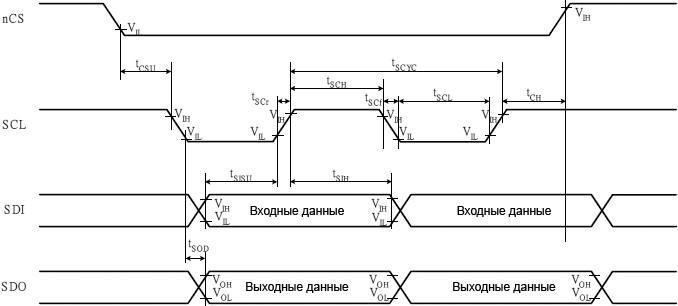

SPI ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ąĮąŠąČąĄą║ IM[3:0] ą▓ čāčĆąŠą▓ąĮąĖ 010x. ąÆ čĆąĄąČąĖą╝ąĄ SPI ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ąĮąŠąČą║ą░ ą▓čŗą▒ąŠčĆą║ąĖ chip select (nCS), ą▓čŗą▓ąŠą┤ čéą░ą║č鹊ą▓ ą┤ą░ąĮąĮčŗčģ (SCL), ą▓čŗą▓ąŠą┤ ą▓čģąŠą┤ą░ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ą┤ą░ąĮąĮčŗčģ ą┤ą░ąĮąĮčŗčģ (SDI) ąĖ ą▓čŗą▓ąŠą┤ ą▓čŗčģąŠą┤ą░ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ą┤ą░ąĮąĮčŗčģ (SDO). ąÆčŗą▓ąŠą┤ ID čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ą╝ą╗ą░ą┤čłąĖą╣ ą▒ąĖčé ą║ąŠą┤ą░ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░čåąĖąĖ. ąÆčŗą▓ąŠą┤čŗ DB[17:0], ą║ąŠč鹊čĆčŗąĄ ą▓ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ, ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą┐ąŠą┤čéčÅąĮčāčéčŗ ą║ GND.

ąĀą░ą▒ąŠčéą░ SPI čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ ą┐ąŠ čüą┐ą░ą┤čā čāčĆąŠą▓ąĮčÅ nCS ąĖ ą┐ąĄčĆąĄą┤ą░čćą░ ą┤ą░ąĮąĮčŗčģ ąĘą░ą║ą░ąĮčćąĖą▓ą░ąĄčéčüčÅ ą┐ąŠ čäčĆąŠąĮčéčā ąĮą░čĆą░čüčéą░ąĮąĖčÅ nCS. ąØą░čćą░ą╗čīąĮčŗą╣ ą▒ą░ą╣čé ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą┤ą╗čÅ ąĘą░ą┐čāčüą║ą░ čéčĆą░ąĮąĘą░ą║čåąĖąĖ, ąĖ ą▓ čŹč鹊ą╝ ą▒ą░ą╣č鹥 ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ąĖąĮč乊čĆą╝ą░čåąĖčÅ ąŠ čćč鹥ąĮąĖąĖ ąĖą╗ąĖ ąĘą░ą┐ąĖčüąĖ, ąĖ ąĖąĮč乊čĆą╝ą░čåąĖčÅ RS. ąÜąŠą│ą┤ą░ ąĮą░čćą░ą╗čīąĮčŗą╣ ą▒ą░ą╣čé ą║ąŠčĆčĆąĄą║č鹥ąĮ, ą┐ąŠčüą╗ąĄą┤čāčÄčēąĖąĄ ą┤ą░ąĮąĮčŗąĄ ą┐čĆąĖąĮąĖą╝ą░čÄčéčüčÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą╝ ILI9325.

ąĪąĄą┤čīą╝ąŠą╣ ą▒ąĖčé ąĮą░čćą░ą╗čīąĮąŠą│ąŠ ą▒ą░ą╣čéą░ čŹč鹊 ą▒ąĖčé RS. ąÜąŠą│ą┤ą░ RS = 0, ą▒čāą┤ąĄčé ą▓čŗą┐ąŠą╗ąĮąĄąĮą░ ąŠą┐ąĄčĆą░čåąĖčÅ ąĘą░ą┐ąĖčüąĖ ąĖąĮą┤ąĄą║čüą░ ąĖą╗ąĖ ąŠą┐ąĄčĆą░čåąĖčÅ čćč鹥ąĮąĖčÅ čüčéą░čéčāčüą░. ąÜąŠą│ą┤ą░ RS = 1, č鹊 ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą╗ąĖą▒ąŠ ąŠą┐ąĄčĆą░čåąĖčÅ ąĘą░ą┐ąĖčüąĖ čĆąĄą│ąĖčüčéčĆą░, ą╗ąĖą▒ąŠ ąŠą┐ąĄčĆą░čåąĖčÅ čćč鹥ąĮąĖčÅ/ąĘą░ą┐ąĖčüąĖ ą×ąŚąŻ. ąÆąŠčüčīą╝ąŠą╣ ą▒ąĖčé ąĮą░čćą░ą╗čīąĮąŠą│ąŠ ą▒ą░ą╣čéą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą░ ąŠą┐ąĄčĆą░čåąĖąĖ čćč鹥ąĮąĖčÅ ąĖą╗ąĖ ąĘą░ą┐ąĖčüąĖ (ą▒ąĖčé R/W). ąöą░ąĮąĮčŗąĄ ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ, ą║ąŠą│ą┤ą░ ą▒ąĖčé R/W = 0, ąĖ ą▓čŗčćąĖčéčŗą▓ą░čÄčéčüčÅ, ą║ąŠą│ą┤ą░ ą▒ąĖčé R/W = 1.

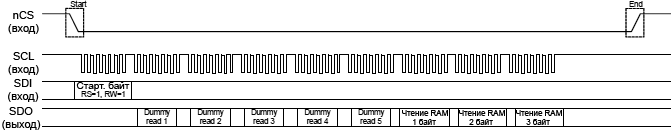

ą¤ąŠčüą╗ąĄ ą┐čĆąĖąĄą╝ą░ čüčéą░čĆč鹊ą▓ąŠą│ąŠ ą▒ą░ą╣čéą░ ILI9325 ąĮą░čćąĮąĄčé ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī ąĖą╗ąĖ ą┐čĆąĖąĮąĖą╝ą░čéčī ą┤ą░ąĮąĮčŗąĄ ą┐ąŠ ą▒ą░ą╣čéą░ą╝, ą║ą░ąČą┤čŗą╣ ą▒ą░ą╣čé ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ, ąĮą░čćąĖąĮą░čÅ čüąŠ čüčéą░čĆčłąĄą│ąŠ ą▒ąĖčéą░ (MSB). ąÆčüąĄ čĆąĄą│ąĖčüčéčĆčŗ ILI9325 16-ą▒ąĖčéąĮčŗąĄ, ąĖ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░ čüąĮą░čćą░ą╗ą░ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ čüčéą░čĆčłąĖą╣ ą▒ą░ą╣čé, ąĘą░ ąĮąĖą╝ ą╝ą╗ą░ą┤čłąĖą╣. ąÆ čĆąĄąČąĖą╝ąĄ SPI ą┐čĆąĖ čćč鹥ąĮąĖąĖ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ą░ ąŠą┐ąĄčĆą░čåąĖčÅ ą┐čāčüč鹊ą│ąŠ čćč鹥ąĮąĖčÅ (dummy read) 5 ą▒ą░ą╣čé, ąĖ ą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗąĄ ą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ąĮą░čćąĖąĮą░čÄčé ą┐ąŠčüčéčāą┐ą░čéčī ąĮą░čćąĖąĮą░čÅ čü 6-ą│ąŠ ą▒ą░ą╣čéą░.

ążąŠčĆą╝ą░čé čüčéą░čĆč鹊ą▓ąŠą│ąŠ ą▒ą░ą╣čéą░:

| ą¤ąĄčĆąĄą┤ą░ąĮąĮčŗąĄ ą▒ąĖčéčŗ |

S |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

| ążąŠčĆą╝ą░čé start-ą▒ą░ą╣čéą░ |

ąØą░čćą░ą╗ąŠ ą┐ąĄčĆąĄą┤ą░čćąĖ |

ąÜąŠą┤ ID čāčüčéčĆąŠą╣čüčéą▓ą░ |

RS |

R/W |

| 0 |

1 |

1 |

1 |

0 |

ID |

1/0 |

1/0 |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ: ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčéą░ ID ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ čāčĆąŠą▓ąĮčÅ ą▓čŗą▓ąŠą┤ą░ IM0/ID. ąÆ čéą░ą▒ą╗ąĖčåąĄ čāą║ą░ąĘą░ąĮą░ ąĮąĄ čĆą░ąĘčĆčÅą┤ąĮąŠčüčéčī ą▒ąĖčé, ą░ ąĖčģ ąĮąŠą╝ąĄčĆ ą▓ ą┐ąŠčĆčÅą┤ą║ąĄ ą┐ąŠčÅą▓ą╗ąĄąĮąĖčÅ (1, 2, .., 8).

ążčāąĮą║čåąĖčÅ ą▒ąĖčé RS ąĖ R/W:

| ążčāąĮą║čåąĖčÅ |

R/W |

RS |

| ąŻčüčéą░ąĮąŠą▓ą║ą░ ąĖąĮą┤ąĄą║čüąĮąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░ (IR) |

0 |

0 |

| ą¦č鹥ąĮąĖąĄ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čüčéą░čéčāčüą░ |

1 |

0 |

| ąŚą░ą┐ąĖčüčī čĆąĄą│ąĖčüčéčĆą░ ąĖą╗ąĖ ą┤ą░ąĮąĮčŗčģ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ GRAM |

0 |

1 |

| ą¦č鹥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ ąĖą╗ąĖ ąĖąĘ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ GRAM |

1 |

1 |

ąĀąĖčü. 7. ążąŠčĆą╝ą░čé ą┤ą░ąĮąĮčŗčģ ąĖąĮč鹥čĆč乥ą╣čüą░ SPI.

(a) ąæą░ąĘąŠą▓ą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░ ą┤ą░ąĮąĮčŗčģ č湥čĆąĄąĘ SPI:

(b) ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░ ą┤ą░ąĮąĮčŗčģ č湥čĆąĄąĘ SPI:

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą┐ąĄčĆą▓čŗą╣ ą▒ą░ą╣čé ą┐ąŠčüą╗ąĄ čüčéą░čĆč鹊ą▓ąŠą│ąŠ ą▓čüąĄą│ą┤ą░ ą┐ąĄčĆąĄą┤ą░ąĄčé čüčéą░čĆčłąĖąĄ 8 ą▒ąĖčé.

(c) ą¤ąĄčĆąĄą┤ą░čćą░ čćč鹥ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ GRAM:

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą┐ąŠčüą╗ąĄ čüčéą░čĆč鹊ą▓ąŠą│ąŠ ą▒ą░ą╣čéą░ čéčĆąĄą▒čāąĄčéčüčÅ ą┐čĆąŠčćąĖčéą░čéčī 5 ąĮąĖč湥ą│ąŠ ąĮąĄ ąĘąĮą░čćą░čēąĖčģ ą▒ą░ą╣čé (Dummy read n), ą║ąŠč鹊čĆčŗąĄ čüąŠą┤ąĄčƹȹ░čé ąĮąĄą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ.

(d) ą¤ąĄčĆąĄą┤ą░čćą░ čćč鹥ąĮąĖčÅ čüčéą░čéčāčüą░ / čĆąĄą│ąĖčüčéčĆąŠą▓:

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą┐ąŠčüą╗ąĄ čüčéą░čĆč鹊ą▓ąŠą│ąŠ ą▒ą░ą╣čéą░ ąĮčāąČąĮąŠ ą┐čĆąŠčćąĖčéą░čéčī ąŠą┤ąĖąĮ ą┐čāčüč鹊ą╣ ą▒ą░ą╣čé (dummy data read).

ąĀąĖčü. 8. ąöąĖą░ą│čĆą░ą╝ą╝čŗ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ č湥čĆąĄąĘ SPI.

(e) ąæą░ąĘąŠą▓ą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░ ą┤ą░ąĮąĮčŗčģ č湥čĆąĄąĘ SPI:

(f) ą¤ąĄčĆąĄą┤ą░čćą░ ąĘą░ą┐ąĖčüąĖ ą┤ą░ąĮąĮčŗčģ ą▓ GRAM:

(g) ą¤ąĄčĆąĄą┤ą░čćą░ čćč鹥ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ąĖąĘ GRAM:

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą┐ąŠčüą╗ąĄ čüčéą░čĆč鹊ą▓ąŠą│ąŠ ą▒ą░ą╣čéą░ ąĮčāąČąĮąŠ ą┐čĆąŠčćąĖčéą░čéčī 5 ą┐čāčüčéčŗčģ ą▒ą░ą╣čé (dummy read).

ąĀąĖčü. 9. ąöąĖą░ą│čĆą░ą╝ą╝čŗ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ č湥čĆąĄąĘ SPI ą┐čĆąĖ TRI=1 ąĖ DFM=10.

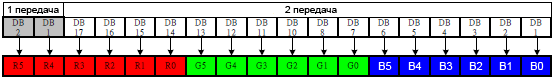

[ąśąĮč鹥čĆč乥ą╣čü VSYNC]

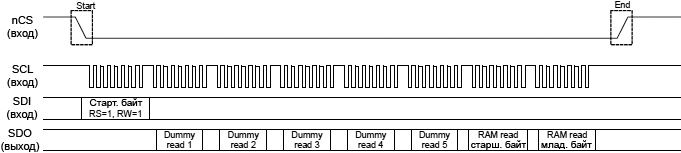

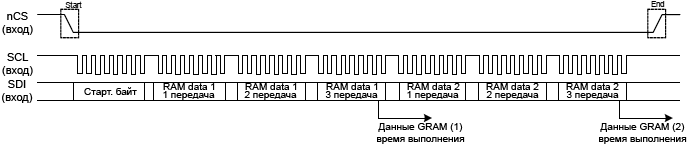

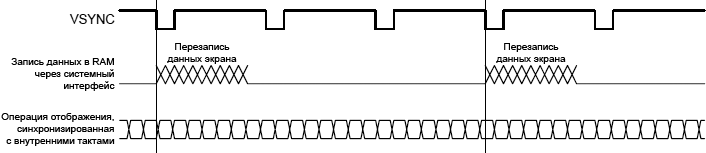

ILI9325 ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ąĖąĮč鹥čĆč乥ą╣čü VSYNC ą▓ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ čü čüąĖą│ąĮą░ą╗ąŠą╝ čüąĖąĮčģčĆąŠąĖą╝ą┐čāą╗čīčüą░ ą║ą░ą┤čĆą░ VSYNC, čćč鹊ą▒čŗ ąŠč鹊ą▒čĆą░ąČą░čéčī ą┤ą▓ąĖąČčāčēčāčÄčüčÅ ą║ą░čĆčéąĖąĮą║čā (ą▓ąĖą┤ąĄąŠ) č湥čĆąĄąĘ čüąĖčüč鹥ą╝ąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü i80. ąÜąŠą│ą┤ą░ ą┤ą╗čÅ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖčÅ ą▓ąĖą┤ąĄąŠ ą▓čŗą▒čĆą░ąĮ ąĖąĮč鹥čĆč乥ą╣čü VSYNC, ą╝ąĖąĮąĖą╝ą░ą╗čīąĮą░čÅ čüą║ąŠčĆąŠčüčéčī ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ GRAM ąŠą│čĆą░ąĮąĖč湥ąĮą░ ąĖąĮč鹥čĆč乥ą╣čüąŠą╝ VSYNC (ą┤ą░ąĮąĮčŗąĄ ą║ą░čĆčéąĖąĮą║ąĖ ąĮčāąČąĮąŠ čāčüą┐ąĄčéčī ą┐ąĄčĆąĄą┤ą░čéčī ąĘą░ ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĖąŠą┤ą░ čćą░čüč鹊čéčŗ ą║ą░ą┤čĆąŠą▓). ąśąĮč鹥čĆč乥ą╣čü VSYNC ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ čāčĆąŠą▓ąĮčÅą╝ąĖ DM[1:0] = 10 ąĖ RM = 0.

ąĀąĖčü. 10. ą¤ąĄčĆąĄą┤ą░čćą░ ą┤ą░ąĮąĮčŗčģ č湥čĆąĄąĘ ąĖąĮč鹥čĆč乥ą╣čü VSYNC.

ąÆ čĆąĄąČąĖą╝ąĄ VSYNC čĆą░ą▒ąŠčéą░ ą┤ąĖčüą┐ą╗ąĄčÅ čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆąŠą▓ą░ąĮą░ čü ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ čćą░čüč鹊č鹊ą╣ ąĖ ą▓čģąŠą┤ąŠą╝ VSYNC, ąĖ čćą░čüč鹊čéą░ čüą╝ąĄąĮčŗ ą║ą░ą┤čĆąŠą▓ (frame rate) ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ čćą░čüč鹊č鹊ą╣ čüąĖąĮčģčĆąŠąĖą╝ą┐čāą╗čīčüąŠą▓ VSYNC. ąÆčüąĄ ą┤ą░ąĮąĮčŗąĄ ą┤ąĖčüą┐ą╗ąĄčÅ čüąŠčģčĆą░ąĮčÅčÄčéčüčÅ ą▓ GRAM, čćč鹊ą▒čŗ ą╝ąĖąĮąĖą╝ąĖąĘąĖčĆąŠą▓ą░čéčī ąŠą▒čēąĖąĄ ą┐ąĄčĆąĄčüčŗą╗ą║ąĖ, ąĮąĄąŠą▒čģąŠą┤ąĖą╝čŗąĄ ą┤ą╗čÅ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖčÅ ąĖąĘą╝ąĄąĮčÅčÄčēąĄą╣čüčÅ ą║ą░čĆčéąĖąĮą║ąĖ.

ąĀąĖčü. 11. ą¤ąĄčĆąĄą┤ą░čćą░ ąĖąĘą╝ąĄąĮčÅčÄčēąĄą╣čüčÅ ą║ą░čĆčéąĖąĮą║ąĖ č湥čĆąĄąĘ ąĖąĮč鹥čĆč乥ą╣čü VSYNC.

ąĀąĖčü. 12. ąĀą░ą▒ąŠčéą░ č湥čĆąĄąĘ ąĖąĮč鹥čĆč乥ą╣čü VSYNC.

ą×ą│čĆą░ąĮąĖč湥ąĮąĖąĄ ą┐ąŠ ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠą╣ čüą║ąŠčĆąŠčüčéąĖ ąĘą░ą┐ąĖčüąĖ ą┤ą░ąĮąĮčŗčģ ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮčÄčÄ ą┐ą░ą╝čÅčéčī GRAM č湥čĆąĄąĘ čüąĖčüč鹥ą╝ąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü ą▓čŗčćąĖčüą╗čÅąĄčéčüčÅ ą┐ąŠ čüą╗ąĄą┤čāčÄčēąĄą╣ č乊čĆą╝čāą╗ąĄ:

fosc = Fframe * (NL + FP + BP) * RTN * Ffl

ąŚą┤ąĄčüčī čüą╝čŗčüą╗ ą┐ąĄčĆąĄą╝ąĄąĮąĮčŗčģ čüą╗ąĄą┤čāčÄčēąĖą╣:

fosc ąÆąĮčāčéčĆąĄąĮąĮčÅčÅ čćą░čüč鹊čéą░ čéą░ą║č鹊ą▓, ąōčå

Fframe ą¦ą░čüč鹊čéą░ ą║ą░ą┤čĆąŠą▓

NL ąÜąŠą╗ąĖč湥čüčéą▓ąŠ ąŠč鹊ą▒čĆą░ąČą░ąĄą╝čŗčģ ąĮą░ 菹║čĆą░ąĮąĄ čüčéčĆąŠą║

FP ąÜąŠą╗ąĖč湥čüčéą▓ąŠ "čäčĆąŠąĮčéą░ą╗čīąĮčŗčģ" čüčéčĆąŠą║ (FrontPorch)

BP ąÜąŠą╗ąĖč湥čüčéą▓ąŠ "ąĘą░ą┤ąĮąĖčģ" čüčéčĆąŠą║ (BackPorch)

RTN ąÜąŠą╗ąĖč湥čüčéą▓ąŠ čéą░ą║č鹊ą▓čŗčģ ąĖą╝ą┐čāą╗čīčüąŠą▓ ąĮą░ čüčéčĆąŠą║čā (ClockCyclePerLines)

Ffl ąÆąŠąĘą╝ąŠąČąĮčŗąĄ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ čćą░čüč鹊čéčŗ (FrequencyFluctuation).

FminRAM = 240 * NL / ((BP + NL - ą│čĆą░ąĮąĖčåčŗ) * 16 (čéą░ą║č鹊ą▓) * 1/fosc)

ąŚą┤ąĄčüčī FminRAM čŹč鹊 ą╝ąĖąĮąĖą╝ą░ą╗čīąĮą░čÅ čüą║ąŠčĆąŠčüčéčī ąĘą░ą┐ąĖčüąĖ ą▓ GRAM, ąōčå.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą║ąŠą│ą┤ą░ ąŠą┐ąĄčĆą░čåąĖčÅ ąĘą░ą┐ąĖčüąĖ ą▓ GRAM ąĮąĄ ąĮą░čćą░ą╗ą░čüčī ą▓ ą╝ąŠą╝ąĄąĮčé čüą┐ą░ą┤ą░ čāčĆąŠą▓ąĮčÅ VSYNC, č鹊 čéą░ą║ąČąĄ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ čāčćąĖčéčŗą▓ą░čéčī ą▓čĆąĄą╝čÅ ąŠčé čüą┐ą░ą┤ą░ VSYNC ą┤ąŠ ąĮą░čćą░ą╗ą░ ąŠą┐ąĄčĆą░čåąĖąĖ ąĘą░ą┐ąĖčüąĖ ą▓ GRAM.

ąØąĖąČąĄ ą┐čĆąĖą▓ąĄą┤ąĄąĮ ą┐čĆąĖą╝ąĄčĆ čĆą░čüč湥čéą░ ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠą╣ čüą║ąŠčĆąŠčüčéąĖ ąĘą░ą┐ąĖčüąĖ ą▓ GRAM ąĖ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ ą▓ čĆąĄąČąĖą╝ąĄ ąĖąĮč鹥čĆč乥ą╣čüą░ VSYNC. ąśčüčģąŠą┤ąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ:

ąĀą░ąĘą╝ąĄčĆ čŹą║čĆą░ąĮą░ 240 RGB x 320 čüčéčĆąŠą║

ą¤čĆąĖ 320 čüčéčĆąŠą║ą░čģ NL = 100111

Back porch 14 čüčéčĆąŠą║ (BP = 1110)

Front porch 2 čüčéčĆąŠą║ąĖ (FP = 0010)

ą¦ą░čüč鹊čéą░ ą║ą░ą┤čĆąŠą▓ 60 ąōčå

Frequency fluctuation: 10%

ąÆąĮčāčéčĆąĄąĮąĮčÅčÅ čćą░čüč鹊čéą░ čéą░ą║č鹊ą▓, ąōčå:

fosc = 60 x [320+ 2 + 14] x 16 čéą░ą║č鹊ą▓ x (1.1/0.9) = 394 ą║ąōčå

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą┐čĆąĖ ą▓čŗčćąĖčüą╗ąĄąĮąĖąĖ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ ąĮčāąČąĮąŠ čāčćąĖčéčŗą▓ą░čéčī ą▓ąŠąĘą╝ąŠąČąĮčŗą╣ ąĄčæ čāčģąŠą┤ (Frequency fluctuation). ąÆ ą▓čŗčłąĄą┐čĆąĖą▓ąĄą┤ąĄąĮąĮąŠą╝ ą┐čĆąĖą╝ąĄčĆąĄ ą▓čŗčćąĖčüą╗ąĄąĮąĖčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ čćą░čüč鹊čéčŗ ą║ą░ą┤čĆąŠą▓ ą┐čĆąĖąĮąĖą╝ą░ąĄčéčüčÅ ą▓ą░čĆąĖą░čåąĖčÅ ą▓ ą┐čĆąĄą┤ąĄą╗ą░čģ ą│čĆą░ąĮąĖčå ┬▒10%. ąŁč鹊čé čāčģąŠą┤ čćą░čüč鹊čéčŗ ą▓ąŠąĘą╝ąŠąČąĄąĮ ąĖąĘ-ąĘą░ čĆą░ąĘą╗ąĖčćąĖą╣ ą▓ čāčüą╗ąŠą▓ąĖčÅčģ č鹥čģą┐čĆąŠčåąĄčüčüą░ LSI, ąĖąĘ-ąĘą░ ąĖąĘą╝ąĄąĮąĄąĮąĖą╣ č鹥ą╝ą┐ąĄčĆą░čéčāčĆčŗ, ąĖąĘ-ąĘą░ čĆą░ąĘą▒čĆąŠčüą░ ąĮąŠą╝ąĖąĮą░ą╗ąŠą▓ ą▓ąĮąĄčłąĮąĖčģ čĆąĄąĘąĖčüč鹊čĆąŠą▓ ąĖ ąĖąĘ-ąĘą░ ąĖąĘą╝ąĄąĮąĄąĮąĖą╣ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ VCI.

ą£ąĖąĮąĖą╝ą░ą╗čīąĮą░čÅ čüą║ąŠčĆąŠčüčéčī ąĘą░ą┐ąĖčüąĖ ą▓ GRAM:

FminRAM = 240 x 320 x 394 ą║ąōčå / ((14 + 320 ŌĆō 2)čüčéčĆąŠą║ x 16 čéą░ą║č鹊ą▓) = 5.7 ą£ąōčå.

ą¤ąŠą╗čāčćąĖą▓čłąĄąĄčüčÅ č鹥ąŠčĆąĄčéąĖč湥čüą║ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą▓čŗčćąĖčüą╗ąĄąĮąŠ ą┤ą╗čÅ čāčüą╗ąŠą▓ąĖą╣, ą║ąŠą│ą┤ą░ ąĘą░ą┐ąĖčüčī ą┤ą░ąĮąĮčŗčģ ą▓ GRAM ILI9325 ąĮą░čćąĖąĮą░ąĄčéčüčÅ ą▓ ą╝ąŠą╝ąĄąĮčé čüą┐ą░ą┤ą░ čāčĆąŠą▓ąĮčÅ VSYNC. ąóčĆąĄą▒čāąĄčéčüčÅ ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ąĖąĮč鹥čĆą▓ą░ą╗ ąĖąĘ 2 čüčéčĆąŠą║ ą╝ąĄąČą┤čā čäąĖąĘąĖč湥čüą║ąŠą╣ čüčéčĆąŠą║ąŠą╣ ą┤ąĖčüą┐ą╗ąĄčÅ ąĖ ą░ą┤čĆąĄčüąŠą╝ čüčéčĆąŠą║ąĖ GRAM, ą║čāą┤ą░ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ąĘą░ą┐ąĖčüčī. ąĪą║ąŠčĆąŠčüčéčī ąĘą░ą┐ąĖčüąĖ ą▓ GRAM 5.7 ą£ąōčå ąĖą╗ąĖ ą▓čŗčłąĄ ą│ą░čĆą░ąĮčéąĖčĆčāąĄčé ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĄ ąŠą┐ąĄčĆą░čåąĖąĖ ąĘą░ą┐ąĖčüąĖ ą▓ GRAM ą┤ąŠ č鹊ą│ąŠ, ą║ą░ą║ ILI9325 ąĮą░čćąĮąĄčé ąŠč鹊ą▒čĆą░ąČą░čéčī ą┤ą░ąĮąĮčŗąĄ ąĮą░ 菹║čĆą░ąĮąĄ, čćč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąŠą▒ąĮąŠą▓ą╗čÅčéčī ą▓čüčÄ ą║ą░čĆčéąĖąĮą║čā ąĮą░ 菹║čĆą░ąĮąĄ ą▒ąĄąĘ ą╝ąĄčĆčåą░ąĮąĖčÅ ąĖ ąĖčüą║ą░ąČąĄąĮąĖčÅ ąĖąĘąŠą▒čĆą░ąČąĄąĮąĖčÅ.

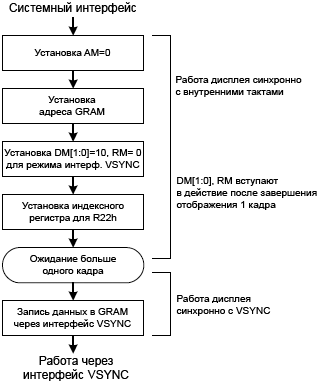

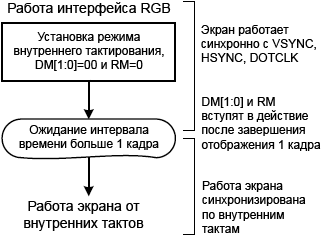

ąŚą░ą╝ąĄčćą░ąĮąĖčÅ ą┐ąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÄ ąĖąĮč鹥čĆč乥ą╣čüą░ VSYNC:

1. ąöąŠą╗ąČąĮąŠ čāą┤ąŠą▓ą╗ąĄčéą▓ąŠčĆčÅčéčīčüčÅ čāčüą╗ąŠą▓ąĖąĄ ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠą╣ čüą║ąŠčĆąŠčüčéąĖ ąĘą░ą┐ąĖčüąĖ ą▓ GRAM, čü čāč湥č鹊ą╝ ą▓ąŠąĘą╝ąŠąČąĮąŠą│ąŠ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ.

2. ą¦ą░čüč鹊čéą░ ą║ą░ą┤čĆąŠą▓ (display frame rate) ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ čćą░čüč鹊č鹊ą╣ VSYNC, ąĖ ą┐ąĄčĆąĖąŠą┤ VSYNC ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą▒ąŠą╗čīčłąĄ, č湥ą╝ ą┐ąĄčĆąĖąŠą┤ čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓čüąĄą╣ ą║ą░čĆčéąĖąĮą║ąĖ.

3. ą¤čĆąĖ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĖ ąĖąĘ čĆąĄąČąĖą╝ą░ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ (DM[1:0] = 00) ą▓ čĆąĄąČąĖą╝ ąĖąĮč鹥čĆč乥ą╣čüą░ VSYNC ąĖą╗ąĖ ąĮą░ąŠą▒ąŠčĆąŠčé, ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ąĮą░čćąĖąĮą░ąĄčéčüčÅ čüąŠ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ čéą░ą║čéą░ VSYNC, čé. ąĄ. ą┐ąŠčüą╗ąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖčÅ ą║ą░ą┤čĆą░.

4. ą¦ą░čüčéąĖčćąĮąŠąĄ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖąĄ (partial display), ą▓ąĄčĆčéąĖą║ą░ą╗čīąĮą░čÅ ą┐čĆąŠą║čĆčāčéą║ą░ (vertical scroll), čäčāąĮą║čåąĖąĖ č湥čĆąĄčüčüčéčĆąŠčćąĮąŠą╣ čĆą░ąĘą▓ąĄčĆčéą║ąĖ čüčéčĆąŠą║ (interlaced scan) ąĮąĄą┤ąŠčüčéčāą┐ąĮčŗ ą▓ čĆąĄąČąĖą╝ąĄ ąĖąĮč鹥čĆč乥ą╣čüą░ VSYNC, ąĖ ą▒ąĖčé AM čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▓ 0 ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ą┤ąĖčüą┐ą╗ąĄčÅ.

ą¤ąĄčĆąĄčģąŠą┤ čüąĖčüč鹥ą╝ąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü

-> ąĖąĮč鹥čĆč乥ą╣čü VSYNC |

ą×ą▒čĆą░čéąĮčŗą╣ ą┐ąĄčĆąĄčģąŠą┤ ąĖąĮč鹥čĆč乥ą╣čü VSYNC

-> čüąĖčüč鹥ą╝ąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü |

|

|

ąĀąĖčü. 13. ą¤ąĄčĆąĄčģąŠą┤čŗ ą╝ąĄąČą┤čā čĆąĄąČąĖą╝ą░ą╝ąĖ VSYNC čĆąĄąČąĖą╝ą░ą╝ąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĖčģ čéą░ą║č鹊ą▓.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą┐čĆąĖ čāčüčéą░ąĮąŠą▓ą║ąĄ ą▒ąĖčé čĆąĄą│ąĖčüčéčĆą░ DM, RM ą▓ą▓ąŠą┤ VSYNC ą▓čüčéčāą┐ą░ąĄčé ą▓ ą┤ąĄą╣čüčéą▓ąĖąĄ ą┐ąŠčüą╗ąĄ ą┐ąĄčĆąĖąŠą┤ą░ ą▓čĆąĄą╝ąĄąĮąĖ ą┐čĆąŠčģąŠąČą┤ąĄąĮąĖčÅ ą▒ąŠą╗čīčłąĄ ąŠą┤ąĮąŠą│ąŠ ą║ą░ą┤čĆą░.

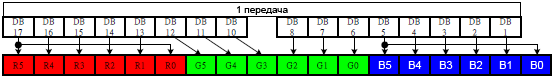

[ąśąĮč鹥čĆč乥ą╣čü RGB]

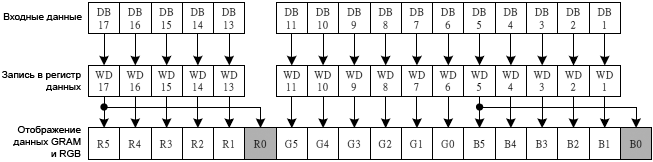

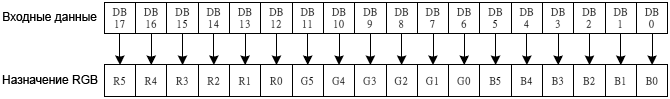

ąĀąĄąČąĖą╝ ąĖąĮč鹥čĆč乥ą╣čüą░ RGB ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčé RIM[1:0] ą┐ąŠ čüą╗ąĄą┤čāčÄčēąĄą╣ čéą░ą▒ą╗ąĖčåąĄ.

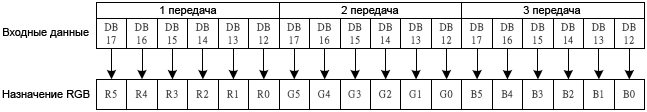

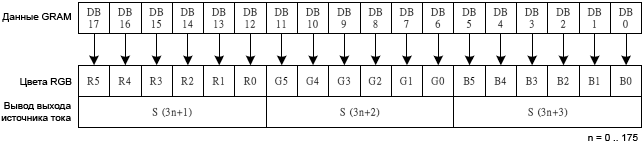

18-ą▒ąĖčé ąĖąĮč鹥čĆč乥ą╣čü RGB (262K čåą▓ąĄč鹊ą▓):

16-ą▒ąĖčé ąĖąĮč鹥čĆč乥ą╣čü RGB (65K čåą▓ąĄč鹊ą▓):

6-ą▒ąĖčé ąĖąĮč鹥čĆč乥ą╣čü RGB (262K čåą▓ąĄč鹊ą▓):

ąĀąĖčü. 14. ążąŠčĆą╝ą░čé ą┤ą░ąĮąĮčŗčģ ąĖąĮč鹥čĆč乥ą╣čüą░ RGB.

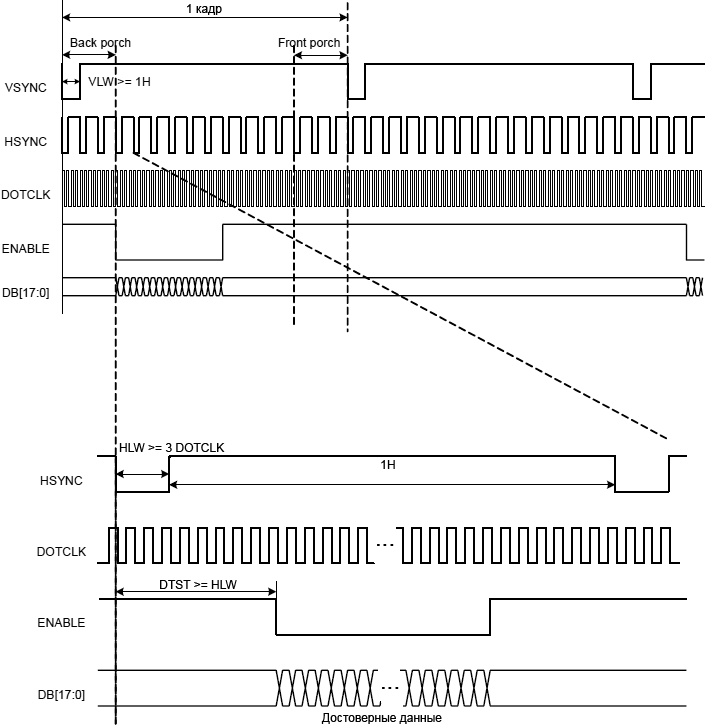

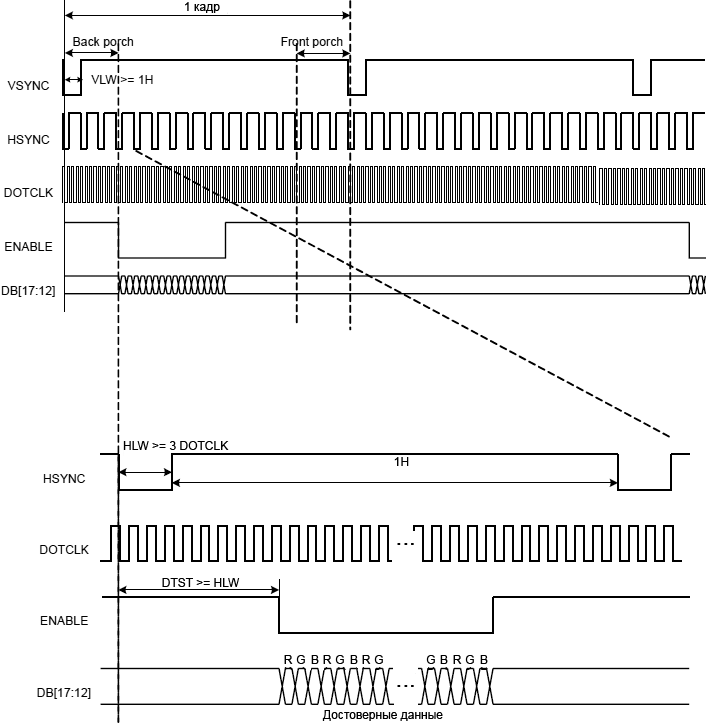

ąĀą░ą▒ąŠčéą░ ą┤ąĖčüą┐ą╗ąĄčÅ ą▓ čĆąĄąČąĖą╝ąĄ RGB čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆčāąĄčéčüčÅ čü čüąĖą│ąĮą░ą╗ą░ą╝ąĖ VSYNC, HSYNC ąĖ DOTCLK. ąśąĮč鹥čĆč乥ą╣čü RGB ą┐ąĄčĆąĄą┤ą░ąĄčé ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą▓ GRAM čäčāąĮą║čåąĖąĄą╣ ą▓čŗčüąŠą║ąŠčüą║ąŠčĆąŠčüčéąĮąŠą╣ ąĘą░ą┐ąĖčüąĖ, ąĖ ąŠą▒ą╗ą░čüčéčī ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ čäčāąĮą║čåąĖąĄą╣ ą░ą┤čĆąĄčüą░čåąĖąĖ ąŠą║ąĮą░. ąöą╗čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ ąĖąĮč鹥čĆą▓ą░ą╗ąŠą▓ ą▓čĆąĄą╝ąĄąĮąĖ ąĖąĮč鹥čĆč乥ą╣čüą░ RGB ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą║ąŠą╗ąĖč湥čüčéą▓ą░ čüčéčĆąŠą║ ąĮą░čćą░ą╗ą░ ą║ą░ą┤čĆą░ (Front porch) ąĖ ą║ąŠąĮčåą░ ą║ą░ą┤čĆą░ (Back porch).

ąĀąĖčü. 15. ąöąŠčüčéčāą┐ ą║ ąŠą▒ą╗ą░čüčéąĖ GRAM č湥čĆąĄąĘ ąĖąĮč鹥čĆč乥ą╣čü RGB.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą¤ąĄčĆąĖąŠą┤ front porch ą┐čĆąŠą┤ąŠą╗ąČą░ąĄčéčüčÅ ą┤ąŠ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ ą▓ą▓ąŠą┤ą░ VSYNC. ąÆąŠ ą▓čĆąĄą╝čÅ ąŠą┐ąĄčĆą░čåąĖąĖ ą┤ąŠčüčéčāą┐ą░ ą┐ąŠą┤ą░čÄčéčüčÅ ą▓čģąŠą┤ąĮčŗąĄ čéą░ą║čéčŗ DOTCLK. ą¤čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄą╝čŗąĄ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ ąĖą╝ą┐čāą╗čīčüąŠą▓ VSYNC, HSYNC ąĖ DOTCLK ą┐ąŠ čćą░čüč鹊č鹥 ą┤ąŠą╗ąČąĮčŗ čāą┤ąŠą▓ą╗ąĄčéą▓ąŠčĆčÅčéčī čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅą╝ čĆą░ąĘčĆąĄčłą░čÄčēąĄą╣ čüą┐ąŠčüąŠą▒ąĮąŠčüčéąĖ ą┐ą░ąĮąĄą╗ąĖ LCD.

ąĀąĖčü. 16. ąöąĖą░ą│čĆą░ą╝ą╝ą░ čüąĖą│ąĮą░ą╗ąŠą▓ ą▓ čĆąĄąČąĖą╝ąĄ ąĖąĮč鹥čĆč乥ą╣čüą░ RGB 18-/16-ą▒ąĖčé.

VLW: VSYNC low (ą┐ąĄčĆąĖąŠą┤ ą╗ąŠą│. 0 čüąĖąĮčģčĆąŠąĖą╝ą┐čāą╗čīčüą░ ą▓ąĄčĆčéąĖą║ą░ą╗čīąĮąŠą╣ čĆą░ąĘą▓ąĄčĆčéą║ąĖ)

HLW: HSYNC low (ą┐ąĄčĆąĖąŠą┤ ą╗ąŠą│. 0 čüąĖąĮčģčĆąŠąĖą╝ą┐čāą╗čīčüą░ ą│ąŠčĆąĖąĘąŠąĮčéą░ą╗čīąĮąŠą╣ čĆą░ąĘą▓ąĄčĆčéą║ąĖ)

DTST: data transfer startup time (ą▓čĆąĄą╝čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ)

ąĀąĖčü. 17. ąöąĖą░ą│čĆą░ą╝ą╝ą░ čüąĖą│ąĮą░ą╗ąŠą▓ ą▓ čĆąĄąČąĖą╝ąĄ ąĖąĮč鹥čĆč乥ą╣čüą░ RGB 6-ą▒ąĖčé.

VLW: VSYNC low (ą┐ąĄčĆąĖąŠą┤ ą╗ąŠą│. 0 čüąĖąĮčģčĆąŠąĖą╝ą┐čāą╗čīčüą░ ą▓ąĄčĆčéąĖą║ą░ą╗čīąĮąŠą╣ čĆą░ąĘą▓ąĄčĆčéą║ąĖ)

HLW: HSYNC low (ą┐ąĄčĆąĖąŠą┤ ą╗ąŠą│. 0 čüąĖąĮčģčĆąŠąĖą╝ą┐čāą╗čīčüą░ ą│ąŠčĆąĖąĘąŠąĮčéą░ą╗čīąĮąŠą╣ čĆą░ąĘą▓ąĄčĆčéą║ąĖ)

DTST: data transfer startup time (ą▓čĆąĄą╝čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ)

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ: ą▓ čĆąĄąČąĖą╝ąĄ 6-ą▒ąĖčé ąĖąĮč鹥čĆč乥ą╣čüą░ RGB ą║ą░ąČą┤čŗą╣ čåą▓ąĄčé č鹊čćą║ąĖ (R, G ąĖ B) ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ čüąĖąĮčģčĆąŠąĮąĮąŠ čü čéą░ą║čéą░ą╝ąĖ DOTCLK. ąØą░ą▒ąŠčĆ čéą░ą║č鹊ą▓ VSYNC, HSYNC ąĖ ENABLE ą┐ąŠ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéąĖ ą┤ąŠą╗ąČąĄąĮ ąĮą░čåąĄą╗ąŠ ą┤ąĄą╗ąĖčéčīčüčÅ ąĮą░ 3 čéą░ą║čéą░ DOTCLK.

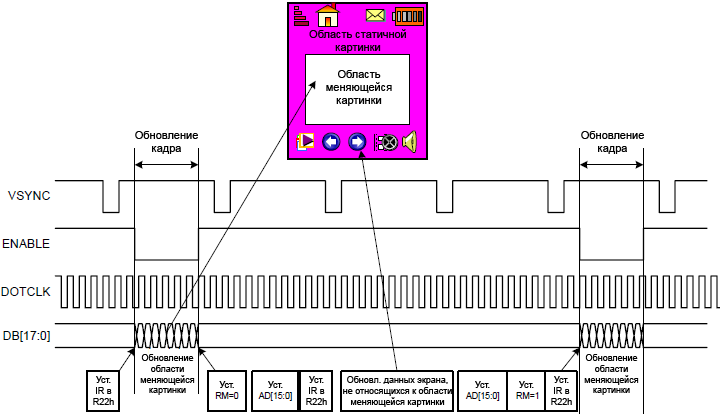

ąśąĘą╝ąĄąĮčÅčÄčēą░čÅčüčÅ ą║ą░čĆčéąĖąĮą║ą░. RGB-ąĖąĮč鹥čĆč乥ą╣čü ILI9325 ąĖą╝ąĄąĄčé ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ąŠč鹊ą▒čĆą░ąČą░čéčī ąĖąĘą╝ąĄąĮčÅąĄą╝čāčÄ ąŠą▒ą╗ą░čüčéčī 菹║čĆą░ąĮą░ ą▓ ą┐ą░ą╝čÅčéąĖ GRAM čüąŠ čüą╗ąĄą┤čāčÄčēąĖą╝ąĖ ą┐čĆąĄąĖą╝čāčēąĄčüčéą▓ą░ą╝ąĖ:

ŌĆó ą×ą┐čĆąĄą┤ąĄą╗ąĄąĮą░ čäčāąĮą║čåąĖčÅ ą░ą┤čĆąĄčüą░čåąĖąĖ ąŠą║ąĮą░ ą┤ą╗čÅ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ ąŠą▒ą╗ą░čüčéąĖ GRAM.

ŌĆó ąÆ GRAM ąŠą▒ąĮąŠą▓ą╗čÅąĄčéčüčÅ č鹊ą╗čīą║ąŠ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮą░čÅ ąŠą▒ą╗ą░čüčéčī 菹║čĆą░ąĮą░.

ŌĆó ą¤čĆąĖ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖąĖ ąĖąĘą╝ąĄąĮčÅčÄčēąĄą╣čüčÅ ą║ą░čĆčéąĖąĮą║ąĖ ą▓ čĆąĄąČąĖą╝ąĄ ąĖąĮč鹥čĆč乥ą╣čüą░ RGB, DB[17:0] ą╝ąŠą│čāčé ą┐ąĄčĆąĄą║ą╗čÄčćą░čéčīčüčÅ ą┤ą╗čÅ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ čĆąĄą│ąĖčüčéčĆąŠą▓ ąĖ "ą┐ąŠčüč鹊čÅąĮąĮąŠą╣" ąŠą▒ą╗ą░čüčéąĖ 菹║čĆą░ąĮą░, ą│ą┤ąĄ ą╝ąŠą│čāčé ą▒čŗčéčī čĆą░čüą┐ąŠą╗ąŠąČąĄąĮčŗ ą┤čĆčāą│ąĖąĄ ą│čĆą░čäąĖč湥čüą║ąĖąĄ 菹╗ąĄą╝ąĄąĮčéčŗ, čéą░ą║ąĖąĄ ą║ą░ą║ ąĖą║ąŠąĮą║ąĖ, ąĘąĮą░čćą║ąĖ, ą║ąĮąŠą┐ą║ąĖ.

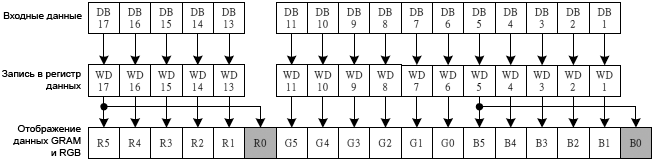

ąöąŠčüčéčāą┐ ą║ GRAM č湥čĆąĄąĘ čüąĖčüč鹥ą╝ąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü ą▓ čĆąĄąČąĖą╝ąĄ ąĖąĮč鹥čĆč乥ą╣čüą░ RGB. ILI9325 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąŠčüčāčēąĄčüčéą▓ą╗čÅčéčī ą┤ąŠčüčéčāą┐ ą║ GRAM č湥čĆąĄąĘ čüąĖčüč鹥ą╝ąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü ą▓ čĆąĄąČąĖą╝ąĄ ąĖąĮč鹥čĆč乥ą╣čüą░ RGB. ą¤čĆąĖ čŹč鹊ą╝ ą┤ą░ąĮąĮčŗąĄ ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮčÄčÄ ą┐ą░ą╝čÅčéčī GRAM čüąĖąĮčģčĆąŠąĮąĮąŠ čü čüąĖą│ąĮą░ą╗ą░ą╝ąĖ DOTCLK ąĖ ENABLE. ąÜąŠą│ą┤ą░ ą┤ą░ąĮąĮčŗąĄ ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮčÄčÄ ą┐ą░ą╝čÅčéčī GRAM č湥čĆąĄąĘ čüąĖčüč鹥ą╝ąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü, ENABLE čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą┤ą╗čÅ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ąĖąĮč鹥čĆč乥ą╣čüą░ RGB ąĖ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ ą▓ čüąĖčüč鹥ą╝ąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü, čćč鹊ą▒čŗ ąŠą▒ąĮąŠą▓ąĖčéčī čĆąĄą│ąĖčüčéčĆčŗ (RM = 0) ąĖ "ą┐ąŠčüč鹊čÅąĮąĮčāčÄ" ąŠą▒ą╗ą░čüčéčī ą║ą░čĆčéąĖąĮą║ąĖ ą▓ GRAM. ąÜąŠą│ą┤ą░ ą┐ąĄčĆąĄąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ ą┤ąŠčüčéčāą┐ ą║ RAM ą▓ čĆąĄąČąĖą╝ąĄ ąĖąĮč鹥čĆč乥ą╣čüą░ RGB, ąŠąČąĖą┤ą░čÄčé ąŠą┤ąĖąĮ čåąĖą║ą╗ čćč鹥ąĮąĖčÅ/ąĘą░ą┐ąĖčüąĖ ąĖ ąĘą░č鹥ą╝ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄčé RM = 1 ąĖ ąĖąĮą┤ąĄą║čüąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ ą▓ R22h, čćč鹊ą▒čŗ ąĮą░čćą░čéčī ą┤ąŠčüčéčāą┐ ą║ GRAM č湥čĆąĄąĘ ąĖąĮč鹥čĆč乥ą╣čü RGB. ąĢčüą╗ąĖ ą║ąŠąĮčäą╗ąĖą║čéčāčÄčé ą┤ą▓ą░ ąĖąĮč鹥čĆč乥ą╣čüą░ ą┐čĆąĖ ą┤ąŠčüčéčāą┐ąĄ ą║ GRAM, ąĮąĄčé ą│ą░čĆą░ąĮčéąĖąĖ, čćč鹊 ą┤ą░ąĮąĮčŗąĄ ą▒čāą┤čāčé ąĘą░ą┐ąĖčüą░ąĮčŗ ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮčÄčÄ ą┐ą░ą╝čÅčéčī GRAM.

ąØą░ čüą╗ąĄą┤čāčÄčēąĄą╝ čĆąĖčüčāąĮą║ąĄ ą┐ąŠą║ą░ąĘą░ąĮą░ čĆą░ą▒ąŠčéą░ ILI9325 ą┐čĆąĖ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖąĖ ą║ą░čĆčéąĖąĮą║ąĖ č湥čĆąĄąĘ ąĖąĮč鹥čĆč乥ą╣čü RGB ąĖ ą┐ąĄčĆąĄąĘą░ą┐ąĖčüčī "ą┐ąŠčüč鹊čÅąĮąĮąŠą╣" ąŠą▒ą╗ą░čüčéąĖ ą┐ą░ą╝čÅčéąĖ č湥čĆąĄąĘ čüąĖčüč鹥ą╝ąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü.

ąĀąĖčü. 18. ą¤čĆąĖą╝ąĄčĆ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ "ą┐ąŠčüč鹊čÅąĮąĮąŠą╣" ąĖ ąĖąĘą╝ąĄąĮčÅčÄčēąĄą╣čüčÅ ą║ą░čĆčéąĖąĮą║ąĖ ąĮą░ 菹║čĆą░ąĮąĄ.

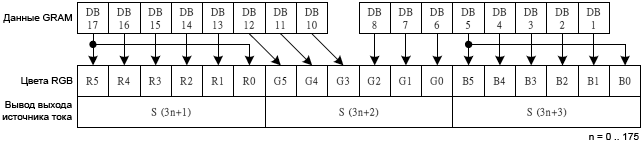

6-ą▒ąĖčéąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü RGB. ąŁč鹊čé čĆąĄąČąĖą╝ ąĖąĮč鹥čĆč乥ą╣čüą░ RGB ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčé RIM[1:0] ą▓ 10. ąĀą░ą▒ąŠčéą░ ą┤ąĖčüą┐ą╗ąĄčÅ čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆčāąĄčéčüčÅ čüąĖą│ąĮą░ą╗ą░ą╝ąĖ VSYNC, HSYNC ąĖ DOTCLK. ą×č鹊ą▒čĆą░ąČą░ąĄą╝čŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮčÄčÄ ą┐ą░ą╝čÅčéčī GRAM čüąĖąĮčģčĆąŠąĮąĮąŠ čĆą░ą▒ąŠč鹊ą╣ 菹║čĆą░ąĮą░ č湥čĆąĄąĘ 6-čĆą░ąĘčĆčÅą┤ąĮčāčÄ čłąĖąĮčā ą┤ą░ąĮąĮčŗčģ RGB (DB[17:12]), ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü čüąĖą│ąĮą░ą╗ąŠą╝ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ (ENABLE). ąØąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą▓čŗą▓ąŠą┤čŗ (DB[11:0]) ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą┐čĆąĖčéčÅąĮčāčéčŗ ą║ ą┐ąŠčüč鹊čÅąĮąĮąŠą╝čā čāčĆąŠą▓ąĮčÄ GND. ąĀąĄą│ąĖčüčéčĆčŗ ą╝ąŠąČąĮąŠ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čéčī č湥čĆąĄąĘ čüąĖčüč鹥ą╝ąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü (i80/SPI).

ąĪąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ą▓ čĆąĄąČąĖą╝ąĄ 6-ą▒ąĖčéąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ RGB. ąŻ ILI9325 ąĄčüčéčī čüč湥čéčćąĖą║ąĖ ą┐ąĄčĆąĄą┤ą░čć ą┤ą░ąĮąĮčŗčģ ą┤ą╗čÅ ą┐ąŠą┤čüč湥čéą░ ą┐ąĄčĆą▓ąŠą╣, ą▓č鹊čĆąŠą╣ ąĖ čéčĆąĄčéčīąĄą╣ ą┐ąĄčĆąĄą┤ą░čć ą┤ą░ąĮąĮčŗčģ ą▓ čĆąĄąČąĖą╝ąĄ ąĖąĮč鹥čĆč乥ą╣čüą░ 6-bit RGB. ąĪč湥čéčćąĖą║ ą┐ąĄčĆąĄą┤ą░čć ą▓čüąĄą│ą┤ą░ čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ą┐ąĄčĆą▓ąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ą┐ąŠ čüą┐ą░ą┤čā čāčĆąŠą▓ąĮčÅ čüąĖą│ąĮą░ą╗ą░ VSYNC. ąĢčüą╗ąĖ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ąĮąĄčüąŠą▓ą┐ą░ą┤ąĄąĮąĖąĄ ą▓ ą║ąŠą╗ąĖč湥čüčéą▓ąĄ ą║ą░ąČą┤ąŠą╣ ąĖąĘ ą┐ąĄčĆąĄą┤ą░čć, č鹊 čüč湥čéčćąĖą║ čüą▒čĆąŠčüąĖčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ą┐ąĄčĆą▓ąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ą▓ ą╝ąŠą╝ąĄąĮčé ąĮą░čćą░ą╗ą░ ą║ą░ą┤čĆą░ (čé. ąĄ. ąĮą░ čüą┐ą░ą┤ąĄ VSYNC) ą┤ą╗čÅ ą┐ąĄčĆąĄąĘą░ą┐čāčüą║ą░ ąĮą░ čüą╗ąĄą┤čāčÄčēąĄą╝ ą║ą░ą┤čĆąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ą▓ ą┐čĆą░ą▓ąĖą╗čīąĮąŠą╝ ą┐ąŠčĆčÅą┤ą║ąĄ. ąŁčéą░ čäčāąĮą║čåąĖčÅ čåąĄą╗ąĄčüąŠąŠą▒čĆą░ąĘąĮą░ ą┤ą╗čÅ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖčÅ ą╝ąĄąĮčÅčÄčēąĄą╣čüčÅ ą║ą░čĆčéąĖąĮą║ąĖ, ą║ąŠč鹊čĆą░čÅ čéčĆąĄą▒čāąĄčé ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ą┐ąĄčĆąĄą┤ą░čć ą┤ą░ąĮąĮčŗčģ ą▓ čüą▓ąĄč鹥 ą╝ąĖąĮąĖą╝ąĖąĘą░čåąĖąĖ čŹčäč乥ą║č鹊ą▓ ąŠčé ąŠčłąĖą▒ąŠčćąĮčŗčģ ą┐ąĄčĆąĄą┤ą░čć ą┤ą░ąĮąĮčŗčģ ąĖ ą┤ą╗čÅ č鹊ą│ąŠ, čćč鹊ą▒čŗ čüąĖčüč鹥ą╝ą░ ą╝ąŠą│ą╗ą░ ą▓ąĄčĆąĮčāčéčīčüčÅ ą║ čüą▓ąŠąĄą╝čā ąĮąŠčĆą╝ą░ą╗čīąĮąŠą╝čā čüąŠčüč鹊čÅąĮąĖčÄ. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ čĆą░ą▒ąŠčéą░ ą┤ąĖčüą┐ą╗ąĄčÅ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą▓ ąĄą┤ąĖąĮąĖčåą░čģ ą┐ąĖą║čüąĄą╗ąĄą╣ (RGB: ą▒ąĄčĆčāčéčüčÅ 3 ą▓čģąŠą┤ą░ DOTCLK). ąĪąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▓čģąŠą┤ąŠą▓ DOTCLK ą▓ ą┐ąĄčĆąĖąŠą┤ąĄ ąŠą┤ąĮąŠą│ąŠ ą║ą░ą┤čĆą░ ą┤ąŠą╗ąČąĮąŠ ą┤ąĄą╗ąĖčéčīčüčÅ ąĮą░ 3 ą┤ą╗čÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą┐ąŠą╗ąĮąŠą╣ ą║ąŠčĆčĆąĄą║čéąĮąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ. ąśąĮą░č湥 čŹč鹊 ą┐ąŠą▓ą╗ąĖčÅąĄčé ąĮą░ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖąĄ č鹥ą║čāčēąĄą│ąŠ ąĖ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ ą║ą░ą┤čĆą░.

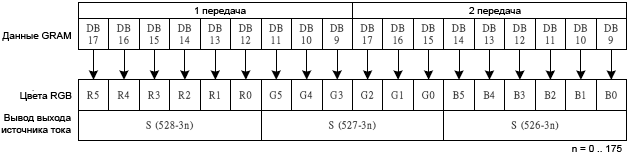

16-ą▒ąĖčéąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü RGB. ąŁč鹊čé čĆąĄąČąĖą╝ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčé RIM[1:0] ą▓ čüąŠčüč鹊čÅąĮąĖąĄ 01. ąĀą░ą▒ąŠčéą░ ą┤ąĖčüą┐ą╗ąĄčÅ čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆčāąĄčéčüčÅ čüąĖą│ąĮą░ą╗ą░ą╝ąĖ VSYNC, HSYNC ąĖ DOTCLK. ą×č鹊ą▒čĆą░ąČą░ąĄą╝čŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮčÄčÄ ą┐ą░ą╝čÅčéčī GRAM čüąĖąĮčģčĆąŠąĮąĮąŠ čü čĆą░ą▒ąŠč鹊ą╣ ą┤ąĖčüą┐ą╗ąĄčÅ č湥čĆąĄąĘ 16-ą▒ąĖčéąĮčāčÄ čłąĖąĮčā ą┤ą░ąĮąĮčŗčģ RGB (DB17-13, DB11-1) ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü čüąĖą│ąĮą░ą╗ąŠą╝ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ (ENABLE). ąĀąĄą│ąĖčüčéčĆčŗ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄčéčüčÅ č鹊ą╗čīą║ąŠ č湥čĆąĄąĘ čüąĖčüč鹥ą╝ąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü.

16-ą▒ąĖčéąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü RGB (65K čåą▓ąĄč鹊ą▓):

18-ą▒ąĖčéąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü RGB. ąŁč鹊čé čĆąĄąČąĖą╝ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčé RIM[1:0] ą▓ čüąŠčüč鹊čÅąĮąĖąĄ 00. ąĀą░ą▒ąŠčéą░ ą┤ąĖčüą┐ą╗ąĄčÅ čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆčāąĄčéčüčÅ čüąĖą│ąĮą░ą╗ą░ą╝ąĖ VSYNC, HSYNC ąĖ DOTCLK. ą×č鹊ą▒čĆą░ąČą░ąĄą╝čŗąĄ ą┤ą░ąĮąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮčÄčÄ ą┐ą░ą╝čÅčéčī GRAM čüąĖąĮčģčĆąŠąĮąĮąŠ čü čĆą░ą▒ąŠč鹊ą╣ ą┤ąĖčüą┐ą╗ąĄčÅ č湥čĆąĄąĘ 18-ą▒ąĖčéąĮčāčÄ čłąĖąĮčā ą┤ą░ąĮąĮčŗčģ RGB (DB17:0) ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü čüąĖą│ąĮą░ą╗ąŠą╝ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ (ENABLE). ąĀąĄą│ąĖčüčéčĆčŗ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄčéčüčÅ č鹊ą╗čīą║ąŠ č湥čĆąĄąĘ čüąĖčüč鹥ą╝ąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü.

18-ą▒ąĖčéąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü RGB:

1. ąĪą╗ąĄą┤čāčÄčēąĖąĄ čäčāąĮą║čåąĖąĖ ąĮąĄą┤ąŠčüčéčāą┐ąĮčŗ ą▓ čĆąĄąČąĖą╝ąĄ ą▓ą▓ąŠą┤ą░ č湥čĆąĄąĘ ąĖąĮč鹥čĆč乥ą╣čü RGB (ą▓ čüčĆą░ą▓ąĮąĄąĮąĖąĖ čü čüąĖčüč鹥ą╝ąĮčŗą╝ ąĖąĮč鹥čĆč乥ą╣čüąŠą╝ i80):

| ążčāąĮą║čåąĖčÅ |

ąśąĮč鹥čĆč乥ą╣čü RGB |

ąśąĮč鹥čĆč乥ą╣čü i80 |

| ą¦ą░čüčéąĖčćąĮąŠąĄ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖąĄ (Partial display) |

ąØąĄą┤ąŠčüčéčāą┐ąĮąŠ |

ąĢčüčéčī |

| ą¤čĆąŠą║čĆčāčéą║ą░ (scroll) |

ąØąĄą┤ąŠčüčéčāą┐ąĮąŠ |

ąĢčüčéčī |

| ą¦ąĄčĆąĄčüčüčéčĆąŠčćąĮą░čÅ čĆą░ąĘą▓ąĄčĆčéą║ą░ (Interlaced scan) |

ąØąĄą┤ąŠčüčéčāą┐ąĮąŠ |

ąĢčüčéčī |

2. ąöąŠą╗ąČąĮčŗ ą▒čŗčéčī ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮčŗ ą┐ąĄčĆąĖąŠą┤ąĖč湥čüą║ąĖąĄ čüąĖą│ąĮą░ą╗čŗ VSYNC, HSYNC ąĖ DOTCLK.

3. ą¤ąĄčĆąĖąŠą┤čŗ, čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗąĄ ą▒ąĖčéą░ą╝ąĖ NO[1:0] (ą┐ąĄčĆąĖąŠą┤ ąĮąĄ ą┐ąĄčĆąĄą║čĆčŗčéąĖčÅ ą▓čŗčģąŠą┤ąŠą▓ ą║ą╗čÄč湥ą╣), ą▒ąĖčéą░ą╝ąĖ STD[1:0] (ą┐ąĄčĆąĖąŠą┤ ąĘą░ą┤ąĄčƹȹ║ąĖ ą▓čŗčģąŠą┤ąŠą▓ ąĖčüč鹊čćąĮąĖą║ąŠą▓ č鹊ą║ą░) ąĖ ą▒ąĖčéą░ą╝ąĖ EQ[1:0] (ą┐ąĄčĆąĖąŠą┤ čĆąĄą│čāą╗ąĖčĆąŠą▓ą░ąĮąĖčÅ), ąŠčüąĮąŠą▓ą░ąĮčŗ ąĮąĄ ąĮą░ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊č鹥, ą░ ąĮą░ čćą░čüč鹊č鹥 DOTCLK.

4. ąÆ čĆąĄąČąĖą╝ąĄ 6-ą▒ąĖčéąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ RGB ą║ą░ąČą┤ą░čÅ č鹊čćą║ą░ RGB ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ čüąĖąĮčģčĆąŠąĮąĮąŠ čü ą▓čģąŠą┤ąŠą╝ DOTCLK. ąöčĆčāą│ąĖą╝ąĖ čüą╗ąŠą▓ą░ą╝ąĖ, ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ąŠą┤ąĮąŠą╣ č鹊čćą║ąĖ ą┐čĆąŠčģąŠą┤ąĖčé 3 ą▓čģąŠą┤ąĮčŗčģ ąĖą╝ą┐čāą╗čīčüą░ DOTCLK. ąÆ čĆąĄąČąĖą╝ąĄ 6-ą▒ąĖčéąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ RGB ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░čéčī čåąĄą╗ąŠčüčéąĮčāčÄ ą┐ąĄčĆąĄą┤ą░čćčā ą┤ą░ąĮąĮčŗčģ ą▓ ąĄą┤ąĖąĮąĖčåą░čģ 3 ąĖą╝ą┐čāą╗čīčüąŠą▓ DOTCLK.

5. ąÆ čĆąĄąČąĖą╝ąĄ 6-ą▒ąĖčéąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ RGB ą┤ą░ąĮąĮčŗąĄ ąŠą┤ąĮąŠą╣ č鹊čćą║ąĖ, ą║ąŠč鹊čĆą░čÅ čüąŠčüč鹊ąĖčé ąĖąĘ č鹊č湥ą║ RGB, ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ą▓ ąĄą┤ąĖąĮąĖčåą░čģ 3 DOTCLK. ąĪąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ čāčüčéą░ąĮąŠą▓ąĖč鹥 čåąĖą║ą╗ ą║ą░ąČą┤ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ą▓ čĆąĄąČąĖą╝ąĄ 6-ą▒ąĖčéąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ (VSYNC, HSYNC, ENABLE, DB[17:0]), čćč鹊ą▒čŗ ą┐čĆąŠąĖčüčģąŠą┤ąĖą╗ąŠ ąĮą░čåąĄą╗ąŠ ą┤ąĄą╗čÅčēąĄąĄčüčÅ ąĮą░ 3 ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▓ą▓ąŠą┤ąŠą▓ DOTCLK ą▓ ąĄą┤ąĖąĮąĖčåą░čģ č鹊č湥ą║.

6. ąÜąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ąĖąĘ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čĆąĄąČąĖą╝ą░ čĆą░ą▒ąŠčéčŗ (ą▓ąĮčāčéčĆąĄąĮąĮąĄąĄ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ) ą▓ čĆąĄąČąĖą╝ ą▓ą▓ąŠą┤ą░ č湥čĆąĄąĘ ąĖąĮč鹥čĆč乥ą╣čü RGB (ąĖą╗ąĖ ąĮą░ąŠą▒ąŠčĆąŠčé), čüą╗ąĄą┤čāą╣č鹥 ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ, ą┐ąŠą║ą░ąĘą░ąĮąĮąŠą╣ ąĮą░ čĆąĖčü. 19.

ą¤ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ čü ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ

ąĮą░ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ąŠčé ąĖąĮč鹥čĆč乥ą╣čüą░ RGB |

ą×ą▒čĆą░čéąĮąŠąĄ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ: čü čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ

ąŠčé ąĖąĮč鹥čĆč乥ą╣čüą░ RGB ąĮą░ ą▓ąĮčāčéčĆąĄąĮąĮąĄąĄ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ |

|

|

ąĀąĖčü. 19. ą¤ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ą╝ąĄąČą┤čā čĆąĄąČąĖą╝ą░ą╝ąĖ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖ ąĖąĮč鹥čĆč乥ą╣čüąŠą╝ RGB.

7. ąÆ čĆąĄąČąĖą╝ąĄ ąĖąĮč鹥čĆč乥ą╣čüą░ RGB, ą┐ąĄčĆąĖąŠą┤ front porch ą┐čĆąŠą┤ąŠą╗ąČą░ąĄčéčüčÅ ą┤ąŠ ą╝ąŠą╝ąĄąĮčéą░ ą┐ąŠčÅą▓ą╗ąĄąĮąĖčÅ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ čüąĖąĮčģčĆąŠąĖą╝ą┐čāą╗čīčüą░ VSYNC ą┐ąŠčüą╗ąĄ ąŠčéčĆąĖčüąŠą▓ą║ąĖ ąŠą┤ąĮąŠą│ąŠ ą║ą░ą┤čĆą░.

8. ąÆ čĆąĄąČąĖą╝ąĄ ąĖąĮč鹥čĆč乥ą╣čüą░ RGB ą░ą┤čĆąĄčü ą×ąŚąŻ (AD[15:0]) čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ą░ą┤čĆąĄčü čüč湥čéčćąĖą║ą░ ą║ą░ąČą┤ąŠą│ąŠ ą║ą░ą┤čĆą░ ąĮą░ ą║ą░ąČą┤ąŠą╝ čüą┐ą░ą┤ąĄ čāčĆąŠą▓ąĮčÅ čüąĖąĮčģčĆąŠąĖą╝ą┐čāą╗čīčüą░ VSYNC.

ą¤ąĄčĆąĄčģąŠą┤ ąŠčé ąĘą░ą┐ąĖčüąĖ ą▓ GRAM č湥čĆąĄąĘ

ąĖąĮč鹥čĆč乥ą╣čü RGB ą║ ąĘą░ą┐ąĖčüąĖ

č湥čĆąĄąĘ čüąĖčüč鹥ą╝ąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü |

ą×ą▒čĆą░čéąĮčŗą╣ ą┐ąĄčĆąĄčģąŠą┤: ąŠčé ąĘą░ą┐ąĖčüąĖ ą▓ GRAM

č湥čĆąĄąĘ čüąĖčüč鹥ą╝ąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü

ą║ ąĘą░ą┐ąĖčüąĖ č湥čĆąĄąĘ ąĖąĮč鹥čĆč乥ą╣čü RGB |

|

|

ąĀąĖčü. 20. ąöąŠčüčéčāą┐ ą║ GRAM ą╝ąĄąČą┤čā čüąĖčüč鹥ą╝ąĮčŗą╝ ąĖąĮč鹥čĆč乥ą╣čüąŠą╝ ąĖ ąĖąĮč鹥čĆč乥ą╣čüąŠą╝ RGB.

ąØąĖąČąĄ ą┐ąŠą║ą░ąĘą░ąĮčŗ ą┤ąĖą░ą│čĆą░ą╝ą╝čŗ čüąĖą│ąĮą░ą╗ąŠą▓ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ą░ąĮąĄą╗ąĖ LCD ą▓ čĆąĄąČąĖą╝ąĄ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖ ą▓ čĆąĄąČąĖą╝ą░čģ RGB.

ąĀąĖčü. 21. ąÆąĘą░ąĖą╝ąŠčüą▓čÅąĘčī ą╝ąĄąČą┤čā čüąĖą│ąĮą░ą╗ą░ą╝ąĖ ąĖąĮč鹥čĆč乥ą╣čüą░ RGB ąĖ čāą┐čĆą░ą▓ą╗čÅčÄčēąĖą╝ąĖ čüąĖą│ąĮą░ą╗ą░ą╝ąĖ ą┐ą░ąĮąĄą╗ąĖ LCD.

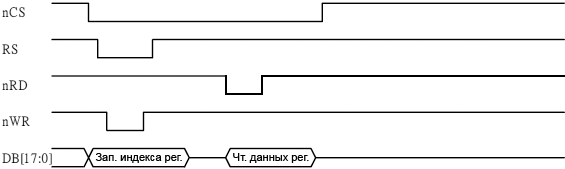

[ą×ą┐ąĖčüą░ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆąŠą▓]

ąöąŠčüčéčāą┐ ą║ čĆąĄą│ąĖčüčéčĆą░ą╝. ILI9325 ą░ą┤ą░ą┐čéąĖčĆčāąĄčé ą░čĆčģąĖč鹥ą║čéčāčĆčā ąĖąĮč鹥čĆč乥ą╣čüą░ 18-ą▒ąĖčéąĮąŠą╣ čłąĖąĮčŗ ą┤ą╗čÅ ą▓čŗčüąŠą║ąŠą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠą│ąŠ ą╝ąĖą║čĆąŠą┐čĆąŠčåąĄčüčüąŠčĆą░. ąÆčüąĄ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮčŗąĄ ą▒ą╗ąŠą║ąĖ ILI9325 ąĮą░čćąĖąĮą░čÄčé čĆą░ą▒ąŠčéą░čéčī ą┐ąŠčüą╗ąĄ ą┐čĆąĖąĄą╝ą░ ą║ąŠčĆčĆąĄą║čéąĮąŠą╣ ąĖąĮčüčéčĆčāą║čåąĖąĖ ąŠčé ą▓ąĮąĄčłąĮąĄą│ąŠ ą╝ąĖą║čĆąŠą┐čĆąŠčåąĄčüčüąŠčĆą░. ąśąĮčüčéčĆčāą║čåąĖčÅ ą┐čĆąĖčģąŠą┤ąĖčé č湥čĆąĄąĘ 18-, 16-, 9-, ąĖą╗ąĖ 8-ą▒ąĖčéąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü. ąśąĮą┤ąĄą║čüąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ (IR) čģčĆą░ąĮąĖčé ą░ą┤čĆąĄčü čĆąĄą│ąĖčüčéčĆą░, ą▓ ą║ąŠč鹊čĆčŗą╣ ą▒čāą┤čāčé ąĘą░ą┐ąĖčüą░ąĮą░ ąĖąĮčüčéčĆčāą║čåąĖčÅ ąĖ ąŠč鹊ą▒čĆą░ąČą░ąĄą╝čŗąĄ ą┤ą░ąĮąĮčŗąĄ. ąĪąĖą│ąĮą░ą╗ ą▓čŗą▒ąŠčĆą░ čĆąĄą│ąĖčüčéčĆą░ (RS), čüąĖą│ąĮą░ą╗čŗ čćč鹥ąĮąĖčÅ/ąĘą░ą┐ąĖčüąĖ (nRD/nWR) ąĖ čłąĖąĮą░ ą┤ą░ąĮąĮčŗčģ D17-0 ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ/ąĘą░ą┐ąĖčüąĖ ąĖąĮčüčéčĆčāą║čåąĖą╣ ąĖ ą┤ą░ąĮąĮčŗčģ ąĖąĘ/ą▓ ILI9325. ąĀąĄą│ąĖčüčéčĆčŗ ILI9325 ą┤ąĄą╗čÅčéčüčÅ ą┐ąŠ čüą╗ąĄą┤čāčÄčēąĖą╝ ą│čĆčāą┐ą┐ąŠą▓čŗą╝ ą║ą░č鹥ą│ąŠčĆąĖčÅą╝.

1. ąŻčüčéą░ąĮąŠą▓ą║ą░ ąĖąĮą┤ąĄą║čüąĮąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░ (IR).

2. ą¦č鹥ąĮąĖąĄ čüčéą░čéčāčüą░.

3. ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┤ąĖčüą┐ą╗ąĄąĄą╝.

4. ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐ąĖčéą░ąĮąĖąĄą╝.

5. ą×ą▒čĆą░ą▒ąŠčéą║ą░ ą│čĆą░čäąĖč湥čüą║ąĖčģ ą┤ą░ąĮąĮčŗčģ.

6. ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ ą░ą┤čĆąĄčüą░ GRAM (AC).

7. ą¤ąĄčĆąĄą╝ąĄčēąĄąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮčÄčÄ ą┐ą░ą╝čÅčéčī GRAM ąĖ ąĖąĘ ąĮąĄčæ (R22).

8. ąÆąĮčāčéčĆąĄąĮąĮčÅčÅ ą│ą░ą╝ą╝ą░-ą║ąŠčĆčĆąĄą║čåąĖčÅ ą│čĆą░ą┤ą░čåąĖą╣ čüąĄčĆąŠą│ąŠ (R30 .. R39).

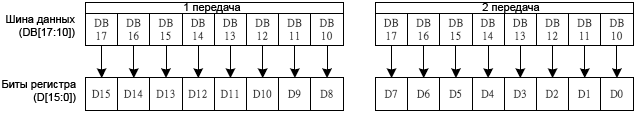

ą×ą▒čŗčćąĮąŠ čćą░čēąĄ ą▓čüąĄą│ąŠ ąŠą▒ąĮąŠą▓ą╗čÅčÄčéčüčÅ ąŠč鹊ą▒čĆą░ąČą░ąĄą╝čŗąĄ ą┤ą░ąĮąĮčŗąĄ (čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ GRAM), ąĖ ą┐ąŠčüą║ąŠą╗čīą║čā ILI9325 ą╝ąŠąČąĄčé ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąŠą▒ąĮąŠą▓ąĖčéčī ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ ą░ą┤čĆąĄčü GRAM, ą┐ąŠą║ą░ ą┤ą░ąĮąĮčŗąĄ ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮčÄčÄ ą┐ą░ą╝čÅčéčī GRAM, ąĖ ąĄčüčéčī ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą╝ąĖąĮąĖą╝ąĖąĘą░čåąĖąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ą┐čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ čäčāąĮą║čåąĖąĖ ą░ą┤čĆąĄčüą░čåąĖąĖ ąŠą║ąĮą░, čüąĮąĖąČą░ąĄčéčüčÅ ąĮą░ą│čĆčāąĘą║ą░ ą┐ąŠ ą┐ąĄčĆąĄą┤ą░č湥 ą┤ą░ąĮąĮčŗčģ ąĮą░ ą╝ąĖą║čĆąŠą┐čĆąŠčåąĄčüčüąŠčĆ. ąÜą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčüčāąĮą║ą░čģ ąĮąĖąČąĄ, čüą┐ąŠčüąŠą▒ ą┤ąŠčüčéčāą┐ą░ ą┤ą░ąĮąĮčŗčģ ą║ ą▒ąĖčéą░ą╝ 16-čĆą░ąĘčĆčÅą┤ąĮčŗčģ čĆąĄą│ąĖčüčéčĆąŠą▓ (D[15:0]) ąĖąĘą╝ąĄąĮčÅąĄčéčüčÅ ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░. ąŻą┐čĆą░ą▓ą╗čÅą╣č鹥 čĆąĄą│ąĖčüčéčĆą░ą╝ąĖ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čüąŠ čüą╗ąĄą┤čāčÄčēąĖą╝ č乊čĆą╝ą░č鹊ą╝ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ.

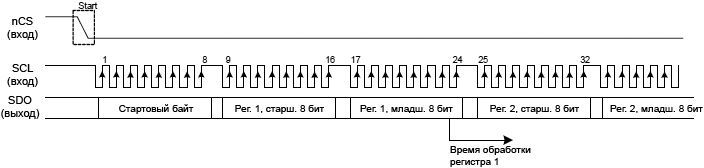

ąöąŠčüčéčāą┐ ą║ čĆąĄą│ąĖčüčéčĆčā č湥čĆąĄąĘ SPI:

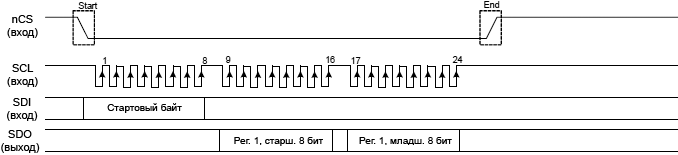

ąĀąĖčü. 22. ąŻčüčéą░ąĮąŠą▓ą║ą░ čĆąĄą│ąĖčüčéčĆą░ č湥čĆąĄąĘ SPI.

ąĪąĖčüč鹥ą╝ąĮą░čÅ 18-ą▒ąĖčéąĮą░čÅ čłąĖąĮą░ ą┤ą░ąĮąĮčŗčģ ąĖąĮč鹥čĆč乥ą╣čüą░ i80/M68:

ąĪąĖčüč鹥ą╝ąĮą░čÅ 16-ą▒ąĖčéąĮą░čÅ čłąĖąĮą░ ą┤ą░ąĮąĮčŗčģ ąĖąĮč鹥čĆč乥ą╣čüą░ i80/M68:

ąĪąĖčüč鹥ą╝ąĮą░čÅ 9-ą▒ąĖčéąĮą░čÅ čłąĖąĮą░ ą┤ą░ąĮąĮčŗčģ ąĖąĮč鹥čĆč乥ą╣čüą░ i80/M68:

ąĪąĖčüč鹥ą╝ąĮą░čÅ 8-ą▒ąĖčéąĮą░čÅ čłąĖąĮą░ ą┤ą░ąĮąĮčŗčģ ąĖąĮč鹥čĆč乥ą╣čüą░ i80/M68 / ąĖąĮč鹥čĆč乥ą╣čü SPI (2/3 ą┐ąĄčĆąĄą┤ą░čćąĖ):

ąĀąĖčü. 23. ąŻčüčéą░ąĮąŠą▓ą║ą░ čĆąĄą│ąĖčüčéčĆą░ č湥čĆąĄąĘ čüąĖčüč鹥ą╝ąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü i80.

ąśąĮč鹥čĆą▓ą░ą╗čŗ ą▓čĆąĄą╝ąĄąĮąĖ ąĘą░ą┐ąĖčüąĖ čĆąĄą│ąĖčüčéčĆą░ čüąĖčüč鹥ą╝ąĮąŠą│ąŠ 18-/16-ą▒ąĖčéąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ i80:

ąśąĮč鹥čĆą▓ą░ą╗čŗ ą▓čĆąĄą╝ąĄąĮąĖ čćč鹥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ čüąĖčüč鹥ą╝ąĮąŠą│ąŠ 18-/16-ą▒ąĖčéąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ i80:

ąśąĮč鹥čĆą▓ą░ą╗čŗ ą▓čĆąĄą╝ąĄąĮąĖ ąĘą░ą┐ąĖčüąĖ čĆąĄą│ąĖčüčéčĆą░ čüąĖčüč鹥ą╝ąĮąŠą│ąŠ 9-/8-ą▒ąĖčéąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ i80:

ąśąĮč鹥čĆą▓ą░ą╗čŗ ą▓čĆąĄą╝ąĄąĮąĖ čćč鹥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆą░ čüąĖčüč鹥ą╝ąĮąŠą│ąŠ 9-/8-ą▒ąĖčéąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ i80:

ąĀąĖčü. 24. ąöąĖą░ą│čĆą░ą╝ą╝čŗ čćč鹥ąĮąĖčÅ/ąĘą░ą┐ąĖčüąĖ ąĖąĮč鹥čĆč乥ą╣čüą░ č湥čĆąĄąĘ čüąĖčüč鹥ą╝ąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü i80.

ąóą░ą▒ą╗ąĖčåą░ ąĖąĮčüčéčĆčāą║čåąĖą╣ ILI9325:

| Ōä¢ |

ążčāąĮą║čåąĖčÅ |

D15 |

D14 |

D13 |

D12 |

D11 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

| IR |

Index Register |

- |

- |

- |

- |

- |

- |

- |

- |

ID7 |

ID6 |

ID5 |

ID4 |

ID3 |

ID2 |

ID1 |

ID0 |

| 00h |

Driver Code Read |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

| 01h |

Driver Output Control 1 |

0 |

0 |

0 |

0 |

0 |

SM |

0 |

SS |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

| 02h |

ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ LCD |

0 |

0 |

0 |

0 |

0 |

0 |

B/C |

EOR |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

| 03h |

Entry Mode |

TRI |

DFM |

0 |

BGR |

0 |

0 |

0 |

0 |

ORG |

0 |

I/D1 |

I/D0 |

AM |

0 |

0 |

0 |

| 04h |

Resize Control |

0 |

0 |

0 |

0 |

0 |

0 |

RCV1 |

RCV0 |

0 |

0 |

RCH1 |

RCH0 |

0 |

0 |

RSZ1 |

RSZ0 |

| 07h |

Display Control 1 |

0 |

0 |

PTDE1 |

PTDE0 |

0 |

0 |

0 |

BASEE |

0 |

0 |

GON |

DTE |

CL |

0 |

D1 |

D0 |

| 08h |

Display Control 2 |

0 |

0 |

0 |

0 |

FP3 |

FP2 |

FP1 |

FP0 |

0 |

0 |

0 |

0 |

BP3 |

BP2 |

BP1 |

BP0 |

| 09h |

Display Control 3 |

0 |

0 |

0 |

0 |

0 |

PTS2 |

PTS1 |

PTS0 |

0 |

0 |

PTG1 |

PTG0 |

ISC3 |

ISC2 |

ISC1 |

ISC0 |

| 0Ah |

Display Control 4 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

FMARKOE |

FMI2 |

FMI1 |

FMI0 |

| 0Ch |

RGB Display Interface Control 1 |

0 |

ENC2 |

ENC1 |

ENC0 |

0 |

0 |

0 |

RM |

0 |

0 |

DM1 |

DM0 |

0 |

0 |

RIM1 |

RIM0 |

| 0Dh |

Frame Maker Position |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

FMP8 |

FMP7 |

FMP6 |

FMP5 |

FMP4 |

FMP3 |

FMP2 |

FMP1 |

FMP0 |

| 0Fh |

RGB Display Interface Control 2 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

VSPL |

HSPL |

0 |

DPL |

EPL |

| 10h |

Power Control 1 |

0 |

0 |

0 |

SAP |

0 |

BT2 |

BT1 |

BT0 |

APE |

AP2 |

AP1 |

AP0 |

0 |

0 |

SLP |

STB |

| 11h |

Power Control 2 |

0 |

0 |

0 |

0 |

0 |

DC12 |

DC11 |

DC10 |

0 |

DC02 |

DC01 |

DC00 |

0 |

VC2 |

VC1 |

VC0 |

| 12h |

Power Control 3 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

VCIRE |

0 |

0 |

PON |

VRH3 |

VRH2 |

VRH1 |

VRH0 |

| 13h |

Power Control 4 |

0 |

0 |

0 |

VDV4 |

VDV3 |

VDV2 |

VDV1 |

VDV0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

| 20h |

Horizontal GRAM Address Set |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

AD7 |

AD6 |

AD5 |

AD4 |

AD3 |

AD2 |

AD1 |

AD0 |

| 21h |

Vertical GRAM Address Set |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

AD16 |

AD15 |

AD14 |

AD13 |

AD12 |

AD11 |

AD10 |

AD9 |

AD8 |

| 22h |

Write Data to GRAM |

ąŚą░ą┐ąĖčüčŗą▓ą░ąĄą╝čŗąĄ ą▓ ą×ąŚąŻ ą┤ą░ąĮąĮčŗąĄ (WD17-0) / čćąĖčéą░ąĄą╝čŗąĄ ą┤ą░ąĮąĮčŗąĄ (RD17-0) ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ č湥čĆąĄąĘ čĆą░ąĘąĮčŗąĄ ą╗ąĖąĮąĖąĖ čłąĖąĮčŗ ą┤ą░ąĮąĮčŗčģ ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čéąĖą┐ą░ ą▓čŗą▒čĆą░ąĮąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░. |

| 29h |

Power Control 7 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

VCM5 |

VCM4 |

VCM3 |

VCM2 |

VCM1 |

VCM0 |

| 2Bh |

Frame Rate and Color Control |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

FRS[3] |

FRS[2] |

FRS[1] |

FRS[0] |

| 30h |

Gamma Control 1 |

0 |

0 |

0 |

0 |

0 |

KP1[2] |

KP1[1] |

KP1[0] |

0 |

0 |

0 |

0 |

0 |

KP0[2] |

KP0[1] |

KP0[0] |

| 31h |

Gamma Control 2 |

0 |

0 |

0 |

0 |

0 |

KP3[2] |

KP3[1] |

KP3[0] |

0 |

0 |

0 |

0 |

0 |

KP2[2] |

KP2[1] |

KP2[0] |

| 32h |

Gamma Control 3 |

0 |

0 |

0 |

0 |

0 |

KP5[2] |

KP5[1] |

KP5[0] |

0 |

0 |

0 |

0 |

0 |

KP4[2] |

KP4[1] |

KP4[0] |

| 35h |

Gamma Control 4 |

0 |

0 |

0 |

0 |

0 |

RP1[2] |

RP1[1] |

RP1[0] |

0 |

0 |

0 |

0 |

0 |

RP0[2] |

RP0[1] |

RP0[0] |

| 36h |

Gamma Control 5 |

0 |

0 |

0 |

VRP1[4] |

VRP1[3] |

VRP1[2] |

VRP1[1] |

VRP1[0] |

0 |

0 |

0 |

0 |

VRP0[3] |

VRP0[2] |

VRP0[1] |

VRP0[0] |

| 37h |

Gamma Control 6 |

0 |

0 |

0 |

0 |

0 |

KN1[2] |

KN1[1] |

KN1[0] |

0 |

0 |

0 |

0 |

0 |

KN0[2] |

KN0[1] |

KN0[0] |

| 38h |

Gamma Control 7 |

0 |

0 |

0 |

0 |

0 |

KN3[2] |

KN3[1] |

KN3[0] |

0 |

0 |

0 |

0 |

0 |

KN2[2] |

KN2[1] |

KN2[0] |

| 39h |

Gamma Control 8 |

0 |

0 |

0 |

0 |

0 |

KN5[2] |

KN5[1] |

KN5[0] |

0 |

0 |

0 |

0 |

0 |

KN4[2] |

KN4[1] |

KN4[0] |

| 3Ch |

Gamma Control 9 |

0 |

0 |

0 |

0 |

0 |

RN1[2] |

RN1[1] |

RN1[0] |

0 |

0 |

0 |

0 |

0 |

RN0[2] |

RN0[1] |

RN0[0] |

| 3Dh |

Gamma Control 10 |

0 |

0 |

0 |

VRN1[4] |

VRN1[3] |

VRN1[2] |

VRN1[1] |

VRN1[0] |

0 |

0 |

0 |

0 |

VRN0[3] |

VRN0[2] |

VRN0[1] |

VRN0[0] |

| 50h |

Horizontal Address Start Position |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

HSA7 |

HSA6 |

HSA5 |

HSA4 |

HSA3 |

HSA2 |

HSA1 |

HSA0 |

| 51h |

Horizontal Address End Position |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

HEA7 |

HEA6 |

HEA5 |

HEA4 |

HEA3 |

HEA2 |

HEA1 |

HEA0 |

| 52h |

Vertical Address Start Position |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

VSA8 |

VSA7 |

VSA6 |

VSA5 |

VSA4 |

VSA3 |

VSA2 |

VSA1 |

VSA0 |

| 53h |

Vertical Address End Position |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

VEA8 |

VEA7 |

VEA6 |

VEA5 |

VEA4 |

VEA3 |

VEA2 |

VEA1 |

VEA0 |

| 60h |

Driver Output Control 2 |

GS |

0 |

NL5 |

NL4 |

NL3 |

NL2 |

NL1 |

NL0 |

0 |

0 |

SCN5 |

SCN4 |

SCN3 |

SCN2 |

SCN1 |

SCN0 |

| 61h |

Base Image Display Control |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

NDL |

VLE |

REV |

| 6Ah |

Vertical Scroll Control |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

VL8 |

VL7 |

VL6 |

VL5 |

VL4 |

VL3 |

VL2 |

VL1 |

VL0 |

| 80h |

Partial Image 1 Display Position |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

PTDP08 |

PTDP07 |

PTDP06 |

PTDP05 |

PTDP04 |

PTDP03 |

PTDP02 |

PTDP01 |

PTDP00 |

| 81h |

Partial Image 1 Area (Start Line) |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

PTSA08 |

PTSA07 |

PTSA06 |

PTSA05 |

PTSA04 |

PTSA03 |

PTSA02 |

PTSA01 |

PTSA00 |

| 82h |

Partial Image 1 Area (End Line) |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

PTEA08 |

PTEA07 |

PTEA06 |

PTEA05 |

PTEA04 |

PTEA03 |

PTEA02 |

PTEA01 |

PTEA00 |

| 83h |

Partial Image 2 Display Position |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

PTDP18 |

PTDP17 |

PTDP16 |

PTDP15 |

PTDP14 |

PTDP13 |

PTDP12 |

PTDP11 |

PTDP10 |

| 84h |

Partial Image 2 Area (Start Line) |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

PTSA18 |

PTSA17 |

PTSA16 |

PTSA15 |

PTSA14 |

PTSA13 |

PTSA12 |

PTSA11 |

PTSA10 |

| 85h |

Partial Image 2 Area (End Line) |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

PTEA18 |

PTEA17 |

PTEA16 |

PTEA15 |

PTEA14 |

PTEA13 |

PTEA12 |

PTEA11 |

PTEA10 |

| 90h |

Panel Interface Control 1 |

0 |

0 |

0 |

0 |

0 |

0 |

DIVI1 |

DIVI00 |

0 |

0 |

0 |

0 |

RTNI3 |

RTNI2 |

RTNI1 |

RTNI0 |

| 92h |

Panel Interface Control 2 |

0 |

0 |

0 |

0 |

0 |

NOWI2 |

NOWI1 |

NOWI0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

| 95h |

Panel Interface Control 4 |

0 |

0 |

0 |

0 |

0 |

0 |

DIVE1 |

DIVE0 |

0 |

0 |

RTNE5 |

RTNE4 |

RTNE3 |

RTNE2 |

RTNE1 |

RTNE0 |

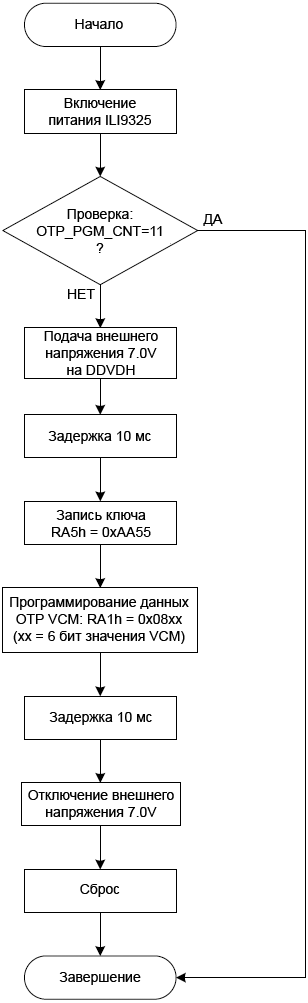

| A1h |

OTP VCM Programming Control |

0 |

0 |

0 |

0 |

OTP_

PGM_EN |

0 |

0 |

0 |

0 |

0 |

VCM_

OTP5 |

VCM_

OTP4 |

VCM_

OTP3 |

VCM_

OTP2 |

VCM_

OTP1 |

VCM_

OTP0 |

| A2h |

OTP VCM Status and Enable |

PGM_

CNT1 |

PGM_

CNT0 |

VCM_

D5 |

VCM_

D4 |

VCM_