|

ąöąŠą▓ąŠą╗čīąĮąŠ ąĮąĄą┤ąŠčĆąŠą│ąŠą╣ čüą┐ąŠčüąŠą▒ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ ą▓čŗčüąŠą║ąŠč鹊čćąĮąŠą│ąŠ čåąĖčäčĆąŠ-ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░č鹥ą╗čÅ (digital-to-analog conversion, DAC) - čüą║ąŠą╝ą▒ąĖąĮąĖčĆąŠą▓ą░čéčī ą▓čŗčģąŠą┤ ą©ąśą£ ąĮą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąĄ (pulse-width-modulate, PWM), č鹊čćąĮčŗą╣ ąĖčüč鹊čćąĮąĖą║ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ, ą║ą╗čÄčćąĖ CMOS ąĖ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗą╣ čäąĖą╗čīčéčĆ [2].

ą×ą┤ąĮą░ą║ąŠ ą▓ ą╗čÄą▒ąŠą╝ čüą╗čāčćą░ąĄ ą”ąÉą¤ ąĮą░ ąŠčüąĮąŠą▓ąĄ PWM čüąŠąĘą┤ą░ąĄčé ą▒ąŠą╗čīčłčāčÄ ą┐čĆąŠą▒ą╗ąĄą╝čā ą┤ą╗čÅ čĆą░ąĘčĆą░ą▒ąŠčéčćąĖą║ą░: ą║ą░ą║ ą░ą┤ąĄą║ą▓ą░čéąĮąŠ ą┐ąŠą┤ą░ą▓ąĖčéčī ąĮą░ ą▓čŗčģąŠą┤ąĄ ą▒ąŠą╗čīčłčāčÄ ą░ą╝ą┐ą╗ąĖčéčāą┤ąĄ ą┐čāą╗čīčüą░čåąĖą╣ čćą░čüč鹊čéčŗ ąĖą╝ą┐čāą╗čīčüąŠą▓ ą©ąśą£? ą¤čĆąŠą▒ą╗ąĄą╝ą░ ą┐ąŠą┤ą░ą▓ą╗ąĄąĮąĖčÅ ąĖą╝ą┐čāą╗čīčüąŠą▓ ą©ąśą£ ąŠčüąŠą▒ąĄąĮąĮąŠ ą░ą║čéčāą░ą╗čīąĮą░, ą║ąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ 16-ą▒ąĖčéąĮčŗą╣ ą©ąśą£ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░, ą┐ąŠč鹊ą╝čā čćč鹊 ąĮąĄ ą┐ąŠą╗čāčćą░ąĄčéčüčÅ čüčéą░ąĮąŠą▓ąĖčéčüčÅ čéčĆčāą┤ąĮčŗą╝ ą▓čŗą▒čĆą░čéčī ą▓čŗčüąŠą║čāčÄ čćą░čüč鹊čéčā ąĖą╝ą┐čāą╗čīčüąŠą▓ ą©ąśą£, čćč鹊ą▒čŗ ąĄčæ ą╝ąŠąČąĮąŠ ą▒čŗą╗ąŠ ą╗ąĄą│ą║ąŠ ąŠčéčäąĖą╗čīčéčĆąŠą▓ą░čéčī ą┐čĆąŠčüčéčŗą╝ ążąØą¦. ąØą░ą┐čĆąĖą╝ąĄčĆ, ą▓čŗčüąŠą║ąŠč鹊čćąĮčŗą╣ 16-ą▒ąĖčéąĮčŗą╣ ą©ąśą£ čéčĆąĄą▒čāąĄčé ąŠčé čüč湥čéčćąĖą║ą░ PWM ąŠą▒čĆą░ą▒ąŠčéą║ąĖ 216 ąŠčéčüč湥č鹊ą▓, ąĖ ąĄčüą╗ąĖ čćą░čüč鹊čéą░ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ čüč湥čéčćąĖą║ą░ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ PWM 16 ą£ąōčå, č鹊 ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮą░čÅ čćą░čüč鹊čéą░ ąĖą╝ą┐čāą╗čīčüąŠą▓ ą©ąśą£ ą┐ąŠą╗čāčćąĖčéčüčÅ 16000000 / 216 = 244 ąōčå. ą¤čĆąĖ čéą░ą║ąĖčģ ąĮąĖąĘą║ąĖčģ čćą░čüč鹊čéą░čģ ą┐čāą╗čīčüą░čåąĖą╣ ą©ąśą£, ąĄčüą╗ąĖ ąĖčģ ą┐ąŠą┤ą░ą▓ą╗čÅčéčī RC-čåąĄą┐ąŠčćą║ąŠą╣ ą┤ąŠ čāčĆąŠą▓ąĮčÅ čåąĄąĮčŗ ąŠą┤ąĮąŠą│ąŠ čĆą░ąĘčĆčÅą┤ą░ 16-ą▒ąĖčéąĮąŠą│ąŠ ą”ąÉą¤ (čé. ąĄ. ą┤ąŠ -96 dB), č鹊 ąĖąĘą╝ąĄąĮąĄąĮąĖąĄ čāčĆąŠą▓ąĮčÅ ąĮą░ ą▓čŗčģąŠą┤ąĄ ą┐ąŠą╗čāčćąĖčéčüčÅ ąŠč湥ąĮčī ą╝ąĄą┤ą╗ąĄąĮąĮčŗą╝ - ąĖąĘą╝ąĄąĮąĄąĮąĖąĄ ą┐ąŠą╗ąĄąĘąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ąŠčé ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠą│ąŠ ą┤ąŠ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ ą▒čāą┤ąĄčé ą┤ą╗ąĖčéčīčüčÅ ą┐ąŠčĆčÅą┤ą║ą░ čüąĄą║čāąĮą┤čŗ, ą░ č鹊 ąĖ ą▒ąŠą╗čīčłąĄ.

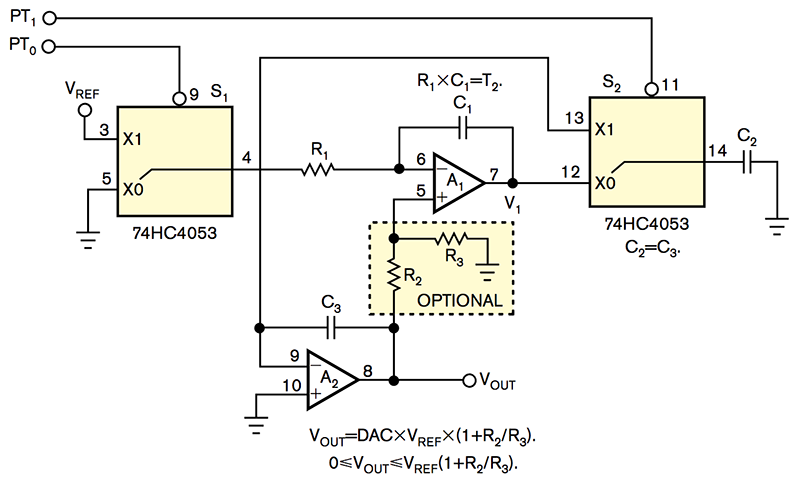

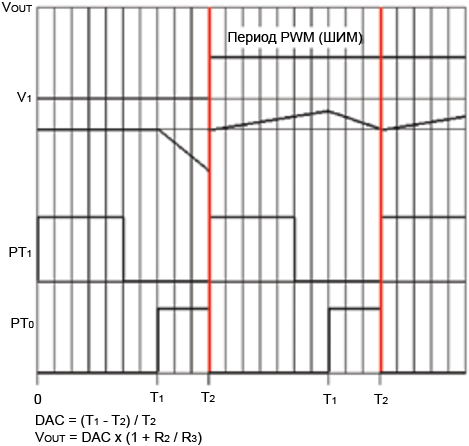

ąĪčģąĄą╝ą░ ąĮą░ čĆąĖčü. 1 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąĖąĘą▒ąĄąČą░čéčī ą▒ąŠą╗čīčłąĖąĮčüčéą▓ą░ ą┐čĆąŠą▒ą╗ąĄą╝ ążąØą¦. ąŁč鹊 ą┤ąŠčüčéąĖą│ą░ąĄčéčüčÅ ą║ąŠą╝ą▒ąĖąĮą░čåąĖąĖ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą│ąŠ ąĖąĮč鹥ą│čĆą░č鹊čĆą░ A1 čü čāčüąĖą╗ąĖč鹥ą╗ąĄą╝ ą▓čŗą▒ąŠčĆą║ąĖ-čģčĆą░ąĮąĄąĮąĖčÅ A2, ą║ąŠč鹊čĆčŗąĄ ą▓čüčéčĆąŠąĄąĮčŗ ą▓ ą┐ąĄčéą╗čÄ ąŠą▒čĆą░čéąĮąŠą╣ čüą▓čÅąĘąĖ, čĆą░ą▒ąŠčéą░čÄčēąĄą╣ čüąĖąĮčģčĆąŠąĮąĮąŠ čü ą┐ąĄčĆąĖąŠą┤ąŠą╝ PWM (T2 ąĮą░ čĆąĖčü. 2). ąĢčüą╗ąĖ čüą┤ąĄą╗ą░čéčī ą┐ąŠčüč鹊čÅąĮąĮčāčÄ ą▓čĆąĄą╝ąĄąĮąĖ ąĖąĮč鹥ą│čĆą░č鹊čĆą░ čĆą░ą▓ąĮąŠą╣ ą┐ąĄčĆąĖąŠą┤čā PWM (R1 ├Ś C1 = T2). ąś ąĄčüą╗ąĖ ąĄą╝ą║ąŠčüčéčī ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆą░ ą▓čŗą▒ąŠčĆą║ąĖ C2 čĆą░ą▓ąĮą░ ąĄą╝ą║ąŠčüčéąĖ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆą░ čģčĆą░ąĮąĄąĮąĖčÅ C3, č鹊 čäąĖą╗čīčéčĆ ą╝ąŠąČąĄčé ąĘą░čģą▓ą░čéąĖčéčī ąĖ čāčüčéą░ąĮąŠą▓ąĖčéčī ąĮąŠą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ DAC čĆąŠą▓ąĮąŠ ąĘą░ 1 ą┐ąĄčĆąĖąŠą┤ PWM. ąźąŠčéčÅ čŹč鹊čé čüą┐ąŠčüąŠą▒ ąĮąĄ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐ąŠą╗čāčćąĖčéčī čĆąĄą░ą╗čīąĮąŠ ą▒čŗčüčéčĆčŗą╣ ąĖ "ą▓čŗčüąŠą║ąŠčüą║ąŠčĆąŠčüčéąĮąŠą╣" ą”ąÉą¤, ąĄą│ąŠ ą▓čĆąĄą╝čÅ čĆąĄą░ą║čåąĖąĖ 10 ą╝čü čŹč鹊 ą▓čüąĄ čĆą░ą▓ąĮąŠ ą▓ 100 čĆą░ąĘ ą╗čāčćčłąĄ, č湥ą╝ ą▓čĆąĄą╝čÅ čĆąĄą░ą║čåąĖąĖ 1 čüąĄą║čāąĮą┤ą░. ąÆą░ąČąĮčŗą╣ ą╝ąŠą╝ąĄąĮčé - ą┐ąŠą▓čŗčłąĄąĮąĖąĄ čüą║ąŠčĆąŠčüčéąĖ čĆą░ą▒ąŠčéčŗ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ąĮąĄ ą▓ čāčēąĄčĆą▒ ą┐ąŠą┤ą░ą▓ą╗ąĄąĮąĖčÄ ą┐čāą╗čīčüą░čåąĖą╣. ą¤ąŠą┤ą░ą▓ą╗ąĄąĮąĖąĄ ą┐čāą╗čīčüą░čåąĖą╣ čüąĖąĮčģčĆąŠąĮąĮąŠą│ąŠ čäąĖą╗čīčéčĆą░ ą┐čĆą░ą║čéąĖč湥čüą║ąĖ ą▒ąĄčüą║ąŠąĮąĄčćąĮąŠ, ąĄą┤ąĖąĮčüčéą▓ąĄąĮąĮčŗą╝ ą┐čĆąĄą┤ąĄą╗ąŠą╝ ąĮą░ ą┐čĆą░ą║čéąĖą║ąĄ čÅą▓ą╗čÅąĄčéčüčÅ ąĮąĄąĮčāą╗ąĄą▓ąŠąĄ ą▓čĆąĄą╝čÅ ąĘą░čĆčÅą┤ą░ C3 č湥čĆąĄąĘ ą║ą╗čÄčć S2. ąĢčüą╗ąĖ ą▓čŗą▒čĆą░čéčī čģąŠčĆąŠčłąĖą╣ ą║ą╗čÄčć S2 ąĖ ą┤ą╗čÅ C3 ąĄą╝ą║ąŠčüčéčī ą┐čĆąĖą╝ąĄčĆąĮąŠ 1 ą╝ą║ąż, č鹊 ą░ą╝ą┐ą╗ąĖčéčāą┤ą░ ą┐čāą╗čīčüą░čåąĖą╣ ą▒čāą┤ąĄčé ą┐ąŠčĆčÅą┤ą║ą░ ą╝ąĖą║čĆąŠą▓ąŠą╗čīčé.

ąĀąĖčü. 1. ąĪčģąĄą╝ą░ čüąĖąĮčģčĆąŠąĮąĮąŠą│ąŠ čäąĖą╗čīčéčĆą░ ąĖą╝ą┐čāą╗čīčüąŠą▓ PWM.

ąĀąĖčü. 2. ąöąĖą░ą│čĆą░ą╝ą╝ą░ čüąĖą│ąĮą░ą╗ąŠą▓ čĆą░ą▒ąŠčéčŗ čüąĖąĮčģčĆąŠąĮąĮąŠą│ąŠ čäąĖą╗čīčéčĆą░.

ą×ą┐čåąĖąŠąĮą░ą╗čīąĮčŗą╣ ą┤ąĄą╗ąĖč鹥ą╗čī ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ąŠą▒čĆą░čéąĮąŠą╣ čüą▓čÅąĘąĖ R2/R3 ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą┐ąŠą┤čüčéčĆąŠą╣ą║ąĖ ą┤ąĖą░ą┐ą░ąĘąŠąĮą░ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ DAC ą┐ąŠ ąŠčéąĮąŠčłąĄąĮąĖčÄ ą║ čāčĆąŠą▓ąĮčÄ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ. ąØą░ą┐čĆąĖą╝ąĄčĆ, ąĄčüą╗ąĖ R2=R3, č鹊 ą┤ąĖą░ą┐ą░ąĘąŠąĮ ą▓čŗčģąŠą┤ąĮčŗčģ čāčĆąŠą▓ąĮąĄą╣ DAC čüąŠčüčéą░ą▓ąĖčé 0 .. 10V ą┐čĆąĖ ąŠą┐ąŠčĆąĮąŠą╝ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĖ 5V. ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠąĄ ą┤ąŠčüč鹊ąĖąĮčüčéą▓ąŠ čŹč鹊ą│ąŠ ą╝ąĄč鹊ą┤ą░ čĆąĄą│čāą╗ąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ čüąŠčüč鹊ąĖčé ą▓ č鹊ą╝, čćč鹊 ą┐čāą╗čīčüą░čåąĖąĖ ąĮą░ ą▓čŗčģąŠą┤ąĄ ąĮąĄ ąĘą░ą▓ąĖčüčÅčé ąŠčé čāčüąĖą╗ąĄąĮąĖčÅ čāčĆąŠą▓ąĮčÅ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ.

[ąĪčüčŗą╗ą║ąĖ]

1. Fast-settling synchronous-PWM-DAC filter has almost no ripple site:edn.com.

2. 16-ą▒ąĖčéąĮčŗą╣ ą©ąśą£ ąŠčüąĮąŠą▓ąĄ ą┤ą▓čāčģ 8-ą▒ąĖčéąĮčŗčģ.

3. ąæčŗčüčéčĆčŗą╣ PWM DAC ą▒ąĄąĘ ą▓čŗčģąŠą┤ąĮčŗčģ ą┐čāą╗čīčüą░čåąĖą╣. |