|

8-čĆą░ąĘčĆčÅą┤ąĮčŗą╣ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ AVR ą╝ąŠąČąĄčé ą▓čŗą┐ąŠą╗ąĮčÅčéčī ą▒ąŠą╗čīčłąĄ č湥ą╝ 100 čĆą░ąĘą╗ąĖčćąĮčŗčģ ąĖąĮčüčéčĆčāą║čåąĖą╣, ąĖ ą╝ąĮąŠą│ąĖąĄ ąĖąĘ ąĮąĖčģ ą▓čŗą┐ąŠą╗ąĮčÅčÄčéčüčÅ ąĘą░ 1 čéą░ą║čé. ąĪąŠą▓čĆąĄą╝ąĄąĮąĮčŗąĄ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ čÅą┤ąĄčĆ AVR (megaAVR, tinyAVR čüąĄčĆąĖą╣ 0 ąĖ 1) čüąĮą░ą▒ąČąĄąĮčŗ ą░ą┐ą┐ą░čĆą░čéąĮčŗą╝ čāą╝ąĮąŠąČąĖč鹥ą╗ąĄą╝, ą▓čŗą┐ąŠą╗ąĮčÅčÄčēąĖą╝ ąŠą┐ąĄčĆą░čåąĖąĖ ąĘą░ 2 čéą░ą║čéą░. ą×ą┤ąĮą░ą║ąŠ ąĮąĄčé č湥čéą║ąŠą│ąŠ ą┐ąŠąĮąĖą╝ą░ąĮąĖčÅ, ą║ą░ą║ čéą░ą║ą░čÅ ą▓čŗčćąĖčüą╗ąĖč鹥ą╗čīąĮą░čÅ ą╝ąŠčēąĮąŠčüčéčī ą╝ąŠąČąĄčé ą▒čŗčéčī ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮą░ ą▓ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅčģ čĆąĄą░ą╗čīąĮąŠą│ąŠ ą╝ąĖčĆą░, ąŠčüąŠą▒ąĄąĮąĮąŠ ą║ąŠą│ą┤ą░ ąĮą░ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéčī ą║ąŠą┤ą░ ąĮą░ą║ą╗ą░ą┤čŗą▓ą░čÄčéčüčÅ ąŠčüąŠą▒ąĄąĮąĮąŠčüčéąĖ ąĮą░ą┐ąĖčüą░ąĮąĖčÅ ą║ąŠą┤ą░ ąĖ ą║ąŠą╝ą┐ąĖą╗čÅč鹊čĆą░ ą▓čŗčüąŠą║ąŠčāčĆąŠą▓ąĮąĄą▓ąŠą│ąŠ čÅąĘčŗą║ą░. ąÆ čŹč鹊ą╣ čüčéą░čéčīąĄ (ą┐ąĄčĆąĄą▓ąŠą┤ ą┤ąŠą║čāą╝ąĄąĮčéą░ [1]) čĆą░čüčüą╝ą░čéčĆąĖą▓ą░čÄčéčüčÅ ąĮąĄą║ąŠč鹊čĆčŗąĄ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ čåąĖčäčĆąŠą▓ąŠą╣ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ čüąĖą│ąĮą░ą╗ą░ (DSP) ąĮą░ ąŠčüąĮąŠą▓ąĄ AVR, ąĖ ą║ą░ą║ąĖąĄ ą┤ą╗čÅ čŹč鹊ą│ąŠ ą┐čĆąŠčåąĄčüčüąŠčĆąĮčŗąĄ čĆąĄčüčāčĆčüčŗ čéčĆąĄą▒čāčÄčéčüčÅ. ąÆ čĆą░čüčüą╝ą░čéčĆąĖą▓ą░ąĄą╝čŗčģ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅčģ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ ą▓ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ AVR (MCU) ą░ąĮą░ą╗ąŠą│ąŠ-čåąĖčäčĆąŠą▓ąŠą╣ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░č鹥ą╗čī (ADC) ą┤ą╗čÅ ąŠčåąĖčäčĆąŠą▓ą║ąĖ ą┐čĆąĖčģąŠą┤čÅčēąĄą│ąŠ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░, ąĖ čÅą┤čĆąŠ AVR ą▓čŗą┐ąŠą╗ąĮčÅąĄčé ąŠą▒čĆą░ą▒ąŠčéą║čā ąŠčåąĖčäčĆąŠą▓ą░ąĮąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░. ąŁč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ ą┤ąŠą╗ąČąĮąŠ ąŠą▒ąĄčüą┐ąĄčćąĖą▓ą░čéčī ąŠą▒čĆą░ą▒ąŠčéą║čā ą┤ą░ąĮąĮčŗčģ ą▓ čĆąĄą░ą╗čīąĮąŠą╝ ą▓čĆąĄą╝ąĄąĮąĖ, čćč鹊ą▒čŗ ą▓čüąĄ ąŠčåąĖčäčĆąŠą▓ą░ąĮąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ą▒čŗą╗ąĖ č湥čéą║ąŠ ąŠą▒čĆą░ą▒ąŠčéą░ąĮčŗ čü čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮčŗą╝ąĖ ąĖąĮč鹥čĆą▓ą░ą╗ą░ą╝ąĖ ą▓čĆąĄą╝ąĄąĮąĖ. ąÜąŠą┤ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ąĮą░ą┐ąĖčüą░ąĮ ąĮą░ čÅąĘčŗą║ąĄ C, ąĘą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ ąĮąĄą║ąŠč鹊čĆčŗčģ čäčāąĮą║čåąĖą╣ ąĮą░ ą░čüčüąĄą╝ą▒ą╗ąĄčĆąĄ, ą▓čŗą┐ąŠą╗ąĮčÅčÄčēąĖčģ čāą╝ąĮąŠąČąĄąĮąĖąĄ 16-ą▒ąĖčéąĮčŗčģ čćąĖčüąĄą╗. ąŁčéąĖ čäčāąĮą║čåąĖąĖ ą▓čŗąĘčŗą▓ą░čÄčéčüčÅ ąĖąĘ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ąĮą░ čÅąĘčŗą║ąĄ C.

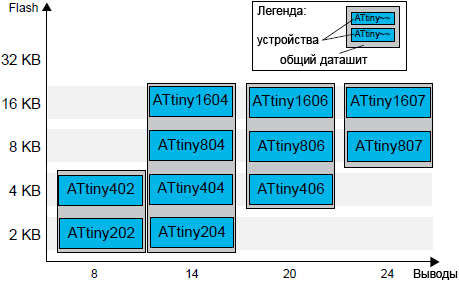

tinyAVR 0-series. ąØą░ čĆąĖčüčāąĮą║ąĄ ąĮąĖąČąĄ ą┐ąŠą║ą░ąĘą░ąĮą░ ą╗ąĖąĮąĄą╣ą║ą░ tinyAVR čüąĄčĆąĖąĖ 0, čü čāą║ą░ąĘą░ąĮąĖąĄą╝ ą▓ą░čĆąĖą░ąĮč鹊ą▓ ą┐ąŠ ą║ąŠą╗ąĖč湥čüčéą▓čā ą▓čŗą▓ąŠą┤ąŠą▓ ąĖ ąŠą▒čŖąĄą╝čā ą┐ą░ą╝čÅčéąĖ.

ŌĆó ą£ąĖą│čĆą░čåąĖčÅ ą║ąŠą┤ą░ ą▓ ą┐ąŠ ą▓ąĄčĆčéąĖą║ą░ą╗čīąĮąŠą╣ ąŠčüąĖ ą▓ąŠąĘą╝ąŠąČąĮą░ ą▒ąĄąĘ ąĘąĮą░čćąĖč鹥ą╗čīąĮąŠą╣ ą╝ąŠą┤ąĖčäąĖą║ą░čåąĖąĖ ą║ąŠą┤ą░, ą┐ąŠčüą║ąŠą╗čīą║čā čāčüčéčĆąŠą╣čüčéą▓ą░ ą┐ąŠą╗ąĮąŠčüčéčīčÄ čüąŠą▓ą╝ąĄčüčéąĖą╝čŗ ą┐ąŠ ą▓čŗą▓ąŠą┤ą░ą╝ ąĖ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮčŗą╝ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčÅą╝.

ŌĆó ąōąŠčĆąĖąĘąŠąĮčéą░ą╗čīąĮą░čÅ ą╝ąĖą│čĆą░čåąĖčÅ ą▓ą╗ąĄą▓ąŠ čüą▓čÅąĘą░ąĮą░ čü čāą╝ąĄąĮčīčłąĄąĮąĖąĄą╝ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ą▓čŗą▓ąŠą┤ąŠą▓, ąĖ ą║ą░ą║ čüą╗ąĄą┤čüčéą▓ąĖąĄ ą▓ąŠąĘą╝ąŠąČąĮąŠ čāą╝ąĄąĮčīčłąĄąĮąĖąĄ ą┤ąŠčüčéčāą┐ąĮčŗčģ čäčāąĮą║čåąĖą╣.

ąĀąĖčü. 1. ą×ą▒ąĘąŠčĆ čüąĄą╝ąĄą╣čüčéą▓ą░ tinyAVR 0-series.

ąŻčüčéčĆąŠą╣čüčéą▓ą░ čü čĆą░ąĘąĮčŗą╝ ąŠą▒čŖąĄą╝ąŠą╝ ą┐ą░ą╝čÅčéąĖ Flash čéą░ą║ąČąĄ ąĖą╝ąĄčÄčé čĆą░ąĘąĮčŗą╣ ąŠą▒čŖąĄą╝ SRAM ąĖ EEPROM.

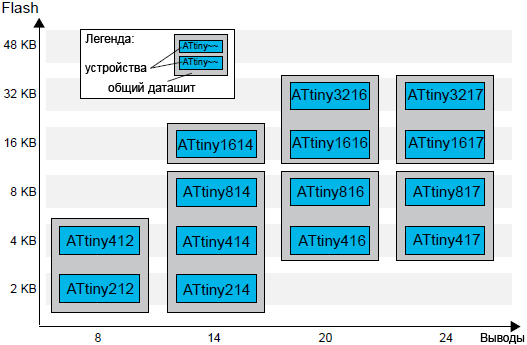

tinyAVR 1-series. ąØą░ čĆąĖčü. ąĮąĖąČąĄ ą┐ąŠą║ą░ąĘą░ąĮą░ ą╗ąĖąĮąĄą╣ą║ą░ čāčüčéčĆąŠą╣čüčéą▓ tinyAVR 1-series, čü čāą║ą░ąĘą░ąĮąĖąĄą╝ ą▓ą░čĆąĖą░ąĮč鹊ą▓ ą┐ąŠ ą║ąŠą╗ąĖč湥čüčéą▓čā ą▓čŗą▓ąŠą┤ąŠą▓ ąĖ ąŠą▒čŖąĄą╝čā ą┐ą░ą╝čÅčéąĖ.

ŌĆó ąÆąĄčĆčéąĖą║ą░ą╗čīąĮą░čÅ ą╝ąĖą│čĆą░čåąĖčÅ ą▓ą▓ąĄčĆčģ ą▓ąŠąĘą╝ąŠąČąĮą░ ą▒ąĄąĘ ą╝ąŠą┤ąĖčäąĖą║ą░čåąĖąĖ ą║ąŠą┤ą░, ą┐ąŠčüą║ąŠą╗čīą║čā čŹčéąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ čüąŠą▓ą╝ąĄčüčéąĖą╝čŗ ą┐ąŠ ą▓čŗą▓ąŠą┤ą░ą╝ ąĖ ąŠą▒ąĄčüą┐ąĄčćąĖą▓ą░čÄčé č鹊čé ąČąĄ ąĖą╗ąĖ čĆą░čüčłąĖčĆąĄąĮąĮčŗą╣ ąĮą░ą▒ąŠčĆ ą▓ąŠąĘą╝ąŠąČąĮąŠčüč鹥ą╣. ą×ą▒čĆą░čéąĮą░čÅ ą╝ąĖą│čĆą░čåąĖčÅ ą┐ąŠčéčĆąĄą▒čāąĄčé ą╝ąŠą┤ąĖčäąĖą║ą░čåąĖąĖ ą║ąŠą┤ą░, ą┐ąŠčüą║ąŠą╗čīą║čā ą▒čāą┤ąĄčé ą╝ąĄąĮčīčłąĄ ą┤ąŠčüčéčāą┐ąĮčŗčģ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓.

ŌĆó ąōąŠčĆąĖąĘąŠąĮčéą░ą╗čīąĮą░čÅ ą╝ąĖą│čĆą░čåąĖčÅ ą▓ą╗ąĄą▓ąŠ čüą▓čÅąĘą░ąĮą░ čü čāą╝ąĄąĮčīčłąĄąĮąĖąĄą╝ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ą▓čŗą▓ąŠą┤ąŠą▓, ąĖ ą║ą░ą║ čüą╗ąĄą┤čüčéą▓ąĖąĄ ą▓ąŠąĘą╝ąŠąČąĮąŠ čāą╝ąĄąĮčīčłąĄąĮąĖąĄ ą┤ąŠčüčéčāą┐ąĮčŗčģ čäčāąĮą║čåąĖą╣.

ąĀąĖčü. 2. ą×ą▒ąĘąŠčĆ čüąĄą╝ąĄą╣čüčéą▓ą░ tinyAVR 1-series.

ąŻčüčéčĆąŠą╣čüčéą▓ą░ čü čĆą░ąĘąĮčŗą╝ ąŠą▒čŖąĄą╝ąŠą╝ ą┐ą░ą╝čÅčéąĖ Flash čéą░ą║ąČąĄ ąĖą╝ąĄčÄčé čĆą░ąĘąĮčŗą╣ ąŠą▒čŖąĄą╝ SRAM ąĖ EEPROM.

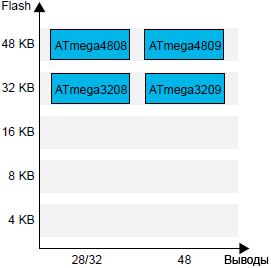

megaAVR 0-series. ąØą░ čüą╗ąĄą┤čāčÄčēąĄą╝ čĆąĖčüčāąĮą║ąĄ ą┐ąŠą║ą░ąĘą░ąĮą░ ą╗ąĖąĮąĄą╣ą║ą░ čāčüčéčĆąŠą╣čüčéą▓ megaAVR 0-series, čü čāą║ą░ąĘą░ąĮąĖąĄą╝ ą▓ą░čĆąĖą░ąĮč鹊ą▓ ą┐ąŠ ą║ąŠą╗ąĖč湥čüčéą▓čā ą▓čŗą▓ąŠą┤ąŠą▓ ąĖ ąŠą▒čŖąĄą╝čā ą┐ą░ą╝čÅčéąĖ.

ŌĆó ą£ąĖą│čĆą░čåąĖčÅ ą║ąŠą┤ą░ ą▓ ą┐ąŠ ą▓ąĄčĆčéąĖą║ą░ą╗čīąĮąŠą╣ ąŠčüąĖ ą▓ąŠąĘą╝ąŠąČąĮą░ ą▒ąĄąĘ ąĘąĮą░čćąĖč鹥ą╗čīąĮąŠą╣ ą╝ąŠą┤ąĖčäąĖą║ą░čåąĖąĖ ą║ąŠą┤ą░, ą┐ąŠčüą║ąŠą╗čīą║čā čāčüčéčĆąŠą╣čüčéą▓ą░ ą┐ąŠą╗ąĮąŠčüčéčīčÄ čüąŠą▓ą╝ąĄčüčéąĖą╝čŗ ą┐ąŠ ą▓čŗą▓ąŠą┤ą░ą╝ ąĖ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮčŗą╝ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčÅą╝.

ŌĆó ąōąŠčĆąĖąĘąŠąĮčéą░ą╗čīąĮą░čÅ ą╝ąĖą│čĆą░čåąĖčÅ ą▓ą╗ąĄą▓ąŠ čüą▓čÅąĘą░ąĮą░ čü čāą╝ąĄąĮčīčłąĄąĮąĖąĄą╝ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ą▓čŗą▓ąŠą┤ąŠą▓, ąĖ ą║ą░ą║ čüą╗ąĄą┤čüčéą▓ąĖąĄ ą▓ąŠąĘą╝ąŠąČąĮąŠ čāą╝ąĄąĮčīčłąĄąĮąĖąĄ ą┤ąŠčüčéčāą┐ąĮčŗčģ čäčāąĮą║čåąĖą╣.

ąĀąĖčü. 3. ą×ą▒ąĘąŠčĆ čüąĄą╝ąĄą╣čüčéą▓ą░ megaAVR 0-series.

ąŻčüčéčĆąŠą╣čüčéą▓ą░ čü čĆą░ąĘąĮčŗą╝ ąŠą▒čŖąĄą╝ąŠą╝ ą┐ą░ą╝čÅčéąĖ Flash čéą░ą║ąČąĄ ąĖą╝ąĄčÄčé čĆą░ąĘąĮčŗą╣ ąŠą▒čŖąĄą╝ SRAM ąĖ EEPROM.

[ąöąĄą╝ąŠą┤čāą╗čÅč鹊čĆ čüąĖą│ąĮą░ą╗ą░ FSK]

ą¤ąĄčĆą▓ąŠąĄ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ, čćč鹊 ą╝čŗ čĆą░čüčüą╝ąŠčéčĆąĖą╝ - ą┤ąĄą╝ąŠą┤čāą╗čÅč鹊čĆ ąĘą▓čāą║ąŠą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ą╝ąŠą┤čāą╗čÅčåąĖąĖ ą┐ąŠ čüą┤ą▓ąĖą│čā čćą░čüč鹊čéčŗ (audio frequency shift keying, AFSK) ą┤ą╗čÅ ą┐čĆąŠč鹊ą║ąŠą╗ą░ Specific Area Message Encoding (SAME), čĆą░ą▒ąŠčéą░čÄčēąĖą╣ ąĮą░ AVR-ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąĄ ATmega328P. ą¤ąŠą┤čĆąŠą▒ąĮąŠąĄ ąŠą▒čŖčÅčüąĮąĄąĮąĖąĄ ą┤ąĖąĘą░ą╣ąĮą░ ą┐čĆąŠč鹊ą║ąŠą╗ą░ ąĖ ą┤ąĄą╝ąŠą┤čāą╗čÅč鹊čĆą░, ą░ čéą░ą║ąČąĄ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ąĖčüčģąŠą┤ąĮčŗą╣ ą║ąŠą┤ ąĮą░ čÅąĘčŗą║ąĄ C, čćč鹊 ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą║ą░ą║ ąĖčüčģąŠą┤ąĮčāčÄ č鹊čćą║čā ą┤ą╗čÅ čüąŠą▒čüčéą▓ąĄąĮąĮąŠą╣ čĆą░ąĘčĆą░ą▒ąŠčéą║ąĖ, čüą╝. ą┐ąŠ čüčüčŗą╗ą║ąĄ [2].

ąÆ ą┐čĆąŠč鹊ą║ąŠą╗ąĄ SAME AFSK ą▒ąĖčéčŗ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ č鹊ąĮą░ą╗čīąĮčŗą╝ąĖ ą┐ąŠčüčŗą╗ą║ą░ą╝ąĖ ą┐ąŠ 1.92 ą╝ąĖą╗ą╗ąĖčüąĄą║čāąĮą┤, ą┐ąŠčŹč鹊ą╝čā čüą║ąŠčĆąŠčüčéčī ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐ąŠą╗čāčćą░ąĄčéčüčÅ 520.83 ą▒ąĖčé/čüąĄą║. ąøąŠą│ąĖč湥čüą║ąĖą╣ 0 ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮ čéčĆąĄą╝čÅ čåąĖą║ą╗ą░ą╝ąĖ č鹊ąĮą░ ąĘą▓čāą║ą░ 1562.5 ąōčå, ąĖ ą╗ąŠą│ąĖč湥čüą║ą░čÅ 1 ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮą░ 4 čåąĖą║ą╗ą░ą╝ąĖ č鹊ąĮą░ ąĘą▓čāą║ą░ 2083.3 ąōčå. ąÆ ąĮą░čćą░ą╗ąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ ąŠčéą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ 16-ą▒ą░ą╣čéąĮą░čÅ ą┐čĆąĄą░ą╝ą▒čāą╗ą░, čćč鹊ą▒čŗ ą┐čĆąĖąĄą╝ąĮąĖą║čā ą▒čŗą╗ąŠ ą╗ąĄą│č湥 ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ą│čĆą░ąĮąĖčåčŗ ą▒ąĖčé ą┐ąĄčĆąĄą┤ ąĮą░čćą░ą╗ąŠą╝ ąĖčģ ą┐ąĄčĆąĄą┤ą░čćąĖ.

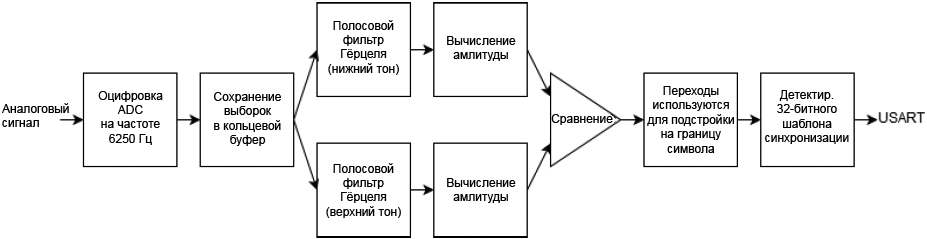

ąźąŠčéčÅ ą┤ąĄą╝ąŠą┤čāą╗čÅč鹊čĆ ąĖąĘąĮą░čćą░ą╗čīąĮąŠ ą▒čŗą╗ čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮ ąĮą░ ATmega328P, čĆą░ą▒ąŠčéą░čÄčēąĄą╝ čü čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊č鹊ą╣ 16 ą£ąōčå, č鹊 ąČąĄ čüą░ą╝ąŠąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮąŠ ąĮą░ ą┤čĆčāą│ąŠą╝ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąĄ AVR. ąóą░ą╣ą╝ąĄčĆ/čüč湥čéčćąĖą║ ąĖ ADC ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ąĮą░čüčéčĆą░ąĖą▓ą░ąĄčéčüčÅ ą┤ą╗čÅ ąŠčåąĖčäčĆąŠą▓ą║ąĖ ą┐čĆąĖčģąŠą┤čÅčēąĄą│ąŠ ąĘą▓čāą║ąŠą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ čü čćą░čüč鹊č鹊ą╣, ą▓ 4 čĆą░ąĘą░ ą┐čĆąĄą▓čŗčłą░čÄčēąĄą╣ čćą░čüč鹊čéčā čüąĖą│ąĮą░ą╗ą░ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ 0, ąĖ 3 čĆą░ąĘą░ ą┐čĆąĄą▓čŗčłą░čÄčēąĄą╣ čćą░čüč鹊čéčā ą┐ąĄčĆąĄą┤ą░čćąĖ 1, ąĖą╗ąĖ 6250 ąōčå. ąŁč鹊 ąĘąĮą░čćąĖčé, čćč鹊 ą┤ą╗čÅ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą║ą░ąČą┤ąŠą╣ ą▓čŗą▒ąŠčĆą║ąĖ čüąĖą│ąĮą░ą╗ą░ ADC ą┤ąŠčüčéčāą┐ąĮąŠ (16 ą£ąōčå/6250 ąōčå) = 2560 čéą░ą║č鹊ą▓ CPU. ąØą░ čüą╗ąĄą┤čāčÄčēąĄą╝ čĆąĖčüčāąĮą║ąĄ ą┐ąŠą║ą░ąĘą░ąĮą░ ą▒ą╗ąŠą║-čüčģąĄą╝ą░ ą┤ąĄą╝ąŠą┤čāą╗čÅč鹊čĆą░.

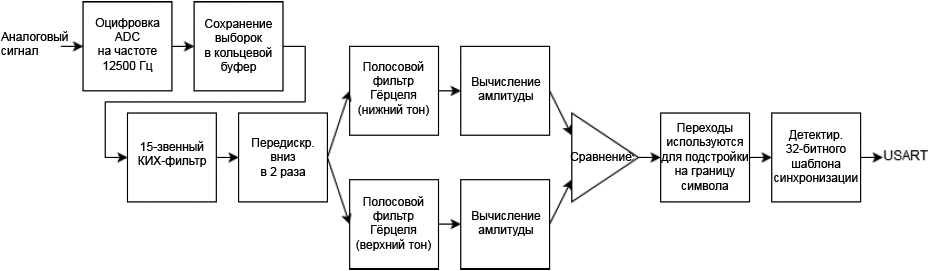

ąĀąĖčü. 4. ąöąĄą╝ąŠą┤čāą╗čÅč鹊čĆ FSK ąĮą░ ąŠčüąĮąŠą▓ąĄ ATmega328.

ąÜą░ąČą┤čŗą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ ąŠčé ADC ą┐čĆąĖčģąŠą┤ąĖčé ąĮąŠą▓ą░čÅ ą▓čŗą▒ąŠčĆą║ą░, ąŠąĮą░ ą┤ąŠą▒ą░ą▓ą╗čÅąĄčéčüčÅ ą▓ ą║ąŠą╗čīčåąĄą▓ąŠą╣ ą▒čāč乥čĆ, čüąŠčüč鹊čÅčēąĖą╣ ąĖąĘ čüą░ą╝čŗčģ čüą▓ąĄąČąĖčģ 12 ą▓čŗą▒ąŠčĆąŠą║ ADC. ąöą▓ą░ čåąĖčäčĆąŠą▓čŗčģ ą┐ąŠą╗ąŠčüąŠą▓čŗčģ čäąĖą╗čīčéčĆą░ ąōčæčĆčåąĄą╗čÅ, ąŠą┤ąĖąĮ ąĮą░čüčéčĆąŠąĄąĮ ąĮą░ čćą░čüč鹊čéčā č鹊ąĮą░ ą╗ąŠą│. 0, ą┤čĆčāą│ąŠą╣ ąĮą░ čćą░čüč鹊čéčā č鹊ąĮą░ ą╗ąŠą│. 1, ąŠą▒ą░ čĆą░ą▒ąŠčéą░čÄčé ąĮą░ ą┐ąŠčüą╗ąĄą┤ąĮąĖčģ 12 ą▓čŗą▒ąŠčĆą║ą░čģ čüąĖą│ąĮą░ą╗ą░ ADC, ąĘą░ ą║ąŠč鹊čĆčŗą╝ąĖ ą▓čŗčćąĖčüą╗čÅąĄčéčüčÅ ą▓čŗčģąŠą┤ąĮą░čÅ ą░ą╝ą┐ą╗ąĖčéčāą┤ą░ čüąĖą│ąĮą░ą╗ą░ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ čäąĖą╗čīčéčĆą░. ąÆčŗčģąŠą┤ąĮčŗąĄ ą░ą╝ą┐ą╗ąĖčéčāą┤čŗ ą┤ą▓čāčģ čäąĖą╗čīčéčĆąŠą▓ čüčĆą░ą▓ąĮąĖą▓ą░čÄčéčüčÅ, čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ą║ą░ą║ąŠą╣ ąĖąĘ čāčĆąŠą▓ąĮąĄą╣ ą▒čŗą╗ ą┐čĆąĖąĮčÅčé - ą▒ąĖčé ąĮčāą╗čÅ ąĖą╗ąĖ ą▒ąĖčé ąĄą┤ąĖąĮąĖčåčŗ. ąÆčŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ąĮąĄą║ąŠč鹊čĆą░čÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮą░čÅ ąŠą▒čĆą░ą▒ąŠčéą║ą░ ą┤ą╗čÅ ąŠą▒ąĮą░čĆčāąČąĄąĮąĖčÅ ą┐ąĄčĆąĄčģąŠą┤ąŠą▓ ą╝ąĄąČą┤čā ą▒ąĖčéą░ą╝ąĖ ąĖ ą┐čĆąĄą░ą╝ą▒čāą╗čŗ, čćč鹊ą▒čŗ ą┐ąŠ ąĮąĖą╝ ąŠą▒ąĄčüą┐ąĄčćąĖčéčī čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖčÄ ą┐čĆąĖąĄą╝ą░ ą┤ą░ąĮąĮčŗčģ. ą¤ąŠčüą╗ąĄ ą┤ąŠčüčéąĖąČąĄąĮąĖčÅ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ą┤ąĄą╝ąŠą┤čāą╗ąĖčĆąŠą▓ą░ąĮąĮčŗąĄ čüąĖą╝ą▓ąŠą╗čŗ ASCII ą▓čŗą▓ąŠą┤čÅčéčüčÅ ą▓ USART.

ą¤čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéčī čÅą┤čĆą░ AVR č鹥čüčéąĖčĆąŠą▓ą░ą╗ą░čüčī ąĮą░ ą║ąŠą┤ąĄ C, čüą║ąŠą╝ą┐ąĖą╗ąĖčĆąŠą▓ą░ąĮąĮąŠą╝ ą▓ Atmel Studio 7.0.1645, ą║ąŠč鹊čĆčŗą╣ čĆą░ą▒ąŠčéą░ą╗ ąĮą░ ąŠčéą╗ą░ą┤ąŠčćąĮąŠą╣ ą┐ą╗ą░č鹥 ATmega328P Xplained Mini. ąæčŗą╗ąĖ čüą┤ąĄą╗ą░ąĮčŗ ąĮąĄą║ąŠč鹊čĆčŗąĄ ąĮąĄąĘąĮą░čćąĖč鹥ą╗čīąĮčŗąĄ ą╝ąŠą┤ąĖčäąĖą║ą░čåąĖąĖ ą║ąŠą┤ą░, čćč鹊ą▒čŗ ą╝ąŠąČąĮąŠ ą▒čŗą╗ąŠ ąŠčåąĄąĮąĖčéčī čāčéąĖą╗ąĖąĘą░čåąĖčÄ ą▓čŗčćąĖčüą╗ąĖč鹥ą╗čīąĮčŗčģ čĆąĄčüčāčĆčüąŠą▓ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░, ąĖ čüą┤ąĄą╗ą░čéčī ą░ą╗ą│ąŠčĆąĖčéą╝ ą▒ąŠą╗ąĄąĄ čāčüč鹊ą╣čćąĖą▓čŗą╝ ą║ ąŠčłąĖą▒ą║ąĄ čćą░čüč鹊čéčŗ ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░ (ą╝ąŠą┤ąĖčäąĖčåąĖčĆąŠą▓ą░ąĮąĮčŗą╣ ą║ąŠą┤, ą░ čéą░ą║ąČąĄ ą▓ąĄčüčī ą║ąŠą┤, čĆą░čüčüą╝ą░čéčĆąĖą▓ą░ąĄą╝čŗą╣ ą▓ ą┐ąŠčüą╗ąĄą┤čāčÄčēąĖčģ čüąĄą║čåąĖčÅčģ, ą╝ąŠąČąĮąŠ ąĮą░ą╣čéąĖ ą▓ ą░čĆčģąĖą▓ąĄ FSK_demod_code_for_AVR_core.zip ąĮą░ ą▓ąĄą▒-čüą░ą╣č鹥 Microchip. ą×čé ą┐ąĄčĆąĄą▓ąŠą┤čćąĖą║ą░). ąÆ čüą░ą╝ąŠą╝ ą┐ą╗ąŠčģąŠą╝ čüą╗čāčćą░ąĄ ą▒čŗą╗ąŠ ąĮą░ą╣ą┤ąĄąĮąŠ, čćč鹊 ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ąĖ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą▓čŗą▒ąŠčĆą║ąĖ ADC čéčĆąĄą▒čāąĄčéčüčÅ 749 čéą░ą║č鹊ą▓ CPU. ąŁč鹊 ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▓ą║ą╗čÄčćą░ąĄčé ą║ą░ą║ ą▓čüčÄ čäąĖą╗čīčéčĆą░čåąĖčÄ ąĖ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖčÄ, čéą░ą║ ąĖ ą┐ąĄčĆąĄą┤ą░čćčā ą┤ąĄą╝ąŠą┤čāą╗ąĖčĆąŠą▓ą░ąĮčŗčģ čüąĖą╝ą▓ąŠą╗ąŠą▓ č湥čĆąĄąĘ USART. ąśąĘ čĆą░čüč湥čéą░ 2560 čéą░ą║č鹊ą▓ CPU ąĮą░ ą▓čŗą▒ąŠčĆą║čā ADC ąĘą░ą│čĆčāąĘą║ą░ čÅą┤čĆą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░ čüąŠčüčéą░ą▓ąĖčé (749/2560)*100% = 29.3%.

ąŁč鹊čé čĆąĄąĘčāą╗čīčéą░čé ą╝ąŠąČąĮąŠ ąĖąĮč鹥čĆą┐čĆąĄčéąĖčĆąŠą▓ą░čéčī ą┐ąŠ-čĆą░ąĘąĮąŠą╝čā. ą×ą║ąŠą╗ąŠ 70% ą┐čĆąŠčåąĄčüčüąŠčĆąĮąŠą╣ ą╝ąŠčēąĮąŠčüčéąĖ čÅą┤čĆą░ AVR ą▓čüąĄ ąĄčēąĄ ąŠčüčéą░ąĄčéčüčÅ ą┤ąŠčüčéčāą┐ąĮčŗą╝, ąĄčüą╗ąĖ ą▓ ą┐čĆąŠąĄą║čé ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ąĮą░ą┤ąŠ ą▒čāą┤ąĄčé ą┤ąŠą▒ą░ą▓ąĖčéčī ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗą╣ čäčāąĮą║čåąĖąŠąĮą░ą╗. ą¤ąŠčŹč鹊ą╝čā ą╝ąŠąČąĮąŠ ą┐ąŠąĮąĖąĘąĖčéčī čéą░ą║č鹊ą▓čāčÄ čćą░čüč鹊čéčā CPU ąŠčé 16 ą£ąōčå ą┤ąŠ 4.8 ą£ąōčå, čćč鹊ą▒čŗ čāą╝ąĄąĮčīčłąĖčéčī ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ 菹ĮąĄčĆą│ąĖąĖ ą▒ąĄąĘ ą┐ąŠč鹥čĆąĖ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠčüčéąĖ ą┤ąĄą╝ąŠą┤čāą╗čÅč鹊čĆą░ AFSK. ąĢčēąĄ ąŠą┤ąĮą░ ąĖąĮč鹥čĆą┐čĆąĄčéą░čåąĖčÅ - ąĄčüą╗ąĖ čćą░čüč鹊čéą░ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ CPU ąŠčüčéą░ąĮąĄčéčüčÅ 16 ą£ąōčå, čüą║ąŠčĆąŠčüčéčī ą▒ąĖčé AFSK, čćą░čüč鹊čéčā ąĘą▓čāą║ą░ ąĖ čćą░čüč鹊čéčā ą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ ADC ą╝ąŠąČąĮąŠ čāą▓ąĄą╗ąĖčćąĖčéčī ą▓ ąĮąĄčüą║ąŠą╗čīą║ąŠ čĆą░ąĘ, ą┤ąŠ 3.4 čĆą░ąĘą░, čćč鹊ą▒čŗ ą┤ąŠčüčéąĖčćčī čüą║ąŠčĆąŠčüčéąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ 1.77 ą║ąĖą╗ąŠą▒ąĖčé/čüąĄą║.

[ąöąĄą╝ąŠą┤čāą╗čÅč鹊čĆ AFSK čü ą┤ą▓čāą║čĆą░čéąĮąŠą╣ čćą░čüč鹊č鹊ą╣ ą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ ąĖ čåąĖčäčĆąŠą▓ąŠą╣ čäąĖą╗čīčéčĆą░čåąĖąĄą╣]

ąöąĄą╝ąŠą┤čāą╗čÅč鹊čĆ AFSK, ą║ąŠč鹊čĆčŗą╣ ą╝čŗ ąŠą▒čüčāą┤ąĖą╗ąĖ ą▓ ą┐čĆąĄą┤čŗą┤čāčēąĄą╝ čĆą░ąĘą┤ąĄą╗ąĄ, ąĮąĄ ąĖą╝ąĄą╗ ąĮąĖą║ą░ą║ąŠą╣ čåąĖčäčĆąŠą▓ąŠą╣ čäąĖą╗čīčéčĆą░čåąĖąĖ, čćč鹊ą▒čŗ ą┐čĆąĄą┤ąŠčéą▓čĆą░čéąĖčéčī ąĮą░ą╗ąŠąČąĄąĮąĖąĄ čćą░čüč鹊čé ą▓čŗčłąĄ ą┐ąŠą╗ąŠą▓ąĖąĮčŗ čćą░čüč鹊čéčŗ ą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ (0.5 * 6250 ąōčå = 3125 ąōčå). ąöą╗čÅ ą┐čĆąĖą╝ąĄčĆą░ ą┐čĆąĄą┤čüčéą░ą▓ąĖą╝, čćč鹊 ąĮą░ ą▓čģąŠą┤ ą┐ąŠčüčéčāą┐ą░ąĄčé č鹊ąĮ ąĘą▓čāą║ąŠą▓ąŠą╣ ą┐ąŠą╝ąĄčģąĖ čü čćą░čüč鹊č鹊ą╣ 4687.5 ąōčå. ą¤ąŠčüą║ąŠą╗čīą║čā čćą░čüč鹊čéą░ ą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ čüąŠčüčéą░ą▓ą╗čÅąĄčé 6250 ąōčå, ą┐ąŠčüą╗ąĄ ą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ č鹊ąĮą░ą╗čīąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ čü čćą░čüč鹊č鹊ą╣ 4687,5 ąōčå ąŠąĮ ą▒čāą┤ąĄčé ą┐ąŠčÅą▓ą╗čÅčéčīčüčÅ ą▓ čåąĖčäčĆąŠą▓ąŠą╣ ąŠą▒ą╗ą░čüčéąĖ ąĮą░ čüąŠą▓ą╝ąĄčēąĄąĮąĮąŠą╣ čćą░čüč鹊č鹥 (6250-4687.5) ąōčå = 1562.5 ąōčå. ą¤ąŠčüą║ąŠą╗čīą║čā čŹč鹊 čéą░ ąČąĄ čćą░čüč鹊čéą░, čćč鹊 ąĖ ąĮčāą╗ąĄą▓ąŠą╣ čüąĖą│ąĮą░ą╗ ą╗ąŠą│ąĖč湥čüą║ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ FSK, ąŠąĮ ą▒čāą┤ąĄčé ą╝ąĄčłą░čéčī ą┤ąĄą╝ąŠą┤čāą╗čÅč鹊čĆčā FSK ąĖ ą┐čĆąĄą┐čÅčéčüčéą▓ąŠą▓ą░čéčī ąĄą│ąŠ ą┐čĆą░ą▓ąĖą╗čīąĮąŠą╝čā čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖčÄ. ąöą╗čÅ ą┐čĆąĄą┤ąŠčéą▓čĆą░čēąĄąĮąĖčÅ čŹč鹊ą╣ ą┐ąŠą╝ąĄčģąĖ ąĄą┤ąĖąĮčüčéą▓ąĄąĮąĮčŗą╝ ą▓ą░čĆąĖą░ąĮč鹊ą╝ čü ą┐čĆąĄą┤čŗą┤čāčēąĖą╝ ą║ąŠą┤ąŠą╝ ą┤ąĄą╝ąŠą┤čāą╗čÅč鹊čĆą░ ą▒čŗą╗ąŠ ą▒čŗ ą┤ąŠą▒ą░ą▓ą╗ąĄąĮąĖąĄ ą░ą┐ą┐ą░čĆą░čéąĮąŠą│ąŠ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ čäąĖą╗čīčéčĆą░ ą┐ąĄčĆąĄą┤ ą▓čģąŠą┤ąŠą╝ ąÉą”ą¤ ą┤ą╗čÅ ąŠčüą╗ą░ą▒ą╗ąĄąĮąĖčÅ čćą░čüč鹊čé čüąĖą│ąĮą░ą╗ą░ ą▓čŗčłąĄ 3125 ąōčå.

ąÉą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčŗą╣ čüą┐ąŠčüąŠą▒ ą┤ą╗čÅ čĆąĄčłąĄąĮąĖčÅ čŹč鹊ą╣ ą┐čĆąŠą▒ą╗ąĄą╝čŗ - ąŠčåąĖčäčĆąŠą▓čŗą▓ą░čéčī čüąĖą│ąĮą░ą╗ ąĮą░ ą┐ąŠą▓čŗčłąĄąĮąĮąŠą╣ čćą░čüč鹊č鹥 ą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ, ą▓čŗą┐ąŠą╗ąĮąĖčéčī ąĮąĄą║čāčÄ čåąĖčäčĆąŠą▓čāčÄ čäąĖą╗čīčéčĆą░čåąĖčÄ ą┤ą╗čÅ ą┐ąŠąĮąĖąČąĄąĮąĖčÅ čüąŠčüčéą░ą▓ą╗čÅčÄčēąĖčģ čüą┐ąĄą║čéčĆą░ ą▓čŗčłąĄ 3125 ąōčå, ąĖ ąĘą░č鹥ą╝ ą┐ąĄčĆąĄą┤ąĖčüą║čĆąĄčéąĖąĘąĖčĆąŠą▓ą░čéčī ą▓ąĮąĖąĘ čćą░čüč鹊čéčā ąŠčåąĖčäčĆąŠą▓ą║ąĖ čüąĖą│ąĮą░ą╗ą░. ąĪąĖą│ąĮą░ą╗ čü ą┐ąŠąĮąĖąČąĄąĮąĮąŠą╣ čćą░čüč鹊č鹊ą╣ ą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ ą┐ąŠčüą╗ąĄ čŹč鹊ą│ąŠ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┤ąĄą╝ąŠą┤čāą╗ąĖčĆąŠą▓ą░ąĮ. ąÜąŠą┤ ą┤ąĄą╝ąŠą┤čāą╗čÅč鹊čĆą░ AFSK, ąŠą┐ąĖčüą░ąĮąĮčŗą╣ ą▓ ą┐čĆąĄą┤čŗą┤čāčēąĄą╝ čĆą░ąĘą┤ąĄą╗ąĄ, ą▒čŗą╗ ą▓ąĘčÅčé ąĘą░ ąŠčüąĮąŠą▓čā ąĖ ąĘą░č鹥ą╝ ą┤ąŠčĆą░ą▒ąŠčéą░ąĮ ą┤ą╗čÅ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ čŹč鹊ą│ąŠ ą┐ąŠą┤čģąŠą┤ą░. ąæą╗ąŠą║-čüčģąĄą╝ą░ ą╝ąŠą┤ąĖčäąĖčåąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ ą┤ąĄą╝ąŠą┤čāą╗čÅč鹊čĆą░ ą┐ąŠą║ą░ąĘą░ąĮą░ ąĮą░ čĆąĖčüčāąĮą║ąĄ ąĮąĖąČąĄ.

ąĀąĖčü. 5. ąöąĄą╝ąŠą┤čāą╗čÅč鹊čĆ FSK čü čåąĖčäčĆąŠą▓ąŠą╣ čäąĖą╗čīčéčĆą░čåąĖąĄą╣.

ą£ąŠą┤ąĖčäąĖčåąĖčĆąŠą▓ą░ąĮąĮčŗą╣ ą║ąŠą┤ ąĖčüą┐ąŠą╗čīąĘčāąĄčé ADC ą┤ą╗čÅ ąŠčåąĖčäčĆąŠą▓ą║ąĖ ą┐čĆąĖčģąŠą┤čÅčēąĄą│ąŠ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ąĮą░ čćą░čüč鹊č鹥 ą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ 12500 ąōčå, čćč鹊 ą▓ 2 čĆą░ąĘą░ ą▓čŗčłąĄ ą┐čĆąĄą┤čŗą┤čāčēąĄą│ąŠ ą▓ą░čĆąĖą░ąĮčéą░ čćą░čüč鹊čéčŗ ą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ 6250 ąōčå. ąÆčŗą▒ąŠčĆą║ąĖ 12500 ąōčå ą┐čĆąŠčģąŠą┤čÅčé č湥čĆąĄąĘ 15-ąĘą▓ąĄąĮąĮčŗą╣ FIR-čäąĖą╗čīčéčĆ, ą║ąŠč鹊čĆčŗą╣ čĆą░ąĘčĆą░ą▒ąŠčéą░ąĮ čéą░ą║, čćč鹊 ąŠčüą╗ą░ą▒ą╗čÅąĄčé ą▒ąŠą╗čīčłąĄ č湥ą╝ ąĮą░ 44 dB čüąŠčüčéą░ą▓ą╗čÅčÄčēąĖąĄ čüą┐ąĄą║čéčĆą░ ą▓čŗčłąĄ čćą░čüč鹊čéčŗ čüčĆąĄąĘą░ 3125 ąōčå. ąŚą▓ąĄąĮčīčÅ FIR-čäąĖą╗čīčéčĆą░ čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮčŗ čü 10-čĆą░ąĘčĆčÅą┤ąĮąŠą╣ č鹊čćąĮąŠčüčéčīčÄ, ąĖ ąĘąĮą░č湥ąĮąĖčÅ ADC čéą░ą║ąČąĄ 10-ą▒ąĖčéąĮčŗąĄ, čéą░ą║ čćč鹊 ą▓ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ FIR-čäąĖą╗čīčéčĆą░ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ąŠą┐ąĄčĆą░čåąĖąĖ čāą╝ąĮąŠąČąĄąĮąĖčÅ 16-ą▒ąĖčé ąĮą░ 16-ą▒ąĖčé. ąÆčŗčģąŠą┤ąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ FIR-čäąĖą╗čīčéčĆą░ ą┐ąĄčĆąĄą┤ąĖčüą║čĆąĄčéąĖąĘąĖčĆčāčÄčéčüčÅ ą▓ąĮąĖąĘ ą▓ 2 čĆą░ąĘą░, čćč鹊ą▒čŗ ą┐ąŠą╗čāčćąĖčéčī ąŠčĆąĖą│ąĖąĮą░ą╗čīąĮčāčÄ čćą░čüč鹊čéčā ą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ 6250 ąōčå, ą┐ąŠčüą╗ąĄ č湥ą│ąŠ čŹč鹊čé čåąĖčäčĆąŠą▓ąŠą╣ čüąĖą│ąĮą░ą╗ ą┐ąŠą┤ą░ąĄčéčüčÅ ą▓ ą║ąŠą┤ ąŠčĆąĖą│ąĖąĮą░ą╗čīąĮąŠą│ąŠ ą┤ąĄą╝ąŠą┤čāą╗čÅč鹊čĆą░ FSK, ą║ąŠč鹊čĆčŗą╣ ą▒čŗą╗ čĆą░ąĘčĆą░ą▒ąŠčéą░ąĮ ą┤ą╗čÅ čćą░čüč鹊čéčŗ ą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ 6250 ąōčå.

ąĀą░čüčüą╝ąŠčéčĆąĖą╝, čćč鹊 ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé, ą║ąŠą│ą┤ą░ ą┐čĆąĖčüčāčéčüčéą▓čāąĄčé čüąĖą│ąĮą░ą╗ čüąĖąĮčāčüąŠąĖą┤ą░ą╗čīąĮąŠą╣ ą┐ąŠą╝ąĄčģąĖ 4687.5 ąōčå. ąśąĘ-ąĘą░ č鹊ą│ąŠ, čćč鹊 čüąĖą│ąĮą░ą╗ ąŠčåąĖčäčĆąŠą▓čŗą▓ą░ąĄčéčüčÅ čü čćą░čüč鹊č鹊ą╣ ą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ 12500 ąōčå, ąĮą░ą╗ąŠąČąĄąĮąĖčÅ čüą┐ąĄą║čéčĆą░ ą┤ą╗čÅ čŹč鹊ą│ąŠ čüąĖą│ąĮą░ą╗ą░ ąĮąĄ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ŌĆō ąŠąĮ ąĮąŠčĆą╝ą░ą╗čīąĮąŠ ą▒čāą┤ąĄčé ą┐čĆąĖčüčāčéčüčéą▓ąŠą▓ą░čéčī ą║ą░ą║ 4687.5 ąōčå ą▓ ąŠčåąĖčäčĆąŠą▓ą░ąĮąĮąŠą╣ ą▓ąĄčĆčüąĖąĖ čüąĖą│ąĮą░ą╗ą░. ąæą╗ą░ą│ąŠą┤ą░čĆčÅ ąŠčüą╗ą░ą▒ą╗ąĄąĮąĖčÄ 44 dB FIR-čäąĖą╗čīčéčĆą░ ą┤ą╗čÅ čćą░čüč鹊čé ą▓čŗčłąĄ 3125 ąōčå, čüąĖą│ąĮą░ą╗ ą┐ąŠą╝ąĄčģąĖ 4687.5 ąōčå ąĮą░ ą▓čŗčģąŠą┤ąĄ FIR-čäąĖą╗čīčéčĆą░ ą▒čāą┤ąĄčé čāą╝ąĄąĮčīčłąĄąĮ ą┤ąŠ čāčĆąŠą▓ąĮčÅ ą╝ąĄąĮąĄąĄ 1% ąŠčé čüą▓ąŠąĄą╣ ąŠčĆąĖą│ąĖąĮą░ą╗čīąĮąŠą╣ ą░ą╝ą┐ą╗ąĖčéčāą┤čŗ. ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ čćą░čüč鹊čéą░ ą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ ą▒čāą┤ąĄčé čüąĮąŠą▓ą░ ą┐ąŠąĮąĖąČąĄąĮą░ ą┤ąŠ 6250 ąōčå, ąĮą░ą╗ąŠąČąĄąĮąĖąĄ čüą┐ąĄą║čéčĆą░ ą┤ą╗čÅ čŹč鹊ą╣ ą┐ąŠą╝ąĄčģąĖ ą▓ąĄčĆąĮąĄčéčüčÅ ąĮą░ čćą░čüč鹊čéčā 1562.5 ąōčå, ąĮąŠ ą▒čāą┤ąĄčé ą┐čĆąĖ čŹč鹊ą╝ ąĘąĮą░čćąĖč鹥ą╗čīąĮąŠ ą┐ąŠąĮąĖąČąĄąĮą░ ą┐ąŠ ą░ą╝ą┐ą╗ąĖčéčāą┤ąĄ, ąĖ ąĮąĄ ąŠą║ą░ąČąĄčé ąĮąĄą│ą░čéąĖą▓ąĮąŠąĄ ą▓ą╗ąĖčÅąĮąĖąĄ ąĮą░ čĆą░ą▒ąŠčéčā ą┤ąĄą╝ąŠą┤čāą╗čÅč鹊čĆą░ FSK.

ąŻą┤ą▓ąŠąĄąĮąĖąĄ čćą░čüč鹊čéčŗ ą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ ą┤ąŠ 12500 ąōčå ą┐čĆąĖ čćą░čüč鹊č鹥 čéą░ą║č鹊ą▓ AVR-čÅą┤čĆą░ 16 ą£ąōčå ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ č鹊ą╝čā, čćč鹊 č鹥ą┐ąĄčĆčī ąĮą░ ą║ą░ąČą┤čāčÄ ą▓čŗą▒ąŠčĆą║čā ą▒čāą┤ąĄčé ą┤ąŠčüčéčāą┐ąĮąŠ (16 ą£ąōčå/12500 ąōčå) = 1280 čéą░ą║č鹊ą▓ CPU. ąæčŗą╗ąŠ ąŠą▒ąĮą░čĆčāąČąĄąĮąŠ, čćč鹊 čāčéąĖą╗ąĖąĘą░čåąĖčÅ CPU čŹč鹊ą│ąŠ ą║ąŠą┤ą░ čüąŠčüčéą░ą▓ąĖą╗ą░ ąĮąĄ ą▒ąŠą╗ąĄąĄ 792 čéą░ą║č鹊ą▓ ąĮą░ ą▓čŗą▒ąŠčĆą║čā ADC, ą┐ąŠčŹč鹊ą╝čā čĆą░čüčģąŠą┤ ą┐čĆąŠčåąĄčüčüąŠčĆąĮąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ čÅą┤čĆą░ AVR čüąŠčüčéą░ą▓ąĖą╗ (792/1280)*100% = 62%.

ąÜą░ą║ ąĖ čĆą░ąĮąĄąĄ, čŹč鹊čé čĆąĄąĘčāą╗čīčéą░čé čéą░ą║ąČąĄ ą╝ąŠąČąĮąŠ ąĖąĮč鹥čĆą┐čĆąĄčéąĖčĆąŠą▓ą░čéčī ą┐ąŠ-čĆą░ąĘąĮąŠą╝čā. ąŻ ąĮą░čü ąŠčüčéą░ą╗ąŠčüčī 38% čüą▓ąŠą▒ąŠą┤ąĮąŠą│ąŠ ą┐čĆąŠčåąĄčüčüąŠčĆąĮąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ, ą║ąŠč鹊čĆąŠąĄ ą╝ąŠąČąĮąŠ ą▒čŗą╗ąŠ ą▒čŗ ą┐ąŠčéčĆą░čéąĖčéčī ąĮą░ ą┤ąŠą▒ą░ą▓ą╗ąĄąĮąĖąĄ/čāą╗čāčćčłąĄąĮąĖąĄ čäčāąĮą║čåąĖąŠąĮą░ą╗ą░ ąĮą░čłąĄą│ąŠ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ. ąØą░ą┐čĆąĖą╝ąĄčĆ, čéą░ą║č鹊ą▓čāčÄ čćą░čüč鹊čéčā CPU ą╝ąŠąČąĮąŠ ą▒čŗą╗ąŠ ą▒čŗ čüąĮąĖąĘąĖčéčī čü 16 ą£ąōčå ą┤ąŠ 10 ą£ąōčå ą▒ąĄąĘ čāčģčāą┤čłąĄąĮąĖčÅ čĆą░ą▒ąŠčéčŗ ą┤ąĄą╝ąŠą┤čāą╗čÅč鹊čĆą░. ąöčĆčāą│ą░čÅ ąĖąĮč鹥čĆą┐čĆąĄčéą░čåąĖčÅ - ąĄčüą╗ąĖ ąŠčüčéą░ą▓ąĖčéčī čćą░čüč鹊čéčā čéą░ą║č鹊ą▓ AVR-čÅą┤čĆą░ 16 ą£ąōčå, č鹊 ą╝ąŠąČąĮąŠ ą▓ 1.6 čĆą░ąĘą░ ą┐ąŠą▓čŗčüąĖčéčī ą┐ą░čĆą░ą╝ąĄčéčĆčŗ čüą║ąŠčĆąŠčüčéąĖ ą▒ąĖčé AFSK, čćą░čüč鹊čéčŗ ąĘą▓čāą║ą░ ąĖą╗ąĖ čćą░čüč鹊čéčŗ ą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ ADC, čćč鹊ą▒čŗ ą┤ąŠčüčéąĖčćčī čüą║ąŠčĆąŠčüčéąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ą┤ąŠ 833 ą▒ąĖčé/čüąĄą║.

[ąöąĄą╝ąŠą┤čāą╗čÅč鹊čĆ FSK ąĮą░ 8-ą║čĆą░čéąĮąŠą╣ čćą░čüč鹊č鹥 ą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ, čü čåąĖčäčĆąŠą▓ąŠą╣ čäąĖą╗čīčéčĆą░čåąĖąĄą╣]

ąÜąŠą┤ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ ą▒čŗą╗ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠ ąĖąĘą╝ąĄąĮąĄąĮ ą┤ą╗čÅ ą┤ąĄą╝ąŠą┤čāą╗čÅčåąĖąĖ ą▒ąŠą╗ąĄąĄ čüą╗ąŠąČąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ FSK. ąöą╗ąĖč鹥ą╗čīąĮąŠčüčéčī ą▒ąĖčé ąŠčüčéą░ą▓ą╗ąĄąĮą░ 1.92 ą╝ąĖą╗ą╗ąĖčüąĄą║čāąĮą┤čŗ, ąŠą┤ąĮą░ą║ąŠ čćą░čüč鹊čéą░ ąĘą▓čāą║ą░ ą▒čŗą╗ą░ ą┐ąŠą▓čŗčłąĄąĮą░ ą┤ąŠ 16666.7 ąōčå ą┤ą╗čÅ ą╗ąŠą│ąĖč湥čüą║ąŠą╣ ąĄą┤ąĖąĮąĖčåčŗ ąĖ 17187.5 ąōčå ą┤ą╗čÅ ą╗ąŠą│ąĖč湥čüą║ąŠą│ąŠ ąĮčāą╗čÅ. ąŁč鹊 čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé č鹊čćąĮąŠ 32 ąĖą╗ąĖ 33 ą┐ąĄčĆąĖąŠą┤ą░ą╝ čüąĖąĮčāčüąŠąĖą┤čŗ ą┤ą╗čÅ ąĖąĮč鹥čĆą▓ą░ą╗ą░ ą▒ąĖčéą░ 1.92 ą╝čü.

ąöą╗čÅ čŹč鹊ą│ąŠ ą▓ą░čĆąĖą░ąĮčéą░ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ čéą░ą╣ą╝ąĄčĆ/čüč湥čéčćąĖą║ ąĖ ADC ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ąĮą░čüčéčĆąŠąĄąĮčŗ ą┤ą╗čÅ ąŠčåąĖčäčĆąŠą▓ą║ąĖ ąĮą░ čćą░čüč鹊č鹥 ą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ 50 ą║ąōčå. ąæą╗ąŠą║-čüčģąĄą╝ą░ ą┤ąĄą╝ąŠą┤čāą╗čÅč鹊čĆą░ ą┐ąŠą║ą░ąĘą░ąĮą░ ąĮą░ čüą╗ąĄą┤čāčÄčēąĄą╝ čĆąĖčüčāąĮą║ąĄ.

ąĀąĖčü. 6. ąöąĄą╝ąŠą┤čāą╗čÅč鹊čĆ FSK, čĆą░ą▒ąŠčéą░čÄčēąĖą╣ ąĮą░ ą┐ąŠą▓čŗčłąĄąĮąĮąŠą╣ čćą░čüč鹊č鹥 ą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ.

ą×ą▒čĆą░ą▒ąŠčéčćąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (ISR) čüąŠčģčĆą░ąĮčÅąĄčé ą┐ąŠčüčéčāą┐ą░čÄčēąĖąĄ ą▓čŗą▒ąŠčĆą║ąĖ ADC ą▓ ą║ąŠą╗čīčåąĄą▓ąŠą╣ ą▒čāč乥čĆ, ą║ąŠč鹊čĆčŗą╣ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčéčüčÅ ą▓ ą│ą╗ą░ą▓ąĮąŠą╝ čåąĖą║ą╗ąĄ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ. ąÆ ą│ą╗ą░ą▓ąĮąŠą╝ čåąĖą║ą╗ąĄ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą▓čŗą▒ąŠčĆą║ąĖ 50 ą║ąōčå ą┐ąŠčüčéčāą┐ą░čÄčé ąĮą░ ą▓čģąŠą┤ 9-ąĘą▓ąĄąĮąĮąŠą│ąŠ FIR-čäąĖą╗čīčéčĆą░, ą║ąŠč鹊čĆčŗą╣ ąĮą░ 40 dB ą┐ąŠąĮąĖąČą░ąĄčé čüąŠčüčéą░ą▓ą╗čÅčÄčēąĖąĄ čüąĖą│ąĮą░ą╗ą░ ąĮąĖąČąĄ 10 ą║ąōčå, čéą░ą║ čćč鹊 ąĘą▓čāą║ąĖ č湥ą╗ąŠą▓ąĄč湥čüą║ąŠą│ąŠ ą│ąŠą╗ąŠčüą░ ąĖ ąĮąĖąĘą║ąŠčćą░čüč鹊čéąĮčŗąĄ čłčāą╝čŗ čāą┤ą░ą╗čÅčÄčéčüčÅ ąĖąĘ čüąĖą│ąĮą░ą╗ą░. FIR-čäąĖą╗čīčéčĆ čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮ čü 10-ą▒ąĖčéąĮąŠą╣ č鹊čćąĮąŠčüčéčīčÄ, ąĖ ąĘąĮą░č湥ąĮąĖčÅ ADC ąĖą╝ąĄčÄčé čĆą░ąĘčĆčÅą┤ąĮąŠčüčéčī 10 ą▒ąĖčé, čéą░ą║ čćč鹊 ą▓ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ FIR-čäąĖą╗čīčéčĆą░ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ąŠą┐ąĄčĆą░čåąĖąĖ čāą╝ąĮąŠąČąĄąĮąĖčÅ 16 ą▒ąĖčé ąĮą░ 16 ą▒ąĖčé.

ąÆčŗčģąŠą┤ FIR-čäąĖą╗čīčéčĆą░ ą┐ąĄčĆąĄą┤ąĖčüą║čĆąĄčéąĖąĘąĖčĆčāąĄčéčüčÅ ą▓ąĮąĖąĘ ą▓ 8 čĆą░ąĘ, čćč鹊ą▒čŗ ą┐ąŠą╗čāčćąĖčéčī čåąĖčäčĆąŠą▓ąŠą╣ čüąĖą│ąĮą░ą╗ čü čćą░čüč鹊č鹊ą╣ ą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ 6250 ąōčå. ą¦ą░čüč鹊čéčŗ ą▓ ą┐ąĄčĆąĄą┤ąĖčüą║čĆąĄčéąĖąĘąĖčĆąŠą▓ą░ąĮąĮąŠą╝ ą▓ąĮąĖąĘ čüąĖą│ąĮą░ą╗ąĄ, ą▒ą╗ąĖąĘą║ąĖąĄ ą║ čāą╗čīčéčĆą░ąĘą▓čāą║čā 16666.7 ąōčå ąĖ 17187.5 ąōčå ąŠč鹊ą▒čĆą░ąČą░čÄčéčüčÅ ąĮą░ čćą░čüč鹊čéčŗ (3*6250 ŌĆō 16666.7) ąōčå ąĖ (3*6250 ŌĆō 17187.5) ąōčå, čé. ąĄ. ąĮą░ 2083.3 ąōčå ąĖ 1562.5 ąōčå čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ. ąŁč鹊 ąĘąĮą░čćąĖčé, čćč鹊 ą┤ą╗čÅ ąĮąĖčģ ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą▓čüąĄ č鹊čé ąČąĄ ą║ąŠą┤ ąŠčĆąĖą│ąĖąĮą░ą╗čīąĮąŠą│ąŠ ą┤ąĄą╝ąŠą┤čāą╗čÅč鹊čĆą░ FSK.

ąĪ čāč湥č鹊ą╝ č鹊ą│ąŠ, čćč鹊 čÅą┤čĆąŠ čĆą░ą▒ąŠčéą░ąĄčé ąĮą░ čćą░čüč鹊č鹥 16 ą£ąōčå, čā ąĮąĄčü ąĄčüčéčī 320 čåąĖą║ą╗ąŠą▓ CPU ąĮą░ ą║ą░ąČą┤čŗą╣ ąĖąĮč鹥čĆą▓ą░ą╗ ą╝ąĄąČą┤čā ą▓čŗą▒ąŠčĆą║ą░ą╝ąĖ 50 ą║ąōčå, ąĖ 2560 čéą░ą║č鹊ą▓ CPU ąĮą░ ą┐ąĄčĆąĄą┤ąĖčüą║čĆąĄčéąĖąĘąĖčĆąŠą▓ą░ąĮąĮčŗą╣ ą┤ąŠ 6250 ąōčå ąĖąĮč鹥čĆą▓ą░ą╗ čüąĖą│ąĮą░ą╗ą░. ąĀą░čüčģąŠą┤ ą┐čĆąŠčåąĄčüčüąŠčĆąĮąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ ą▒čŗą╗ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮ čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝:

ŌĆó ą¤ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ISR: 65 čéą░ą║č鹊ą▓ ąĮą░ ą▓čŗą▒ąŠčĆą║čā 50 ą║ąōčå = (65/320)*100% = 20.3% čāčéąĖą╗ąĖąĘą░čåąĖąĖ CPU.

ŌĆó 9-ąĘą▓ąĄąĮąĮčŗą╣ FIR-čäąĖą╗čīčéčĆ ąĖ ąĮą░ą║ą╗ą░ą┤ąĮčŗąĄ čĆą░čüčģąŠą┤čŗ: 468 čéą░ą║č鹊ą▓ ąĮą░ 6250 ąōčå = (468/2560)*100% = 18.3% čāčéąĖą╗ąĖąĘą░čåąĖąĖ CPU.

ŌĆó ąöąĄą╝ąŠą┤čāą╗čÅč鹊čĆ FSK (ą▓ą║ą╗čÄčćą░čÅ ą▓čŗą▓ąŠą┤ ą▓ USART): 718 čéą░ą║č鹊ą▓ ąĮą░ 6250 ąōčå = (718/2560)*100% = 28.0% čāčéąĖą╗ąĖąĘą░čåąĖąĖ CPU.

ą¤ąŠą╗čāčćą░ąĄčéčüčÅ, čćč鹊 ąŠą▒čēąĖą╣ čĆą░čüčģąŠą┤ ą┐čĆąŠčåąĄčüčüąŠčĆąĮąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ CPU čüąŠčüčéą░ą▓ąĖą╗ 20.3% + 18.3% + 28.0% = 66.6%, čéą░ą║ čćč鹊 ąĄčēąĄ čéčĆąĄčéčī čéą░ą║č鹊ą▓ CPU ąŠčüčéą░ąĄčéčüčÅ ą┤ąŠčüčéčāą┐ąĮąŠą╣ ą┤ą╗čÅ ą┤čĆčāą│ąŠą╣ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ. ą£ąŠąČąĮąŠ ą┐ąŠąĮąĖąĘąĖčé čéą░ą║č鹊ą▓čāčÄ čćą░čüč鹊čéčā čü 16 ą£ąōčå ą┤ąŠ 10.7 ą£ąōčå ą▒ąĄąĘ ą┐ąŠč鹥čĆąĖ čäčāąĮą║čåąĖąŠąĮą░ą╗ą░ ą┤ąĄą╝ąŠą┤čāą╗čÅč鹊čĆą░. ąĢčüą╗ąĖ ąČąĄ ąŠčüčéą░ą▓ąĖčéčī čćą░čüč鹊čéčā čéą░ą║č鹊ą▓ 16 ą£ąōčå, č鹊 čćą░čüč鹊čéčŗ ą▒ąĖčé FSK ą╝ąŠąČąĮąŠ ą┐čĆąŠą┐ąŠčĆčåąĖąŠąĮą░ą╗čīąĮąŠ ą┐ąŠą▓čŗčüąĖčéčī ą▓ 1.5 čĆą░ąĘą░.

[ą×ą▒čēąĖąĄ ą▓čŗą▓ąŠą┤čŗ]

ąŻčéąĖą╗ąĖąĘą░čåąĖčÅ ą┐čĆąŠčåąĄčüčüąŠčĆąĮąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ čÅą┤čĆą░ AVR čüą▓ąĄą┤ąĄąĮą░ ą▓ čüą╗ąĄą┤čāčÄčēčāčÄ čéą░ą▒ą╗ąĖčåčā. ąæčŗą╗ čéą░ą║ąČąĄ ą┤ąŠą▒ą░ą▓ą╗ąĄąĮ čüč鹊ą╗ą▒ąĄčå ą┤ą╗čÅ čćą░čüč鹊čéčŗ čéą░ą║č鹊ą▓ CPU 20 ą£ąōčå, ą┐ąŠčüą║ąŠą╗čīą║čā ą╝ąĮąŠą│ąĖąĄ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčŗ AVR ą╝ąŠą│čāčé čĆą░ą▒ąŠčéą░čéčī ąĮą░ čéą░ą║ąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊č鹥.

ąóąĖą┐ ą┤ąĄą╝ąŠą┤čāą╗čÅč鹊čĆą░

|

ą¦ą░čüč鹊čéą░ ą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ

|

ąÜąŠą╗ąĖčć. ąĘą▓ąĄąĮčīąĄą▓ ąÜąśąź-čäąĖą╗čīčéčĆą░

|

ąÜąŠčŹčä. ą┐ąĄčĆąĄą┤ąĖčüą║čĆ. ą▓ąĮąĖąĘ

|

ąŚą░ą│čĆčāąĘą║ą░ čÅą┤čĆą░ (16 ą£ąōčå)

|

| 16 ą£ąōčå |

20 ą£ąōčå |

| AFSK |

6250 ąōčå |

- |

1 |

29.3% |

23.4% |

| AFSK čü ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ čäąĖą╗čīčéčĆą░čåąĖąĄą╣ |

12500 ąōčå |

15 |

2 |

61.9% |

49.5% |

| FSK ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ, ą▒ą╗ąĖąĘą║ąŠą╝ ą║ čāą╗čīčéčĆą░ąĘą▓čāą║čā |

50000 ąōčå |

9 |

8 |

66.6% |

53.3% |

ąŁčéąĖ čĆąĄąĘčāą╗čīčéą░čéčŗ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ą░čÄčé, čćč鹊 8-ą▒ąĖčéąĮąŠąĄ čÅą┤čĆąŠ AVR ą╝ąŠąČąĄčé ą┐čĆąĄą┤ąŠčüčéą░ą▓ąĖčéčī ą┤ąŠčüčéą░č鹊čćąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéąĖ ą┤ą░ąČąĄ ą┤ą╗čÅ ąĮąĄą║ąŠč鹊čĆąŠą╣ čåąĖčäčĆąŠą▓ąŠą╣ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ čüąĖą│ąĮą░ą╗ą░ ąĖ ąĮą░ą┐ąĖčüą░ąĮąĖčÅ ą║ąŠą┤ą░ ąĮą░ čÅąĘčŗą║ąĄ ą▓čŗčüąŠą║ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ. ąÆ čüą╗ąĄą┤čāčÄčēąĖą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ ą▒čāą┤ąĄč鹥 ą┐čĆąĖąĮąĖą╝ą░čéčī čĆąĄčłąĄąĮąĖąĄ, ą║ą░ą║ąŠą╣ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą▓čŗą▒čĆą░čéčī ą┤ą╗čÅ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ ą┐čĆąŠąĄą║čéą░, čĆą░čüčüą╝ąŠčéčĆąĖč鹥 ą▓ą░čĆąĖą░ąĮčé ą┐čĆąŠč鹊čéąĖą┐ą░ ąĮą░ ąŠčüąĮąŠą▓ąĄ 8-ą▒ąĖčéąĮąŠą│ąŠ AVR. ąĢą│ąŠ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéčī ą▓ą╝ąĄčüč鹥 čü ąĮąĖąĘą║ąĖą╝ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄą╝ ąĖ čåąĄąĮąŠą╣ ą┐ąŠąĘą▓ąŠą╗čÅčé ą▓ ą╝ąĮąŠą│ąĖčģ čüą╗čāčćą░čÅčģ čĆą░ąĘčĆą░ą▒ąŠčéą░čéčī ąŠč湥ąĮčī čŹčäč乥ą║čéąĖą▓ąĮąŠąĄ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ.

[ąĪą╗ąŠą▓ą░čĆąĖą║]

FIR Finite Impulse Response, čäąĖą╗čīčéčĆ čü ą║ąŠąĮąĄčćąĮąŠą╣ ąĖą╝ą┐čāą╗čīčüąĮąŠą╣ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąŠą╣, ąÜąśąź-čäąĖą╗čīčéčĆ.

[ąĪčüčŗą╗ą║ąĖ]

1. AN2701 Digital Signal Processing Performance of the 8-bit AVR Core site:microchip.com.

2. Specific Area Message Encoding site:swfltek.com.

3. ąÉą╗ą│ąŠčĆąĖčéą╝ ąōčæčĆčåąĄą╗čÅ site:wikipedia.org.

3. ąæąĖą▒ą╗ąĖąŠč鹥ą║ą░ DSP čĆąĄą░ą╗čīąĮąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ ą┤ą╗čÅ Arduino.

4. ą×ą▒čĆą░ą▒ąŠčéą║ą░ ąĘą▓čāą║ą░ ą▓ čĆąĄą░ą╗čīąĮąŠą╝ ą▓čĆąĄą╝ąĄąĮąĖ čü ą┐ąŠą╝ąŠčēčīčÄ Arduino.

5. AVR223: Digital Filters with AVR (čåąĖčäčĆąŠą▓čŗąĄ čäąĖą╗čīčéčĆčŗ ąĮą░ AVR).

6. AVR335: čåąĖčäčĆąŠą▓ąŠą╣ čĆąĄą║ąŠčĆą┤ąĄčĆ ąĘą▓čāą║ą░ ąĮą░ AVR ąĖ DataFlash.

7. ąŻą╗čāčćčłąĄąĮąĖąĄ ąŠčåąĖčäčĆąŠą▓ą║ąĖ čü ą┐ąŠą╝ąŠčēčīčÄ ą┐ąĄčĆąĄą┤ąĖčüą║čĆąĄčéąĖąĘą░čåąĖąĖ ąĖ čāčüčĆąĄą┤ąĮąĄąĮąĖčÅ.

8. FSK Demodulation in GNU Radio site:wirelesspi.com.

9. 230628AN2701.zip - ą┤ą░čéą░čłąĖčéčŗ, ą┤ąŠą║čāą╝ąĄąĮčéą░čåąĖčÅ. |