|

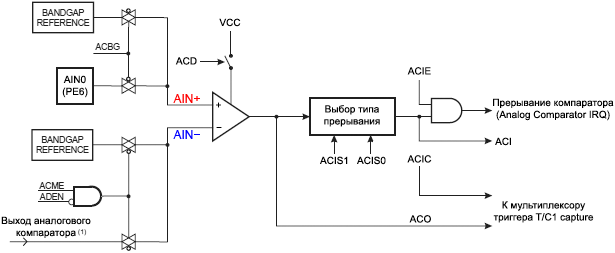

ąÆ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąĄ ATmega32U4 (ą░ čéą░ą║ąČąĄ ą▓ ąĄą│ąŠ čāčĆąĄąĘą░ąĮąĮąŠą╣ ą▓ąĄčĆčüąĖąĖ ATmega16U4) ą┐čĆąĖčüčāčéčüčéą▓čāąĄčé ą░ą┐ą┐ą░čĆą░čéąĮčŗą╣ čāąĘąĄą╗ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ (Analog Comparator). ą×ąĮ čüčĆą░ą▓ąĮąĖą▓ą░ąĄčé ą┤čĆčāą│ čü ą┤čĆčāą│ąŠą╝ ą▓čģąŠą┤ąĮčŗąĄ (ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮčŗąĄ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ GND) ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ čüąĖą│ąĮą░ą╗ąŠą▓ AIN+ (ąĮąĄ ąĖąĮą▓ąĄčĆčüąĮčŗą╣ ą▓čģąŠą┤) ąĖ AIN- (ąĖąĮą▓ąĄčĆčüąĮčŗą╣ ą▓čģąŠą┤). ąÜąŠą│ą┤ą░ čāčĆąŠą▓ąĄąĮčī ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ąĮą░ AIN+ ą▓čŗčłąĄ, č湥ą╝ čāčĆąŠą▓ąĄąĮčī ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ąĮą░ AIN-, čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▓ ą╗ąŠą│. 1 čāčĆąŠą▓ąĄąĮčī ąĮą░ ą▓čŗčģąŠą┤ąĄ Analog Comparator (čüąĖą│ąĮą░ą╗ ACO).

ąÆčŗčģąŠą┤ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĮą░čüčéčĆąŠąĄąĮ ą┤ą╗čÅ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖčÅ čäčāąĮą║čåąĖąĖ Input Capture čéą░ą╣ą╝ąĄčĆą░/čüč湥čéčćąĖą║ą░ 1 (Timer/Counter1). ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠ čüąĖą│ąĮą░ą╗ ąĮą░ ą▓čŗčģąŠą┤ąĄ Analog Comparator ą╝ąŠąČąĄčé ąĘą░ą┐čāčüą║ą░čéčī čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĄ ąŠčéą┤ąĄą╗čīąĮąŠą│ąŠ, čüą┐ąĄčåąĖą░ą╗čīąĮąŠ ą▓čŗą┤ąĄą╗ąĄąĮąĮąŠą│ąŠ ą▓ąĄą║č鹊čĆą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ą¤ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą╝ąŠąČąĄčé ą▓čŗą▒čĆą░čéčī ą╝ąŠą╝ąĄąĮčé čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ čäčĆąŠąĮčéčā ąĮą░čĆą░čüčéą░ąĮąĖčÅ čāčĆąŠą▓ąĮčÅ ACO, ą┐ąŠ ąĄą│ąŠ čüą┐ą░ą┤čā ąĖą╗ąĖ ą┐ąŠ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÄ ą▓ ą┐čĆąŠčéąĖą▓ąŠą┐ąŠą╗ąŠąČąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ. ąæą╗ąŠą║-čüčģąĄą╝ą░ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ ąĖ ąĄą│ąŠ ąŠą║čĆčāąČą░čÄčēąĄą╣ ą╗ąŠą│ąĖą║ąĖ ą┐ąŠą║ą░ąĘą░ąĮą░ ąĮą░ čĆąĖčü. 23-1.

ąĀąĖčü. 23-1. ąæą╗ąŠą║ čüčģąĄą╝ą░ Analog Comparator(2).

ą¤čĆąĖą╝ąĄčćą░ąĮąĖčÅ:

1. ąĪą╝. čéą░ą▒ą╗ąĖčåčā 23-2 ąĮąĖąČąĄ.

2. ąĪą╝. čĆą░ąĘą▓ąŠą┤ą║čā ą▓čŗą▓ąŠą┤ąŠą▓ ąĮą░ ą║ą░čĆčéąĖąĮą║ąĄ ąĮąĖąČąĄ, ąĖ čéą░ą▒ą╗ąĖčåčā 10-3 ąĖąĘ ą┤ą░čéą░čłąĖčéą░ [1], ą│ą┤ąĄ ą┐ąŠą║ą░ąĘą░ąĮąŠ čĆą░ąĘą╝ąĄčēąĄąĮąĖąĄ ą▓čŗą▓ąŠą┤ąŠą▓ Analog Comparator.

ąĪąĖą│ąĮą░ą╗ AIN+ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą╗ąĖą▒ąŠ ą║ ą▓ąĮąĄčłąĮąĄą╝čā ą▓čŗą▓ąŠą┤čā AIN0 (ąĮąŠąČą║ą░ ą┐ąŠčĆčéą░ PE6), ąĖą╗ąĖ ą║ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╝čā ąŠą┐ąŠčĆąĮąŠą╝čā ąĮą░ą┐čĆčÅąČąĄąĮąĖčÄ Bandgap. ąĪąĖą│ąĮą░ą╗ AIN- ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮ č鹊ą╗čīą║ąŠ ą║ ą▓čŗčģąŠą┤čā ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąŠčĆą░ ADC (ąÉą”ą¤).

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▓ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąĄ ATmega16U4/ATmega32U4 ąĖą╝ąĄąĄčéčüčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ ąĖčüč鹊čćąĮąĖą║ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ, čéą░ą║ ąĮą░ąĘčŗą▓ą░ąĄą╝čŗą╣ čŹčéą░ą╗ąŠąĮąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī ąĘą░ą┐čĆąĄčēąĄąĮąĮąŠą╣ ąĘąŠąĮčŗ (bandgap). ąŁč鹊čé ąĖčüč鹊čćąĮąĖą║ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čäčāąĮą║čåąĖąĖ ą▓čŗčģąŠą┤ą░ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ ąĘą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╣ ą┐čĆąĄą┤ąĄą╗ (Brown-out Detection), ąĖ ąŠąĮ čéą░ą║ąČąĄ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą║ą░ą║ ąŠą┐ąŠčĆąĮčŗą╣ ą▓čģąŠą┤ąĮąŠą╣ čāčĆąŠą▓ąĄąĮčī ą┤ą╗čÅ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ ąĖą╗ąĖ ąÉą”ą¤ (ADC). ą£ąĖąĮąĖą╝ą░ą╗čīąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ bandgap čüąŠčüčéą░ą▓ą╗čÅąĄčé 1.0V, ąĮąŠą╝ąĖąĮą░ą╗čīąĮčŗą╣ 1.1V, ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮčŗą╣ 1.2V.

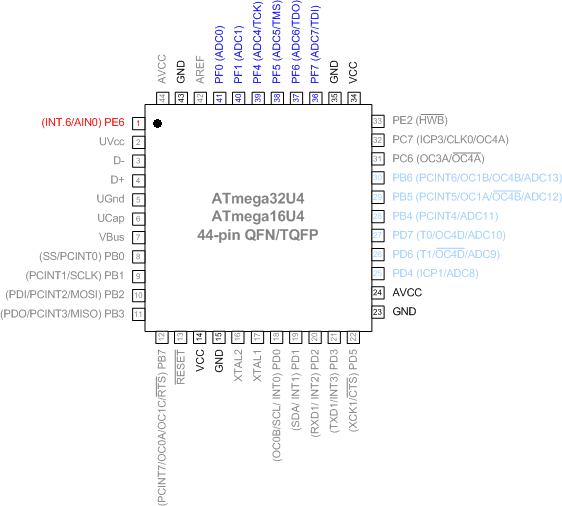

ąĀą░čüą┐ąŠą╗ąŠąČąĄąĮąĖąĄ ą▓čŗą▓ąŠą┤ąŠą▓, ą║ ą║ąŠč鹊čĆčŗą╝ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮ Analog Comparator, ąĮą░ ą║ąŠčĆą┐čāčüąĄ QFN44/TQFP44 ATmega32U4:

ąÆ čŹč鹊ą╣ ą▓čĆąĄąĘą║ąĄ ą┐ąŠą║ą░ąĘą░ąĮčŗ ą▓čŗą▓ąŠą┤čŗ, ą║ąŠč鹊čĆčŗąĄ ąĖą╝ąĄčÄčé ąŠčéąĮąŠčłąĄąĮąĖąĄ ą║ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆčā (ą╝ąŠą│čāčé ą┤ą╗čÅ ąĮąĄą│ąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ).

[ą¤ąŠčĆčéčŗ PB]

| ą¤ąŠčĆčé |

ąÉą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčŗąĄ čäčāąĮą║čåąĖąĖ |

| PB6 |

OC1B/PCINT6/OC.4B/ADC13 (ą▓čŗčģąŠą┤ Output Compare ąĖ PWM B ą┤ą╗čÅ Timer/Counter1, ąĖą╗ąĖ Pin Change Interrupt 6, ąĖą╗ąĖ ą▓čŗčģąŠą┤ Timer 4 Compare B / PWM, ąĖą╗ąĖ ą║ą░ąĮą░ą╗ 13 ąÉą”ą¤) |

| PB5 |

OC1A/PCINT5/~OC.4B/ADC12 (ą▓čŗčģąŠą┤ Output Compare ąĖ PWM A ą┤ą╗čÅ Timer/Counter1, ąĖą╗ąĖ Pin Change Interrupt 5, ąĖą╗ąĖ ą║ąŠą╝ą┐ą╗ąĄą╝ąĄąĮčéą░čĆąĮčŗą╣ ą▓čŗčģąŠą┤ Timer 4 Compare B / PWM, ąĖą╗ąĖ ą║ą░ąĮą░ą╗ 12 ąÉą”ą¤) |

| PB4 |

PCINT4/ADC11 (Pin Change Interrupt 4 ąĖą╗ąĖ ą║ą░ąĮą░ą╗ 11 ąÉą”ą¤) |

[ą¤ąŠčĆčéčŗ PD]

| ą¤ąŠčĆčé |

ąÉą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčŗąĄ čäčāąĮą║čåąĖąĖ |

| PD7 |

T0/OC.4D/ADC10 (ą▓čģąŠą┤ čéą░ą║č鹊ą▓ Timer/Counter0, ąĖą╗ąĖ ą▓čŗčģąŠą┤ Timer 4 Compare D / PWM, ąĖą╗ąĖ ą║ą░ąĮą░ą╗ 10 ąÉą”ą¤) |

| PD6 |

T1/~OC.4D/ADC9 (ą▓čģąŠą┤ čéą░ą║č鹊ą▓ Timer/Counter1, ąĖą╗ąĖ ą║ąŠą╝ą┐ą╗ąĄą╝ąĄąĮčéą░čĆąĮčŗą╣ ą▓čŗčģąŠą┤ Timer 4 Compare D / PWM, ąĖą╗ąĖ ą║ą░ąĮą░ą╗ 9 ąÉą”ą¤) |

| PD4 |

ICP1/ADC8 (čéčĆąĖą│ą│ąĄčĆ Timer/Counter1 Input Capture, ąĖą╗ąĖ ą║ą░ąĮą░ą╗ 8 ąÉą”ą¤) |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: čüą║ąŠčĆąĄąĄ ą▓čüąĄą│ąŠ, ą┐ąŠčĆčéčŗ PB ąĖ PD ą┤ą╗čÅ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ąĮąĄą╗čīąĘčÅ, čüą╝. čéą░ą▒ą╗ąĖčåčā 23-2 ąĖ ą┐čĆąĖą╝ąĄčćą░ąĮąĖąĄ ą┐ąŠčüą╗ąĄ ąĮąĄčæ.

[ą¤ąŠčĆčé PE6]

| ą¤ąŠčĆčé |

ąÉą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčŗąĄ čäčāąĮą║čåąĖąĖ |

| PE6 |

INT6/AIN0 (ą▓čģąŠą┤ External Interrupt 6, ąĖą╗ąĖ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮčŗą╣, ąĮąĄ ąĖąĮą▓ąĄčĆčüąĮčŗą╣ ą▓čģąŠą┤ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░) |

[ą¤ąŠčĆčéčŗ PF]

| ą¤ąŠčĆčé |

ąÉą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčŗąĄ čäčāąĮą║čåąĖąĖ |

| PF7 |

ADC7/TDI (ą║ą░ąĮą░ą╗ 7 ąÉą”ą¤ ąĖą╗ąĖ JTAG TDI) |

| PF6 |

ADC6/TDO (ą║ą░ąĮą░ą╗ 6 ąÉą”ą¤ ąĖą╗ąĖ JTAG TDO) |

| PF5 |

ADC5/TMS (ą║ą░ąĮą░ą╗ 5 ąÉą”ą¤ ąĖą╗ąĖ JTAG TMS) |

| PF4 |

ADC4/TCK (ą║ą░ąĮą░ą╗ 4 ąÉą”ą¤ ąĖą╗ąĖ JTAG TCK) |

| PF1 |

ADC1 (ą║ą░ąĮą░ą╗ 1 ąÉą”ą¤) |

| PF0 |

ADC0 (ą║ą░ąĮą░ą╗ 0 ąÉą”ą¤) |

[ą×ą┐ąĖčüą░ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆąŠą▓ ąĖ ą▒ąĖčé, ąŠčéąĮąŠčüčÅčēąĖčģčüčÅ ą║ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆčā]

ADC Control and Status Register B ŌĆō ADCSRB

| ąĀą░ąĘčĆčÅą┤ |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

| |

ADHSM |

ACME |

MUX5 |

- |

ADTS3 |

ADTS2 |

ADTS1 |

ADTS0 |

ADCSRB |

| ą¦č鹥ąĮąĖąĄ/ąĘą░ą┐ąĖčüčī |

R |

R/W |

R/W |

R |

R |

R/W |

R/W |

R/W |

|

| ąśčüčģ. ąĘąĮą░č湥ąĮąĖąĄ |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

ąæąĖčé 6 ACME: Analog Comparator Multiplexer Enable

ąÜąŠą│ą┤ą░ ą▓ ACME ąĘą░ą┐ąĖčüą░ąĮą░ ą╗ąŠą│. 1, ąĖ ADC ą▓čŗą║ą╗čÄč湥ąĮ (ADEN ą▓ čĆąĄą│ąĖčüčéčĆąĄ ADCSRA čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ ą╗ąŠą│. 0), ą▓čŗčģąŠą┤ ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąŠčĆą░ ADC ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą║ ąĖąĮą▓ąĄčĆčüąĮąŠą╝čā ą▓čģąŠą┤čā AIN- ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░. ąÜąŠą│ą┤ą░ ą▓ ACME ąĘą░ą┐ąĖčüą░ąĮ ą╗ąŠą│. 0, ąĮą░ čŹč鹊čé ą▓čģąŠą┤ AIN- ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ ą┐ąŠą┤ą║ą╗čÄč湥ąĮą░ ąĖčüč鹊čćąĮąĖą║ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ Bandgap (čüą╝. čĆą░ąĘą┤ąĄą╗ "Internal Voltage Reference" ą┤ą░čéą░čłąĖčéą░ [1]). ą¤ąŠą┤čĆąŠą▒ąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ čŹč鹊ą│ąŠ ą▒ąĖčéą░ čüą╝. ąĮąĖąČąĄ ą▓ čĆą░ąĘą┤ąĄą╗ąĄ "ą£čāą╗čīčéąĖą┐ą╗ąĄą║čüąĖčĆąŠą▓ą░ąĮąĮčŗą╣ ą▓čģąŠą┤ Analog Comparator".

Analog Comparator Control and Status Register ŌĆō ACSR

| ąĀą░ąĘčĆčÅą┤ |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

| |

ACD |

ACBG |

ACO |

ACI |

ACIE |

ACIC |

ACIS1 |

ACIS0 |

ADCSRB |

| ą¦č鹥ąĮąĖąĄ/ąĘą░ą┐ąĖčüčī |

R/W |

R/W |

R |

R/W |

R/W |

R/W |

R/W |

R/W |

|

| ąśčüčģ. ąĘąĮą░č湥ąĮąĖąĄ |

0 |

0 |

N/A |

0 |

0 |

0 |

0 |

0 |

|

ąæąĖčé 7 ACD: Analog Comparator Disable

ąÜąŠą│ą┤ą░ čŹč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ ą╗ąŠą│. 1, ą┐ąĖčéą░ąĮąĖąĄ Analog Comparator ą▓čŗą║ą╗čÄč湥ąĮąŠ. ąŁč鹊čé ą▒ąĖčé ą╝ąŠąČąĄčé ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ ą╗čÄą▒ąŠąĄ ą▓čĆąĄą╝čÅ čü čåąĄą╗čīčÄ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ Analog Comparator, čćč鹊 čüąĮąĖąĘąĖčé ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ ą╝ąŠčēąĮąŠčüčéąĖ ą▓ čĆąĄąČąĖą╝ą░čģ Active ąĖ Idle. ąÜąŠą│ą┤ą░ ą╝ąĄąĮčÅąĄčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčéą░ ACD, ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ Analog Comparator ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ąĘą░ą┐čĆąĄčēąĄąĮąŠ ąŠčćąĖčüčéą║ąŠą╣ ą▒ąĖčéą░ ACIE ą▓ čĆąĄą│ąĖčüčéčĆąĄ ACSR. ąÆ ą┐čĆąŠčéąĖą▓ąĮąŠą╝ čüą╗čāčćą░ąĄ ą┐čĆąĖ ąĖąĘą╝ąĄąĮąĄąĮąĖąĖ ą▒ąĖčéą░ ACD ą╝ąŠąČąĄčé ą┐čĆąŠąĖąĘąŠą╣čéąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░.

ąæąĖčé 6 ACBG: Analog Comparator Bandgap Select

ąÜąŠą│ą┤ą░ čŹč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮąŠąĄ ąŠą┐ąŠčĆąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ (fixed bandgap reference) ąĘą░ą╝ąĄąĮčÅąĄčé čāčĆąŠą▓ąĄąĮčī ąĮą░ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą╝ ą▓čģąŠą┤ąĄ AIN+ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░. ąÜąŠą│ą┤ą░ čŹč鹊čé ą▒ąĖčé ąŠčćąĖčēąĄąĮ, AIN0 ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą║ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą╝čā ą▓čģąŠą┤čā AIN+ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░. ąĪą╝. čĆą░ąĘą┤ąĄą╗ "Internal Voltage Reference" ą┤ą░čéą░čłąĖčéą░ [1].

ąæąĖčé 5 ACO: Analog Comparator Output

ąŁč鹊čé ą▒ąĖčé ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆąŠą▓ą░ąĮąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ąĮą░ ą▓čŗčģąŠą┤ąĄ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░. ąŚą░ą┤ąĄčƹȹ║ą░ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ čüąŠčüčéą░ą▓ą╗čÅąĄčé 1 ąĖą╗ąĖ 2 čéą░ą║čéą░ čÅą┤čĆą░.

ąæąĖčé 4 ACI: Analog Comparator Interrupt Flag

ąŁč鹊čé ą▒ąĖčé čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé čüąŠą▒čŗčéąĖąĄ ąĖąĘą╝ąĄąĮąĄąĮąĖąĄ čāčĆąŠą▓ąĮčÅ ąĮą░ ą▓čŗčģąŠą┤ąĄ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü čĆąĄąČąĖą╝ąŠą╝, ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗą╝ ą▒ąĖčéą░ą╝ąĖ ACIS1 ąĖ ACIS0. ą×ą▒čĆą░ą▒ąŠčéčćąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (ISR) Analog Comparator ą▓čŗą┐ąŠą╗ąĮąĖčéčüčÅ, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé ACIE ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ I-ą▒ąĖčé (ą│ą╗ąŠą▒ą░ą╗čīąĮąŠąĄ čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣) ą▓ čĆąĄą│ąĖčüčéčĆąĄ SREG. ACI ąŠčćąĖčēą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ, ą║ąŠą│ą┤ą░ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▓ąĄą║č鹊čĆ ISR. ąÉą╗čīč鹥čĆąĮą░čéąĖą▓ąĮąŠ ACI ąŠčćąĖčēą░ąĄčéčüčÅ ąĘą░ą┐ąĖčüčīčÄ ą▓ ąĮąĄą│ąŠ ą╗ąŠą│. 1.

ąæąĖčé 3 ACIE: Analog Comparator Interrupt Enable

ąÜąŠą│ą┤ą░ ą▓ ą▒ąĖčé ACIE ąĘą░ą┐ąĖčüą░ąĮą░ ą╗ąŠą│. 1, ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ I-ą▒ąĖčé ą▓ Status Register (SREG), ą░ą║čéąĖą▓ąĖčĆčāąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ Analog Comparator. ąÜąŠą│ą┤ą░ ą▓ ACIE ąĘą░ą┐ąĖčüą░ąĮ ą╗ąŠą│. 0, ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ ąĘą░ą┐čĆąĄčēą░ąĄčéčüčÅ.

ąæąĖčé 2 ACIC: Analog Comparator Input Capture Enable

ąÜąŠą│ą┤ą░ ą▓ čŹč鹊čé ą▒ąĖčé ąĘą░ą┐ąĖčüą░ąĮą░ ą╗ąŠą│. 1, č鹊 čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ čäčāąĮą║čåąĖčÅ ąĘą░čģą▓ą░čéą░ ą┐ąŠ ą▓čģąŠą┤čā čéą░ą╣ą╝ąĄčĆą░ 1 (input capture Timer/Counter1), ąĘą░ą┐čāčüą║ą░ąĄą╝ą░čÅ ąŠčé ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ą▓čŗčģąŠą┤ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ ąĮą░ą┐čĆčÅą╝čāčÄ ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčéčüčÅ ą║ ą╗ąŠą│ąĖą║ąĄ input capture, čü ą┐čĆąĖą╝ąĄąĮąĄąĮąĖąĄą╝ čäčāąĮą║čåąĖą╣ ą┐ąŠą┤ą░ą▓ą╗ąĄąĮąĖčÅ čłčāą╝ą░ (noise canceler) ąĖ ą▓čŗą▒ąŠčĆą░ ą┐ąĄčĆąĄą┐ą░ą┤ą░ (edge select) ą┤ą╗čÅ Timer/Counter1 Input Capture interrupt. ąÜąŠą│ą┤ą░ ą▓ ą▒ąĖčé ACIC ąĘą░ą┐ąĖčüą░ąĮ ą╗ąŠą│. 0, ąŠčéčüčāčéčüčéą▓čāąĄčé čüąŠąĄą┤ąĖąĮąĄąĮąĖąĄ ą╝ąĄąČą┤čā ą▓čŗčģąŠą┤ąŠą╝ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ ąĖ čäčāąĮą║čåąĖąĄą╣ ą▓čģąŠą┤ą░ ąĘą░čģą▓ą░čéą░. ą¦č鹊ą▒čŗ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆ ą▓čŗąĘčŗą▓ą░ą╗ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ Timer/Counter1 Input Capture, ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé ICIE1 ą▓ Timer Interrupt Mask Register (TIMSK1).

ąæąĖčéčŗ 1 ąĖ 0, ACIS1, ACIS0: Analog Comparator Interrupt Mode Select

ąŁčéąĖ ą▒ąĖčéčŗ ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčé, ą║ą░ą║ąŠąĄ ąĖąĘ čüąŠą▒čŗčéąĖą╣ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ čāčĆąŠą▓ąĮčÅ ąĮą░ ą▓čŗčģąŠą┤ąĄ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖčÄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ Analog Comparator. ąÆ čéą░ą▒ą╗ąĖčåąĄ ąĮąĖąČąĄ ą┐ąĄčĆąĄčćąĖčüą╗ąĄąĮčŗ ą▓ąŠąĘą╝ąŠąČąĮčŗąĄ ąĮą░čüčéčĆąŠą╣ą║ąĖ ą┤ą╗čÅ čŹčéąĖčģ ą▒ąĖčé.

ąóą░ą▒ą╗ąĖčåą░ 23-1. ąæąĖčéčŗ ACIS1/ACIS0, ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčēąĖąĄ čüąŠą▒čŗčéąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĮą░ ą▓čŗčģąŠą┤ąĄ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆąĄ.

| ACIS1 |

ACIS0 |

ąĀąĄąČąĖą╝ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ |

| 0 |

0 |

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čüčĆą░ą▒ą░čéčŗą▓ą░ąĄčé ą┐čĆąĖ ąĖąĘą╝ąĄąĮąĄąĮąĖąĖ ą╗ąŠą│. čāčĆąŠą▓ąĮčÅ ąĮą░ ą▓čŗčģąŠą┤ąĄ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░. |

| 0 |

1 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

| 1 |

0 |

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐čĆąĖ čüą┐ą░ą┤ąĄ čāčĆąŠą▓ąĮčÅ ąĮą░ ą▓čŗčģąŠą┤ąĄ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ (ą┐ąĄčĆąĄčģąŠą┤ 1 -> 0). |

| 1 |

1 |

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐čĆąĖ ąĮą░čĆą░čüčéą░ąĮąĖąĖ čāčĆąŠą▓ąĮčÅ ąĮą░ ą▓čŗčģąŠą┤ąĄ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ (ą┐ąĄčĆąĄčģąŠą┤ 0 -> 1). |

ąÜąŠą│ą┤ą░ ą╝ąĄąĮčÅčÄčéčüčÅ ą▒ąĖčéčŗ ACIS1/ACIS0, ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ąĘą░ą┐čĆąĄčēąĄąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ Analog Comparator ą┐čāč鹥ą╝ ąŠčćąĖčüčéą║ąĖ ą▒ąĖčéą░ ACIE ą▓ čĆąĄą│ąĖčüčéčĆąĄ ACSR. ąÆ ą┐čĆąŠčéąĖą▓ąĮąŠą╝ čüą╗čāčćą░ąĄ ą╝ąŠąČąĄčé ą┐čĆąŠąĖąĘąŠą╣čéąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░.

Digital Input Disable Register 1 ŌĆō DIDR1

| ąĀą░ąĘčĆčÅą┤ |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

| |

- |

- |

- |

- |

- |

- |

- |

AIN0D |

ADCSRB |

| ą¦č鹥ąĮąĖąĄ/ąĘą░ą┐ąĖčüčī |

R |

R |

R |

R |

R |

R |

R |

R/W |

|

| ąśčüčģ. ąĘąĮą░č湥ąĮąĖąĄ |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

ąæąĖčé 0 AIN0D: AIN0 Digital Input Disable

ąÜąŠą│ą┤ą░ ą▓ čŹč鹊čé ą▒ąĖčé ąĘą░ą┐ąĖčüą░ąĮą░ ą╗ąŠą│. 1, č鹊 ąĘą░ą┐čĆąĄčēą░ąĄčéčüčÅ ą▓čģąŠą┤ąĮąŠą╣ čåąĖčäčĆąŠą▓ąŠą╣ ą▒čāč乥čĆ ą▓čŗą▓ąŠą┤ą░ AIN0. ąĪąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé čĆąĄą│ąĖčüčéčĆą░ PIN ą▒čāą┤ąĄčé ą▓čüąĄą│ą┤ą░ čćąĖčéą░čéčīčüčÅ ą║ą░ą║ 0, ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé AIN0D. ąÜąŠą│ą┤ą░ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗą╣ čüąĖą│ąĮą░ą╗ ą┐čĆąĖą║ą╗ą░ą┤čŗą▓ą░ąĄčéčüčÅ ą║ ą▓čŗą▓ąŠą┤čā AIN0, ąĖ ąĮąĄ čéčĆąĄą▒čāąĄčéčüčÅ ą┐ąŠą┤ą░čćą░ čåąĖčäčĆąŠą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ čü čŹč鹊ą│ąŠ ą▓čŗą▓ąŠą┤ą░, ą▓ ą▒ąĖčé AIN0D čüą╗ąĄą┤čāąĄčé ąĘą░ą┐ąĖčüą░čéčī ą╗ąŠą│. 1, čćč鹊ą▒čŗ čāą╝ąĄąĮčīčłąĖčéčī ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ ą╝ąŠčēąĮąŠčüčéąĖ ą▓ čåąĖčäčĆąŠą▓ąŠą╝ ą▓čģąŠą┤ąĮąŠą╝ ą▒čāč乥čĆąĄ.

[ą£čāą╗čīčéąĖą┐ą╗ąĄą║čüąĖčĆąŠą▓ą░ąĮąĮčŗą╣ ą▓čģąŠą┤ Analog Comparator]

ą£ąŠąČąĮąŠ ą▓čŗą▒čĆą░čéčī ą╗čÄą▒ąŠą╣ ąĖąĘ ą▓čŗą▓ąŠą┤ąŠą▓ ADC13..0 (ą║čĆąŠą╝ąĄ ADC2 ąĖ ADC4, čŹčéąĖčģ ą▓čģąŠą┤ąŠą▓ ąĮąĄčé ąĮą░ ą║ąŠčĆą┐čāčüąĄ čćąĖą┐ą░), čćč鹊ą▒čŗ ą┐ąŠą┤ą░čéčī čü ąĮąĖčģ čüąĖą│ąĮą░ą╗ ąĮą░ ąĖąĮą▓ąĄčĆčüąĮčŗą╣ ą▓čģąŠą┤ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ AIN-. ą£čāą╗čīčéąĖą┐ą╗ąĄą║čüąŠčĆ ADC ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą░ čŹč鹊ą│ąŠ ą▓čģąŠą┤ą░, čéą░ą║ čćč鹊 ą┤ą╗čÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ čŹč鹊ą╣ čäčāąĮą║čåąĖąĖ ADC ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą▓čŗą║ą╗čÄč湥ąĮąŠ. ąĢčüą╗ąĖ ą▒ąĖčé Analog Comparator Multiplexer Enable (ACME ą▓ čĆąĄą│ąĖčüčéčĆąĄ ADCSRB) čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ąĖ ADC ą▓čŗą║ą╗čÄč湥ąĮ (ADEN ą▓ čĆąĄą│ąĖčüčéčĆąĄ ADCSRA ą▓ ą╗ąŠą│. 0), č鹊 ą▒ąĖčéčŗ MUX2..0 ą▓ ADMUX ą▓čŗą▒ąĖčĆą░čÄčé ą▓čģąŠą┤ąĮąŠą╣ ą▓čŗą▓ąŠą┤, čćč鹊ą▒čŗ ąĘą░ą╝ąĄąĮąĖčéčī ąĄą│ąŠ čāčĆąŠą▓ąĮąĄą╝ čüąĖą│ąĮą░ą╗ ąĮą░ ąĖąĮą▓ąĄčĆčüąĮąŠą╝ ą▓čģąŠą┤ąĄ Analog Comparator, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▓ čéą░ą▒ą╗ąĖčåąĄ ąĮąĖąČąĄ. ąĢčüą╗ąĖ ą▒ąĖčé ACME ąŠčćąĖčēąĄąĮ, ąĖą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé ADEN, č鹊 ąĮą░ ąĖąĮą▓ąĄčĆčüąĮčŗą╣ ą▓čģąŠą┤ Analog Comparator ą┐ąŠą┤ą░ąĄčéčüčÅ ąŠą┐ąŠčĆąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ (Bandgap reference).

ąóą░ą▒ą╗ąĖčåą░ 23-2. ą£čāą╗čīčéąĖą┐ą╗ąĄą║čüąĖčĆąŠą▓ą░ąĮąĖąĄ ą▓čģąŠą┤ą░ Analog Comparator.

| ACME |

ADEN |

MUX2..0 |

ąśąĮą▓ąĄčĆčüąĮčŗą╣ ą▓čģąŠą┤ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆą░ (AIN-) |

| 0 |

x |

xxx |

ą×ą┐ąŠčĆąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī Bandgap. |

| 1 |

1 |

xxx |

ą×ą┐ąŠčĆąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī Bandgap. |

| 1 |

0 |

000 |

ADC0 |

| 001 |

ADC1 |

| 010 |

ąØąĄ ą┐čĆąĖą╝ąĄąĮąĖą╝ąŠ |

| 011 |

| 100 |

ADC4 |

| 101 |

ADC5 |

| 110 |

ADC6 |

| 111 |

ADC7 |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▓ ą┐čĆąĄą┤čŗą┤čāčēąĄą╝ ą┐čĆąĄą┤ą╗ąŠąČąĄąĮąĖąĖ ąŠčłąĖą▒ą║ą░, ą┐ąŠč鹊ą╝čā čćč鹊 čāčéą▓ąĄčƹȹ┤ąĄąĮąĖąĄ, čćč鹊 ą▓čŗą▒ąŠčĆ ą▓čģąŠą┤ą░ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą▒ąĖčéą░ą╝ąĖ MUX2..0 (čćč鹊 čéą░ą║ąČąĄ ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▓ čéą░ą▒ą╗ąĖčåąĄ 23-2) ą┐čĆąŠčéąĖą▓ąŠčĆąĄčćąĖčé čü č鹥ą╝, čćč鹊 čÅą║ąŠą▒čŗ ą╝ąŠąČąĮąŠ ą▓čŗą▒čĆą░čéčī ą╗čÄą▒ąŠą╣ ąĖąĘ ą▓čŗą▓ąŠą┤ąŠą▓ ADC13..0.

[ąĪčüčŗą╗ą║ąĖ]

1. ATmega16U4/ATmega32U4 DATASHEET site:microchip.com.

2. ATmega16 (32): ą░ąĮą░ą╗ąŠą│ąŠ-čåąĖčäčĆąŠą▓ąŠą╣ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░č鹥ą╗čī (ADC). |