|

ą¤ąĄčĆąĄą▓ąŠą┤ ą┤ą░čéą░čłąĖčéą░ Atmel ąĮą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ATmega16, ATmega32, ą║ą░čüą░čÄčēąĖą╣čüčÅ ADC.

[ą×čéą╗ąĖčćąĖč鹥ą╗čīąĮčŗąĄ ąŠčüąŠą▒ąĄąĮąĮąŠčüčéąĖ]

- 10-čĆą░ąĘčĆčÅą┤ąĮąŠąĄ čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ

- ąśąĮč鹥ą│čĆą░ą╗čīąĮą░čÅ ąĮąĄą╗ąĖąĮąĄą╣ąĮąŠčüčéčī 0.5 ą╝ą╗. čĆą░ąĘčĆ.

- ąÉą▒čüąŠą╗čÄčéąĮą░čÅ ą┐ąŠą│čĆąĄčłąĮąŠčüčéčī ┬▒2 ą╝ą╗. čĆą░ąĘčĆ.

- ąÆčĆąĄą╝čÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ 13 - 260 ą╝ą║čü.

- ą¦ą░čüč鹊čéą░ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą┤ąŠ 15 čéčŗčü. ą┐čĆąĄąŠą▒čĆ. ą▓ čüąĄą║. ą┐čĆąĖ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą╝ čĆą░ąĘčĆąĄčłąĄąĮąĖąĖ

- 8 ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąĖčĆąŠą▓ą░ąĮąĮčŗčģ ąŠą┤ąĮąŠą┐ąŠą╗čÅčĆąĮčŗčģ ą║ą░ąĮą░ą╗ąŠą▓ (ą▓čģąŠą┤ąŠą▓)

- 7 ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗčģ ą║ą░ąĮą░ą╗ąŠą▓ (ą▓čģąŠą┤ąŠą▓)

2 ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗčģ ą║ą░ąĮą░ą╗ą░ (ą▓čģąŠą┤ą░) čü ą┐ąŠą┤ą║ą╗čÄčćą░ąĄą╝čŗą╝ čāčüąĖą╗ąĄąĮąĖąĄą╝ ąĮą░ 10 ąĖ 200

- ą¤čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮąĖąĄ čĆąĄąĘčāą╗čīčéą░čéą░ čü ą╗ąĄą▓ąŠčüč鹊čĆąŠąĮąĮąĖą╝ ąĖą╗ąĖ ą┐čĆą░ą▓ąŠčüč鹊čĆąŠąĮąĮąĖą╝ ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖąĄą╝ ą▓ 16-čĆą░ąĘčĆ. čüą╗ąŠą▓ąĄ

- ąöąĖą░ą┐ą░ąĘąŠąĮ ą▓čģąŠą┤ąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ADC 0ŌĆ”VCC

- ąÆčŗą▒ąŠčĆąŠčćąĮčŗą╣ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ ąśą×ąØ (Reference Voltage) ąĮą░ 2.56 ąÆ

- ąĀąĄąČąĖą╝čŗ ąŠą┤ąĖąĮąŠčćąĮąŠą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ąĖ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą│ąŠ ą┐ąĄčĆąĄąĘą░ą┐čāčüą║ą░

- ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ADC

- ą£ąĄčģą░ąĮąĖąĘą╝ ą┐ąŠą┤ą░ą▓ą╗ąĄąĮąĖčÅ čłčāą╝ąŠą▓ ą▓ čĆąĄąČąĖą╝ąĄ čüąĮą░

ąŚą░ą╝ąĄčćą░ąĮąĖąĄ: ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗąĄ ą║ą░ąĮą░ą╗čŗ ąĮąĄ č鹥čüčéąĖčĆąŠą▓ą░ą╗ąĖčüčī ą┤ą╗čÅ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ ą▓ ą║ąŠčĆą┐čāčüąĄ PDIP40. ąĀą░ą▒ąŠčéą░ ą▓ čéą░ą║ąŠą╝ čĆąĄąČąĖą╝ąĄ ą│ą░čĆą░ąĮčéąĖčĆčāąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ ą▓ ą║ąŠčĆą┐čāčüą░čģ TQFP ąĖ QFN/MLF.

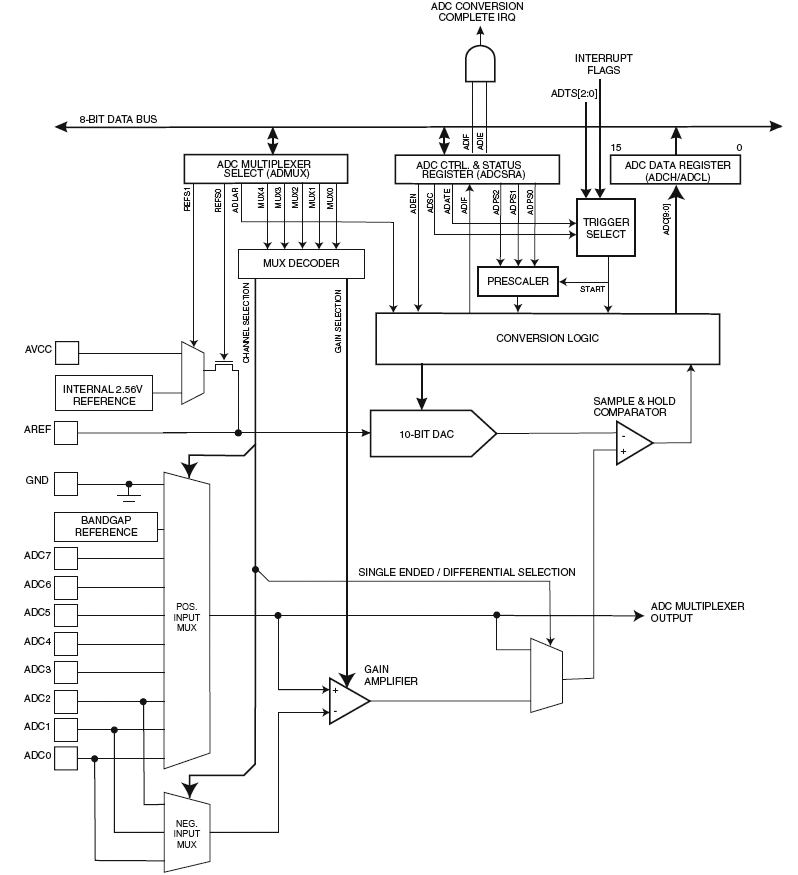

ATmega16 čüąŠą┤ąĄčƹȹĖčé 10-čĆą░ąĘčĆ. ADC ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ą┐čĆąĖą▒ą╗ąĖąČąĄąĮąĖčÅ. ADC čüą▓čÅąĘą░ąĮ čü 8-ą║ą░ąĮą░ą╗čīąĮčŗą╝ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗą╝ ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąŠčĆąŠą╝, 8 ąŠą┤ąĮąŠą┐ąŠą╗čÅčĆąĮčŗčģ (ąĮąĄą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗčģ) ą▓čģąŠą┤ąŠą▓ ą║ąŠč鹊čĆąŠą│ąŠ čüą▓čÅąĘą░ąĮčŗ čü ąĮąŠąČą║ą░ą╝ąĖ ą┐ąŠčĆčéą░ A. ąØąĄą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗąĄ ą▓čģąŠą┤čŗ ąĖąĘą╝ąĄčĆčÅčÄčé ą┐ąŠč鹥ąĮčåąĖą░ą╗ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ą┐čĆąŠą▓ąŠą┤ą░ 0 ąÆ (čé. ąĄ. čüą▓čÅąĘą░ąĮąĮąŠą│ąŠ čü GND).

ADC čéą░ą║ąČąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé 16 ą▓ą░čĆąĖą░ąĮč鹊ą▓ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą┤ą╗čÅ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗčģ ą▓čģąŠą┤ąŠą▓. ąöą▓ą░ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗčģ ą▓čģąŠą┤ą░ (ADC1, ADC0 ąĖ ADC3, ADC2) čüąŠą┤ąĄčƹȹ░čé ą║ą░čüą║ą░ą┤ čüąŠ čüčéčāą┐ąĄąĮčćą░čéčŗą╝ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗą╝ čāčüąĖą╗ąĄąĮąĖąĄą╝: 0 ą┤ąæ (1x), 20 ą┤ąæ (10x), ąĖą╗ąĖ 46 ą┤ąæ (200x) ŌĆō ąĮąĄą┐ąŠčüčĆąĄą┤čüčéą▓ąĄąĮąĮąŠ ą┐ąĄčĆąĄą┤ ą░ąĮą░ą╗ąŠą│ąŠ-čåąĖčäčĆąŠą▓čŗą╝ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄą╝. ąĪąĄą╝čī ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗčģ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗčģ ą║ą░ąĮą░ą╗ąŠą▓ ąĖčüą┐ąŠą╗čīąĘčāčÄčé ąŠą▒čēąĖą╣ ąĖąĮą▓ąĄčĆčéąĖčĆčāčÄčēąĖą╣ ą▓čģąŠą┤ (ADC1), ą░ ą▓čüąĄ ąŠčüčéą░ą╗čīąĮčŗąĄ ą▓čģąŠą┤čŗ ADC ą▓čŗą┐ąŠą╗ąĮčÅčÄčé čäčāąĮą║čåąĖčÄ ąĮąĄąĖąĮą▓ąĄčĆčéąĖčĆčāčÄčēąĖčģ ą▓čģąŠą┤ąŠą▓. ąĢčüą╗ąĖ ą▓čŗą▒čĆą░ąĮąŠ čāčüąĖą╗ąĄąĮąĖąĄ 1x ąĖą╗ąĖ 10x, č鹊 ą╝ąŠąČąĮąŠ ąŠąČąĖą┤ą░čéčī 8-čĆą░ąĘčĆčÅą┤ąĮąŠąĄ čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ, ą░ ąĄčüą╗ąĖ 200x, č鹊 7-čĆą░ąĘčĆčÅą┤ąĮąŠąĄ.

ADC čüąŠą┤ąĄčƹȹĖčé ąŻąÆąź (Sample and Hold circuit, čāčüčéčĆąŠą╣čüčéą▓ąŠ ą▓čŗą▒ąŠčĆą║ąĖ-čģčĆą░ąĮąĄąĮąĖčÅ), ą║ąŠč鹊čĆąŠąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé ąĮą░ ą┐ąŠčüč鹊čÅąĮąĮąŠą╝ čāčĆąŠą▓ąĮąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮą░ ą▓čģąŠą┤ąĄ ADC ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ. ążčāąĮą║čåąĖąŠąĮą░ą╗čīąĮą░čÅ čüčģąĄą╝ą░ ADC ą┐ąŠą║ą░ąĘą░ąĮą░ ąĮą░ čĆąĖčüčāąĮą║ąĄ 98.

ADC ąĖą╝ąĄąĄčé ąŠčéą┤ąĄą╗čīąĮčŗą╣ ą▓čŗą▓ąŠą┤ ą┐ąĖčéą░ąĮąĖčÅ AVCC (ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠąĄ ą┐ąĖčéą░ąĮąĖąĄ). AVCC ąĮąĄ ą┤ąŠą╗ąČąĄąĮ ąŠčéą╗ąĖčćą░čéčīčüčÅ ą▒ąŠą╗ąĄąĄ č湥ą╝ ąĮą░ ┬▒0.3ąÆ ąŠčé VCC. ąĪą╝. ą┐ą░čĆą░ą│čĆą░čä ŌĆ£ą¤ąŠą┤ą░ą▓ąĖč鹥ą╗čī čłčāą╝ąŠą▓ ADC (ADC Noise Canceler)ŌĆØ, ą│ą┤ąĄ ą┐čĆąĖą▓ąĄą┤ąĄąĮčŗ čĆąĄą║ąŠą╝ąĄąĮą┤ą░čåąĖąĖ ą┐ąŠ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÄ čŹč鹊ą│ąŠ ą▓čŗą▓ąŠą┤ą░.

ąÆ ą║ą░č湥čüčéą▓ąĄ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą╝ąŠąČąĄčé ą▓čŗčüčéčāą┐ą░čéčī ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąŠčé ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ ąśą×ąØ (Reference Voltage, ąśčüč鹊čćąĮąĖą║ ą×ą┐ąŠčĆąĮąŠą│ąŠ ąØą░ą┐čĆčÅąČąĄąĮąĖčÅ) ąĮą░ 2.56ąÆ ąĖą╗ąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ AVCC. ąöą╗čÅ čāą╝ąĄąĮčīčłąĄąĮąĖčÅ čłčāą╝ą░ ą║ ą▓čŗą▓ąŠą┤čā AREF ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą▓ąĮąĄčłąĮąĖą╣ ą▒ą╗ąŠą║ąĖčĆąŠą▓ąŠčćąĮčŗą╣ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ.

ąĀąĖčüčāąĮąŠą║ 98. ąæą╗ąŠą║ąŠą▓ą░čÅ čüčģąĄą╝ą░ ADC.

[ą¤čĆąĖąĮčåąĖą┐ ą┤ąĄą╣čüčéą▓ąĖčÅ]

ADC ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓čŗą▓ą░ąĄčé ą▓čģąŠą┤ąĮąŠąĄ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą▓ 10-čĆą░ąĘčĆ. ą║ąŠą┤ ą╝ąĄč鹊ą┤ąŠą╝ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ą┐čĆąĖą▒ą╗ąĖąČąĄąĮąĖą╣. ą£ąĖąĮąĖą╝ą░ą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé čāčĆąŠą▓ąĮčÄ GND, ą░ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠąĄ čāčĆąŠą▓ąĮčÄ AREF ą╝ąĖąĮčāčü 1 ą╝ą╗. čĆą░ąĘčĆ. ąÜ ą▓čŗą▓ąŠą┤čā AREF ą┐ąŠ ą▓čŗą▒ąŠčĆčā ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ AVCC ąĖą╗ąĖ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ ąśą×ąØ ąĮą░ 2.56ąÆ ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖčģ ąĘąĮą░č湥ąĮąĖą╣ ą▓ ą▒ąĖčéčŗ REFSn čĆąĄą│ąĖčüčéčĆą░ ADMUX. ąØąĄčüą╝ąŠčéčĆčÅ ąĮą░ č鹊, čćč鹊 ąśą×ąØ ąĮą░ 2.56ąÆ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ąĮčāčéčĆąĖ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░, ą║ ąĄą│ąŠ ą▓čŗčģąŠą┤čā ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą▒ą╗ąŠą║ąĖčĆąŠą▓ąŠčćąĮčŗą╣ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ ą┤ą╗čÅ čüąĮąĖąČąĄąĮąĖčÅ čćčāą▓čüčéą▓ąĖč鹥ą╗čīąĮąŠčüčéąĖ ą║ čłčāą╝ą░ą╝, čé.ą║. ąŠąĮ čüą▓čÅąĘą░ąĮ čü ą▓čŗą▓ąŠą┤ąŠą╝ AREF.

ąÜą░ąĮą░ą╗ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ą▓ą▓ąŠą┤ą░ ąĖ ą║ą░čüą║ą░ą┤ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą│ąŠ čāčüąĖą╗ąĄąĮąĖčÅ ą▓čŗą▒ąĖčĆą░čÄčéčüčÅ ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ ą▒ąĖčé MUX ą▓ čĆąĄą│ąĖčüčéčĆ ADMUX. ąÆ ą║ą░č湥čüčéą▓ąĄ ąŠą┤ąĮąŠą┐ąŠą╗čÅčĆąĮąŠą│ąŠ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ą▓čģąŠą┤ą░ ADC ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą▒čĆą░ąĮ ąŠą┤ąĖąĮ ąĖąĘ ą▓čģąŠą┤ąŠą▓ ADC0ŌĆ”ADC7, ą░ čéą░ą║ąČąĄ GND ąĖ ą▓čŗčģąŠą┤ čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮąŠą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ (fixed bandgap voltage reference). ąÆ čĆąĄąČąĖą╝ąĄ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą│ąŠ ą▓ą▓ąŠą┤ą░ ą┐čĆąĄą┤čāčüą╝ąŠčéčĆąĄąĮą░ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą▓čŗą▒ąŠčĆą░ ąĖąĮą▓ąĄčĆčéąĖčĆčāčÄčēąĖčģ ąĖ ąĮąĄąĖąĮą▓ąĄčĆčéąĖčĆčāčÄčēąĖčģ ą▓čģąŠą┤ąŠą▓ ą║ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą│ąŠ čāčüąĖą╗ąĖč鹥ą╗čÅ.

ąĢčüą╗ąĖ ą▓čŗą▒čĆą░ąĮ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣ čĆąĄąČąĖą╝ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ą▓ą▓ąŠą┤ą░, č鹊 ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣ čāčüąĖą╗ąĖč鹥ą╗čī ą▒čāą┤ąĄčé čāčüąĖą╗ąĖą▓ą░čéčī čĆą░ąĘąĮąŠčüčéčī ąĮą░ą┐čĆčÅąČąĄąĮąĖą╣ ą╝ąĄąČą┤čā ą▓čŗą▒čĆą░ąĮąĮąŠą╣ ą┐ą░čĆąŠą╣ ą▓čģąŠą┤ąŠą▓ ąĮą░ ąĘą░ą┤ą░ąĮąĮčŗą╣ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé čāčüąĖą╗ąĄąĮąĖčÅ. ąŻčüąĖą╗ąĄąĮąĮąŠąĄ čéą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝ ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠčüčéčāą┐ą░ąĄčé ąĮą░ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ą▓čģąŠą┤ ADC. ąĢčüą╗ąĖ ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ąŠą┤ąĮąŠą┐ąŠą╗čÅčĆąĮčŗą╣ čĆąĄąČąĖą╝ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ą▓ą▓ąŠą┤ą░, č鹊 ą║ą░čüą║ą░ą┤ čāčüąĖą╗ąĄąĮąĖčÅ ą┐čĆąŠą┐čāčüą║ą░ąĄčéčüčÅ.

ąĀą░ą▒ąŠčéą░ ADC čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ ADEN ą▓ čĆąĄą│ąĖčüčéčĆąĄ ADCSRA. ąÆčŗą▒ąŠčĆ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ ąĖ ą║ą░ąĮą░ą╗ą░ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ąĮąĄ ą┐čĆąŠąĖąĘą▓ąŠą┤čÅčé čŹčäč乥ą║čéą░ ą┤ąŠ čāčüčéą░ąĮąŠą▓ą║ąĖ ADEN. ąĢčüą╗ąĖ ADEN = 0, č鹊 ADC ąĮąĄ ą┐ąŠčéčĆąĄą▒ą╗čÅąĄčé č鹊ą║, ą┐ąŠčŹč鹊ą╝čā, ą┐čĆąĖ ą┐ąĄčĆąĄą▓ąŠą┤ąĄ ą▓ 菹║ąŠąĮąŠą╝ąĖčćąĮčŗąĄ čĆąĄąČąĖą╝čŗ čüąĮą░ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮąŠ ąŠčéą║ą╗čÄčćąĖčéčī ADC.

ADC ą│ąĄąĮąĄčĆąĖčĆčāąĄčé 10-čĆą░ąĘčĆčÅą┤ąĮčŗą╣ čĆąĄąĘčāą╗čīčéą░čé, ą║ąŠč鹊čĆčŗą╣ ą┐ąŠą╝ąĄčēą░ąĄčéčüčÅ ą▓ ą┐ą░čĆčā čĆąĄą│ąĖčüčéčĆąŠą▓ ą┤ą░ąĮąĮčŗčģ ADC ADCH ąĖ ADCL. ą¤ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ čĆąĄąĘčāą╗čīčéą░čé ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ čĆą░ąĘą╝ąĄčēą░ąĄčéčüčÅ ą▓ ą╝ą╗ą░ą┤čłąĖčģ 10-čéąĖ čĆą░ąĘčĆčÅą┤ą░čģ 16-čĆą░ąĘčĆ. čüą╗ąŠą▓ą░ (ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖąĄ čüą┐čĆą░ą▓ą░), ąĮąŠ ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠą┐čåąĖąŠąĮą░ą╗čīąĮąŠ čĆą░ąĘą╝ąĄčēąĄąĮ ą▓ čüčéą░čĆčłąĖčģ 10-čéąĖ čĆą░ąĘčĆčÅą┤ą░čģ (ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖąĄ čüą╗ąĄą▓ą░) ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ ADLAR ą▓ čĆąĄą│ąĖčüčéčĆąĄ ADMUX.

ą¤čĆą░ą║čéąĖč湥čüą║ą░čÅ ą┐ąŠą╗ąĄąĘąĮąŠčüčéčī ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮąĖčÅ čĆąĄąĘčāą╗čīčéą░čéą░ čü ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖąĄą╝ čüą╗ąĄą▓ą░ čüčāčēąĄčüčéą▓čāąĄčé, ą║ąŠą│ą┤ą░ ą┤ąŠčüčéą░č鹊čćąĮąŠ 8-čĆą░ąĘčĆčÅą┤ąĮąŠąĄ čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ, čé.ą║. ą▓ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ čüčćąĖčéą░čéčī č鹊ą╗čīą║ąŠ čĆąĄą│ąĖčüčéčĆ ADCH. ąÆ ą┤čĆčāą│ąŠą╝ ąČąĄ čüą╗čāčćą░ąĄ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ą┐ąĄčĆą▓čŗą╝ čüčćąĖčéą░čéčī čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ čĆąĄą│ąĖčüčéčĆą░ ADCL, ą░ ąĘą░č鹥ą╝ ADCH, č湥ą╝ ą│ą░čĆą░ąĮčéąĖčĆčāąĄčéčüčÅ, čćč鹊 ąŠą▒ą░ ą▒ą░ą╣čéą░ čÅą▓ą╗čÅčÄčéčüčÅ čĆąĄąĘčāą╗čīčéą░č鹊ą╝ ąŠą┤ąĮąŠą│ąŠ ąĖ č鹊ą│ąŠ ąČąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ. ąÜą░ą║ č鹊ą╗čīą║ąŠ ą▓čŗą┐ąŠą╗ąĮąĄąĮąŠ čćč鹥ąĮąĖąĄ ADCL, ą▒ą╗ąŠą║ąĖčĆčāąĄčéčüčÅ ą┤ąŠčüčéčāą┐ ą║ čĆąĄą│ąĖčüčéčĆą░ą╝ ą┤ą░ąĮąĮčŗčģ čüąŠ čüč鹊čĆąŠąĮčŗ ADC. ąŁč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ąĄčüą╗ąĖ čüčćąĖčéą░ąĮ ADCL ąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ąĘą░ą▓ąĄčĆčłą░ąĄčéčüčÅ ą┐ąĄčĆąĄą┤ čćč鹥ąĮąĖąĄą╝ čĆąĄą│ąĖčüčéčĆą░ ADCH, č鹊 ąĮąĖ ąŠą┤ąĖąĮ ąĖąĘ čĆąĄą│ąĖčüčéčĆąŠą▓ ąĮąĄ ą╝ąŠąČąĄčé ą╝ąŠą┤ąĖčäąĖčåąĖčĆąŠą▓ą░čéčīčüčÅ ąĖ čĆąĄąĘčāą╗čīčéą░čé ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ č鹥čĆčÅąĄčéčüčÅ. ą¤ąŠčüą╗ąĄ čćč鹥ąĮąĖčÅ ADCH ą┤ąŠčüčéčāą┐ ą║ čĆąĄą│ąĖčüčéčĆą░ą╝ ADCH ąĖ ADCL čüąŠ čüč鹊čĆąŠąĮčŗ ADC čüąĮąŠą▓ą░ čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ.

ADC ą│ąĄąĮąĄčĆąĖčĆčāąĄčé čüąŠą▒čüčéą▓ąĄąĮąĮčŗą╣ ąĘą░ą┐čĆąŠčü ąĮą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ. ąĢčüą╗ąĖ ą╝ąĄąČą┤čā čćč鹥ąĮąĖąĄą╝ čĆąĄą│ąĖčüčéčĆąŠą▓ ADCH ąĖ ADCL ąĘą░ą┐čĆąĄčēąĄąĮ ą┤ąŠčüčéčāą┐ ą║ ą┤ą░ąĮąĮčŗą╝ ą┤ą╗čÅ ADC, č鹊 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą▓ąŠąĘąĮąĖą║ąĮąĄčé, ą┤ą░ąČąĄ ąĄčüą╗ąĖ čĆąĄąĘčāą╗čīčéą░čé ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą▒čāą┤ąĄčé ą┐ąŠč鹥čĆčÅąĮ.

[ąŚą░ą┐čāčüą║ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ]

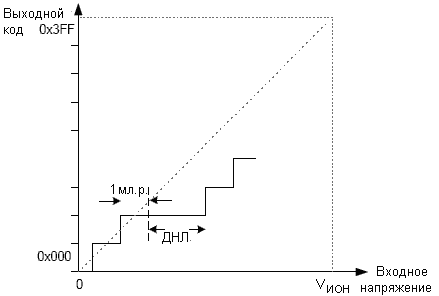

ą×ą┤ąĖąĮąŠčćąĮąŠąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ ą╗ąŠą│. 1 ą▓ ą▒ąĖčé ąĘą░ą┐čāčüą║ą░ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ADC ADSC (čĆąĄą│ąĖčüčéčĆ ADCSRA). ąöą░ąĮąĮčŗą╣ ą▒ąĖčé ąŠčüčéą░ąĄčéčüčÅ ą▓ ą▓čŗčüąŠą║ąŠą╝ čüąŠčüč鹊čÅąĮąĖąĖ ą▓ ą┐čĆąŠčåąĄčüčüąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ąĖ čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ ą┐ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ. ąĢčüą╗ąĖ ą▓ ą┐čĆąŠčåąĄčüčüąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą┐ąĄčĆąĄą║ą╗čÄčćą░ąĄčéčüčÅ ą║ą░ąĮą░ą╗ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ą▓ą▓ąŠą┤ą░, č鹊 ADC ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąĘą░ą▓ąĄčĆčłąĖčé č鹥ą║čāčēąĄąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ą┐čĆąĄąČą┤ąĄ, č湥ą╝ ą┐ąĄčĆąĄą║ą╗čÄčćąĖčé ą║ą░ąĮą░ą╗.

ąöčĆčāą│ąŠą╣ ą▓ą░čĆąĖą░ąĮčé ąĘą░ą┐čāčüą║ą░ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ŌĆō ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖą╣ ąĘą░ą┐čāčüą║ ą┐ąŠ čüąĖą│ąĮą░ą╗čā ąĖąĘ čĆą░ąĘą╗ąĖčćąĮčŗčģ ąĖčüč鹊čćąĮąĖą║ąŠą▓. ąÆ čĆąĄąČąĖą╝ąĄ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą│ąŠ ą┐ąĄčĆąĄąĘą░ą┐čāčüą║ą░ ADC ąĮąĄą┐čĆąĄčĆčŗą▓ąĮąŠ ąŠčåąĖčäčĆąŠą▓čŗą▓ą░ąĄčé ą░ąĮą░ą╗ąŠą│ąŠą▓čŗą╣ čüąĖą│ąĮą░ą╗ ąĖ ąŠą▒ąĮąŠą▓ą╗čÅąĄčé čĆąĄą│ąĖčüčéčĆ ą┤ą░ąĮąĮčŗčģ ADC. ąöą░ąĮąĮčŗą╣ čĆąĄąČąĖą╝ ąĘą░ą┤ą░ąĄčéčüčÅ ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ ą╗ąŠą│. 1 ą▓ ą▒ąĖčé ADATE čĆąĄą│ąĖčüčéčĆą░ ADCSRA. ą£ąŠąČąĮąŠ čéą░ą║ąČąĄ ą▓čŗą▒čĆą░čéčī ąĖčüč鹊čćąĮąĖą║ ą┐ąĄčĆąĄąĘą░ą┐čāčüą║ą░ ą▒ąĖčéą░ą╝ąĖ ADTS čĆąĄą│ąĖčüčéčĆą░ SFIOR (čüą╝. ąŠą┐ąĖčüą░ąĮąĖąĄ ą▒ąĖč鹊ą▓ ADTS ą┤ą╗čÅ čüą┐ąĖčüą║ą░ ąĖčüč鹊čćąĮąĖą║ąŠą▓ ąĘą░ą┐čāčüą║ą░). ąÜąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮčŗą╣ ą┐ąĄčĆąĄą┐ą░ą┤ ą▓čŗą▒čĆą░ąĮąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ą┐ąĄčĆąĄąĘą░ą┐čāčüą║ą░, čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ ą┐čĆąĄčüą║ą░ą╗ąĄčĆ ADC ąĖ ąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ. ąŁč鹊 ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą╝ąĄč鹊ą┤ ąĘą░ą┐čāčüą║ą░ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą▓ čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮčŗąĄ ąĖąĮč鹥čĆą▓ą░ą╗čŗ ą▓čĆąĄą╝ąĄąĮąĖ. ąĢčüą╗ąĖ čüąĖą│ąĮą░ą╗ ąĘą░ą┐čāčüą║ą░ ą▓čüąĄ ąĄčēąĄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ą║ąŠą│ą┤ą░ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąŠ, ąĮąŠą▓ąŠąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ąĮąĄ ąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ. ąĢčüą╗ąĖ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮčŗą╣ ą┐ąĄčĆąĄą┐ą░ą┤ ą▓čŗą▒čĆą░ąĮąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ą┐ąĄčĆąĄąĘą░ą┐čāčüą║ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ, čŹč鹊čé ą┐ąĄčĆąĄą┐ą░ą┤ ą▒čāą┤ąĄčé ąĖą│ąĮąŠčĆąĖčĆąŠą▓ą░ąĮ. ąÆąĮąĖą╝ą░ąĮąĖąĄ ŌĆō čäą╗ą░ą│ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ADIF ą▒čāą┤ąĄčé ą▓čüąĄ čĆą░ą▓ąĮąŠ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ą┤ą░ąČąĄ ąĄčüą╗ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ ąĖą╗ąĖ ą▒ąĖčé ą│ą╗ąŠą▒ą░ą╗čīąĮąŠą│ąŠ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ čĆąĄą│ąĖčüčéčĆą░ SREG čüą▒čĆąŠčłąĄąĮ, ą┐čĆąĖ čŹč鹊ą╝ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ąĘą░ą┐čāčüčéąĖčéčüčÅ ą▒ąĄąĘ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ą×ą┤ąĮą░ą║ąŠ čäą╗ą░ą│ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ADIF ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąŠčćąĖčēąĄąĮ, čćč鹊ą▒čŗ ąĘą░ą┐čāčüčéąĖą╗ąŠčüčī ąĮąŠą▓ąŠąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ą┐čĆąĖ čüą╗ąĄą┤čāčÄčēąĄą╝ čüąŠą▒čŗčéąĖąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

ąĀąĖčüčāąĮąŠą║ 99. ąøąŠą│ąĖą║ą░ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą│ąŠ ąĘą░ą┐čāčüą║ą░ ADC.

ąśčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ čäą╗ą░ą│ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ADC (ADIF) ą║ą░ą║ ąĖčüč鹊čćąĮąĖą║ą░ ąĘą░ą┐čāčüą║ą░ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ąĘą░ą┐čāčüą║ą░ąĄčé ąĮąŠą▓ąŠąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ, ą║ą░ą║ č鹊ą╗čīą║ąŠ č鹥ą║čāčēąĄąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ąĘą░ą▓ąĄčĆčłą░ąĄčéčüčÅ. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ADC čĆą░ą▒ąŠčéą░ąĄčé ą▓ čĆąĄąČąĖą╝ąĄ ą░ą▓č鹊ąĘą░ą┐čāčüą║ą░ - ąĮąĄą┐čĆąĄčĆčŗą▓ąĮąŠ ąŠčåąĖčäčĆąŠą▓čŗą▓ą░ąĄčé ą░ąĮą░ą╗ąŠą│ąŠą▓čŗą╣ čüąĖą│ąĮą░ą╗ ąĖ ąŠą▒ąĮąŠą▓ą╗čÅąĄčé čĆąĄą│ąĖčüčéčĆ ą┤ą░ąĮąĮčŗčģ ADC. ą¤ąĄčĆą▓ąŠąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ąĖąĮąĖčåąĖąĖčĆčāąĄčéčüčÅ ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ ą╗ąŠą│. 1 ą▓ ą▒ąĖčé ADSC čĆąĄą│ąĖčüčéčĆą░ ADCSRA. ąÆ ą┤ą░ąĮąĮąŠą╝ čĆąĄąČąĖą╝ąĄ ADC ą▓čŗą┐ąŠą╗ąĮčÅąĄčé ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ, ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé č鹊ą│ąŠ - čüą▒čĆąŠčłąĄąĮ čäą╗ą░ą│ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ADC ADIF ąĖą╗ąĖ ąĮąĄčé.

ąĢčüą╗ąĖ čĆą░ąĘčĆąĄčłąĄąĮ ą░ą▓č鹊ąĘą░ą┐čāčüą║ (čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé ADATE čĆąĄą│ąĖčüčéčĆą░ ADCSRA), ąŠą┤ąĖąĮąŠčćąĮčŗąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą╝ąŠą│čāčé ąĘą░ą┐čāčüą║ą░čéčīčüčÅ ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ ą╗ąŠą│. 1 ą▓ ą▒ąĖčé ADSC čĆąĄą│ąĖčüčéčĆą░ ADCSRA. ąæąĖčé ADSC ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ, ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ąĖą╗ąĖ ąĮąĄčé ą▓ ąĮą░čüč鹊čÅčēąĖą╣ ą╝ąŠą╝ąĄąĮčé ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ. ąæąĖčé ADSC ą▒čāą┤ąĄčé čćąĖčéą░čéčīčüčÅ ą║ą░ą║ 1 ą▓ąŠ ą▓čĆąĄą╝čÅ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ, ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé č鹊ą│ąŠ, ą║ą░ą║ ąŠąĮąŠ ą▒čŗą╗ąŠ ąĘą░ą┐čāčēąĄąĮąŠ.

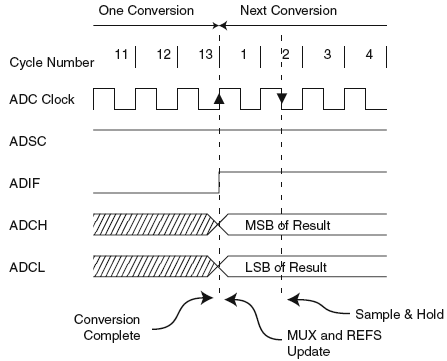

[ą¤čĆąĄą┤ą┤ąĄą╗ąĖč鹥ą╗čī (ą┐čĆąĄčüą║ą░ą╗ąĄčĆ) ąĖ ą▓čĆąĄą╝ąĄąĮąĮą░čÅ ą┤ąĖą░ą│čĆą░ą╝ą╝ą░ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ]

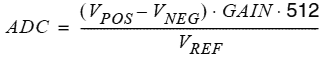

ąĀąĖčüčāąĮąŠą║ 100. ą¤čĆąĄčüą║ą░ą╗ąĄčĆ ADC.

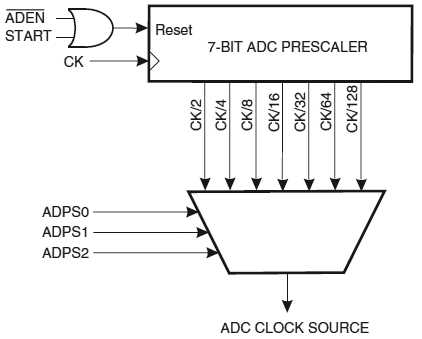

ąĢčüą╗ąĖ čéčĆąĄą▒čāąĄčéčüčÅ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮą░čÅ čĆą░ąĘčĆąĄčłą░čÄčēą░čÅ čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī (10 čĆą░ąĘčĆčÅą┤ąŠą▓), č鹊 čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ ą┤ą╗čÅ ADC ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ą┐čĆąĖą▒ą╗ąĖąČąĄąĮąĖčÅ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ 50ŌĆ”200 ą║ąōčå. ąĢčüą╗ąĖ ą┤ąŠčüčéą░č鹊čćąĮąŠ čĆą░ąĘčĆąĄčłąĄąĮąĖąĄ ą╝ąĄąĮąĄąĄ 10 čĆą░ąĘčĆčÅą┤ąŠą▓, č鹊 ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ą▒ąŠą╗ąĄąĄ ą▓čŗčüąŠą║ąŠą╣ čćą░čüč鹊čéčŗ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ ADC ą╝ąŠąČąĄčé ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮą░ čüą▓čŗčłąĄ 200 ą║ąōčå.

ą£ąŠą┤čāą╗čī ADC čüąŠą┤ąĄčƹȹĖčé ą┐čĆąĄą┤ą┤ąĄą╗ąĖč鹥ą╗čī, ą║ąŠč鹊čĆčŗą╣ č乊čĆą╝ąĖčĆčāąĄčé čćą░čüč鹊čéčŗ čéą░ą║č鹊ą▓ ADC ąĖąĘ ą╗čÄą▒čŗčģ čćą░čüč鹊čé čÅą┤čĆą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ čüą▓čŗčłąĄ 100 ą║ąōčå. ąÜąŠčŹčäčäąĖčåąĖąĄąĮčé ą┤ąĄą╗ąĄąĮąĖčÅ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ čü ą┐ąŠą╝ąŠčēčīčÄ ą▒ąĖčé ADPS ą▓ čĆąĄą│ąĖčüčéčĆąĄ ADCSRA. ą¤čĆąĄą┤ą┤ąĄą╗ąĖč鹥ą╗čī ąĮą░čćąĖąĮą░ąĄčé čüč湥čé čü ą╝ąŠą╝ąĄąĮčéą░ ą▓ą║ą╗čÄč湥ąĮąĖčÅ ADC čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ ADEN ą▓ čĆąĄą│ąĖčüčéčĆąĄ ADCSRA. ą¤čĆąĄą┤ą┤ąĄą╗ąĖč鹥ą╗čī čĆą░ą▒ąŠčéą░ąĄčé, ą┐ąŠą║ą░ ą▒ąĖčé ADEN = 1, ąĖ ą┐ąŠčüč鹊čÅąĮąĮąŠ čüą▒čĆąŠčłąĄąĮ, ą║ąŠą│ą┤ą░ ADEN=0.

ąĢčüą╗ąĖ ąĖąĮąĖčåąĖąĖčĆčāąĄčéčüčÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ąĮąĄ ą▓ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą╝ čĆąĄąČąĖą╝ąĄ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ ADSC ą▓ čĆąĄą│ąĖčüčéčĆąĄ ADCSRA, č鹊 ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ąĮą░čćąĖąĮą░ąĄčéčüčÅ čüąŠ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ ąĮą░čĆą░čüčéą░čÄčēąĄą│ąŠ čäčĆąŠąĮčéą░ čéą░ą║č鹊ą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ADC. ą×čüąŠą▒ąĄąĮąĮąŠčüčéąĖ ą▓čĆąĄą╝ąĄąĮąĮąŠą╣ ą┤ąĖą░ą│čĆą░ą╝ą╝čŗ ą▓ čĆąĄąČąĖą╝ąĄ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮčŗ ą▓ čĆą░ąĘą┤ąĄą╗ąĄ ŌĆ£ąÜą░ąĮą░ą╗čŗ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą│ąŠ čāčüąĖą╗ąĄąĮąĖčÅŌĆØ.

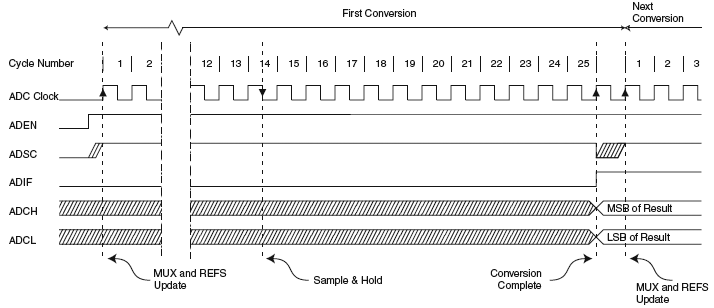

ąØąŠčĆą╝ą░ą╗čīąĮąŠąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ čéčĆąĄą▒čāąĄčé 13 čéą░ą║č鹊ą▓ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ADC. ą¤ąĄčĆą▓ąŠąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ą┐ąŠčüą╗ąĄ ą▓ą║ą╗čÄč湥ąĮąĖčÅ ADC (čāčüčéą░ąĮąŠą▓ą║ą░ ADEN ą▓ ADCSRA) čéčĆąĄą▒čāąĄčé 25 čéą░ą║č鹊ą▓ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ADC ąĘą░ čüč湥čé ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéąĖ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą╣ čüčģąĄą╝čŗ.

ą¤ąŠčüą╗ąĄ ąĮą░čćą░ą╗ą░ ąĮąŠčĆą╝ą░ą╗čīąĮąŠą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ąĮą░ ą▓čŗą▒ąŠčĆą║čā-čģčĆą░ąĮąĄąĮąĖąĄ ąĘą░čéčĆą░čćąĖą▓ą░ąĄčéčüčÅ 1.5 čéą░ą║čéą░ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ADC, ą░ ą┐ąŠčüą╗ąĄ ąĮą░čćą░ą╗ą░ ą┐ąĄčĆą▓ąŠą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ŌĆō 13,5 čéą░ą║č鹊ą▓. ą¤ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ čĆąĄąĘčāą╗čīčéą░čé ą┐ąŠą╝ąĄčēą░ąĄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆčŗ ą┤ą░ąĮąĮčŗčģ ADC ąĖ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ čäą╗ą░ą│ ADIF. ąÆ čĆąĄąČąĖą╝ąĄ ąŠą┤ąĖąĮąŠčćąĮąŠą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ ą▒ąĖčé ADSC. ą¤čĆąŠą│čĆą░ą╝ą╝ąĮąŠ ą▒ąĖčé ADSC ą╝ąŠąČąĄčé ą▒čŗčéčī čüąĮąŠą▓ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ąĖ ąĮąŠą▓ąŠąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ą▒čāą┤ąĄčé ąĖąĮąĖčåąĖąĖčĆąŠą▓ą░ąĮąŠ ą┐ąĄčĆą▓čŗą╝ ąĮą░čĆą░čüčéą░čÄčēąĖą╝ čäčĆąŠąĮč鹊ą╝ čéą░ą║č鹊ą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ADC.

ąÆ čĆąĄąČąĖą╝ąĄ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą│ąŠ ą┐ąĄčĆąĄąĘą░ą┐čāčüą║ą░ ą┐čĆąĄčüą║ą░ą╗ąĄčĆ (ą┐čĆąĄą┤ą┤ąĄą╗ąĖč鹥ą╗čī) čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ ą┐čĆąĖ ą║ą░ąČą┤ąŠą╝ čüąŠą▒čŗčéąĖąĖ ąĘą░ą┐čāčüą║ą░. ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ čüčģąĄą╝ą░ ą▓čŗą▒ąŠčĆą║ąĖ-čģčĆą░ąĮąĄąĮąĖčÅ čéčĆąĄą▒čāąĄčé 2 čéą░ą║čéą░ ADC ą┐ąŠčüą╗ąĄ ąĮą░čĆą░čüčéą░čÄčēąĄą│ąŠ čäčĆąŠąĮčéą░ čüąĖą│ąĮą░ą╗ą░ ąĘą░ą┐čāčüą║ą░. 3 ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗčģ čåąĖą║ą╗ą░ čÅą┤čĆą░ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą╗ąŠą│ąĖą║ąĖ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ. ąÆ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą╝ čĆąĄąČąĖą╝ąĄ, ąĄčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą░ą▓č鹊ąĘą░ą┐čāčüą║ ąŠčé ą╗čÄą▒ąŠą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░, ą║čĆąŠą╝ąĄ ┬½ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ADC┬╗, ą║ą░ąČą┤ąŠąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ čéčĆąĄą▒čāąĄčé 25 čéą░ą║č鹊ą▓ ADC. ąŁč鹊 ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ąĖąĘ-ąĘą░ č鹊ą│ąŠ, čćč鹊 ADC ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ą┐čĆąĄčēąĄąĮ ąĖ čüąĮąŠą▓ą░ čĆą░ąĘčĆąĄčłąĄąĮ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ.

ąÆ čĆąĄąČąĖą╝ąĄ ą┐ąŠčüč鹊čÅąĮąĮąŠą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ (Free Running) ąĮąŠą▓ąŠąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ąĮą░čćąĖąĮą░ąĄčéčüčÅ čüčĆą░ąĘčā ą┐ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĖ ą┐čĆąĄą┤čŗą┤čāčēąĄą│ąŠ, ą┐ąŠą║ą░ ą▒ąĖčé ADSC ąŠčüčéą░ąĄčéčüčÅ ą▓ ą▓čŗčüąŠą║ąŠą╝ čüąŠčüč鹊čÅąĮąĖąĖ. ąÆčĆąĄą╝ąĄąĮą░ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čĆą░ąĘą╗ąĖčćąĮčŗčģ čĆąĄąČąĖą╝ąŠą▓ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮčŗ ą▓ čéą░ą▒ą╗ąĖčåąĄ 81.

ąĀąĖčüčāąĮąŠą║ 101. ąÆčĆąĄą╝ąĄąĮąĮąÉčÅ ą┤ąĖą░ą│čĆą░ą╝ą╝ą░ ADC, ą┐ąĄčĆą▓ąŠąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ (čĆąĄąČąĖą╝ ąŠą┤ąĖąĮąŠčćąĮąŠą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ).

ąĀąĖčüčāąĮąŠą║ 102. ąÆčĆąĄą╝ąĄąĮąĮąÉčÅ ą┤ąĖą░ą│čĆą░ą╝ą╝ą░ ADC, ąŠą┤ąĖąĮąŠčćąĮąŠąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ.

ąĀąĖčüčāąĮąŠą║ 103. ąÆčĆąĄą╝ąĄąĮąĮąÉčÅ ą┤ąĖą░ą│čĆą░ą╝ą╝ą░ ADC, ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ čü ą░ą▓č鹊ąĘą░ą┐čāčüą║ąŠą╝.

ąĀąĖčüčāąĮąŠą║ 104. ąÆčĆąĄą╝ąĄąĮąĮąÉčÅ ą┤ąĖą░ą│čĆą░ą╝ą╝ą░ ADC, ąĮąĄą┐čĆąĄčĆčŗą▓ąĮąŠąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ (Free Running conversion).

ąóą░ą▒ą╗ąĖčåą░ 81. ąÆčĆąĄą╝čÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ADC.

|

ąŻčüą╗ąŠą▓ąĖąĄ

|

ą▓čŗą▒ąŠčĆą║ą░ ąĖ čģčĆą░ąĮąĄąĮąĖąĄ (ą▓ čåąĖą║ą╗ą░čģ ADC ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ąĮą░čćą░ą╗ą░ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ)

|

ą▓čĆąĄą╝čÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą▓ čåąĖą║ą╗ą░čģ ADC

|

| ą¤ąĄčĆą▓ąŠąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ |

13.5 |

25 |

| ąØąĄą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠąĄ ąŠą▒čŗčćąĮąŠąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ |

1.5 |

13 |

| ą¤čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ čü ą░ą▓č鹊ąĘą░ą┐čāčüą║ąŠą╝ |

2 |

13.5 |

| ąöąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠąĄ ąŠą▒čŗčćąĮąŠąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ |

1.5/2.5 |

13/14 |

[ąÜą░ąĮą░ą╗čŗ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą│ąŠ čāčüąĖą╗ąĄąĮąĖčÅ]

ąĢčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą║ą░ąĮą░ą╗čŗ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą│ąŠ čāčüąĖą╗ąĄąĮąĖčÅ, č鹊 ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ą┐čĆąĖąĮčÅčéčī ą▓ąŠ ą▓ąĮąĖą╝ą░ąĮąĖąĄ ąĮąĄą║ąŠč鹊čĆčŗąĄ ąŠčüąŠą▒ąĄąĮąĮąŠčüčéąĖ.

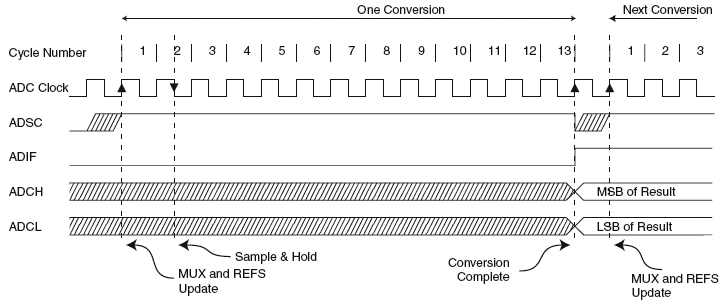

ąöąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆąŠą▓ą░ąĮčŗ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊č鹊ą╣ CKADC2, čćą░čüč鹊ą│ąŠ ą║ąŠč鹊čĆąŠą│ąŠ čĆą░ą▓ąĮą░ ą┐ąŠą╗ąŠą▓ąĖąĮąĄ čćą░čüč鹊čéčŗ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ADC. ąöą░ąĮąĮą░čÅ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖčÅ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąĖąĮč鹥čĆč乥ą╣čüąŠą╝ ADC čéą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, čćč鹊ą▒čŗ ą▓čŗą▒ąŠčĆą║ą░-čģčĆą░ąĮąĄąĮąĖąĄ ąĖąĮąĖčåąĖąĖčĆąŠą▓ą░ą╗ą░čüčī ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗą╝ čäą░ąĘąŠą╣ CKADC2. ąĢčüą╗ąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ (ą▓čüąĄ ąŠą┤ąĖąĮąŠčćąĮčŗąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ąĖ ą┐ąĄčĆą▓ąŠąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ą▓ čĆąĄąČąĖą╝ąĄ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą│ąŠ ą┐ąĄčĆąĄąĘą░ą┐čāčüą║ą░) ąĖąĮąĖčåąĖąĖčĆąŠą▓ą░ą╗ąŠčüčī ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╝, ą║ąŠą│ą┤ą░ CKADC2 ąĮą░čģąŠą┤ąĖą╗čüčÅ ą▓ ąĮąĖąĘą║ąŠą╝ ą╗ąŠą│. čüąŠčüč鹊čÅąĮąĖąĖ, č鹊 ąĄą│ąŠ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī ą▒čāą┤ąĄčé 菹║ą▓ąĖą▓ą░ą╗ąĄąĮčéą░ ąĮąĄą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą╝čā ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÄ (13 čéą░ą║č鹊ą▓ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ADC ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ čéą░ą║čéą░). ąĢčüą╗ąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ąĖąĮąĖčåąĖąĖčĆčāąĄčéčüčÅ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╝, ą║ąŠą│ą┤ą░ CKADC2 čĆą░ą▓ąĄąĮ ą╗ąŠą│. 1 , ąŠąĮąŠ ą▒čāą┤ąĄčé ą┤ą╗ąĖčéčīčüčÅ 14 čéą░ą║č鹊ą▓ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ADC ą▓čüą╗ąĄą┤čüčéą▓ąĖąĄ čĆą░ą▒ąŠčéčŗ ą╝ąĄčģą░ąĮąĖąĘą╝ą░ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ. ąÆ čĆąĄąČąĖą╝ąĄ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą│ąŠ ą┐ąĄčĆąĄąĘą░ą┐čāčüą║ą░ (Free Running mode) ąĮąŠą▓ąŠąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ąĖąĮąĖčåąĖąĖčĆčāąĄčéčüčÅ čüčĆą░ąĘčā ą┐ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĖ ą┐čĆąĄą┤čŗą┤čāčēąĄą│ąŠ, ą░ čé.ą║. ą▓ čŹč鹊čé ą╝ąŠą╝ąĄąĮčé CKADC2 čĆą░ą▓ąĄąĮ ą╗ąŠą│. 1, č鹊 ą▓čüąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ, ą║ąŠč鹊čĆčŗąĄ ą▒čŗą╗ąĖ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą┐ąĄčĆąĄąĘą░ą┐čāčēąĄąĮčŗ (čé. ąĄ. ą▓čüąĄ, ą║čĆąŠą╝ąĄ ą┐ąĄčĆą▓ąŠą│ąŠ), ą▒čāą┤čāčé ą┤ą╗ąĖčéčīčüčÅ 14 čéą░ą║č鹊ą▓ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ADC.

ąŻčüąĖą╗ąĖč鹥ą╗čīąĮčŗą╣ ą║ą░čüą║ą░ą┤ ąŠą┐čéąĖą╝ąĖąĘąĖčĆąŠą▓ą░ąĮ ą┐ąŠą┤ čćą░čüč鹊čéąĮčŗą╣ ą┤ąĖą░ą┐ą░ąĘąŠąĮ ą┤ąŠ 4 ą║ąōčå ą┤ą╗čÅ ą╗čÄą▒čŗčģ ą║ąŠčŹčäčäąĖčåąĖąĄąĮč鹊ą▓ čāčüąĖą╗ąĄąĮąĖčÅ. ąŻčüąĖą╗ąĄąĮąĖąĄ čüąĖą│ąĮą░ą╗ąŠą▓ ą▒ąŠą╗ąĄąĄ ą▓čŗčüąŠą║ąĖčģ čćą░čüč鹊čé ą▒čāą┤ąĄčé ąĮąĄą╗ąĖąĮąĄą╣ąĮčŗą╝. ą¤ąŠčŹč鹊ą╝čā, ąĄčüą╗ąĖ ą▓čģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ čüąŠą┤ąĄčƹȹĖčé čćą░čüč鹊čéąĮčŗąĄ čüąŠčüčéą░ą▓ą╗čÅčÄčēąĖąĄ ą▓čŗčłąĄ čćą░čüč鹊čéąĮąŠą│ąŠ ą┤ąĖą░ą┐ą░ąĘąŠąĮą░ čāčüąĖą╗ąĖč鹥ą╗čīąĮąŠą│ąŠ ą║ą░čüą║ą░ą┤ą░, č鹊 ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ čāčüčéą░ąĮąŠą▓ąĖčéčī ą▓ąĮąĄčłąĮąĖą╣ čäąĖą╗čīčéčĆ ąĮąĖąĘą║ąĖčģ čćą░čüč鹊čé. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 čćą░čüč鹊čéą░ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ADC ąĮąĄ čüą▓čÅąĘą░ąĮą░ čü ąŠą│čĆą░ąĮąĖč湥ąĮąĖąĄą╝ ą┐ąŠ čćą░čüč鹊čéąĮąŠą╝čā ą┤ąĖą░ą┐ą░ąĘąŠąĮčā čāčüąĖą╗ąĖč鹥ą╗čīąĮąŠą│ąŠ ą║ą░čüą║ą░ą┤ą░. ąØą░ą┐čĆąĖą╝ąĄčĆ, ą┐ąĄčĆąĖąŠą┤ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ADC ą╝ąŠąČąĄčé ą▒čŗčéčī 6 ą╝ą║čü, ą┐čĆąĖ ą║ąŠč鹊čĆąŠą╝ čćą░čüč鹊čéą░ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą║ą░ąĮą░ą╗ą░ čĆą░ą▓ąĮą░ 12 čéčŗčü. ą┐čĆąĄąŠą▒čĆ. ą▓ čüąĄą║čāąĮą┤čā, ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé čćą░čüč鹊čéąĮąŠą│ąŠ ą┤ąĖą░ą┐ą░ąĘąŠąĮą░ čŹč鹊ą│ąŠ ą║ą░ąĮą░ą╗ą░.

ąĢčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą║ą░ąĮą░ą╗čŗ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą│ąŠ čāčüąĖą╗ąĄąĮąĖčÅ ąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ąĘą░ą┐čāčēąĄąĮąŠ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖą╝ ąĘą░ą┐čāčüą║ąŠą╝, č鹊 ADC ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą▓čŗą║ą╗čÄč湥ąĮ ą╝ąĄąČą┤čā ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅą╝ąĖ. ą¤čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą│ąŠ ąĘą░ą┐čāčüą║ą░ ą┐čĆąĄčüą║ą░ą╗ąĄčĆ ADC čüą▒čĆąŠčłąĄąĮ ą┐ąĄčĆąĄą┤ ąĘą░ą┐čāčüą║ąŠą╝ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ. ą¤ąŠčüą║ąŠą╗čīą║čā ą║ą░čüą║ą░ą┤ čāčüąĖą╗ąĄąĮąĖčÅ ąĘą░ą▓ąĖčüąĖčé ąŠčé čüčéą░ą▒ąĖą╗čīąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ ADC ą┐ąĄčĆąĄą┤ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄą╝, č鹊 čŹč鹊 ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ą▒čāą┤ąĄčé ąĮąĄą┤ąĄą╣čüčéą▓ąĖč鹥ą╗čīąĮčŗą╝. ą¤čāč鹥ą╝ ąĘą░ą┐čĆąĄčēąĄąĮąĖčÅ ąĖ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ADC ą╝ąĄąČą┤čā ą║ą░ąČą┤čŗą╝ąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅą╝ąĖ (čü ą┐ąŠą╝ąŠčēčīčÄ ąĘą░ą┐ąĖčüąĖ 0 ąĖ 1 čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ ą▓ ą▒ąĖčé ADEN čĆąĄą│ąĖčüčéčĆą░ ADCSRA) ą▓čŗą┐ąŠą╗ąĮčÅčÄčéčüčÅ č鹊ą╗čīą║ąŠ čĆą░čüčłąĖčĆąĄąĮąĮčŗąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ. ąĀąĄąĘčāą╗čīčéą░čé čĆą░čüčłąĖčĆąĄąĮąĮąŠą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą▒čāą┤ąĄčé ą┤ąĄą╣čüčéą▓ąĖč鹥ą╗čīąĮčŗą╝. ąĪą╝. ą┐ąŠą┤čĆąŠą▒ąĮąĄąĄ čĆą░ąĘą┤ąĄą╗ ┬½ą¤čĆąĄą┤ą┤ąĄą╗ąĖč鹥ą╗čī (ą┐čĆąĄčüą║ą░ą╗ąĄčĆ) ąĖ ą▓čĆąĄą╝ąĄąĮąĮą░čÅ ą┤ąĖą░ą│čĆą░ą╝ą╝ą░ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ┬╗.

[ąśąĘą╝ąĄąĮąĄąĮąĖąĄ ą║ą░ąĮą░ą╗ą░ ąĖą╗ąĖ ą▓čŗą▒ąŠčĆ ąĖčüč鹊čćąĮąĖą║ą░ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ]

ąæąĖčéčŗ MUXn ąĖ REFS1:0 ą▓ čĆąĄą│ąĖčüčéčĆąĄ ADMUX ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé ąŠą┤ąĮąŠčüčéčāą┐ąĄąĮčćą░čéčāčÄ ą▒čāč乥čĆąĖąĘą░čåąĖčÄ č湥čĆąĄąĘ ą▓čĆąĄą╝ąĄąĮąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ. ąŁčéąĖą╝ ą│ą░čĆą░ąĮčéąĖčĆčāąĄčéčüčÅ, čćč鹊 ąĮąŠą▓čŗąĄ ąĮą░čüčéčĆąŠą╣ą║ąĖ ą║ą░ąĮą░ą╗ą░ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ąĖ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ ą▓čüčéčāą┐čÅčé ą▓ čüąĖą╗čā ą▓ ą▒ąĄąĘąŠą┐ą░čüąĮčŗą╣ ą╝ąŠą╝ąĄąĮčé ą┤ą╗čÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ. ąøčÄą▒čŗąĄ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ą║ą░ąĮą░ą╗ą░ ąĖ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ ą┐ąŠčüč鹊čÅąĮąĮąŠ ą▓čüčéčāą┐ą░čÄčé ą▓ čüąĖą╗čā ą▓ ą╝ąŠą╝ąĄąĮčé ąĮą░čćą░ą╗ą░ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ. ąÜą░ą║ č鹊ą╗čīą║ąŠ ąĮą░čćąĖąĮą░ąĄčéčüčÅ ą┐čĆąŠčåąĄčüčü ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą┤ąŠčüčéčāą┐ ą║ ąĖąĘą╝ąĄąĮąĄąĮąĖčÄ ą║ą░ąĮą░ą╗ą░ ąĖ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ ą▒ą╗ąŠą║ąĖčĆčāąĄčéčüčÅ, č湥ą╝ ą│ą░čĆą░ąĮčéąĖčĆčāąĄčéčüčÅ ą┤ąŠčüčéą░č鹊čćąĮąŠčüčéčī ą▓čĆąĄą╝ąĄąĮąĖ ąĮą░ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ą┤ą╗čÅ ADC. ąØąĄą┐čĆąĄčĆčŗą▓ąĮąŠčüčéčī ą╝ąŠą┤ąĖčäąĖą║ą░čåąĖąĖ ą▓ąŠčüčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ąĮą░ ą┐ąŠčüą╗ąĄą┤ąĮąĄą╝ čéą░ą║č鹥 ADC ą┐ąĄčĆąĄą┤ ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĄą╝ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ (ą┐čĆąĖ čāčüčéą░ąĮąŠą▓ą║ąĄ čäą╗ą░ą│ą░ ADIF ą▓ čĆąĄą│ąĖčüčéčĆąĄ ADCSRA). ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ąĮą░čćąĖąĮą░ąĄčéčüčÅ čüą╗ąĄą┤čāčÄčēąĖą╝ ąĮą░čĆą░čüčéą░čÄčēąĖą╝ čäčĆąŠąĮč鹊ą╝ čéą░ą║č鹊ą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ADC ą┐ąŠčüą╗ąĄ ąĘą░ą┐ąĖčüąĖ ADSC. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÄ ąĮąĄ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ąĘą░ą┐ąĖčüčŗą▓ą░čéčī ąĮąŠą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą║ą░ąĮą░ą╗ą░ ąĖą╗ąĖ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ ą▓ ADMUX ą┤ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ 1-ą│ąŠ čéą░ą║čéą░ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ADC ą┐ąŠčüą╗ąĄ ąĘą░ą┐ąĖčüąĖ ADSC.

ąĢčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą░ą▓č鹊ąĘą░ą┐čāčüą║ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ, č鹊 ąĮąĄą╗čīąĘčÅ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī č鹊čćąĮąŠąĄ ą▓čĆąĄą╝čÅ čüąŠą▒čŗčéąĖčÅ ąĘą░ą┐čāčüą║ą░. ąØąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ą▓ąĮąĖą╝ą░č鹥ą╗čīąĮąŠ ąŠą▒ąĮąŠą▓ą╗čÅčéčī čĆąĄą│ąĖčüčéčĆ ADMUX, čćč鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī, ą║ą░ą║ąŠąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ą▒čāą┤ąĄčé čüąŠąŠčéą▓ąĄčéčüčéą▓ąŠą▓ą░čéčī ąĮąŠą▓čŗą╝ čāčüčéą░ąĮąŠą▓ą║ą░ą╝.

ąĢčüą╗ąĖ ąŠą▒ą░ ą▒ąĖčéą░ ADATE ąĖ ADEN čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą▓ ą╗ąŠą│. 1, čüąŠą▒čŗčéąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą╝ąŠąČąĄčé ą┐čĆąŠąĖąĘąŠą╣čéąĖ ą▓ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé. ąĢčüą╗ąĖ čĆąĄą│ąĖčüčéčĆ ADMUX ą▒čŗą╗ ąĖąĘą╝ąĄąĮąĄąĮ ą▓ čŹč鹊čé ą┐ąĄčĆąĖąŠą┤, č鹊 ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ąĮąĄ ą╝ąŠąČąĄčé čüą║ą░ąĘą░čéčī, ą┐čĆąŠąĖąĘąŠčłą╗ąŠ čŹč鹊 ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ąĮą░ ąŠčüąĮąŠą▓ąĄ čüčéą░čĆčŗčģ ąĖą╗ąĖ ąĮąŠą▓čŗčģ čāčüčéą░ąĮąŠą▓ąŠą║. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ADMUX ą┤ąŠą╗ąČąĄąĮ ą╝ąŠą┤ąĖčäąĖčåąĖčĆąŠą▓ą░čéčīčüčÅ čüą╗ąĄą┤čāčÄčēąĖą╝ąĖ čüą┐ąŠčüąŠą▒ą░ą╝ąĖ:

- ąÜąŠą│ą┤ą░ ąŠčćąĖčēąĄąĮčŗ ą▒ąĖčé ADATE ąĖą╗ąĖ ADEN.

- ąÆąŠ ą▓čĆąĄą╝čÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ, ą╝ąĖąĮąĖą╝čāą╝ ąŠą┤ąĖąĮ čåąĖą║ą╗ ADC ą┐ąŠčüą╗ąĄ čüąŠą▒čŗčéąĖčÅ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖčÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ.

- ą¤ąŠčüą╗ąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ, ą┐ąĄčĆąĄą┤ č鹥ą╝ ą║ą░ą║ čäą╗ą░ą│ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ADIF ąŠčćąĖčēąĄąĮ ą┤ą╗čÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą║ą░ą║ ąĖčüč鹊čćąĮąĖą║ čüąŠą▒čŗčéąĖčÅ ąĘą░ą┐čāčüą║ą░.

ąÜąŠą│ą┤ą░ čĆąĄą│ąĖčüčéčĆ ADMUX ąŠą▒ąĮąŠą▓ą╗čÅąĄčéčüčÅ čü čüąŠą▒ą╗čÄą┤ąĄąĮąĖąĄą╝ čŹčéąĖčģ čāčüą╗ąŠą▓ąĖą╣, č鹊 ąĮąŠą▓čŗąĄ čāčüčéą░ąĮąŠą▓ą║ąĖ ąĮą░čćąĮčāčé čĆą░ą▒ąŠčéą░čéčī ą▓ąŠ ą▓čĆąĄą╝čÅ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ADC.

ą×čüąŠą▒čŗąĄ ą╝ąĄčĆčŗ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ą┐čĆąĄą┤ą┐čĆąĖąĮčÅčéčī ą┐čĆąĖ ąĖąĘą╝ąĄąĮąĄąĮąĖąĖ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗčģ ą║ą░ąĮą░ą╗ąŠą▓. ąÜą░ą║ č鹊ą╗čīą║ąŠ ąŠčüčāčēąĄčüčéą▓ą╗ąĄąĮ ą▓čŗą▒ąŠčĆ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą│ąŠ ą║ą░ąĮą░ą╗ą░, čāčüąĖą╗ąĖč鹥ą╗čīąĮąŠą╝čā ą║ą░čüą║ą░ą┤čā čéčĆąĄą▒čāąĄčéčüčÅ 125 ą╝ą║čü ą┤ą╗čÅ čüčéą░ą▒ąĖą╗ąĖąĘą░čåąĖąĖ ąĮąŠą▓ąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ. ąĪą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ, ą┐ąŠčüą╗ąĄ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą│ąŠ ą║ą░ąĮą░ą╗ą░ ą▓ č鹥č湥ąĮąĖąĄ ą┐ąĄčĆą▓čŗčģ 125 ą╝ą║čü ąĮąĄ ą┤ąŠą╗ąČąĮąŠ čüčéą░čĆč鹊ą▓ą░čéčī ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ. ąĢčüą╗ąĖ ąČąĄ ą▓ čŹč鹊čé ą┐ąĄčĆąĖąŠą┤ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą▓čüąĄ-čéą░ą║ąĖ ą▓čŗą┐ąŠą╗ąĮčÅą╗ąĖčüčī, č鹊 ąĖčģ čĆąĄąĘčāą╗čīčéą░čé ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ąĖą│ąĮąŠčĆąĖčĆąŠą▓ą░čéčī.

ąóą░ą║čāčÄ ąČąĄ ąĘą░ą┤ąĄčƹȹ║čā ąĮą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖąĄ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ą▓ą▓ąĄčüčéąĖ ą┐čĆąĖ ą┐ąĄčĆą▓ąŠą╝ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą╝ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĖ ą┐ąŠčüą╗ąĄ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ąĖčüč鹊čćąĮąĖą║ą░ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┤ą╗čÅ ADC (ą┐čāč鹥ą╝ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ą▒ąĖčé REFS1:0 ą▓ ADMUX).

[ąÆčģąŠą┤ąĮčŗąĄ ą║ą░ąĮą░ą╗čŗ ADC]

ą¤čĆąĖ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĖ ą▓čģąŠą┤ąĮąŠą│ąŠ ą║ą░ąĮą░ą╗ą░ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ čāč湥čüčéčī ąĮąĄą║ąŠč鹊čĆčŗąĄ čĆąĄą║ąŠą╝ąĄąĮą┤ą░čåąĖąĖ, ą║ąŠč鹊čĆčŗąĄ ąĖčüą║ą╗čÄčćą░čé ąĮąĄą║ąŠčĆčĆąĄą║čéąĮąŠčüčéčī ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ.

ąÆ čĆąĄąČąĖą╝ąĄ ąŠą┤ąĖąĮąŠčćąĮąŠą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ą║ą░ąĮą░ą╗ą░ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ą▓čŗą┐ąŠą╗ąĮčÅčéčī ą┐ąĄčĆąĄą┤ ąĮą░čćą░ą╗ąŠą╝ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ. ą¤ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ą║ą░ąĮą░ą╗ą░ ą╝ąŠąČąĄčé ą┐čĆąŠąĖąĘąŠą╣čéąĖ č鹊ą╗čīą║ąŠ ą▓ č鹥č湥ąĮąĖąĄ ąŠą┤ąĮąŠą│ąŠ čéą░ą║čéą░ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ADC ą┐ąŠčüą╗ąĄ ąĘą░ą┐ąĖčüąĖ ą╗ąŠą│. 1 ą▓ ADSC. ą×ą┤ąĮą░ą║ąŠ čüą░ą╝čŗą╝ ą┐čĆąŠčüčéčŗą╝ ą╝ąĄč鹊ą┤ąŠą╝ čÅą▓ą╗čÅąĄčéčüčÅ ąŠąČąĖą┤ą░ąĮąĖąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą┐ąĄčĆąĄą┤ ą▓čŗą▒ąŠčĆąŠą╝ ąĮąŠą▓ąŠą│ąŠ ą║ą░ąĮą░ą╗ą░.

ąÆ čĆąĄąČąĖą╝ąĄ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą│ąŠ ą┐ąĄčĆąĄąĘą░ą┐čāčüą║ą░ (Free Running mode) ą║ą░ąĮą░ą╗ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ą▓čŗą▒ąĖčĆą░čéčī ą┐ąĄčĆąĄą┤ ąĮą░čćą░ą╗ąŠą╝ ą┐ąĄčĆą▓ąŠą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ. ą¤ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ą║ą░ąĮą░ą╗ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą░ąĮą░ą╗ąŠą│ąĖčćąĮąŠ - ą▓ č鹥č湥ąĮąĖąĄ ąŠą┤ąĮąŠą│ąŠ čéą░ą║čéą░ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ADC ą┐ąŠčüą╗ąĄ ąĘą░ą┐ąĖčüąĖ ą╗ąŠą│. 1 ą▓ ADSC. ąØąŠ čüą░ą╝čŗą╝ ą┐čĆąŠčüčéčŗą╝ ą╝ąĄč鹊ą┤ąŠą╝ čÅą▓ą╗čÅąĄčéčüčÅ ąŠąČąĖą┤ą░ąĮąĖąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐ąĄčĆą▓ąŠą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ, ą░ ąĘą░č鹥ą╝ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ą║ą░ąĮą░ą╗ą░. ą¤ąŠčüą║ąŠą╗čīą║čā čüą╗ąĄą┤čāčÄčēąĄąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ čāąČąĄ ąĘą░ą┐čāčēąĄąĮąŠ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ, č鹊 čüą╗ąĄą┤čāčÄčēąĖą╣ čĆąĄąĘčāą╗čīčéą░čé ą▒čāą┤ąĄčé čüąŠąŠčéą▓ąĄčéčüčéą▓ąŠą▓ą░čéčī ą┐čĆąĄą┤čŗą┤čāčēąĄą╝čā ą║ą░ąĮą░ą╗čā. ą¤ąŠčüą╗ąĄą┤čāčÄčēąĖąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ąŠčéčĆą░ąČą░čÄčé čĆąĄąĘčāą╗čīčéą░čé ą┤ą╗čÅ ąĮąŠą▓ąŠą│ąŠ ą▓čŗą▒čĆą░ąĮąĮąŠą│ąŠ ą║ą░ąĮą░ą╗ą░.

ą¤čĆąĖ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĖ ąĮą░ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣ ą║ą░ąĮą░ą╗ ą┐ąĄčĆą▓ąŠąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ą▒čāą┤ąĄčé čģą░čĆą░ą║č鹥čĆąĖąĘąŠą▓ą░čéčīčüčÅ ą┐ą╗ąŠčģąŠą╣ č鹊čćąĮąŠčüčéčīčÄ ąĖąĘ-ąĘą░ ą┐ąĄčĆąĄčģąŠą┤ąĮąŠą│ąŠ ą┐čĆąŠčåąĄčüčüą░ ą▓ čüčģąĄą╝ąĄ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą╣ čĆąĄą│čāą╗ąĖčĆąŠą▓ą║ąĖ čüą╝ąĄčēąĄąĮąĖčÅ. ąĪą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ, ą┐ąĄčĆą▓čŗą╣ čĆąĄąĘčāą╗čīčéą░čé čéą░ą║ąŠą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ąĖą│ąĮąŠčĆąĖčĆąŠą▓ą░čéčī.

[ąśčüč鹊čćąĮąĖą║ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ADC]

ąśčüč鹊čćąĮąĖą║ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ (ąśą×ąØ) ą┤ą╗čÅ ADC (VREF) ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ą┤ąĖą░ą┐ą░ąĘąŠąĮ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ADC. ąĢčüą╗ąĖ ą▓ ąĮąĄą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą╝ čĆąĄąČąĖą╝ąĄ čāčĆąŠą▓ąĄąĮčī čüąĖą│ąĮą░ą╗ą░ čüą▓čŗčłąĄ VREF, č鹊 čĆąĄąĘčāą╗čīčéą░č鹊ą╝ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą▒čāą┤ąĄčé 0x3FF. ąÆ ą║ą░č湥čüčéą▓ąĄ VREF ą╝ąŠą│čāčé ą▓čŗčüčéčāą┐ą░čéčī AVCC, ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ ąśą×ąØ 2,56ąÆ ąĖą╗ąĖ ą▓ąĮąĄčłąĮąĖą╣ ąśą×ąØ, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗą╣ ą║ ą▓čŗą▓. AREF.

AVCC ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčéčüčÅ ą║ ADC č湥čĆąĄąĘ ą┐ą░čüčüąĖą▓ąĮčŗą╣ ą║ą╗čÄčć. ąÆąĮčāčéčĆąĄąĮąĮąĄąĄ ąŠą┐ąŠčĆąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ 2,56ąÆ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╝ čŹčéą░ą╗ąŠąĮąĮčŗą╝ ąĖčüč鹊čćąĮąĖą║ąŠą╝ (Bandgap Reference) VBG, ą▒čāč乥čĆąĖąĘąŠą▓ą░ąĮąĮąŠą│ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╝ čāčüąĖą╗ąĖč鹥ą╗ąĄą╝. ąÆ ą╗čÄą▒ąŠą╝ čüą╗čāčćą░ąĄ ą▓ąĮąĄčłąĮąĖą╣ ą▓čŗą▓ąŠą┤ AREF čüą▓čÅąĘą░ąĮ ąĮąĄą┐ąŠčüčĆąĄą┤čüčéą▓ąĄąĮąĮąŠ čü ADC, ąĖ ą┐ąŠčŹč鹊ą╝čā ą╝ąŠąČąĮąŠ čüąĮąĖąĘąĖčéčī ą▓ą╗ąĖčÅąĮąĖąĄ čłčāą╝ąŠą▓ ąĮą░ ąŠą┐ąŠčĆąĮčŗą╣ ąĖčüč鹊čćąĮąĖą║ ąĘą░ čüč湥čé ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆą░ ą╝ąĄąČą┤čā ą▓čŗą▓ąŠą┤ąŠą╝ AREF ąĖ ąŠą▒čēąĖą╝ ą┐čĆąŠą▓ąŠą┤ąŠą╝ (GND). ąØą░ą┐čĆčÅąČąĄąĮąĖąĄ VREF čéą░ą║ąČąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĖąĘą╝ąĄčĆąĄąĮąŠ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ AREF ą▓čŗčüąŠą║ąŠąŠą╝ąĮčŗą╝ ą▓ąŠą╗čīčéą╝ąĄčéčĆąŠą╝. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 VREF čÅą▓ą╗čÅąĄčéčüčÅ ą▓čŗčüąŠą║ąŠąŠą╝ąĮčŗą╝ ąĖčüč鹊čćąĮąĖą║ąŠą╝, ąĖ ą┐ąŠčŹč鹊ą╝čā ą▓ąĮąĄčłąĮąĄ ą║ ąĮąĄą╝čā ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠą┤ą║ą╗čÄč湥ąĮą░ č鹊ą╗čīą║ąŠ ąĄą╝ą║ąŠčüčéąĮą░čÅ ąĮą░ą│čĆčāąĘą║ą░.

ąĢčüą╗ąĖ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą▓ąĮąĄčłąĮąĖą╣ ąŠą┐ąŠčĆąĮčŗą╣ ąĖčüč鹊čćąĮąĖą║, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗą╣ ą║ ą▓čŗą▓. AREF, č鹊 ąĮąĄ ą┤ąŠą┐čāčüą║ą░ąĄčéčüčÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ ą┤čĆčāą│ąŠą╣ ąŠą┐čåąĖąĖ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░, čé. ą║. čŹč鹊 ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ čłčāąĮčéąĖčĆąŠą▓ą░ąĮąĖčÄ ą▓ąĮąĄčłąĮąĄą│ąŠ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ. ąĢčüą╗ąĖ ą║ ą▓čŗą▓. AREF ąĮąĄ ą┐čĆąĖą╗ąŠąČąĄąĮąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ, č鹊 ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą╝ąŠąČąĄčé ą▓čŗą▒čĆą░čéčī AVCC ąĖ 2.56ąÆ ą║ą░č湥čüčéą▓ąĄ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░. ąĀąĄąĘčāą╗čīčéą░čé ą┐ąĄčĆą▓ąŠą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą┐ąŠčüą╗ąĄ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ ą╝ąŠąČąĄčé čģą░čĆą░ą║č鹥čĆąĖąĘąŠą▓ą░čéčīčüčÅ ą┐ą╗ąŠčģąŠą╣ č鹊čćąĮąŠčüčéčīčÄ ąĖ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čÄ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ąĄą│ąŠ ąĖą│ąĮąŠčĆąĖčĆąŠą▓ą░čéčī.

ąĢčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗąĄ ą║ą░ąĮą░ą╗čŗ, č鹊 ą▓čŗą▒čĆą░ąĮąĮčŗą╣ ąŠą┐ąŠčĆąĮčŗą╣ ąĖčüč鹊čćąĮąĖą║ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą╝ąĄąĮčīčłąĄ čāčĆąŠą▓ąĮčÅ AVCC, čćč鹊 ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▓ čéą░ą▒ą╗. 122.

ą¦ą░čüčéčī čéą░ą▒ą╗ąĖčåčŗ 122. ąŻčĆąŠą▓ąĄąĮčī ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ADC.

| ąĪąĖą╝ą▓ąŠą╗ |

ą¤ą░čĆą░ą╝ąĄčéčĆ |

ąĀąĄąČąĖą╝ |

Min |

ąØąŠą╝ąĖąĮą░ą╗ |

Max |

ąĢą┤ąĖąĮąĖčåčŗ |

|

VREF

|

ą×ą┐ąŠčĆąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ |

ąØąĄą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣ |

2.0 |

|

AVCC |

ąÆ |

| ąöąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣ |

2.0 |

|

AVCC - 0.2 |

ąÆ |

[ą¤ąŠą┤ą░ą▓ąĖč鹥ą╗čī čłčāą╝ąŠą▓ ADC (ADC Noise Canceler)]

ADC ąĖą╝ąĄąĄčé ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ ą┐ąŠą┤ą░ą▓ąĖč鹥ą╗čī čłčāą╝ąŠą▓, ą║ąŠč鹊čĆčŗą╣ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖčéčī ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ą▓ čĆąĄąČąĖą╝ąĄ čüąĮą░ (sleep mode), čćč鹊 čāą╝ąĄąĮčīčłą░ąĄčé ą▓ą╗ąĖčÅąĮąĖąĄ čłčāą╝ąŠą▓, ą▓čŗąĘą▓ą░ąĮąĮčŗčģ čĆą░ą▒ąŠč鹊ą╣ čÅą┤čĆą░ ą”ą¤ąŻ ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ą▓ą▓ąŠą┤ą░-ą▓čŗą▓ąŠą┤ą░. ą¤ąŠą┤ą░ą▓ąĖč鹥ą╗čī čłčāą╝ąŠą▓ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮ čüąŠą▓ą╝ąĄčüčéąĮąŠ čü čĆąĄąČąĖą╝ą░ą╝ąĖ čüąĮąĖąČąĄąĮąĖčÅ čłčāą╝ąŠą▓ ADC (ADC Noise Reduction) ąĖ ą▓ čĆąĄąČąĖą╝ąĄ čģąŠą╗ąŠčüč鹊ą│ąŠ čģąŠą┤ą░ (Idle mode). ą¤čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ ą┤ą░ąĮąĮąŠą╣ čäčāąĮą║čåąĖąĖ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ą┐čĆąĖą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ čüą╗ąĄą┤čāčÄčēąĄą╣ ą┐čĆąŠčåąĄą┤čāčĆčŗ:

- ąŻą▒ąĄą┤ąĖč鹥čüčī, čćč鹊 čĆą░ą▒ąŠčéą░ ADC čĆą░ąĘčĆąĄčłąĄąĮą░ ąĖ ąŠąĮ ąĮąĄ ą▓čŗą┐ąŠą╗ąĮčÅąĄčé ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ. ąöąŠą╗ąČąĄąĮ ą▒čŗčéčī ą▓čŗą▒čĆą░ąĮ čĆąĄąČąĖą╝ ąŠą┤ąĖąĮąŠčćąĮąŠą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ąĖ čĆą░ąĘčĆąĄčłąĄąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ.

- ąŚą░ą┐čāčüčéąĖč鹥 čĆąĄąČąĖą╝ čāą╝ąĄąĮčīčłąĄąĮąĖčÅ čłčāą╝ąŠą▓ ADC (ADC Noise Reduction mode) ąĖą╗ąĖ čĆąĄąČąĖą╝ čģąŠą╗ąŠčüč鹊ą│ąŠ čģąŠą┤ą░ (Idle mode). ADC ąĘą░ą┐čāčüčéąĖčé ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ, ą║ą░ą║ č鹊ą╗čīą║ąŠ ąŠčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą”ą¤ąŻ.

- ąĢčüą╗ąĖ ą┤ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ąĮąĄ ą▓ąŠąĘąĮąĖą║ą░ąĄčé ą┤čĆčāą│ąĖčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣, č鹊 ą┐ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ADC čĆą░ąĘą▒čāą┤ąĖčé ą”ą¤ąŻ ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┐ąĄčĆąĄą╣ą┤ąĄčé ąĮą░ ą▓ąĄą║č鹊čĆ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ, ADC Conversion Complete). ąĢčüą╗ąĖ ą┤ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą┤čĆčāą│ąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐čĆąŠą▒čāąČą┤ą░ąĄčé ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ, č鹊 čŹč鹊 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčéčüčÅ, ą░ ą┐ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ąĘą░ą┐čĆąŠčü ąĮą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ. ADC ąŠčüčéą░ąĄčéčüčÅ ą▓ ą░ą║čéąĖą▓ąĮąŠą╝ čĆąĄąČąĖą╝ąĄ ą┐ąŠą║ą░ ąĮąĄ ą▒čāą┤ąĄčé ą▓čŗą┐ąŠą╗ąĮąĄąĮą░ ąŠč湥čĆąĄą┤ąĮą░čÅ ą║ąŠą╝ą░ąĮą┤ą░ sleep.

ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ADC ąĮąĄ ąŠčéą║ą╗čÄčćą░ąĄčéčüčÅ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą┐čĆąĖ ą┐ąĄčĆąĄą▓ąŠą┤ąĄ ą▓ąŠ ą▓čüąĄ ą┤čĆčāą│ąĖąĄ čĆąĄąČąĖą╝čŗ čüąĮą░, ą║čĆąŠą╝ąĄ čĆąĄąČąĖą╝ą░ čģąŠą╗ąŠčüč鹊ą│ąŠ čģąŠą┤ą░ (Idle mode) ąĖ čĆąĄąČąĖą╝ą░ čüąĮąĖąČąĄąĮąĖčÅ čłčāą╝ąŠą▓ ADC (ADC Noise Reduction mode). ą¤ąŠčŹč鹊ą╝čā ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą┤ąŠą╗ąČąĄąĮ ą┐čĆąĄą┤čāčüą╝ąŠčéčĆąĄčéčī ąĘą░ą┐ąĖčüčī ą╗ąŠą│. 0 ą▓ ą▒ąĖčé ADEN ą┐ąĄčĆąĄą┤ ą┐ąĄčĆąĄą▓ąŠą┤ąŠą╝ ą▓ čéą░ą║ąĖąĄ čĆąĄąČąĖą╝čŗ čüąĮą░, ą▓ąŠ ąĖąĘą▒ąĄąČą░ąĮąĖąĄ čćčĆąĄąĘą╝ąĄčĆąĮąŠą│ąŠ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ. ąĢčüą╗ąĖ čĆą░ą▒ąŠčéą░ ADC ą▒čŗą╗ą░ čĆą░ąĘčĆąĄčłąĄąĮą░ ą▓ čéą░ą║ąĖčģ čĆąĄąČąĖą╝ą░čģ čüąĮą░ ąĖ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ąČąĄą╗ą░ąĄčé ą▓čŗą┐ąŠą╗ąĮąĖčéčī ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ, č鹊 ą┐ąŠčüą╗ąĄ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ ADC ąĮčāąČąĮąŠ ą▓čŗą║ą╗čÄčćąĖčéčī, ą░ ąĘą░č鹥ą╝ ą▓ą║ą╗čÄčćąĖčéčī ą┤ą╗čÅ ąĖąĮąĖčåąĖą░čåąĖąĖ čĆą░čüčłąĖčĆąĄąĮąĮąŠą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ, č湥ą╝ ą▒čāą┤ąĄčé ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░ąĮąŠ ą┐ąŠą╗čāč湥ąĮąĖąĄ ą┤ąĄą╣čüčéą▓ąĖč鹥ą╗čīąĮąŠą│ąŠ čĆąĄąĘčāą╗čīčéą░čéą░.

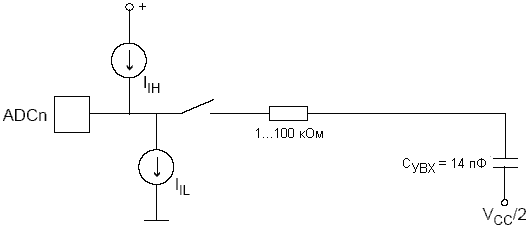

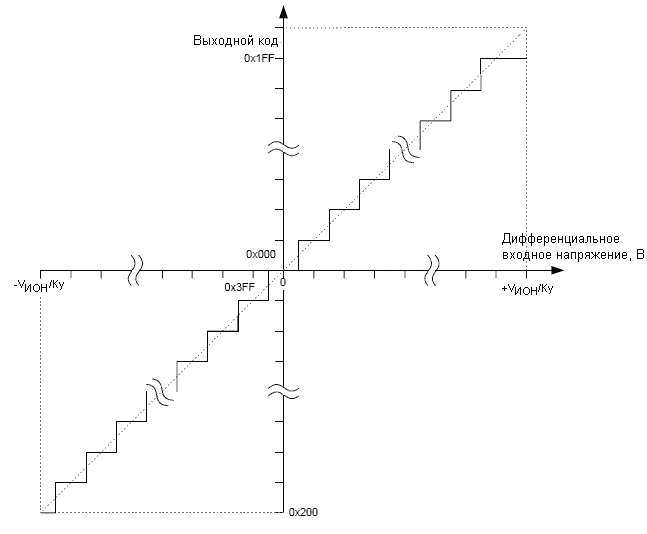

[ąĪčģąĄą╝ą░ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ą▓čģąŠą┤ą░]

ąĪčģąĄą╝ą░ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ą▓čģąŠą┤ą░ ą┤ą╗čÅ ąĮąĄą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗčģ ą║ą░ąĮą░ą╗ąŠą▓ ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮą░ ąĮą░ čĆąĖčüčāąĮą║ąĄ 105. ąØąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé č鹊ą│ąŠ, ą║ą░ą║ąŠą╣ ą║ą░ąĮą░ą╗ ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą║ ADC, ą░ąĮą░ą╗ąŠą│ąŠą▓čŗą╣ čüąĖą│ąĮą░ą╗, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗą╣ ą║ ą▓čŗą▓. ADCn, ąĮą░ą│čĆčāąČą░ąĄčéčüčÅ ąĄą╝ą║ąŠčüčéčīčÄ ą▓čŗą▓ąŠą┤ą░ ąĖ ą▓čģąŠą┤ąĮčŗą╝ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄą╝ čāč鹥čćą║ąĖ. ą¤ąŠčüą╗ąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ą║ą░ąĮą░ą╗ą░ ą║ ADC ą▓čģąŠą┤ąĮąŠą╣ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗą╣ čüąĖą│ąĮą░ą╗ ą▒čāą┤ąĄčé čüą▓čÅąĘą░ąĮ čü ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆąŠą╝ ą▓čŗą▒ąŠčĆą║ąĖ-čģčĆą░ąĮąĄąĮąĖčÅ č湥čĆąĄąĘ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ čĆąĄąĘąĖčüč鹊čĆ, čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ ą║ąŠč鹊čĆąŠą│ąŠ 菹║ą▓ąĖą▓ą░ą╗ąĄąĮčéąĮąŠ ą▓čüąĄą╣ ą▓čģąŠą┤ąĮąŠą╣ čåąĄą┐ąĖ.

ADC ąŠą┐čéąĖą╝ąĖąĘąĖčĆąŠą▓ą░ąĮ ą┐ąŠą┤ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗąĄ čüąĖą│ąĮą░ą╗čŗ čü ą▓čŗčģąŠą┤ąĮčŗą╝ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄą╝ 10 ą║ą×ą╝ ąĖą╗ąĖ ą╝ąĄąĮčīčłąĄ. ąĢčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čéą░ą║ąŠą╣ ąĖčüč鹊čćąĮąĖą║ čüąĖą│ąĮą░ą╗ą░, č鹊 ą▓čĆąĄą╝čÅ ą▓čŗą▒ąŠčĆą║ąĖ ąĮąĄąĘąĮą░čćąĖč鹥ą╗čīąĮąŠ. ąĢčüą╗ąĖ ąČąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ąĖčüč鹊čćąĮąĖą║ čü ą▒ąŠą╗ąĄąĄ ą▓čŗčüąŠą║ąĖą╝ ą▓čģąŠą┤ąĮčŗą╝ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄą╝, č鹊 ą▓čĆąĄą╝čÅ ą▓čŗą▒ąŠčĆą║ąĖ ą▒čāą┤ąĄčé ąŠą┐čĆąĄą┤ąĄą╗čÅčéčīčüčÅ ą▓čĆąĄą╝ąĄąĮąĄą╝, ą║ąŠč鹊čĆąŠąĄ čéčĆąĄą▒čāąĄčéčüčÅ ą┤ą╗čÅ ąĘą░čĆčÅą┤ą║ąĖ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆą░ ą▓čŗą▒ąŠčĆą║ąĖ-čģčĆą░ąĮąĄąĮąĖčÅ ąŠčé ąĖčüč鹊čćąĮąĖą║ą░ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░. ąĀąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ąĖčüč鹊čćąĮąĖą║ąĖ č鹊ą╗čīą║ąŠ čü ą╝ą░ą╗čŗą╝ ą▓čŗčģąŠą┤ąĮčŗą╝ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄą╝ ąĖ ą╝ąĄą┤ą╗ąĄąĮąĮąŠ ąĖąĘą╝ąĄąĮčÅčÄčēąĖą╝ąĖčüčÅ čüąĖą│ąĮą░ą╗ą░ą╝ąĖ, čé.ą║. ą▓ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ą▒čāą┤ąĄčé ą┤ąŠčüčéą░č鹊čćąĮąŠ ą▒čŗčüčéčĆčŗą╝ ąĘą░čĆčÅą┤ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆą░ ą▓čŗą▒ąŠčĆą║ąĖ-čģčĆą░ąĮąĄąĮąĖčÅ.

ąĪ ą║ą░ąĮą░ą╗ą░ą╝ąĖ čü ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╝ čāčüąĖą╗ąĄąĮąĖąĄą╝ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čüąĖą│ąĮą░ą╗čŗ čü ą▓ąĮčāčéčĆąĄąĮąĮąĖą╝ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄą╝ ą┤ąŠ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ čüąŠč鹥ąĮ ą║ą×ą╝.

ąĪą╗ąĄą┤čāąĄčé ą┐čĆąĄą┤čāčüą╝ąŠčéčĆąĄčéčī, čćč鹊ą▒čŗ ą▓ ą┐čĆąĄą┤ą▓ą░čĆąĖč鹥ą╗čīąĮčŗčģ ą║ą░čüą║ą░ą┤ą░čģ č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ą║ąŠ ą▓čģąŠą┤čā ADC ąĮąĄ ą▓ąĮąŠčüąĖą╗ąĖčüčī čćą░čüč鹊čéčŗ ą▓čŗčłąĄ fADC/2, ą▓ ą┐čĆąŠčéąĖą▓ąĮąŠą╝ čüą╗čāčćą░ąĄ čĆąĄąĘčāą╗čīčéą░čé ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĮąĄą║ąŠčĆčĆąĄą║čéąĮčŗą╝ (čüą▓čÅąĘą░ąĮąŠ čü čāčüą╗ąŠą▓ąĖąĄą╝ ąØą░ą╣ą║ą▓ąĖčüčéą░/ąÜąŠč鹥ą╗čīąĮąĖą║ąŠą▓ą░). ąĢčüą╗ąĖ ą▓ąĄčĆąŠčÅčéąĮąŠčüčéčī ą┐čĆąŠąĮąĖą║ąĮąŠą▓ąĄąĮąĖčÅ ą▓čŗčüąŠą║ąĖčģ čćą░čüč鹊čé čüčāčēąĄčüčéą▓čāąĄčé, č鹊 čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ą┐ąĄčĆąĄą┤ ADC čāčüčéą░ąĮąŠą▓ąĖčéčī čäąĖą╗čīčéčĆ ąĮąĖąĘą║ąĖčģ čćą░čüč鹊čé.

ąĀąĖčüčāąĮąŠą║ 105. ąĪčģąĄą╝ą░ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ą▓čģąŠą┤ą░

[ąĀąĄą║ąŠą╝ąĄąĮą┤ą░čåąĖąĖ ą┐ąŠ čüąĮąĖąČąĄąĮąĖčÄ ą▓ą╗ąĖčÅąĮąĖčÅ čłčāą╝ąŠą▓ ąĮą░ čĆąĄąĘčāą╗čīčéą░čé ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ]

ąĀą░ą▒ąŠčéą░ čåąĖčäčĆąŠą▓čŗčģ čāąĘą╗ąŠą▓ ą▓ąĮčāčéčĆąĖ ąĖ čüąĮą░čĆčāąČąĖ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ čüą▓čÅąĘą░ąĮą░ čü ą│ąĄąĮąĄčĆą░čåąĖąĄą╣ 菹╗ąĄą║čéčĆąŠą╝ą░ą│ąĮąĖčéąĮčŗčģ ąĖąĘą╗čāč湥ąĮąĖą╣ ąĖ čłčāą╝ąŠą▓, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠą│čāčé ąĮąĄą│ą░čéąĖą▓ąĮąŠ čüą║ą░ąĘą░čéčīčüčÅ ąĮą░ č鹊čćąĮąŠčüčéčī ąĖąĘą╝ąĄčĆąĄąĮąĖčÅ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░. ąĢčüą╗ąĖ č鹊čćąĮąŠčüčéčī ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ čÅą▓ą╗čÅąĄčéčüčÅ ą║čĆąĖčéąĖč湥čüą║ąĖą╝ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą╝, č鹊 čāčĆąŠą▓ąĄąĮčī čłčāą╝ąŠą▓ ą╝ąŠąČąĮąŠ čüąĮąĖąĘąĖčéčī, ą┐čĆąĖą┤ąĄčƹȹĖą▓ą░čÅčüčī čüą╗ąĄą┤čāčÄčēąĖčģ čĆąĄą║ąŠą╝ąĄąĮą┤ą░čåąĖą╣:

- ąÆčŗą┐ąŠą╗ąĮčÅą╣č鹥 ą┐čāčéčī ą░ąĮą░ą╗ąŠą│ąŠą▓čŗčģ čüąĖą│ąĮą░ą╗ąŠą▓ ą║ą░ą║ ą╝ąŠąČąĮąŠ ą▒ąŠą╗ąĄąĄ ą║ąŠčĆąŠčéą║ąĖą╝. ąĪą╗ąĄą┤ąĖč鹥, čćč鹊ą▒čŗ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗąĄ čüąĖą│ąĮą░ą╗čŗ ą┐čĆąŠčģąŠą┤ąĖą╗ąĖ ąĮą░ą┤ ą┐ą╗ąŠčüą║ąŠčüčéčīčÄ (čüą╗ąŠąĄą╝) čü ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą╣ ąĘąĄą╝ą╗ąĄą╣ (菹║čĆą░ąĮąŠą╝) ąĖ ą┤ą░ą╗ąĄą║ąŠ ąŠčé ą┐čĆąŠą▓ąŠą┤ąĮąĖą║ąŠą▓, ą┐ąĄčĆąĄą┤ą░čÄčēąĖčģ ą▓čŗčüąŠą║ąŠčüą║ąŠčĆąŠčüčéąĮčŗąĄ čåąĖčäčĆąŠą▓čŗąĄ čüąĖą│ąĮą░ą╗čŗ.

- ąÆčŗą▓ąŠą┤ AVCC ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ čüą▓čÅąĘą░čéčī čü čåąĖčäčĆąŠą▓čŗą╝ ą┐ąĖčéą░ąĮąĖąĄą╝ VCC č湥čĆąĄąĘ LC-čåąĄą┐čī ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü čĆąĖčü. 106.

- ąśčüą┐ąŠą╗čīąĘčāą╣č鹥 čäčāąĮą║čåąĖčÄ ą┐ąŠą┤ą░ą▓ą╗ąĄąĮąĖčÅ čłčāą╝ąŠą▓ ADC (ADC noise canceler) ą┤ą╗čÅ čāą╝ąĄąĮčīčłąĄąĮąĖčÅ čłčāą╝ąŠą▓, ą▓ąĮąĄčüąĄąĮąĮčŗčģ čĆą░ą▒ąŠč鹊ą╣ čÅą┤čĆą░ ą”ą¤ąŻ.

- ąĢčüą╗ąĖ ą║ą░ą║ąŠą╣-ą╗ąĖą▒ąŠ ąĖąĘ ą▓čŗą▓ąŠą┤ąŠą▓ ADC ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą║ą░ą║ čåąĖčäčĆąŠą▓ąŠą╣ ą▓čŗčģąŠą┤, č鹊 čćčĆąĄąĘą▓čŗčćą░ą╣ąĮąŠ ą▓ą░ąČąĮąŠ ąĮąĄ ą┤ąŠą┐čāčüčéąĖčéčī ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ čüąŠčüč鹊čÅąĮąĖčÅ čŹč鹊ą│ąŠ ą▓čŗčģąŠą┤ą░ ą▓ ą┐čĆąŠčåąĄčüčüąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ.

ąĀąĖčüčāąĮąŠą║ 106. ą¤ąŠą┤ą║ą╗čÄč湥ąĮąĖąĄ ą┐ąĖčéą░ąĮąĖčÅ ą║ ADC

[ąĪčģąĄą╝čŗ ą║ąŠą╝ą┐ąĄąĮčüą░čåąĖąĖ čüą╝ąĄčēąĄąĮąĖčÅ]

ąŻčüąĖą╗ąĖč鹥ą╗čīąĮčŗą╣ ą║ą░čüą║ą░ą┤ ąĖą╝ąĄąĄčé ą▓čüčéčĆąŠąĄąĮąĮčāčÄ čüčģąĄą╝čā ą║ąŠą╝ą┐ąĄąĮčüą░čåąĖąĖ čüą╝ąĄčēąĄąĮąĖčÅ (offset cancellation circuit), ą║ąŠč鹊čĆą░čÅ čüčéčĆąĄą╝ąĖčéčüčÅ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠ ą┐čĆąĖą▒ą╗ąĖąĘąĖčéčī ą║ ąĮčāą╗čÄ čüą╝ąĄčēąĄąĮąĖąĄ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą│ąŠ ąĖąĘą╝ąĄčĆąĄąĮąĖčÅ. ą×čüčéą░ą▓čłąĄąĄčüčÅ čüą╝ąĄčēąĄąĮąĖąĄ ą╝ąŠąČąĮąŠ ąĖąĘą╝ąĄčĆąĖčéčī, ąĄčüą╗ąĖ ą▓ ą║ą░č湥čüčéą▓ąĄ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗčģ ą▓čģąŠą┤ąŠą▓ ADC ą▓čŗą▒čĆą░čéčī ąŠą┤ąĖąĮ ąĖ č鹊čé ąČąĄ ą▓čŗą▓ąŠą┤ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░. ąśąĘą╝ąĄčĆąĄąĮąĮąŠąĄ čéą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝ ąŠčüčéą░č鹊čćąĮąŠąĄ čüą╝ąĄčēąĄąĮąĖąĄ ą╝ąŠąČąĮąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ ą▓čŗč湥čüčéčī ąĖąĘ čĆąĄąĘčāą╗čīčéą░čéą░ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ. ąśčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ ą░ą╗ą│ąŠčĆąĖčéą╝ą░ ą║ąŠčĆčĆąĄą║čåąĖąĖ čüą╝ąĄčēąĄąĮąĖčÅ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé čāą╝ąĄąĮčīčłąĖčéčī čüą╝ąĄčēąĄąĮąĖąĄ ąĮąĖąČąĄ ąŠą┤ąĮąŠą│ąŠ ą╝ą╗. čĆą░ąĘčĆ.

[ą×ą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ ą┐ąŠą│čĆąĄčłąĮąŠčüčéąĖ (č鹊čćąĮąŠčüčéąĖ) ą░ąĮą░ą╗ąŠą│ąŠ-čåąĖčäčĆąŠą▓ąŠą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ]

n-čĆą░ąĘčĆčÅą┤ąĮčŗą╣ ąŠą┤ąĮąŠą┐ąŠą╗čÅčĆąĮčŗą╣ ADC ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓čŗą▓ą░ąĄčé ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą╗ąĖąĮąĄą╣ąĮąŠ ą╝ąĄąČą┤čā GND ąĖ VREF čü ą║ąŠą╗ąĖč湥čüčéą▓ąŠą╝ čłą░ą│ąŠą▓ 2n (ą╝ą╗. čĆą░ąĘčĆčÅą┤ąŠą▓). ą£ąĖąĮąĖą╝ą░ą╗čīąĮčŗą╣ ą║ąŠą┤ = 0, ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮčŗą╣ = 2n-1. ą×čüąĮąŠą▓ąĮčŗąĄ ą┐ąŠą│čĆąĄčłąĮąŠčüčéąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ čÅą▓ą╗čÅčÄčéčüčÅ ąŠčéą║ą╗ąŠąĮąĄąĮąĖąĄą╝ čĆąĄą░ą╗čīąĮąŠą╣ čäčāąĮą║čåąĖąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ąŠčé ąĖą┤ąĄą░ą╗čīąĮąŠą╣. ąÜ ąĮąĖą╝ ąŠčéąĮąŠčüčÅčéčüčÅ:

ąĪą╝ąĄčēąĄąĮąĖąĄ ŌĆō ąŠčéą║ą╗ąŠąĮąĄąĮąĖąĄ ą┐ąĄčĆą▓ąŠą│ąŠ ą┐ąĄčĆąĄčģąŠą┤ą░ (ąŠčé ą║ąŠą┤ą░ 0x000 ąĮą░ ą║ąŠą┤ 0x001) ą┐ąŠ čüčĆą░ą▓ąĮąĄąĮąĖčÄ čü ąĖą┤ąĄą░ą╗čīąĮčŗą╝ ą┐ąĄčĆąĄčģąŠą┤ąŠą╝ (čé. ąĄ. ą┐čĆąĖ 0.5 ą╝ą╗. čĆą░ąĘčĆ.). ąśą┤ąĄą░ą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ: 0 ą╝ą╗. čĆą░ąĘčĆ.

ąĀąĖčüčāąĮąŠą║ 107. ą¤ąŠą│čĆąĄčłąĮąŠčüčéčī čüą╝ąĄčēąĄąĮąĖčÅ.

ą¤ąŠą│čĆąĄčłąĮąŠčüčéčī čāčüąĖą╗ąĄąĮąĖčÅ. ą¤ąŠčüą╗ąĄ ą║ąŠčĆčĆąĄą║čéąĖčĆąŠą▓ą║ąĖ čüą╝ąĄčēąĄąĮąĖčÅ ą┐ąŠą│čĆąĄčłąĮąŠčüčéčī čāčüąĖą╗ąĄąĮąĖčÅ ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé čüąŠą▒ąŠą╣ ąŠčéą║ą╗ąŠąĮąĄąĮąĖąĄ ą┐ąŠčüą╗ąĄą┤ąĮąĄą│ąŠ ą┐ąĄčĆąĄčģąŠą┤ą░ (čü 0x3FE ąĮą░ 0x3FF) ąŠčé ąĖą┤ąĄą░ą╗čīąĮąŠą│ąŠ ą┐ąĄčĆąĄčģąŠą┤ą░ (čé. ąĄ. ąŠčéą║ą╗ąŠąĮąĄąĮąĖąĄ ą┐čĆąĖ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą╝ ąĘąĮą░č湥ąĮąĖąĖ ą╝ąĖąĮčāčü 1.5 ą╝ą╗. čĆą░ąĘčĆ.). ąśą┤ąĄą░ą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ: 0 ą╝ą╗. čĆą░ąĘčĆ.

ąĀąĖčüčāąĮąŠą║ 108. ą¤ąŠą│čĆąĄčłąĮąŠčüčéčī čāčüąĖą╗ąĄąĮąĖčÅ

ąśąĮč鹥ą│čĆą░ą╗čīąĮą░čÅ ąĮąĄą╗ąĖąĮąĄą╣ąĮąŠčüčéčī (Integral Non-linearity, INL). ą¤ąŠčüą╗ąĄ ą║ąŠčĆčĆąĄą║čéąĖčĆąŠą▓ą║ąĖ čüą╝ąĄčēąĄąĮąĖčÅ ąĖ ą┐ąŠą│čĆąĄčłąĮąŠčüčéąĖ čāčüąĖą╗ąĄąĮąĖčÅ INL ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé čüąŠą▒ąŠą╣ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠąĄ ąŠčéą║ą╗ąŠąĮąĄąĮąĖąĄ čĆąĄą░ą╗čīąĮąŠą╣ čäčāąĮą║čåąĖąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ąŠčé ąĖą┤ąĄą░ą╗čīąĮąŠą╣ ą┤ą╗čÅ ą╗čÄą▒ąŠą│ąŠ ą║ąŠą┤ą░. ąśą┤ąĄą░ą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ąśąØąø = 0 ą╝ą╗. čĆą░ąĘčĆ.

ąĀąĖčüčāąĮąŠą║ 109. ąśąĮč鹥ą│čĆą░ą╗čīąĮą░čÅ ąĮąĄą╗ąĖąĮąĄą╣ąĮąŠčüčéčī (ąśąØąø)

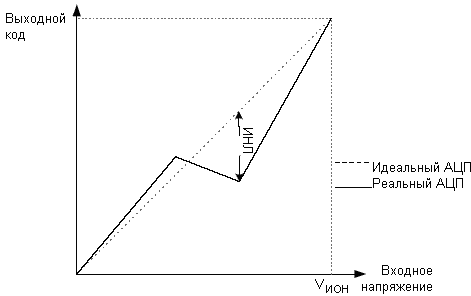

ąöąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮą░čÅ ąĮąĄą╗ąĖąĮąĄą╣ąĮąŠčüčéčī (DNL). ą£ą░ą║čüąĖą╝ą░ą╗čīąĮąŠąĄ ąŠčéą║ą╗ąŠąĮąĄąĮąĖąĄ ą╝ąĄąČą┤čā čłąĖčĆąĖąĮąŠą╣ čäą░ą║čéąĖč湥čüą║ąŠą│ąŠ ą║ąŠą┤ą░ (ąĖąĮč鹥čĆą▓ą░ą╗ ą╝ąĄąČą┤čā ą┤ą▓čāą╝čÅ čüą╝ąĄąČąĮčŗą╝ąĖ ą┐ąĄčĆąĄčģąŠą┤ą░ą╝ąĖ) ąŠčé čłąĖčĆąĖąĮčŗ ąĖą┤ąĄą░ą╗čīąĮąŠą│ąŠ ą║ąŠą┤ą░ (1 ą╝ą╗. čĆą░ąĘčĆ.). ąśą┤ąĄą░ą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ: 0 ą╝ą╗. čĆą░ąĘčĆ.

ąĀąĖčüčāąĮąŠą║ 110. ąöąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮą░čÅ ąĮąĄą╗ąĖąĮąĄą╣ąĮąŠčüčéčī (DNL)

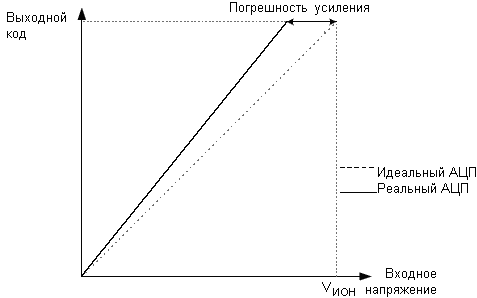

ą¤ąŠą│čĆąĄčłąĮąŠčüčéčī ą║ą▓ą░ąĮč鹊ą▓ą░ąĮąĖčÅ. ąÆąŠąĘąĮąĖą║ą░ąĄčé ąĖąĘ-ąĘą░ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą▓čģąŠą┤ąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą▓ ą║ąŠąĮąĄčćąĮąŠąĄ čćąĖčüą╗ąŠ ą║ąŠą┤ąŠą▓. ą¤ąŠą│čĆąĄčłąĮąŠčüčéčī ą║ą▓ą░ąĮč鹊ą▓ą░ąĮąĖčÅ - ąĖąĮč鹥čĆą▓ą░ą╗ ą▓čģąŠą┤ąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐čĆąŠčéčÅąČąĄąĮąĮąŠčüčéčīčÄ 1 ą╝ą╗. čĆą░ąĘčĆ. (čłą░ą│ ą║ą▓ą░ąĮč鹊ą▓ą░ąĮąĖčÅ ą┐ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÄ), ą║ąŠč鹊čĆčŗą╣ čģą░čĆą░ą║č鹥čĆąĖąĘčāąĄčéčüčÅ ąŠą┤ąĮąĖą╝ ąĖ č鹥ą╝ ąČąĄ ą║ąŠą┤ąŠą╝. ąÆčüąĄą│ą┤ą░ čĆą░ą▓ąĄąĮ ┬▒0.5 ą╝ą╗. čĆą░ąĘčĆ.

ąÉą▒čüąŠą╗čÄčéąĮą░čÅ ą┐ąŠą│čĆąĄčłąĮąŠčüčéčī. ą£ą░ą║čüąĖą╝ą░ą╗čīąĮąŠąĄ ąŠčéą║ą╗ąŠąĮąĄąĮąĖąĄ čĆąĄą░ą╗čīąĮąŠą╣ (ą▒ąĄąĘ ą┐ąŠą┤čüčéčĆąŠą╣ą║ąĖ) čäčāąĮą║čåąĖąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ąŠčé čĆąĄą░ą╗čīąĮąŠą╣ ą┐čĆąĖ ą╗čÄą▒ąŠą╝ ą║ąŠą┤ąĄ. ą»ą▓ą╗čÅąĄčéčüčÅ čĆąĄąĘčāą╗čīčéą░č鹊ą╝ ą┤ąĄą╣čüčéą▓ąĖčÅ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ čŹčäč乥ą║č鹊ą▓: čüą╝ąĄčēąĄąĮąĖąĄ, ą┐ąŠą│čĆąĄčłąĮąŠčüčéčī čāčüąĖą╗ąĄąĮąĖčÅ, ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮą░čÅ ą┐ąŠą│čĆąĄčłąĮąŠčüčéčī, ąĮąĄą╗ąĖąĮąĄą╣ąĮąŠčüčéčī ąĖ ą┐ąŠą│čĆąĄčłąĮąŠčüčéčī ą║ą▓ą░ąĮč鹊ą▓ą░ąĮąĖčÅ. ąśą┤ąĄą░ą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ: ┬▒0.5 ą╝ą╗. čĆą░ąĘčĆ.

[ąĀąĄąĘčāą╗čīčéą░čé ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ADC]

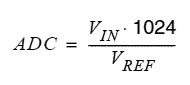

ą¤ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ (ADIF = 1) čĆąĄąĘčāą╗čīčéą░čé ą╝ąŠąČąĄčé ą▒čŗčéčī čüčćąĖčéą░ąĮ ąĖąĘ ą┐ą░čĆčŗ čĆąĄą│ąĖčüčéčĆąŠą▓ čĆąĄąĘčāą╗čīčéą░čéą░ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ADC (ADCL, ADCH). ąöą╗čÅ ąĮąĄą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ:

ą│ą┤ąĄ VIN ŌĆō čāčĆąŠą▓ąĄąĮčī ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ąĮą░ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮąŠą╝ ą║ ADC ą▓čģąŠą┤ąĄ, VREF ŌĆō ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą▓čŗą▒čĆą░ąĮąĮąŠą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ (čüą╝. čéą░ą▒ą╗. 83 ąĖ čéą░ą▒ą╗. 84). ąÜąŠą┤ 0x000 čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé čāčĆąŠą▓ąĮčÄ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą╣ ąĘąĄą╝ą╗ąĖ, ą░ 0x3FF - čāčĆąŠą▓ąĮčÄ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ąśą×ąØ ą╝ąĖąĮčāčü 1 čłą░ą│ ą║ą▓ą░ąĮč鹊ą▓ą░ąĮąĖčÅ ą┐ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÄ.

ą¤čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą│ąŠ ą║ą░ąĮą░ą╗ą░

ąŚą┤ąĄčüčī VPOS ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮą░ ┬½ą┐ą╗čÄčüąŠą▓ąŠą╝┬╗ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą╝ ą▓čģąŠą┤ąĄ, ą░ VNEG ŌĆō ąĮą░ ┬½ą╝ąĖąĮčāčüąŠą▓ąŠą╝┬╗, GAIN ŌĆō ą▓čŗą▒čĆą░ąĮąĮčŗą╣ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé čāčüąĖą╗ąĄąĮąĖčÅ, VREF ŌĆō ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą▓čŗą▒čĆą░ąĮąĮąŠą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ. ąĀąĄąĘčāą╗čīčéą░čé ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčéčüčÅ ą▓ ą║ąŠą┤ąĄ ą┤ą▓ąŠąĖčćąĮąŠą│ąŠ ą┤ąŠą┐ąŠą╗ąĮąĄąĮąĖčÅ, ąĮą░čćąĖąĮą░čÅ čü 0x200 (-512d) ą┤ąŠ 0x1FF (+511d). ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ą┐čĆąĖ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéąĖ ą▒čŗčüčéčĆąŠ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī ą┐ąŠą╗čÅčĆąĮąŠčüčéčī čĆąĄąĘčāą╗čīčéą░čéą░ ą┤ąŠčüčéą░č鹊čćąĮąŠ ąŠą┐čĆąŠčüąĖčéčī čüčéą░čĆčłąĖą╣ ą▒ąĖčé čĆąĄąĘčāą╗čīčéą░čéą░ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ (ADC9 ą▓ ADCH). ąĢčüą╗ąĖ ą┤ą░ąĮąĮčŗą╣ ą▒ąĖčé čĆą░ą▓ąĄąĮ ą╗ąŠą│. 1, č鹊 čĆąĄąĘčāą╗čīčéą░čé ąŠčéčĆąĖčåą░č鹥ą╗čīąĮčŗą╣, ąĄčüą╗ąĖ ąČąĄ ą╗ąŠą│. 0, č鹊 ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮčŗą╣. ąØą░ čĆąĖčüčāąĮą║ąĄ 111 ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮą░ čäčāąĮą║čåąĖčÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ADC ą▓ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą╝ čĆąĄąČąĖą╝ąĄ.

ąÆ čéą░ą▒ą╗ąĖčåąĄ 82 ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮčŗ čĆąĄąĘčāą╗čīčéąĖčĆčāčÄčēąĖąĄ ą▓čŗčģąŠą┤ąĮčŗąĄ ą║ąŠą┤čŗ ą┤ą╗čÅ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą╣ ą┐ą░čĆčŗ ą║ą░ąĮą░ą╗ąŠą▓ (ADCn - ADCm) čü ą║ąŠčŹčäčäąĖčåąĖąĄąĮč鹊ą╝ čāčüąĖą╗ąĄąĮąĖčÅ GAIN (ąÜčā) ąĖ ąŠą┐ąŠčĆąĮčŗą╝ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄą╝ VREF (Vąśą×ąØ).

ąĀąĖčüčāąĮąŠą║ 111. ążčāąĮą║čåąĖčÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ADC ą┐čĆąĖ ąĖąĘą╝ąĄčĆąĄąĮąĖąĖ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░

ąóą░ą▒ą╗ąĖčåą░ 82. ąĪą▓čÅąĘčī ą╝ąĄąČą┤čā ą▓čģąŠą┤ąĮčŗą╝ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄą╝ ąĖ ą▓čŗčģąŠą┤ąĮčŗą╝ąĖ ą║ąŠą┤ą░ą╝ąĖ

|

VADC, čĆą░ąĘąĮąĖčåą░ ąĮą░ą┐čĆčÅąČąĄąĮąĖą╣ ą▓čģąŠą┤ąŠą▓ (VADCn - VADCm)

|

čüčćąĖčéčŗą▓ą░ąĄą╝čŗą╣ ą║ąŠą┤ |

čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ ą┤ąĄčüčÅčéąĖčćąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ |

| + VREF / GAIN |

0x1FF |

511 |

| + (511/512) VREF / GAIN |

0x1FF |

511 |

| + (510/512) VREF / GAIN |

0x1FE |

510 |

| ŌĆ” |

... |

... |

| + (1/512) VREF / GAIN |

0x001 |

1 |

| 0 |

0x000 |

0 |

| - (1/512) VREF / GAIN |

0x3FF |

-1 |

| ŌĆ” |

... |

... |

| - (511/512) VREF / GAIN |

0x201 |

-511 |

| ŌĆō VREF / GAIN |

0x200 |

-512 |

ą¤čĆąĖą╝ąĄčĆ: ADMUX = 0xED (ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮą░čÅ ą┐ą░čĆą░ ą▓čģąŠą┤ąŠą▓ ADC3 - ADC2, GAIN = 10, VREF =2.56ąÆ, čĆąĄąĘčāą╗čīčéą░čé čü ą╗ąĄą▓ąŠčüč鹊čĆąŠąĮąĮąĖą╝ ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖąĄą╝), ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąĮą░ ą▓čģąŠą┤ąĄ ADC3 = 300 ą╝ąÆ, ą░ ąĮą░ ą▓čģąŠą┤ąĄ ADC2 = 500 ą╝ąÆ, č鹊ą│ą┤ą░:

ADCR = 512 * 10 * (300 - 500) / 2560 = -400 = 0x270

ąĪ čāč湥č鹊ą╝ ą▓čŗą▒čĆą░ąĮąĮąŠą│ąŠ č乊čĆą╝ą░čéą░ čĆą░ąĘą╝ąĄčēąĄąĮąĖčÅ čĆąĄąĘčāą╗čīčéą░čéą░ (ą╗ąĄą▓ąŠčüč鹊čĆąŠąĮąĮąĖą╣) ADCL = 0x00, ą░ ADCH = 0x9C. ąĢčüą╗ąĖ ąČąĄ ą▓čŗą▒čĆą░ąĮ ą┐čĆą░ą▓ąŠčüč鹊čĆąŠąĮąĮąĖą╣ č乊čĆą╝ą░čé (ADLAR=0), č鹊 ADCL = 0x70, ADCH = 0x02.

[ąĀąĄą│ąĖčüčéčĆčŗ ADC]

ąśąĮč鹥čĆč乥ą╣čü čĆą░ą▒ąŠčéčŗ čü ADC ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ ATmega16 (ATmega32) čćčĆąĄąĘą▓čŗčćą░ą╣ąĮąŠ ą┐čĆąŠčüčé - ąĮčāąČąĮąŠ ąĘąĮą░čéčī č鹊ą╗čīą║ąŠ 5 čĆąĄą│ąĖčüčéčĆąŠą▓ - ADMUX, ADCSRA, ADCL, ADCH, SFIOR.

| ąĀą░ąĘčĆčÅą┤ |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

| |

REFS1 |

REFS0 |

ADLAR |

MUX4 |

MUX3 |

MUX2 |

MUX1 |

MUX0 |

ADMUX |

| ą¦č鹥ąĮąĖąĄ/ąĘą░ą┐ąĖčüčī |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

|

| ąśčüčģ. ąĘąĮą░č湥ąĮąĖąĄ |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

ąĀą░ąĘčĆčÅą┤ 7:6 ŌĆō REFS1:0: ąæąĖčéčŗ ą▓čŗą▒ąŠčĆą░ ąĖčüč鹊čćąĮąĖą║ą░ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ

ąöą░ąĮąĮčŗąĄ ą▒ąĖčéčŗ ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčé ą║ą░ą║ąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ą▒čāą┤ąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą▓ ą║ą░č湥čüčéą▓ąĄ ąŠą┐ąŠčĆąĮąŠą│ąŠ ą┤ą╗čÅ ADC (čüą╝. čéą░ą▒ą╗. 83). ąĢčüą╗ąĖ ąĖąĘą╝ąĄąĮąĖčéčī ąĘąĮą░č湥ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ą▒ąĖčé ą▓ ą┐čĆąŠčåąĄčüčüąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ, č鹊 ąĮąŠą▓čŗąĄ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▓čüčéčāą┐čÅčé ą▓ čüąĖą╗čā č鹊ą╗čīą║ąŠ ą┐ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĖ č鹥ą║čāčēąĄą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ (čé. ąĄ. ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé ADIF ą▓ čĆąĄą│ąĖčüčéčĆąĄ ADCSRA). ąÆąĮčāčéčĆąĄąĮąĮąĖą╣ ąśą×ąØ ą╝ąŠąČąĮąŠ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī, ąĄčüą╗ąĖ ą║ ą▓čŗą▓ąŠą┤čā AREF ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą▓ąĮąĄčłąĮąĖą╣ ąŠą┐ąŠčĆąĮčŗą╣ ąĖčüč鹊čćąĮąĖą║.

ąóą░ą▒ą╗ąĖčåą░ 83. ąÆčŗą▒ąŠčĆ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ ADC

| REFS1 |

REFS0 |

ąśčüč鹊čćąĮąĖą║ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ADC |

| 0 |

0 |

ąÆąĮąĄčłąĮąĖą╣ ąĖčüč鹊čćąĮąĖą║, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗą╣ ą║ AREF, ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ VREF ąŠčéą║ą╗čÄč湥ąĮ |

| 0 |

1 |

AVCC čü ą▓ąĮąĄčłąĮąĖą╝ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆąŠą╝ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ AREF |

| 1 |

0 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

| 1 |

1 |

ąÆąĮčāčéčĆąĄąĮąĮąĖą╣ ąĖčüč鹊čćąĮąĖą║ ąŠą┐ąŠčĆąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ 2.56ąÆ čü ą▓ąĮąĄčłąĮąĖą╝ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆąŠą╝ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ AREF |

ąĀą░ąĘčĆčÅą┤ 5 ŌĆō ADLAR: ąæąĖčé čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮąĖąĄą╝ čĆąĄąĘčāą╗čīčéą░čéą░ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ

ąæąĖčé ADLAR ą▓ą╗ąĖčÅąĄčé ąĮą░ ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮąĖąĄ čĆąĄąĘčāą╗čīčéą░čéą░ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą▓ ą┐ą░čĆąĄ čĆąĄą│ąĖčüčéčĆąŠą▓ čĆąĄąĘčāą╗čīčéą░čéą░ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ADC. ąĢčüą╗ąĖ ADLAR = 1, č鹊 čĆąĄąĘčāą╗čīčéą░čé ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą▒čāą┤ąĄčé ąĖą╝ąĄčéčī ą╗ąĄą▓ąŠčüč鹊čĆąŠąĮąĮąĖą╣ č乊čĆą╝ą░čé, ą▓ ą┐čĆąŠčéąĖą▓ąĮąŠą╝ čüą╗čāčćą░ąĄ - ą┐čĆą░ą▓ąŠčüč鹊čĆąŠąĮąĮąĖą╣. ąöąĄą╣čüčéą▓ąĖąĄ ą▒ąĖčéą░ ADLAR ą▓čüčéčāą┐ą░ąĄčé ą▓ čüąĖą╗čā čüčĆą░ąĘčā ą┐ąŠčüą╗ąĄ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ, ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé ą▓čŗą┐ąŠą╗ąĮčÅčÄčēąĄą│ąŠčüčÅ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ. ą¤ąŠą╗ąĮąŠąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ ą┤ąĄą╣čüčéą▓ąĖčÅ ą┤ą░ąĮąĮąŠą│ąŠ ą▒ąĖčéą░ ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮąŠ ą▓ąŠ ą▓čĆąĄąĘą║ąĄ "ąĀąĄą│ąĖčüčéčĆčŗ ą┤ą░ąĮąĮčŗčģ ADC: ADCL ąĖ ADCH".

ąĀą░ąĘčĆčÅą┤čŗ 4:0 ŌĆō MUX4:0: ąæąĖčéčŗ ą▓čŗą▒ąŠčĆą░ ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ą║ą░ąĮą░ą╗ą░ ąĖ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéą░ čāčüąĖą╗ąĄąĮąĖčÅ

ąöą░ąĮąĮčŗąĄ ą▒ąĖčéčŗ ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčé ą║ą░ą║ąĖąĄ ąĖąĘ ąĖą╝ąĄčÄčēąĖčģčüčÅ ą░ąĮą░ą╗ąŠą│ąŠą▓čŗčģ ą▓čģąŠą┤ąŠą▓ ą┐ąŠą┤ą║ą╗čÄčćą░čÄčéčüčÅ ą║ ADC. ąÜčĆąŠą╝ąĄ č鹊ą│ąŠ, čü ąĖčģ ą┐ąŠą╝ąŠčēčīčÄ ą╝ąŠąČąĮąŠ ą▓čŗą▒čĆą░čéčī ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé čāčüąĖą╗ąĄąĮąĖčÅ ą┤ą╗čÅ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗčģ ą║ą░ąĮą░ą╗ąŠą▓ (čüą╝. čéą░ą▒ą╗. 84). ąĢčüą╗ąĖ ąĘąĮą░č湥ąĮąĖčÅ ą▒ąĖčé ąĖąĘą╝ąĄąĮąĖčéčī ą▓ ą┐čĆąŠčåąĄčüčüąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ, č鹊 ąĮąŠą▓čŗąĄ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▓čüčéčāą┐čÅčé ą▓ čüąĖą╗čā č鹊ą╗čīą║ąŠ ą┐ąŠčüą╗ąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ č鹥ą║čāčēąĄą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ (ą┐ąŠčüą╗ąĄ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ ADIF ą▓ čĆąĄą│ąĖčüčéčĆąĄ ADCSRA).

ąóą░ą▒ą╗ąĖčåą░ 84. ąÆčŗą▒ąŠčĆ ą▓čģąŠą┤ąĮąŠą│ąŠ ą║ą░ąĮą░ą╗ą░ ąĖ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéą░ čāčüąĖą╗ąĄąĮąĖčÅ

| MUX4..0 |

ąØąĄą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣ ą▓čģąŠą┤ |

ąØąĄąĖąĮą▓ąĄčĆčéąĖčĆčāčÄčēąĖą╣ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣ ą▓čģąŠą┤ |

ąśąĮą▓ąĄčĆčéąĖčĆčāčÄčēąĖą╣ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣ ą▓čģąŠą┤ |

ąÜąŠčŹčäčäąĖčåąĖąĄąĮčé čāčüąĖą╗ąĄąĮąĖčÅ, GAIN (ąÜčā) |

| 00000 |

ADC0 |

ąöąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗčģ ą▓čģąŠą┤ąŠą▓ ąĖ čāčüąĖą╗ąĄąĮąĖčÅ ąĮąĄčé |

| 00001 |

ADC1 |

| 00010 |

ADC2 |

| 00011 |

ADC3 |

| 00100 |

ADC4 |

| 00101 |

ADC5 |

| 00110 |

ADC6 |

| 00111 |

ADC7 |

| 01000 |

ąØąĄą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗčģ ą▓čģąŠą┤ąŠą▓ ąĮąĄčé |

ADC0 |

ADC0 |

10x |

| 01001 |

ADC1 |

ADC0 |

10x |

| 01010(1) |

ADC0 |

ADC0 |

200x |

| 01011(1) |

ADC1 |

ADC0 |

200x |

| 01100 |

ADC2 |

ADC2 |

10x |

| 01101 |

ADC3 |

ADC2 |

10x |

| 01110(1) |

ADC2 |

ADC2 |

200x |

| 01111(1) |

ADC3 |

ADC2 |

200x |

| 10000 |

ADC0 |

ADC1 |

1x |

| 10001 |

ADC1 |

ADC1 |

1x |

| 10010 |

ADC2 |

ADC1 |

1x |

| 10011 |

ADC3 |

ADC1 |

1x |

| 10100 |

ADC4 |

ADC1 |

1x |

| 10101 |

ADC5 |

ADC1 |

1x |

| 10110 |

ADC6 |

ADC1 |

1x |

| 10111 |

ADC7 |

ADC1 |

1x |

| 11000 |

ADC0 |

ADC2 |

1x |

| 11001 |

ADC1 |

ADC2 |

1x |

| 11010 |

ADC2 |

ADC2 |

1x |

| 11011 |

ADC3 |

ADC2 |

1x |

| 11100 |

ADC4 |

ADC2 |

1x |

| 11101 |

ADC5 |

ADC2 |

1x |

| 11110 |

1.22 ąÆ (VBG) |

ąöąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗčģ ą▓čģąŠą┤ąŠą▓ ąĖ čāčüąĖą╗ąĄąĮąĖčÅ ąĮąĄčé |

| 11111 |

0 ąÆ (GND) |

|

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: 1. ąöąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗąĄ ą║ą░ąĮą░ą╗čŗ ąĮąĄ č鹥čüčéąĖčĆąŠą▓ą░ą╗ąĖčüčī ą┤ą╗čÅ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ ą▓ ą║ąŠčĆą┐čāčüąĄ PDIP40. ąĀą░ą▒ąŠčéą░ ą▓ čéą░ą║ąŠą╝ čĆąĄąČąĖą╝ąĄ ą│ą░čĆą░ąĮčéąĖčĆčāąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ ą▓ ą║ąŠčĆą┐čāčüą░čģ TQFP ąĖ QFN/MLF.

| ąĀą░ąĘčĆčÅą┤ |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

| |

ADEN |

ADSC |

ADFR |

ADIF |

ADIE |

ADPS2 |

ADPS1 |

ADPS0 |

ADCSRA |

| ą¦č鹥ąĮąĖąĄ/ąĘą░ą┐ąĖčüčī |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

|

| ąśčüčģ. ąĘąĮą░č湥ąĮąĖąĄ |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

ąĀą░ąĘčĆčÅą┤ 7 ŌĆō ADEN: ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ čĆą░ą▒ąŠčéčŗ ADC

ąŚą░ą┐ąĖčüčī ą▓ ą┤ą░ąĮąĮčŗą╣ ą▒ąĖčé ą╗ąŠą│. 1 čĆą░ąĘčĆąĄčłą░ąĄčé čĆą░ą▒ąŠčéčā ADC. ąĢčüą╗ąĖ ą▓ ą┤ą░ąĮąĮčŗą╣ ą▒ąĖčé ąĘą░ą┐ąĖčüą░čéčī ą╗ąŠą│. 0, č鹊 ADC ąŠčéą║ą╗čÄčćą░ąĄčéčüčÅ, ą┤ą░ąČąĄ ąĄčüą╗ąĖ ąŠąĮ ąĮą░čģąŠą┤ąĖą╗čüčÅ ą▓ ą┐čĆąŠčåąĄčüčüąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ.

ąĀą░ąĘčĆčÅą┤ 6 ŌĆō ADSC: ąŚą░ą┐čāčüą║ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ADC

ąÆ čĆąĄąČąĖą╝ąĄ ąŠą┤ąĖąĮąŠčćąĮąŠą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ čāčüčéą░ąĮąŠą▓ą║ą░ ą┤ą░ąĮąĮąŠą│ąŠ ą▒ąĖčéą░ ąĖąĮąĖčåąĖąĖčĆčāąĄčé čüčéą░čĆčé ą║ą░ąČą┤ąŠą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ. ąÆ čĆąĄąČąĖą╝ąĄ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą│ąŠ ą┐ąĄčĆąĄąĘą░ą┐čāčüą║ą░ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ čŹč鹊ą│ąŠ ą▒ąĖčéą░ ąĖąĮąĖčåąĖąĖčĆčāąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą┐ąĄčĆą▓ąŠąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ, ą░ ą▓čüąĄ ąŠčüčéą░ą╗čīąĮčŗąĄ ą▓čŗą┐ąŠą╗ąĮčÅčÄčéčüčÅ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ. ą¤ąĄčĆą▓ąŠąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ą┐ąŠčüą╗ąĄ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ čĆą░ą▒ąŠčéčŗ ADC, ąĖąĮąĖčåąĖąĖčĆąŠą▓ą░ąĮąĮąŠąĄ ą▒ąĖč鹊ą╝ ADSC (ąĖą╗ąĖ ąĄčüą╗ąĖ ą▓ ADSC ąĘą░ą┐ąĖčüą░ą╗ąĖ 1 ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ čü čĆą░ąĘčĆąĄčłąĄąĮąĖąĄą╝ čĆą░ą▒ąŠčéčŗ ADC), ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ąĘą░ 25 čéą░ą║č鹊ą▓ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ADC, ą▓ą╝ąĄčüč鹊 ąŠą▒čŗčćąĮčŗčģ 13 čéą░ą║č鹊ą▓. ąŁč鹊 čüą▓čÅąĘą░ąĮąŠ čü ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéčīčÄ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ ADC ą┐čĆąĖ ą┐ąĄčĆą▓ąŠą╝ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĖ.

ąÆ ą┐čĆąŠčåąĄčüčüąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą┐čĆąĖ ąŠą┐čĆąŠčüąĄ ą▒ąĖčéą░ ADSC ą▓ąŠąĘą▓čĆą░čēą░ąĄčéčüčÅ ą╗ąŠą│. 1, ą░ ą┐ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ŌĆō ą╗ąŠą│. 0. ąŚą░ą┐ąĖčüčī ą╗ąŠą│. 0 ą▓ ą┤ą░ąĮąĮčŗą╣ ą▒ąĖčé ą▓ąŠąĘą╝ąŠąČąĮąŠ, ąĮąŠ ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ ą┤ąĄą╣čüčéą▓ąĖčÅ.

ąĀą░ąĘčĆčÅą┤ 5 ŌĆō ADATE: ąÆą║ą╗čÄč湥ąĮąĖąĄ čĆąĄąČąĖą╝ą░ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą│ąŠ ąĘą░ą┐čāčüą║ą░ ADC

ąĢčüą╗ąĖ ą▓ ą┤ą░ąĮąĮčŗą╣ ą▒ąĖčé ąĘą░ą┐ąĖčüą░čéčī ą╗ąŠą│. 1, č鹊 ADC ą┐ąĄčĆąĄą╣ą┤ąĄčé ą▓ čĆąĄąČąĖą╝ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą│ąŠ ą┐ąĄčĆąĄąĘą░ą┐čāčüą║ą░. ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ADC ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąĘą░ą┐čāčüą║ą░ąĄčé ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ą┐ąŠ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą╝čā čäčĆąŠąĮčéčā ą▓čŗą▒čĆą░ąĮąĮąŠą│ąŠ ąĘą░ą┐čāčüą║ą░čÄčēąĄą│ąŠ čüąĖą│ąĮą░ą╗ą░. ąÆčŗą▒ąŠčĆ ąĖčüč鹊čćąĮąĖą║ą░ ąĘą░ą┐čāčüą║ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą▒ąĖčéą░ą╝ąĖ ADTS čĆąĄą│ąĖčüčéčĆą░ SFIOR.

ąĀą░ąĘčĆčÅą┤ 4 ŌĆō ADIF: ążą╗ą░ą│ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ADC

ąöą░ąĮąĮčŗą╣ čäą╗ą░ą│ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą┐ąŠčüą╗ąĄ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ADC ąĖ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ čĆąĄą│ąĖčüčéčĆąŠą▓ ą▓čŗčģąŠą┤ąĮčŗčģ ą┤ą░ąĮąĮčŗčģ (ADCH:ADCL). ąĢčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą▒ąĖčéčŗ ADIE ąĖ I (čĆąĄą│ąĖčüčéčĆ SREG), č鹊 ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą▓čŗąĘąŠą▓ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ. ążą╗ą░ą│ ADIF čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéąĮąŠ ą┐čĆąĖ ą┐ąĄčĆąĄčģąŠą┤ąĄ ąĮą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▓ąĄą║č鹊čĆ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ. ąÉą╗čīč鹥čĆąĮą░čéąĖą▓ąĮąŠ čäą╗ą░ą│ ADIF čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ ą╗ąŠą│. 1 ą▓ ąĮąĄą│ąŠ. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ą┐čĆąĖ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĖ ą║ąŠą╝ą░ąĮą┤čŗ "čćč鹥ąĮąĖąĄ-ą╝ąŠą┤ąĖčäąĖą║ą░čåąĖčÅ-ąĘą░ą┐ąĖčüčī" čü čĆąĄą│ąĖčüčéčĆąŠą╝ ADCSRA ąŠąČąĖą┤ą░ąĄą╝ąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąĄčēąĄąĮąŠ. ąĪą║ą░ąĘą░ąĮąĮąŠąĄ čéą░ą║ąČąĄ ą┤ąĄą╣čüčéą▓ąĖč鹥ą╗čīąĮąŠ, ąĄčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ąĖąĮčüčéčĆčāą║čåąĖąĖ SBI ąĖ CBI.

ąĀą░ąĘčĆčÅą┤ 3 ŌĆō ADIE: ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ADC

ąÜąŠą│ą┤ą░ čŹč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ ą╗ąŠą│. 1, ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé I ą▓ čĆąĄą│ąĖčüčéčĆąĄ SREG, čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ADC.

ąĀą░ąĘčĆčÅą┤čŗ 2:0 ŌĆō ADPS2:0: ąæąĖčéčŗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐čĆąĄą┤ą┤ąĄą╗ąĖč鹥ą╗ąĄą╝ ADC

ąöą░ąĮąĮčŗąĄ ą▒ąĖčéčŗ ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčé ąĮą░ ą║ą░ą║ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ ą”ą¤ąŻ ą▒čāą┤ąĄčé ąŠčéą╗ąĖčćą░čéčīčüčÅ ąŠčé čćą░čüč鹊čéčŗ ą▓čģąŠą┤ąĮąŠą╣ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ADC.

ąóą░ą▒ą╗ąĖčåą░ 85. ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą┐čĆąĄą┤ą┤ąĄą╗ąĖč鹥ą╗ąĄą╝ (ą┐čĆąĄčüą║ą░ą╗ąĄčĆąŠą╝) ADC

| ADPS2 |

ADPS1 |

ADPS0 |

ąÜąŠčŹčäčäąĖčåąĖąĄąĮčé ą┤ąĄą╗ąĄąĮąĖčÅ |

| 0 |

0 |

0 |

2 |

| 0 |

0 |

1 |

2 |

| 0 |

1 |

0 |

4 |

| 0 |

1 |

1 |

8 |

| 1 |

0 |

0 |

16 |

| 1 |

0 |

1 |

32 |

| 1 |

1 |

0 |

64 |

| 1 |

1 |

1 |

128 |

ADLAR = 0:

| ąĀą░ąĘčĆčÅą┤ |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

|

| |

- |

- |

- |

- |

- |

- |

ADC9 |

ADC8 |

ADCH |

| |

ADC7 |

ADC6 |

ADC5 |

ADC4 |

ADC3 |

ADC2 |

ADC1 |

ADC0 |

ADCL |

| |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

| ą¦č鹥ąĮąĖąĄ/ąĘą░ą┐ąĖčüčī |

R |

R |

R |

R |

R |

R |

R |

R |

|

| |

R |

R |

R |

R |

R |

R |

R |

R |

|

| ąśčüčģ. ąĘąĮą░č湥ąĮąĖąĄ |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

| |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

ADLAR = 1:

| ąĀą░ąĘčĆčÅą┤ |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

|

| |

ADC9 |

ADC8 |

ADC7 |

ADC6 |

ADC5 |

ADC4 |

ADC3 |

ADC2 |

ADCH |

| |

ADC1 |

ADC0 |

- |

- |

- |

- |

- |

- |

ADCL |

| |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

| ą¦č鹥ąĮąĖąĄ/ąĘą░ą┐ąĖčüčī |

R |

R |

R |

R |

R |

R |

R |

R |

|

| |

R |

R |

R |

R |

R |

R |

R |

R |

|

| ąśčüčģ. ąĘąĮą░č湥ąĮąĖąĄ |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

| |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

ą¤ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ čĆąĄąĘčāą╗čīčéą░čé ą┐ąŠą╝ąĄčēą░ąĄčéčüčÅ ą▓ čŹčéąĖčģ ą┤ą▓čāčģ čĆąĄą│ąĖčüčéčĆą░čģ. ą¤čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮąŠą│ąŠ čĆąĄąČąĖą╝ą░ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ čĆąĄąĘčāą╗čīčéą░čé ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčéčüčÅ ą▓ ą║ąŠą┤ąĄ ą┤ą▓ąŠąĖčćąĮąŠą│ąŠ ą┤ąŠą┐ąŠą╗ąĮąĄąĮąĖčÅ.

ąĢčüą╗ąĖ ą▓čŗą┐ąŠą╗ąĮąĄąĮąŠ čćč鹥ąĮąĖąĄ ADCL, č鹊 ą┤ąŠčüčéčāą┐ ą║ čŹčéąĖą╝ čĆąĄą│ąĖčüčéčĆą░ą╝ ą┤ą╗čÅ ADC ą▒čāą┤ąĄčé ąĘą░ą▒ą╗ąŠą║ąĖčĆąŠą▓ą░ąĮ (čé. ąĄ. ADC ąĮąĄ čüą╝ąŠąČąĄčé ą▓ ą┤ą░ą╗čīąĮąĄą╣čłąĄą╝ ą╝ąŠą┤ąĖčäąĖčåąĖčĆąŠą▓ą░čéčī čĆąĄąĘčāą╗čīčéą░čé ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ), ą┐ąŠą║ą░ ąĮąĄ ą▒čāą┤ąĄčé čüčćąĖčéą░ąĮ čĆąĄą│ąĖčüčéčĆ ADCH.

ążąŠčĆą╝ą░čé ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮąĖčÅ čĆąĄąĘčāą╗čīčéą░čéą░ (ą╗ąĄą▓ąŠčüč鹊čĆąŠąĮąĮąĄąĄ ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖąĄ ąĖą╗ąĖ ą┐čĆą░ą▓ąŠčüč鹊čĆąŠąĮąĮąĄąĄ ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖąĄ) ąĘą░ą▓ąĖčüąĖčé ąŠčé čüąŠčüč鹊čÅąĮąĖčÅ ą▒ąĖčéą░ ADLAR ąĖ ąŠčé čüąŠčüč鹊čÅąĮąĖčÅ ą▒ąĖč鹊ą▓ MUXn ą▓ čĆąĄą│ąĖčüčéčĆąĄ ADMUX. ąøąĄą▓ąŠčüč鹊čĆąŠąĮąĮąĖą╣ č乊čĆą╝ą░čé ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮąĖčÅ čĆąĄąĘčāą╗čīčéą░čéą░ čāą┤ąŠą▒ąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī, ąĄčüą╗ąĖ ą┤ąŠčüčéą░č鹊čćąĮąŠ 8 čĆą░ąĘčĆčÅą┤ąŠą▓. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ 8-čĆą░ąĘčĆčÅą┤ąĮčŗą╣ čĆąĄąĘčāą╗čīčéą░čé čģčĆą░ąĮąĖčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ ADCH ąĖ, čüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ, čćč鹥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ ADCL ą╝ąŠąČąĮąŠ ąĮąĄ ą▓čŗą┐ąŠą╗ąĮčÅčéčī. ą¤čĆąĖ ą┐čĆą░ą▓ąŠčüč鹊čĆąŠąĮąĮąĄą╝ č乊čĆą╝ą░č鹥 ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ čüąĮą░čćą░ą╗ą░ čüčćąĖčéą░čéčī ADCL, ą░ ąĘą░č鹥ą╝ ADCH.

ADC9:0: ąĀąĄąĘčāą╗čīčéą░čé ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ADC

ąöą░ąĮąĮčŗąĄ ą▒ąĖčéčŗ ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅčÄčé čĆąĄąĘčāą╗čīčéą░čé ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ. ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. čĆą░ąĘą┤ąĄą╗ ┬½ąĀąĄąĘčāą╗čīčéą░čé ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ADC┬╗.

| ąĀą░ąĘčĆčÅą┤ |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

| |

ADTS2 |

ADTS1 |

ADTS0 |

- |

ACME |

PUD |

PSR2 |

PSR10 |

SFIOR |

| ą¦č鹥ąĮąĖąĄ/ąĘą░ą┐ąĖčüčī |

R/W |

R/W |

R/W |

R |

R/W |

R/W |

R/W |

R/W |

|

| ąśčüčģ. ąĘąĮą░č湥ąĮąĖąĄ |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

ąĀą░ąĘčĆčÅą┤čŗ 7:5 ŌĆō ADTS2:0: ąæąĖčéčŗ ą▓čŗą▒ąŠčĆą░ ąĖčüč鹊čćąĮąĖą║ą░ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą│ąŠ ąĘą░ą┐čāčüą║ą░ ADC

ąĢčüą╗ąĖ ADATE ą▓ čĆąĄą│ąĖčüčéčĆąĄ ADCSRA ąĘą░ą┐ąĖčüą░ąĮ ą▓ ą╗ąŠą│. 1, ąĘąĮą░č湥ąĮąĖčÅ ą▒ąĖčé ADTS ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčé, ą║ą░ą║ąŠą╣ ą▒čāą┤ąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ąĖčüč鹊čćąĮąĖą║ ą┤ą╗čÅ ąĘą░ą┐čāčüą║ą░ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ. ąĢčüą╗ąĖ ADATE ą▓ čĆąĄą│ąĖčüčéčĆąĄ ADCSRA ąĘą░ą┐ąĖčüą░ąĮ ą▓ ą╗ąŠą│. 0, ąĘąĮą░č湥ąĮąĖčÅ ą▒ąĖčé ADTS ąĮąĖą║ą░ą║ąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ ąĮąĄ ąĖą╝ąĄčÄčé. ą¤čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ą▒čāą┤ąĄčé ąĘą░ą┐čāčüą║ą░čéčīčüčÅ ą┐ąŠ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą╝čā čäčĆąŠąĮčéčā (ąĮą░čĆą░čüčéą░ąĮąĖąĄ čüąĖą│ąĮą░ą╗ą░) ą▓čŗą▒čĆą░ąĮąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░. ąÆąĮąĖą╝ą░ąĮąĖąĄ ŌĆō čüąŠą▒čŗčéąĖąĄ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ ąŠčé ąŠčćąĖčēąĄąĮąĮąŠą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ ąĘą░ą┐čāčüą║ą░ ą║ ąĖčüč鹊čćąĮąĖą║čā ąĘą░ą┐čāčüą║ą░, ą║ąŠč鹊čĆčŗą╣ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ą▒čāą┤ąĄčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮčŗą╣ čäčĆąŠąĮčé čüąĖą│ąĮą░ą╗ą░ ąĘą░ą┐čāčüą║ą░, ąĖ ąĄčüą╗ąĖ ą▒ąĖčé ADEN ą▓ čĆąĄą│ąĖčüčéčĆąĄ ADCSRA čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, č鹊 ąĘą░ą┐čāčüčéąĖčéčüčÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ. ą¤ąĄčĆąĄą║ą╗čÄč湥ąĮąĖąĄ ą▓ čĆąĄąČąĖą╝ ą┐ąŠčüč鹊čÅąĮąĮąŠą│ąŠ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ (Free Running mode, ADTS[2:0]=0) ąĮąĄ ą│ąĄąĮąĄčĆąĖčĆčāąĄčé čüąŠą▒čŗčéąĖąĄ ąĘą░ą┐čāčüą║ą░, ą┤ą░ąČąĄ ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čäą╗ą░ą│ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ADC (ADC Interrupt Flag).

| ADTS2 |

ADTS1 |

ADTS0 |

ąśčüč鹊čćąĮąĖą║ ąĘą░ą┐čāčüą║ą░ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ADC |

| 0 |

0 |

0 |

ą¤ąŠčüč鹊čÅąĮąĮąŠąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ (Free Running mode) |

| 0 |

0 |

1 |

ąÉąĮą░ą╗ąŠą│ąŠą▓čŗą╣ ą║ąŠą╝ą┐ą░čĆą░č鹊čĆ |

| 0 |

1 |

0 |

ąÆąĮąĄčłąĮąĖą╣ ąĘą░ą┐čĆąŠčü ąĮą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ 0 |

| 0 |

1 |

1 |

Timer/Counter0 Compare Match |

| 1 |

0 |

0 |

Timer/Counter0 Overflow |

| 1 |

0 |

1 |

Timer/Counter1 Compare Match B |

| 1 |

1 |

0 |

Timer/Counter1 Overflow |

| 1 |

1 |

1 |

Timer/Counter1 Capture Event |

ąĀą░ąĘčĆčÅą┤ 4 ŌĆō Res: ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąĮčŗą╣ ą▒ąĖčé

ąŁč鹊čé ą▒ąĖčé ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮ ą┤ą╗čÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą▓ ą▒čāą┤čāčēąĄą╝. ąöą╗čÅ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖčÅ čüąŠą▓ą╝ąĄčüčéąĖą╝ąŠčüčéąĖ čü ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ą╝ąĖ, ą║ąŠč鹊čĆčŗąĄ ą▒čāą┤čāčé čĆą░ąĘčĆą░ą▒ąŠčéą░ąĮčŗ ą▓ ą▒čāą┤čāčēąĄą╝, ą┐čĆąĖ ąĘą░ą┐ąĖčüąĖ ą▓ čĆąĄą│ąĖčüčéčĆ SFIOR čŹč鹊čé ą▒ąĖčé ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ ą╗ąŠą│. 0.

[ąŻčüčéčĆą░ąĮąĄąĮąĖąĄ ą┐čĆąŠą▒ą╗ąĄą╝, FAQ]

Q001. ą£ąĮąĄ ąĮčāąČąĮąŠ, čćč鹊ą▒čŗ ADC ą▓čŗą┐ąŠą╗ąĮčÅą╗ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖąĄ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠ ą▒čŗčüčéčĆąŠ. ą¤ąŠč湥ą╝čā ą║ąŠą│ą┤ą░ čÅ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░čÄ ą╝ą░ą╗ąĄąĮčīą║ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┤ąĄą╗ąĖč鹥ą╗čÅ ą▒ąĖčéą░ą╝ąĖ ADPS2..0 (ADPS2:ADPS0=000 ąĖą╗ąĖ ADPS2:ADPS0=001), č鹊 ADC čā ą╝ąĄąĮčÅ ąĮąĄ čĆą░ą▒ąŠčéą░ąĄčé?

A001. ADC ąĖą╝ąĄąĄčé ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠ ą┤ąŠą┐čāčüčéąĖą╝ąŠąĄ ą▓čĆąĄą╝čÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ, ą┐ąŠčŹč鹊ą╝čā ąĄčüą╗ąĖ čā ąÆą░čü čĆą░ą▒ąŠčćą░čÅ čćą░čüč鹊čéą░ čÅą┤čĆą░ CPU čüą╗ąĖčłą║ąŠą╝ ą▒ąŠą╗čīčłą░čÅ (16 ą£ąōčå ąĖ ą▓čŗčłąĄ), č鹊 ą┐čĆąĖ ą╝ą░ą╗ąĄąĮčīą║ąĖčģ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéą░čģ ą┤ąĄą╗ąĄąĮąĖčÅ ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ ą┤ą╗čÅ ADC ą╝ąŠąČąĄčé ąŠą║ą░ąĘą░čéčīčüčÅ čüą╗ąĖčłą║ąŠą╝ ą▓čŗčüąŠą║ąŠą╣. ą¤ąŠčŹč鹊ą╝čā ą┐čĆąŠčüč鹊 ą┐ąŠą┤ą▒ąĄčĆąĖč鹥 ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┤ąĄą╗ąĖč鹥ą╗čÅ, ą┐čĆąĖ ą║ąŠč鹊čĆąŠą╝ ADC ąĮą░čćąĖąĮą░ąĄčé čĆą░ą▒ąŠčéą░čéčī. ąØą░ą┐čĆąĖą╝ąĄčĆ, čā ą╝ąĄąĮčÅ čü ATmega32A čĆą░ą▒ąŠč湥ąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┤ąĄą╗ąĖč鹥ą╗čÅ ąŠą║ą░ąĘą░ą╗ąŠčüčī ąĮąĄ ą╝ąĄąĮčīčłąĄ 4 (ADPS2:ADPS0=010).

[ąĪčüčŗą╗ą║ąĖ]

1. ąĪąŠą┤ąĄčƹȹĖą╝ąŠąĄ čŹč鹊ą╣ čüčéą░čéčīąĖ ą▓ č乊čĆą╝ą░č鹥 doc.

2. ąÉą▓č鹊ą╝ą░čé čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąŠčüą▓ąĄčēąĄąĮąĖąĄą╝ ledlight - čĆą░ą▒ąŠčćąĖą╣ ą┐čĆąŠąĄą║čé AVR Studio ą║ą░ą║ ą┐čĆąĖą╝ąĄčĆ čĆą░ą▒ąŠčéčŗ čü ADC.

3. AVR-USB-MEGA16: ąĘą░ą╝ąĄąĮą░ GC7137AD (ICL7137) ąĮą░ ATmega32 ąĖ OP291. |